Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

658 results about "Critical path method" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The critical path method (CPM), or critical path analysis (CPA), is an algorithm for scheduling a set of project activities. It is commonly used in conjunction with the program evaluation and review technique (PERT). A critical path is determined by identifying the longest stretch of dependent activities and measuring the time required to complete them from start to finish.

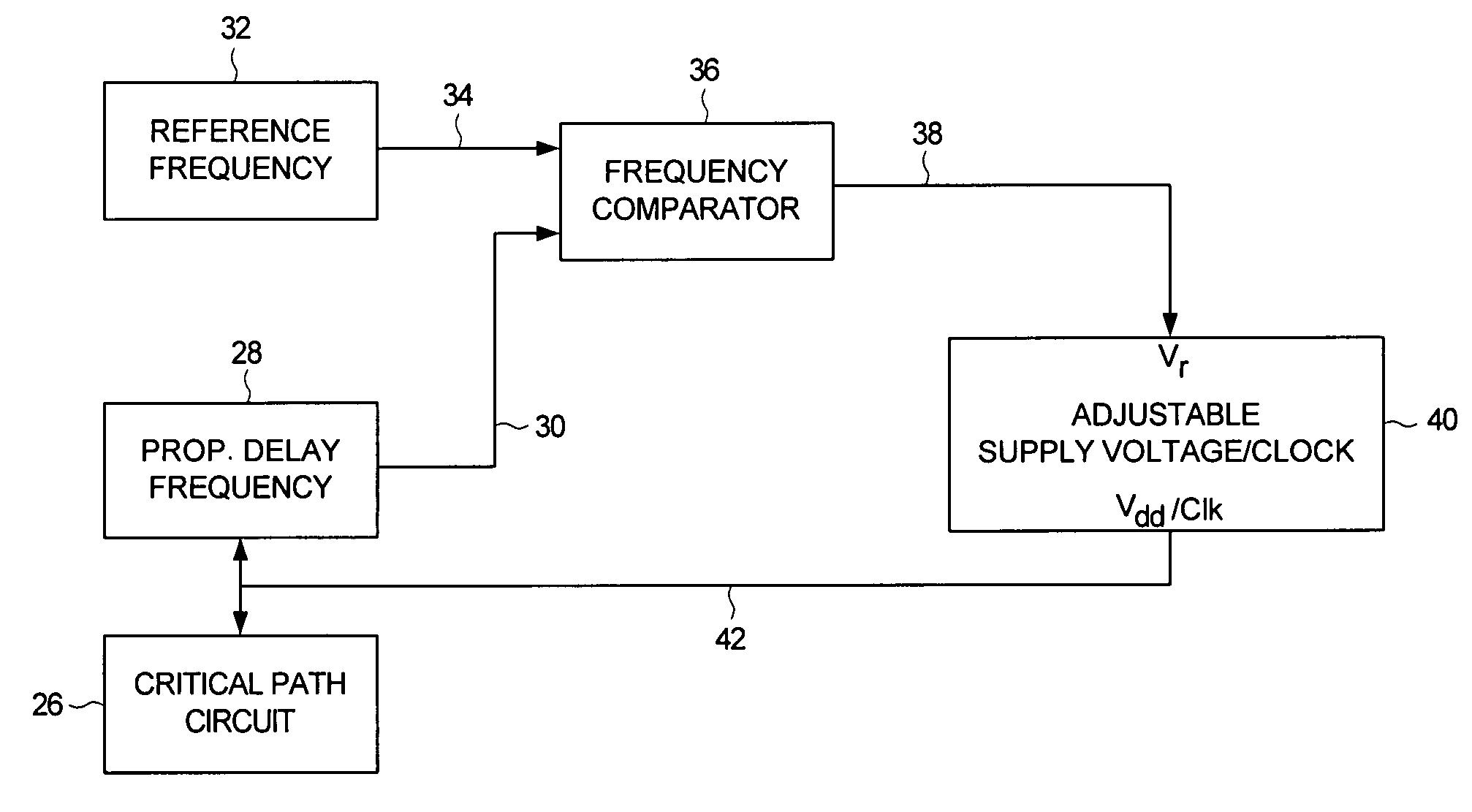

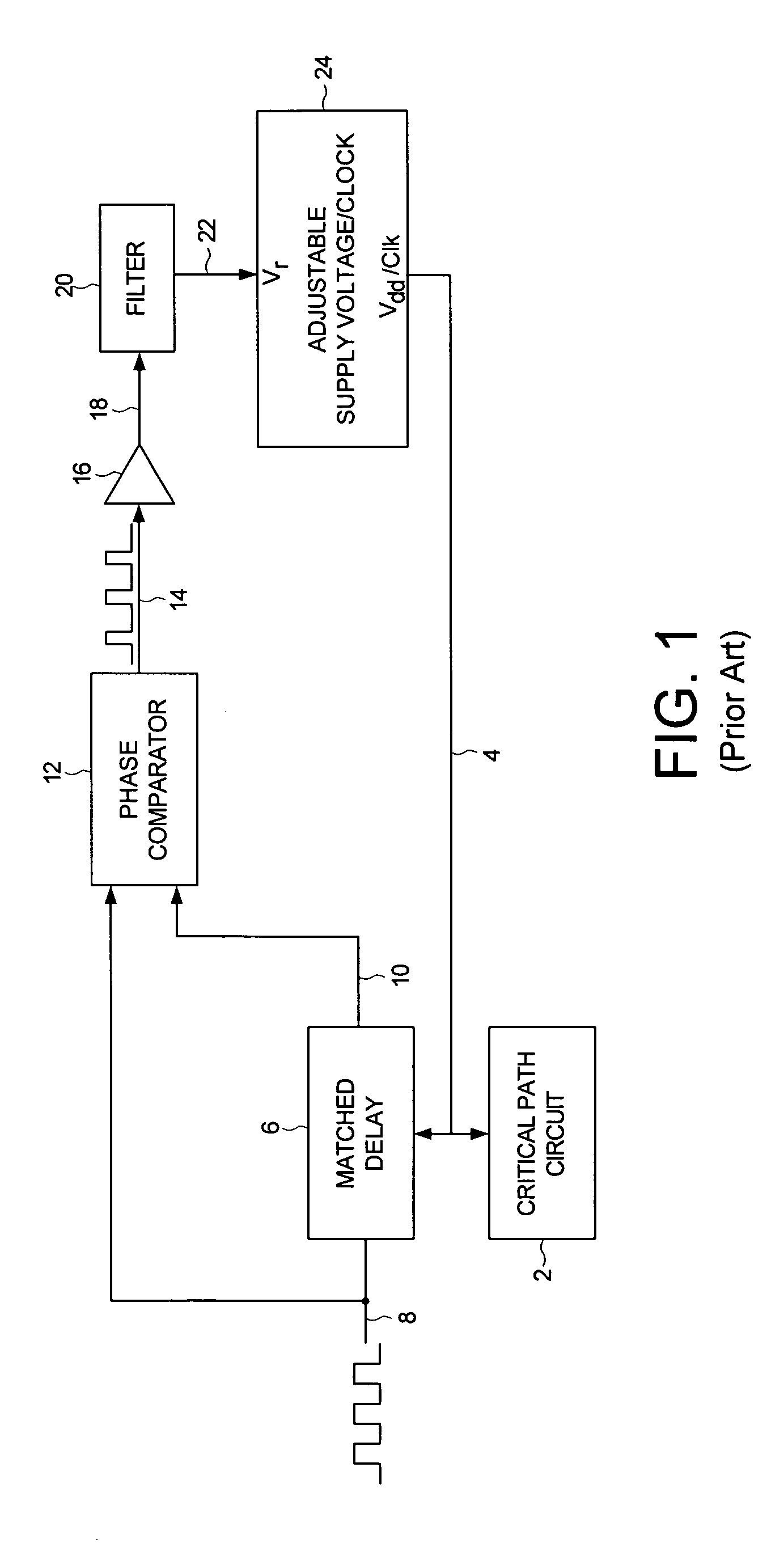

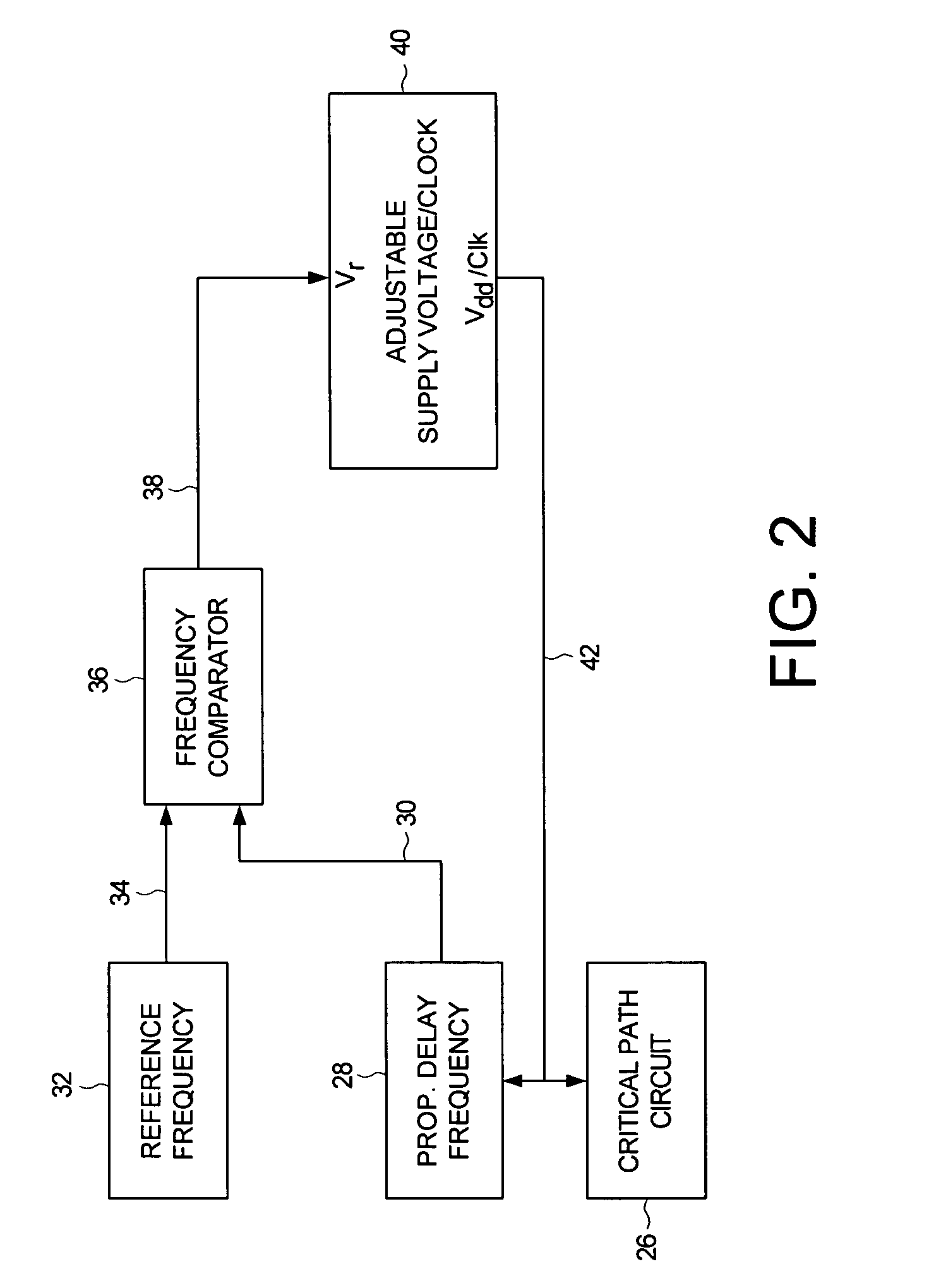

Adjusting power consumption of digital circuitry by generating frequency error representing error in propagation delay

A method and apparatus is disclosed for adjusting at least one of a supply voltage and a clocking frequency applied to digital circuitry of a computing device, wherein the digital circuitry comprises a critical path circuit. A propagation delay frequency representing a propagation delay of the critical path circuit is generated, and a frequency error signal is generated representing a difference between a reference frequency and the propagation delay frequency. At least one of the supply voltage and the clocking frequency is adjusted in response to the frequency error signal.

Owner:WESTERN DIGITAL TECH INC

Multi-activity offshore exploration and/or development drilling method and apparatus

Owner:TRANSOCEAN OFFSHORE DEEPWATER DRILLING

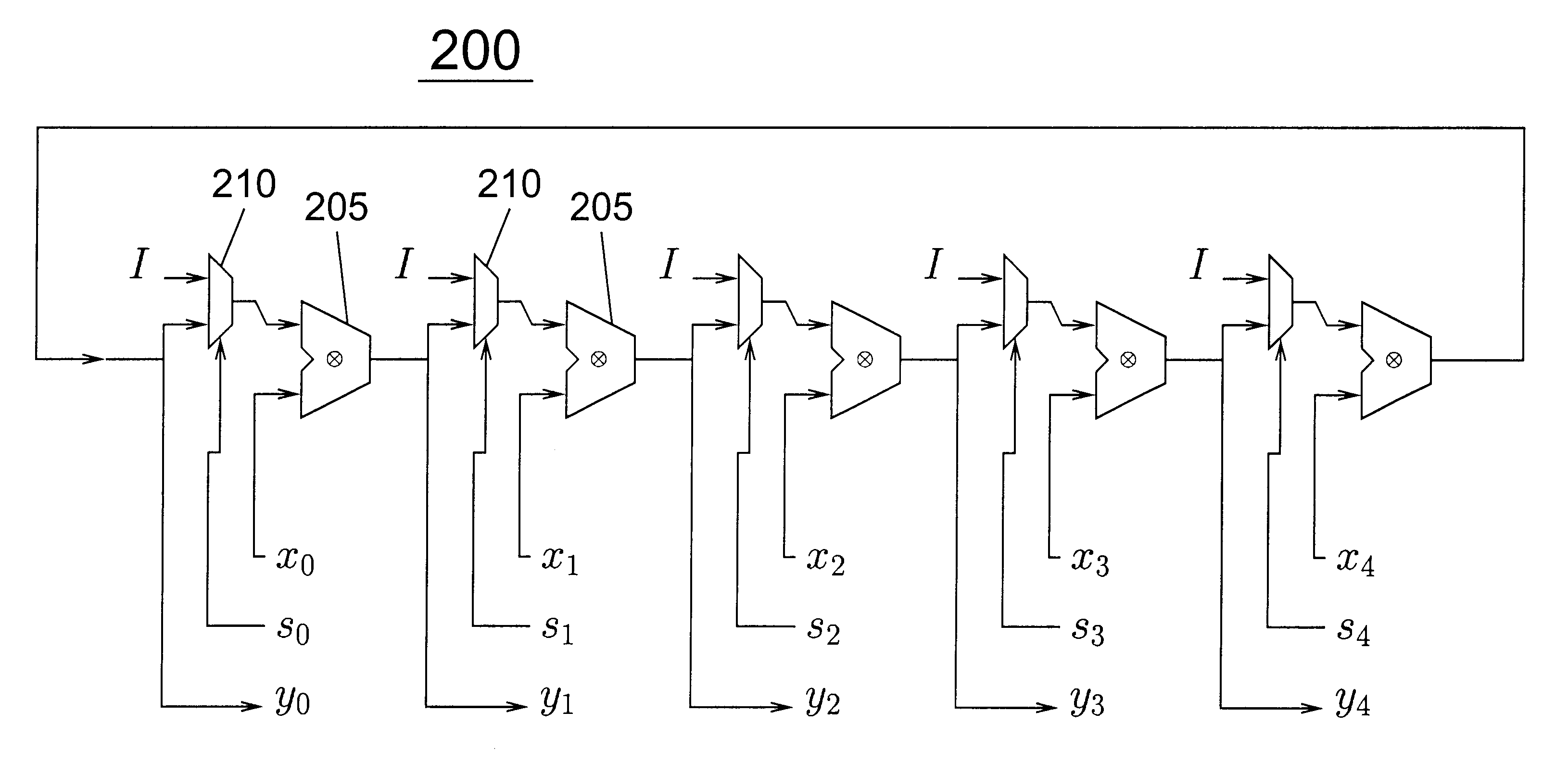

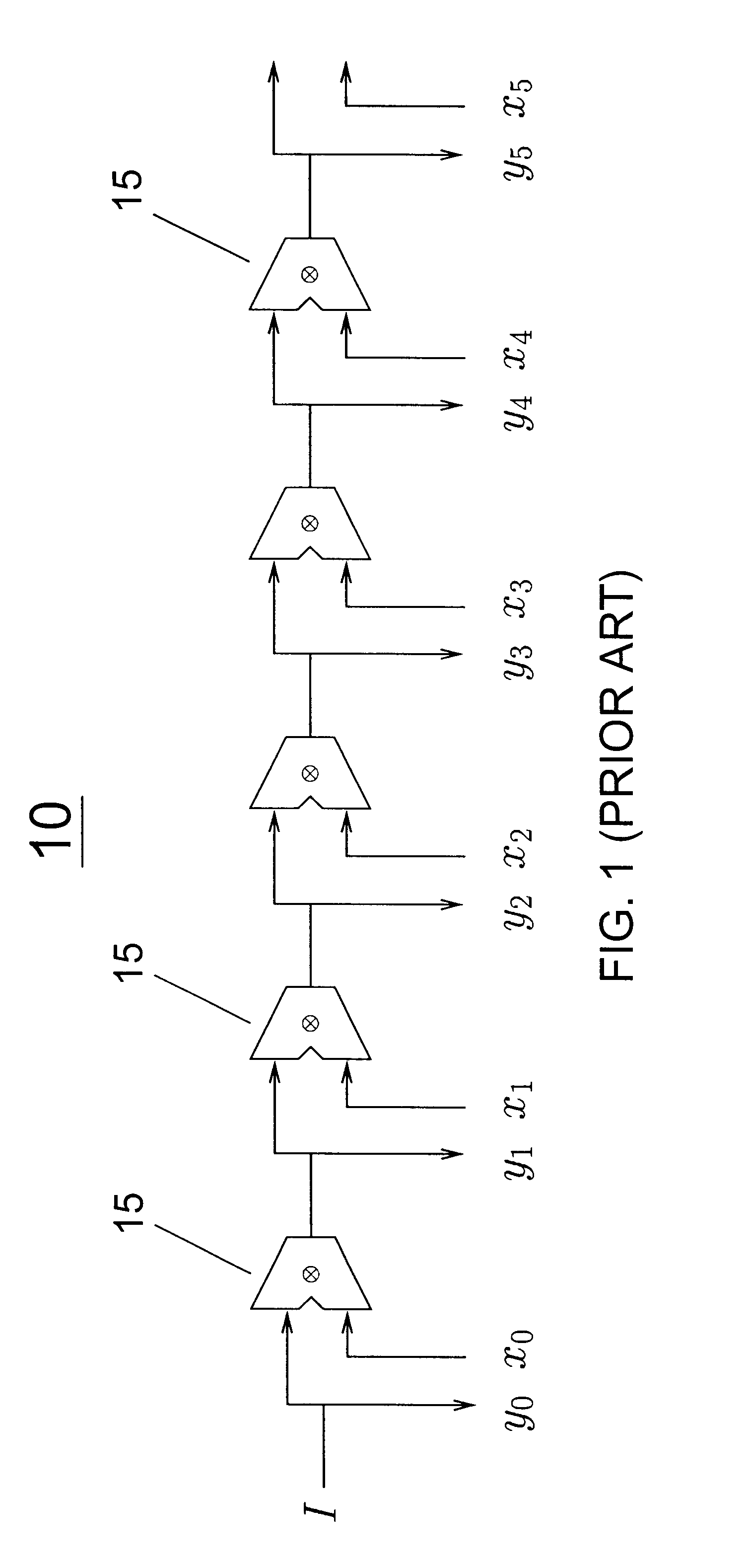

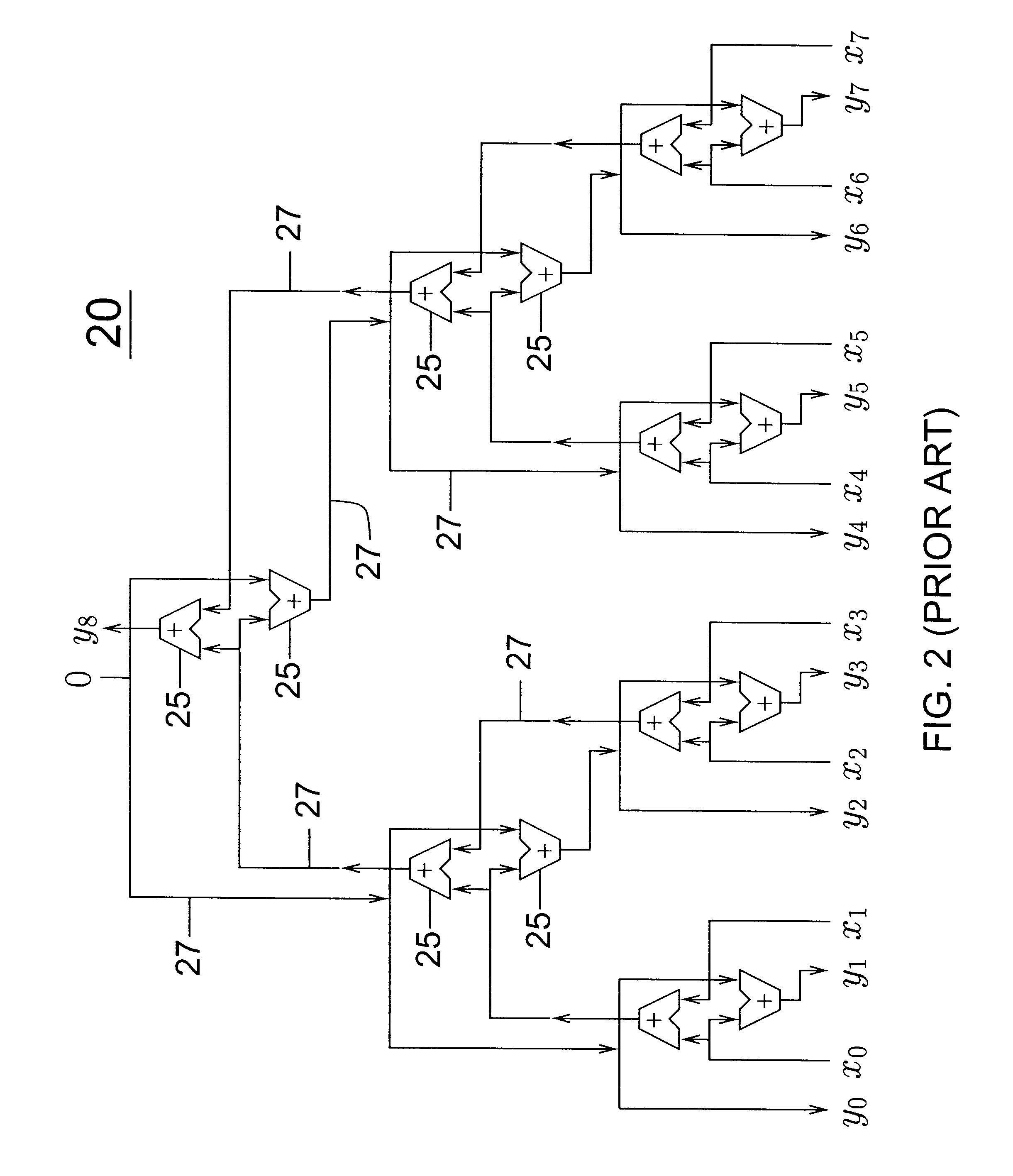

Cycle segmented prefix circuits

InactiveUS6609189B1Improve performanceAvoid performanceComputation using non-contact making devicesGeneral purpose stored program computerExtensibilityScalar processor

The poor scalability of existing superscalar processors has been of great concern to the computer engineering community. In particular, the critical-path delays of many components in existing implementations grow quadratically with the issue width and the window size. This patent presents a novel way to reimplement these components and reduce their critical-path delay growth. It then describes an entire processor microarchitecture, called the Ultrascalar processor, that has better critical-path delay growth than existing superscalars. Most of our scalable designs are based on a single circuit, a cyclic segmented parallel prefix (cspp). We observe that processor components typically operate on a wrap-around sequence of instructions, computing some associative property of that sequence. For example, to assign an ALU to the oldest requesting instruction, each instruction in the instruction sequence must be told whether any preceding instructions are requesting an ALU. Similarly, to read an argument register, an instruction must somehow communicate with the most recent preceding instruction that wrote that register. A cspp circuit can implement such functions by computing for each instruction within a wrap-around instruction sequence the accumulative result of applying some associative operator to all the preceding instructions. A cspp circuit has a critical path gate delay logarithmic in the length of the instruction sequence. Depending on its associative operation and its layout, a cspp circuit can have a critical path wire delay sublinear in the length of the instruction sequence.

Owner:YALE UNIV

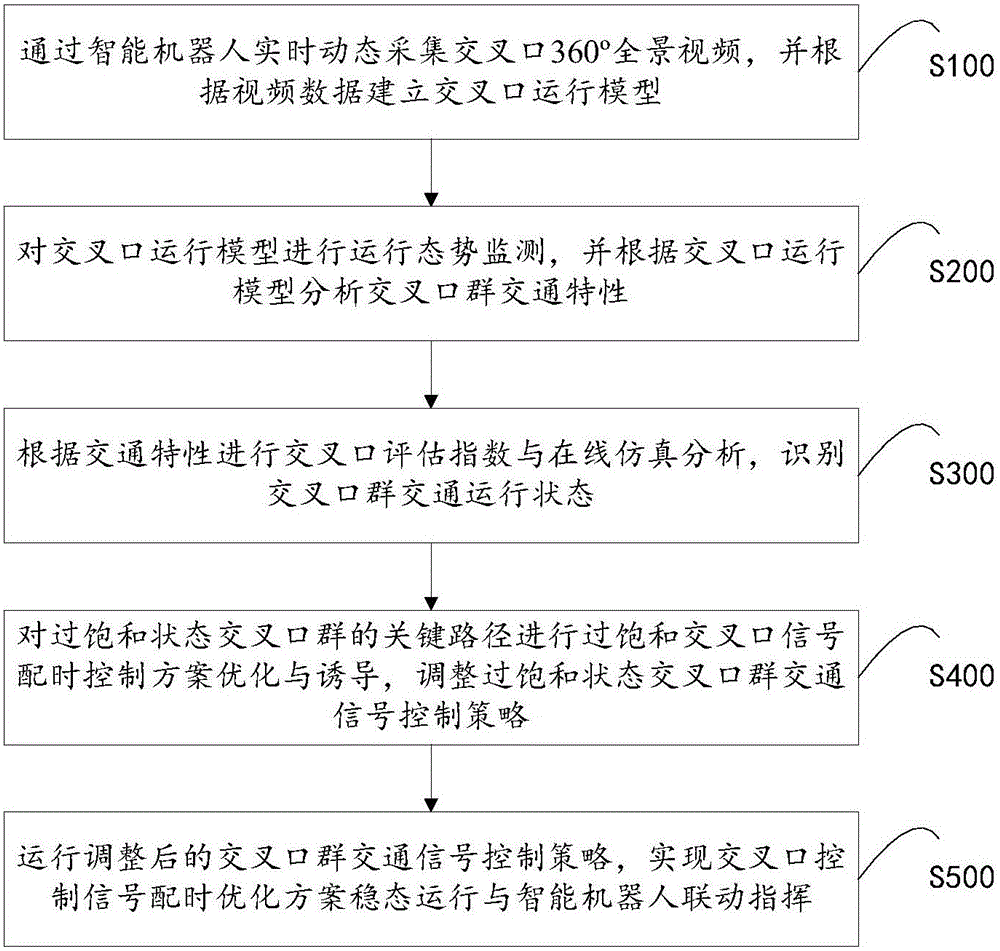

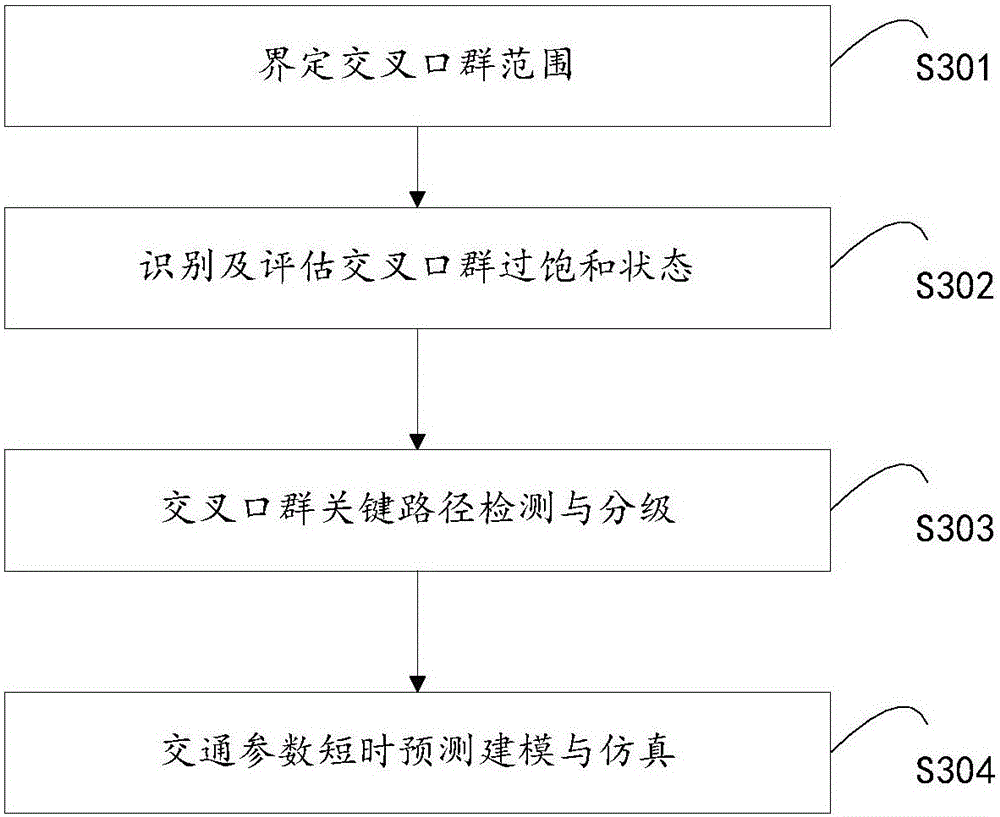

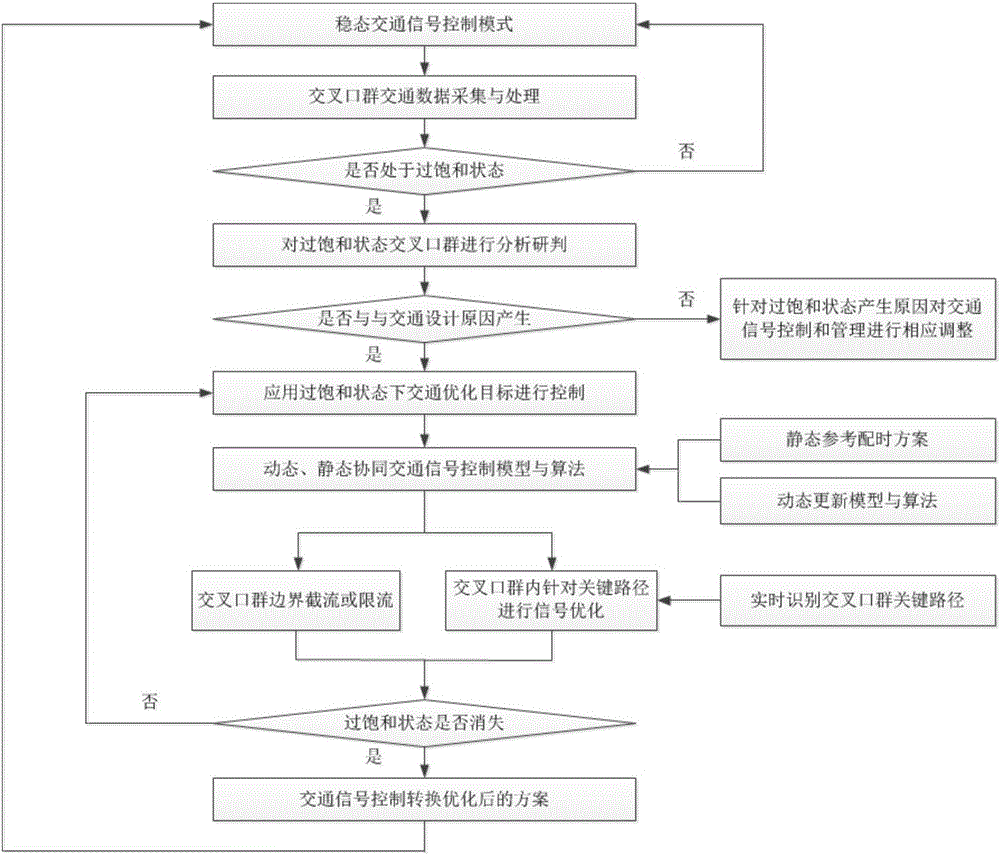

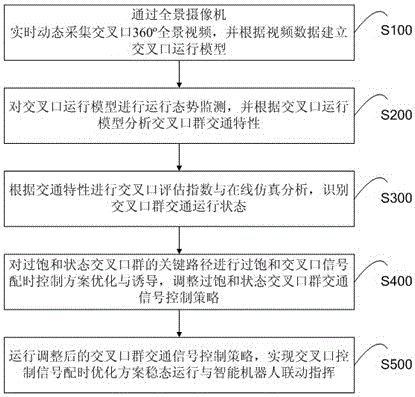

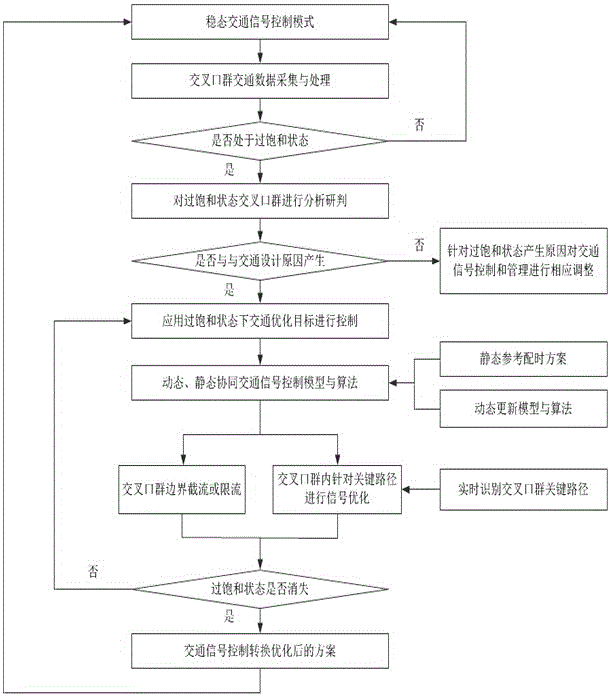

Traffic control method and system based on intersection group

InactiveCN105809958AEase traffic congestionSolve overeatingControlling traffic signalsDetection of traffic movementTraffic characteristicControl signal

The invention relates to a traffic control method and system based on an intersection group.The method comprises the steps that 1, 360-degree panoramic video of intersections is dynamically collected in real time through an intelligent robot, an intersection operation model is established according to video data, and traffic characteristics of the intersection group are analyzed according to the intersection operation model; 2, intersection index evaluation and online simulation analysis are conducted according to the traffic characteristics, and the traffic operation state of the intersection group is identified; 3, supersaturation state intersection signal timing control scheme optimization is conducted on critical paths of a supersaturation state intersection group, and a supersaturation state intersection group traffic signal control strategy is adjusted; 4, the adjusted intersection group traffic signal control strategy is operated, and steady-state operation of an intersection control signal timing optimization scheme and linkage command of the intelligent robot are achieved.By means of the traffic control method and system based on the intersection group, traffic efficiency and service level of intersection single point control can be improved, and therefore the operation efficiency of an urban traffic system is greatly improved, and urban traffic jams are relieved.

Owner:SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI

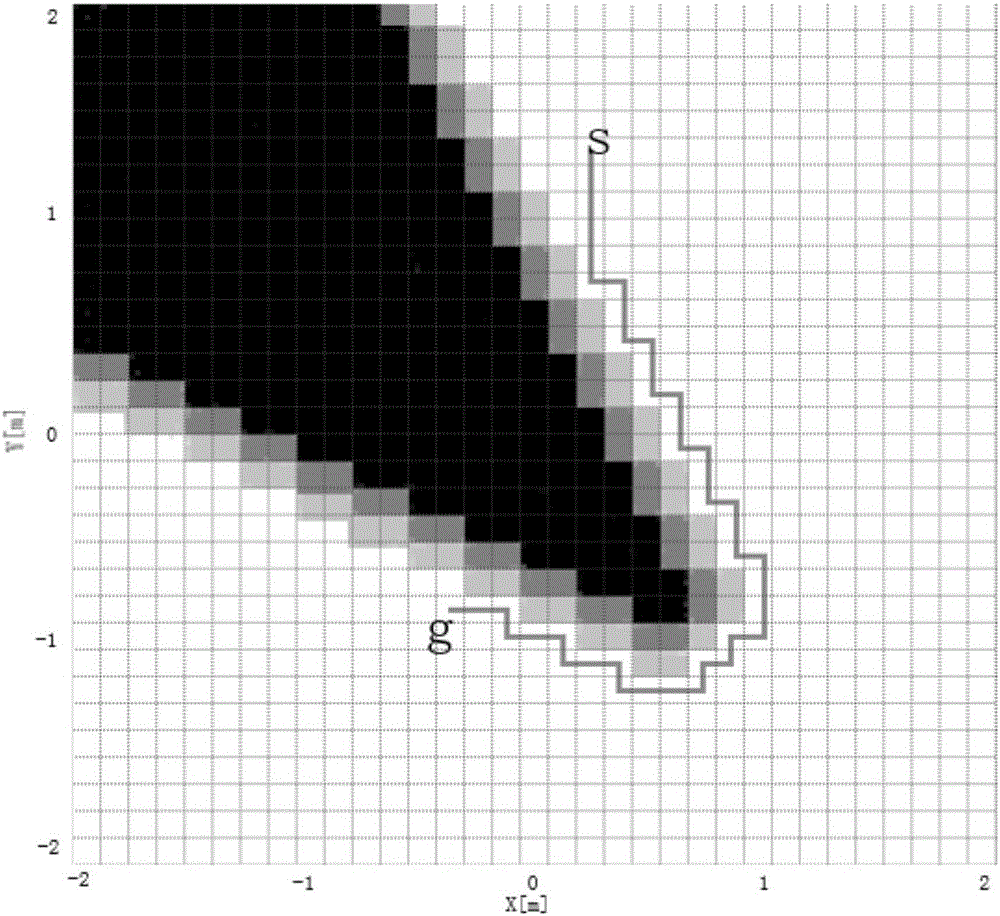

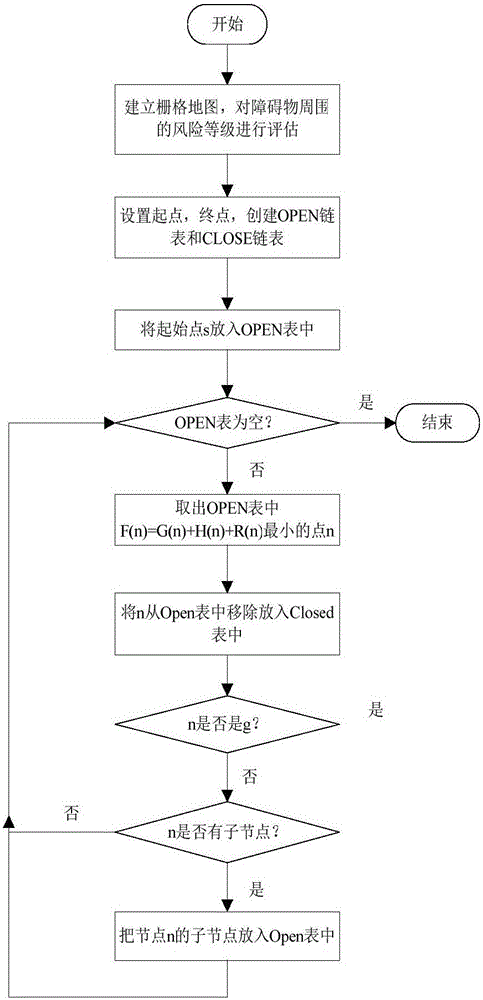

AGV path tracking and obstacle avoiding coordination method based on A* extraction guide point

The invention discloses an AGV path tracking and obstacle avoiding coordination method based on an A* extraction guide point, and relates to the field of mobile robot navigation. The method can achieve the coordination of path tracking and obstacle avoiding. The method comprises the steps: planning a safe global path; building an initial grid map according to the environment information; carrying out the evaluation of the risk level of surrounding nodes of an obstacle avoiding object through a risk evaluation function R(n); obtaining a new safety grid map with a risk region; extracting a key path point from the global path obtained through planning. For the path tracking and obstacle avoiding coordination, the method employs a dynamic window based on a laser sensor for obstacle avoiding, takes the key path point as the guide point, carries out the updating of the guide point, and achieves the coordination of the path tracking and obstacle avoiding.

Owner:XIAMEN UNIV

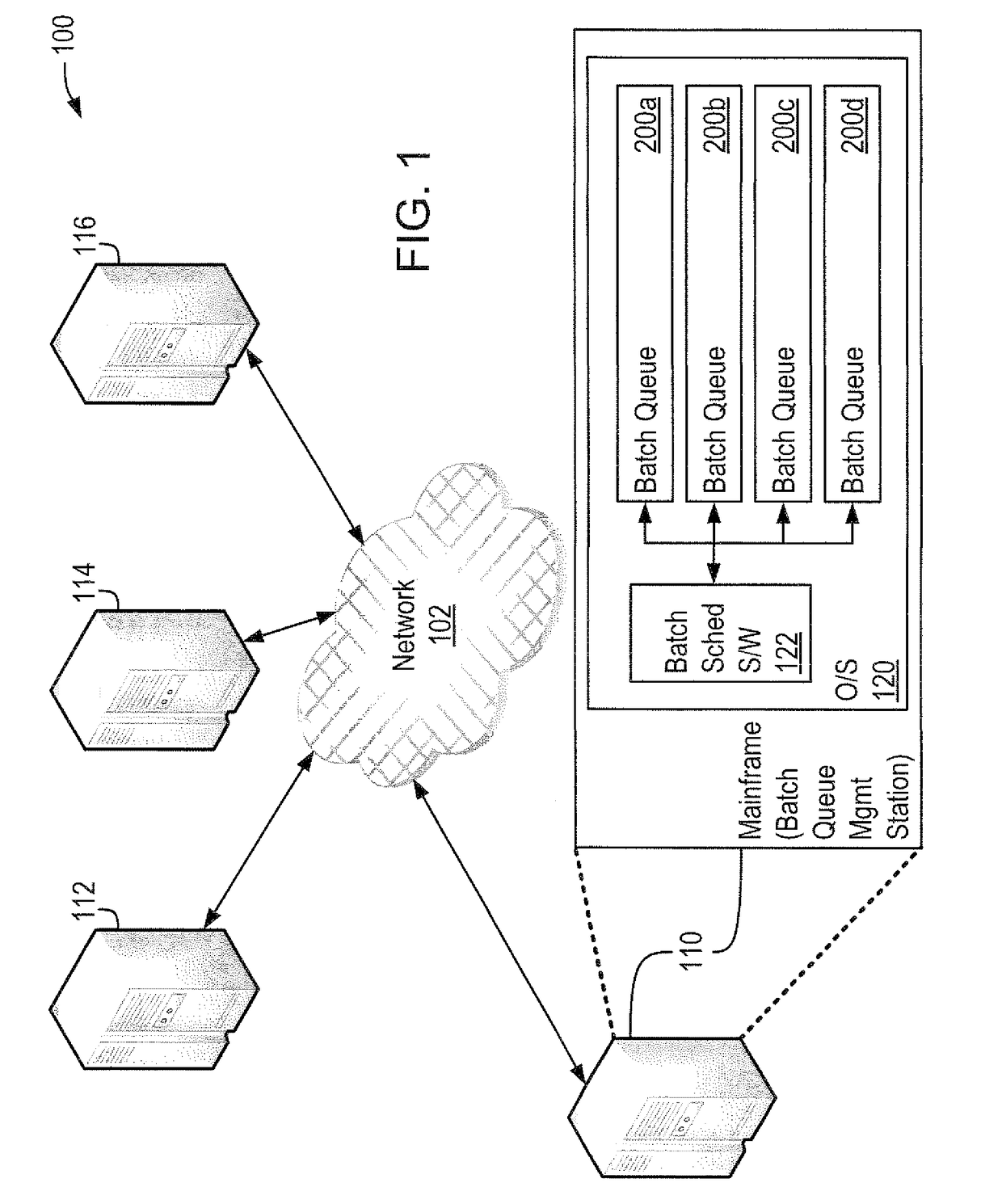

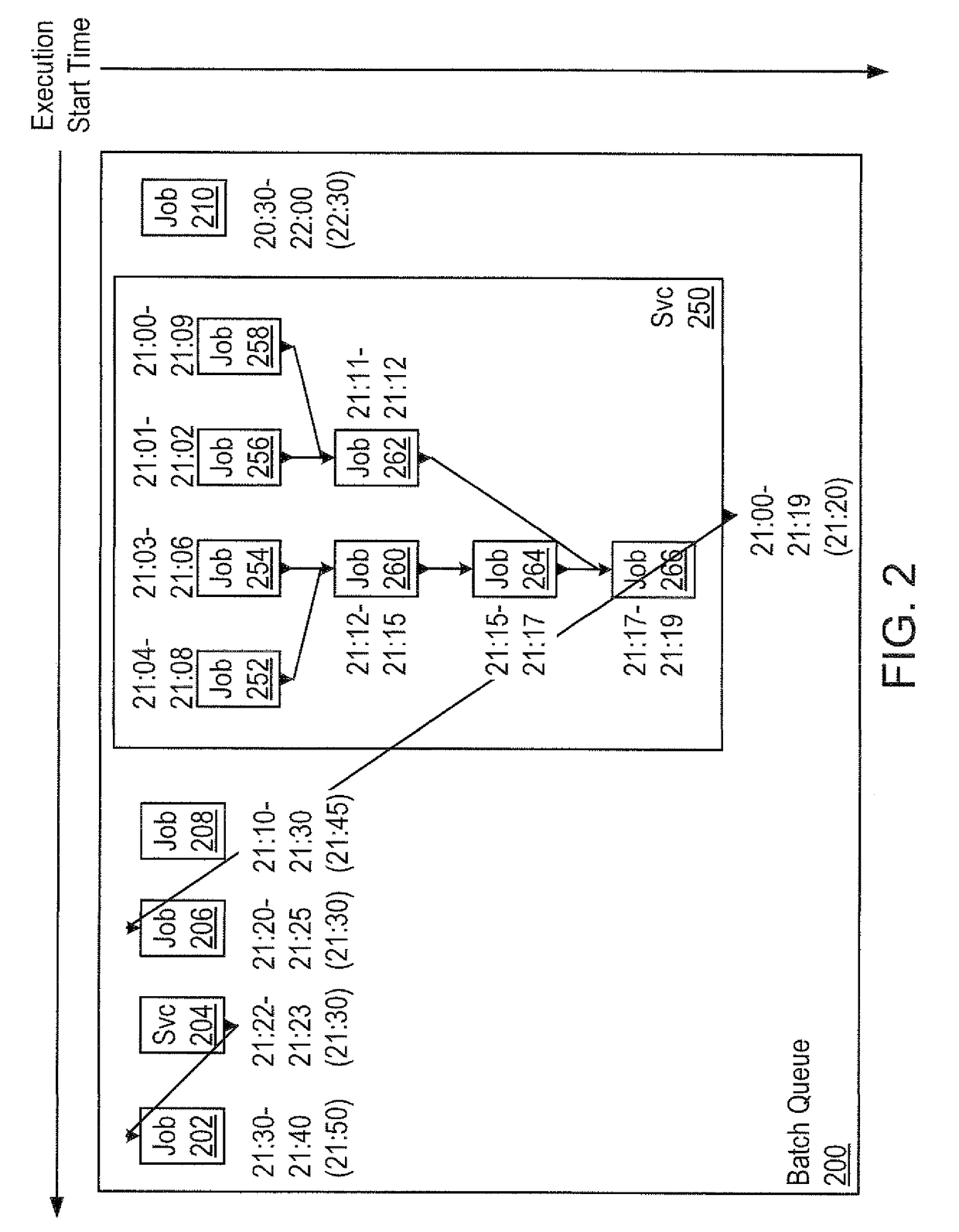

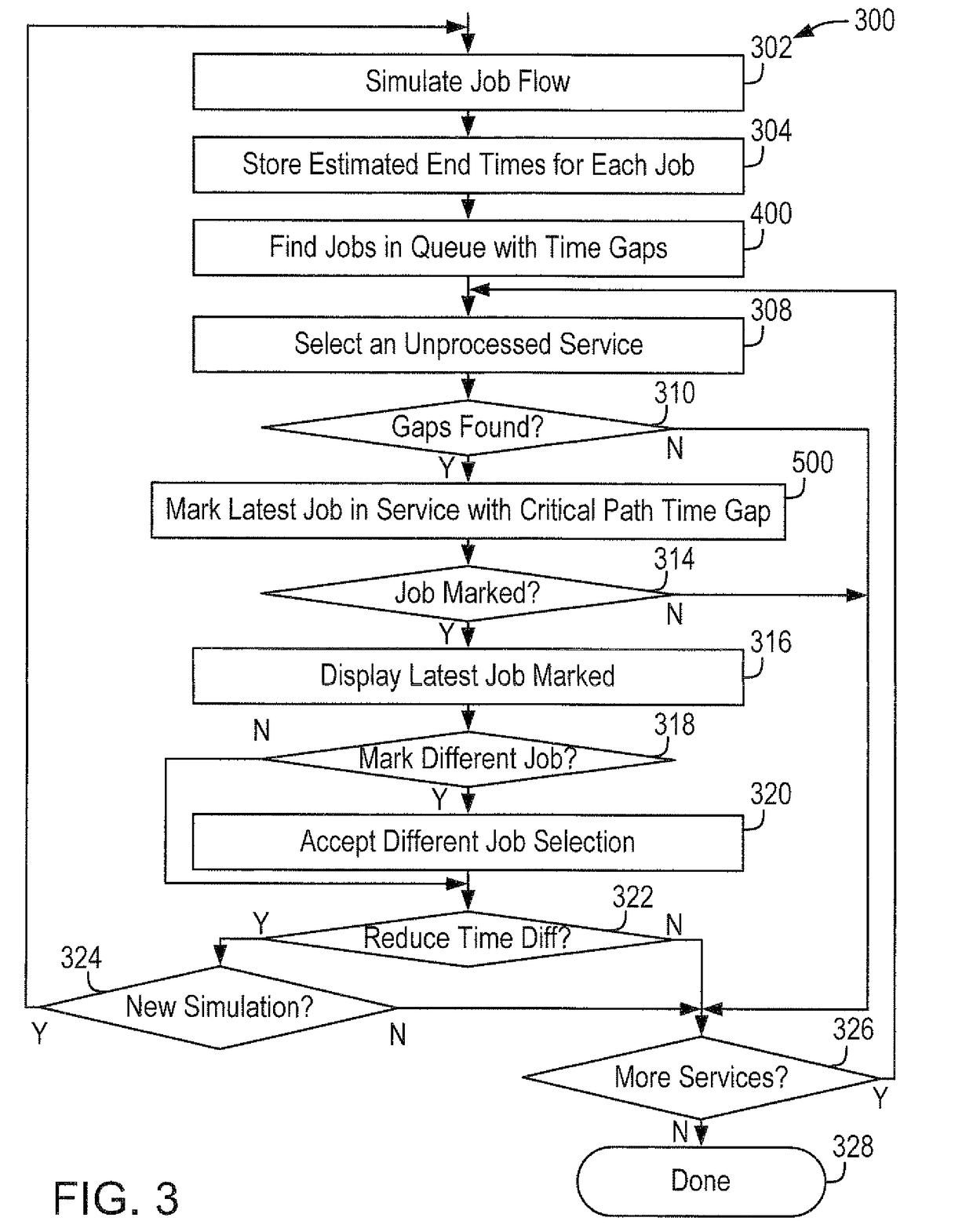

Method and system for traversing in reverse chronological order along a critical path of a plurality of jobs, and reducing time gaps between jobs until an estimated end time of the last job is less than or equal to a target end time

ActiveUS8473951B2Easy to manageMultiprogramming arrangementsMemory systemsStart timeComputerized system

Systems and methods for improved batch flow management are described. At least some embodiments include a computer system for managing a job flow including a memory storing a plurality of batch queue jobs grouped into Services each including a job and a predecessor job. A time difference is the difference between a scheduled job start time and an estimated predecessor job end time. Jobs with a preceding time gap include jobs immediately preceded only by non-zero time differences. The job start depends upon the predecessor job completion. The computer system further includes a processing unit that identifies jobs preceded by a time gap, selects one of the Services, and traverses in reverse chronological order a critical path of dependent jobs within the Service until a latest job with a preceding time gap is identified or at least those jobs along the critical path preceded by another job are traversed.

Owner:BMC SOFTWARE

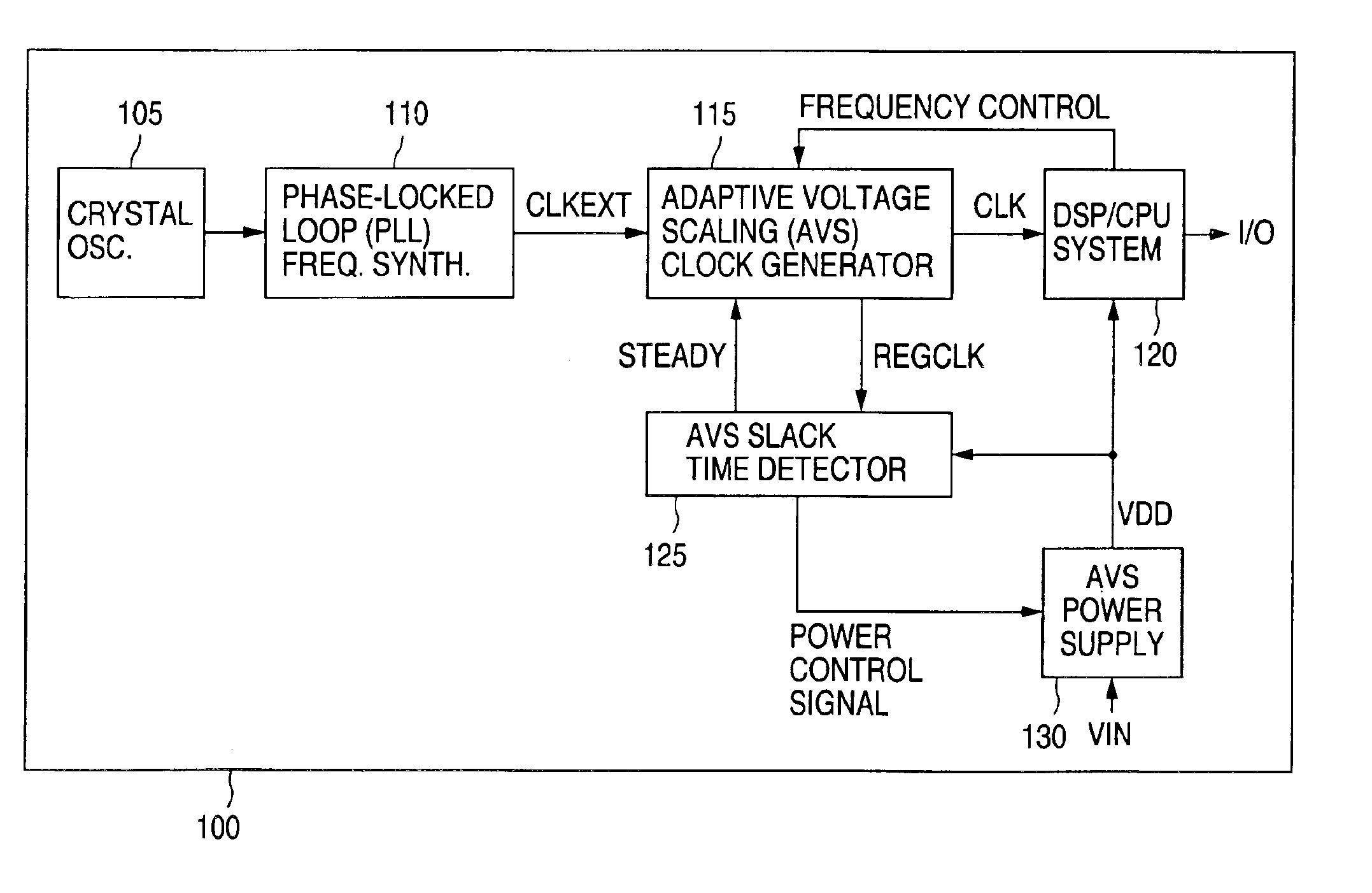

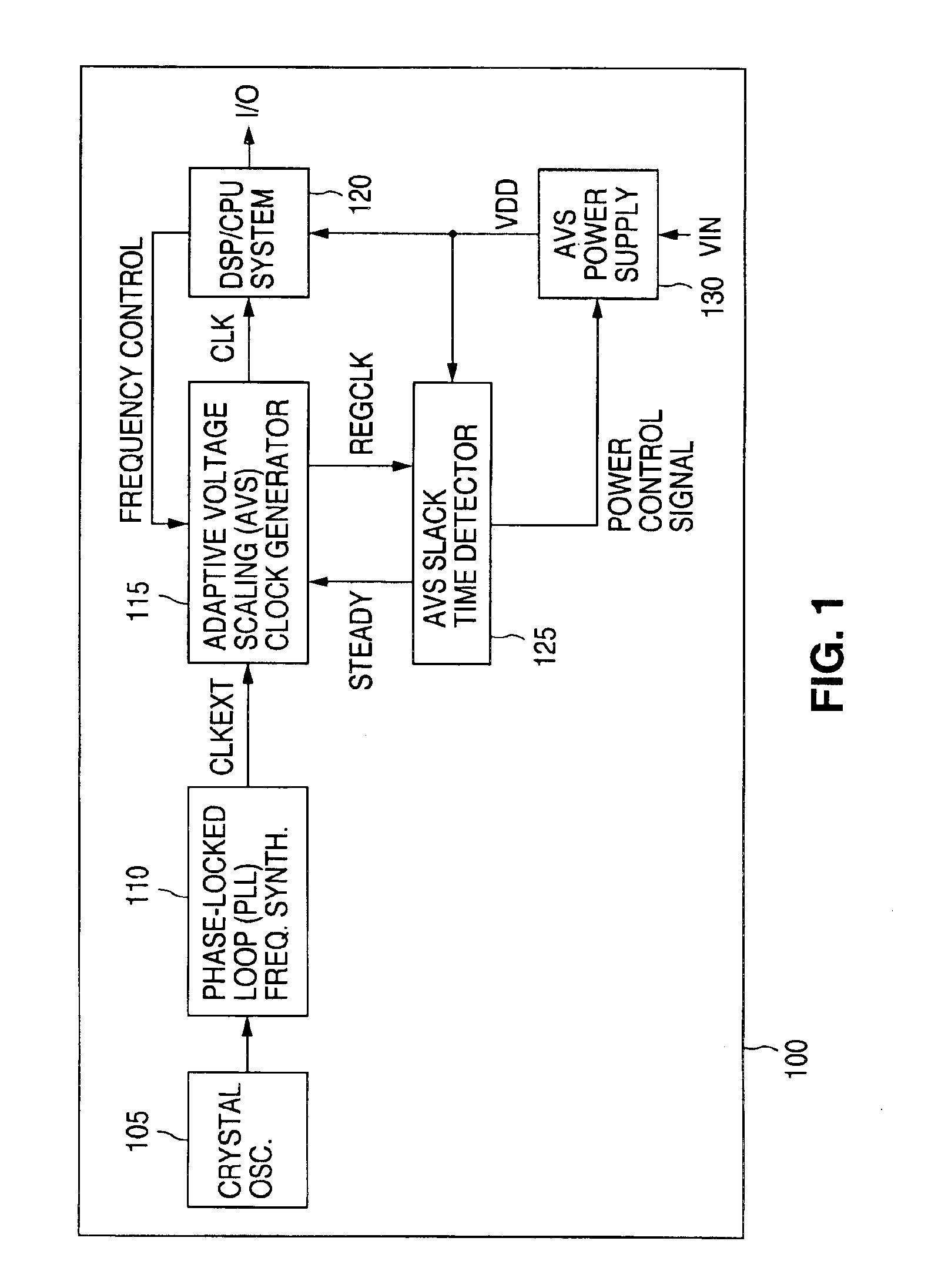

Adaptive voltage scaling digital processing component and method of operating the same

There is disclosed a digital circuit comprising a digital processing component, an adjustable power supply and power supply adjustment circuitry. The digital processing component is capable of operating at a plurality of selected clock frequencies, wherein a maximum delay time of a critical path in the digital processing component is determined by a level of a power supply, VDD, of the digital processing component. The adjustable power supply is capable of supplying VDD to the digital processing component. The power supply adjustment circuitry is operable to receive a first selected clock signal and adjusts the level of VDD such that the maximum delay time of the critical path of the digital processing component is less than a pulse-width duration between a first clock edge of the first selected clock signal and a second clock edge of the first selected clock signal immediately following the first clock edge.

Owner:NAT SEMICON CORP

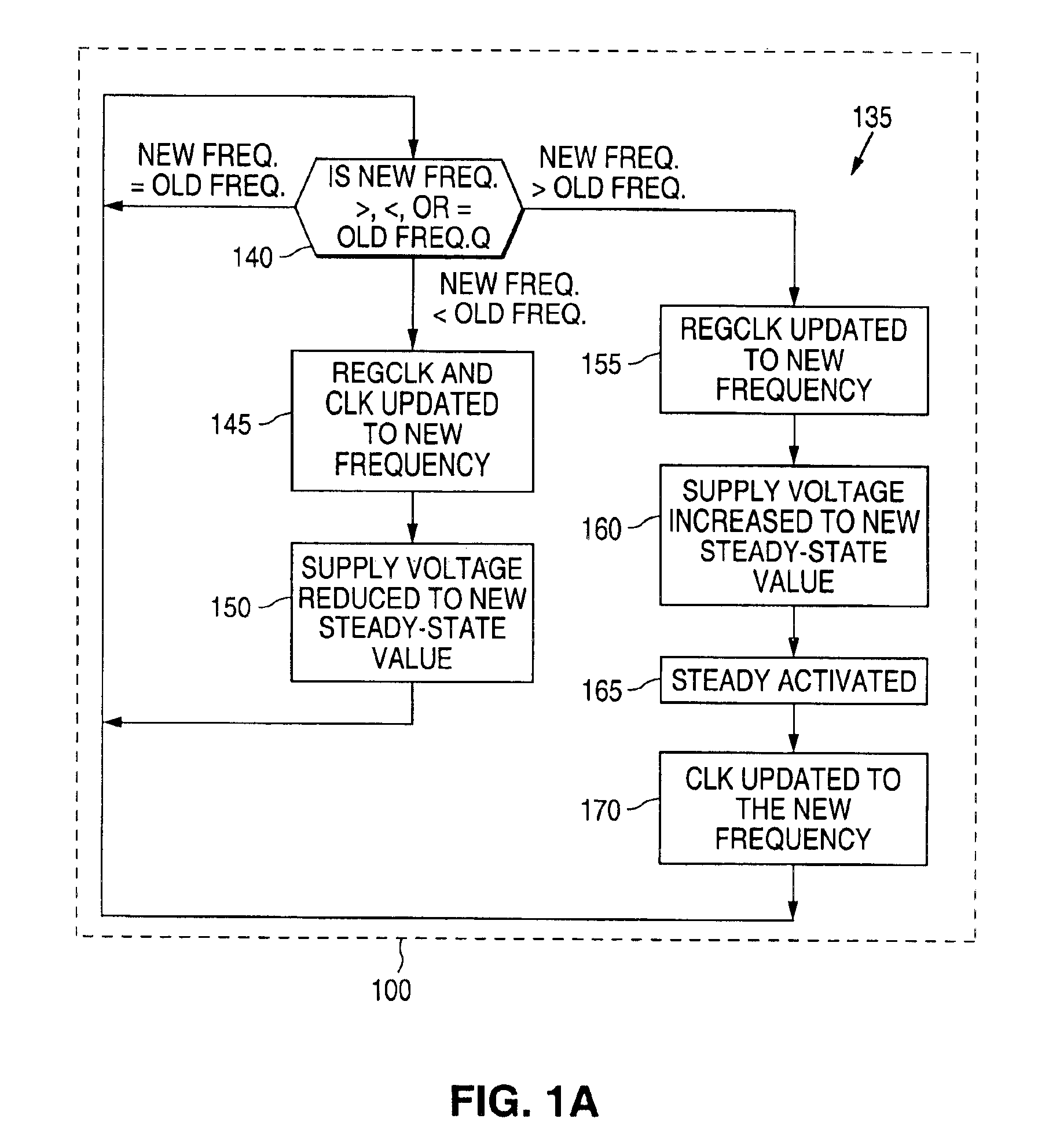

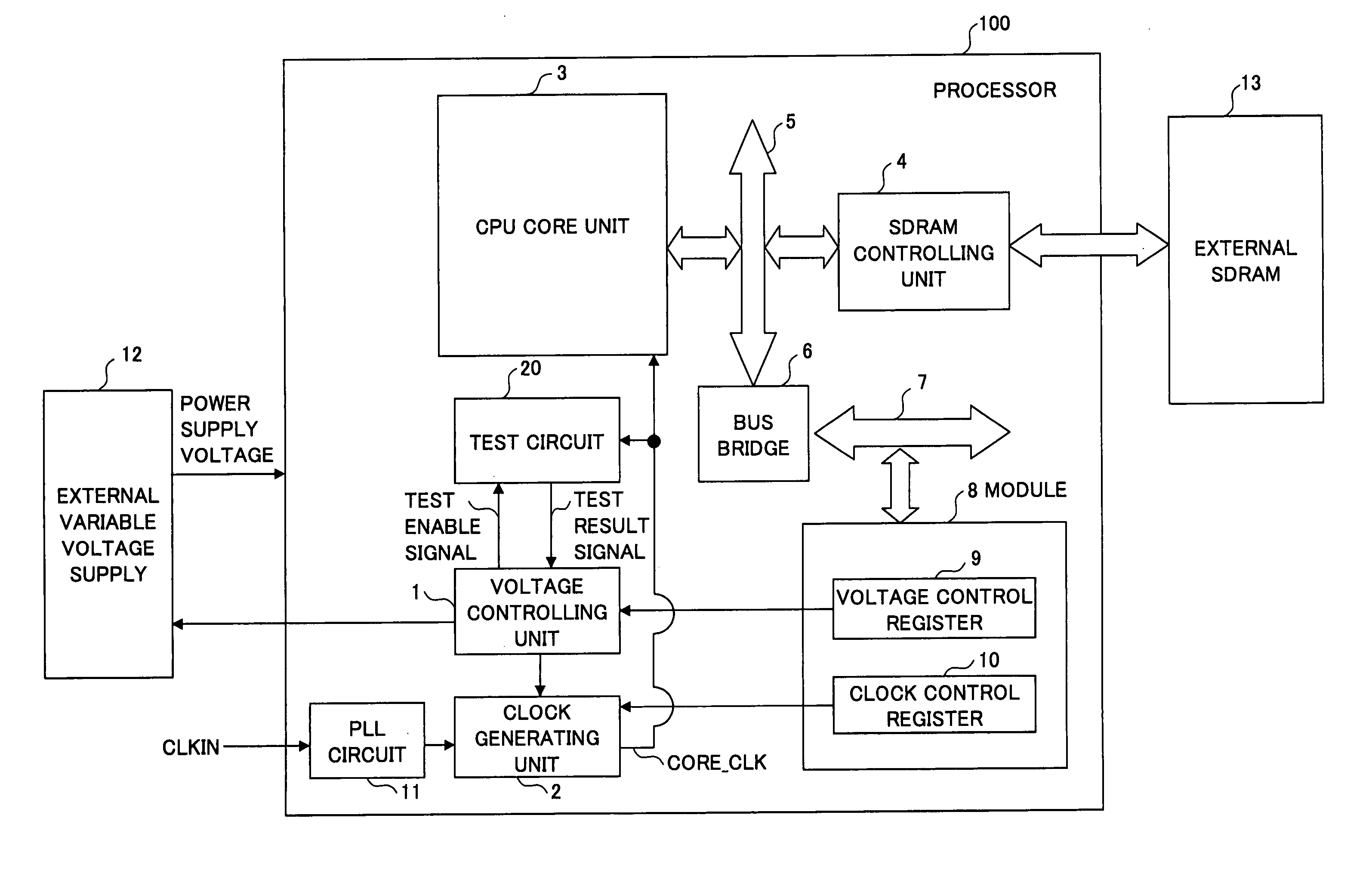

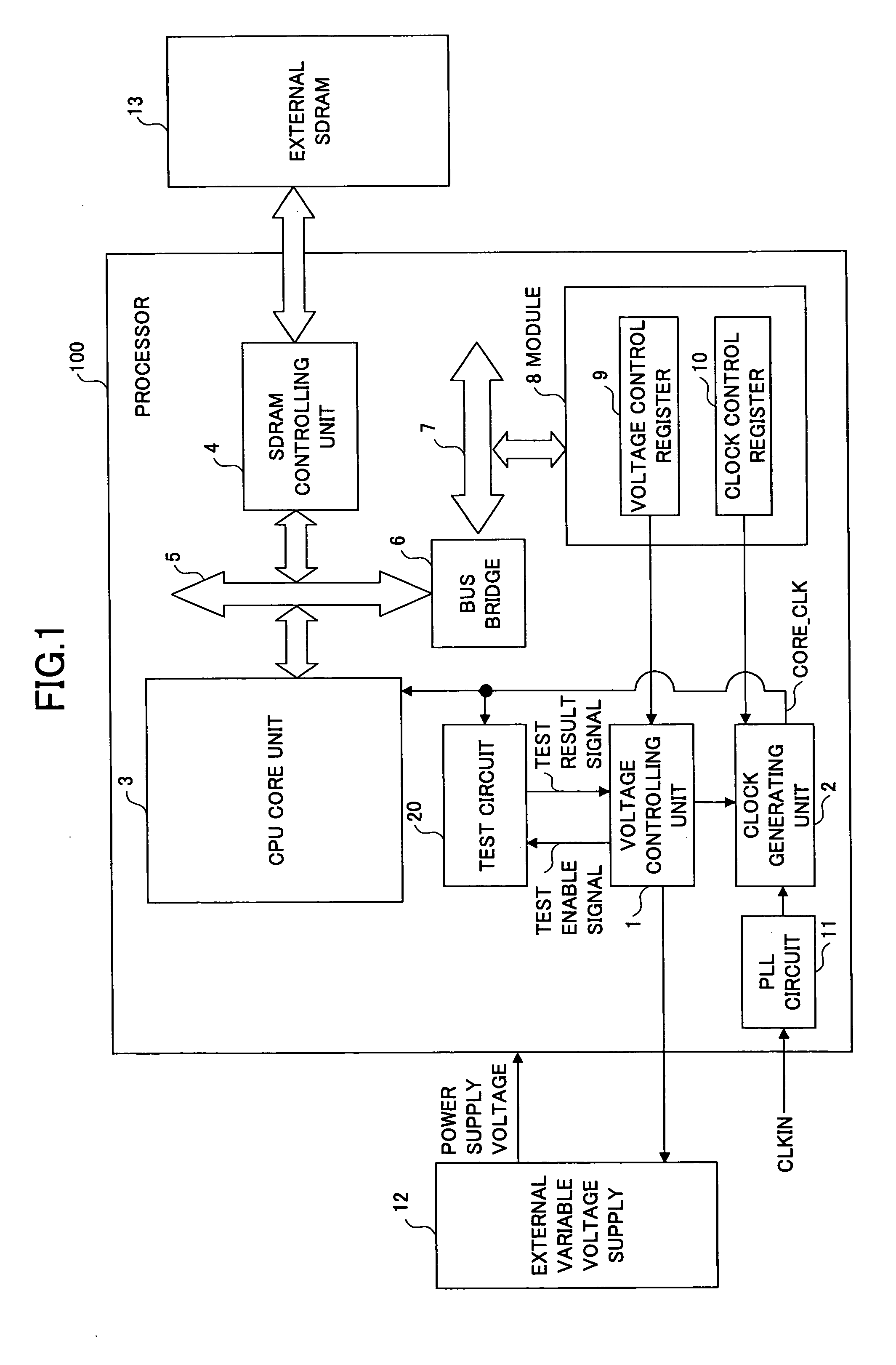

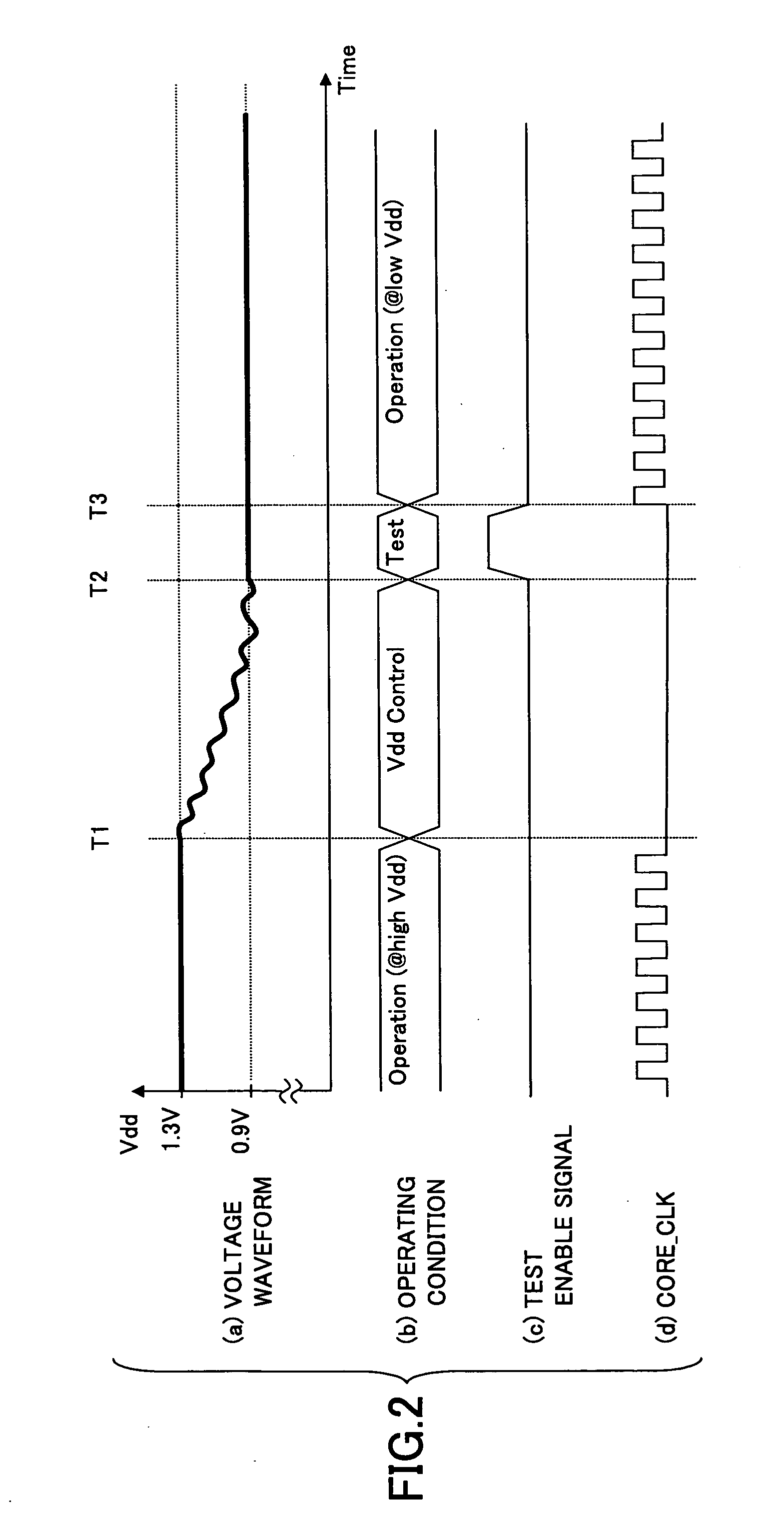

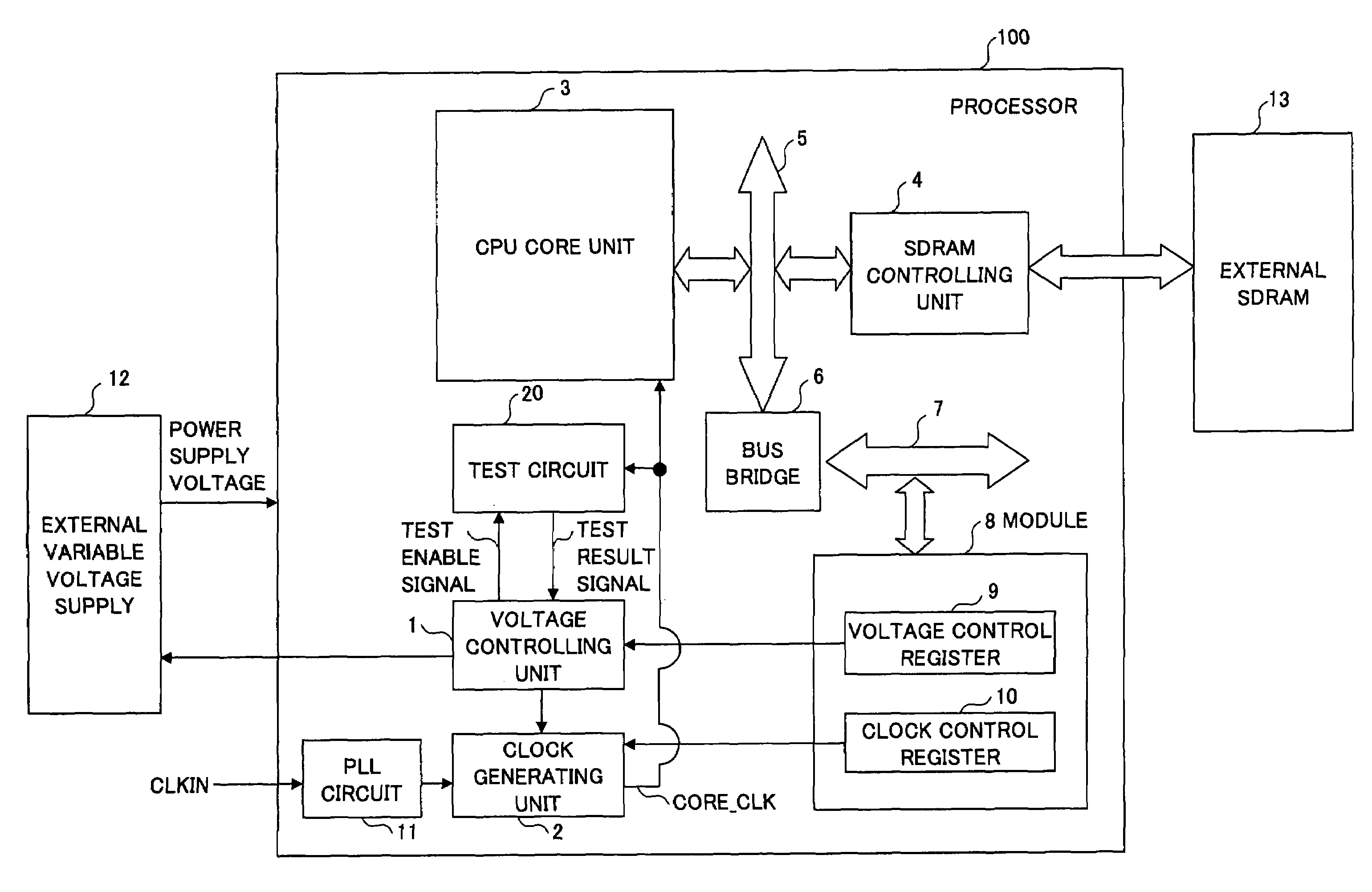

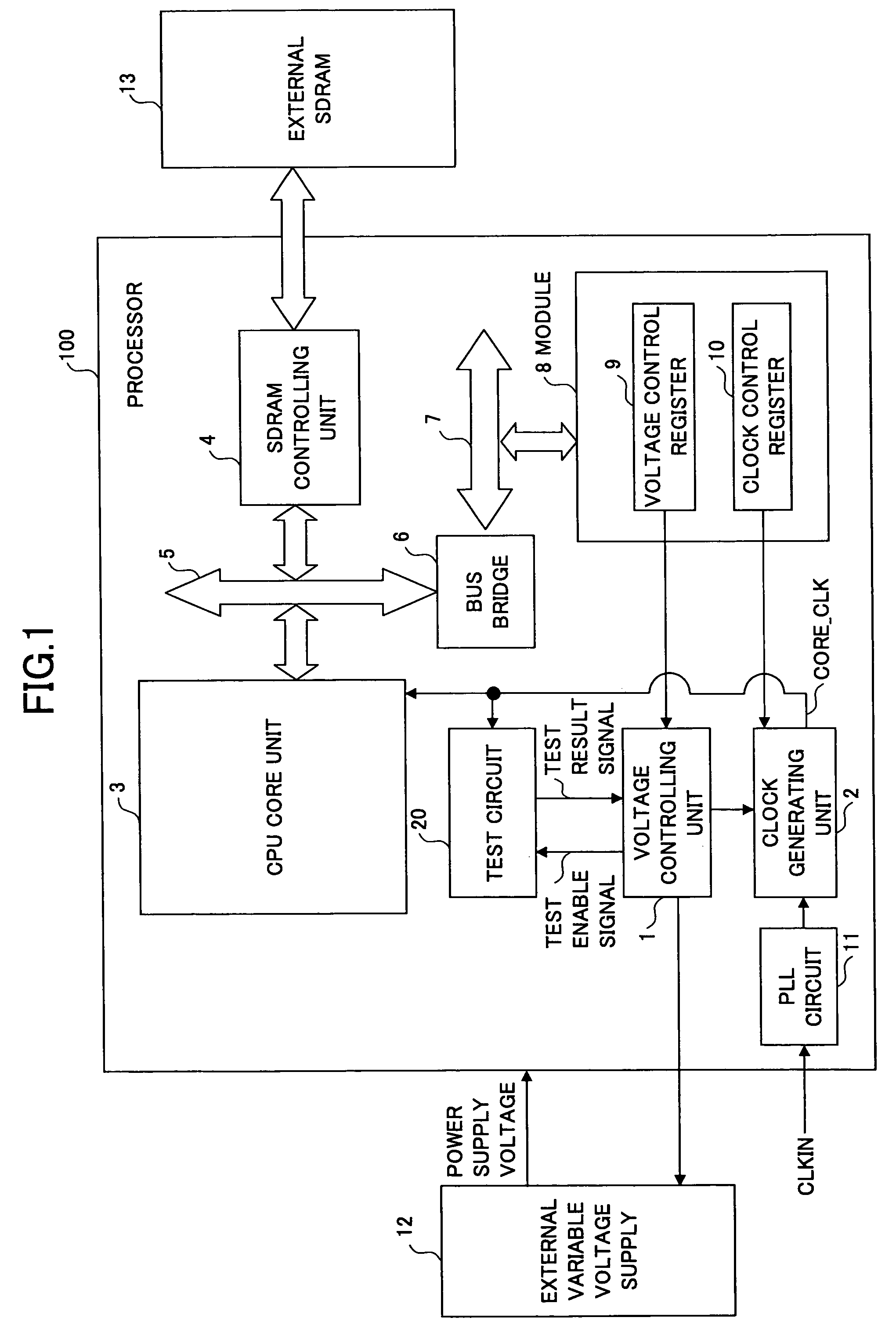

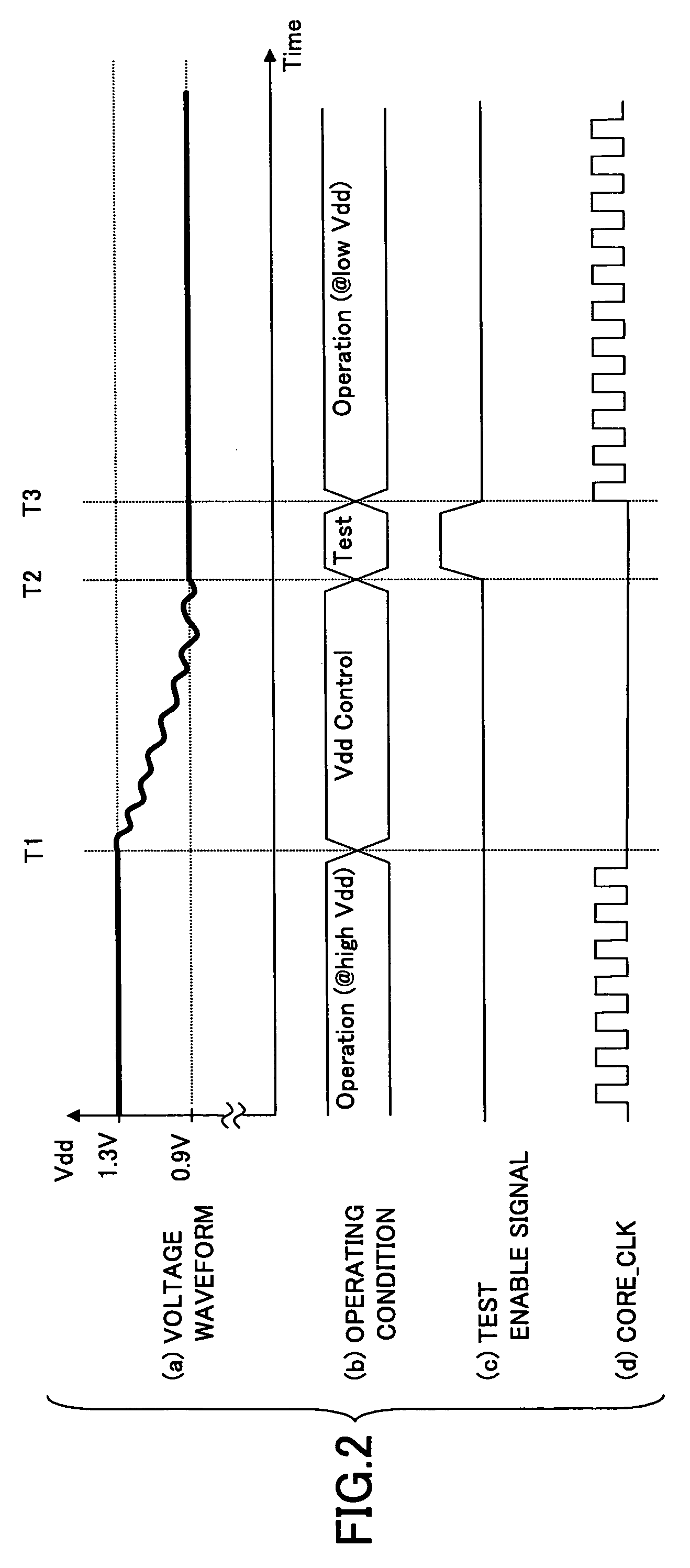

Changing of operating voltage in semiconductor integrated circuit

InactiveUS20050283630A1Avoid failureEnergy efficient ICTVolume/mass flow measurementCritical path methodEngineering

A semiconductor integrated circuit includes a module configured to operate based on a clock signal, a voltage controlling unit configured to change a power supply voltage supplied to the module, a clock generating unit configured to supply the clock signal to the module, and a test circuit configured to operate at the power supply voltage based on the clock signal to emulate a delay of a critical path provided in the module, thereby testing whether the module properly operates at the power supply voltage, wherein the clock generating unit supplies a different signal, in place of the clock signal, to the module while the voltage controlling unit is changing the power supply voltage.

Owner:SOCIONEXT INC

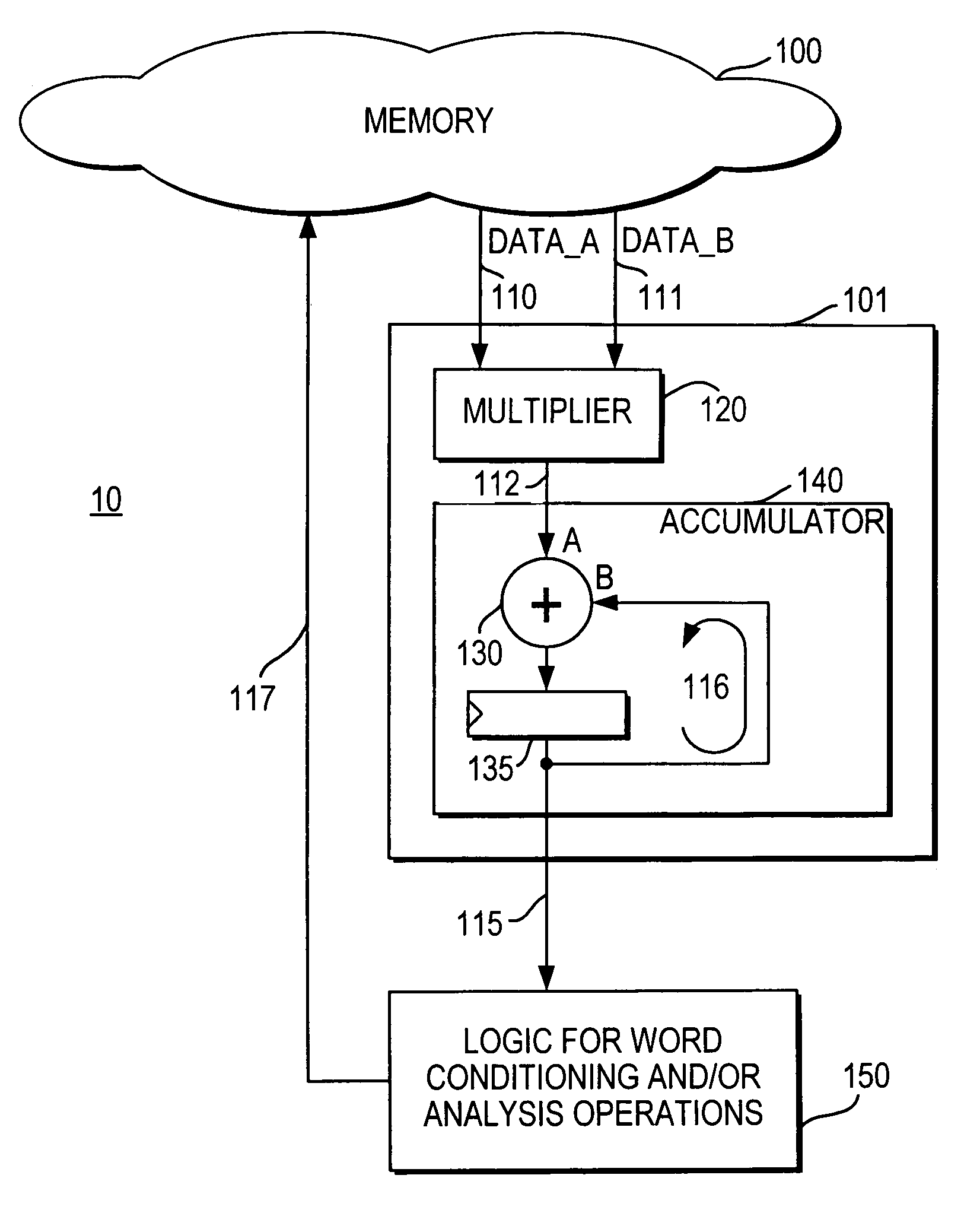

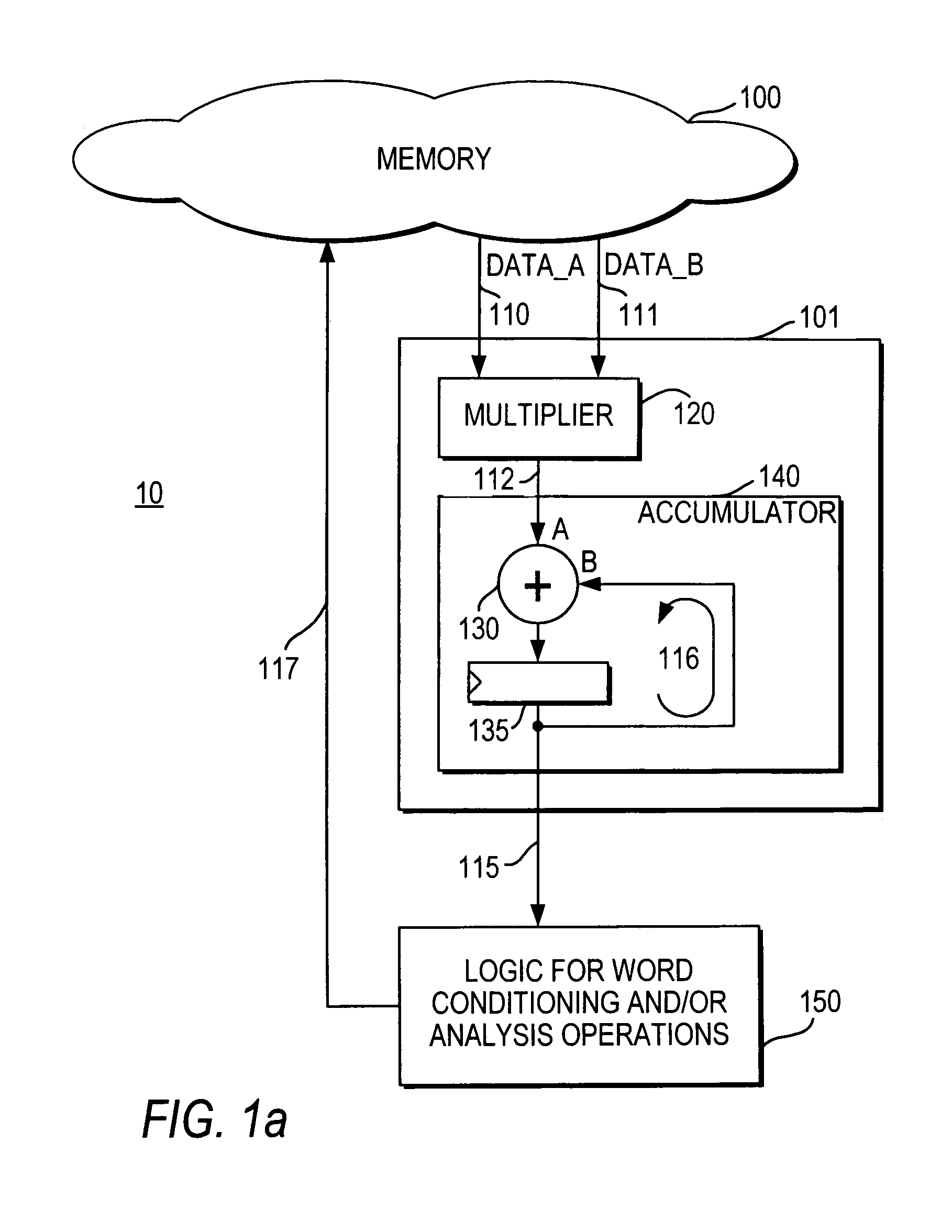

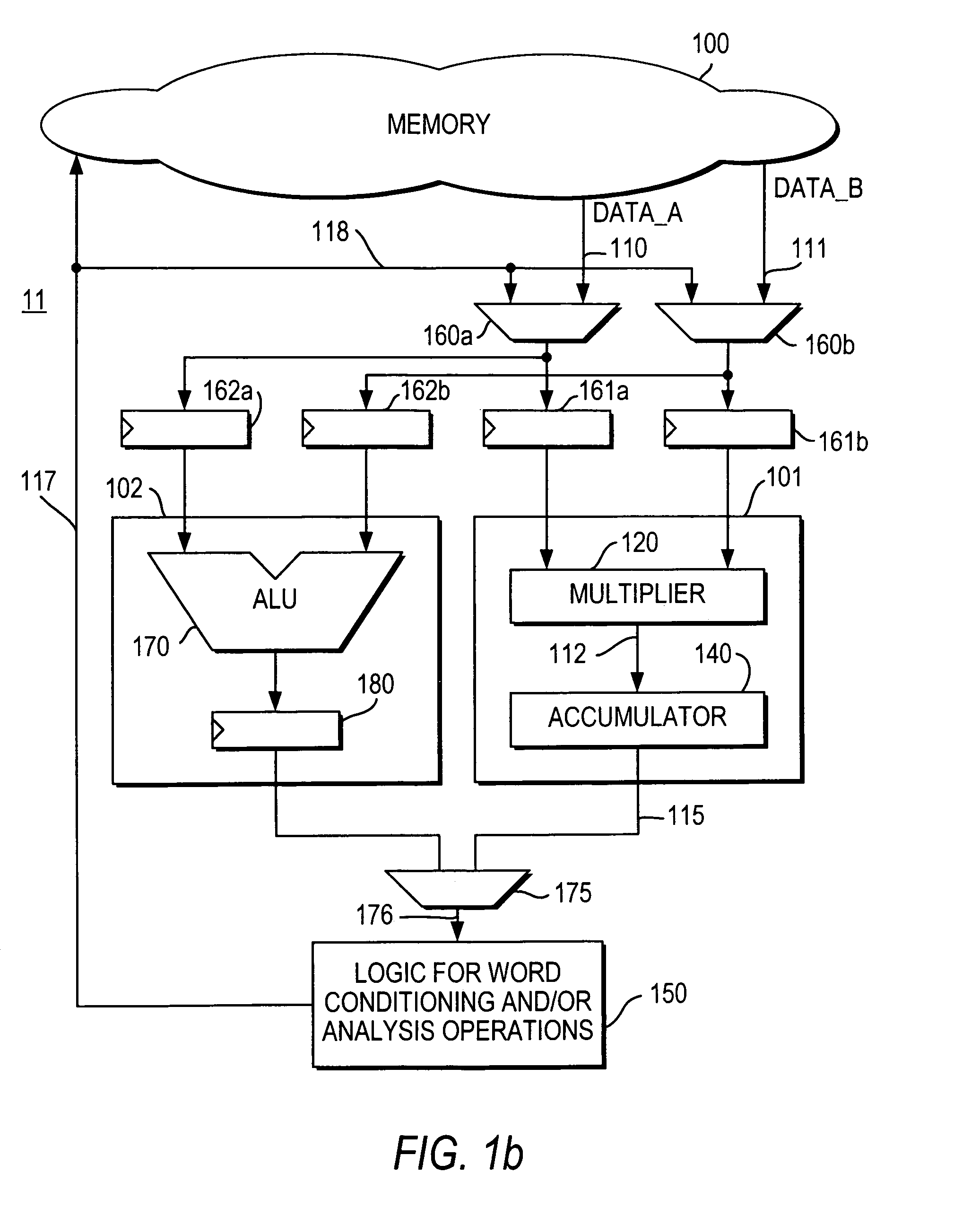

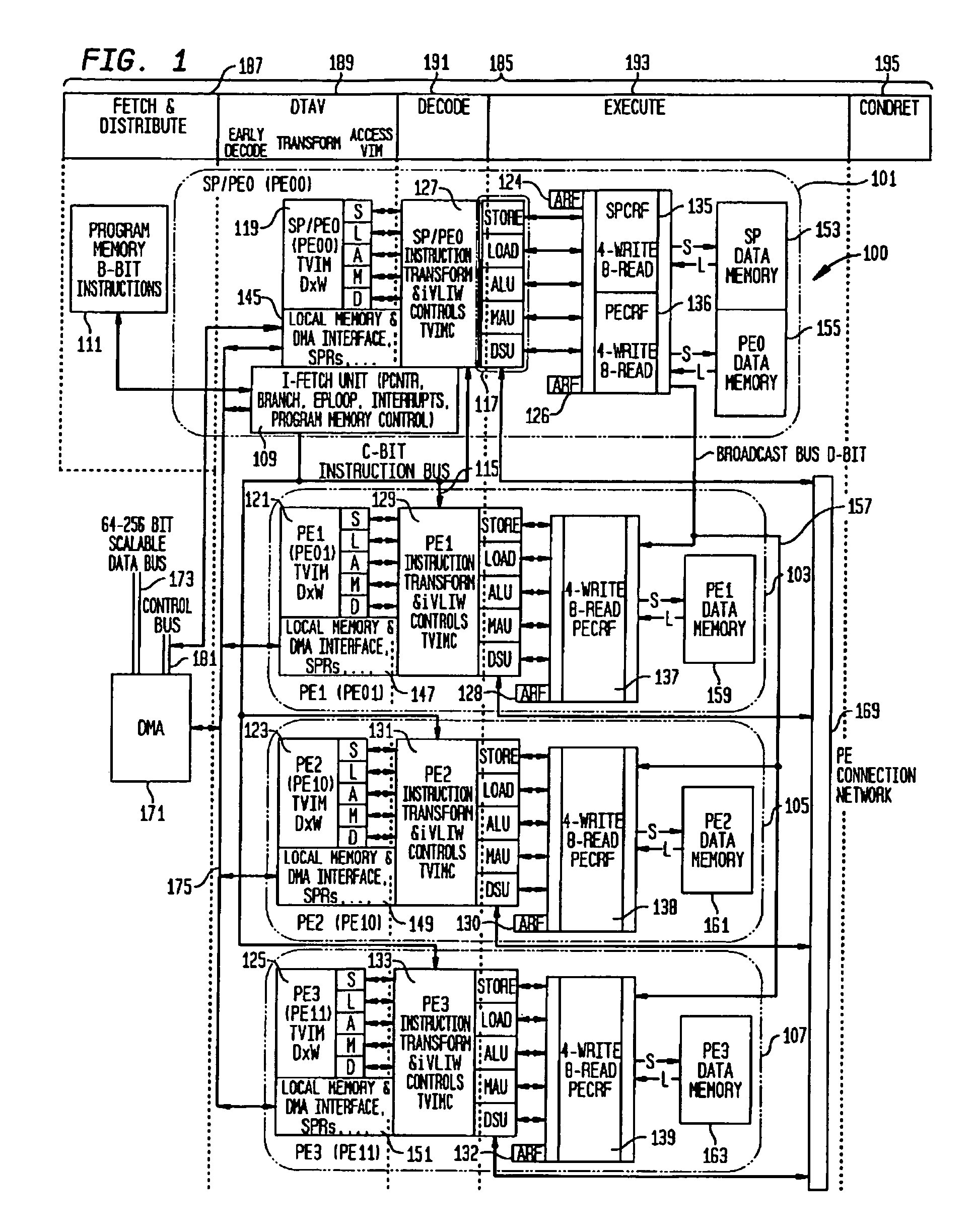

DSP processor architecture with write datapath word conditioning and analysis

InactiveUS6978287B1Improve throughputReduce delaysDigital computer detailsProgram controlRoundingBlock floating-point

Owner:ALTERA CORP

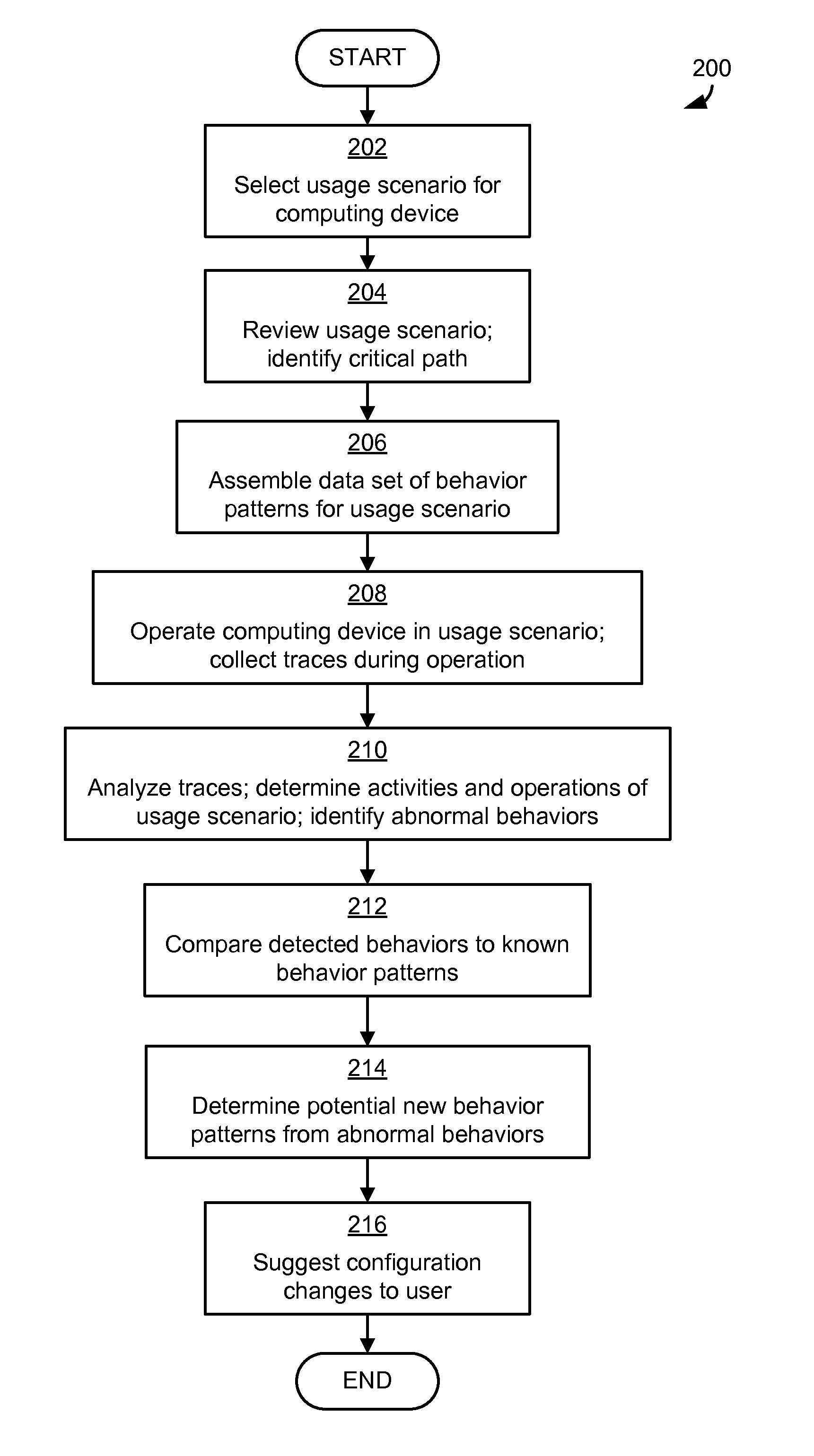

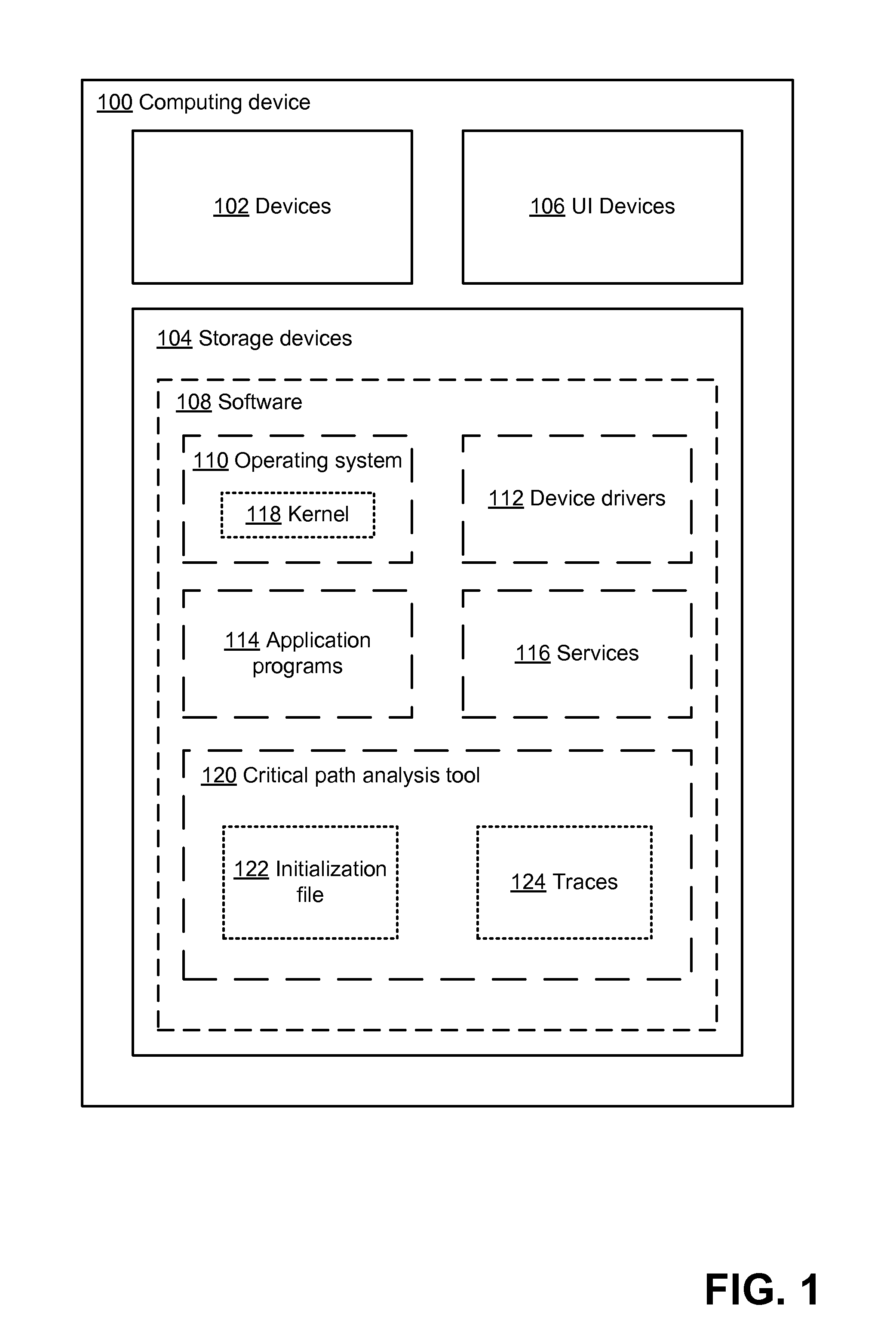

Analyzing performance of computing devices in usage scenarios

ActiveUS20120124363A1Affect performanceInformation can be usedError detection/correctionData resettingCritical path methodReal-time computing

Techniques for conducting an automated analysis of operations carried out during the critical path for a usage scenario and suggesting ways in which the configuration of the computing device could be changed to affect performance of the computing device. Computing devices can be operated in a variety of usage scenarios and users may notice the performance of a computing device in certain usage scenarios more particularly. Critical path analysis of operations conducted in these usage scenarios can be used to identify a critical path of the usage scenario, from which changes that could be made to the computing device to affect performance could be identified. Once the changes that could be made are identified, suggestions can be made to the user, such that a user is able to make changes to the configuration to affect performance when the user has little knowledge about how to improve configurations.

Owner:MICROSOFT TECH LICENSING LLC

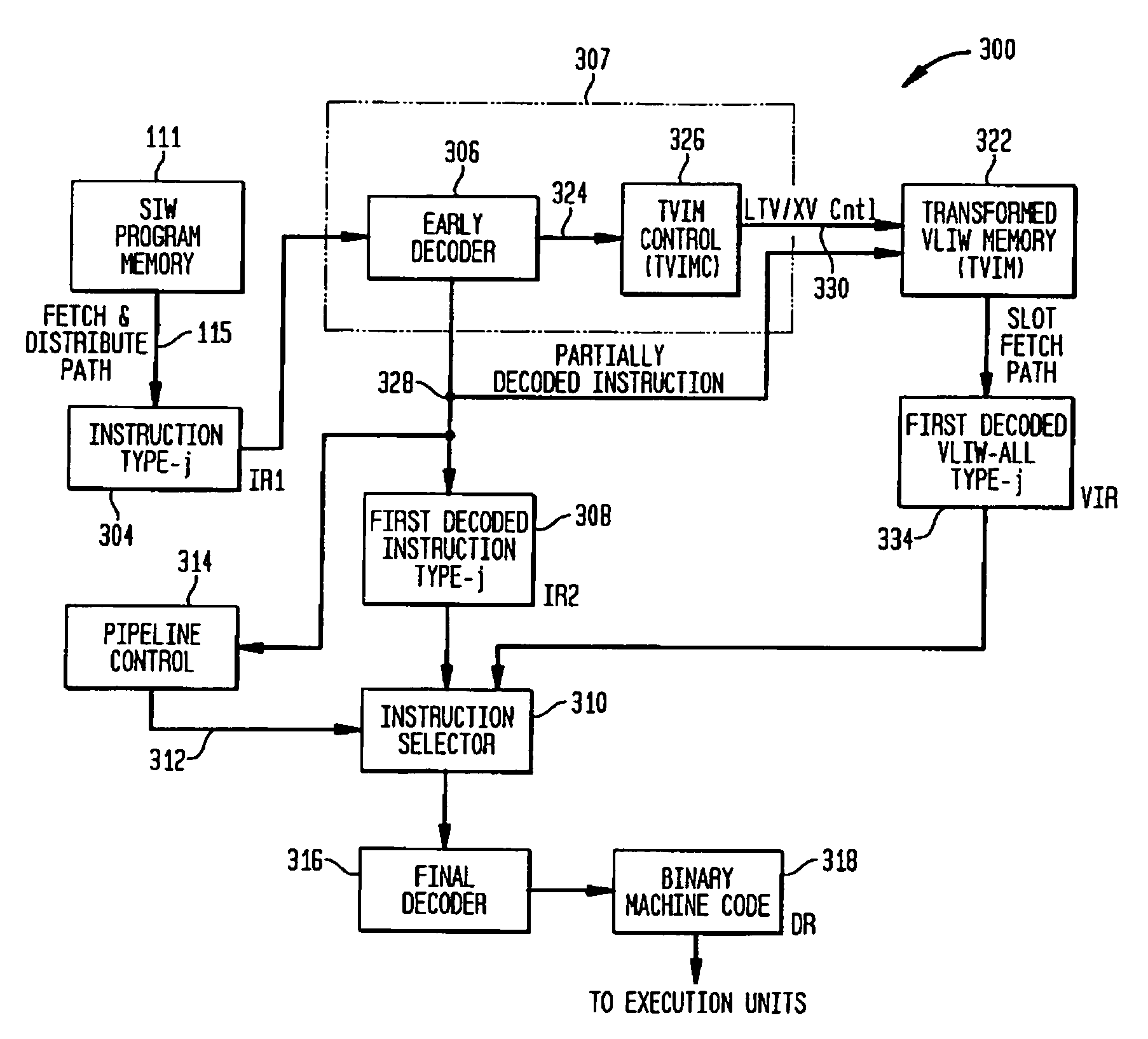

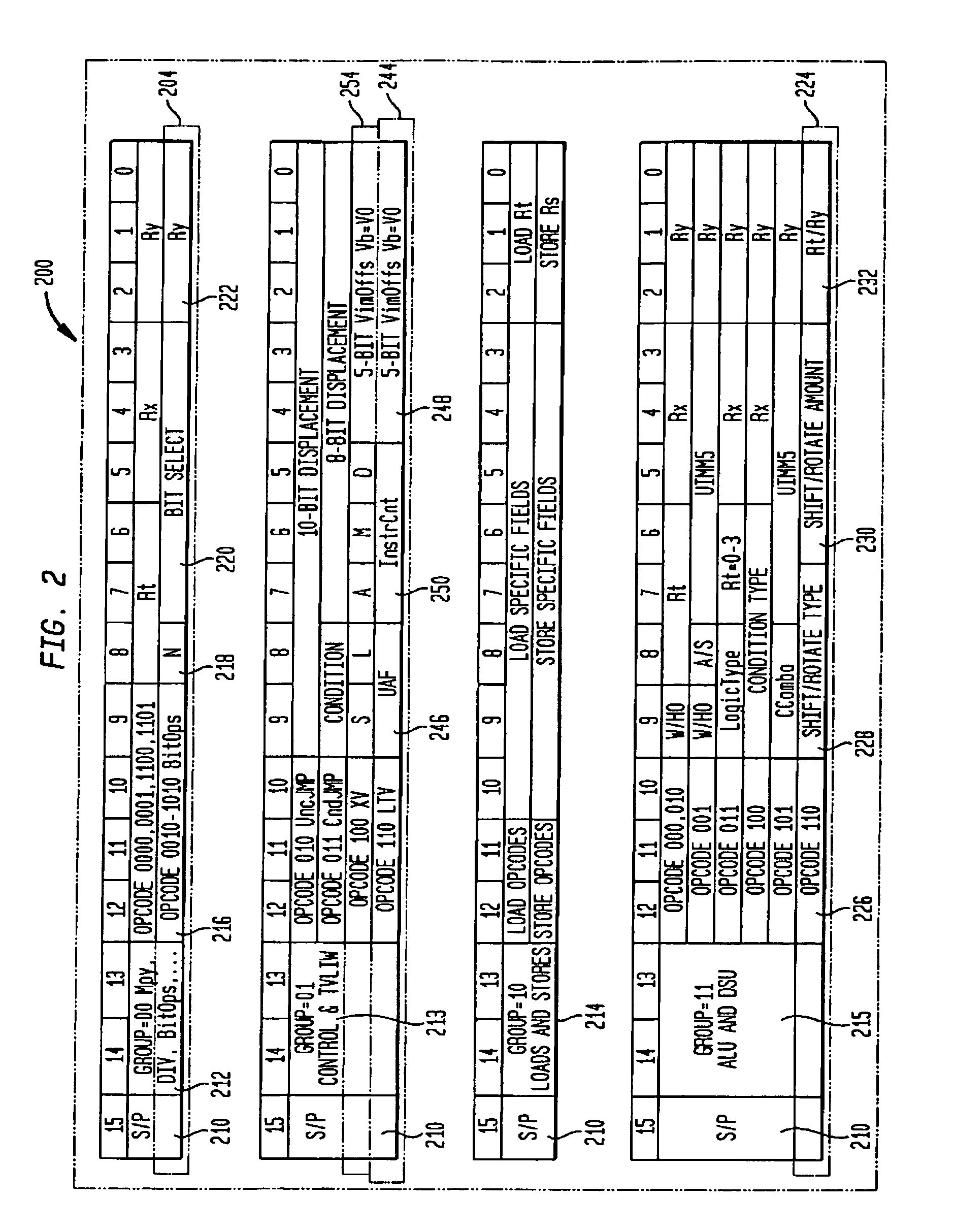

Methods and apparatus for transforming, loading, and executing super-set instructions

InactiveUS7493474B1Eliminate decode stageMinimization of actionRegister arrangementsInstruction analysisInstruction memoryLoad instruction

Techniques are described for loading decoded instructions and super-set instructions in a memory for later access. For loading a decoded instruction, the decoded instruction is a transformed form of an original instruction that was stored in the program memory. The transformation is from an encoded assembly level format to a binary machine level format. In one technique, the transformation mechanism is invoked by a transform and load instruction that causes an instruction retrieved from program memory to be transformed into a new language format and then loaded into a transformed instruction memory. The format of the transformed instruction may be optimized to the implementation requirements, such as improving critical path timing. The transformation of instructions may extend to other needs beyond timing path improvement, for example, requiring super-set instructions for increased functionality and improvements to instruction level parallelism. Techniques for transforming, loading, and executing super-set instructions are described.

Owner:ALTERA CORP

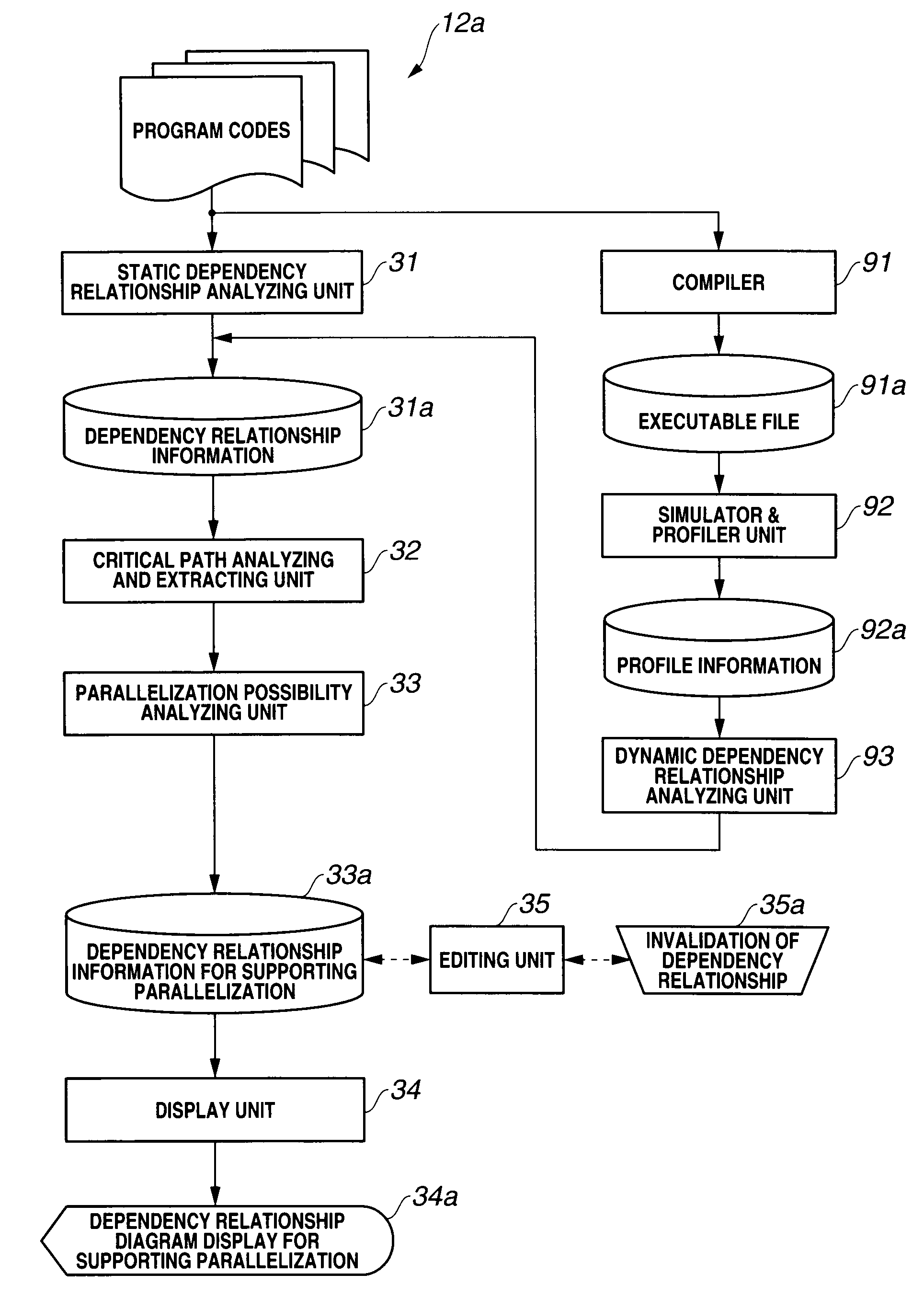

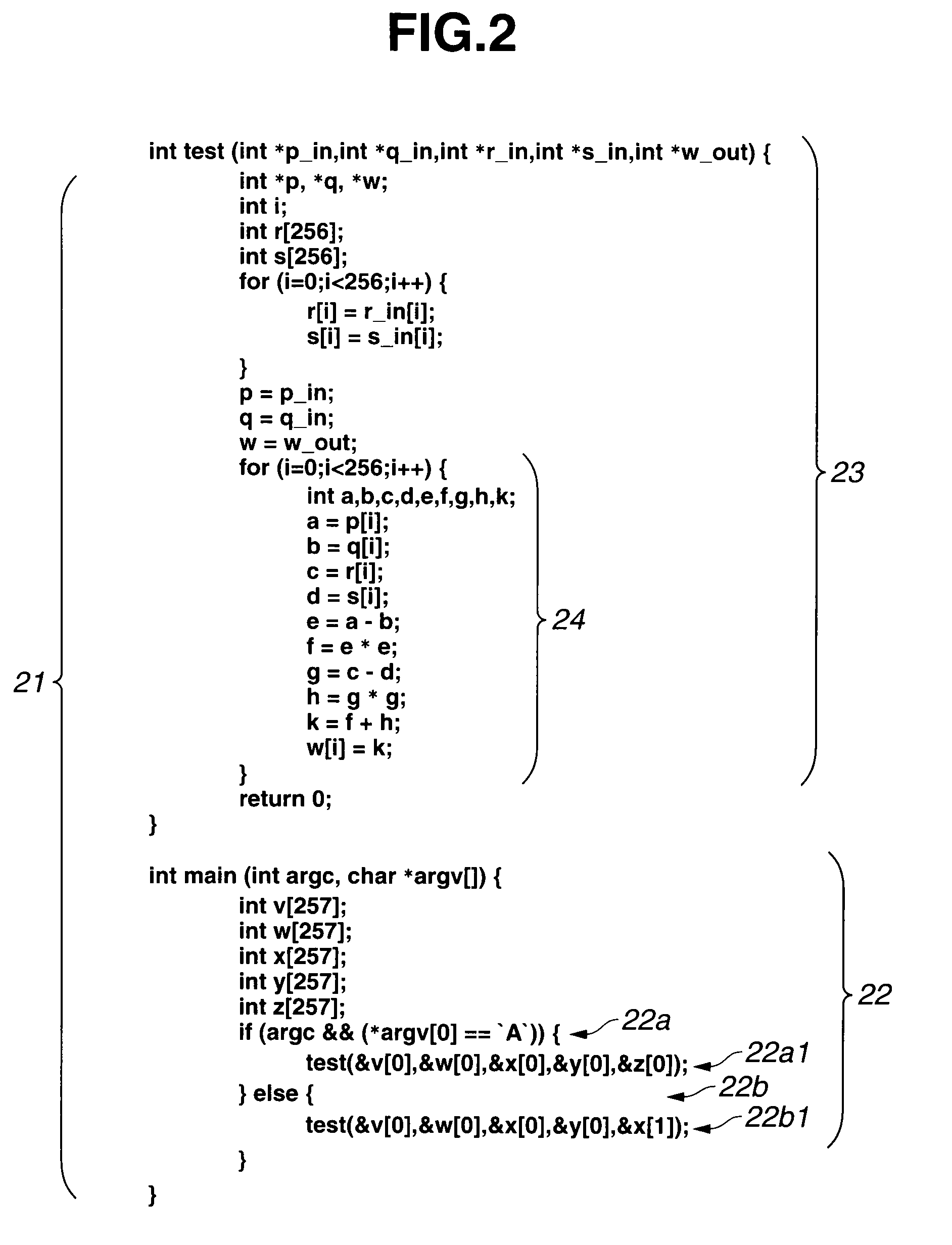

Program parallelization supporting apparatus and program parallelization supporting method

InactiveUS20090138862A1Reduce in quantitySoftware engineeringProgram controlProcessing InstructionCritical path method

A program parallelization supporting apparatus determines a determinacy in at least one dependency relationship of a data dependency, a control dependency and a pointer dependency in a program, extracts a critical path in the program, and extracts a processing instruction which exists on the critical path and has a non-deterministic determinacy in the dependency relationship. Furthermore, if a process related to a path of the extracted non-deterministic processing instruction is parallelized and the path of the non-deterministic processing instruction is deleted, the program parallelization supporting apparatus outputs parallelization labor hour information depending on the number of dependency relationships disturbing the parallelization and parallelization effect information depending on the number of processing instructions which are shortened by the parallelization.

Owner:KK TOSHIBA

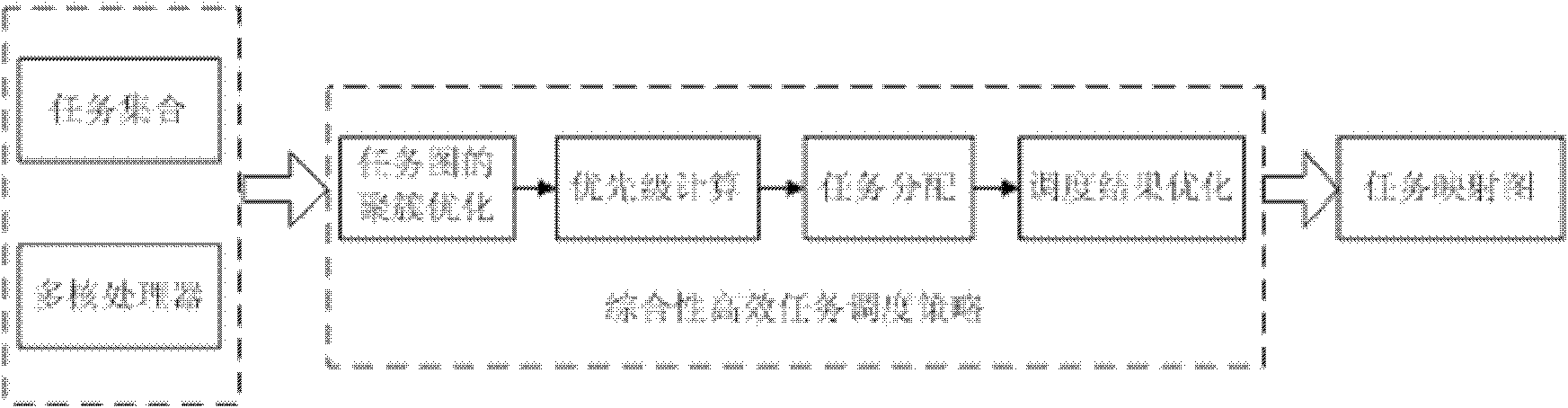

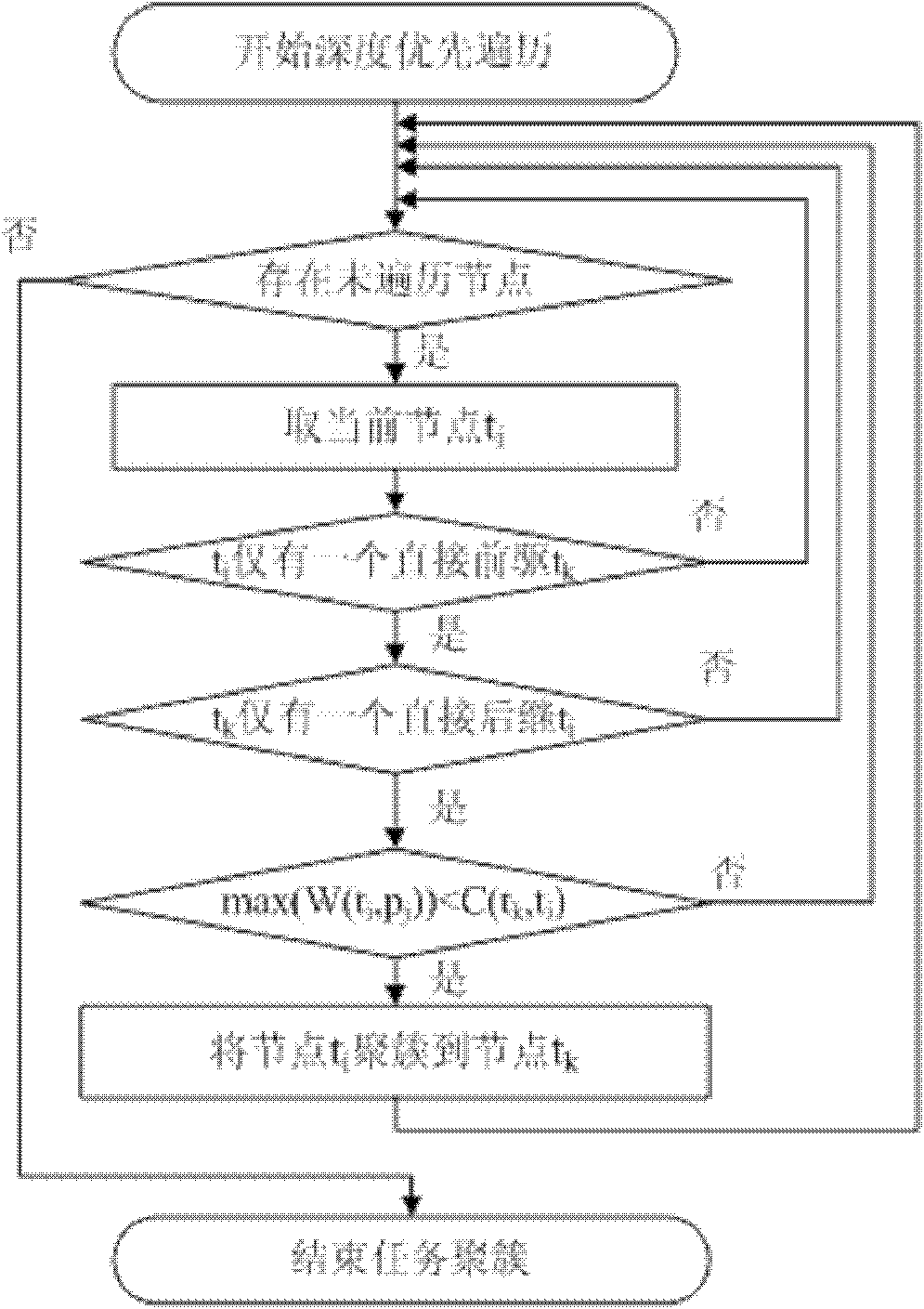

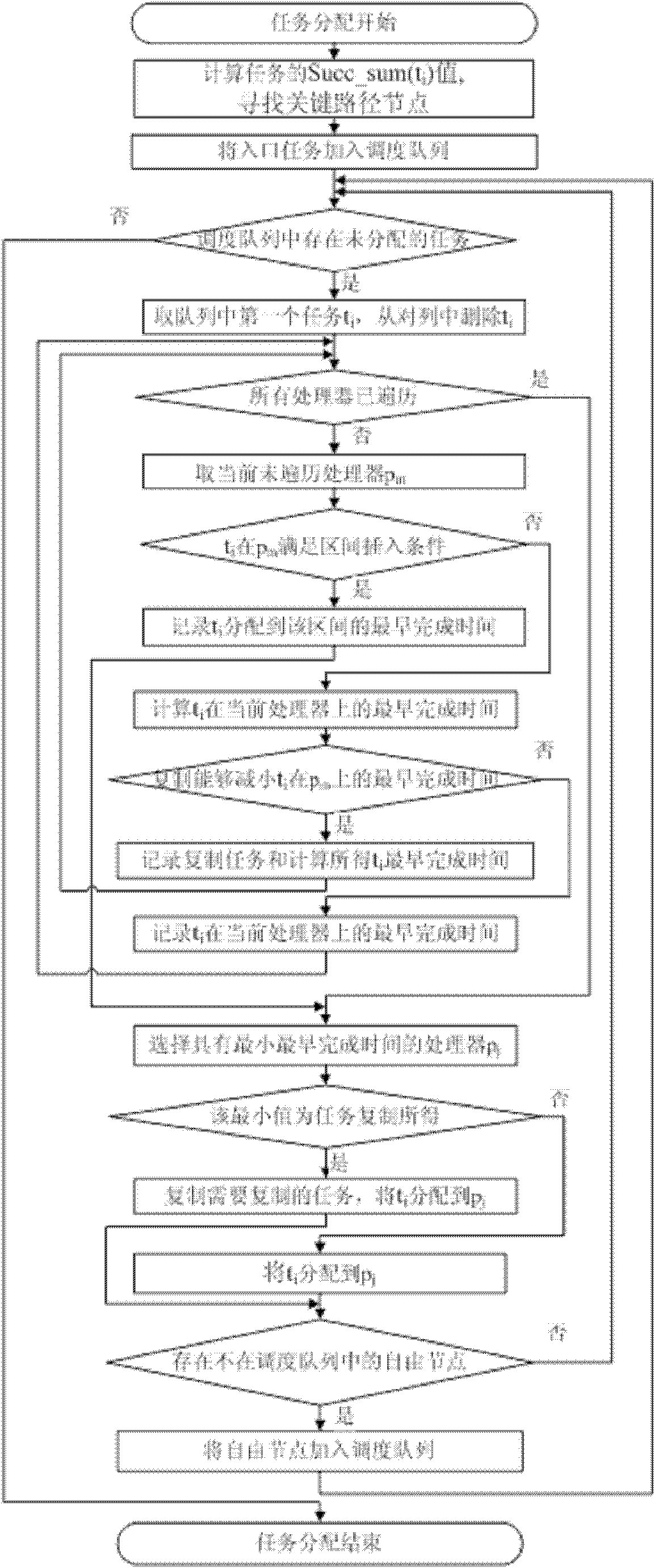

Method for high-efficiency task scheduling of heterogeneous multi-core processor

InactiveCN102193826ARaise priorityOptimize calculation resultsEnergy efficient ICTResource allocationEarliest finish timeCritical path method

The invention provides a method for high-efficiency task scheduling of a heterogeneous multi-core processor. The method comprises the following steps of: clustering certain special tasks which are large in communication overhead and easy to cluster in a task image to a precursor node of the tasks by adopting a linear task clustering method; starting from a topological structure of the whole task image, selecting parameters capable of comprehensively reflecting the importance of the task in the whole task image as priority weights; selecting a free critical path node to perform allocation first, and if multiple free critical path nodes exist, allocating the free critical path nodes in a sequence from high to low according to the node priority weights, and allocating all non-critical path free nodes in a sequence from high to low according to the priority weights; performing redundancy judgment, and deleting redundant tasks in a scheduling result; and performing adjustment according to the scheduling result after deleting the redundant tasks, and recalculating the earliest finish time of each task. According to the method, the efficiency of the task scheduling of the heterogeneous multi-core processor is improved, the power consumption of the processor is reduced, and the performance of the multi-core processor is promoted.

Owner:HARBIN ENG UNIV

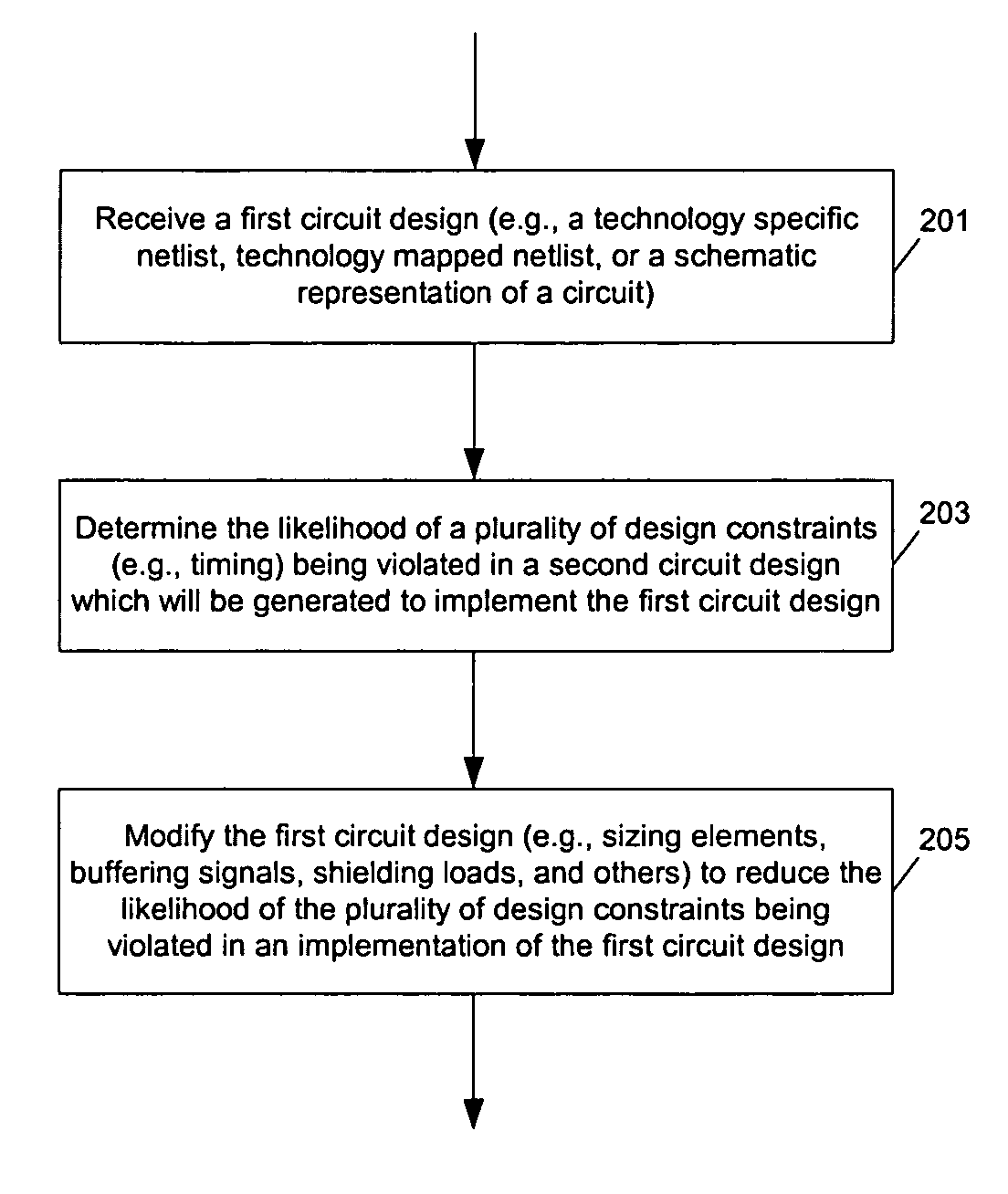

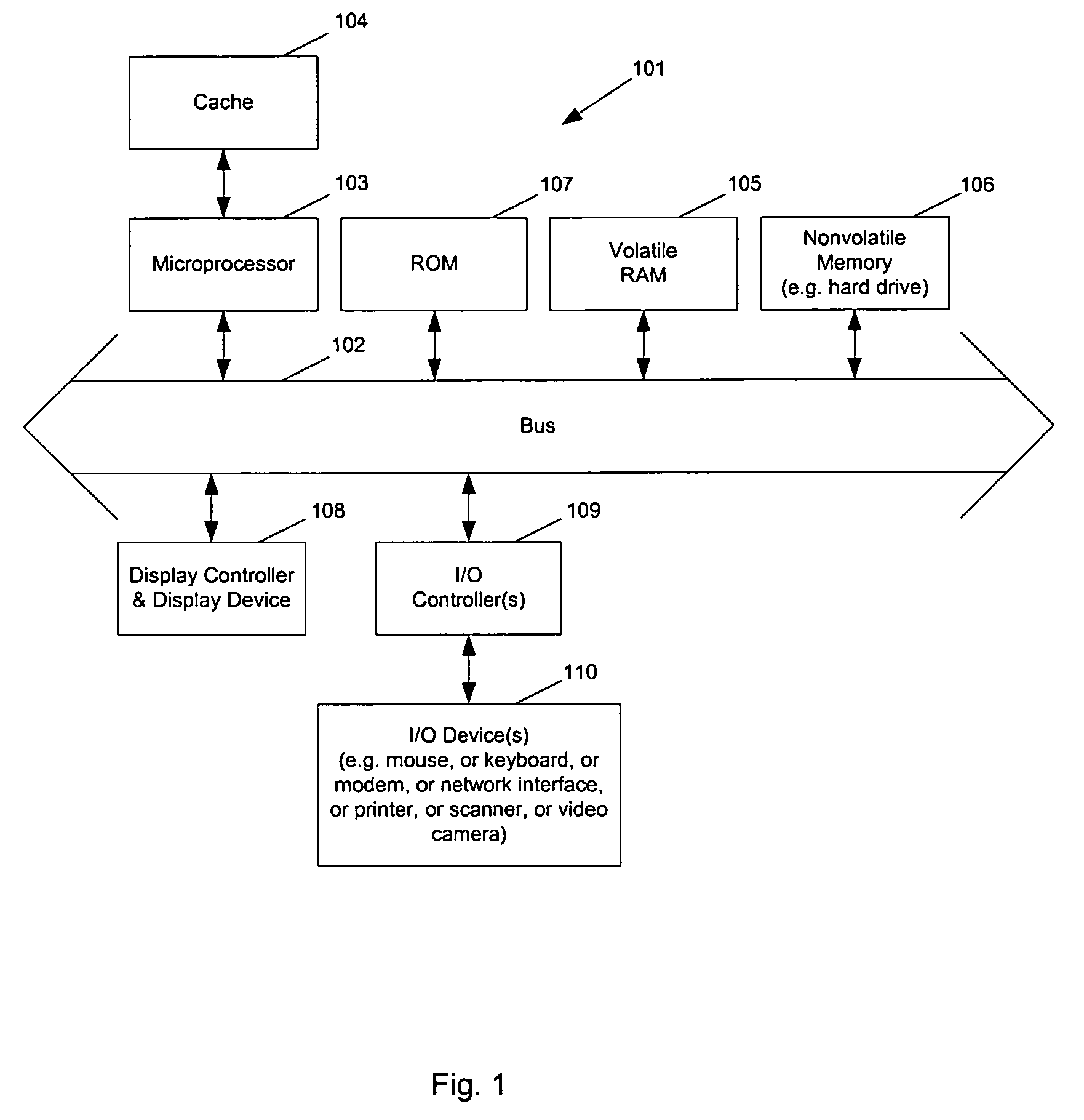

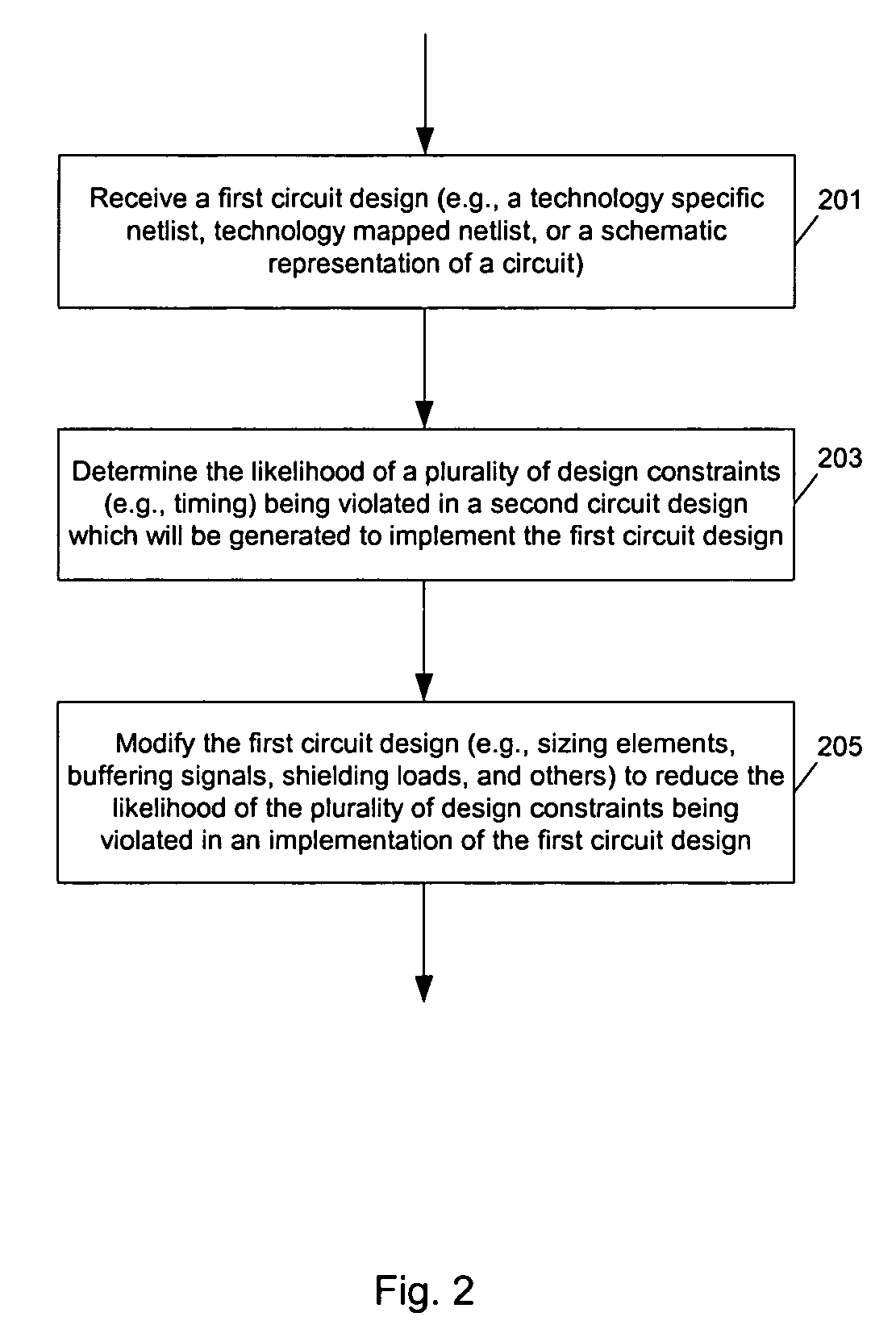

Method and apparatus for automated circuit design

ActiveUS7251800B2CAD circuit designSoftware simulation/interpretation/emulationCritical path methodCircuit design

Methods and apparatuses to automatically modify a circuit design according to the possible deviation in the subsequent implementation of the circuit. In one aspect, a method to design a circuit includes: determining whether a design constraint is likely to be violated during a subsequent routing implementation of a design of the circuit; and, modifying the design of the circuit to reduce likelihood of the design constraint being violated during a subsequent implementation. For example, a route for a net with a number of fanout larger than two and on a timing critical or near-critical path may be considered sensitive to route topology such that an alternative routing path may lead to a violation in timing constraint; to reduce the possibility of a timing problem in a subsequent routing solution, a transformation can be selectively applied to the circuit design to an extent not worsening a cost function.

Owner:SYNOPSYS INC

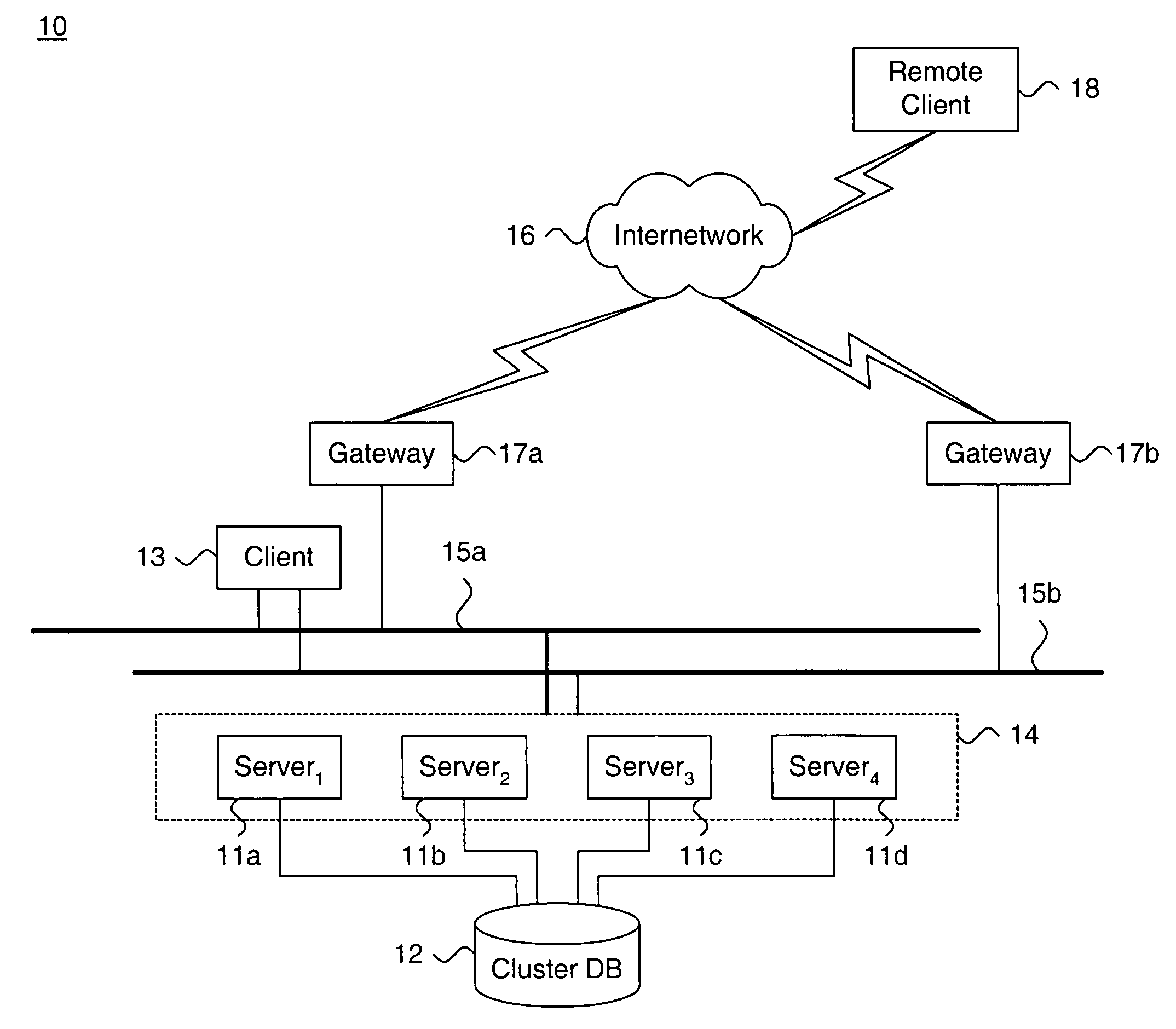

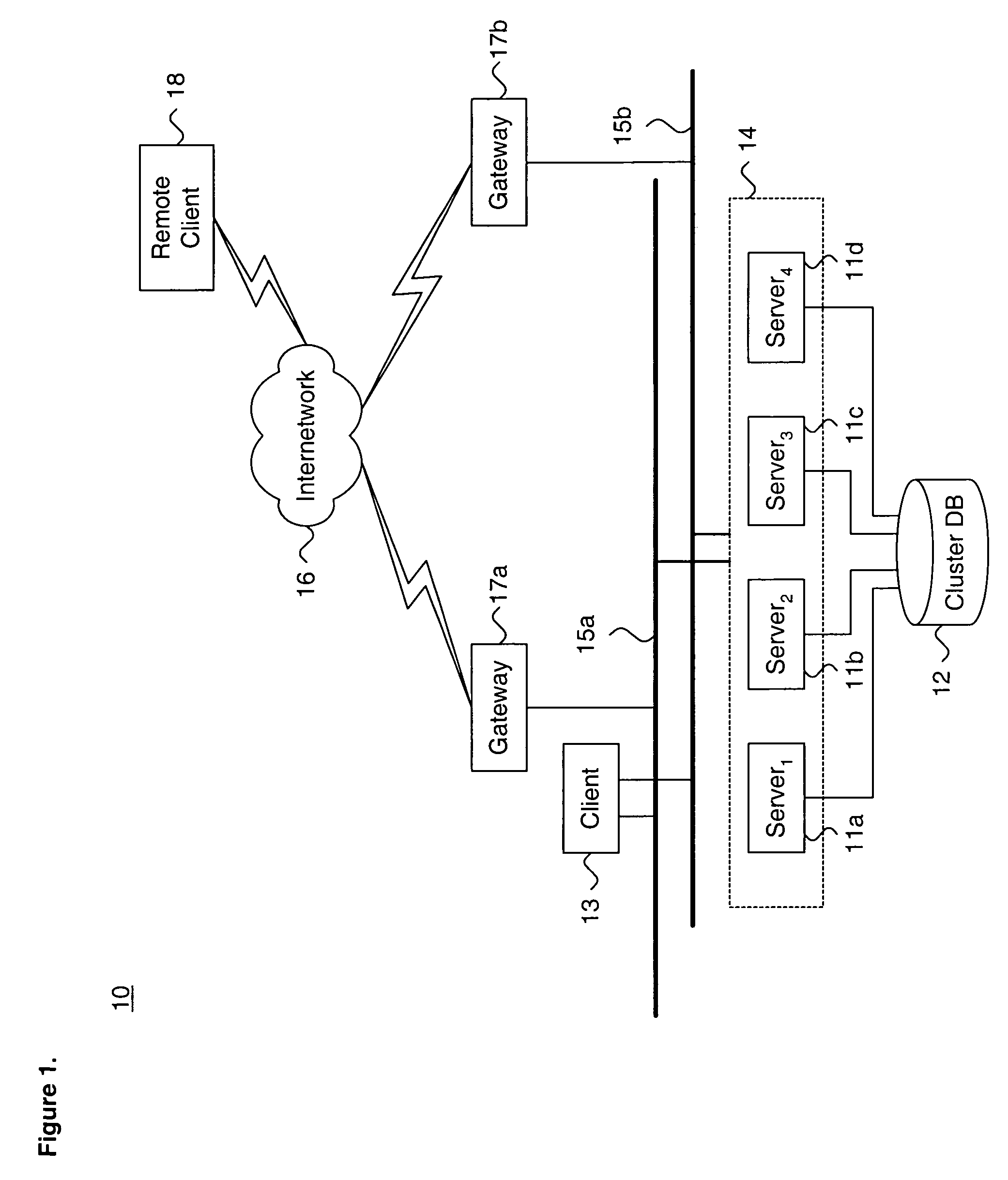

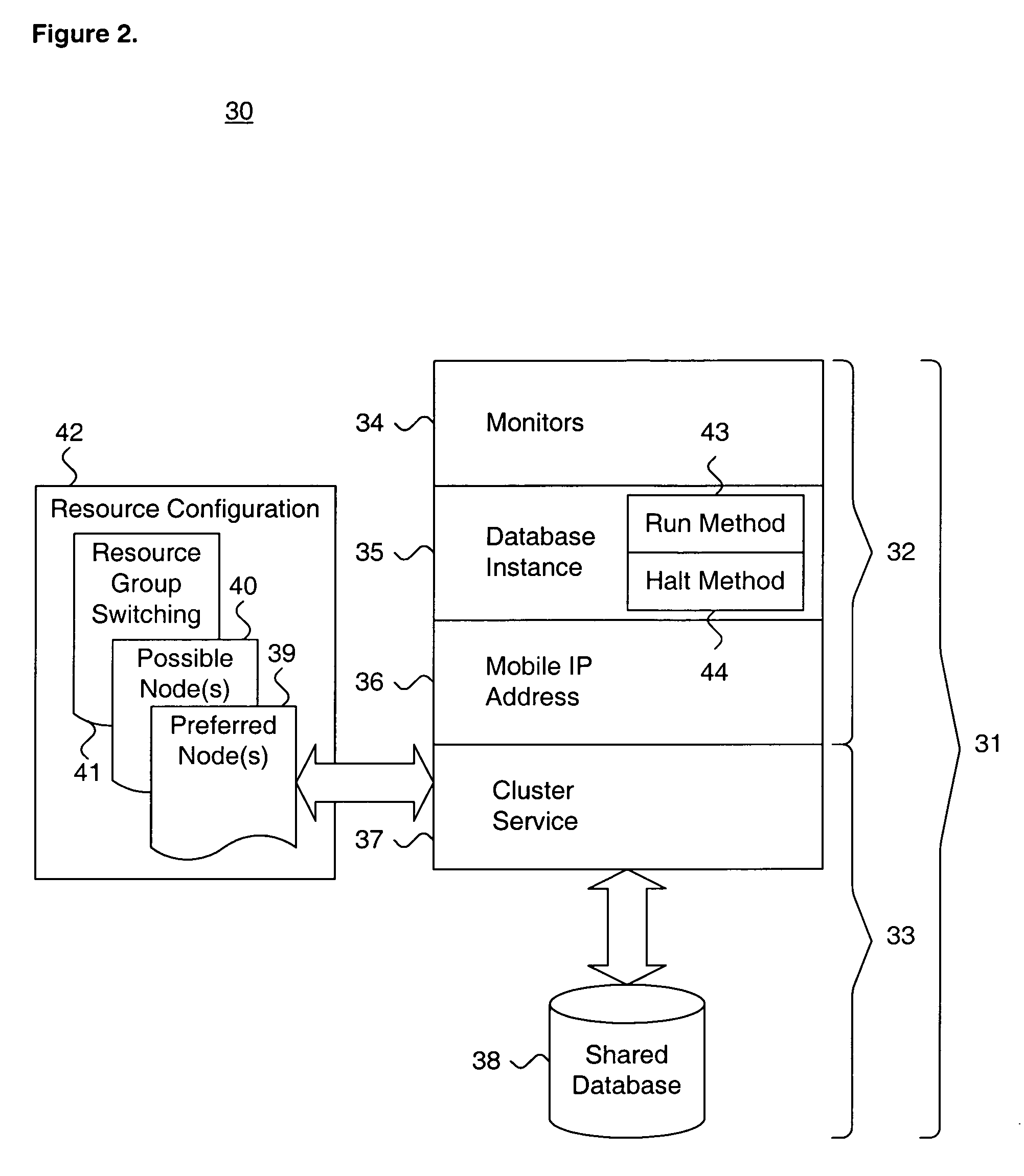

System and method for providing cooperative resource groups for high availability applications

InactiveUS7444335B1Eliminates TCP/IP timeout errorEliminate errorsDigital data processing detailsDigital computer detailsClustered dataHigh availability

A system and method for providing cooperative resource groups for high availability applications, such as cluster databases, is described. A cluster framework, including a plurality of nodes, is built. A plurality of cooperative resource groups is formed, each including a logical network address, at least one monitor and an application providing services and externally accessed using the logical network address. A plurality of resources is structured, each including a cluster service supporting the services provided by each application. A preferred node for execution is designated for each cooperative resource group and one or more possible nodes are provided as standby nodes for each other cooperative resource group. The services are restarted on a surviving node off a critical path of the preferred node upon an unavailability of the preferred node, while the logical network address is kept available on each possible node for the cooperative resource group.

Owner:ORACLE INT CORP

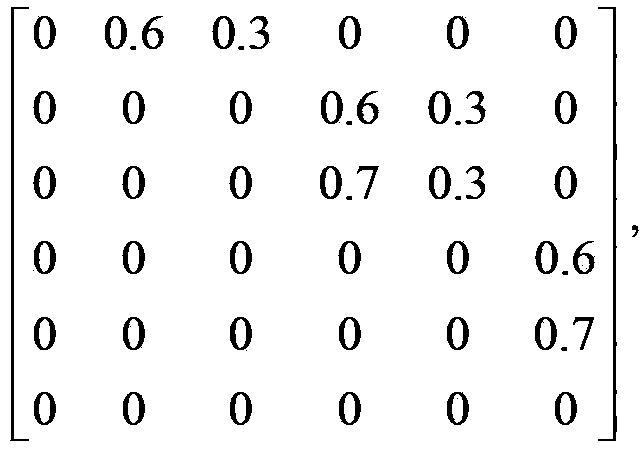

Network security evaluation device based on attack graph adjacent matrix

The invention provides a network security evaluation device based on an attack graph adjacent matrix. The network security evaluation device comprises an information collection device, an atom attack graph generation device, a matrix calculation device, a network safety analyzing device and a result appearing device, wherein the information collection device is used for collecting all information in a network; the atom attack graph generation device is used for generating an initial atom attack graph between a main engine pair needed for carrying out subsequent analysis on network safety; the matrix calculation device is used for converting the generated atom attack graph into the corresponding adjacent matrix and is also used for calculating a corresponding iteration matrix of the adjacent matrix through setting iteration times; the network safety analyzing device is used for obtaining information including a key main engine, a key path and the like on the basis of the finally-generated iteration matrix; the result appearing device is used for visually appearing the found key main engine and key path and a network vulnerability index. The network security evaluation device disclosed by the invention is high in efficiency and is suitable for large-scale and high-speed networks. The network security evaluation device can improve the instantaneity of evaluating a target network. The evaluation accuracy rate is high, and the key path and the key main engine can be accurately recognized. The visualization degree is high so that the network security evaluation device is convenient for a manager to check, analyze and maintain.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

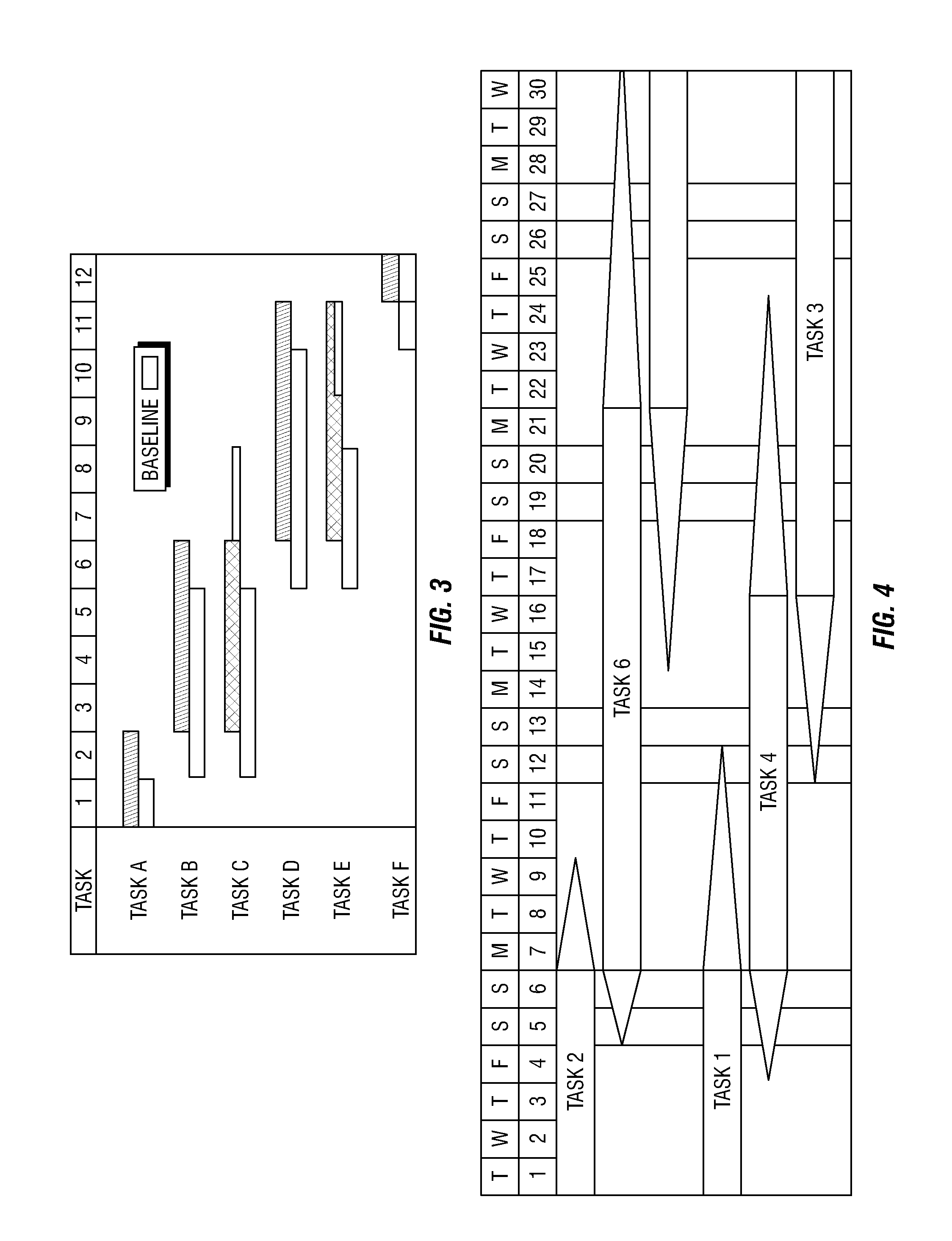

Determining a Critical Path in Statistical Project Management

An apparatus for a Gantt chart includes a processing unit which determines a range of dates for an end date for completing a task. The range comprises a first date and a final date. The apparatus includes a display which shows the range of dates for the task completion. A method for a Gantt chart includes the steps of determining a range of dates for an end date for completing a task with a processing unit. The range comprises a first date and a final date. There is the step of showing on a display the range of dates for the task completion. There is the step of showing on a display the range of the end date. An apparatus for establishing a project's performance. A method for establishing a project's performance.

Owner:TELEFON AB LM ERICSSON (PUBL)

Path metric normalization

ActiveUS7400688B2Speed up the processWithout executionData representation error detection/correctionError preventionAlgorithmCritical path method

Path metric normalization in calculating trellis-based algorithms is improved by normalizing the path metric with an average value (rather than a maximum or a minimum) of the path metrics. Using an average rather than a maximum or a minimum provides various advantages without adversely affecting the execution of the trellis-based algorithm. Due to the relatively faster computation time available when an average is computed, average value normalization can be applied every cycle, because its critical path is less than that of the ACS unit.

Owner:WSOU INVESTMENTS LLC +1

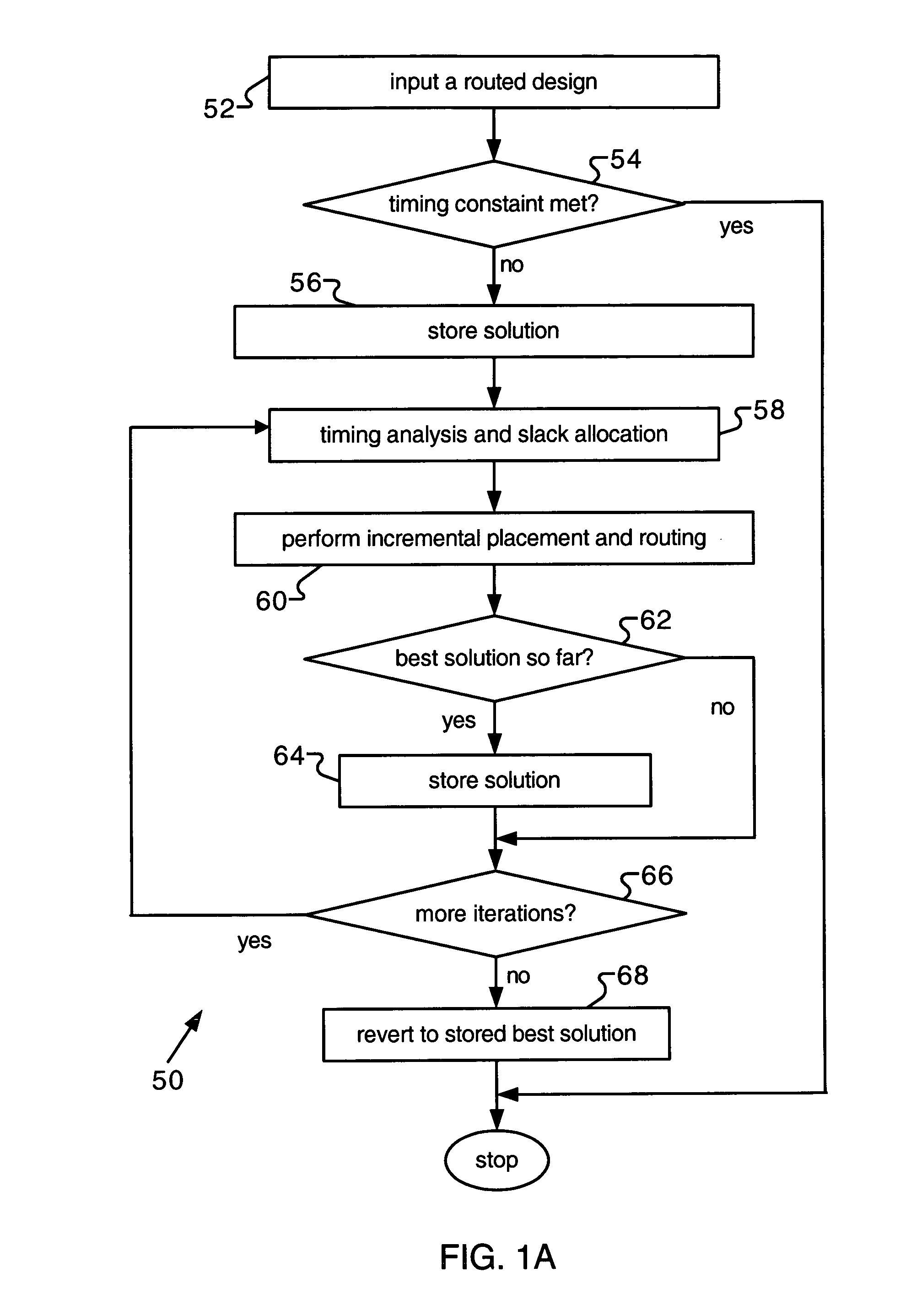

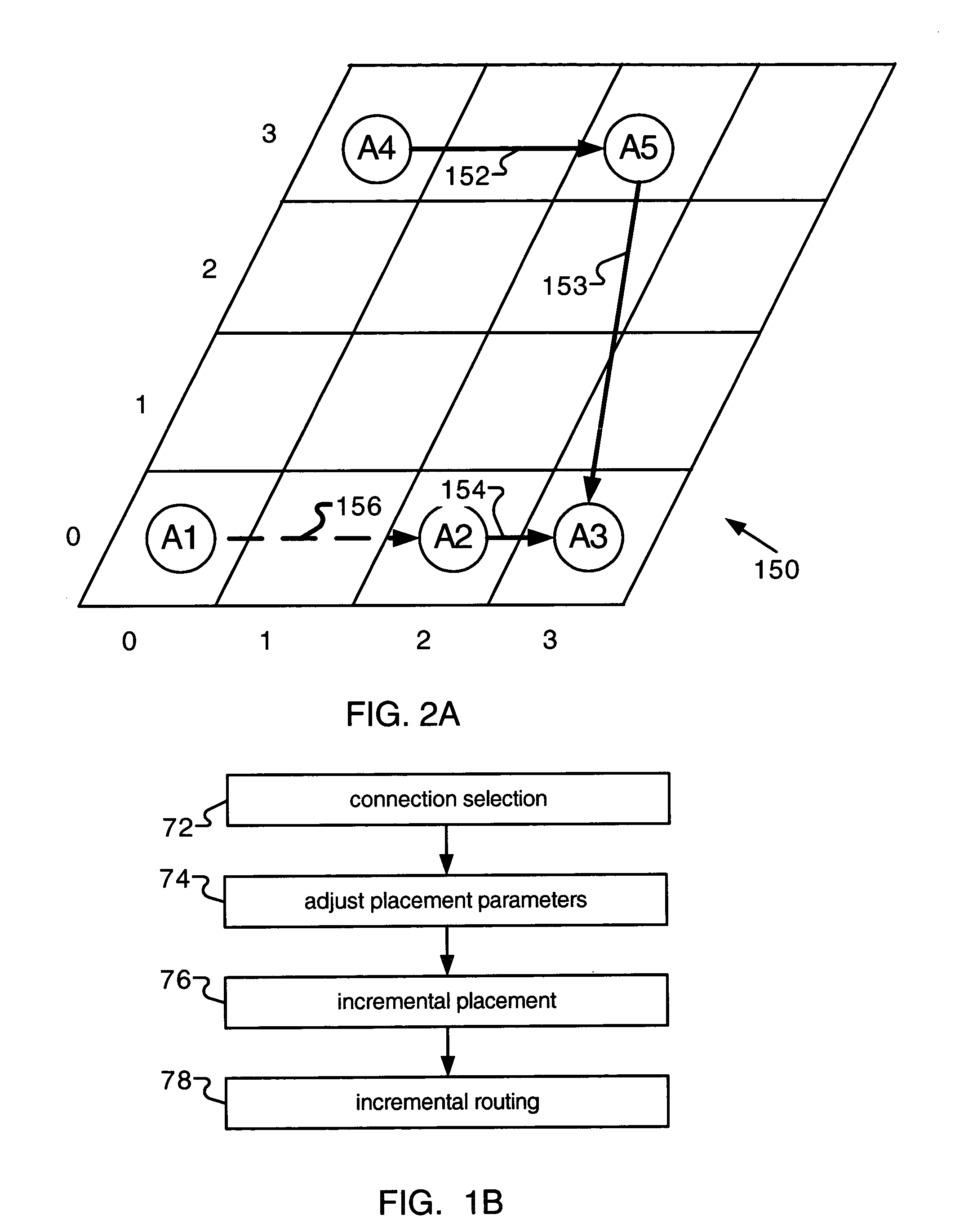

Post-layout optimization in integrated circuit design

ActiveUS7111268B1Computer programmed simultaneously with data introductionComputer aided designComputer architectureCritical path method

A method for post-layout timing optimization is disclosed. The method performs timing analysis on a design to obtain timing information such as critical paths and slack values. Incremental placement based on the timing information is performed. A new routed design is generated by applying incremental routing to the result of incremental placement. The routed design is stored if its performance is better than the previous routed design. The above steps are repeated until a predetermined criterion is met.

Owner:XILINX INC

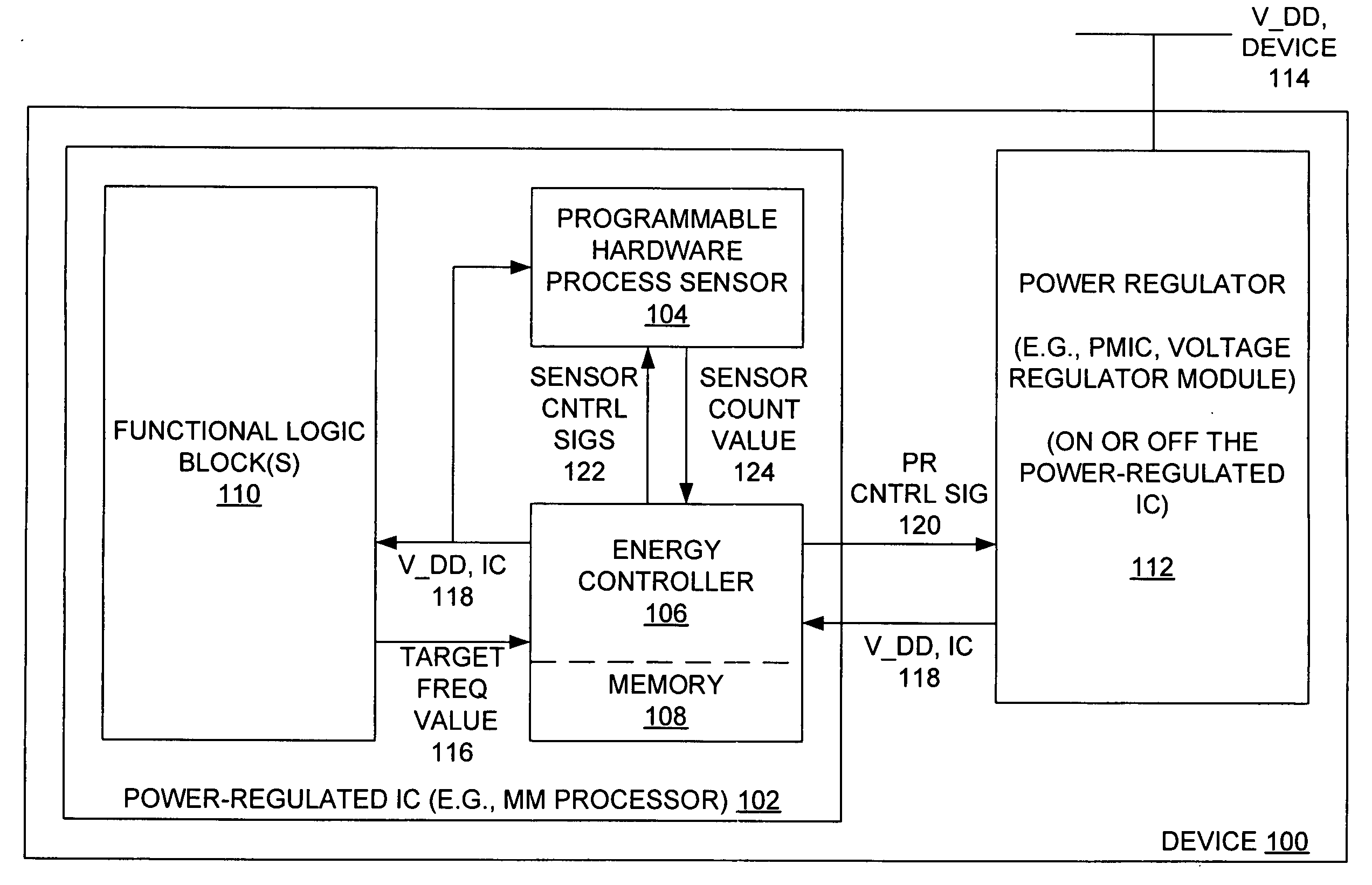

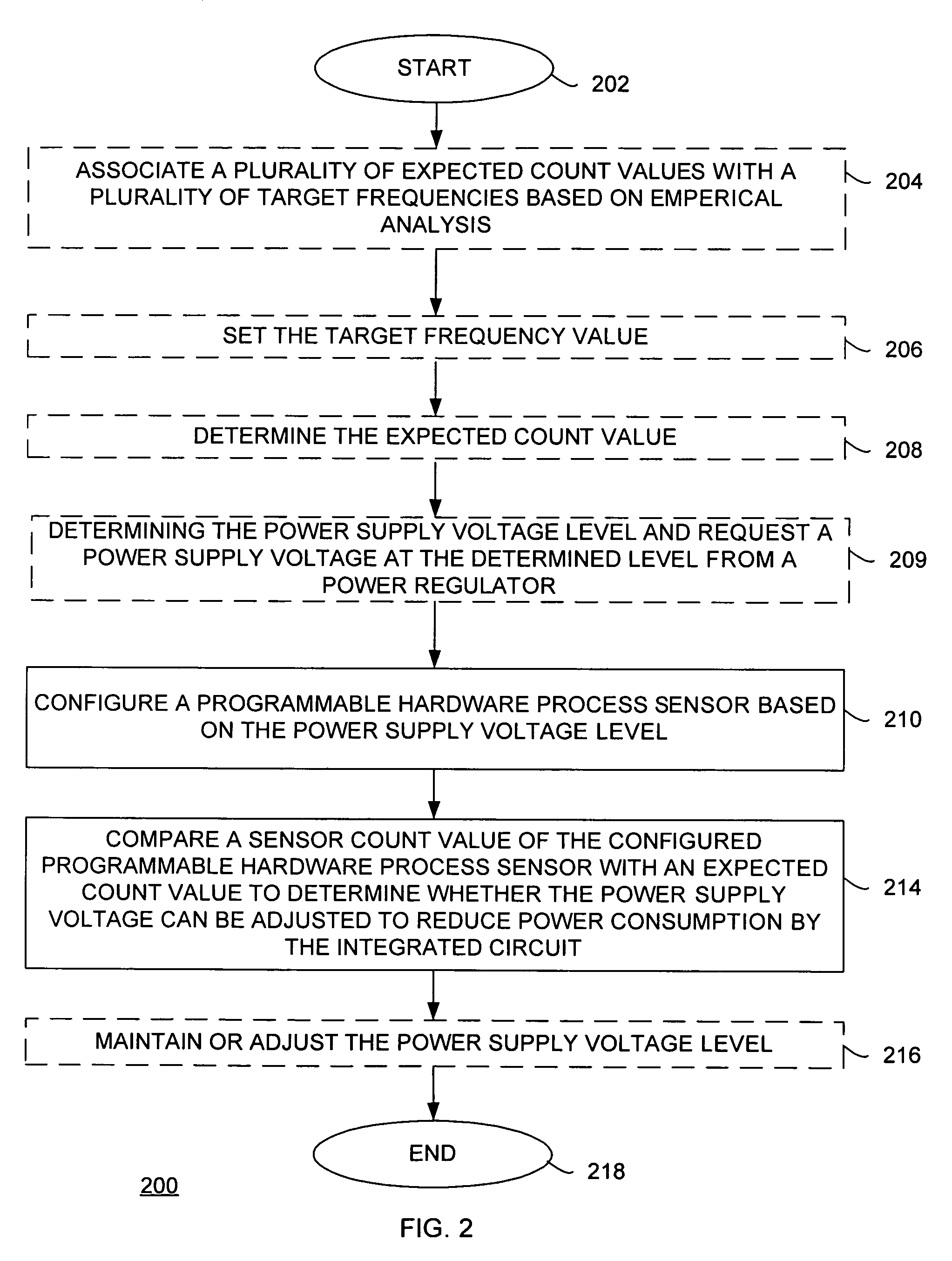

Apparatus and method for reducing power consumption by an integrated circuit

An integrated circuit includes an energy controller that generates a power supply voltage level for the integrated circuit based on a desired target frequency value for the integrated circuit. The energy controller configures a programmable hardware process sensor based on the power supply voltage level such that the programmable hardware process sensor is capable of mimicking the electrical characteristics of a predetermined critical path associated with the integrated circuit when operating at the power supply voltage level. By monitoring the frequency of the programmable hardware process sensor over a period of time, the energy controller can compare the monitored frequency to an expected value and determine whether the power supply voltage level can be adjusted or whether it should be maintained.

Owner:ADVANCED MICRO DEVICES INC

Driverless vehicle local path planning method with time consistency

ActiveCN108088456ASolve the problem of inter-consistencyGuaranteed ModularityInstruments for road network navigationPlanning approachDegrees of freedom

The invention discloses a driverless vehicle local path planning method with time consistency. The method comprises the steps: firstly, vehicle motion differential constraints are increased for a planning path curve, so that a vehicle can track a generated trajectory accurately; secondly, model parameters of a path planning trajectory curve model are promoted, a greater degree of freedom is increased for the planning path, and a curvature constraint problem is conveniently transformed into a mathematical solving optimization problem; and finally, results of periodic optimization before and after the local path method is obtained through periodic optimization solving have large difference, and the problem of jitter of the vehicle during real-time path tracking is caused. A local path planning section is divided into two parts, namely a weak planning section and a strong planning section; the weak planning section is obtained by a strong planning result of a last planning period; throughplanned segmentation, the time consistency of the planning results can be guaranteed, and the local path planning can also have high obstacle avoidance ability.

Owner:BEIJING UNIV OF TECH

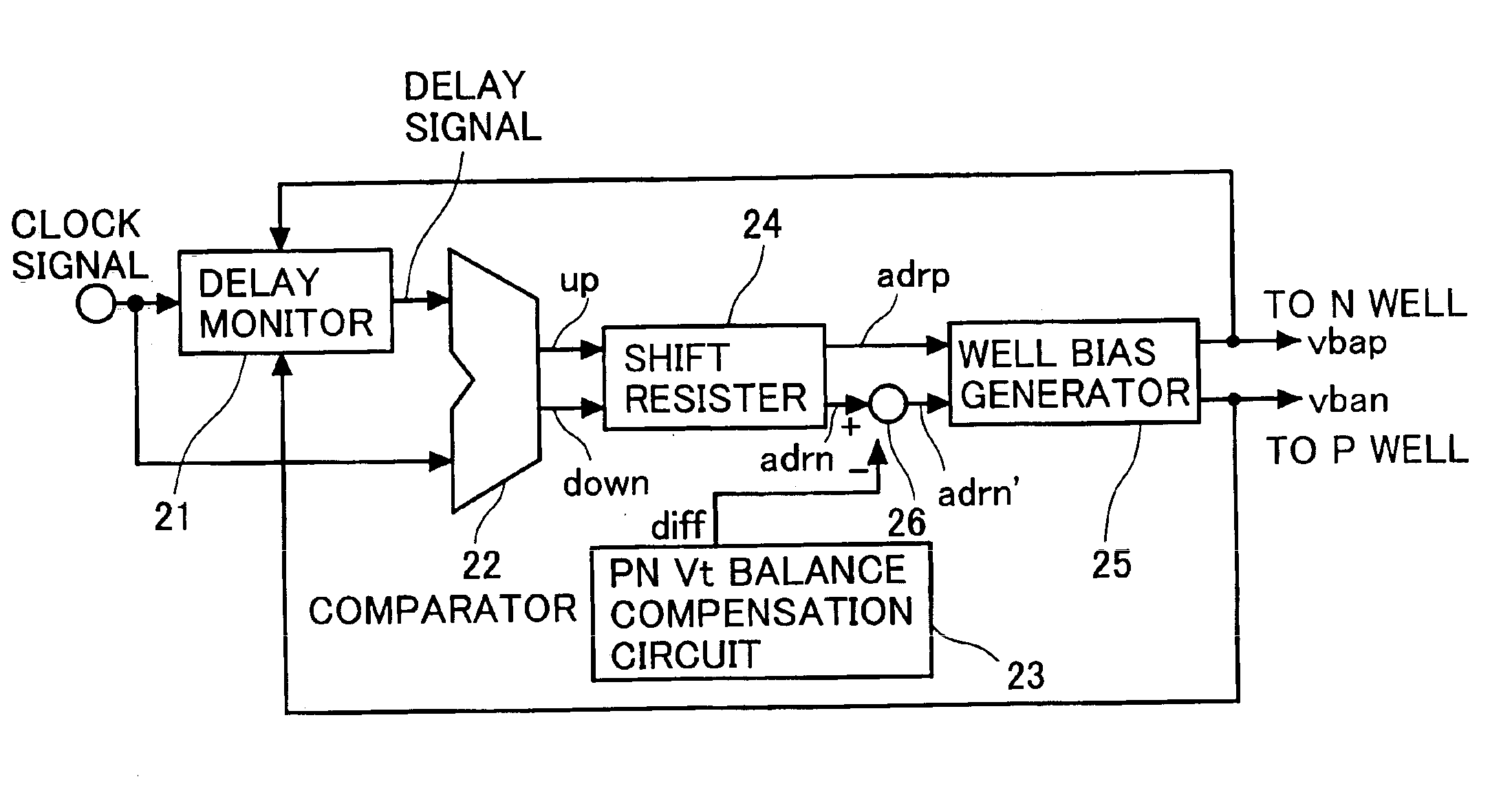

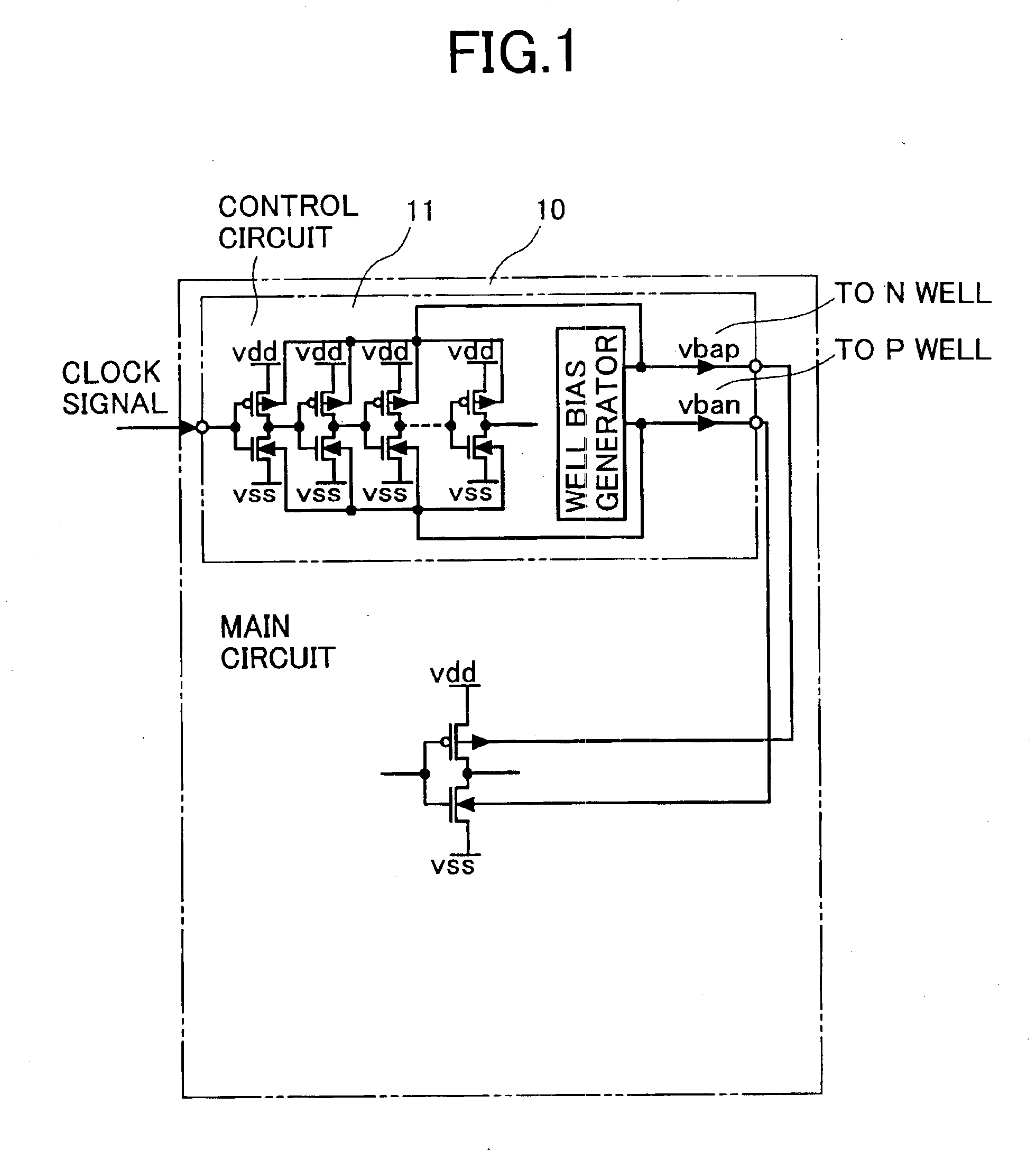

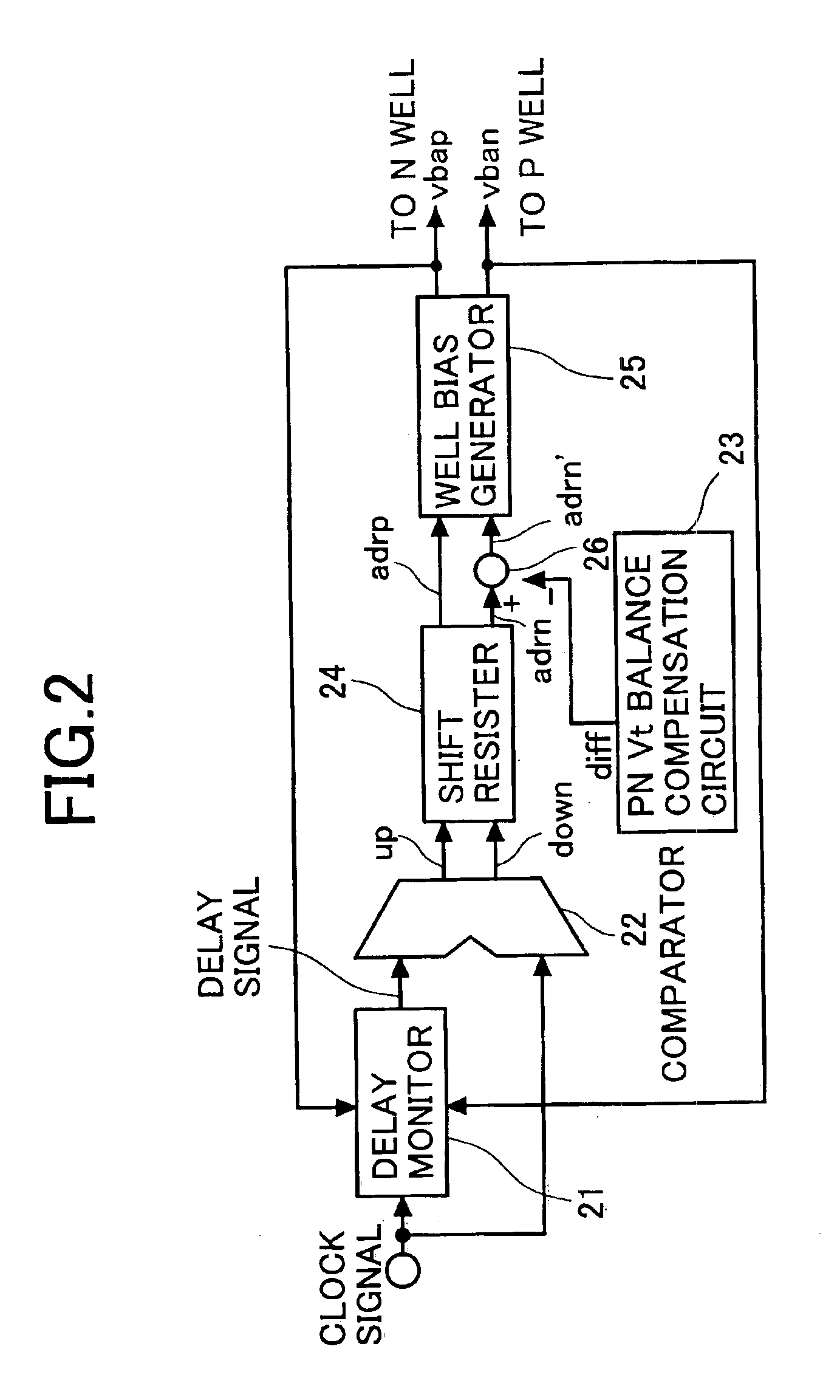

Well bias voltage control circuit and method

InactiveUS6847252B1Improve leakage currentRatio of power consumptionTransistorReliability increasing modificationsCMOSEngineering

A semiconductor integrated circuit device having a mechanism of compensating not only circuit operational speed but also variations in leakage current, which includes: a main circuit constructed with CMOS device, a delay monitor for simulating a critical path of the main circuit constructed by a CMOS and monitoring a delay of the path, a PN Vt balance compensation circuit for detecting a threshold voltage difference between a PMOS transistor and an NMOS transistor, and a well bias generating circuit for receiving outputs of the delay monitor and the PN Vt balance compensation circuit and applying a well bias to the delay monitor and the main circuit so as to compensate the operation speed of the delay monitor to a desired speed and reduce a threshold voltage difference between the PMOS and NMOS transistors.

Owner:RENESAS ELECTRONICS CORP

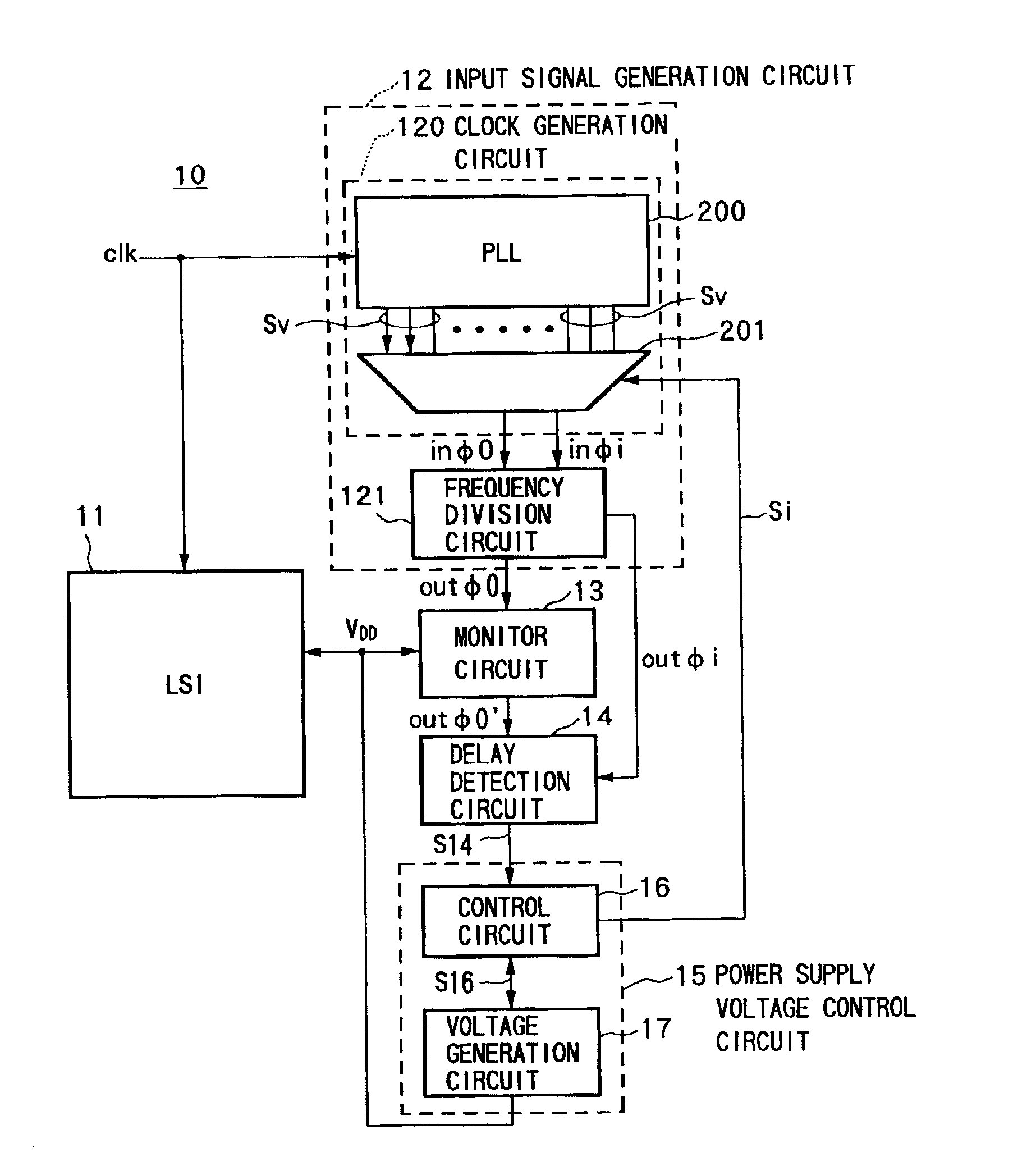

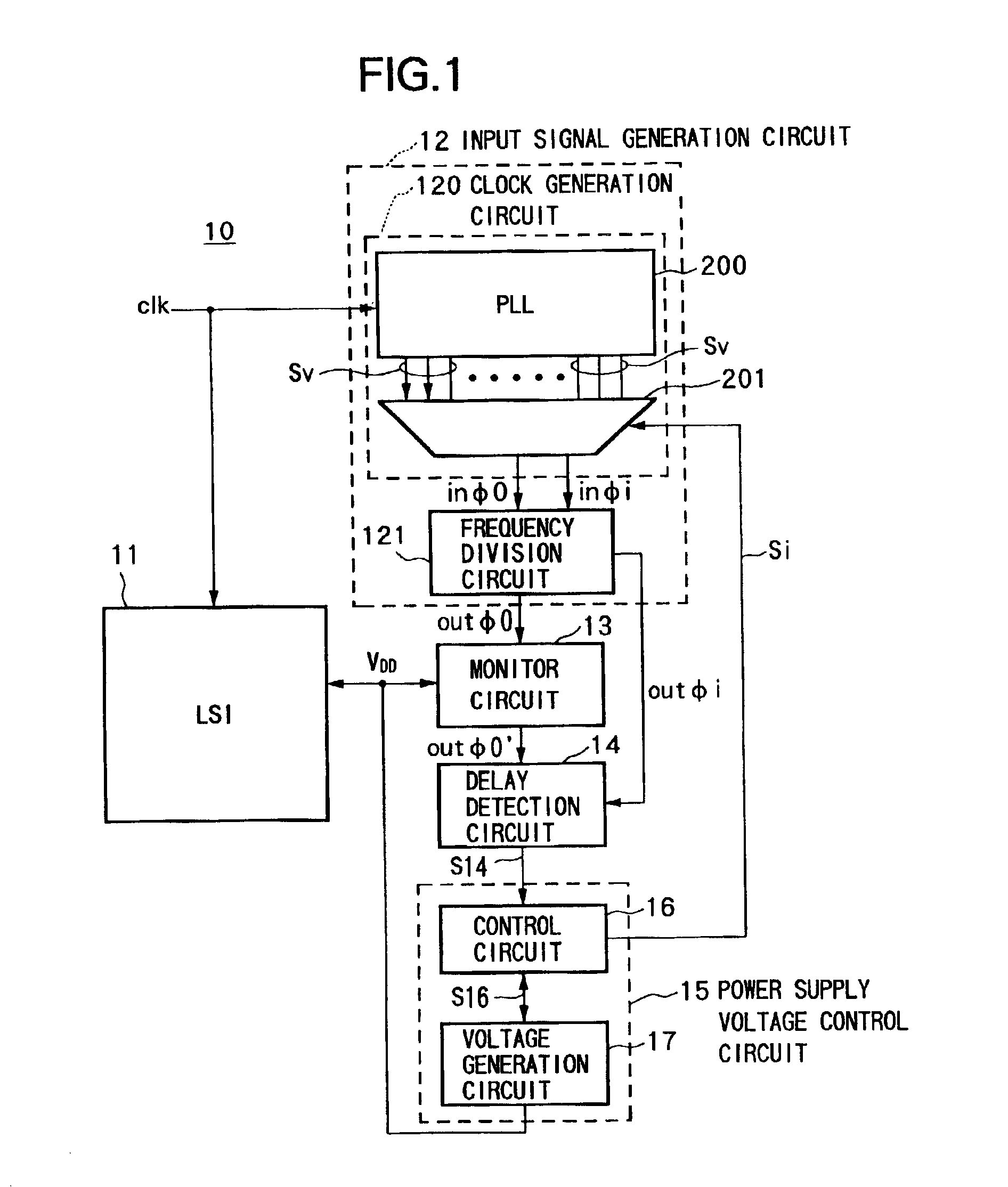

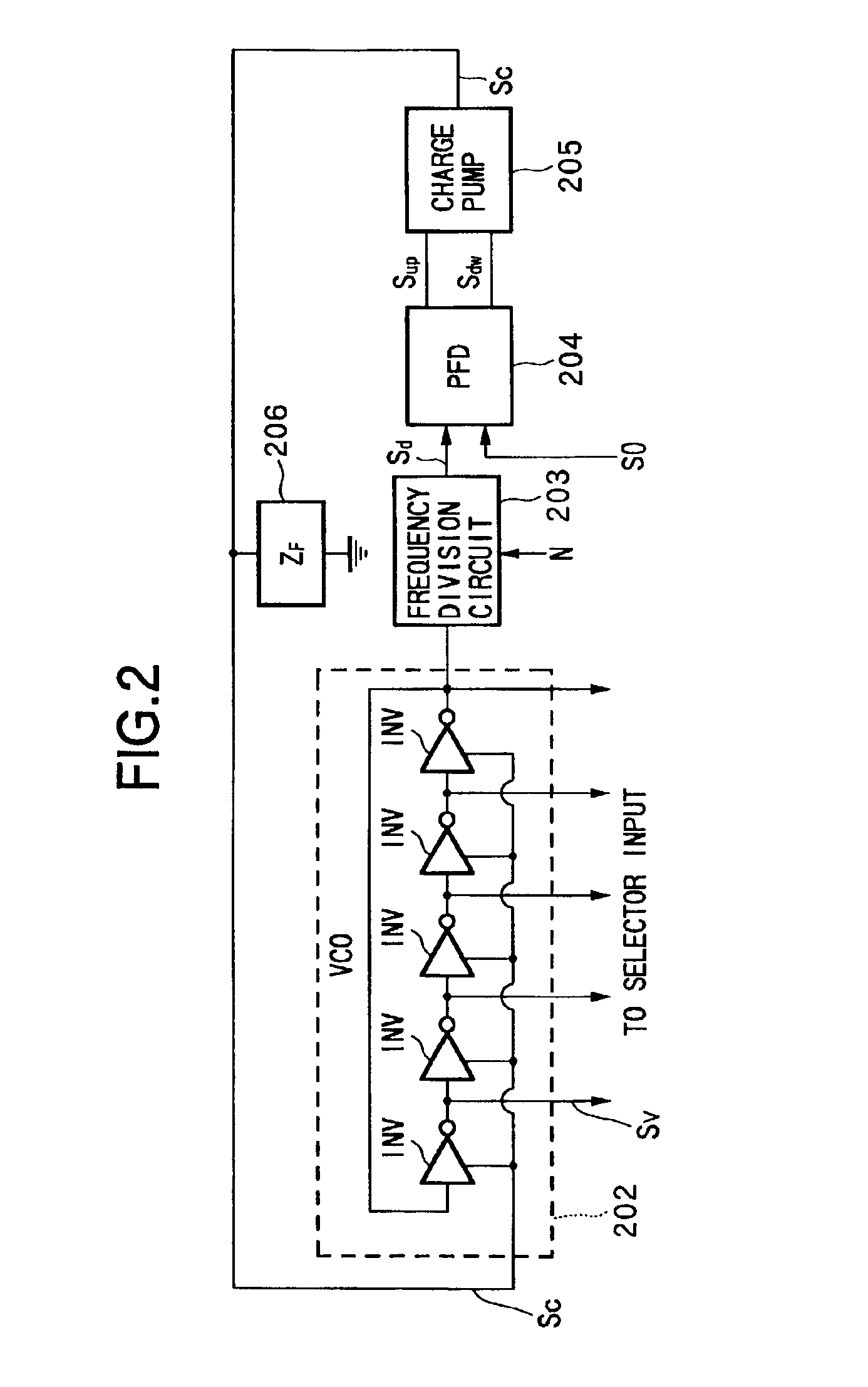

Power supply control device, semiconductor device and method of driving semiconductor device

InactiveUS6924679B2Increase in sizeSolve low usageEnergy efficient ICTPulse automatic controlPhase differenceControl signal

A power supply voltage control apparatus including an input signal generation circuit of wide uses or a small-sized monitor circuit of a novel configuration, and a semiconductor circuit and a method for driving the same, having a semiconductor circuit 11, an input signal generation circuit 12 able to change the phase difference i of a reference signal outφi and an input signal outφ0 in accordance with a control signal Si when generating the two signals from a clock, a monitor circuit 13 having a characteristic between a power supply voltage and delay the same as that of a critical path of the semiconductor circuit 11, propagating the input signal outφ0, and outputting a delayed signal outφ0′ to be delayed exactly by a time equivalent to a delay of the critical path (or smaller by a constant ratio), a delay detection circuit 14 for detecting a delay of the delayed signal outφ0′ relative to the reference signal outφi, and a power supply voltage control circuit 15 for controlling a power supply voltage VDD supplied to the semiconductor device 11 and the monitor circuit 13 based on the detection result.

Owner:SONY CORP

Novel control system and novel control method for sensing and controlling road intersection group signals

InactiveCN105844927AEase traffic congestionSolve run optimization problemsRoad vehicles traffic controlTraffic signalSimulation

The invention discloses a novel control system and a novel control method for sensing and controlling road intersection group signals. Through constructing a method containing four steps of 360-DEG intersection panorama video real time monitoring and modeling, intersection assessment index and online simulation analysis, supersaturated intersection key path and control strategy optimization and intersection signal control optimization and panorama video acquisition robot linkage command and establishing an intelligent city traffic control robot based on an intersection group, a city road supersaturated intersection single-point operation optimization problem is solved, an intelligent command city road intersection, supersaturated intersection and supersaturated intersection group traffic control and optimization scheme is formed, moreover, the intelligent city traffic control robot based on the intersection group is employed, linkage between a panorama video acquisition robot and a traffic signals controller is realized, traffic efficiency and the service level of intersection single-point control are improved, so operation efficiency of a city traffic system is greatly improved, and city traffic jams are alleviated.

Owner:SHENZHEN RONGHENG IND GRP

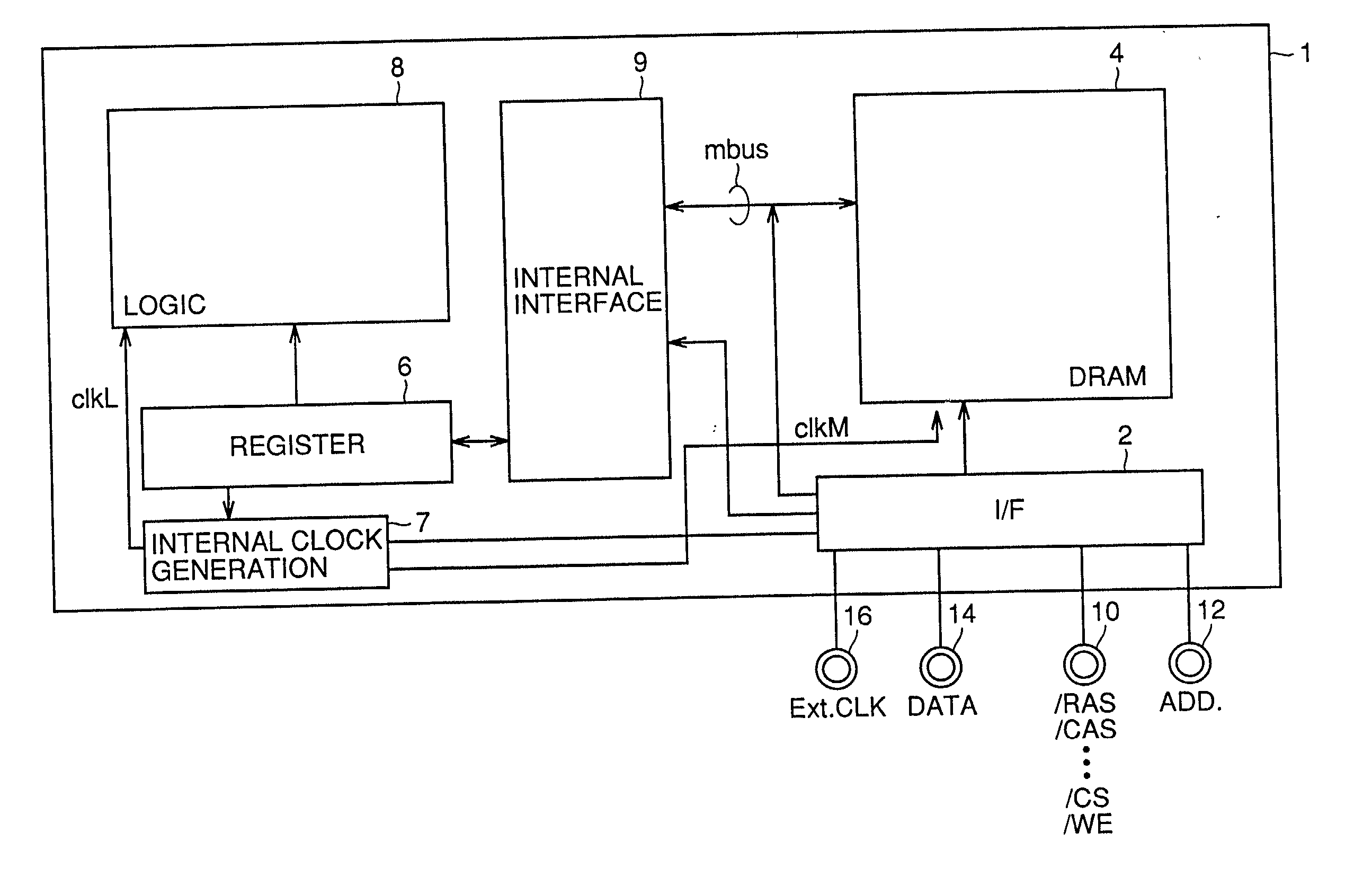

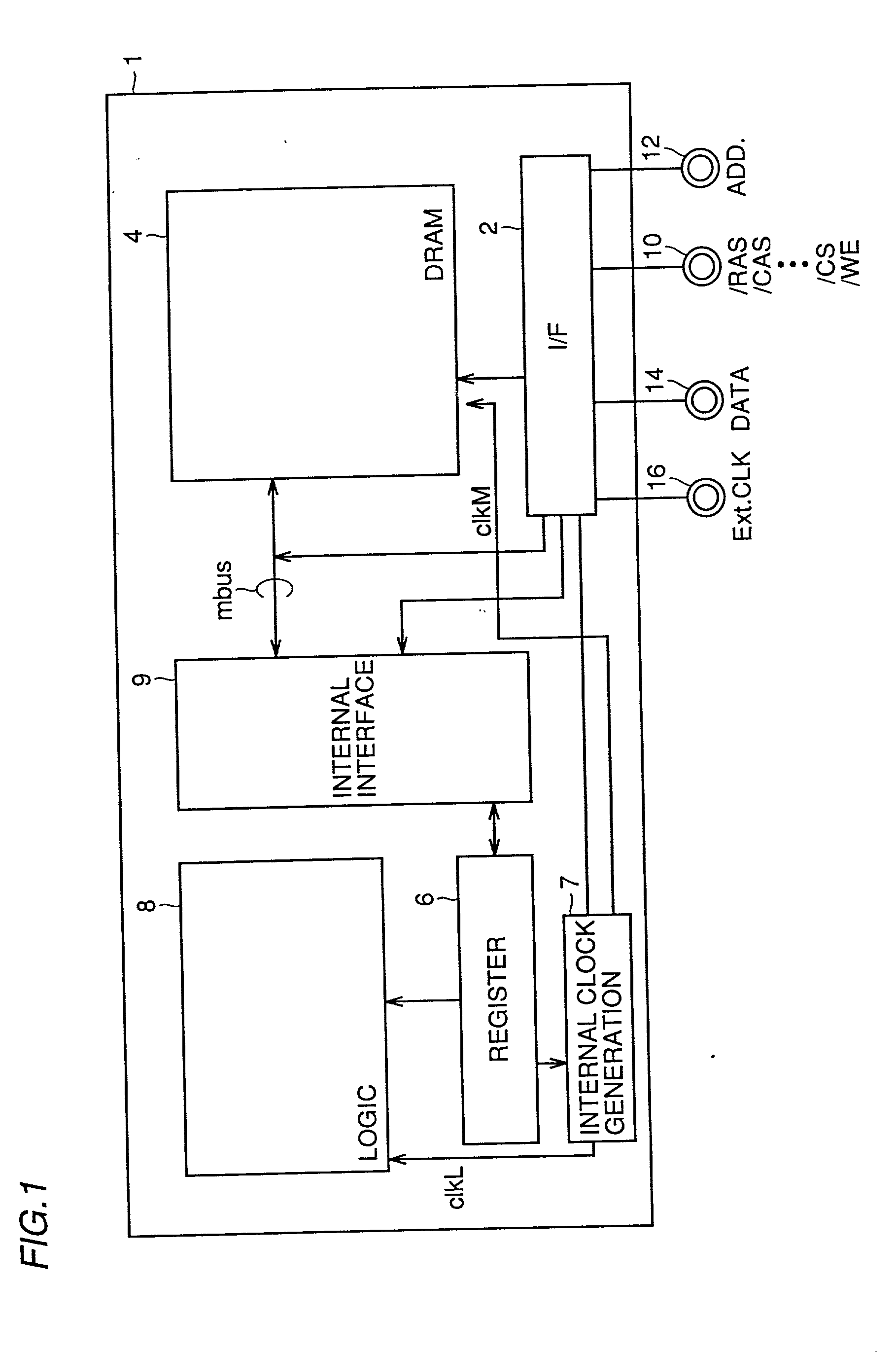

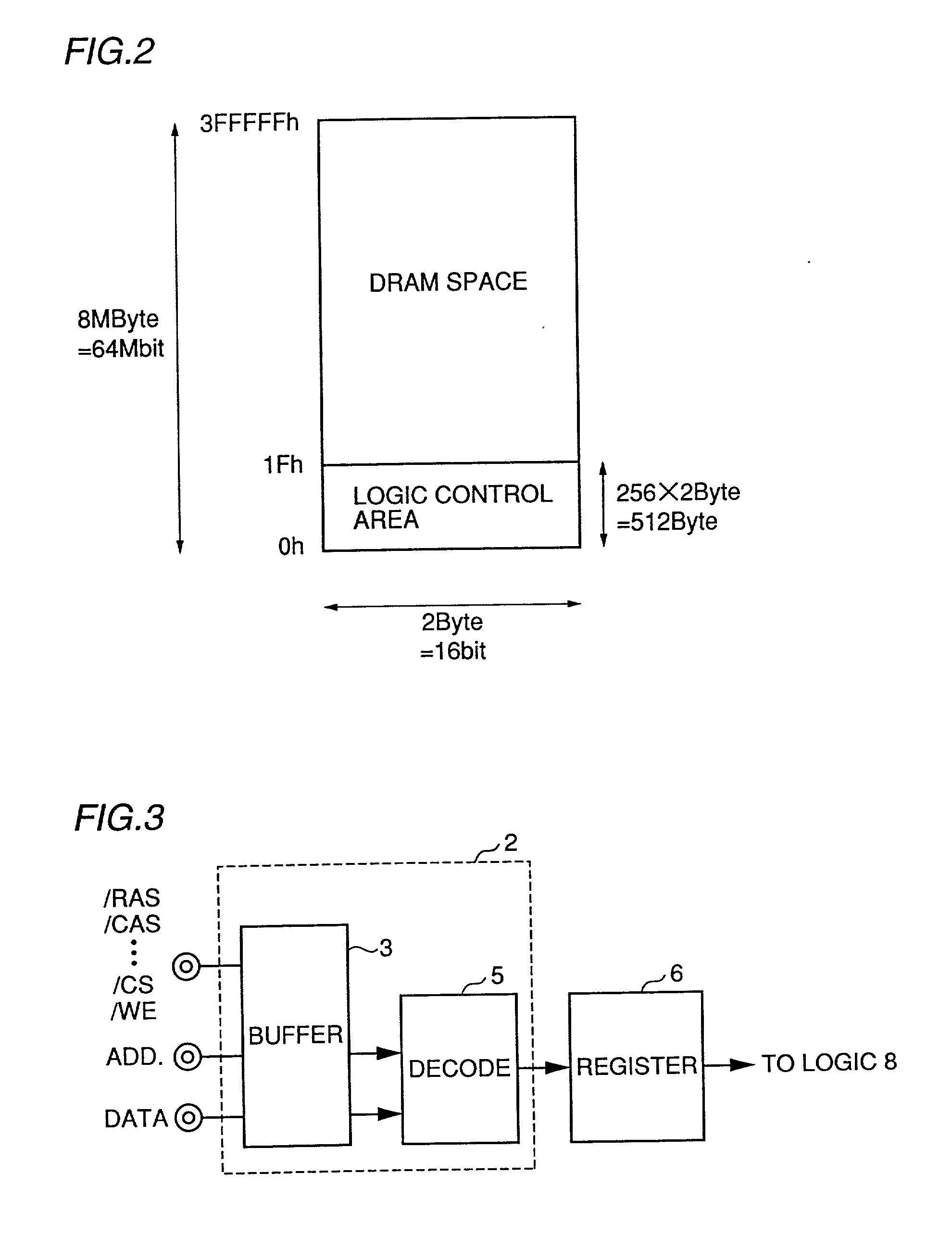

Simply interfaced semiconductor integrated circuit device including logic circuitry and embedded memory circuitry

InactiveUS20020040420A1Public key for secure communicationUser identity/authority verificationControl signalData store

An interface circuit performs supply / reception of data with a register instead of supply / reception of data with DRAM when an area specified by an address signal is a logic control area. Data signals in the case are a control command for a logic circuit held in a register and input data to be processed. The logic circuit takes charge of a critical path in processing time such as cryptographic processing and image processing. A processing result is held in the register. The register circuit switches between storage data stored in DRAM and data given from a terminal group to select data to be processed according to a control signal.

Owner:RENESAS ELECTRONICS CORP

Storage network adapter of supporting virtual interface

InactiveCN1761222AIncrease flexibilityHigh bandwidthData switching by path configurationMemory systemsInteroperability ProblemSoftware

Thorough mode of combining software with hardware in FPGA chip, the invention realizes protocol of virtual interface. The invention includes host interface, system on chip, Ethernet interface, and dedicated logic circuit for virtual interface. Through bus of system on chip, the system on chip is connected to Ethernet interface each other. Using communication mechanism sharing memory between host interface and system on chip realizes interlinkage and communication. Advantages are: reducing communication overhead of communication, obtaining more high transmission performance; using communication protocol in VIA lightweight level, the invention reduces data copy in communication process, shortens key path of storing data; Ethernet as transmission media is adopted at bottom layer so as to guarantee interlinkage and interoperability to current network; collaborative work between software and hardware speeds up procedure for processing protocol.

Owner:HUAZHONG UNIV OF SCI & TECH

Method and apparatus for finance-based scheduling of construction projects

a method and apparatus is disclosed for scheduling construction projects based on the available finance using integer programming. This method renders CPM / PERT schedules of construction projects executable using bank overdrafts of specified credit limits. Conveniently, the method is organized in three stages; input preparation, schedule extension, and model formulation. Input preparation stage supports preparing CPM / PERT schedule and financial data of the project. Schedule extension stage supports developing a scheme for schedule extension. The scheme is a framework of the original schedule that allows a definite extension increment in the critical path of the CPM. Model formulation stage supports building an integer programming model for the scheme and involves the components of formulating an objective function, setting constraints, and searching for a model solution. The model solution determines the activities' shifts that fulfill the constraints of the specified credit limit while minimizing the schedule extension. A search for a solution of the model is performed. If no solution is found, a repetition of the last two stages of the method is performed after allowing longer extension increment.

Owner:KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS

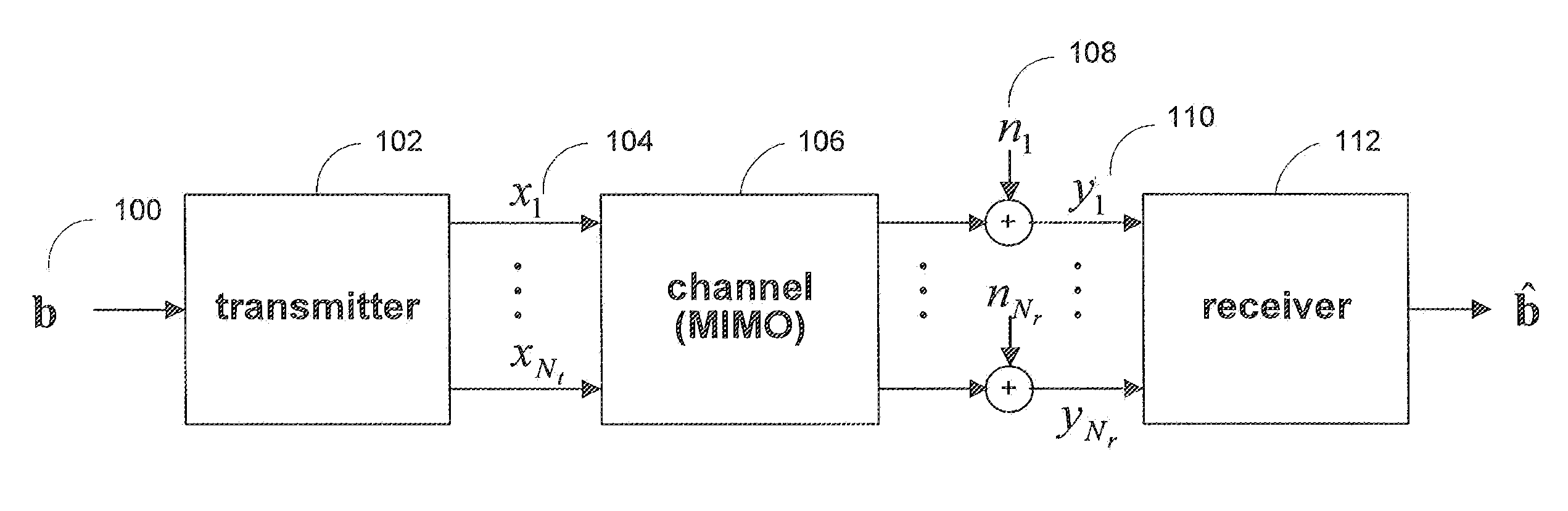

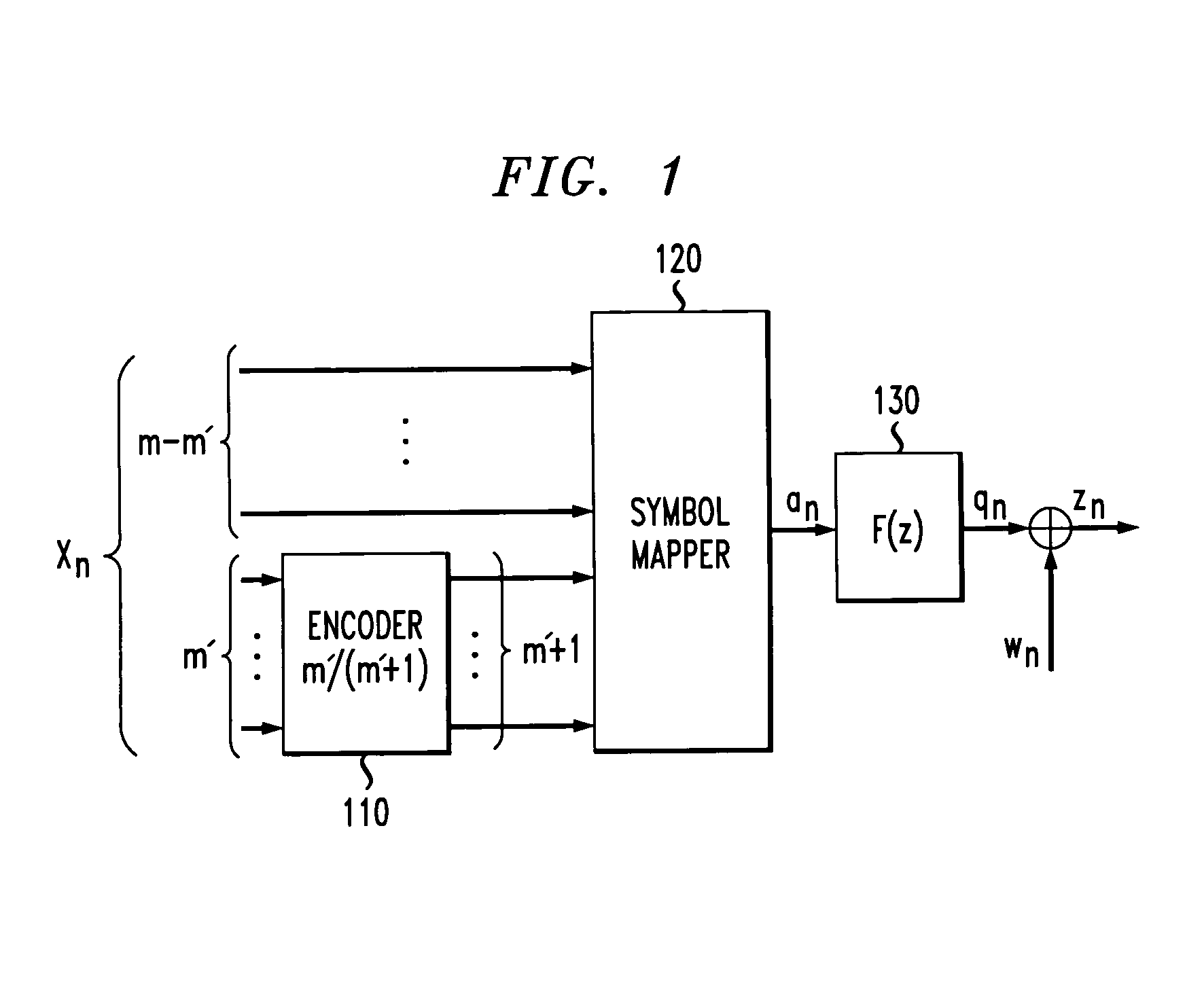

Symbol-level combining for MIMO systems with HARQ and/or repetition coding

ActiveUS20080025427A1Reduce decoding complexityWhitens noiseSpatial transmit diversityModulated-carrier systemsCritical path methodMimo systems

Systems and methods are provided for decoding signal vectors in multiple-input multiple-output (MIMO) systems, where the receiver has received one or more signal vectors from the same transmitted vector. The symbols of the received signal vectors are combined, forming a combined received signal vector that may be treated as a single received signal vector. The combined signal vector is then decoded using a maximum-likelihood decoder. In some embodiments, the combined received signal vector may be processed prior to decoding. Systems and methods are also provided for computing soft information from a combined signal vector based on a decoding metric. Computationally intensive calculations can be extracted from the critical path and implemented in preprocessors and / or postprocessors.

Owner:NXP USA INC

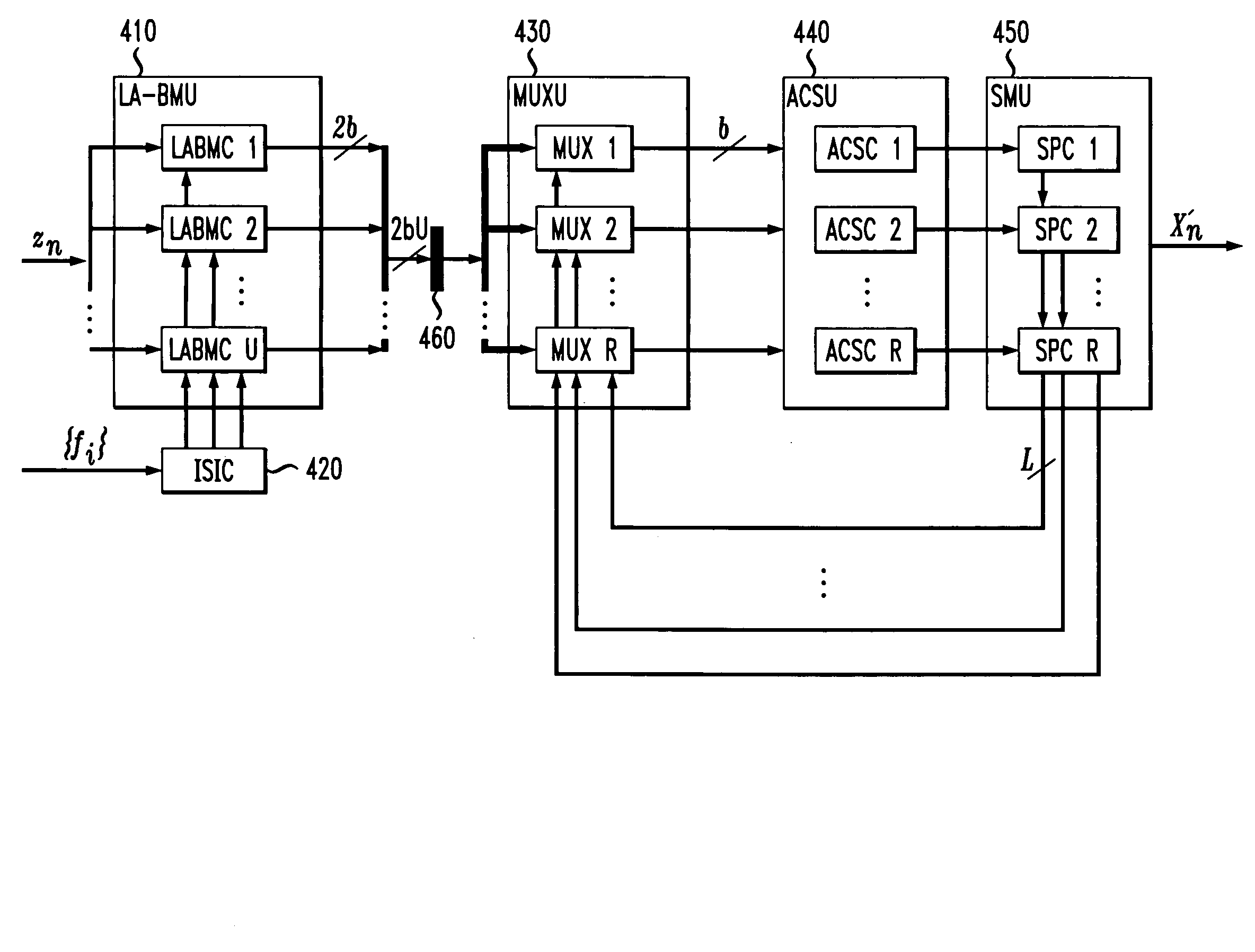

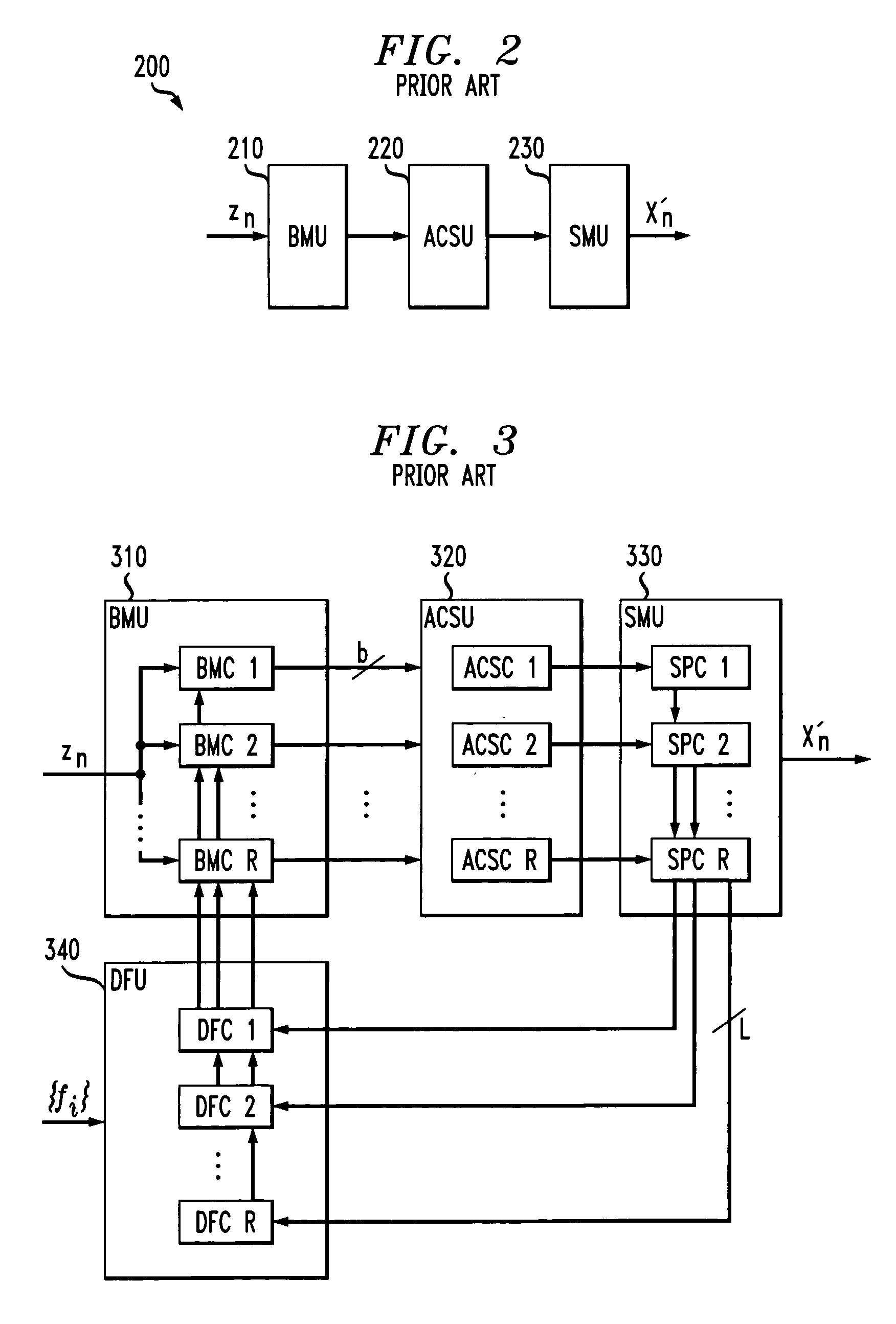

Method and apparatus for shortening the critical path of reduced complexity sequence estimation techniques

InactiveUS6999521B1Reduce computing loadReduce complexityData representation error detection/correctionOther decoding techniquesMultiplexerPrecomputation

A method and apparatus are disclosed for improving the processing time of reduced complexity sequence estimation techniques, such as reduced state sequence estimation. Precomputing the branch metrics for all possible symbol combinations in the channel memory makes it possible to remove the branch metrics unit and decision-feedback unit from the feedback loop, thereby reducing the critical path. A set of multiplexers select the appropriate branch metrics based on the survivor symbols in the corresponding survivor path cells. The computational load of the precomputations is reduced for multi-dimensional trellis codes by precomputing each dimension of the multi-dimensional trellis code separately. A hybrid survivor memory architecture is also disclosed for a RSSE for a channel having a channel memory of length L, where the survivors corresponding to the L past decoding cycles are stored in a register exchange architecture (REA), and survivors corresponding to later decoding cycles are stored in a trace-back architecture (TBA) or REA.

Owner:WSOU INVESTMENTS LLC +1

Changing of operating voltage in semiconductor integrated circuit

InactiveUS7392413B2Avoid failureEnergy efficient ICTVolume/mass flow measurementEngineeringCritical path method

A semiconductor integrated circuit includes a module configured to operate based on a clock signal, a voltage controlling unit configured to change a power supply voltage supplied to the module, a clock generating unit configured to supply the clock signal to the module, and a test circuit configured to operate at the power supply voltage based on the clock signal to emulate a delay of a critical path provided in the module, thereby testing whether the module properly operates at the power supply voltage, wherein the clock generating unit supplies a different signal, in place of the clock signal, to the module while the voltage controlling unit is changing the power supply voltage.

Owner:SOCIONEXT INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com