Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

225 results about "Programmable hardware" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

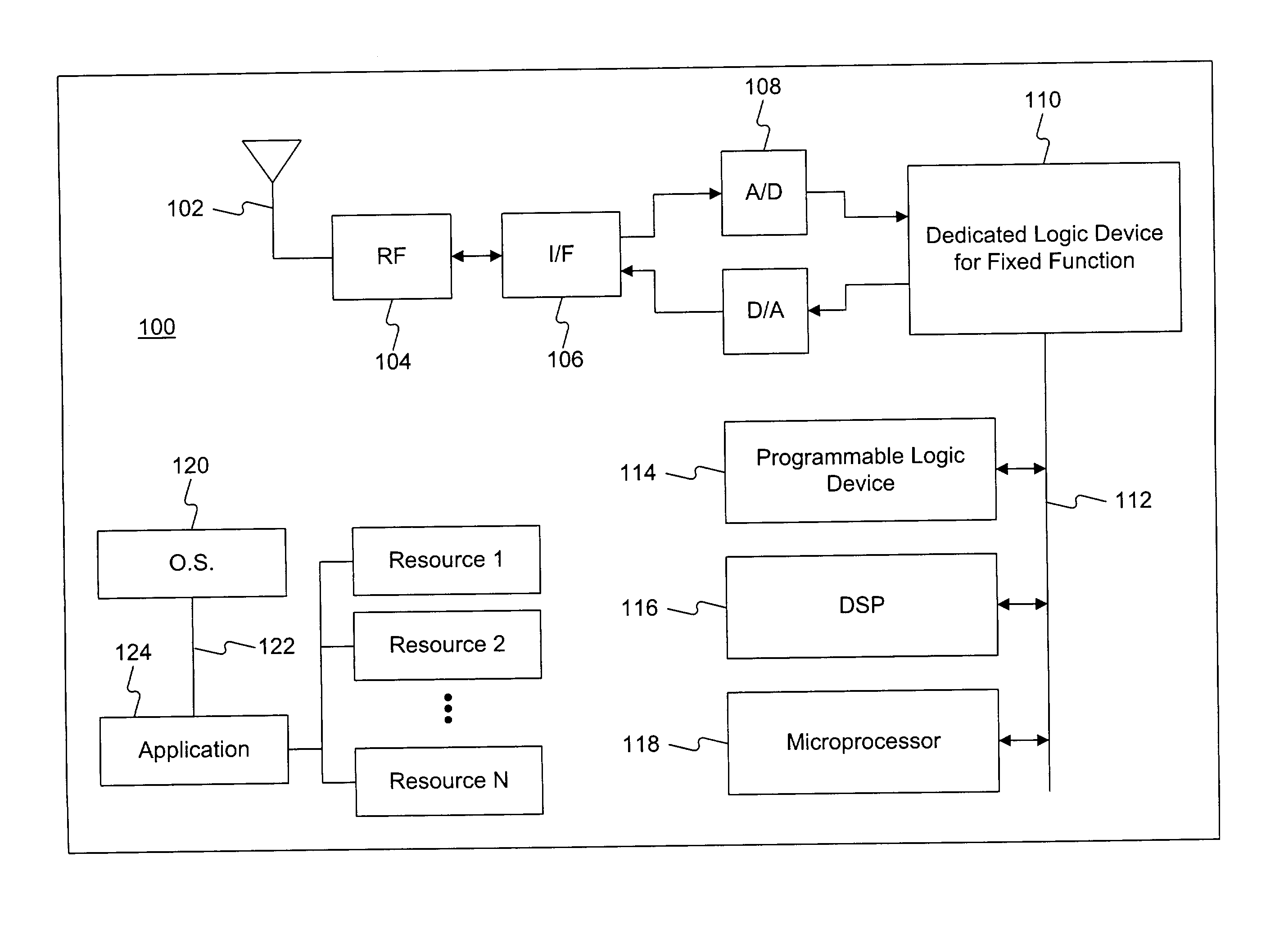

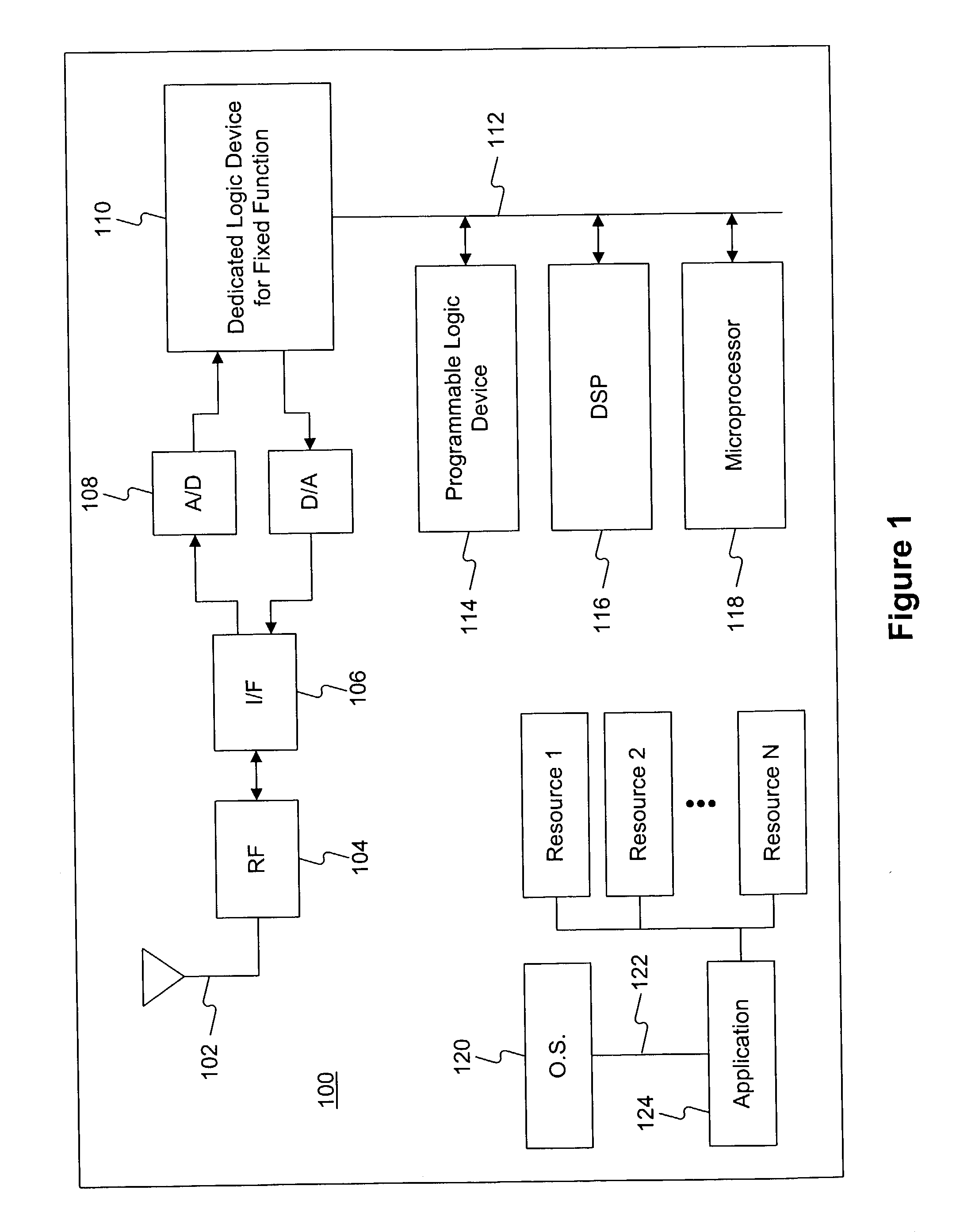

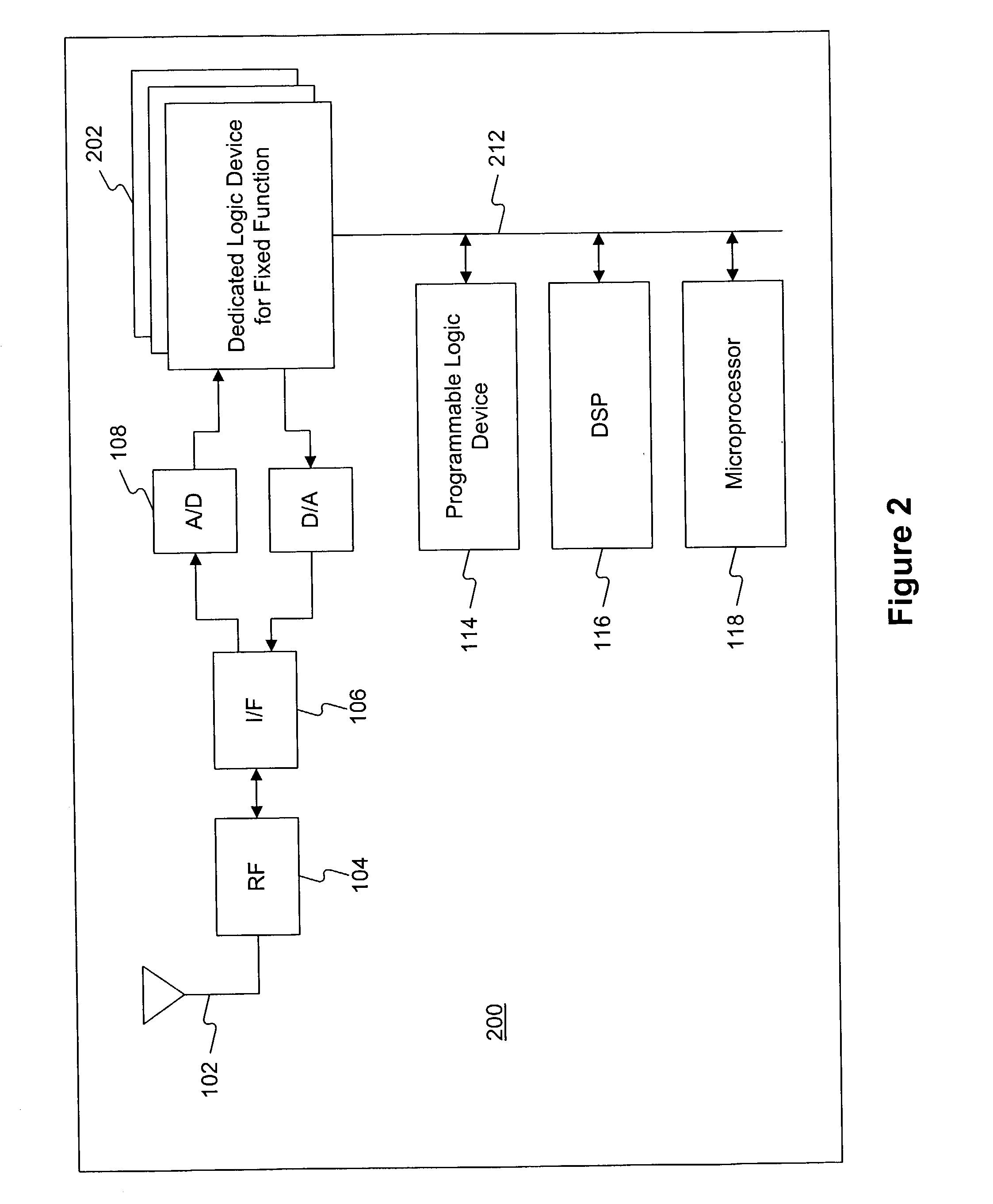

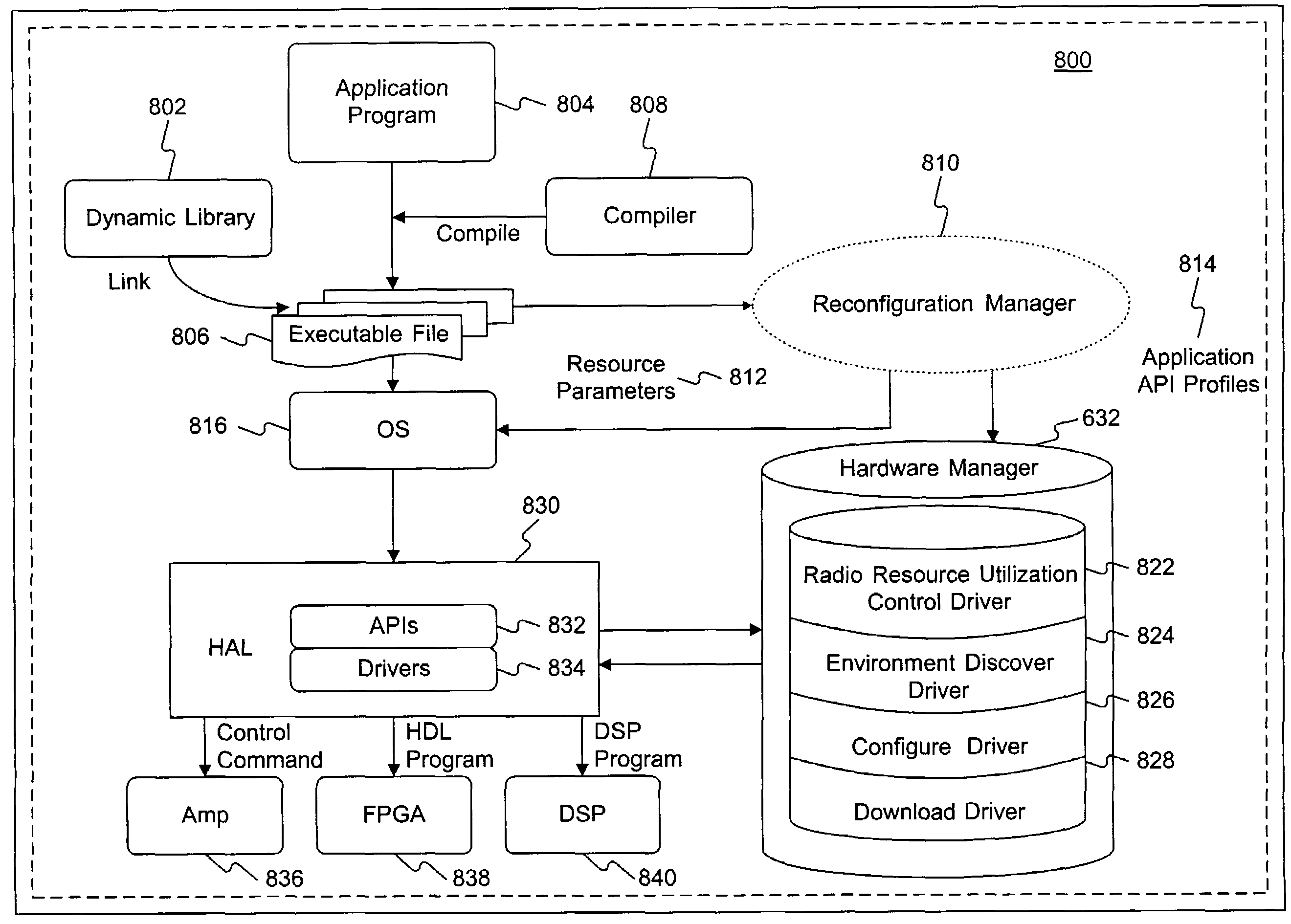

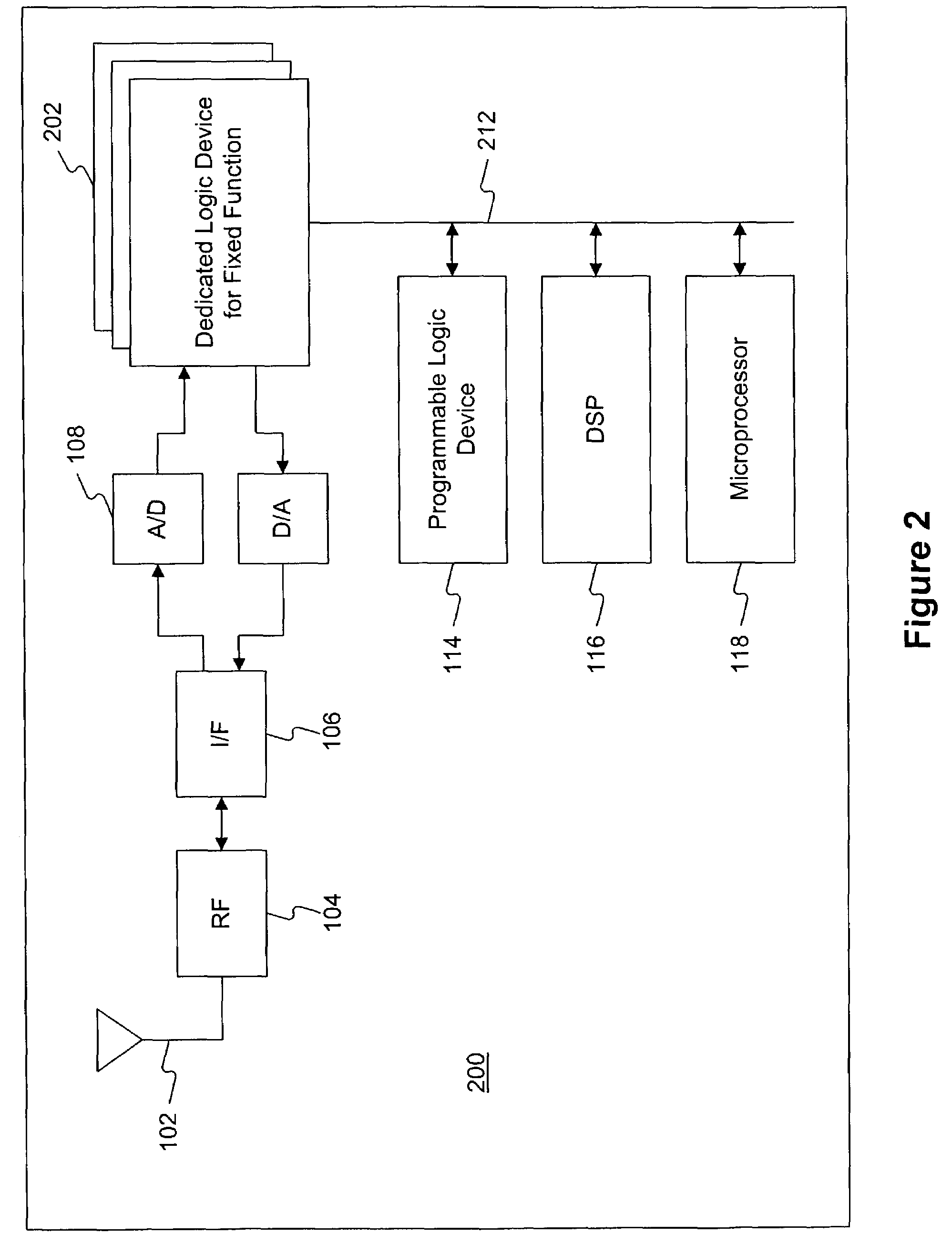

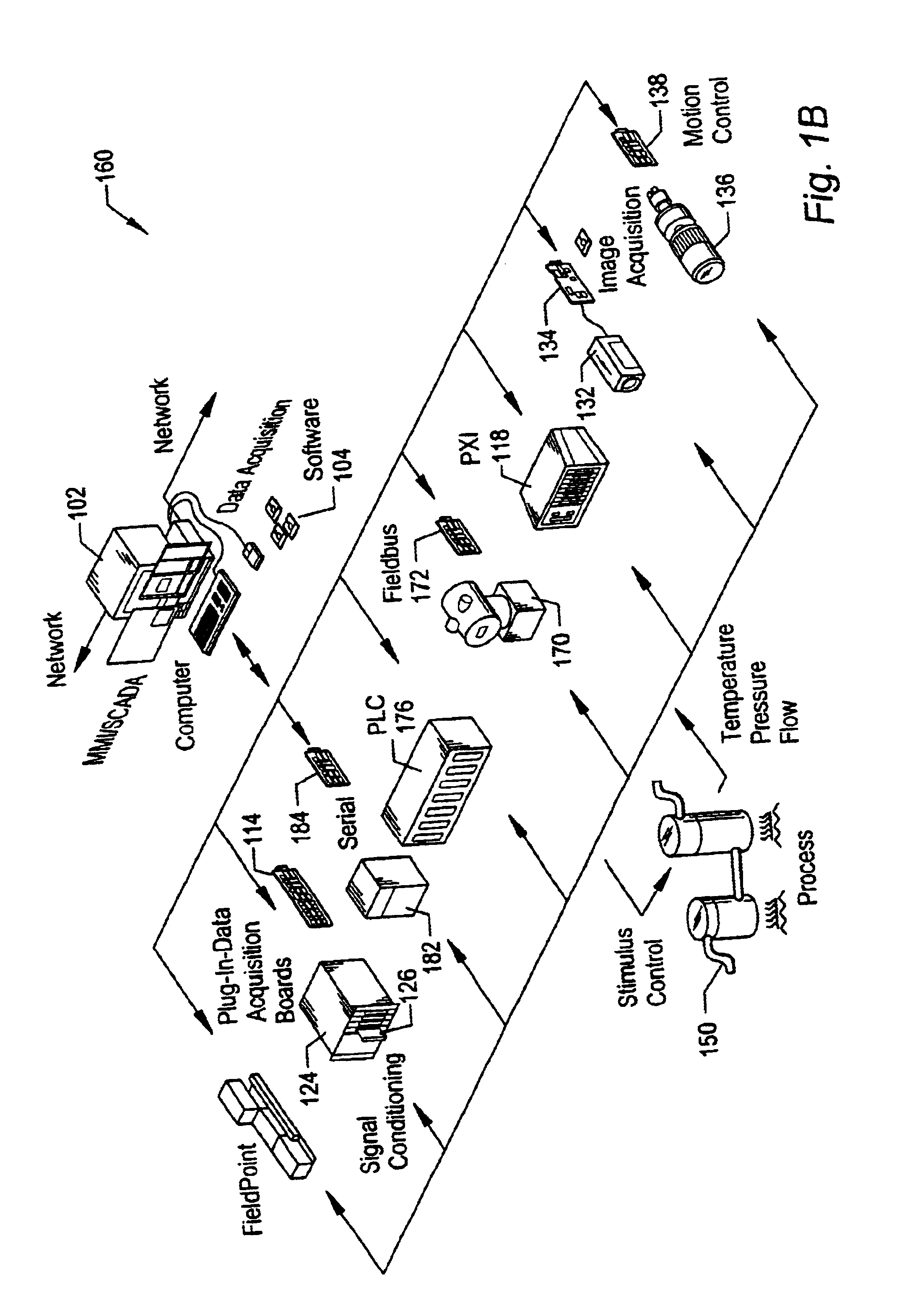

Software defined radio (SDR) architecture for wireless digital communication systems

InactiveUS20030050055A1Special service for subscribersDigital computer detailsSoftware define radioCommunications system

A system and method for providing one hardware platform to implement multiple wireless communication standards, services and applications. The kernel oriented macro based software defined radio (SDR) architecture provides a configurable and programmable hardware platform to implement multiple wireless communication standards, services and applications.

Owner:MEDIATEK INC

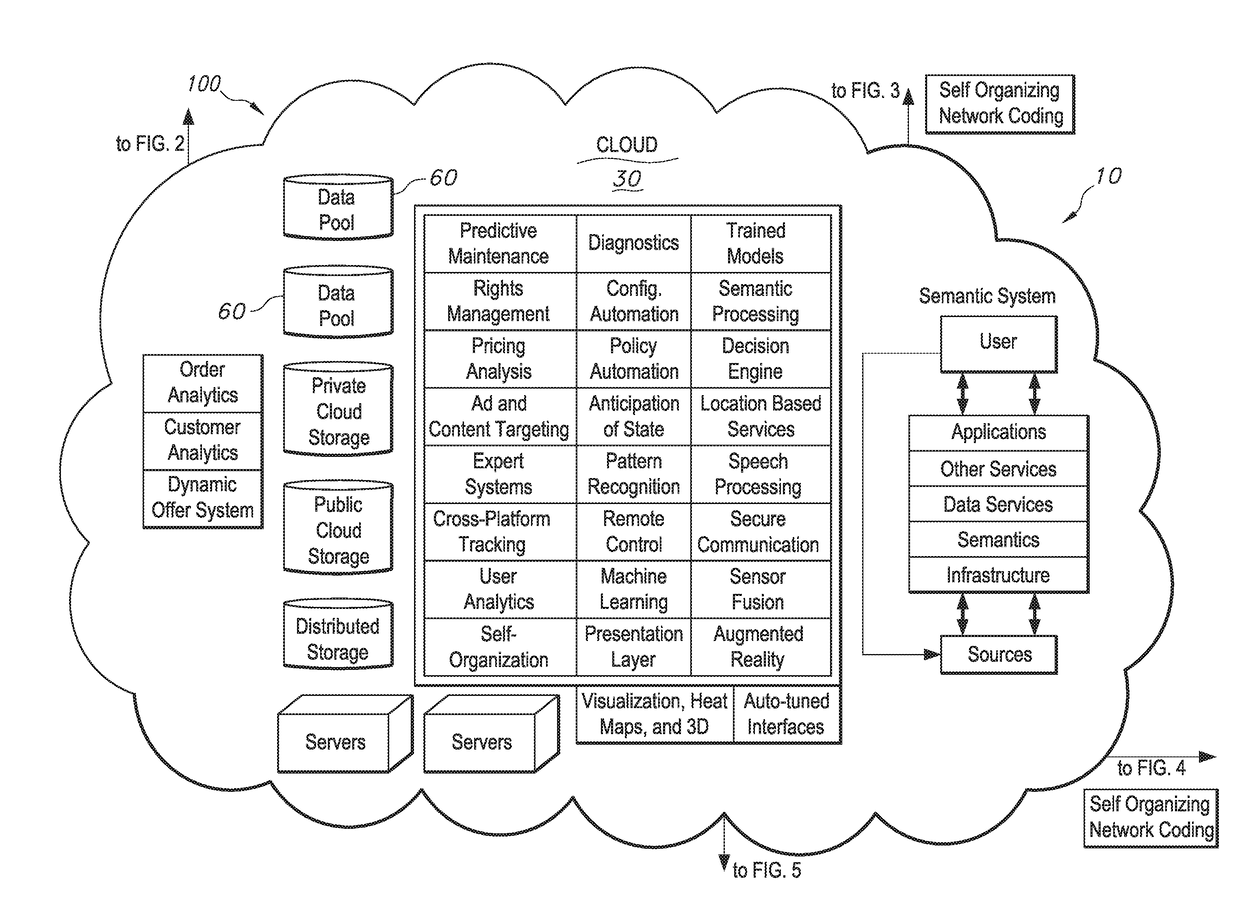

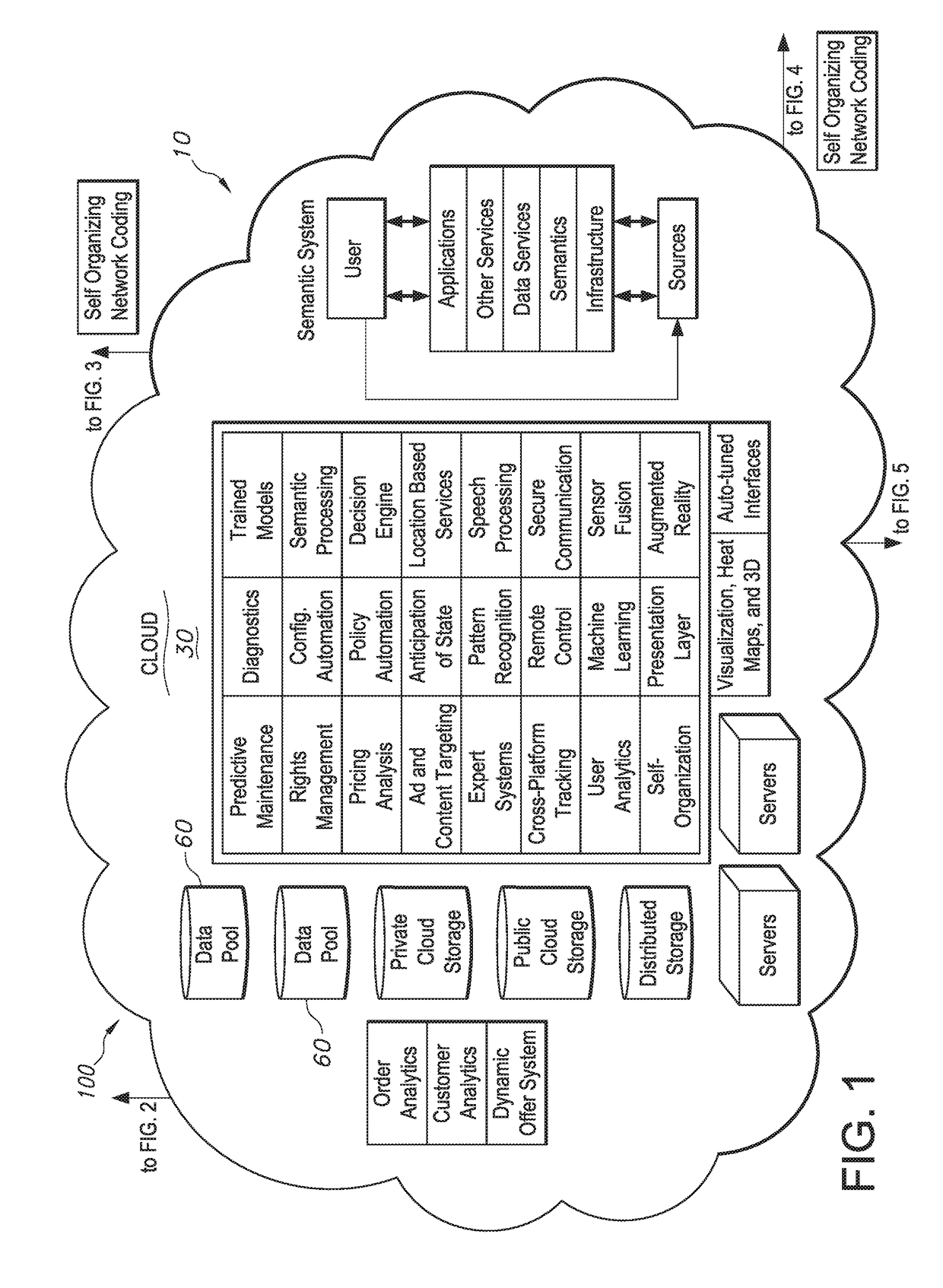

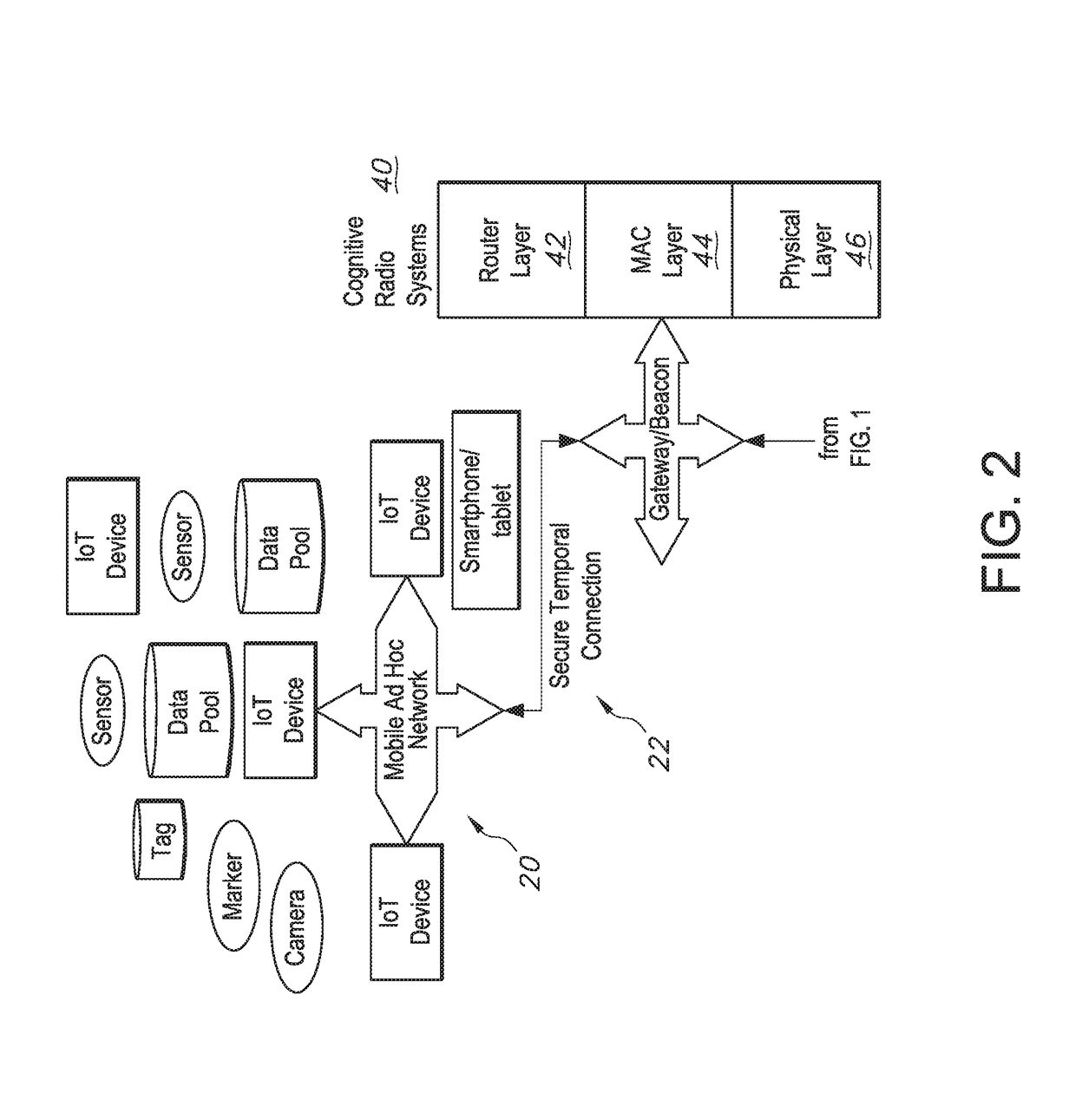

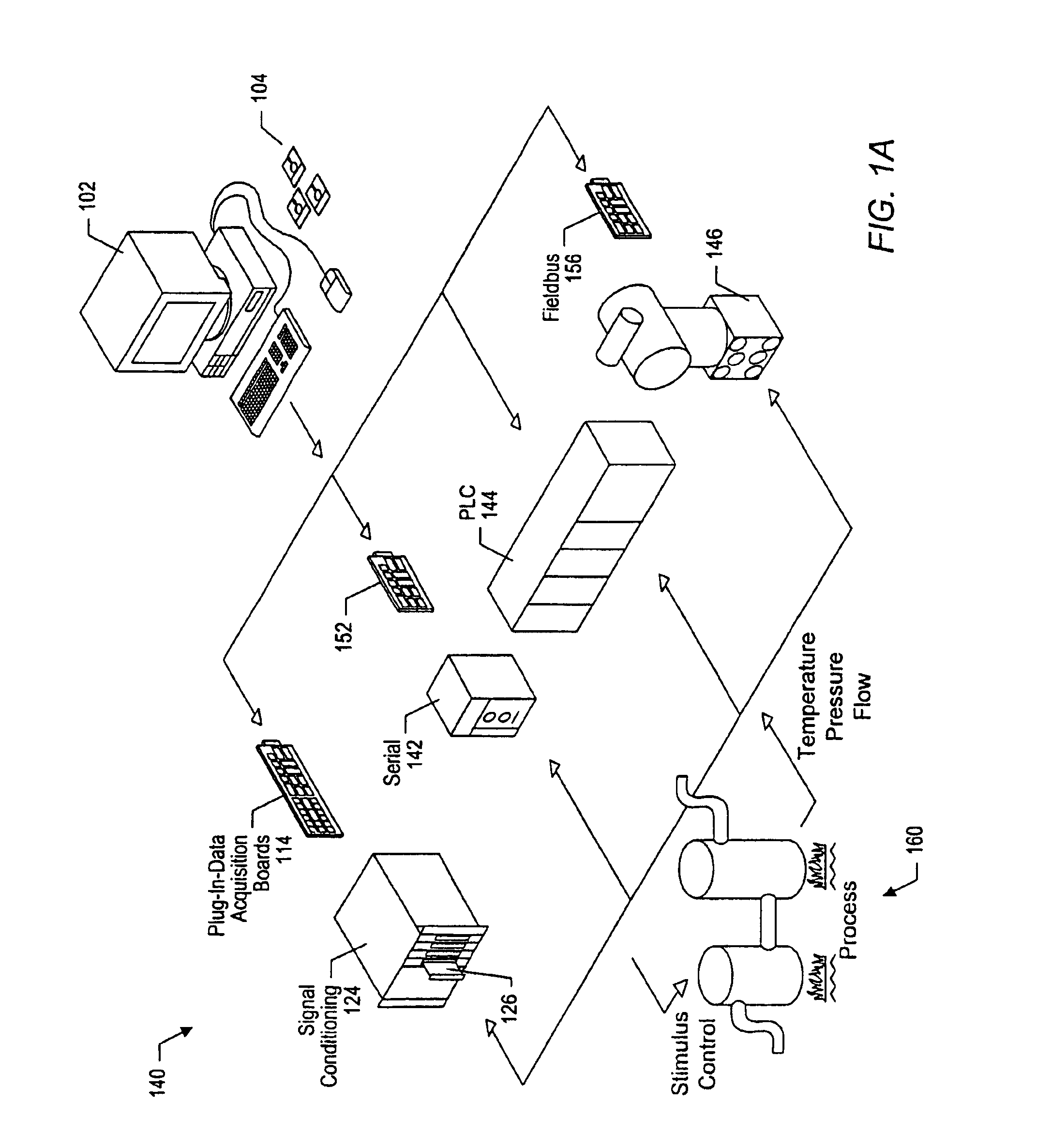

Methods and systems for the industrial internet of things

ActiveUS20180188704A1Improve signal-to-noise ratioLow sampling rateVibration measurement in solidsMachine part testingData streamData acquisition

The system generally includes a crosspoint switch in the local data collection system having multiple inputs and multiple outputs including a first input connected to the first sensor and a second input connected to the second sensor. The multiple outputs include a first output and a second output configured to be switchable between a condition in which the first output is configured to switch between delivery of the first sensor signal and the second sensor signal and a condition in which there is simultaneous delivery of the first sensor signal from the first output and the second sensor signal from the second output. Each of multiple inputs is configured to be individually assigned to any of the multiple outputs. Unassigned outputs are configured to be switched off producing a high-impedance state. The local data collection system includes multiple multiplexing units and multiple data acquisition units receiving multiple data streams from multiple machines in the industrial environment. The local data collection system includes distributed complex programmable hardware device (CPLD) chips each dedicated to a data bus for logic control of the multiple multiplexing units and the multiple data acquisition units that receive the multiple data streams from the multiple machines in the industrial environment. The local data collection system is configured to manage data collection bands.

Owner:STRONG FORCE IOT

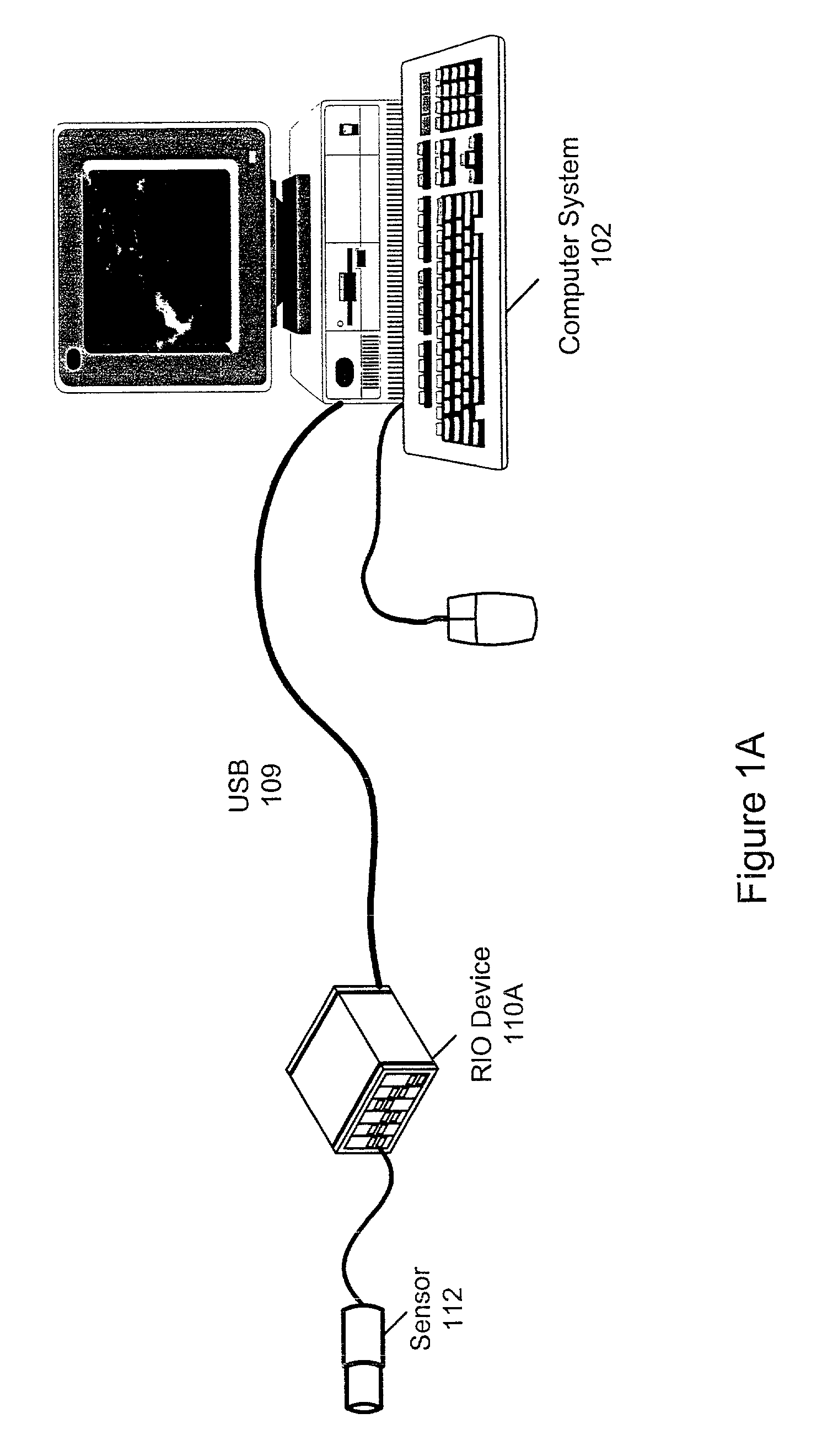

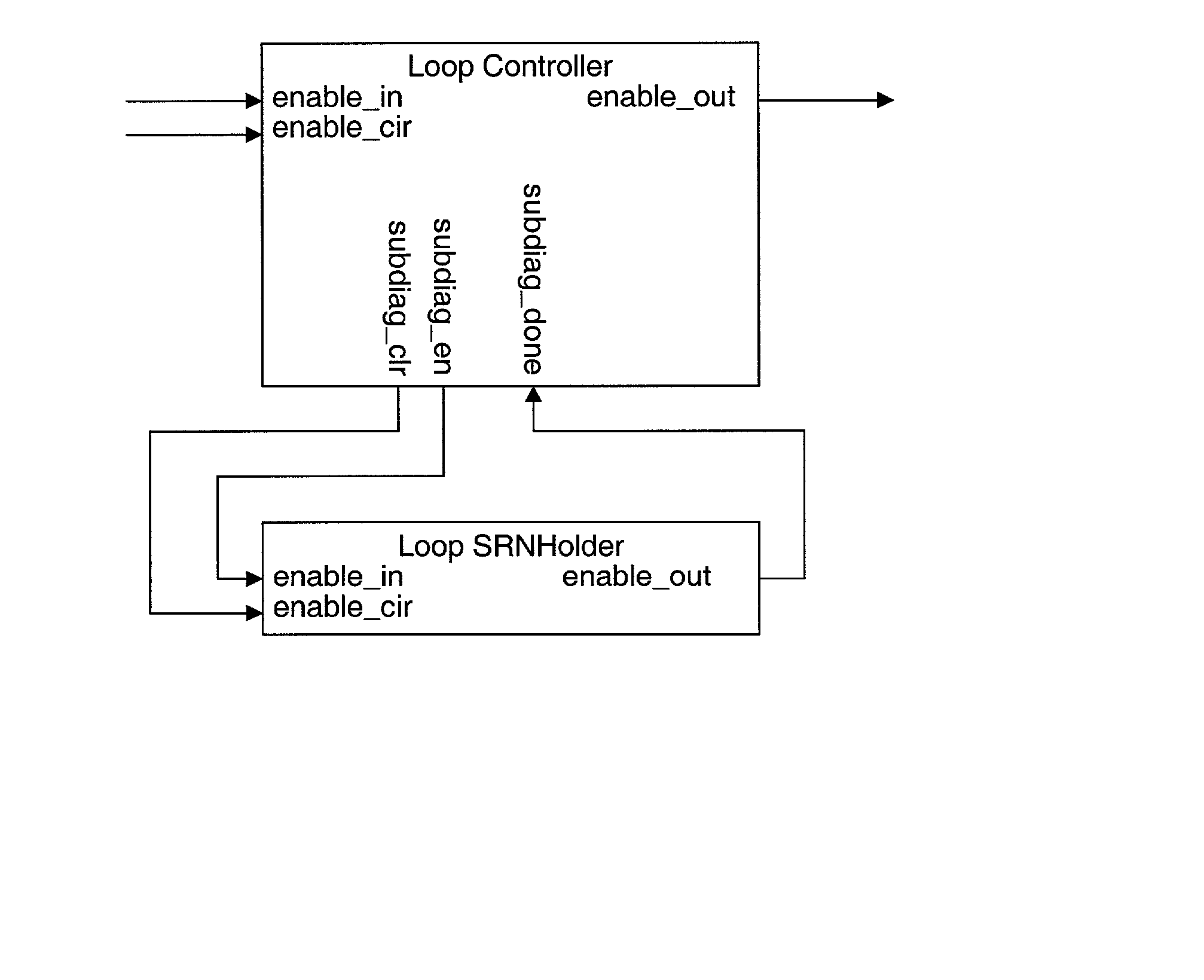

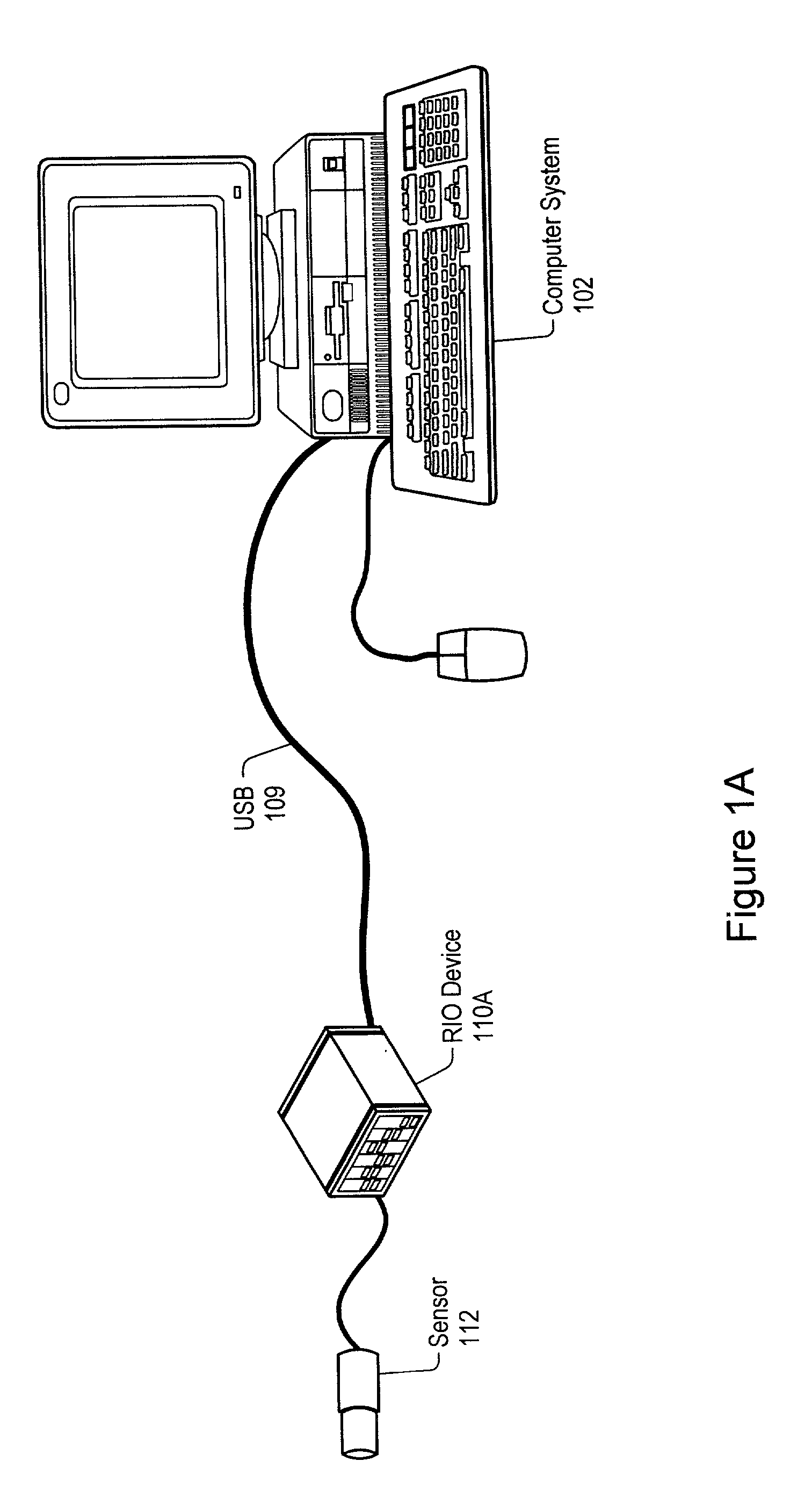

System and method for debugging a software program

InactiveUS20030192032A1Fast and Accurate TestingAccurate and efficient matchingDetecting faulty computer hardwareCAD circuit designComputerized systemProgrammable hardware

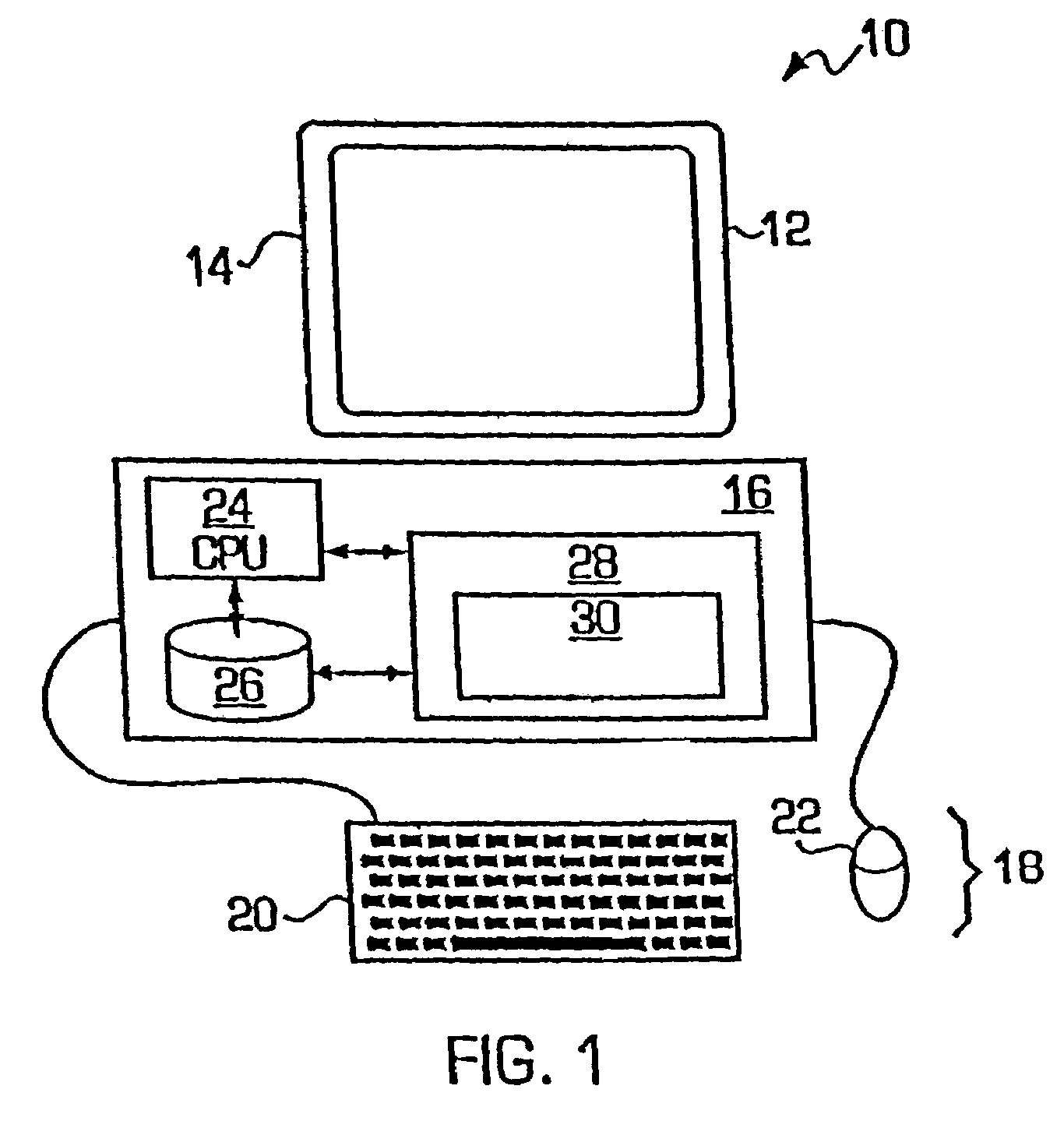

A system and method for debugging a program which is intended to execute on a reconfigurable device. A computer system stores a program that specifies a function, and which is convertible into a hardware configuration program (HCP) and deployable onto a programmable hardware element comprised on the device. The HCP is generated based on the program, specifies a configuration for the programmable hardware element that implements the function, and further specifies usage of one or more fixed hardware resources by the programmable hardware element in performing the function. A test configuration is deployable on the programmable hardware element by a deployment program, where, after deployment, the programmable hardware element provides for communication between the fixed hardware resources and the program. The program is executable by a processor in the computer system, where during execution the program communicates with the one or more fixed hardware resources through the programmable hardware element.

Owner:NATIONAL INSTRUMENTS

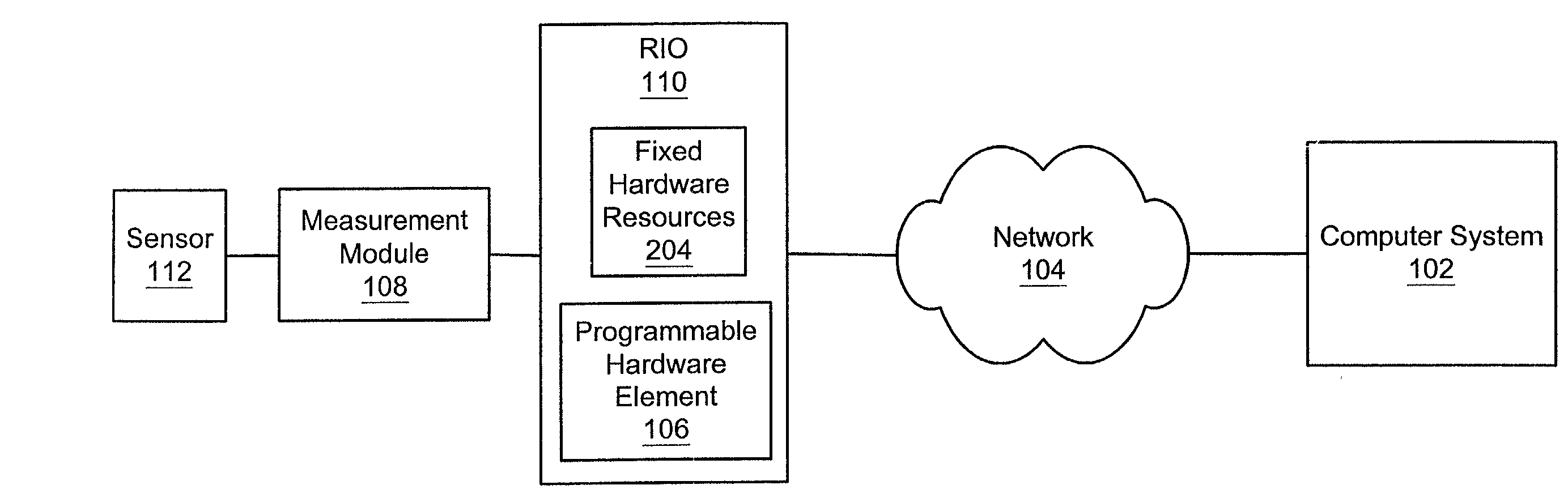

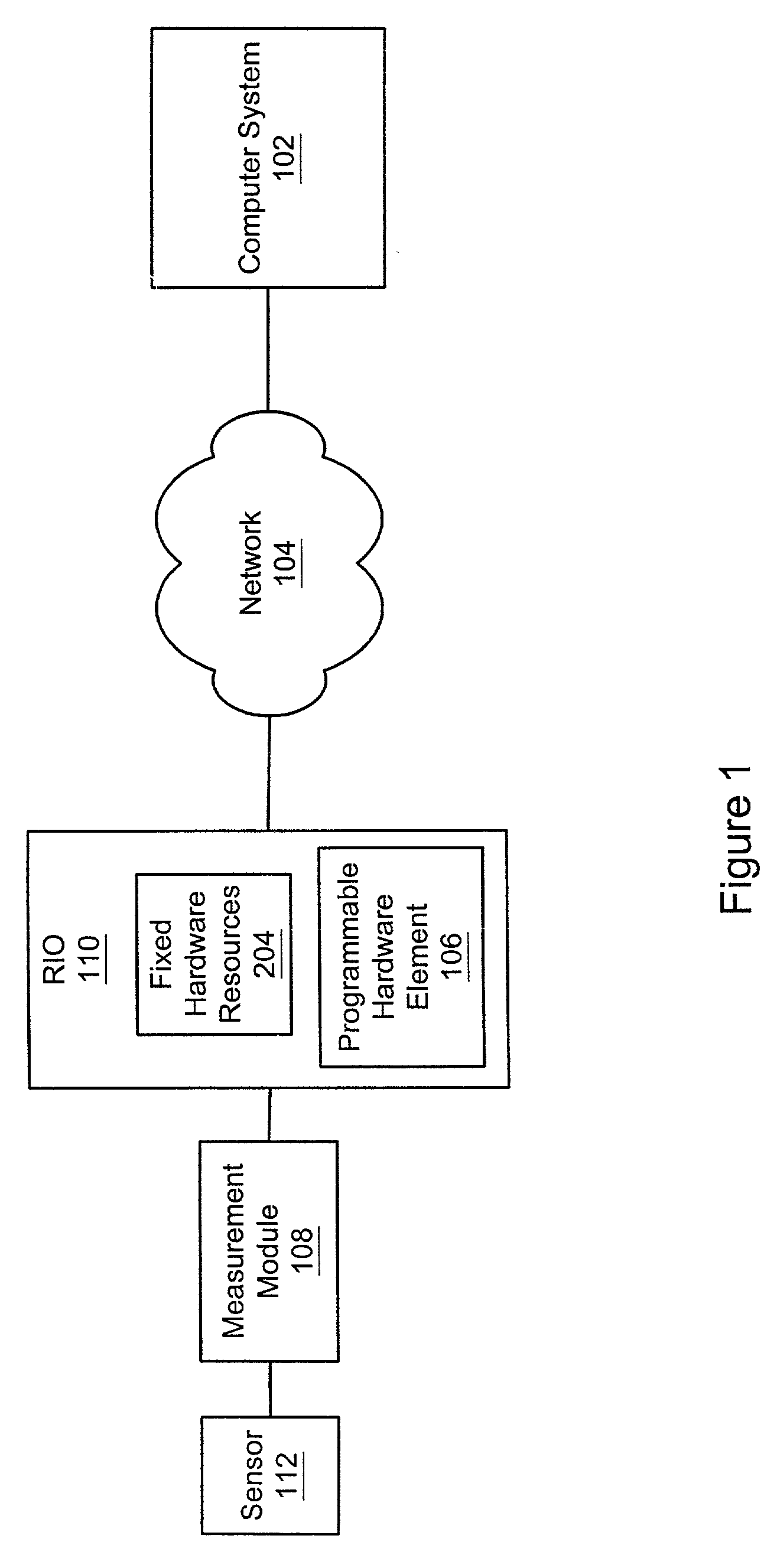

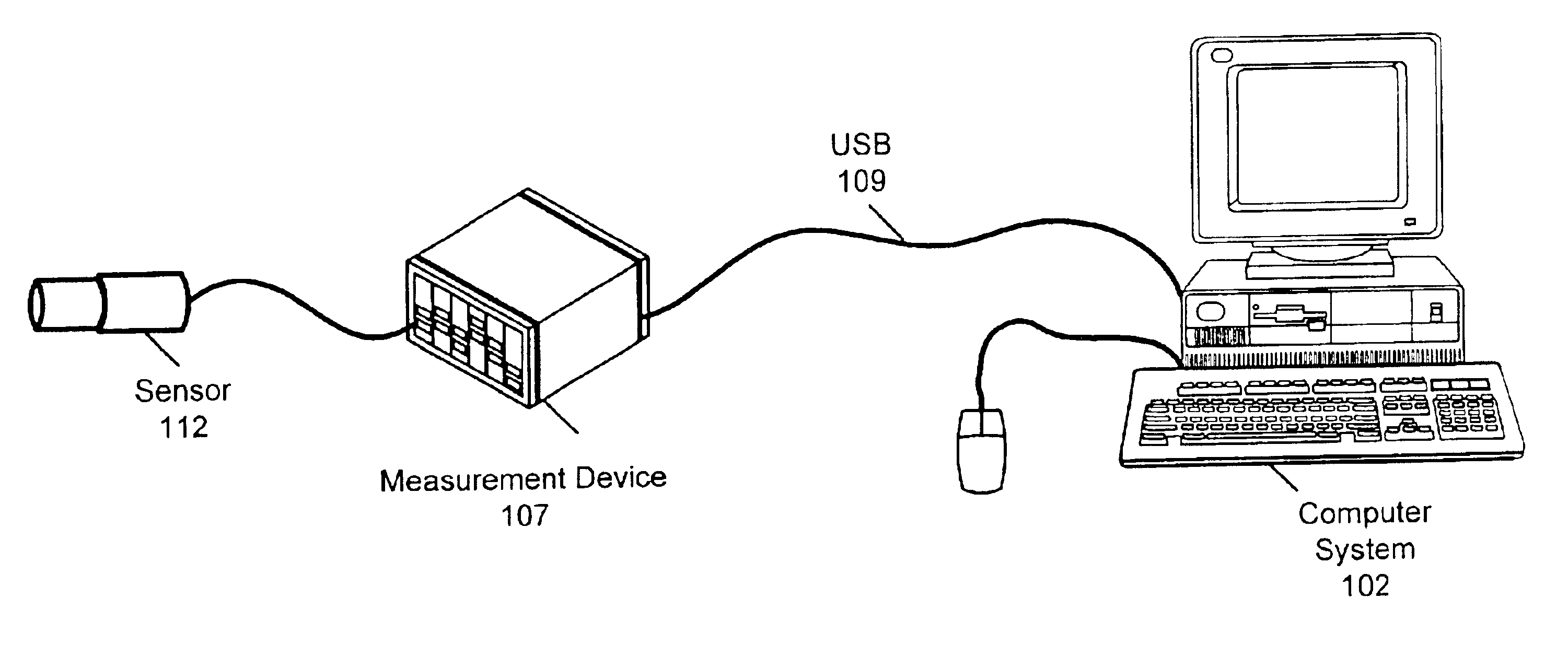

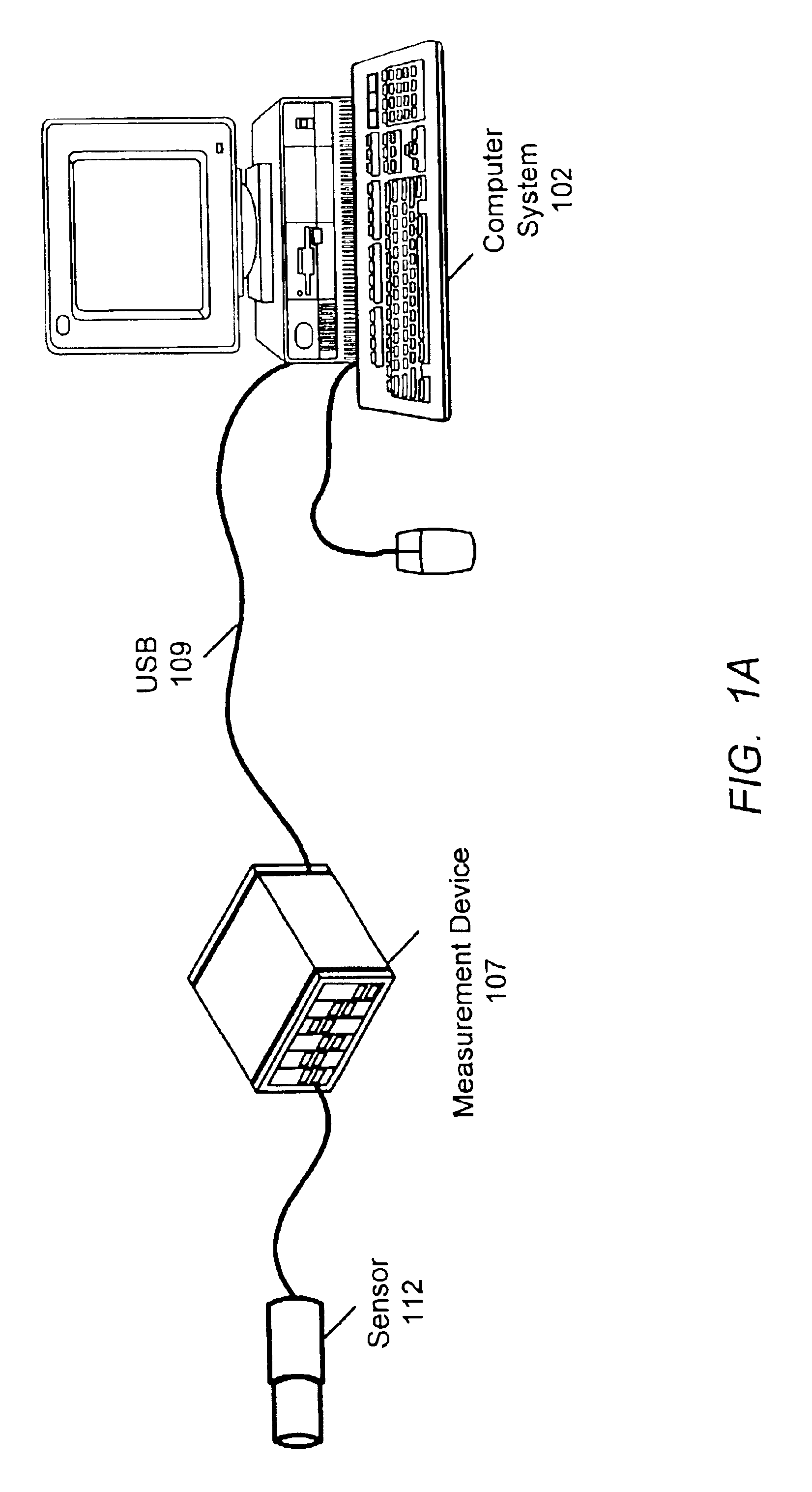

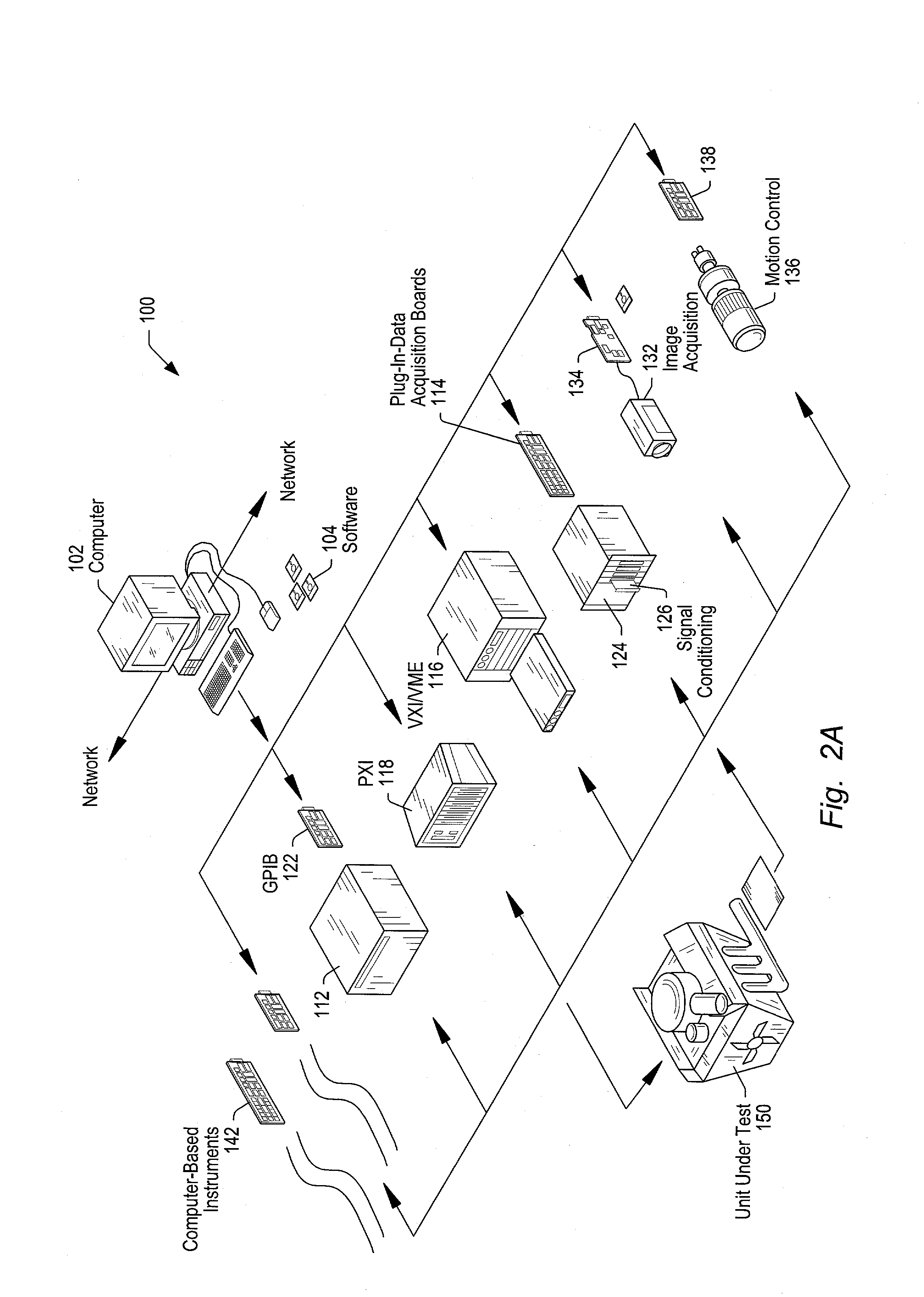

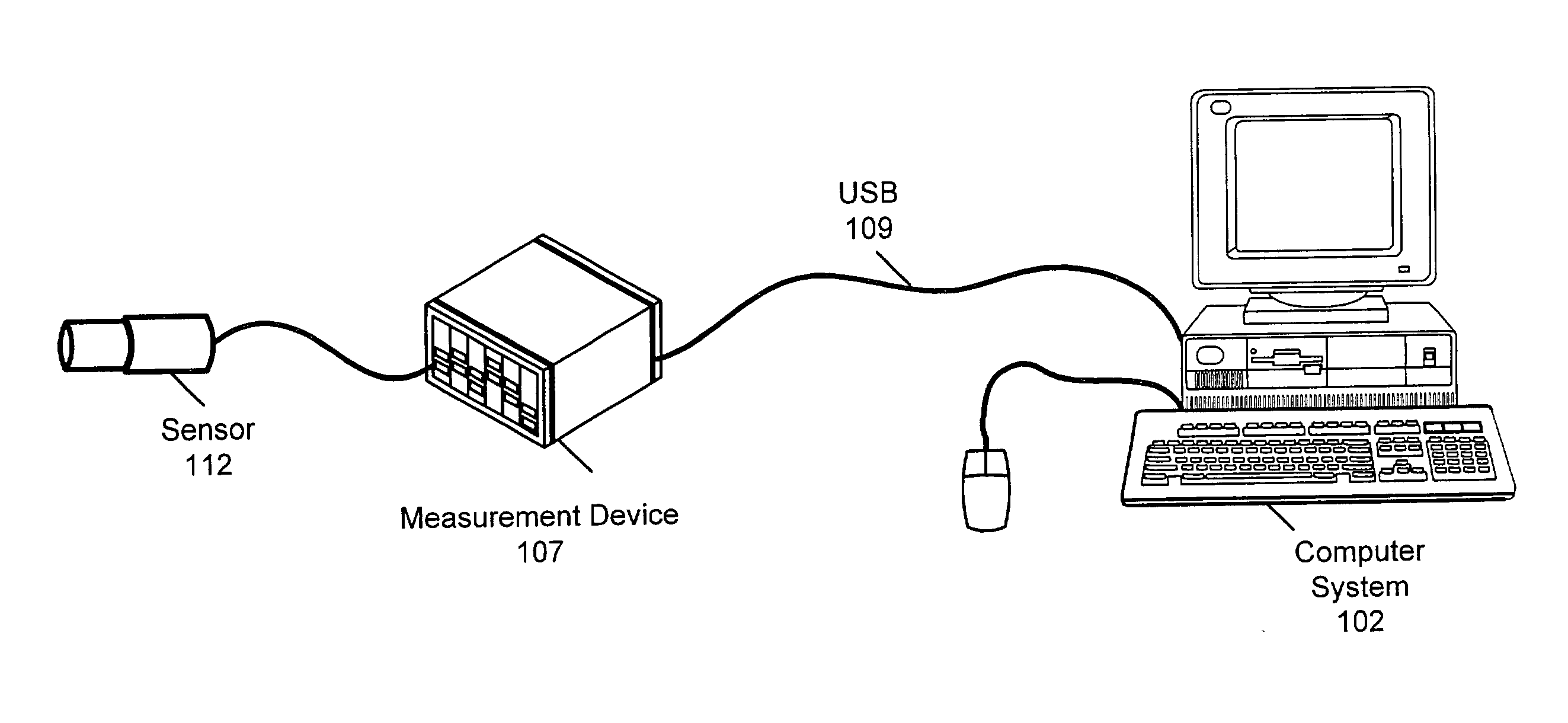

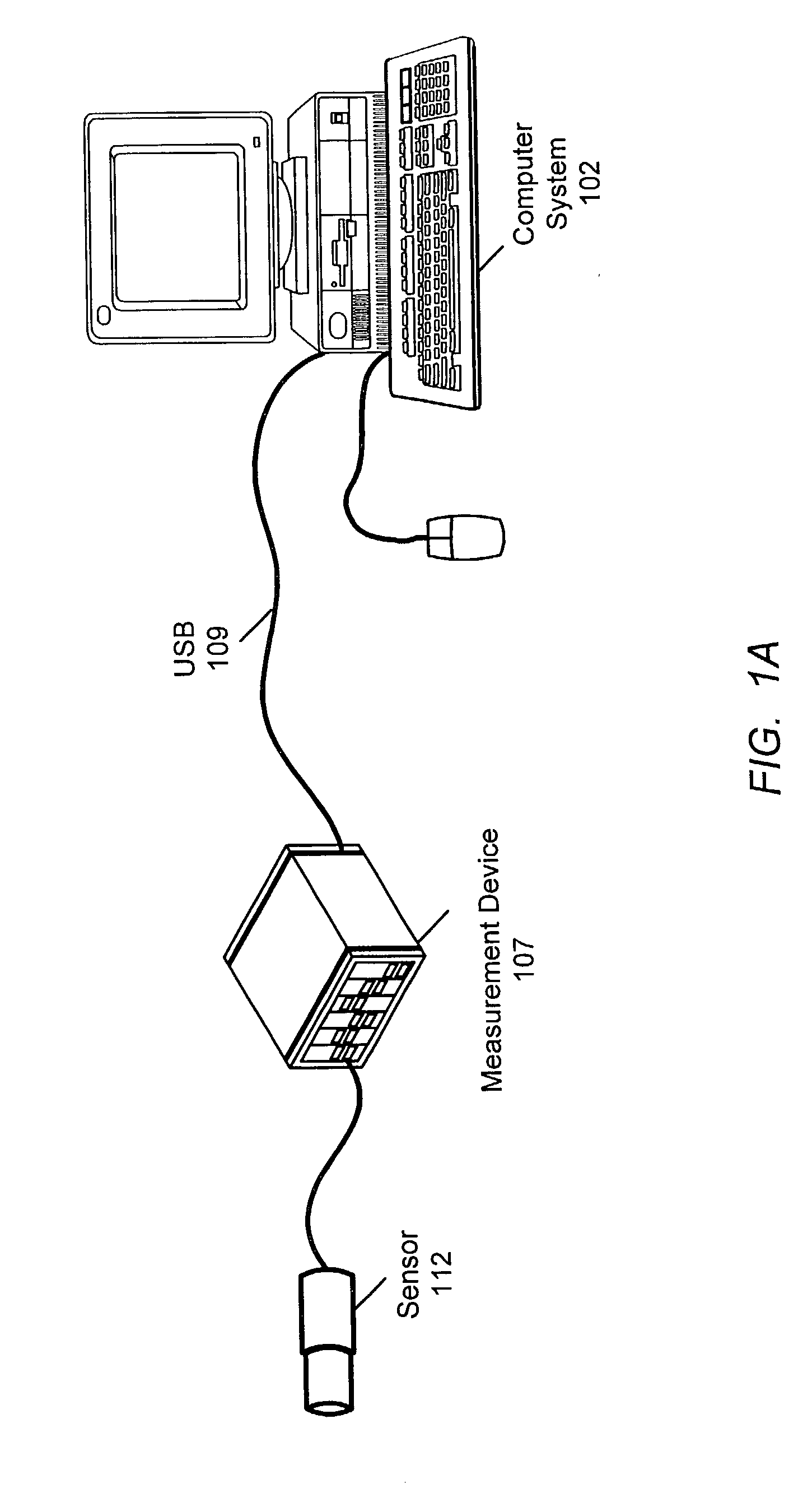

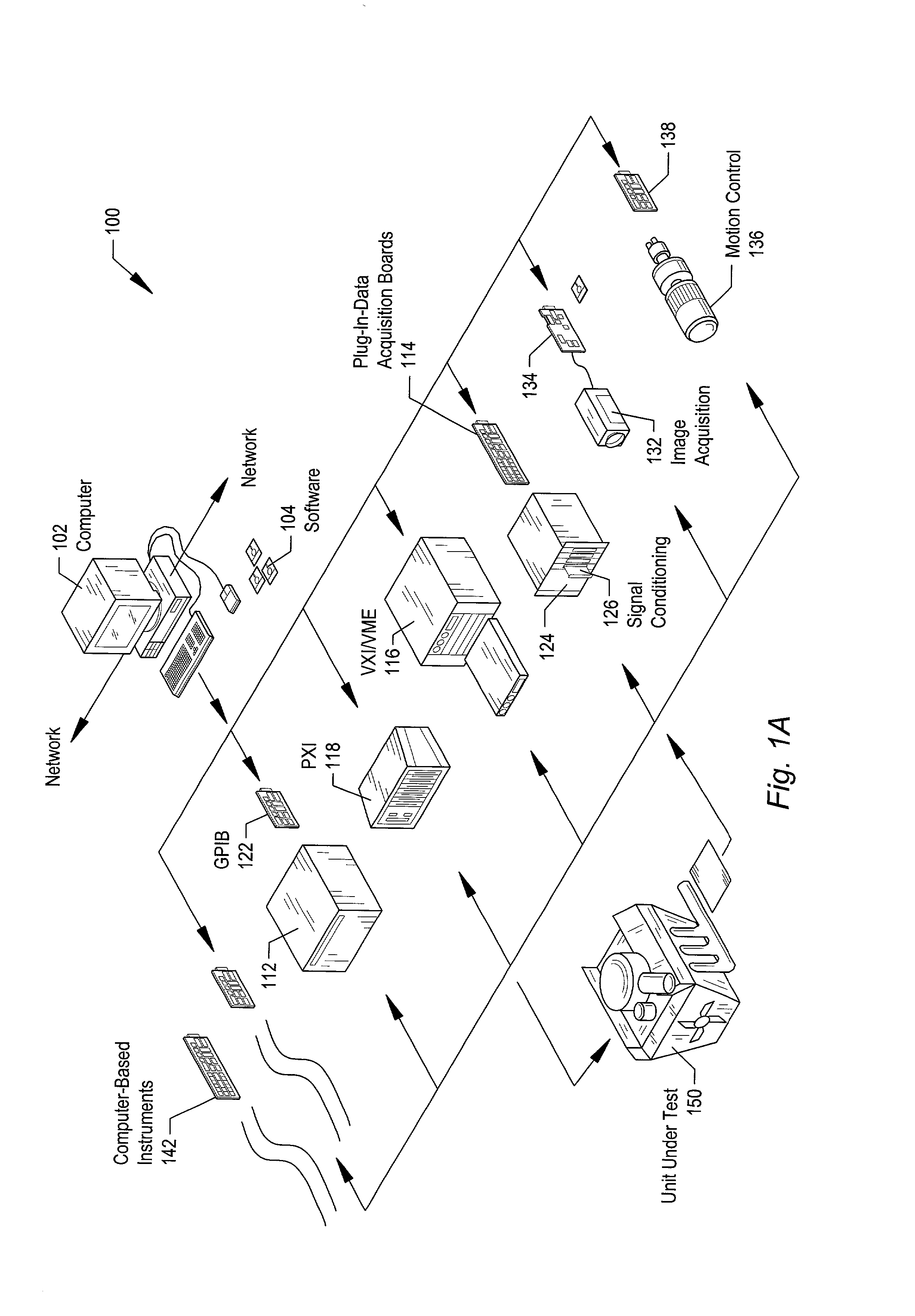

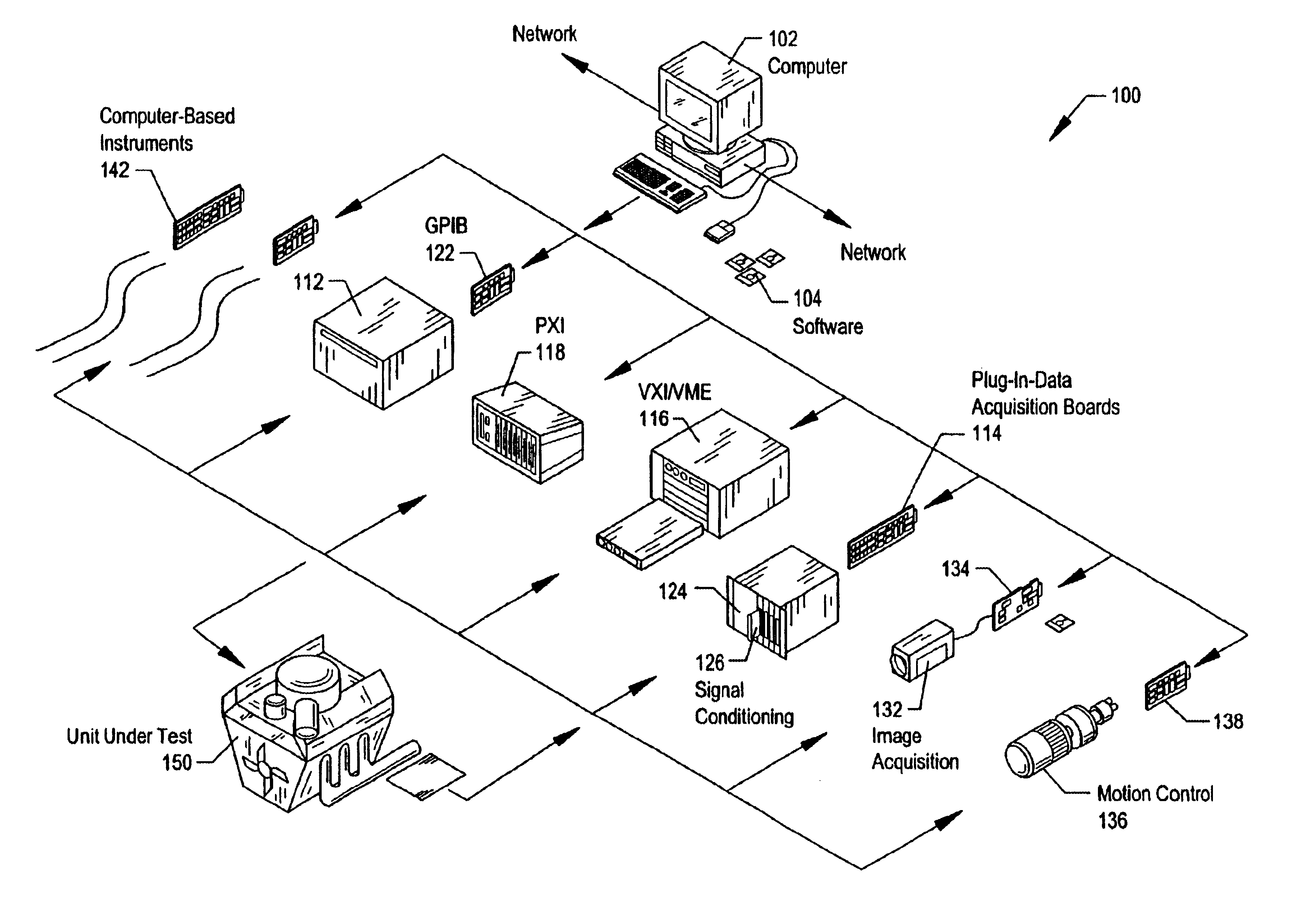

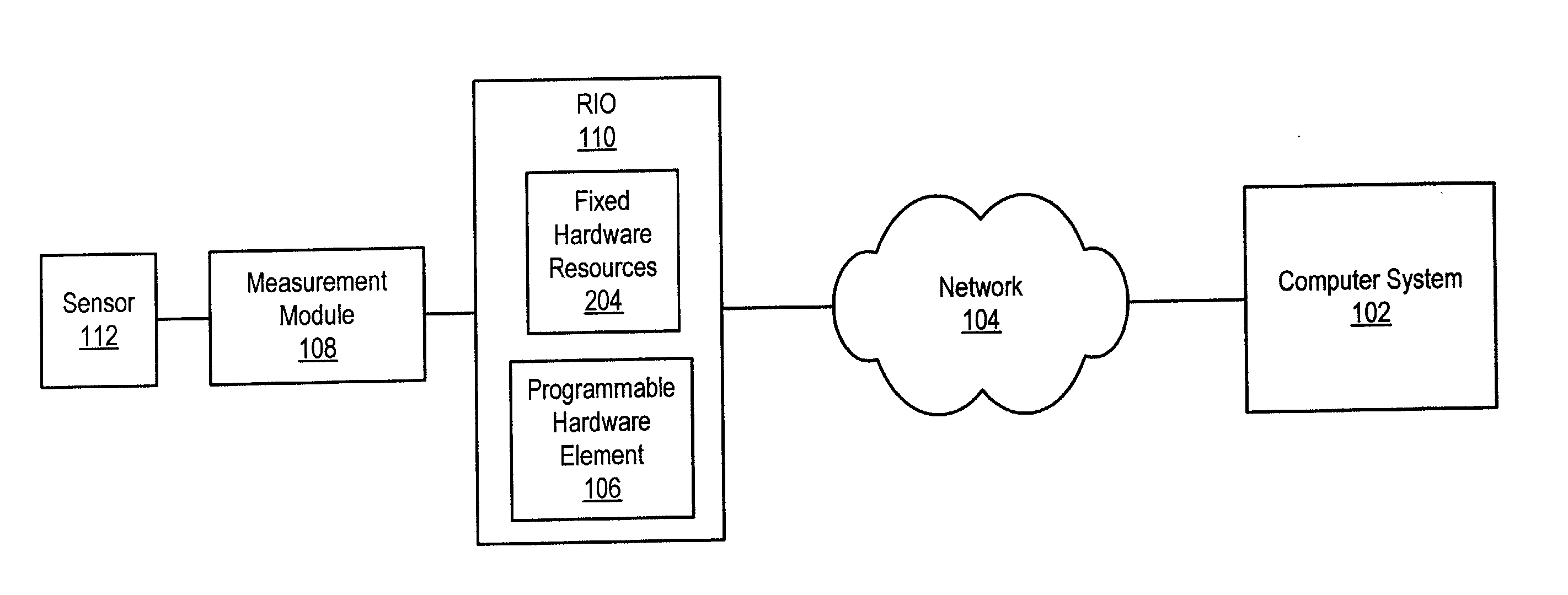

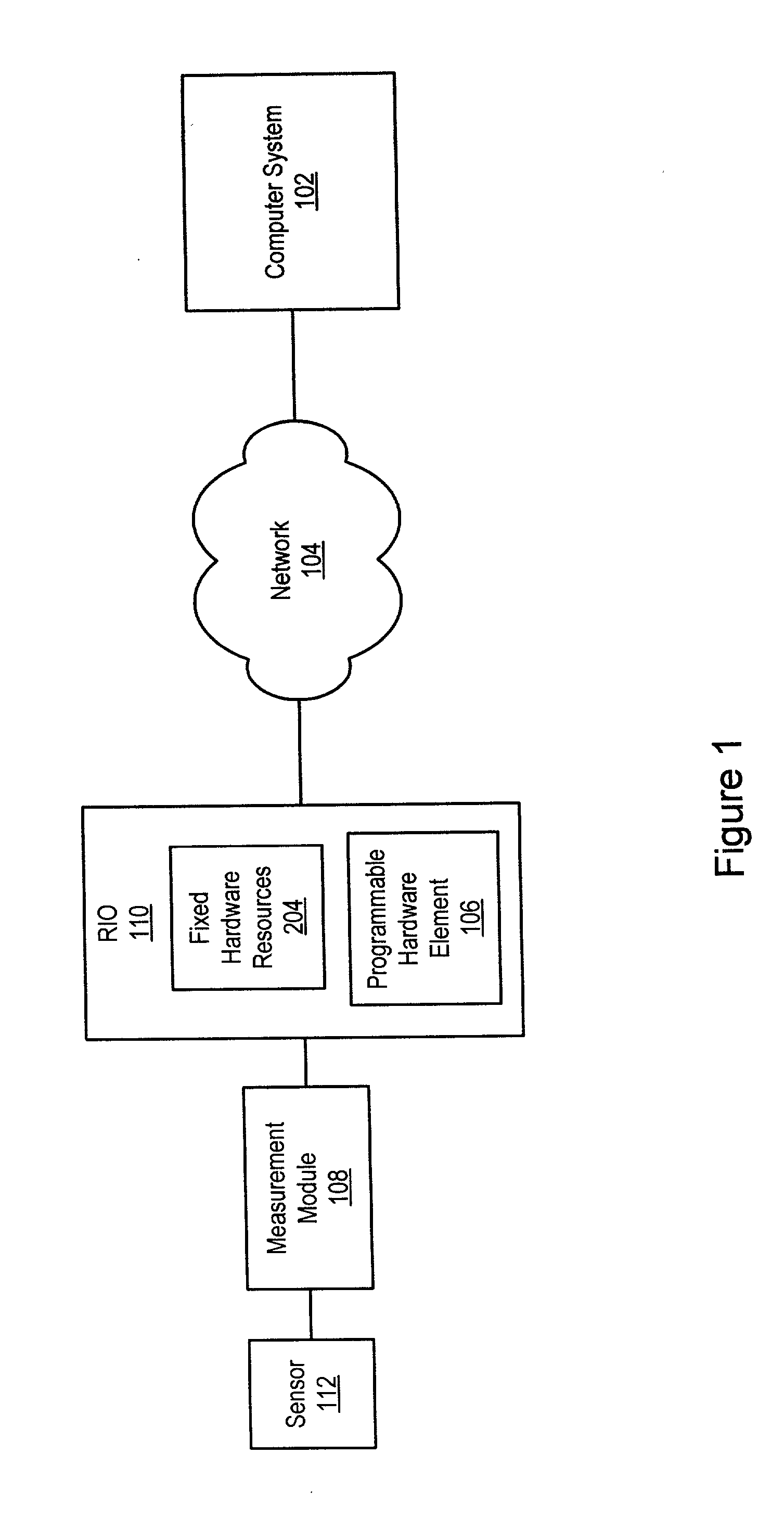

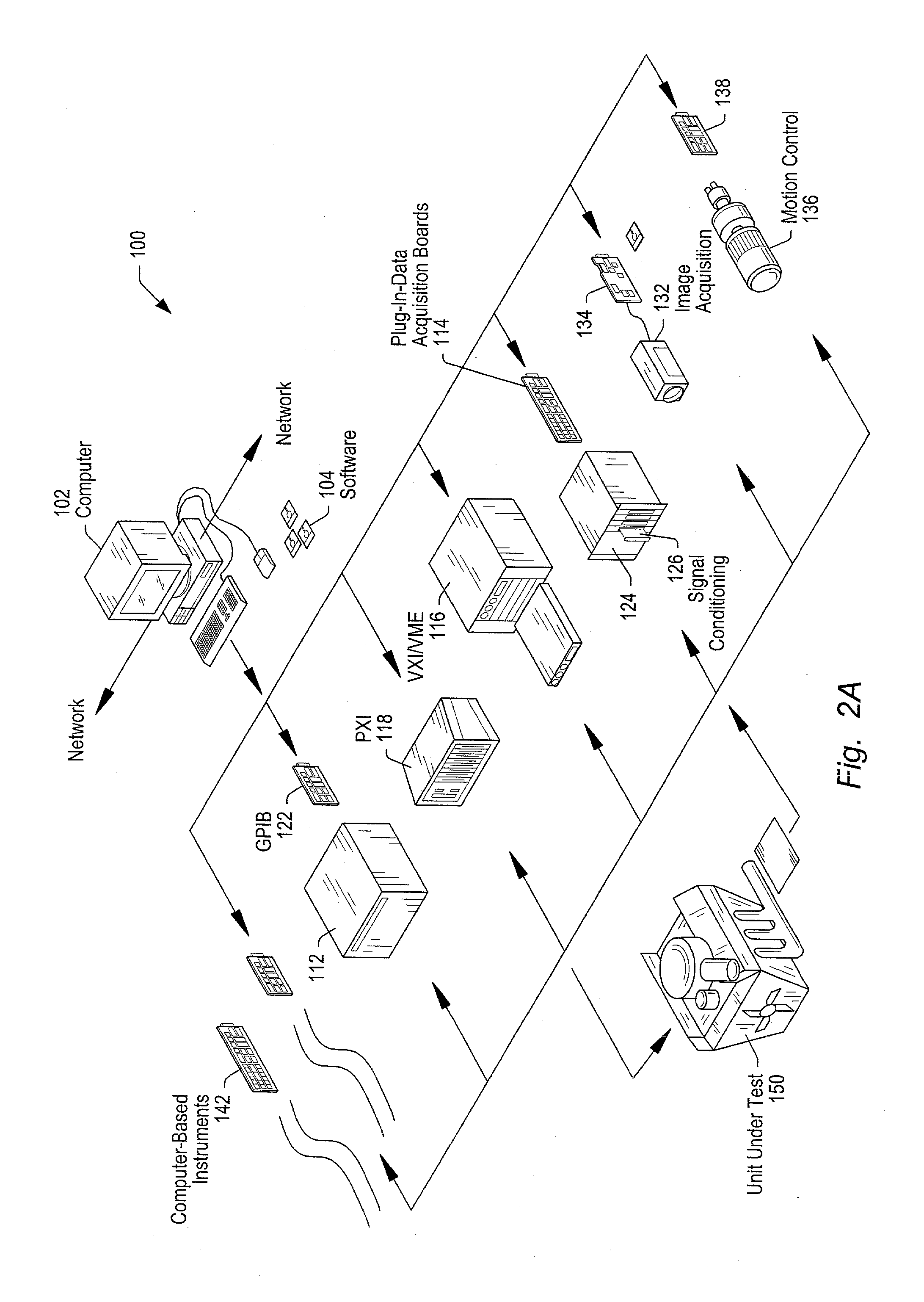

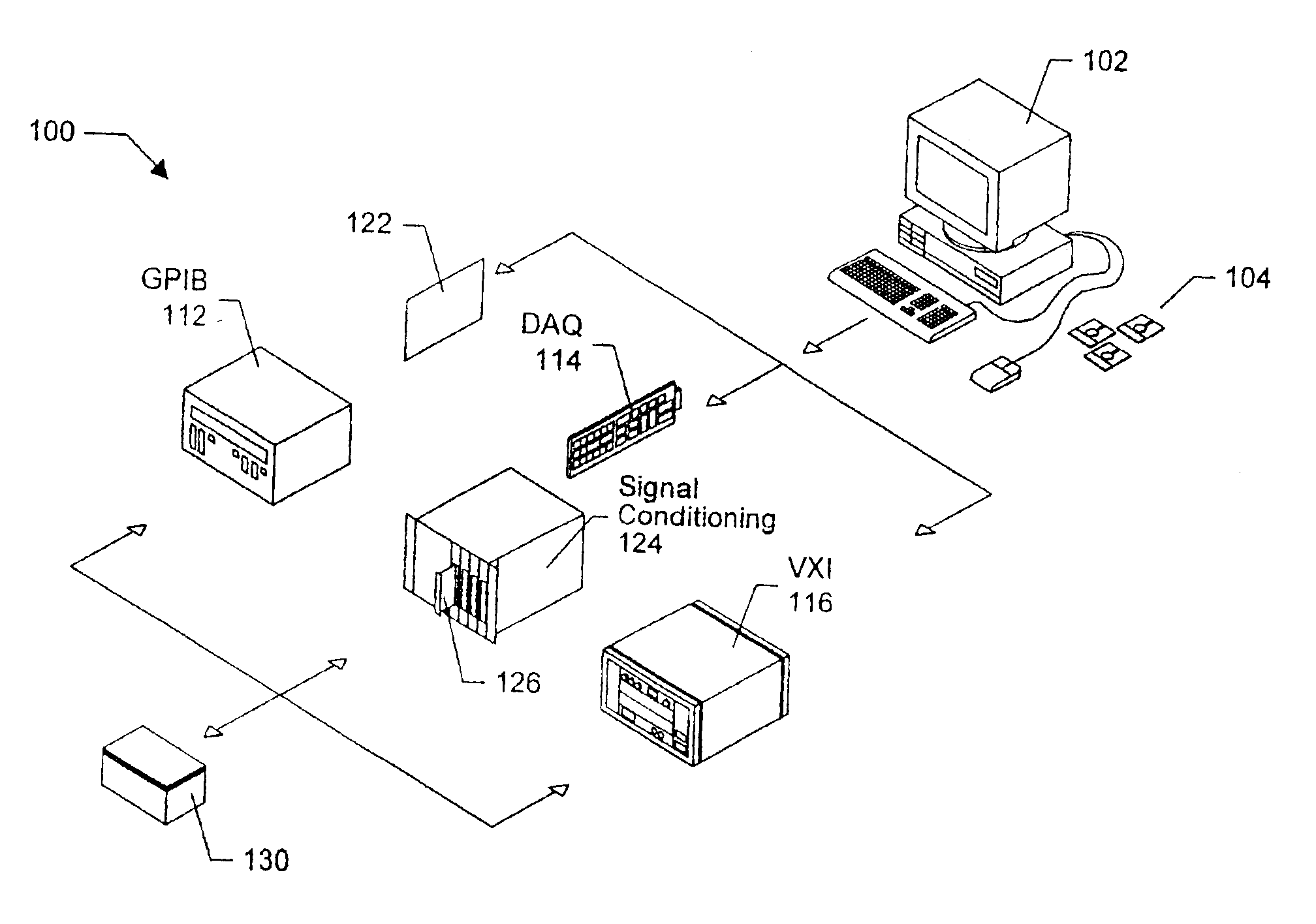

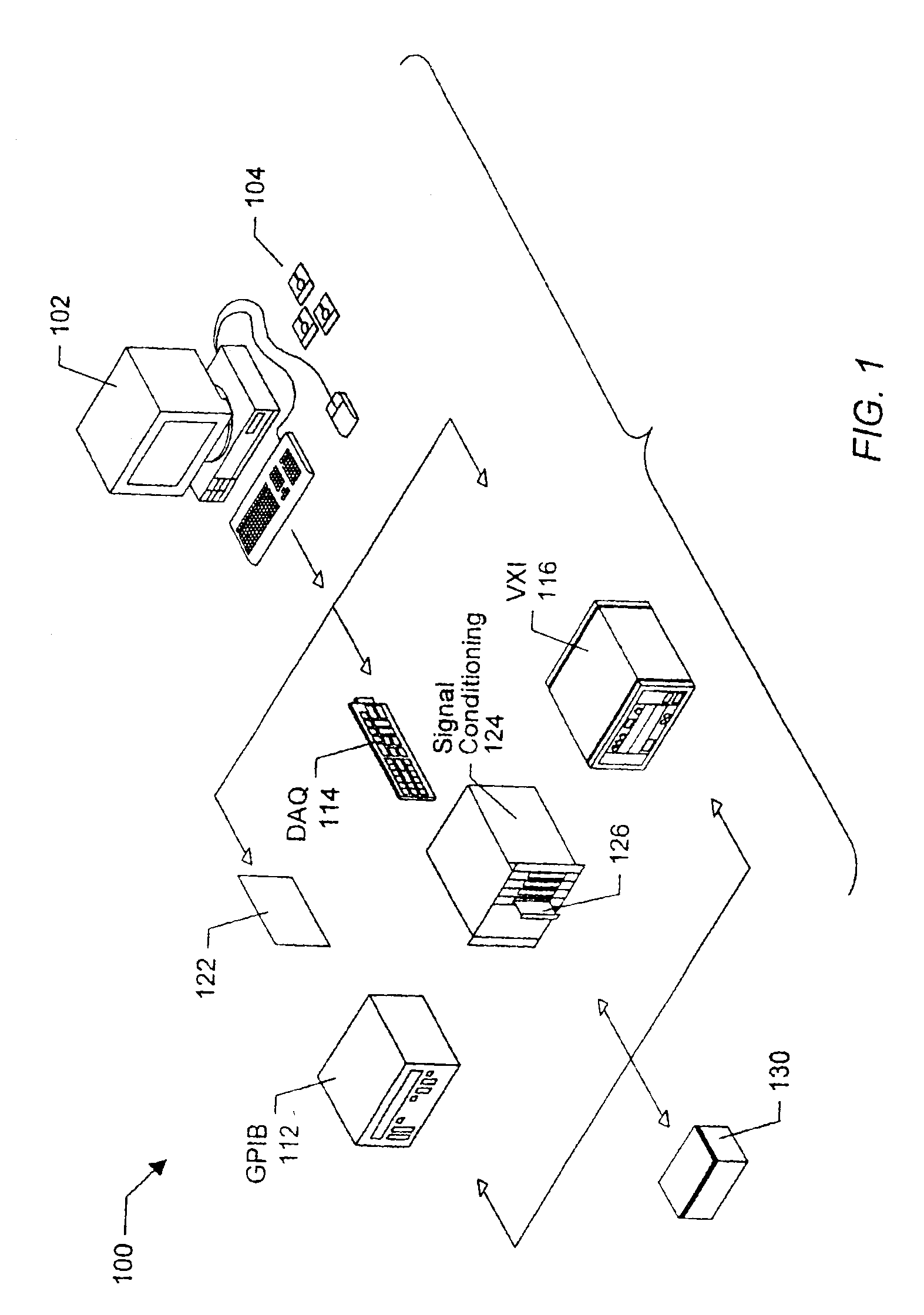

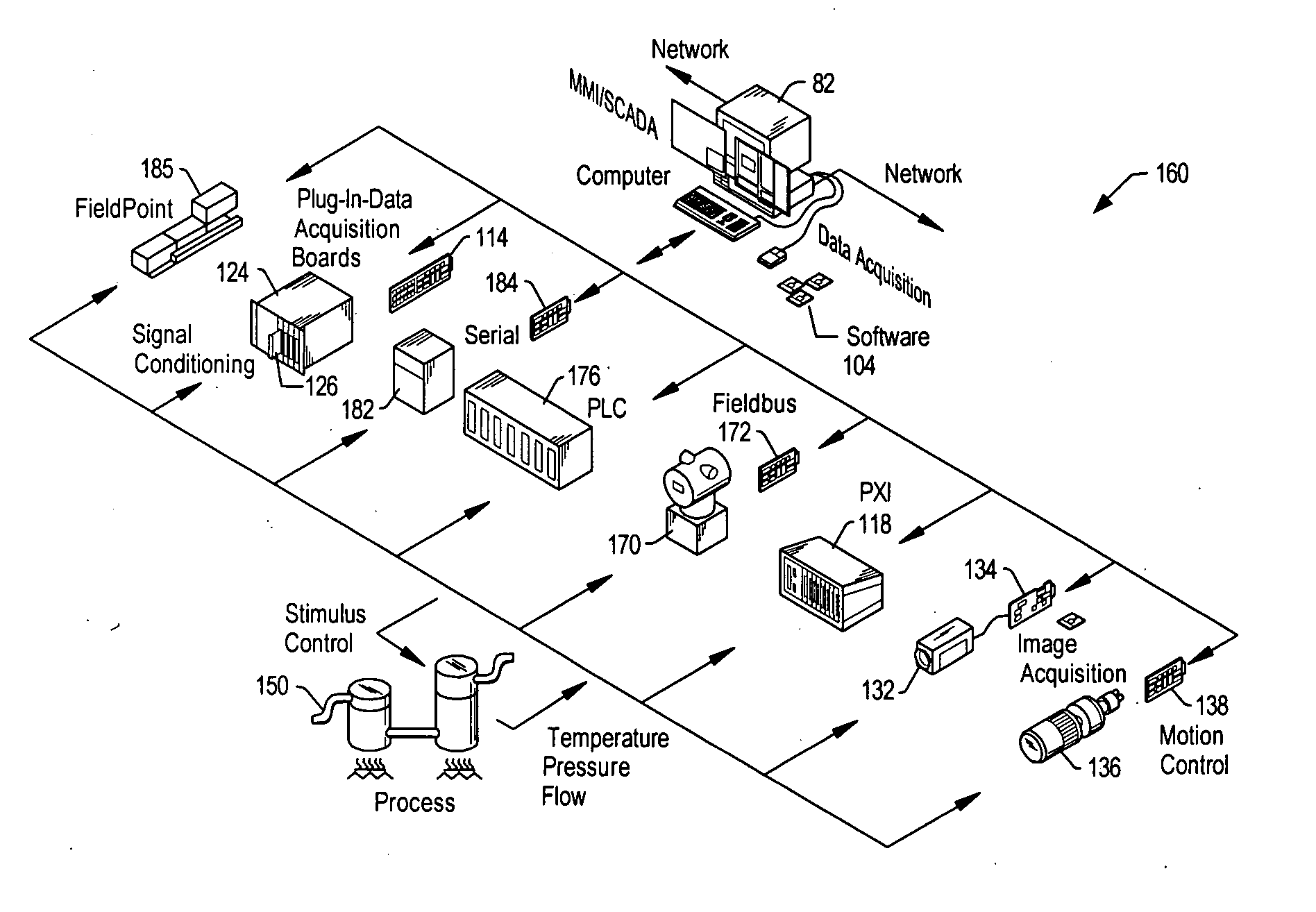

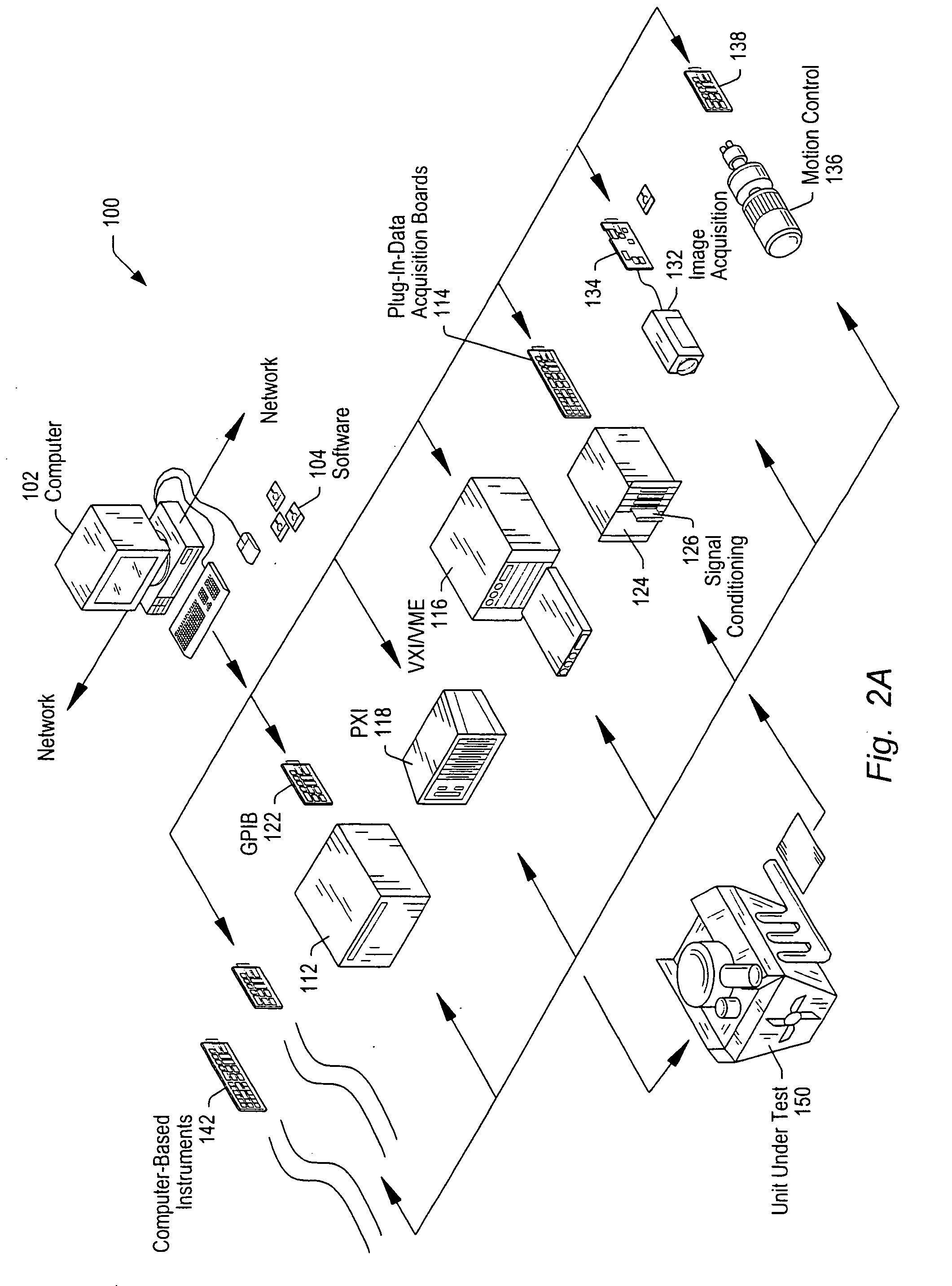

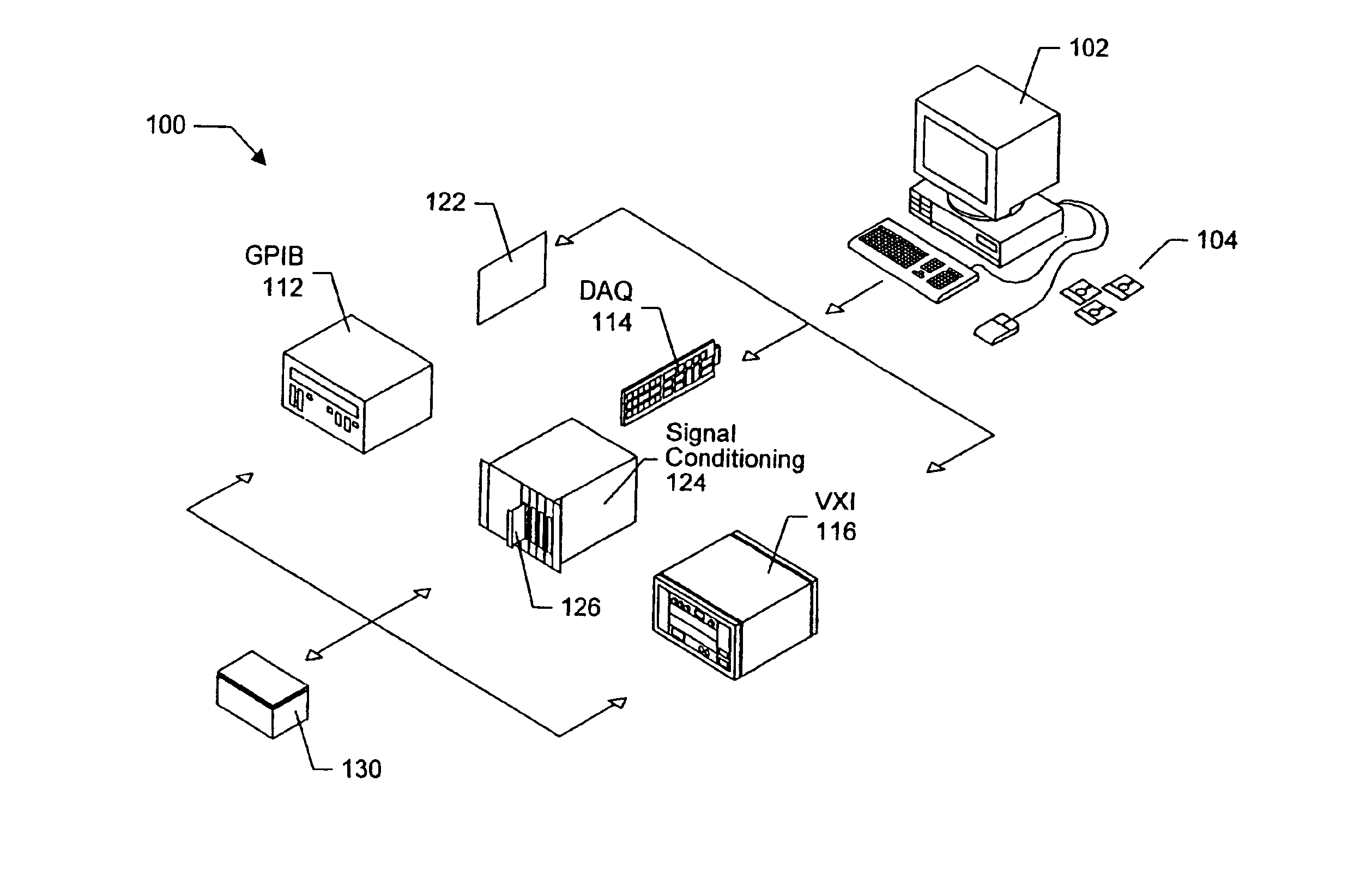

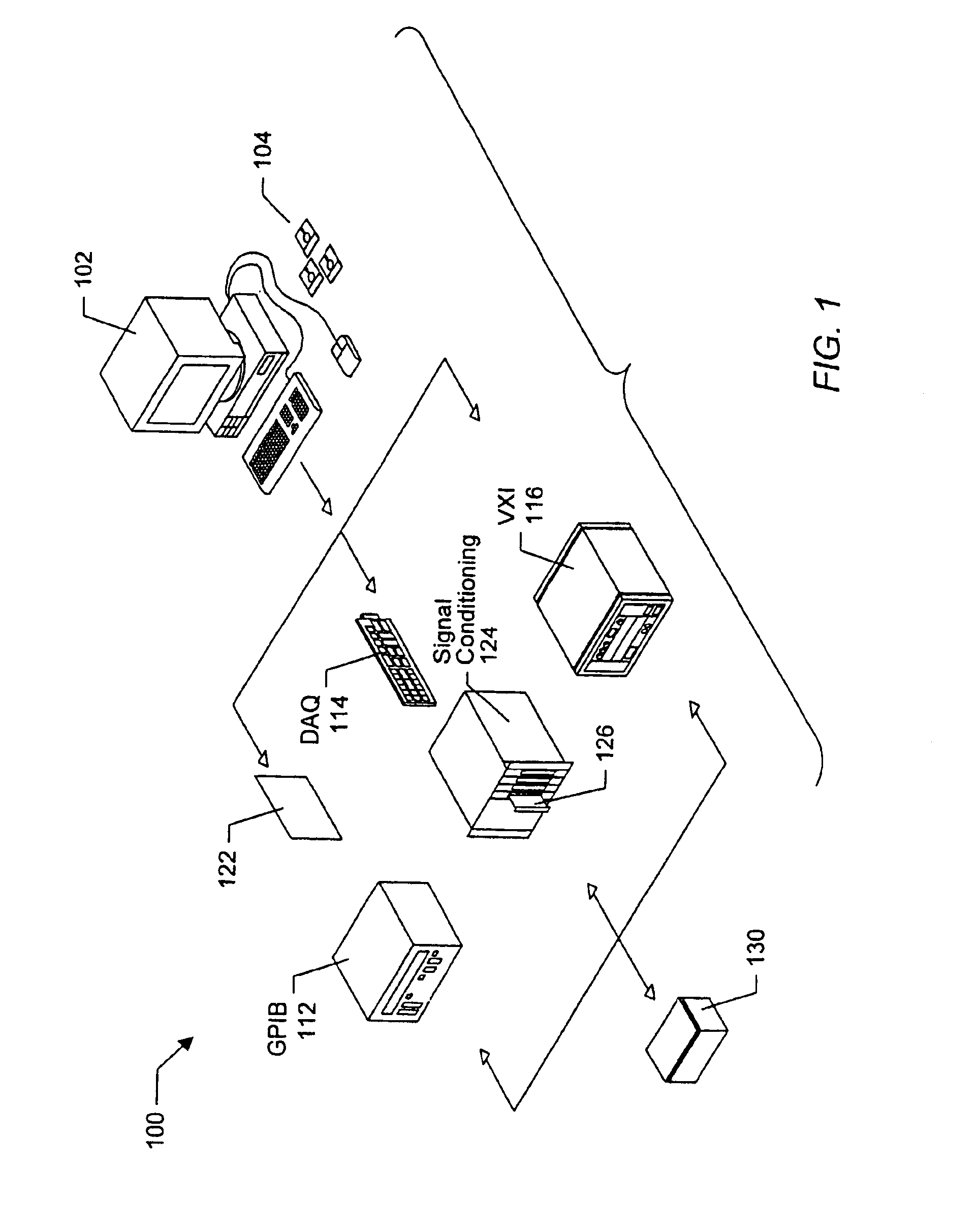

Measurement system including a programmable hardware element and measurement modules that convey interface information

InactiveUS6823283B2Local control/monitoringError detection/correctionMeasurement deviceSignal conditioning

System and method for measurement, DAQ, and control operations. A measurement module includes measurement circuitry for performing signal conditioning and / or signal conversion, and interface circuitry which provides an interface for the measurement circuitry. A carrier unit couples to the interface circuitry of the module. A computer system couples to the carrier unit and stores one or more hardware configuration programs. The interface circuitry communicates an interface protocol describing the interface, e.g., to the carrier unit or the computer system. The computer system provides a hardware configuration program in response to the communicated interface protocol, and programs one or more programmable hardware elements on the carrier unit with the hardware configuration program. After being configured, the programmable hardware elements interface with the measurement module in accordance with the communicated interface protocol. The measurement module and the programmed carrier unit may perform together as a DAQ device, measurement device, and / or control device.

Owner:NATIONAL INSTRUMENTS

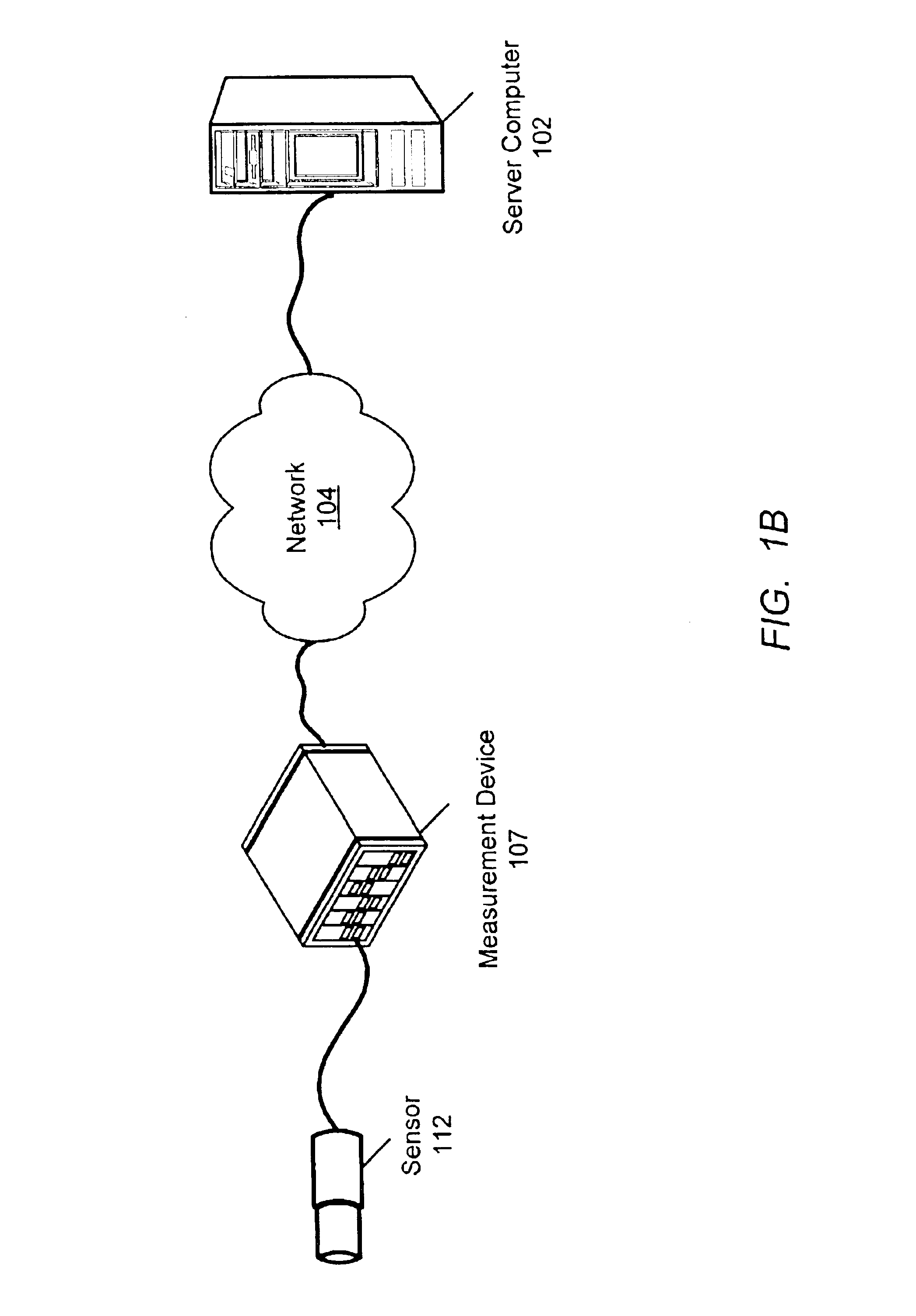

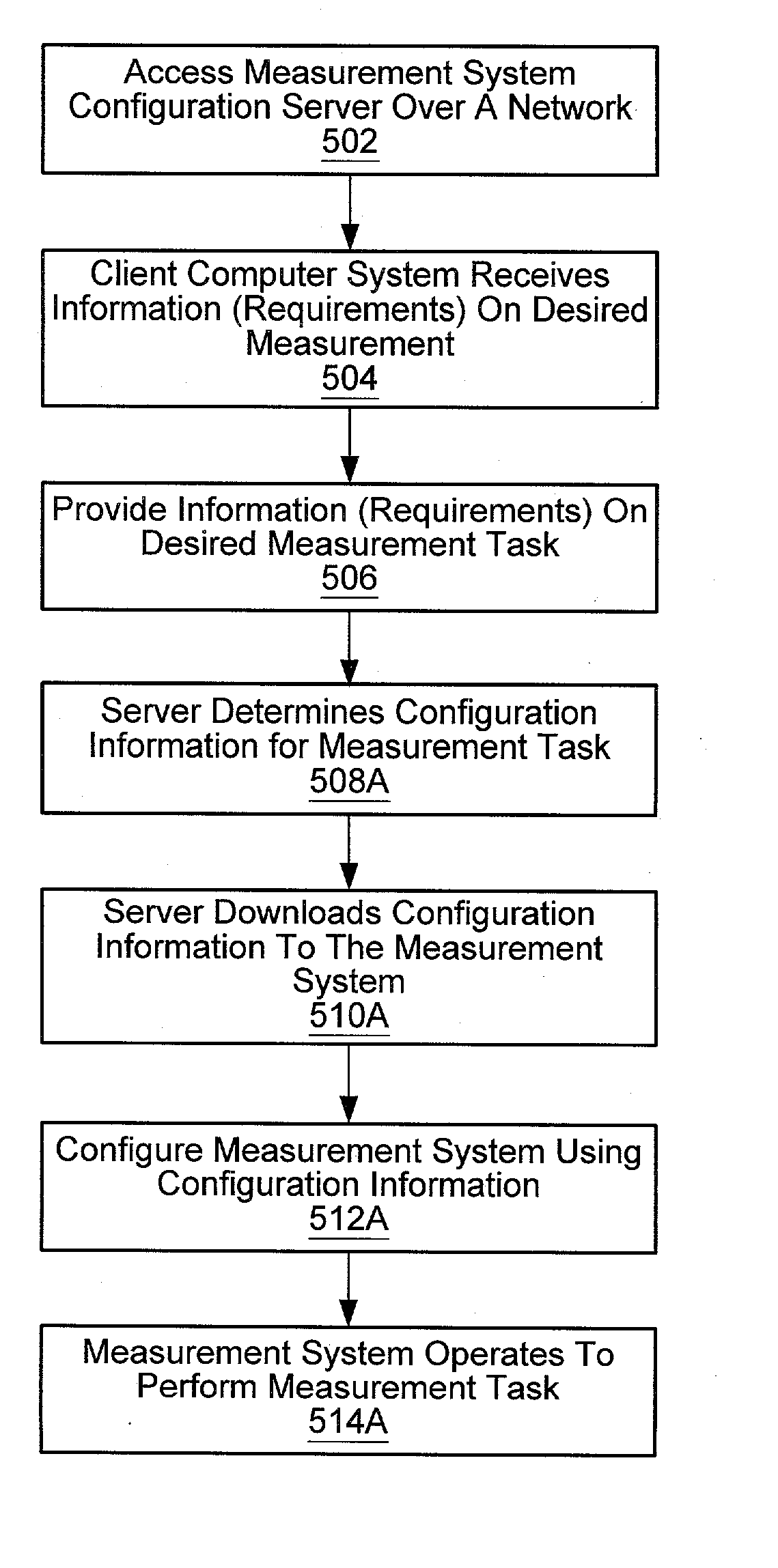

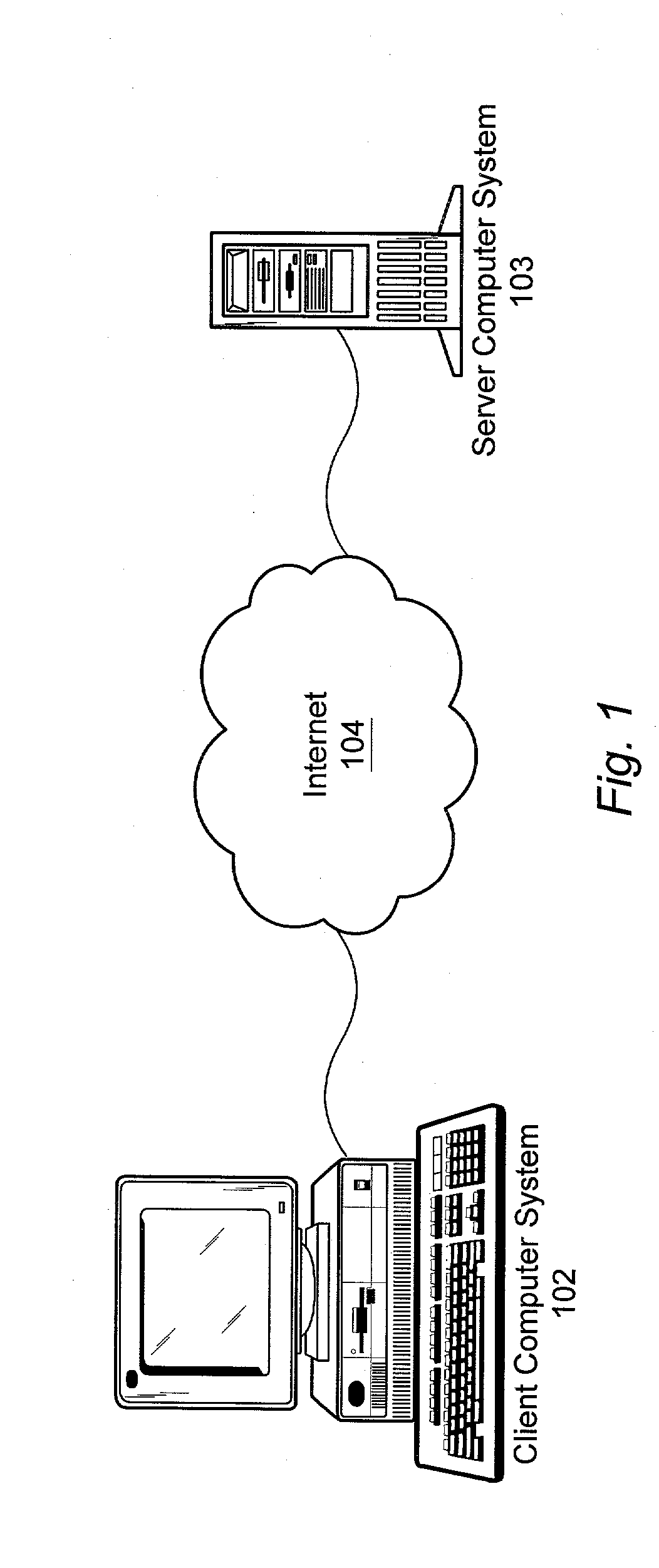

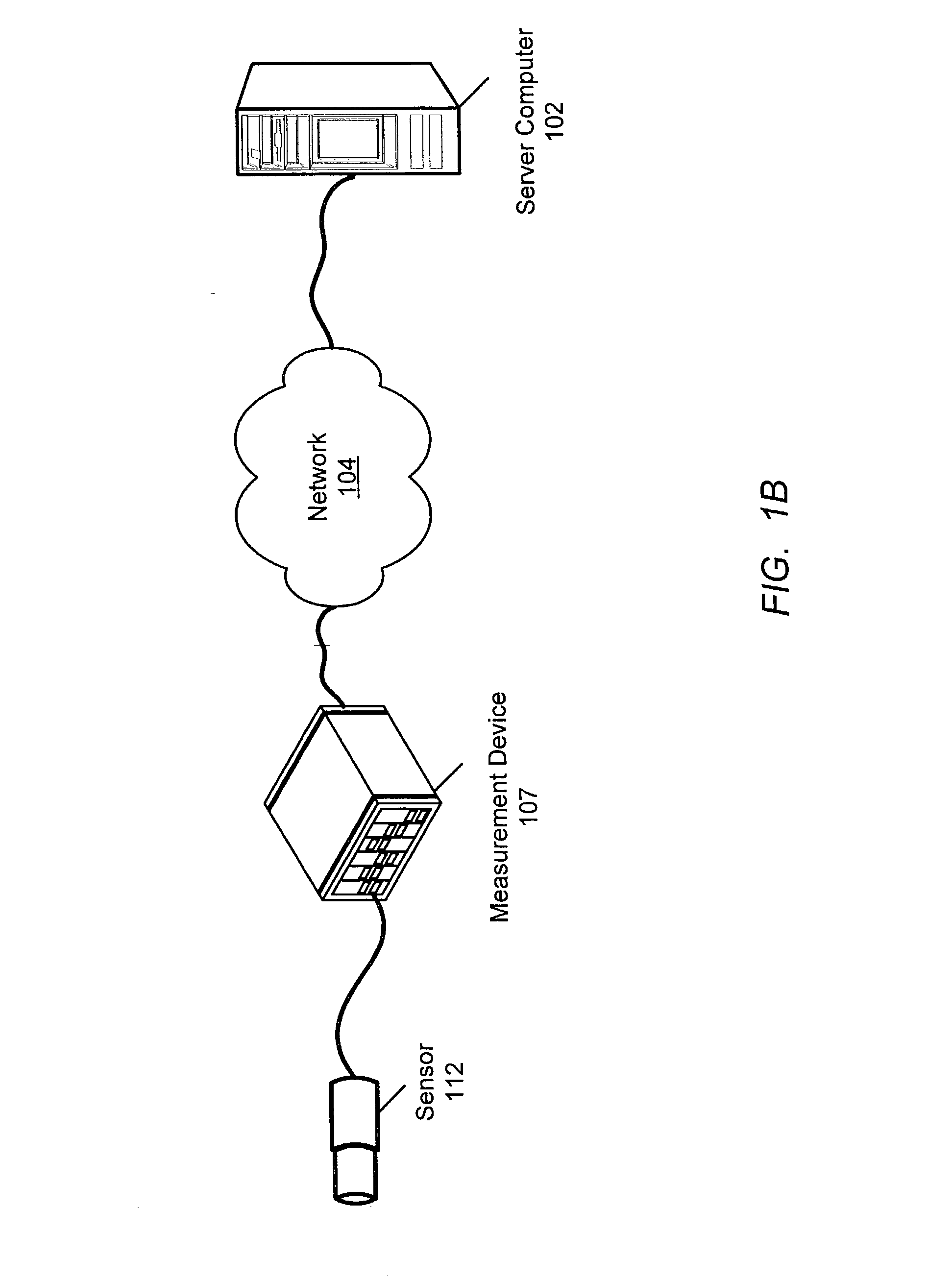

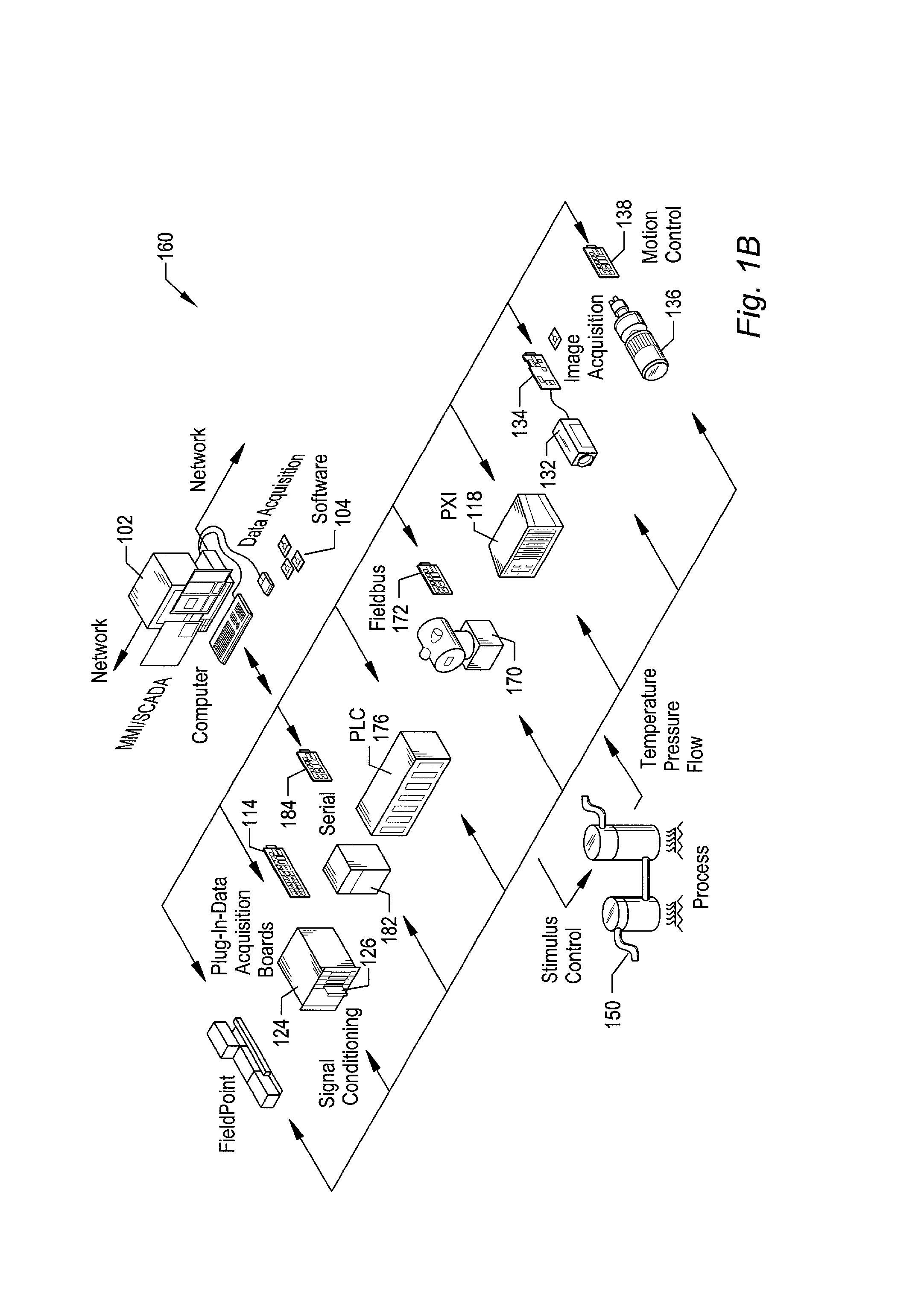

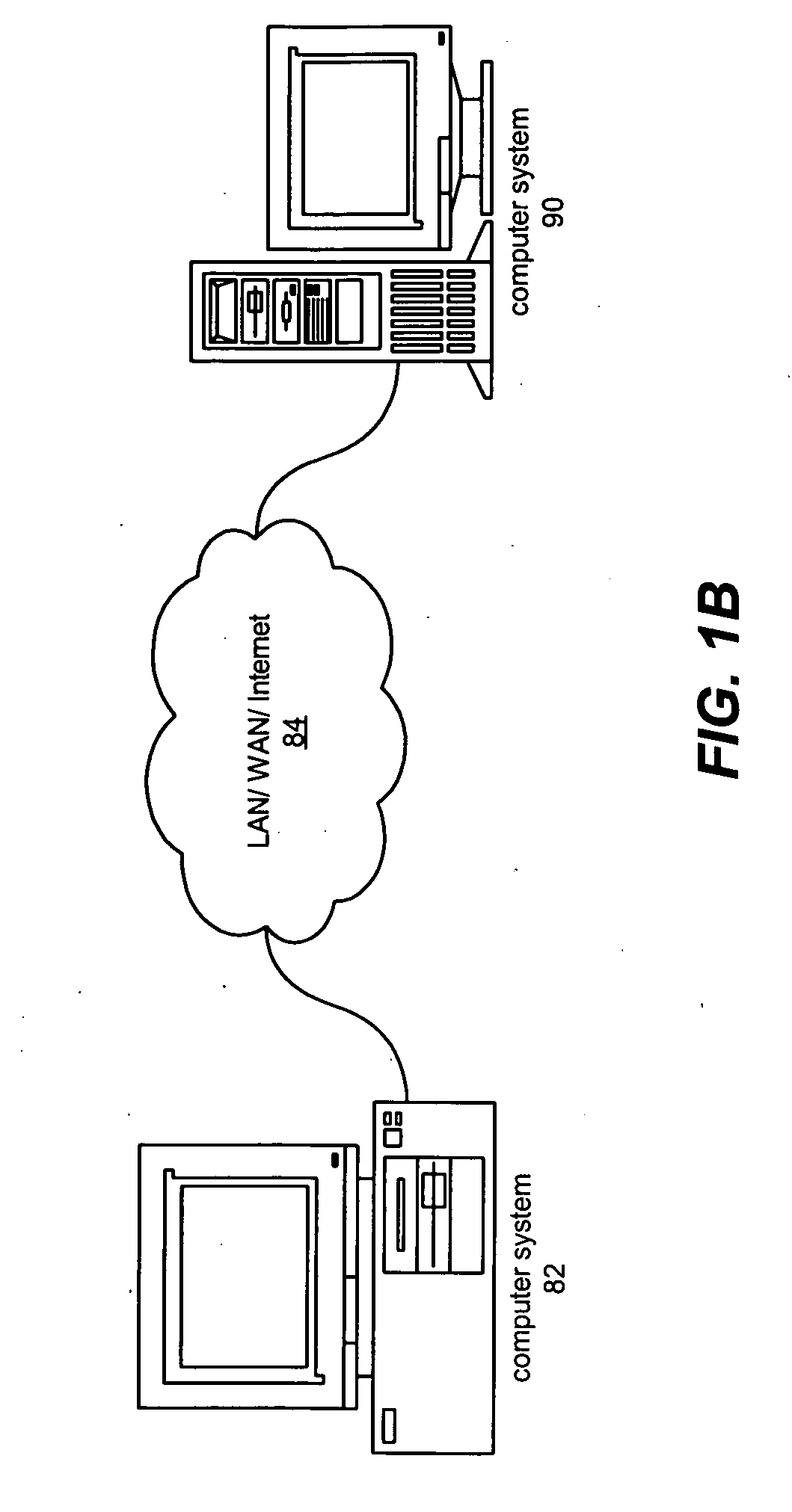

Network-based system for configuring a measurement system using configuration information generated based on a user specification

InactiveUS20030036876A1Measurement arrangements for variableStructural/machines measurementComputer hardwareAuto-configuration

System and method for online configuration of a device for a measurement system. The user accesses a server with a client computer over a network and specifies a task. If the user lacks the hardware to perform the task, hardware specifications are sent to a manufacturer, who sends the hardware to the user. The hardware may be re-configurable hardware (a programmable hardware element or processor / memory based device). Software products (programs and / or data) for configuring measurement system hardware (and / or software) to perform the task may be sent to the user. The hardware may be configured automatically or by the user. The software products may include programs usable by the measurement system to perform the task, configuration information for configuring the client computer or other measurement device, and / or hardware configuration program(s) for configuring a programmable hardware element. Thus, hardware and / or software specific to the user's application are be provided to the user.

Owner:NATIONAL INSTRUMENTS

Measurement system including a programmable hardware element and measurement modules that convey interface information

InactiveUS20030040881A1Local control/monitoringError detection/correctionMeasurement deviceSignal conditioning

System and method for measurement, DAQ, and control operations. A measurement module includes measurement circuitry for performing signal conditioning and / or signal conversion, and interface circuitry which provides an interface for the measurement circuitry. A carrier unit couples to the interface circuitry of the module. A computer system couples to the carrier unit and stores one or more hardware configuration programs. The interface circuitry communicates an interface protocol describing the interface, e.g., to the carrier unit or the computer system. The computer system provides a hardware configuration program in response to the communicated interface protocol, and programs one or more programmable hardware elements on the carrier unit with the hardware configuration program. After being configured, the programmable hardware elements interface with the measurement module in accordance with the communicated interface protocol. The measurement module and the programmed carrier unit may perform together as a DAQ device, measurement device, and / or control device.

Owner:NATIONAL INSTRUMENTS

Software defined radio (SDR) architecture for wireless digital communication systems

InactiveUS7151925B2Special service for subscribersDigital computer detailsSoftware define radioCommunications system

A system and method for providing one hardware platform to implement multiple wireless communication standards, services and applications. The kernel oriented macro based software defined radio (SDR) architecture provides a configurable and programmable hardware platform to implement multiple wireless communication standards, services and applications.

Owner:MEDIATEK INC

System and method for configuring an instrument to perform measurement functions utilizing conversion of graphical programs into hardware implementations

InactiveUS20020080174A1Detecting faulty hardware by remote testCathode-ray tube indicatorsGraphicsComputer hardware

A computer-implemented system and method for generating a hardware implementation of graphical code. The method may operate to configure an instrument to perform measurement functions, wherein the instrument includes a programmable hardware element. The method comprises first creating a graphical program, wherein the graphical program may implement a measurement function. A portion of the graphical program may be converted into a hardware implementation on a programmable hardware element, and a portion may optionally be compiled into machine code for execution by a CPU. The programmable hardware element is thus configured utilizing a hardware description and implements a hardware implementation of at least a portion of the graphical program.

Owner:NATIONAL INSTRUMENTS

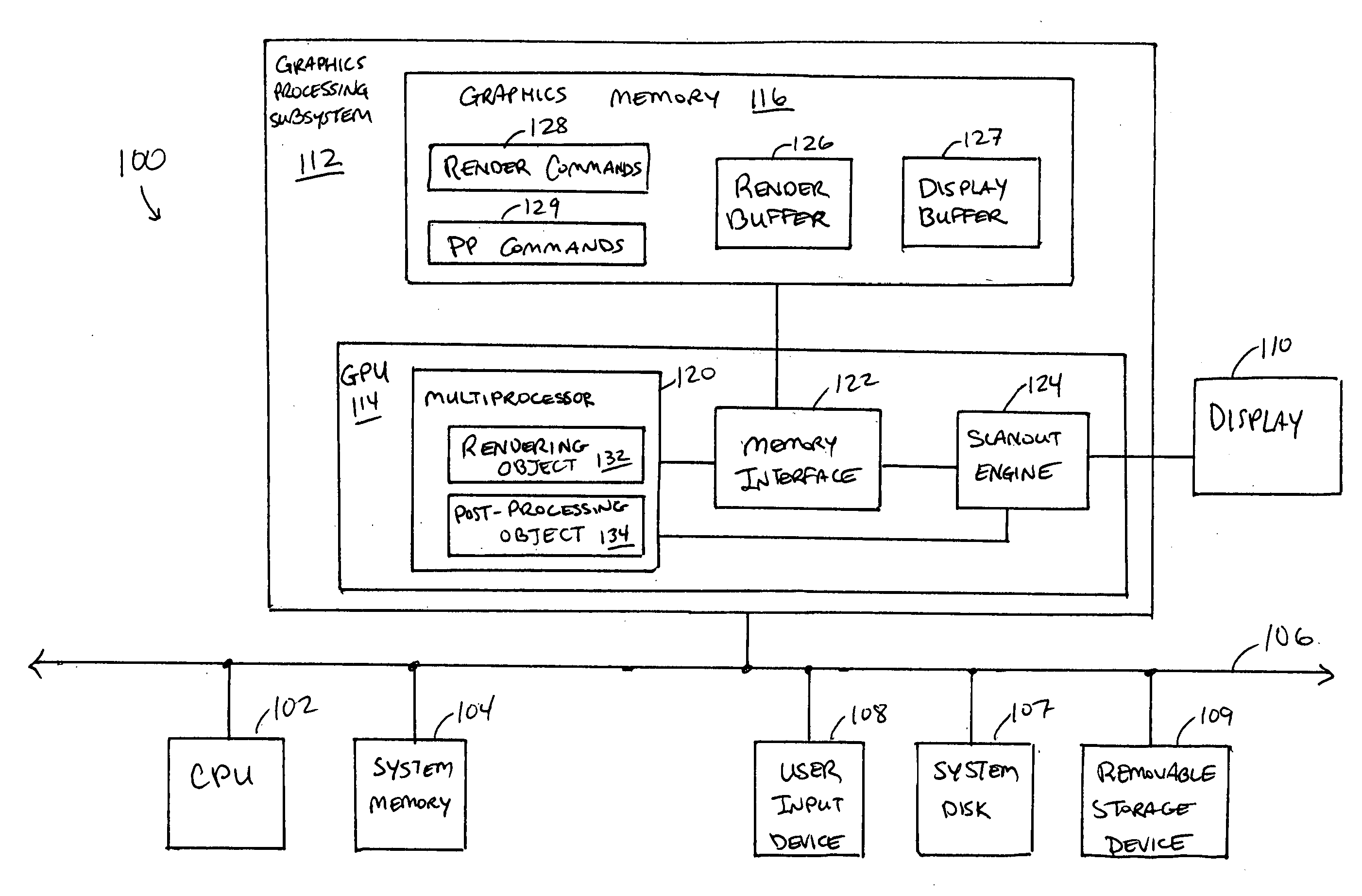

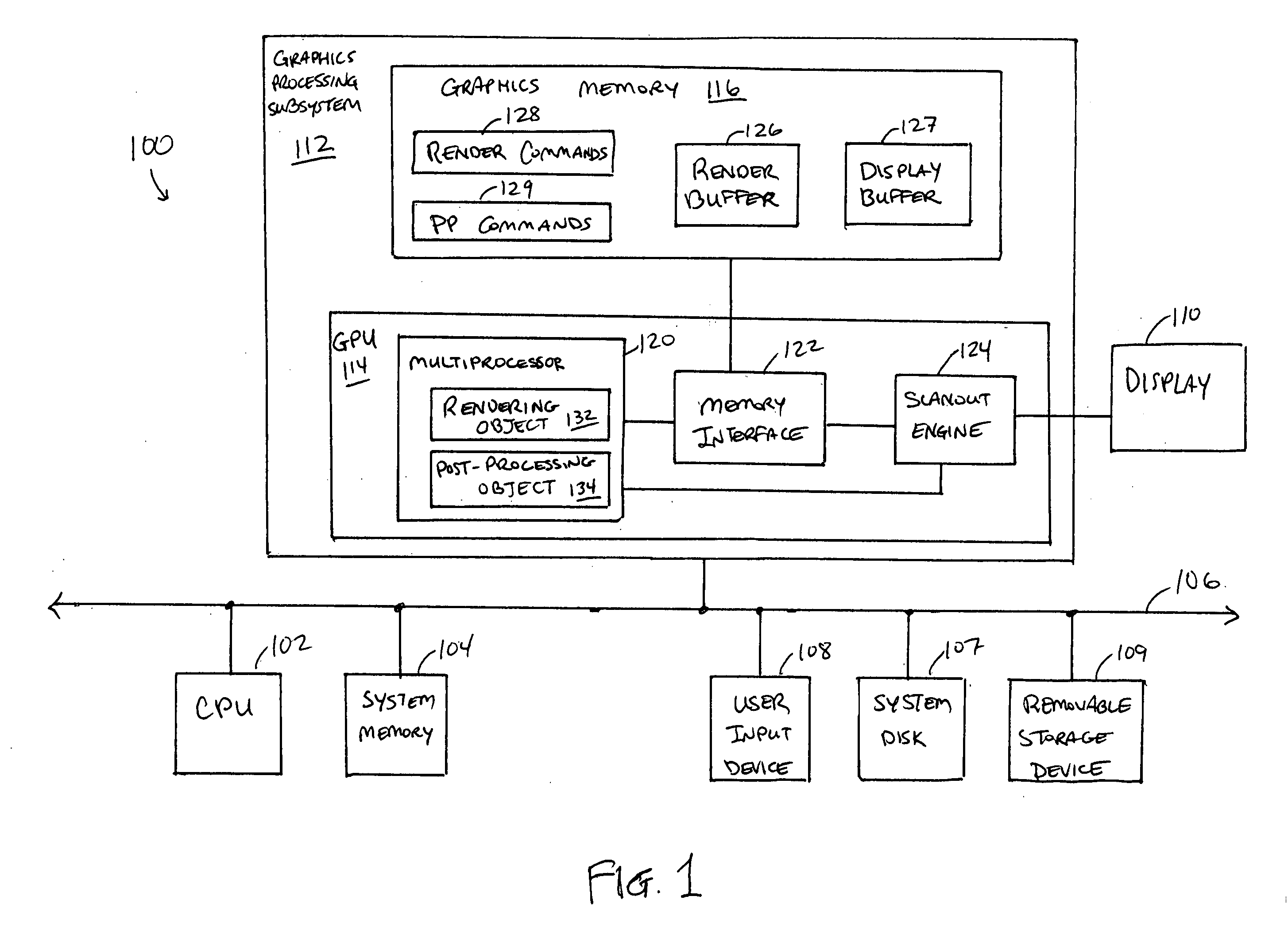

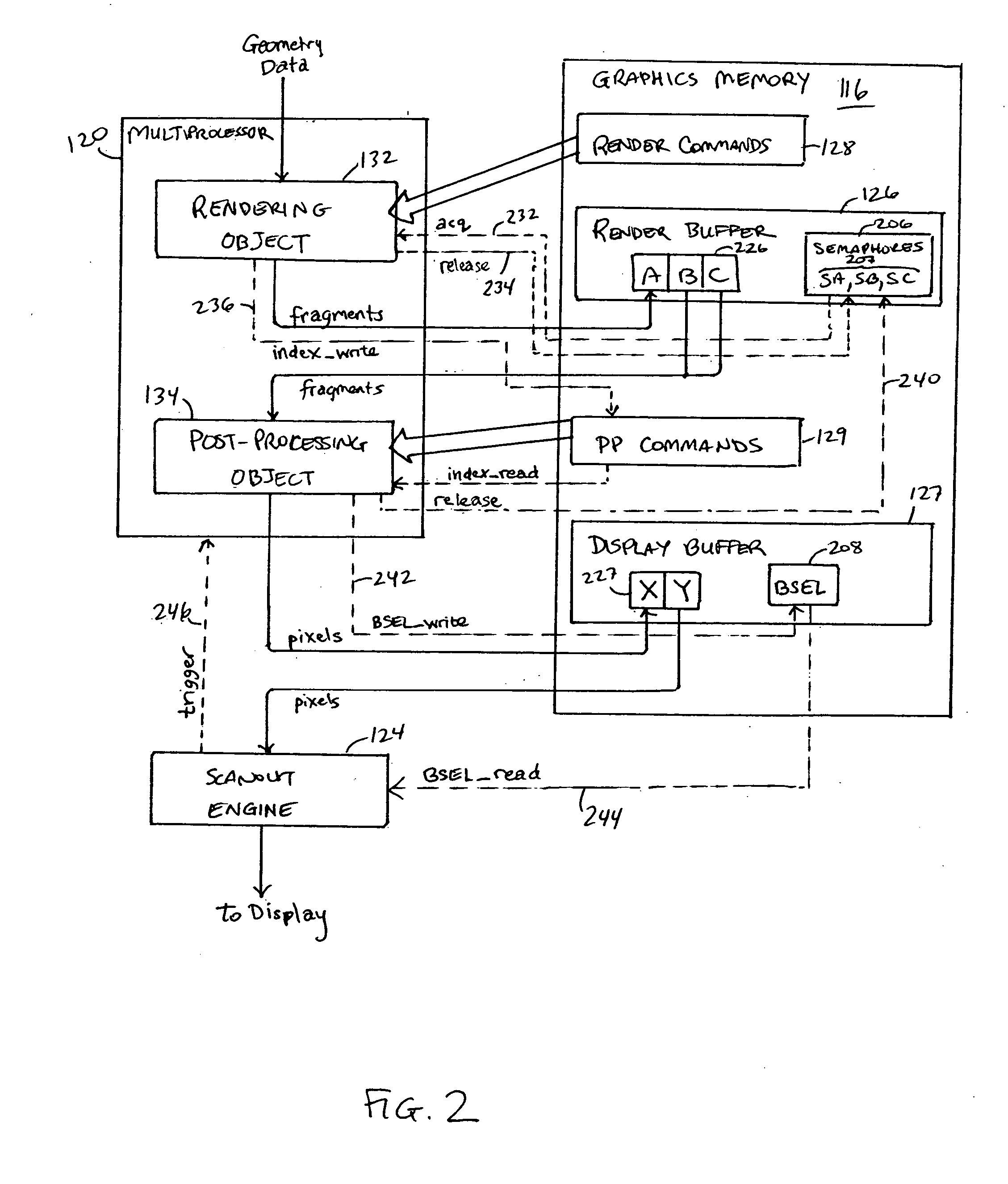

Real-time display post-processing using programmable hardware

ActiveUS20060132491A1Image memory managementMultiprogramming arrangementsDisplay deviceProgrammable hardware

In a graphics processor, a rendering object and a post-processing object share access to a host processor with a programmable execution core. The rendering object generates fragment data for an image from geometry data. The post-processing object operates to generate a frame of pixel data from the fragment data and to store the pixel data in a frame buffer. In parallel with operations of the host processor, a scanout engine reads pixel data for a previously generated frame and supplies the pixel data to a display device. The scanout engine periodically triggers the host processor to operate the post-processing object to generate the next frame. Timing between the scanout engine and the post-processing object can be controlled such that the next frame to be displayed is ready in a frame buffer when the scanout engine finishes reading a current frame.

Owner:NVIDIA CORP

System and method for configuring an instrument to perform measurement functions utilizing conversion of graphical programs into hardware implementations

InactiveUS6784903B2Detecting faulty hardware by remote testCathode-ray tube indicatorsGraphicsComputer hardware

A computer-implemented system and method for generating a hardware implementation of graphical code. The method may operate to configure an instrument to perform measurement functions, wherein the instrument includes a programmable hardware element. The method comprises first creating a graphical program, wherein the graphical program may implement a measurement function. A portion of the graphical program may be converted into a hardware implementation on a programmable hardware element, and a portion may optionally be compiled into machine code for execution by a CPU. The programmable hardware element is thus configured utilizing a hardware description and implements a hardware implementation of at least a portion of the graphical program.

Owner:NATIONAL INSTRUMENTS

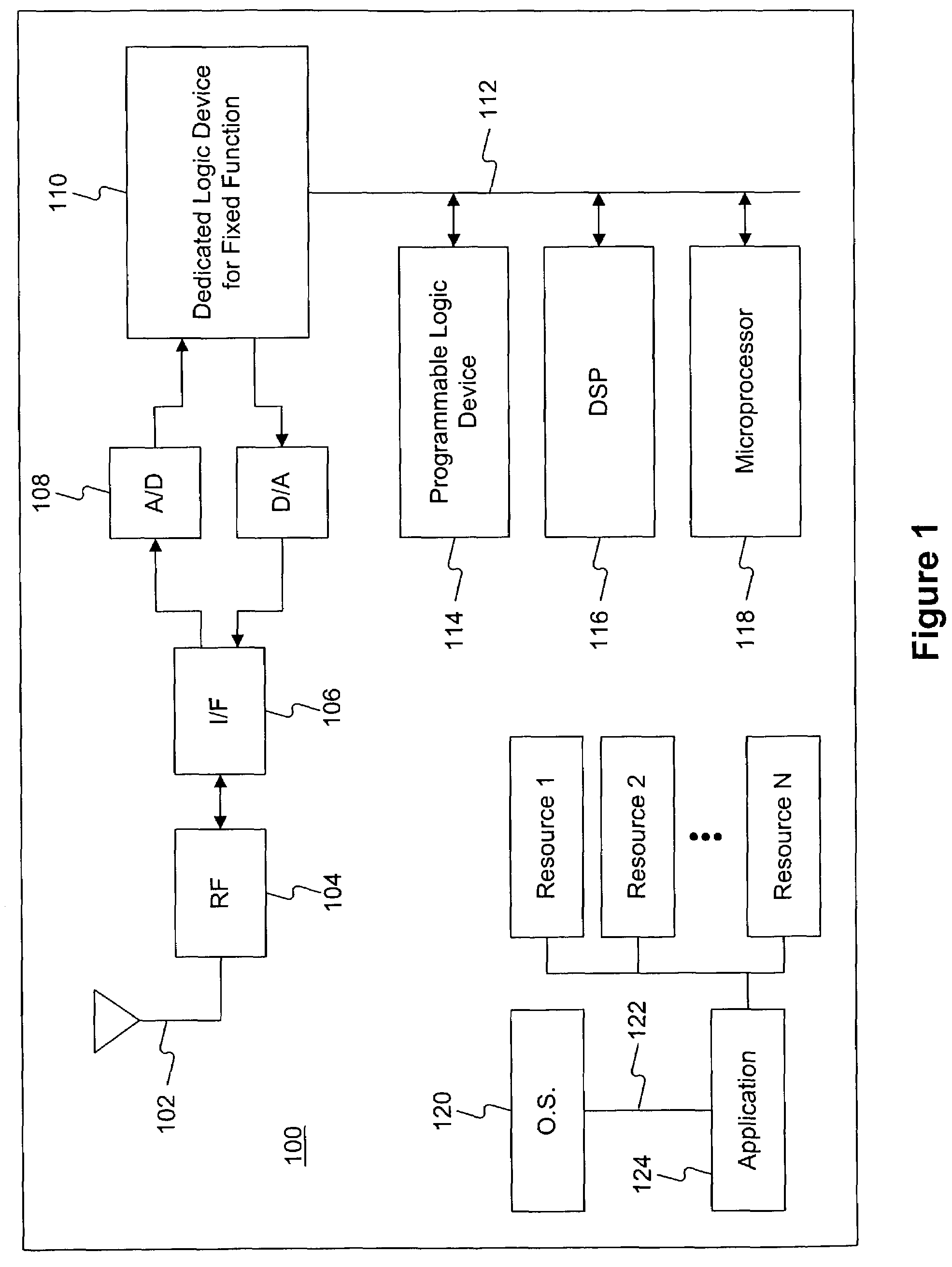

Reconfigurable measurement system utilizing a programmable hardware element and fixed hardware resources

InactiveUS20050143968A9Accurate and efficient matchingEfficient and flexibleError detection/correctionDigital computer detailsComputer hardwareSignal conditioning

Owner:NATIONAL INSTRUMENTS

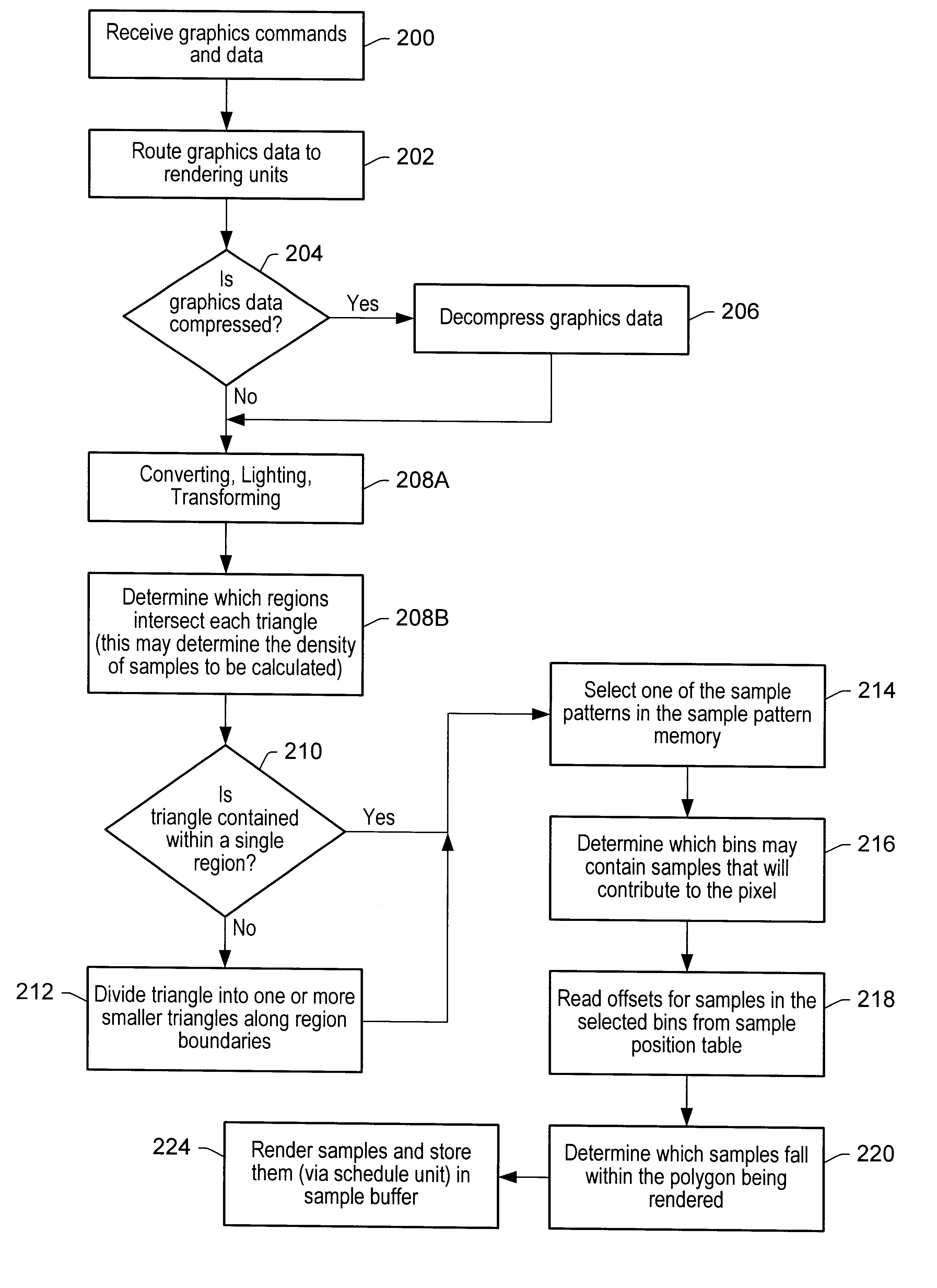

Graphics system with programmable sample positions

A method and computer graphics system for rendering images using programmable sample positions is disclosed. In one embodiment, the computer graphics system may comprise a graphics processor, a sample buffer, and a sample-to-pixel calculation unit. The graphics processor may be configured to generate a plurality of samples using a sample positioning algorithm selected from a programmable memory or generated by programmable hardware. The sample buffer, which is coupled to the graphics processor, may be configured to store the samples. The sample buffer may be super-sampled and double buffered. The sample-to-pixel calculation unit is programmable to select a variable number of stored samples from the sample buffer to filter into an output pixel. The sample-to-pixel calculation unit performs the filter process in real-time, and may use a number of different filter types. The algorithms used to position the samples may position the samples according to a regular grid, a perturbed regular grid, or a stochastic grid.

Owner:ORACLE INT CORP

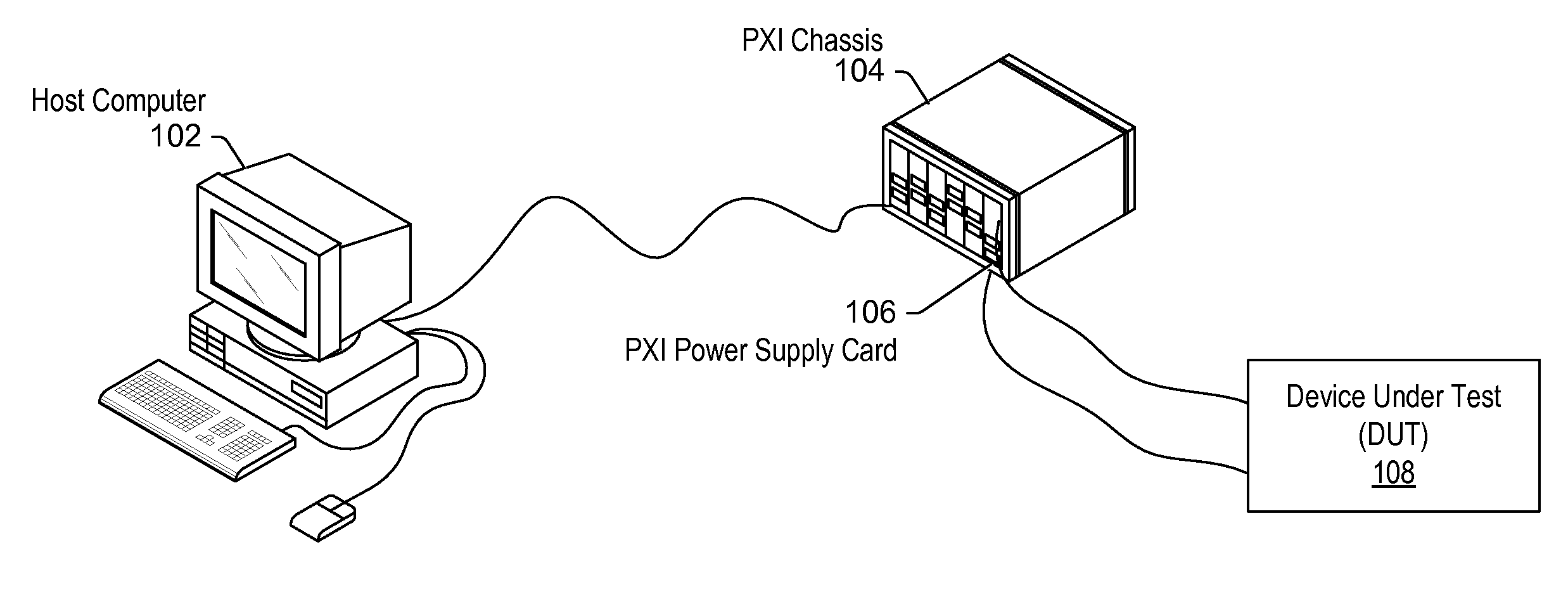

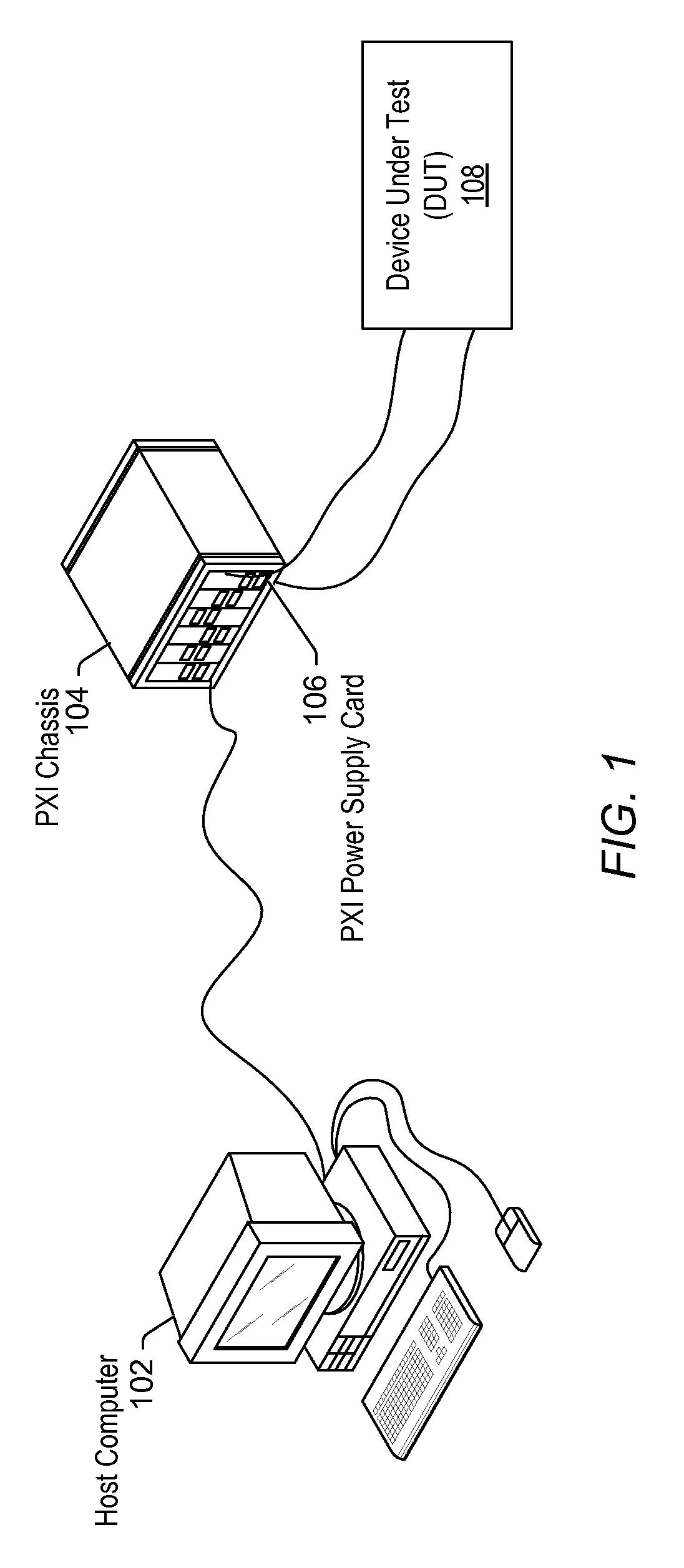

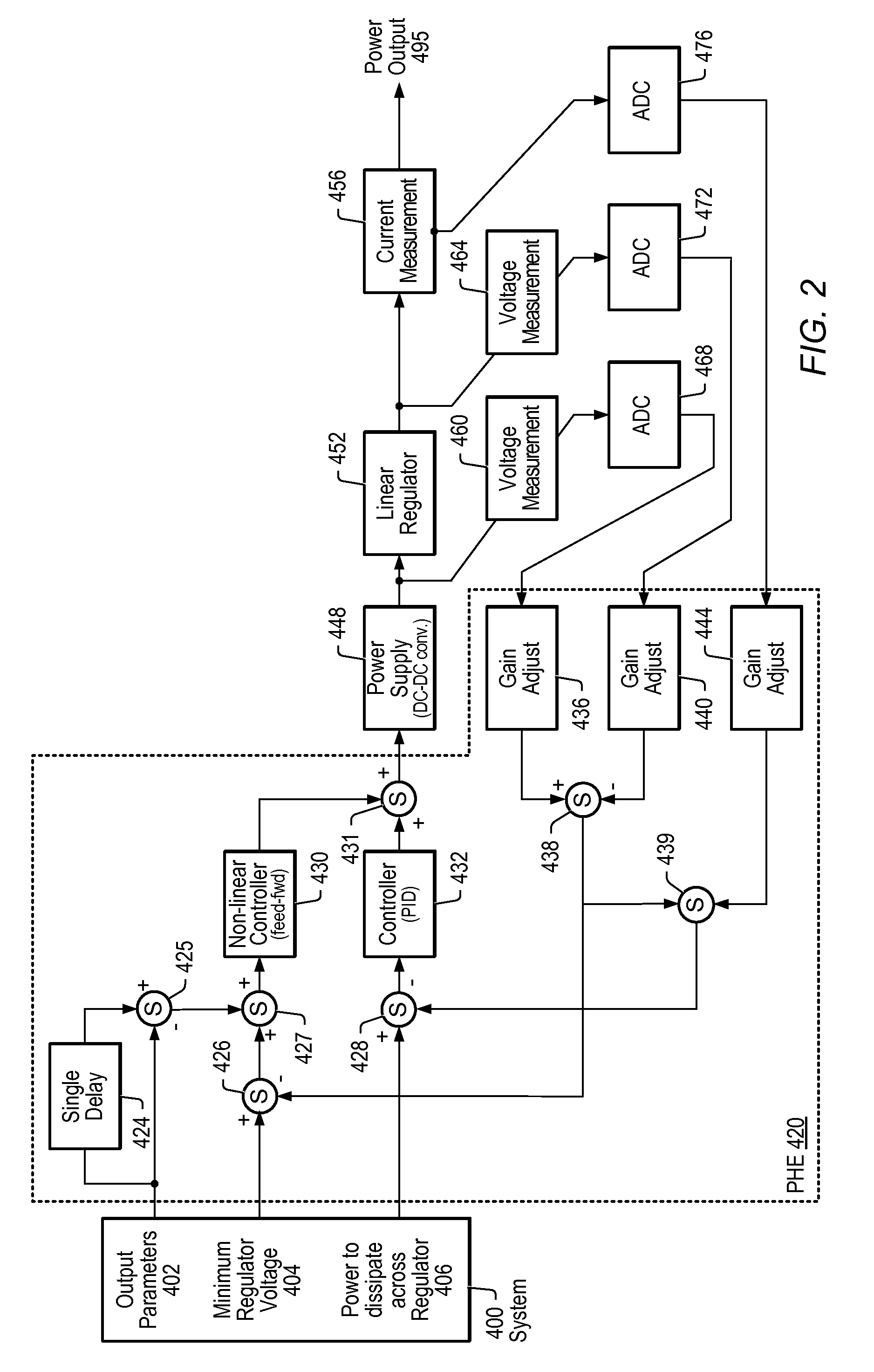

Programmable Hardware Element Pre-Regulator

ActiveUS20070185590A1Fast and efficient modificationMaximize power outputDc-dc conversionElectric controllersProgrammable hardwareLinear control

System and method for providing a programmable power supply. The programmable power supply may include a programmable hardware element (PHE) that couples to a power supply (DC-DC converter) and which in turn couples to a linear regulator. The PHE may implement a PID control algorithm that receives a measurement of the output power and may use PID and / or non-linear control to ensure that the power supply and the linear regulator maintain similar power levels. The PHE may be configured based on a graphical program, thus enabling fast and efficient modifications to the programmable power supply.

Owner:NATIONAL INSTRUMENTS

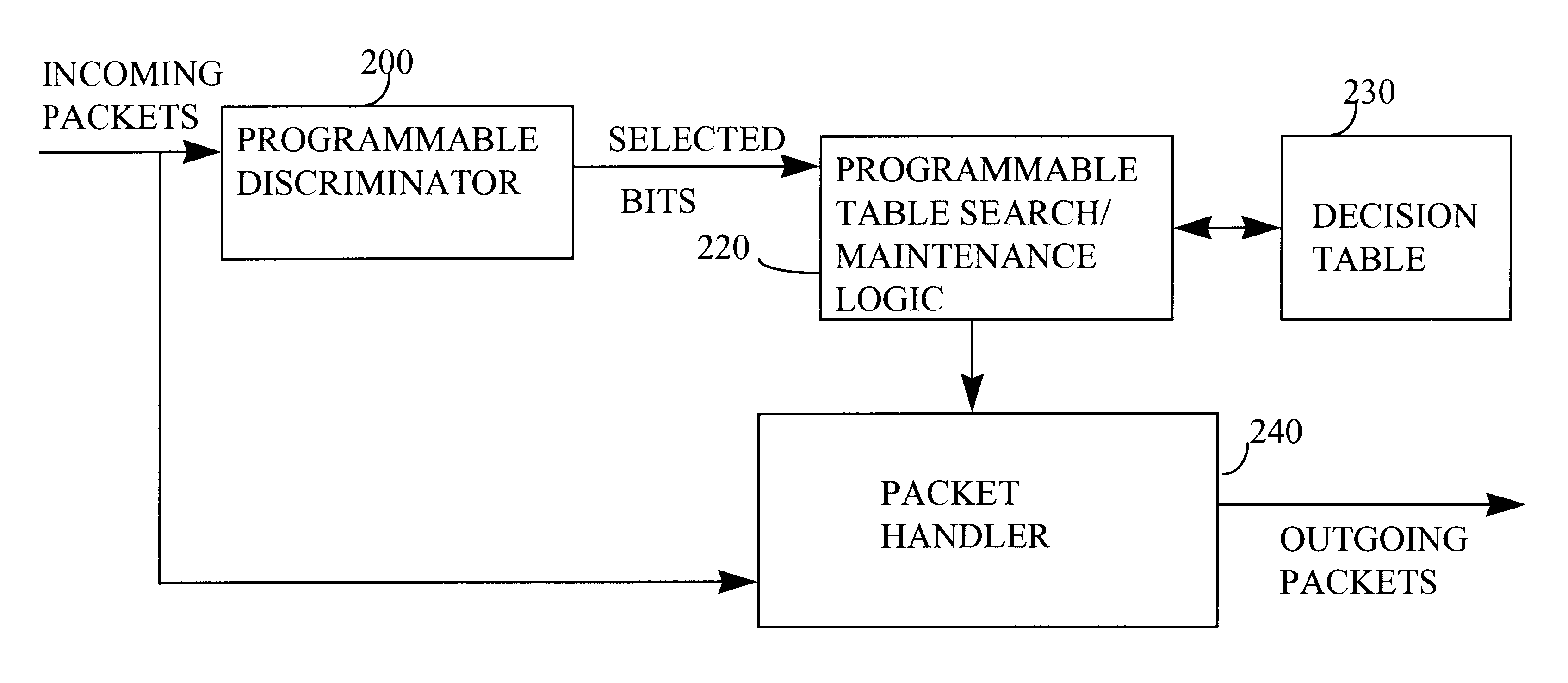

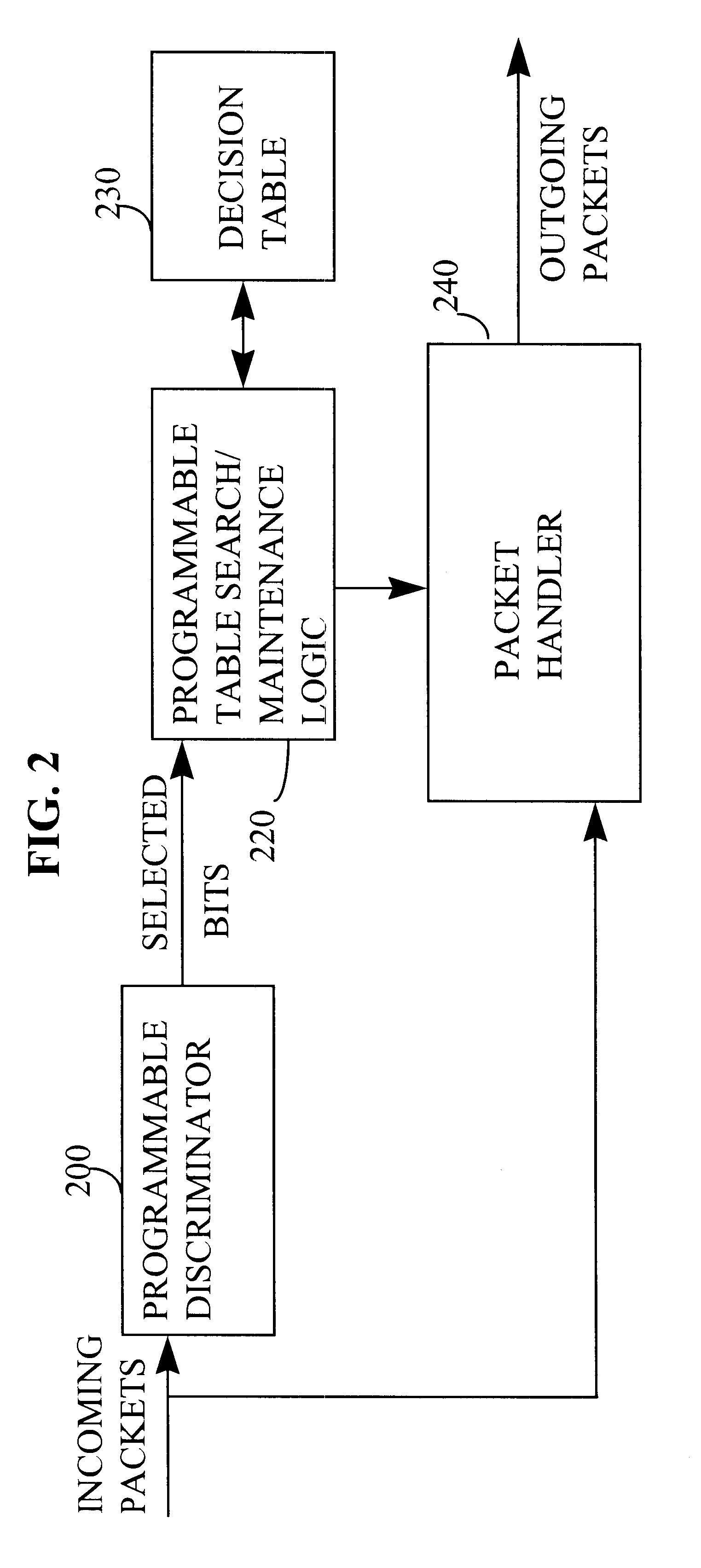

Programmable packet switching device

Owner:RPX CORP +1

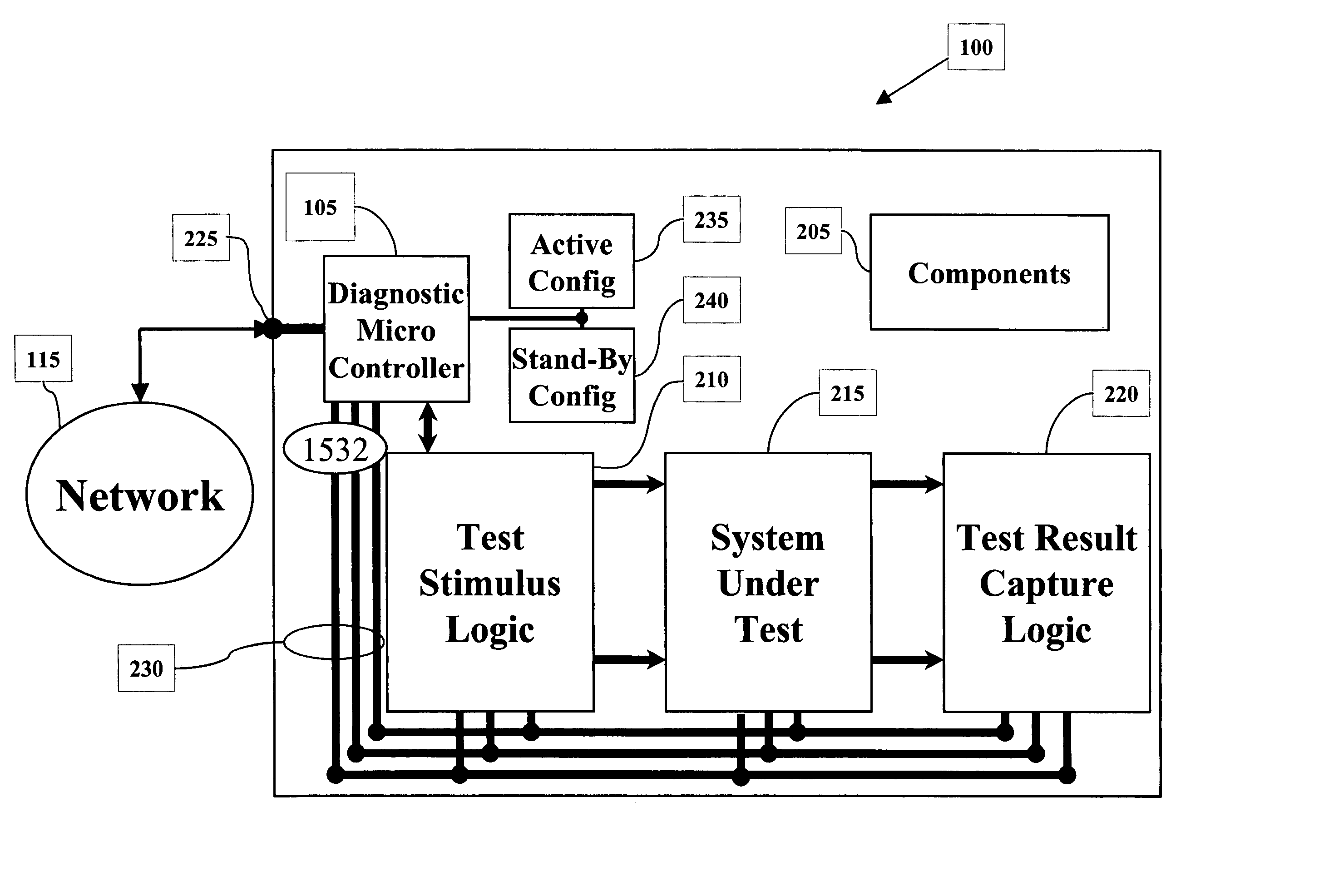

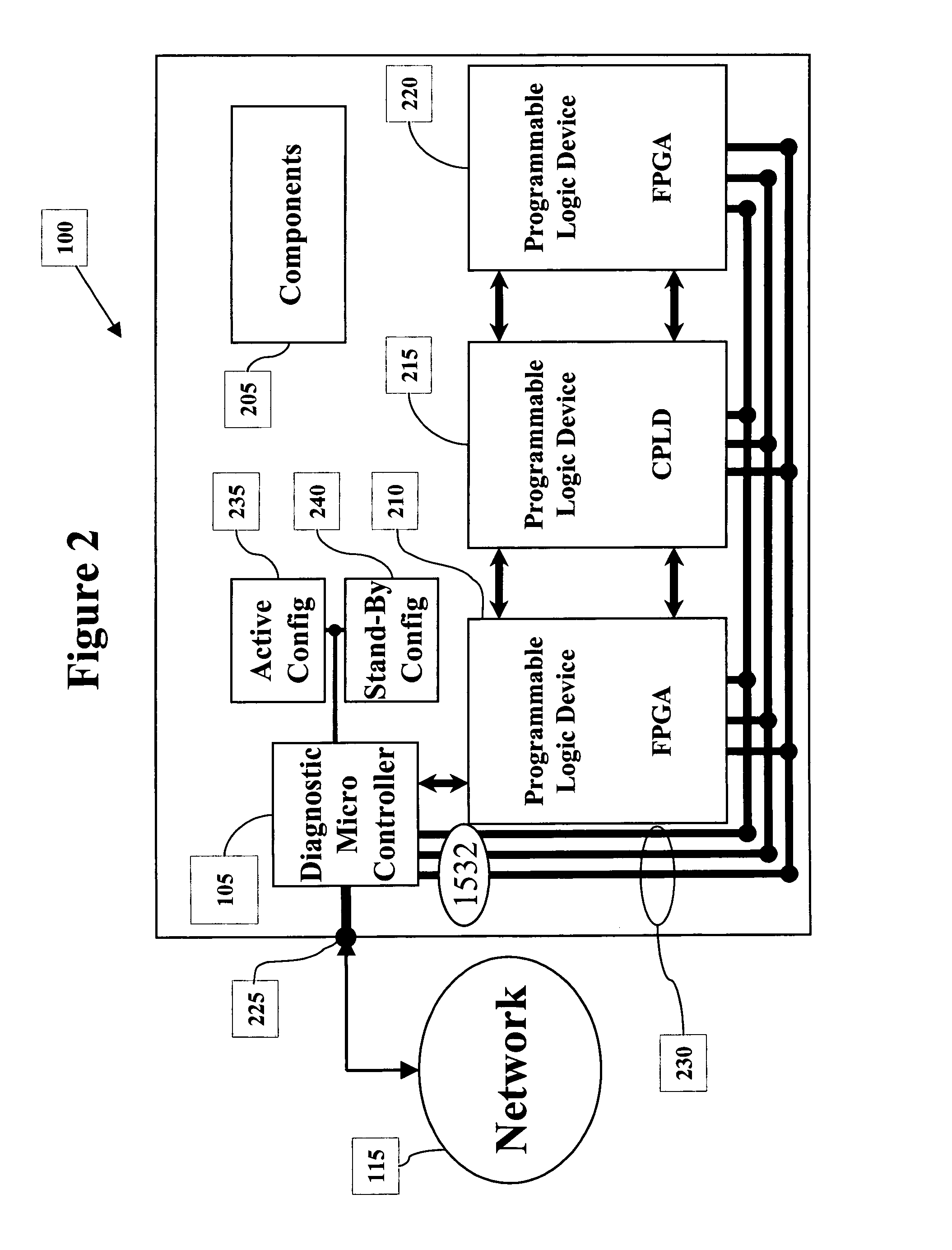

Network based diagnostic system and method for programmable hardware

InactiveUS7133822B1Obvious advantagesDetecting faulty hardware by remote testElectronic switchingMicrocontrollerProgrammable logic device

A system and method for diagnosing an electronic device remotely using a network is provided. The electronic device includes one or more programmable logic devices that are configurable. A diagnostic microcontroller functions to communicate to the programmable logic devices and to communicate to the network. To diagnose the electronic device, communication is established to the network and to a diagnostic / repair center. The diagnostic / repair center selects diagnostic commands and transmits them to the electronic device. The diagnostic microcontroller initiates the diagnostic commands on the one or more programmable logic devices to test their configuration and / or functionality. Test results are collected and transmitted back to the diagnostic / repair center for analysis. Based on the analysis, if appropriate, reconfiguration commands are sent to reconfigure the programmable logic device to correct identified errors.

Owner:XILINX INC

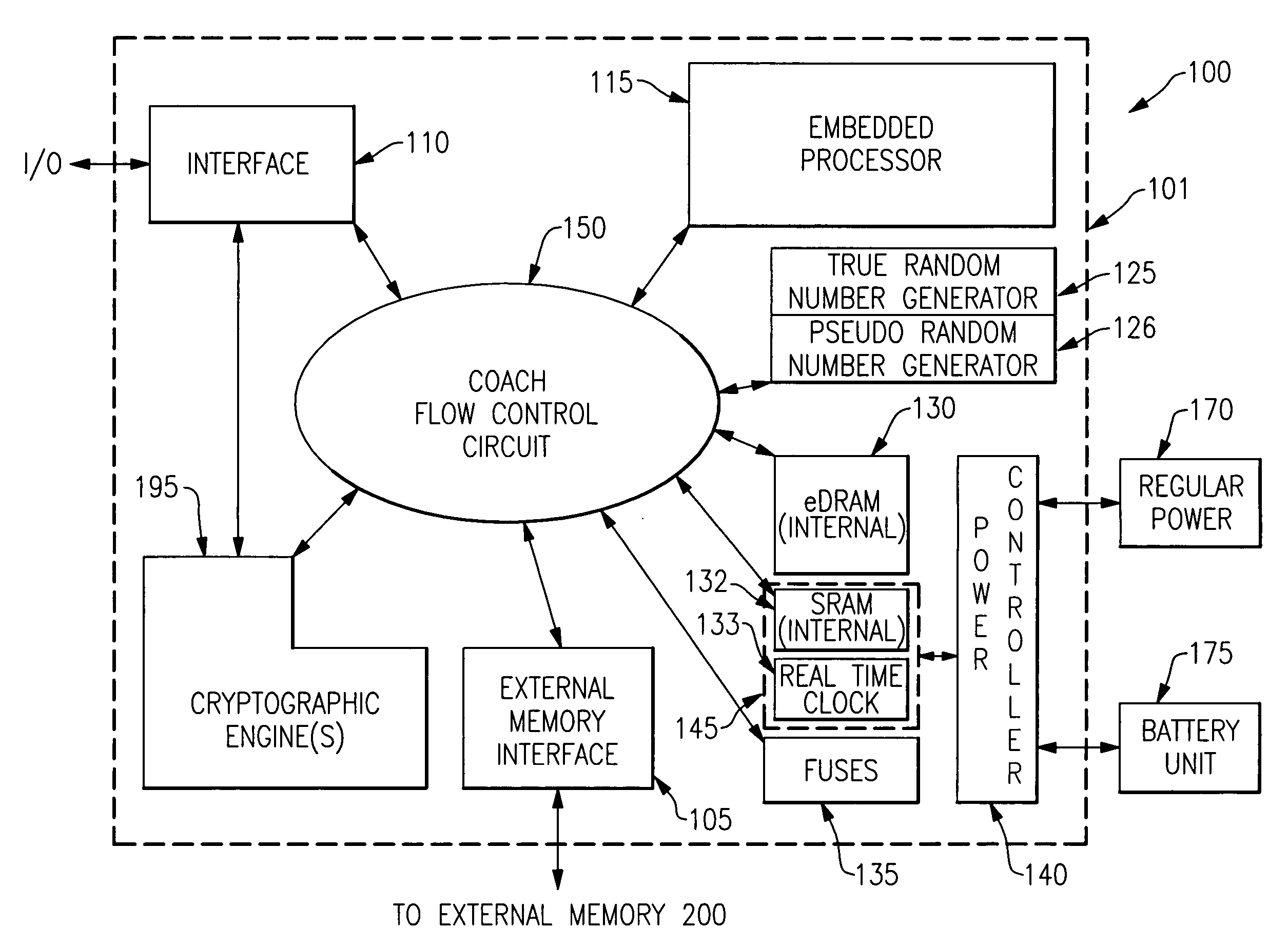

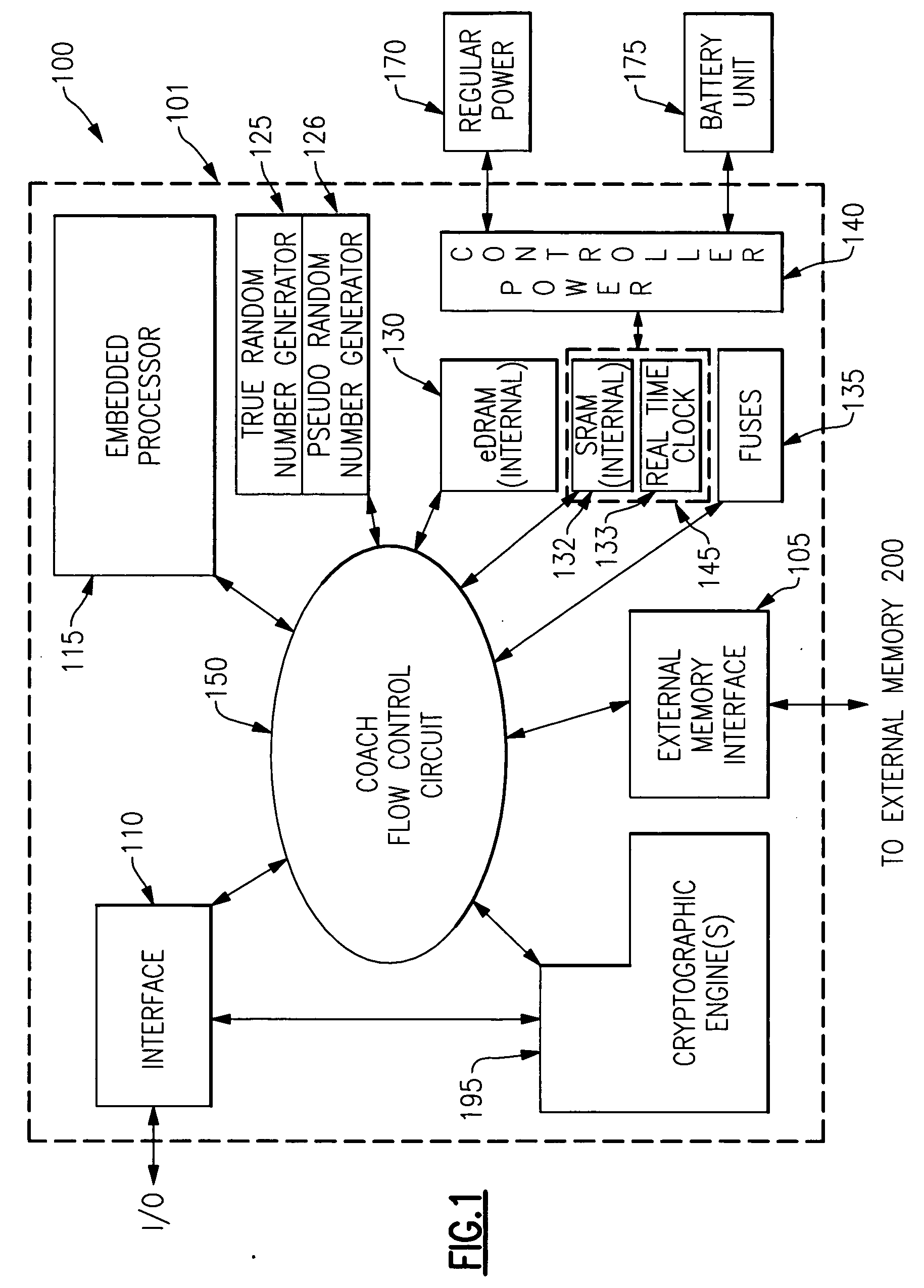

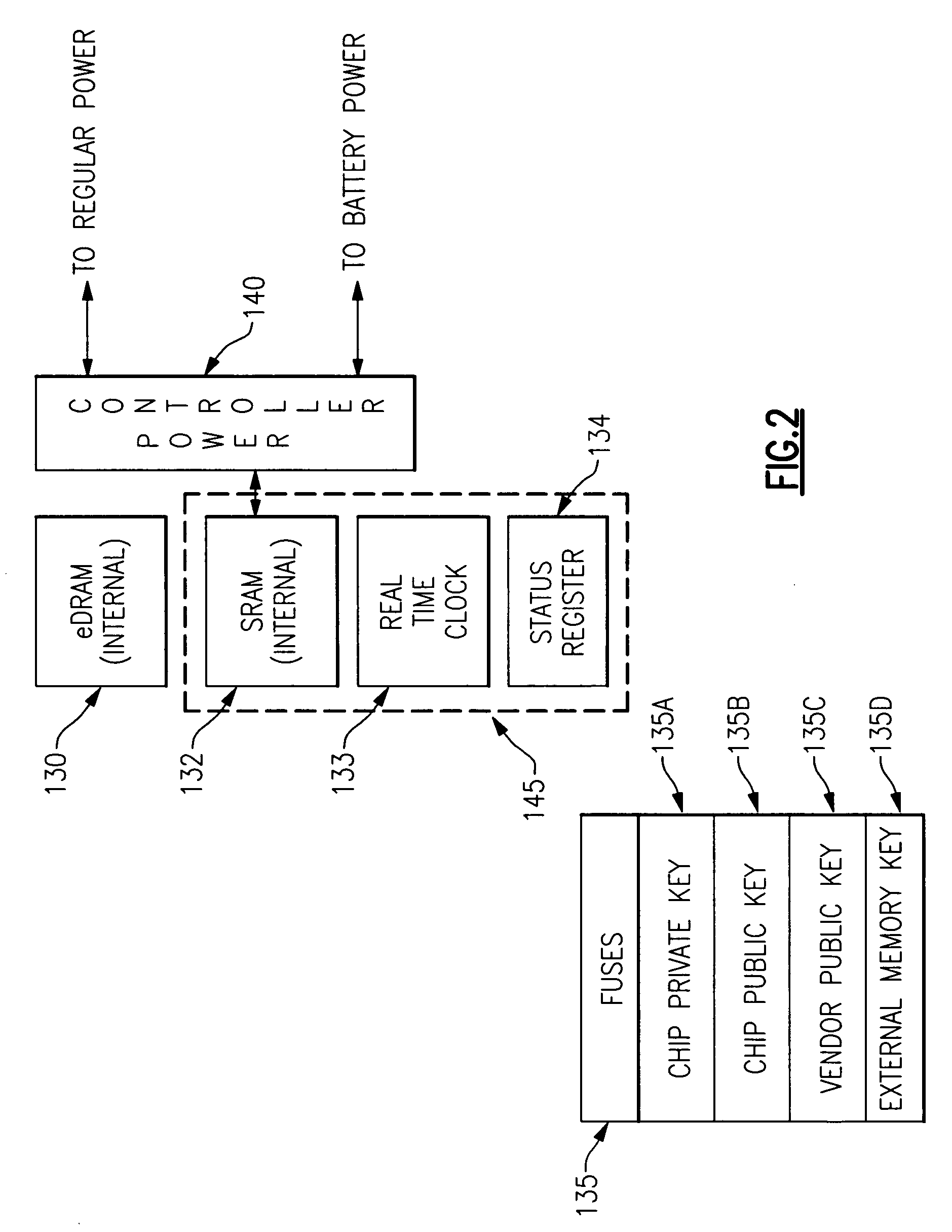

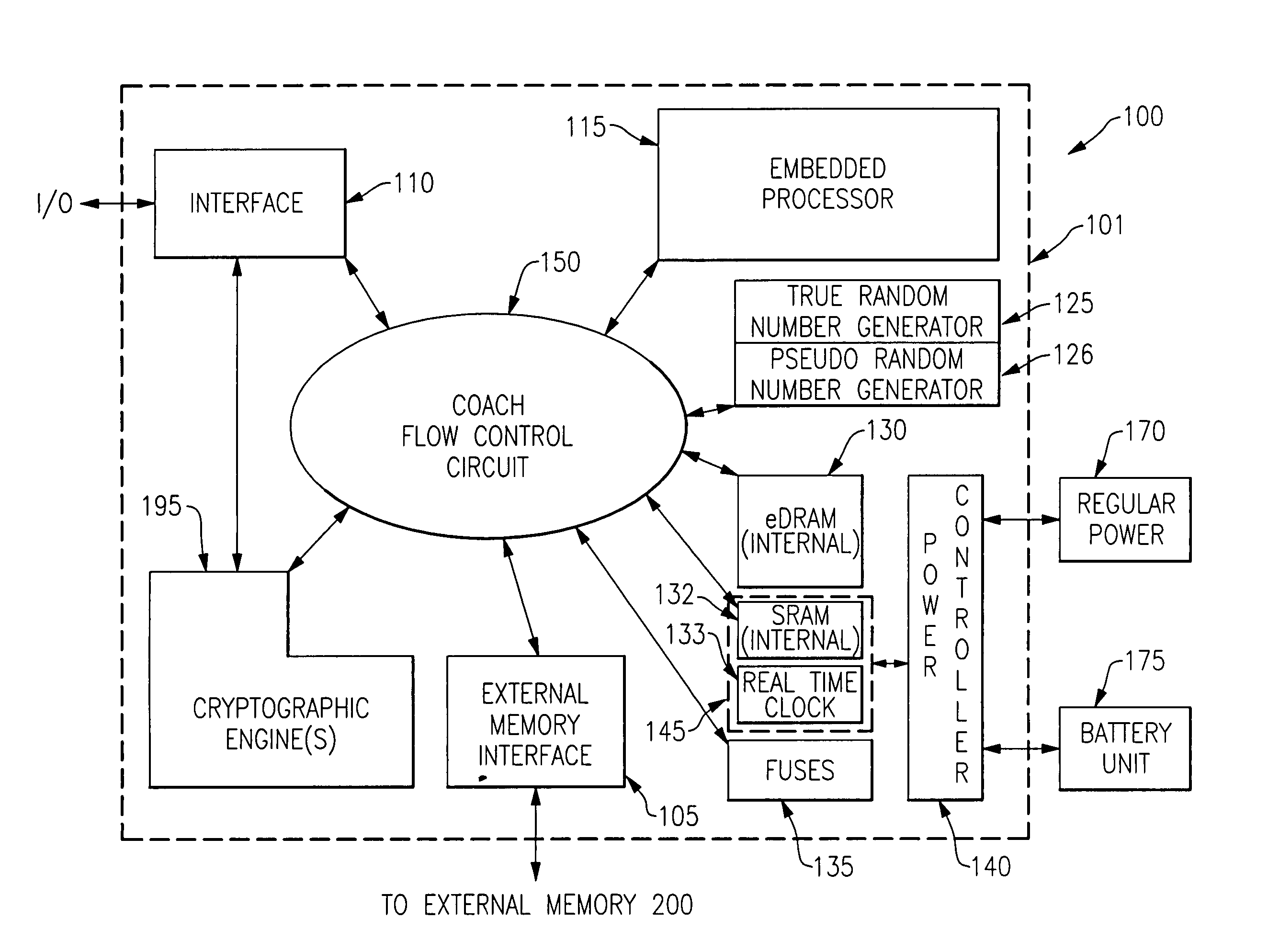

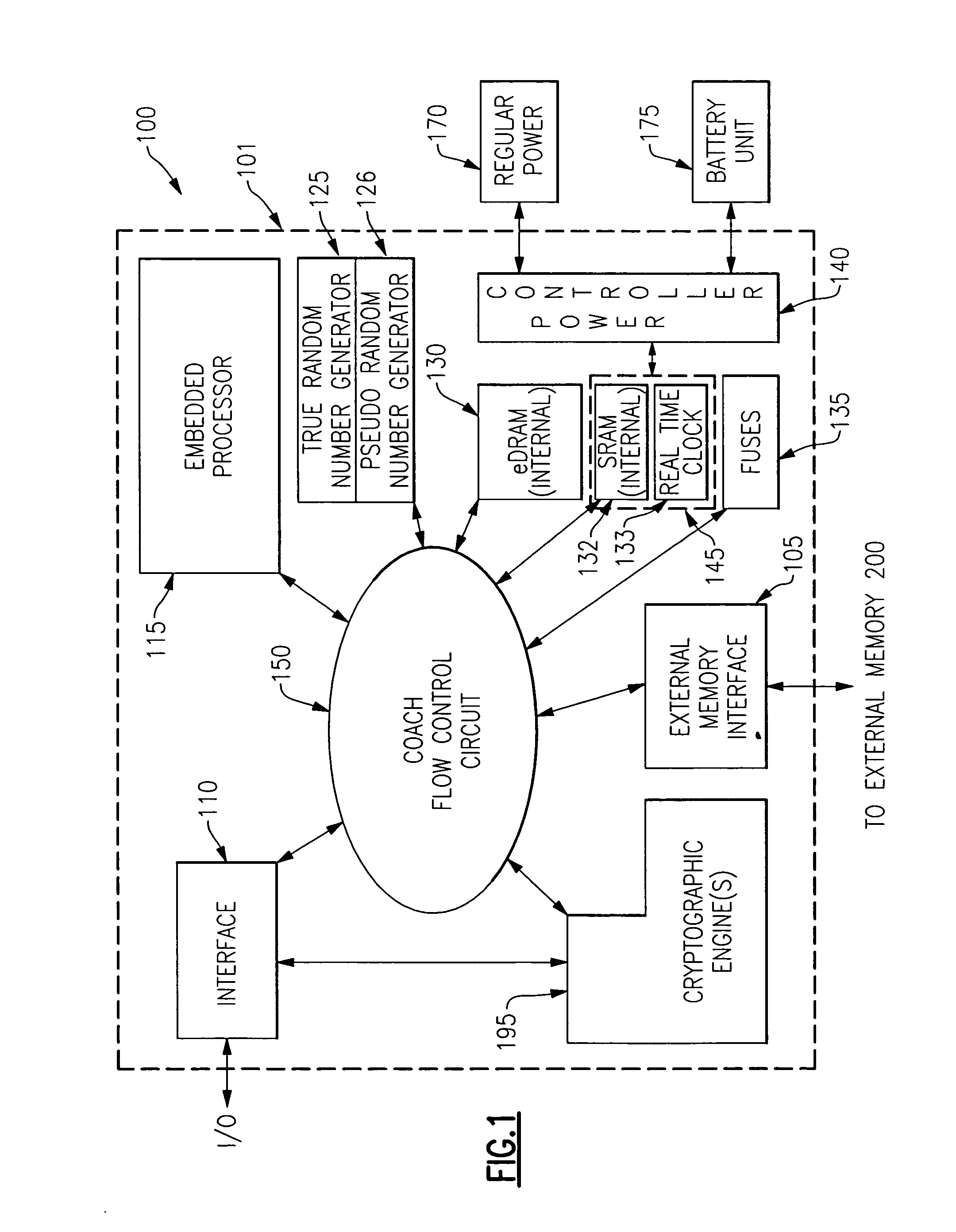

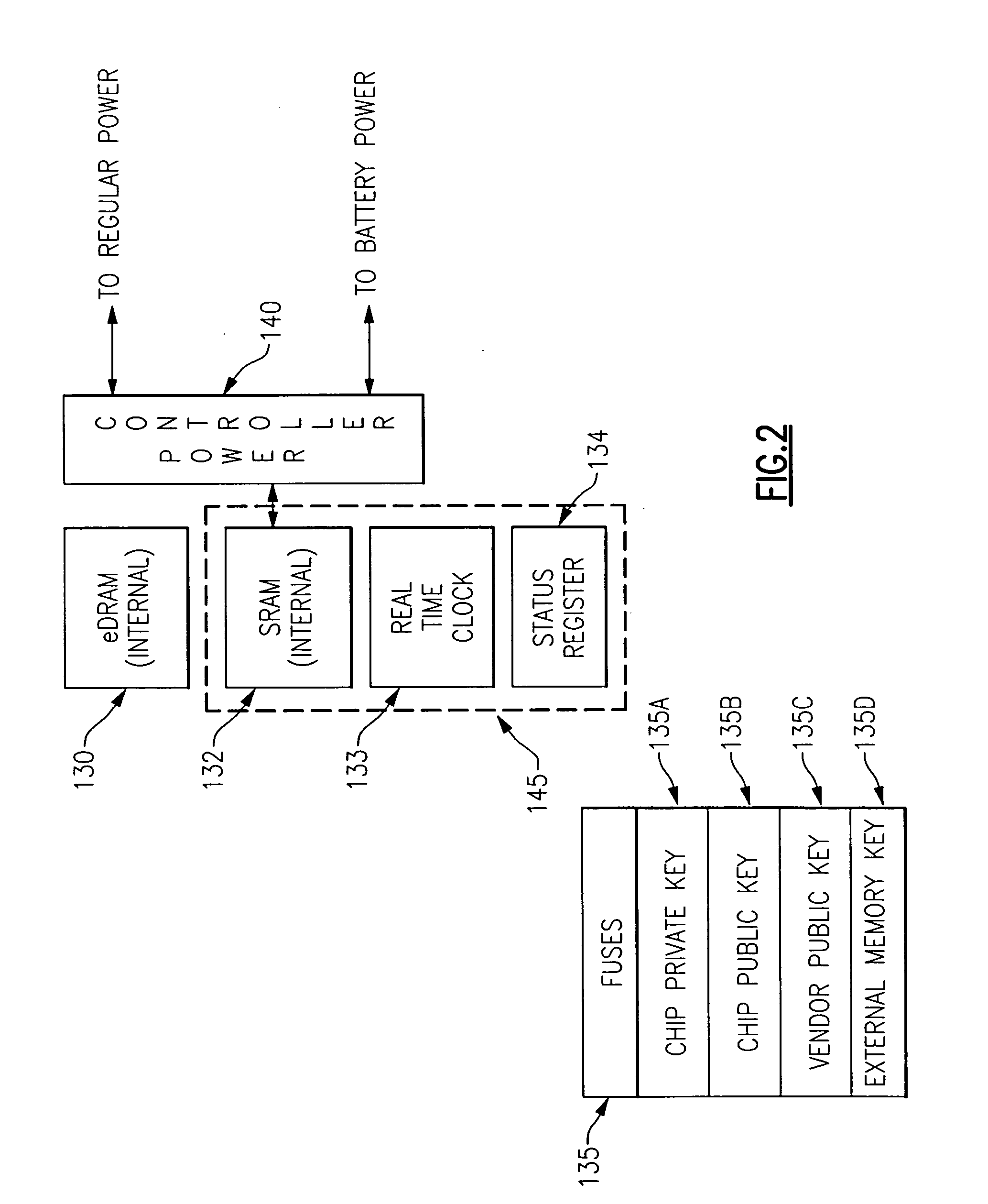

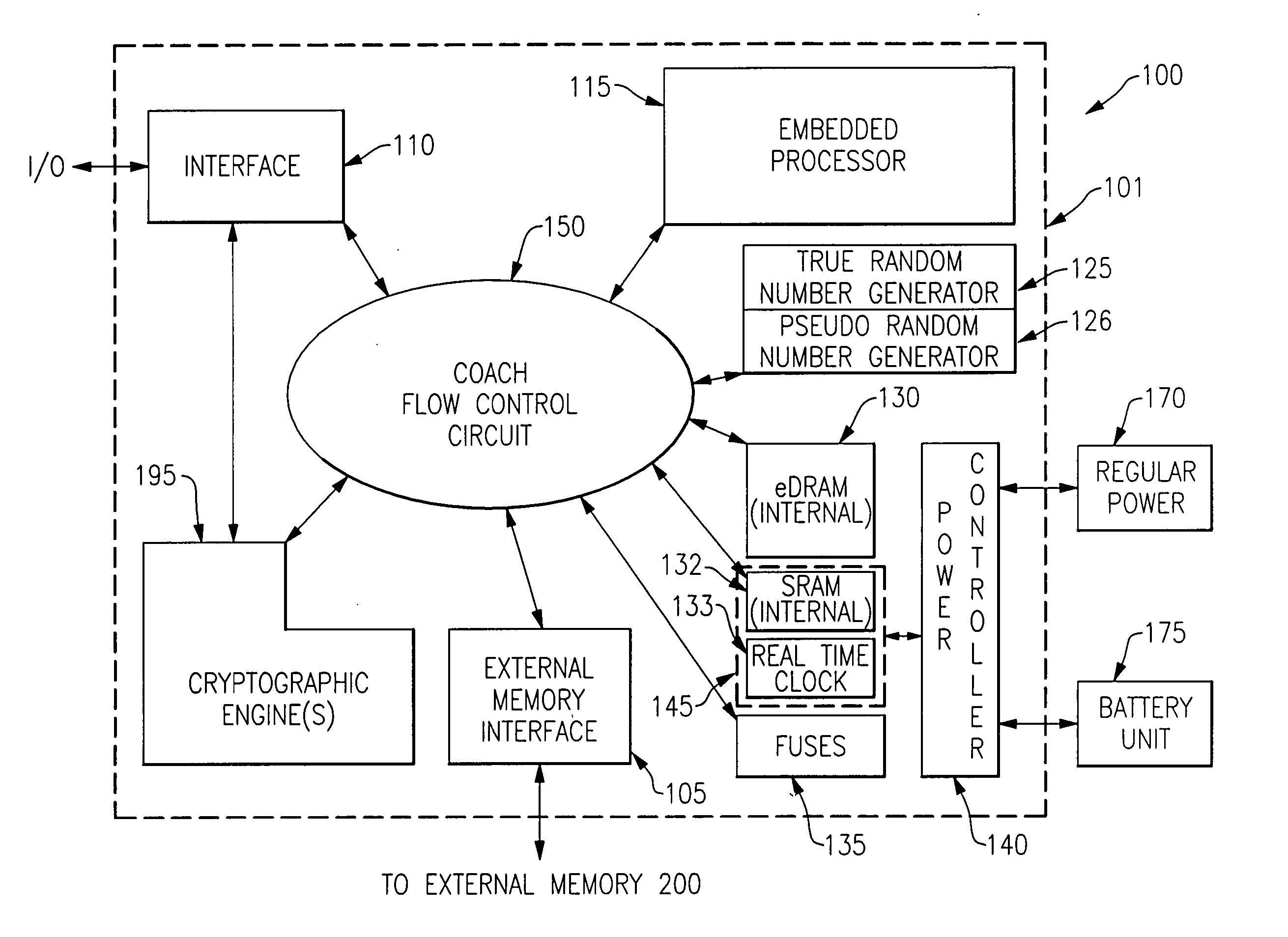

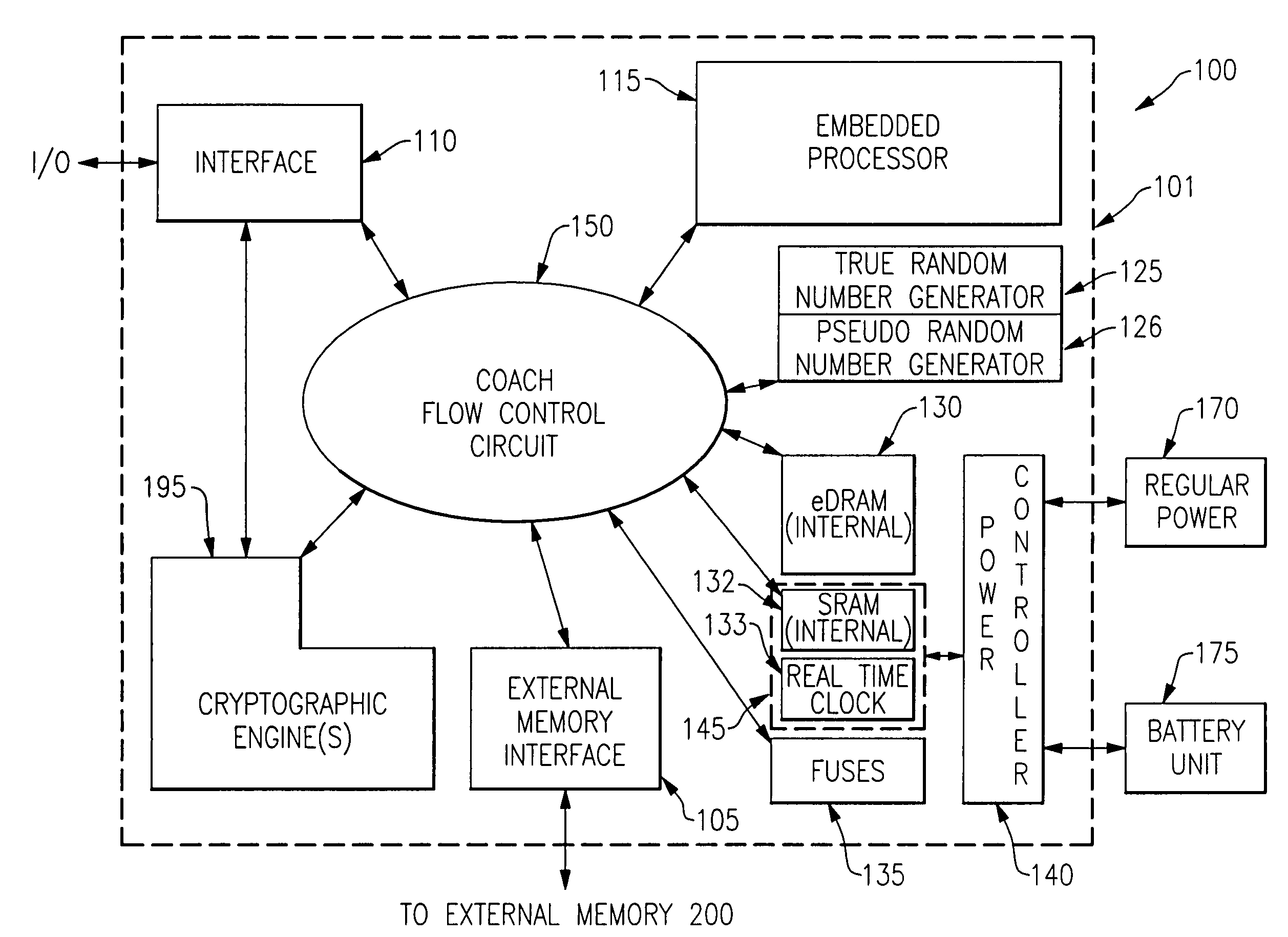

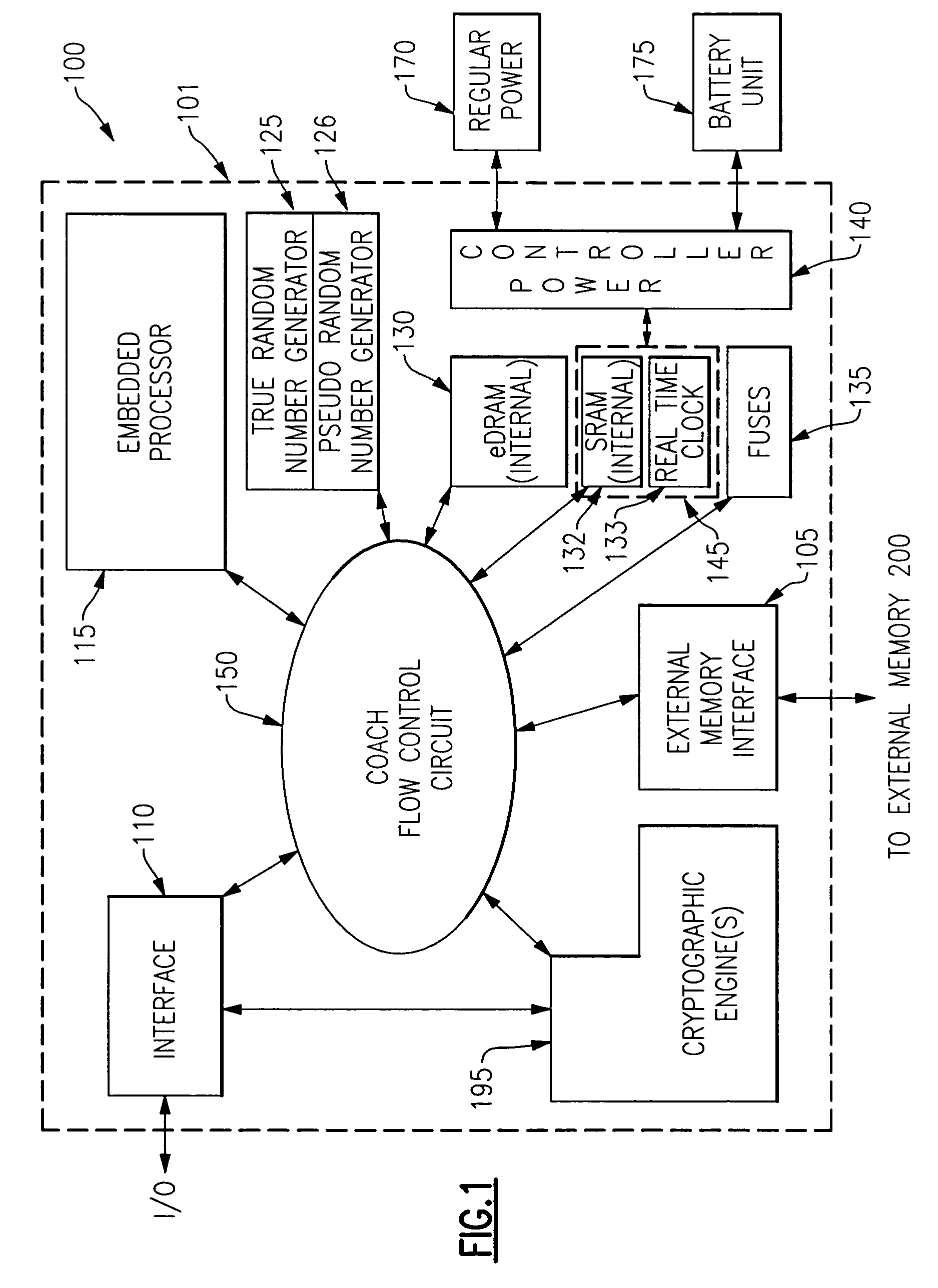

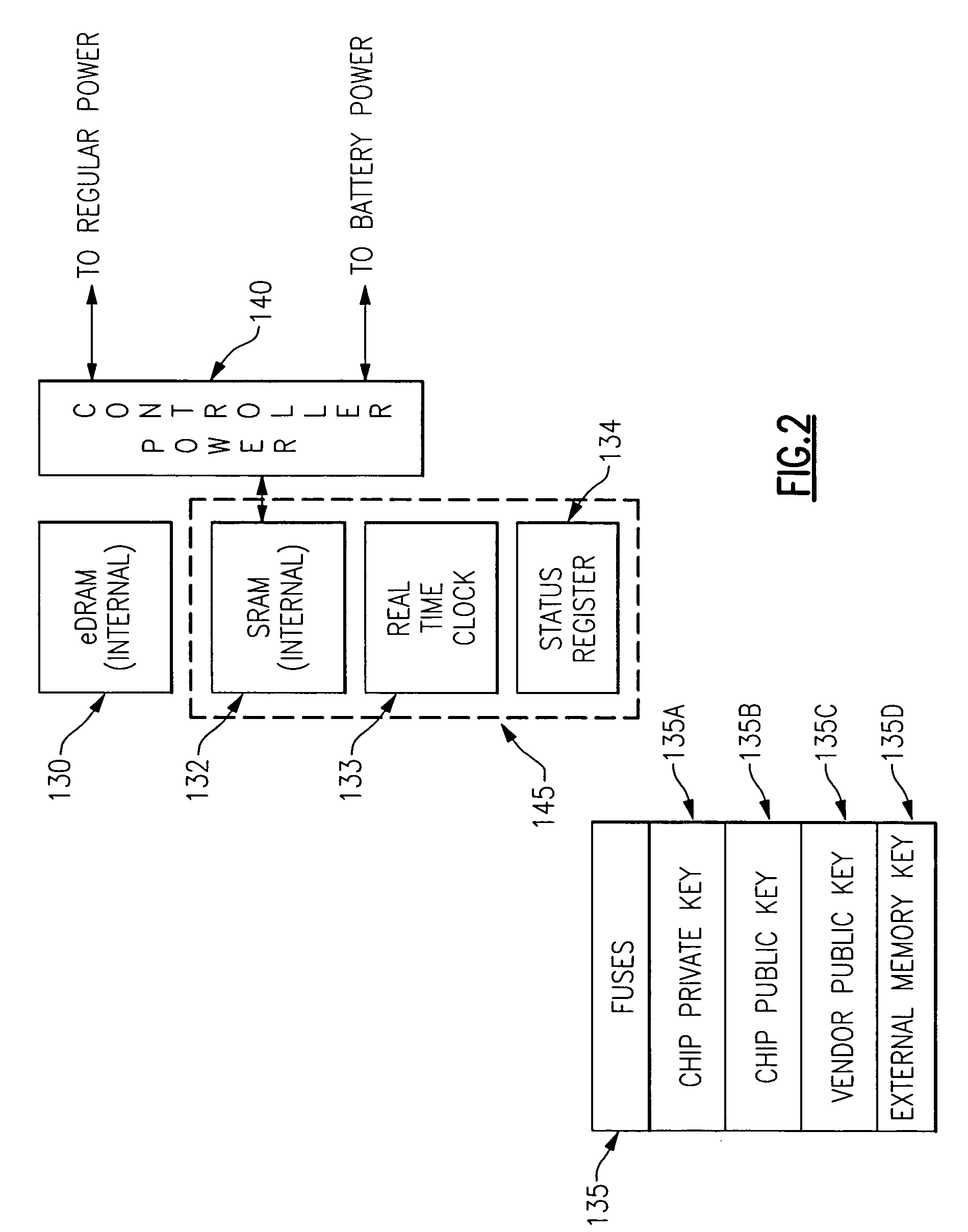

Circuit chip for cryptographic processing having a secure interface to an external memory

InactiveUS20060059369A1Improve process capabilityInhibit involvementUser identity/authority verificationUnauthorized memory use protectionInternal memoryStatic random-access memory

A mechanism is provided in which a secure chip for performing cryptographic and / or other functions is able to securely access a separate random access memory externally disposed with respect to a secure chip boundary. Addressing of the external memory is controlled so as to define certain regions therein which receive and store only encrypted information from the chip. Other regions of the external memory are set aside for the receipt and storage of unencrypted information. Access to the external memory is provided through a controlled interface which communicates with internal chip hardware which operates to control the flow of communication between various internal components such as cryptographic engines, data processors, internal memory of both the volatile and the nonvolatile variety and an external interface which provides the only other access to the chip. The internal chip hardware with which the external memory interface communicates is implemented as a combined ASIC and programmable hardware circuit, wherein the programmable hardware circuit is also securely configurable.

Owner:IBM CORP

System for securely configuring a field programmable gate array or other programmable hardware

InactiveUS20060059574A1Improve process capabilityInhibit involvementError detection/correctionVolume/mass flow measurementProgrammable logic deviceProgrammable hardware

A system and method are provided for securely providing configuration information, that is, programming, to programmable hardware such as a Field Programmable Gate Array (FPGA) or a Programmable Logic Device (PLD). Security is provided by first verifying authority to enter configuration information via the decryption of an encrypted certificate of authority. The decryption is carried out using a cryptography engine disposed on the chip containing the programmable hardware. Additionally, the configuration information is itself provided in an encrypted form which requires recognition of the certificate of authority in order to decrypt it and to place it in storage locations within the programmable hardware. In this manner, the flexibility advantages of programmable hardware are fully met without the disadvantage of the programmable hardware being compromised by other users.

Owner:IBM CORP

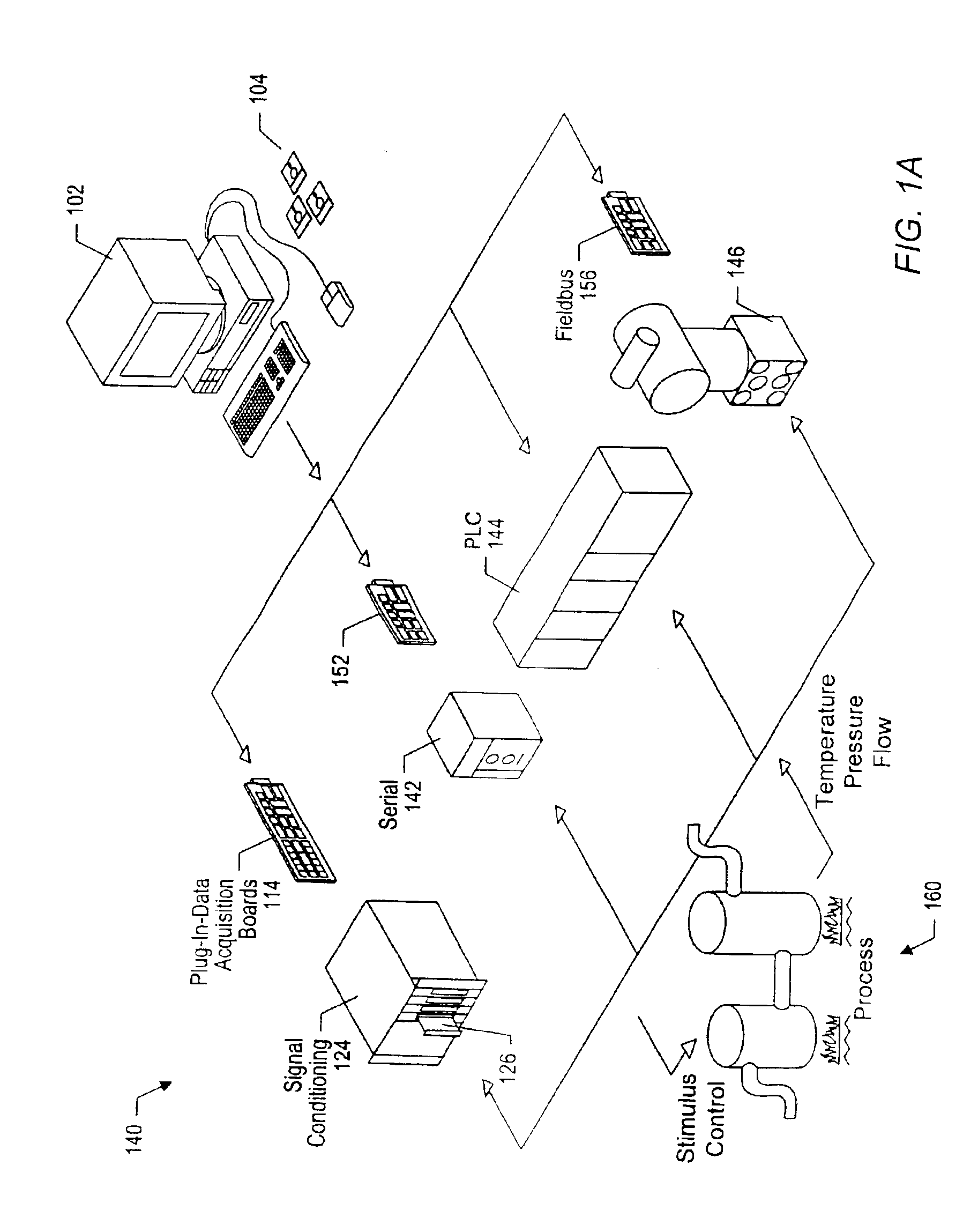

System and method for online specification of measurement hardware

InactiveUS20030036871A1Error preventionFrequency-division multiplex detailsComputer hardwareGraphics

A system and method for online configuration of a measurement device for a measurement system. The user accesses a server with a client computer over a network and specifies a desired measurement task. If the user lacks the hardware required to perform the task, hardware specifications and configuration software and / or data specific to the user's application, i.e., to perform the task, are sent to a manufacturer, who pre-configures the hardware with the configuration software and / or data to perform the task and sends the pre-configured hardware to the user. The hardware may be re-configurable hardware, such as a programmable hardware element or processor / memory based device. Configuration software and / or data for configuring the user's measurement system hardware (and / or software) to perform the desired task may also be sent to the user. The configuration software sent to the user may comprise a graphical program usable by the measurement system to perform the task.

Owner:NATIONAL INSTRUMENTS

Integrated circuit chip for encryption and decryption having a secure mechanism for programming on-chip hardware

InactiveUS20060059372A1Improve process capabilityInhibit involvementUnauthorized memory use protectionHardware monitoringHard codingChip architecture

An integrated circuit chip is provided which contains one or more processors and one or more cryptographic engines. A flow control circuit having a command processor accepts requests and data via a secure external interface through which only encrypted information is passed. The flow control circuit mediates decryption of this information using cryptographic keys that are present in hard coded form on the chip. In particular the flow control circuit includes a programmable hardware portion which is configurable in a secure manner to create a flexible internal chip architecture. The chip also includes a volatile memory disposed on a voltage island on which is maintained either through a battery backup or from a fixed power source (mains). The chip is thus enabled to securely perform cryptographic operations with the processors controlling the cryptographic engines through the flow control circuit.

Owner:IBM CORP

Specifying and targeting portions of a graphical program for execution by multiple targets

InactiveUS6934668B2Detecting faulty hardware by remote testComputation using non-denominational number representationGraphicsComputer architecture

A computer-implemented system and method for generating a hardware implementation of graphical code. The method comprises first creating a graphical program. A first portion of the graphical program may optionally be compiled into machine code for execution by a CPU. A second portion of the graphical program is converted into a hardware implementation according to the present invention. The operation of converting the graphical program into a hardware implementation comprises exporting the second portion of the graphical program into a hardware description, wherein the hardware description describes a hardware implementation of the second portion of the graphical program, and then configuring a programmable hardware element utilizing the hardware description to produce a configured hardware element. The configured hardware element thus implements a hardware implementation of the second portion of the graphical program.

Owner:NATIONAL INSTRUMENTS

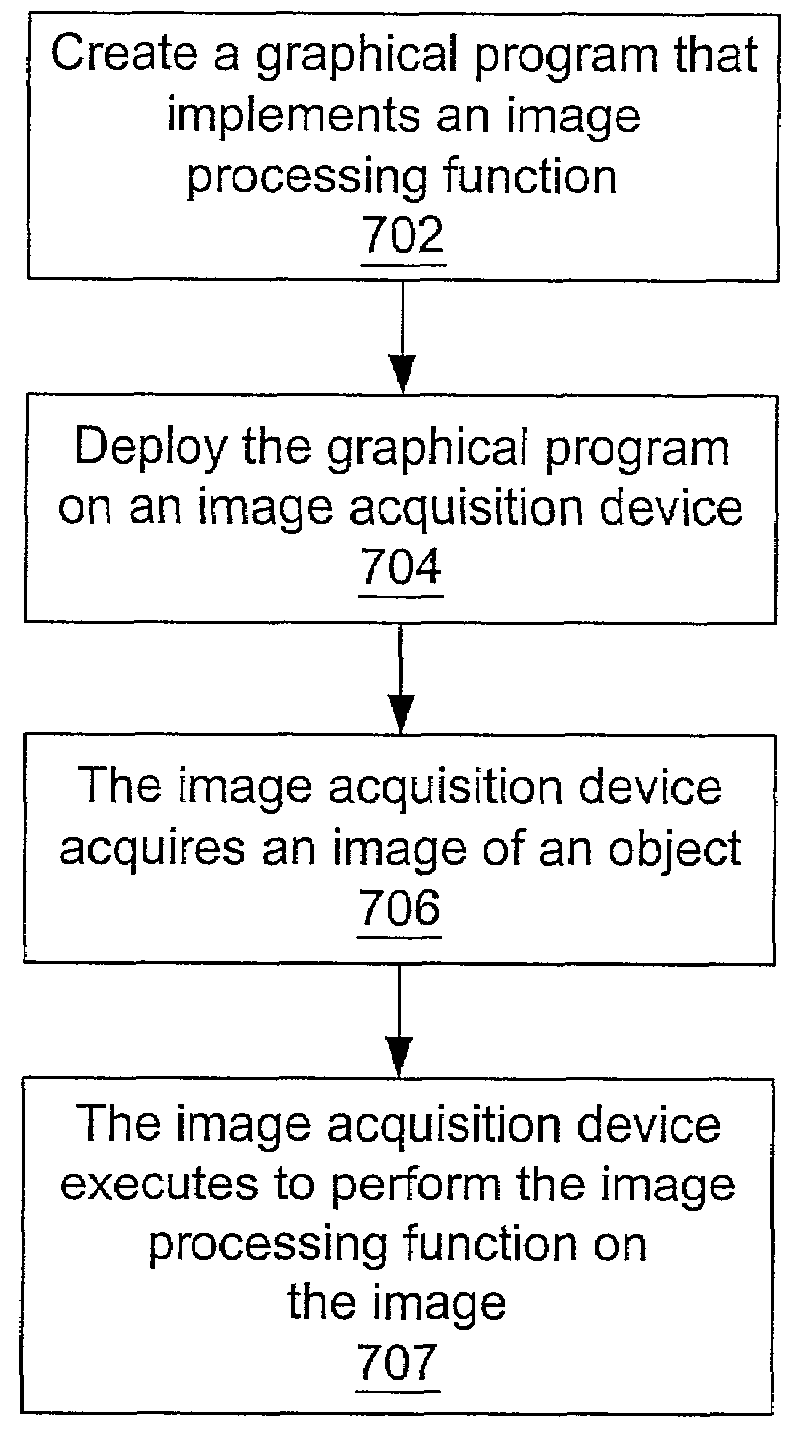

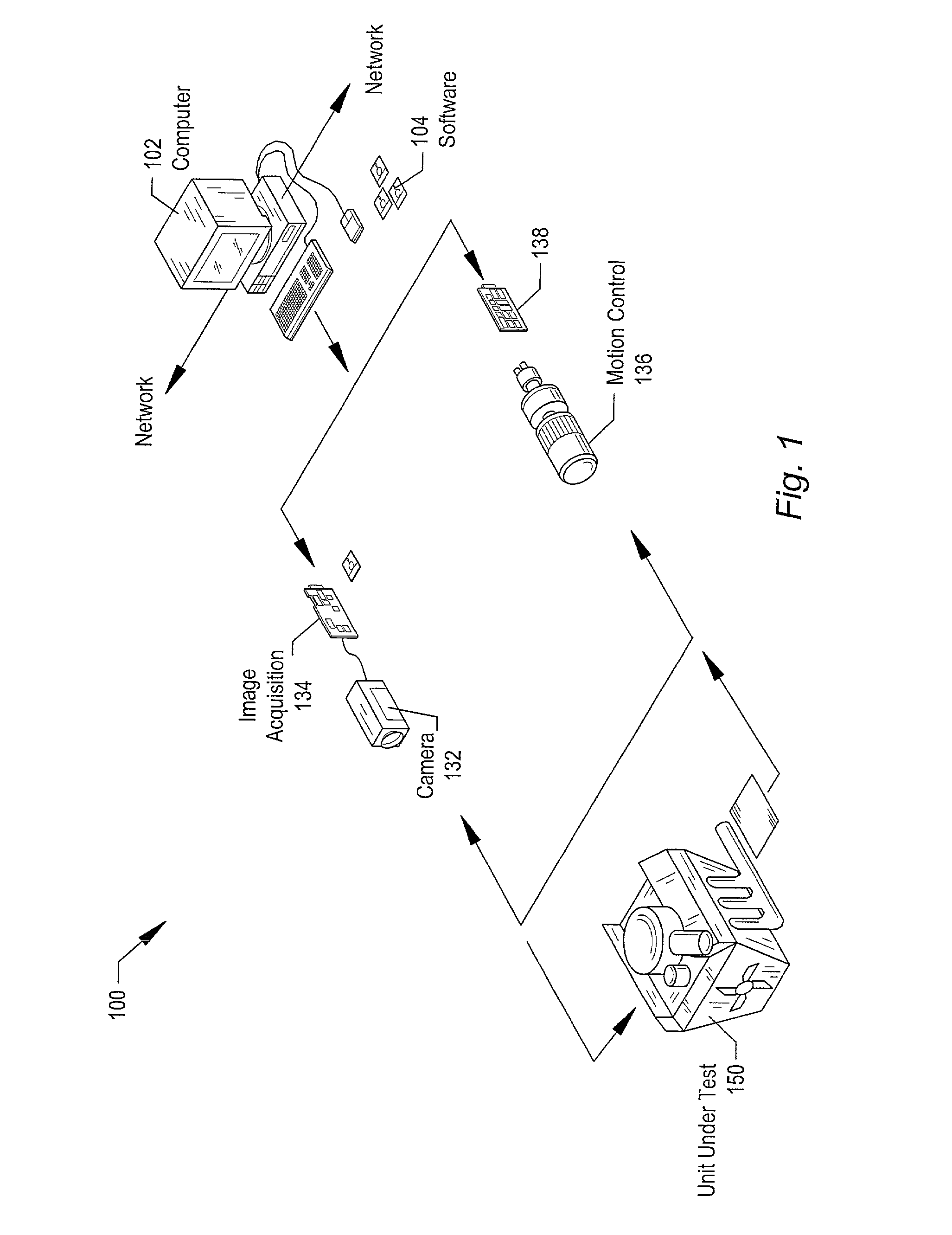

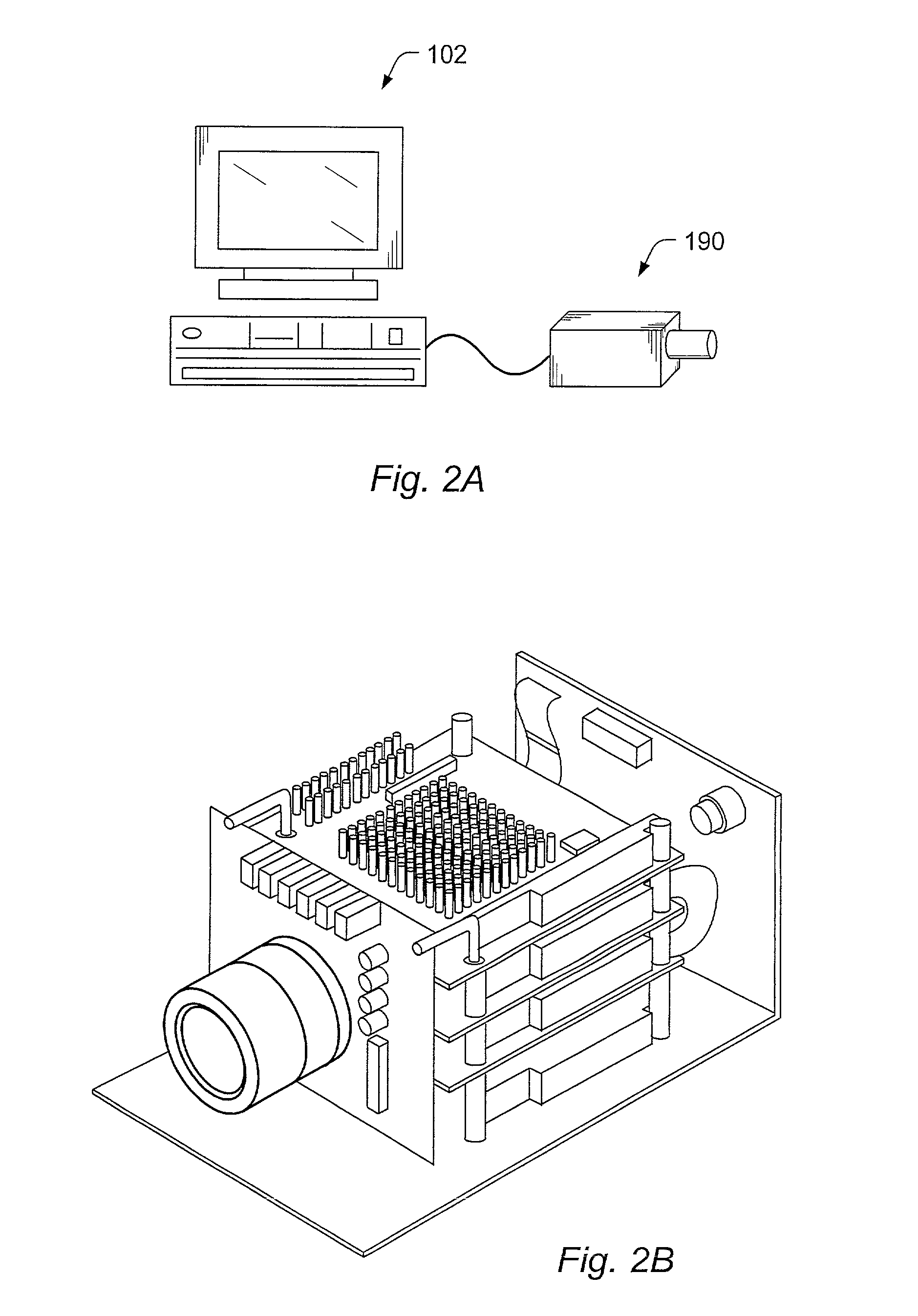

System and method for deploying a graphical program on an image acquisition device

InactiveUS6971066B2Television system detailsDetecting faulty hardware by remote testComputer hardwareComputer architecture

A computer-implemented system and method for deploying a graphical program onto an image acquisition (IMAQ) device. The method may operate to configure an image acquisition (IMAQ) device to perform image processing or machine vision functions, wherein the device includes a programmable hardware element and / or a processor and memory. The method comprises first creating a graphical program which implements the image processing or machine vision function. A portion of the graphical program may be converted into a hardware implementation on a programmable hardware element, and a portion may optionally be compiled into machine code for execution by a CPU. The programmable hardware element is thus configured utilizing a hardware description and implements a hardware implementation of at least a portion of the graphical program. The CPU-executable code may be executed by a computer coupled to the IMAQ device, or by a processor / memory on the IMAQ device.

Owner:NATIONAL INSTRUMENTS

Implementation of packet-based communications in a reconfigurable hardware element

In some embodiments, a user may select an elemental function such as read, write, or configuration from a graphical programming environment. A file may be created that instantiates functionality into a programmable hardware element to allow it to send a command across a serial protocol to peripheral interface circuitry and ultimately to peripheral chips (e.g., network chips on a CAN). The elemental node concept may be generic to any network chip because the node may contain only the general data of a packet (e.g., command type, value of data bytes, etc). The actual interface to a network chip may be handled inside the peripheral interface circuitry. The peripheral interface circuitry may have the details of the network chip in which it interfaces and may abstract details of the network chip from the target programmable hardware element through the serial protocol.

Owner:NATIONAL INSTRUMENTS

System and method for processing by distinct entities securely configurable circuit chips

InactiveUS20060059368A1Improve process capabilityInhibit involvementUser identity/authority verificationUnauthorized memory use protectionHard codingThird party

A system and method are provided in which a third party chip vendor is enabled to securely program an electronic circuit chip supplied from a chip manufacturer. The chip vendor supplies a vendor's public cryptography key to the chip manufacturer who hard codes it on the chip along with a chip private key and a chip public key. One or more cryptographic engines on the chip, which preferably has a tamper resistant / detecting boundary, are used to decrypt program instructions supplied to the chip after having been encrypted with the vendor's private key and the chip public key. The chip includes a processor and an associated memory which receives a version of the instructions decrypted with the chip private key and the vendor's public key. The chip also preferably includes programmable hardware which is also securely programmable by the downstream chip vendor. The chip, as processed by the chip vendor is shipped with a battery in place to provide power for maintaining data held in volatile memory portions of the chip.

Owner:IBM CORP

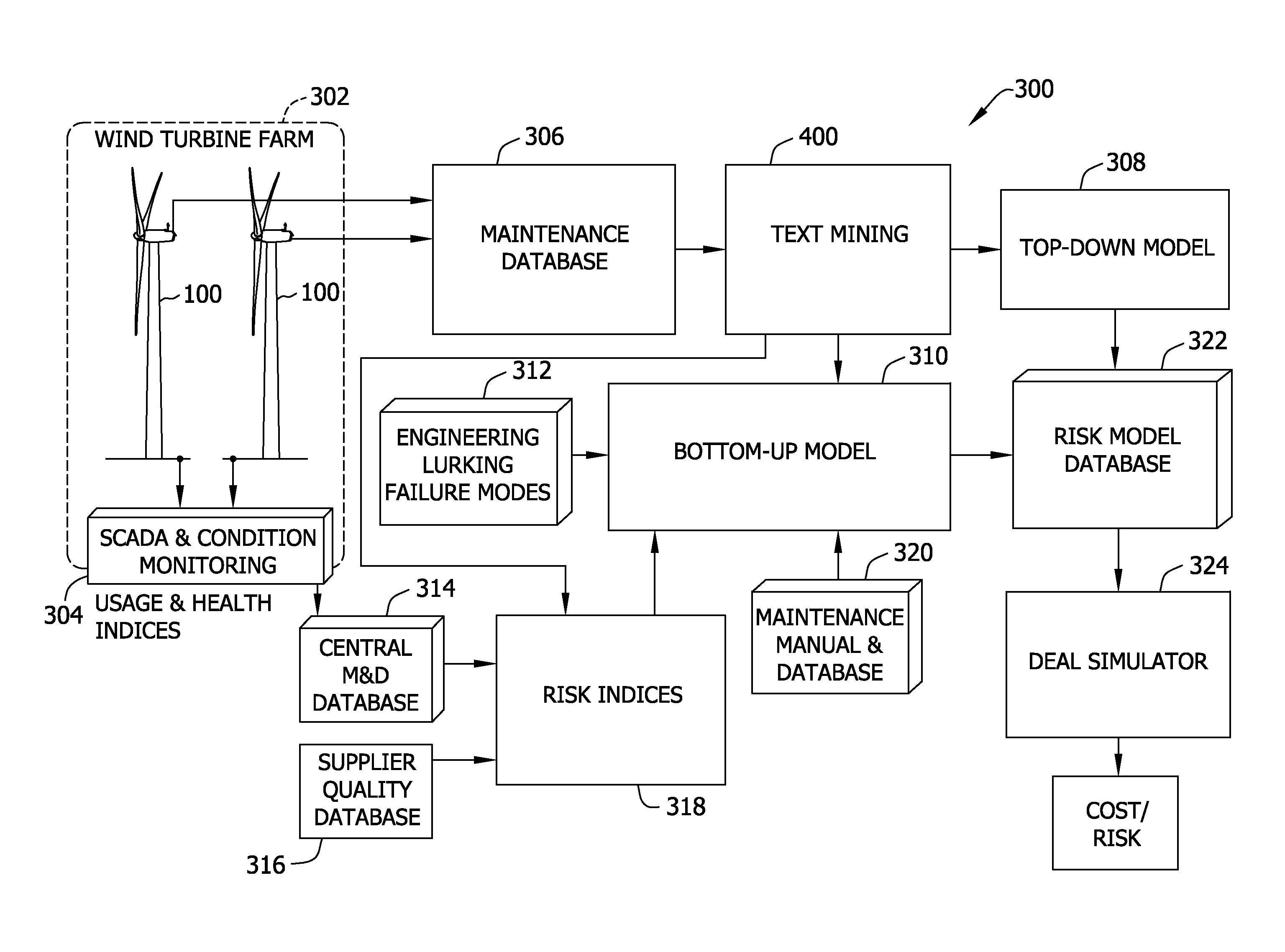

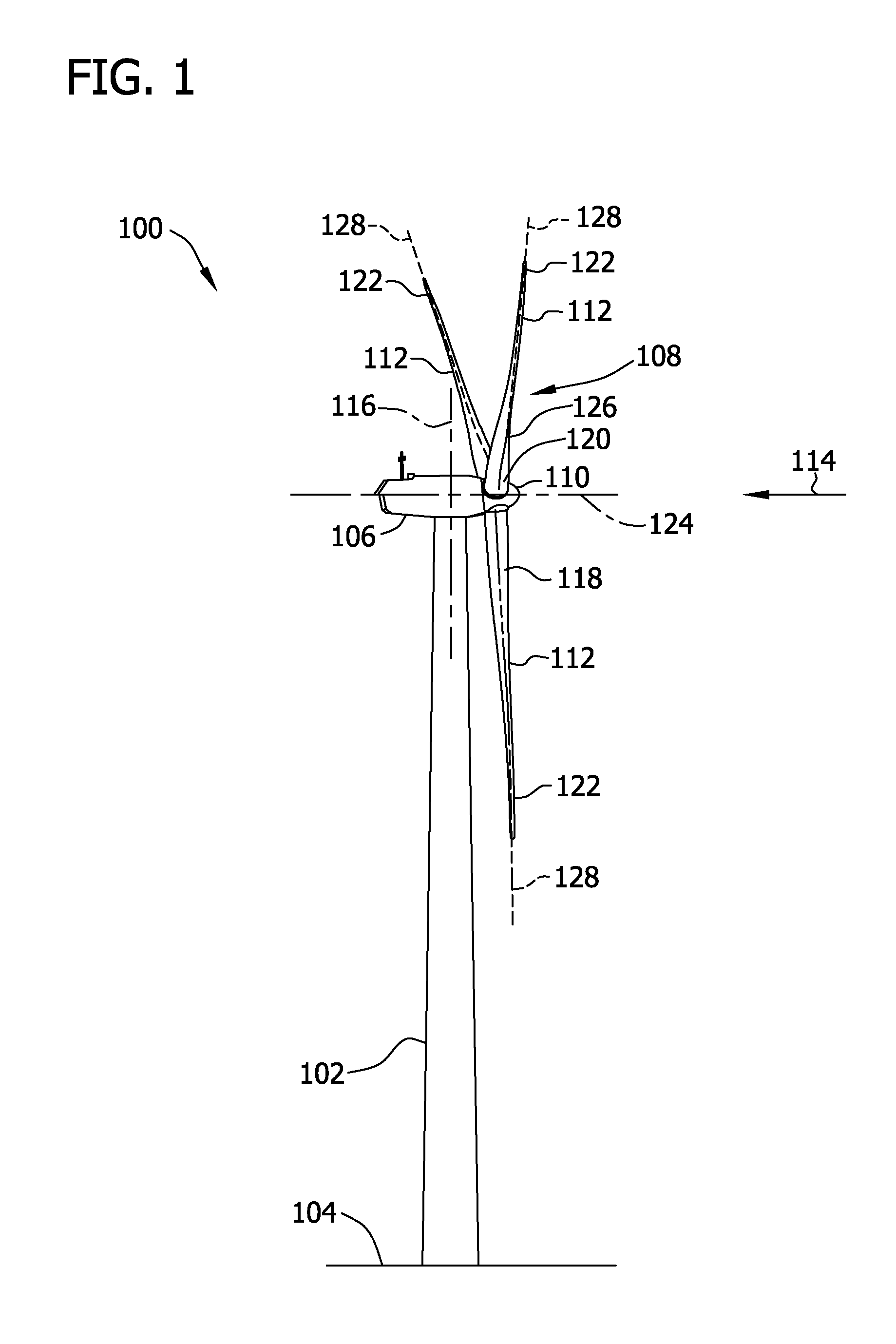

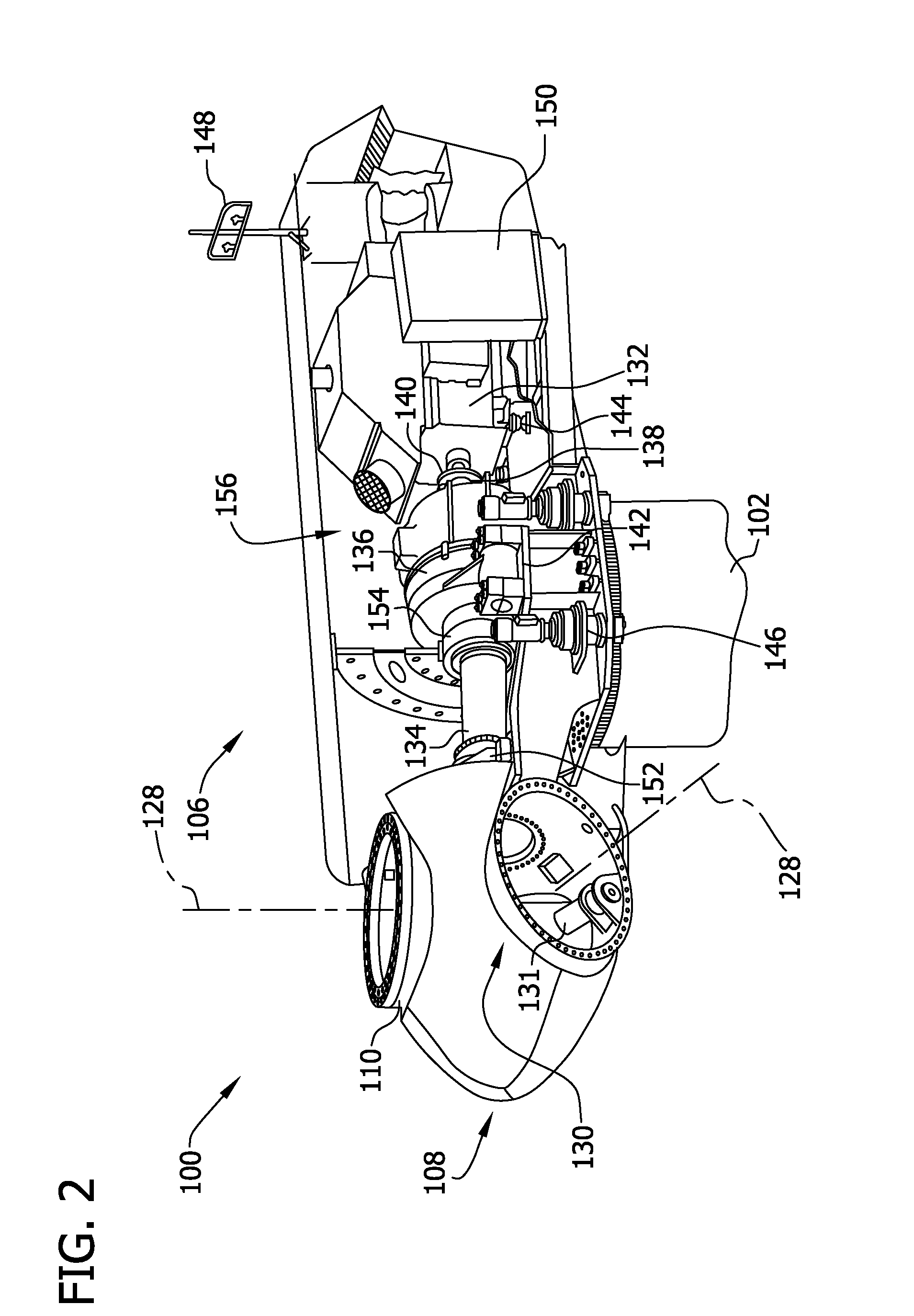

Risk management system for use with service agreements

A system for use with a risk management system is provided. The system includes a memory device configured to store data including at least historical service records of at least one wind turbine and new service records of the at least one wind turbine and a processor unit coupled to the memory device. The processor unit includes a programmable hardware component that is programmed. The processor unit is configured to analyze, by a processing system, text of the historical service records to generate a prediction model including a plurality of failure categories; and analyze, by a monitoring system, text of the new service records to classify each new service record based on the prediction model.

Owner:GENERAL ELECTRIC CO

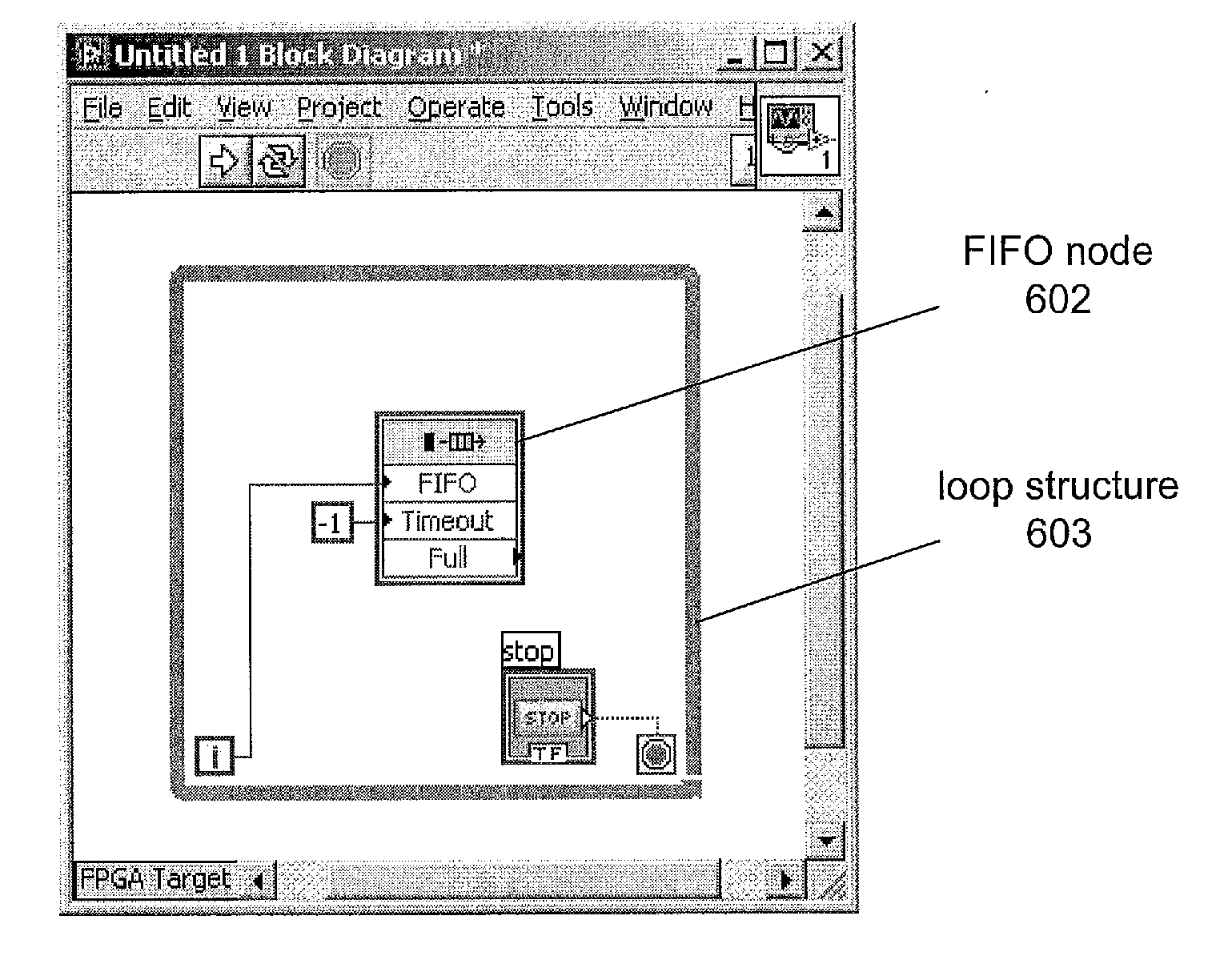

Graphical Programs With FIFO Structure For Controller/FPGA Communications

ActiveUS20070089063A1Facilitates direct memory access of memoryEasy accessAnalogue computers for electric apparatusCAD circuit designGraphicsDirect memory access

System and method for communicating between graphical programs executing on respective devices, e.g., a programmable hardware element (PHE) and a controller. The system includes a first node representing a first in, first out (FIFO) structure, and a second node providing a controller interface to the FIFO structure. A first portion of the FIFO is implemented on the PHE, and a second portion of the FIFO is implemented in memory of the controller. The first and second nodes are operable to be included respectively in first and second graphical programs, where the first graphical program is deployable to the PHE, where the second graphical program is deployable to the controller, and where the graphical programs communicate via the FIFO in cooperatively performing a specified task. The FIFO may implement a Direct Memory Access (DMA) FIFO, where at least part of a DMA controller is implemented on or coupled to the PHE.

Owner:NATIONAL INSTRUMENTS

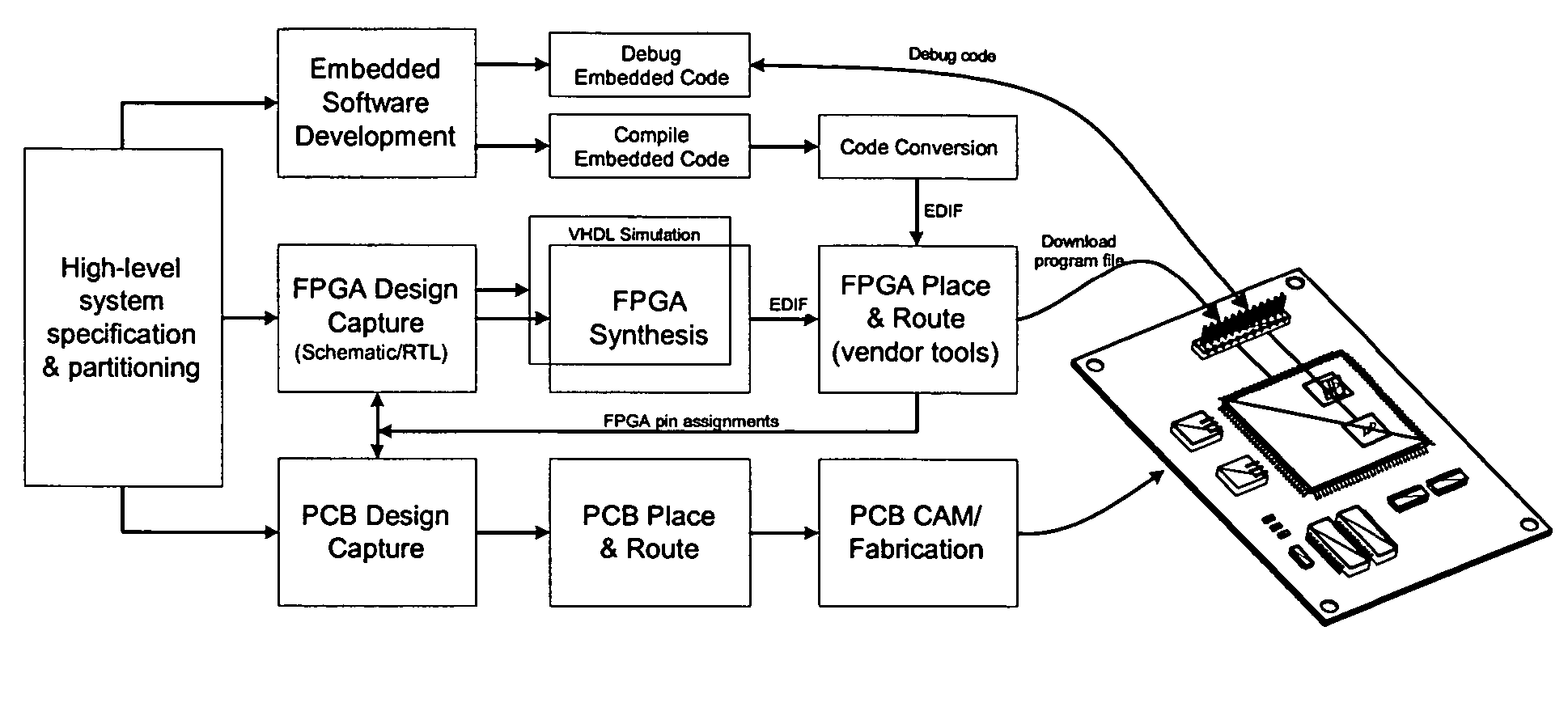

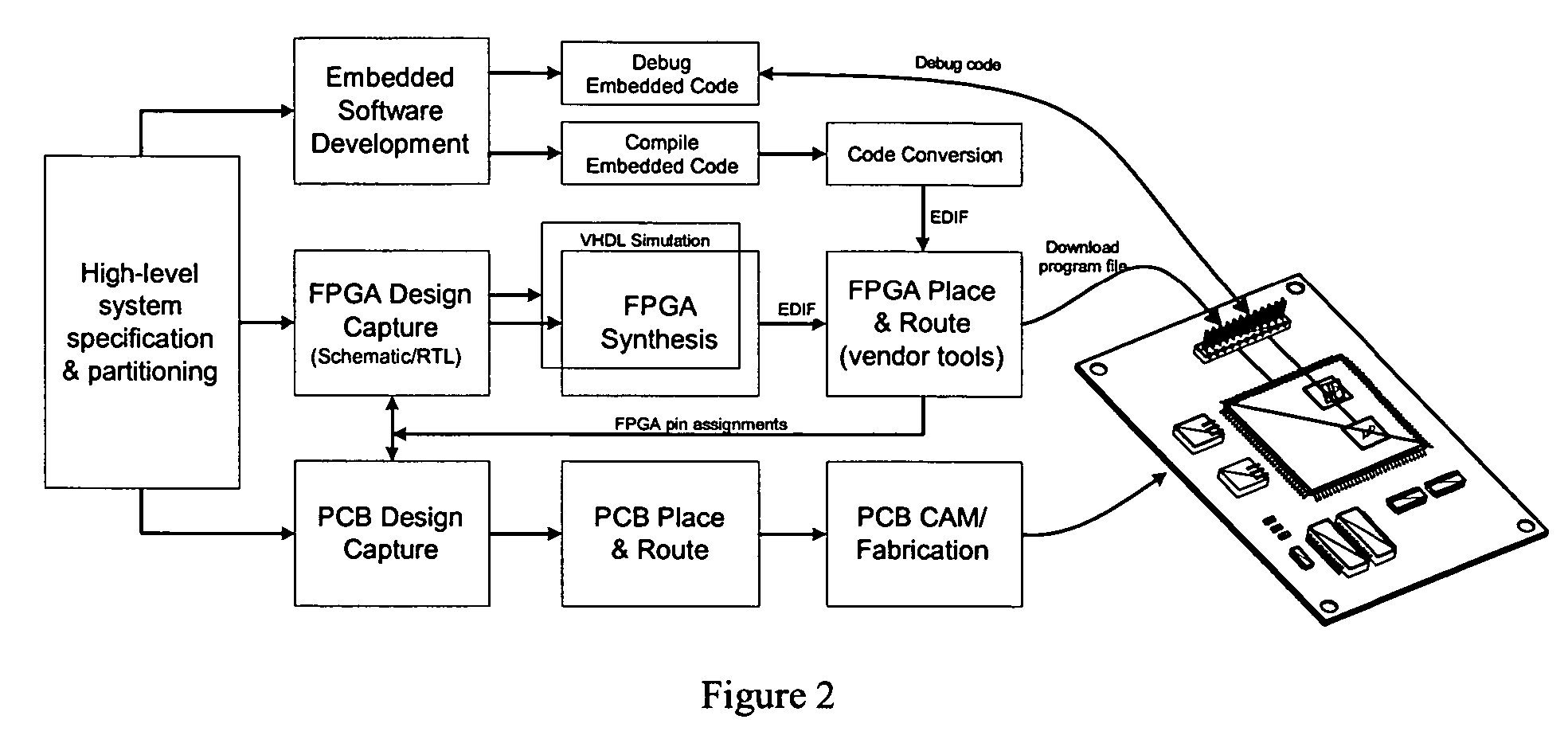

System for designing re-programmable digital hardware platforms

InactiveUS7340693B2Assembly is complexEasy to moveCAD circuit designSpecial data processing applicationsComputer hardwareComputer architecture

A digital design system and method are provided for re-programmable hardware platforms, such as field programmable gate arrays (FPGAs) and other re-programmable system designs. The design system and method bridge the gap between what has previously been a development and prototyping platform used during the design phase of an electronic design system (EDS) project, and commercially viable re-programmable product platforms to replace non-programmable platforms, such as discrete processors and ASICs.

Owner:MITSUBISHI CABLE IND LTD

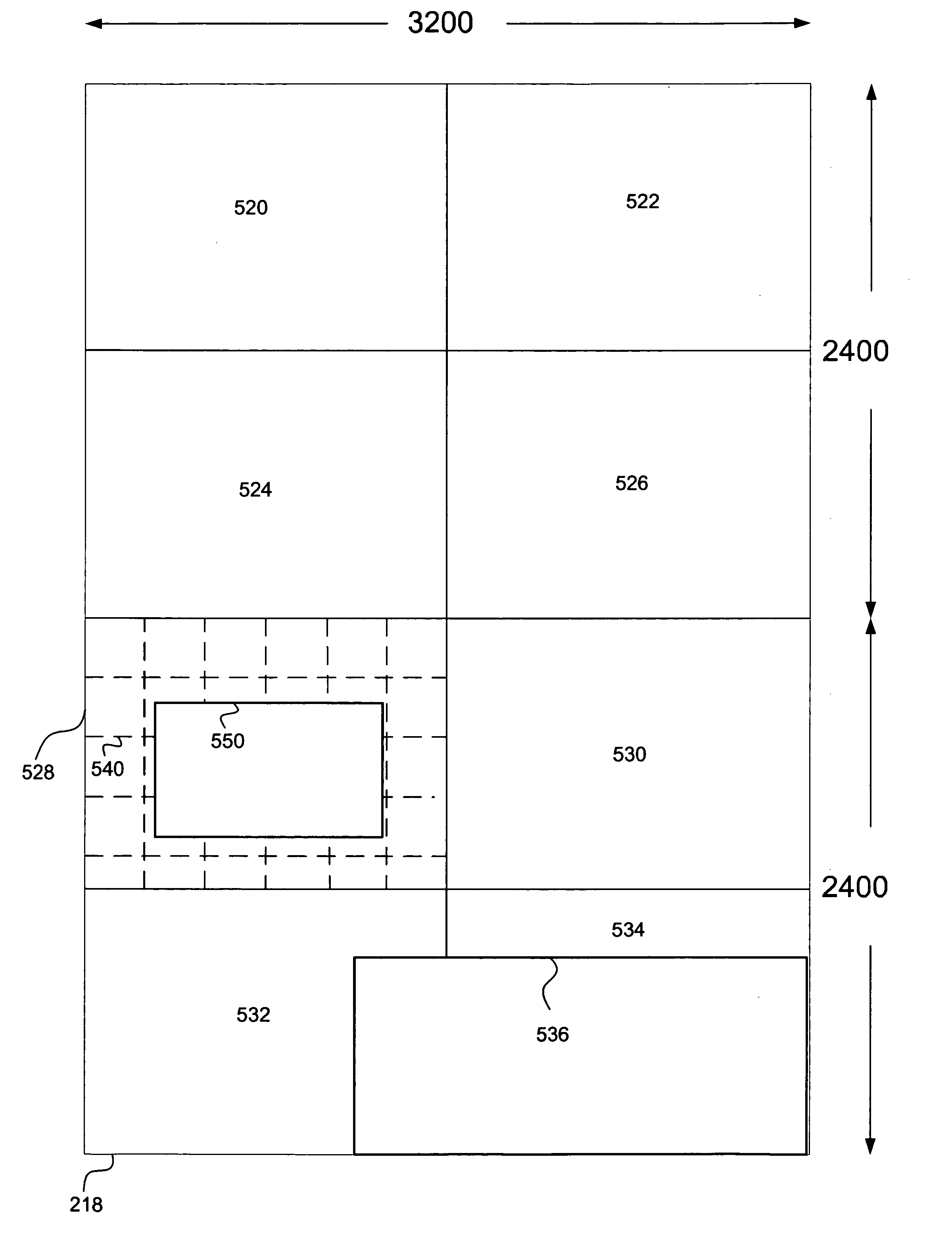

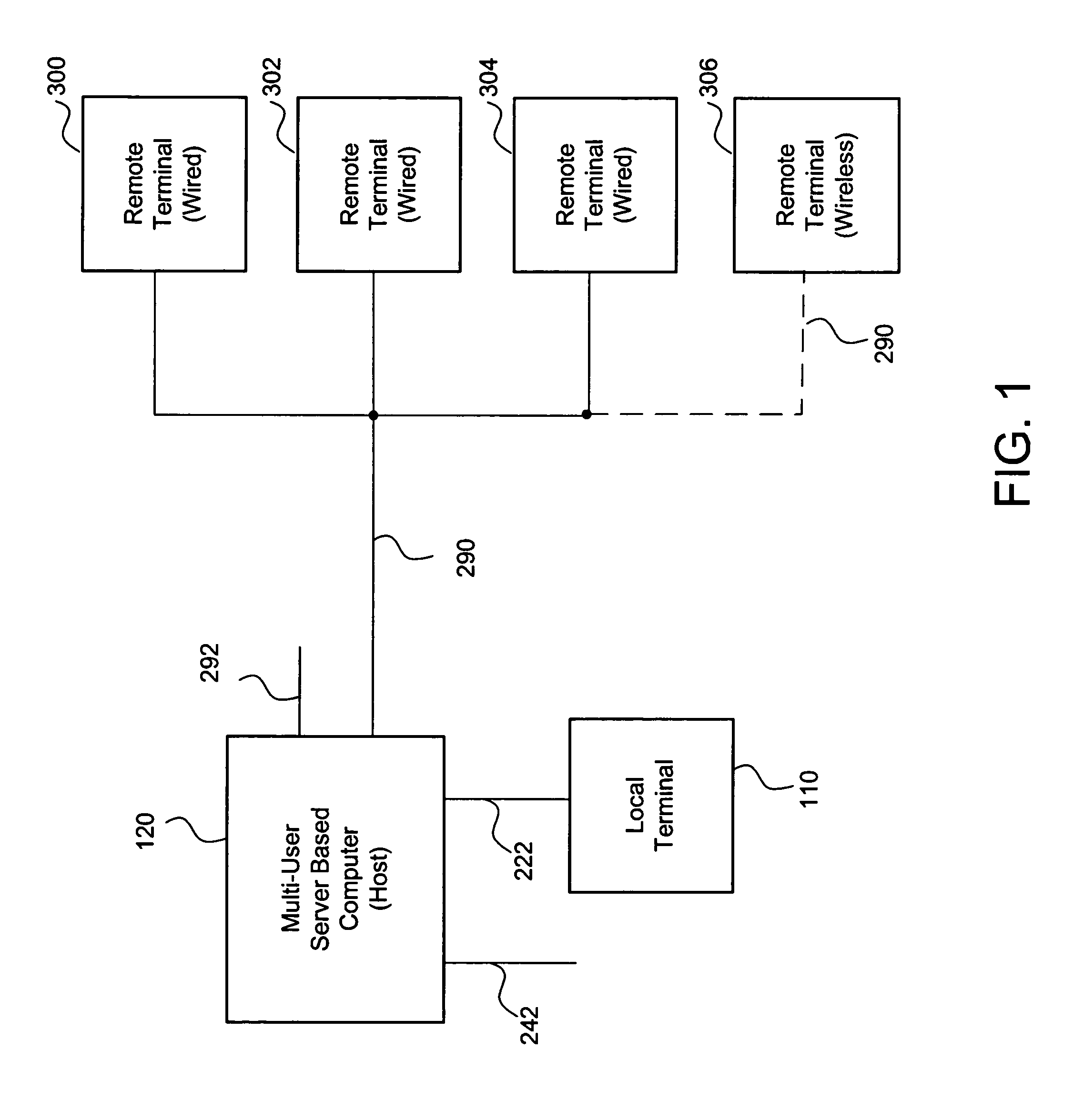

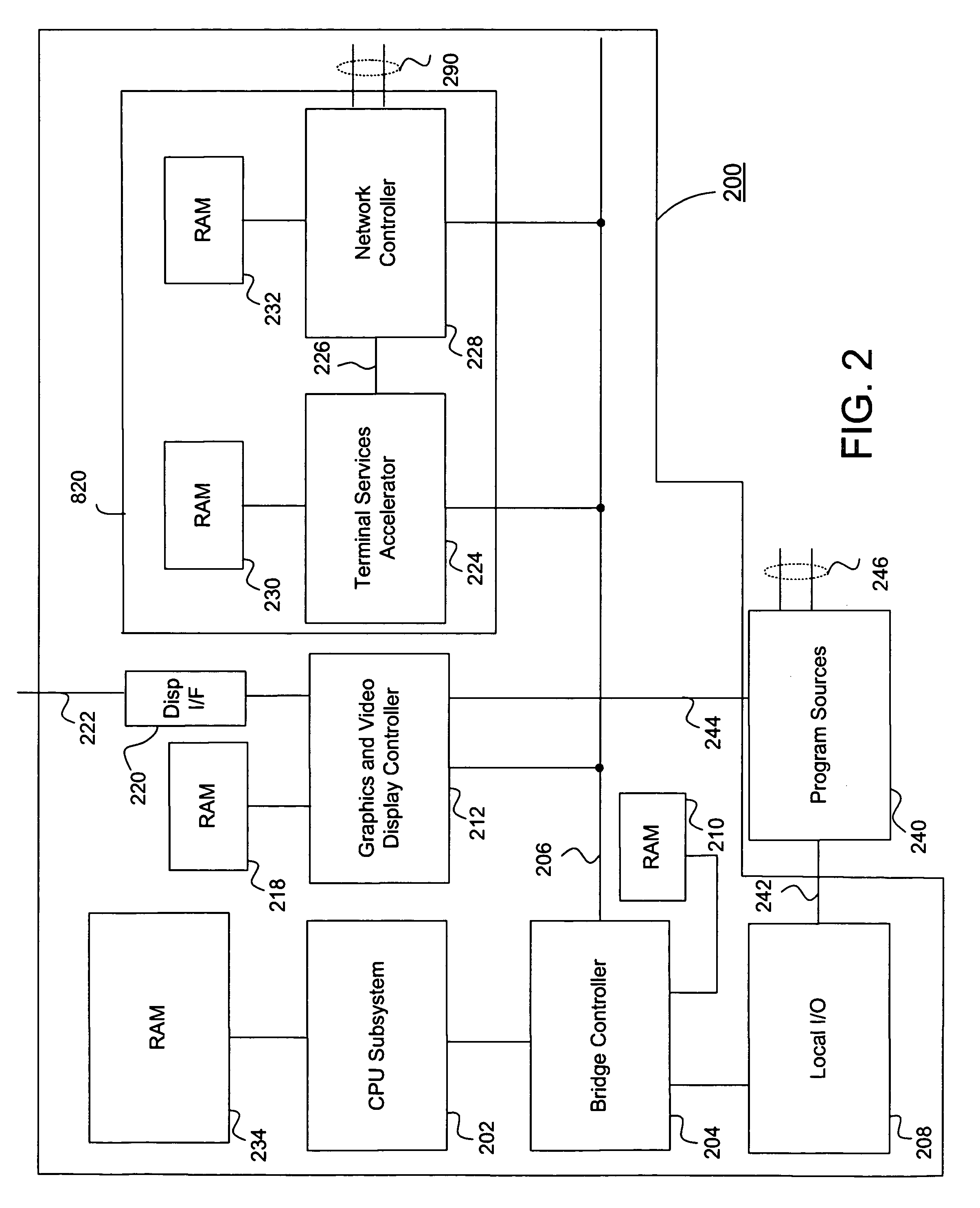

Multi-user terminal services accelerator

InactiveUS7899864B2Efficient architectureEasy to useDigital data processing detailsCathode-ray tube indicatorsGraphicsData stream

A multi-user host computer system comprises a host computer that processes applications and the desktop environments for multiple remote terminals. The host computer includes a terminal services offload processor to supplement the processing of the host CPU. For each remote terminal, the terminal services offload processor may improve the video and graphics performance and allow the multi-user host computer system to more efficiently support multiple users. The host computer may include a graphics processor that manages a virtual display for each remote terminal and provides selective updates of sub frame data. Where appropriate, the sub frame data is encoded and transmitted over the network to the remote terminals. Video data streams are also optimized by the terminal services offload processor and optimized for the intended remote terminals and their respective network connections. The terminal services offload processor may be implemented in programmable hardware and may be a separate subsystem or may also be used to perform other offload tasks.

Owner:MICROSOFT TECH LICENSING LLC

Network-based system for configuring a programmable hardware element in a modeling system using hardware configuration programs determined based on a user specification

InactiveUS20050137840A1Facilitating native executionAnalogue computers for electric apparatusMeasurement arrangements for variableComputer hardwareGraphics

A system and method for online configuration of a measurement system. The user may access a server over a network and specify a desired task, e.g., a measurement task, and receive programs and / or configuration information which are usable to configure the user's measurement system hardware (and / or software) to perform the desired task. Additionally, if the user does not have the hardware required to perform the task, the required hardware may be sent to the user, along with programs and / or configuration information. The hardware may be reconfigurable hardware, such as an FPGA or a processor / memory based device. In one embodiment, the required hardware may be pre-configured to perform the task before being sent to the user. In another embodiment, the system and method may provide a graphical program in response to receiving the user's task specification, where the graphical program may be usable by the measurement system to perform the task.

Owner:NATIONAL INSTRUMENTS

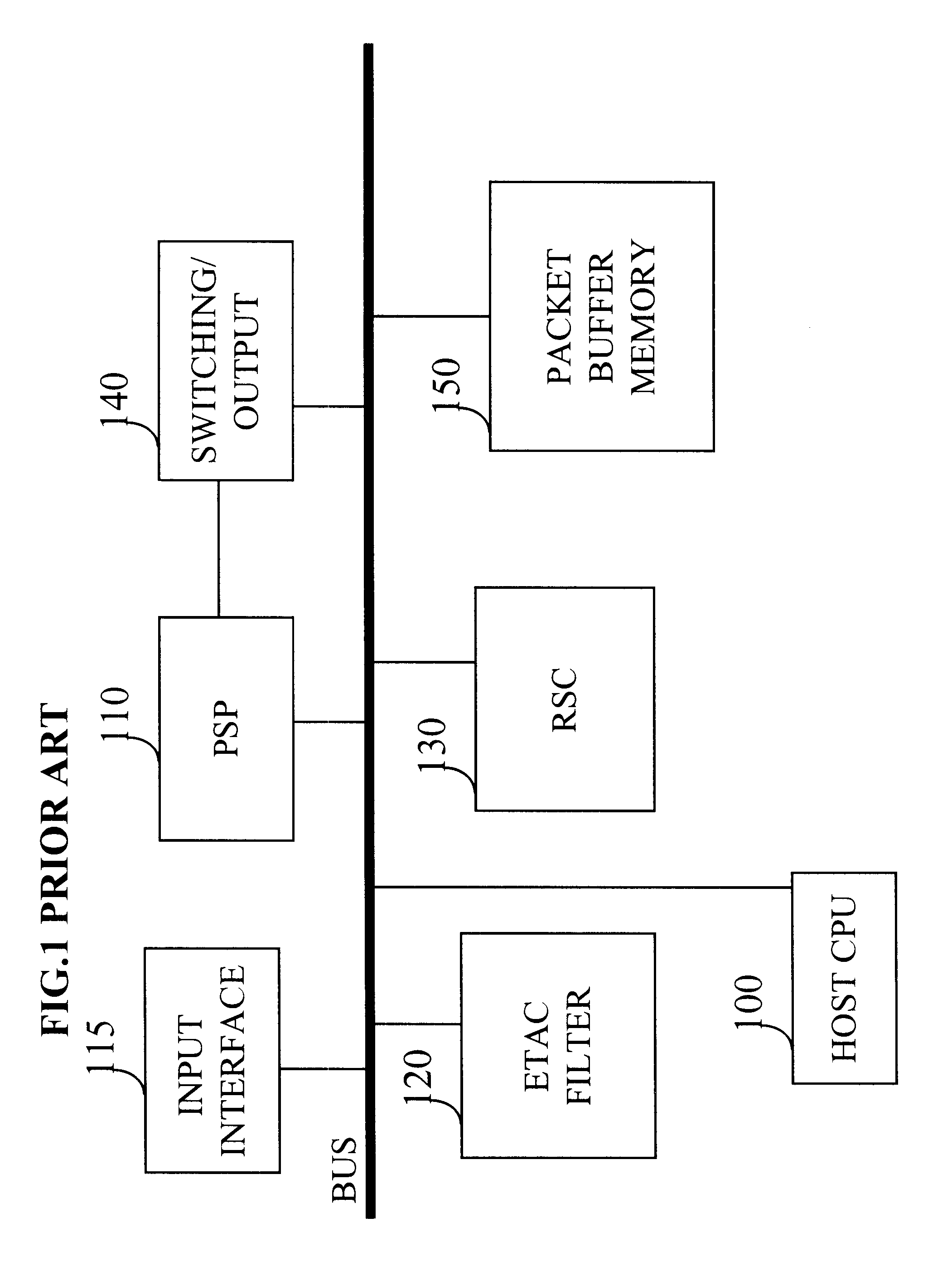

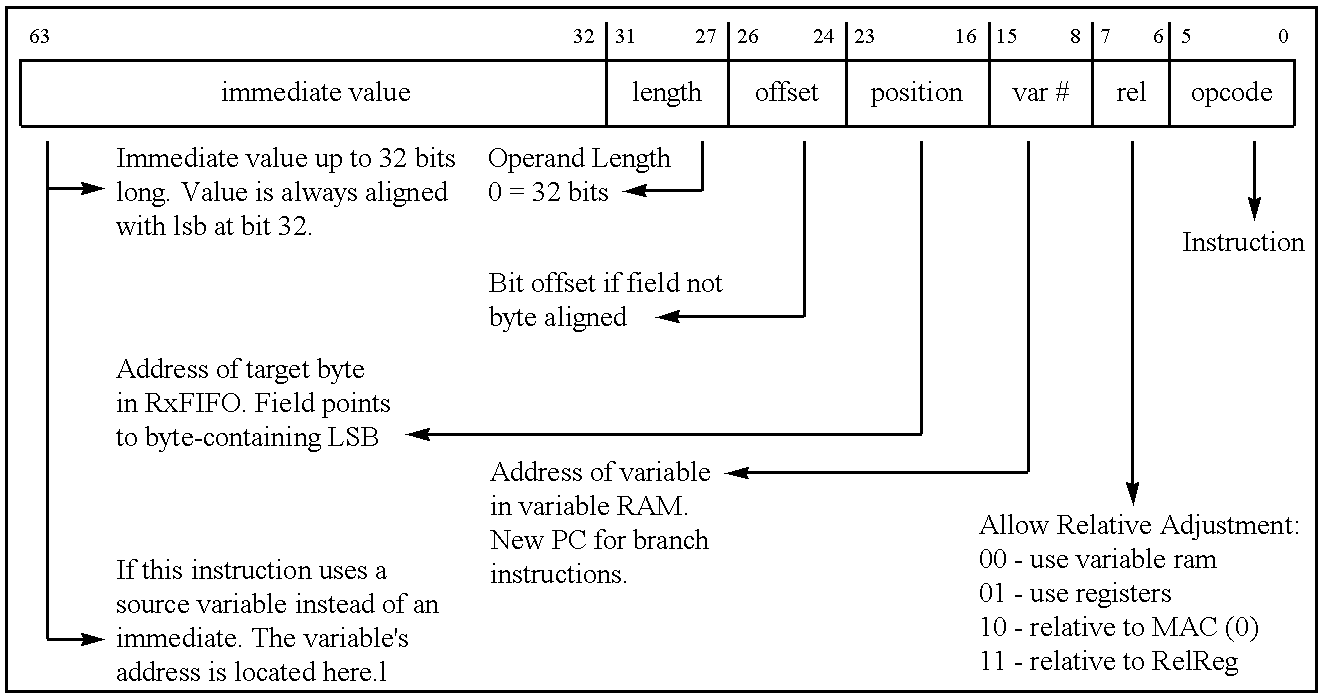

Method and apparatus for performing frame processing for a network

InactiveUS20020010793A1Easy to handleError preventionFrequency-division multiplex detailsMedia access controlProgrammable hardware

An improved frame processing apparatus for a network that supports high speed frame processing is disclosed. The frame processing apparatus uses a combination of fixed hardware and programmable hardware to implement network processing, including frame processing and media access control (MAC) processing. Although generally applicable to frame processing for networks, the improved frame processing apparatus is particular suited for token-ring networks and ethernet networks. The invention can be implemented in numerous ways, including as an apparatus, an integrated circuit and network equipment.

Owner:AVAYA MANAGEMENT LP

Graphical program with various function icons and method for conversion into hardware implementation

InactiveUS6954724B2Detecting faulty hardware by remote testComputation using non-denominational number representationGraphicsComputer architecture

A computer-implemented system and method for generating a hardware implementation of graphical code. The method comprises first creating a graphical program. A first portion of the graphical program may optionally be compiled into machine code for execution by a CPU. A second portion of the graphical program is converted into a hardware implementation according to the present invention. The operation of converting the graphical program into a hardware implementation comprises exporting the second portion of the graphical program into a hardware description, wherein the hardware description describes a hardware implementation of the second portion of the graphical program, and then configuring a programmable hardware element utilizing the hardware description to produce a configured hardware element. The configured hardware element thus implements a hardware implementation of the second portion of the graphical program.

Owner:NATIONAL INSTRUMENTS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com