Method and apparatus for performing frame processing for a network

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0130]

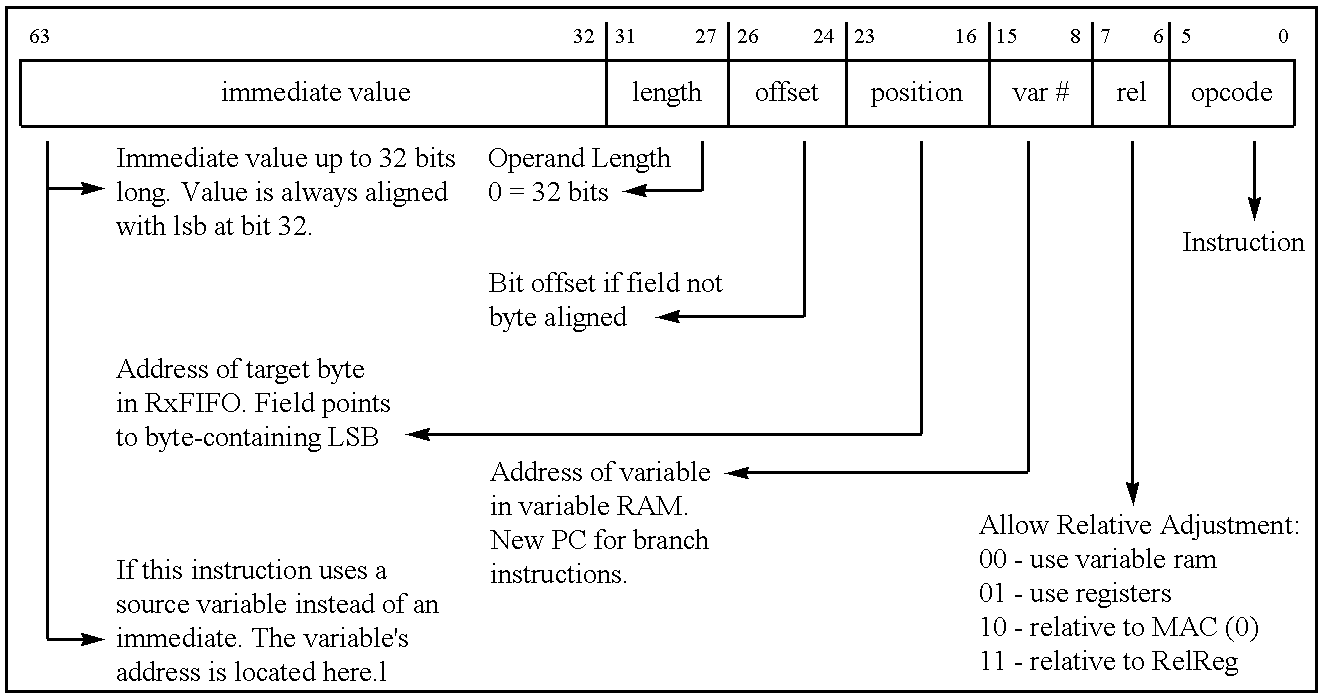

3 Opcode Instruction Effect 00 halt # Stop processing until restart at next frame, optionally abort frame 01 jmp # jmp to immediate location 02 sti #,d1 store immediate to RxFIFO, variable ram or registers 03 or #,s mem[d] = mem[s] OR immediate, if only s specified, d=s 04 xor #,s mem[d] = mem[s] XOR immediate, if only s specified, d=s 05 and #,s mem[d] = mem[s] AND immediate, if only s specified, d=s 06 sub #,s, mem[d] = mem[s] - immediate, if only s specified, d =s 07 add #,s, mem[d] = mem[s] + immediate, if only s specified, d=s 08 cje #,s,pc compare mem[s] with immediate; jump to PC if result zero 09 cjne #,s,pc compare mem[s] with immediate; jump to PC if result non-zero 0A cjgte #,s,pc compare mem[s] with immediate; jump to PC if greater or equal 0B cjlt #,s,pc compare mem[s] with immediate; jump to PC if less than 0C subje #,s,pc mem[s] = (mem[s] - immediate); jump to PC if result non-zero 0D subjne #,s,pc mem[s] = (mem[s] - immediate); jump to PC if result zero 0E cjin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com