Universal single event effect detecting method of memory circuit

A memory circuit and single event effect technology, applied in static memory, instruments, etc., can solve the problems of difficult positioning, multi-bit flipping and statistics, lack of versatility, difficulty in data analysis of memory circuits, etc., to achieve rich test methods and detection functions full effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

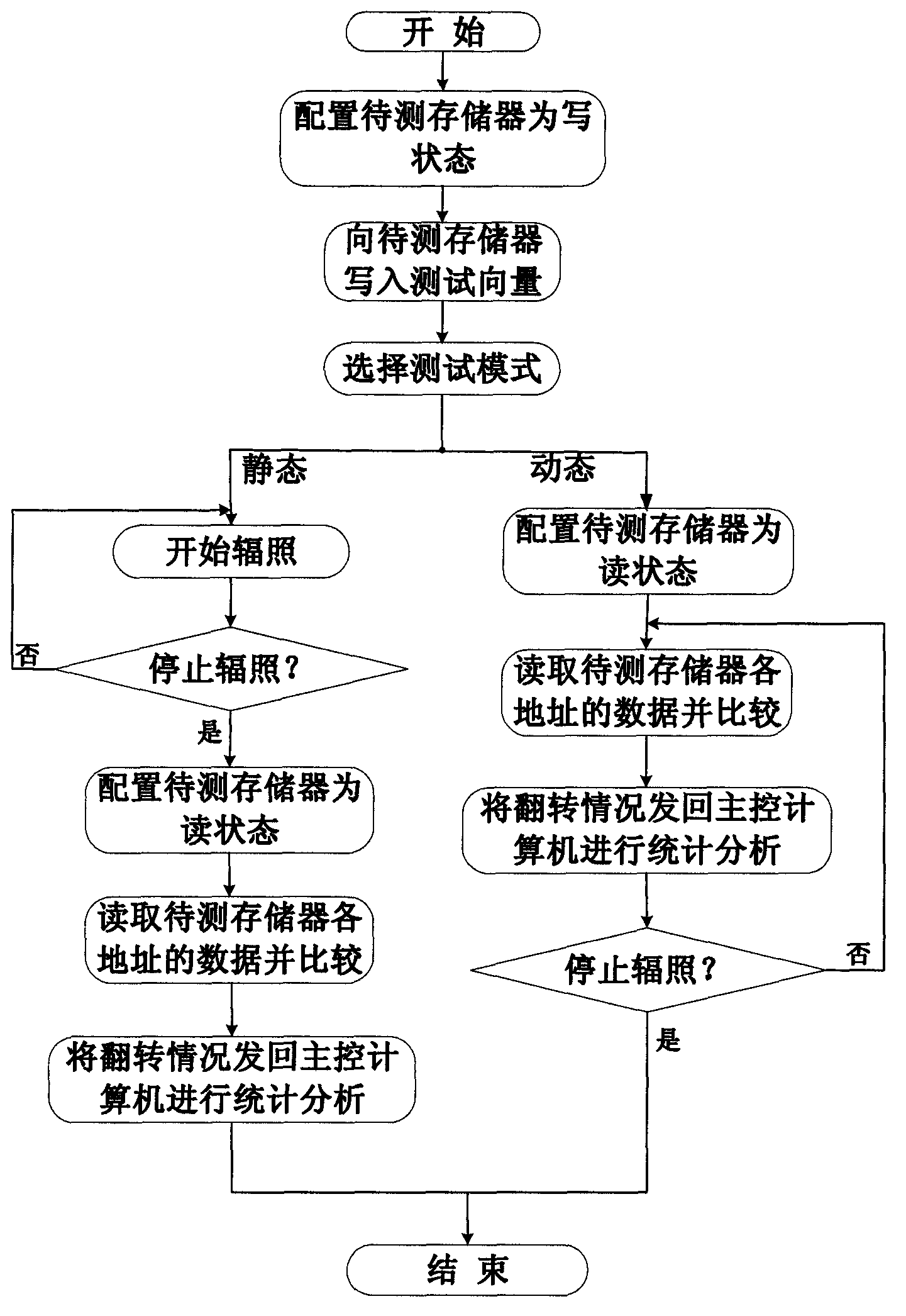

[0025] Such as figure 1 As shown in FIG. 2 , it is a flow chart of the general single event effect detection method for the memory circuit of the present invention. After starting the test, firstly, by configuring the pin signals of the memory device to be tested, the memory to be tested is made to work in three different working modes: write state, read state, or non-read and non-write state.

[0026] In the write state, according to the test instruction, write the test vector ("00", "FF", "55", "AA", "55"+"AA", "00"+" FF”, MARCH, etc.). In the test process, the required test vector can be selected through the input command of the host computer so that the storage state and working state of the unit of the memory circuit are in a specific state, and then the anti-single event effect performance of the memory circuit is comprehensively assessed.

[0027] In the read state, the data output terminal of the memory to be tested is detected, and the received data is compared with...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com