Python language based Rapidio switcher logic simulation verification platform and method

A logic simulation and verification platform technology, applied in the field of cloud computing, to improve writing efficiency and reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

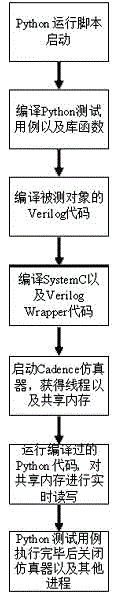

Image

Examples

Embodiment Construction

[0040] The present invention will be further described below in conjunction with specific embodiments by accompanying drawings of description:

[0041] A logic simulation and verification platform for Rapidio switchers based on the Python language. The verification platform includes: a SystemC interface function that interprets Python semantics, a DPI interface function that calls SystemVerilog from SystemC, a test case implemented by Python, and a running script.

[0042] The implementation steps of the verification platform are as follows:

[0043] 1) Instantiate the object under test of the Rapidio switch written in Verilog;

[0044] 2) Use Verilog program to write basic stimulus input and response output DPI functions to interact with the outer SystemC environment;

[0045] 3) Write a SystemC interpreter for Python;

[0046] 4) Write the underlying library functions of Python;

[0047] 5) Write Python test cases and run scripts.

[0048] The logic simulation verificati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com