Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

143 results about "Process patterns" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Process patterns can be defined as the set of activities, actions, work tasks or work products and similar related behaviour followed in a software development life cycle. Process patterns can be more easily understood by dividing it into terms, Process which means the steps followed to achieve a task and patterns which means the recurrence of same basic features during the lifecycle of a process. Thus in a more universal term process patterns are common or general solution for a complexity.

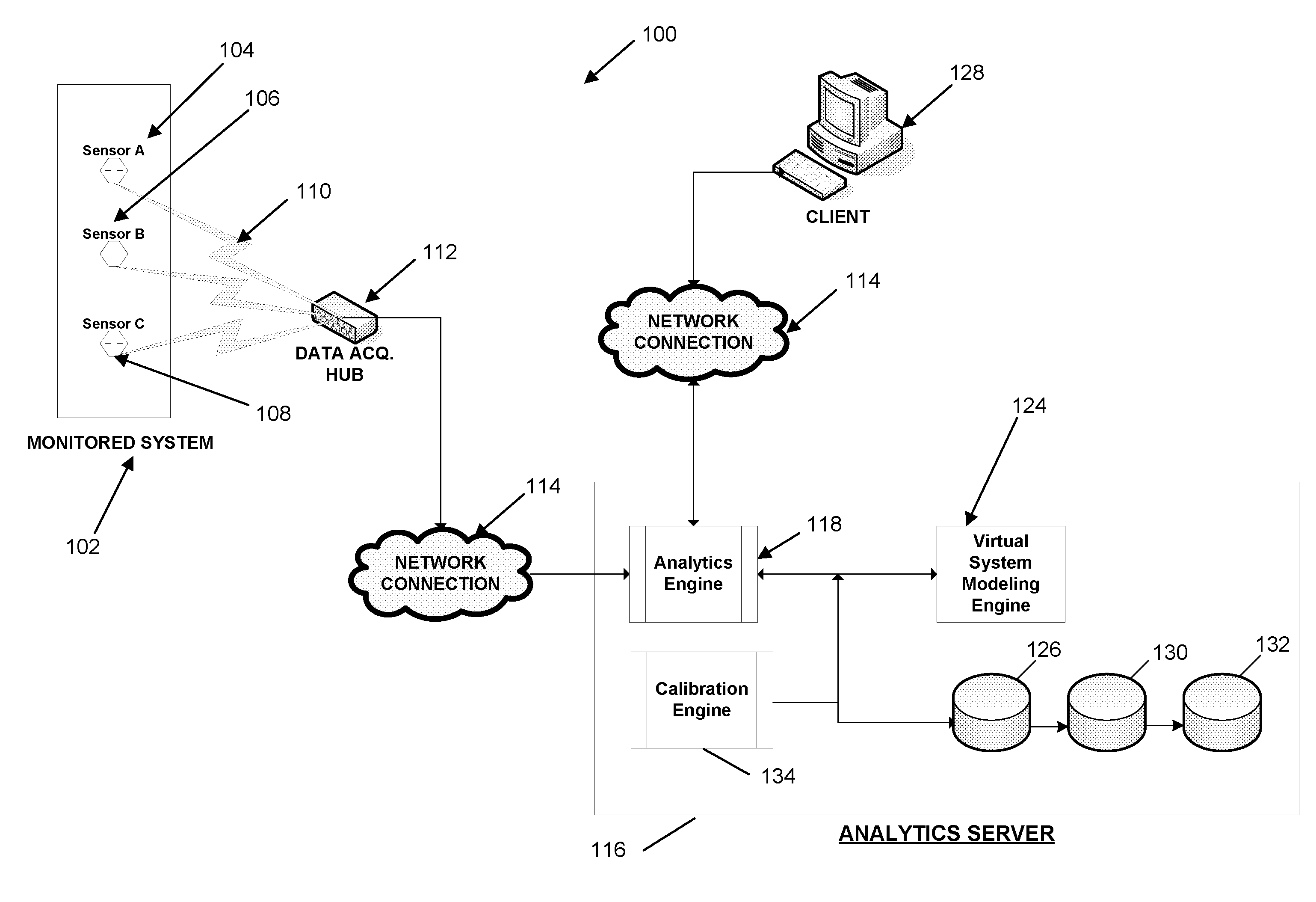

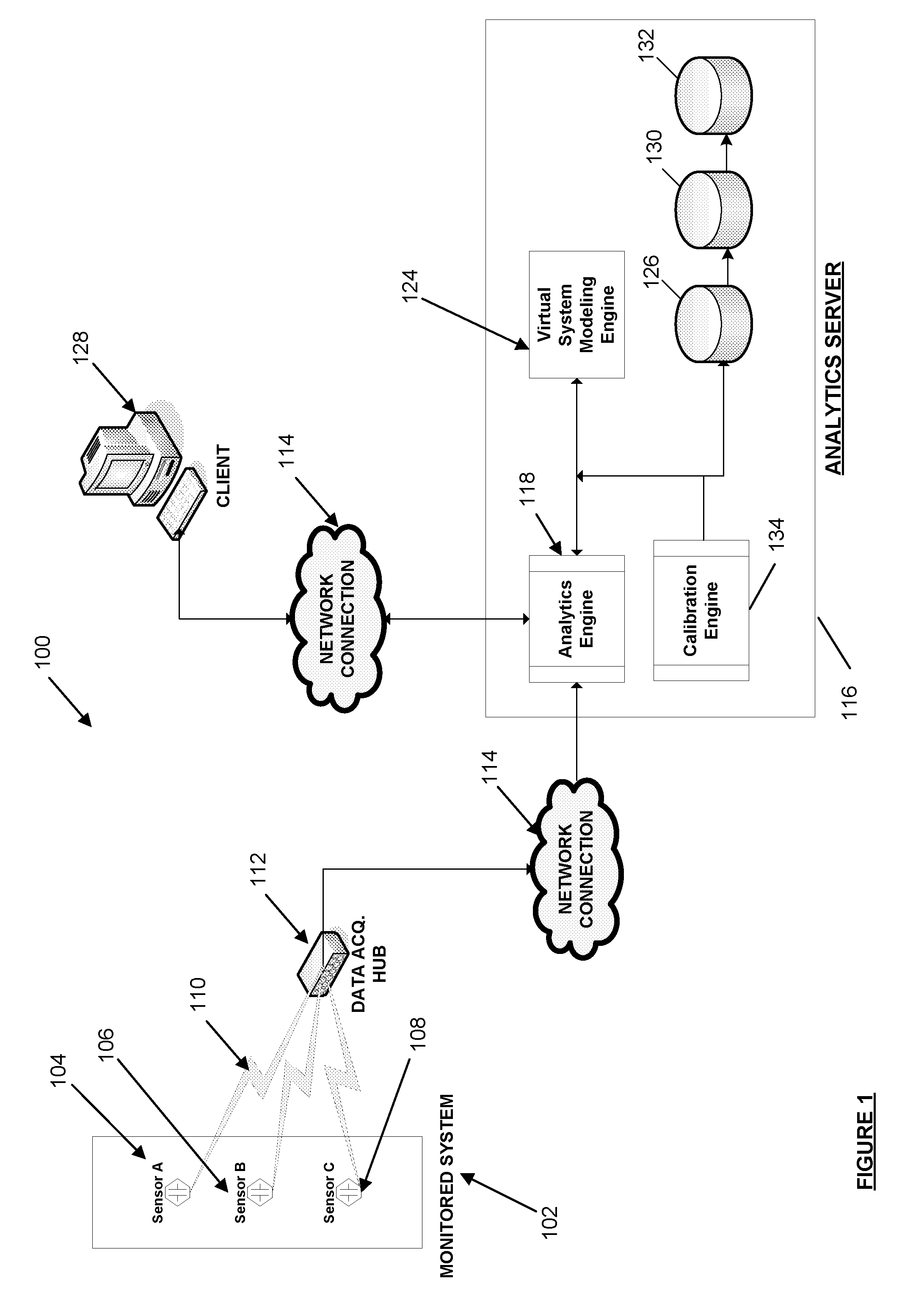

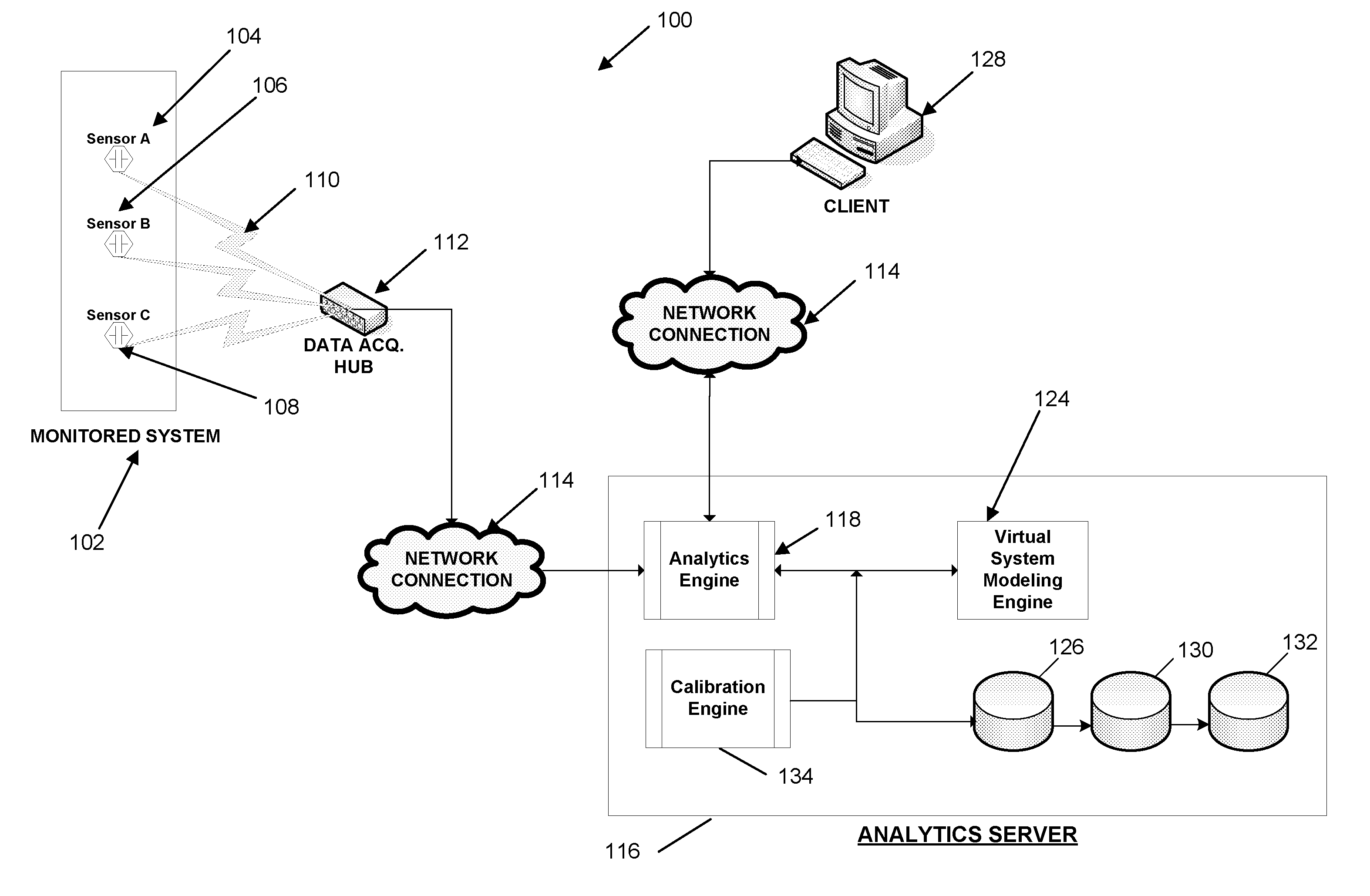

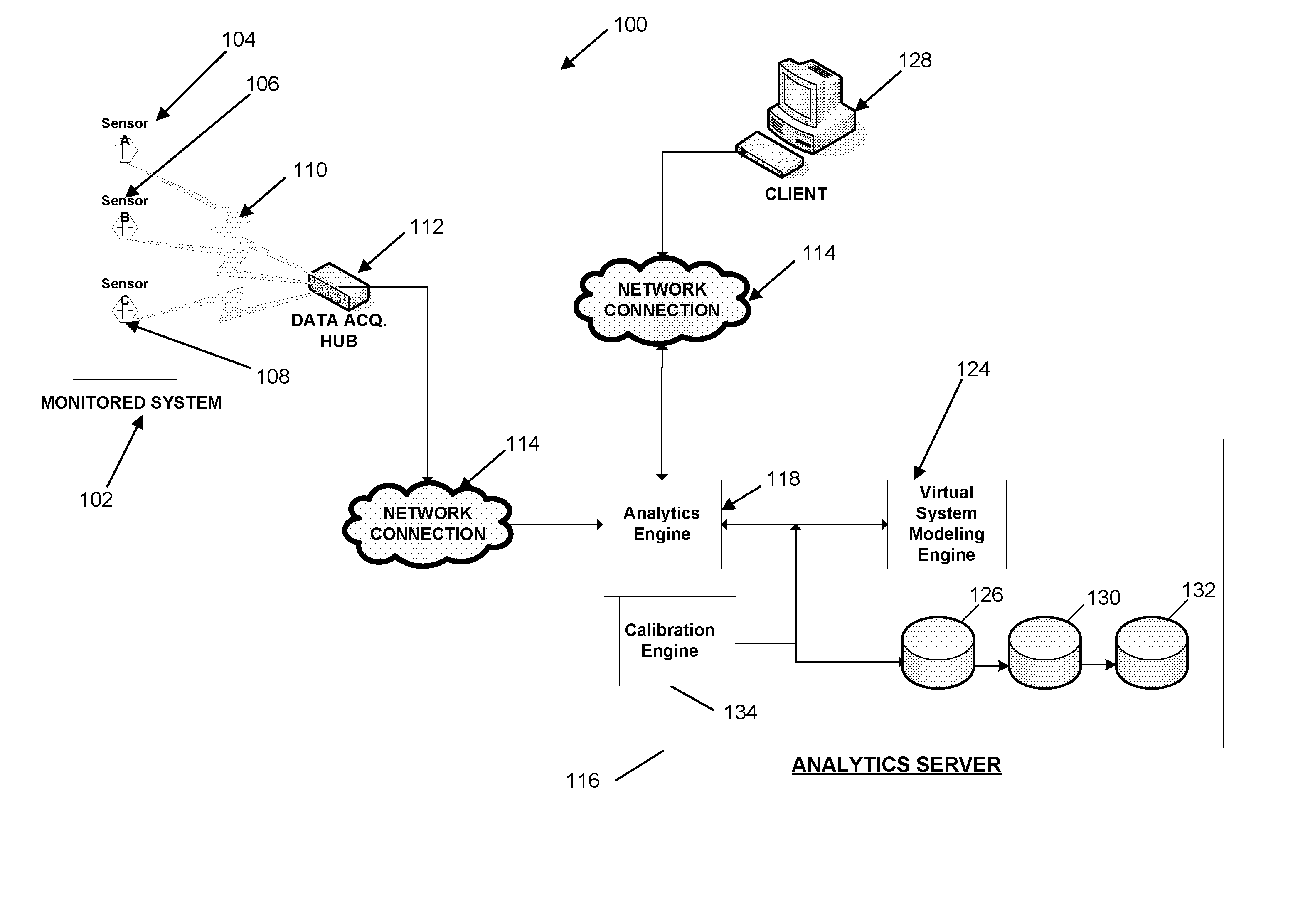

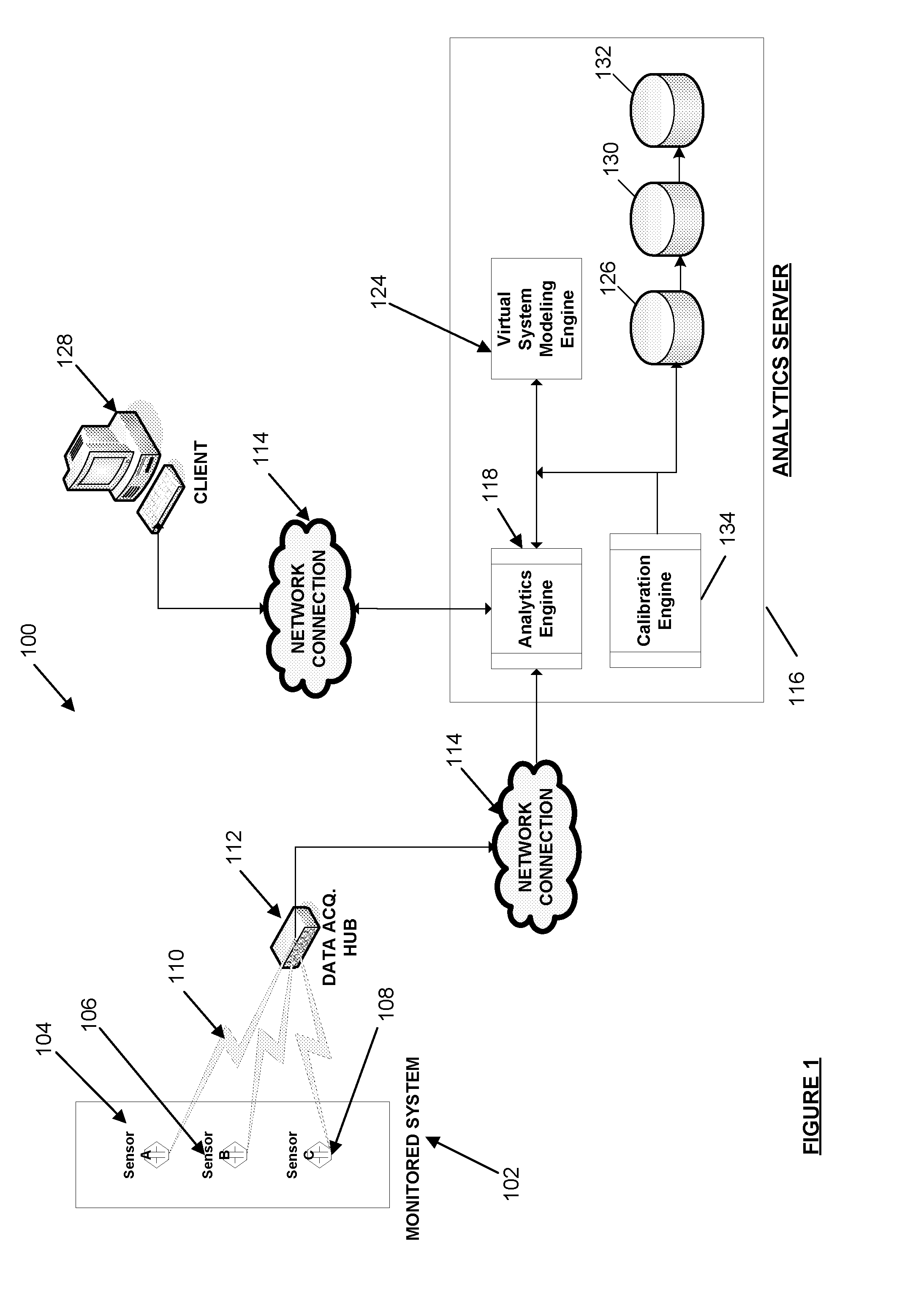

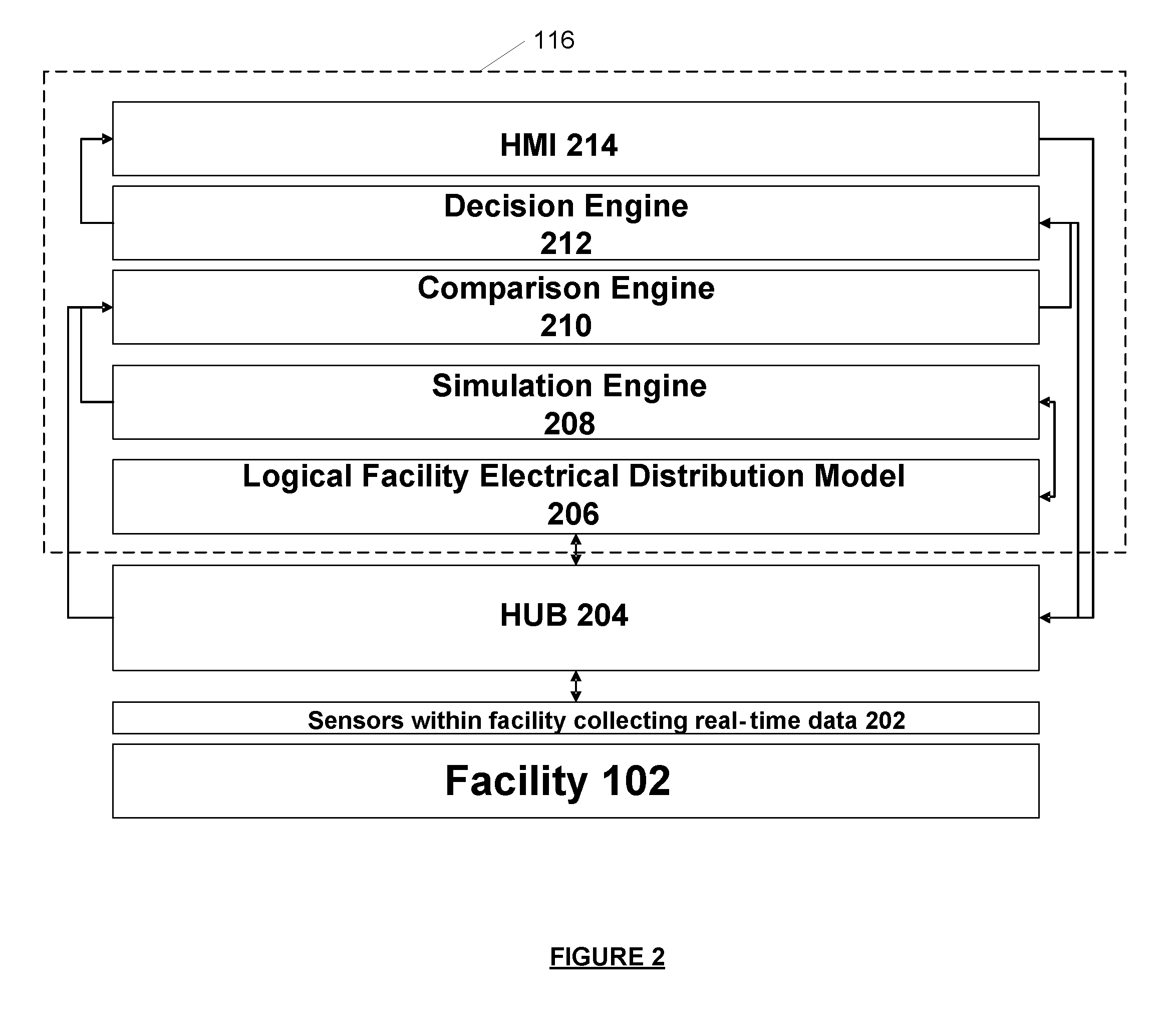

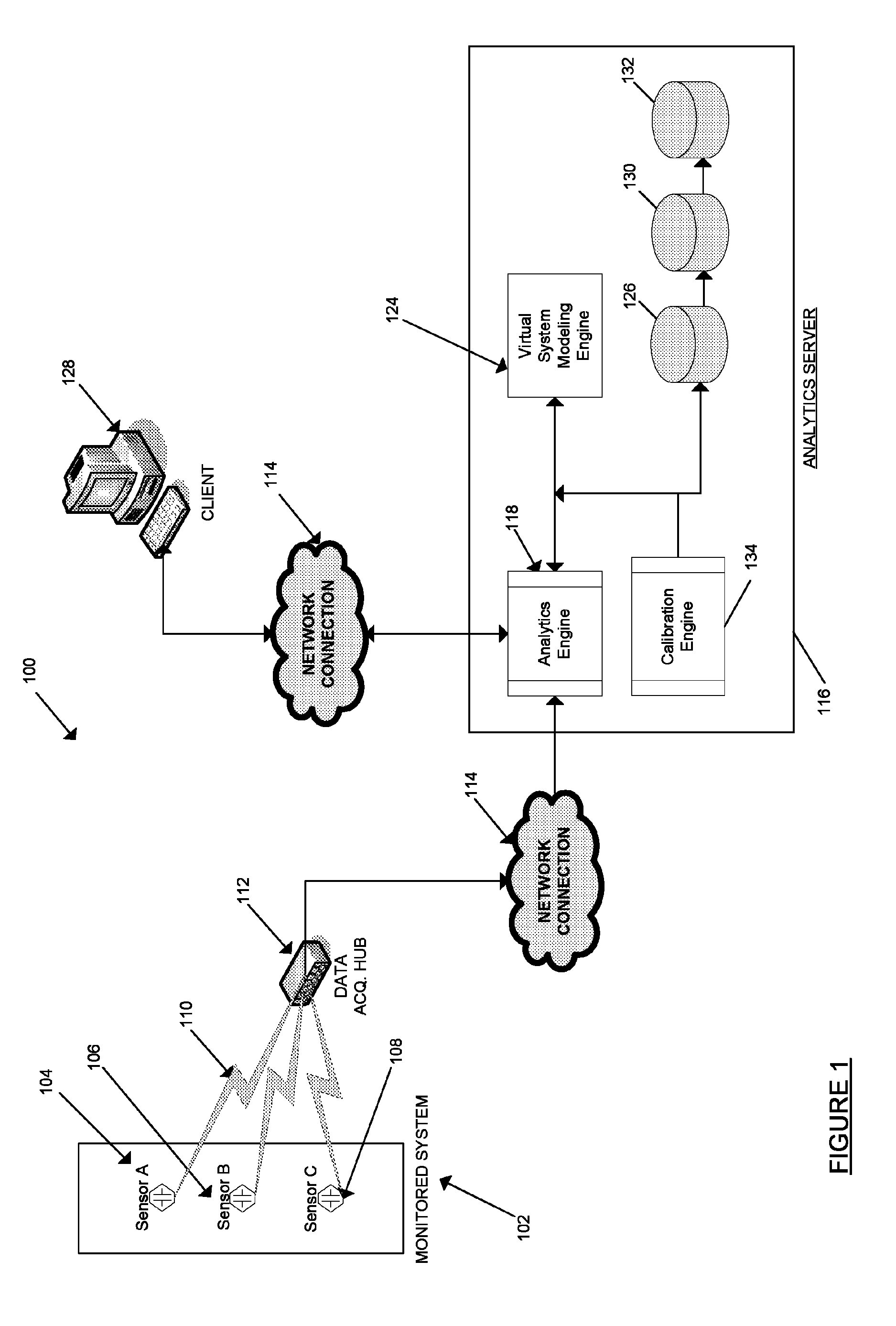

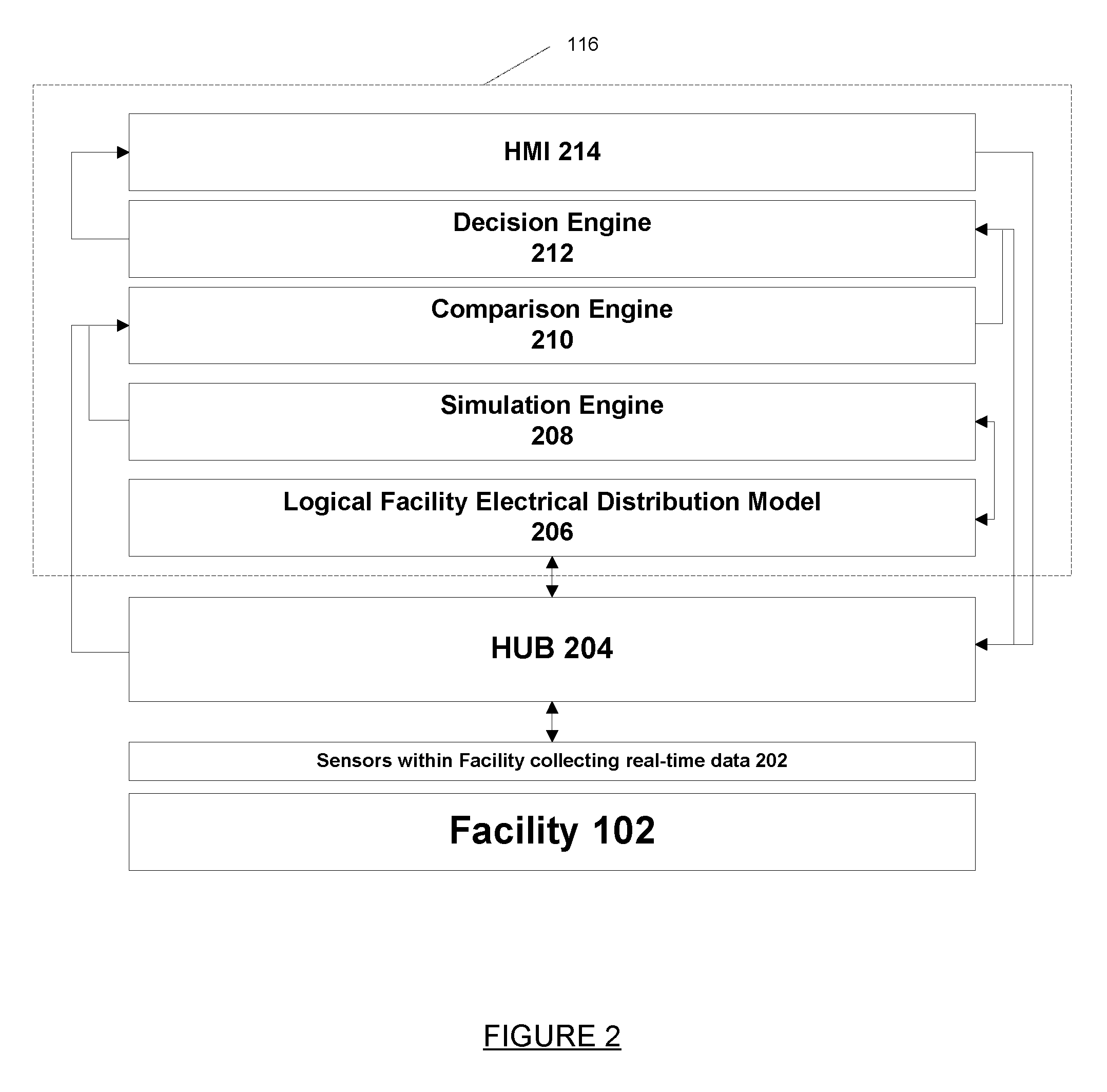

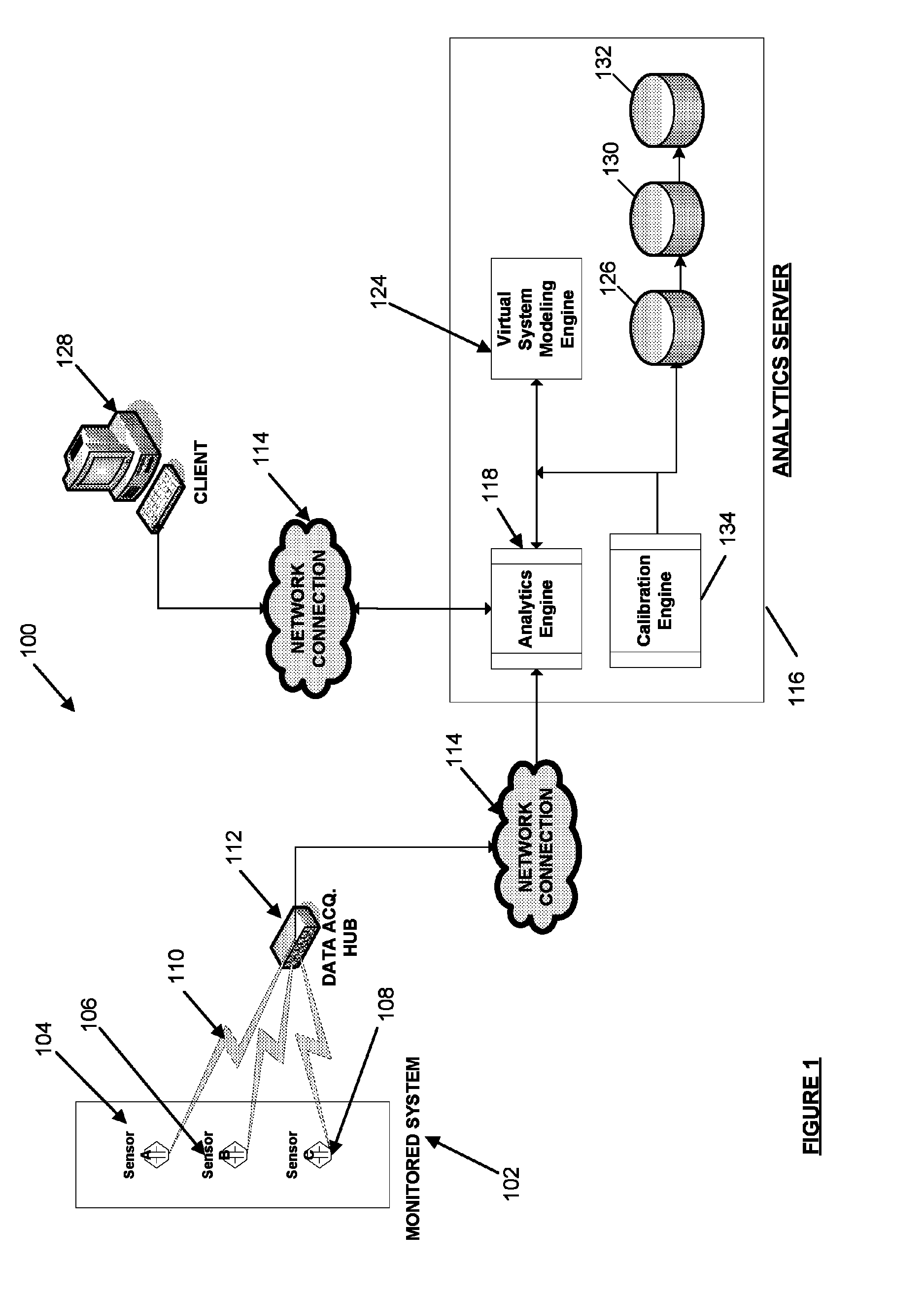

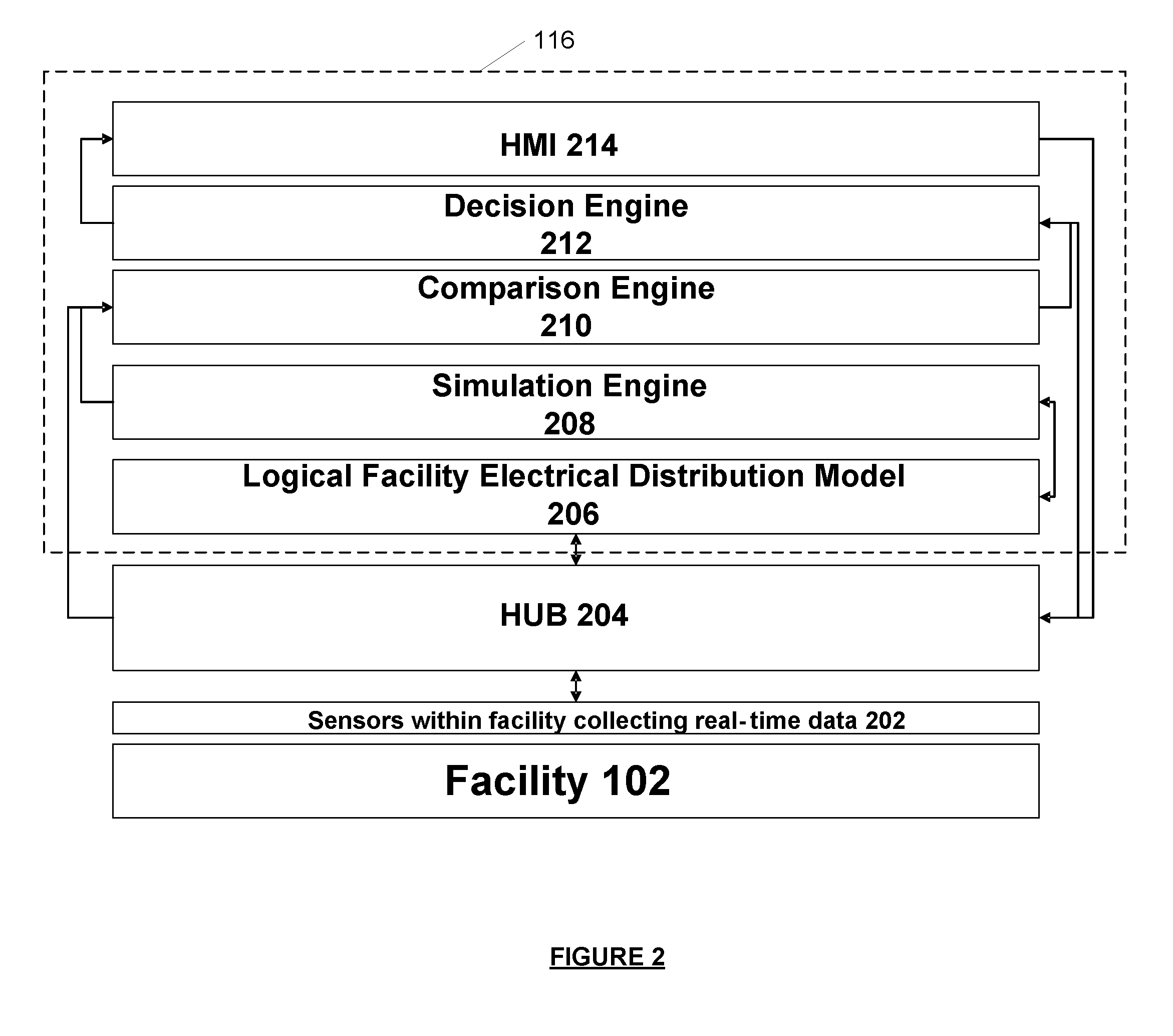

Real-time predictive systems for intelligent energy monitoring and management of electrical power networks

A system for intelligent monitoring and management of an electrical system is disclosed. The system includes a data acquisition component, a power analytics server and a client terminal. The data acquisition component acquires real-time data output from the electrical system. The power analytics server is comprised of a real-time energy pricing engine, virtual system modeling engine, an analytics engine, a machine learning engine and a schematic user interface creator engine. The real-time energy pricing engine generates real-time utility power pricing data. The virtual system modeling engine generates predicted data output for the electrical system. The analytics engine monitors real-time data output and predicted data output of the electrical system. The machine learning engine stores and processes patterns observed from the real-time data output and the predicted data output to forecast an aspect of the electrical system.

Owner:POWER ANALYTICS CORP

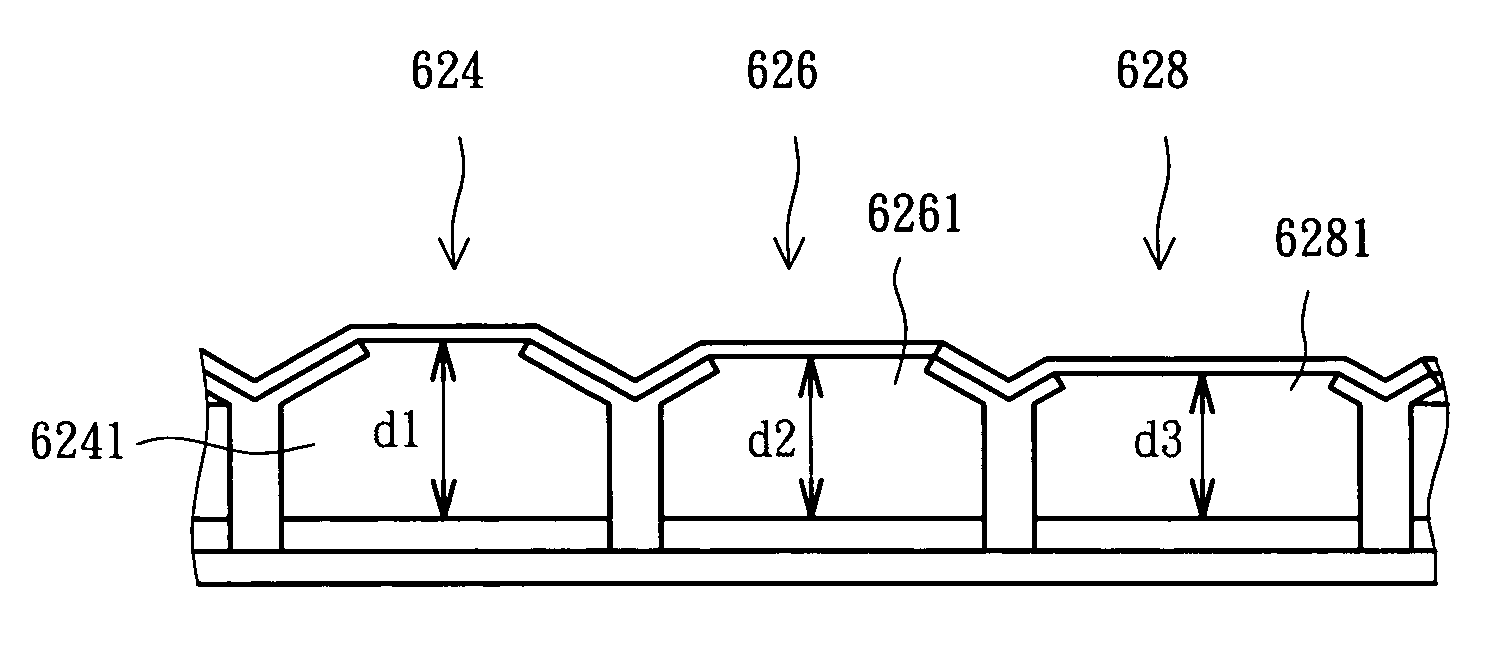

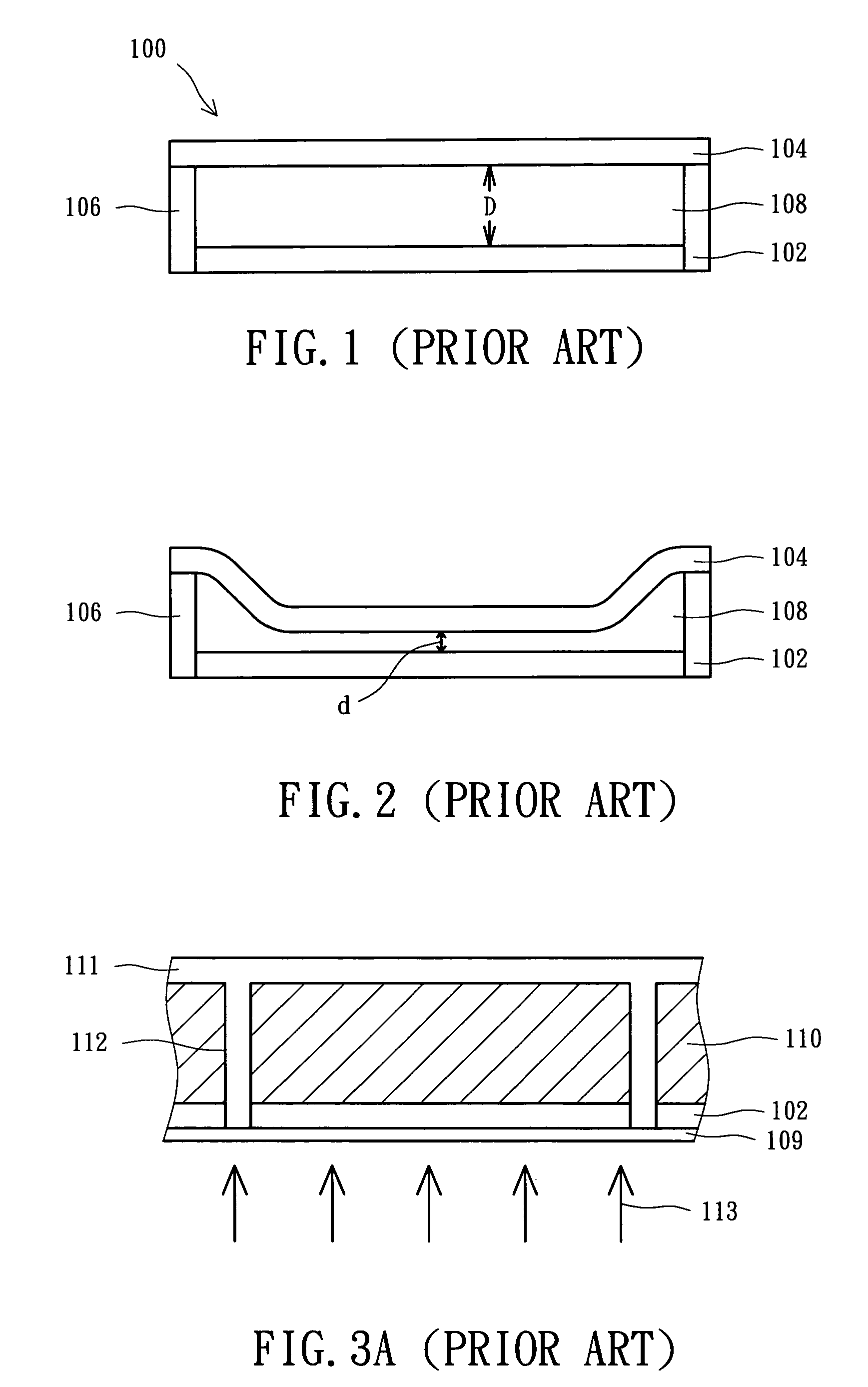

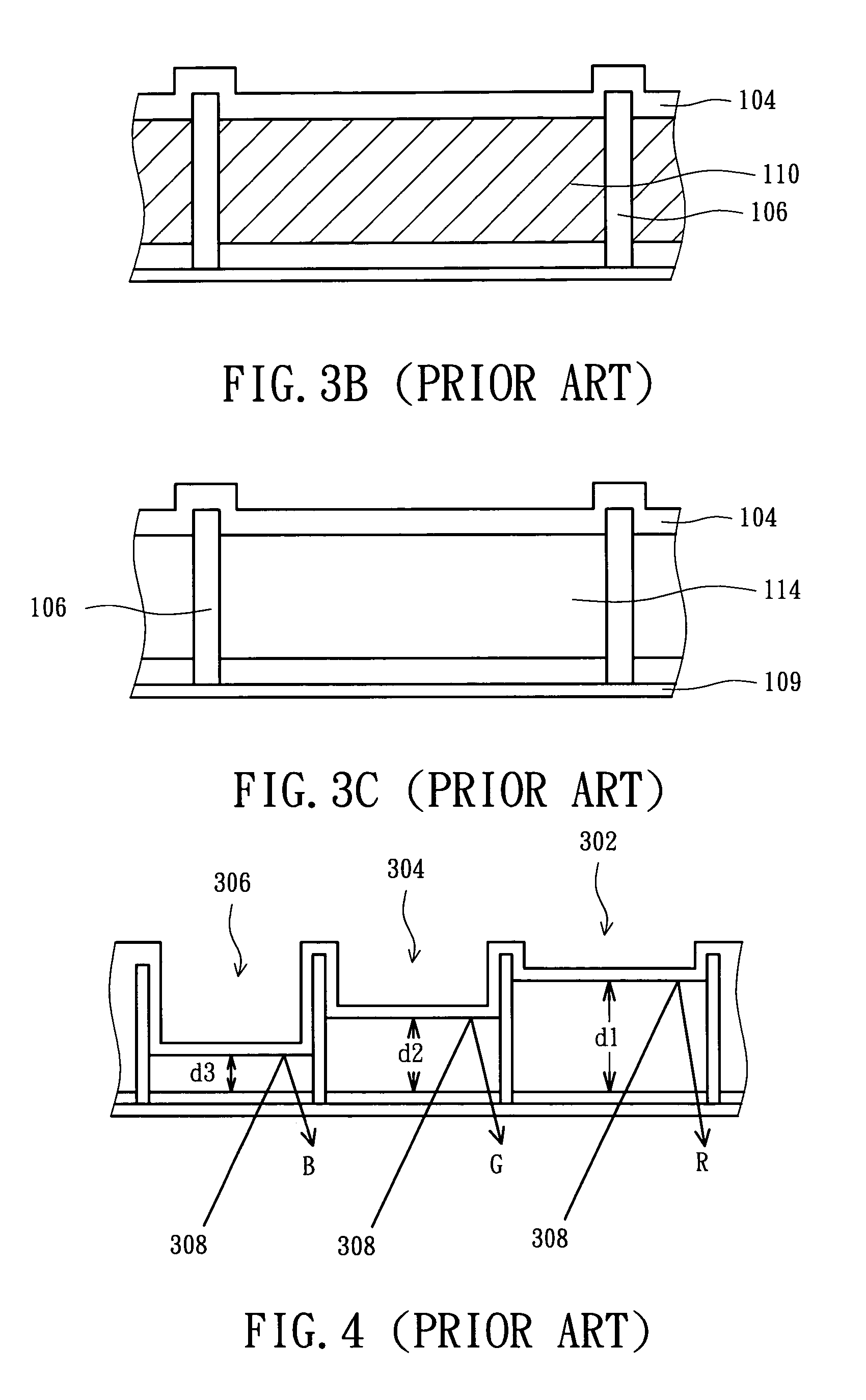

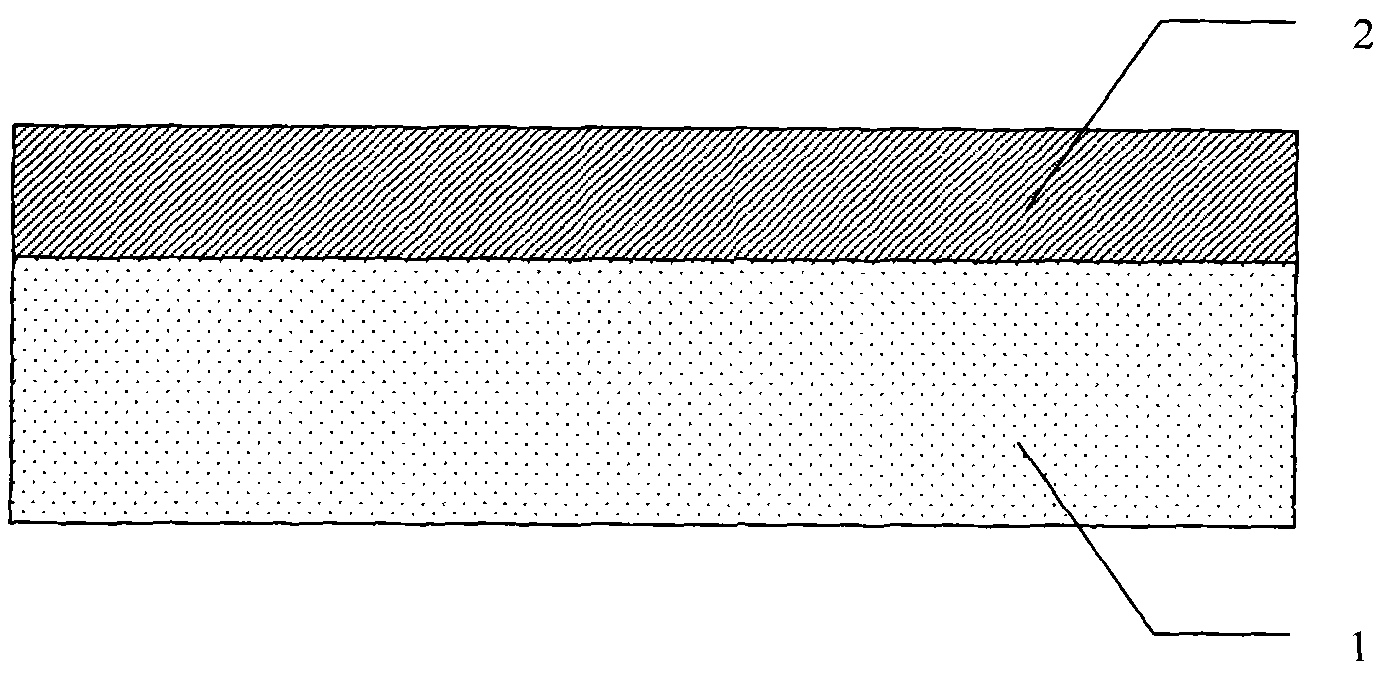

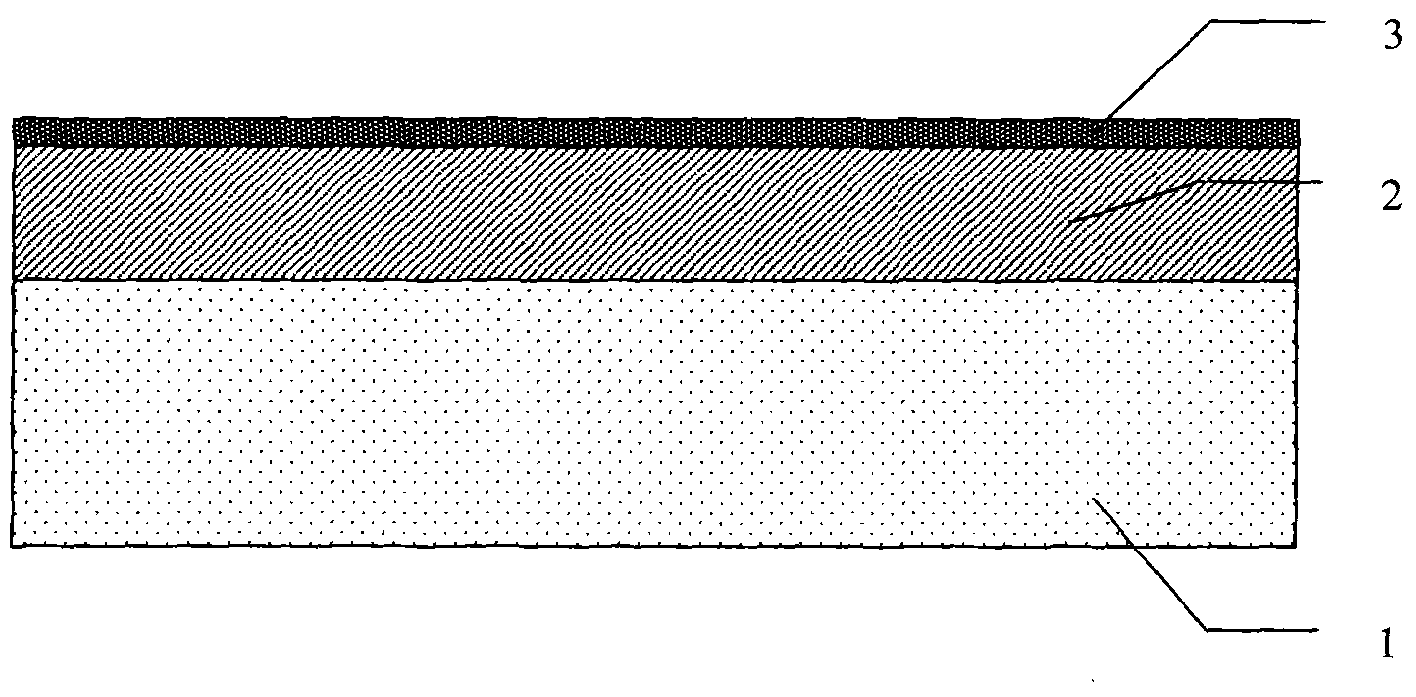

Method for fabricating an interference display unit

InactiveUS7198973B2Increase brightnessSimple and easy manufacturing processPhotomechanical apparatusSemiconductor/solid-state device manufacturingProcess patternsEngineering

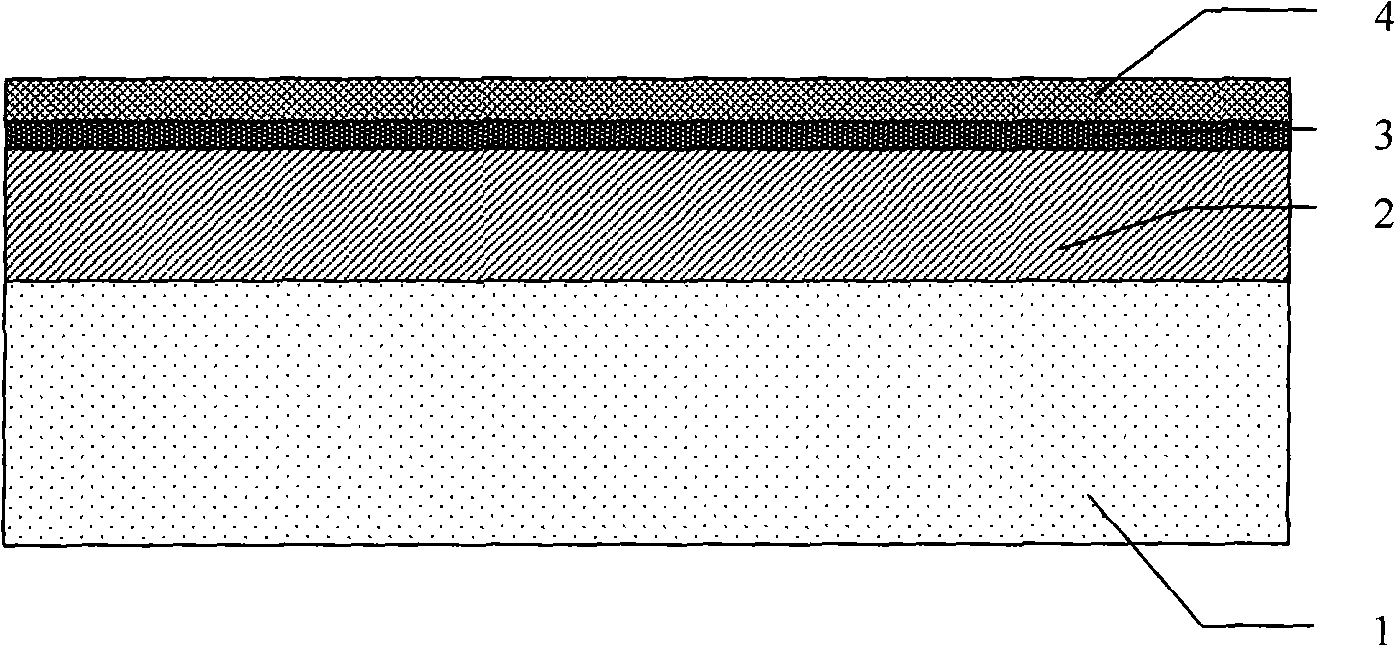

A method for fabricating an interference display unit is provided. A first plate and a sacrificial layer are formed in order on a substrate and at least two openings are formed in the first plate and the sacrificial layer. A photoresist layer is spin-coated on the sacrificial layer and fills the openings. A photolithographic process patterns the photoresist layer to define a support with an arm. A second plate is formed on the sacrificial layer and posts. The arm's stress is released through a thermal process. The position of the arm is shifted and the distance between the first plate and the second plate is therefore defined. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

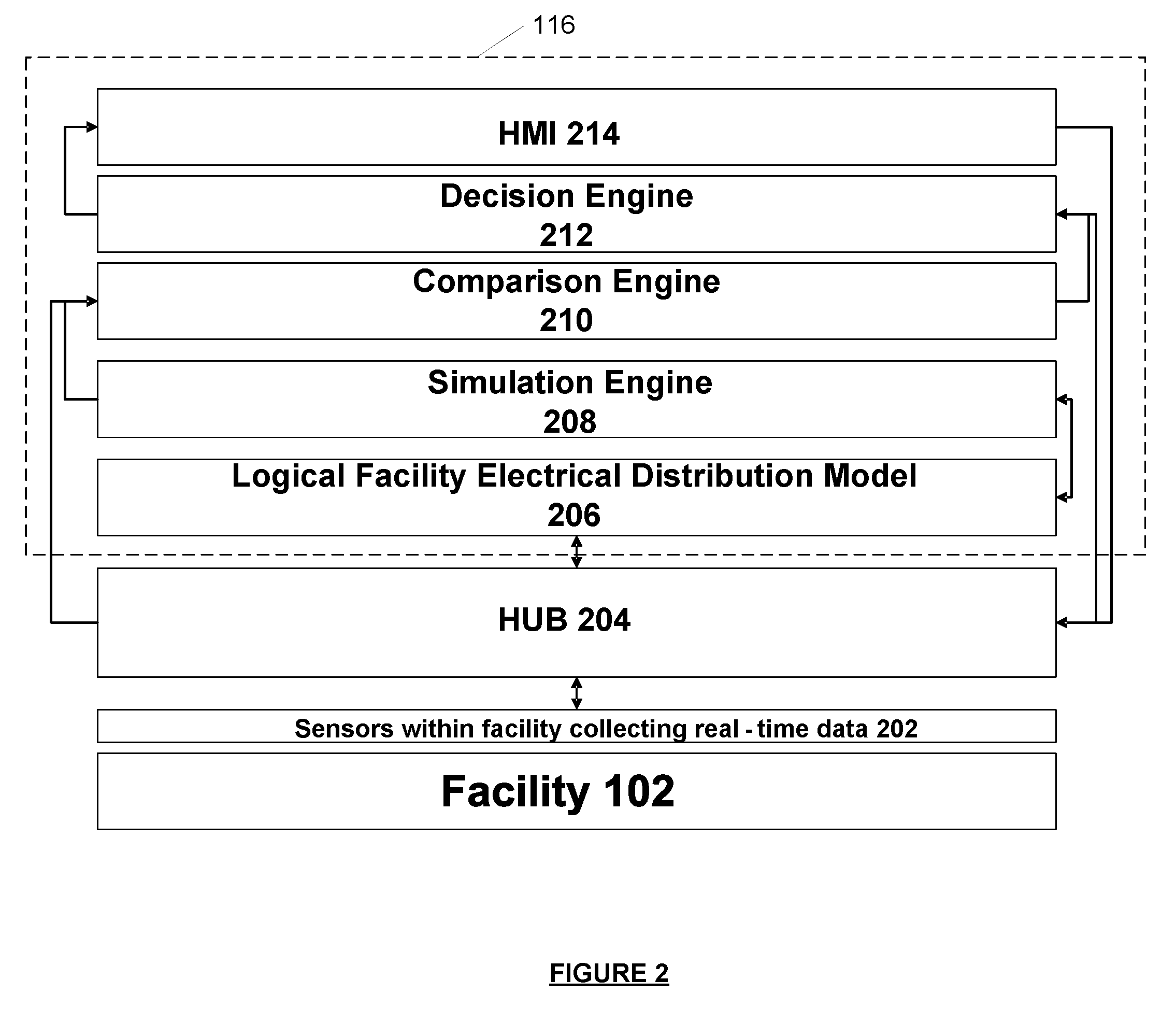

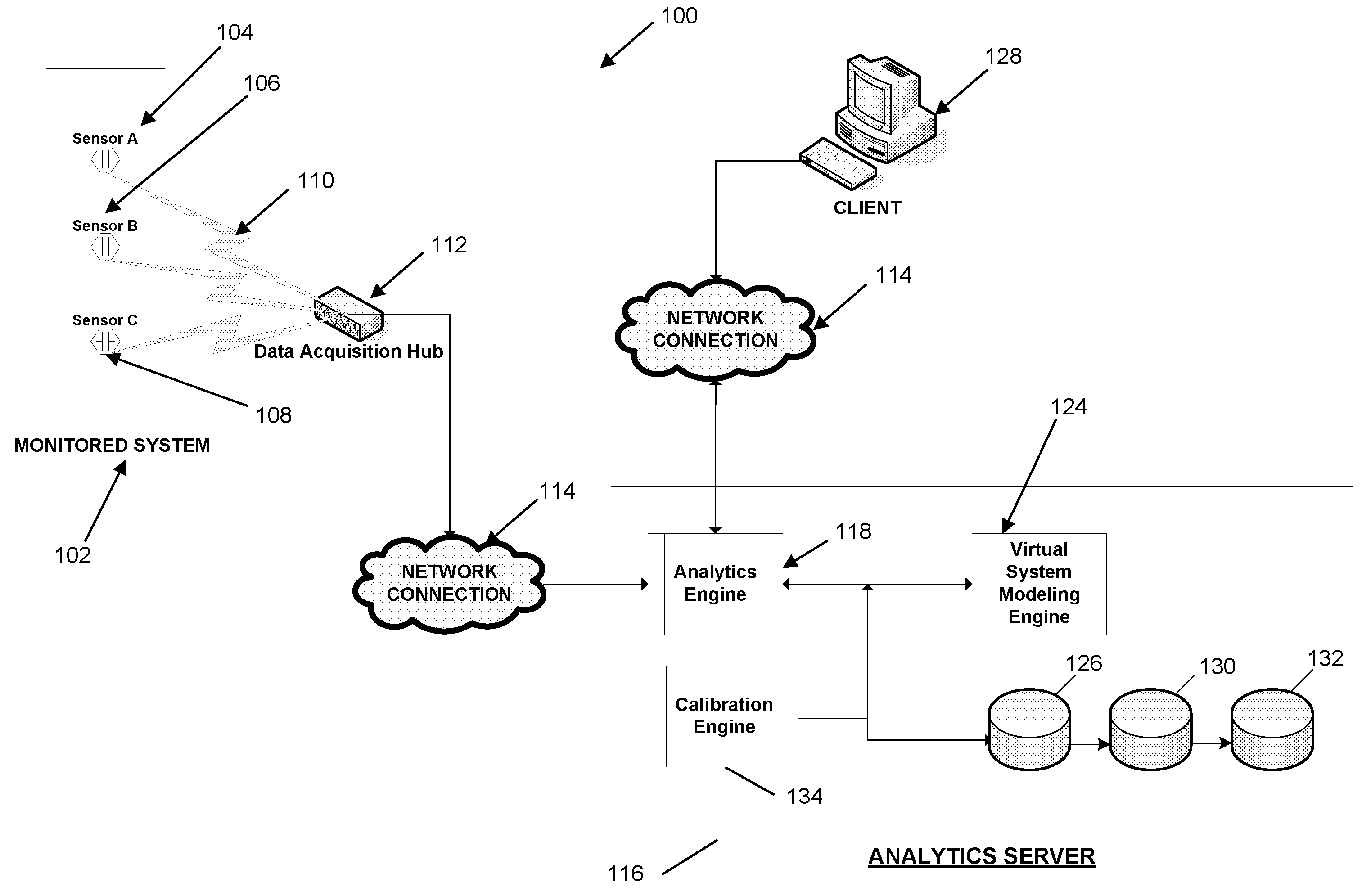

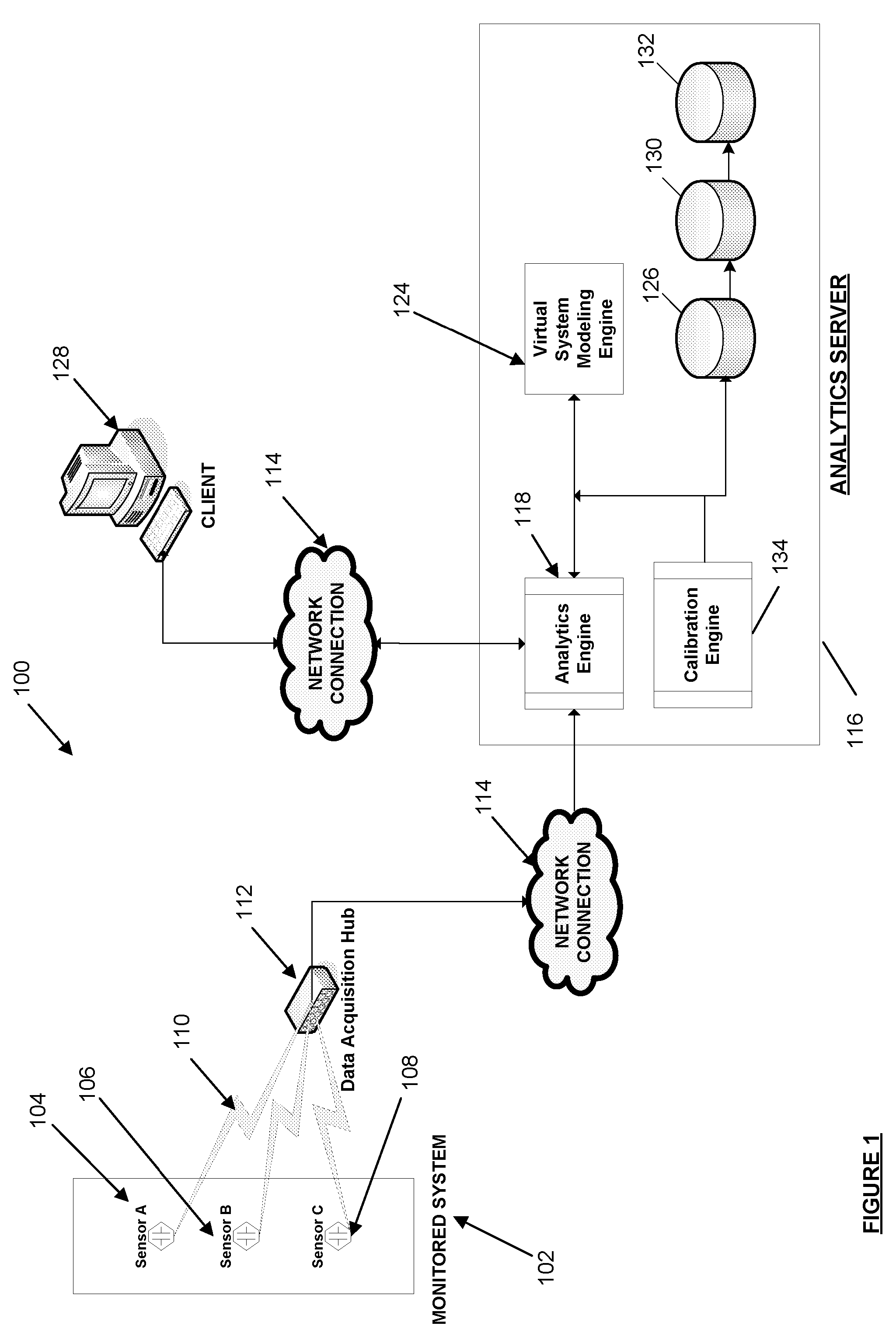

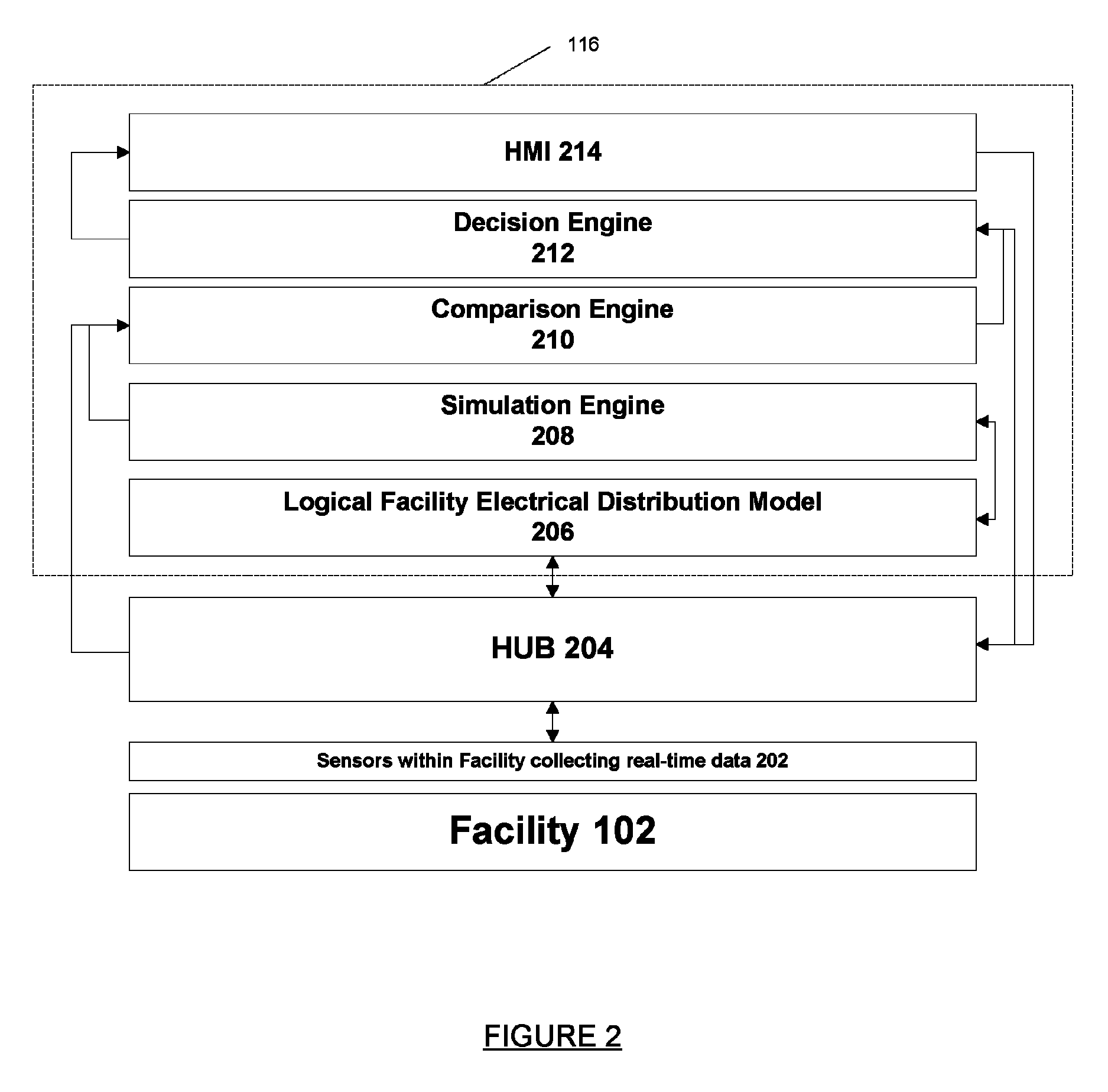

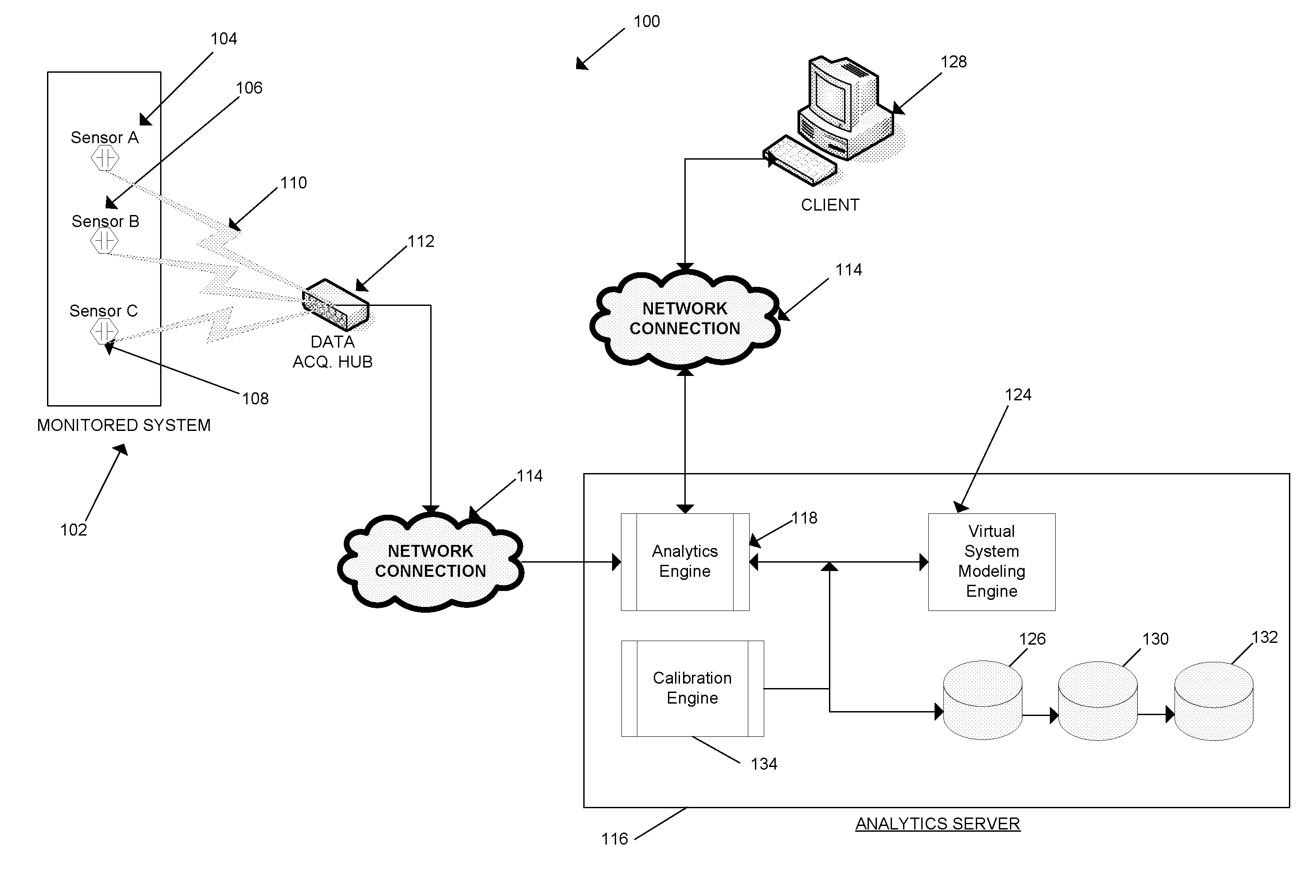

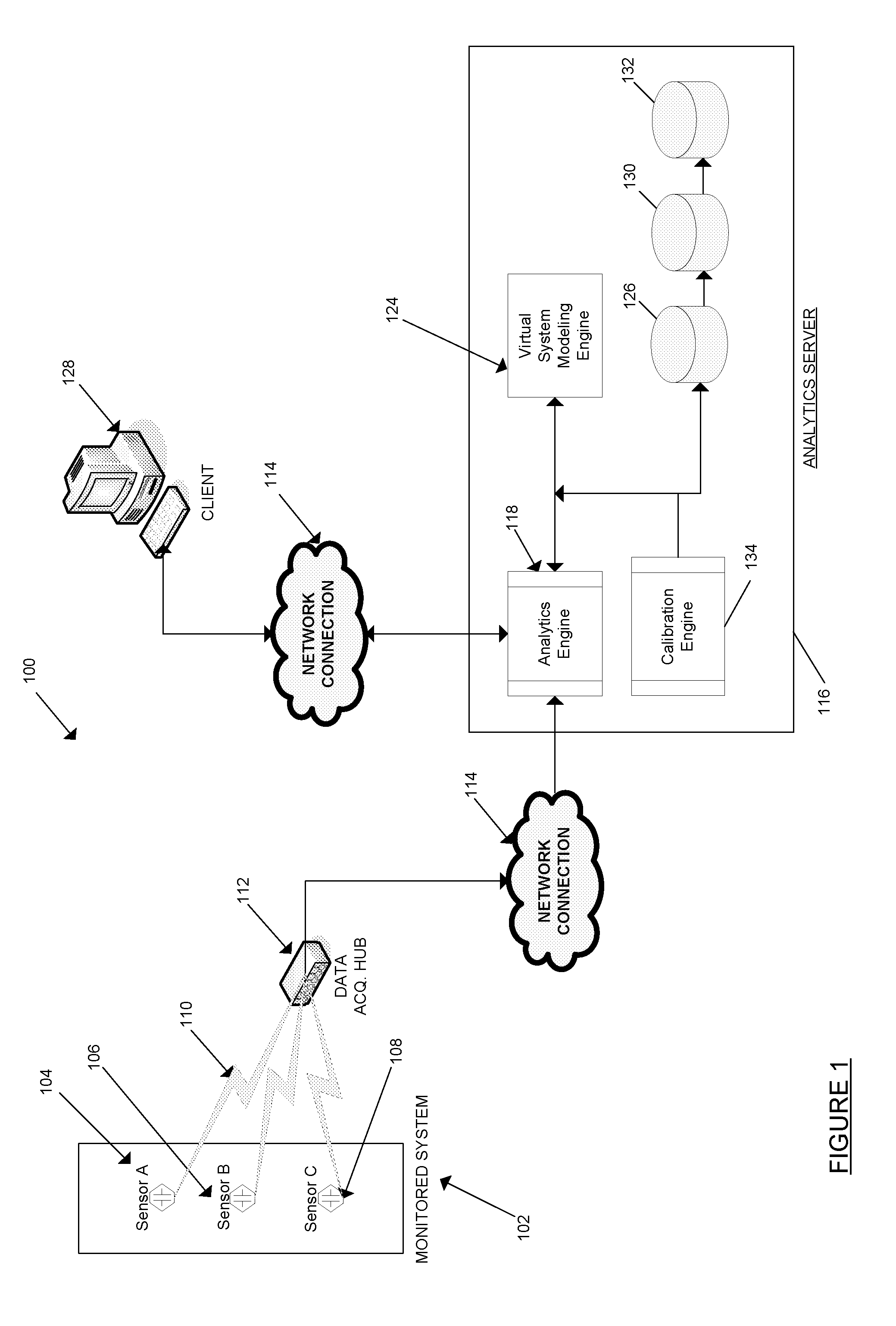

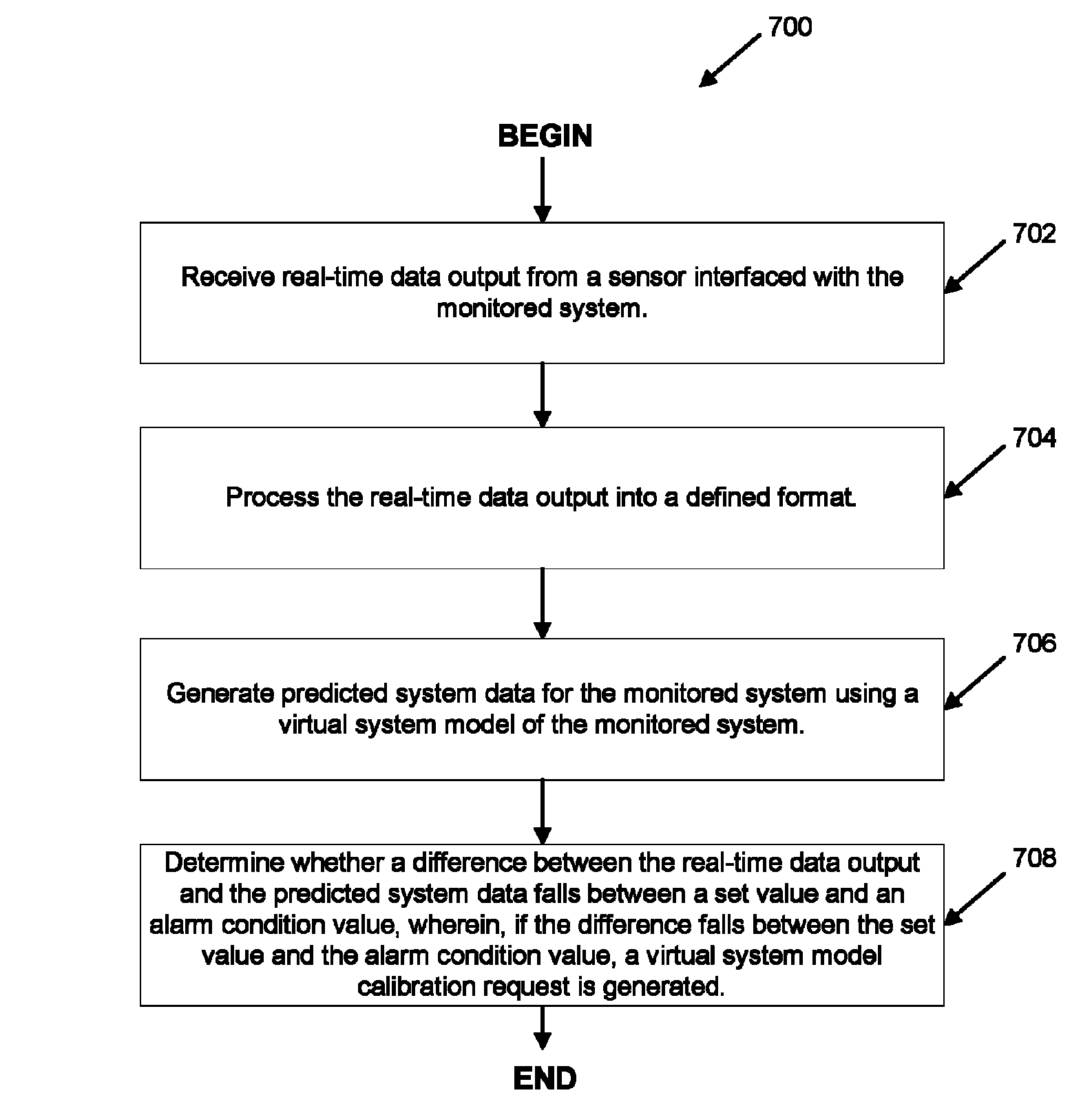

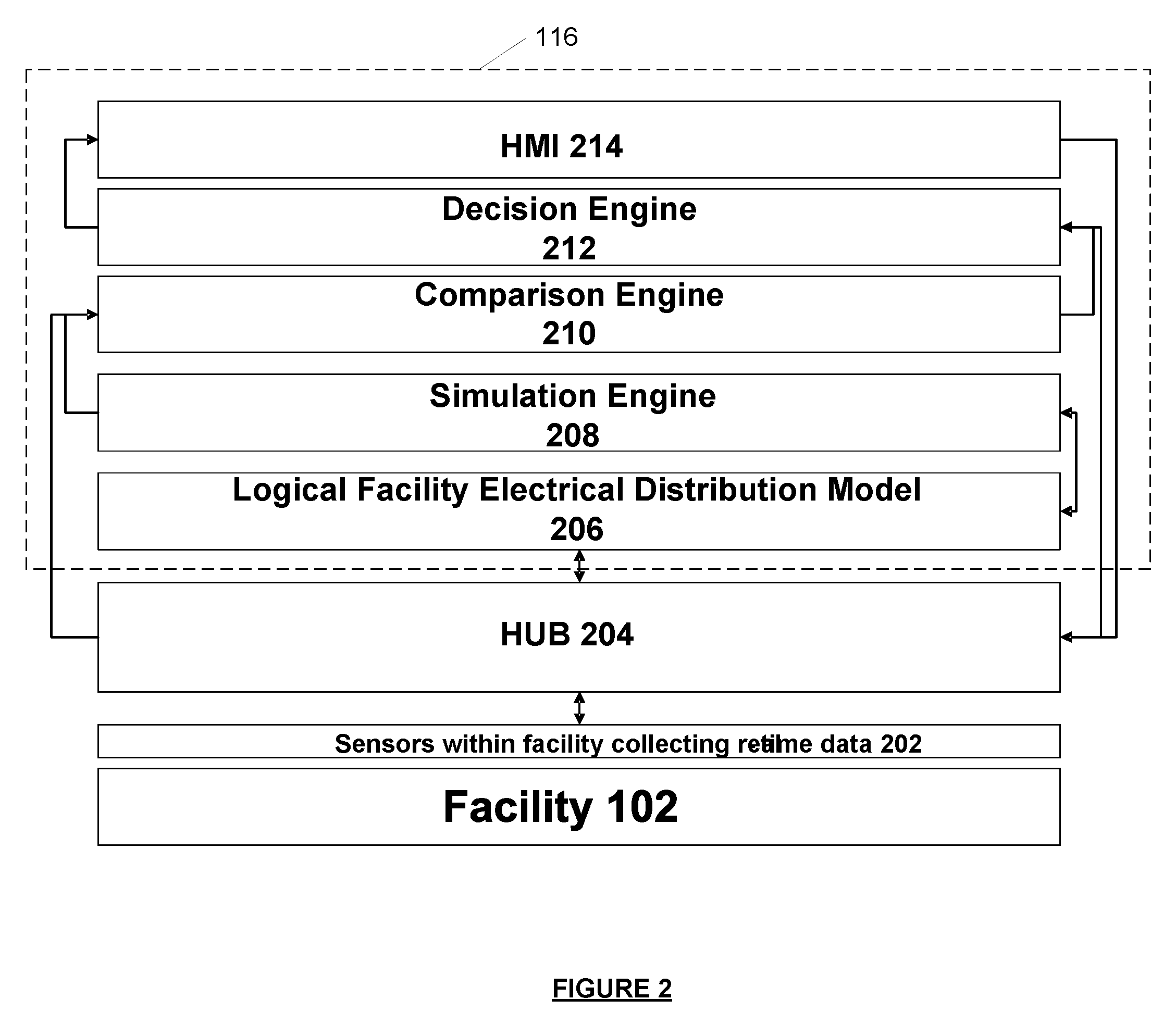

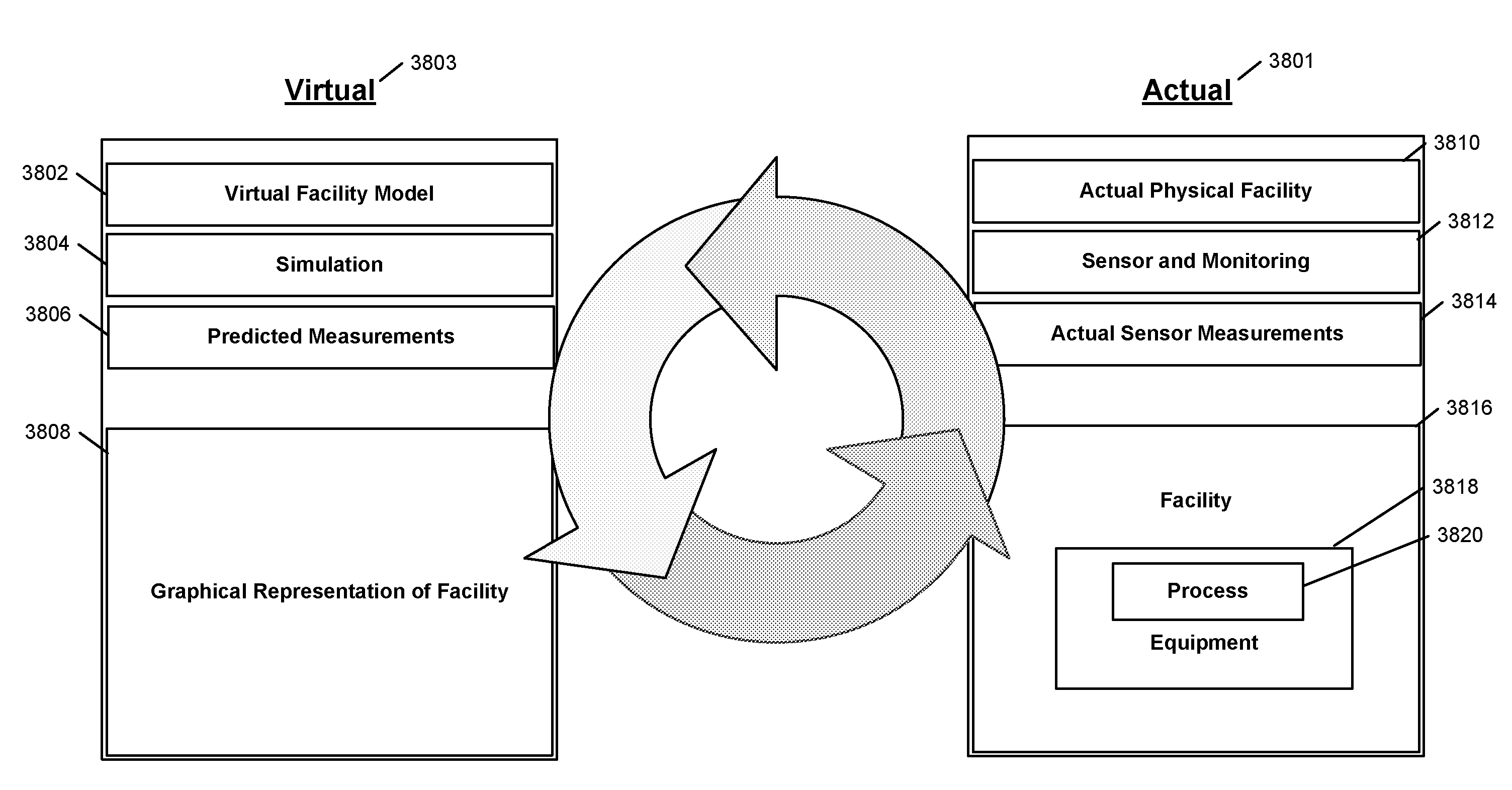

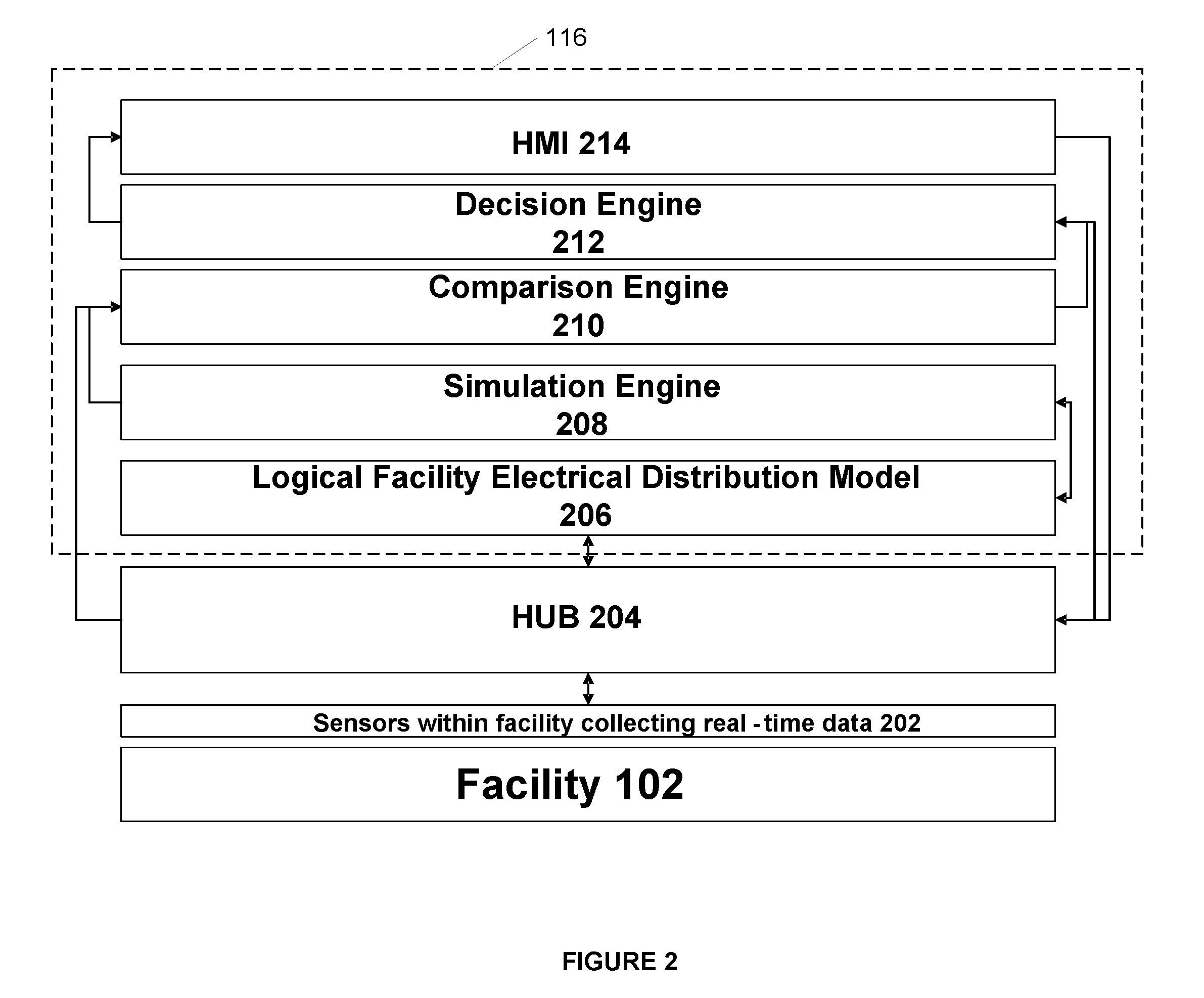

Systems and methods for real-time advanced visualization for predicting the health, reliability and performance of an electrical power system

ActiveUS20080049013A1Circuit arrangementsTesting/monitoring control systemsReal-time dataComputer terminal

A system for real-time three-dimensional (3D) visualization of an electrical system is disclosed. The system includes a data acquisition component, a power analytics server and a client terminal. The data acquisition component acquires real-time data output from the electrical system. The power analytics server is comprised of a virtual system modeling engine, an analytics engine, a machine learning engine and a 3D visualization engine. The virtual system modeling engine generates predicted data output for the electrical system. The analytics engine monitors real-time data output and predicted data output of the electrical system. The machine learning engine stores and processes patterns observed from the real-time data output and the predicted data output to forecast an aspect of the electrical system. The 3D visualization engine renders the virtual system model and the forecasted aspect into a 3D visual model.

Owner:POWER ANALYTICS CORP

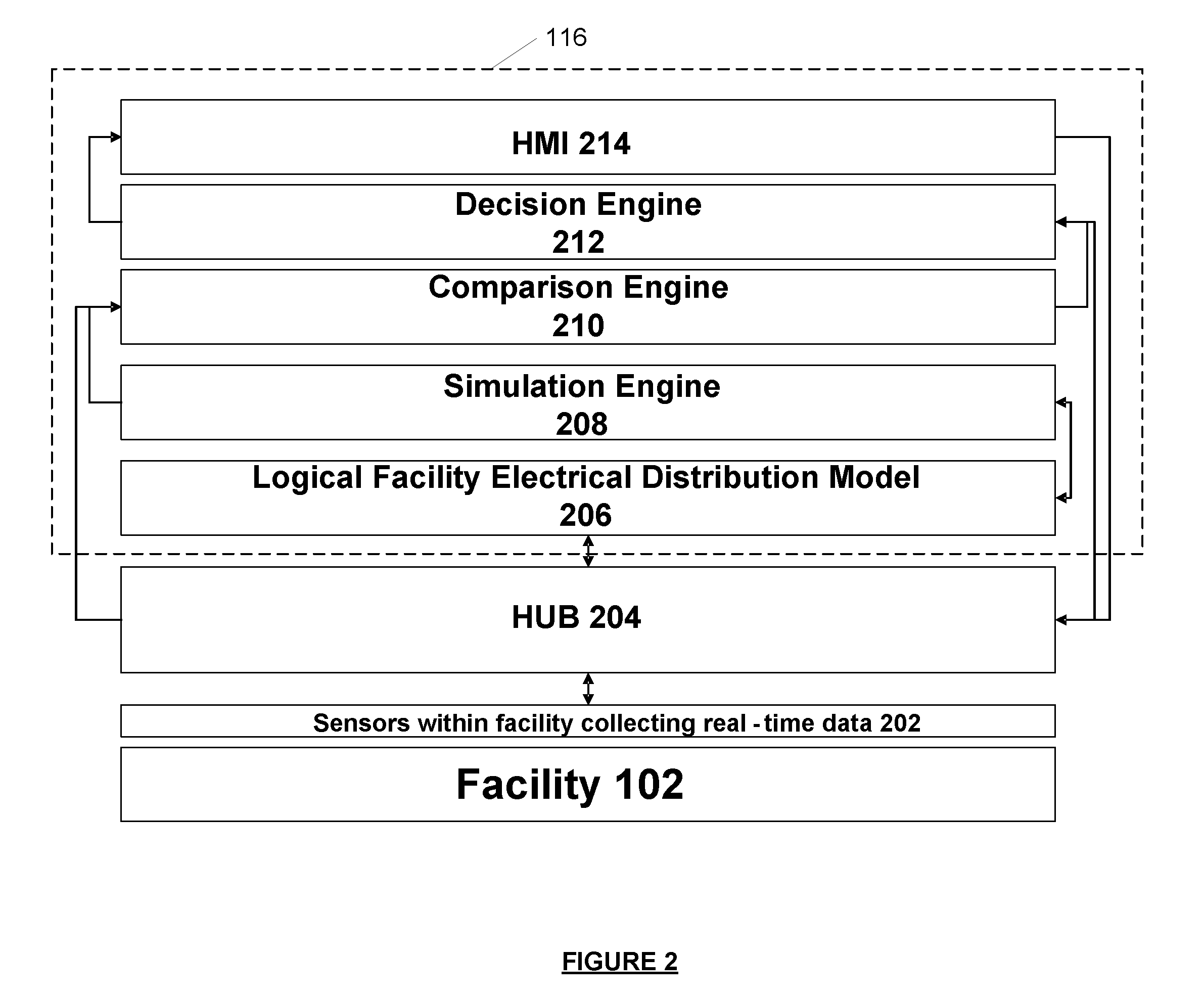

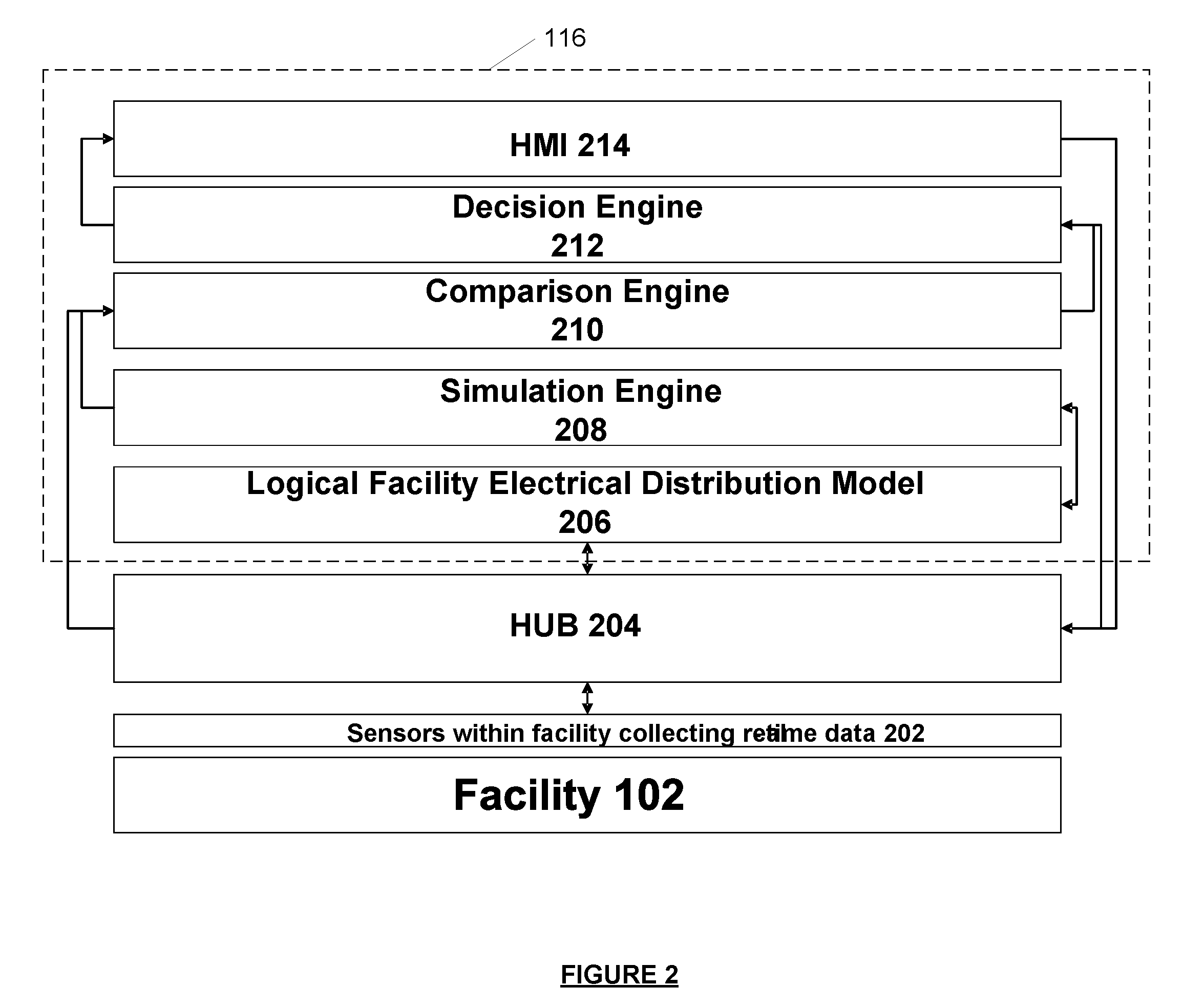

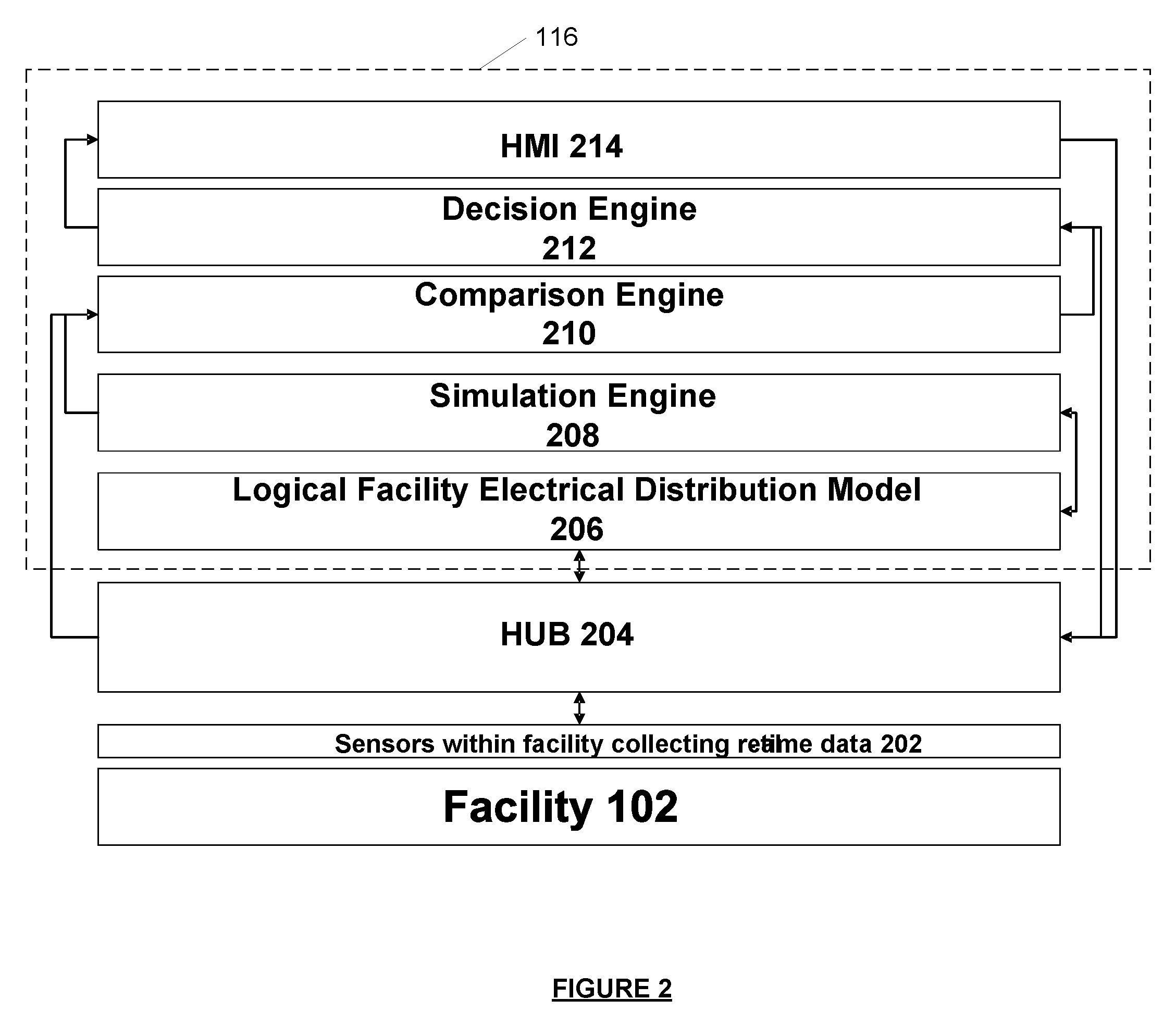

Systems and methods for a real-time synchronized electrical power system simulator for "what-if" analysis and prediction over electrical power networks

ActiveUS20080109205A1Easy to modifyAnalogue computers for nuclear physicsDesign optimisation/simulationPower system simulatorReal-time data

A system for real-time modeling of electrical system performance is disclosed. The system includes a data acquisition component, a power analytics server and a client terminal. The power analytics server is comprised of a virtual system modeling engine, an analytics engine and a power system simulation engine. The virtual system modeling engine is configured to generate predicted data output utilizing a first virtual system model. The analytics engine is configured to synchronize the first virtual system model when a difference between the real-time data output and the predicted data output exceeds a threshold. The power system simulation engine is configured to store and process patterns and facilitate modification of parameters on the first virtual system model to create a second virtual system model; and forecast an aspect of the electrical system operating under parameters of the second virtual system model. The client terminal displays the forecasted aspects.

Owner:BENTLEY SYST INC +1

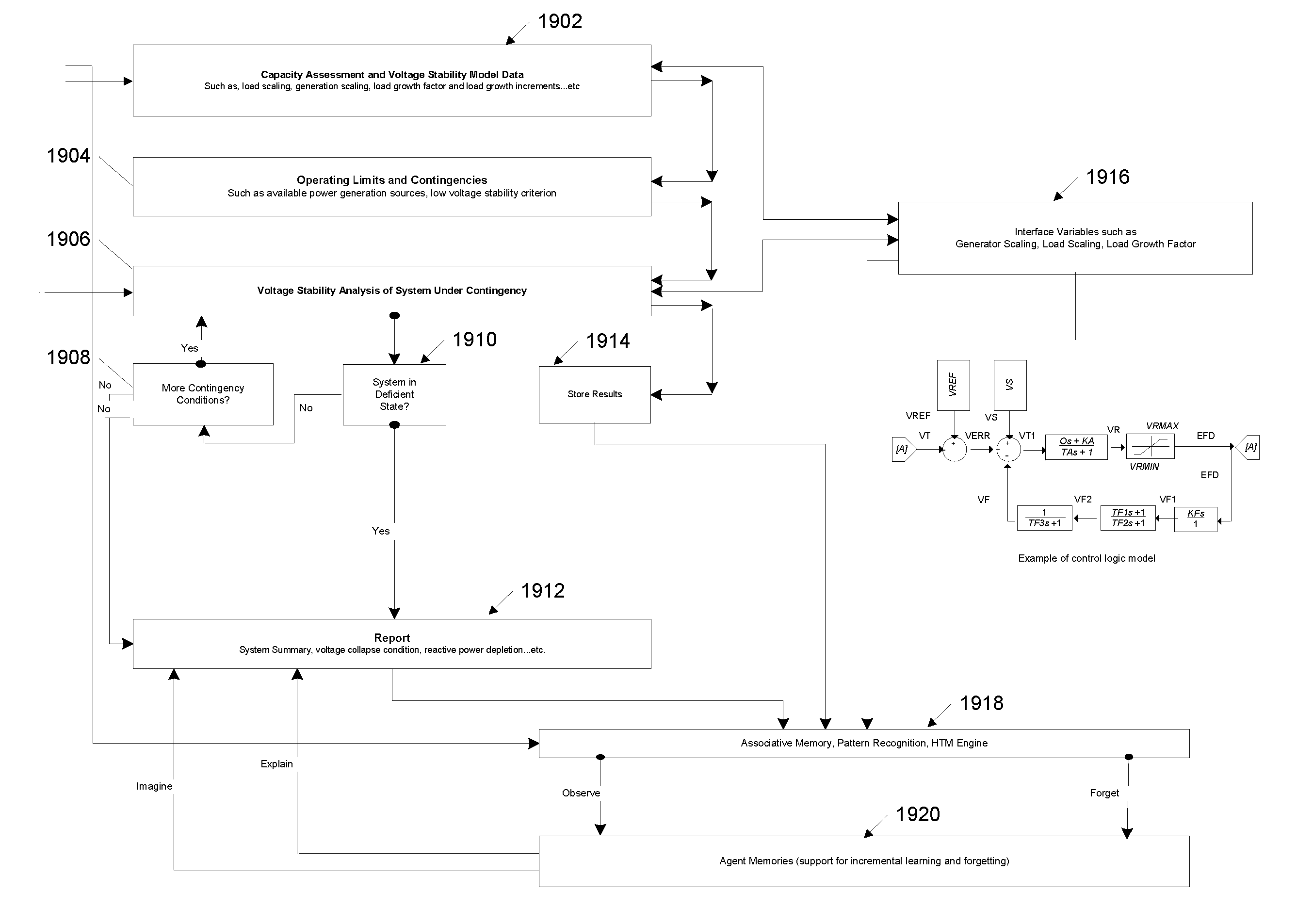

Systems and methods for automatic real-time capacity assessment for use in real-time power analytics of an electrical power distribution system

A system for conducting a real-time power capacity assessment of an electrical system is disclosed. The system includes a data acquisition component, a power analytics server and a client terminal. The data acquisition component is communicatively connected to a sensor configured to acquire real-time data output from the electrical system. The power analytics server is communicatively connected to the data acquisition component and is comprised of a virtual system modeling engine, an analytics engine and a machine learning engine. The machine learning engine is configured to store and process patterns observed from the real-time data output and the predicted data output, forecasting power capacity of the electrical system subjected to a simulated contingency event.

Owner:POWER ANALYTICS CORP

Systems and methods for performing automatic real-time harmonics analyses for use in real-time power analytics of an electrical power distribution system

A system for conducting performing real-time harmonics analysis of an electrical power distribution and transmission system is disclosed. The system includes a data acquisition component, a power analytics server and a client terminal. The data acquisition component is communicatively connected to a sensor configured to acquire real-time data output from the electrical system. The power analytics server is communicatively connected to the data acquisition component and is comprised of a virtual system modeling engine, an analytics engine and a machine learning engine. The machine learning engine is configured to store and process patterns observed from the real-time data output and the predicted data output, forecasting harmonic distortions in the electrical system subjected to a simulated contingency event.

Owner:POWER ANALYTICS CORP

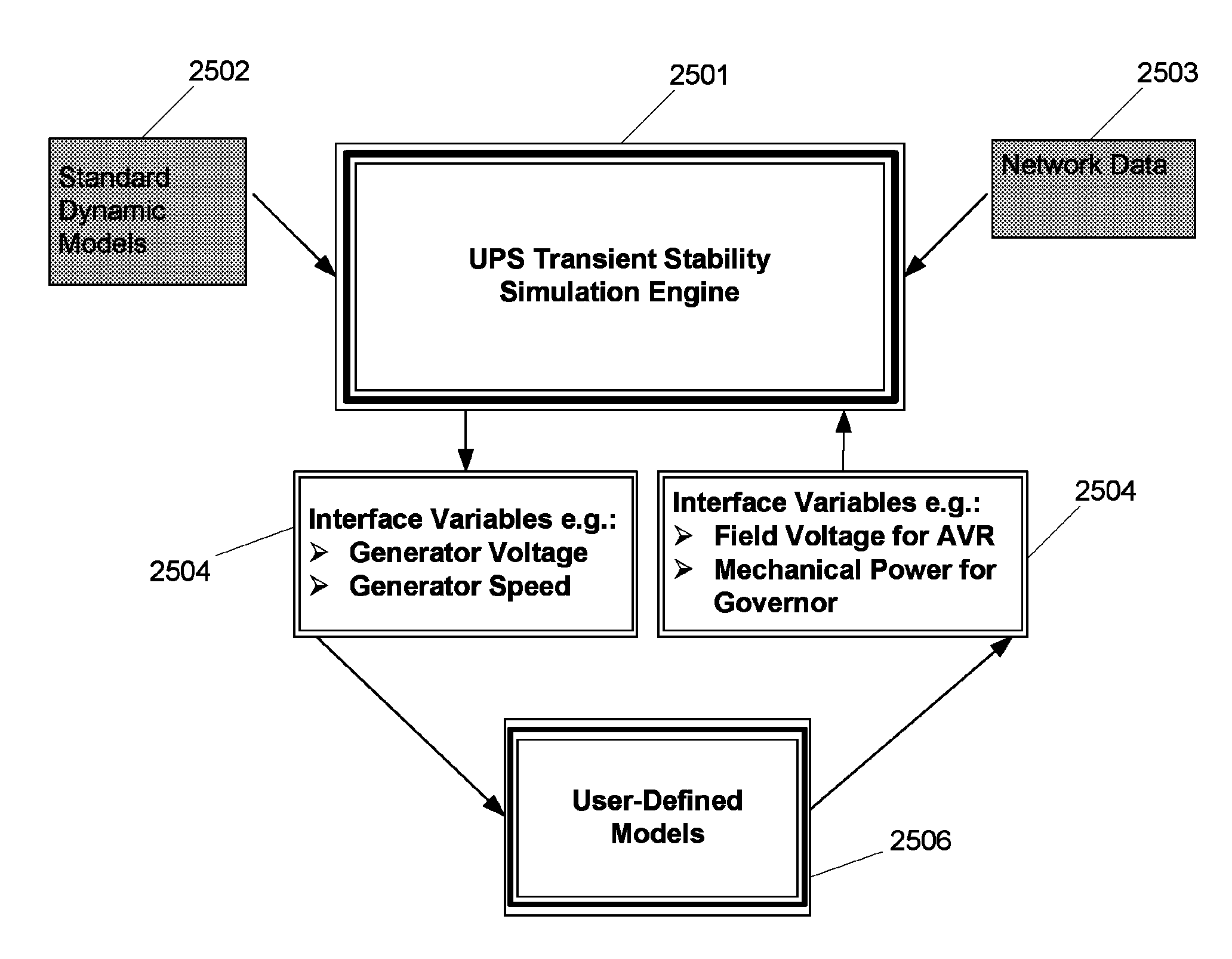

Systems and methods for real-time dynamic simulation of uninterruptible power supply solutions and their control logic systems

InactiveUS7844440B2Current/voltage measurementAnalogue computers for electric apparatusReal-time dataControl system

Owner:POWER ANALYTICS CORP

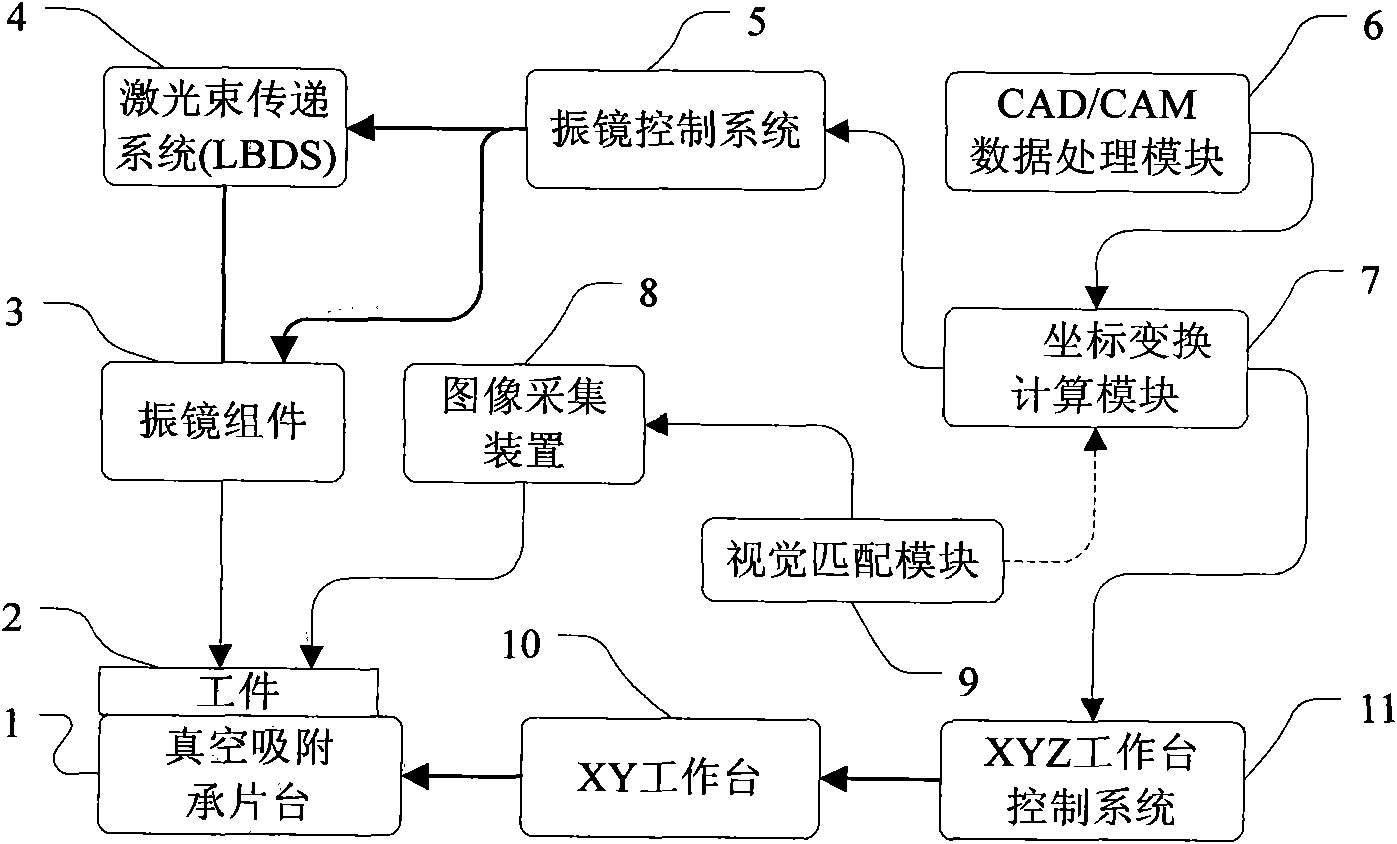

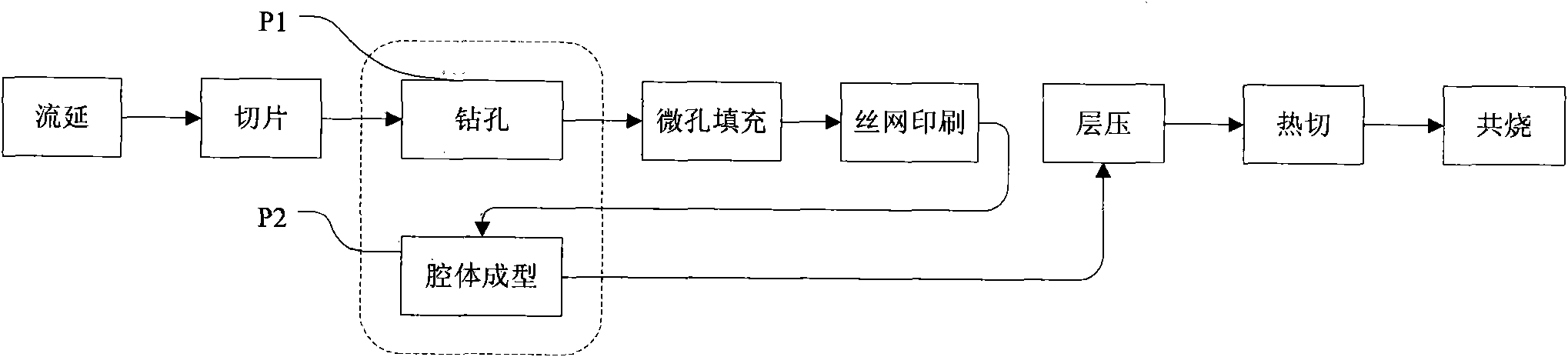

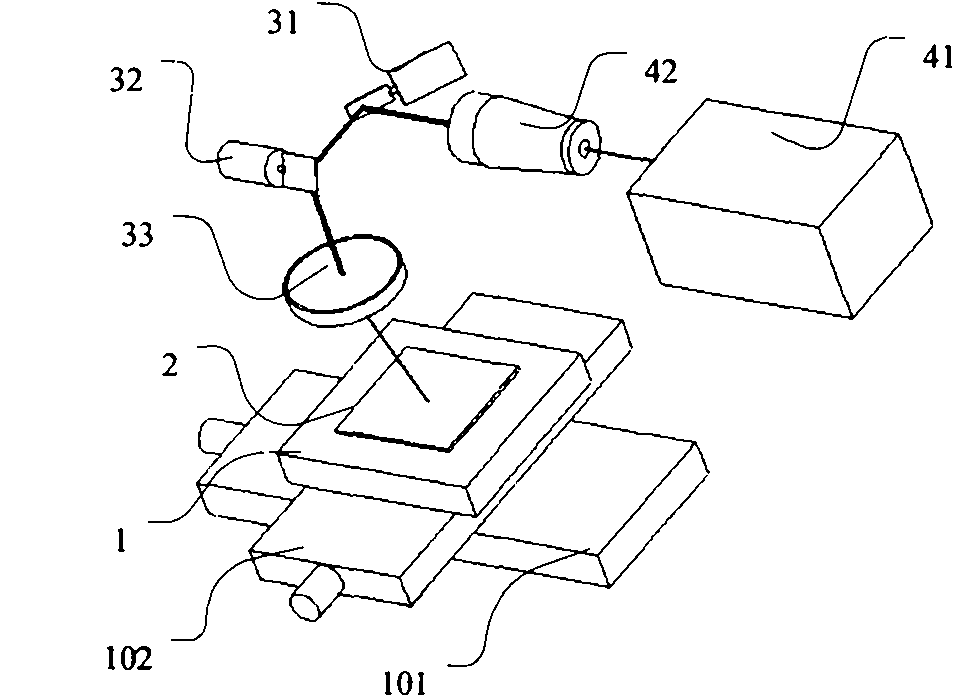

Double-workbench drive laser processing machine and processing method thereof

InactiveCN101870039AAddress flexibilitySolve efficiency problemsLaser beam welding apparatusProduction lineLaser processing

The invention provides a double-workbench drive laser processing machine and a processing method thereof, and relates to the technical field of laser precision processing equipment. The double-workbench drive laser processing machine is provided with a first workbench, a second workbench, a laser beam transfer device (LBDS), a vacuum adsorption chuck and an image acquisition device. The processing method comprises the following steps: carrying out P1 non-contraposition and P2 contraposition on the basis of a unified affine transformation model; mapping a workpiece coordinate space to a processing coordinate space, i.e. a first workbench processing coordinate and a second workbench processing coordinate; and transferring a CAD data pattern to the workpiece, thereby controlling a feature position error of the processed pattern within an ideal accuracy range. By using the invention, the working efficiency of the P1 procedure can be effectively enhanced and the problem of automatic visual contraposition accuracy caused by workpiece deformation in the P2 procedure can be effectively solved, thereby reducing the cost and enhancing the productive capacity. The invention has the advantages of simple structure, and unique principle and method. The invention is especially suitable to be used on a large-scale LTCC / HTCC production line of processing technology.

Owner:THE 45TH RES INST OF CETC

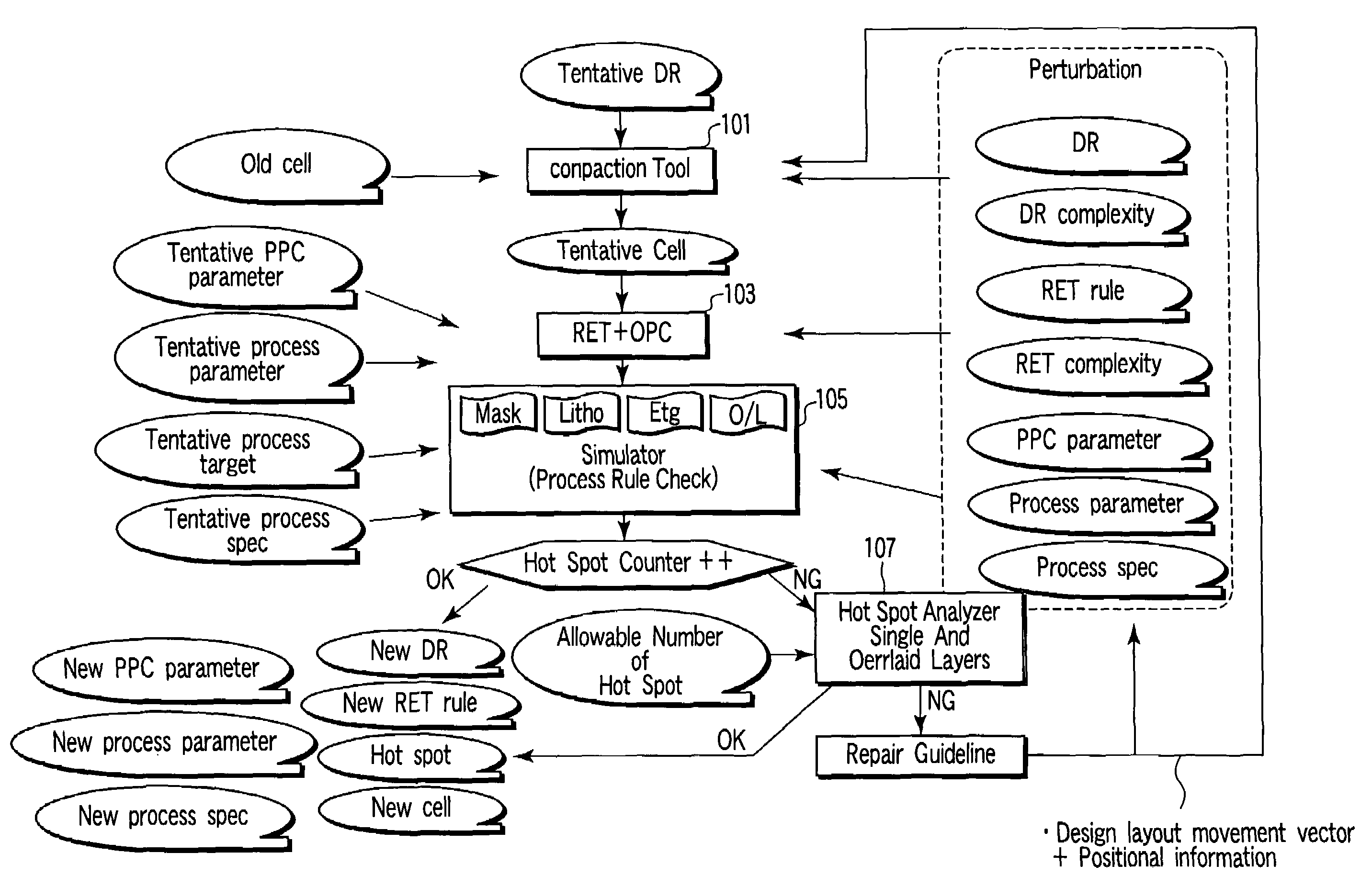

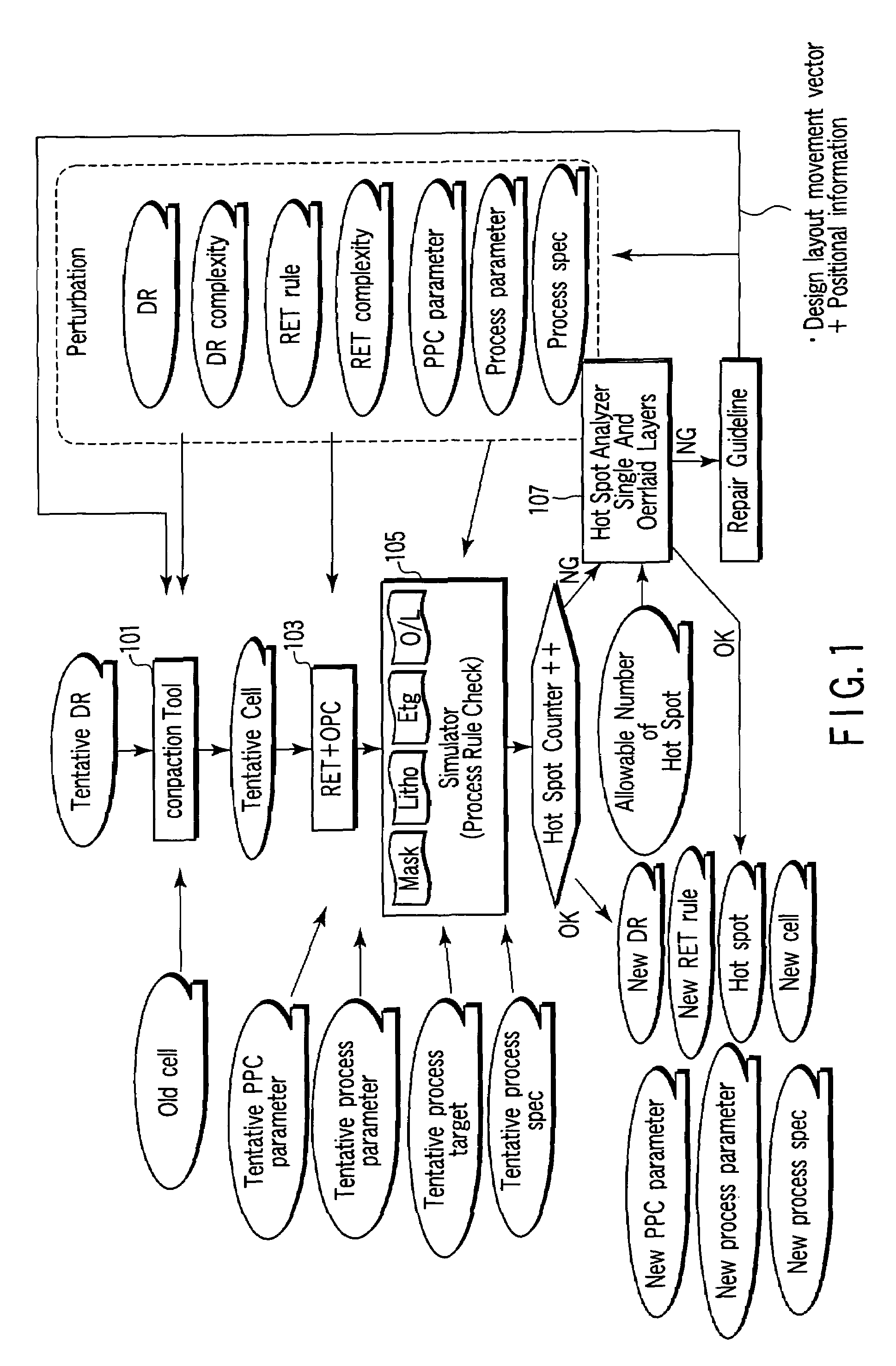

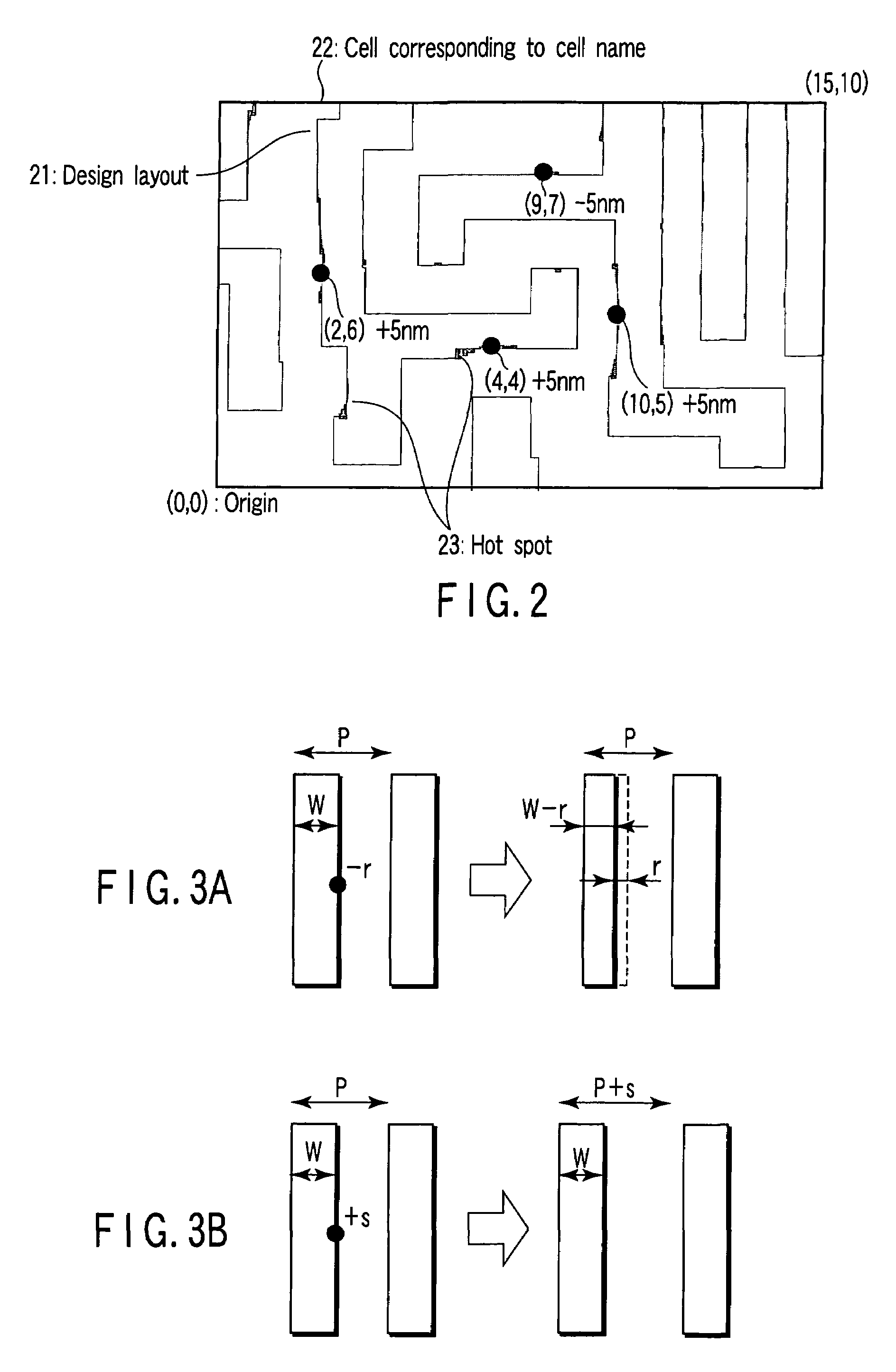

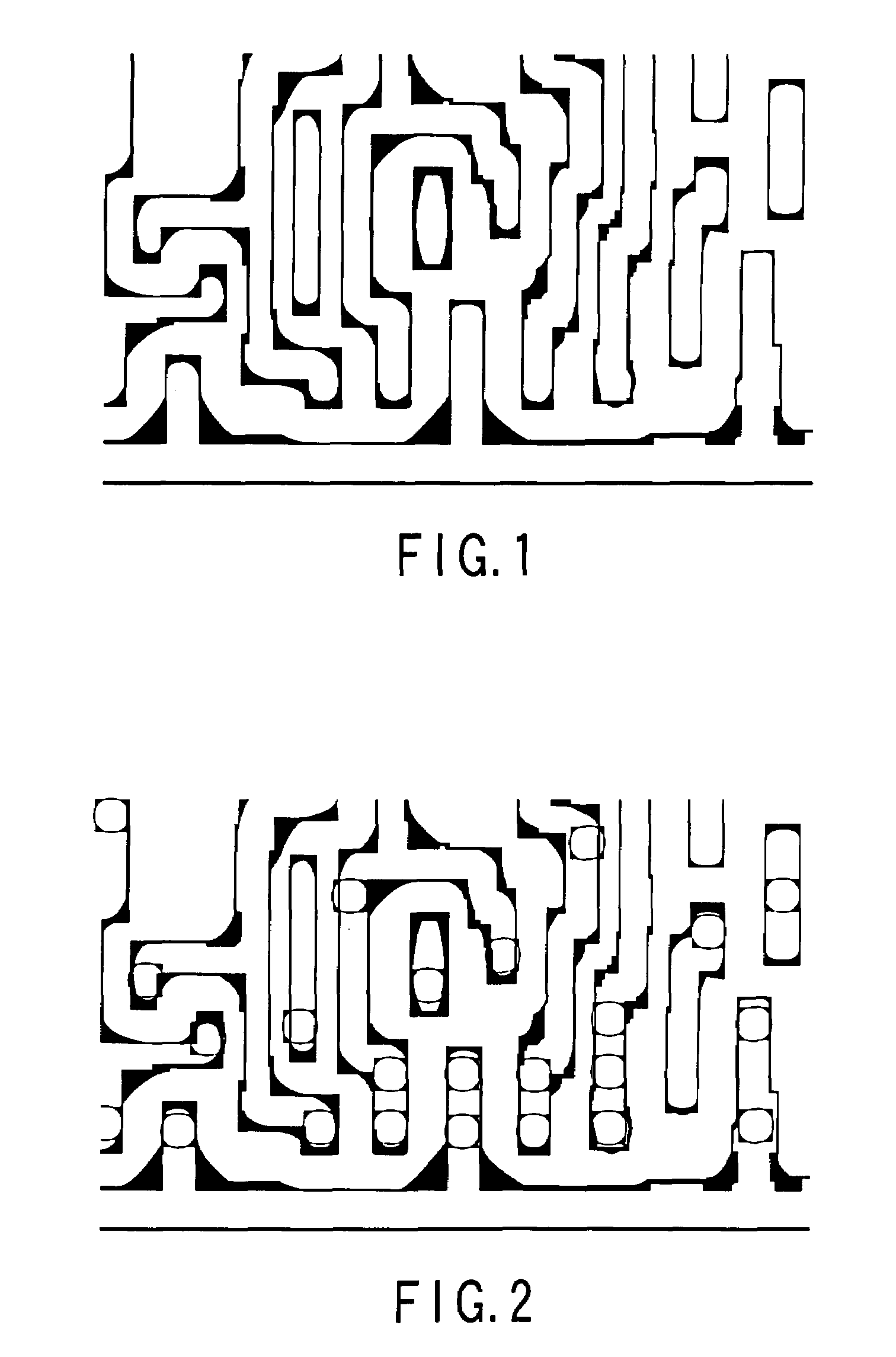

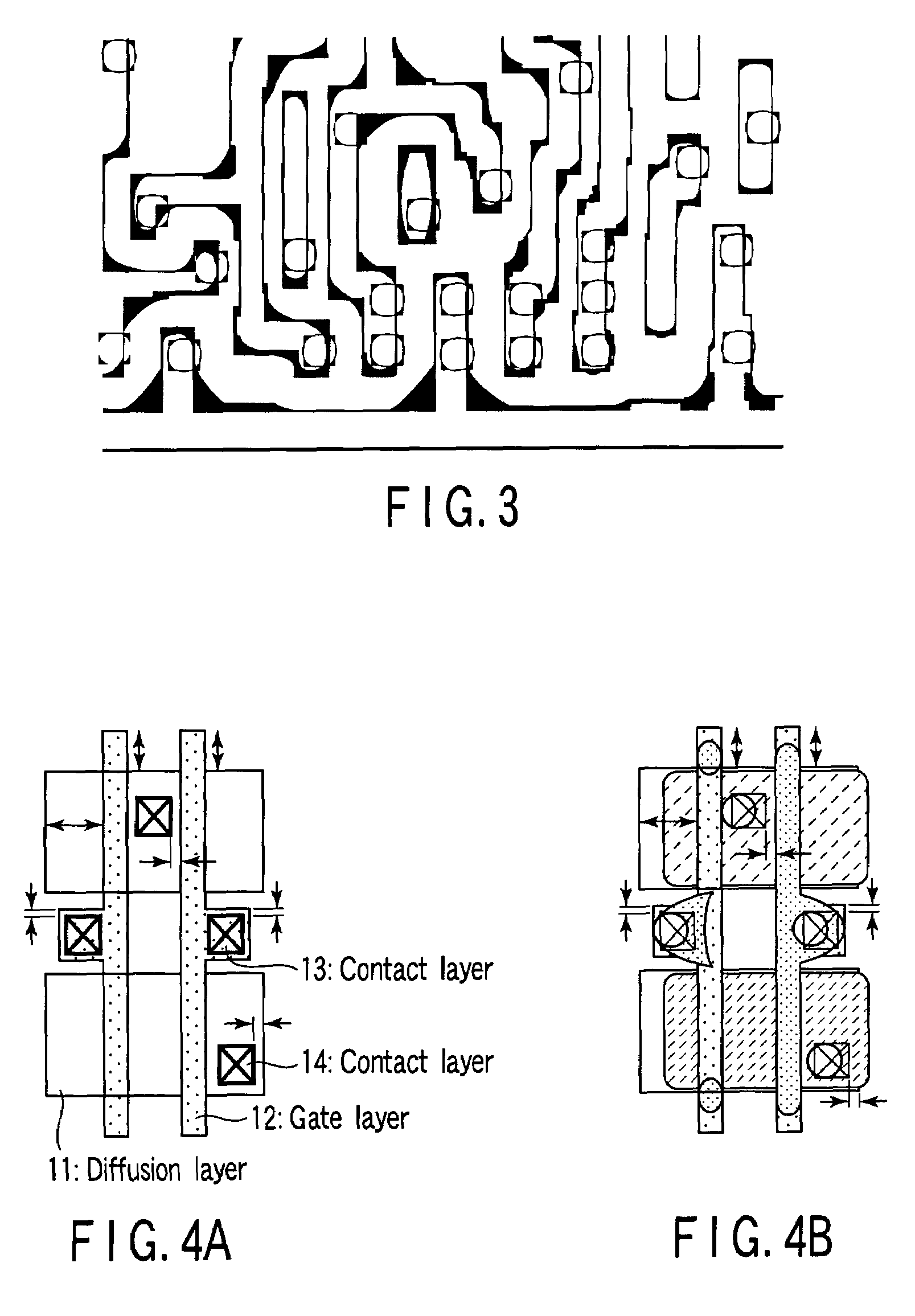

Design layout preparing method

ActiveUS7194704B2Semiconductor/solid-state device manufacturingOriginals for photomechanical treatmentEngineeringProcess patterns

There is disclosed a method of producing a design layout by optimizing at least one of design rule, process proximity correction parameter and process parameter, including calculating a processed pattern shape based on a design layout and a process parameter, extracting a dangerous spot having an evaluation value with respect to the processed pattern shape, which does not satisfy a predetermined tolerance, generating a repair guideline of the design layout based on a pattern included in the dangerous spot, and repairing that portion of the design layout which corresponds to the dangerous spot based on the repair guideline.

Owner:KIOXIA CORP

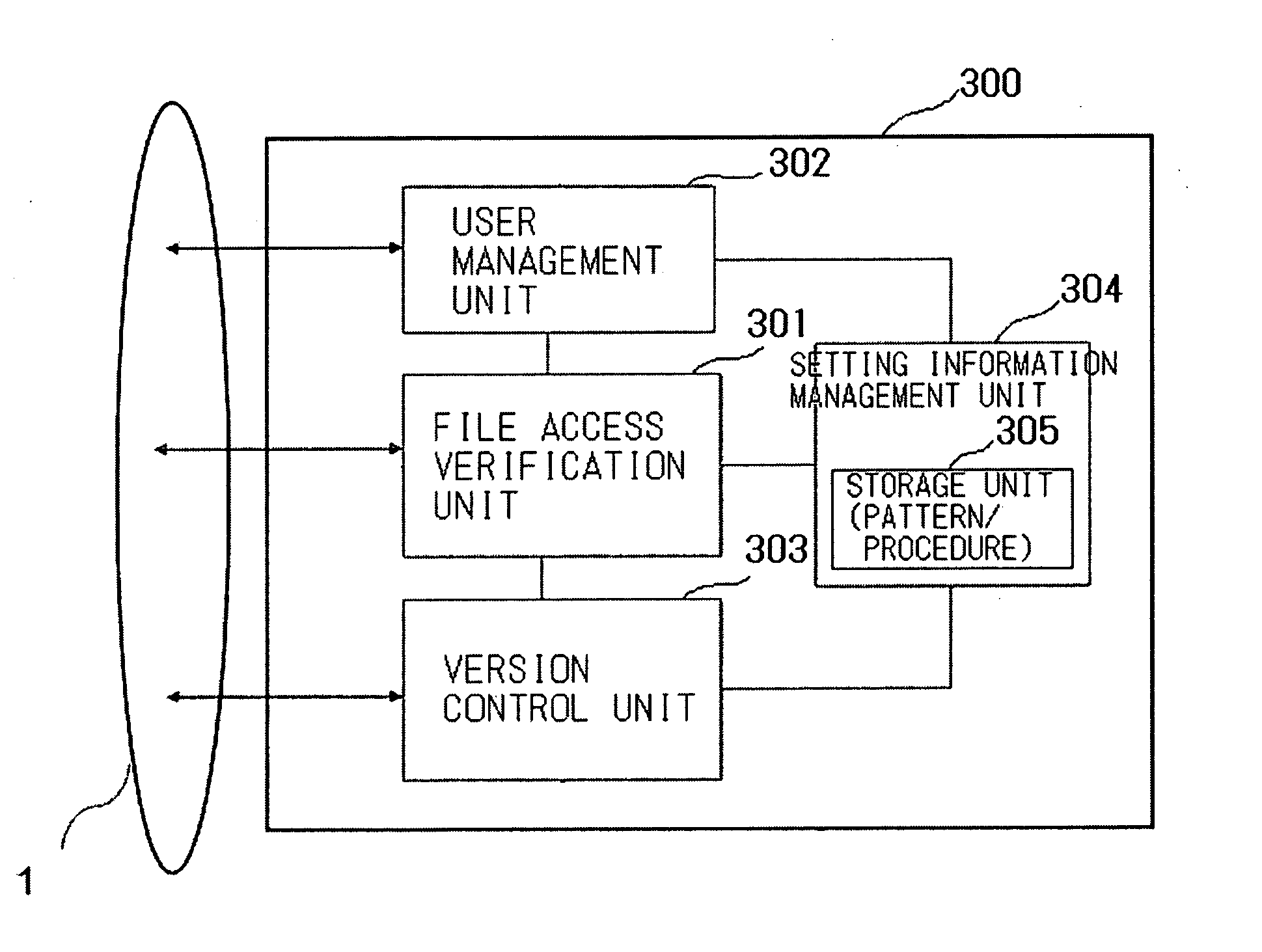

File version management device, method, and program

InactiveUS20060288056A1Avoid wastingAvoid dataDigital data information retrievalSpecial data processing applicationsManagement unitPattern matching

Disclosed is a version management device which comprises a file access verification unit that receives a request packet sent from the client and a response packet sent from the server, extracts a processing request and a response result from the packets, and checks if the processing request and the response result match an access pattern corresponding to a file data update processing operation by an application running on the client; a user management unit that manages user information in a format defined for each file access protocol to verify from which user the processing request, included in the request packet from the client, is issued; a version control unit that controls the creation operation of a version management file when it is found that an operation corresponding to processing pattern corresponding to file data update processing by the application running on the client is executed in the file access verification unit; and a setting information management unit that holds operation setting information required by the file access verification unit, the user management unit, and the version control unit for their operation.

Owner:NEC CORP

Systems and methods for real-time dynamic simulation of uninterruptible power supply solutions and their control logic systems

InactiveUS20080215302A1Current/voltage measurementAnalogue computers for electric apparatusReal-time dataControl system

A system for real-time modeling of uninterruptible power supply (UPS) control elements protecting an electrical system is disclosed. The system includes a data acquisition component, a power analytics server and a client terminal. The data acquisition component acquires real-time data output from the electrical system. The power analytics server is comprised of a virtual system modeling engine, an analytics engine and a UPS transient stability simulation engine.The virtual system modeling engine generates predicted data output for the electrical system. The analytics engine monitors real-time data output and predicted data output of the electrical system. The UPS transient stability simulation engine stores and processes patterns observed from the real-time data output and utilizes a user-defined UPS control logic model to forecast an aspect of the interaction between UPS control elements and the electrical system subjected to a simulated contingency event.

Owner:POWER ANALYTICS CORP

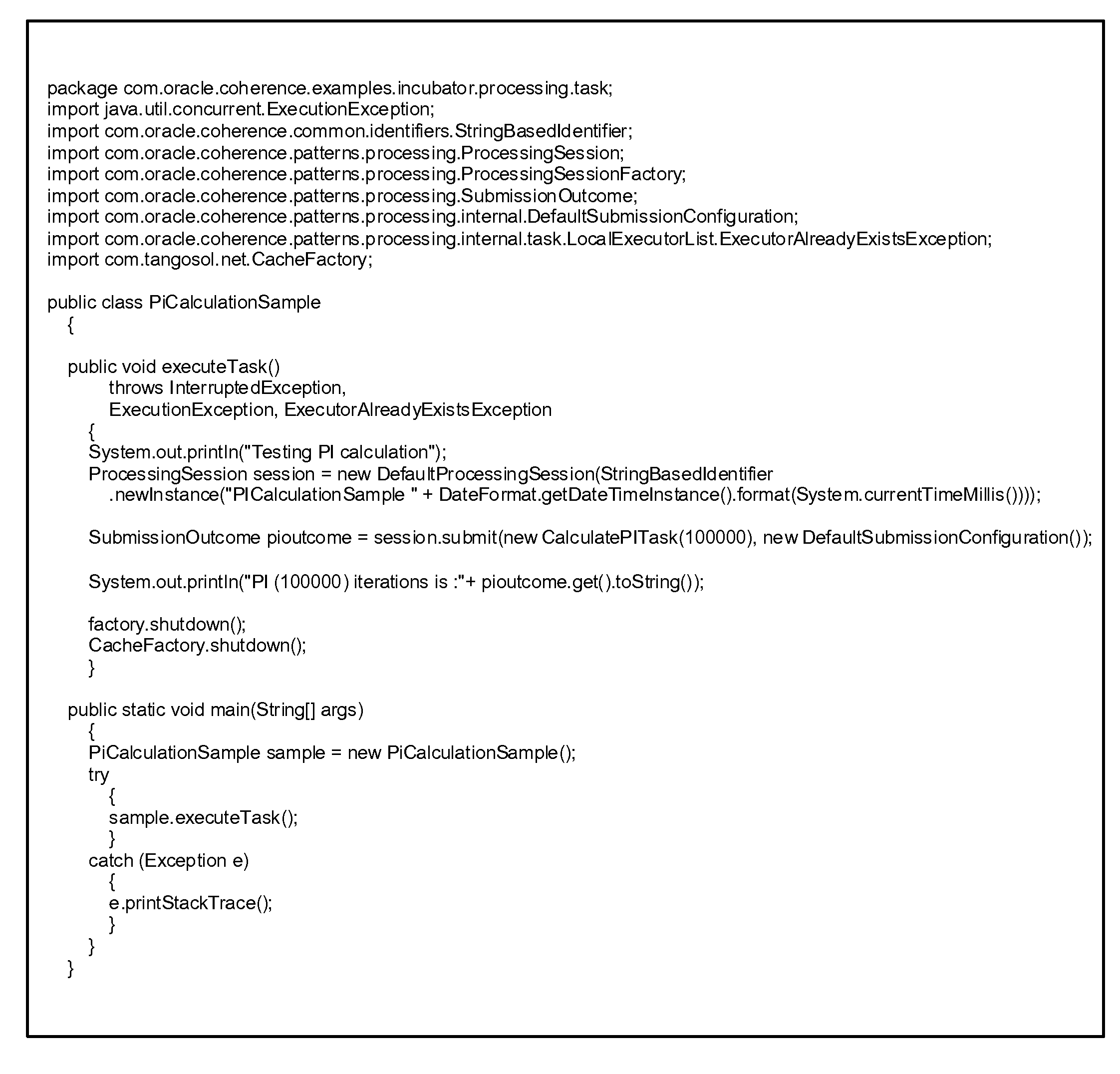

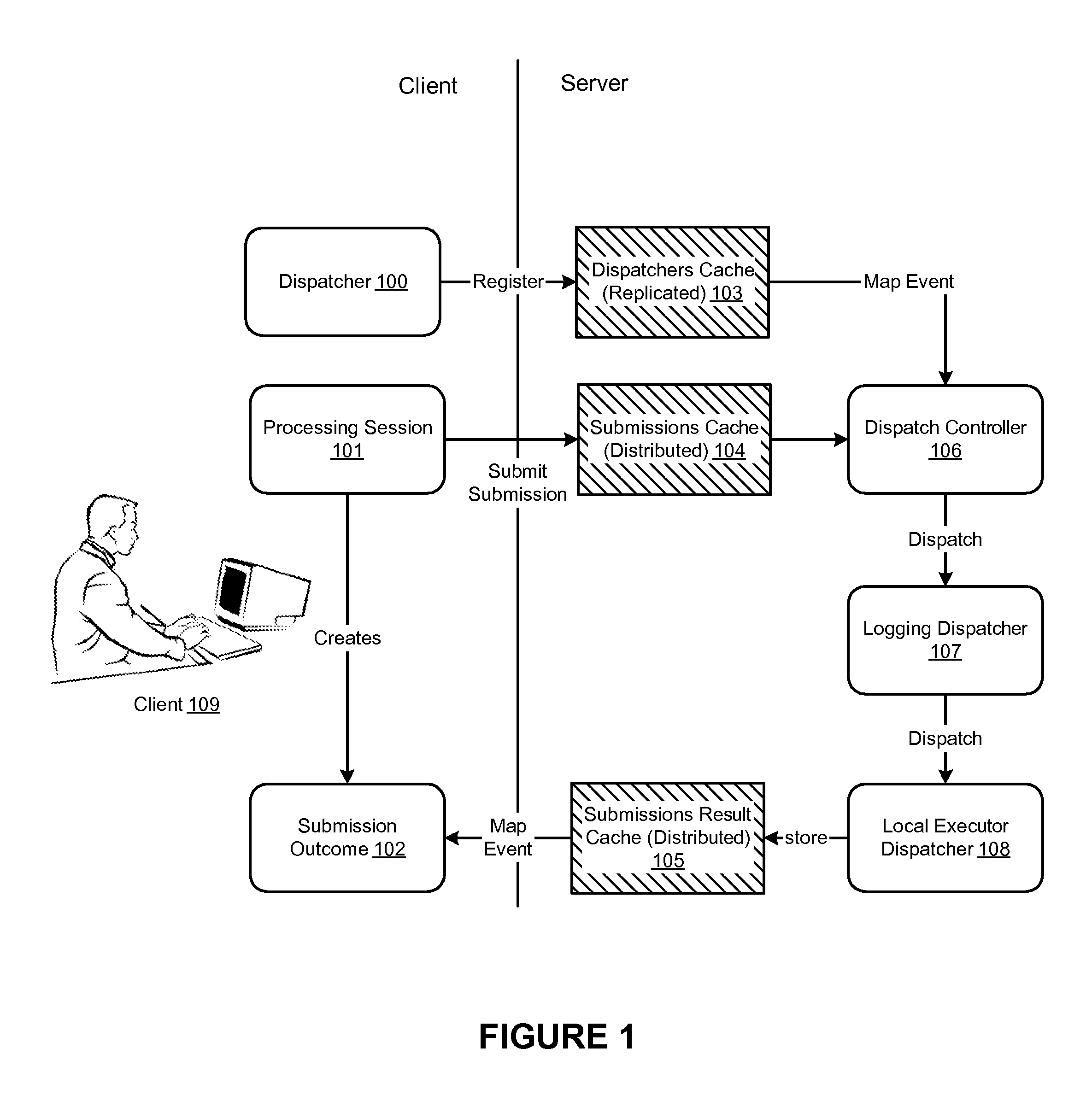

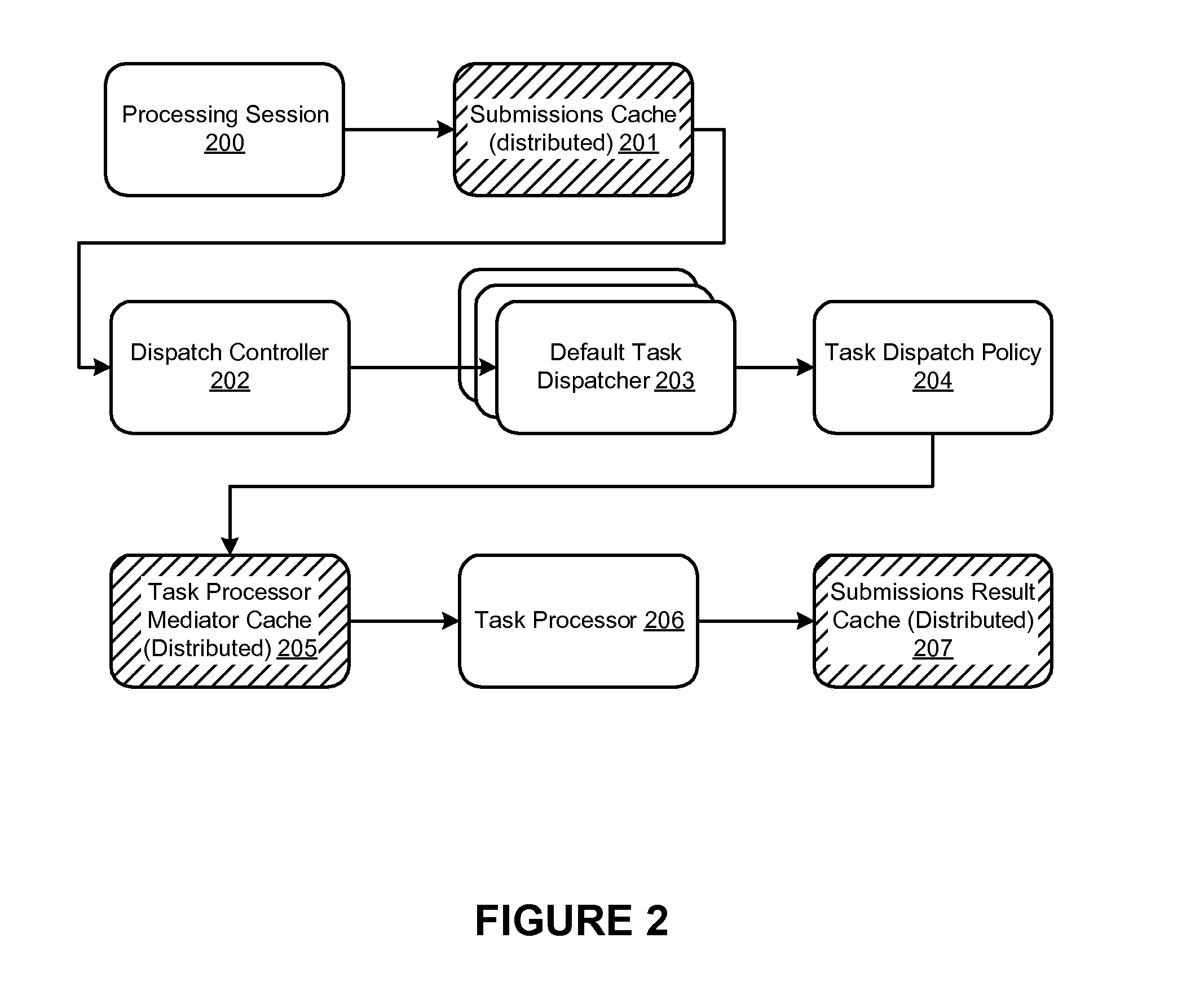

Processing pattern framework for dispatching and executing tasks in a distributed computing grid

ActiveUS20120197959A1Program initiation/switchingMultiple digital computer combinationsProcess patternsClient-side

A processing pattern is described for dispatching and executing tasks in a distributed computing grid, such as a cluster network. The grid includes a plurality of computer nodes that store a set of data and perform operations on that data. The grid provides an interface that allows clients to submit tasks to the cluster for processing. The interface can be used to establish a session between the client and the cluster, which will be used to submit a task for processing by the plurality of computer nodes of the cluster. A dispatcher receives a submission of the task over the interface and routes the task to at least one node in the cluster that is designated to process the task. A task processor then processes the task on the designated node(s), generates a submission outcome and indicates to the client that the submission outcome is available.

Owner:ORACLE INT CORP

Systems and methods for performing automatic real-time harmonics analyses for use in real-time power analytics of an electrical power distribution system

Owner:POWER ANALYTICS CORP

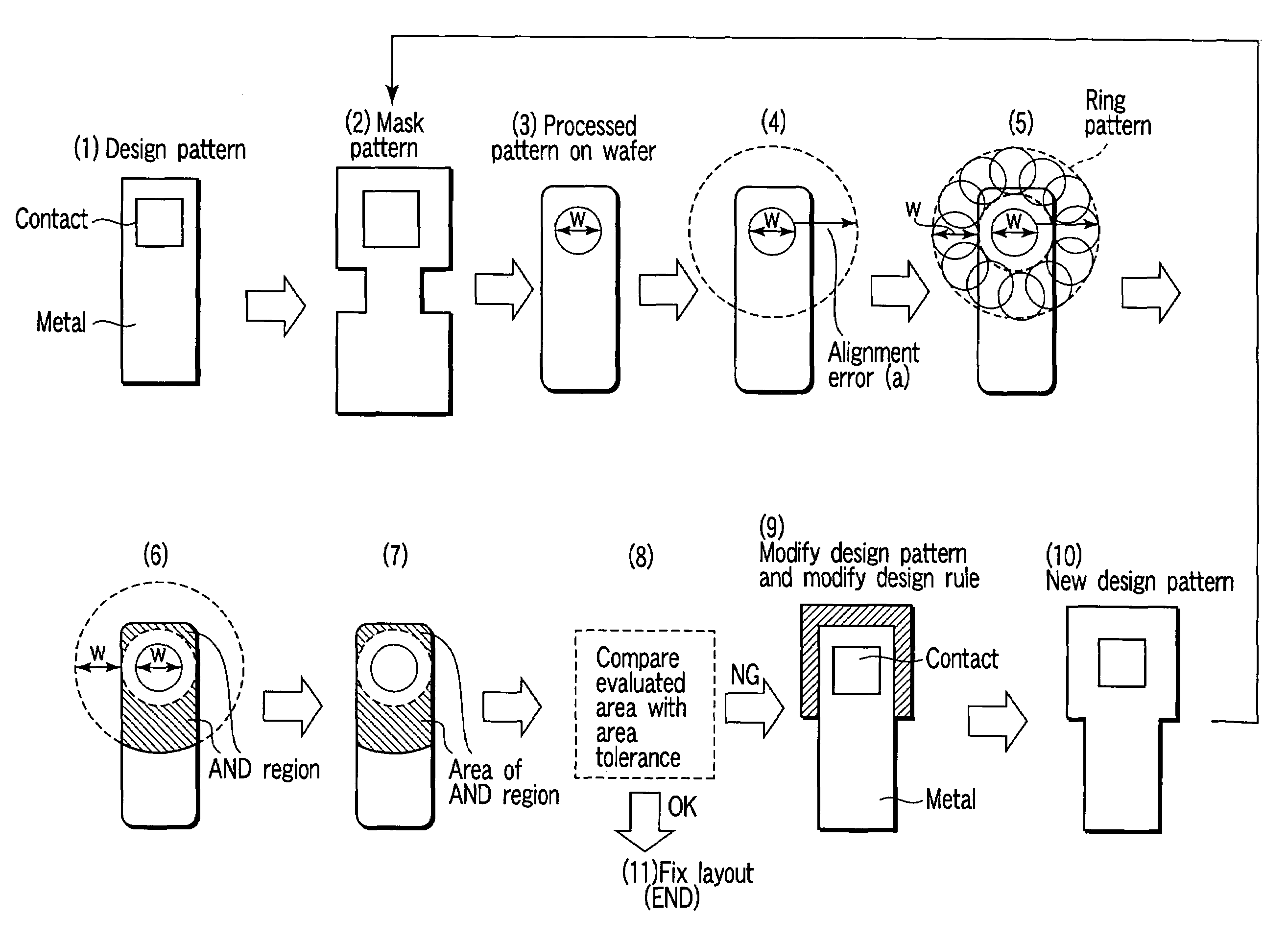

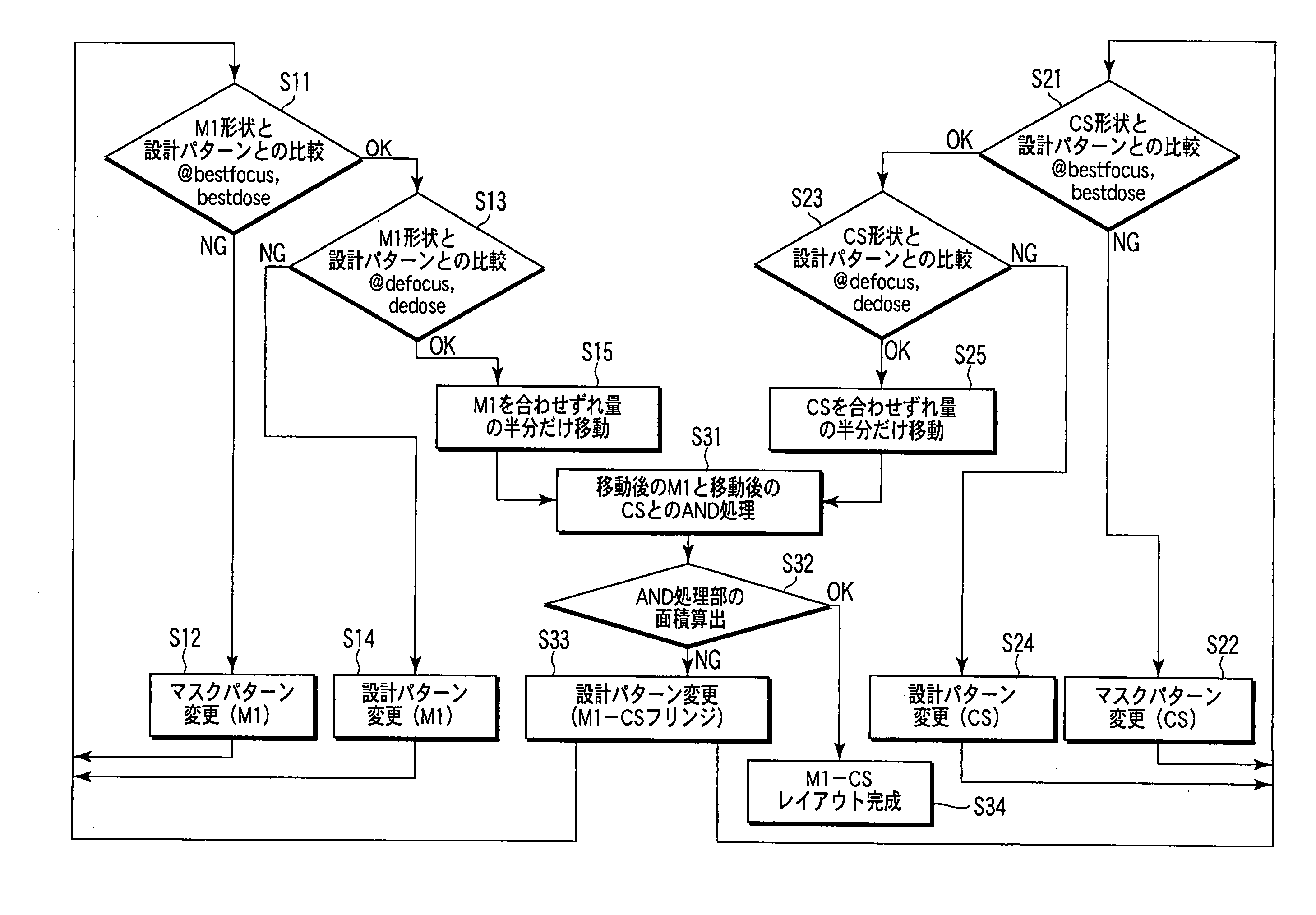

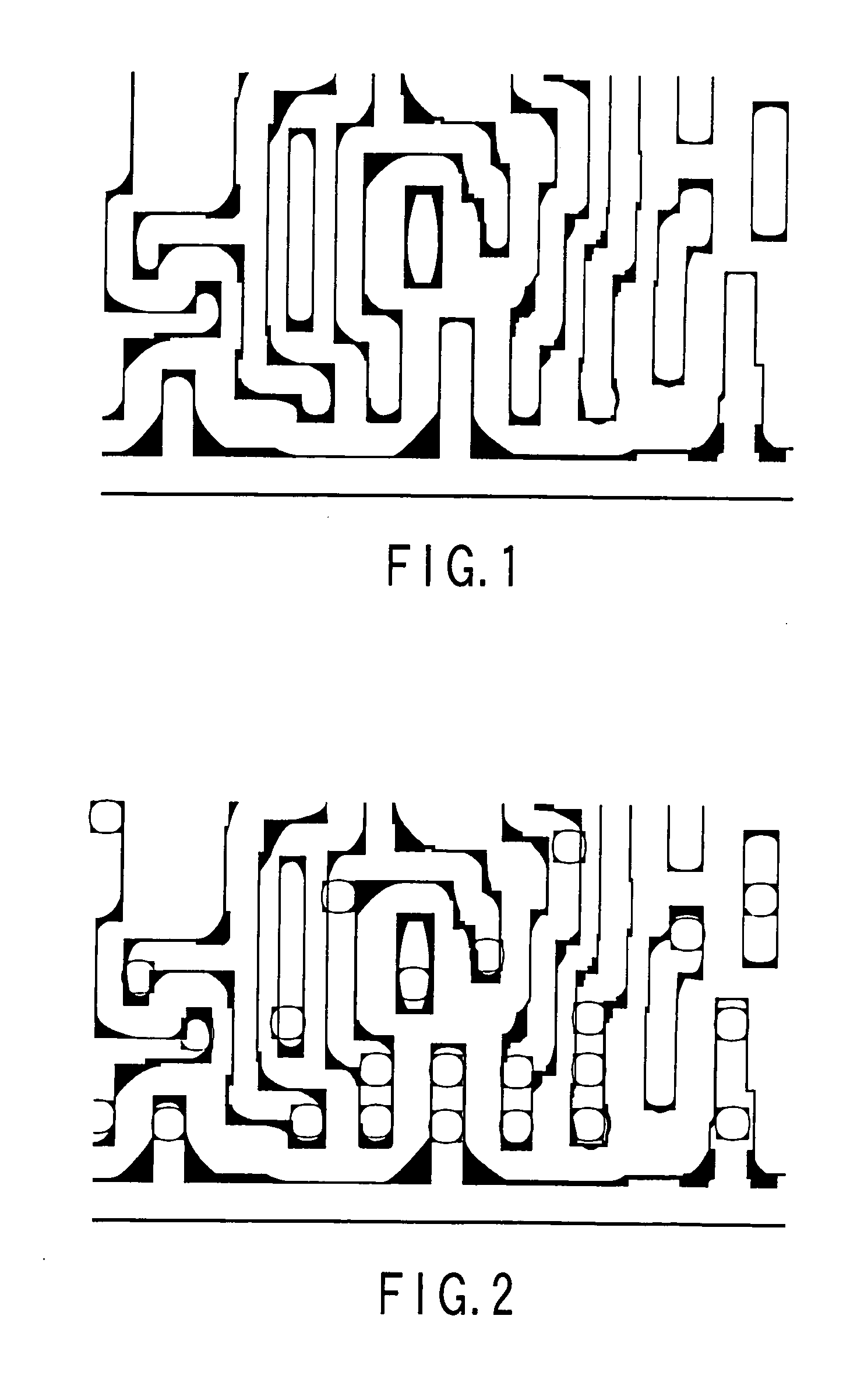

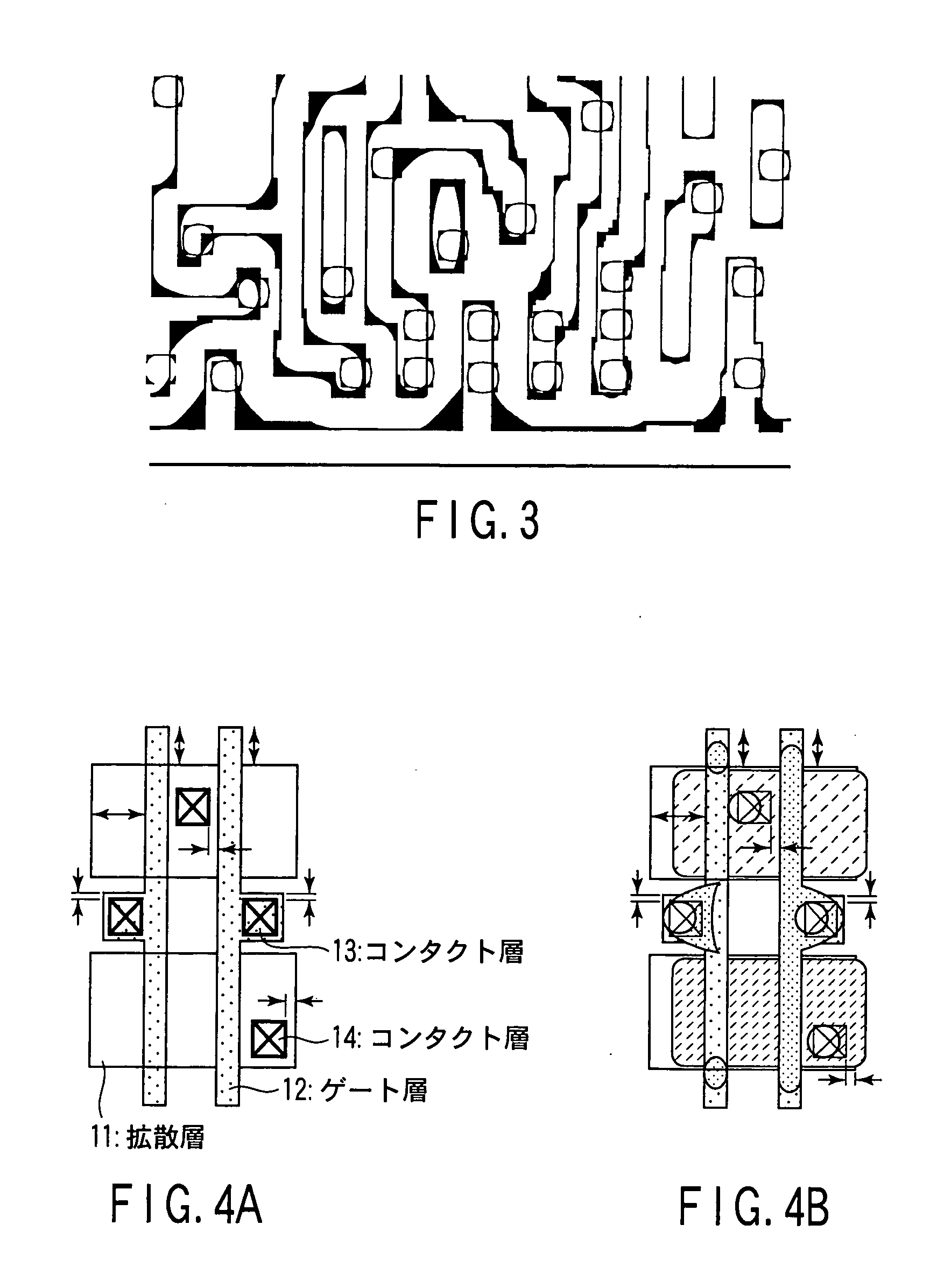

Design pattern correction method and mask pattern producing method

ActiveUS7266801B2Semiconductor/solid-state device manufacturingOriginals for photomechanical treatmentProcess patternsEngineering

Owner:KIOXIA CORP

Method for preparing micro-nano-scale patterned electrospun fiber membrane

InactiveCN102260963AEasy to processHigh degree of automationNew-spun product collectionFilament/thread formingFiberMicro nano

The invention relates to a method for preparing a micro-nano-scale patterned electrospun fiber membrane. The method comprises the following steps: A) using a computer to draw a required pattern through layout design software; B) inputting the pattern into a micro-electrical mechanical system and using the micro-electrical mechanical system to deposit metal onto a non-metal base material according to the input pattern so as to get a receiving plate with the micro-nano-scale pattern; and C) taking the receiving plate with the micro-nano-scale pattern as the receiving plate of an electrospinning device and performing electrostatic spinning so as to get the micro-nano-scale patterned electrospun fiber membrane. By adopting the method, the patterned electrospun fiber membrane with micro-nano-scale minimal unit size of the pattern can be prepared, and the patterned electrospun fiber membrane has good application prospects in repair and manufacturing of micro-electronic devices, sensors, ultrafine filters and human tissues. Furthermore, the preparation process is simple and convenient, the degree of automation is high and the processed pattern is precise, controllable and good in repeatability.

Owner:SOUTHWEST JIAOTONG UNIV

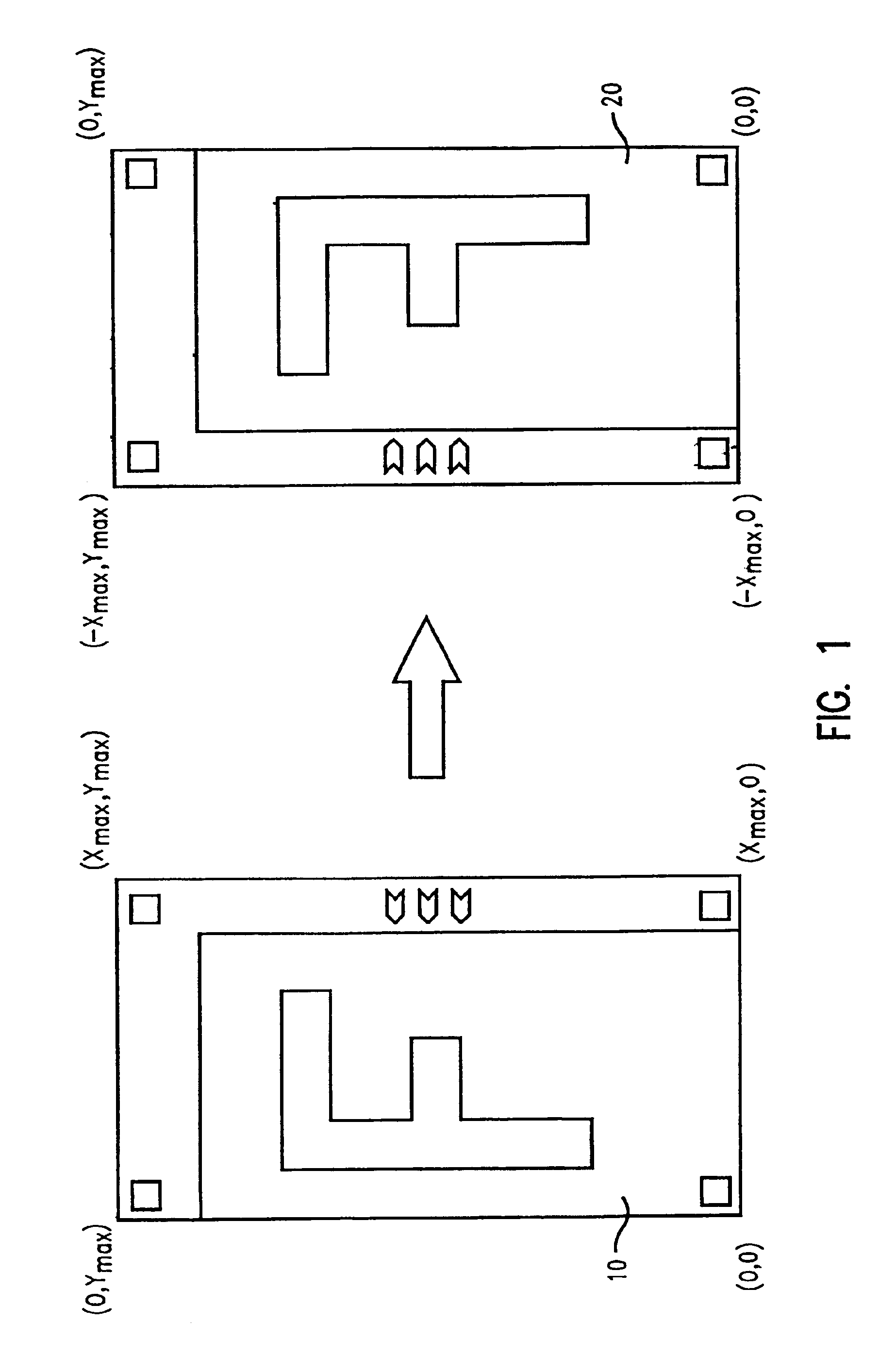

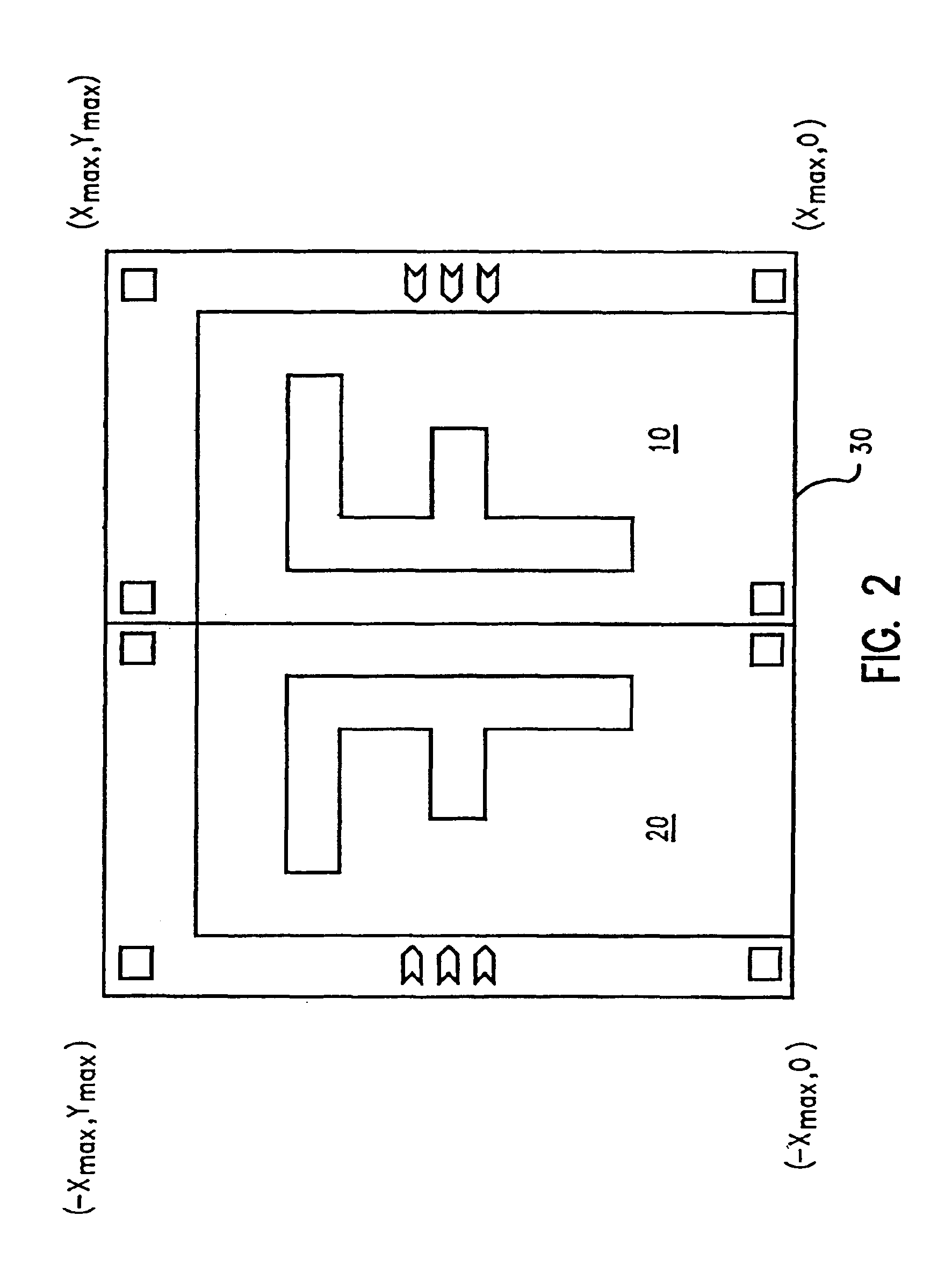

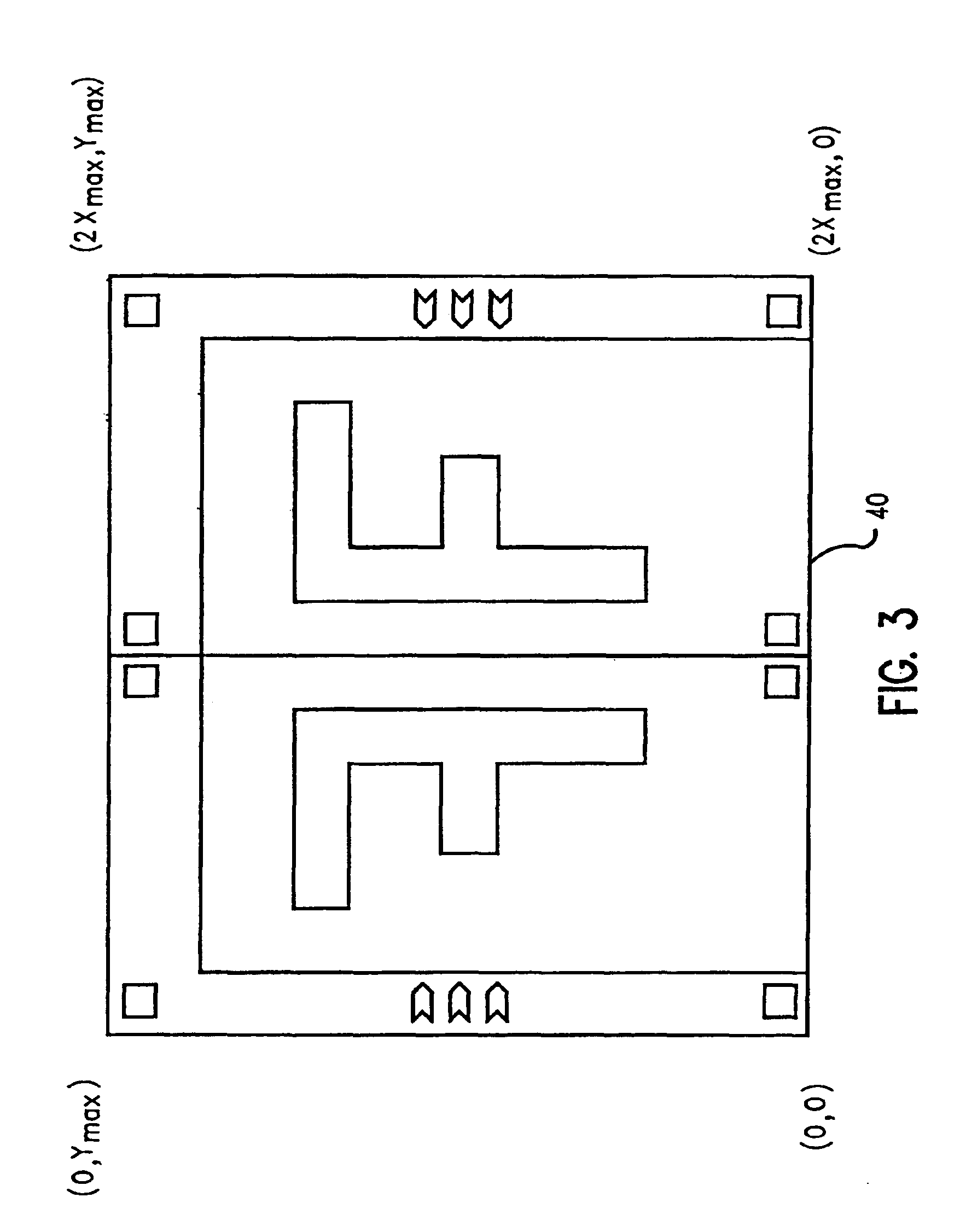

Method for backside alignment of photo-processes using standard front side alignment tools

InactiveUS6861186B1Semiconductor/solid-state device manufacturingUsing optical meansLithographic artistEngineering

An image of an integrated circuit chip and optical kerf and their mirror image are formed within a single optical field. When a substrate pattern using this process is flipped over or reversed, the processed pattern appears the same as on the first side, equal to its own mirror image. Prior to the backside lithography, a portion of the second side is removed to allow detection of alignment marks on the first side from the second side of the substrate. Once the alignment marks are detected, the lithography continues as though the substrate was not flipped over at all.

Owner:IBM CORP

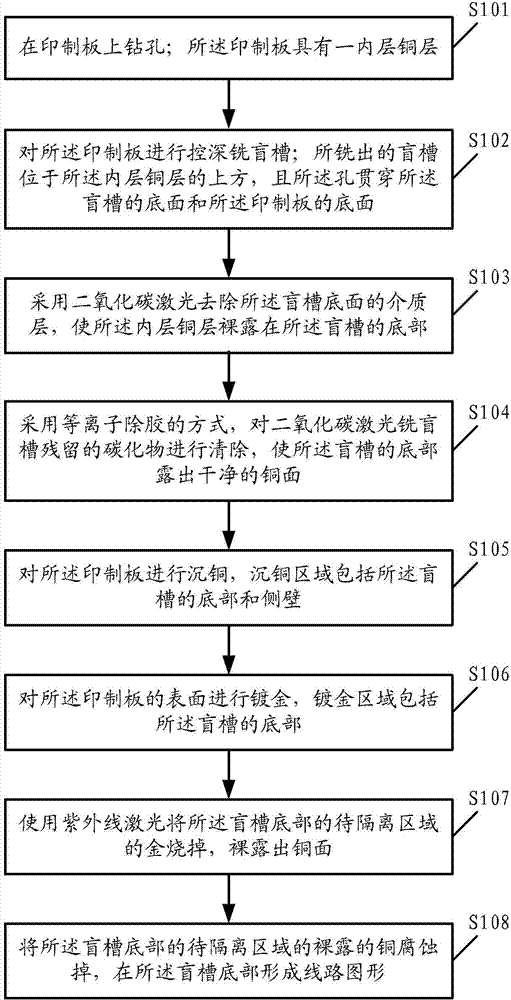

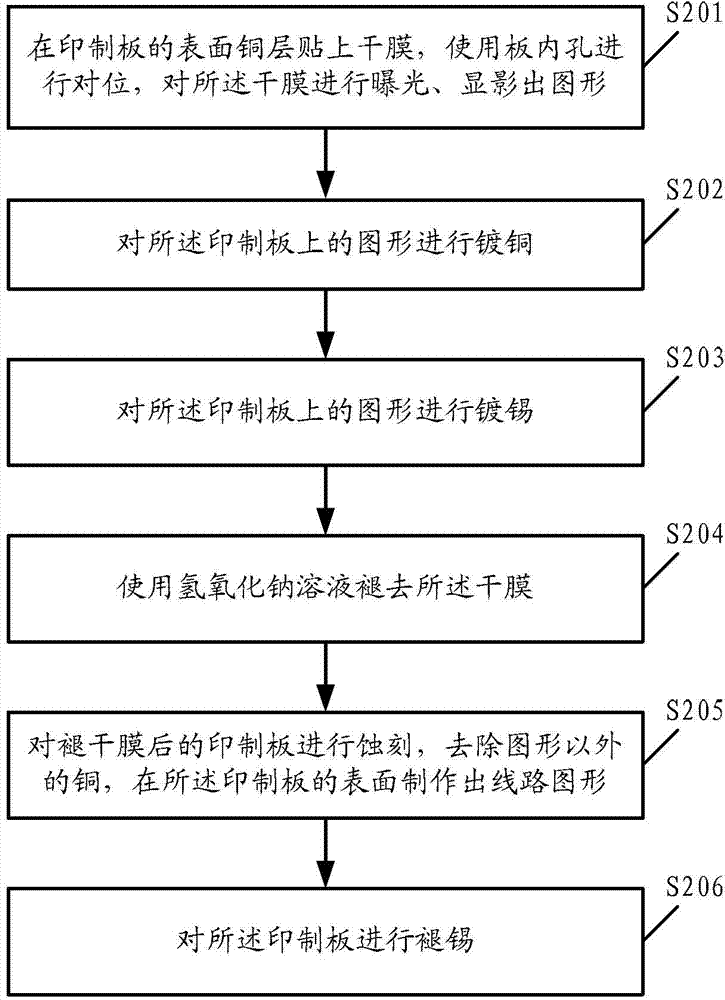

Method for processing patterns in blind slot of printed circuit board

ActiveCN103079350AMeet design and assembly performance requirementsImprove pass rateConductive material chemical/electrolytical removalCopper platingProcess patterns

The invention discloses a method for processing patterns in a blind slot of a printed circuit board. The method comprises the following steps of drilling a hole in the printed circuit board; forming an inner copper layer on the printed circuit board; milling the blind slot with controlled depth on the printed circuit board; exposing the inner copper layer at the bottom of the blind slot; carrying out electroless copper plating on the printed circuit board, wherein the electroless copper plating areas comprise the bottom and the side walls of the blind slot; plating gold on the surface of the printed circuit board, wherein the gold plating area comprises the bottom of the blind slot; using an ultraviolet ray to burn the gold on the area to be isolated at the bottom of the blind slot, and exposing the copper surface; and corroding the exposed copper on the area to be isolated at the bottom of the blind slot, so as to form a circuit pattern at the bottom of the blind slot. The method disclosed by the embodiment of the invention has the advantages that the metallizing of the side wall of the blind slot is realized, the metallic through hole and the circuit pattern are manufactured at the bottom of the blind slot, and the qualified rate of the pattern is improved.

Owner:GCI SCI & TECH

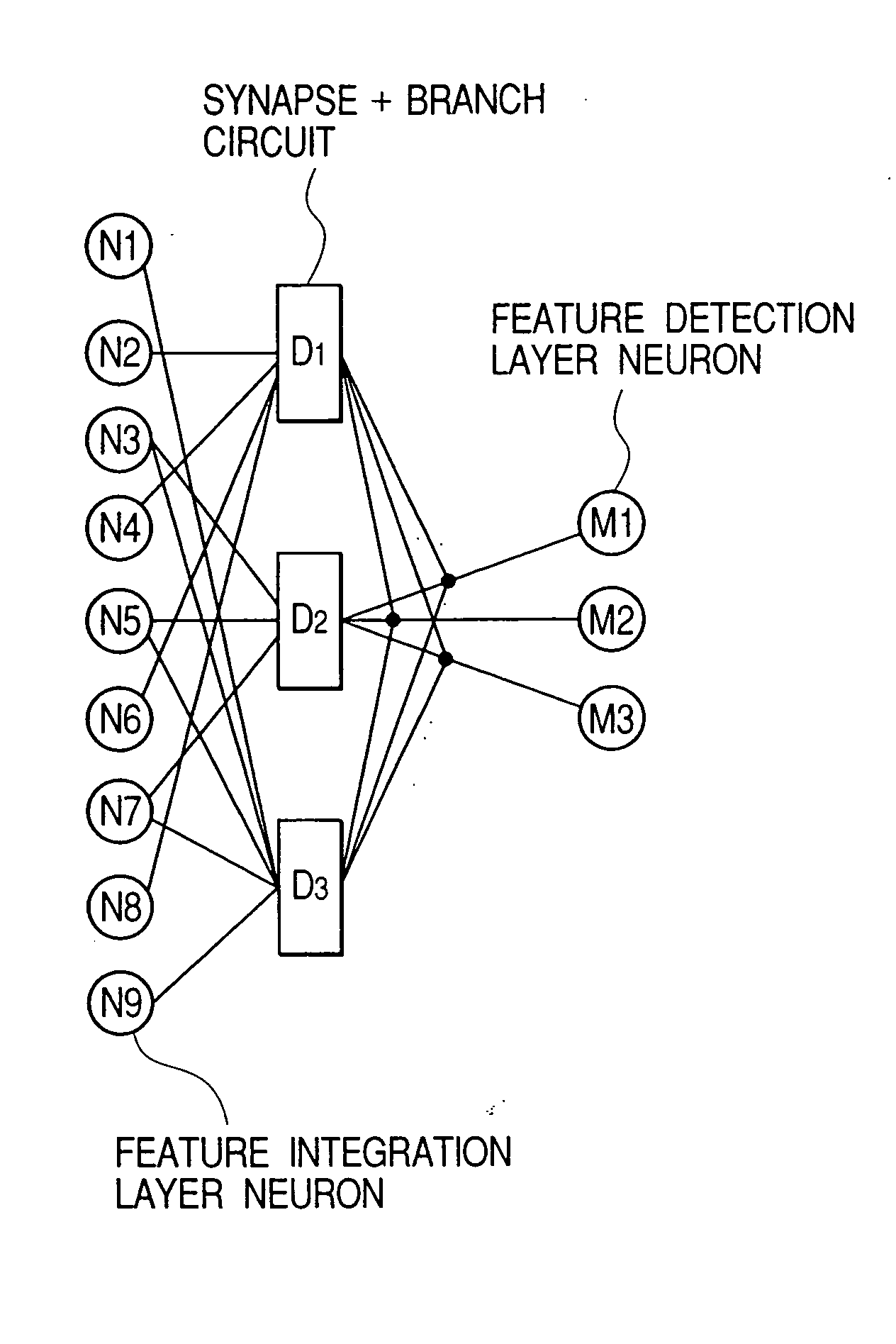

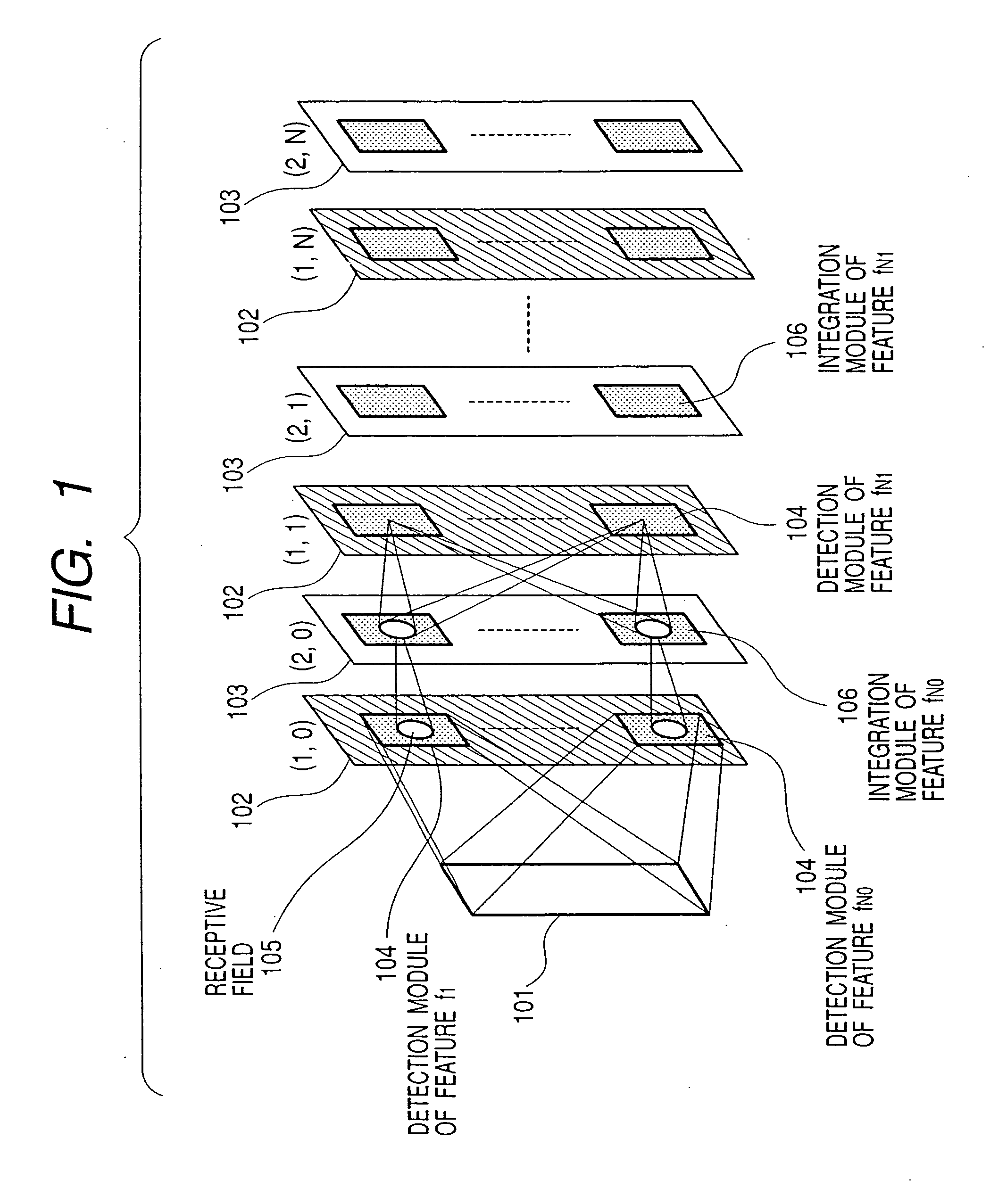

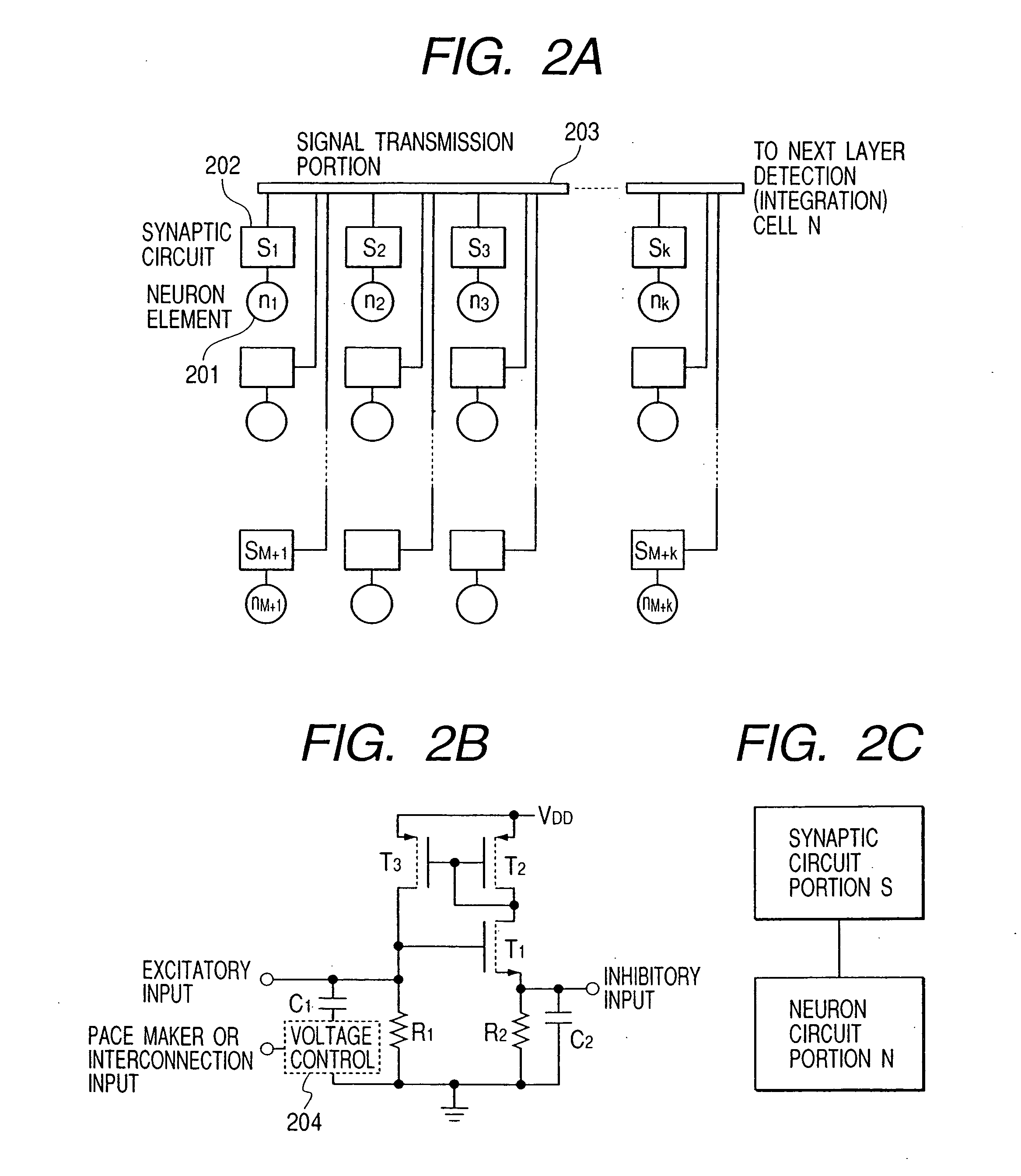

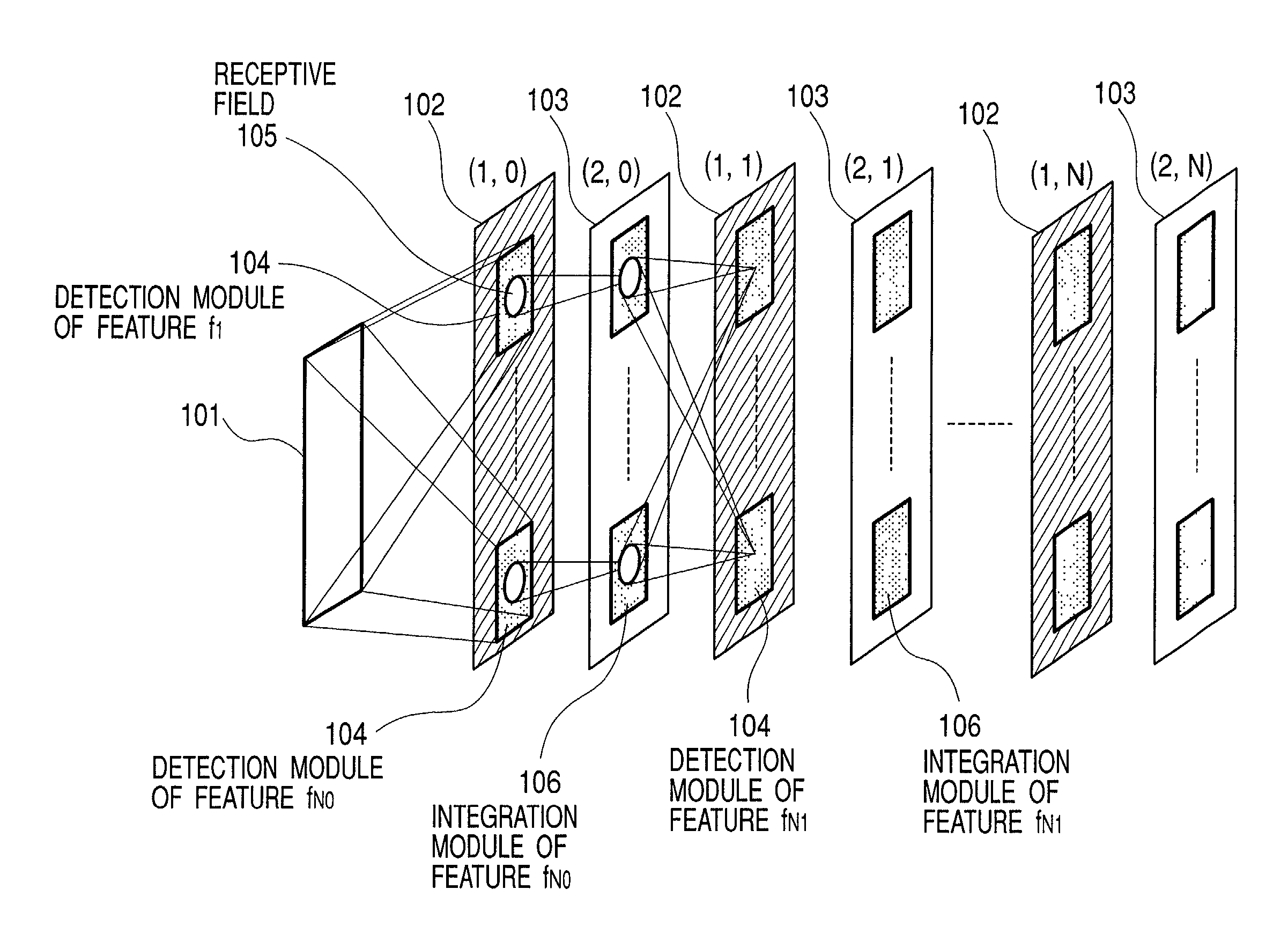

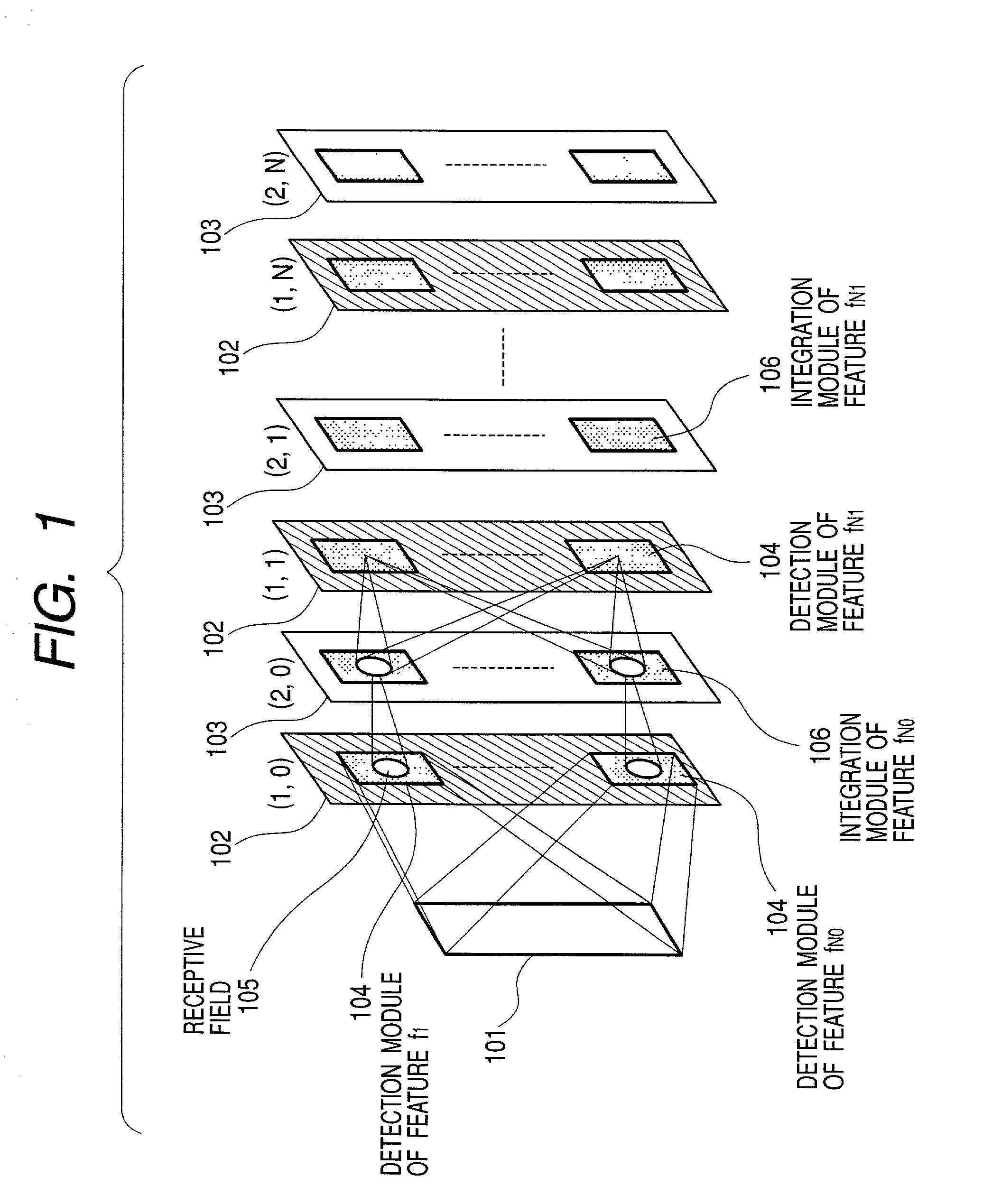

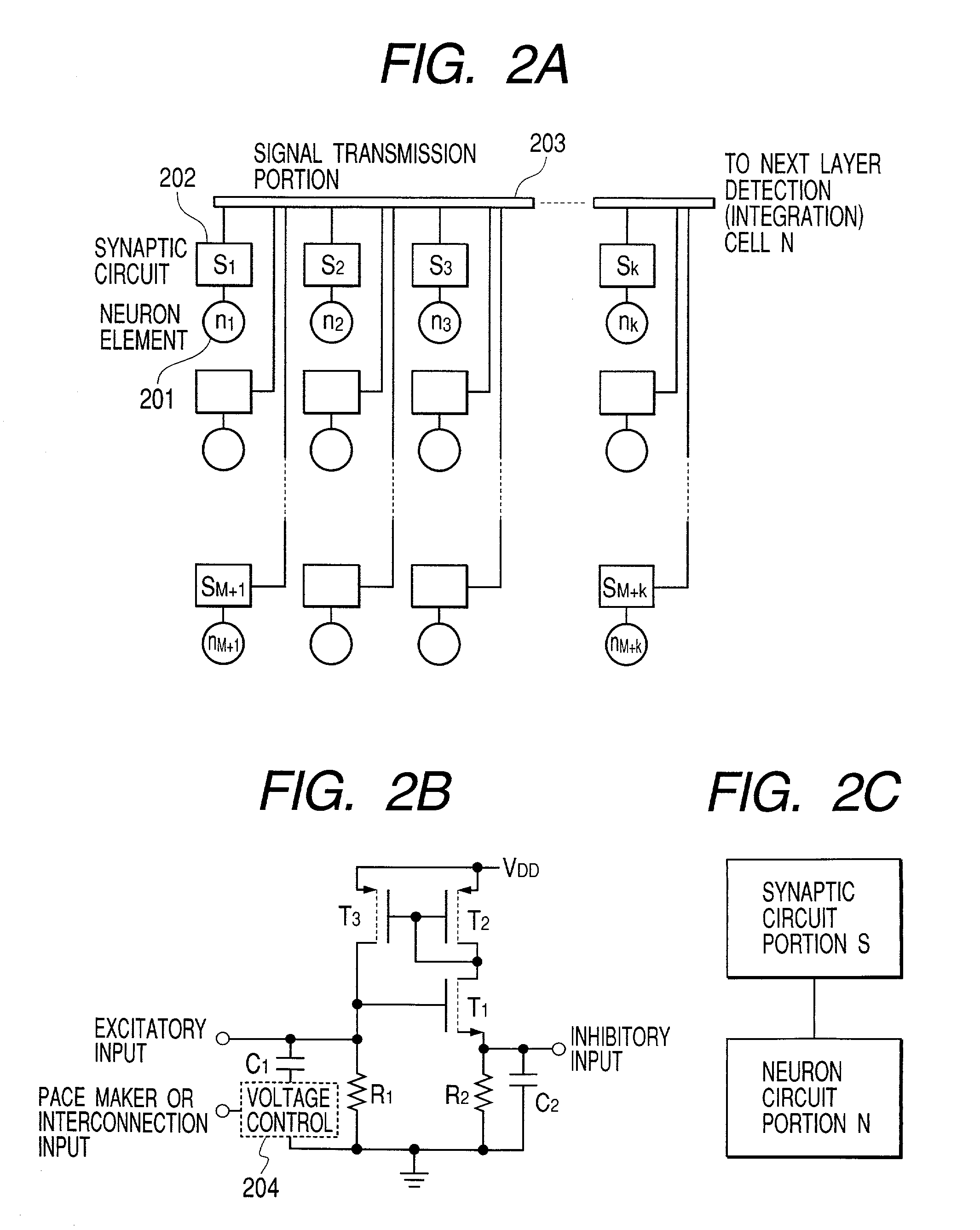

Pulse signal circuit, parallel processing circuit, pattern recognition system, and image input system

InactiveUS20070011120A1Image analysisCharacter and pattern recognitionProcess patternsParallel processing

A synaptic connection element for connecting neuron elements inputs a plurality of pulsed signals from different neuron elements N1 through N4, effects a common modulation (time window integration or pulse phase / width modulation) on a plurality of predetermined signals among the plurality of pulse signals, and outputs the modulated pulse signals to different signal lines to a neuron element M1. A neural network for representing and processing pattern information by the pulse modulation is thereby downsized in scale.

Owner:CANON KK

Systems and methods for a real-time synchronized electrical power system simulator for “what-if” analysis and prediction over electrical power networks

ActiveUS8180622B2Analogue computers for nuclear physicsDesign optimisation/simulationPower system simulatorReal-time data

A system for real-time modeling of electrical system performance is disclosed. The system includes a data acquisition component, a power analytics server and a client terminal. The power analytics server is comprised of a virtual system modeling engine, an analytics engine and a power system simulation engine. The virtual system modeling engine is configured to generate predicted data output utilizing a first virtual system model. The analytics engine is configured to synchronize the first virtual system model when a difference between the real-time data output and the predicted data output exceeds a threshold. The power system simulation engine is configured to store and process patterns and facilitate modification of parameters on the first virtual system model to create a second virtual system model; and forecast an aspect of the electrical system operating under parameters of the second virtual system model. The client terminal displays the forecasted aspects.

Owner:BENTLEY SYST INC +1

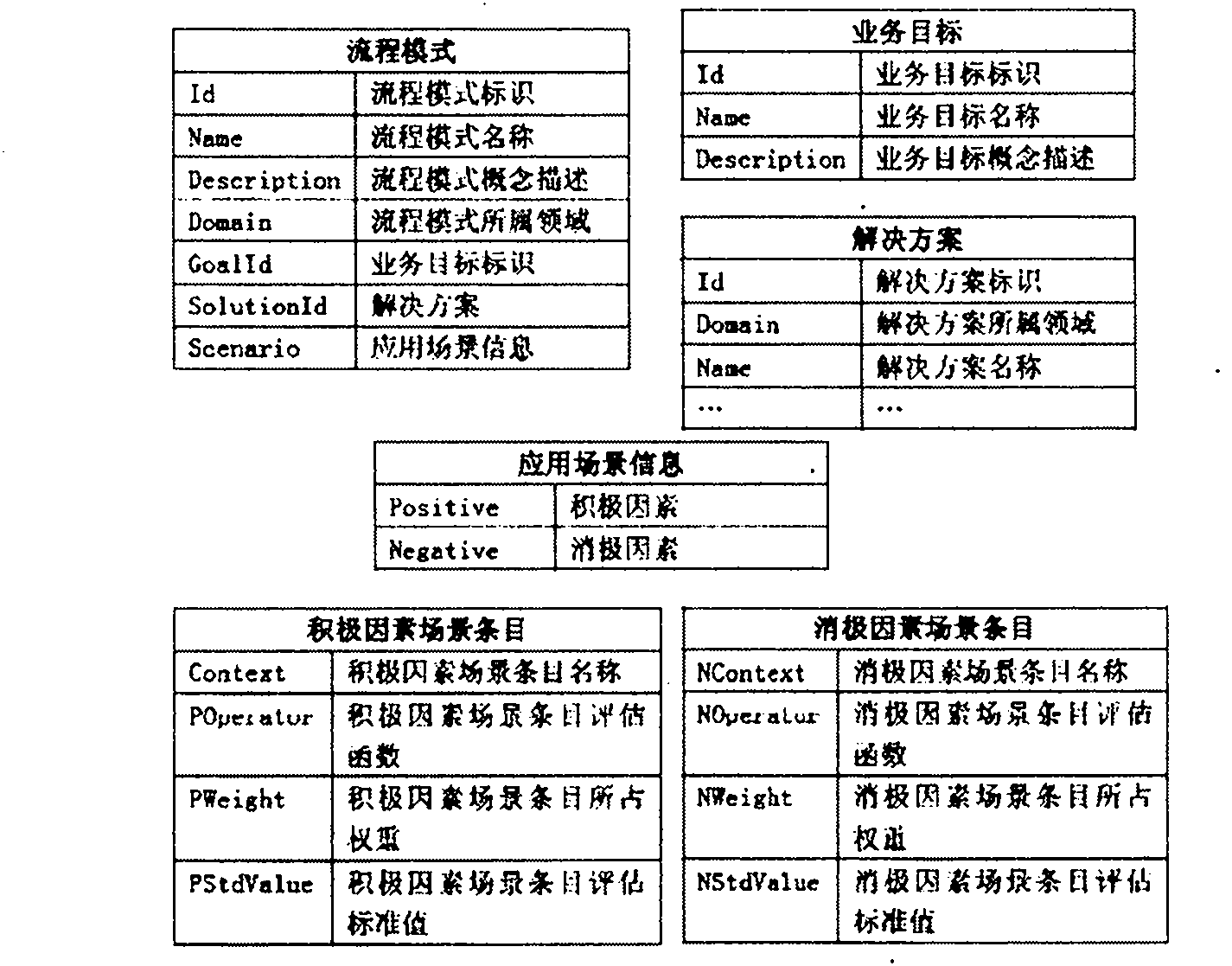

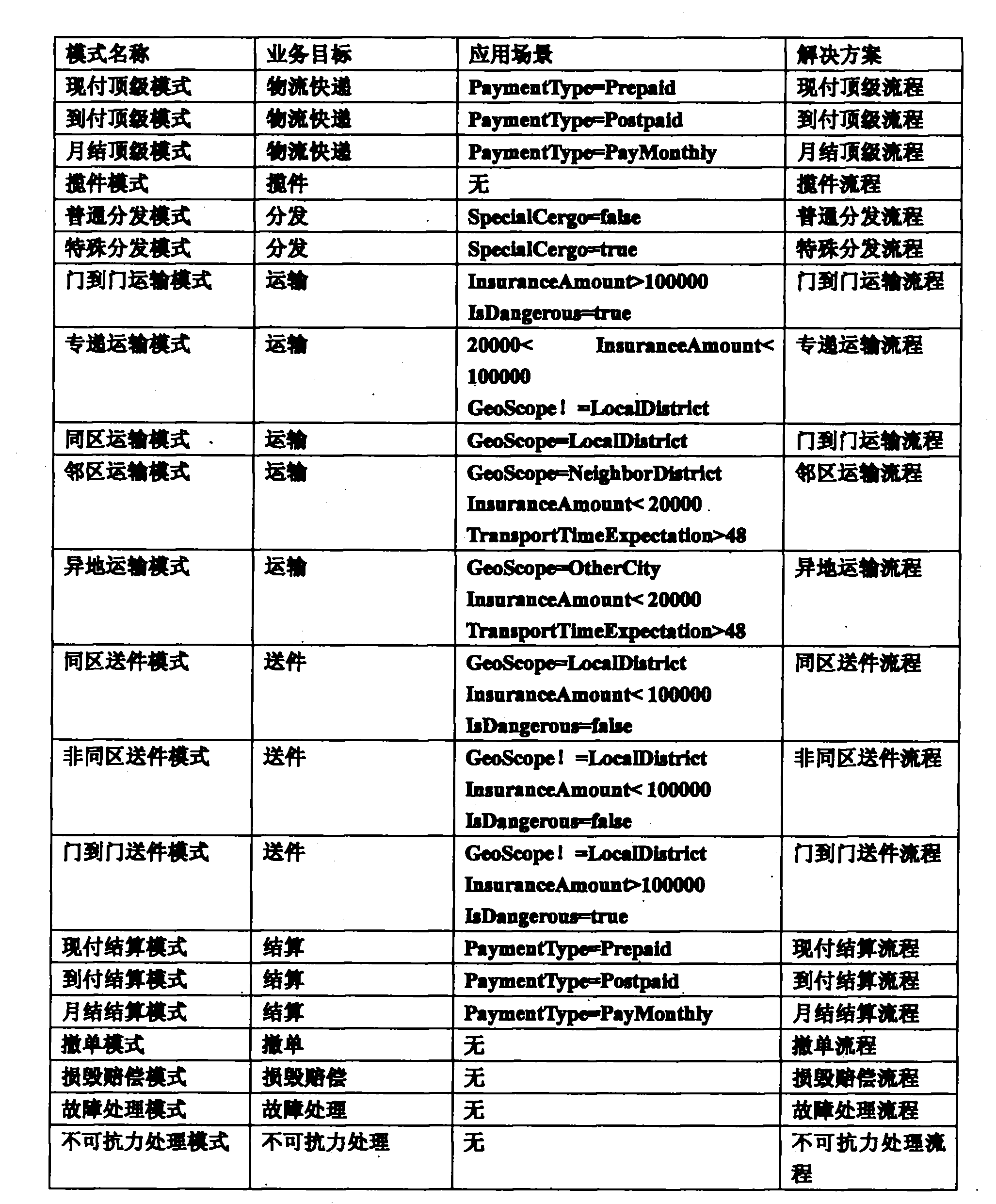

Workflow static planning method based on process mode

Owner:TSINGHUA UNIV

Real-time predictive systems for intelligent energy monitoring and management of electrical power networks

ActiveUS9557723B2Market predictionsAnalogue computers for electric apparatusUser interfaceElectric power

A system for intelligent monitoring and management of an electrical system is disclosed. The system includes a data acquisition component, a power analytics server and a client terminal. The data acquisition component acquires real-time data output from the electrical system. The power analytics server is comprised of a real-time energy pricing engine, virtual system modeling engine, an analytics engine, a machine learning engine and a schematic user interface creator engine. The real-time energy pricing engine generates real-time utility power pricing data. The virtual system modeling engine generates predicted data output for the electrical system. The analytics engine monitors real-time data output and predicted data output of the electrical system. The machine learning engine stores and processes patterns observed from the real-time data output and the predicted data output to forecast an aspect of the electrical system.

Owner:POWER ANALYTICS CORP

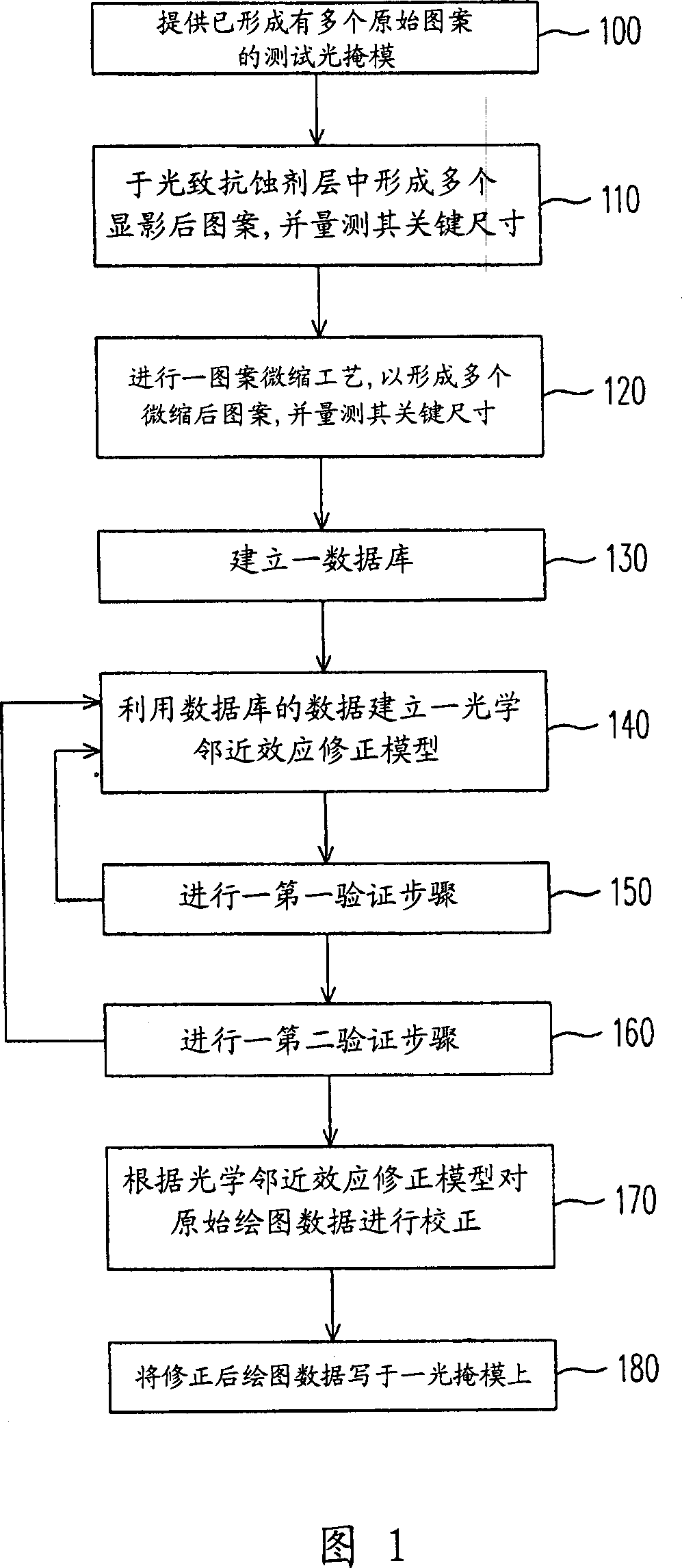

Optical mask pattern correcting method and its formation

InactiveCN1940715AReduce processing costsHigh yieldSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusProcess patternsEngineering

A method for calibrating photomask pattern includes providing a test photomask and transferring original pattern on test photomask to the first photoresist layer for obtaining multiple developed pattern then measuring out their first size, carrying out pattern micro process on developed pattern to obtain micro processed pattern then measuring out their second size, calculate out deviate of two said sizes and utilizing two said sizes and deviate as well as original plotting data to form a databank, using databank to set up optical near effect revision model then utilizing said model to calibrate original plotting data for obtaining calibrated plotting data.

Owner:POWERCHIP SEMICON CORP

Design pattern correction method and mask pattern producing method

ActiveUS20050235245A1Semiconductor/solid-state device manufacturingOriginals for photomechanical treatmentEngineeringProcess patterns

There is disclosed a method of correcting a design pattern considering a process margin between layers of a semiconductor integrated circuit, including calculating a first pattern shape corresponding to a processed pattern shape of a first layer based on a first design pattern, calculating a second pattern shape corresponding to a processed pattern shape of a second layer based on a second design pattern, calculating a third pattern shape using a Boolean operation between the first and second pattern shapes, determining whether or not an evaluation value obtained from the third pattern shape satisfies a predetermined value, and correcting at least one of the first and second design patterns if it is determined that the evaluation value does not satisfy the predetermined value.

Owner:KIOXIA CORP

Pulse signal circuit, parallel processing circuit, pattern recognition system, and image input system

ActiveUS7085749B2Equal performanceImage analysisCharacter and pattern recognitionPulse-code modulationProcess patterns

A synaptic connection element for connecting neuron elements inputs a plurality of pulsed signals from different neuron elements N1 through N4, effects a common modulation (time window integration or pulse phase / width modulation) on a plurality of predetermined signals among the plurality of pulse signals, and outputs the modulated pulse signals to different signal lines to a neuron element M1. A neural network for representing and processing pattern information by the pulse modulation is thereby downsized in scale.

Owner:CANON KK

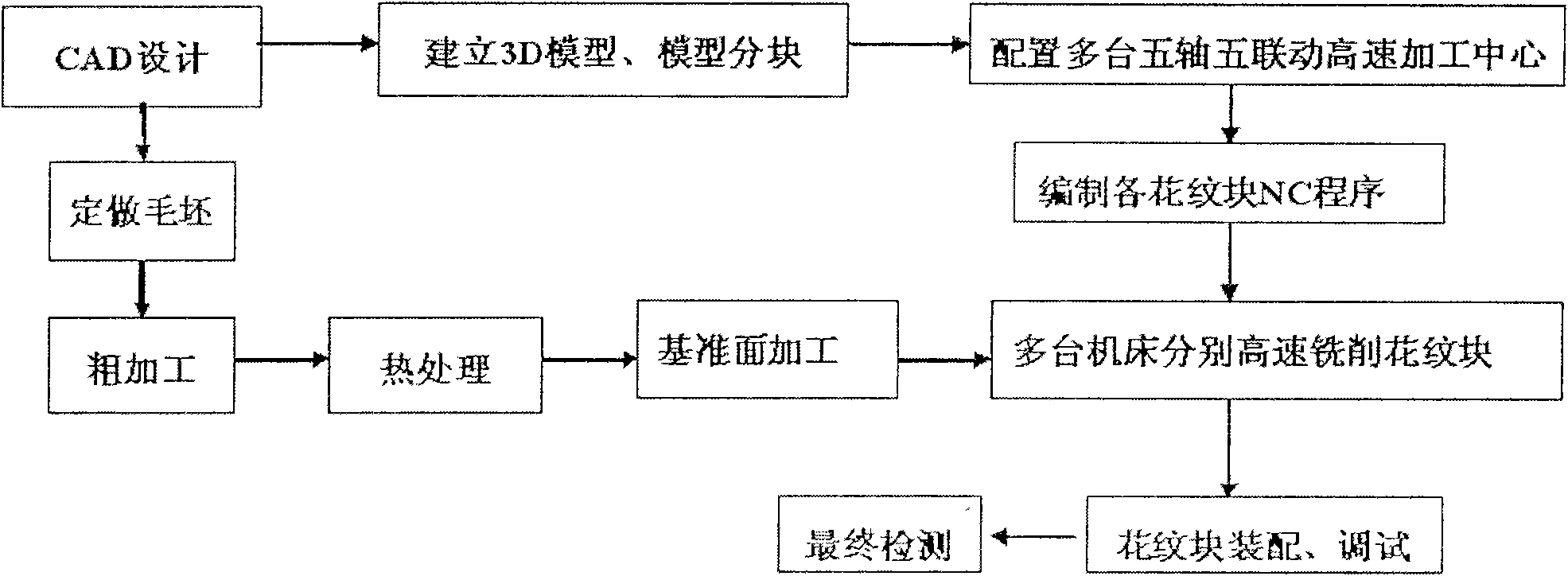

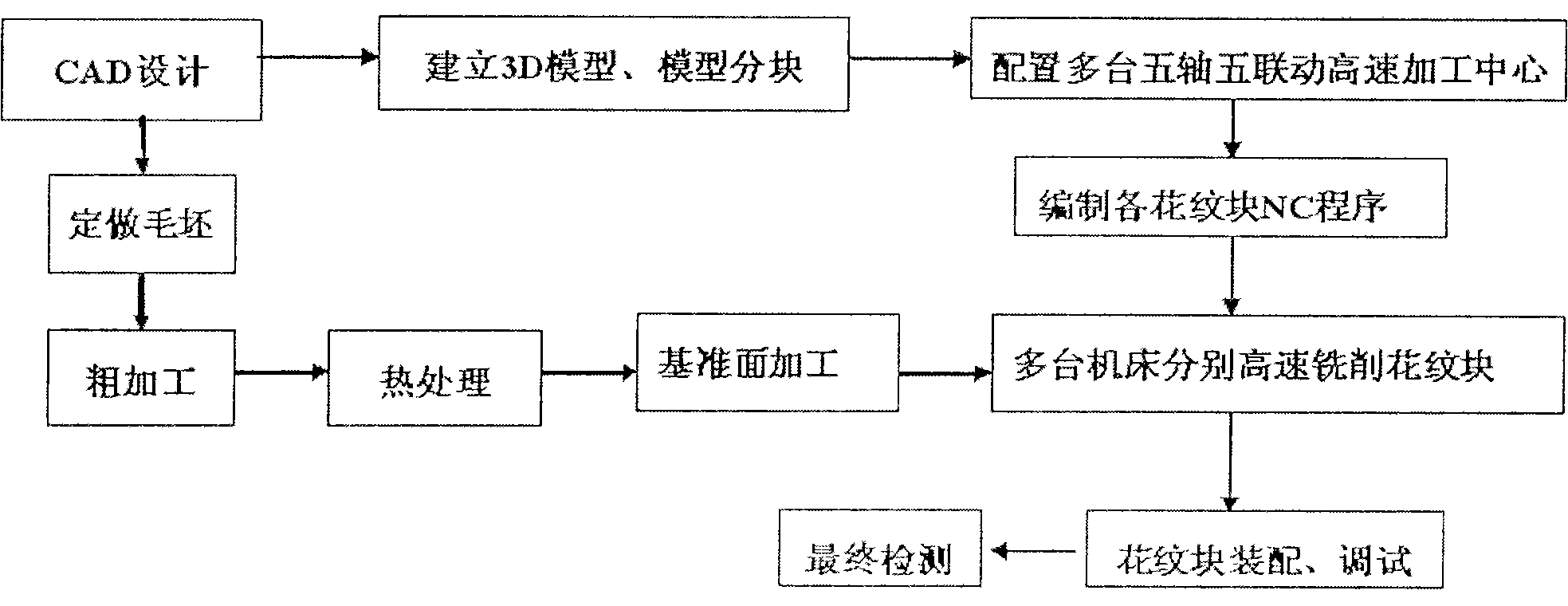

Manufacturing method of pattern ring of segmented mold of radial tyre

InactiveCN101890625AReduce turnover timesImprove interchangeabilityMilling equipment detailsThermal deformationProcess patterns

The invention discloses a manufacturing method of a pattern ring of a segmented mold of a radial tyre. The manufacturing method comprises the following steps of: performing a CAD design on the pattern ring, establishing a 3D model of the pattern ring, then dividing the 3D model into corresponding single pattern blocks according to requirements, and simultaneously customizing a pattern ring blank, finishing preliminary works such as rough machining, heat treatment, reference plane machining and the like of the pattern ring; configuring a plurality of machine tools and completing the preparation work before production; establishing part processing cutter tracks required by each machine tool, generating semi-finishing, finishing and corner cleaning procedures of each pattern block according to the configured condition of the machine tools, and establishing a procedure list; executing the processing procedures according to a procedure list sequence; and assembling and debugging the plurality of processed pattern blocks. The manufacturing method has the advantages of simple process, difficult generation of thermal deformation on a workpiece during production, short production cycle, high production efficiency and high accuracy, and ensures the assembly accuracy of the a tyre mold.

Owner:山东金利轮胎装备有限公司

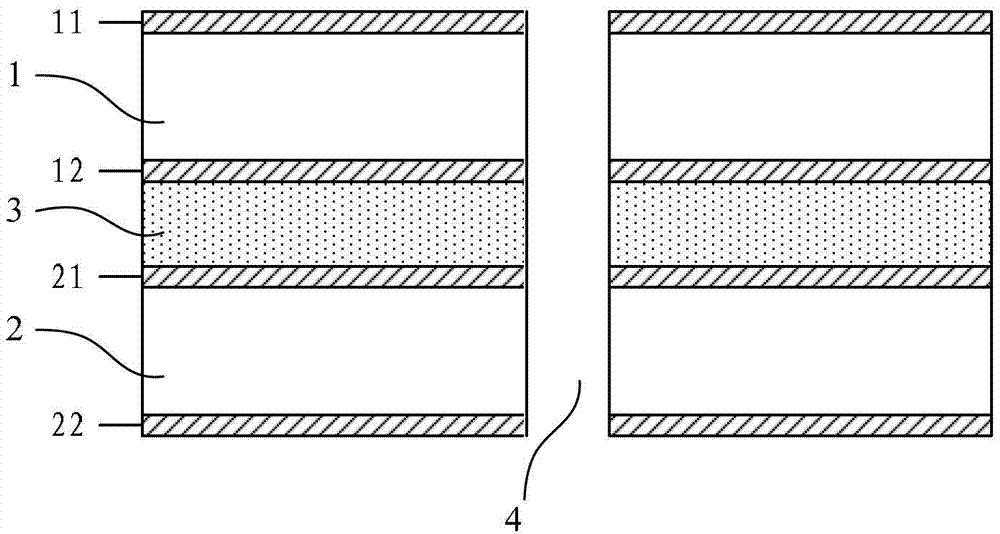

Two-board-in-one processing method for substrate manufacture of printed circuit board or integrated circuit package

InactiveCN101359601ALow costIncrease productivitySemiconductor/solid-state device manufacturingMultilayer circuit manufactureElectrical conductorProcess patterns

Disclosed is a method for combining two plates in the fabrication process of an enclosure baseplate of a printed circuit or an integrated circuit. The method includes the following steps: splicing two chip plates through a bonding sheet so as to make a machining plate which is big in thickness, higher in rigidity and can satisfy common equipment machining requirements; processing pattern transfer to the spliced machining plate and developing a necessary circuit diagram of a conductor on the surface of the machining plate; developing an insulating medium layer and a conducting copper layer on the surface of the newly developed circuit diagram of the conductor through the method of lamination; repeating above processes so as to form a multilayer machining plate; separating the machining plate at two sides of the splicing sheet from the splicing sheet after the machining plate reaches certain thickness and rigidity, thus forming two machining plates; and respectively processing the two machining plates through regular lamination, boring, electroplating and pattern transfer techniques until the necessary circuit board and the enclosure baseplate are finished. The method requires no special equipment or machining tools and can reduce cost by a large margin and improve production efficiency and yield.

Owner:SHANGHAI MEADVILLE SCI & TECH +2

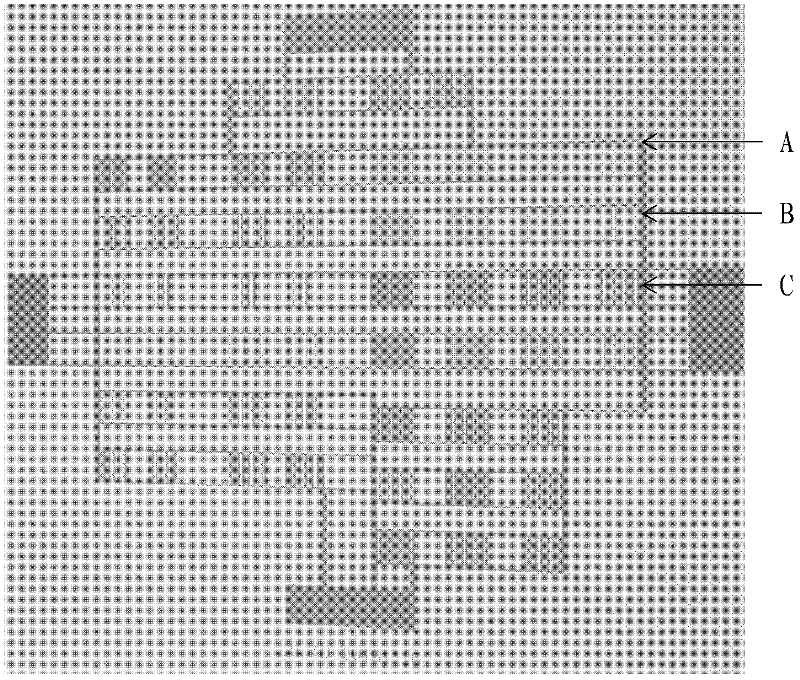

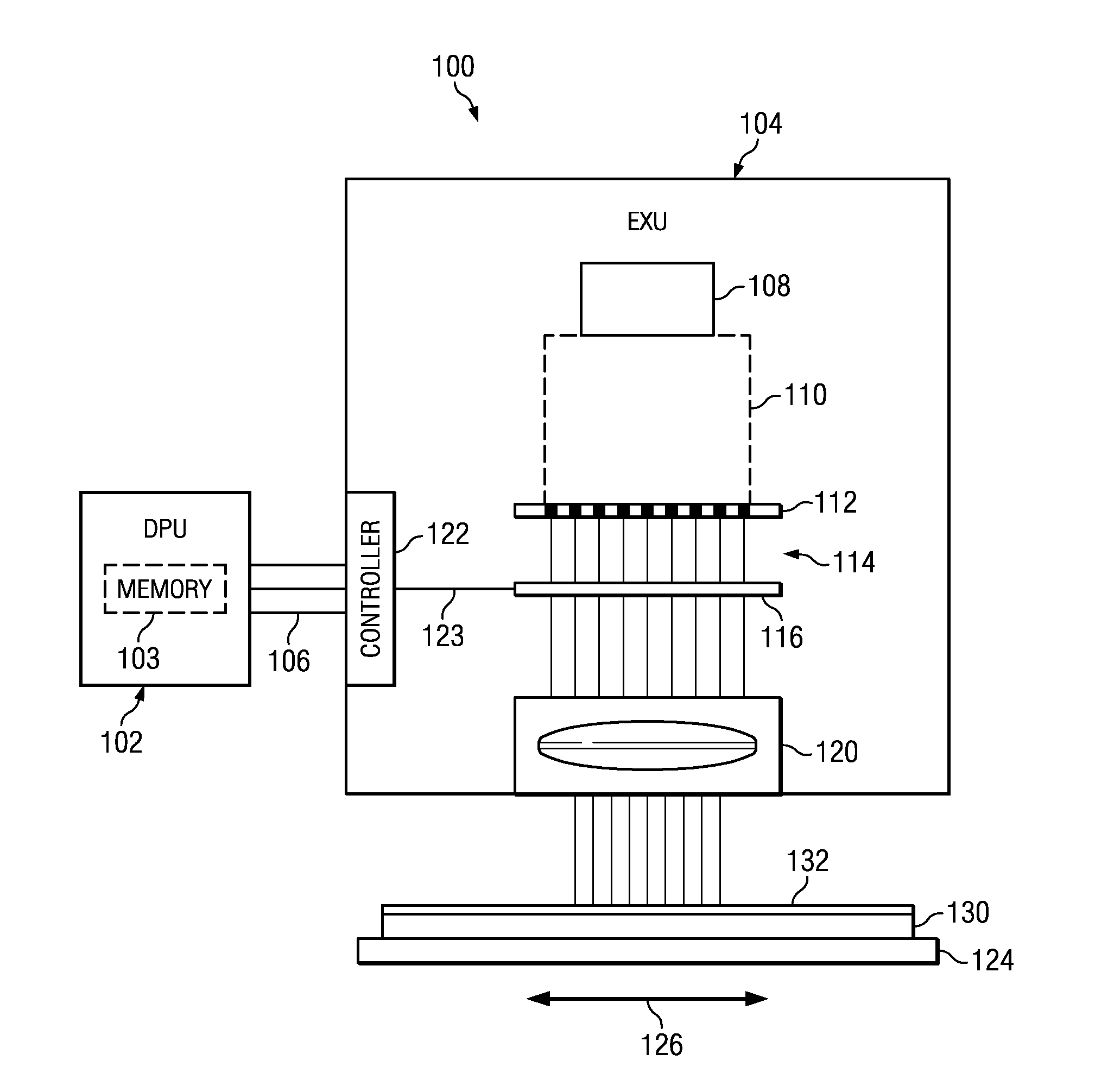

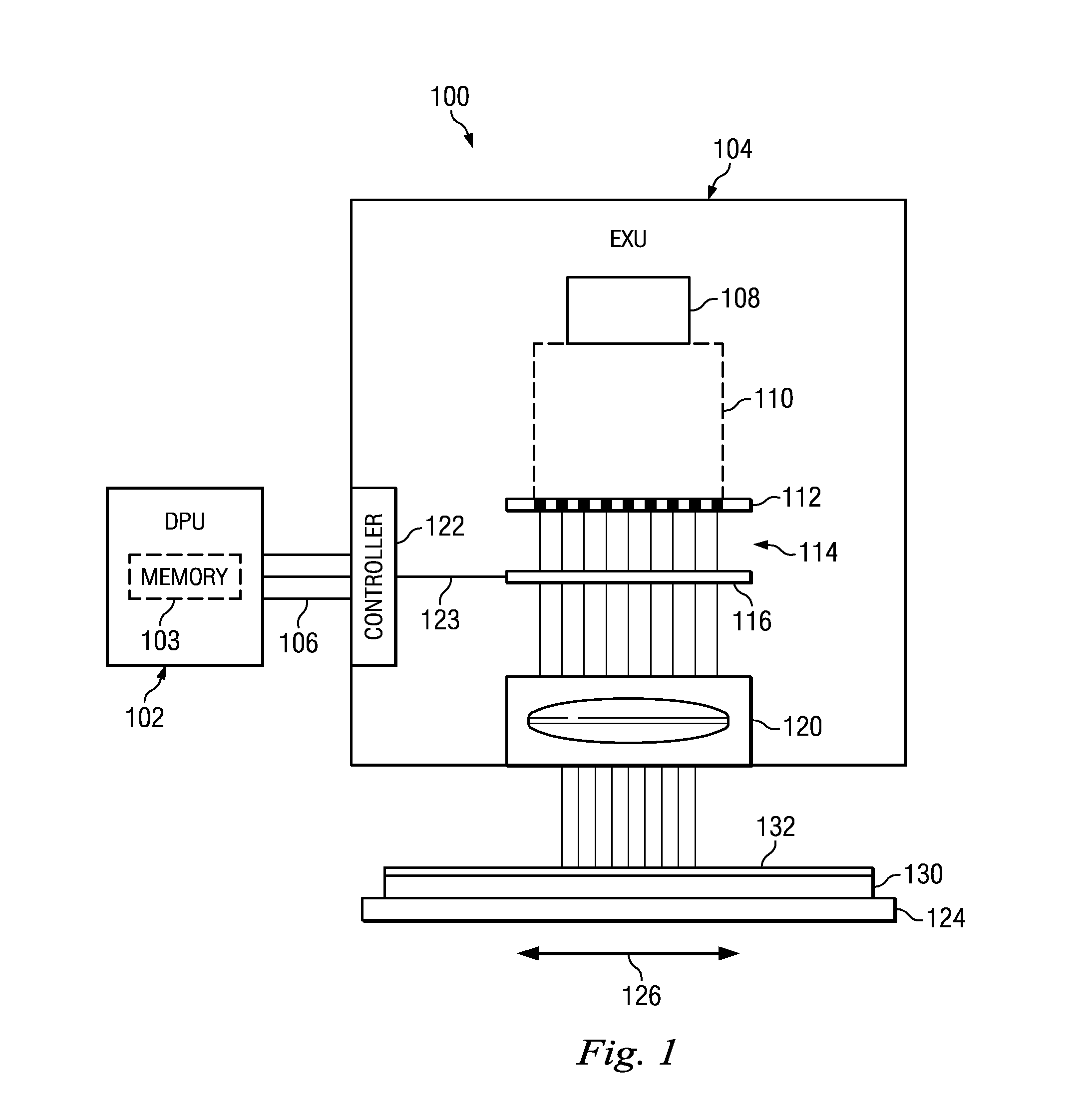

Method for performing full-chip manufacturing reliability checking and correction

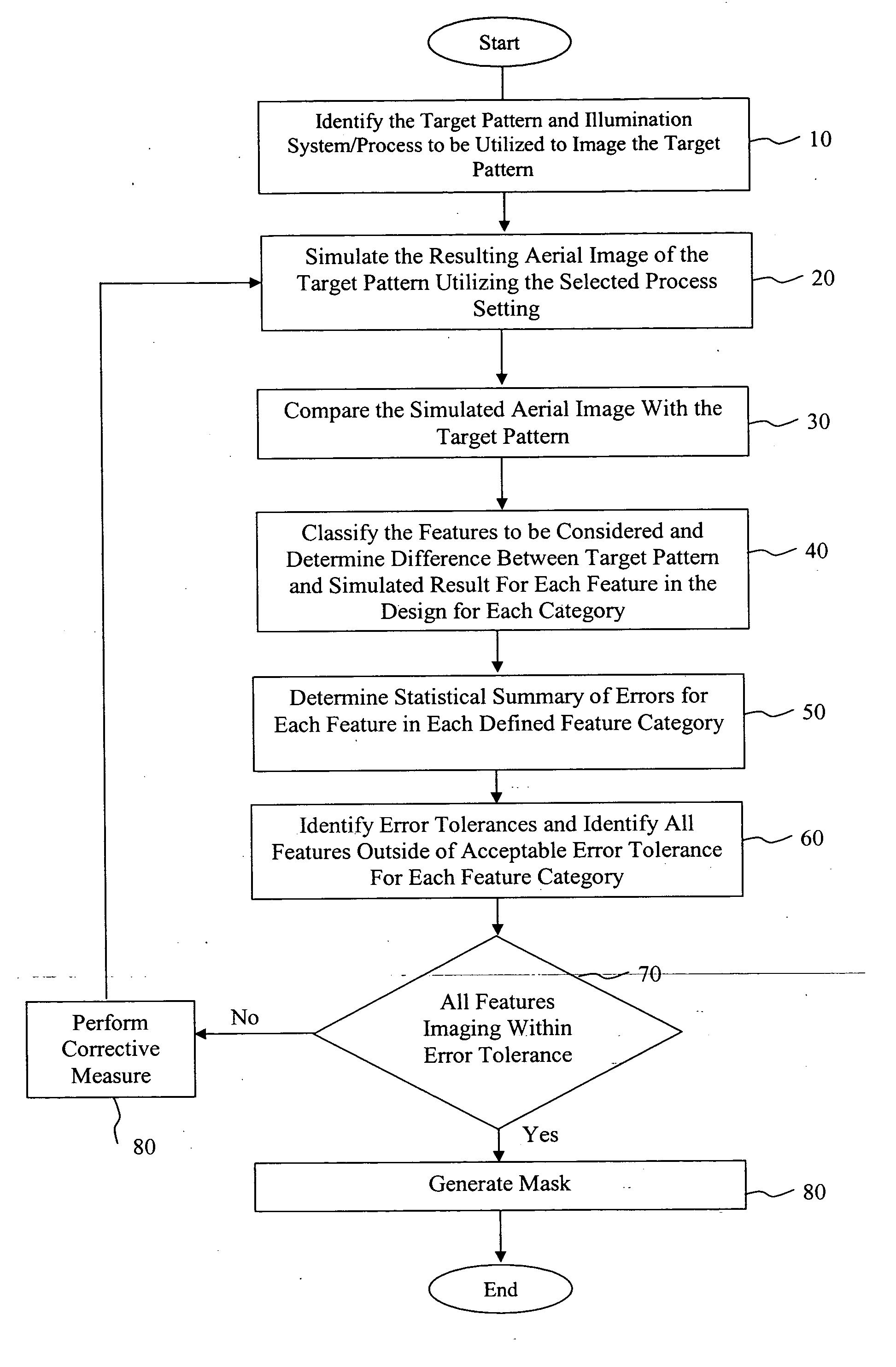

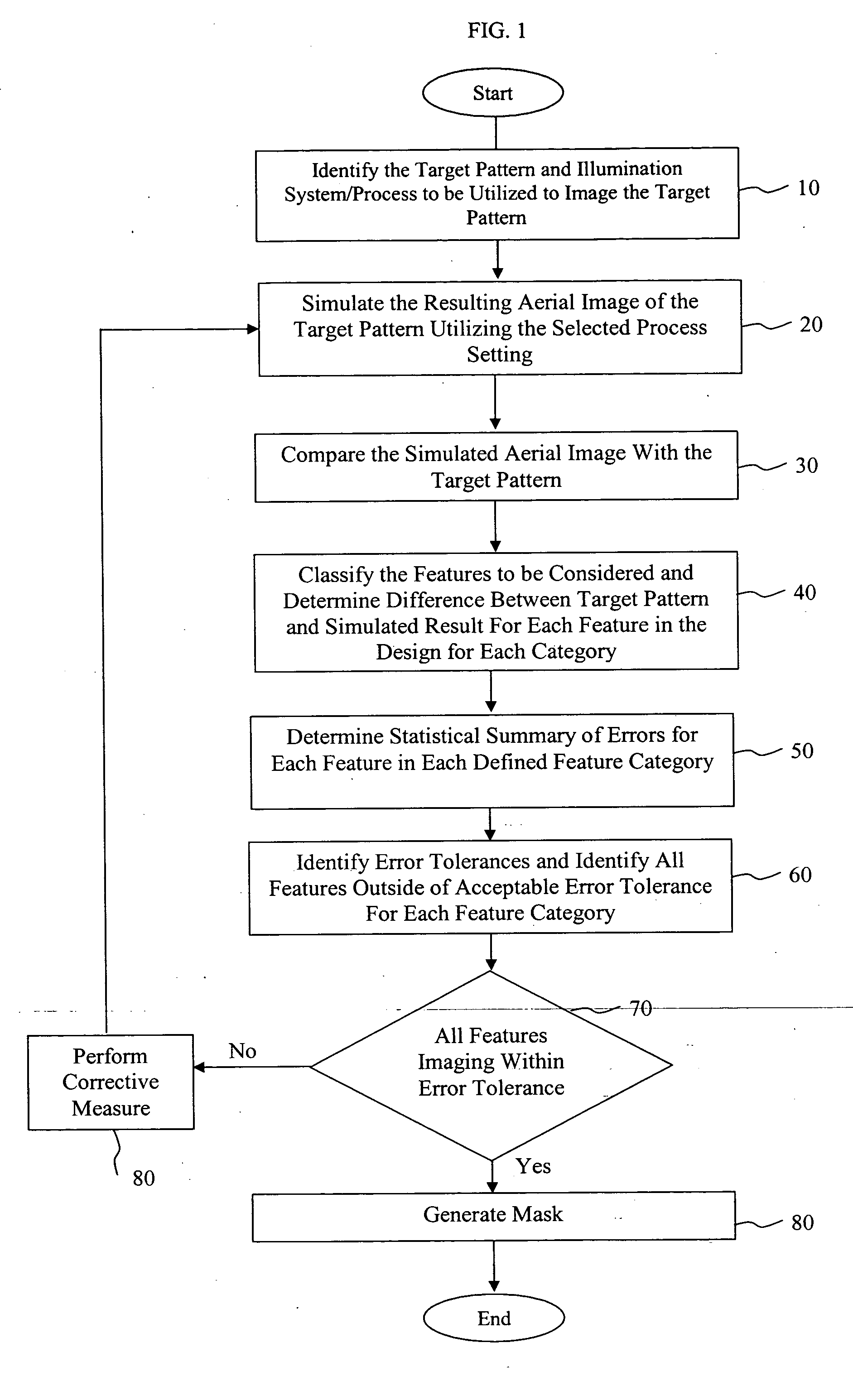

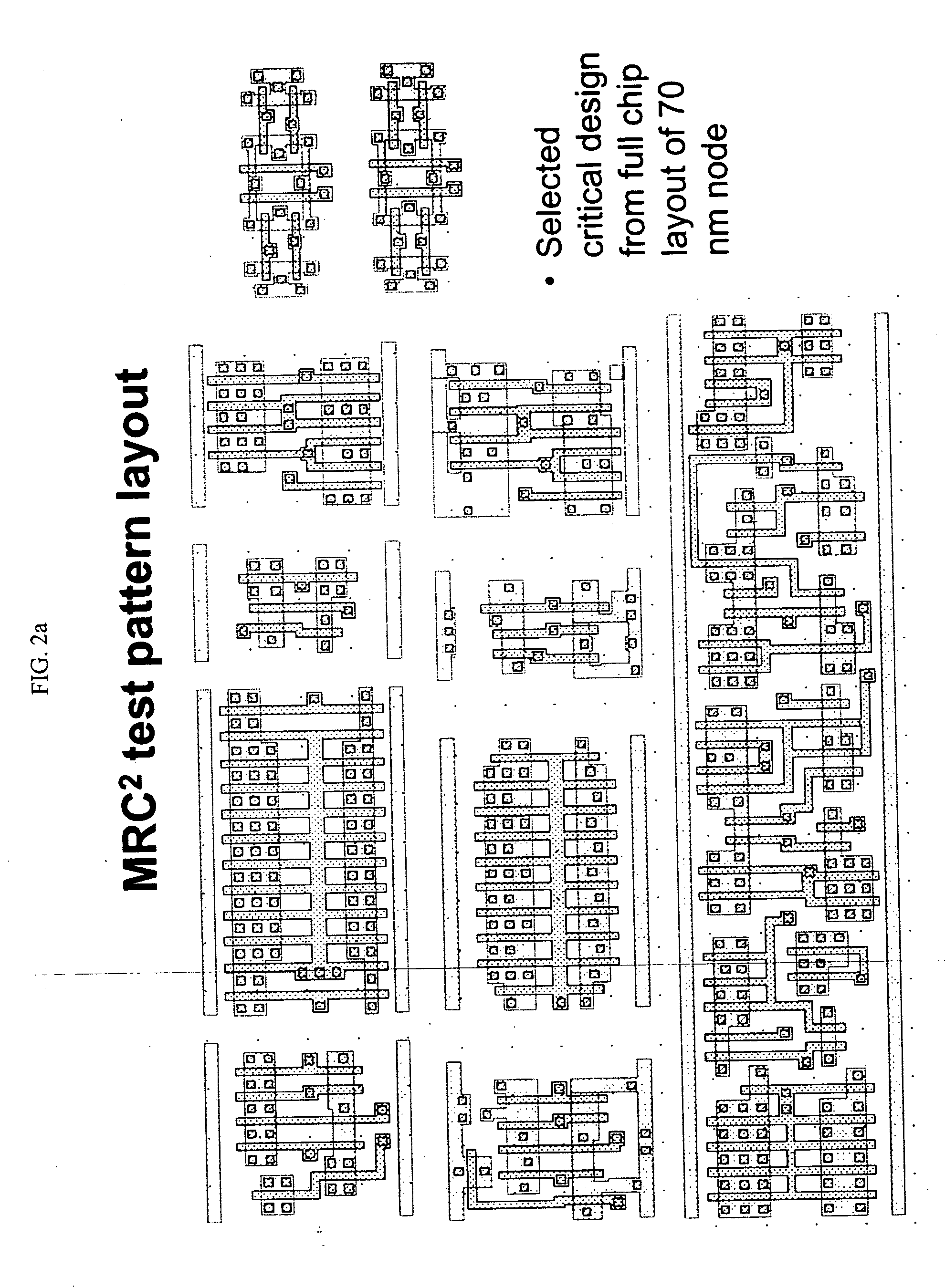

ActiveUS20060080633A1Suitable for useMinimize timePhotomechanical apparatusCharacter and pattern recognitionPattern recognitionProcess patterns

A method of generating a mask for use in an imaging process pattern. The method includes the steps of: (a) obtaining a desired target pattern having a plurality of features to be imaged on a substrate; (b) simulating a wafer image utilizing the target pattern and process parameters associated with a defined process; (c) defining at least one feature category; (d) identifying features in the target pattern that correspond to the at least one feature category, and recording an error value for each feature identified as corresponding to the at least one feature category; and (e) generating a statistical summary which indicates the error value for each feature identified as corresponding to the at least one feature category.

Owner:ASML NETHERLANDS BV

Systems and methods for automatic real-time capacity assessment for use in real-time power analytics of an electrical power distribution system

ActiveUS8959006B2Level controlDigital data processing detailsReal-time dataDistribution power system

A system for conducting a real-time power capacity assessment of an electrical system is disclosed. The system includes a data acquisition component, a power analytics server and a client terminal. The data acquisition component is communicatively connected to a sensor configured to acquire real-time data output from the electrical system. The power analytics server is communicatively connected to the data acquisition component and is comprised of a virtual system modeling engine, an analytics engine and a machine learning engine. The machine learning engine is configured to store and process patterns observed from the real-time data output and the predicted data output, forecasting power capacity of the electrical system subjected to a simulated contingency event.

Owner:POWER ANALYTICS CORP

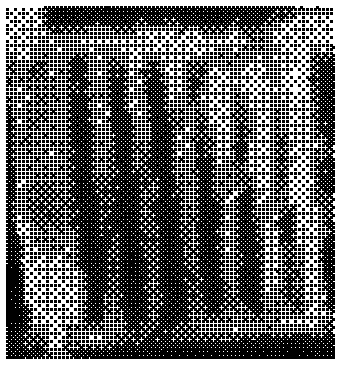

Method for preparing periodic nanostructure with high aspect ratio

InactiveCN102096317AAdd depthIncrease steepnessNanotechnologyPhotosensitive materials for photomechanical apparatusCooking & bakingGrating

The invention discloses a method for preparing a periodic nanostructure with high aspect ratio. The method is characterized by comprising the following steps of: selecting a polished substrate; coating a layer of photoresist with the thickness of greater than or equal to 300 nm on the surface of the polished substrate by a spin-coating method; depositing a SiO2 film with the thickness of 20 nm on the surface of the photoresist by a magnetron sputtering method; coating a layer of high-resolution photoresist with the thickness of 50 to 100 nm on the surface of the SiO2 film by the spin-coating method; exposing and developing the surface high-resolution photoresist by utilizing laser interference photolithography; hardening the three-layer adhesive structure in a heating plate or a baking oven; selecting a fluorine-base gas; transferring a surface photoresist pattern to the SiO2 layer by utilizing reactive ion etching; selecting and using oxygen; taking the SiO2 layer as a hard mask layer; and transferring a pattern on the SiO2 layer to the bottom photoresist by utilizing the reactive ion etching to obtain a photoresist pattern with high resolution and high aspect ratio. The method has low cost, large area of processed pattern area, and a broad application prospect in the aspects of the manufacturing and the application research of sub-wavelength gratings and photonic crystals.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

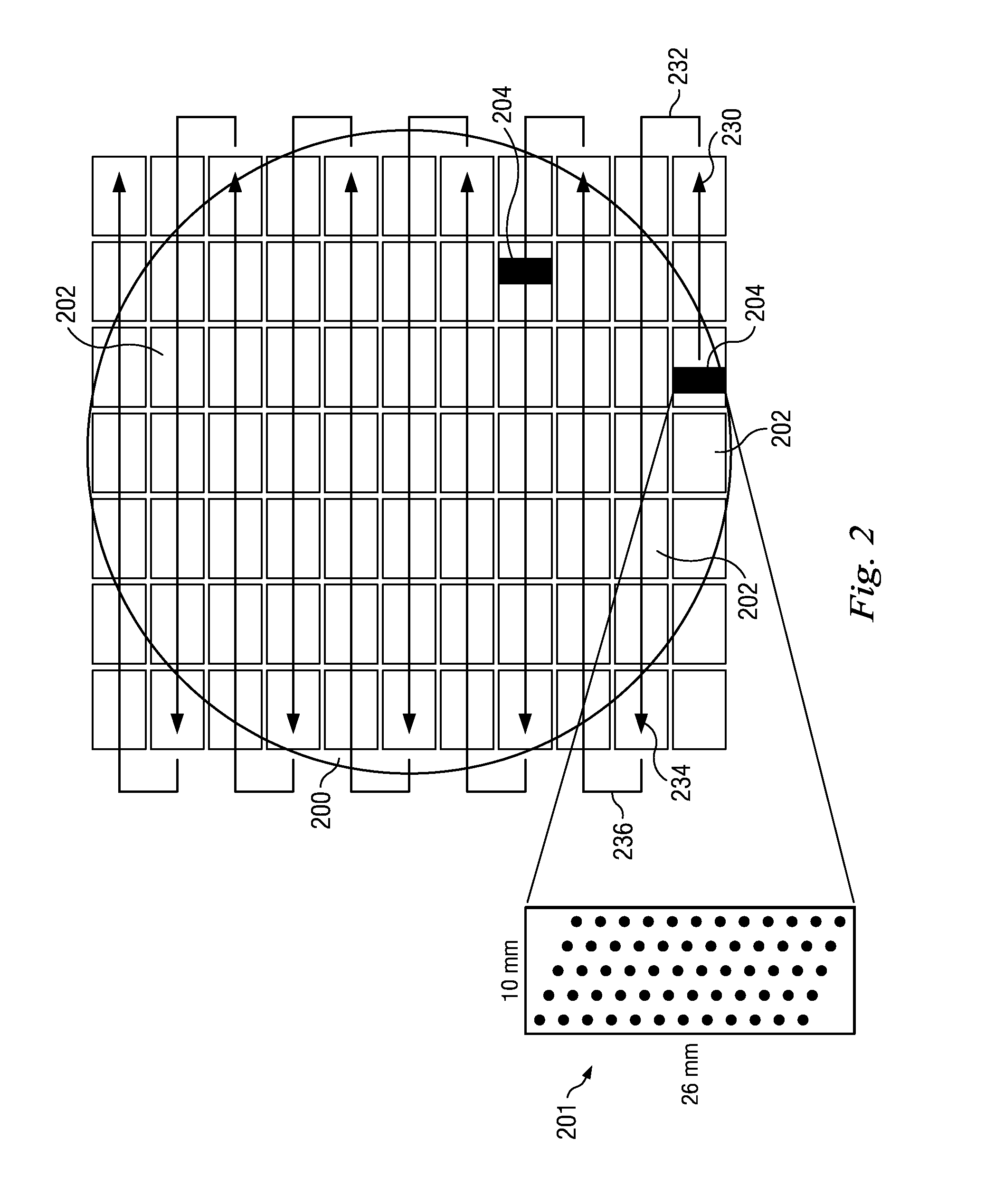

System and method for generating direct-write pattern

A direct-write system is provided which includes a stage for holding a substrate, a processing module for processing pattern data and generating instructions associated with the pattern data, and an exposure module that includes beams that are focused onto the substrate and a beam controller that controls the beams in accordance with the instructions. The processing module includes vertex pair processors each having bit inverters. Each vertex pair processor is operable to process a respective vertex pair of an input scan line to generate an output scan line. Each bit inverter is operable to invert a respective input bit of the input scan line to generate a respective output bit of the output scan line if a bit position is located between the respective vertex pair, otherwise the respective input bit is copied to the respective output bit. The instructions correspond to the output bits for each beam.

Owner:TAIWAN SEMICON MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com