Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

153results about How to "Reduce load effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

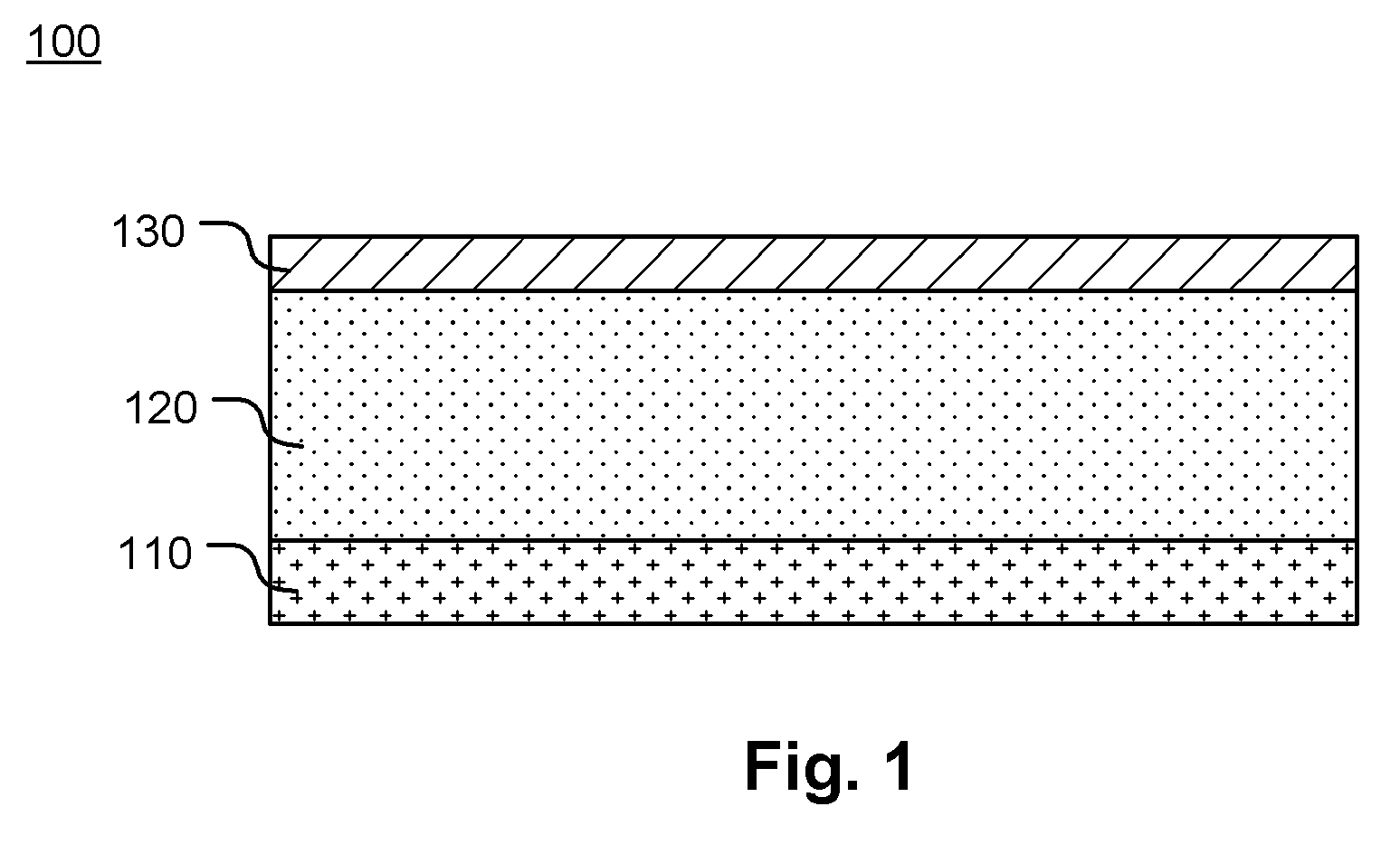

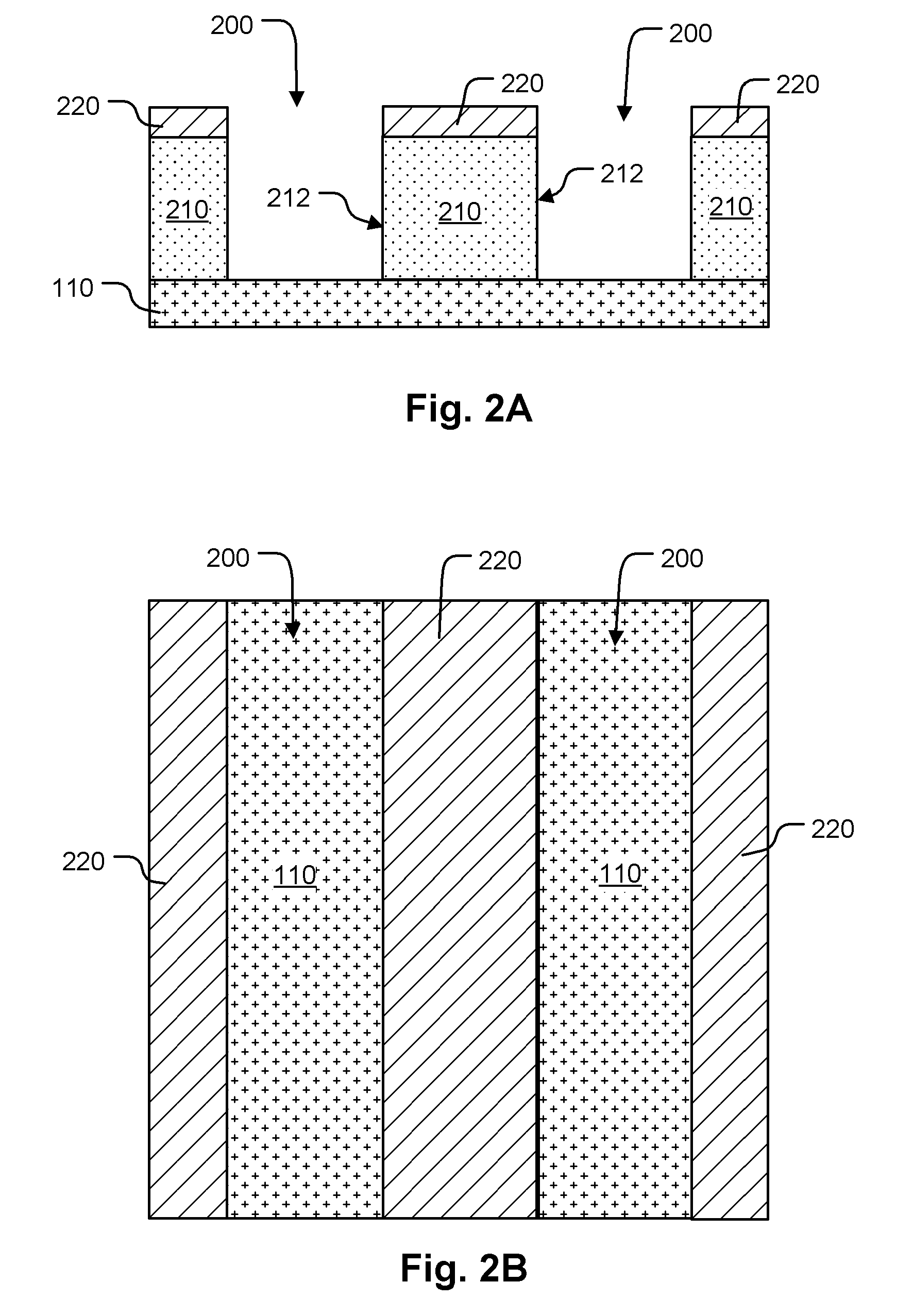

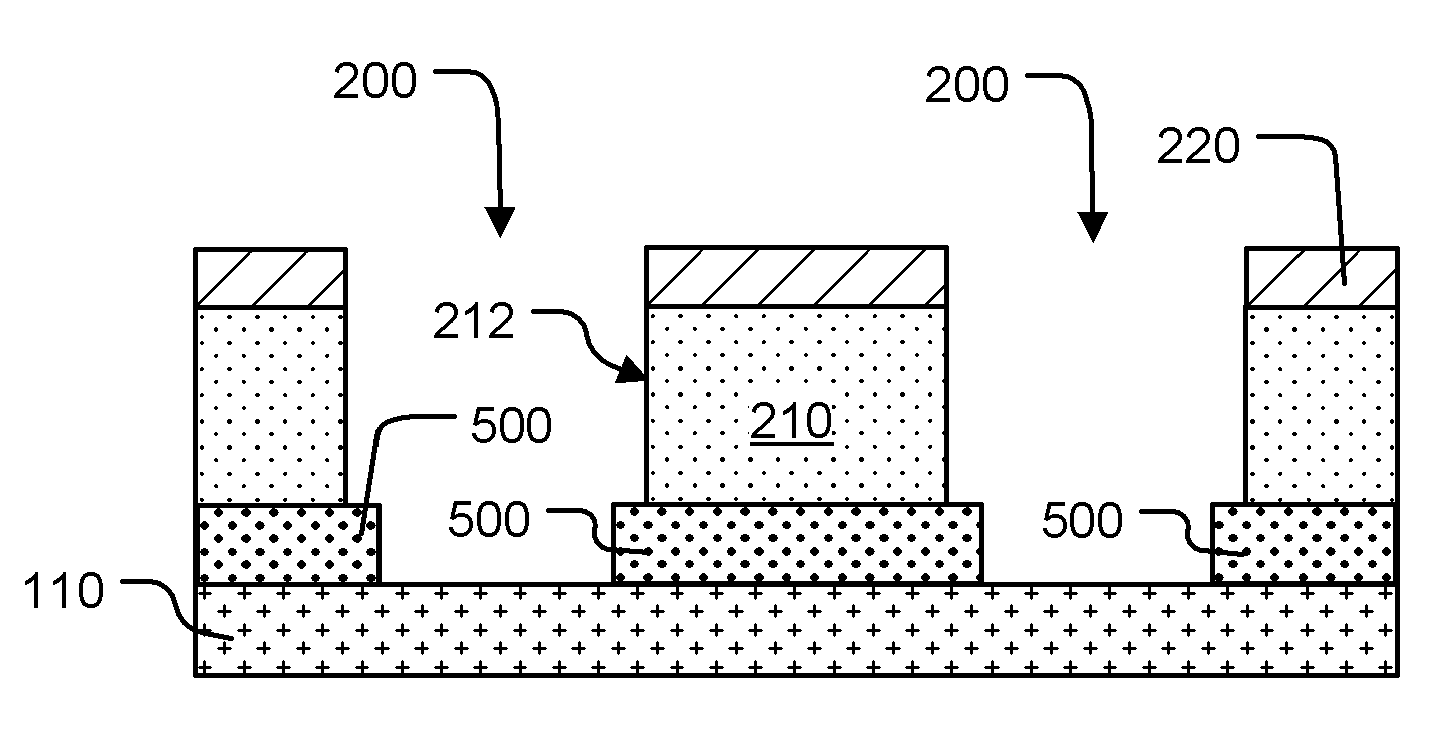

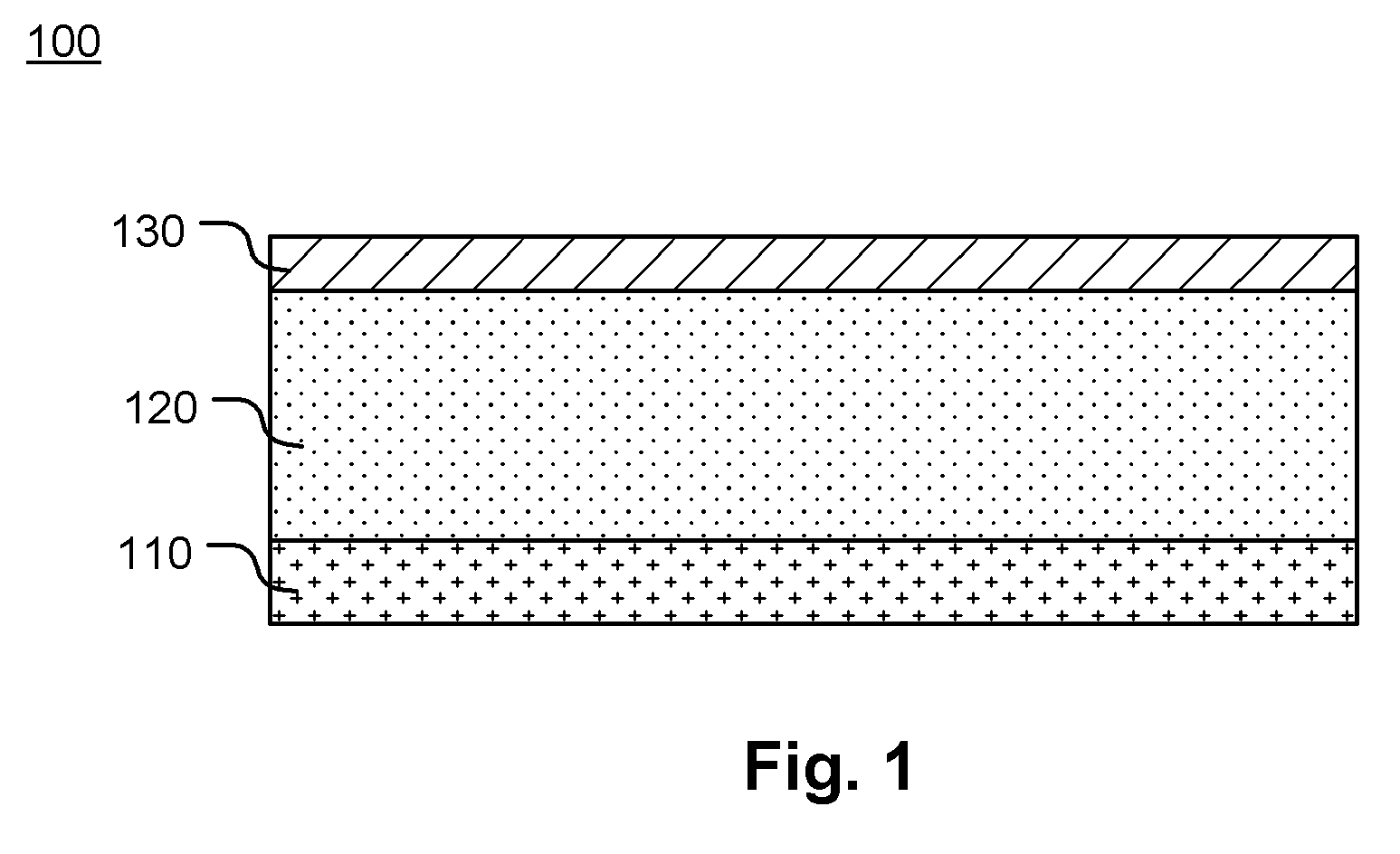

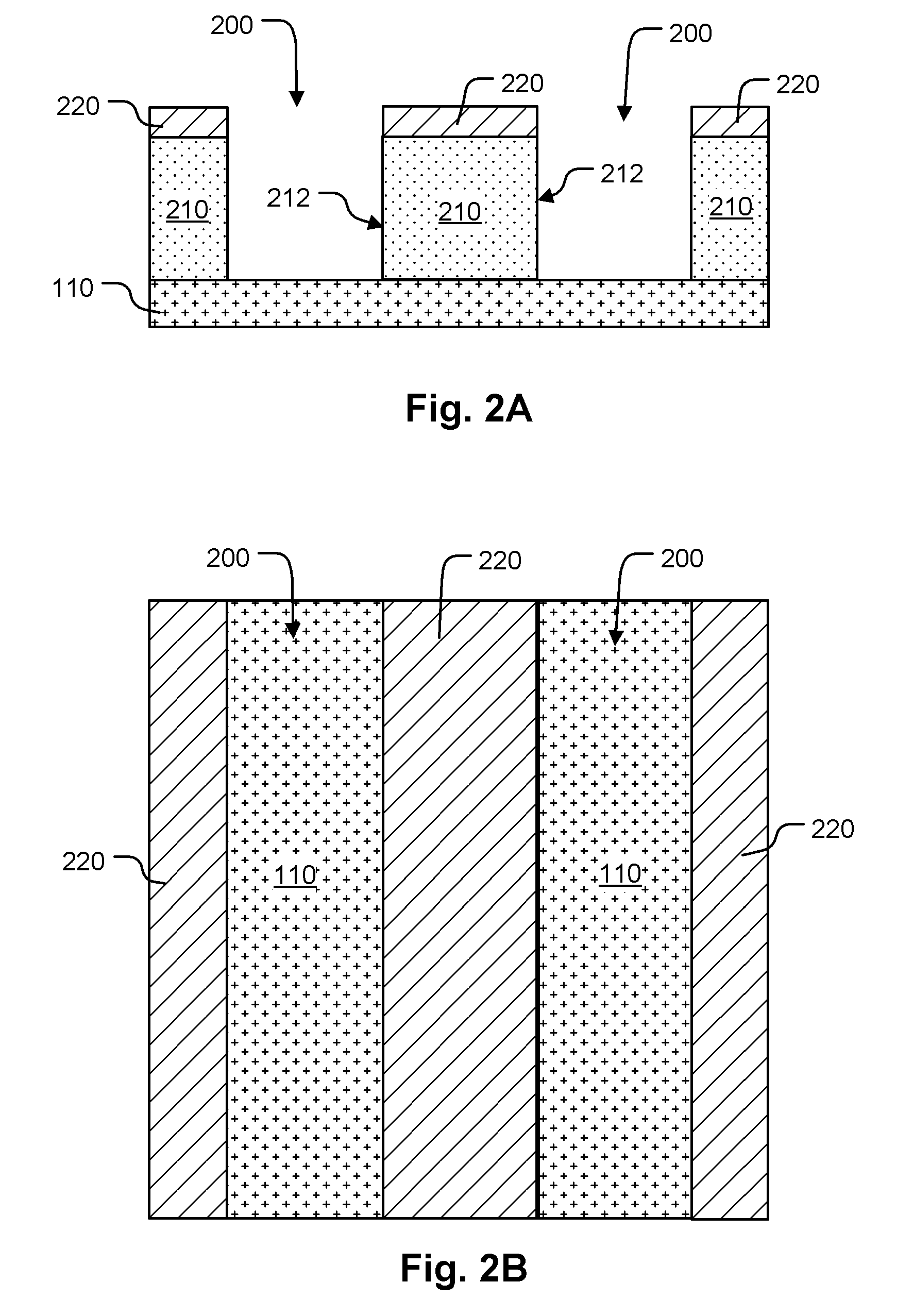

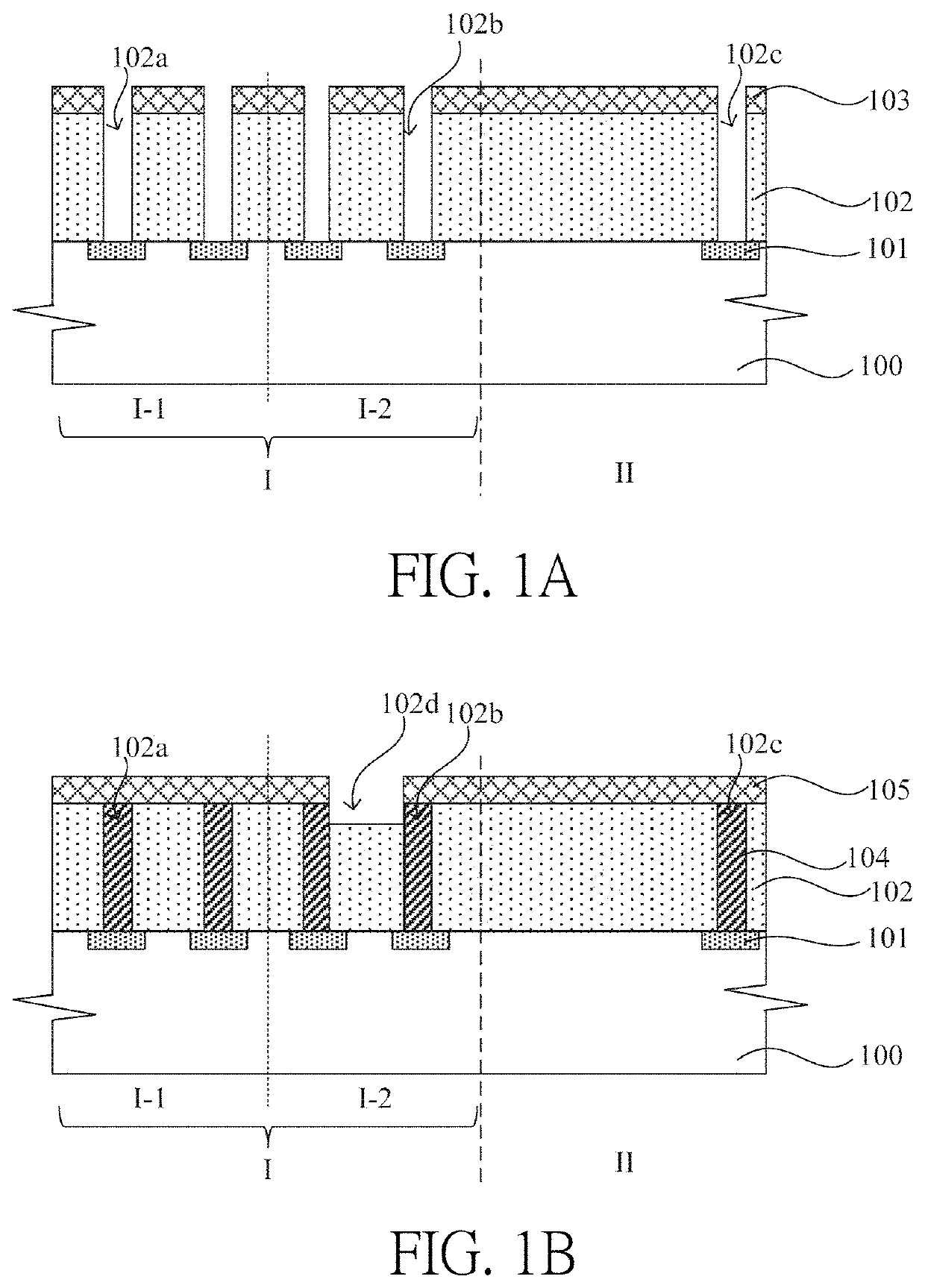

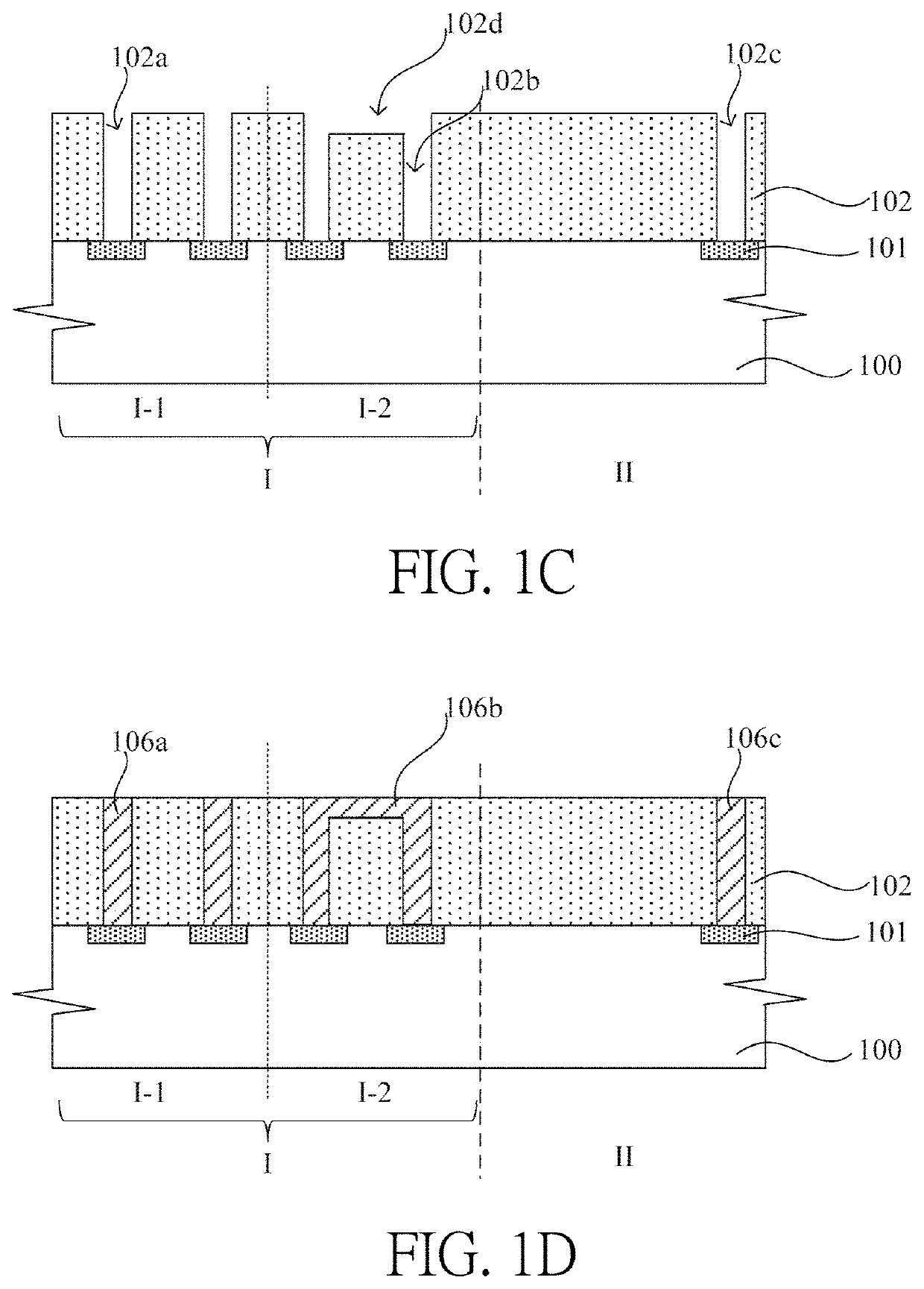

Buried silicide structure and method for making

ActiveUS20100301304A1Easy to manufactureImprove conductivitySolid-state devicesSemiconductor/solid-state device manufacturingSalicideHigh density

Methods for manufacturing buried silicide lines are described herein, along with high density stacked memory structures. A method for manufacturing an integrated circuit as described herein includes forming a semiconductor body comprising silicon. A plurality of trenches are formed in the semiconductor body to define semiconductor lines comprising silicon between adjacent trenches, the semiconductor lines having sidewalls. A silicide precursor is deposited within the trenches to contact the sidewalls of the semiconductor lines, and a portion of the silicide precursor is removed to expose upper portions of the sidewalls and leave remaining strips of silicide precursor along the sidewalls. Silicide conductors are then formed by inducing reaction of the strips of silicide with the silicon of the semiconductor lines.

Owner:MACRONIX INT CO LTD

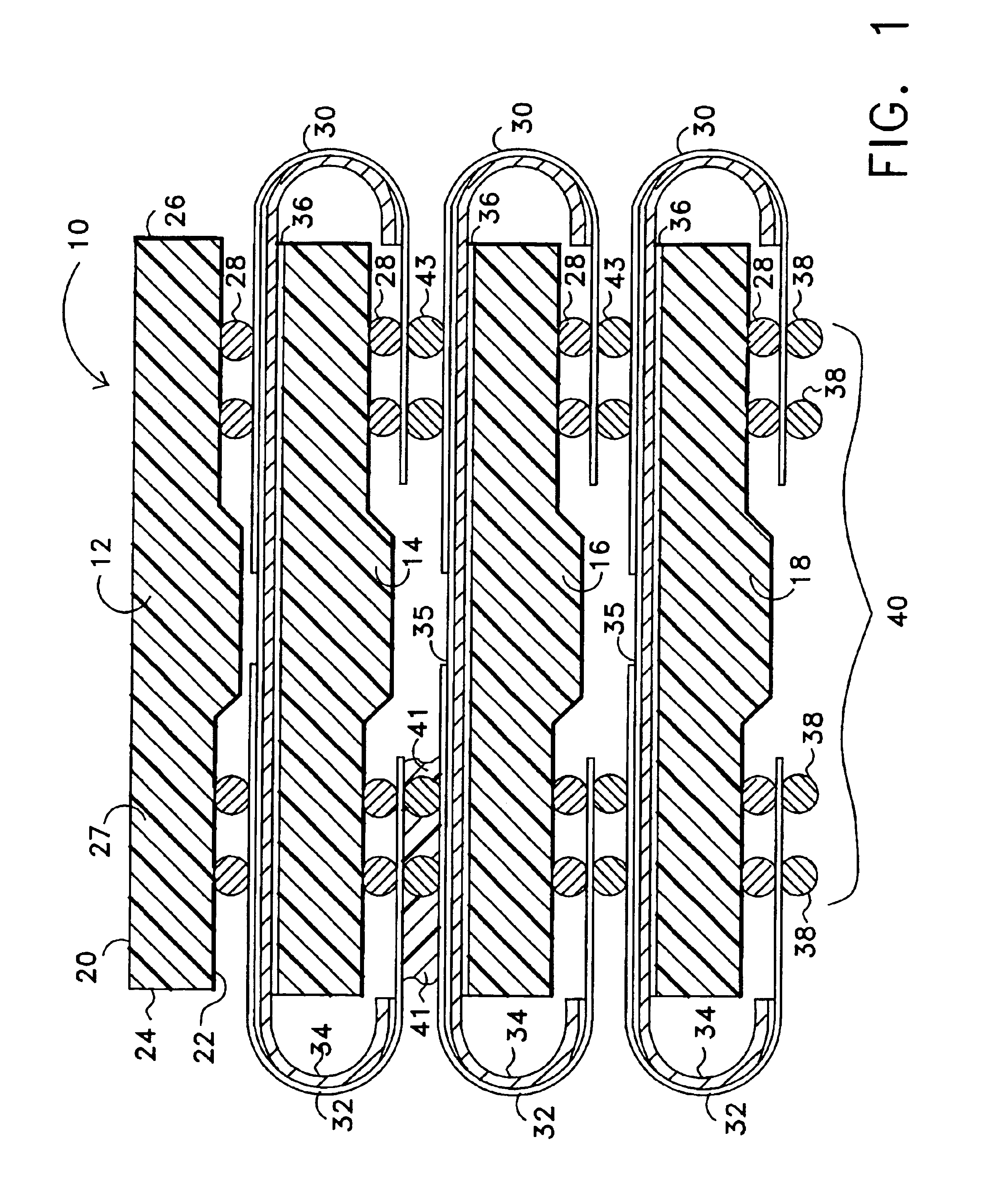

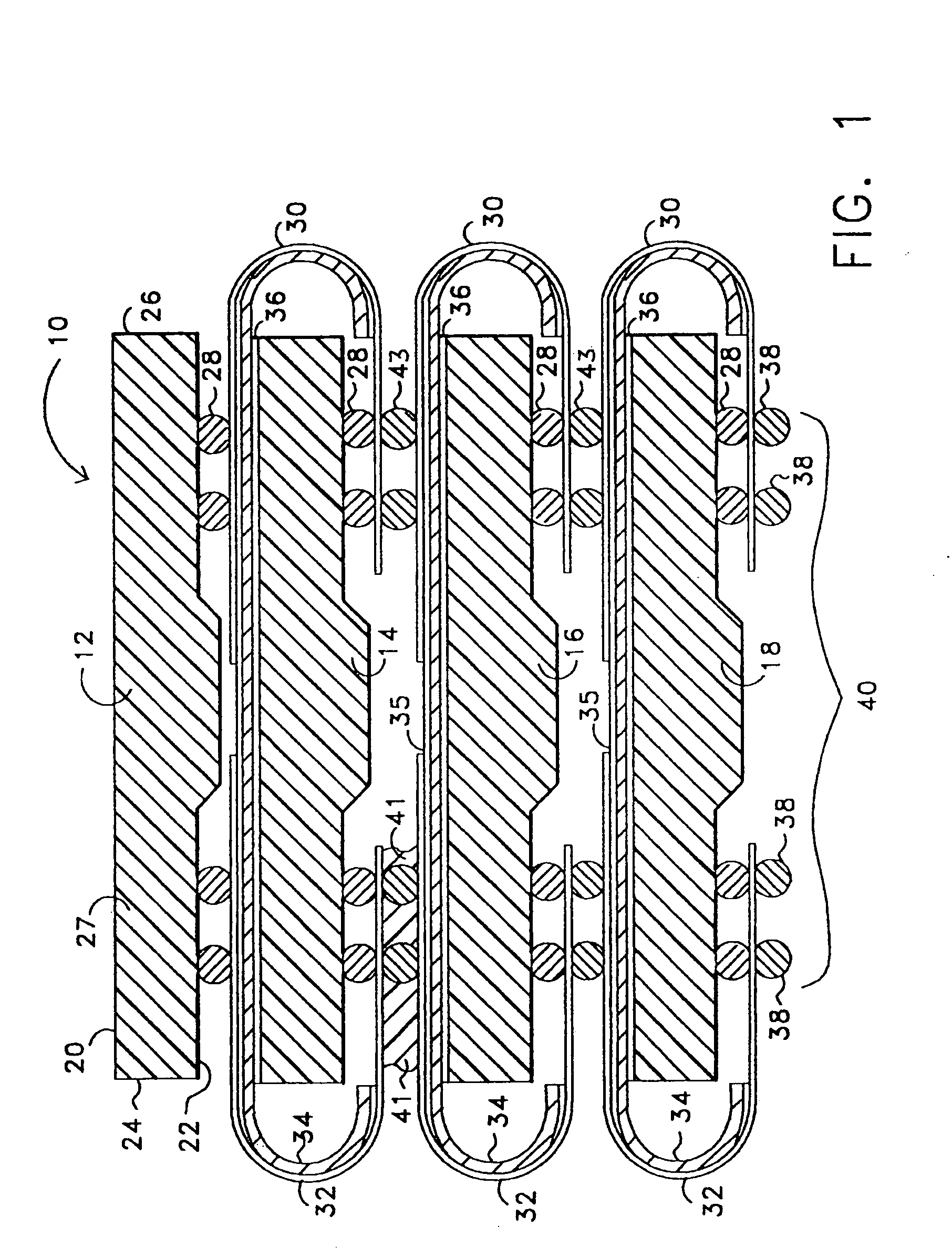

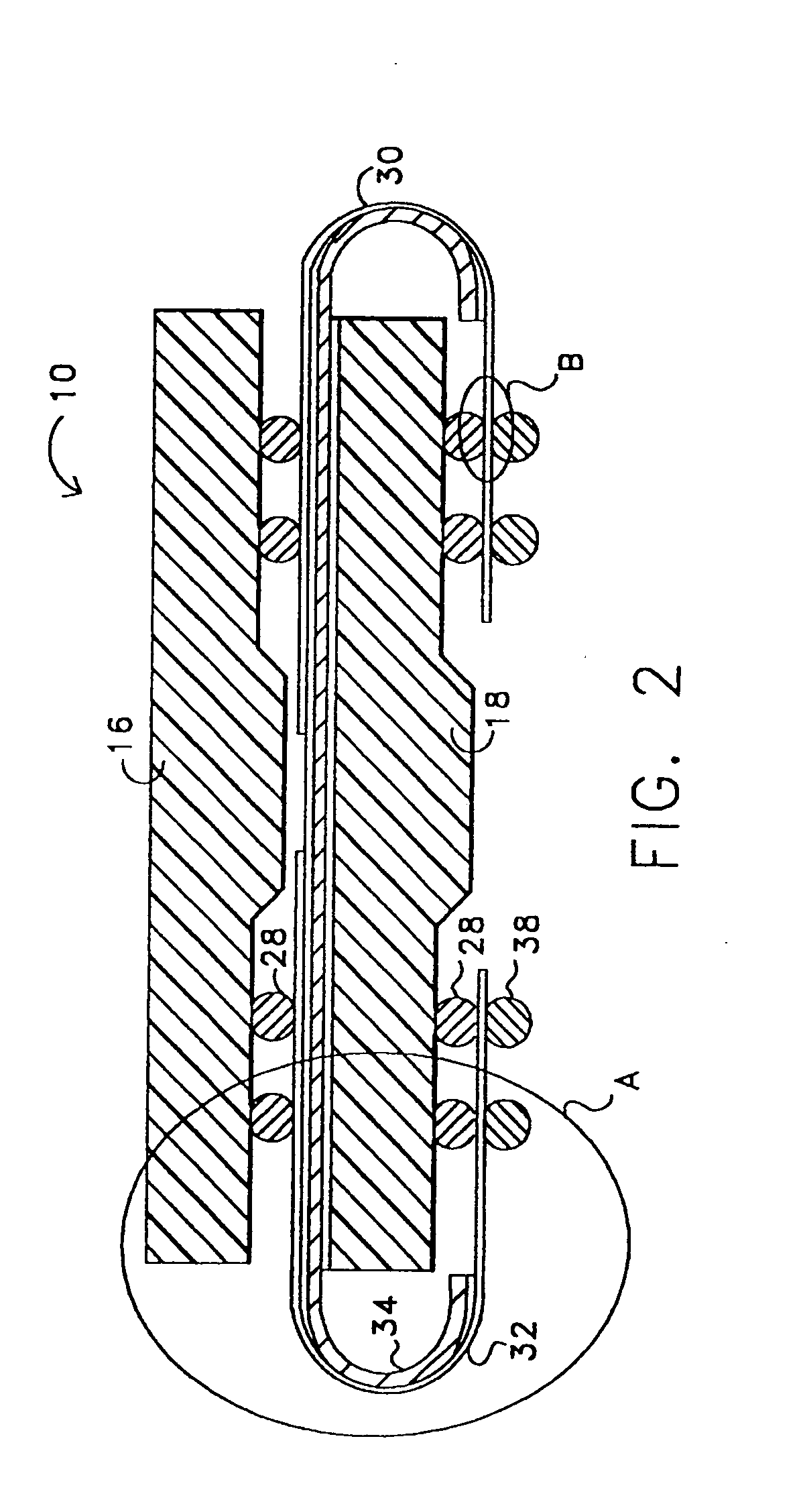

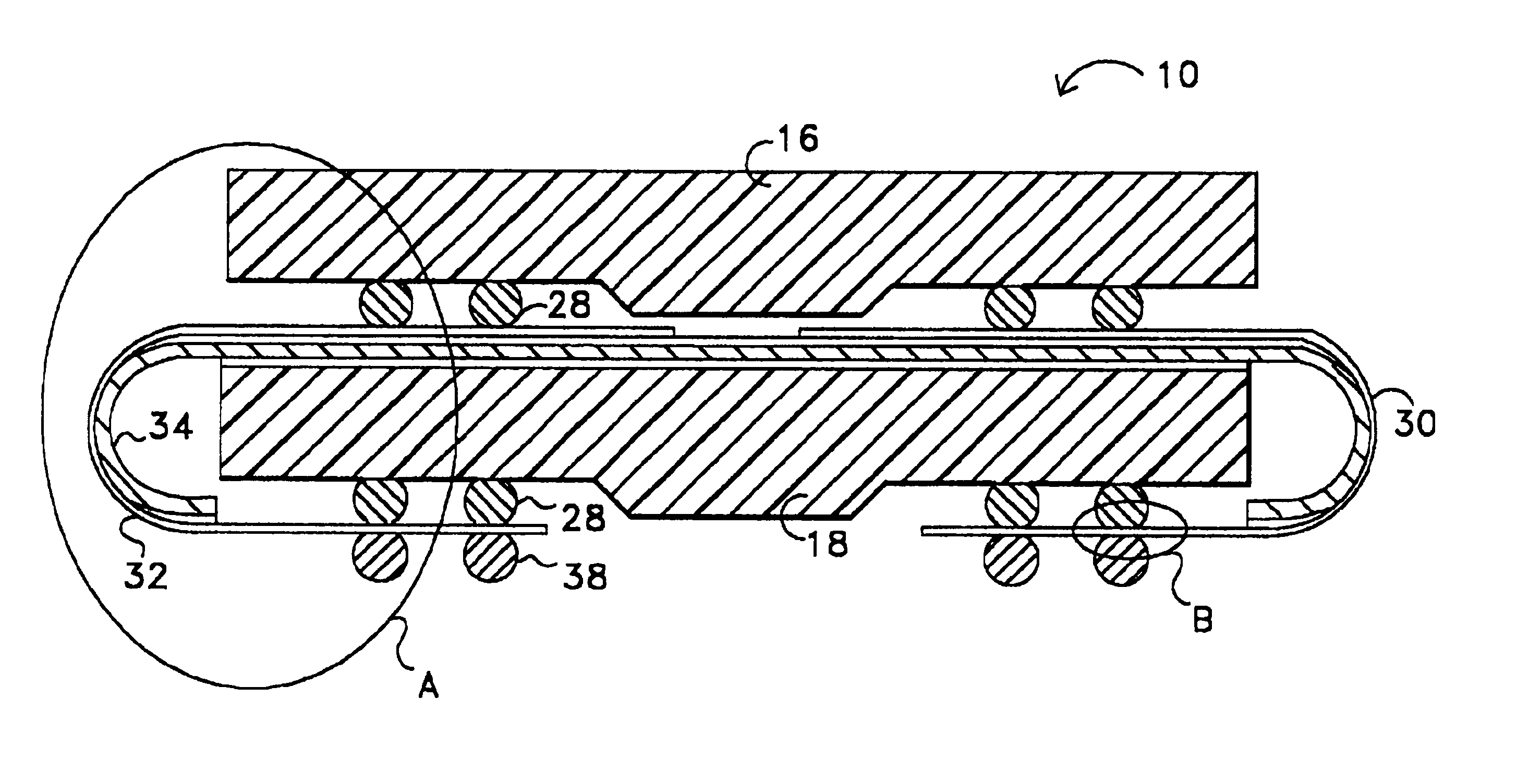

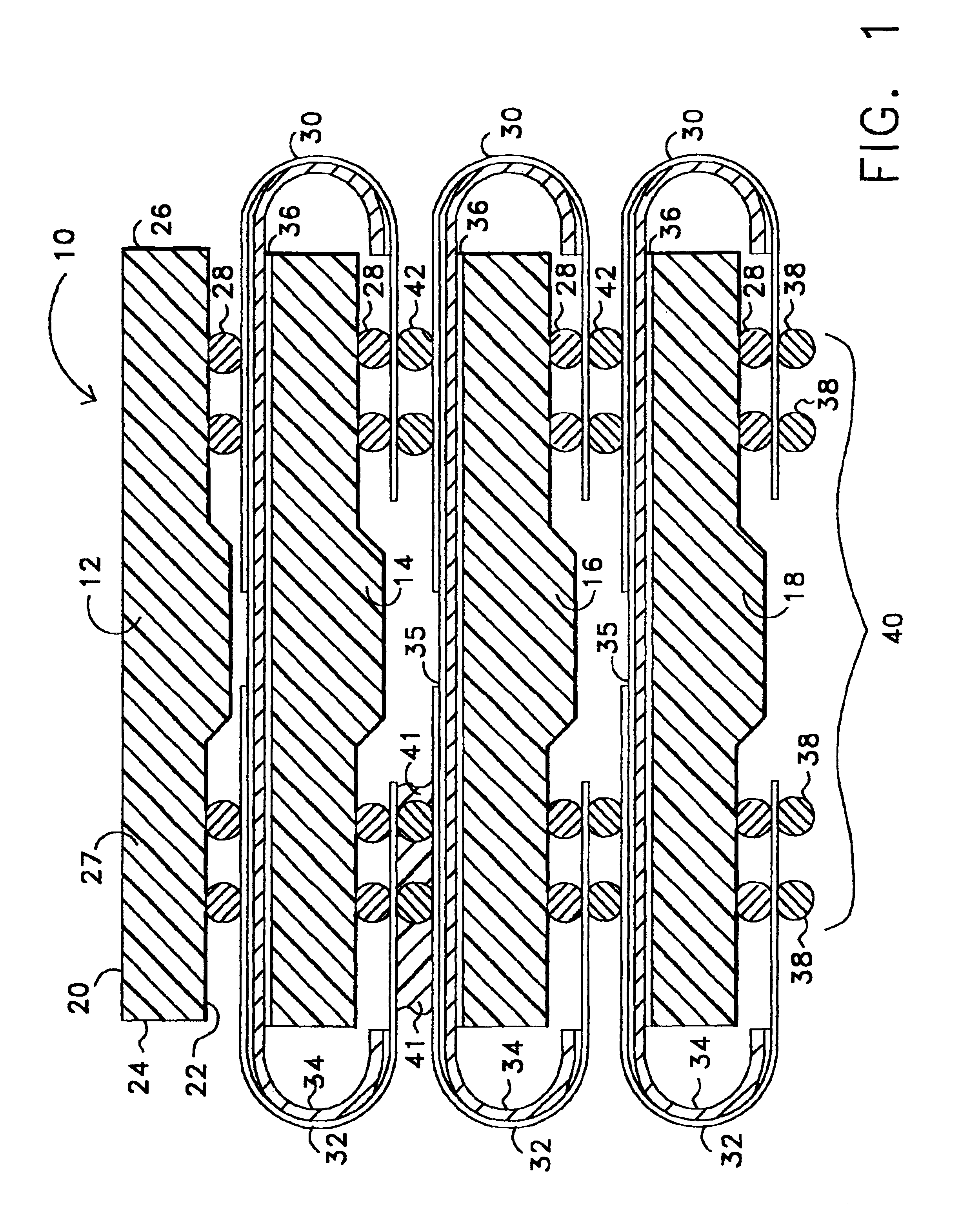

Integrated circuit stacking system and method

InactiveUS6956284B2Improve thermal efficiencyReduced footprintPrinted circuit assemblingSemiconductor/solid-state device detailsCapacitanceMemory address

The present invention stacks integrated circuits (ICs) into modules that conserve PWB or other board surface area. In another aspect, the invention provides a lower capacitance memory expansion addressing system and method and preferably with the CSP stacked modules provided herein. In a preferred embodiment in accordance with the invention, a form standard provides a physical form that allows many of the varying package sizes found in the broad family of CSP packages to be used to advantage while employing a standard connective flex circuitry design. In a preferred embodiment, the form standard will be devised of heat transference material such as copper to improve thermal performance. In an alternative embodiment, the form standard may include a heat spreader portion with mounting feet. In a preferred embodiment of the memory addressing system, a high speed switching system selects a data line associated with each level of a stacked module to reduce the loading effect upon data signals in memory access.

Owner:TAMIRAS PER PTE LTD LLC

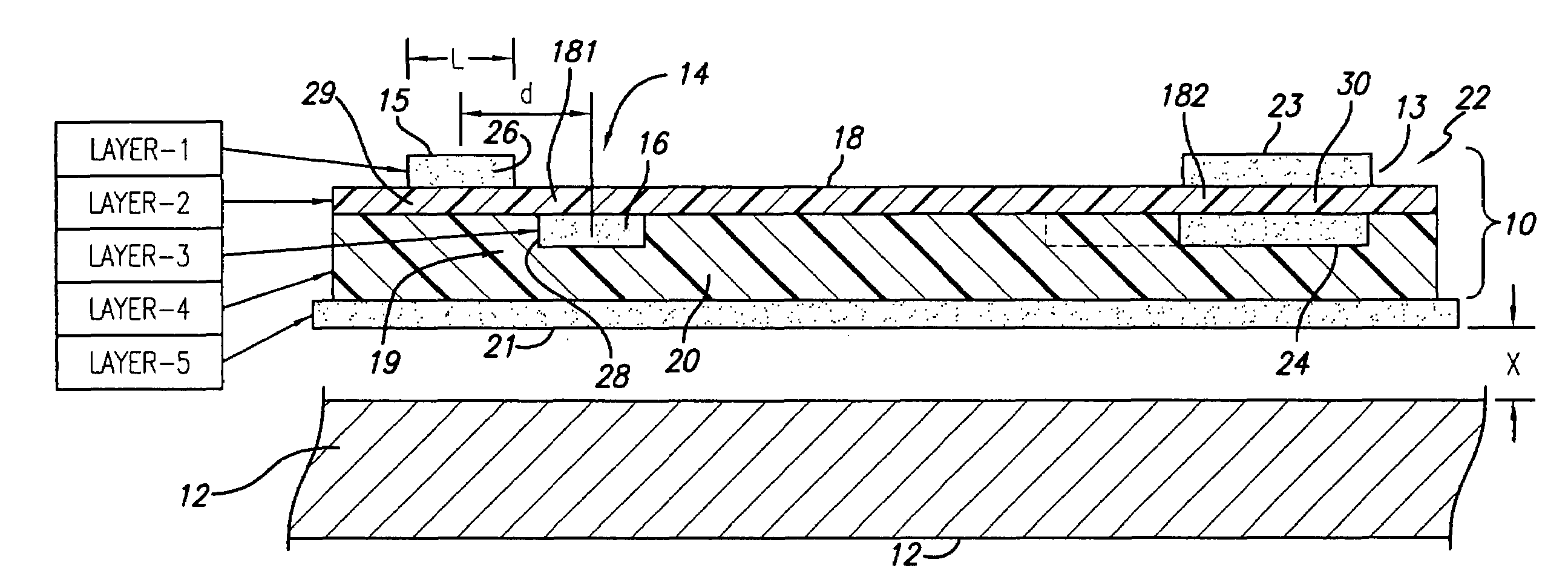

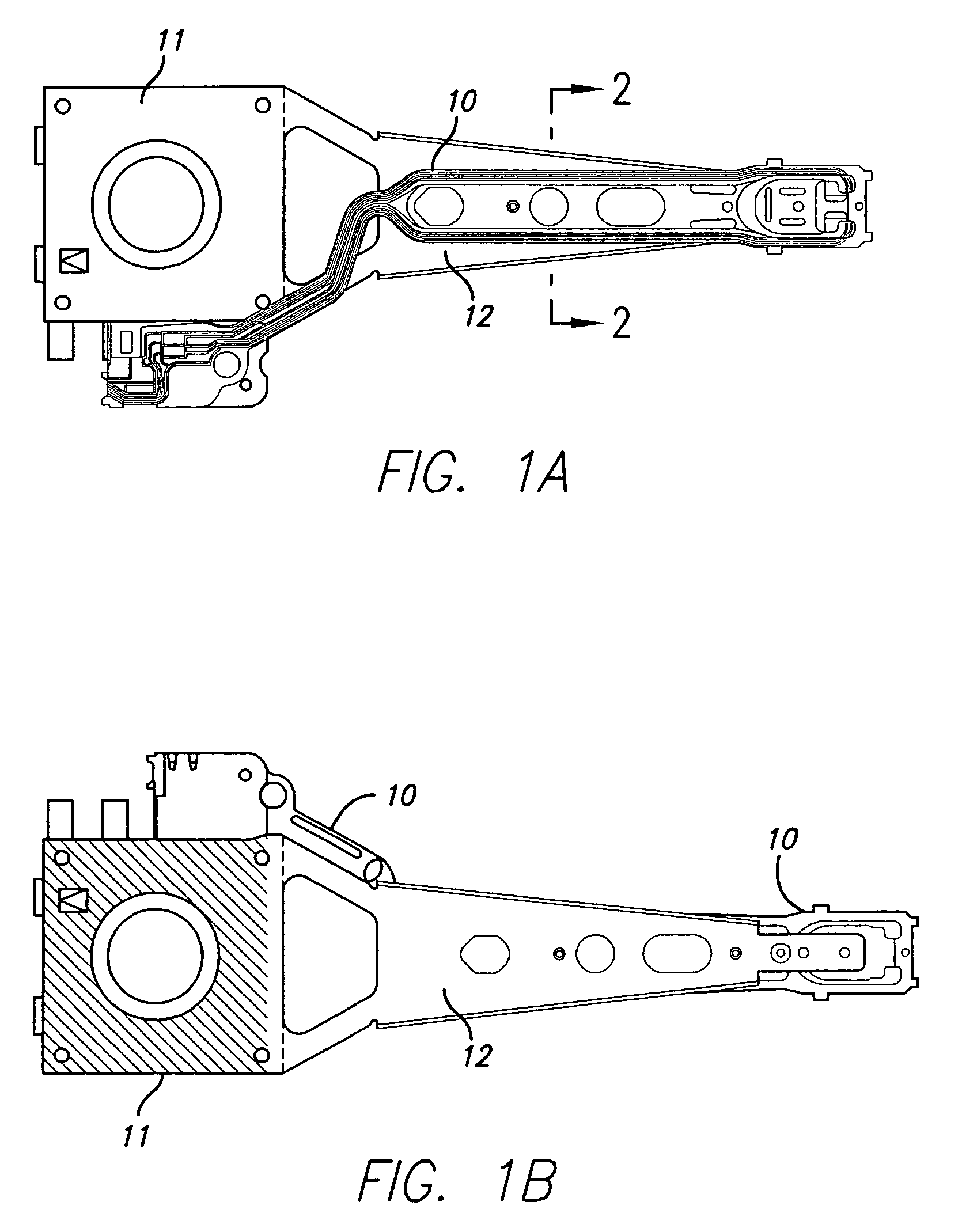

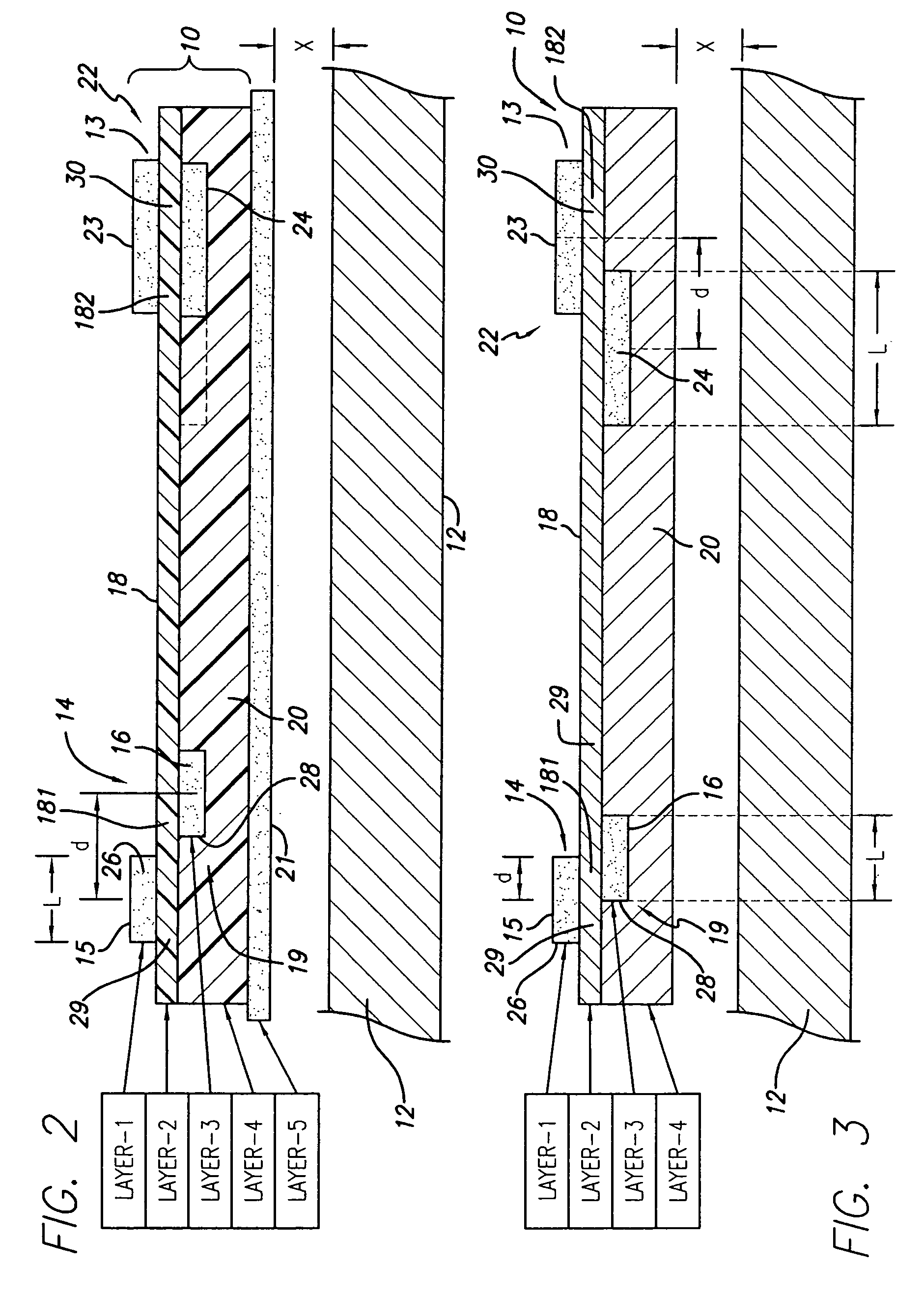

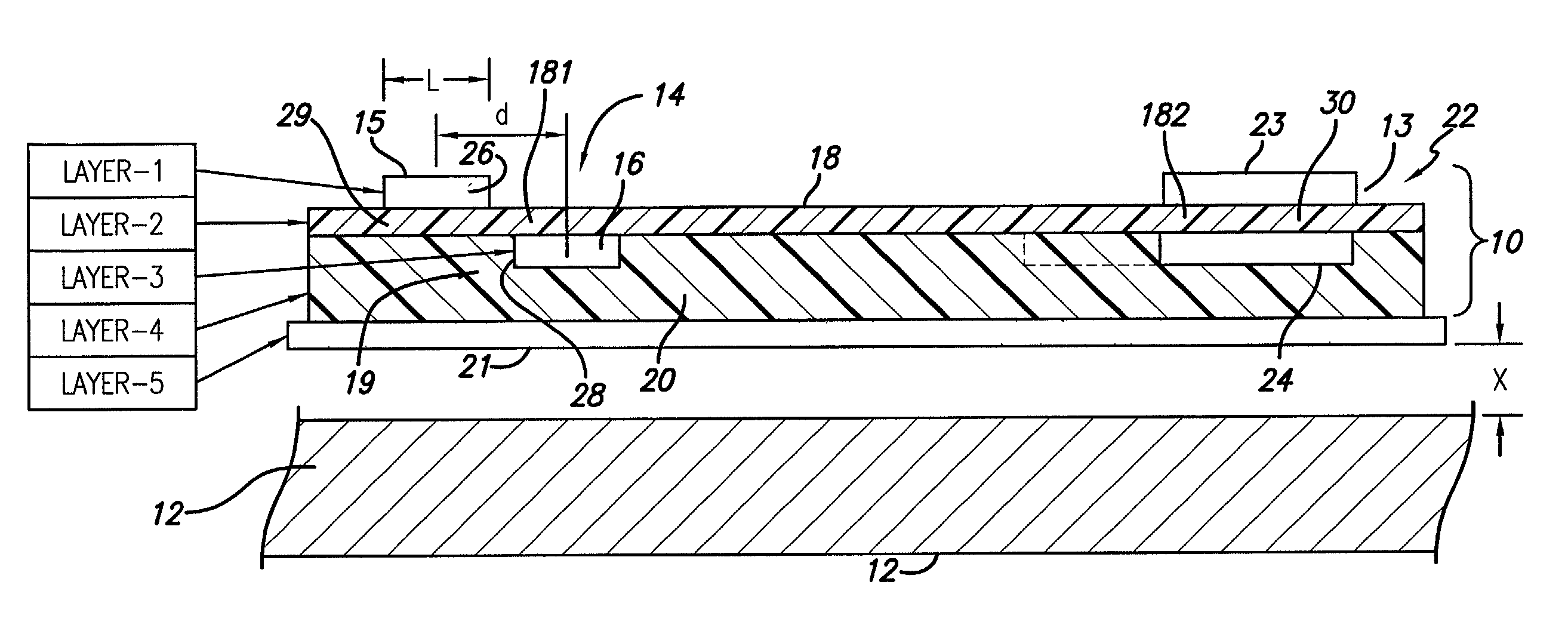

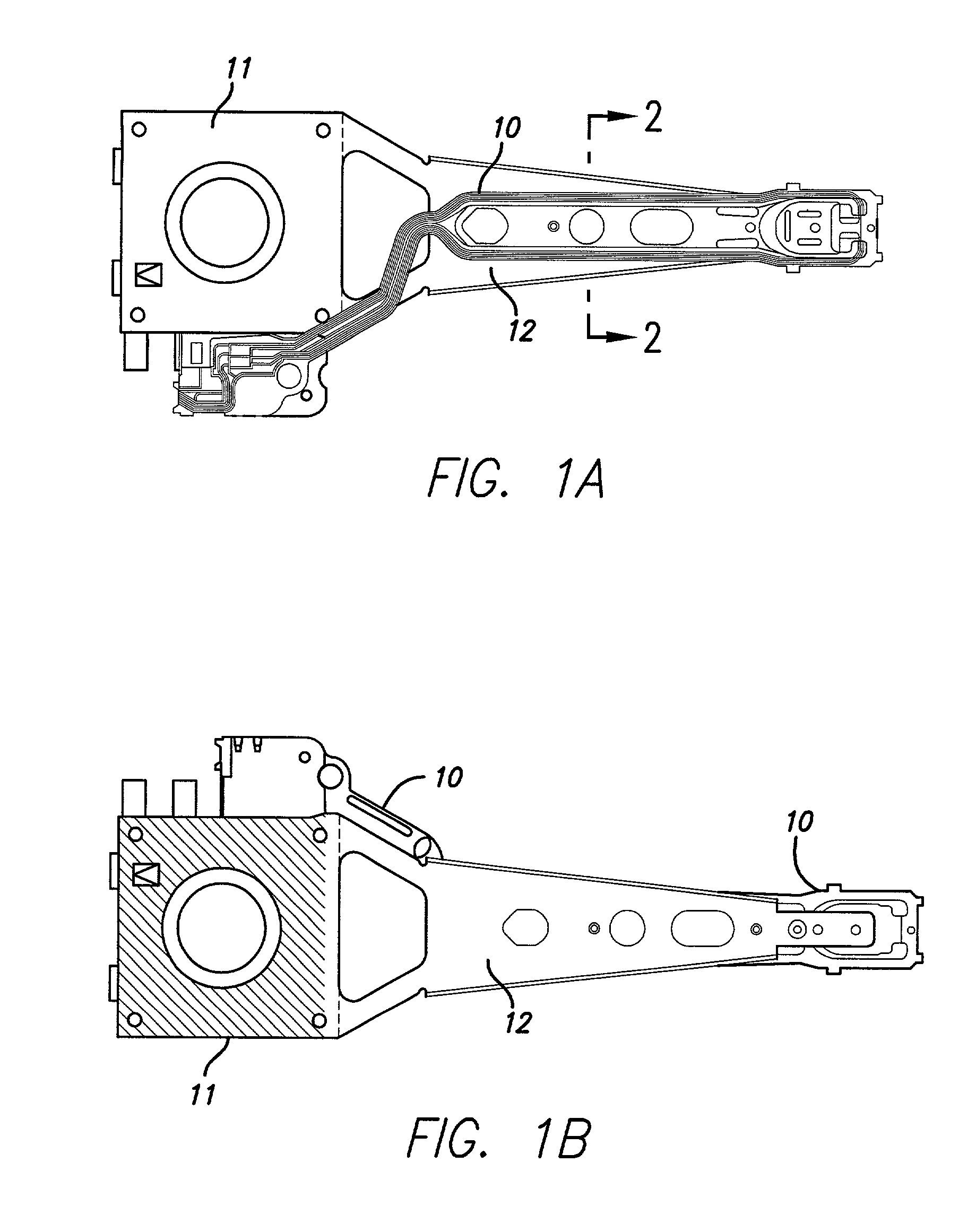

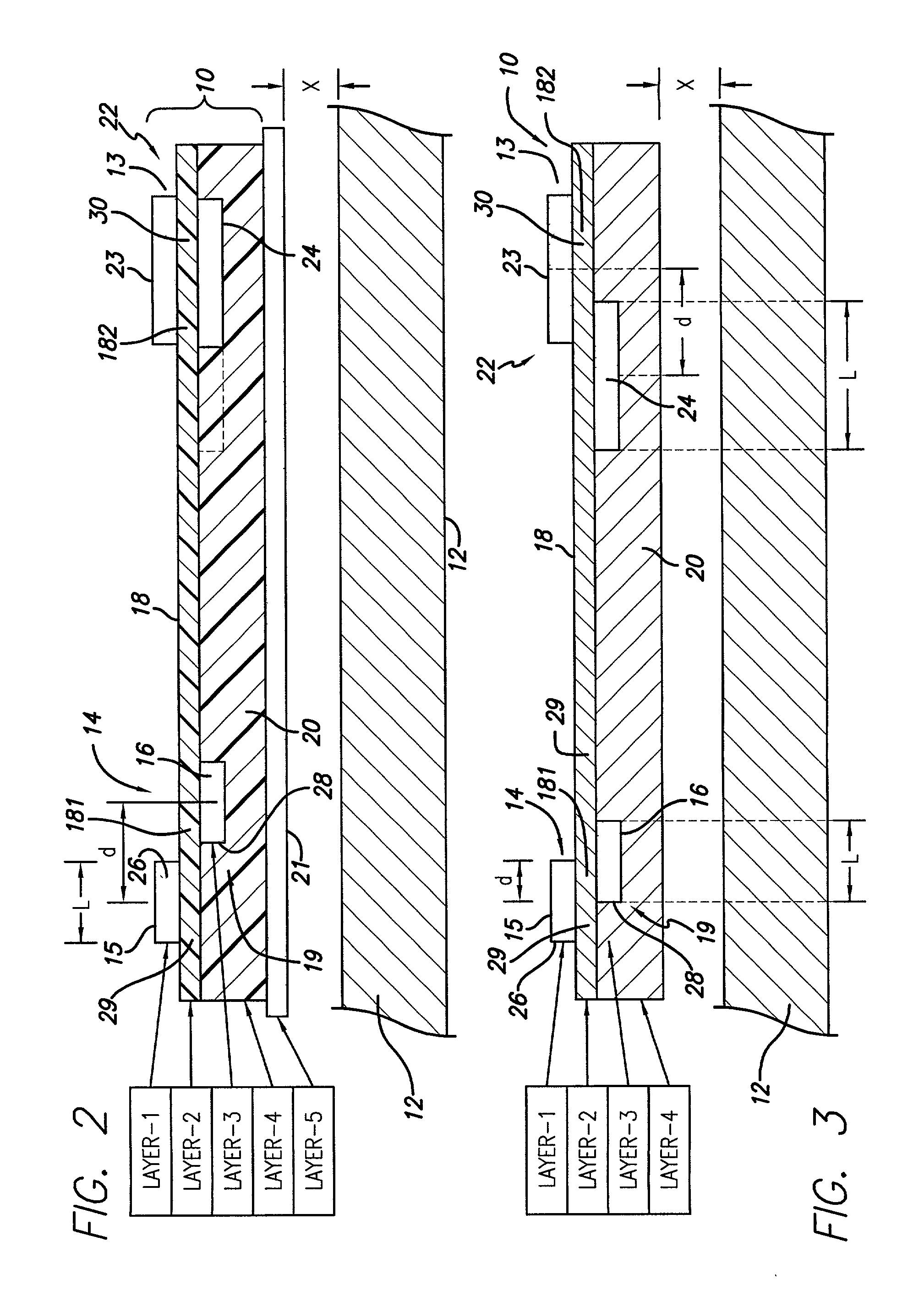

Additive-process suspension interconnect with controlled noise

InactiveUS7079357B1Increase electrical couplingLess sensitiveRecord information storageStructure of arm assemblyAdditive processElectrical interconnect

A disk drive electrical interconnect assembly and additive method therefor. The interconnect assembly has a supporting or fifth layer of metal, a fourth layer of a polyimide precursor or a polyimide with a first face directed away from the fifth layer, a third layer directly attached to the first face and defining a first subset of one or more conductive trace pair members, a second layer on the third and fourth layers of a polyimide precursor or a polyimide with a second face directed away from the third layer, and a first layer directly attached to the second layer and defining a second subset of one or more conductive trace pair members in spaced, paired and laterally offset relation respectively with one or more of the first subset pair members.

Owner:MAGNECOMP

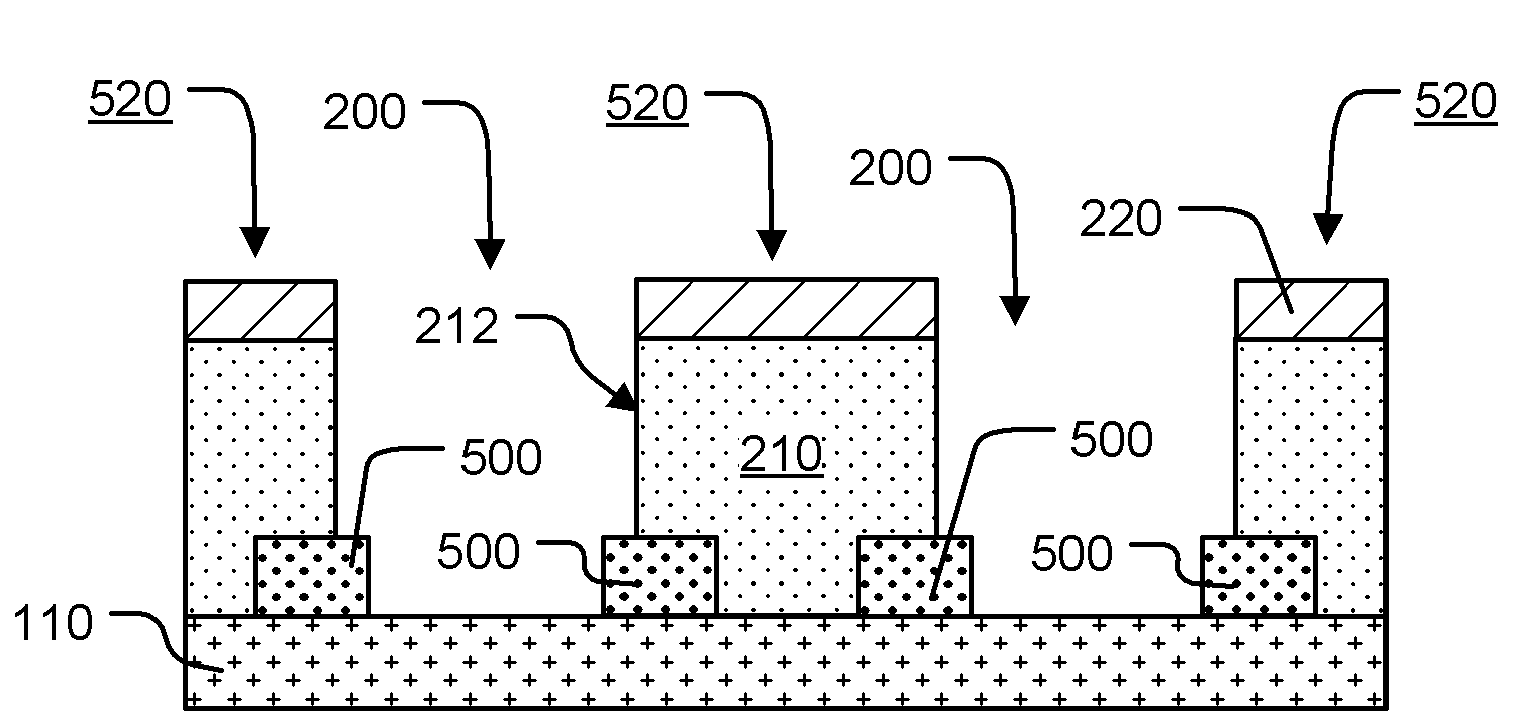

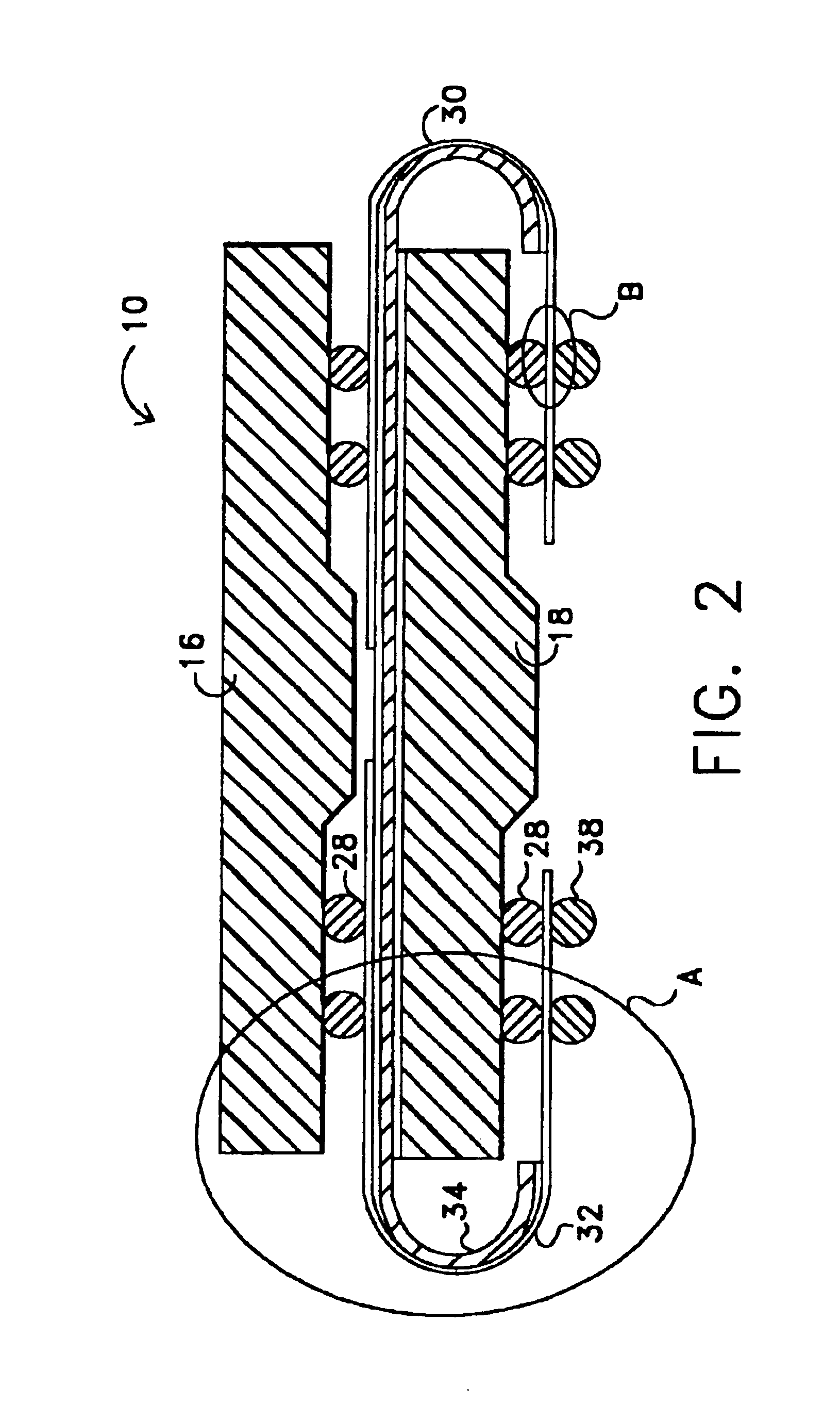

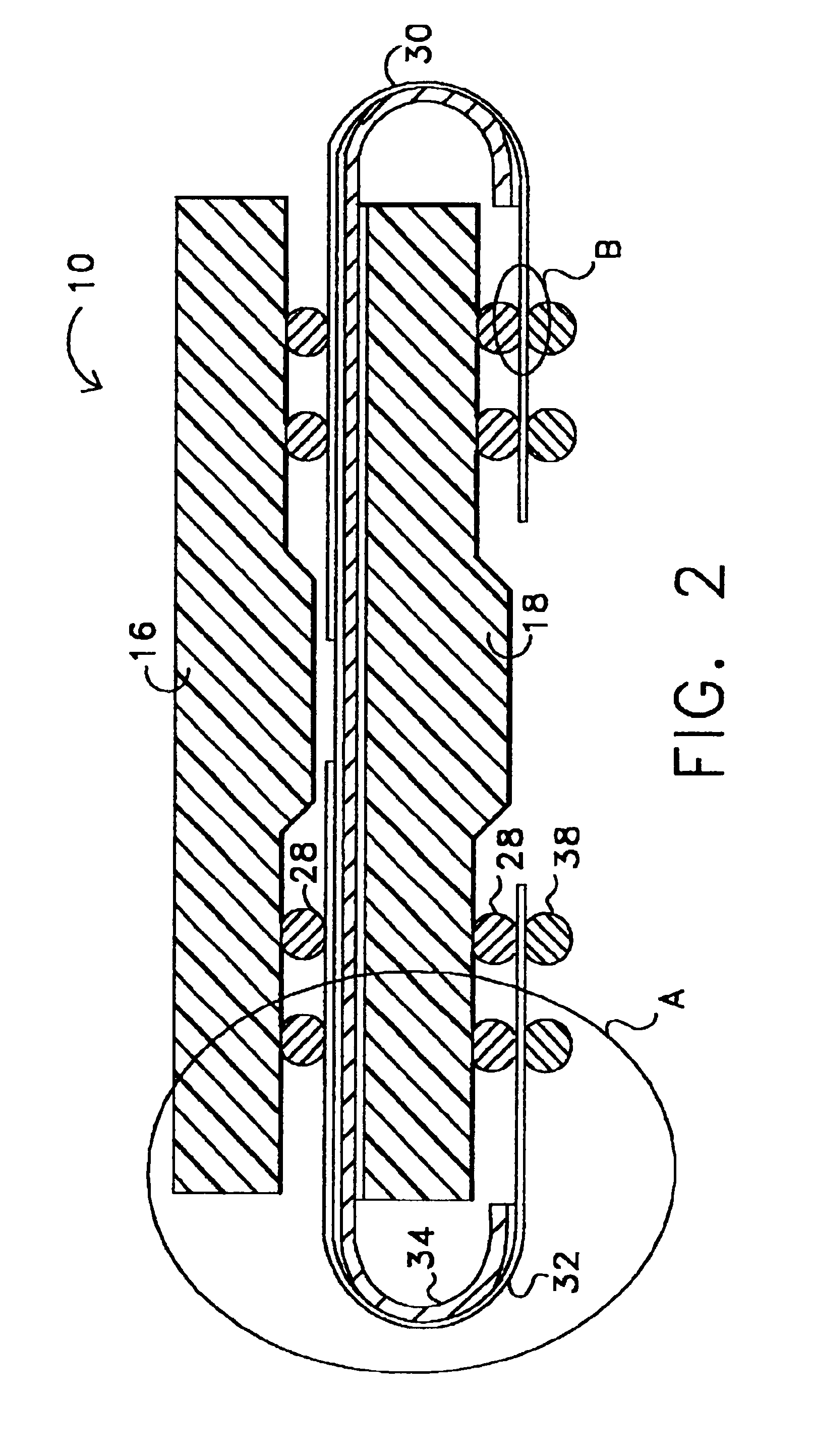

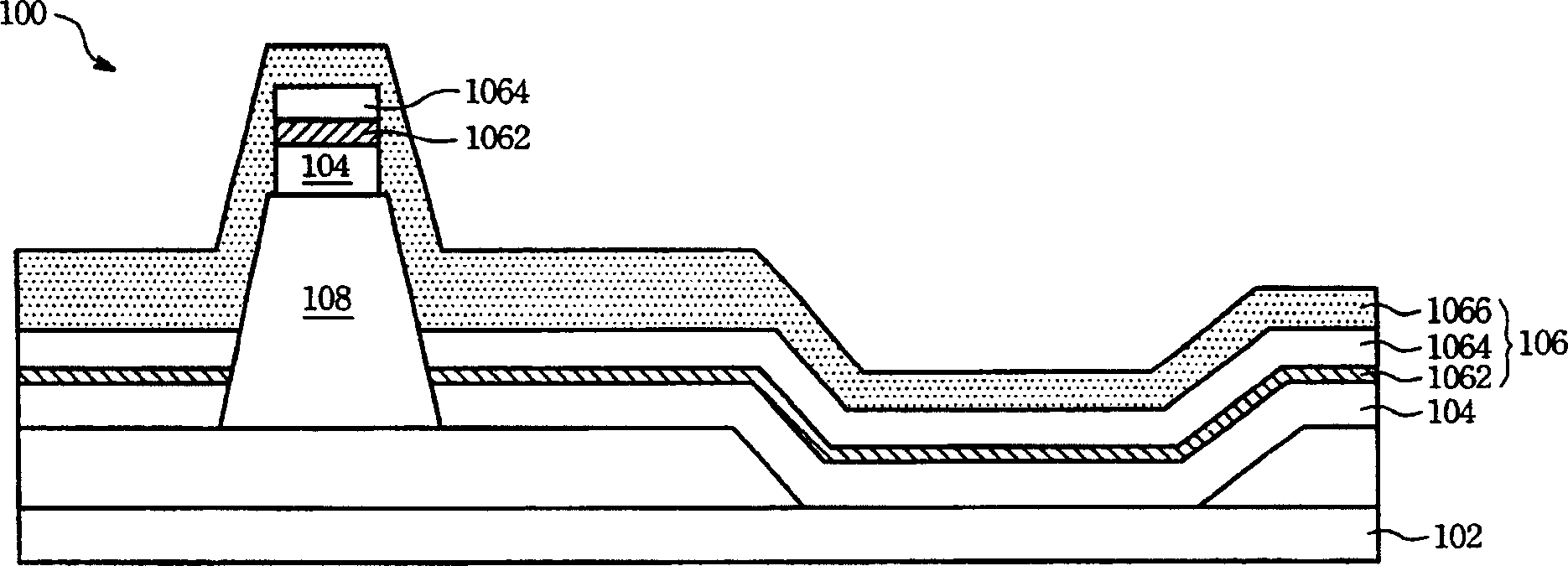

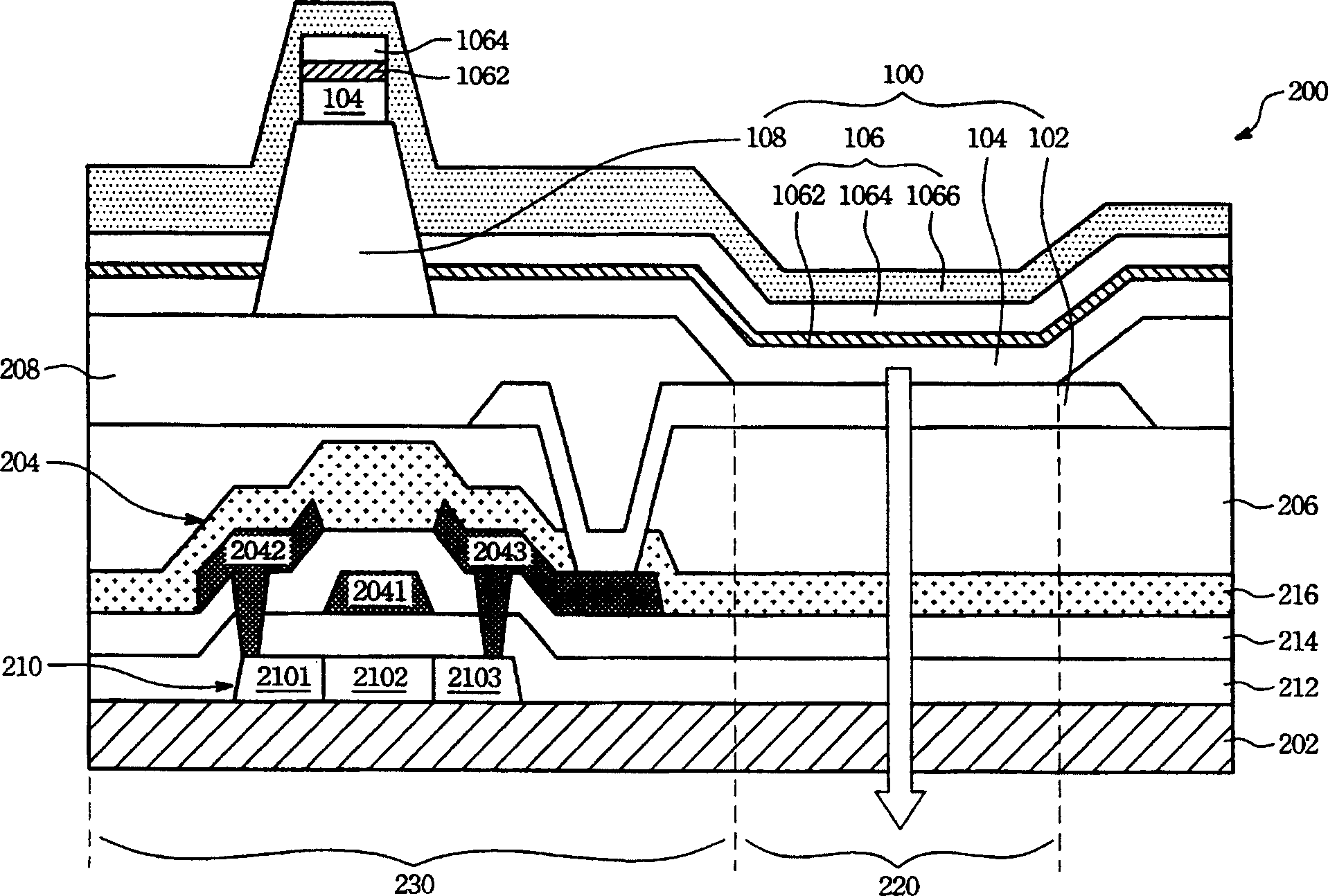

Buried silicide structure and method for making

ActiveUS8168538B2Improve conductivityReduce load effectTransistorSemiconductor/solid-state device detailsSalicideHigh density

Methods for manufacturing buried silicide lines are described herein, along with high density stacked memory structures. A method for manufacturing an integrated circuit as described herein includes forming a semiconductor body comprising silicon. A plurality of trenches are formed in the semiconductor body to define semiconductor lines comprising silicon between adjacent trenches, the semiconductor lines having sidewalls. A silicide precursor is deposited within the trenches to contact the sidewalls of the semiconductor lines, and a portion of the silicide precursor is removed to expose upper portions of the sidewalls and leave remaining strips of silicide precursor along the sidewalls. Silicide conductors are then formed by inducing reaction of the strips of silicide with the silicon of the semiconductor lines.

Owner:MACRONIX INT CO LTD

Suspension interconnect with controlled noise

InactiveUS6975488B1Improved disk drive suspensionIncrease electrical couplingCross-talk/noise/interference reductionPrinted circuit aspectsEngineeringMetal

A disk drive suspension and method has a metal load beam and an electrical interconnect assembly. The interconnect assembly has an insulative layer, a read pair of forward and return path conductive traces, a write pair of forward and return path conductive traces that are supported by the insulative layer, preferably in offset relation across the insulative layer, and a metal layer for grounding and mounted on the insulative plastic layer in fixed spaced relation to the conductive traces to be between the interconnect assembly and the load beam. The metal layer shields the conductive traces from variations in impedance occasioned by varying distances between said electrical interconnect and said load beam.

Owner:MAGNECOMP

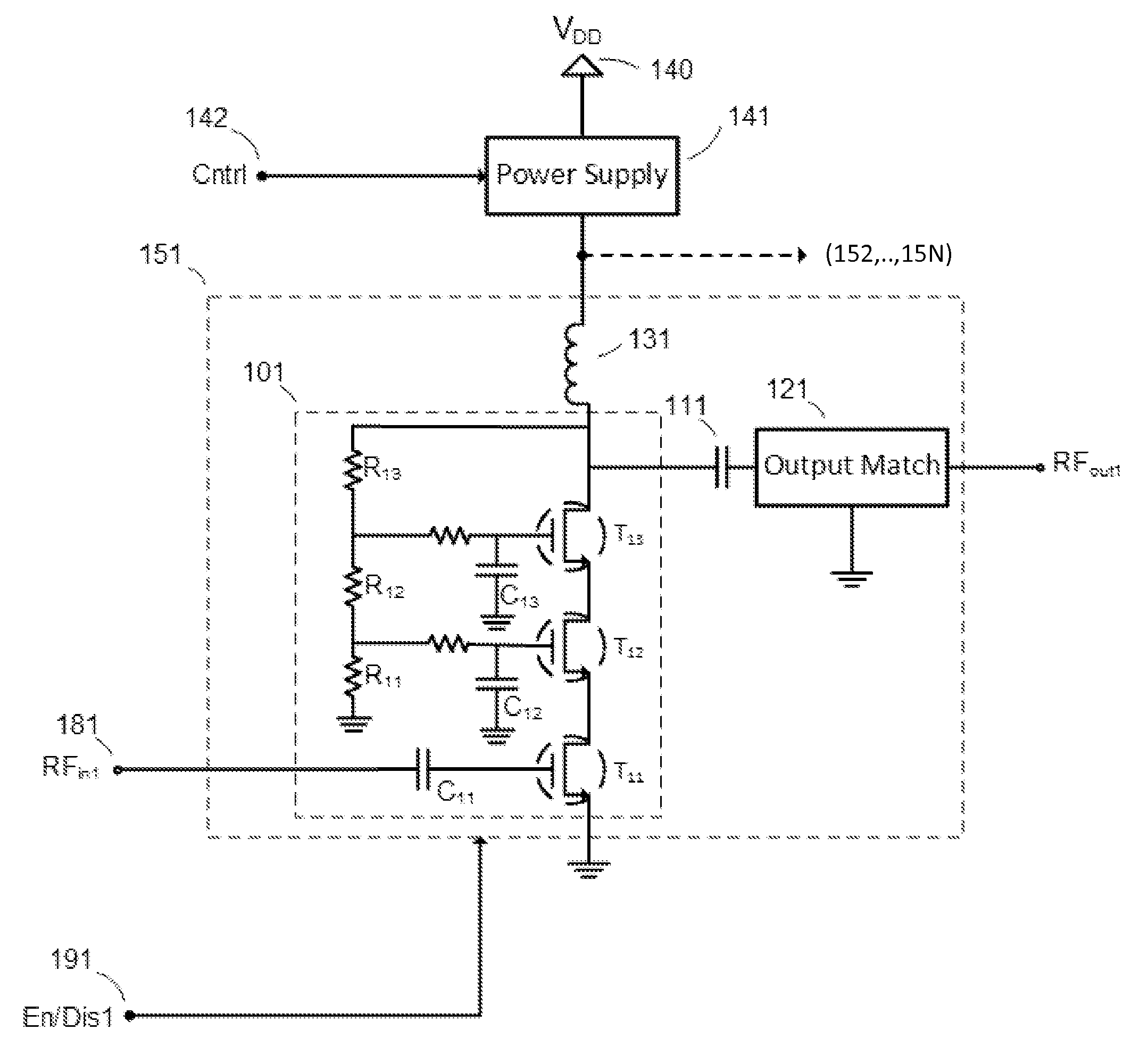

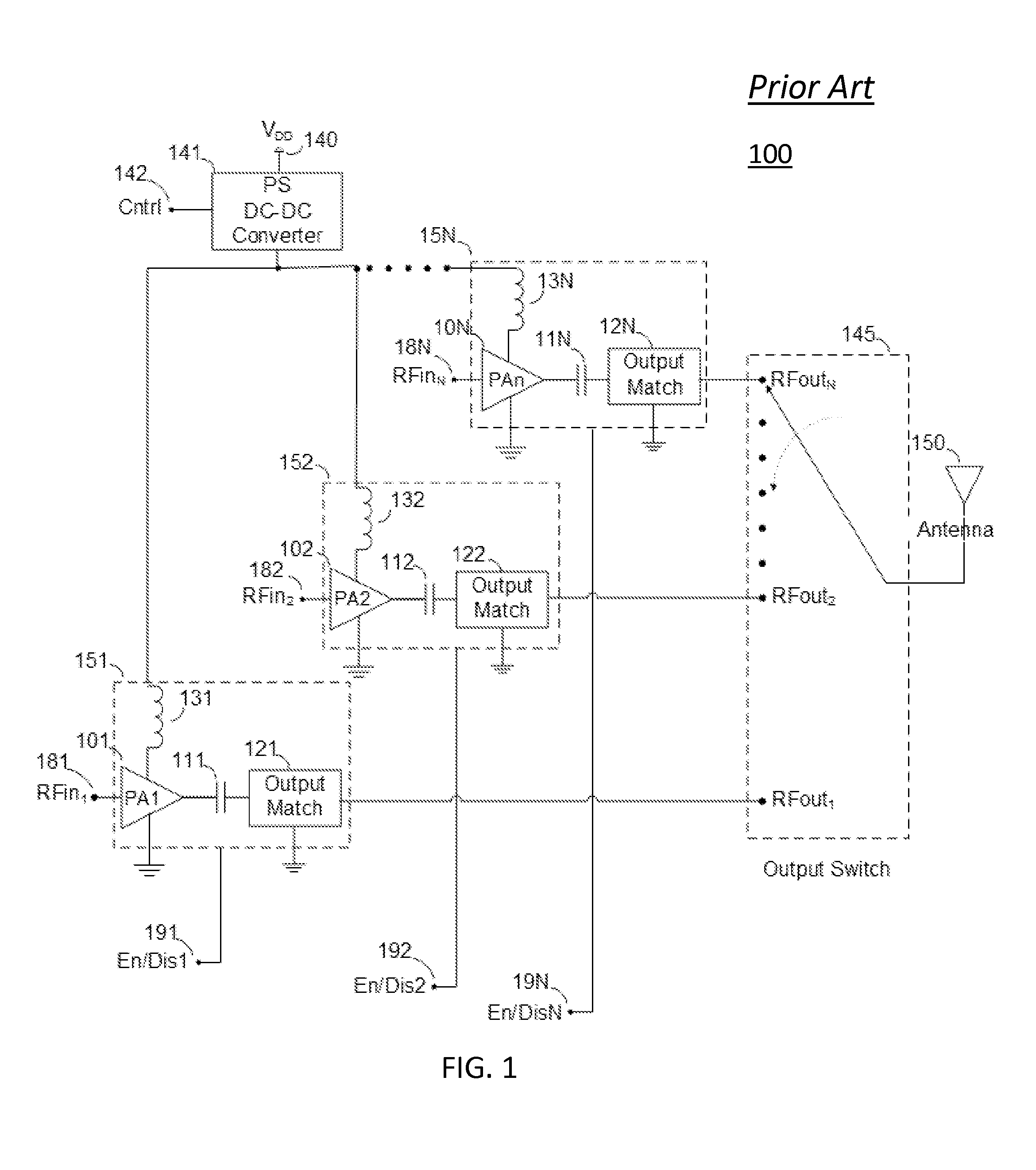

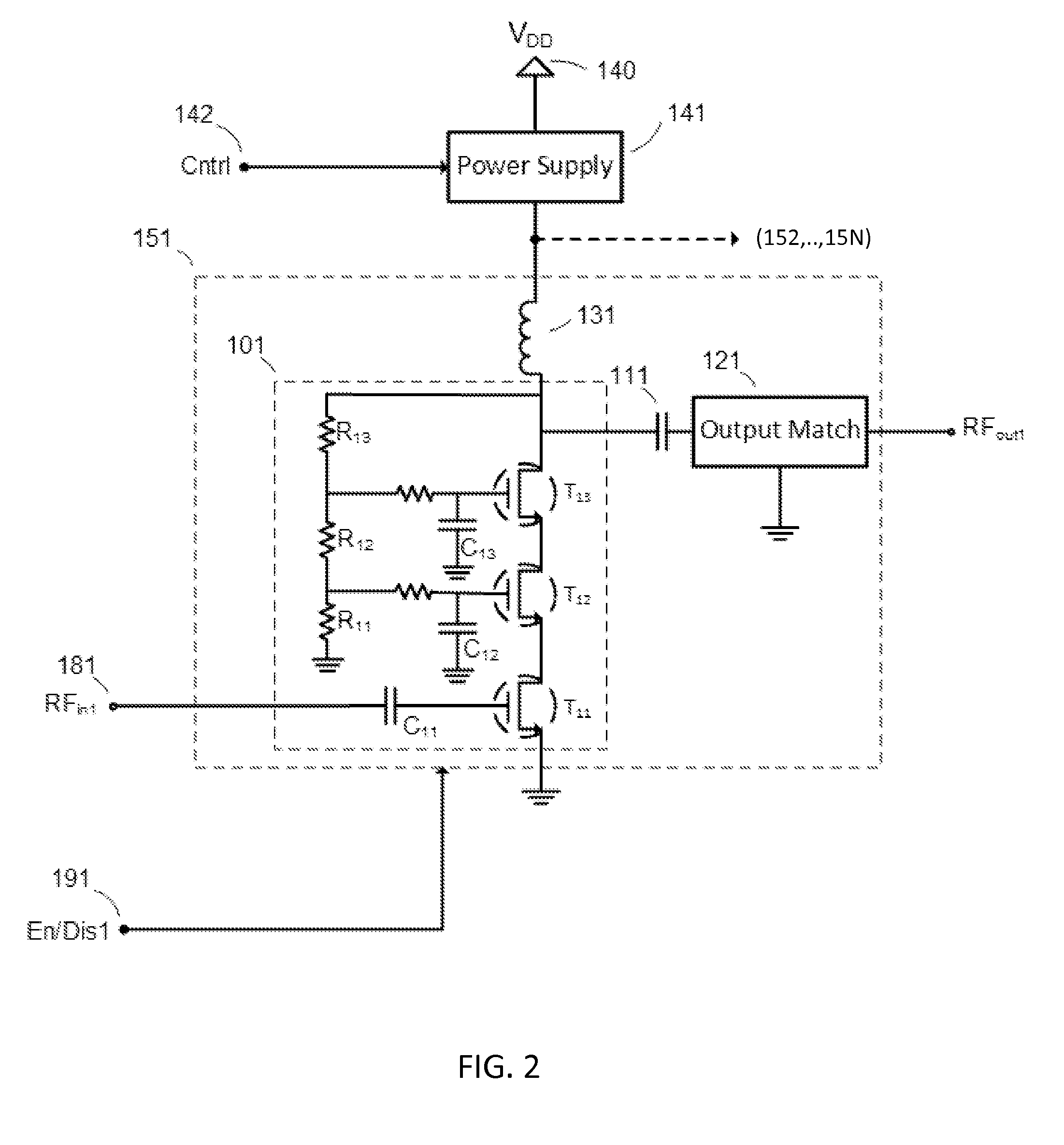

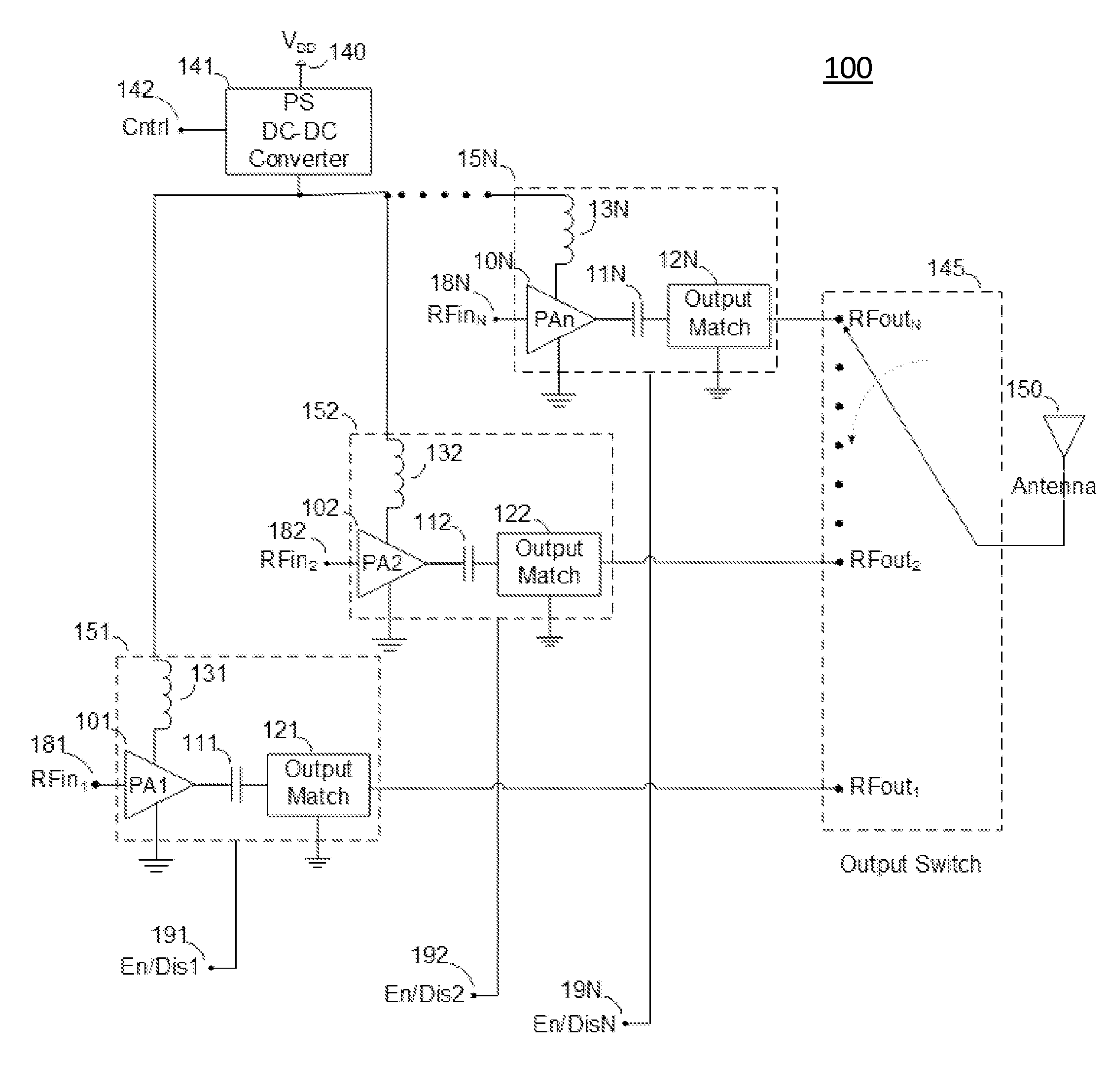

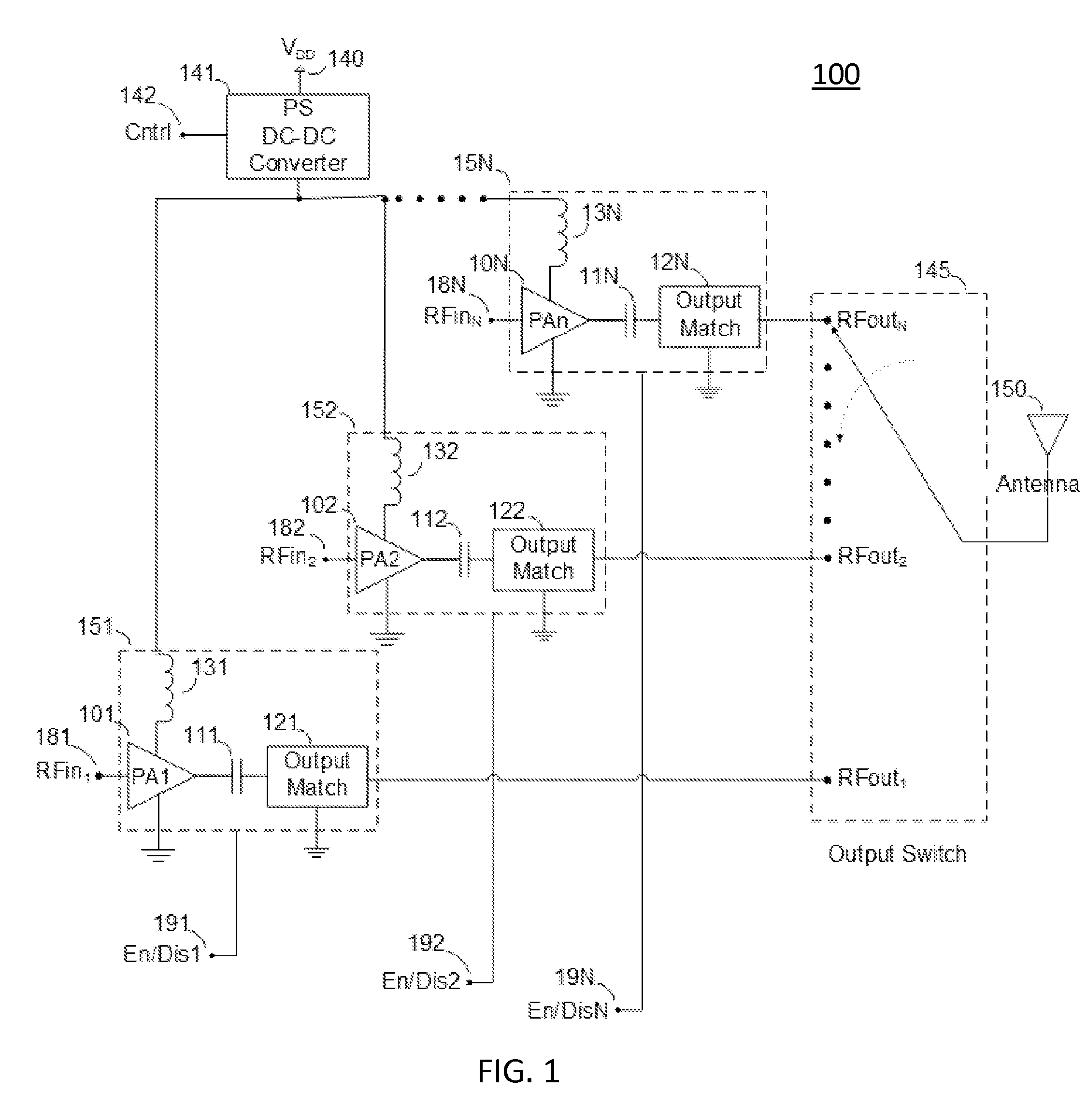

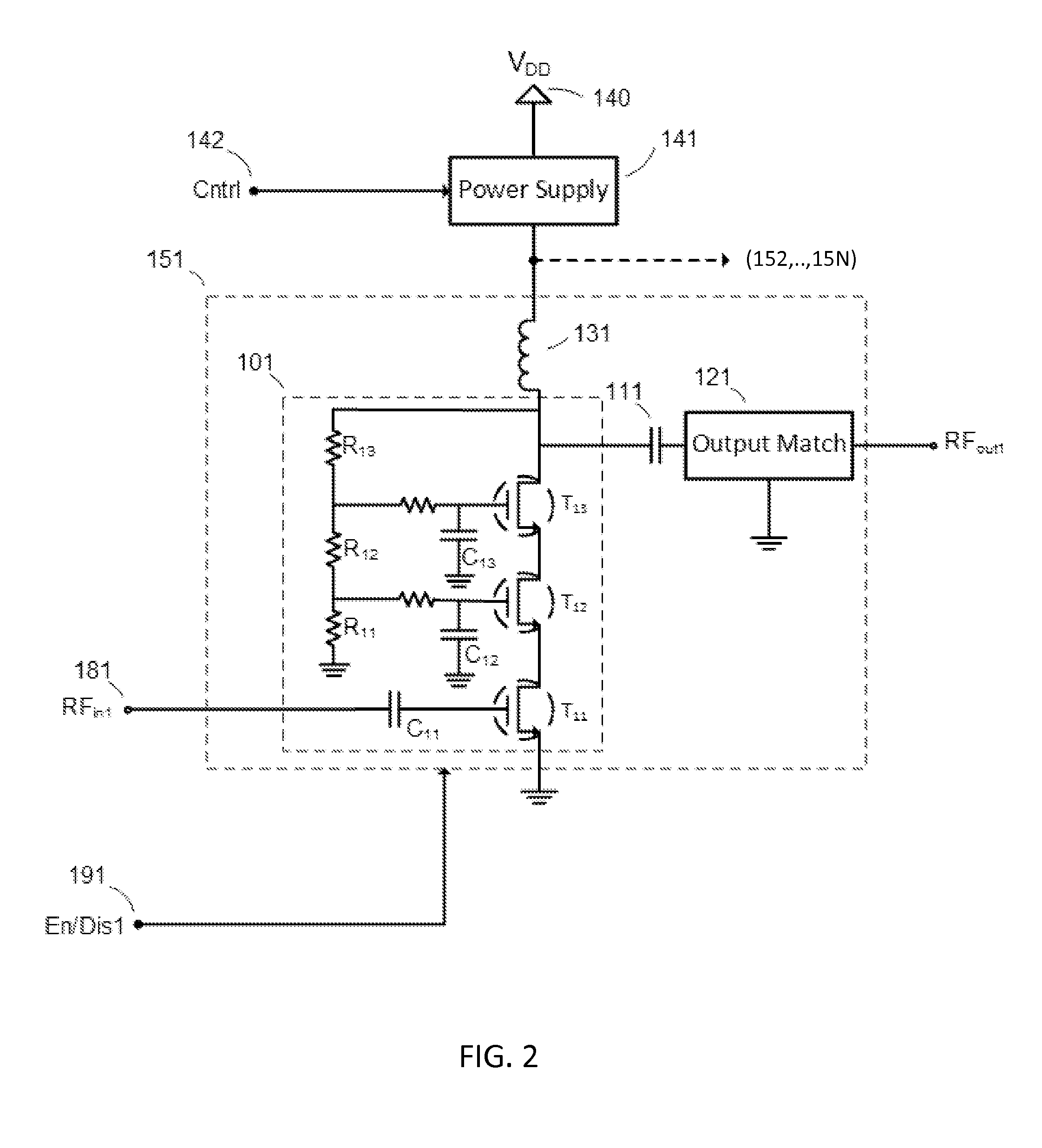

Load compensation in RF amplifiers

ActiveUS9160292B2Reduce power supplyReduce load effectHigh frequency amplifiersPower amplifiersRF power amplifierParasitic load

Methods and systems for reducing parasitic loading on a power supply output in RF amplifier arrangements used in multiband and / or multitude RF circuits are presented. Such RF circuits can comprise a plurality of RF amplifiers of which only one is activated for a given desired transmission mode and / or band.

Owner:PSEMI CORP

Load Compensation in RF Amplifiers

ActiveUS20150097624A1Reduce load effectReduce power supplyHigh frequency amplifiersPower amplifiersTransfer modeEngineering

Methods and systems for reducing parasitic loading on a power supply output in RF amplifier arrangements used in multiband and / or multitude RF circuits are presented. Such RF circuits can comprise a plurality of RF amplifiers of which only one is activated for a given desired transmission mode and / or band.

Owner:PSEMI CORP

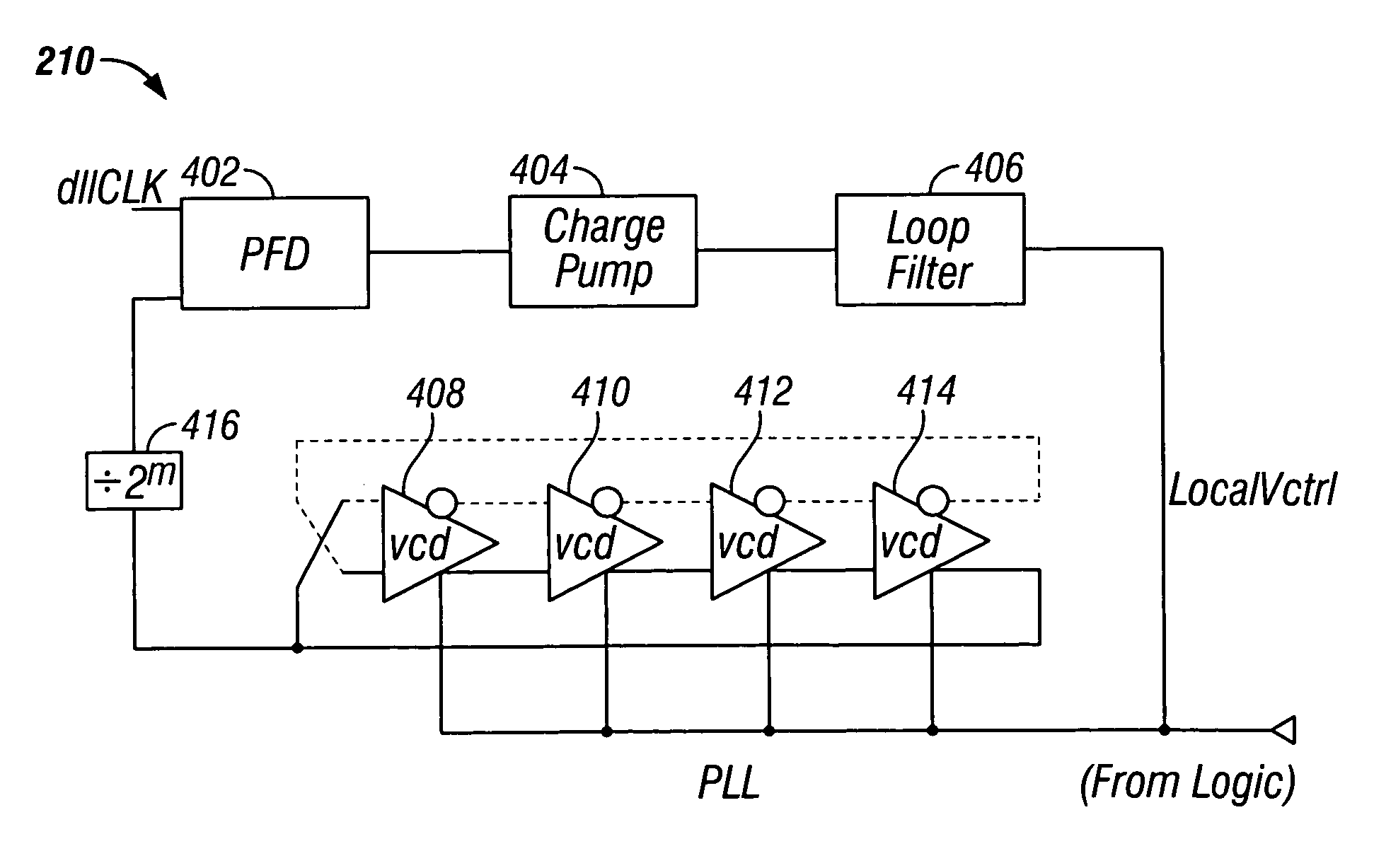

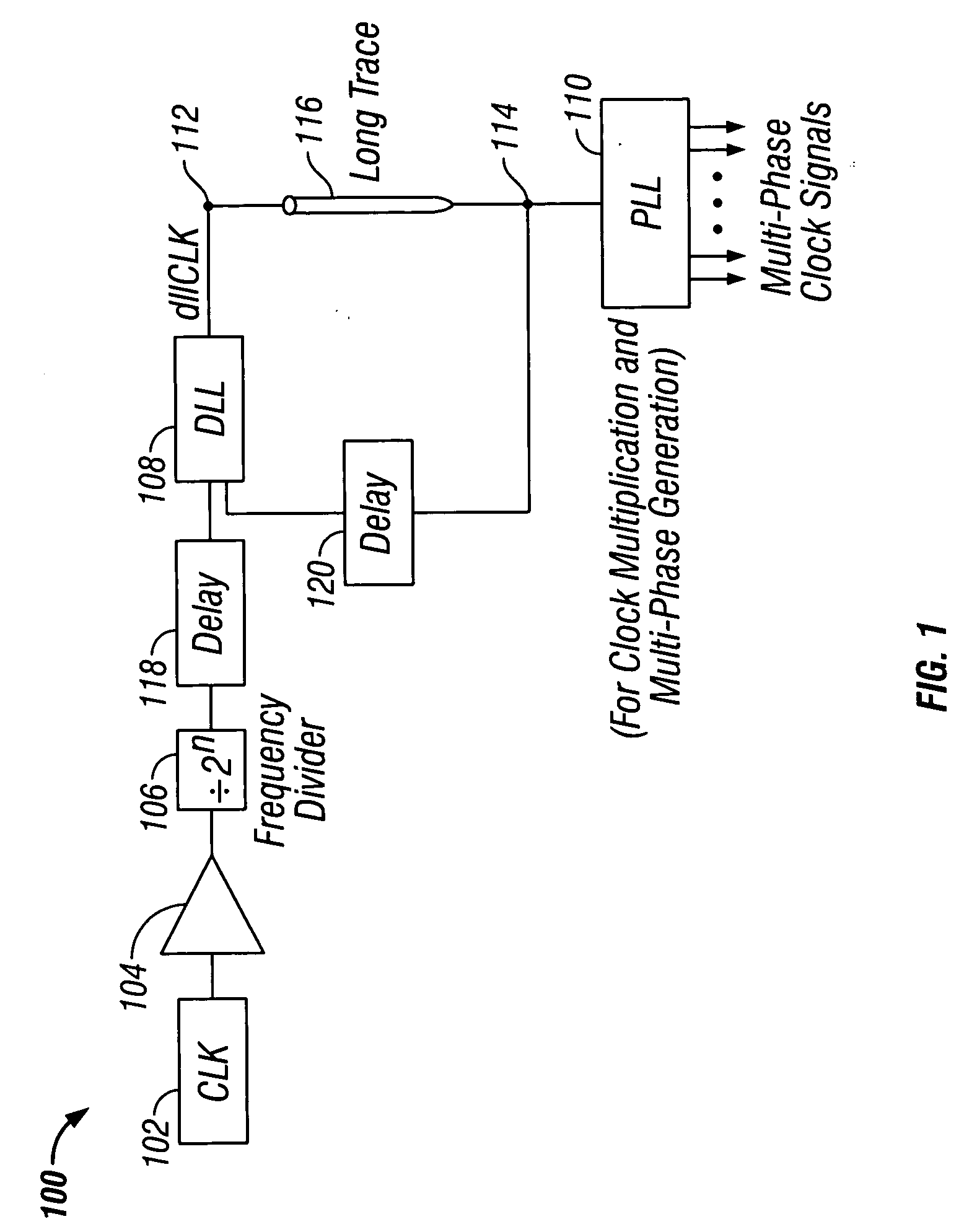

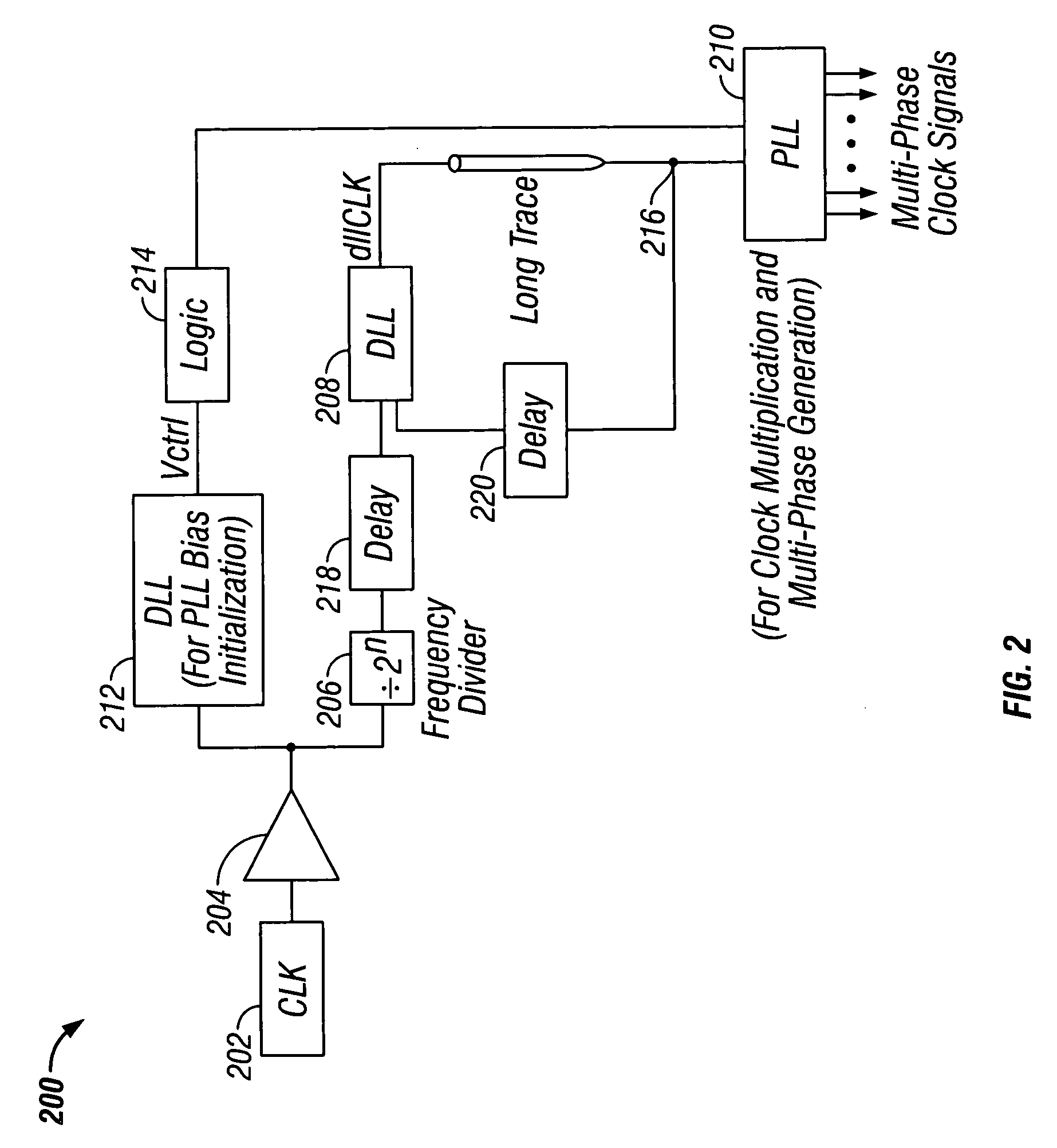

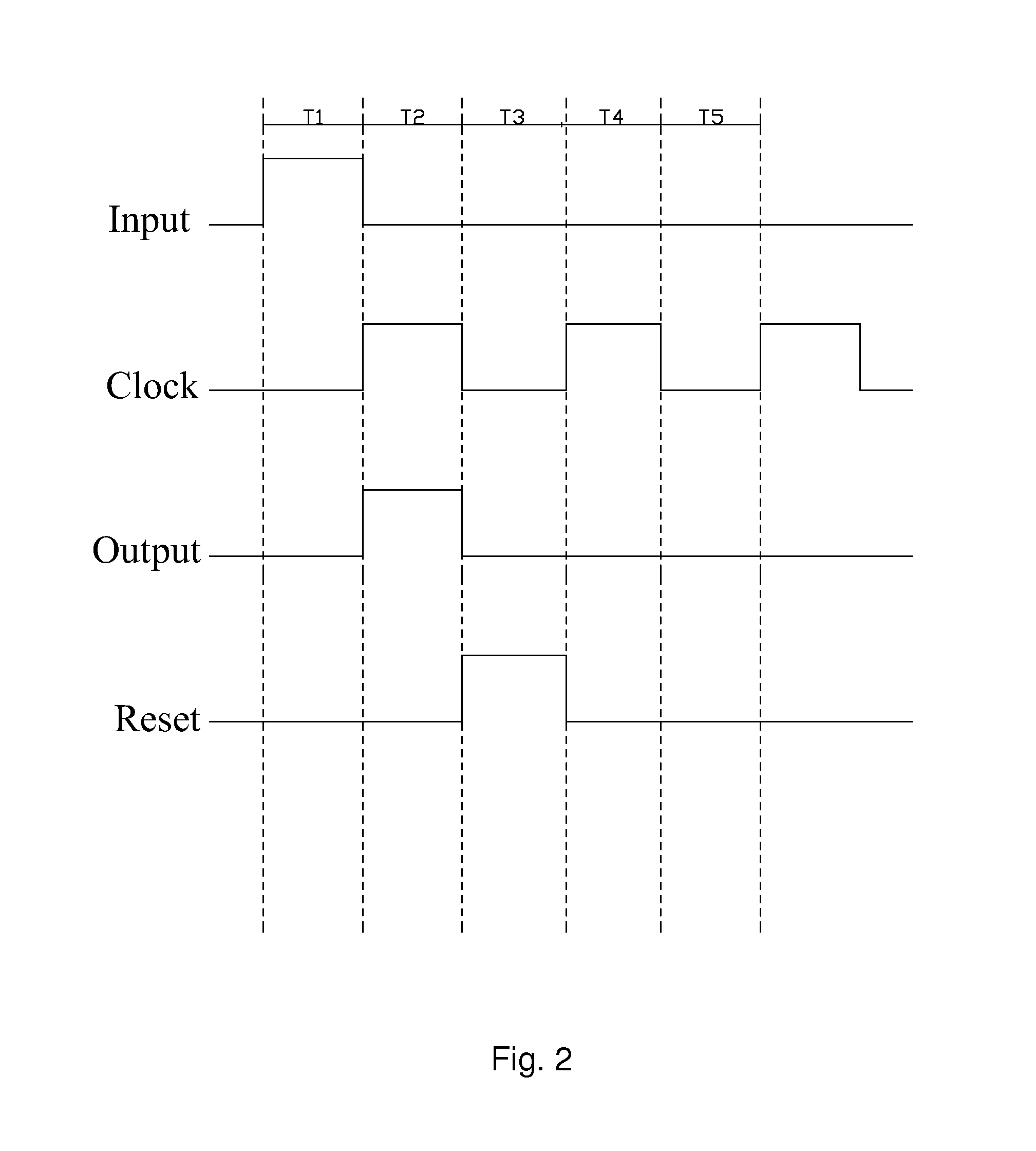

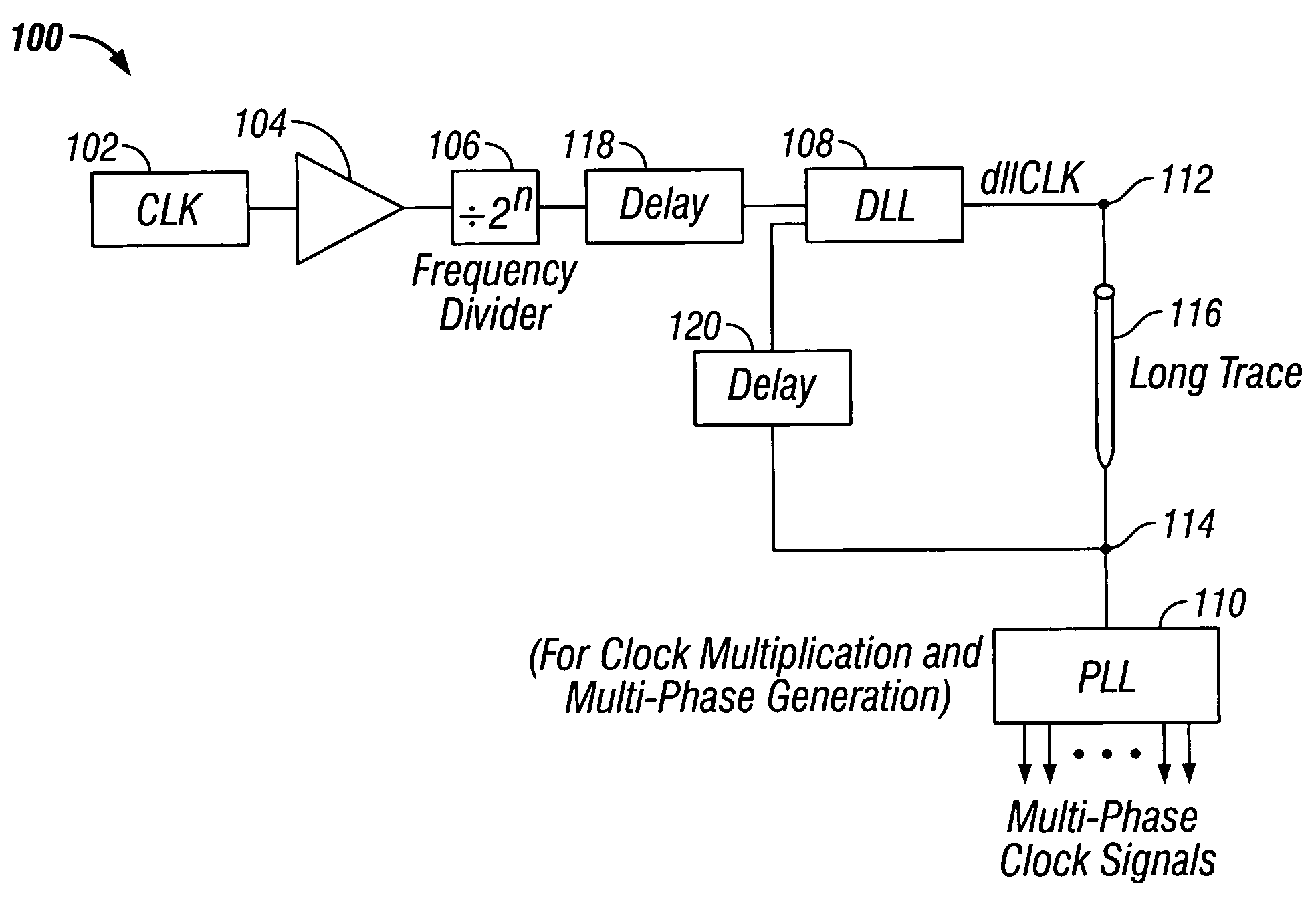

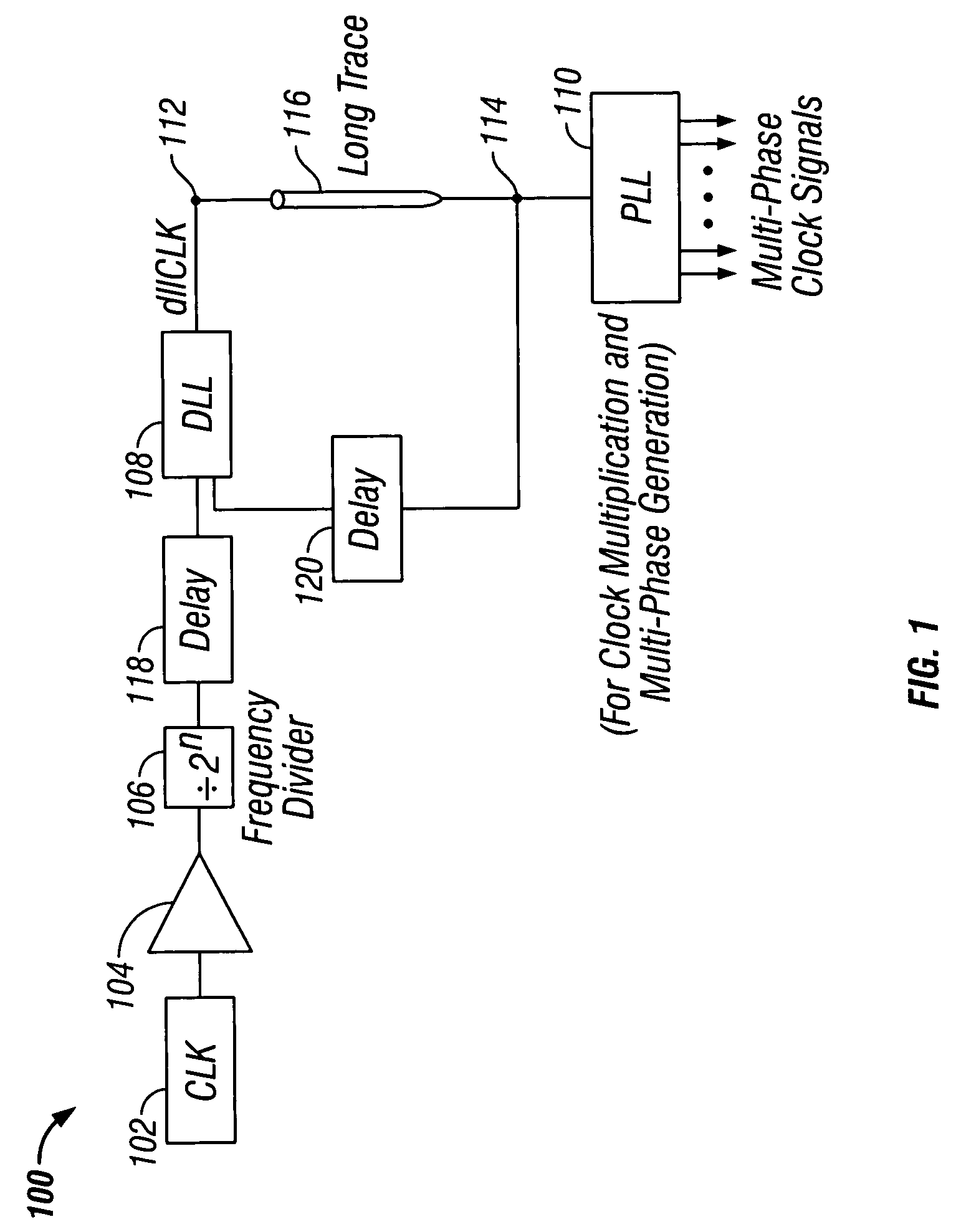

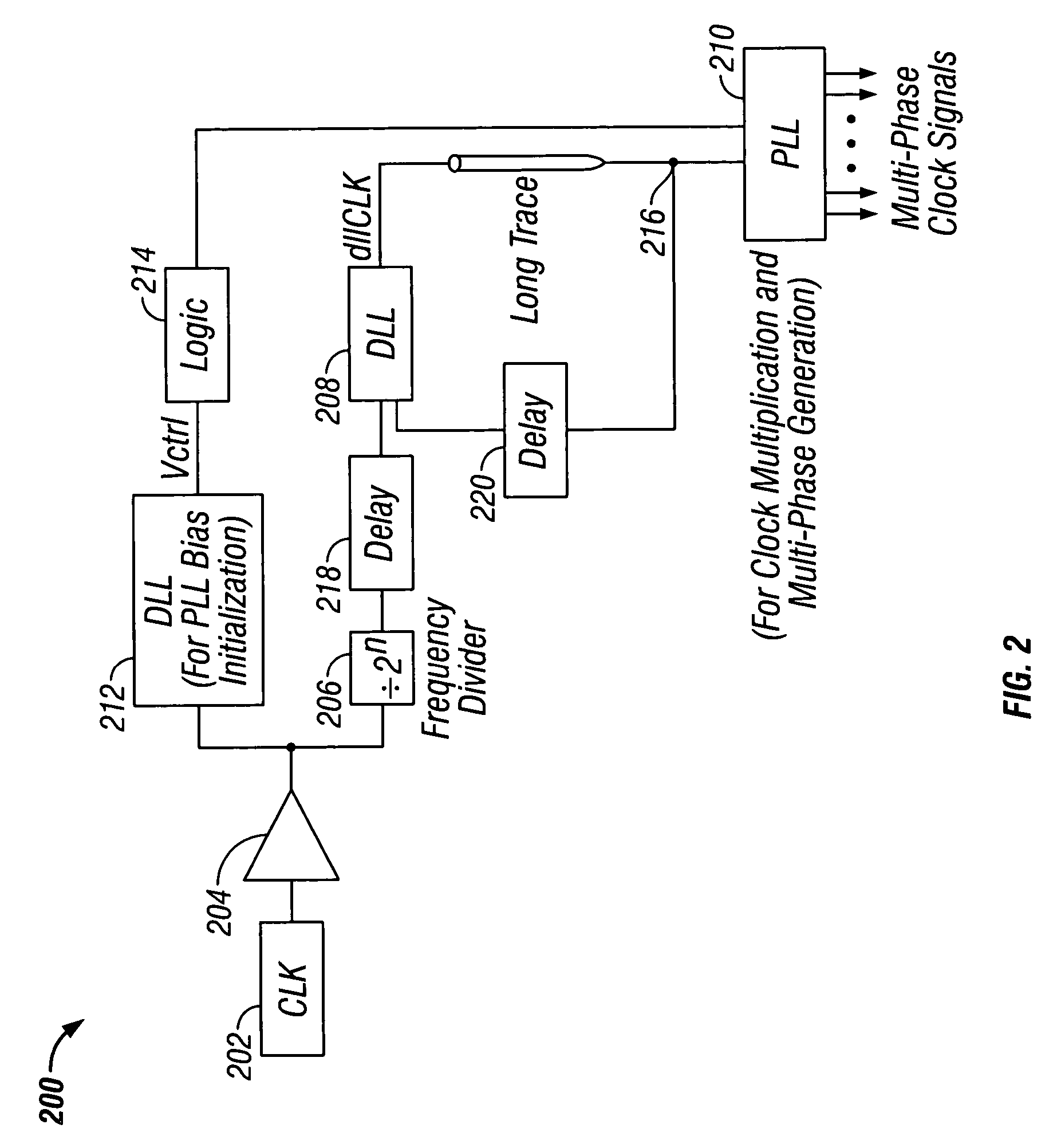

Clock signal distribution with reduced parasitic loading effects

ActiveUS20050134337A1Reduced parasitic loading effectReduce load effectPulse automatic controlGenerating/distributing signalsDelay-locked loopDistribution system

Clock signal distribution systems with reduced parasitic loading effects are provided. A reference clock is frequency-divided to produce a lower frequency clock signal. A delay-locked loop (DLL) circuit locks to the lower frequency clock signal, and outputs a corresponding lower frequency clock signal for distribution over a long trace. Power consumption caused by parasitic capacitance of the trace is thereby reduced. Parasitic effects associated with clock jitter are also reduced. A frequency multiplying phase-locked loop (PLL) circuit locks to the lower frequency clock signal, and outputs at least one clock signal having a higher frequency than the lower frequency signal.

Owner:MICRON TECH INC

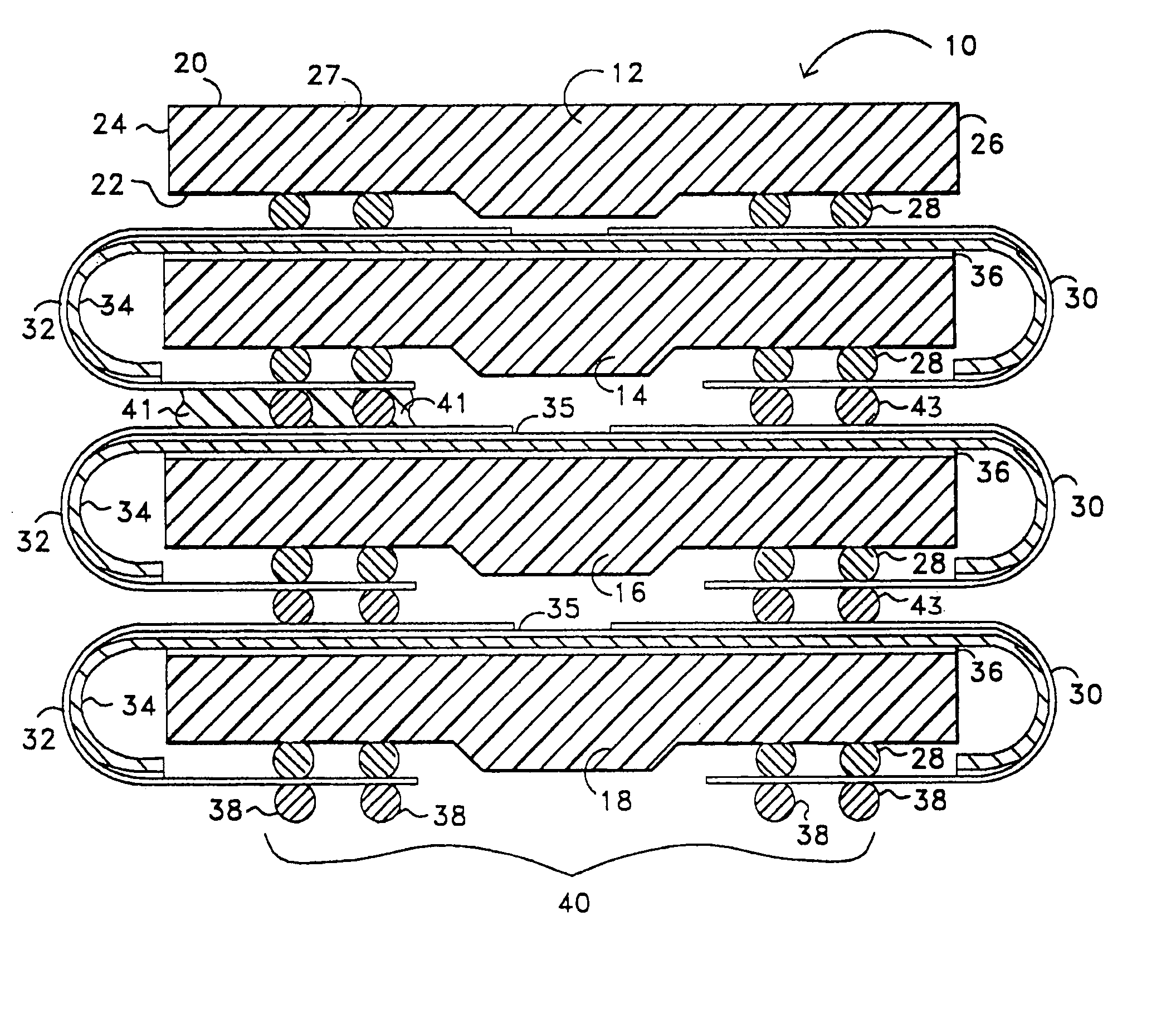

Memory expansion and integrated circuit stacking system and method

ActiveUS20050057911A1Improve thermal efficiencyReduced footprintElectrically conductive connectionsSemiconductor/solid-state device detailsMemory addressCapacitance

The present invention stacks integrated circuits (ICs) into modules that conserve PWB or other board surface area. In another aspect, the invention provides a lower capacitance memory expansion addressing system and method and preferably with the CSP stacked modules provided herein. In a preferred embodiment in accordance with the invention, a form standard provides a physical form that allows many of the varying package sizes found in the broad family of CSP packages to be used to advantage while employing a standard connective flex circuitry design. In a preferred embodiment, the form standard will be devised of heat transference material such as copper to improve thermal performance. In a preferred embodiment of the memory addressing system, a high speed switching system selects a data line associated with each level of a stacked module to reduce the loading effect upon data signals in memory access.

Owner:TAMIRAS PER PTE LTD LLC

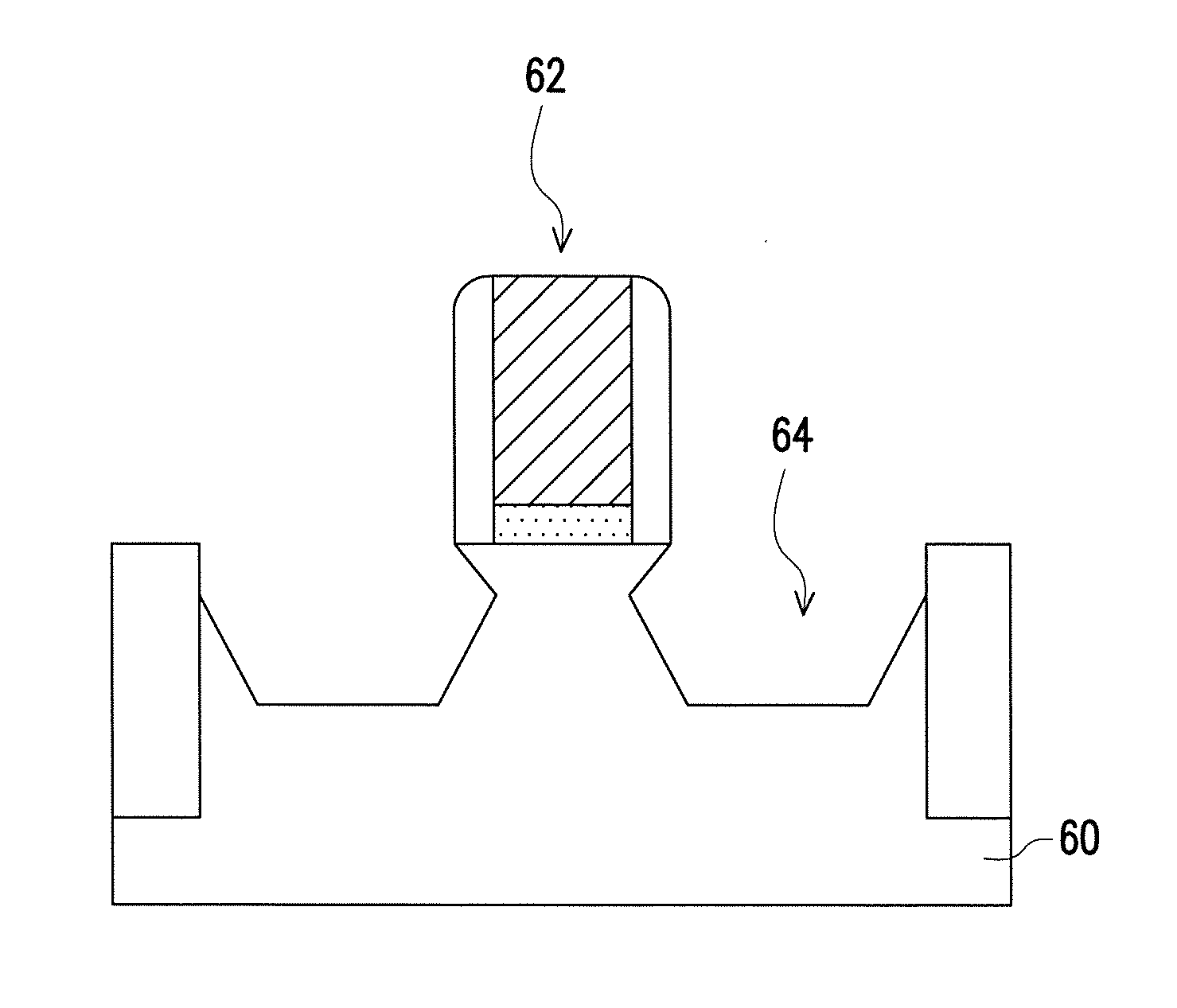

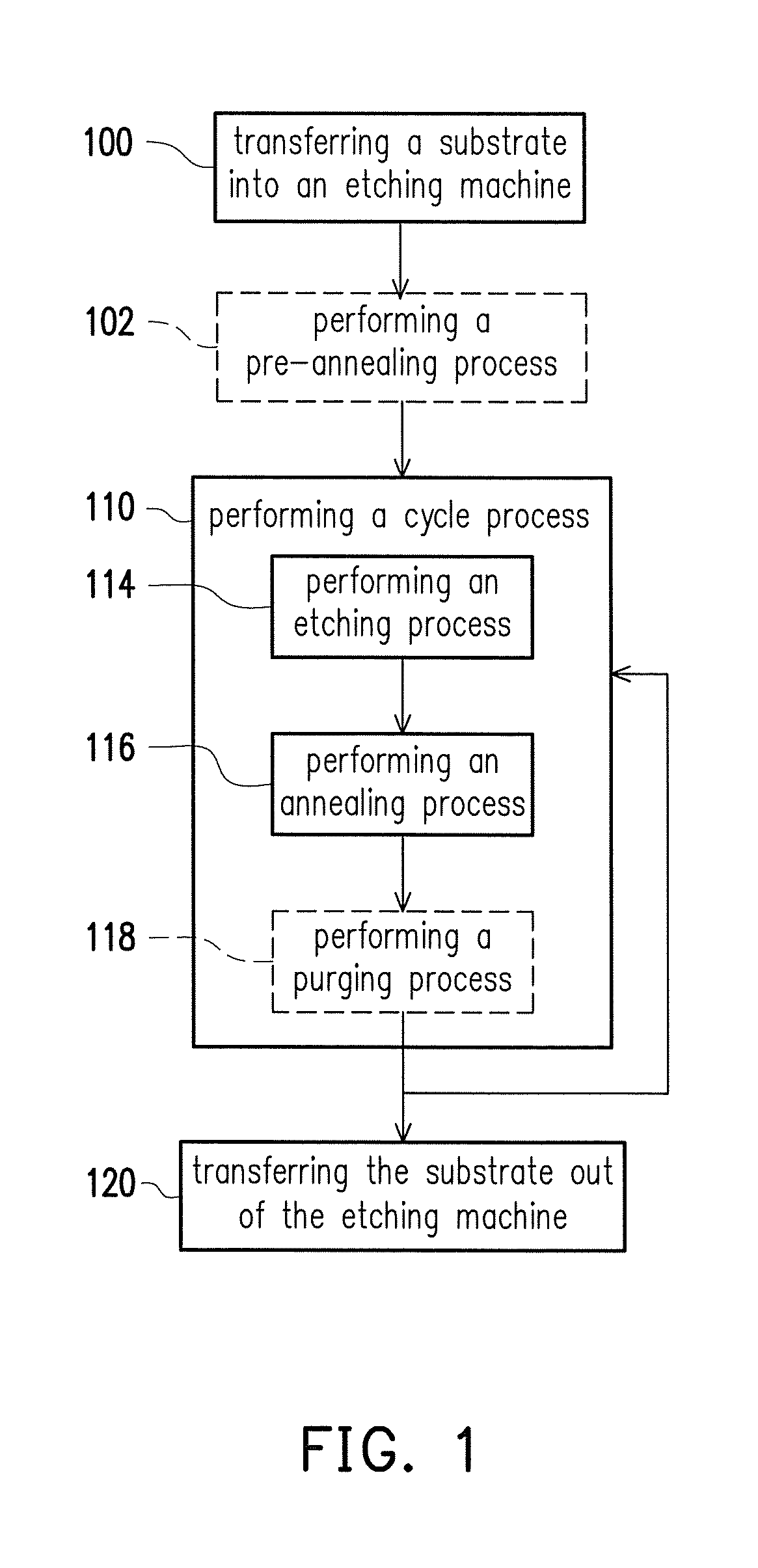

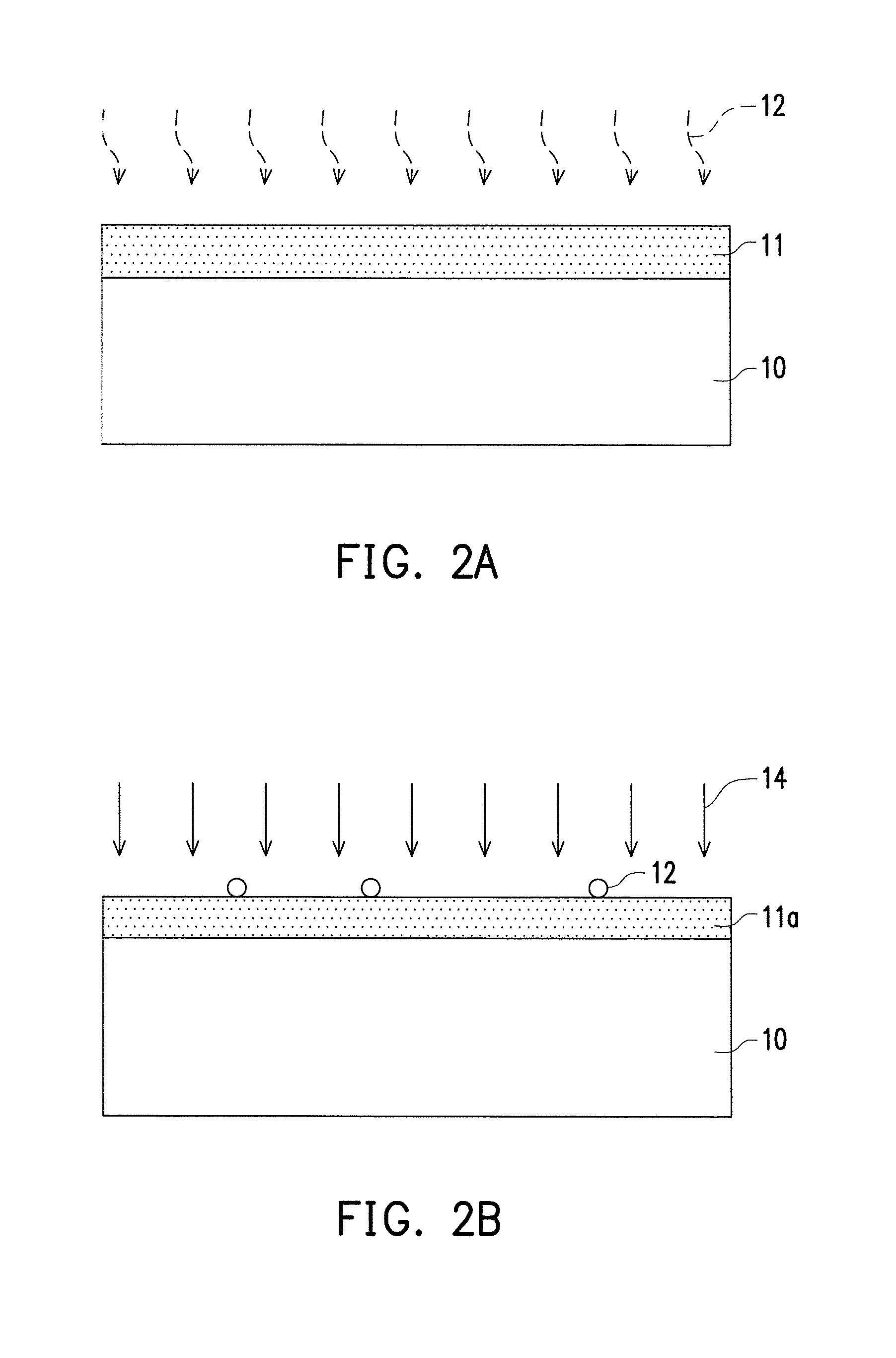

Removing method

ActiveUS20150044879A1Effectively remove the material layerReduce load effectSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringBy-product

A removing method including the following steps. A substrate is transferred into an etching machine, wherein the substrate has a material layer formed thereon. A cycle process is performed. The cycle process includes performing an etching process to remove a portion of the material layer, and performing an annealing process to remove a by-product generated by the etching process. The cycle process is repeated at least one time. The substrate is transferred out of the etching machine. In the removing method of the invention, the cycle process is performed multiple times to effectively remove the undesired thickness of the material layer and reduce the loading effect.

Owner:UNITED MICROELECTRONICS CORP

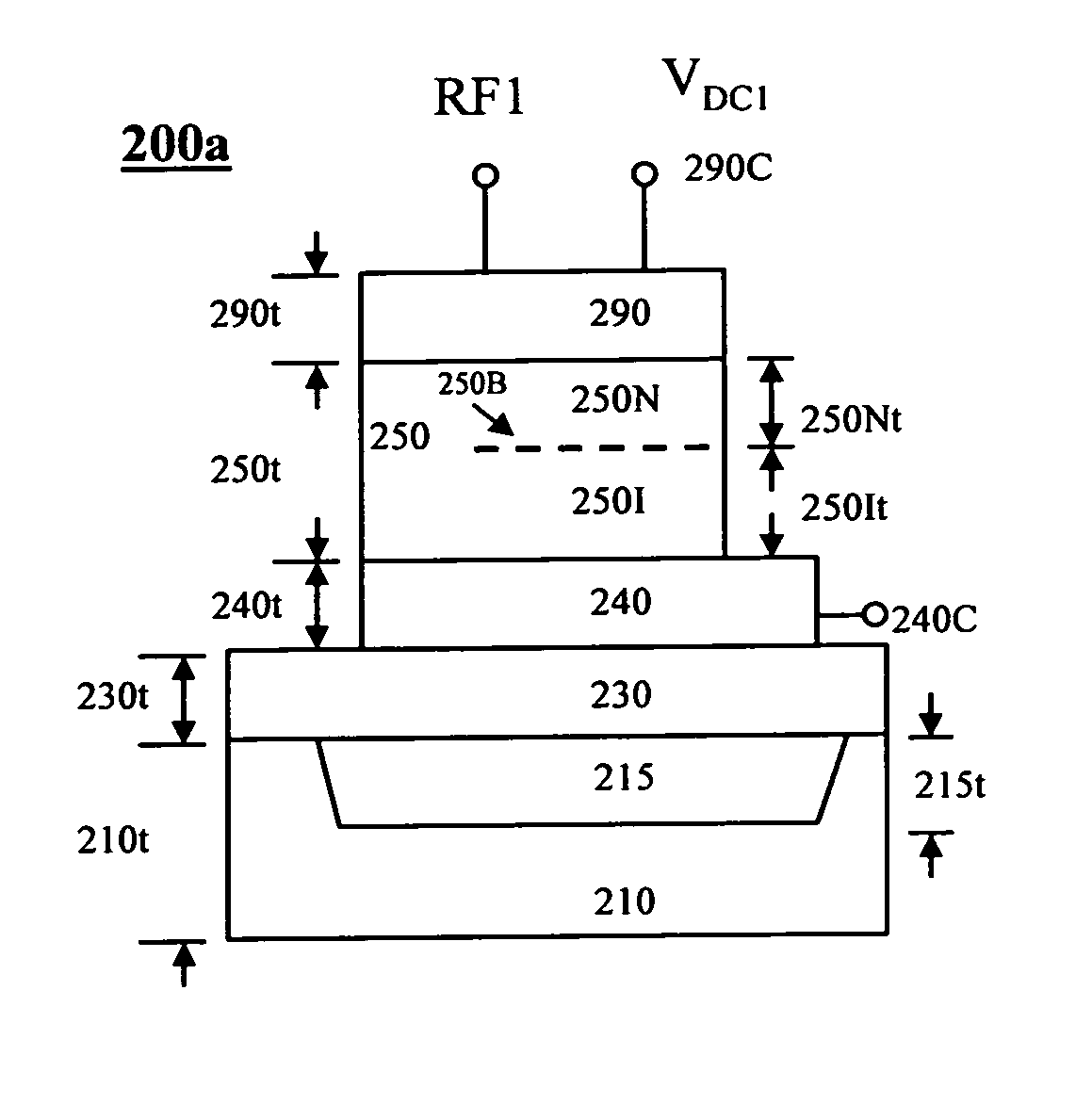

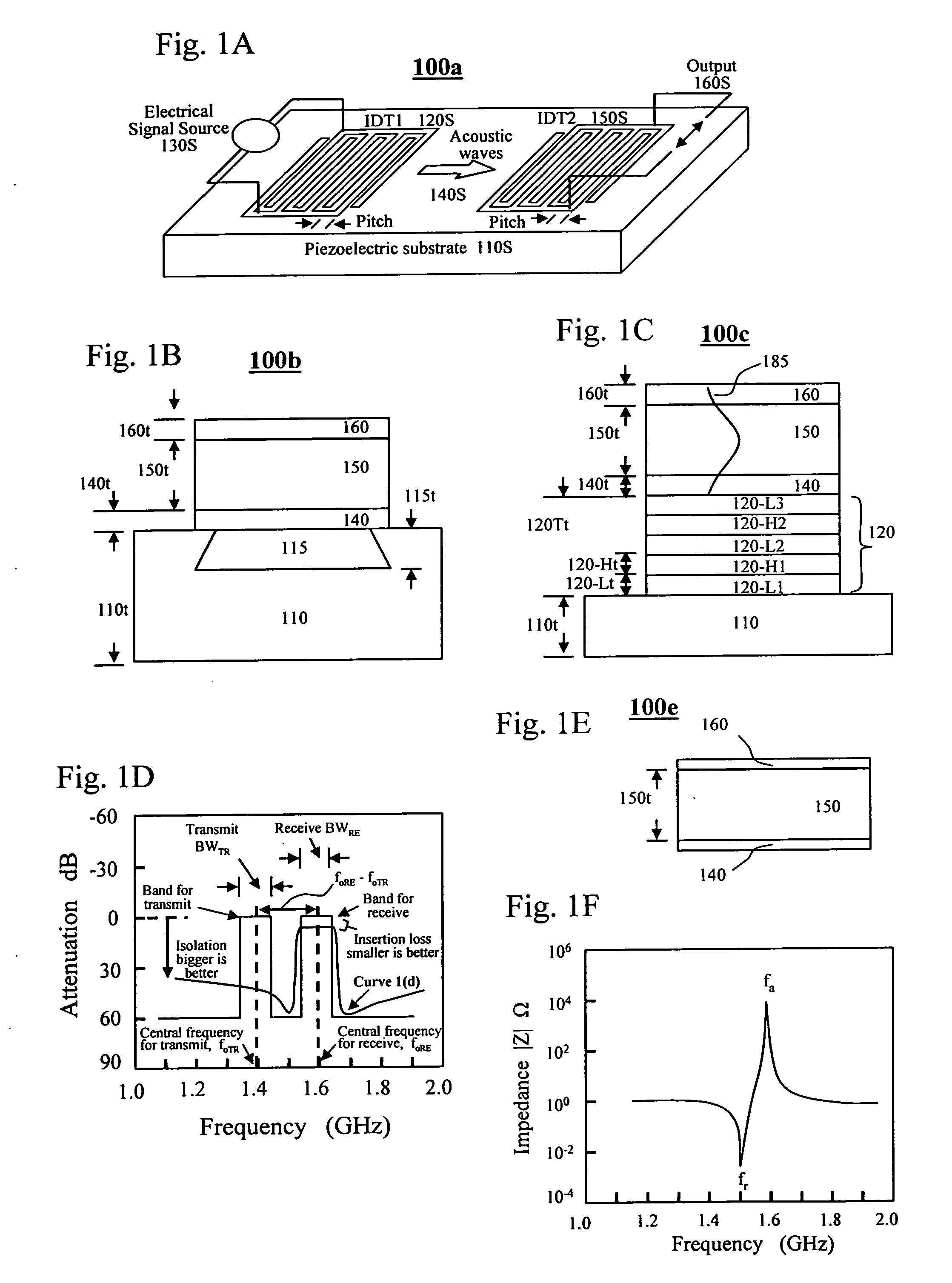

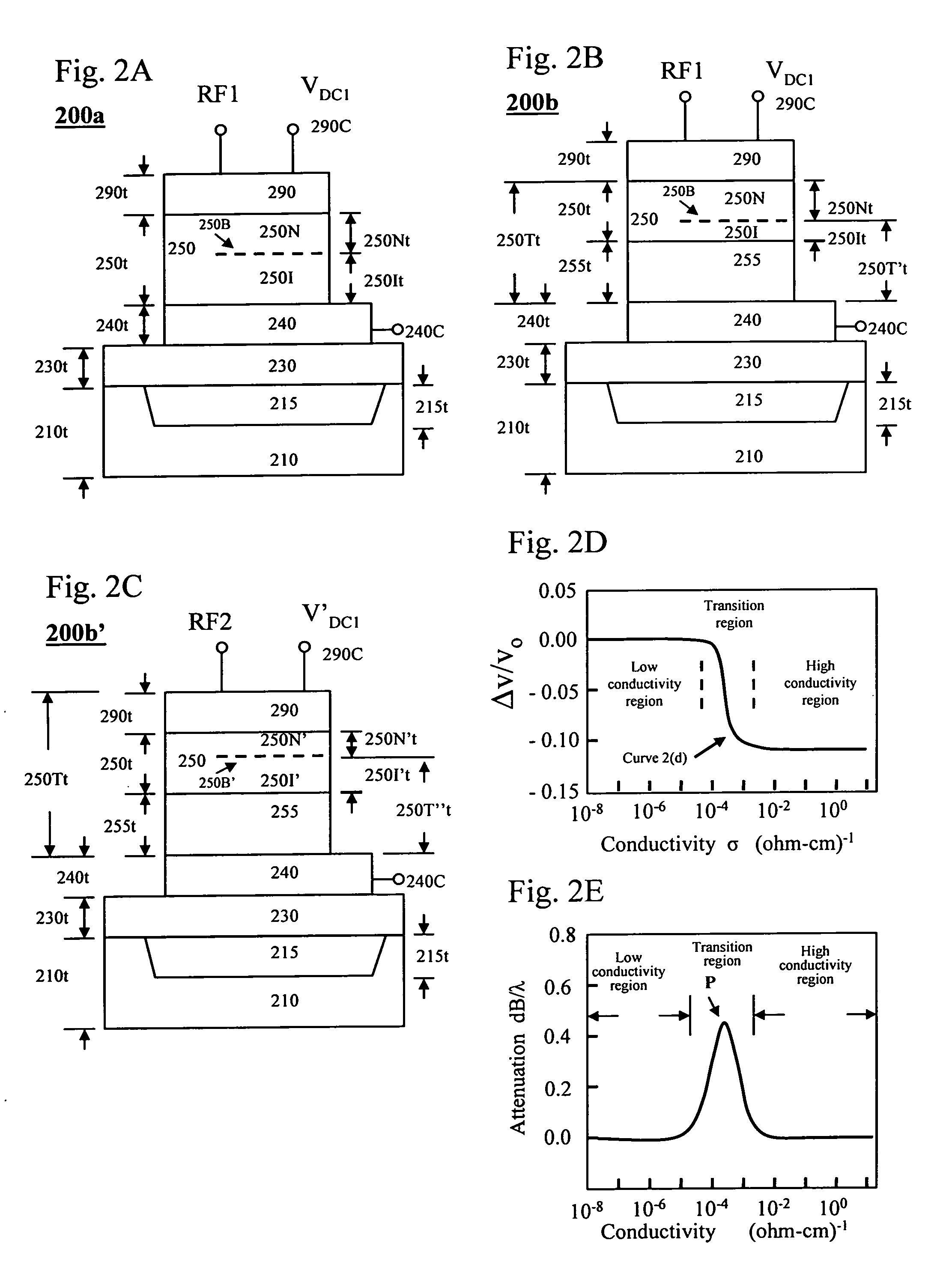

Tunable film bulk acoustic resonators and filters

ActiveUS20170025596A1Decrease in piezoelectric active layer thicknessReduce load effectImpedence networksPiezoelectric/electrostrictive/magnetostrictive devicesCommunication unitResonance

In wireless communications, many radio frequency bands are used. For each frequency band, there are two frequencies, one for transmitting and the other for receiving. As the band widths are small and separation between adjacent bands is also small, many band pass filters with different band pass frequencies are required for each communication unit such as mobile handset. The invention provides tunable film bulk acoustic resonators TFBARs containing semiconducting piezoelectric layers and methods for tuning and adjusting the resonant properties. When a DC biasing voltage is varied, both the depletion region thickness and neutral region thickness associated in the semiconducting piezoelectric layers varies leading to changes in equivalent capacitances, inductance and resistances and hence the resonance properties and frequencies. A plurality of the present TFBARs are connected into a tunable oscillator or a tunable and selectable microwave filter for selecting and adjusting of the bandpass frequency by varying the biasing voltages.

Owner:QIU CINDY X +5

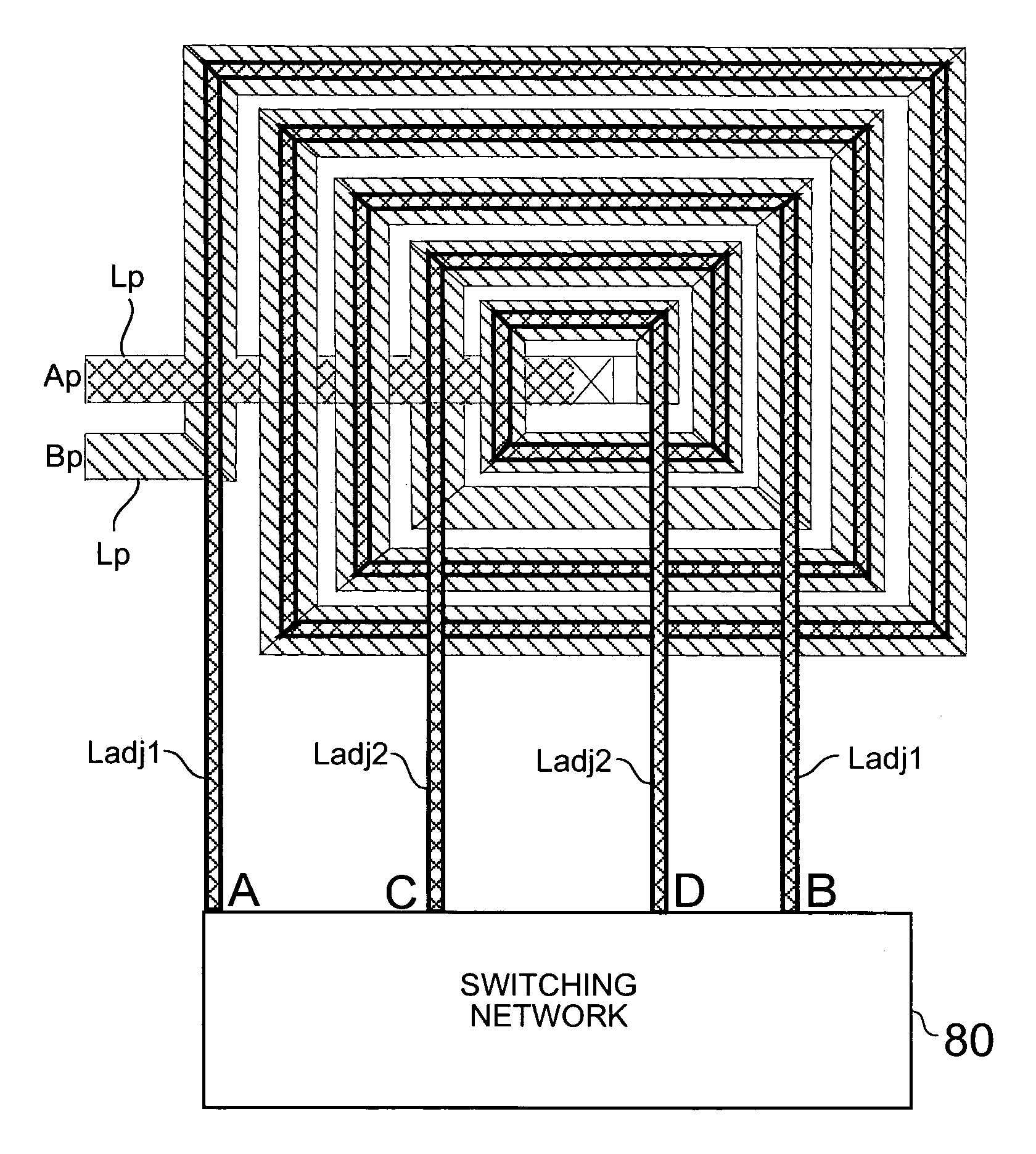

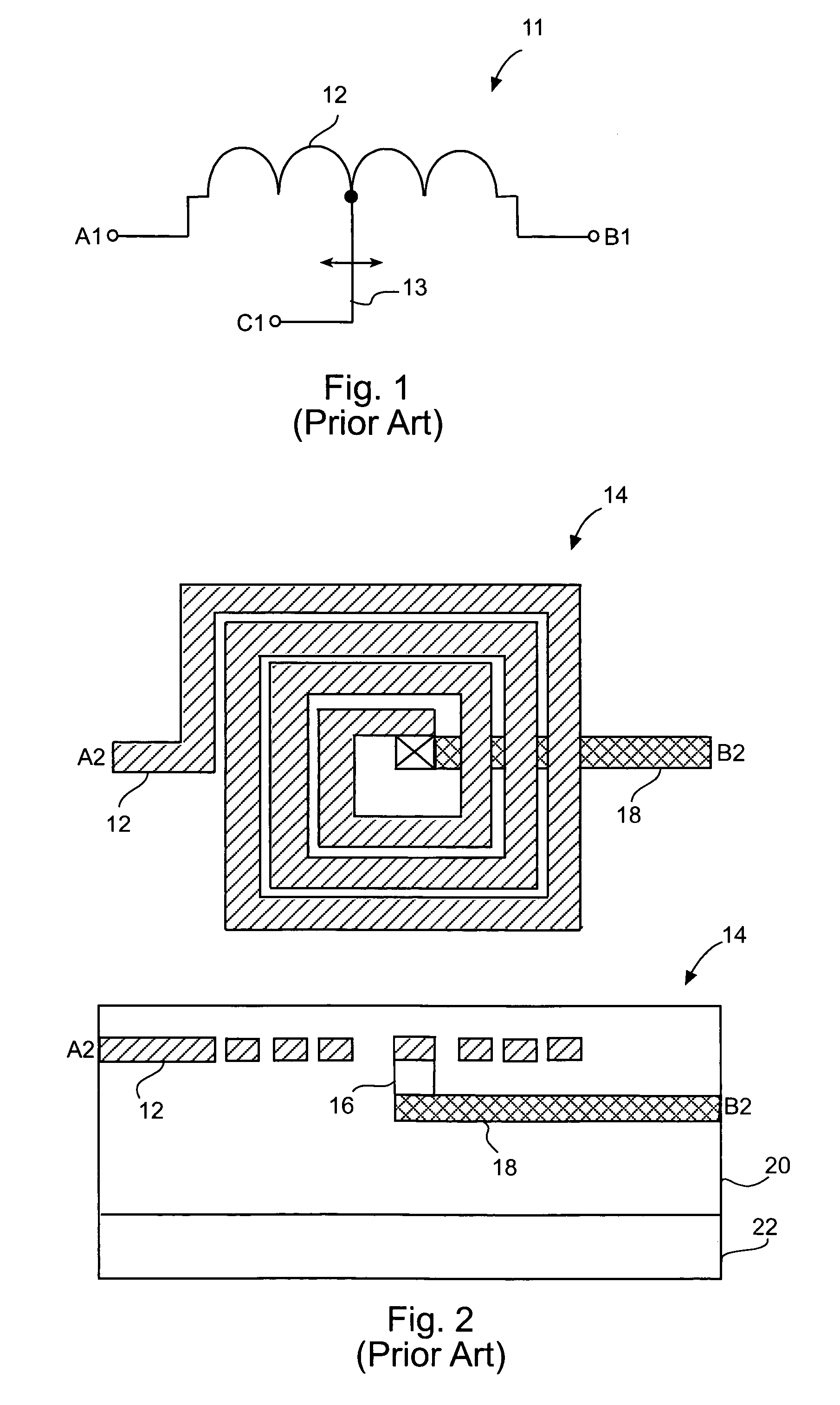

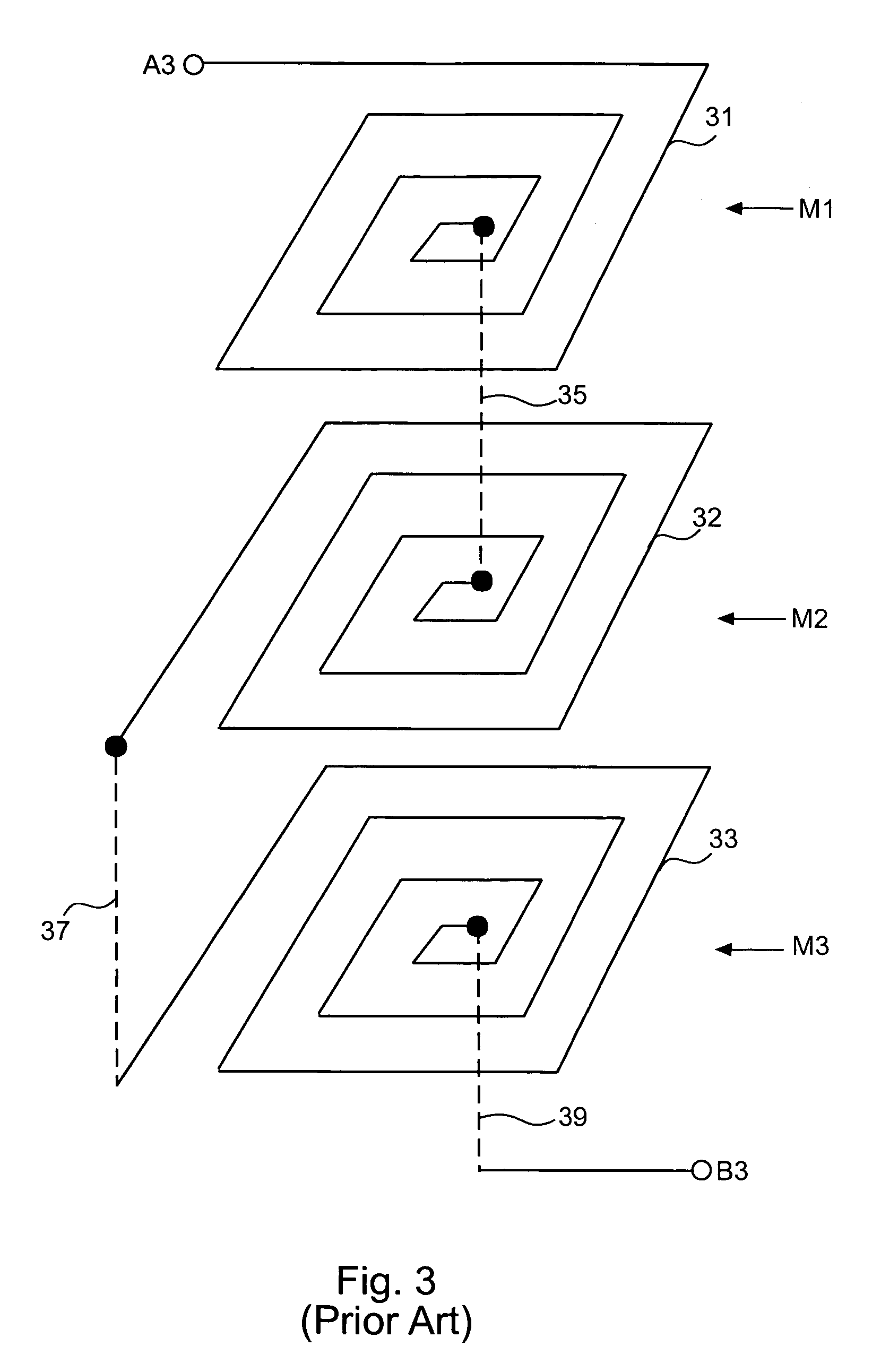

Variable inductor technique

InactiveUS7598838B2Increased and decreasedReduce load effectMultiple-port networksResonant circuit tuningClosed loopEngineering

An integrated variable inductor is achieved by placing a second closed-loop inductor immediately above or below a primary inductor. The closed-loop configuration of the second inductor may be broken on-chip by several ways, including use of a transistor to selectively short together both ends of the second inductor. If one wishes to alter the inherent inductance characteristics of the primary inductor, the transistor coupling both ends of the second inductor is actuated. Thus, a current applied to the primary inductor induces a current in the second inductor by inductive coupling. The second current in the second inductor then alters the impedance of the primary inductor by mutual inductance. Thus, the inductance value of the primary inductor is altered. To remove the influence of the second inductor on the primary inductor, the closed-loop configuration of the second inductor is broken.

Owner:138 EAST LCD ADVANCEMENTS LTD

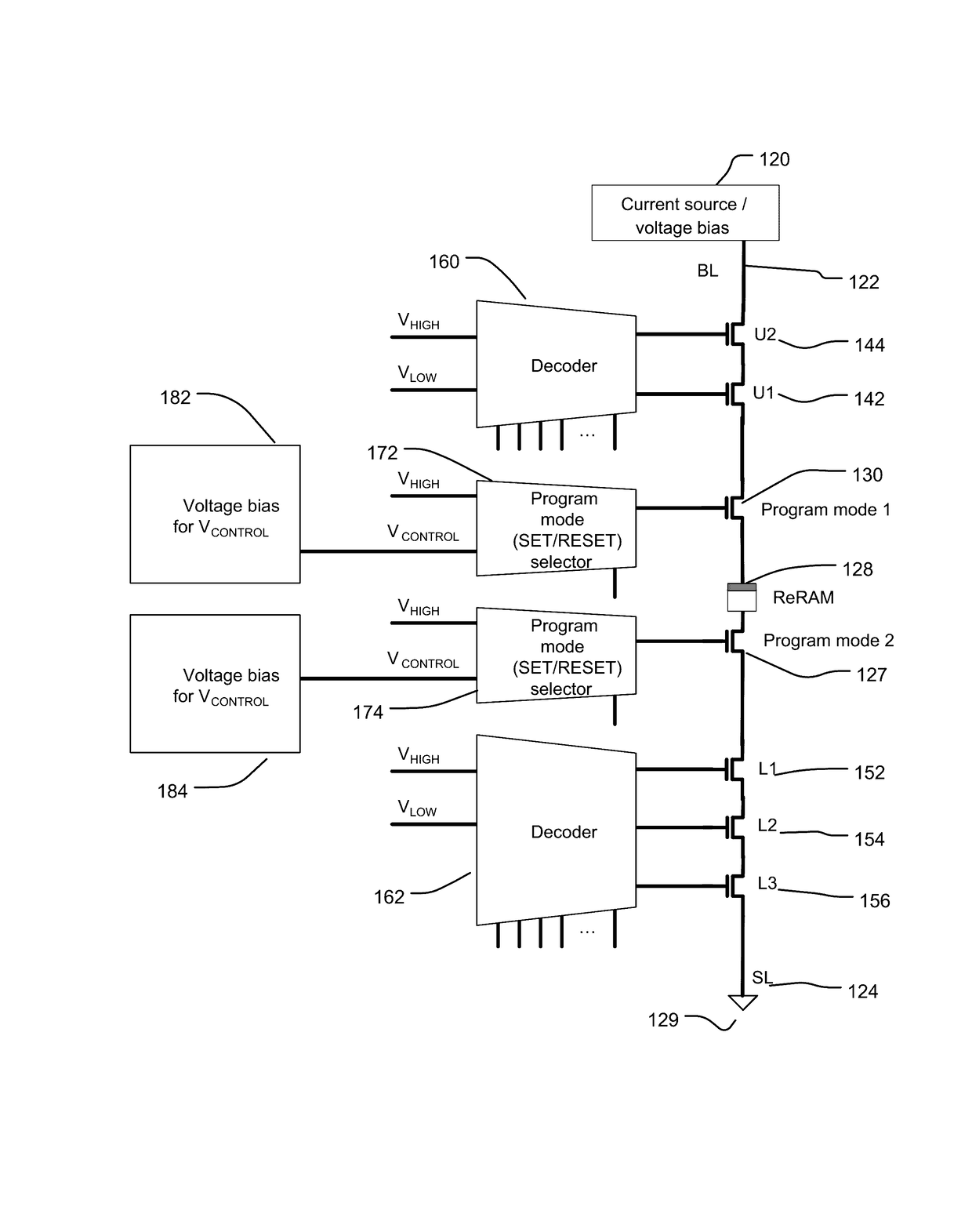

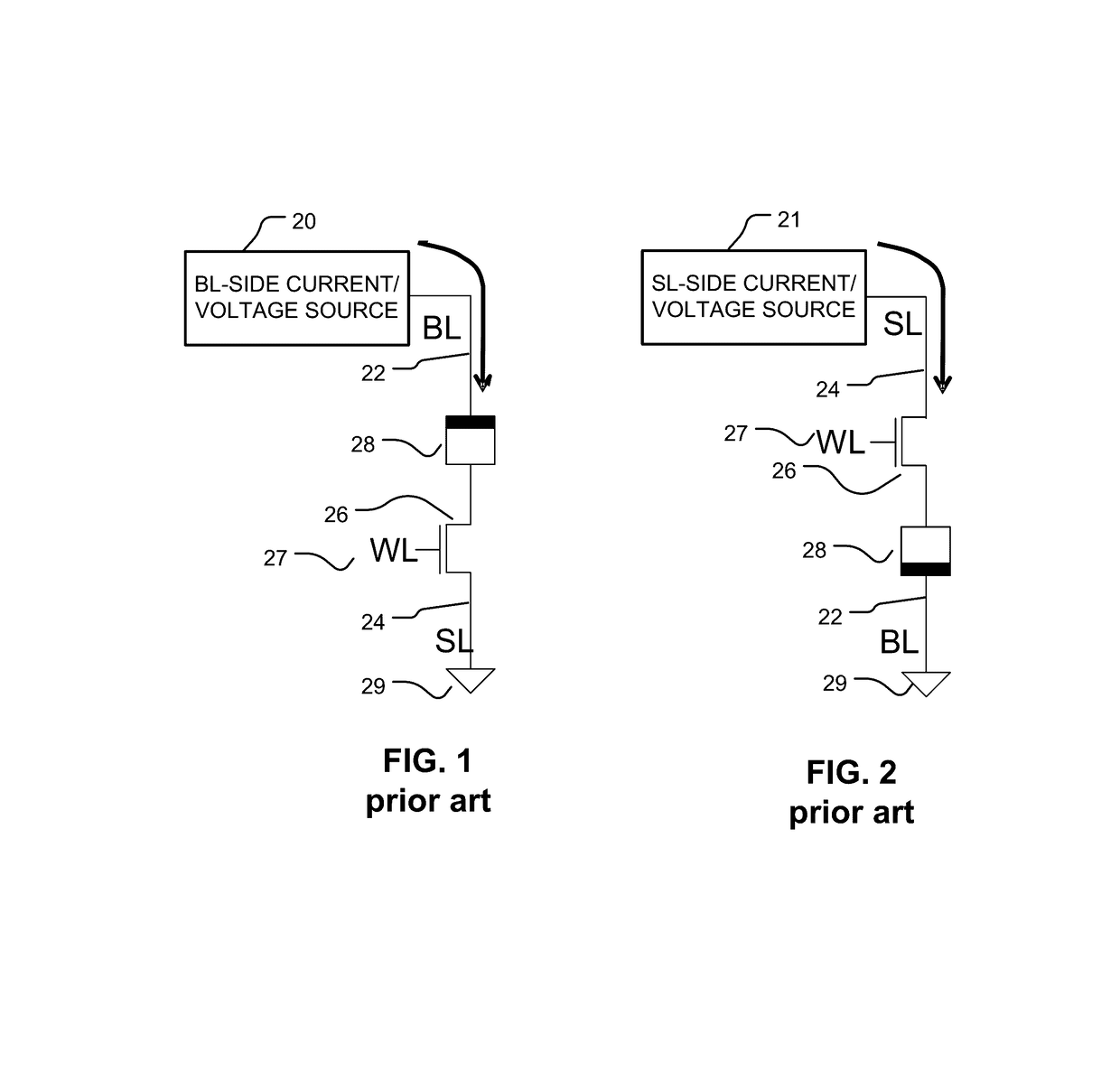

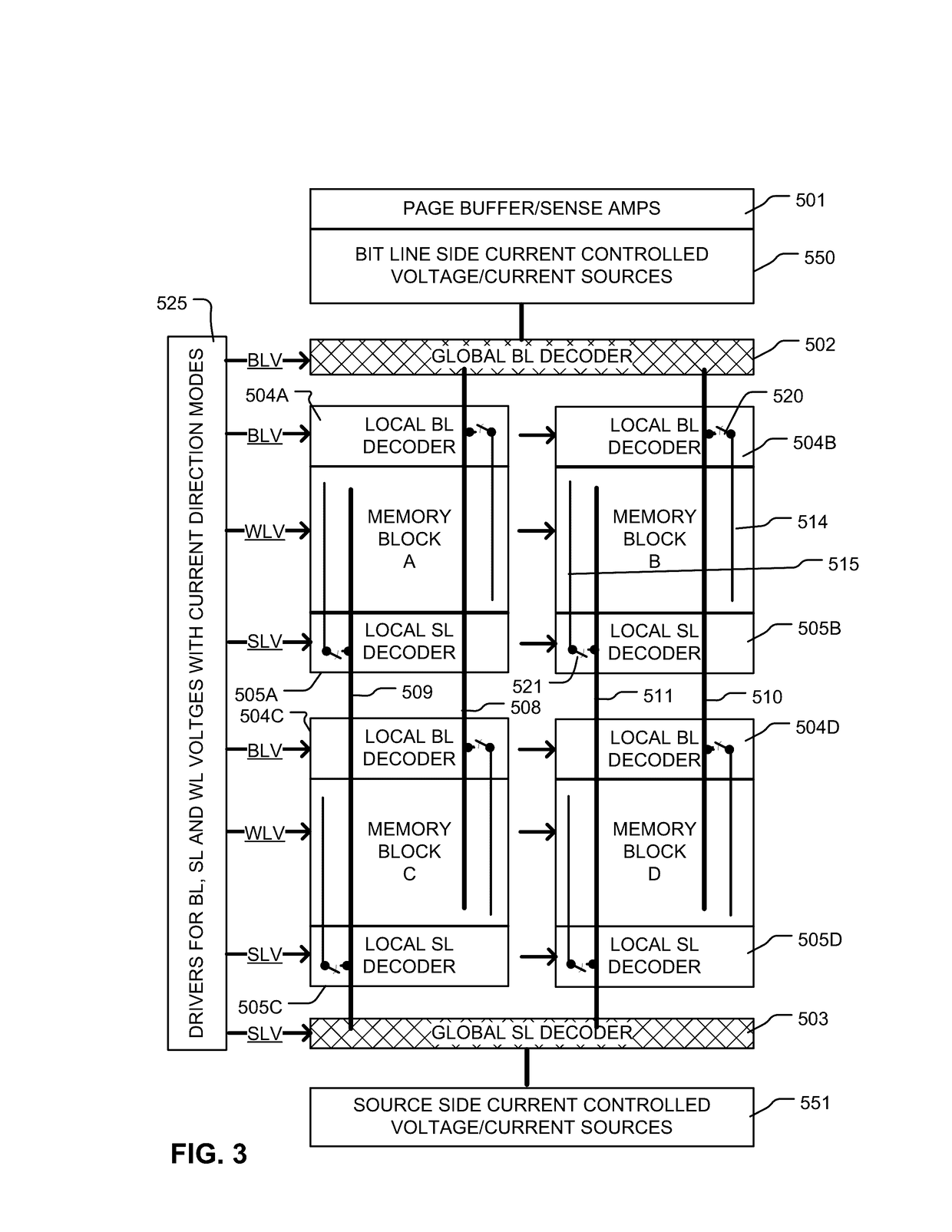

ReRAM array configuration for bipolar operation

ActiveUS9691478B1Improve uniformityExtended operating rangeSolid-state devicesDigital storageCell basedOxide

A memory architecture has improved controllability of operations for bipolar current directions used to write data in programmable resistance memory cells, including ReRAM cells based on metal oxide memory materials. Instead of a fixed gate voltage on a specific decoder transistor or cell selection device, and a control voltage set to values that cause the decoder transistor or cell selection device to operate in a fully-on mode for one current direction or in a current moderating mode with opposite current direction. Using this technology allows symmetrical or close to symmetrical operation in both current directions with little or no effect on the array complexity.

Owner:MACRONIX INT CO LTD

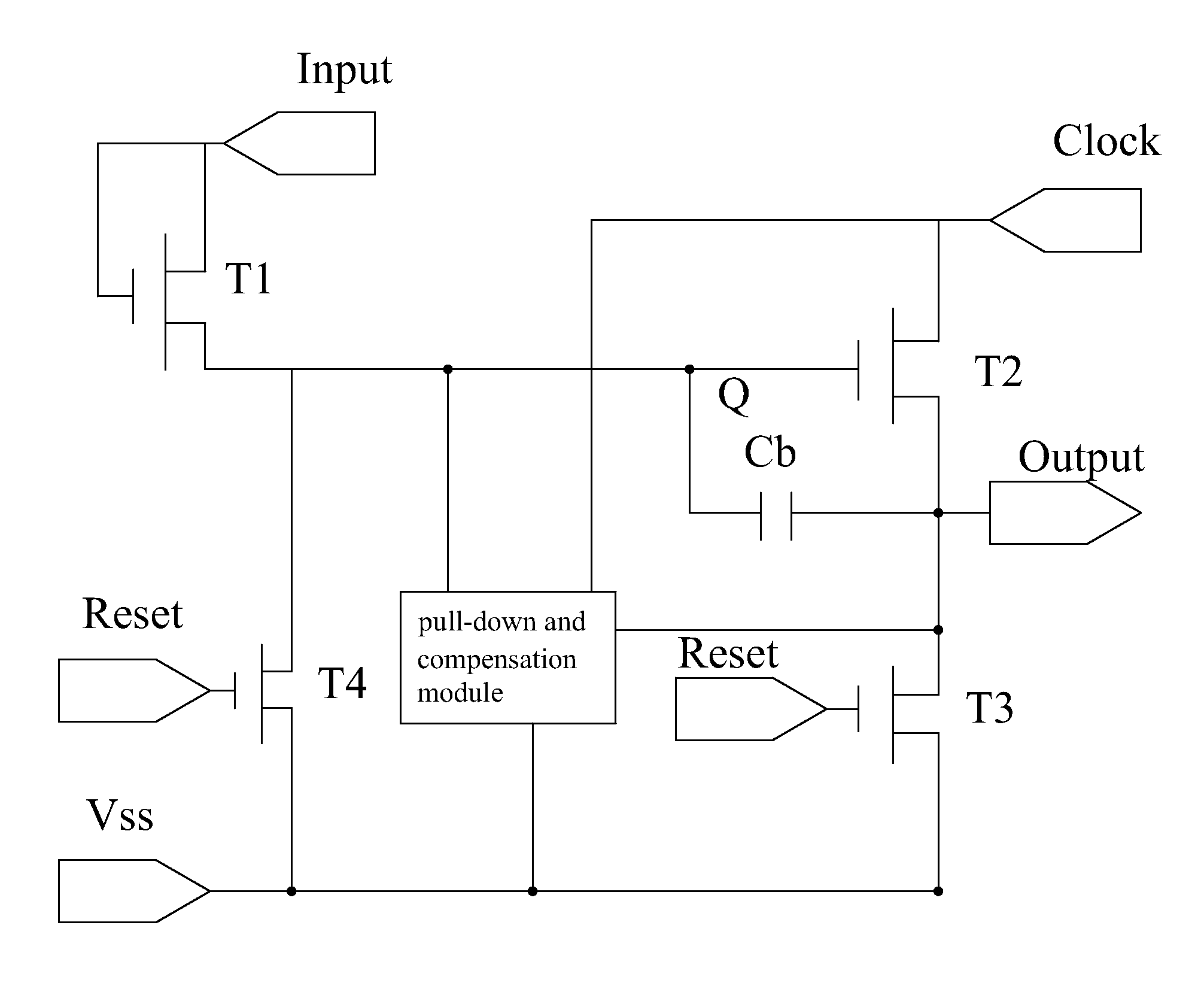

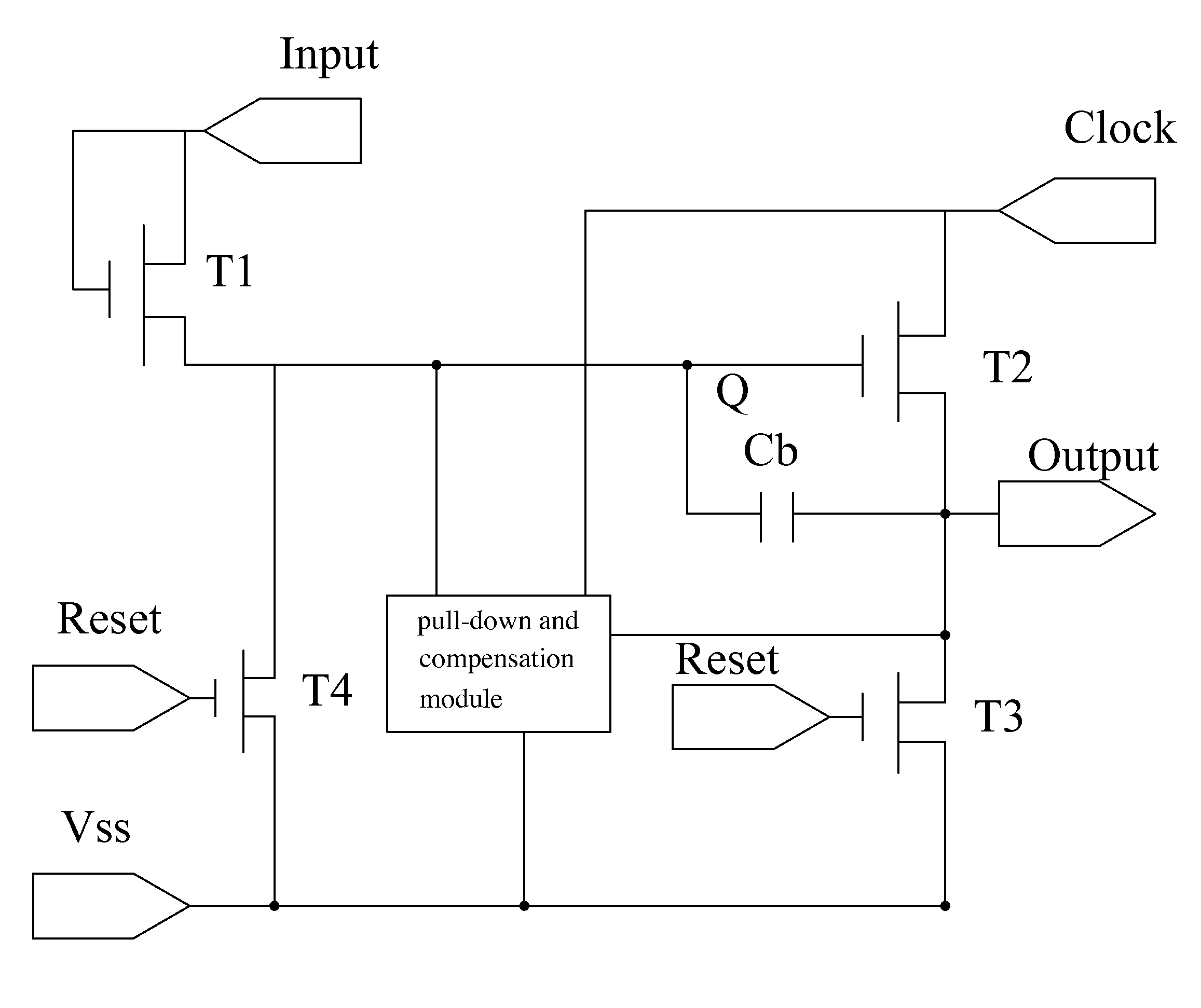

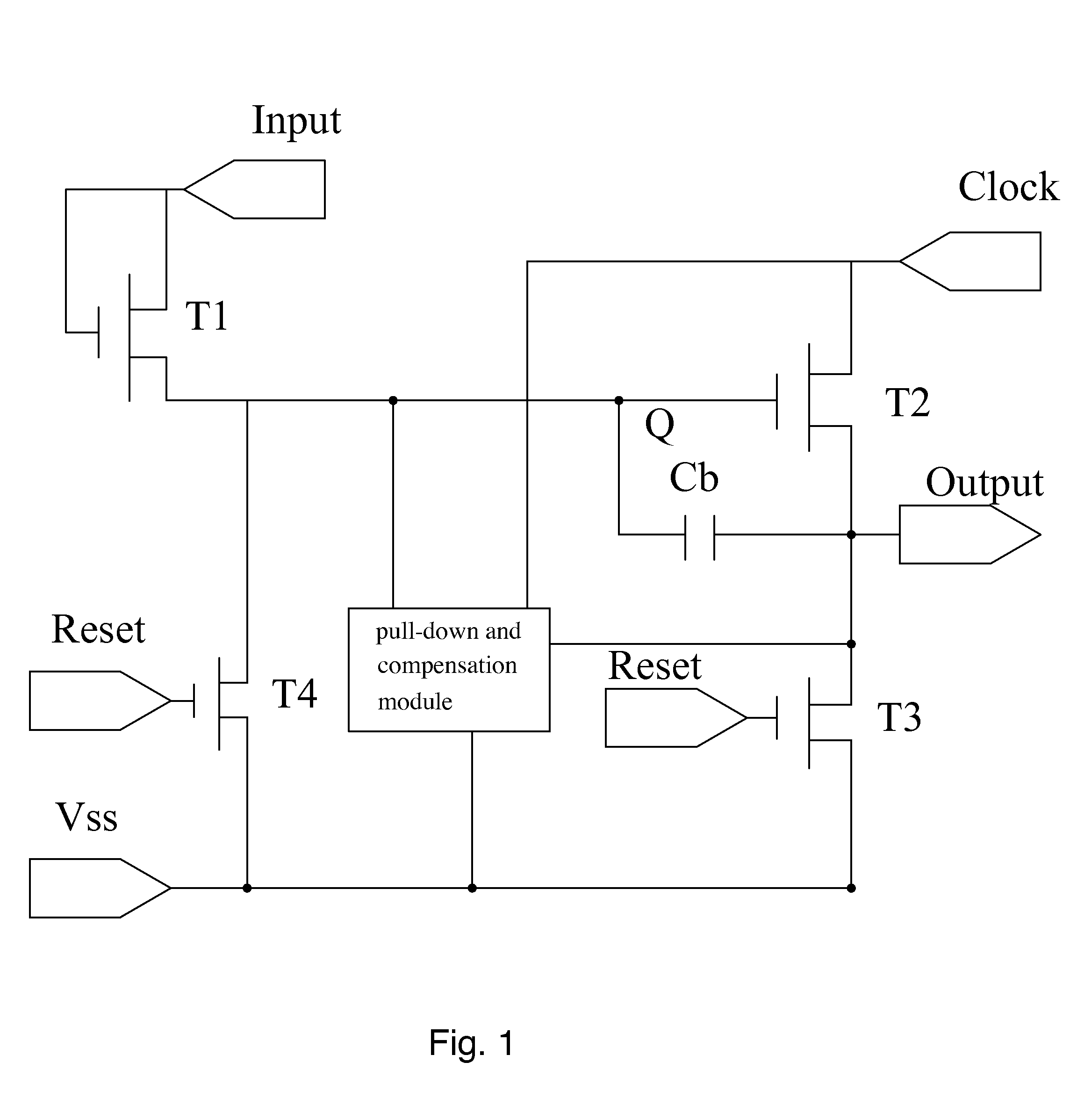

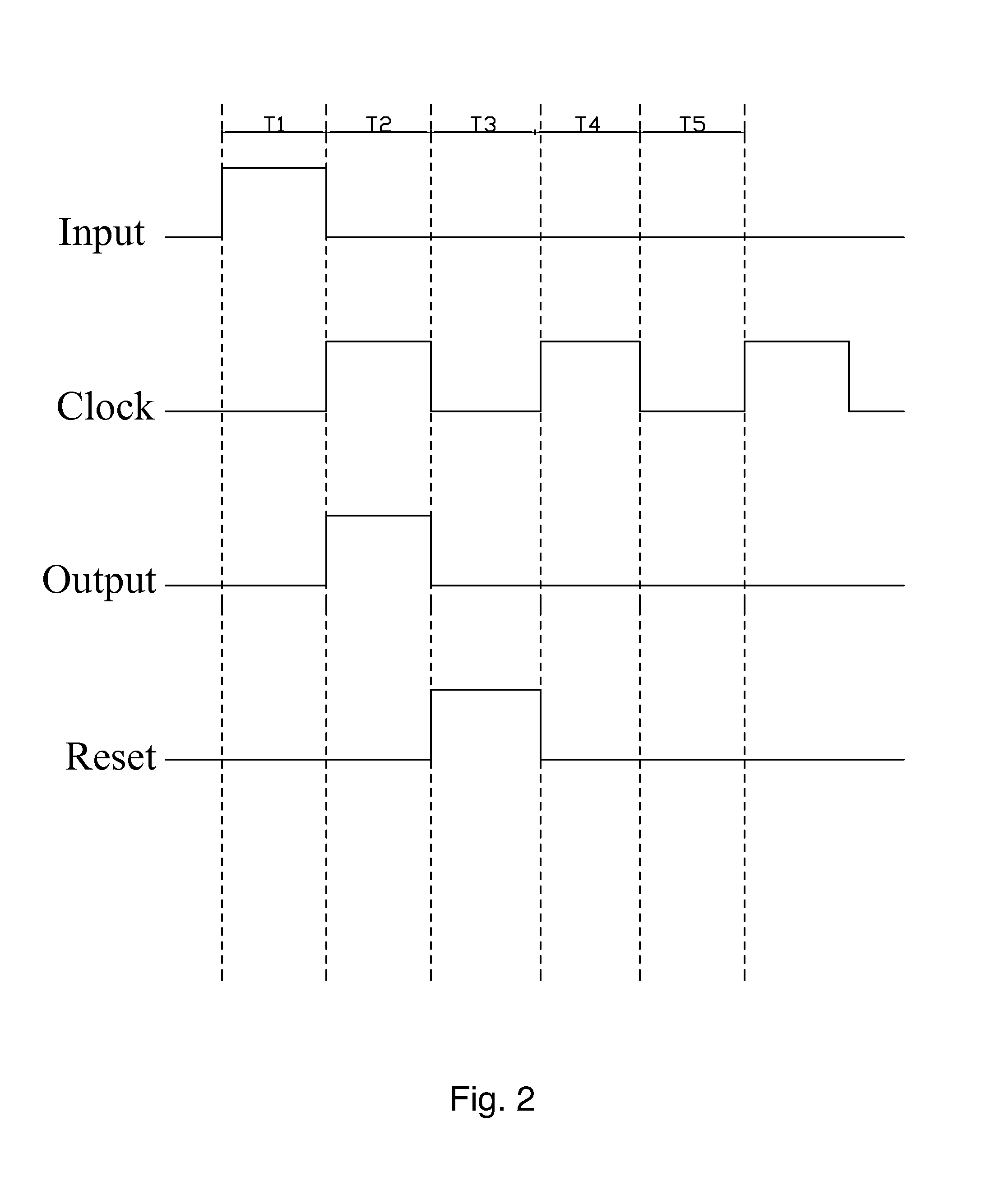

A gate driver circuit basing on igzo process

ActiveUS20160247476A1Reduce load effectImprove stabilityStatic indicating devicesDigital storageDriver circuitEngineering

The present invention provides a gate driver basing on IGZO process, comprising: GOAs in cascade connection comprising a Nth-stage GOA, wherein the Nth-stage GOA further comprising: a pull-up control part 100, a pull-up part 200, a transfer part 300, a pull-down part 400, a pull-down holding part 500, a boost part 600, a first negative supply VSS1, a second negative supply VSS2, a third negative supply VSS3, which are three gradually decreasing negative supplies and pull down an output terminal G(N), a first node Q(N), a second node P(N), and a driving single ST(N) to prevent the electrical leakage of TFTs effectively. And channels of the TFT switches of the gate driver basing on the IGZO process are oxide semiconductor channels.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

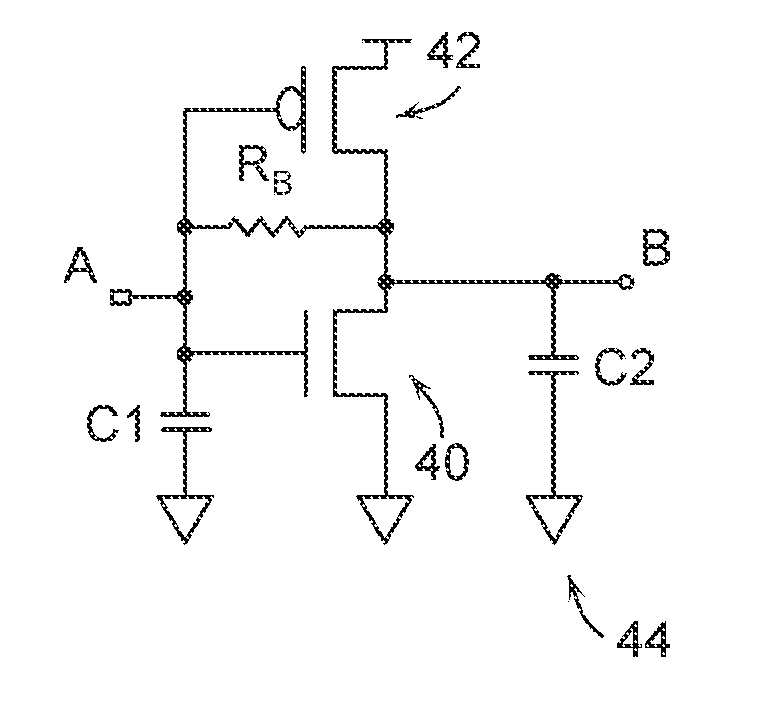

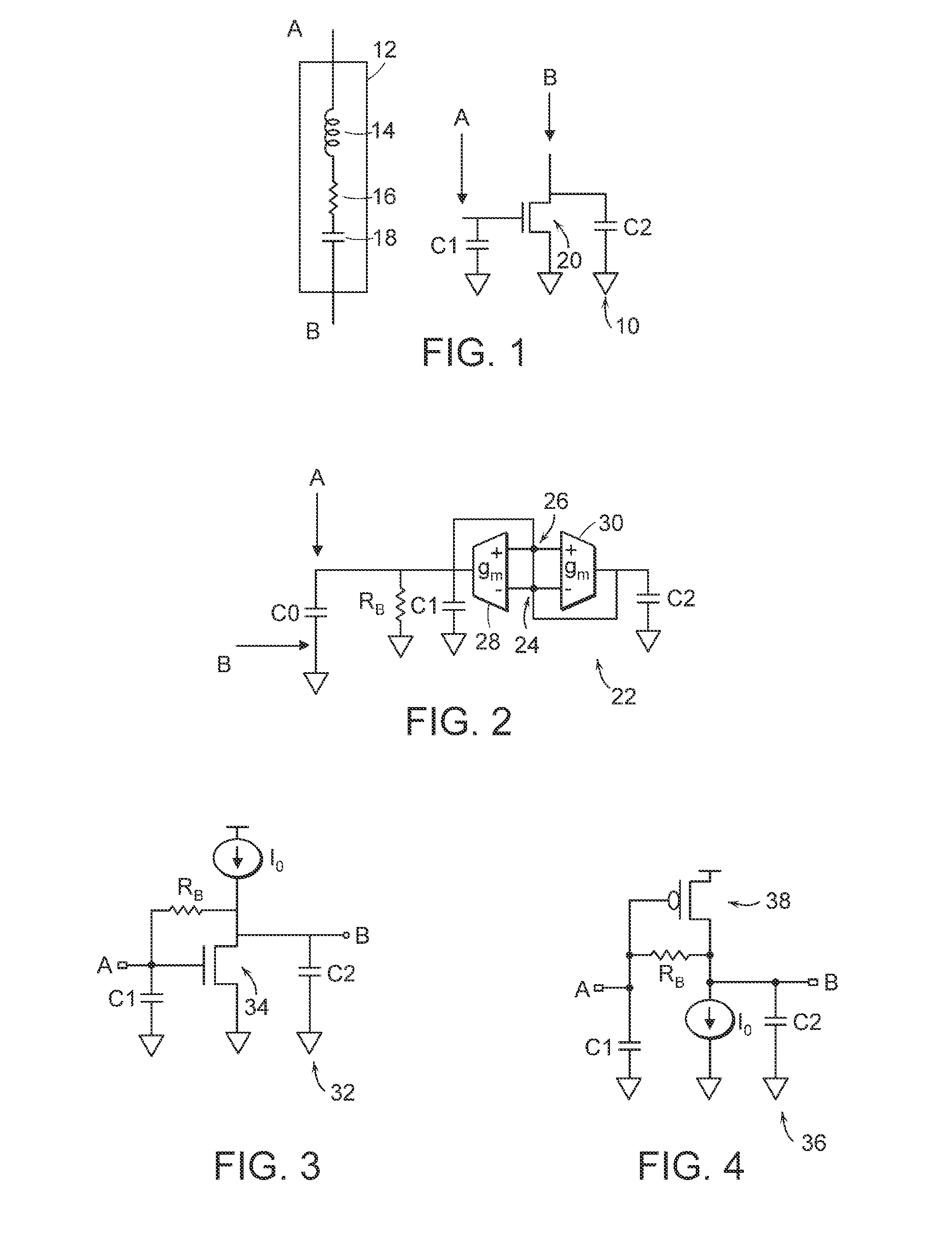

High gain, high frequency CMOS oscillator circuit and method

ActiveUS20070188256A1Reduce load effectHigh impedancePulse automatic controlOscillations generatorsResonatorShunt capacitors

An oscillator amplifier circuit is provided. The amplifier circuit can be used with a resonator to amplify and form a resonating oscillator. The amplifier circuit comprises an active circuit which includes an inverter and a current-controlled biasing circuit. One transistor of the inverter receives a voltage produced from the biasing circuit in order to place a gate terminal of that transistor at approximately a threshold voltage. The other transistor can be biased using a passive circuit element, such as a resistor. Therefore, both transistors are biased independent of each other within the optimal gain region. Large shunt capacitors are not required and the total current consumption is controlled through a variable resistor coupled to the source terminal of either the first transistor, second transistor, or possibly both transistors of the inverter to adjust the amplitude of the oscillating output.

Owner:MONTEREY RES LLC

Clock signal distribution with reduced parasitic loading effects

ActiveUS7528638B2Reduce load effectReduce power lossPulse automatic controlGenerating/distributing signalsDelay-locked loopDistribution system

Clock signal distribution systems with reduced parasitic loading effects are provided. A reference clock is frequency-divided to produce a lower frequency clock signal. A delay-locked loop (DLL) circuit locks to the lower frequency clock signal, and outputs a corresponding lower frequency clock signal for distribution over a long trace. Power consumption caused by parasitic capacitance of the trace is thereby reduced. Parasitic effects associated with clock jitter are also reduced. A frequency multiplying phase-locked loop (PLL) circuit locks to the lower frequency clock signal, and outputs at least one clock signal having a higher frequency than the lower frequency signal.

Owner:MICRON TECH INC

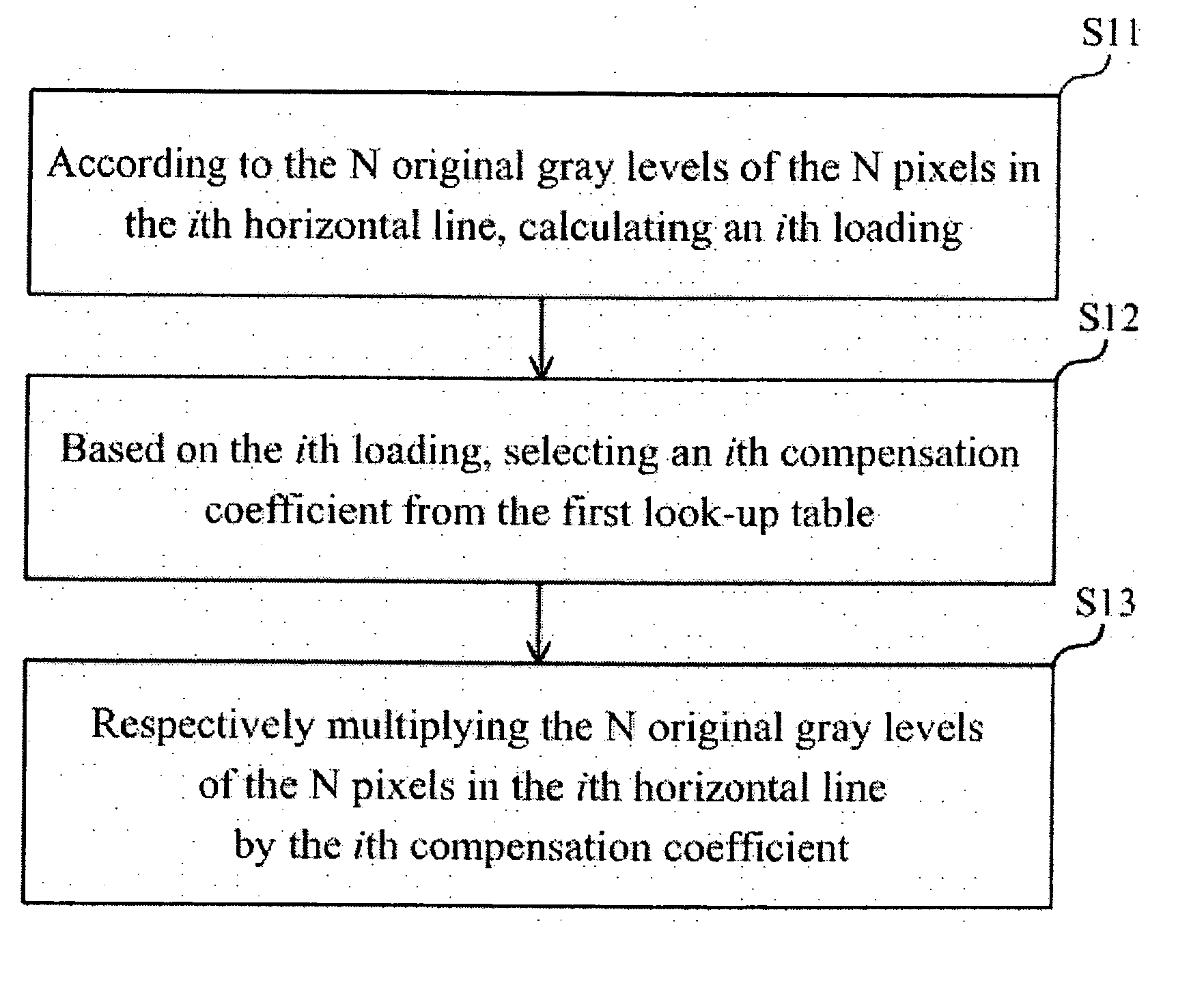

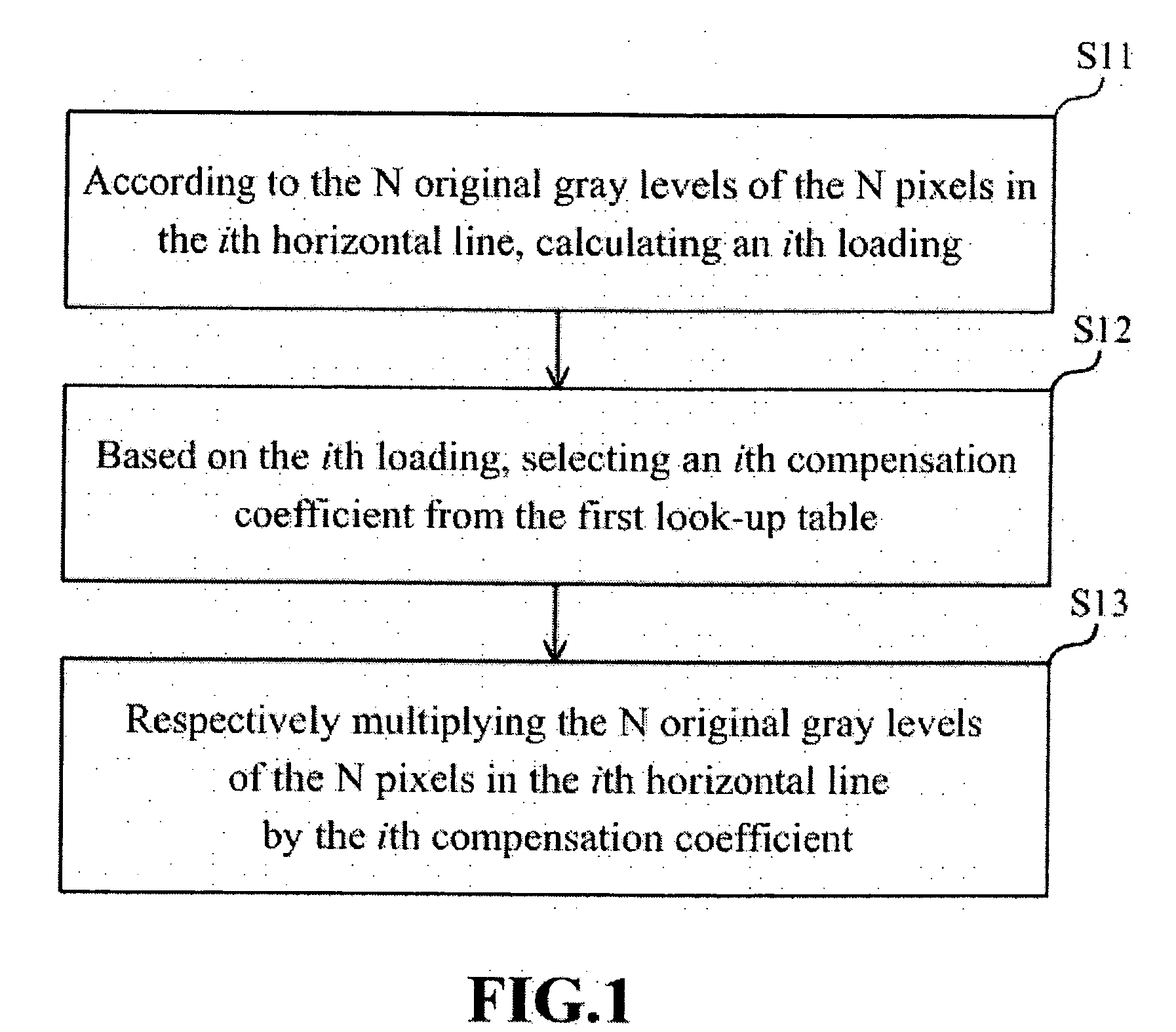

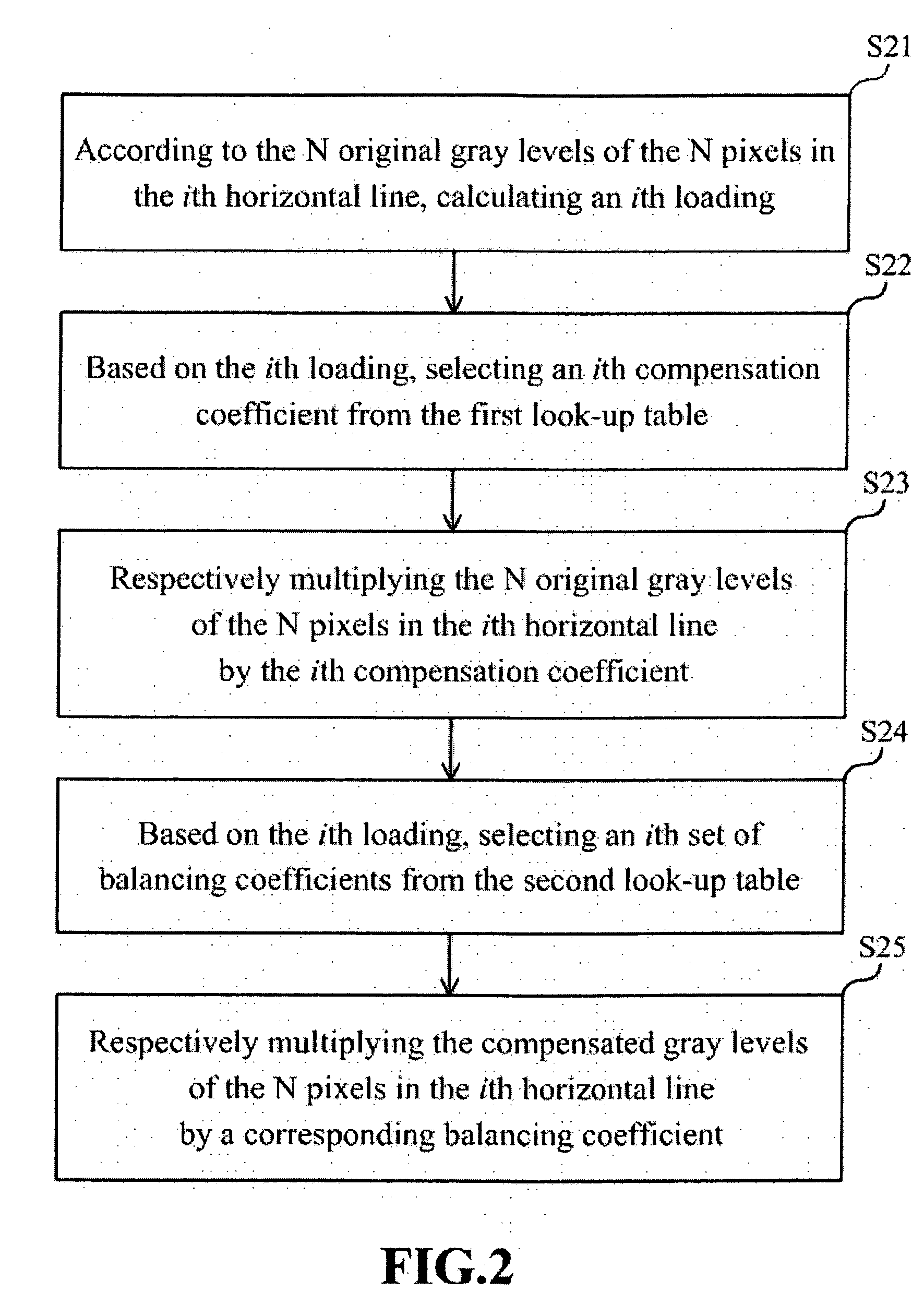

Apparatus and method for adjusting image on the basis of characteristics of display system

InactiveUS20070126661A1Reduce load effectTelevision system detailsColor signal processing circuitsGray levelLevel line

A method for adjusting an image on the basis of characteristics of a display system is provided. The image includes M horizontal lines. Each of the M horizontal lines respectively includes N pixels. Each pixel has an original gray level. A look-up table previously stores a plurality of conversion coefficients related to the characteristics of the display system. The method first calculates an ith loading according to the N original gray levels of the N pixels in the ith horizontal line. Based on the ith loading, an ith conversion coefficient corresponding to the ith loading is selected from the plurality of conversion coefficients in the look-up table. The method respectively multiplies the N original gray levels of the N pixels in the ith horizontal line by the ith conversion coefficient to generate N new gray levels for the N pixels in the ith horizontal line, whereby the image is adjusted.

Owner:MARKETECH INT

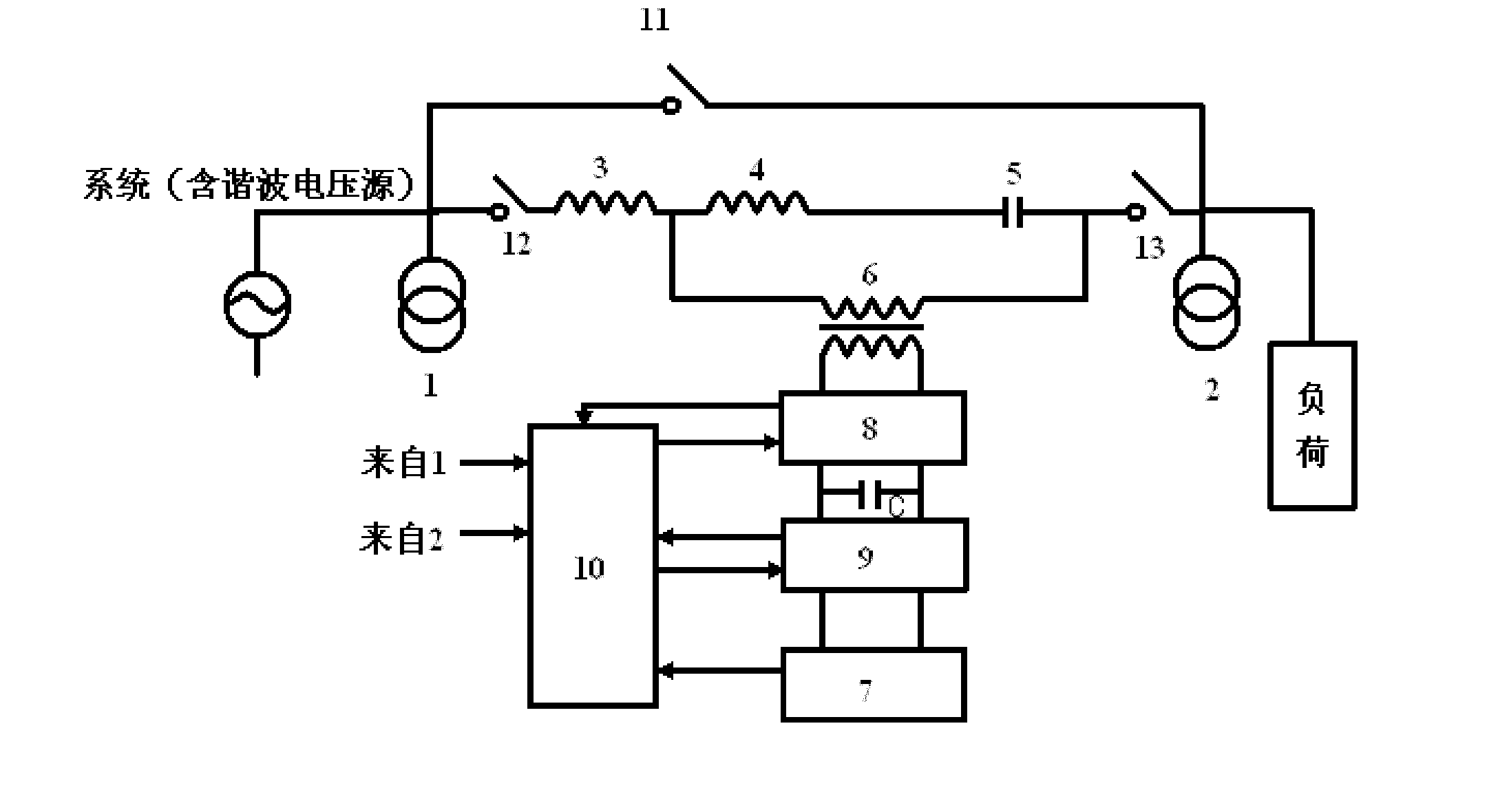

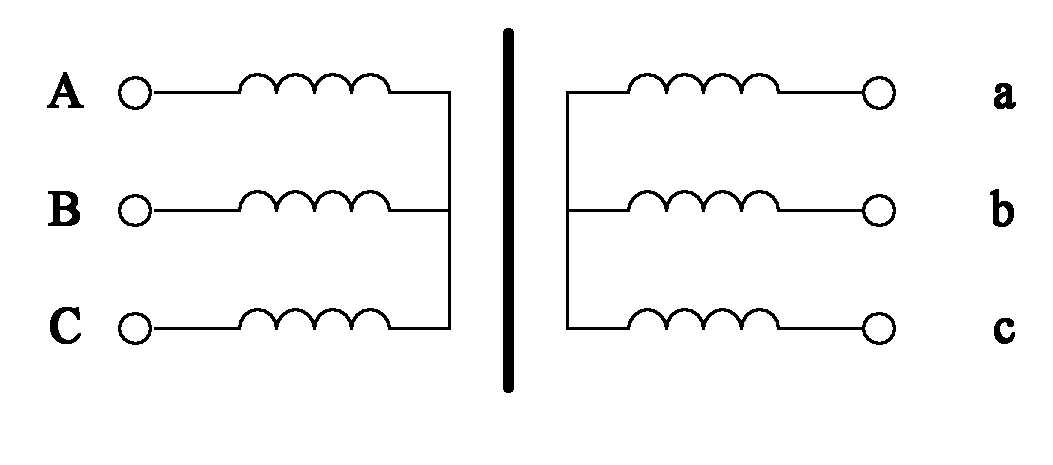

Device for eliminating voltage harmonics of power system

ActiveCN102157940AEliminate load effectsQuick responseActive power filteringHarmonic reduction arrangementElectric power systemTransformer

The invention relates to a device for eliminating voltage harmonics of a power system, which comprises a harmonic voltage source detection device, a fundamental wave filter, a high frequency transformer, an AC (Alternating Current) power source, a power unit, a rectifying unit, a filtering unit and a controller, wherein the fundamental wave filter is formed by connecting a reactor 1, a reactor 2 and a capacitor in series; the harmonic voltage source detection device collects the real-time harmonic voltage of the system and inputs a harmonic voltage signal to the controller; the controller calculates out a voltage which is equal to the harmonic voltage in magnitude and opposite to the harmonic voltage in direction; the power unit inputs the voltage into an LC (Loop Circuit) branch, formed by connecting the reactors and the capacitor in series, through the high frequency transformer, and the voltage and the harmonic voltage are superposed so that the output harmonic voltage becomes zeroand the effect of filtering out the harmonic voltage in a power grid is achieved; and the controller is connected with the AC power source, the rectifying unit and the power unit respectively. In thedevice, based on the superposition principle, the purpose of eliminating the influence of a power-side higher harmonic voltage source to a load can be achieved by connecting the harmonic voltage sources in series, and the response speed is high.

Owner:RONGXIN HUIKO ELECTRIC TECH CO LTD +1

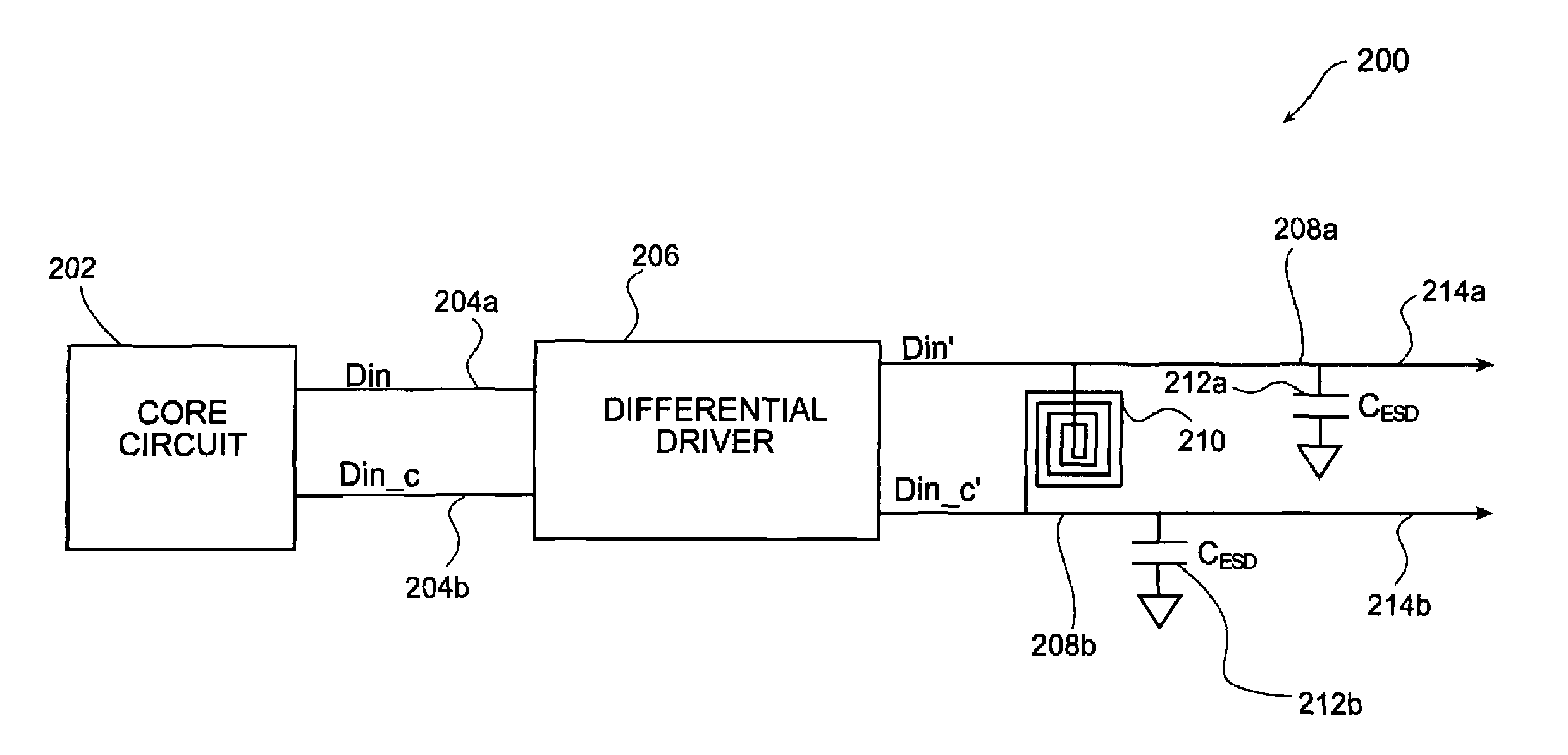

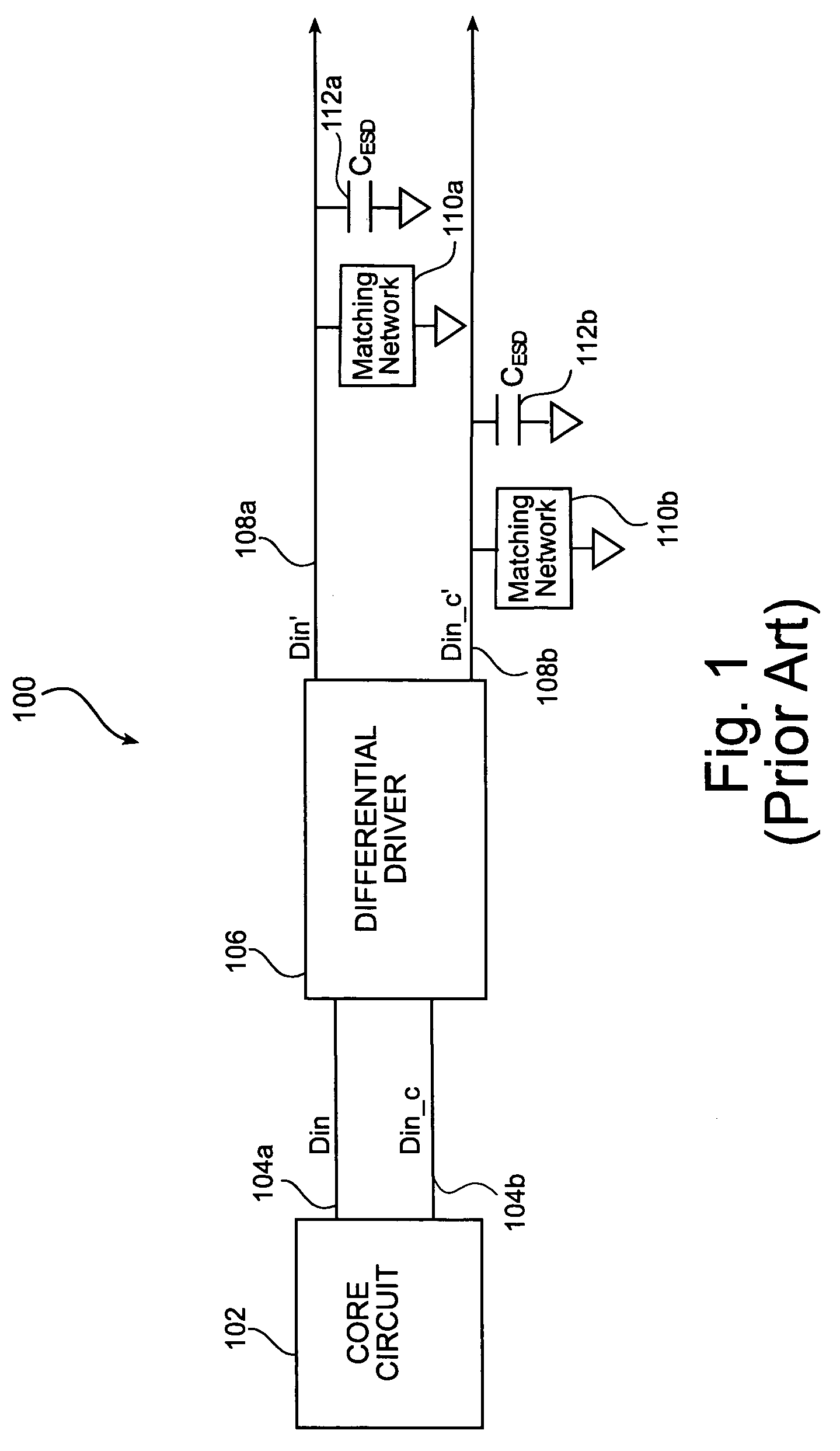

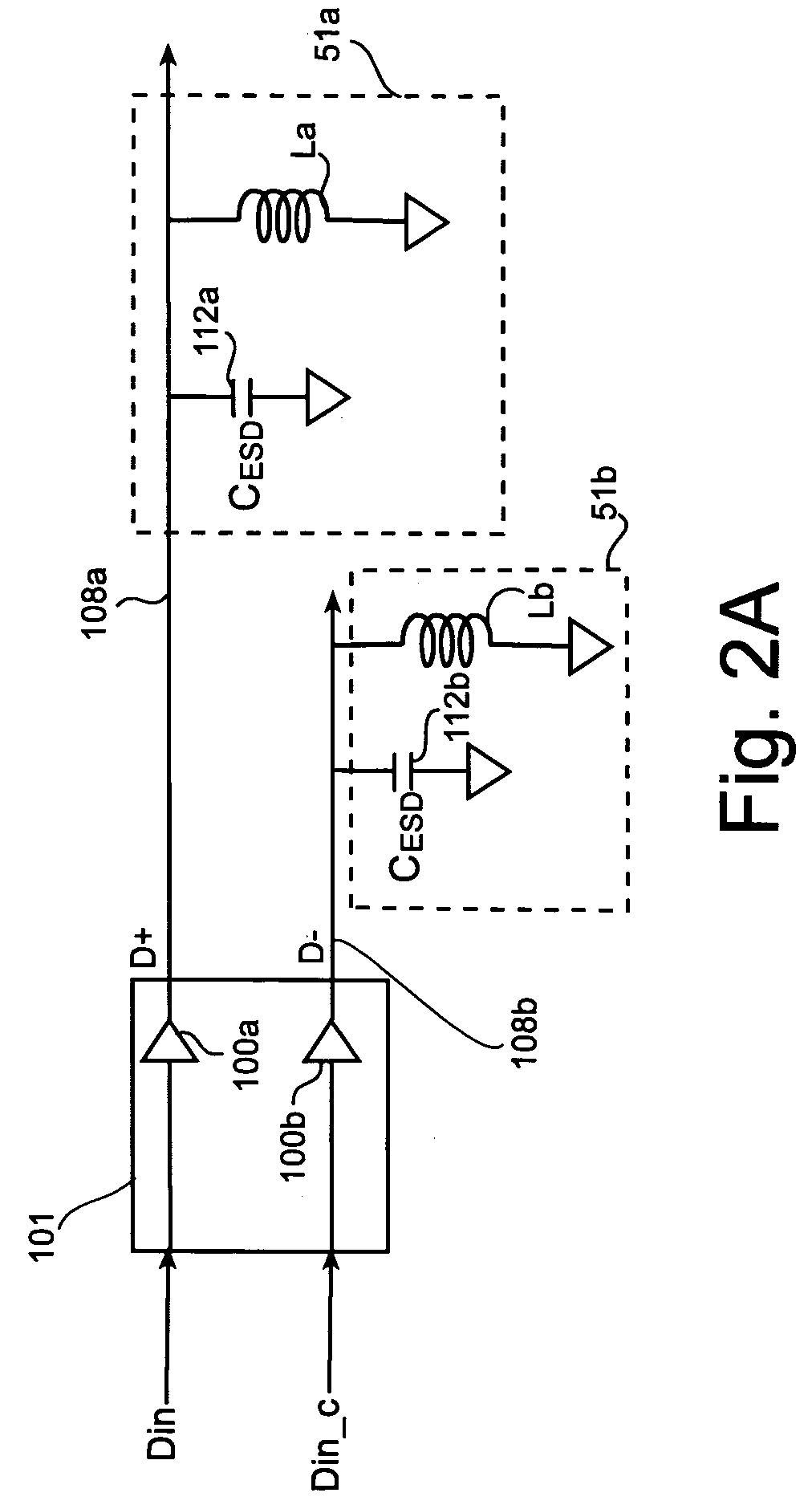

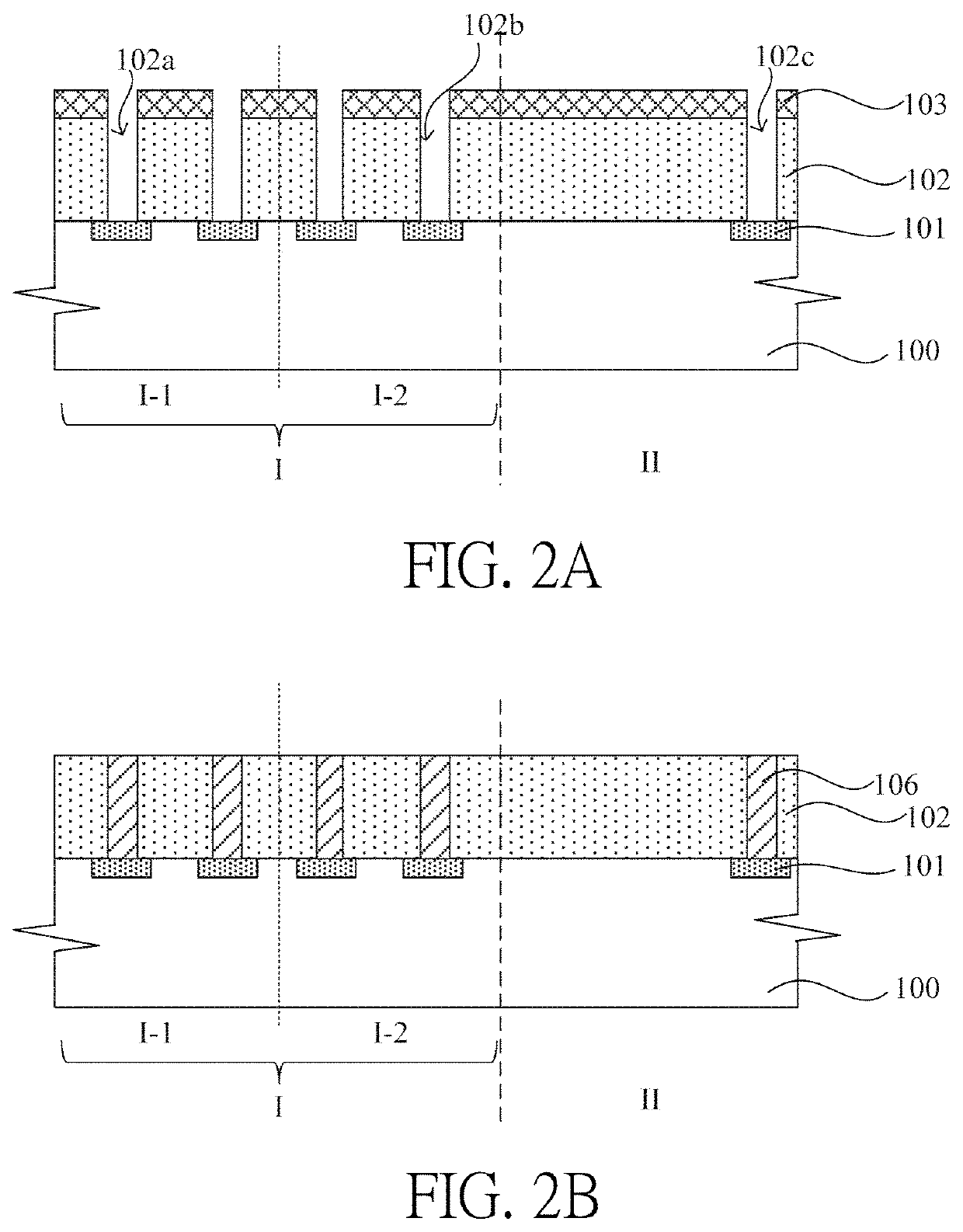

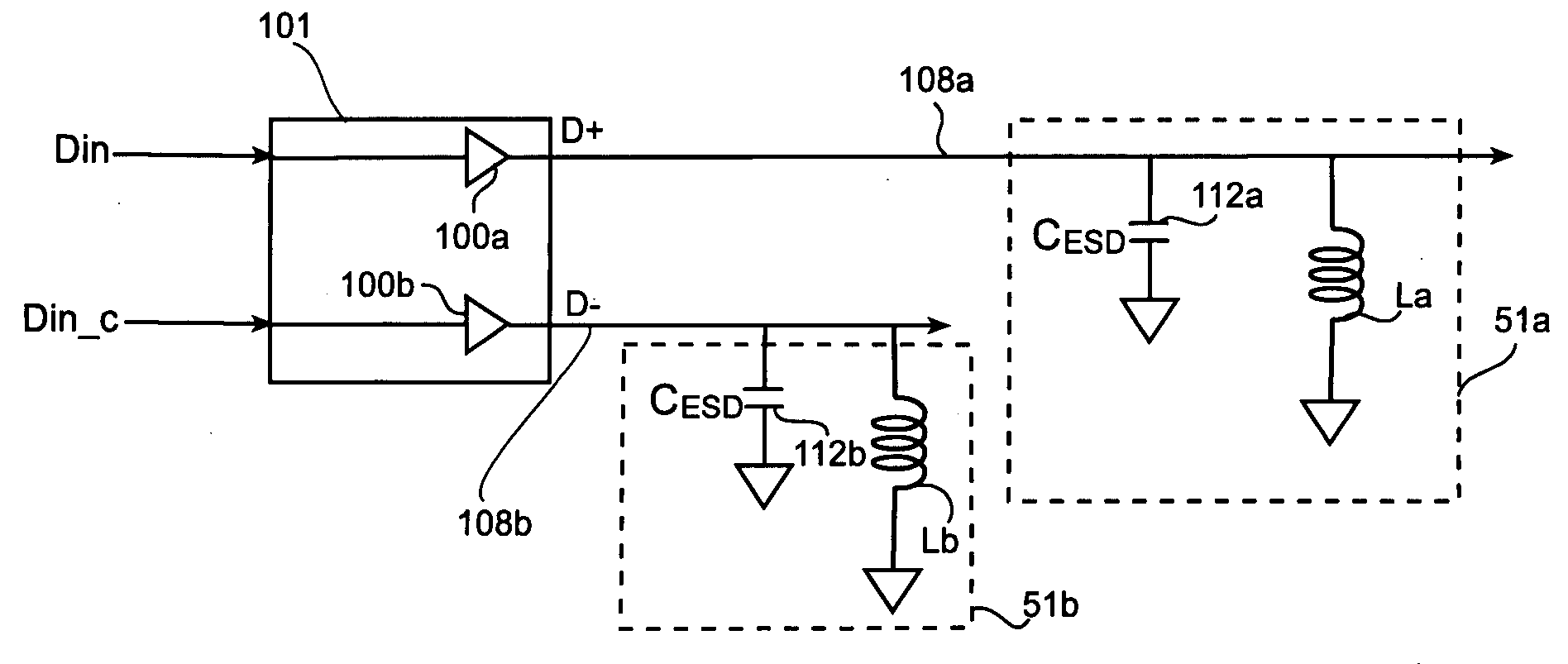

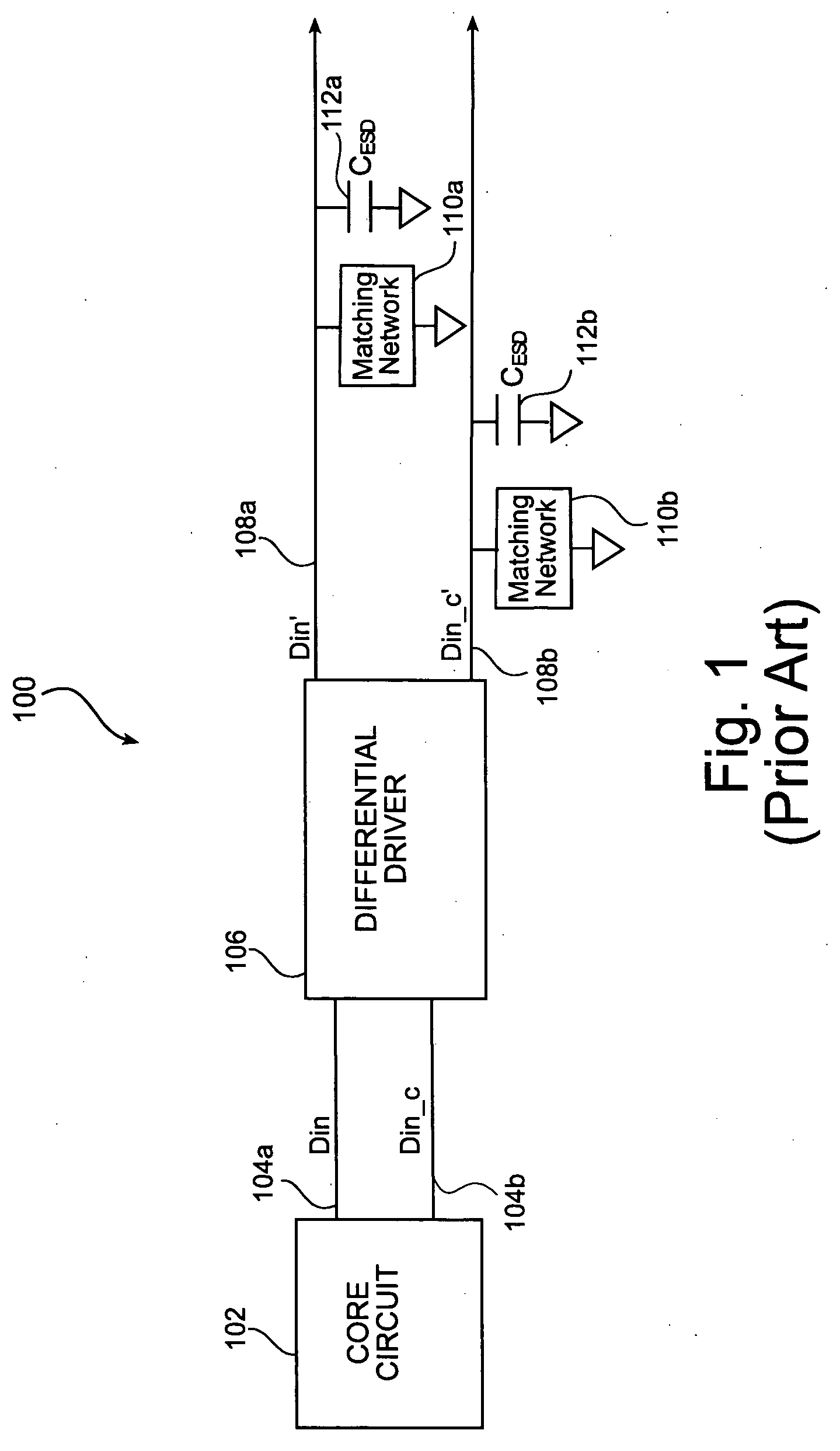

Methods and systems for rise-time improvements in differential signal outputs

InactiveUS7224180B2Reduce load effectSwitching accelaration modificationsMultiple-port networksCapacitanceDifferential signaling

A method for maintaining signal integrity of a differential output signal generated from a differential driver is disclosed. The method includes receiving the differential output signal from the differential driver. Once received, the method includes tuning the differential output signal by exposing the differential output signal to an inductance. The inductance is configured to reduce signal mismatch between complementary signals of the differential output signal. The signal mismatch is a result of having each of the complementary signals exposed to different capacitive loading. A device and system is also provided, which include integrating an inductor between the output leads of a differential driver. The inductor is sized for the particular frequency of operation, and the inductor provides an inductance that assists in eliminating mismatch between the complementary signals of the differential output. A reduction and / or elimination of the mismatch will assist in improving the rise-time of the differential signals.

Owner:SEIKO EPSON CORP

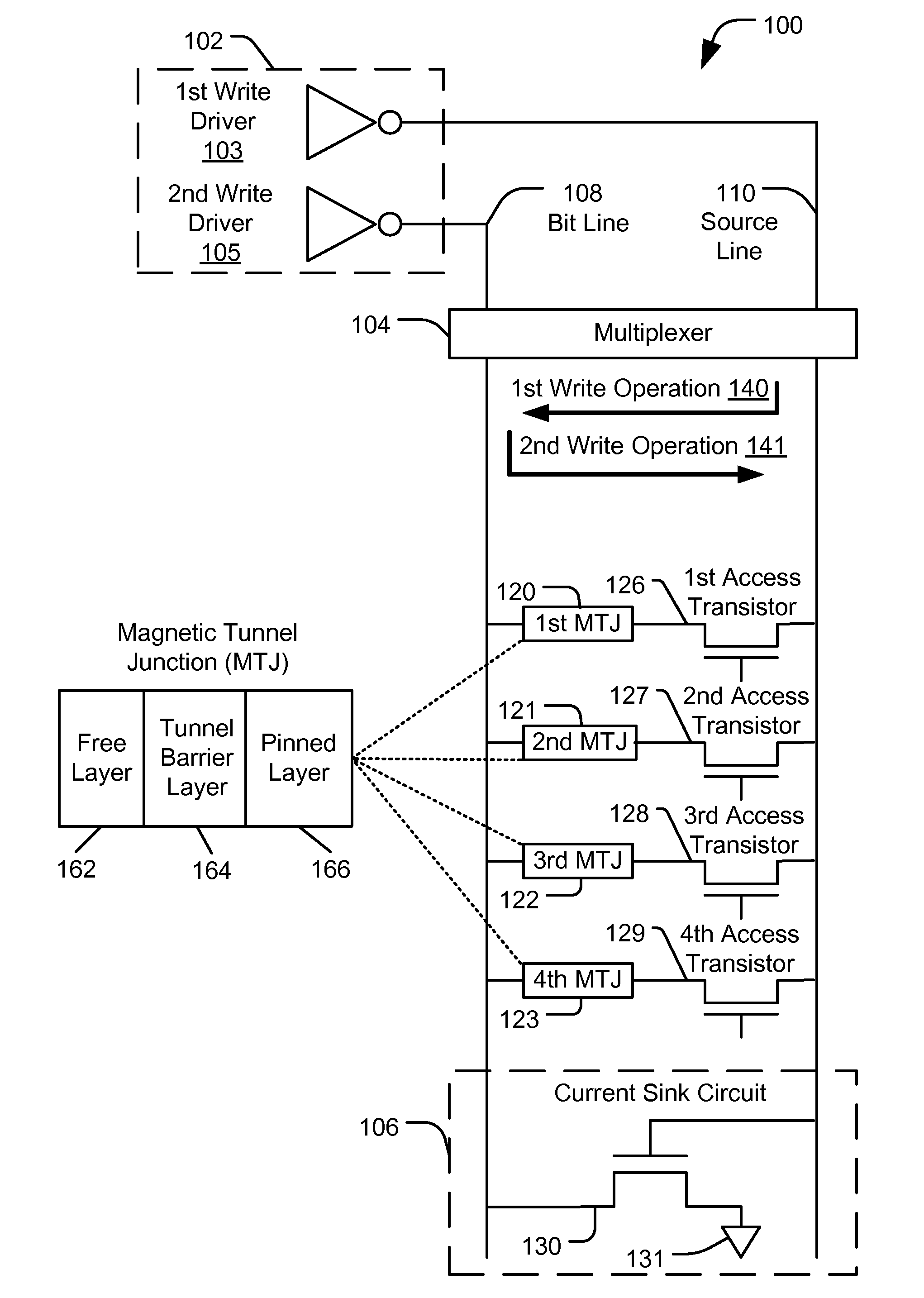

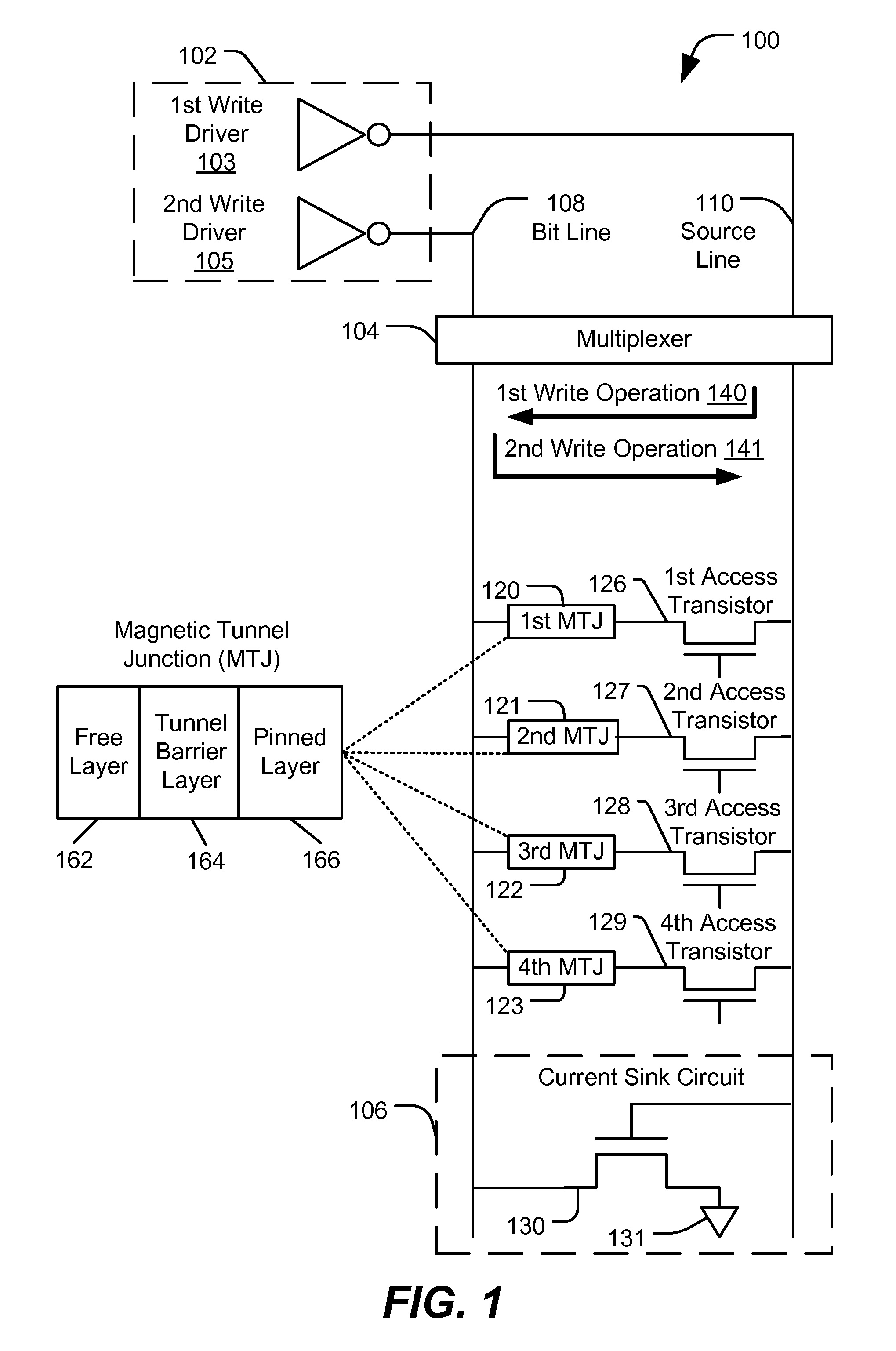

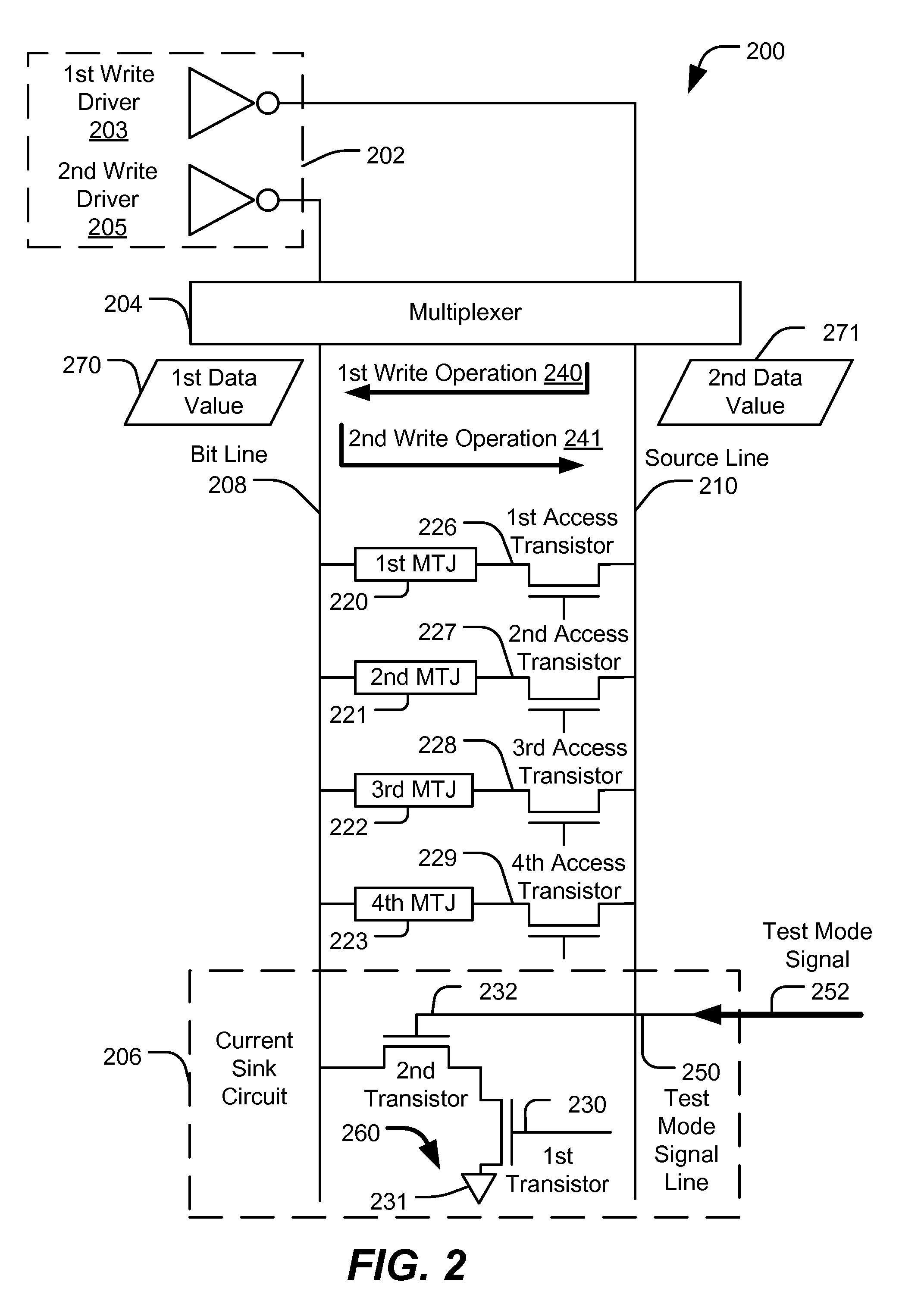

Memory Device Having A Local Current Sink

ActiveUS20110280057A1Reduce parasitic resistanceReduce load effectDigital storageSpecial data processing applicationsBit lineEngineering

A memory device having a local current sink is disclosed. In a particular embodiment, an electronic device is disclosed. The electronic device includes one or more write drivers. The electronic device includes at least one Magnetic Tunnel Junction (MTJ) coupled to a bit line and coupled to a source line. The electronic device also includes a current sink circuit comprising a single transistor, the single transistor coupled to the bit line and to the source line.

Owner:QUALCOMM INC

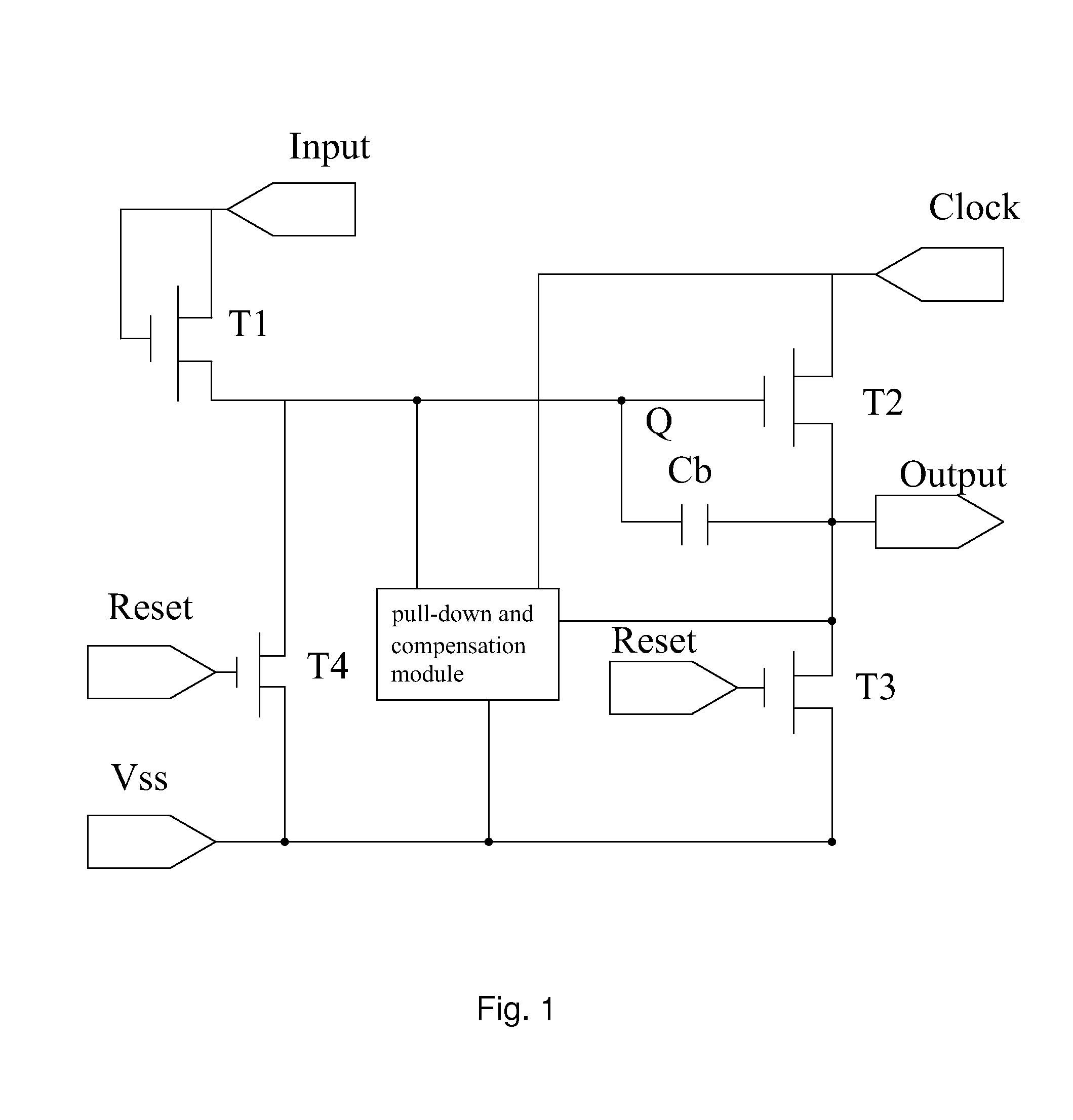

Gate driver circuit basing on igzo process

ActiveUS20160267864A1Effectively minimize amountSave packing timeStatic indicating devicesDigital storageDriver circuitEngineering

The present invention provides a gate driver circuit basing on IGZO process, comprising GOAs in cascade connection comprising a Nth-stage GOA, wherein the Nth-stage GOA further comprising a pull-up control part 100, a pull-up part 200, a transfer part 300, a pull-down part 400, a pull-down holding part 500, a boost part 600, a first negative supply VSS1, a second negative supply VSS2, a third negative supply VSS3, which are three gradually decreasing negative supplies and pull down an output terminal G(N), a first node Q(N), a second node P(N), and a driving single ST(N) to prevent the electrical leakage of TFTs effectively. And channels of the TFT switches of the gate driver circuit basing on the IGZO process are oxide semiconductor channels.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

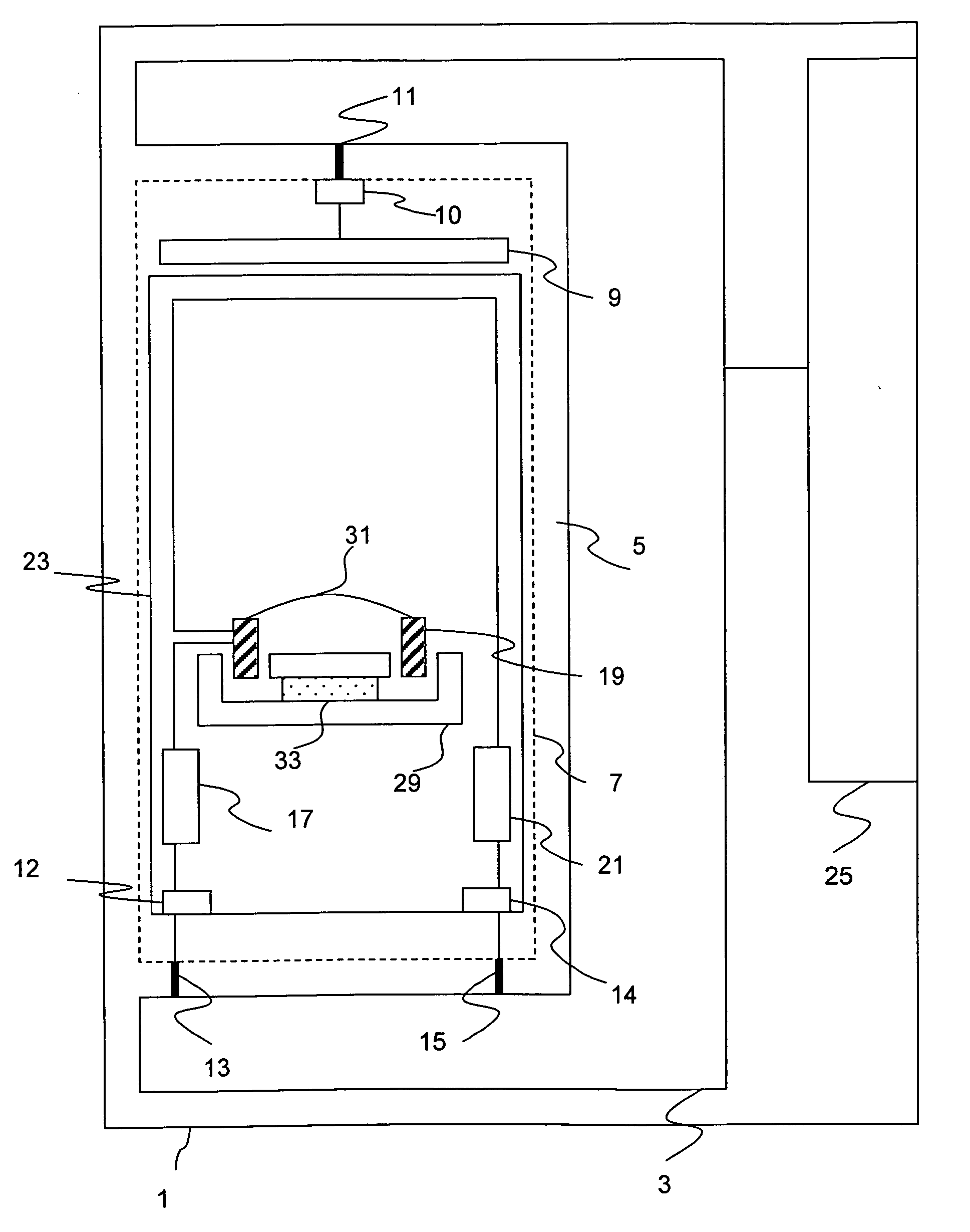

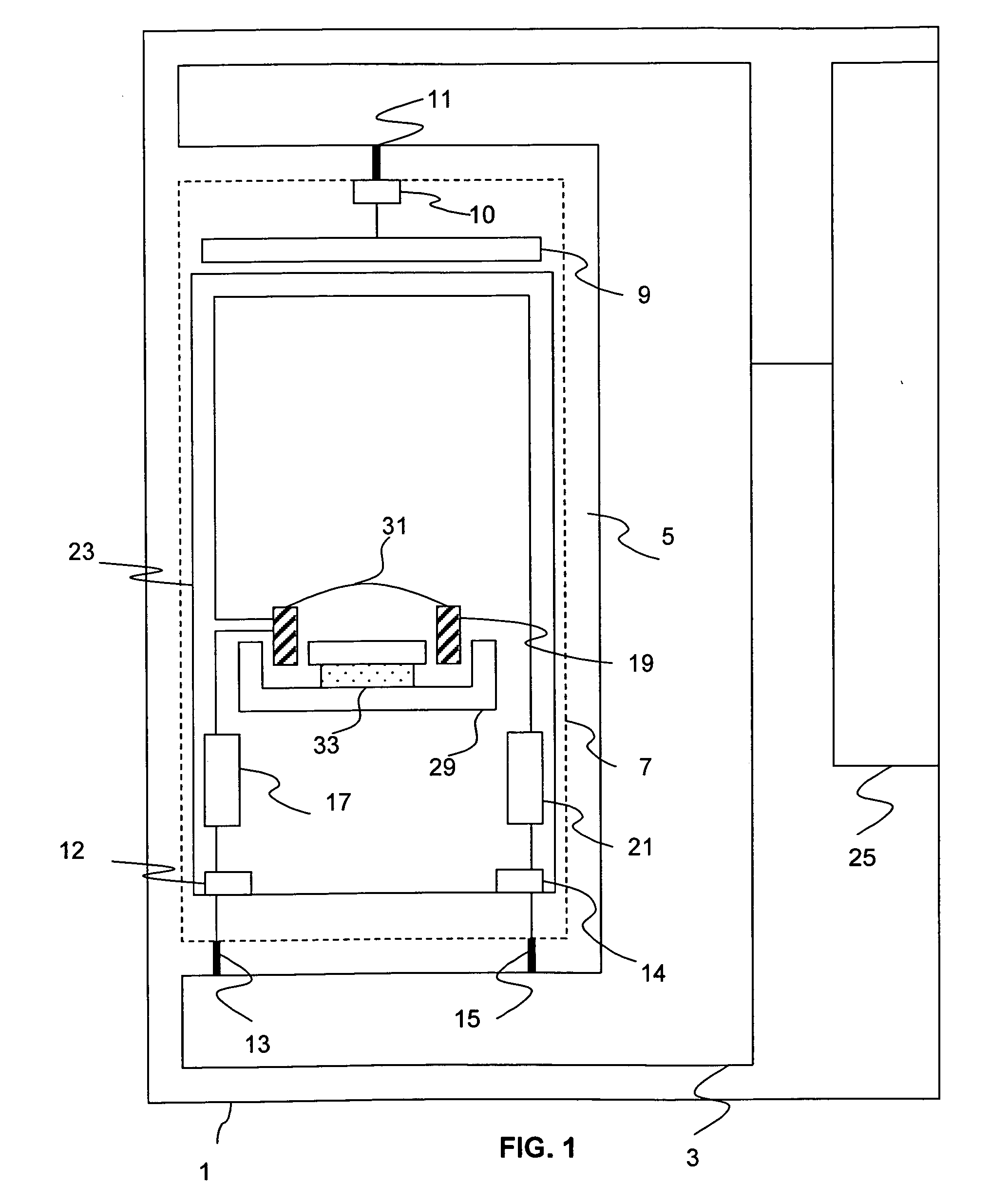

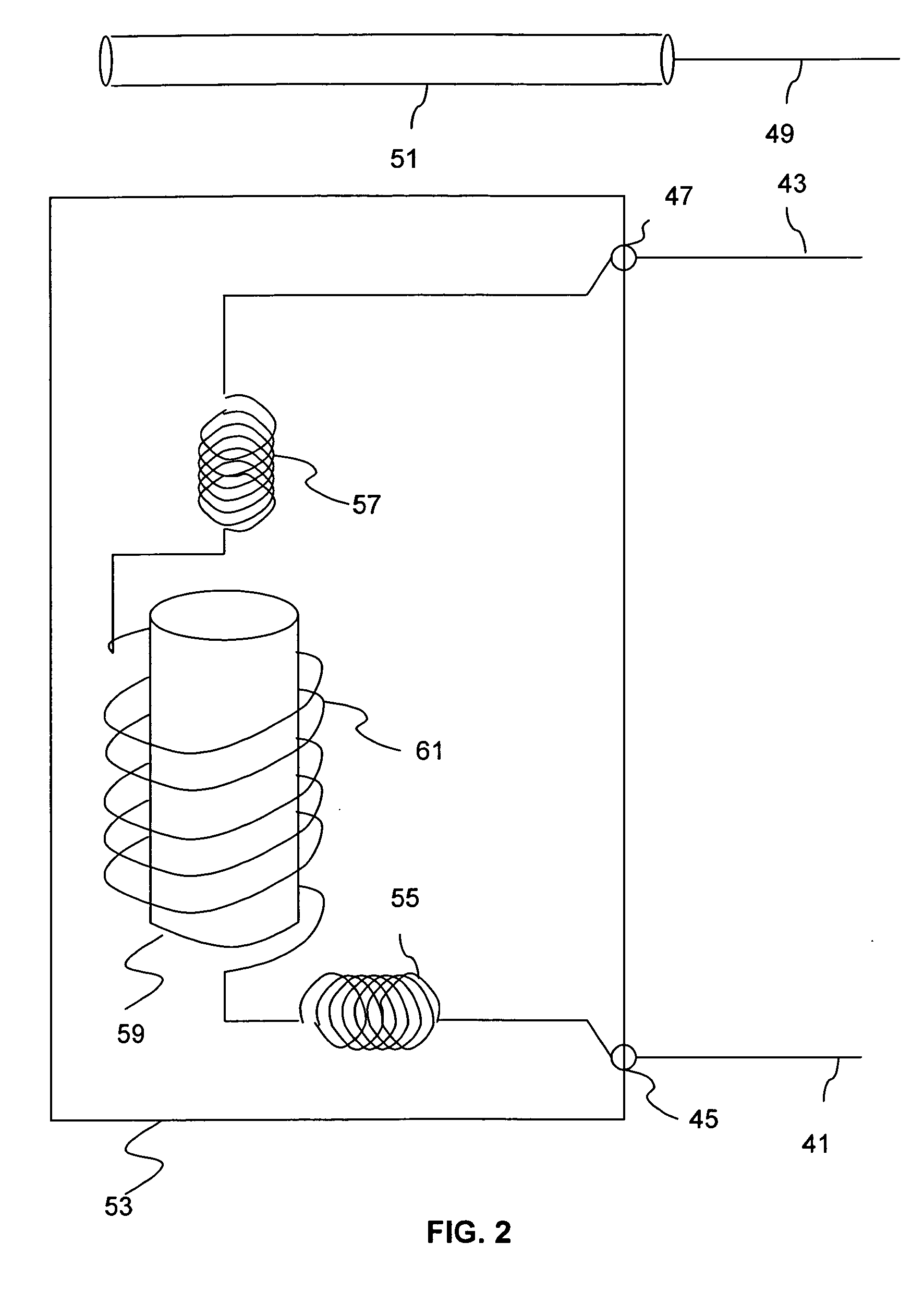

Memory expansion and chip scale stacking system and method

InactiveUS6955945B2Improve thermal efficiencyReduce load effectPrinted circuit assemblingSemiconductor/solid-state device detailsCapacitanceDIMM

The present invention stacks chip scale-packaged integrated circuits (CSPs) into modules that conserve PWB or other board surface area. In another aspect, the invention provides a lower capacitance memory expansion addressing system and method and preferably with the CSP stacked modules provided herein. In a preferred embodiment in accordance with the invention, a form standard is disposed between the flex circuitry and the IC package over which a portion of the flex circuitry is laid. In a preferred embodiment, the form standard will be devised of heat transference material such as copper to improve thermal performance. In a preferred embodiment, a high speed switching system selects a data line associated with each level of a stacked module to reduce the loading effect upon data signals in memory access. This favorably changes the impedance characteristics exhibited by a DIMM board populated with stacked modules. In a preferred embodiment, FET multiplexers for example, under logic control select particular data lines associated with particular levels of stacked modules populated upon a DIMM for connection to a controlling chip set in a memory expansion system.

Owner:TAMIRAS PER PTE LTD LLC

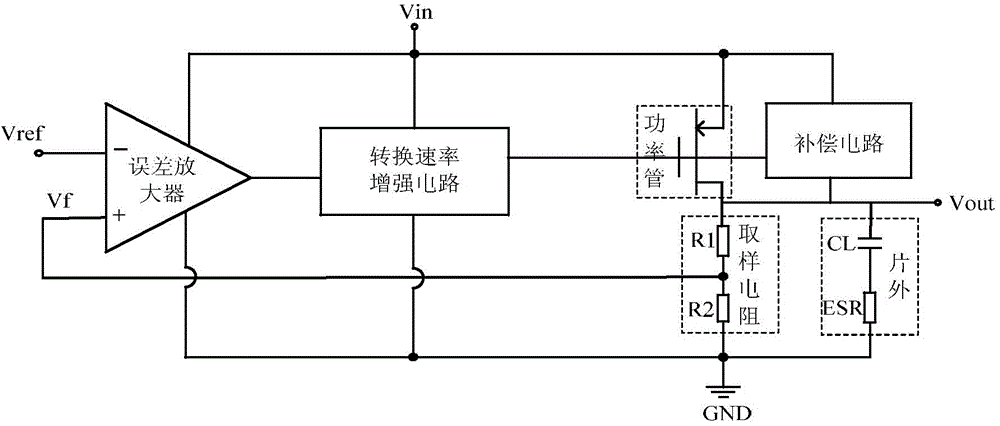

Quick transient response CMOS (Complementary Metal Oxide Semiconductor) low-dropout regulator

ActiveCN104679086AFast charging and dischargingAmplifies the gate input currentElectric variable regulationCMOSElectrical resistance and conductance

The invention discloses a quick transient response CMOS (Complementary Metal Oxide Semiconductor) low-dropout regulator. The inverted input end of an error amplification circuit is connected with reference voltage Vref, the in-phase input end of the error amplification circuit is connected with the sampling output end Vf of a sampling resistor circuit, and the output end of the error amplification circuit is connected with the gate of a power tube through a conversion rate increasing circuit. The positive power end of the error amplification circuit, the positive power end of the conversion rate increasing circuit and the source of the power tube are connected to form the input end Vin of a regulator body. The drain of the power tube and the positive power end of the sampling resistor circuit are connected to form the output end Vout of the regulator body. The negative power end of the error amplification circuit, the negative power end of the conversion rate increasing circuit and the negative power end of the sampling resistor circuit are connected to form the ground end GND of the regulator body. The quick transient response CMOS low-dropout regulator is higher in conversion rate and quicker in transient response.

Owner:GUILIN UNIV OF ELECTRONIC TECH

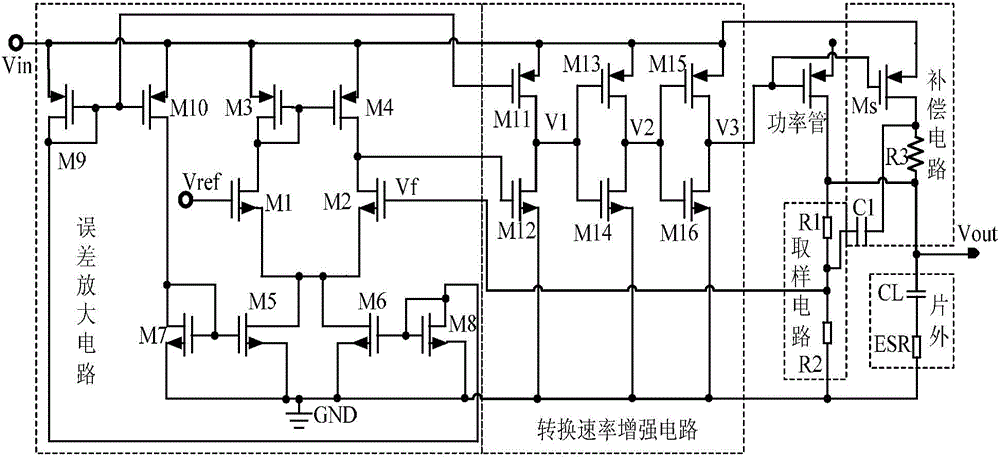

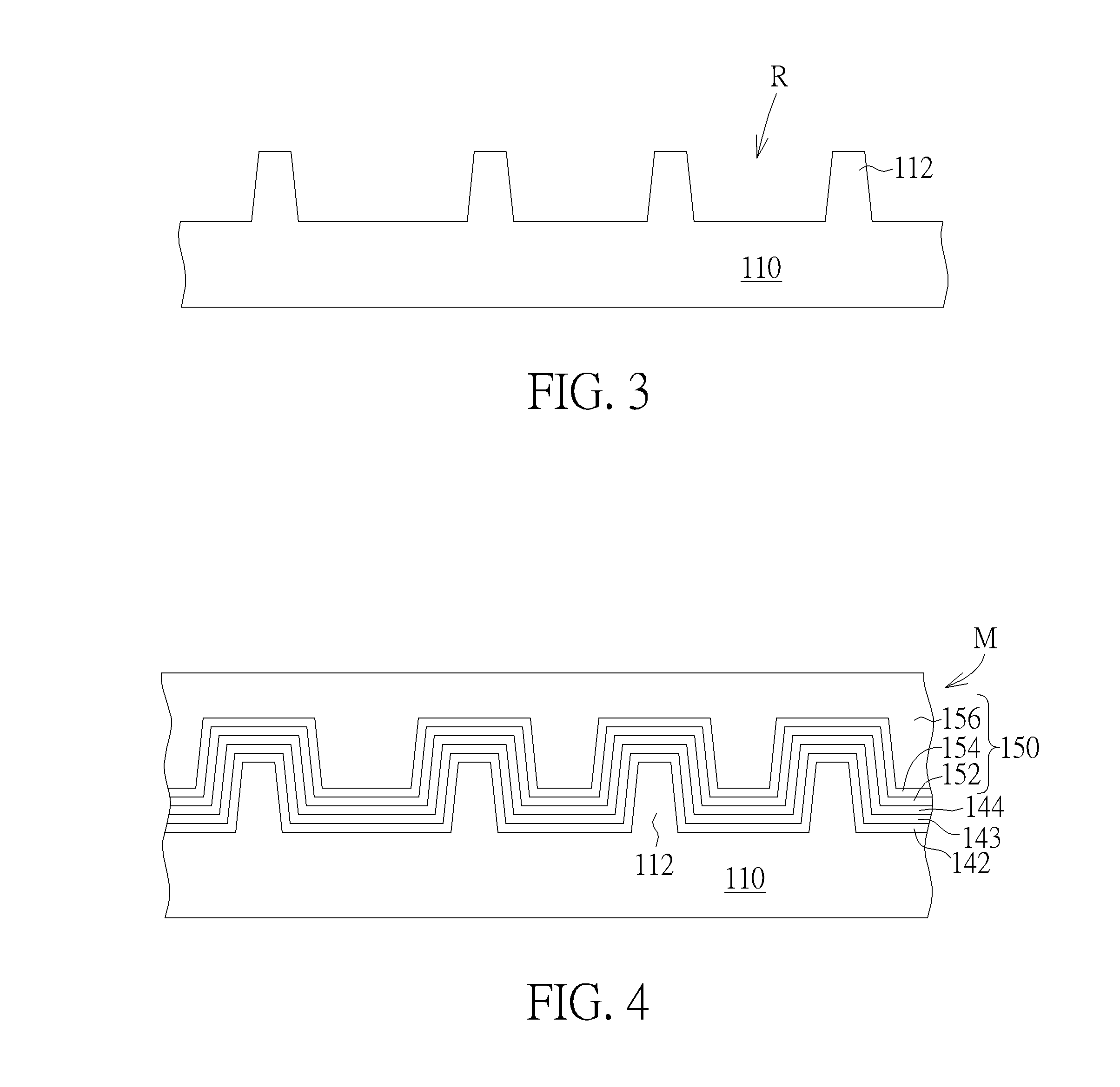

Semiconductor structure and process thereof

ActiveUS20160300755A1Short heightProcessing problemSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

A semiconductor process includes the following step. A metal gate strip and a cap layer are sequentially formed in a trench of a dielectric layer. The cap layer and the metal gate strip are cut off to form a plurality of caps on a plurality of metal gates, and a gap isolates adjacent caps and adjacent metal gates. An isolation material fills in the gap. The present invention also provides semiconductor structures formed by said semiconductor process. For example, the semiconductor structure includes a plurality of stacked structures in a trench of a dielectric layer, where each of the stacked structures includes a metal gate and a cap on the metal gate, where an isolation slot isolates and contacts adjacent stacked structures at end to end, and the isolation slot has same level as the stacked structures.

Owner:MARLIN SEMICON LTD

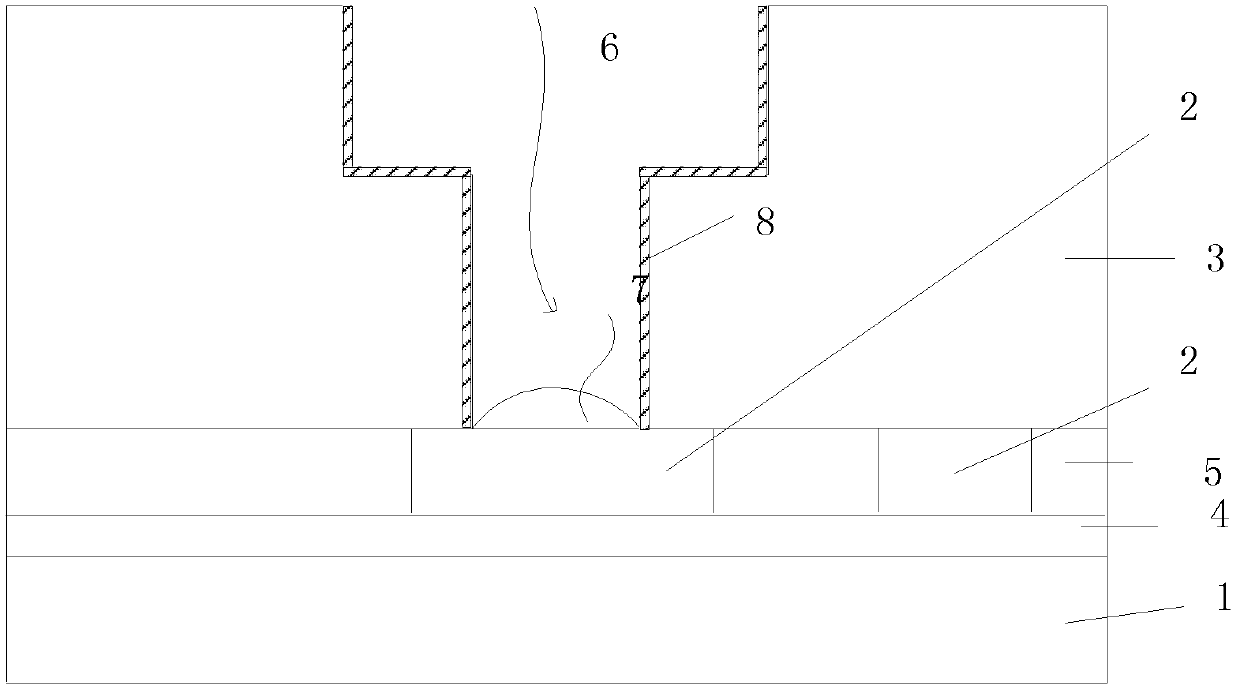

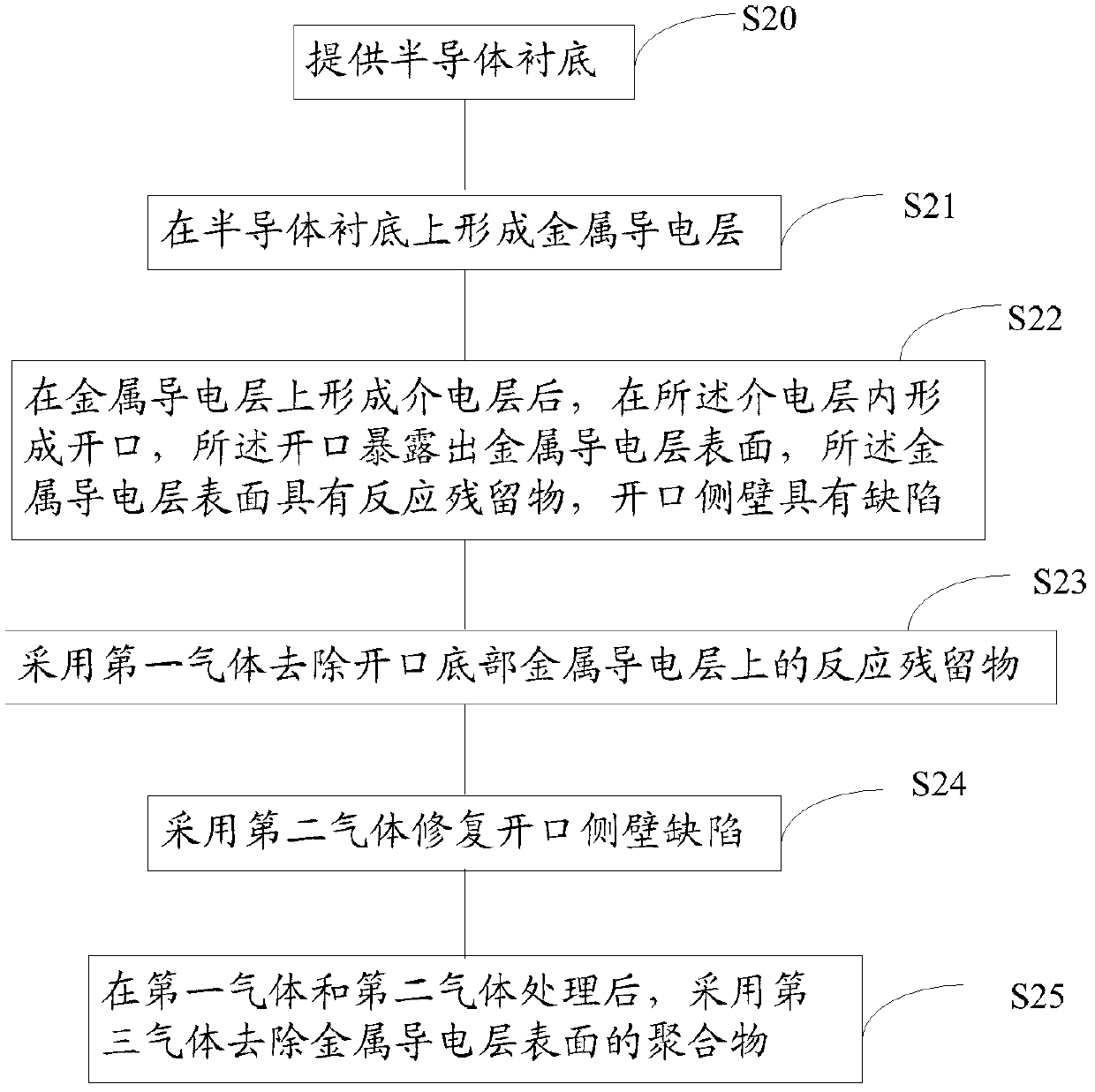

Method of forming opening

ActiveCN103377913AImprove yieldImprove reliabilitySemiconductor/solid-state device manufacturingAfter treatmentDielectric layer

Disclosed is a method of forming an opening. The method comprises the steps of providing a semiconductor substrate; forming a metal conductive layer on the semiconductor substrate; forming a dielectric layer on the metal conductive layer and forming an opening in the dielectric layer with the opening exposing a surface of the metal conductive layer, the surface of the metal conductive layer having a reaction residue and a side wall of the opening having a defect; removing the reaction residue on the metal conductive layer at the bottom of the opening by use of a first gas; repairing the defect on the side wall of the opening by use of a second gas; and removing, after treatment of the first gas and the second gas, a polymer on the surface of the metal conductive layer by use of a third gas. The method of forming the opening is used for improving electrical properties, stability and yield of an integrated circuit.

Owner:SEMICON MFG INT (SHANGHAI) CORP

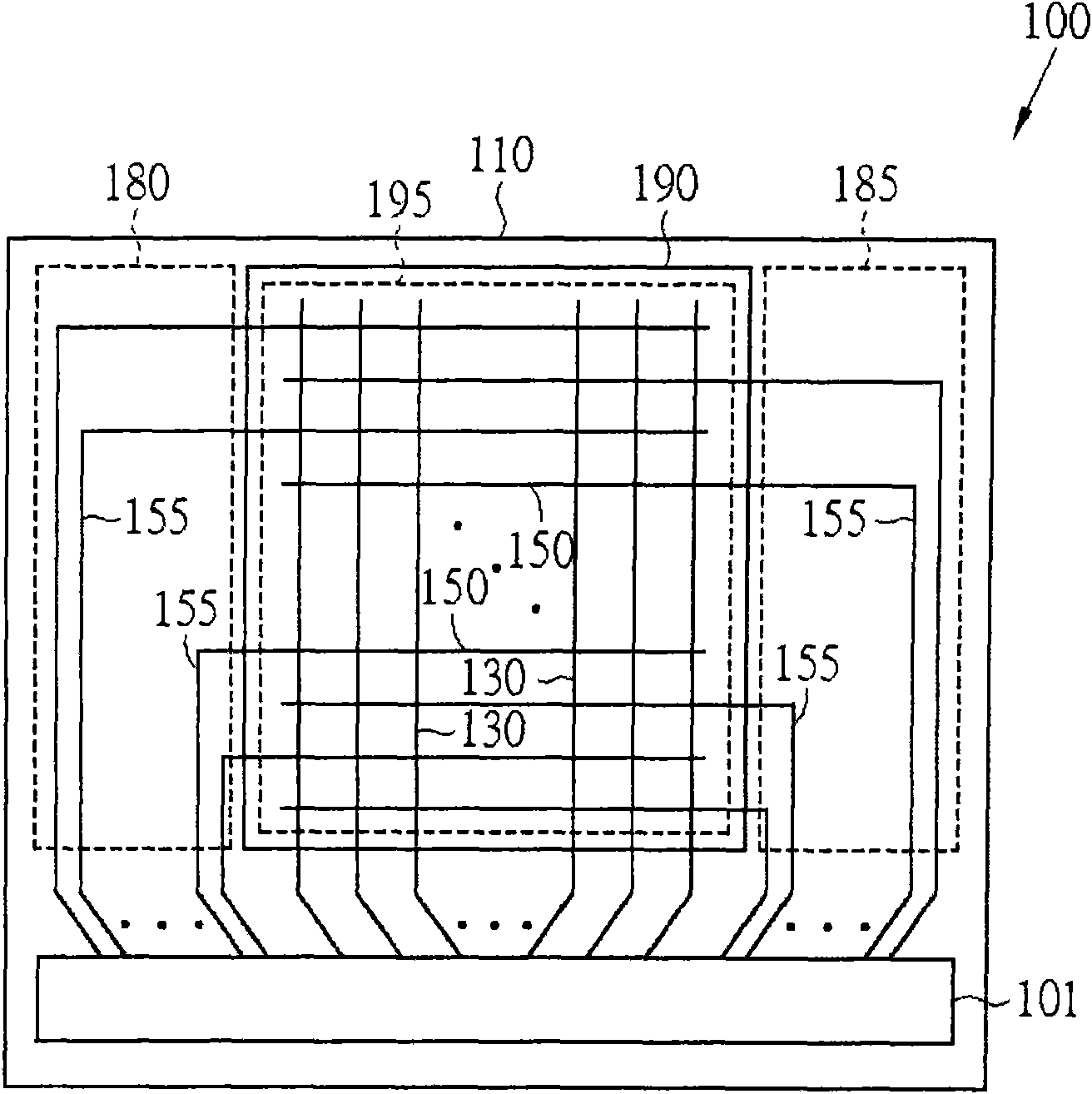

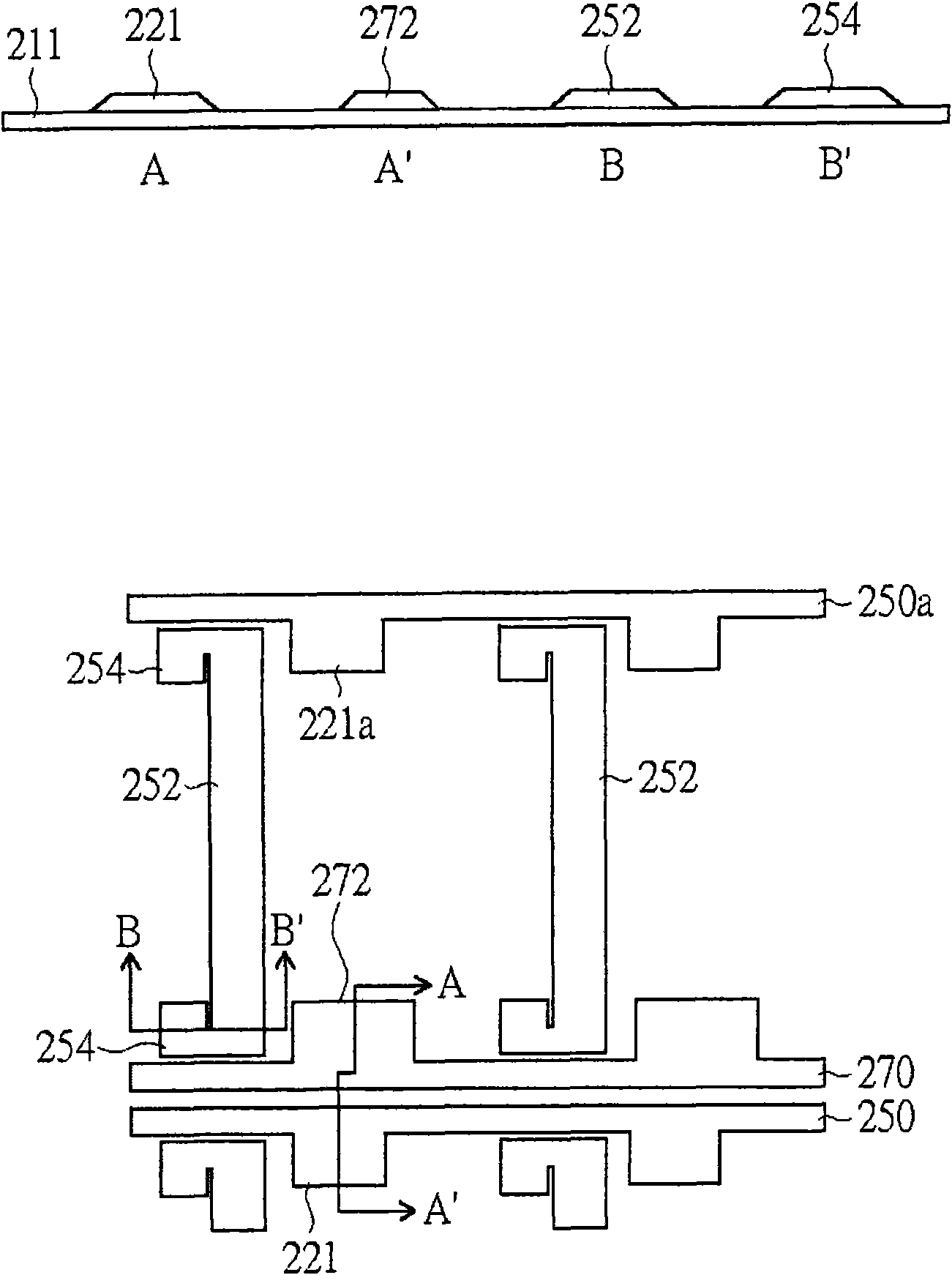

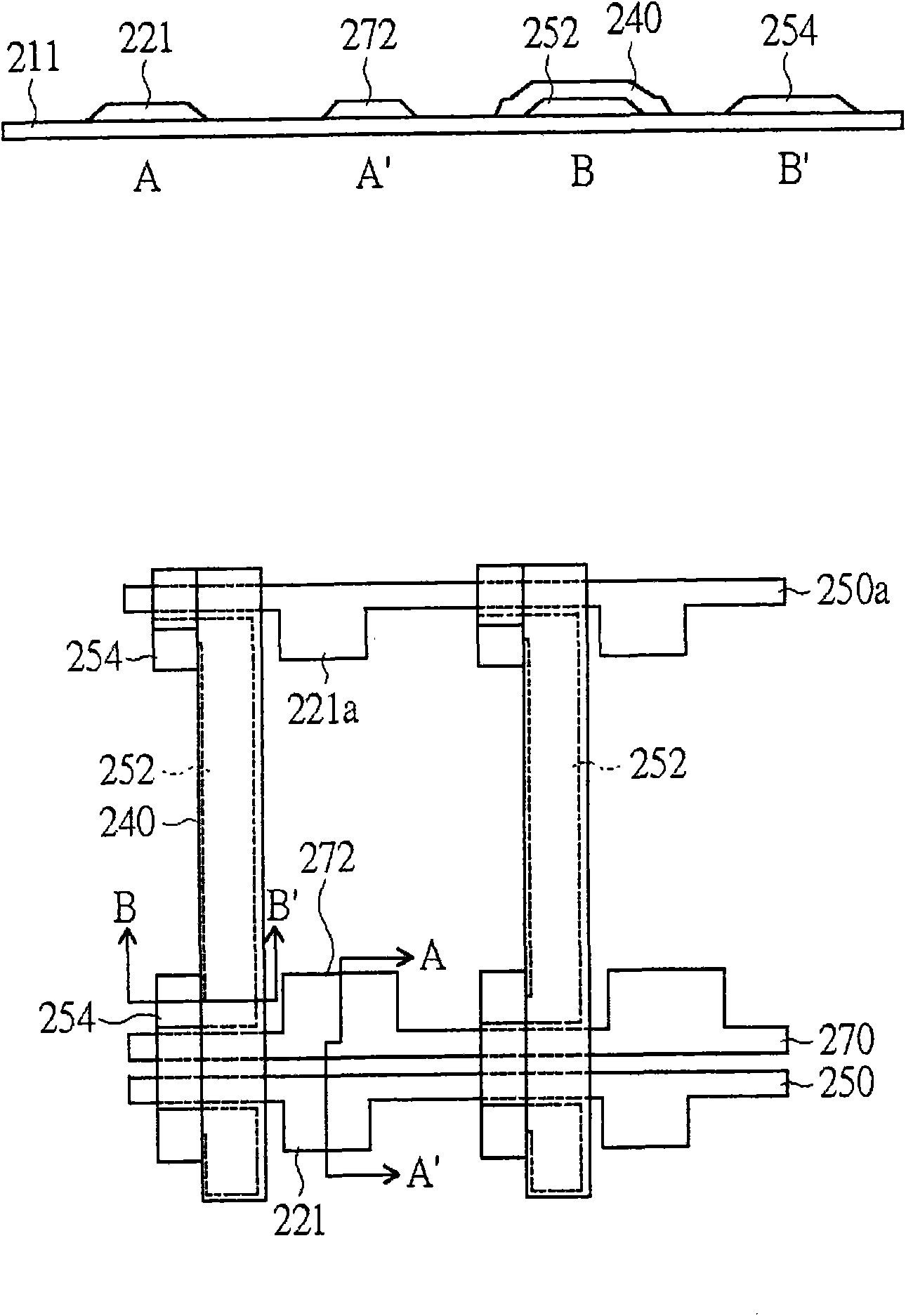

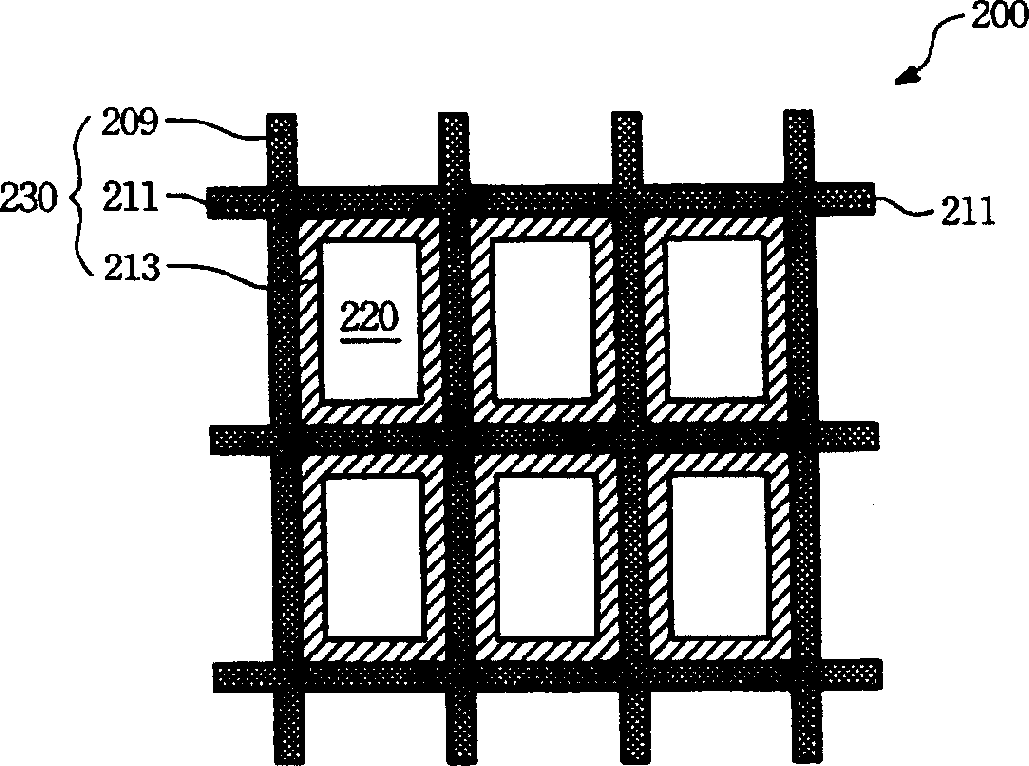

Active array substrate, liquid crystal display panel and method for manufacturing active array substrate

ActiveCN101561609AAvoid loading effectImprove display qualitySemiconductor/solid-state device detailsSolid-state devicesLiquid-crystal displayEngineering

The invention provides an active array substrate, a liquid crystal display panel and a method for manufacturing the active array substrate. The active array substrate comprises a substrate, a plurality of scanning lines, a plurality of data wires and a plurality of grid electrode patch cords arranged on the substrate, wherein the grid electrode patch cords have a plurality of first parts, a plurality of patch cord parts connected with the corresponding first parts, a plurality of connection holes and a plurality of second parts. The second parts and the first parts are not arranged at the same layer and one of the second parts is electrically connected with the corresponding first part by one of the connection holes.

Owner:AU OPTRONICS CORP

Organic light-emitting diode and display

ActiveCN1828966AImprove current injection effectReduce reflectivityElectroluminescent light sourcesSolid-state devicesPhotoluminescenceDisplay device

An organic LED includes a transparency electrode, an organic luminescent layer, an antireflection and an auxiliary electrode. Said Organic luminescent layer is located between transparency electrode and antireflection electrode, antireflection electrode including first conducting layer, a second conducting layer and a nonmetal layer, said first conducting layer located between organic luminescent layer and nonmetal layer, said nonmetal layer located between first conducting layer and second conducting layer, auxiliary electrode penetration nonmetal layer and connecting said first conducting layer to second conducting layer. Above-mentioned organic LED can be used in an organic electro photoluminescence display.

Owner:AU OPTRONICS CORP

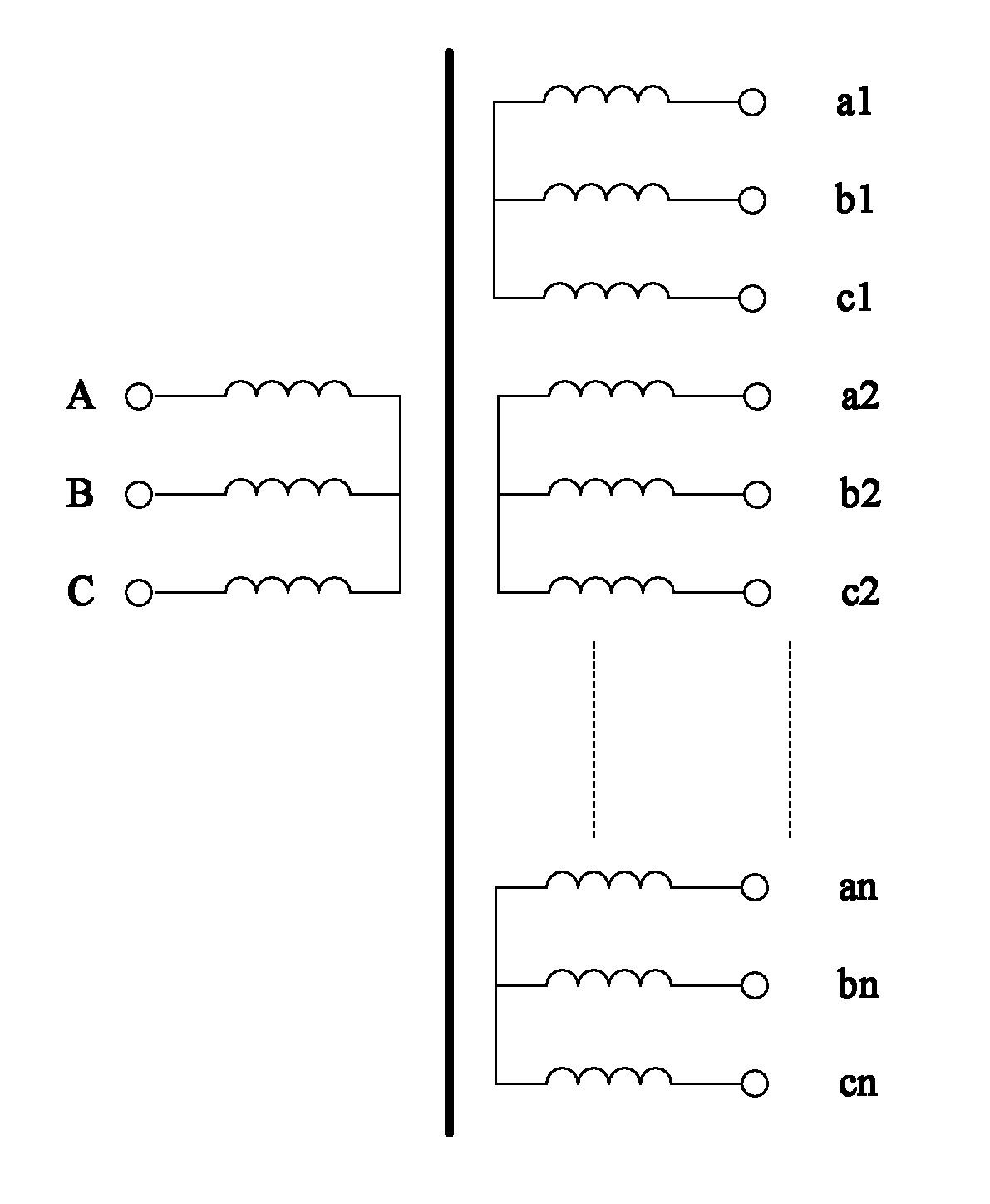

Reduction in interference between components

ActiveUS20100137019A1Easy to addImprove performanceTransformers/inductances coils/windings/connectionsSubstation equipmentTransducerElectrical connection

An apparatus is disclosed comprising a transducer, which transducer comprises at least one electrical connection point configured to enable an external electrical connection of the transducer. The transducer further comprises at least one decoupling coil configured to electrically decouple the transducer from the at least one electrical connection point at a frequency above an operating frequency of the transducer. Moreover, a method for assembling the described apparatus is disclosed.

Owner:RPX CORP

Contact structure, contact pad layout and structure, mask combination and manufacturing method thereof

PendingUS20210272961A1SizeImprove performanceTransistorSolid-state devicesElectrical resistance and conductanceContact pad

A contact structure, contact pad layout and structure, mask combination and manufacturing method thereof is provided in the present invention. Through the connection of tops of at least two contact plugs in the boundary of core region, an integrated contact with larger cross-sectional area is formed in the boundary of core region. Accordingly, the process of forming electronic components on the contact structure in the boundary of core region may be provided with sufficient process window to increase the size of electronic components in the boundary, lower contact resistance, and the electronic component with increased size in the boundary buffer the density difference of circuit patterns between the core region and the peripheral region, thereby improving optical proximity effect and ensuring the uniformity of electronic components on the contact plugs inside the boundary of core region, and avoiding the collapse of electronic components on the contact plug in the boundary.

Owner:FUJIAN JINHUA INTEGRATED CIRCUIT CO LTD

Methods and systems for rise-time improvements in differential signal outputs

InactiveUS20060103418A1Reduce load effectSwitching accelaration modificationsSemiconductor/solid-state device detailsCapacitanceDifferential signaling

A method for maintaining signal integrity of a differential output signal generated from a differential driver is disclosed. The method includes receiving the differential output signal from the differential driver. Once received, the method includes tuning the differential output signal by exposing the differential output signal to an inductance. The inductance is configured to reduce signal mismatch between complementary signals of the differential output signal. The signal mismatch is a result of having each of the complementary signals exposed to different capacitive loading. A device and system is also provided, which include integrating an inductor between the output leads of a differential driver. The inductor is sized for the particular frequency of operation, and the inductor provides an inductance that assists in eliminating mismatch between the complementary signals of the differential output. A reduction and / or elimination of the mismatch will assist in improving the rise-time of the differential signals.

Owner:SEIKO EPSON CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com