Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

53results about How to "Avoid loading effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

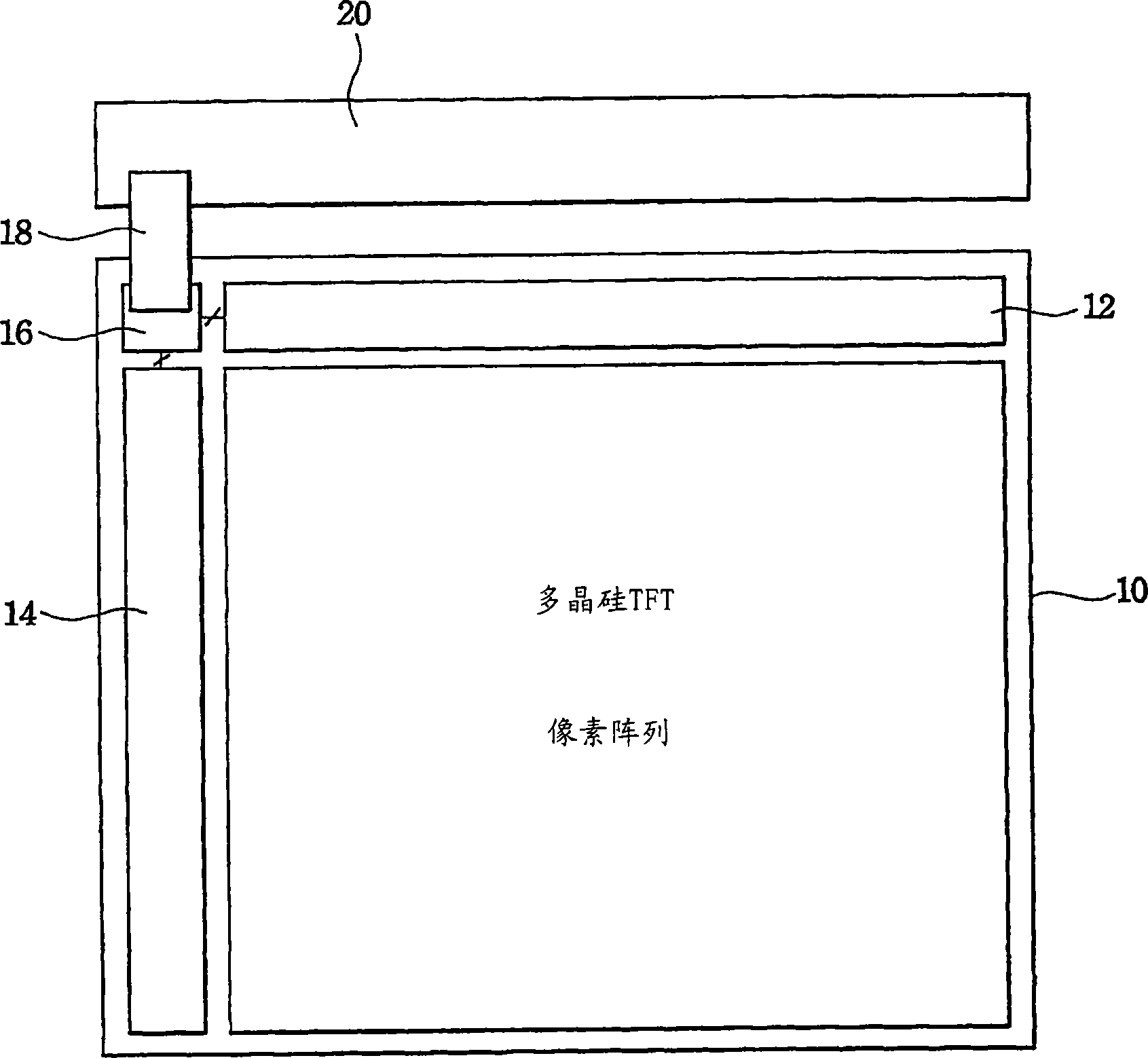

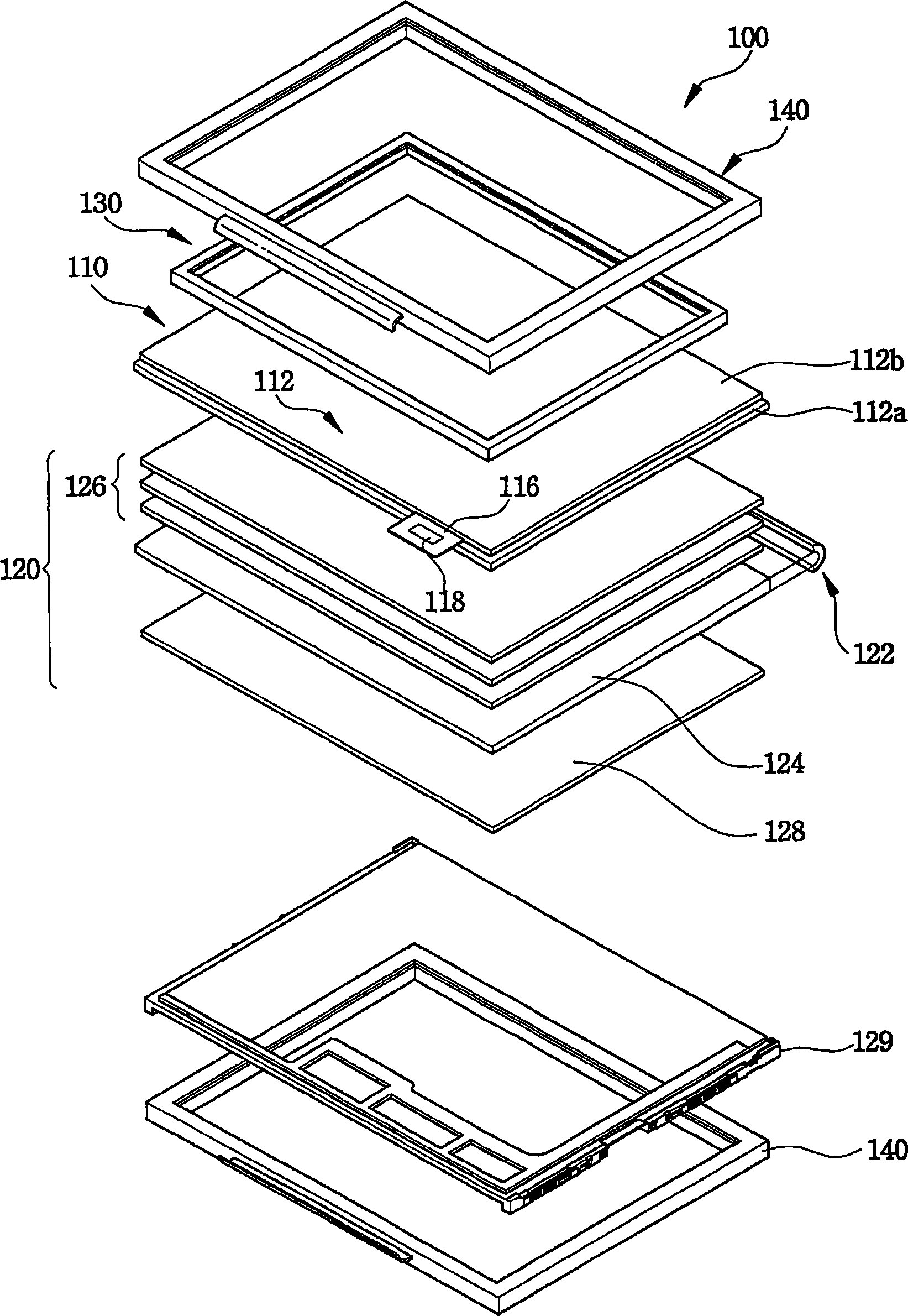

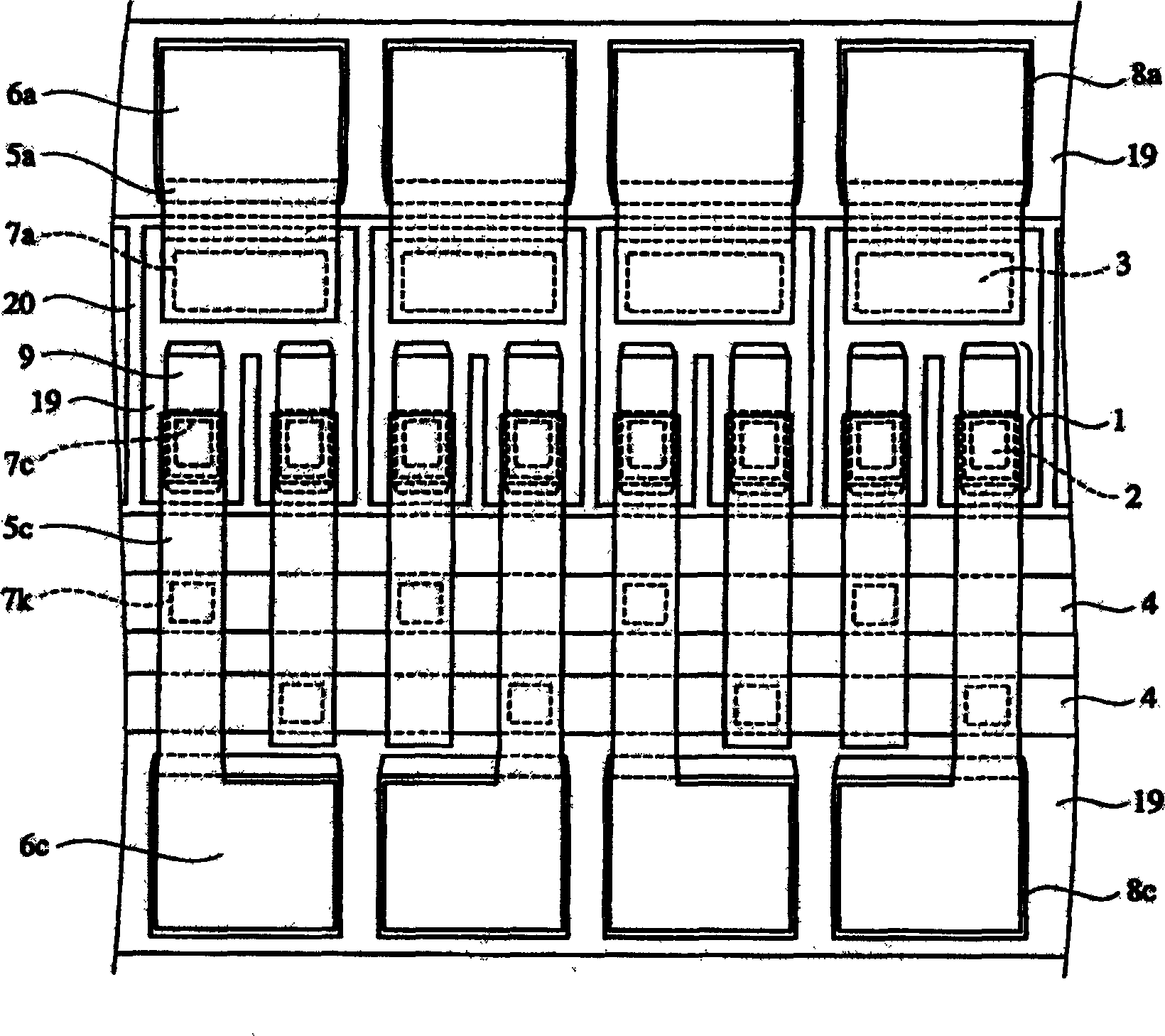

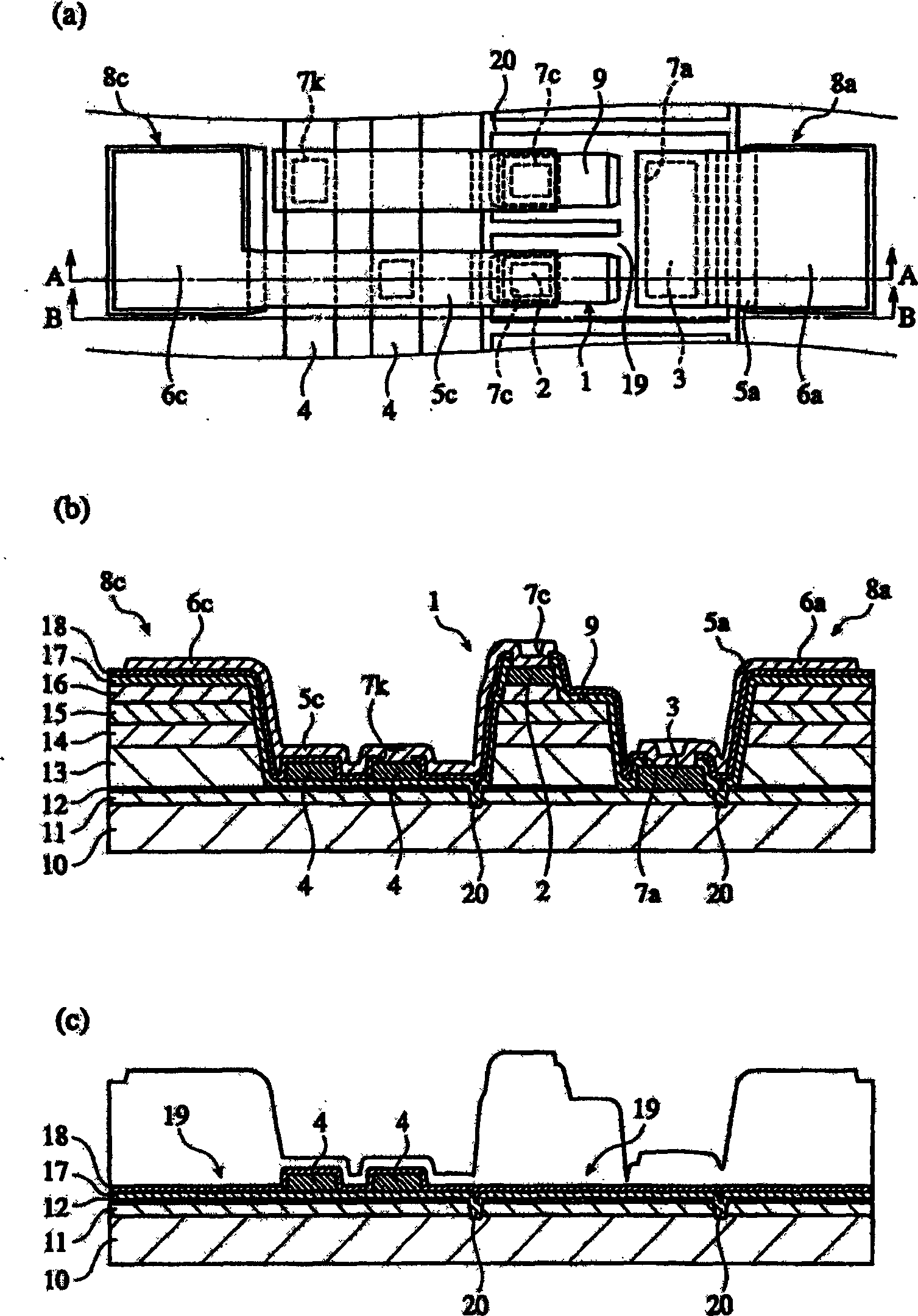

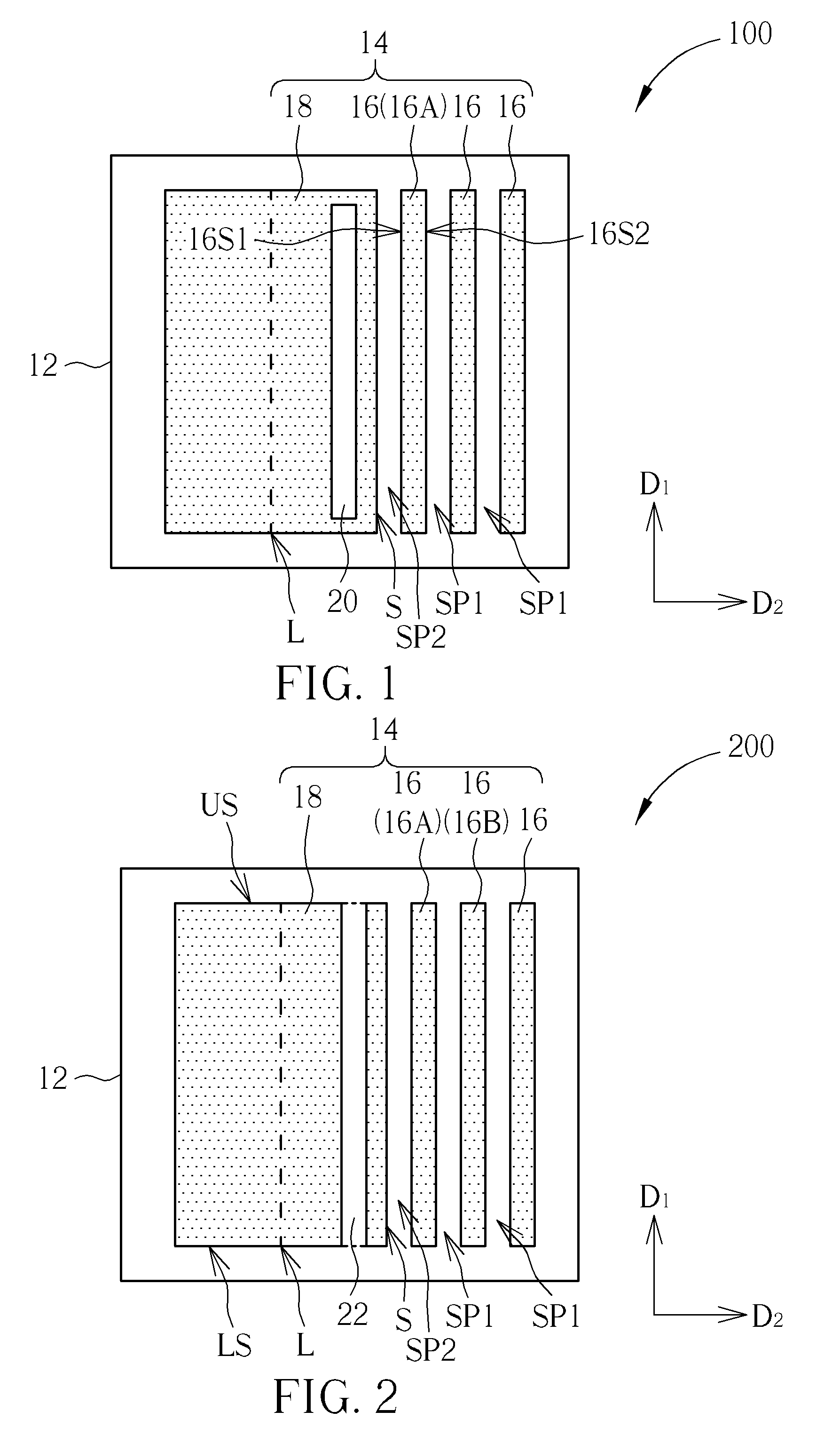

Method of driving a shift register, a shift register, a liquid crystal display device having the shift register

InactiveCN1860519ADelay minimizationAvoid loading effectStatic indicating devicesDigital storageShift registerLiquid-crystal display

In a shift register and LCD device having the shift register that may be employed in the liquid crystal display device having a large screen size and a large resolution, the shift register includes stages connected with each other and each of the stages have a carry buffer for generating a carry signal. The pull-down transistor of each of the stages of the shift register is divided into a first pull-down transistor and a second pull-down transistor. A power voltage Vona larger than the power voltage Von applied to a clock generator is applied to the shift register. A signal delay due to the RC delay of the gate lines may be minimized, the shift register is independent of the variation of the threshold voltage of the TFTs, and image display quality may not be deteriorated.

Owner:SAMSUNG DISPLAY CO LTD

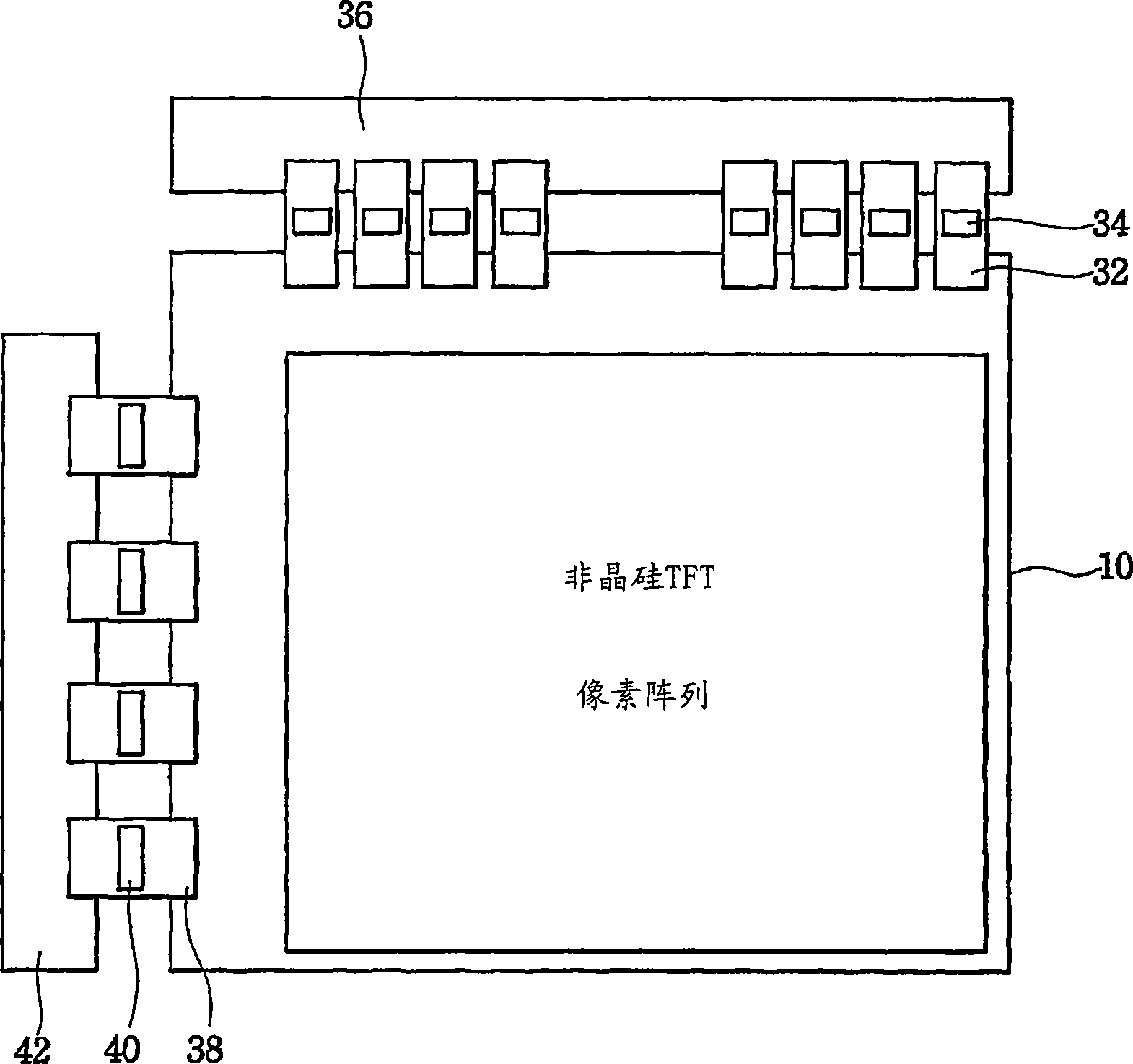

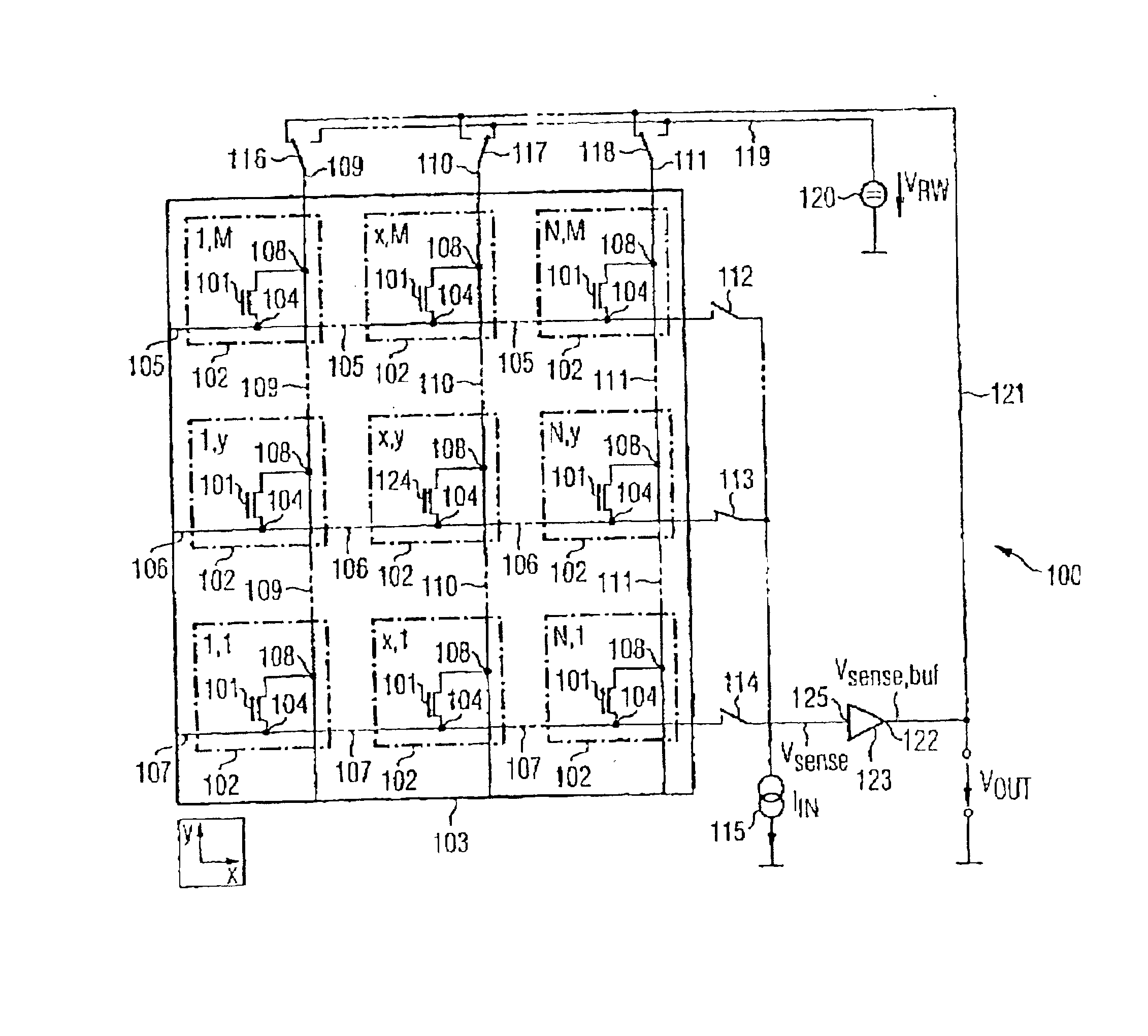

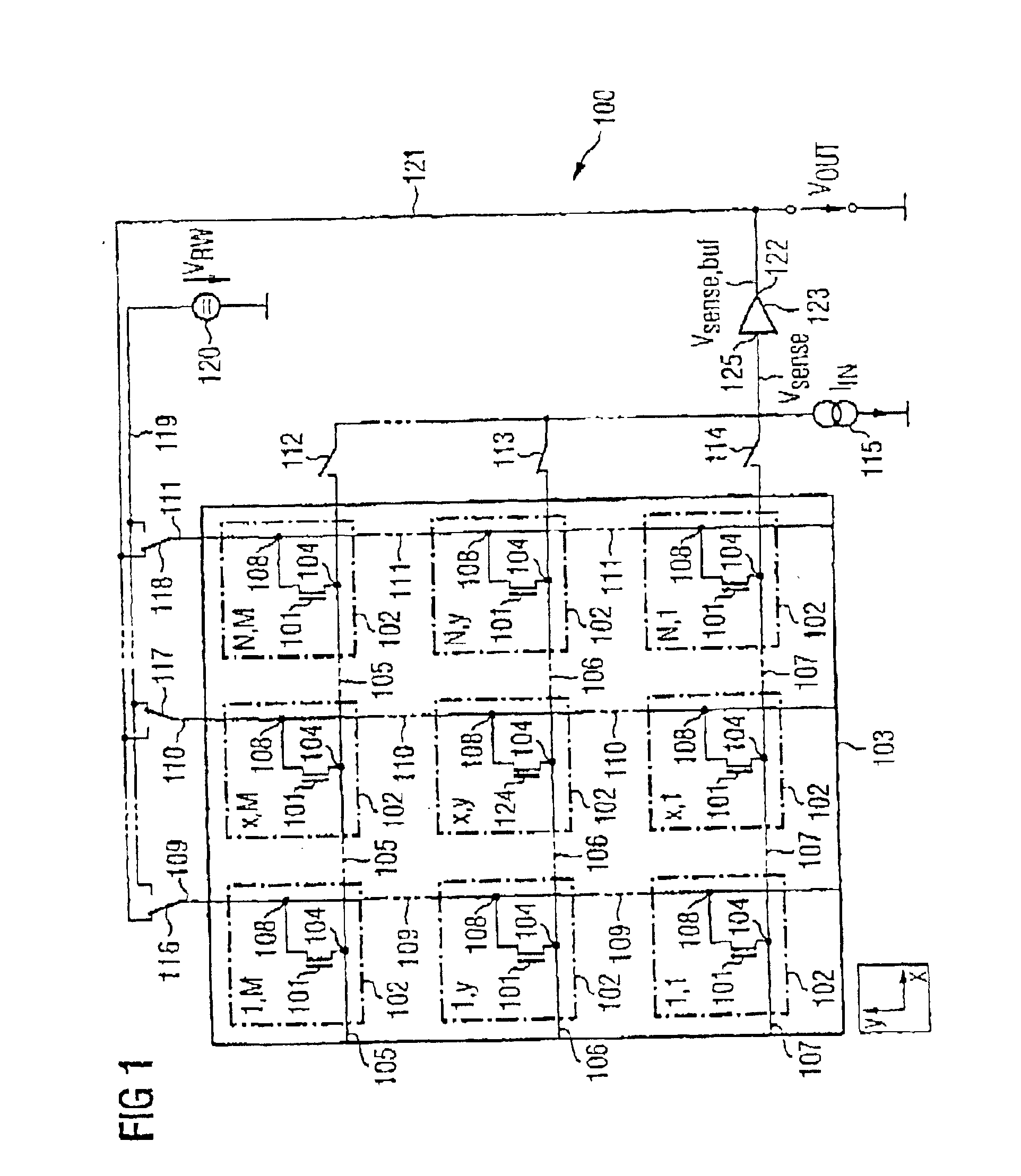

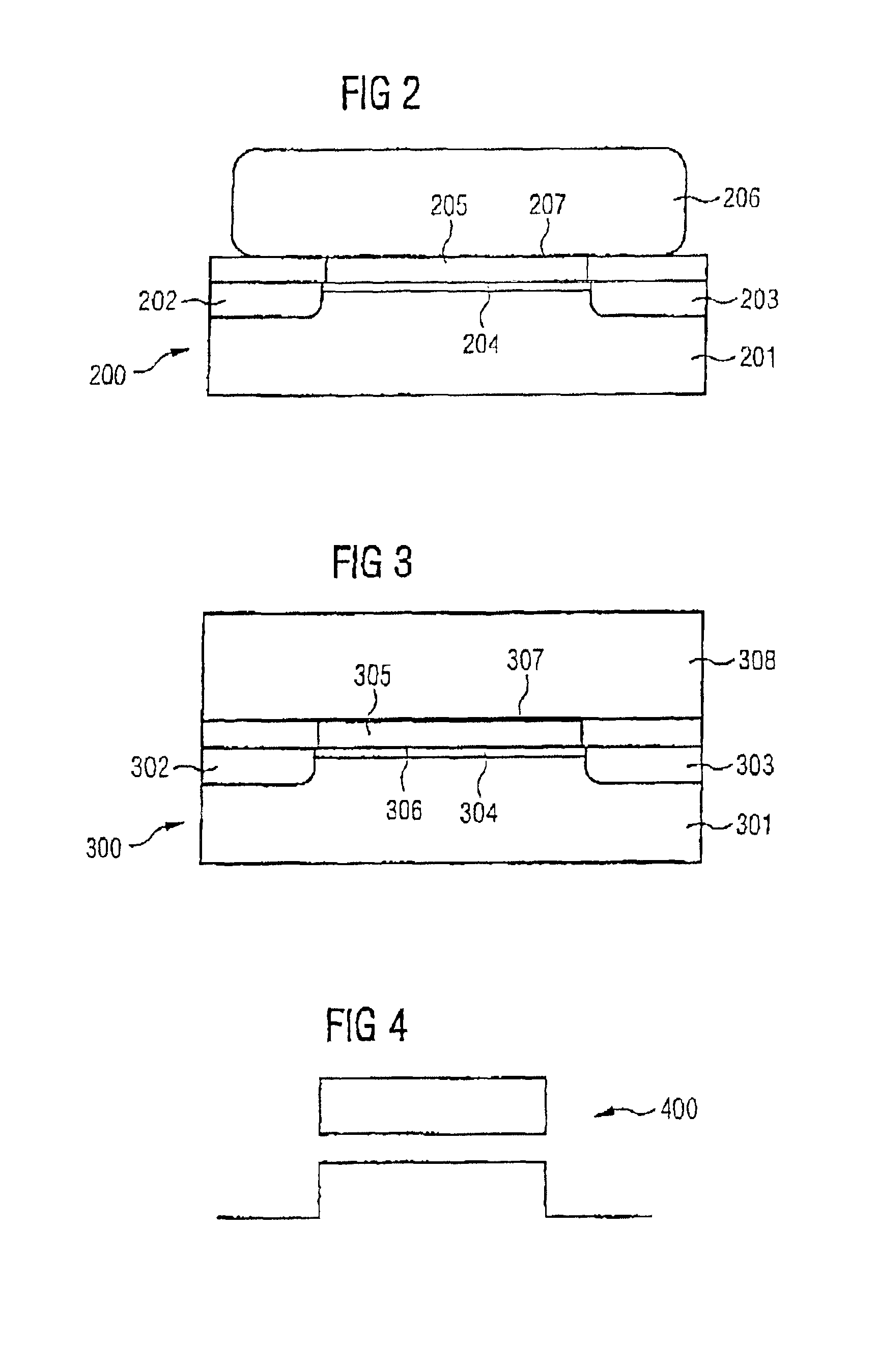

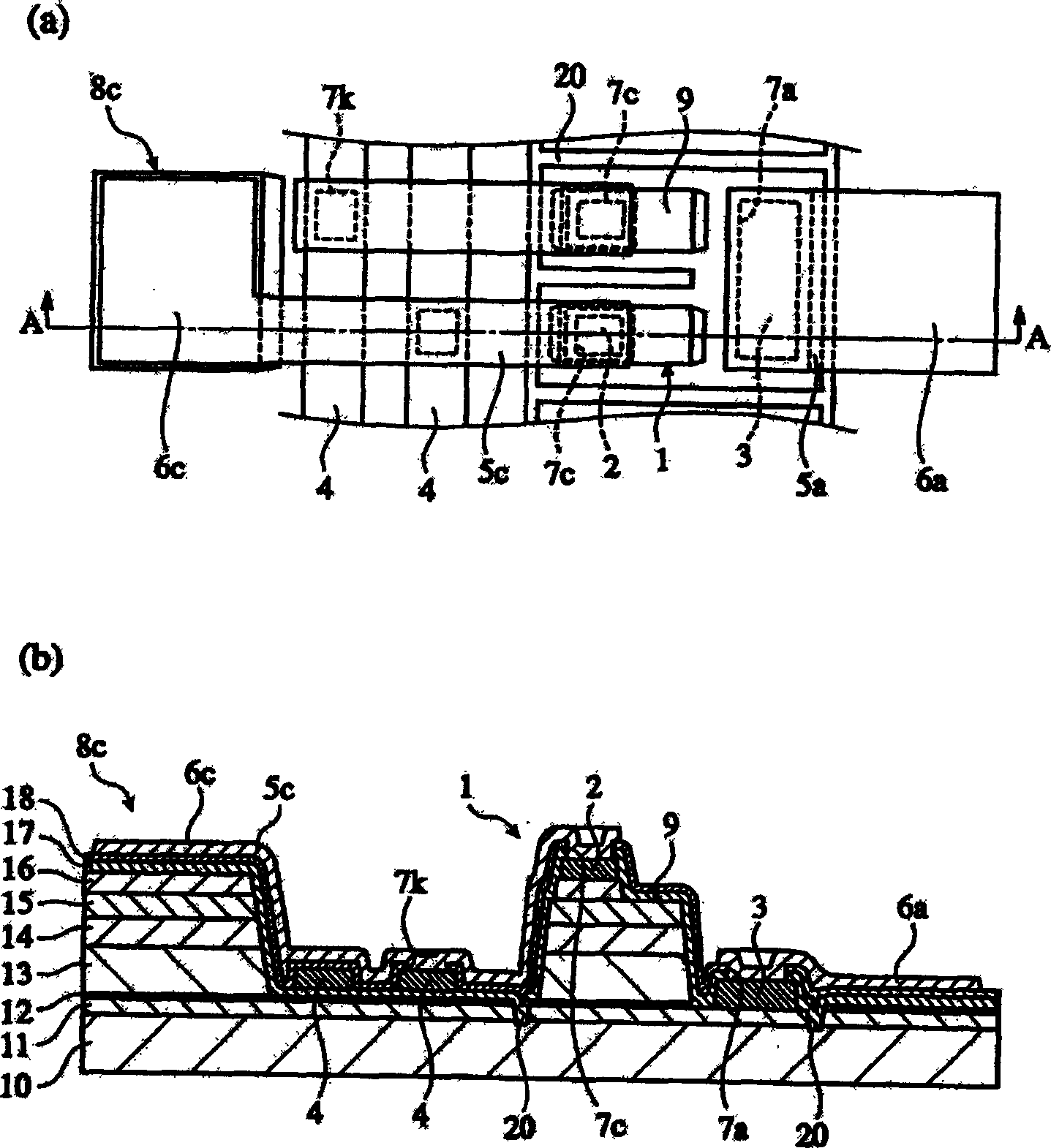

Sensor array and method for detecting the condition of a transistor in a sensor array

InactiveUS6856161B2High levelHigh resolutionDigital circuit testingMaterial analysis by electric/magnetic meansSensor arrayField-effect transistor

A sensor array is provided including transistors that are coupled together. The transistors are designed as sensors and wherein the sensor array has switching devices for selecting a transistor and wherein the selected transistor's condition may be detected. The sensor array is set up so that the selected transistor is driven as a source follower and at least some of the transistors are MOS field effect transistors that are configured so that at least some of the transistors are capable of detecting biological material.

Owner:SIEMENS AG

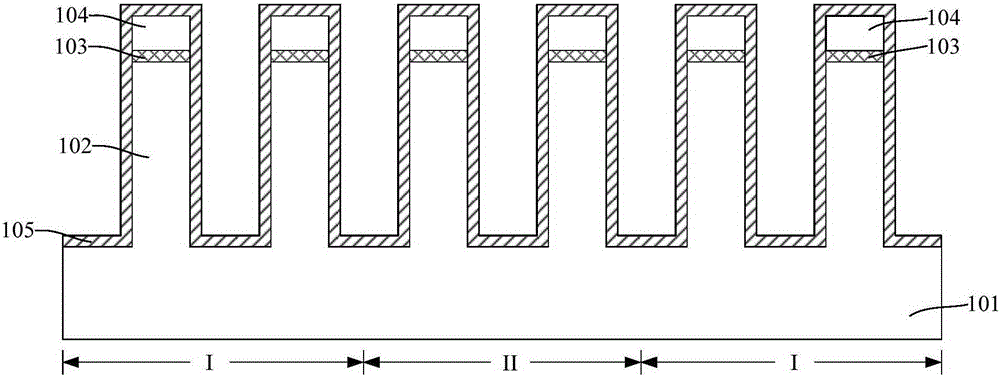

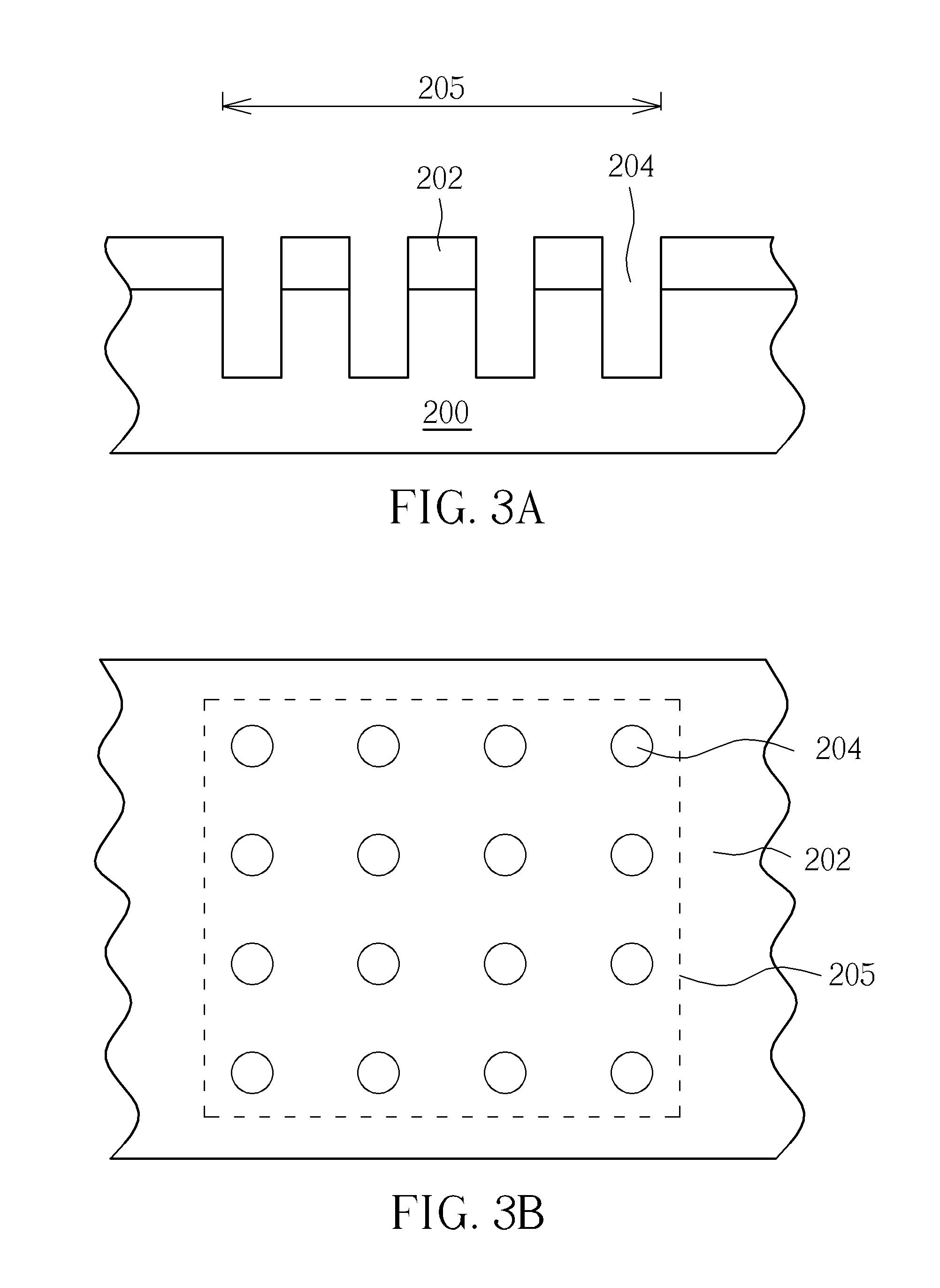

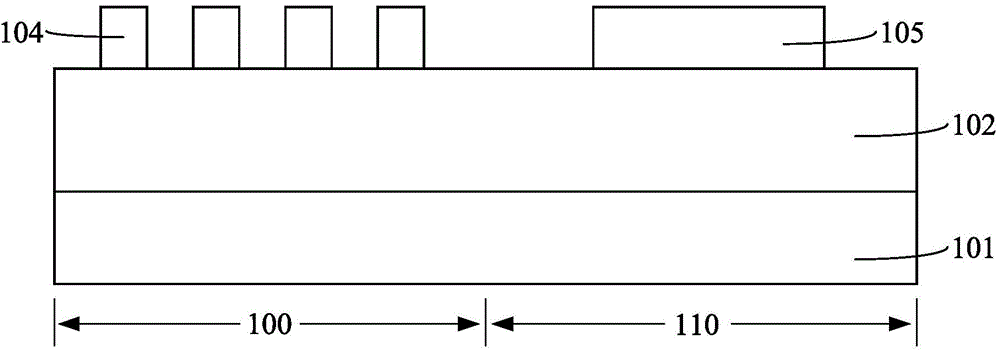

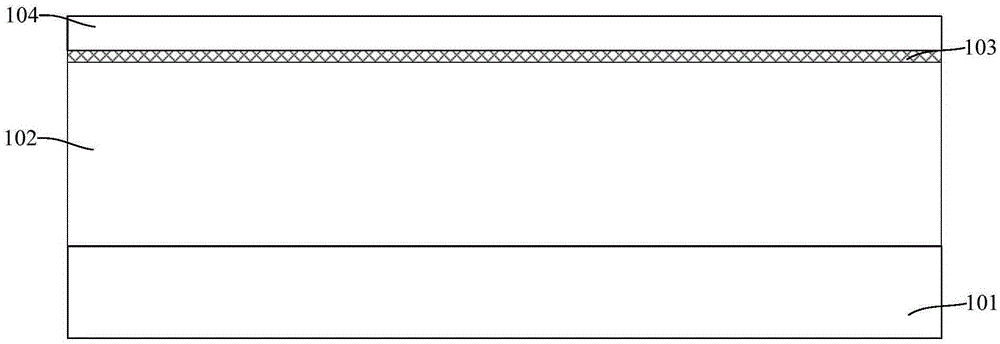

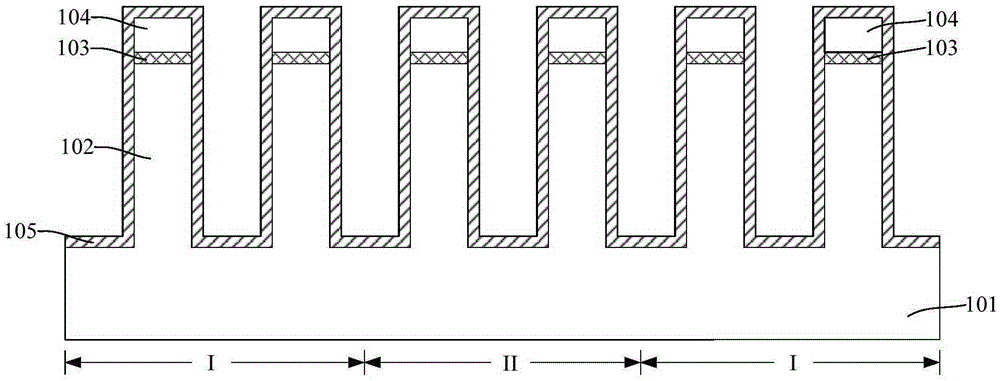

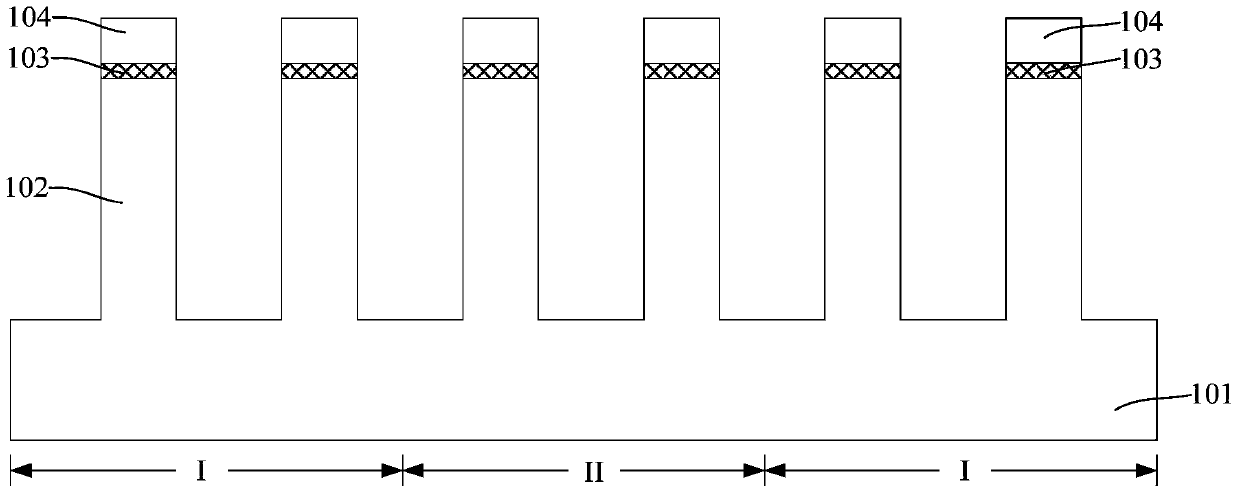

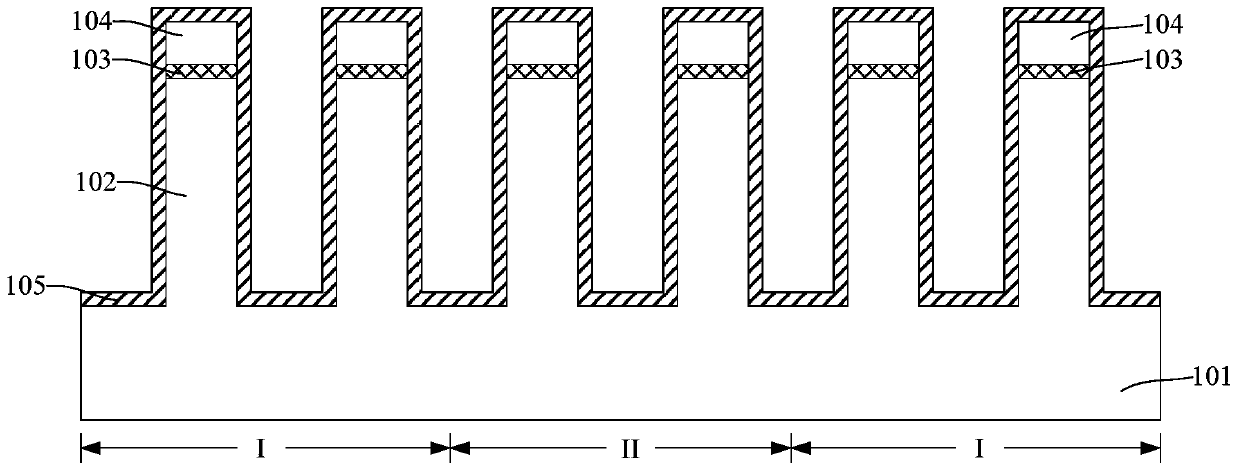

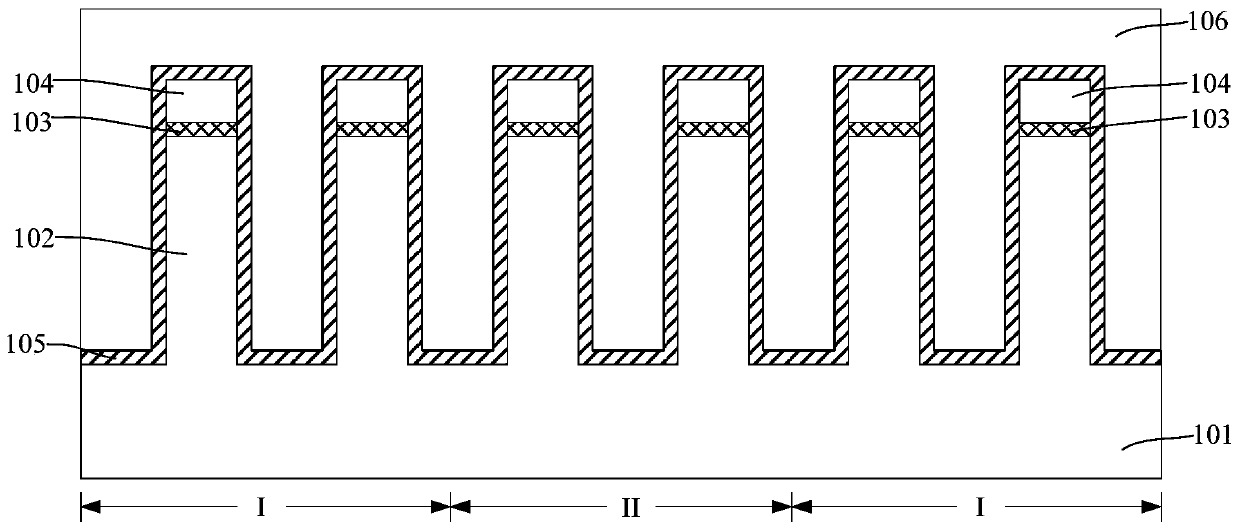

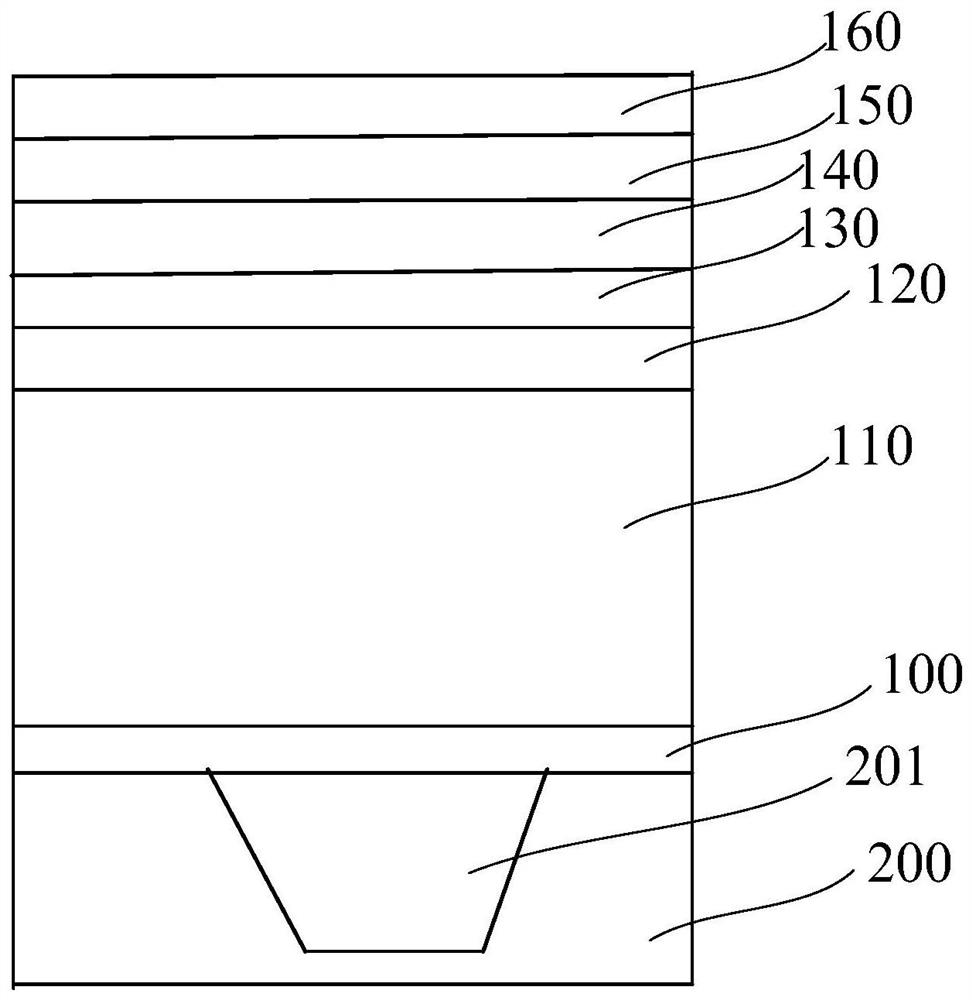

Method for forming fin field effect transistor

ActiveCN106571336AImprove electrical performanceGood feature sizeSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectrical performance

A method for forming a fin field effect transistor comprises: providing a substrate, wherein the substrate includes first regions and second regions located between adjacent first regions, a plurality of discrete fins are formed on the surface of the substrate, and the distances between the adjacent fins are the same; fully filling the surface of the substrate between the adjacent fins with a first dielectric layer, wherein the first dielectric layer covers the sidewall surfaces of the fins; removing the first dielectric layer of the second regions to expose the sidewall surfaces of the fins in the second regions; oxidizing the fins of the second regions to convert the fins of the second regions into an oxidizing structure; forming a second dielectric layer on the substrate in the second regions, wherein the second dielectric layer also covers the sidewall surface of the oxidizing structure, and the sidewall surface of the first dielectric layer in the first regions; etching back a part of thickness of the first dielectric layer, the second dielectric layer, and the oxidizing structure. The method forms a number of fins with different pattern densities and with good feature sizes and morphology so as to improve the electrical performance of the fin field effect transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

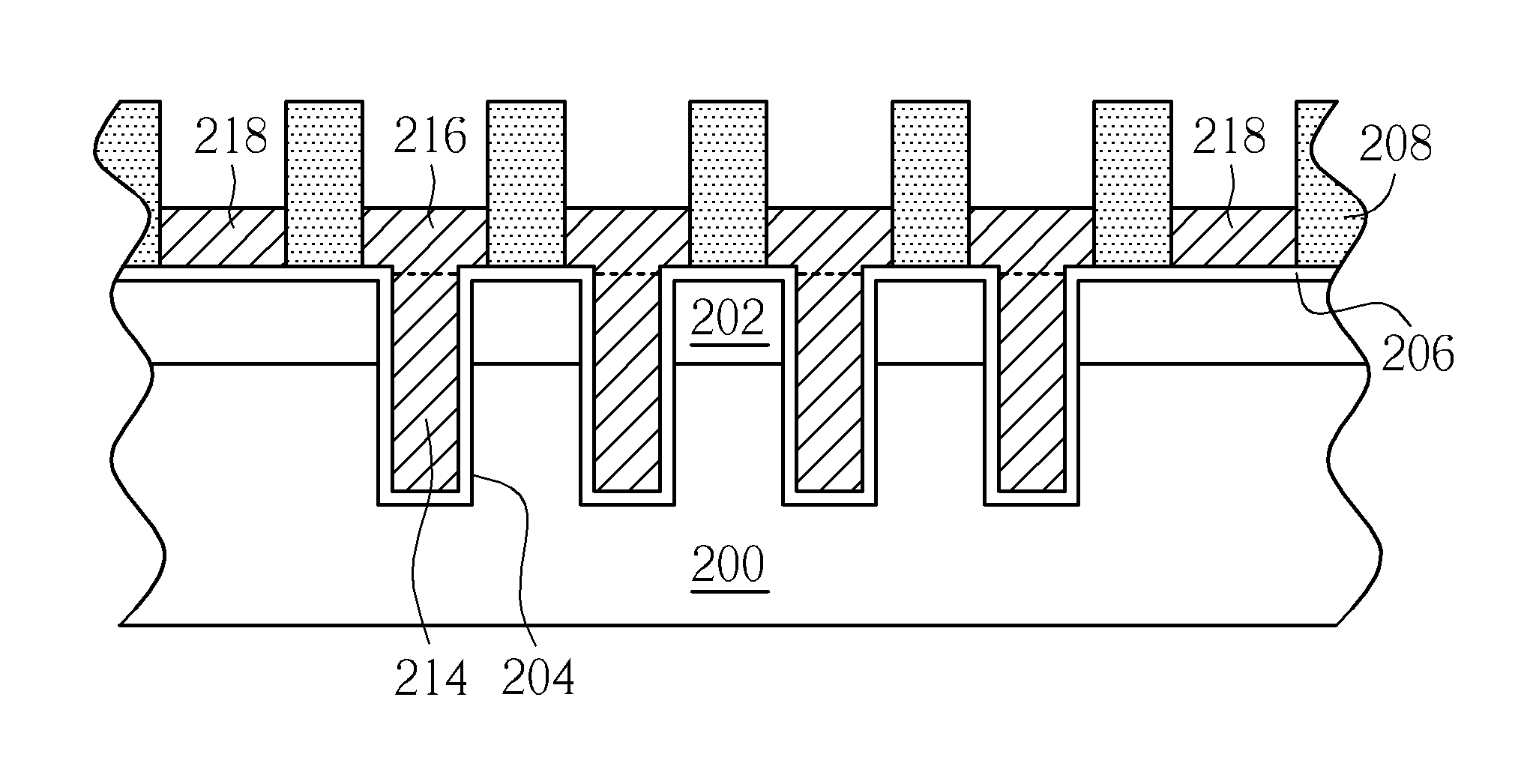

Through Silicon Via and Method of Manufacturing the Same

InactiveUS20130140688A1Improve filling uniformityImprove methodSemiconductor/solid-state device detailsSolid-state devicesEngineeringThrough-silicon via

The present invention discloses a through silicon via and method of manufacturing the same comprising the steps of providing a substrate, forming a plurality of through silicon via (TSV) holes in said substrate, forming a seed layer on the surface of said substrate and said a plurality of TSV holes, forming a patterned mask on said substrate, wherein said patterned mask comprises a plurality of first openings corresponding to said TSV holes and a plurality of second openings adjacent to or surrounding said a plurality of first openings, forming a material layer on said substrate, wherein said material layer is filled into said TSV holes and said first openings to form a plurality of through silicon vias, and said material layer is filled into said second openings to form a plurality of dummy bumps.

Owner:UNITED MICROELECTRONICS CORP

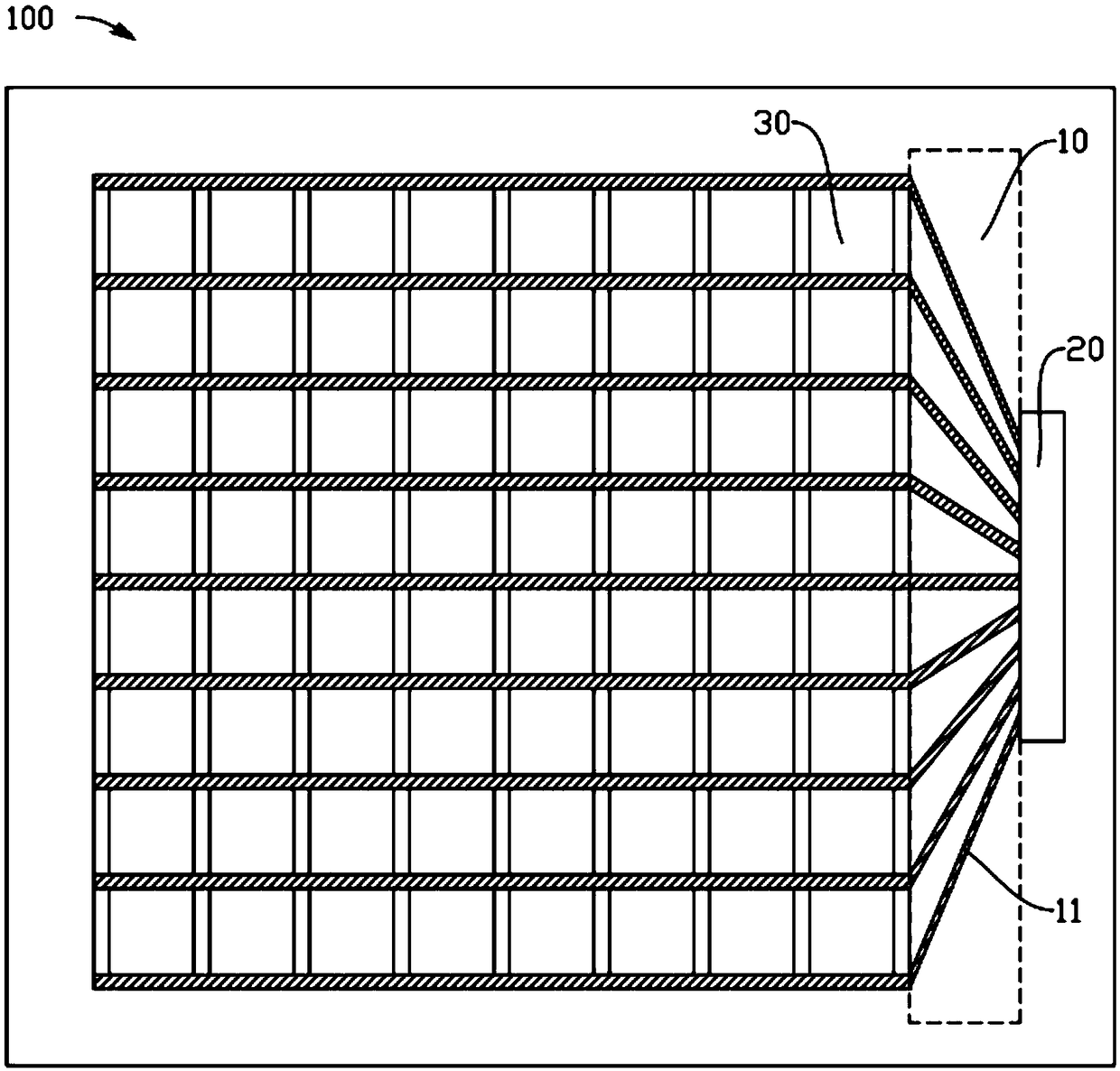

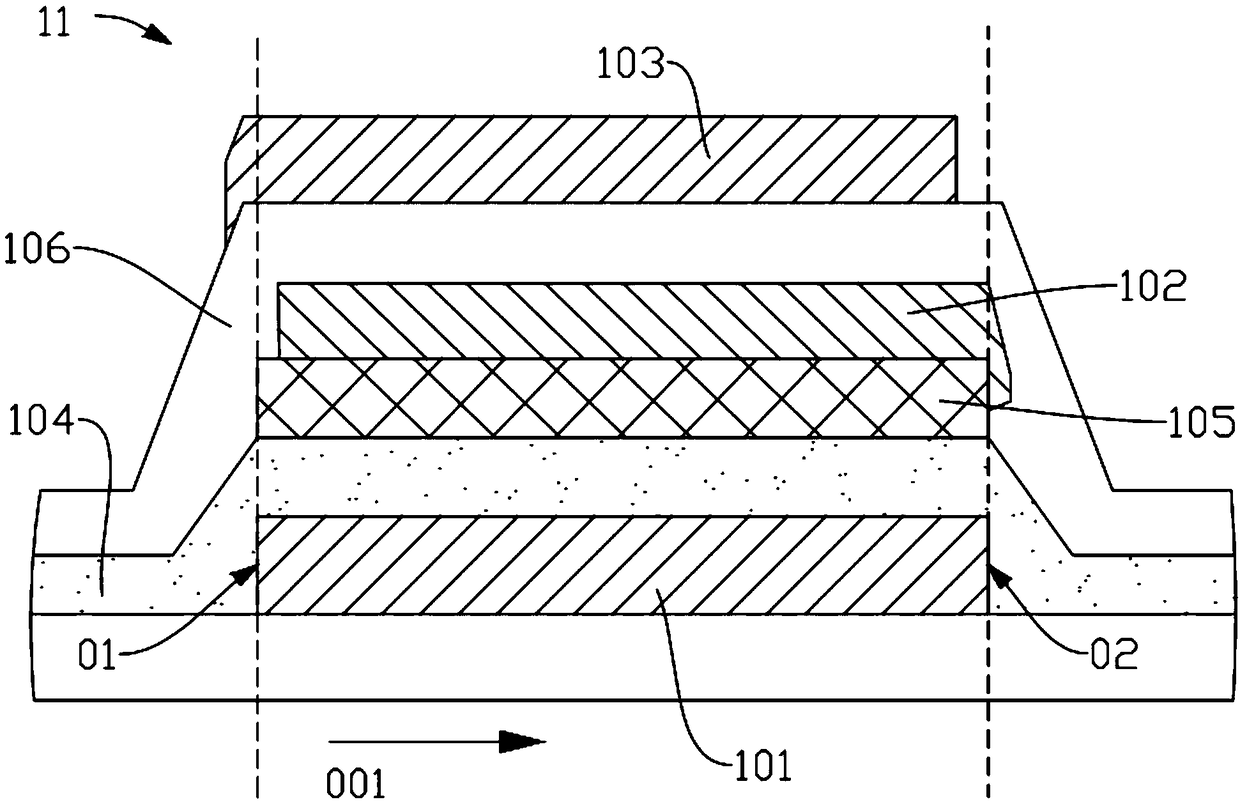

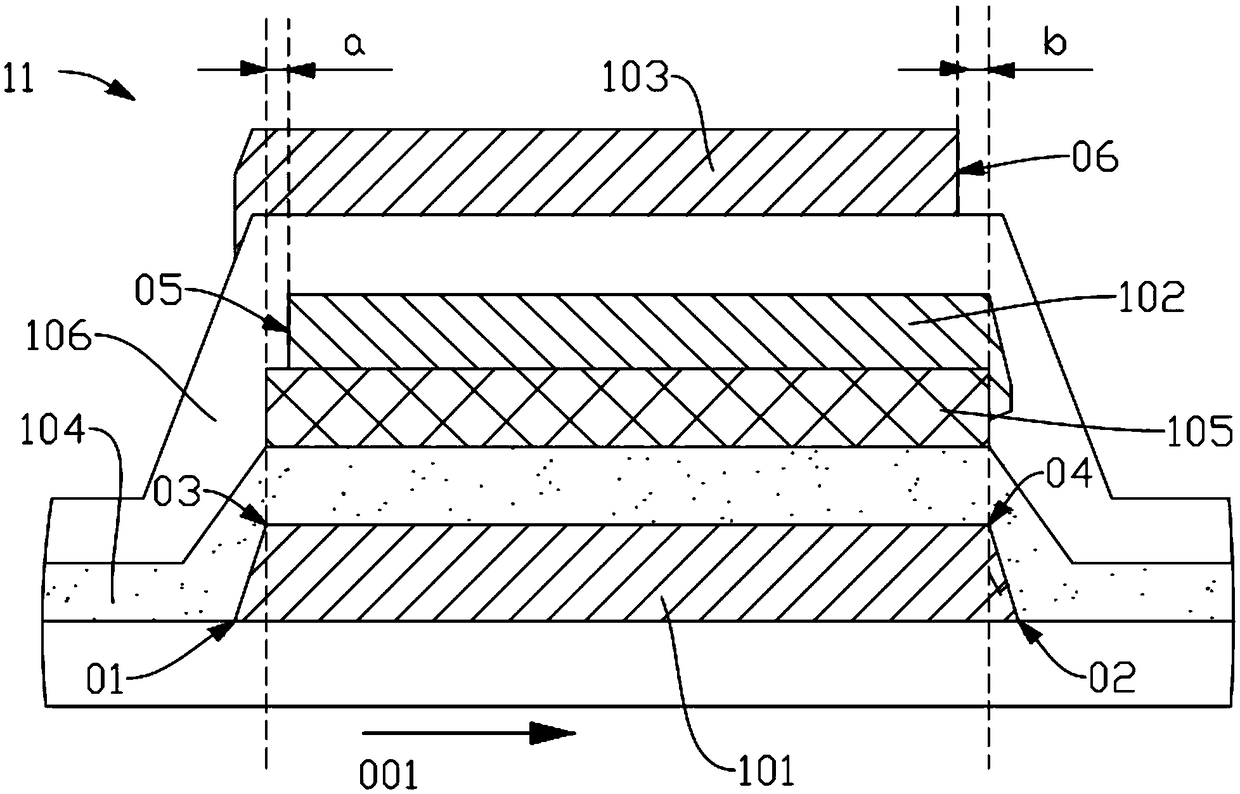

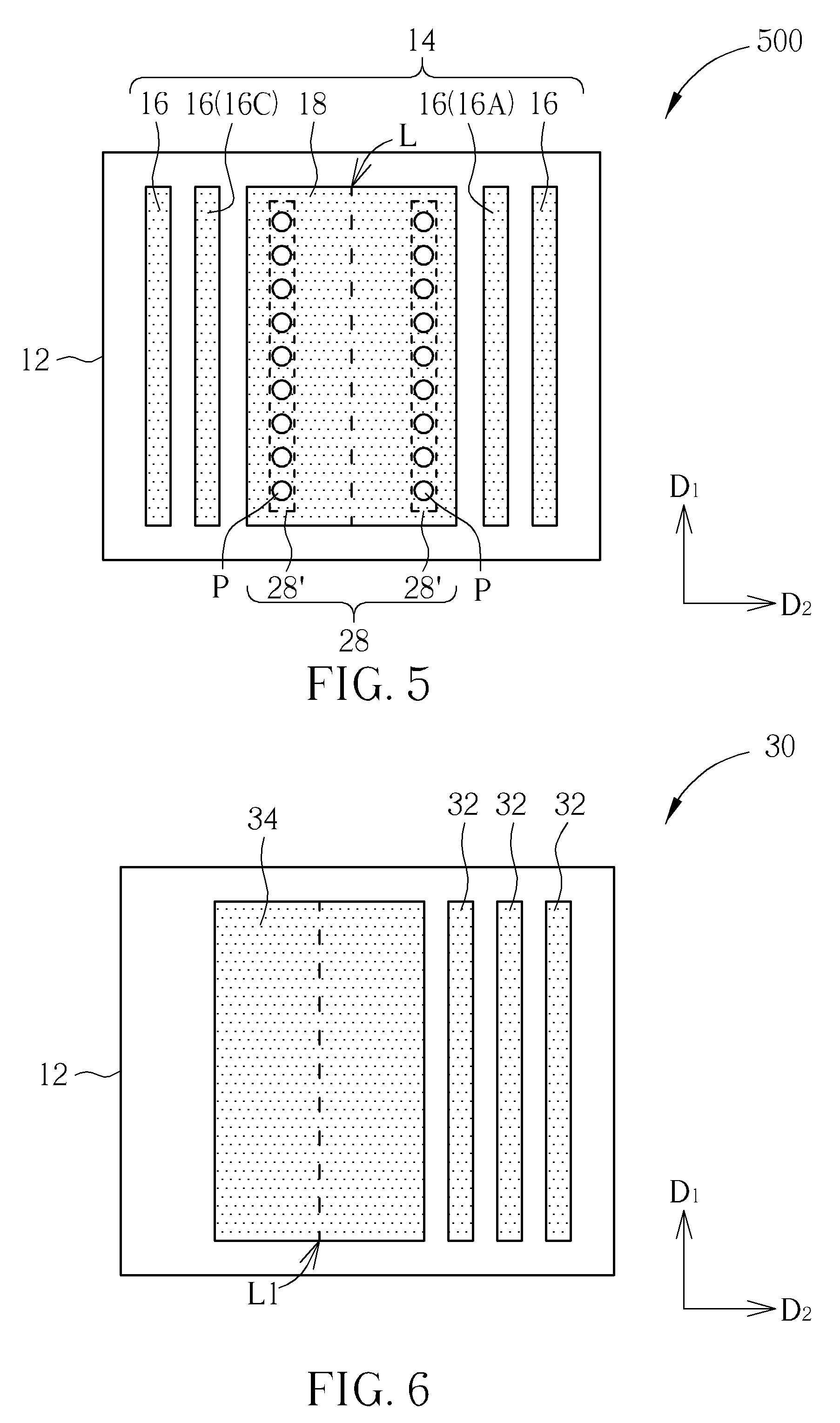

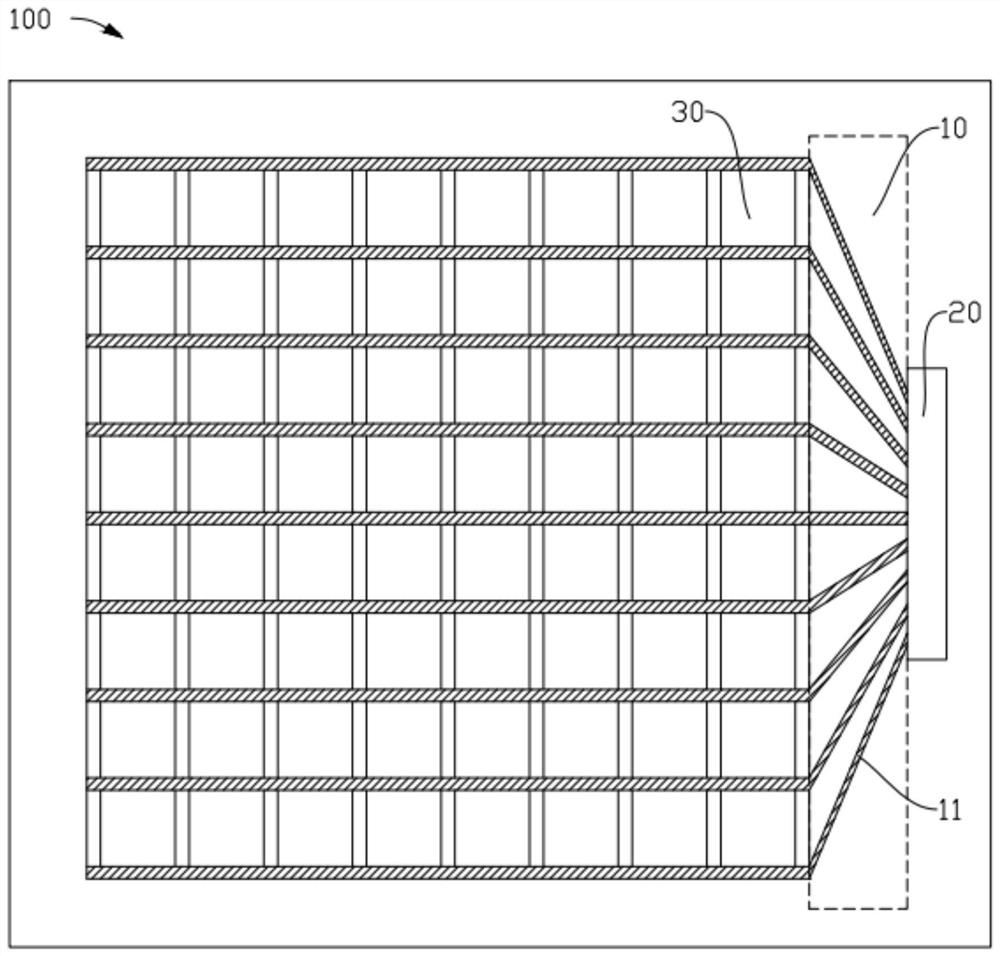

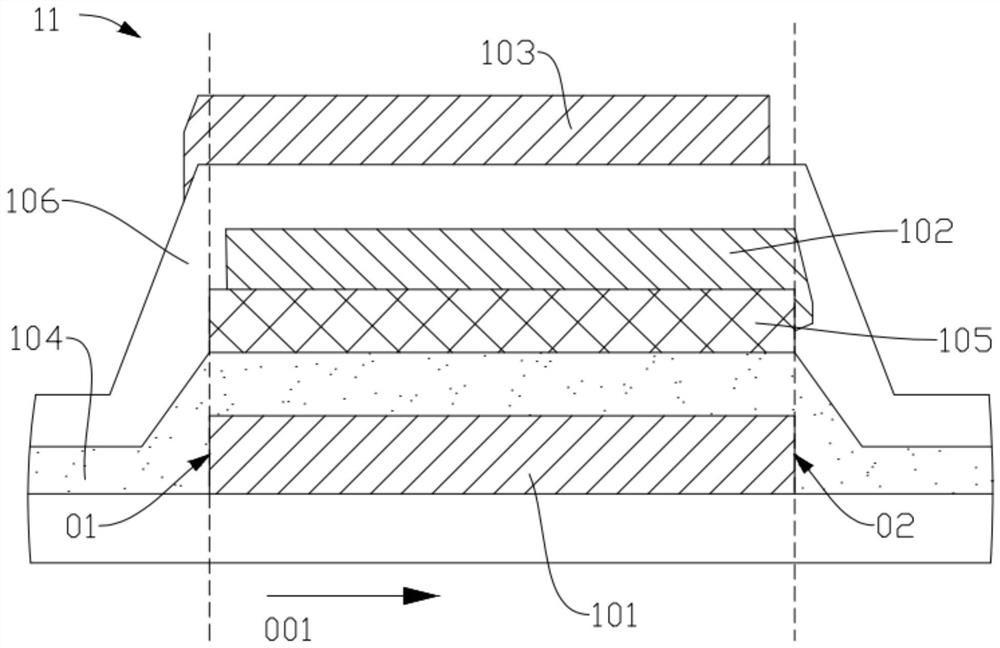

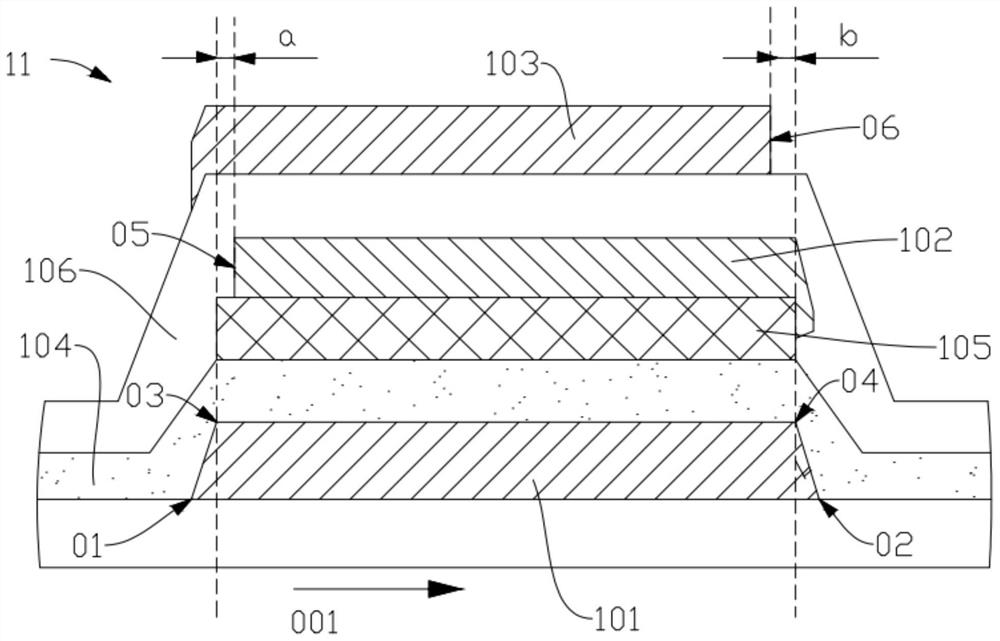

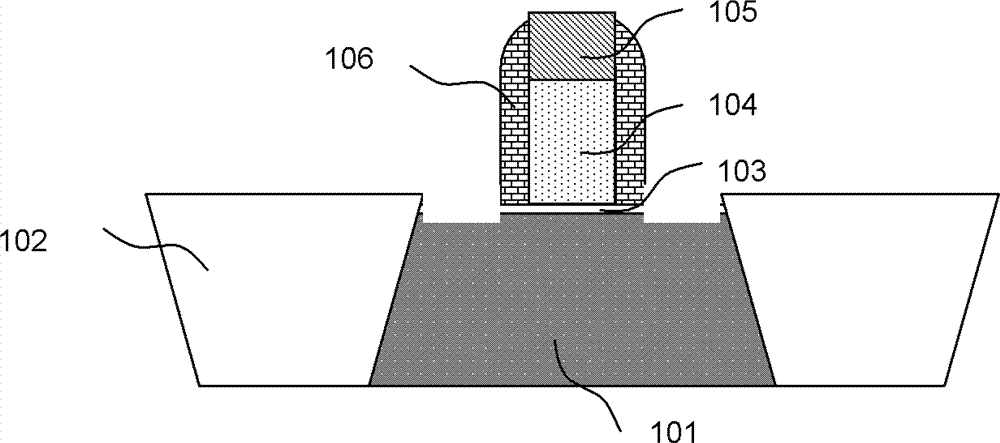

Array substrate, liquid crystal display and electronic apparatus

ActiveCN108614378ANo short circuit failureImprove yield rateNon-linear opticsLiquid-crystal displayEngineering

The invention relates to an array substrate. A first metal wire, a second metal wire and a common electrode line which are mutually insulated and sequentially stacked in a fan-out area of the array substrate, on any section of the first metal line extension path, the first metal line comprises a first end point and a second end point in a first direction, the second metal wire does not exceed thefirst end point in the first direction, and the common electrode line does not exceed the second end point in the first direction. The second metal wire and the common electrode wire form a staggeredlaminated structure in the first direction, and the conduction of the second metal wire and the common electrode wire can be avoided under the condition of poor cutting, so that the array substrate does not cause a short circuit fault. The invention also relates to a liquid crystal display and an electronic device equipped with the above-mentioned array substrate.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

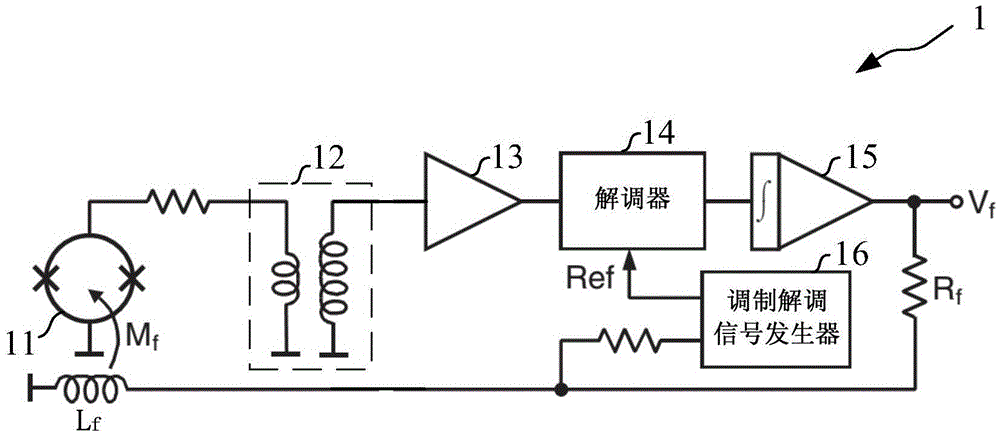

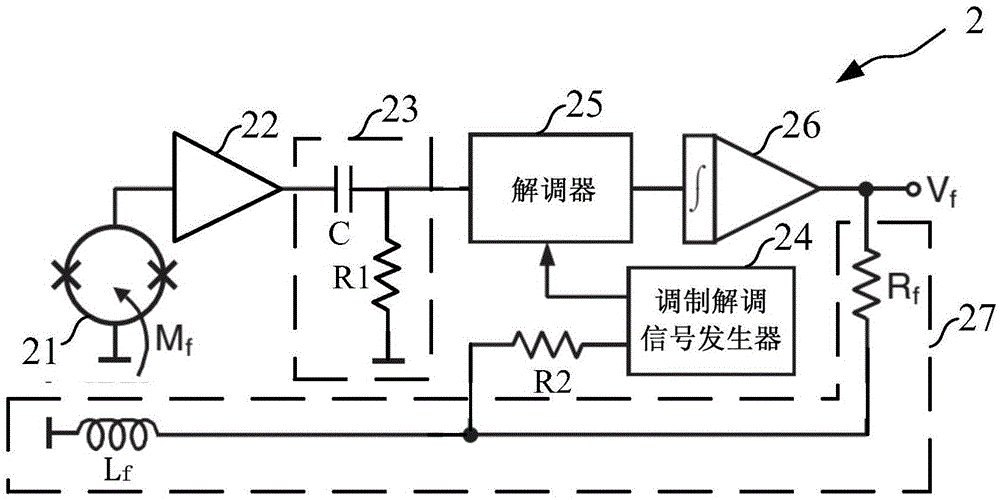

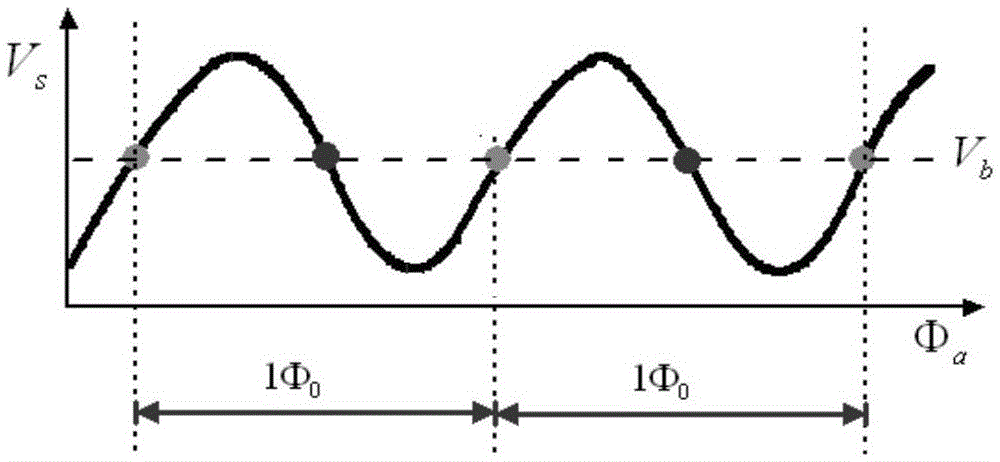

Direct-reading magnetic flux modulation reading circuit and method

InactiveCN105676152AAvoid loading effectImproved noise suppressionMagnetic field measurement using superconductive devicesIntegratorTransformer

The invention provides a direct-reading magnetic flux modulation reading circuit and method. The reading circuit comprises a SQUID device, a pre-amplifier for amplifying the output signal of the SQUID device, a high-pass filter for filtering a DC component and low-frequency noise, a modulation / demodulation signal generator, a demodulator for demodulating the output signal of the high-pass filter, an integrator for carrying out integration and generating a response voltage signal, and a feedback module for feeding back the response voltage signal to the SQUID device. Through modulation, the working point of the SQUID device is allowed to be switched between two working points, and the change trends of the two working points are opposite; and the measured signal is subjected to amplification, high-pass filtering, demodulation and integration, and then, is fed back to the SQUID device, so that the working point is locked. Isolation of the low-frequency noise and the output DC bias of the pre-amplifier is realized through the high-pass filter; the SQUID magnetic flux-voltage conversion coefficient does not reduce due to the load effect; higher harmonic distortion does not occur to a SQUID magnetic flux-voltage curve; the problem of thermal noise of a transformer is prevented; and the circuit is simpler in structure and higher in practicality.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

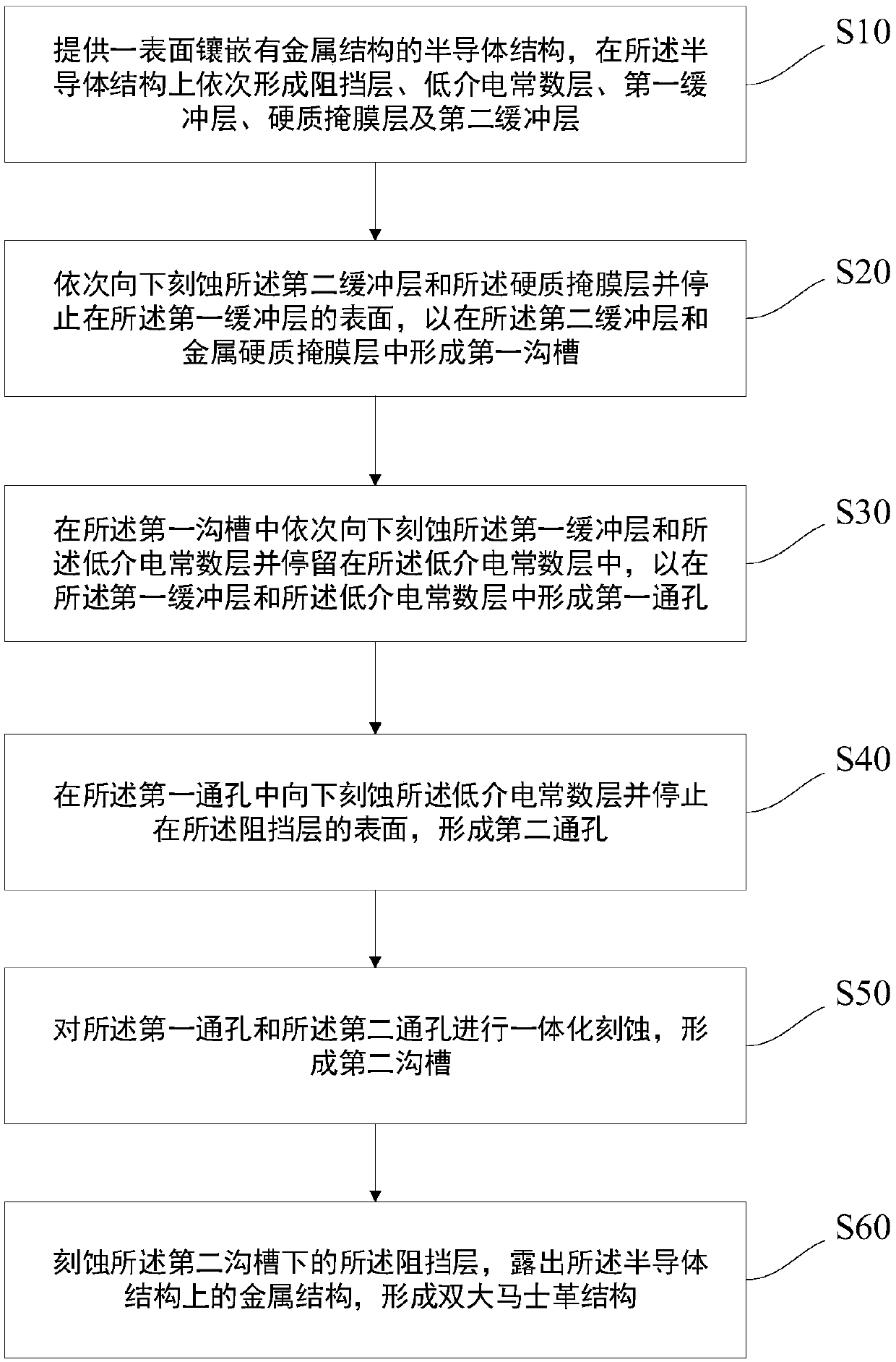

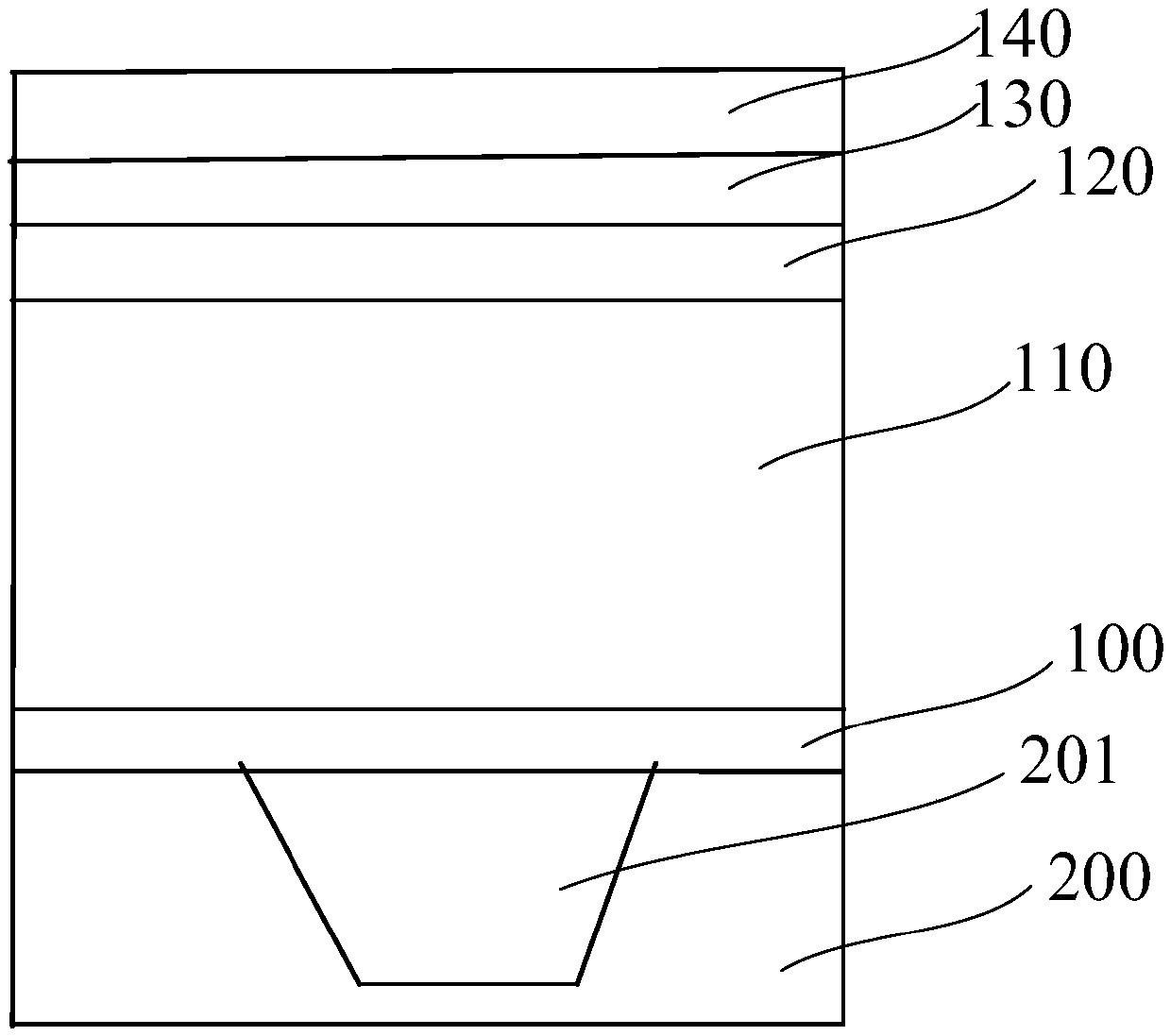

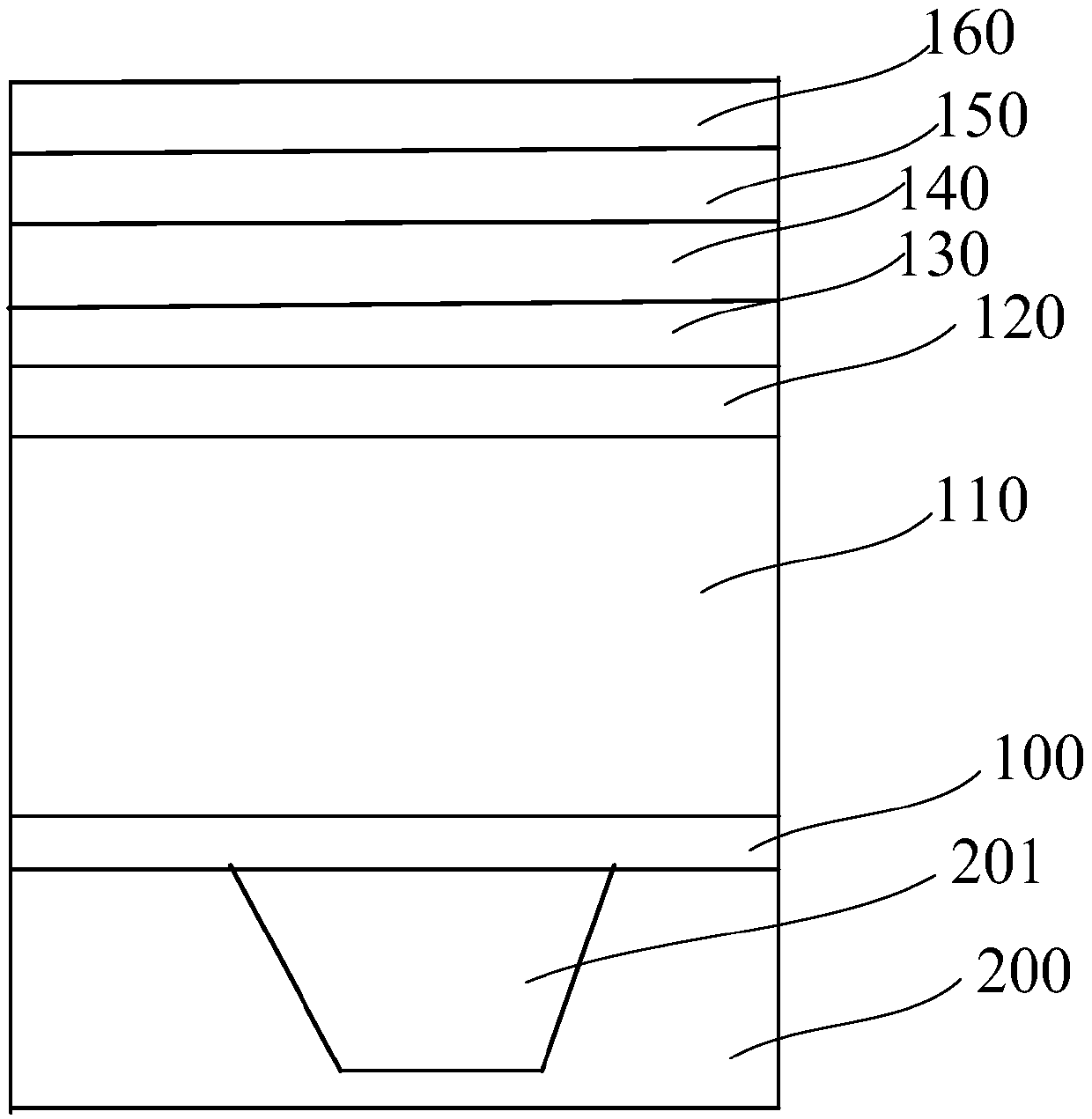

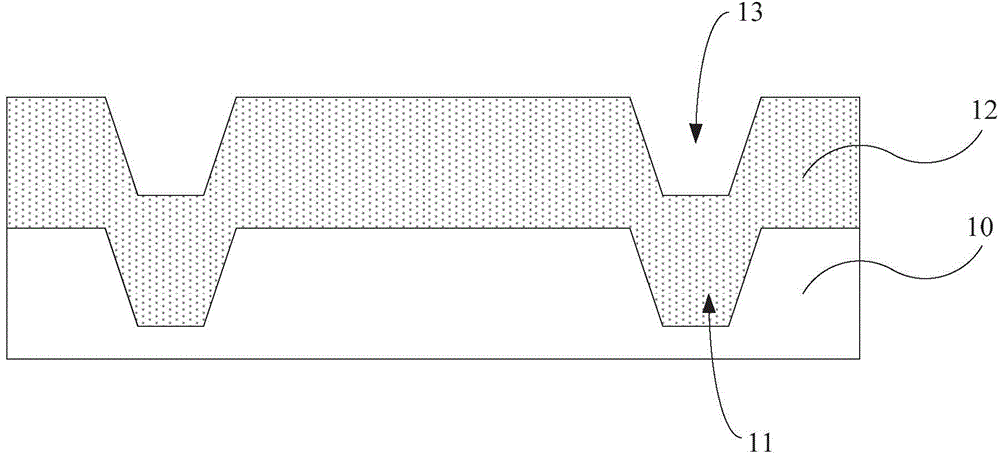

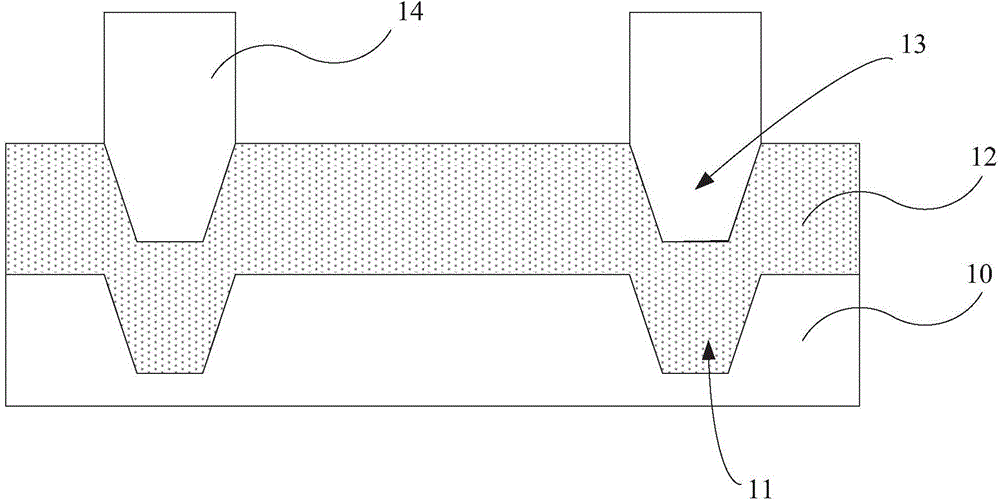

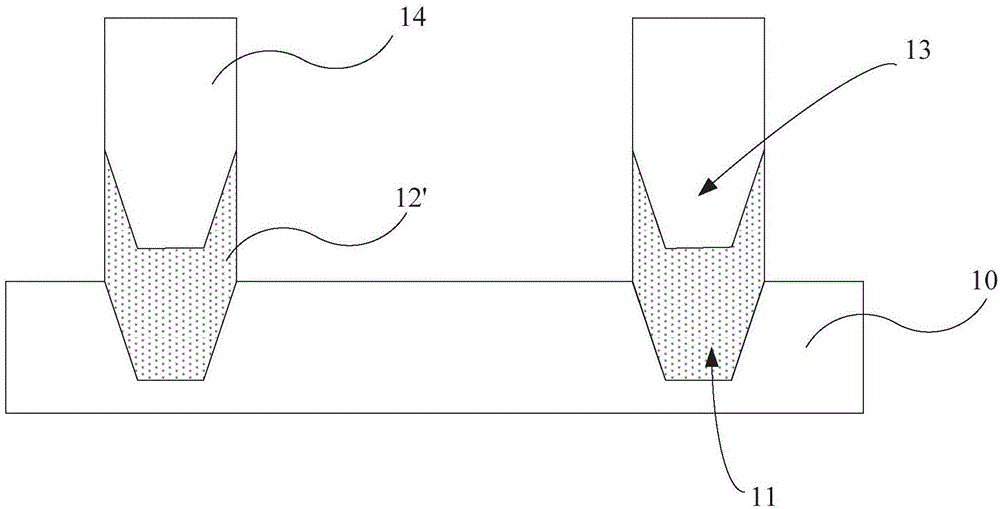

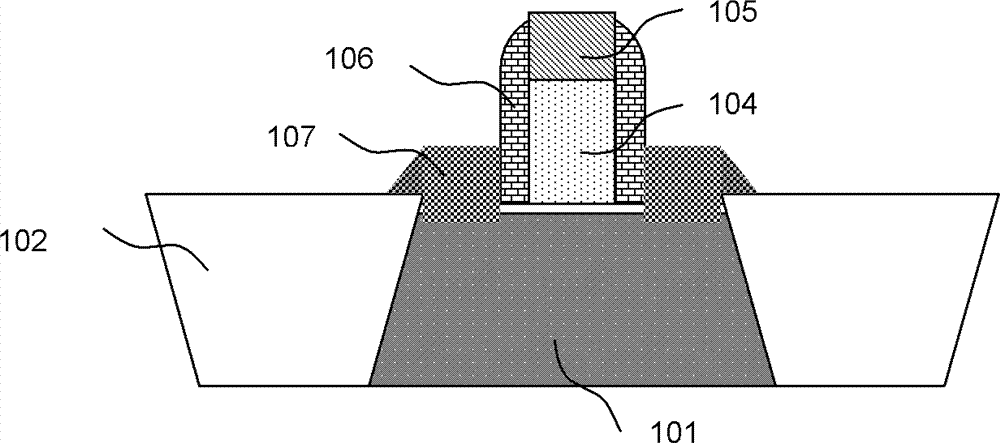

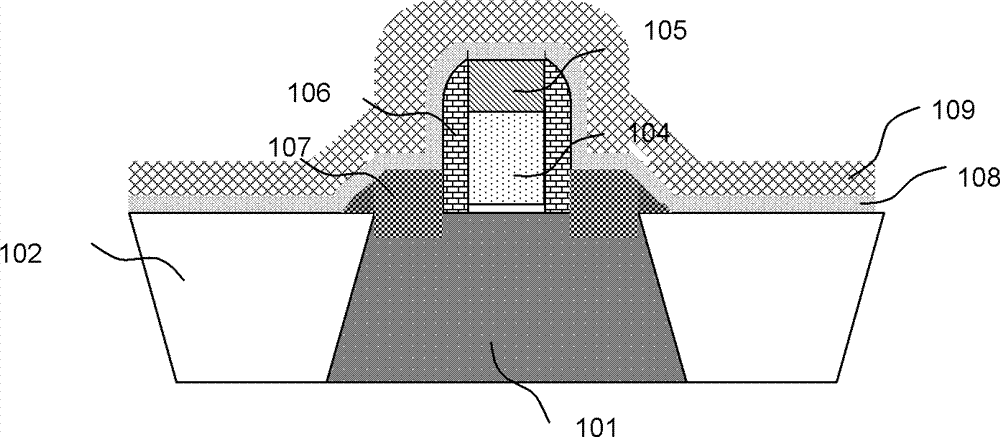

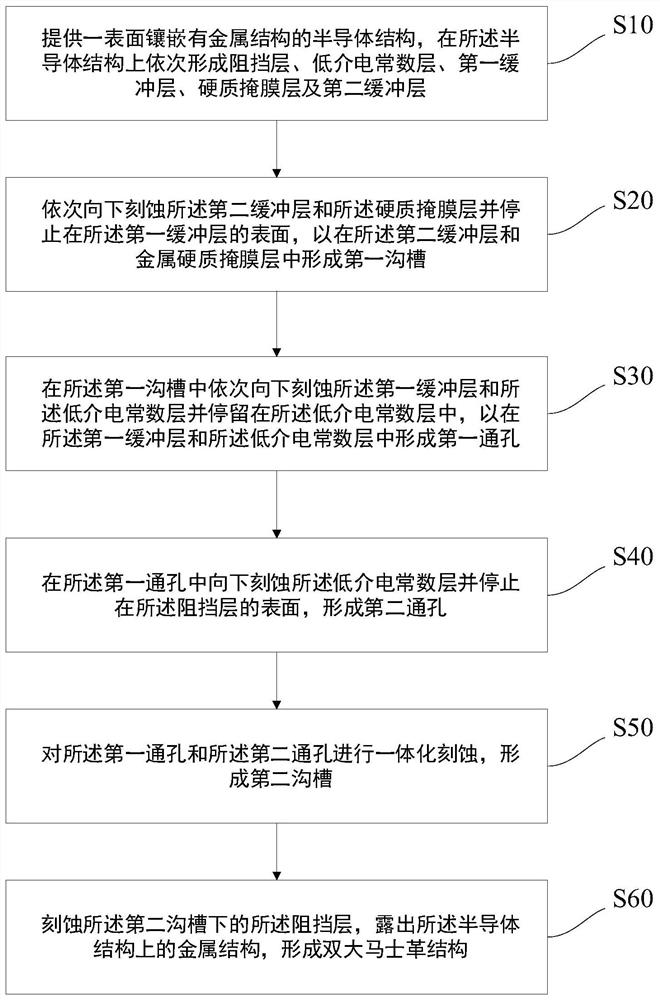

Method for forming dual-damascene structure

ActiveCN109585364AImprove etch defectsGood lookingSemiconductor/solid-state device detailsSolid-state devicesEtchingSemiconductor structure

The present invention provides a method for forming a dual-damascene structure. The method comprises successively forming a barrier layer, a low dielectric constant layer, a first buffer layer, a hardmask layer, and a second buffer layer on the surface of a semiconductor structure in which a metal structure is embedded; etching the second buffer layer and the hard mask layer to form a first trench; etching the first buffer layer and the low dielectric constant layer to form a first via hole; downwards etching the low dielectric constant layer to form a second via hole; integrally etching thefirst via hole and the second via hole to form a second trench; opening the barrier layer to expose the metal structure so as to form the dual-damascene structure. Performing local via hole etching twice can well solve a load effect caused by etching and improve the dual-damascene etching defect, thereby improving the dual-damascene shape. Further, the second trench formed by the integral etchingis favorable for subsequent copper filling, which improves the reliability of the dual-damascene structure.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

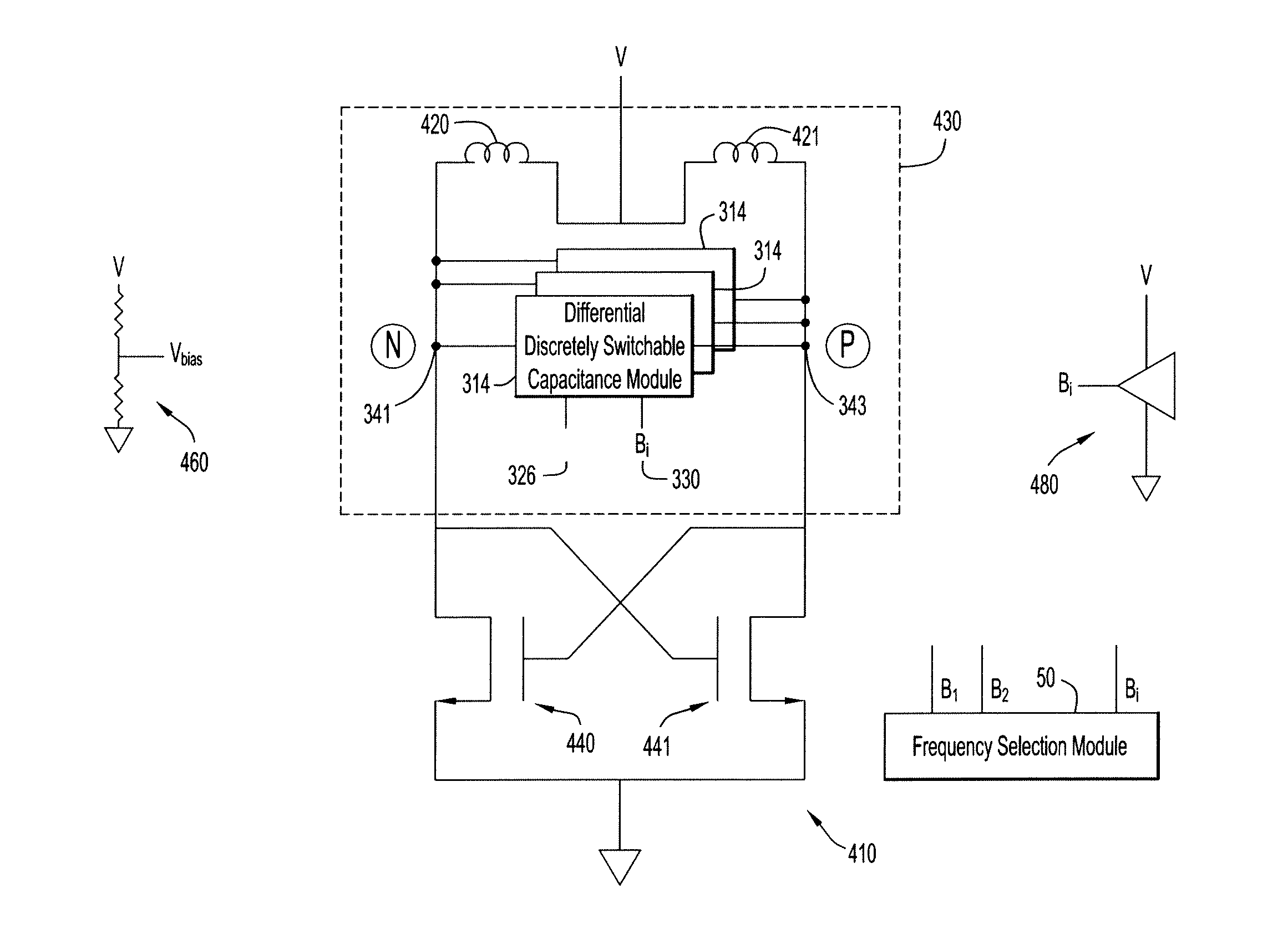

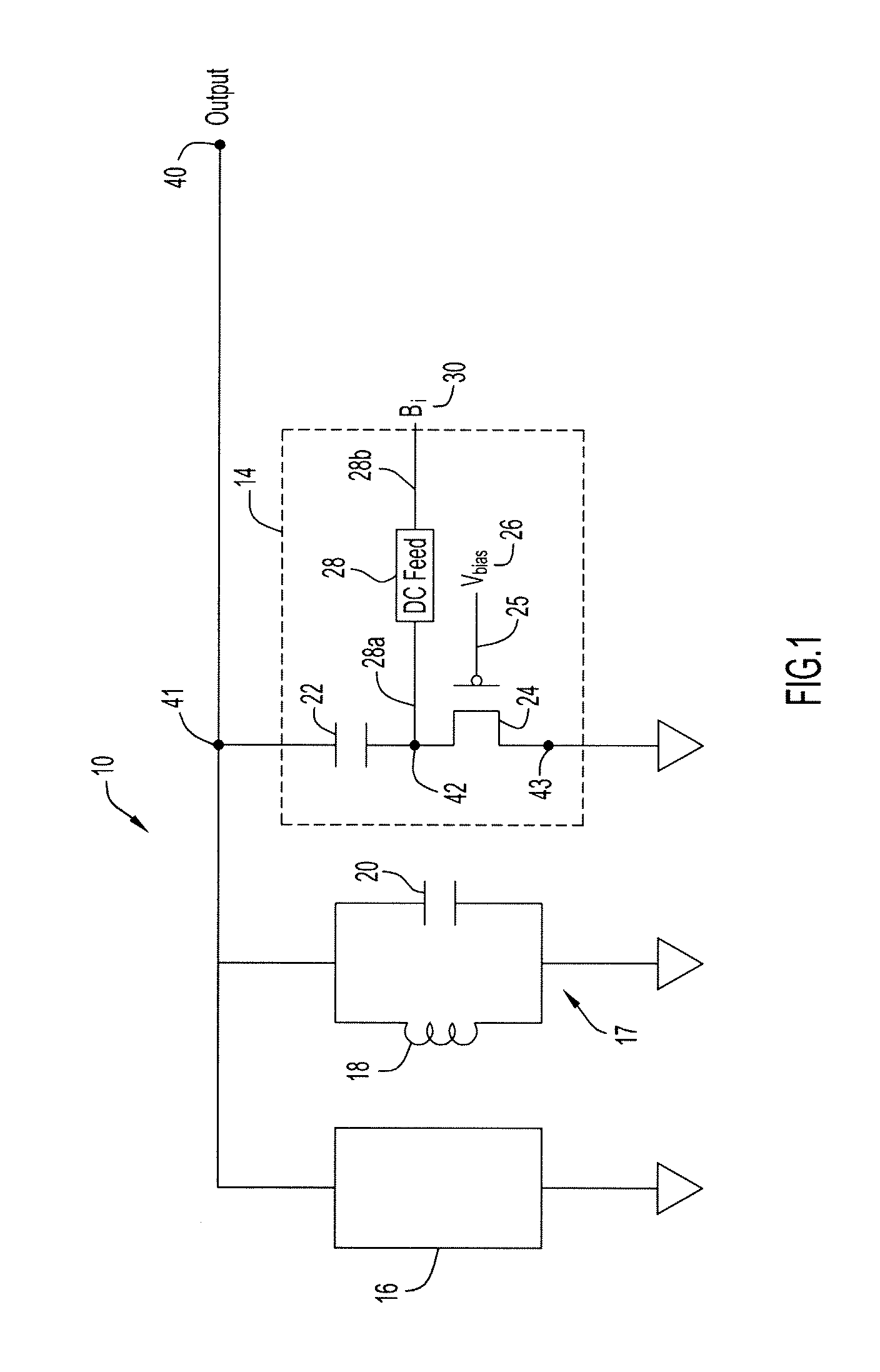

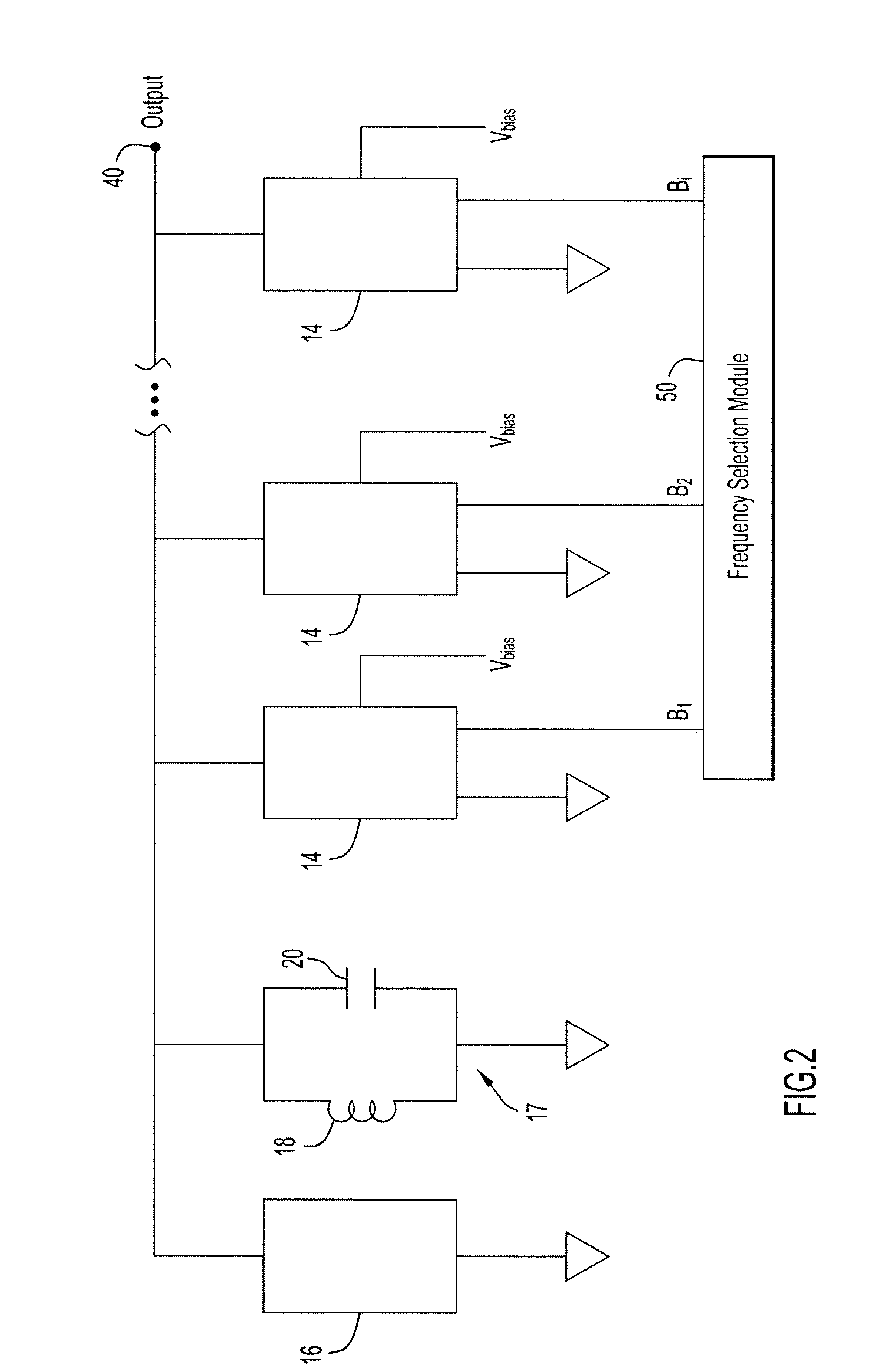

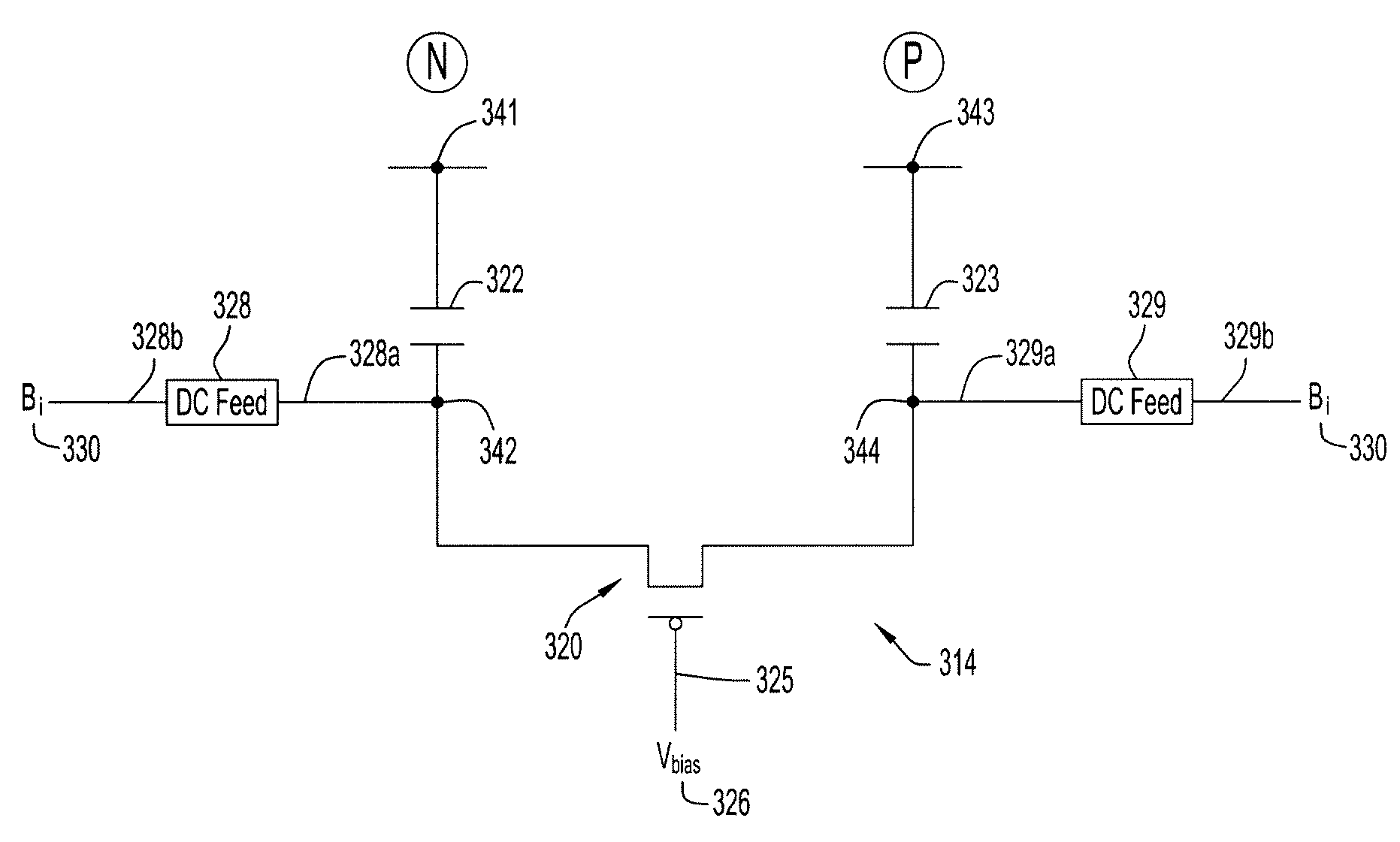

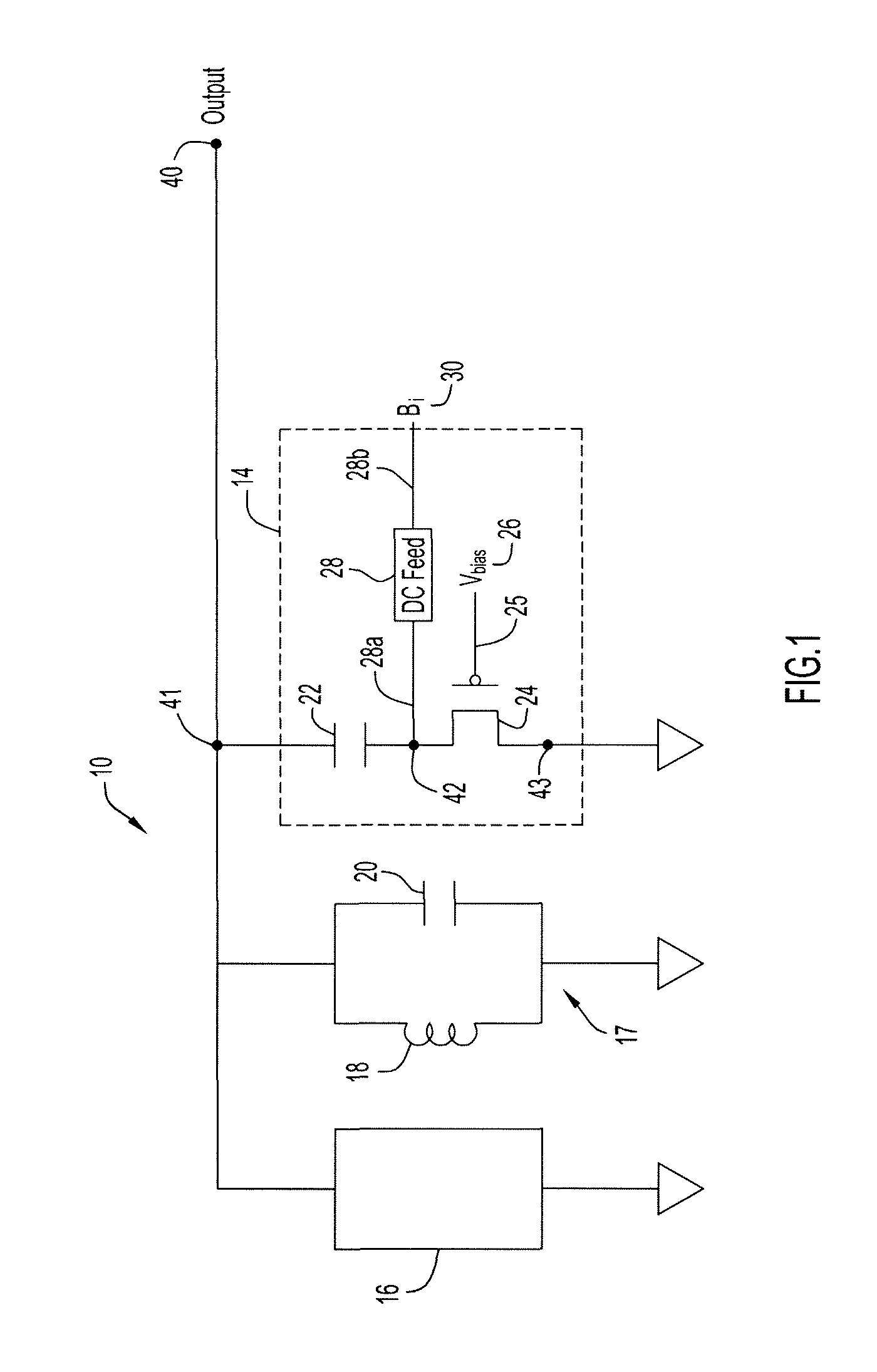

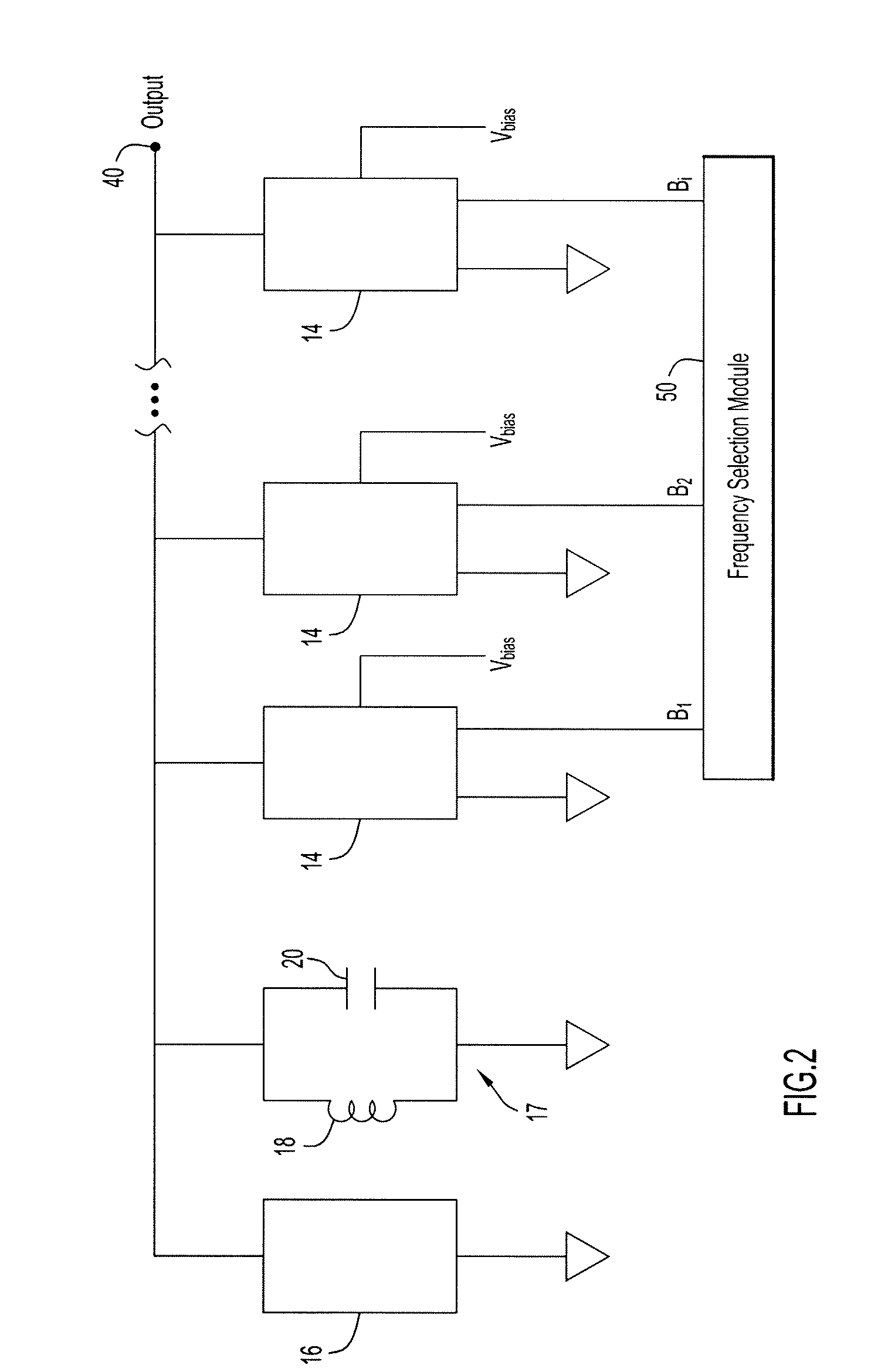

Apparatus and Method for Digitally Controlling Capacitance

ActiveUS20110319036A1Avoid loading effectPulse automatic controlElectric pulse generatorCapacitanceControl signal

An oscillator circuit having a source of an oscillating signal, a tank circuit including an inductor and a capacitor, and a discretely switchable capacitance module configured to control an amount of capacitance in the oscillator circuit. The discretely switchable capacitance module includes, in one embodiment, a capacitor coupled between a first node and a second node, a switch, having a control node, coupled between the second node and a third node; and a DC feed circuit, having a first end coupled to the second node and a second end configured to receive a first or second control signal. The control node of the switch is tied to a predetermined bias voltage. When the first control signal is applied, the capacitor is coupled between the first node and the third node via the switch such that the capacitor is coupled in parallel with the capacitor of the tank circuit, and when the second control signal is applied the capacitor is decoupled from the tank circuit.

Owner:RICHWAVE TECH CORP

Method of driving a shift register, a shift register, a liquid crystal display device having the shift register

InactiveCN100476941CDelay minimizationAvoid loading effectStatic indicating devicesDigital storageShift registerLiquid-crystal display

Owner:SAMSUNG DISPLAY CO LTD

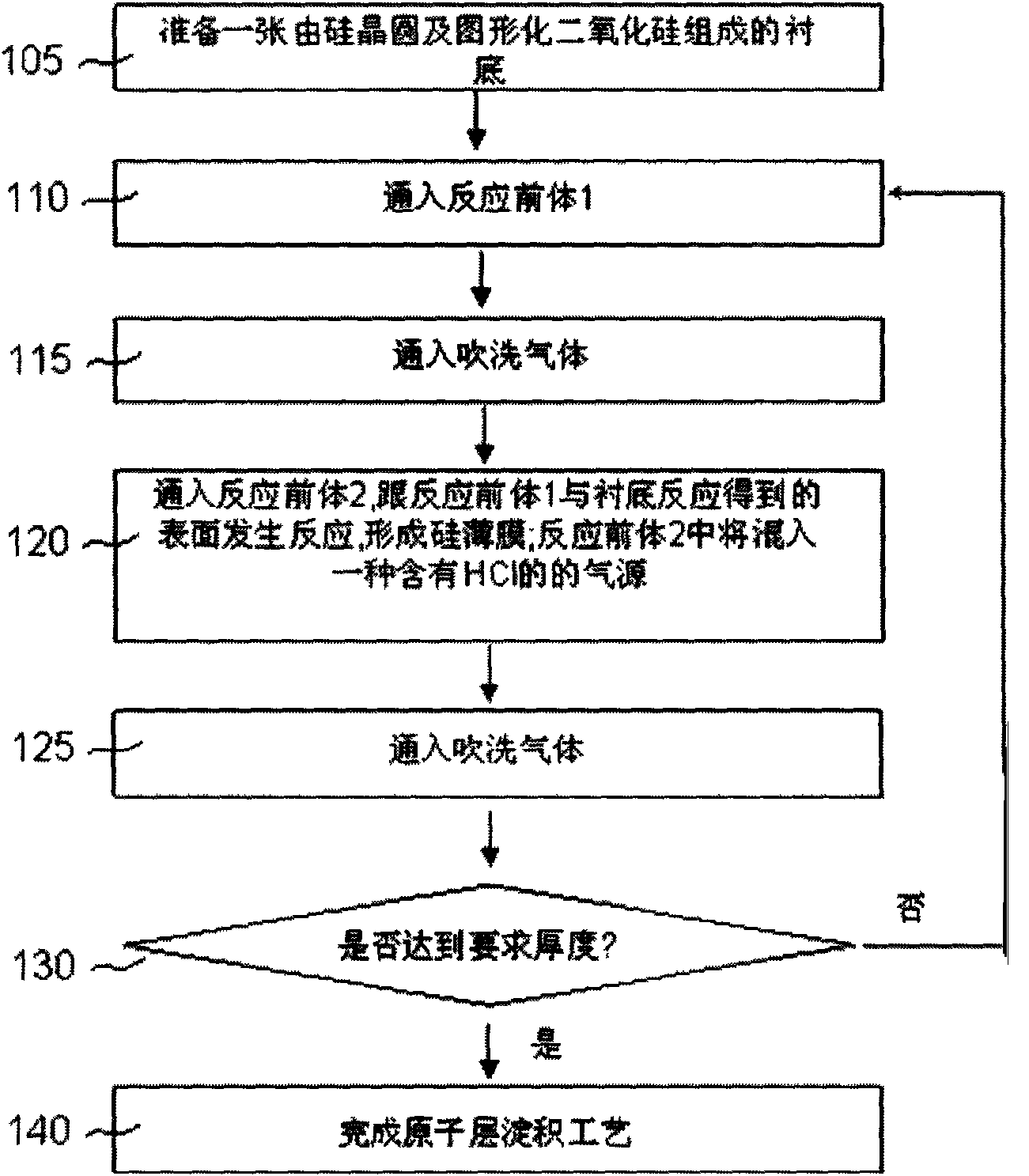

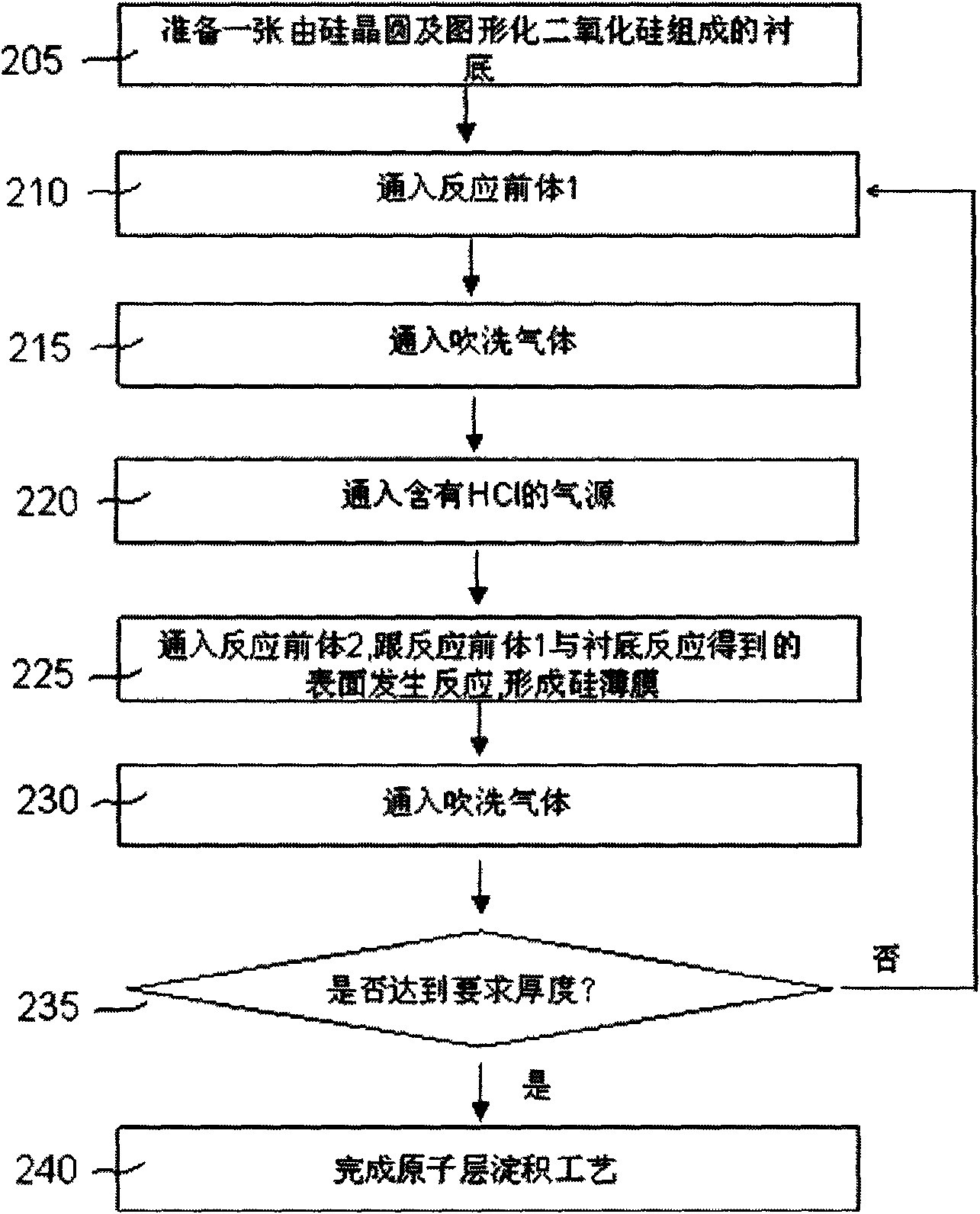

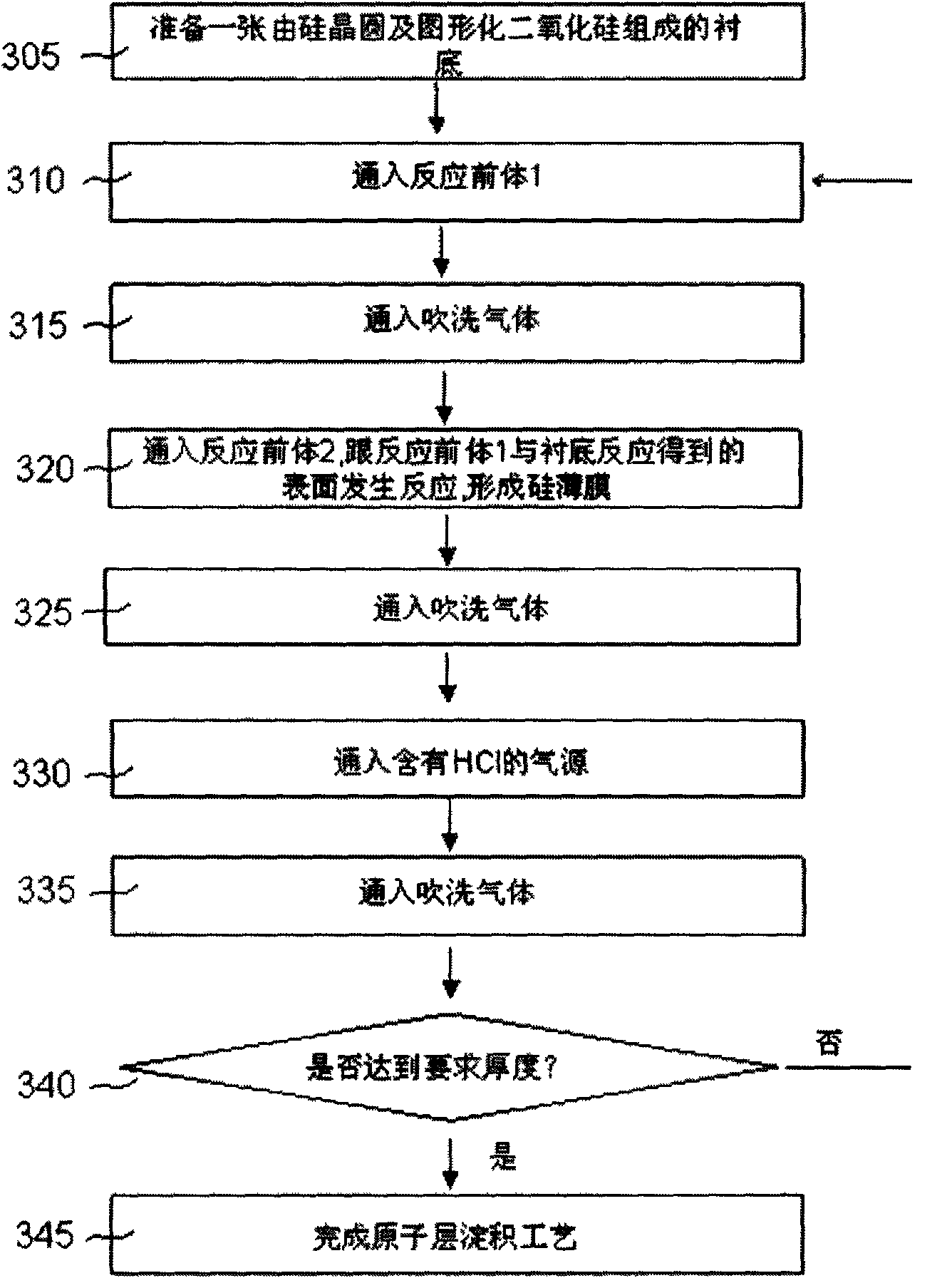

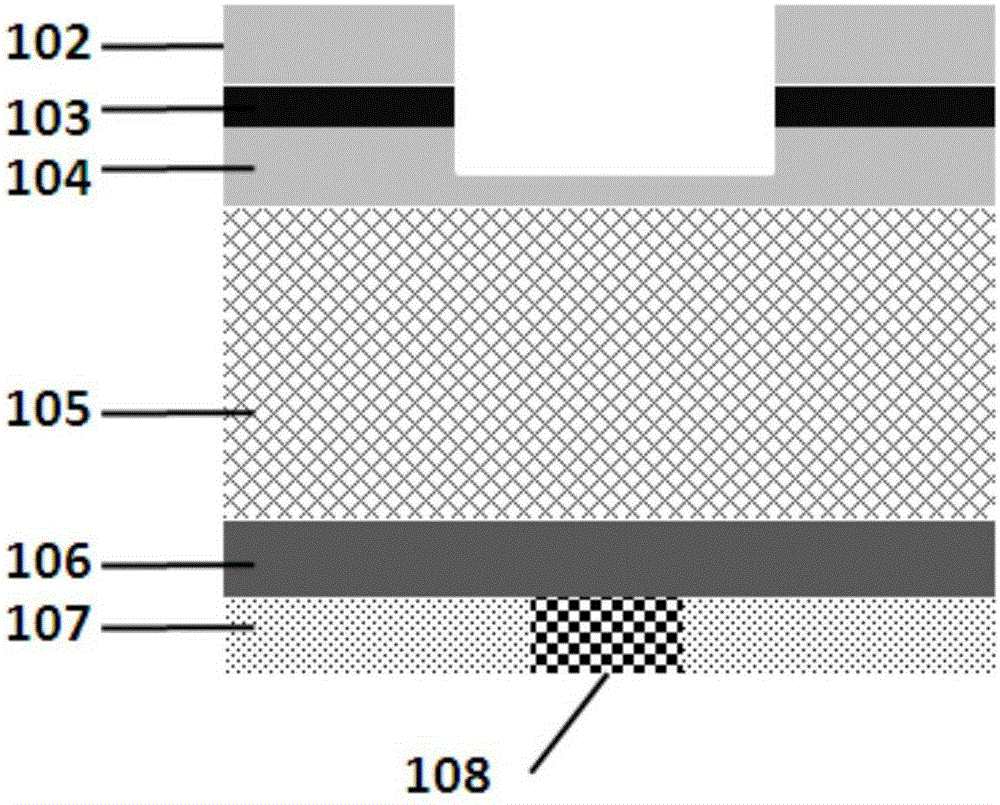

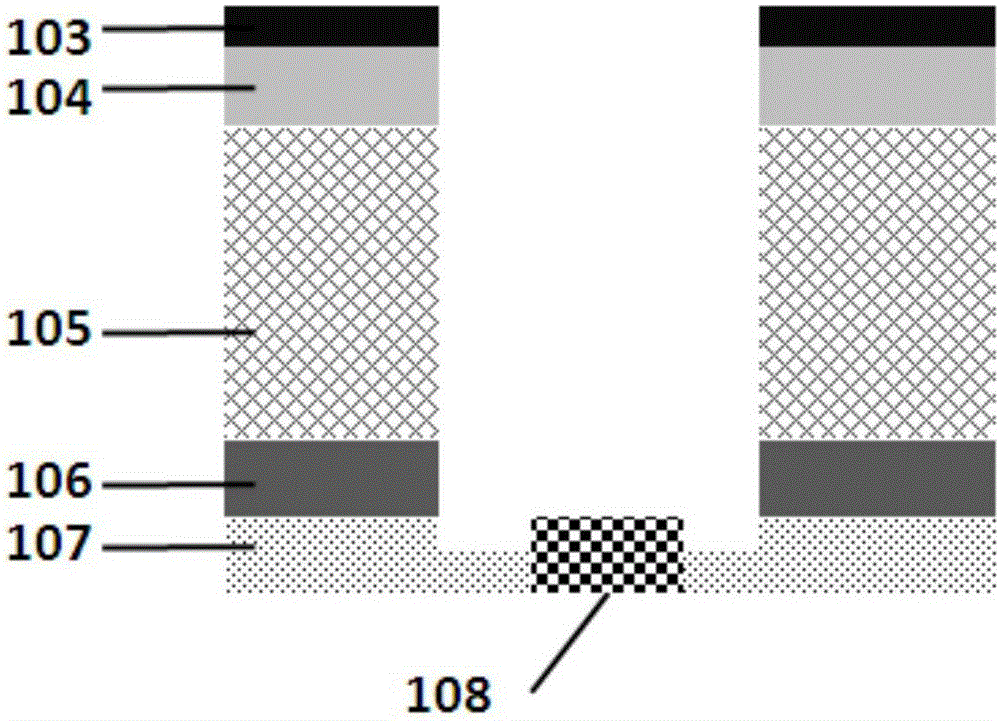

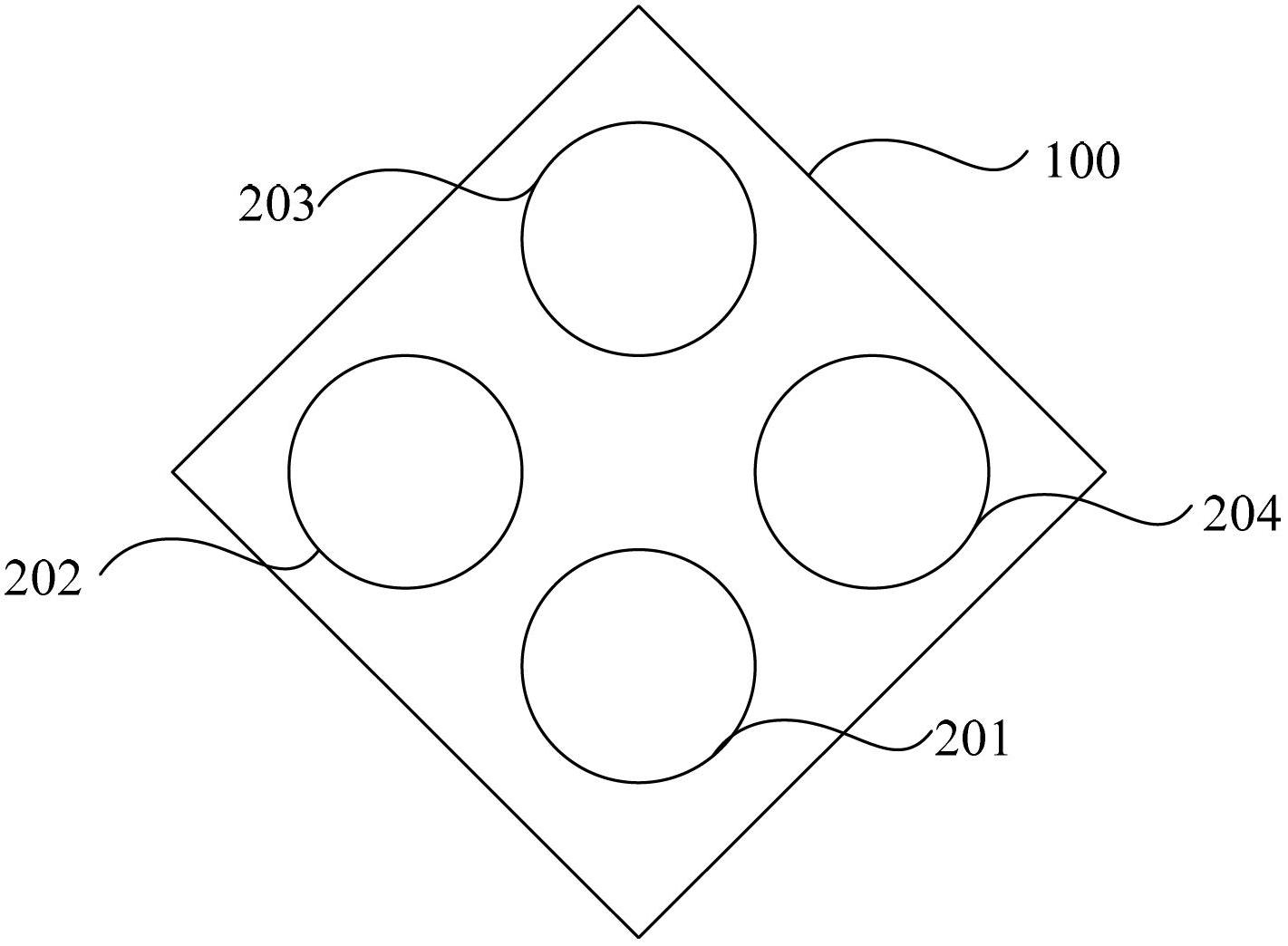

Method for selectively depositing thin film on substrate by utilizing atomic layer deposition

InactiveCN102031501AAvoid loading effectSemiconductor/solid-state device manufacturingChemical vapor deposition coatingWaferingDevice material

The invention relates to a thin film deposition technology for preparing semiconductor devices, in particular to a method for selectively growing silicon, germanium silicon and derivative thin films thereof on a substrate by utilizing an atomic layer deposition technology. The substrate is heated to the preset temperature during the growth process against the substrate comprising a semiconductor wafer and oxide thin films with different density patterns, the atomic layer deposition method is utilized for growing the thin film on the surface of the substrate, and the effect of inhibiting the growth of the thin film on an oxide layer can be realized by doping HCl (hydrochloric acid) in a reaction precursor of the atomic layer deposition or independently introducing pulses of the HCl in the technological process. The thin film is deposited in a selected region and does not need to be deposited in other unnecessary places; by utilizing the method, the traditional selective deposition and growth way of depositing the thin film with load effect on the surfaces with the different density patterns can be solved; and the traditional lithography technology is not required, and the need of introducing the follow-up thin film etching process due to the use of the traditional lithography technology can be also omitted.

Owner:FUDAN UNIV

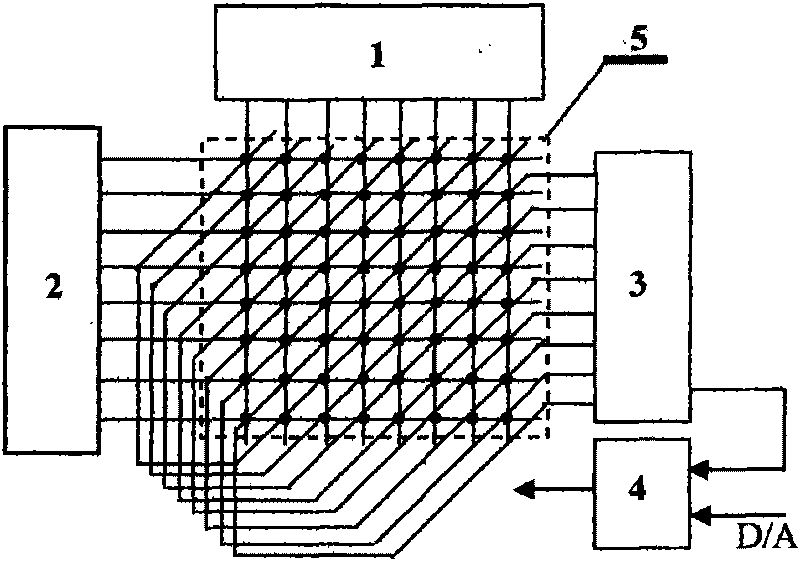

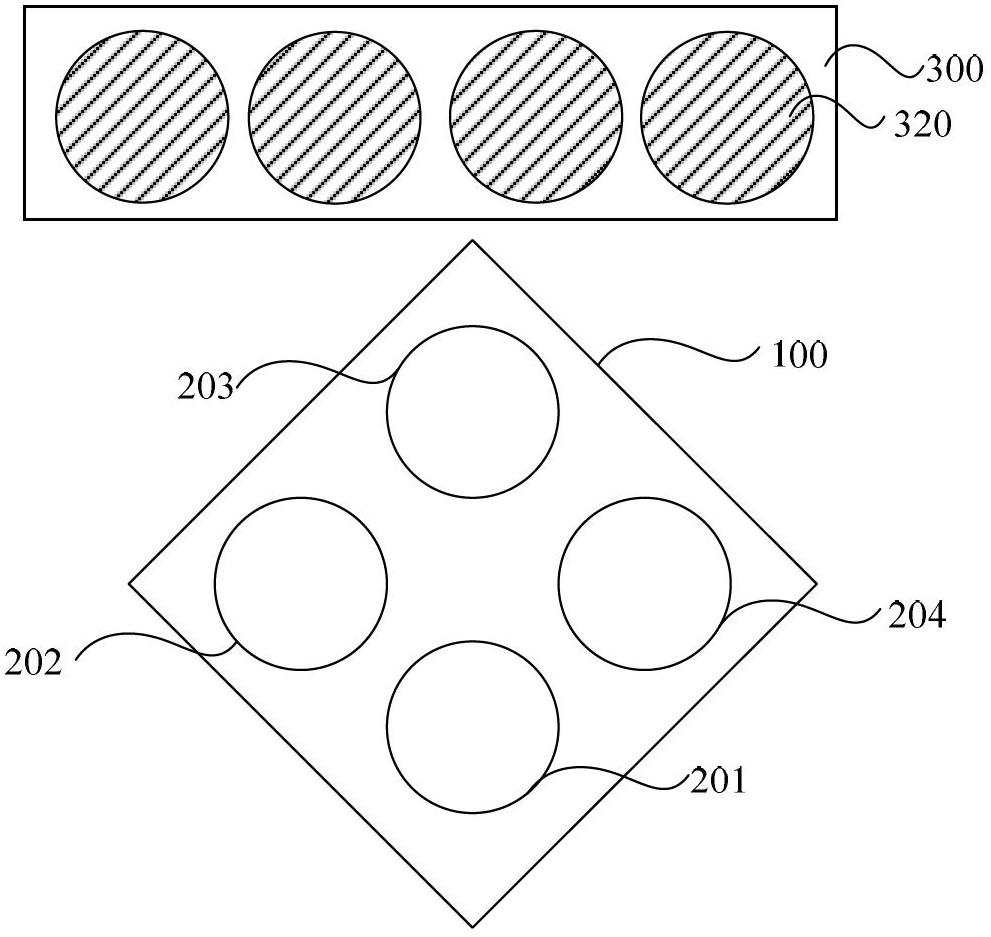

Magnetic image sensor

InactiveCN101738586AImplement detectionSimple designMagnitude/direction of magnetic fieldsPhysicsTime-sharing

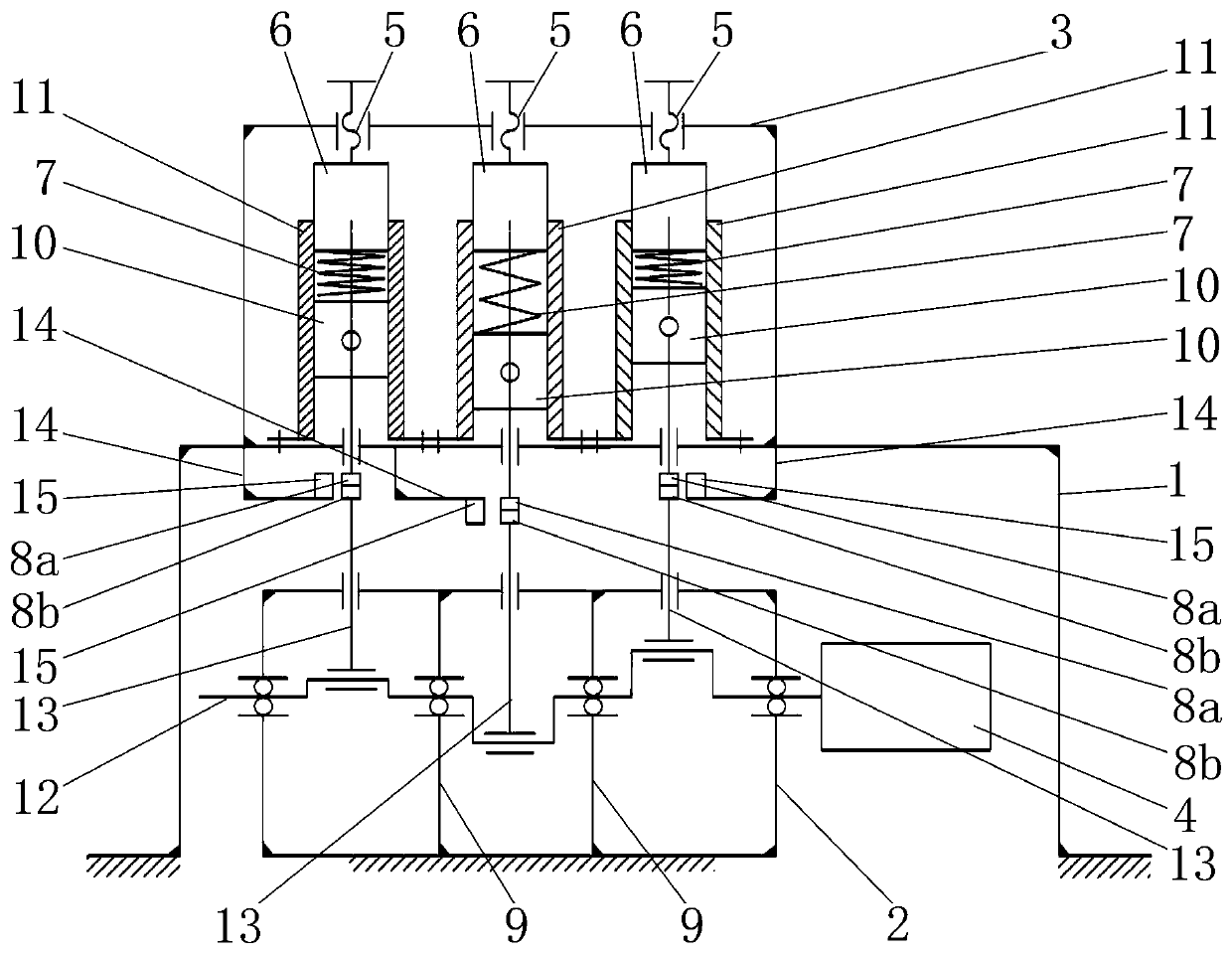

The invention relates to a magnetic image sensor, in particular to a sensor for detecting distribution rule of a magnetic field, which comprises an 8*8 image pixel matrix consisting of 64 SS495 linear hall sensors, three one-out-of-eight multiway switches and a zero correction amplifier. The structural principle of the magnetic image sensor is shown in attached figure 1, wherein (1) represents the line power supplying one-out-of-eight multiway switch; (2) represents the row power supplying one-out-of-eight multiway switch; (3) represents the output one-out-of-eight multiway switch; (4) represents a zero correcting and amplifying circuit; (5) represents the 8*8 image pixel matrix consisting of the 64 SS495 linear hall sensors. Dynamic power supply is performed on the 64 sensors. The output ends of 64 magnetic pixels are arranged towards the direction of 45 degrees, and eight magnetic pixels form one group in parallel. The output of the eight groups of sensors are communicated with the same-phase input end of the zero correcting and amplifying circuit in time sharing. The connecting method has the advantages that the 64 sensors realize three-dimensional matrix connection by the three multiway switches; the three-dimensional matrix connection completely avoids the loading effect of the non-working magnetic pixels on the working magnetic pixels, and greatly enhances the sensitivity of the working magnetic pixels. Only one amplifier can realize time-sharing amplification on the output signals of the 64 pixels, therefore reducing the hardware cost. The switching between the magnetic pixels of the sensors adopts a digital switching method. The zero deviation of the sensors adopts a dynamic correction technology, i.e. the output of the zero correction amplifier is sampled when the sensors do not work, and the sampling data of the 64 pixels is stored in 64 correcting units; when the sensors work.

Owner:XIANGTAN UNIV +1

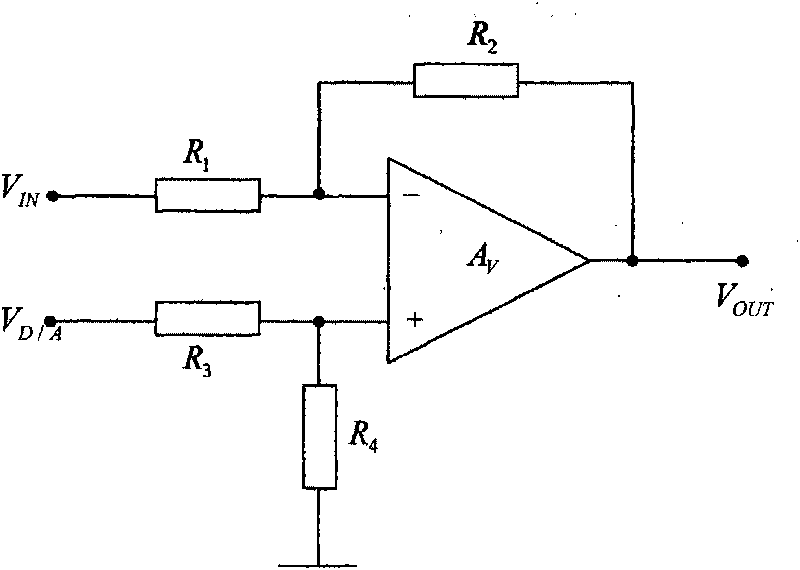

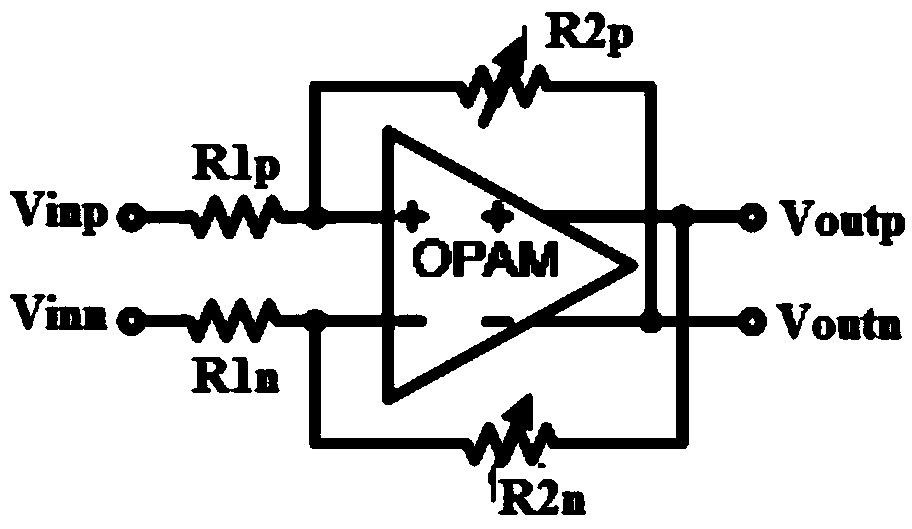

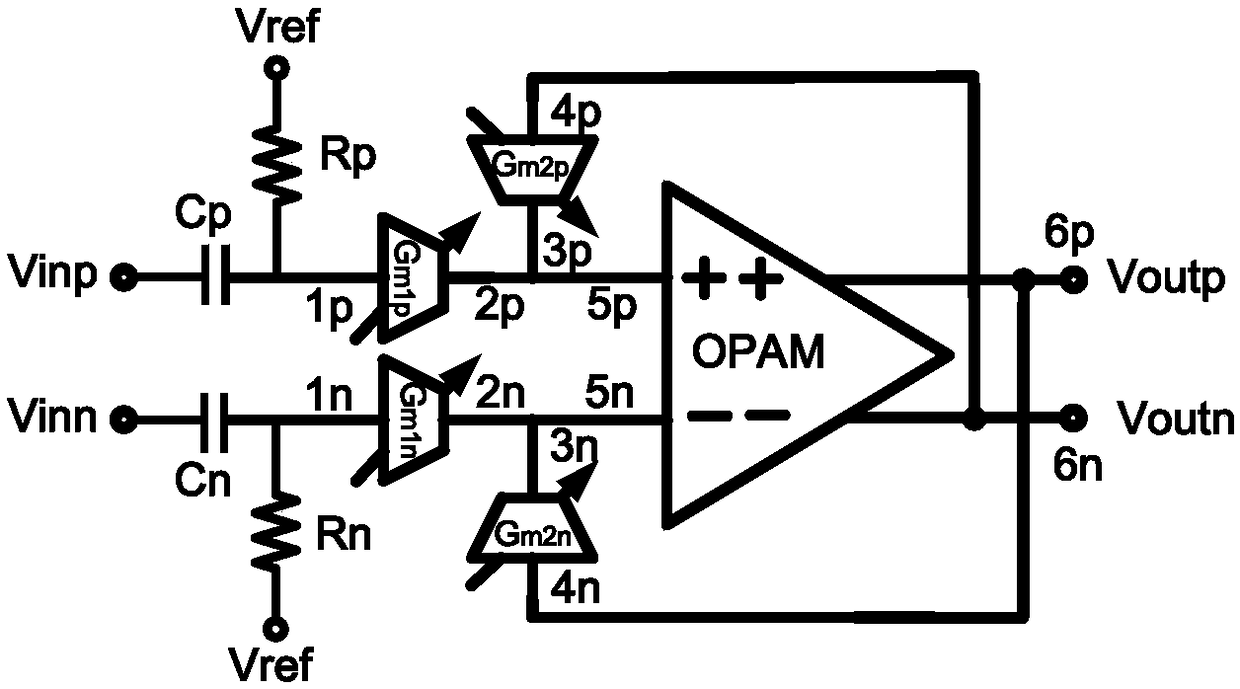

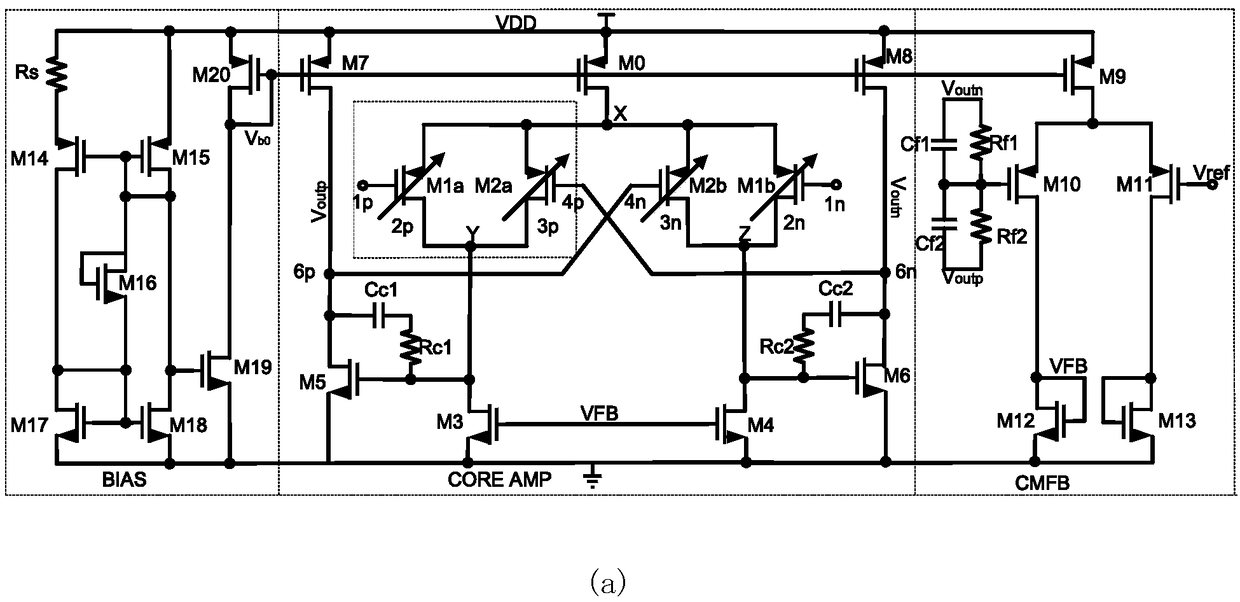

Programmable gain amplifier circuit based on transconductance feedback unit

InactiveCN108768325ATroubleshoot loading effectsSolve the problem of large gain errorGain controlDifferential amplifiersCapacitanceTransistor array

The invention discloses a programmable gain amplifier circuit based on a transconductance feedback unit, and belongs to the design field of analog integrated circuits. The amplifier circuit is composed of a direct current offset suppression circuit, an input transconductance unit, a feedback transconductance unit, and an operational amplifier; the direct current offset suppression circuit is composed of a resistor and a capacitor; the input transconductance unit and the feedback transconductance unit are respectively composed of an MOS transistor array; the operational amplifier is composed ofan amplifying circuit, a bias circuit and a common-mode feedback circuit; the amplifying circuit is a two-stage Miller amplifier; the bias circuit is a voltage bias circuit proportional to temperature; and the common-mode feedback circuit is a differential common-mode feedback circuit. According to the programmable gain amplifier circuit based on the transconductance feedback unit provided by theinvention, the load effect problem in a traditional feedback structure can be effectively solved, and the gain error is reduced; on the premise that the power consumption is not changed, the bandwidth can be greatly improved and the layout area can be reduced, therefore the performance of the programmable gain amplifier can be improved.

Owner:TSINGHUA UNIV

Luminous diode array

InactiveCN1527411AWill not short circuitDoes not increase the etch areaLaser detailsSolid-state devicesEngineeringLight-emitting diode

A light-emitting diode array comprising a conductive layer formed on a substrate, separate light-emitting portions formed on the conductive layer, a first electrode formed on at least part of an upper surface of each light-emitting portion, and a second electrode formed on the conductive layer adjacent to the light-emitting portions; the first electrode comprising a common switching electrode matrix; the second electrode comprising a common electrode divided such that one second electrode exists in every block; and at least one of bonding pads extending to the first common electrode and the second common electrode being formed on a bonding portion formed on the conductive layer like an island, whereby the bonding pads are separate from each other.

Owner:LEXTAR ELECTRONICS CORP

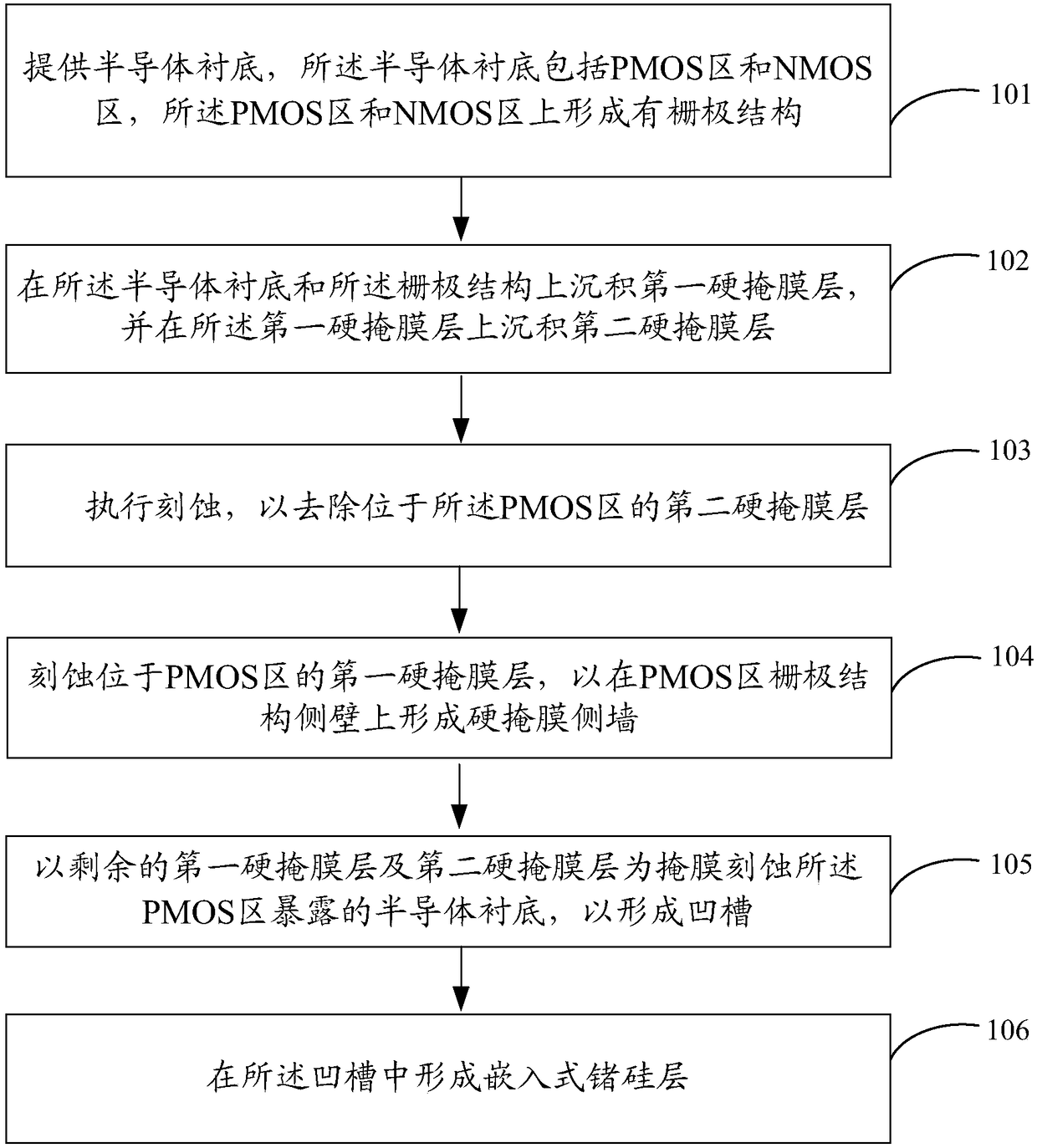

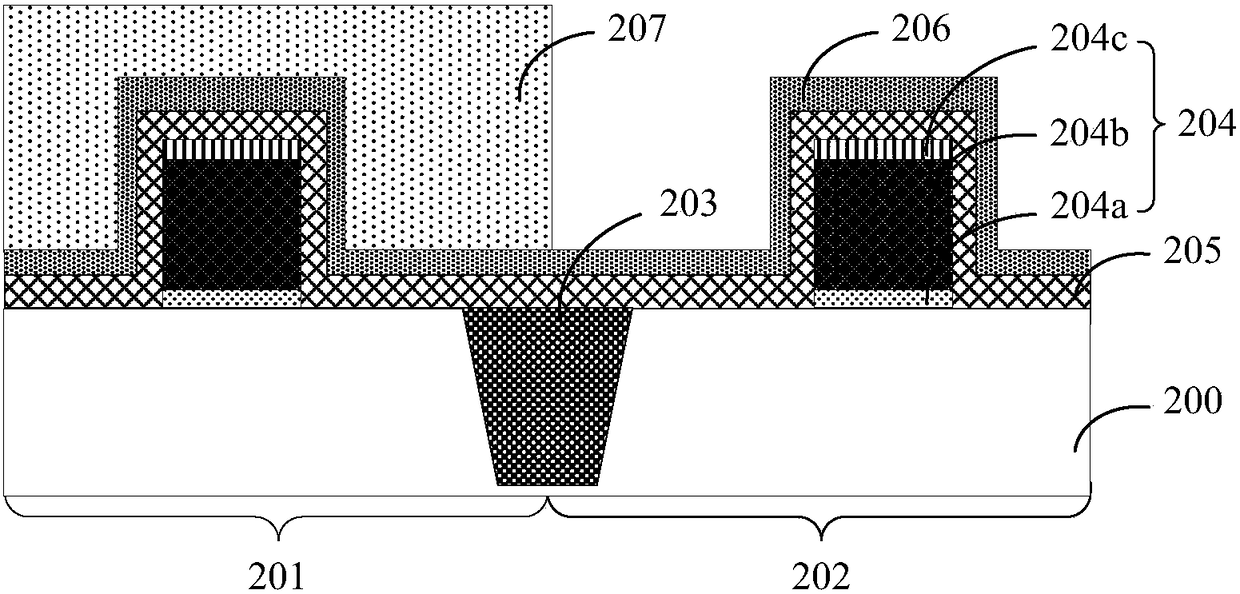

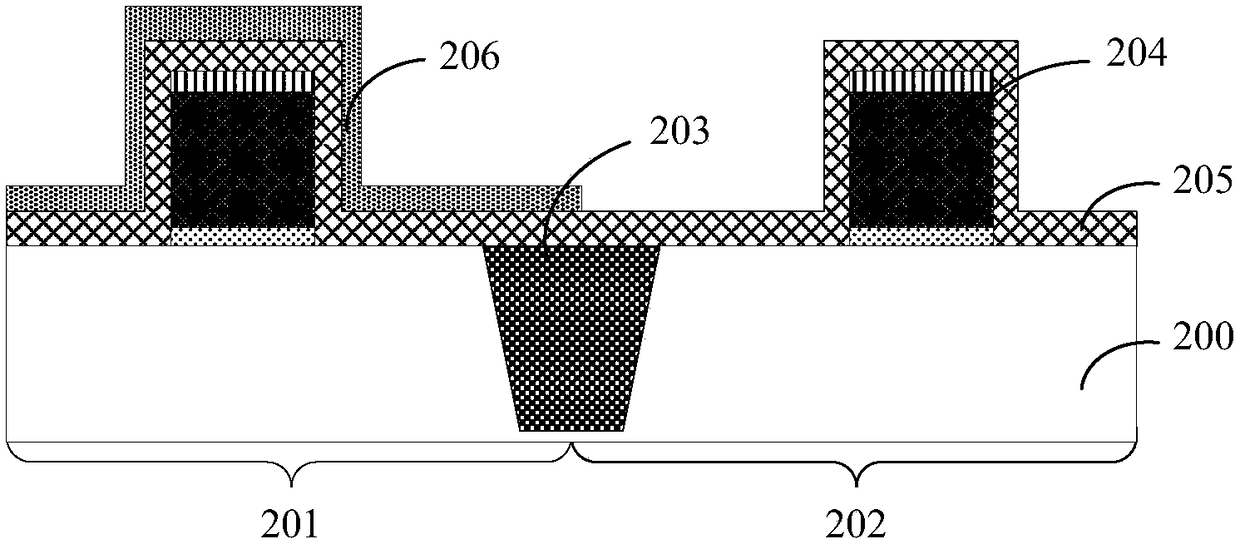

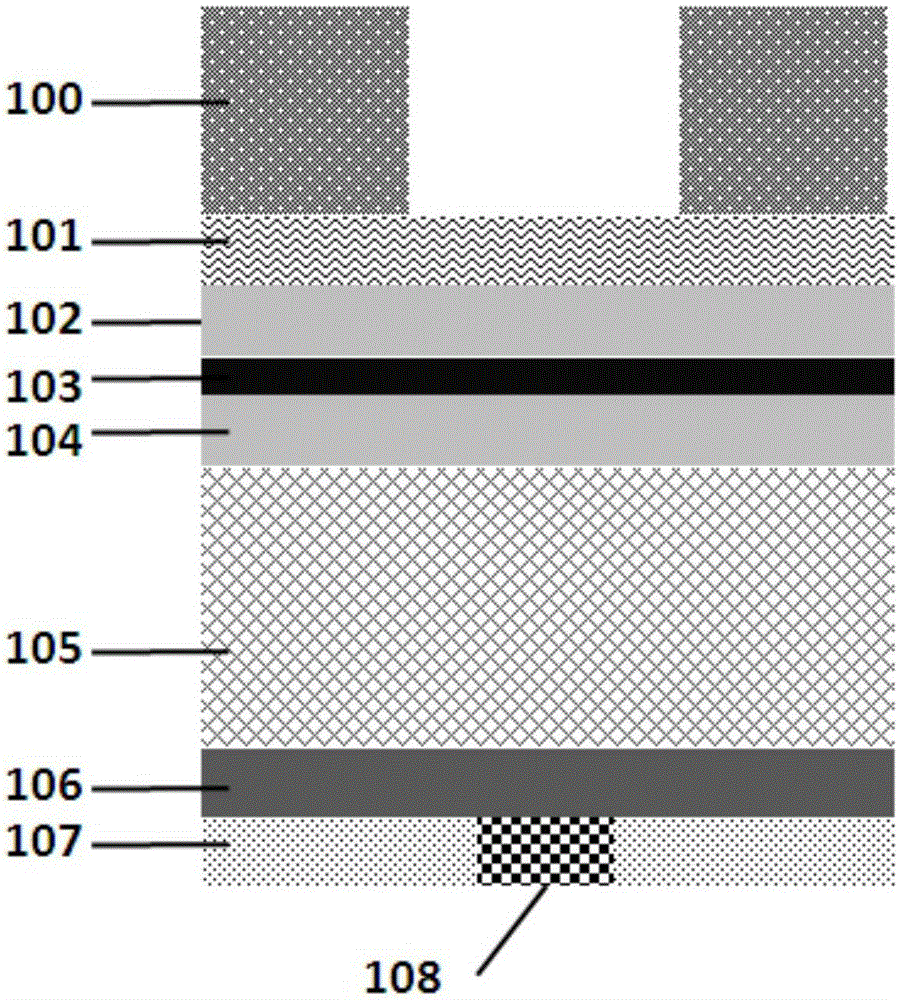

Formation method of semiconductor device

ActiveCN104952782AEasy to shapeGood lookingSemiconductor/solid-state device manufacturingComputational physicsSemiconductor

A formation method of a semiconductor device includes providing a substrate having a to-be-etched layer including a graph dense zone and a graph sparse zone; forming a first mask layer having sparse images on the surface of the graph sparse zone of the to-be-etched layer; forming a photo-etching layer covering the surface of the to-be-etched layer and the surface of the first mask layer; performing exposure development on the photo-etching layer and forming a second mask layer having dense images on the image dense zone of the to-be-etched layer and the surface of the first mask layer; etching the graph dense zone of to-be-etched layer by taking the second mask layer as a mask and etching the graph sparse zone of the to-be-etched layer by taking the second mask layer and the first mask layer as the mask until the surface of the substrate is exposed. By adopting the invention, problems caused by load effect during an etching process can be solved, so that the etching layer formed after the etching process of the graph sparse zone has a good appearance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

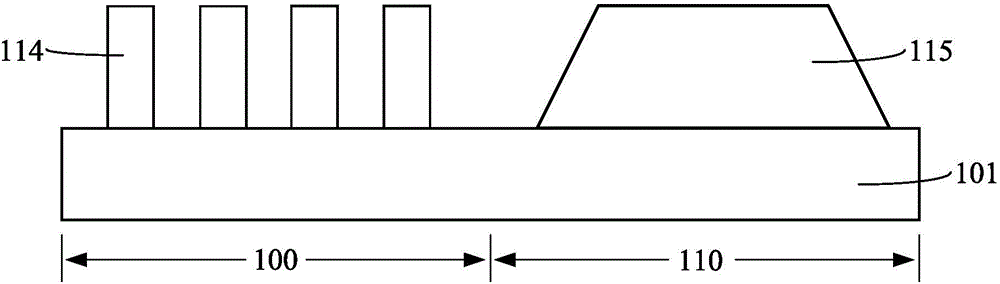

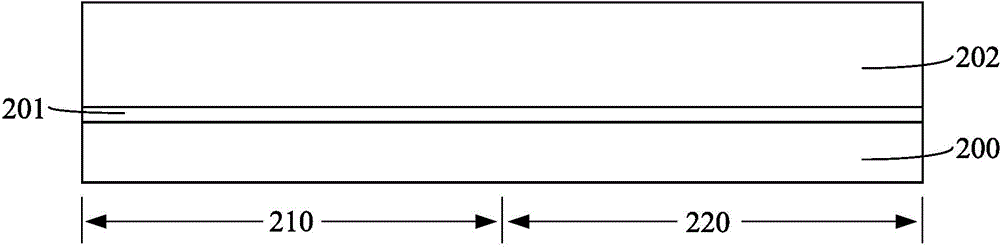

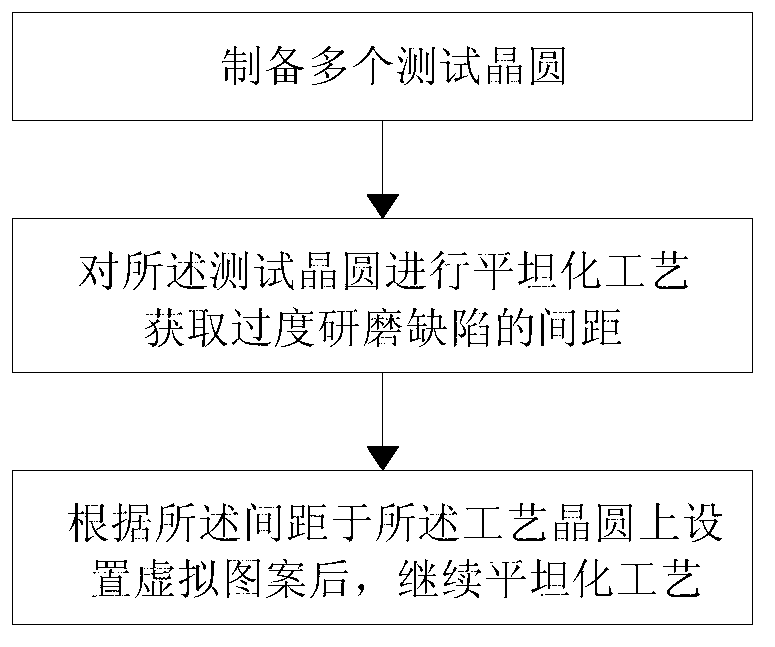

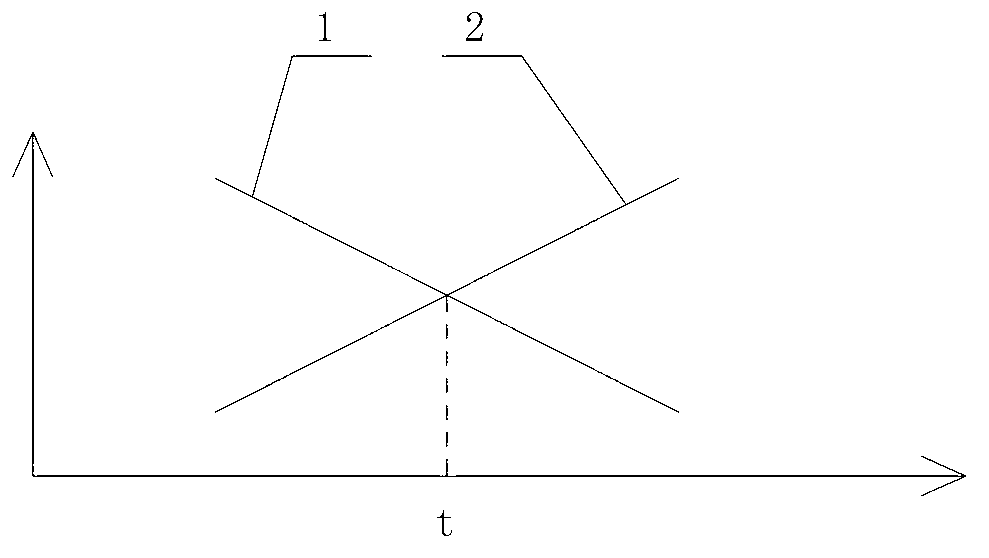

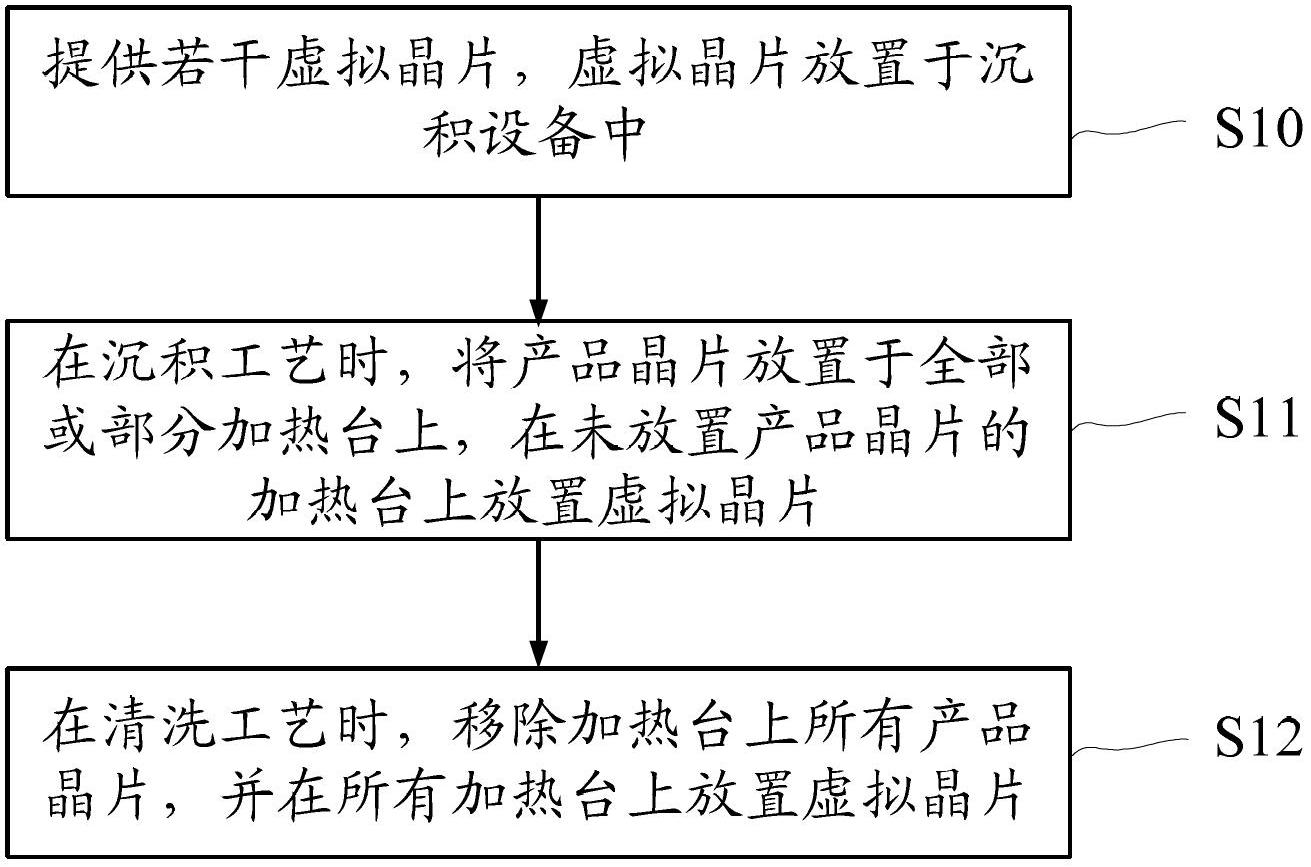

Method for detecting load effect of grinding process

The invention relates to the field of semiconductor fabrication, in particular to a method for detecting a load effect of a grinding process. A test wafer is adopted to test a grinding defect spacing of a planarization process and optimal process time of the grinding process, virtual patterns corresponding to the spacing are arranged on a process wafer, a planarization process of the optimal process time is carried out on the process wafer, and therefore generation of the load effect caused by different densities of pictures on the wafers can be effectively avoided, the product performance is improved, and meanwhile the product yield is increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Semiconductor device and manufacturing method thereof

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

First layer metal trench etching method

ActiveCN105226014AGood lookingConducive to loadSemiconductor/solid-state device manufacturingDry etchingMetal

The invention provides a first layer metal trench etching method. The ILD dielectric of a contact hole layer in a wafer front-layer process is SiO2, and contact hole WCMP is completed. The method comprises the steps that etching stop layers are deposited; a Low-k dielectric layer is deposited; by introducing the mask plate and the shrinkage plate of a first layer metal trench, metal hard mask etching and Low-k dielectric layer etching are separated; by using the difference between etching selection ratio of different materials, two times of etching stop at the etching stop layers which are respectively located at the top and the bottom of the Low-k dielectric layer; and great uniformity of wet etching is used to reduce an etching loading effect. Compared with a first layer metal trench dry etching method in the prior art, the method provided by the invention has the advantages that a better optimization loading effect is realized without affecting the morphology of the first layer metal trench; the consistency of process parameters of first layer metal is ensured; and the uniformity of process parameters of the whole device is optimized.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for eliminating load effect of multi sequence single deposition device

InactiveCN102664146AStable thicknessStress stabilizationSemiconductor/solid-state device manufacturingEngineeringMechanical engineering

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Planarization method

ActiveCN105990130AAvoid loading effectReduce processing costsSemiconductor/solid-state device manufacturingEtchingEngineering

Owner:SEMICON MFG INT (SHANGHAI) CORP

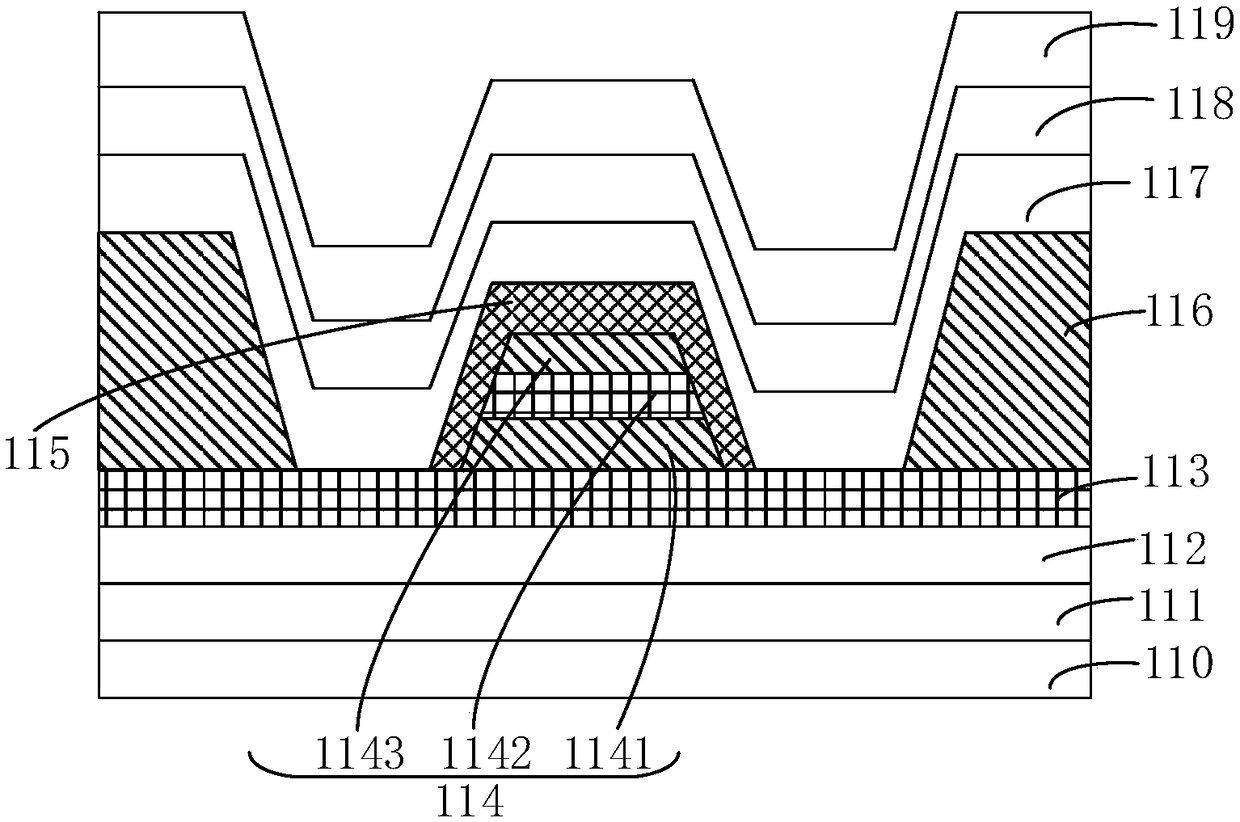

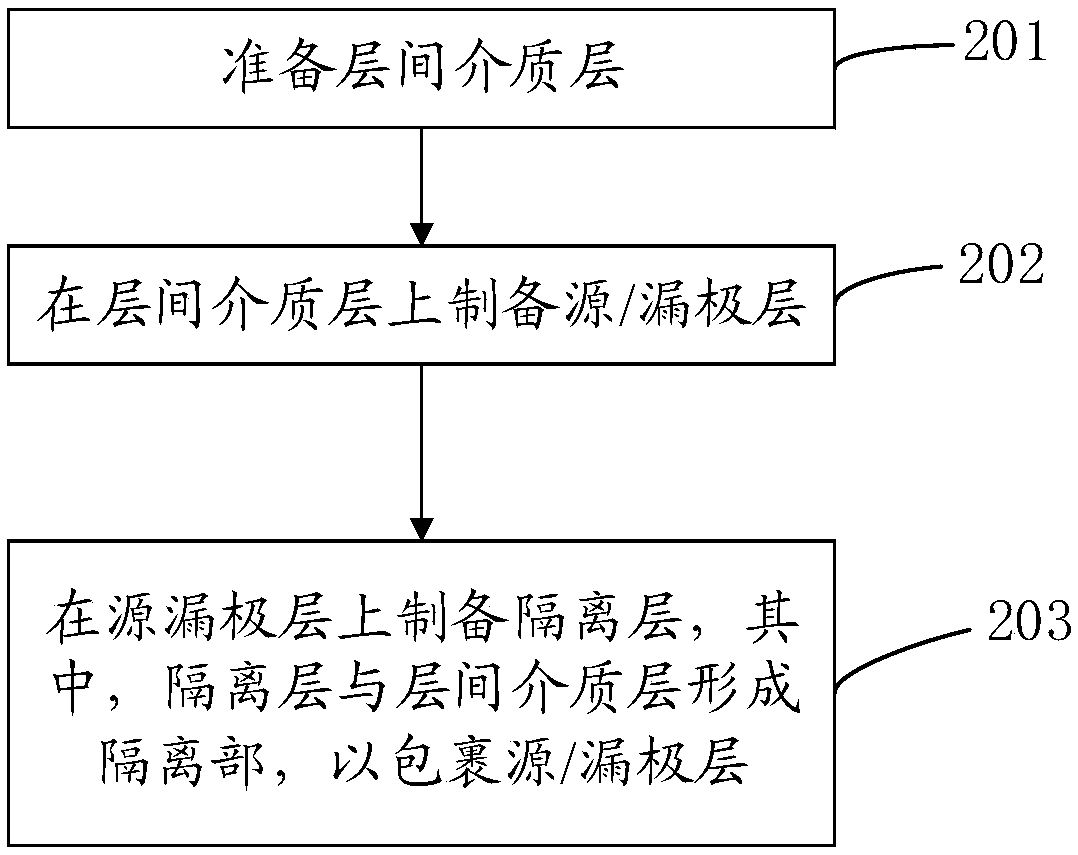

Display device and fabrication method thereof

InactiveCN108878448AIncrease coverageImprove reliabilityTransistorSolid-state devicesIsolation layerDisplay device

The invention discloses a display device and a fabrication method thereof. The display device comprises an interlayer dielectric layer, a source / drain layer and an isolation layer which are sequentially arranged, wherein the isolation layer and the interlayer dielectric layer form an isolation part to wrap the source / drain layer. In the display device, the source / drain layer is wrapped by the isolation layer and the interlayer dielectric layer, so that the source / drain layer is prevented from being corroded by an etching liquid in subsequent processes, the coverage of a film layer can be improved, a load effect is prevented, and the reliability is improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

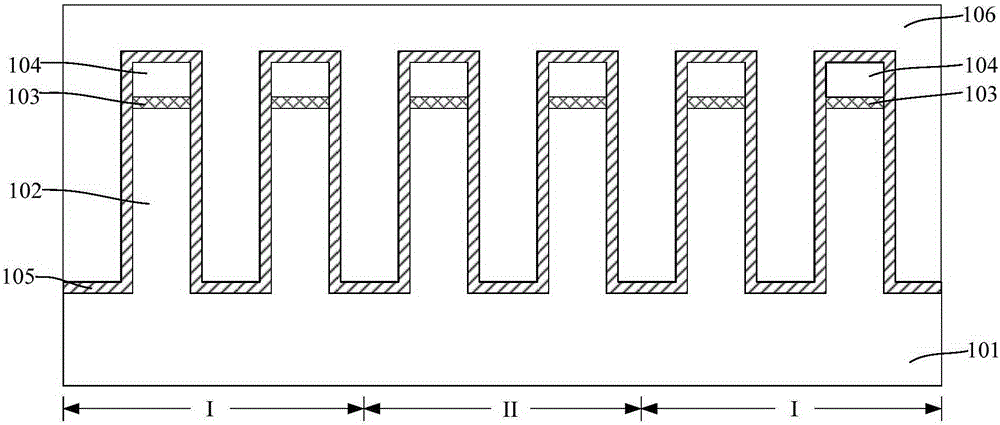

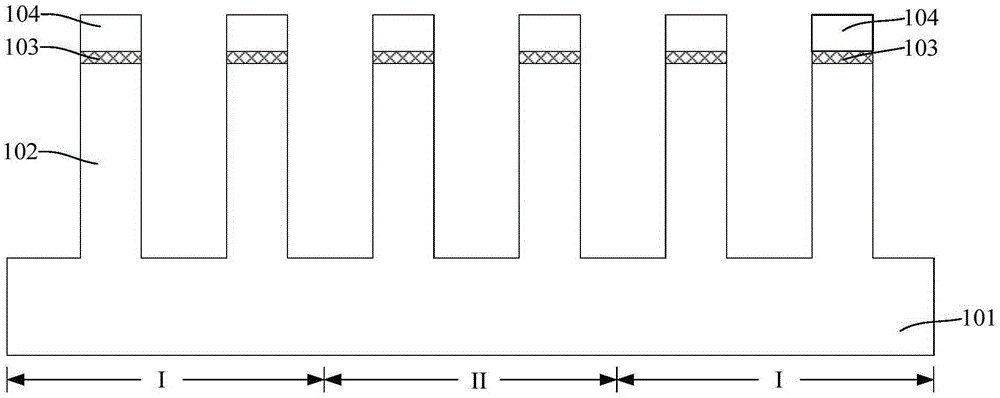

Forming method of fin type field-effect tube

ActiveCN106653604AImprove electrical performanceGood feature sizeSemiconductor/solid-state device manufacturingSemiconductor devicesFeature DimensionEtching

The invention relates to a forming method of a fin type field-effect tube. The forming method comprises: a substrate including a first region and a second region adjacent to the first region is provided, wherein a plurality of discrete fin parts are formed on the surface of the substrate and the fin parts are arranged at equal intervals; the intervals between the adjacent fin parts are filled with first dielectric layers, wherein the first dielectric layers cover the surfaces of the side walls of the fins; the fin parts in the second area are removed and thus the substrate surface in the second area is exposed; a second dielectric layer is formed on the substrate in the second area, wherein the second dielectric layer also covers the surfaces of the side walls of the first dielectric layers in the first area and the tops of the first dielectric layers are flush with the top of the second dielectric layer; and back etching is carried out to remove the first dielectric layers and the second dielectric layer at the certain thicknesses and thus the partial side wall surfaces of the fin parts in the first area are exposed. According to the forming method, the plurality of fin parts with different graphic densities are formed and the fin parts have excellent feature dimensions and forms, so that the electrical performances of the fin type field-effect tube can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Apparatus and method for digitally controlling capacitance

ActiveUS8275336B2Avoid loading effectAngle modulation by variable impedencePulse automatic controlCapacitanceControl signal

Owner:RICHWAVE TECH CORP

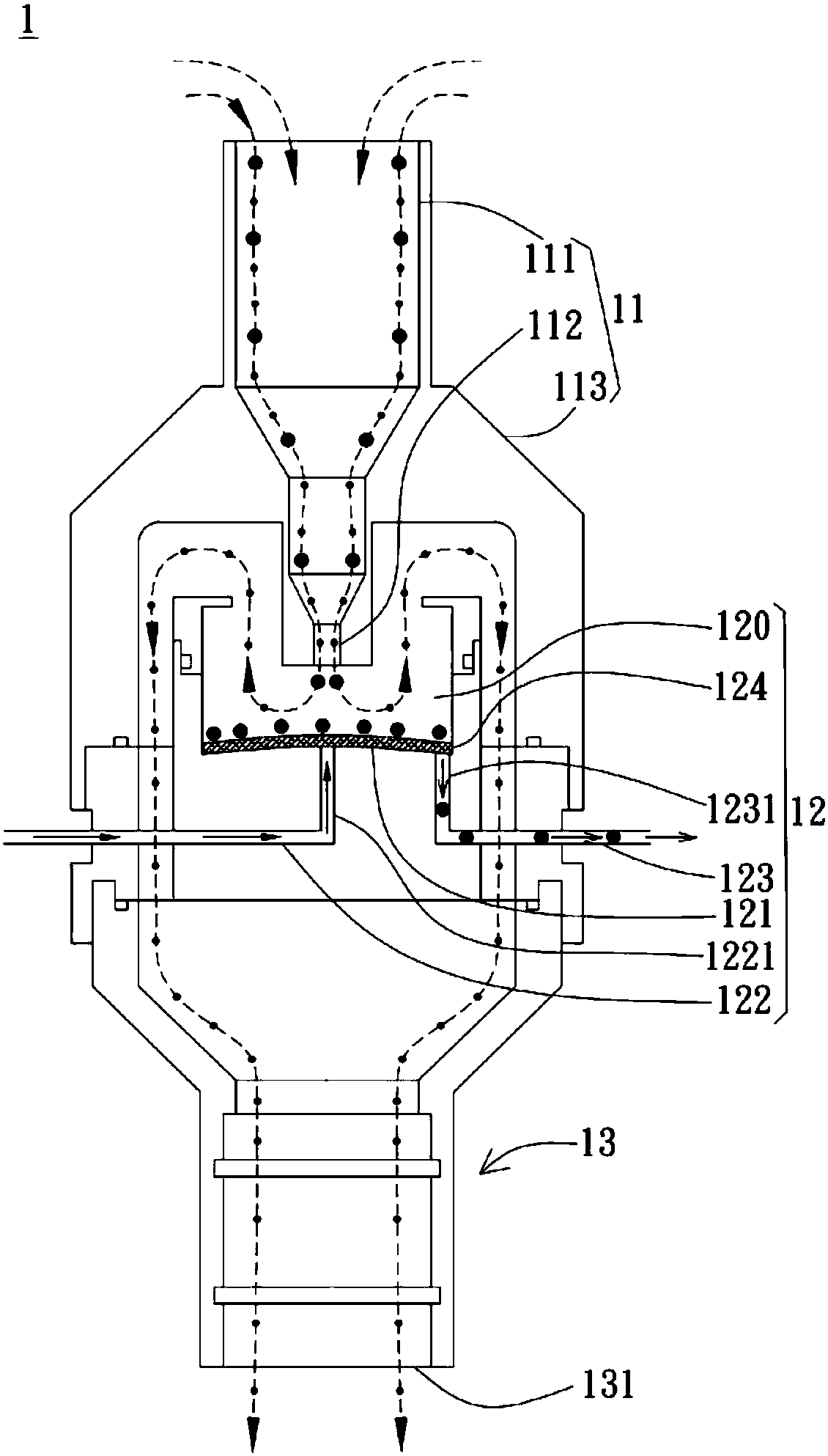

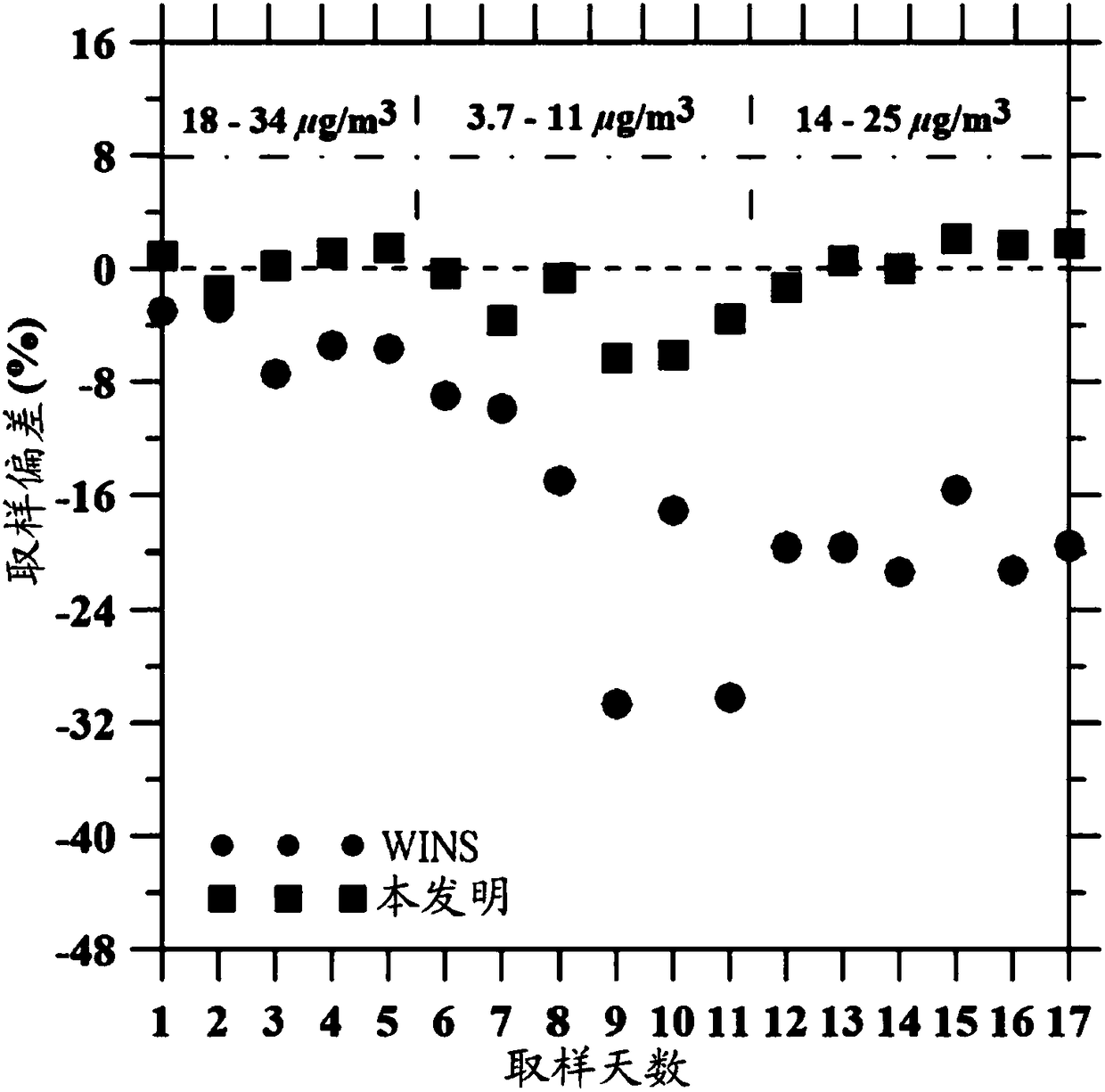

Inertial impactor with wetted impaction surface to prevent particle loading effect

InactiveCN109406354AAvoid loading effectPrevent reboundParticle suspension analysisEngineeringParticle sampling

The invention discloses an inertial impactor with a wetted impaction surface to prevent the particle loading effect. The inertial impactor can prevent the particle loading effect and is composed of anupper shell, an impacting part, and a lower shell. The upper shell is provided with an air inlet and a round nozzle that is connected to the air inlet. The impacting part comprises an impacting well,and the lower part of the impacting well is an impacting surface. The nozzle is right opposite to and is above the center of the impacting surface. The center of the impacting surface is provided with a liquid inlet. Liquid is continuously or intermittently introduced to the impacting surface so as to wet the impacting surface and remove particles, at the same time, the liquid is discharged froma liquid discharge route in the impacting surface, and the lower shell is provided with an air outlet channel, which is connected to a particle sampling or monitoring device.

Owner:SPRING FOUND OF NCTU

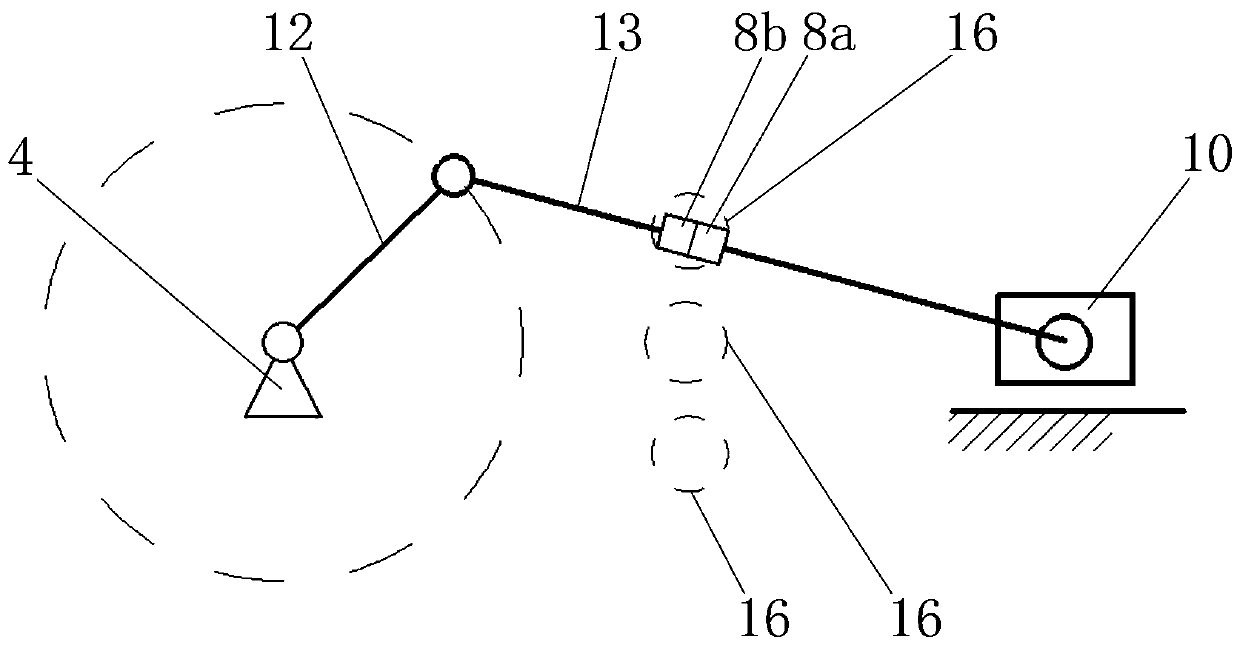

High-speed multi-station piston ring-cylinder liner sliding pair friction test machine

PendingCN111089815ASpeed up the testing processAvoid loading effectTransmission systemsInvestigating abrasion/wear resistancePhysicsElectric machinery

The invention relates to friction test machines, in particular to a high-speed multi-station piston ring-cylinder liner sliding pair friction test machine. The problems that the test process of a traditional friction test machine is slow, the mutual-affected frictional wear state among piston cavities cannot be tested, and the traditional friction test machine is not suitable for high-speed occasions are solved. The high-speed multi-station piston ring-cylinder liner sliding pair friction test machine includes a first box-shaped machine frame, a second box-shaped machine frame, a third box-shaped machine frame, a crank connecting rod mechanism, a variable frequency motor, N loading screws, N pressure sensors, N compression springs, N wireless passive strain sensors and N wireless passive inclination sensors, wherein N is a positive integer, and N is more than or equal to 2; an output shaft of the variable frequency motor is connected to the free end of a crank of the crank connecting rod mechanism; the N loading screws penetrate through N screw holes one to one; and the N pressure sensors are fixed to the lower ends of the N loading screws one to one. The high-speed multi-station piston ring-cylinder liner sliding pair friction test machine is suitable for a friction test of a piston ring-cylinder liner sliding pair.

Owner:山西交通职业技术学院

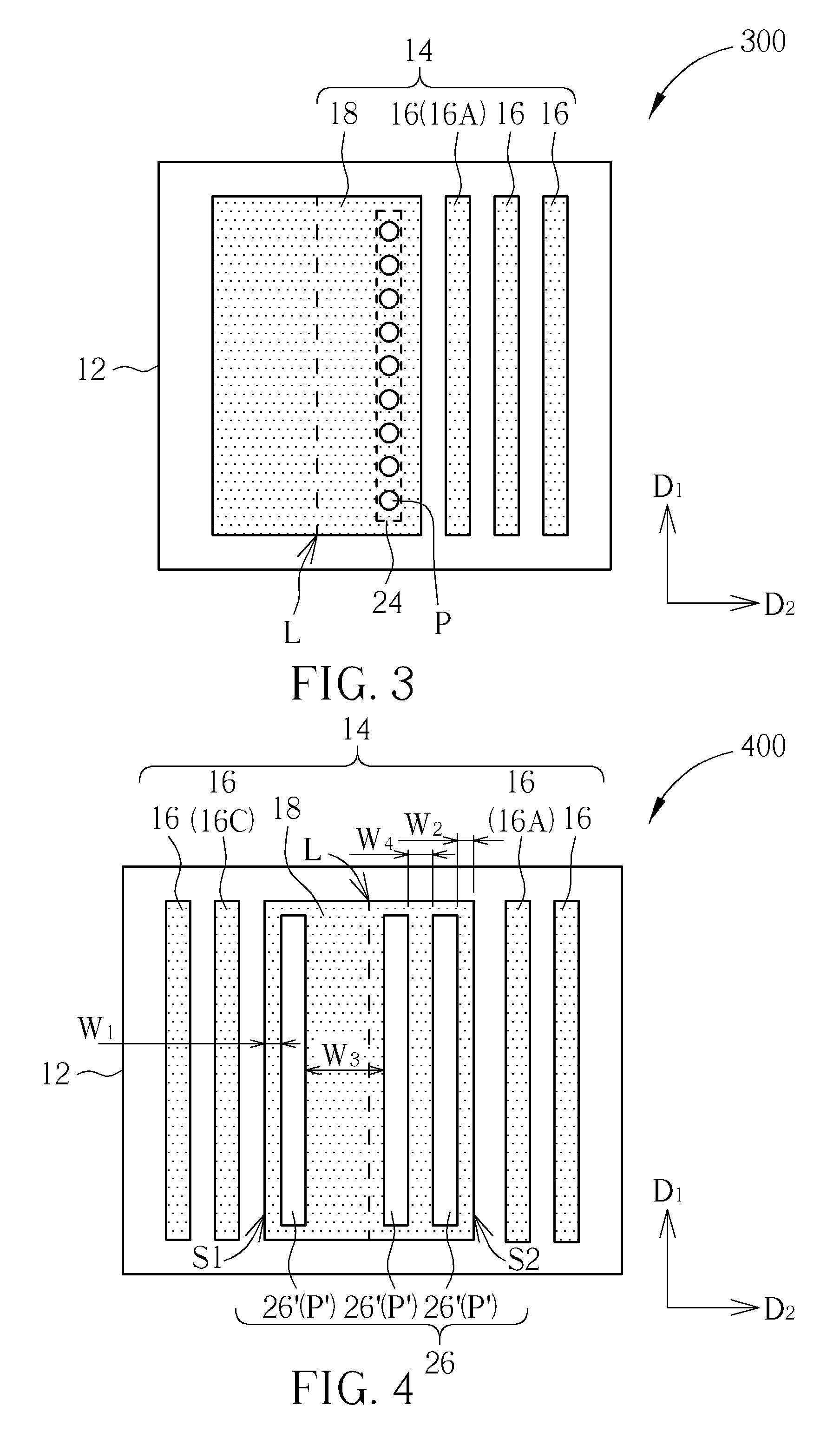

Mask and method of forming pattern by using the same

ActiveUS8962221B2Improve accuracyAvoid loading effectPhotomechanical apparatusCAD circuit designEngineering

Owner:UNITED MICROELECTRONICS CORP

A metal groove etching method

ActiveCN105226014BDoes not affect shapeThe size is smaller than the process requirementSemiconductor/solid-state device manufacturingDry etchingMetal

The invention provides a first layer metal trench etching method. The ILD dielectric of a contact hole layer in a wafer front-layer process is SiO2, and contact hole WCMP is completed. The method comprises the steps that etching stop layers are deposited; a Low-k dielectric layer is deposited; by introducing the mask plate and the shrinkage plate of a first layer metal trench, metal hard mask etching and Low-k dielectric layer etching are separated; by using the difference between etching selection ratio of different materials, two times of etching stop at the etching stop layers which are respectively located at the top and the bottom of the Low-k dielectric layer; and great uniformity of wet etching is used to reduce an etching loading effect. Compared with a first layer metal trench dry etching method in the prior art, the method provided by the invention has the advantages that a better optimization loading effect is realized without affecting the morphology of the first layer metal trench; the consistency of process parameters of first layer metal is ensured; and the uniformity of process parameters of the whole device is optimized.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Formation method of fin field effect transistor

ActiveCN106571336BImprove electrical performanceGood lookingSemiconductor/solid-state device manufacturingSemiconductor devicesField effectElectrical performance

A method for forming a fin field effect transistor comprises: providing a substrate, wherein the substrate includes first regions and second regions located between adjacent first regions, a plurality of discrete fins are formed on the surface of the substrate, and the distances between the adjacent fins are the same; fully filling the surface of the substrate between the adjacent fins with a first dielectric layer, wherein the first dielectric layer covers the sidewall surfaces of the fins; removing the first dielectric layer of the second regions to expose the sidewall surfaces of the fins in the second regions; oxidizing the fins of the second regions to convert the fins of the second regions into an oxidizing structure; forming a second dielectric layer on the substrate in the second regions, wherein the second dielectric layer also covers the sidewall surface of the oxidizing structure, and the sidewall surface of the first dielectric layer in the first regions; etching back a part of thickness of the first dielectric layer, the second dielectric layer, and the oxidizing structure. The method forms a number of fins with different pattern densities and with good feature sizes and morphology so as to improve the electrical performance of the fin field effect transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Array substrate, liquid crystal display and electronic equipment

ActiveCN108614378BNo short circuit failureImprove yield rateNon-linear opticsLiquid-crystal displayDisplay device

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Integrated method of raise source leakage structure complementary metal-oxide-semiconductor transistor (CMOS) and Bipolar device

ActiveCN103151292BPrecise thickness controlSolve the problem of limited design sizeSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPolycrystalline silicon

The invention discloses an integrated method of a raise source leakage structure complementary metal-oxide-semiconductor transistor (CMOS) and a Bipolar device. The integrated method of the raise source leakage structure CMOS and the Bipolar device comprises forming a grid structure on a traditional shallow groove isolation structure, wherein a certain etch quantity of a silicon substrate is caused by side wall etch, using selective epitaxy to develop polycrystalline silicon in a source leakage area so as to form a raise source leakage area, depositing dielectric film again to protect a CMOS area; forming a polycrystalline silicon side wall after base polycrystalline silicon etch is carried out, removing dielectric film of the CMOS area, and keeping dielectric film under the polycrystalline silicon side wall; using emitting electrode polycrystalline silicon as expansion of the raise source leakage area to a shallow trench isolation (STI) area and a connecting line of a CMOS local area, coating a layer of filling materials after imaging is carried out, carrying out backward etch on the filling materials and the emitting electrode polycrystalline silicon above the source leakage area, and stopping etch on the dielectric film; at last, removing the filling materials and an etch stopping layer, and finishing source leakage injection, follow-up contact holes and a metal connecting line technology. The integrated method of the raise source leakage structure CMOS and the Bipolar device has the advantages of being capable of effectively reducing the size from an active area to a grid, increasing amount of transistors in unit area, enlarging a technology window, reducing source leakage parasitic capacitance, and improving a short-channel effect.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A method for forming a double damascene structure

ActiveCN109585364BImprove etch defectsGood lookingSemiconductor/solid-state device detailsSolid-state devicesEtchingSemiconductor structure

The present invention provides a method for forming a dual-damascene structure. The method comprises successively forming a barrier layer, a low dielectric constant layer, a first buffer layer, a hardmask layer, and a second buffer layer on the surface of a semiconductor structure in which a metal structure is embedded; etching the second buffer layer and the hard mask layer to form a first trench; etching the first buffer layer and the low dielectric constant layer to form a first via hole; downwards etching the low dielectric constant layer to form a second via hole; integrally etching thefirst via hole and the second via hole to form a second trench; opening the barrier layer to expose the metal structure so as to form the dual-damascene structure. Performing local via hole etching twice can well solve a load effect caused by etching and improve the dual-damascene etching defect, thereby improving the dual-damascene shape. Further, the second trench formed by the integral etchingis favorable for subsequent copper filling, which improves the reliability of the dual-damascene structure.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com