Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

630 results about "Programmable-gain amplifier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A programmable-gain amplifier (PGA) is an electronic amplifier (typically an operational amplifier) whose gain can be controlled by external digital or analog signals. The gain can be set from less than 1V/V to over 100V/V. Examples for the external digital signals can be SPI, I²C while the latest PGAs can also be programmed for offset voltage trimming, as well as active output filters. Popular applications for these products are motor control, signal and sensor conditioning.

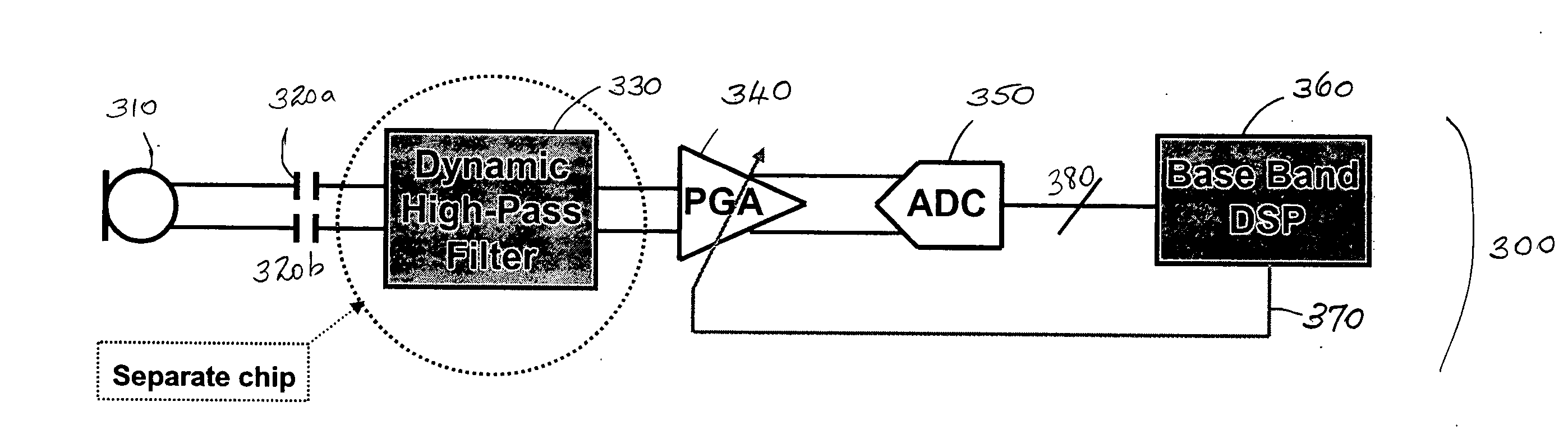

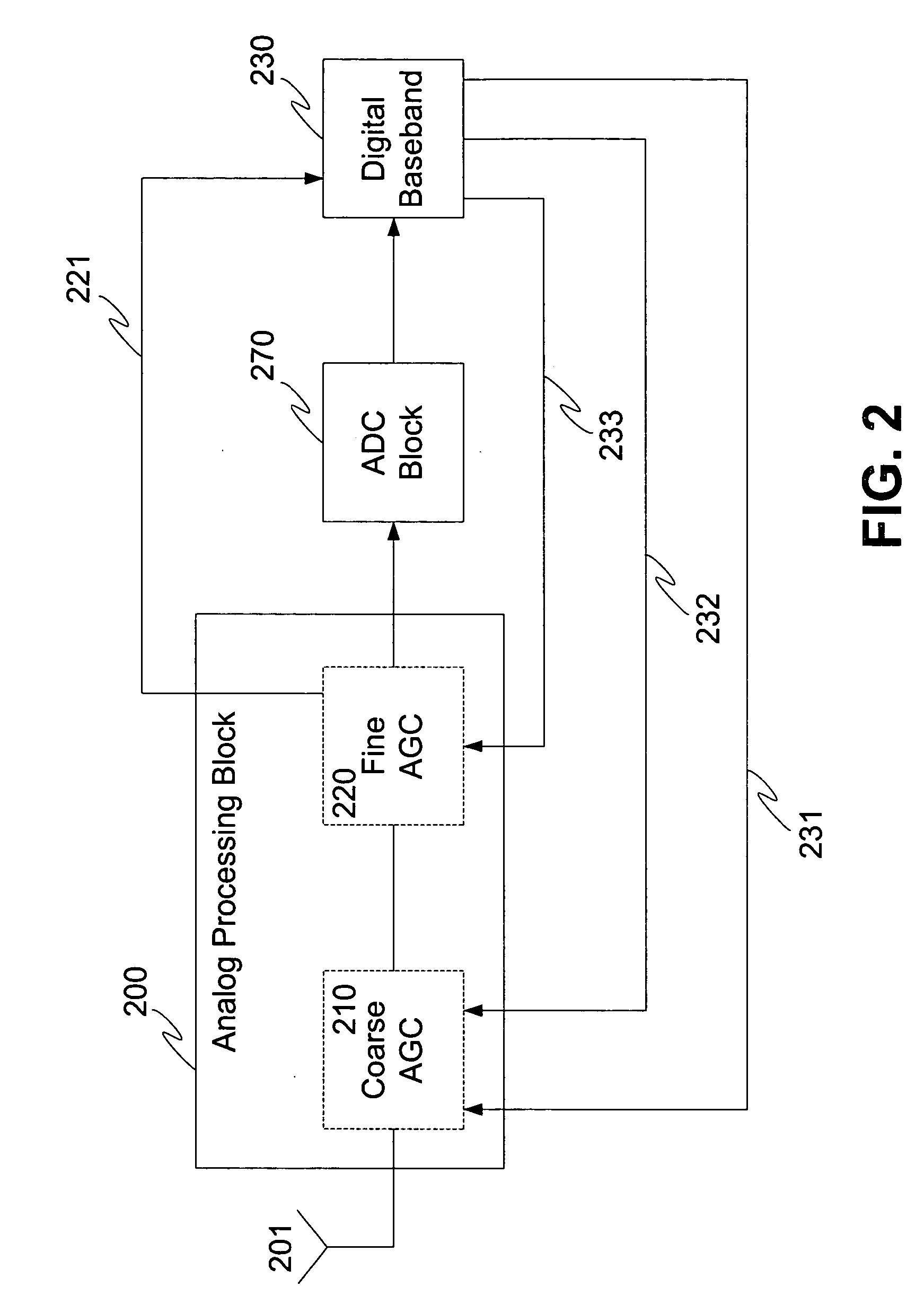

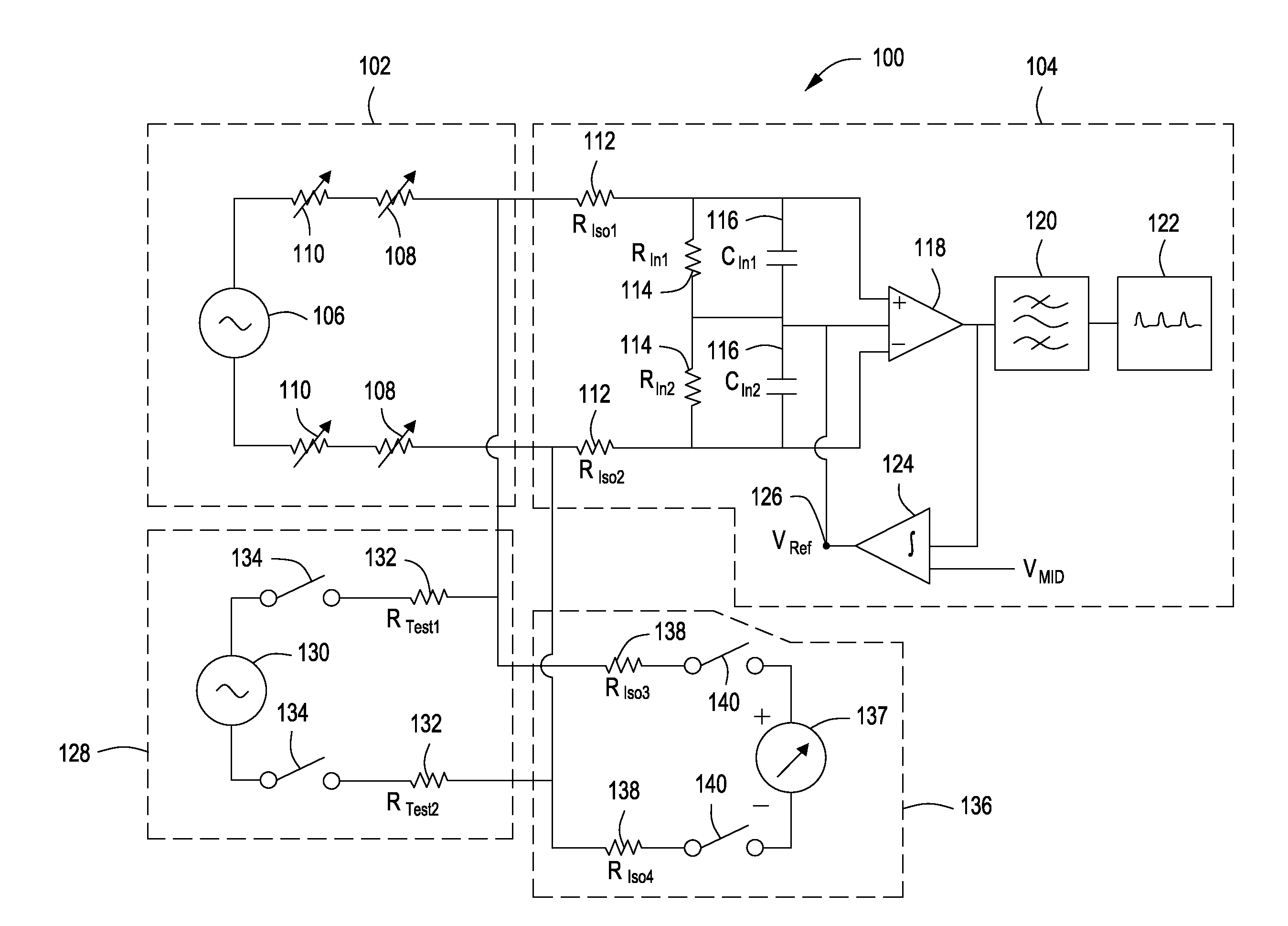

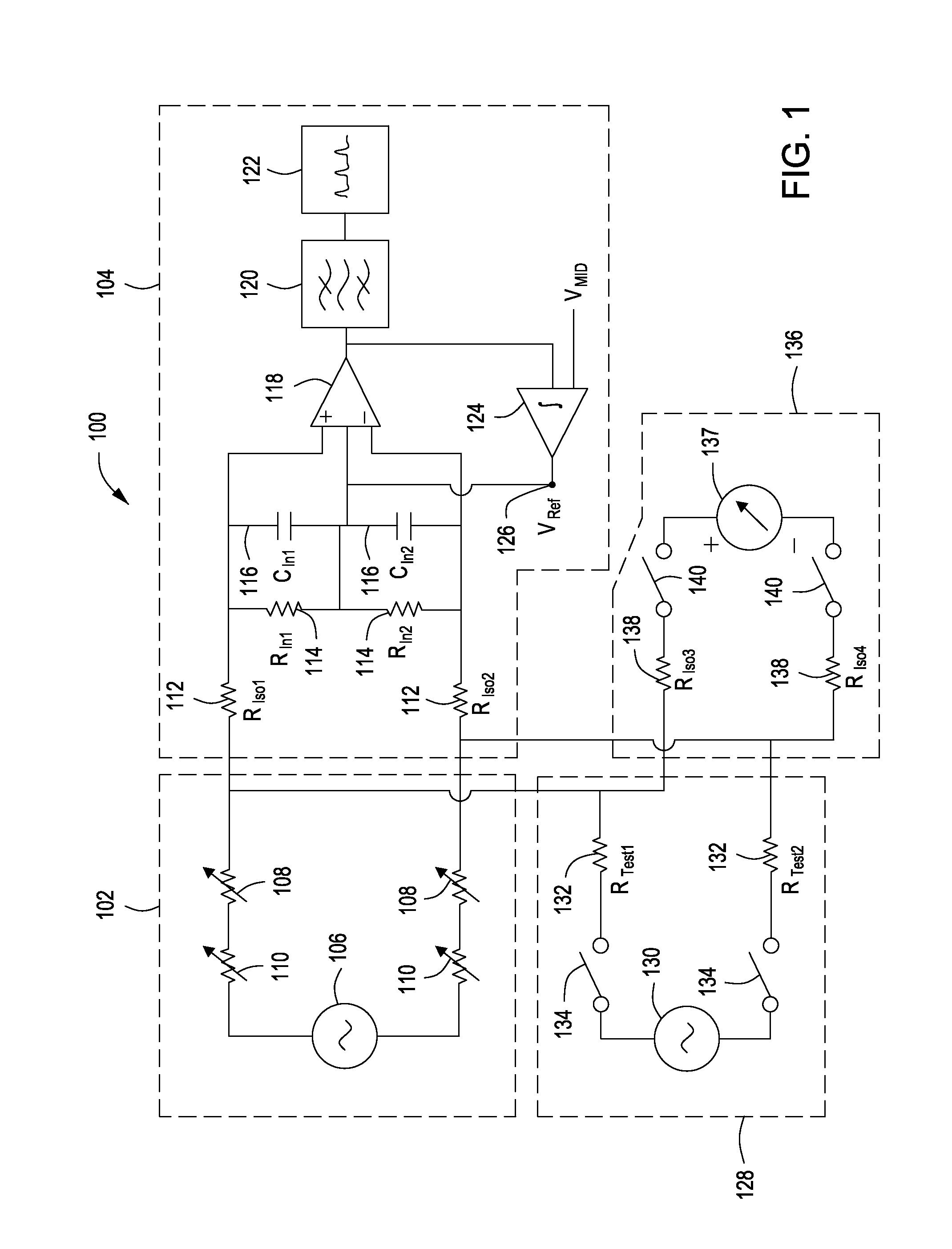

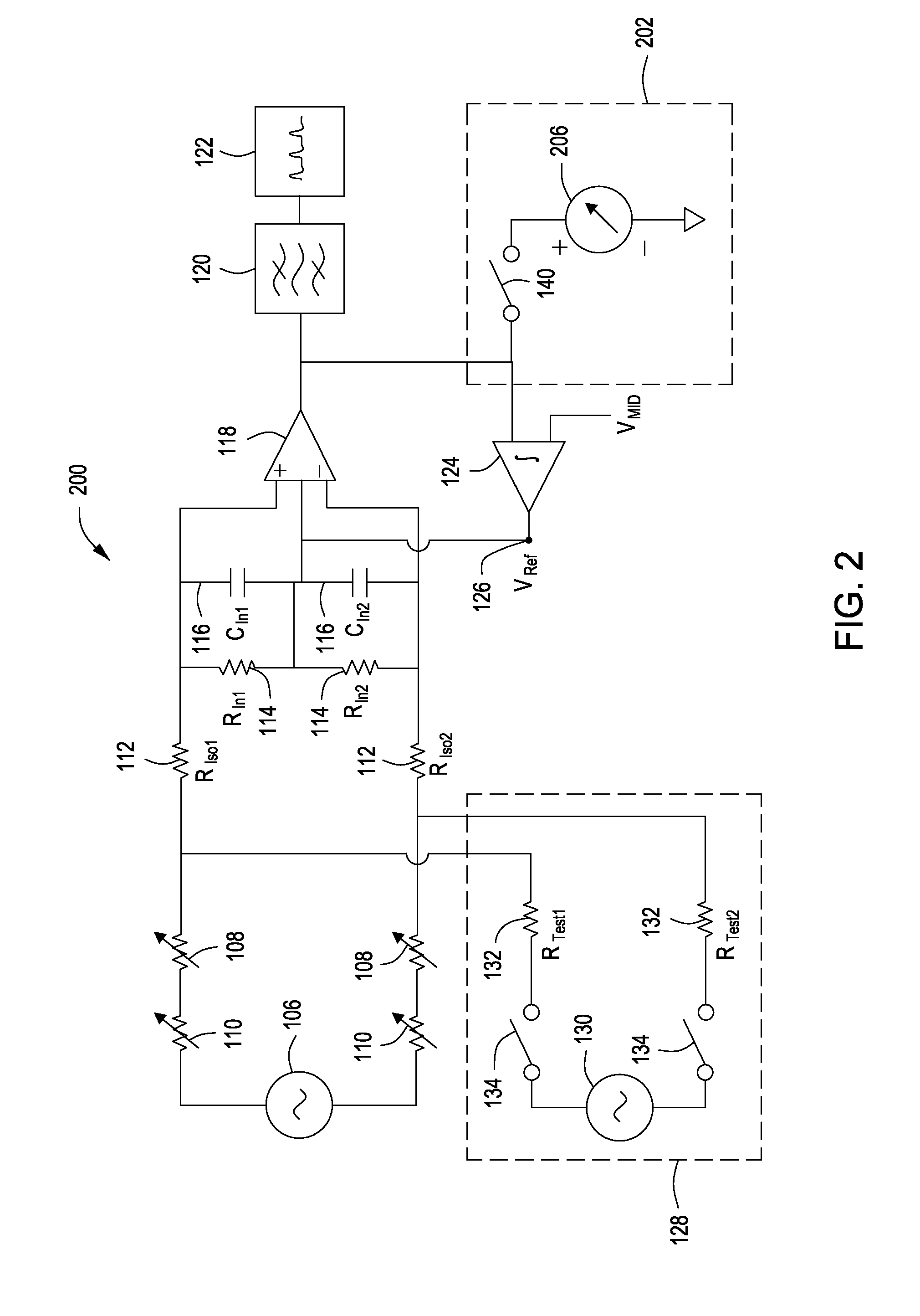

Low frequency noise reduction circuit architecture for communications applications

ActiveUS20080069373A1Economical yet effective high-pass filterAchieve adaptiveFrequency response correctionTransmission noise suppressionCapacitanceLow noise

A noise reduction circuit for reducing the effects of low frequency noise such as wind noise in communications applications is described. In one embodiment, the noise reduction circuit features a high pass filter formed by exploiting the existing off-chip AC coupling capacitances in making the connection to the source of audio signals. The filter may be adaptive to environmental low frequency noise level through programming the shunt resistances. A low-noise wide dynamic range programmable gain amplifier is also described. Adaptive equalization of the audio signal is also described through the utilization of programmable front-end resistors and a back-end audio equalizer.

Owner:AVAGO TECH INT SALES PTE LTD

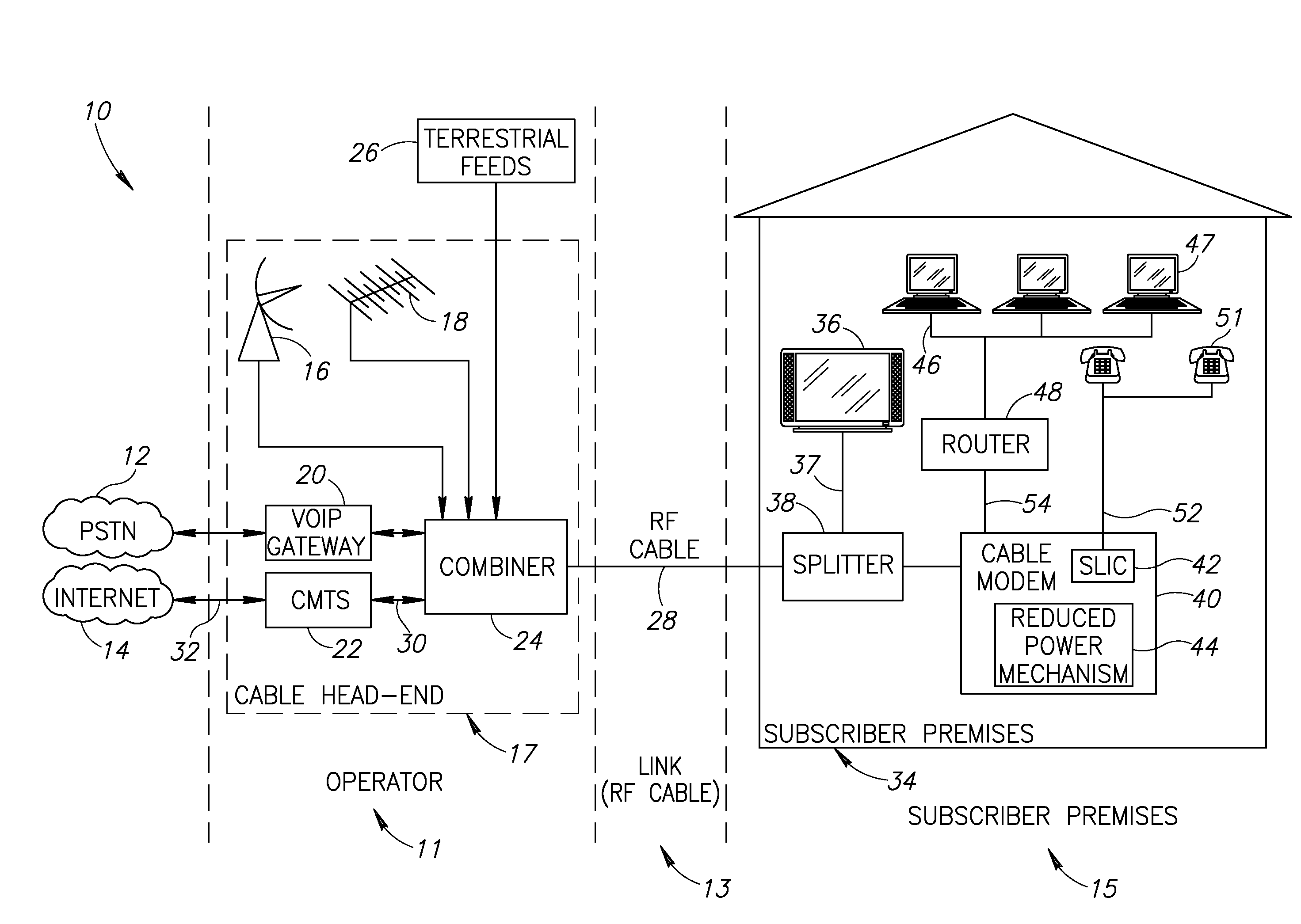

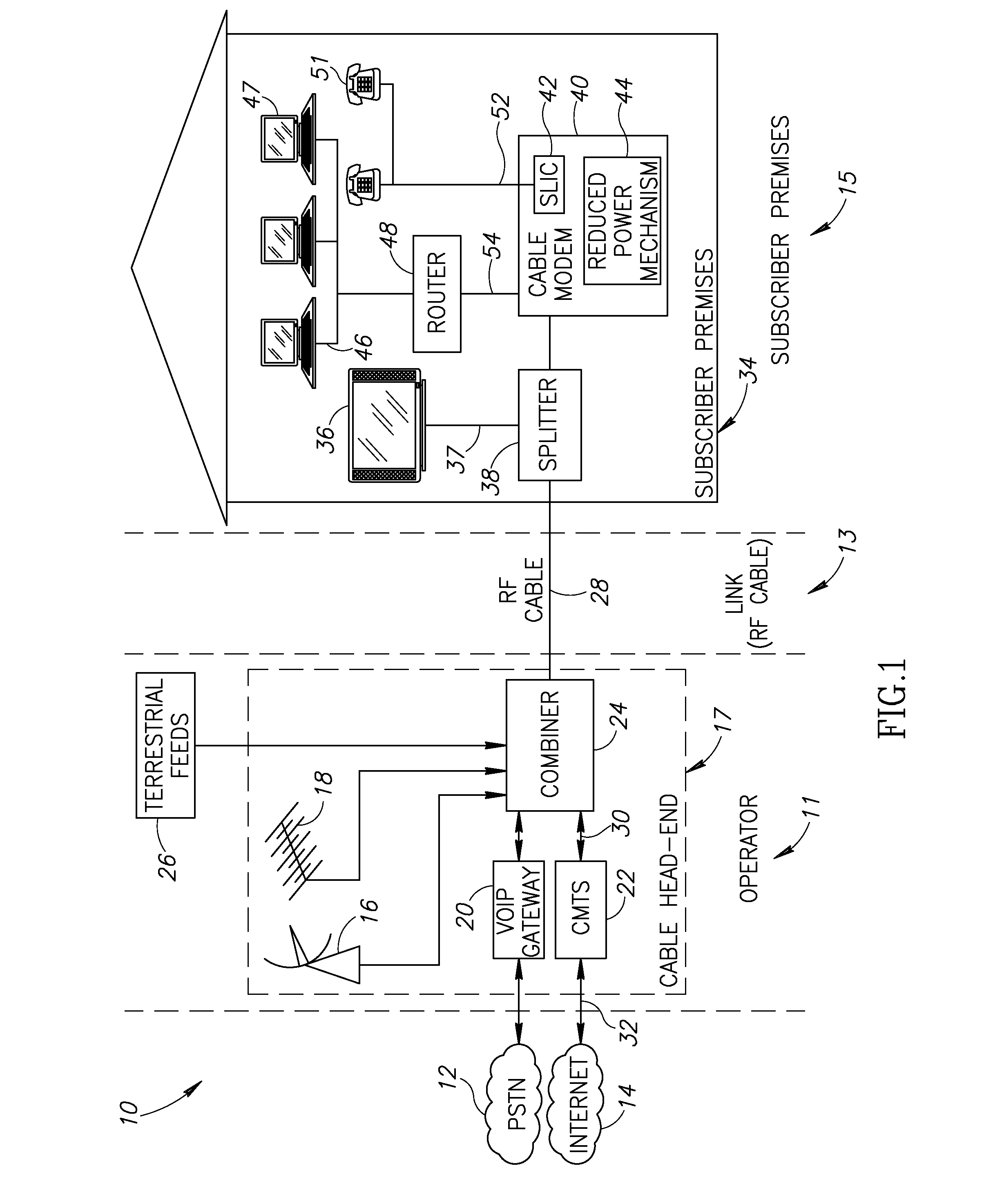

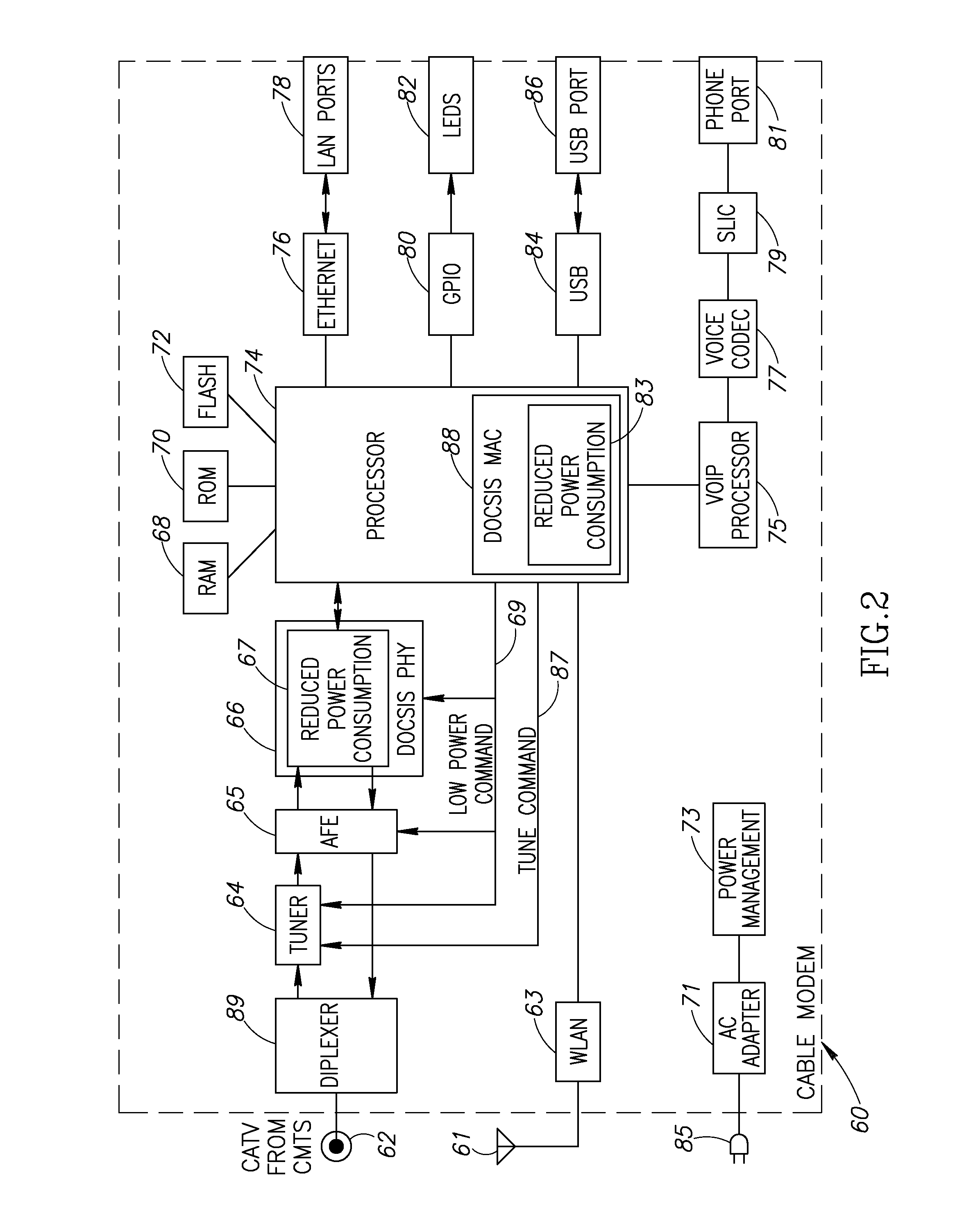

Apparatus for and method of reducing power consumption in a cable modem

ActiveUS20080018427A1Reduce power consumptionReduce MechanismsError preventionFrequency-division multiplex detailsDOCSISBandwidth requirement

A novel apparatus and method of reduced power consumption for battery backup operation of a communication device such as a cable modem. When the cable modem senses a failure of the external power source it requests from the cable head-end to switch from multi-channel DOCSIS 3.0 operation to single-channel DOCSIS 2.0 operation. In response to approval by the cable head-end, the cable modem shuts down multi-channel circuits in the PHY such as the wideband analog to digital converter (ADC) which is normally used during multi-channel operation. In its place, it activates narrowband circuitry such as a narrowband ADC which consumes far less power. Tuner filter circuits are also swapped to match the reduced bandwidth requirements of battery backup operation. To further reduce power, the narrower bandwidth requirements during battery backup operation permit the linearity of a programmable gain amplifier (PGA) in the upstream path to be reduced.

Owner:MAXLINEAR INC

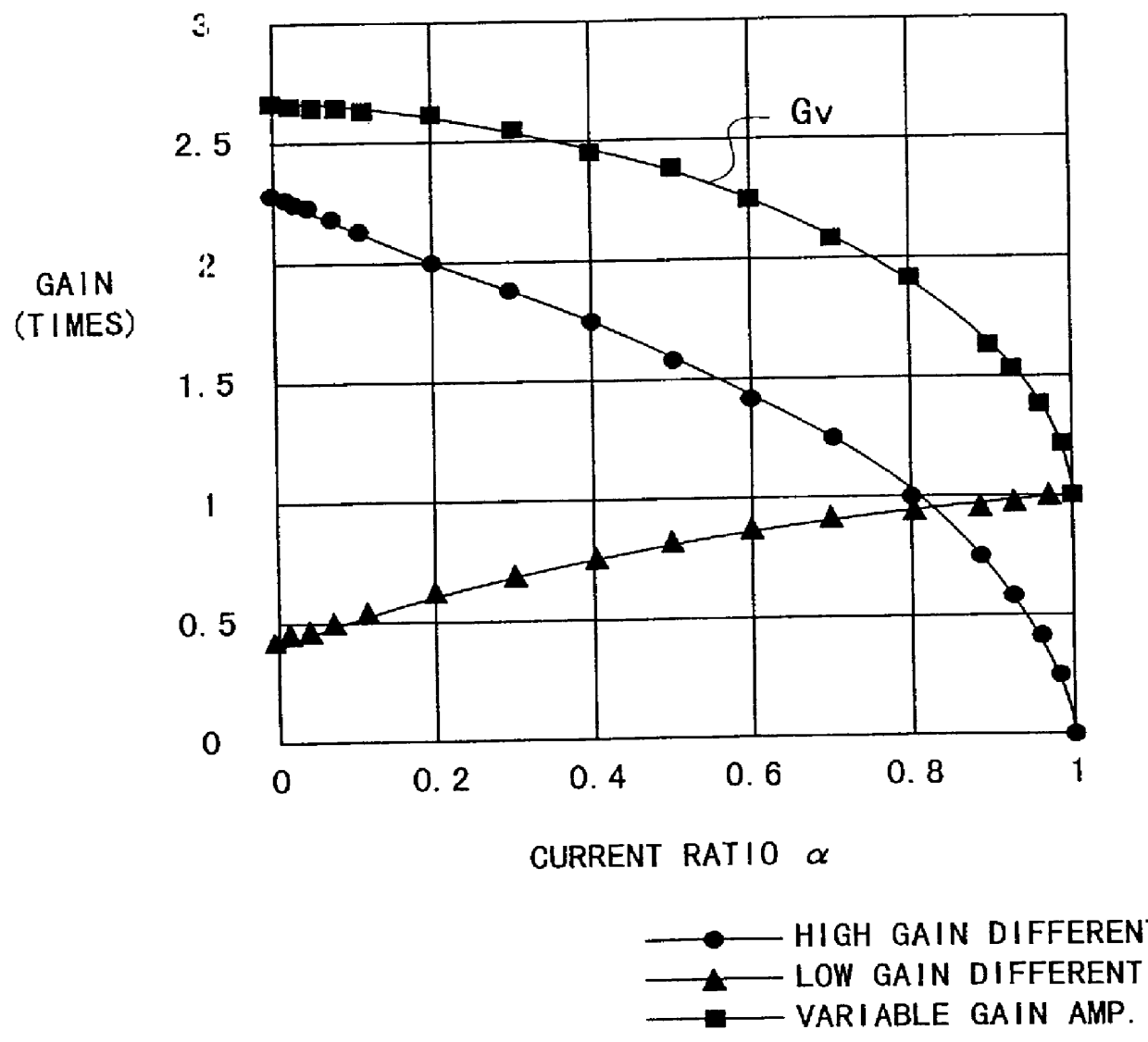

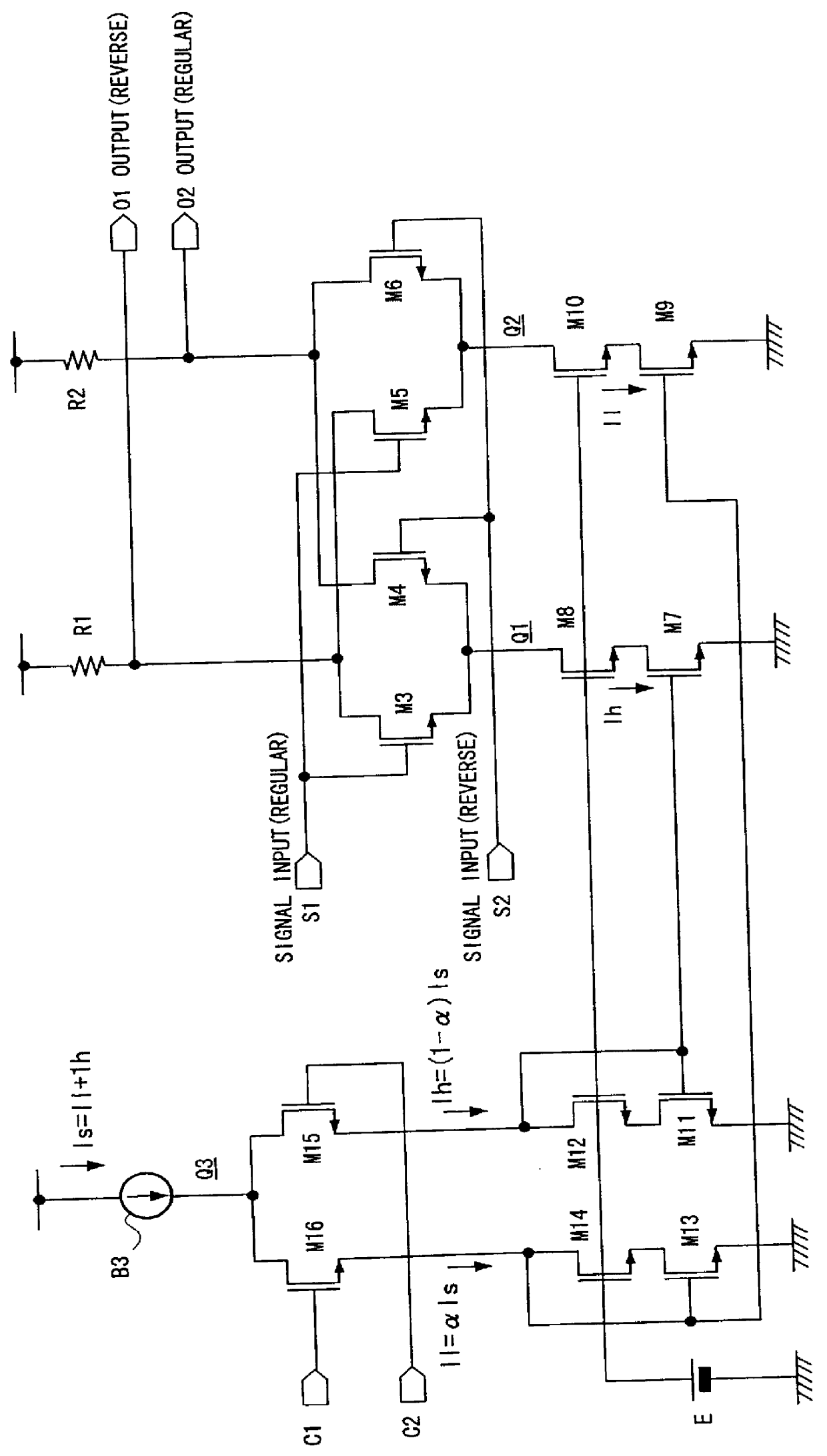

Variable gain amplifier

InactiveUS6163215AComputations using contact-making devicesGain controlAudio power amplifierVariable-gain amplifier

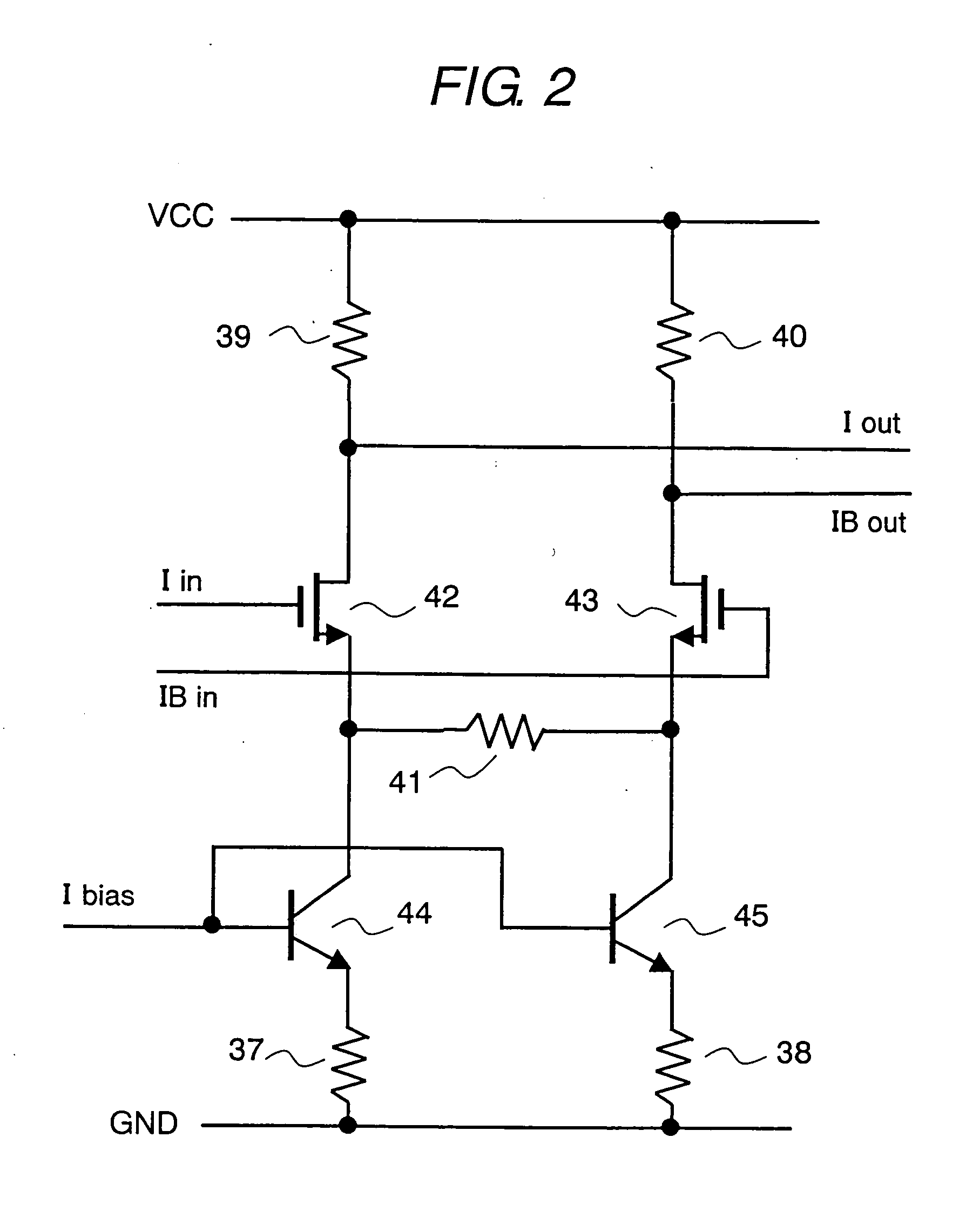

In a variable gain amplifier controlling a gain by using differential amplifiers with a gain control signal, a gain switchover differential amplifier or a bias circuit which composes a current mirror with the gain switchover differential amplifier is connected between a high and a low gain differential amplifier for the same bias current which are mutually connected to share load resistances for the same output polarity and a bias current source common to both of the differential amplifiers, to perform switchover operations of the high and the low differential amplifier by a gain control signal, and a current source which flows a fixed offset current through at least the low one of the high and the low differential amplifier is provided.

Owner:FUJITSU LTD

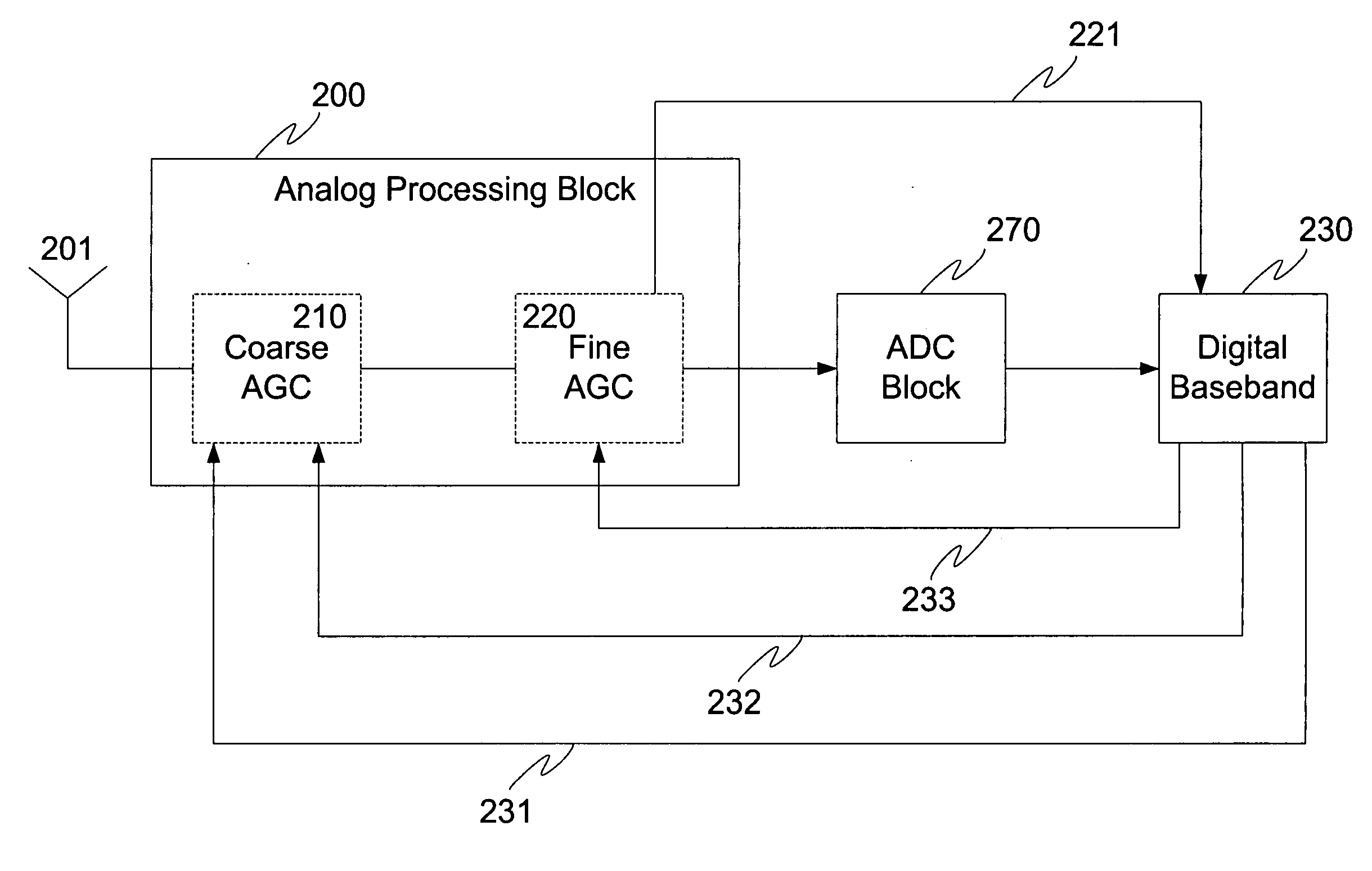

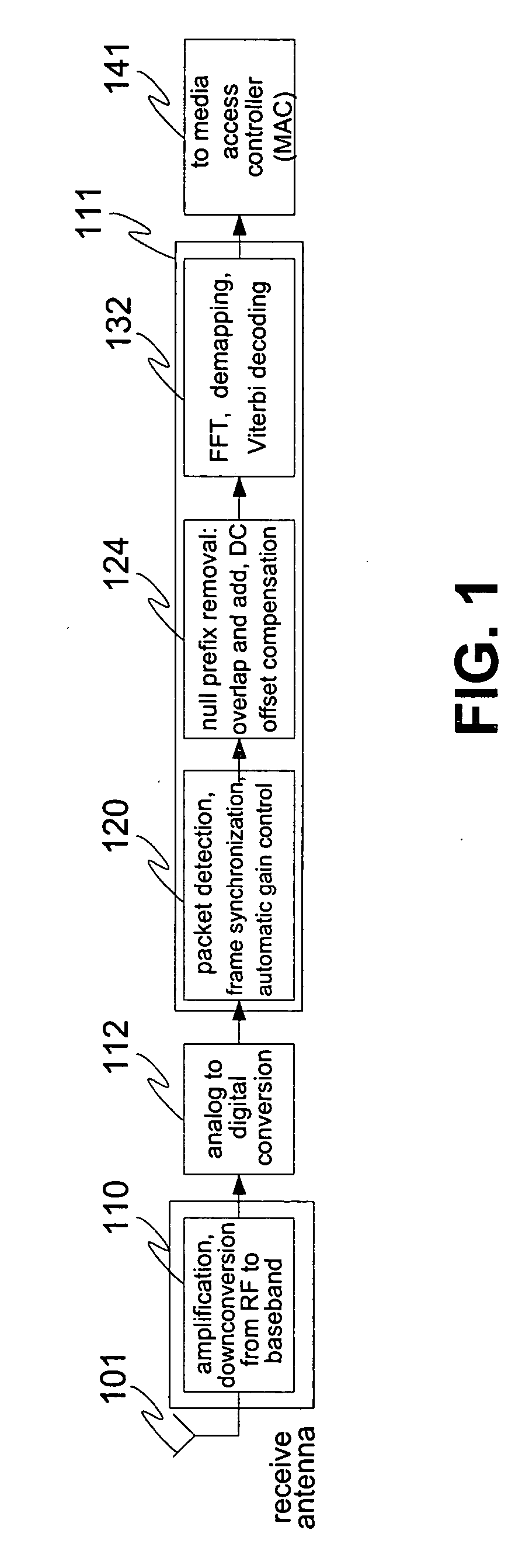

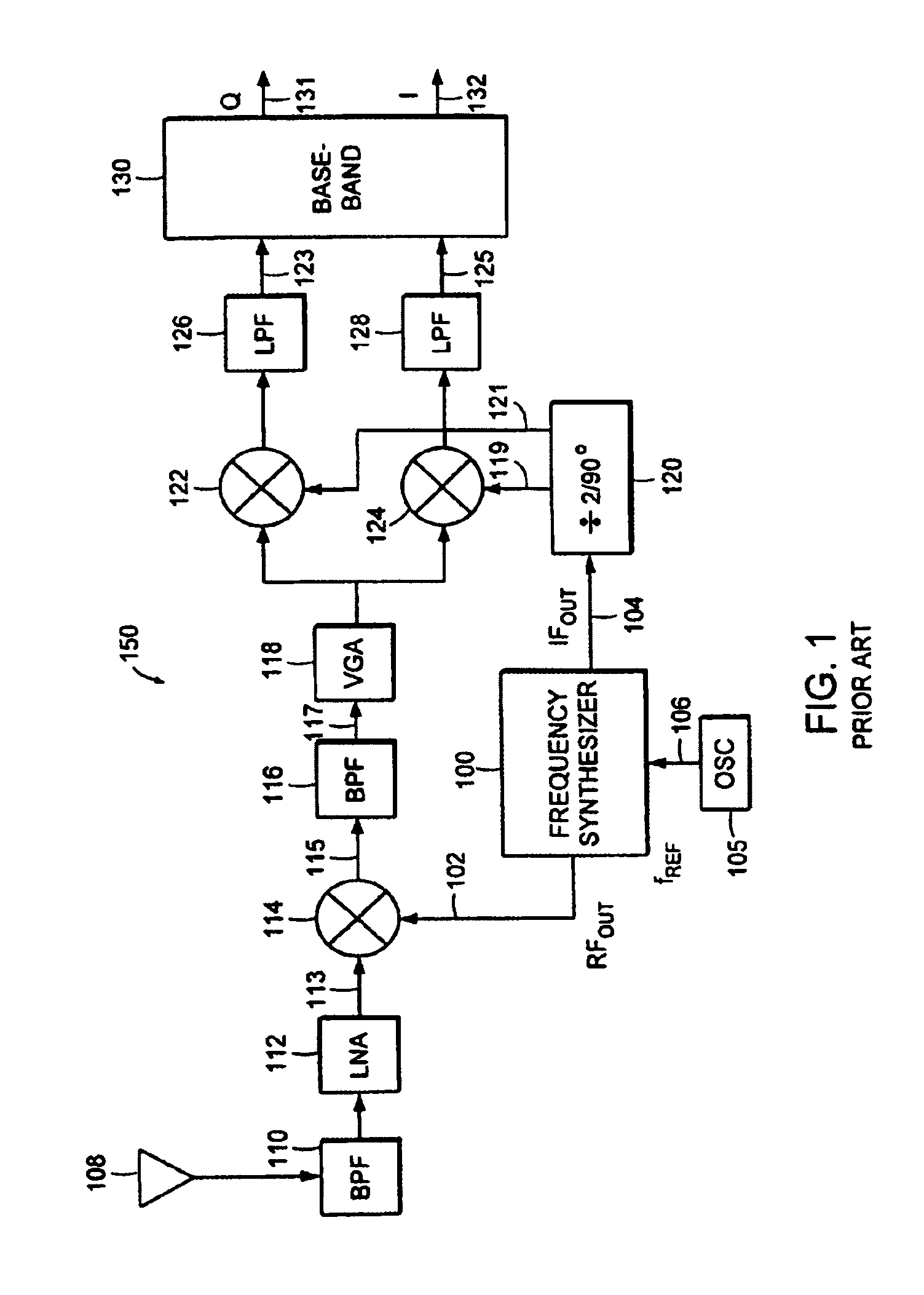

Automatic gain control for frequency-hopped OFDM

ActiveUS20070058739A1Gain controlAmplitude-modulated carrier systemsAudio power amplifierFrequency mixer

An automatic gain control method and system for use in signal processing of OFDM symbols at a receiver. Two stages of coarse and fine automatic gain control are implemented that adjust different gains in an analog RF processing stage of the receiver. Gain of a low noise amplifier and a mixer are adjusted during a first and coarse automatic gain control stage based on feedback from a digital baseband stage. During a subsequent fine gain control period, the gain of a programmable gain amplifier is adjusted separately for each frequency band used by the OFDM symbols based on a histogram bin that counts the number of output samples of an analog to digital converter whose magnitude falls within certain ranges. Coarse and fine gains are updated after each OFDM symbol.

Owner:REALTEK SEMICON CORP +1

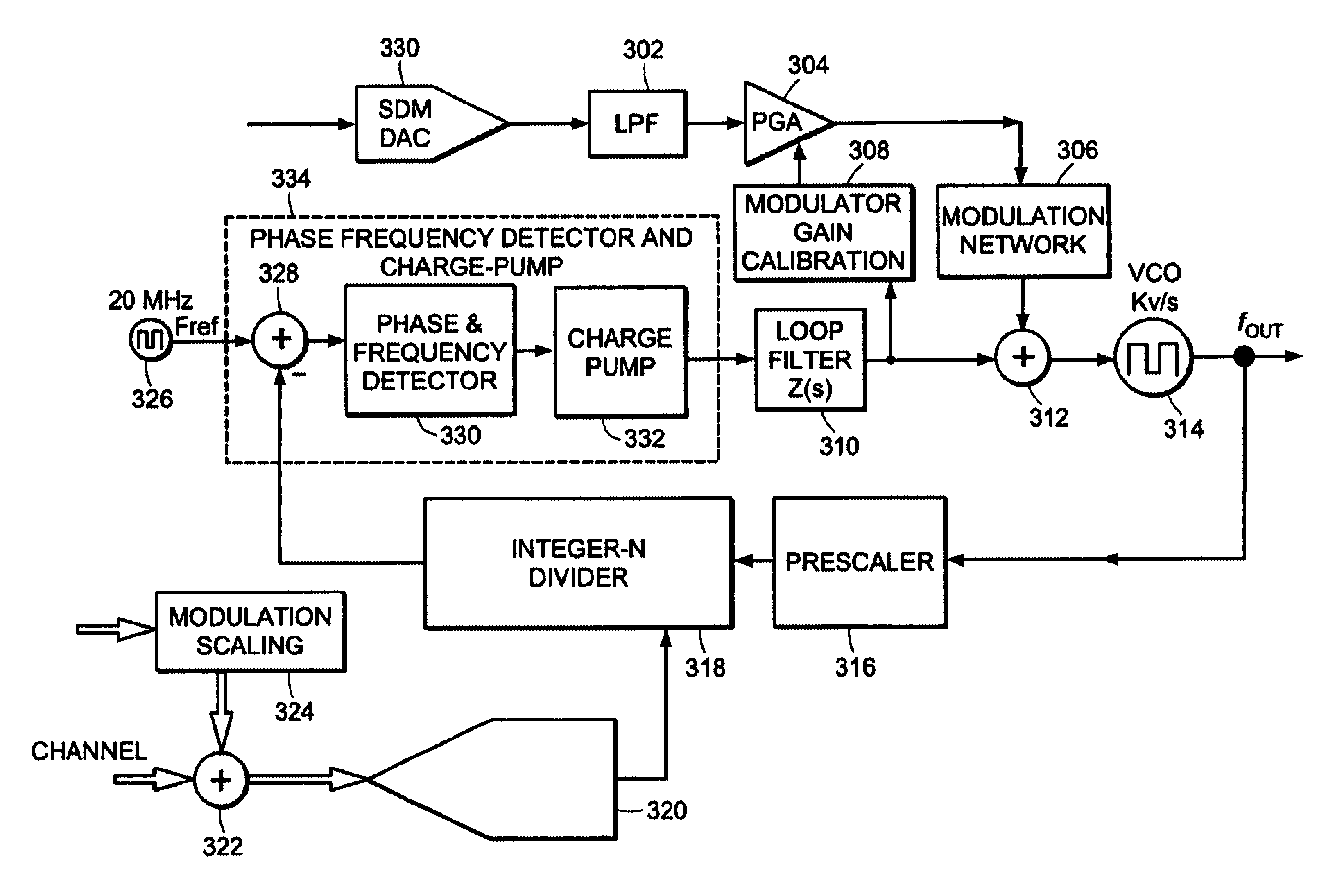

Method of modulation gain calibration and system thereof

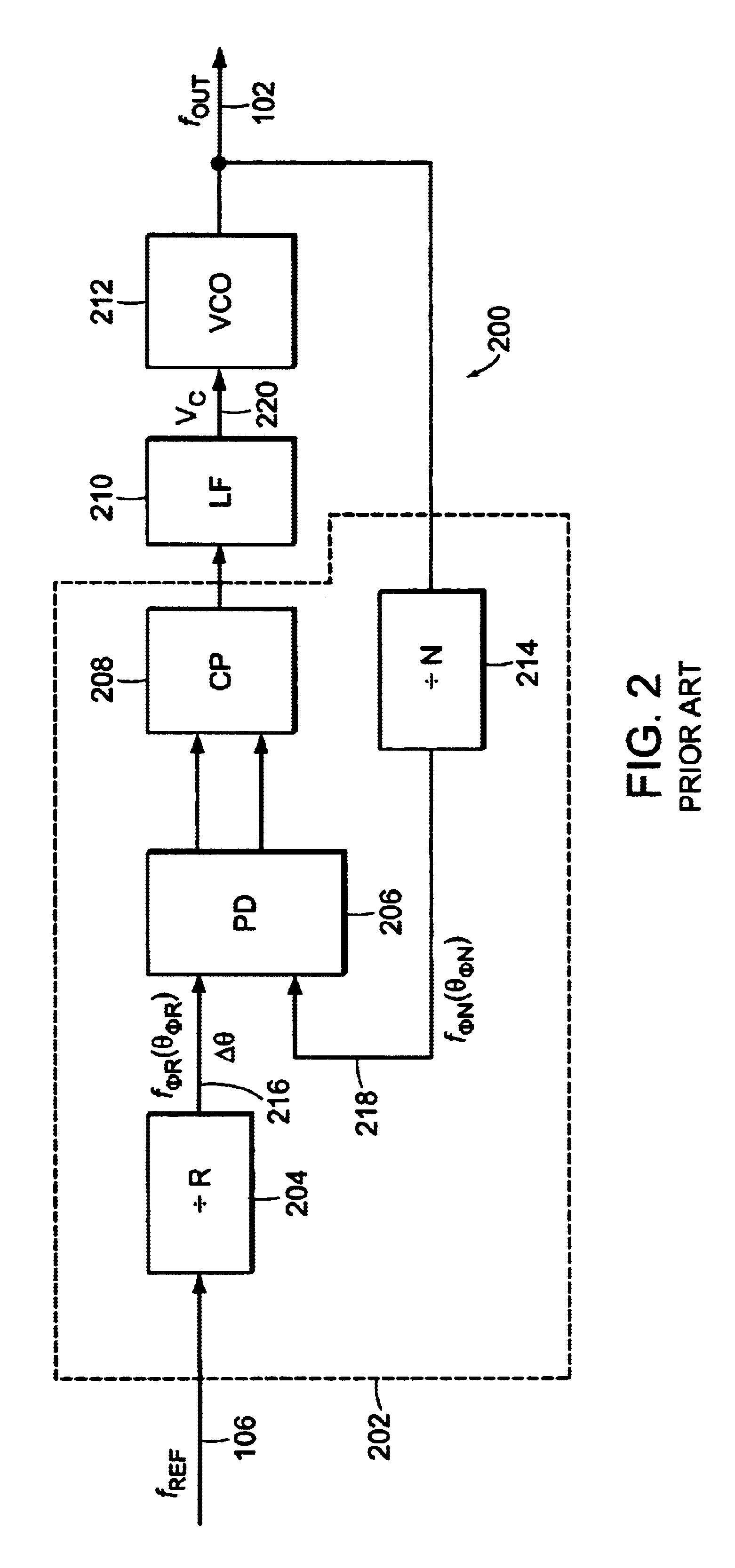

A wideband impedance attenuator includes a phase-locked loop filter, a voltage-controlled oscillator connected to the phase-locked loop filter during transmit, and an impedance circuit connected to the phase-locked loop filter and the voltage controlled oscillator. The impedance circuit is a scaled version of the phase-locked loop filter. Moreover, the wideband impedance attenuator attenuates a Gaussian frequency shift key modulation signal by a factor of 1 / (N+1) using the impedance circuit, which has an impedance of N*Z(s), and the phase-locked loop filter, which has an impedance of Z(s). An output frequency is generated using a voltage-controlled oscillator wherein the output frequency corresponds to the attenuated Gaussian frequency shift key modulation signal. In addition, a comparator compares a voltage of an output from the programmable gain amplifier with a voltage necessary to produce a predetermined frequency shift in a voltage-controlled oscillator to produce a gain signal. A gain controller, in response to the gain signal produced by the comparator, controls a gain of the programmable gain amplifier.

Owner:MEDIATEK INC

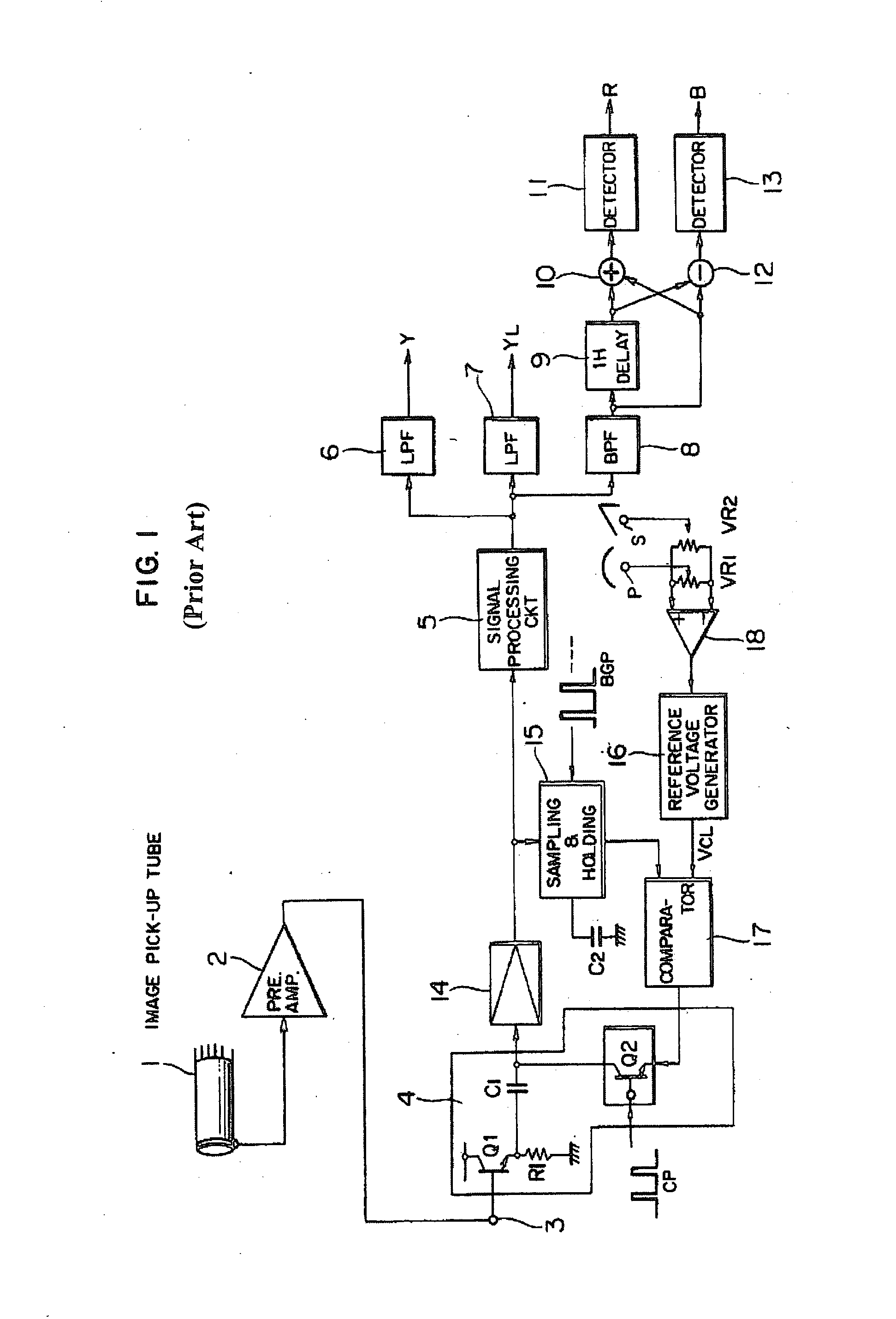

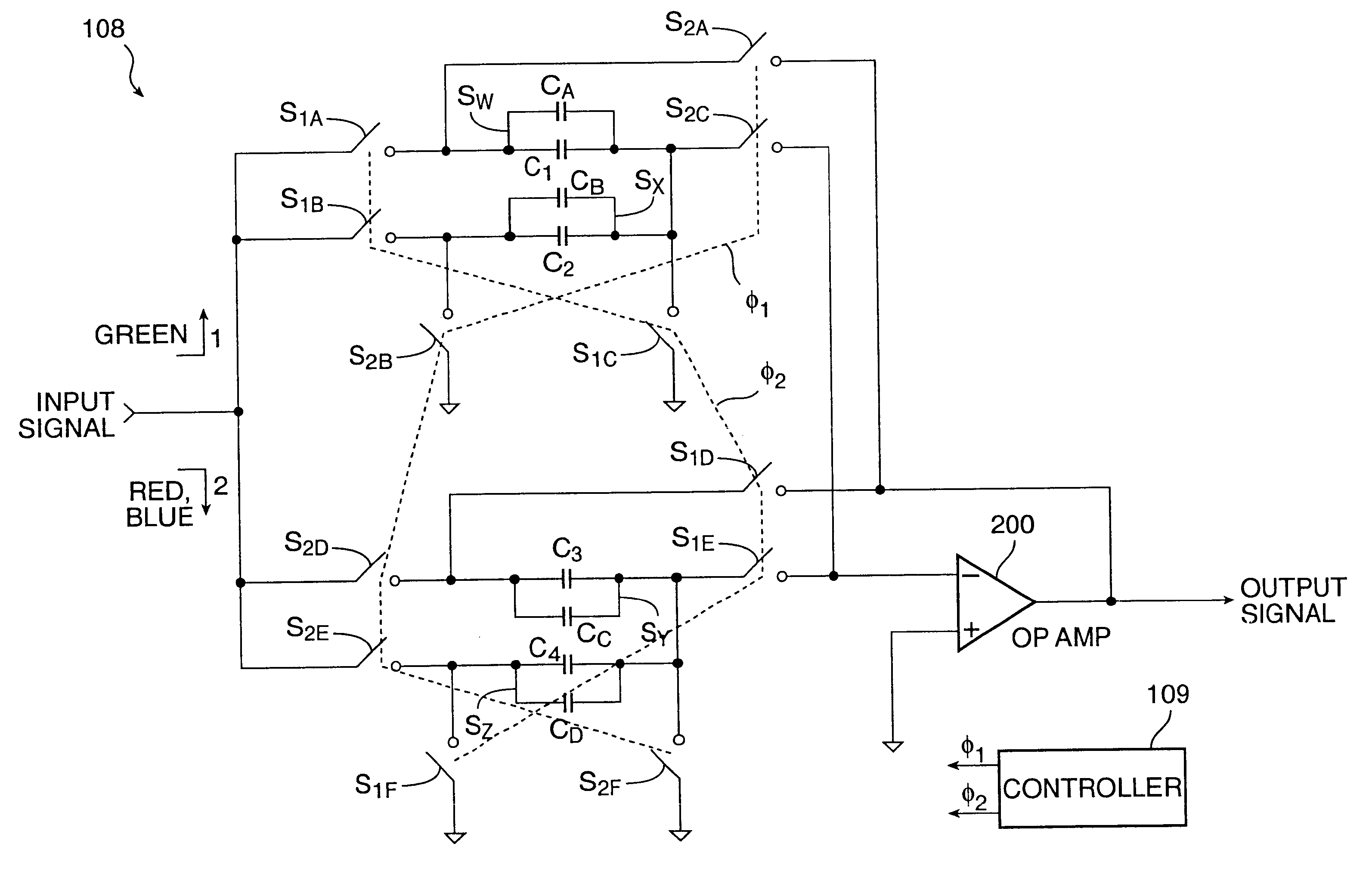

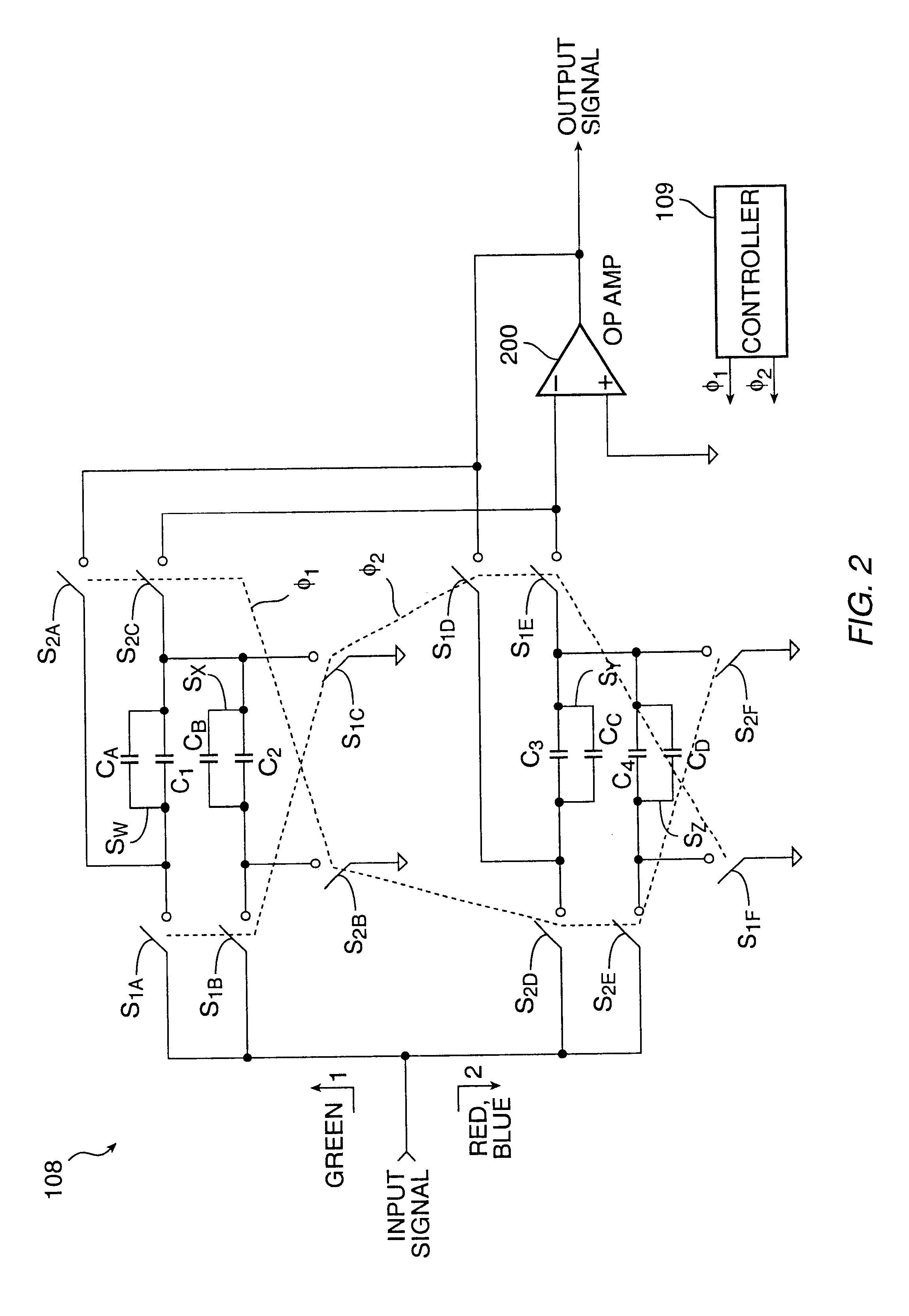

Cross-coupled differential Dac-based black clamp circuit

InactiveUS20080218609A1Television system detailsColor signal processing circuitsEngineeringGain setting

A black clamp circuit for an image sensor utilizes a differential programmable gain amplifier and a feed-back loop to adjust a black level based on comparison to a reference black level. The gain (and therefore step size and range) of the feed-back loop constant for all programmable gain amplifier gain settings. The gain of the fee-back loop is kept constant by adjusting the values of programmable capacitors in the circuit.

Owner:ALTASENS

Phase-locked loop filter with out of band rejection in low bandwidth mode

A wideband impedance attenuator includes a phase-locked loop filter, a voltage-controlled oscillator connected to the phase-locked loop filter during transmit, and an impedance circuit connected to the phase-locked loop filter and the voltage controlled oscillator. The impedance circuit is a scaled version of the phase-locked loop filter. Moreover, the wideband impedance attenuator attenuates a Gaussian frequency shift key modulation signal by a factor of 1 / (N+1) using the impedance circuit, which has an impedance of N*Z(s), and the phase-locked loop filter, which has an impedance of Z(s). An output frequency is generated using a voltage-controlled oscillator wherein the output frequency corresponds to the attenuated Gaussian frequency shift key modulation signal. In addition, a comparator compares a voltage of an output from the programmable gain amplifier with a voltage necessary to produce a predetermined frequency shift in a voltage-controlled oscillator to produce a gain signal. A gain controller, in response to the gain signal produced by the comparator, controls a gain of the programmable gain amplifier.

Owner:MEDIATEK INC

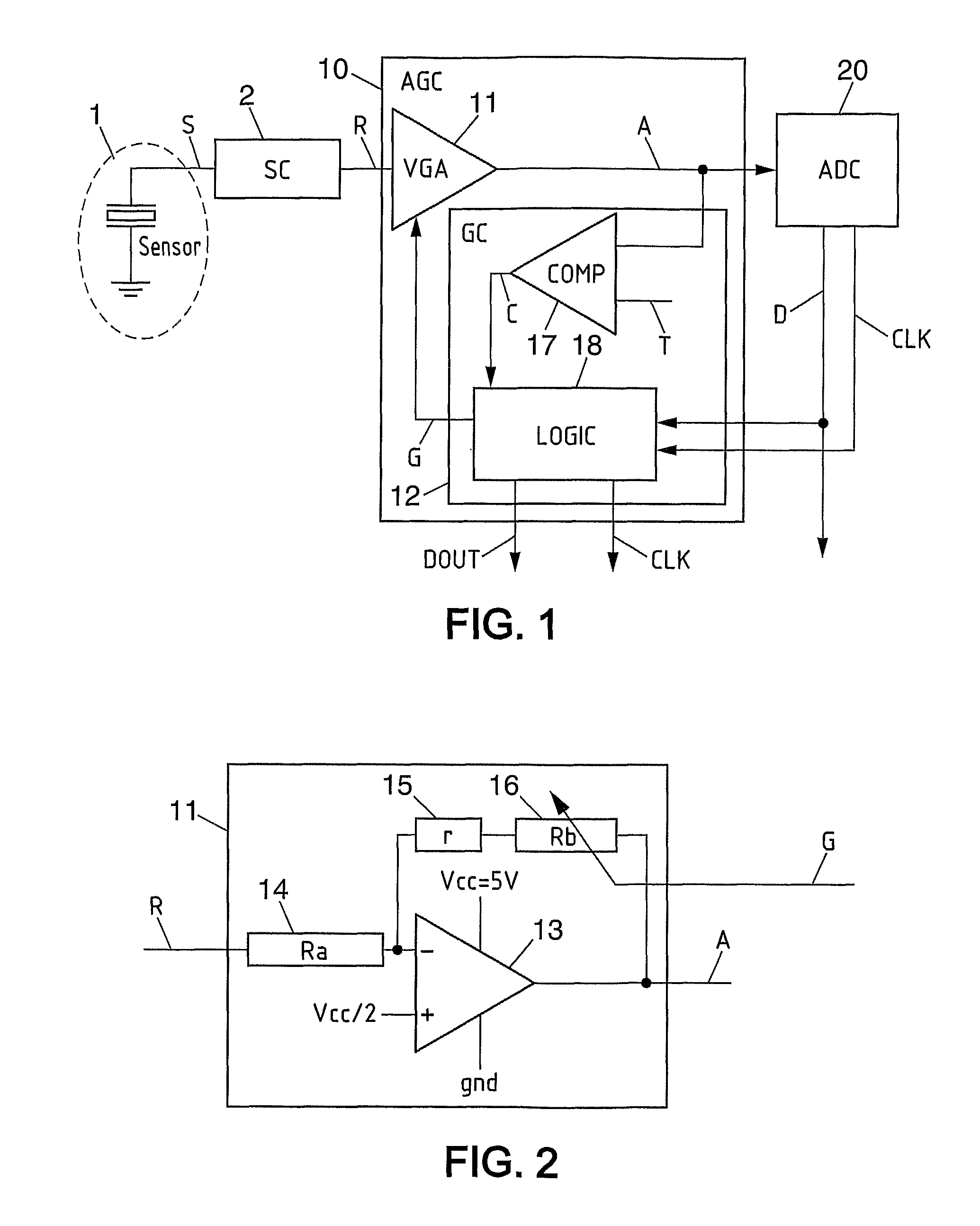

Automatic gain control circuit

ActiveUS8228121B2Constant rateLow costNegative-feedback-circuit arrangementsVolume compression/expansion having semiconductor devicesAudio power amplifierVariable-gain amplifier

An automatic gain control circuit including a variable gain amplifier (11) adapted to receive a received signal (R) and to output an amplified signal (A) to an analog to digital converter (20), and a gain controller (12) which is connected to said variable gain amplifier (11) for receiving said amplified signal (A) and for controlling a gain of said variable gain amplifier (11). The gain controller (12) is adapted to determine an occurrence of a threshold event each time the amplified signal (A) has reached a predetermined threshold, decrease the gain of the variable gain amplifier (11) at each occurrence of a threshold event, measure a delay since the last threshold event, increase the gain of the variable gain amplifier (11) if the delay is greater than a delay specified value and if the gain of the variable gain amplifier (11) is not maximum.

Owner:ELO TOUCH SOLUTIONS INC

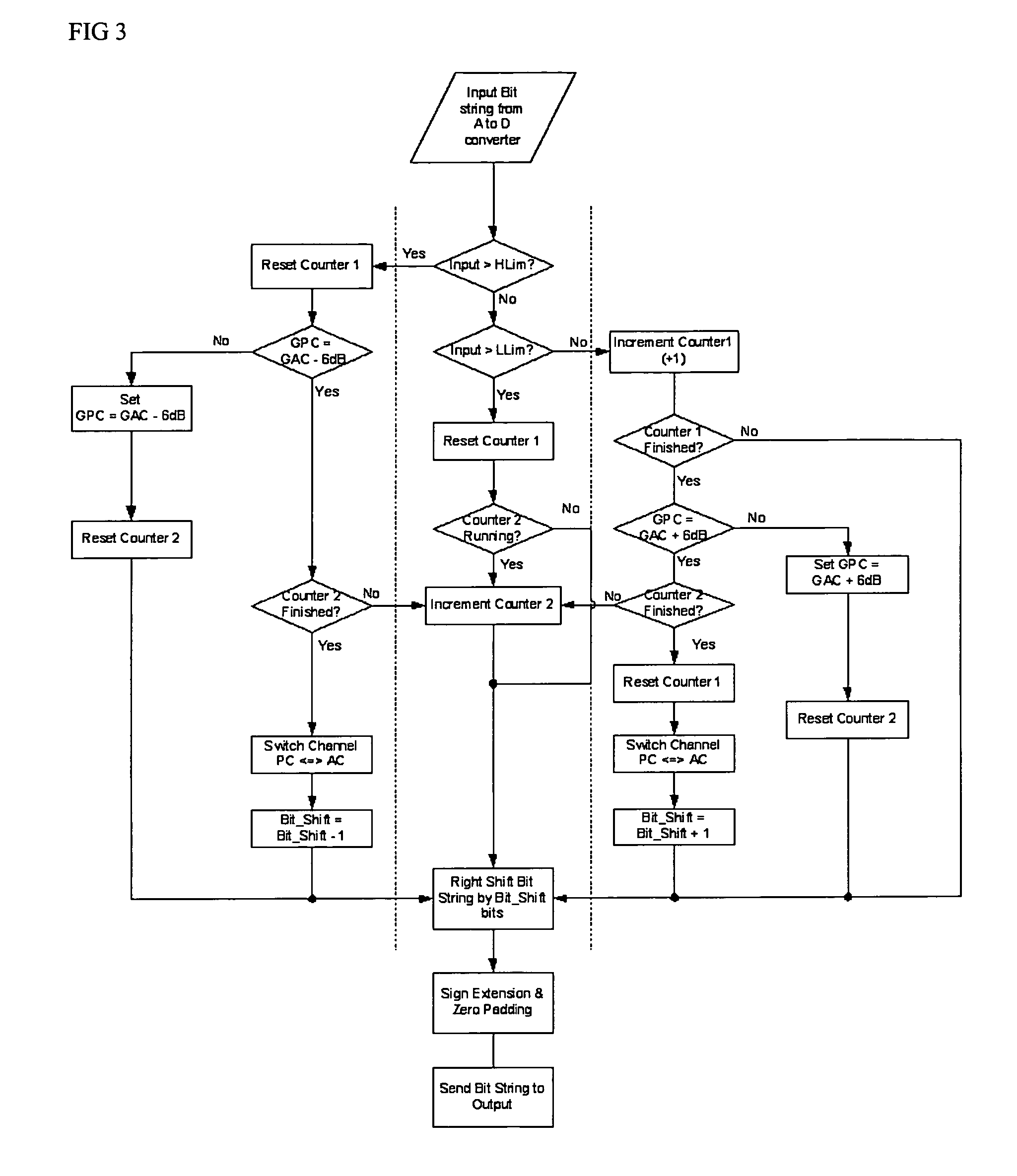

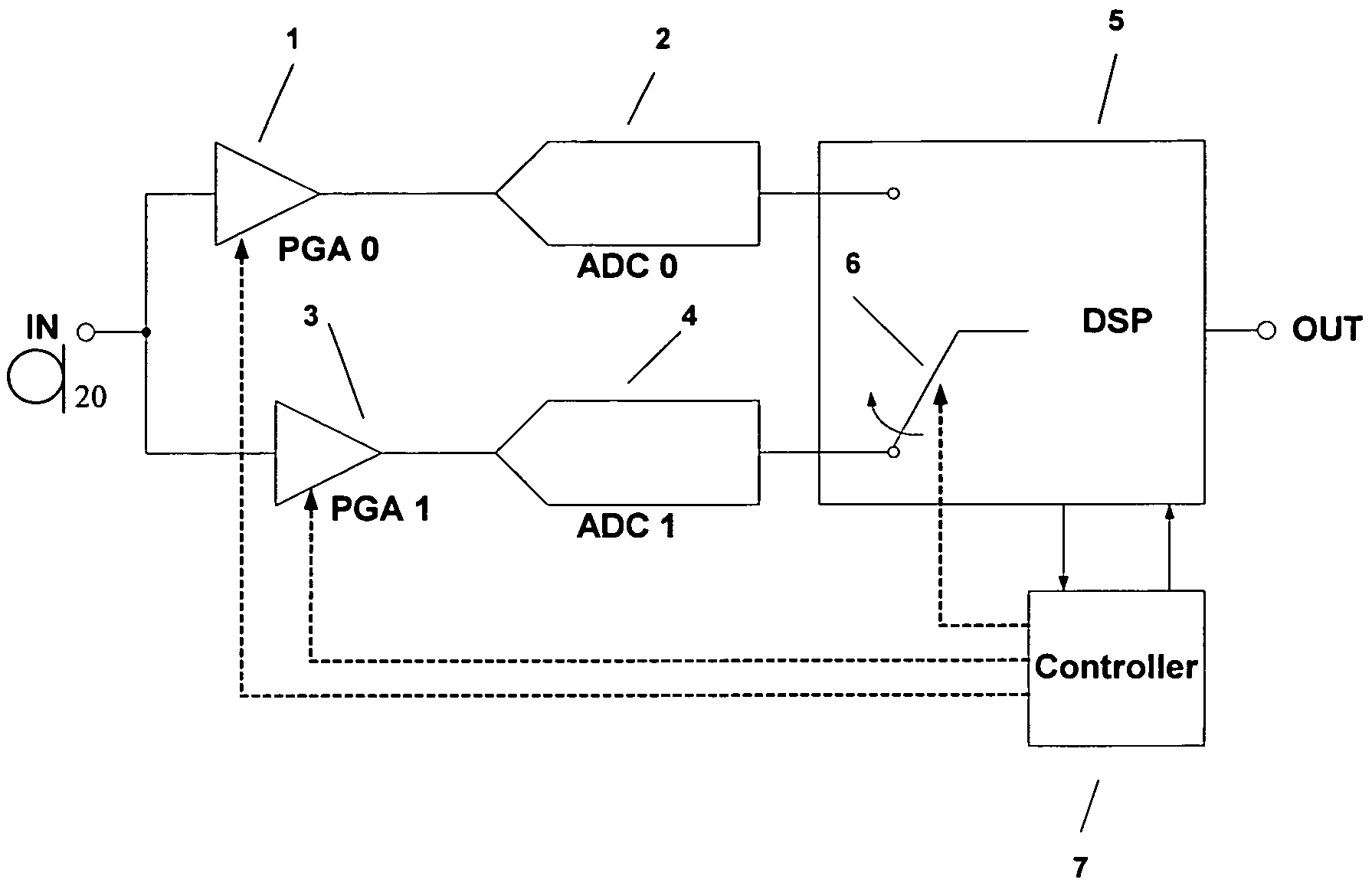

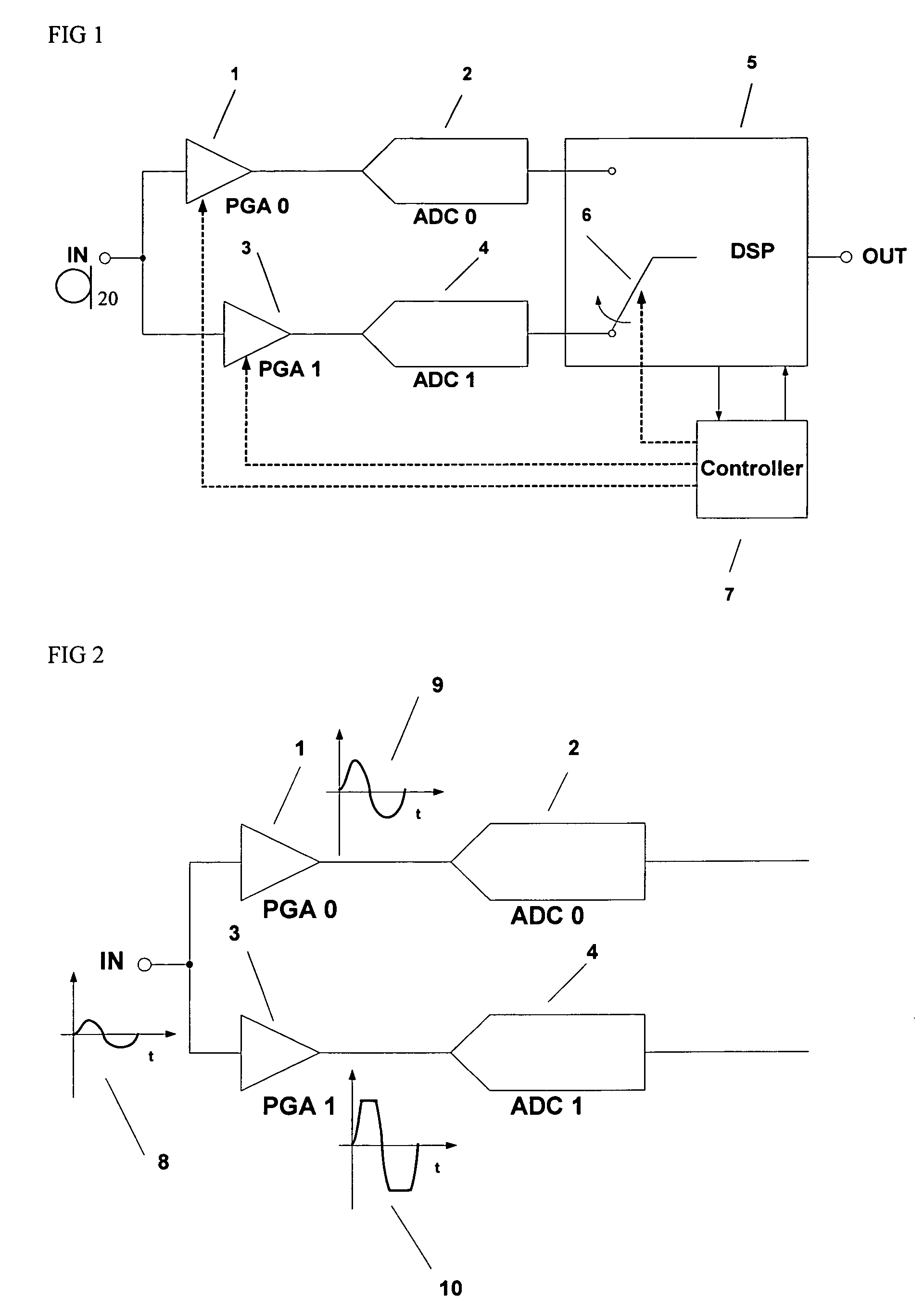

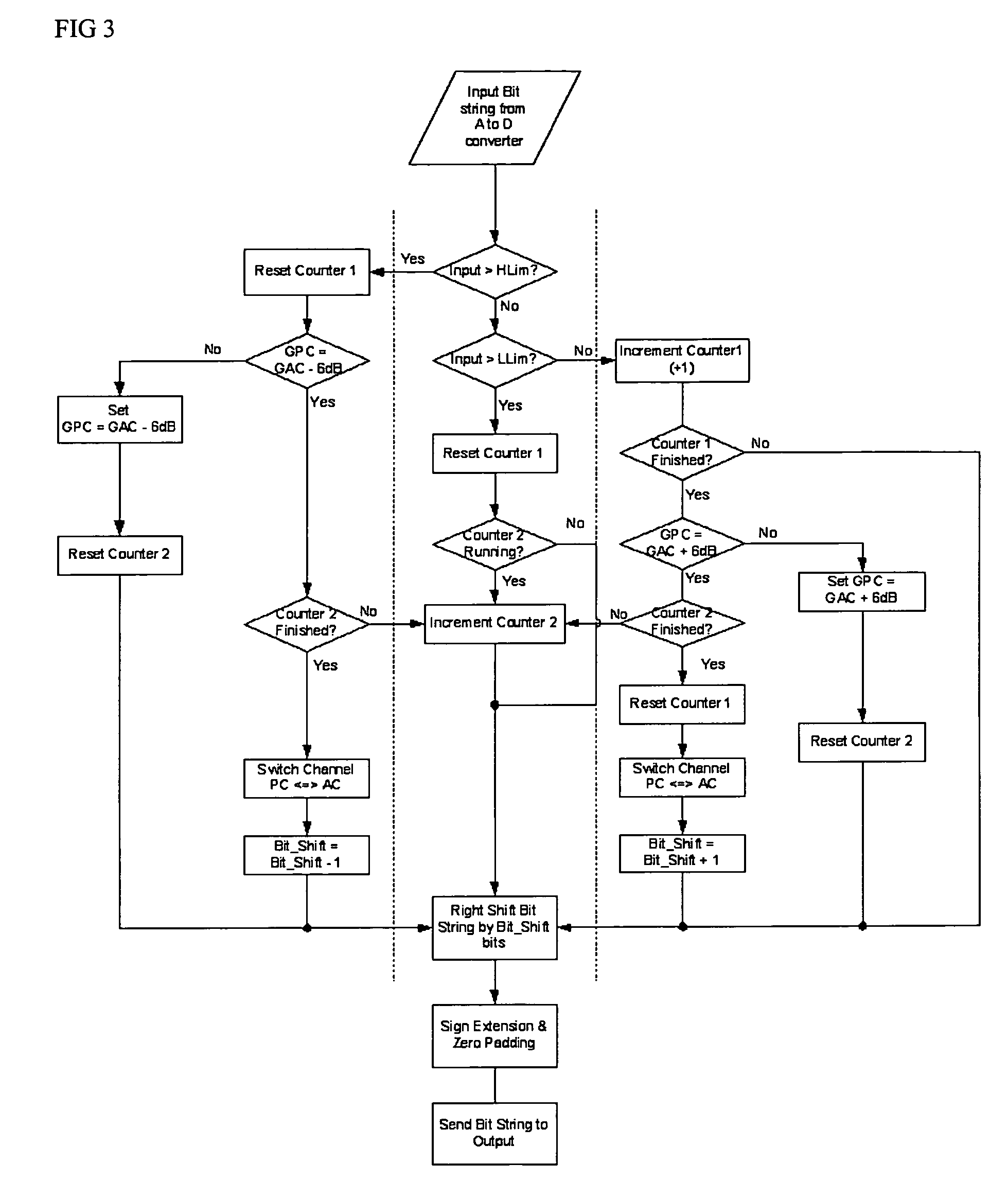

ADC with dynamic range extension

ActiveUS20070120721A1Easy to quantifyDifferent gain levelTelevision system detailsElectric signal transmission systemsAudio power amplifierHearing aid

ADC circuitry has a first programmable gain amplifier to amplify an analog input, a first analog to digital converter coupled to an output of the first amplifier, a second programmable gain amplifier, to amplify the analog input, a second analog to digital converter coupled to an output of the second amplifier, and a digital circuit for deriving a digital output from the outputs of the first and second converters and a controller for controlling the gains of the first and second amplifiers, according to the outputs of the first and second converters. Such programmable gain pre amplifiers help enable effective dynamic range to be extended without unduly increasing the number of quantisation bits, or the number of components or the power dissipation. It can be used in applications sensitive to size and power, such as DSP based acoustic devices including hearing aids.

Owner:HIMPP

ADC with dynamic range extension

ActiveUS7365664B2Easy to quantifyDifferent gain levelTelevision system detailsElectric signal transmission systemsAudio power amplifierHearing aid

ADC circuitry has a first programmable gain amplifier to amplify an analog input, a first analog to digital converter coupled to an output of the first amplifier, a second programmable gain amplifier, to amplify the analog input, a second analog to digital converter coupled to an output of the second amplifier, and a digital circuit for deriving a digital output from the outputs of the first and second converters and a controller for controlling the gains of the first and second amplifiers, according to the outputs of the first and second converters. Such programmable gain pre amplifiers help enable effective dynamic range to be extended without unduly increasing the number of quantisation bits, or the number of components or the power dissipation. It can be used in applications sensitive to size and power, such as DSP based acoustic devices including hearing aids.

Owner:HIMPP

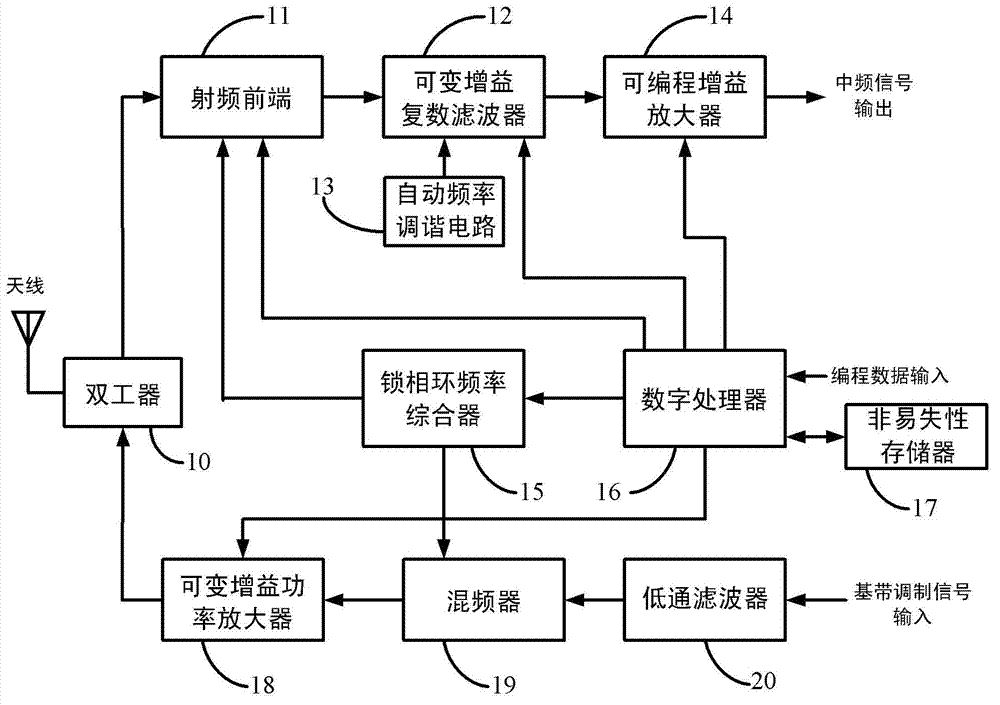

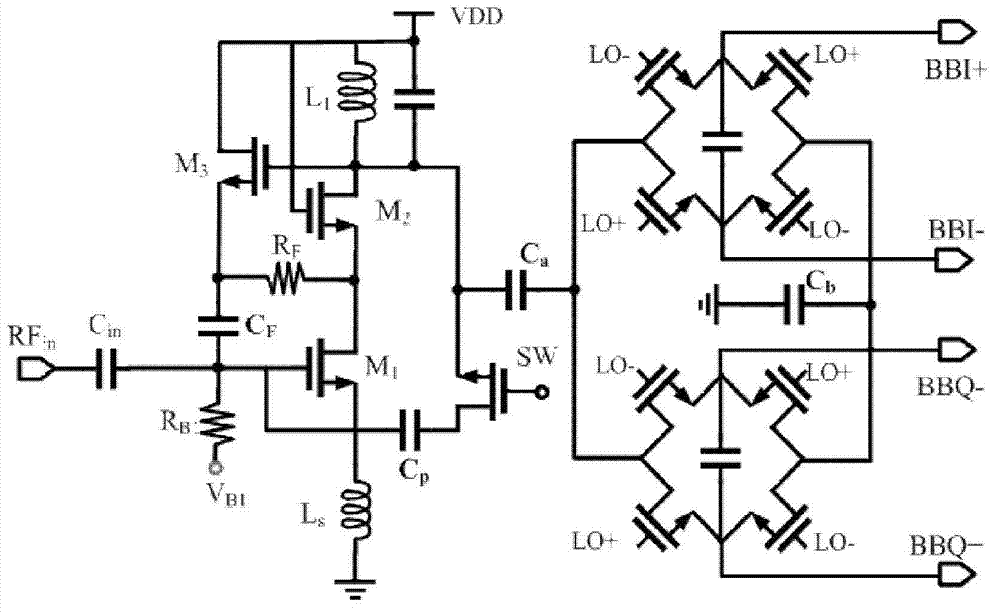

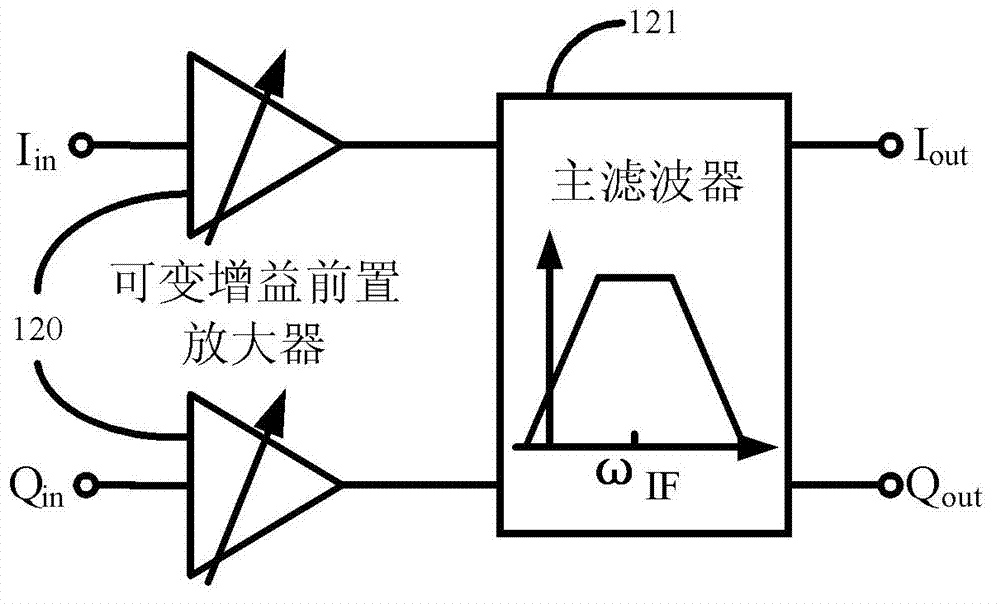

Wireless sensor network application-oriented low-power consumption radio frequency receiving and sending device

ActiveCN102970053ALow cost requirementsReduce power consumptionNetwork topologiesTransmissionIntermediate frequencyLow-pass filter

The invention discloses a wireless sensor network application-oriented low-power consumption radio frequency receiving and sending device which comprises a duplexer, a radio frequency front end, a variable gain complex filter, an automatic frequency tuning circuit, a programmable gain amplifier, a phase-locked loop frequency synthesizer, a digital processor, a storage, a variable gain power amplifier, a mixer and a low pass filter, wherein the duplexer, the radio frequency front end, the variable gain complex filter, the automatic frequency tuning circuit and the programmable gain amplifier form a receiving link which is used for receiving and processing a radio frequency signal and converting the radio frequency signal into a low-medium frequency digital signal so that the signal can be conveniently processed by a subsequent analog-digital converter later; the duplexer, the variable gain power amplifier, the mixer and the low pass filter form an emitting link which is used for mixing a baseband analog modulation signal into a carrier frequency and sending a wireless signal; and the receiving link and the emitting link share the duplexer. The wireless sensor network application-oriented low-power consumption radio frequency receiving and sending device realizes singlechip integration by adopting a standard CMOS (Complementary Metal Oxide Semiconductor) process, is simple in structure and low in power consumption, and is applicable to a wireless sensor network.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Radio frequency automatic gain control amplifier

ActiveCN102868369AReduce signal to noise ratioSimple designAmplifier modifications to reduce noise influenceLow-pass filterIntermediate frequency

The invention discloses a radio frequency automatic gain control amplifier. The radio frequency automatic gain control amplifier comprises a radio frequency receiving unit, a radio frequency amplifier control unit and an intermediate frequency amplifier, wherein the radio frequency receiving unit is composed of an adjustable low noise amplifier (LNA), a programmable gain amplifier (PGA), a down-conversion frequency mixer and a low-pass filter; the radio frequency amplifier control unit comprises a signal strength detector, a DAC (digital-to-analog converter), a comparator and a decoder; the signal strength detector is used for detecting the strength of an intermediate frequency signal; a comparator circuit is used for comparing an output signal of the signal strength detector with a fixed comparing level output from the DAC so as to output a comparison result; the decoder is used for inputting the comparison result into a gain control digital module and outputting a digital control signal so as to carry out the feedback control to the signal at the front end of the radio frequency, so that the gains of the LNA and the PGA are controlled, the signal to noise ratio of a receiving system is increased, and the requirements on dynamic ranges and high linearity of an input signal are met. The automatic gain control amplifier can be used in various radio frequency receiving chips flexibly, and particularly is applicable to radio frequency front-end circuit which has a wider input range of a radio frequency signal.

Owner:杭州中科微电子有限公司

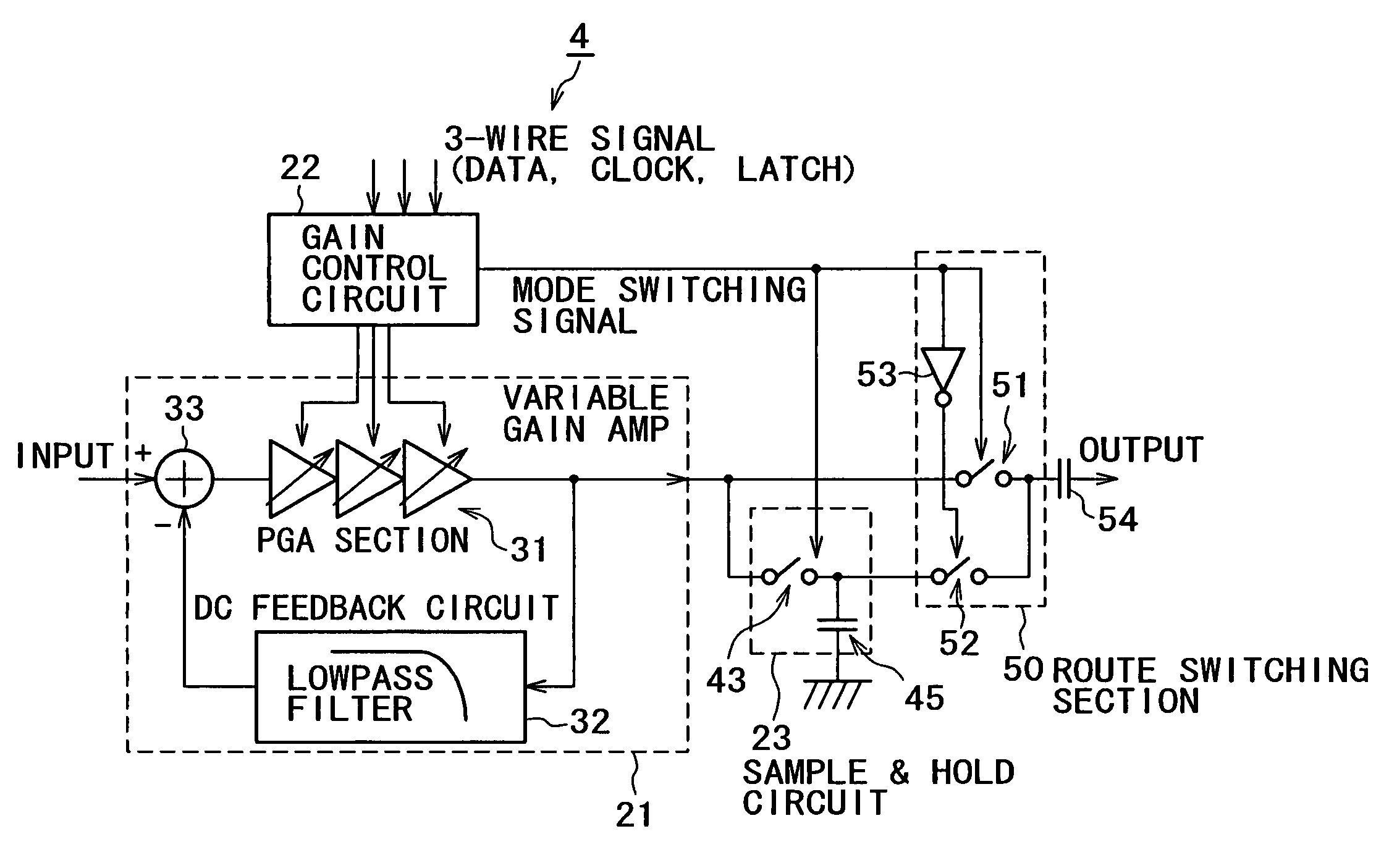

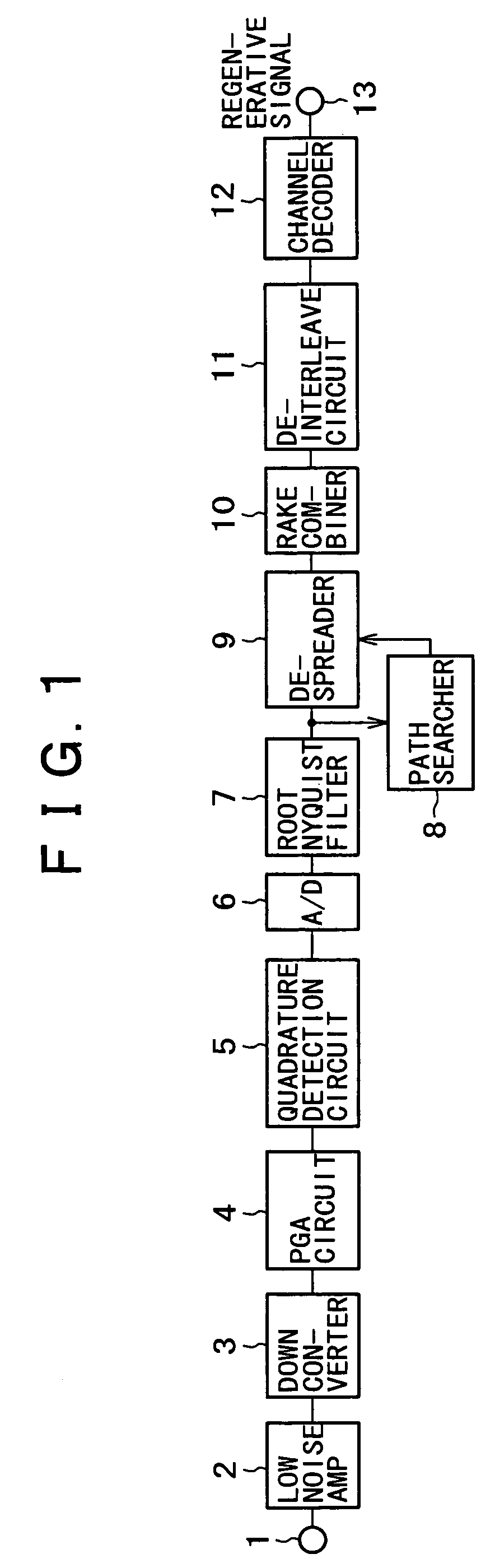

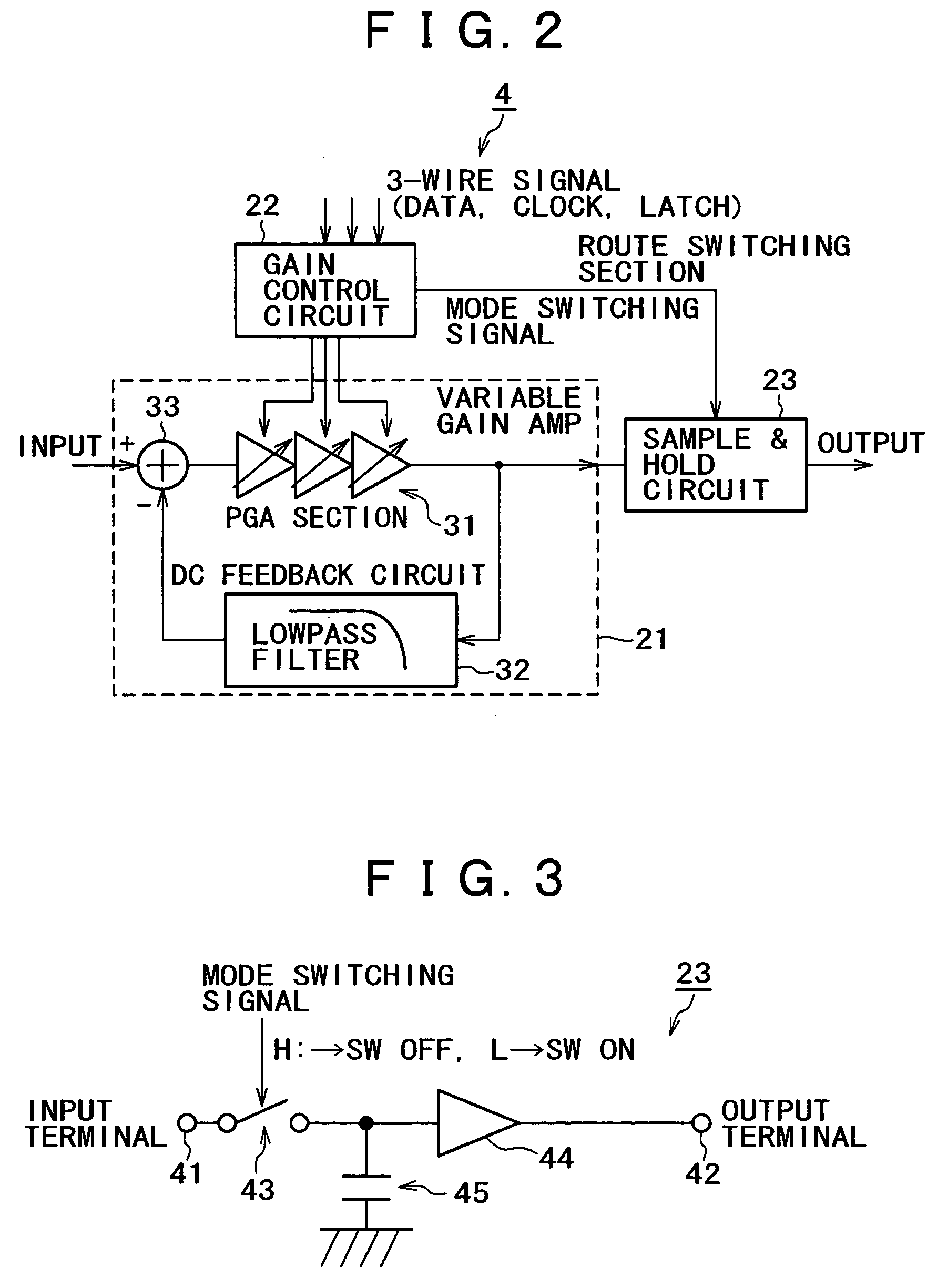

Mobile communication terminal device and variable gain circuit

InactiveUS7149487B2Guaranteed uptimeError preventionGain controlVariable-gain amplifierGain-switching

In receiver systems for cellular phones using the W-CDMA method, the change in DC voltage occurring when the gain of a programmable gain amplifier (PGA circuit) is switched to adjust the gain for a received signal, can be suppressed. A sample-and-hold circuit is installed containing a “sample” mode for directly outputting a signal from the PGA section and also containing a “hold” mode for outputting the electric charge of a specified voltage stored in a capacitor. This sample-and-hold circuit normally operates in “sample” mode so the output signal from the PGA section is directly output, but is operated in “hold” mode at the gain switching timing of the PGA circuit, so that the electric charge of the specified voltage stored in the capacitor is output for a specified length of time (equal to the time required for the DC voltage change to converge to a stable level).

Owner:SONY ERICSSON MOBILE COMM JAPAN INC

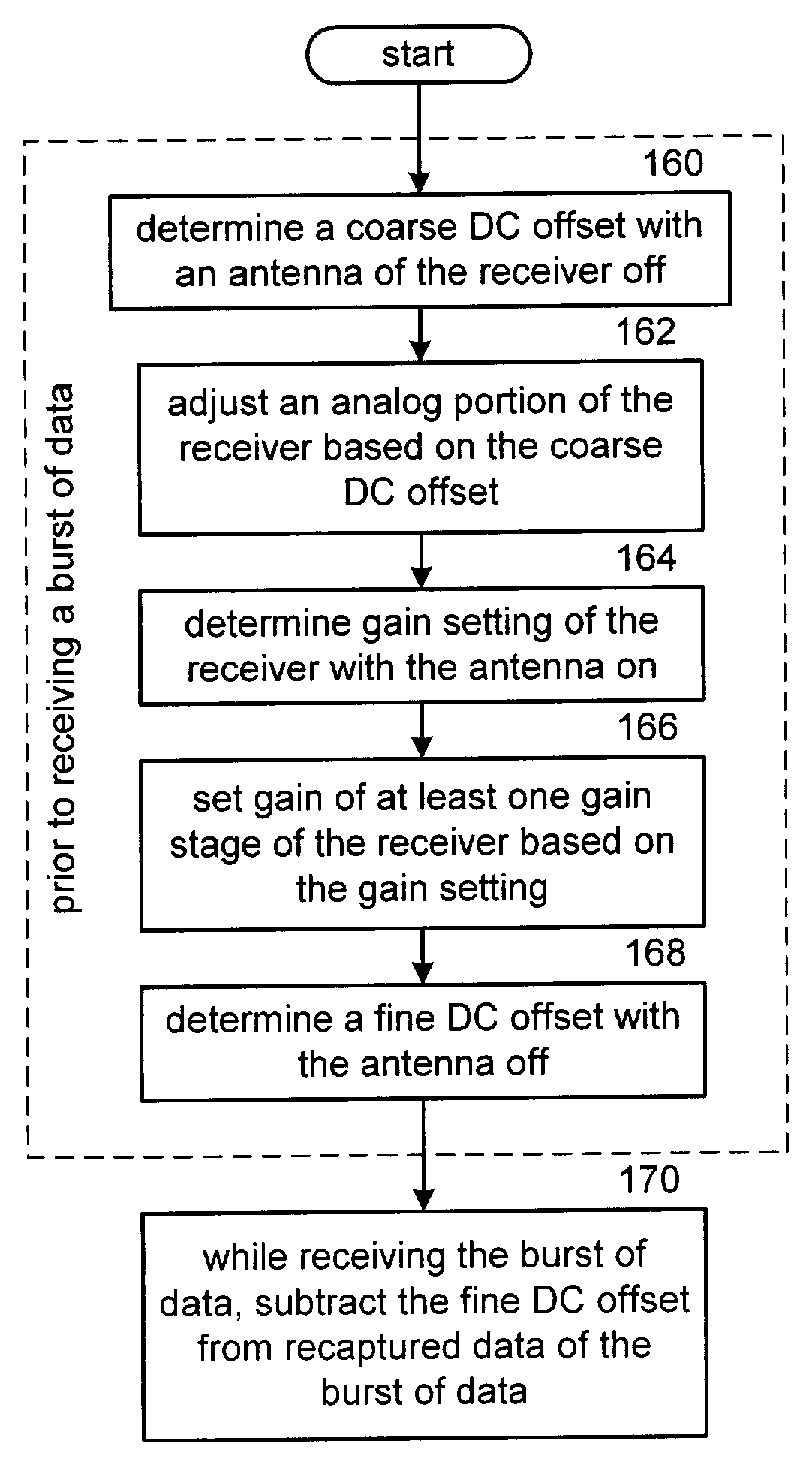

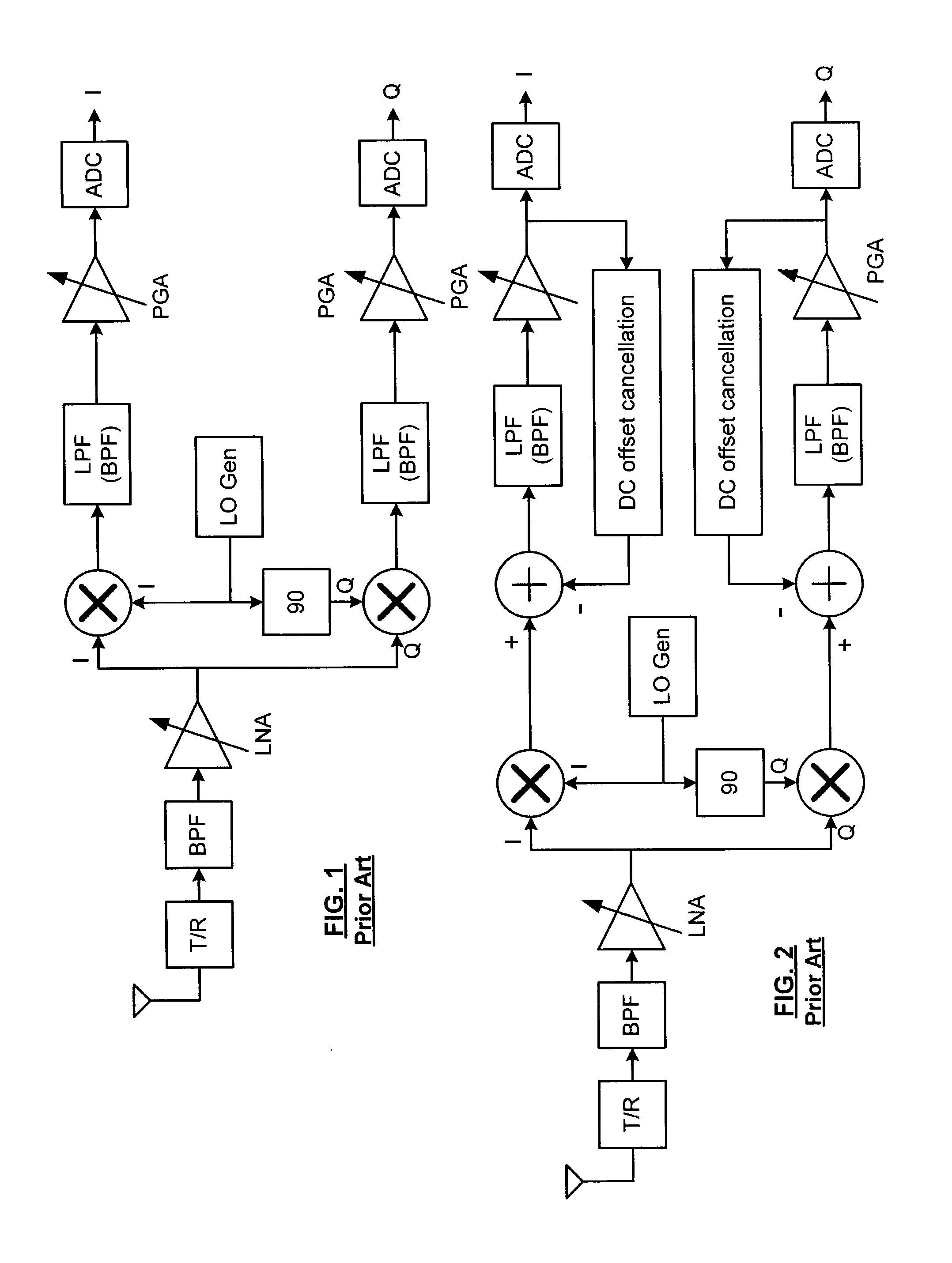

DC offset correcting in a direct conversion or very low IF receiver

InactiveUS7136431B2Reduce cancellationDc level restoring means or bias distort correctionLine balance variation compensationEngineeringLow IF receiver

A direct conversion or VLIF receiver corrects DC offset by, prior to receiving a burst of data, the receiver determines a coarse DC offset with the antenna of the receiver switched off. The receiver then adjusts an analog portion of the receiver (e.g., the output of the mixers) based on the coarse DC offset. The receiver then determines a gain setting of the receiver (e.g., for the low noise amplifier and / or programmable gain amplifiers) with the antenna on. The receiver then sets the gain of at least one gain stage of the receiver based on the gain setting. The receiver then determines a fine DC offset with the antenna off. The receiver then, while receiving a burst of data, subtracts the fine DC offset from the digital baseband or low IF signal prior to data recovery.

Owner:AVAGO TECH INT SALES PTE LTD

Method and apparatus to determine impedance variations in a skin/electrode interface

InactiveUS20110251817A1Testing/calibration apparatusSpeed measurement using gyroscopic effectsElectrode impedanceImpedance variation

The present invention relates to a system for measuring the impedance of a skin / electrode interface and selectively modifying the system gain of the monitoring circuit to compensate for errors introduced by variations in the skin / electrode impedance. More particularly, a simplified, low-cost method for measuring and compensating for skin / electrode impedance variations is provided. The skin / electrode impedance measuring circuit and determines a system gain correction factor which may be applied to the measured signal using a software algorithm, thereby eliminating the need to change the circuit topology with a programmable gain amplifier or programmable resistor network.

Owner:REPRODIVE RES TECH

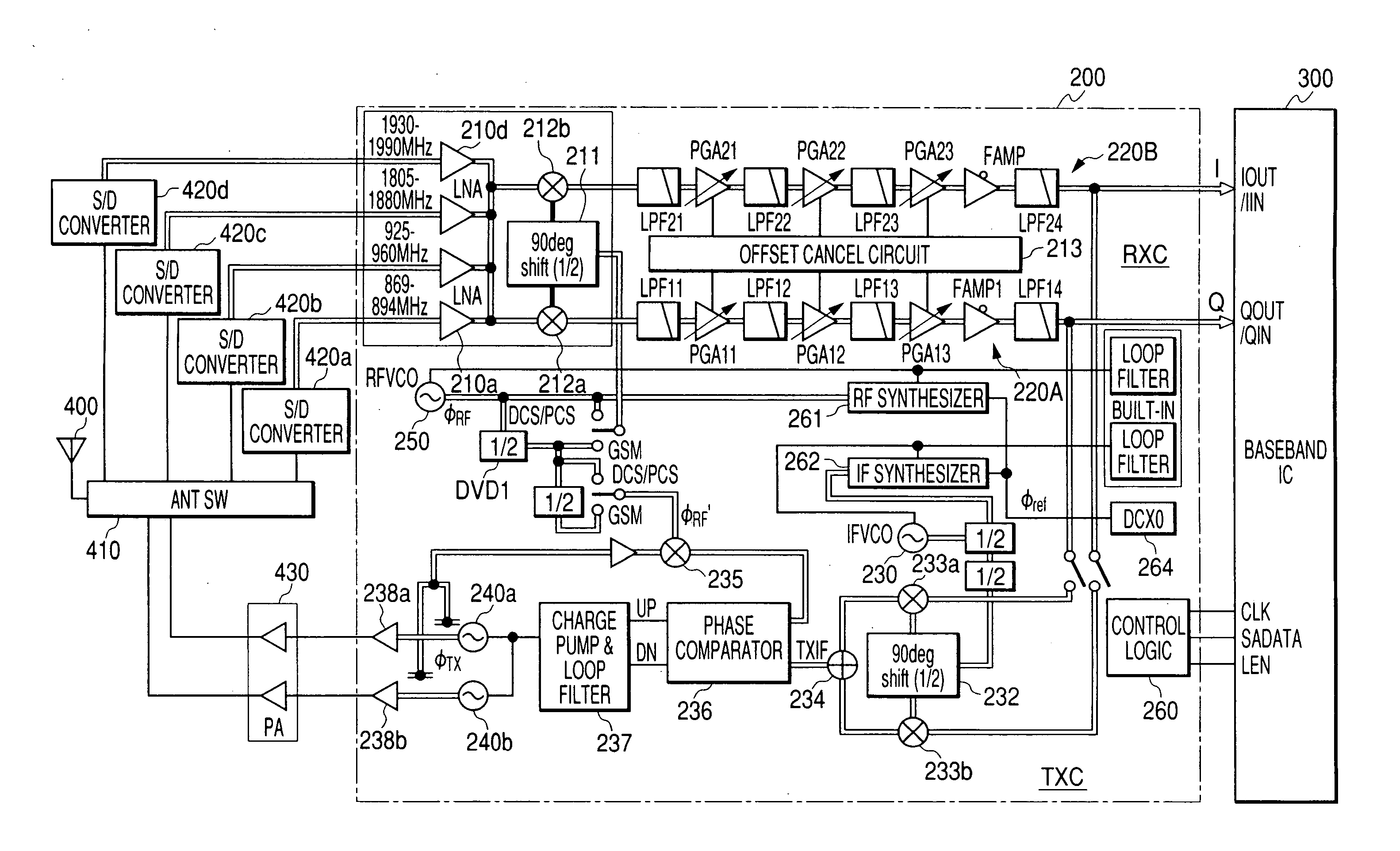

Wireless communication semiconductor integrated circuit device and wireless communication system

InactiveUS20070202814A1Improve receiver sensitivityNarrow rangeModulated-carrier systemsGain controlCommunications systemAudio power amplifier

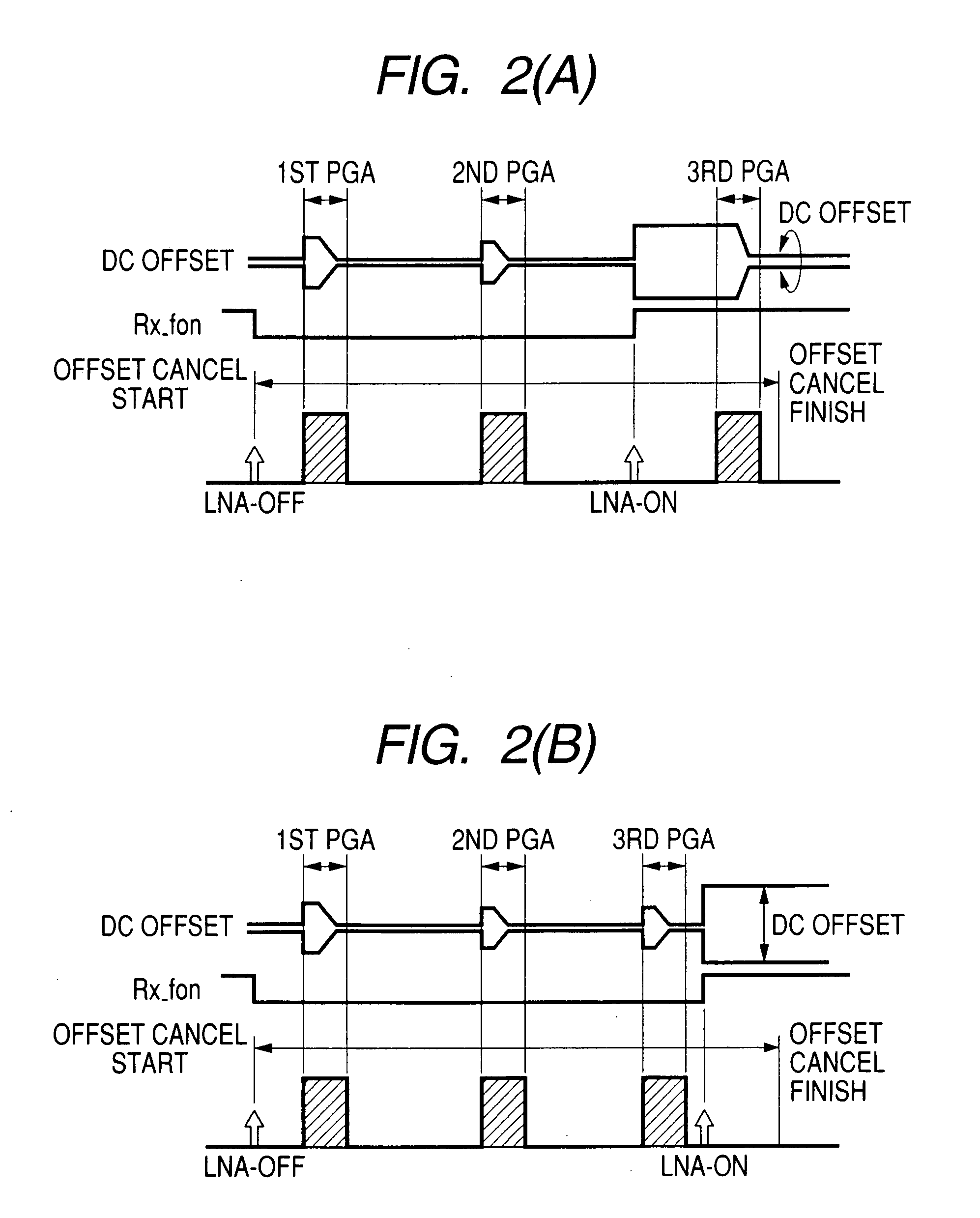

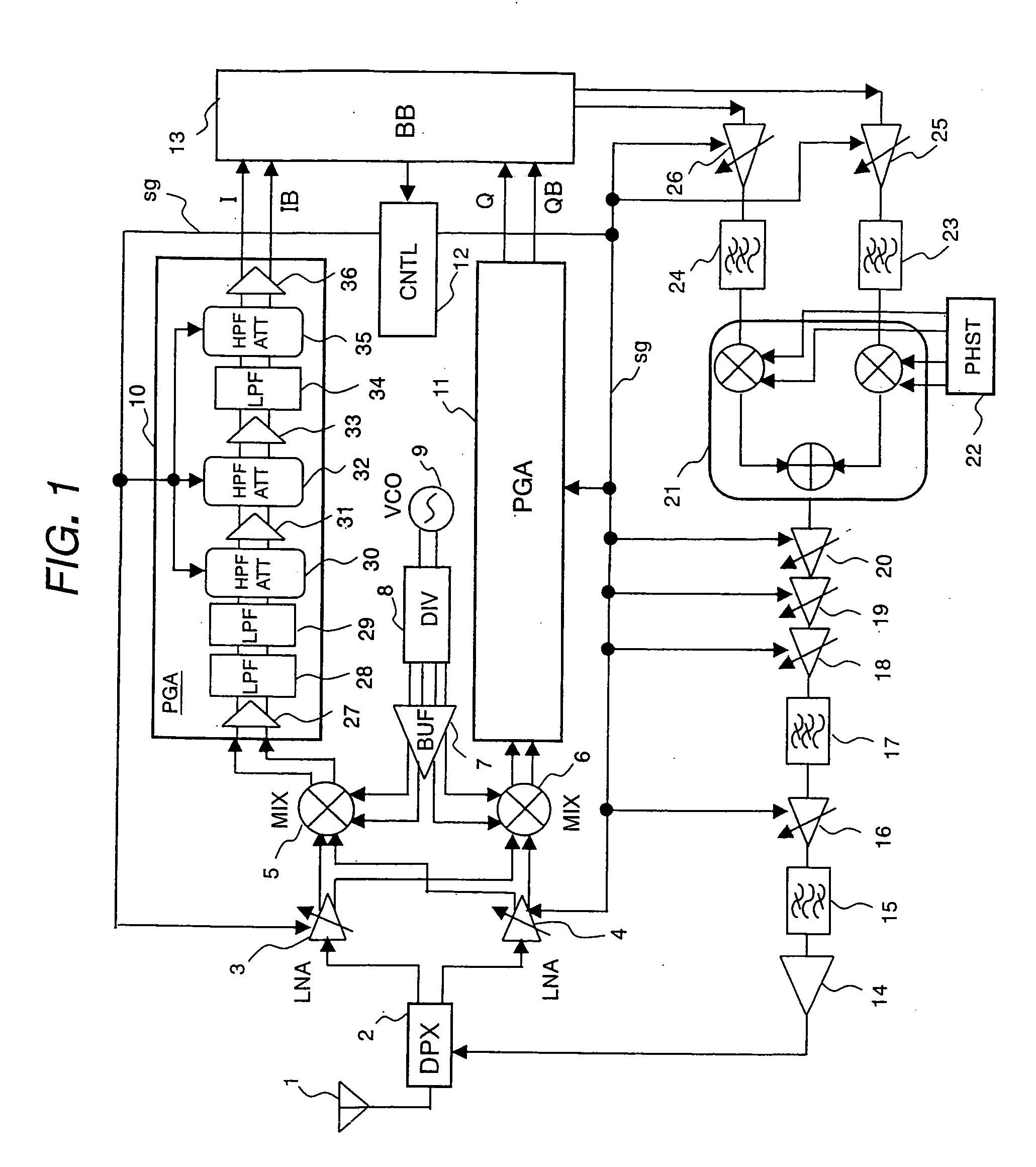

A receiving circuit of a direct conversion system which includes a differential amplifier circuit which amplifies a received signal, a mixer which combines the amplified received signal and an oscillation signal having a predetermined frequency to perform frequency conversion, and a high gain amplifier circuit in which programmable gain amplifiers and filters which eliminate noise of the received signal, are connected in a multistage and which is configured such that an amplification factor is varied according to the level of the received signal. In the receiving circuit, the low noise amplifier is brought to a non-operating state to allow execution of a DC offset cancel operation of the programmable gain amplifier on the pre-stage side of the high gain amplifier circuit. Thereafter, the low noise amplifier is brought to an operating state to allow execution of a DC offset cancel operation of the final-stage programmable gain amplifier.

Owner:ONO IKUYA +1

Wireless communication receiver

InactiveUS20060128334A1Reduce circuit areaSuppression of levelEnergy efficient ICTGain controlControl signalQ-switching

To reduce circuit area and power consumption and suppress transient response occurring at switching in PGA of a programmable gain amplifier is provided a wireless communication receiver comprising PGAs for adjusting the gain of a received signal down-converted by mixers and sending it to base-band block. Within PGAs are provided HPFATT circuits formed of capacitors arranged in series, and ladder resistors arranged in parallel, with signal lines, and a plurality of switches. HPFATT is a circuit serving as a high-pass filter and an attenuator for gain switching, wherein switches are controlled by control signal sg from a controller. Amplifiers connected to the rear stage of the HPFATT circuit are formed of MOS transistors.

Owner:RENESAS TECH CORP

Apparatus and method for stabilizing image sensor black level

ActiveUS7760258B2Superior black level stabilizationMaximize dynamic rangeTelevision system detailsTelevision system scanning detailsEngineeringAnalog signal

A black clamp stabilization circuit for an image sensor utilizes a mixed-signal SoC block comprising sub-blocks to dynamically and precisely adjust the black level based on comparison to a reference black level. The black level adjustments include a first level regulation using digital control of an analog signal in a feedback loop that includes a programmable gain amplifier and high-resolution A / D converter. By applying the black clamping in the analog domain, dynamic range is extended. Additional black level regulation is subsequently performed in the digital domain to differentially eliminate line noise and column noise generated within the imaging System-on-Chip. By providing information between the sub-blocks, the algorithms can converge more quickly. The technique enables multiple signal paths to separately handle individual colors and to increase imaging data throughput.

Owner:SAMSUNG ELECTRONICS CO LTD

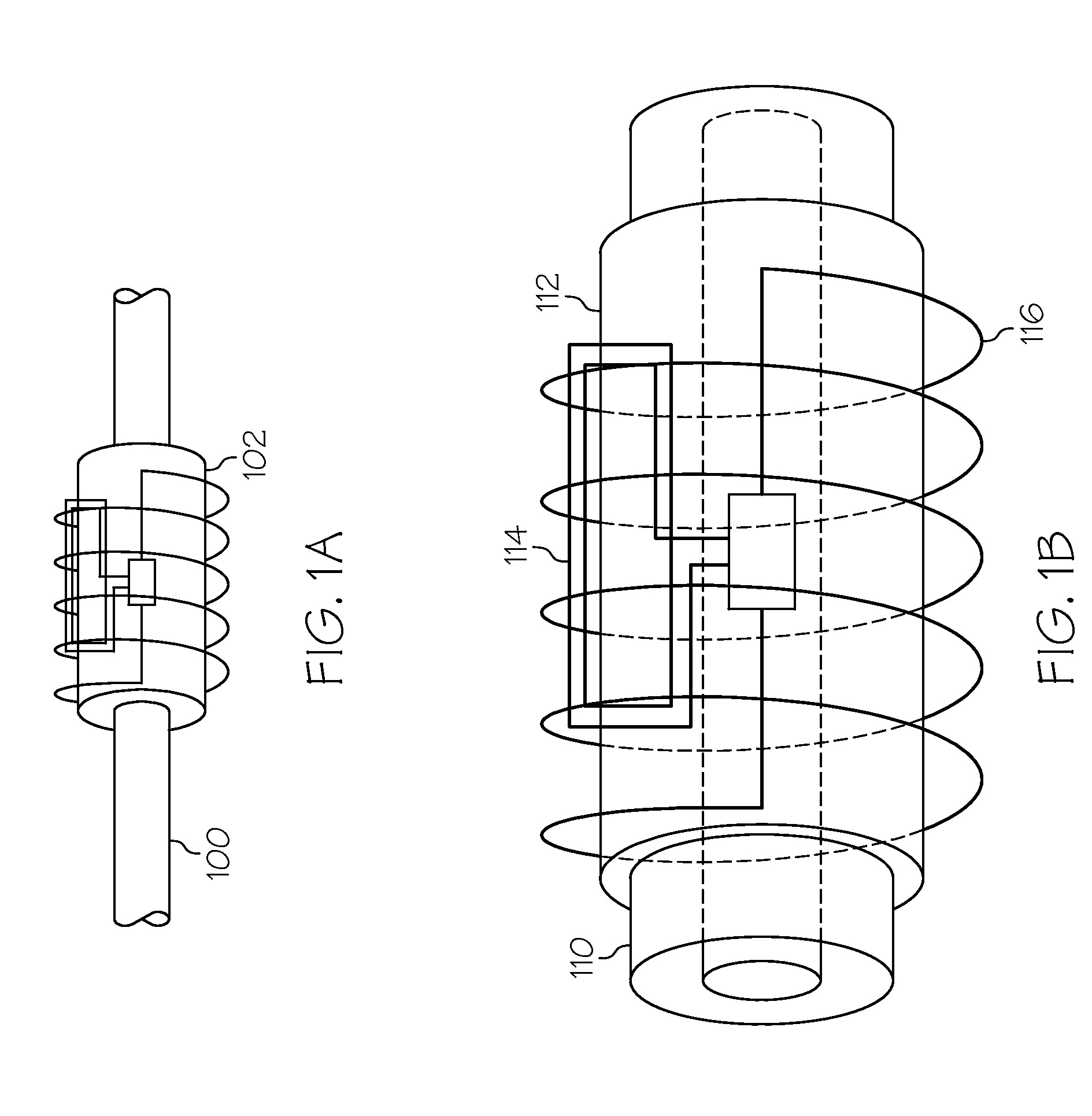

Rfid-based electricity metering system

InactiveUS20120280828A1Accurate scaleElectric signal transmission systemsWireless architecture usageProgrammable-gain amplifierRadio frequency

Embodiments of the present invention provide a radio frequency identification (RFID) based electricity metering system enabled to meter energy consumption of individual devices. Specifically, embodiments of this invention provide a set (a least one) of RFID sensor units, each RFID sensor unit comprising: an inductor affixed to the power line of an electronic device configured to produce an induced current using the power line of the electronic device through inductive coupling; a programmable gain amplifier (PGA) coupled to the inductor configured to provide gain or attenuation control on the induced current so that the induced current is properly scaled; an analog-to-digital converter (ADC) configured to convert the amplitude of the induced current to a digital value representing the energy consumption of the electronic device; a central processing unit (CPU) coupled to the ADC configured to receive the digital value from the ADC; a memory unit configured to store the digital value from the CPU; an antenna coupled to the CPU configured to transmit the digital value within a frequency band; and an RFID reader configured to receive the digital value transmitted by the RFID sensor unit.

Owner:KIM MOON J

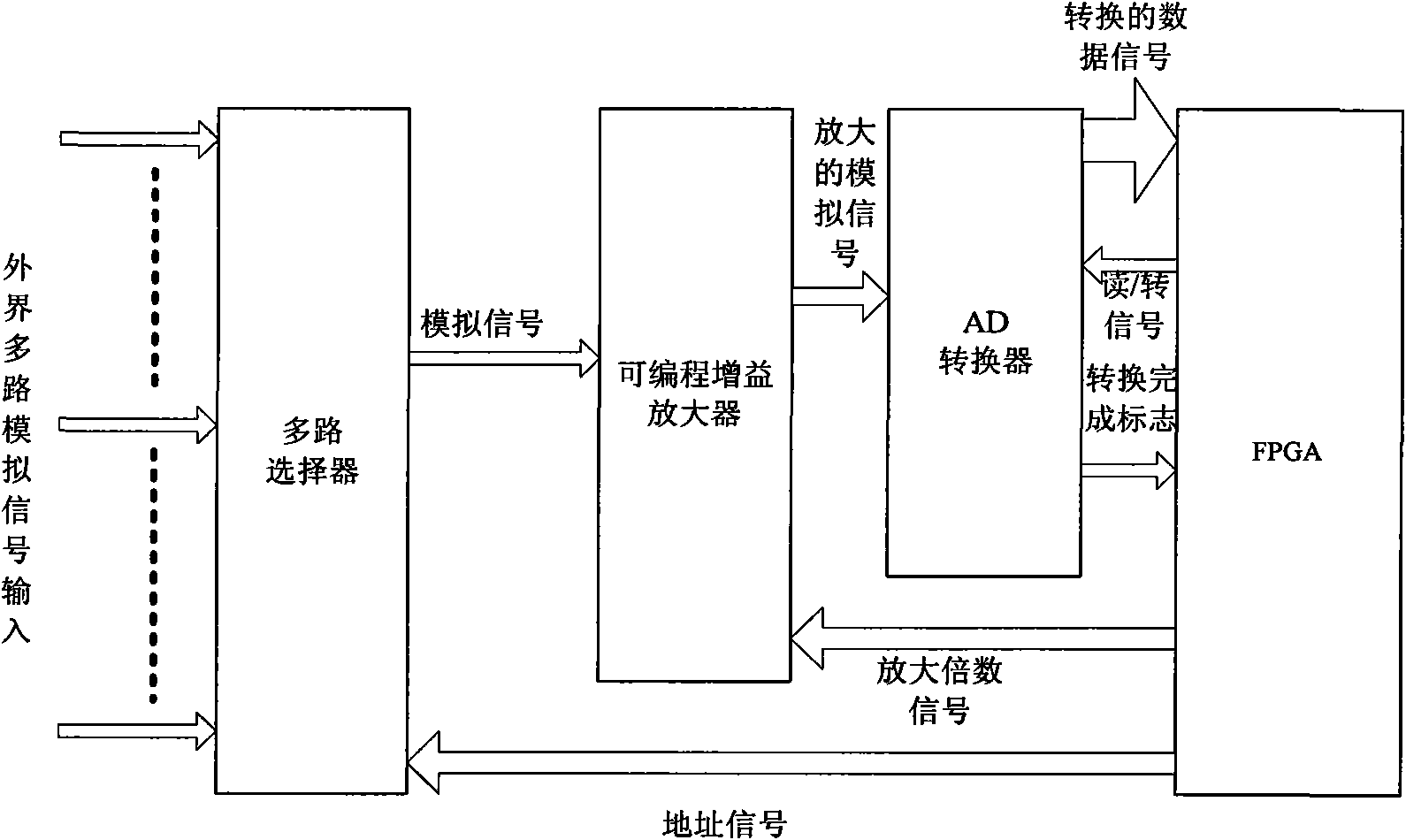

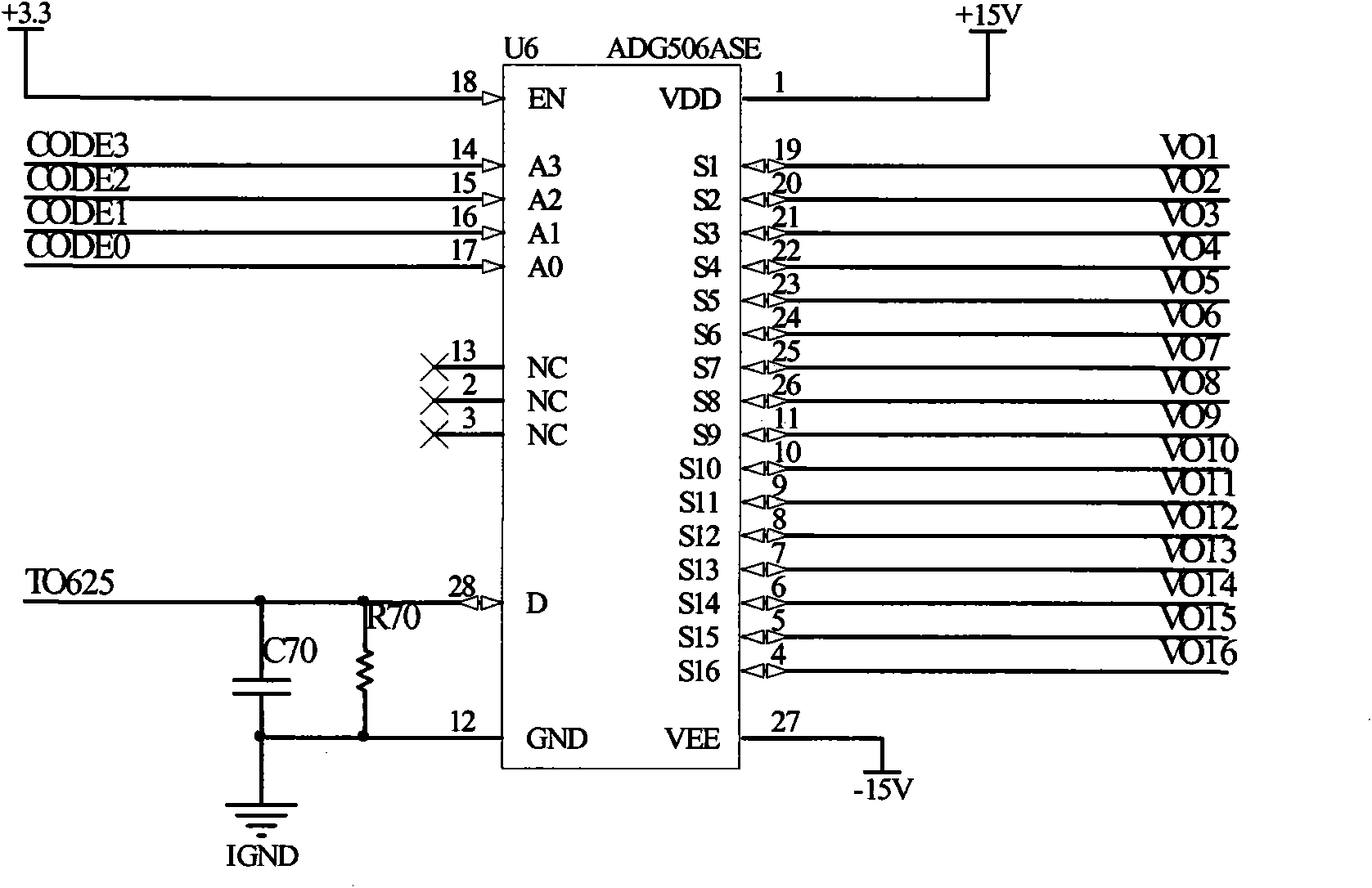

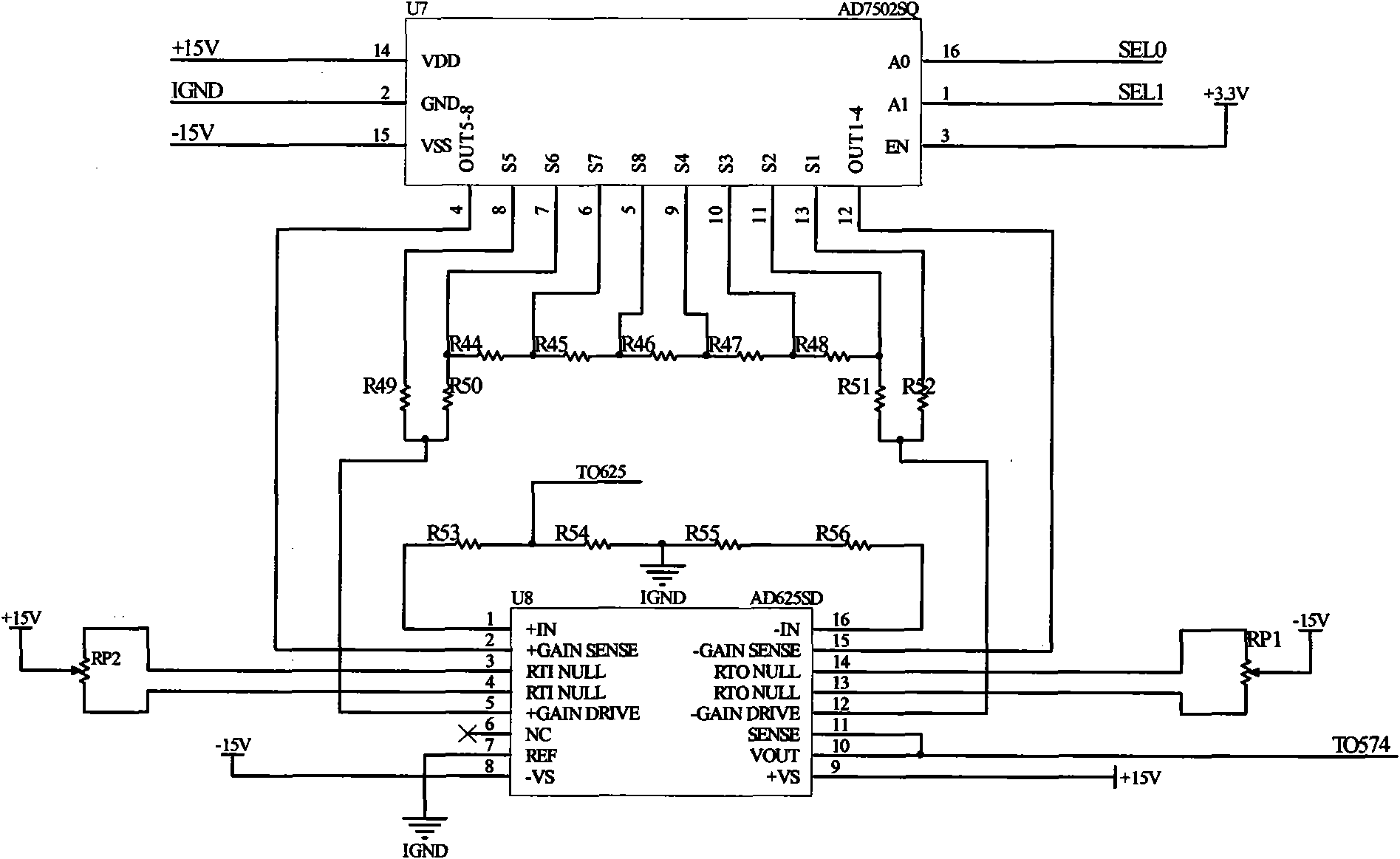

Multi-path data acquiring system based on FPGA

ActiveCN101615010AWide input rangeGuaranteed accuracyProgramme controlComputer controlIndustrial monitoringData acquisition

The invention discloses a multi-path data acquiring system based on FPGA, which mainly solves the problems of small signal acquiring range and poor acquiring precision of the prior multi-path acquiring system. The multi-path data acquiring system comprises a multi-path selector, a programmable-gain amplifier, an AD converter and an FPGA data processing module, wherein the FPGA data processing module sends an address signal to the multi-path selector and also sends a magnification signal to the programmable-gain amplifier; the multi-path selector selects an external analog signal according to the address signal to enter the programmable-gain amplifier; after amplifying the input analog signal, the programmable-gain amplifier outputs the analog signal to the AD converter; the AD converter samples the input analog signal, quantifies the analog signal to form a digital signal and transmits the digital signal to the FPGA data processing module; and the FPGA data processing module transmits the input data to a host computer after sequencing, wave filtering and table searching. The invention has the advantages of wide signal acquisition range, high precision can convenient acquisition path expansion, thereby being suitable for the signal acquisition of an industrial monitoring and sensing network.

Owner:XIDIAN UNIV

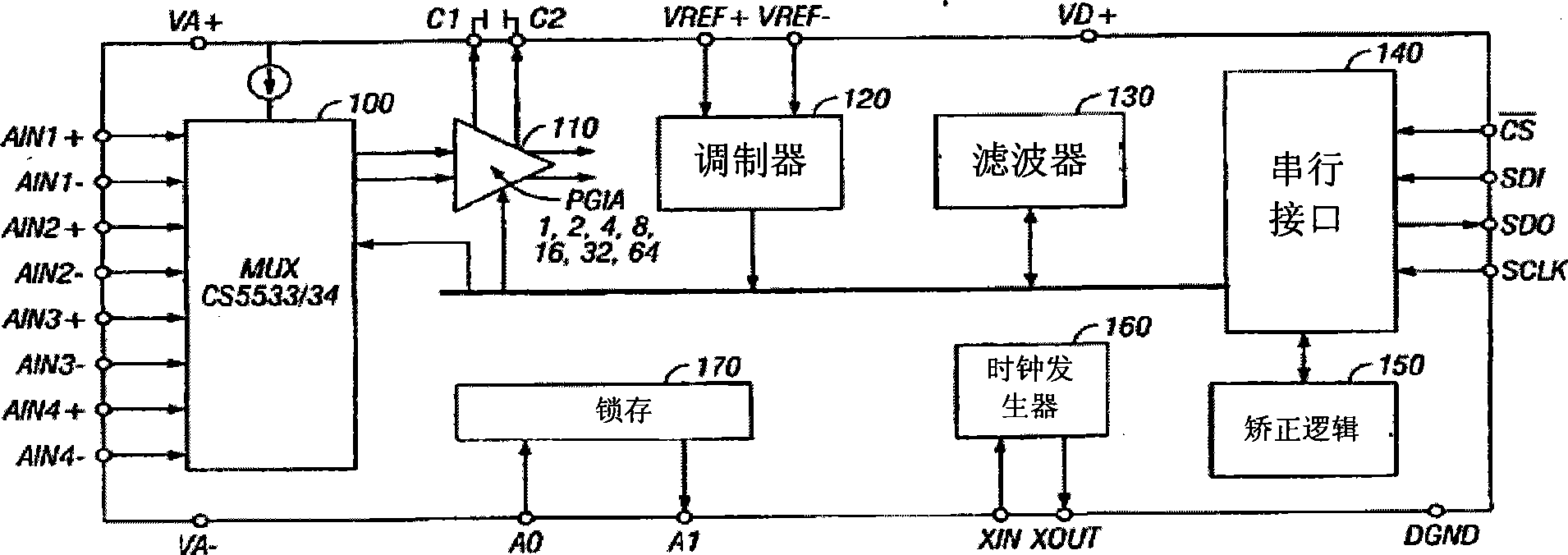

Multi-channel programmable gain amplifier controlled with a serial interface

InactiveUS6847904B2Simple interfaceAmplifier with semiconductor-devices/discharge-tubesAnalog signal digital controlMultiplexerProgrammable-gain amplifier

Owner:MICROCHIP TECH INC

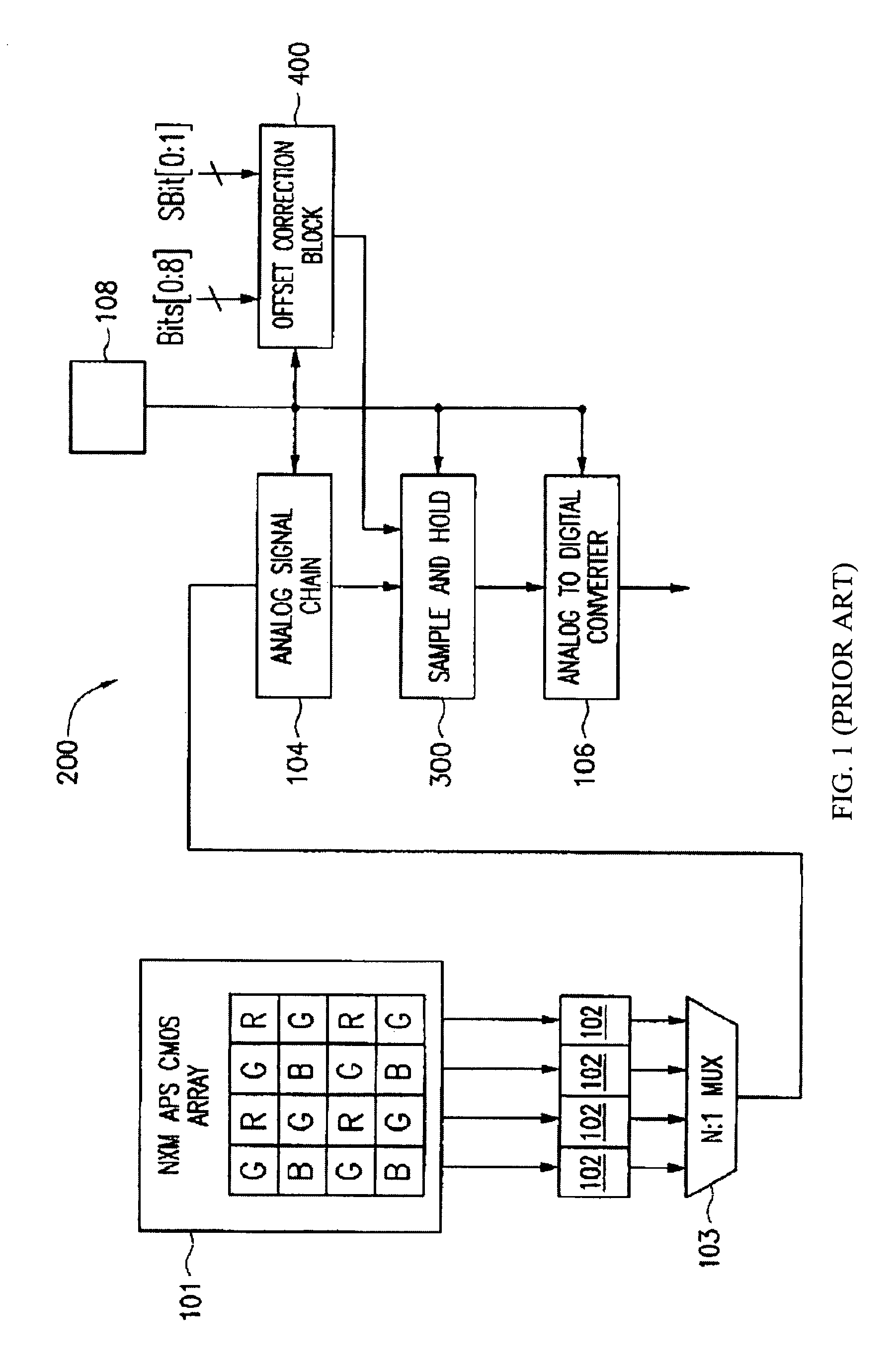

Power saving method using interleaved programmable gain amplifier and A/D converters for digital imaging devices

InactiveUS6342919B2Television system detailsColor signal processing circuitsDigital imagingĆuk converter

For use in a low-power digital imaging devices, for example a low-power single CCD-based digital camera, particularly in a battery-operated camera, a method for implementing video signal processing is provided wherein a single amplifier is employed in switched but parallel and uncorrelated signal paths in a manner which avoids fixed pattern noise that would be introduced by mismatches in gain and offset in various paths. The desired effect is achieved through use of a controller that switches appropriate sets of capacitors in parallel paths to establish different gains for each pixel component. The invention achieves power savings and flexibility to independently control gain of each color component.

Owner:MEDIATEK SINGAPORE PTE LTD SINGAPORE

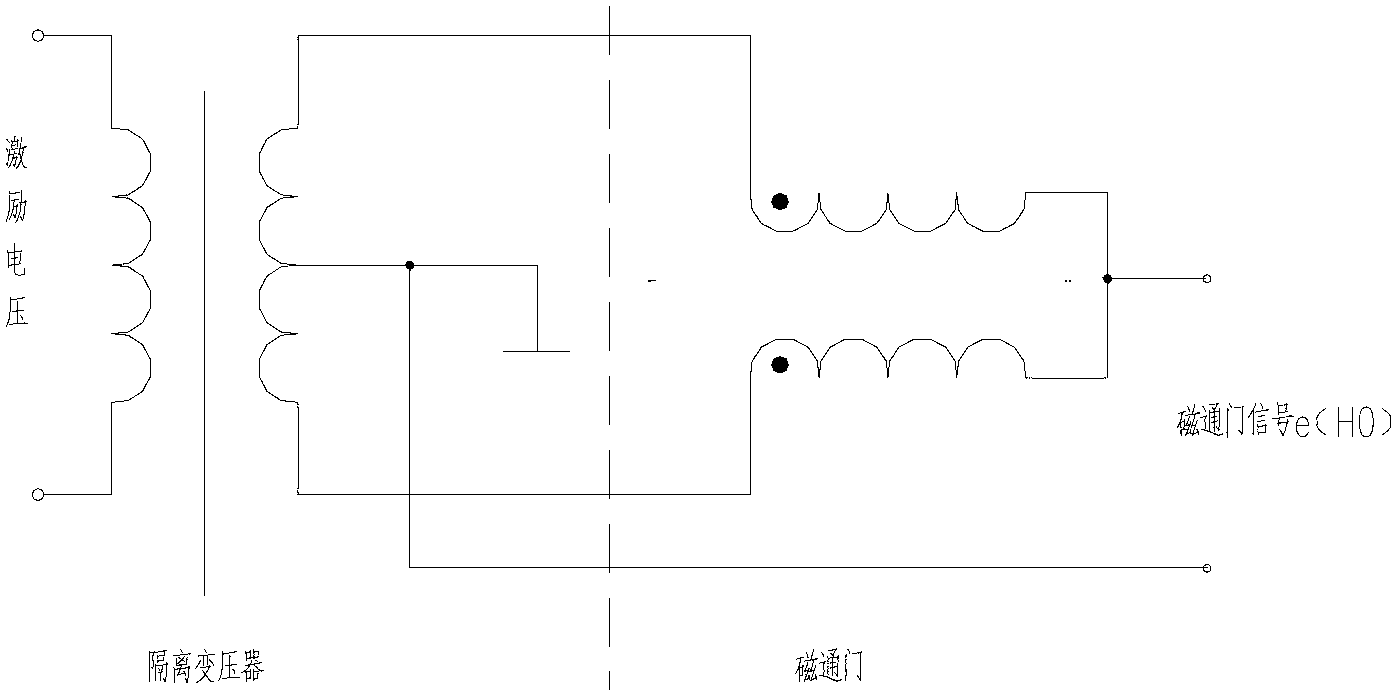

Signal processing circuit of fluxgate sensor

InactiveCN102830371AHighly integratedImprove anti-interference abilityMagnetic field measurement using flux-gate principleMeasurement using digital techniquesSignal processing circuitsDigital down converter

The invention discloses a signal processing circuit of a fluxgate sensor. The signal processing circuit of the fluxgate sensor comprises a DSP (digital signal processor) and a signal feedback unit; an environment voltage signal collected by a fluxgate probe is linked with a digital signal processor through a bridging circuit and a programmable gain amplifier; the signal feedback unit feeds the processing signal of the digital signal processor back to the front end of the bridging circuit; the DSP comprises an analogue-digital converter, a digital frequency selector, a phase sensitive detector and a magnetic field calibrating module; the signal feedback unit comprises an interpolation calculation module, the analogue-digital converter and the programmable gain amplifier; the DSP receives the signal of the fluxgate probe, and outputs the size of the tested environment magnetic field by means of analogue-digital conversion, digital frequency selecting filtering, phase-sensitive rectifying and magnetic field calibration orderly; the measurement precision and the product performance of the fluxgate sensor are improved by digital treatment of the environment signal, so that adjustment and upgrade of the system are more convenient.

Owner:BC P INC CHINA NAT PETROLEUM CORP +1

Multi-axis integrated inertial sensing device

ActiveUS20150276407A1Television system detailsAcceleration measurement using interia forcesLow noiseGyroscope

A system comprising an integrated multi-axis MEMS inertial sensor architecture. The system can include a MEMS gyroscope having a MEMS resonator and a MEMS accelerometer overlying a CMOS IC substrate. The CMOS IC substrate can include low noise Charge Sense amplifiers to process the sensed signals, programmable gain amplifiers, a demodulator, mixer, an AGC loop circuit coupled to the MEMS gyroscope to drive MEMS resonator. The CMOS IC also includes programmable Quadrature cancellation, Analog and digital phase shifters are implemented in the architecture to ensure quadrature cancellation and demodulation to achieve optimal performance. The AGC loop acts in a way such that generated desired signal amplitude out of the drive signal maintains MEMS resonator velocity at a desired frequency and amplitude while consuming low power. The MEMS gyroscope and accelerometer can be coupled to an input multiplexer configured to operate in a time-multiplexed manner.

Owner:MCUBE INC

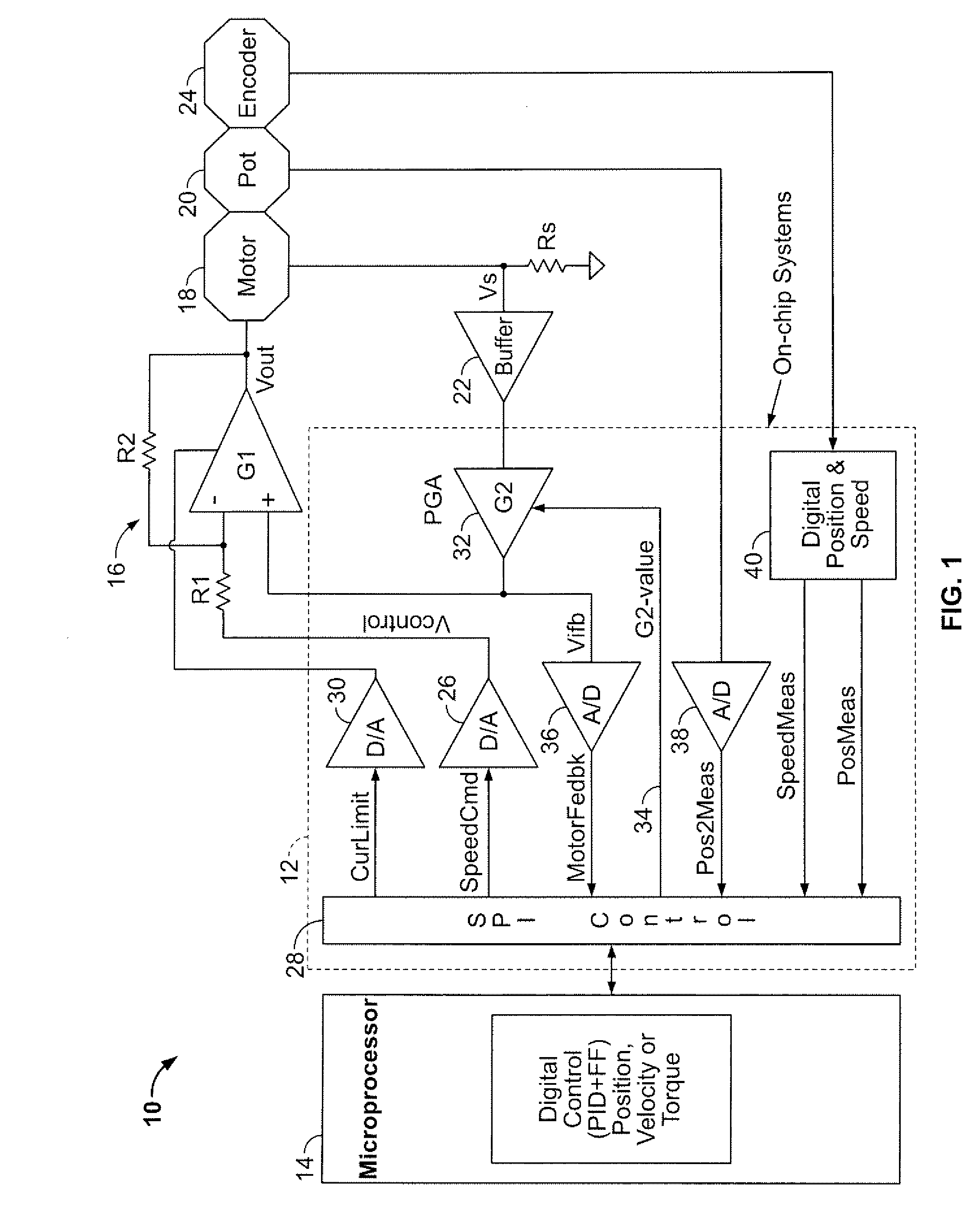

Adaptive and reconfigurable system for DC motor control

ActiveUS20080247735A1Digital variable displayAcceleration measurement using interia forcesDigital analog converterControl signal

An integrated circuit for controlling a DC motor is disclosed. The integrated circuit includes at least one digital position and speed circuit (DPS) for providing measurements of speed, position, and direction of the motor, the DPS being in signal communication with the motor for receiving a pair of signals having a quadrature relationship; and at least one programmable gain amplifier (PGA) electrically coupled to the motor, the PGA being configured to receive a feedback signal indicative of current flowing through the motor and to apply a second signal to the motor for adjusting the speed of the motor; and at least two analog-to-digital converters (A / D), one A / D being used to quantize the output of the PGA for an off-chip processor; and another A / D to provide motor reference position from an analog sensor, such as a potentiometer; and at least two digital-to-analog converters (D / A), one D / A used to set the motor voltage; and another D / A used to set the motor current limit. The integrated circuit can be incorporated into a larger motor control loop which further includes a summing amplifier for providing the feedback signal to the motor that is indicative of current flowing through the motor; a buffer amplifier electrically for sensing the output current of the motor, and a processor for providing control signals to the system monolithic module and for receiving the measurements of speed, position, and direction of the motor.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

Wireless communication semiconductor integrated circuit device and wireless communication system

ActiveUS7257385B2Improve receiver sensitivityNarrow rangeModulated-carrier systemsGain controlDifferential amplifierAmplification factor

A receiving circuit of a direct conversion system is provided which includes a differential amplifier circuit which amplifies a received signal, a mixer which combines the amplified received signal and an oscillation signal having a predetermined frequency to thereby perform frequency conversion, and a high gain amplifier circuit in which a plurality of programmable gain amplifiers and a plurality of filters which eliminate noise of the received signal and an unnecessary wave, are connected in a multistage and which is configured such that an amplification factor is varied according to the level of the received signal. In the receiving circuit, the low noise amplifier is brought to a non-operating state to thereby allow execution of a DC offset cancel operation of the corresponding programmable gain amplifier on the pre-stage side of the high gain amplifier circuit. Thereafter, the low noise amplifier is brought to an operating state to thereby allow execution of a DC offset cancel operation of the final-stage programmable gain amplifier.

Owner:RENESAS ELECTRONICS CORP

System and method for eliminating fixed mode noise by dummy pixels

InactiveCN101309359AEliminate Row FPNPlay a compensatory roleInput/output for user-computer interactionTelevision system detailsCompensation effectComputer science

The invention discloses a system used for eliminating the Fixed Pattern Noise (FPN). The system includes a pixel array, a reading circuit used for reading the pixel value of each pixel unit, a programmable gain amplifier (PGA) algorithm unit, an A / D conversion unit and an FPN elimination unit; the system adopts the dummy pixel values of the current row and the current column for compensation; the invention also discloses an implementation method for eliminating the FPN, including that the pixel array is read; the read result is inputted to the PGA algorithm unit; a pixel offset is added to each pixel unit; the operation result is processed with A / D conversion; the dummy pixel values of the current row and the current column are used for compensation. Based on the system and the method for eliminating the FPN, each pixel in the pixel array not only can use the dummy pixel of the current row to eliminate the column FPN, but also can use the dummy pixel of the current column to eliminate the row FPN; besides, because the data of the dummy pixels in the pixel array are acquired real-timely, the dummy pixel data have certain compensation effect on the FPN caused by the power disturbance.

Owner:APEXONE MICROELECTRONICS SHANGHAI +1

Analog optical black clamping circuit for a charge coupled device having wide programmable gain range

ActiveUS6940548B2Overall design flexibilityHighly programmableTelevision system detailsColor signal processing circuitsIntegratorAudio power amplifier

An image processing apparatus (200) for a charge coupled device including analog front end circuitry having optical black and offset correction, whereby the offset and optical black correction circuit is programmable. The present invention includes a first circuit (202, 204, 206, 208, 210) to sample the incoming optical black signal output from a CCD. This first circuit includes a correlated double sampler (202) coupled to a first programmable gain amplifier (204). An adder (206) connects between the first programmable gain amplifier (204) and a second gain amplifier (208) for adding in the optical black offset to the optical black signal input from the CCD. A second circuit (212, 214) includes a reverse programmable gain amplifier (212) connected to the output of the second programmable gain amplifier (208) to amplify the optical black level inversely proportional to the gain from the second programmable gain amplifier (208). The second circuit (212, 214) also includes an integrator (214) coupled to the reverse programmable gain amplifier (212) to integrate the difference between the incoming signal and the desired optical black value. The second circuit (212, 214) couples to the adder (206) to add the positive and negative difference to the optical black signal. An analog-to-digital converter (210) converts the sampled signal for further processing at the output of the image processing apparatus (200).

Owner:TEXAS INSTR INC

Image sampling circuit with a blank reference combined with the video input

ActiveUS6952240B2Without adversely affectingEnhanced signalTelevision system detailsElectric signal transmission systemsCapacitanceAudio power amplifier

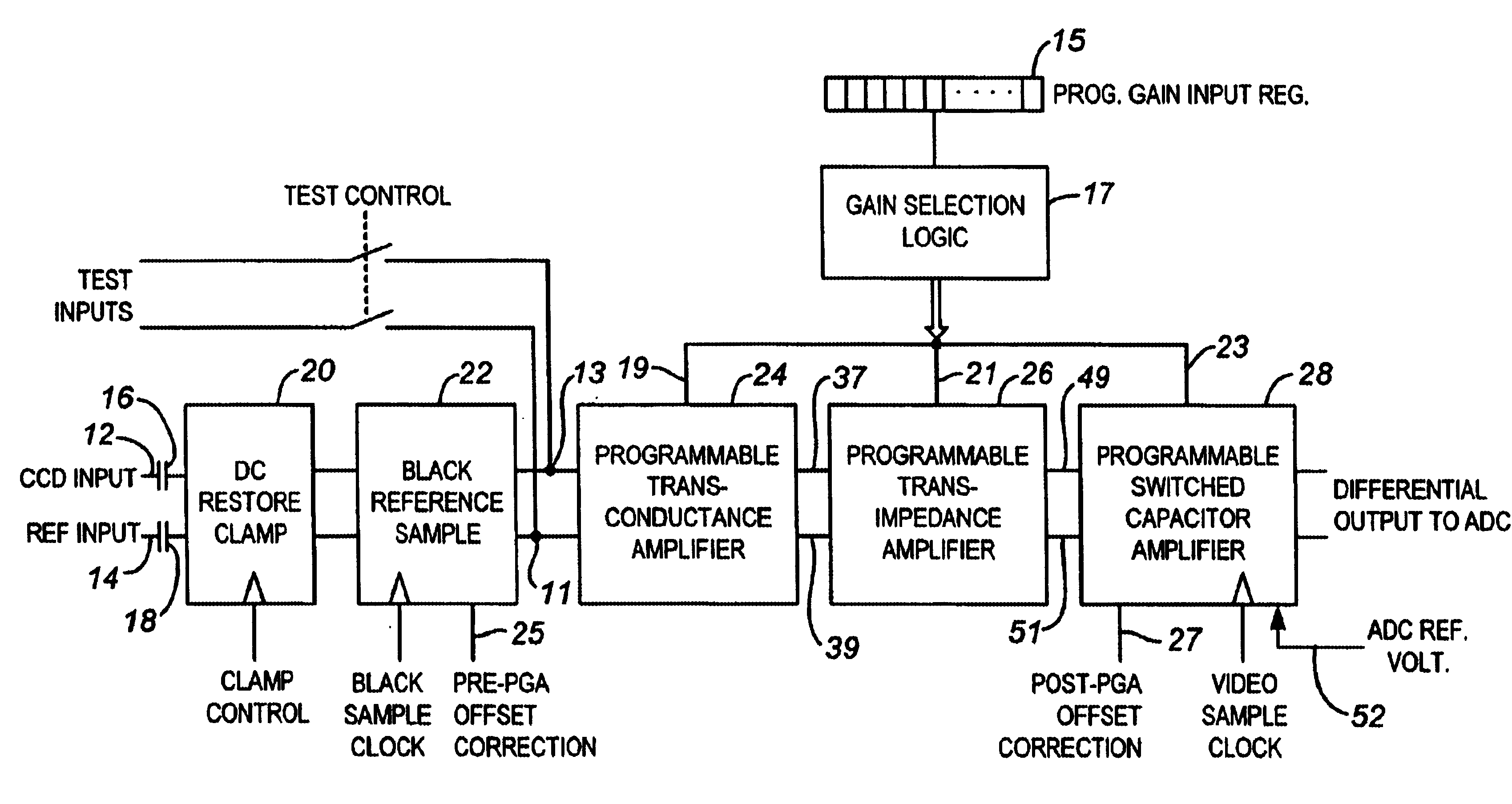

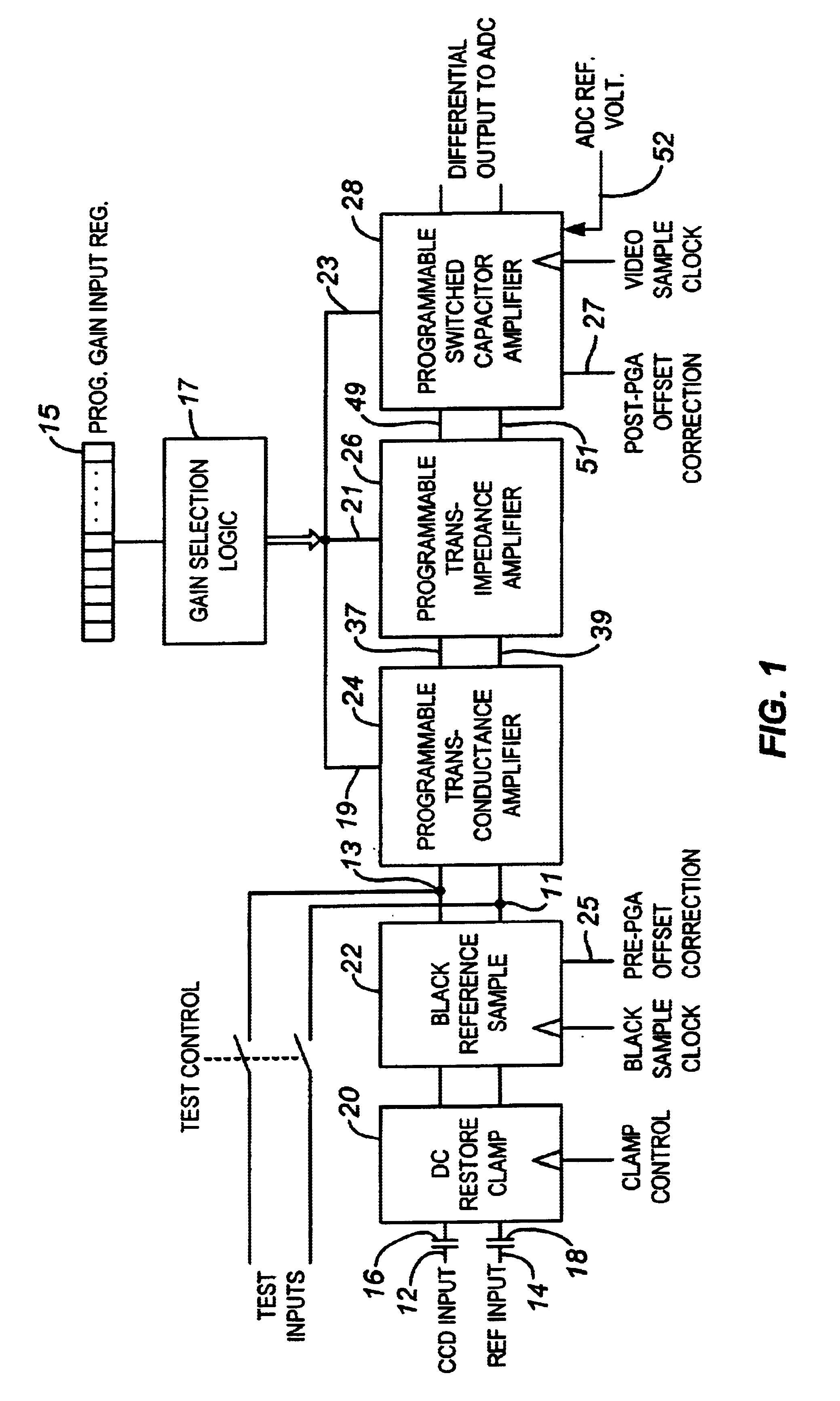

A programmable gain amplifier having three separately programmable amplifiers. A programmable transconductance amplifier is followed by a programmable transimpedance amplifier, then a programmable switched capacitor amplifier. In one embodiment, this programmable gain amplifier is implemented in an analog front-end (AFE) circuit. One AFE embodiment provides a coarse pre-gain offset a black reference level sampler, and a fine post-gain offset in the programmable switched capacitor amplifier. In one embodiment, an ADC reference is sampled, and is subtracted directly from the video signal in the switched capacitor amplifier so that the zero level of the video signal is made to correspond to the zero level of the ADC. In another embodiment, a piece-wise linear approximation of an exponential gain function is implemented by programming the transconductance and transimpedance amplifiers to provide exponential jumps in gain, while the switched capacitor amplifier is programmed to interpolate as needed between the exponential gain levels.

Owner:EXAR CORP

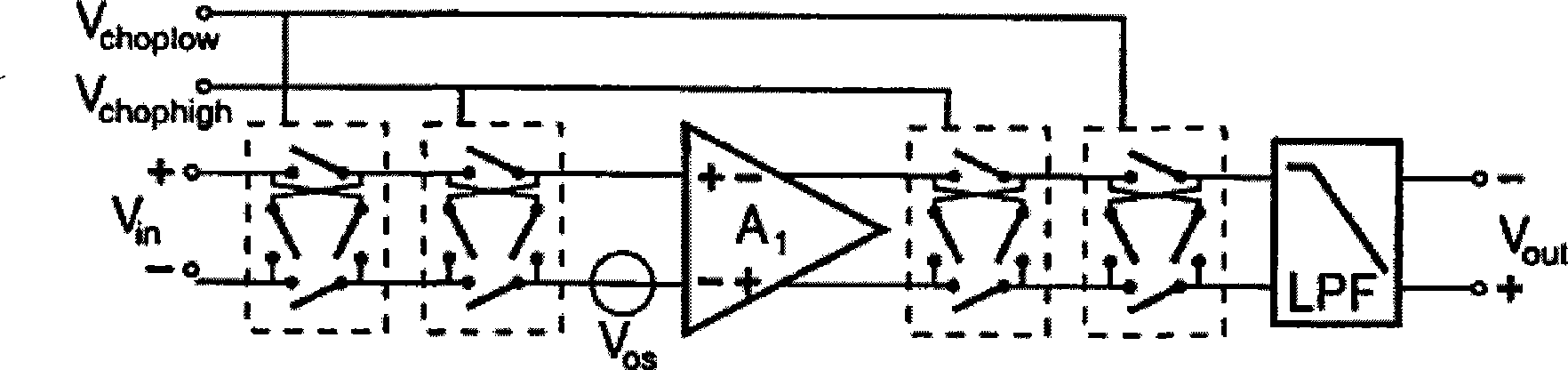

Signal conditioning circuit and dual sampling-hold circuit applying the conditioning method

ActiveCN101394163AAvoid residual dysregulation problemsEasy to integrateDigital technique networkElectric analogue storesSignal conditioning circuitsDigital down converter

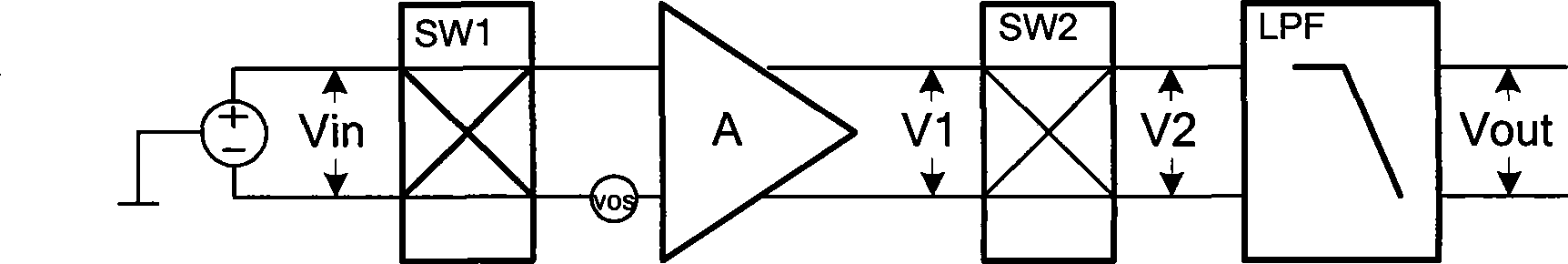

The invention discloses a signal conditioning circuit, a conditioning method thereof and a double sampling retaining circuit. The signal conditioning circuit comprises a first chopping switch, a programmable gain amplifier, a second chopping switch, a double sampling retaining circuit, an analog-to-digital converter, and a digital reduction sampling filter which are connected in sequence. The double sampling retaining circuit samples outputs of the programmable gain amplifier in two-phase positions of a chopping clock, and the results of two samplings are added. and an added output voltage is transmitted to and processed by the analog-to-digital converter, and the digital reduction sampling filter. Since the double sampling retaining circuit is added, the invention avoids the residual and off-tune problem in a chopping amplifier. Meanwhile, the invention facilitates the integration of a single chip, without the need of external filtering capacitor. Furthermore, a novel sequential control reduces the consumption of a digital signal conditioning circuit based on a chopping amplifier.

Owner:豪威国际控股有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com