Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

663results about "Line balance variation compensation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

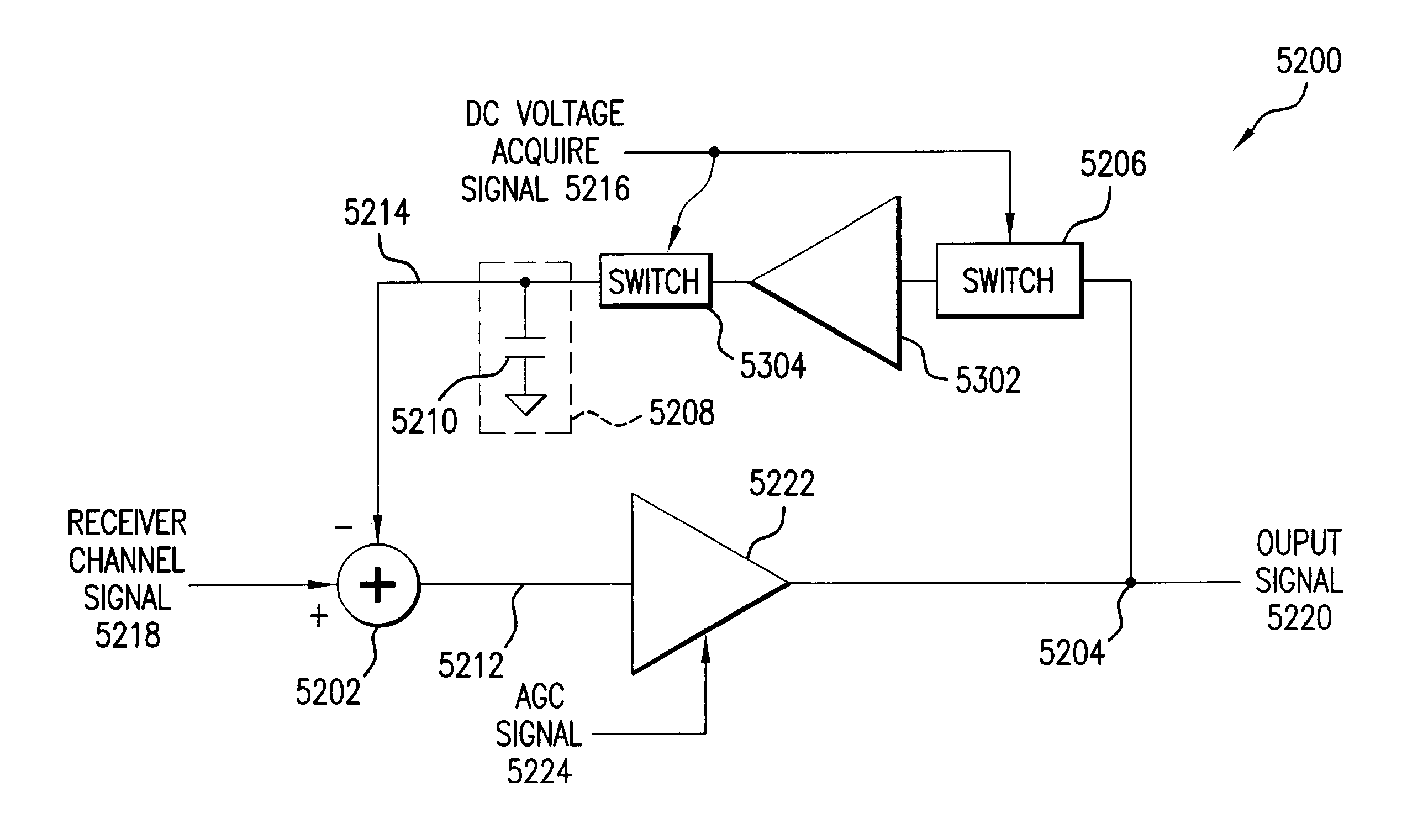

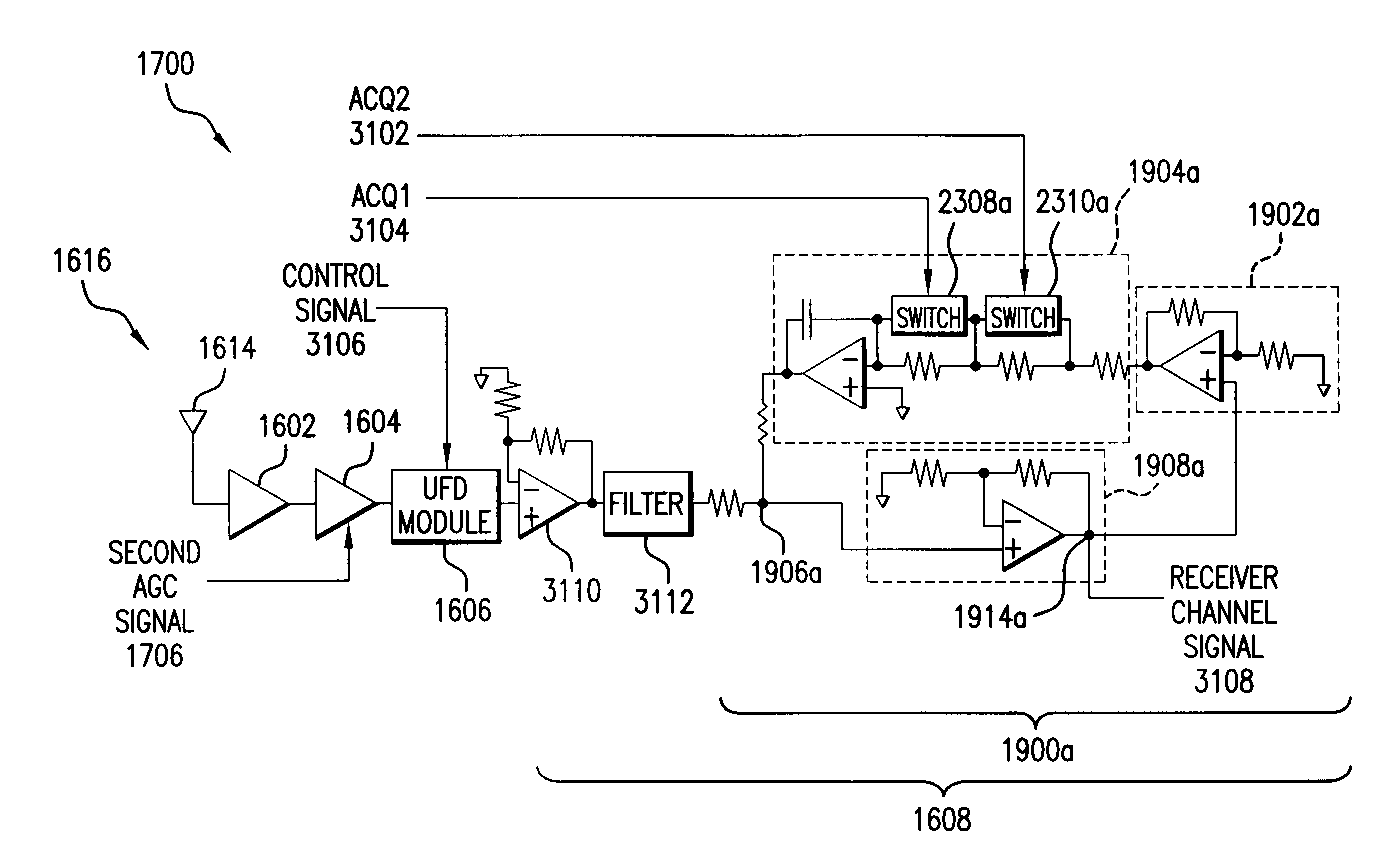

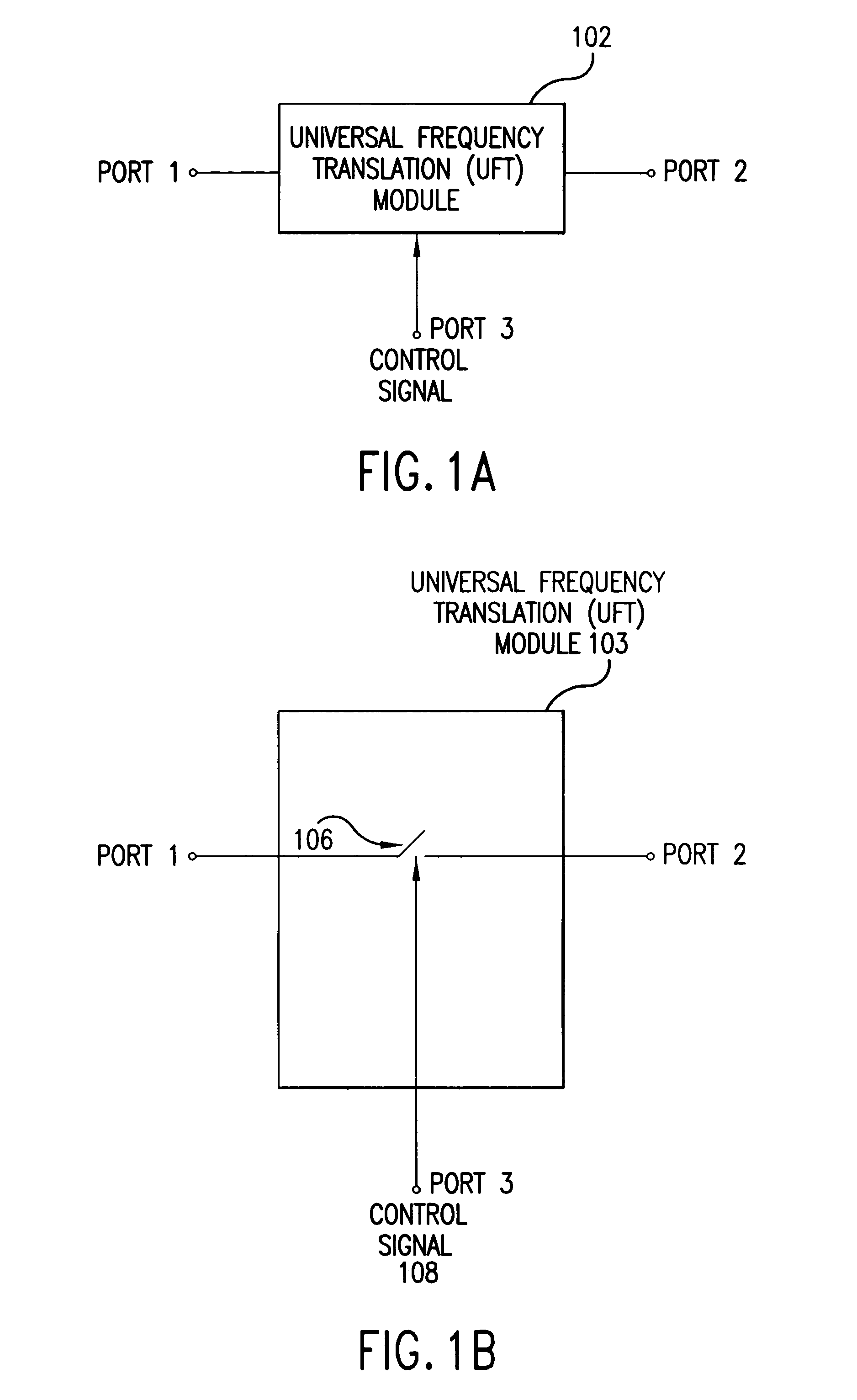

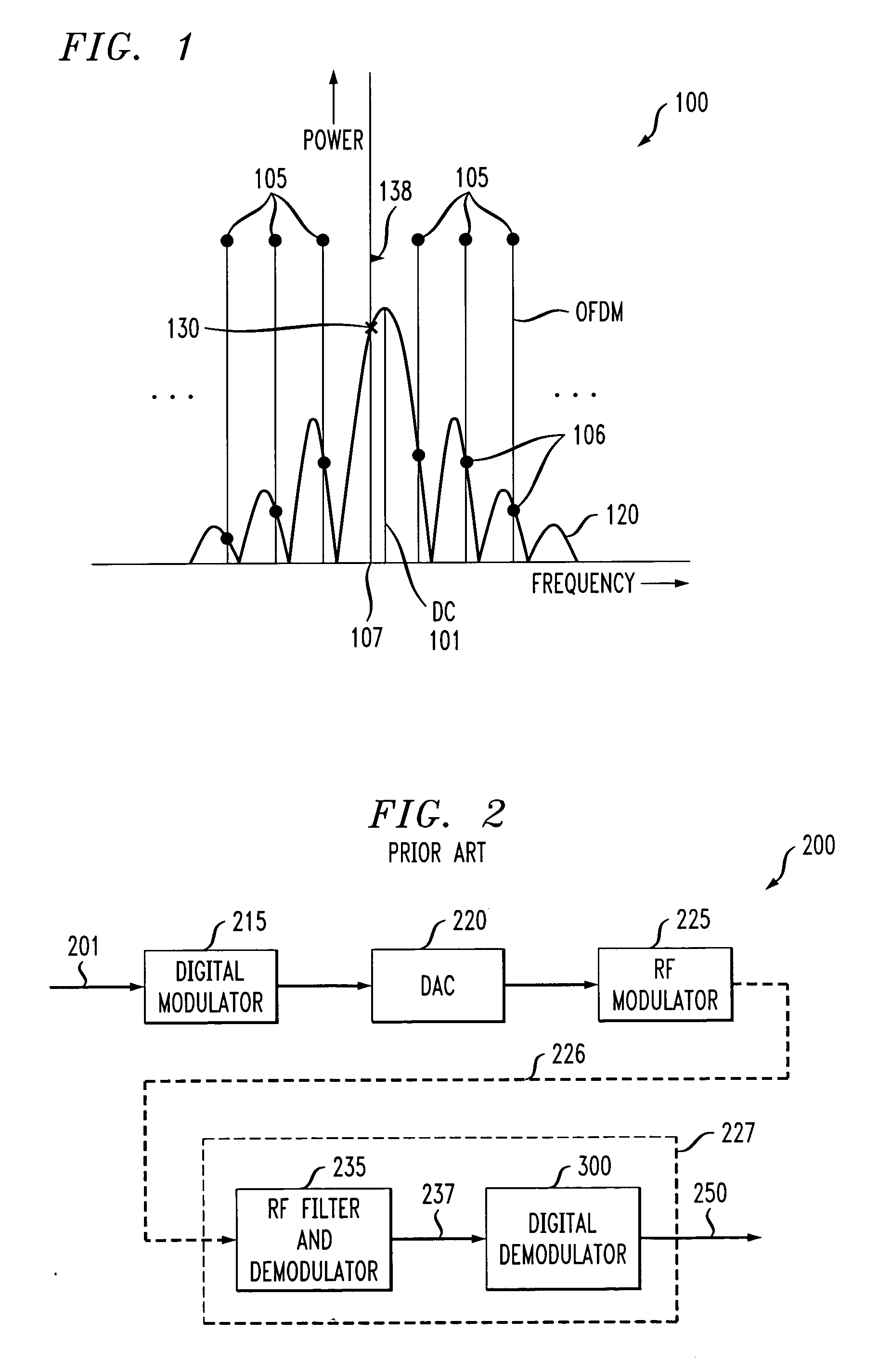

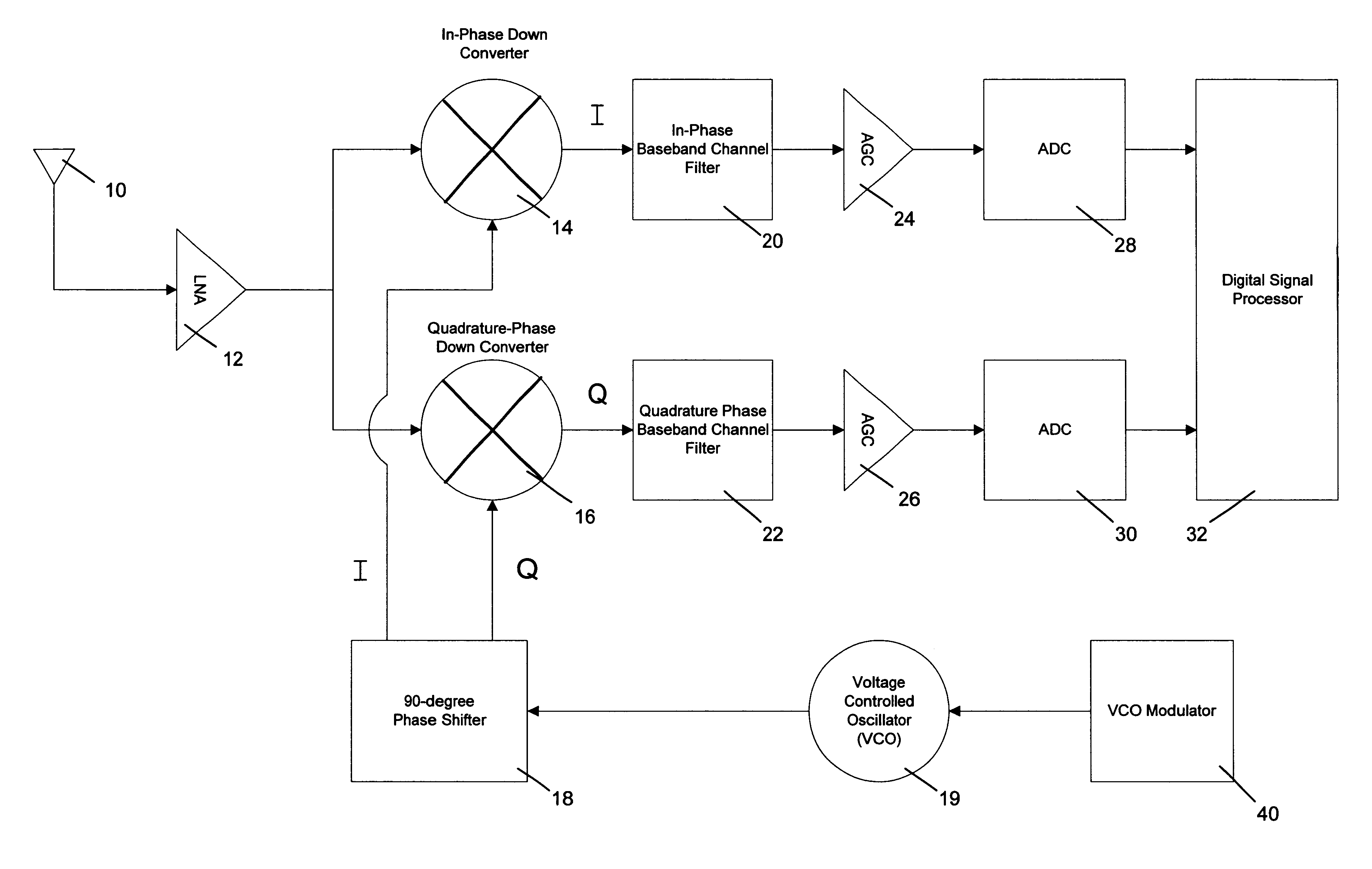

Method and apparatus for reducing DC offsets in a communication system

InactiveUS7072427B2Reduce DC offsetError preventionGain controlCommunications systemAudio power amplifier

Methods and apparatuses for reducing DC offsets in a communication system are described. In a first aspect, a feedback loop circuit reduces DC offset in a wireless local area network (WLAN) receiver channel. The frequency response of the feedback loop circuit can be variable. In a second aspect, a circuit provides gain control in a WLAN receiver channel. The stored DC offset is subtracted from the receiver channel. First and second automatic gain control (AGC) amplifiers are coupled in respective portions of the receiver channel. In a third aspect, a feedback loop circuit reduces DC offset in a WLAN receiver channel. The feedback loop circuit includes a storage element that samples and stores receiver channel DC offset. The loop is opened, and the DC offset stored in the storage element is subtracted from the receiver channel. Circuits for monitoring DC offset, and for providing control signals for controlling the frequency response of the DC offset reducing circuits are also provided.

Owner:PARKER VISION INC

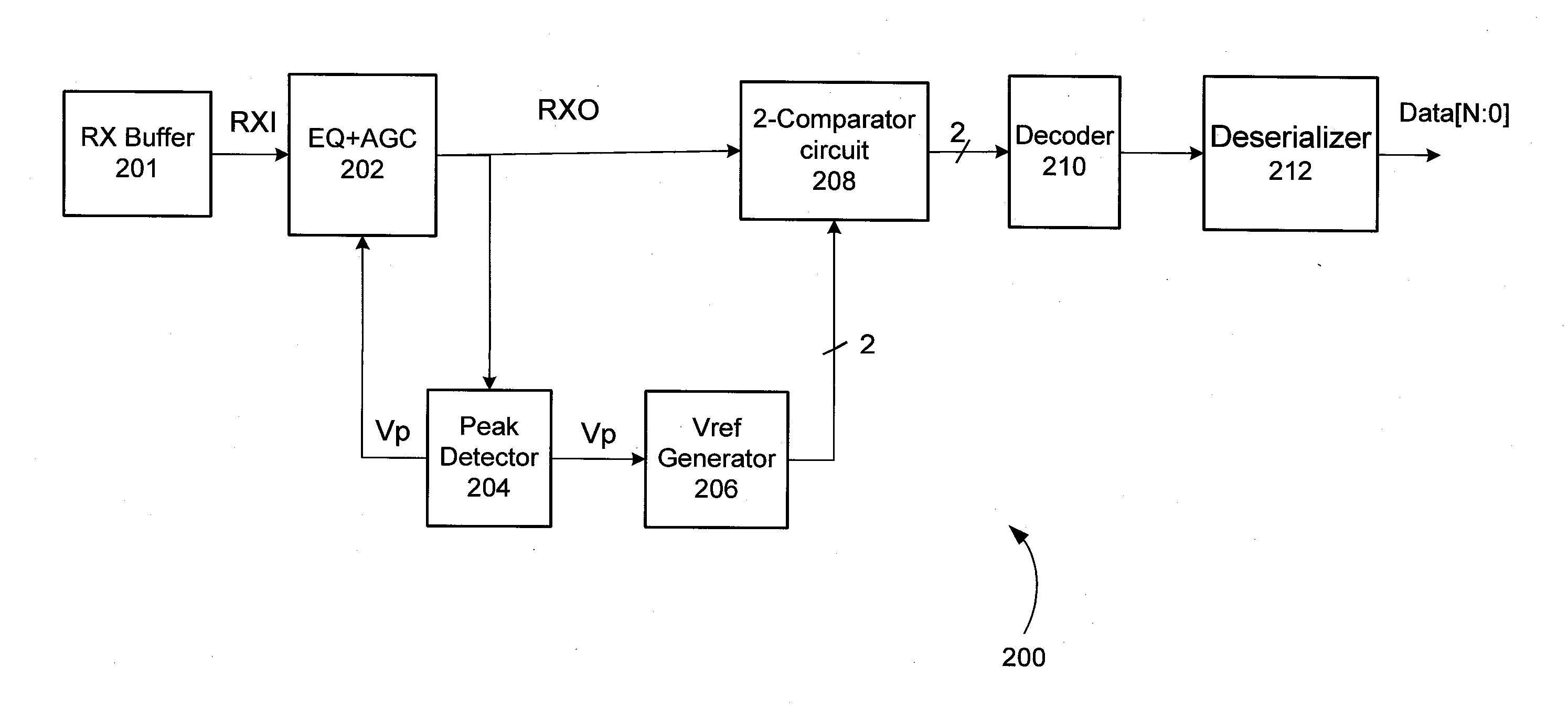

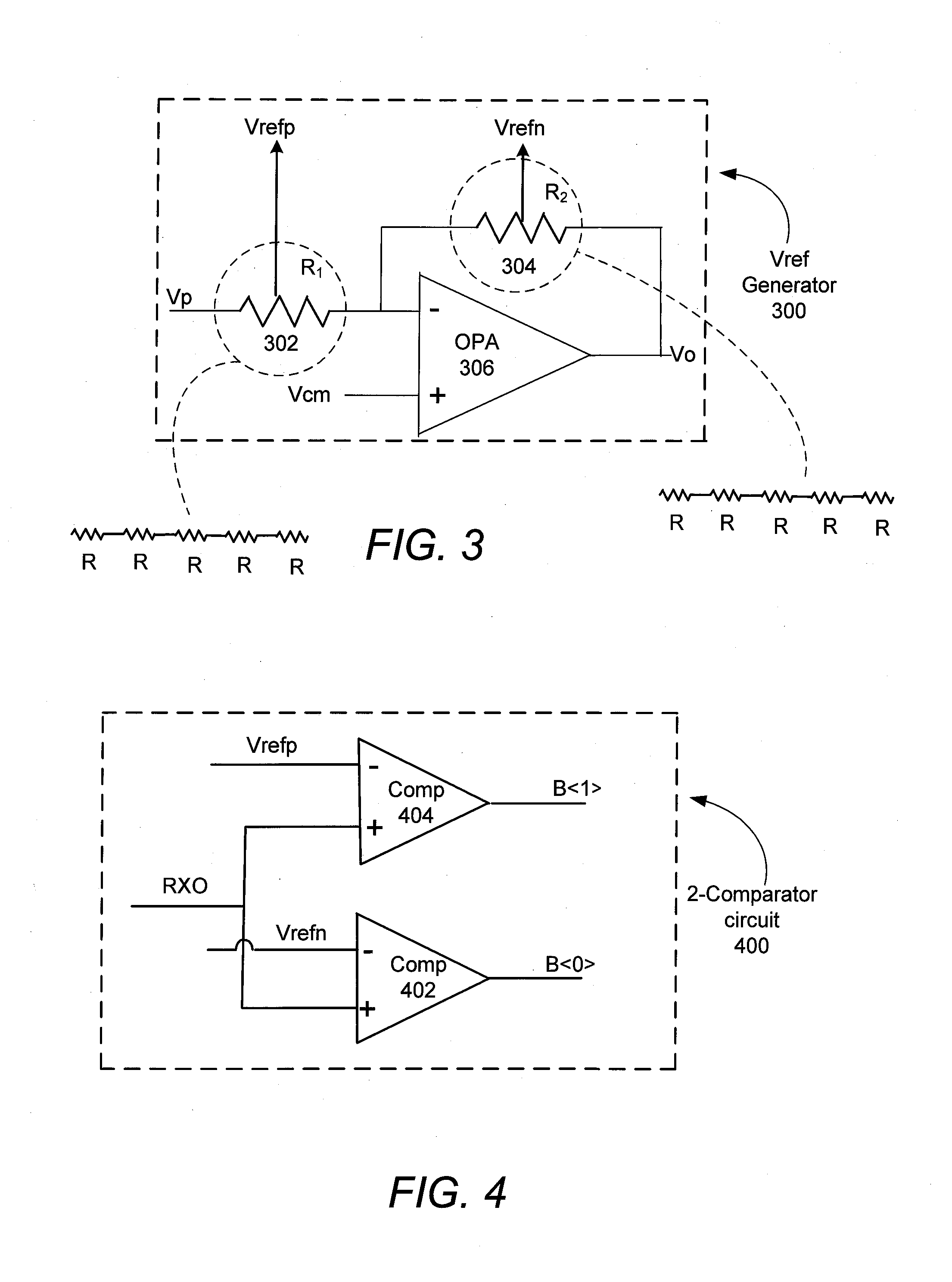

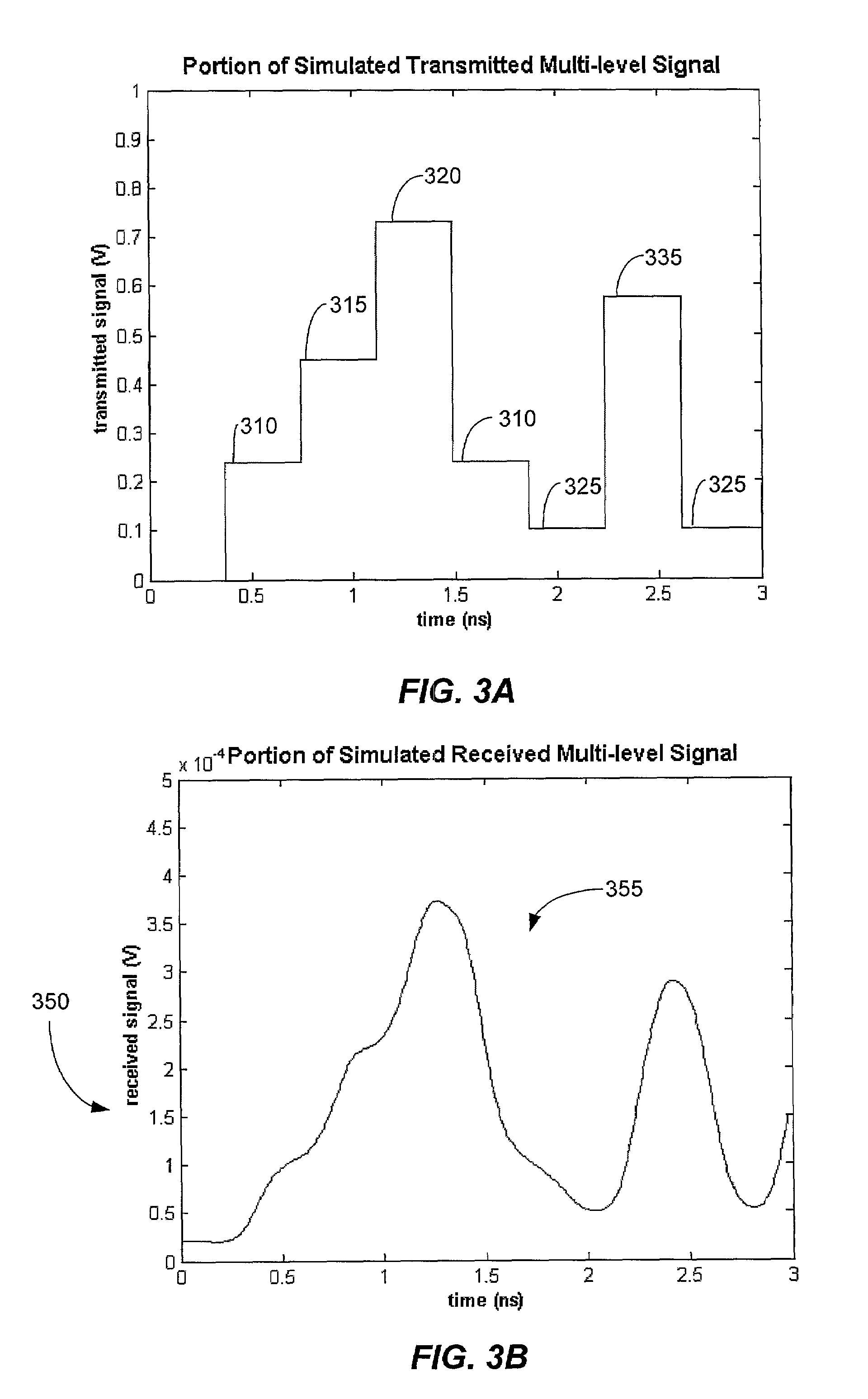

Multi-level amplitude signaling receiver

ActiveUS20130195155A1Dc level restoring means or bias distort correctionLine balance variation compensationVoltage generatorComparators circuits

One embodiment relates to a receiver circuit for multi-level amplitude signaling which includes at least three amplitude levels for each symbol period. The receiver circuit includes a peak detector, a reference voltage generator, and a comparator circuit. The peak detector is arranged to detect a peak voltage of the multi-level amplitude signal, and the reference voltage generator uses the peak voltage to generate multiple reference voltages. The comparator circuit uses the multiple reference voltages to detect an amplitude level of the multi-level amplitude signal. Other embodiments and features are also disclosed.

Owner:ALTERA CORP

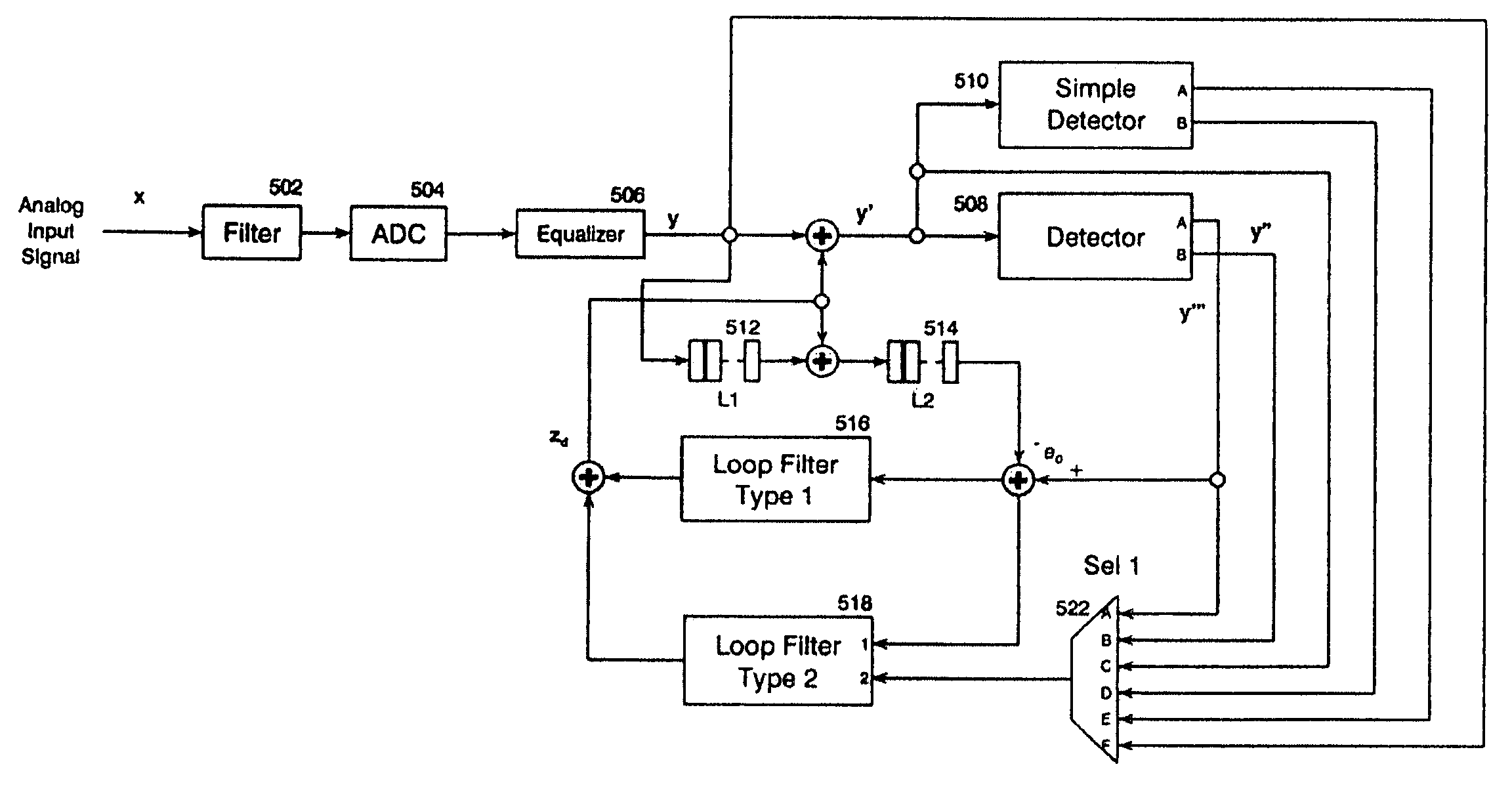

DC-offset compensation loops for magnetic recording system

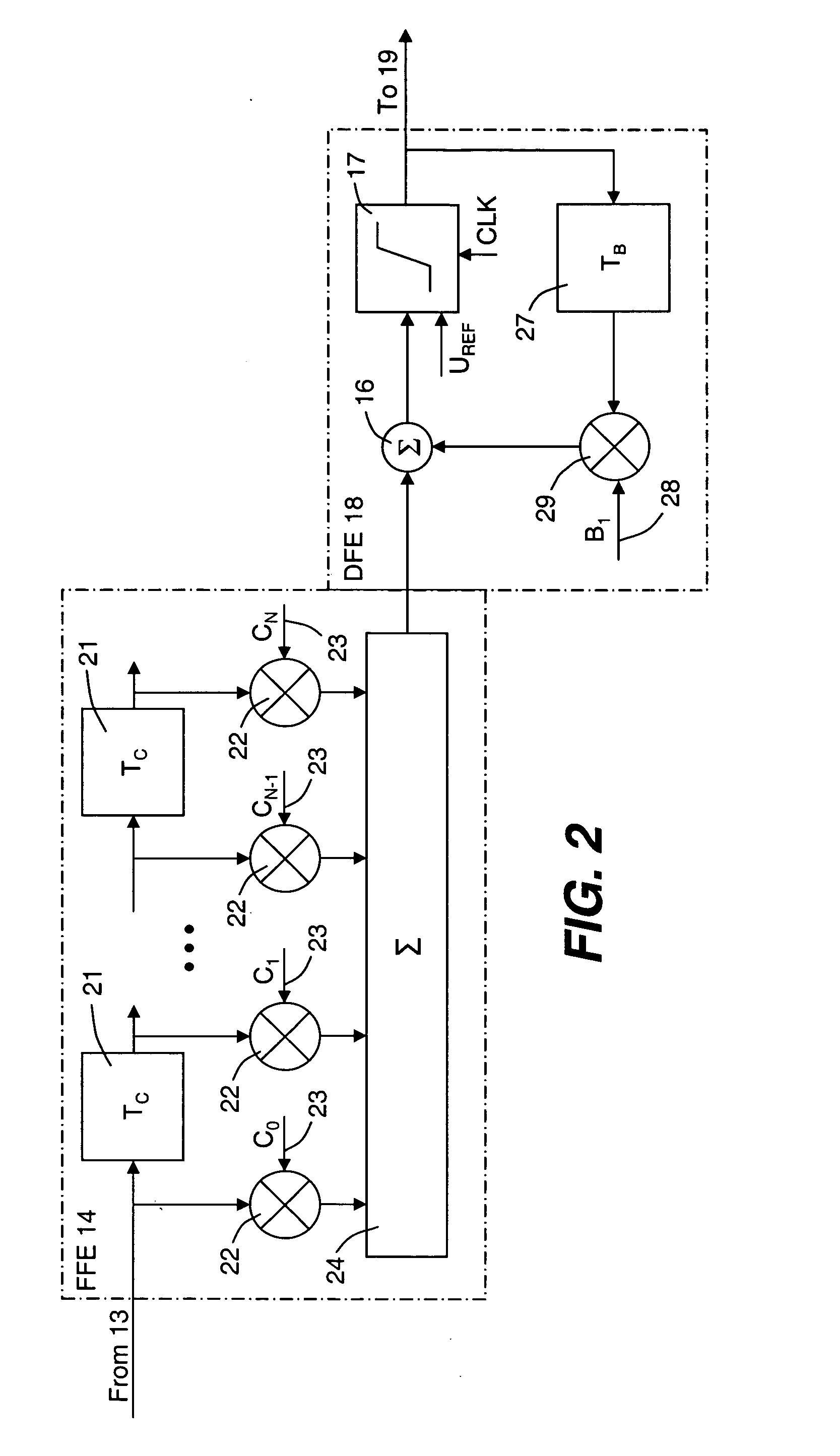

InactiveUS7116504B1Reducing baseline wanderReducing dc offsetPulse automatic controlDc level restoring means or bias distort correctionAdaptive filterAnalog signal

An apparatus, method, and system for providing dc offset reduction in a communications channel include two or more feedback loops to generate dc offset correction signals, which in turn are combined with an input analog signal and a processed digital signal thereby reducing dc offset. Each feedback loop may include an adaptive filter. At least one feedback loop may be responsive to an error signal that represents the difference between the delayed input of a first detector, and its output. Further, the dc offset correction signal, partially delayed, may be added to the error signal, thereby improving the response time of the dc offset correction loop.

Owner:MARVELL INT LTD

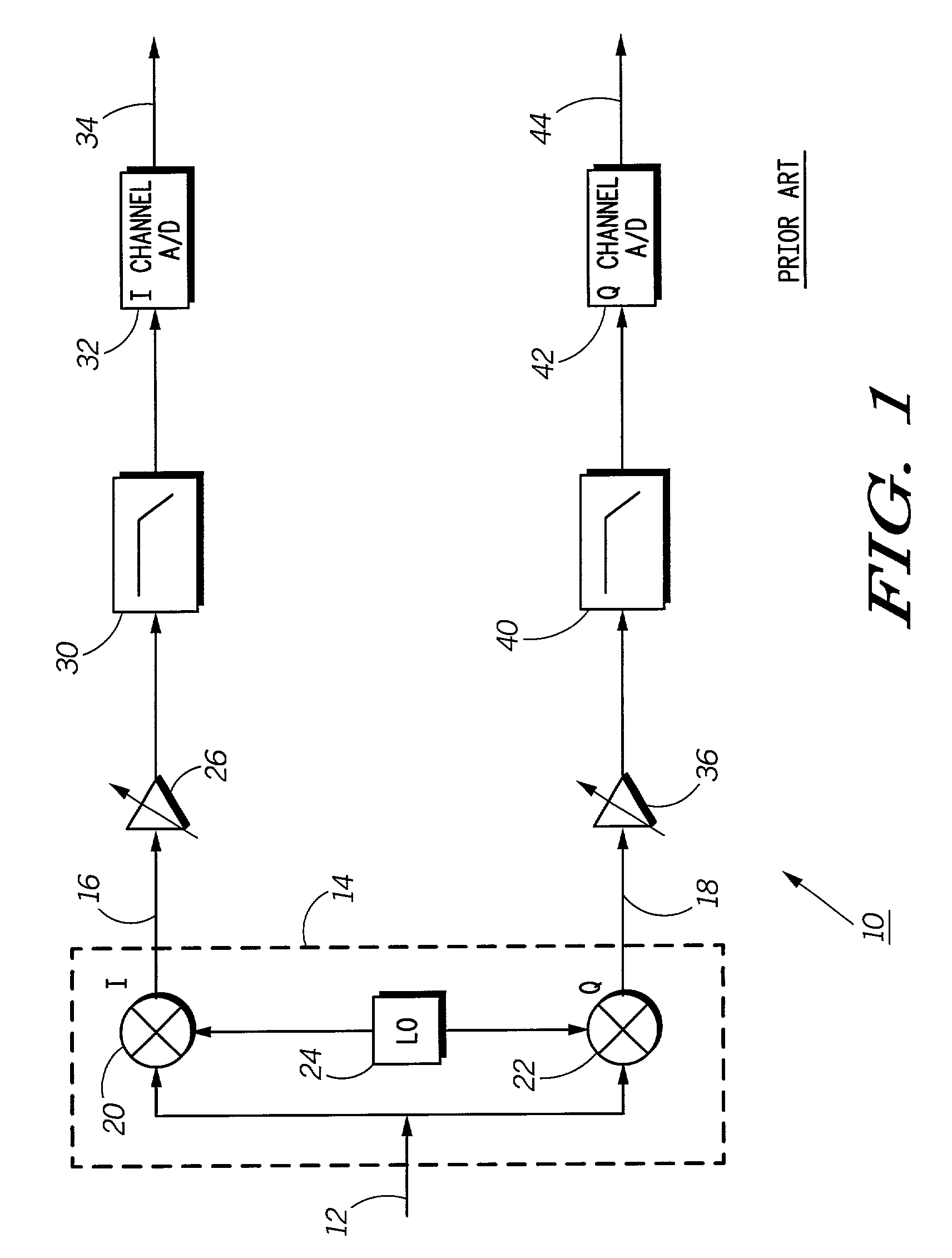

Compensation of i-q imbalance in digital transceivers

A transceiver includes a switching unit configurable for isolating an input of a receiver from an output of a transmitter during a local calibration mode. A known signal present at the output at a first power level during the calibration mode will also be present at the input at a second power level lower than the first power level and will be converted by the quadrature demodulator. A compensation factor is estimated for compensating the receiver section for imbalances in the in-phase and quadrature phase signals resulting from conversion of the known signal. Remote calibration is implemented using a method for remotely compensating for I-Q imbalance wherein a data packet having a known signal is transmitted to a receiver for conversion by a quadrature demodulator and compensation factors are estimated for compensating for imbalances in the in-phase and quadrature phase signals resulting from conversion of the known signal.

Owner:MICROCHIP TECH INC

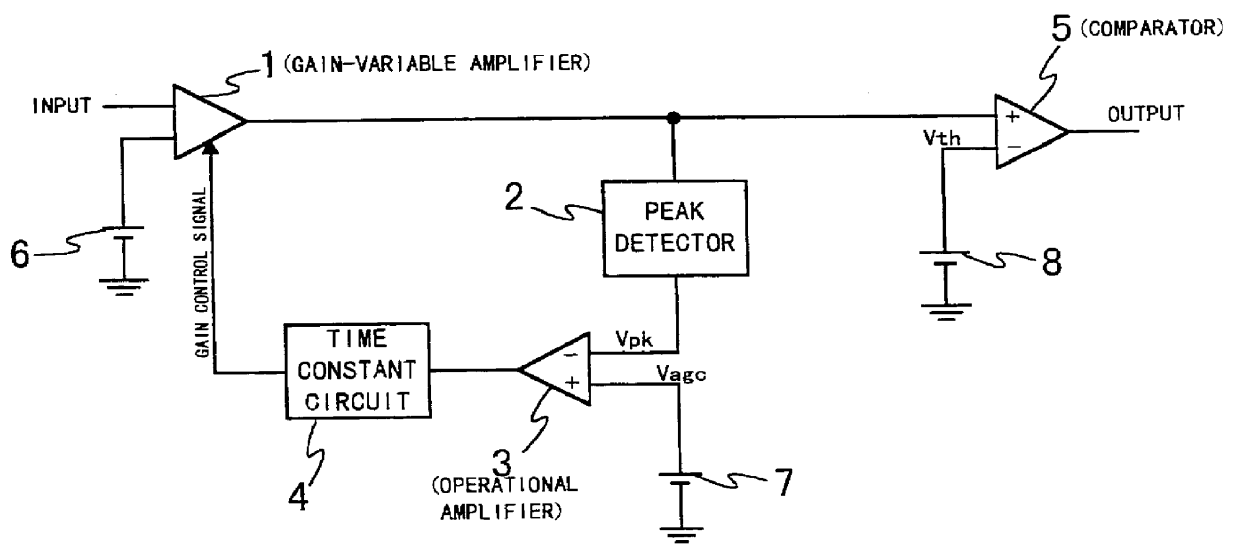

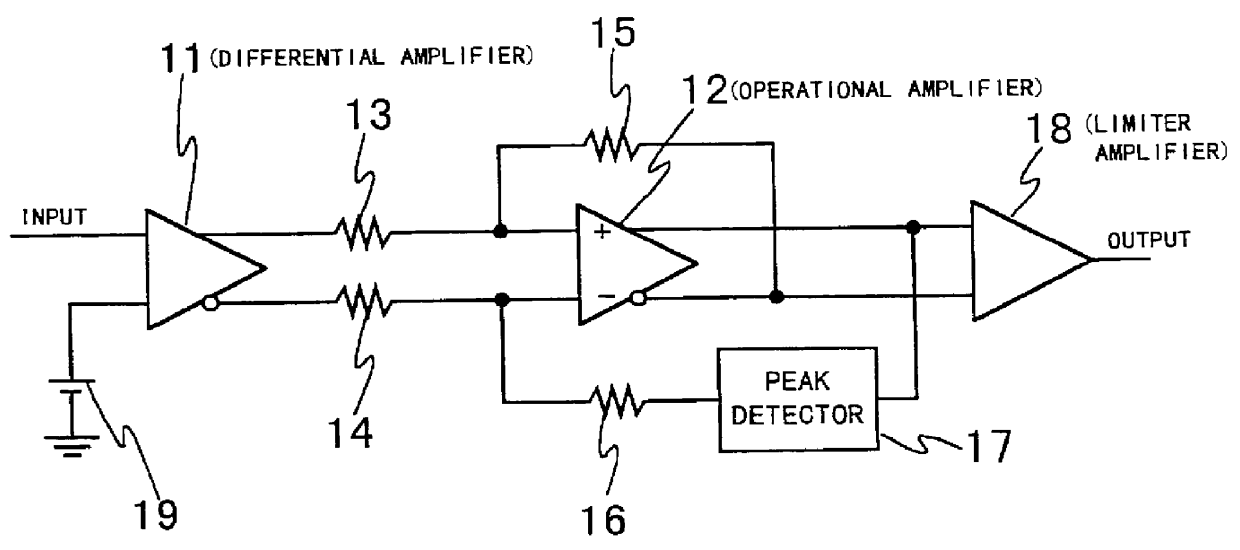

Method and apparatus for level decision and optical receiver using same

InactiveUS6151150ASimple designStart fastLaser detailsDc level restoring means or bias distort correctionPeak valueEngineering

In a method for deciding the level of an input signal, positive and negative signals are provided in response to the input signal. A peak of the positive signal is detected to provide a positive-peak value. A peak of the negative signal is detected to provide a negative-peak value. The positive signal and the negative-peak value are combined to provide a first combination signal. The negative signal and the positive-peak value are combined to provide a second combination signal. The first and second combination signals are compared to provide an output signal of zero or one.

Owner:LAPIS SEMICON CO LTD

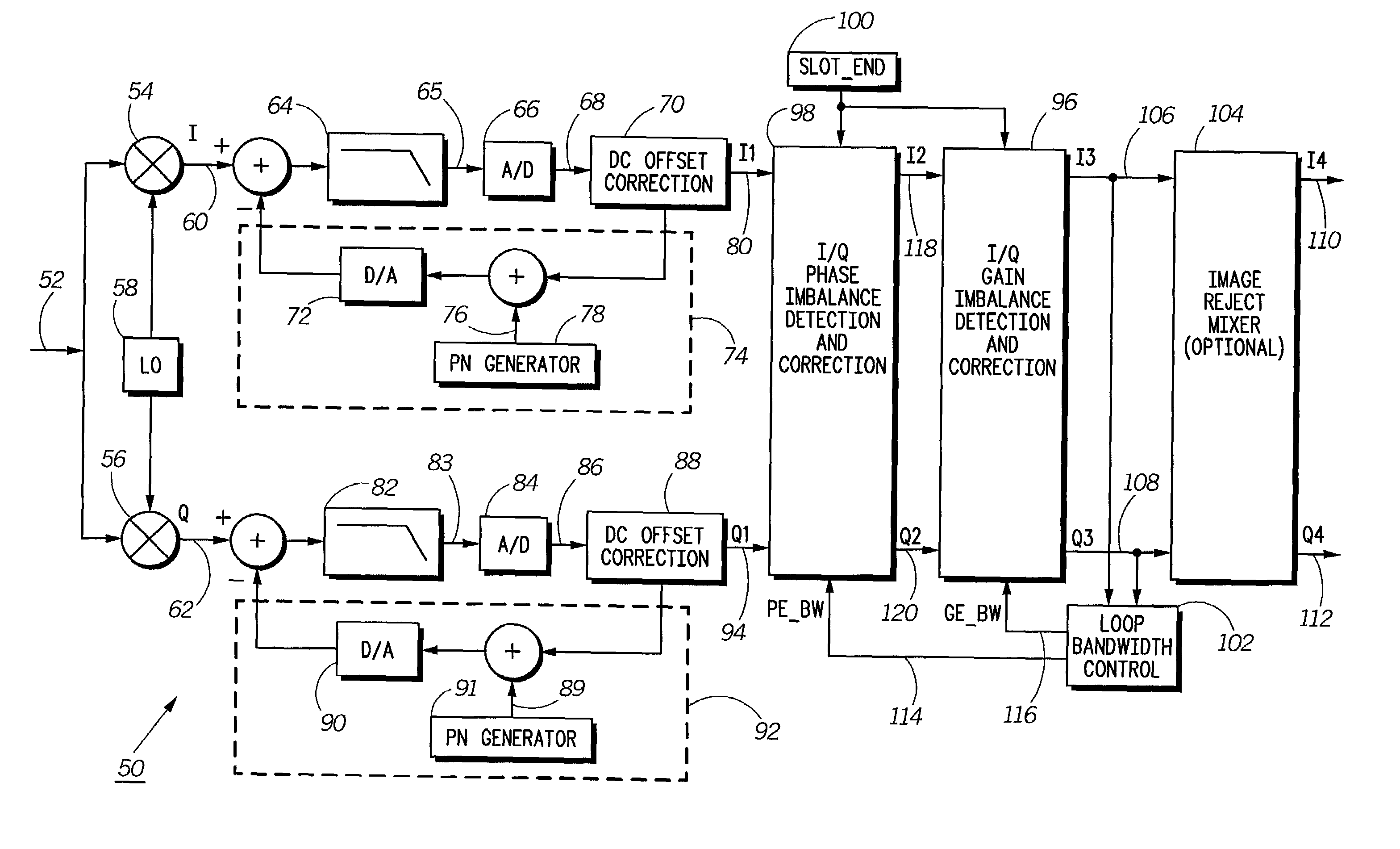

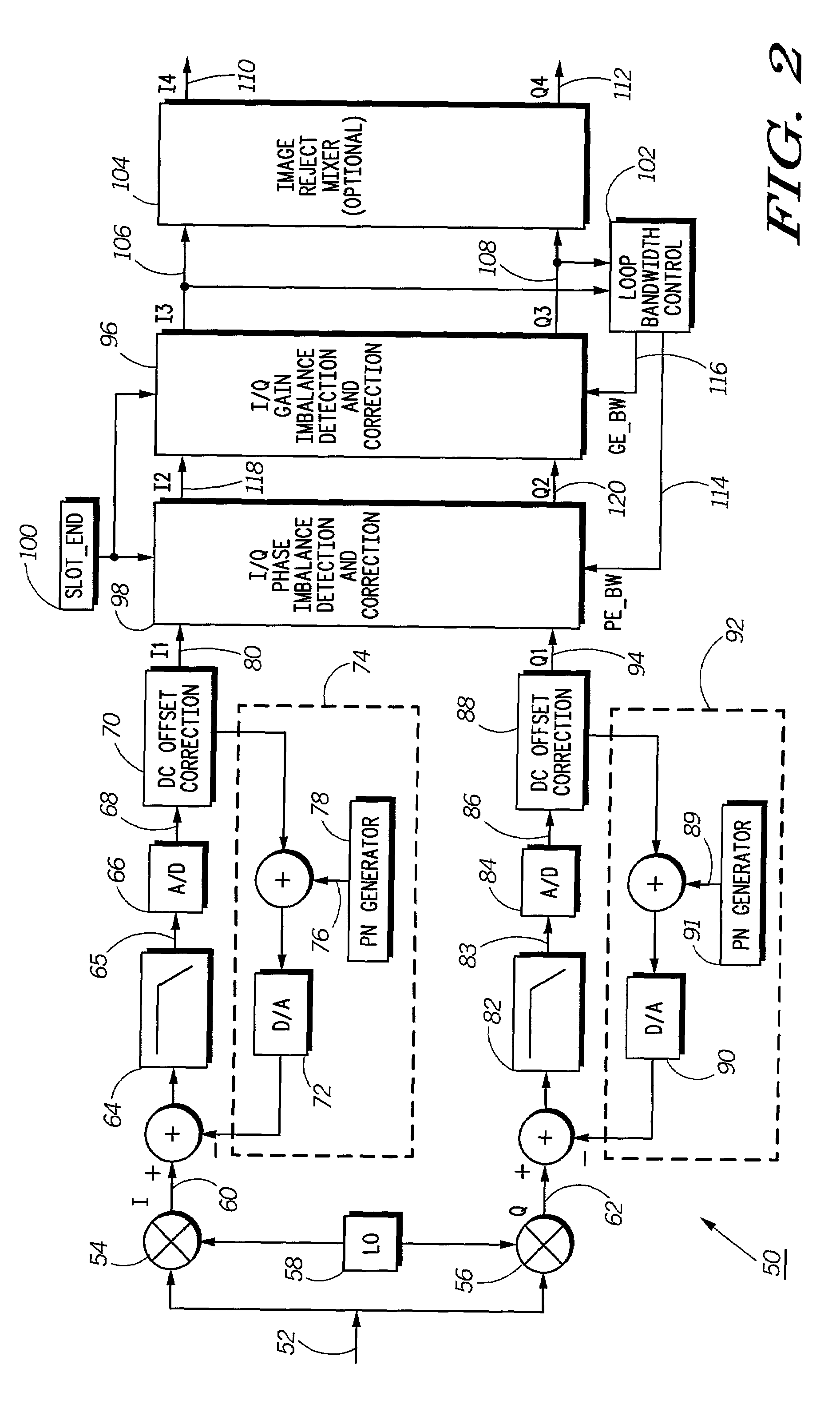

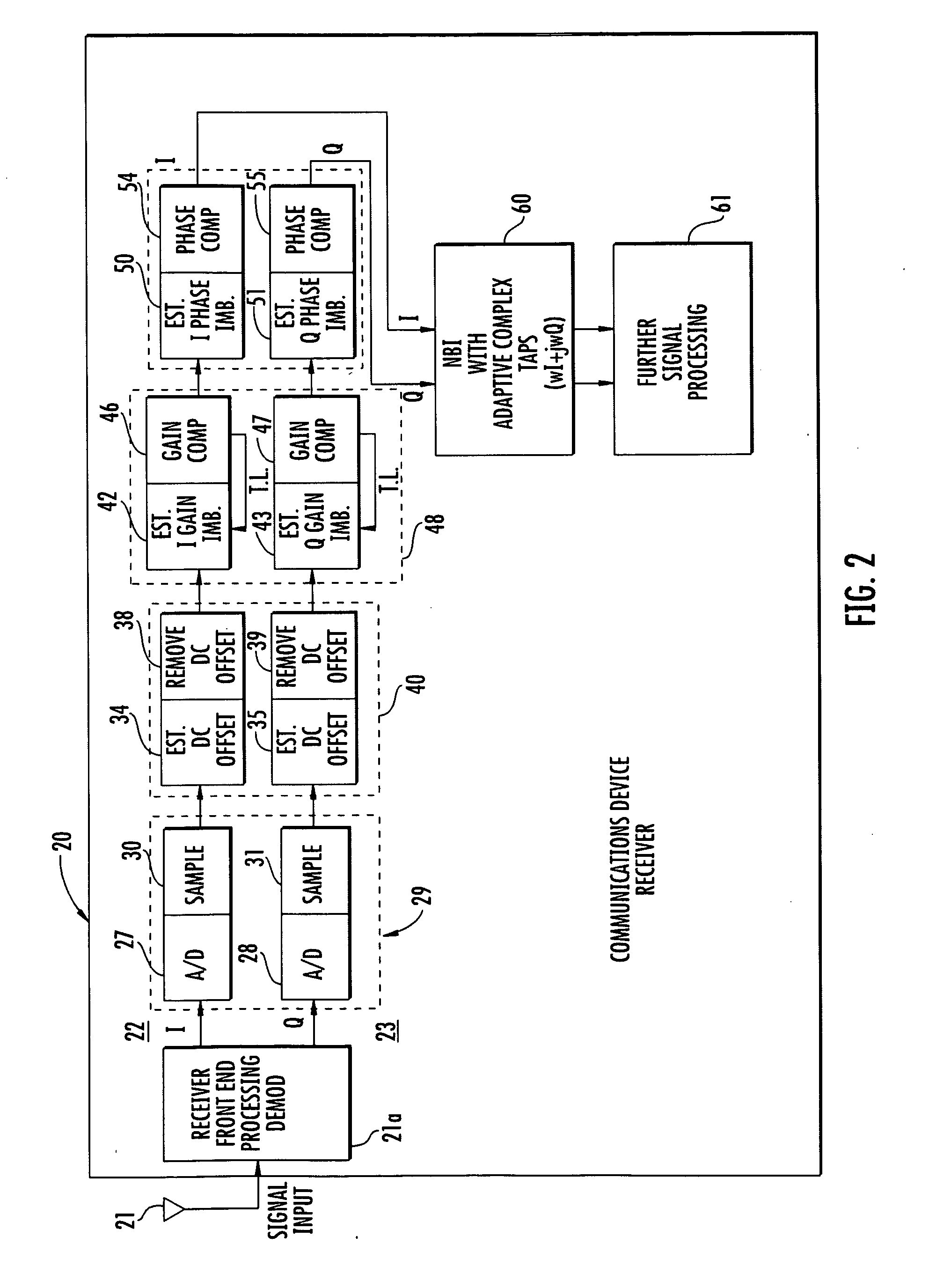

Self calibrating receive path correction system in a receiver

ActiveUS7130359B2Dc level restoring means or bias distort correctionLine balance variation compensationPhase imbalanceRelative phase

A receiver (50) includes a self-calibrating receive path correction system for correction of I / Q gain and phase imbalances in a radio frequency signal. The system includes a signal-processing block (53), an I / Q phase imbalance detection and correction circuit (98), an I / Q gain imbalance detection and correction circuit (96), and an adaptive loop bandwidth control circuit (102). The I / Q phase imbalance detection and correction circuit (98) equalizes for the relative phase imbalance and the I / Q gain imbalance detection and correction circuit (96) equalizes for the relative gain imbalance between the I and Q channels created by the analog portion of a quadrature receiver. The adaptive loop bandwidth control circuit (102) dynamically adjusts at least one loop bandwidth for the I / Q gain imbalance detection and correction circuit (96) and the I / Q phase imbalance detection and correction circuit (98) on a slot boundary.

Owner:GOOGLE TECH HLDG LLC

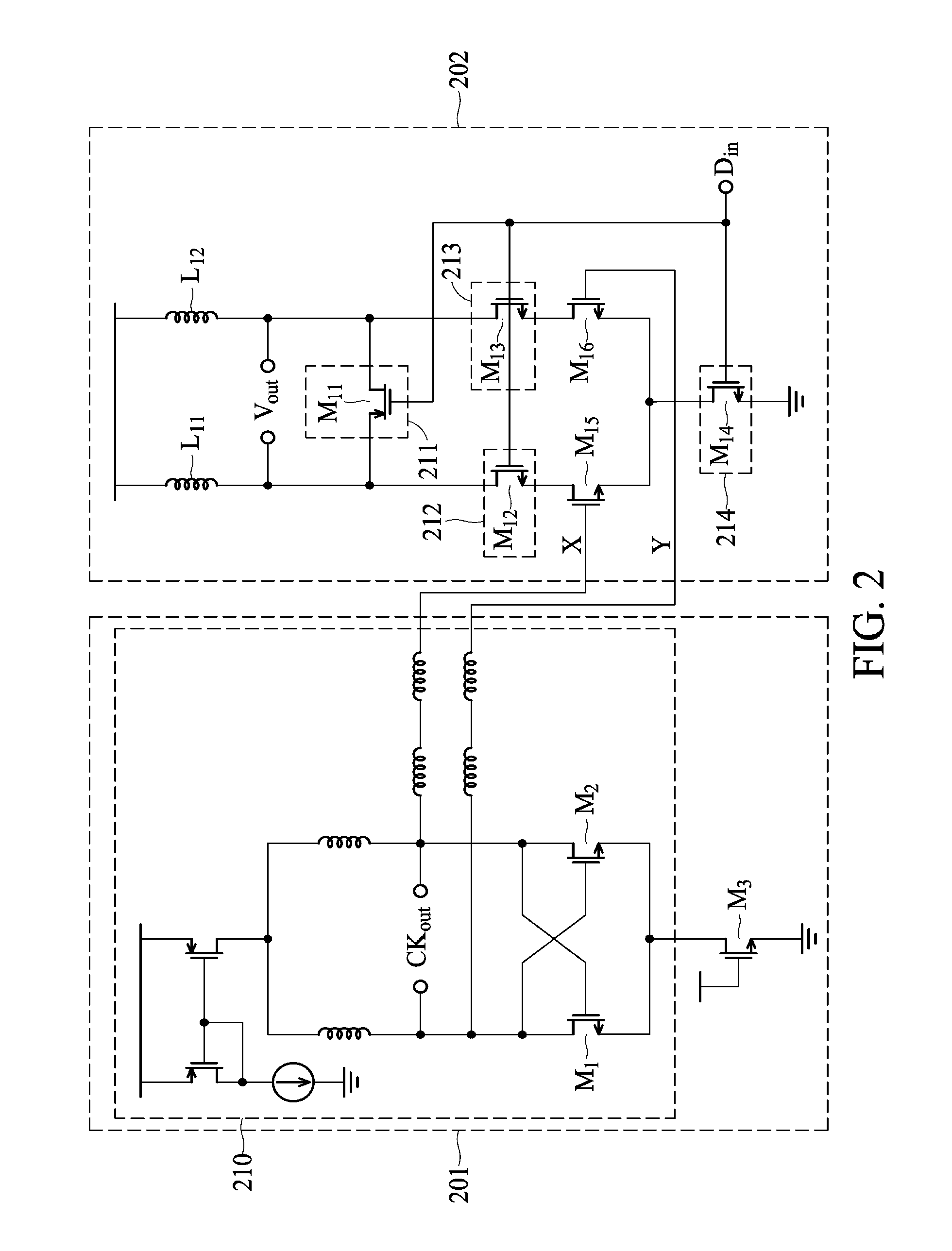

Wireless radio frequency signal transceiving system

ActiveUS20100202499A1Modulation transferenceDc level restoring means or bias distort correctionAudio power amplifierRadio frequency signal

A differential radio frequency signal transmitter is provided. The differential radio frequency signal transmitter includes an oscillator, a modulator and an amplifier module. The oscillator generates a pair of differential oscillation signals. The modulator generates a pair of differential modulated signals according to an input signal and the pair of differential oscillation signals. The input signal is a digital signal. When the input signal is at a first state, the modulator outputs the pair of differential oscillation signals as the pair of differential modulated signals, and when the input signal is at a second state, the modulator outputs a constant voltage signal as the pair of differential modulated signals. The amplifier module receives and amplifies the pair of differential modulated signals and generates a pair of differential radio frequency signals, accordingly.

Owner:NAT TAIWAN UNIV

Method and system for decoding multilevel signals

ActiveUS7215721B2Efficient processingMinimizes average error probabilityRepeater/relay circuitsDc level restoring means or bias distort correctionNormal densityAutomatic control

A multilevel optical receiver can comprise a plurality of comparators that generally correspond with the number of levels in a multilevel data stream. Each comparator can be individually controlled and fed a decision threshold in order to decode a multilevel signal. The multilevel optical receiver can generate a statistical characterization of the received symbols in the form of a marginal cumulative distribution function (CDF) or probability density function (pdf). This characterization can be used to produce a set of ε-support estimates from which conditional pdfs are derived for each of the transmission symbols. These conditional pdfs may then be used to determine decision thresholds for decoding the received signal. The conditional pdfs may further be used to continuously estimate the fidelity or error rate of the received signal without the transmission of a testing sequence. The ε-supports may further be used to automatically control the gain on the receiver.

Owner:INTERSIL INC

Staggered AGC with digitally controlled VGA

ActiveUS20050058228A1Reduce gain requirementsSimple designDc level restoring means or bias distort correctionLine balance variation compensationVariable-gain amplifierA d converter

The invention relates to the field of wireless communications, more particularly to a method of and device for automatic gain control (AGC) incorporating digitally controlled variable gain amplifiers (VGAs). The invention provides an AGC circuit comprising an I / Q baseband strip comprising multiple AGC stages wherein each of the AGC stages comprises: respective I and Q VGAs; a detector for detecting respective I and Q output signals received from the respective I and Q VGAs; an analogue to digital converter (ADC) for converting the detected I and Q output signals; and a digital engine for adjusting the respective I and Q VGAs for differences between the detected I and Q output signals and a reference signal. The use of staggered AGCs incorporating respective I and Q VGAs means that the total dynamic range is split between n-stages, thereby allowing for reduced gain requirements in the VGAs. Additionally, the use of digital control for setting the VGA gains means that analogue variations and I / Q gain imbalances are reduced. Additionally, the use of multiple update rates or magnitudes in the VGA control improves the dynamic settling time.

Owner:ZARBANA DIGITAL FUND

Method and apparatus for reducing DC offsets in a communication system

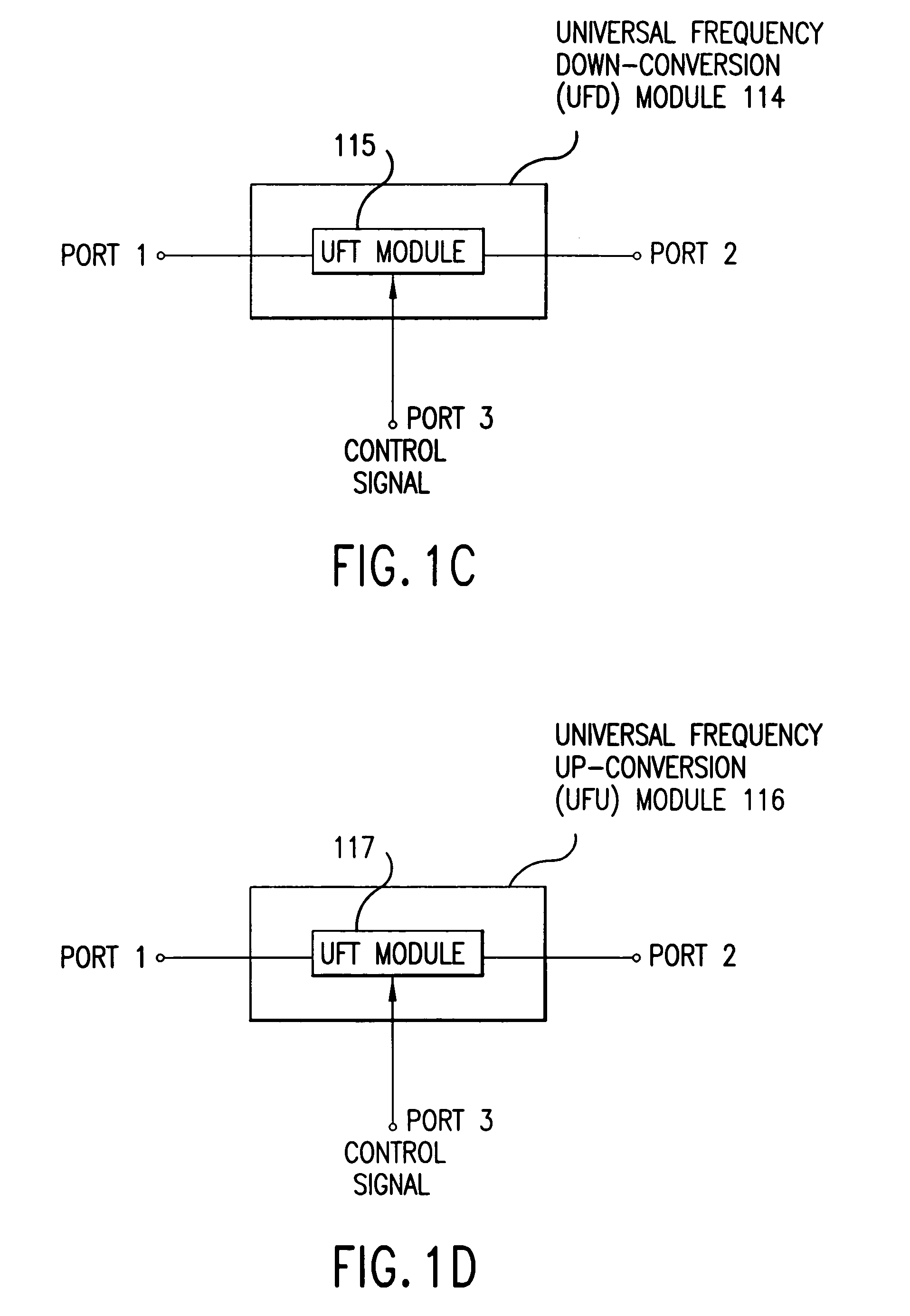

InactiveUS7085335B2Reduce DC offsetError preventionDc level restoring means or bias distort correctionCommunications systemControl signal

Methods and apparatuses for reducing DC offsets in a communication system are described. In a first aspect, a feedback loop circuit reduces DC offset in a wireless local area network (WLAN) receiver channel. The frequency response of the feedback loop circuit can be variable. In a second aspect, a circuit provides gain control in a WLAN receiver channel. First and second automatic gain control (AGC) amplifiers are coupled in respective portions of the receiver channel. Circuits for monitoring DC offset, and for providing control signals for controlling the frequency response of the DC offset reducing circuits are also provided.

Owner:PARKER VISION INC

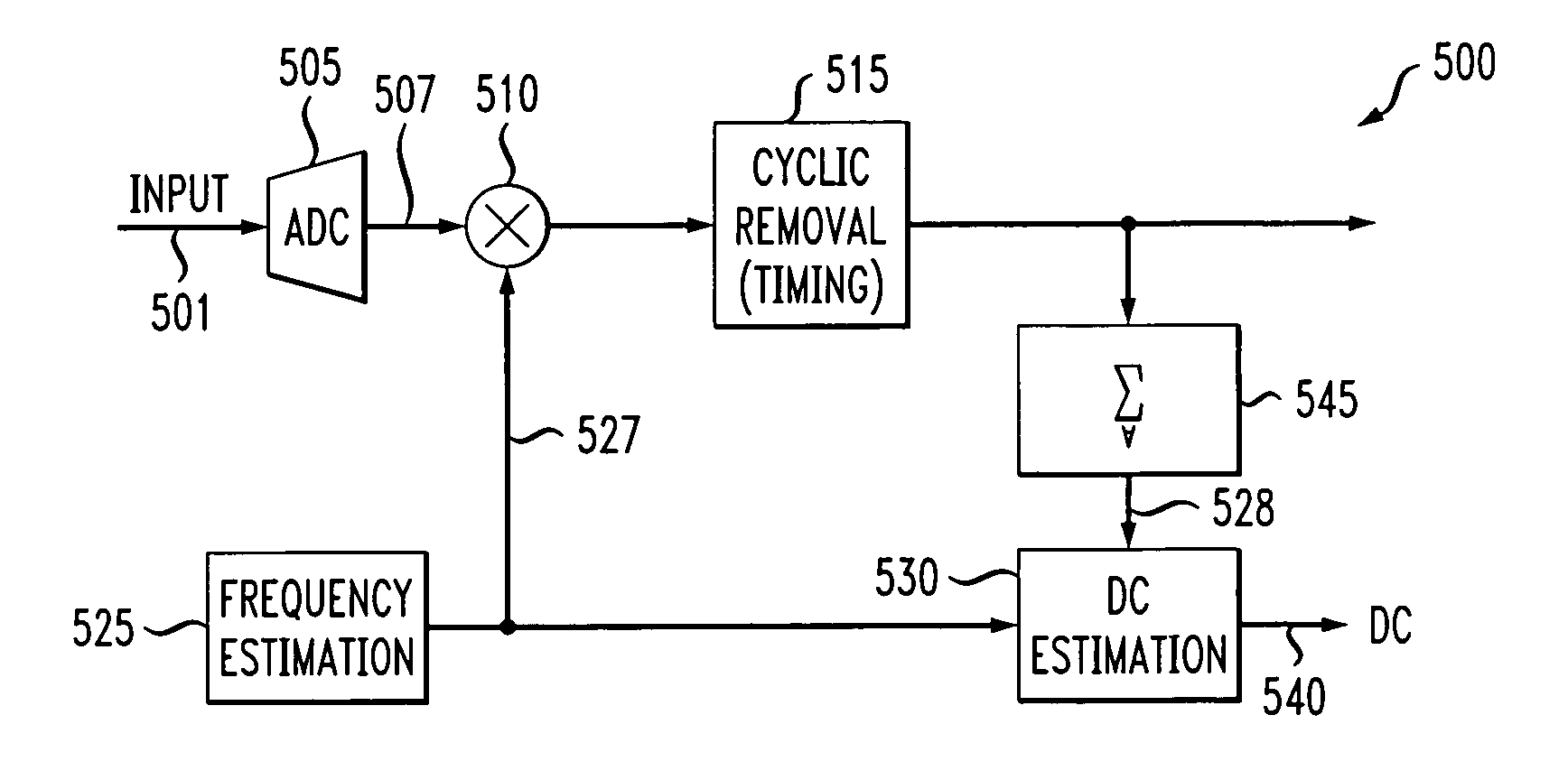

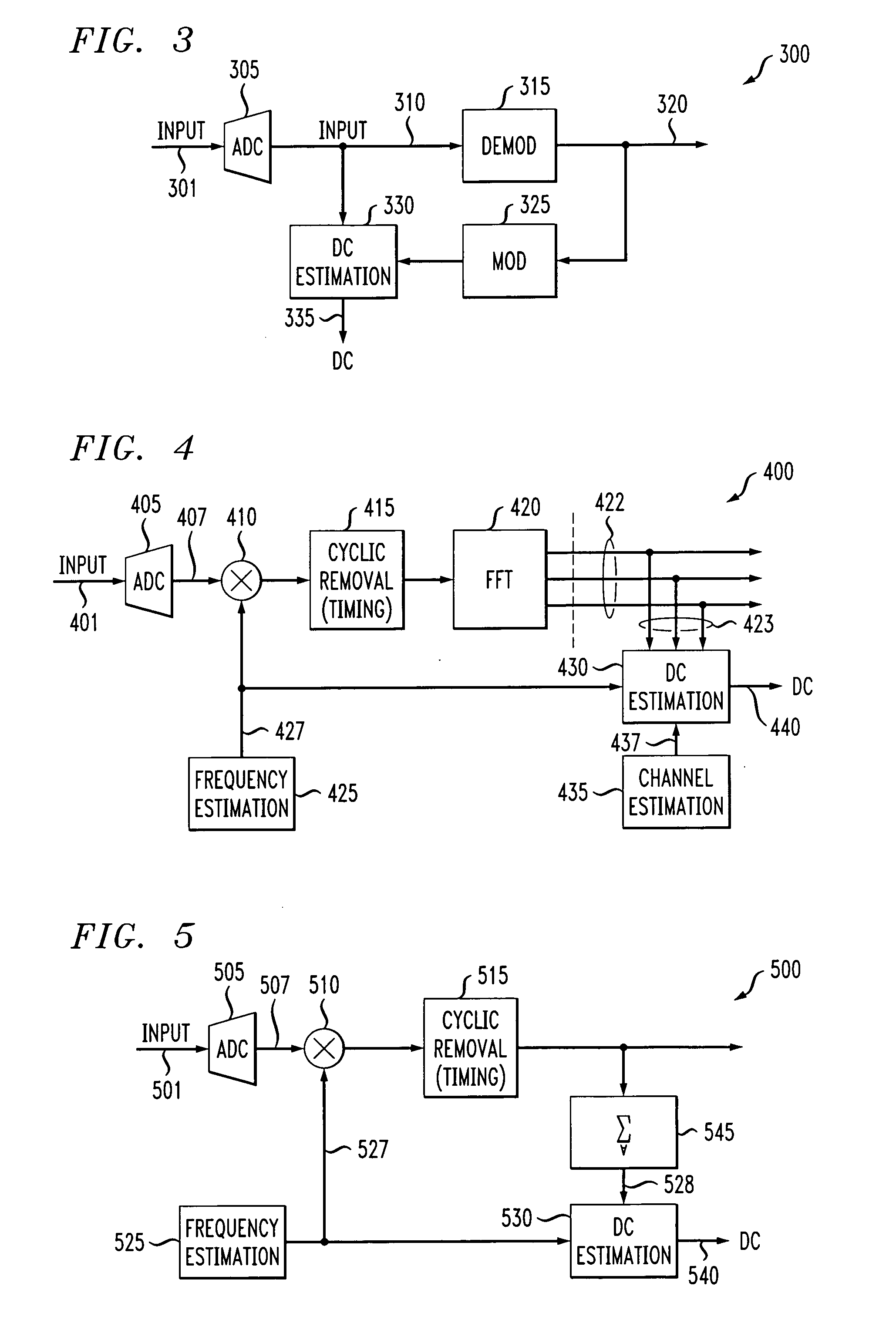

Method and apparatus for estimating DC offset in an orthogonal frequency division multiplexing system

InactiveUS20050111525A1Reduce and eliminate distortionDc level restoring means or bias distort correctionLine balance variation compensationTime domainEngineering

Methods and apparatus are disclosed for DC offset estimation and for DC offset compensation that collectively reduce or eliminate the distortion of subcarriers due to DC offset in an OFDM receiver. The DC offset estimation is obtained by subtracting a sum of time domain samples of an OFDM symbol for two consecutive OFDM symbols or subtracting a known transmitted OFDM symbol and a frequency domain representation of a received version of the known OFDM symbol (at least one of which is adjusted to compensate for channel distortion). The DC offset compensation is accomplished by removing the estimated DC offset from the received signal. The DC estimation process and the DC compensation process can be connected in disclosed feed-forward or feedback configurations.

Owner:AVAGO TECH INT SALES PTE LTD

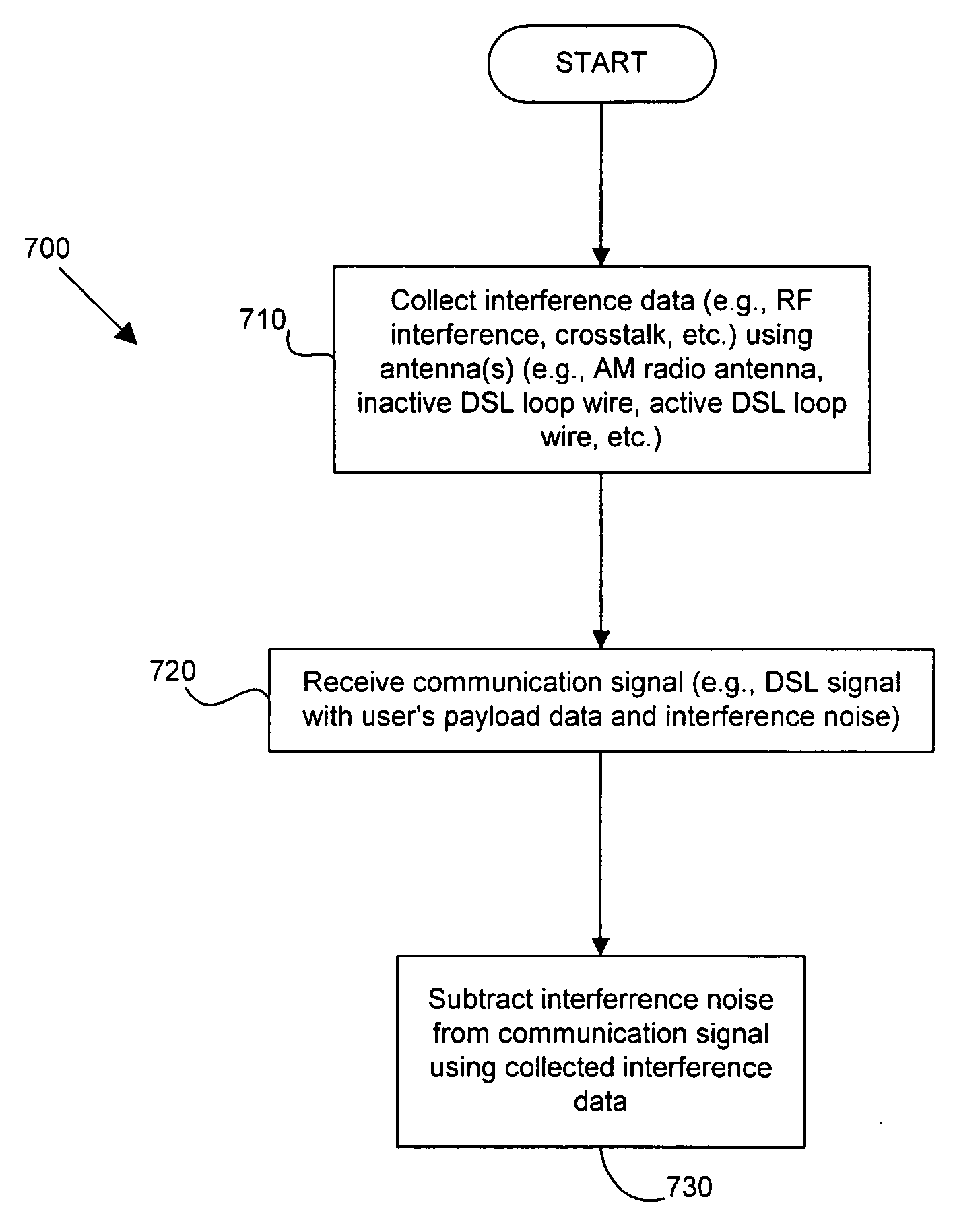

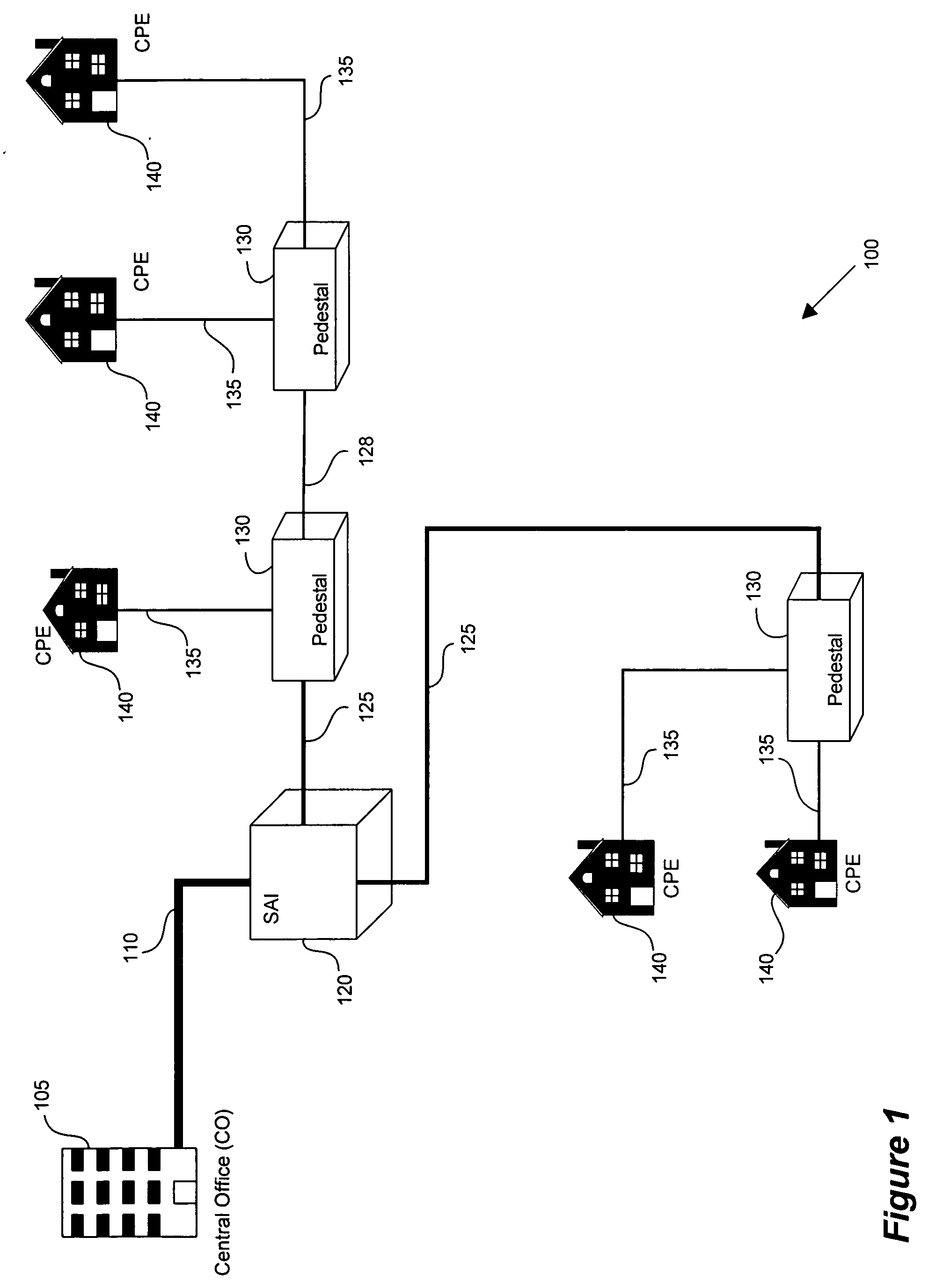

Interference cancellation system

ActiveUS20060039454A1Two-way loud-speaking telephone systemsError preventionInterference cancelationInterference canceller

A DSL or other communication system includes a modem or other communication device having at least one antenna that is configured to collect interference data relating to interference noise affecting communication signals being received by the communication device. The interference may include RF interference, such as AM radio interference, crosstalk and other types of interference from various sources. The interference data collected by the antenna is used by an interference canceller to remove and / or cancel some or all of the interference affecting received signals. In some embodiments of the present invention, more than one antenna may be used, wherein each antenna can collect interference data pertaining to a single source of interference noise. Where a modem or other communication device is coupled to multiple telephone lines, only one of which is being used as the active DSL line, wires in the remaining telephone lines or loops can be used as antennas. Moreover, the antenna may be an antenna, per se, such as a compact AM radio antenna or any other suitable structure or device for collecting the type(s) of interference affecting signals received by the communication device.

Owner:ASSIA SPE LLC CO THE CORP TRUST CO

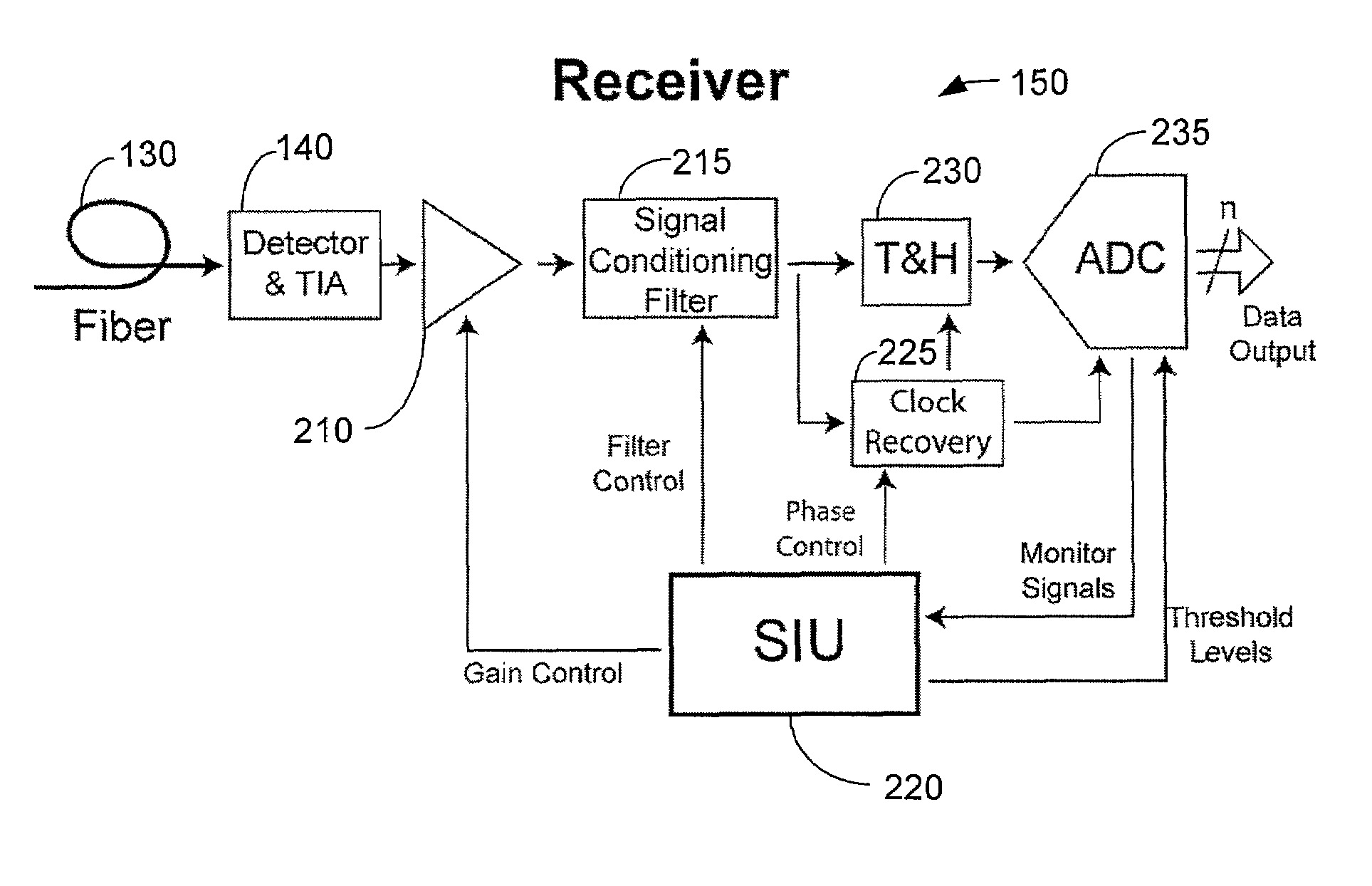

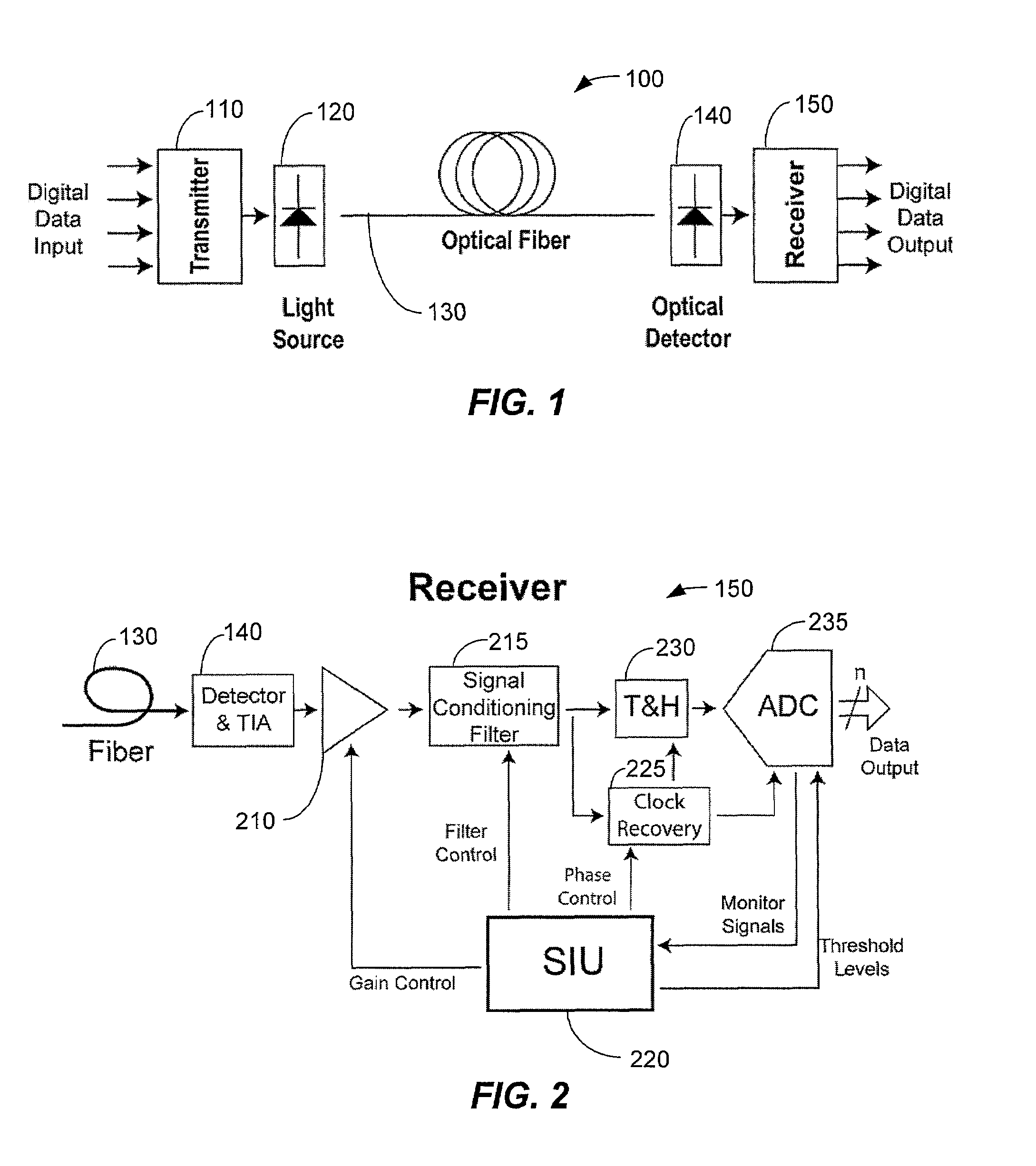

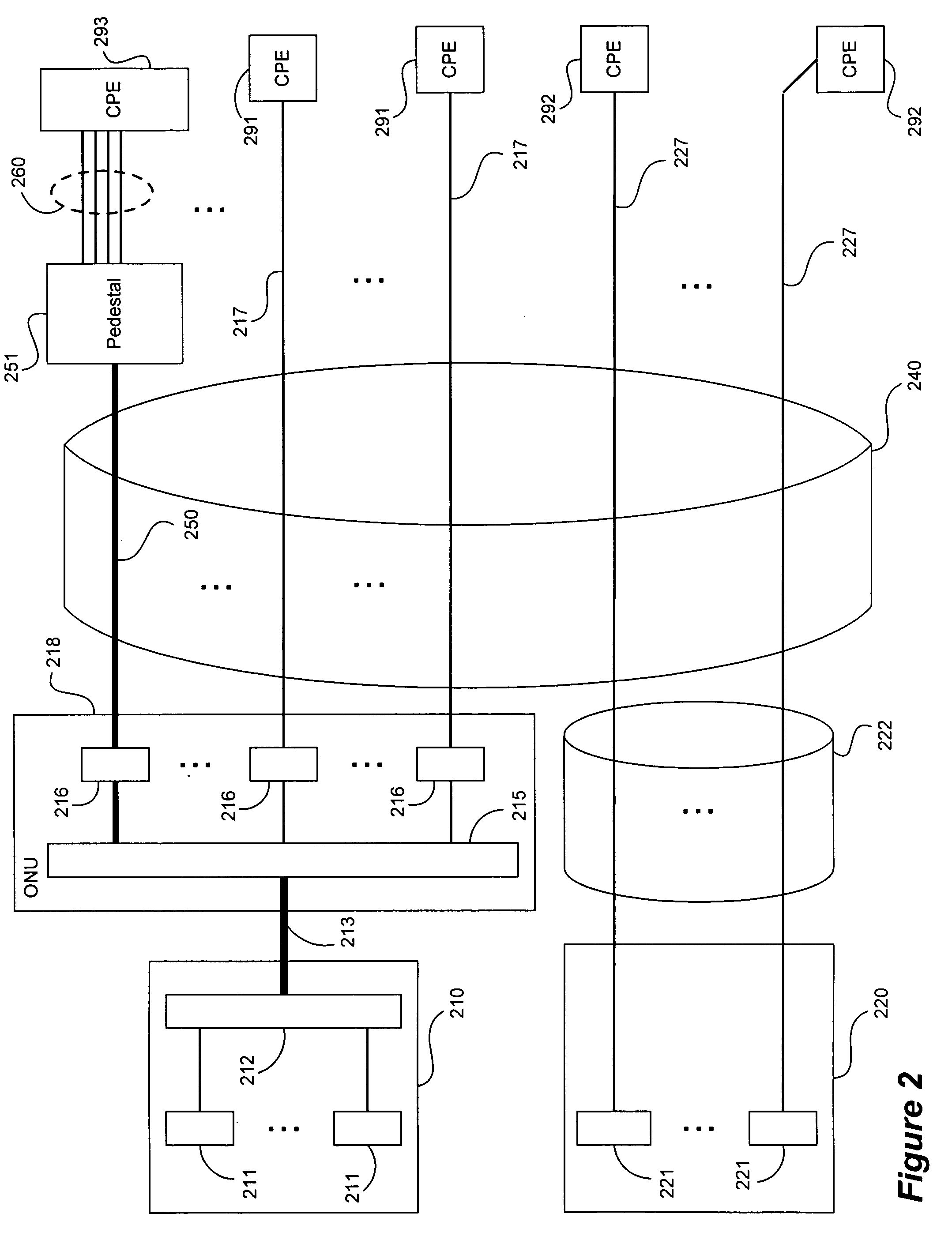

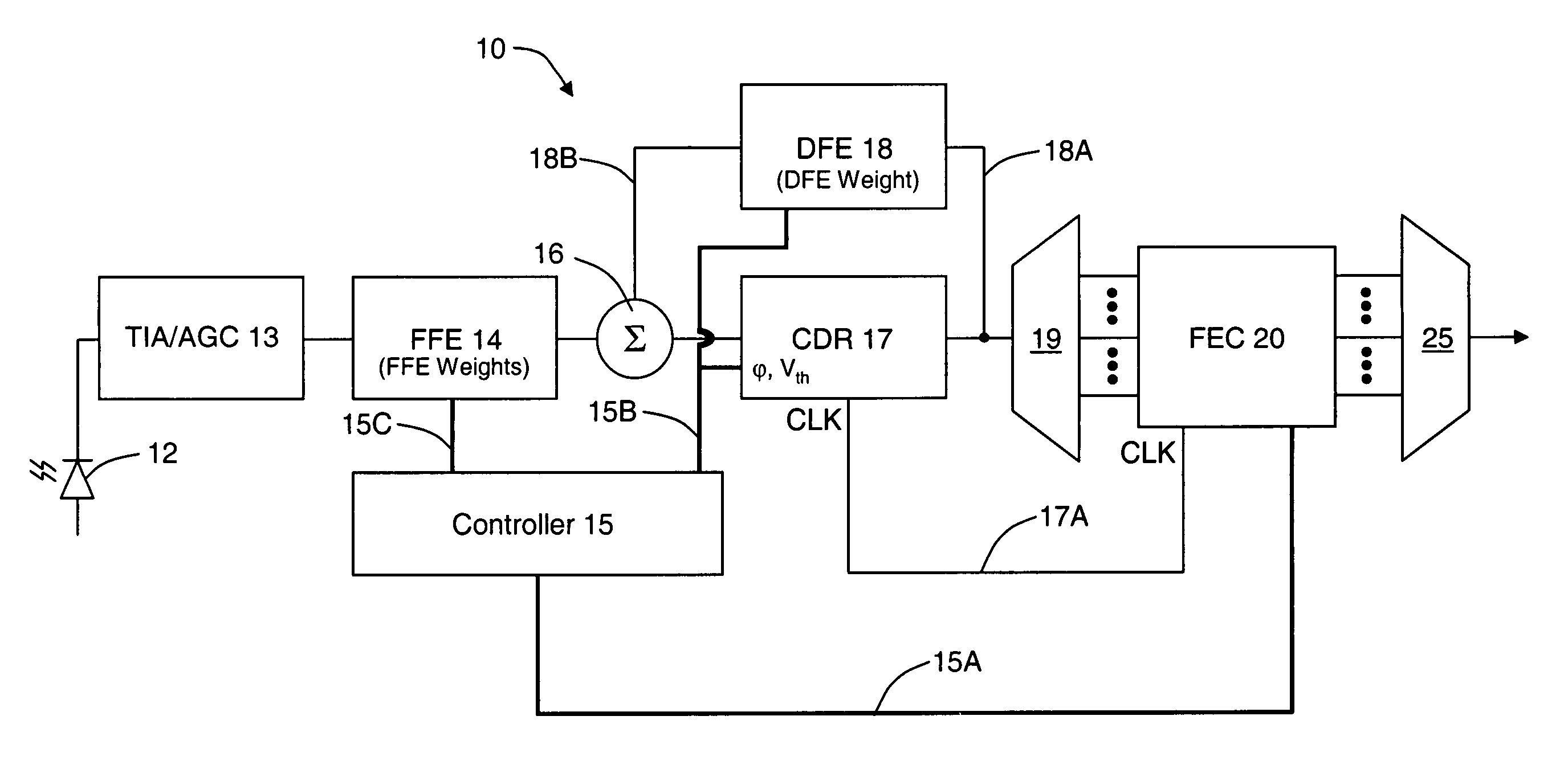

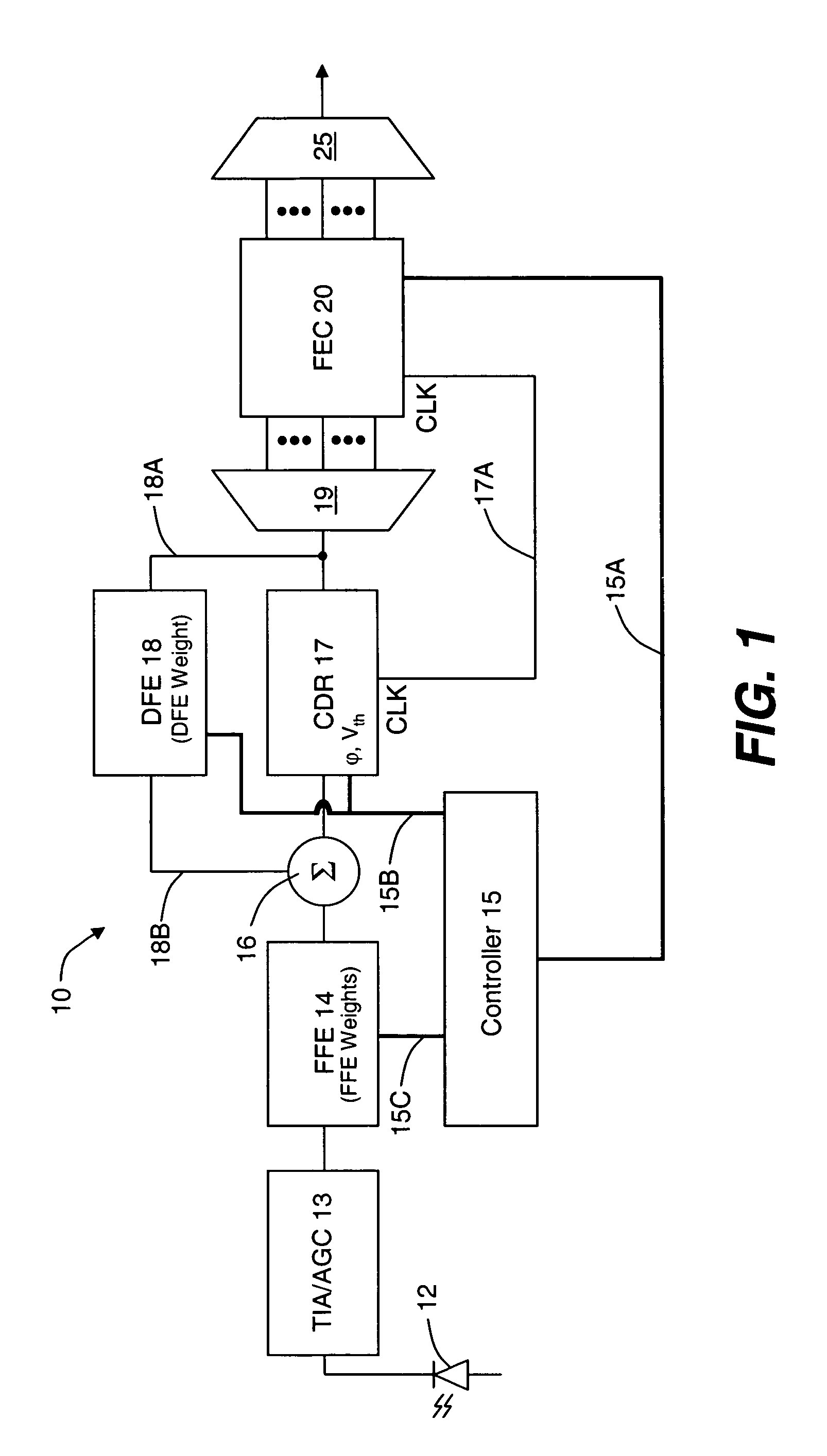

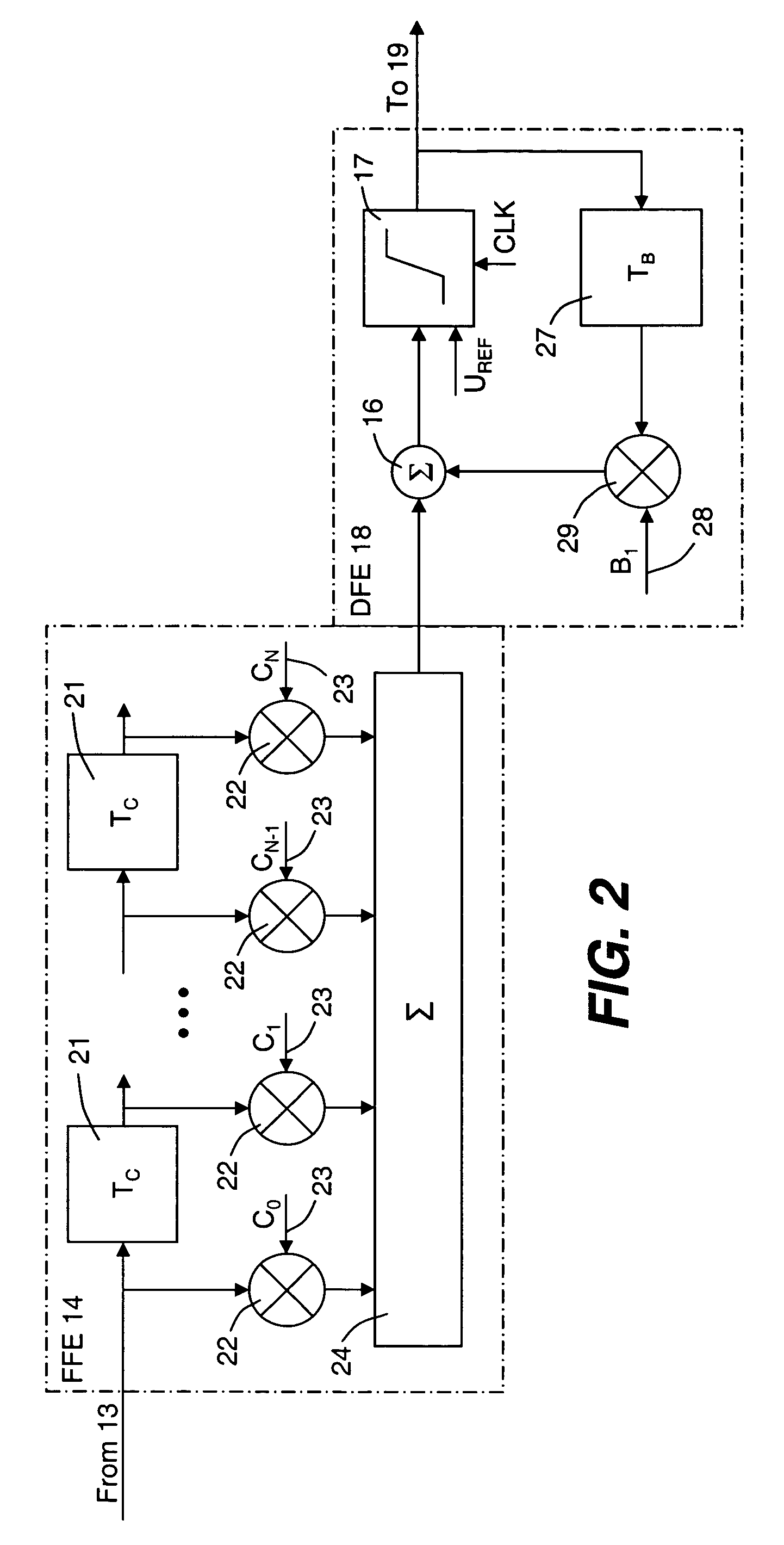

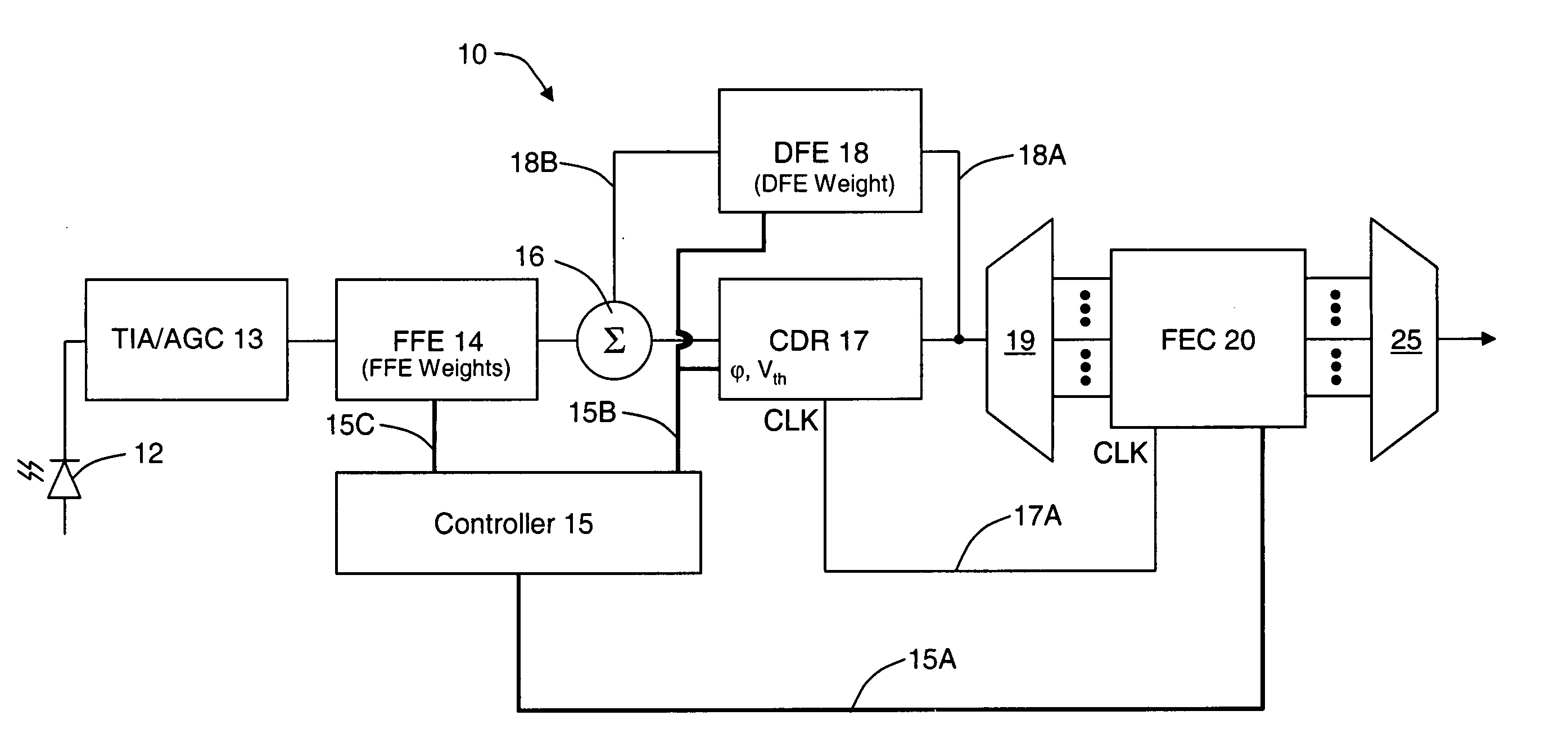

Pattern-dependent error counts for use in correcting operational parameters in an optical receiver

ActiveUS7574146B2Accurate methodReduce manufacturing costMultiple-port networksError detection/prevention using signal quality detectorWeight coefficientSemiconductor chip

An optical transmission network includes an optical transmitter photonic integrated circuit (TxPIC) chip, utilized in an optical transmitter and has a plurality of monolithic modulated sources integrated for multiple signal channels on the same semiconductor chip is provided with channel equalization at the optical receiver side of the network that permits one or more such integrated modulated sources in the TxPIC chip to be out of specification thereby increasing the chip yield and reducing manufacturing costs in the deployment of such TxPIC chips. FEC error counts at the FEC decoder on the optical receiver side of the network includes counters that accumulate a plurality of bit pattern-dependent error counts based on different N-bit patterns in the received data bit stream. The accumulated counts of different N-bit patterns are utilized to provide for corrections to threshold and phase relative to the bit eye pattern as well as provided for weight coefficients for the optical receiver equalization system. The deployment of this type of equalization in a digital OEO REGEN network substantially reduces, if not eliminates, the need for dispersion compensating fiber (DCF) or EDFAs in an optical link of the network and enhances the optical receiver tolerance to chromatic dispersion (CD) so that an increase in chip yield is realized for TxPIC chips not operating with acceptable operational parameters, particularly with a desired frequency chirp parameter relative to at least one of the TxPIC modulated sources.

Owner:INFINERA CORP

Pattern-dependent error counts for use in correcting operational parameters in an optical receiver

ActiveUS20060008279A1Accurate methodReduce manufacturing costMultiple-port networksError detection/prevention using signal quality detectorWeight coefficientSemiconductor chip

An optical transmission network includes an optical transmitter photonic integrated circuit (TxPIC) chip, utilized in an optical transmitter and has a plurality of monolithic modulated sources integrated for multiple signal channels on the same semiconductor chip is provided with channel equalization at the optical receiver side of the network that permits one or more such integrated modulated sources in the TxPIC chip to be out of specification thereby increasing the chip yield and reducing manufacturing costs in the deployment of such TxPIC chips. FEC error counts at the FEC decoder on the optical receiver side of the network includes counters that accumulate a plurality of bit pattern-dependent error counts based on different N-bit patterns in the received data bit stream. The accumulated counts of different N-bit patterns are utilized to provide for corrections to threshold and phase relative to the bit eye pattern as well as provided for weight coefficients for the optical receiver equalization system. The deployment of this type of equalization in a digital OEO REGEN network substantially reduces, if not eliminates, the need for dispersion compensating fiber (DCF) or EDFAs in an optical link of the network and enhances the optical receiver tolerance to chromatic dispersion (CD) so that an increase in chip yield is realized for TxPIC chips not operating with acceptable operational parameters, particularly with a desired frequency chirp parameter relative to at least one of the TxPIC modulated sources.

Owner:INFINERA CORP

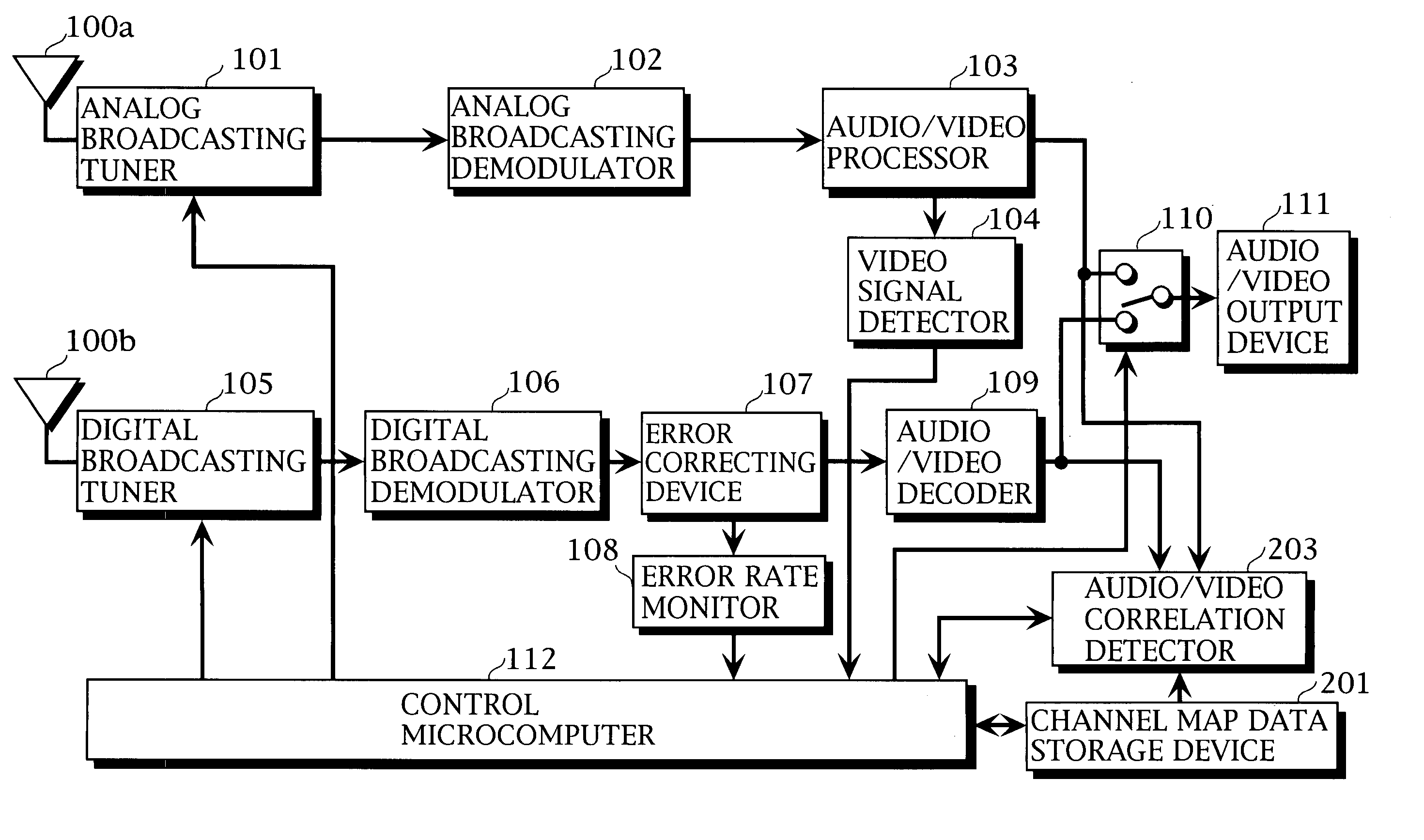

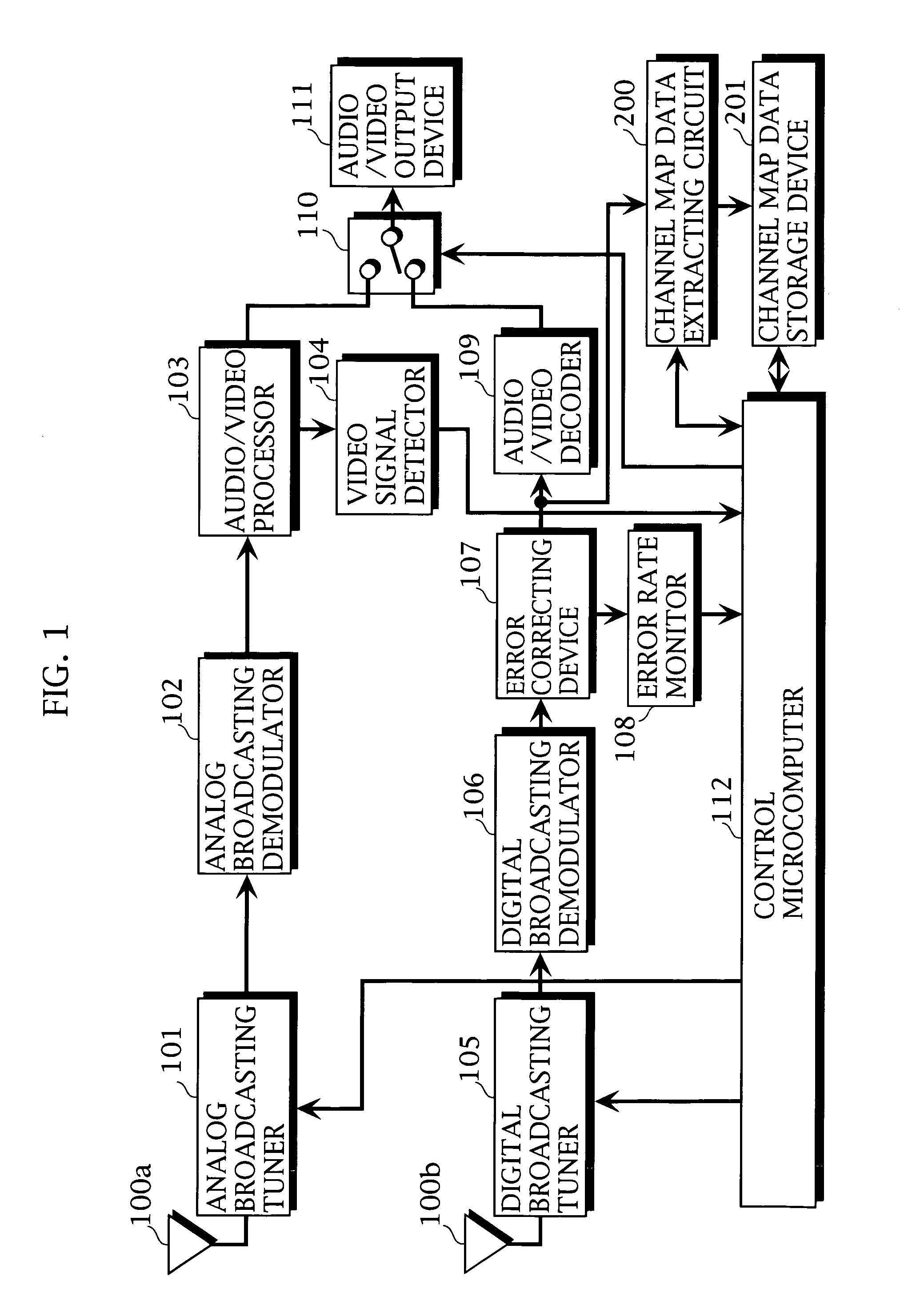

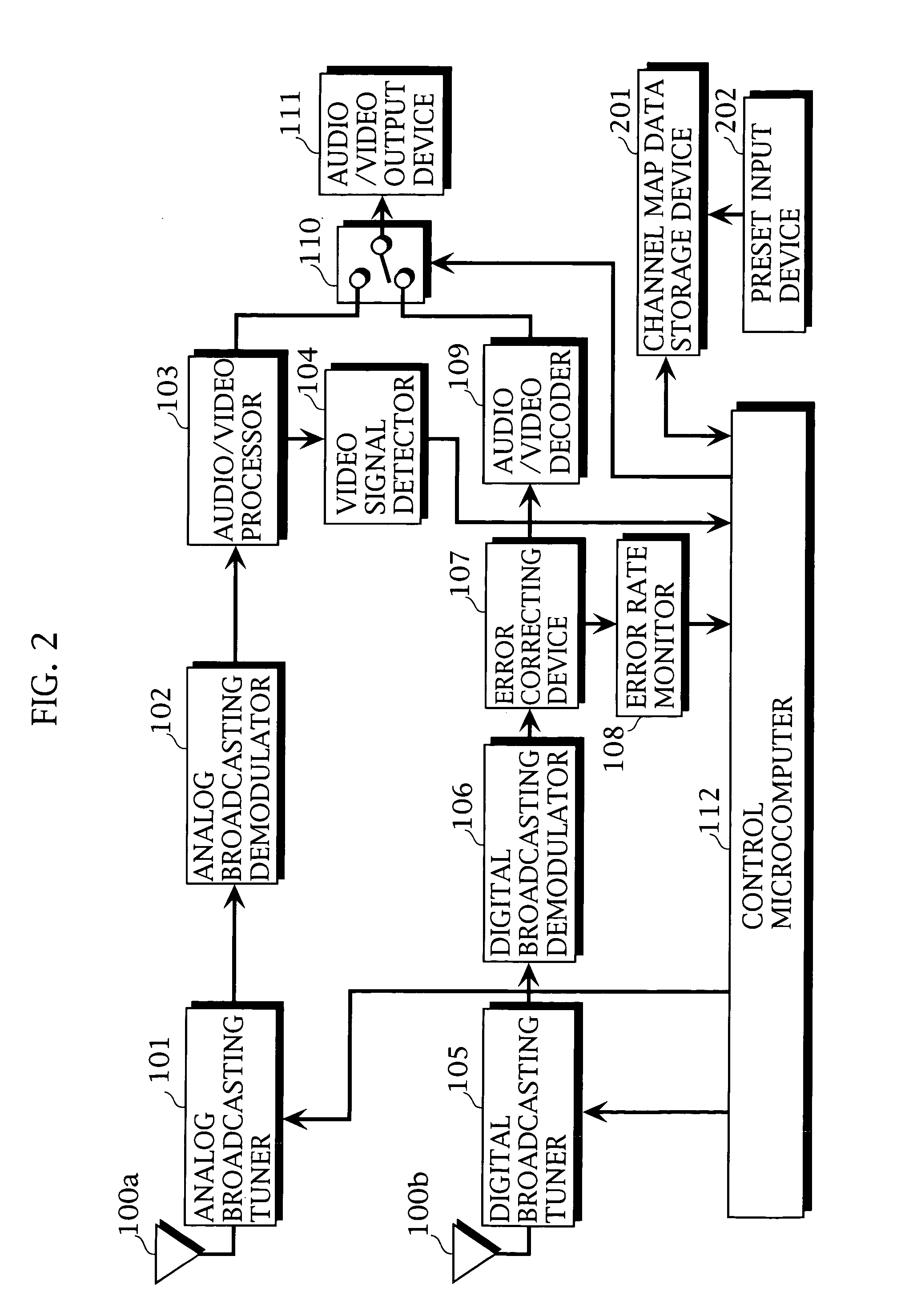

Television receiving method and television receiver

InactiveUS7061542B1Easy to receiveTelevision system detailsColor signal processing circuitsTelevision receiversDigital Video Broadcasting

A receiving section for digital television broadcasting and a receiving section for analog television broadcasting are provided. When a digital television broadcasting program is selected, it is judged whether or not an analog television broadcasting program having the same contents as those of the selected digital television broadcasting program is being broadcast. In a case where the analog television broadcasting program having the same contents as those of the selected digital television broadcasting program is being broadcast, when the digital television broadcasting program cannot be received, the analog television broadcasting program having the same contents as those of the selected digital television broadcasting program is received and outputted.

Owner:SANYO ELECTRIC CO LTD

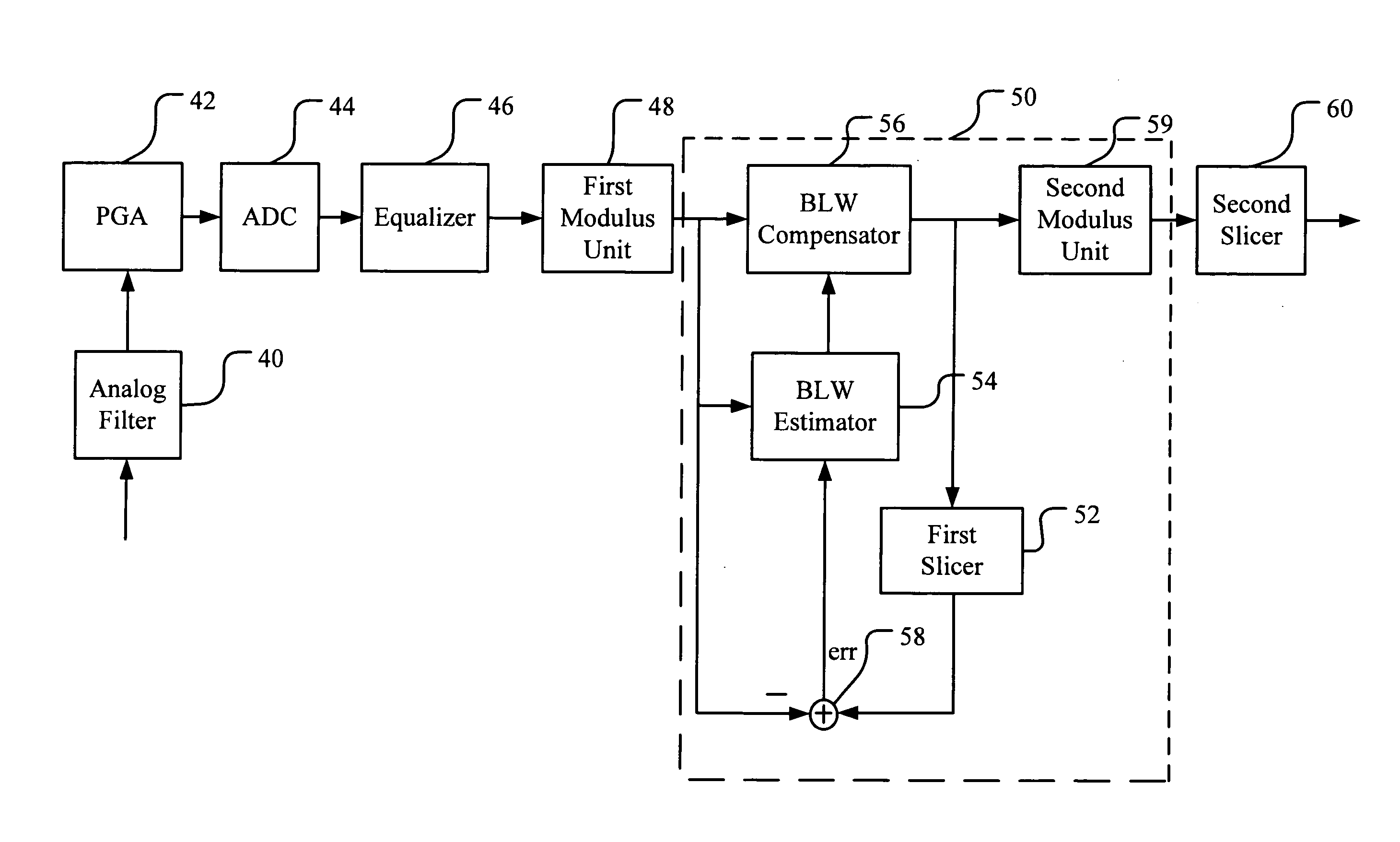

Method and apparatus for baseline wander compensation in Ethernet application

ActiveUS20080212715A1Reduce impactInaccurate estimationError preventionDc level restoring means or bias distort correctionCommunications systemError mitigation

An embodiment of the proposed invention is primarily applied to compensate the BLW in communication systems using THPs in their transmitters, especially suitable for the 10GBase-T Ethernet application. The present apparatus includes an additional decision device (slicer) used to generate DC offset information (error signal) and an extra modulus unit after our BLW compensator to reconvert compensated symbols to correct 16-PAM signals. In addition, the estimated error signals in our method are generated from the difference between the input of the BLW compensator and the output of the decision device. These error signals are then weighted to alleviate the impact of erroneous DC offset information on the performance of the BLW compensator. Therefore, a more direct and accurate DC offset information can be derived to improve the inaccurate BLW estimation in previous works.

Owner:REALTEK SEMICON CORP

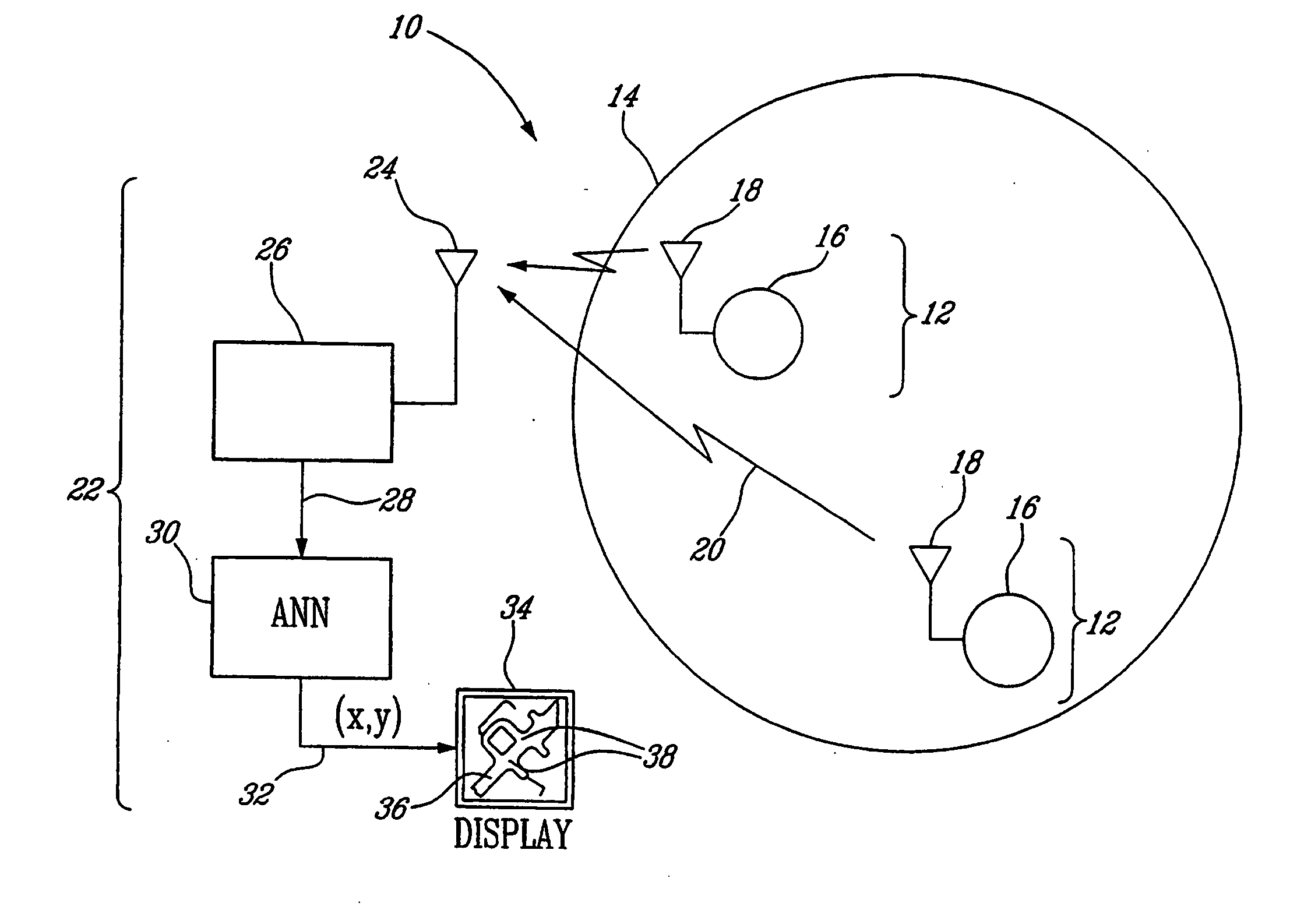

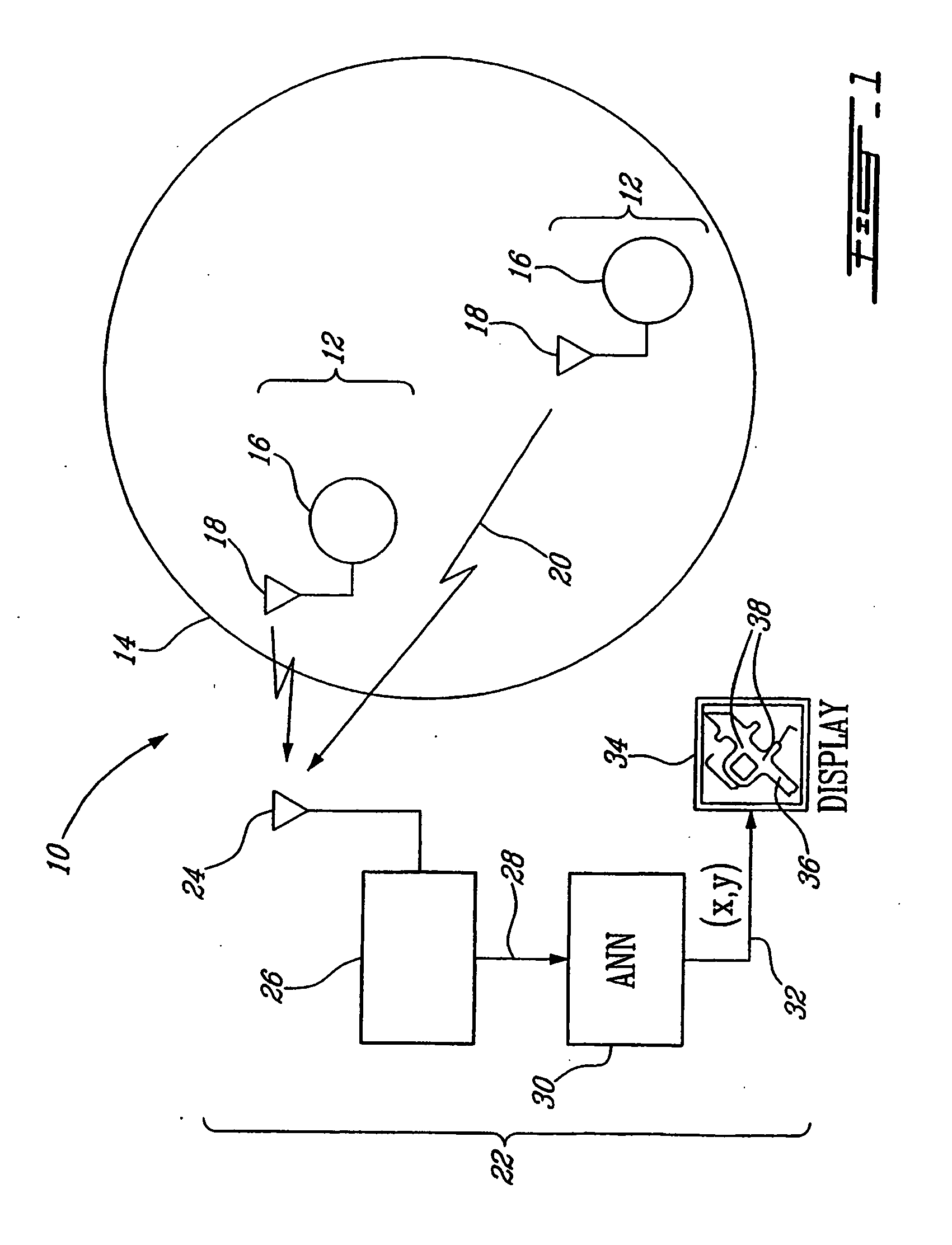

Method and system for indoor geolocation using an impulse response fingerprinting technique

ActiveUS20070010956A1Minimize error functionPolarisation/directional diversityDc level restoring means or bias distort correctionData setIndoor geolocation

A system and method for predicting the location of a transmitter in an indoor zone of interest, including fixed receiver for receiving a signal from the transmitter, the receiver deriving a fingerprint from the received signal, and a trained neural network. The trained neural network predicts the transmitter location from the fingerprint. The method includes receiving a signal transmitted from the transmitter at a fixed-location receiver, deriving a fingerprint from the received signal, supplying the fingerprint to a trained neural network, and reading the predicted location from the neural network. The artificial neural network may further be trained and include a plurality of weights and biases is also shown. The method may include collecting a training data set of fingerprints and corresponding locations, inputting the training data set to the neural network, and adjusting the weights and biases by minimising a sum of squares error function.

Owner:INSTITUT NATIONAL DE LA RECHERCHE SCIENTIFIQUE +1

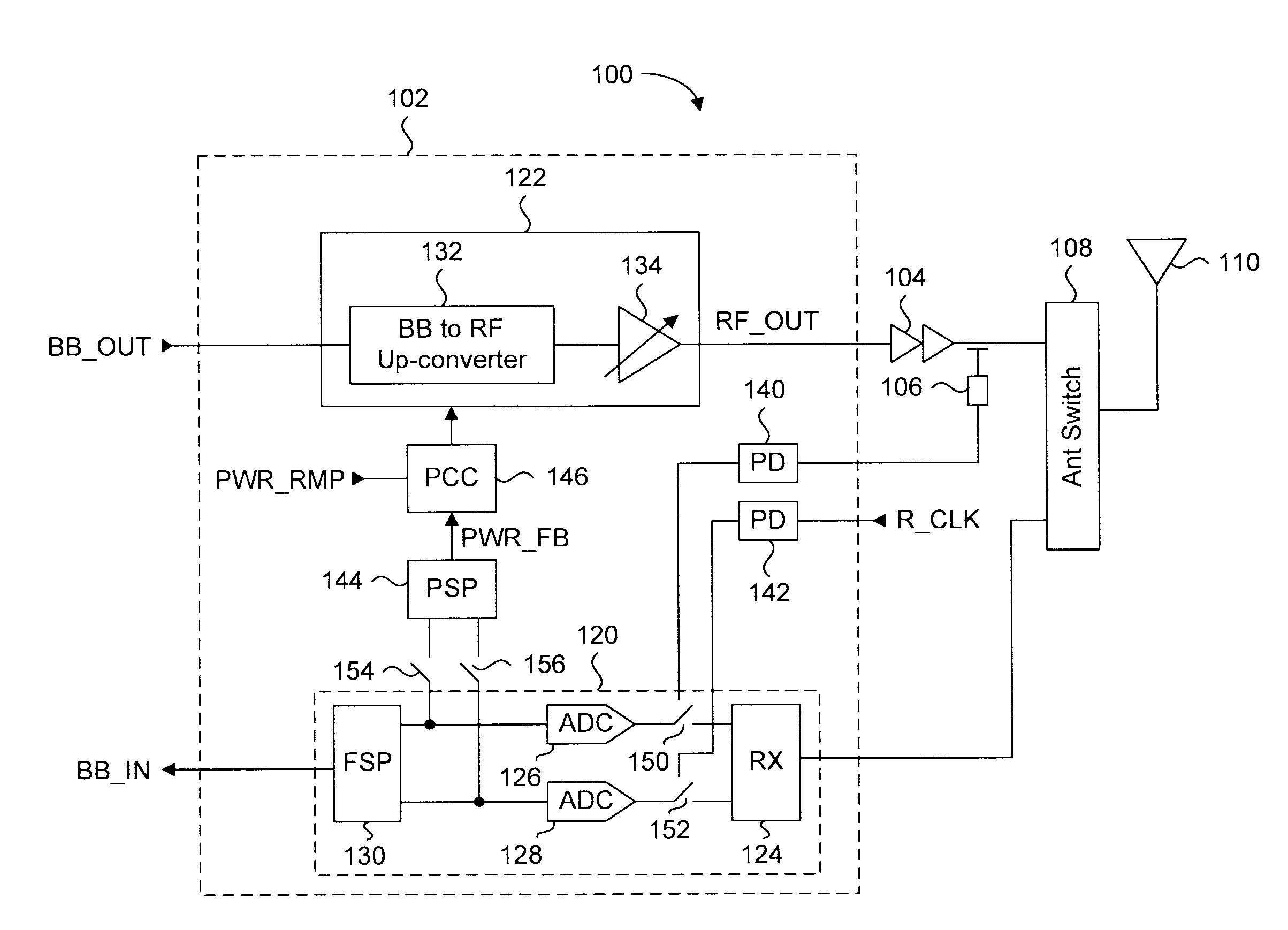

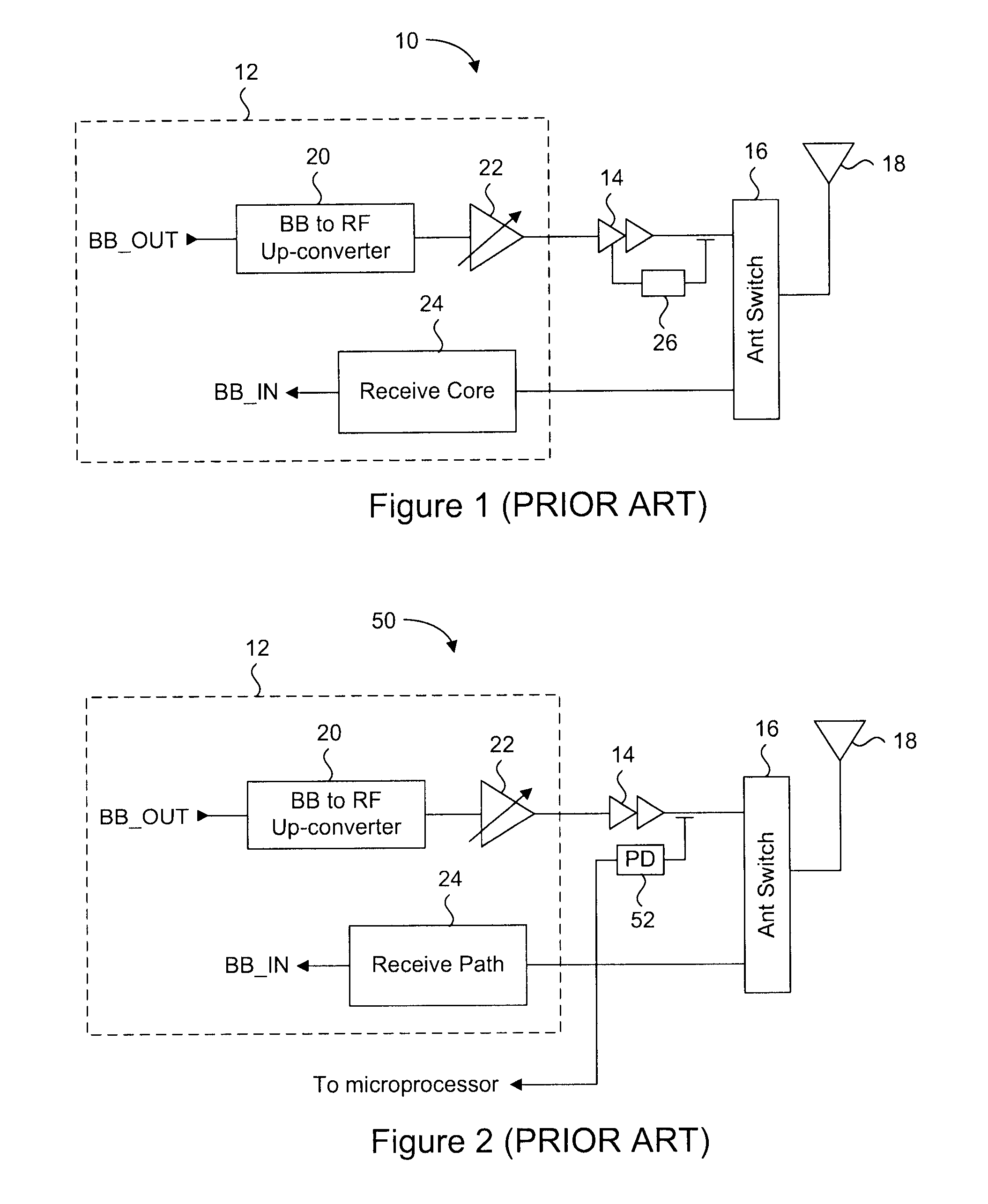

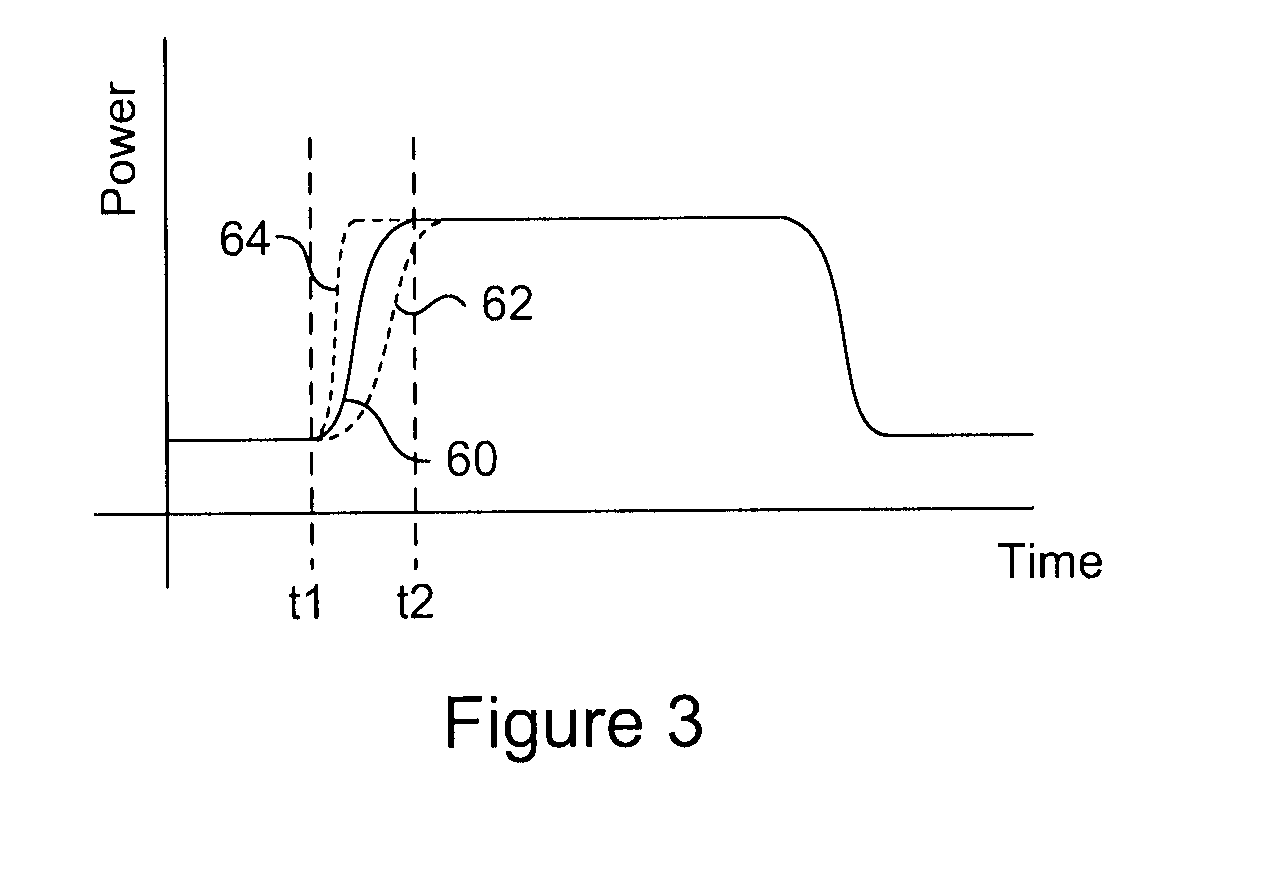

Closed-loop digital power control for a wireless transmitter

ActiveUS20100027596A1Gain controlDc level restoring means or bias distort correctionWireless transceiverTransceiver

A closed loop power output calibration system for variable power output wireless devices. The wireless device includes a wireless transceiver having a transmit core coupled to a discrete power amplifier. Power detection circuitry formed in the wireless transceiver provides a detected power level of the power amplifier, and a reference power level, both of which are converted to digital signals using existing I and Q signal analog to digital converters in the receiver core. The digital signals are processed to cancel power distortion and temperature effects to provide a resulting power feedback signal. Corrective control signals are generated in response to the power feedback signal relative to a desired power output level. The gain in the transmit core is then adjusted in response to the corrective control signals such that the power amplifier outputs the target output power level.

Owner:ICERA CANADA ULC

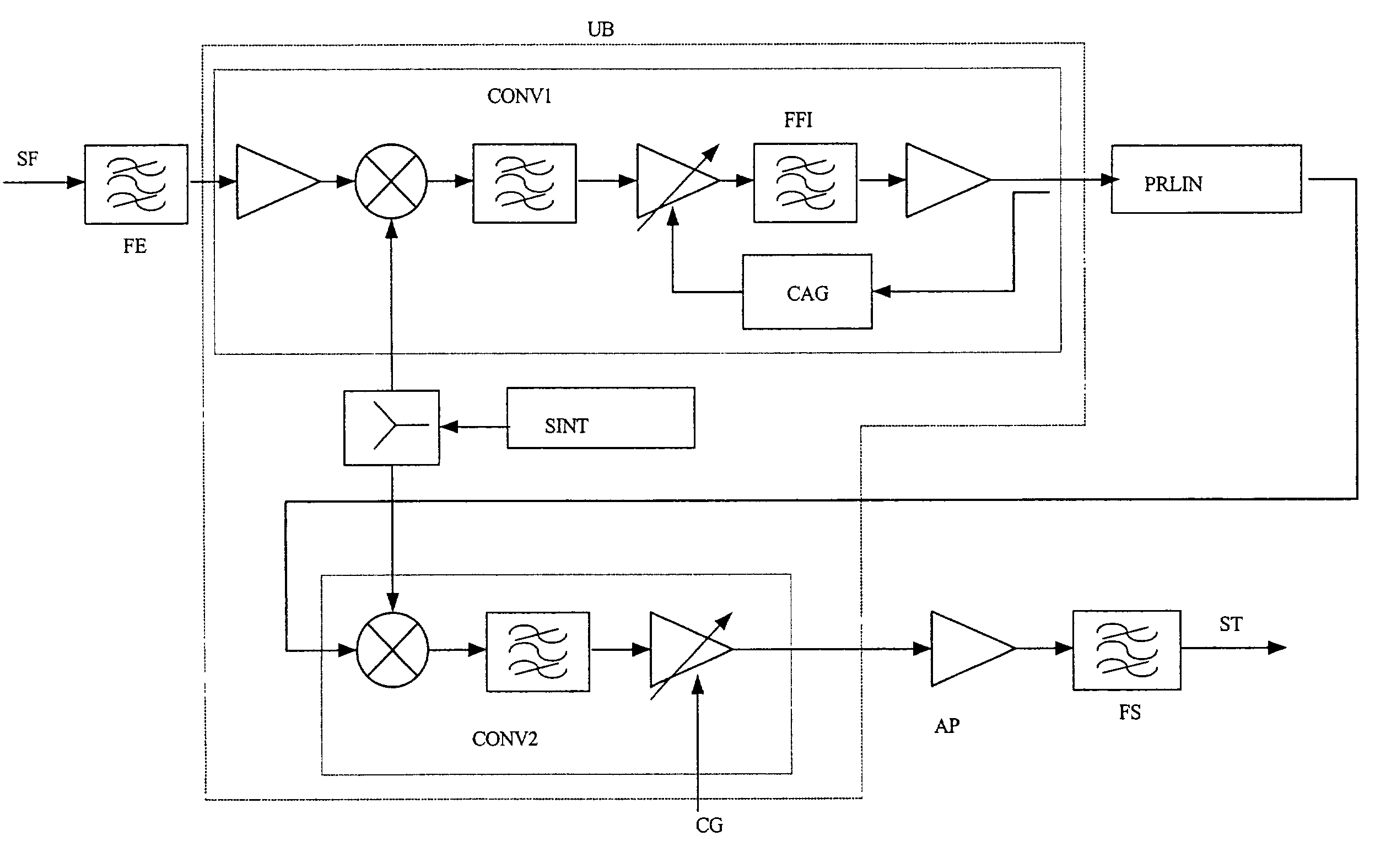

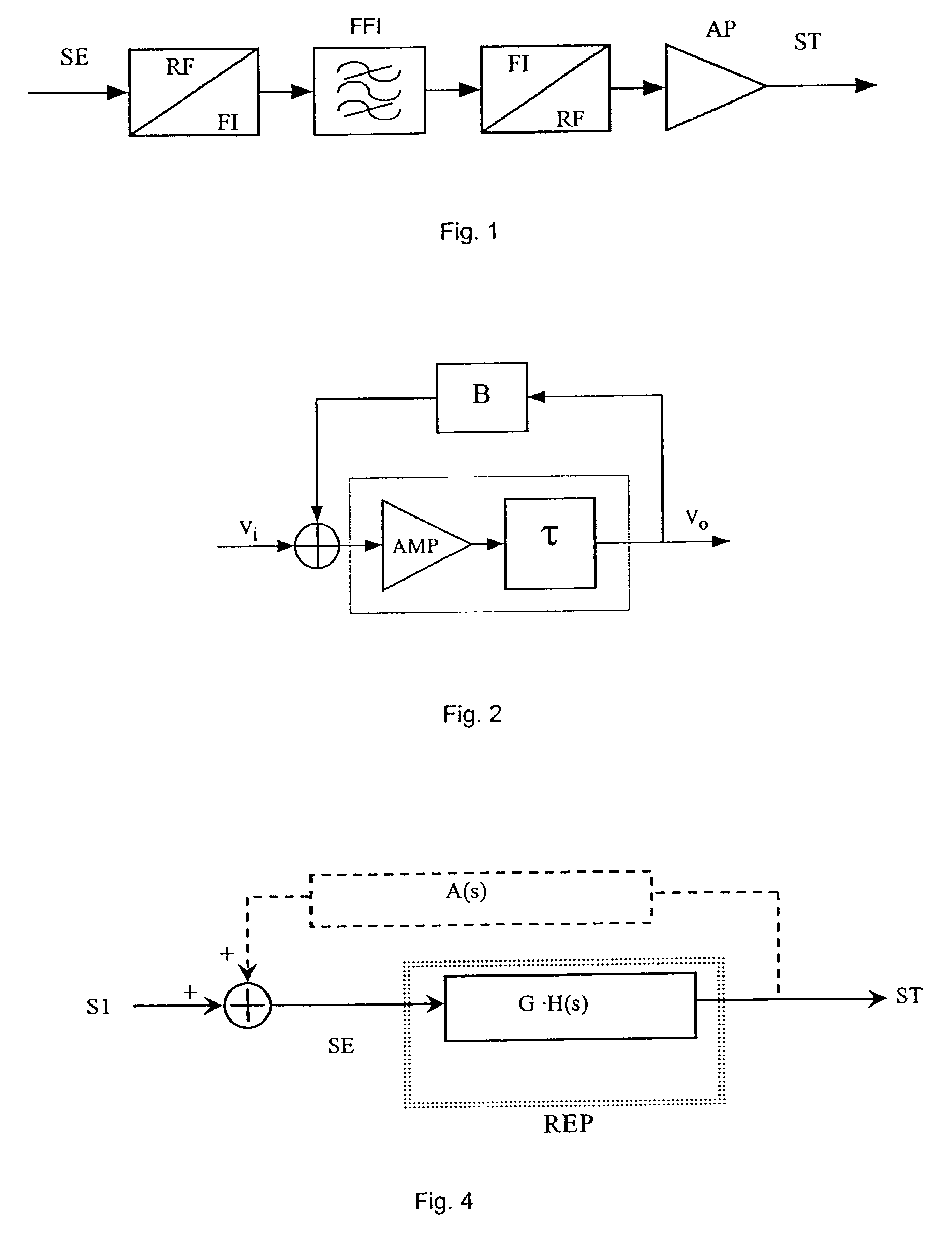

Process for re-transmitting single frequency signals and a single frequency signal repeater

InactiveUS7043203B2Limit resultSimple filterEcho effect reductionModulated-carrier systemsAutomatic controlCoupling

The invention discloses a process for re-transmitting single frequency signals and a single frequency signal repeater, where coupling occurs between the transmitting antenna and the receiving antenna, and where the process is of the type used in a single frequency signal repeater and comprises the steps of: [a] receiving a first radio frequency signal having a particular receiving power, [b] optionally converting said first radio frequency signal into a process signal, [c] filtering, amplification and automatically controlling the gain of said signal, [d] canceling said coupling between said transmitting antenna and said receiving antenna, [e] reconverting, as the case may be, said process signal into a second radio frequency signal, [f] amplifying the power of said second radio frequency signal, [g] output filtering, and [g] transmission.

Owner:MIER COMMUNICACIONES SA

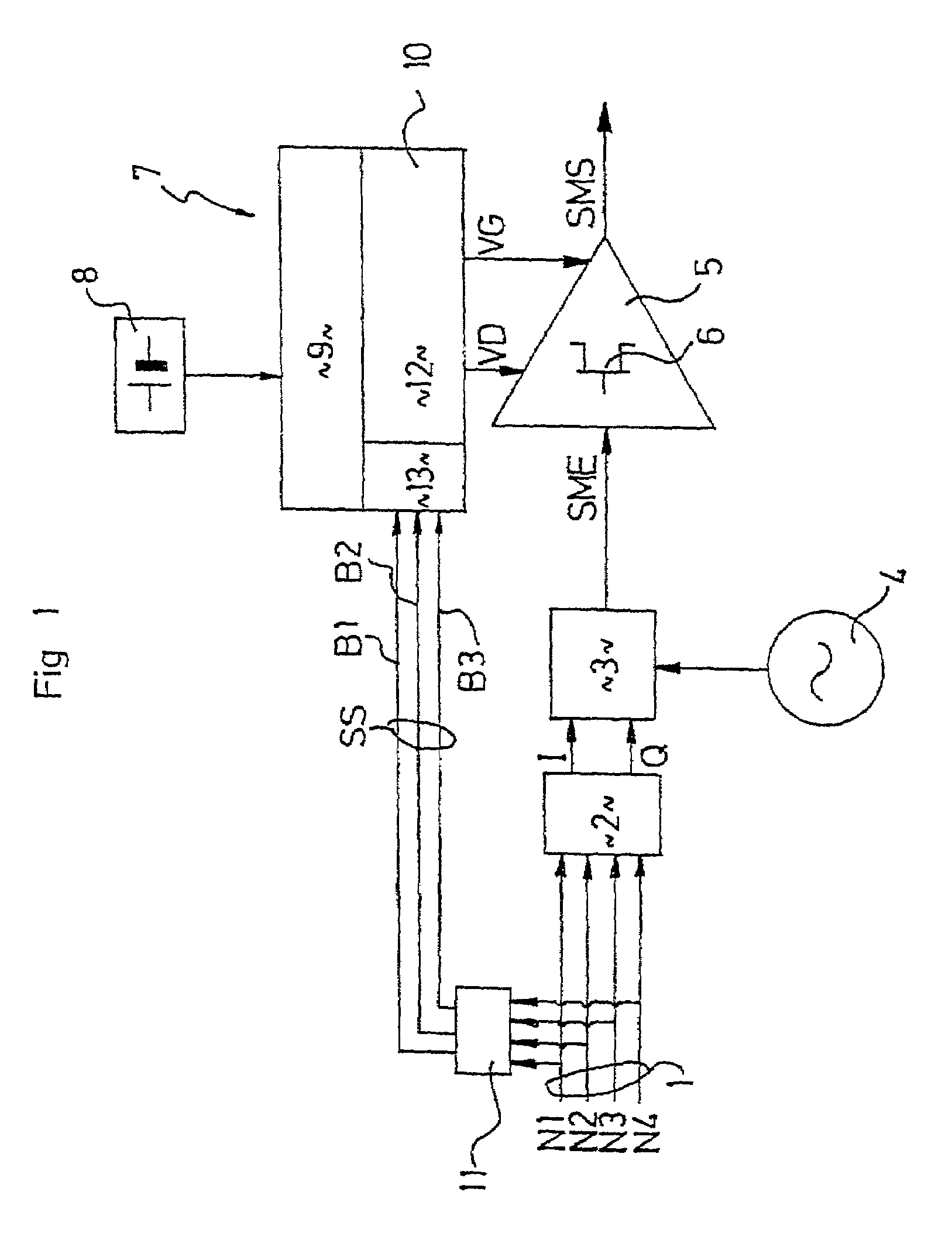

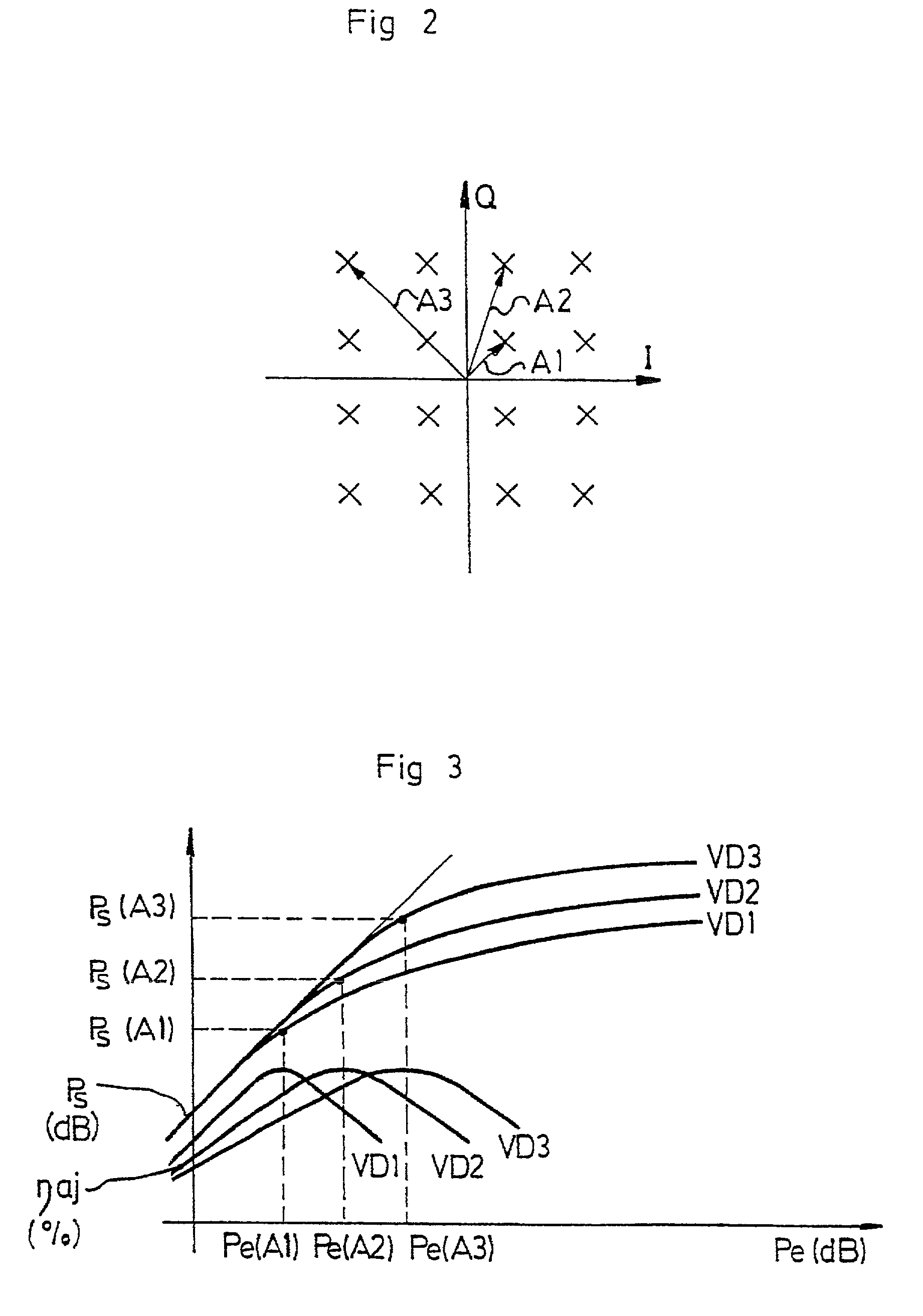

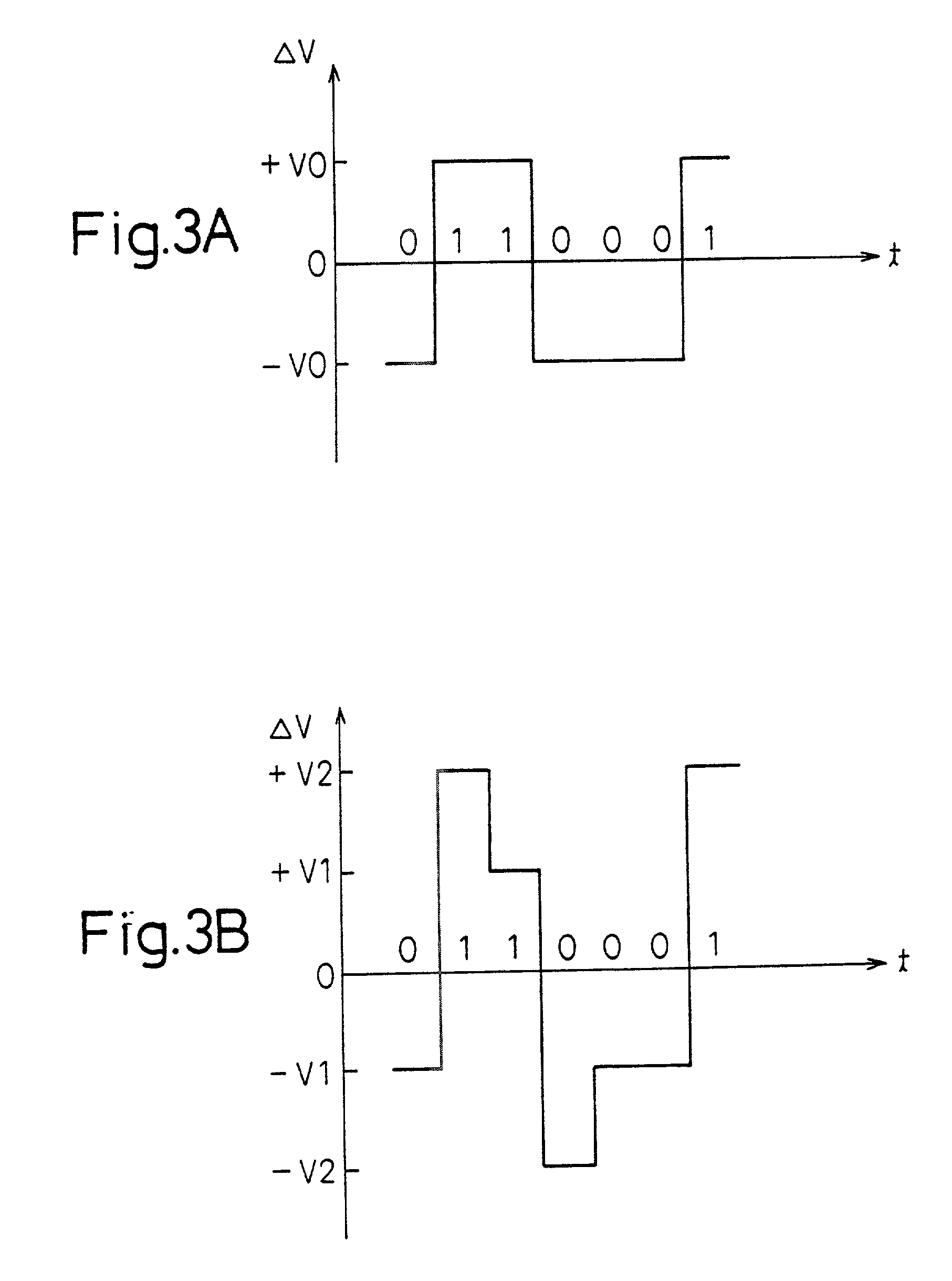

Modulated radio signal transmitter with self-adapted amplification polarization

InactiveUS7103114B1Simple and inexpensive to produceEfficient use ofResonant long antennasModulated-carrier systemsControl signalEngineering

The invention relates to a transmitter of radio signals (SMS), which are amplitude-modulated according to a discrete plurality of amplitude levels, in which at least one output power transistor (6) receives, on one of its terminals, a bias-voltage level which is adapted to the amplitude level represented by the instantaneous value of a selection signal (SS) generated by analysis means (11) on the basis of the digital control signals (1). The electrical consumption is hence optimized.

Owner:CENT NAT DETUD SPATIALES C N E S

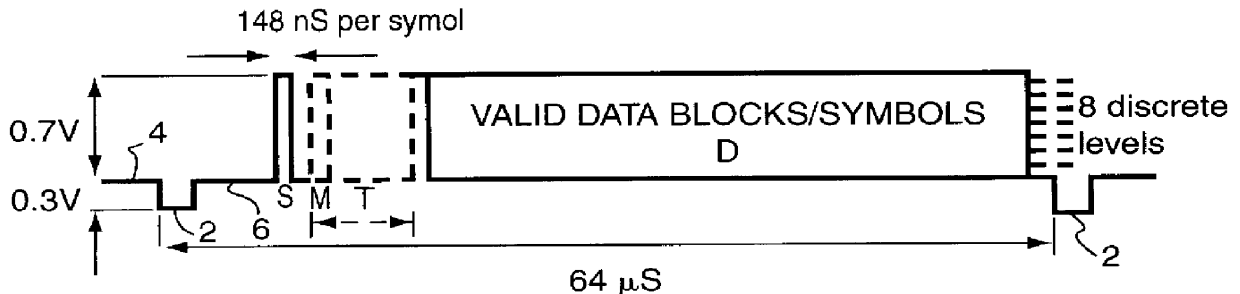

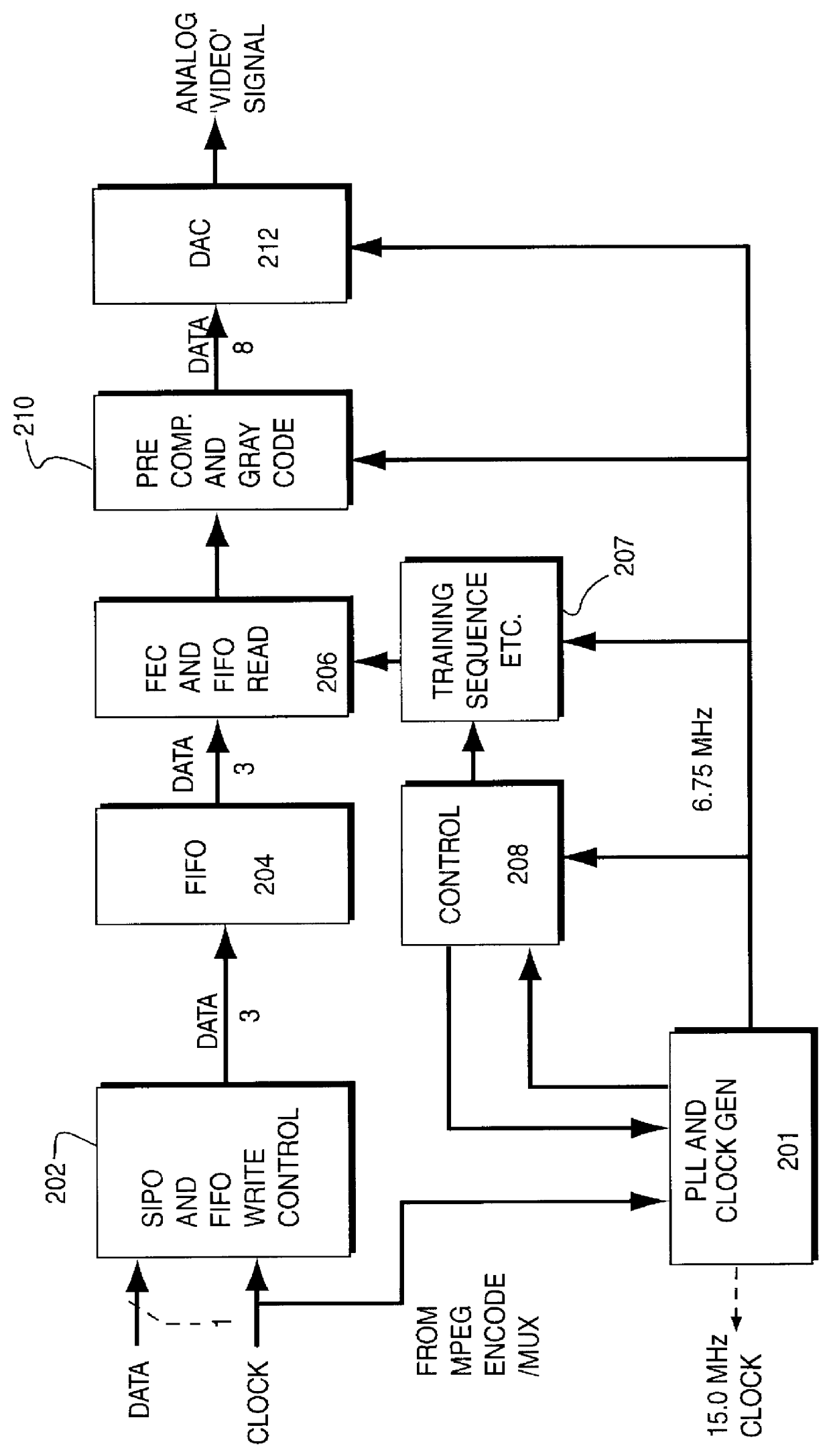

Data transmission

InactiveUS6094461AImprove data throughputSimple designError preventionDc level restoring means or bias distort correctionData transmissionData sequences

A transmitter (20) having means (206, 207) to encode an input signal to form coded data, each element of said coded data having one of at least two discrete signal magnitude levels, the encoding means including in the coded data a periodic training sequence of data (T); and a receiver (30) to receive the coded data and, on the basis of the received training sequence, to adapt a threshold or thresholds to allow the discrete levels to be distinguishable from each other. The training sequence T may comprise a plurality of elements at least one of which, in turn, represents each one of the discrete signal levels. The receiver generates a look-up-table to store the adapted thresholds.

Owner:BRITISH TELECOMM PLC

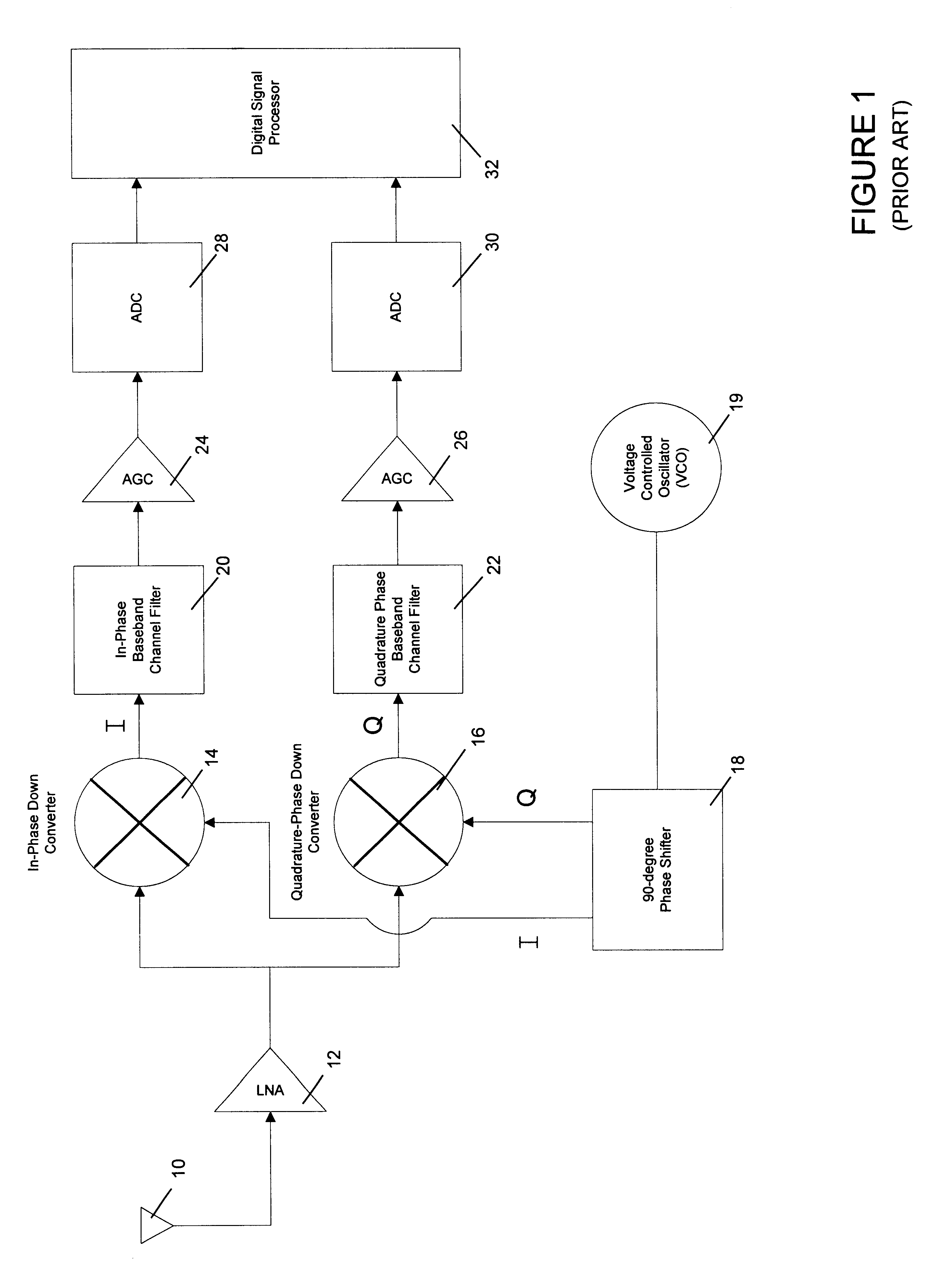

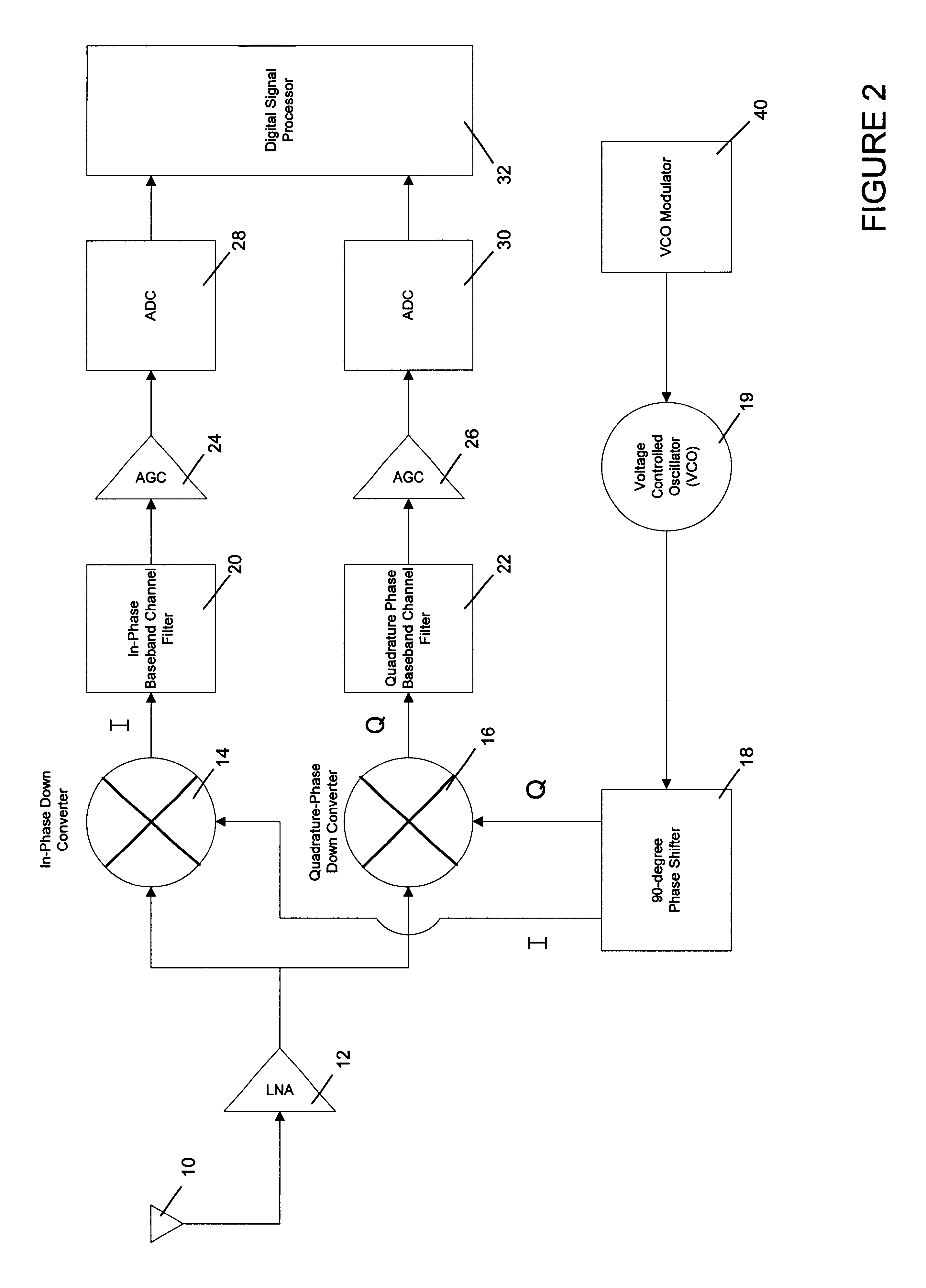

Method and apparatus for calibrating DC-offsets in a direct conversion receiver

InactiveUS6868128B1Reduce sizeSmall sizeDc level restoring means or bias distort correctionCarrier regulationDirect-conversion receiverOffset calibration

A novel method and apparatus for calibrating DC offsets in a direct conversion receiver. The present DC offset calibration method and apparatus comprises a direct conversion receiver equipped with a frequency shifter means and a DC offset measurement and correction technique. In accordance with the present invention, DC offsets are calibrated in direct conversion receivers through an inventive method including two steps: a DC offset measurement step and a DC offset correction step. In the DC offset measurement step the frequency of a local oscillation signal (typically generated by a voltage-controlled oscillator (VCO)) is shifted by a selected frequency shift value during the inactive time intervals of the receiver. DC offsets are measured while the frequency of the down-conversion oscillation signal is shifted by the frequency shift value. Before the inactive time interval expires, the frequency of the down-conversion oscillator signal is shifted back to its original value. In the DC offset correction step of the present invention incoming signals are corrected using a correction means that removes the DC offset measured during the DC offset measurement step.

Owner:QUALCOMM INC

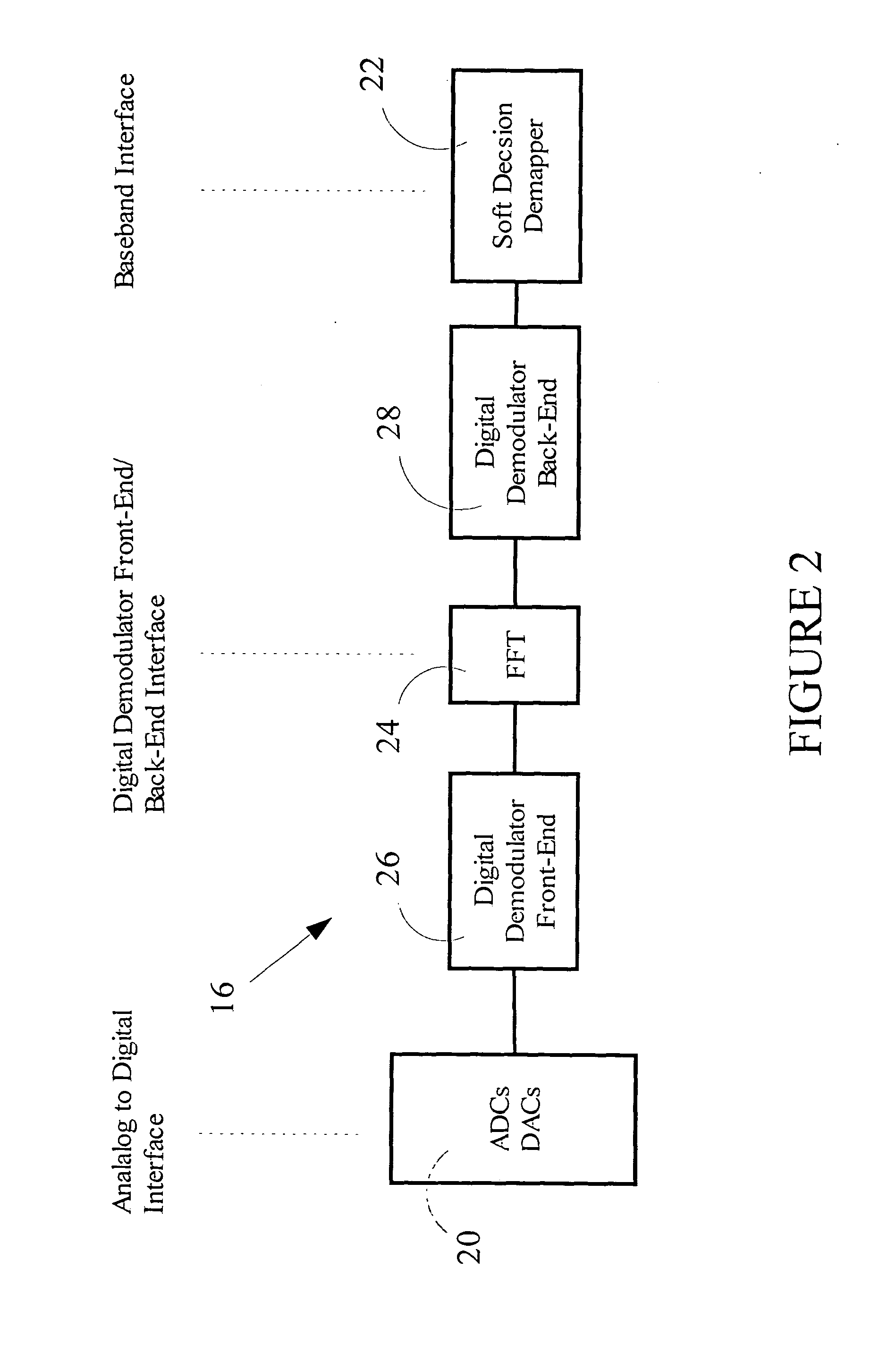

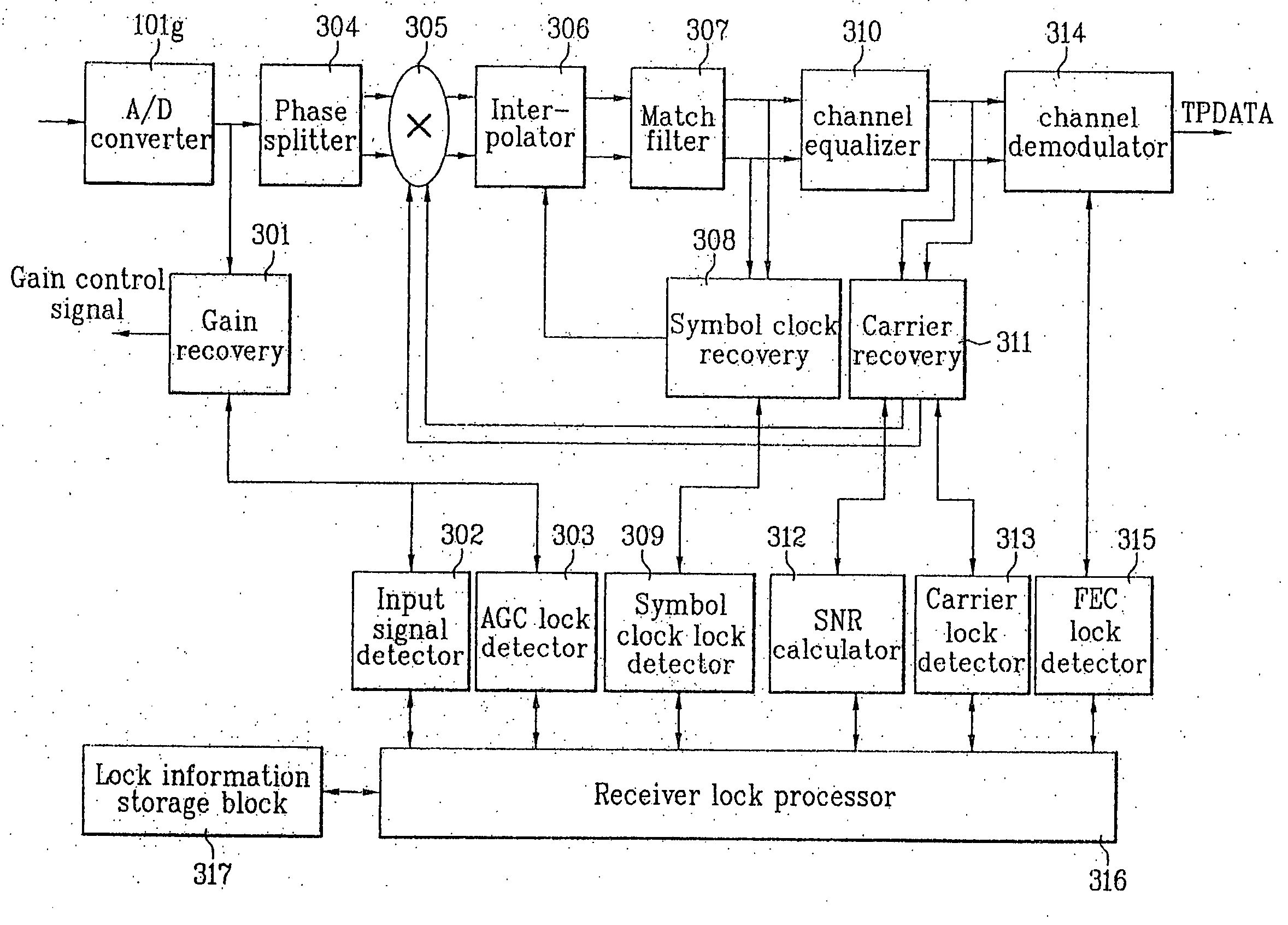

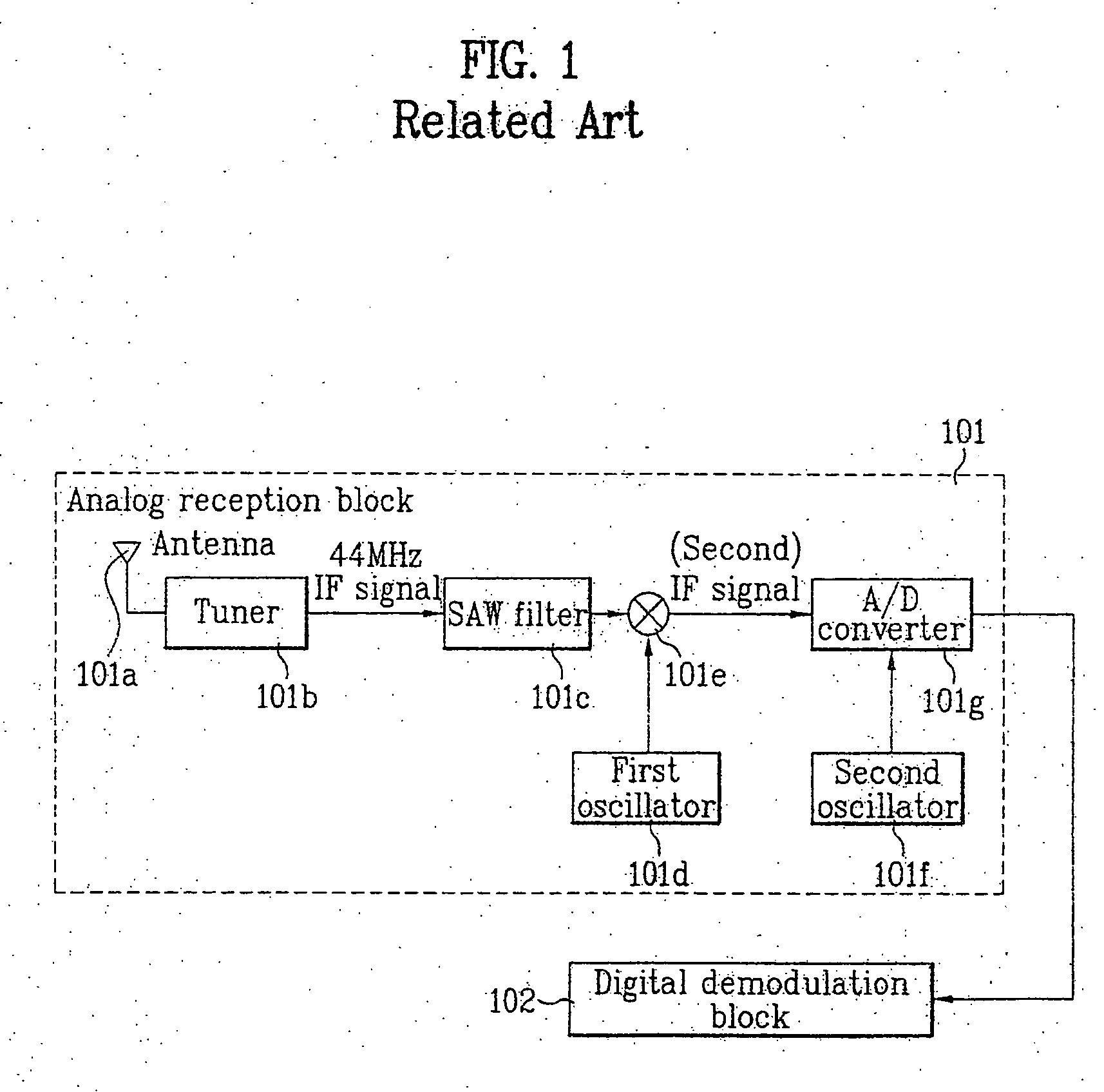

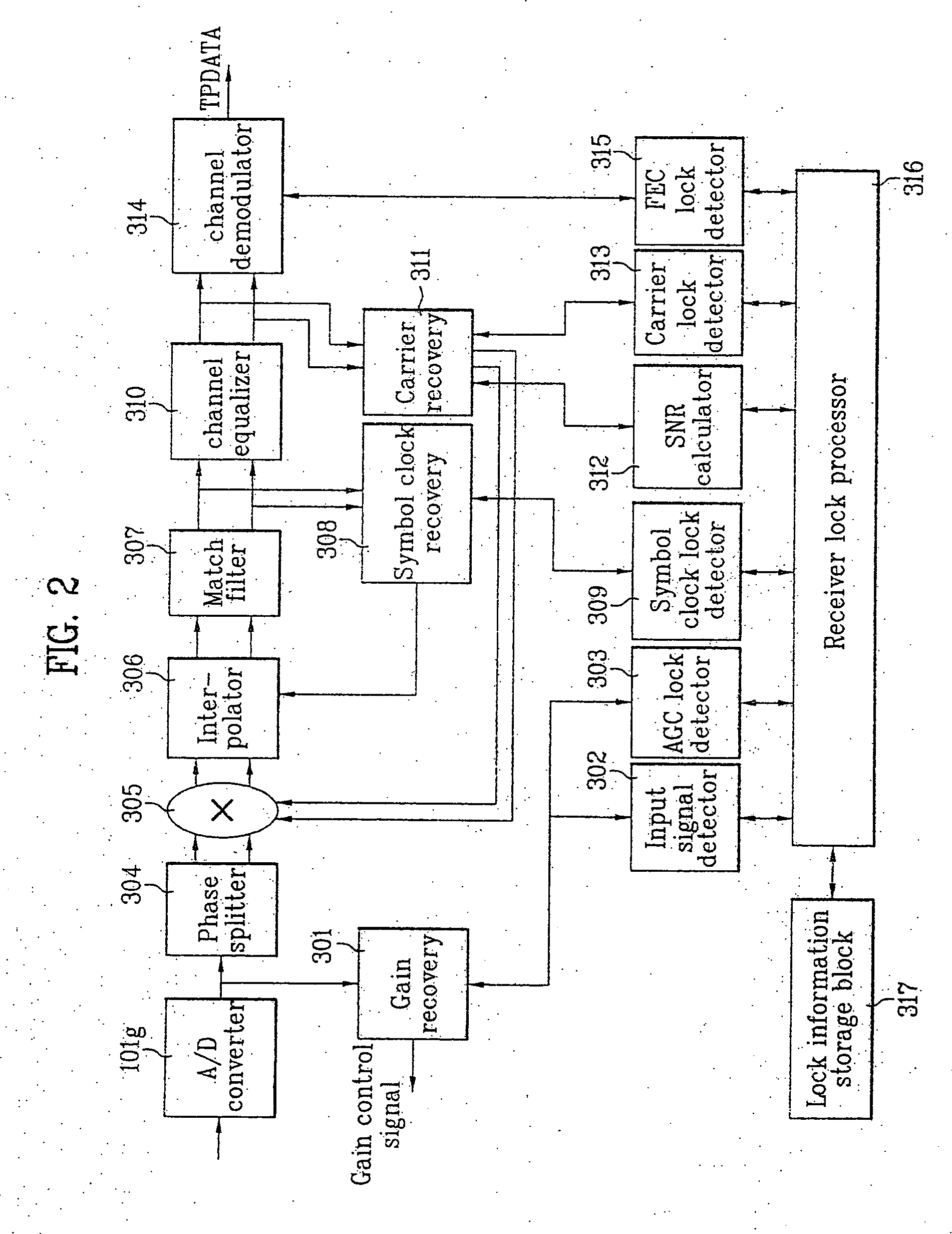

Digital broadcasting receiver, driving method, and self-diagnosis method thereof, and self-diagnosis method thereof

InactiveUS20050058192A1Guaranteed uptimeAcquisition speed is fastError preventionDc level restoring means or bias distort correctionDiagnosis methodsEngineering

A digital broadcasting receiver, a driving method, and a self-diagnosis method thereof, are provided. The digital broadcasting receiver includes: a digital demodulator for demodulating a digital broadcasting signal; a lock detector for detecting lock signals from the digital demodulator; and a lock processor for controlling the digital demodulator according to the detected lock signal.

Owner:LG ELECTRONICS INC

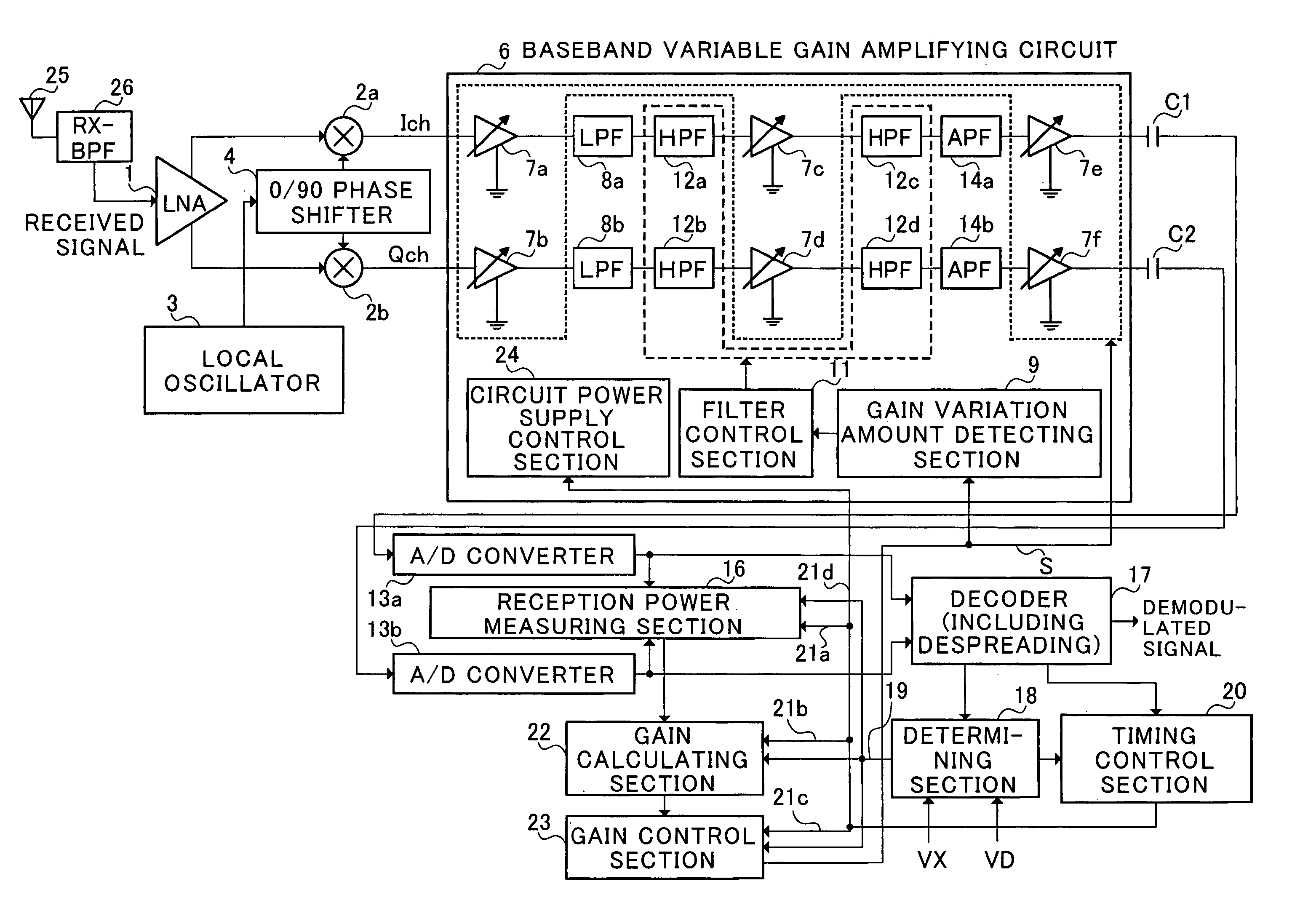

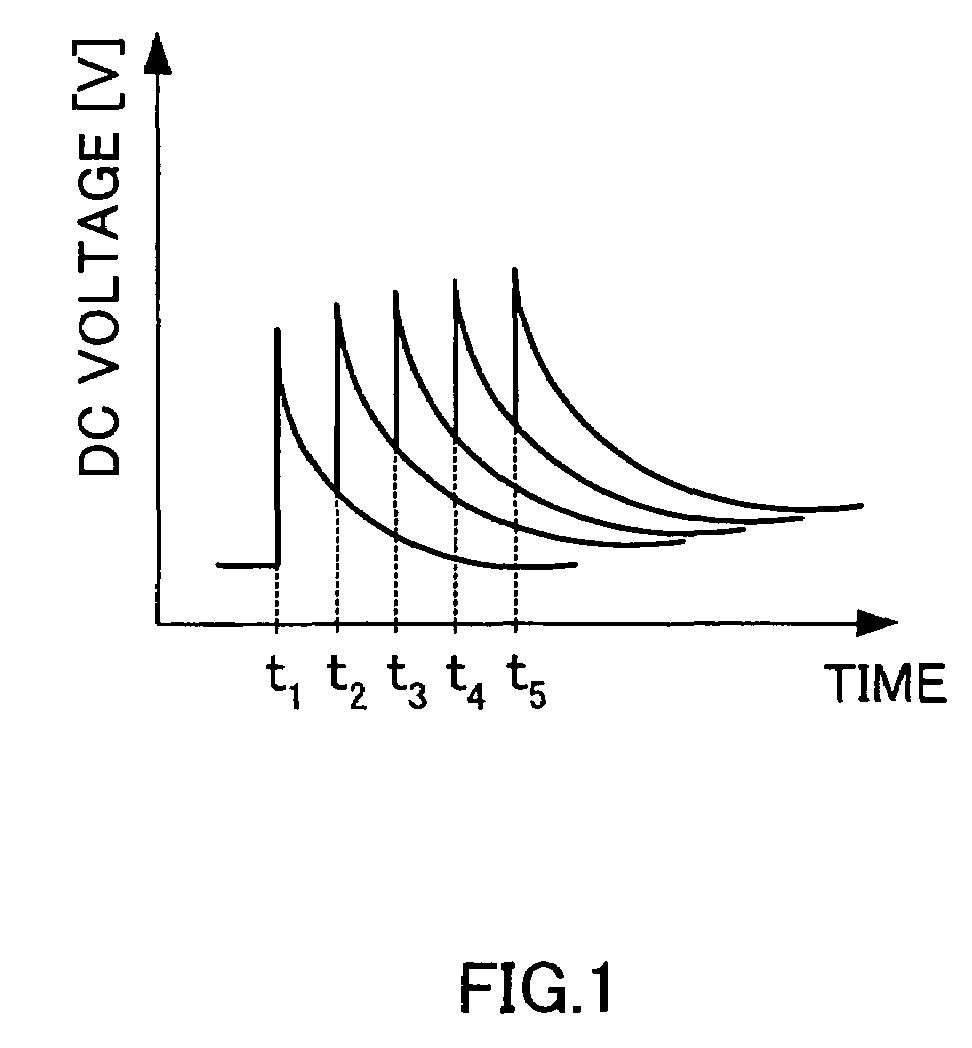

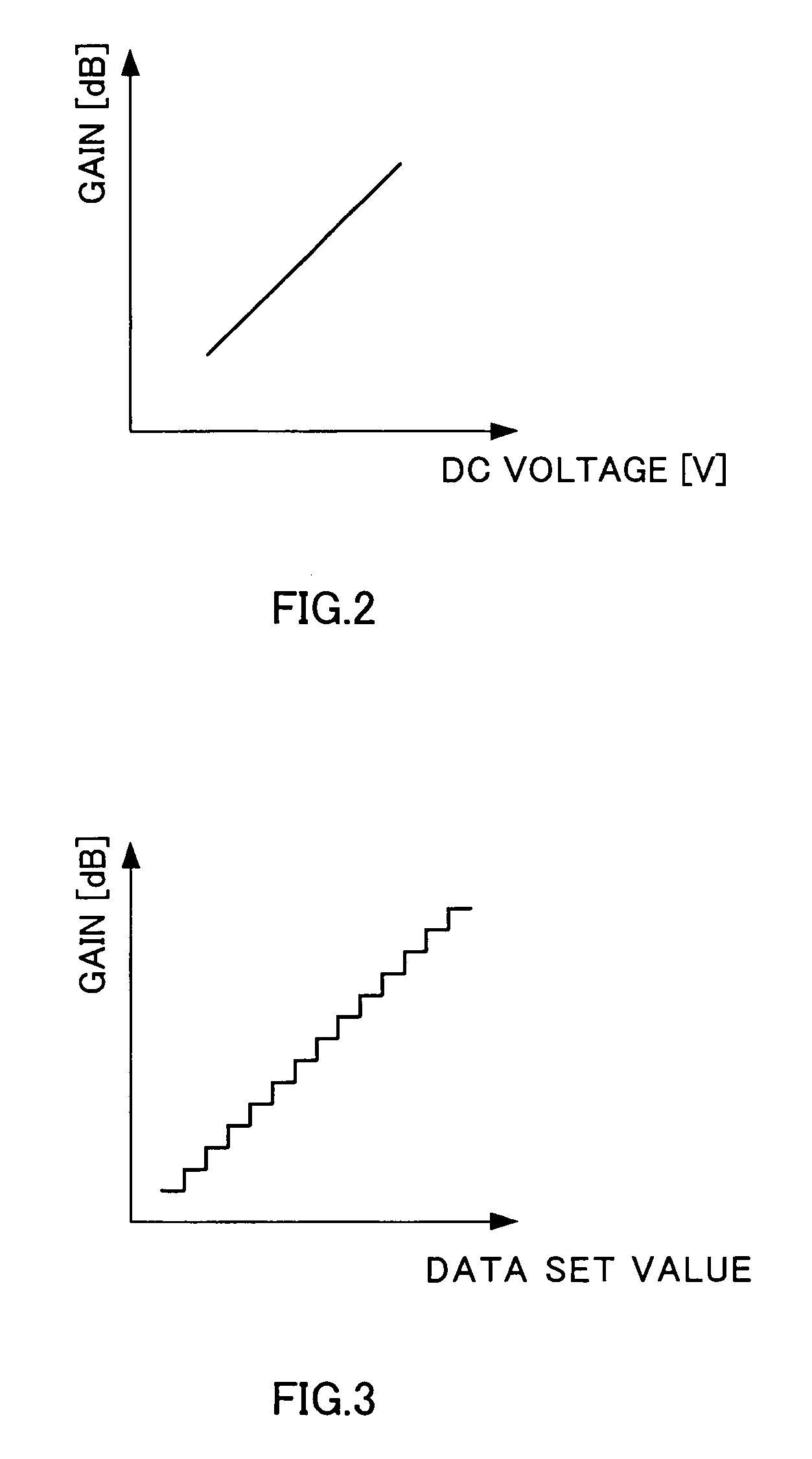

Direct conversion receiver and DC offset reducing method

InactiveUS7171185B2Reduced DC offsetAccurate and fast AGCGain controlDc level restoring means or bias distort correctionDirect-conversion receiverEngineering

A determining section (18) and gain variation amount detecting section (9) detect a period having a possibility of a DC-component offset in an internal circuit of a direct conversion receiver increasing beyond an allowable value due to AGC operation, and during the period, a cut-off frequency of each of high-pass filters (12a to 12d) is set at a frequency higher than that in general operation, thereby rapidly converging transient responses of signals passed through the high-pass filters, while controlling precisely operation timings of reception power measuring section (16), gain calculating section (22), gain control section (23) and circuit power supply control section (24) composing an AGC loop, whereby the DC offset is prevented from increasing and stable circuit operation is assured. It is thereby possible to achieve further reductions in size and power consumption of a CDMA receiver using the direct conversion receiver.

Owner:PANASONIC CORP

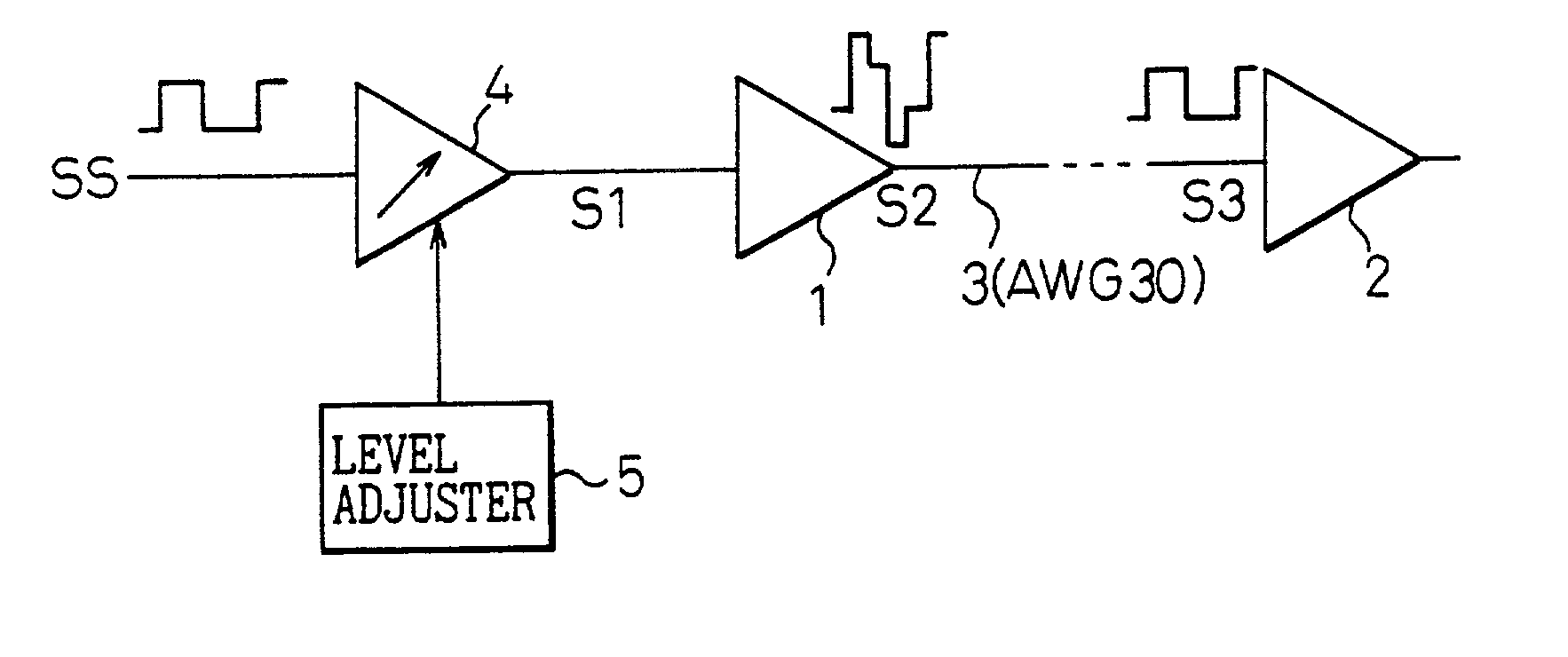

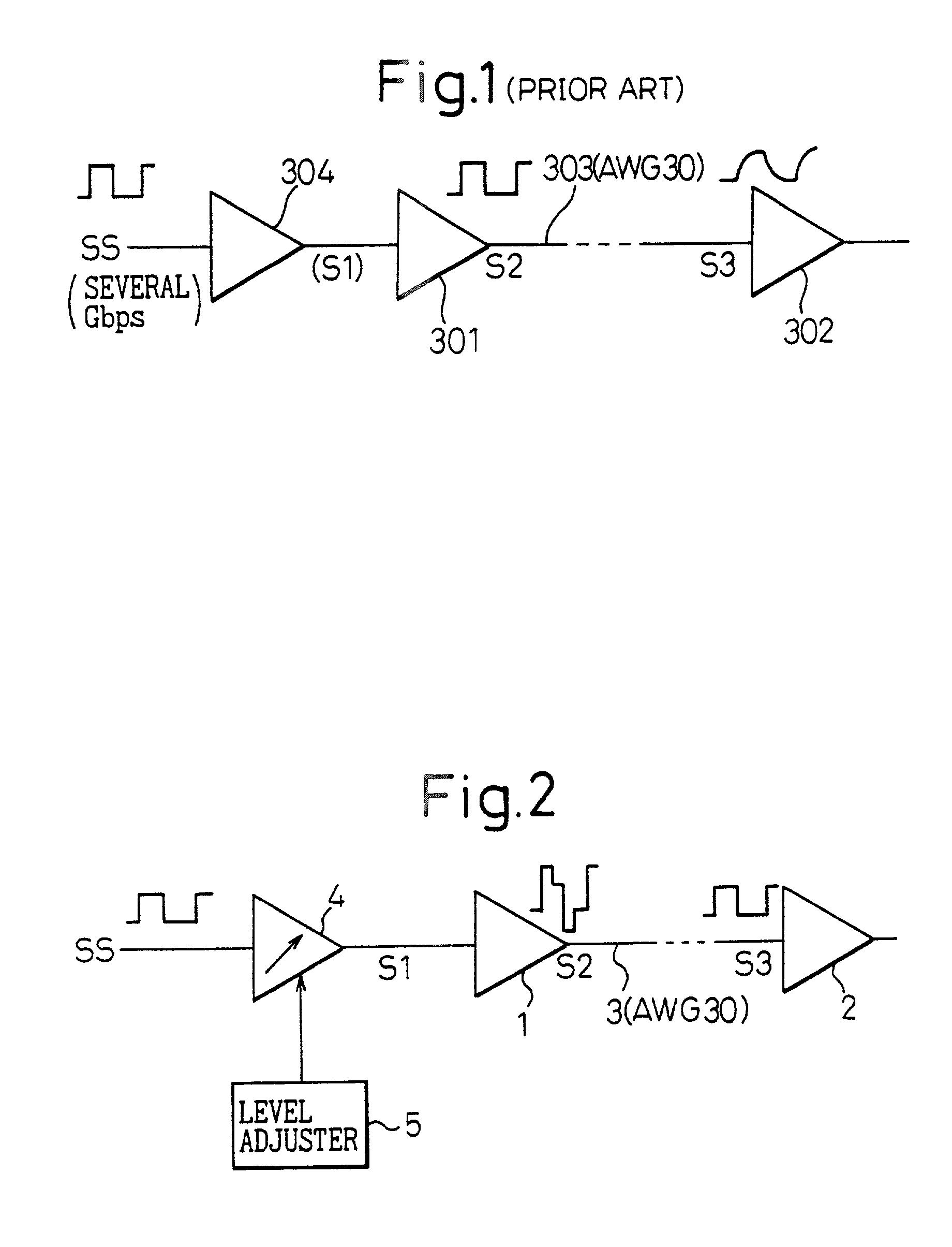

Method of and apparatus for correctly transmitting signals at high speed without waveform distortion

InactiveUS20020125933A1Eliminate distractionsAccurate transmissionCovering/liningsPulse automatic controlDriver circuitEngineering

A driver circuit transmits a signal to a receiver circuit through a signal transmission line. The driver circuit has an output driver, a front driver, and a level adjuster. The front driver drives the output driver, and the level adjuster adjusts the output level of the front driver. The output driver generates a signal whose level is variable in response to an output level of the front driver.

Owner:FUJITSU LTD

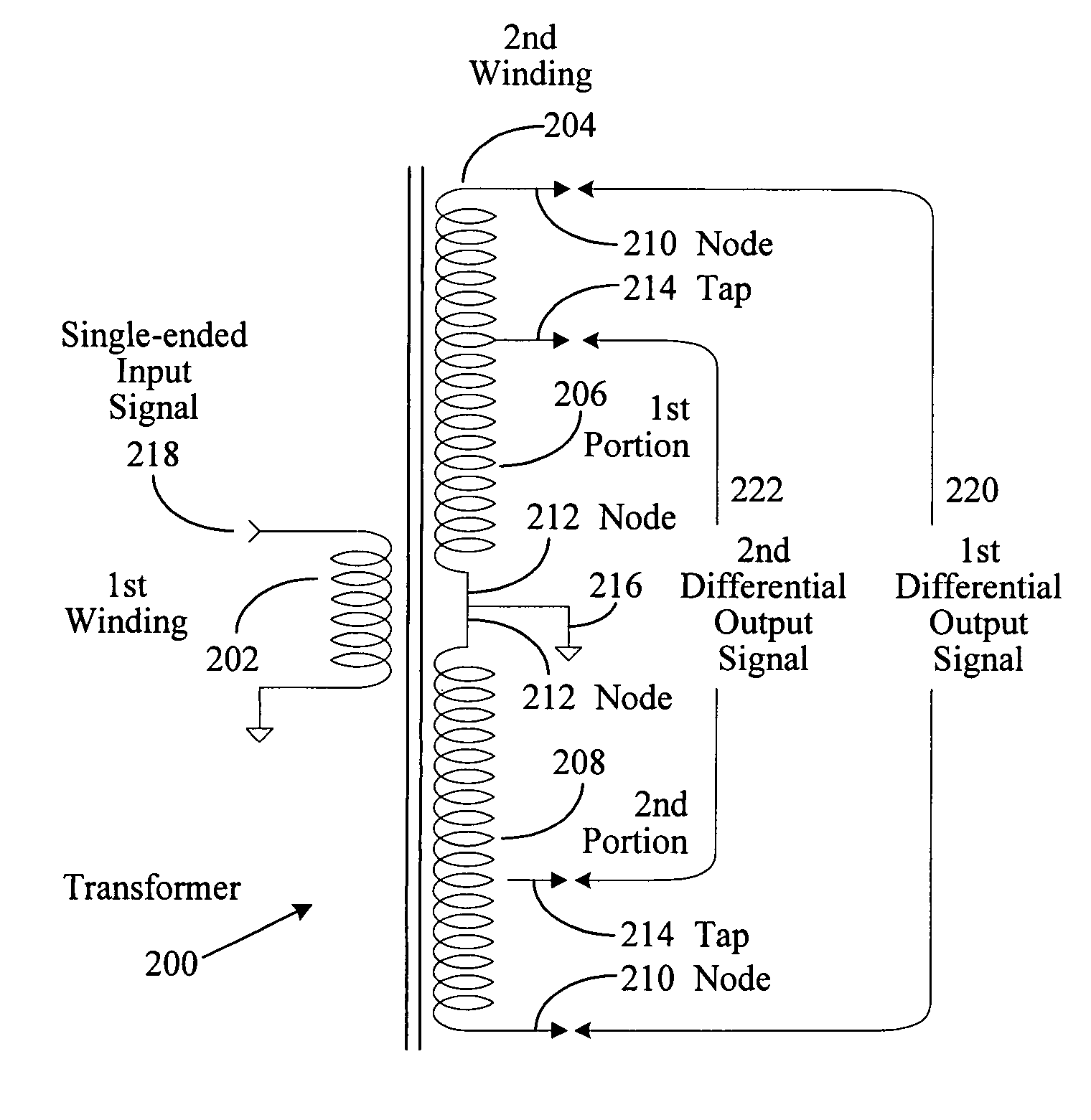

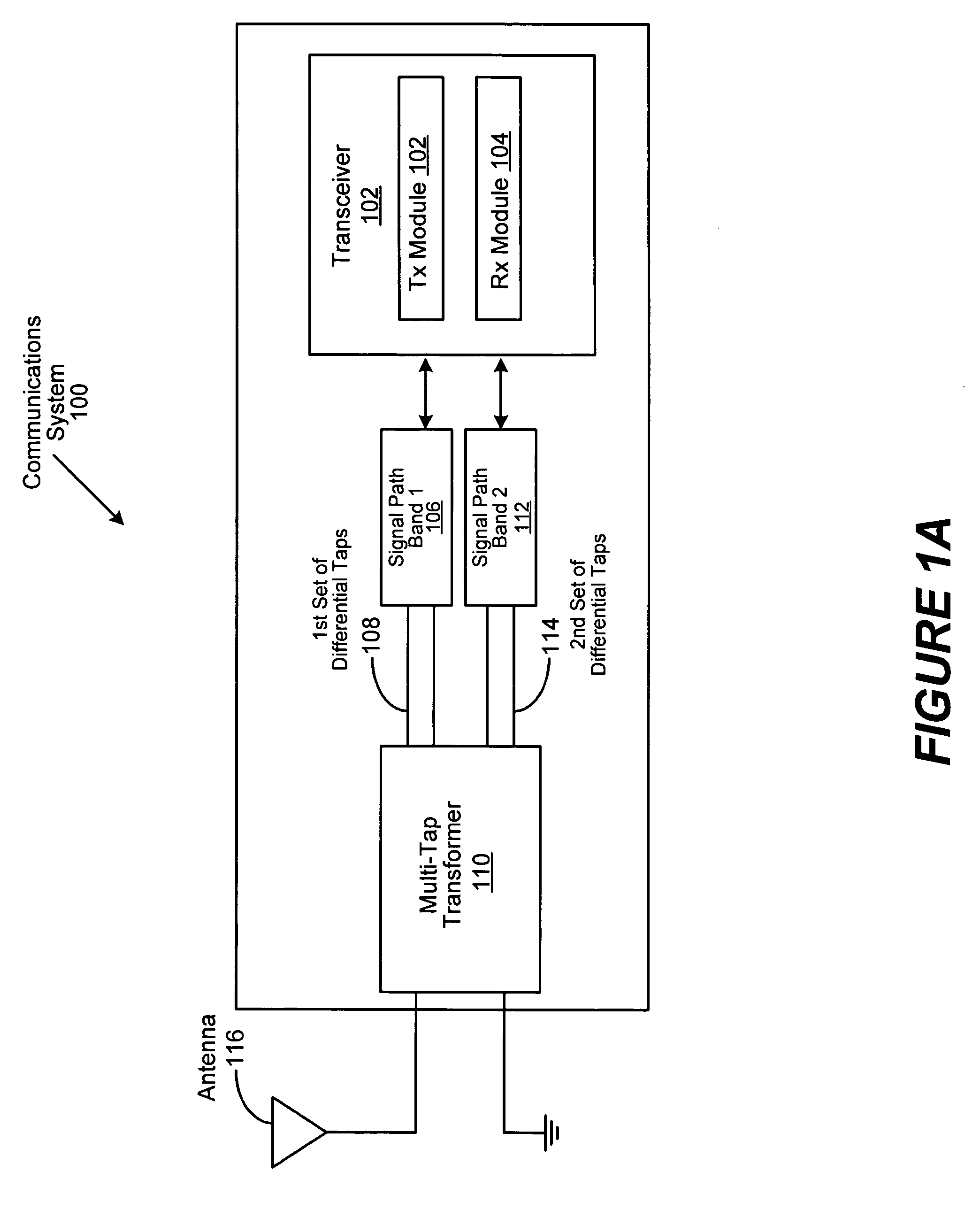

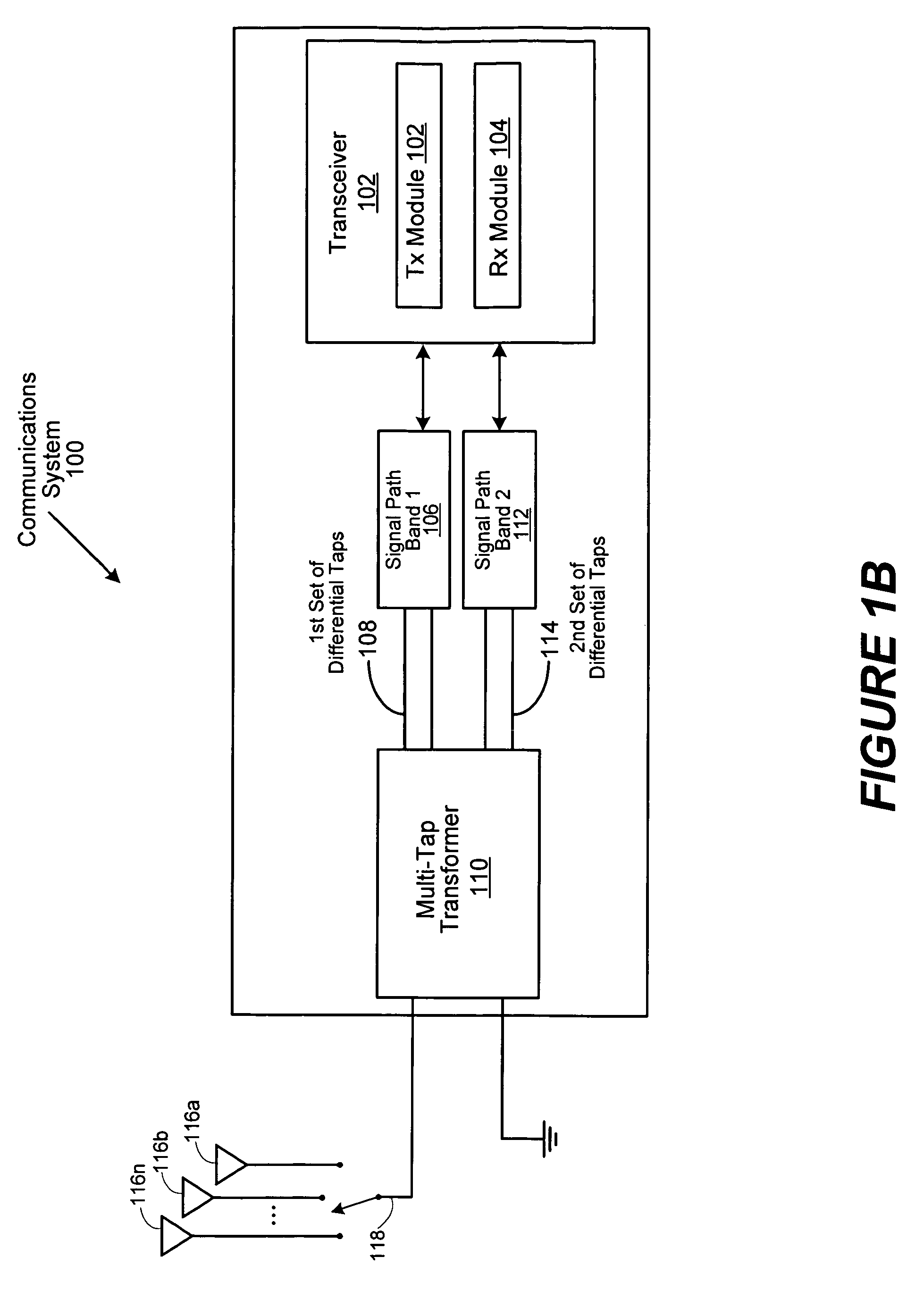

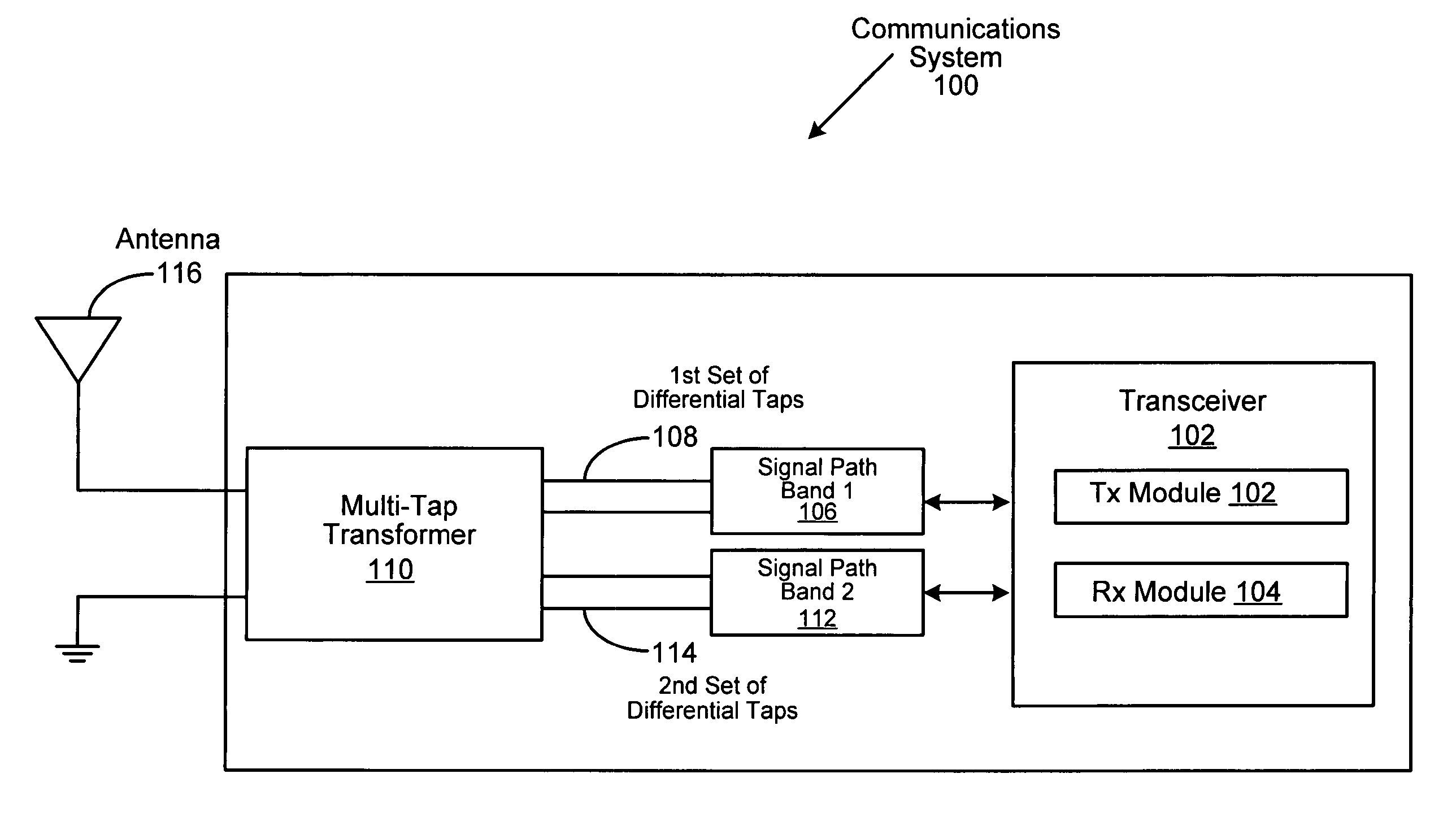

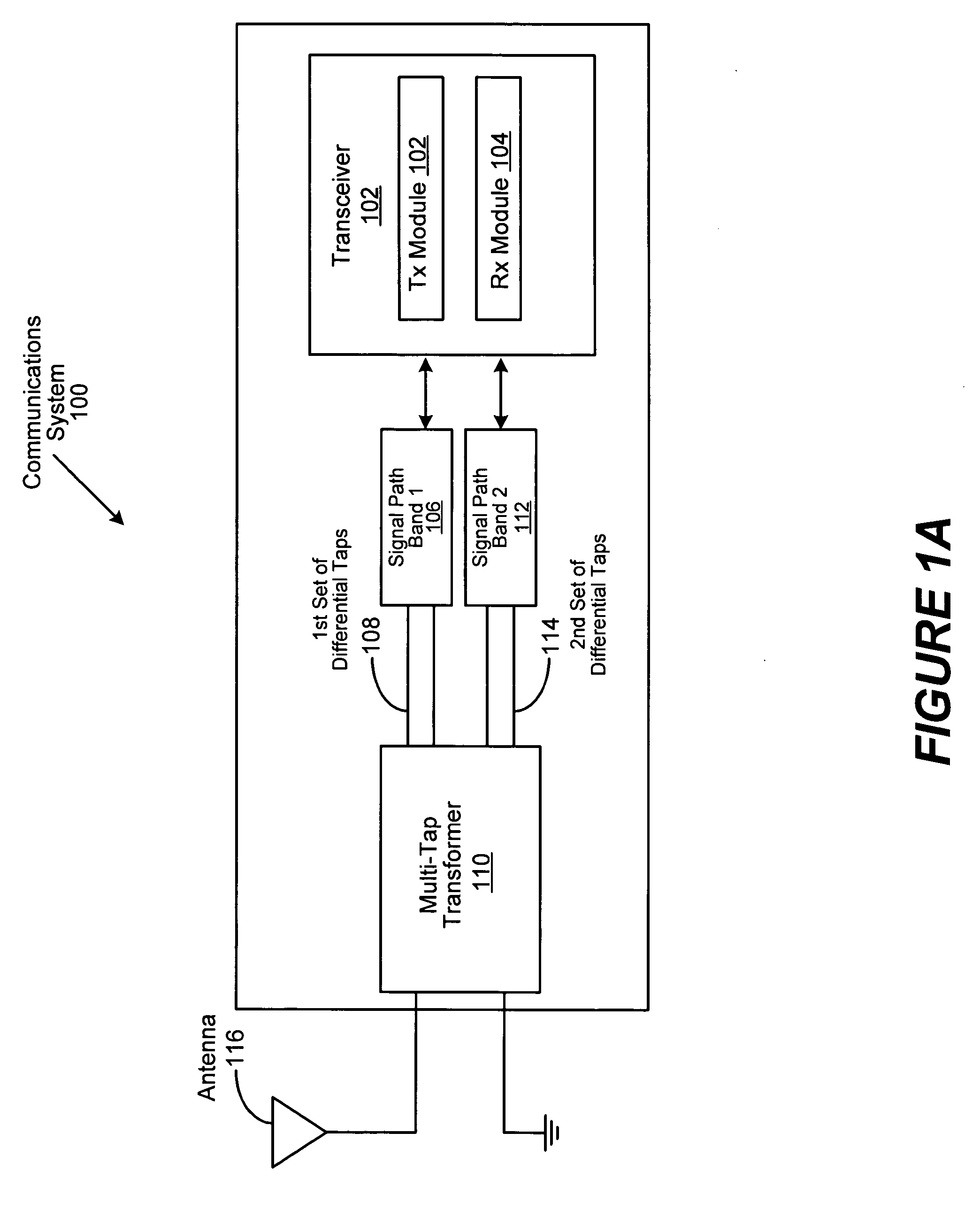

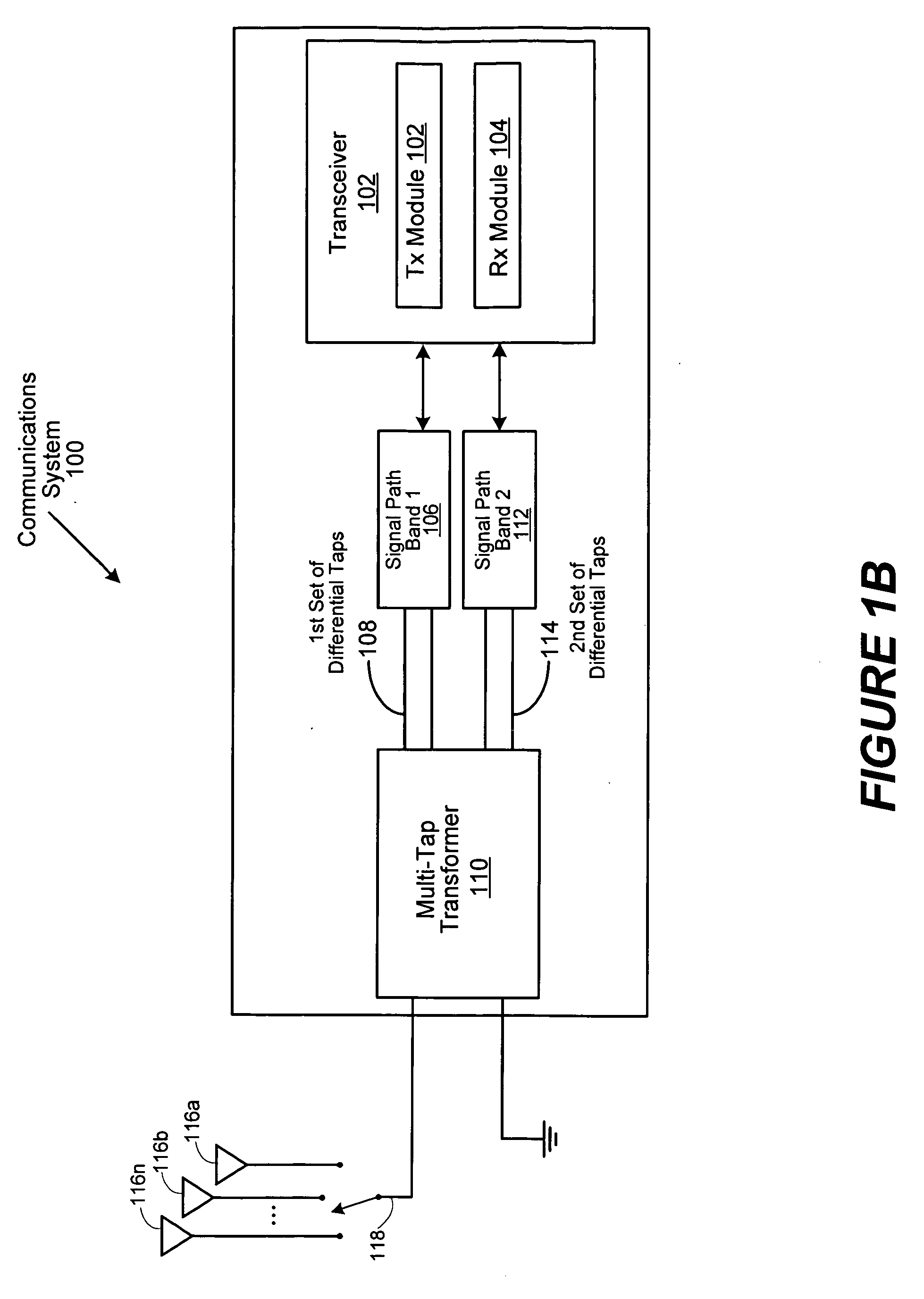

Transformer-based multi-band RF front-end architecture

InactiveUS7526256B2Reduce area requirementsOne-port networksDc level restoring means or bias distort correctionMulti bandTransformer

Owner:AVAGO TECH INT SALES PTE LTD

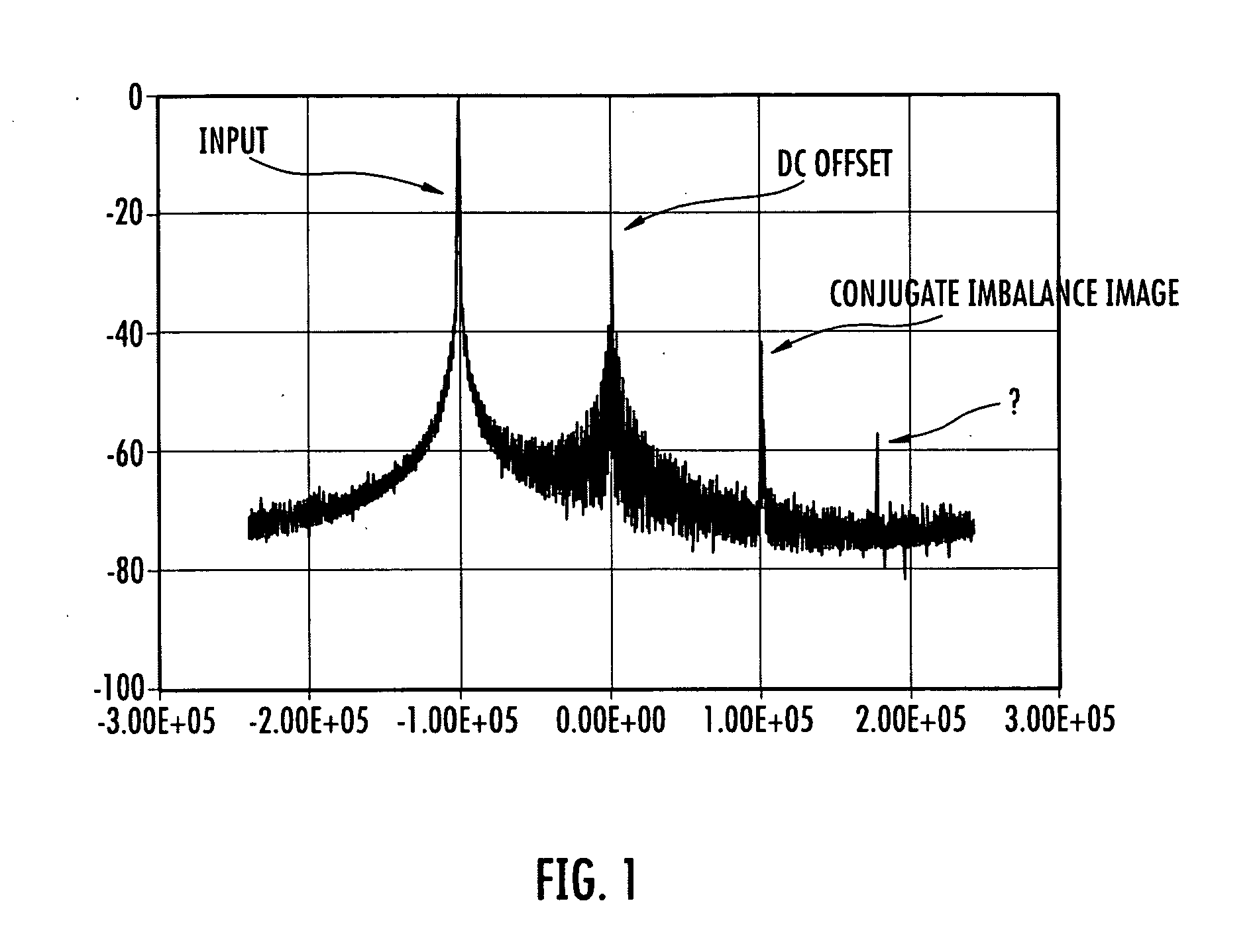

Communications device with in-phase/quadrature (i/q) DC offset, gain and phase imbalance compensation and related method

ActiveUS20100215125A1Component can be removedModulated-carrier systemsDc level restoring means or bias distort correctionPhase imbalanceEngineering

A DC offset estimator and removal circuit removes the DC offsets for each of the I and Q signal components in a received signal. A gain imbalance estimator and compensator circuit estimates and compensates for gain imbalances within the I and Q signal components. A phase imbalance estimator and compensator circuit estimates and compensates for phase imbalances within the I and Q signal components to produce a communications signal that is compensated for received DC offsets and gain and phase imbalances within the I and Q signal components.

Owner:HARRIS GLOBAL COMM INC

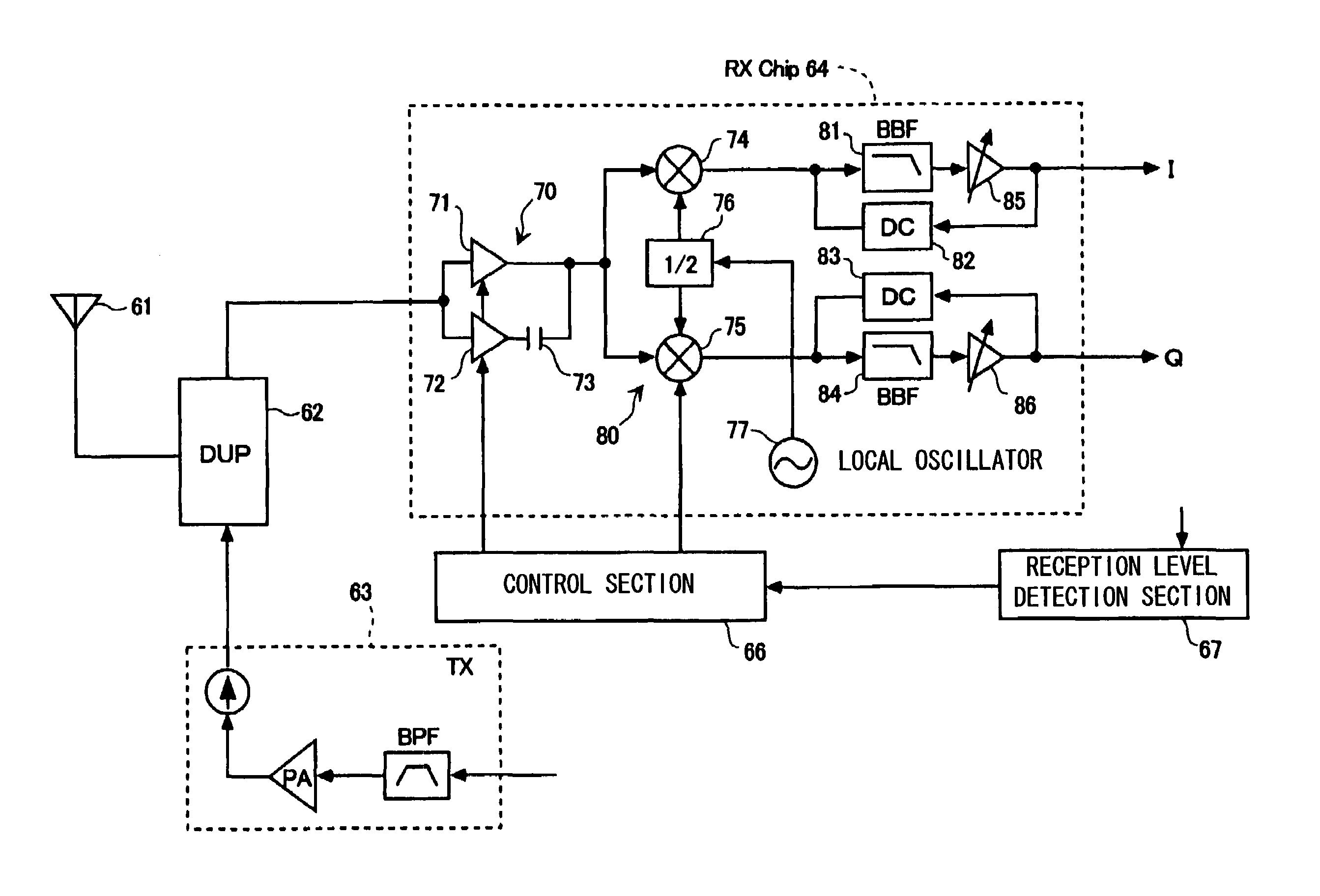

Receiver circuit and radio communication terminal apparatus

ActiveUS7221919B2Reduce power consumptionReduce areaGain controlDc level restoring means or bias distort correctionCapacitanceAudio power amplifier

There are provided, as a low noise amplifier (70) a low noise amplifier (71) with a low gain and a low noise amplifier (72) with a high gain, selectively operable under control of a bias current, and an output from the low noise amplifier (72) and a quadrature demodulator (80) are connected with a serial capacitance (73) and also an output from the low noise amplifier (71) and the quadrature demodulator (80) are serially connected. A control section (66) controls a reception circuit so that the low noise amplifier (71) operates when a reception signal level is high and the low noise amplifier (72) operates when the reception signal level is low. When the low noise amplifier (72) operates, a DC bias current thereof is made flow separately from a DC bias current of the quadrature demodulator (80), and, when the low noise amplifier (71) operates, a DC bias current thereof is shared with the quadrature demodulator.

Owner:SNAPTRACK

Transformer-based multi-band RF front-end architecture

InactiveUS20060270377A1Reduce area requirementsOne-port networksDc level restoring means or bias distort correctionMulti bandRF front end

An apparatus and method for allowing two different signal paths to be coupled to a multi-tap transformer balun. The multi-tap transformer has a first port, which is coupled to a single antenna, and two or more differential secondary ports. Each port has one or more taps, which are optimized separately for each of the signal paths, allowing each of the two or more signal paths to operate in different frequency bands. Use of the method of the invention can decrease the number of external components and integrated circuit package pins, and reduce the area required for each signal path on an integrated circuit die, a printed circuit board, or the like.

Owner:AVAGO TECH INT SALES PTE LTD

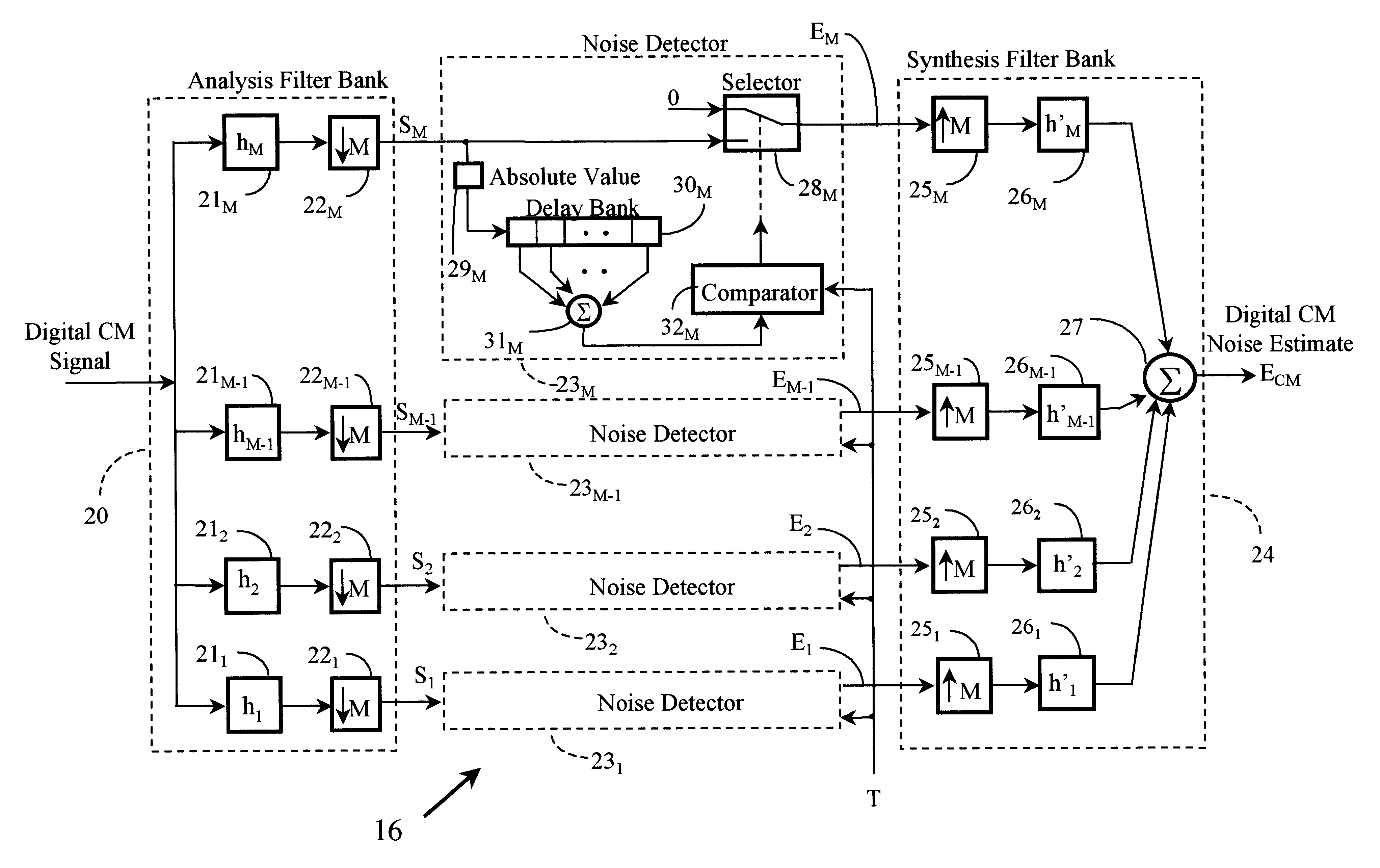

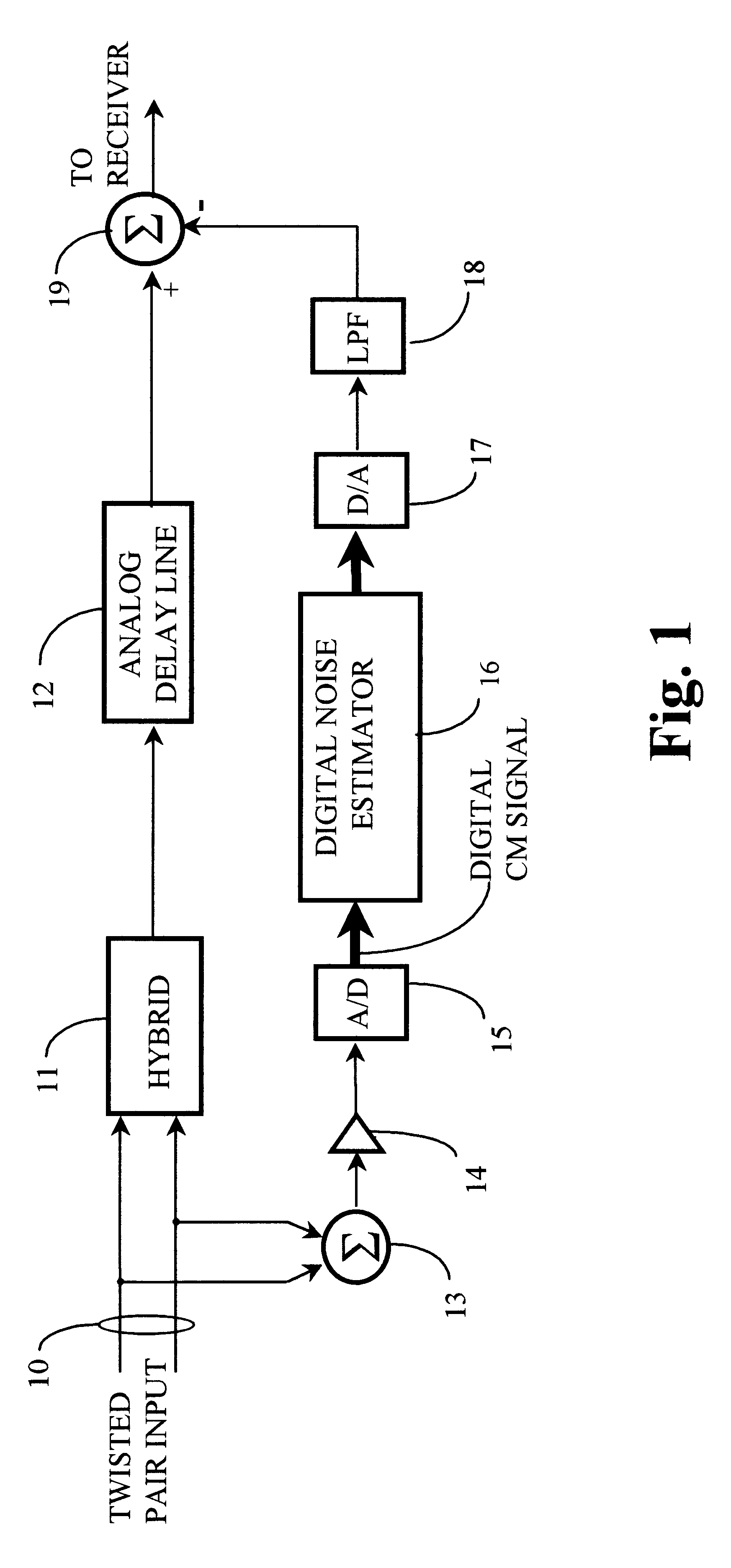

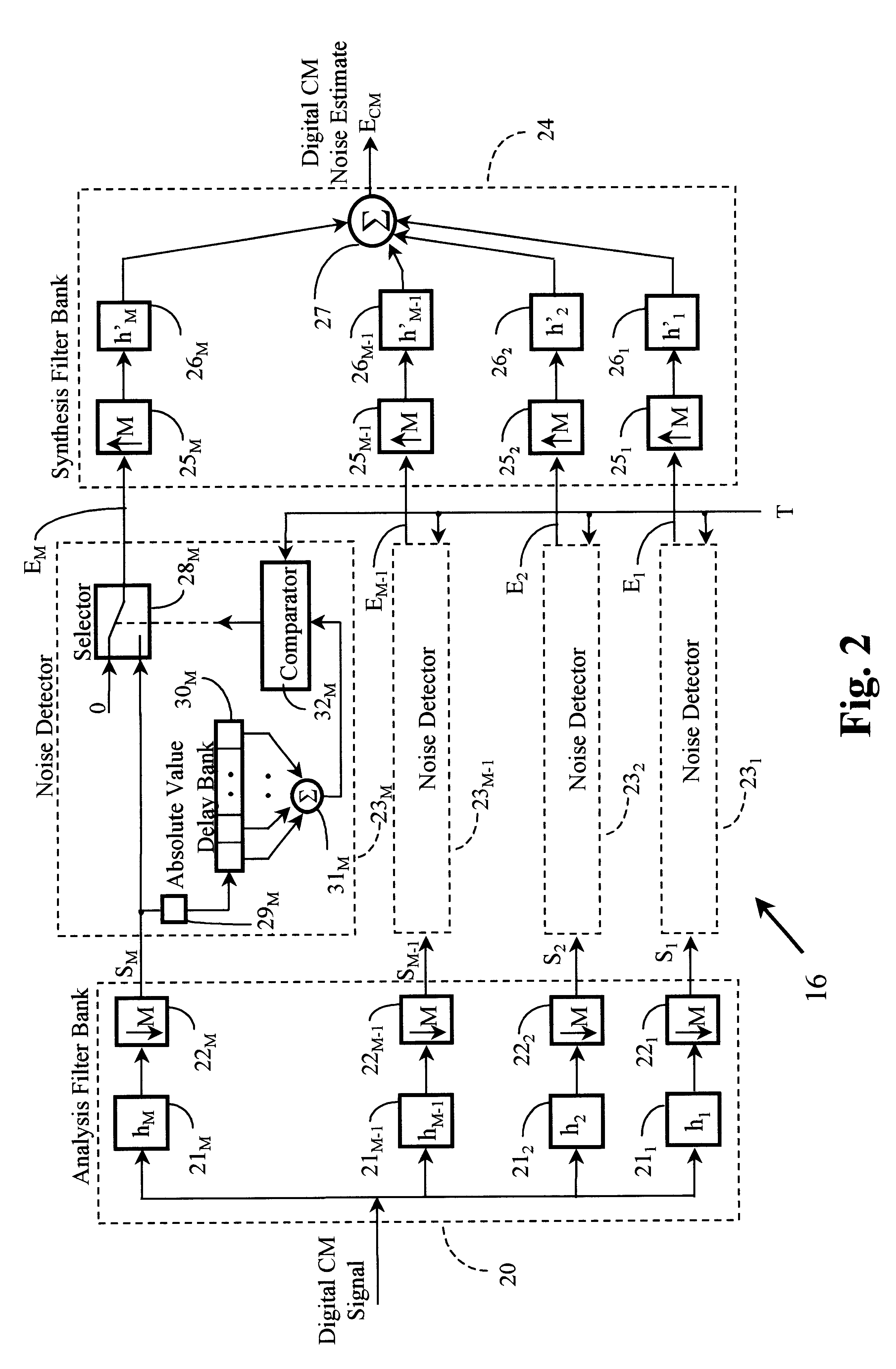

Suppression of radio frequency interference and impulse noise in communications channels

InactiveUS6546057B1Error preventionUnbalanced current interference reductionDifferential signalingEngineering

A noise suppression circuit for a communications channel (10) comprises a hybrid device (11) coupled to the channel for providing a differential output signal corresponding to a received signal. A delay unit (12) delays the differential signal by a suitable amount to allow for the generation and subtraction of a noise estimate. A summing device (13) extracts a digital common mode signal from the channel, and a noise estimation unit (16) provides a common mode noise estimate signal in dependence upon a history of the common mode signal over a predetermined period of time and over a plurality of frequency bands. The common mode noise estimate signal is combined subtractively (19) with the delayed differential signal to cancel common mode noise elements of the delayed differential signal. The noise estimation unit may comprise an analysis filter bank (20) for producing a plurality of subband signals (S1-SM), each at a different one of a plurality of different frequencies, a plurality of noise detection circuits (231-23M), each for processing a respective one of the plurality of subband signals to provide a component of the common mode noise estimate signal, and a synthesis filter bank (24) for processing the common mode noise signal components to provide the noise estimate signal.

Owner:BELL CANADA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com