Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

548 results about "Eye pattern" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

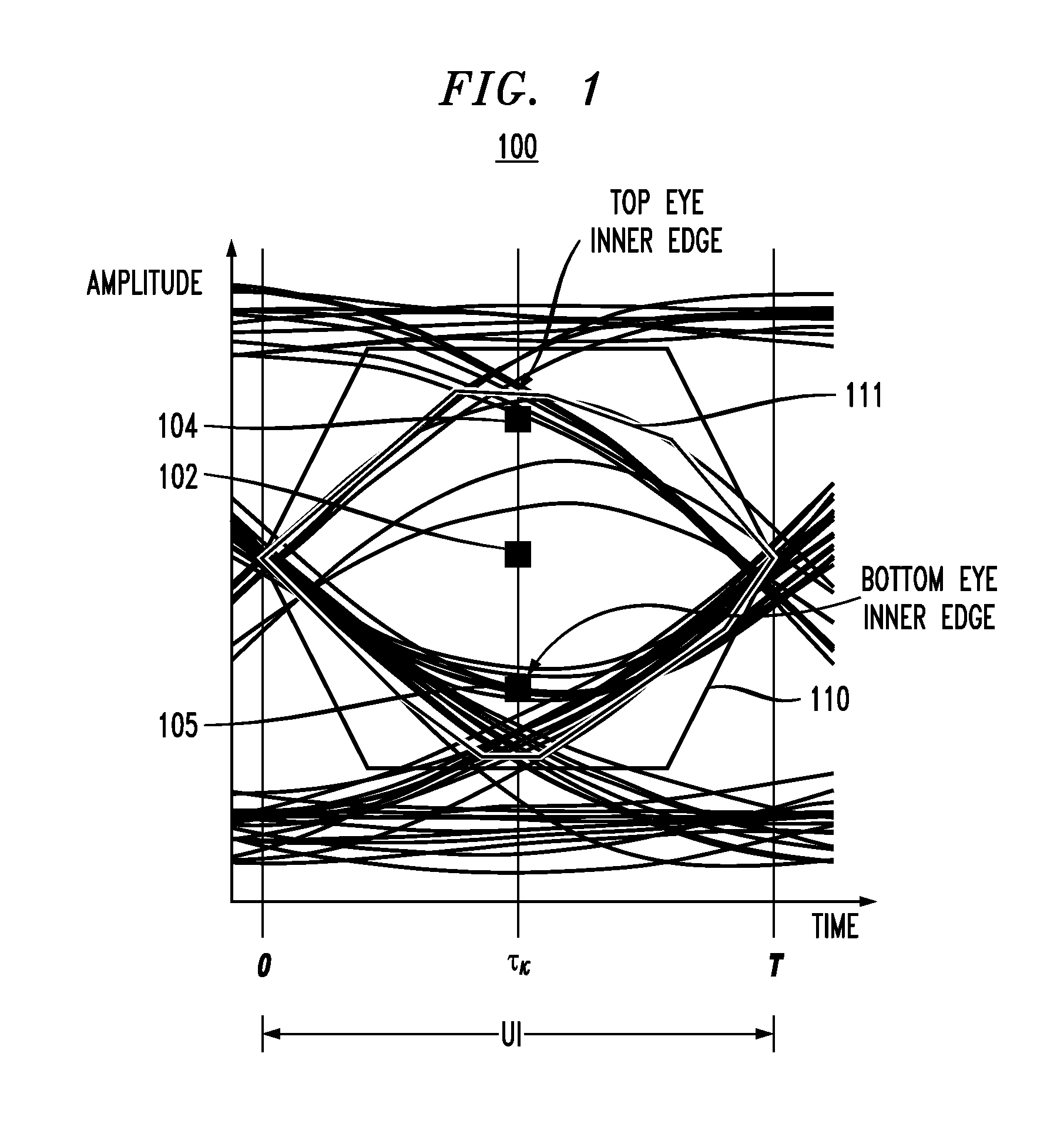

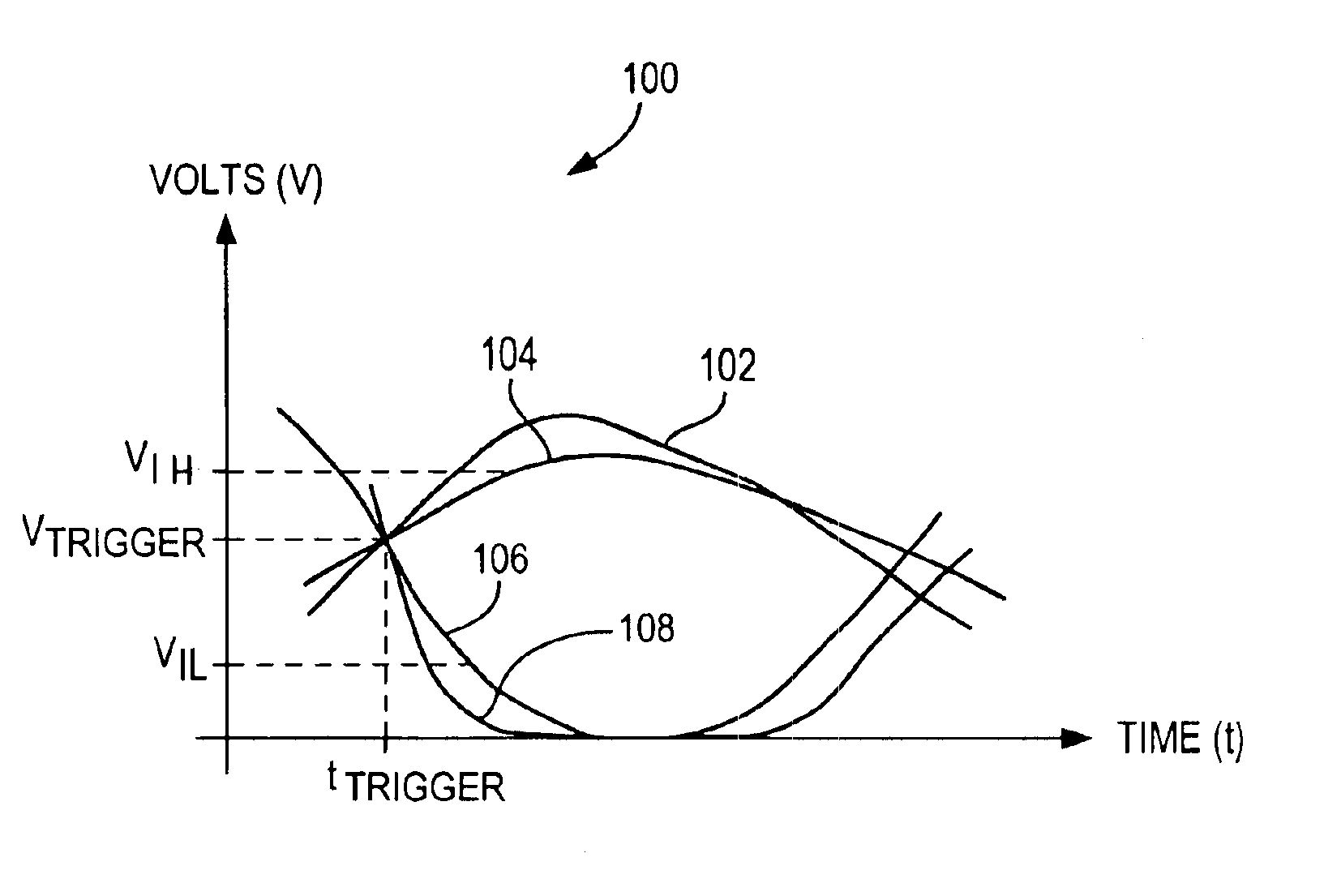

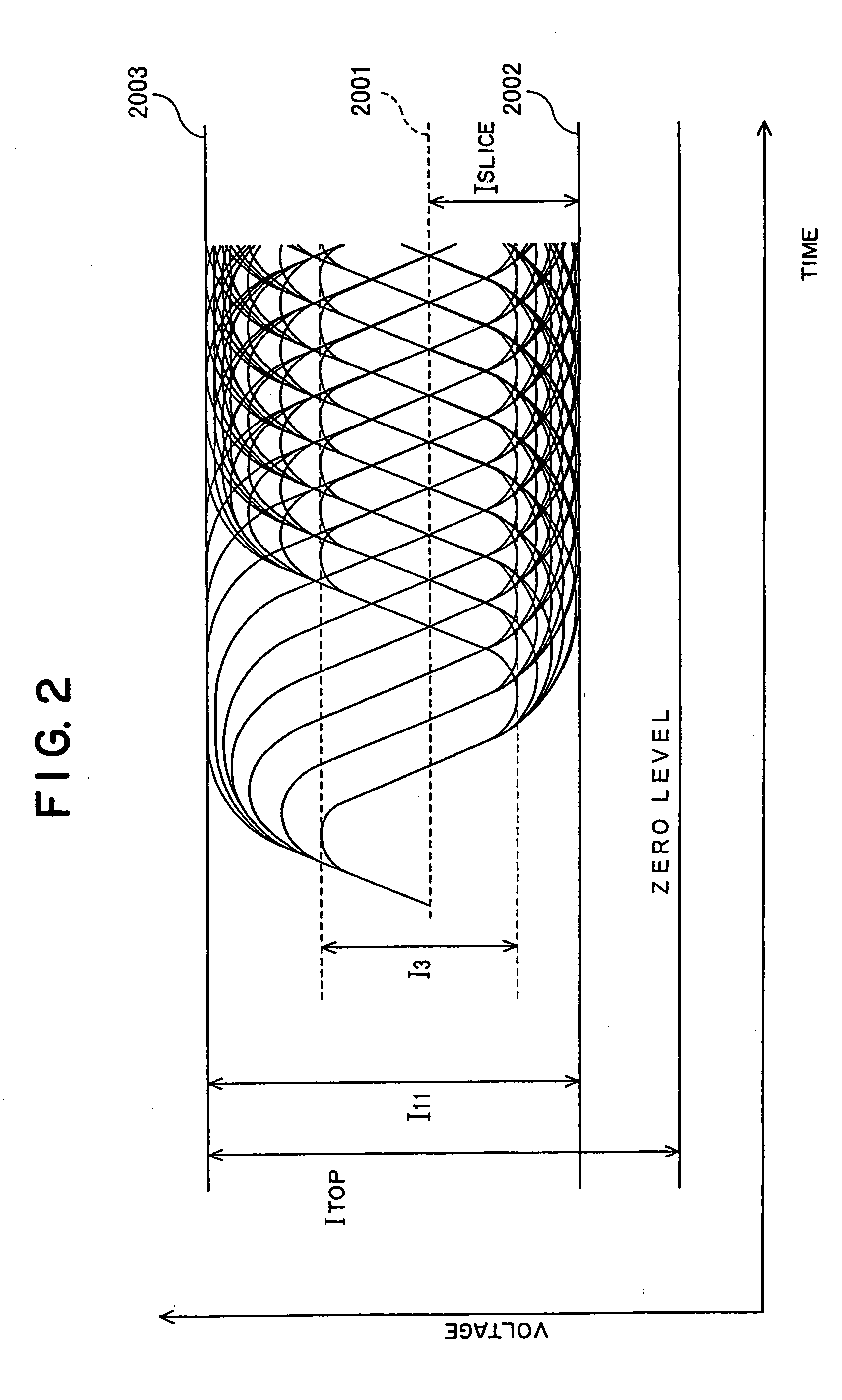

In telecommunication, an eye pattern, also known as an eye diagram, is an oscilloscope display in which a digital signal from a receiver is repetitively sampled and applied to the vertical input, while the data rate is used to trigger the horizontal sweep. It is so called because, for several types of coding, the pattern looks like a series of eyes between a pair of rails. It is a tool for the evaluation of the combined effects of channel noise and intersymbol interference on the performance of a baseband pulse-transmission system. It is the synchronised superposition of all possible realisations of the signal of interest viewed within a particular signaling interval.

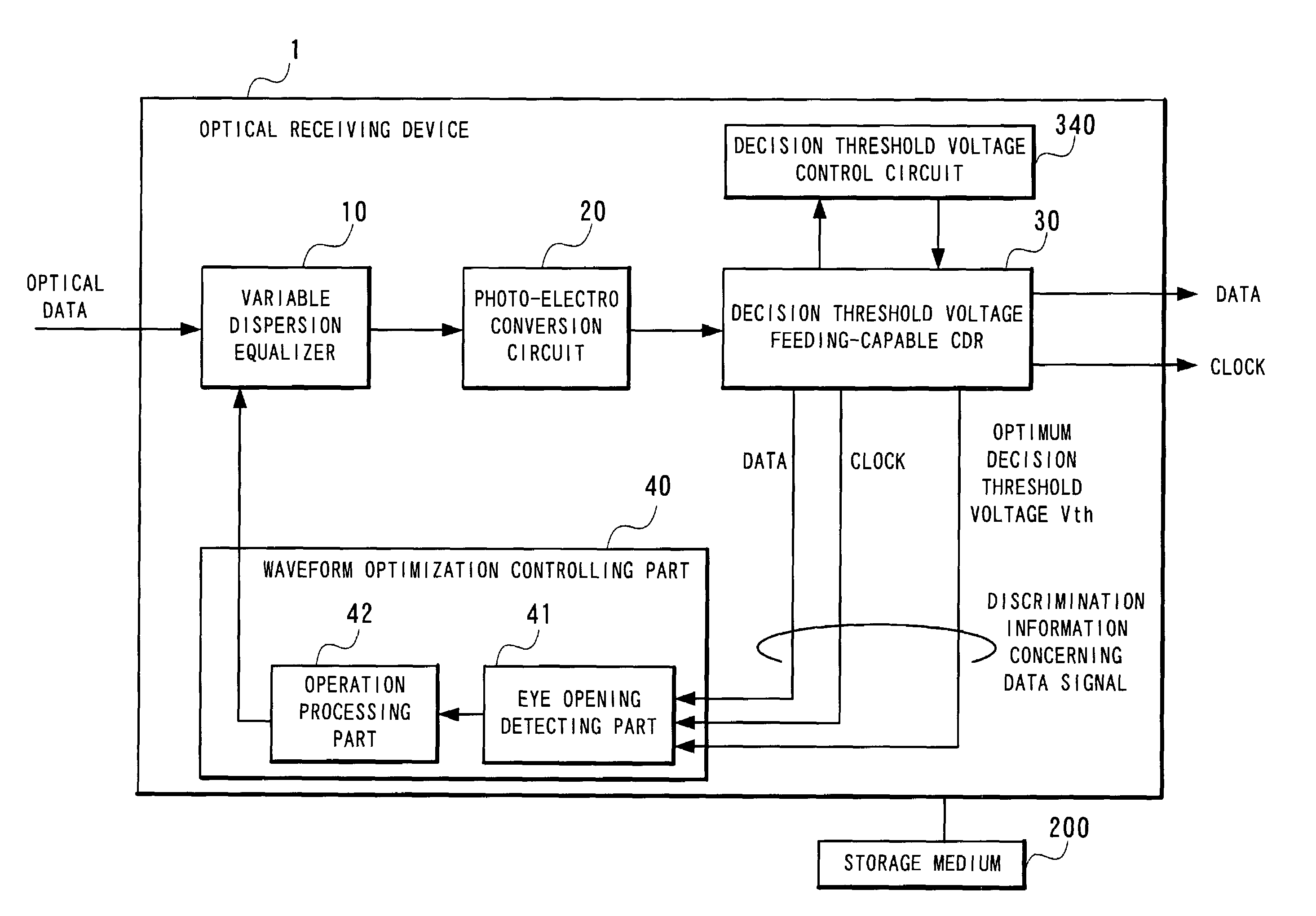

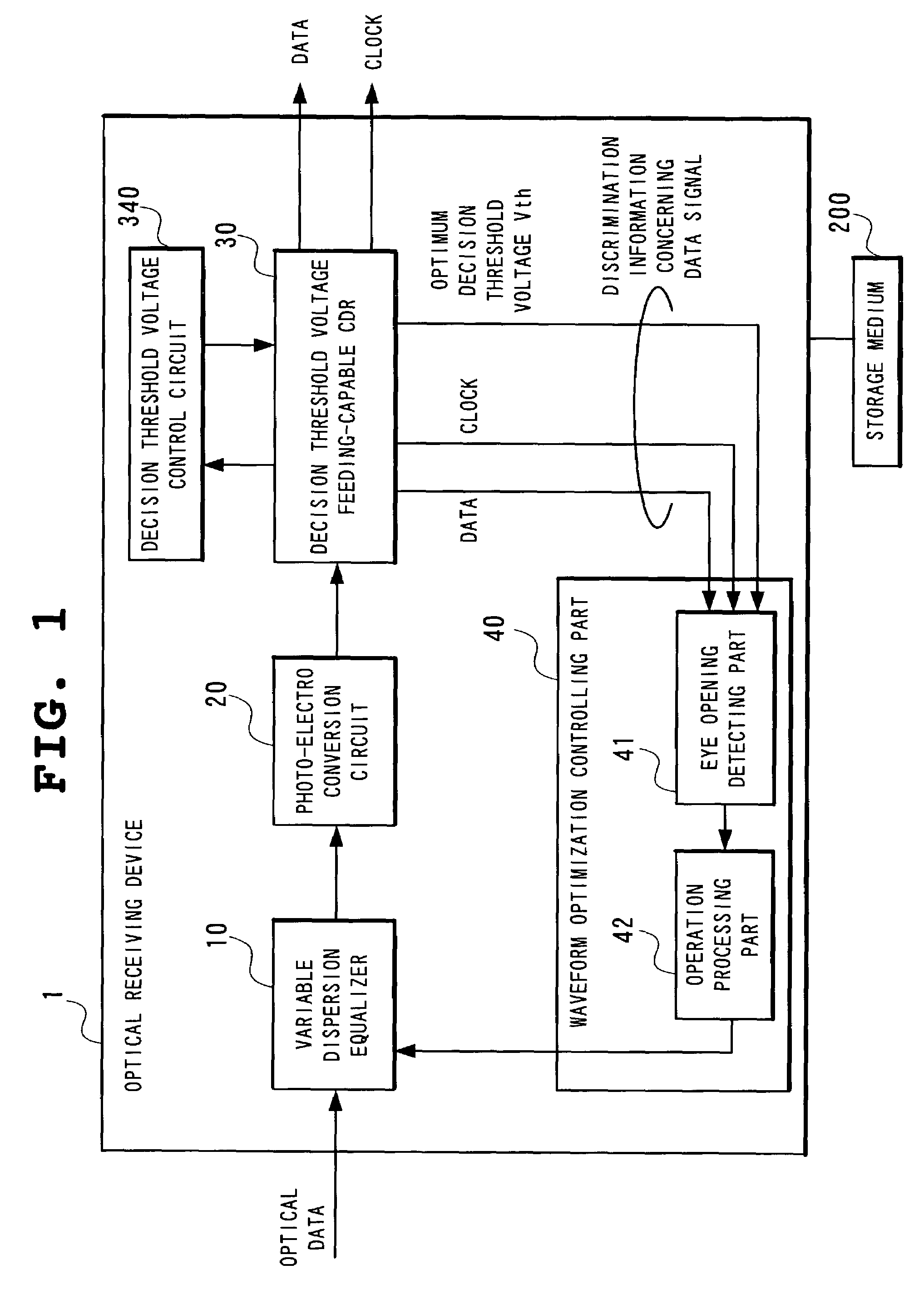

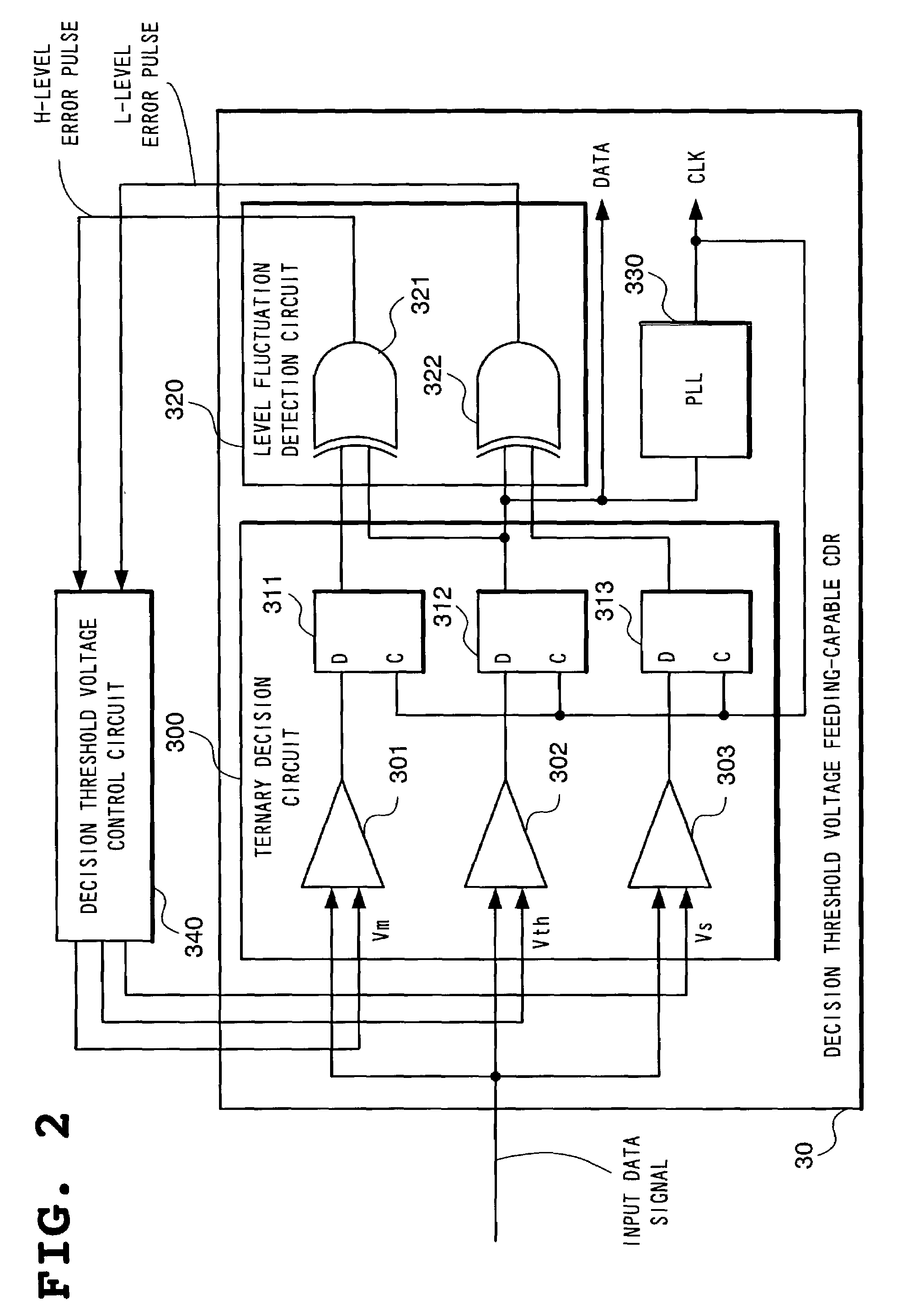

Optical receiving device, waveform optimization method for optical data signals, and waveform optimization program for optical data signals

InactiveUS7123846B2Improve waveformOptimize optical waveformTelevision system detailsFilamentary/web record carriersData signalControl data

This optical receiving device for discriminating and recovering a data signal, which results from converting an optical signal input through a dispersion equalizer into an electrical signal and amplifying it to a pre-determined amplitude, by using a clock and data recovery circuit for discriminating a data signal at the decision point controlled to achieve the optimum position controls the dispersion characteristics of a dispersion equalizer so that the error count in the recovered data signal by using a clock and data recovery circuit will be minimized by controlling the eye pattern of the data signal which has been amplified to a pre-determined amplitude.

Owner:NEC CORP

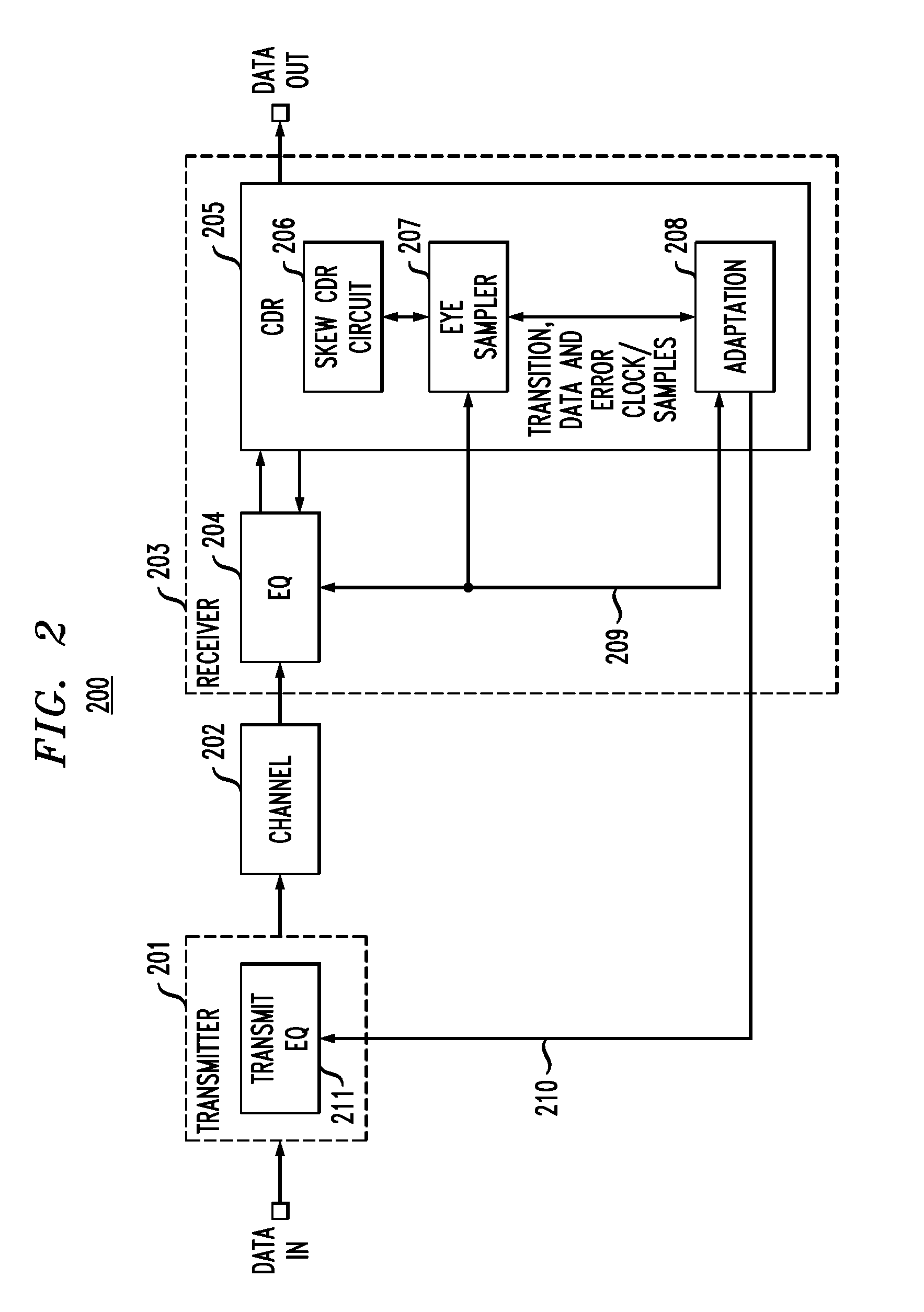

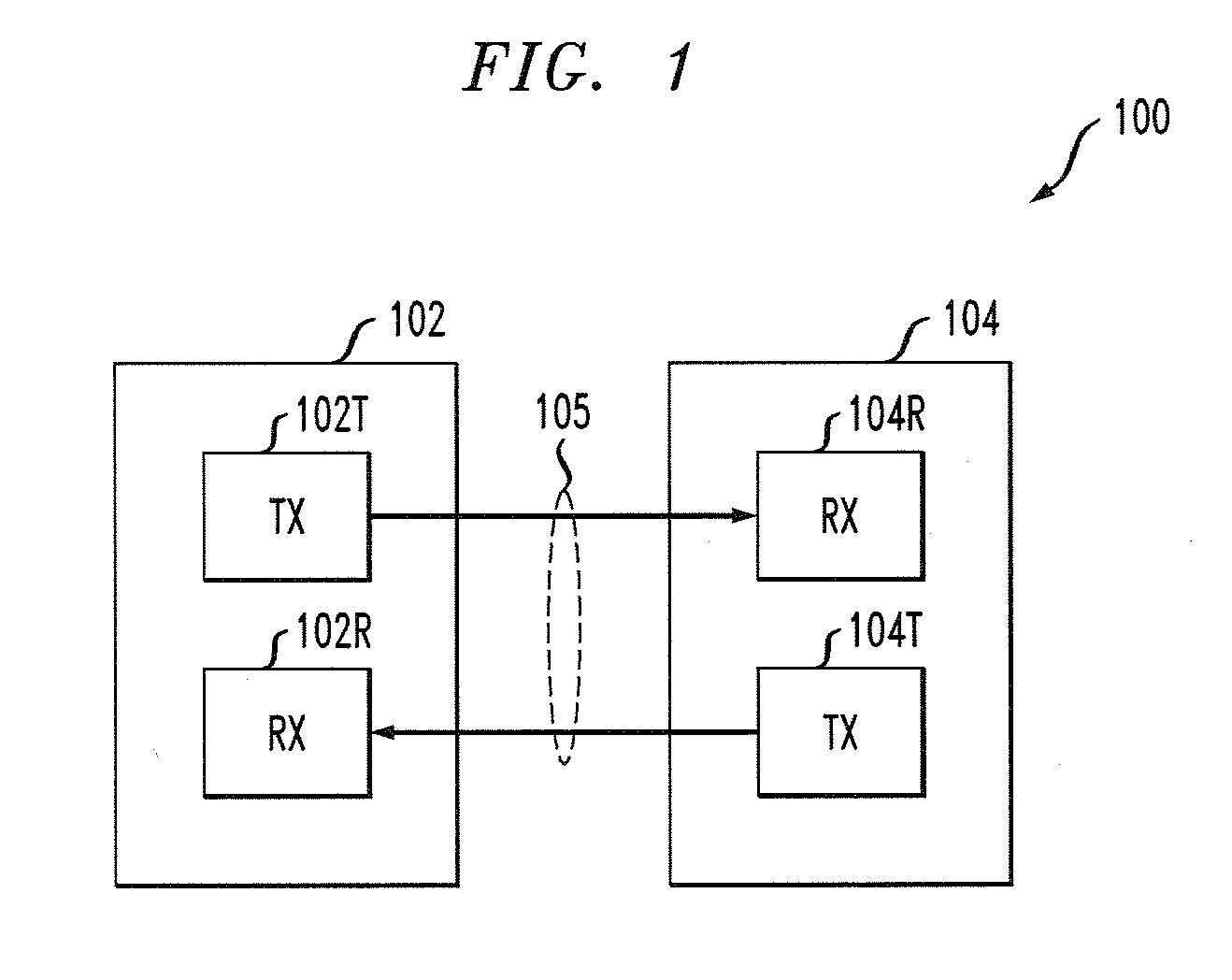

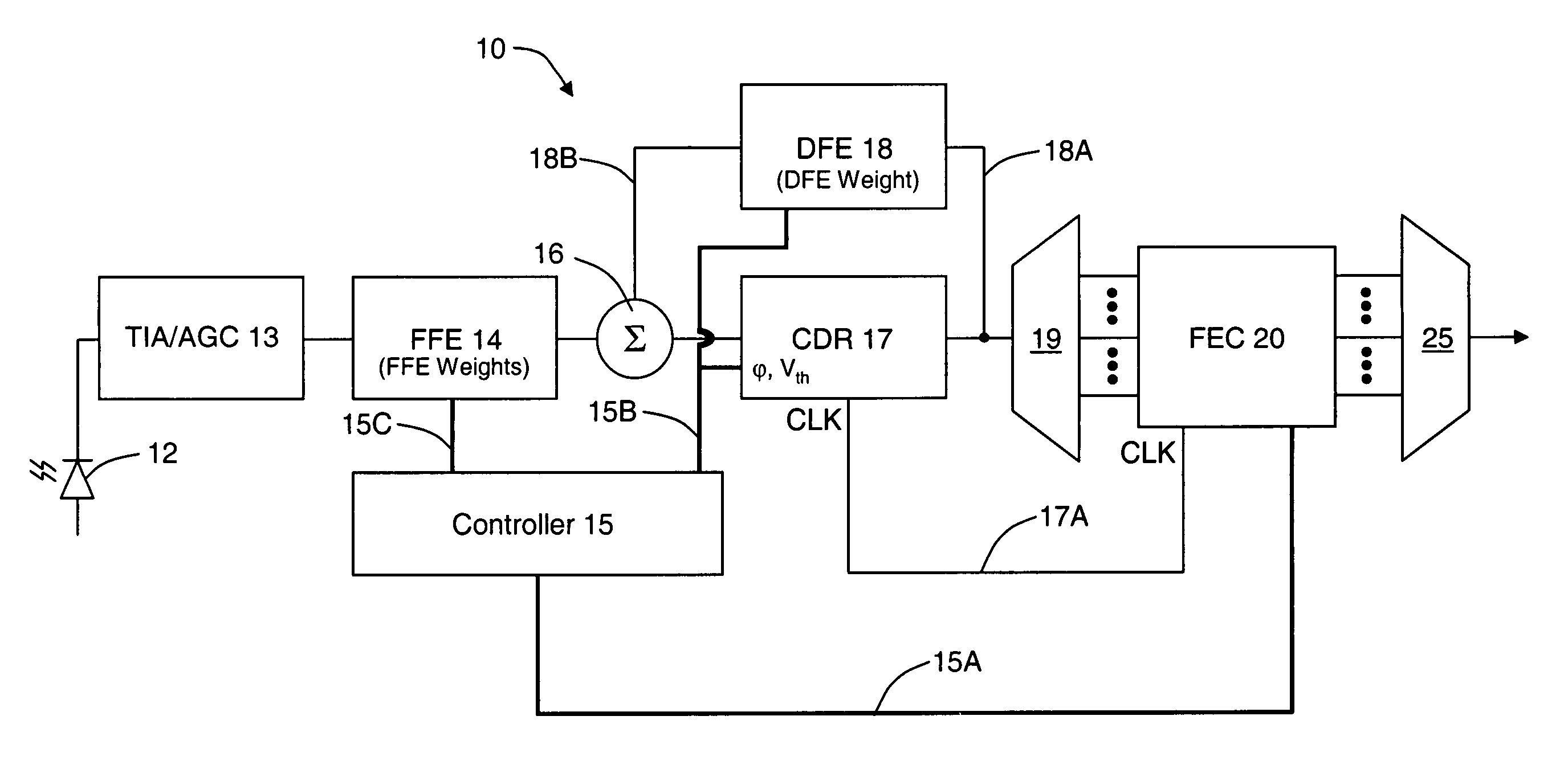

Adjusting sampling phase in a baud-rate CDR using timing skew

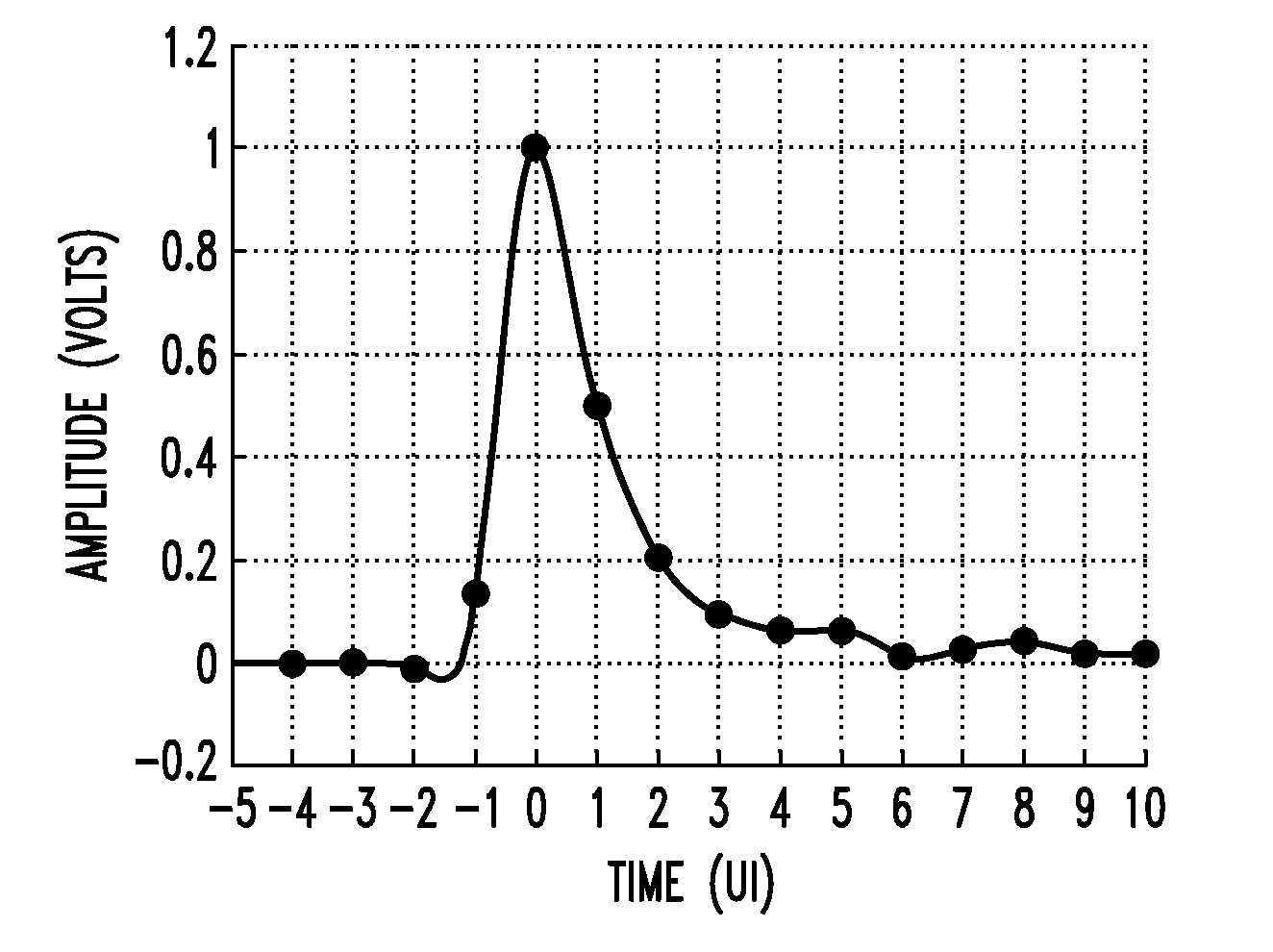

In described embodiments, a transceiver includes a baud-rate clock and data recovery (CDR) module with an eye sampler, and an adaptation module for adaptively setting parameters of various circuit elements, such as timing, equalizer and gain elements. Data sampling clock phase of the CDR module is set for sampling at, for example, near the center of a data eye detected by the eye sampler, and the phase of data error sampling latch(es) is skewed by the CDR module with respect to the phase of the data sampling latch. Since the error signal driving the timing adaptation contains the information of the pulse response that the CDR module encounters, the phase of timing error sampling latch(es) of the CDR module is skewed based on maintaining a relative equivalence of input pulse response residual pre-cursor and residual post-cursor with respect to the timing error sampling clock phase.

Owner:AVAGO TECH INT SALES PTE LTD

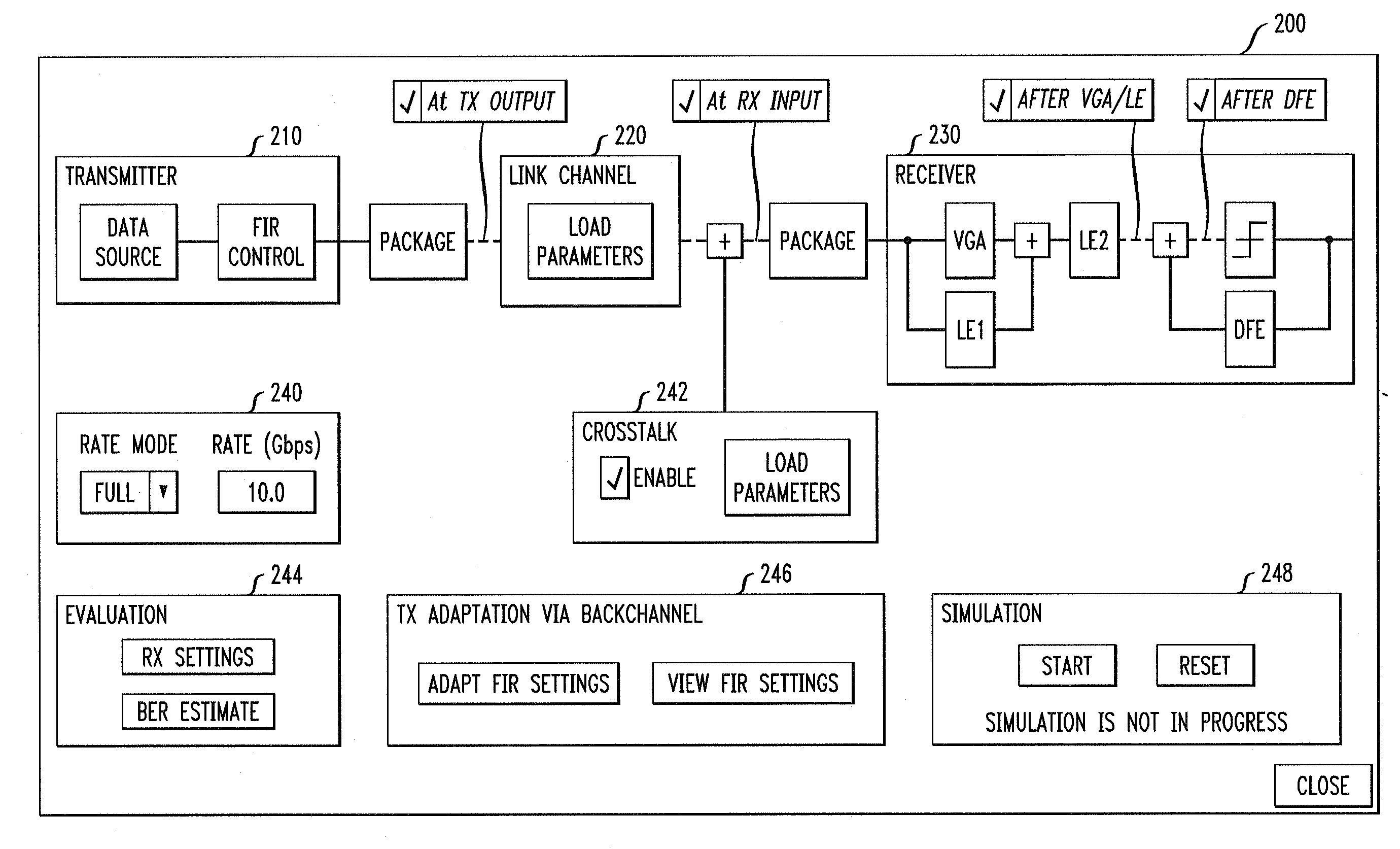

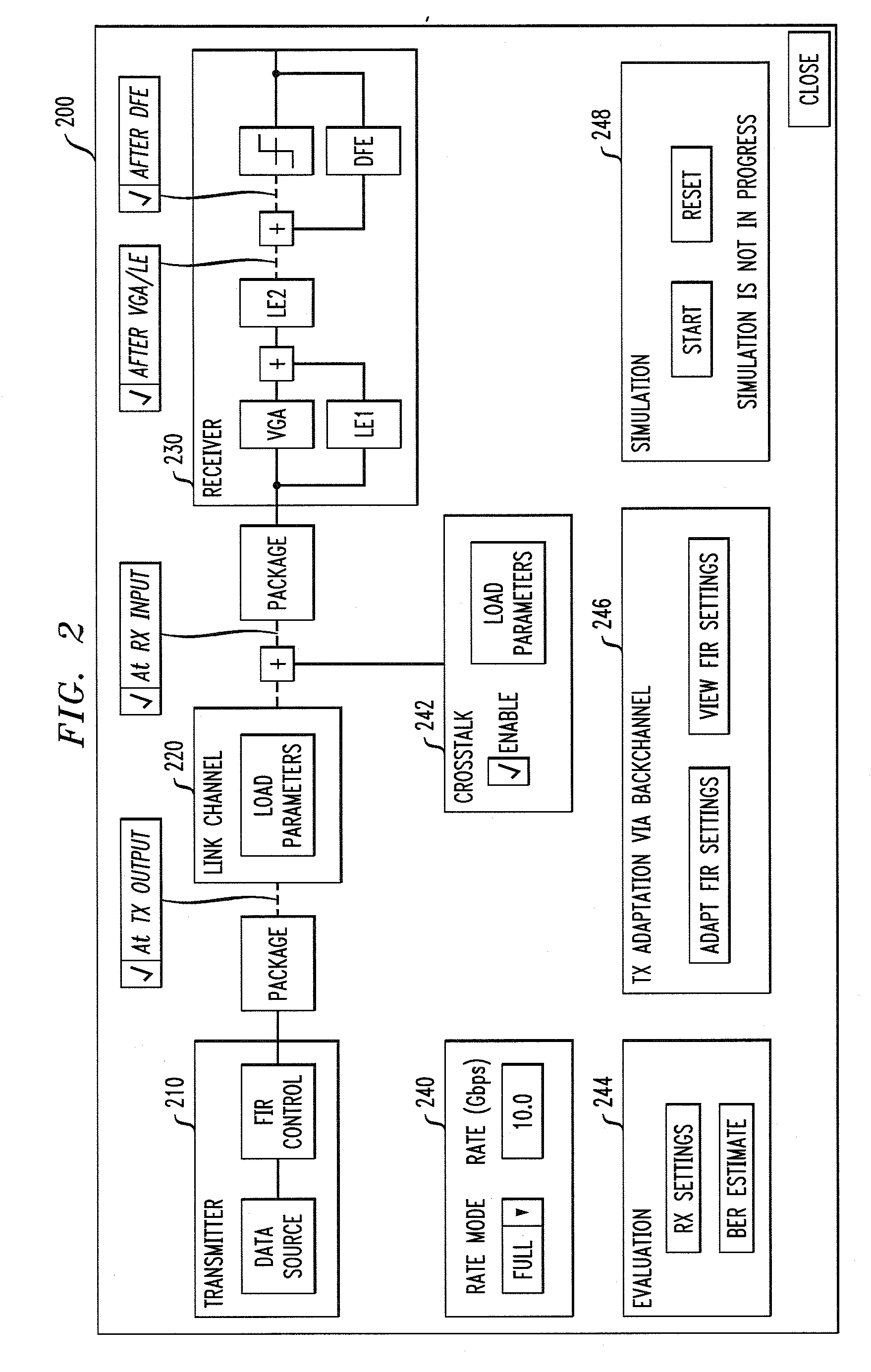

System Optimization Using Soft Receiver Masking Technique

Communication system optimization using a soft receiver masking technique is disclosed. For example, a method for testing a communication device comprises obtaining a software representation of a receiver portion of a given communication device. A data signal received from a transmitter through a given link channel is then processed, wherein the processing step is performed using the software representation of the receiver portion of the communication device. An output signal is caused to be generated by the software representation of the receiver portion. An eye mask test is then applied to the output signal. Based on a result of the eye mask test, one or more parameters of the transmitter may be adjusted.

Owner:LSI CORP

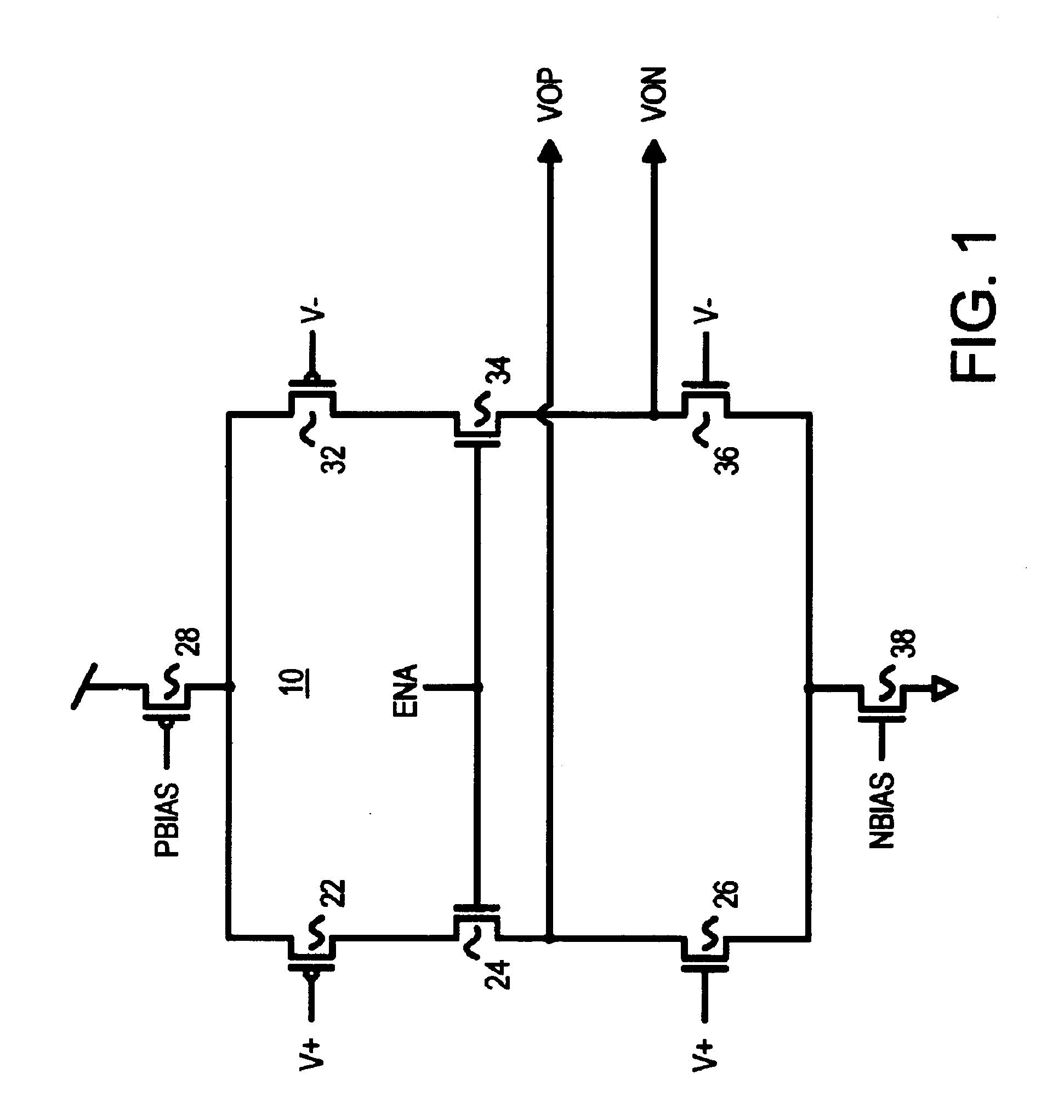

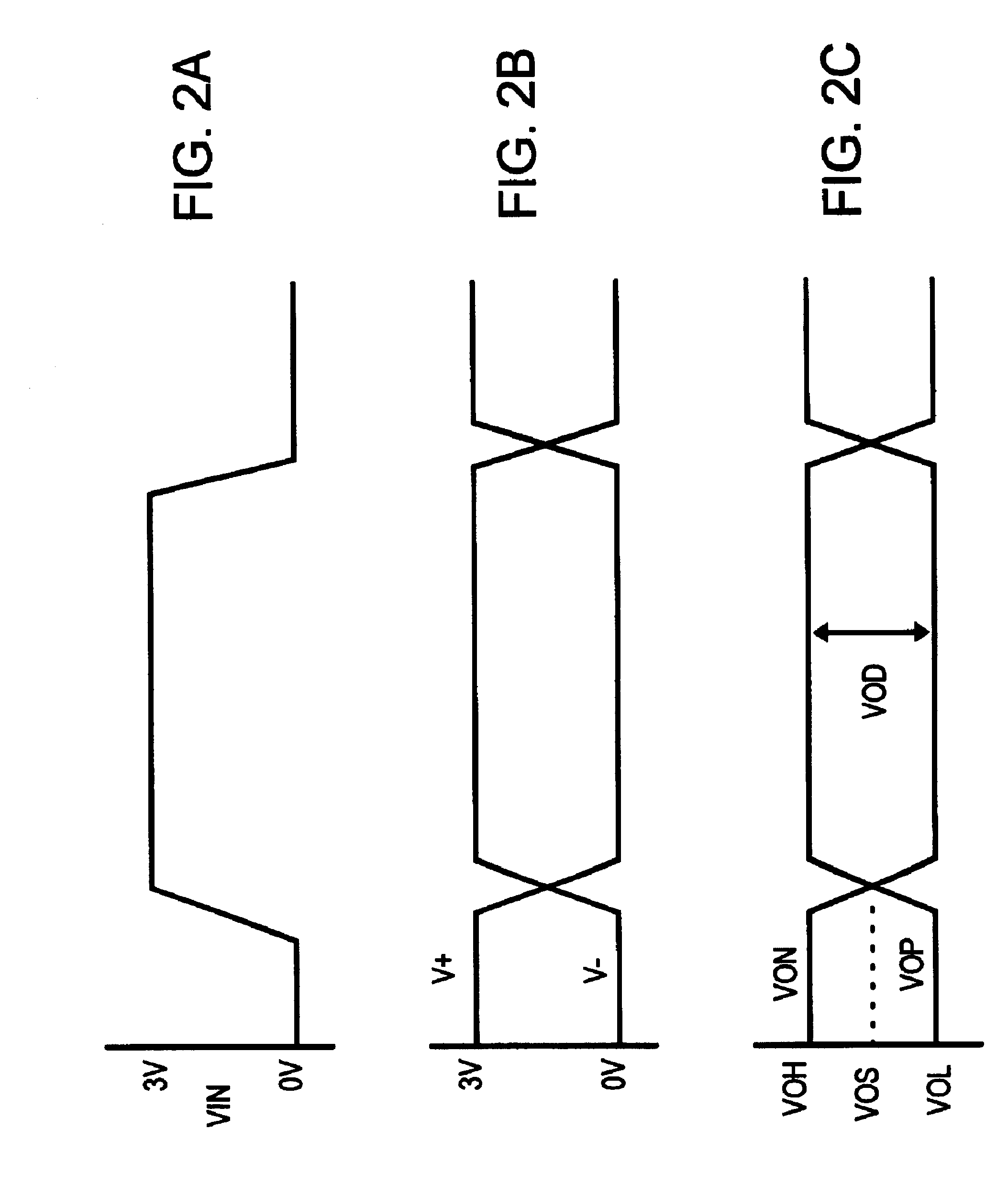

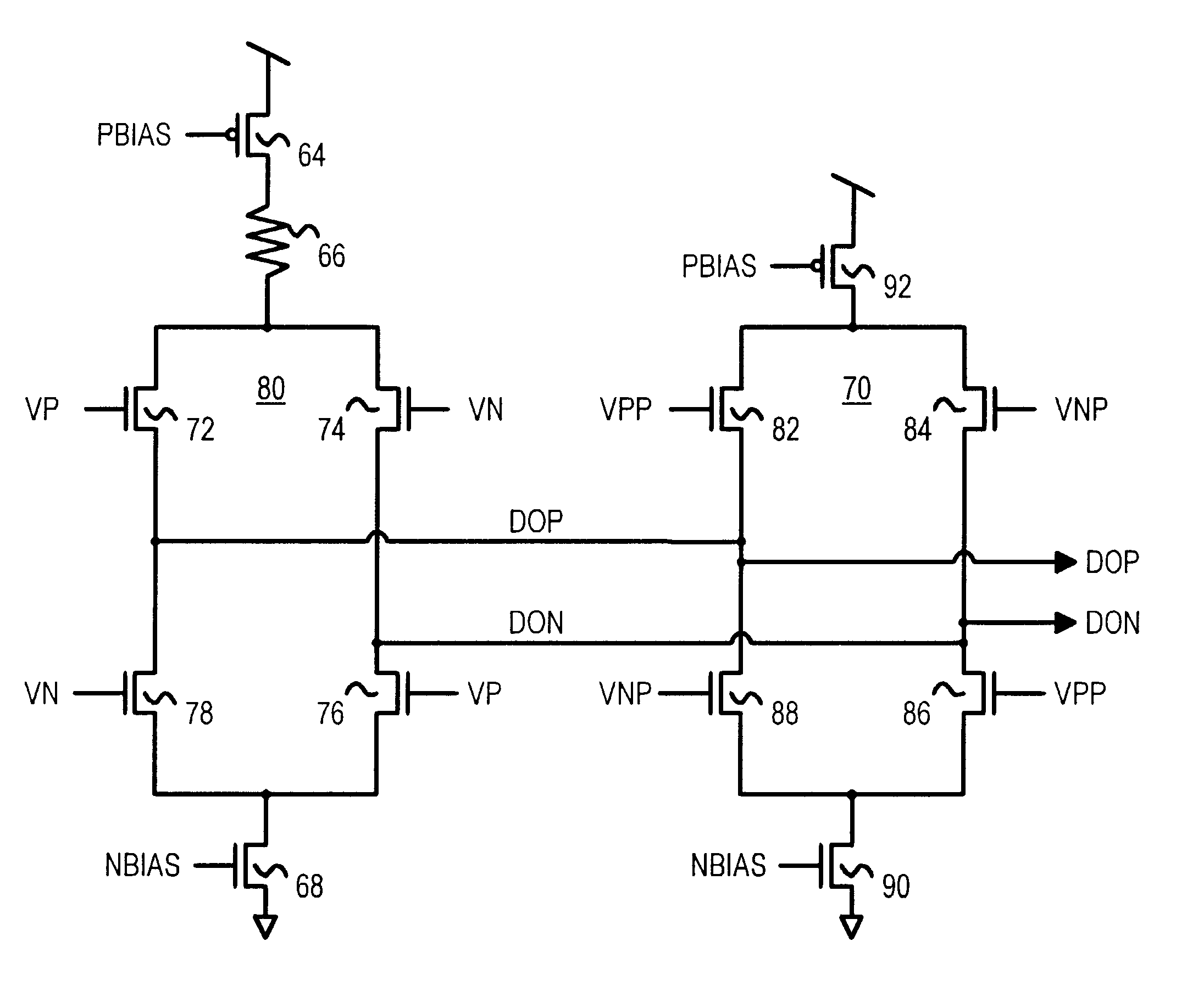

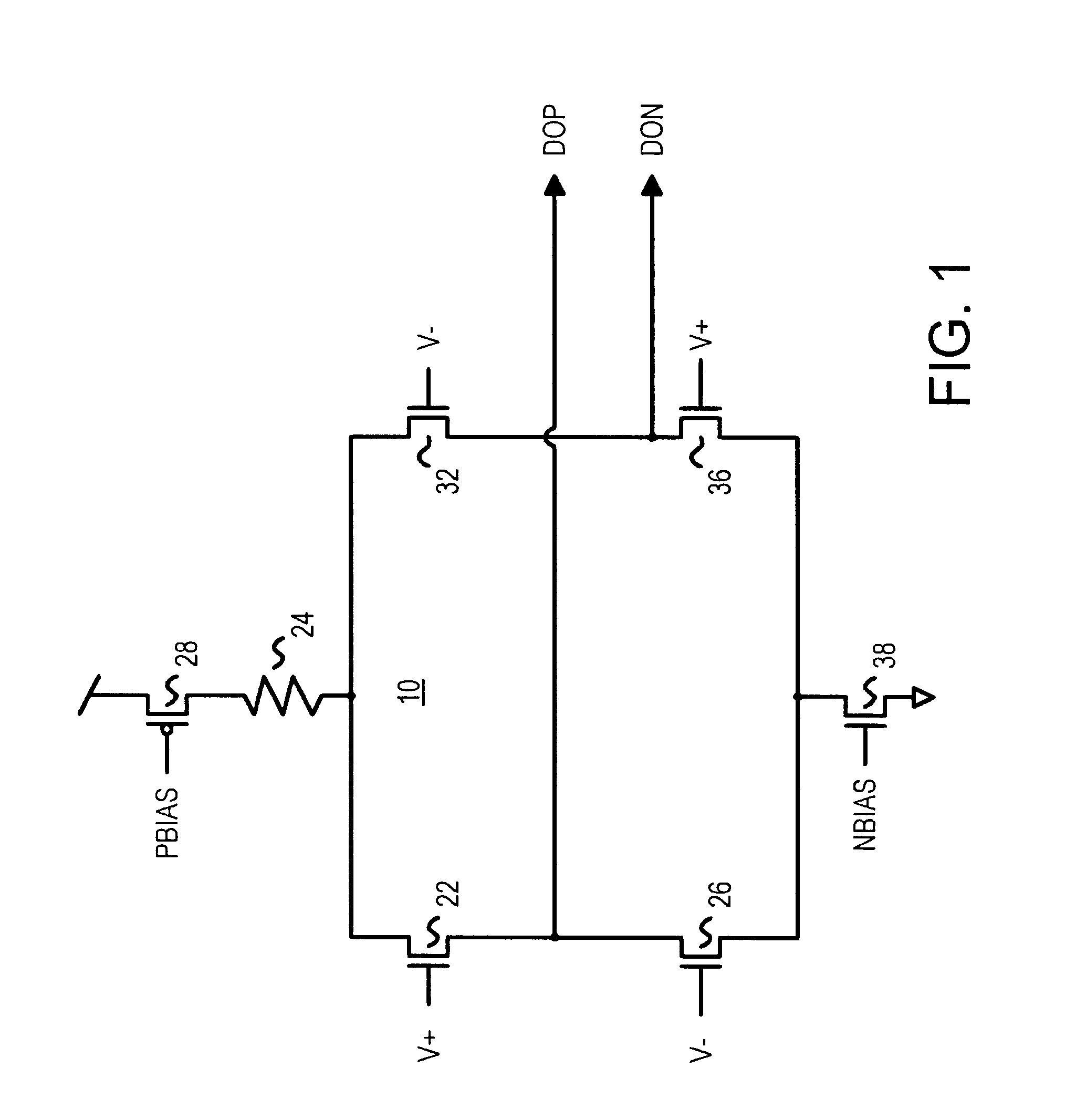

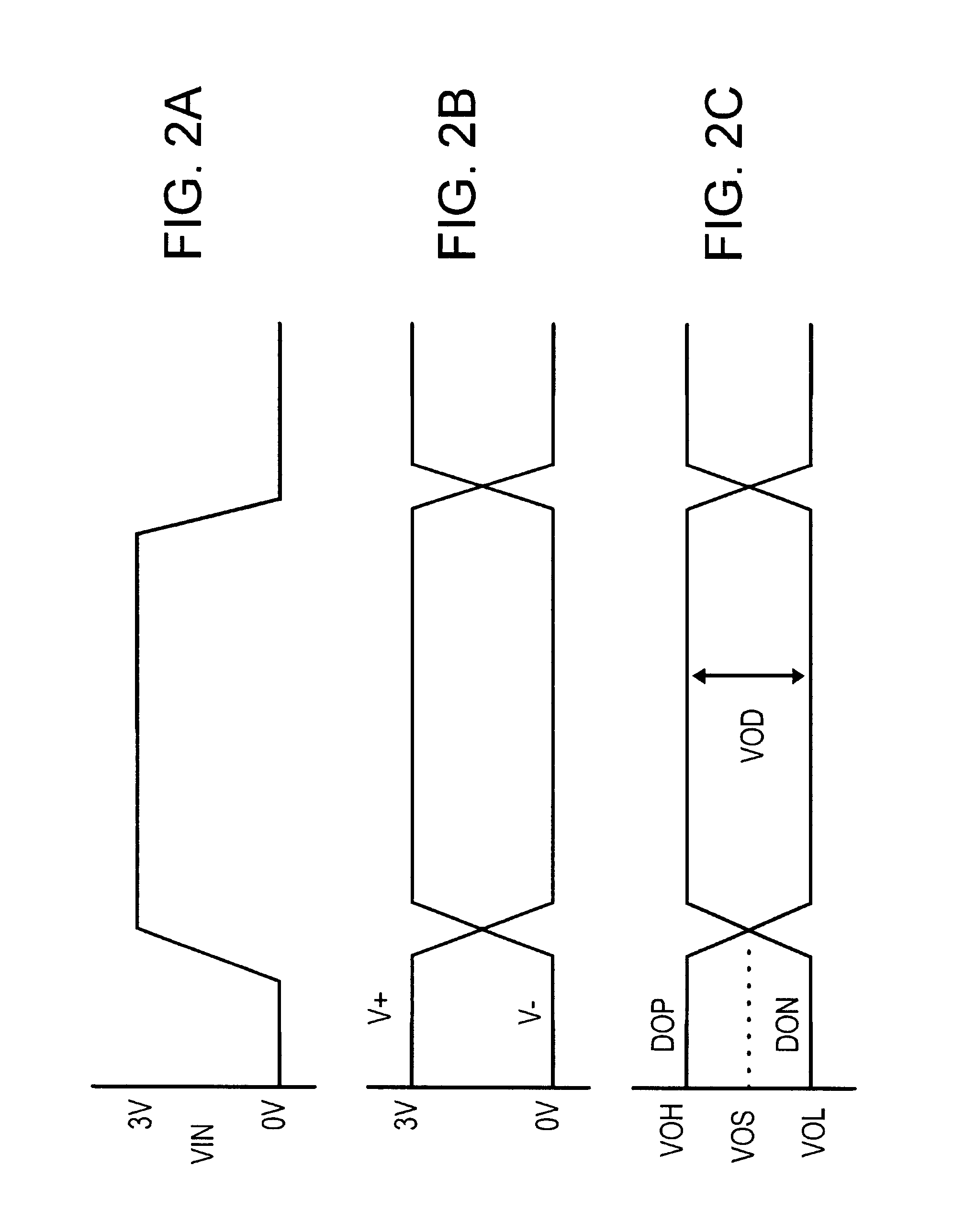

Low-voltage differential-signalling output buffer with pre-emphasis

InactiveUS6288581B1Multiple input and output pulse circuitsPulse automatic controlLow voltageEngineering

A low-voltage differential signaling (LVDS) output buffer has an improved eye pattern. The LVDS buffer has two parallel stages. A primary stage generates enough current to generate a first voltage drop across a load resistor. At higher frequencies, parasitic capacitive coupling reduces this first voltage drop, closing the eye pattern. A boost stage generates an additional boost current through the load resistor, adding to the voltage drop and opening the eye pattern. The boost stage is coupled to the outputs by link transistors that are enabled by a pre-emphasis signal generated by resetable pulse generators. When outputs switch, the pre-emphasis signal pulses the link transistors on, adding the boost current. At high frequencies, the pulse generators are reset before the pre-emphasis signal ends. The boost current is continuously added at high frequencies, but at low frequencies the boost current only occurs during the pre-emphasis period after outputs switch.

Owner:DIODES INC

Pattern-dependent error counts for use in correcting operational parameters in an optical receiver

ActiveUS7574146B2Accurate methodReduce manufacturing costMultiple-port networksError detection/prevention using signal quality detectorWeight coefficientSemiconductor chip

An optical transmission network includes an optical transmitter photonic integrated circuit (TxPIC) chip, utilized in an optical transmitter and has a plurality of monolithic modulated sources integrated for multiple signal channels on the same semiconductor chip is provided with channel equalization at the optical receiver side of the network that permits one or more such integrated modulated sources in the TxPIC chip to be out of specification thereby increasing the chip yield and reducing manufacturing costs in the deployment of such TxPIC chips. FEC error counts at the FEC decoder on the optical receiver side of the network includes counters that accumulate a plurality of bit pattern-dependent error counts based on different N-bit patterns in the received data bit stream. The accumulated counts of different N-bit patterns are utilized to provide for corrections to threshold and phase relative to the bit eye pattern as well as provided for weight coefficients for the optical receiver equalization system. The deployment of this type of equalization in a digital OEO REGEN network substantially reduces, if not eliminates, the need for dispersion compensating fiber (DCF) or EDFAs in an optical link of the network and enhances the optical receiver tolerance to chromatic dispersion (CD) so that an increase in chip yield is realized for TxPIC chips not operating with acceptable operational parameters, particularly with a desired frequency chirp parameter relative to at least one of the TxPIC modulated sources.

Owner:INFINERA CORP

Pattern-dependent error counts for use in correcting operational parameters in an optical receiver

ActiveUS20060008279A1Accurate methodReduce manufacturing costMultiple-port networksError detection/prevention using signal quality detectorWeight coefficientSemiconductor chip

An optical transmission network includes an optical transmitter photonic integrated circuit (TxPIC) chip, utilized in an optical transmitter and has a plurality of monolithic modulated sources integrated for multiple signal channels on the same semiconductor chip is provided with channel equalization at the optical receiver side of the network that permits one or more such integrated modulated sources in the TxPIC chip to be out of specification thereby increasing the chip yield and reducing manufacturing costs in the deployment of such TxPIC chips. FEC error counts at the FEC decoder on the optical receiver side of the network includes counters that accumulate a plurality of bit pattern-dependent error counts based on different N-bit patterns in the received data bit stream. The accumulated counts of different N-bit patterns are utilized to provide for corrections to threshold and phase relative to the bit eye pattern as well as provided for weight coefficients for the optical receiver equalization system. The deployment of this type of equalization in a digital OEO REGEN network substantially reduces, if not eliminates, the need for dispersion compensating fiber (DCF) or EDFAs in an optical link of the network and enhances the optical receiver tolerance to chromatic dispersion (CD) so that an increase in chip yield is realized for TxPIC chips not operating with acceptable operational parameters, particularly with a desired frequency chirp parameter relative to at least one of the TxPIC modulated sources.

Owner:INFINERA CORP

Low-voltage differential driver with opened eye pattern

A differential output buffer has a primary stage and a secondary stage that each directly drive differential outputs. Link transistors between the secondary stage and the differential outputs are eliminated. The primary stage continuously receives differential inputs applied to gates of n-channel sourcing and sinking transistors. The sources of the sourcing transistors and the drains of the sinking transistors are connected to the true and complement differential outputs. The secondary stage also has n-channel sourcing and sinking transistors directly connected to the differential outputs. Pulsed inputs applied to secondary-stage gates are normally low, disabling the sourcing and sinking transistors in the secondary stage to disable the secondary stage. However, during a switching transient, the pulsed inputs are pulsed on, allowing the secondary stage to drive a boost current to the differential outputs. This boost current sharpens rise and fall edges to compensate parasitic capacitances, opening the eye pattern.

Owner:DIODES INC

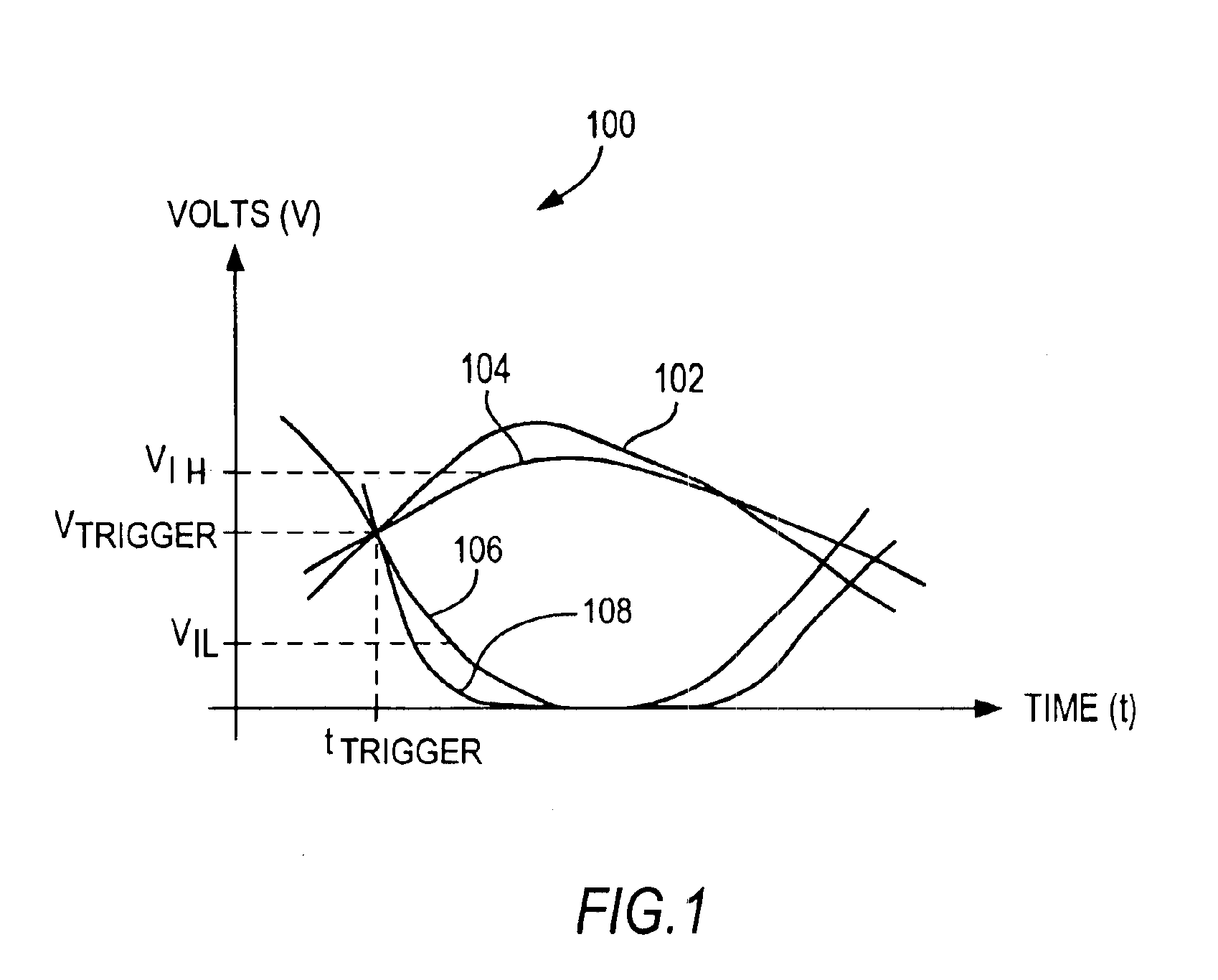

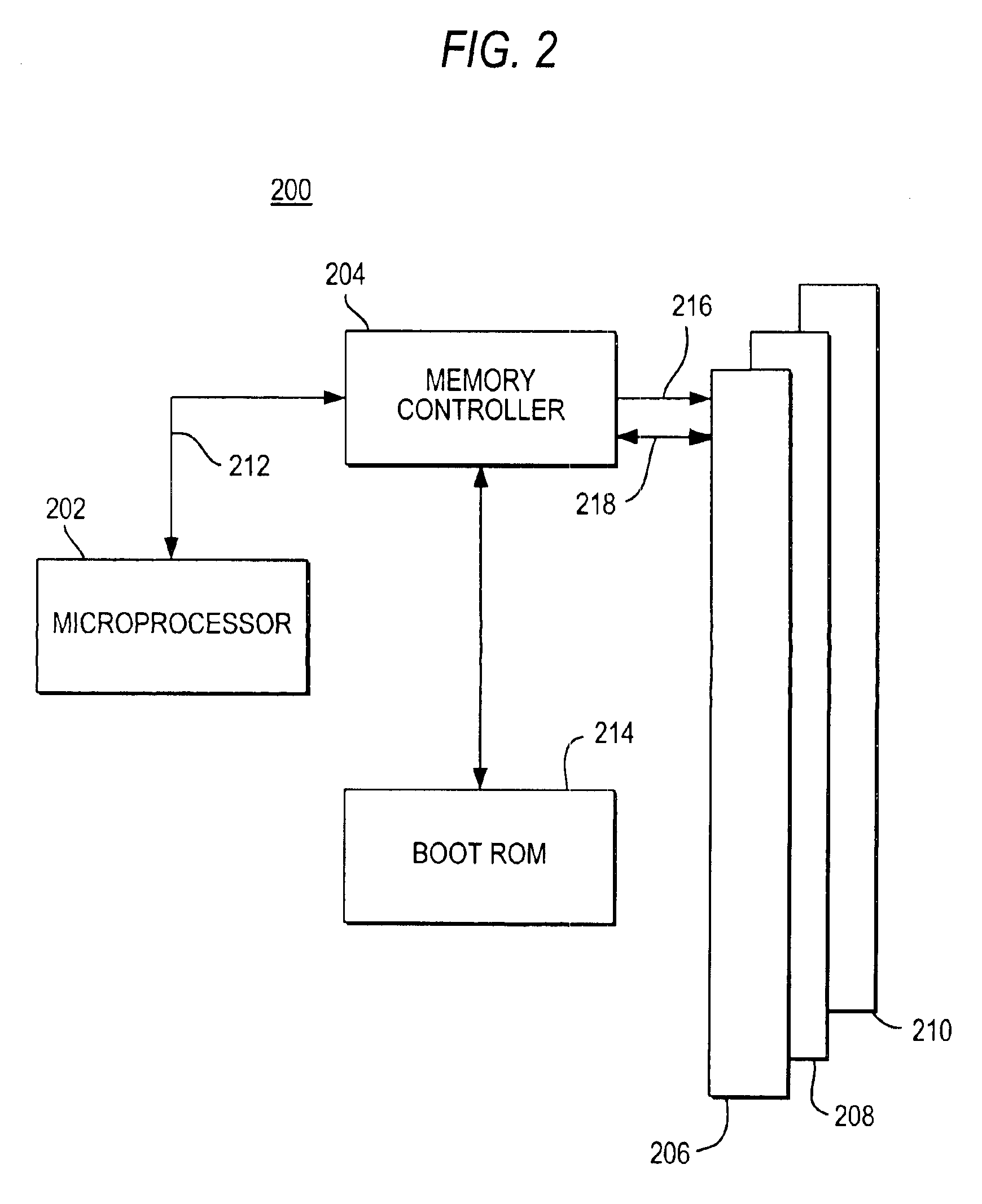

Calibration of memory circuits

A method for calibration of memory circuits is provided that adjusts memory circuit output parameters based on data eye measurements. Data eye patterns from the memory circuit outputs are measured by the memory controller for different settings of the memory circuit output parameters. Memory circuit output parameters can be adjusted to settings that correspond to widest average data eye widths, highest average data eye heights, or other suitable criteria.

Owner:ROUND ROCK RES LLC

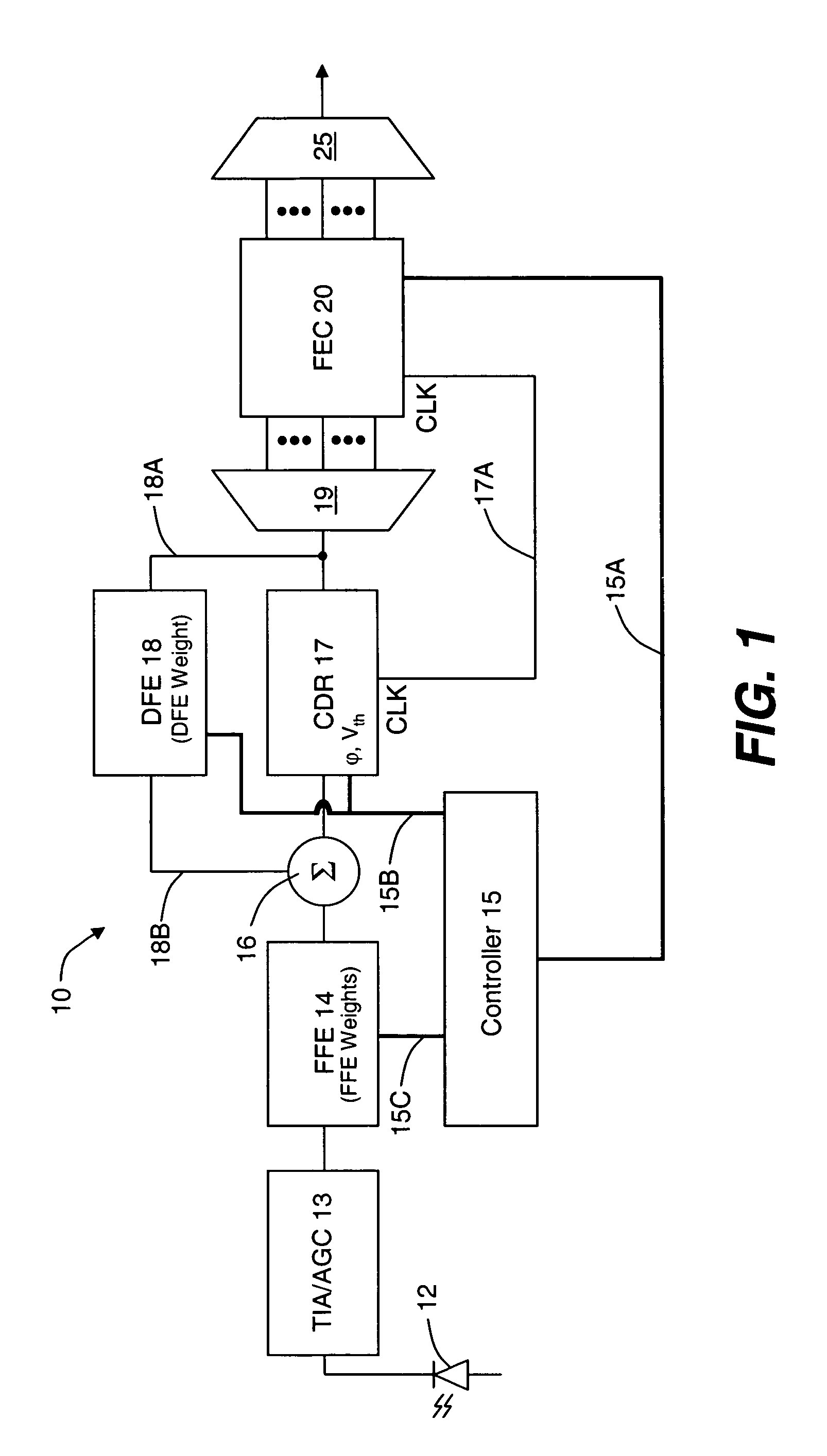

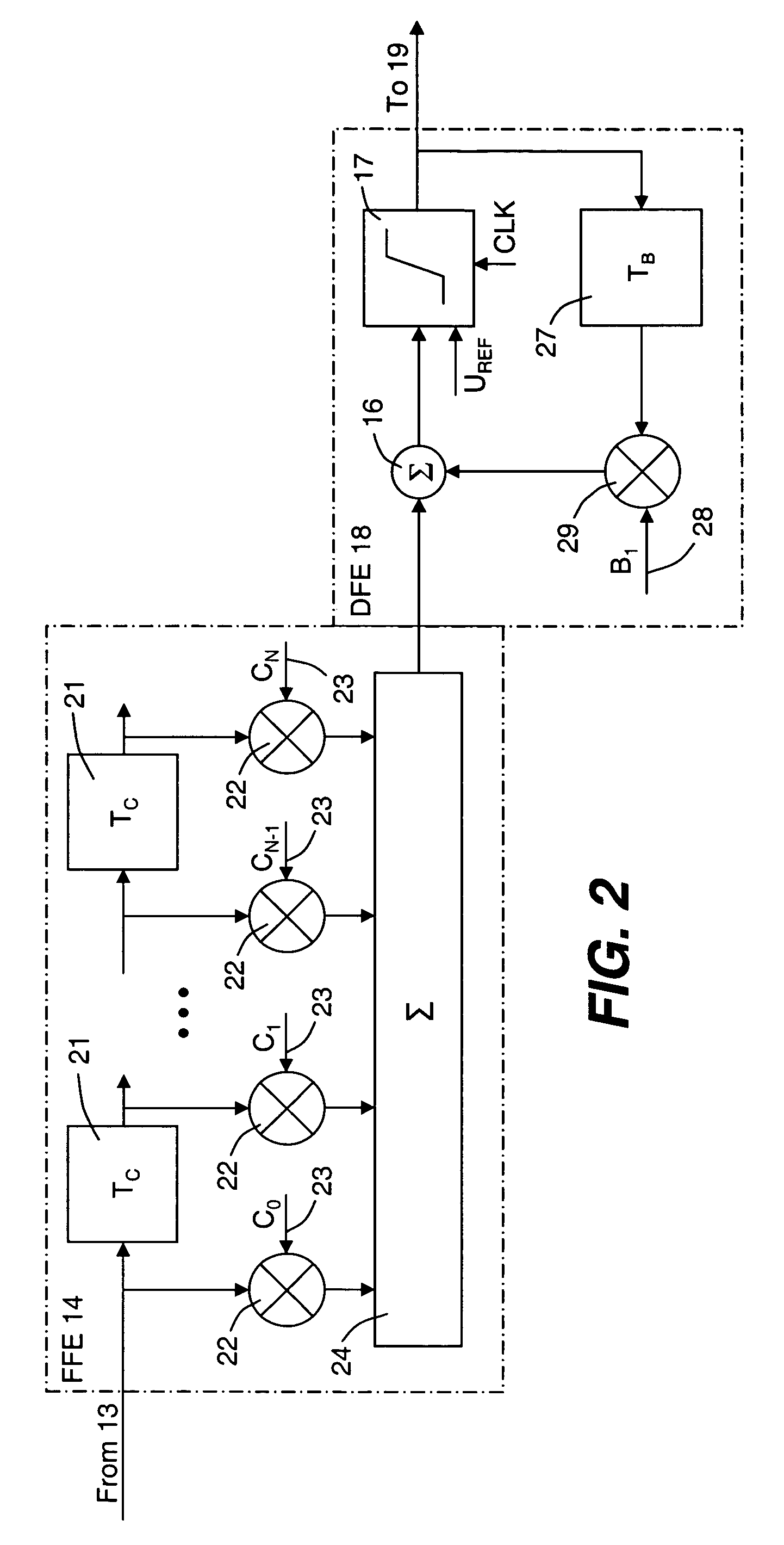

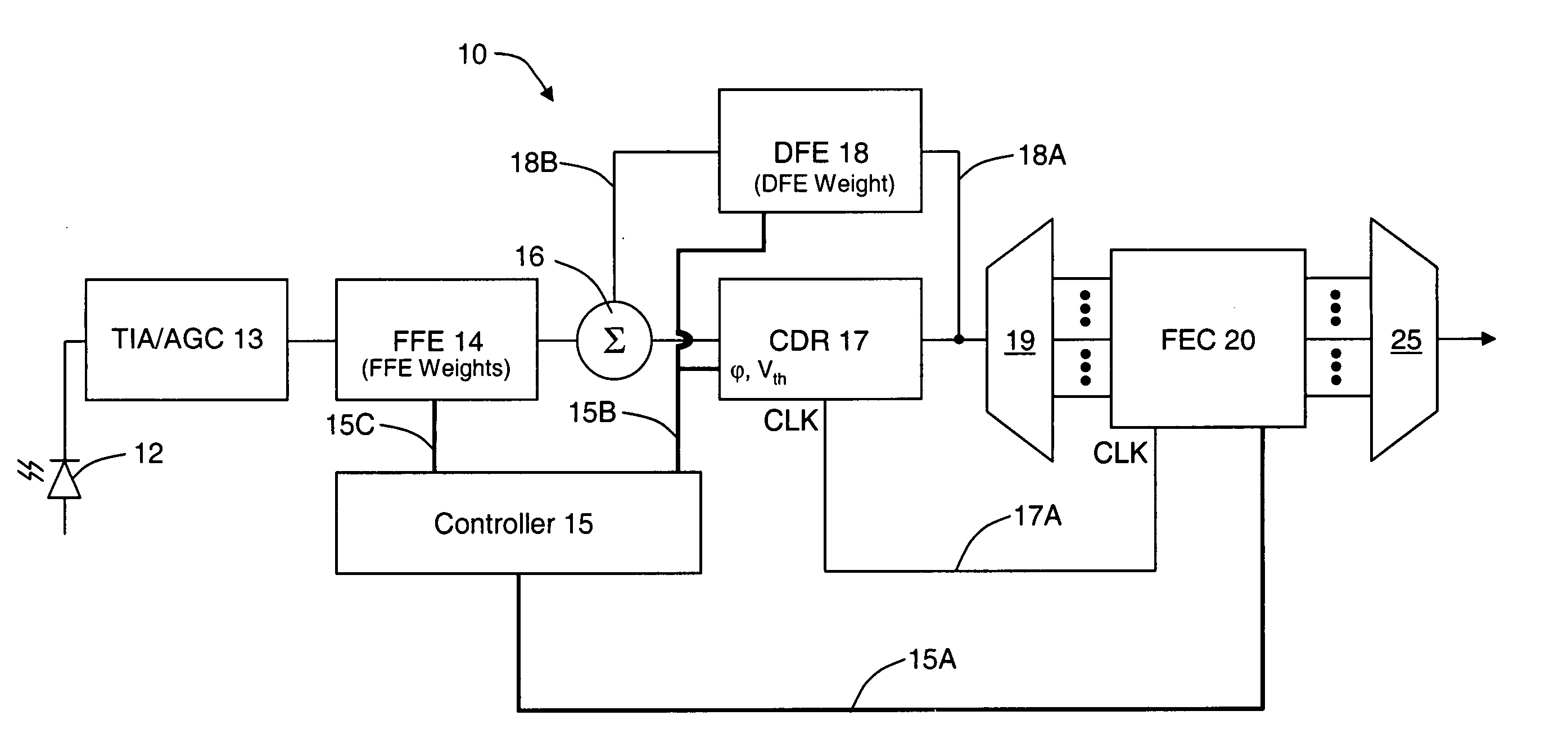

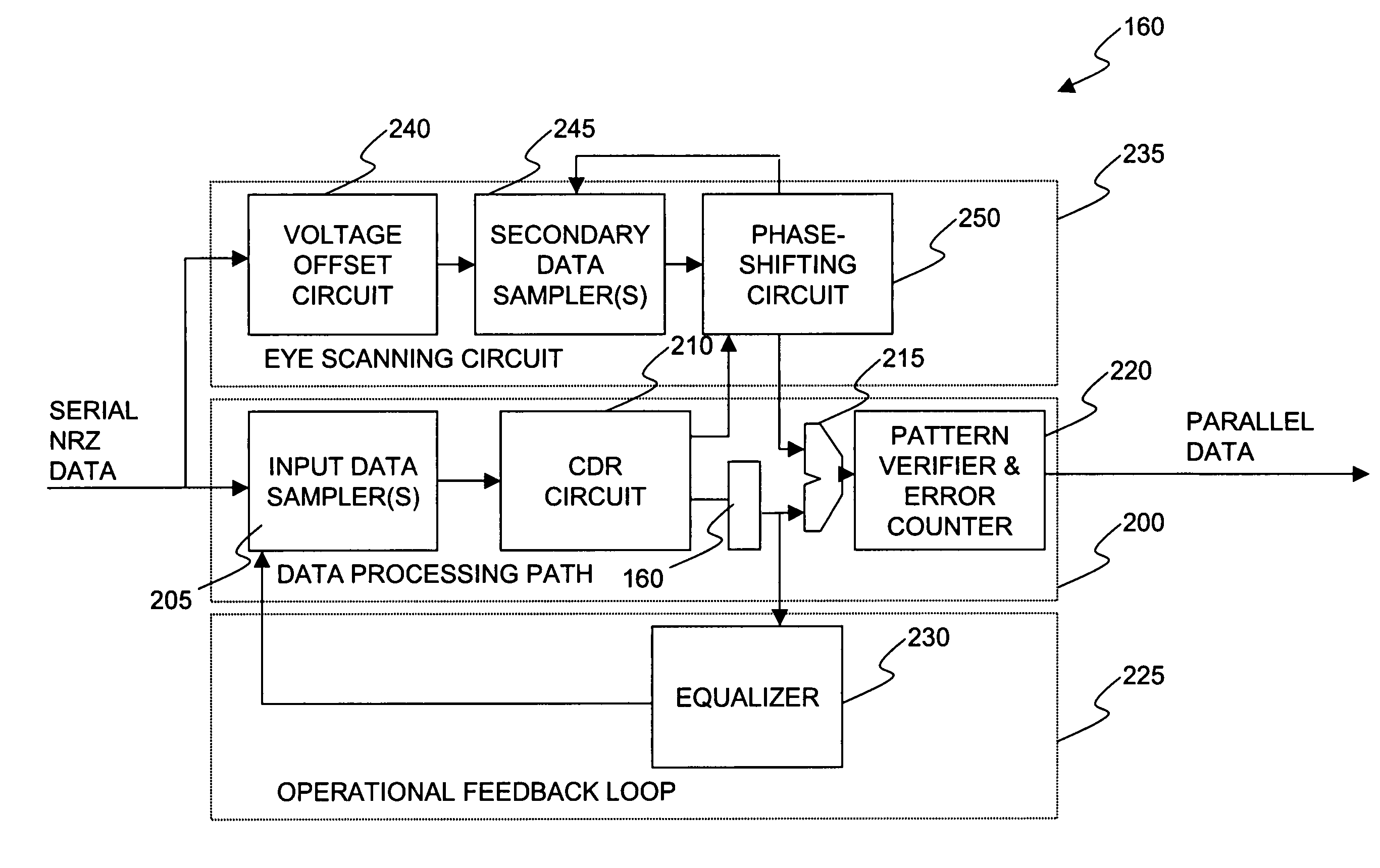

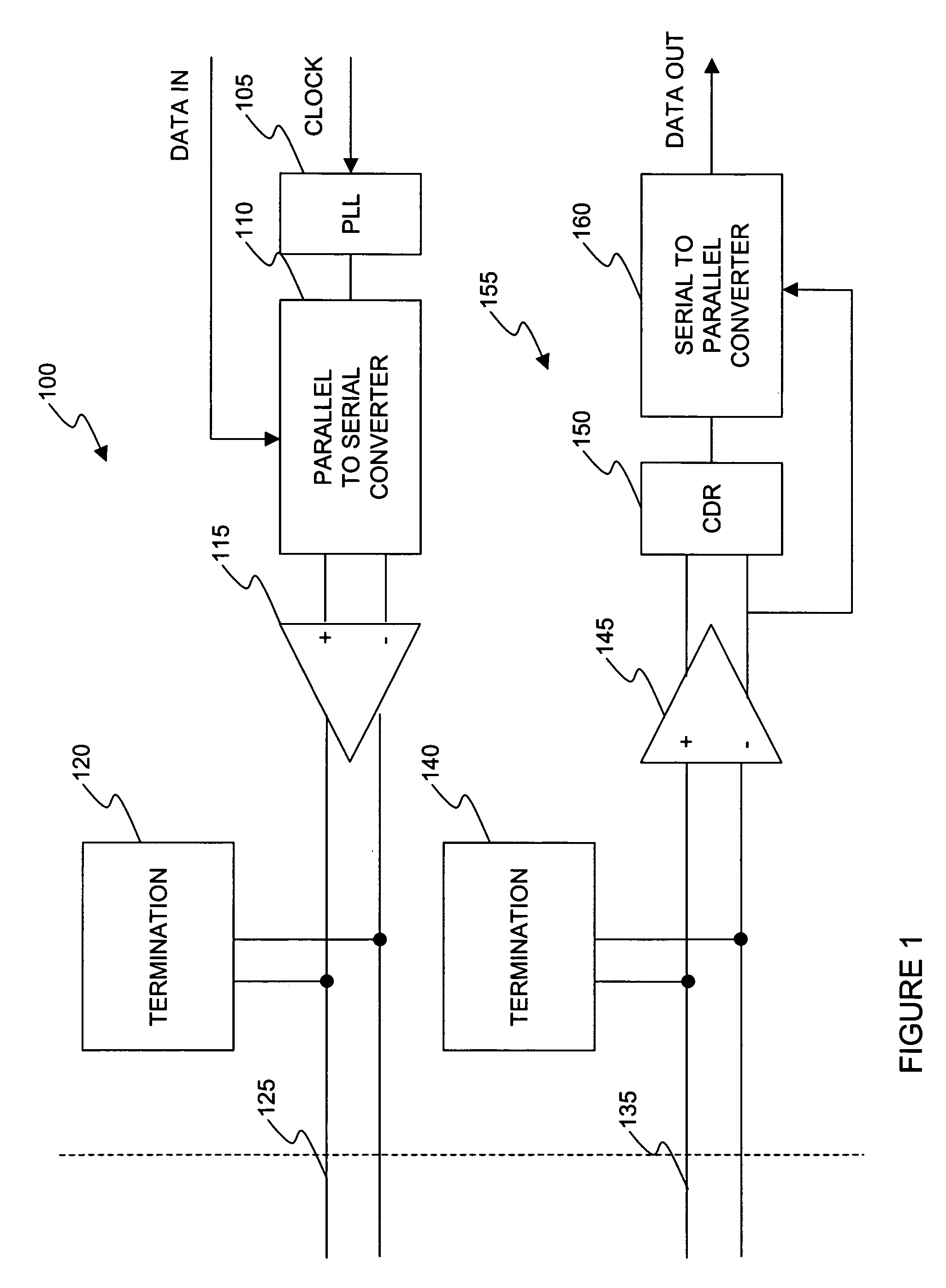

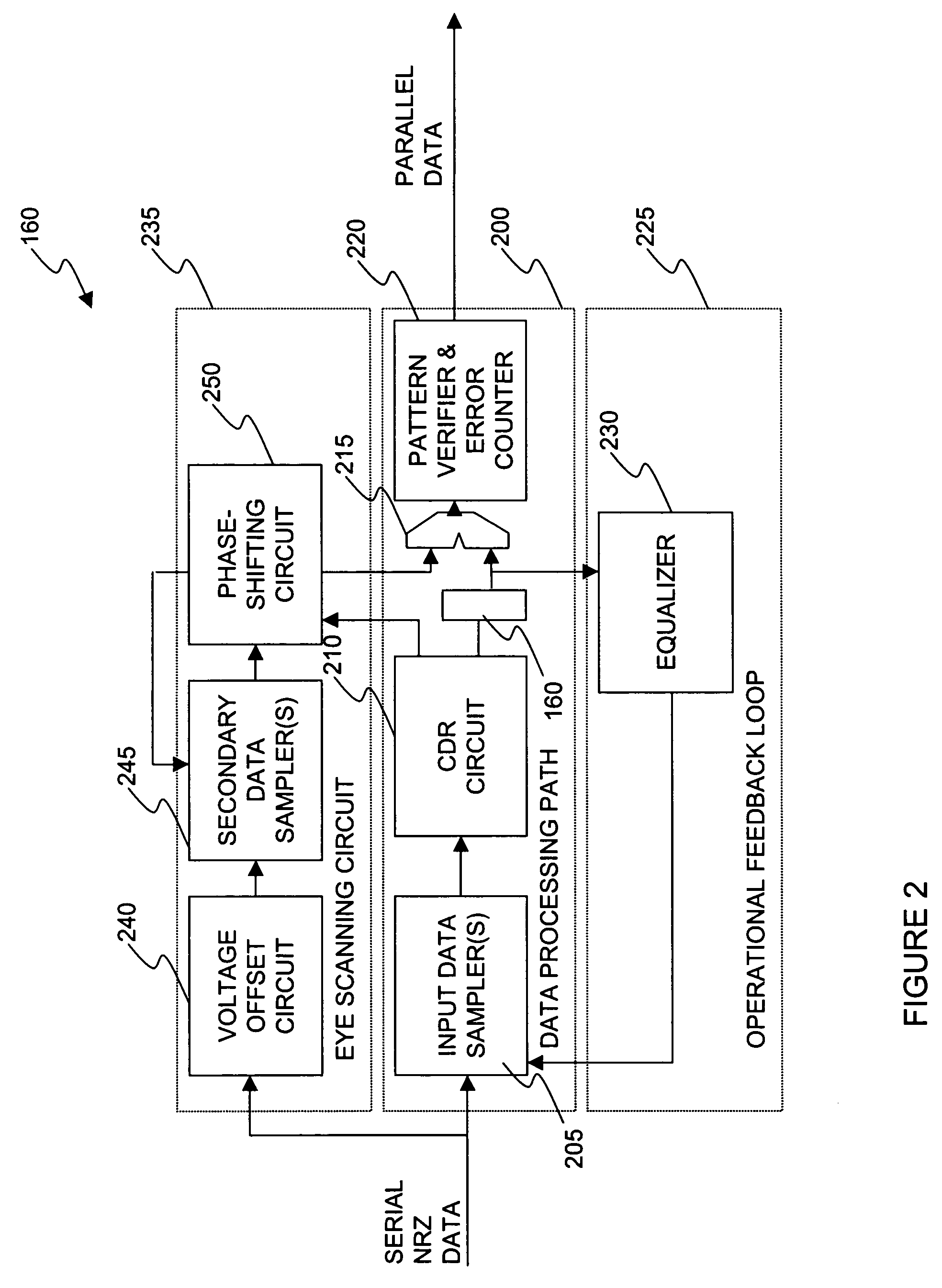

Circuit and method for evaluating the performance of an adaptive decision feedback equalizer-based serializer deserializer and serdes incorporating the same

A circuit and method for evaluating serializer deserializer (SERDES) performance that is particularly advantageous when the SERDES has a decision feedback equalizer (DFE). In one embodiment, the circuit has a data processing path and an operational feedback loop coupled to said data processing path and containing an equalizer, perhaps a DFE. In that embodiment, the circuit includes an eye scanning circuit coupled to said data processing path but separate from said equalizer and configured to measure at least one dimension of an eye relative to which said equalizer is configured for operation without substantially affecting said operation.

Owner:TEXAS INSTR INC

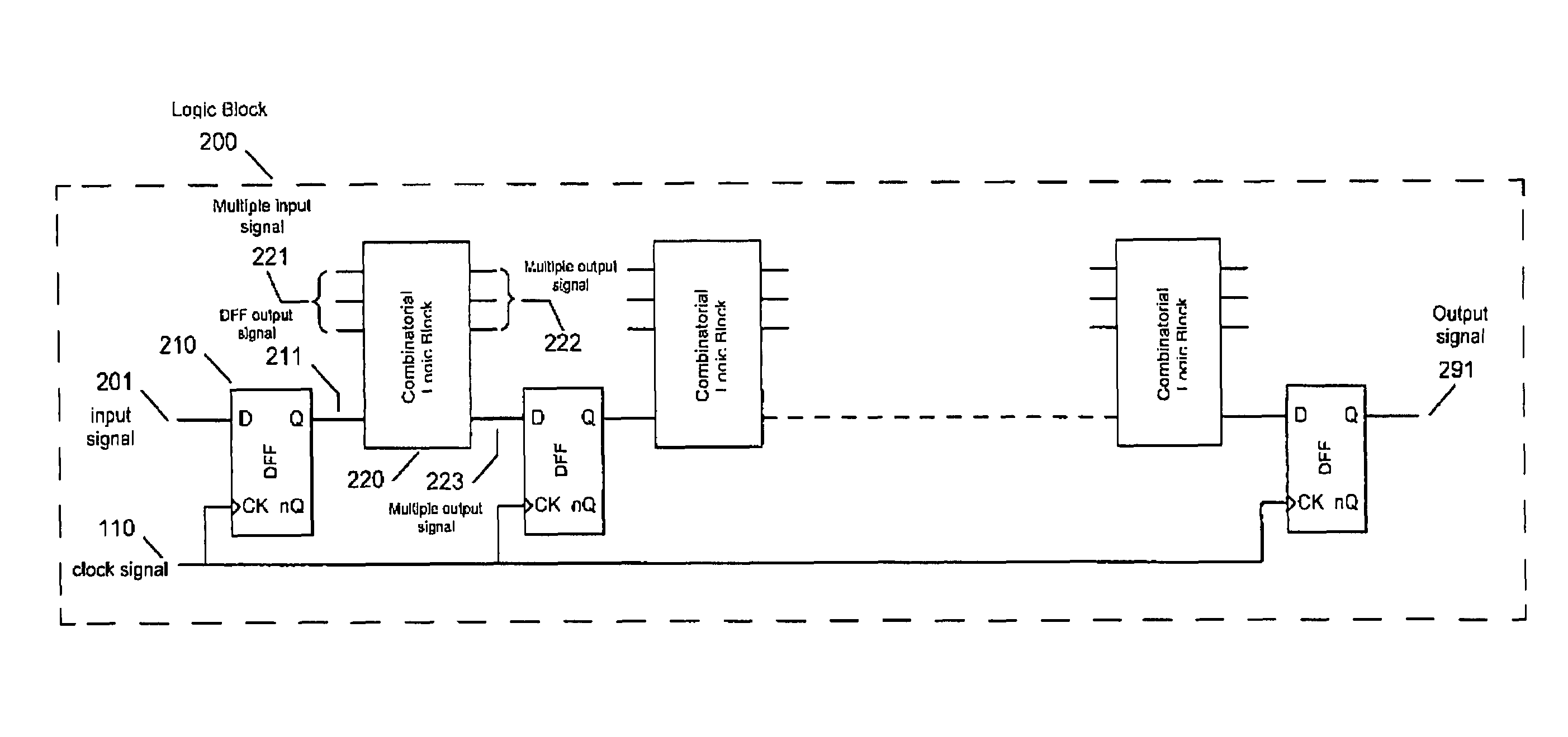

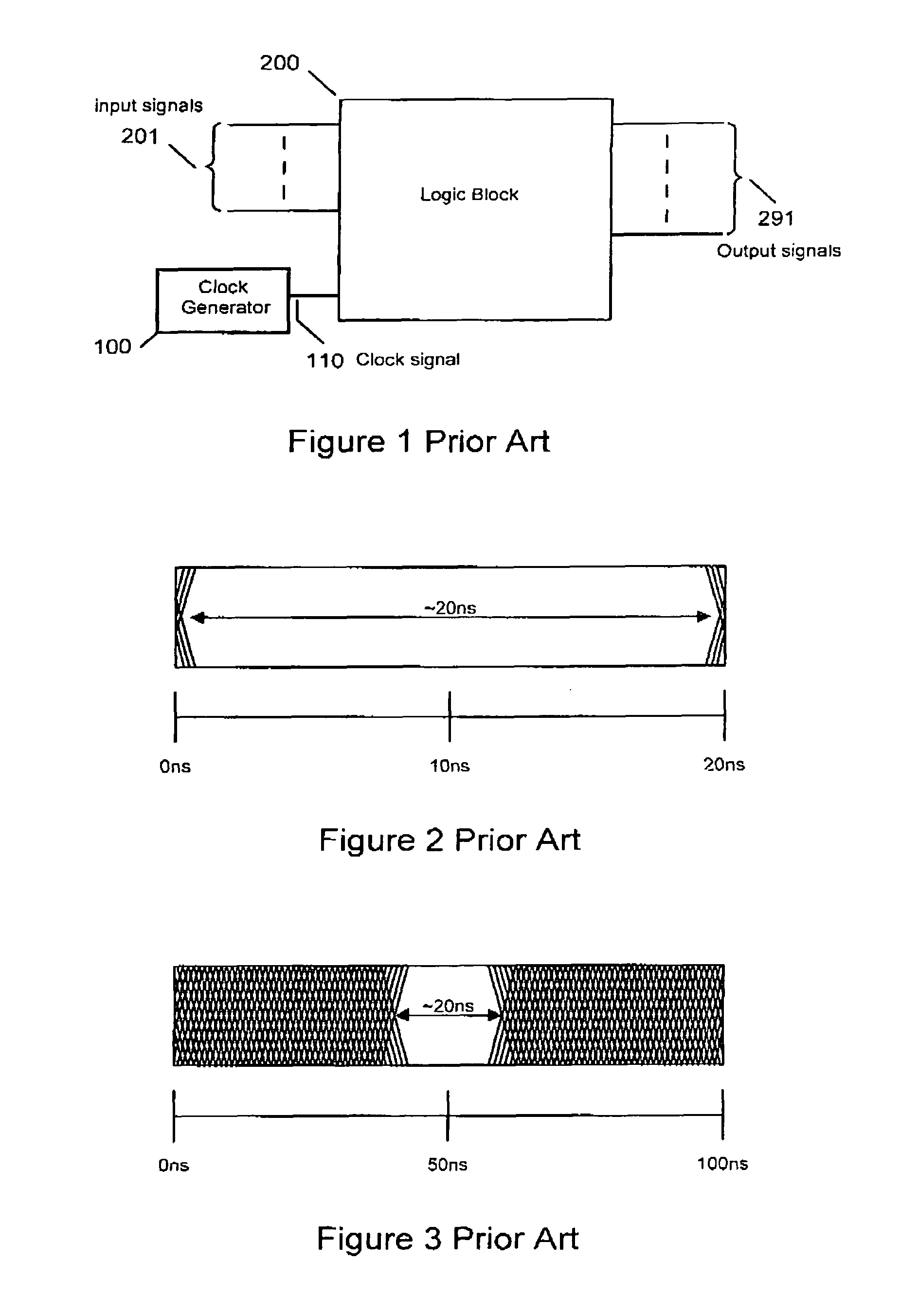

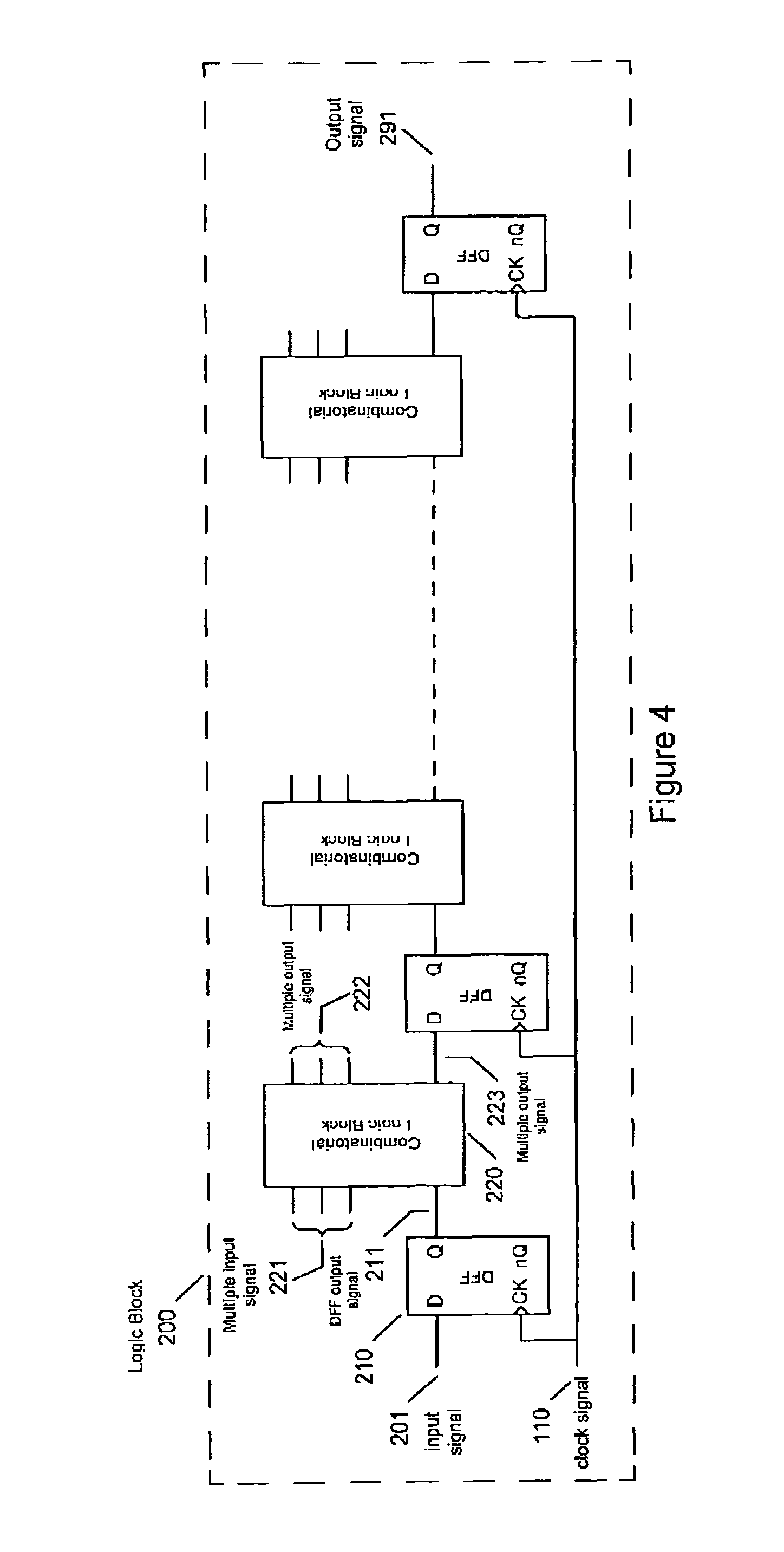

Logic system with resistance to side-channel attack by exhibiting a closed clock-data eye diagram

InactiveUS20110285420A1Improve the immunityReduce sensitivityComputer security arrangementsElectric pulse generatorMonitoring systemEngineering

An improvement in the security of a logic system by minimising observable features such as the power supply or electromagnetic radiation, so called, “side-channel attacks”. Specifically, the present invention comprises a technique and methods for reducing the ability of an intruder to monitor the relationship between currents in the system and the data in the system through the use of a randomised clock wherein the clock eye diagram is closed and without significant reduction in maximum operating speed compared to the reduction in maximum operating frequency that occurs when using conventional means of additive jitter. A system where the clock eye diagram is completely closed is provably more secure than systems where the clock eye diagram is partially open.

Owner:DEAS ALEXANDER ROGER +1

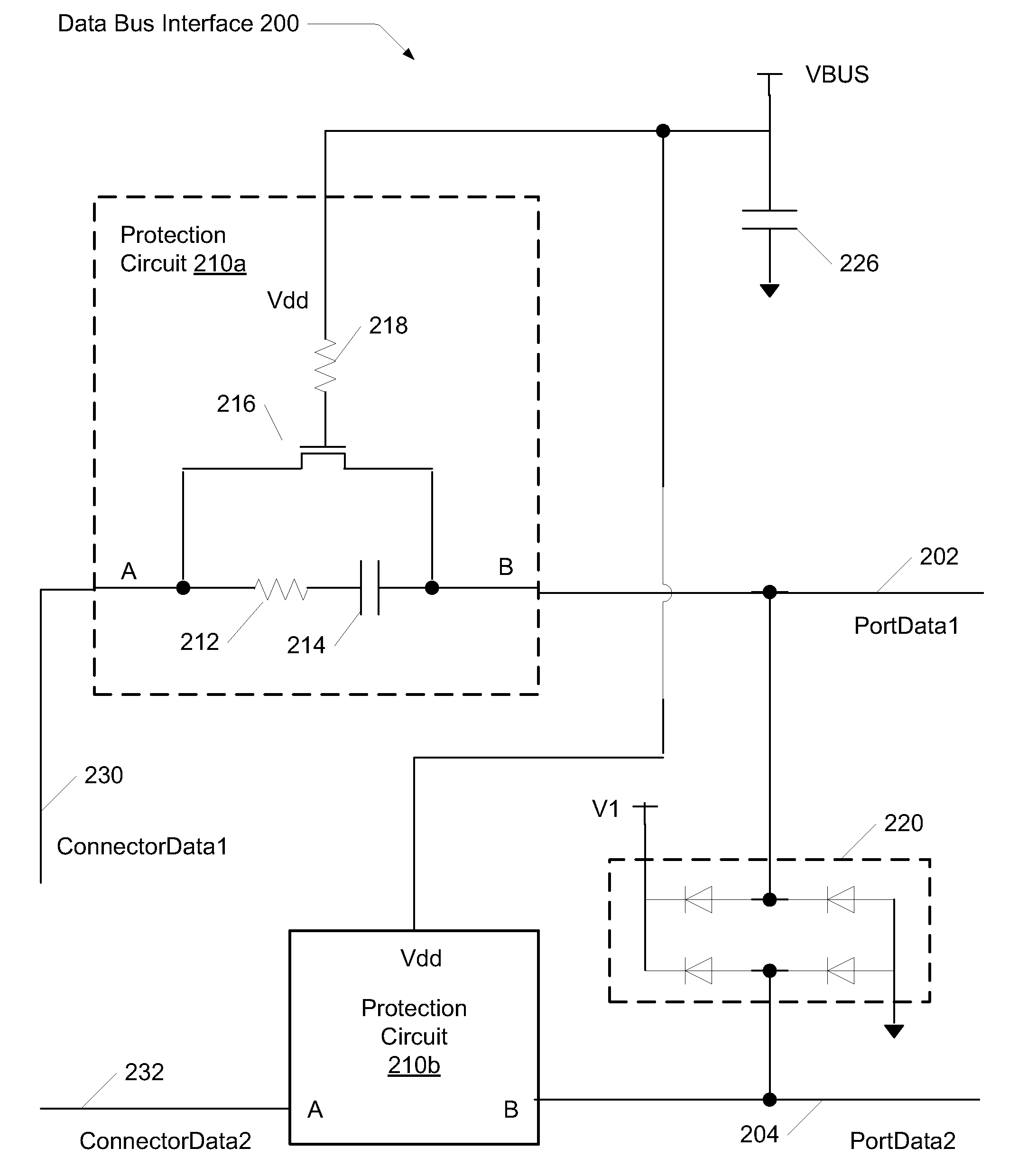

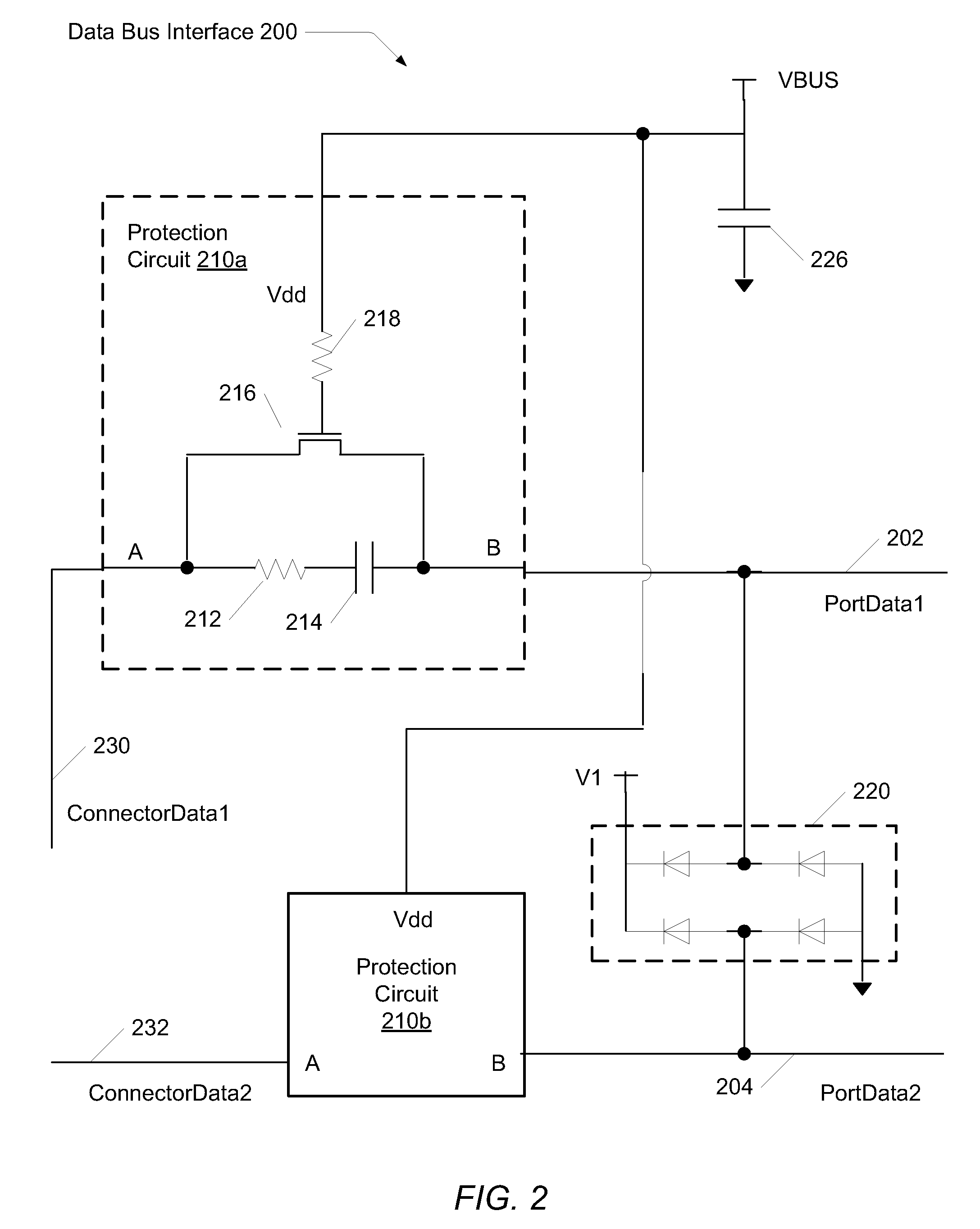

USB port overvoltage protection

ActiveUS20100073837A1Electric digital data processingEmergency protective arrangements for limiting excess voltage/currentOvervoltageUltrasound attenuation

A system and method for efficient input / output (I / O) port overvoltage protection of a high-speed port. An interfacing system for connecting peripheral devices to a computing system comprises ports for conveying serial communications bidirectional signals and an overvoltage protection circuit. The protection circuit prevents an overvoltage condition on one port in response to an overvoltage event on a corresponding second port. In one embodiment, the interfacing system connects USB peripheral devices to an automotive infotainment system comprising an automotive battery potiential greater than a USB power supply. In addition, the overvoltage protection circuit is able to transmit signals between the two ports without signal attenuation defined by an industry standard specification such as Universal Serial Bus (USB) Implementers Forum (IF) eye pattern diagram test. The overvoltage protection circuit is configured to have a small footprint, and, therefore, does not utilize a power reference and comparator circuit.

Owner:MICROCHIP TECH INC

Method of producing a two-dimensional probability density function (PDF) eye diagram and Bit Error Rate eye arrays

InactiveUS20060018374A1Noise figure or signal-to-noise ratio measurementError preventionNormal densityPortable document format

A method of producing of a two-dimensional probability density function eye diagram and Bit Error Rate eye arrays generates a two-dimensional PDF array of a correlated waveform record of a data pattern under test which is convolved with a two-dimensional probability density function (PDF) array of the uncorrelated jitter and noise in the data pattern under test. The resulting aggregate two dimensional PDF array of the correlated waveform record pattern with uncorrelated jitter and noise is divided into unit intervals and the unit intervals are summed to generated a two-dimensional PDF eye diagram array. The two-dimensional PDF eye diagram is processed to generate a two-dimensional Bit Error Rate eye array.

Owner:TEKTRONIX INC

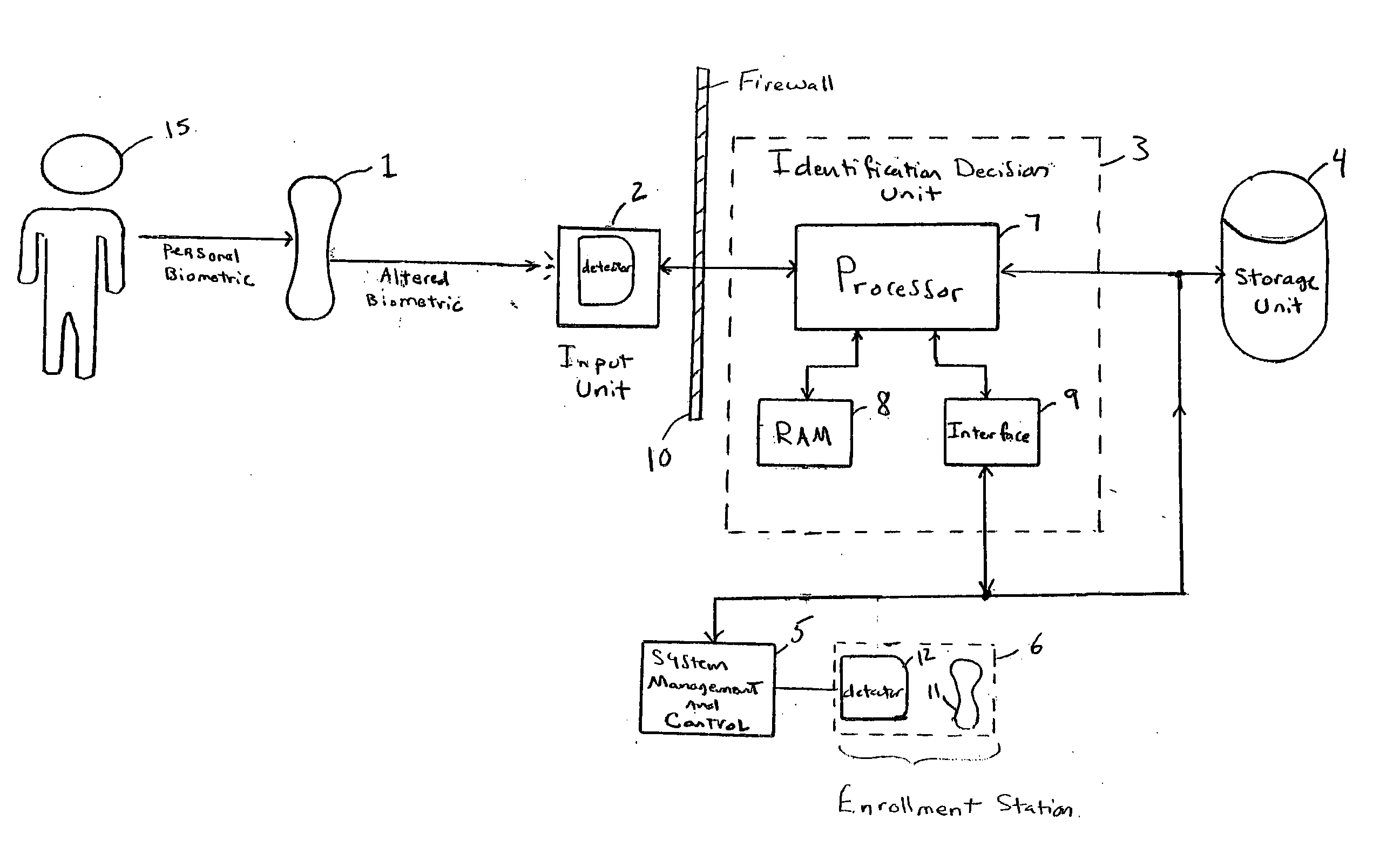

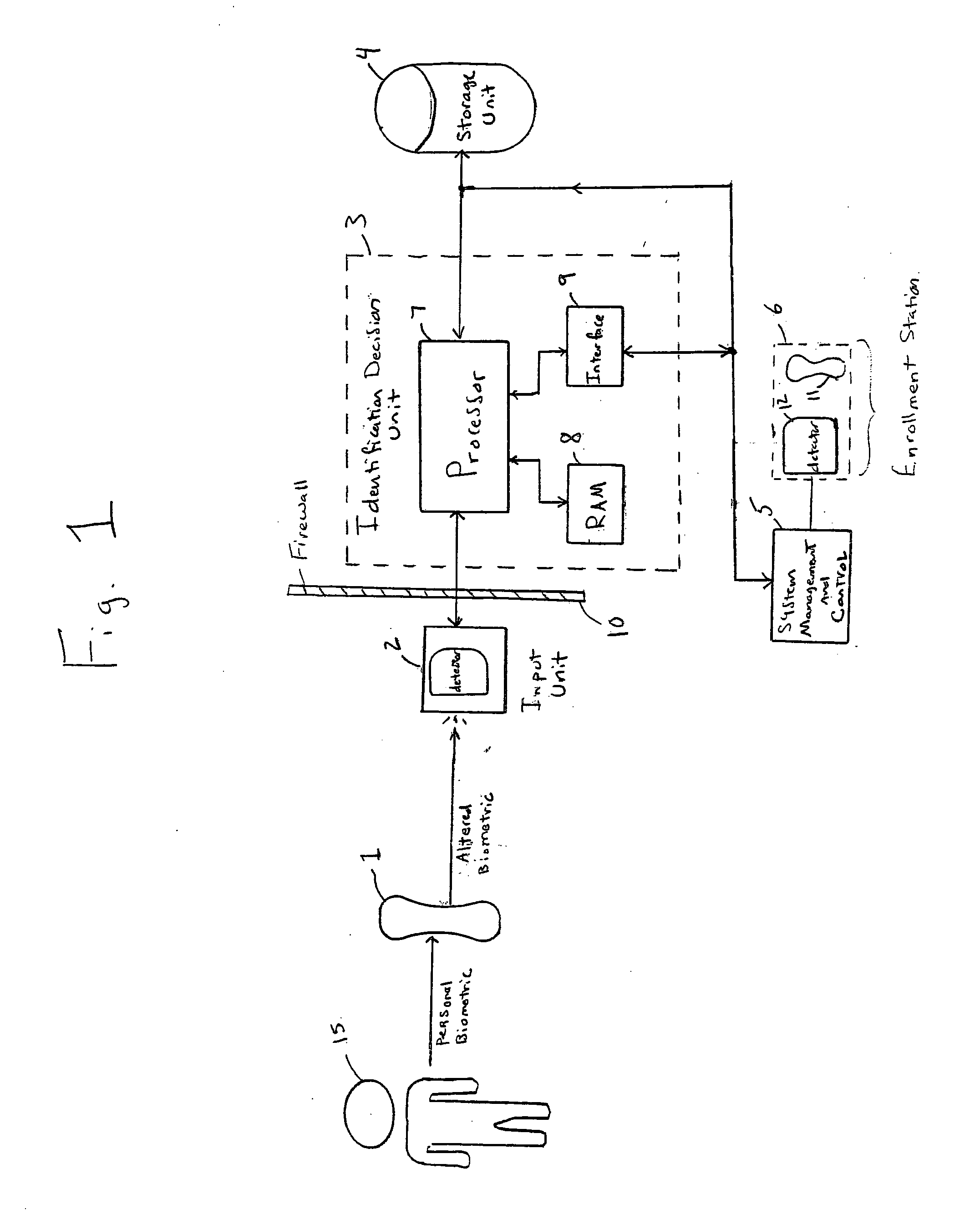

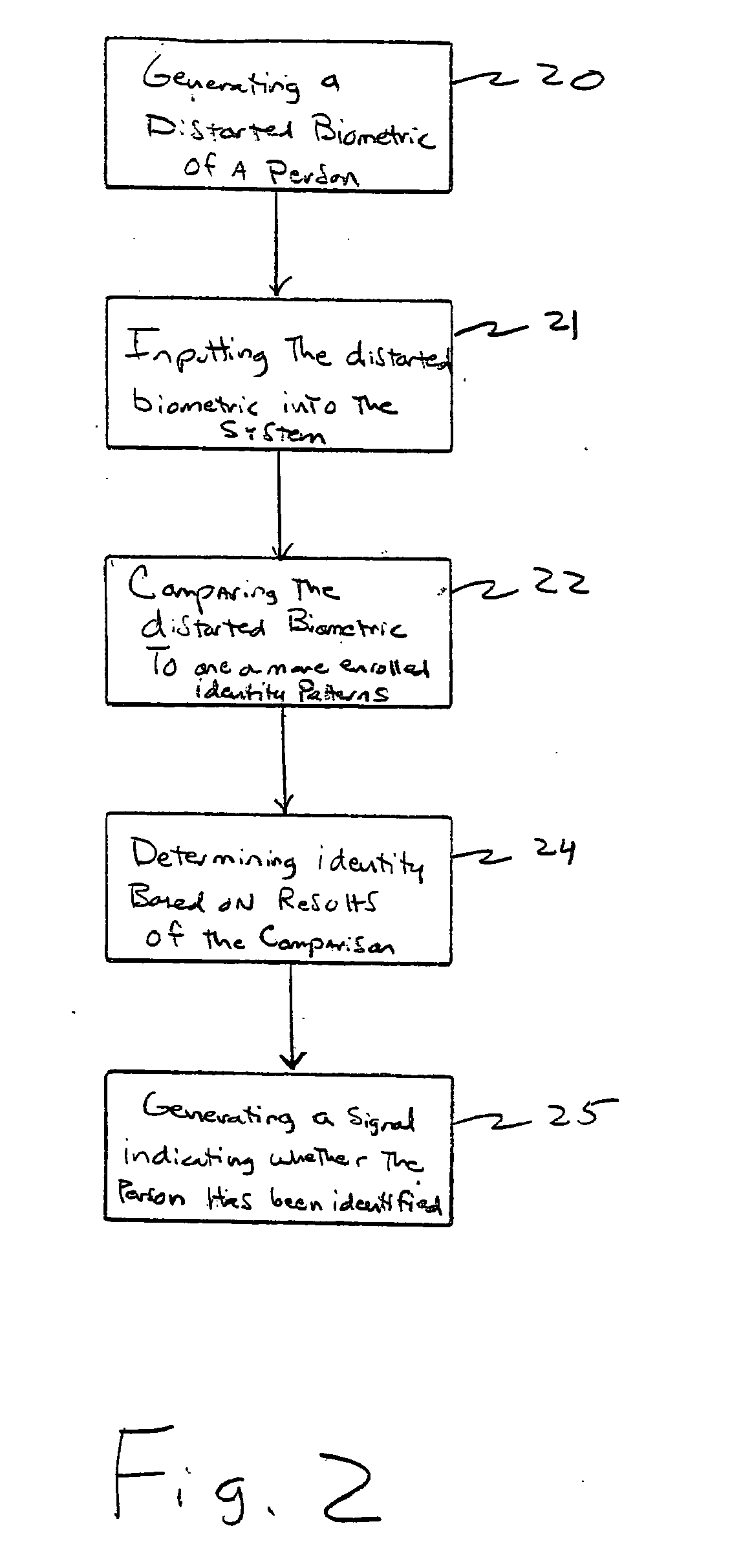

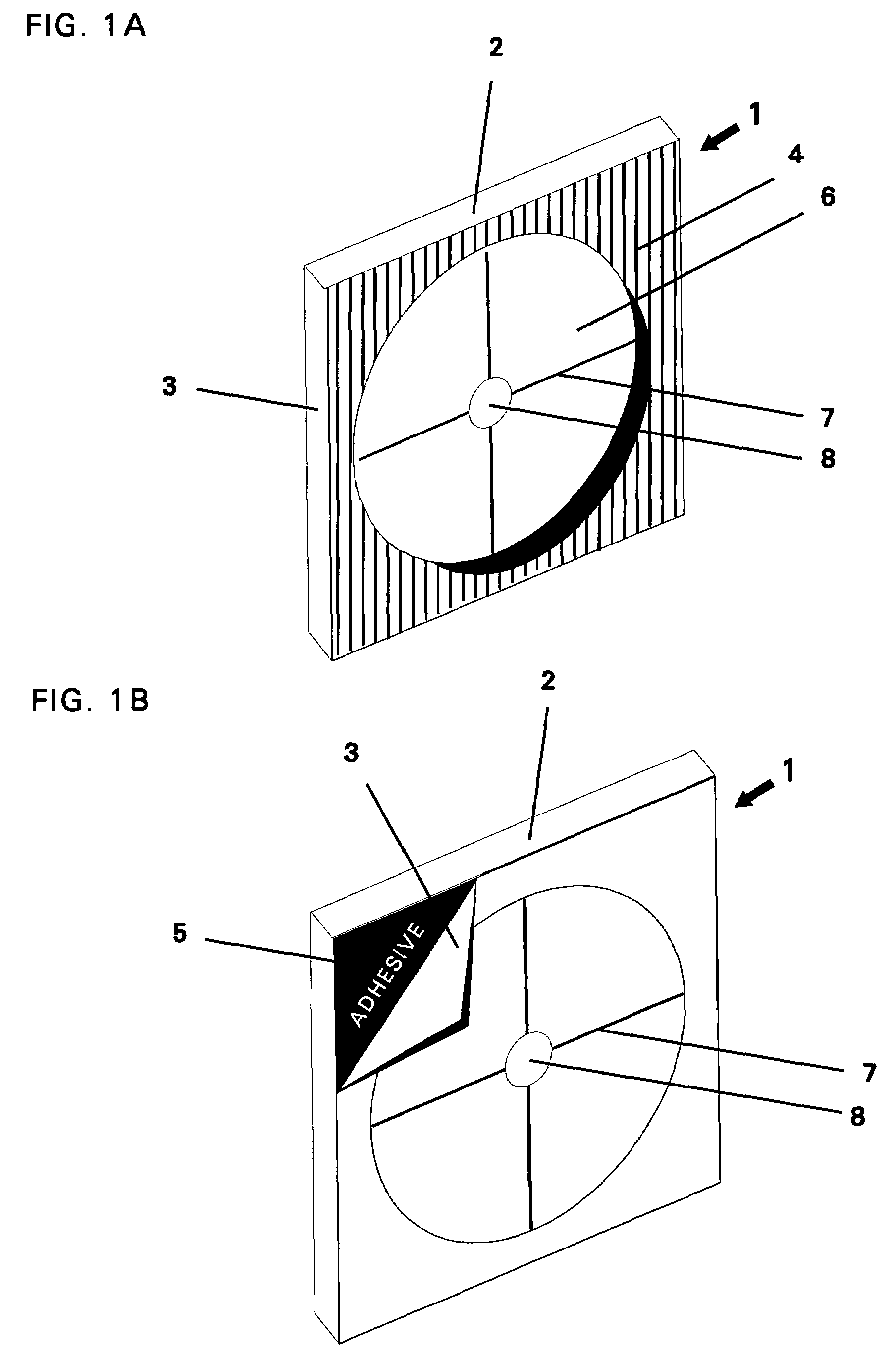

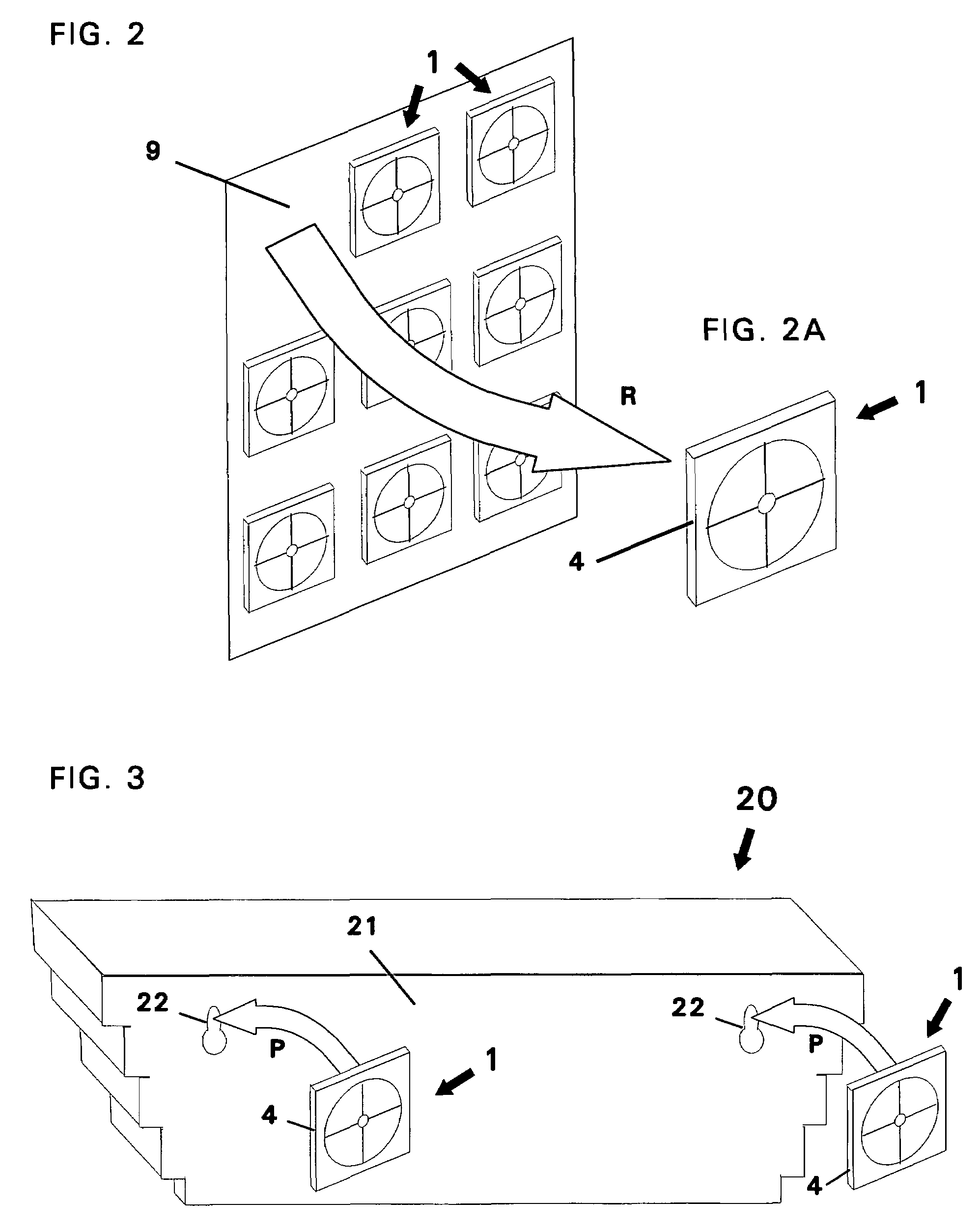

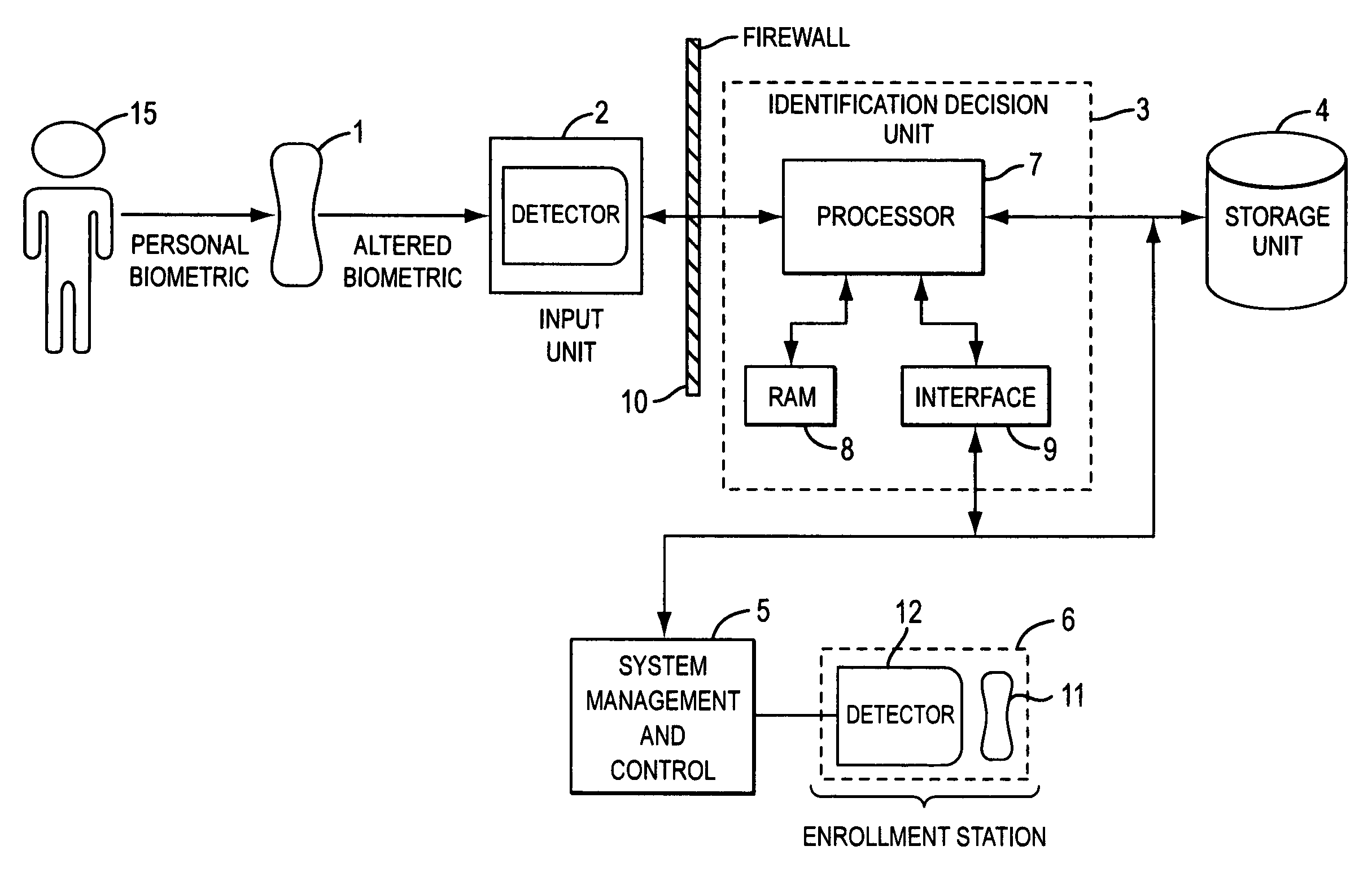

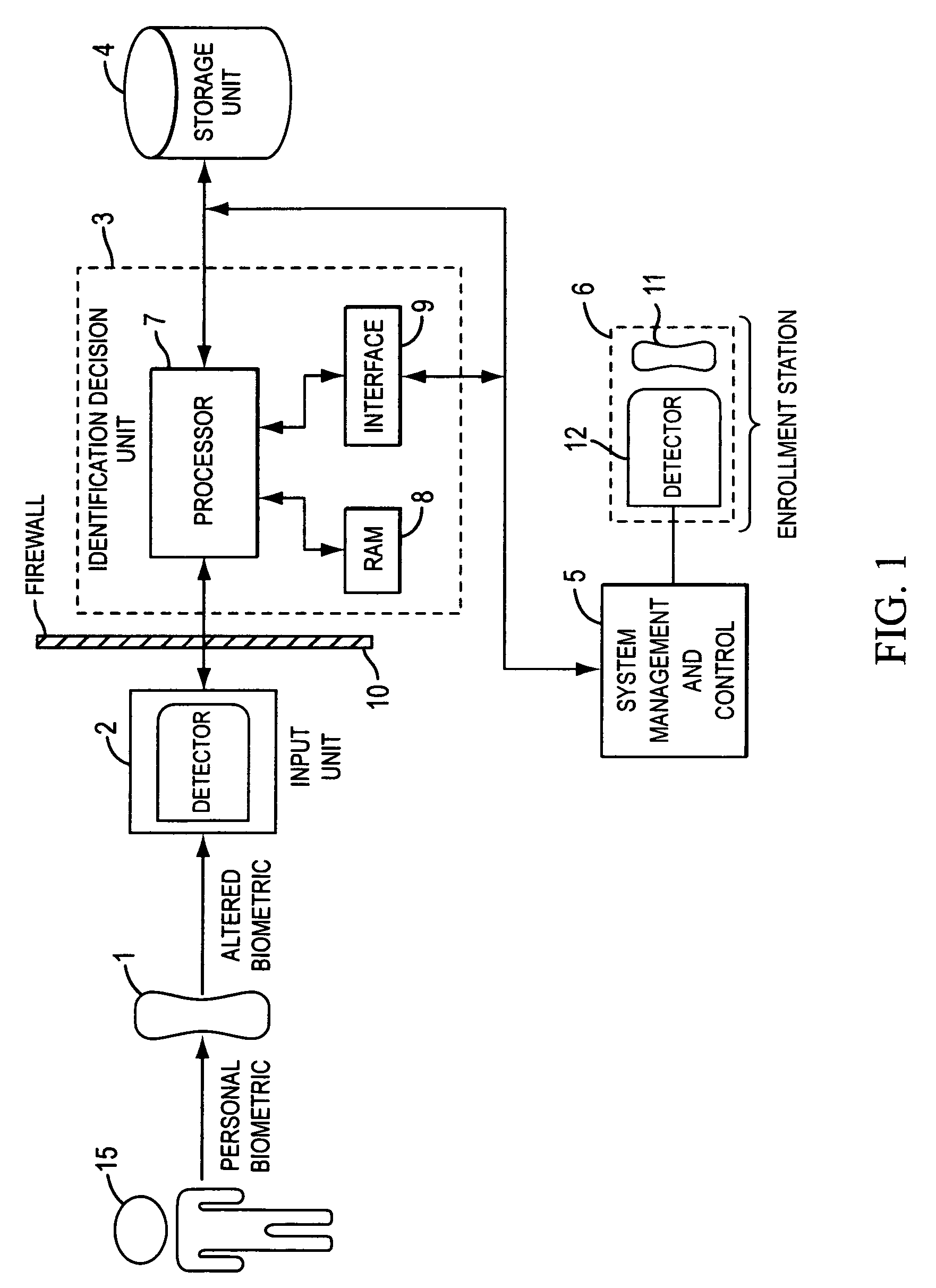

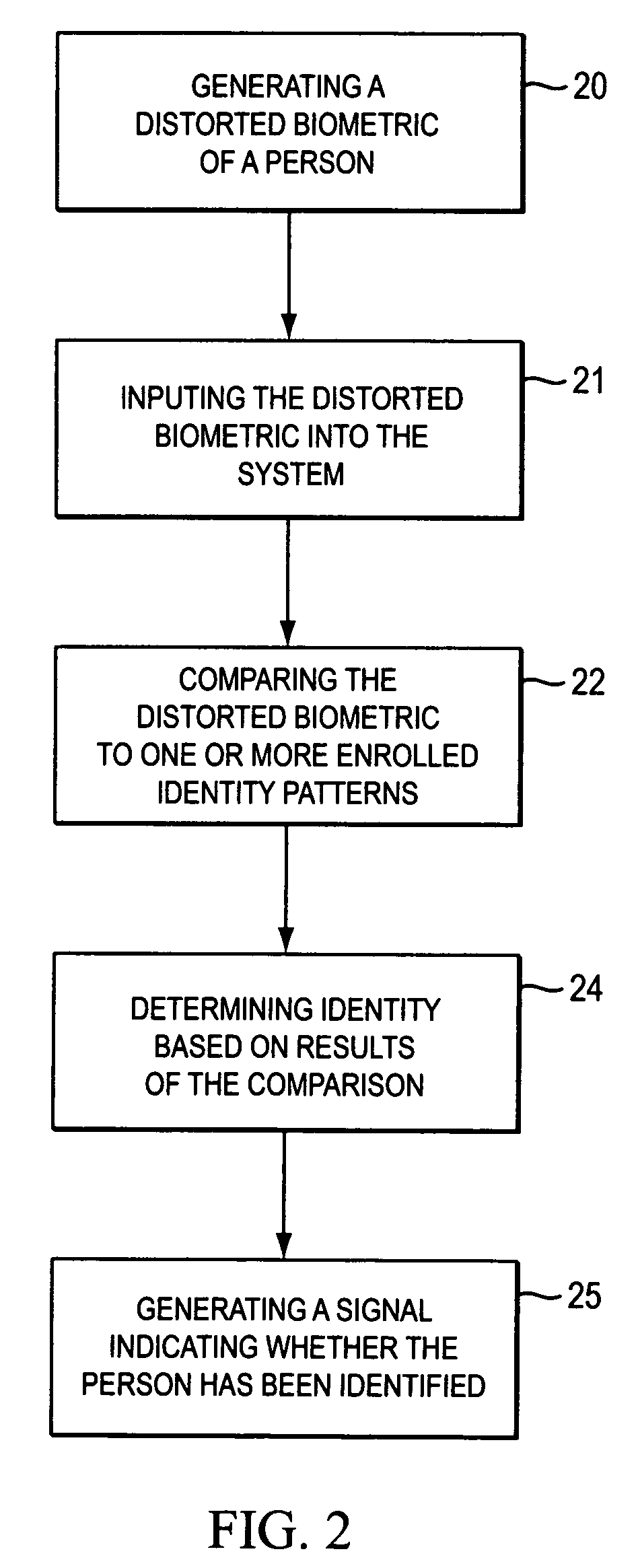

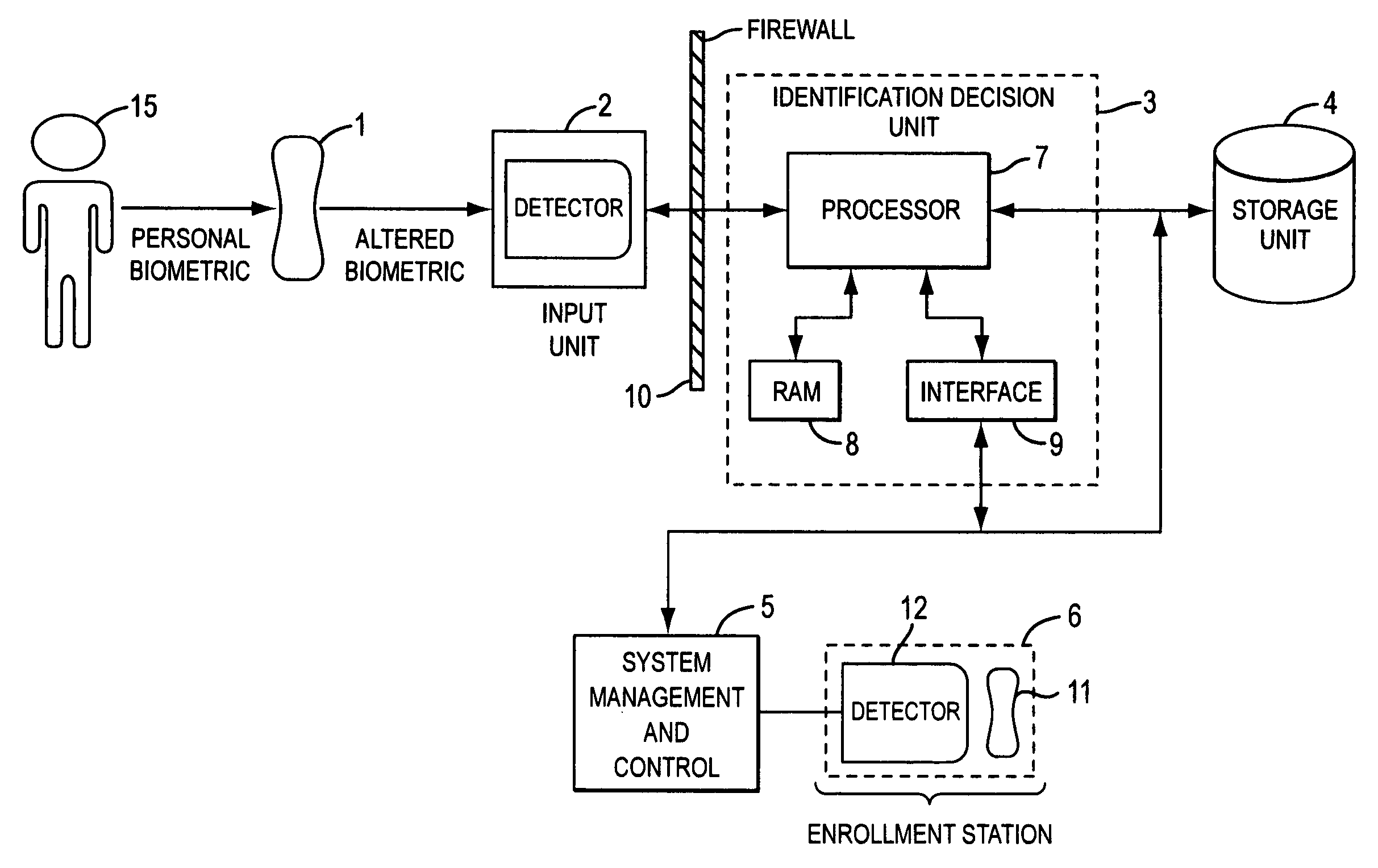

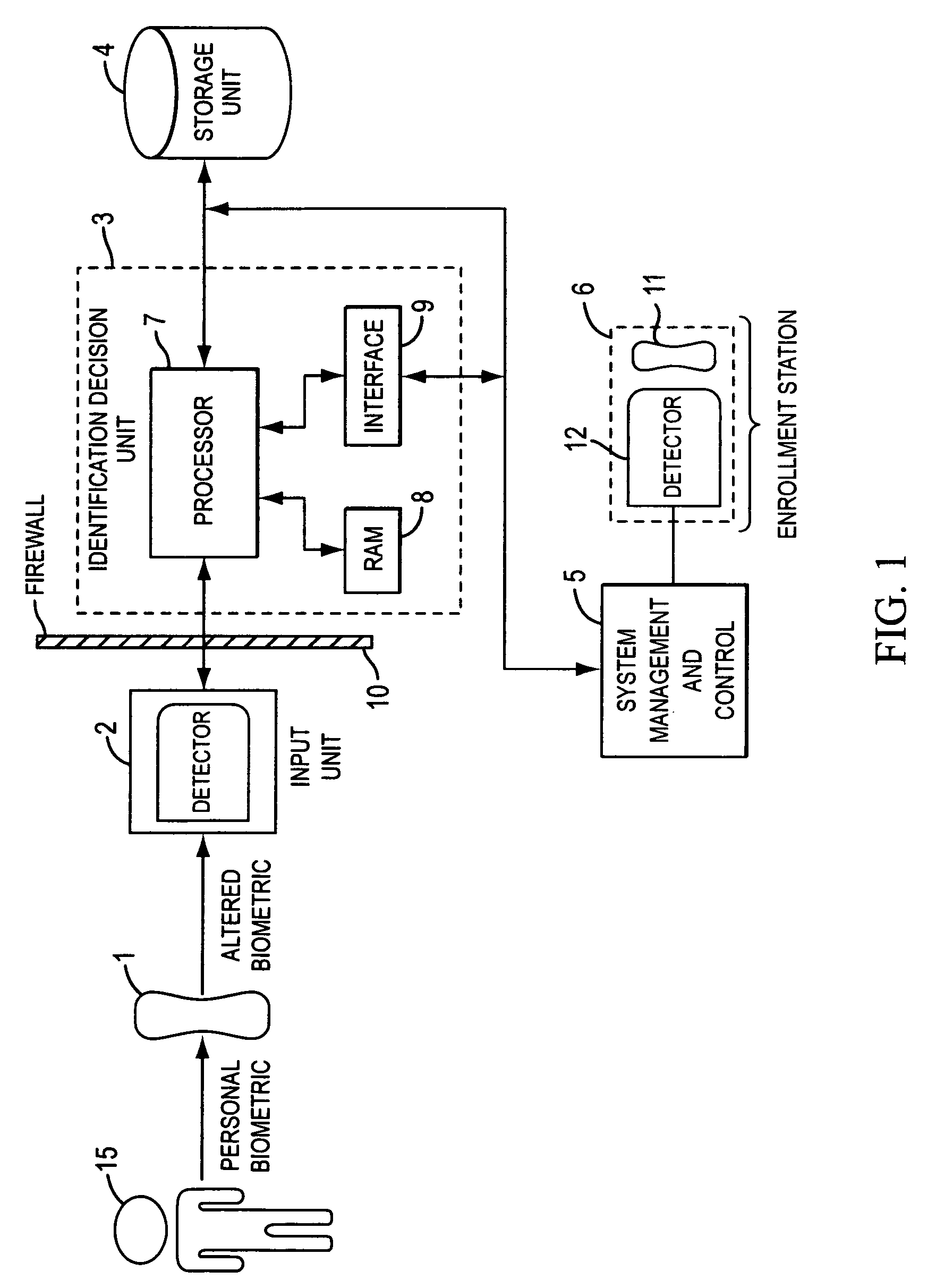

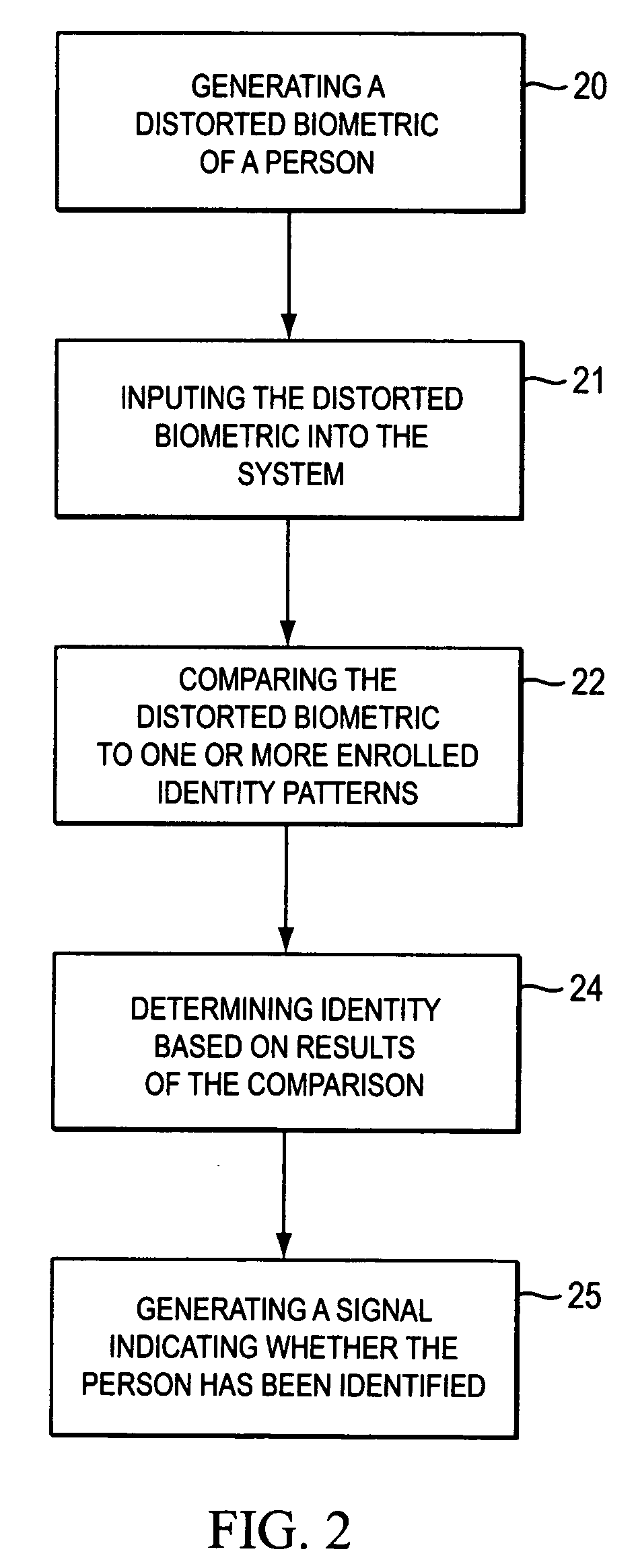

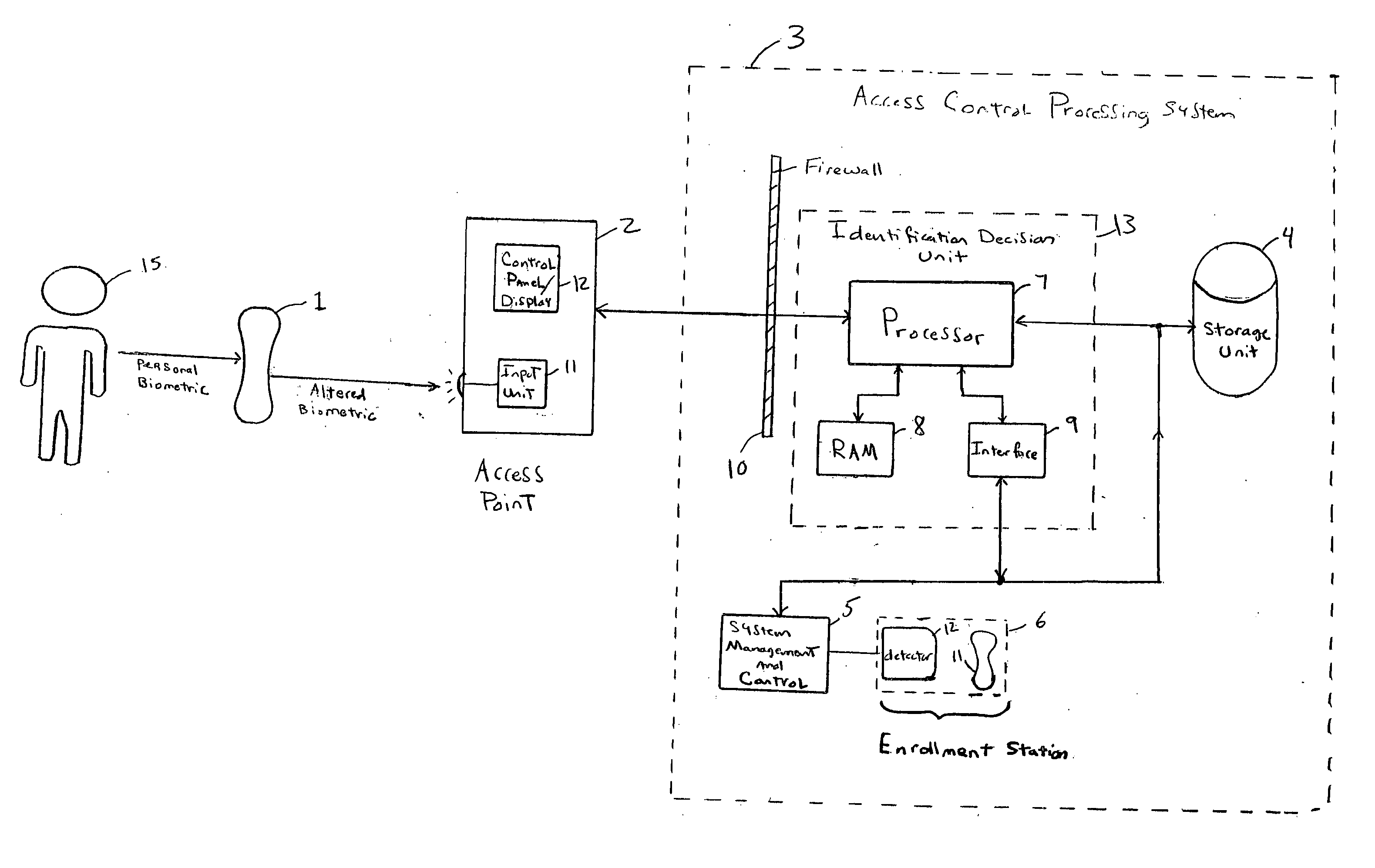

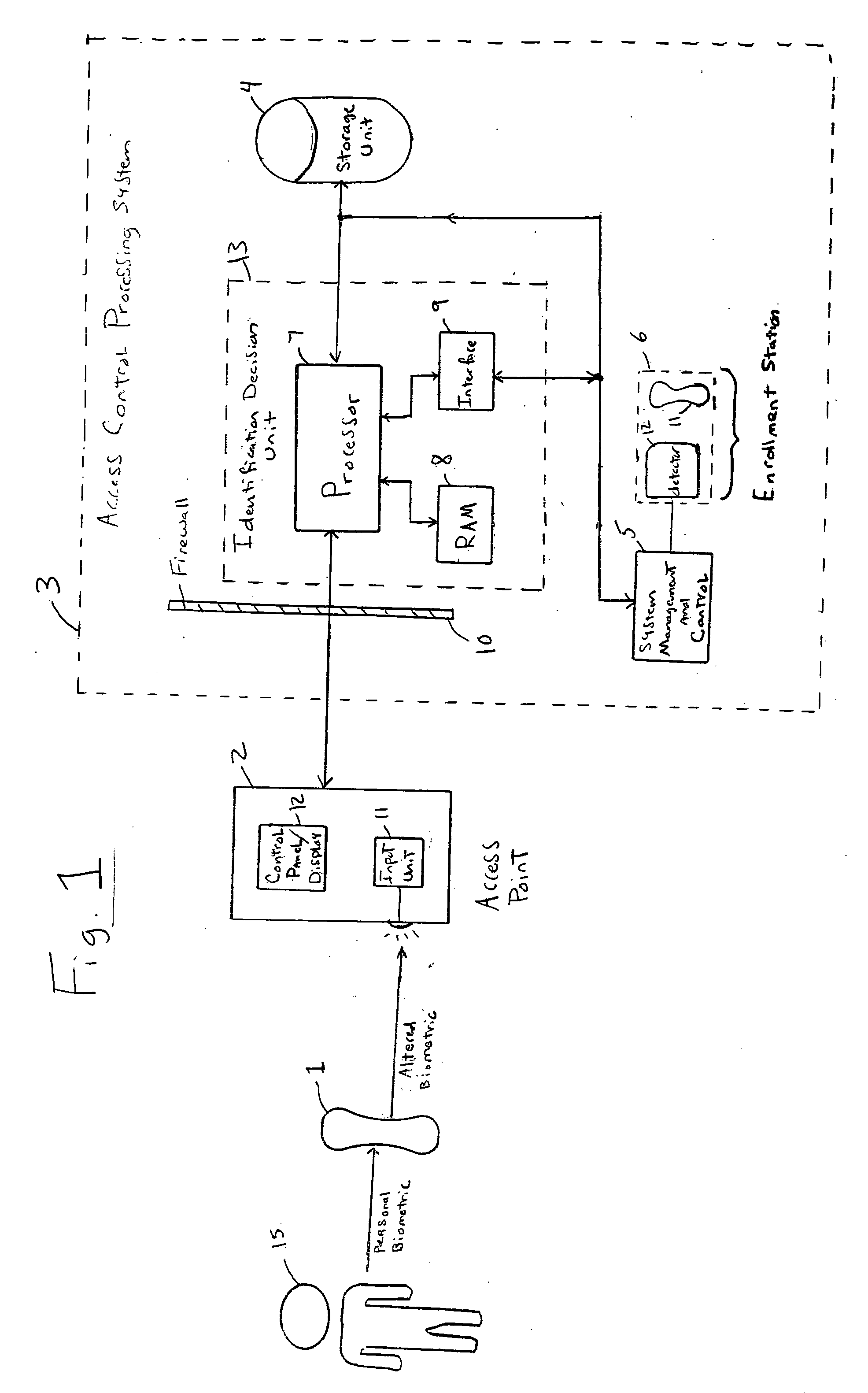

Recoverable biometric identity system and method

InactiveUS20060133651A1Great level of securityIncrease elasticitySpeech analysisAcquiring/recognising eyesHandwritingPalm print

A method for identifying persons based on biometric data achieves enhanced security and increased accuracy compared with other systems by distorting one or more biometrics prior to detection and recognition. The method includes detecting a distorted biometric for input into an identification system, comparing the distorted biometric to one or more distortion patterns, and determining an identity of the person based on results of the comparison. The biometric may be an eye pattern, a fingerprint or palm print, a voice print, a handwriting sample, a DNA sample, a facial image, or any other type of characteristic or behavioral attribute of a person. The biometric may be distorted in any one of a variety of ways for comparison to previously enrolled biometrics which have been distorted using the same or similar element. A system and program embodied within a computer-readable medium performs the steps of the method.

Owner:POLCHA ANDREW J +1

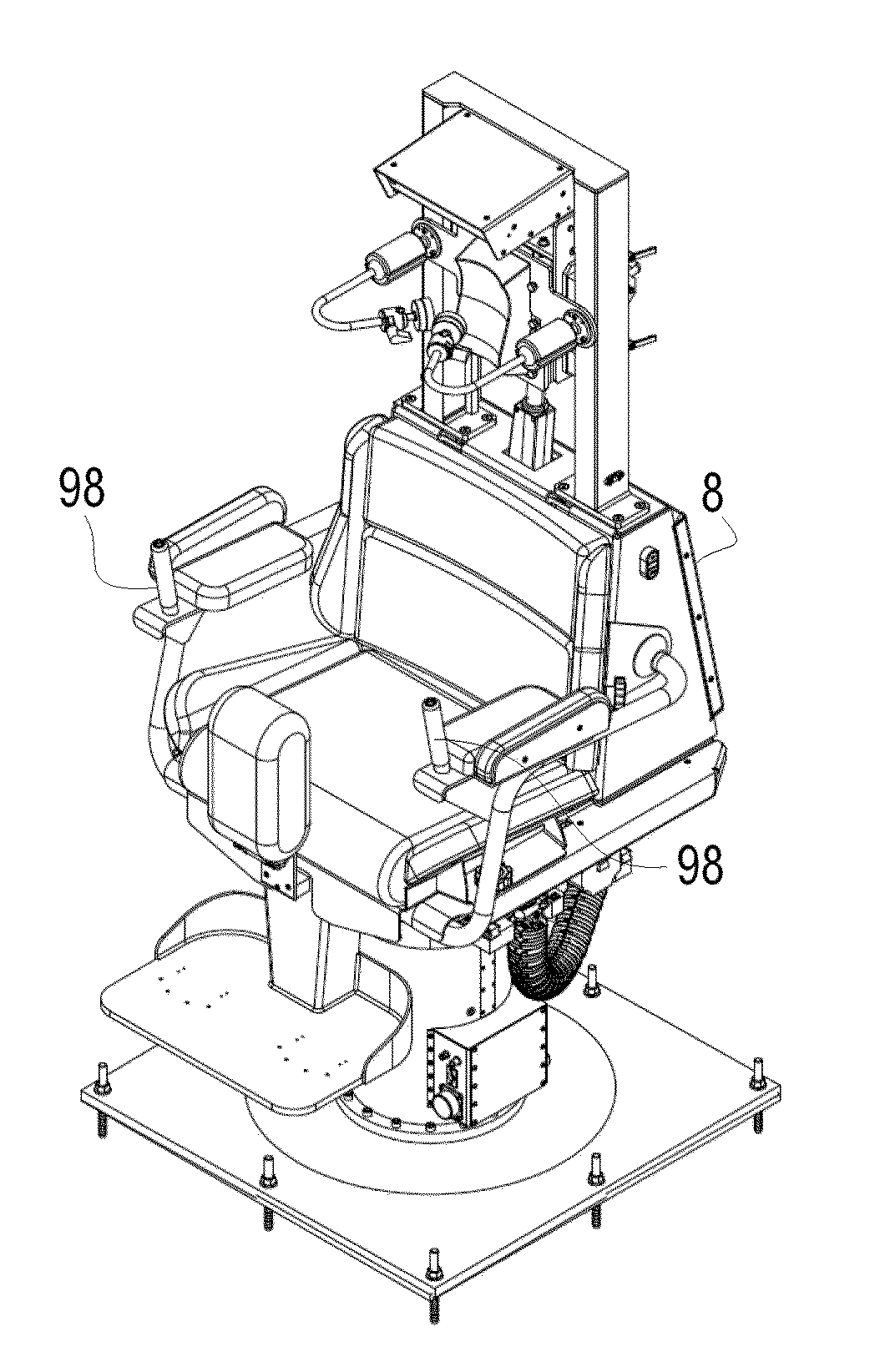

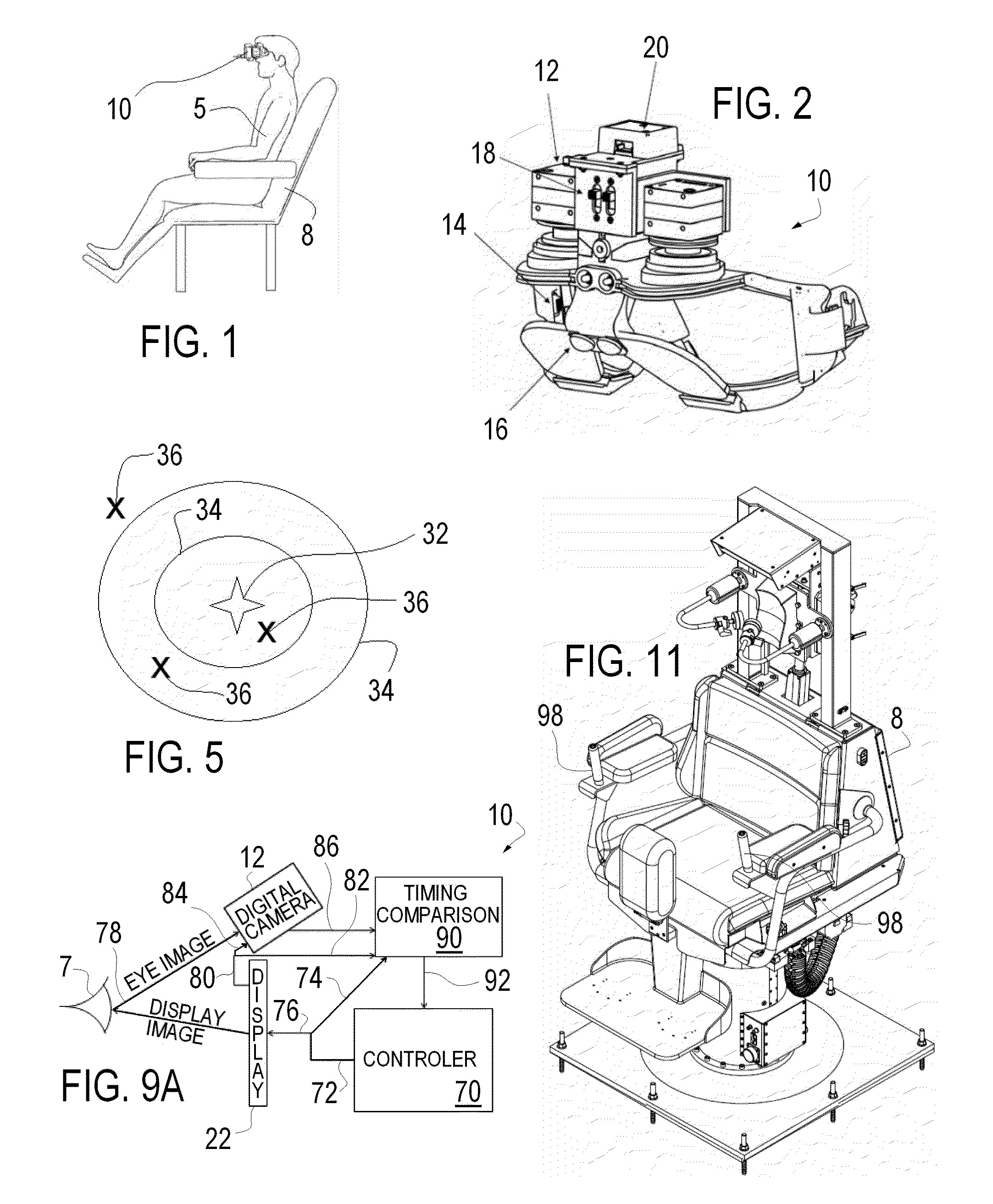

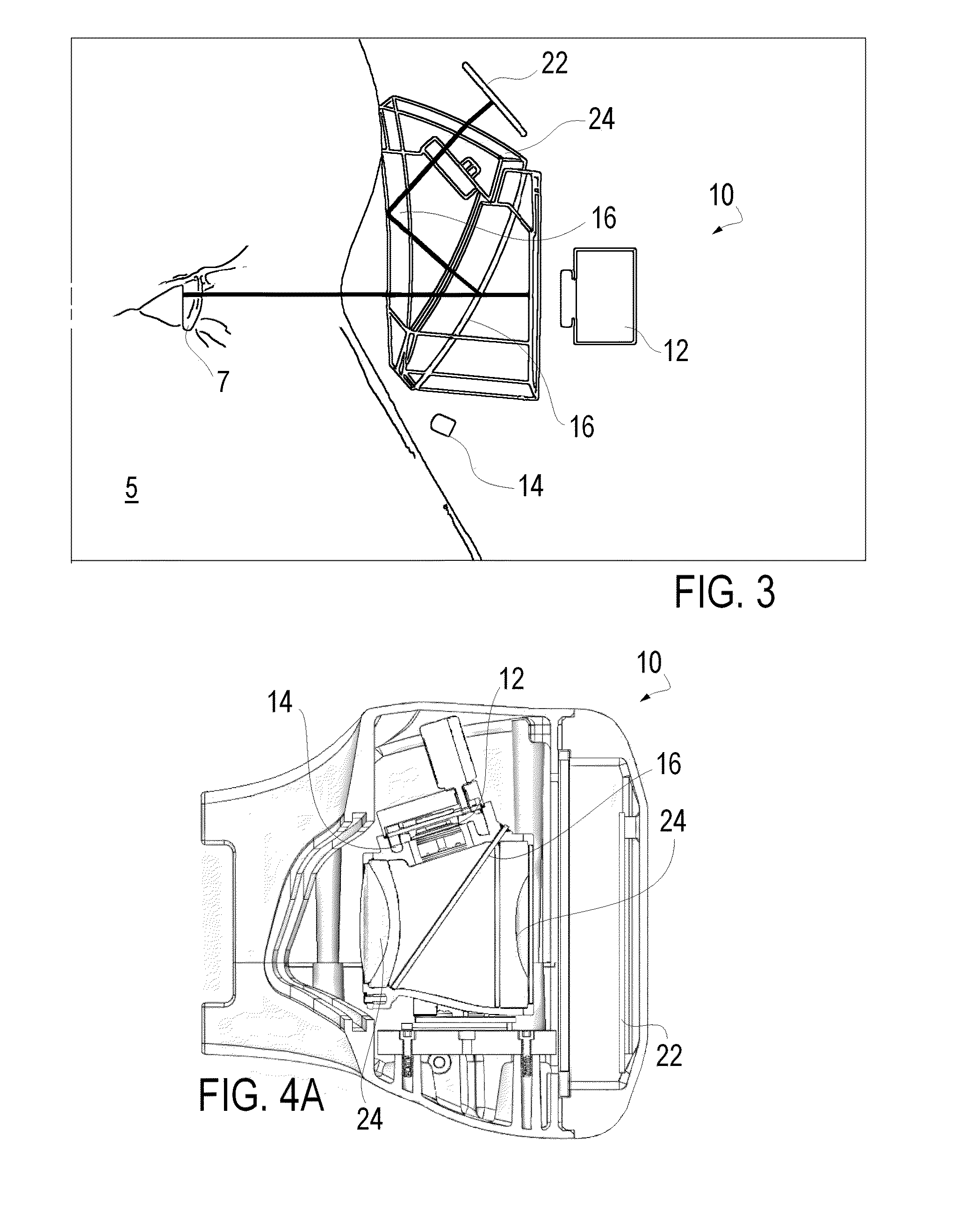

Method of measuring and analyzing ocular response in a subject using stable pupillary parameters with video oculography system

A method of measuring and analyzing an ocular response in a subject comprising the steps of: Providing a video oculography based system for the subject with the system configured to collect eye images in excess of 60 hz and configured to resolve eye movements smaller than at least 3 degrees of motion; Collecting eye data with the video oculography based system wherein at least one stimulus is presented to only one eye of the subject and configured to yield a pupil eye response from at least one eye of the subject; Calculating pupilometry measurements from the eye data, wherein the pupil measurements are calculated independently for the subject's left and right eyes for each stimulus presented to the subject, and wherein comparative left and right pupilometry measurements from the eye data are calculated; analyzing a subject's ocular response based upon at least one of the calculated pupilometry measurements.

Owner:128 GAMMA LIQUIDATING TRUST +1

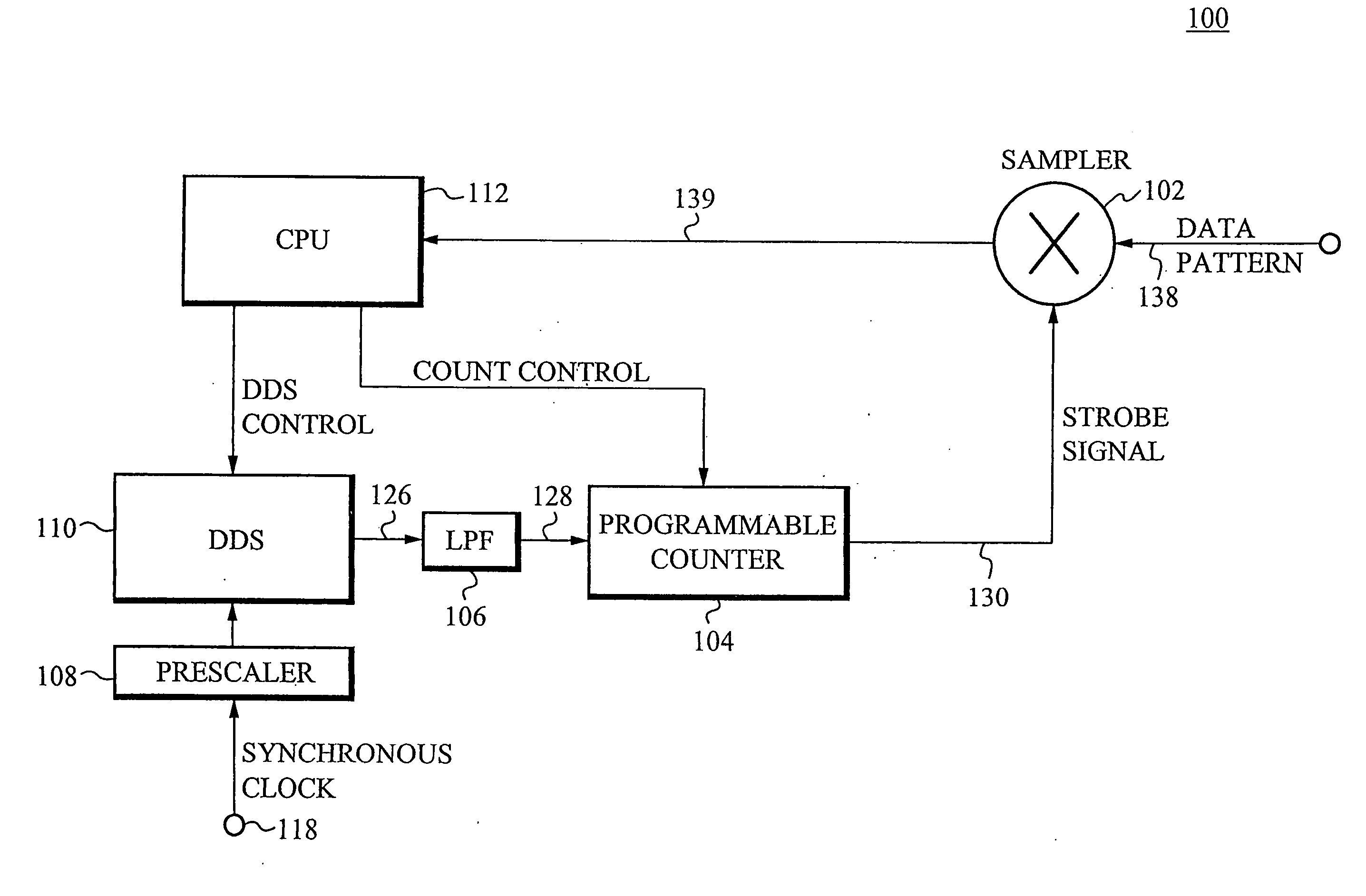

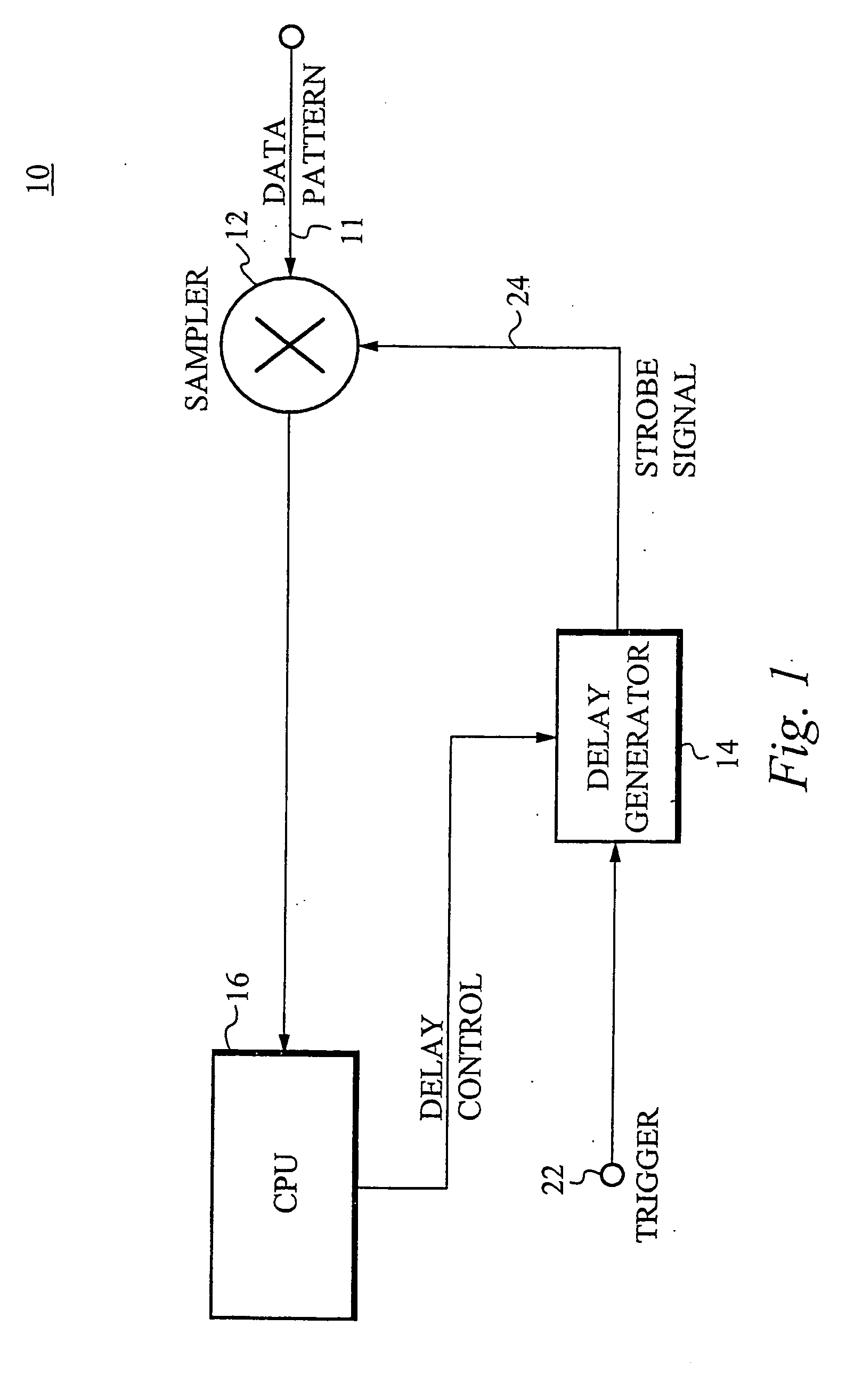

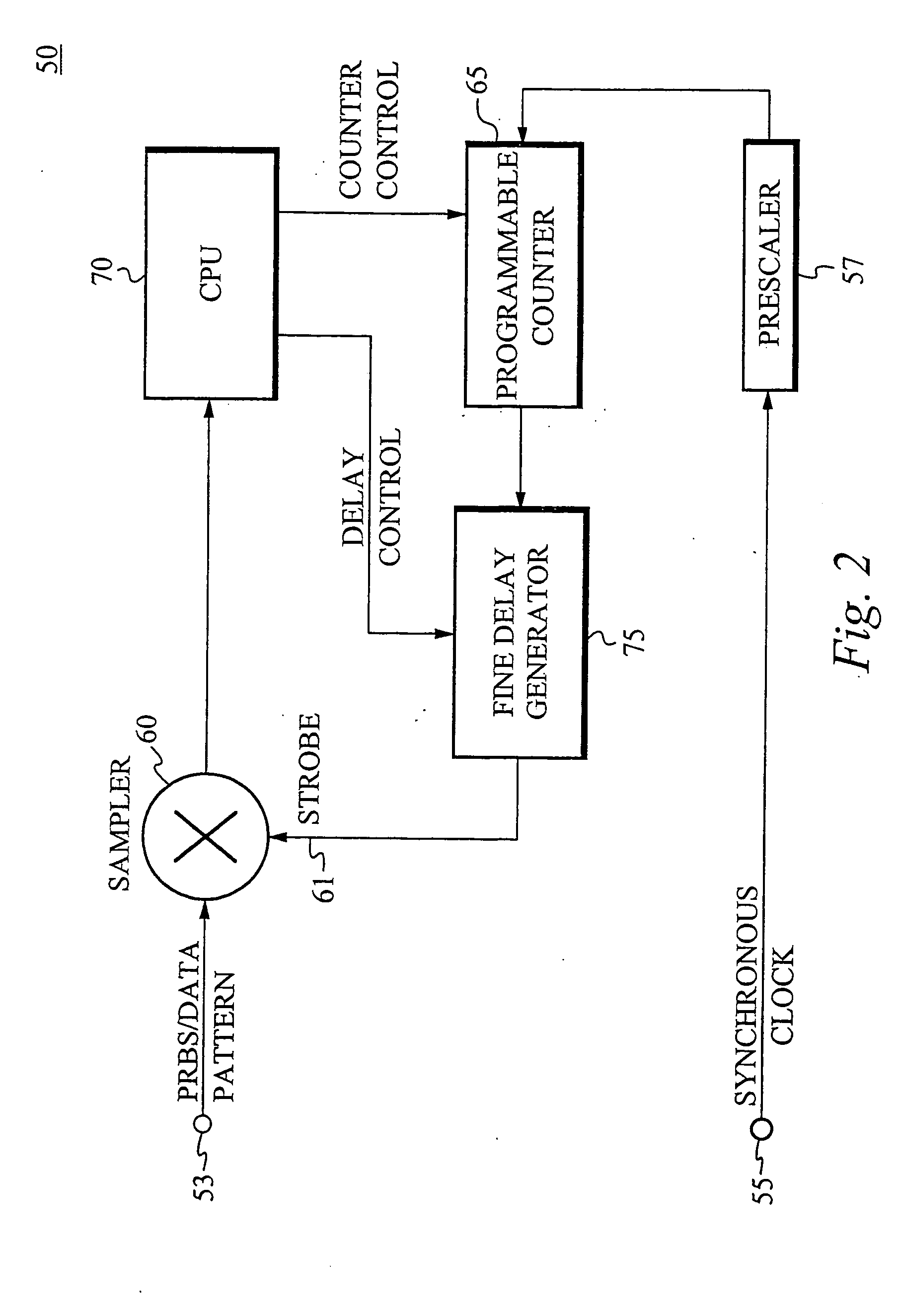

Method of and apparatus for measuring jitter and generating an eye diagram of a high speed data signal

InactiveUS20050177758A1Frequency stabilisation mechanismResistance/reactance/impedenceData signalComputer science

A sampling system is disclosed which measures high speed data signals by performing sampling events at intervals determined by a programmable DDS output frequency and a programmable counter. The reference frequency of the DDS is that of a clock signal that is synchronous with the data signal to be measured. The present invention is able to arrange the sample points to form an eye diagram of the input signal. In addition, the present invention is capable of sampling synchronously with the data clock and controlling the phase of the synthesized signal such that the samples are localized around the rising and falling edges of the data waveform. The present invention is thereby able to determine the location of the edges of the data signal and analyze the deterministic jitter of the waveform.

Owner:ANRITSU CORP

Dot marks the spot

Owner:GRILLO SUSAN KAY

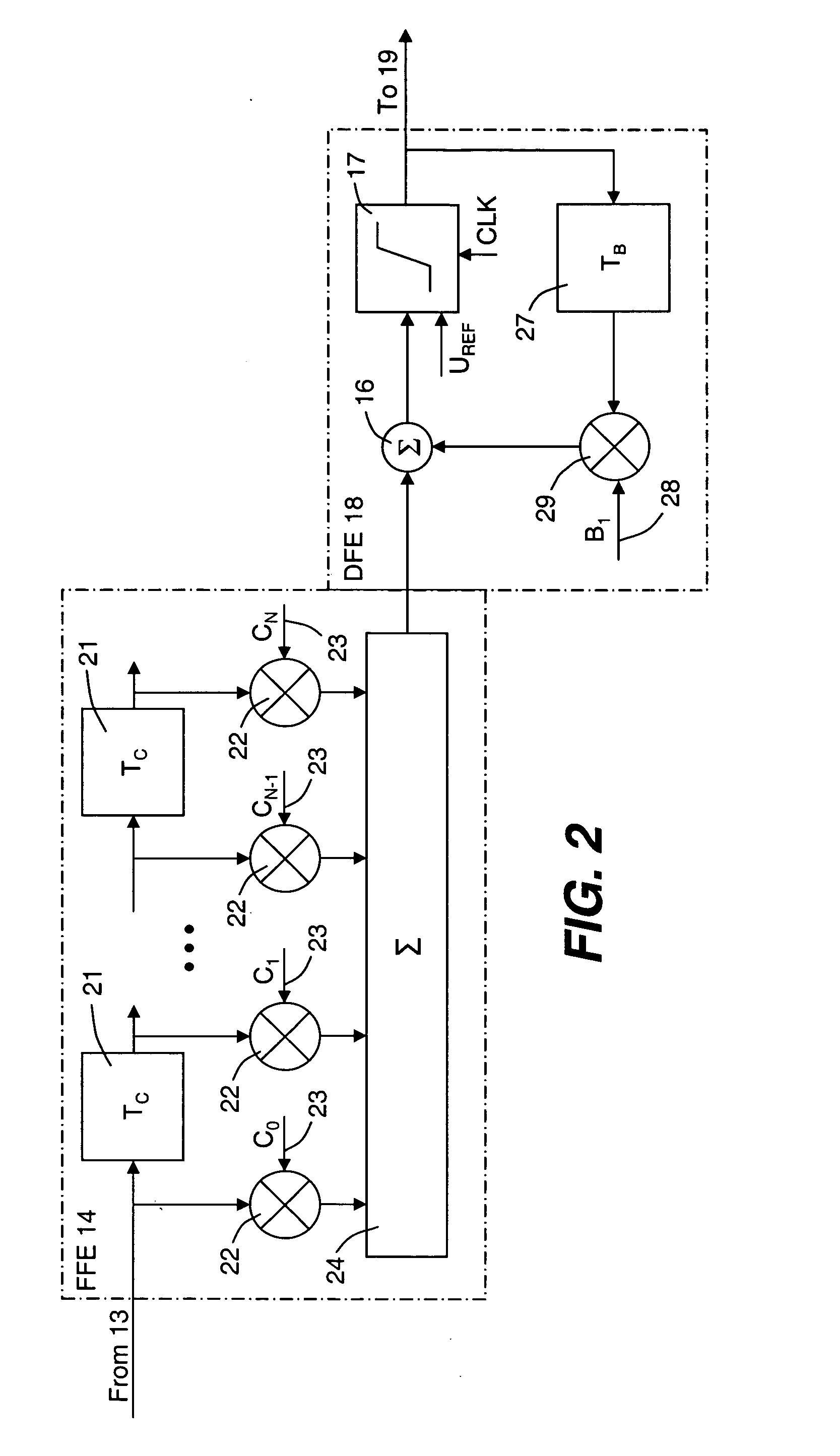

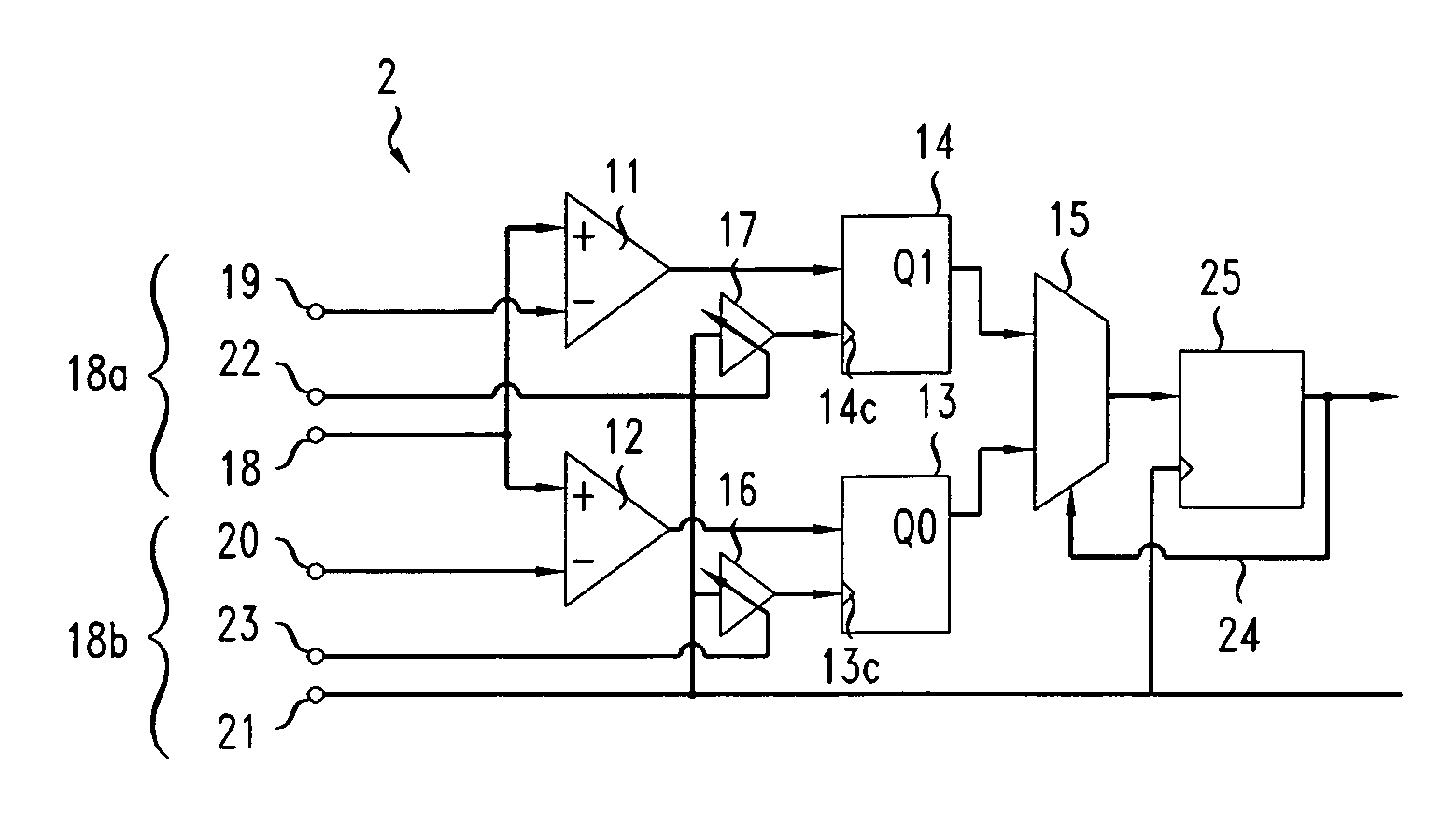

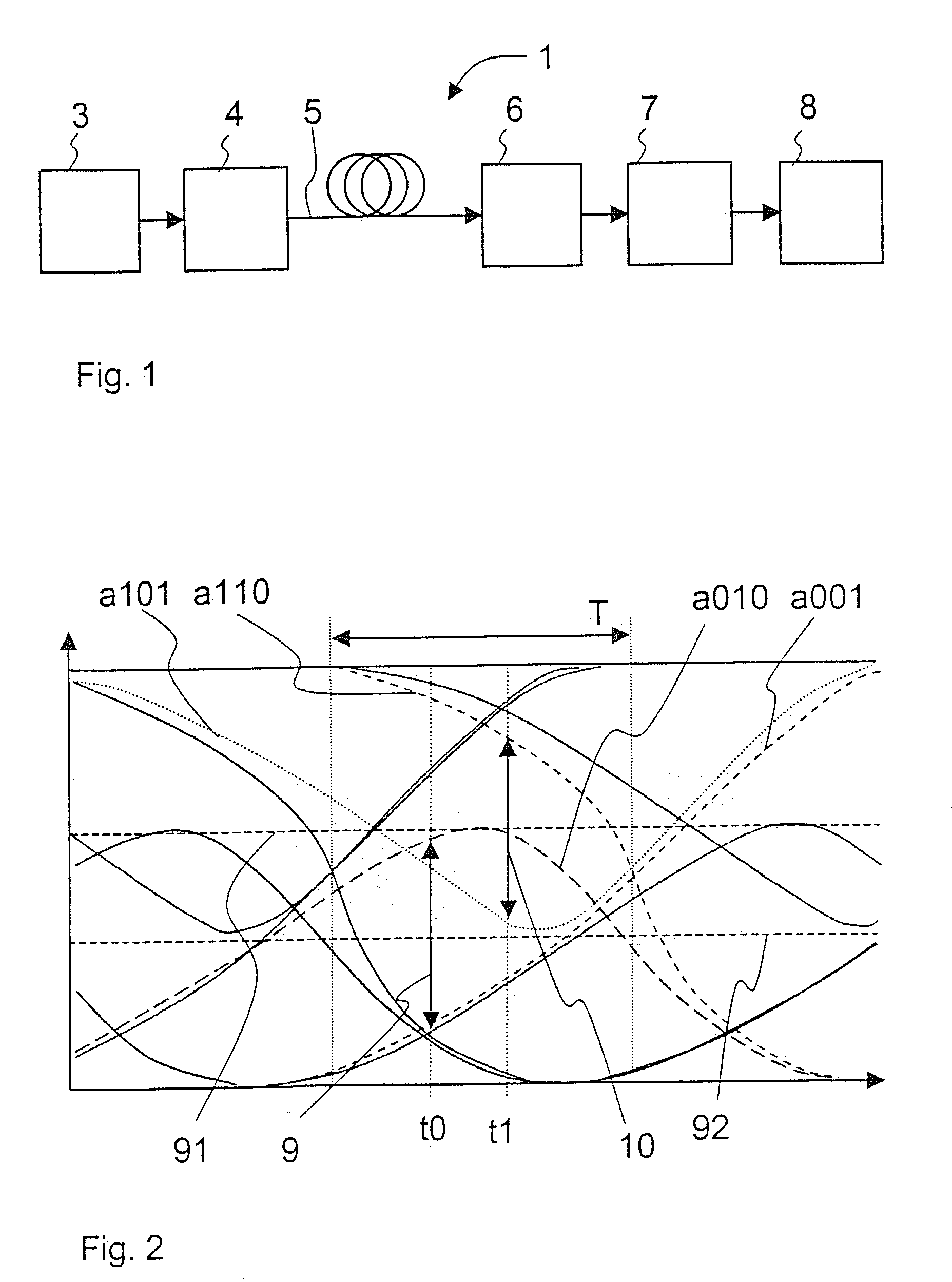

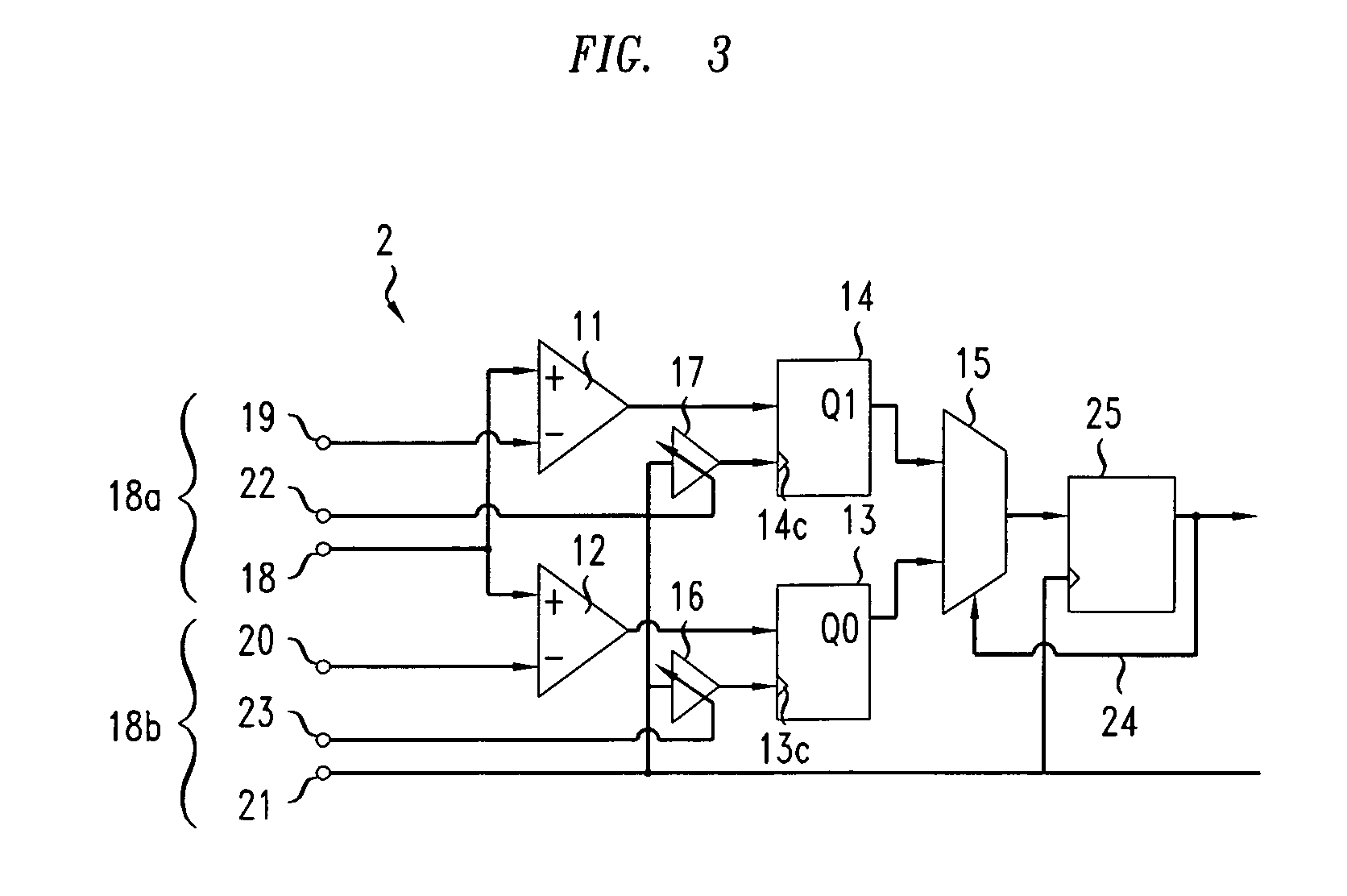

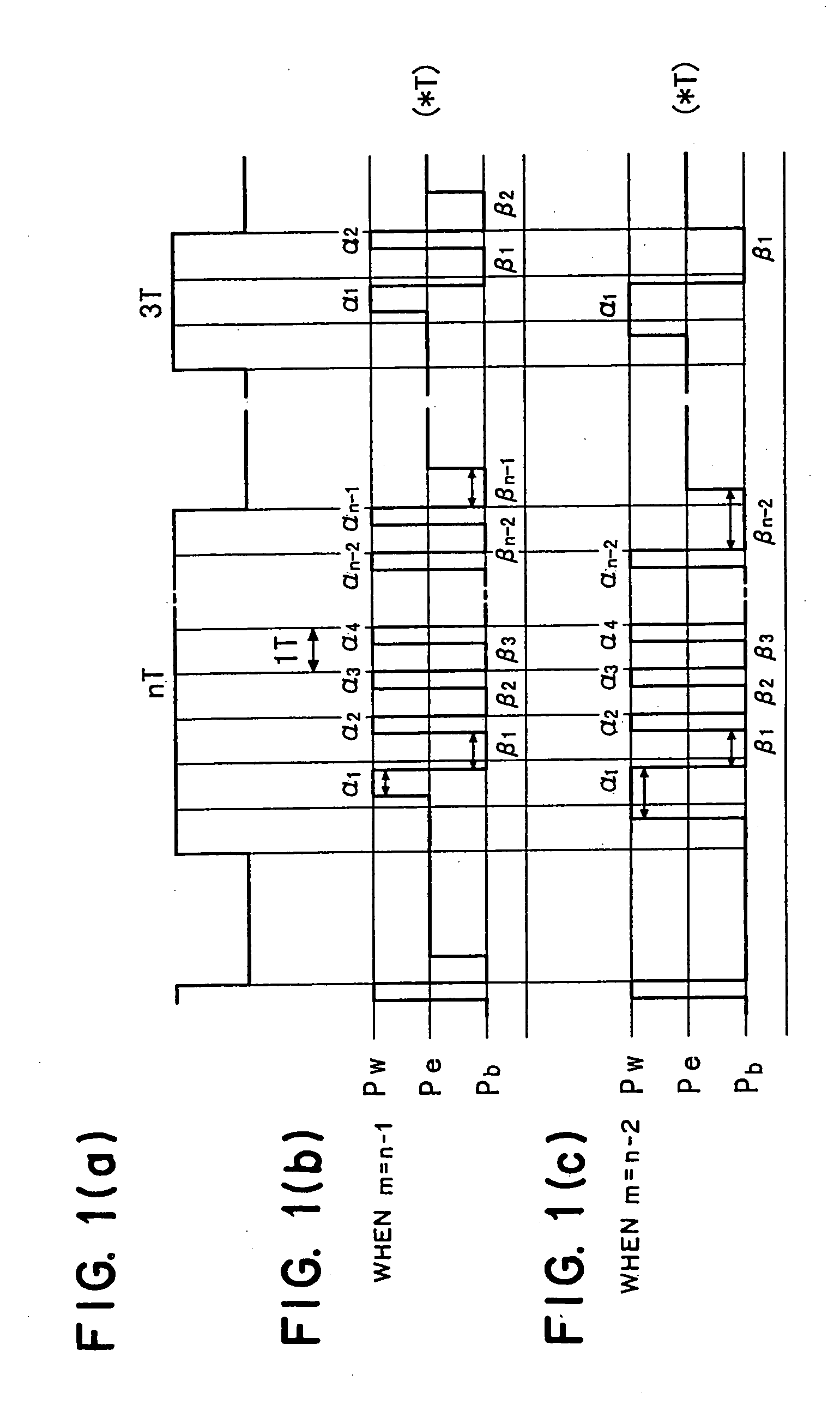

Decision feedback structure with selective sampling phase control

ActiveUS7184477B2Good synchronizationImprove method performanceMultiple-port networksError preventionSampling instantAlgorithm

A decision feedback structure for recovering a bit stream out of received signals is disclosed, wherein the sampling instant may be tuned in dependence of the sequence or pattern of the preceding bits so as to follow the bit sequence dependent instant of the maximum eye opening. The decision-feedback equalizer structure includes decision means for making a bit value decision at a sampling instant, a feedback path to feed back bit values to said decision means and means for adapting the sampling instant for a bit value decision made by said decision means with respect to the sampling phase depending on the bit values of preceding bits, in particular depending on the bit value of the previous bit.

Owner:LUCENT TECH INC

Recoverable biometric identity system and method

ActiveUS8160307B2Increase elasticityElectric signal transmission systemsDigital data processing detailsPattern recognitionHandwriting

A method for identifying persons based on biometric data achieves enhanced security and increased accuracy compared with other systems by distorting one or more biometrics prior to detection and recognition. The method includes detecting a distorted biometric for input into an identification system, comparing the distorted biometric to one or more distortion patterns, and determining an identity of the person based on results of the comparison. The biometric may be an eye pattern, a fingerprint or palm print, a voice print, a handwriting sample, a DNA sample, a facial image, or any other type of characteristic or behavioral attribute of a person. The biometric may be distorted in any one of a variety of ways for comparison to previously enrolled biometrics which have been distorted using the same or similar element. A system and program embodied within a computer-readable medium performs the steps of the method.

Owner:POLCHA ANDREW J +1

Dot marks the spot

Owner:GRILLO SUSAN KAY

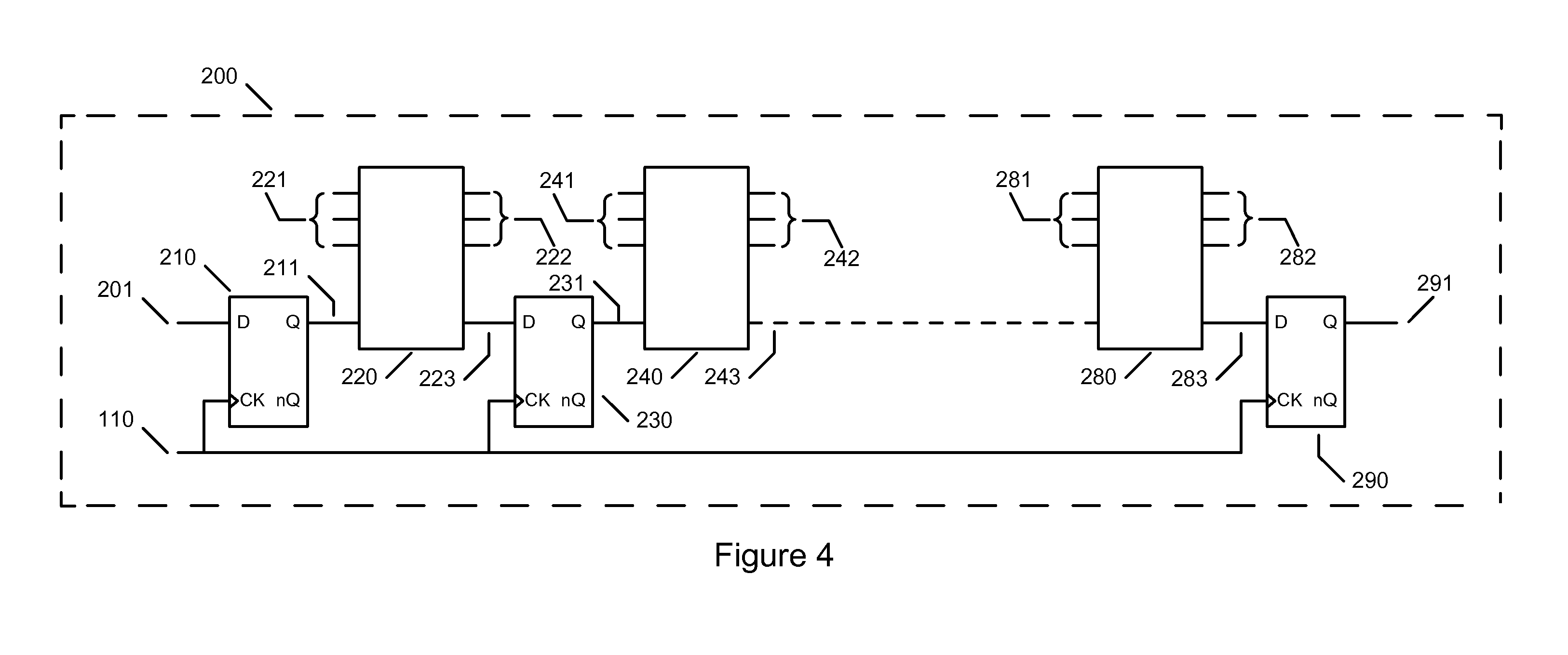

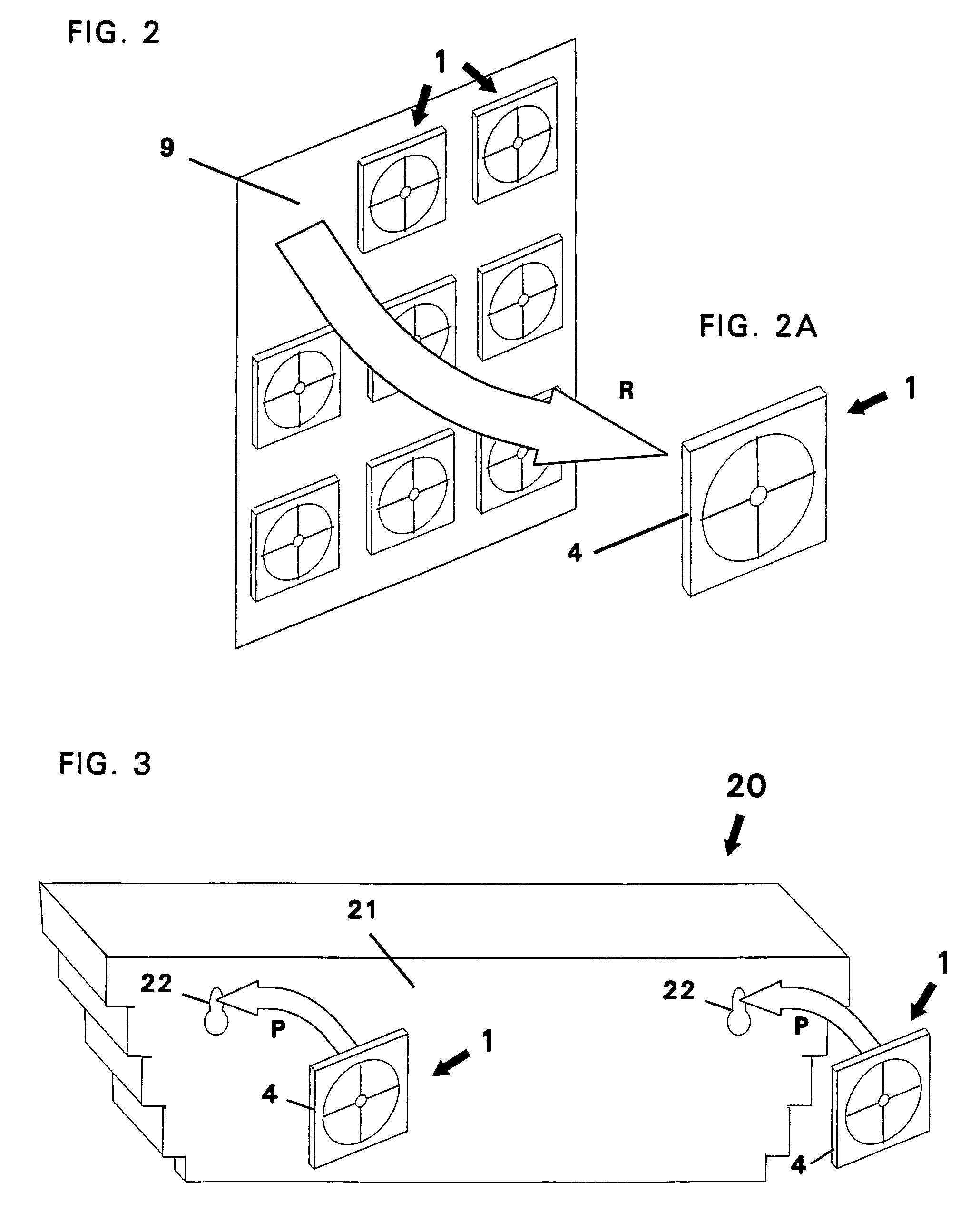

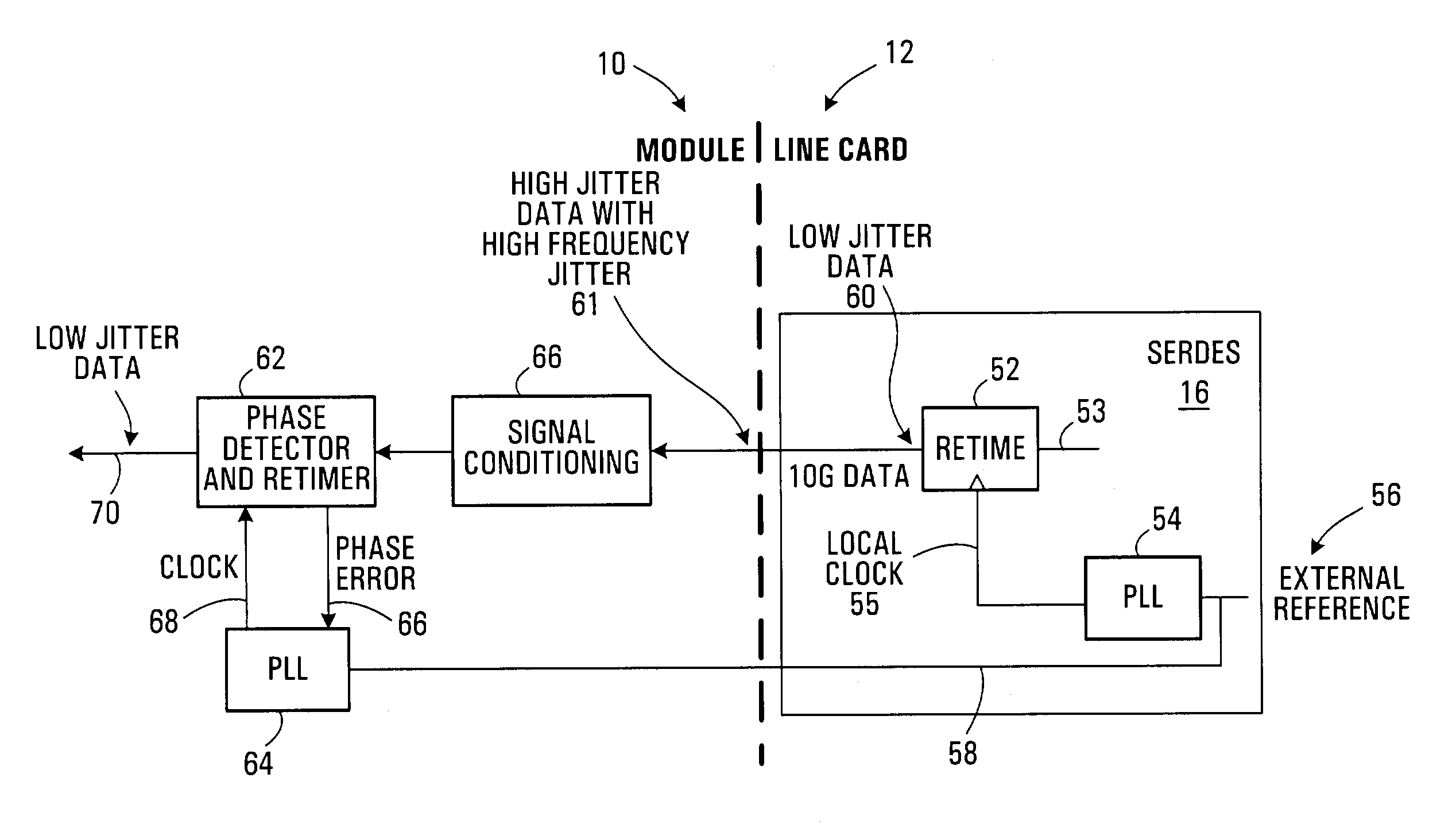

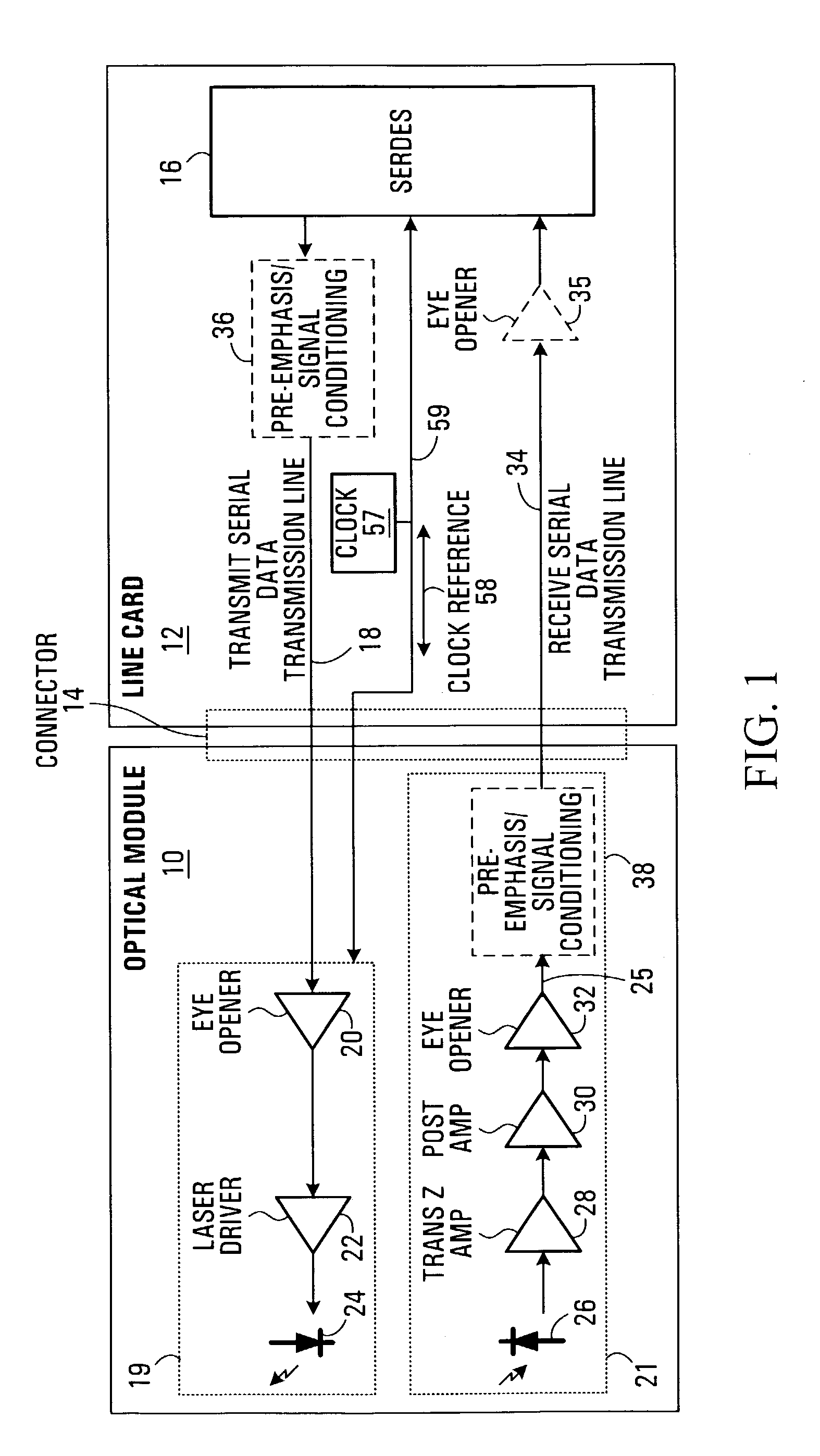

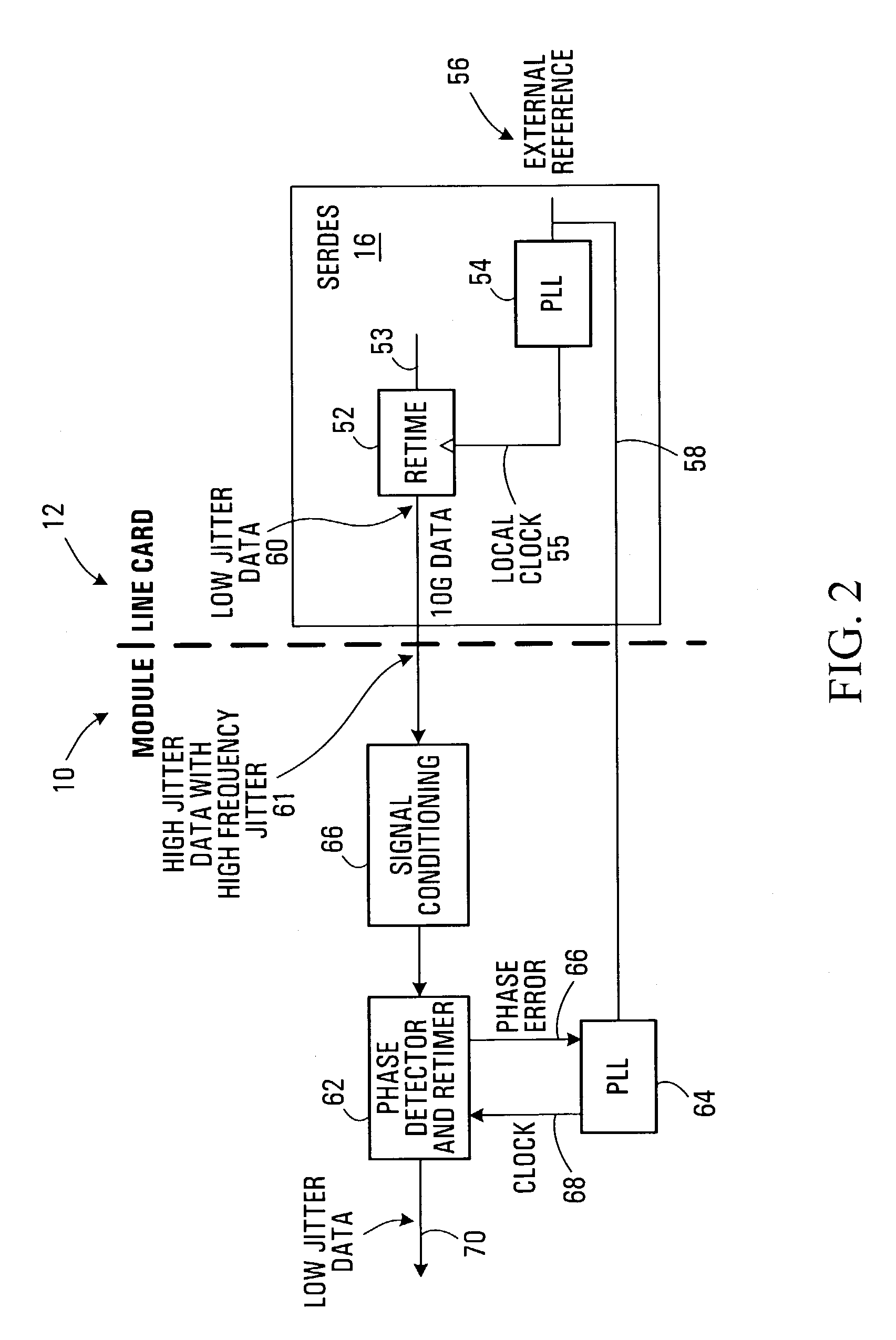

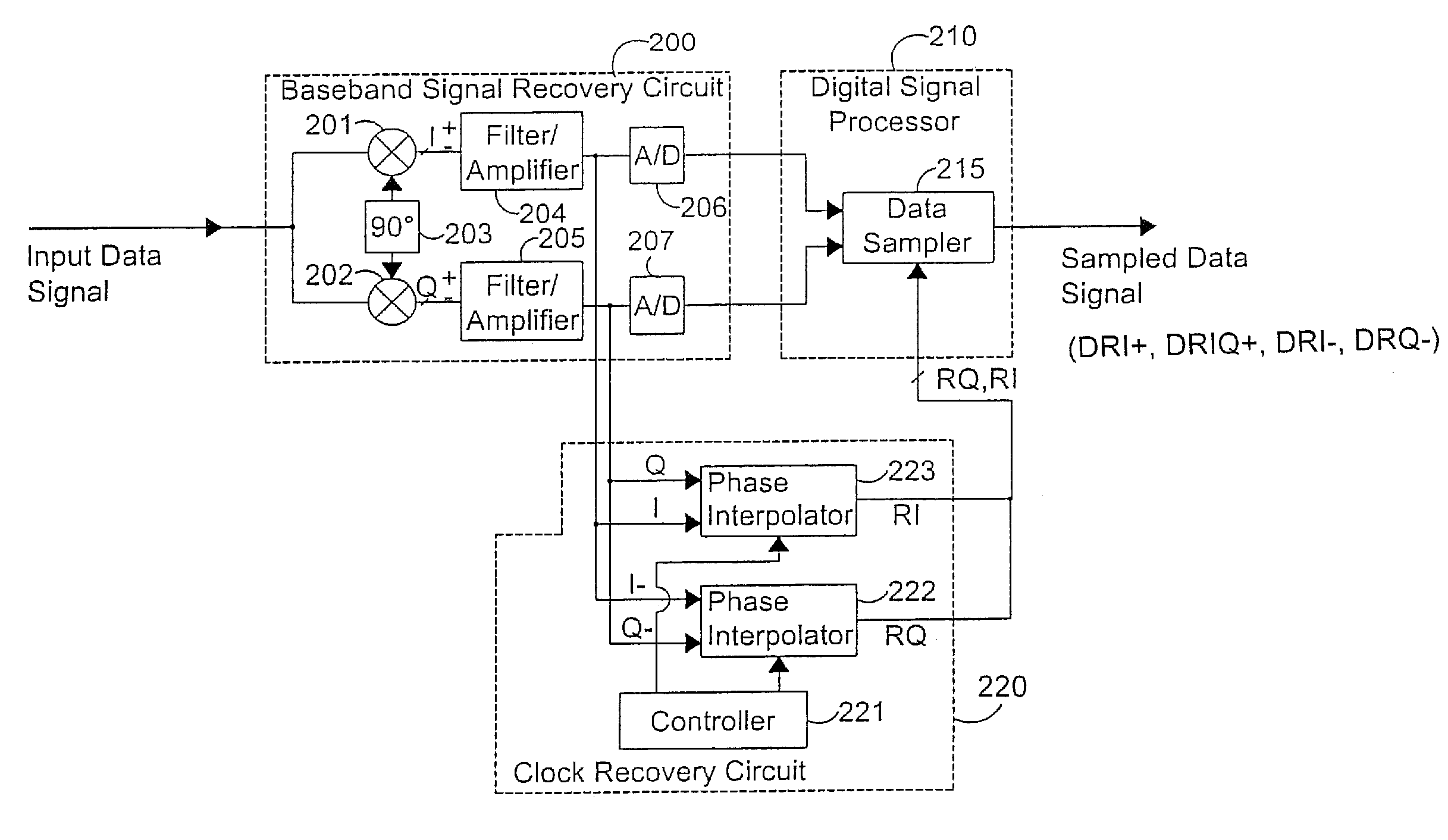

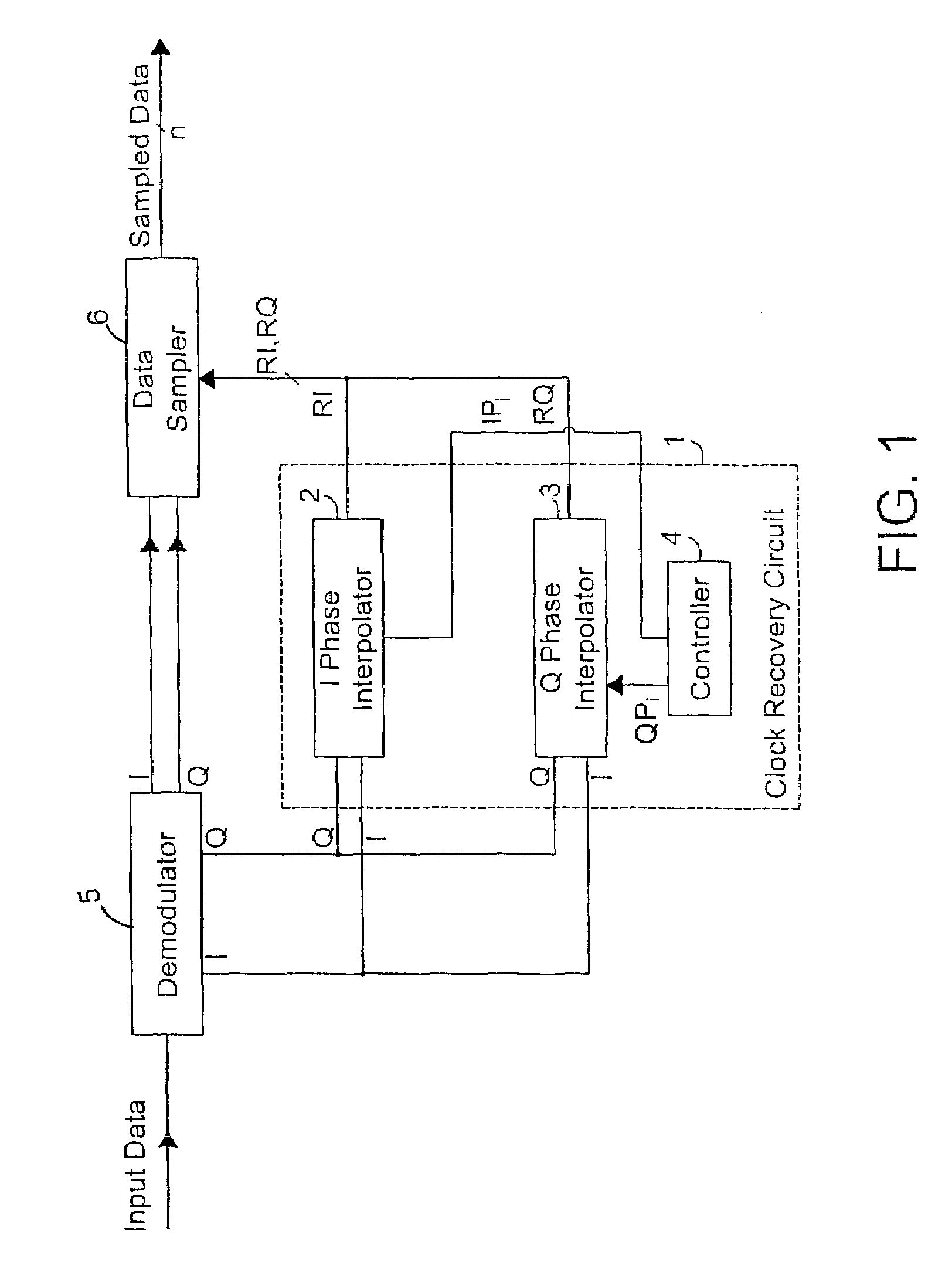

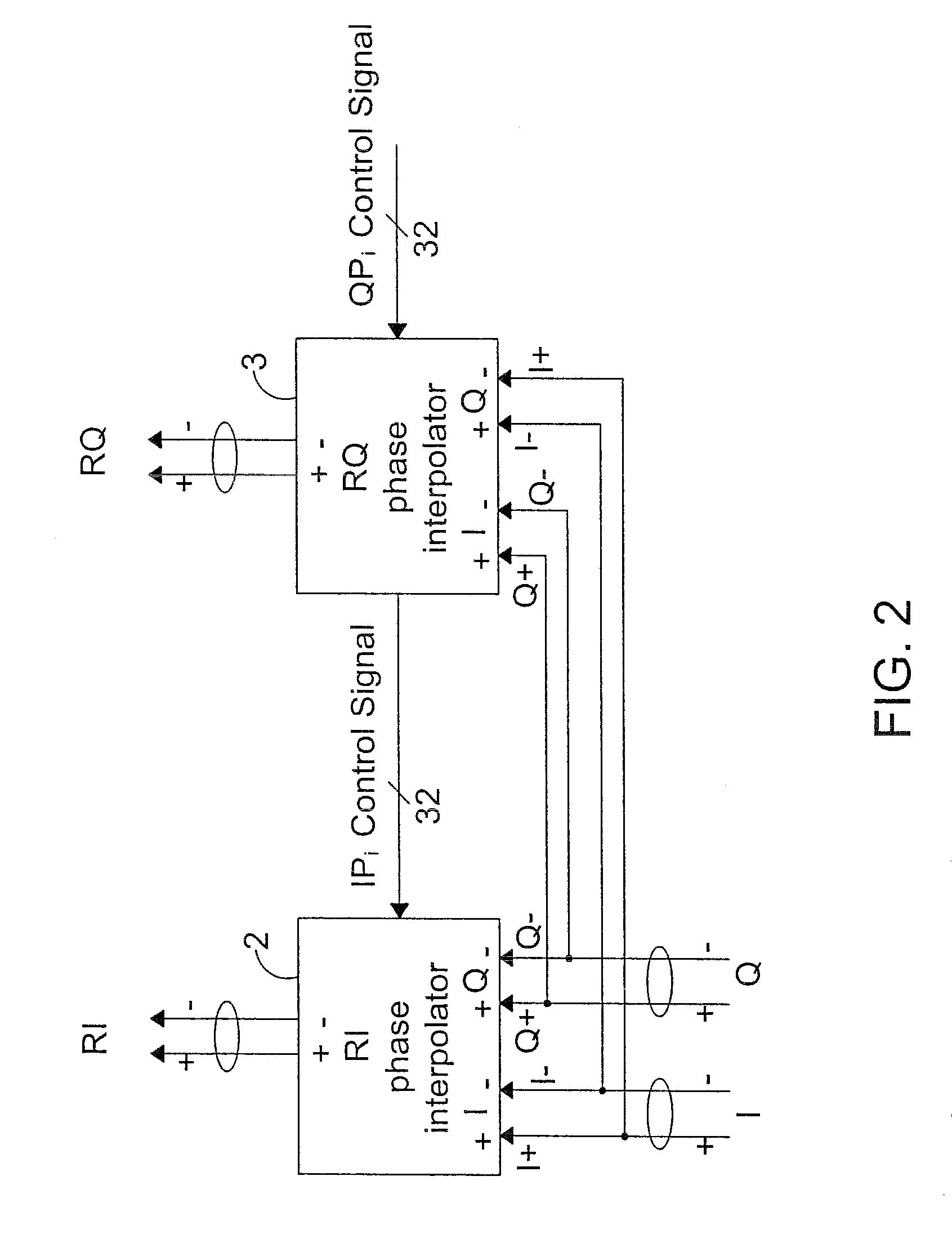

Self correcting data re-timing circuit and method

ActiveUS7308060B1Reduce jitterPulse automatic controlAngle demodulation by phase difference detectionEye patternData signal

An eye opener circuit is provided which performs a data re-timing / eye opening function on a data signal after having been corrupted by jitter. The circuit uses a PLL driven by a clock source which was the same clock source used in timing the data signal originally. The PLL generates a local clock used to re-time the data. A phase error may be introduced into the PLL, or into the data signal.

Owner:MARVELL ASIA PTE LTD

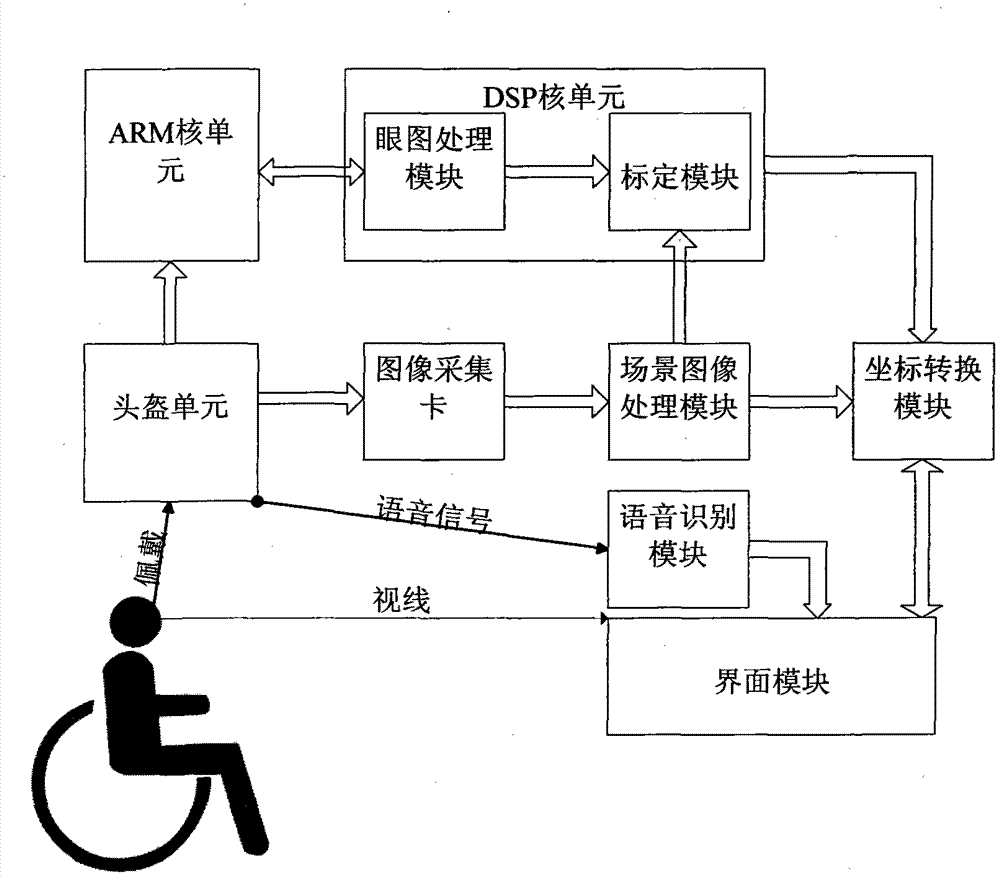

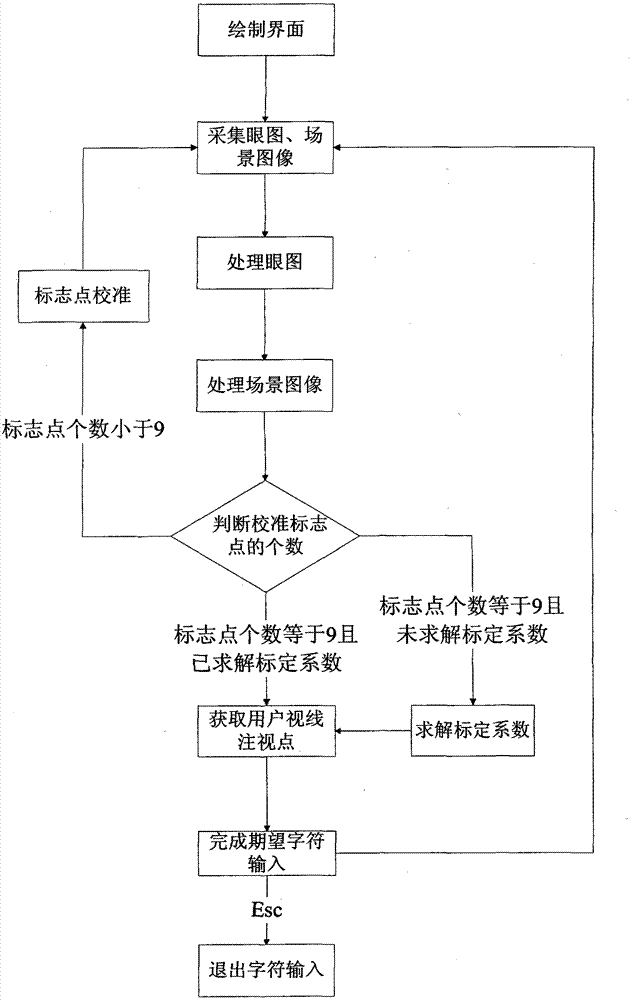

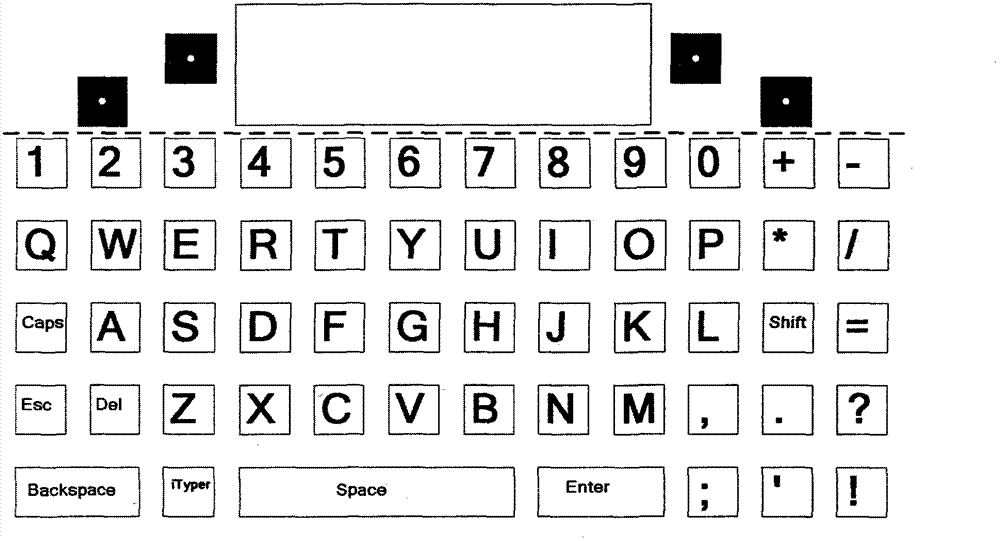

Character input device and method based on eye-gaze tracking and speech recognition

InactiveCN103076876APrecise positioningOvercome the disadvantage of low gaze precisionInput/output for user-computer interactionSpeech recognitionFixation pointSpeech identification

The invention discloses a character input device and method based on eye-gaze tracking and speech recognition. The device comprises a helmet unit, an ARM (advanced RISC machine) core unit, an image acquisition card, a voice identification module, a DSP (digital signal processor) core unit, a scene image processing module, a coordinate conversion module and an interface module. The method comprises the following steps of: on the basis of collecting and processing an eye pattern, a scene image and a user voice signal, calibrating to obtain a calibration coefficient; solving a two-dimensional calibration equation and a coordinate transformation matrix to obtain the coordinate value of a user sight fixation point in an interface coordinate system; finally, obtaining a character which is expected to be input; and cooperating with the user voice information to finish the operations of character input and the four arithmetic operation. The invention has the advantages of high character input fixation precision, big head moving range, simpleness in operation and good practicality and maneuverability.

Owner:XIDIAN UNIV

Recoverable biometric identity system and method

ActiveUS20090175506A1Increase elasticityAcquiring/recognising eyesBiometric pattern recognitionPattern recognitionHandwriting

A method for identifying persons based on biometric data achieves enhanced security and increased accuracy compared with other systems by distorting one or more biometrics prior to detection and recognition. The method includes detecting a distorted biometric for input into an identification system, comparing the distorted biometric to one or more distortion patterns, and determining an identity of the person based on results of the comparison. The biometric may be an eye pattern, a fingerprint or palm print, a voice print, a handwriting sample, a DNA sample, a facial image, or any other type of characteristic or behavioral attribute of a person. The biometric may be distorted in any one of a variety of ways for comparison to previously enrolled biometrics which have been distorted using the same or similar element. A system and program embodied within a computer-readable medium performs the steps of the method.

Owner:POLCHA ANDREW J +1

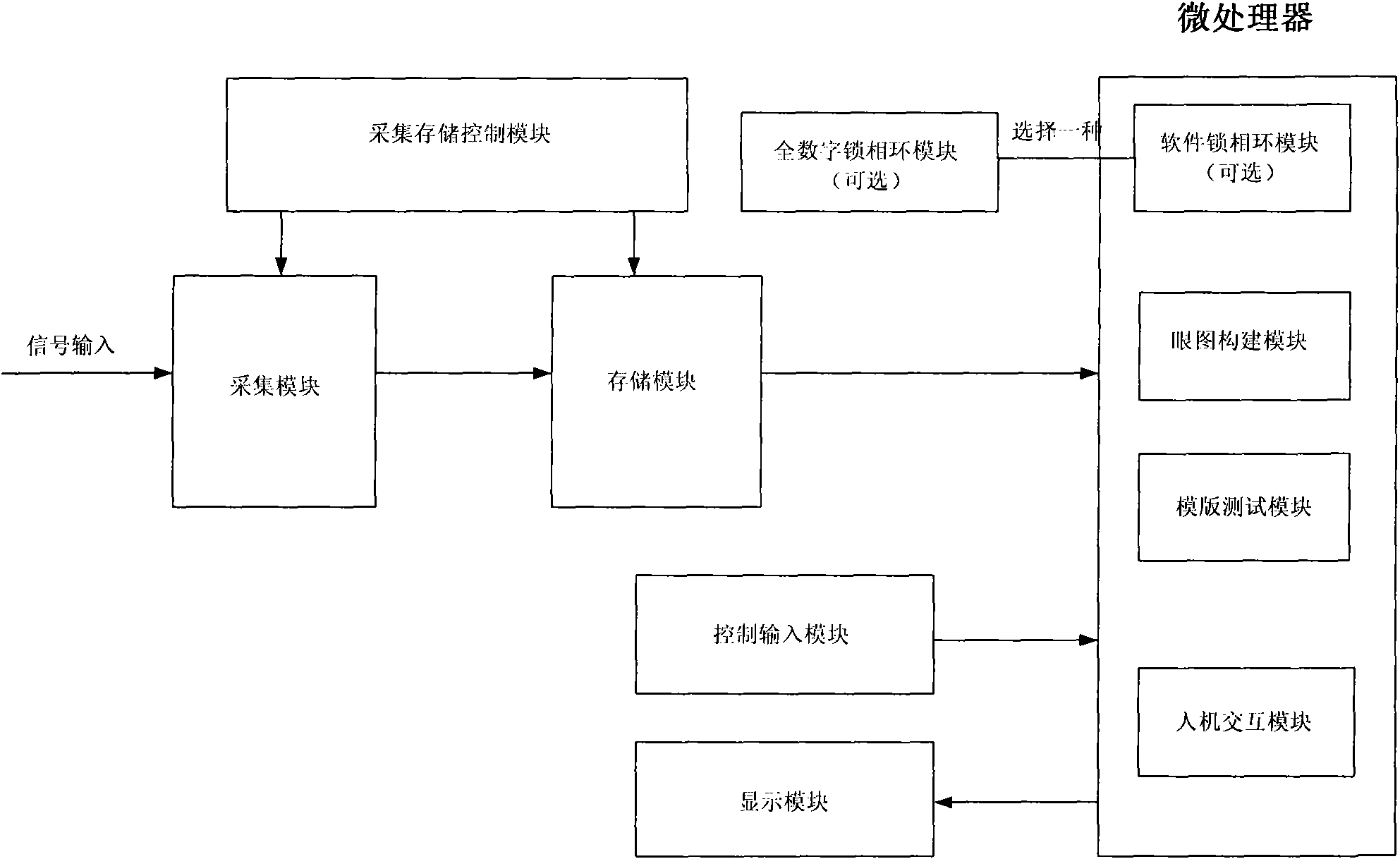

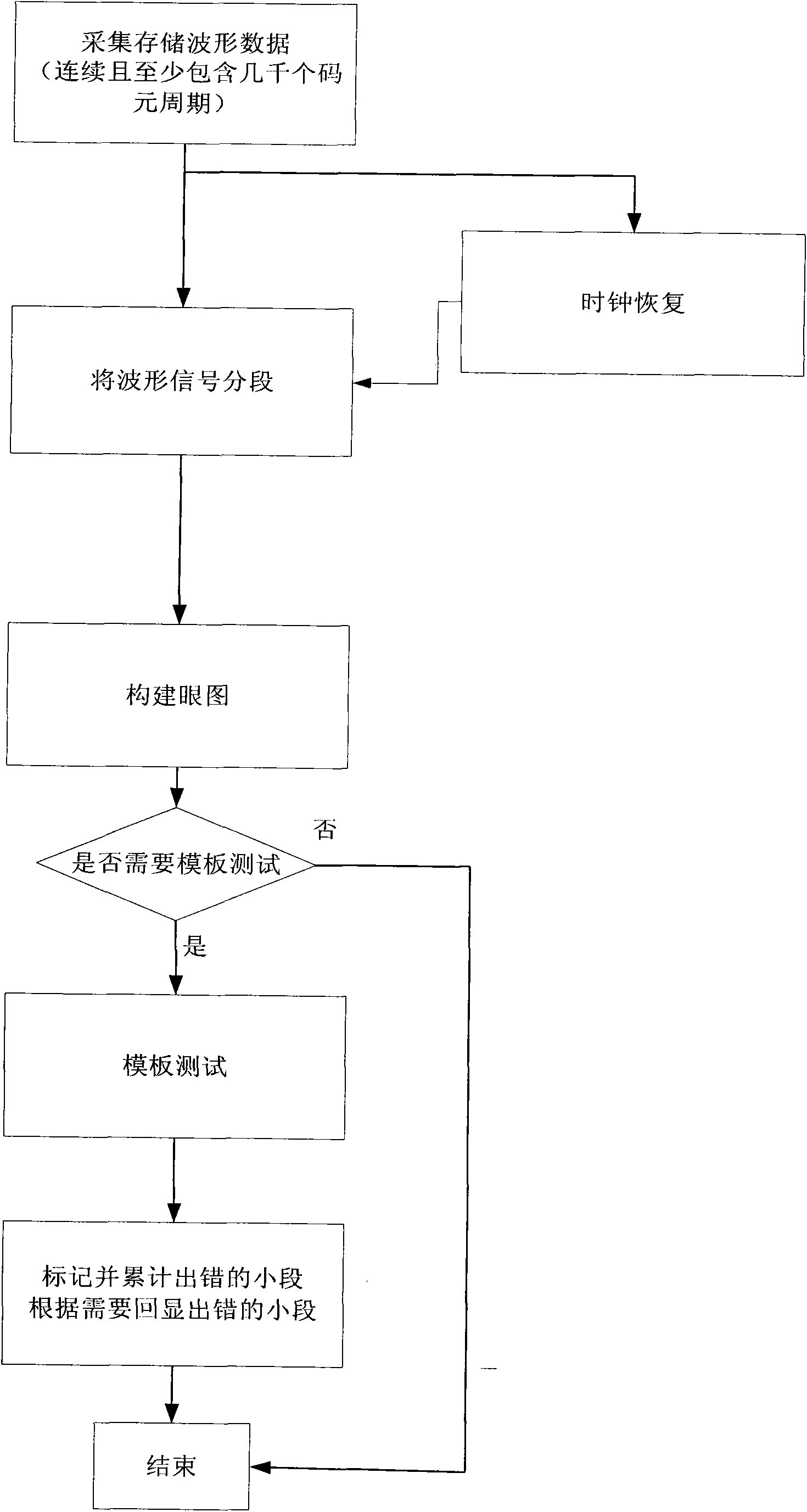

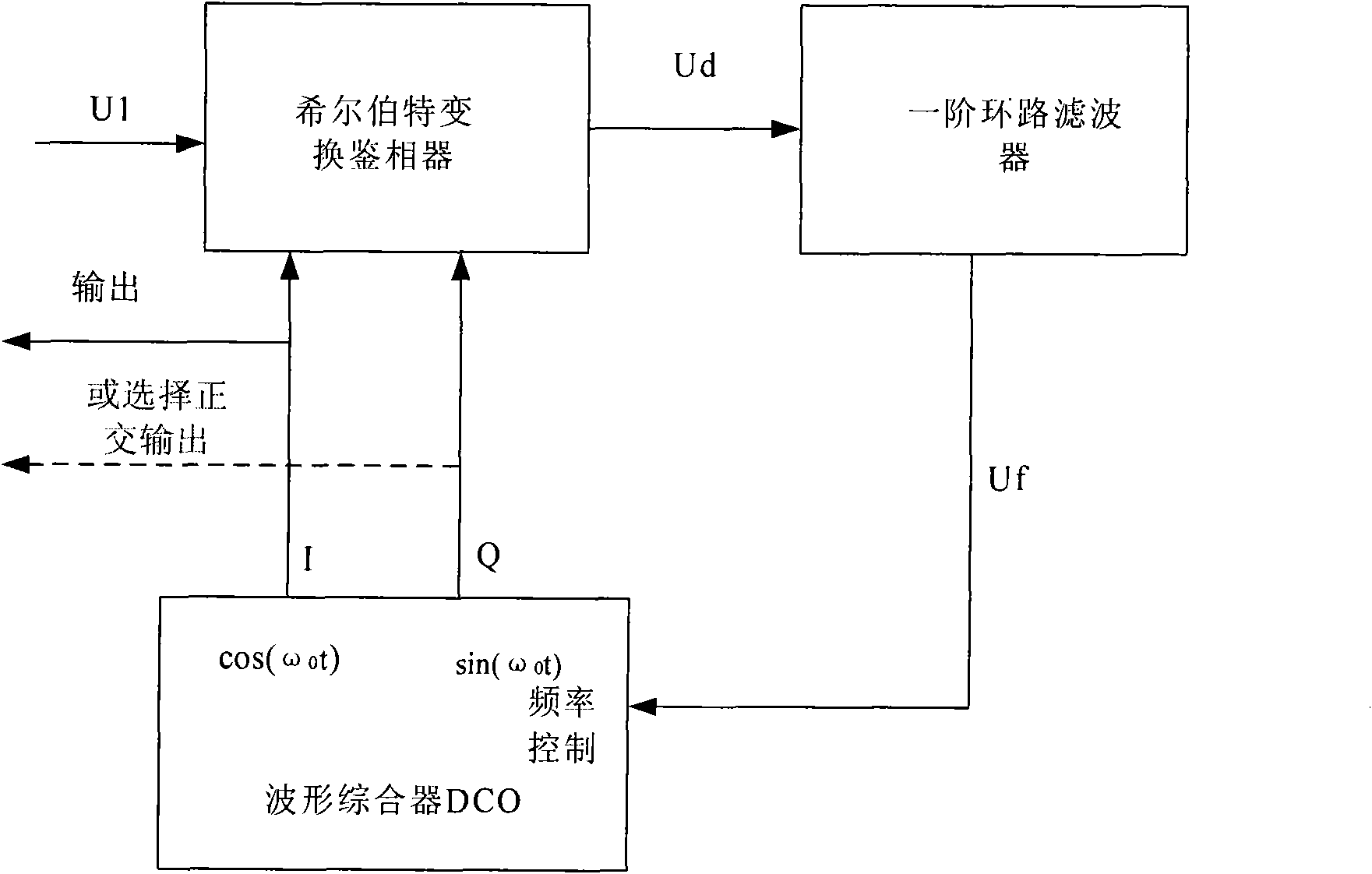

Method for building eye pattern and carrying out eye pattern template test

The invention discloses a method for building an eye pattern and carrying out an eye pattern template test, which comprises the following steps that: firstly, a signal acquisition module is triggered once to acquire a string of continuous data signals without acquisition bland space; secondly, the acquired signals are stored in a storage module and a software phase-locked loop is used to recover a clock signal from the stored data; thirdly, according to the recovered clock signal, a stored waveform signal is divided into data segments with a fixed length, and the data segments are aligned one by one and overlapped together to form an eye pattern; and finally, the formed eye pattern is compared with a template to complete the template test.

Owner:SOUTHEAST UNIV

Logic system with resistance to side-channel attack by exhibiting a closed clock-data eye diagram

InactiveUS8427194B2Reduce sensitivityImprove securityComputer security arrangementsElectric pulse generatorMonitoring systemElectromagnetic radiation

An improvement in the security of a logic system by minimizing observable features such as the power supply or electromagnetic radiation, so called, “side-channel attacks”. Specifically, the present invention comprises a technique and methods for reducing the ability of an intruder to monitor the relationship between currents in the system and the data in the system through the use of a randomized clock wherein the clock eye diagram is closed and without significant reduction in maximum operating speed compared to the reduction in maximum operating frequency that occurs when using conventional means of additive jitter. A system where the clock eye diagram is completely closed is provably more secure than systems where the clock eye diagram is partially open.

Owner:DEAS ALEXANDER ROGER +1

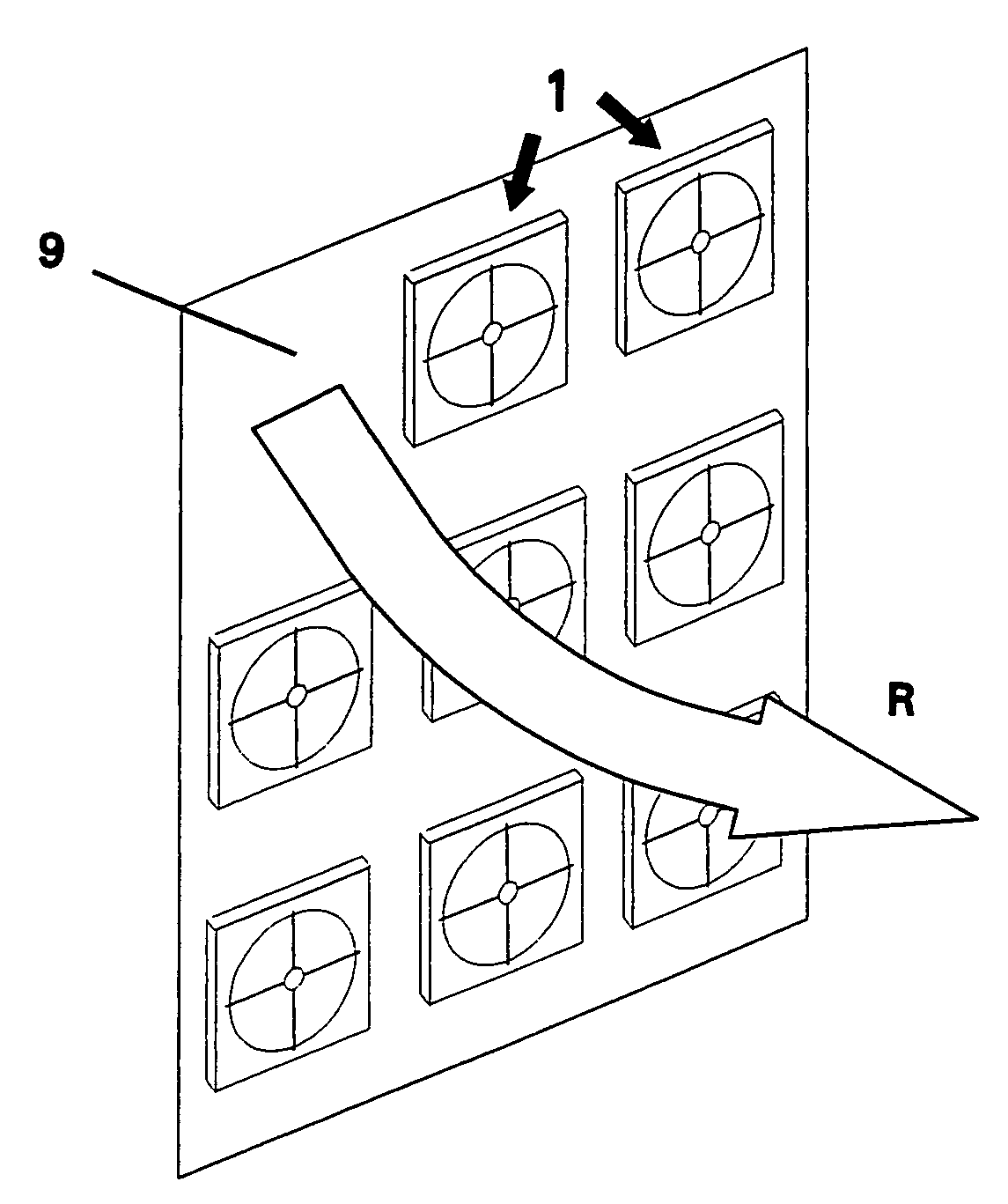

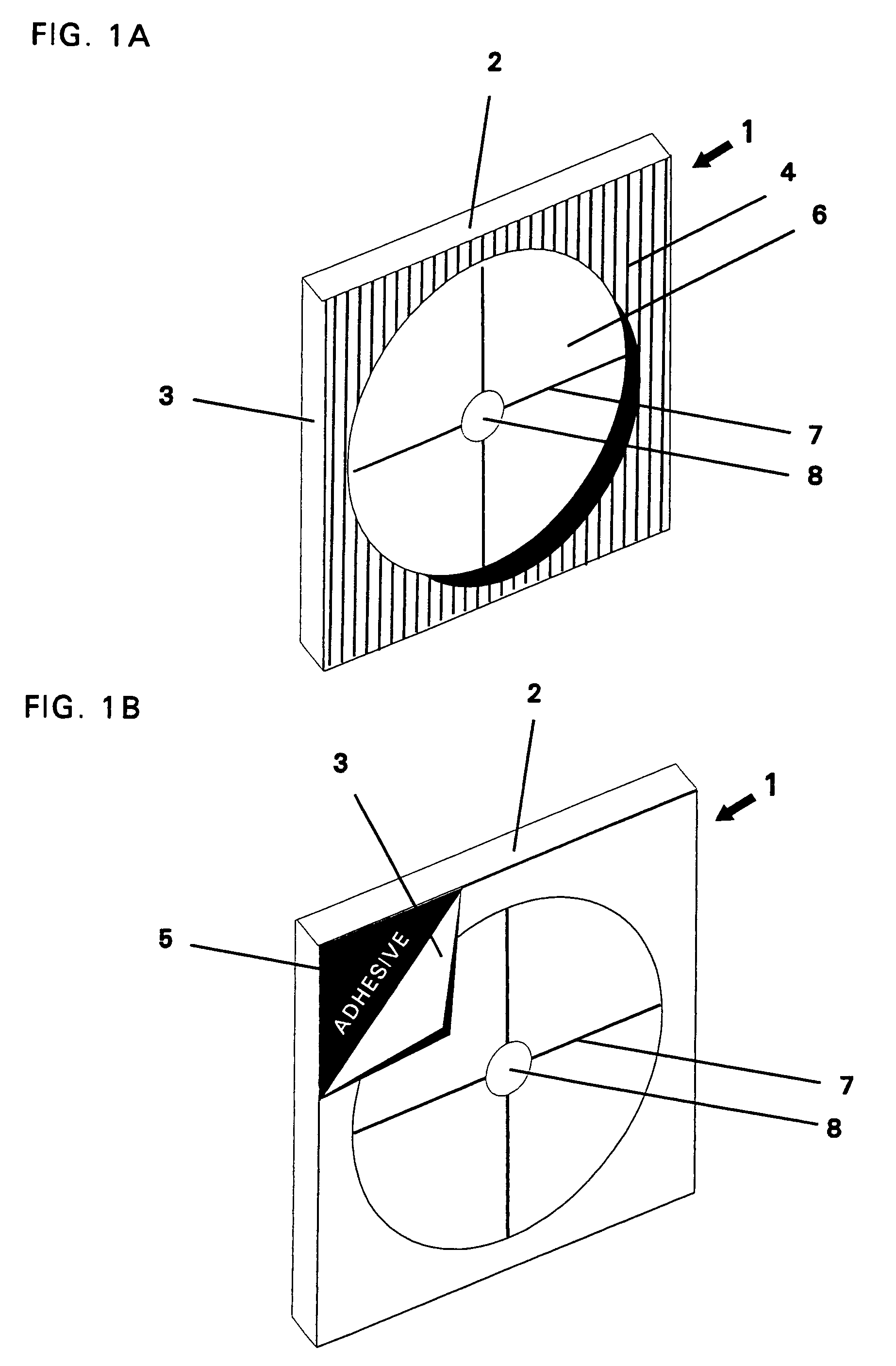

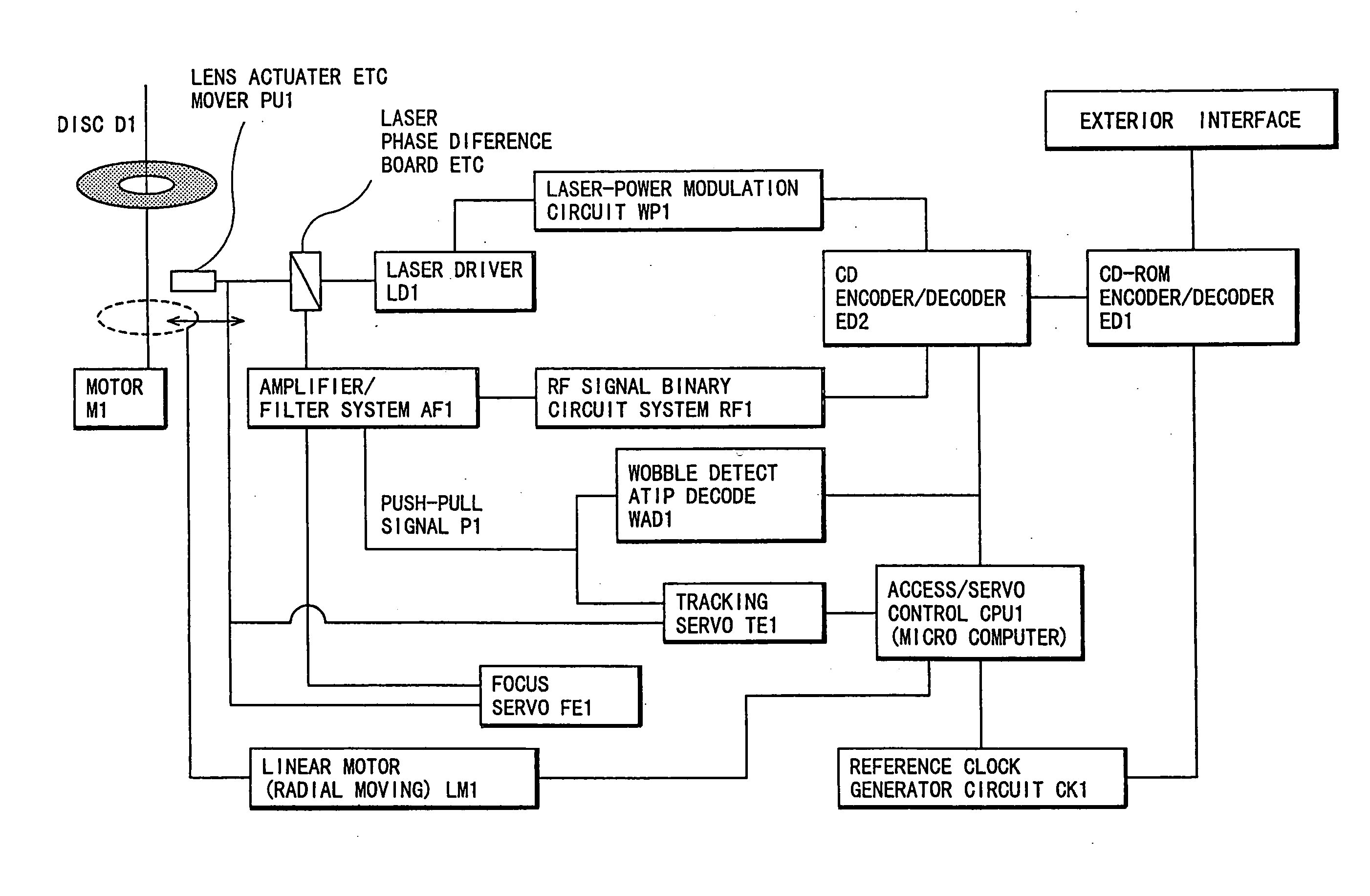

Rewritable optical recording medium, recording method on the same, and optical disc recording/retrieving apparatus

InactiveUS20040190407A1Filamentary/web record carriersOptical beam sourcesRecord statusRewritable compact disc

In a rewritable compact disc having a wobble groove on a substrate, crystal and amorphous states of a phase-change recording layer are an unrecorded / erased state and a recorded state, respectively. When the recording layer is exposed to recording light, amorphous marks assuming the recorded state are formed. At any of 2-, 4- and 8-times velocities with respect to a reference velocity (1-times velocity) whose linear velocity is 1.2-1.4 m / s, modulation m11 of a recorded signal when the recording light of approximately 780 nm in wavelength irradiates the recording layer via an optical system with NA=0.5 or 0.55 is 60-80%. A topmost level Rtop of reflectivity of the eye pattern of the recorded signal during retrieving at the 1-times velocity is 15-25%, and a jitter of the individual length of marks and inter-mark spaces during retrieving at 1-times velocity is 35 ns or less. Recording at 8-times or higher velocities is thereby realized without any risk of impairing the read-compatibility with the conventional CD-RW specifications at least at 4-times velocity.

Owner:CMC MAGNETICS CORPORATION

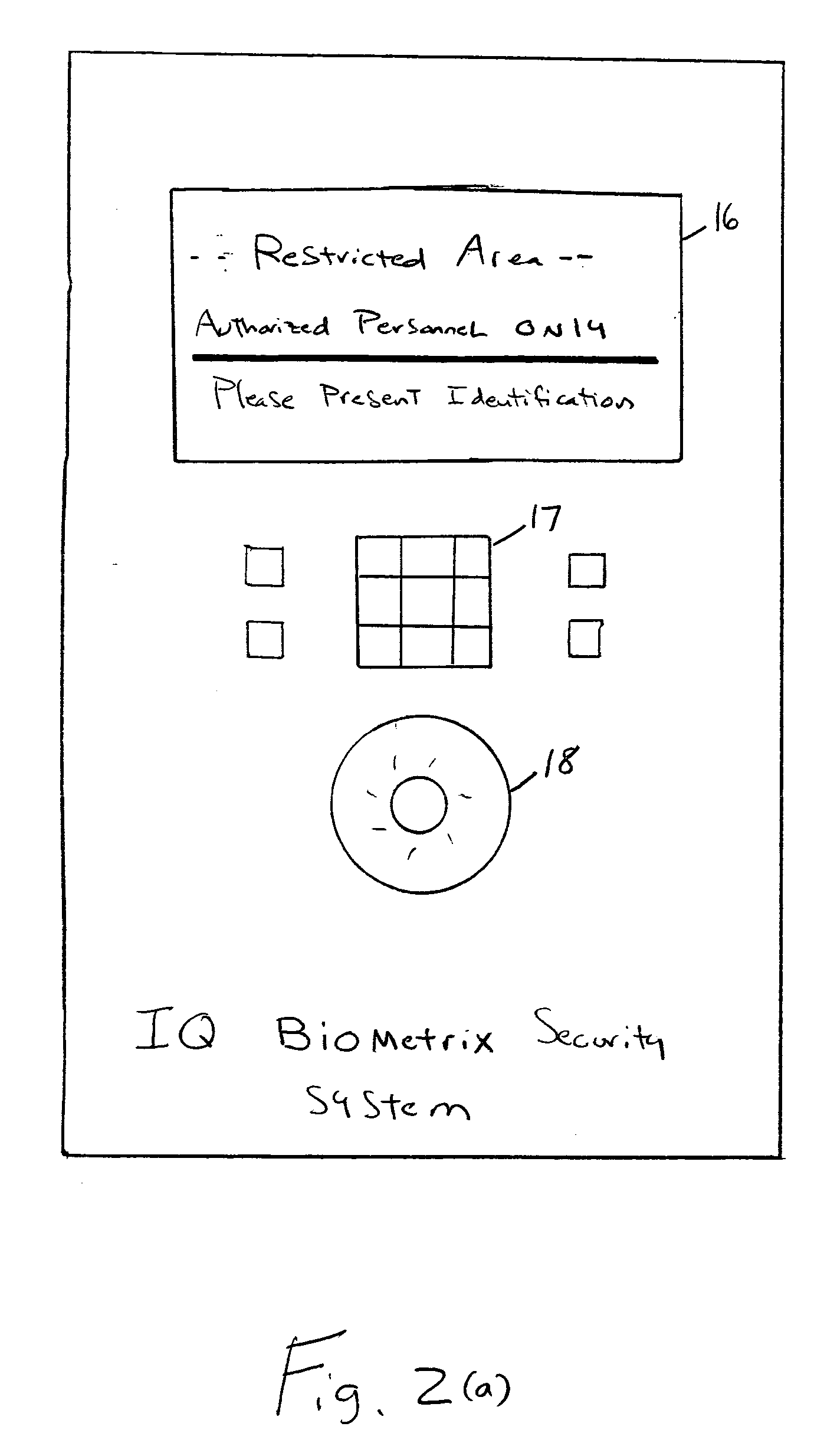

System and method for performing security access control based on modified biometric data

InactiveUS20060136743A1Great level of securityIncrease elasticityDigital data processing detailsPayment architectureHandwritingPalm print

An access control method achieves enhanced security and accuracy compared with other systems through recognition of one or more distorted biometrics. The method includes detecting a distorted biometric for input into an identification system, comparing the distorted biometric to one or more distortion patterns, and controlling access to a restricted item based on results of the comparison. The biometric may be an eye pattern, a fingerprint or palm print, a voice print, a handwriting sample, a DNA sample, a facial image, or any other type of characteristic or behavioral attribute of a person. The biometric may be distorted in any one of a variety of ways for comparison to previously enrolled biometrics which have been distorted using the same or similar element. A system and program embodied within a computer-readable medium performs the steps of the method.

Owner:POLCHA ANDREW J +1

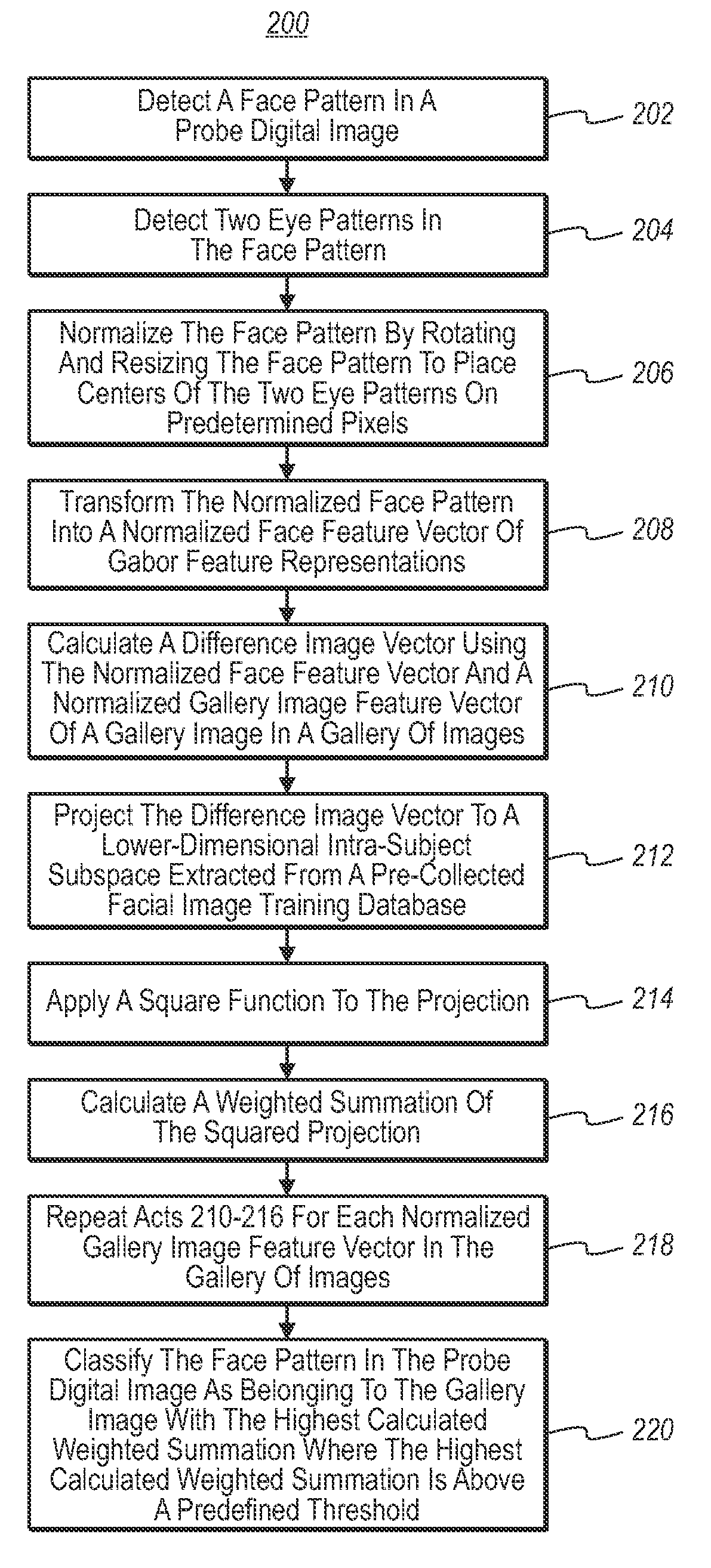

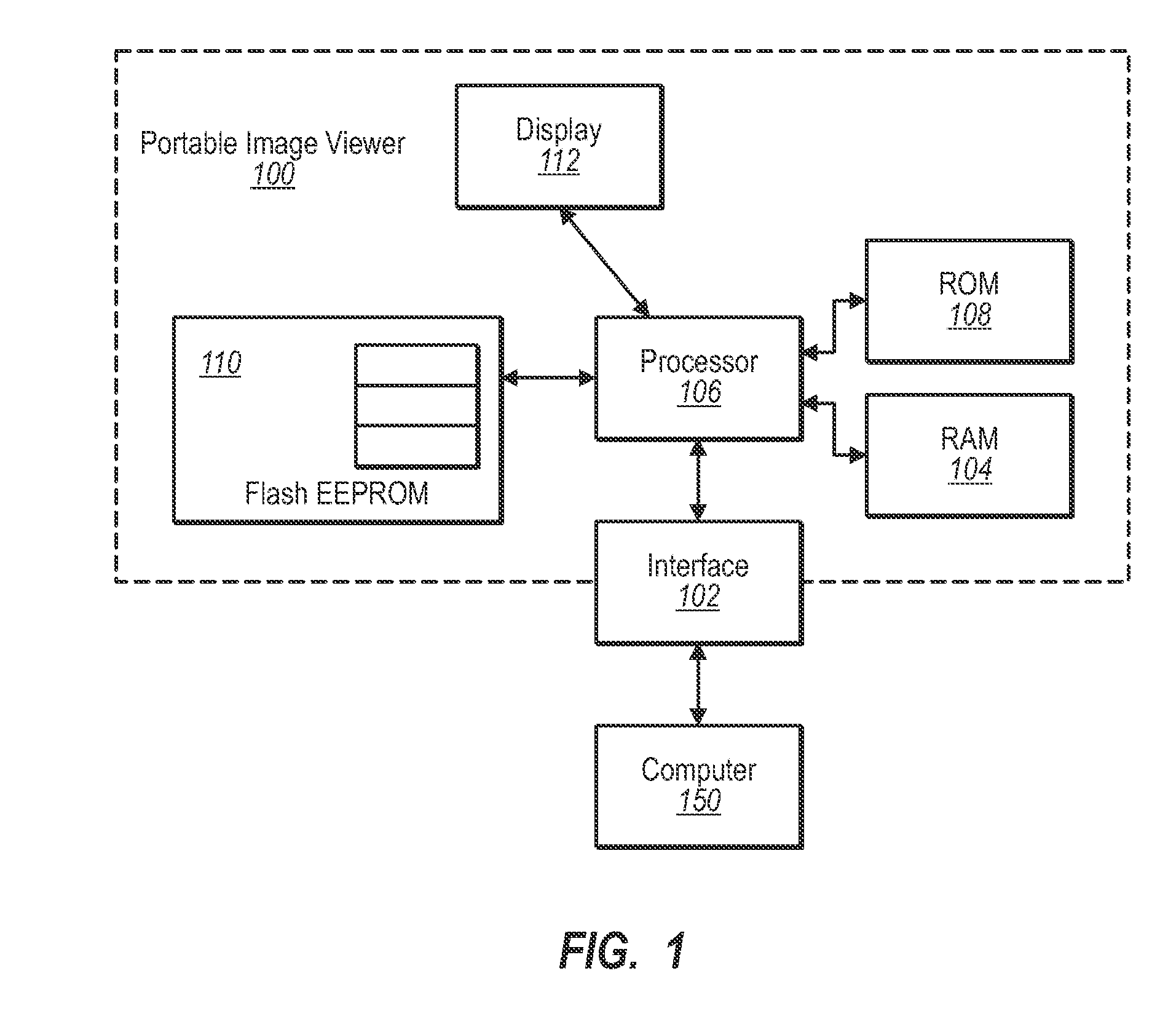

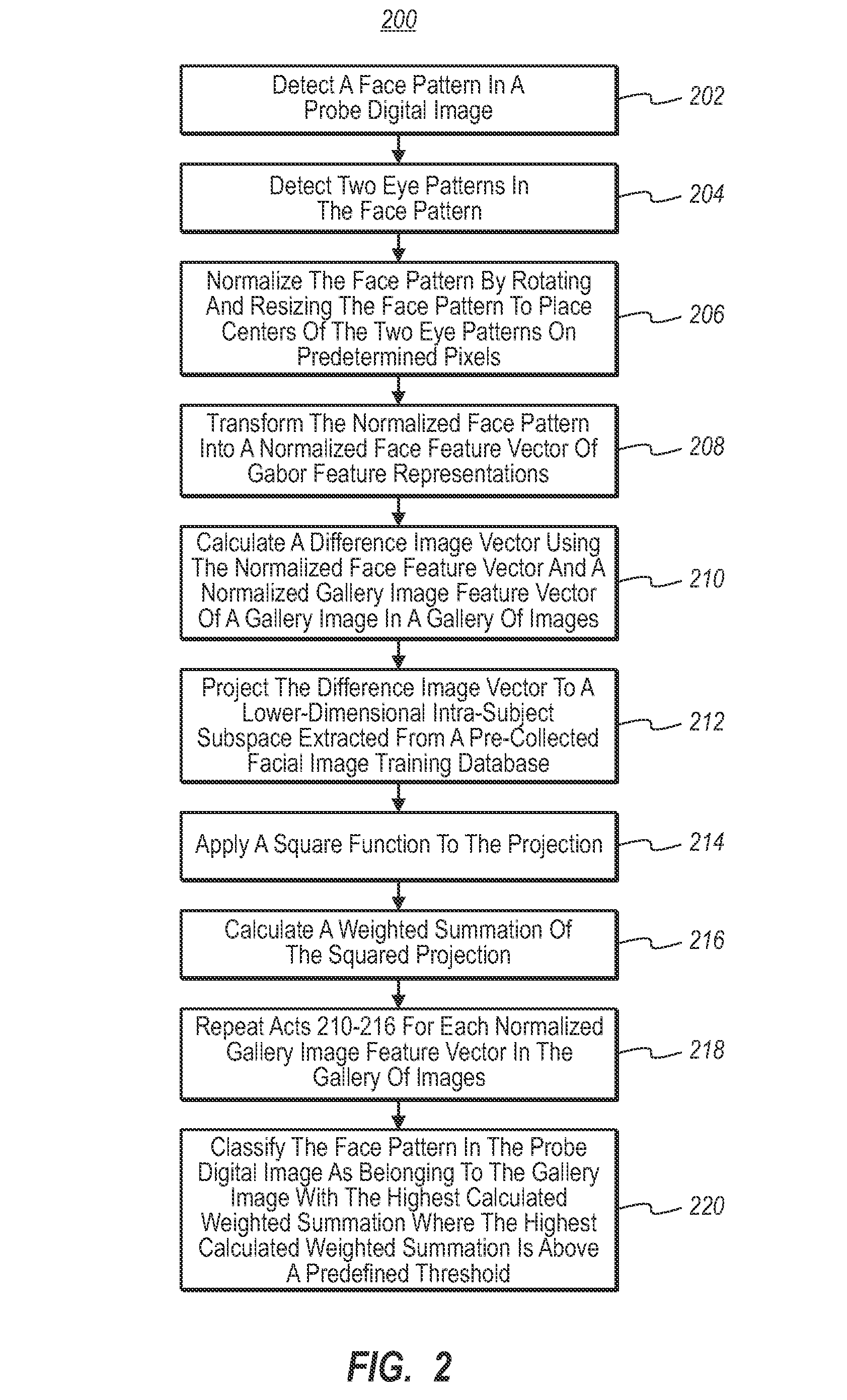

Automatic Face Recognition

Automatic face recognition. In a first example embodiment, a method for automatic face recognition includes several acts. First, a face pattern and two eye patterns are detected. Then, the face pattern is normalized. Next, the normalized face pattern is transformed into a normalized face feature vector of Gabor feature representations. Then, a difference image vector is calculated. Next, the difference image vector is projected to a lower-dimensional intra-subject subspace extracted from a pre-collected training face database. Then, a square function is applied to each component of the projection. Next, a weighted summation of the squared projection is calculated. Then, the previous four acts are repeated for each normalized gallery image feature vector. Finally, the face pattern in the probe digital image is classified as belonging to the gallery image with the highest calculated weighted summation where the highest calculated weighted summation is above a predefined threshold.

Owner:138 EAST LCD ADVANCEMENTS LTD

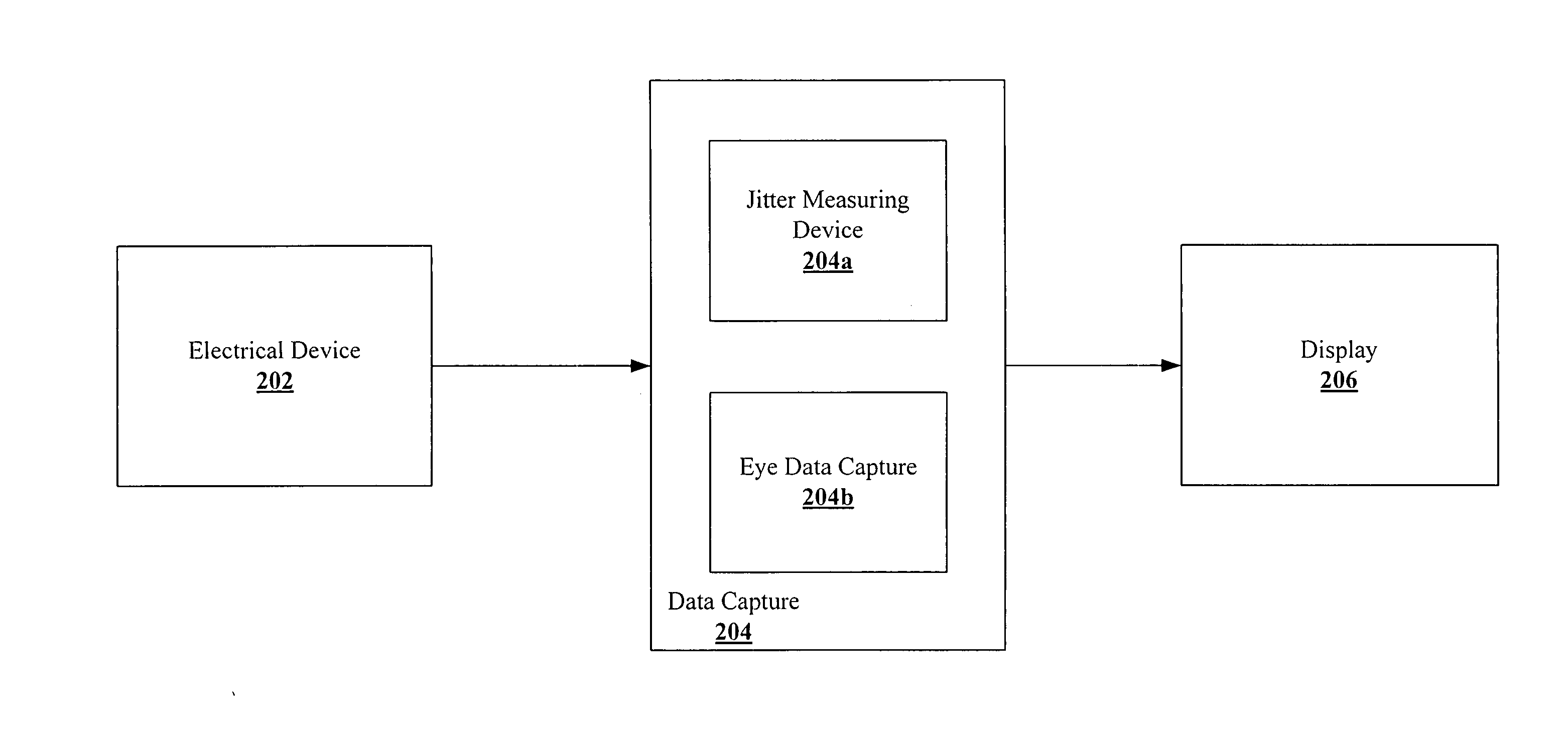

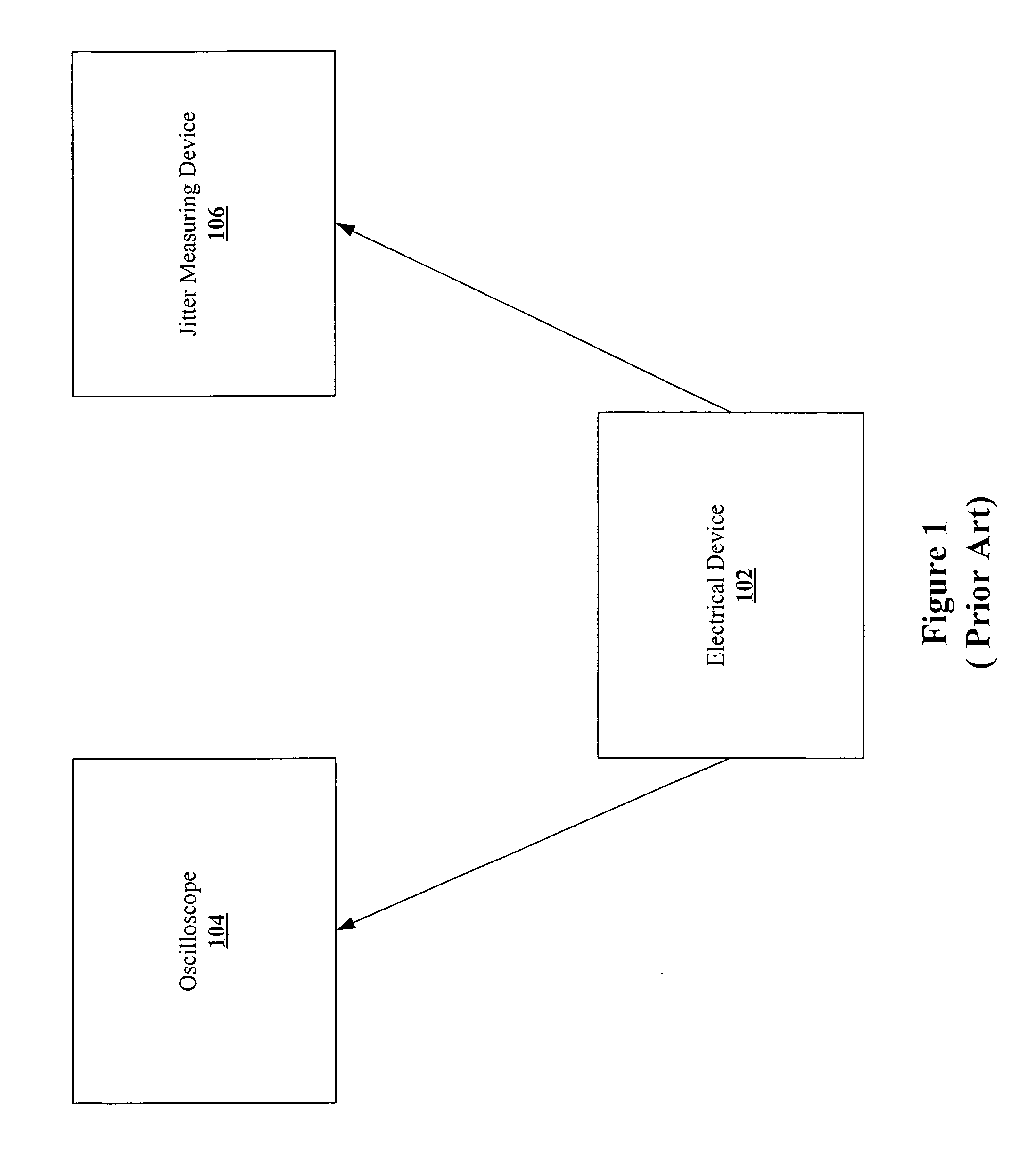

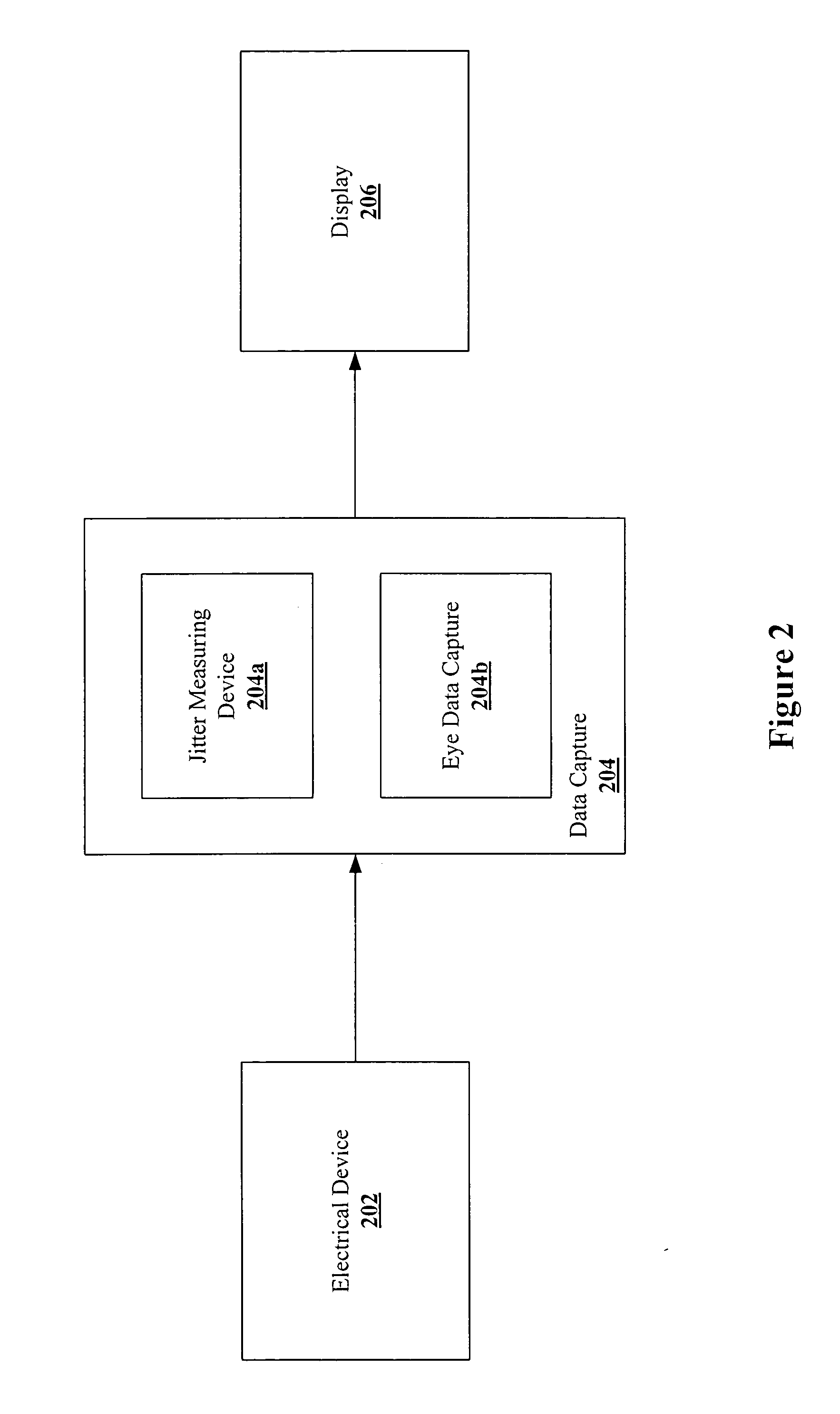

Simultaneous display of eye diagram and jitter profile during device characterization

InactiveUS20070156360A1Easily measure random jitterEasily relationshipNoise figure or signal-to-noise ratio measurementElectrical testingDisplay deviceElectrical devices

A system, apparatus and method for testing and optimizing an electrical device using a simultaneous display of both a signal's eye diagram and total jitter profile are described. In one embodiment of the invention, a data capture module capable of obtaining and separating the total jitter present in a signal into deterministic and random jitter, as well as other eye diagram information, is coupled to the electrical device and one or more display devices. These one or more display devices provide a user a simultaneous visual display of both random jitter and an eye diagram. This simultaneous display allows a user to test and optimize the electrical device without having to attach and detach the electrical device to multiple measuring devices.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

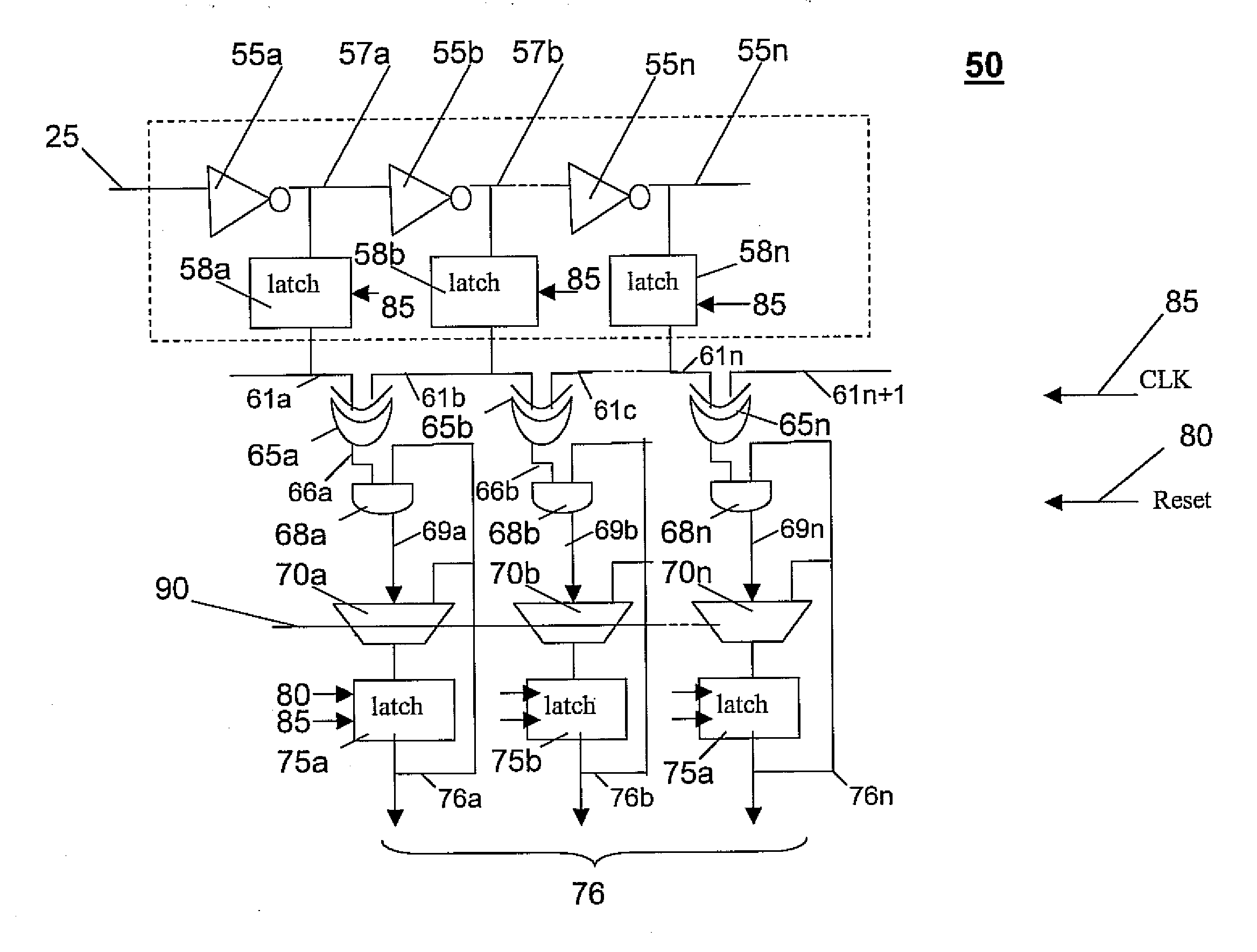

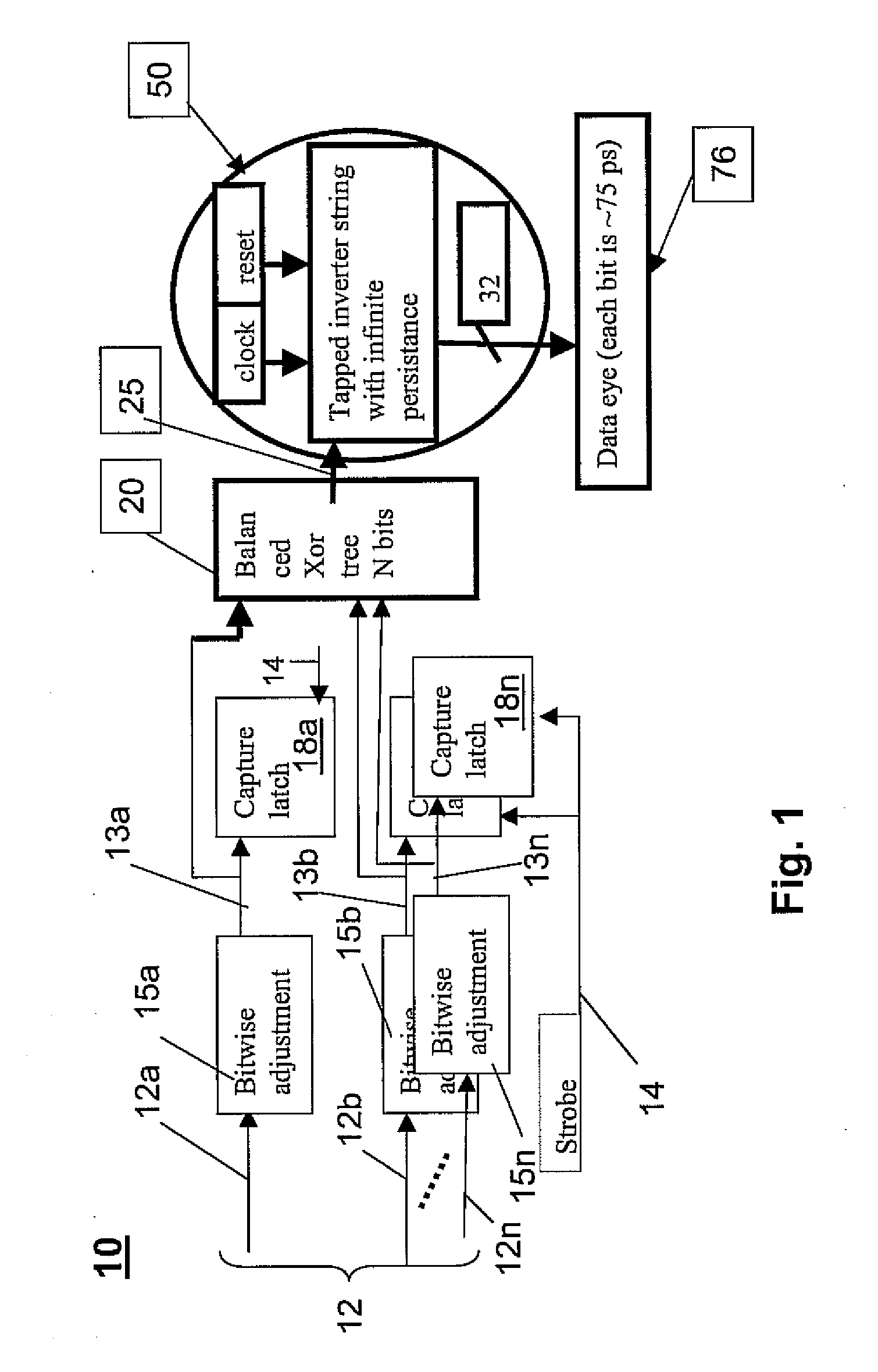

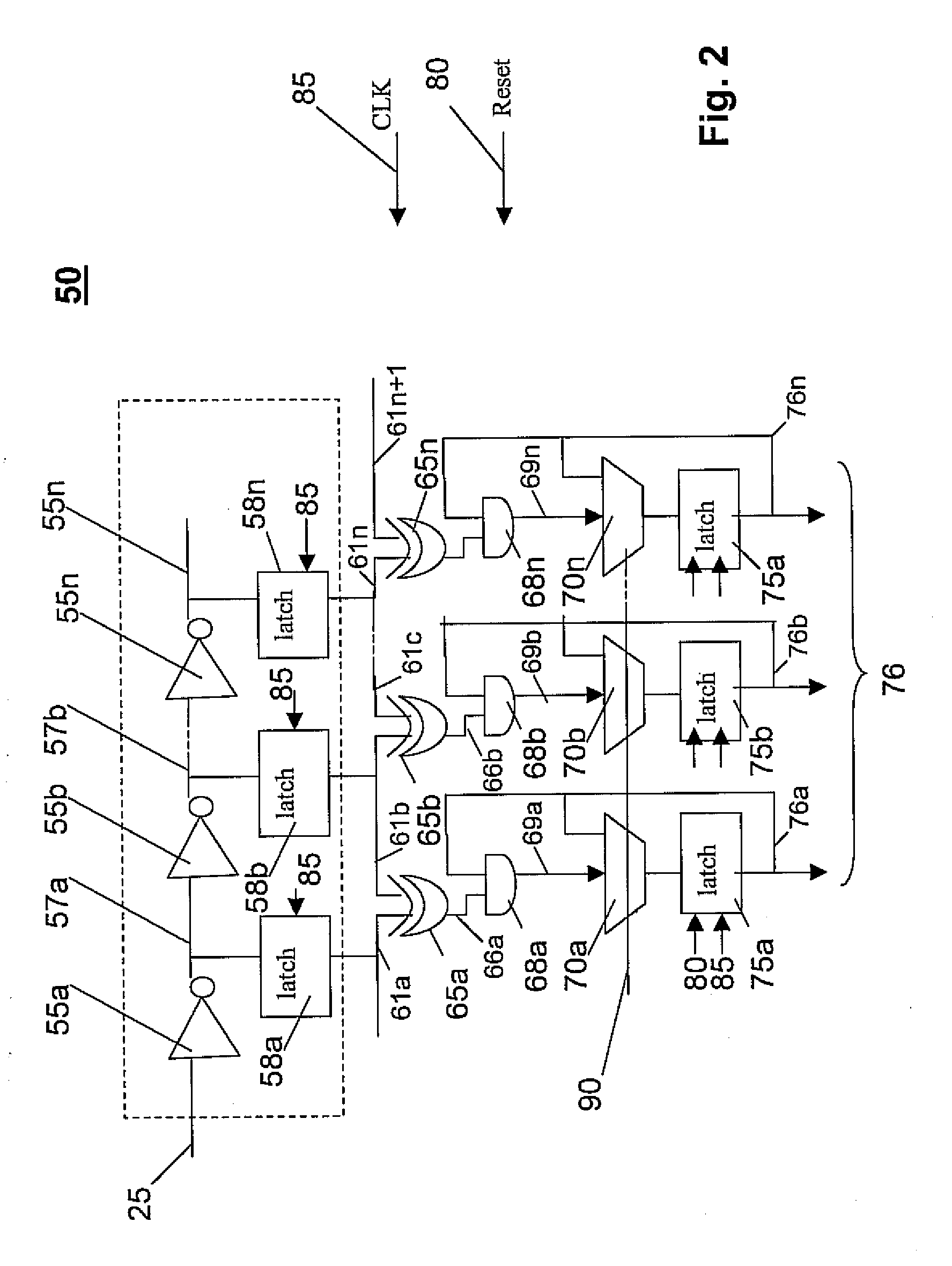

Data eye monitor method and apparatus

InactiveUS20090006730A1Improve data eye centeringRecord information storageMagnetic recordingImage resolutionData signal

An apparatus and method for providing a data eye monitor. The data eye monitor apparatus utilizes an inverter / latch string circuit and a set of latches to save the data eye for providing an infinite persistent data eye. In operation, incoming read data signals are adjusted in the first stage individually and latched to provide the read data to the requesting unit. The data is also simultaneously fed into a balanced XOR tree to combine the transitions of all incoming read data signals into a single signal. This signal is passed along a delay chain and tapped at constant intervals. The tap points are fed into latches, capturing the transitions at a delay element interval resolution. Using XORs, differences between adjacent taps and therefore transitions are detected. The eye is defined by segments that show no transitions over a series of samples. The eye size and position can be used to readjust the delay of incoming signals and / or to control environment parameters like voltage, clock speed and temperature.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com