Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

92results about How to "Reduce Capacitive Coupling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

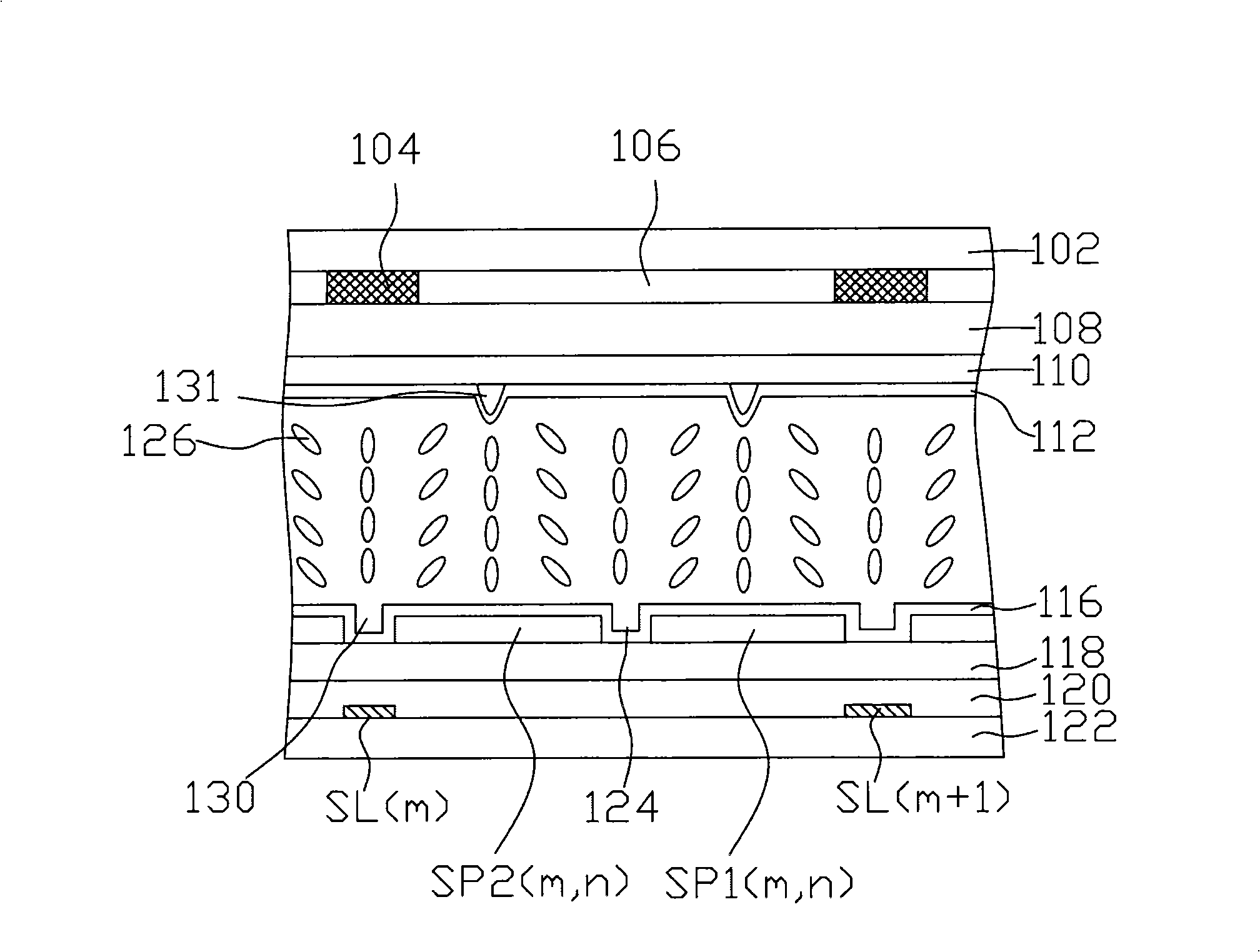

Shielded planar capacitor

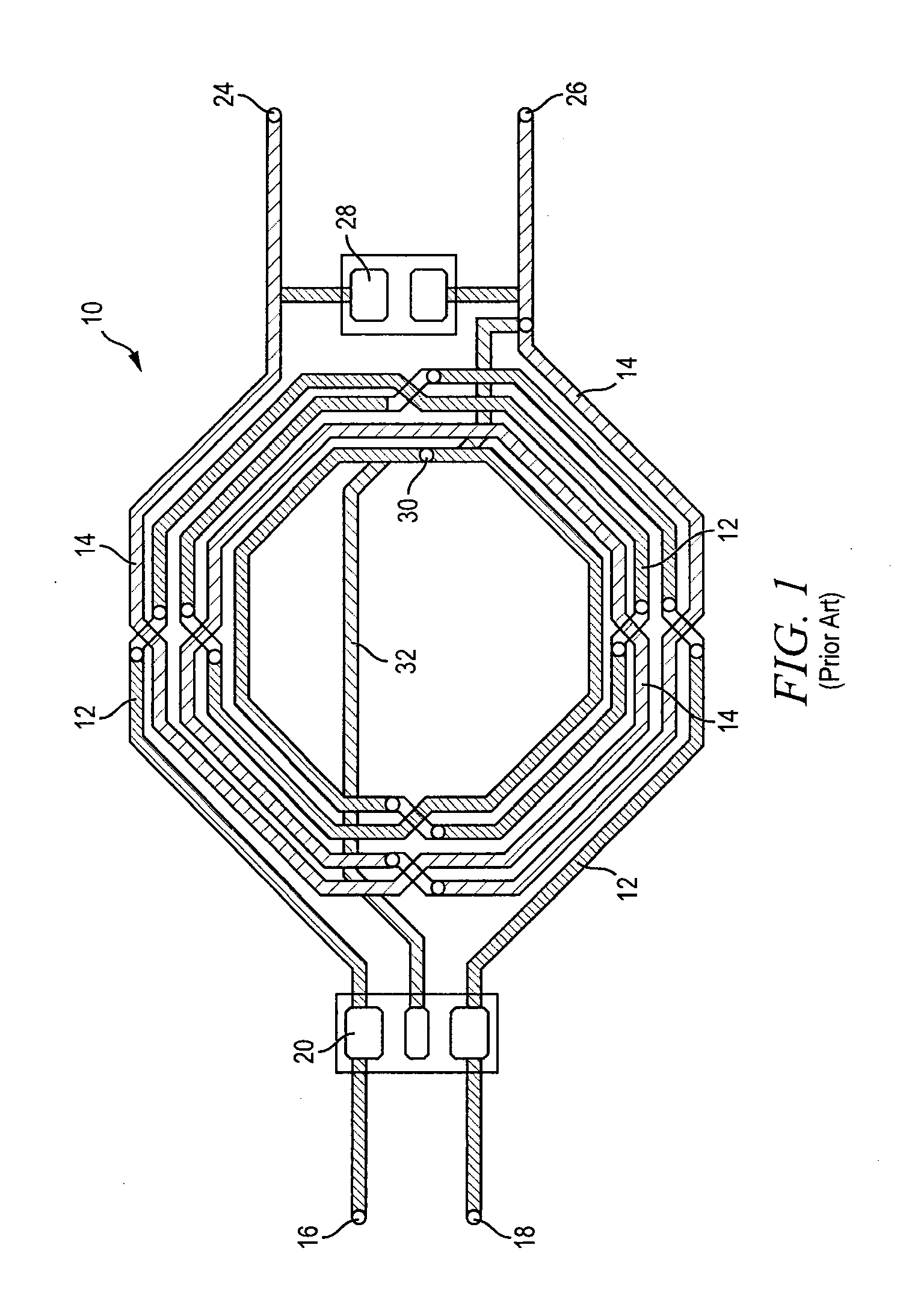

ActiveUS6903918B1Mitigate eddy current lossMinimize eddy current lossSemiconductor/solid-state device detailsFixed capacitor dielectricIsolation layerParasitic capacitance

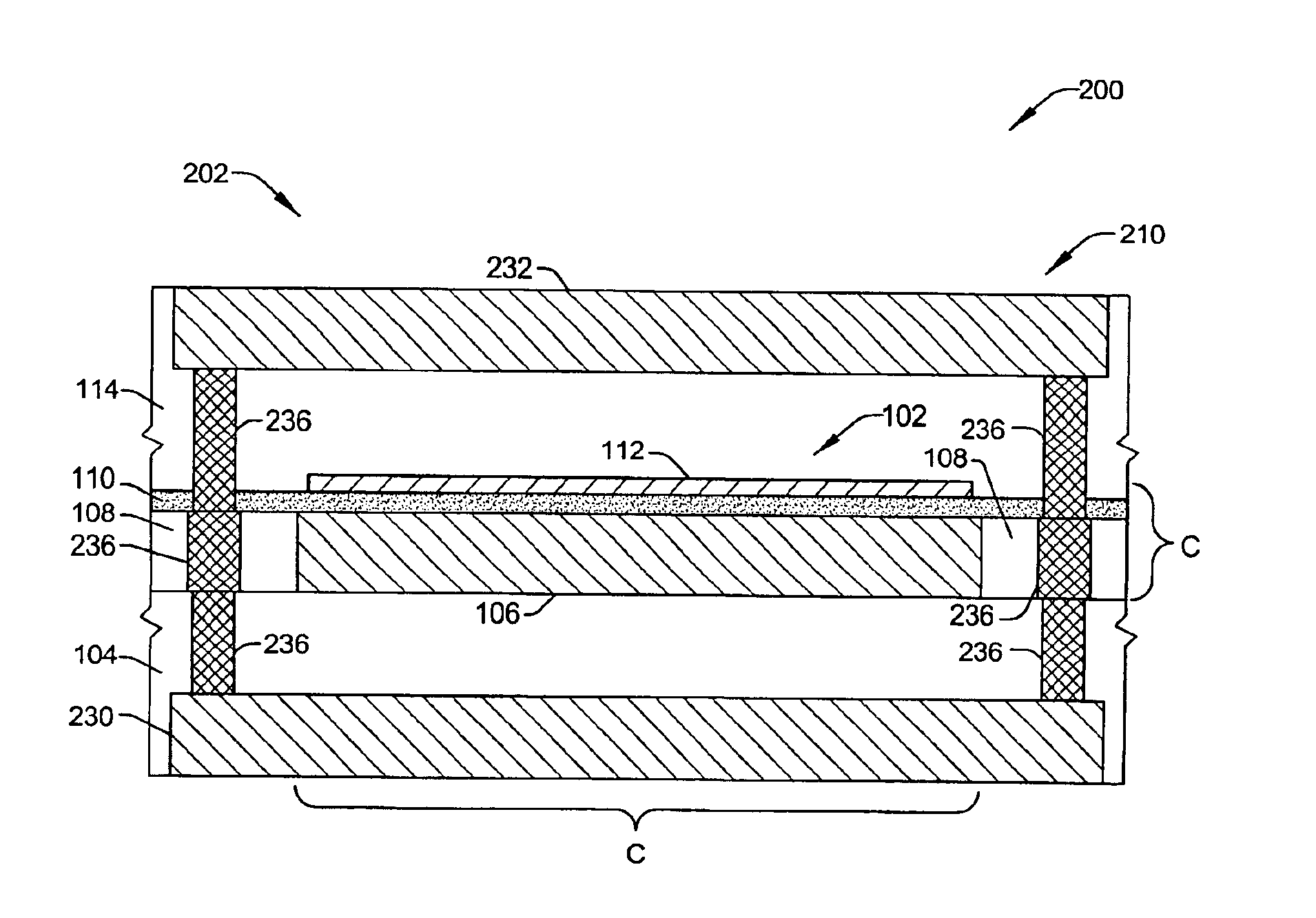

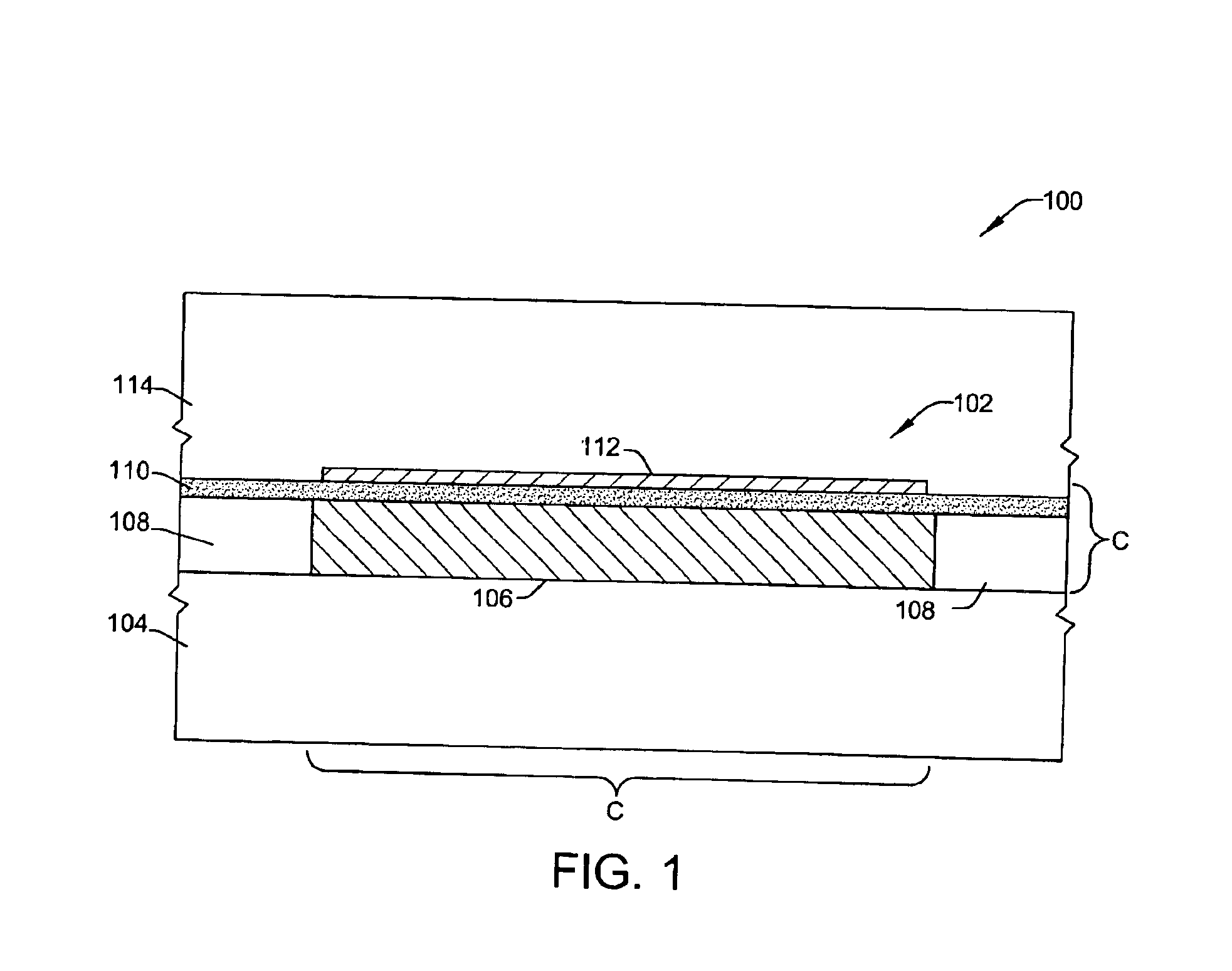

A shielded planar capacitor structure (202) is discussed, formed within a Faraday cage (210) in an integrated circuit device (200). The capacitor structure (202) reduces parasitic capacitances within the integrated circuit device (200). The capacitor (202) comprises a capacitor stack (102) formed between a first and second metal layers (230,232) of the integrated circuit. The capacitor stack (102) has a first conductive layer formed from a third metal layer (106) disposed between the first and second metal layers (230,232) of the integrated circuit, a dielectric isolation layer (110) disposed upon the first conductive layer (106); and a second conductive layer (112) disposed upon the dielectric isolation layer (110) and overlying the first conductive layer (106). The structure (202) further has a first and second isolation layers (104,114) disposed upon opposite sides of the capacitor stack (102). The Faraday cage (210) is formed between the first and second metal layers (230,232) of the integrated circuit (200), comprising a first and second shield layers (402,414) each having a plurality of mutually electrically conductive spaced apart traces (404). The first and second isolation layers (404,414) and the capacitor stack (102,434) are sandwiched between the first and second shield layers (402,414). Conductive elements (432) are distributed around the periphery of the capacitor stack (102,434) and the first and second isolation layers (404,412). The conductive traces (424) of the first shield layer (402) are connected to the conductive traces (424) of the second shield layer (414) through the conductive elements (432).

Owner:TEXAS INSTR INC

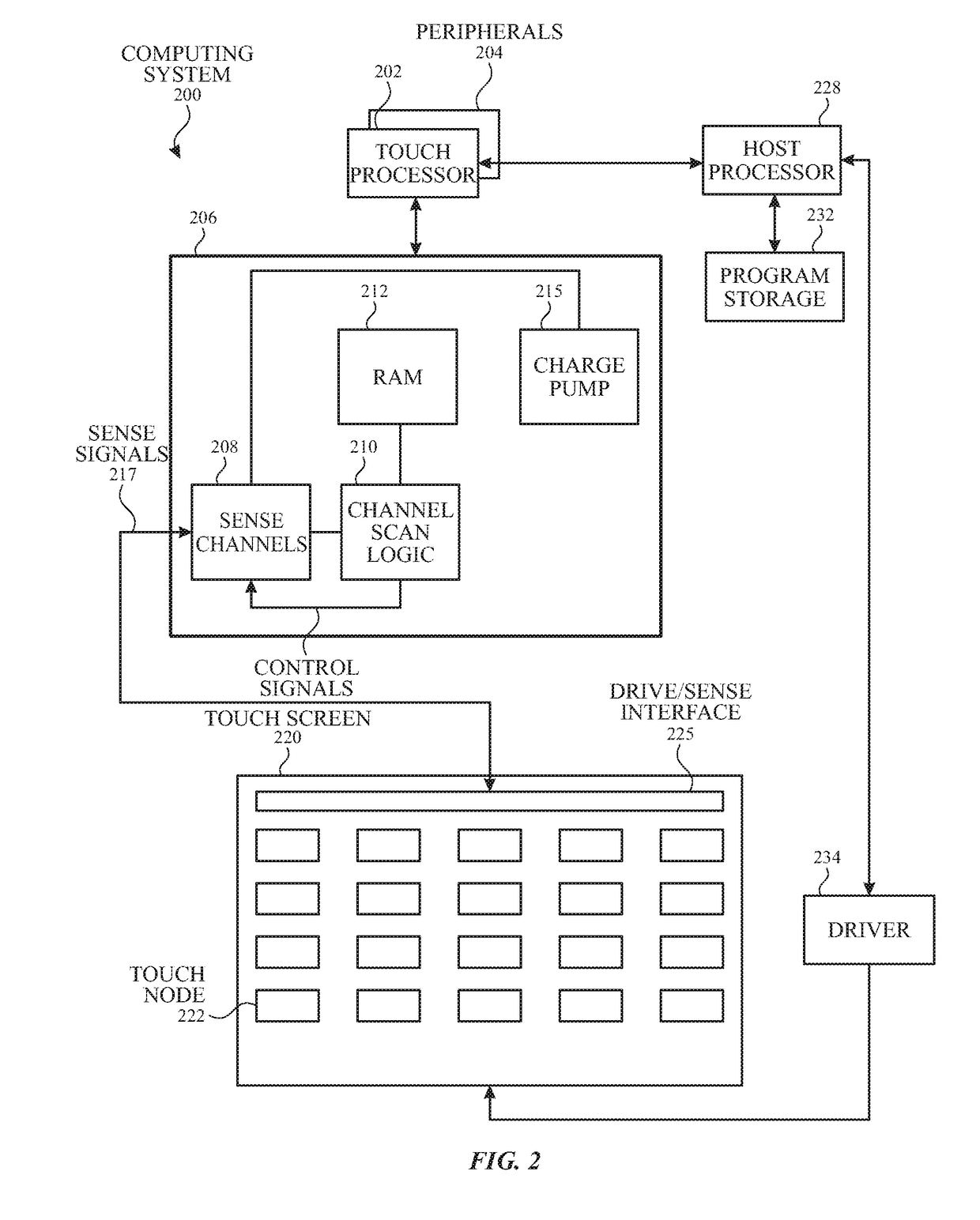

Capacitive coupling reduction in touch sensor panels

ActiveUS20180157354A1Improve performanceReduce Capacitive CouplingInput/output processes for data processingCapacitanceCapacitive coupling

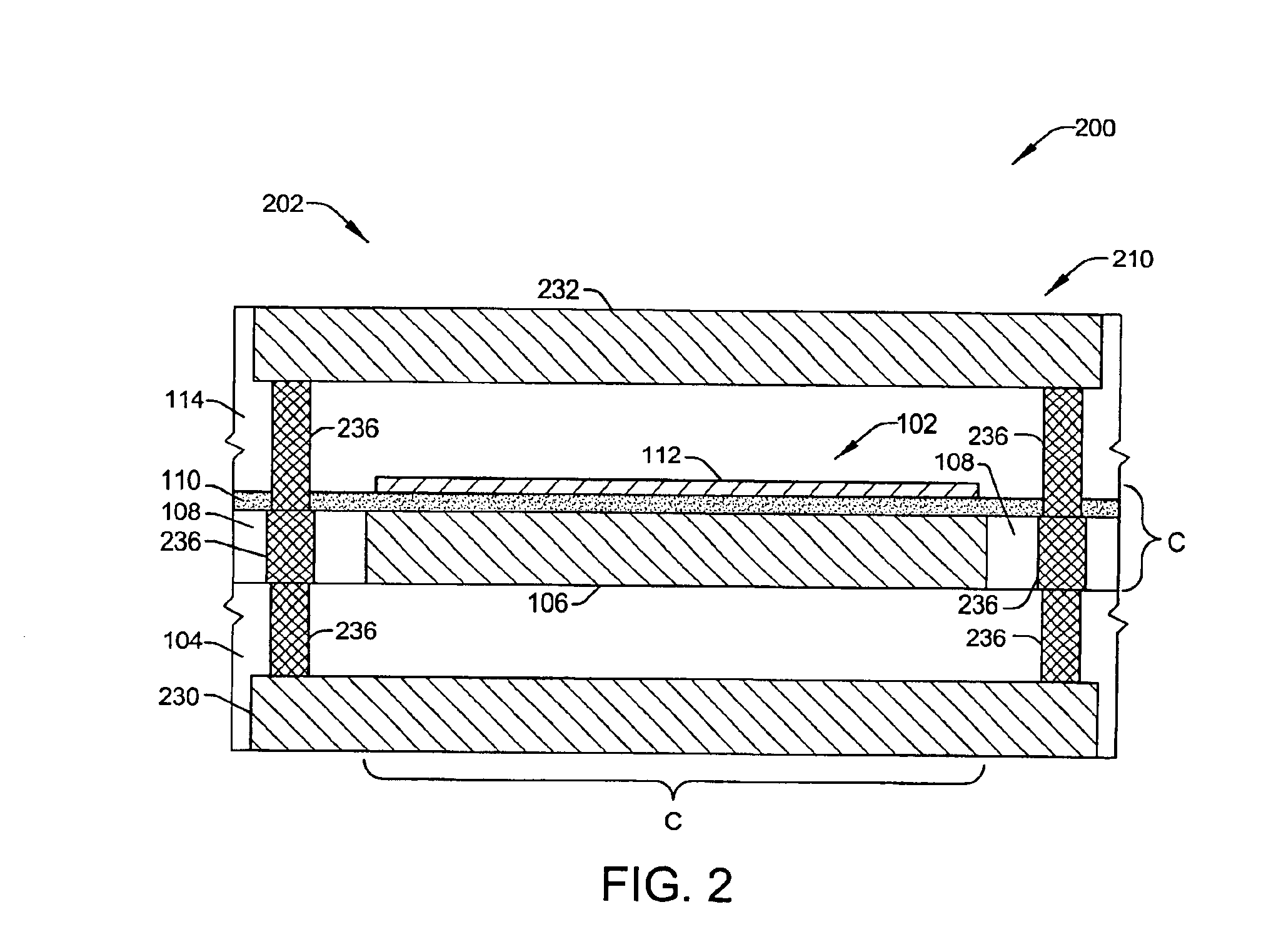

Touch sensor panel configurations and methods for improving touch sensitivity of some or all of the electrodes or portions of the touch sensor panel are disclosed. The touch sensor panel configurations can allow increased speed at which the panel can operate. In some examples, the performance of a given touch electrode can differ from the performance of another touch electrode due to differences in capacitance and / or resistance. The performance of the touch sensor panel can be limited by the touch electrode with the lowest performance relative to the other touch electrodes. The configurations and methods can increase the performance of the touch sensor panel by minimizing the capacitive coupling and / or resistance of touch electrodes. Examples of the disclosure can provide configurations of touch sensor panels and methods for improving optical uniformity of the panel.

Owner:APPLE INC

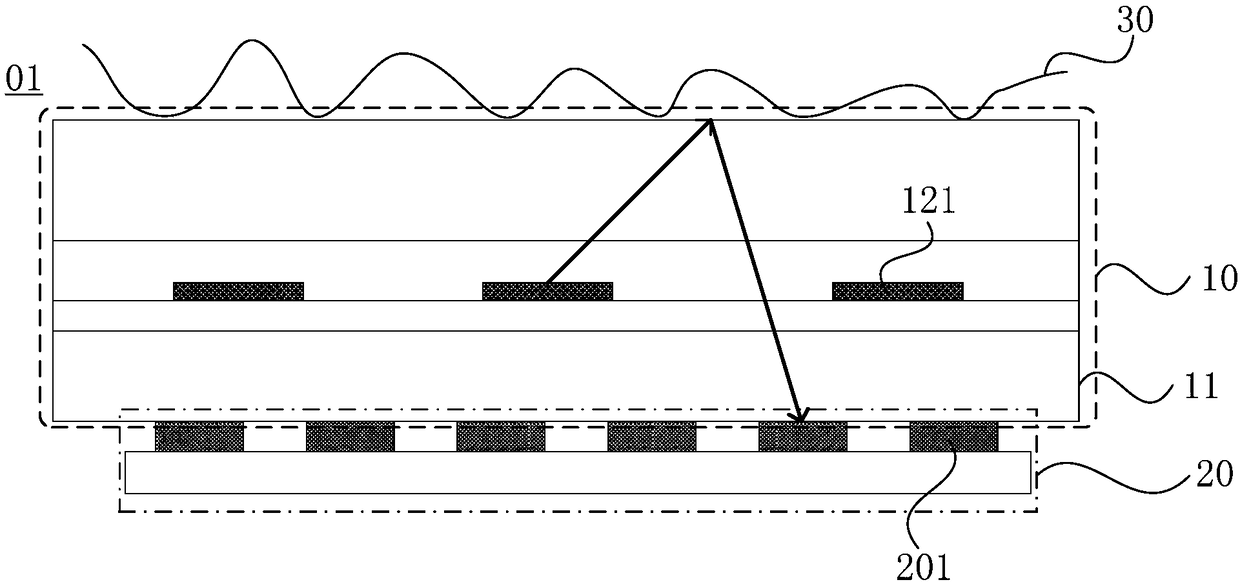

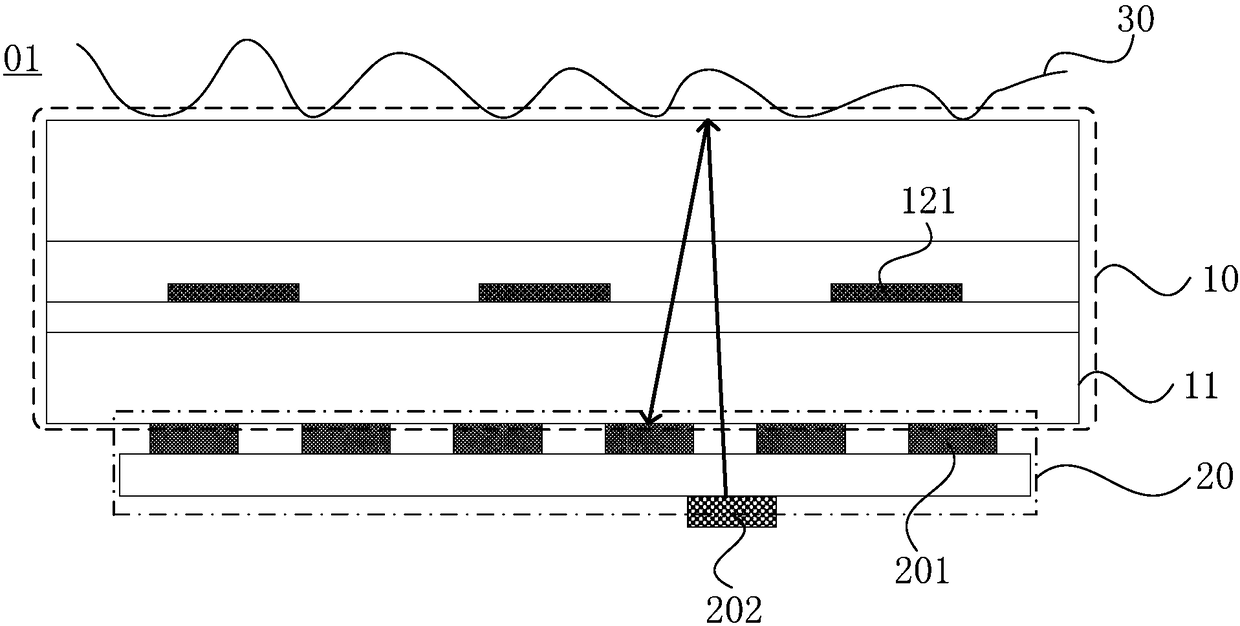

Display panel and display device

ActiveCN108597374AImprove image displayReduce the impactStatic indicating devicesPrint image acquisitionVertical projectionCapacitance

The embodiment of the invention discloses a display panel and a display device. The display panel comprises a display module and a fingerprint identification module, wherein the display module comprises a substrate base plate, a plurality of pixel units positioned on one side of the substrate base plate, and first scanning lines extending along the first direction, each pixel unit comprises a pixel drive unit and a light-emitting unit positioned on the side, far away from the substrate base plate, of the pixel drive unit, and the light-emitting unit comprises a metal anode; the fingerprint identification module is used for carrying out fingerprint identification according to light rays reflected to a fingerprint identification unit through a touch main body; the vertical projection of thefirst scanning lines on the substrate base plate and the vertical projection of the metal anode on the substrate base plate have an overlapped area. For the display panel provided by the embodiment ofthe invention, shielding electrodes are arranged between the film layer where the first scanning lines are located and the film layer where drain electrodes are located, the shielding electrodes andthe drain electrodes are insulated, the vertical projection of the shielding electrodes on the substrate base plate and the overlapped area are overlapped, the capacity coupling between the metal anode and the first scanning lines can be reduced, and thus the image display effect is improved.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

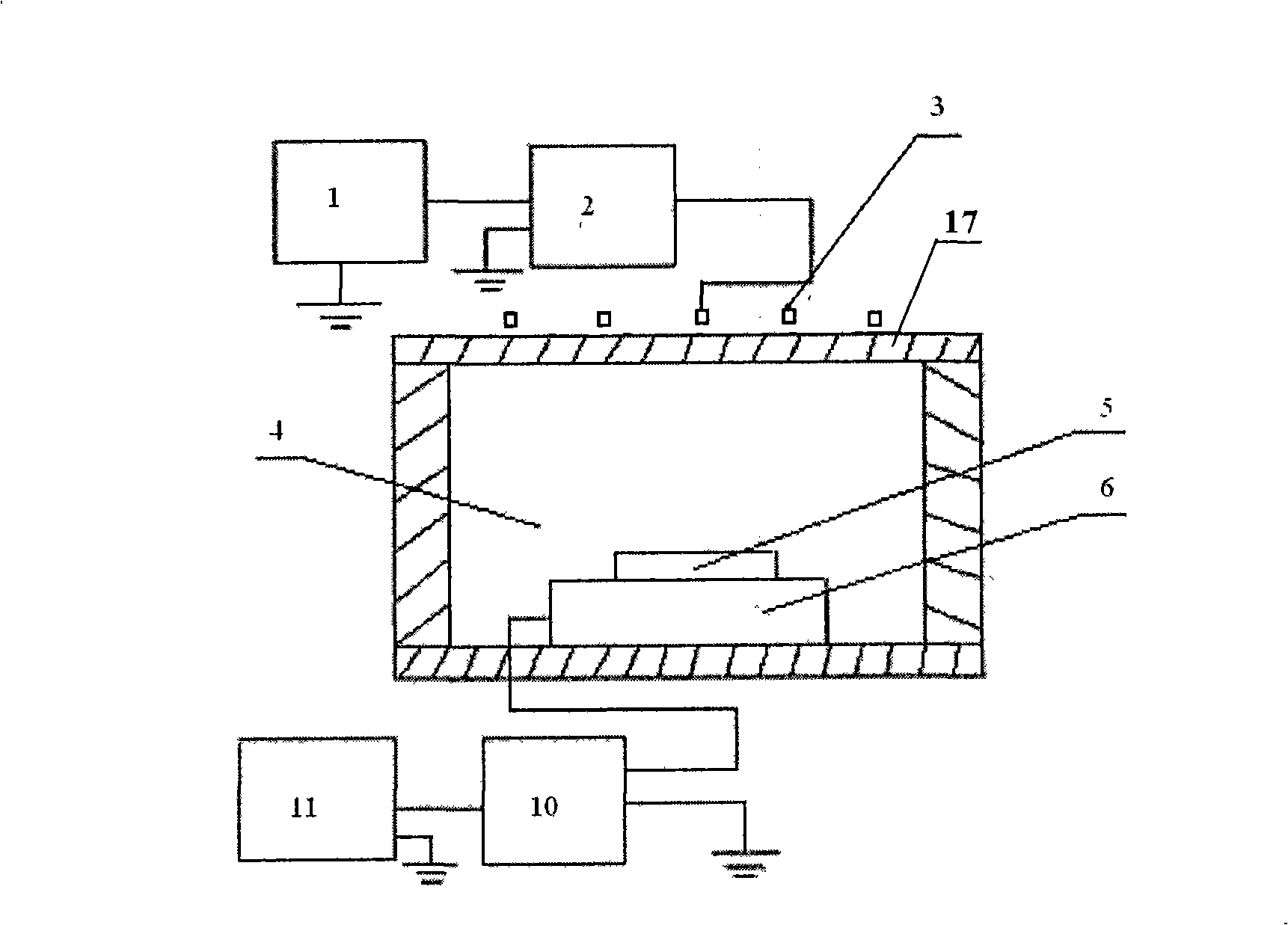

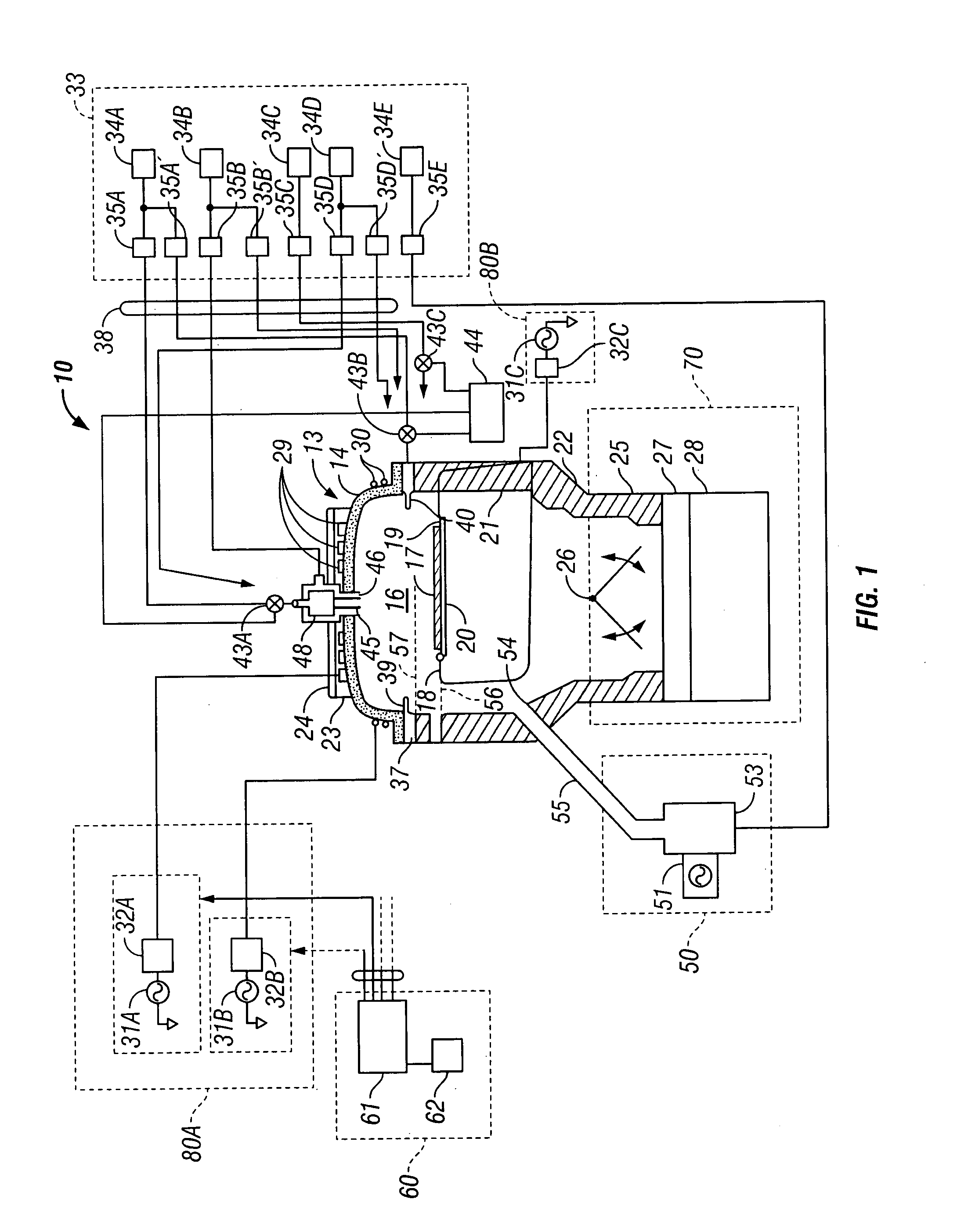

High density plasma CVD chamber

InactiveUS20060191478A1Easy temperature controlFacilitates gapfillElectric discharge tubesChemical vapor deposition coatingHigh densityEngineering

The present invention is directed to the design of a plasma CVD chamber which provides more uniform conditions for forming thin CVD films on a substrate. In one embodiment, an apparatus for processing semiconductor substrates comprises a chamber defining a plasma processing region therein. The chamber includes a bottom, a side wall, and a dome disposed on top of the side wall. The dome has a dome top and having a side portion defining a chamber diameter. A top RF coil is disposed above the dome top. A side RF coil is disposed adjacent the side portion of the dome. The side RF coil is spaced from the top RF coil by a coil separation. A ratio of the coil separation to the chamber diameter is typically at least about 0.15, more desirably about 0.2-0.25.

Owner:APPLIED MATERIALS INC

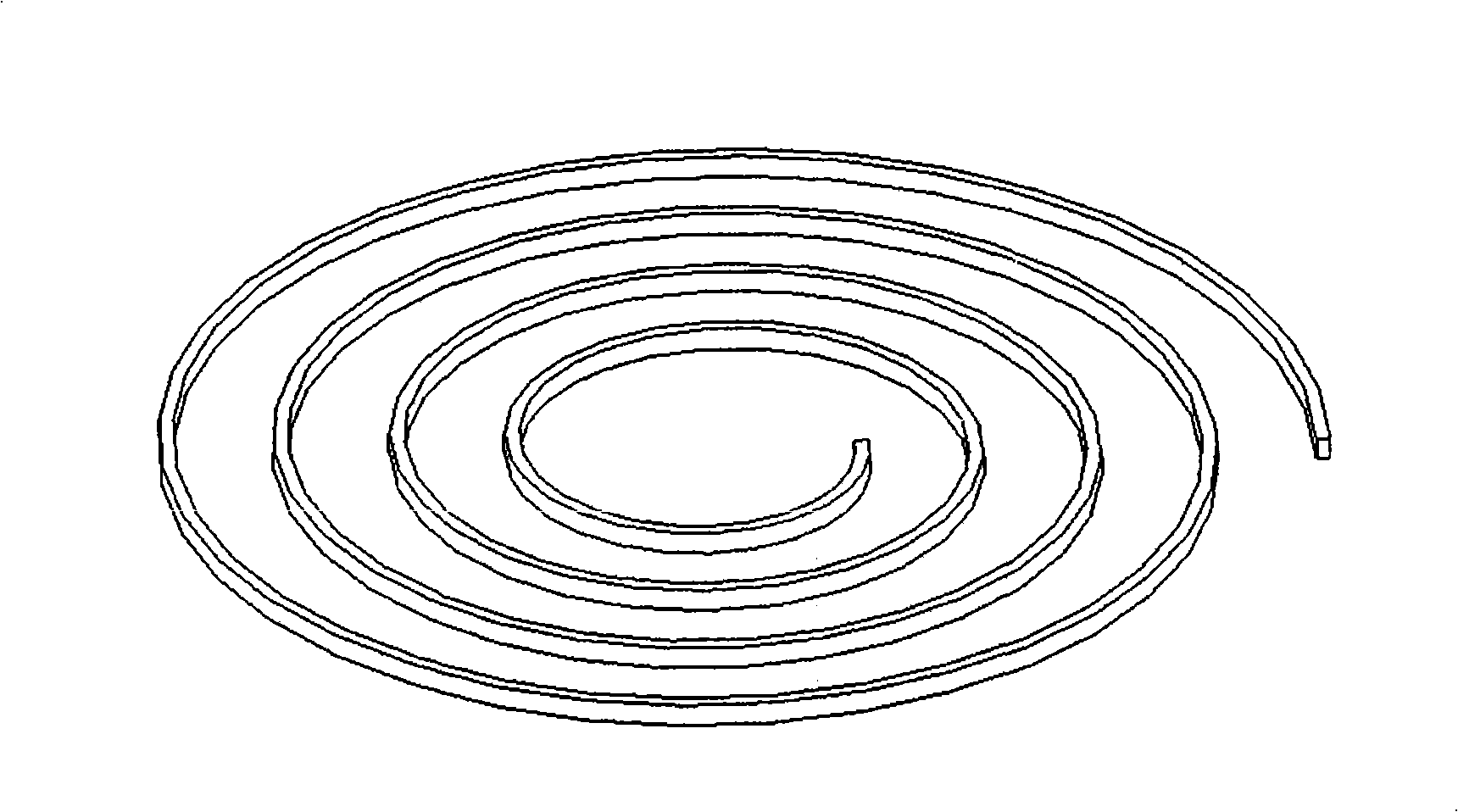

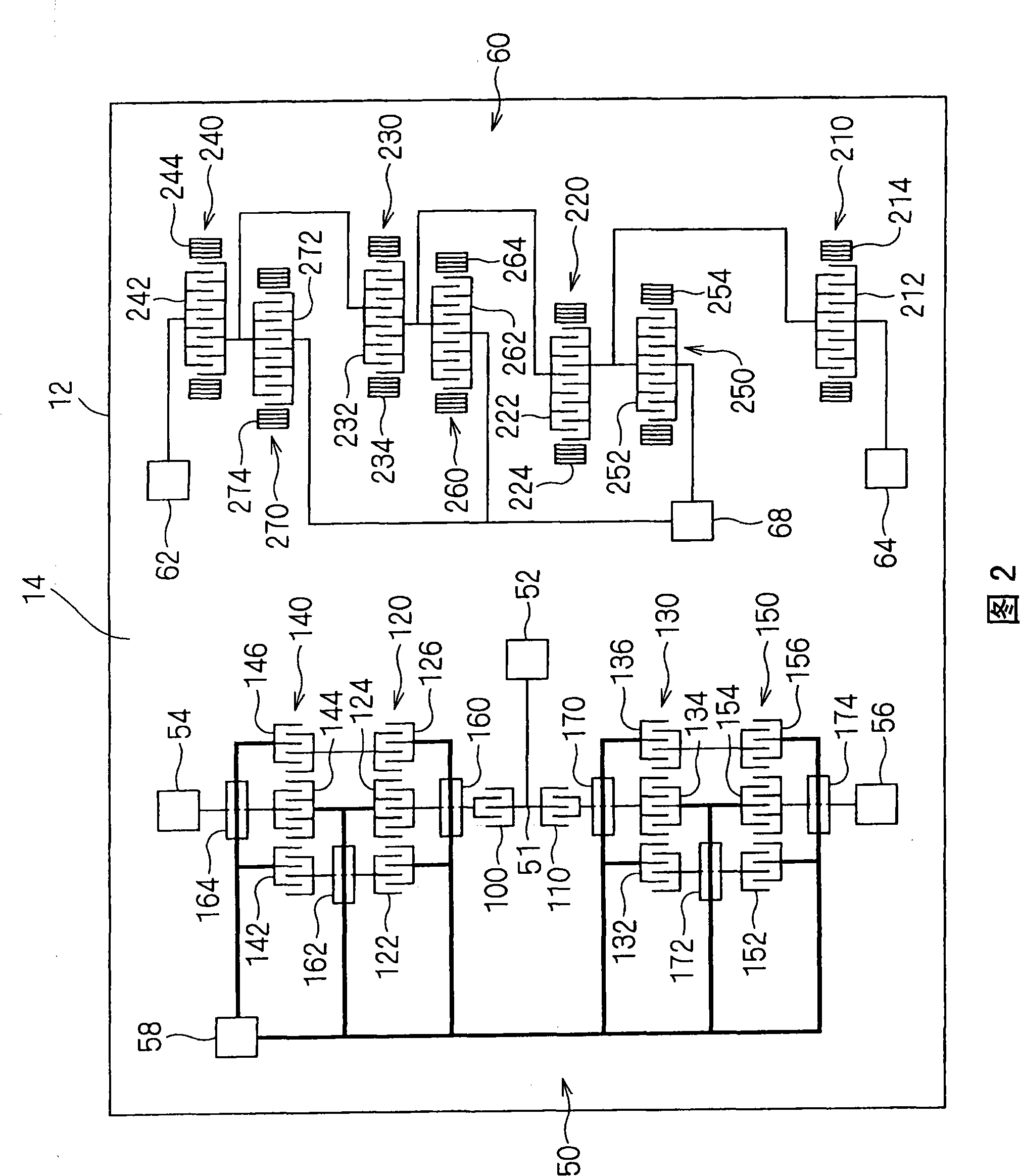

Inductance coupling coil and plasma processing device adopting same

ActiveCN101515498AEvenly distributedUniform induced electromagnetic fieldTransformersSemiconductor/solid-state device manufacturingConductor CoilRadio frequency

The invention discloses an inductance coupling coil, which comprises at least two groups of mutually nested coil windings with different diameters, wherein the upper surfaces of at least two groups of the coil windings in the coil windings are at planes with different heights for the convenience of obtaining plasmas which are distributed evenly. Besides, the invention also discloses a plasma processing device comprising a reaction chamber; a dielectric window is arranged on the upper part of the reaction chamber, and the inductance coupling coil is arranged above the dielectric window; and the inductance coupling coil is connected with a radio frequency power supply through a radio frequency matcher so as to obtain the plasmas distributed evenly in the reaction chamber. The inductance coupling coil and the plasma processing device can obtain the plasmas which are distributed evenly, and can obtain an excellent and even processing / handling result.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

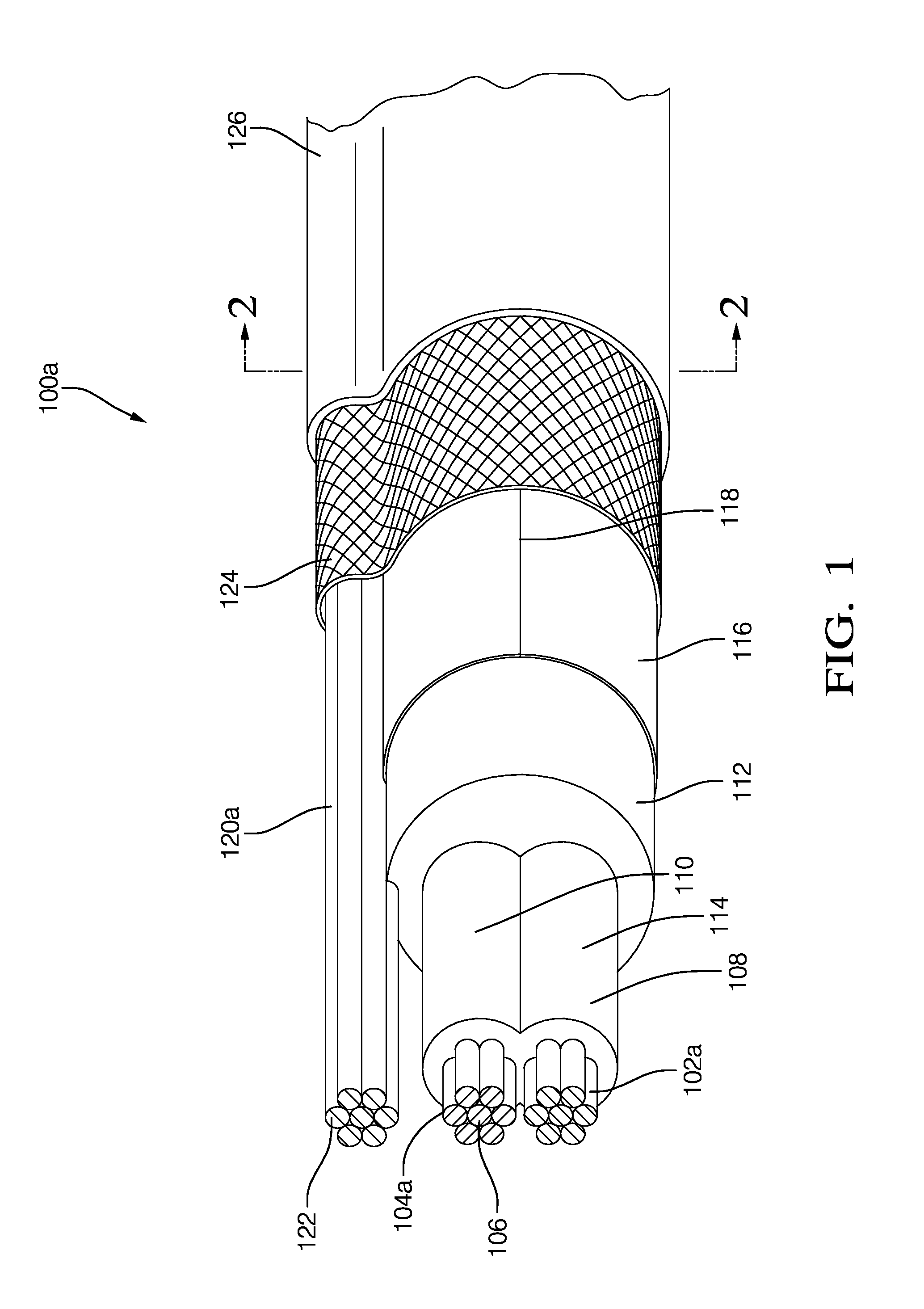

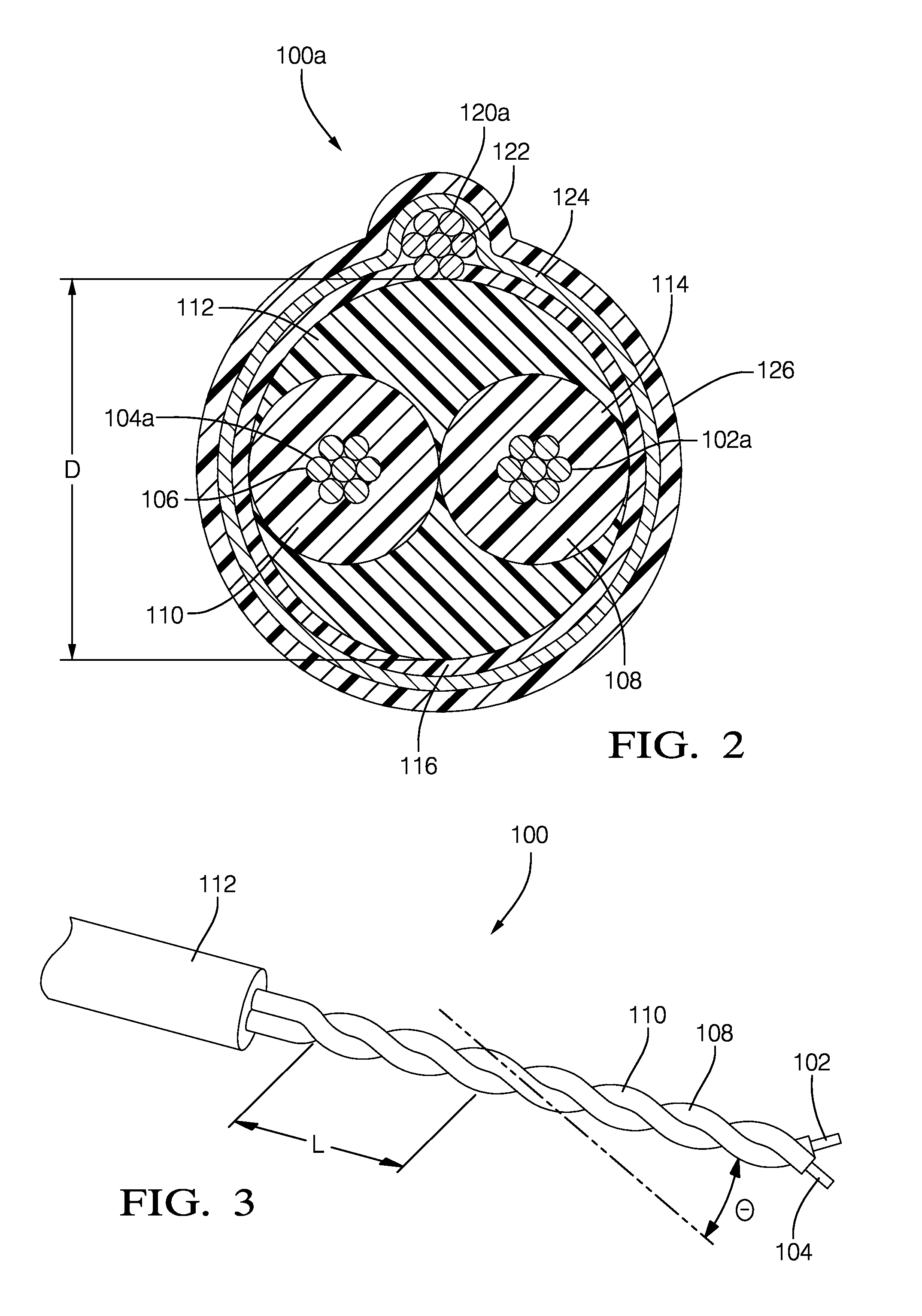

Toroidal conductivity probe with integrated circuitry

InactiveUS20120326711A1Avoid low frequency operationLow L valueComponent separationMaterial analysis by electric/magnetic meansCapacitive couplingGround plane

An apparatus and process for making noncontact measurements of liquid conductivity are disclosed. This apparatus forms a conductivity cell and uses two toroids, one to generate a magnetic field and another to sense the magnetic field, placed in an enclosure which allows liquid to pass through it for measurement. Ground planes constructed preferably of printed circuit boards with conductive layers are used to reduce capacitive coupling between the toroids and provide better shielding. Circuitry on or near these circuit boards are used to convert local, low level signals from a sensing toroid to signals which can be more readily passed to and from a recording system or operator without degradation. Sensors on or near these circuit boards can be used to sense environmental conditions in order to improve operation and stability of the conductivity cell. Methods and apparatus for increasing circuit sensitivity and calibrating the sensor are also disclosed.

Owner:SGS INSTR

System for non-real time reprogramming of non-volatile memory to achieve tighter distribution of threshold voltages

ActiveUS20070297245A1Reduce Capacitive CouplingReduce couplingRead-only memoriesDigital storageNon real timeReprogramming

A set of non-volatile storage elements undergoes initial programming, after which a reprogramming, with higher verify levels, is performed in non-real time, such as when a control enters a standby mode, when no other read or write tasks are pending. The reprogramming can program pages in the set one at a time, stopping at a page boundary when another read or write task is pending, and restarting when the control become available again. Status flags can be provided to identify whether a page and / or the set has completed the reprogramming. In another aspect, a higher pass voltage is applied to unselected word lines during the reprogramming. In another aspect, an error count is determined using a default set of read voltages, and an alternative set of read voltages is selected if the count exceeds a threshold.

Owner:SANDISK TECH LLC

High density plasma CVD chamber

InactiveUS7074298B2Improved temperature controlImprove uniformityElectric discharge tubesSemiconductor/solid-state device manufacturingThin membranePlasma treatment

The present invention is directed to the design of a plasma CVD chamber which provides more uniform conditions for forming thin CVD films on a substrate. In one embodiment, an apparatus for processing semiconductor substrates comprises a chamber defining a plasma processing region therein. The chamber includes a bottom, a side wall, and a dome disposed on top of the side wall. The dome has a dome top and having a side portion defining a chamber diameter. A top RF coil is disposed above the dome top. A side RF coil is disposed adjacent the side portion of the dome. The side RF coil is spaced from the top RF coil by a coil separation. A ratio of the coil separation to the chamber diameter is at least about 0.15, more desirably about 0.2–0.25.

Owner:APPLIED MATERIALS INC

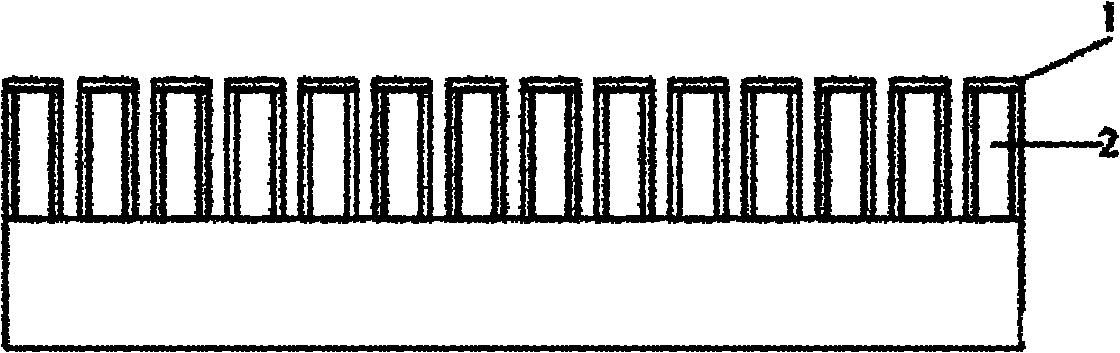

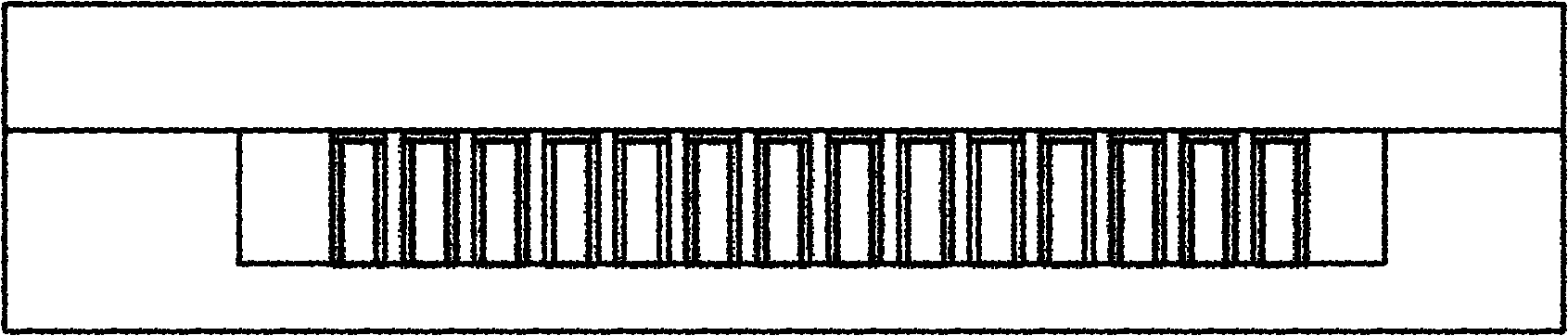

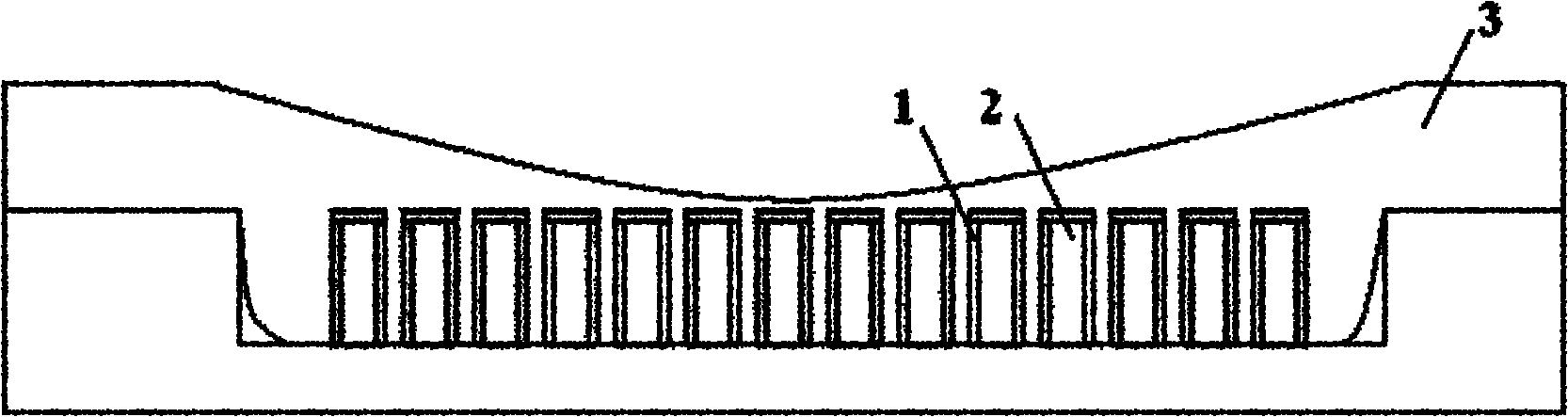

Preparation method for high-density interposer for microelectronic system-in-package

ActiveCN102070120AImprove reliabilitySmall coefficient of thermal expansionDecorative surface effectsChemical vapor deposition coatingThermal dilatationElectrical conductor

The invention discloses a preparation method for a high-density interposer for microelectronic system-in-package. The preparation method comprises the following steps of: 1, preparing a drectionally growing carbon nanotube bundle array, wherein the diameter of each carbon nanotube bundle is 0.5 to 30 microns, the gap of the carbon nanotube bundle is 0.8 to 100 microns, and the carbon nanotube bundle is 40 to 500 microns long; 2, depositing metal tungsten on the surface of the drectionally growing carbon nanotube bundle so as to form a conductor array; 3, melting borosilicate glass and compounding the melted borosilicate glass with the conductor array so as to form a compound body; and 4, grinding the upper surface and the lower surface of the formed compound body so as to expose the end of the carbon nanotube bundle deposited with the metal tungsten, and obtaining the high-density interposer for the system-in-package. The material adopted by the preparation method has low thermal expansivity and the process method is low in time consumption, so the prepared high-density interposer has the advantages of high density, high reliability and low cost.

Owner:SOUTHEAST UNIV

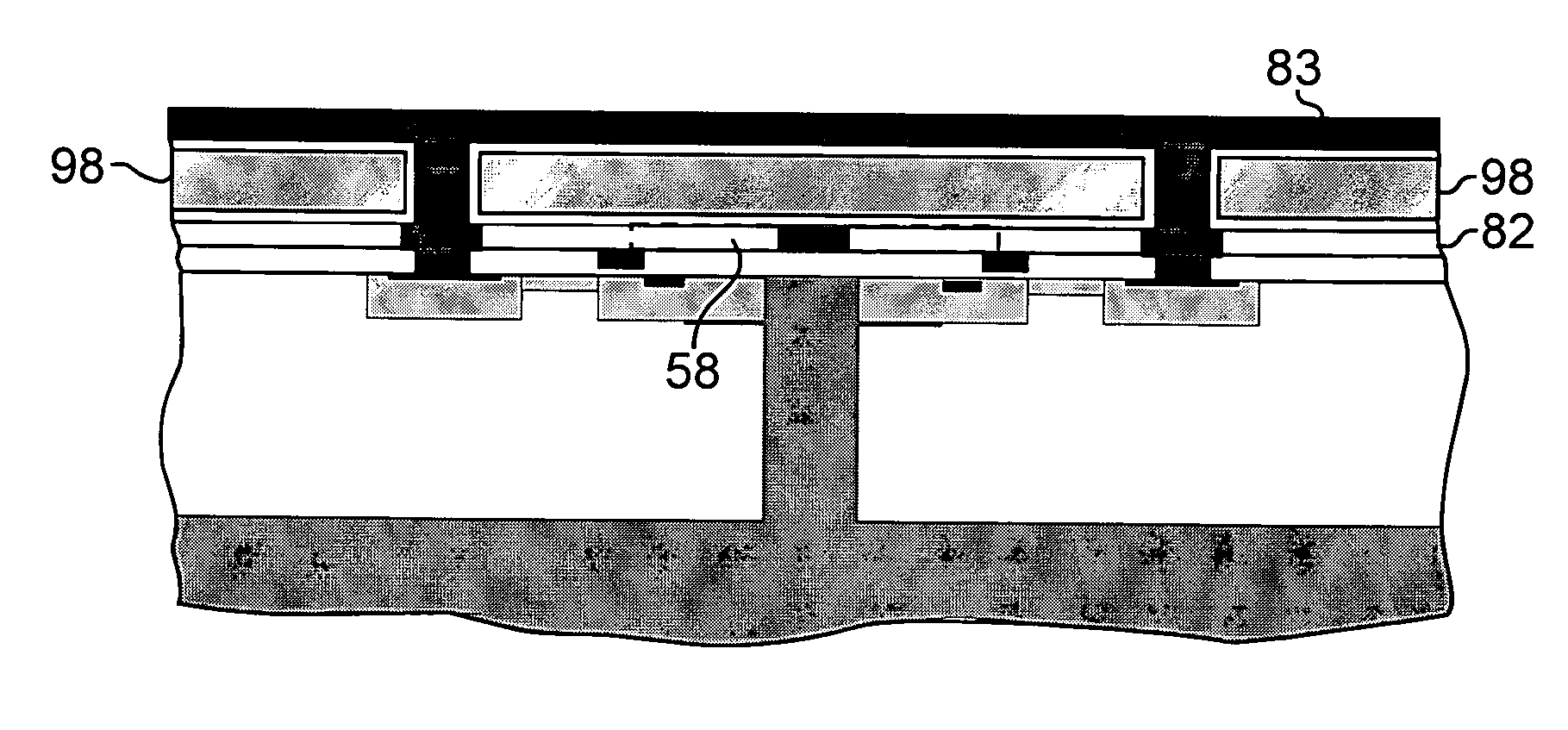

Semiconductor Device and Method of Forming RF Balun Having Reduced Capacitive Coupling and High CMRR

ActiveUS20110241793A1Reduce capacitive couplingHigh CMRROne-port networksSemiconductor/solid-state device detailsCapacitive couplingMicrometer

Owner:JCET SEMICON (SHAOXING) CO LTD

Surface acoustic wave device and boundary acoustic wave device

ActiveCN101361267AReduce Capacitive CouplingImpedence networksSolid-state devicesCapacitanceCapacitive coupling

A surface acoustic wave device and a boundary acoustic wave device capable of reducing capacitive coupling are provided. A piezoelectric substrate (12) is joined to a cover (32) with a support layer 30 therebetween and with a spacing kept therebetween. A transmission surface acoustic wave filter and a reception surface acoustic wave filter are formed on a major surface (14) of the piezoelectric substrate (12) adjacent to the cover (32) and inside the support layer (30). External electrodes (28) are provided on the side of the cover (32) opposite that facing the piezoelectric substrate (12).; The external electrodes (28) include an antenna terminal electrically connected to the transmission surface acoustic wave filter and the reception surface acoustic wave filter, a transmission input terminal electrically connected to the transmission surface acoustic wave filter, and a reception output terminal electrically connected to the reception surface acoustic wave filter. Part of an interconnection line that electrically connects the reception surface acoustic wave filter to the antenna terminal is disposed on the cover (32).

Owner:MURATA MFG CO LTD

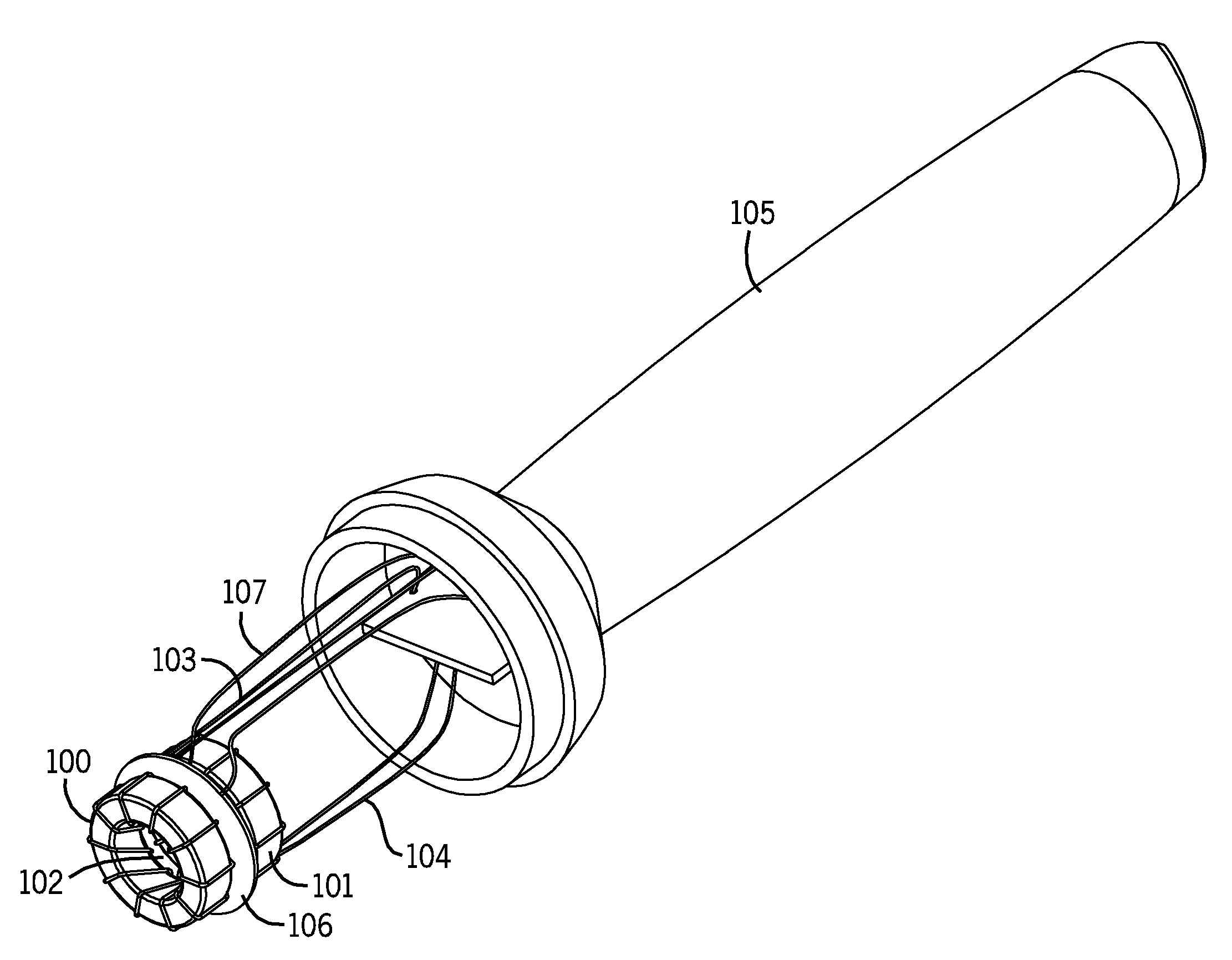

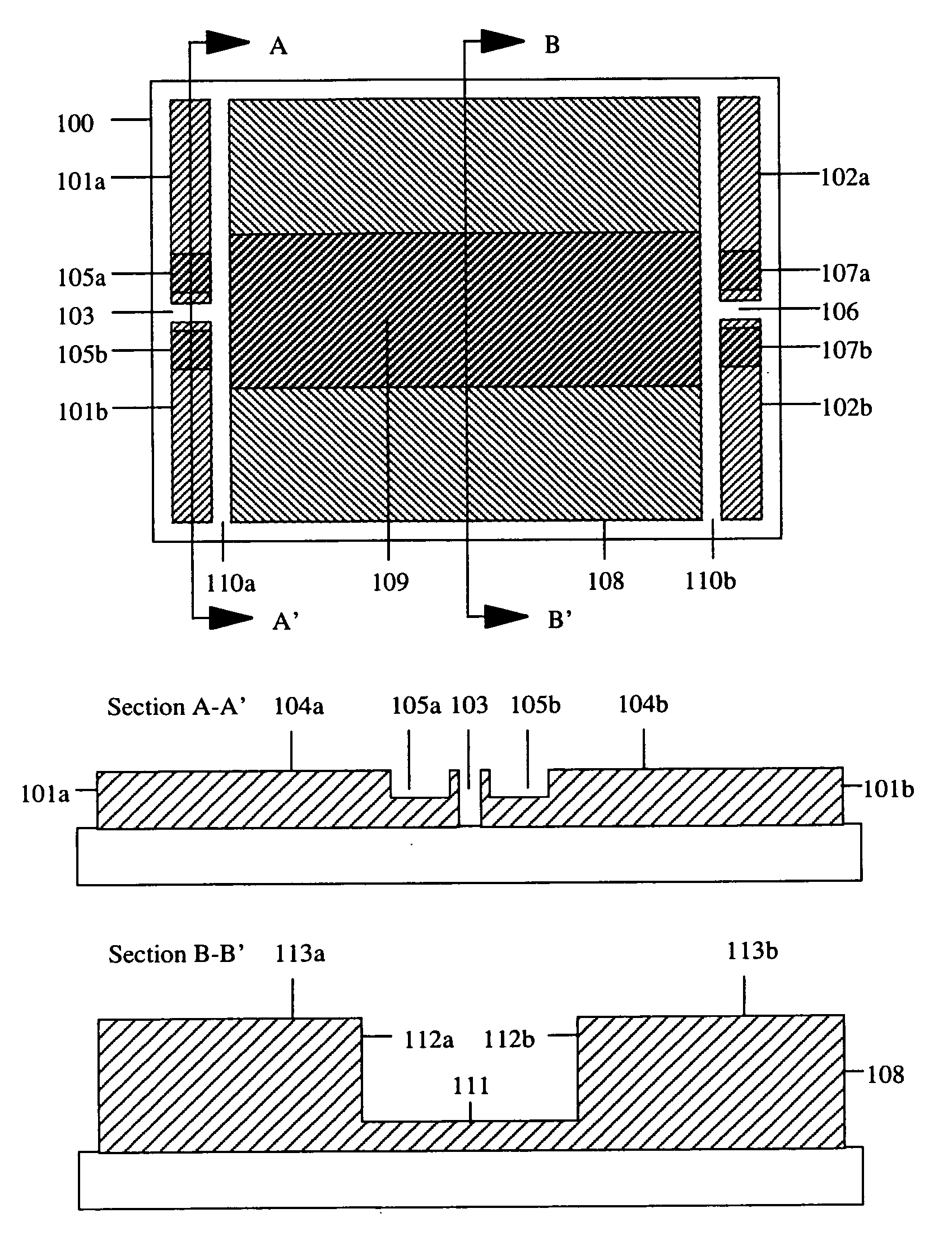

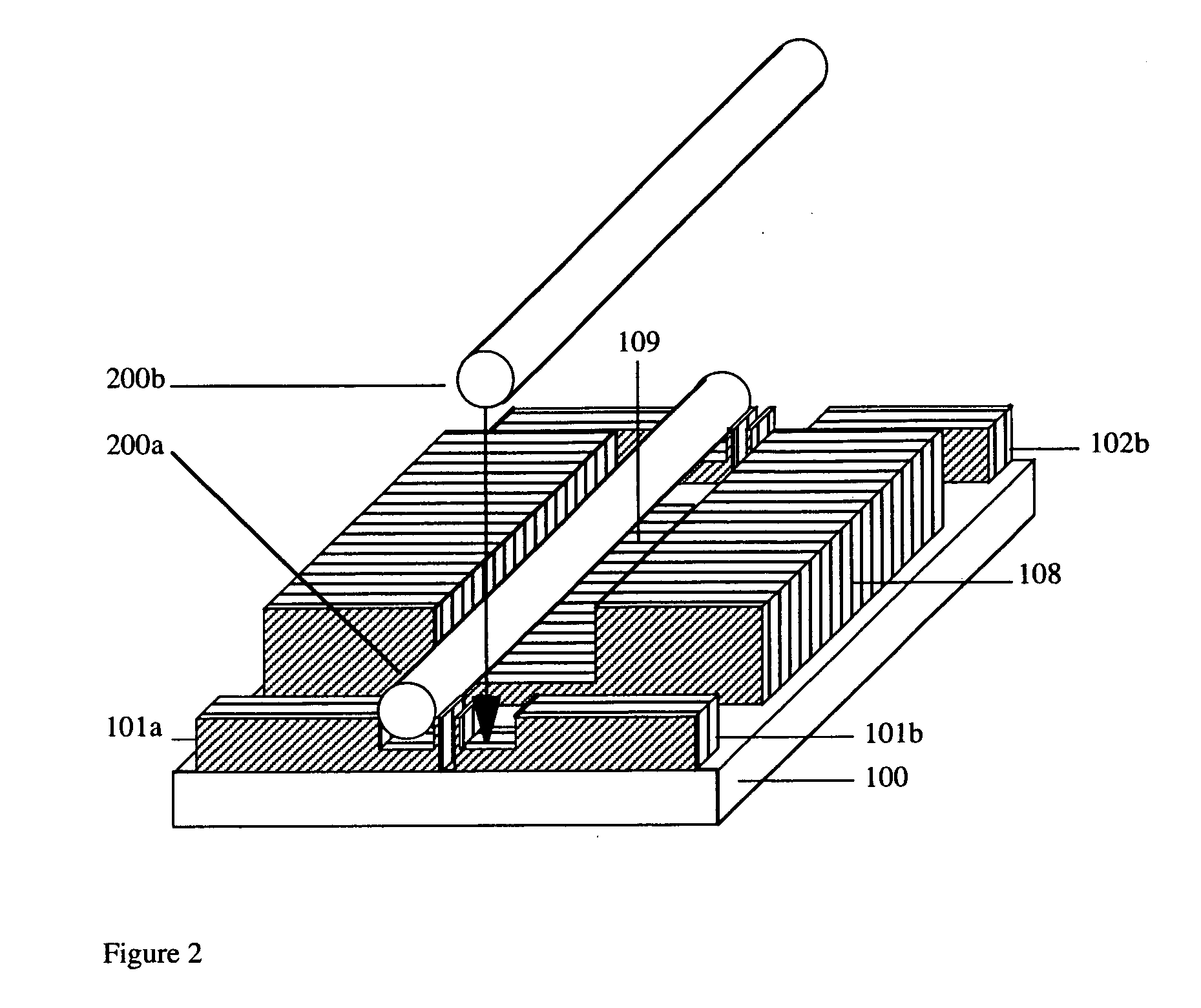

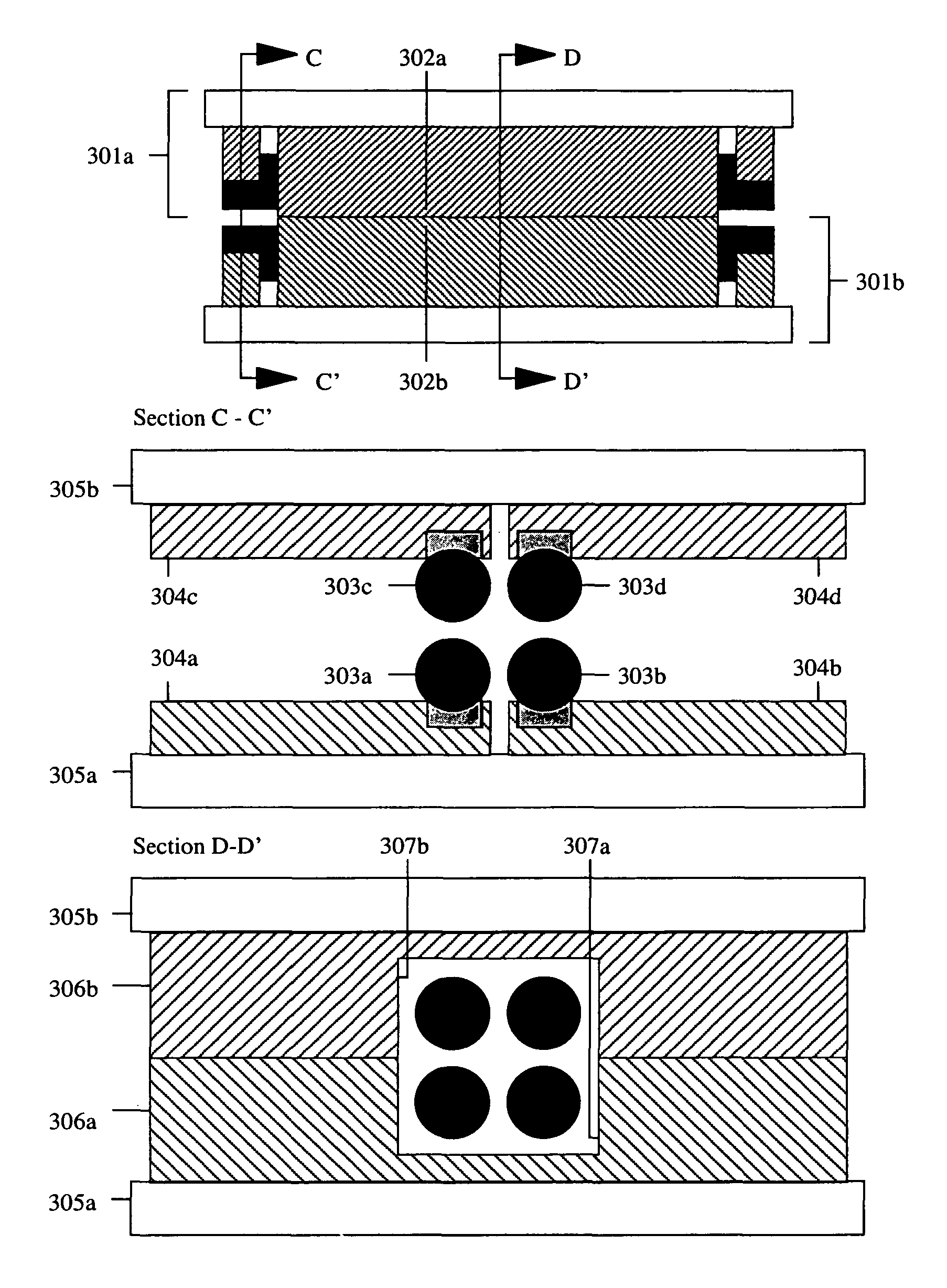

High performance micro-fabricated electrostatic quadrupole lens

ActiveUS20080185518A1Reduce Capacitive CouplingHigh sensitivityStability-of-path spectrometersBeam/ray focussing/reflecting arrangementsCapacitanceCapacitive coupling

A method of aligning sets of cylindrical electrodes in the geometry of a miniature quadrupole electrostatic lens, which can act as a mass filter in a quadrupole mass spectrometer is provided. The electrodes are mounted in pairs on microfabricated supports, which are formed from conducting parts on an insulating substrate. Complete segmentation of the conducting parts provides low capacitative coupling between co-planar cylindrical electrodes, and allows incorporation of a Brubaker prefilter to improve sensitivity at a given mass resolution. A complete quadrupole is constructed from two such supports, which are spaced apart by further conducting spacers. The spacers are continued around the electrodes to provide a conducting screen.

Owner:MICROSAIC SYST

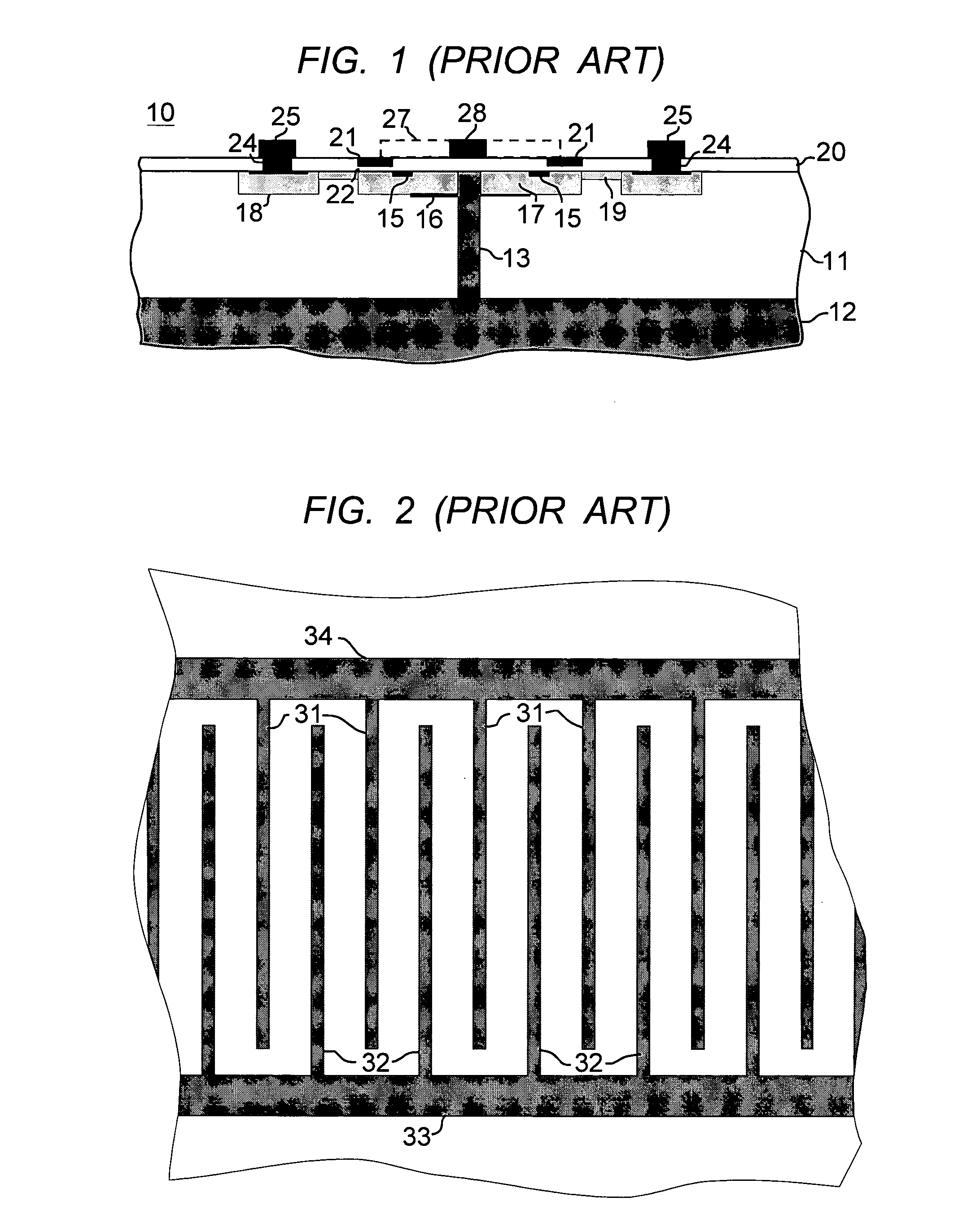

Scrambling method to reduce wordline coupling noise

ActiveUS20060081944A1Reduce coupleReduce array noiseSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCoupling noise

A memory circuit and method to reduce array noise due to wordline coupling is disclosed. The circuit includes a plurality of memory cells arranged in rows (702, 704, and 706) and columns (750, 752). Each row has a first part (1102) and a second part (1108). A first conductor (750) is coupled to a respective column of memory cells in each first part. A second conductor (752) is coupled to a respective column in each second part. A third conductor is coupled to a control terminal of each memory cell in the first part (1102) of a first row and the second part (1108) of a second row.

Owner:TEXAS INSTR INC

LCD device and image element array substrates

ActiveCN101295115AReduce Capacitive CouplingReduce flicker (Flicker) phenomenonSolid-state devicesNon-linear opticsLiquid-crystal displayElectrical polarity

The invention provides a liquid crystal display device and a pixel array substrate thereof, wherein, the pixel array substrate includes: a plurality of pixel electrodes formed on the substrate, and each pixel electrode is provided with two sub-pixel electrodes; a plurality of switching elements formed on the substrate, and each switching element is electrically connected with one sub-pixel electrode; a plurality of data lines formed on the substrate, electrically connected with the switching elements corresponding to a plurality of sub-pixels, and used for exerting voltage signals with opposite polarities to two neighboring sub-pixel electrodes. The liquid crystal display device and the pixel array substrate thereof are used for solving the control problem of the sub-pixels and improving the expressive capability of picture quality.

Owner:KUSN INFOVISION OPTOELECTRONICS

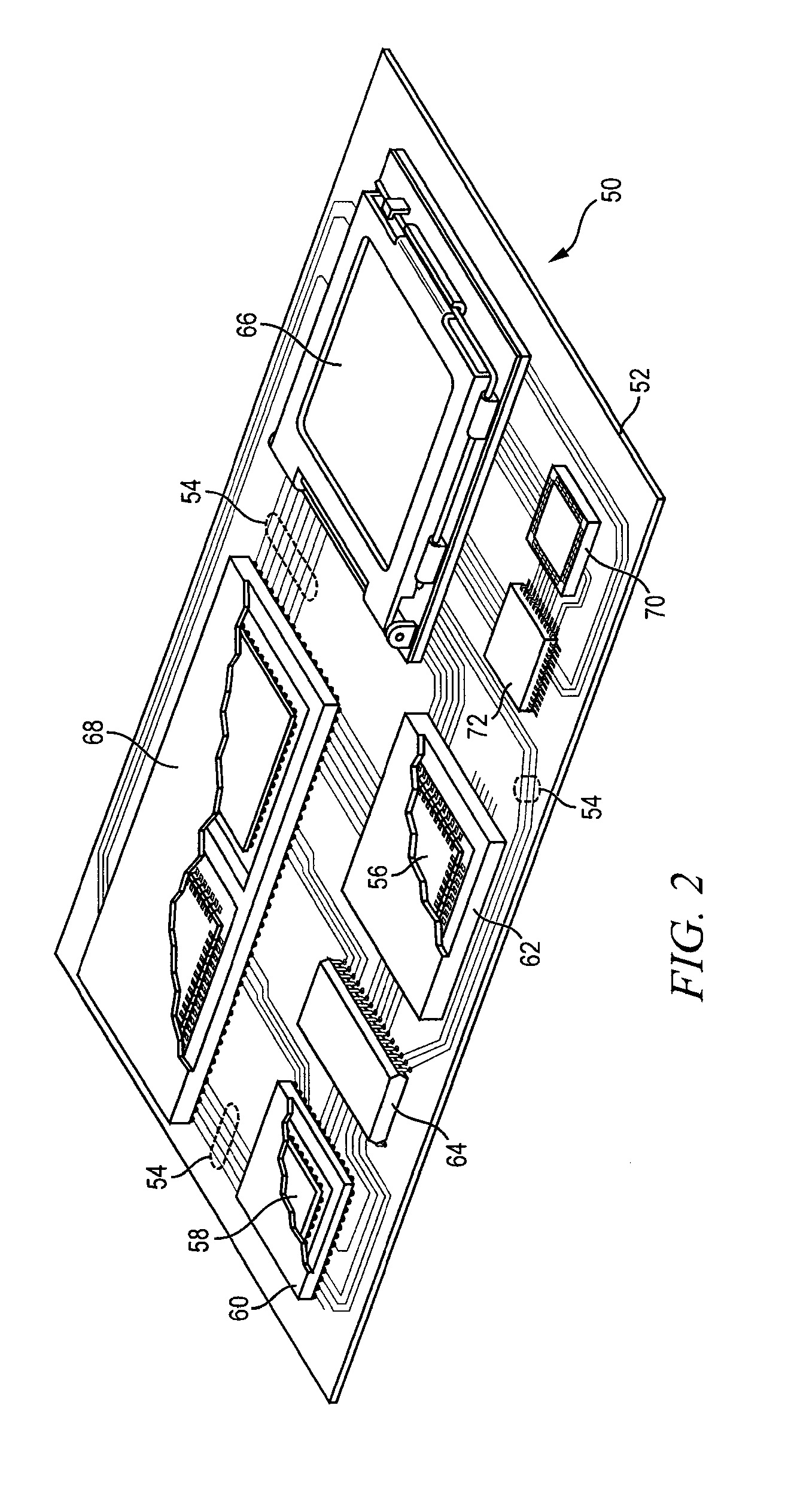

Lateral double diffused MOS transistors

InactiveUS20060091480A1Simple mechanical structureIncreases likelihood of mechanical failureTransistorSemiconductor/solid-state device detailsCross connectionMechanical integrity

The specification describes an improved mechanical electrode structure for MOS transistor devices with elongated runners. It recognizes that shrinking the geometry increases the likelihood of mechanical failure of comb electrode geometries. The mechanical integrity of a comb electrode is improved by interconnecting the electrode fingers in a cross-connected grid. In one embodiment, the transistor device is interconnected with gate fingers on a lower metaliization level, typically the first level metal, with the drain interconnected at a higher metal level. That allows the drain fingers to be cross-connected with a vertical separation between drain and gate comb electrodes. The cross-connect members may be further stabilized by adding beam extensions to the cross-connect members. The beam extensions may be anchored in an interlevel dielectric layer for additional support.

Owner:BELL SEMICON LLC

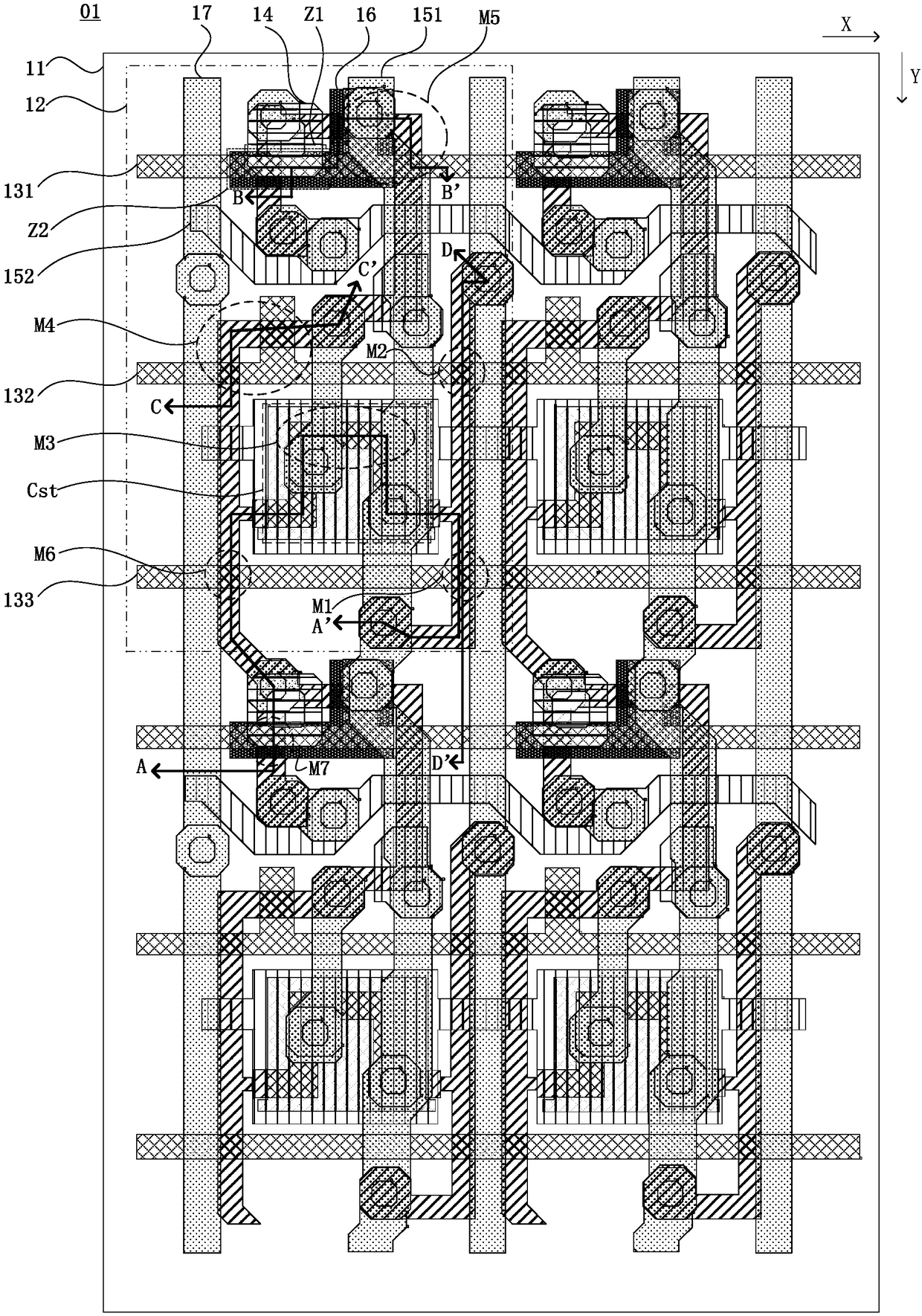

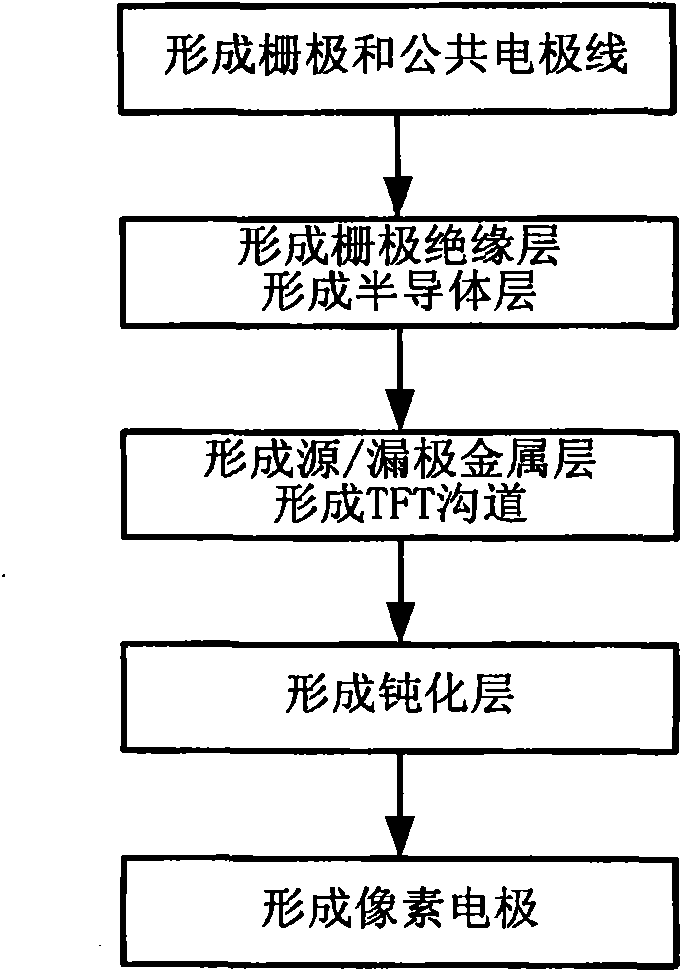

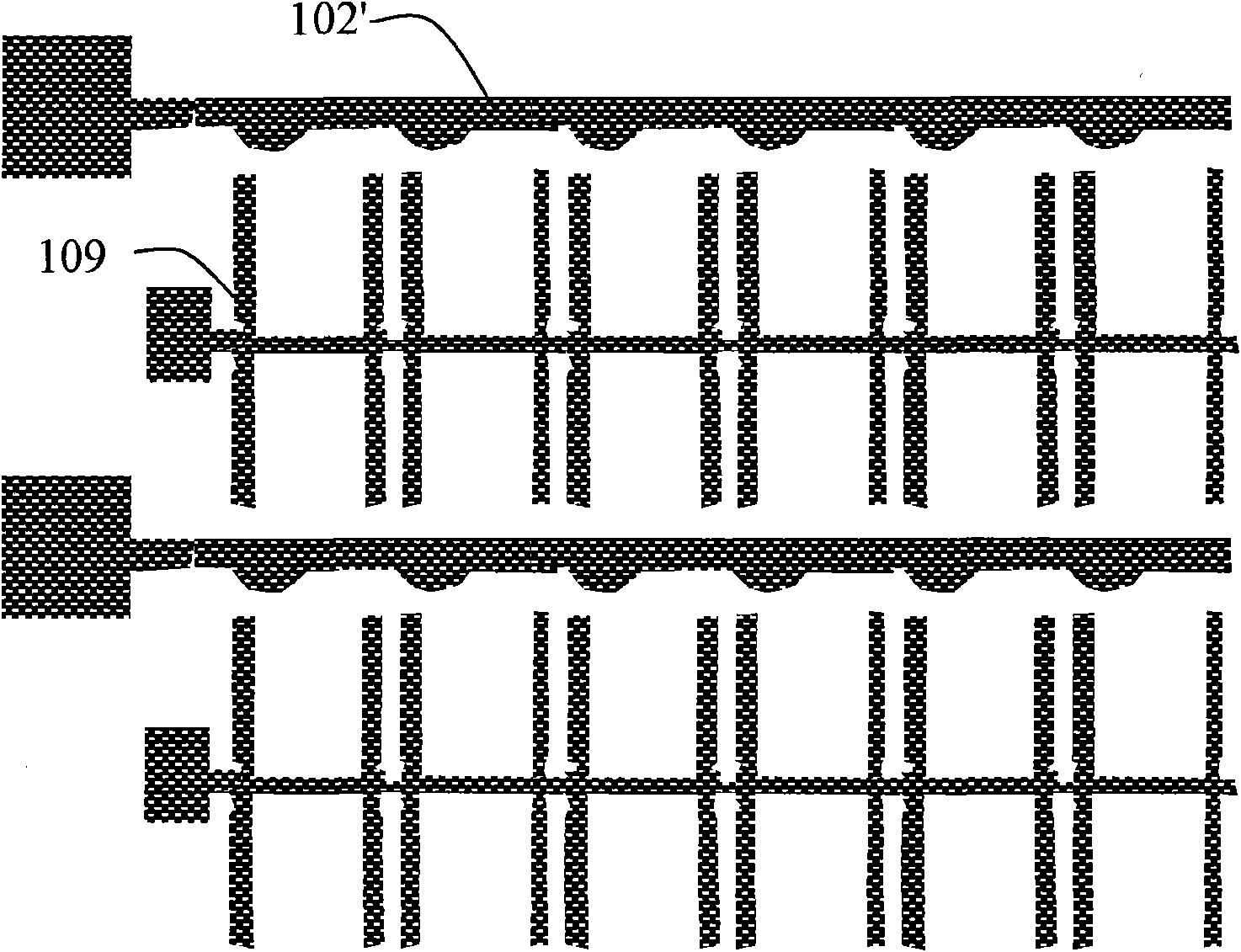

Thin-film-transistor array substrate and forming method thereof

ActiveCN101599497AIncrease opening ratioImprove display qualitySemiconductor/solid-state device detailsSolid-state devicesTransistor arraySilicon

The invention relates to a thin-film-transistor array substrate and a forming method thereof. The array substrate comprises an insulating base, a first metal layer, a grid insulting layer, a noncrystalline silicon layer, a first conducting transparent material layer, a doped noncrystalline silicon layer, a second metal layer, a passivated layer and a second conducting transparent material layer, wherein the first metal layer is positioned above the insulating base, and a first part of the first metal layer forms a TFT grid which is electrically connected with a scanning line; the grid insulating layer is covered above the first metal layer and the insulating base; the noncrystalline silicon layer and the first conducting transparent material layer are both positioned above the grid insulating layer; the doped noncrystalline silicon layer is positioned above the noncrystalline silicon layer and forms a TFT semiconductor layer together with the noncrystalline silicon layer; the second metal layer is positioned above the doped noncrystalline silicon layer and the first conducting transparent material layer, a first part of the second metal layer forms a source electrode and a drain electrode of the TFT, and the source electrode is electrically connected with a data wire; the passivated layer is positioned above the second metal layer and is used as an insulator; the second conducting transparent material layer is positioned above the passivated layer, and a first part of the second conducting transparent material layer forms a pixel electrode connected with the drain electrode; and the first conducting transparent material layer forms part of a common electrode.

Owner:KUSN INFOVISION OPTOELECTRONICS

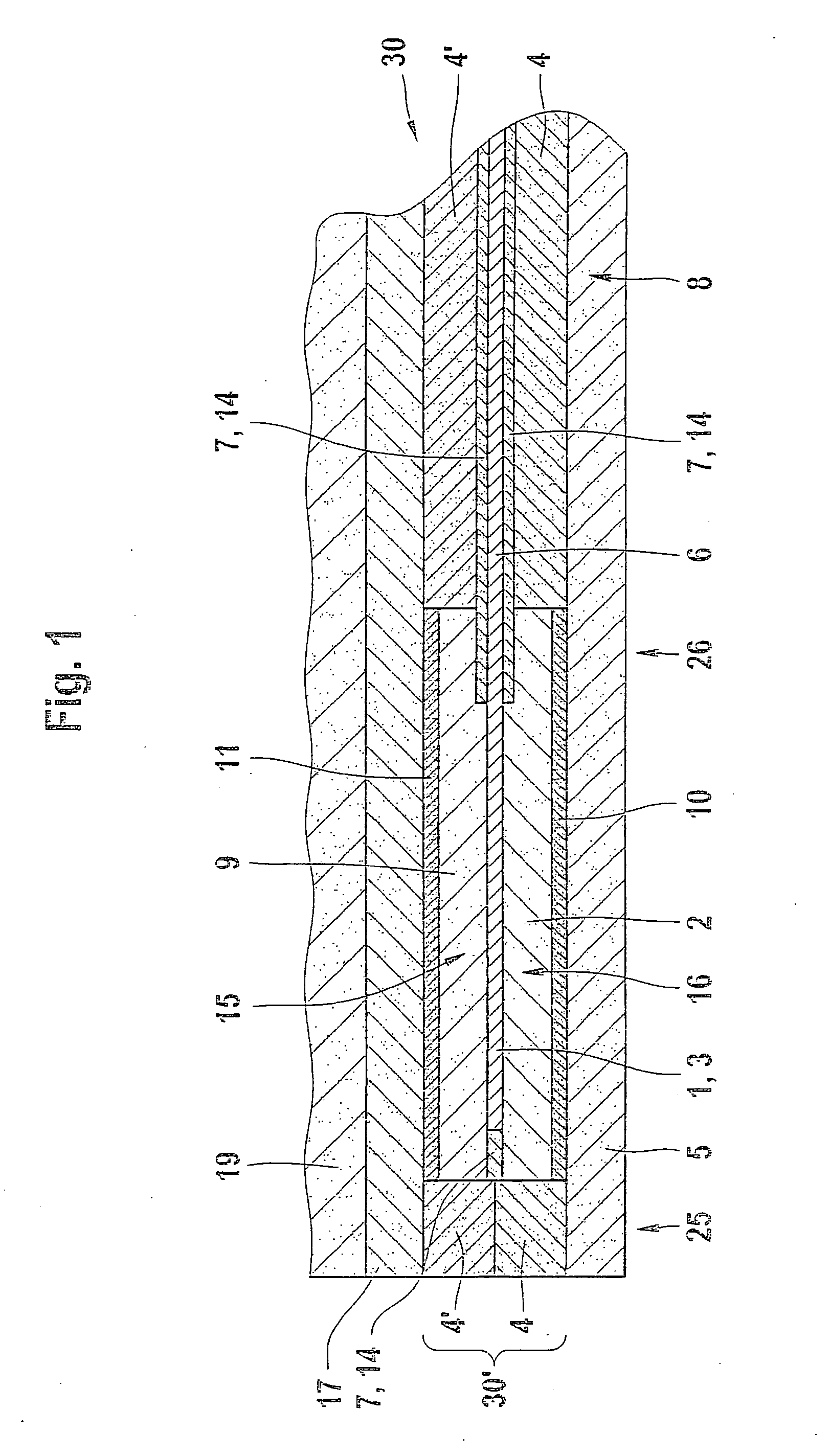

Sensor element, in particular a planar gas sensor element

InactiveUS20050160793A1Improve heat transfer performancePrevents unwanted heat dissipationOhmic-resistance heatingMaterial thermal analysisElectricityEngineering

Owner:ROBERT BOSCH GMBH

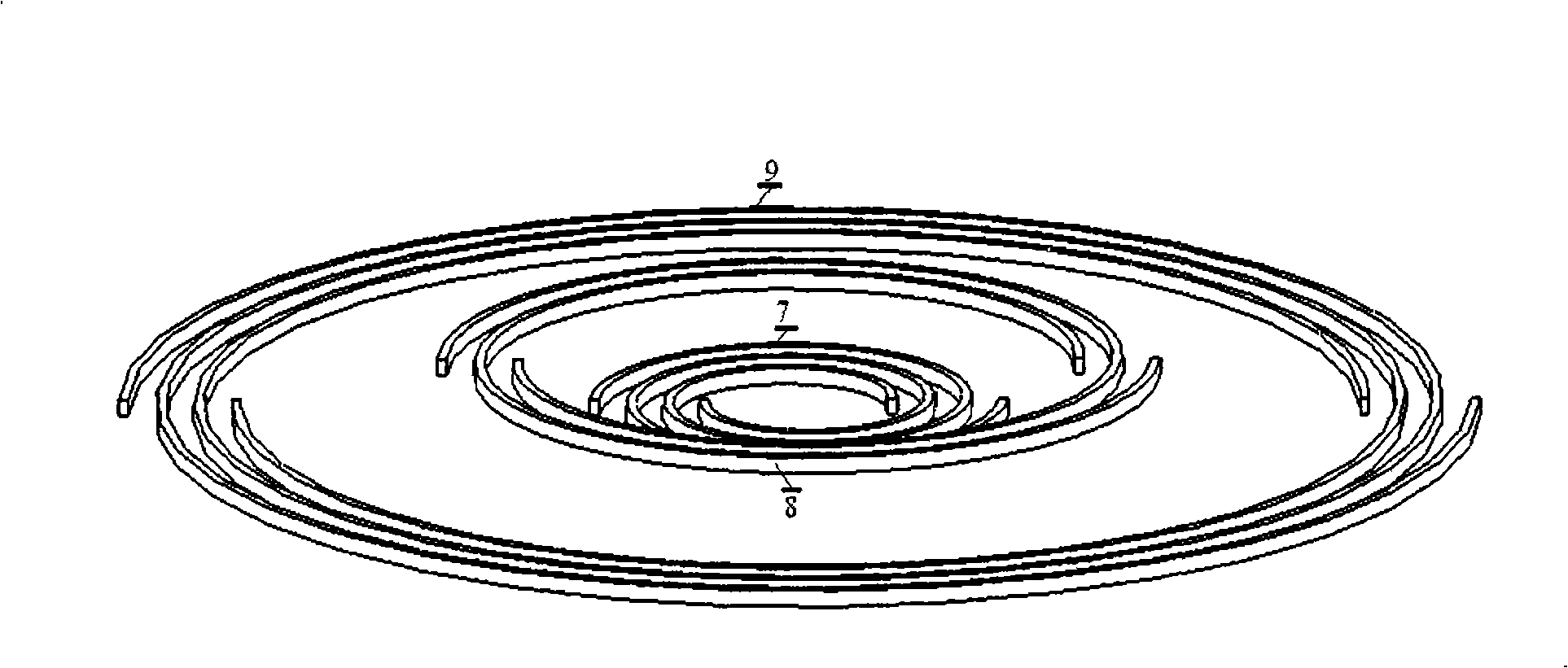

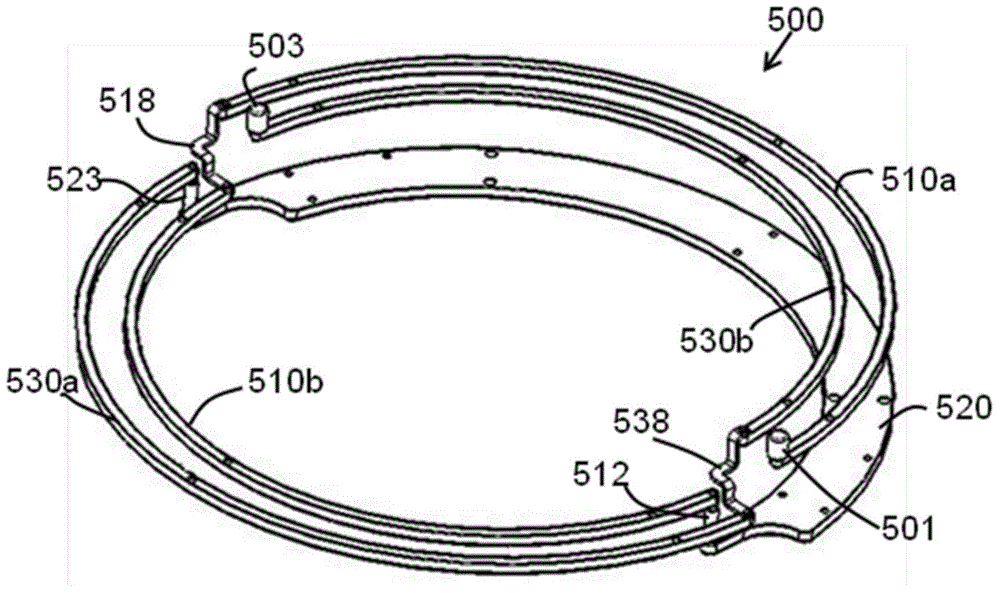

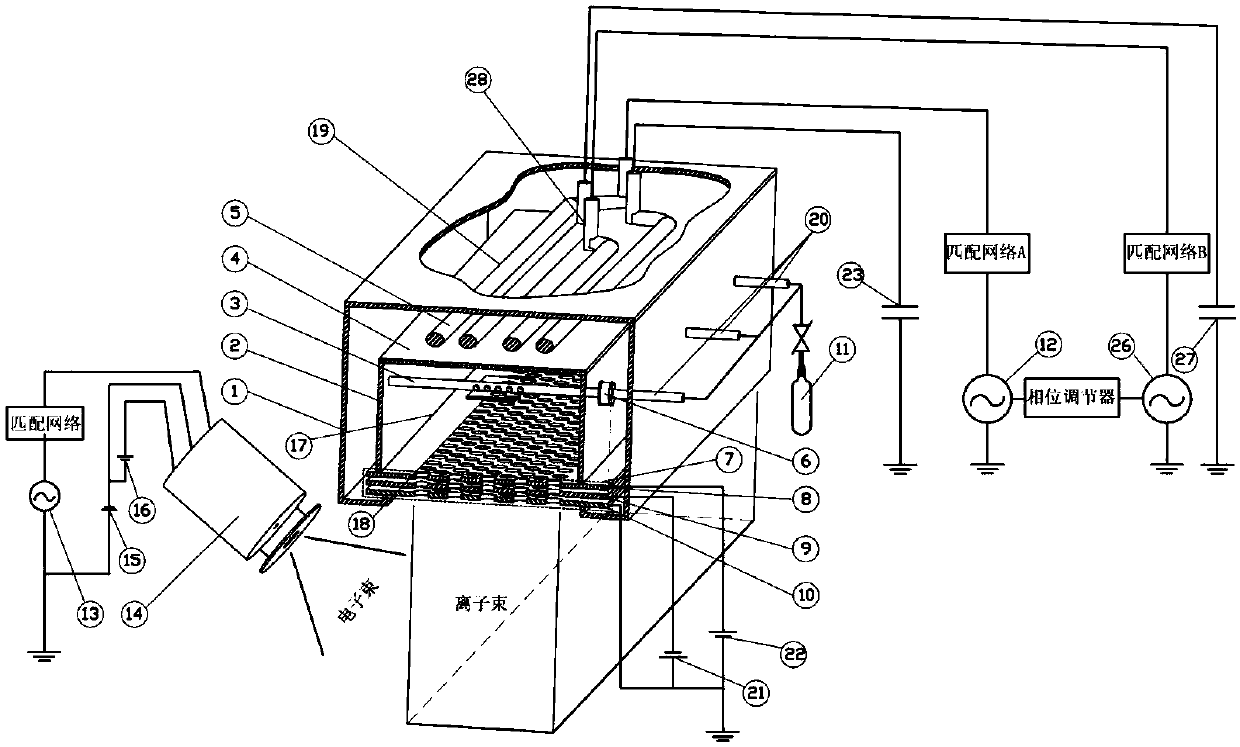

Inductive coil group and inductive coupling plasma processing device

ActiveCN104684235AReduce Capacitive CouplingDoes not reduce the efficiency of feeding magnetic field energy into the reaction chamberPlasma techniqueCapacitanceCapacitive coupling

The invention discloses a plasma processing device. The plasma processing device comprises an air-tight reaction chamber, wherein the reaction chamber comprises a reaction chamber sidewall and a top insulating material window, and the reaction chamber therein comprises a base for supporting a substrate to be processed; a self-shielding inductive coil group is fixedly arranged above the insulating material window. The plasma processing device is characterized in that the self-shielding inductive coil group comprises a plurality of inductive coils, each inductive coil comprises a flat-plate-shaped intermediate coil, a plurality of intermediate coils are combined to form a shielding ring, the two ends of each intermediate coil respectively comprise an input coil and an output coil, wherein the input coil and the output coil are spirally upward from the two ends of the intermediate coil and are respectively connected to a radio-frequency power supply and a regulating circuit, and downward projections of the input coil and the output coil are located on at least one intermediate coil. By adopting the inductive coil structure disclosed by the invention, the capacity coupling of the inductive coil towards the inside of the reaction chamber can be reduced and the service life of the insulating material window can be improved.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

Method for manufacturing an integrated semiconductor device

InactiveUS20070069327A1Preventing an electrical break downPrevent intrusionSemiconductor/solid-state device detailsSolid-state devicesCapacitanceCapacitive coupling

In a method for manufacturing an integrated semiconductor device with low capacitive coupling between a conductive member and a via, a semiconductor substrate with a surface is provided. The conductive member is formed on the surface of the substrate wherein the conductive member is provided for conducting a current in a direction parallel to the surface of the substrate. A sacrifice structure is produced. A via is formed for conducting a current in a direction vertical to the surface of the substrate. The sacrifice structure at least partially defines the shape and position of the via and separates the conductive member and the via. The sacrifice structure is removed thereby generating a void in place of the sacrifice structure.

Owner:INFINEON TECH AG

Microfabricated optical apparatus with flexible electrical connector

InactiveUS20180180829A1Reduce Capacitive CouplingHigh densityLaser detailsDecorative surface effectsEngineeringElectrical connector

A microfabricated optical apparatus that includes a light source driven by a waveform, wherein the waveform is delivered to the light source by at least one through silicon via. The microfabricated optical apparatus may also include a light-sensitive receiver which generates an electrical signal in response to an optical signal. An optical source may be attached to a carrier substrate with the TOSA by a flexible connector, in order to align the optical source before affixing it permanently.

Owner:INNOVATIVE MICRO TECH

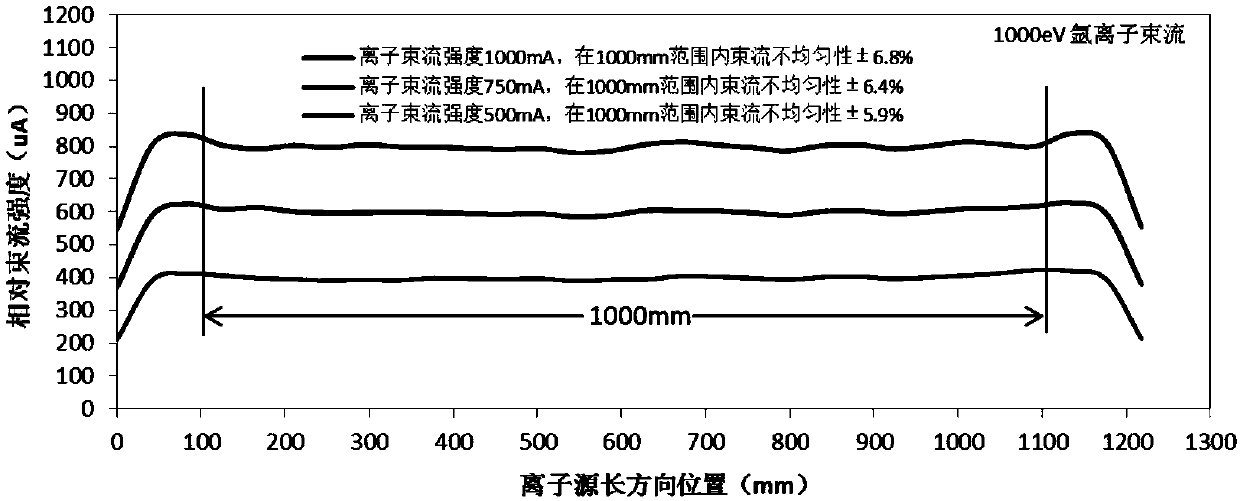

Radio-frequency inductive coupling linear ion source

PendingCN111385953AReduce thicknessReduce processing difficultyPlasma techniqueIon beamParticle physics

The invention belongs to the technical field of ion beam control, and particularly relates to a radio-frequency inductive coupling linear ion source. The radio-frequency inductive coupling linear ionsource comprises an ion source shielding shell, a radio frequency coupling antenna, a dielectric coupling window used for transmitting radio-frequency power and isolating a discharge chamber from an antenna chamber, a plasma discharge chamber side wall used for accommodating discharge plasmas, a multi-grid ion beam extraction system used for extracting ion beams from the plasma discharge chamber,and a radio-frequency neutralizer used for providing initial electrons into the discharge chamber and providing neutralized electrons into the ion beams and a base material. The radio-frequency inductive coupling linear ion source can generate high-uniformity large-area narrow and long linear ion beams in a large size range, and is suitable for processes of ion beam cleaning, etching, thin film deposition and the like of large-area base materials.

Owner:中核同创(成都)科技有限公司

Electrical connection system

ActiveUS20150162692A1Decrease capacitive couplingReduce Capacitive CouplingElectrically conductive connectionsTwo pole connectionsData transmissionElectricity

An electrical connection system configured to terminate electrical connectors and to transmit digital electrical signals having a data transfer rate of 5 Gigabits per second (Gb / s) or higher. The system includes a first parallel mirrored pair of terminals having a planar connection portion and a second pair of parallel mirrored terminals having a cantilever beam portion and a contact points configured to contact the first terminals. The cantilever beam portions are generally perpendicular to the planar connection portions. The terminals cooperate to provide consistent characteristic impedance. The connection system further includes an electromagnetic shield that longitudinally surrounds the terminals. The connection system is suited for terminating wire cables transmitting digital signals using data transfer protocols such as Universal Serial Bus (USB) 3.0 and High Definition Multimedia Interface (HDMI) 1.3

Owner:APTIV TECH LTD

High performance micro-fabricated electrostatic quadrupole lens

ActiveUS7893407B2Reduce Capacitive CouplingHigh sensitivityStability-of-path spectrometersBeam/ray focussing/reflecting arrangementsCapacitanceImage resolution

A method of aligning sets of cylindrical electrodes in the geometry of a miniature quadrupole electrostatic lens, which can act as a mass filter in a quadrupole mass spectrometer is provided. The electrodes are mounted in pairs on microfabricated supports, which are formed from conducting parts on an insulating substrate. Complete segmentation of the conducting parts provides low capacitative coupling between co-planar cylindrical electrodes, and allows incorporation of a Brubaker prefilter to improve sensitivity at a given mass resolution. A complete quadrupole is constructed from two such supports, which are spaced apart by further conducting spacers. The spacers are continued around the electrodes to provide a conducting screen.

Owner:MICROSAIC SYST

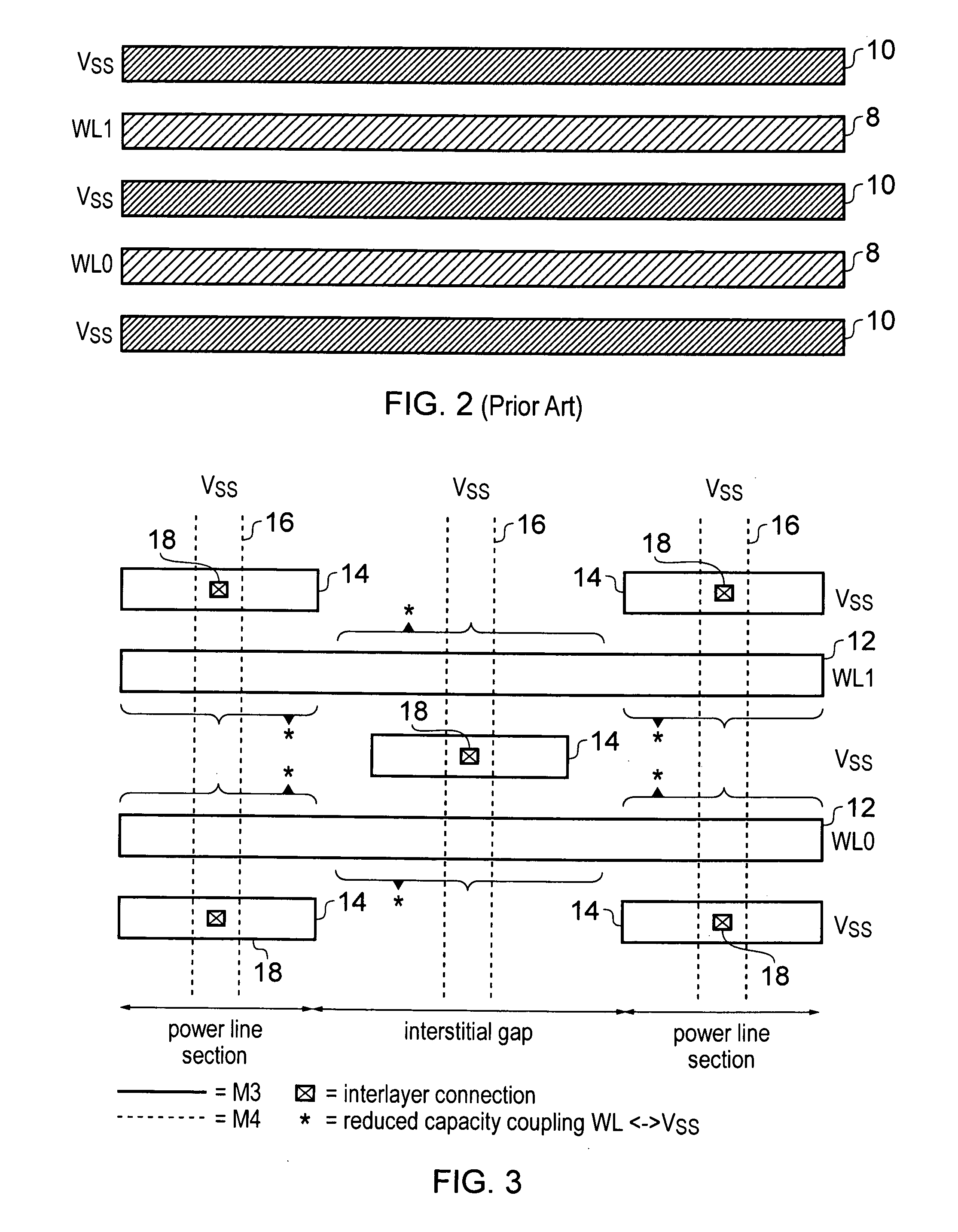

Word line and power conductor within a metal layer of a memory cell

ActiveUS20130182484A1Reduce RC valueImprove scalabilitySolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorEngineering

A memory cell 6 includes a M3 metal layer which incorporate continuous word lines 12 and power conductors formed of a plurality of separate power line sections 14 running parallel to the word lines. Interstitial gaps between the separate power line sections are larger in size than the power line sections themselves. The power line sections are disposed in a staggered arrangement either side of the word lines.

Owner:ARM LTD

Metal conducting wire mosaic structure and method of manufacture

ActiveCN101192592AReduce Capacitive CouplingReduce RC delay and leakage currentSemiconductor/solid-state device detailsSolid-state devicesCapacitive couplingCapacitance

The invention relates to a mosaic structure of metal wires, which includes a basement, a dielectric layer and a plurality of metal wires. The dielectric layer is arranged at the basement, which has a plurality of grooves. The metal wires are inlayed in the plurality of grooves. The dielectric layer includes at least two sub-dielectric layers which are positioned by layer-cake and an air gap is kept between at least a sub-dielectric layer and the metal wires. The mosaic structure of the metal wires can effectively reduce capacitance coupling among the metal wires as well as RC delay and leakage current caused by the capacitance coupling. The invention also provides a method for manufacturing the mosaic structure of the metal wires.

Owner:INNOCOM TECH SHENZHEN +1

Toroidal conductivity probe with integrated circuitry

InactiveUS9310327B2Reduce Capacitive CouplingEasy to getComponent separationMaterial impedanceCapacitanceHemt circuits

Owner:SGS INSTR

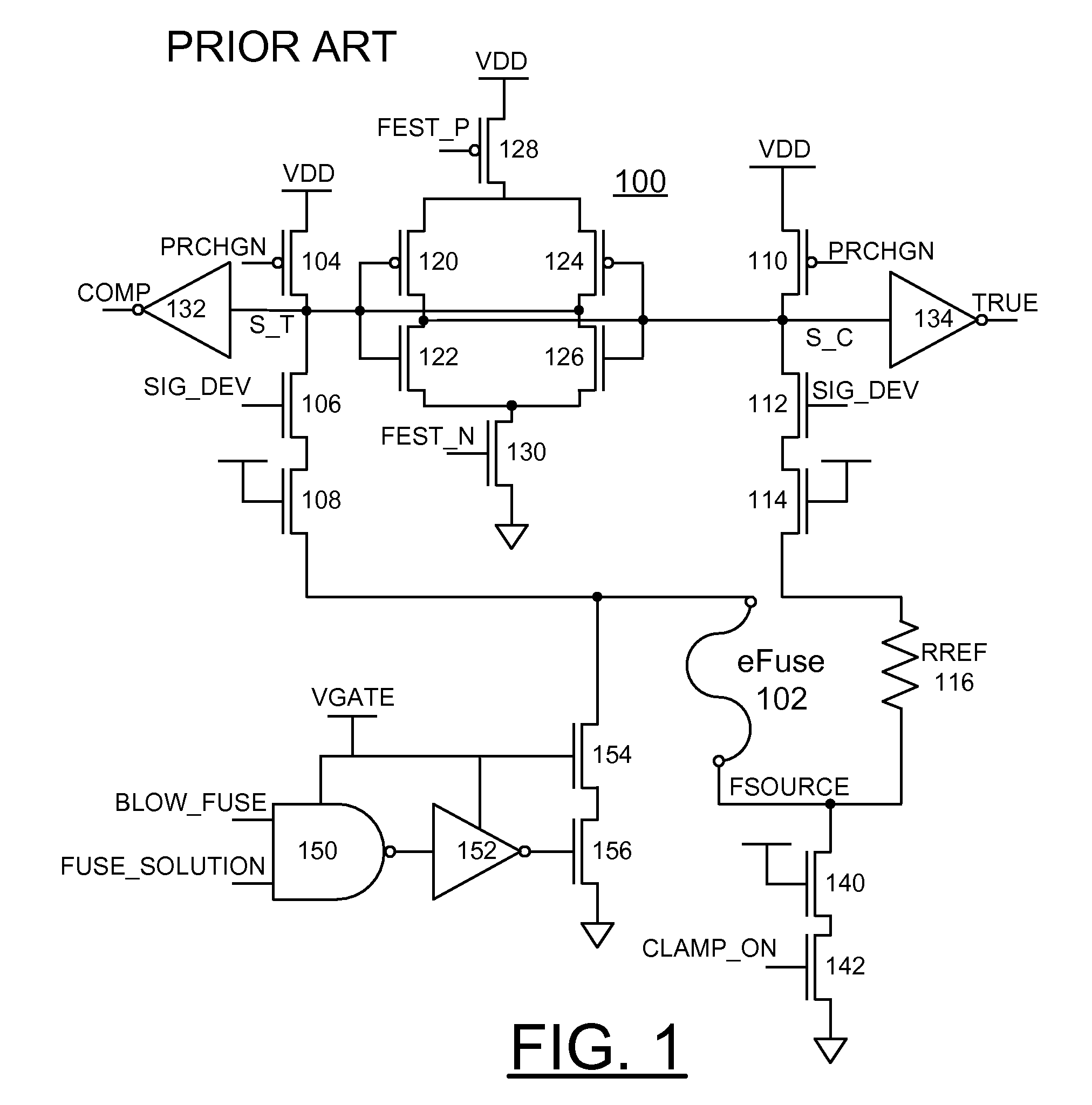

Method and circuit for implementing enhanced eFuse sense circuit

InactiveUS7729188B2Reduces voltage threshold (Vt) scatter effectReduce Capacitive CouplingRead-only memoriesDigital storageAudio power amplifierPull-up resistor

Owner:INT BUSINESS MASCH CORP

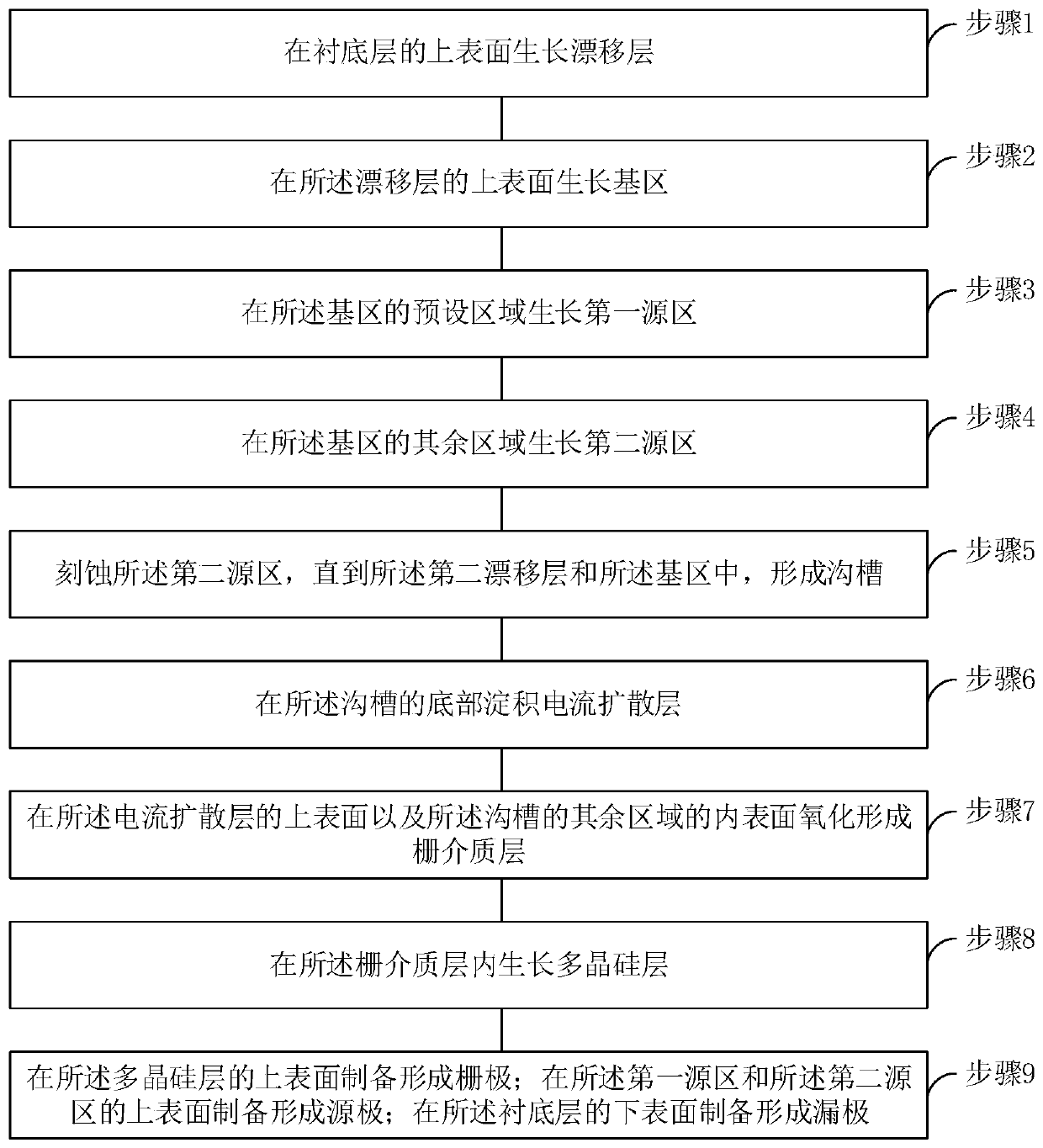

MOSFET device with silicon carbide single-side deep L-shaped base region structure and preparation method of MOSFET device

InactiveCN110212020AReduce aggregationImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

The invention relates to an MOSFET device with a silicon carbide single-side deep L-shaped base region structure and a preparation method of the MOSFET device. The MOSFET device comprises a gate dielectric layer, a base region which comprises a first base region and a second base region located on the two sides of the gate dielectric layer respectively, a current diffusion layer located between the gate dielectric layer and the second base region, a drift layer located on the lower surfaces of the base region and the current diffusion layer, a substrate layer located on the lower surface of the drift layer, a drain electrode located on the lower surface of the substrate layer, a polycrystalline silicon layer positioned on the inner surface of the gate dielectric layer, a gate electrode located on the upper surface of the polycrystalline silicon layer, a first source region located on the upper surface of a preset region of the base region, a second source region located on the upper surface of the rest region of the base region, and a source electrode located on the upper surfaces of the first source region and the second source region. According to the MOSFET device, by changing the structure of the single-side P-type base region, under the condition that the cell area of the device is not enlarged, the electric field aggregation at the groove-gate corner is reduced, and the breakdown voltage of the device is improved.

Owner:XIDIAN UNIV

Inductance coil and inductance coupling plasma processing device

ActiveCN104637767AReduce Capacitive CouplingNo reduction in efficiency of feed into reaction chamberTransformersElectric discharge tubesVoltage amplitudeCoupling

The invention discloses a plasma processing device which comprises an airtight reaction cavity. The reaction cavity comprises reaction cavity side walls and an insulating material window at the top, a base used for supporting a to-be-processed substrate is arranged in the reaction cavity, and a self-shielding inductance coil is fixed above the insulating material window. The plasma processing device is characterized in that the self-shielding inductance coil comprises a first coil, a middle coil and a third coil which are serially connected with one another, the middle coil is positioned below the first coil and the third coil, width of the middle coil is larger than that of the first coil or the third coil, a radio frequency power source applies a radio frequency electric field to space between an input end of the first coil and an output end of the third coil of the self-shielding inductance coil, the output end of the third coil is further connected with a balance adjusting circuit to enable standing waves on the self-shielding inductance coil, and voltage amplitude of the middle coil is smaller than that on the first coil or the third coil.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

Scrambling method to reduce wordline coupling noise

ActiveUS7244995B2Reduce Capacitive CouplingReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorEngineering

A memory circuit and method to reduce array noise due to wordline coupling is disclosed. The circuit includes a plurality of memory cells arranged in rows (702, 704, and 706) and columns (750, 752). Each row has a first part (1102) and a second part (1108). A first conductor (750) is coupled to a respective column of memory cells in each first part. A second conductor (752) is coupled to a respective column in each second part. A third conductor is coupled to a control terminal of each memory cell in the first part (1102) of a first row and the second part (1108) of a second row.

Owner:TEXAS INSTR INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com