Preparation method for high-density interposer for microelectronic system-in-package

A system-in-package, high-density technology, applied in the process of producing decorative surface effects, microstructure devices, manufacturing microstructure devices, etc. Irregular shape and other problems, to achieve the effects of good thermal stability, low thermal expansion coefficient, and precise adjustable length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0030] A method for preparing a high-density adapter board for microelectronic system-in-package, comprising the following steps:

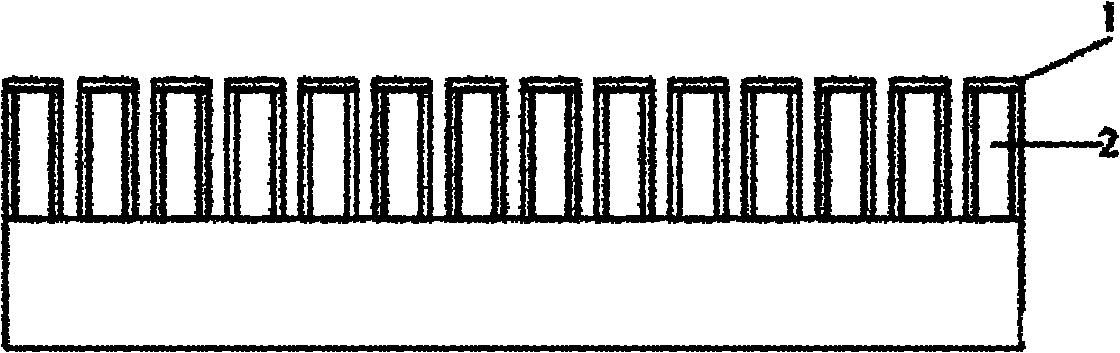

[0031] The first step is to prepare an array 2 of oriented carbon nanotube bundles, the diameter of the carbon nanotube bundles is 0.5-30 microns, such as 0.8 microns, 2 microns, 3 microns, 5 microns, 10 microns, 20 microns, and the spacing is 0.8-100 microns Micron, such as 1 micron, 3 micron, 5 micron, 8 micron, 10 micron, 20 micron, 30 micron, 50 micron, 80 micron, the length is 40-500 micron, such as 45 micron, 60 micron, 100 micron, 200 microns, 300 microns, 400 microns;

[0032] In the second step, metal tungsten 1 is deposited on the surface of the above-mentioned directional growth carbon nanotube bundle to form a conductor array; the thickness of tungsten is 0.1-20 microns, for example, it can be 0.2 microns, 0.8 microns, 1 micron, 5 microns, 10 microns, 15 microns .

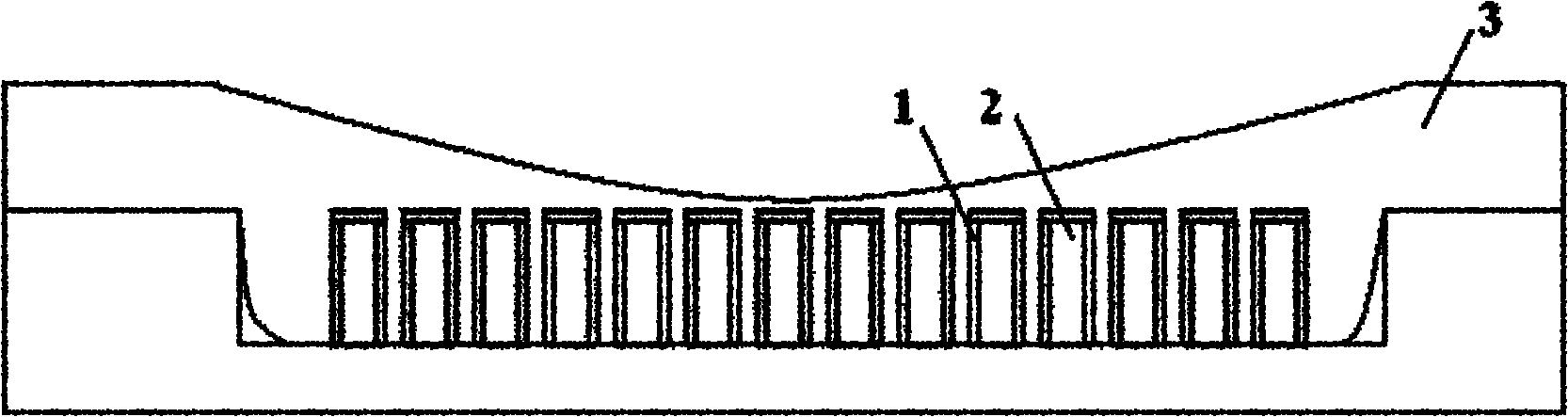

[0033] The third step is to make the borosilicate glass and the cond...

Embodiment 2

[0037] A method for preparing a high-density adapter board for microelectronic system-in-package, comprising the following steps:

[0038] The first step is to prepare a directional growth carbon nanotube bundle array, the carbon nanotube bundle has a diameter of 3 microns, a spacing of 5 microns, and a length of 200 microns; the growth method is a plasma-enhanced vapor deposition method, etc.,

[0039] The second step is to deposit metal tungsten on the surface of the above-mentioned carbon nanotube bundle; a layer of tungsten can be prepared on the surface of the carbon nanotube, and the thickness of tungsten is 3 microns. The preparation method can be sputtering, electron beam evaporation or electroplating. , Electron beam evaporation (Ebeam) can make the surface of the carbon nanotube array covered with uniform thickness of tungsten, and has a low surface roughness.

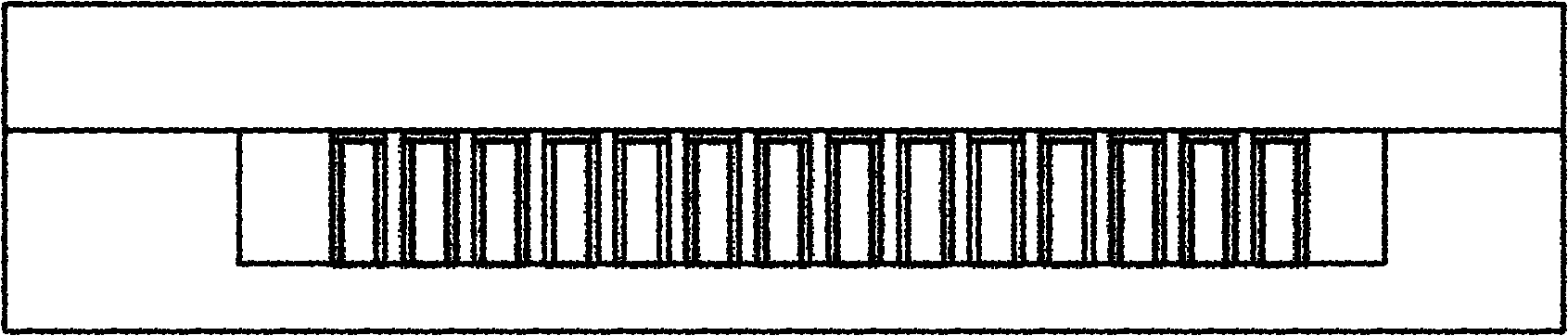

[0040] The third step is to transfer the above-mentioned metallized carbon nanotube bundles into the pre-pre...

Embodiment 3

[0045] A method for preparing a high-density adapter plate for microelectronic system-level packaging, comprising the following steps: the first step is to grow a carbon nanotube bundle array on a silicon wafer; the second step is to use the above-mentioned carbon nanotube bundle Array metallization; the third step is to put the above-mentioned metal array into the pre-prepared silicon cavity, and anodically bond the BOROFLOAT33 glass to the silicon cavity; the fourth step is to place the above-mentioned bonded two wafers in the Under one atmospheric pressure, heat the BOROFLOAT33 glass to melt it, make it well combined with the above-mentioned metal array, cool, and anneal the above-mentioned wafer to relieve stress; the fifth step is to remove the silicon for growing carbon nanotubes, and finally A method for preparing a high-density interposer board for microelectronic system-in-package is obtained.

[0046] In the above technical solution, the method for preparing the carb...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com