Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

121results about How to "Current loss" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

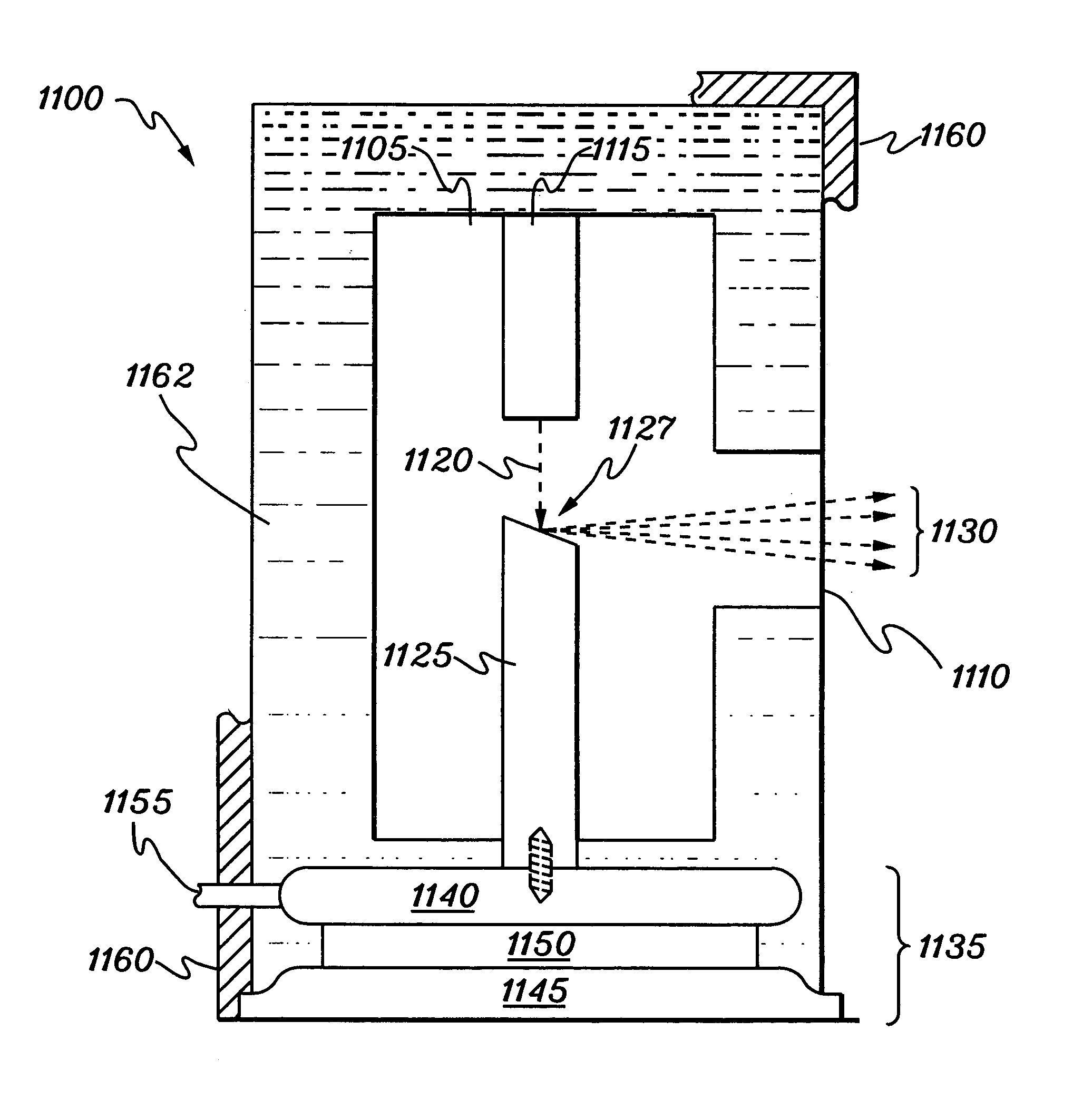

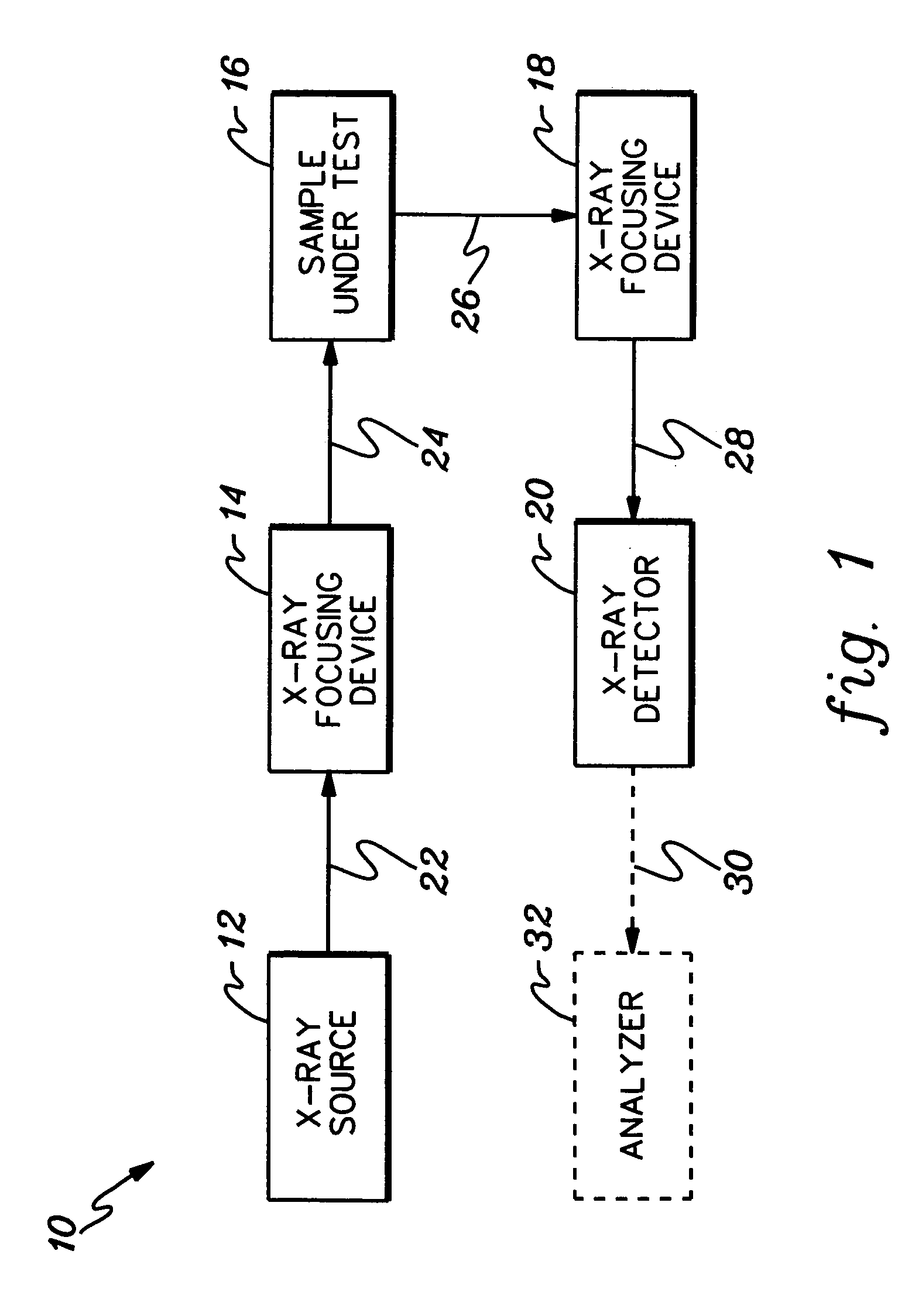

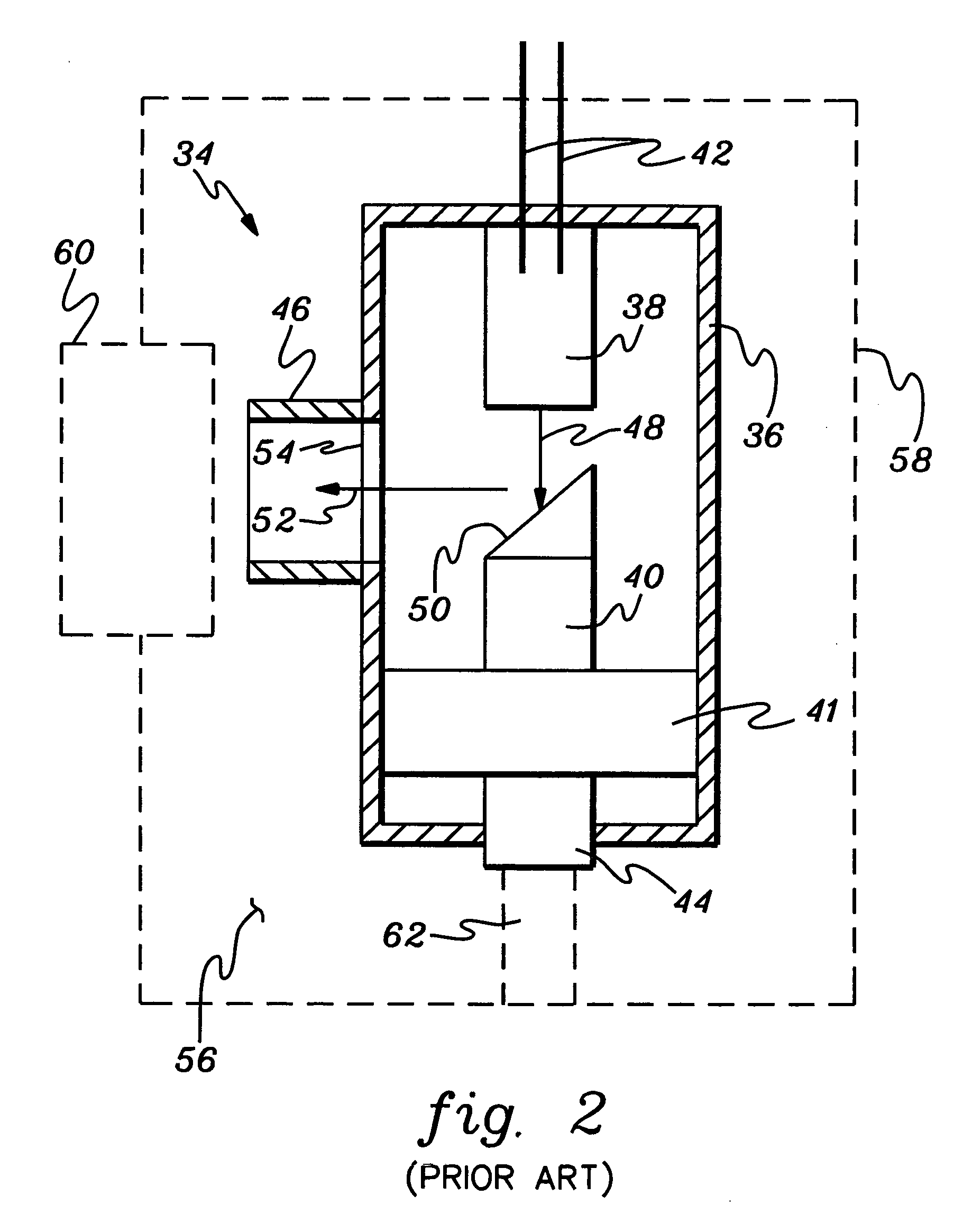

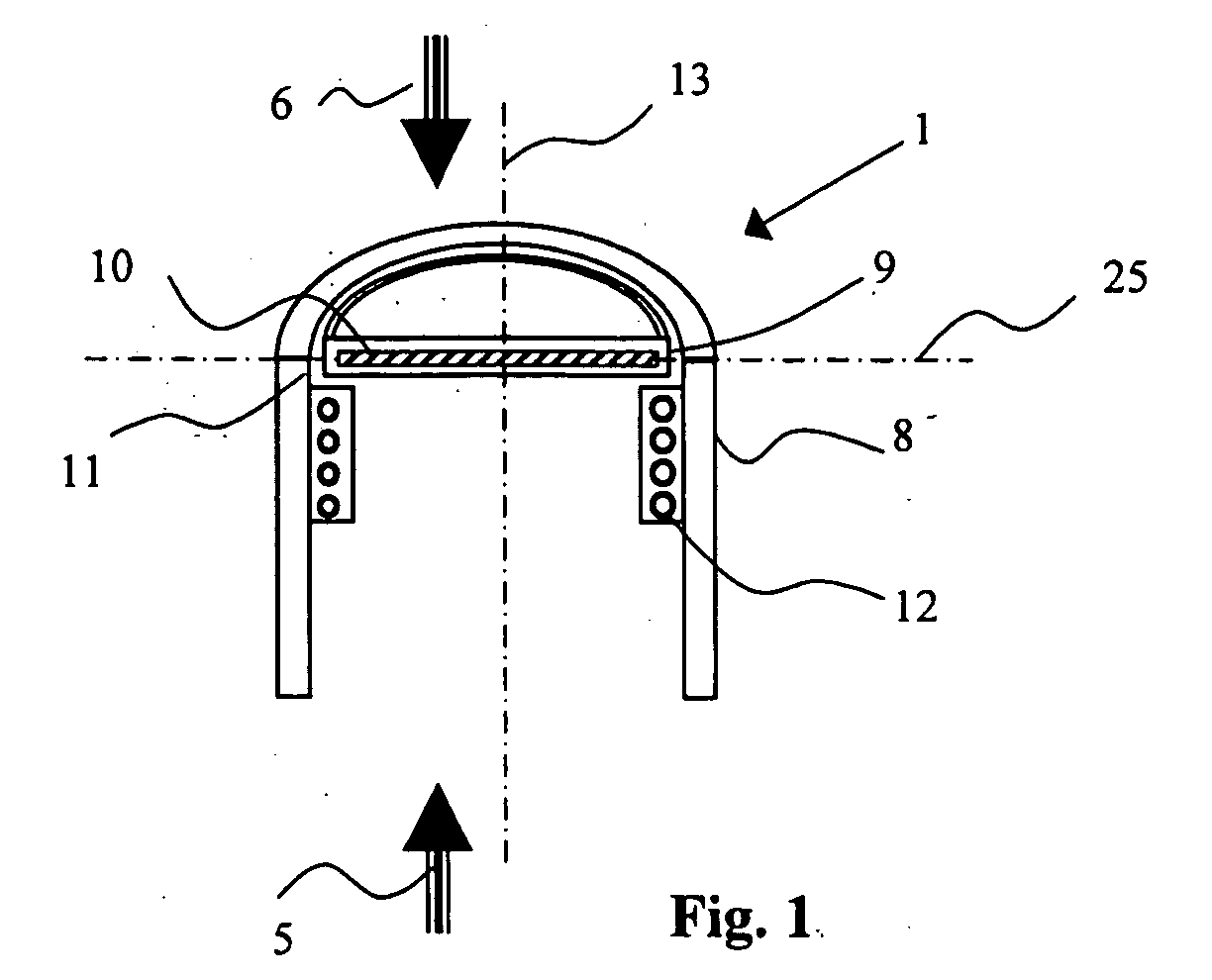

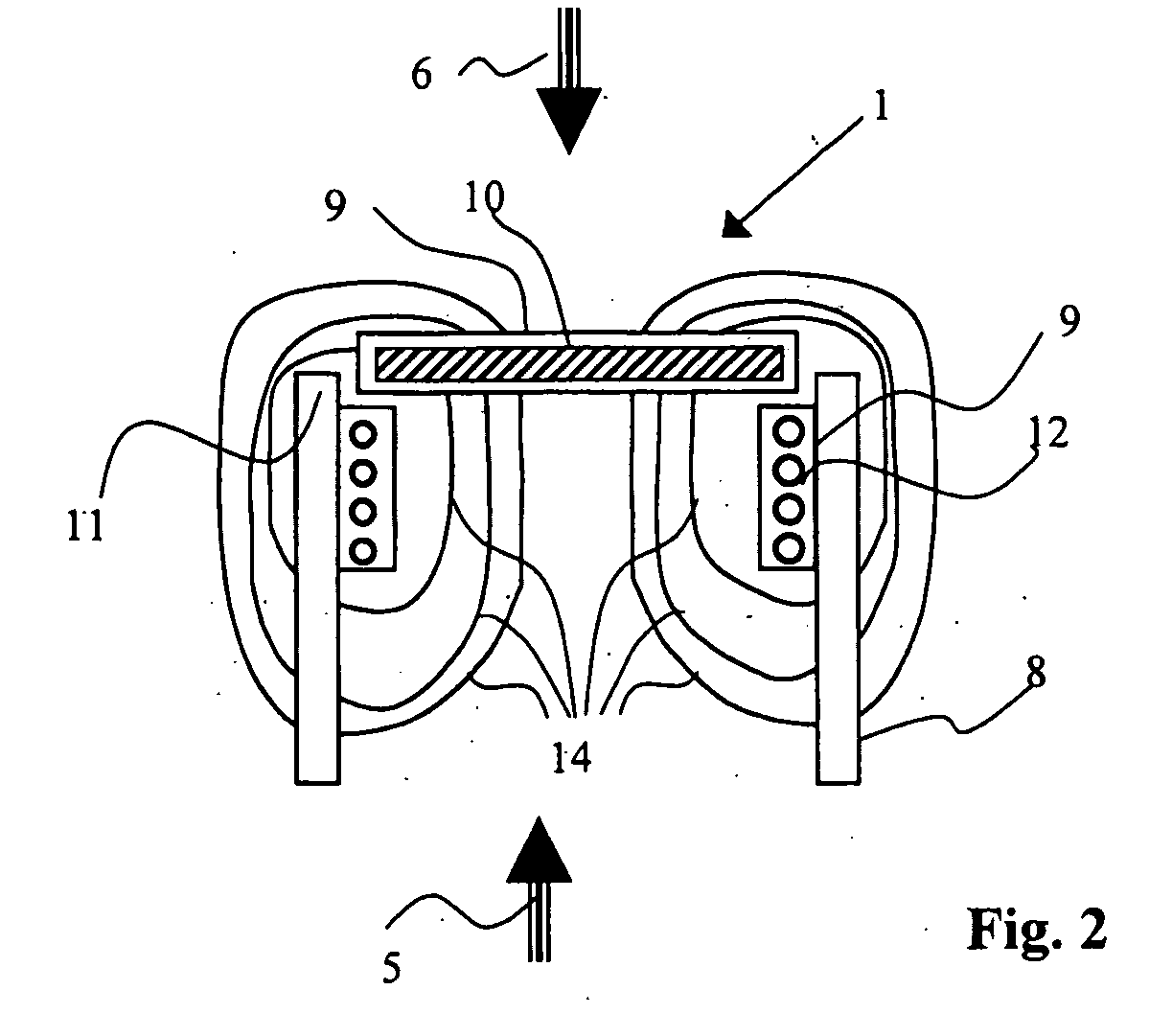

Method and device for cooling and electrically insulating a high-voltage, heat-generating component such as an x-ray tube for analyzing fluid streams

InactiveUS7110506B2Minimise currentCurrent lossElectrically conductive connectionsX-ray tube electrodesX-rayHigh pressure

Owner:S RAY OPTICAL SYST

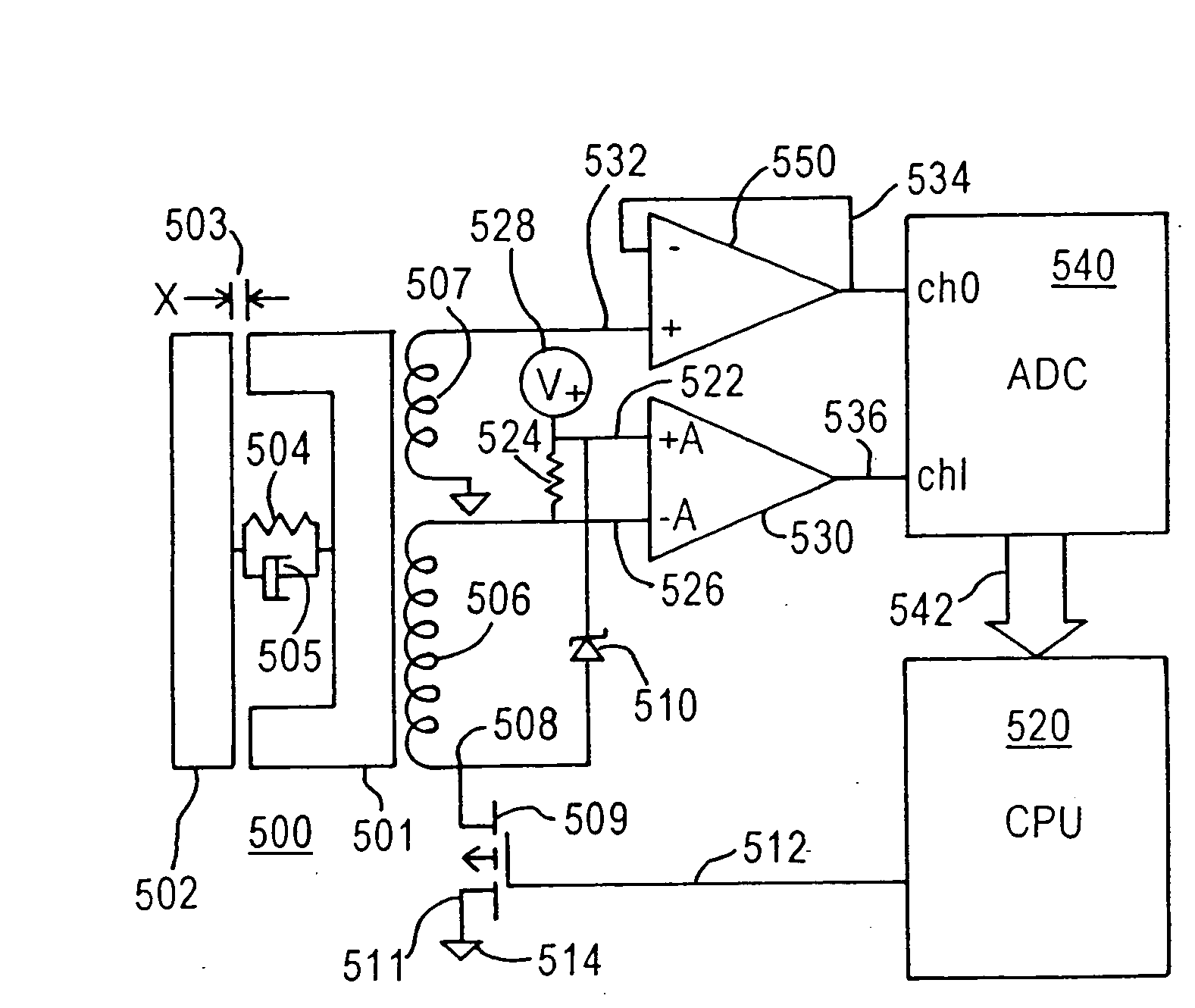

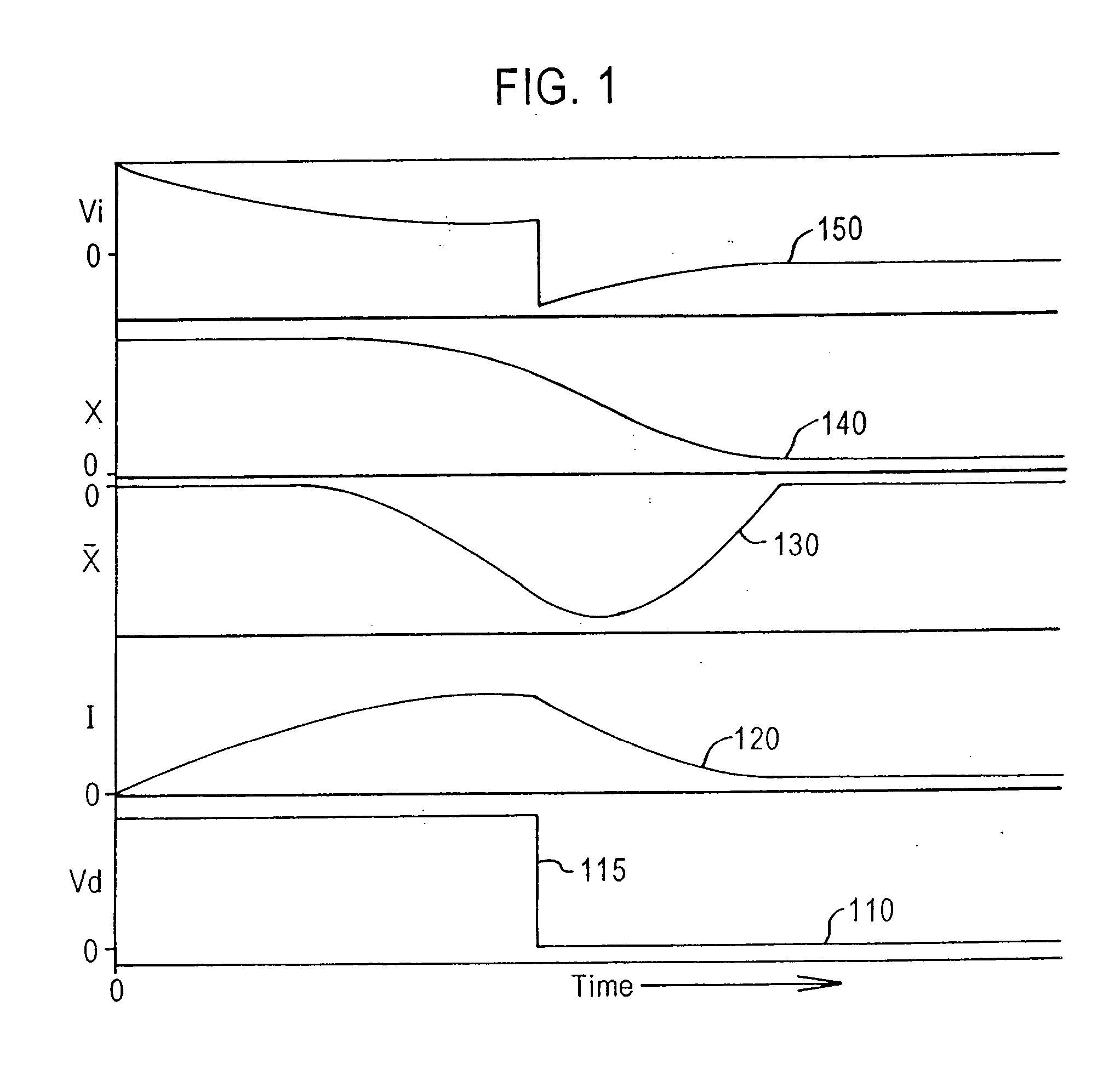

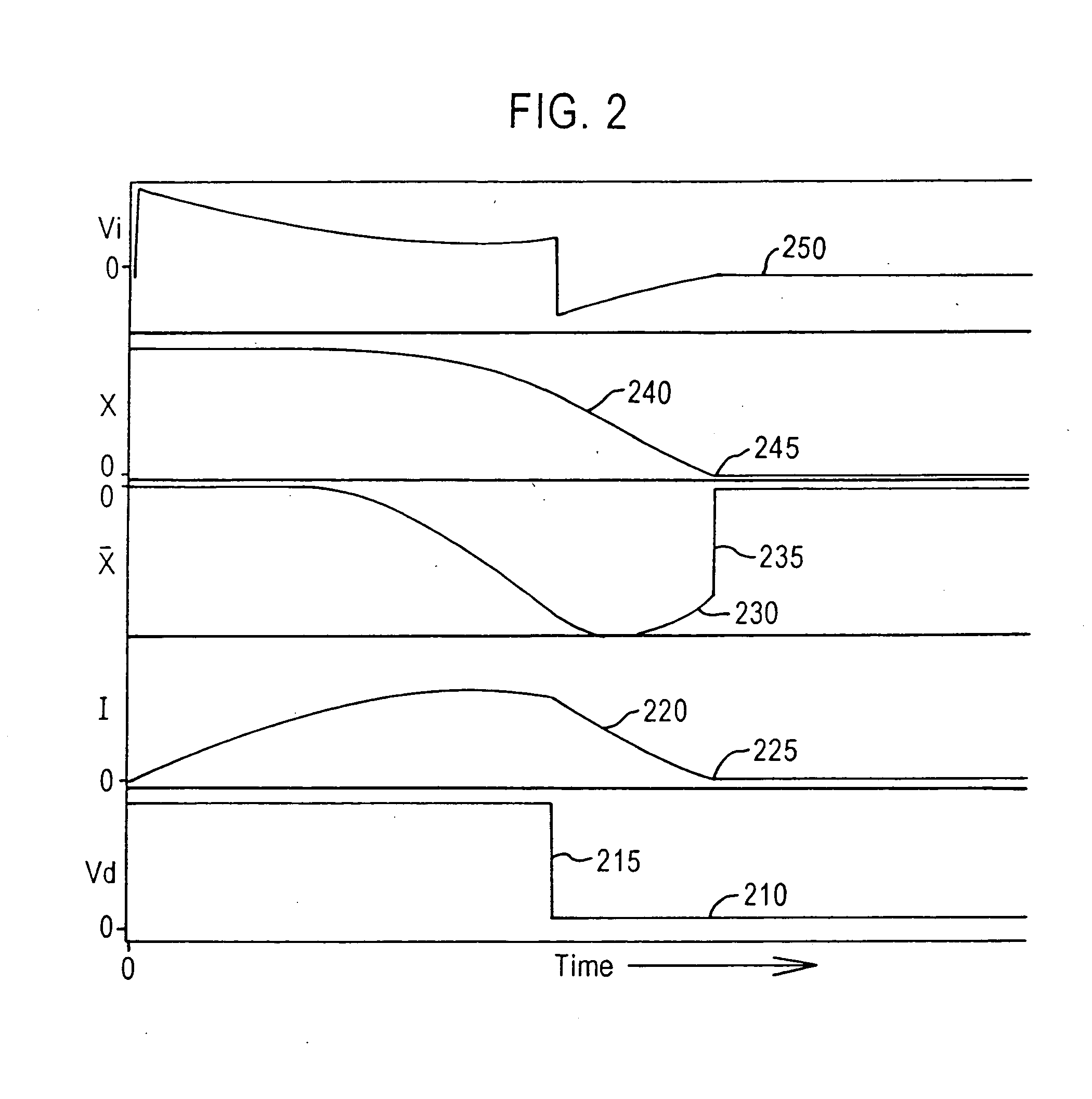

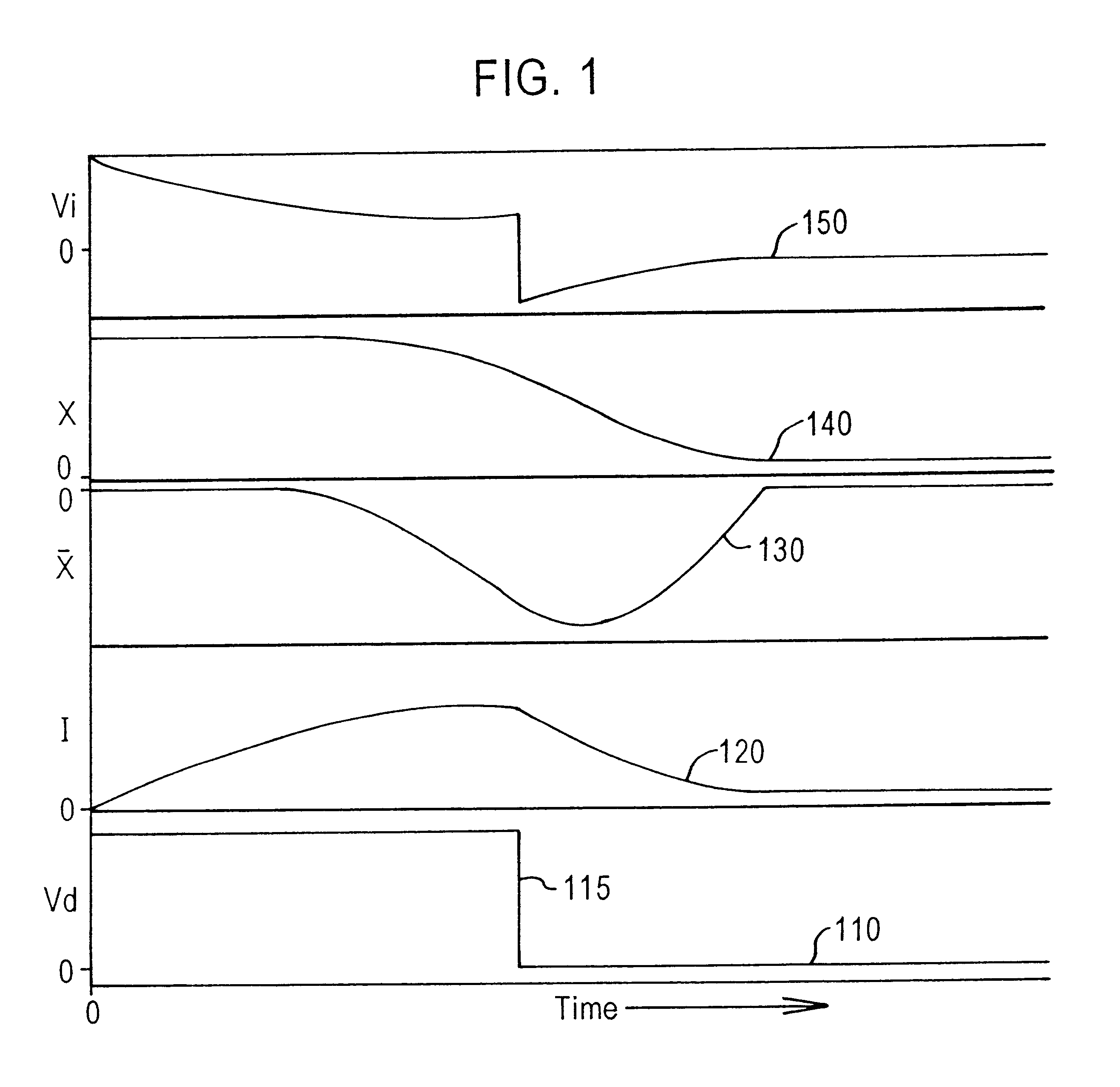

System and method for servo control of nonlinear electromagnetic actuators

InactiveUS20060171091A1Eliminate impactRemove noiseElectrical controlAC motor controlResonance measurementInstability

Servo control using ferromagnetic core material and electrical windings is based on monitoring of winding currents and voltages and inference of magnetic flux, a force indication; and magnetic gap, a position indication. Third order nonlinear servo control is split into nested control loops: a fast nonlinear first-order inner loop causing flux to track a target by varying a voltage output; and a slower almost linear second-order outer loop causing magnetic gap to track a target by controlling the flux target of the inner loop. The inner loop uses efficient switching regulation, preferably based on controlled feedback instabilities, to control voltage output. The outer loop achieves damping and accurate convergence using proportional, time-integral, and time-derivative gain terms. The time-integral feedback may be based on measured and target solenoid drive currents, adjusting the magnetic gap for force balance at the target current. Incorporation of permanent magnet material permits the target current to be zero, achieving levitation with low power, including for a monorail deriving propulsion from the levitation magnets. Linear magnetic approximations lead to the simplest controller, but nonlinear analog computation in the log domain yields a better controller with relatively few parts. When servo-controlled solenoids provide actuation of a pump piston and valves, electronic LC resonance measurements determine liquid volume and gas bubble volume.

Owner:SEALE JOSEPH B +1

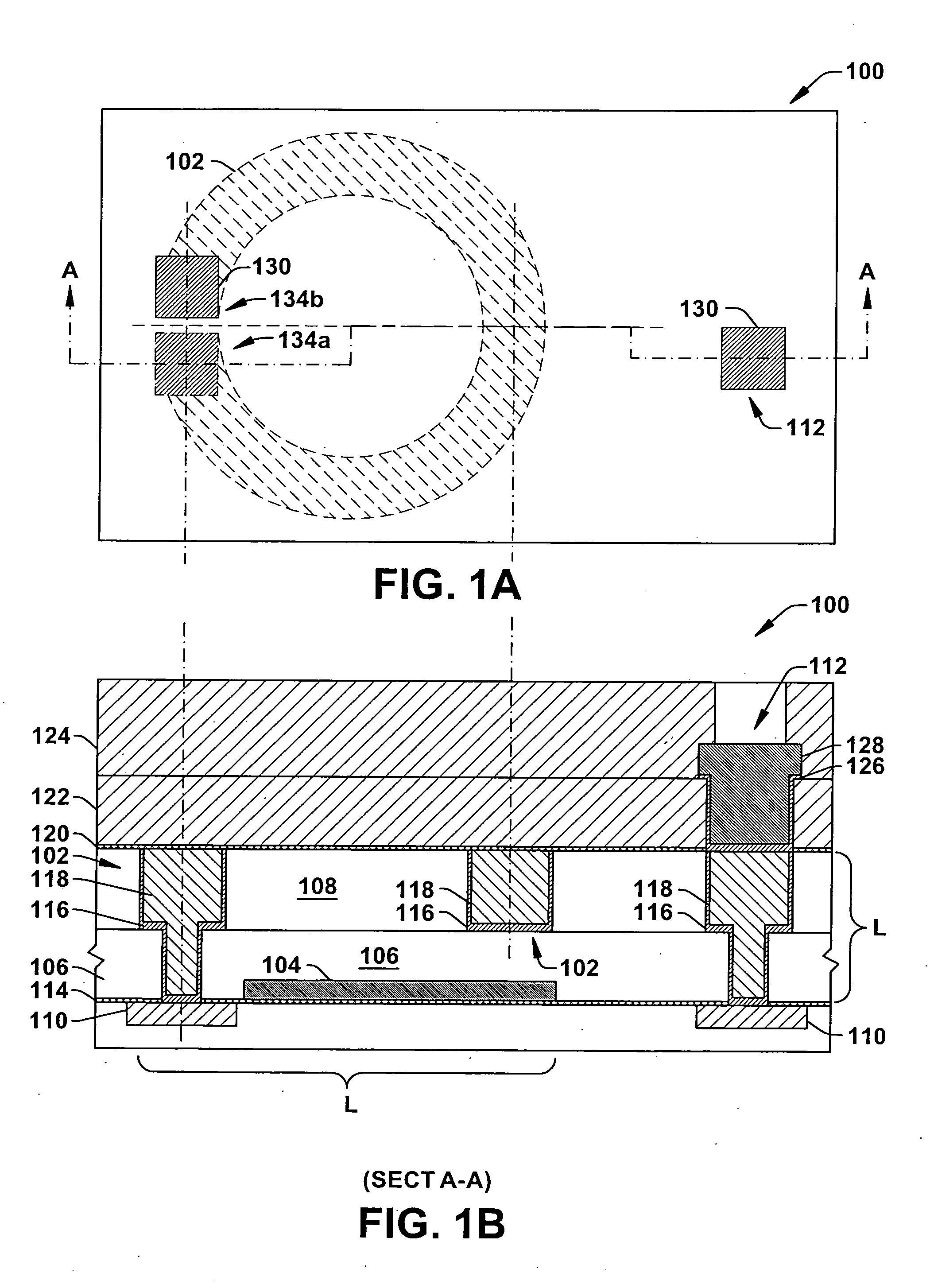

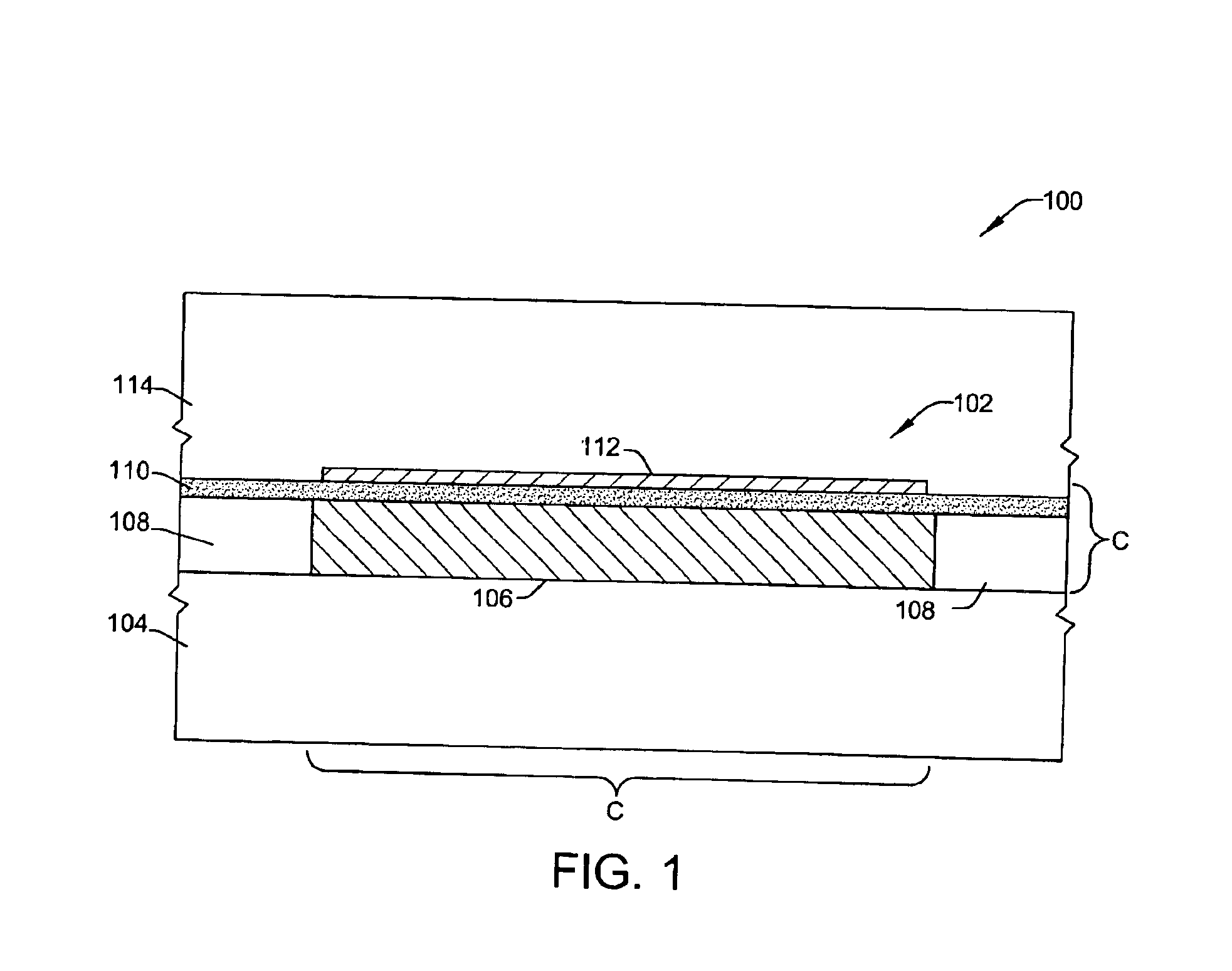

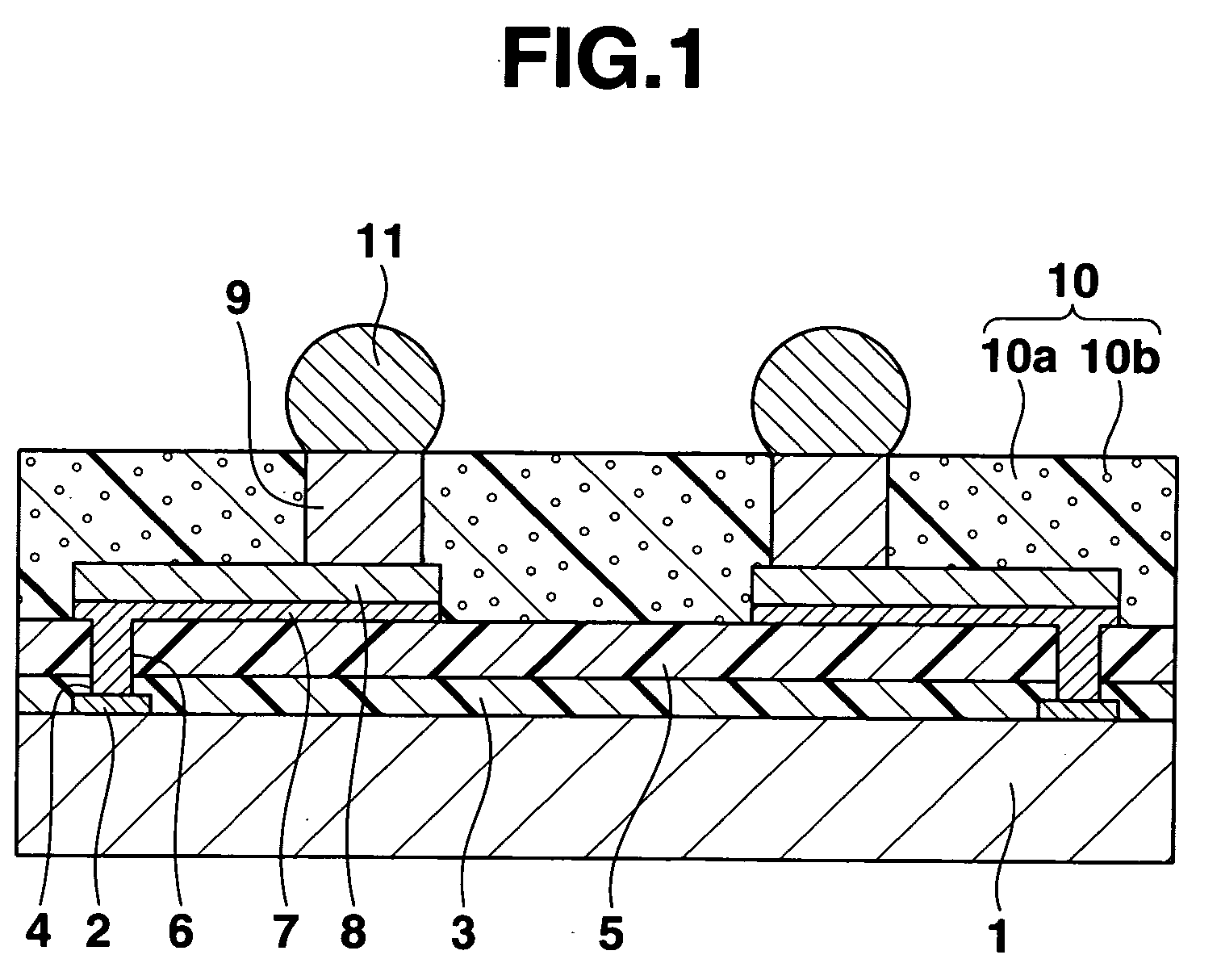

Method to improve inductance with a high-permeability slotted plate core in an integrated circuit

ActiveUS20060022787A1Mitigate eddy current lossIncrease inductanceSemiconductor/solid-state device detailsSolid-state devicesInductorIntegrated circuit

An inductor structure (102) formed in an integrated circuit (100) is disclosed, and includes a first isolation layer (106) and a first core plate (104) disposed over or within the first isolation layer (106, 114). The first core plate (104) includes a plurality of electrically coupled conductive traces composed of a conductive ferromagnetic material layer. A second isolation layer (108) overlies the first isolation layer and an inductor coil (102) composed of a conductive material layer (118) is formed within the second isolation layer (108). Another core plate may be formed over the coil. The one or more core plates increase an inductance (L) of the inductor coil (102).

Owner:TEXAS INSTR INC

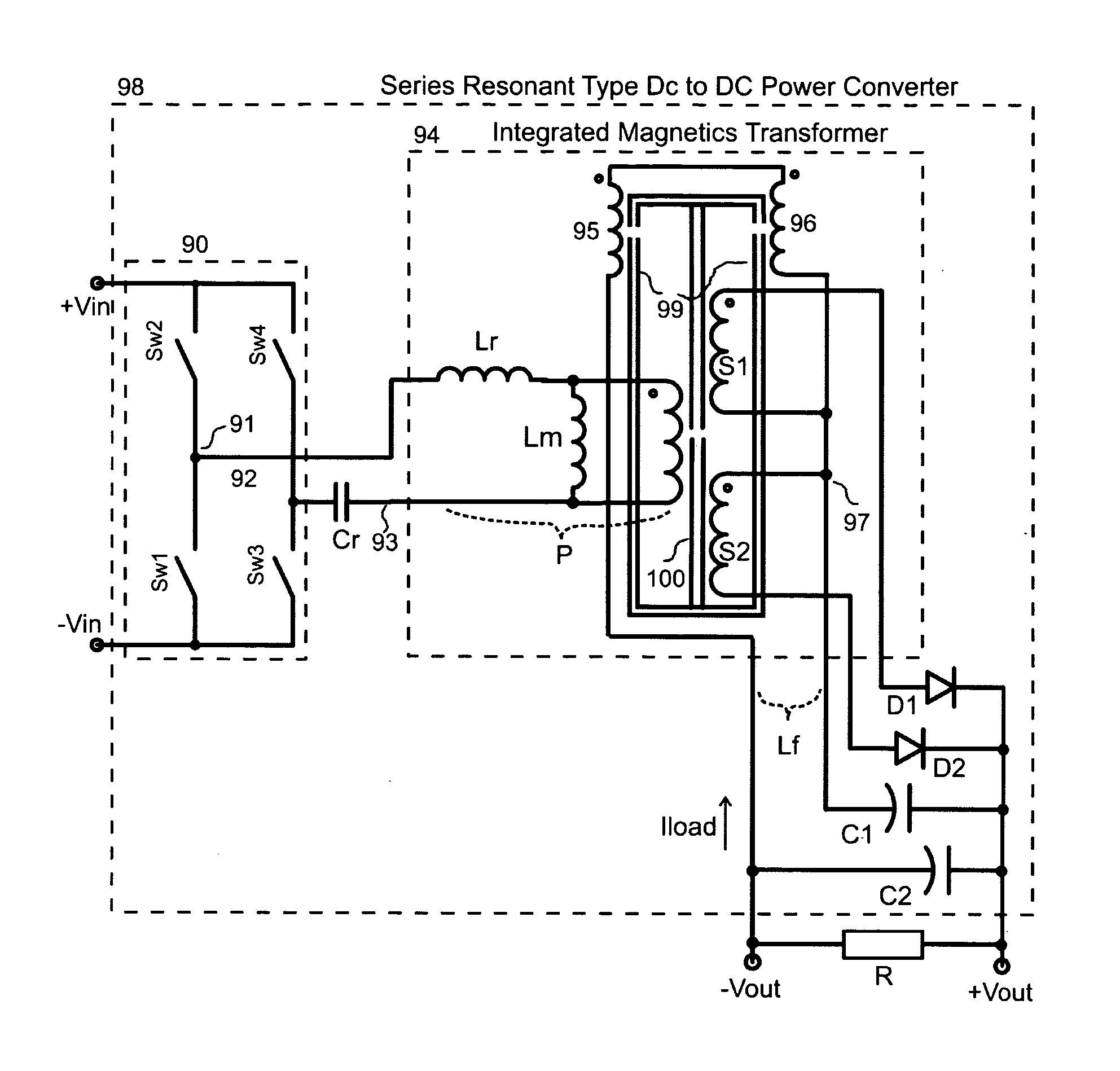

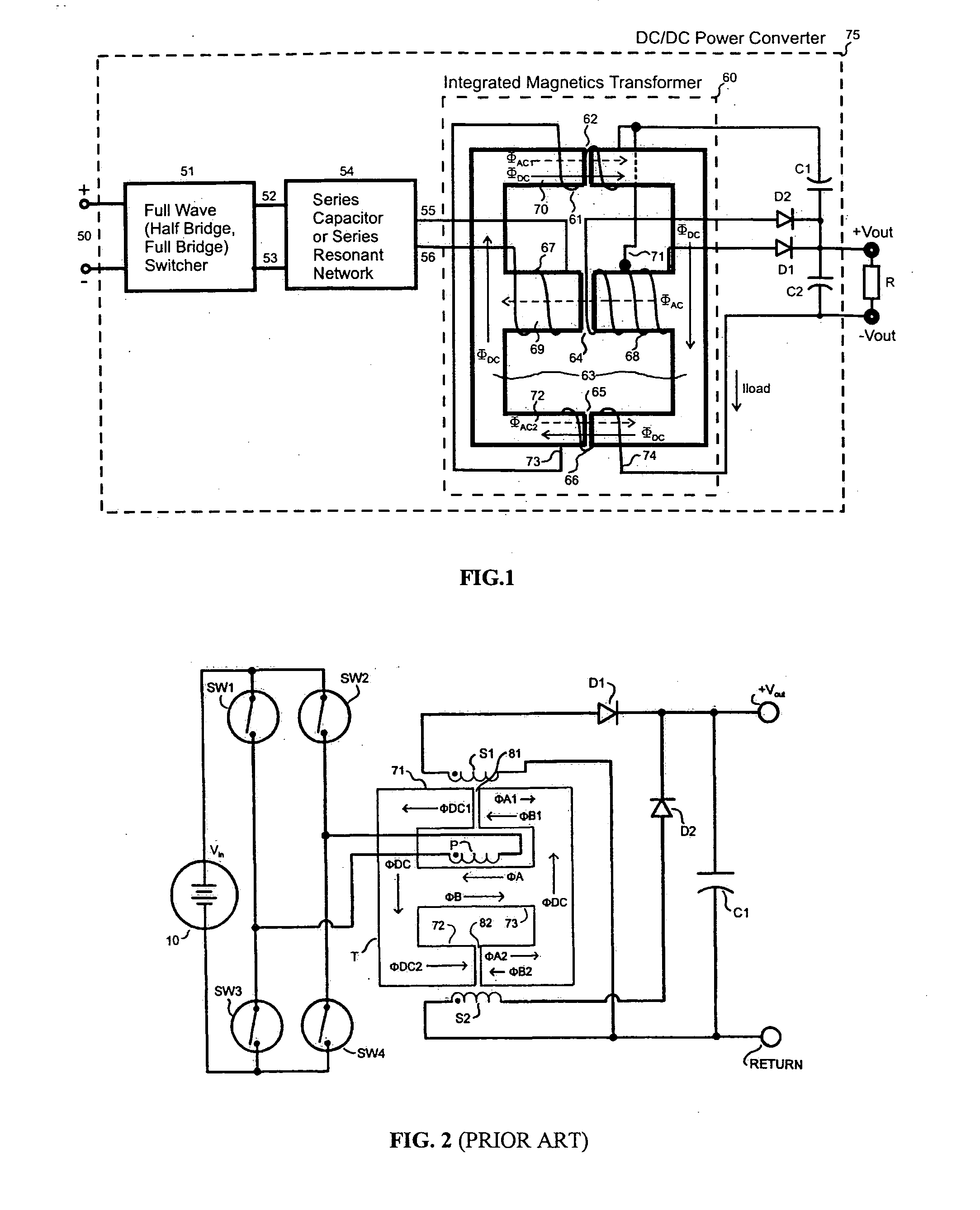

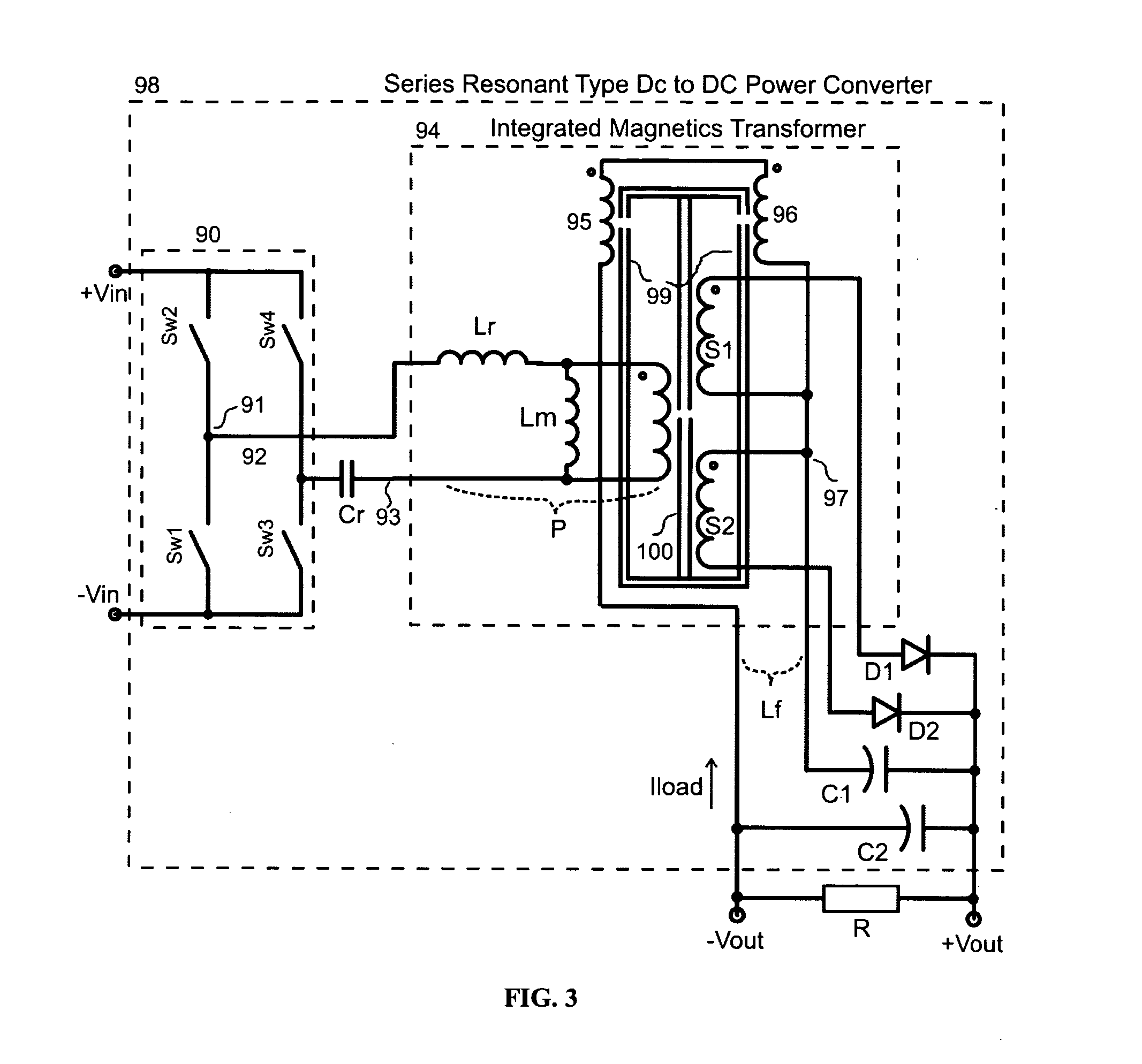

Full wave series resonant type DC to DC power converter with integrated magnetics

ActiveUS20050286270A1Current lossImproved power converter densityAc-dc conversion without reversalTransformersMagnetic coreInductor

A full wave DC / DC converter magnetically integrates into the transformer assembly the functions of the resonant inductor, magnetizing inductor and the output filter inductor. The primary and the secondary windings are assembled on a gapped center leg of an E-core, while two output filter windings with an equal number of turns are assembled on gapped left and gapped opposed side legs of the E-core. The length of the gaps in the side legs is selected so that the DC current does not saturate the side legs. The two filter windings are connected in series and are oppositely polarized so that the voltages induced in these windings by the primary winding flux cancel each other.

Owner:PETKOV ROUMEN D +1

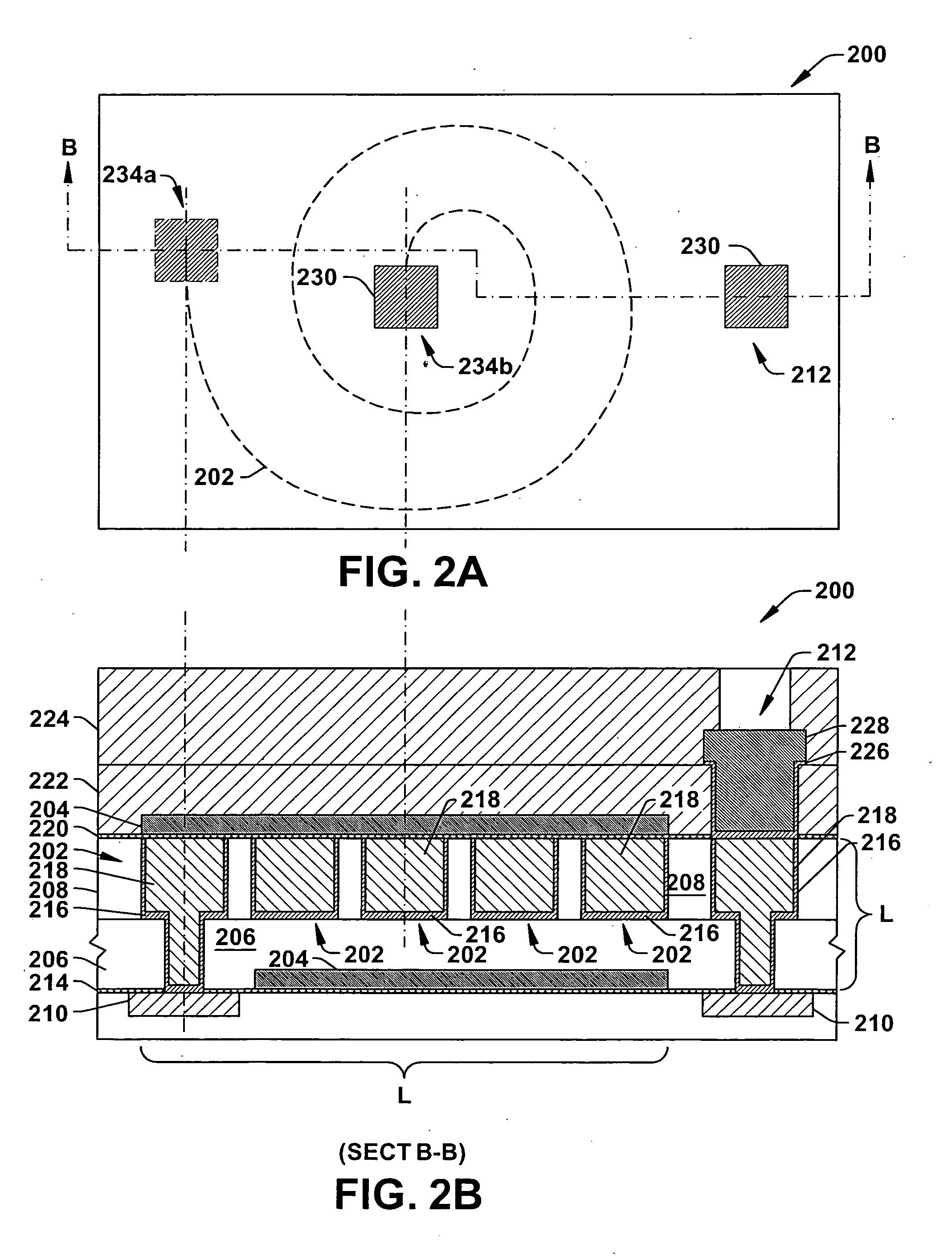

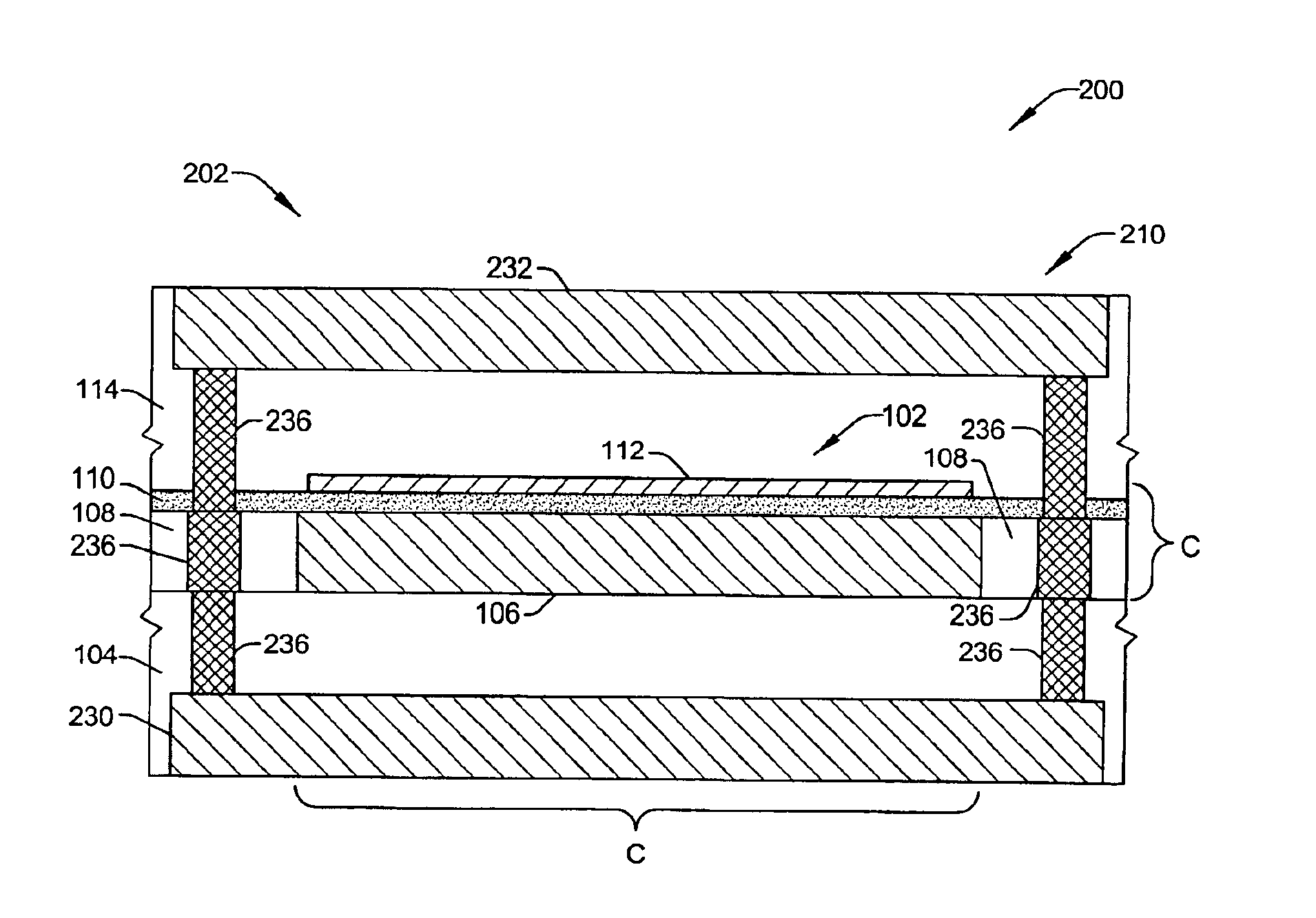

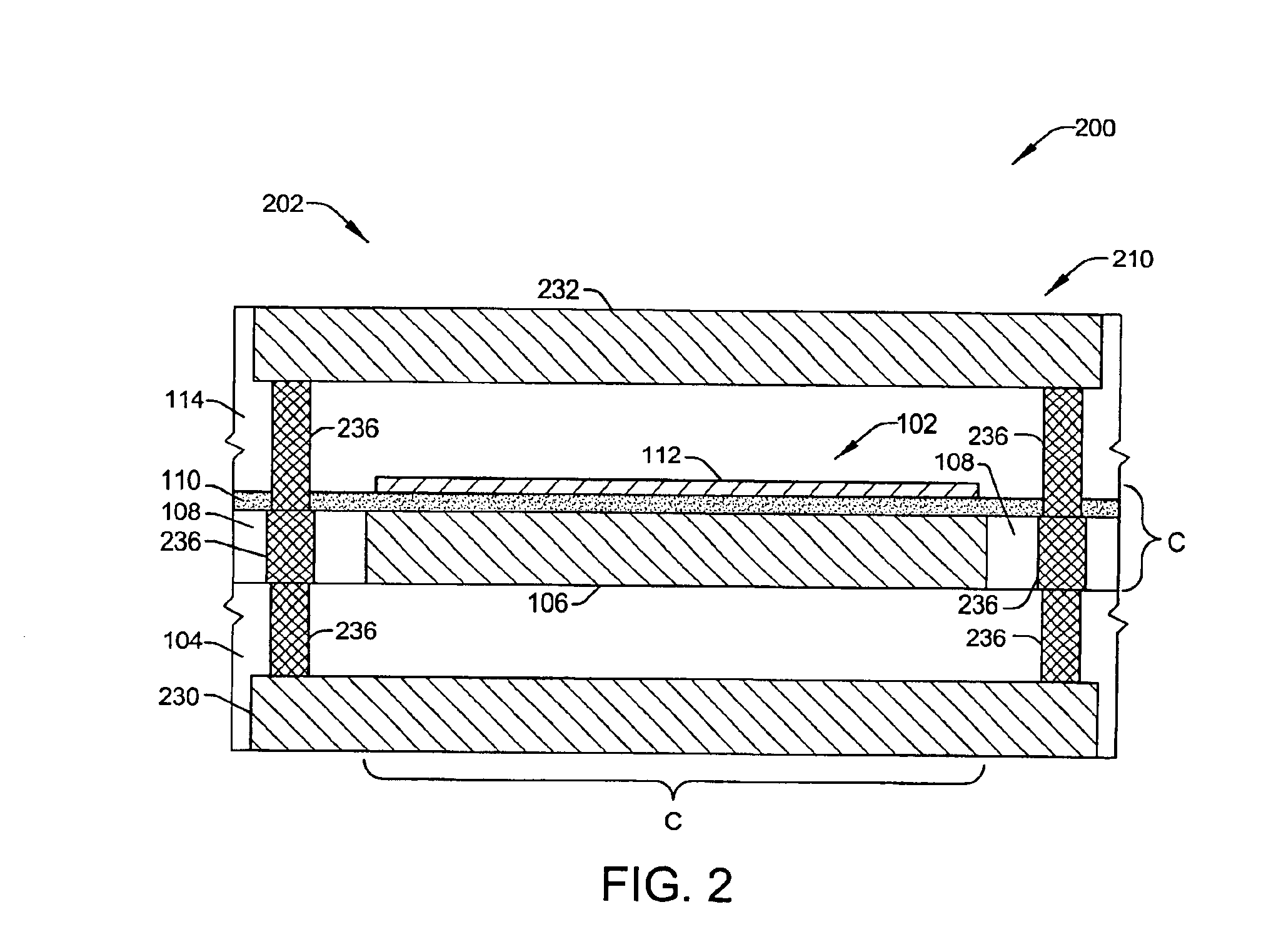

Shielded planar capacitor

ActiveUS6903918B1Mitigate eddy current lossMinimize eddy current lossSemiconductor/solid-state device detailsFixed capacitor dielectricIsolation layerParasitic capacitance

A shielded planar capacitor structure (202) is discussed, formed within a Faraday cage (210) in an integrated circuit device (200). The capacitor structure (202) reduces parasitic capacitances within the integrated circuit device (200). The capacitor (202) comprises a capacitor stack (102) formed between a first and second metal layers (230,232) of the integrated circuit. The capacitor stack (102) has a first conductive layer formed from a third metal layer (106) disposed between the first and second metal layers (230,232) of the integrated circuit, a dielectric isolation layer (110) disposed upon the first conductive layer (106); and a second conductive layer (112) disposed upon the dielectric isolation layer (110) and overlying the first conductive layer (106). The structure (202) further has a first and second isolation layers (104,114) disposed upon opposite sides of the capacitor stack (102). The Faraday cage (210) is formed between the first and second metal layers (230,232) of the integrated circuit (200), comprising a first and second shield layers (402,414) each having a plurality of mutually electrically conductive spaced apart traces (404). The first and second isolation layers (404,414) and the capacitor stack (102,434) are sandwiched between the first and second shield layers (402,414). Conductive elements (432) are distributed around the periphery of the capacitor stack (102,434) and the first and second isolation layers (404,412). The conductive traces (424) of the first shield layer (402) are connected to the conductive traces (424) of the second shield layer (414) through the conductive elements (432).

Owner:TEXAS INSTR INC

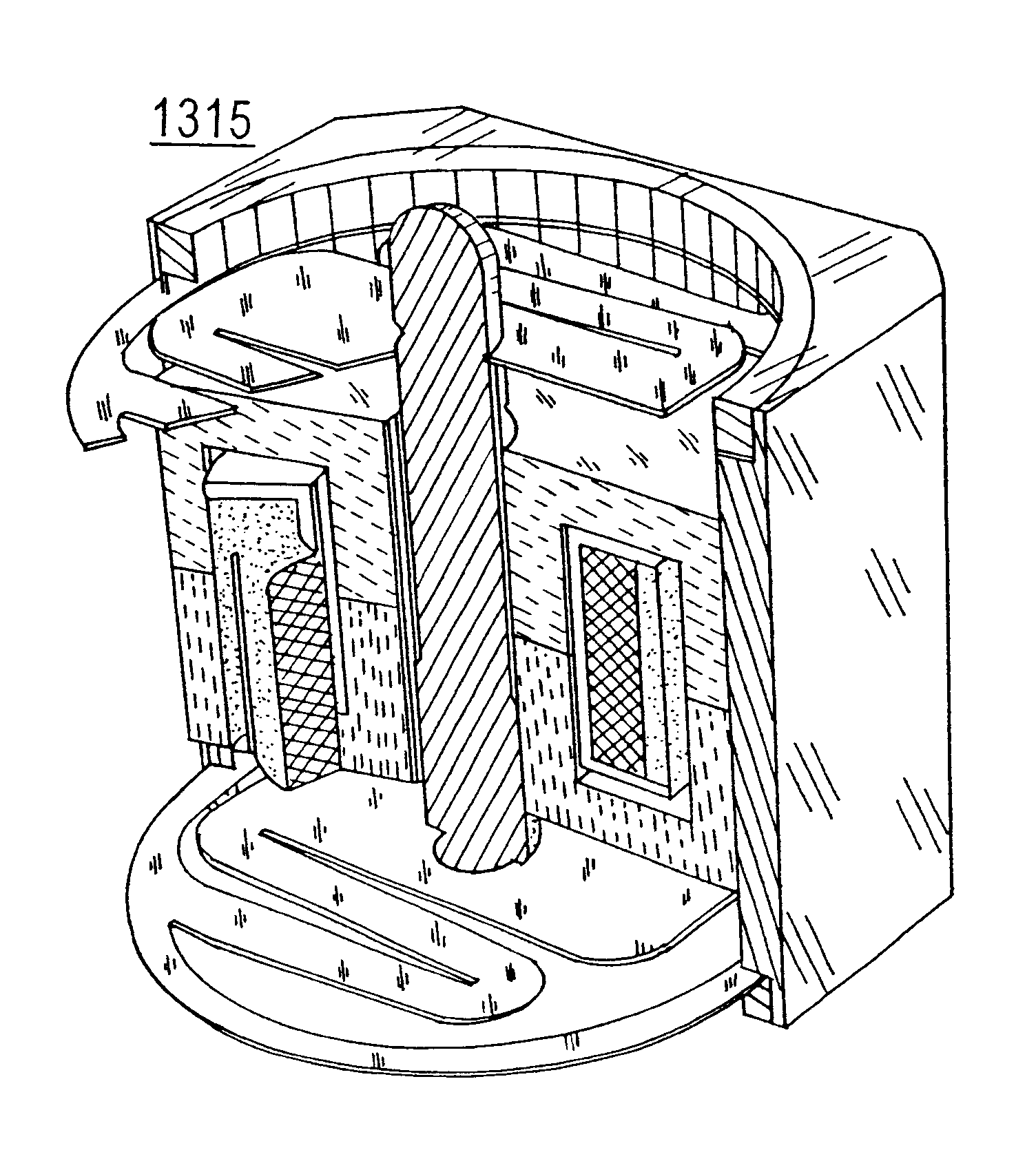

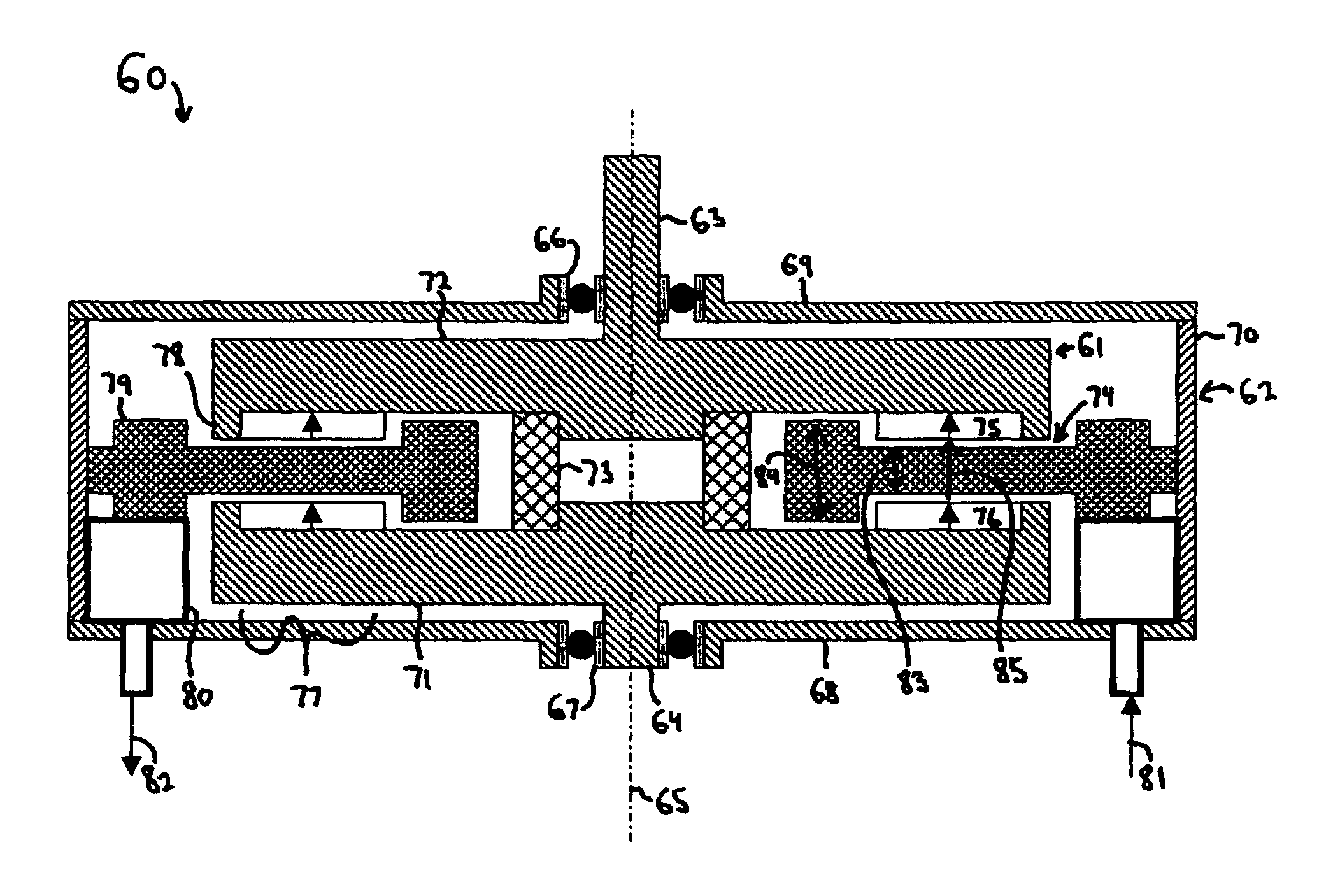

Solenoid cassette pump with servo controlled volume detection

InactiveUS6942469B2Eliminate closure impactEliminate associated noiseAC motor controlElectrical controlResonance measurementDriving current

Servo controlled solenoids provide actuation of a pump piston and valves, and electronic LC resonance measurements to determine liquid volume and gas bubble volume. Third order nonlinear servo control is split into nested control loops: a fast nonlinear first-order inner loop causing flux to track a target by varying a voltage output, and a slower almost linear second-order outer loop causing magnetic gap to track a target by controlling the flux target or the inner loop. The inner loop uses efficient switching regulation, preferably based on controlled feedback instabilities, to control voltage output. The outer loop achieves damping and accurate convergence using proportional, time-integral, and time-derivative gain terms. The time-integral feedback may be based on measured and target solenoid drive currents, adjusting the magnetic gap for force balance at the target current.

Owner:THISTLE ADVISORS

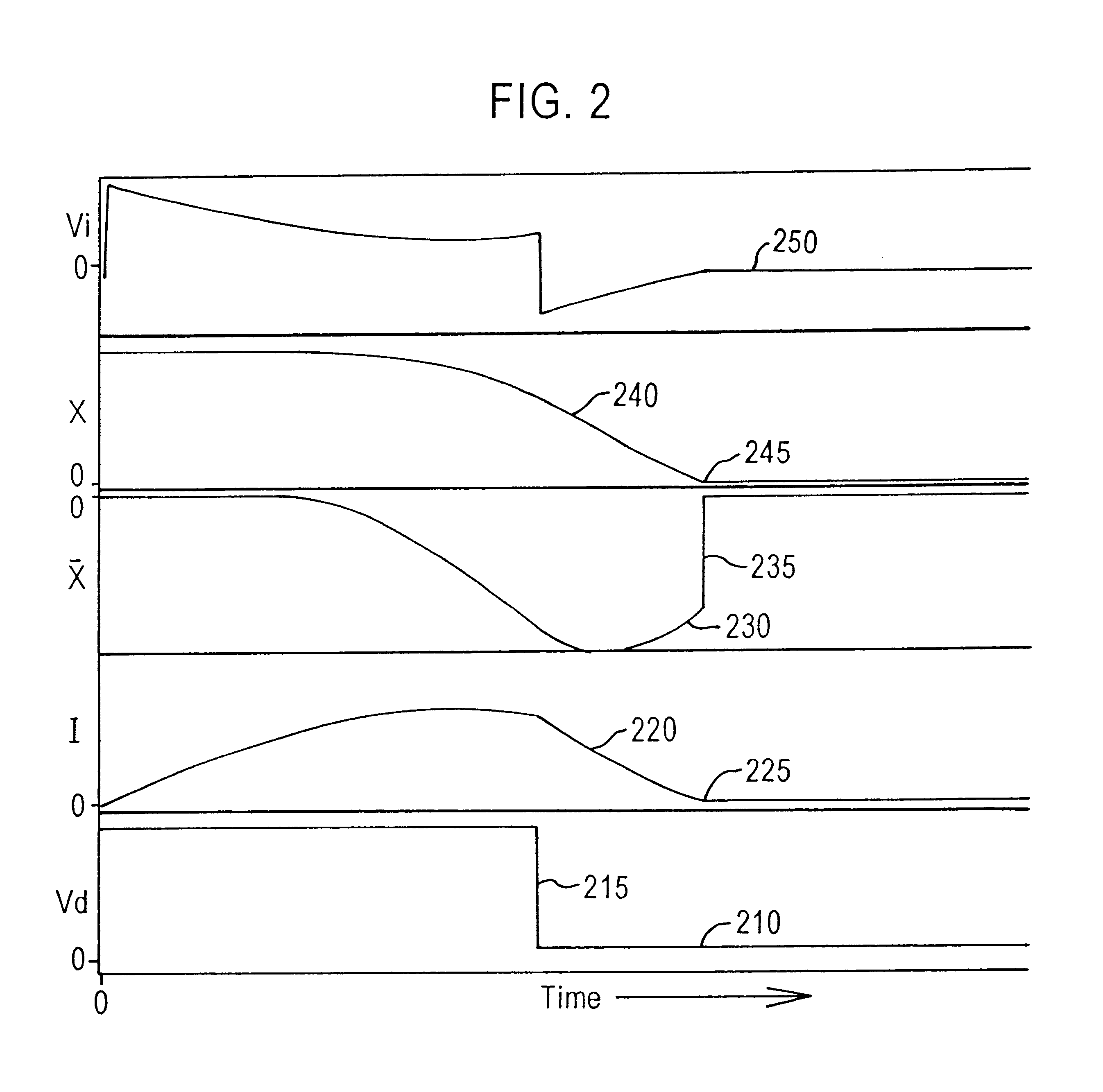

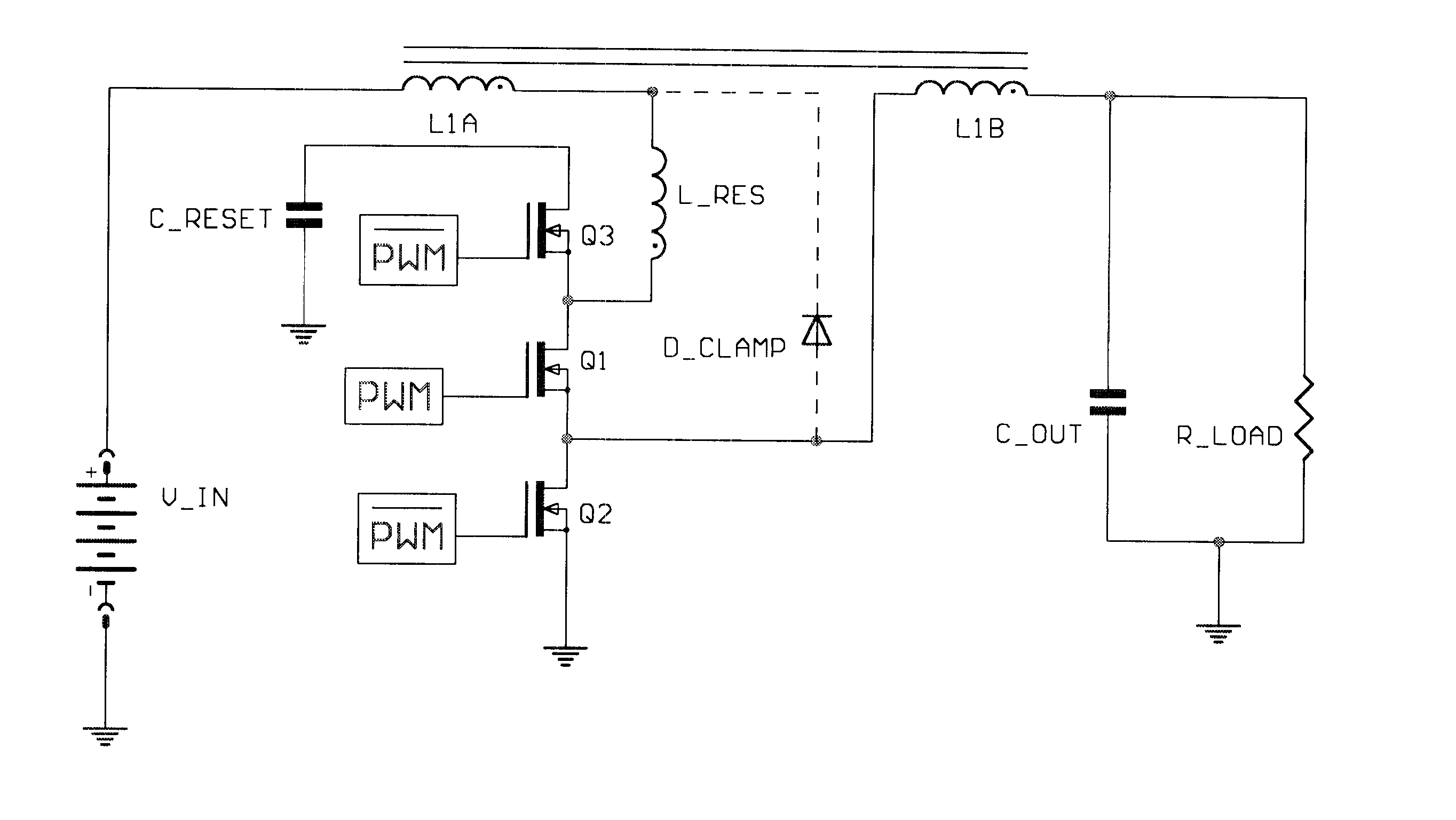

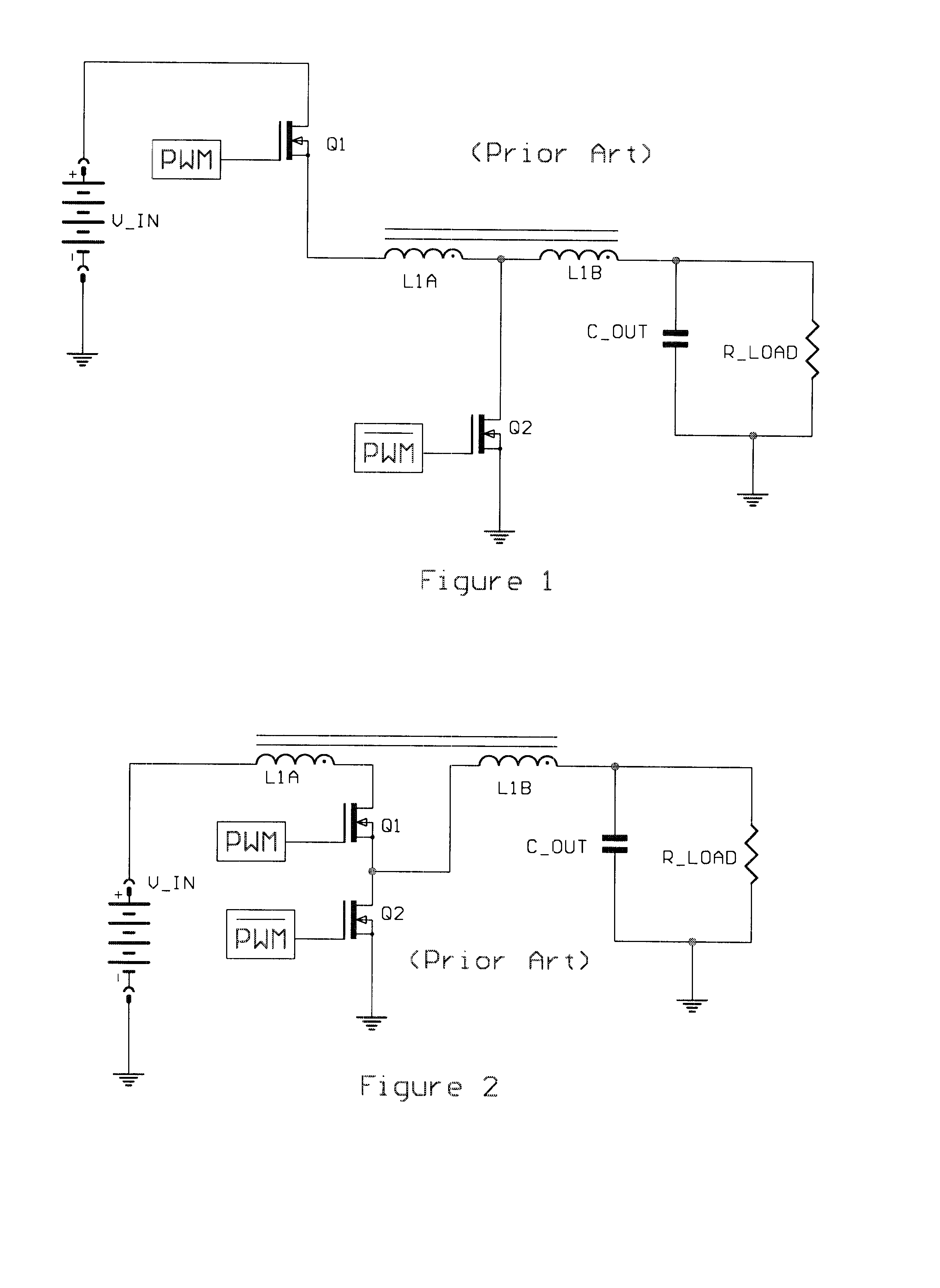

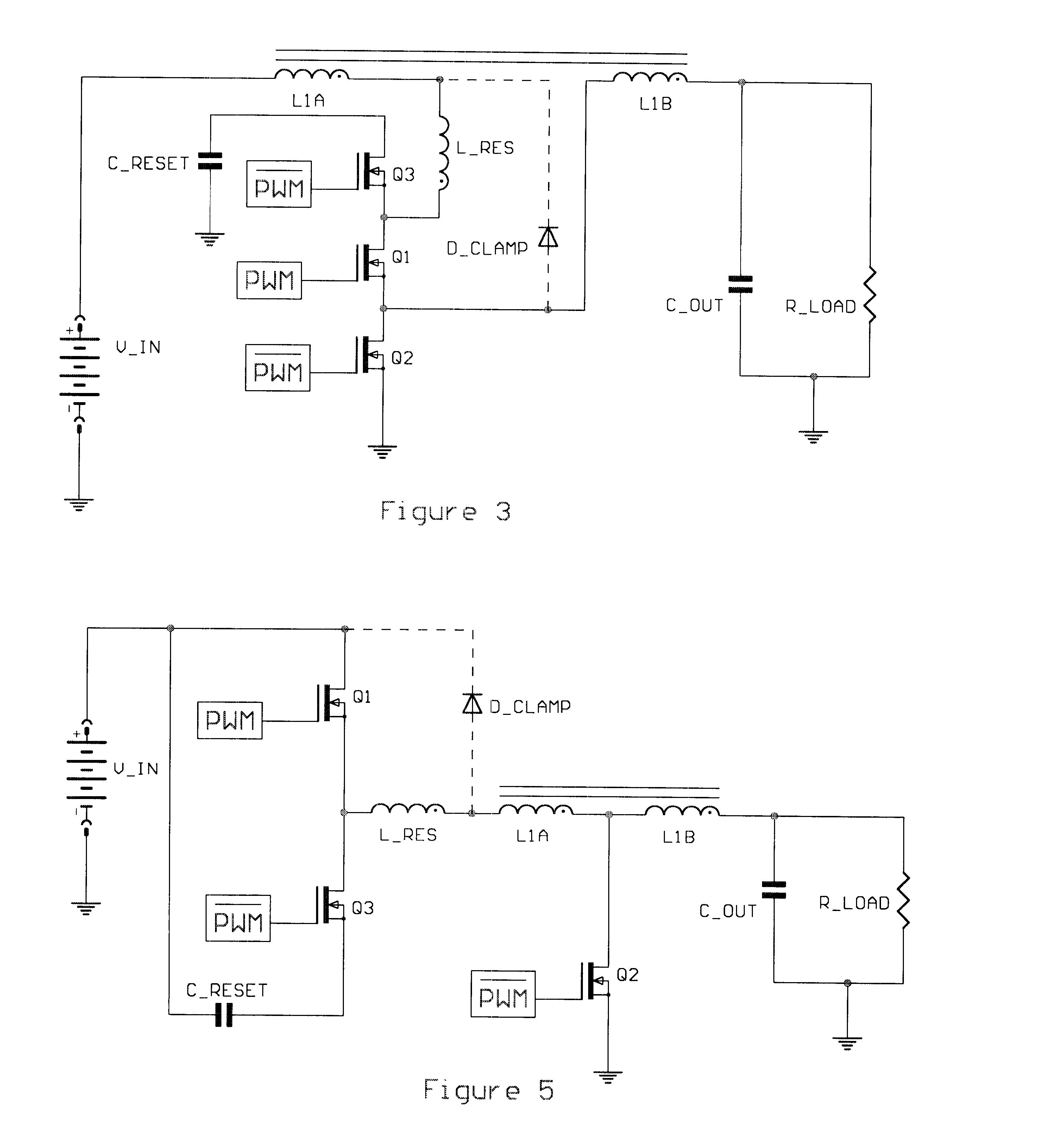

Zero voltage switching power conversion circuits

InactiveUS6462963B1Optimal switch timingCurrent lossEfficient power electronics conversionAc-dc conversionBuck converterEnergy source

A tapped inductor buck converter which achieves zero voltage switching and continuous input and output terminal currents is revealed. To achieve these results an additional switch, a small inductor, and a capacitor are required. The small inductor serves as a source of energy for driving the critical turn on transition of the main switch and the same small inductor also serves as a filter component for smoothing the input and output terminal currents. Simple adaptive gate drive circuits are revealed that improve the timing for turn on of zero voltage switches and reduce gate drive losses. A synchronous rectifier self drive mechanism is revealed which is universally applicable to zero voltage switching power converters with a single main switch which rely on an auxiliary inductor to drive the critical turn on transition of the single main switch. The wave form generated by the auxiliary inductor is ideally suited to synchronous rectifier self drive. Finally, peak current sensing techniques are revealed which are universally applicable to zero voltage switching power converters with a single main switch and an auxiliary switch which rely on an auxiliary inductor to drive the critical turn on transition of the single main switch. The current sensing techniques sense a winding voltage of the auxiliary inductor during the on time of the auxiliary switch. The winding voltage is directly related to the peak current in the main winding of the auxiliary inductor and the peak current in the single main switch of the power converter. The novel current sensing techniques are low noise, reliable, and lossless.

Owner:TECHN WITTS

Linear oscillator

InactiveUS6958553B2Reduce vibrationLittle noiseMechanical energy handlingMetal working apparatusResonanceReciprocating motion

Owner:HEWLETT PACKARD DEV CO LP

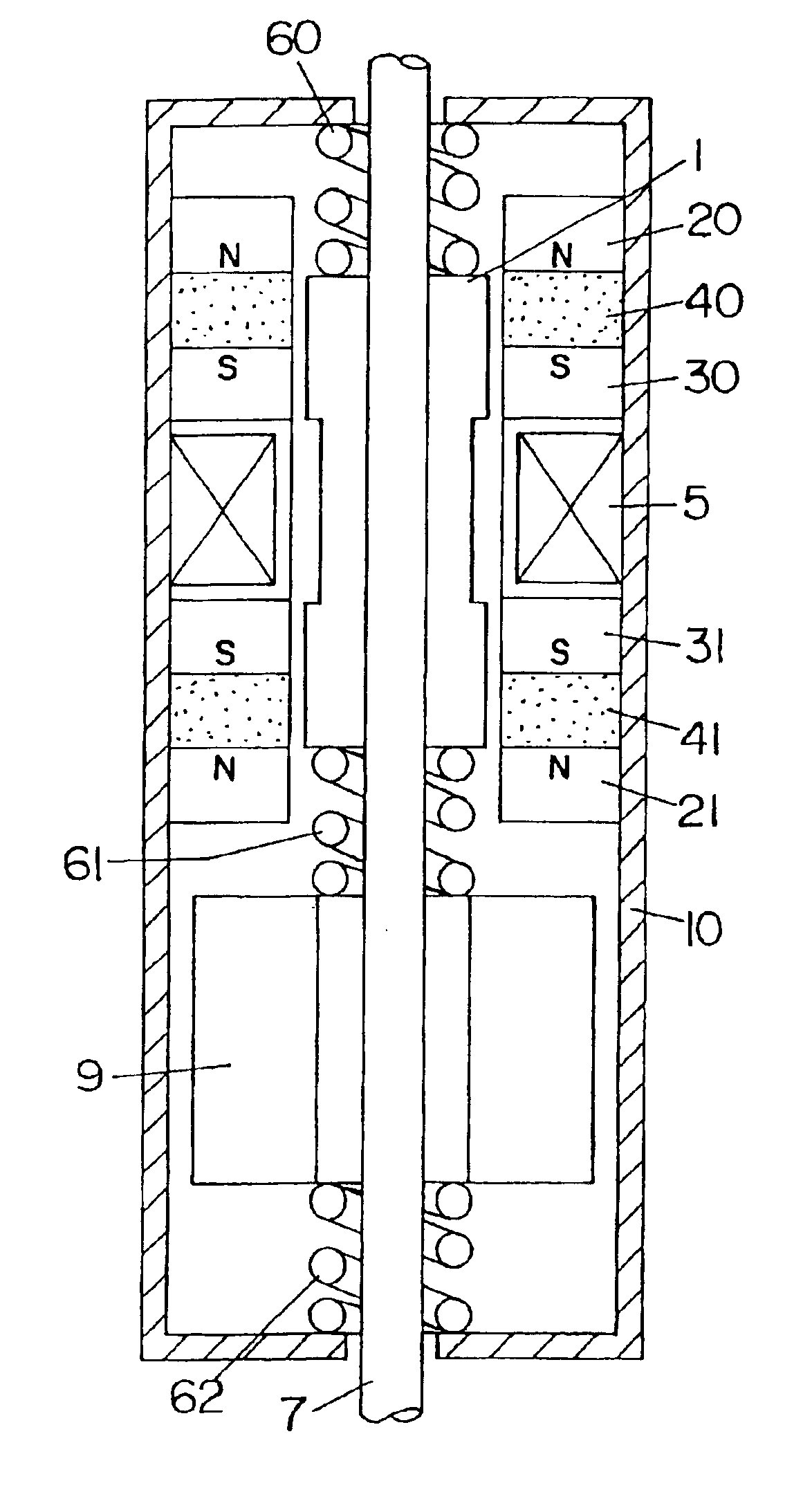

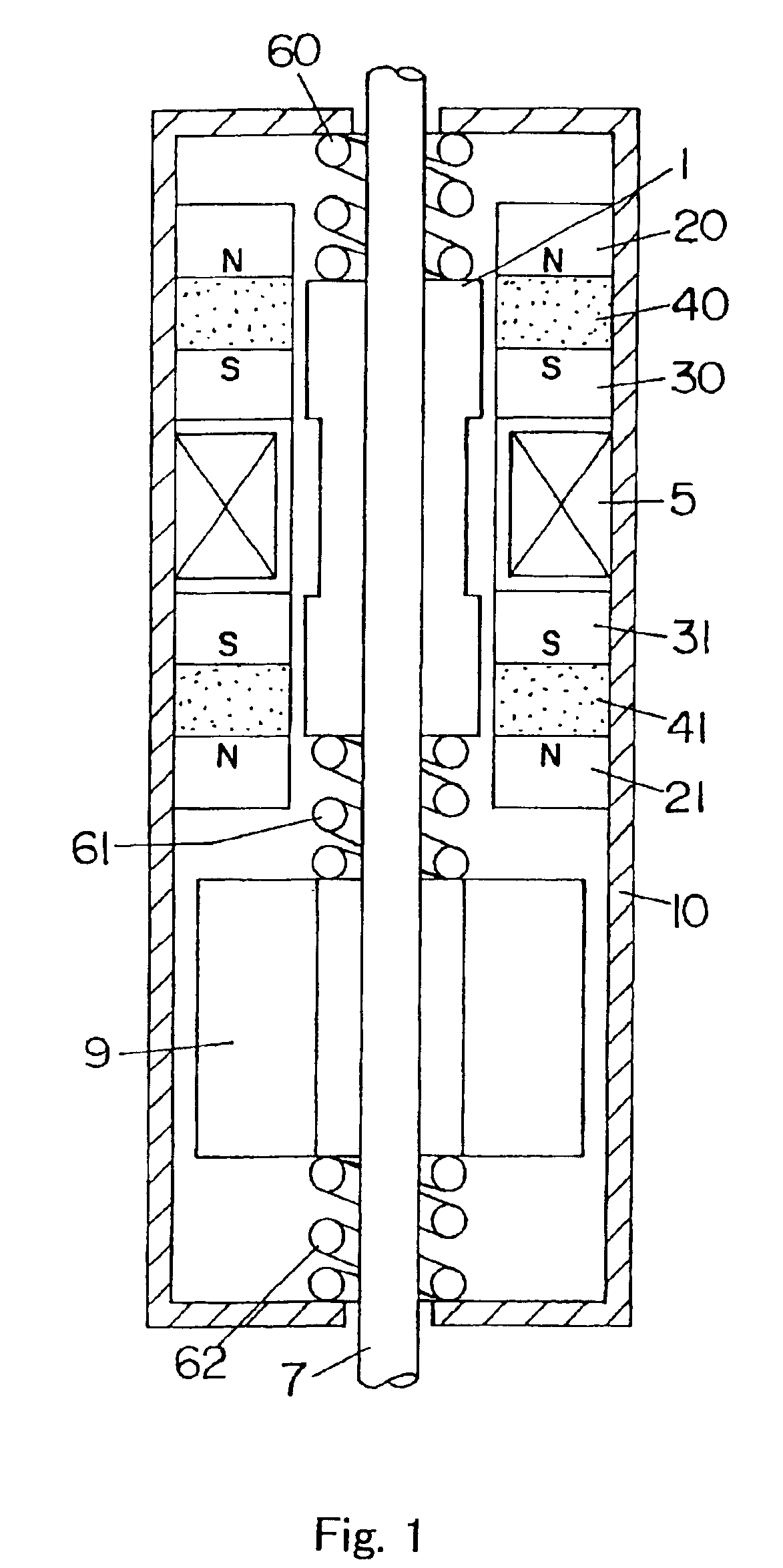

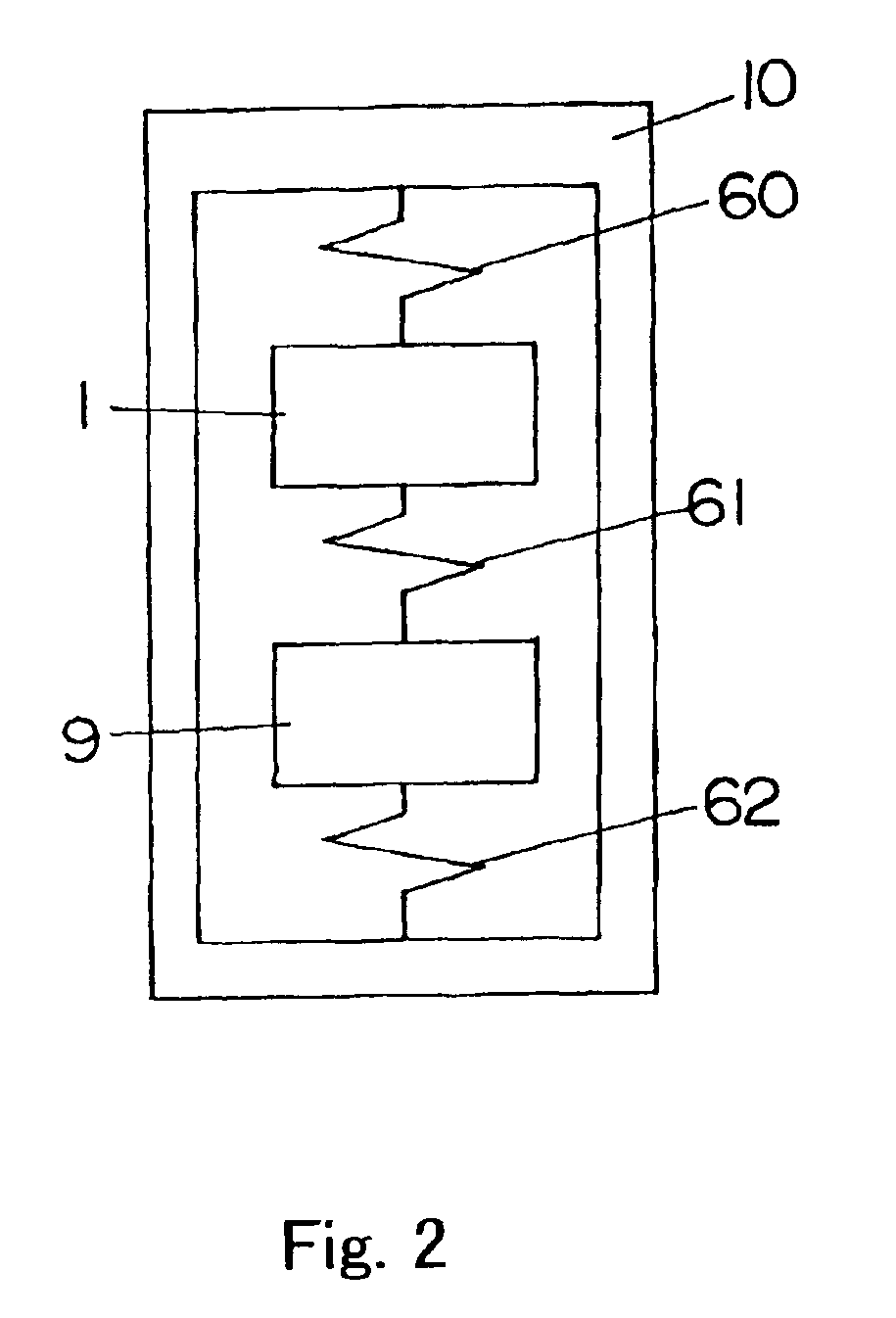

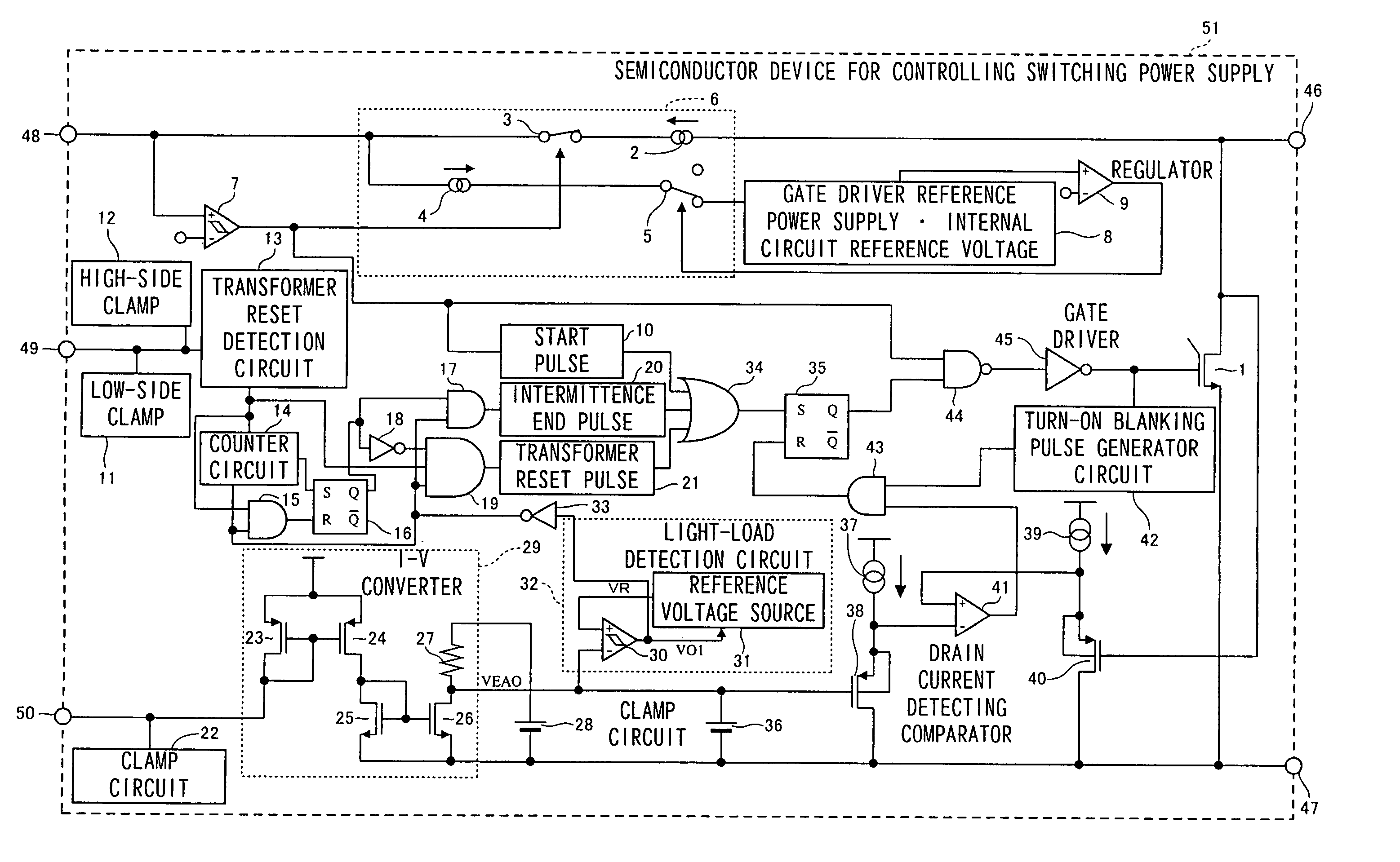

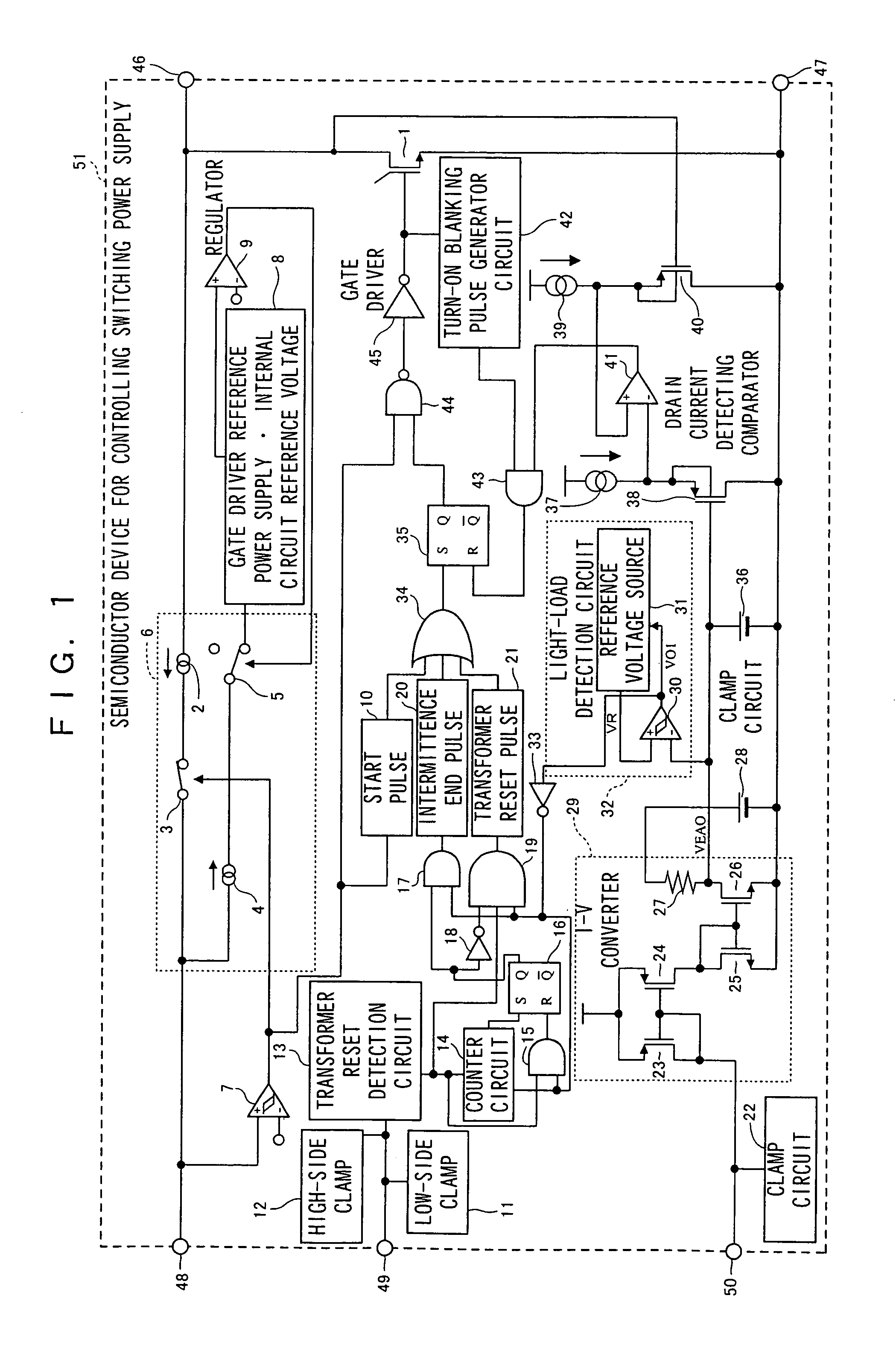

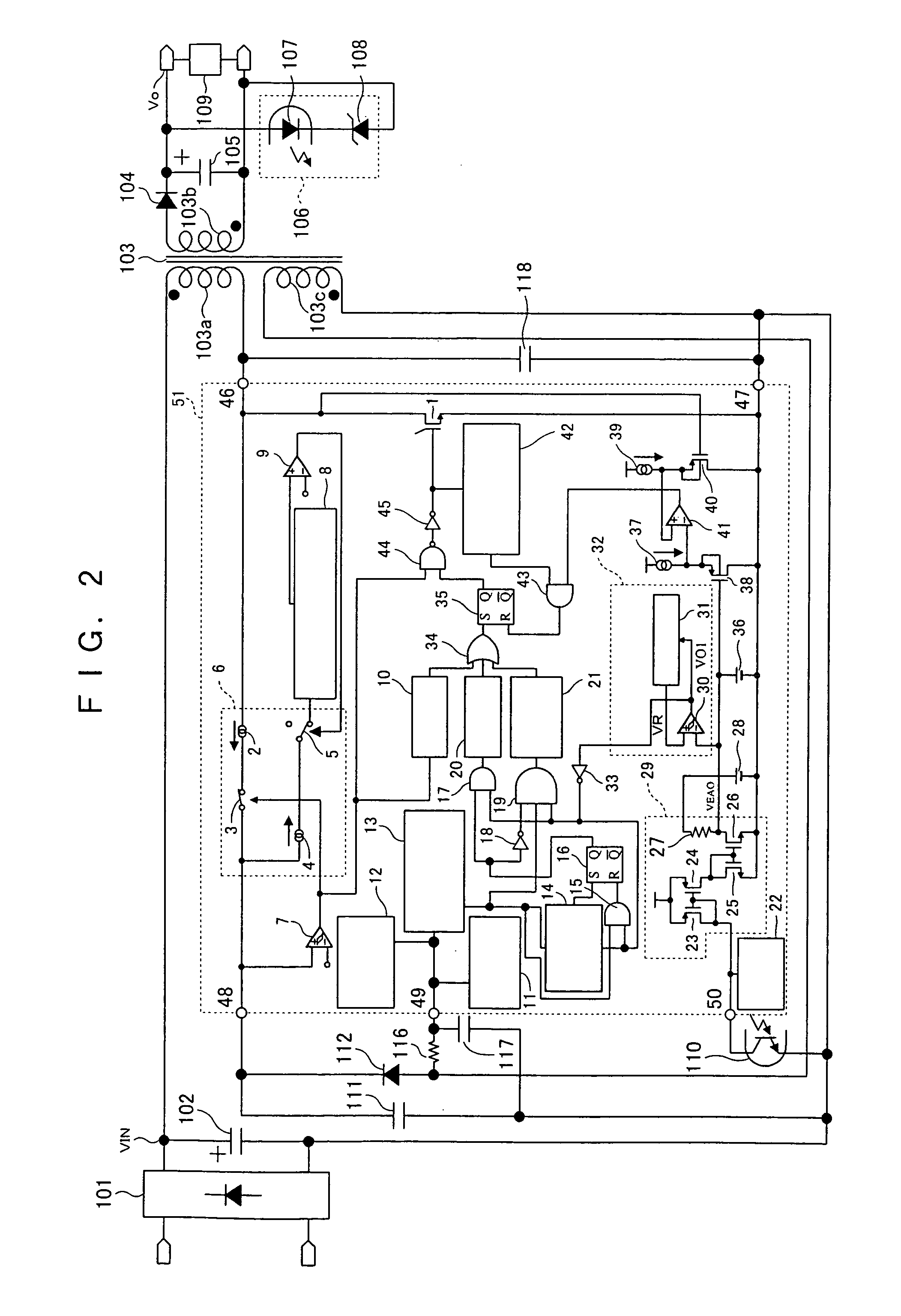

Semiconductor device for controlling switching power supply

InactiveUS7075802B2Light lossReduce power consumptionEfficient power electronics conversionApparatus with intermediate ac conversionTransformerEngineering

A semiconductor device (51) for controlling a switching power supply, includes a switching element (1) and a switching control circuit. During an intermittent switching operation of the switching element (1), when a return signal is outputted from a light load detection circuit (32) before the counting of a counter circuit (14), the switching operation of the switching element (1) is restarted at the timing of a transformer reset signal from a transformer reset detection circuit (13) after the return signal is outputted. When the return signal is outputted from the light load detection circuit (32) after the counting of the counter circuit (14), the switching operation of the switching element (1) is restarted, regardless of the transformer reset signal, only when the return signal is outputted.

Owner:PANASONIC CORP

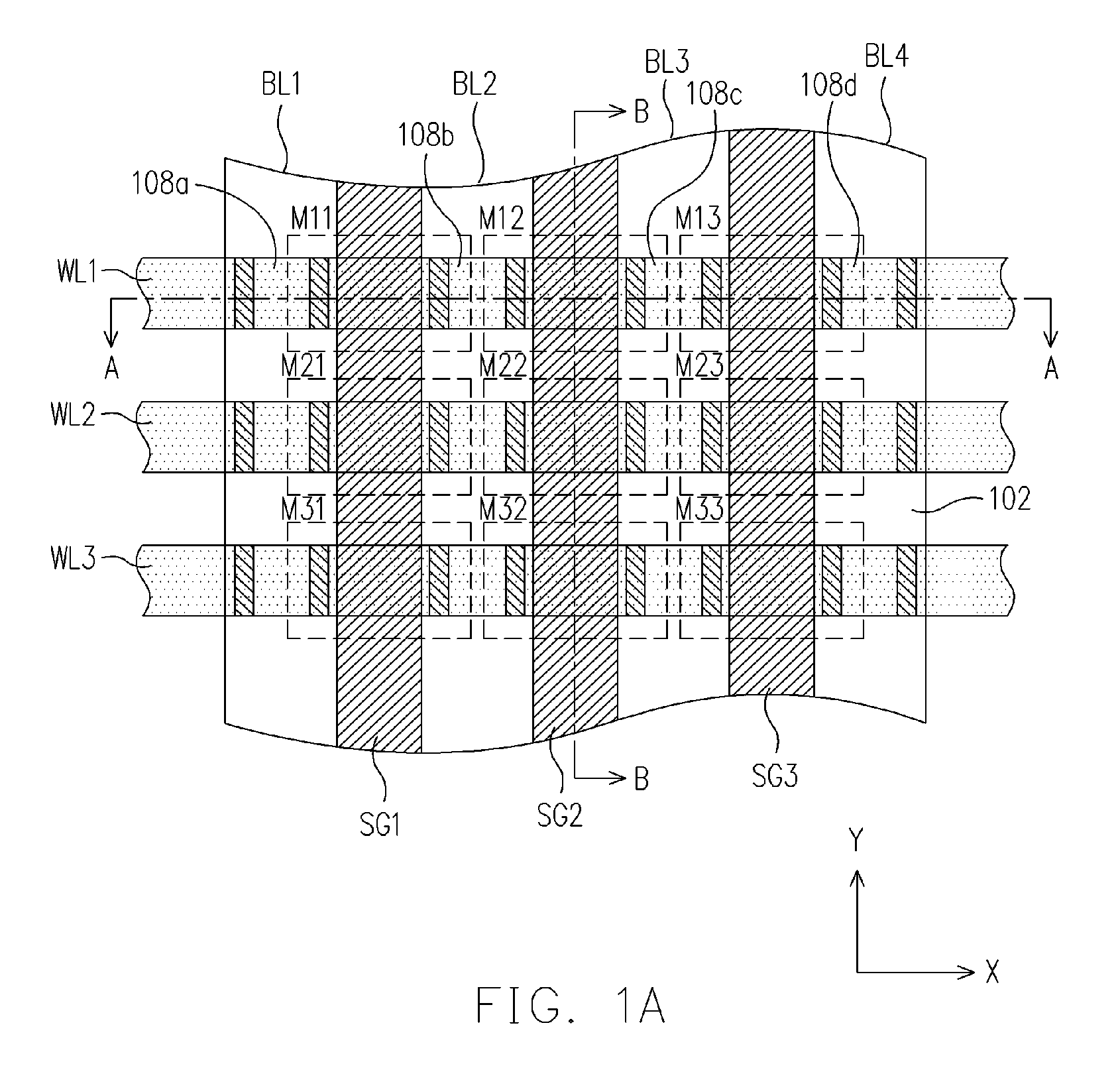

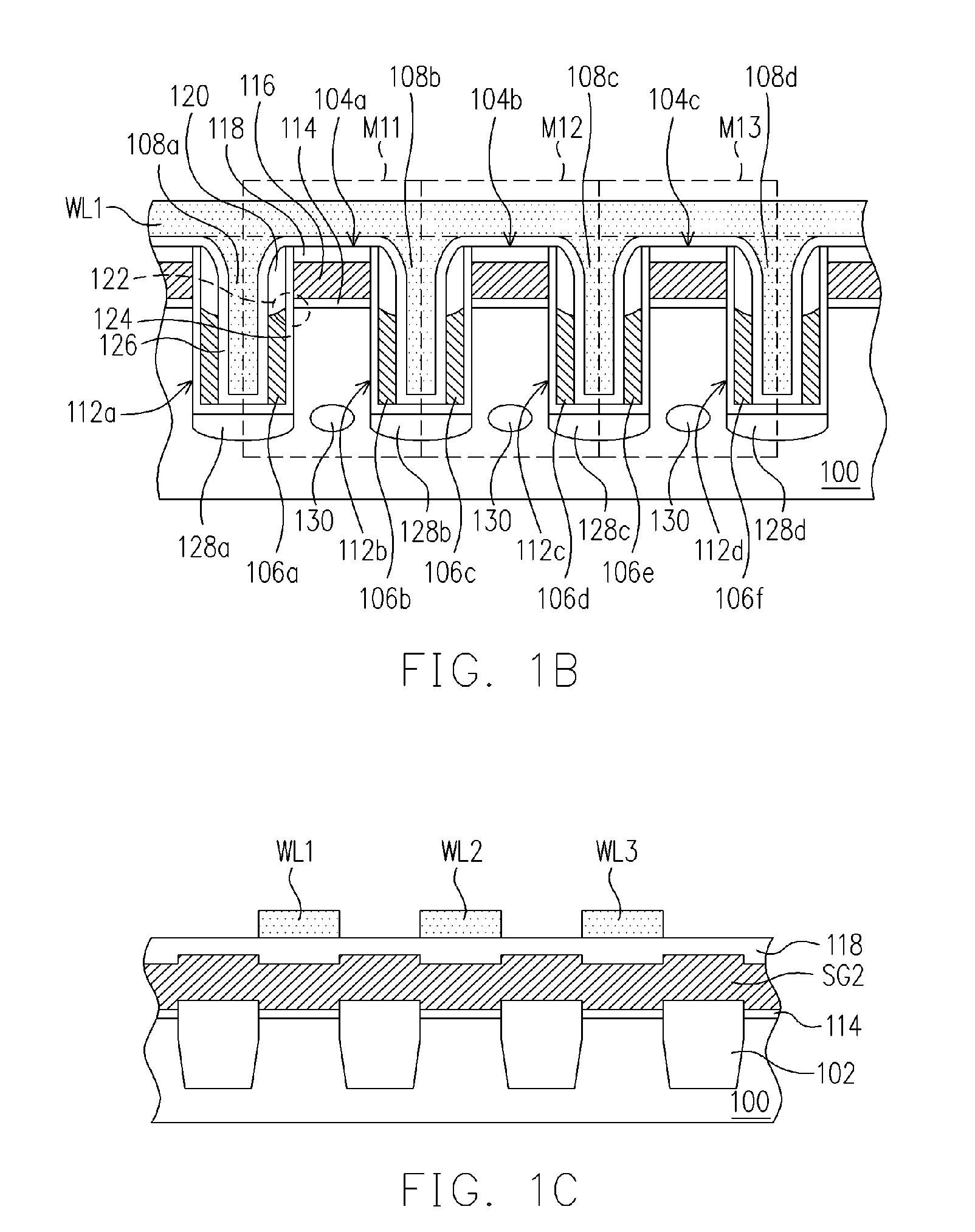

Non-volatile memory, manufacturing and operating method thereof

InactiveUS20060291281A1Total current dropHigh speedSolid-state devicesRead-only memoriesEngineeringNon-volatile memory

A non-volatile memory having a substrate, a select gate, a pair of charge storage layers, a pair of source / drain regions and a control gate is provided. At least a pair of trenches are formed in the substrate. The select gate is formed on the substrate between the pair of trenches. A pair of charge storage layers is formed on the sidewalls of the trenches next to the select gate. A pair of source / drain regions is formed in the substrate at the bottom of the trenches. The control gate is formed on the substrate to fill the trenches completely.

Owner:POWERCHIP SEMICON CORP

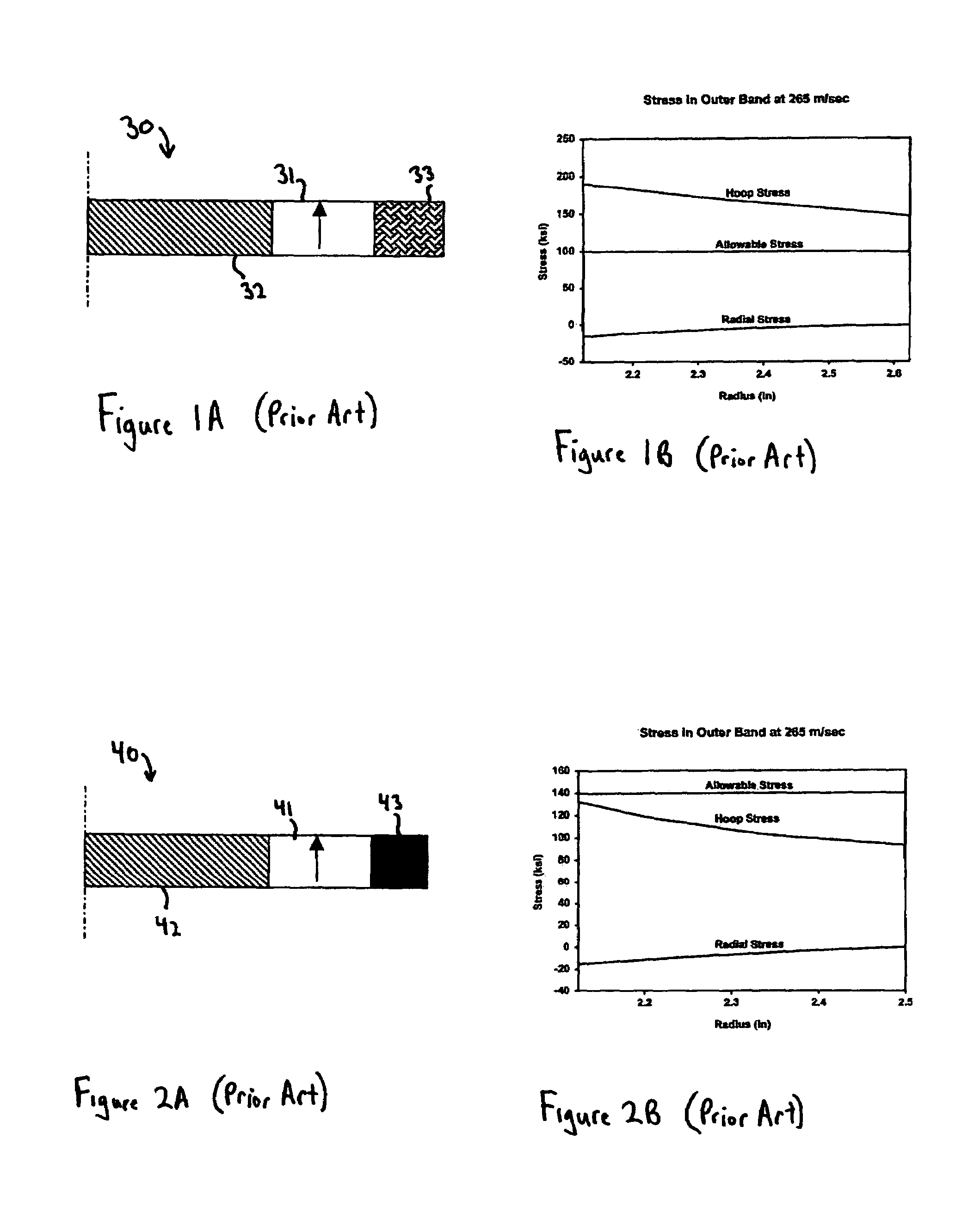

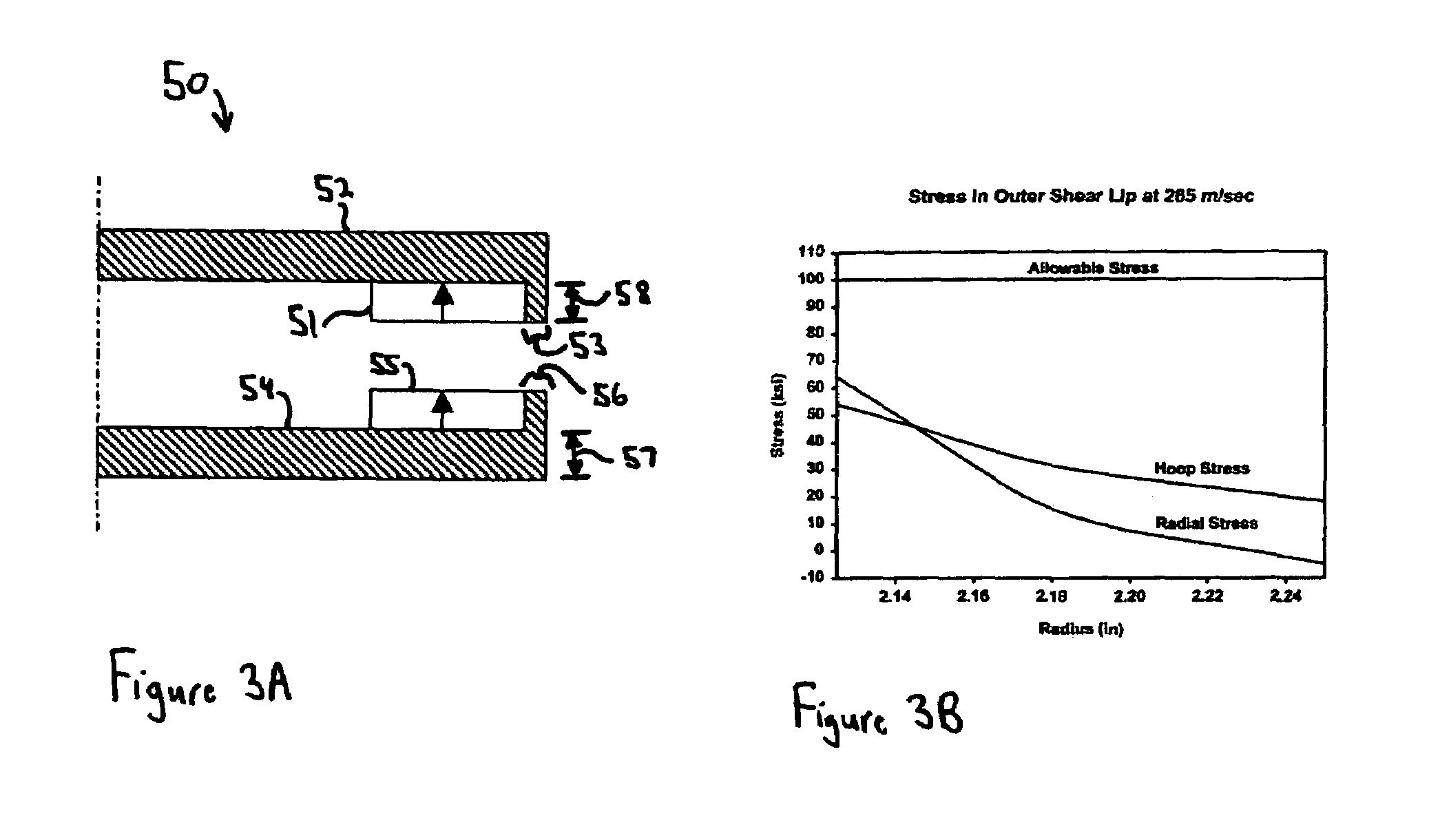

Low cost high speed electrical machine

InactiveUS7084548B1Improve power densityReduce construction costsWindingsMagnetic circuit rotating partsAir coreConductor Coil

A high speed brushless axial gap air core electrical machine includes a rotor mounted for rotation about an axis, and a stationary stator that magnetically interacts with the rotor. The rotor has two discs that are axially spaced apart to form an armature airgap. A stationary air core armature, with windings made of multiple individually insulated strand conductor wire for providing energy conversion, is located in the armature airgap. At least one of the discs carries a circumferential array of multiple alternating axial polarity permanent magnet poles facing the armature airgap. The magnets drive magnetic flux circumferentially through ferromagnetic portions of the discs and axially through the armature airgap. The discs have an integral axially extending circumferentially continuous lip outside of the array of magnet poles. The lip has a integral shear connection with the disc that substantially reduces the hoop stress in the lip that would otherwise occur from the radial containment of the magnet poles when rotated to high speed.

Owner:REVOLUTION ELECTRIC MOTOR

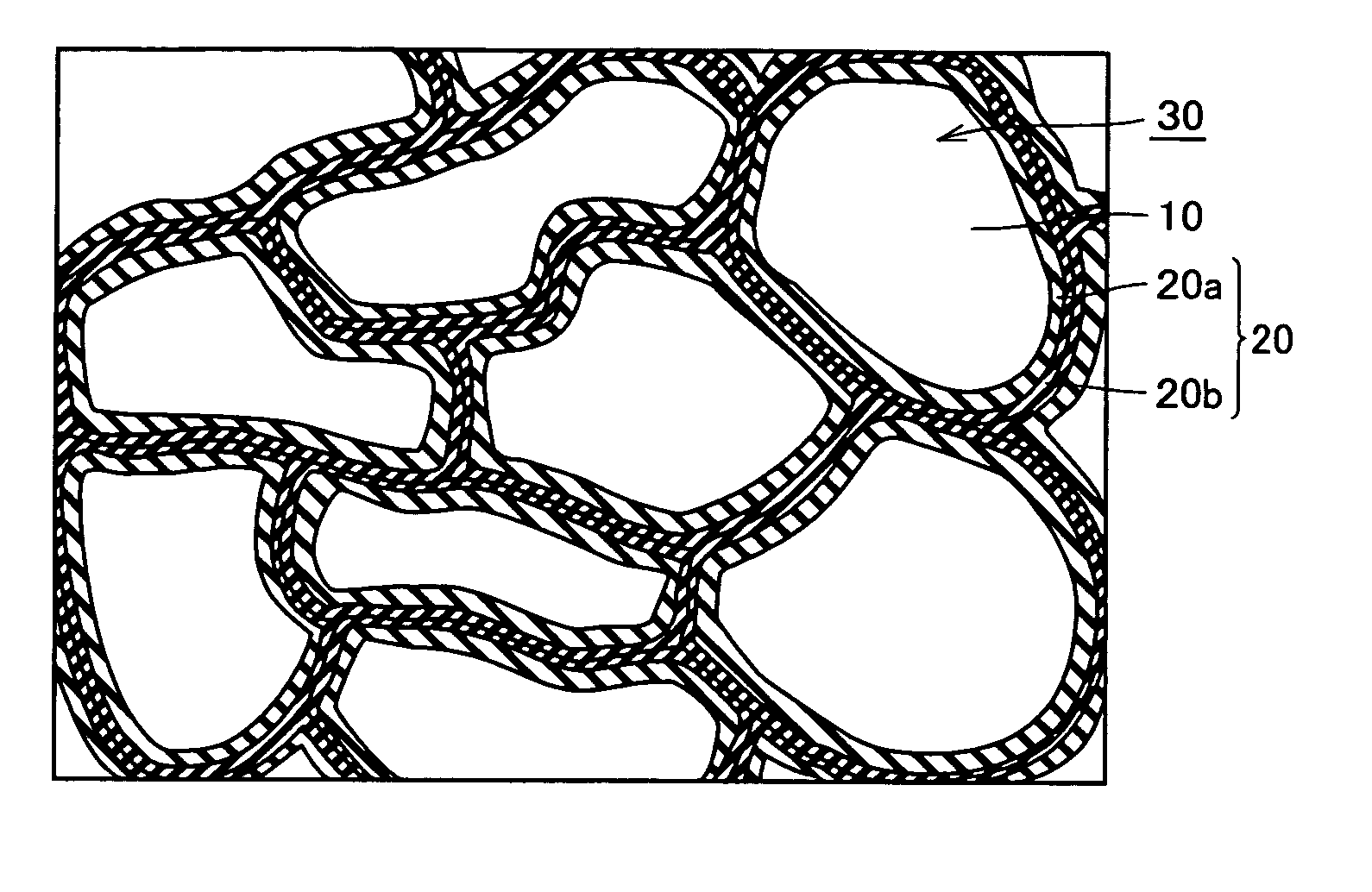

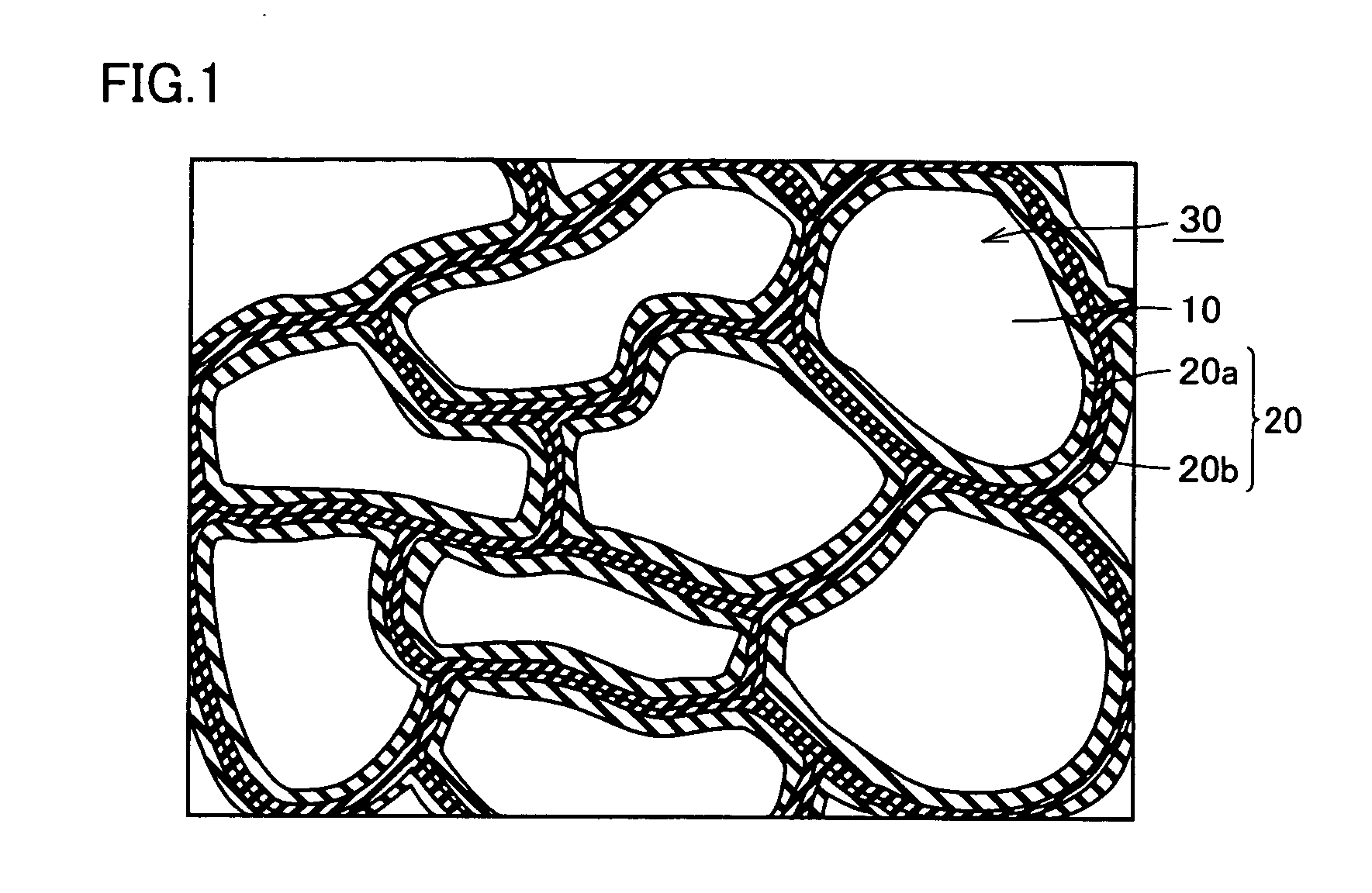

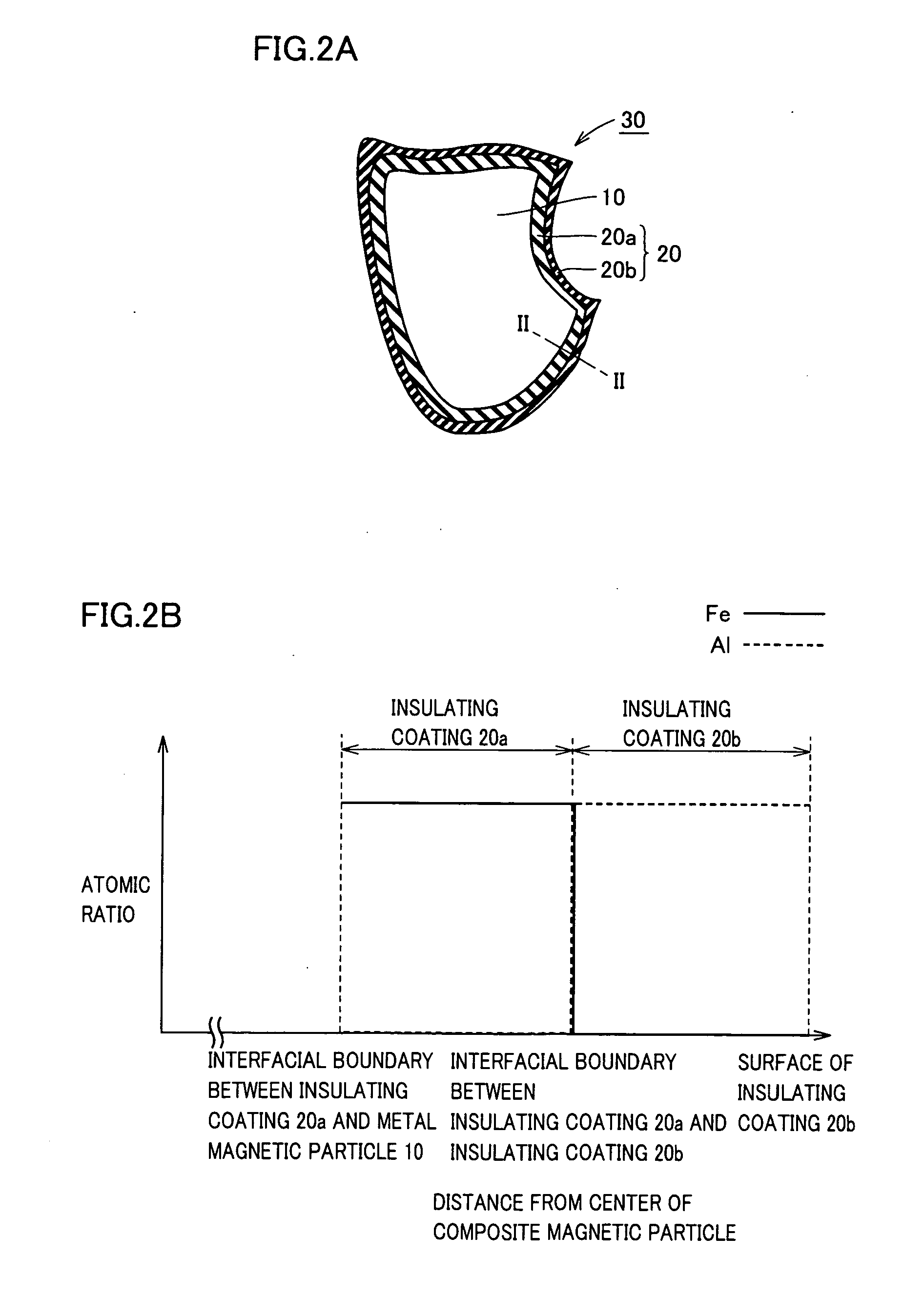

Soft Magnetic Material, Powder Magnetic Core and Method of Manufacturing Soft Magnetic Material

ActiveUS20070235109A1Increase currentImprove heat resistanceMetal-working apparatusInorganic material magnetismPhosphoric acidMagnetic core

A soft magnetic material is a soft magnetic material including a composite magnetic particle (30) having a metal magnetic particle (10) mainly composed of Fe and an insulating coating (20) covering metal magnetic particle (10), and insulating coating (20) contains an iron phosphate compound and an aluminum phosphate compound. The atomic ratio of Fe contained in a contact surface of insulating coating (20) in contact with metal magnetic particle (10) is larger than the atomic ratio of Fe contained in the surface of insulating coating (20). The atomic ratio of Al contained in the contact surface of insulating coating (20) in contact with metal magnetic particle (10) is smaller than the atomic ratio of Al contained in the surface of insulating coating (20). Thus, iron loss can be reduced.

Owner:SUMITOMO ELECTRIC IND LTD +1

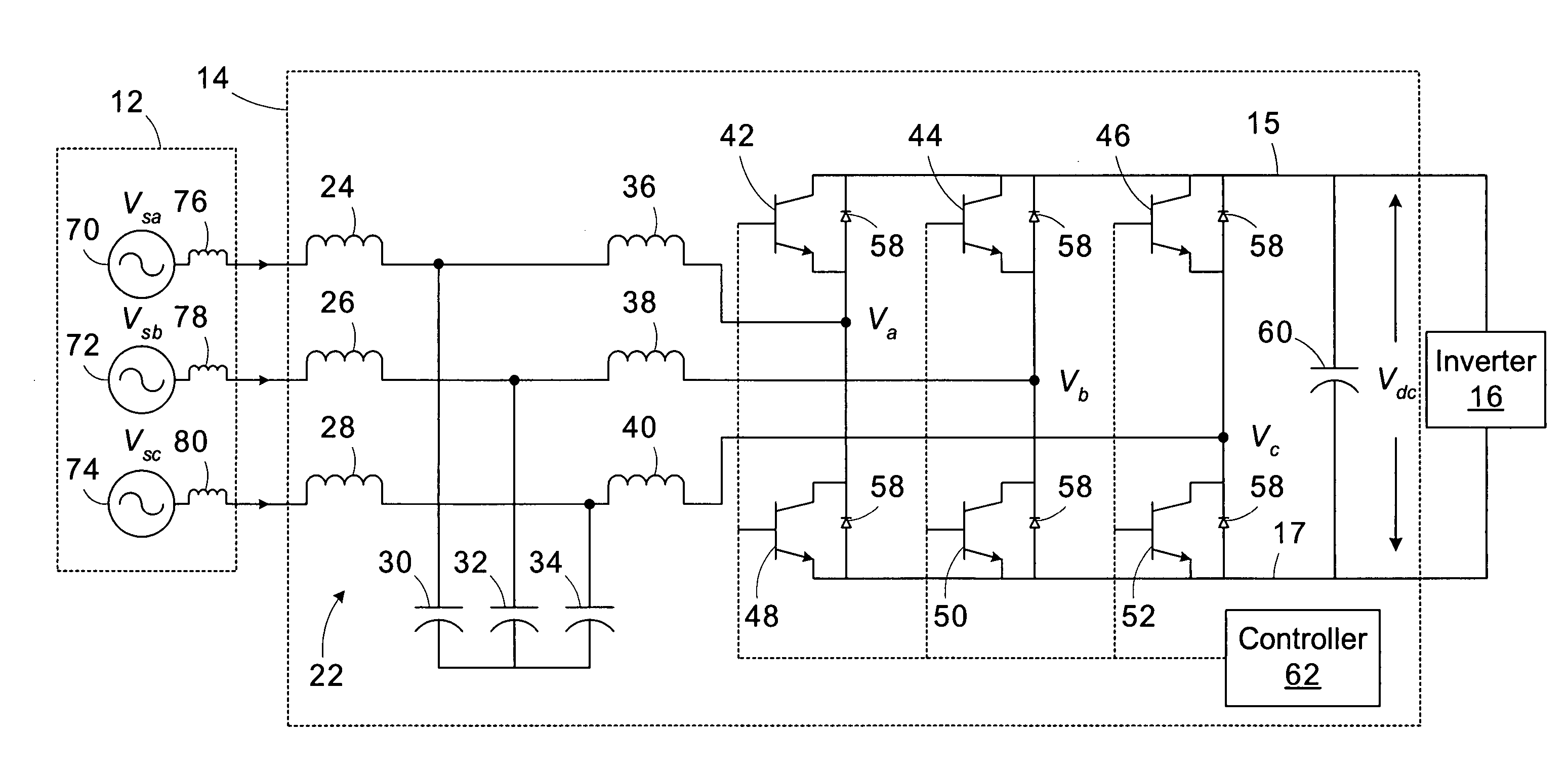

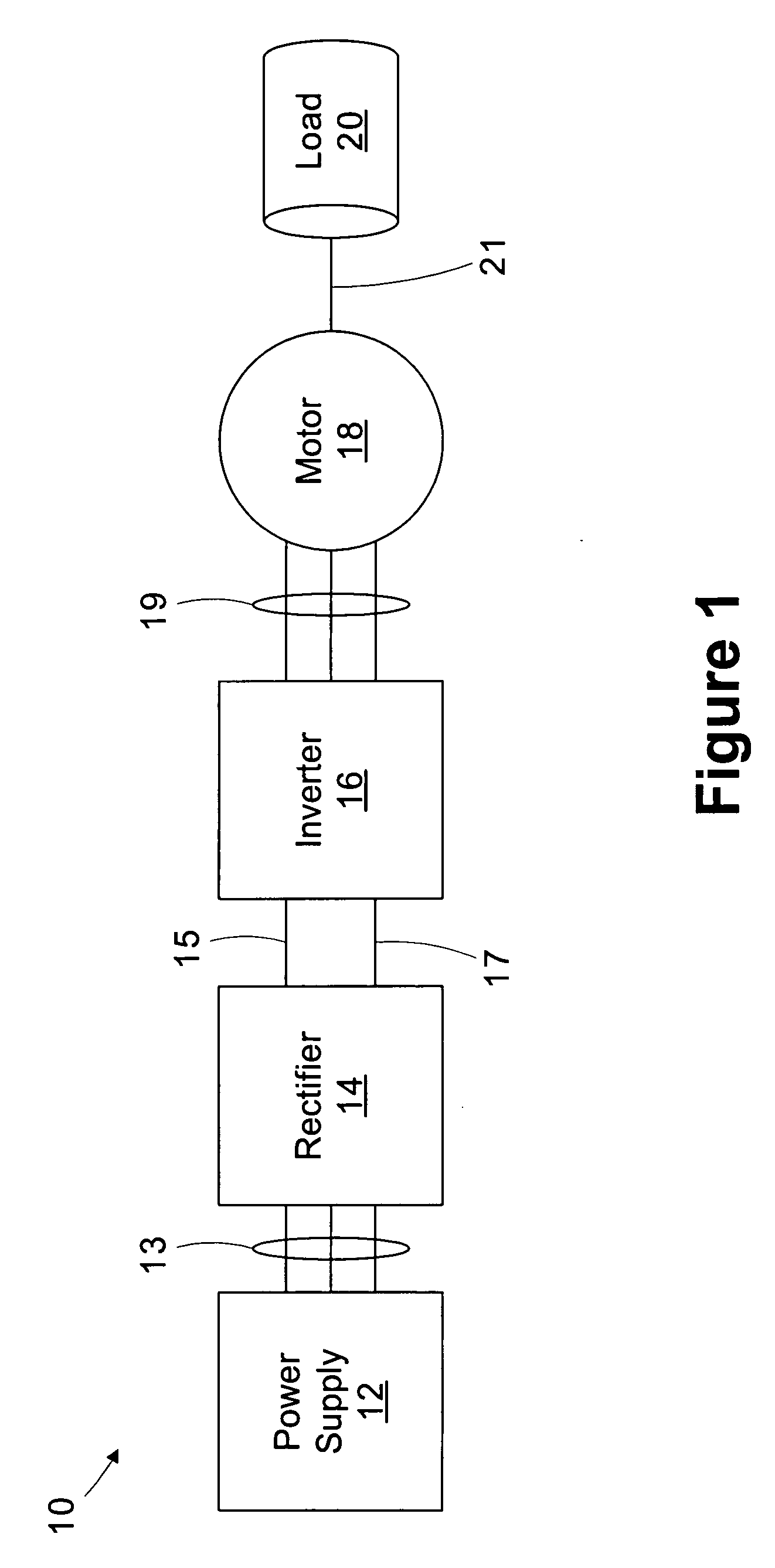

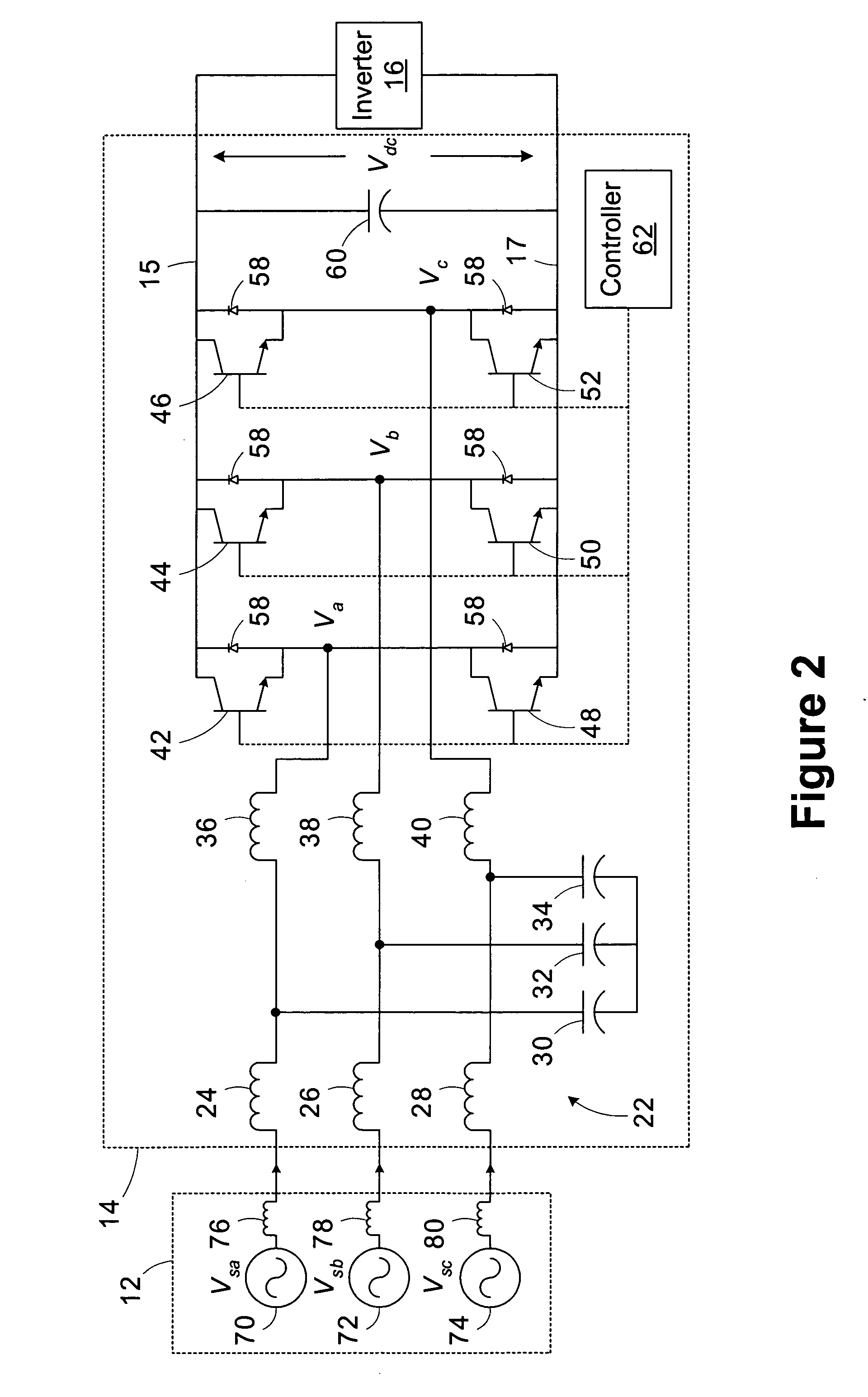

Pulse width modulation (PWM) rectifier with variable switching frequency

InactiveUS20060267542A1Low costIncrease the scope of applicationSingle-phase induction motor startersMotor/generator/converter stoppersSwitching signalSwitching frequency

A method for controlling a device including a plurality of switching devices operated in accordance with a pulse width modulation technique includes receiving a reference voltage signal associated with a first pair of the switching devices. A switching signal is generated. The first pair of switching devices are controlled based on the reference voltage signal and the switching signal in accordance with the pulse width modulation technique. A frequency of the switching signal is varied based on the value of the reference voltage signal.

Owner:ROCKWELL AUTOMATION TECH

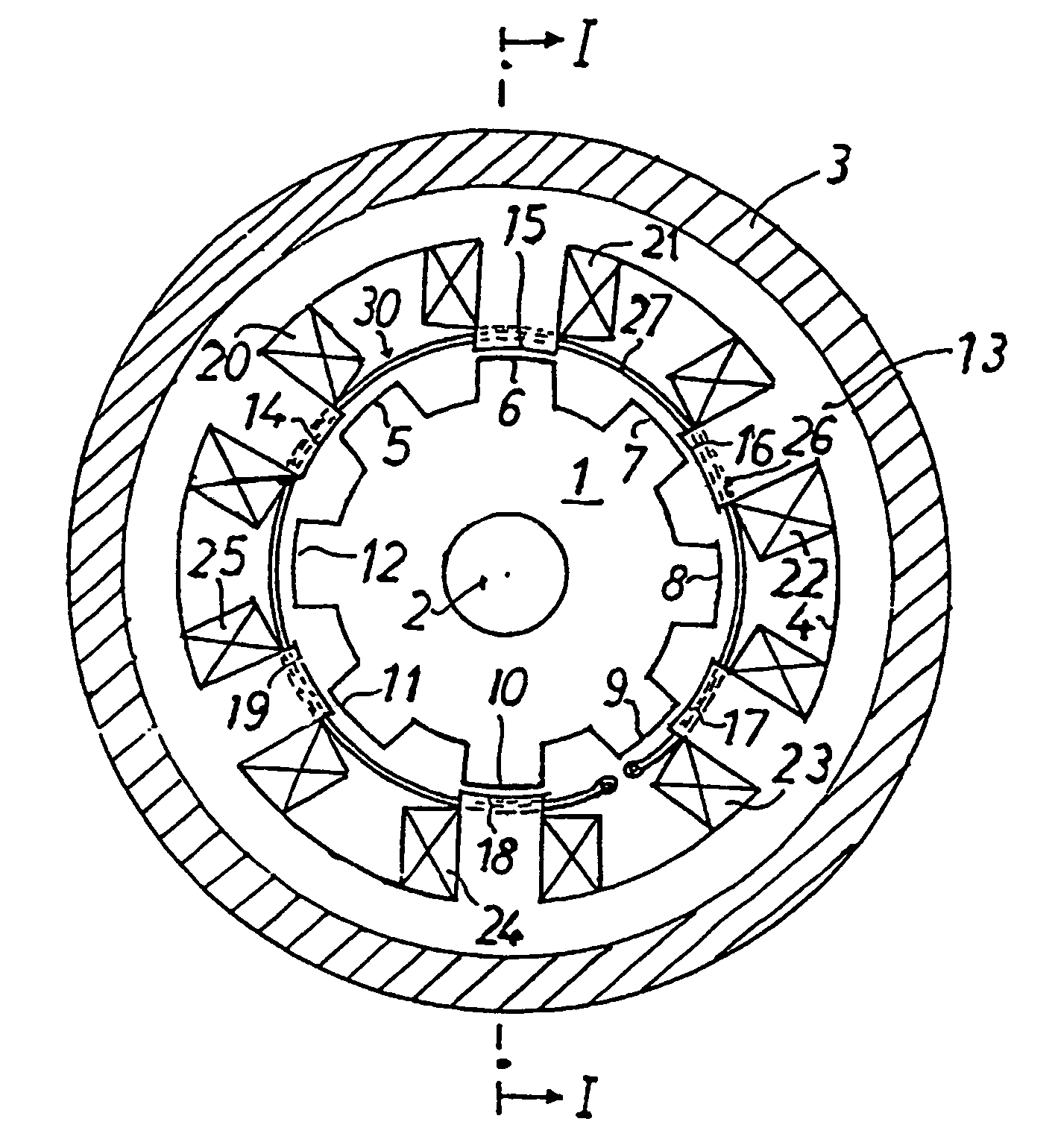

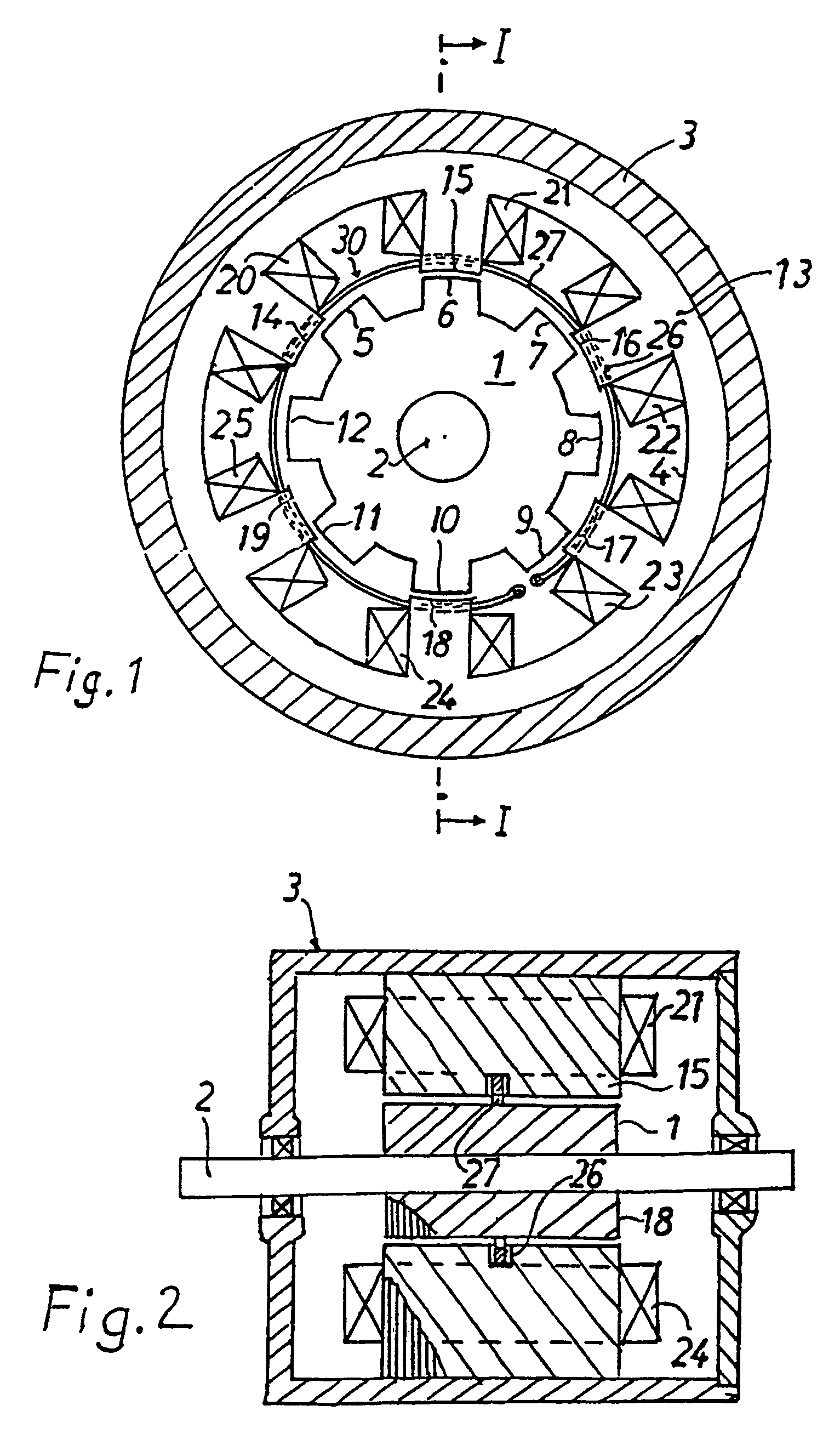

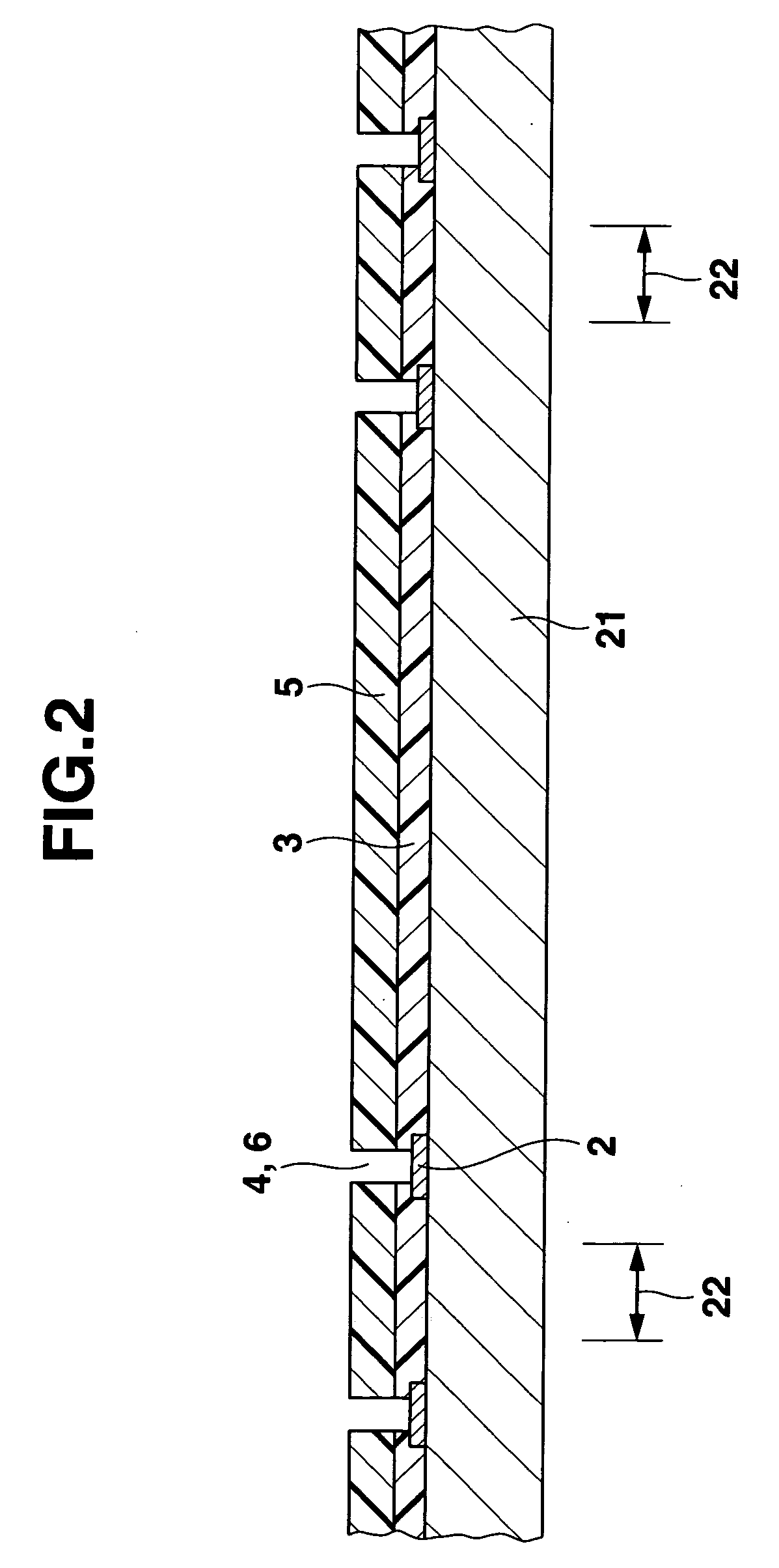

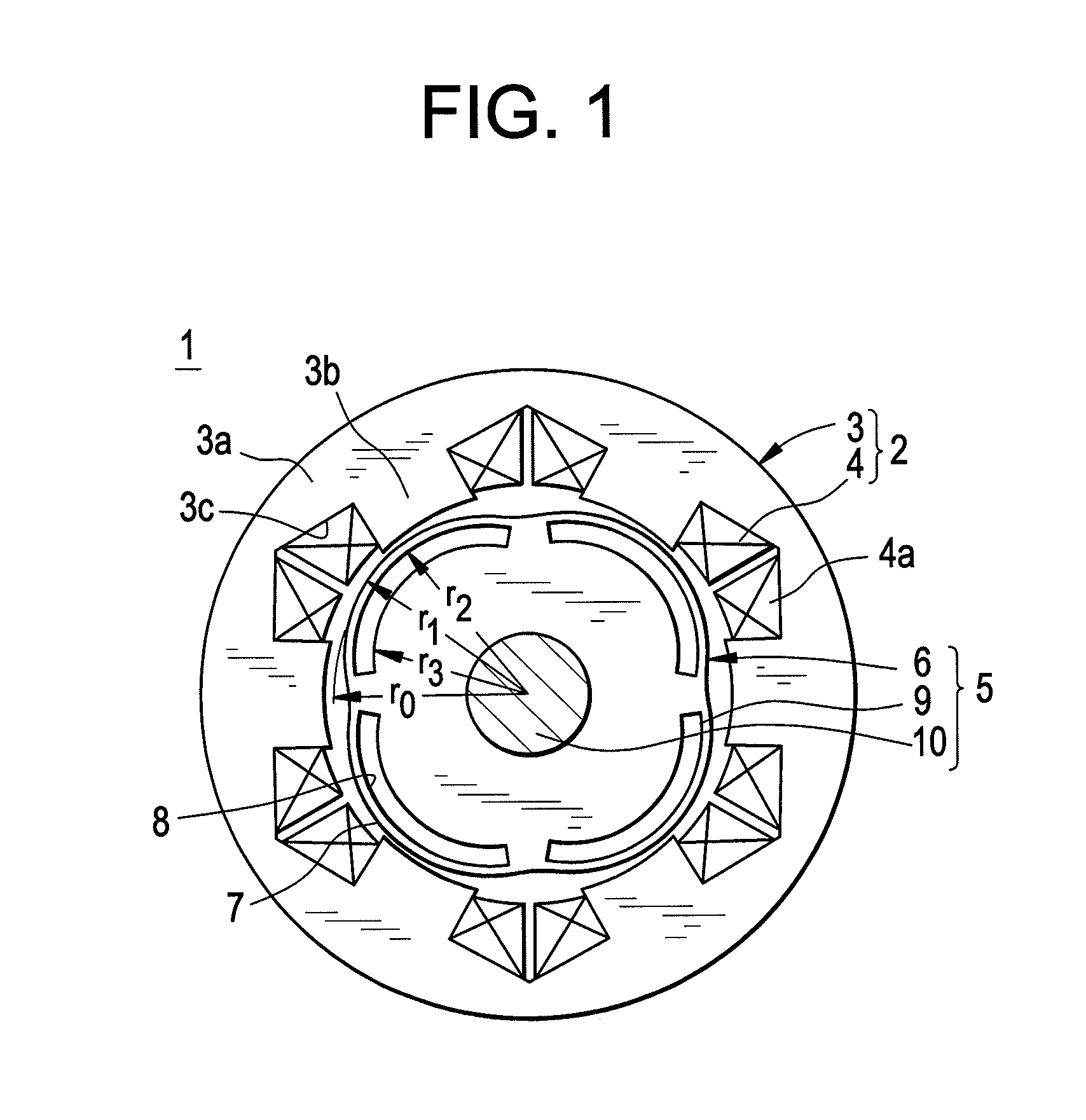

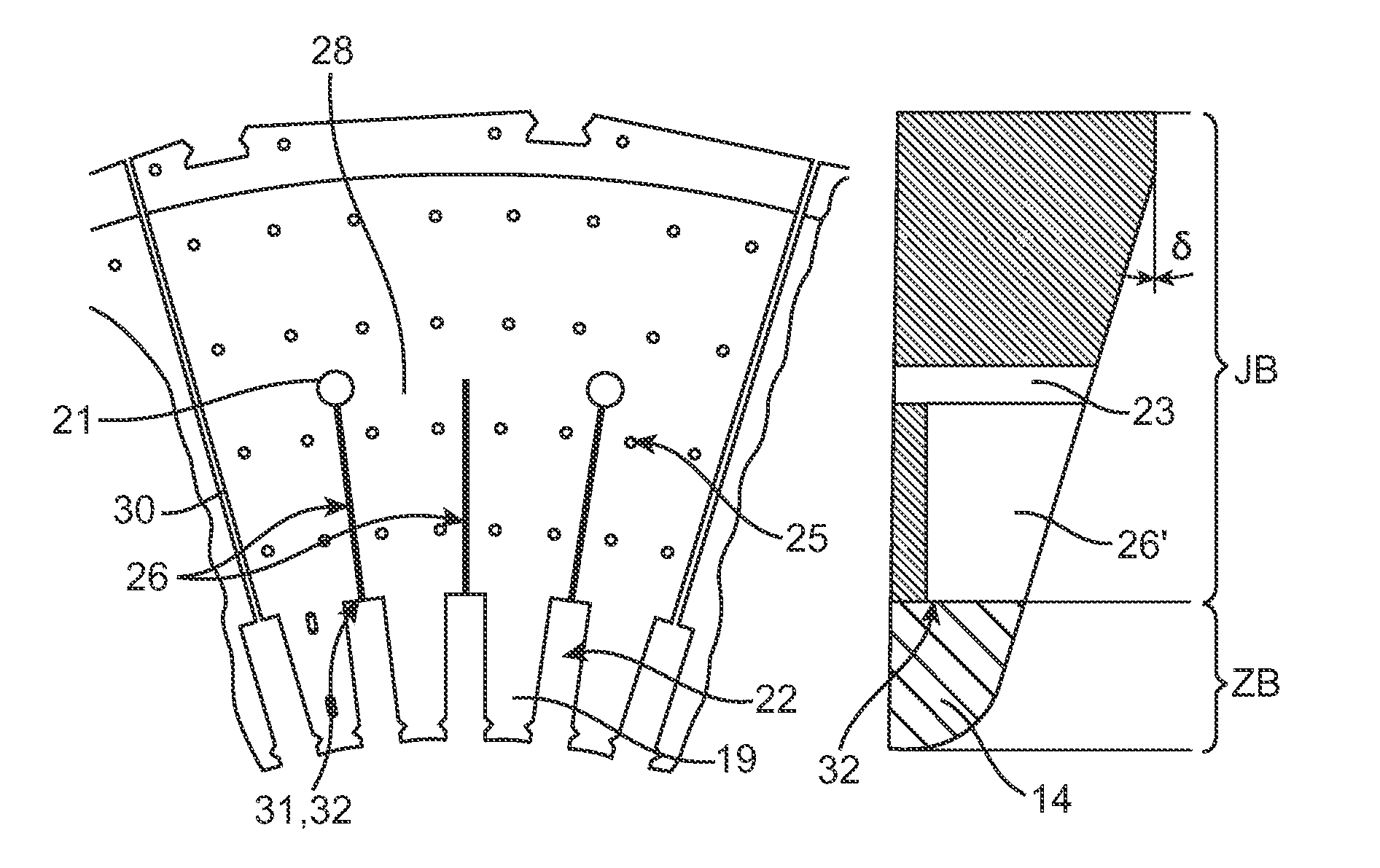

Rotor of a permanent magnet synchronous machine

InactiveUS20120025654A1Increase powerReduction in the harmonics of the magnetic air-gap fieldMagnetic circuit rotating partsSynchronous machines with stationary armatures and rotating magnetsPermanent magnet synchronous machineMagnetic poles

A rotor for a permanent magnet synchronous machine includes a basic body defining a center. Permanent magnets are arranged on a circumferential surface of the basic body to thereby form magnetic poles. Each magnetic pole is formed in a circumferential direction by at least two permanent magnets and defined by a pole center and a pole edge, wherein the pole edge is spaced from the center of the basic body at a distance which is smaller than a distance of the pole center to the center of the basic body. Positioned in sections between the pole centers of adjacent pole are filling elements, with a banding securing the filling elements on the permanent magnets in such a way that the rotor has a substantially cylindrical circumferential surface.

Owner:SIEMENS AG

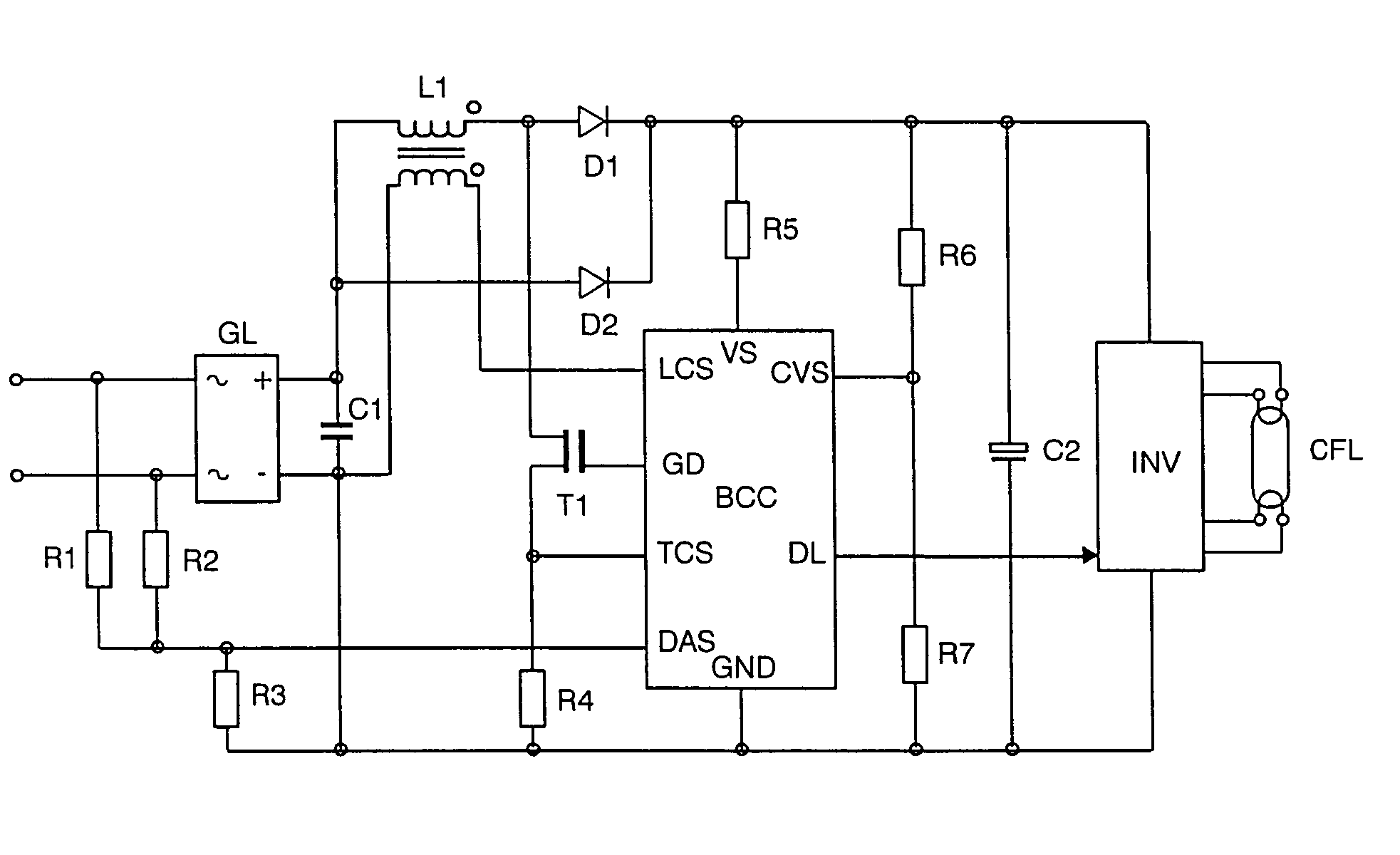

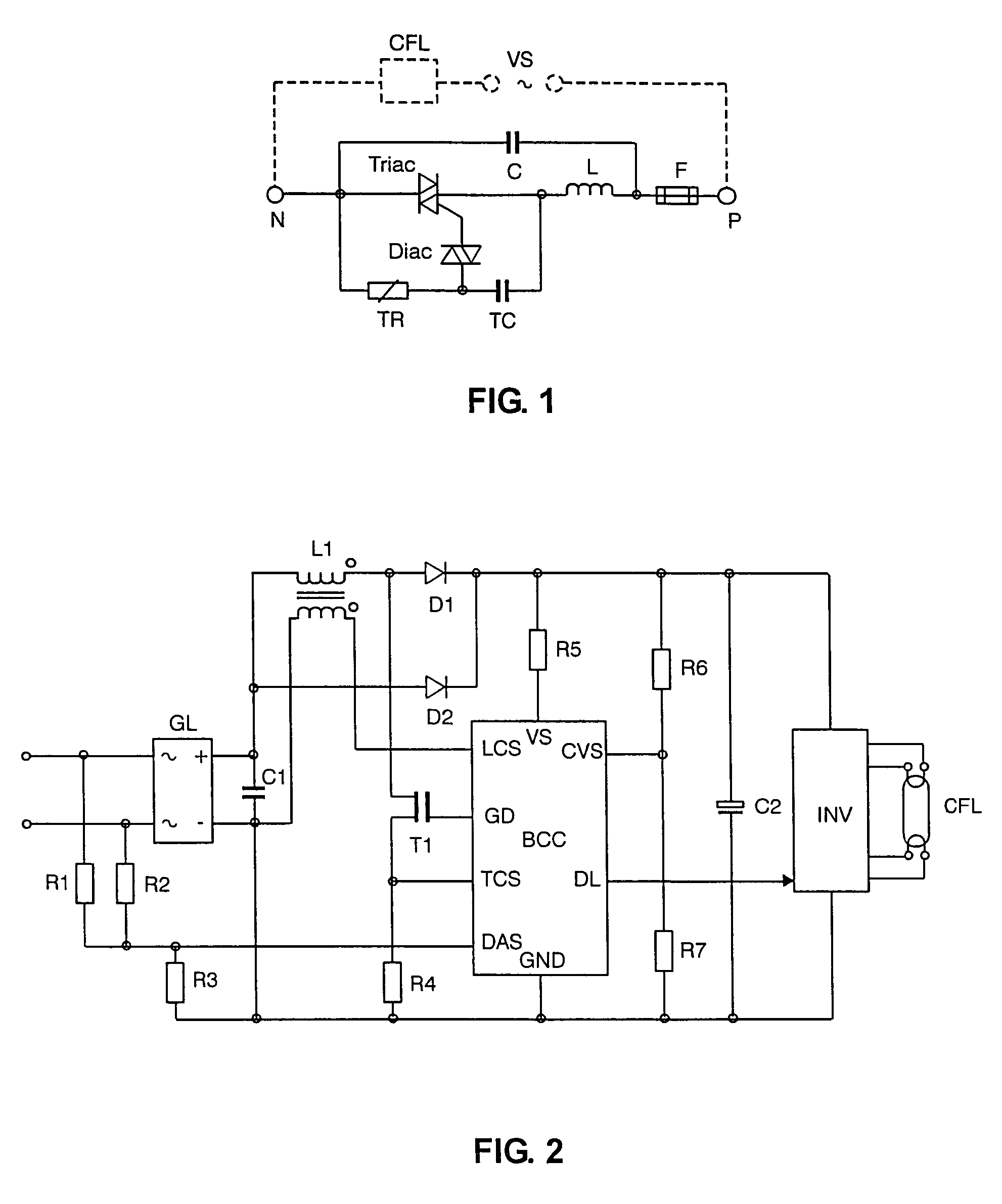

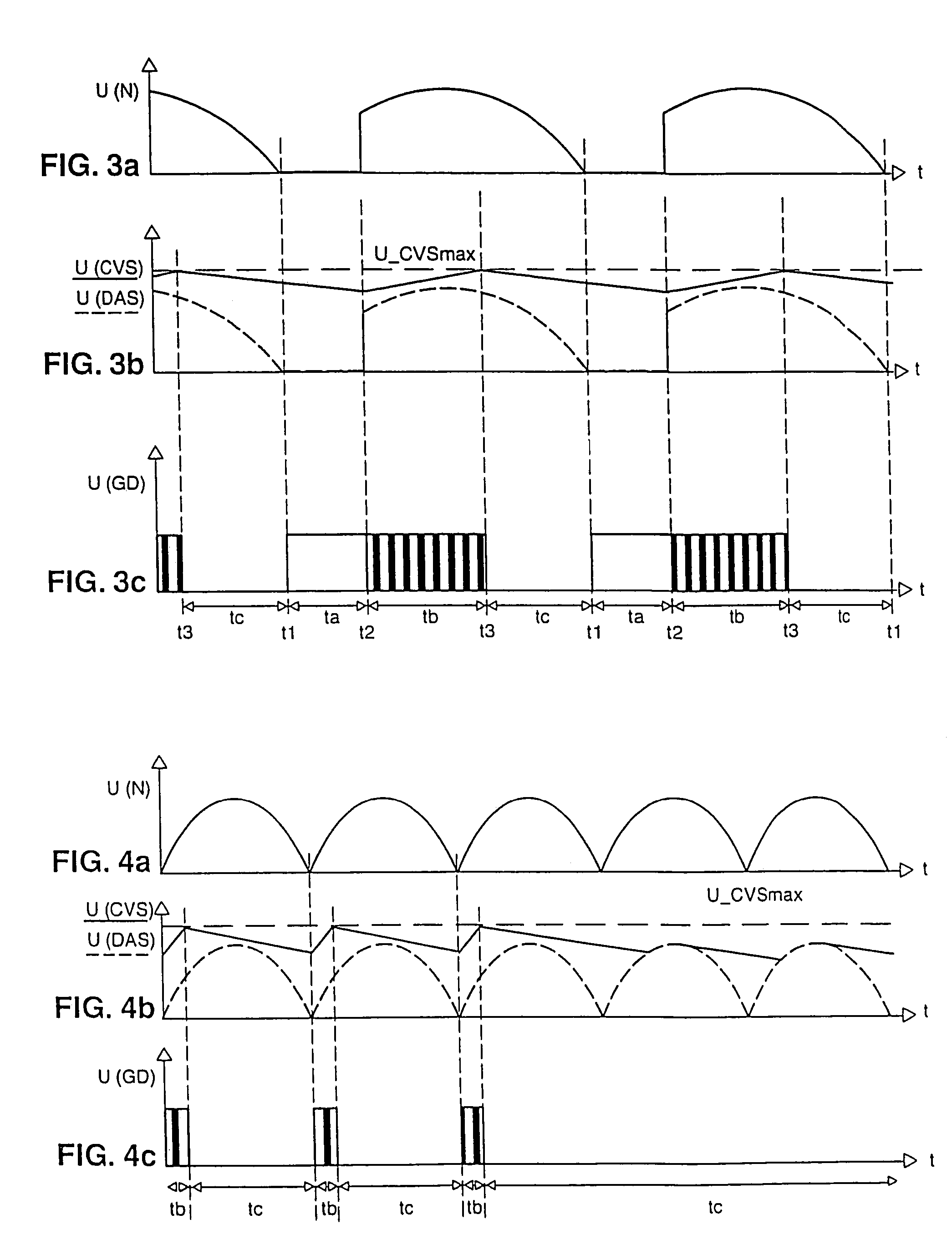

Method for varying the power consumption of capacitive loads

ActiveUS7132802B2Avoid Overvoltage ProblemsLife of lamp can be influencedAc-dc conversion without reversalConversion with intermediate conversion to dcDimmerCapacitor

Method for varying the power consumption of capacitive loads, in particular compact fluorescent lamps which are operated using a phase-gating dimmer by a converter (step-up converter). According to the invention, in the case of a nonconducting dimmer (i.e. no system power supply to the load), the switch (T1) in the converter (step-up converter) is closed. In the case of a conducting dimmer (i.e. when a system voltage is applied to the load), the step-up converter operation takes place until a predetermined maximum voltage is reached across the smoothing capacitor of the load.

Owner:ABL IP HLDG

Linear motor with reduced cogging force

ActiveUS6949846B2Reduce cogging forceEasy to shapeManufacturing dynamo-electric machinesPropulsion systemsMagnetic polesEngineering

Owner:SANYO DENKI CO LTD

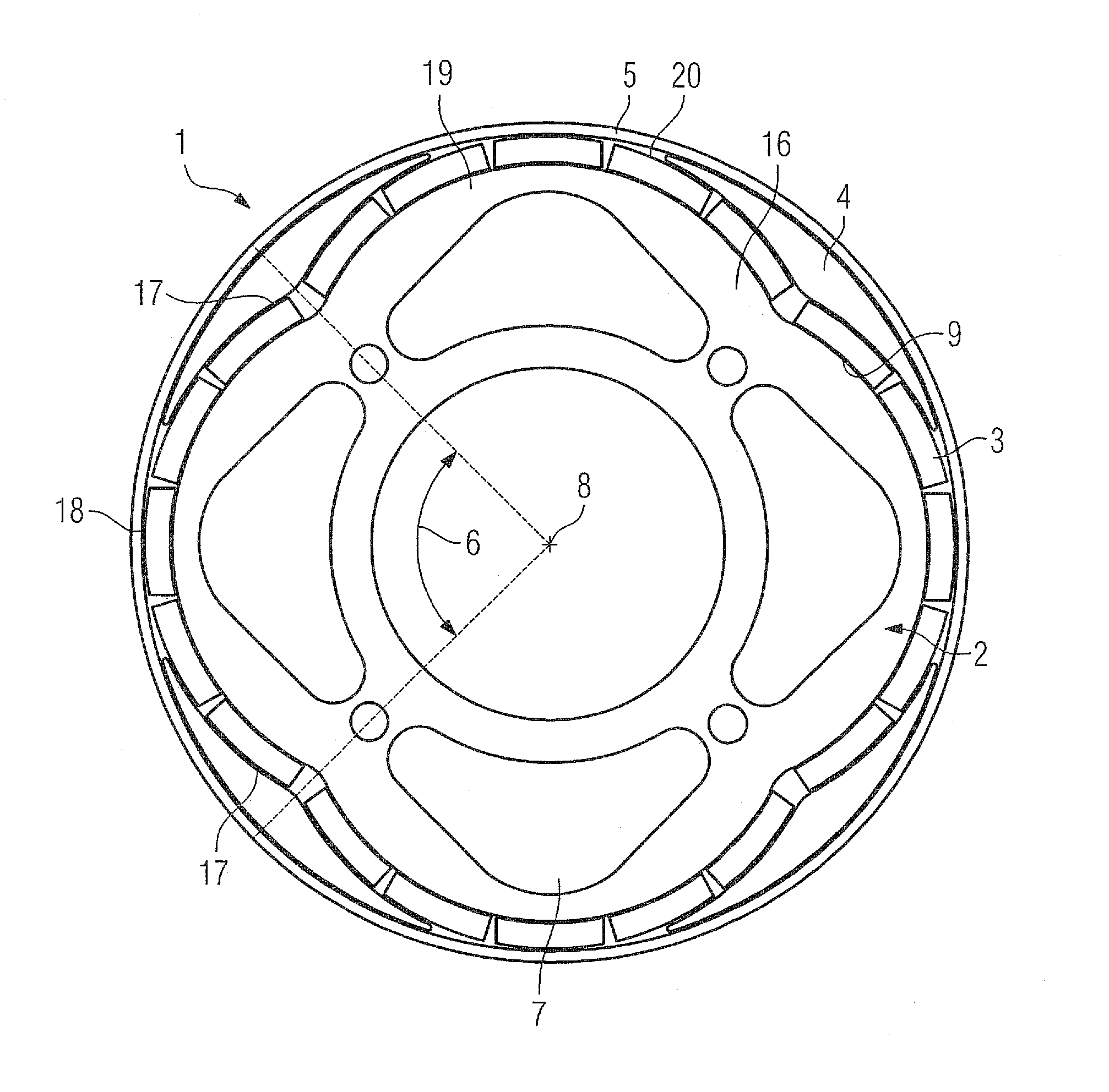

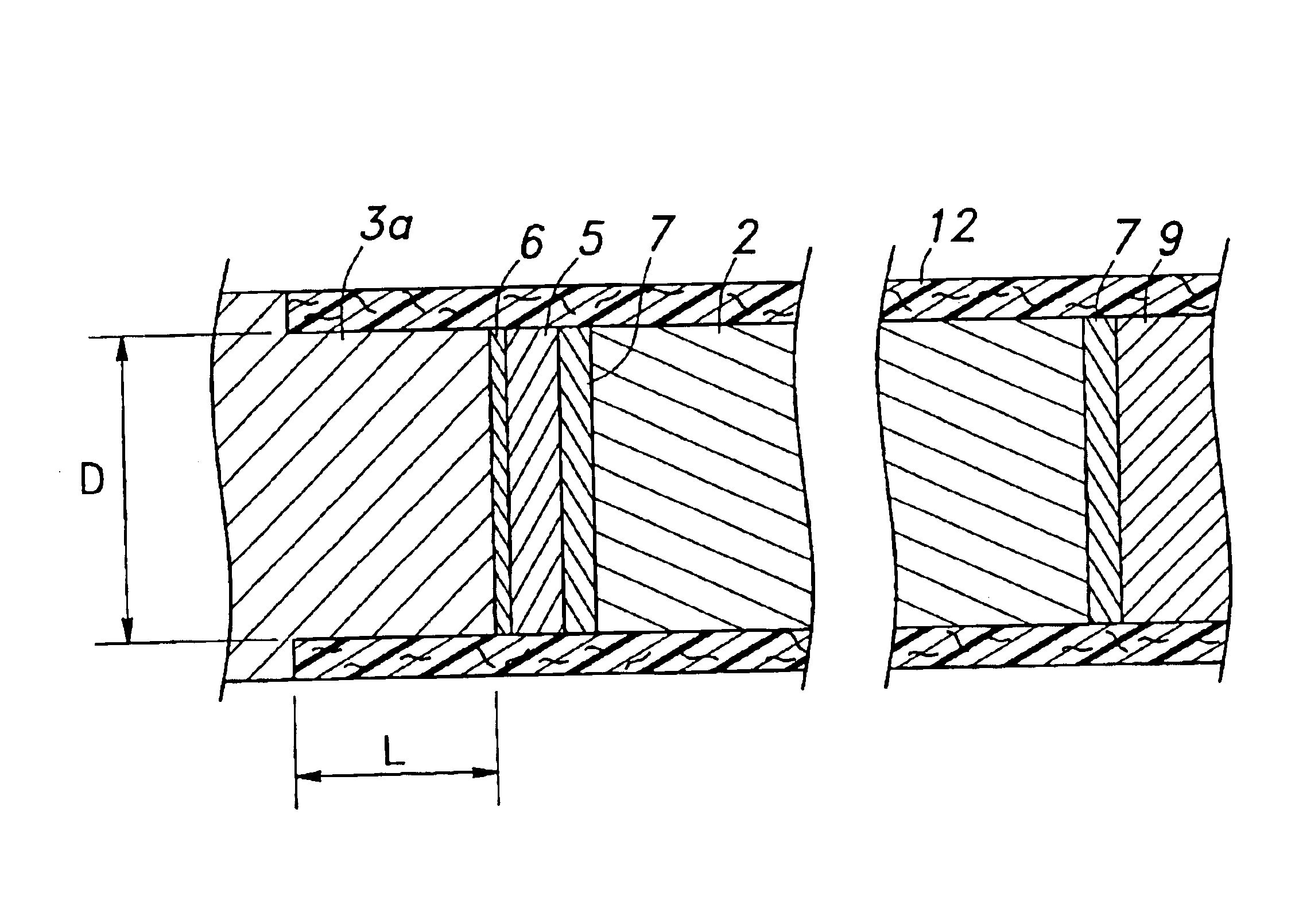

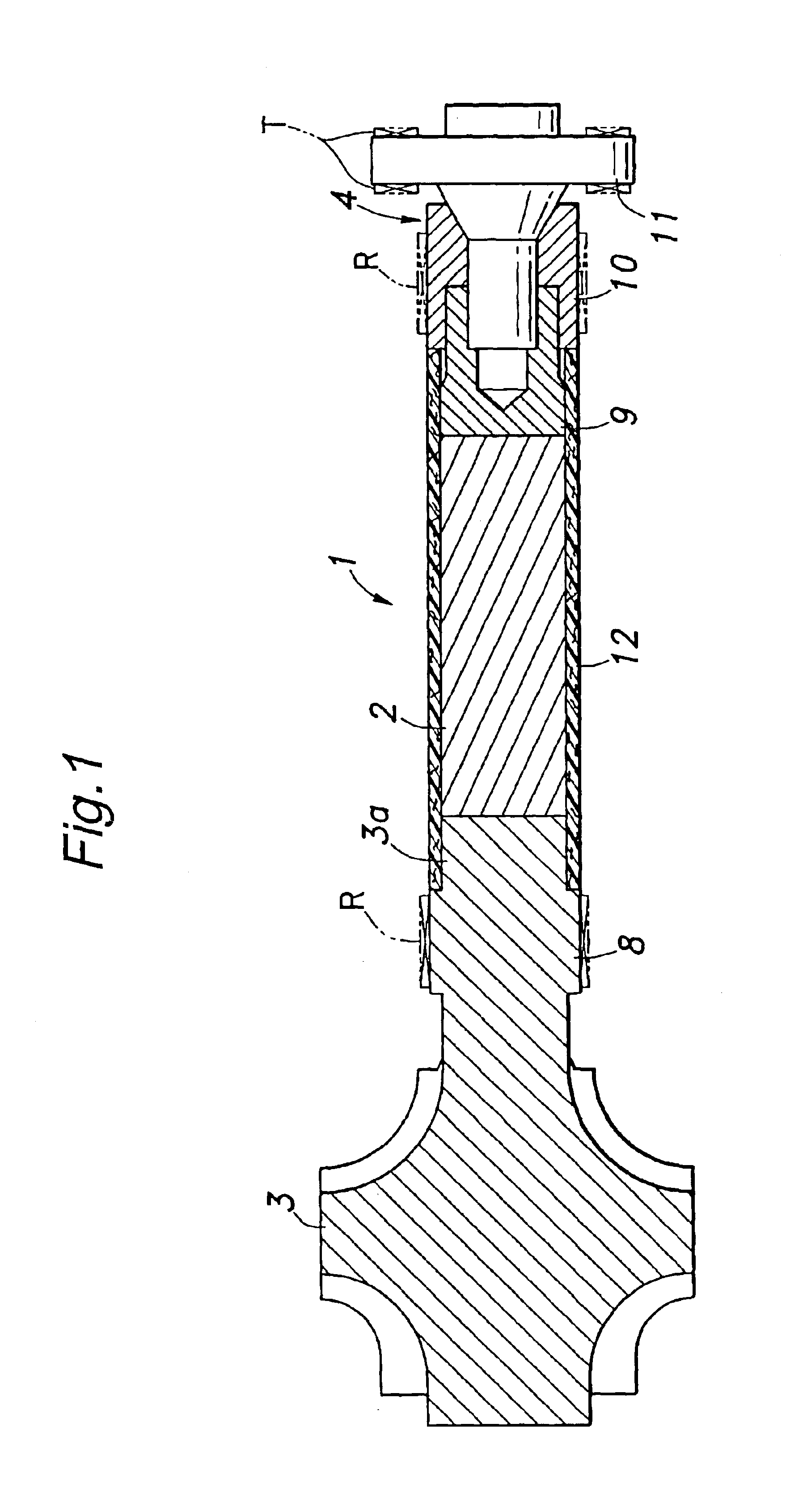

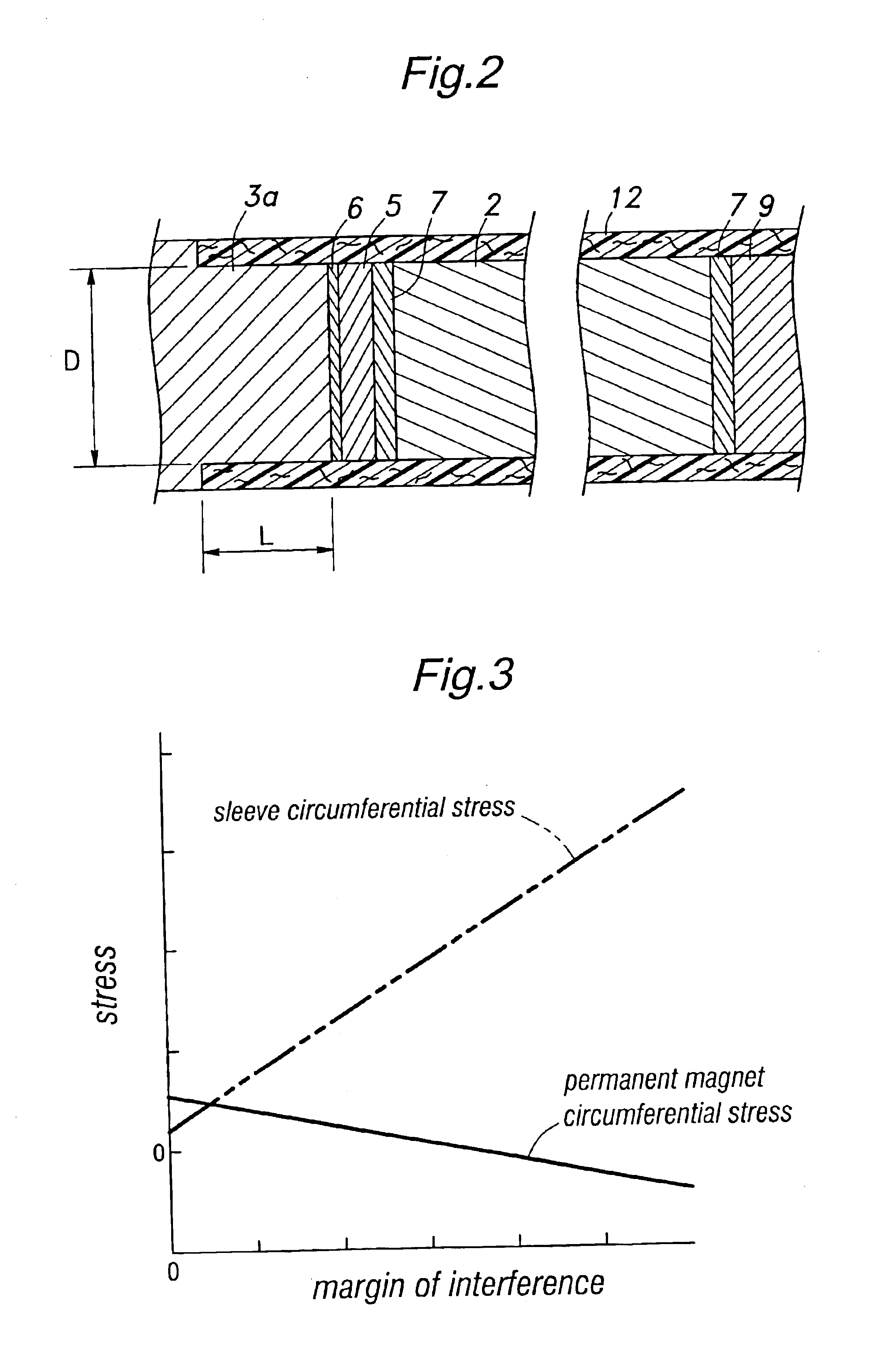

Permanent magnet rotor

InactiveUS6841912B2Increase axial dimensionReduction in cross sectional area can be avoidedMagnetic circuit rotating partsPump componentsPermanent magnet rotorEngineering

In a permanent magnet rotor, a power transmitting shaft is connected to an axial end of a solid cylindrical permanent magnet, and a reinforcement sleeve is fitted on the outer circumferential surface of the permanent magnet. Thus, the shaft is not required to be passed through the permanent magnet as was the case with the conventional permanent magnet rotor for the purpose of transmitting the rotational torque and increasing the overall rigidity, and the increase in the axial dimension of the rotor due to the reduction in the cross sectional area of the permanent magnet can be avoided. Also, because the sleeve surrounds the permanent magnet, the resistance to centrifugal stress resulting from a high speed rotation and repeated bending stress owing to vibrations can be improved.

Owner:HONDA MOTOR CO LTD

Fuel cell

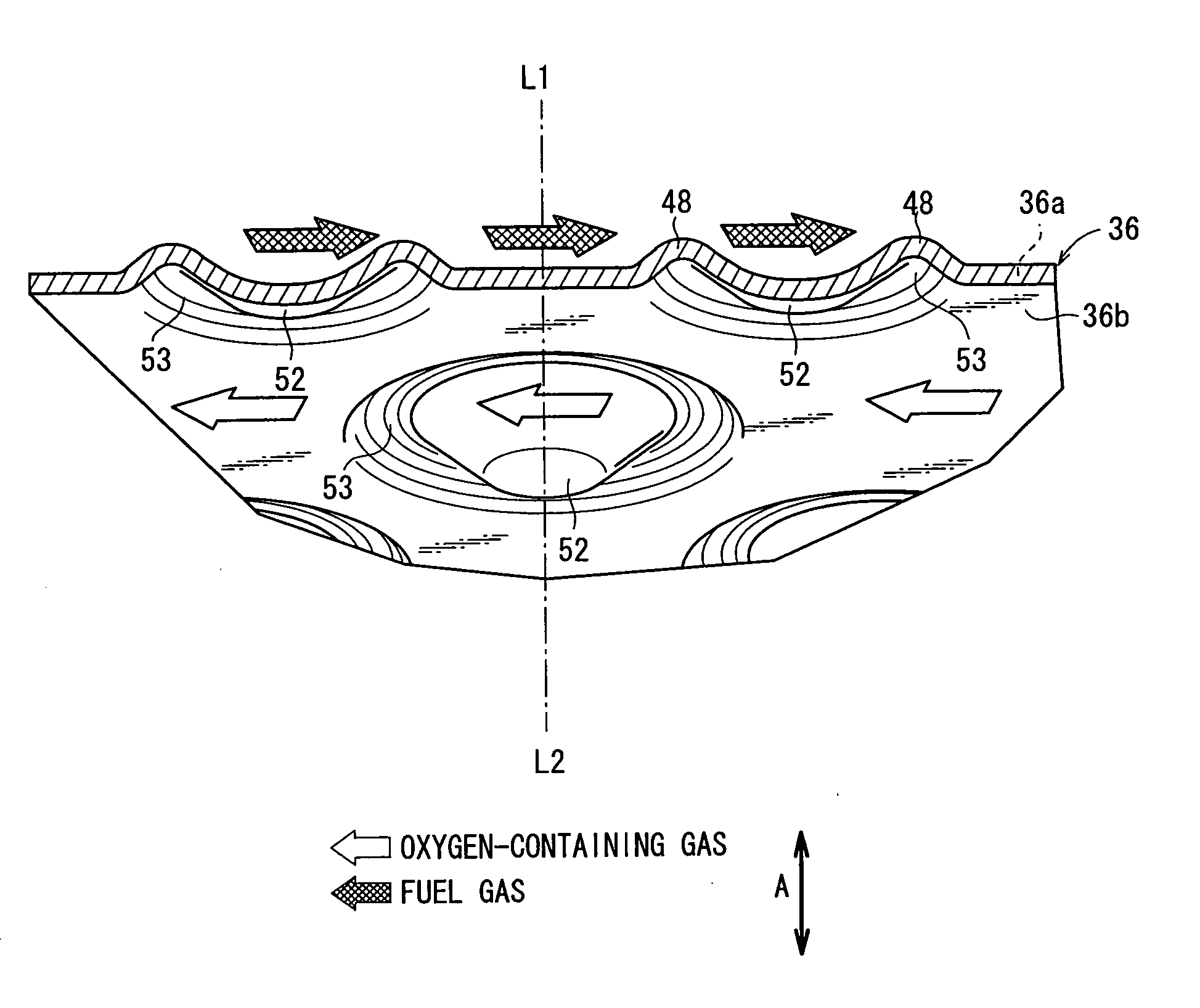

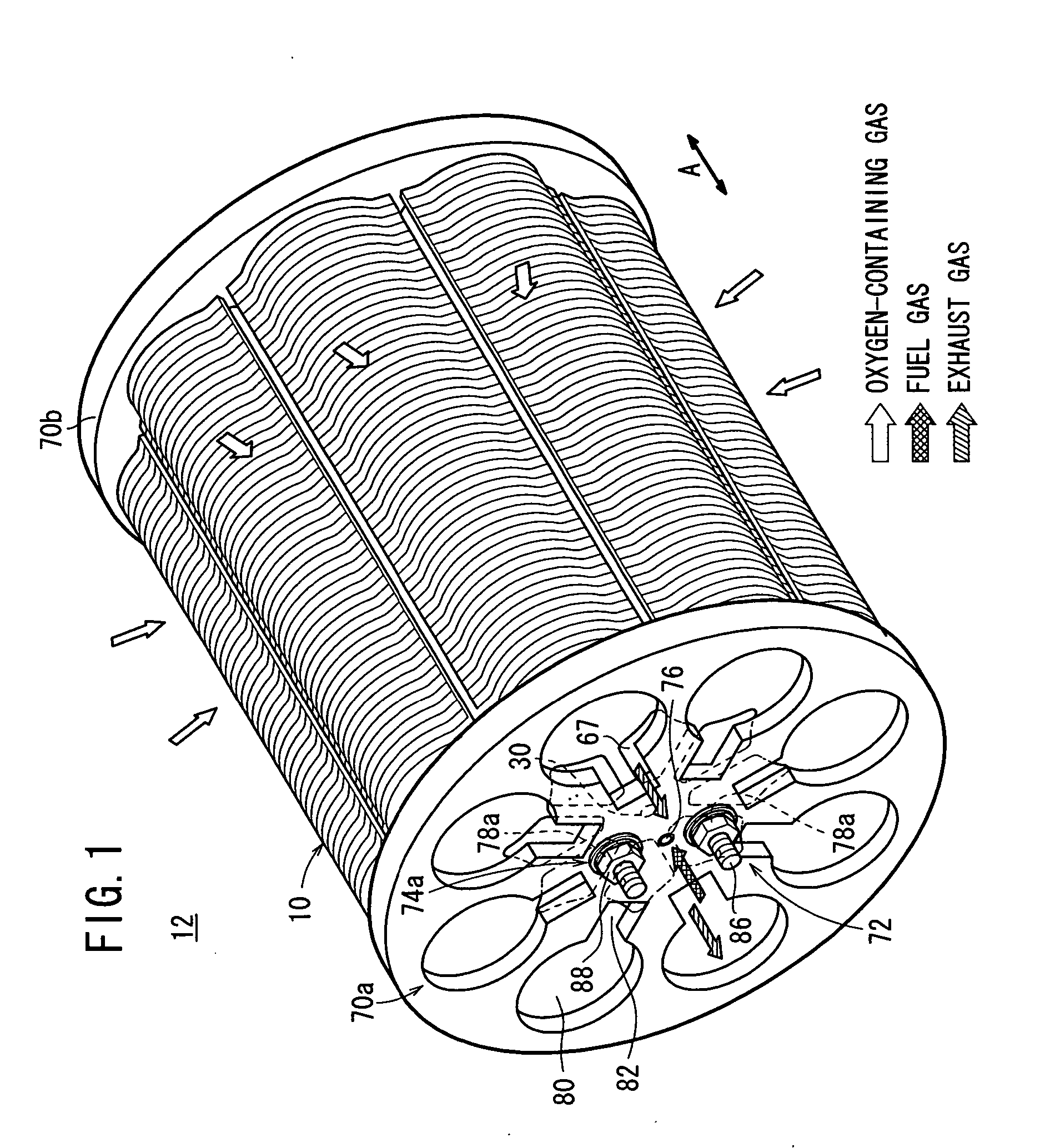

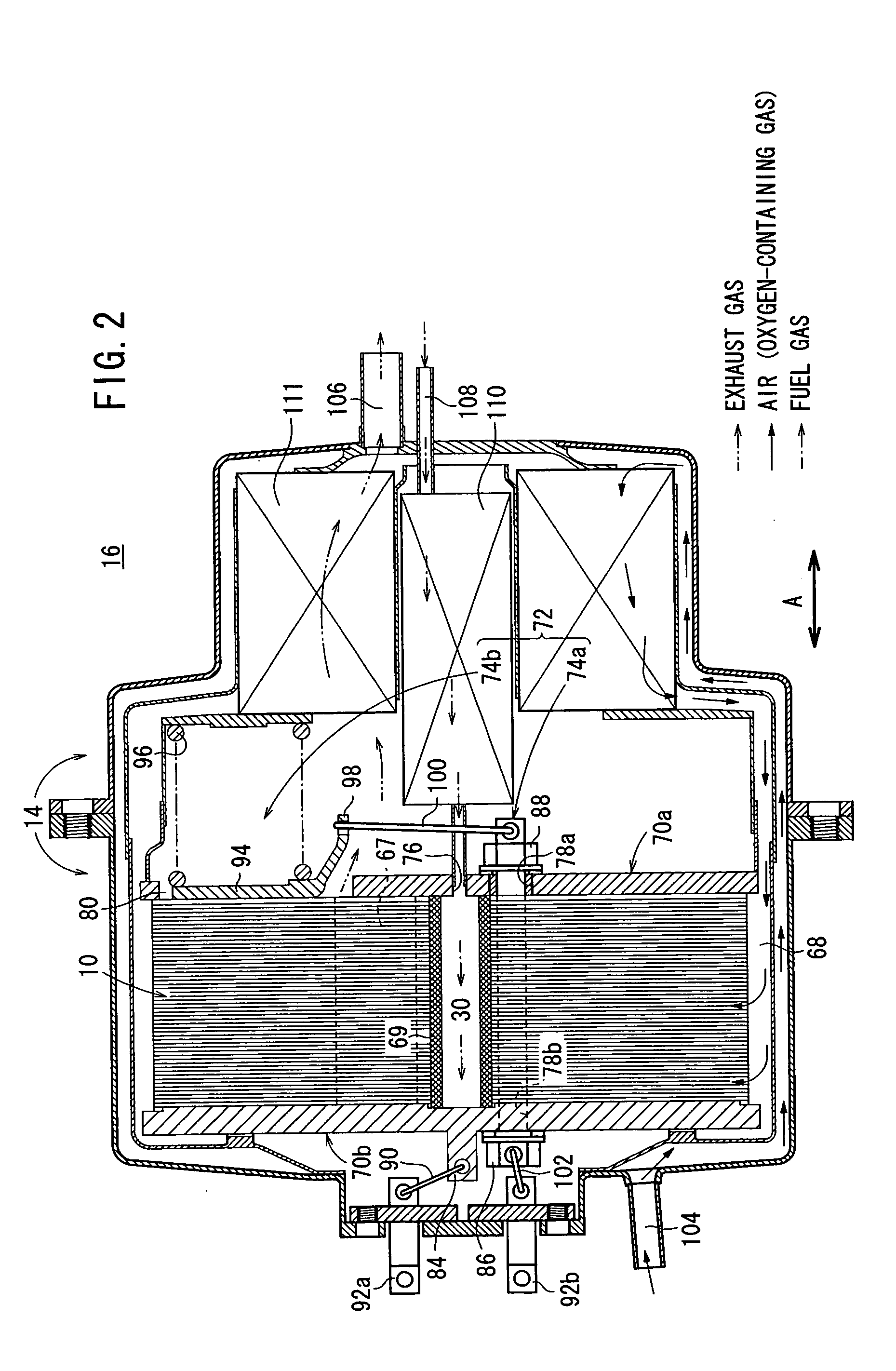

InactiveUS20050142427A1Suppress tightening loadSimple and compact structureFuel cells groupingFuel cell auxillariesFuel cellsSingle plate

A fuel cell includes an electrolyte electrode assembly and a pair of separators sandwiching the electrolyte electrode assembly. Each of the separators is a single plate, and includes a plurality of circular disks. First protrusions and second protrusions are provided on both surfaces of the circular disk. The first protrusions contact the anode of the electrolyte electrode assembly to form a fuel gas flow field, and the second protrusions contact the cathode of the electrolyte electrode assembly to form an oxygen-containing gas flow field. The shape of the first protrusion is different from the shape of the second protrusion. The first and second protrusions are coaxial with each other.

Owner:HONDA MOTOR CO LTD

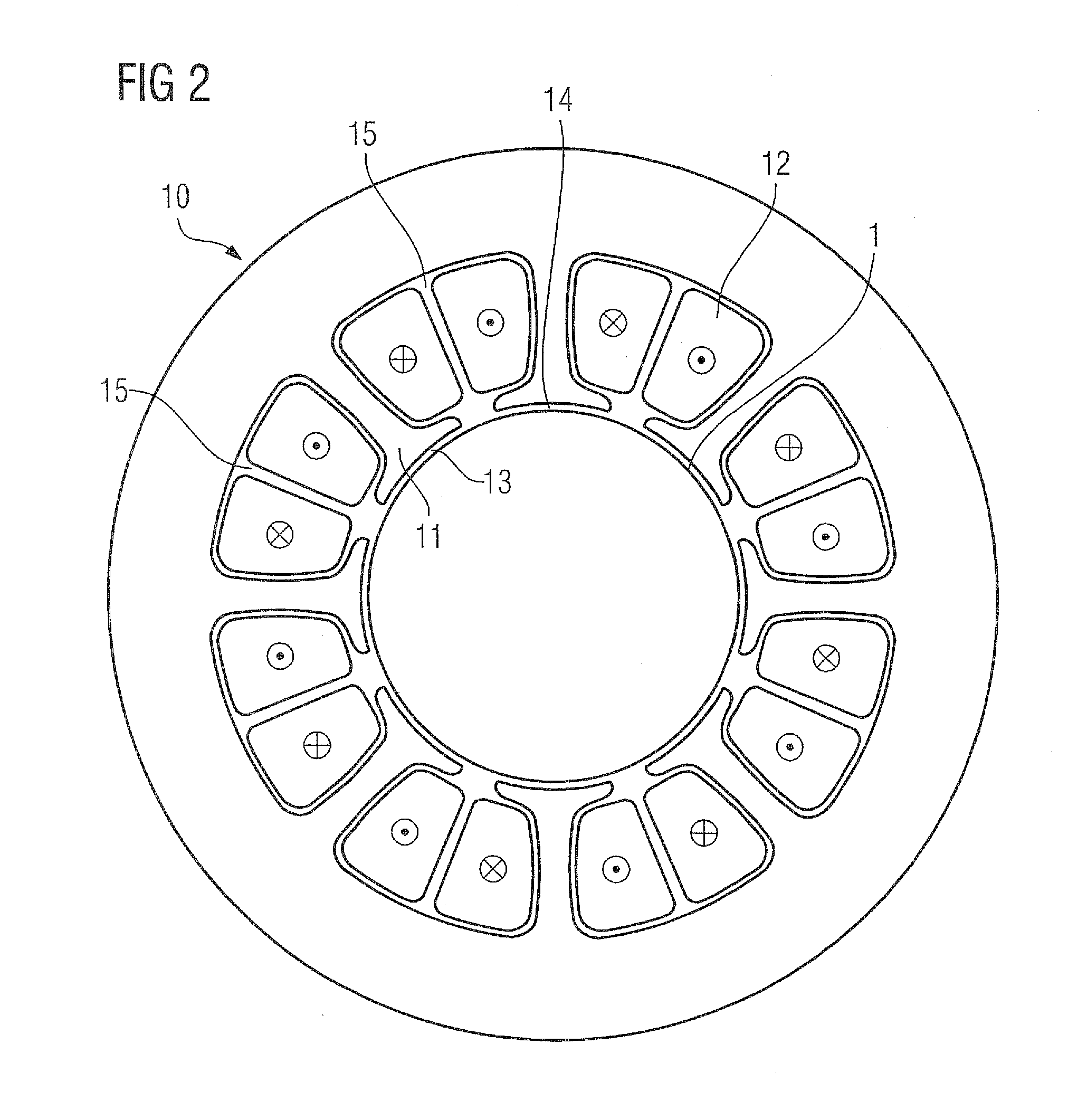

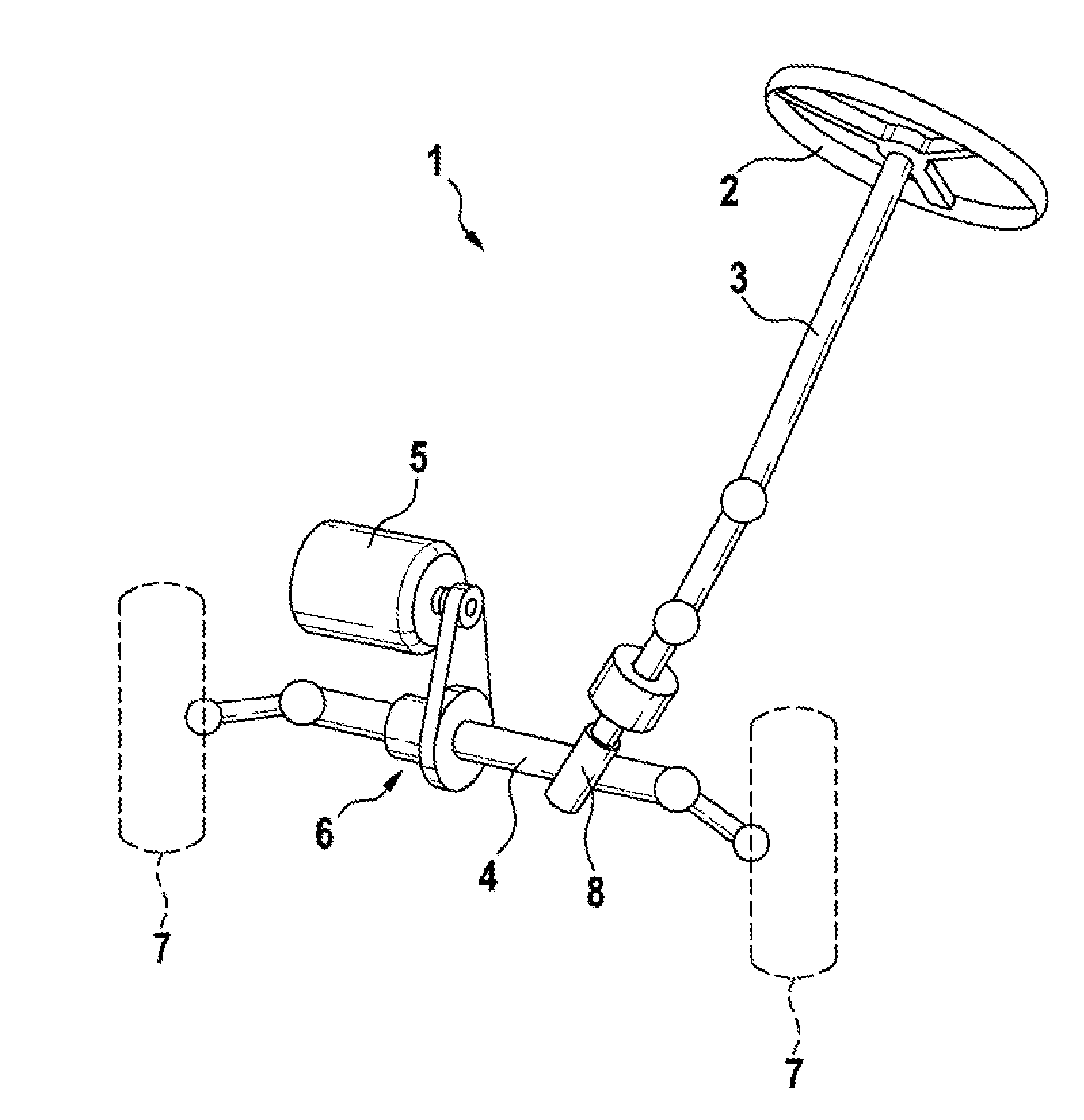

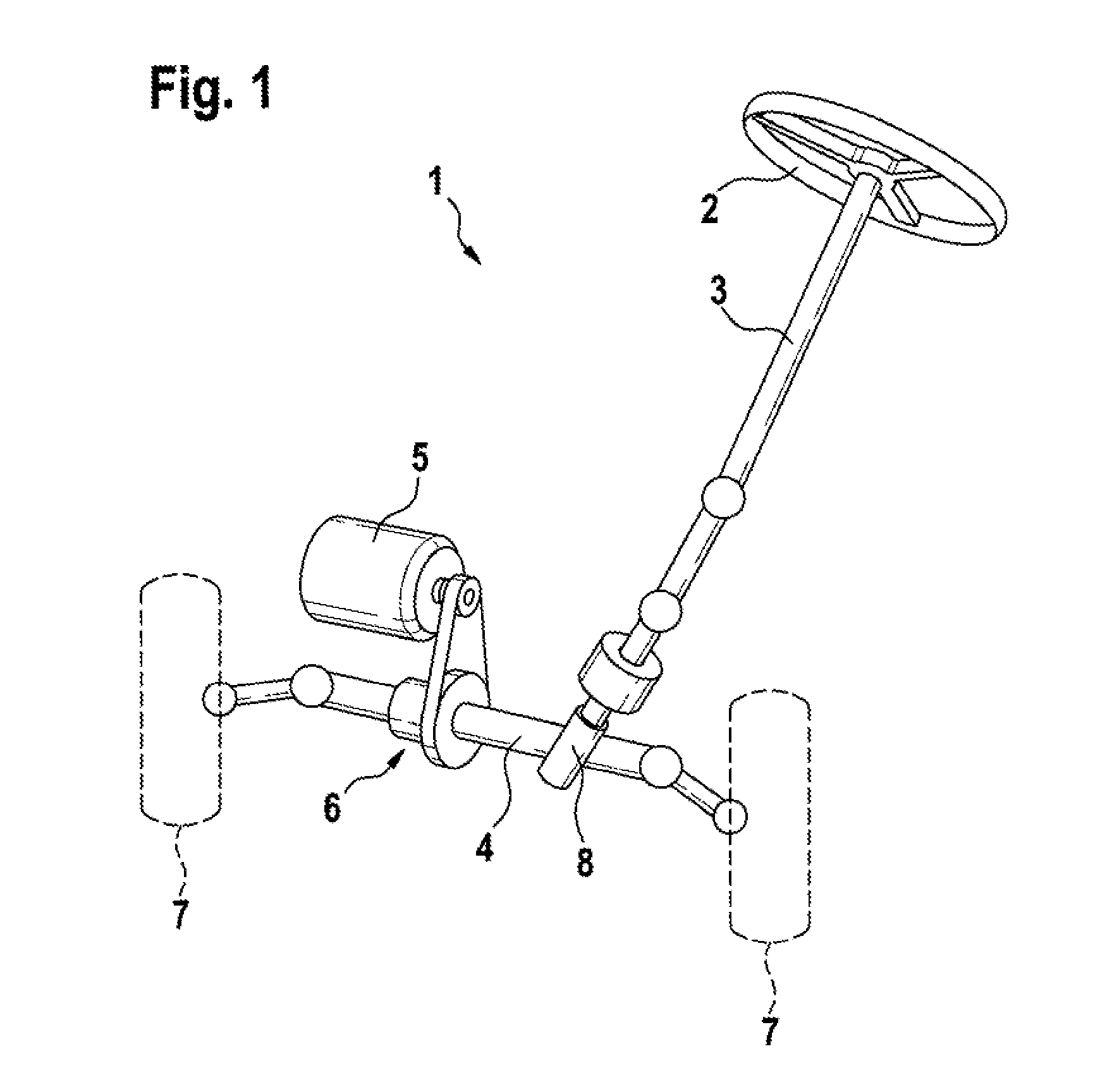

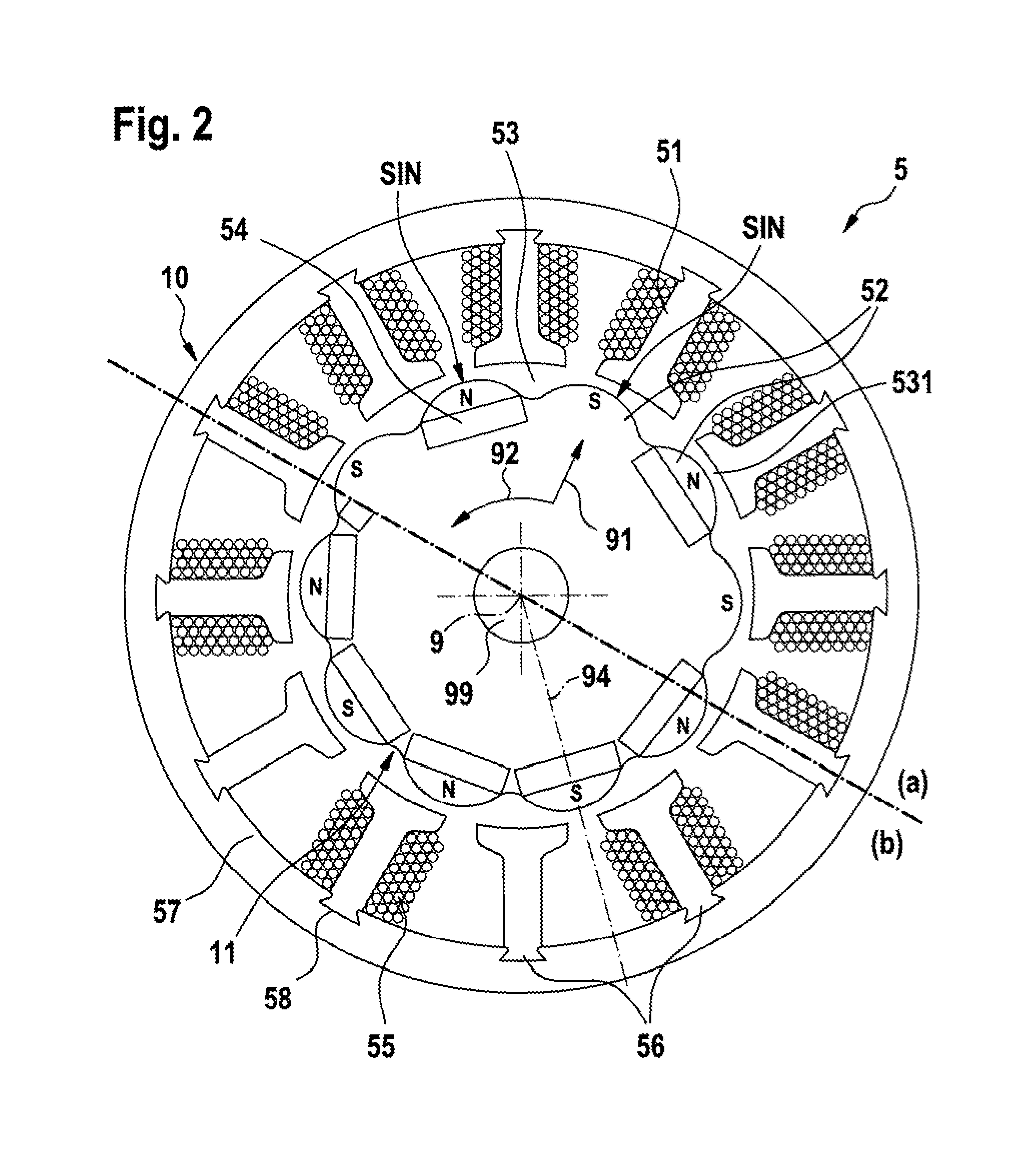

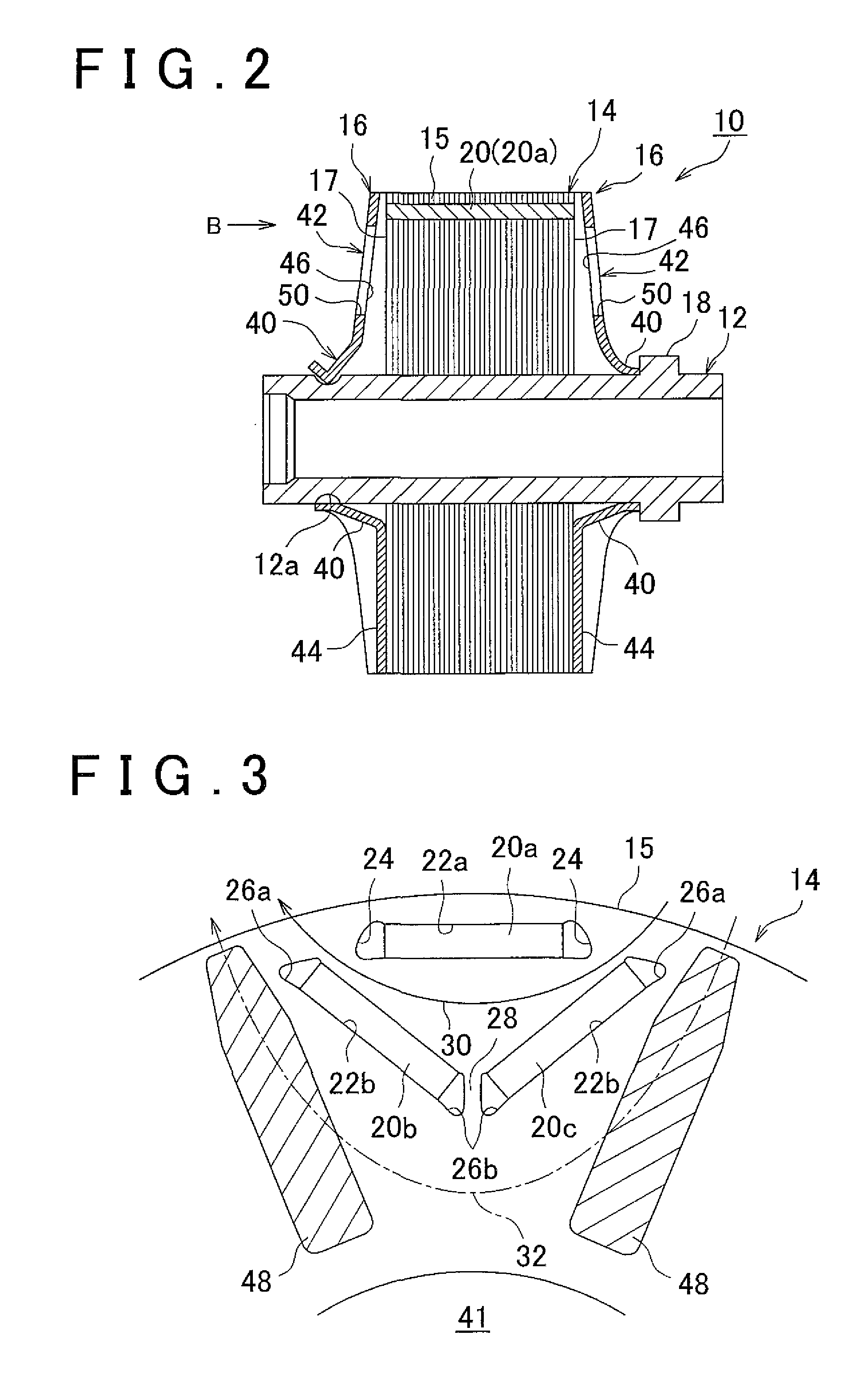

Steering drive for a motor vehicle

ActiveUS20110290581A1Reduce eddy current lossReduces detent torqueMagnetic circuitElectrical steeringSteering wheelSteering column

A steering drive for a motor vehicle comprising a steering wheel, a steering column, on which the steering wheel is disposed, a connecting rod, which interacts with the steering column to deflect the wheels of the motor vehicle, an electric motor, which is provided for boosting the steering thrust, as well as a belt drive, the electric motor interacting with the connecting rod via the belt drive. Said electric motor comprises a stator having twelve stator teeth as well as a rotor having ten rotor poles, the rotor poles being spaced apart from each other by an air gap and embodied as sinus poles.

Owner:ROBERT BOSCH GMBH

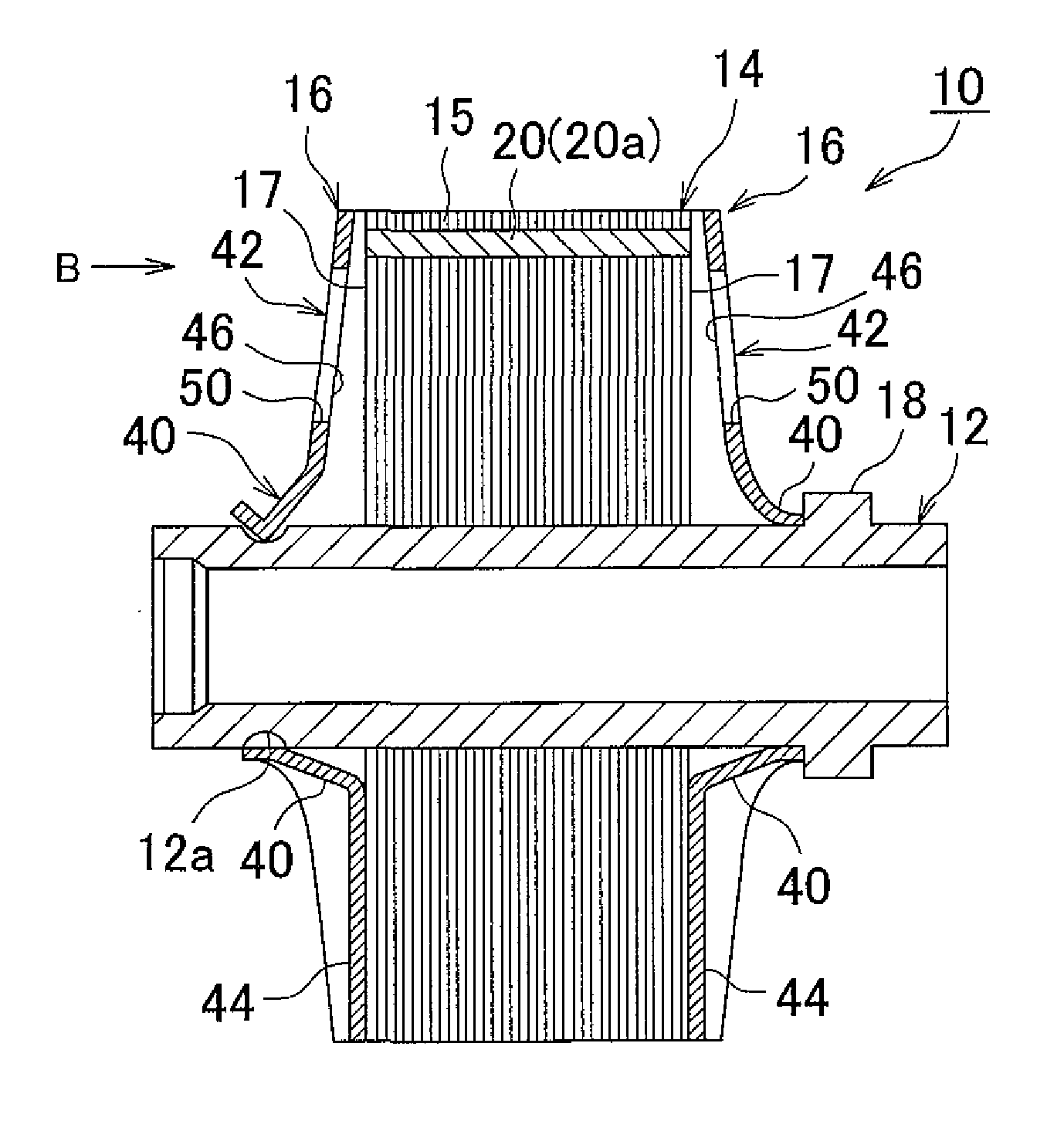

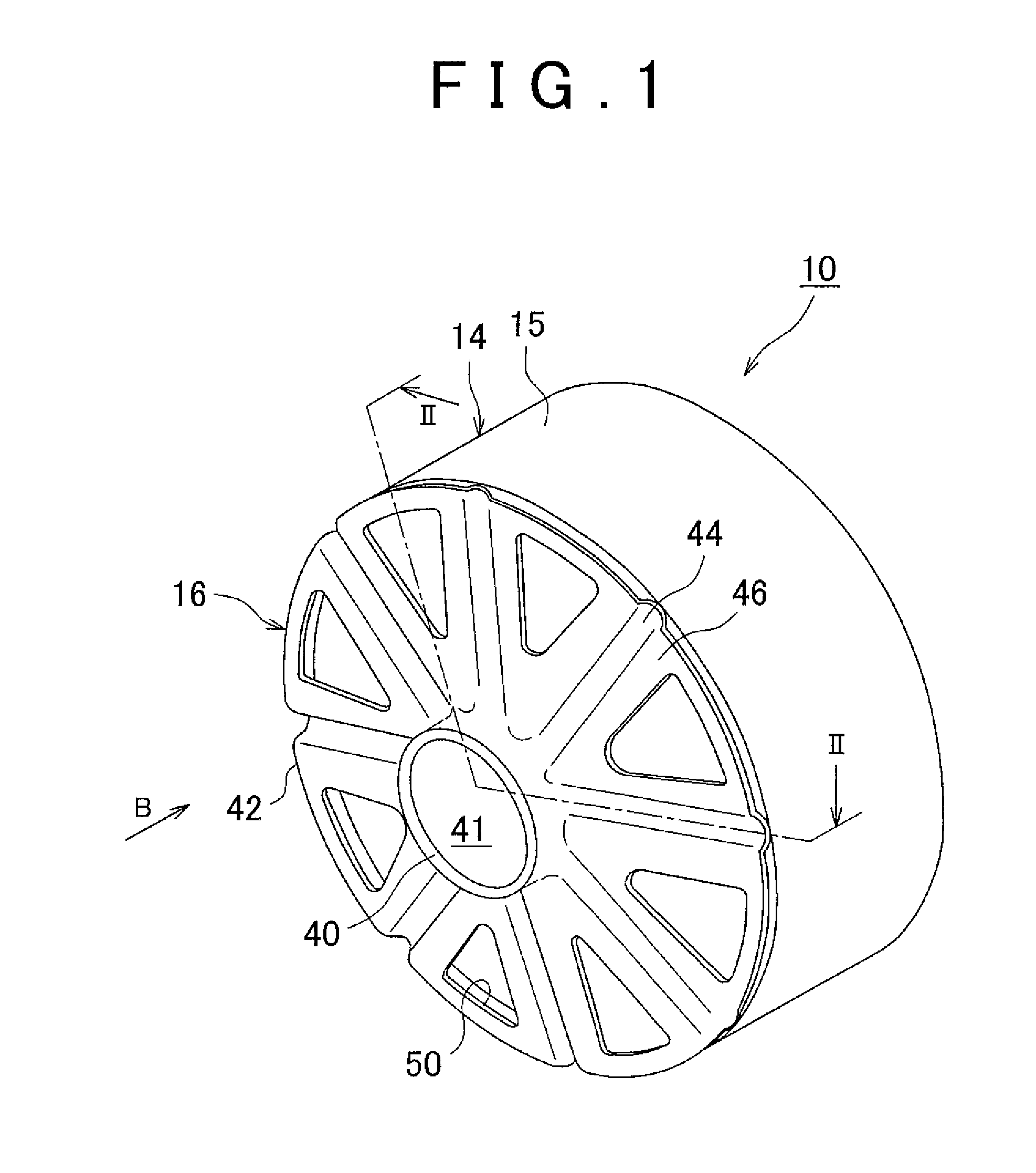

End plate, and rotor for rotary electric machine which employs the end plate

InactiveUS20120139382A1Avoid it happening againLow production costMagnetic circuit rotating partsSynchronous machines with stationary armatures and rotating magnetsElectric machineEngineering

An end plate is made of a magnetic material, and holds an axis-direction end surface of a rotor core in which a permanent magnet is buried. The end plate includes: a protruded portion constructed so as to be caused to pressingly contact the axis-direction end surface of the rotor core when mounted in the rotor; and a depressed portion constructed so as not to contact the axis-direction end surface. The protruded portion is formed so as to contact only one of a d-axis magnetic path region and a q-axis magnetic path region that are formed by the permanent magnet within the rotor core.

Owner:TOYOTA JIDOSHA KK

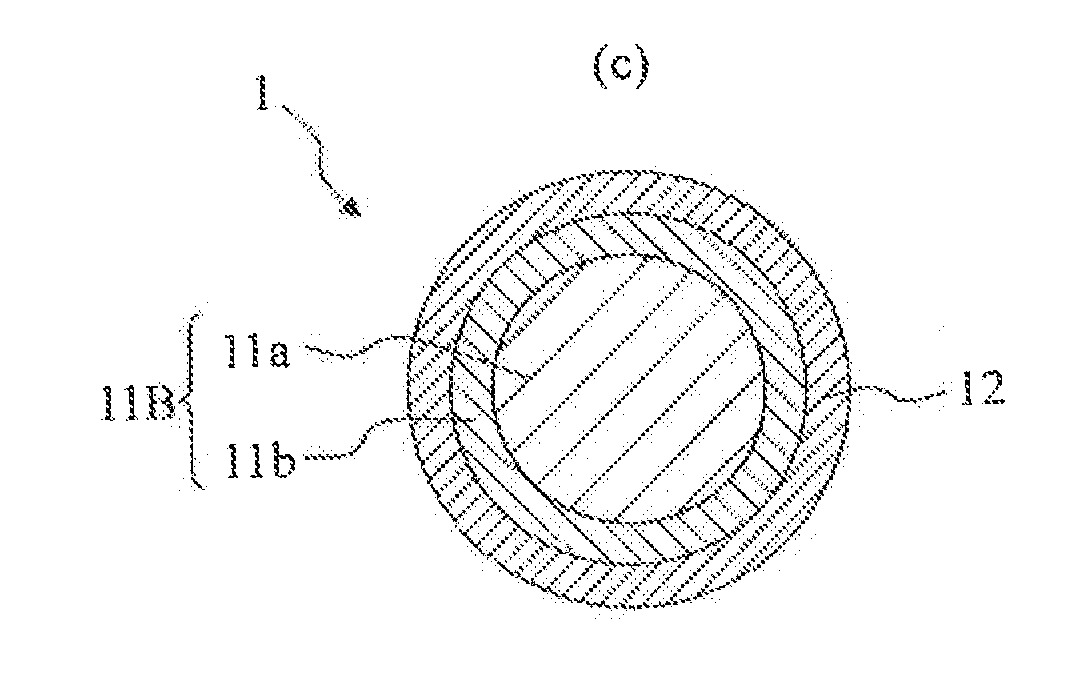

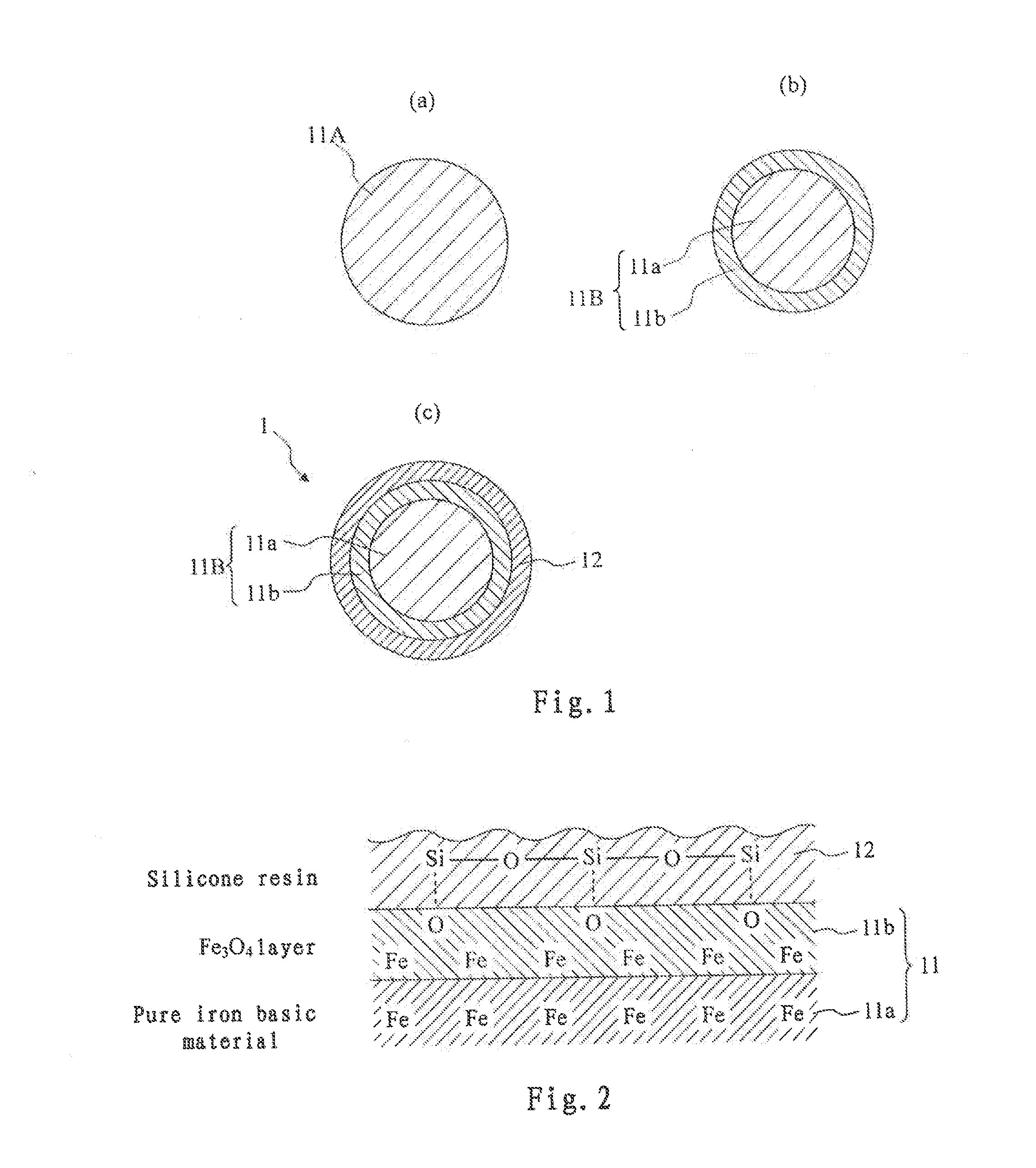

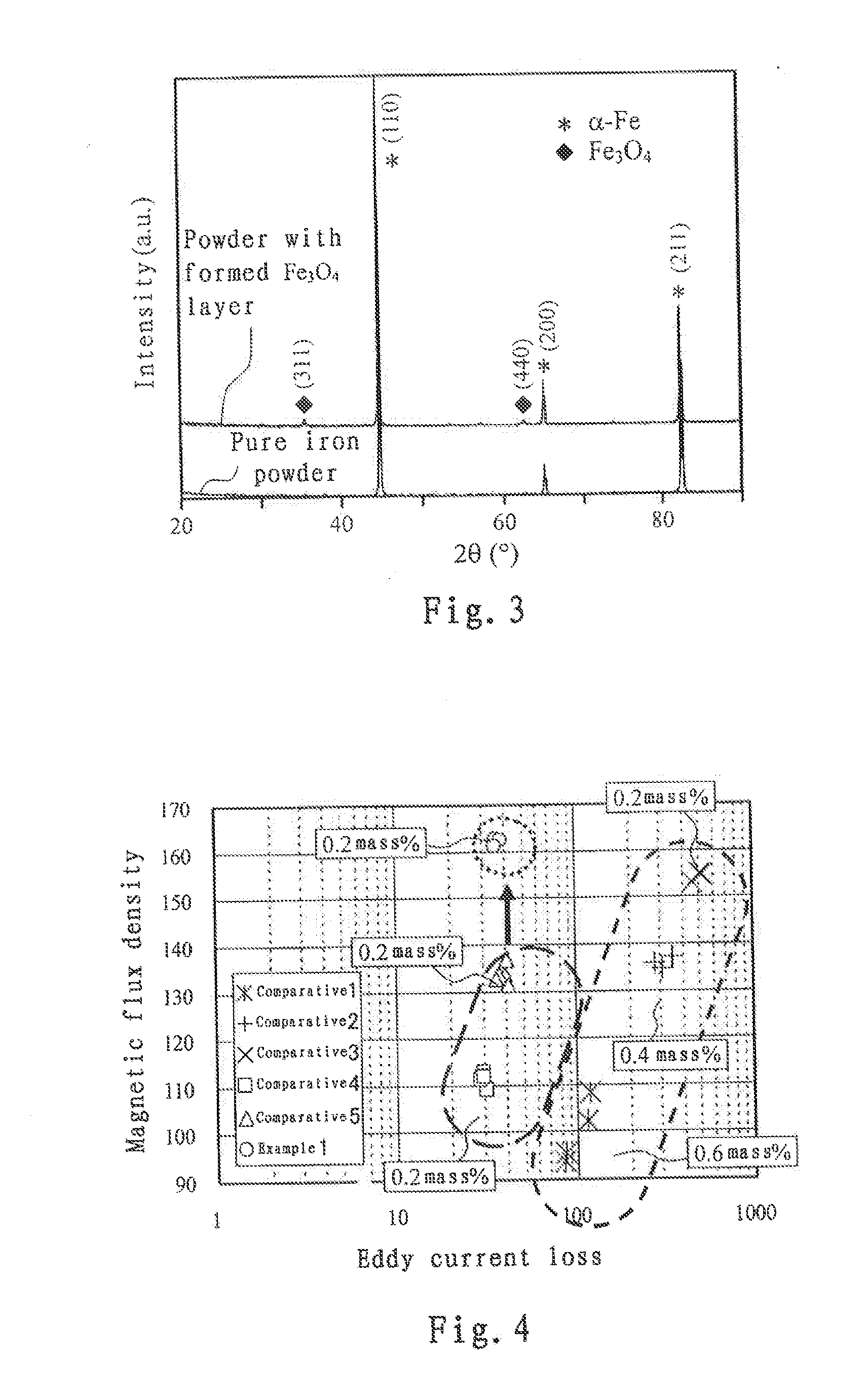

Composite soft magnetic powder, composite soft magnetic powder core, and preparation method therefor

InactiveUS20140104023A1Reduce lossHigh magnetic flux densitySynthetic resin layered productsMetal-working apparatusIron powderHigh density

The present invention discloses a composite soft magnetic powder core and a preparation method therefor, which belong to the technical fields of soft magnetic materials and preparation thereof. An Fe / Fe3O4 shell layer is generated in situ on surfaces of iron powder particles through a controlled oxidation process, to prepare Fe / Fe3O4 composite soft magnetic powder having a uniform structure. The Fe / Fe3O4 composite soft magnetic powder is mixed with suitable amount of silicone resin, and prepared into a high-performance Fe / Fe3O4 composite soft magnetic powder core by using a powder metallurgy compaction process. Such magnetic powder core has a high density, a high magnetic conductivity, a high magnetic flux density, a low loss, and a high breaking strength, and is useful in a large-power and low-loss application scenario. The present invention has the advantages of being rich in raw material resources, simple in process and environmentally friendly, and being suitable for industrial production.

Owner:TSINGHUA UNIV +1

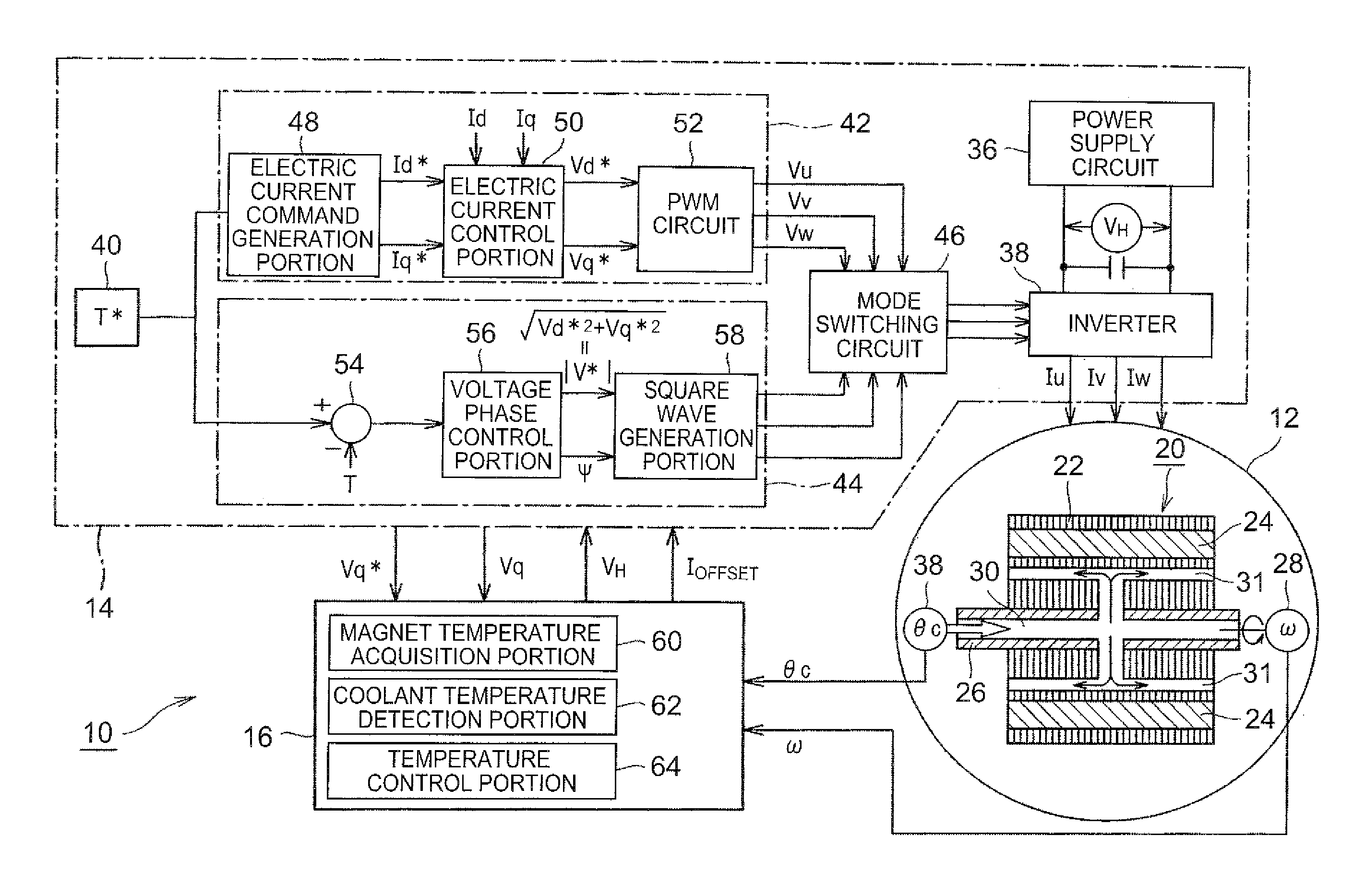

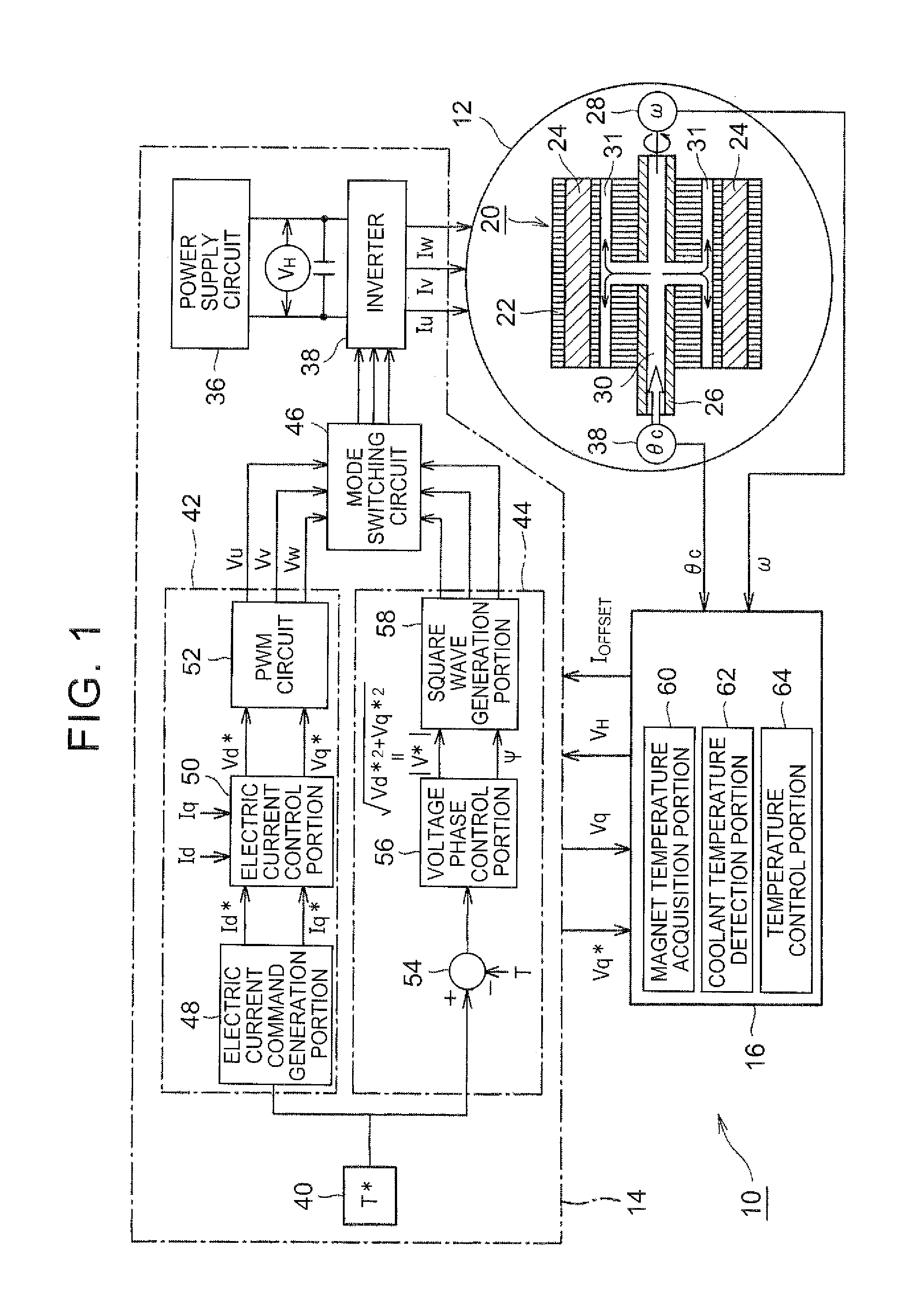

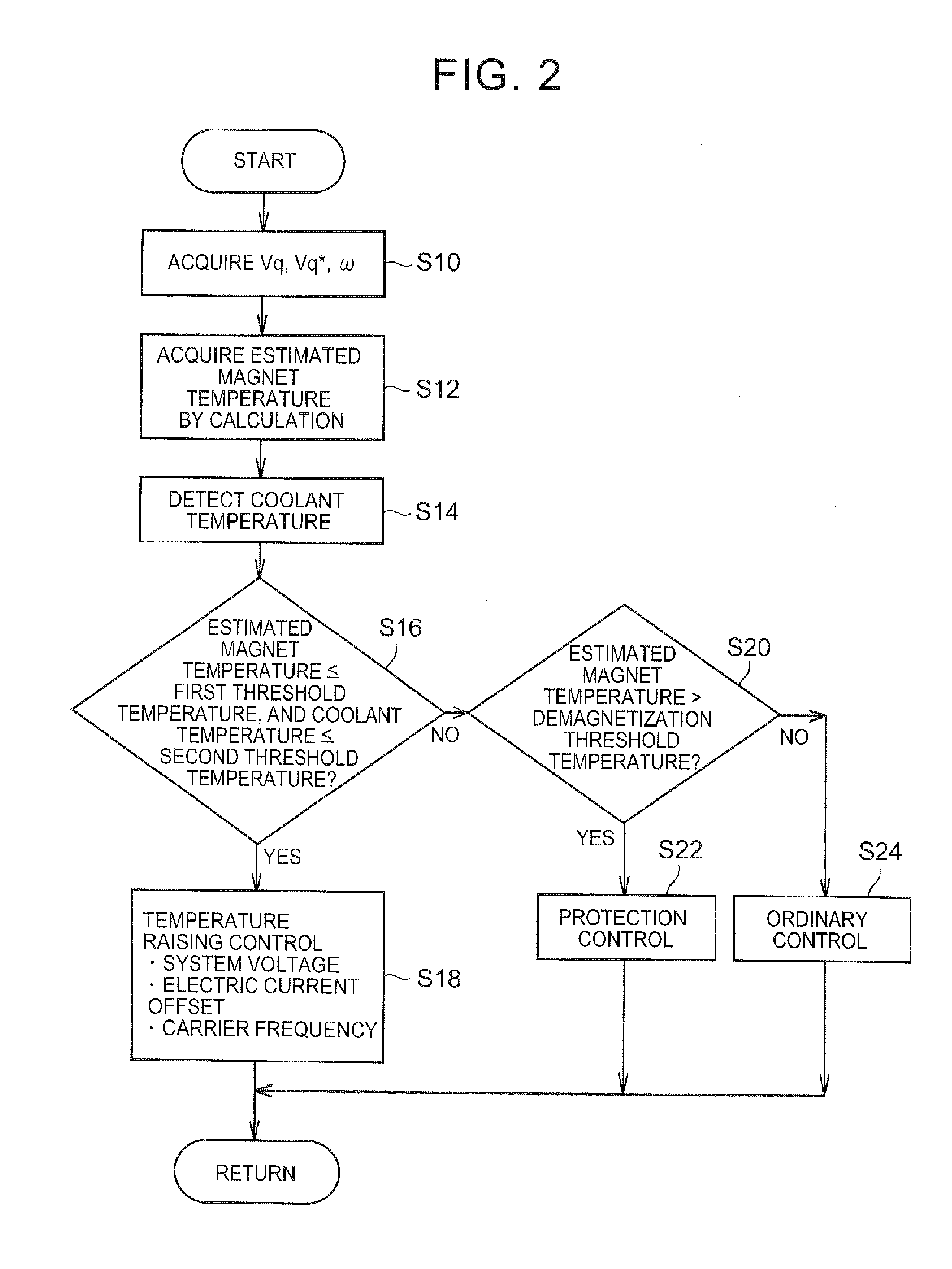

Control apparatus for rotary electric machine, rotary electric machine drive system, and control method for rotary electric machine

InactiveUS20140054986A1Improve energy efficiencyAvoid demagnetizationElectronic commutation motor controlAC motor controlTemperature controlElectric machine

A control apparatus for a rotary electric machine, which has a rotary element that includes a permanent magnet, includes a magnet temperature acquisition portion, a coolant temperature detection portion and a temperature control portion. The magnet temperature acquisition portion acquires information about temperature of the permanent magnet. The coolant temperature detection portion detects temperature of a coolant that cools at least the rotary element. The temperature control portion performs a temperature raising control of the permanent magnet when the temperature of the permanent magnet is less than or equal to a first threshold temperature and the temperature of the coolant is less than or equal to a second threshold temperature.

Owner:TOYOTA JIDOSHA KK

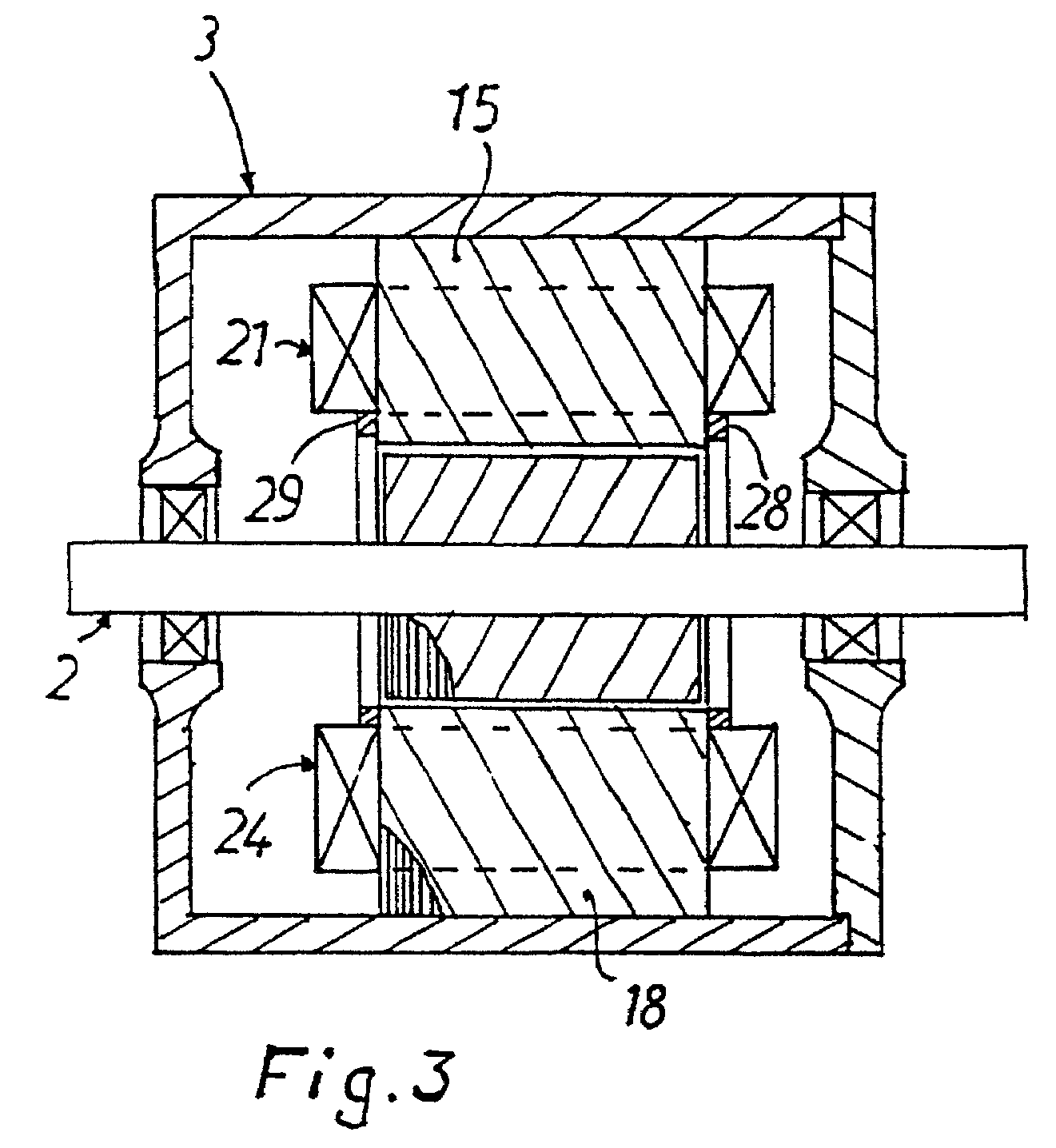

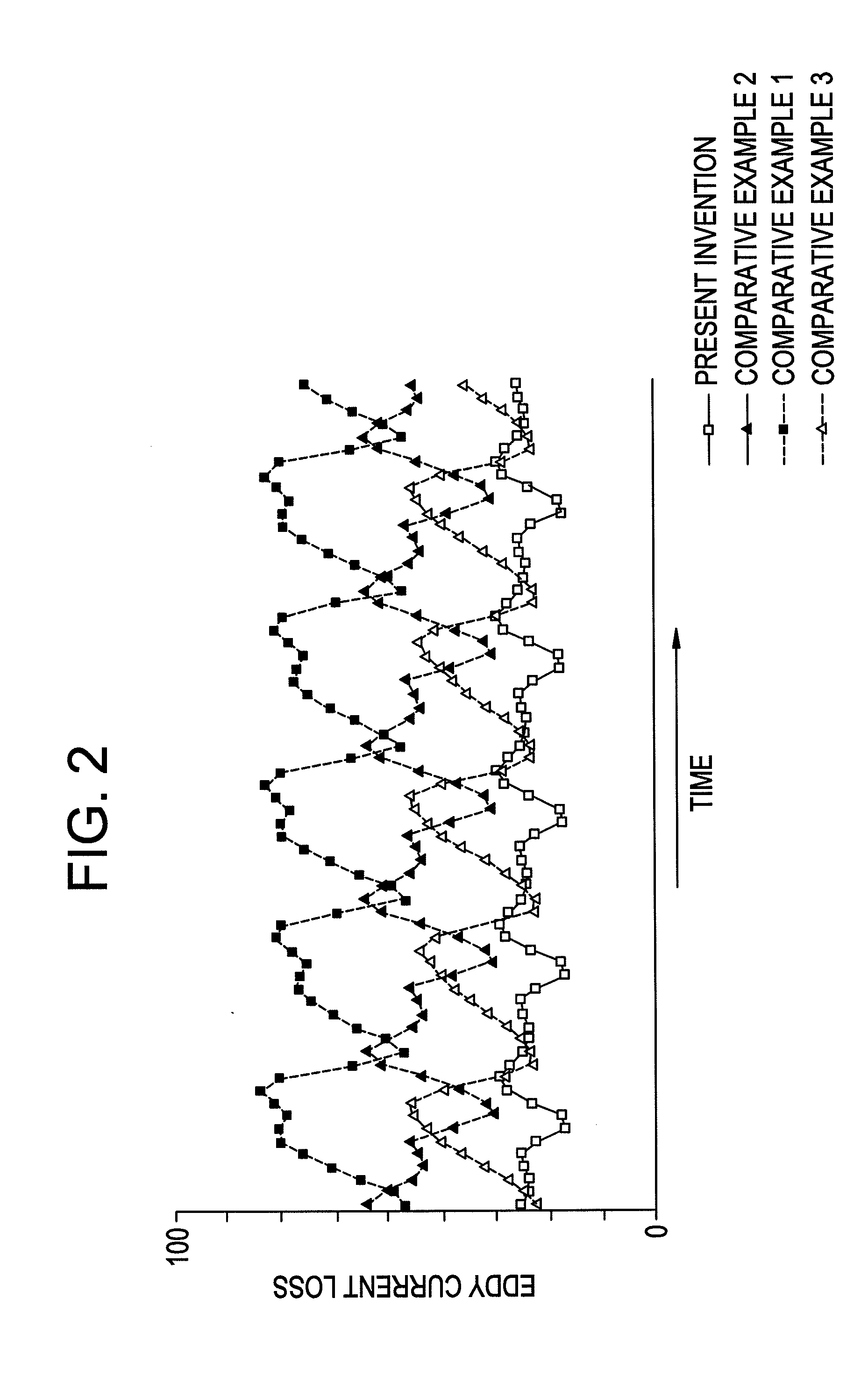

Reluctance motor with at least two salient poles each provided with an exciter winding, and method for manufacturing the stator of such reluctance motor

InactiveUS7215059B1Evenly distributedCurrent lossWindingsMagnetic circuit rotating partsSpring forceReluctance motor

A reluctance motor in which at least one snap ring engages the ends of the exciter coils remote from the stator yoke with radially outward acting spring force.

Owner:DAIMLER AG

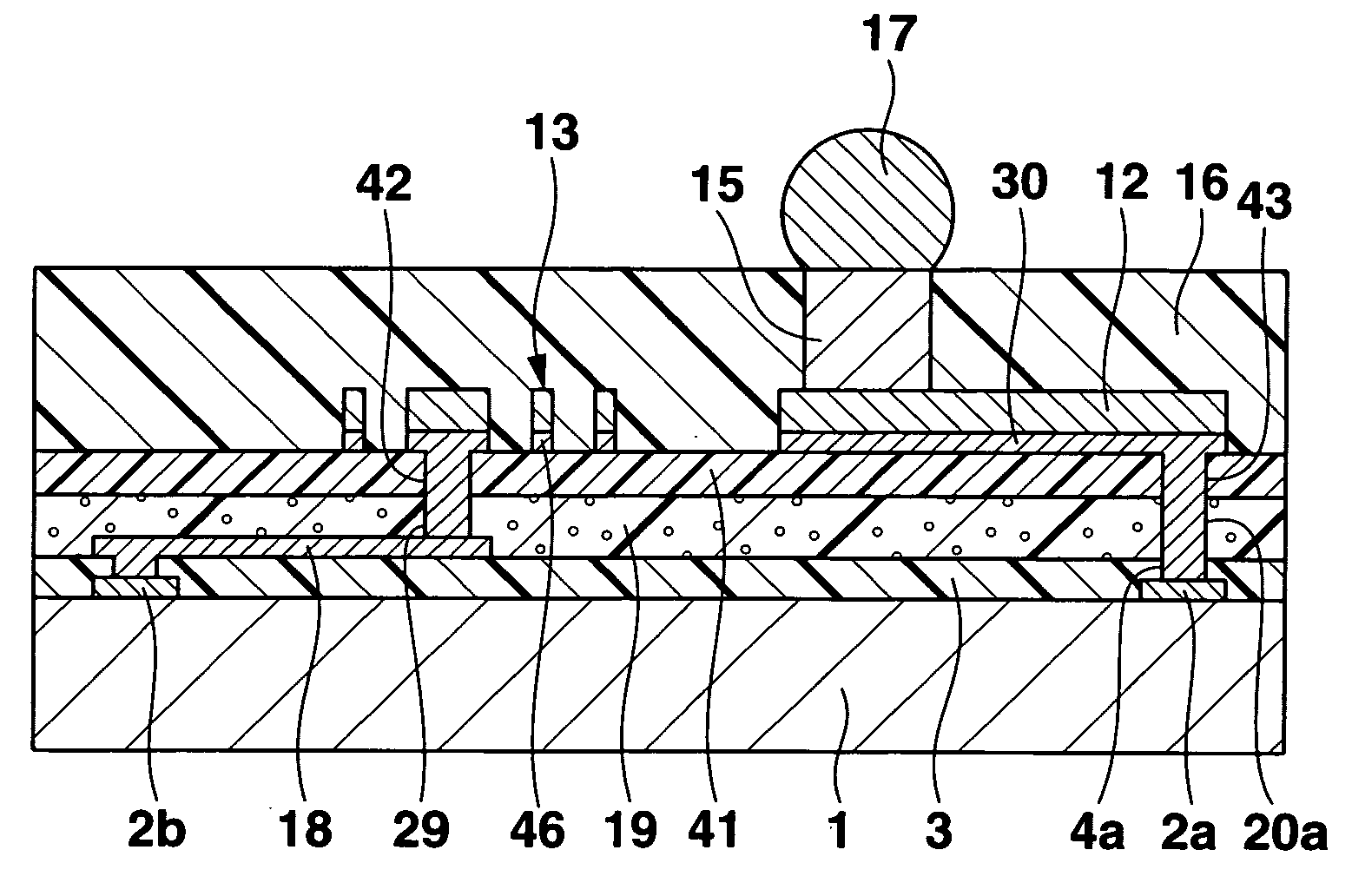

Semiconductor device with magnetic powder mixed therein and manufacturing method thereof

InactiveUS20080191349A1Suppress unnecessary radiant noiseReduce eddy current lossSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A semiconductor device includes a semiconductor substrate on one side of which an integrated circuit and a plurality of connection pads connected to the integrated circuit are provided. An insulating film is provided on the plurality of connection pads except for parts of the connection pads and on the one side of the semiconductor substrate. A plurality of wiring lines are provided to be electrically connected to the integrated circuit via the connection pads, each of the wiring lines having a connection pad portion. A plurality of columnar electrodes are respectively provided on one side of the connection pad portions of the wiring lines. A sealing film is provide on the peripheries of the columnar electrodes to cover the integrated circuit and which is provided. At least one of the insulating film and the sealing film is formed of a resin in which magnetic powder is mixed.

Owner:AOI ELECTRONICS CO LTD

Ring coil motor

InactiveUS7915777B2Simple and cost-effective to manufactureHighly suitableSynchronous generatorsAsynchronous induction motorsElectric machineEngineering

Owner:SIEMENS AG

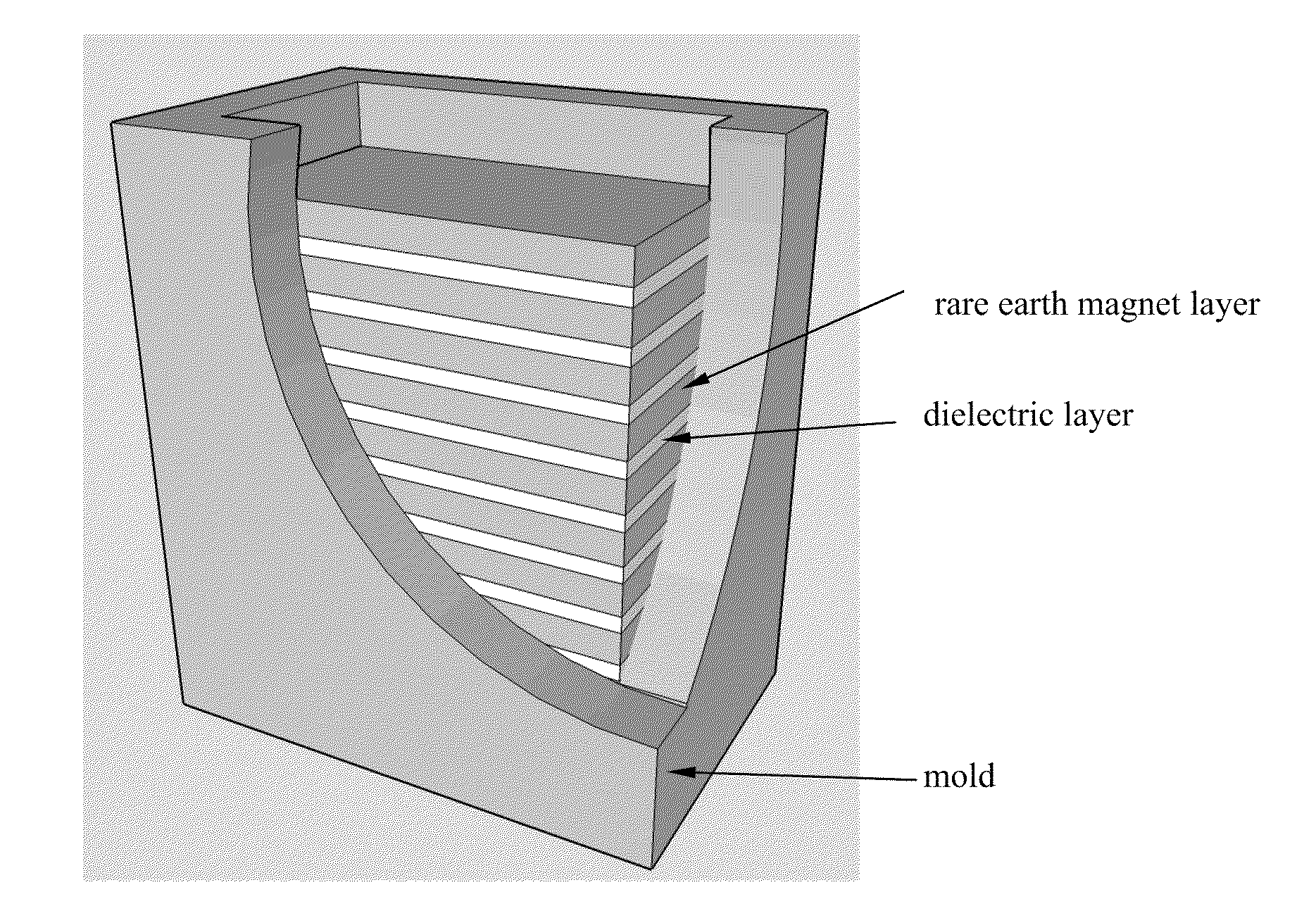

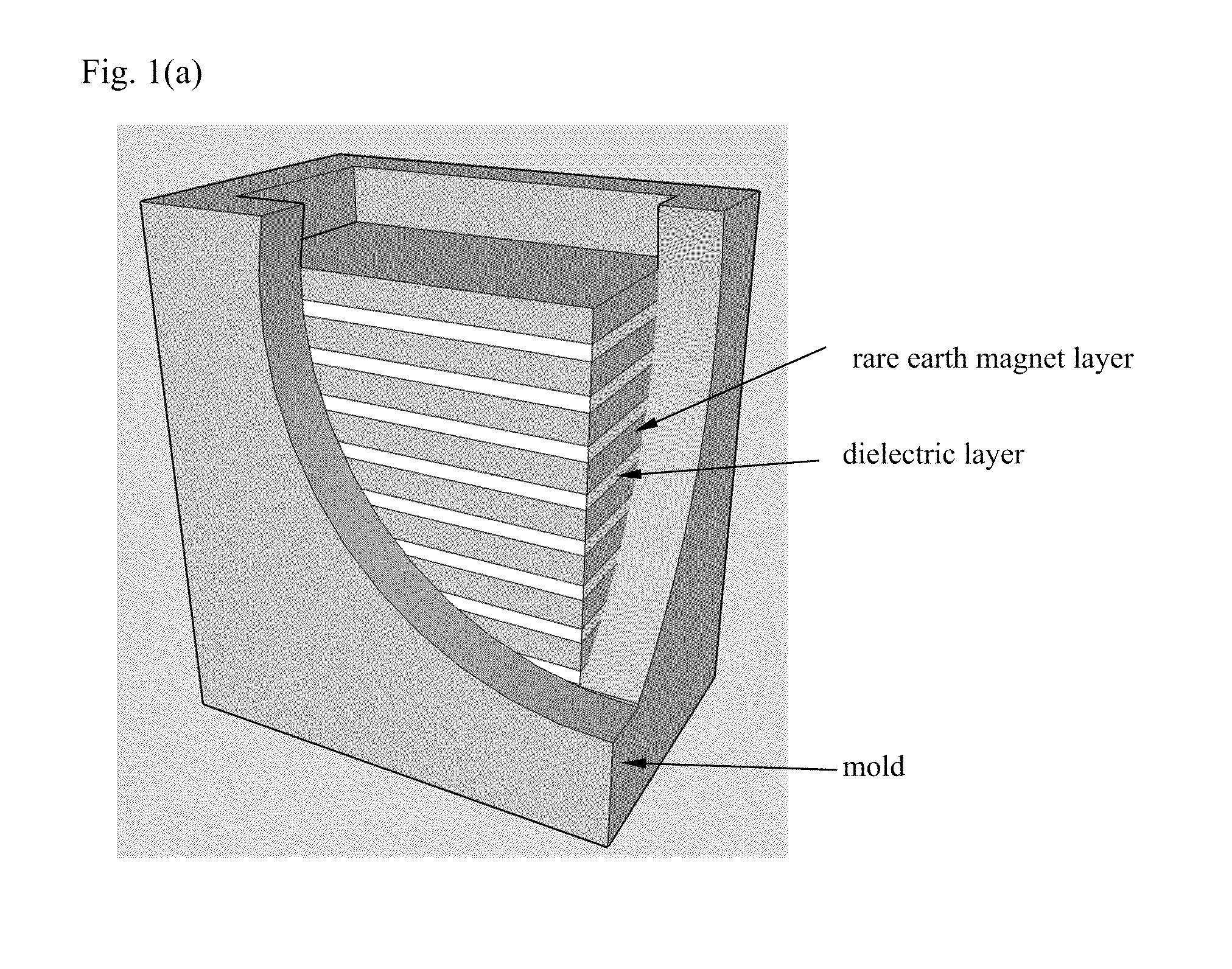

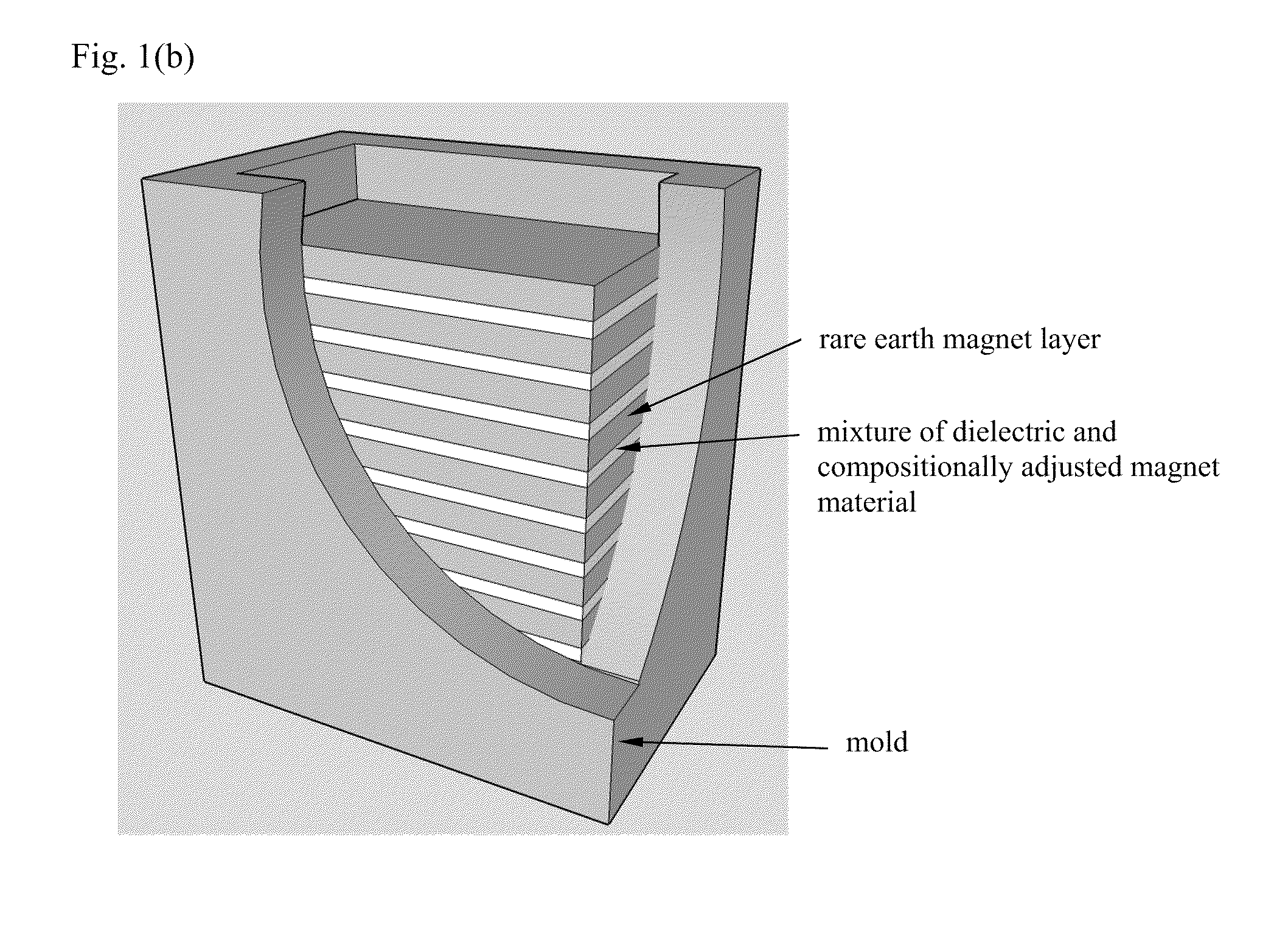

Rare Earth Laminated, Composite Magnets With Increased Electrical Resistivity

InactiveUS20110200839A1Increased electrical resistivityReduce lossNanomagnetismPermanent magnetsHigh resistivityMagnet

Laminated, composite, permanent magnets comprising layers of permanent magnets separated by layers of dielectric or high electrical resistivity substances, wherein the laminated magnets indicate increased electrical resistivity.

Owner:ELECTRON ENERGY CORP

Embedded permanent magnet electric motor

InactiveUS20120267975A1Total current dropDecrease in magnetic fluxMagnetic circuit rotating partsSynchronous machines with stationary armatures and rotating magnetsStator coilPermanent magnet motor

The embedded permanent magnet electric motor includes: a rotor having: a rotor core that has an outer circumferential surface that is constituted by a plurality of convex surfaces that are circular arc-shaped curved surfaces that are arranged continuously at a uniform angular pitch circumferentially; and a plurality of permanent magnets that are embedded in the rotor core so as to be positioned on a radially inner side of each of the circular arc-shaped curved surfaces; and a stator having: a stator core in which teeth are respectively disposed so as to extend radially inward from an annular core back and are arranged at a uniform angular pitch circumferentially to configure open slots; and a stator coil that is constituted by a plurality of concentrated winding coils that are wound into concentrated windings on each of the teeth.

Owner:MITSUBISHI ELECTRIC CORP

Device for determining a condition of flow in a respiration system

InactiveUS20090312661A1Function increaseReduce the possibility of errorRespiratorsMedical devicesCheck valveMedical device

A device for detecting the condition of flow in a respiration system combines the function of a nonreturn valve with the function of flow measurement in a common device. The device includes a valve arrangement (1) with a valve disk (9) and with a valve body (8), wherein the position of a valve disk (9) in relation to a valve seat (11) is detected. An indicator for a flow and a direction of flow (5), (6) is determined from the position of the valve disk (9). The position of the valve disk (9) can be determined inductively, electrically, electromechanically or optically. The flow and direction of flow (5), (6) determined can be used to control the respiration in a medical device.

Owner:DRAGERWERK AG

Rotating electrical machine

ActiveUS7872392B2Total current dropCurrent lossMagnetic circuit rotating partsPrevention/reducing eddy-current losses in winding headsEddy currentMechanical engineering

Owner:GENERAL ELECTRIC TECH GMBH

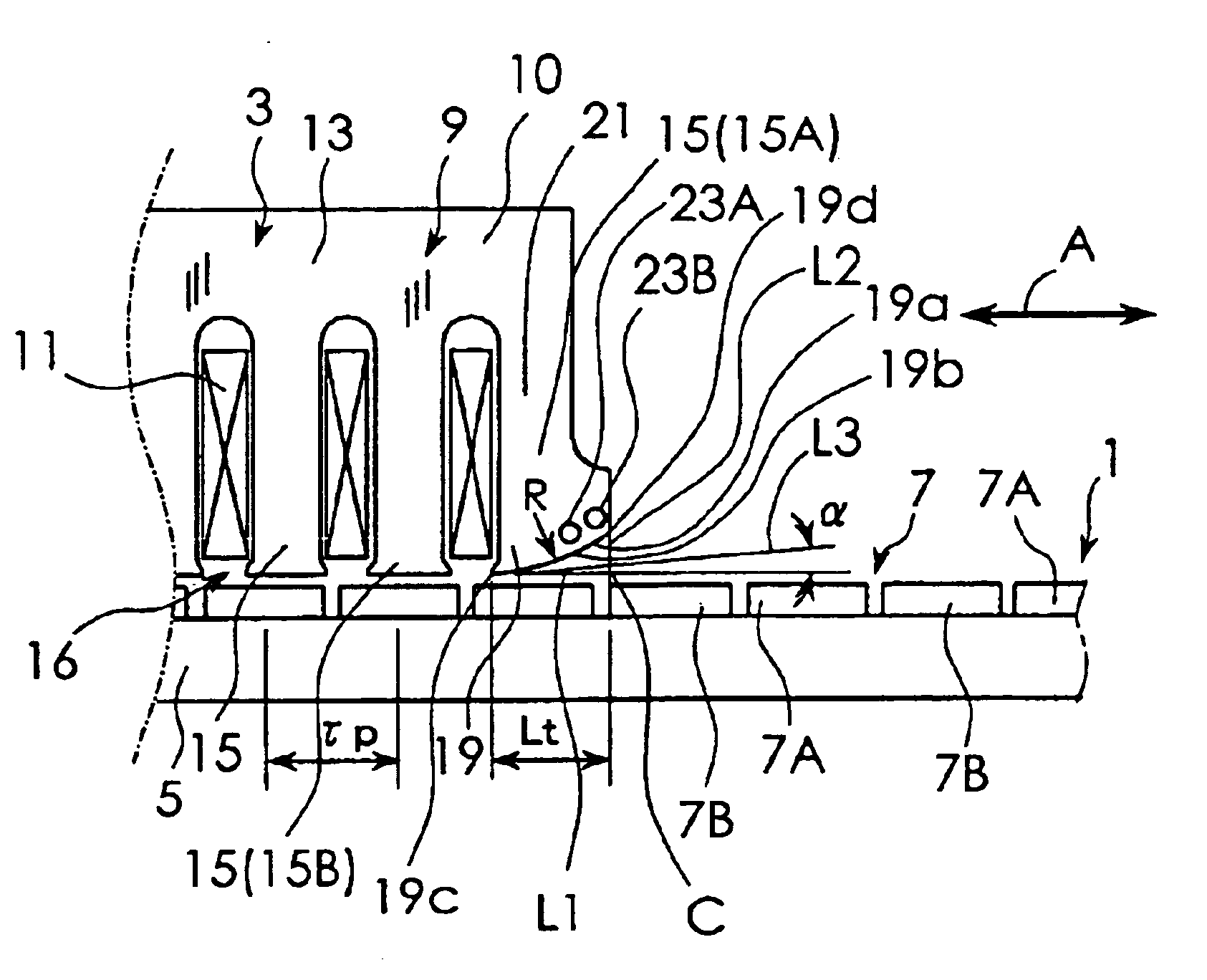

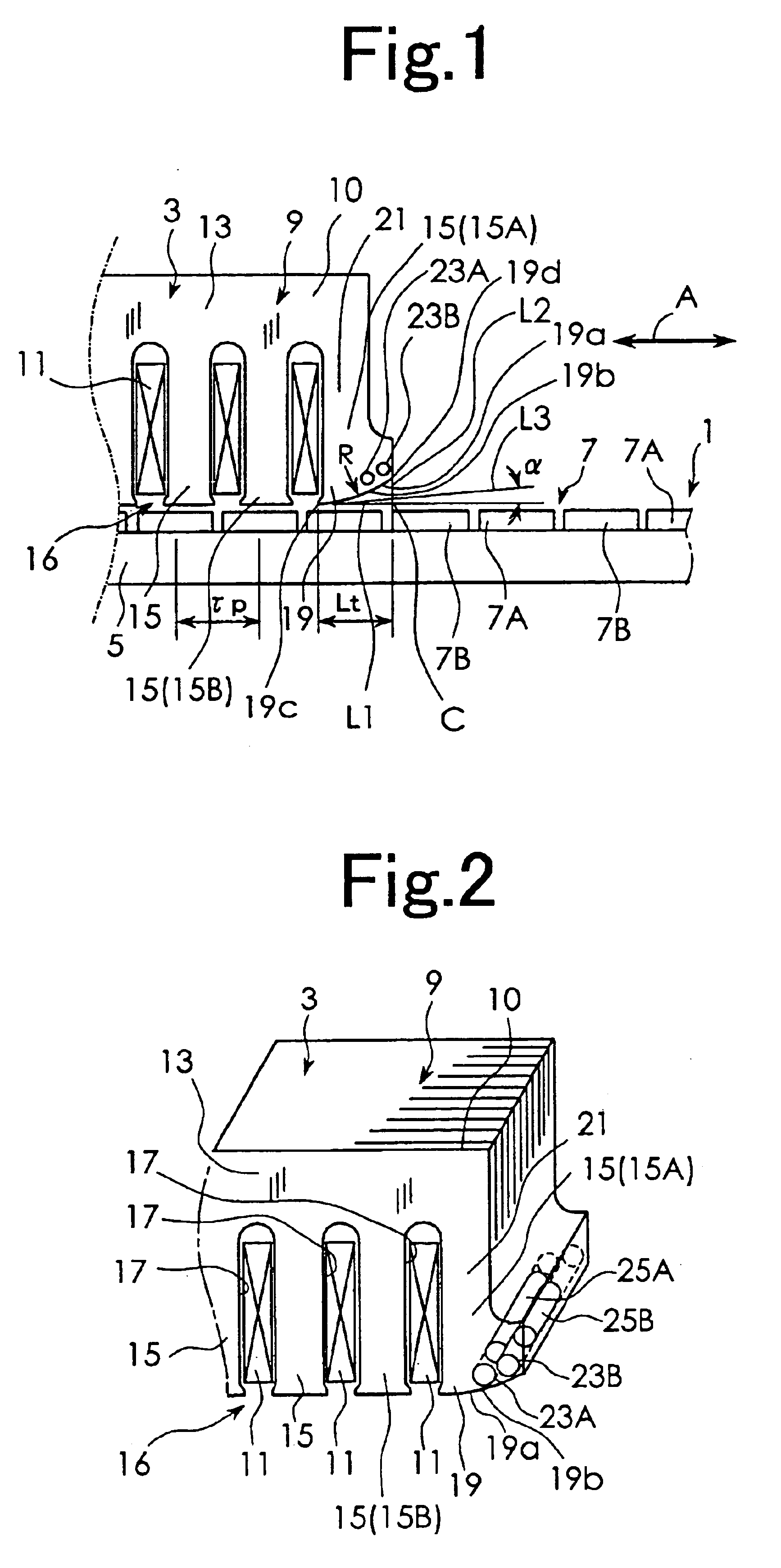

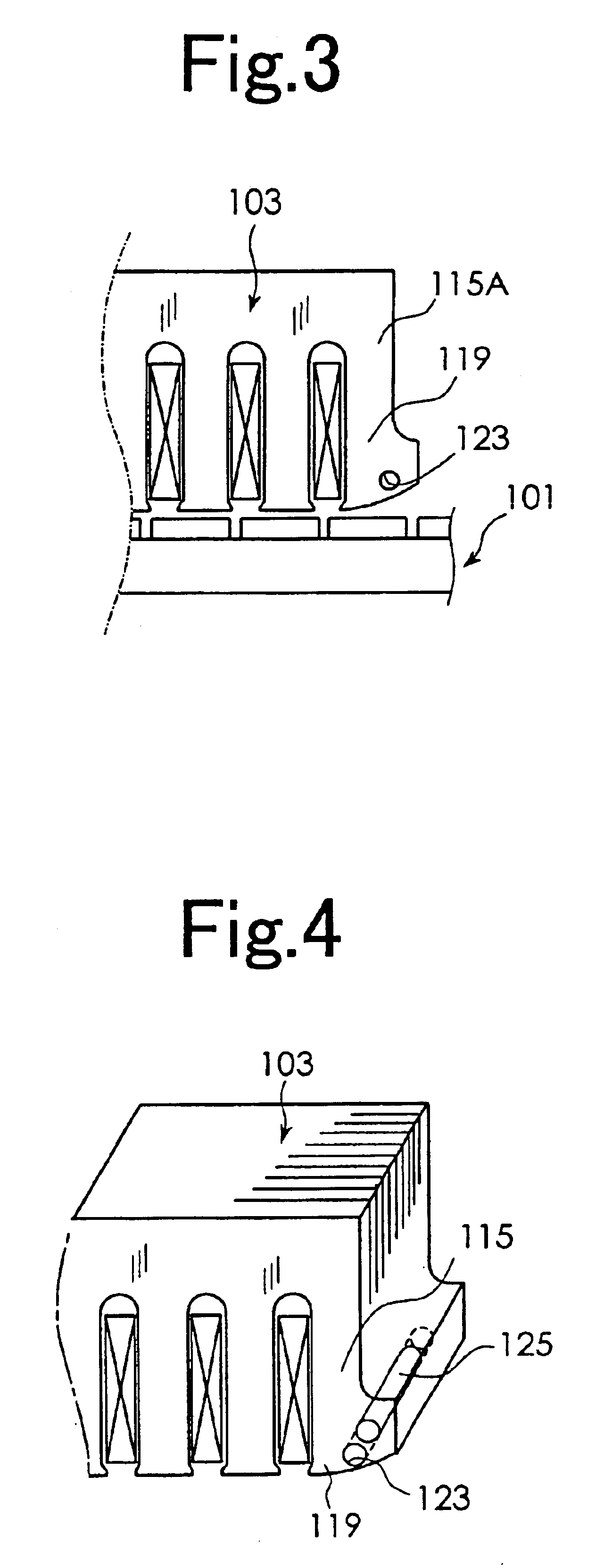

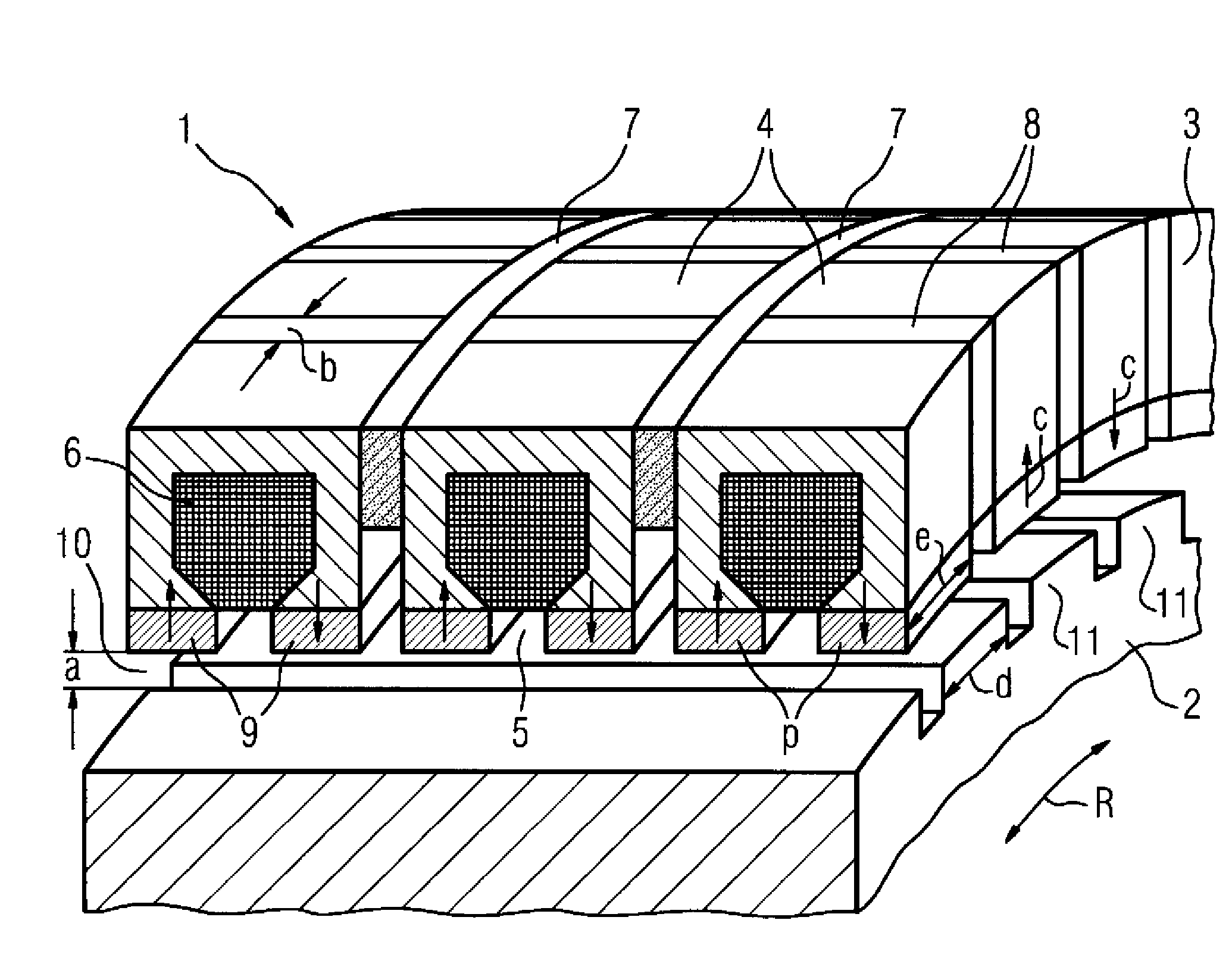

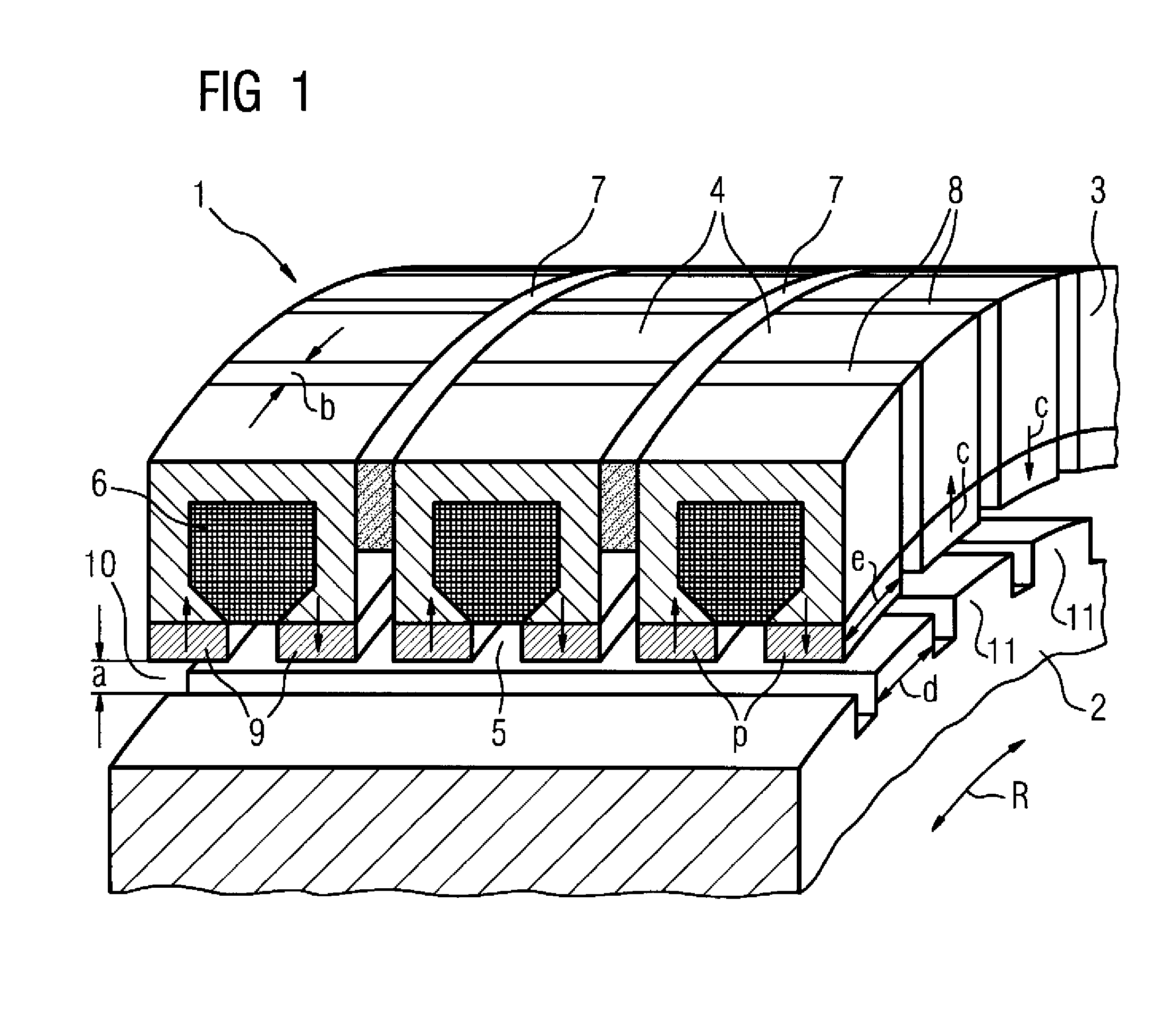

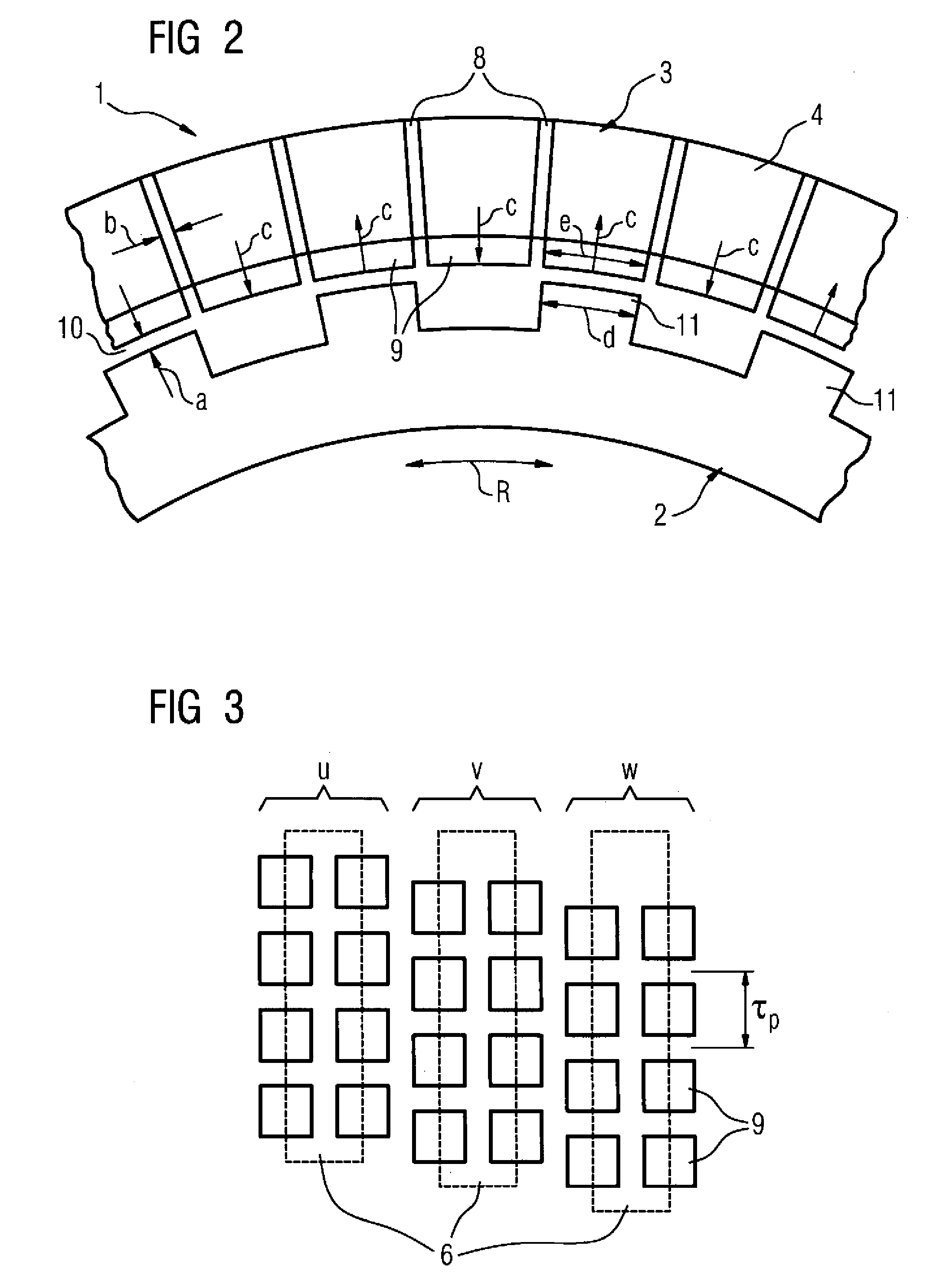

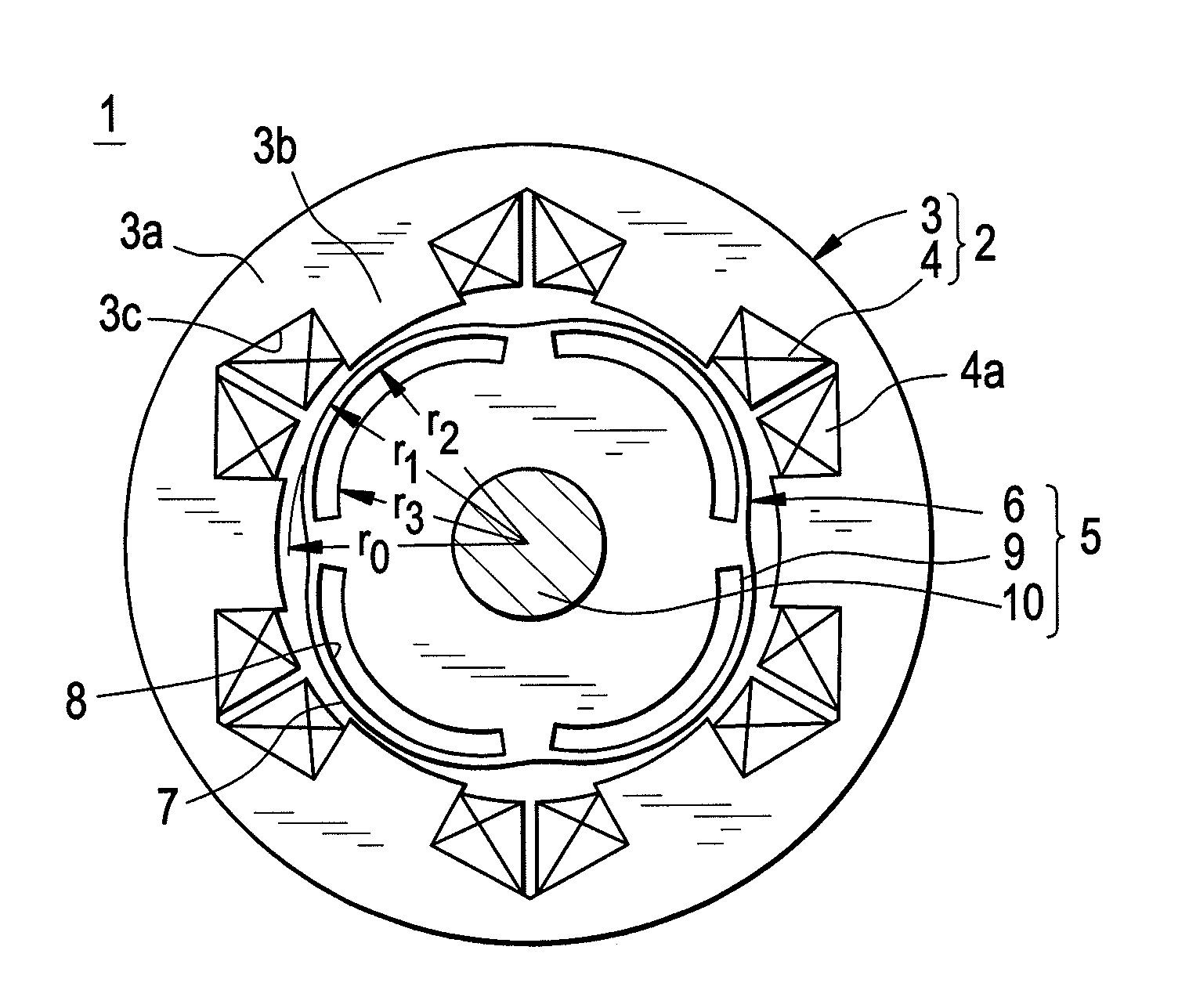

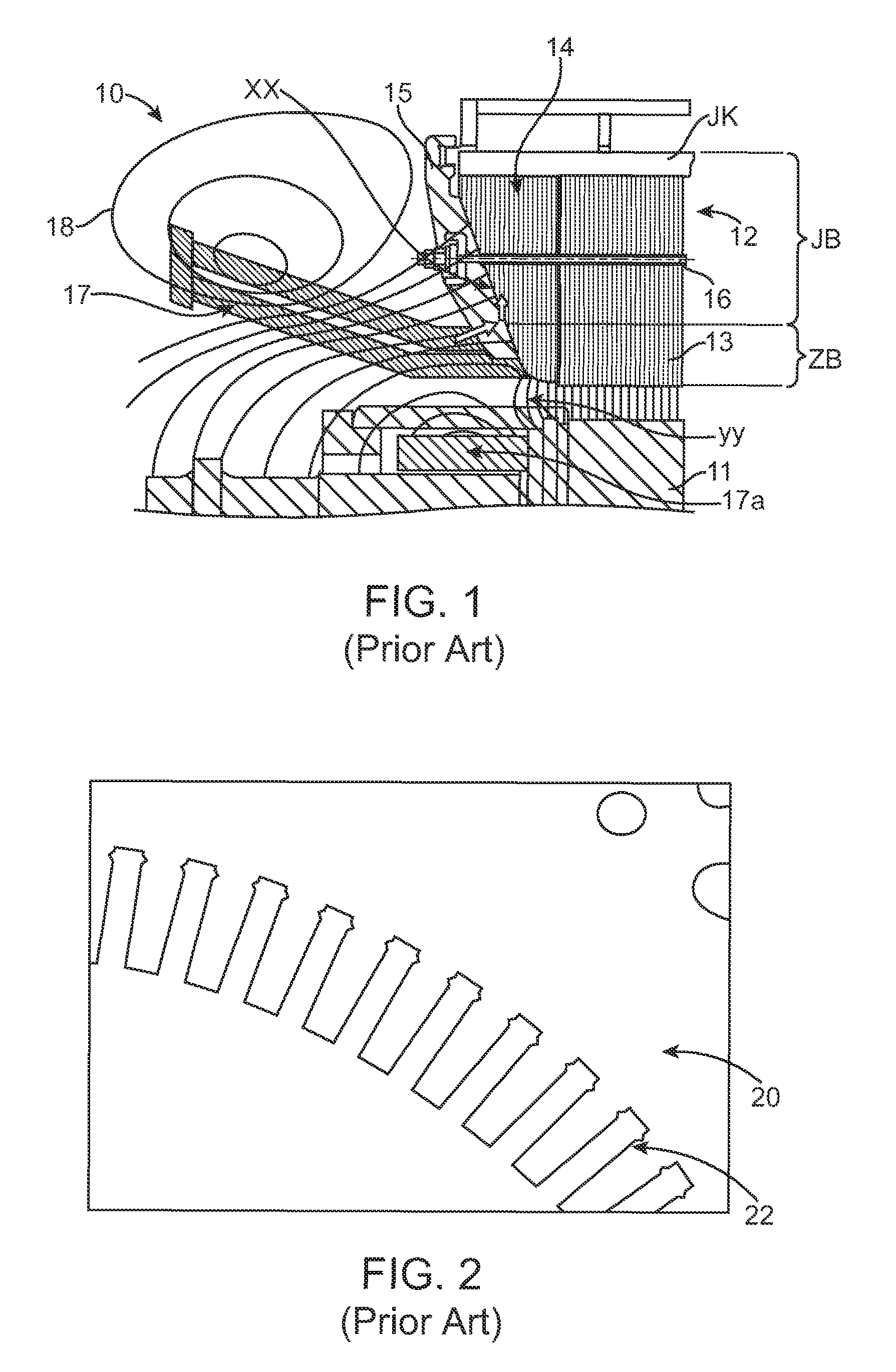

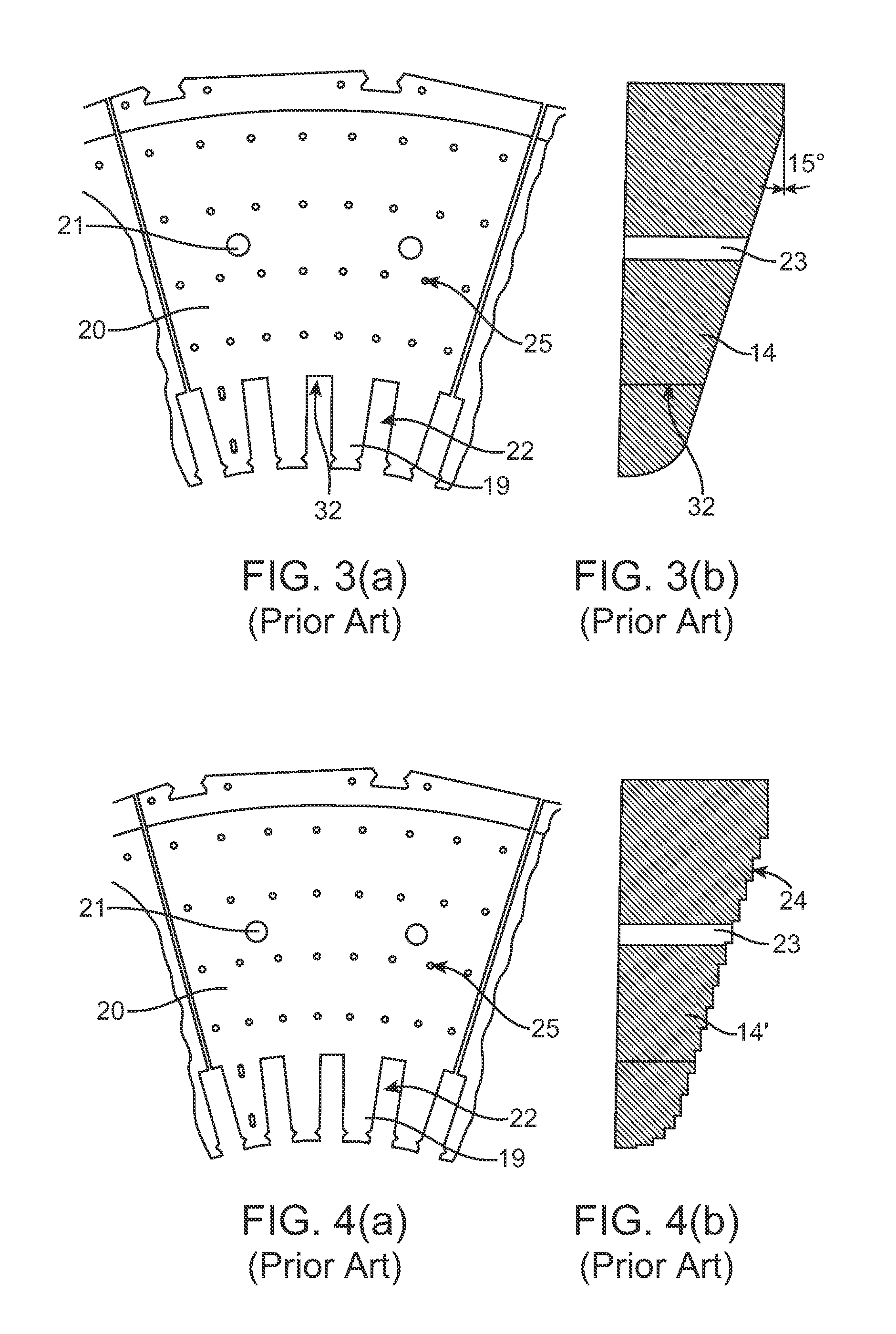

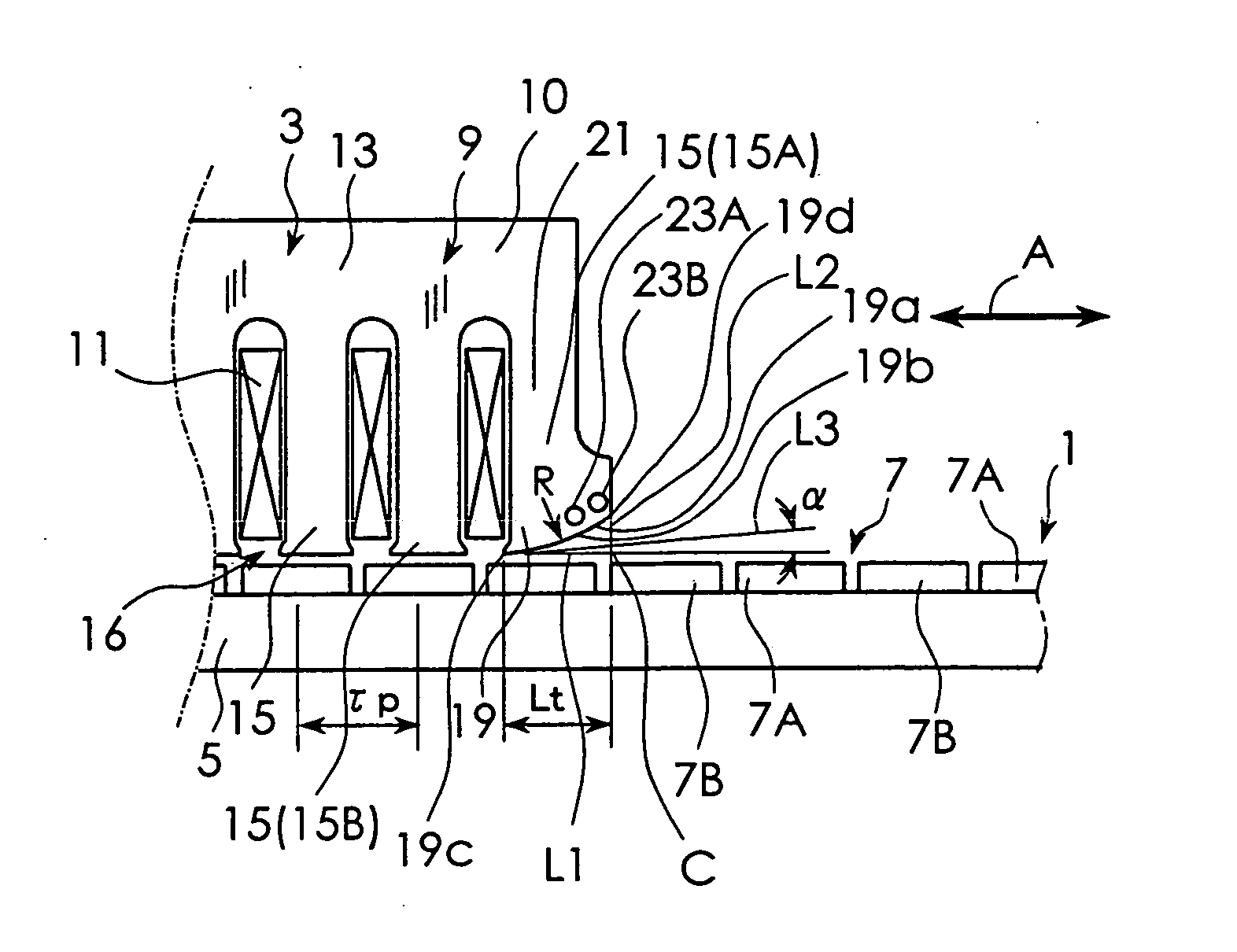

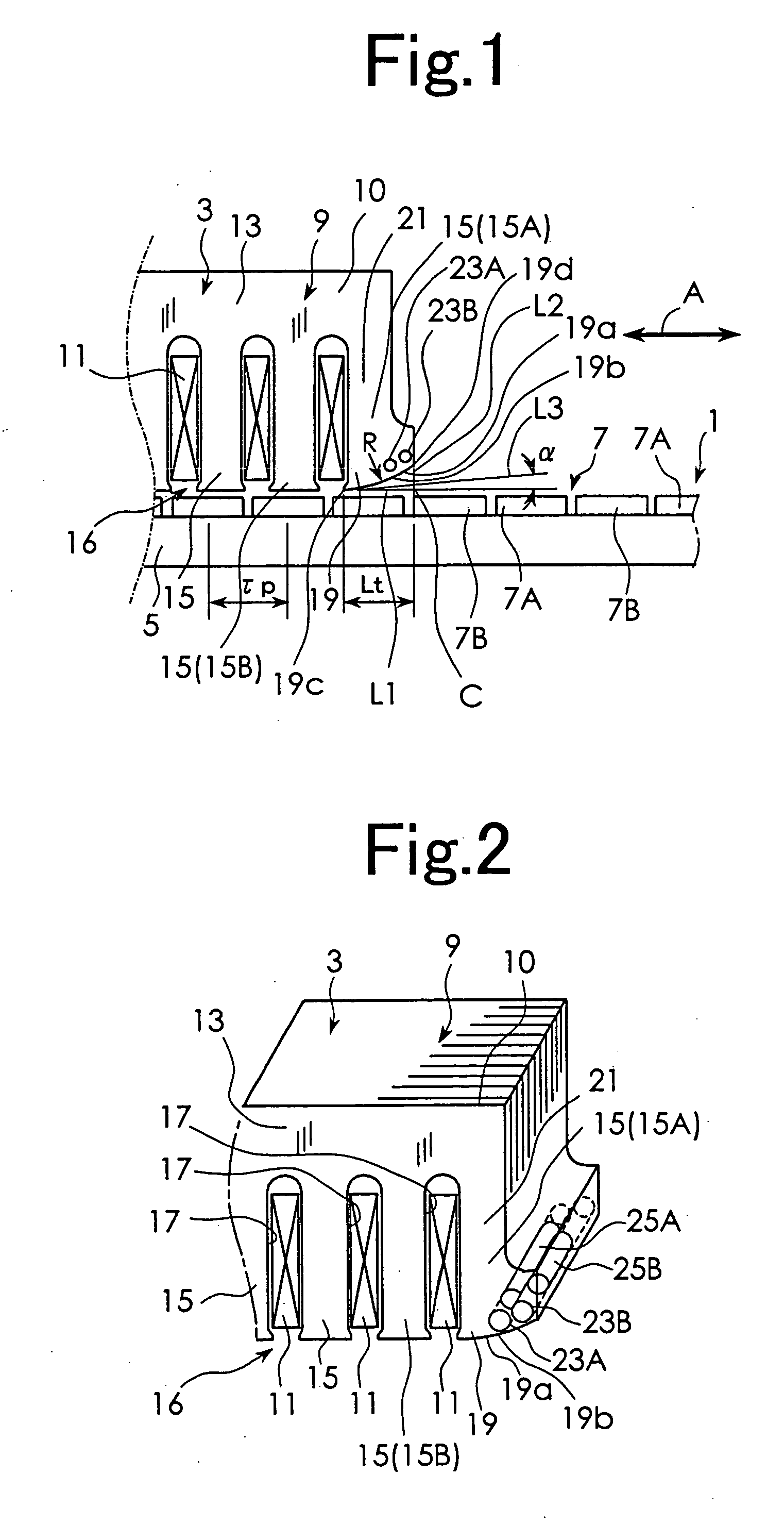

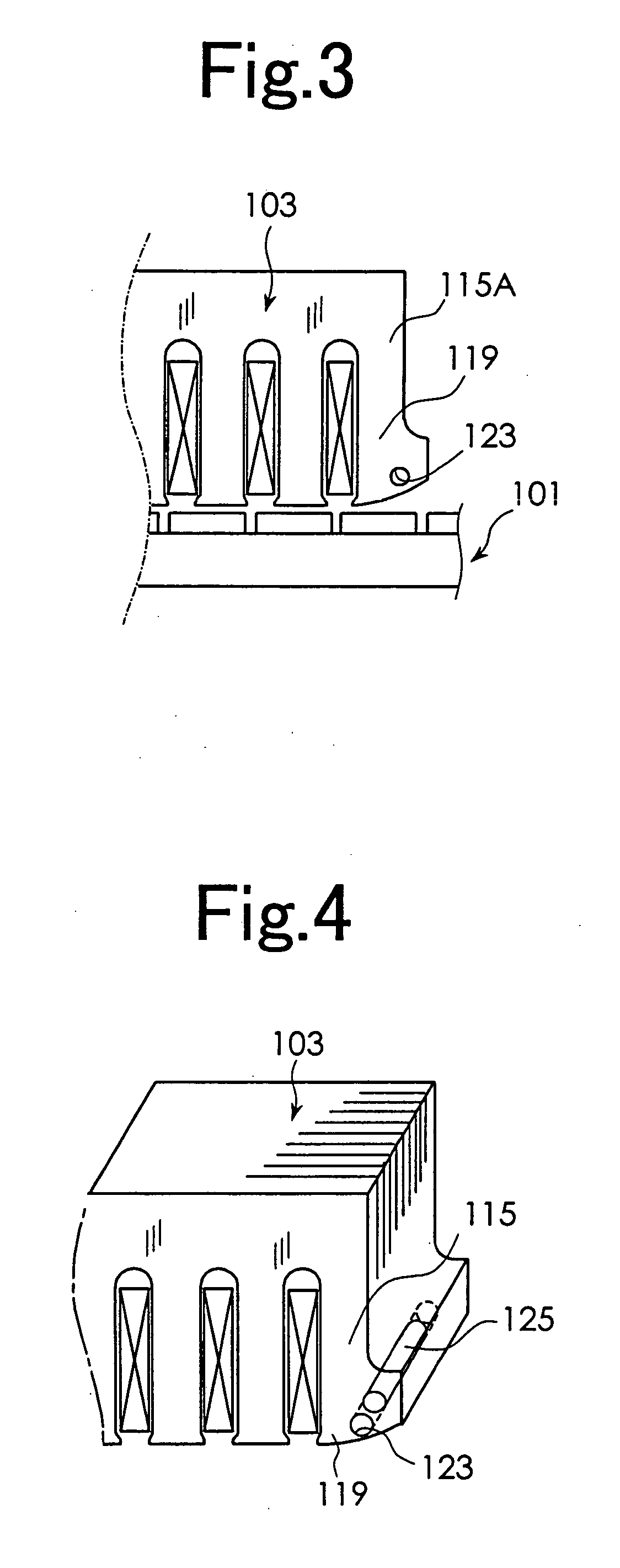

Linear motor with reduced cogging force

ActiveUS20050046281A1Reduce variationReduce cogging forceManufacturing dynamo-electric machinesPropulsion systemsMagnetic polesEngineering

A linear motor in which the shape of magnetic pole surfaces of pole teeth located at both ends of a plurality of pole teeth can be easily formed to be suitable for reducing cogging force. Each of magnetic pole surfaces 19a of pole teeth 15A located at both ends of a plurality of pole teeth 15 is constituted by an arc-shaped curved surface that is curved so that gap from a stator 1 increases with increasing distance from other adjacent pole tooth 15B. Through holes 23A and 23B that extend in the laminating direction of electromagnetic steel plates 10 are formed in the vicinity of the magnetic pole surfaces 19a of the pole teeth 15A. Inside the through holes 23A and 23B, magnetic pieces, which are shorter than the thickness of the electromagnetic steel plates in their laminating direction, are arranged so as to leave spaces at both ends of the through holes 23A and 23B.

Owner:SANYO DENKI CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com