Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

208results about How to "Minimum power consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

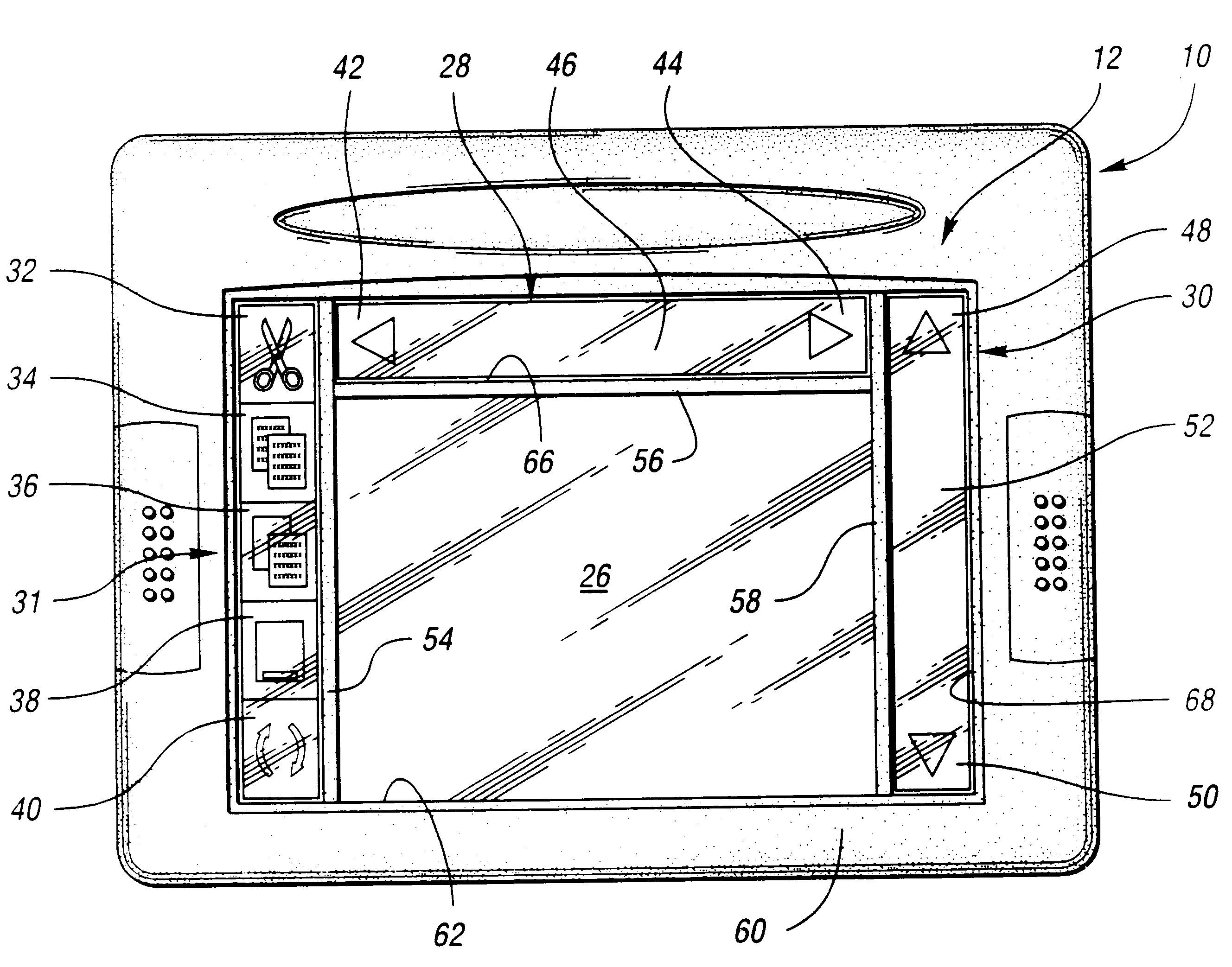

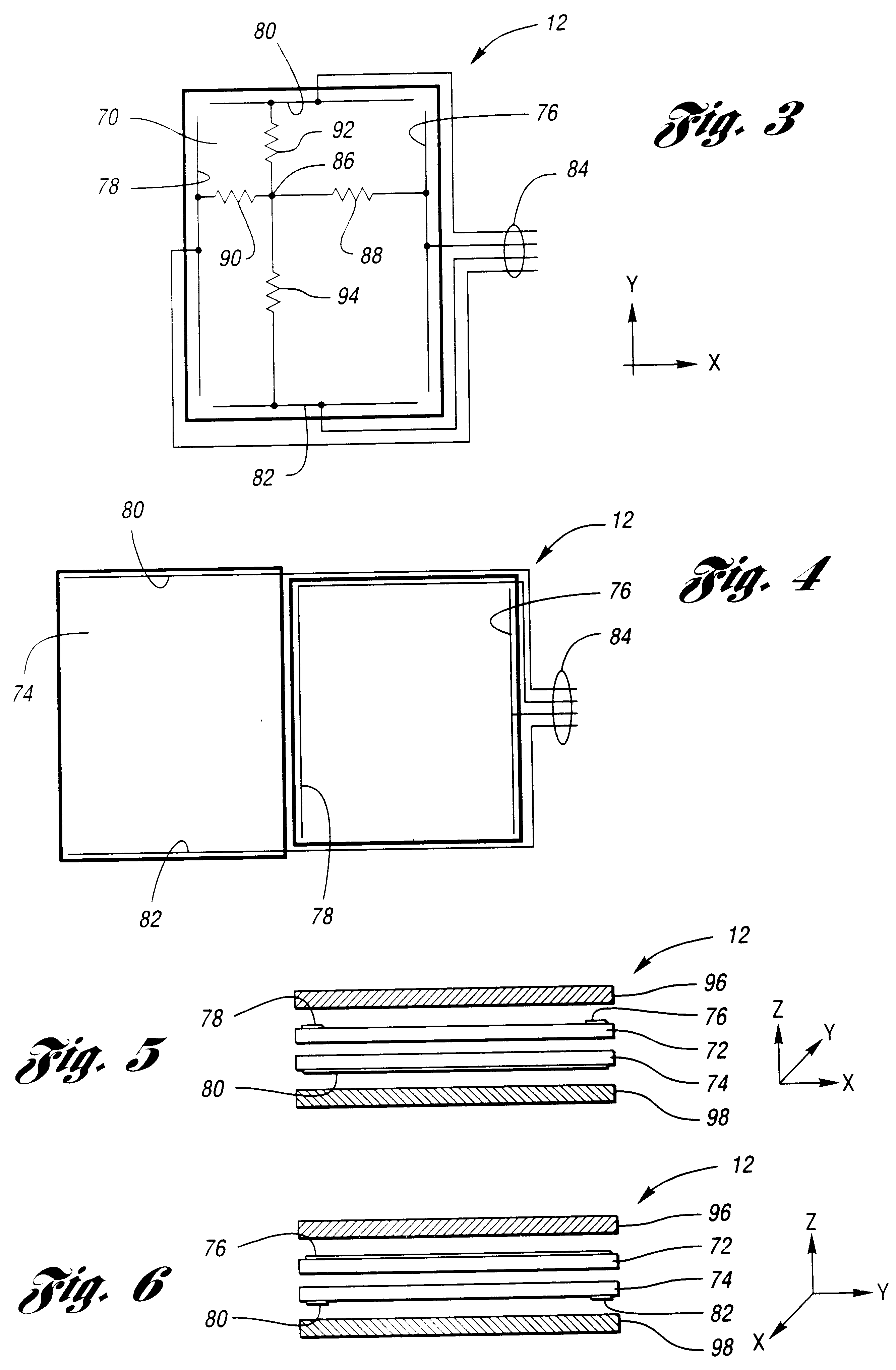

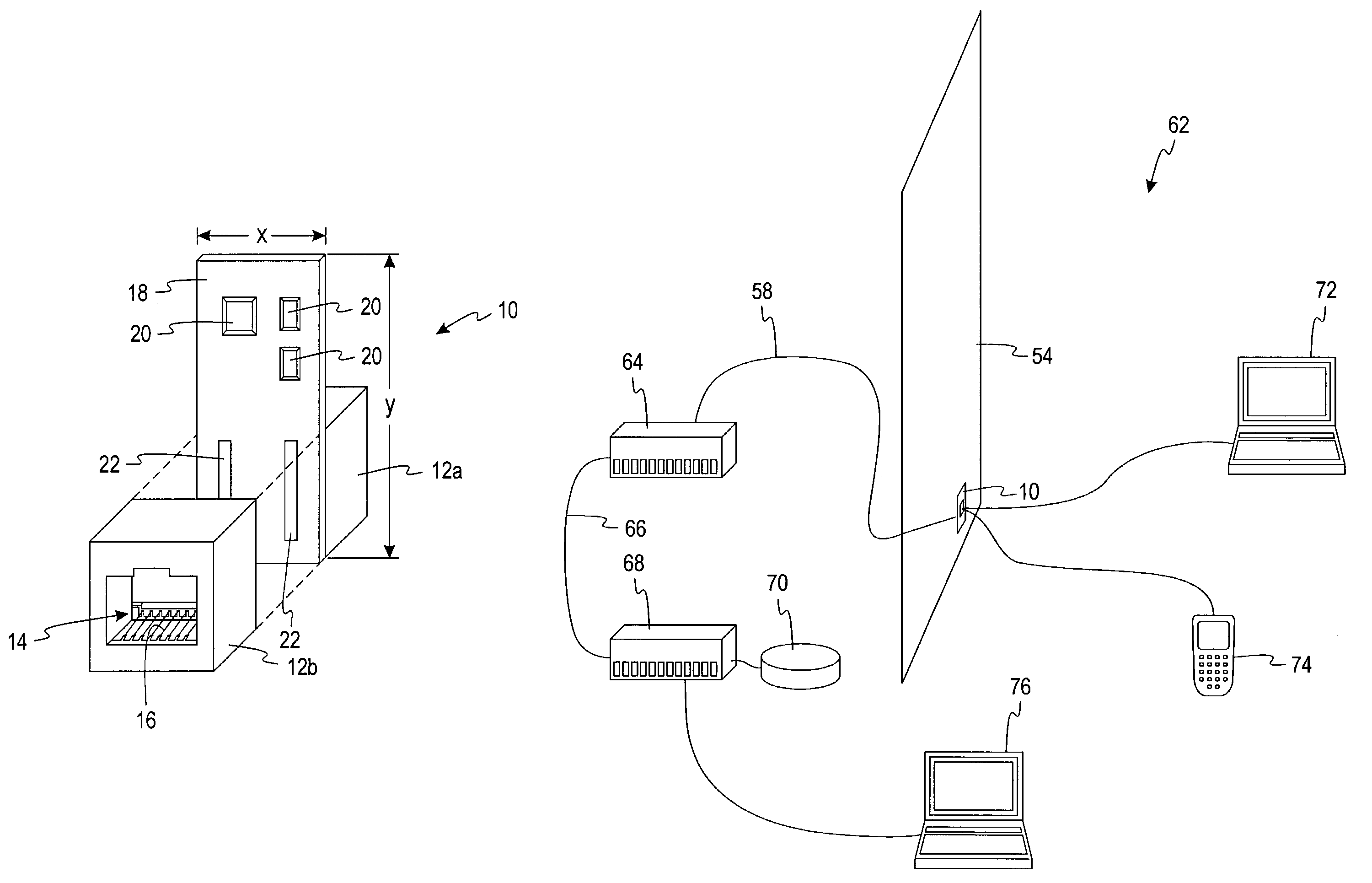

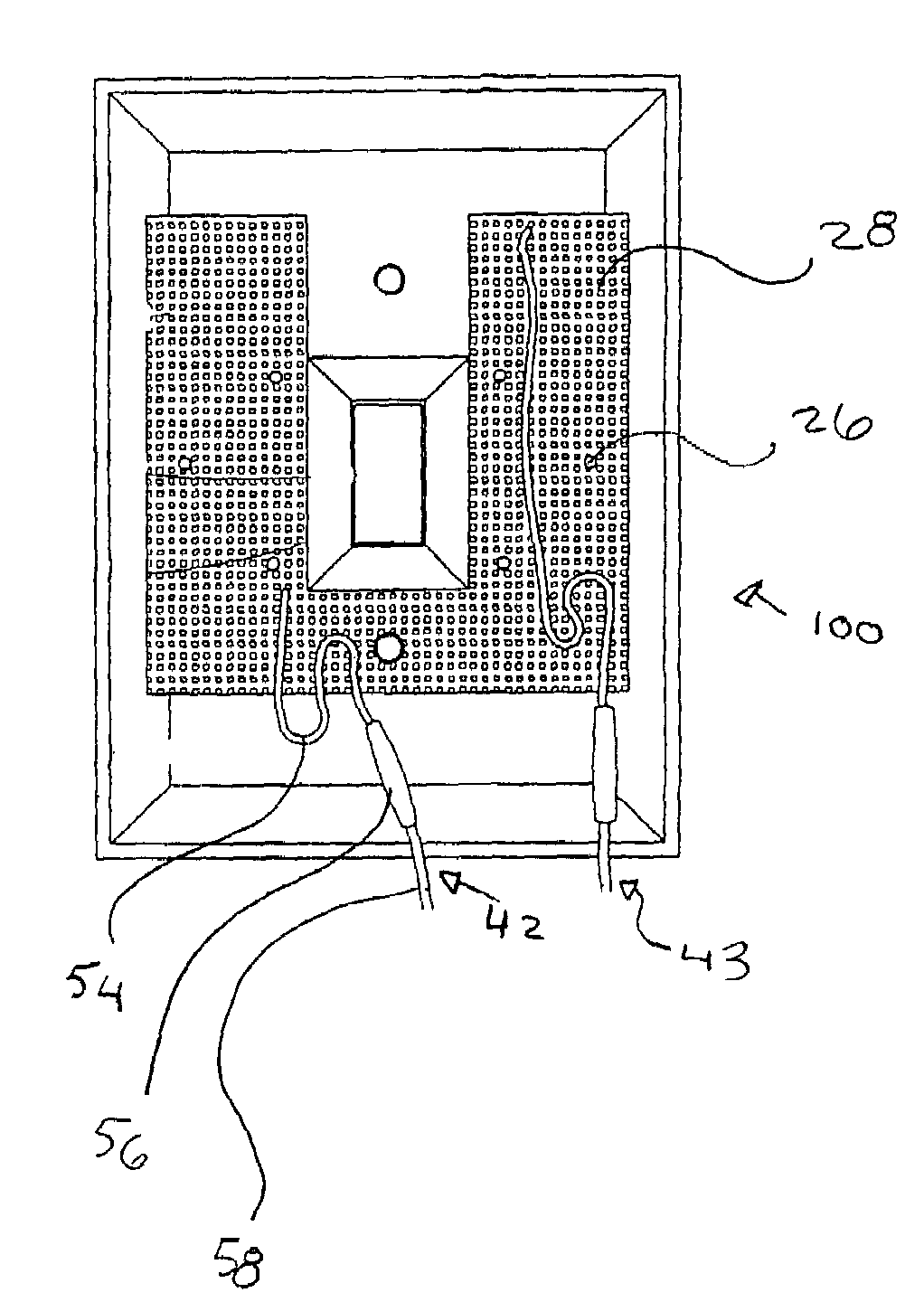

Force sensing semiconductive touchpad

InactiveUS6239790B1Minimum power consumptionLarge excursionTransmission systemsCathode-ray tube indicatorsPressure sensitiveEngineering

A touchpad assembly and method for providing a signal to a computer indicative of the location and applied pressure of an object touching the touchpad assembly is provided. The touchpad assembly includes X and Y position and pressure sensitive semiconductor resistance sensor layers. The X and Y sensors have a pair of spaced apart X and Y conductive traces running across opposite ends such that a resistance RX connects the pair of X traces and a resistance RY connects the pair of Y traces. The X and Y sensors come into contact at a contact point when an object asserts a pressure on the touchpad. The contact point is connected to each trace by a variable pressure resistance RZ associated with the X and Y sensors and variable position resistances of the X and Y resistances. First and second pair of timing capacitors are connected to respective ones of the pairs of X and Y traces. A microprocessor controls and monitors charging time of the capacitors to determine the position and asserted pressure of the object touching the touchpad.

Owner:INTERLINK ELECTRONICS

Novel massively parallel supercomputer

InactiveUS20090259713A1Low costReduced footprintError preventionProgram synchronisationSupercomputerPacket communication

Owner:INT BUSINESS MASCH CORP

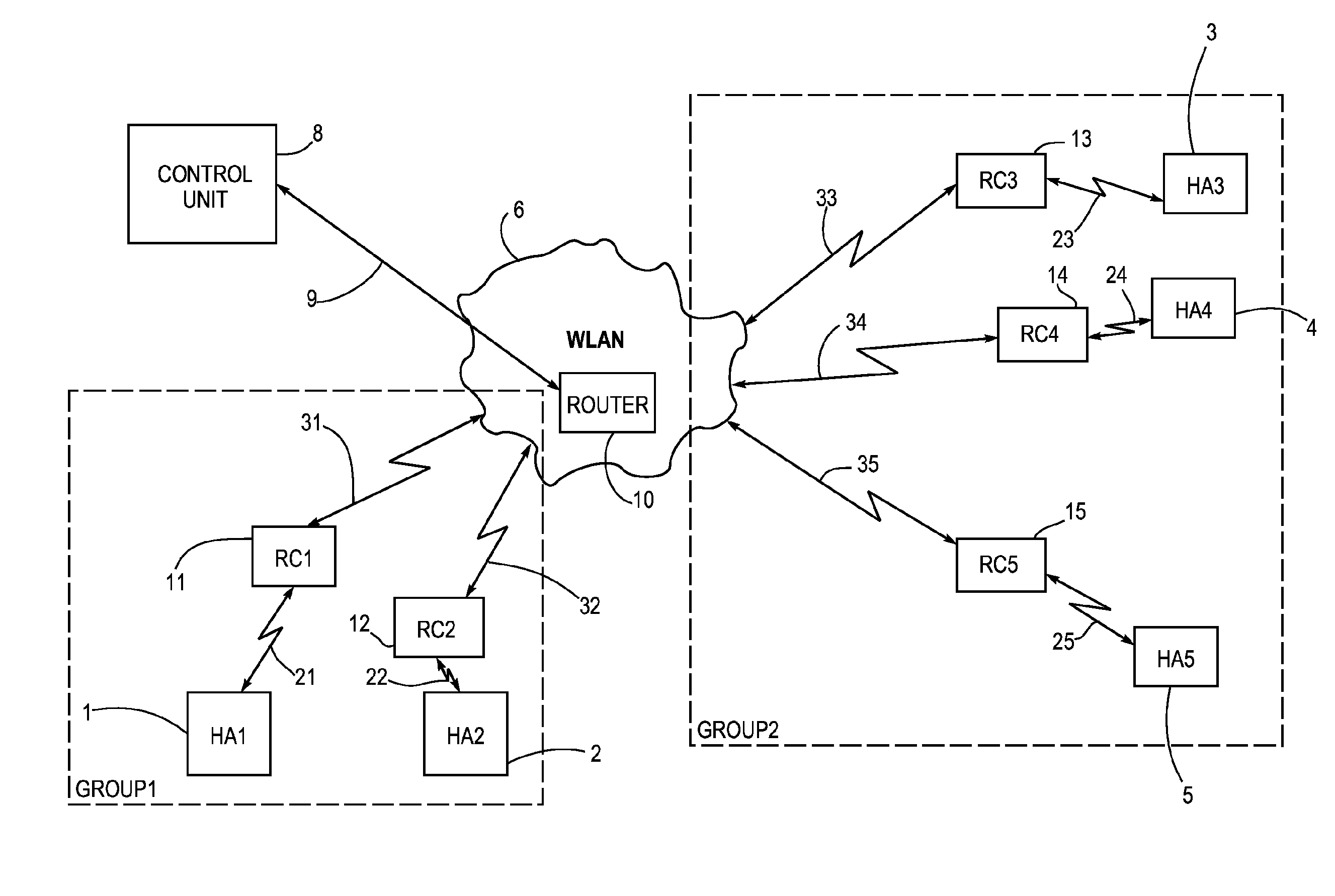

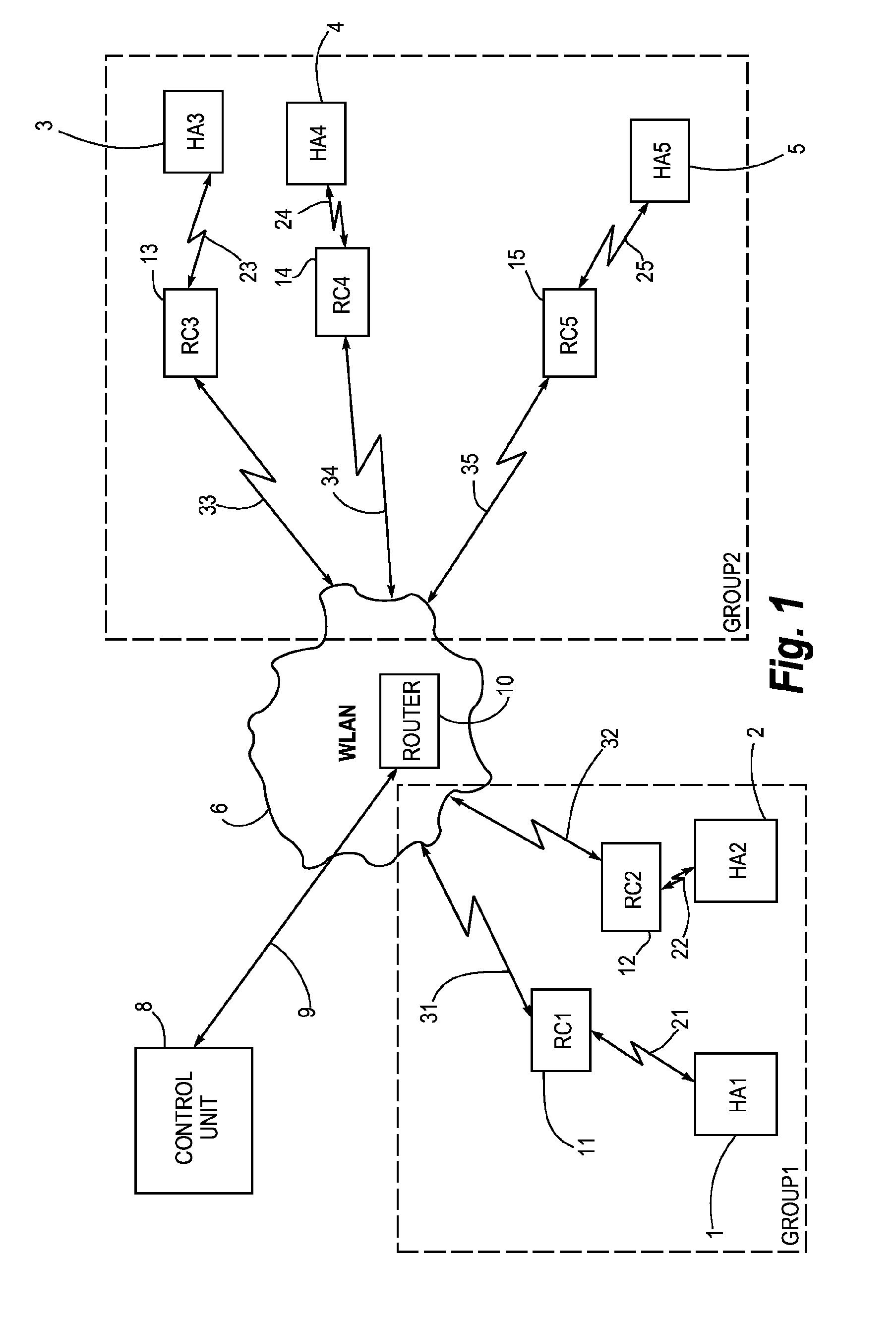

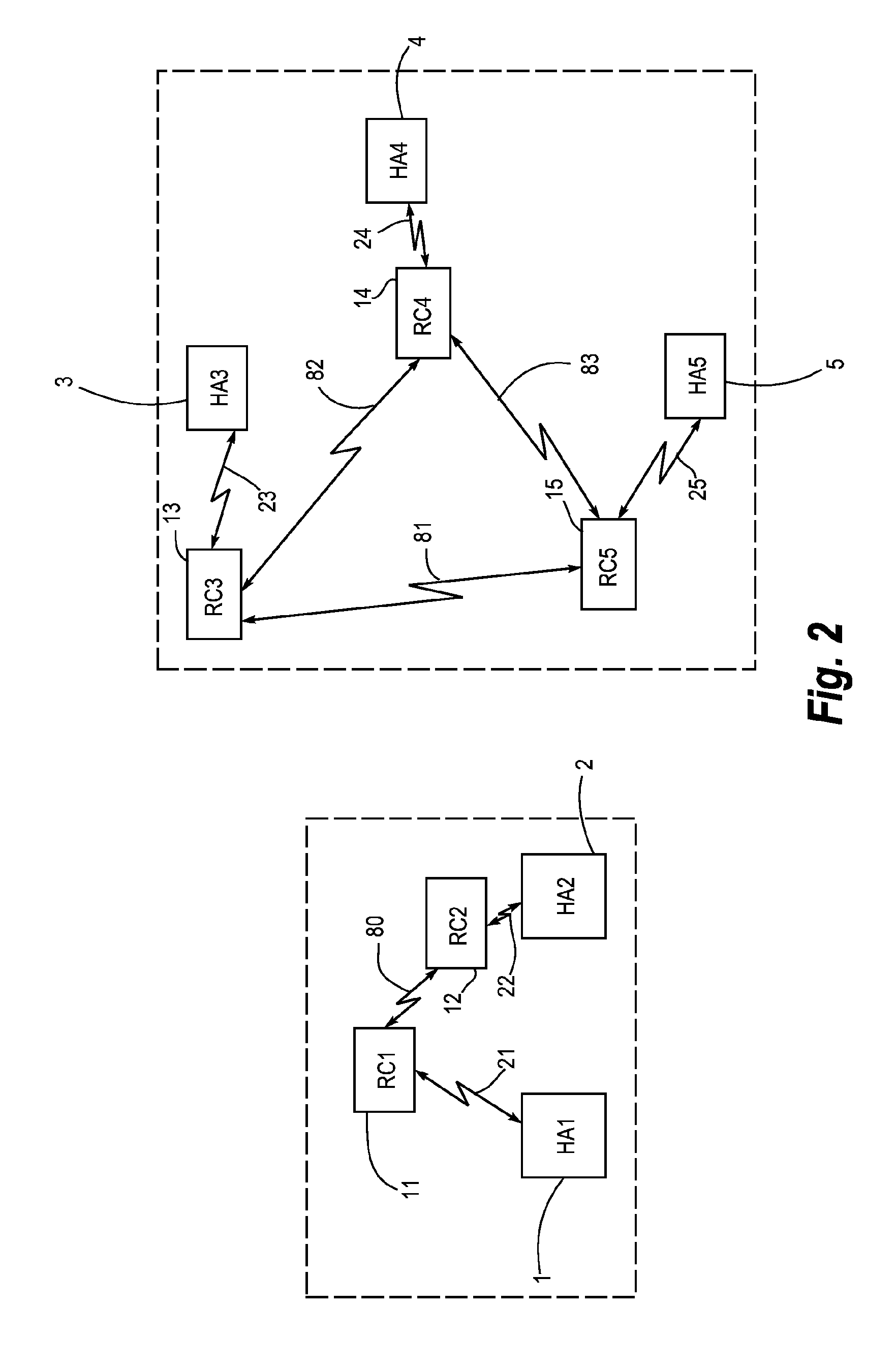

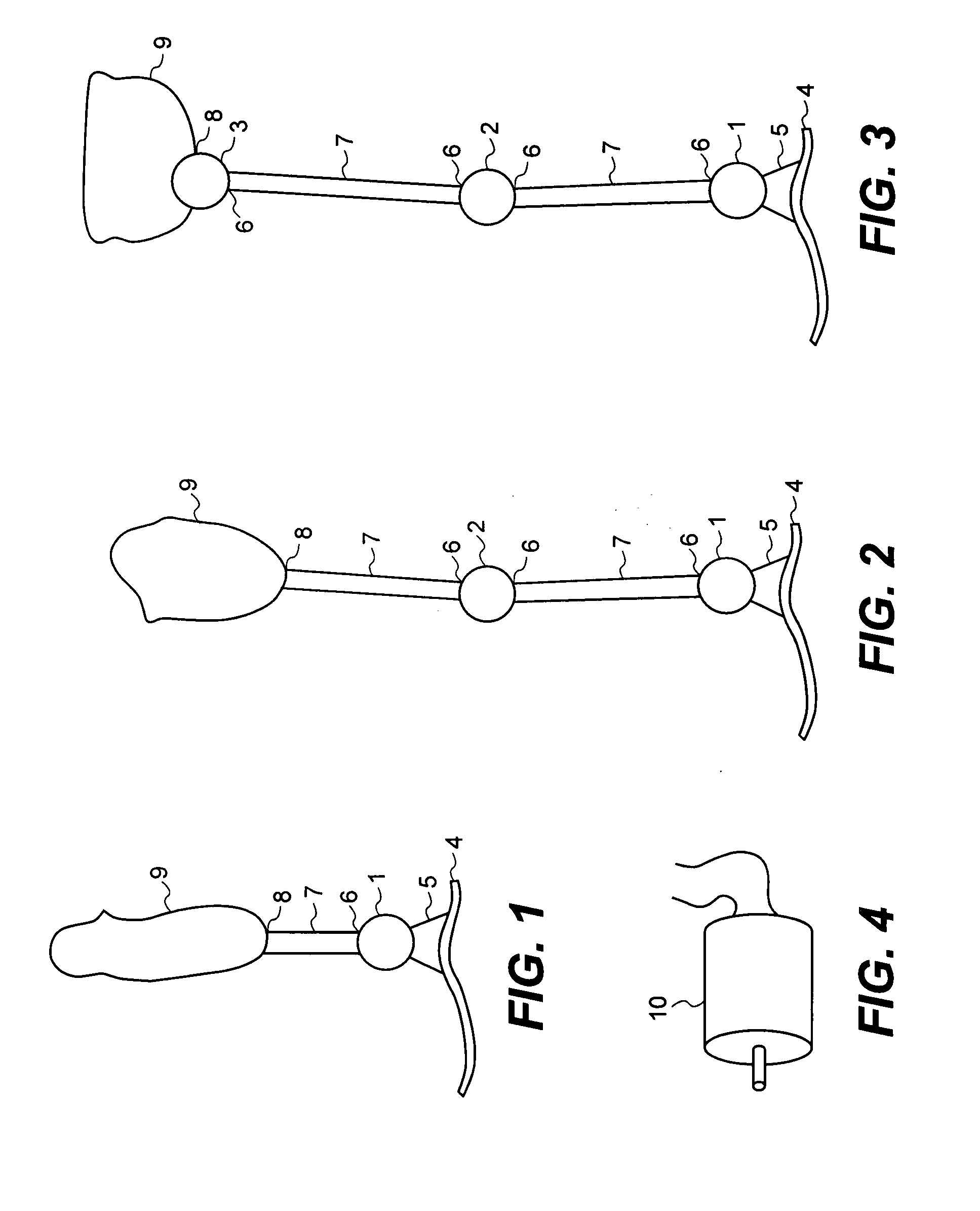

Hearing aid system for establishing a conversation group

ActiveUS20100086152A1Small sizePower transmissionFrequency-division multiplex detailsTime-division multiplexEngineeringHearing aid

A hearing aid system adapted for establishing a conversation group with other hearing aid systems used by different users, comprises a hearing aid (1, 2, 3, 4, 5) with an associated relay device (11, 12, 13, 14, 15). The relay device is (11, 12, 13, 14, 15) adapted for wireless communication (21, 22, 23, 24, 25) with said hearing aid and for wireless communication (31, 32, 33, 34, 35) with a second hearing aid system. The relay device (11, 12, 13, 14, 15) is also adapted for receiving and displaying information about said second hearing aid systems being available for participation in said conversation group, and it comprises means for selection of said other hearing aid systems for inclusion into the conversation group. The invention further provides a method for establishing a conversation group among hearing aid users.

Owner:WIDEX AS

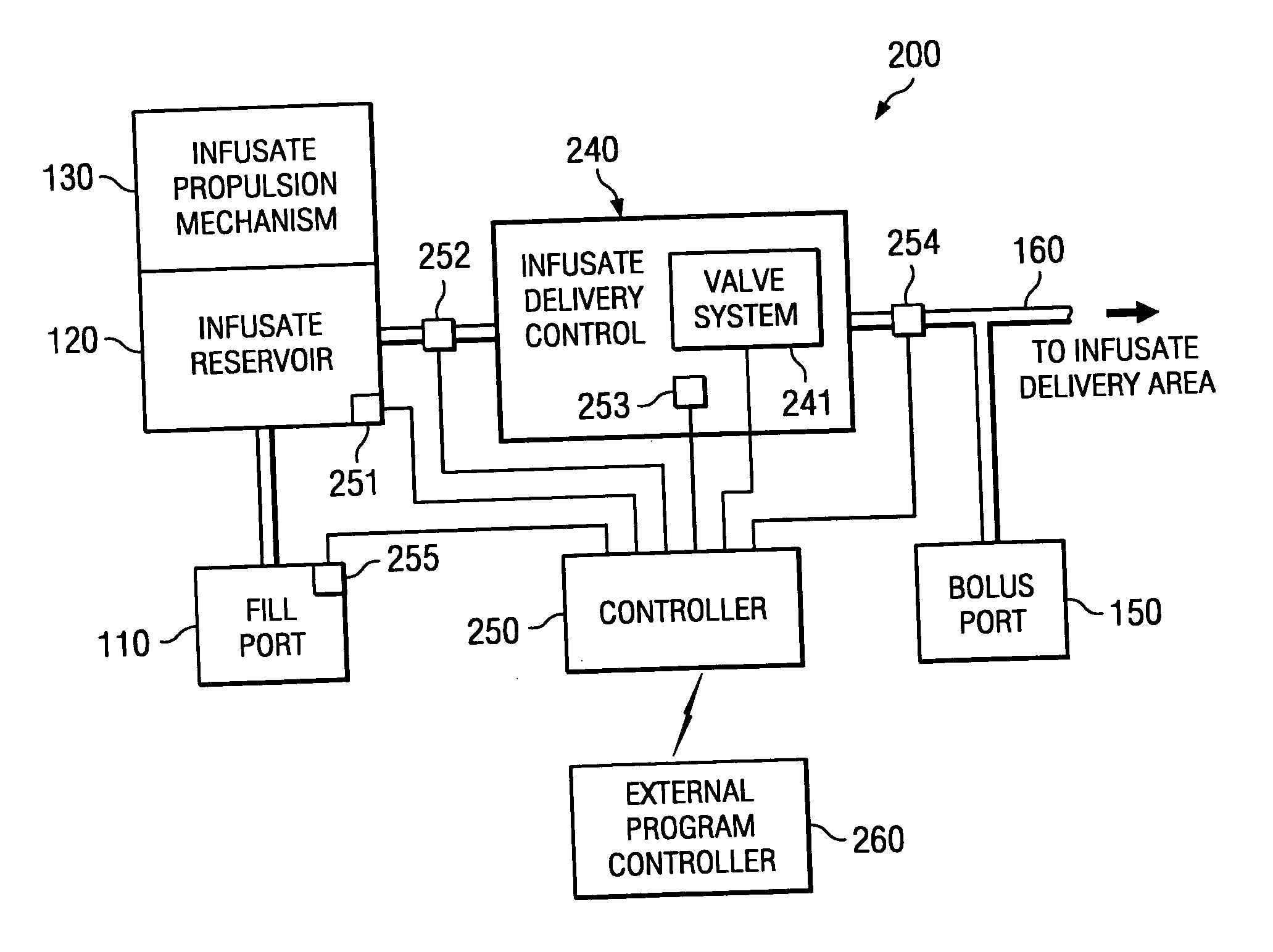

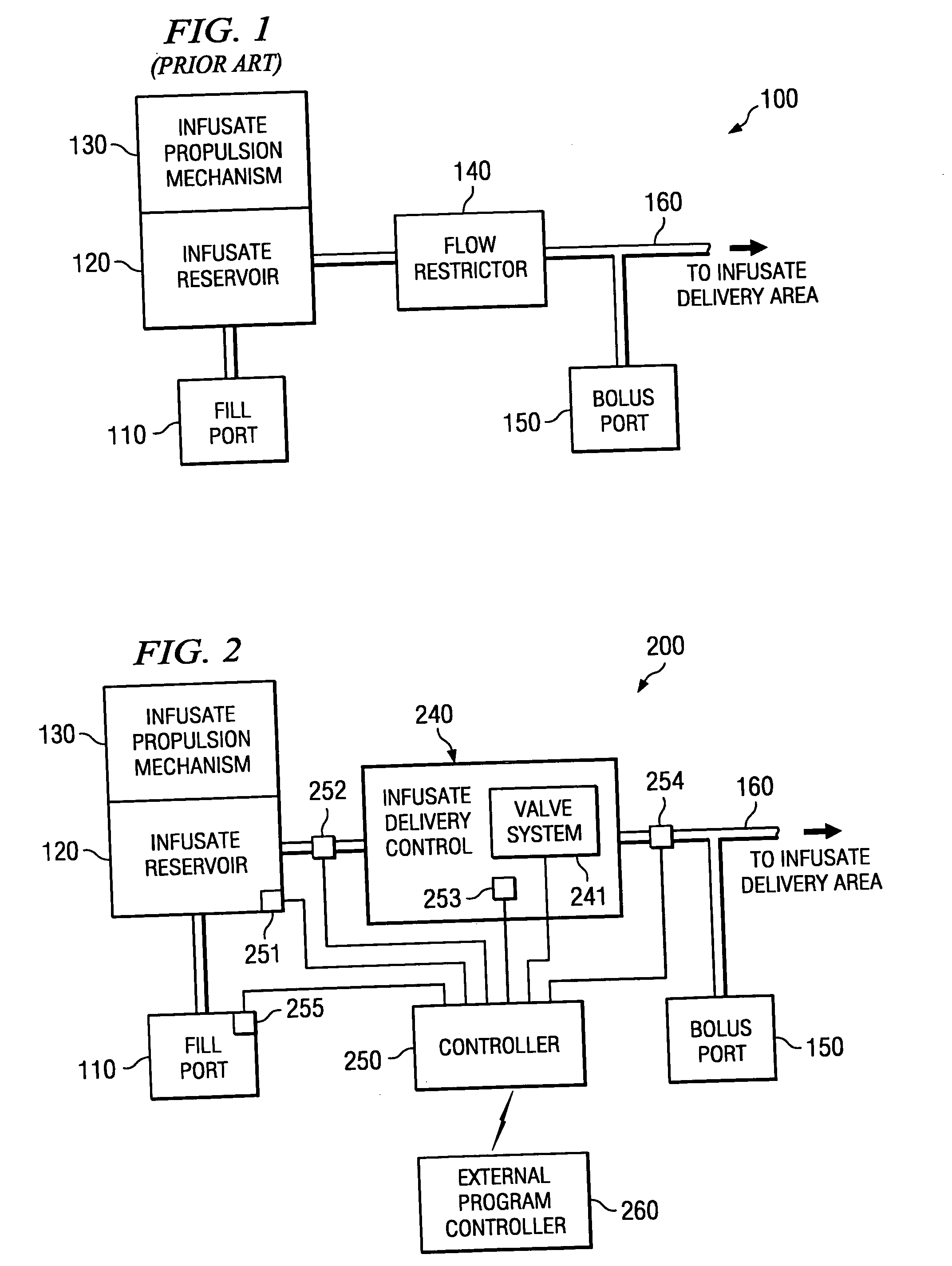

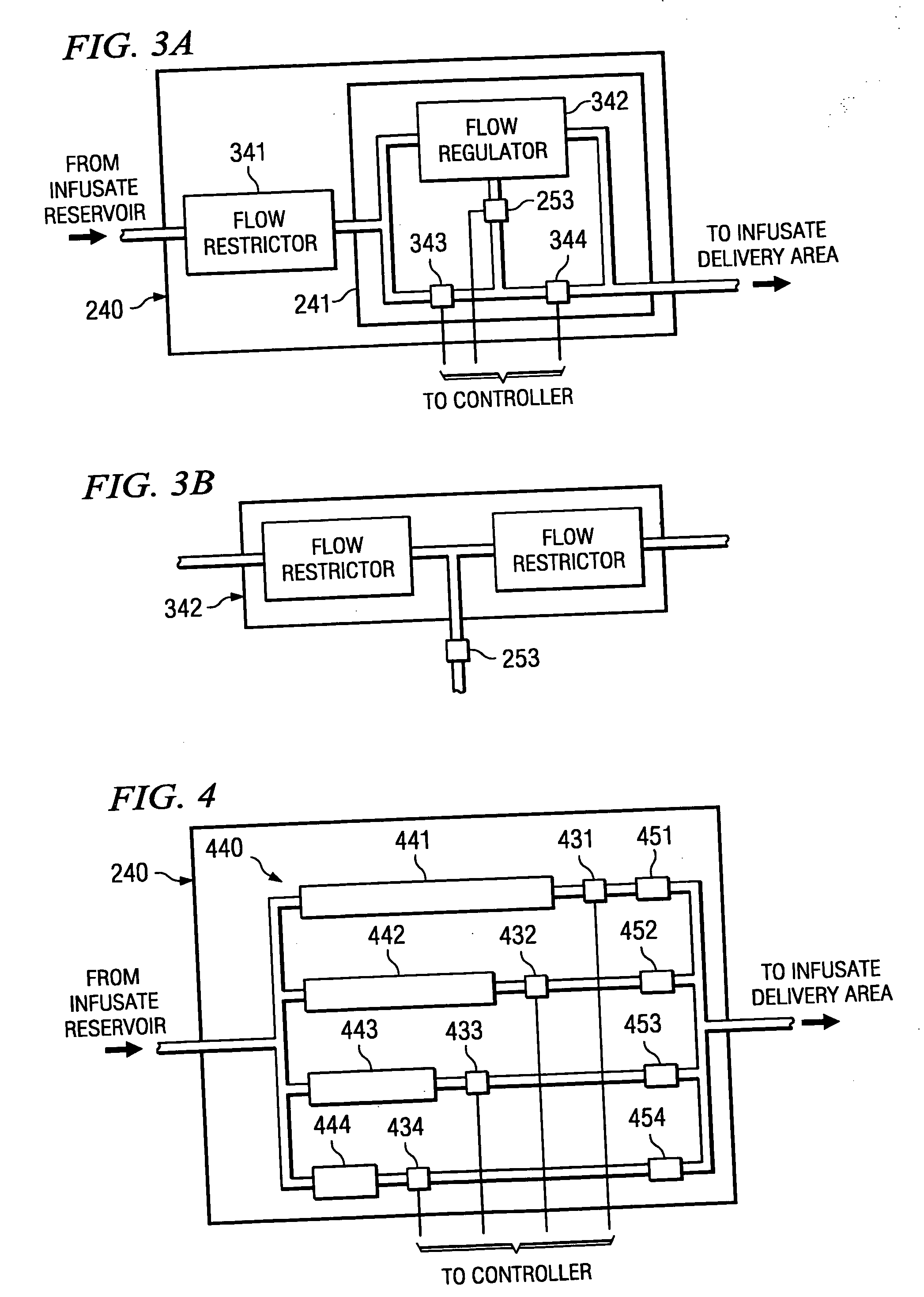

Reduced size programmable drug pump

InactiveUS20050187515A1Guaranteed uptimeMinimum power consumptionMedical devicesPressure infusionReduced sizeEngineering

Systems and methods provide a programmable or controllable infusate delivery with minimal power consumption using controllable valves and with safe and reliable operation of the delivery system. Embodiments provide programmable control without the need for implantable power sources using multi-stable valves and / or mono-stable valves which are powered externally when activated. Embodiments provide for very low power programmable control, such as by employing micro-electromechanical system valves and a flow restrictor array. An external program controller may be utilized to provide a user interface and which may communicate with the controllable infusate delivery system using wireless links. Internal controller circuitry may provide for flow control changes for different activities or times of day and / or in response to changes in pressure, temperature, etcetera. A safety valve configuration may be implemented which provides a safety flow valve configuration which responds in an opposite manner to particular events than does a corresponding primary flow valve.

Owner:ADVANCED NEUROMODULATION SYST INC

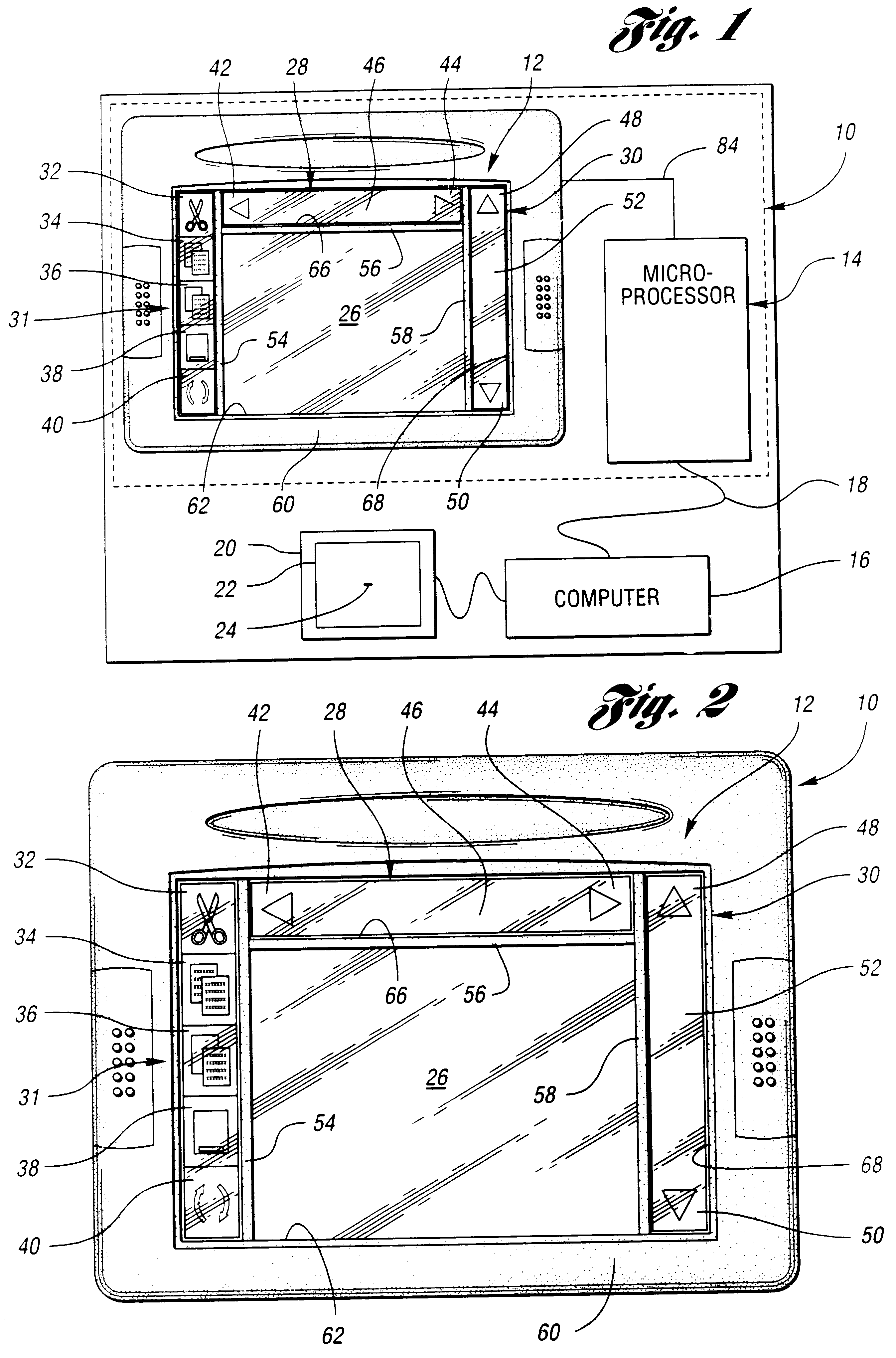

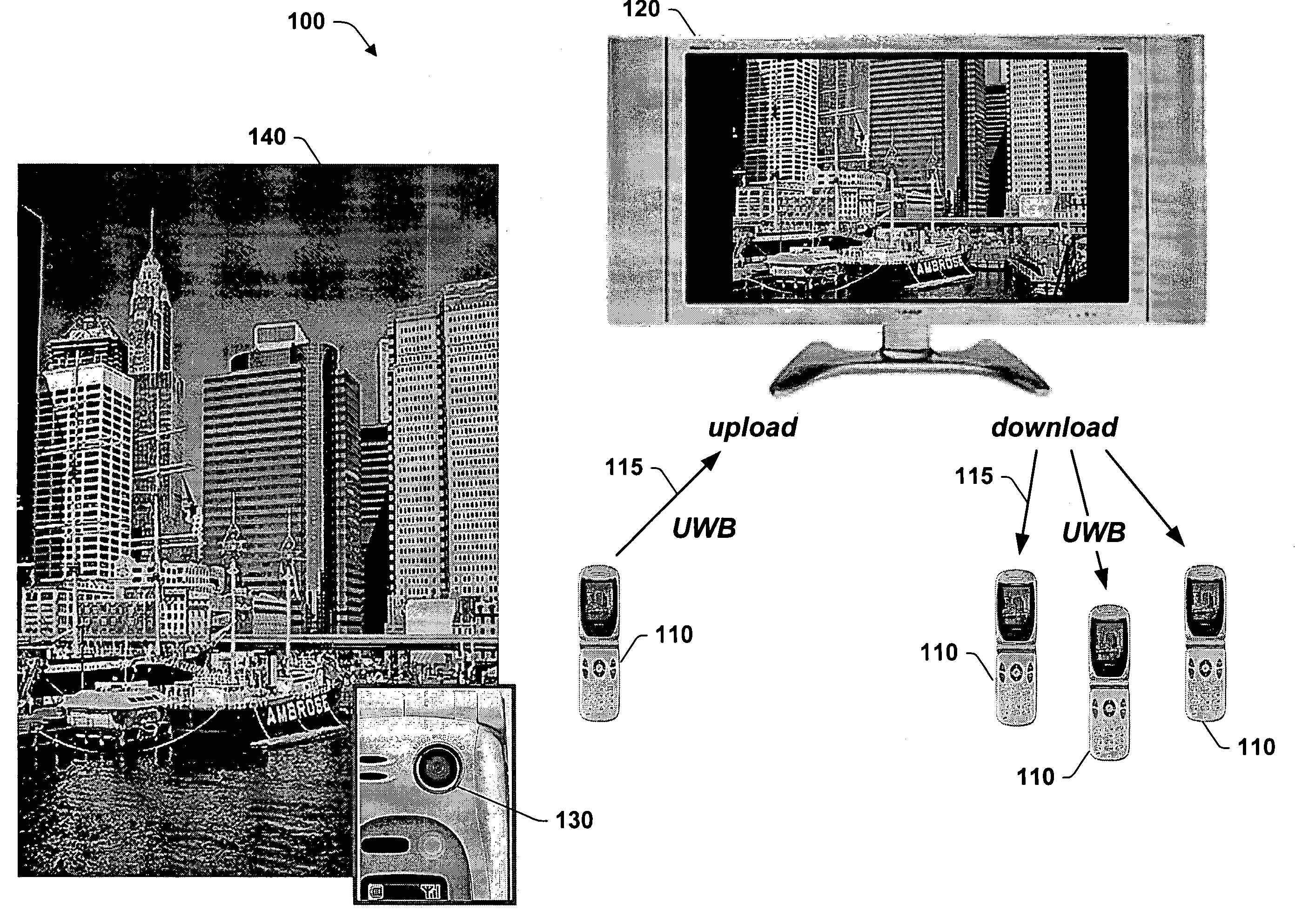

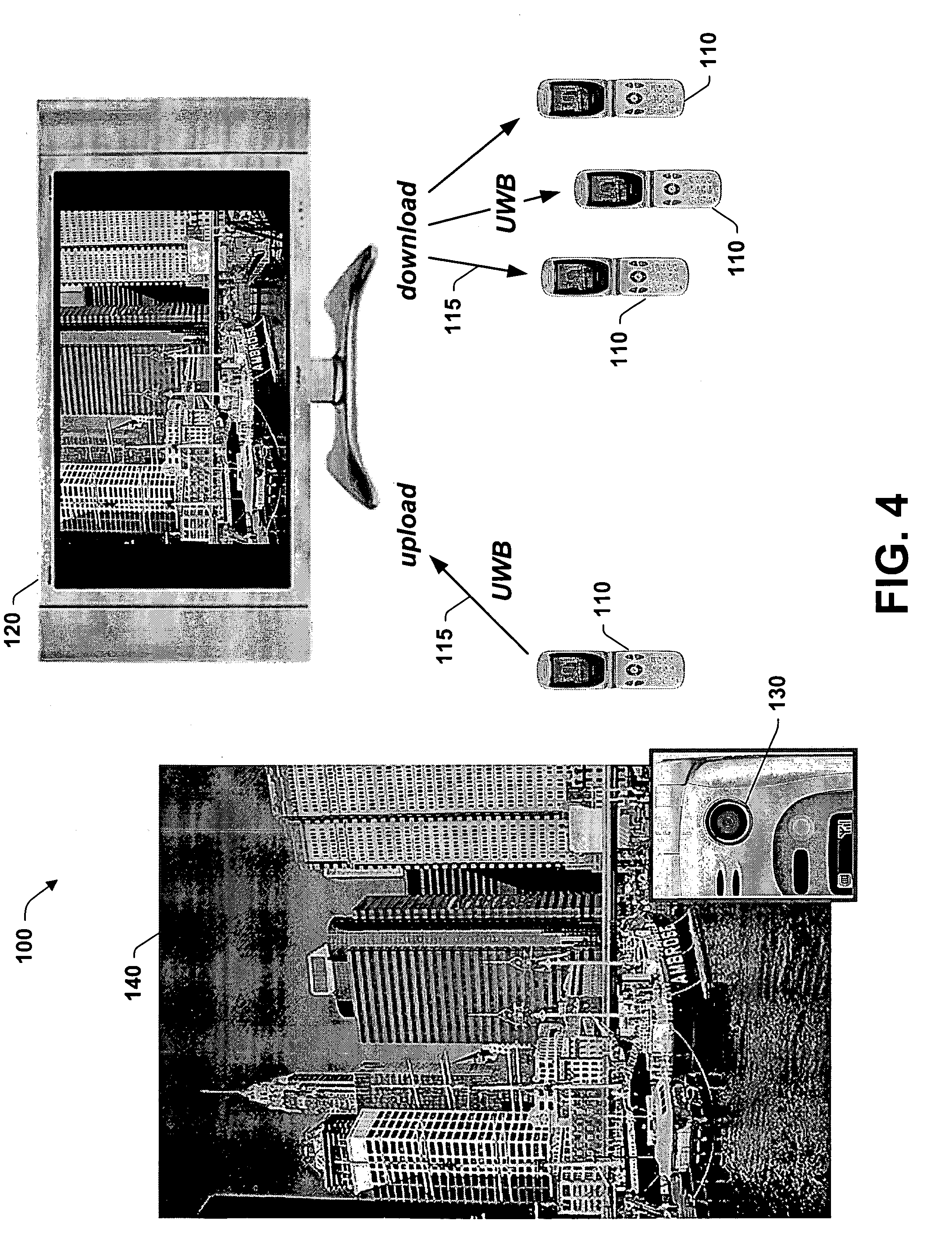

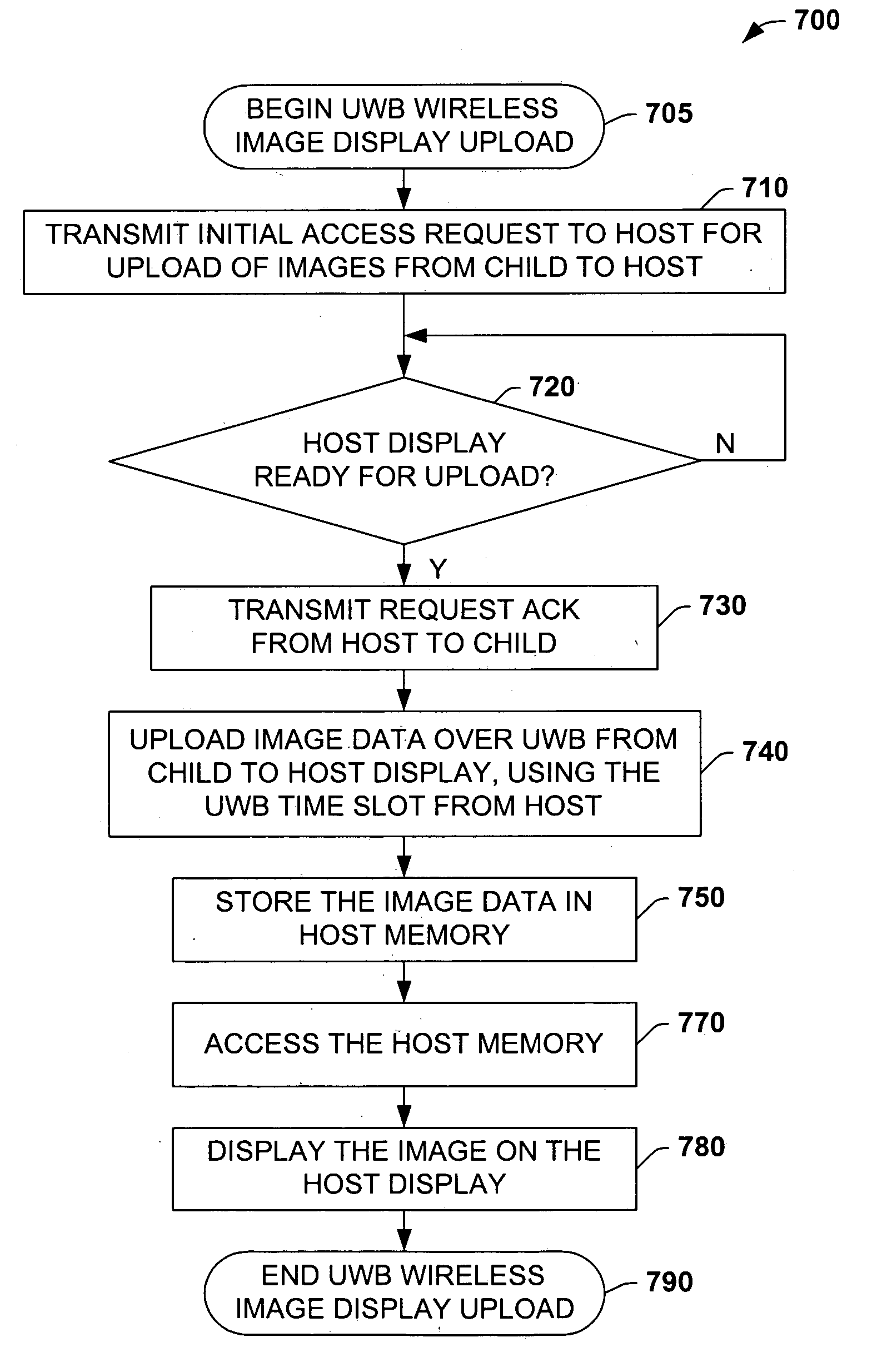

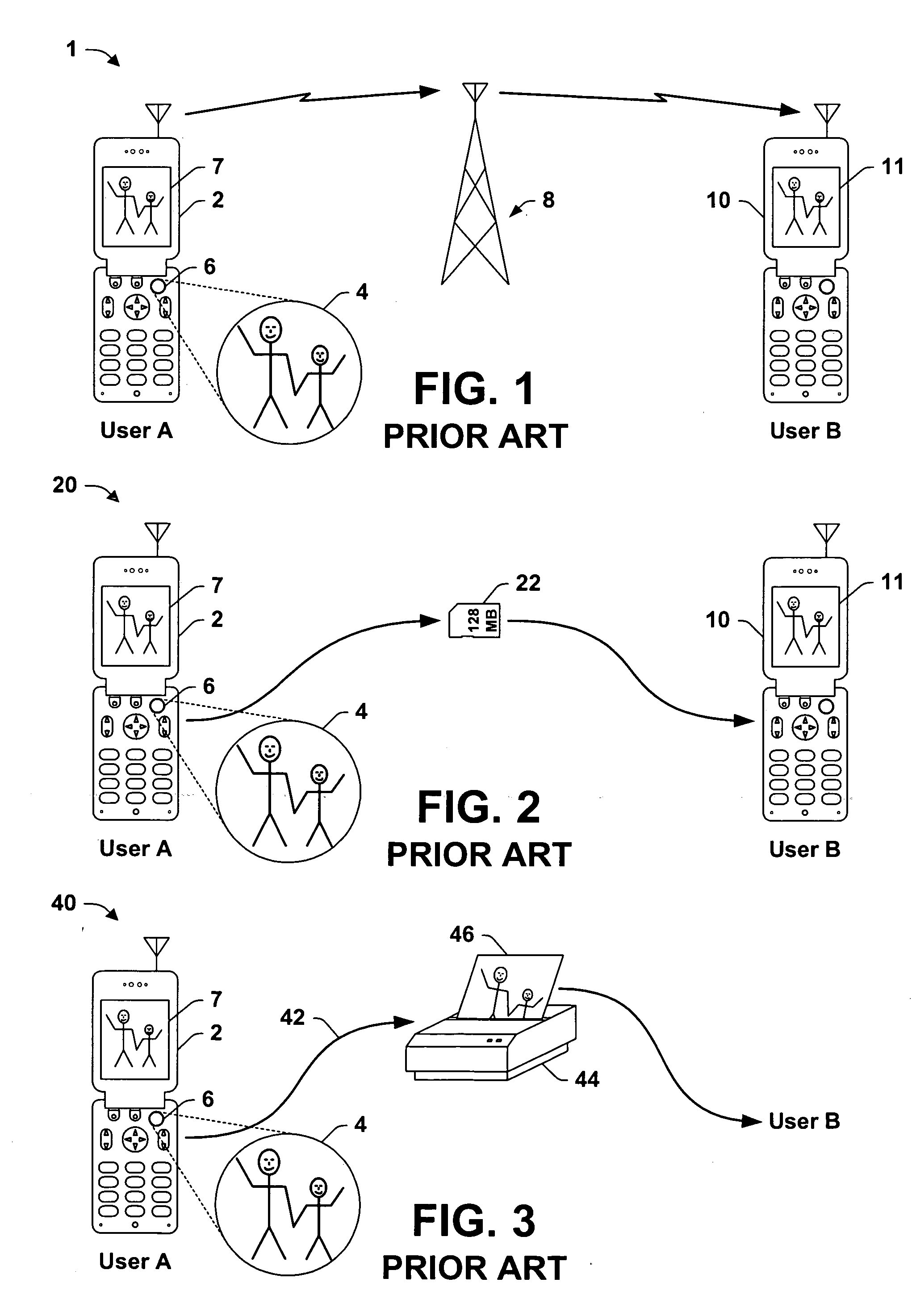

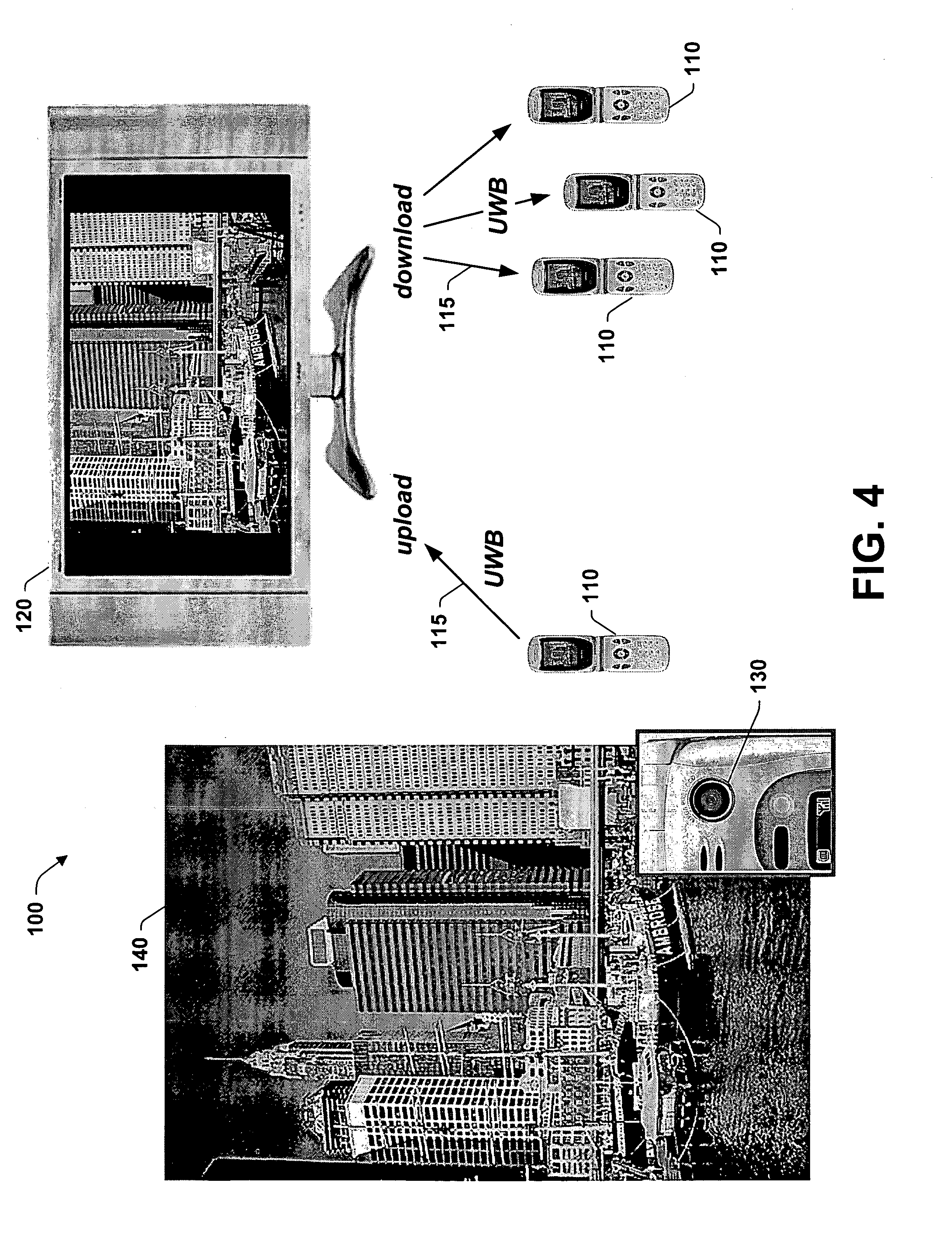

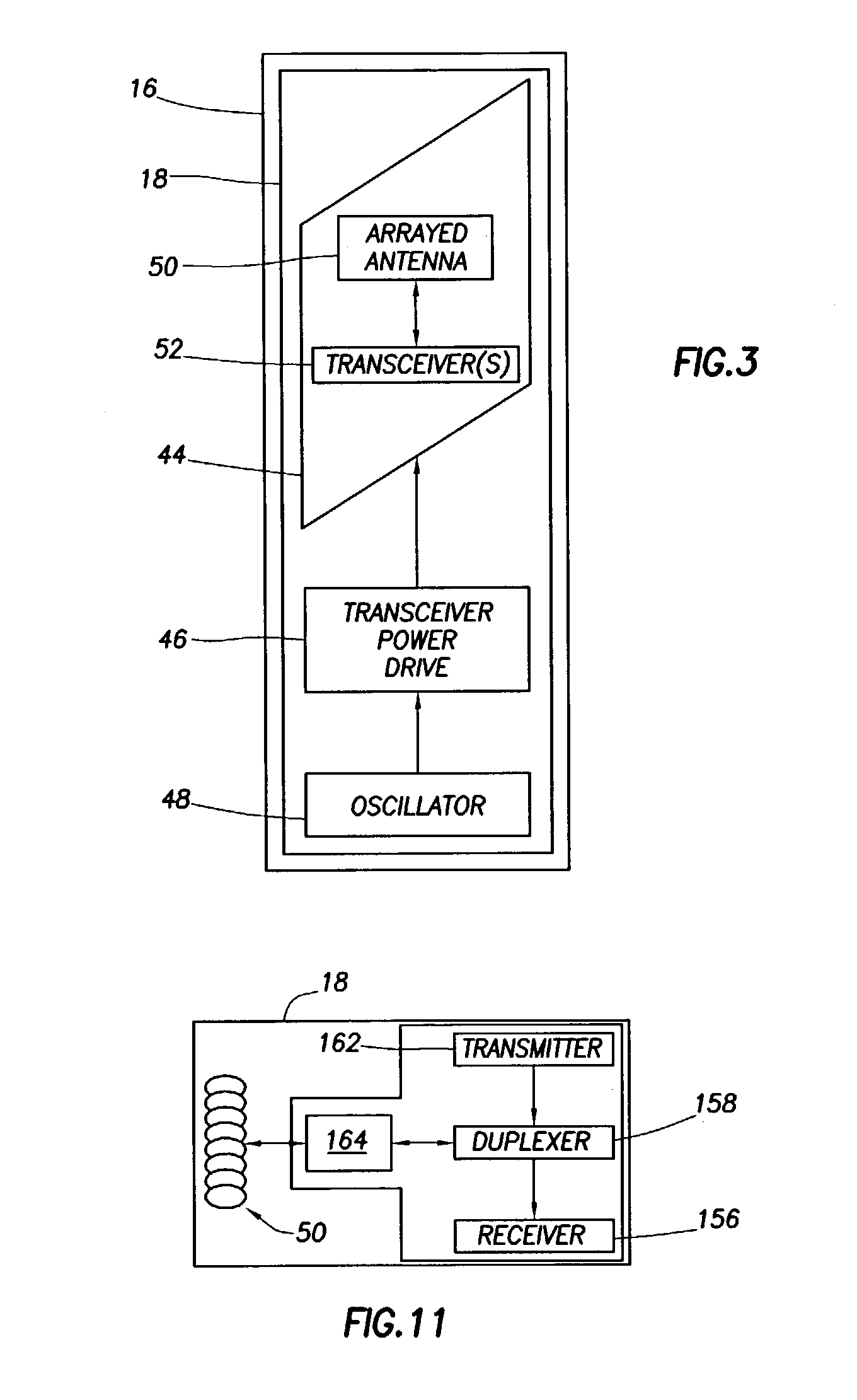

Home picture/video display system with ultra wide-band technology

ActiveUS7327385B2Easy to demonstrateEnhanced personal enjoymentTelevision system detailsColor television detailsUltra-widebandTransceiver

A new display system and method is described, utilizing a cellular telephone having digital camera capability and a television linked directly over a UWB wireless signal forming a UWB wireless video pico-net. The system utilizes a digital camera unit to capture picture or video images for UWB transmission directly to the television acting as a pico-net host controller, either independently or together with the cellular telephone operating as a pico-net child. The display system comprises and one or more remote devices and a host display communicating on a UWB wireless network. The host display comprises a display for presentation of the picture or video images and a UWB transceiver for processing image data from the picture or video images, for selectively sending and receiving the image data based on a request from the child. The one or more remote devices comprise a digital camera for capturing the picture or video images and another UWB transceiver as used in the host display. The host display has a generally larger display for improved presentation of the captured picture or video images useful and amusing for group, party, wedding, and conference viewing, or simply for enhanced personal enjoyment. For picture or video image sharing, the system further facilitates downloading the current picture or video images from the host display television to a requesting cellular telephone or digital camera equipped with the UWB transceiver. The UWB display system provides sufficient bandwidth to support numerous such download requests simultaneously, while utilizing a transmission technology having minimal power consumption.

Owner:TEXAS INSTR INC

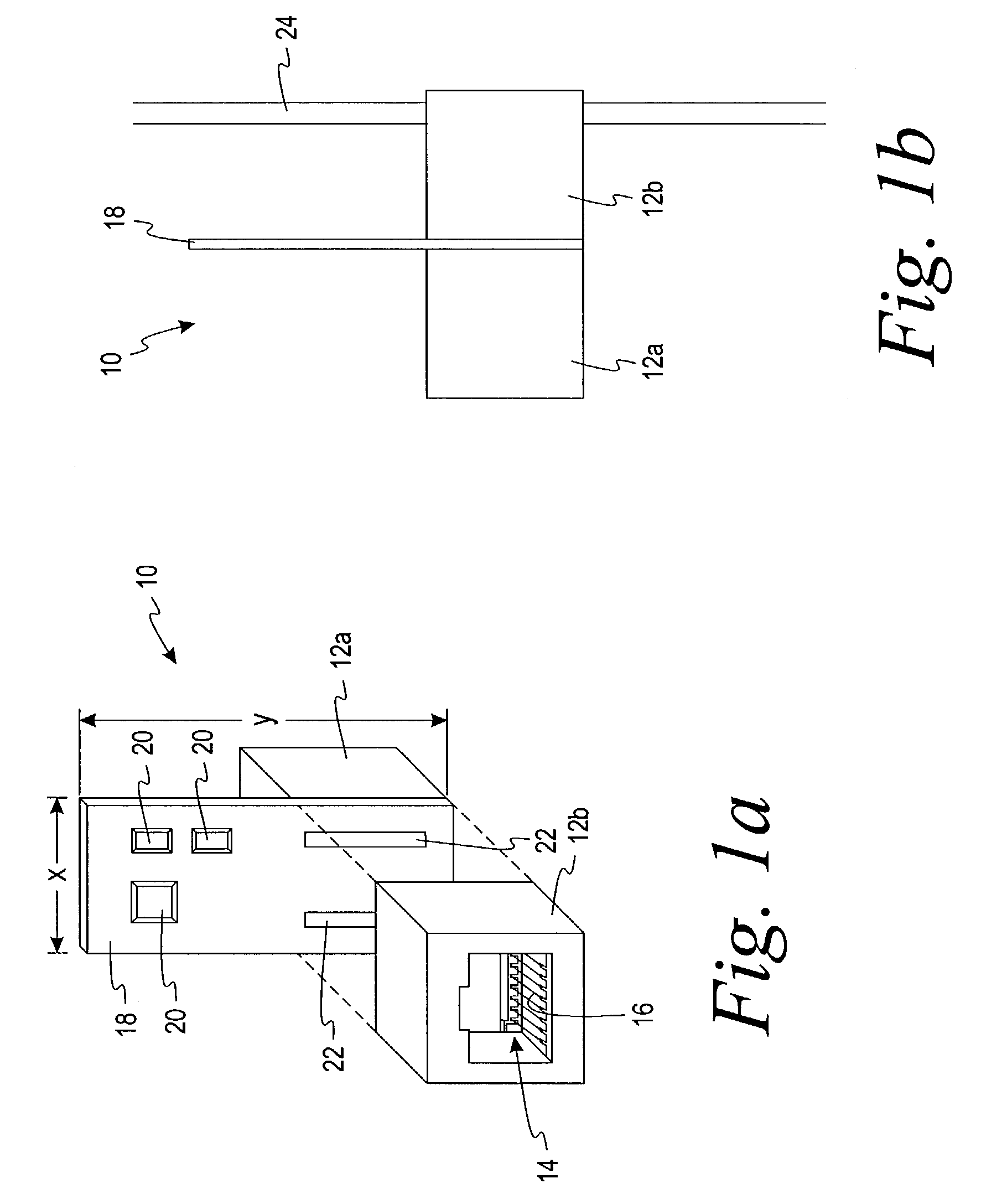

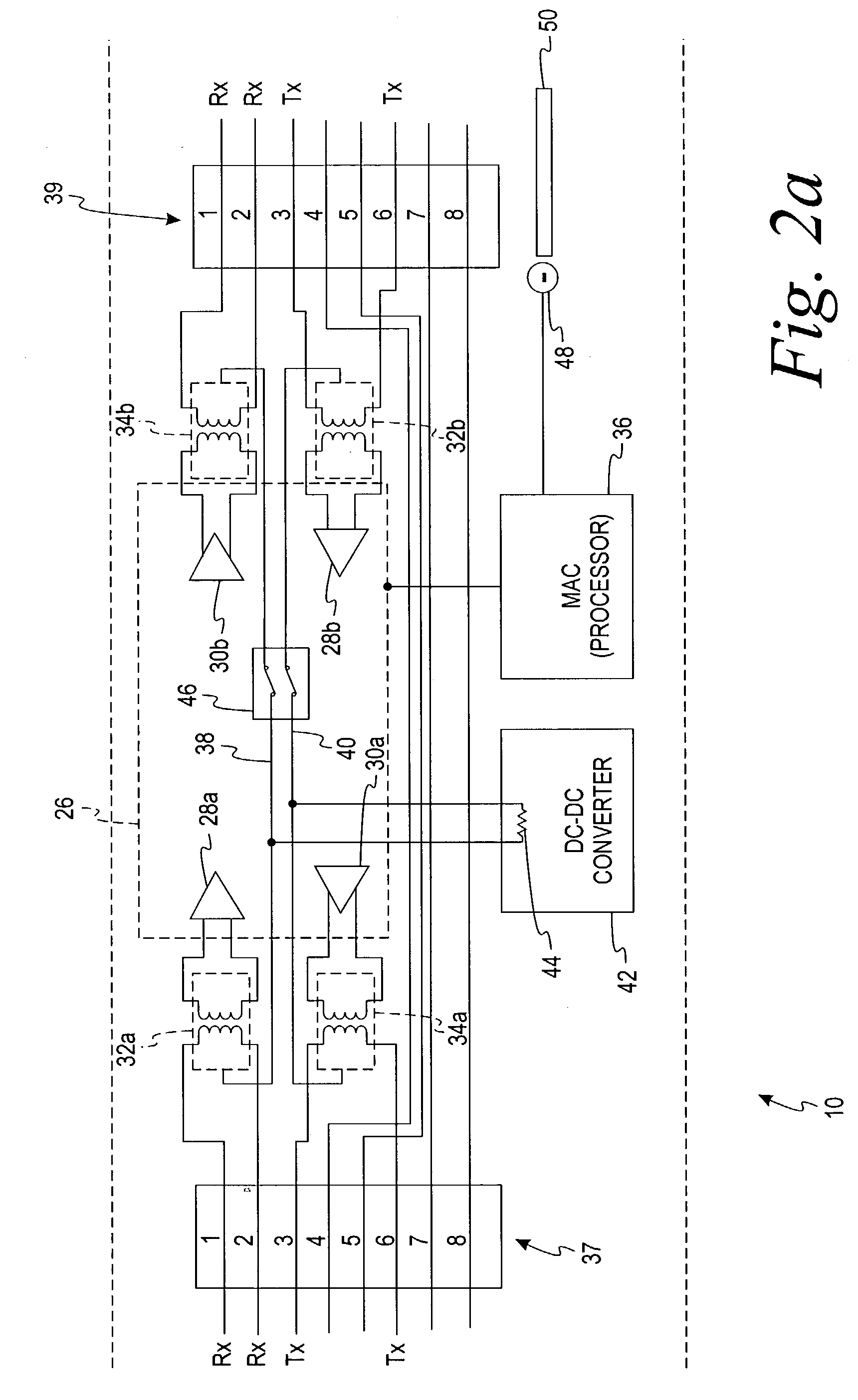

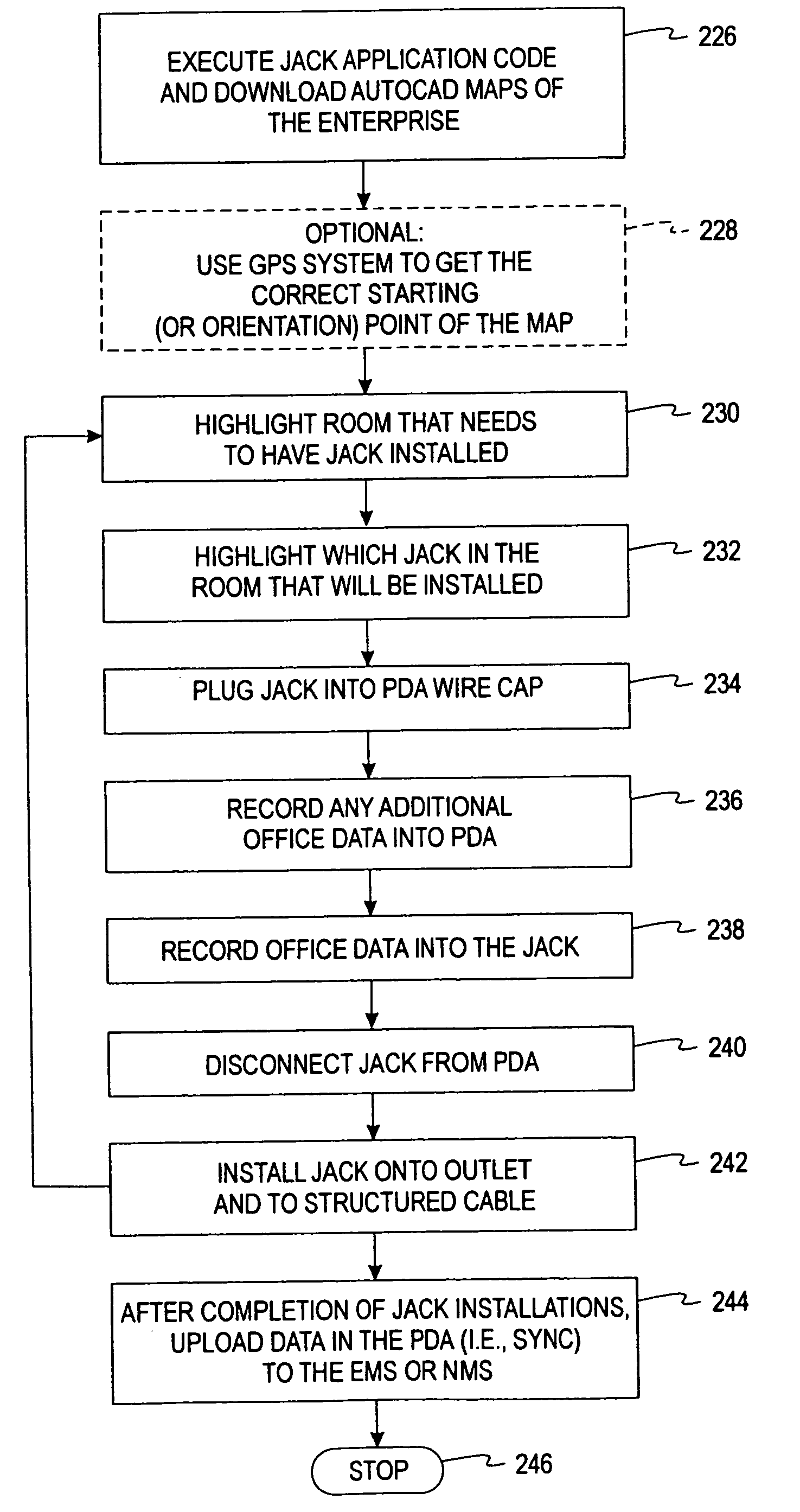

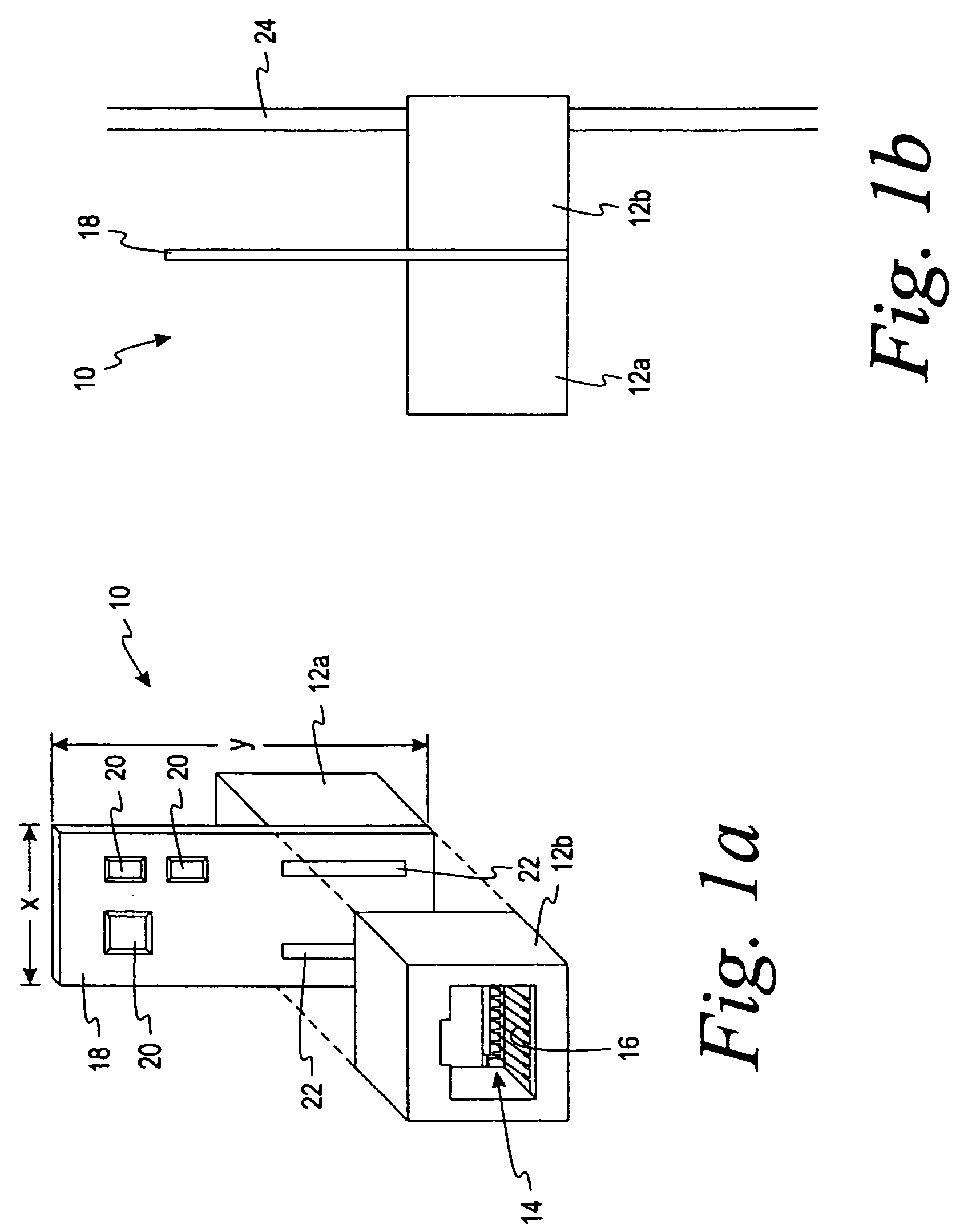

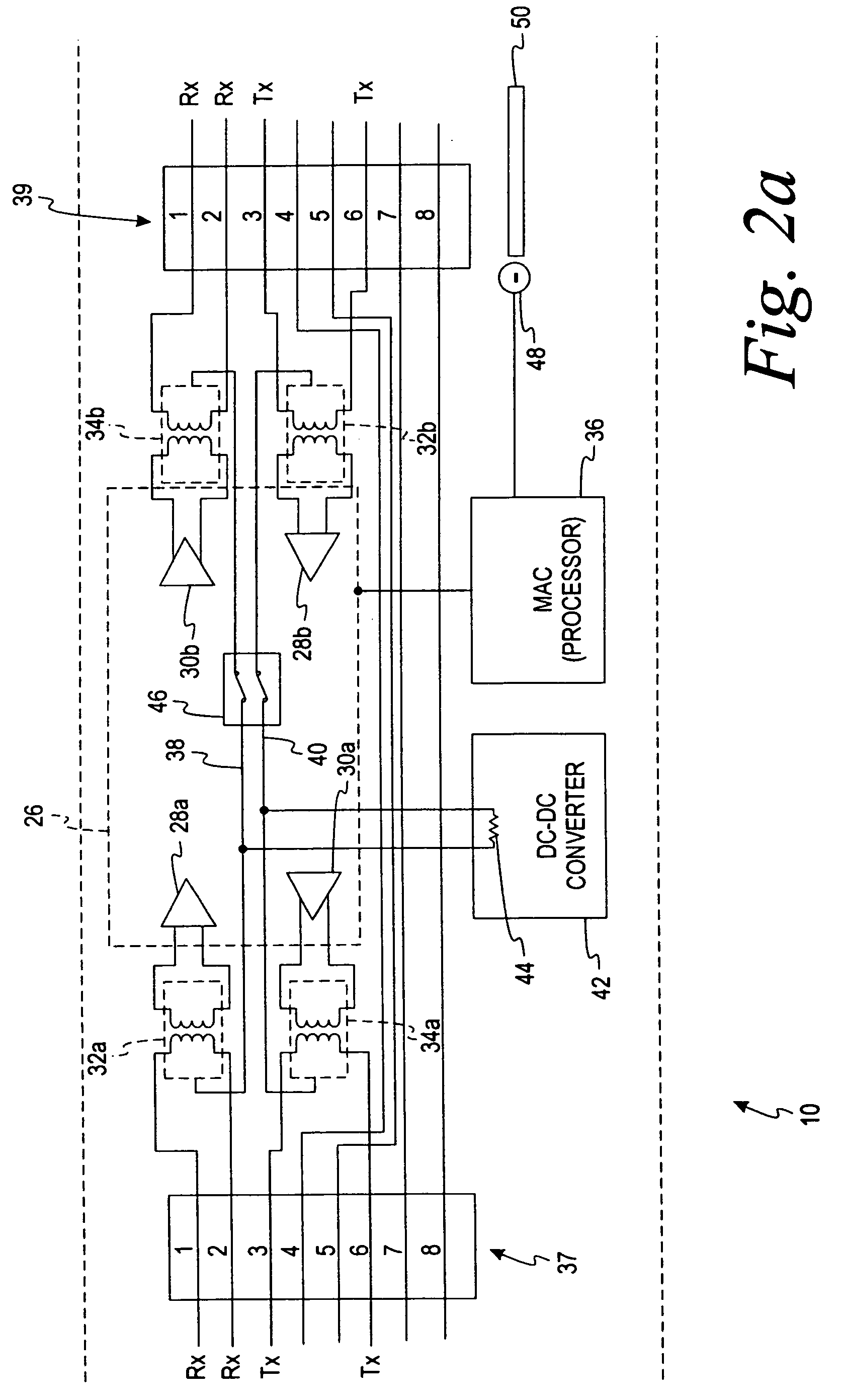

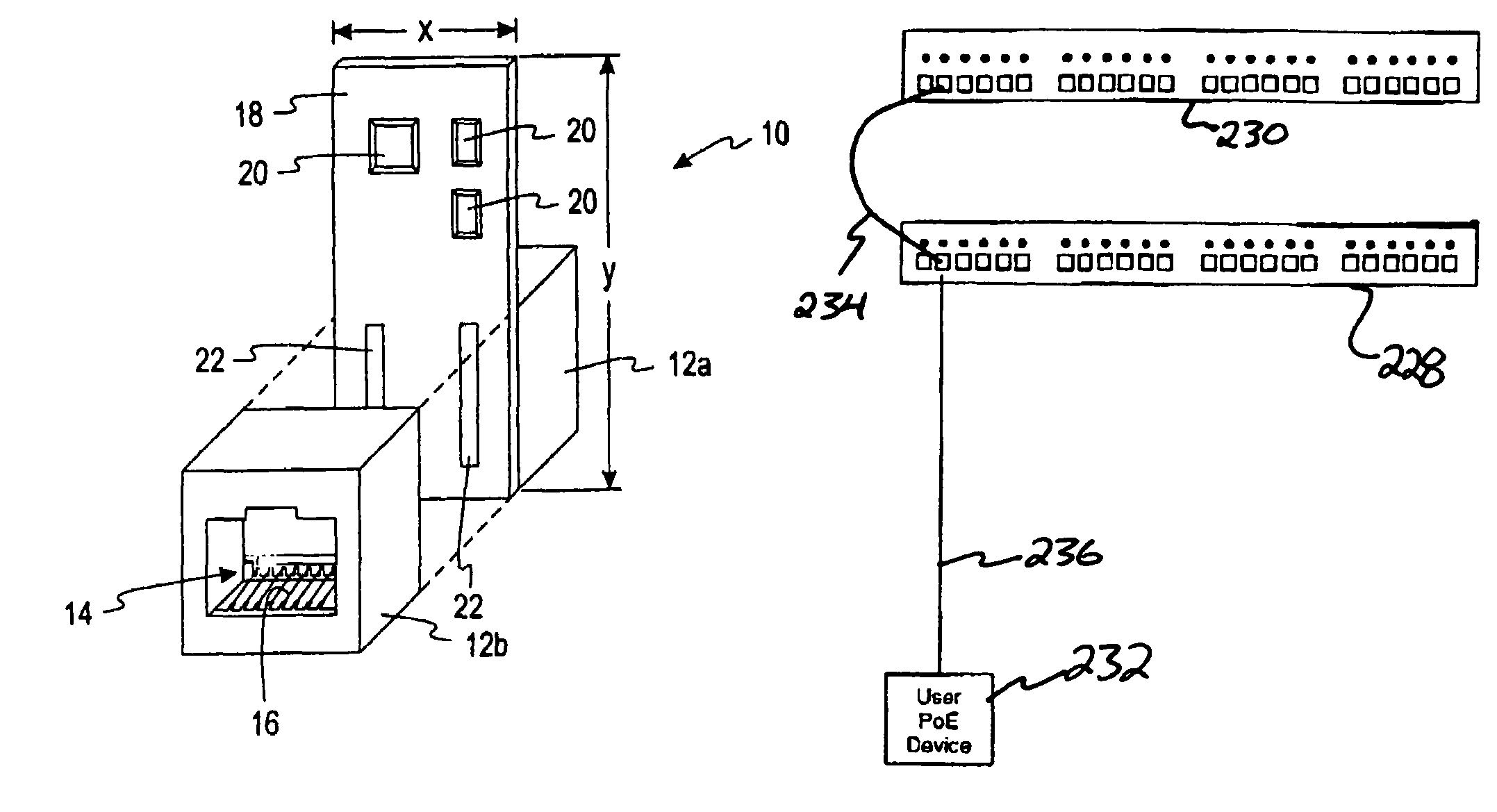

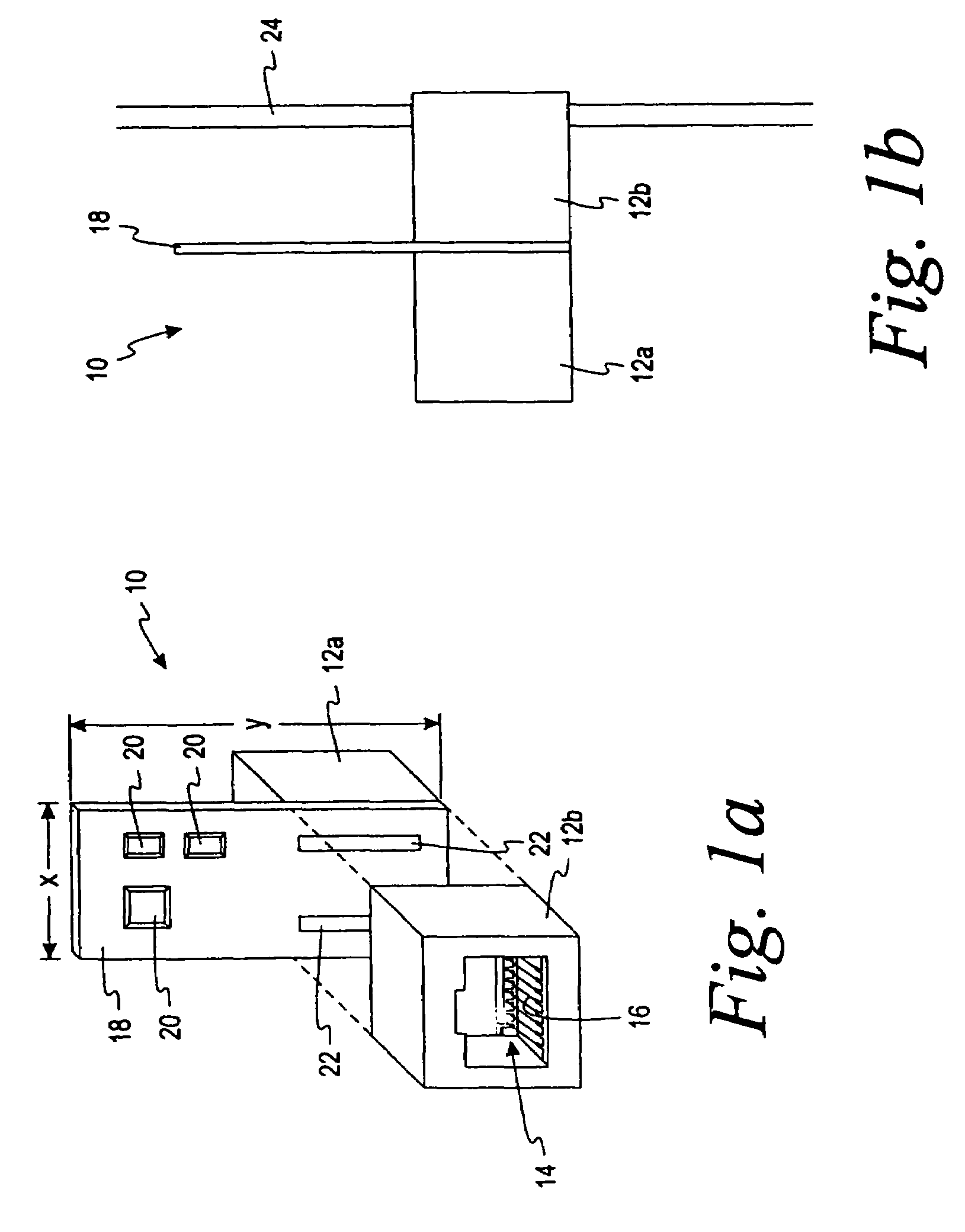

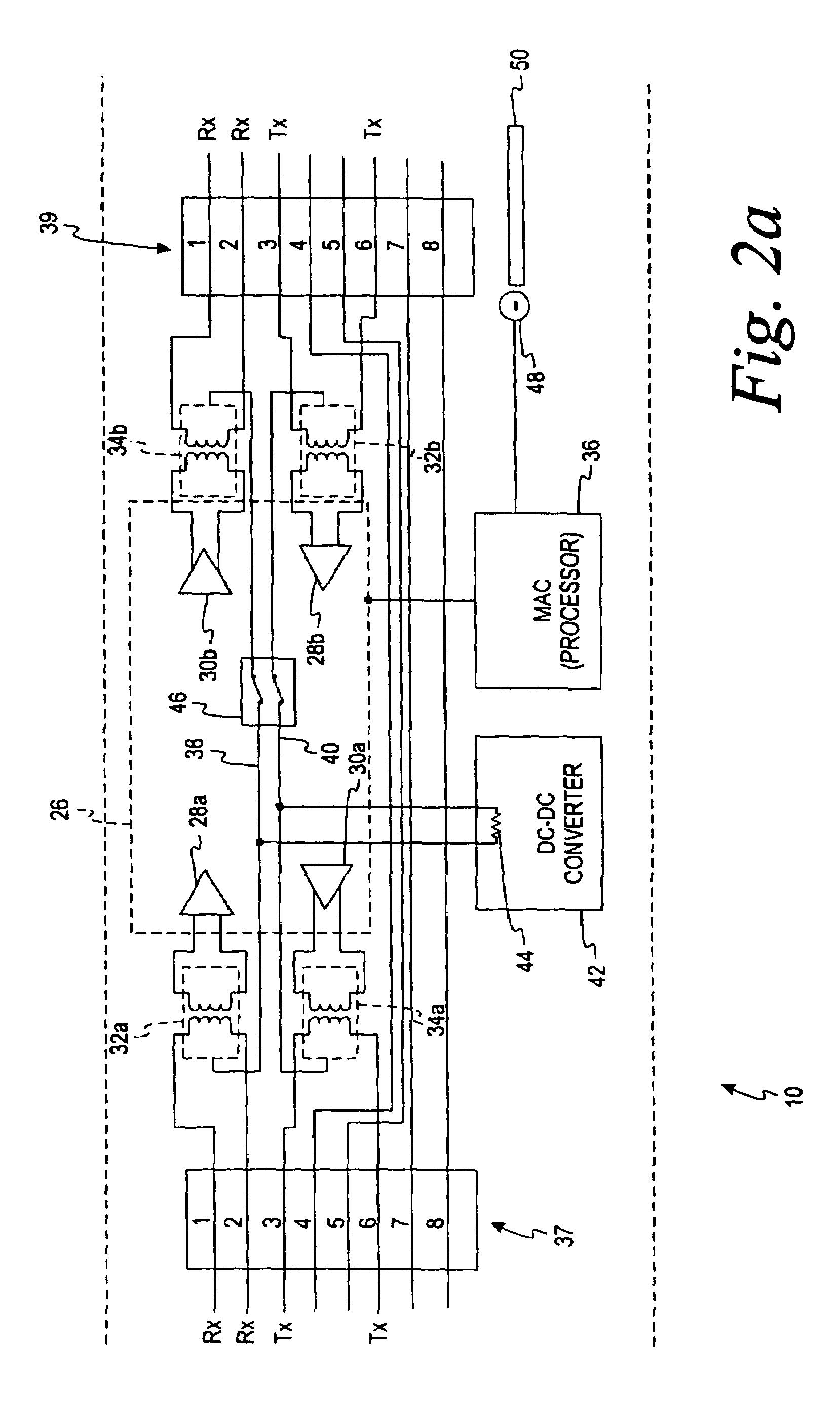

Systems and methods for managing a network

InactiveUS7519000B2Minimum power consumptionEasy to manageError preventionFrequency-division multiplex detailsDocumentation procedureEngineering

A system for managing and documenting a local area communications network is provided which deploys power sourcing equipment and powered devices by the use of active electronic modules, having an Ethernet controller and Power over Ethernet forwarding capabilities, as integral, managed components within the cable plant, to enhance management, documentation, security and emergency 911 aspects of the network as well as extending the physical reach of the network.

Owner:PANDUIT

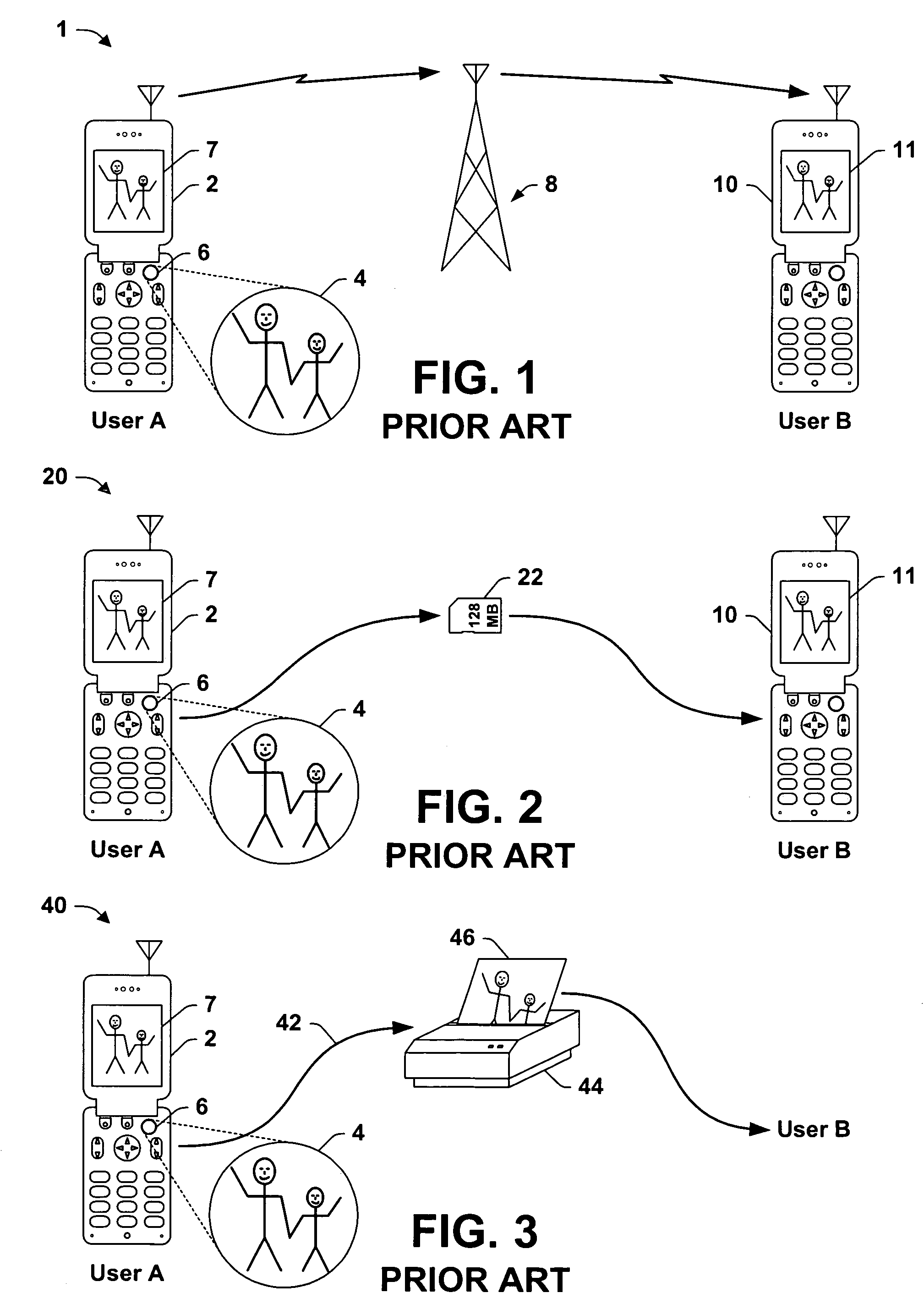

Home picture/video display system with ultra wide-band technology

ActiveUS20050120381A1Easy to demonstrateEnhanced personal enjoymentData switching by path configurationClosed circuit television systemsTransceiverDisplay device

A new display system and method is described, utilizing a cellular telephone having digital camera capability and a television linked directly over a UWB wireless signal forming a UWB wireless video pico-net. The system utilizes a digital camera unit to capture picture or video images for UWB transmission directly to the television acting as a pico-net host controller, either independently or together with the cellular telephone operating as a pico-net child. The display system comprises and one or more remote devices and a host display communicating on a UWB wireless network. The host display comprises a display for presentation of the picture or video images and a UWB transceiver for processing image data from the picture or video images, for selectively sending and receiving the image data based on a request from the child. The one or more remote devices comprise a digital camera for capturing the picture or video images and another UWB transceiver as used in the host display. The host display has a generally larger display for improved presentation of the captured picture or video images useful and amusing for group, party, wedding, and conference viewing, or simply for enhanced personal enjoyment. For picture or video image sharing, the system further facilitates downloading the current picture or video images from the host display television to a requesting cellular telephone or digital camera equipped with the UWB transceiver. The UWB display system provides sufficient bandwidth to support numerous such download requests simultaneously, while utilizing a transmission technology having minimal power consumption.

Owner:TEXAS INSTR INC

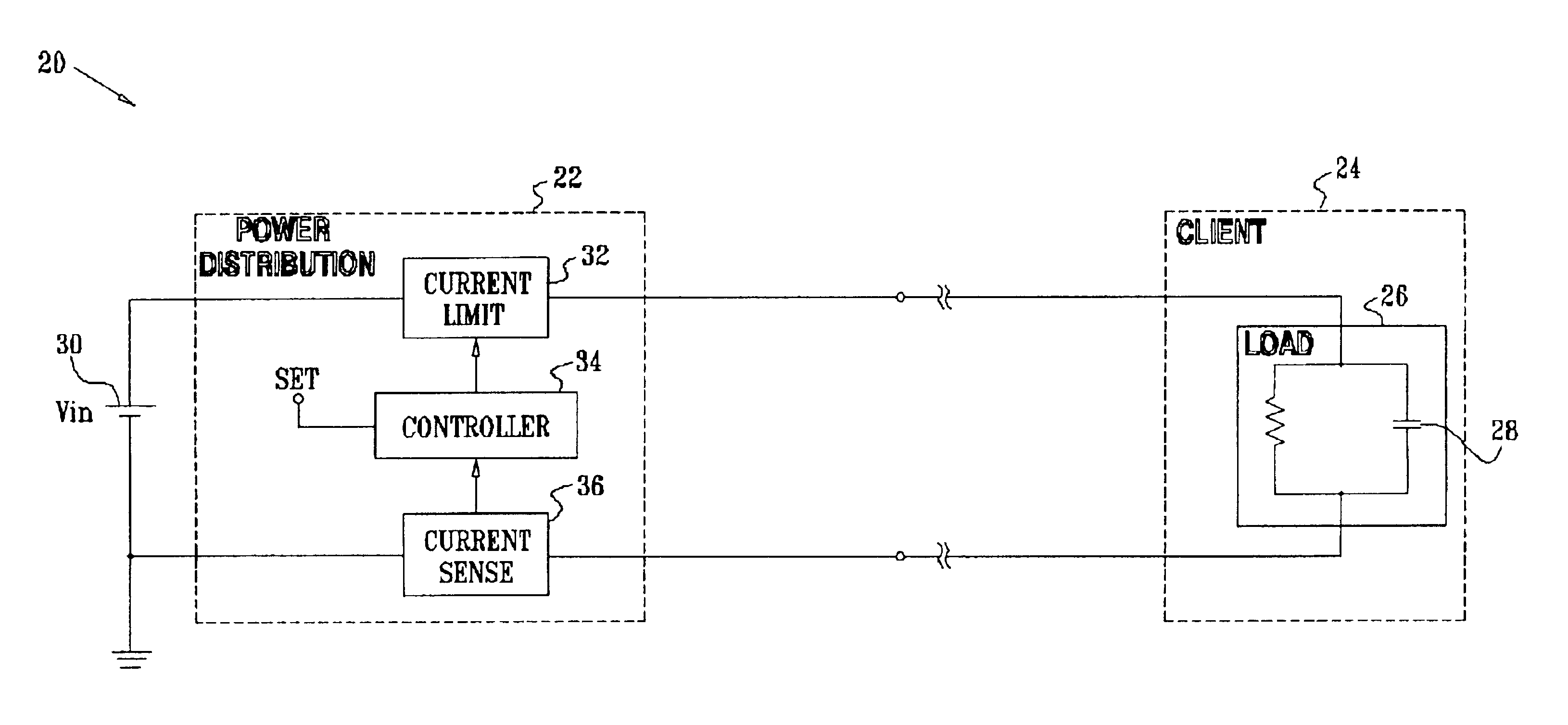

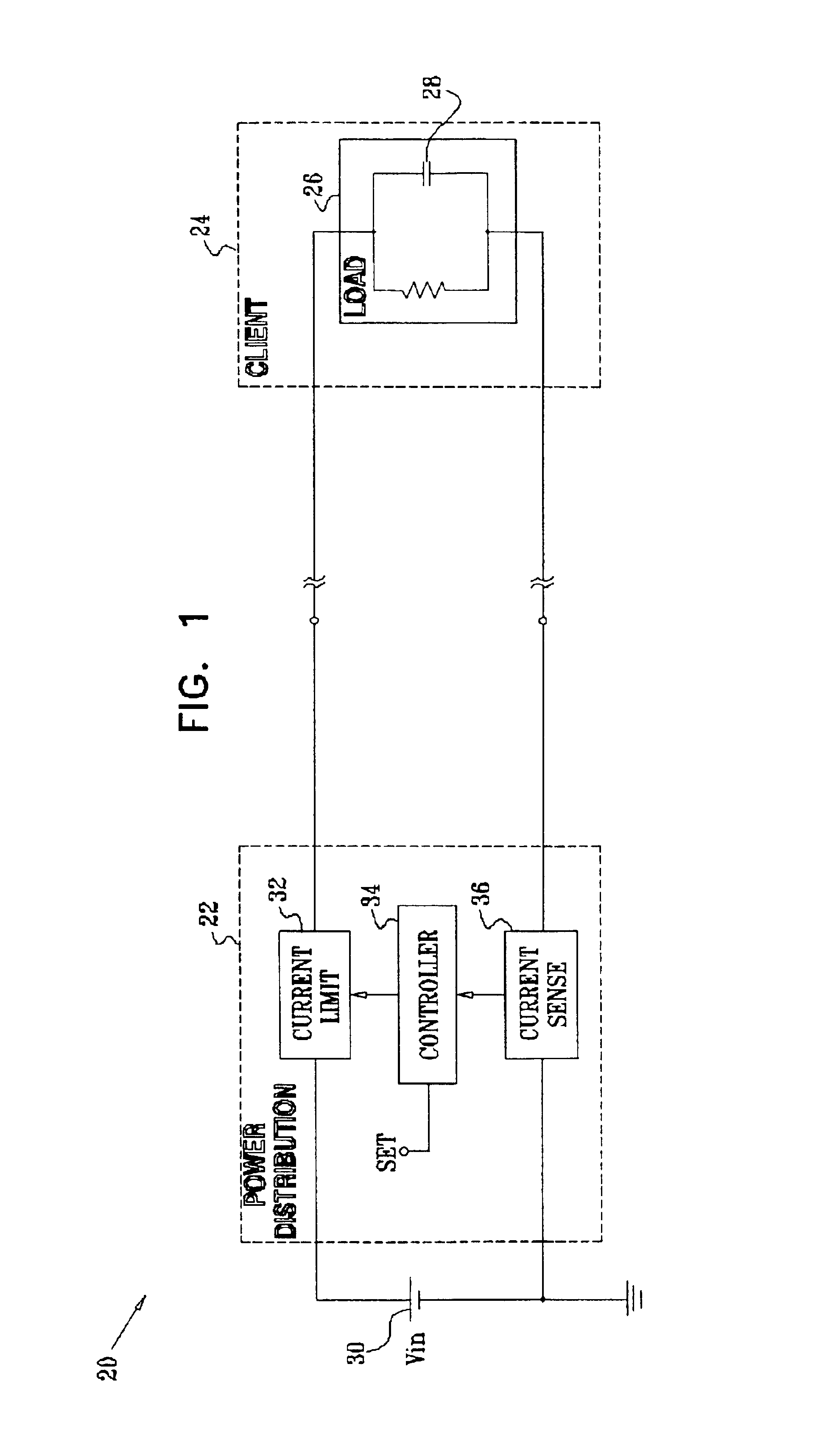

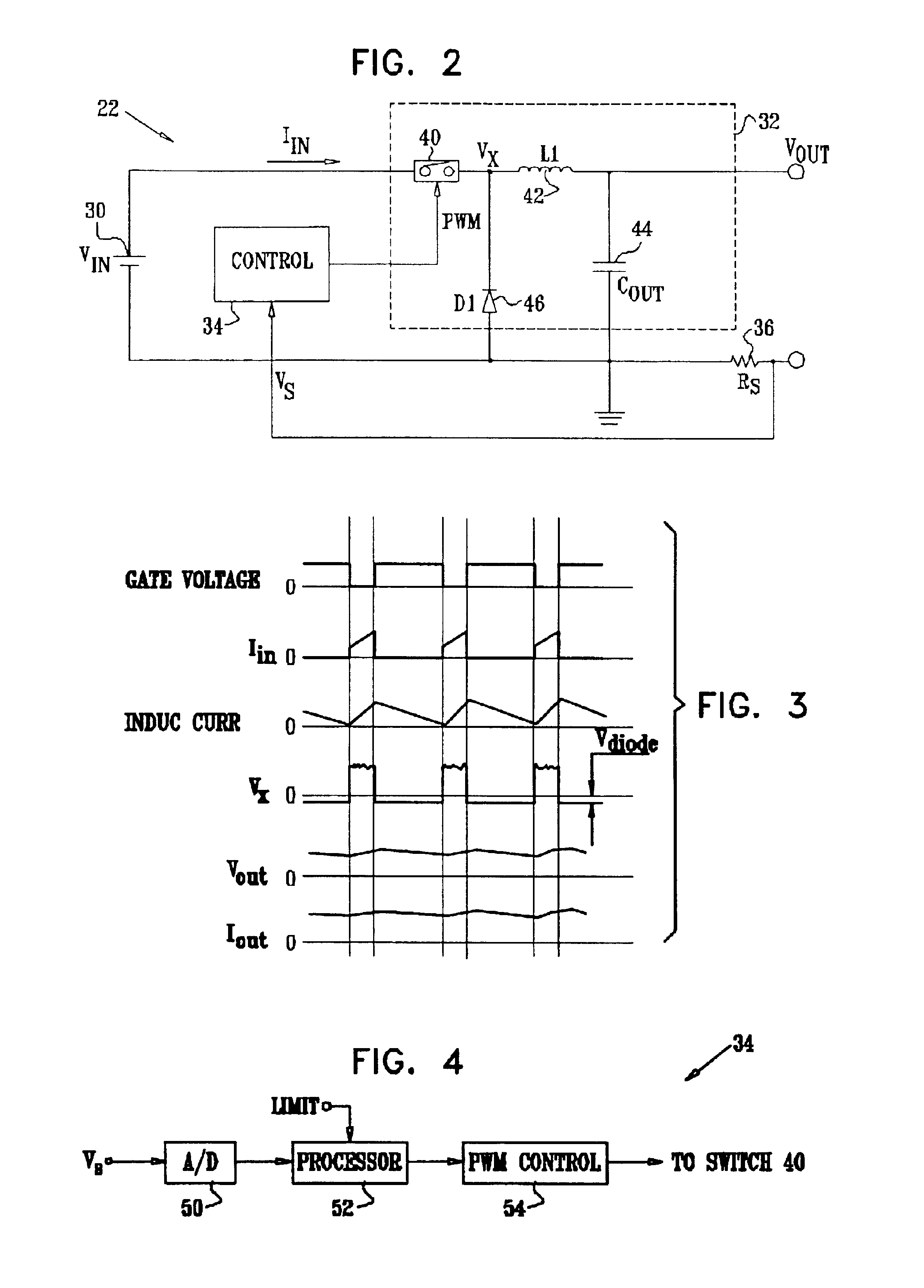

Power distribution with digital current control

InactiveUS6841979B2Minimum power consumptionEfficient power electronics conversionAc-dc conversionControl powerCurrent sensor

Power distribution apparatus, for controlling supply of a current from an electrical power source to at least one load, includes a current sensor, which is coupled to provide an indication of a magnitude of the current flowing to the at least one load. A current limiter is adapted, responsive to the indication, to apply a pulse width modulation to the current drawn from the source so as to maintain the magnitude of the current flowing to the at least one load within a predetermined limit.

Owner:CISCO TECH INC

Network managed device installation and provisioning technique

InactiveUS20050141431A1Minimum power consumptionEasy to manageError preventionTransmission systemsDocumentation procedureEngineering

A system for managing and documenting a local area communications network is provided which deploys power sourcing equipment and powered devices by the use of active electronic modules, having an Ethernet controller and Power over Ethernet forwarding capabilities, as integral, managed components within the cable plant, to enhance management, documentation, security and emergency 911 aspects of the network as well as extending the physical reach of the network.

Owner:PANDUIT

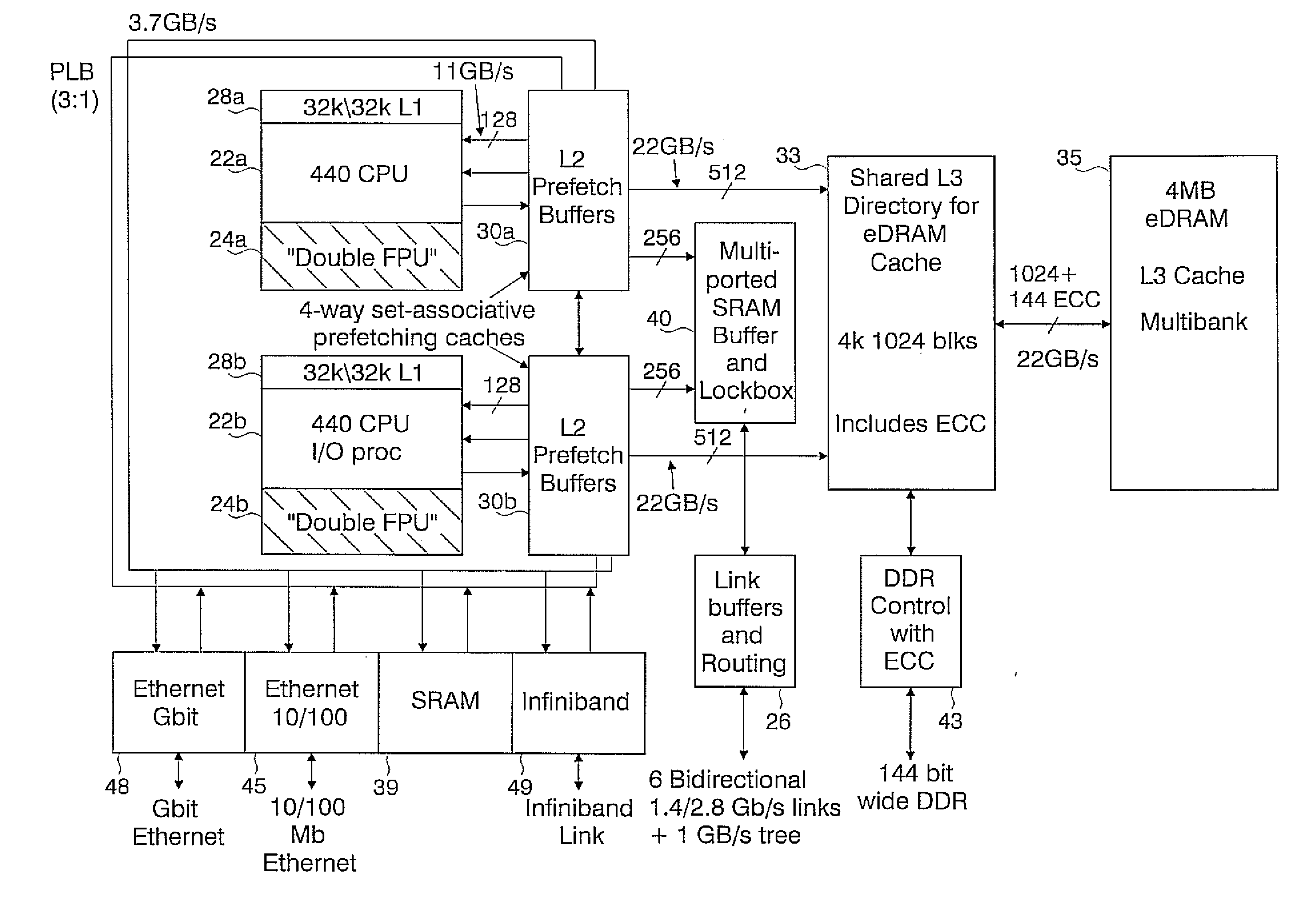

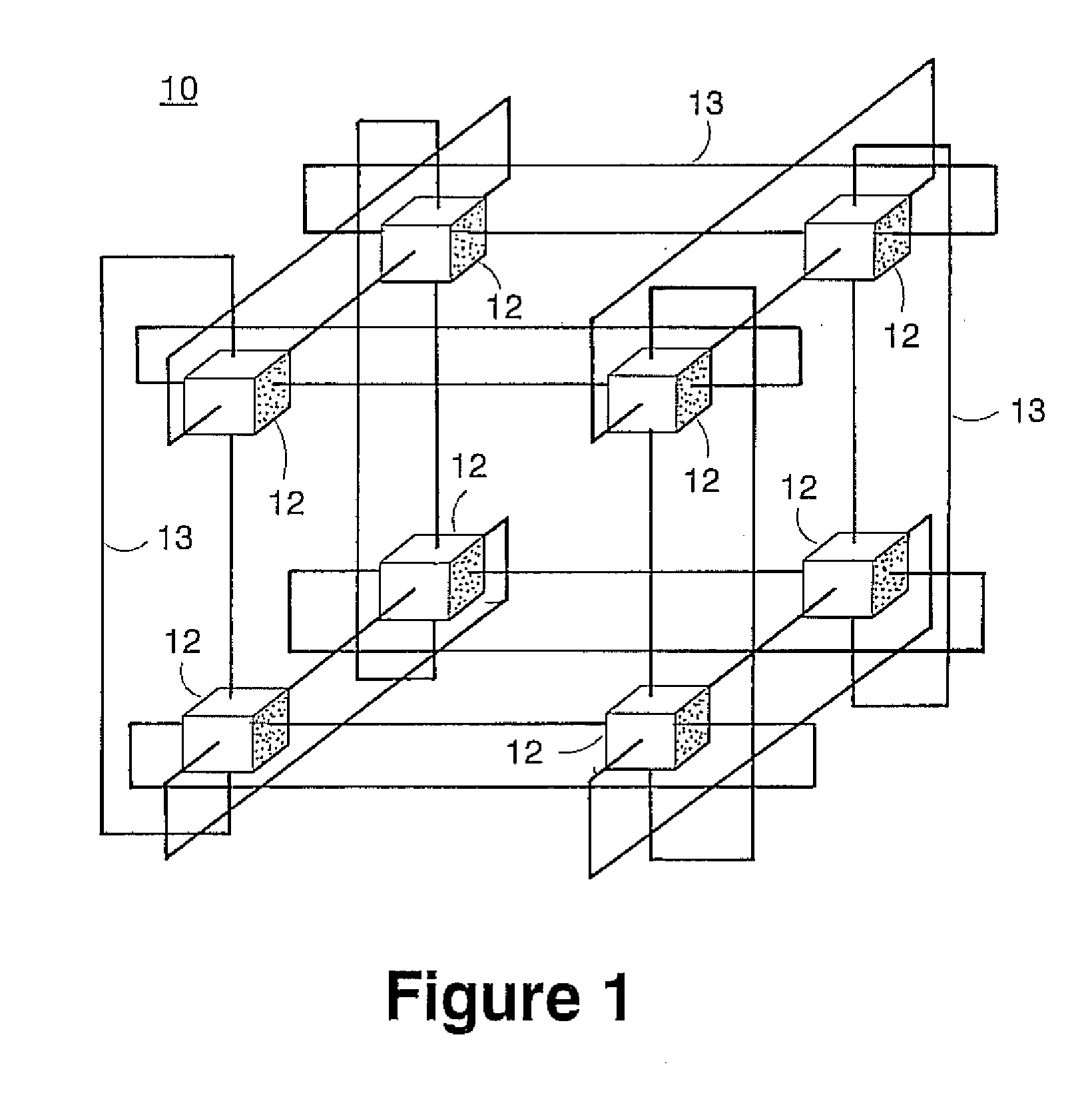

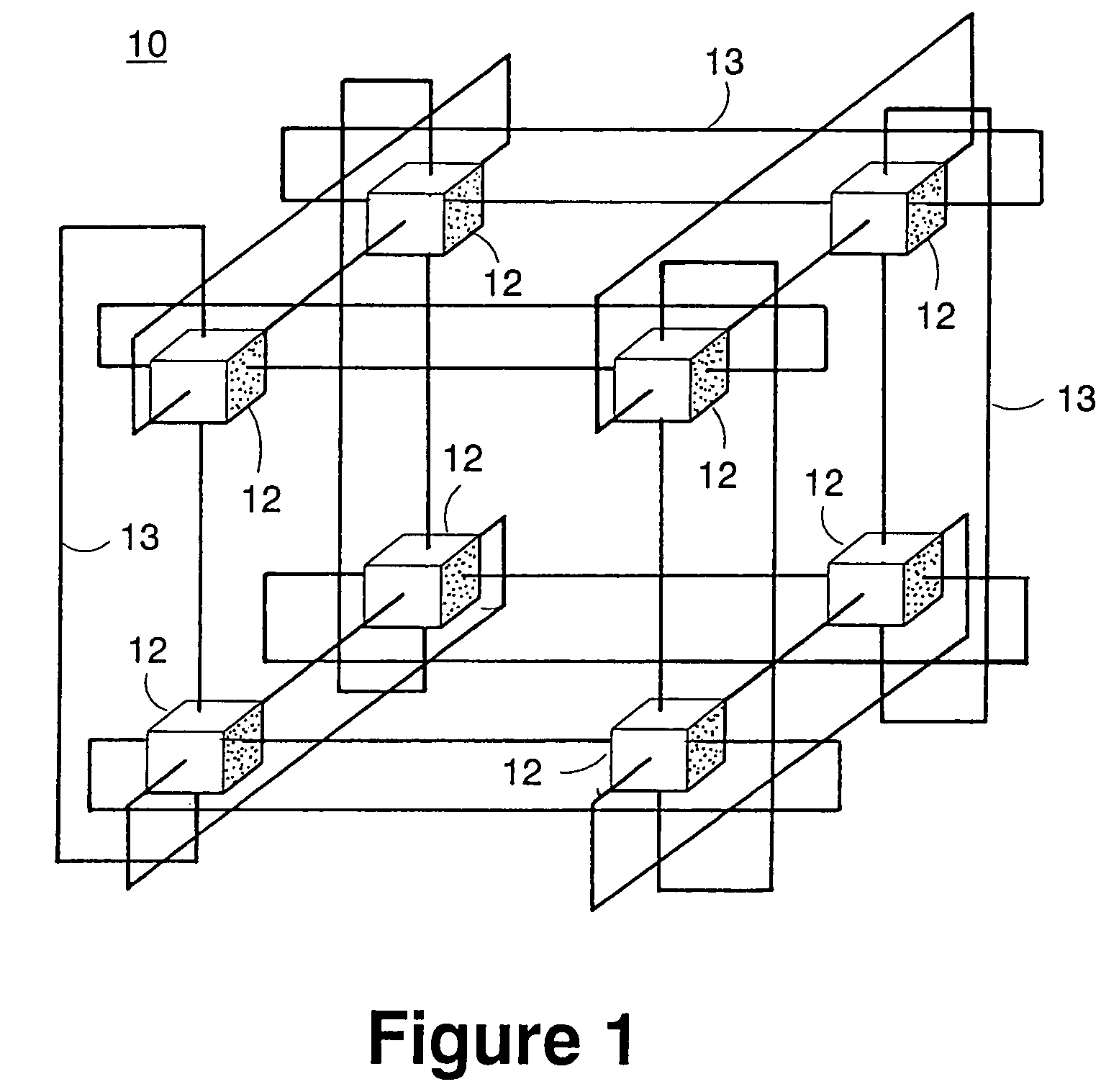

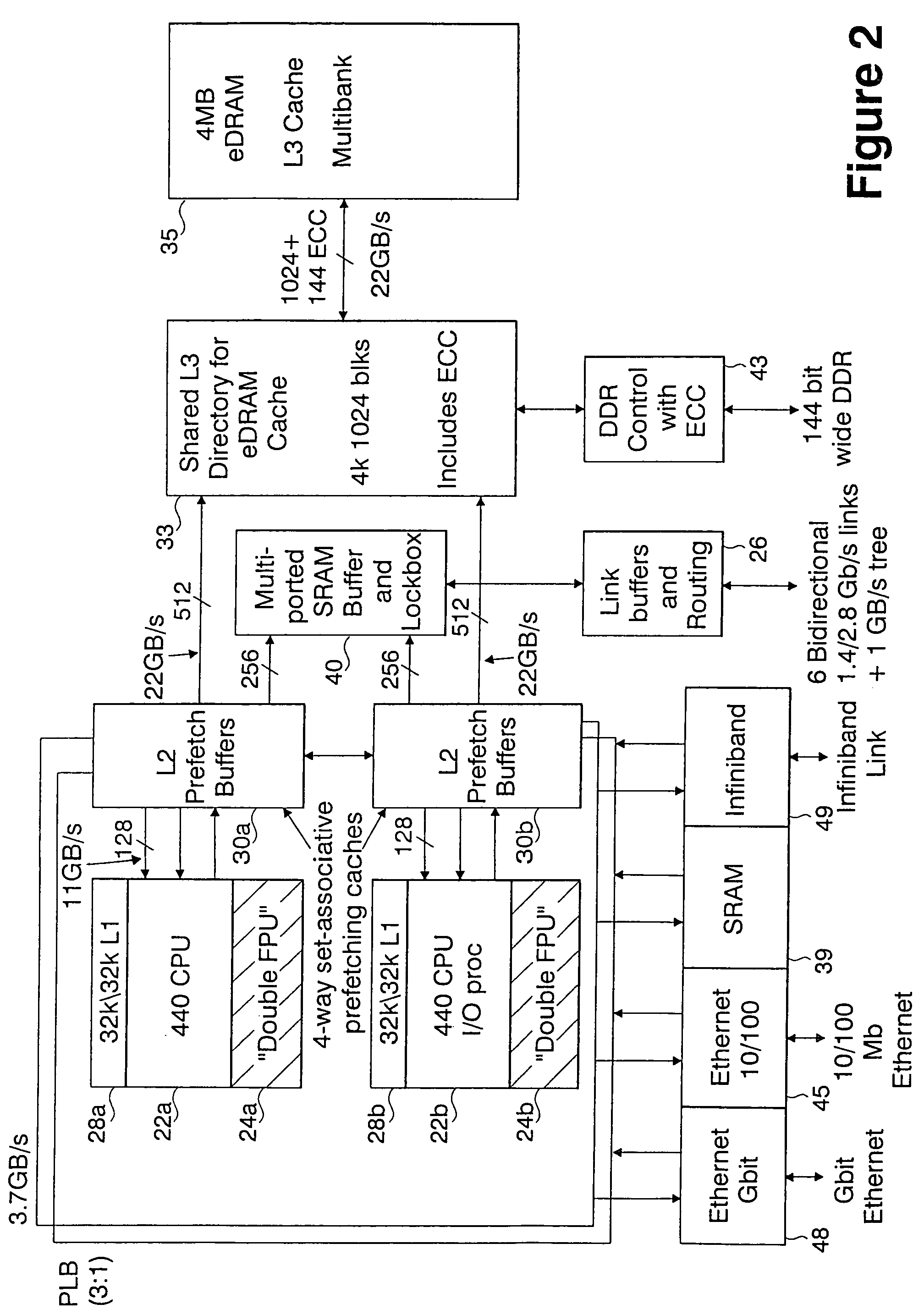

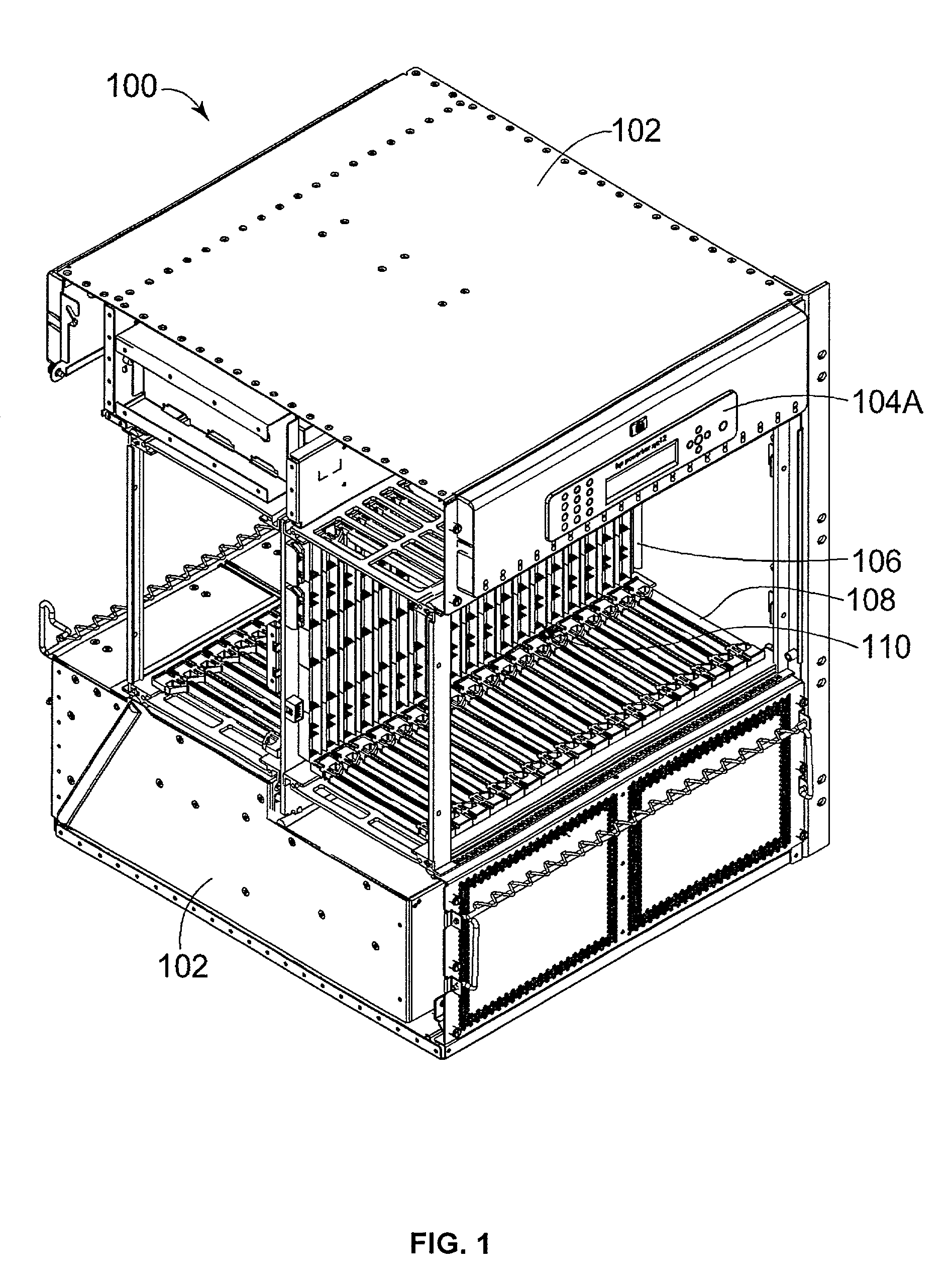

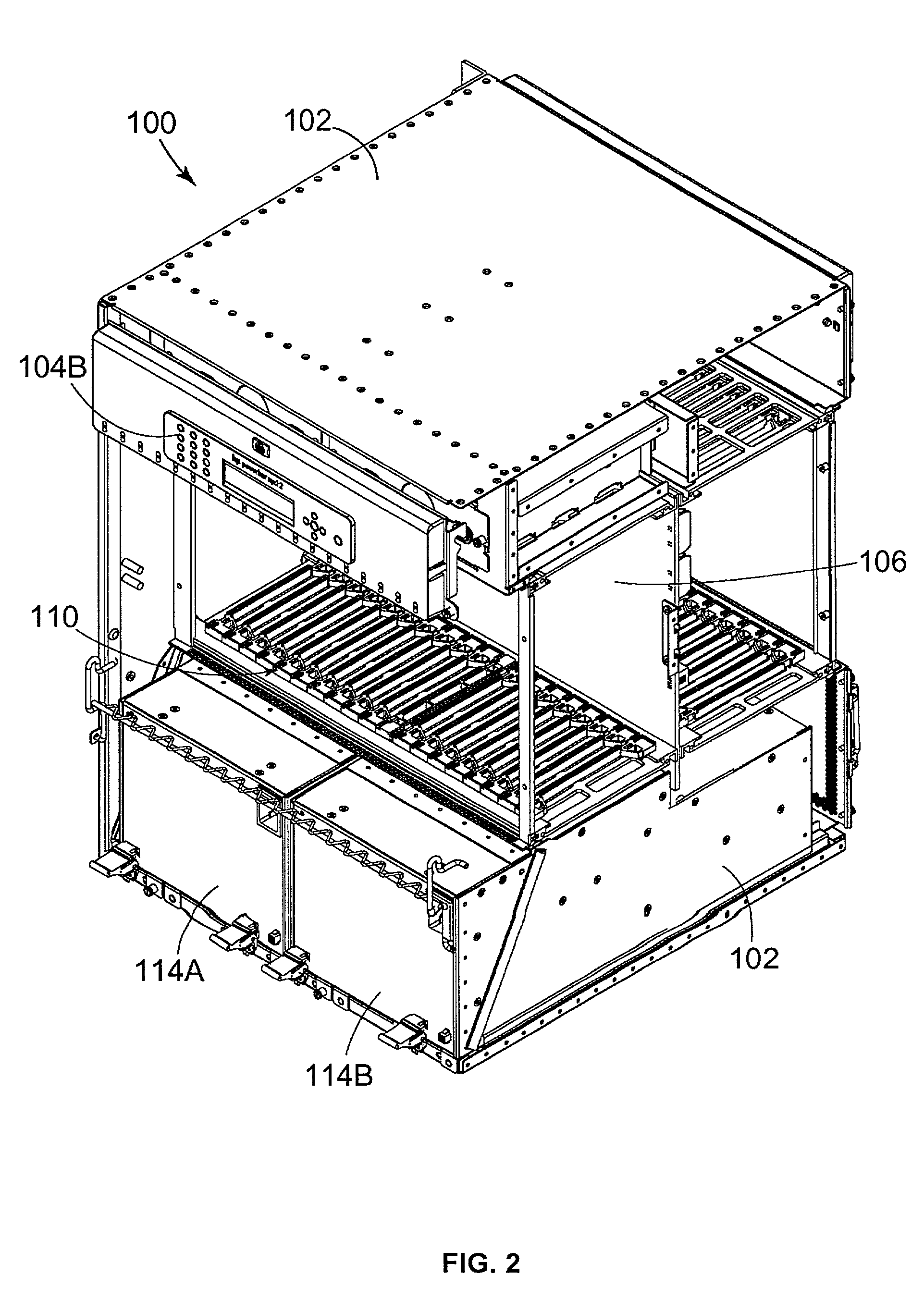

Massively parallel supercomputer

InactiveUS7555566B2Massive level of scalabilityUnprecedented level of scalabilityError preventionProgram synchronisationPacket communicationSupercomputer

A novel massively parallel supercomputer of hundreds of teraOPS-scale includes node architectures based upon System-On-a-Chip technology, i.e., each processing node comprises a single Application Specific Integrated Circuit (ASIC). Within each ASIC node is a plurality of processing elements each of which consists of a central processing unit (CPU) and plurality of floating point processors to enable optimal balance of computational performance, packaging density, low cost, and power and cooling requirements. The plurality of processors within a single node may be used individually or simultaneously to work on any combination of computation or communication as required by the particular algorithm being solved or executed at any point in time. The system-on-a-chip ASIC nodes are interconnected by multiple independent networks that optimally maximizes packet communications throughput and minimizes latency. In the preferred embodiment, the multiple networks include three high-speed networks for parallel algorithm message passing including a Torus, Global Tree, and a Global Asynchronous network that provides global barrier and notification functions. These multiple independent networks may be collaboratively or independently utilized according to the needs or phases of an algorithm for optimizing algorithm processing performance. For particular classes of parallel algorithms, or parts of parallel calculations, this architecture exhibits exceptional computational performance, and may be enabled to perform calculations for new classes of parallel algorithms. Additional networks are provided for external connectivity and used for Input / Output, System Management and Configuration, and Debug and Monitoring functions. Special node packaging techniques implementing midplane and other hardware devices facilitates partitioning of the supercomputer in multiple networks for optimizing supercomputing resources.

Owner:IBM CORP

Energy delivery system and uses thereof

InactiveUS20070288079A1Reduce undesired heatingMinimizing invasivenessElectrotherapySurgical instruments for heatingAbnormal tissue growthThrombus

The present invention relates to systems and devices for delivering energy to tissue for a wide variety of applications, including medical procedures (e.g., tissue ablation, resection, cautery, vascular thrombosis, treatment of cardiac arrhythmias and dysrhythmias, electrosurgery, tissue harvest, etc.). In particular, the present invention relates to systems and devices for the delivery of energy with optimized characteristic impedance. In certain embodiments, methods are provided for treating a tissue region (e.g., a tumor) through application of energy with the systems and devices of the present invention.

Owner:NEUWAVE MEDICAL

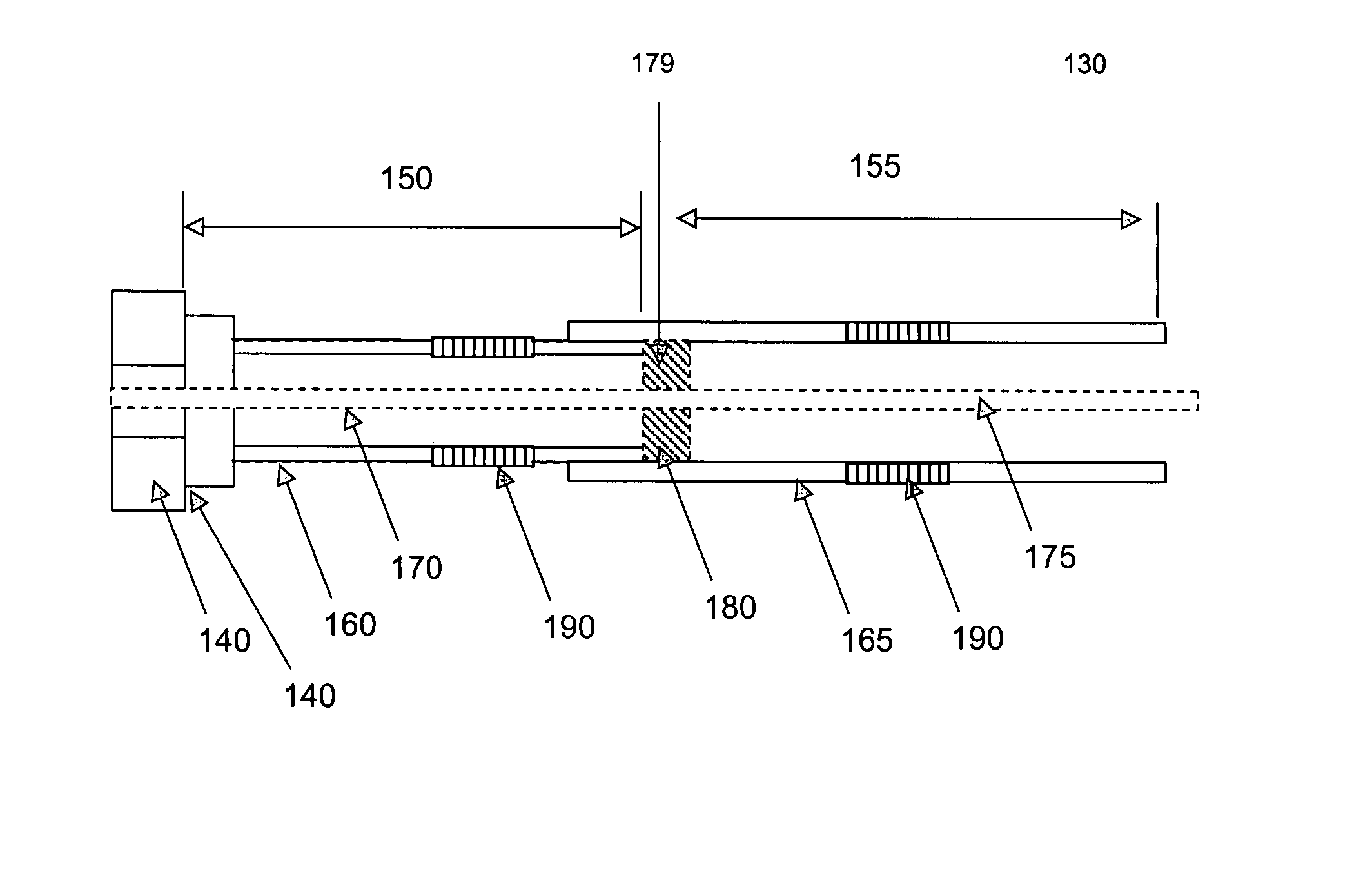

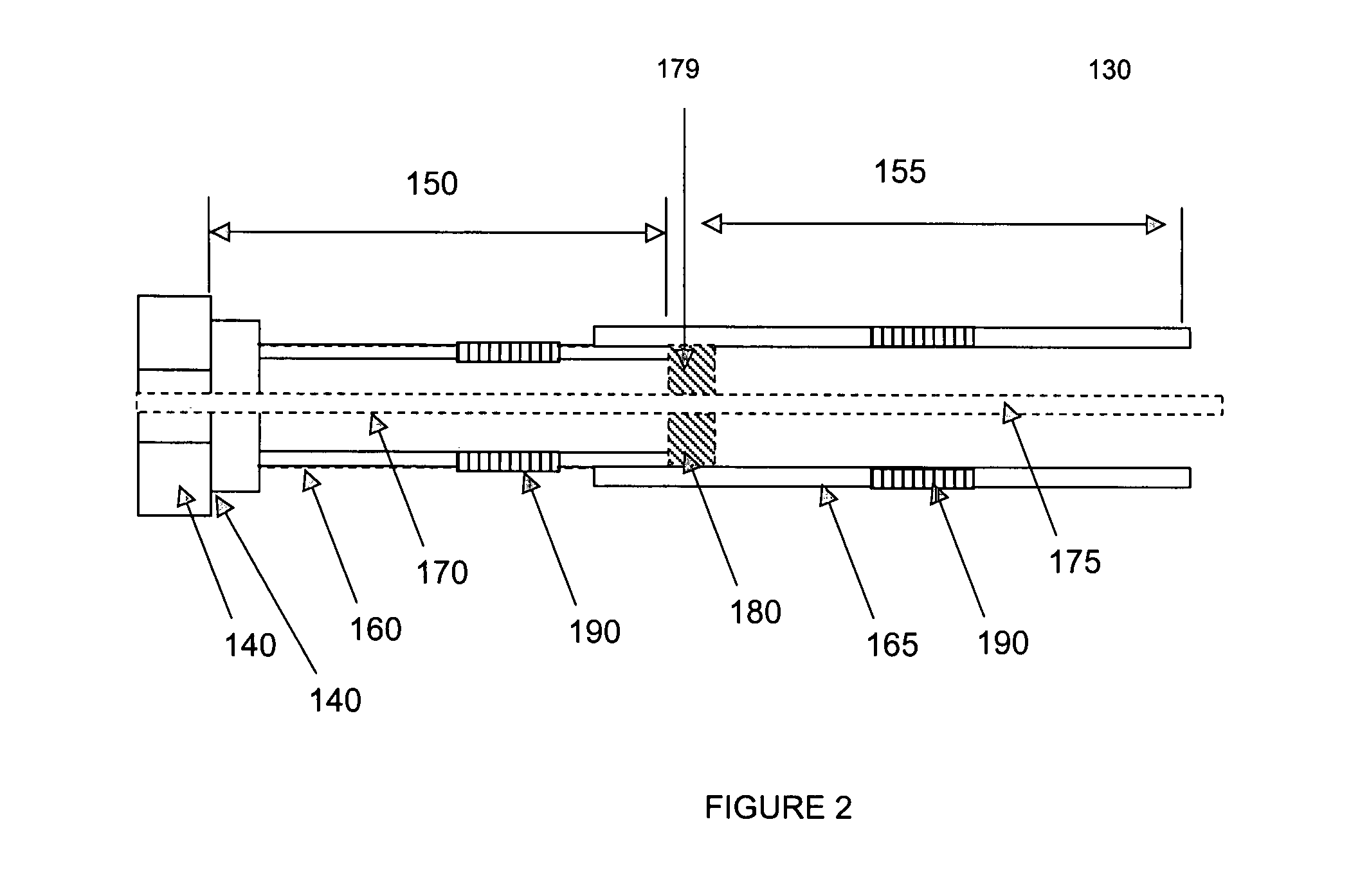

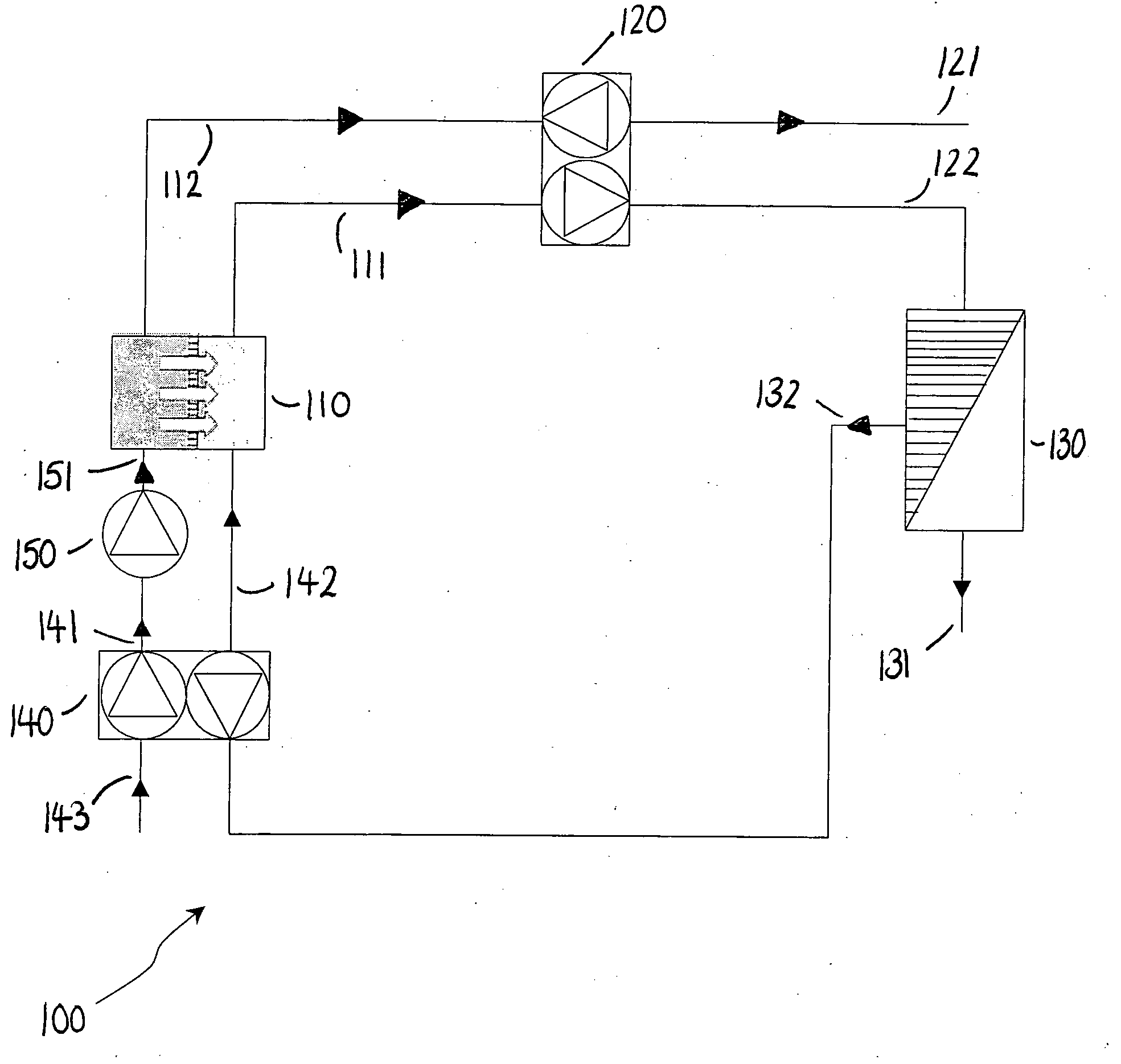

Process and systems

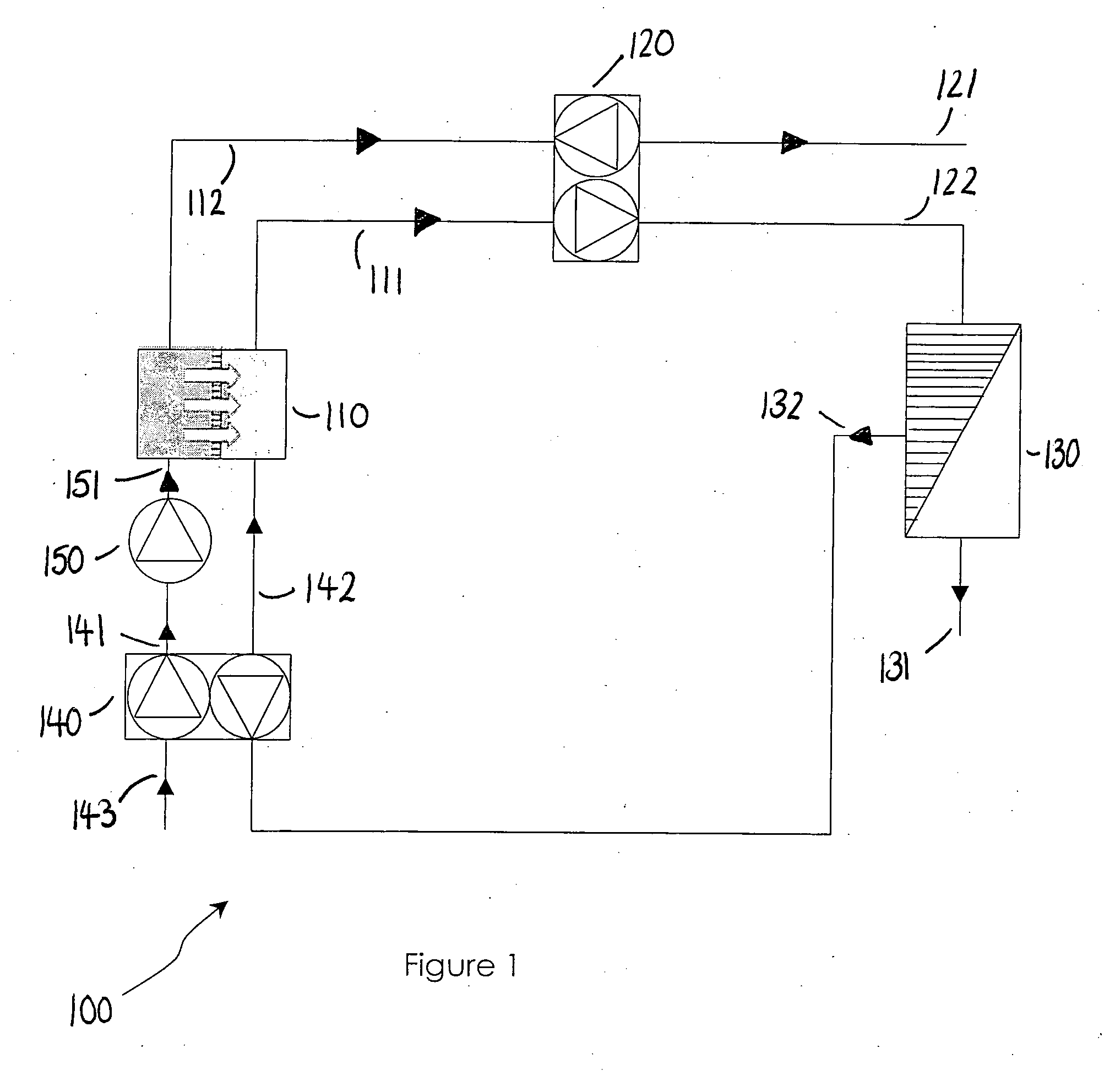

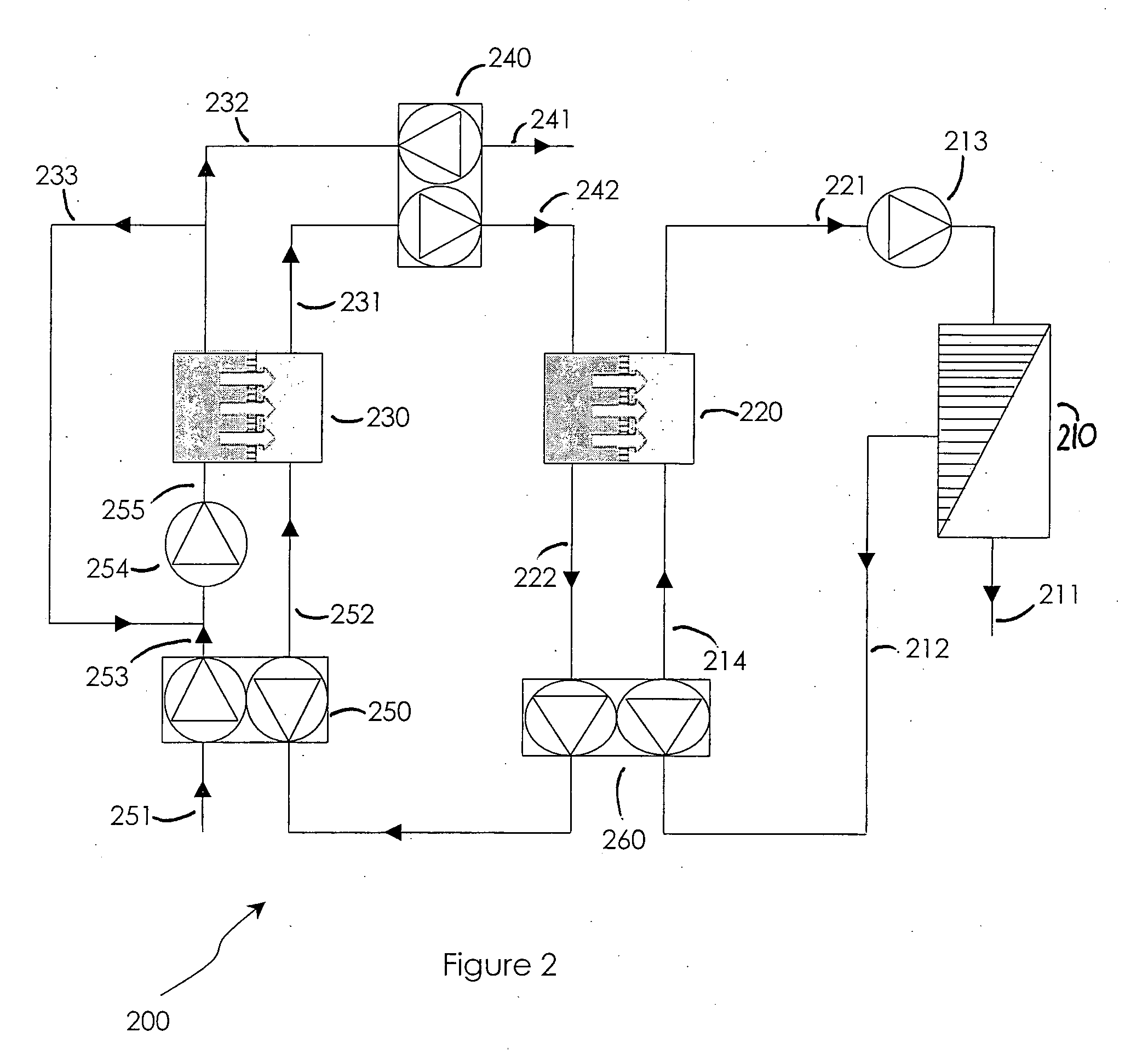

InactiveUS20100192575A1Minimise heat lossHigh working pressureMembranesGeneral water supply conservationProcess engineeringReverse osmosis

An apparatus for recovering energy from an osmotic system, said apparatus comprising: (i) a feed stream (143,251); (ii) pressure means (140,150, 250, 254) to pressurise said feed stream; (iii) a manipulated osmosis unit (110,220,230); (iv) an energy recovery unit (120, 240, 260) in fluid connection with second solution side of the manipulated osmosis unit; (v) a reverse osmosis unit (130) receiving a feed from the energy recovery unit.

Owner:AL MAYAHI ABDULSALAM +1

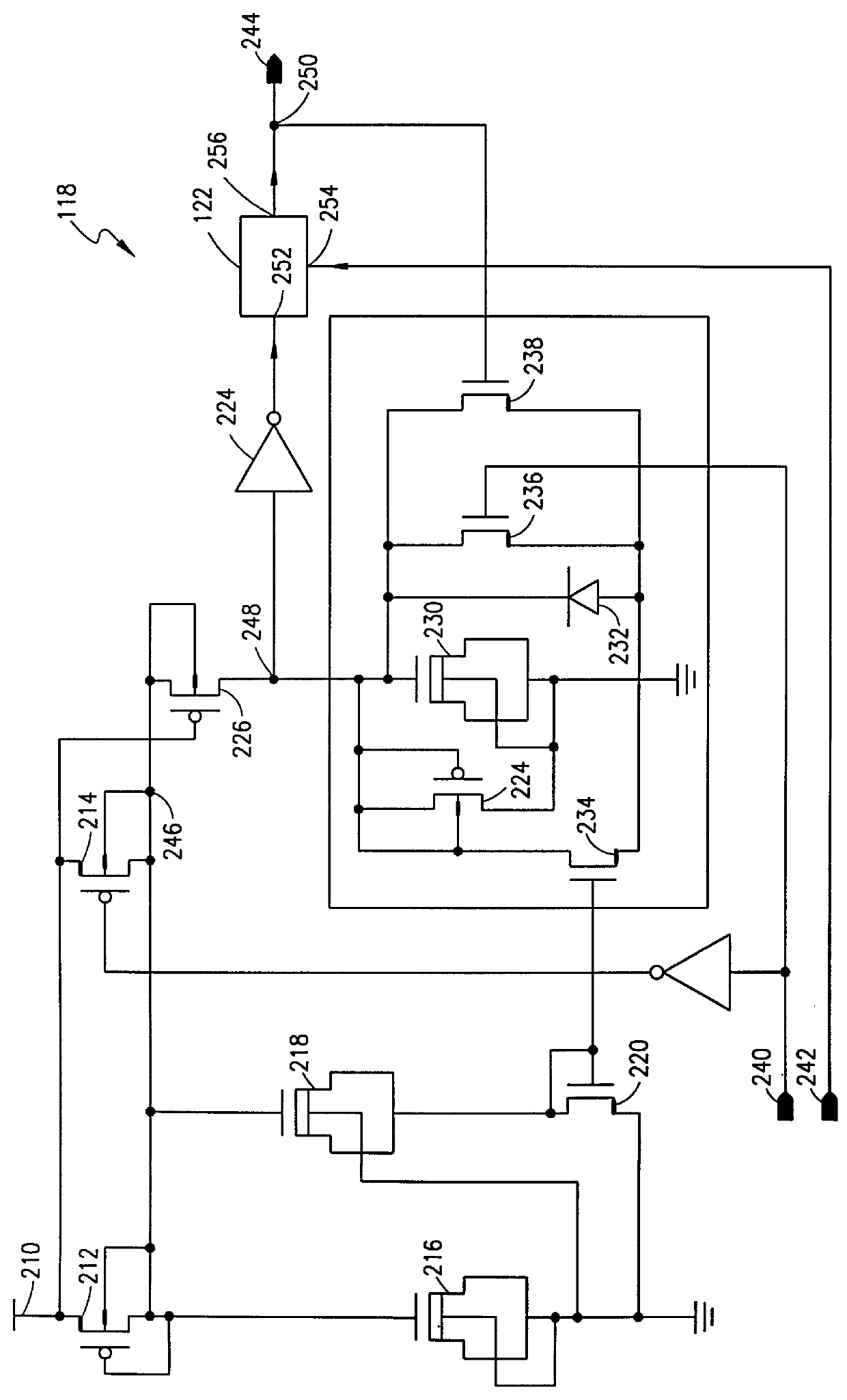

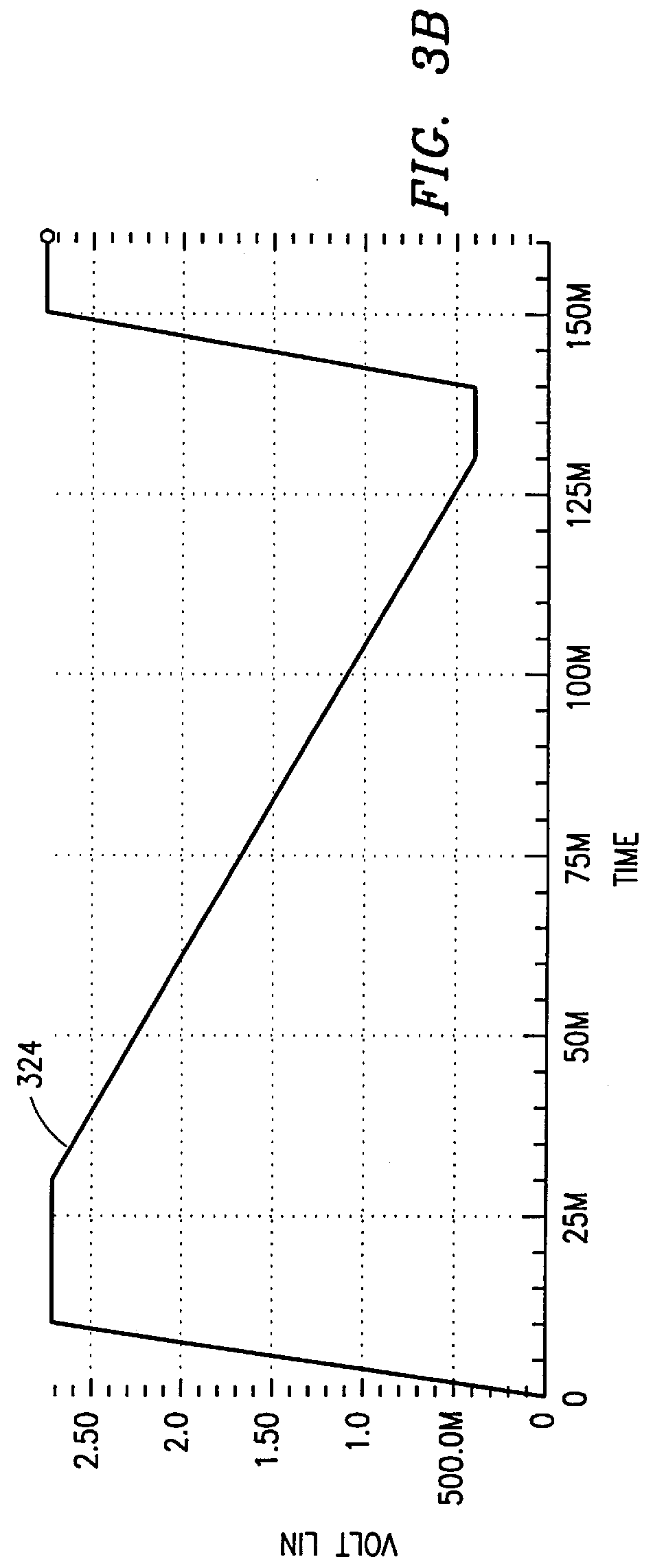

Method for initializing an electronic device using a dual-state power-on-reset circuit

InactiveUS6141764AMinimum power consumptionPulse automatic controlVolume/mass flow measurementPower-on resetElectricity

An initializer that responds to change in a power supply potential level, for generating an initialize signal to initialize a circuit to a select state, the initializer includes a power-on reset circuit that switches between an active and a powered-down state, and is for generating the initialize signal. The initializer also includes a wake-up circuit that monitors the power supply potential level and switches the power-on reset circuit from the powered-down state to the active state when selected change in the power supply potential level occurs.

Owner:MAXIM INTEGRATED PROD INC

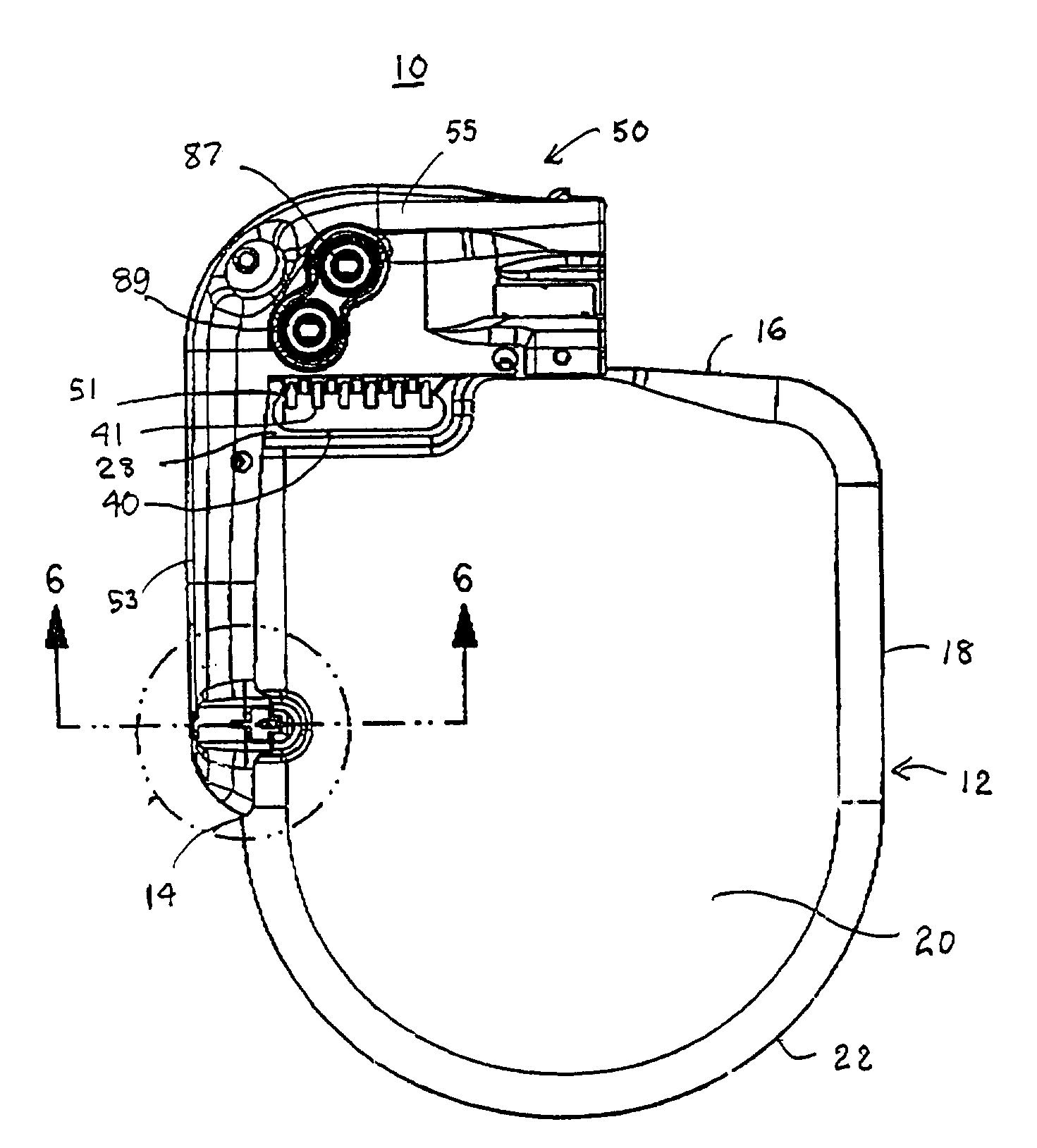

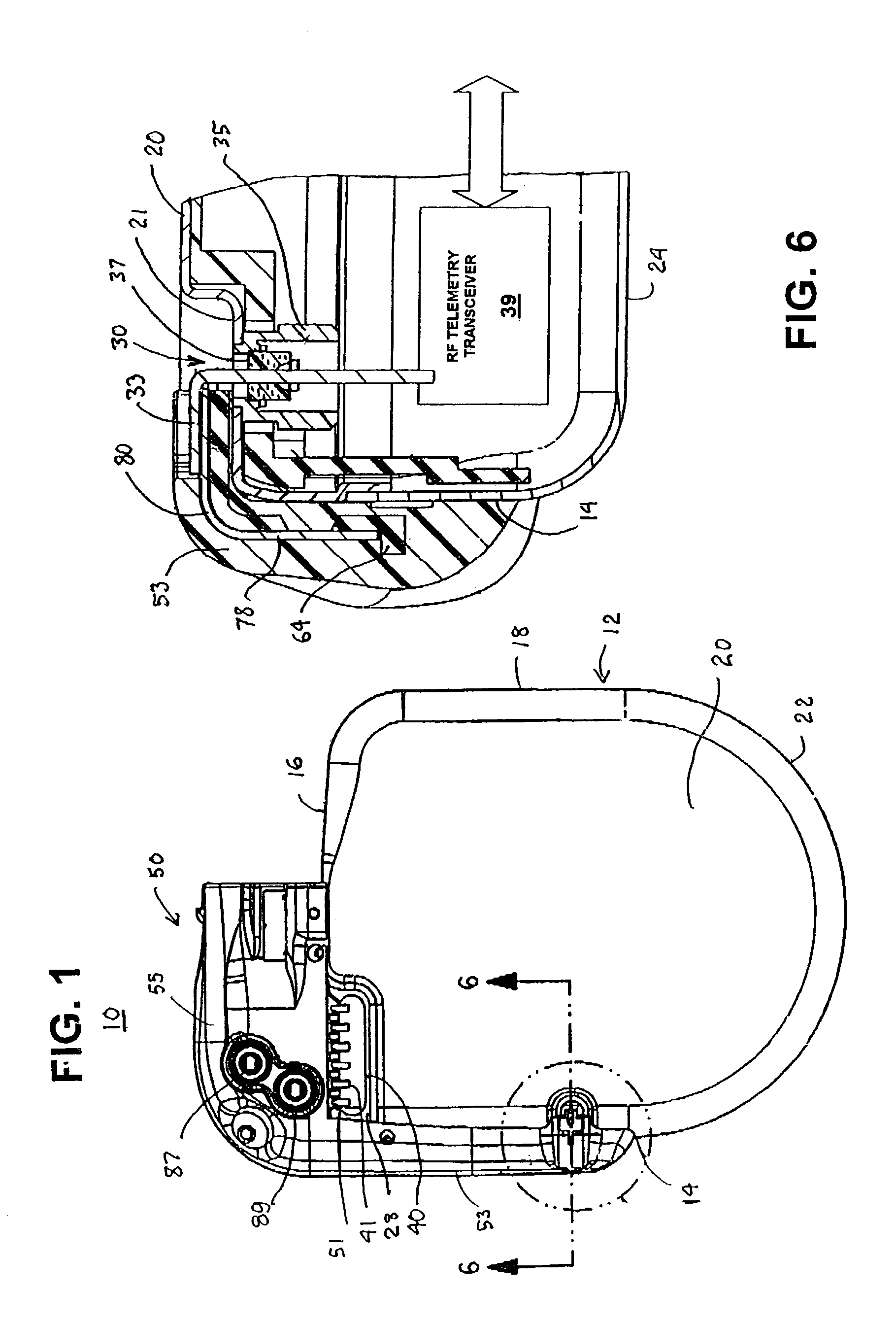

Telemetry antenna for an implantable medical device

InactiveUS7016733B2Minimizing packaging volumeHigh rateHeart stimulatorsSpatial OrientationsEngineering

Improved telemetry antennas and methods of fabrication for an implantable medical device (IMD) for use in uplink telemetry (UT) and downlink telemetry (DT) transmissions between the IMD and an external medical device (EMD) are disclosed. A first telemetry antenna element is supported to extend in a first direction along a minor side of the IMD housing by a first header segment, and a second antenna element is supported to extend in a second direction along a second minor side of the IMD housing by a second header segment. The first and second antenna elements are supported to extend apart at substantially 90° to one another, i.e., substantially orthogonally, in substantially a common plane to optimize UT transmission and DT reception of UHF telemetry signals by at least one of the first and second antenna elements depending upon the mutual spatial orientation with the antenna elements of an EMD antenna.

Owner:MEDTRONIC INC

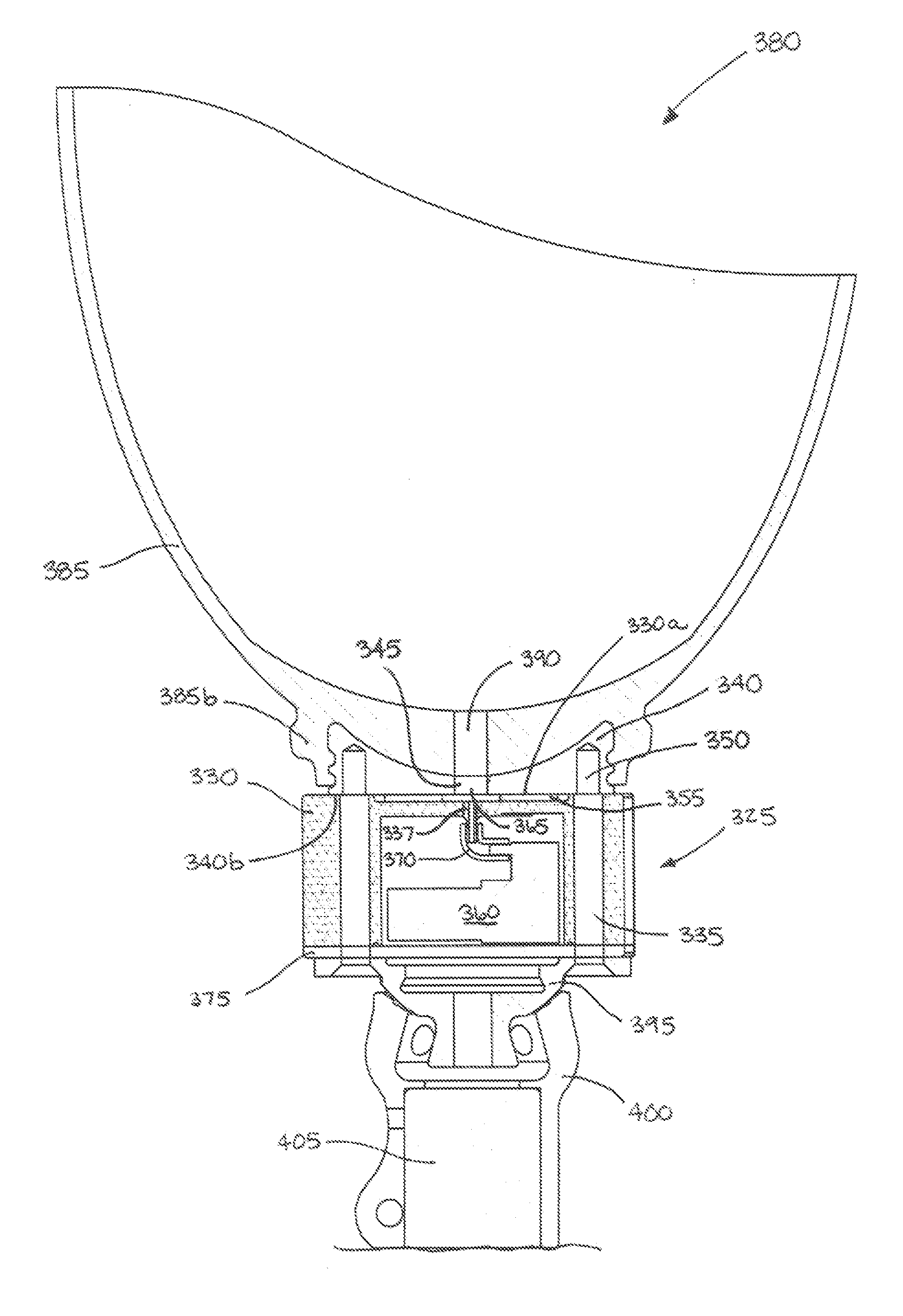

Passive electro-magnetically damped joint

InactiveUS20090192619A1Improving cosmetic appearanceEasy to walkJoint implantsArtificial legsElectrical resistance and conductanceControl system

The present invention comprises an apparatus, system and method utilizing a passive electro-magnetically damped joint for prosthetics or orthotics. Such as system may be controlled through changing the resistive nature of the circuit in which a braking or damping mechanism can sufficiently replicate and augment biomechanical movement. This may be accomplished through electronic circuitry means only, or through the use of intelligent control through a microprocessor and dynamic ambulation replication algorithms.

Owner:ORTHOCARE INNOVATIONS

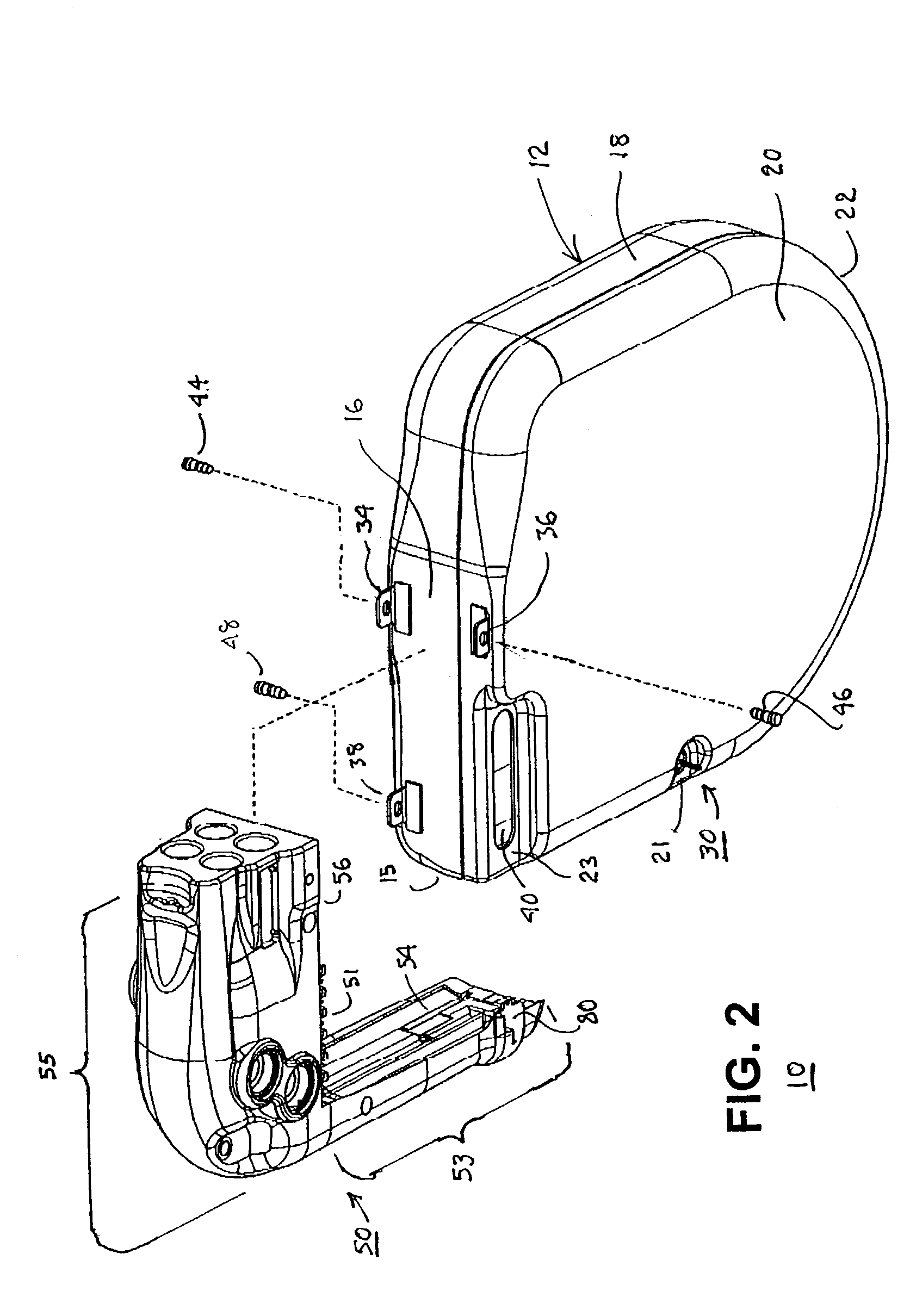

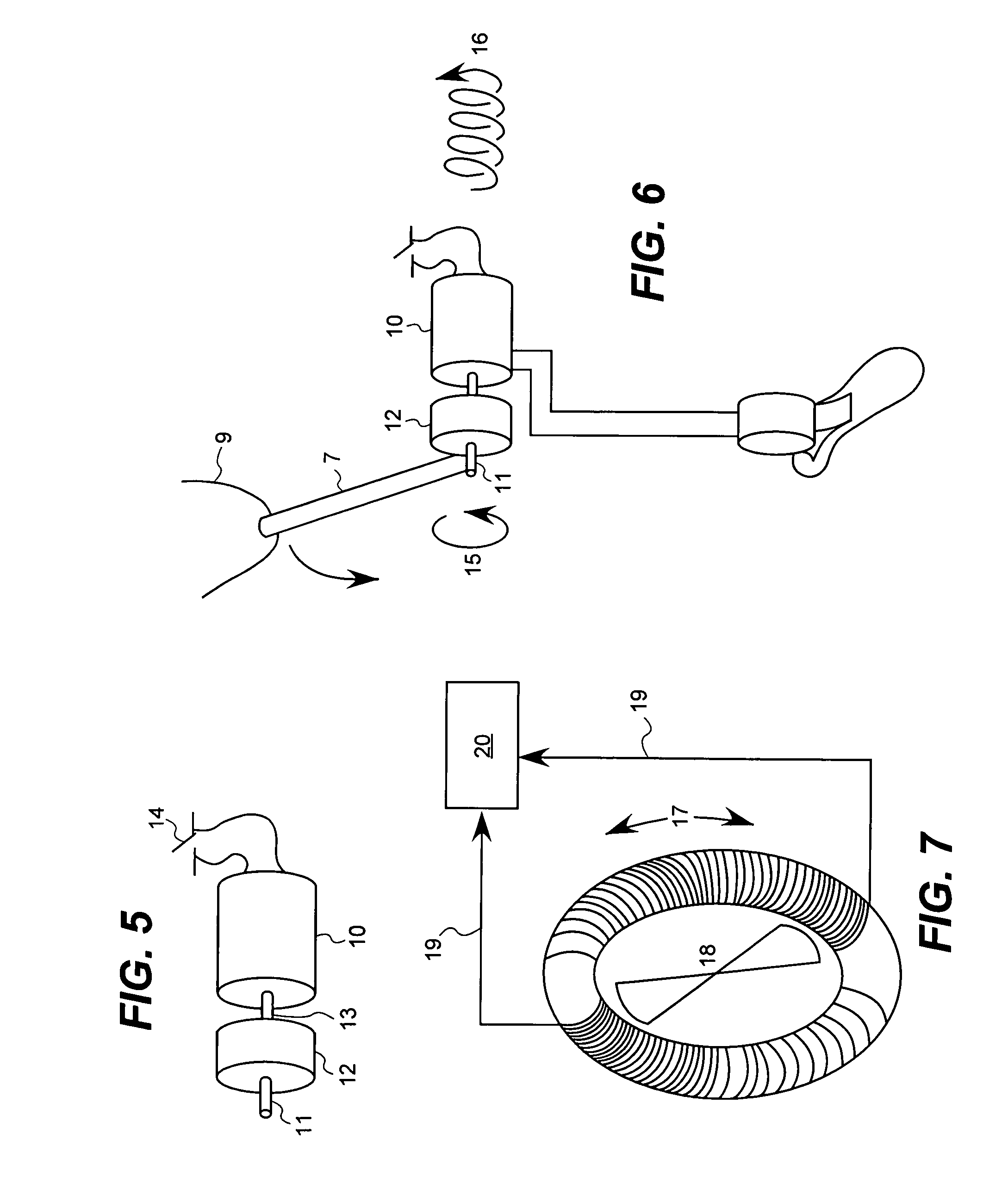

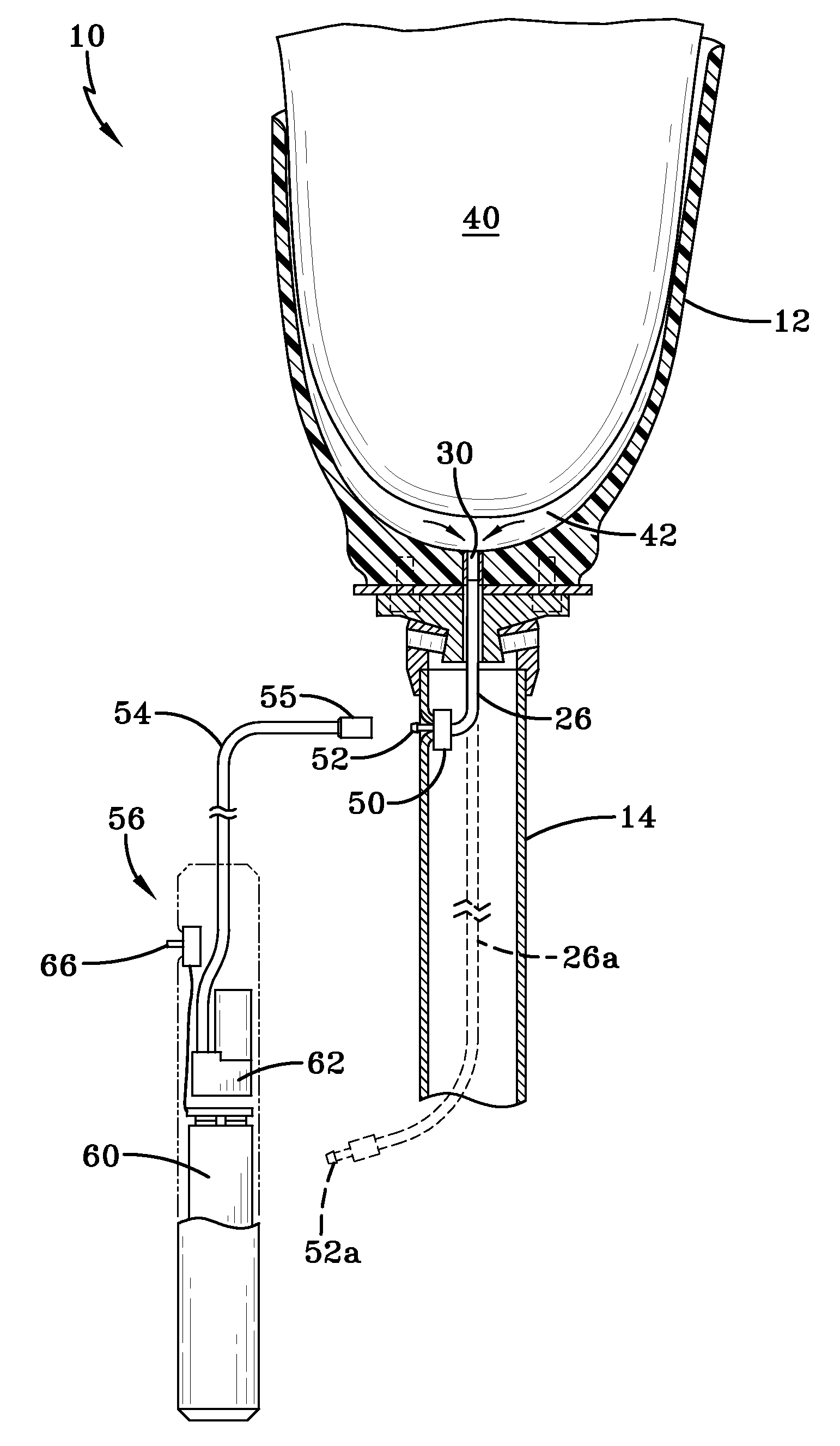

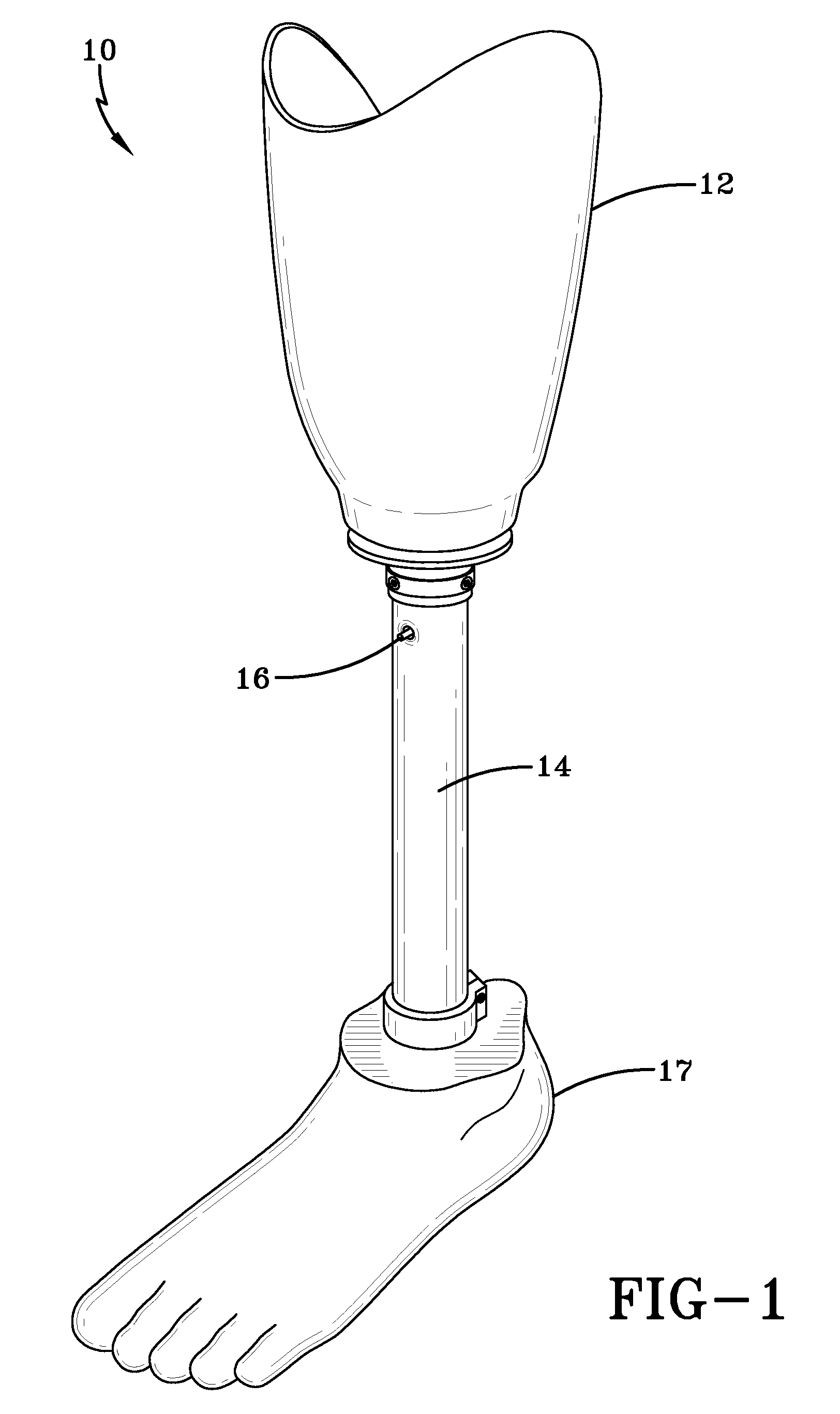

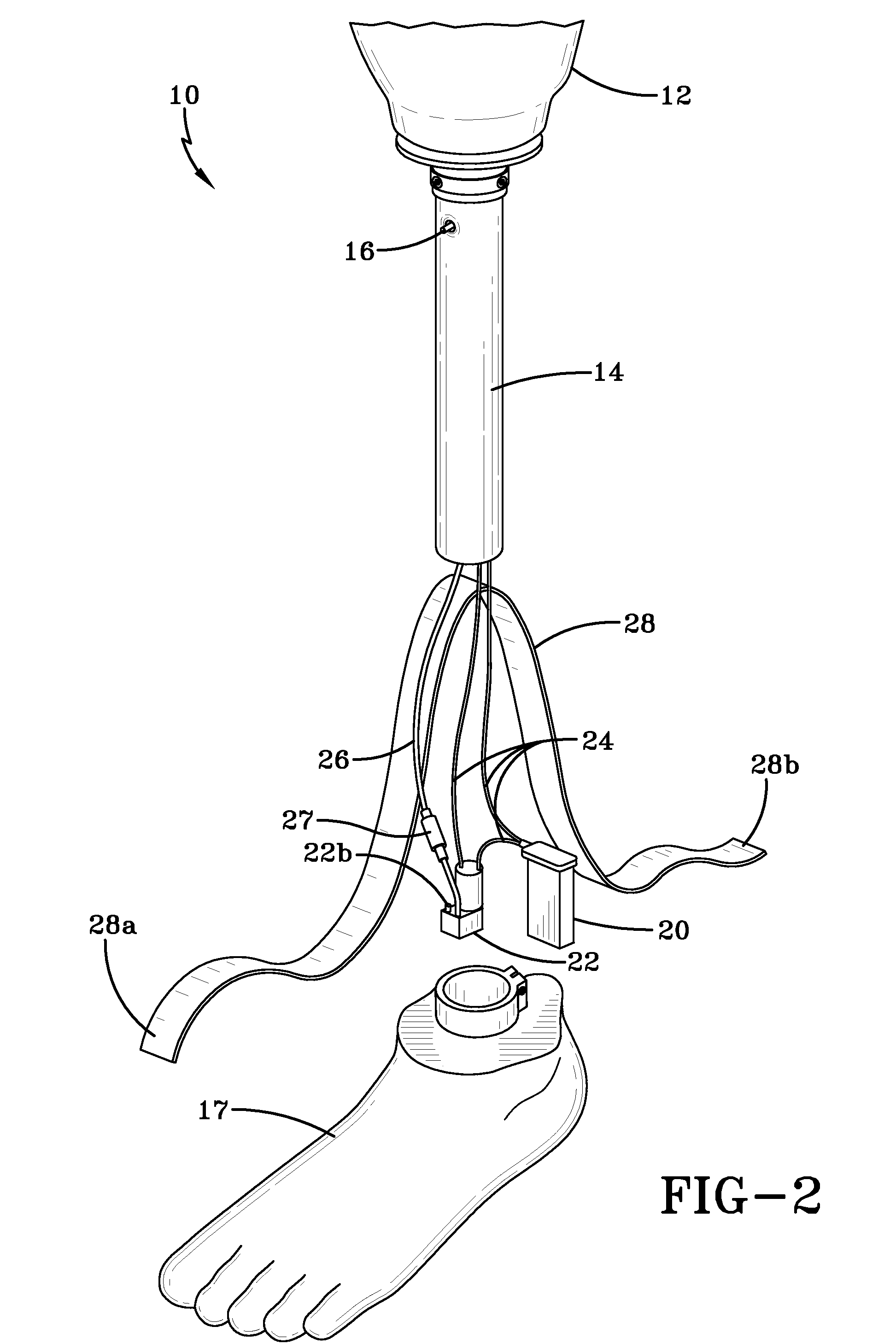

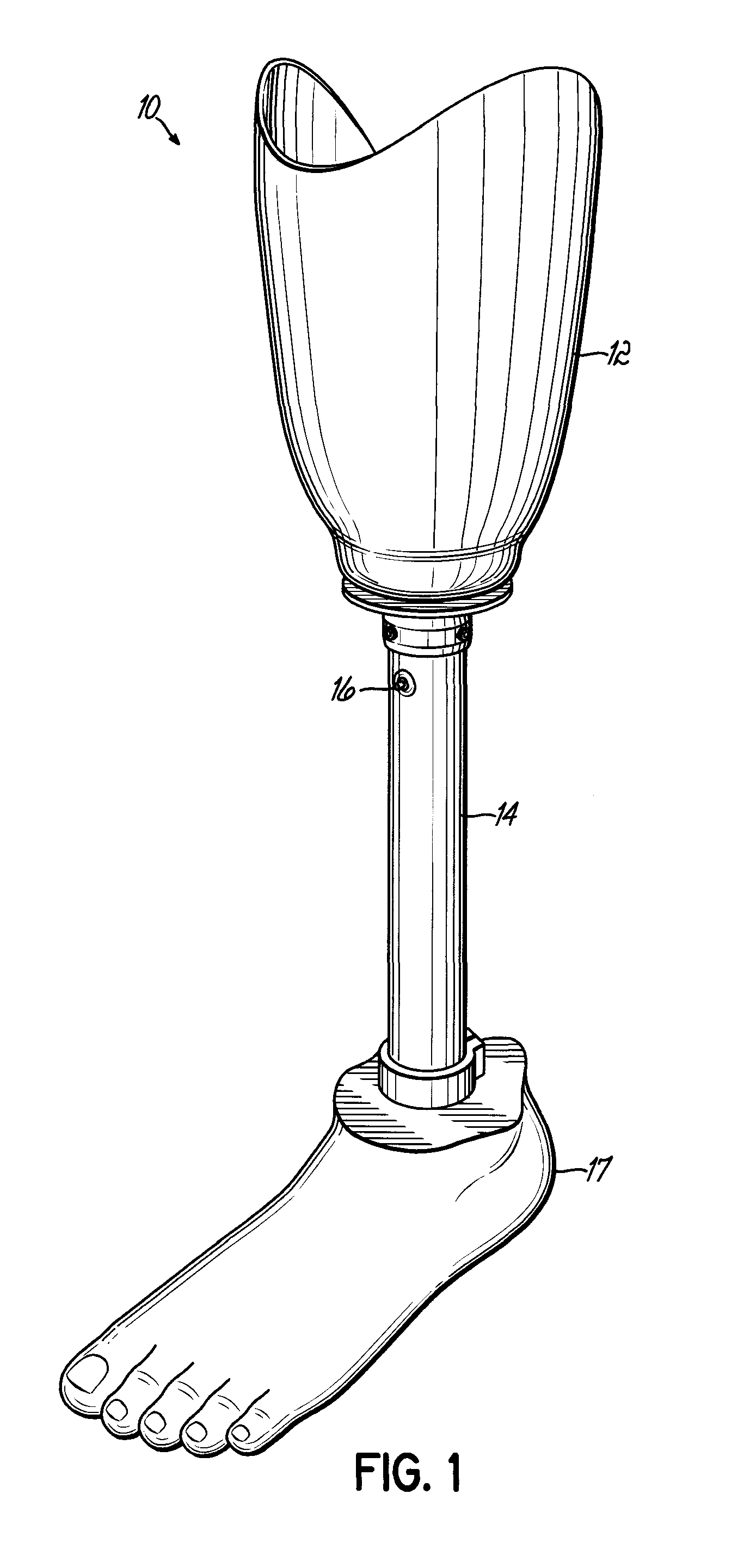

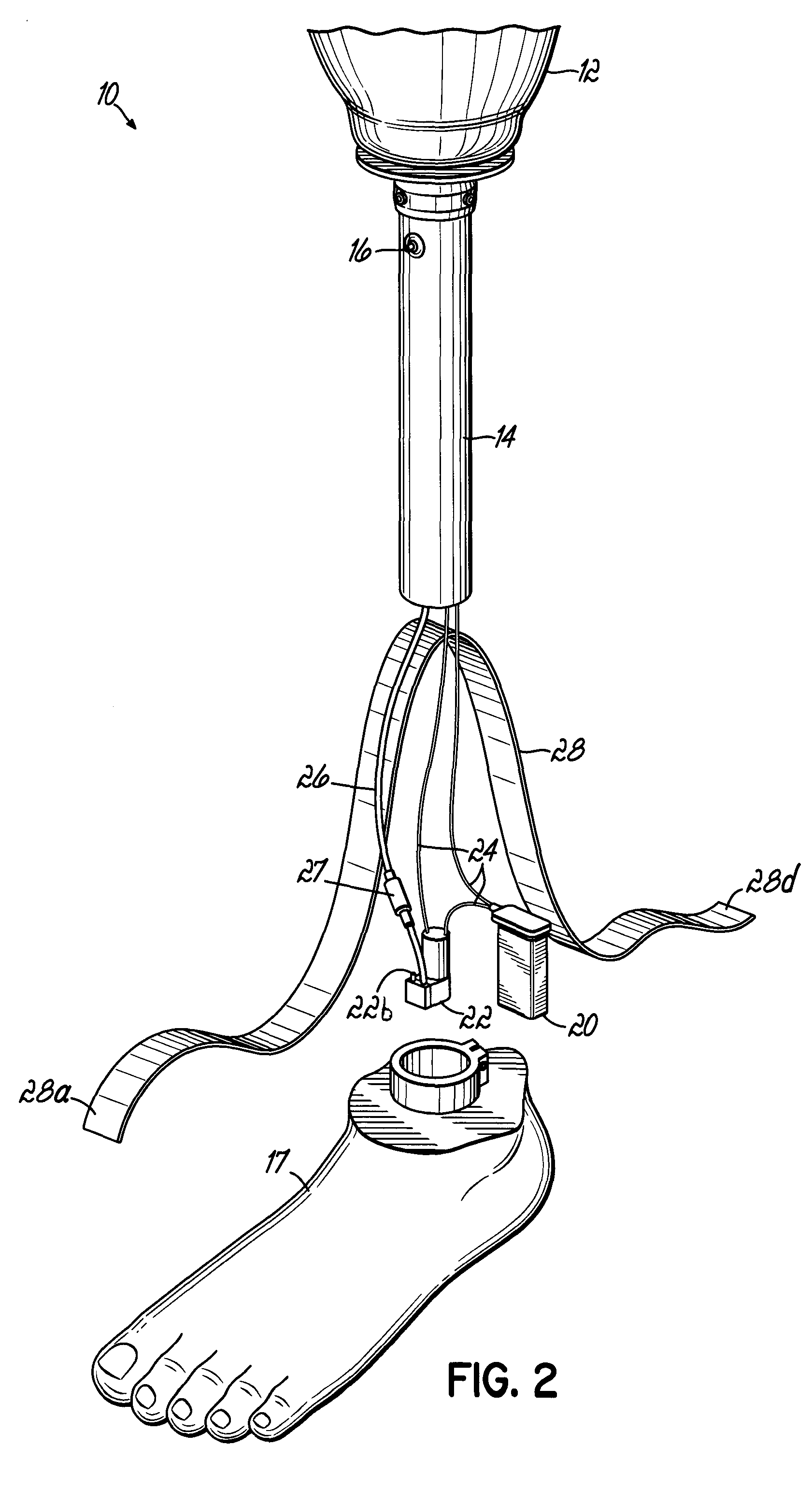

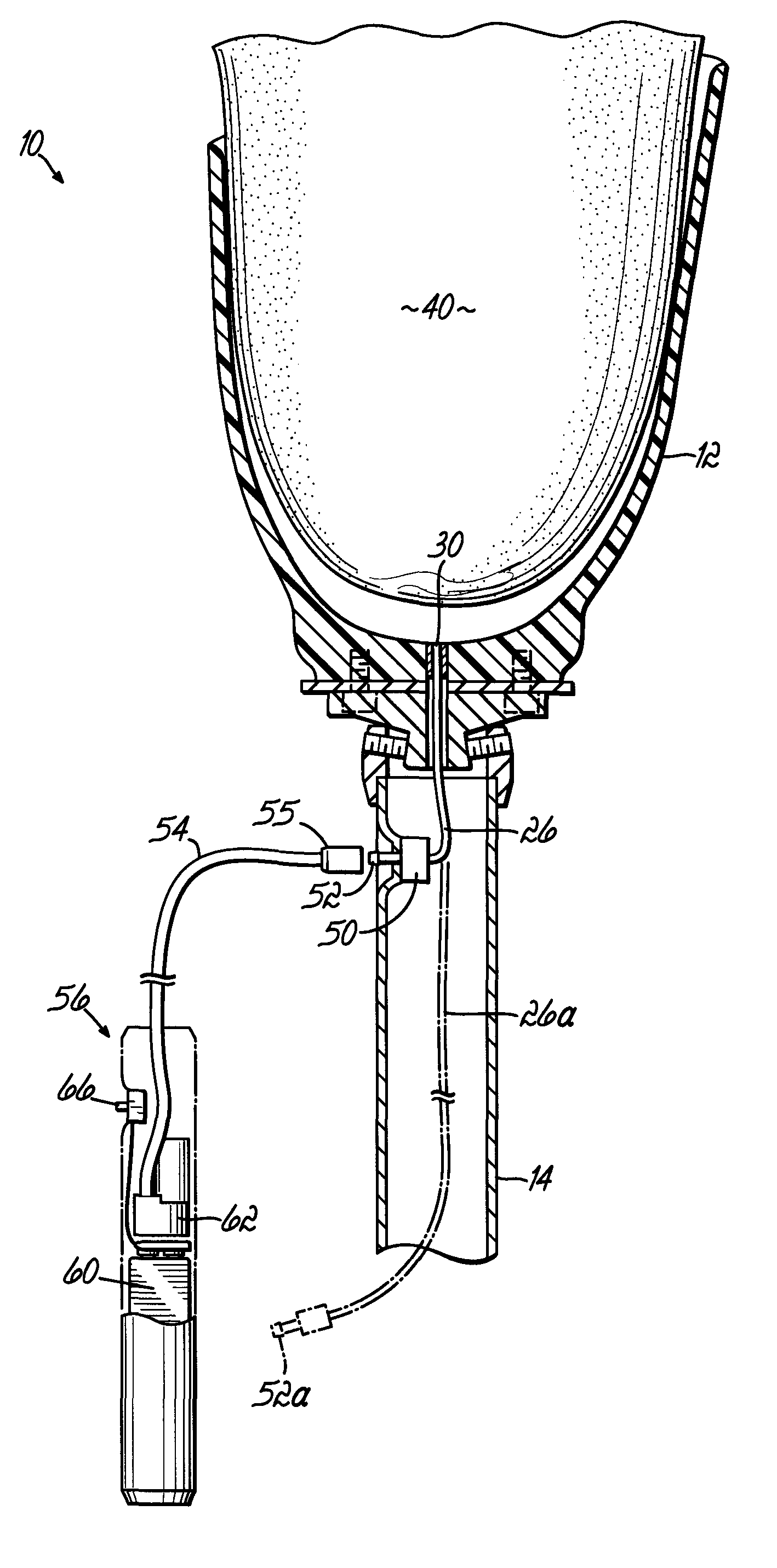

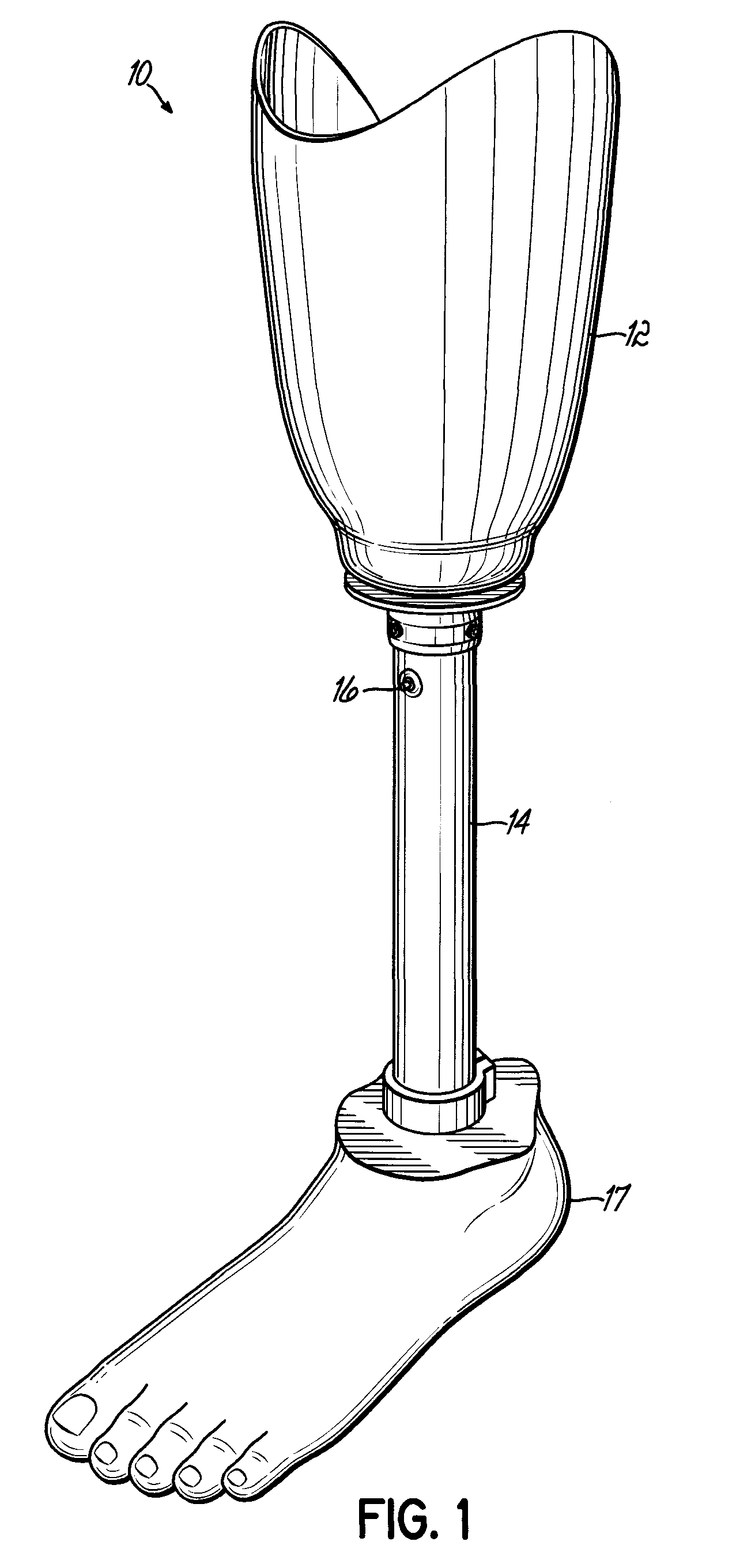

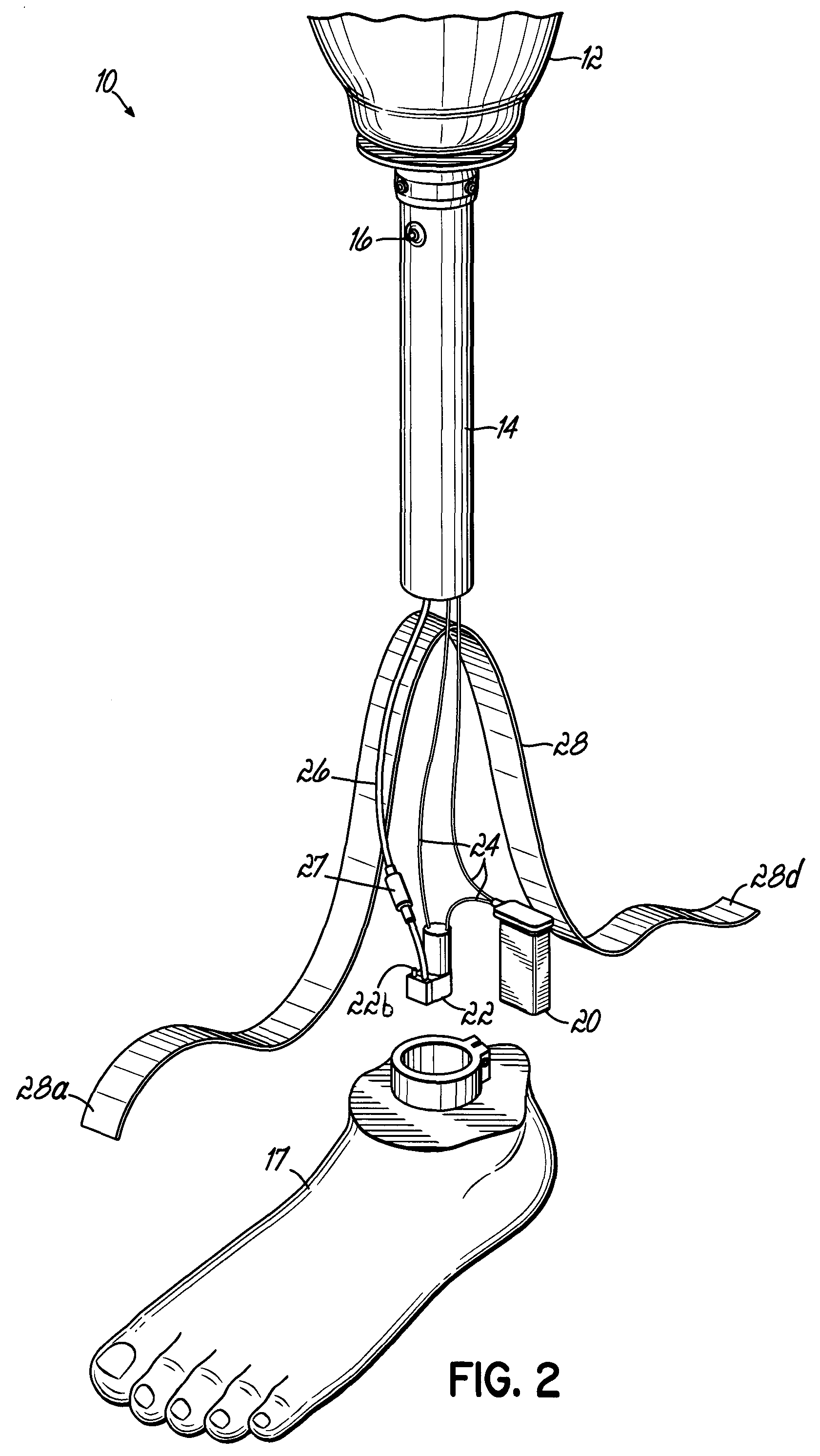

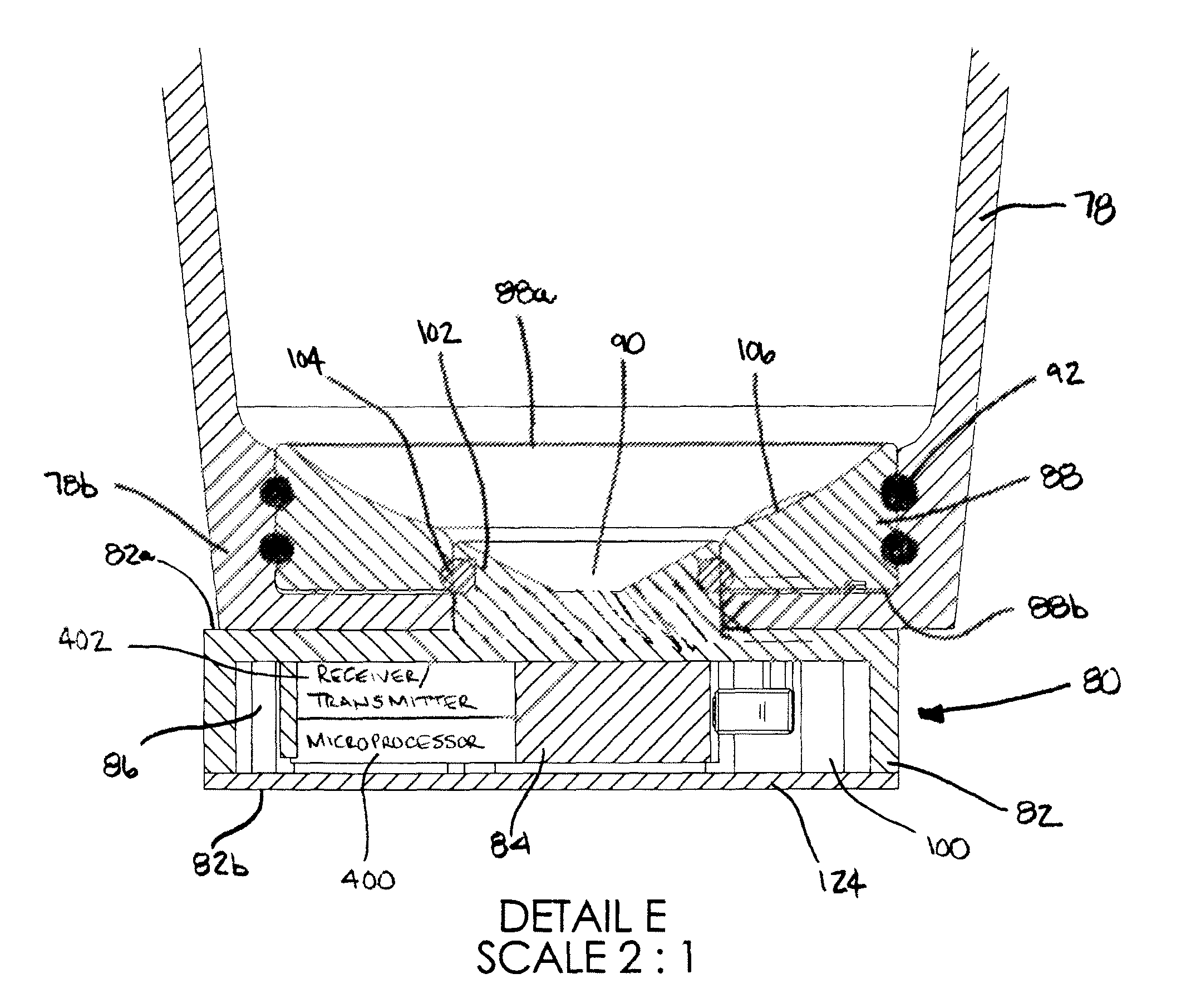

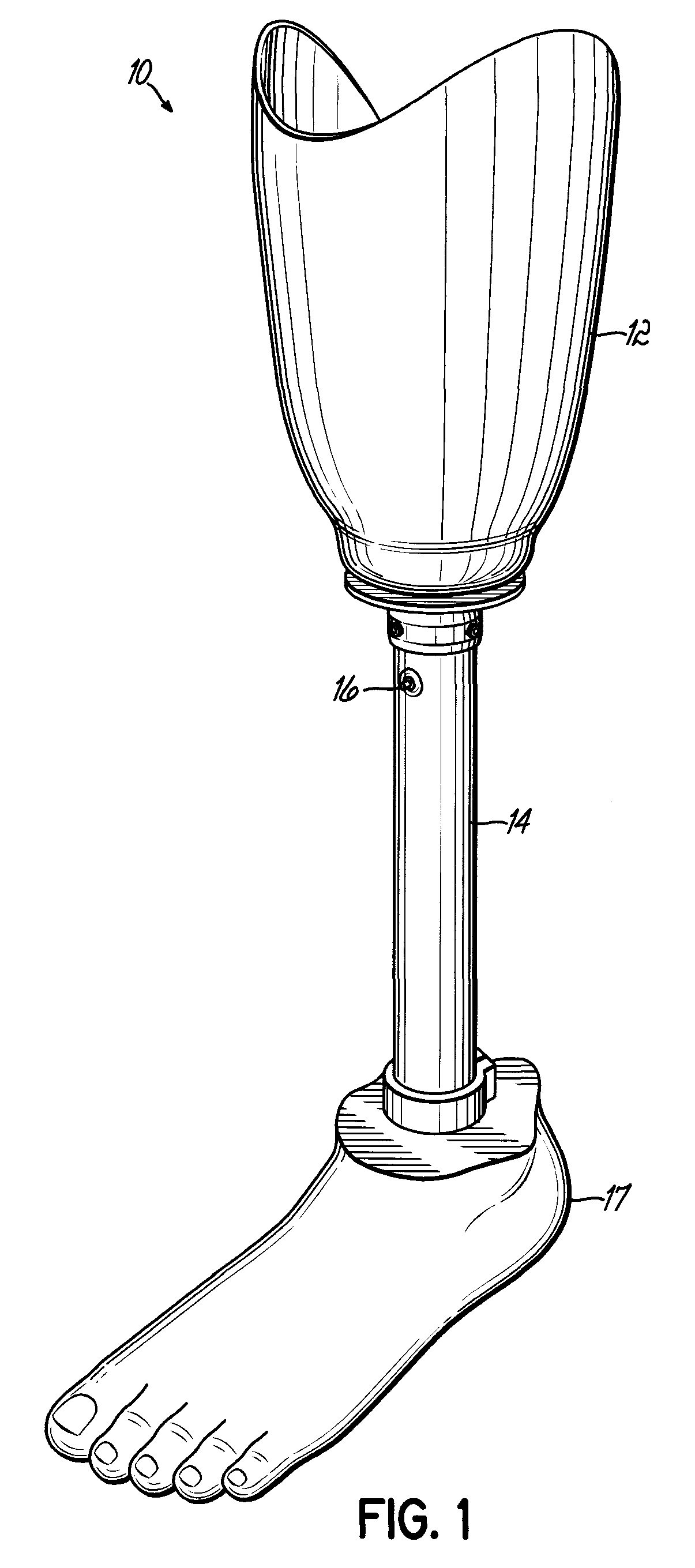

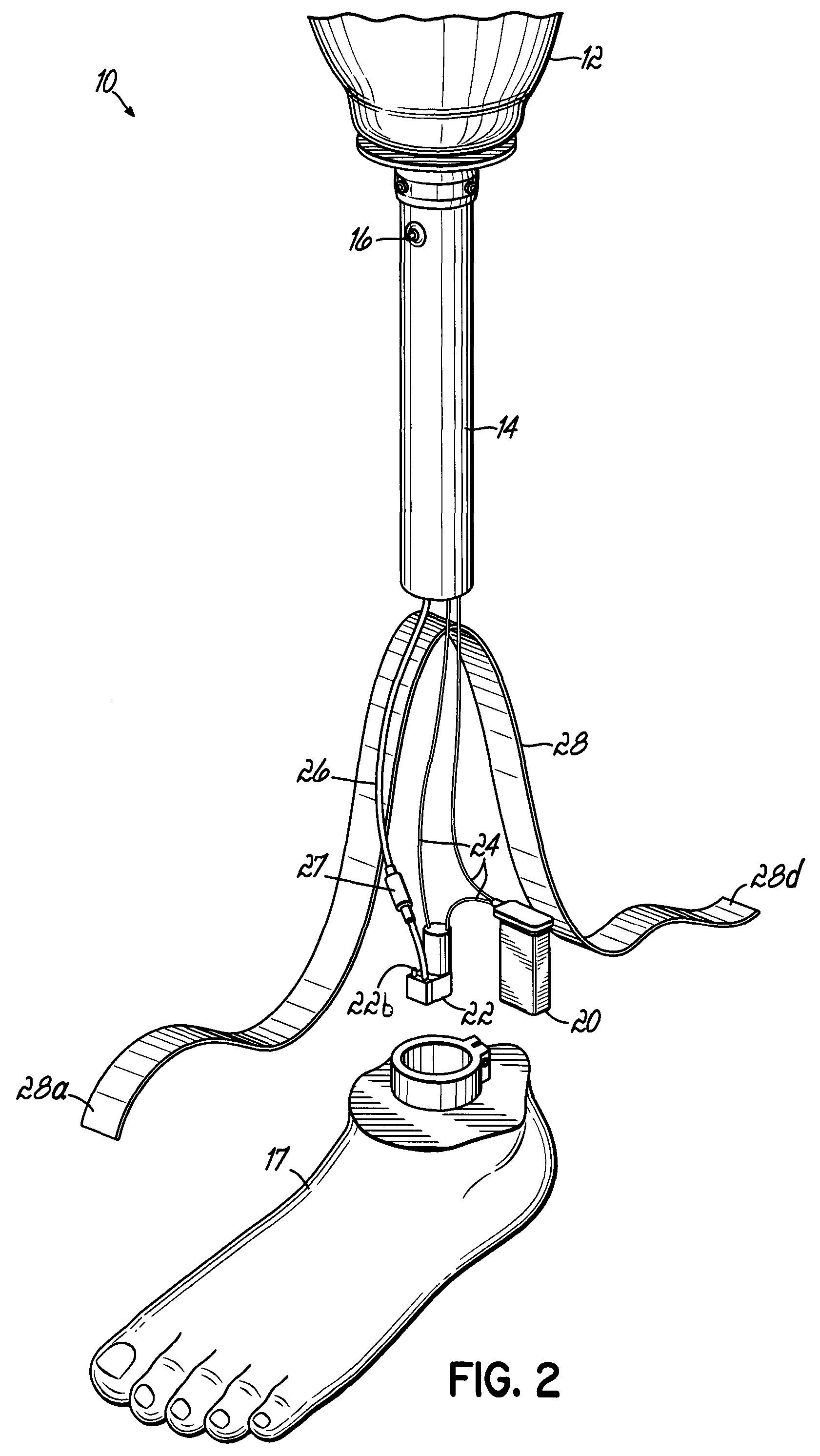

Prosthetic device utilizing electric vacuum pump

ActiveUS20080243266A1Easy to useReadily incorporated into/onto prosthesisArtificial legsArtificial handsControl systemVacuum level

Prosthetic devices having vacuum components operative to evacuate the interior of a prosthetic socket thereof, and control systems for use therewith. The evacuation devices preferably include at least an electrically powered vacuum pump and associated power source, and a vacuum accumulator connected to the vacuum pump. Associated control systems may be of various designs and may employ wired or wireless communication. Control of an evacuation device may be based on vacuum level, residual limb volume, residual limb motion, user activity level or other device parameters.

Owner:WILLOWWOOD GLOBAL LLC

Prosthetic device utilizing electric vacuum pump

ActiveUS20070191965A1Easy to useReadily incorporated into/onto prosthesisArtificial legsArtificial handsControl systemHand held

A prosthetic device and prosthetic assembly operative to evacuate an interior of a prosthetic socket, and control systems for use therewith. The prosthetic device and prosthetic assembly employ evacuation devices for evacuating the socket. The evacuation devices preferably include at least an electrically powered vacuum pump and a power source, and are adapted for mounting to a universal adapter that is installed to the distal end of a prosthetic socket. Associated control systems may be of various design and may employ wired or wireless communication. When wireless communication is employed, a hand held controller may be used to remotely control operation of the evacuation device.

Owner:WILLOWWOOD GLOBAL LLC

Prosthetic device utilizing electric vacuum pump

Evacuation devices for evacuating the socket of a prosthetic limb, and prosthetic limb systems employing such vacuum devices. The evacuation devices each preferably include at least an electrically powered vacuum pump and a power source. Such evacuation devices can be attached at various locations on or in a prosthetic limb. Because the electrically powered pump does not require manual manipulation to create vacuum, it is substantially easier to use than a manual pump. Due to the small size and small power source required by such an electrically powered pump, an evacuation device may be readily incorporated into a prosthesis.

Owner:WILLOWWOOD GLOBAL LLC

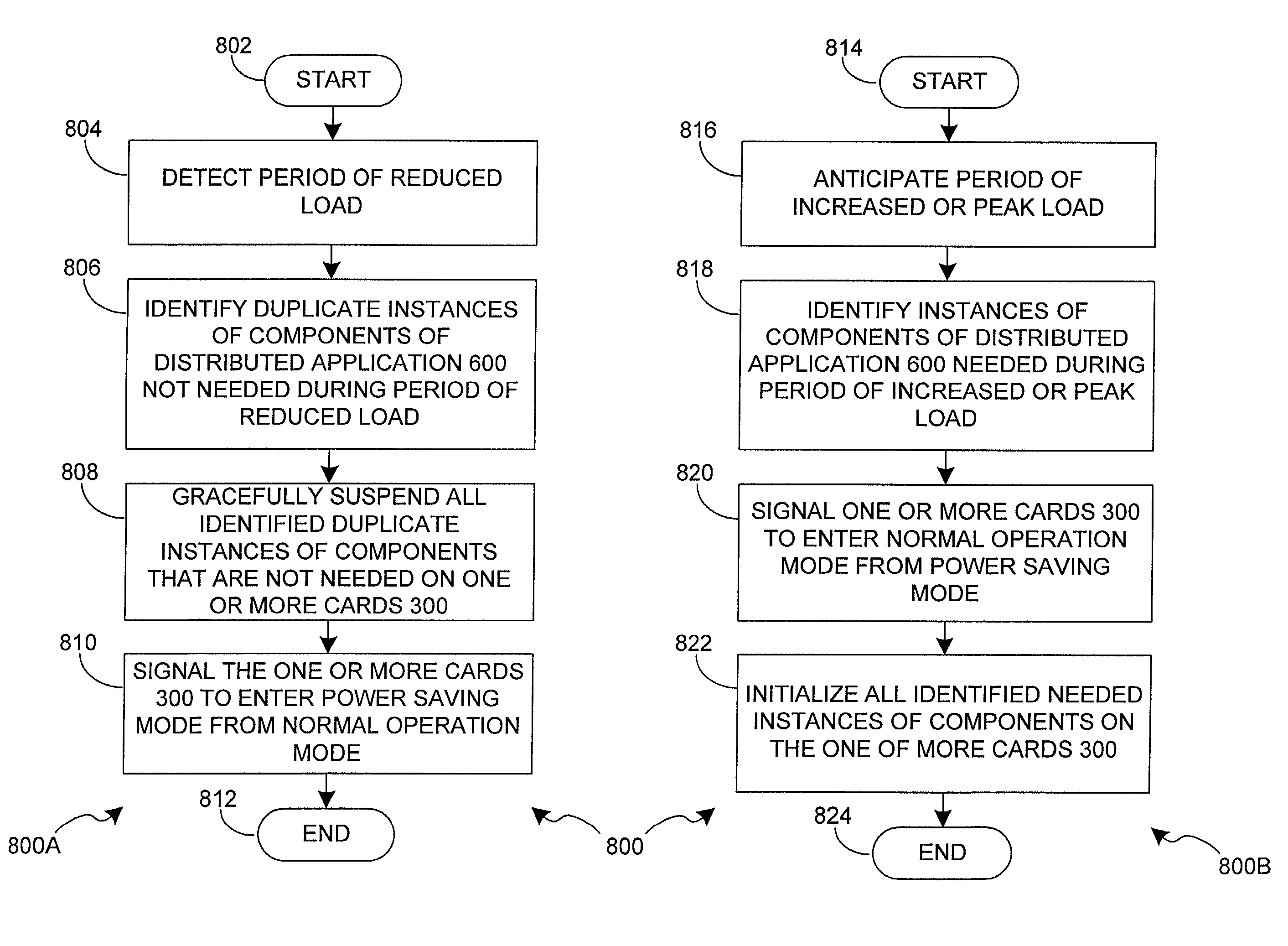

System and method for intelligent control of power consumption of distributed services during periods when power consumption must be reduced

InactiveUS7043650B2Minimum power consumptionIncrease redundancyEnergy efficient ICTVolume/mass flow measurementControl powerComputerized system

A system and method intelligently control power consumption of distributed services using a computer system that provides independent computing elements each capable of entering a power saving mode. In accordance with the present invention, three different algorithms are disclosed. The first algorithm is a reduced load power saving algorithm. As the load decreases, duplicate instances of services can be gracefully suspended and the host processor cards hosting these instances can enter a power saving mode. The second algorithm is a priority-based power consumption reduction algorithm. If power consumption must be reduced, services having less of a contribution to revenue are suspended before components that having a higher contribution to revenue. The third algorithm is a minimal power-consuming redundant computing hardware algorithm that allows a “cold spare” host processing card to be pressed into service if another card fails.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Powered patch panel

InactiveUS7455527B2Minimum power consumptionEasy to manageSubstation/switching arrangement detailsCoupling device detailsPatch panelTelecommunications

A powered communications patch panel is adapted to power network devices connected to the communications patch panel. Power is supplied to the network devices by the powered communications patch panel over the communication cabling. The powered communications patch panel may be provided with a management port to allow remote management of the patch panel via a network connection. Multiple management ports may be provided, allowing patch panels to be connected to one another in a daisy-chain configuration.

Owner:PANDUIT

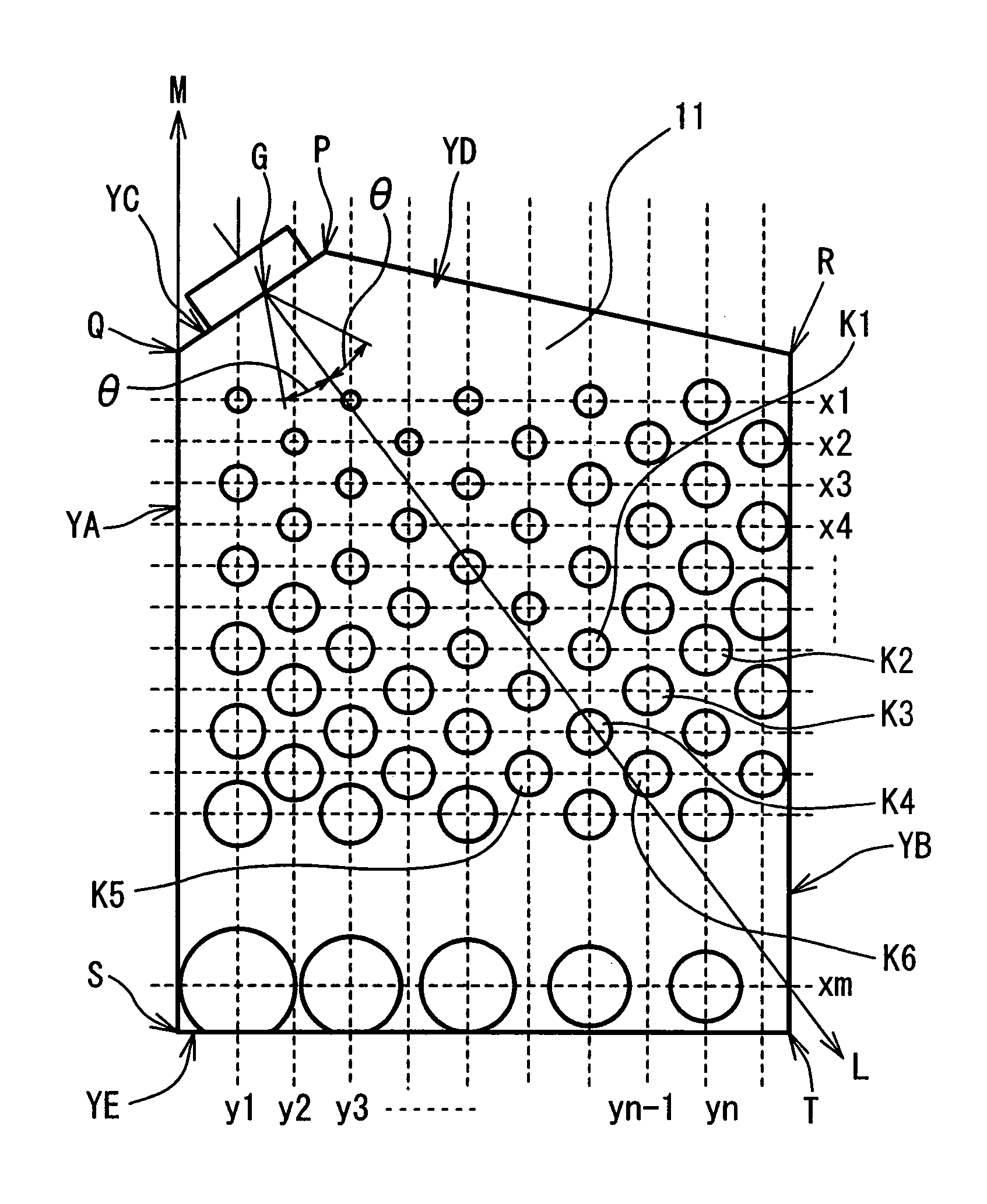

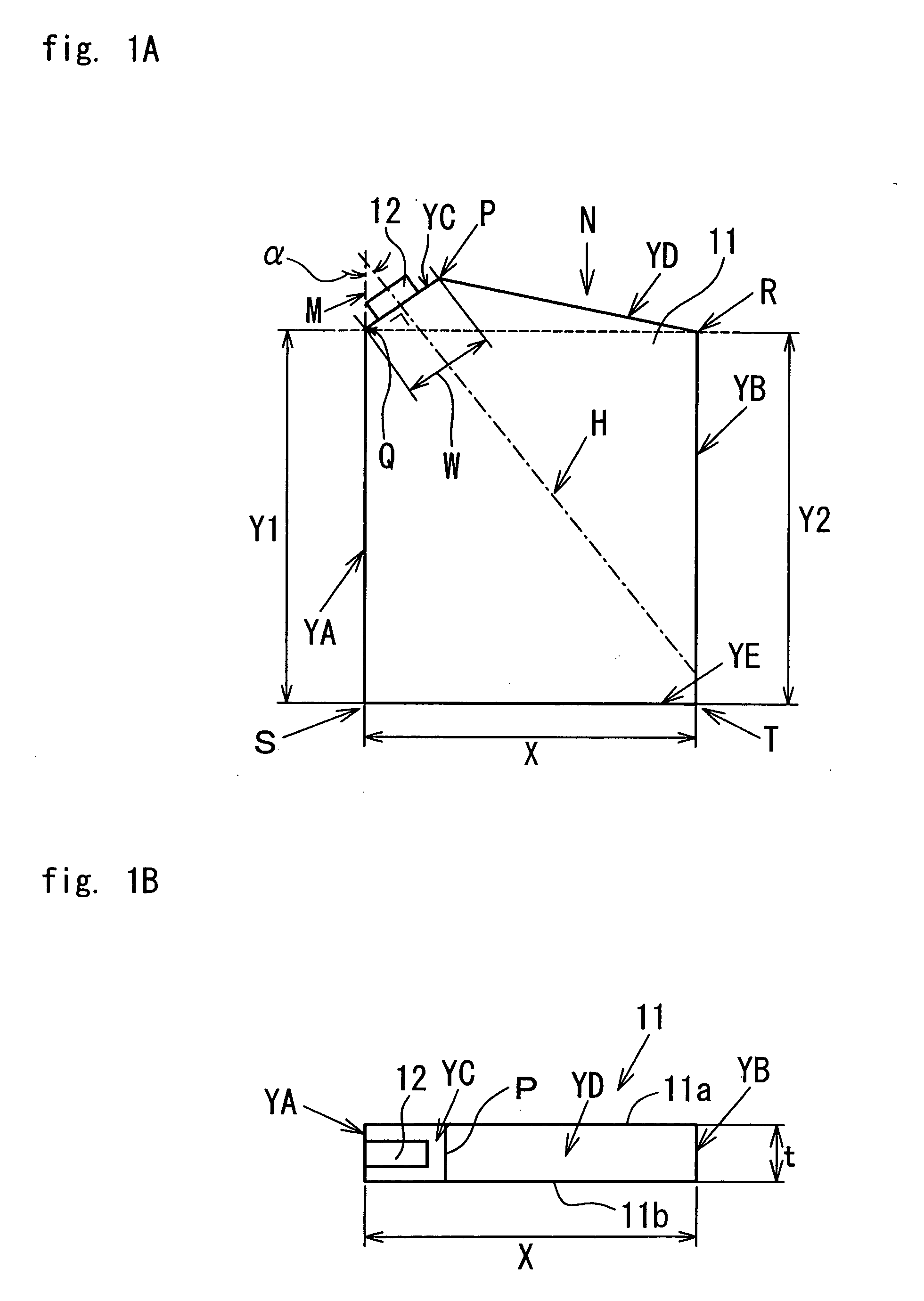

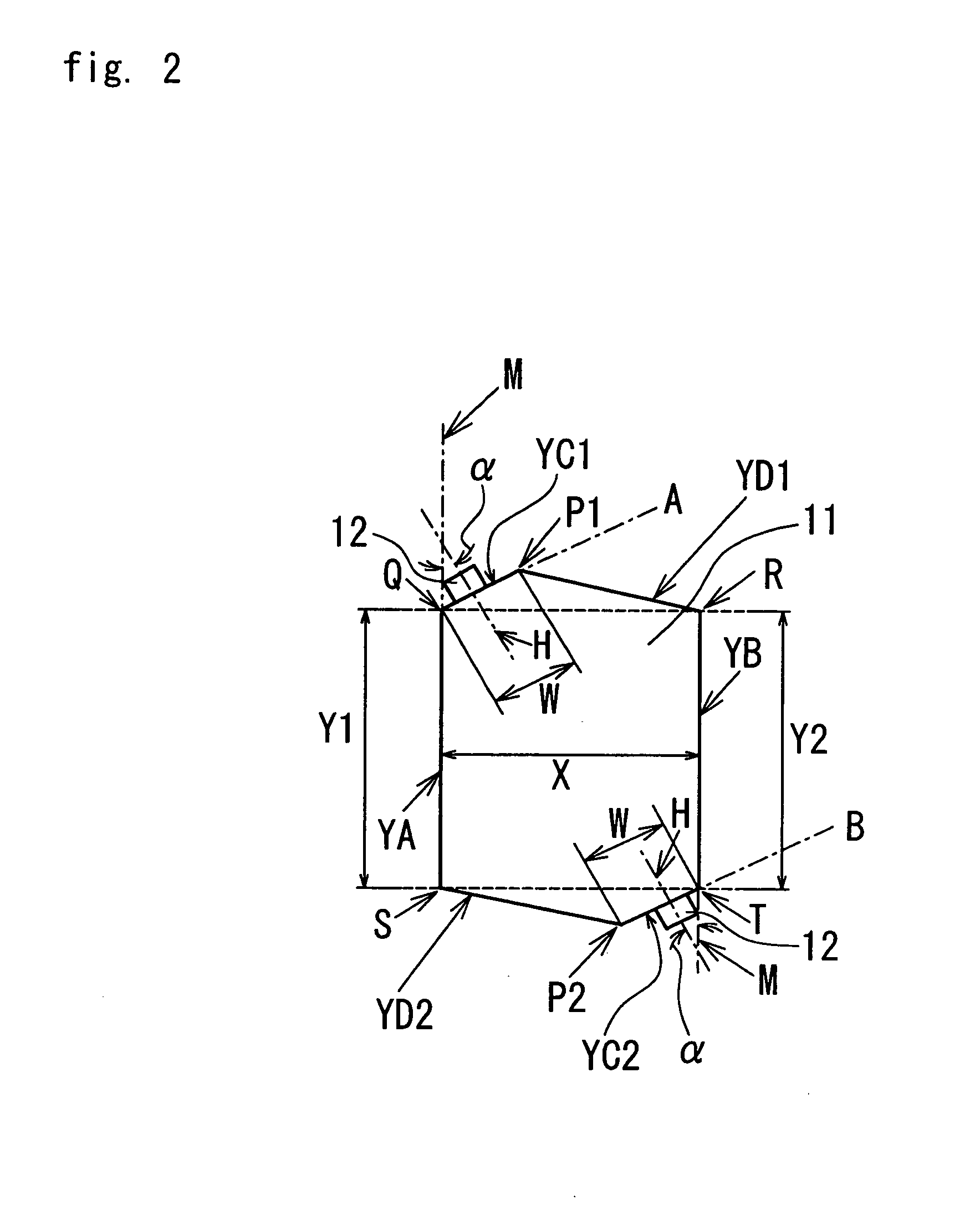

Spread illuminating apparatus with light conductive plate having polygonal configuration

InactiveUS20050259438A1Efficient illuminationMinimum power consumptionMechanical apparatusPoint-like light sourceLight guideOptoelectronics

In a spread illuminating apparatus comprising a spot-like light source, and a light conductive plate, the light conductive plate is shaped into a pentagon which has two sides thereof substantially parallel to each other, and which includes, as a part thereof, a triangle having its base defined by an imaginary line connecting respective straightly opposing ends of the two parallel sides, and the spot-like light source is disposed at a side of the pentagon constituting one of two hypotenuses of the triangle.

Owner:MINEBEA CO LTD

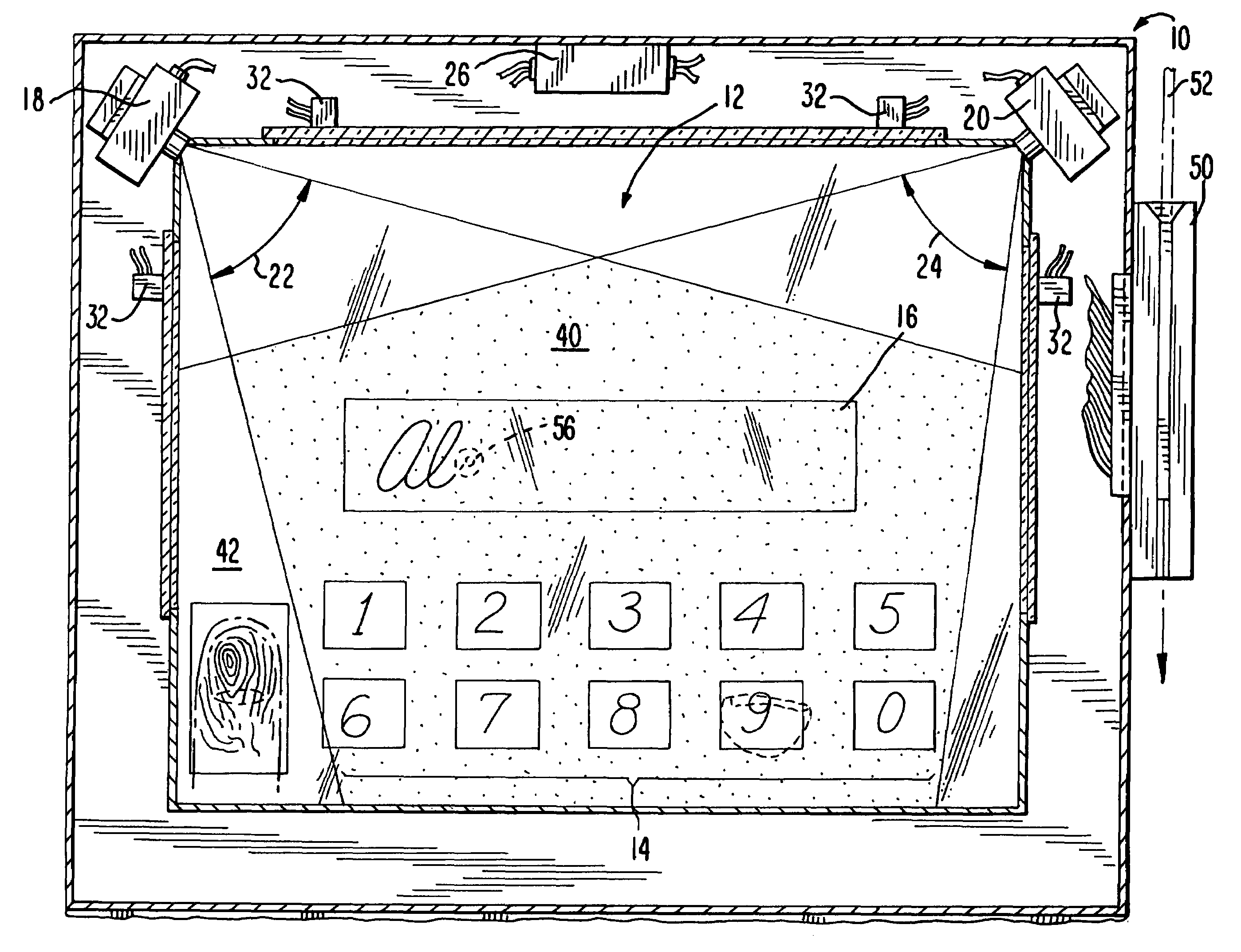

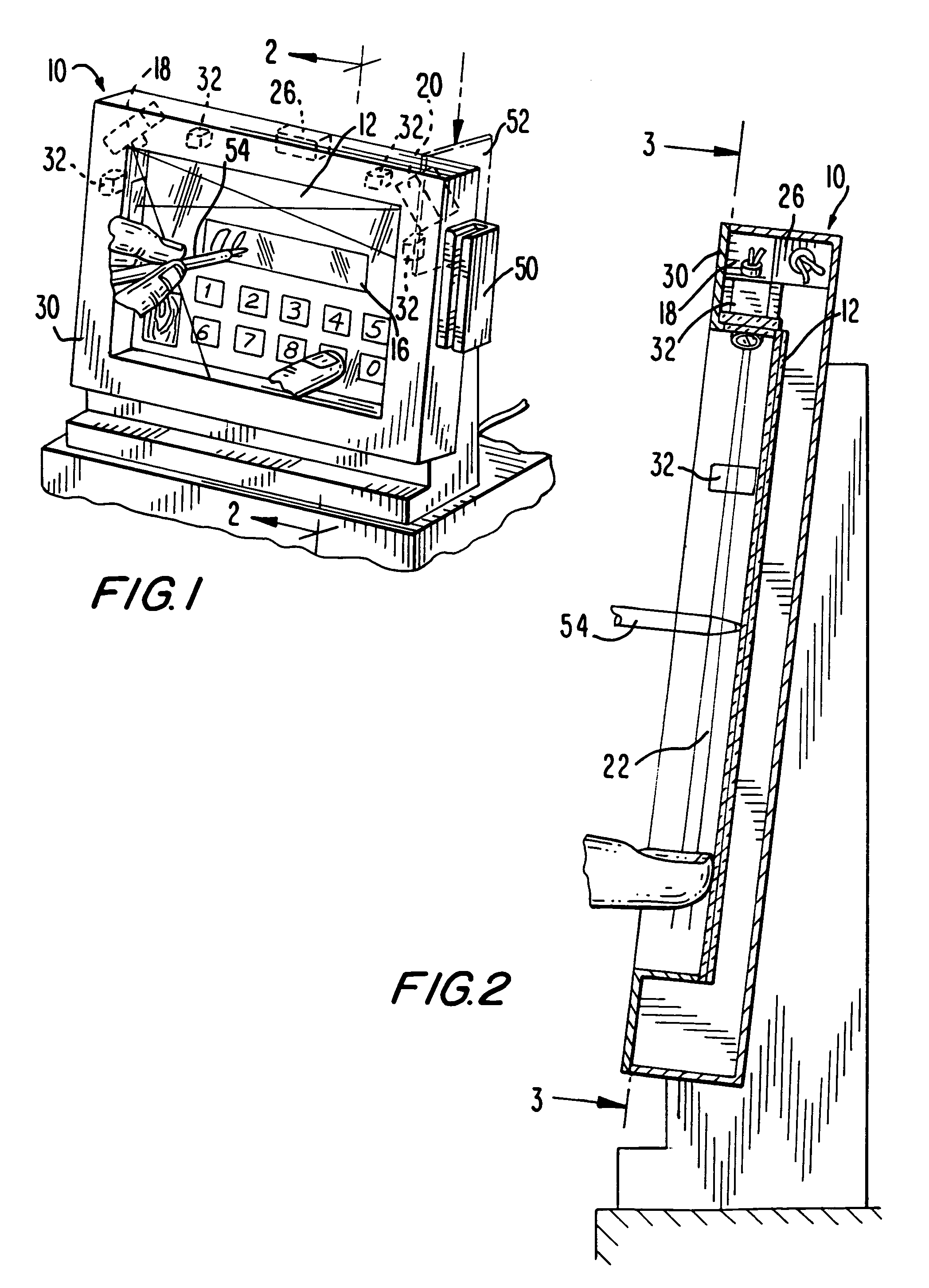

Optical touch screen arrangement

ActiveUS7355594B2Increase brightnessIncrease contrastCathode-ray tube indicatorsInput/output processes for data processingHuman–computer interactionVisual perception

Owner:SYMBOL TECH LLC

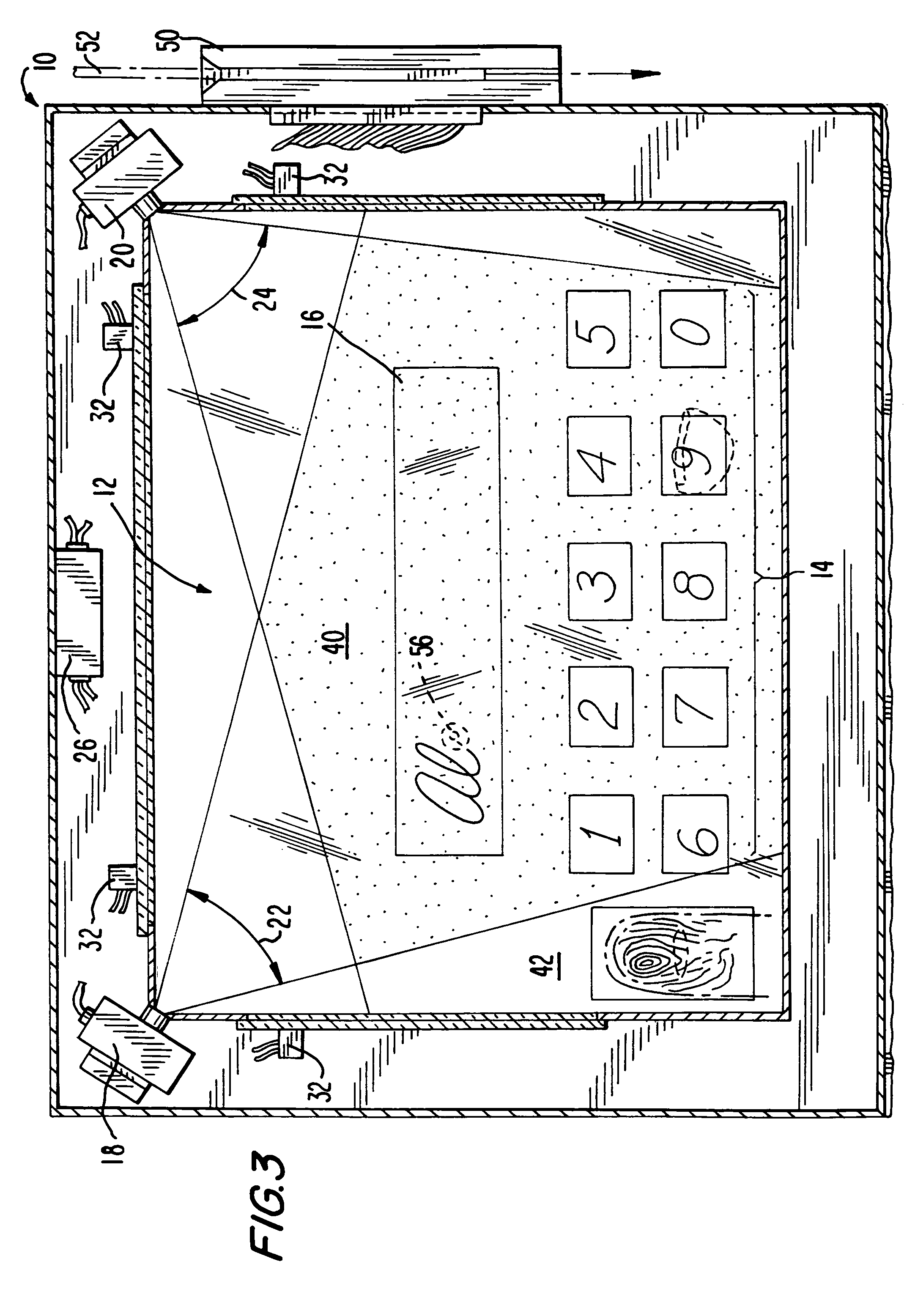

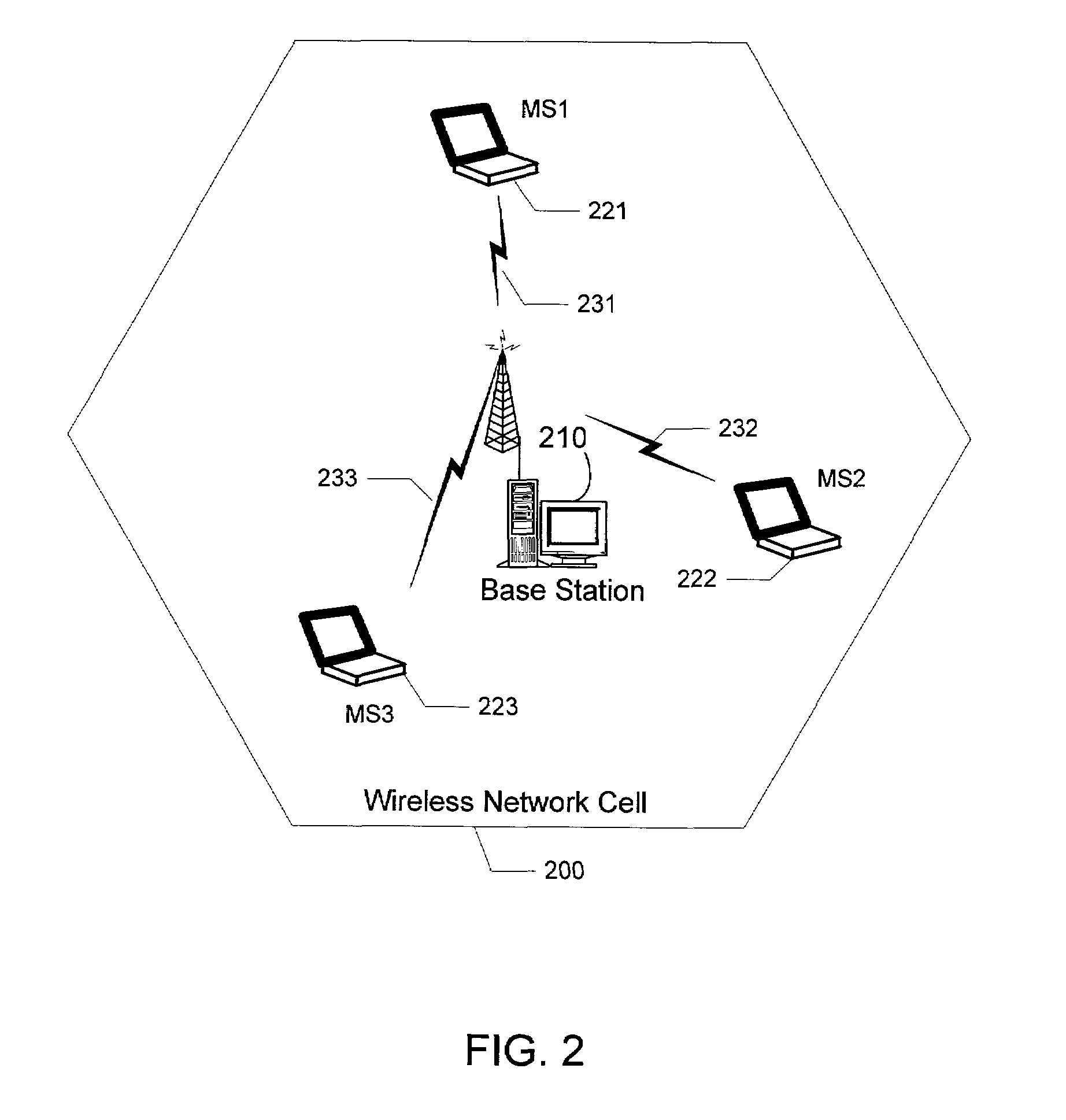

System and method for reducing power consumption for wireless communications by mobile devices

InactiveUS7096034B2Maximize system capacityReduce transmit powerPower managementEnergy efficient ICTSignal qualitySystem capacity

A power control scheme for a wireless network communication system that includes a base station and multiple wireless mobile device dynamically adjusts transmission power of a mobile device in conjunction with adjusting its bit allocation in source coding and channel coding to minimize its total power consumption while maximizing the system capacity in terms of the total effective transmission rates received by the base station. The base station sets a target signal quality value for each mobile station, and the target values are determined by the base station such that the total effective data rate from all the mobile devices is maximized under constraints of the total received power and the error protection level requirements for the mobile devices. The base station periodically measures a signal quality value, such as a signal-to-interference ratio (SIR), from transmissions received by the base from each mobile device, compares it with the measured signal quality value for that mobile device, and sends a control signal instructing the mobile device to increase or decrease its transmission power based on the result of the comparison. When the mobile device receives the control signal, it determines an amount of adjustment to its transmission power by performing a minimum calculation under constraints on the total data distortion and the maximum transmission rate to adjust the parameters for source coding, channel coding, and transmission under the constraints to result in a redistribution of power between the components that provides the minimized total power consumption.

Owner:MICROSOFT TECH LICENSING LLC

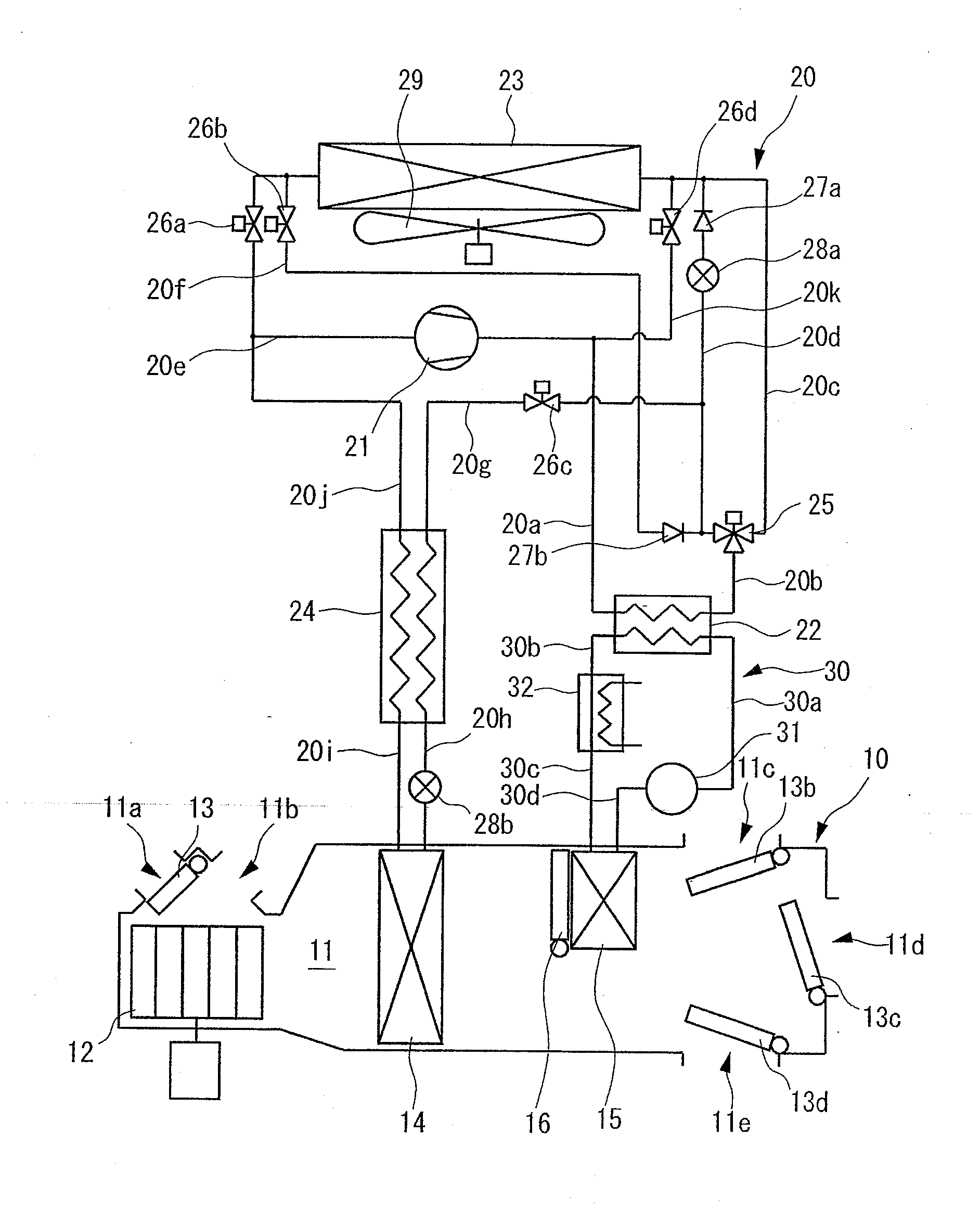

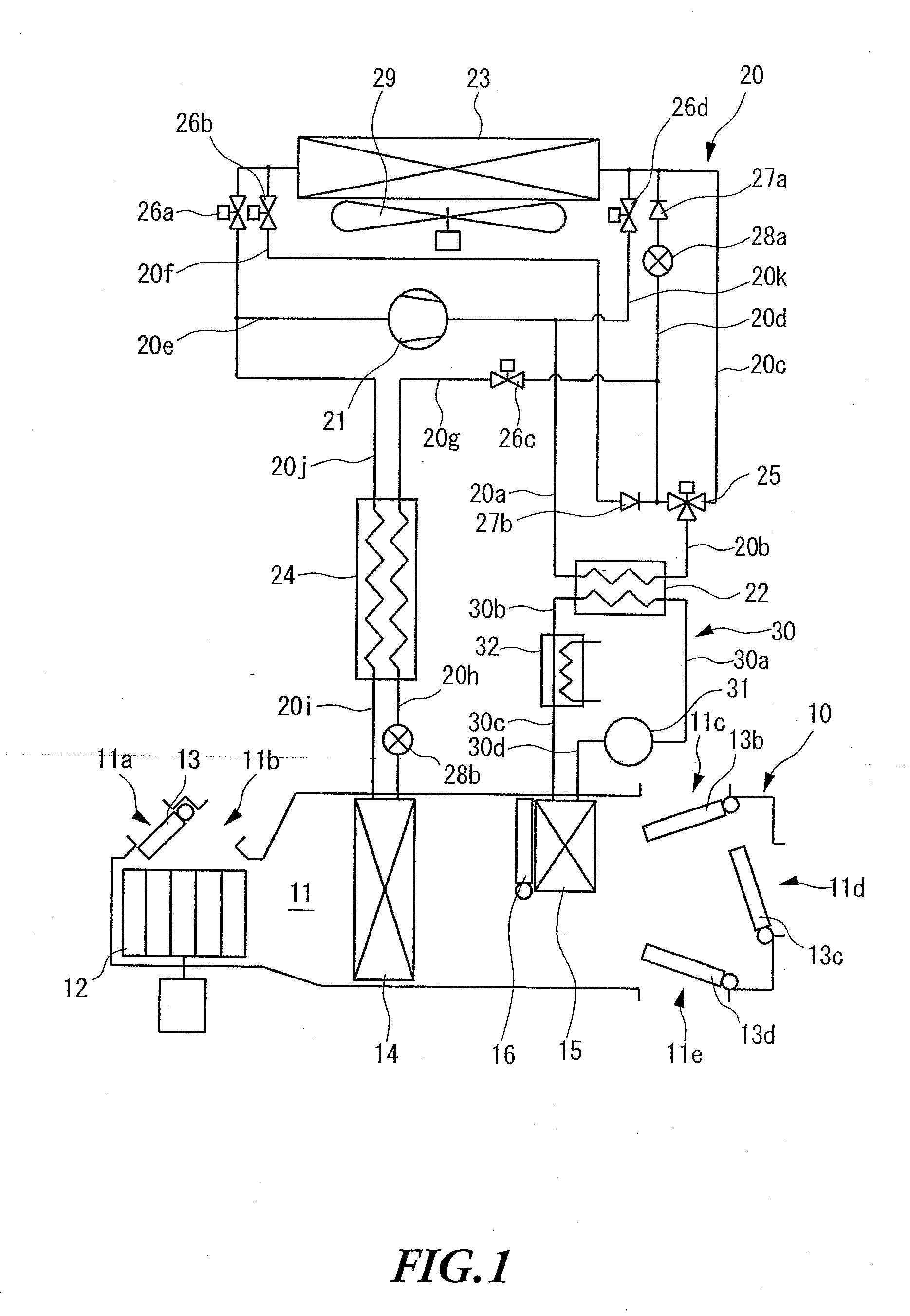

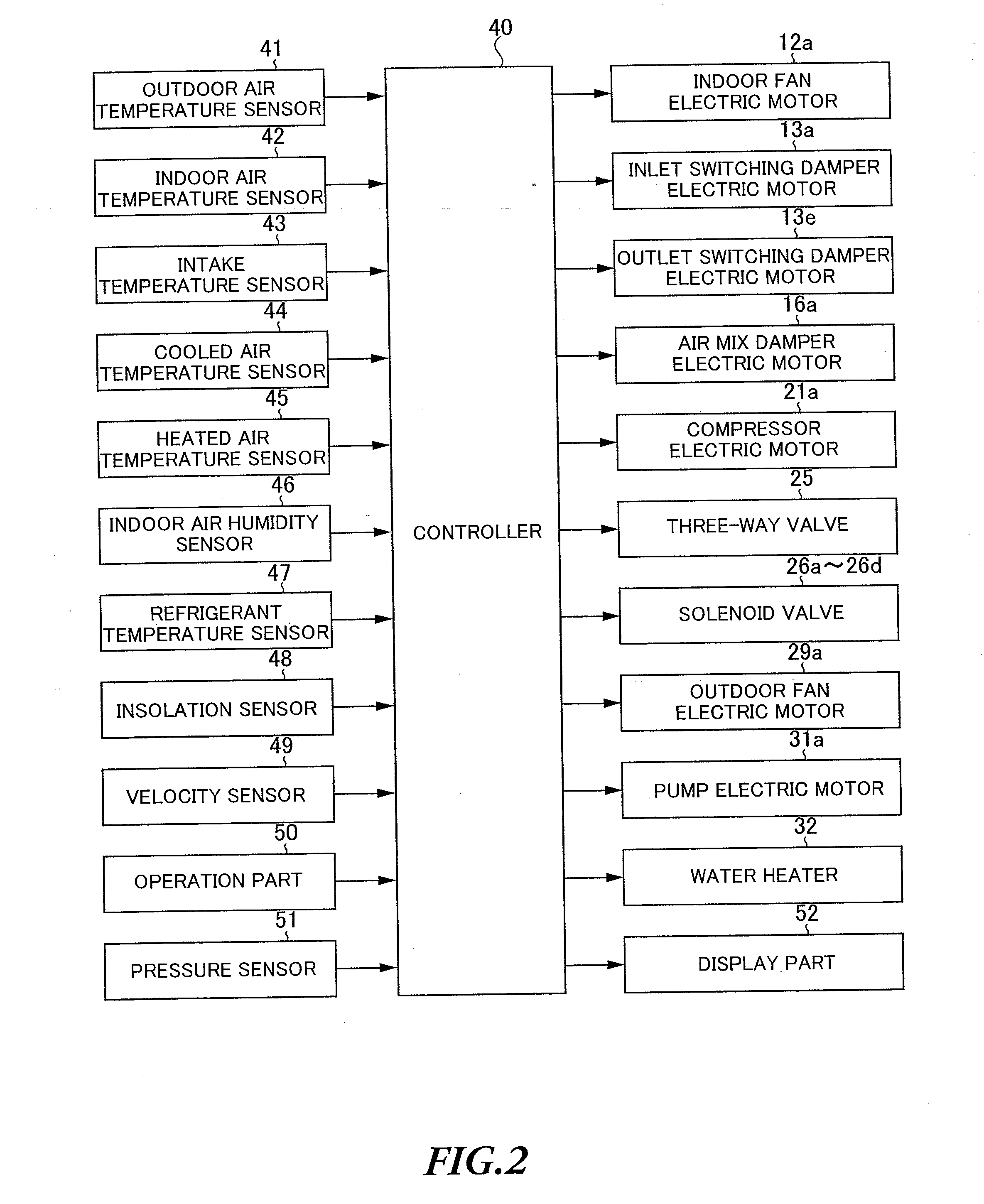

Air Conditioning Device for Vehicle

ActiveUS20130291577A1Reduce power consumptionIncrease mileageLighting and heating apparatusPower to auxillary motorsEngineeringPower sharing

A vehicle air conditioning apparatus is provided that can extend the mileage of a vehicle by reducing the power consumed by the operation of a compressor and a heater. When a required quantity of heating Q_req is acquired, the minimum power sharing ratio between quantity of heat release Q_hpof a water-refrigerant heat exchanger 22 and quantity of heat release Q_htrof a water heater 32 is calculated, which allows the power consumption W_total to be minimized, and a compressor 21 and the water heater 32 is operated based on the result of the calculation.

Owner:SANDEN CORP

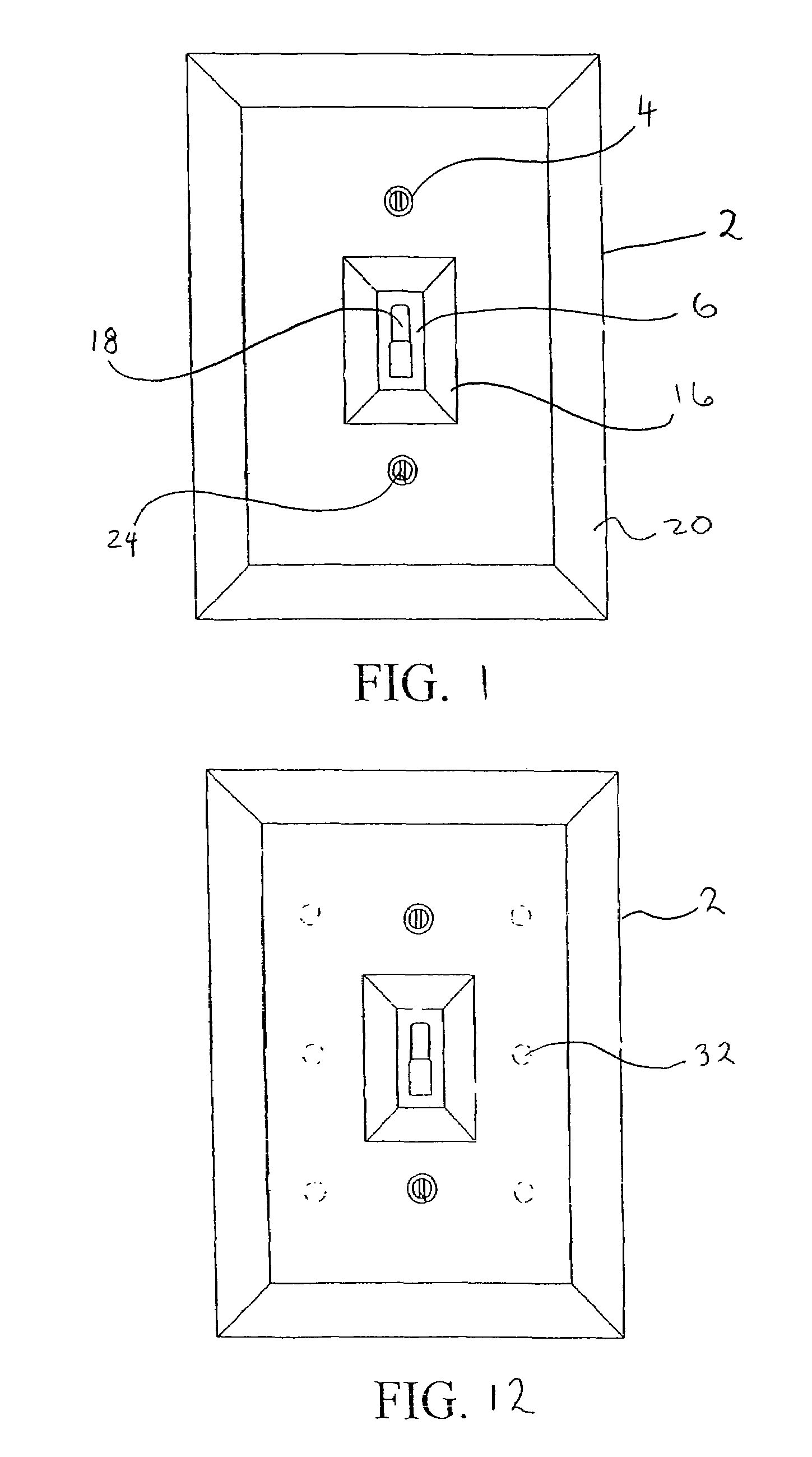

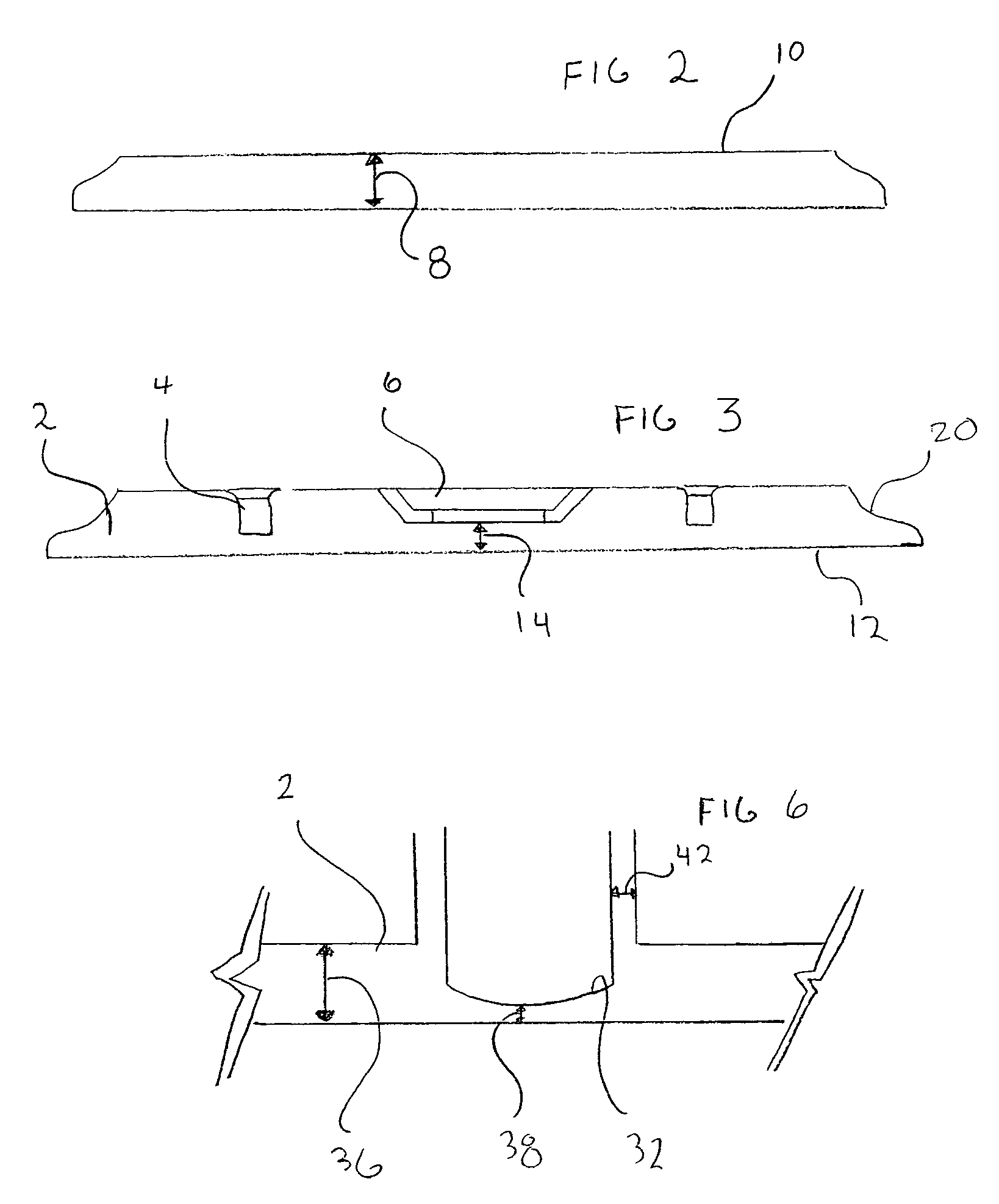

Illuminated electrical box cover plate

InactiveUS7547131B2Reduce heatReduced operating requirementsCoupling device connectionsNon-electric lightingEngineeringLight switch

The present invention is a low power and low heat dissipating, low illumination system that is based in an electrical box cover plate, preferably in a light switch cover plate. It allows for the maintenance of an electrical bleed current through the fluorescent light controlled by that light switch so as to keep a minimal thermal differential between the unlit and lit light. The light switch cover plate has a series of imbedded LEDs that illuminate an area all around the light switch. The unit is retrofittable on conventional light switches.

Owner:FAUNCE MICHAEL JOSEPH

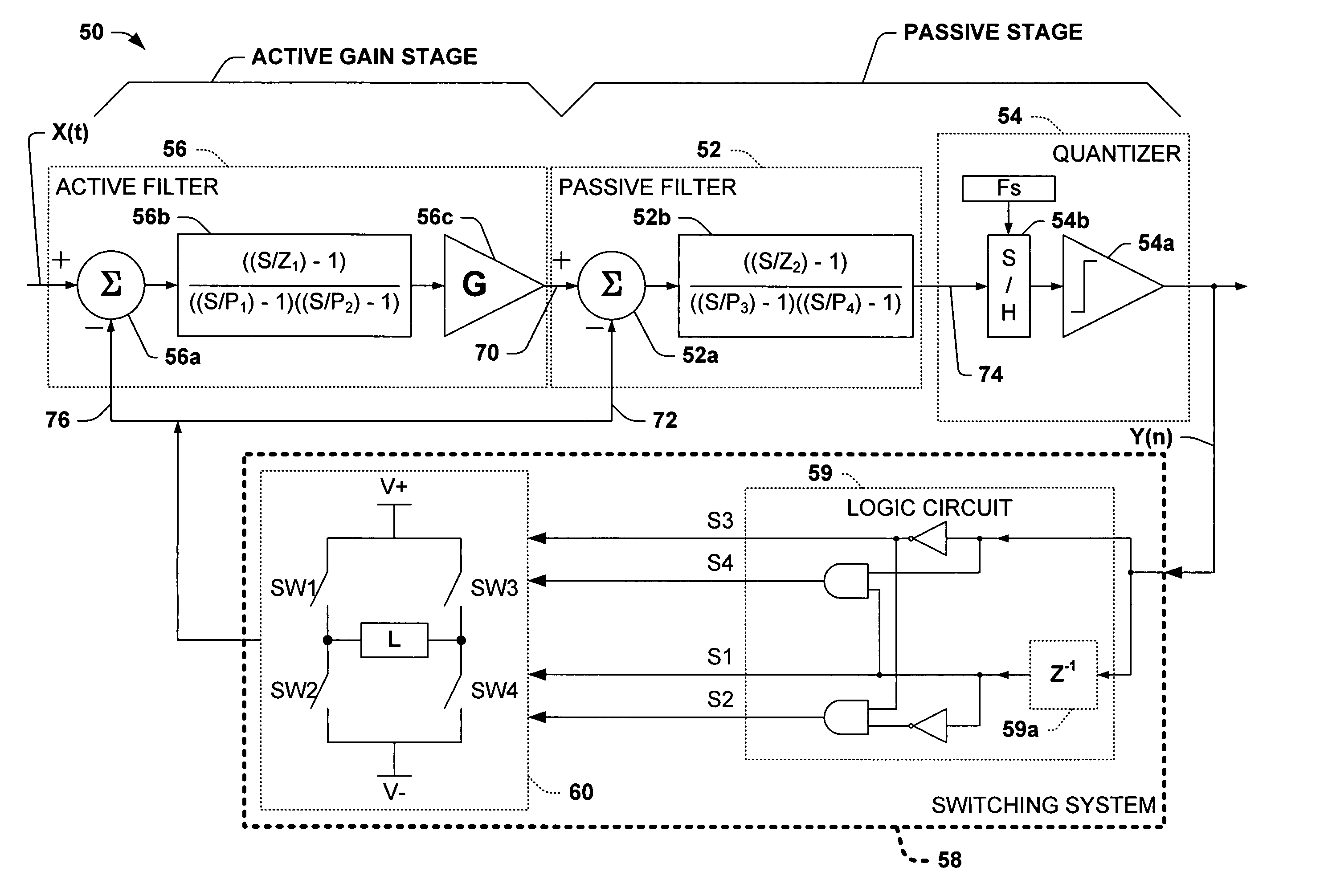

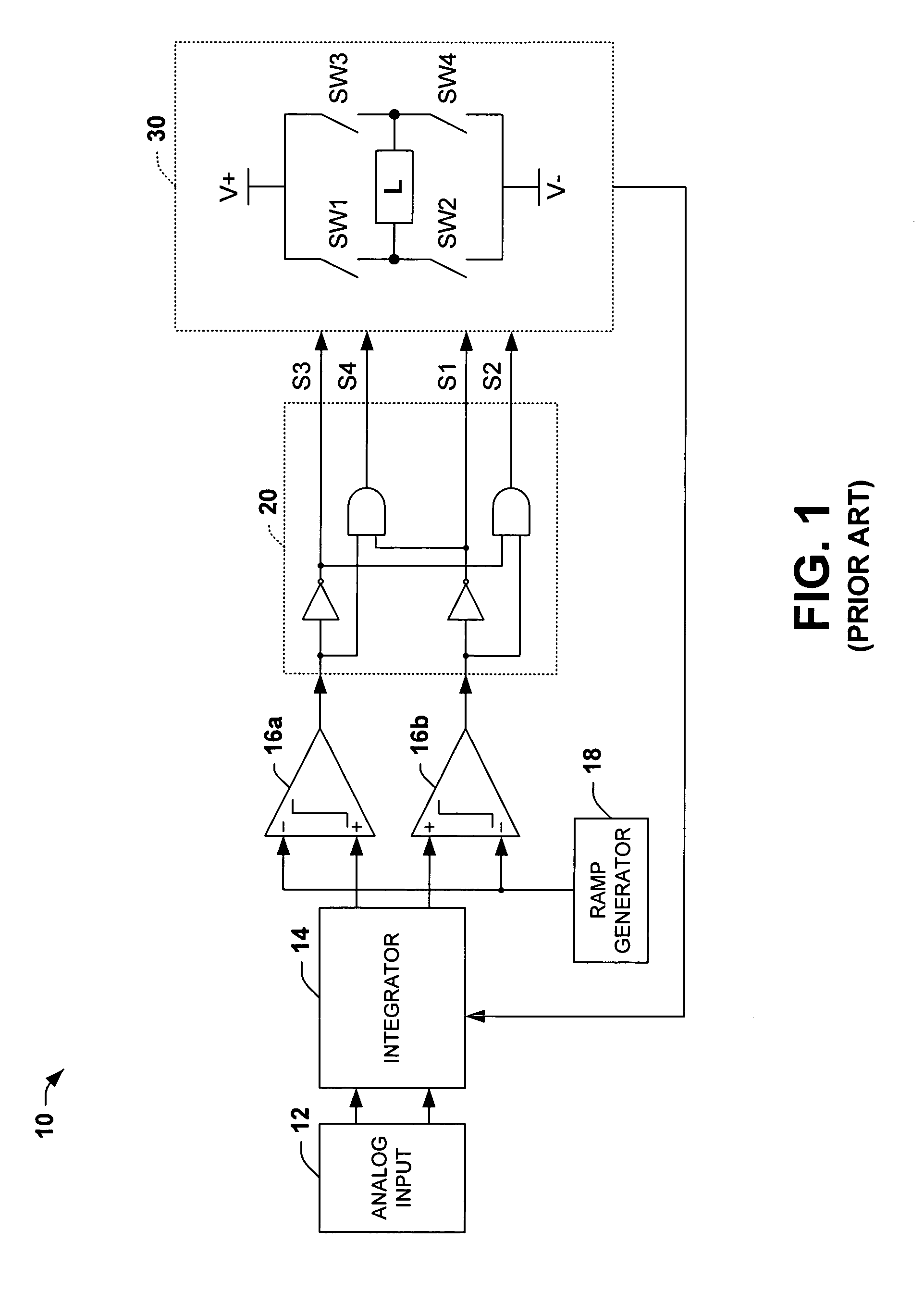

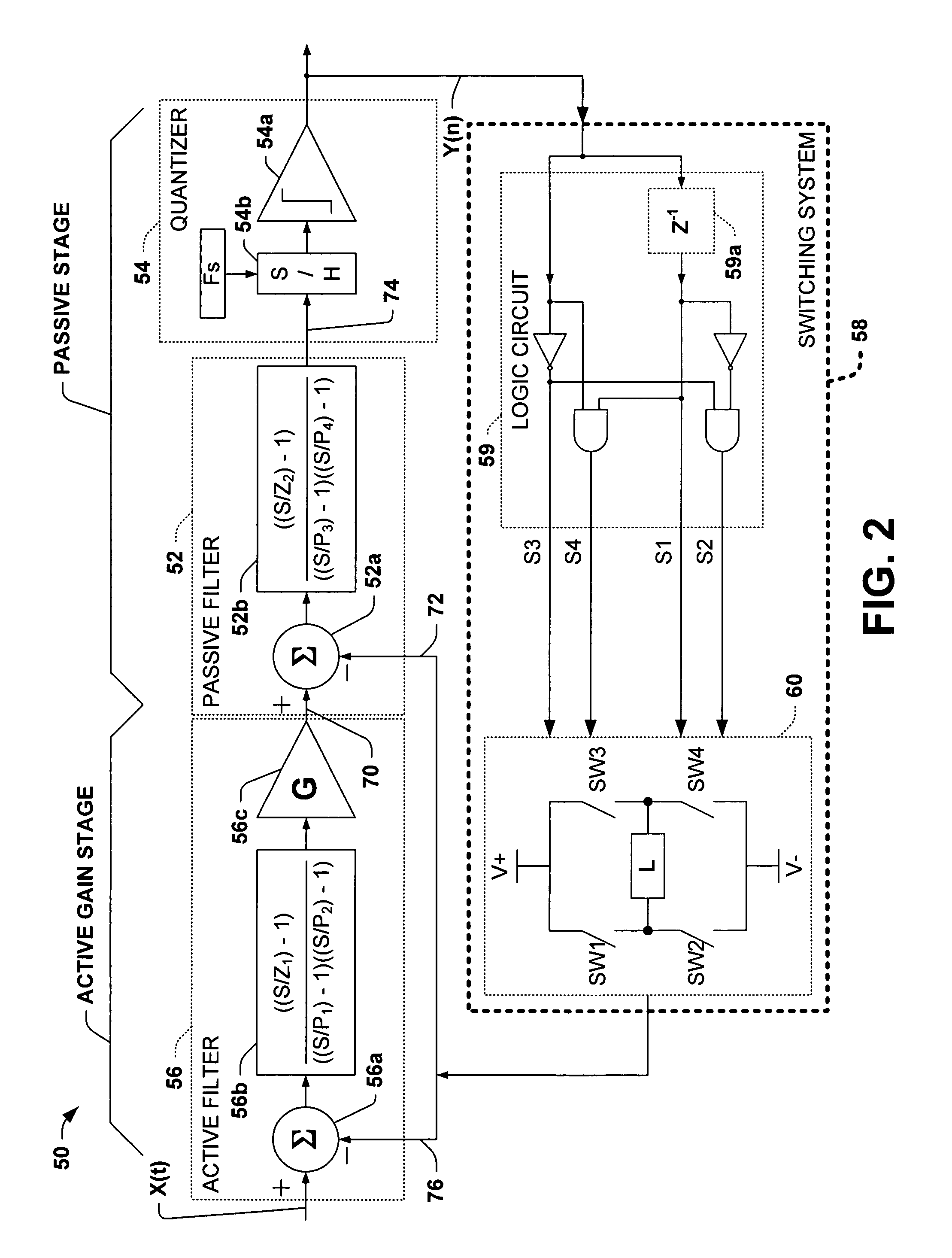

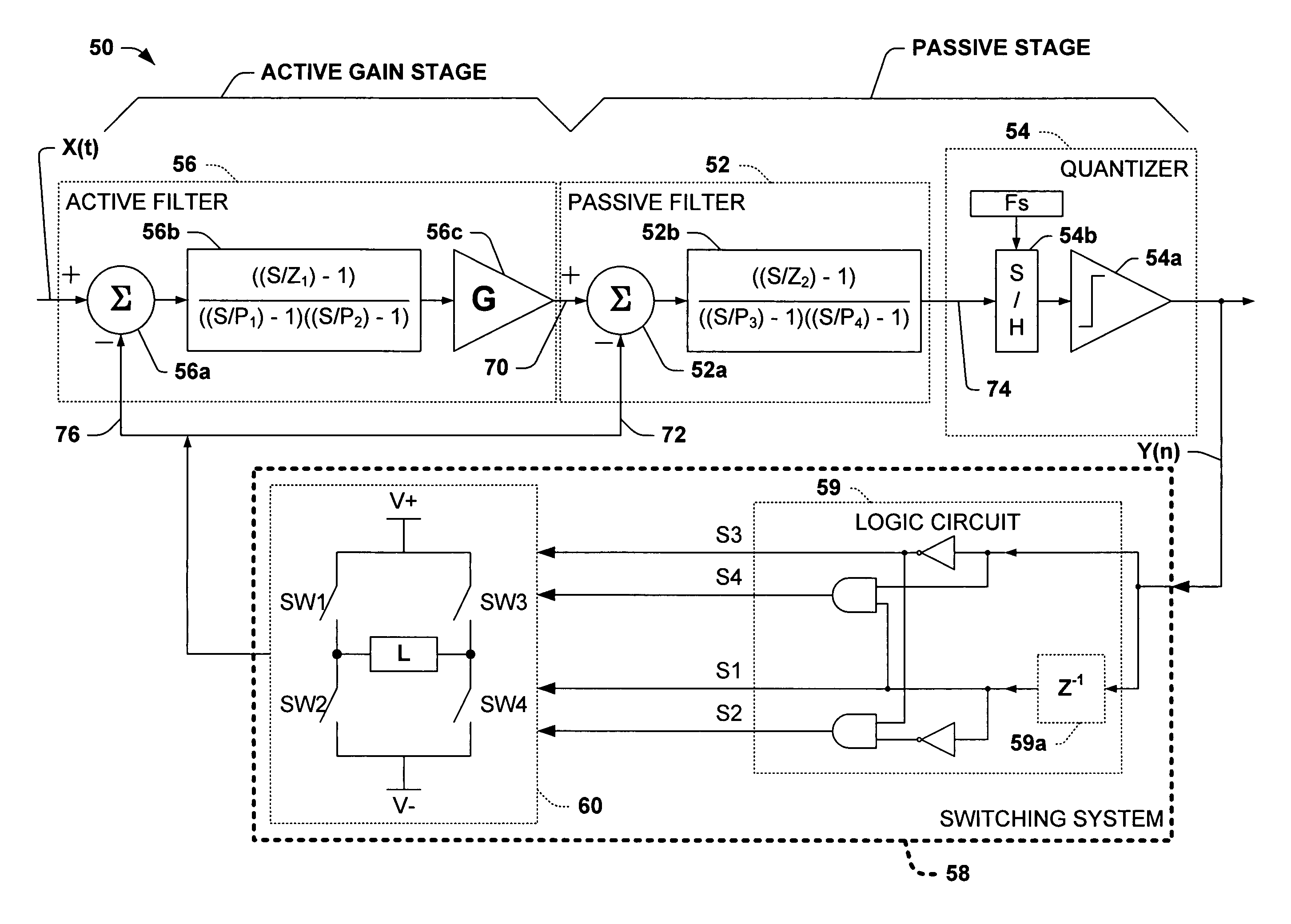

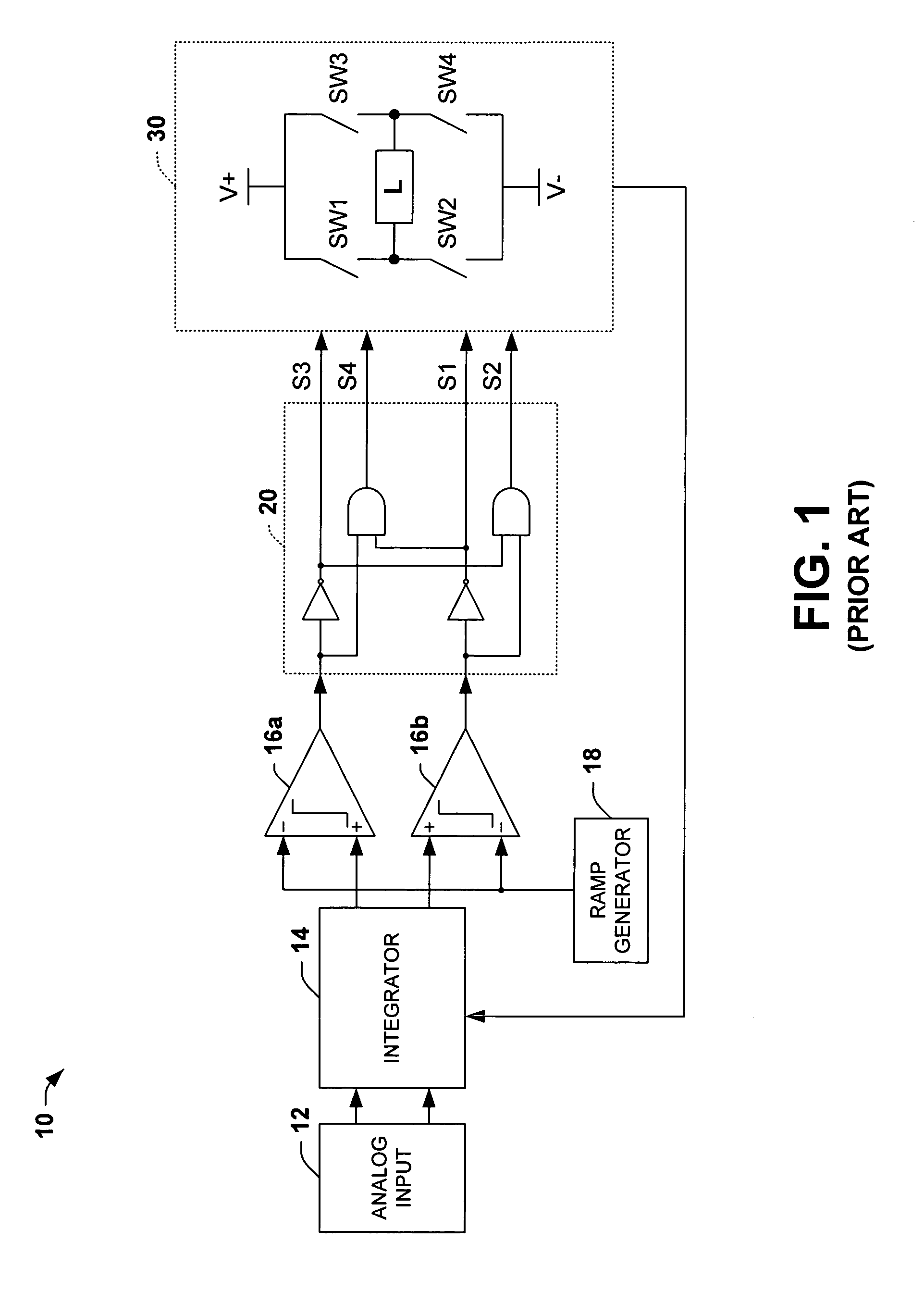

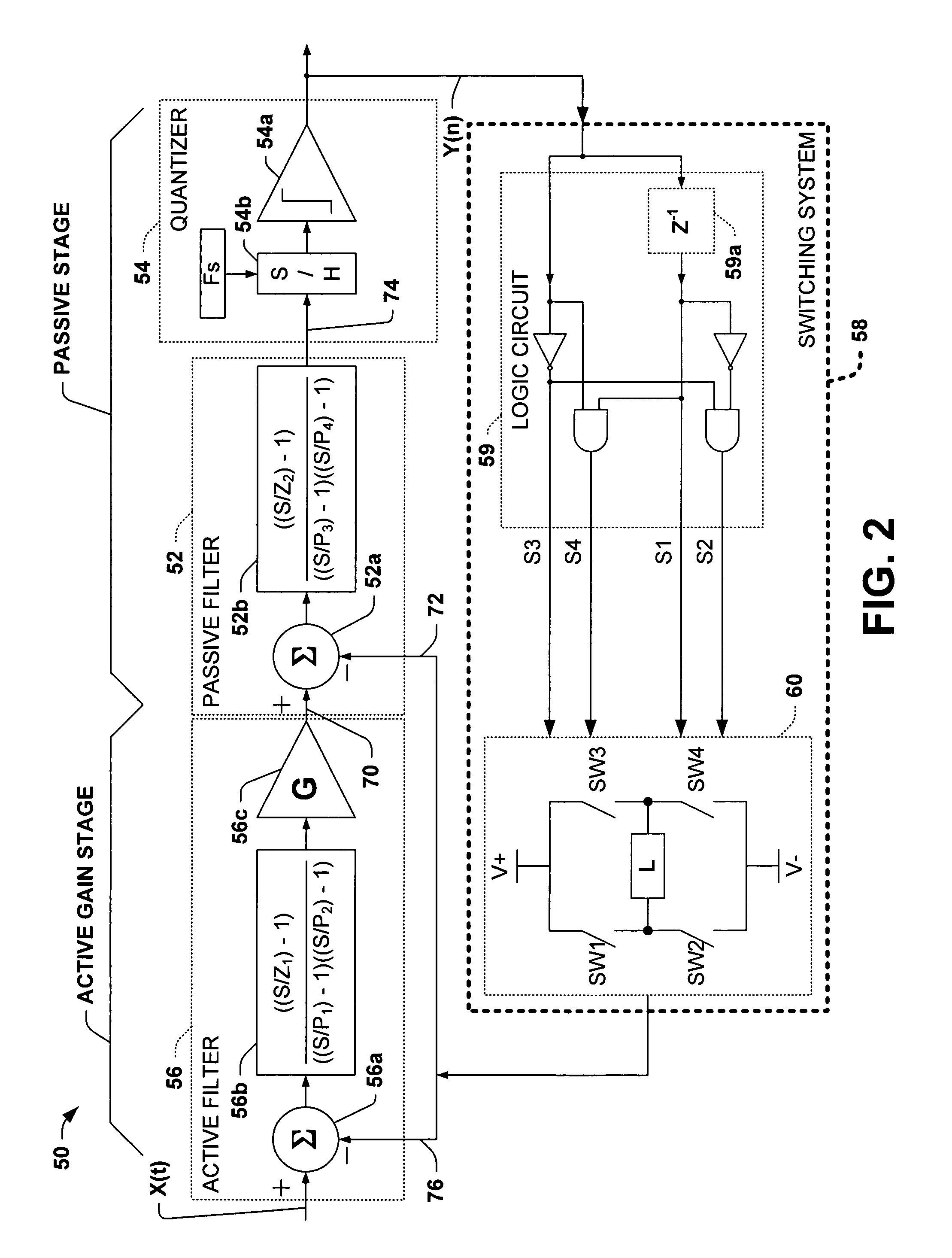

Amplifier using delta-sigma modulation

ActiveUS20050162222A1High SNDR performancePrevent harmonic distortionAnalogue conversionDc amplifiers with modulator-demodulatorGreek letter sigmaDelta-sigma modulation

An amplifier and a driver circuit therefor are presented for driving a load according to a system analog input. The amplifier comprises a passive delta-sigma modulator with a passive filter providing a first filtered signal according to a passive filter input and according to a feedback signal, a quantizer coupled with the passive filter and providing a quantized output according to the first filtered signal, and a switching system coupled with the the passive filter and the quantizer. The switching system selectively providing power to a load according to the quantized output and provides the feedback signal to the passive input, wherein a gain amplifier is provided in a feedback loop around the passive delta-sigma modulator.

Owner:TEXAS INSTR INC

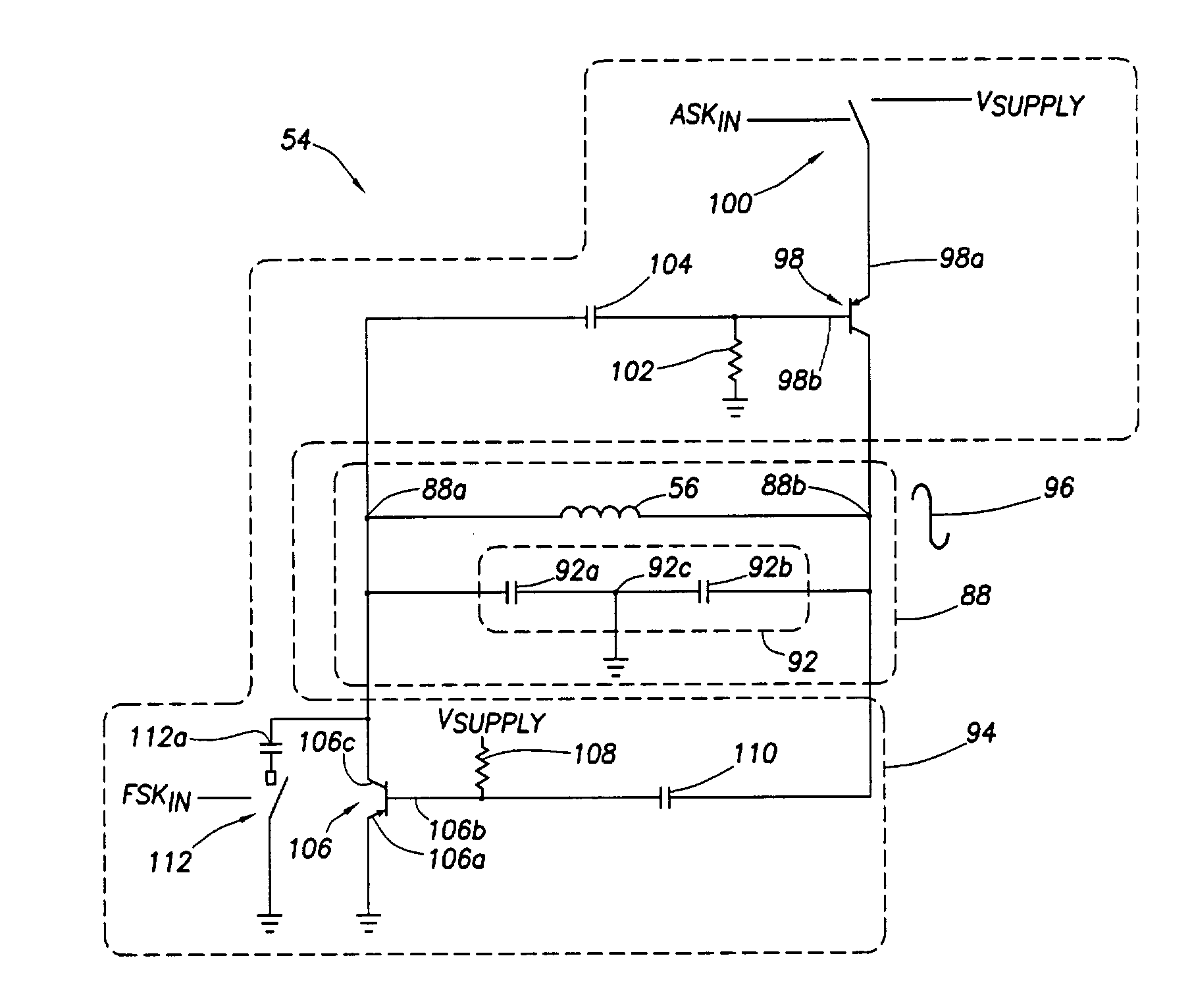

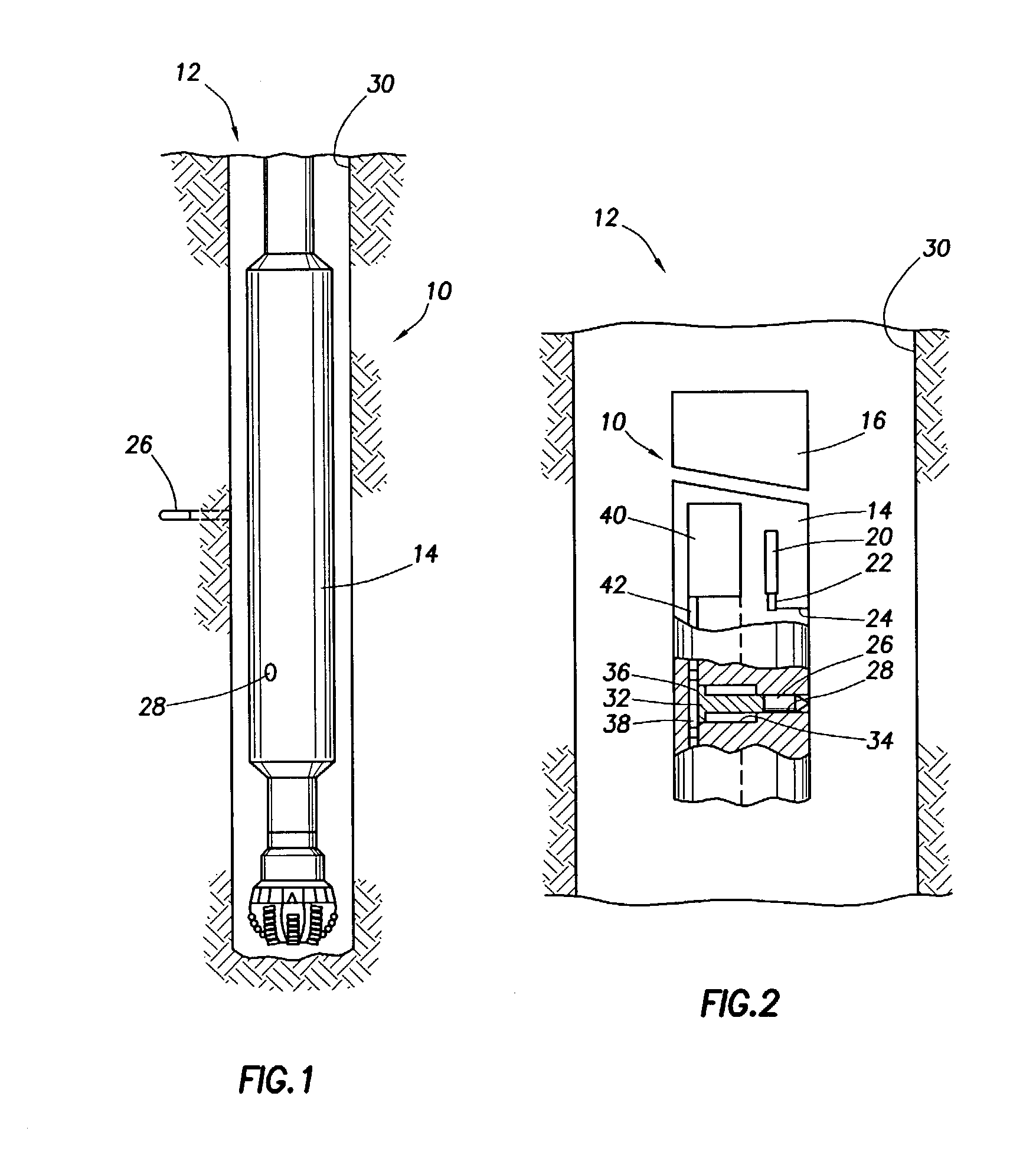

Wireless communication circuit

ActiveUS7158049B2Minimum power consumptionMaximising amplitudeSimultaneous amplitude and angle modulationSurveyInductorEngineering

The invention includes a wireless communication circuit and a method of communicating with wireless signals that feature a tank circuit having an inductor connected in parallel with a capacitor circuit. The capacitor circuit includes a pair of capacitors coupled in series. Each of the capacitors is connected in common to ground and has a capacitive value associated. A feedback network is connected to selectively bias the tank circuit to produce a signal having an amplitude. The amplitude of the signal is a function of a ratio of the capacitive values associated with the capacitor circuit. The frequency of the signal is defined by the inductor and the capacitor circuit. The tank circuit is multifunctional in that it may be biased to function as a transmitter and a receiver.

Owner:SCHLUMBERGER TECH CORP

Prosthetic device utilizing electric vacuum pump

ActiveUS7947085B2Easy to useReadily incorporated into/onto prosthesisArtificial legsArtificial handsEngineeringVacuum pump

Owner:WILLOWWOOD GLOBAL LLC

Amplifier using delta-sigma modulation

ActiveUS6998910B2Reduce adverse effectsSacrificing power consumption advantageAnalogue conversionDc amplifiers with modulator-demodulatorDriver circuitAudio power amplifier

An amplifier and a driver circuit therefor are presented for driving a load according to a system analog input. The amplifier comprises a passive delta-sigma modulator with a passive filter providing a first filtered signal according to a passive filter input and according to a feedback signal, a quantizer coupled with the passive filter and providing a quantized output according to the first filtered signal, and a switching system coupled with the the passive filter and the quantizer. The switching system selectively providing power to a load according to the quantized output and provides the feedback signal to the passive input, wherein a gain amplifier is provided in a feedback loop around the passive delta-sigma modulator.

Owner:TEXAS INSTR INC

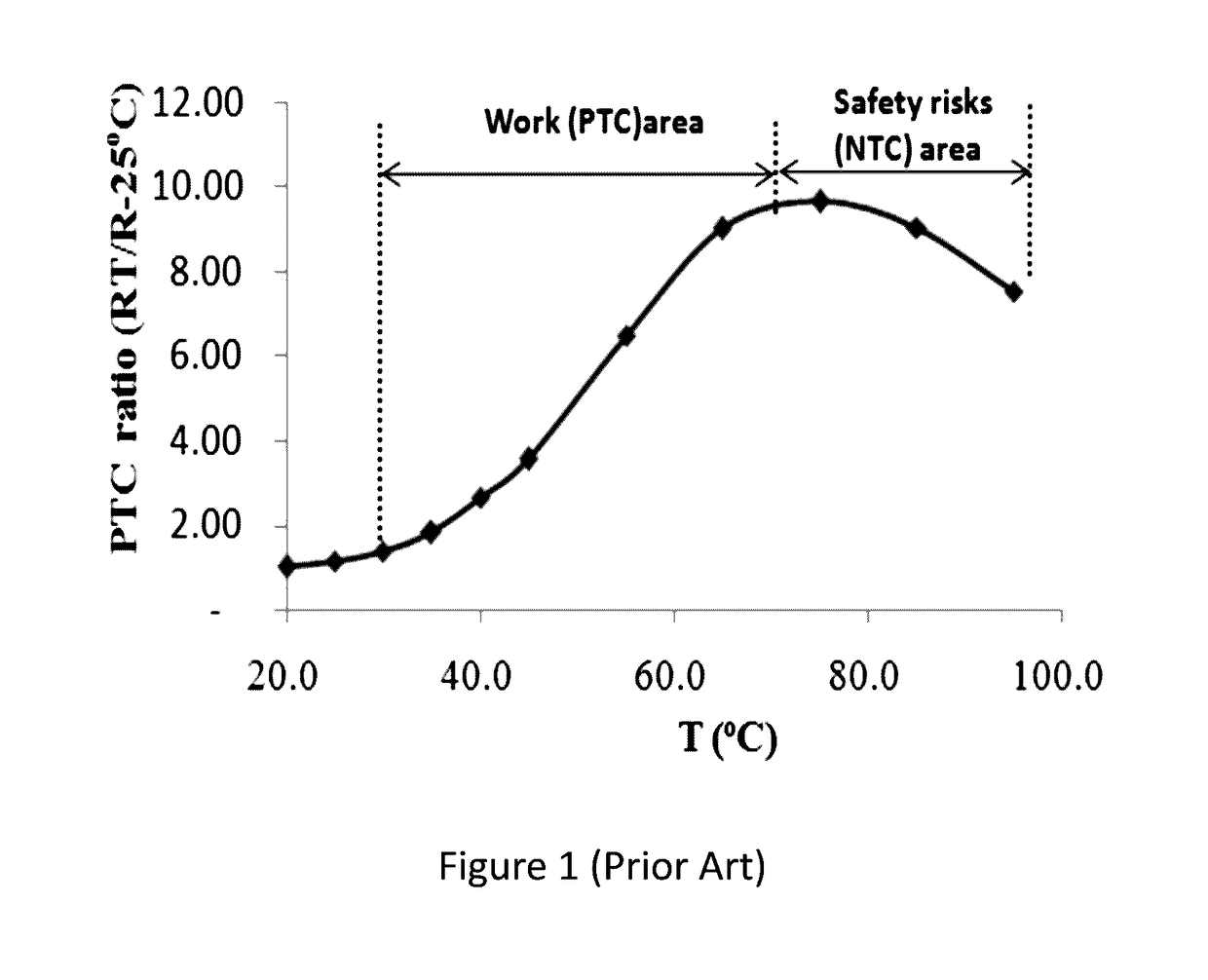

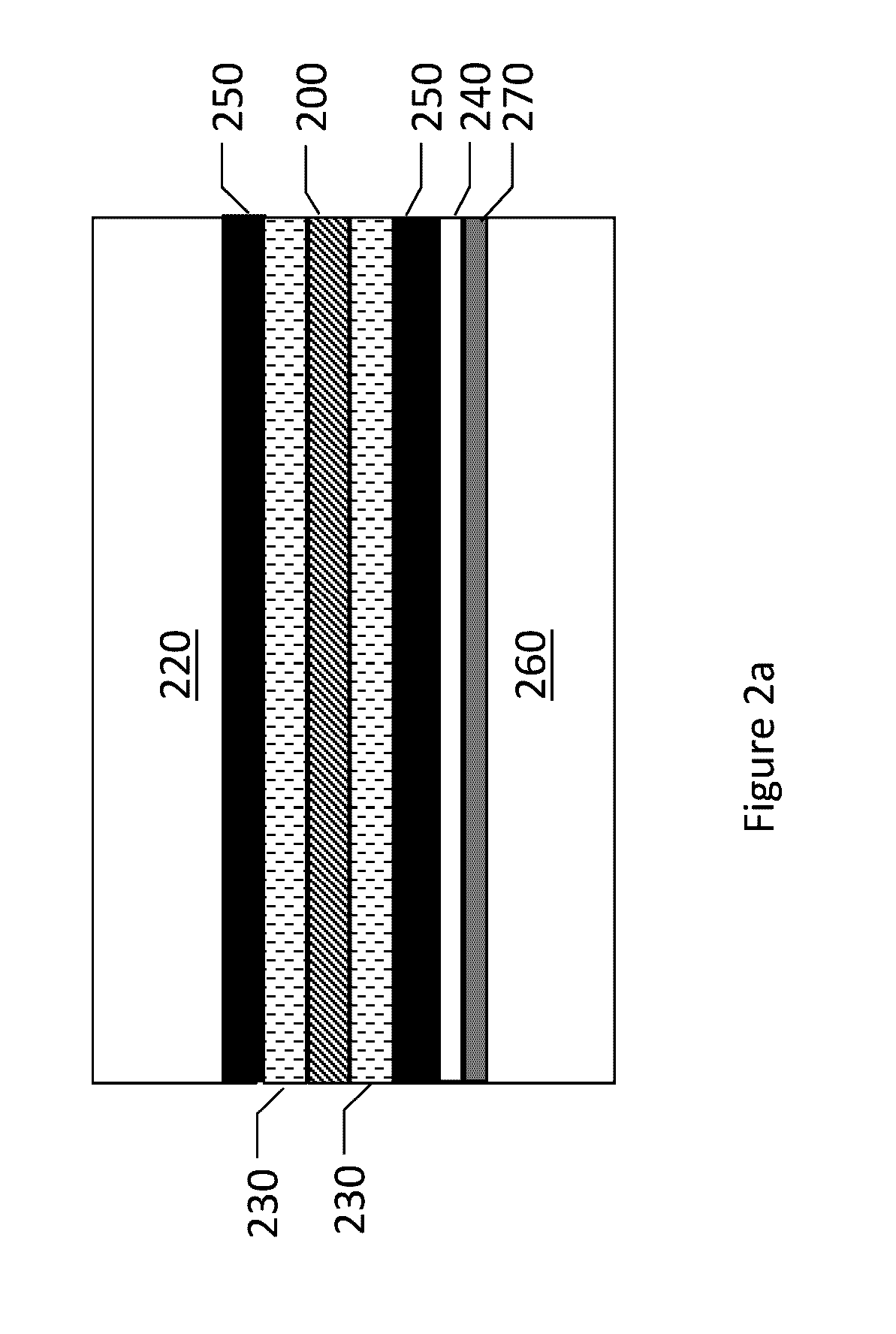

Electrically conductive PTC ink with double switching temperatures and applications thereof in flexible double-switching heaters

ActiveUS20170158898A1Eliminate the effects ofHigh PTC characteristicLighting and heating apparatusIce productionPolyesterCarbon composites

A double-switching heater includes a double-switching PTC ink deposited on a substrate to form one or more resistors. The double-switching PTC ink has a first resin that provides a first PTC effect at a first temperature range and a second resin that provides a second PTC effect at a second temperature range, where the second temperature range is higher than the first temperature range. The substrate may be a flexible substrate or a rigid substrate, and may bedeformable to generate a three-dimensional structure. The substrate may be: polyester, polyimide, polyamide, polypropylene, thermoplastic polyurethane, fiberglass, cement board, carbon composite materials, polyethylene terephthalate, polyethylene, aluminum, steel, glass composite, molded plastic, high-density polyethylene or styrene ethylene butylene styrene.

Owner:LMS CONSULTING GRP LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com