Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

197 results about "Asynchronous network" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

1) In telecommunication signaling within a network or between networks, an asynchronous signal is one that is transmitted at a different clock rate than another signal.

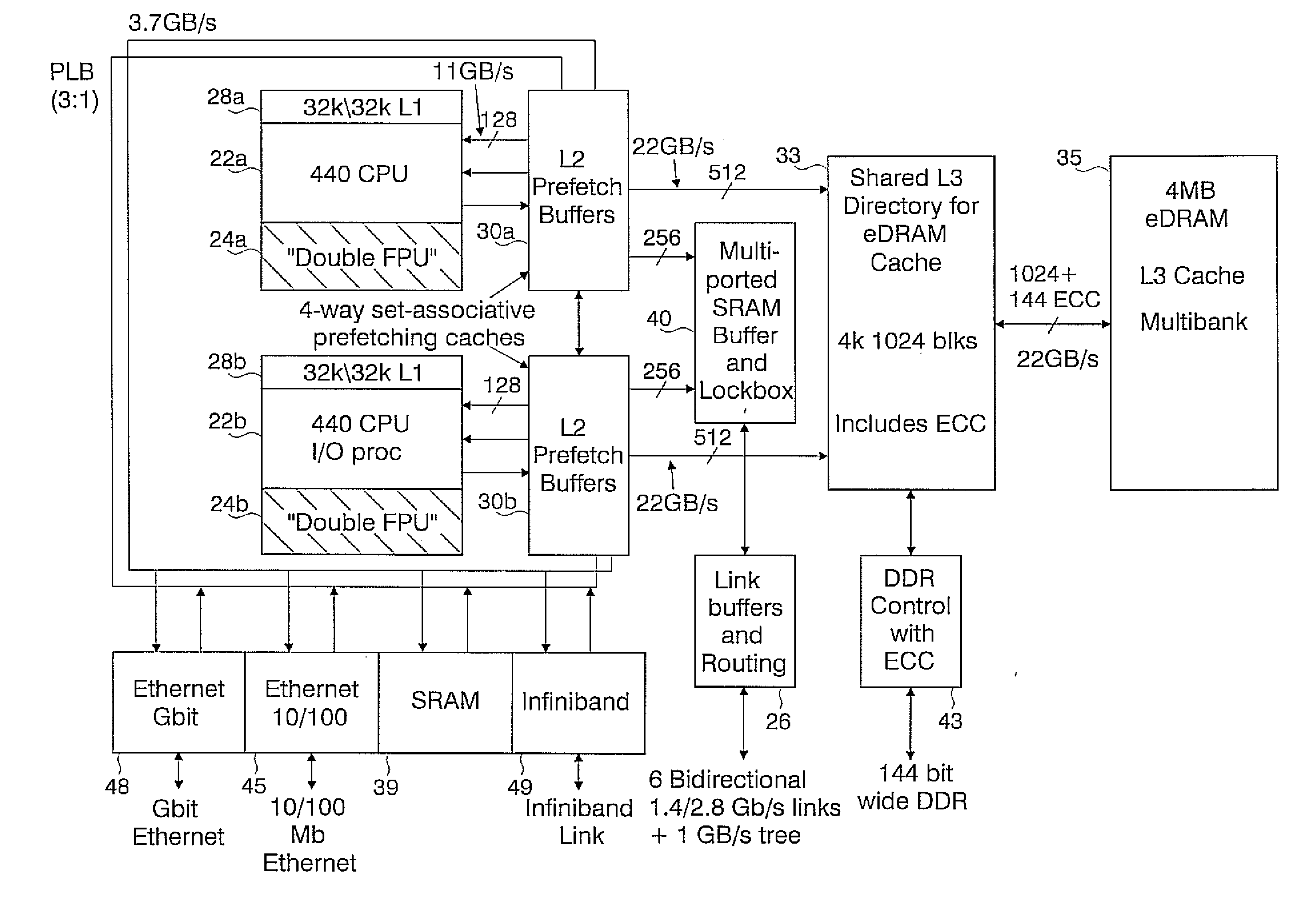

Novel massively parallel supercomputer

InactiveUS20090259713A1Low costReduced footprintError preventionProgram synchronisationSupercomputerPacket communication

Owner:INT BUSINESS MASCH CORP

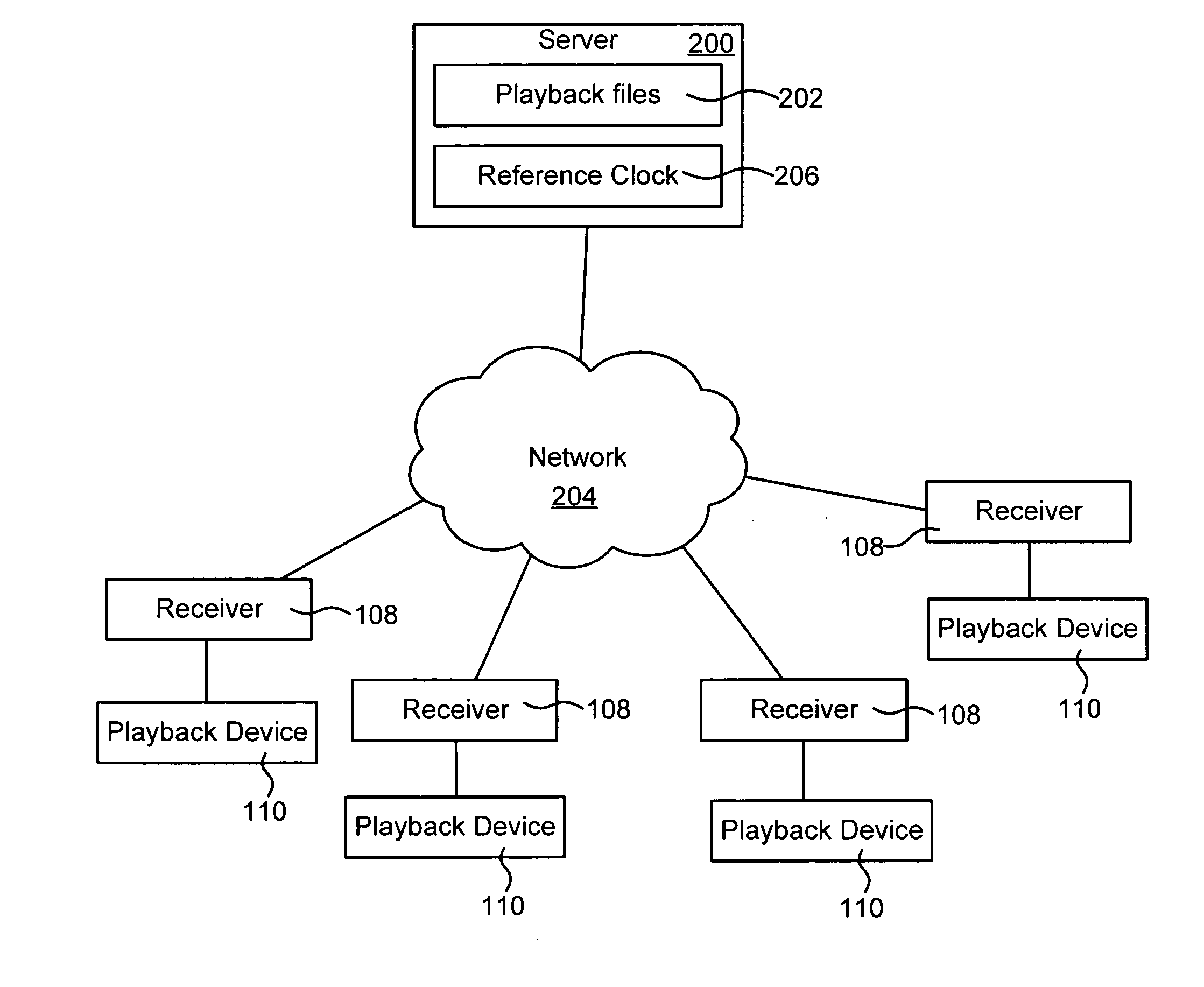

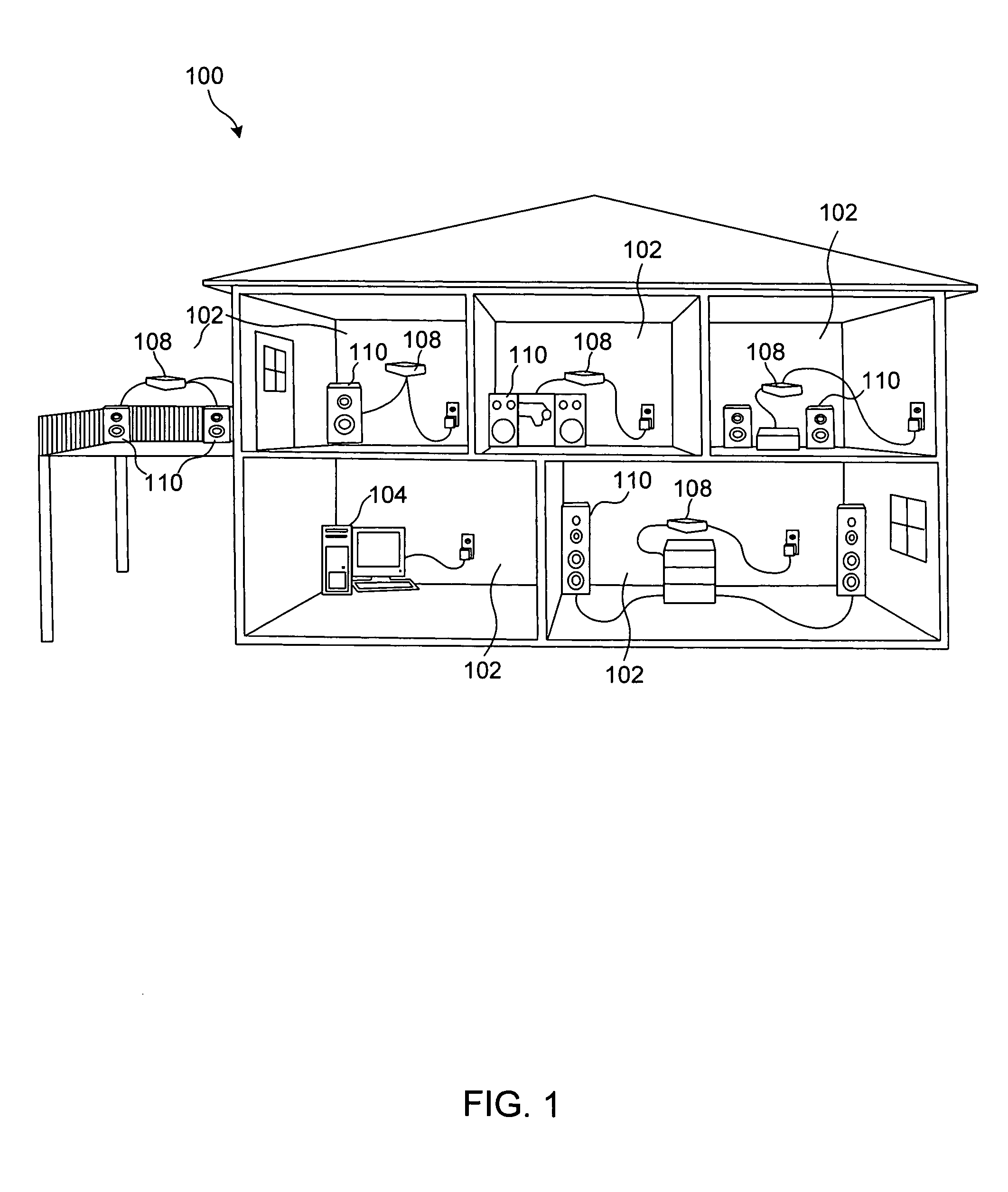

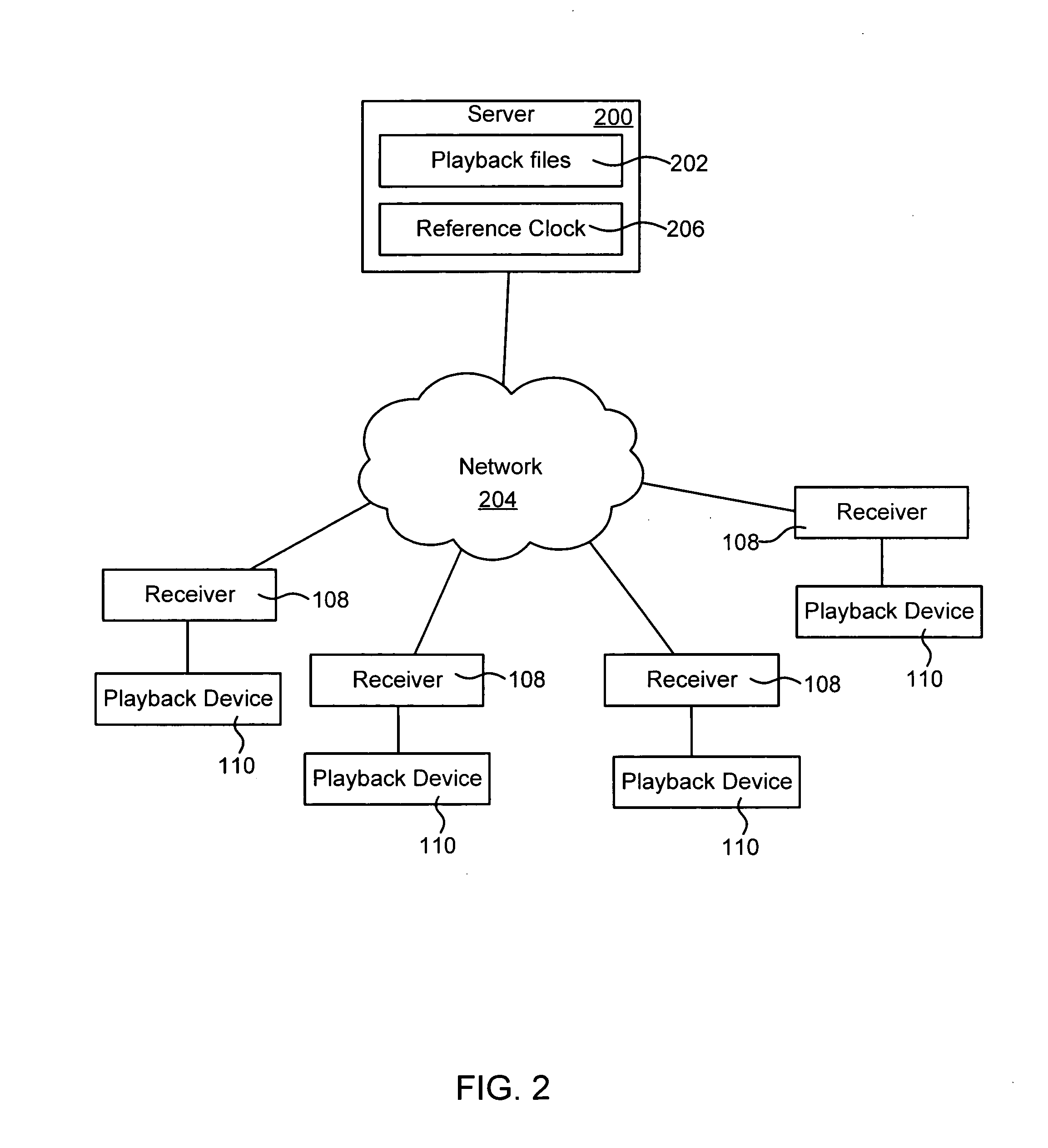

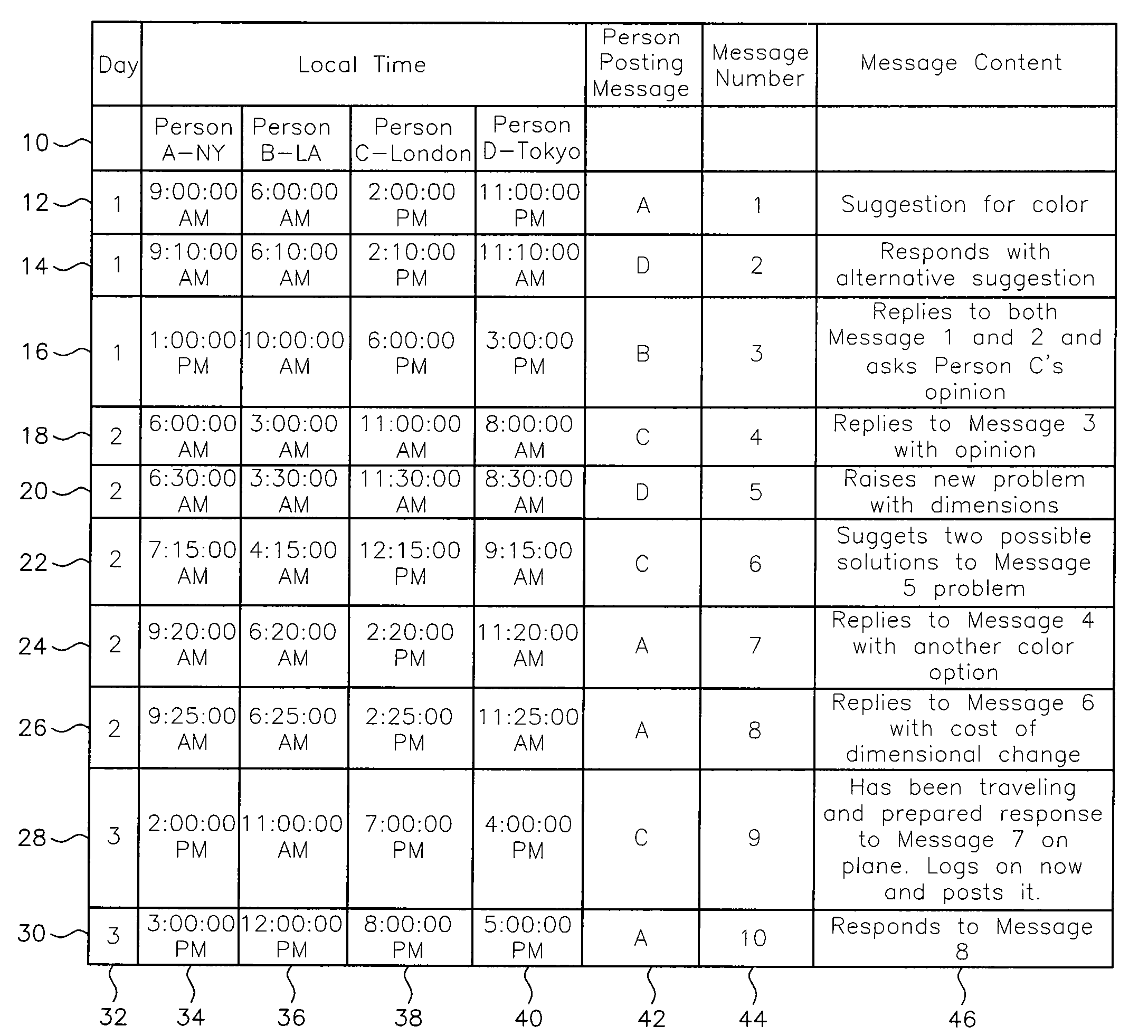

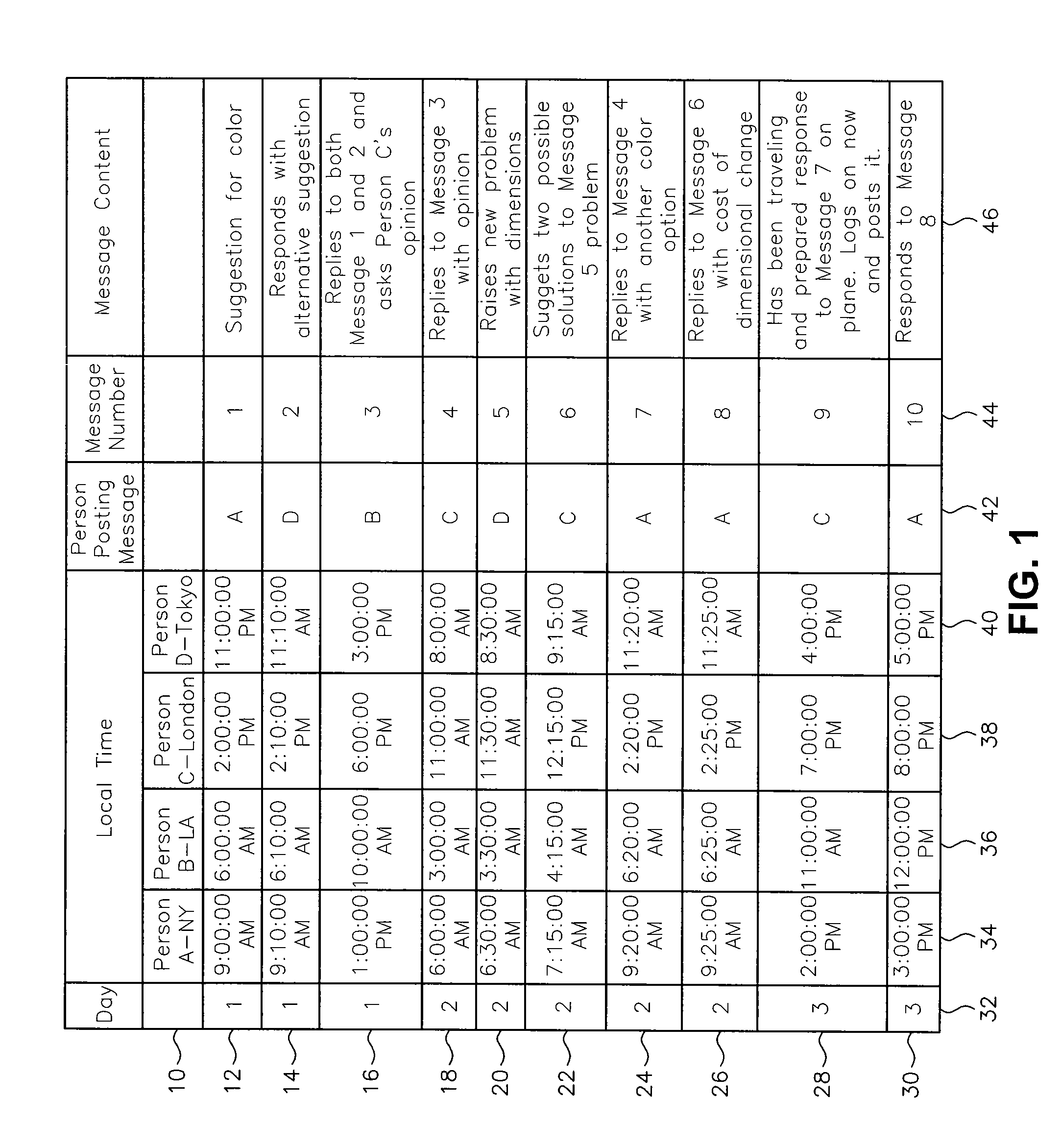

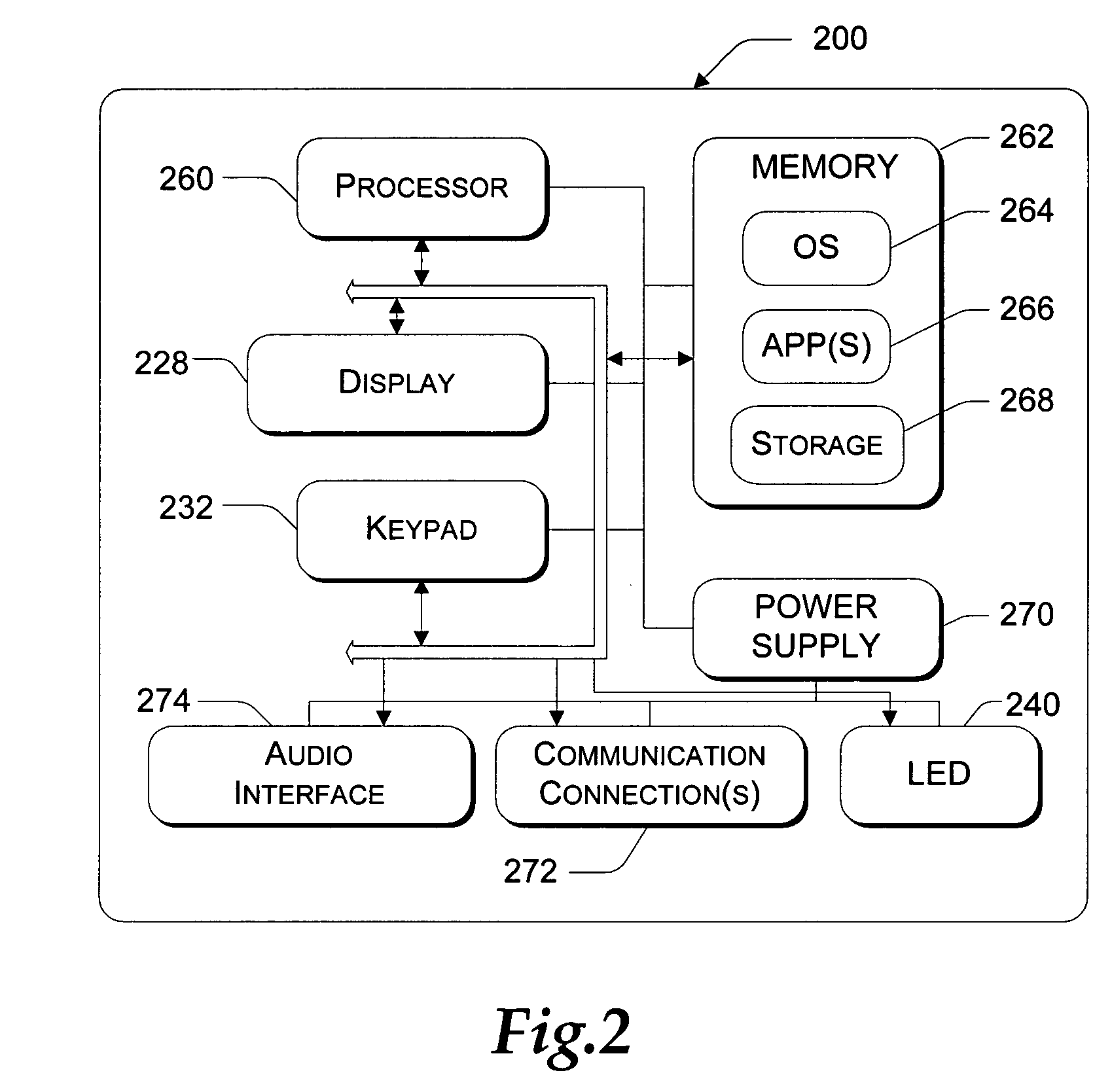

Apparatus, system and method for synchronized playback of data transmitted over an asynchronous network

InactiveUS20050166135A1Compensation differenceDigital computer detailsTime-division multiplexComputer hardwareAsynchronous network

An apparatus, system and method for synchronizing the playback of data transmitted over an asynchronous network. An initialization module may initialize at least two receivers to receive playback data from a transmission module. The transmission module may then transmit to the receivers the playback data, and, in some embodiments, synchronization data. Synchronization data may include a playback indicator by which the receivers may determine an appropriate playback data consumption rate. A buffer module may buffer a predetermined amount of playback data which may be played in response to a start signal individually addressed to the receivers.

Owner:BURKE DAVID G +5

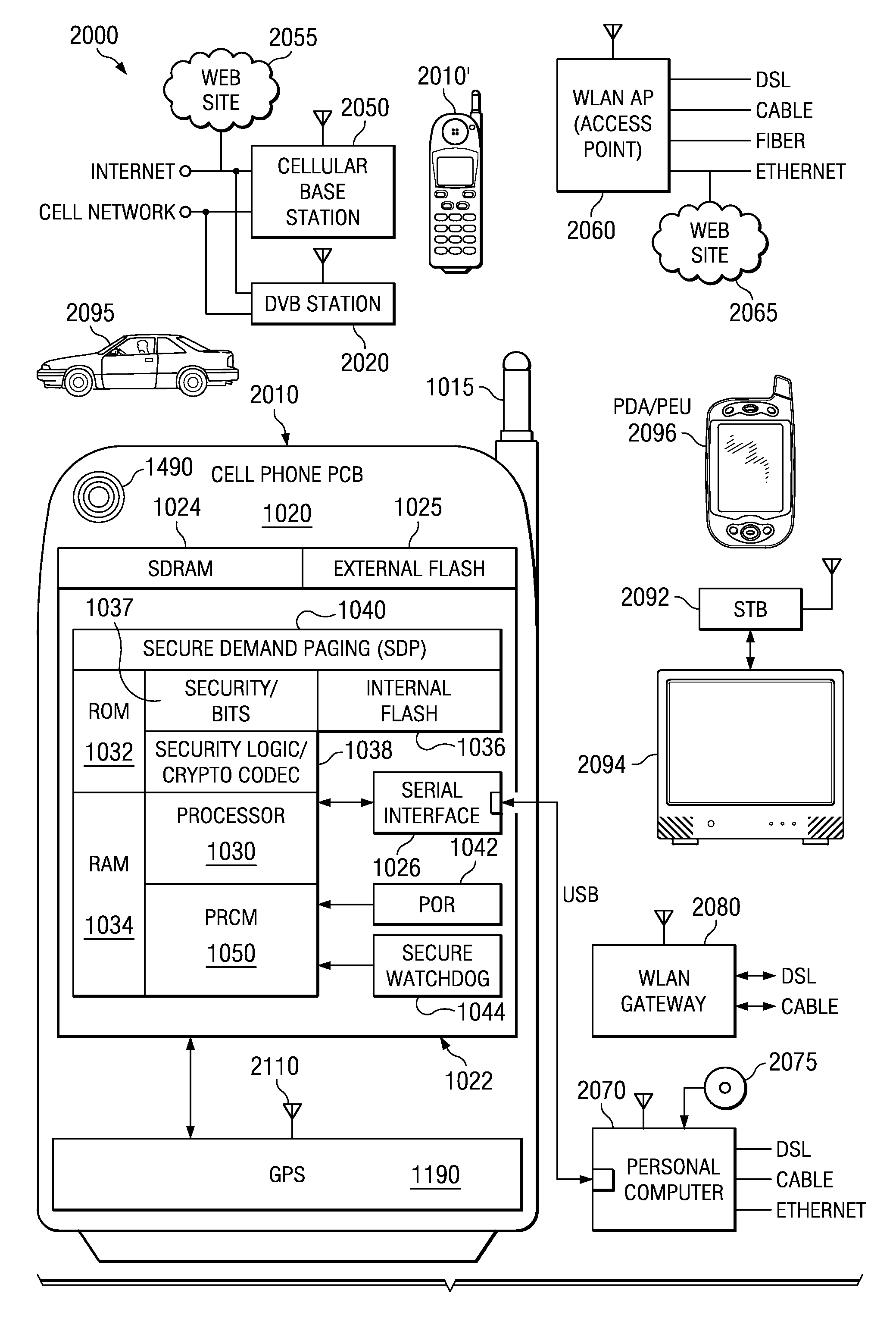

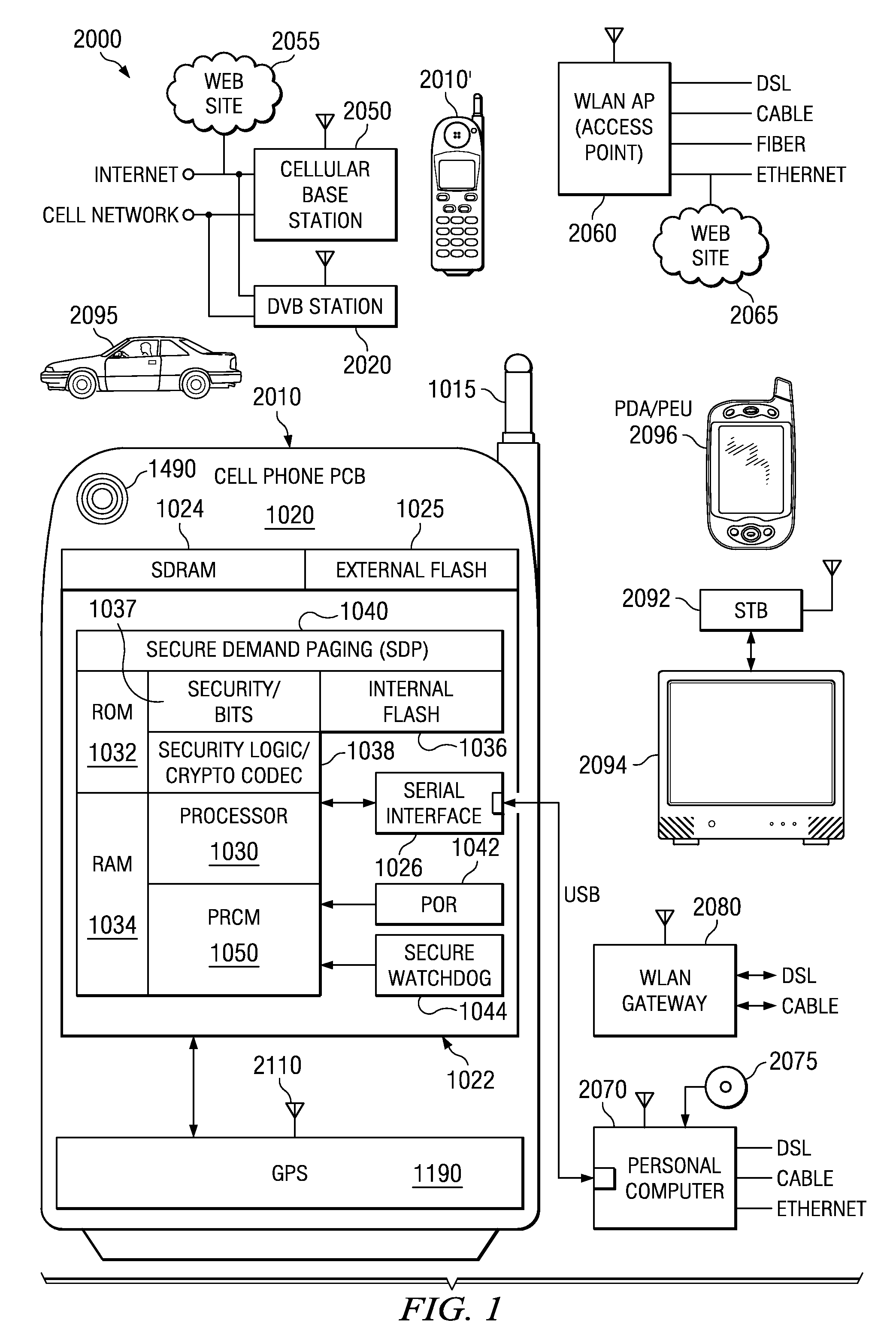

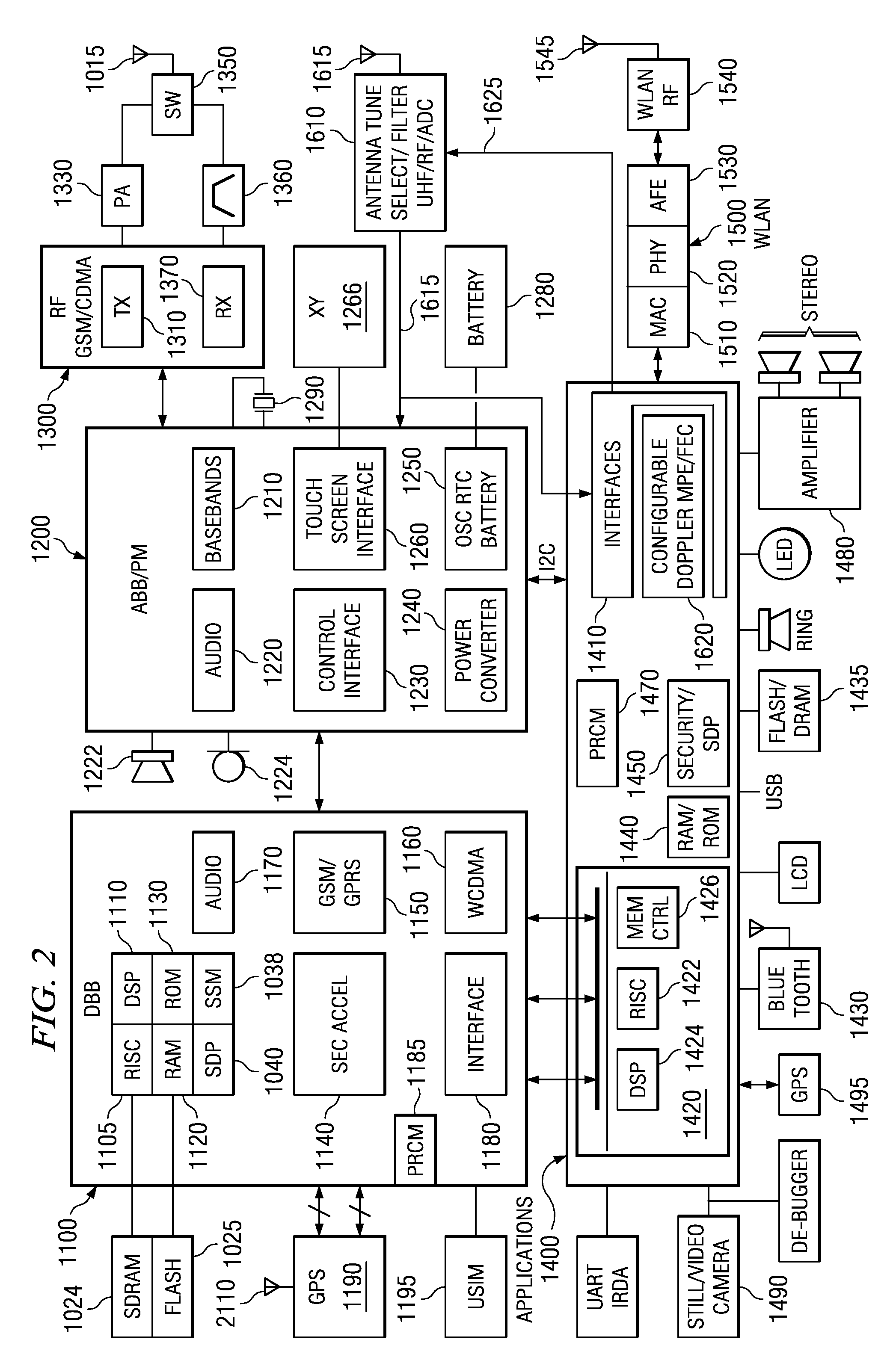

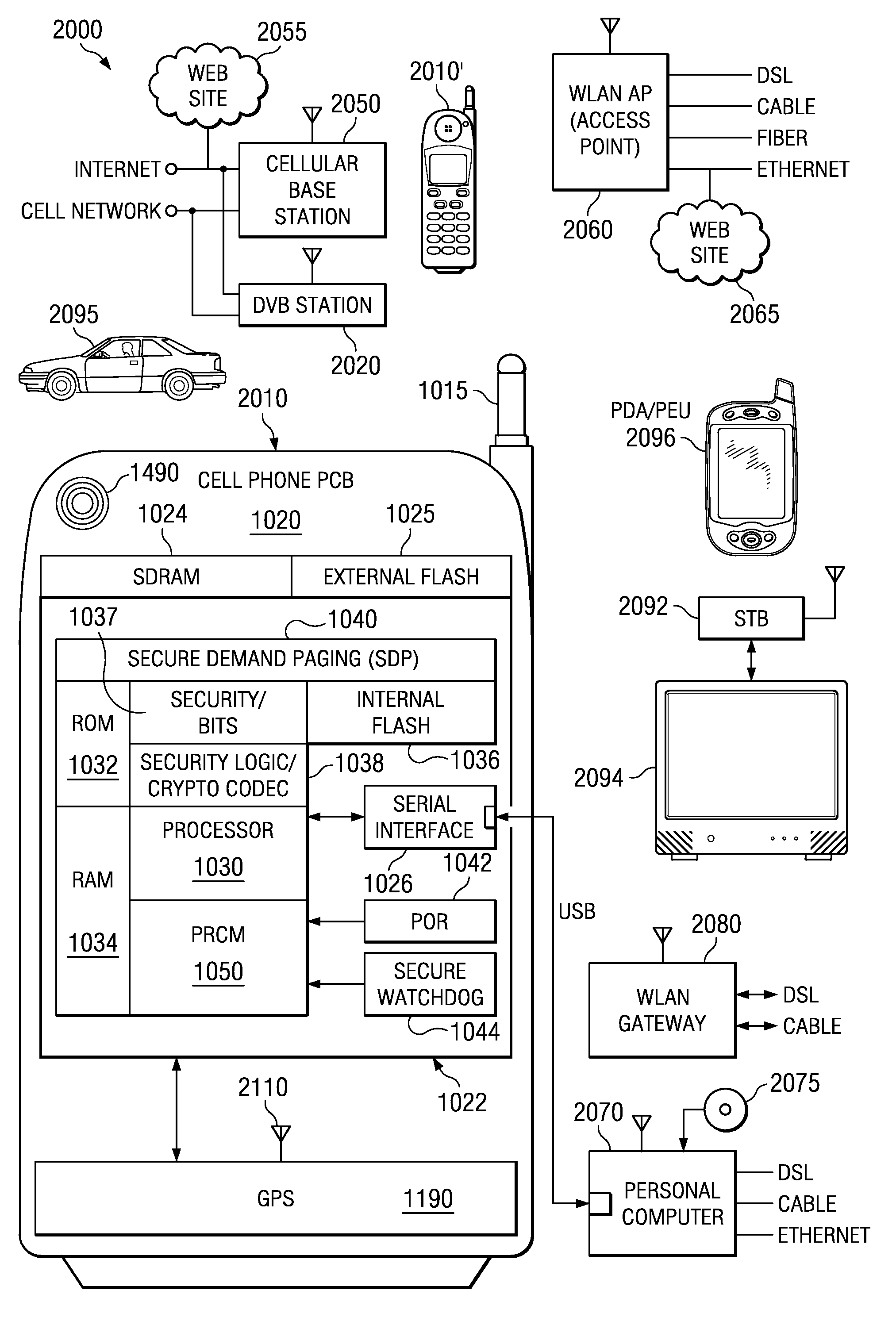

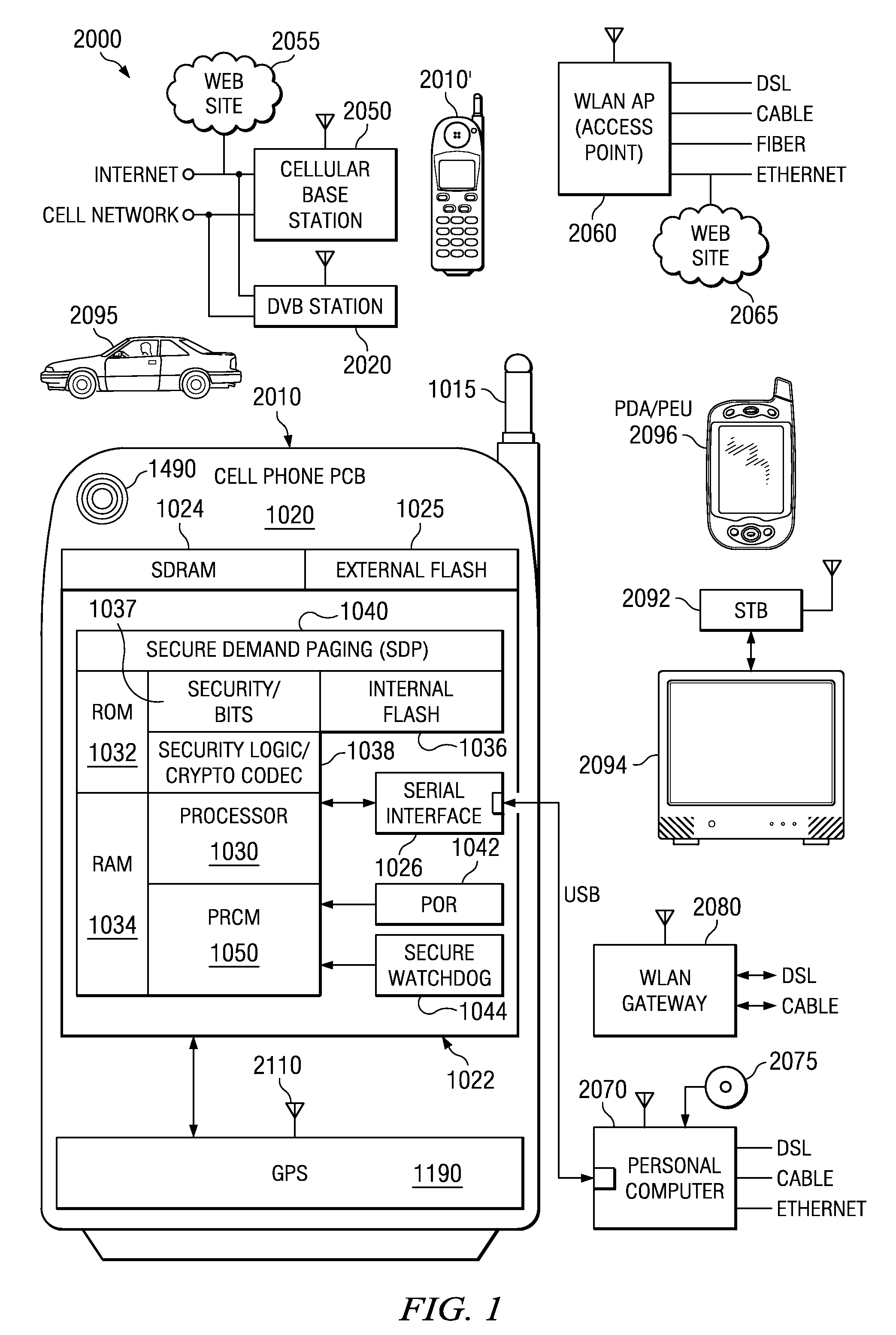

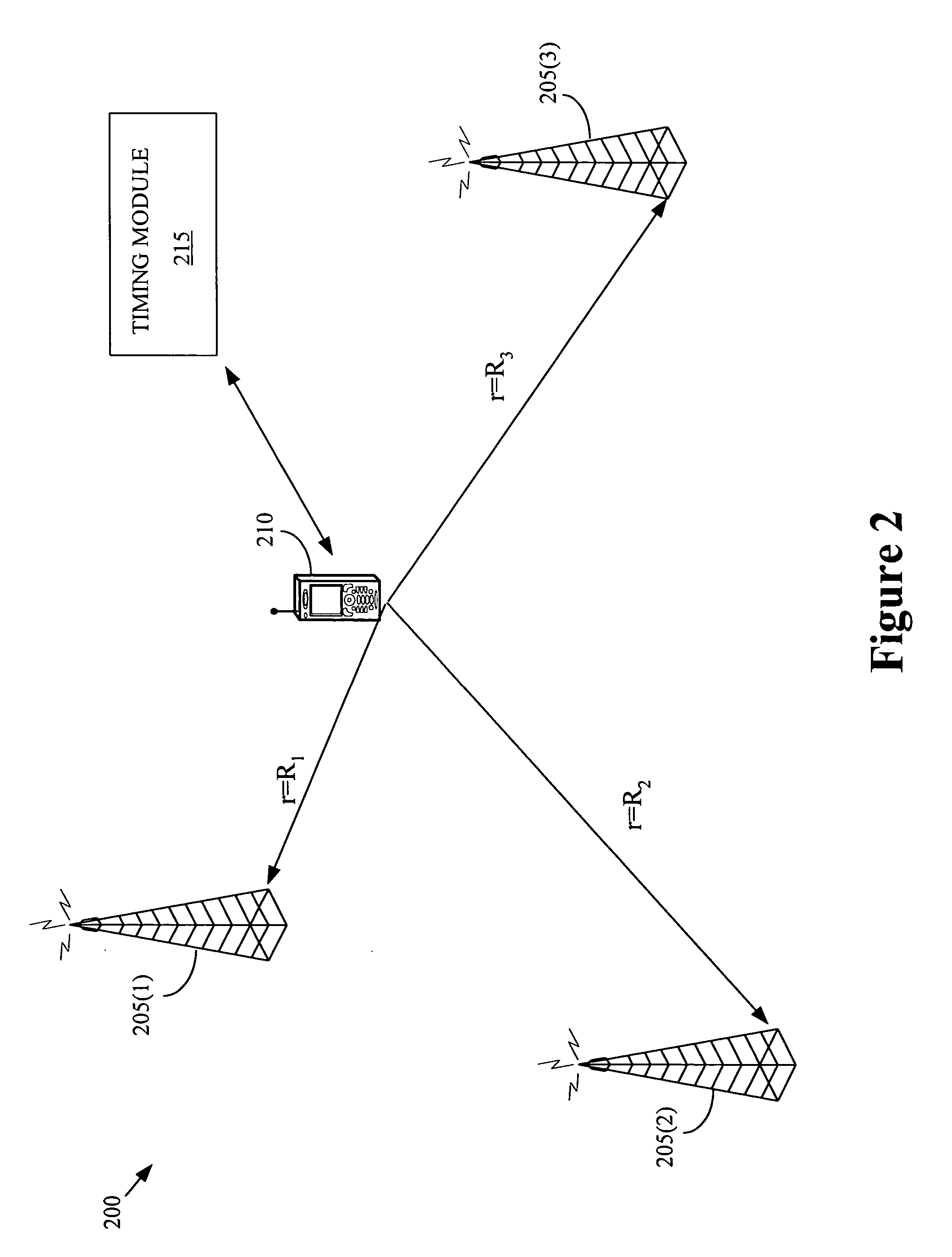

Satellite (GPS) assisted clock apparatus, circuits, systems and processes for cellular terminals on asynchronous networks

ActiveUS20090054075A1Fixed lengthRadio/inductive link selection arrangementsRadio transmissionAsynchronous networkComputer terminal

A wireless circuit (1100, 1190) for tracking an incoming signal and for use in a network (2000) having handover from one part (Cell A) of the network to another part (Cell B). The wireless circuit includes a processor (CE 1100) responsive to the incoming signal, the processor (CE 1100) operable to generate pulse edges representing network-based receiver synchronization instances (RSIs), and a timekeeping circuitry (2420, 2430, 2450) including an oscillator circuitry (2162), the timekeeping circuitry (2420, 2430) operable to maintain a set of counter circuitries (2422-2428) including a counter circuitry (2422) operable to maintain at least one network time component based on the RSIs and another counter circuitry (2428) operable at least during handover and during loss of network coverage for maintaining at least one internal time component (NC) based on the oscillator circuitry (2162), the set of counter circuitries (2422-2428) operable to account for elapsing time substantially gaplessly and substantially without overlap between the time components during a composite of network coverage, loss of network coverage and handover, and the timekeeping circuitry further including a time generator (2450) for combining the time components from the set of counter circuitries (2422-2428) to generate an approximate absolute time (SGTB). Other electronic circuits, positioning systems, methods of operation, and processes of manufacture are also disclosed and claimed.

Owner:TEXAS INSTR INC

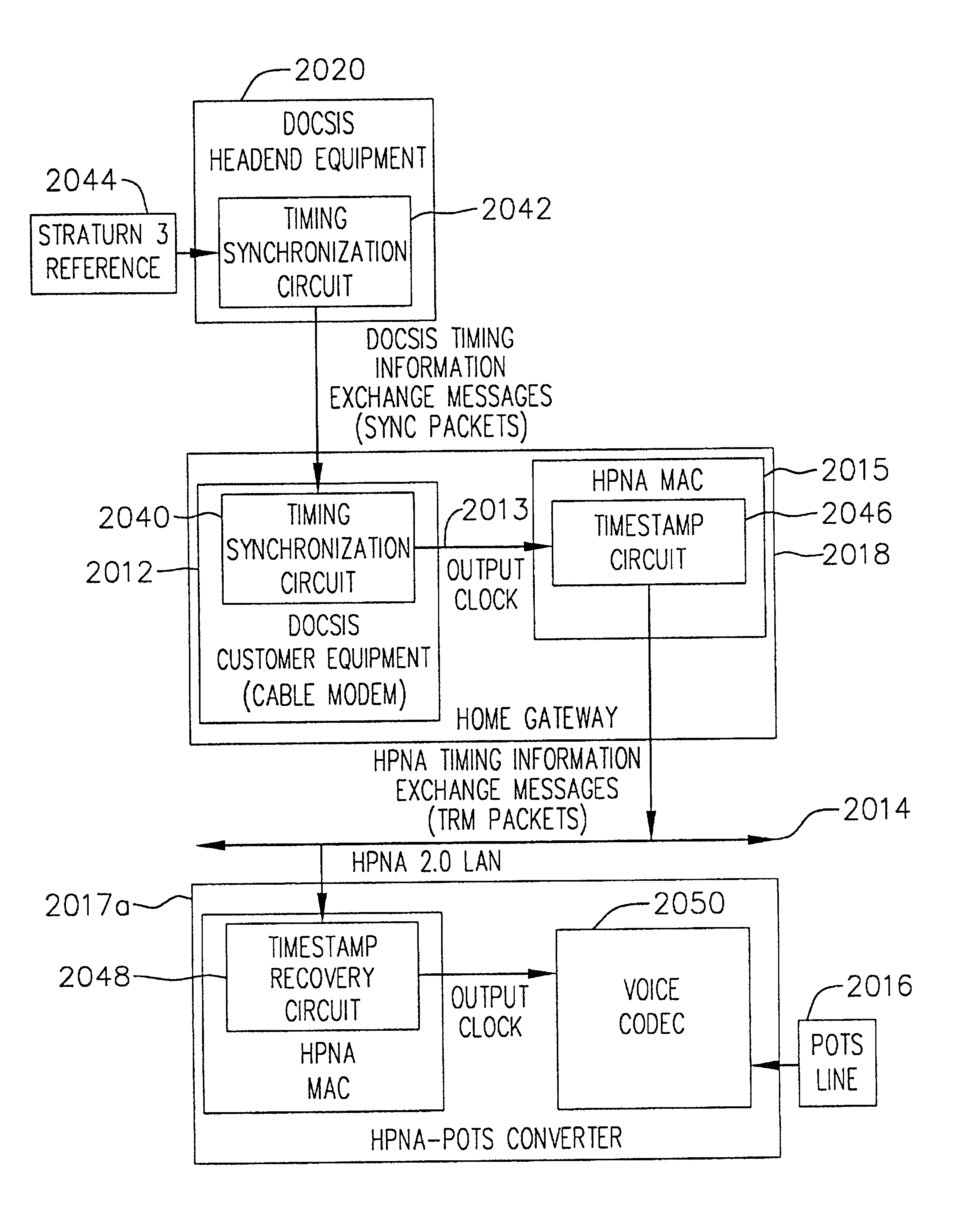

Method of controlling data sampling clocking of asynchronous network nodes in a frame-based communications network

InactiveUS6975655B2Energy efficient ICTError prevention/detection by using return channelTimestampFrame based

Owner:AVAGO TECH INT SALES PTE LTD

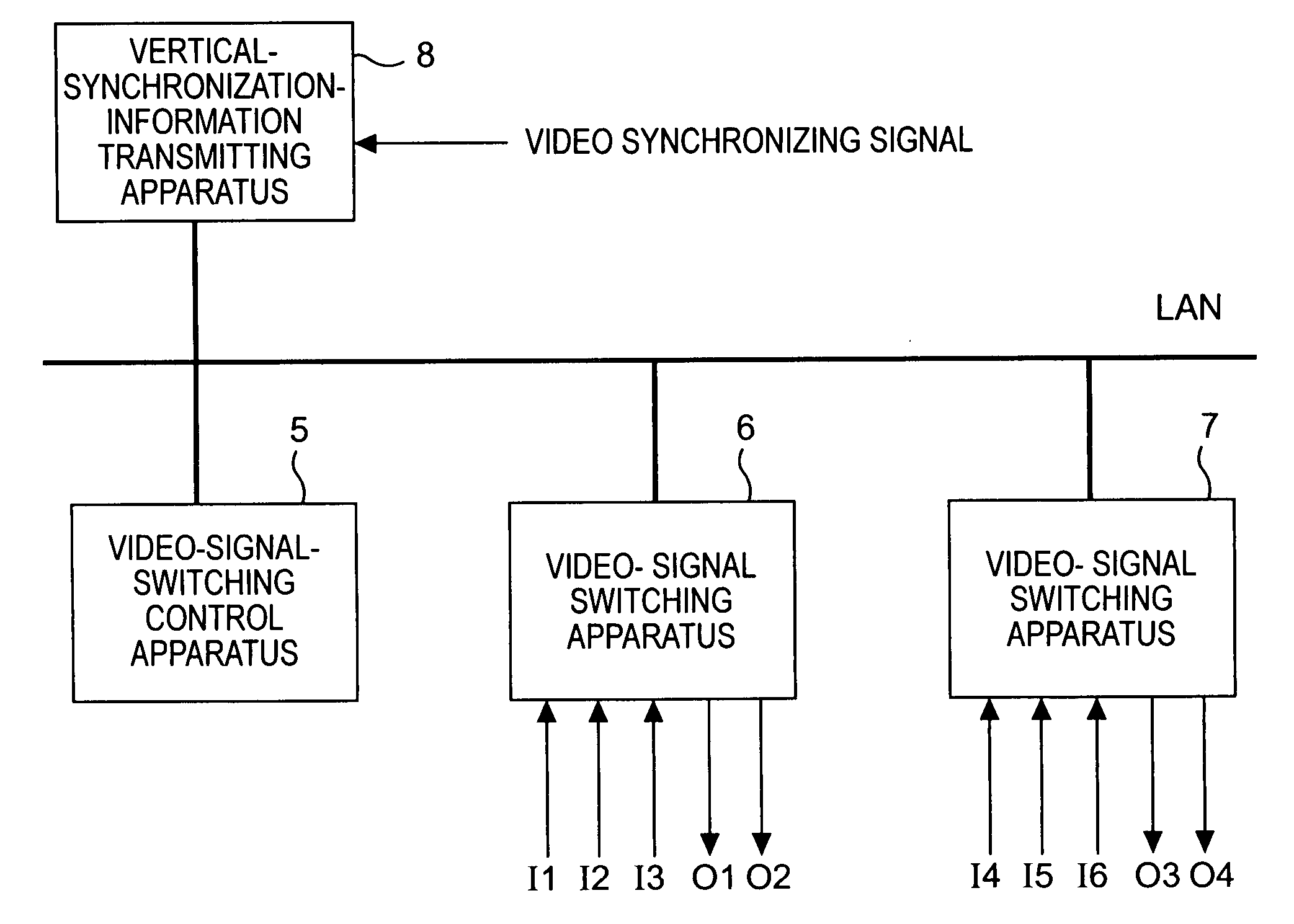

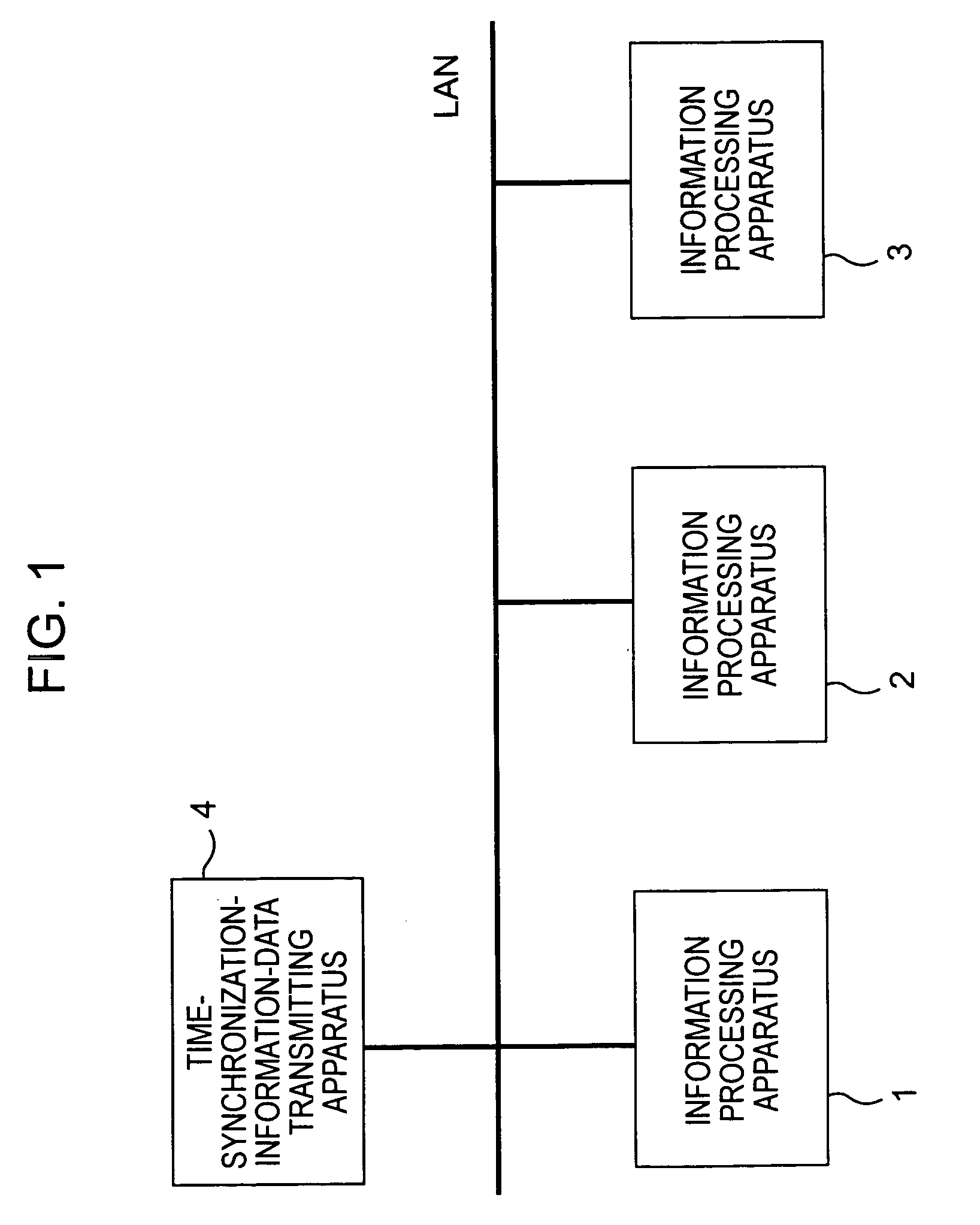

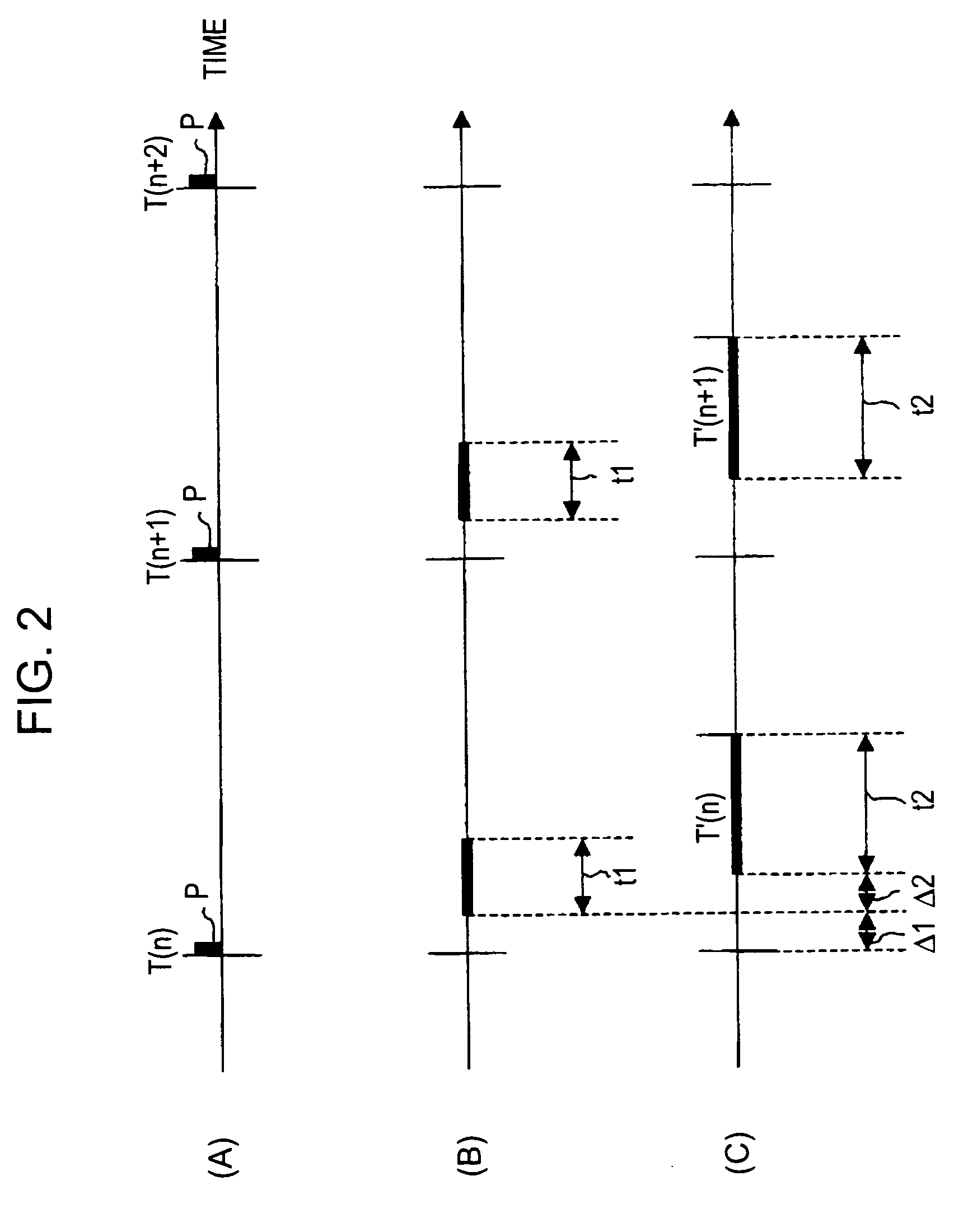

Asynchronous network system, information processing apparatus, data-transmission managing method, data-reception managing method, and program

InactiveUS20060109860A1Data switching by path configurationTwo-way working systemsInformation processingTime information

An asynchronous network system includes a transmitting apparatus which transmits time-synchronization-information data through an asynchronous network, and information processing apparatuses which share identical time information by receiving the time-synchronization-information data. At least one data item whose transmission and reception within a predetermined reaching time are requested to be guaranteed is transmitted by one information processing apparatus among the information processing apparatuses to at least one of the other information processing apparatuses in a state in which the one information processing apparatus occupies a first interval on a communication schedule based on time-synchronization information represented by the time-synchronization-information data.

Owner:SONY CORP

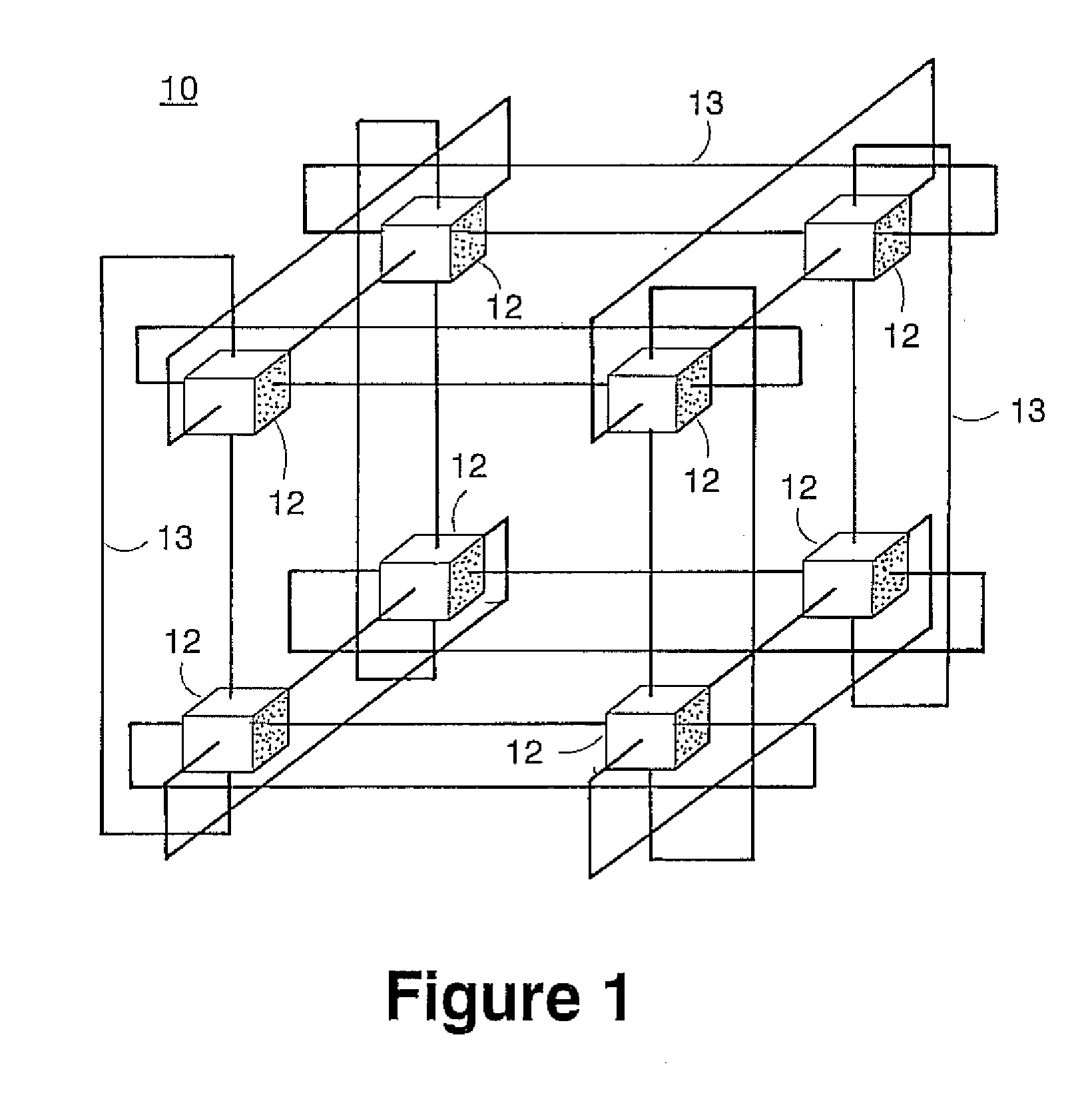

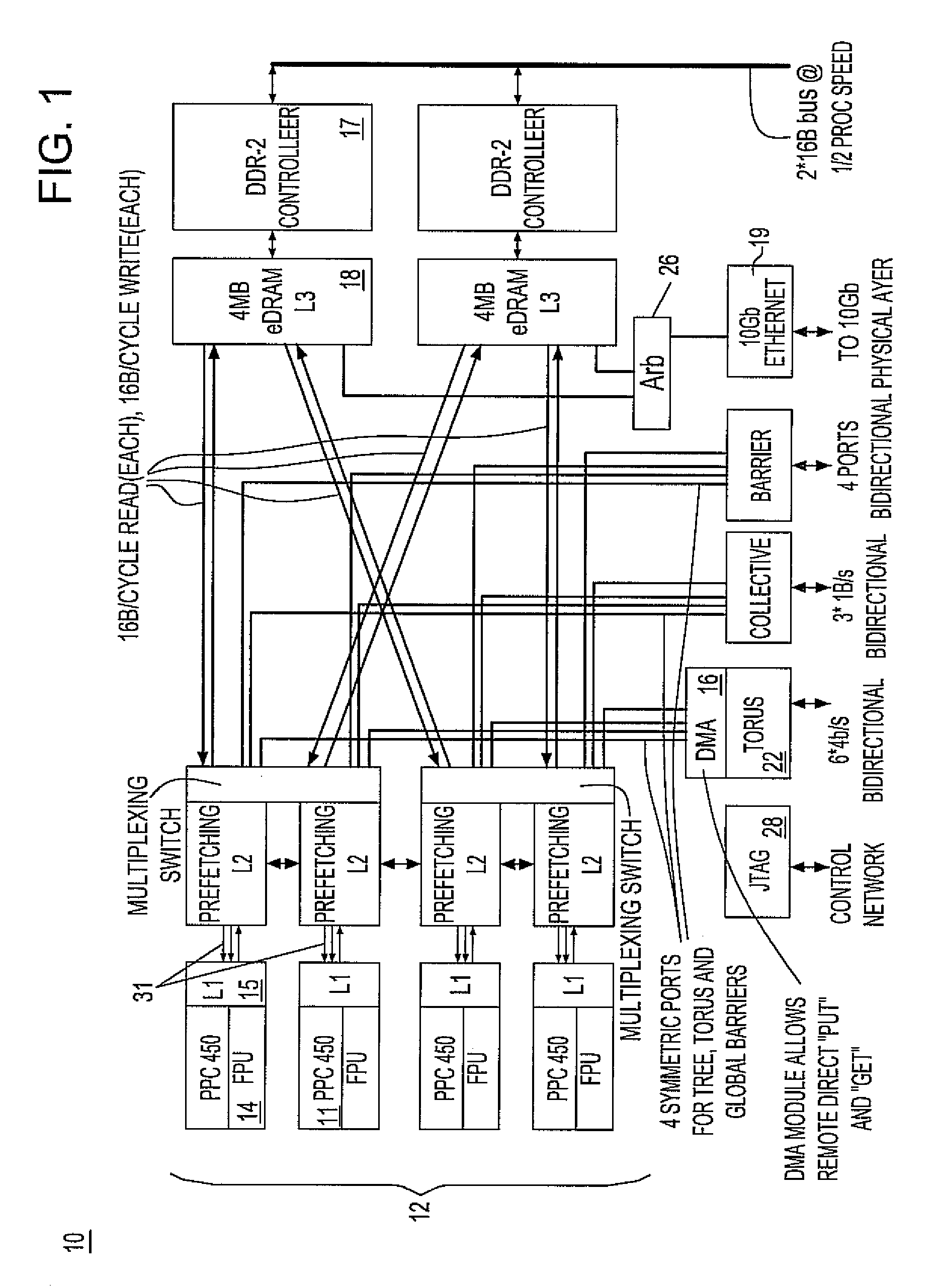

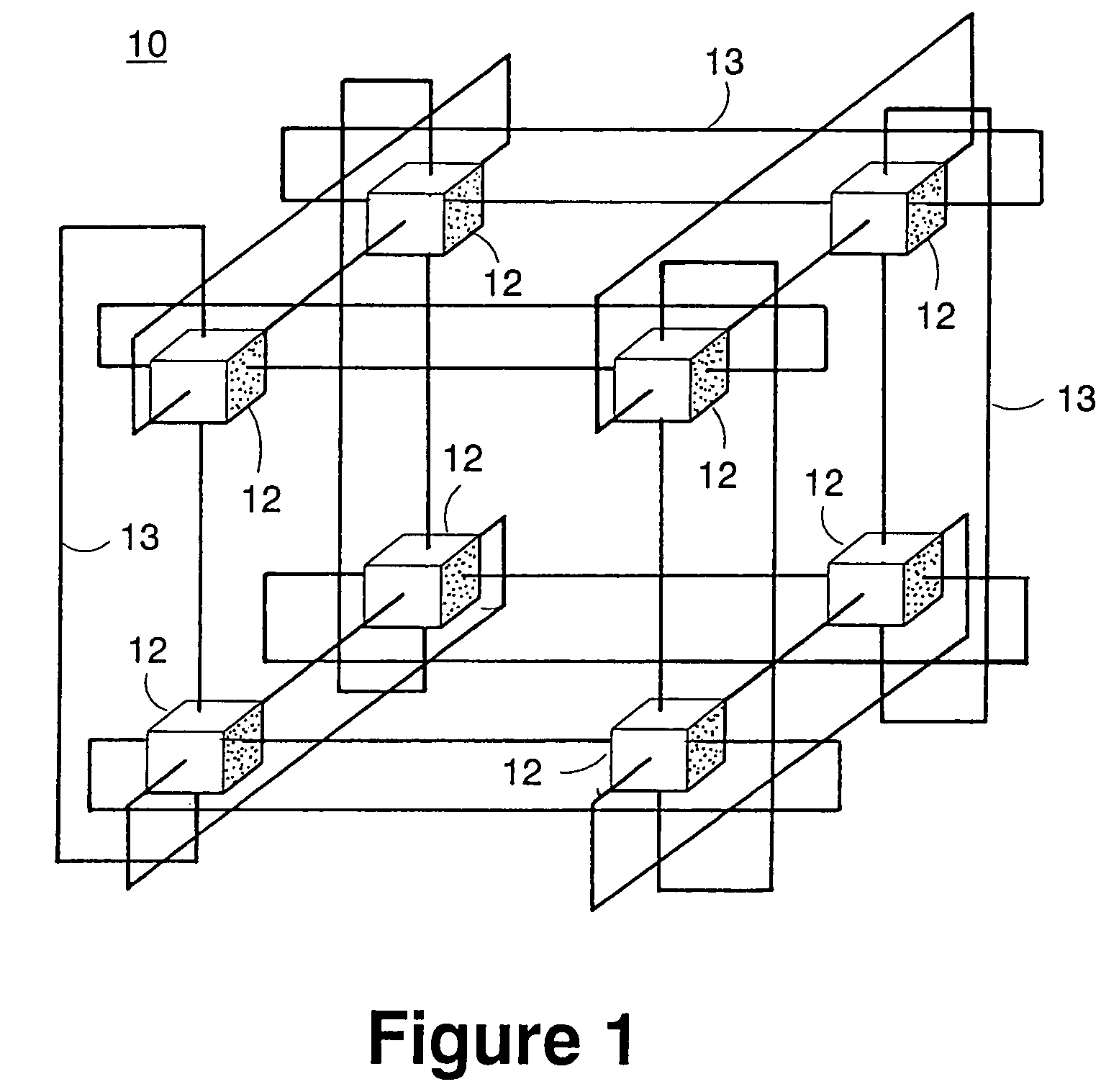

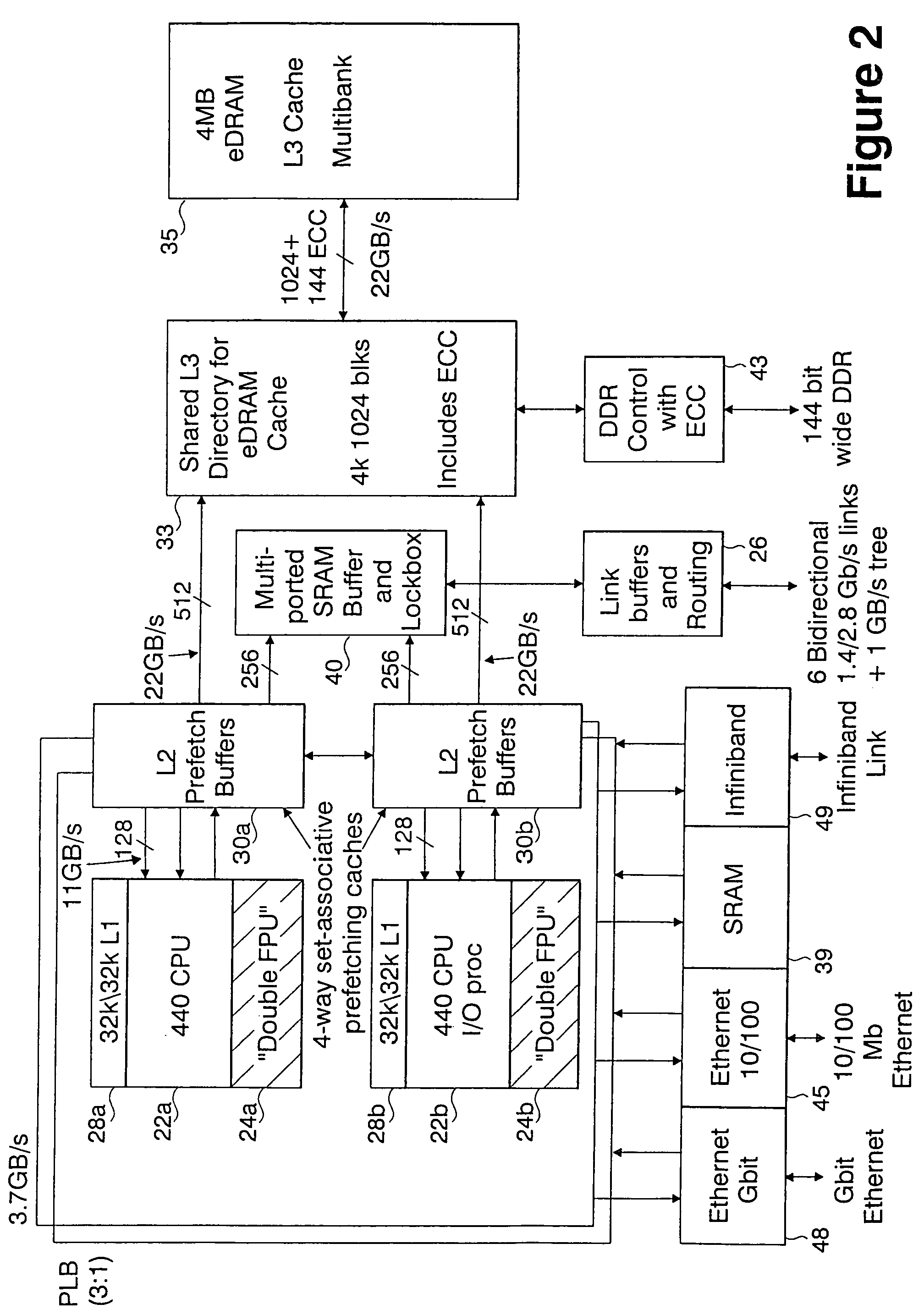

Ultrascalable petaflop parallel supercomputer

InactiveUS7761687B2Maximize throughputDelay minimizationGeneral purpose stored program computerElectric digital data processingSupercomputerPacket communication

A massively parallel supercomputer of petaOPS-scale includes node architectures based upon System-On-a-Chip technology, where each processing node comprises a single Application Specific Integrated Circuit (ASIC) having up to four processing elements. The ASIC nodes are interconnected by multiple independent networks that optimally maximize the throughput of packet communications between nodes with minimal latency. The multiple networks may include three high-speed networks for parallel algorithm message passing including a Torus, collective network, and a Global Asynchronous network that provides global barrier and notification functions. These multiple independent networks may be collaboratively or independently utilized according to the needs or phases of an algorithm for optimizing algorithm processing performance. The use of a DMA engine is provided to facilitate message passing among the nodes without the expenditure of processing resources at the node.

Owner:INT BUSINESS MASCH CORP

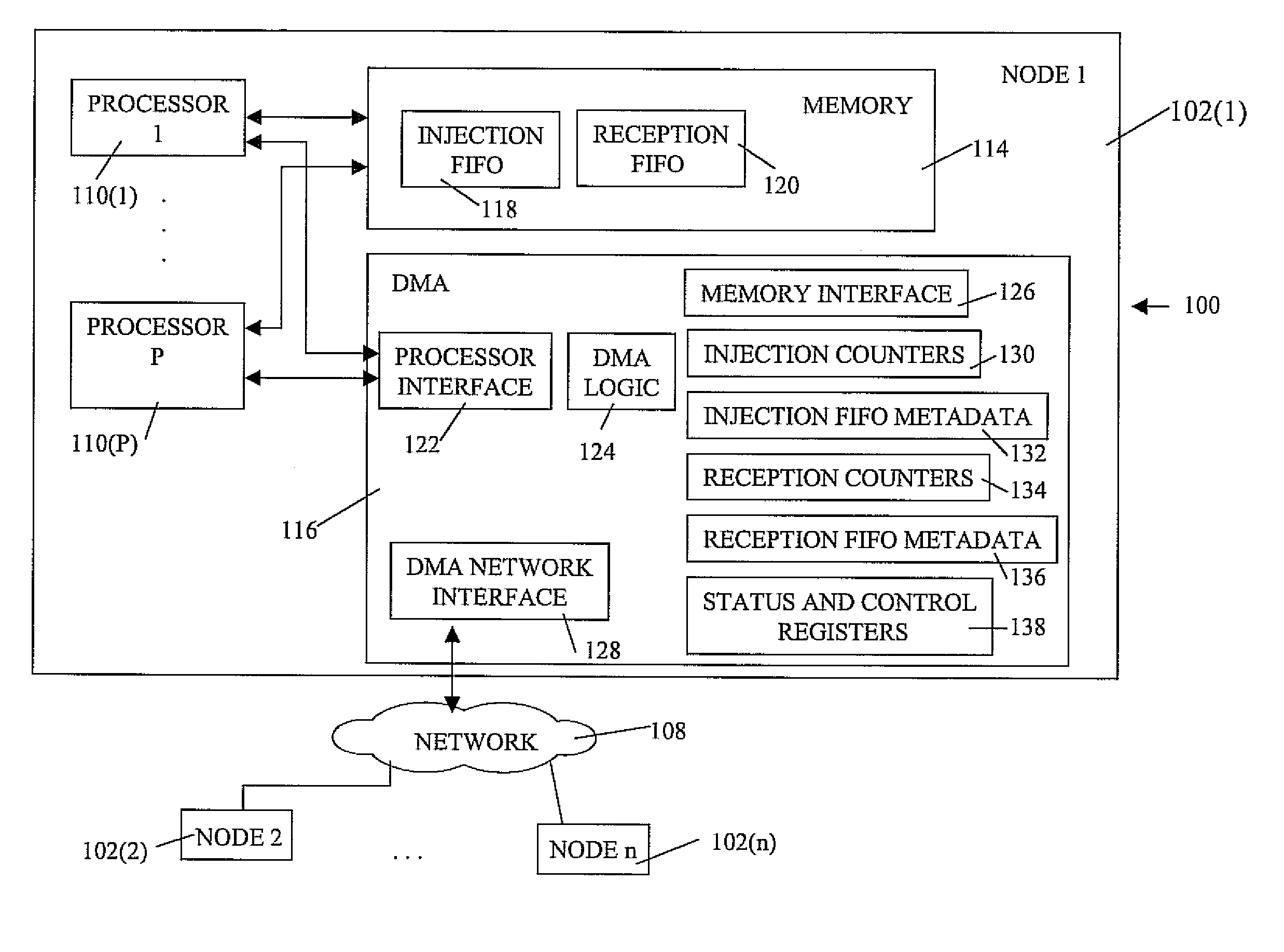

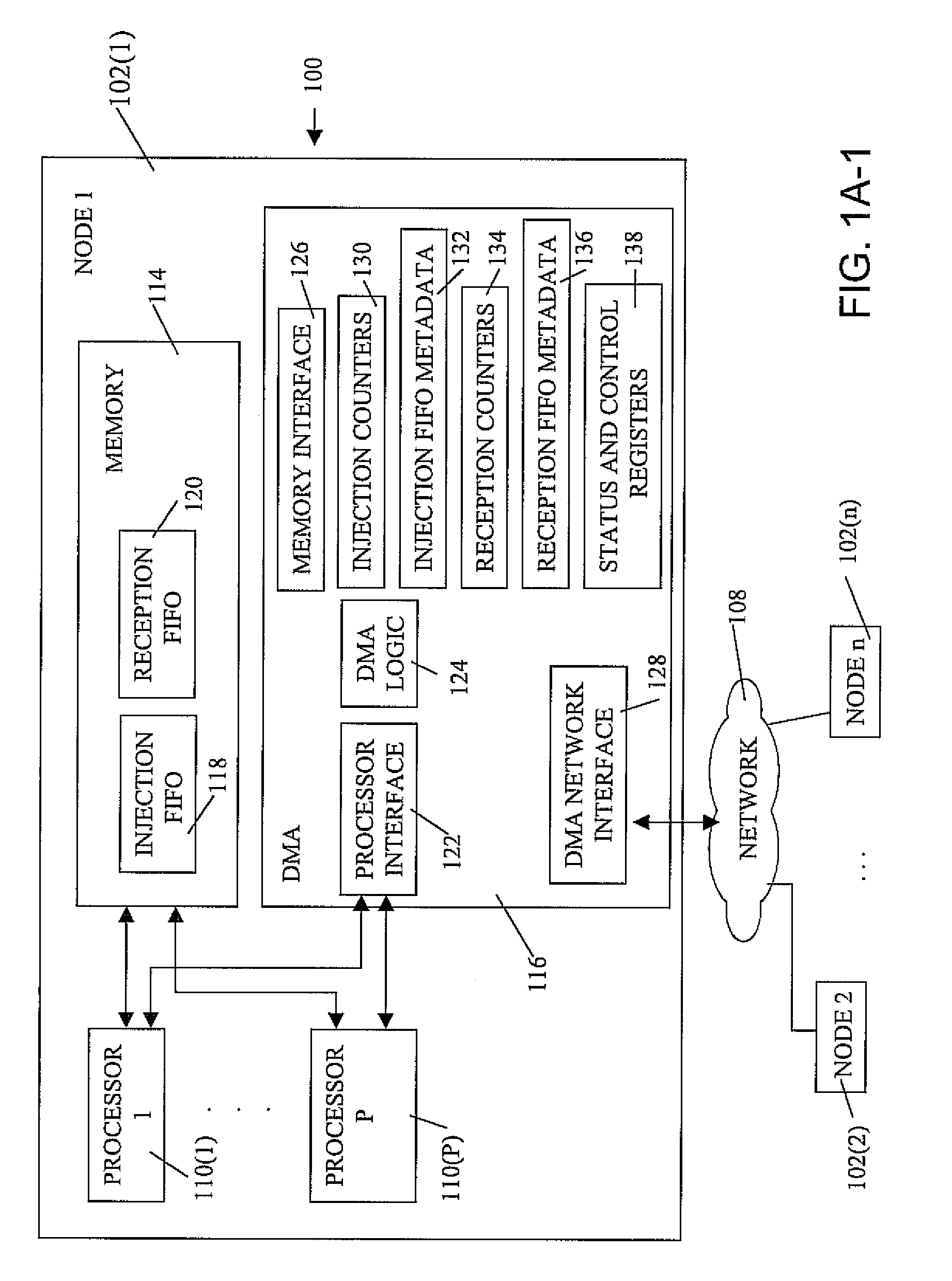

Massively parallel supercomputer

InactiveUS7555566B2Massive level of scalabilityUnprecedented level of scalabilityError preventionProgram synchronisationPacket communicationSupercomputer

A novel massively parallel supercomputer of hundreds of teraOPS-scale includes node architectures based upon System-On-a-Chip technology, i.e., each processing node comprises a single Application Specific Integrated Circuit (ASIC). Within each ASIC node is a plurality of processing elements each of which consists of a central processing unit (CPU) and plurality of floating point processors to enable optimal balance of computational performance, packaging density, low cost, and power and cooling requirements. The plurality of processors within a single node may be used individually or simultaneously to work on any combination of computation or communication as required by the particular algorithm being solved or executed at any point in time. The system-on-a-chip ASIC nodes are interconnected by multiple independent networks that optimally maximizes packet communications throughput and minimizes latency. In the preferred embodiment, the multiple networks include three high-speed networks for parallel algorithm message passing including a Torus, Global Tree, and a Global Asynchronous network that provides global barrier and notification functions. These multiple independent networks may be collaboratively or independently utilized according to the needs or phases of an algorithm for optimizing algorithm processing performance. For particular classes of parallel algorithms, or parts of parallel calculations, this architecture exhibits exceptional computational performance, and may be enabled to perform calculations for new classes of parallel algorithms. Additional networks are provided for external connectivity and used for Input / Output, System Management and Configuration, and Debug and Monitoring functions. Special node packaging techniques implementing midplane and other hardware devices facilitates partitioning of the supercomputer in multiple networks for optimizing supercomputing resources.

Owner:IBM CORP

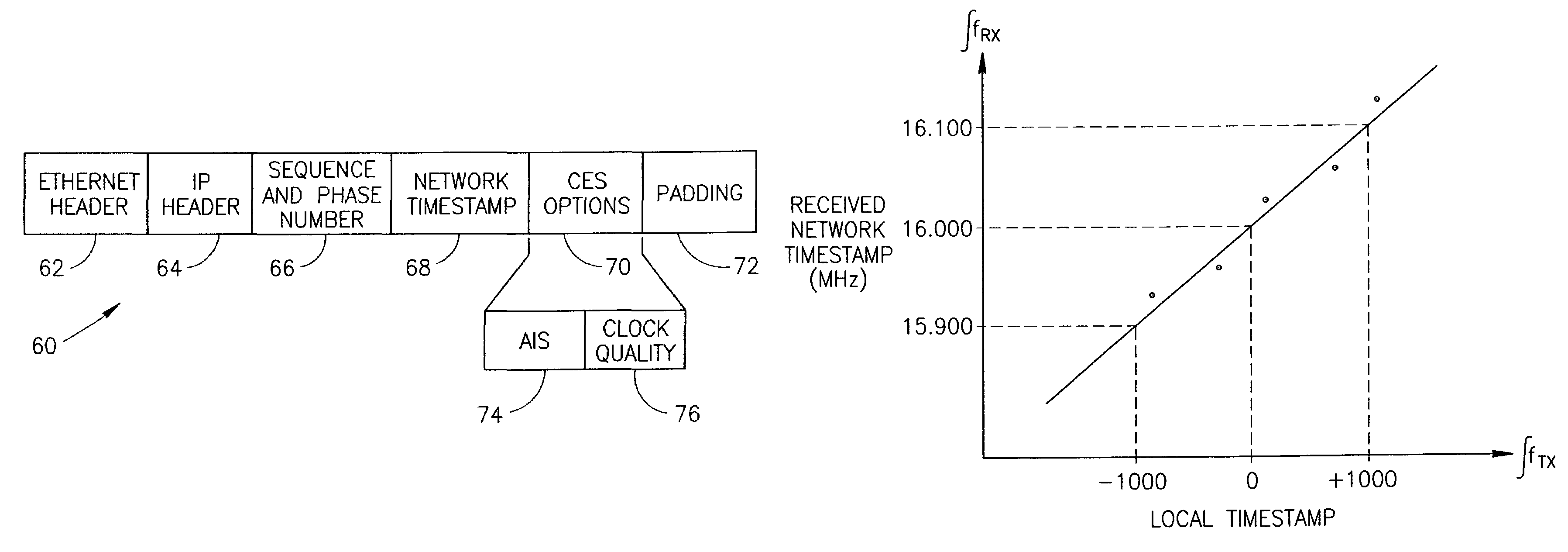

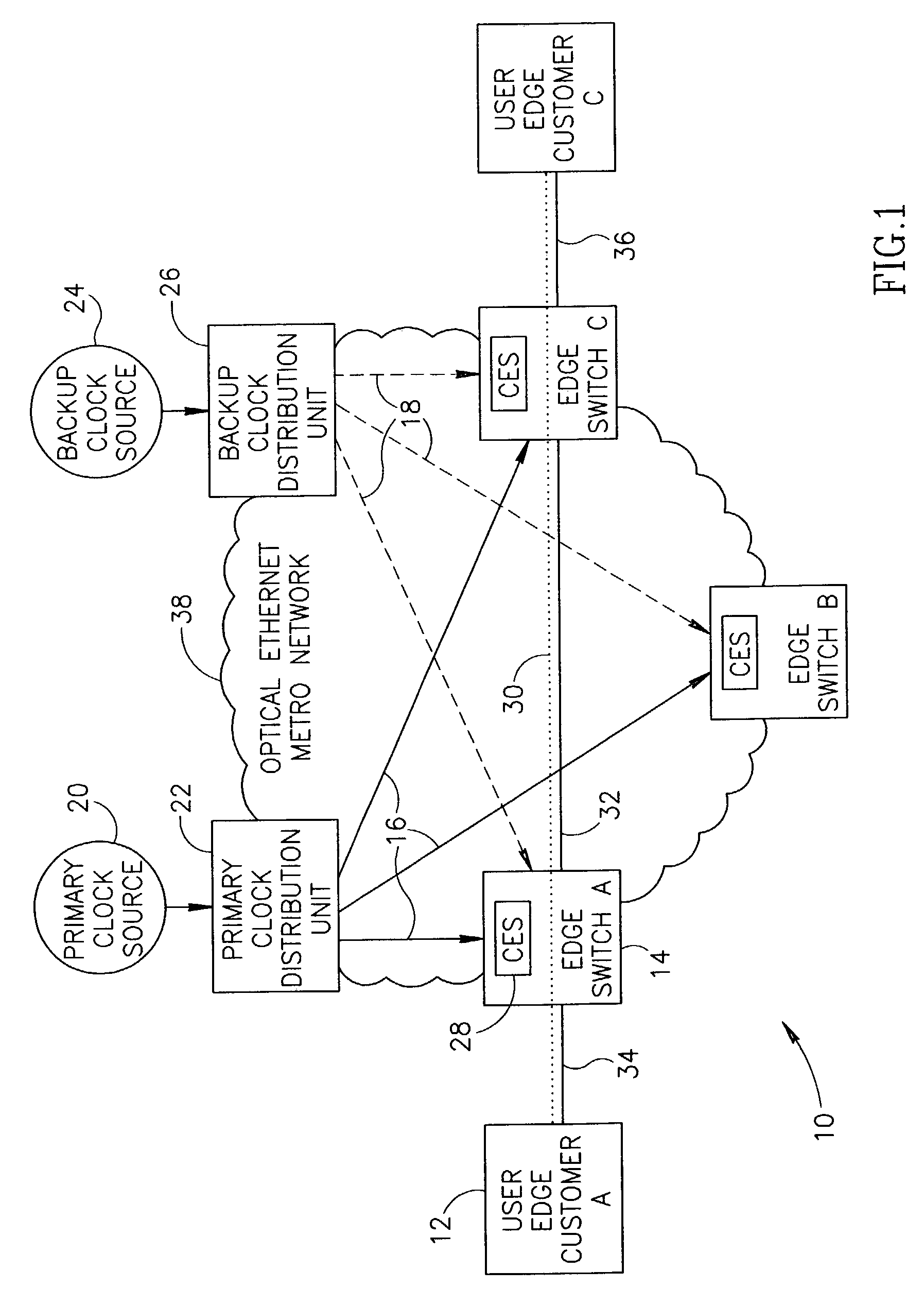

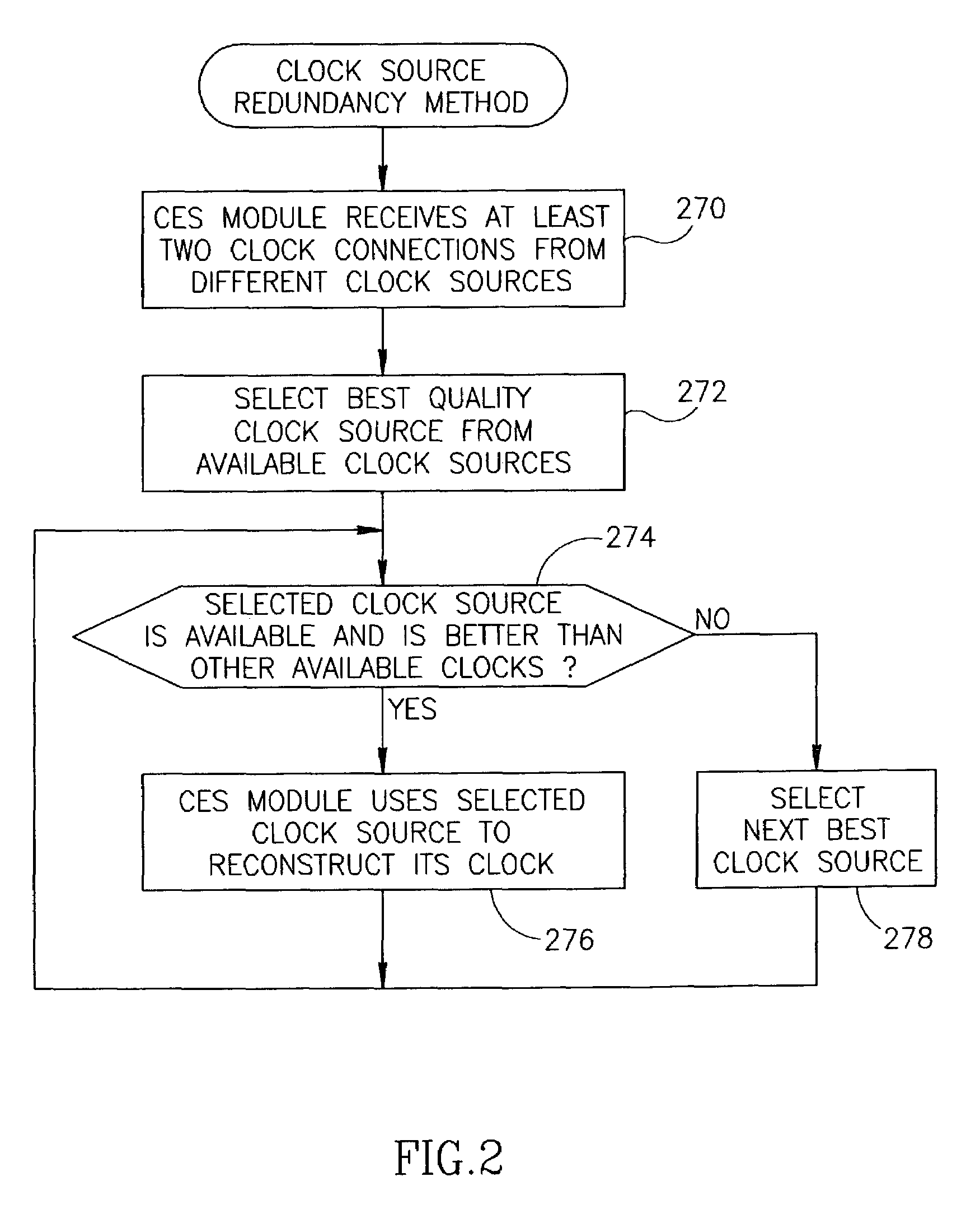

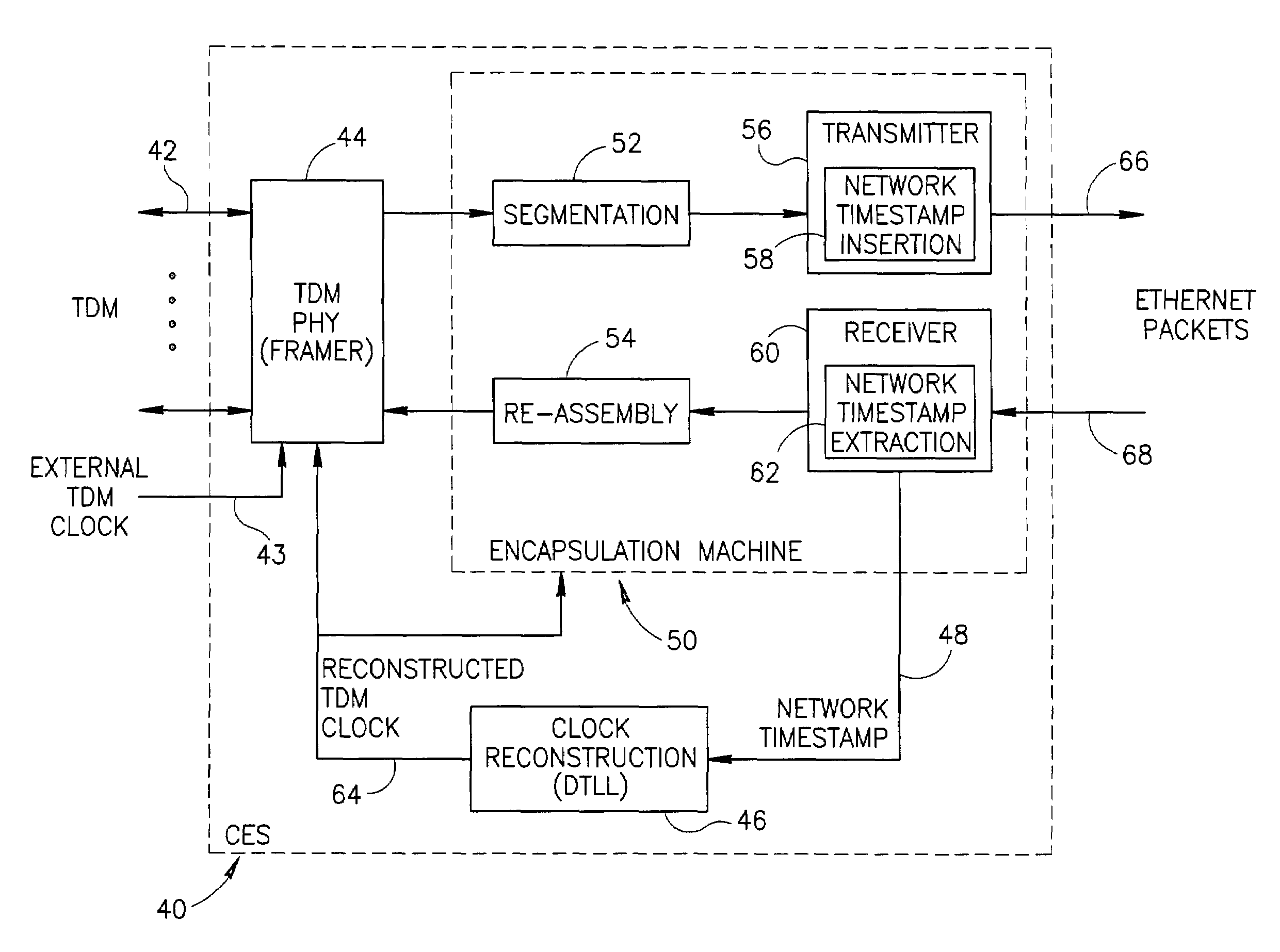

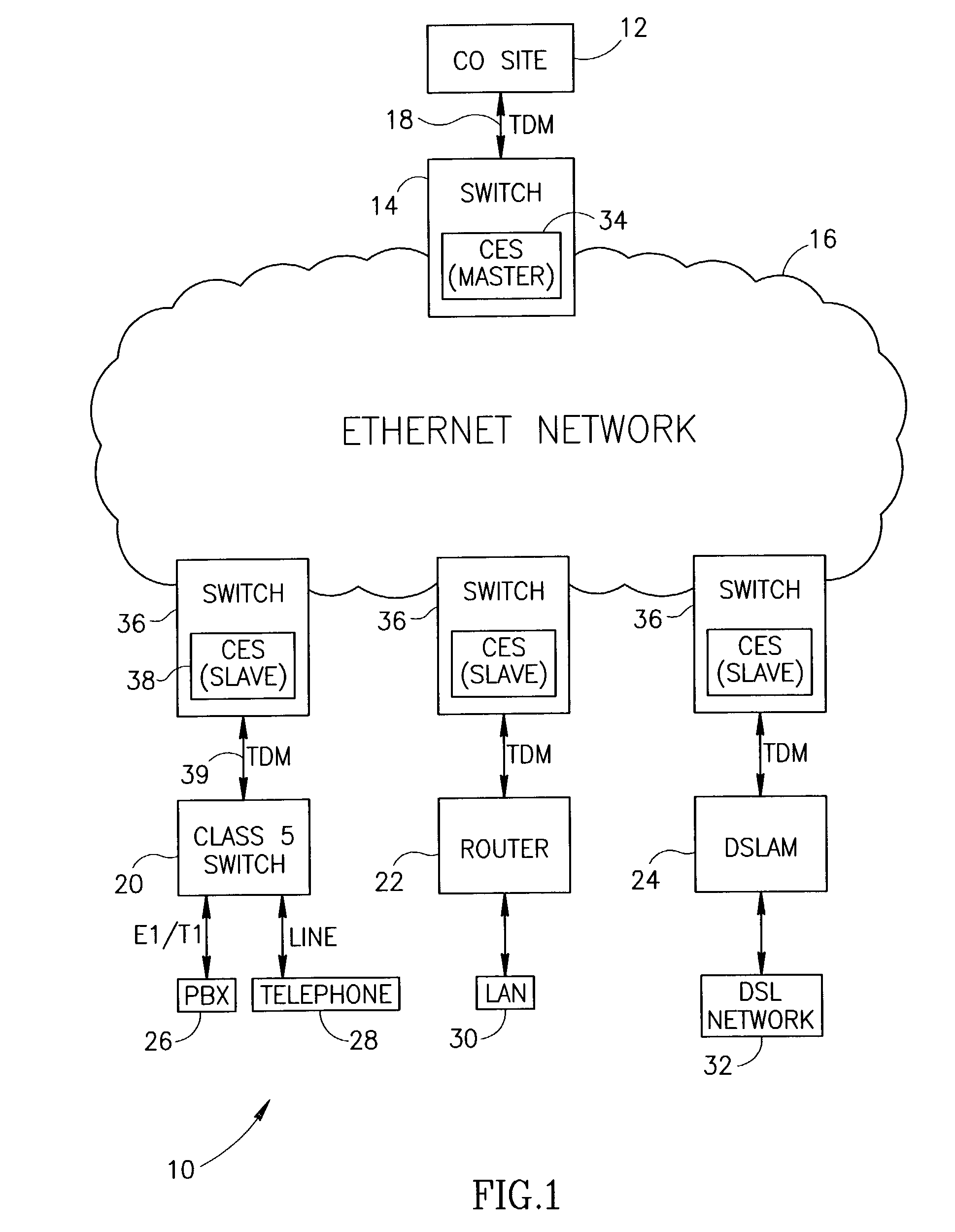

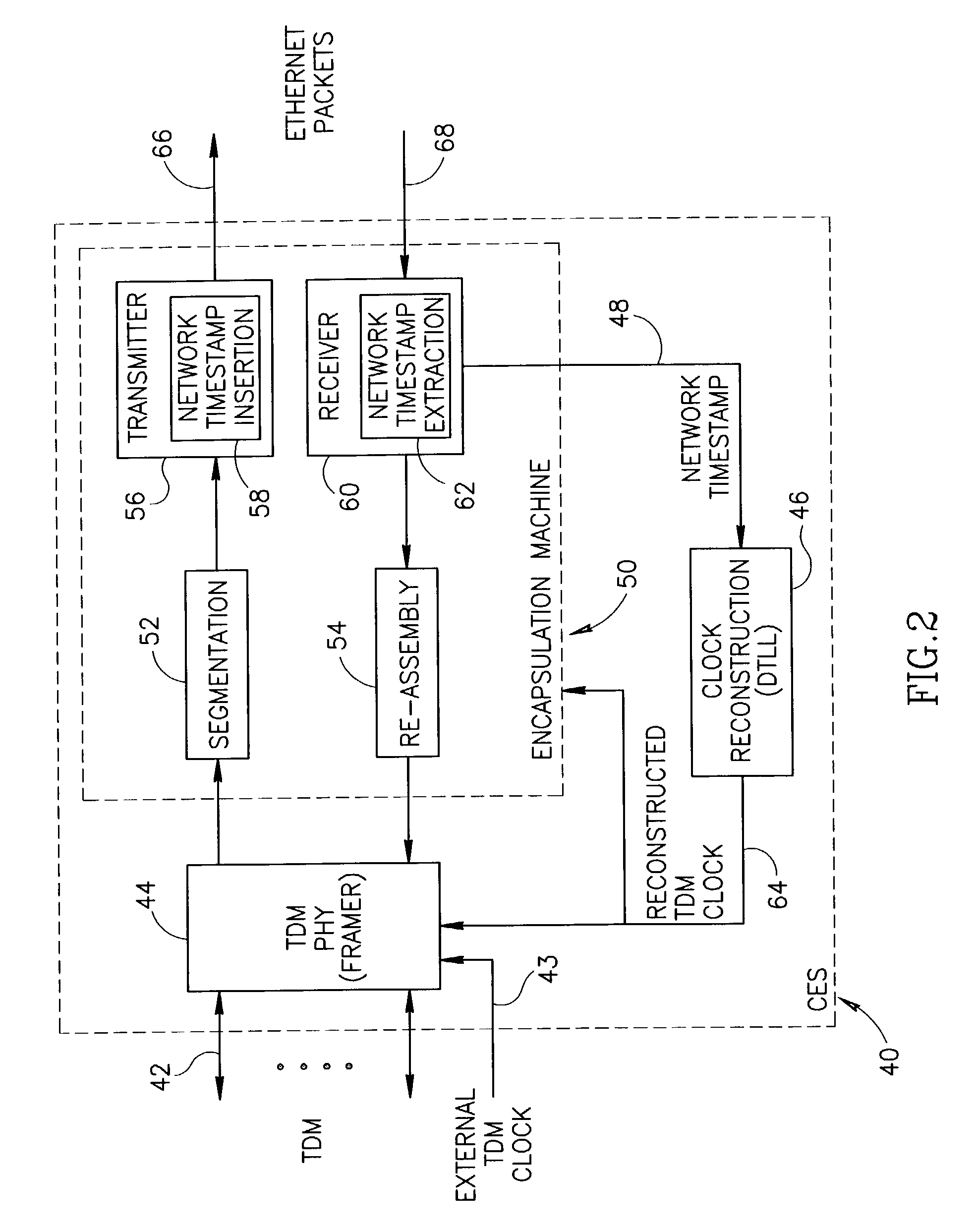

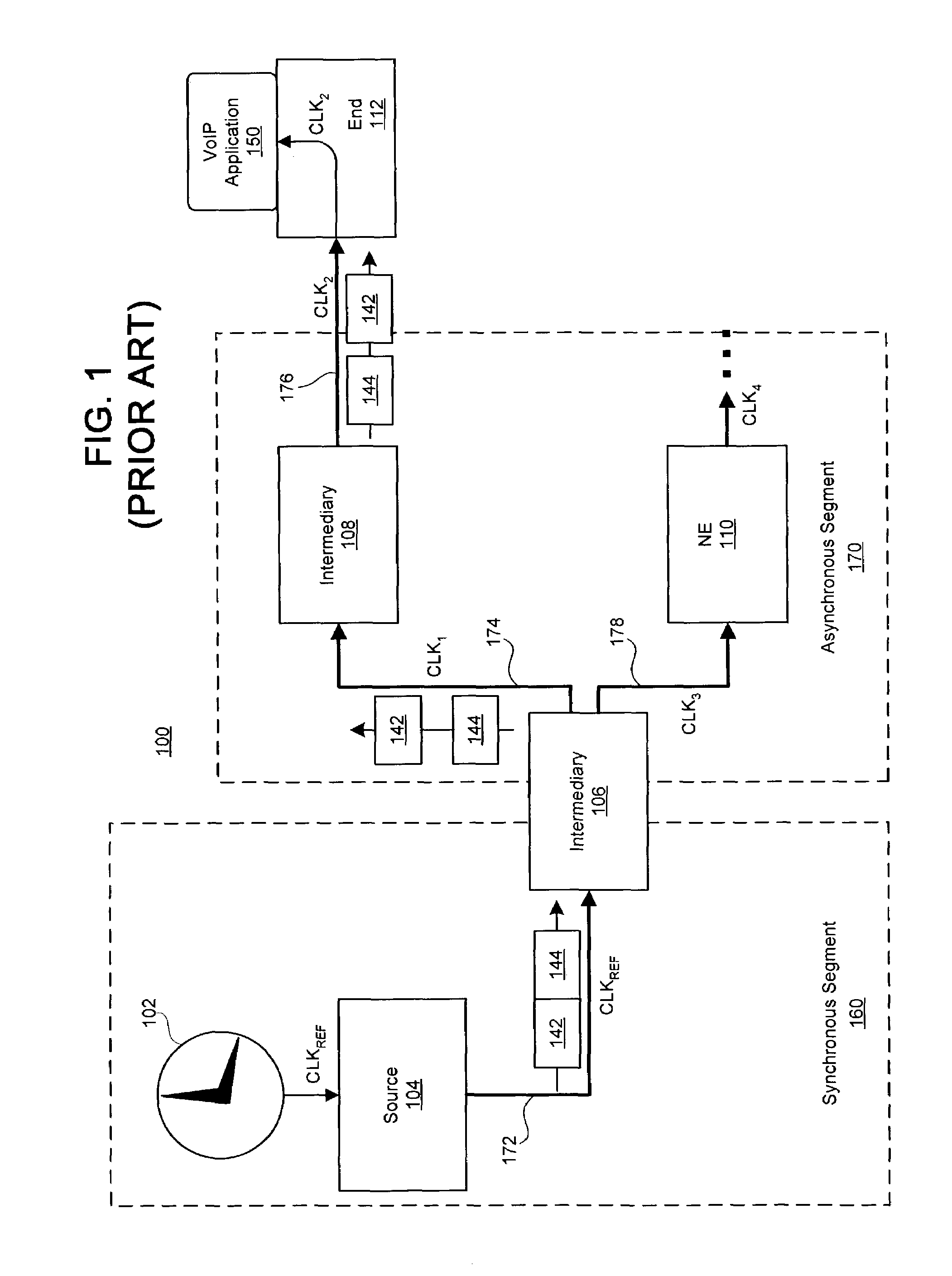

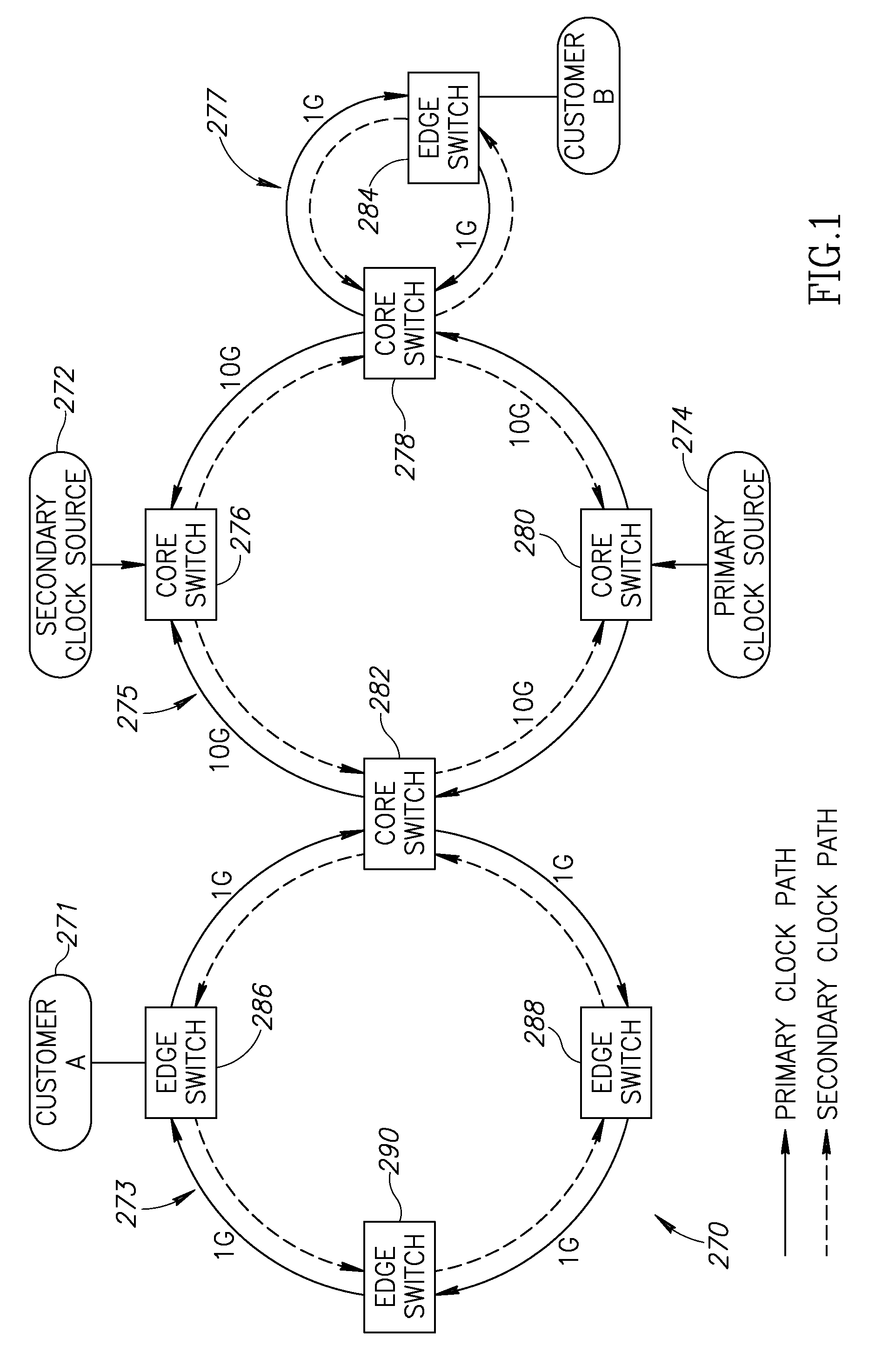

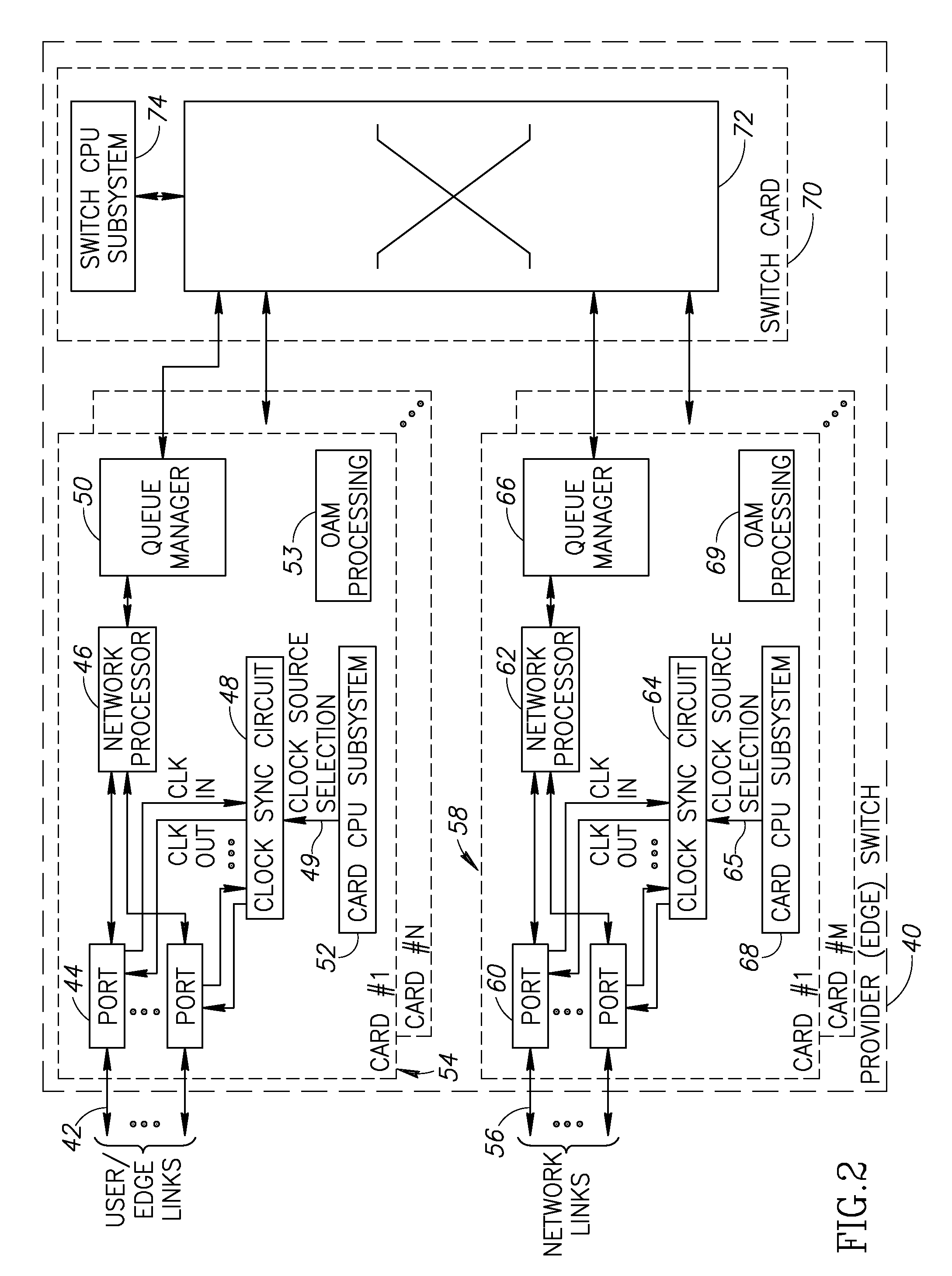

Centralized clock synchronization for time division multiplexed traffic transported over Ethernet networks

InactiveUS7613212B1Improve accuracyImprove clock reliabilityTime-division multiplexTransmissionTraffic capacityAsynchronous network

A centralized clock distribution mechanism for synchronous TDM communications traffic transported over asynchronous networks such as Ethernet networks. The centralized clocking mechanism of the present invention distributes a high accuracy central clock source to a plurality of CES modules over an Ethernet network. Clock synchronization information based on a high quality clock reference source is distributed to circuit emulation service (CES) modules in the network. CES modules receive the clock synchronization information and use it to reconstruct a local clock. A plurality of clock distributors provide clock redundancy whereby each CES module selects the best clock source to use in reconstructing the local clock.

Owner:RPX CORP +1

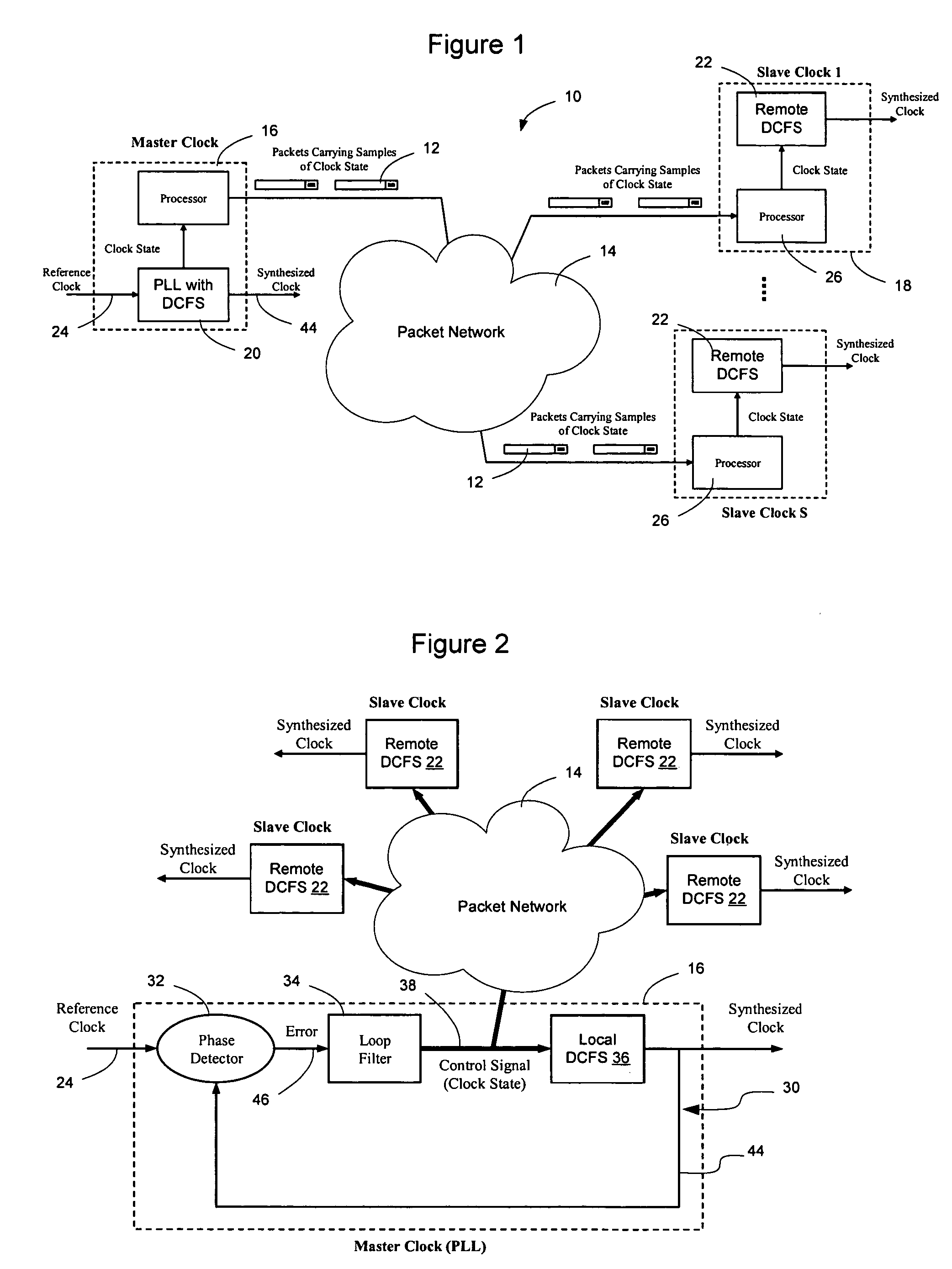

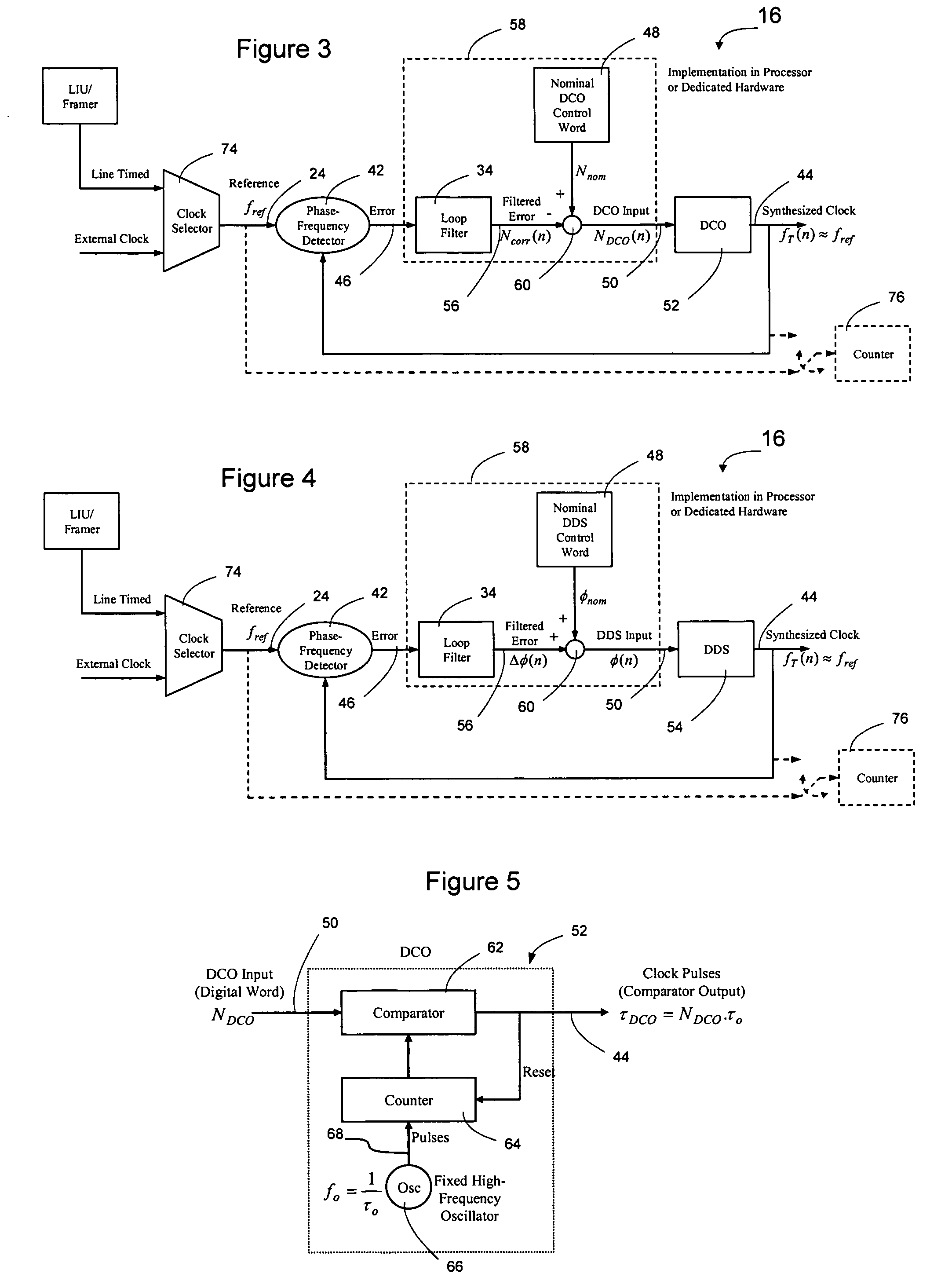

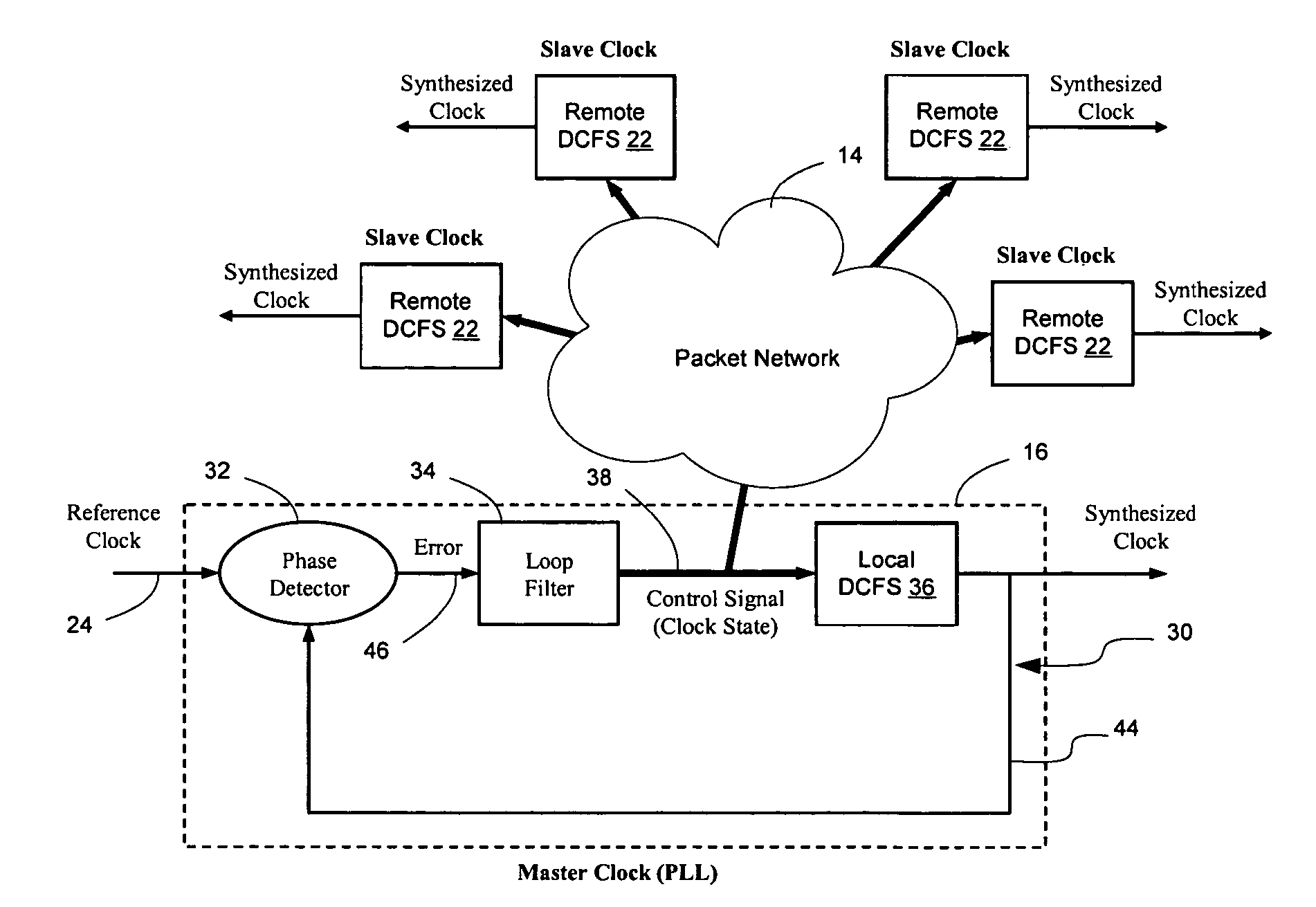

Method and apparatus for synchronizing clock timing between network elements

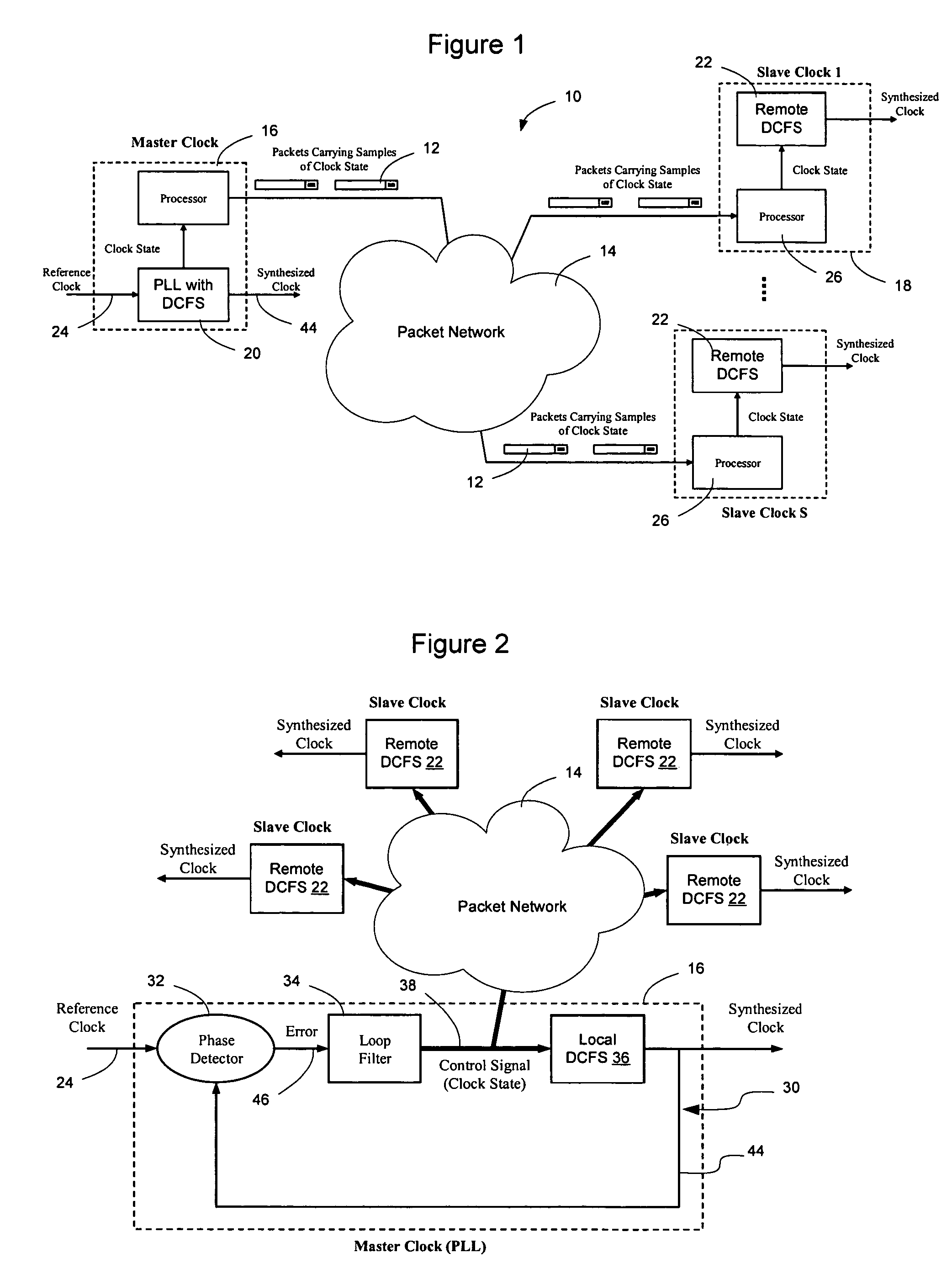

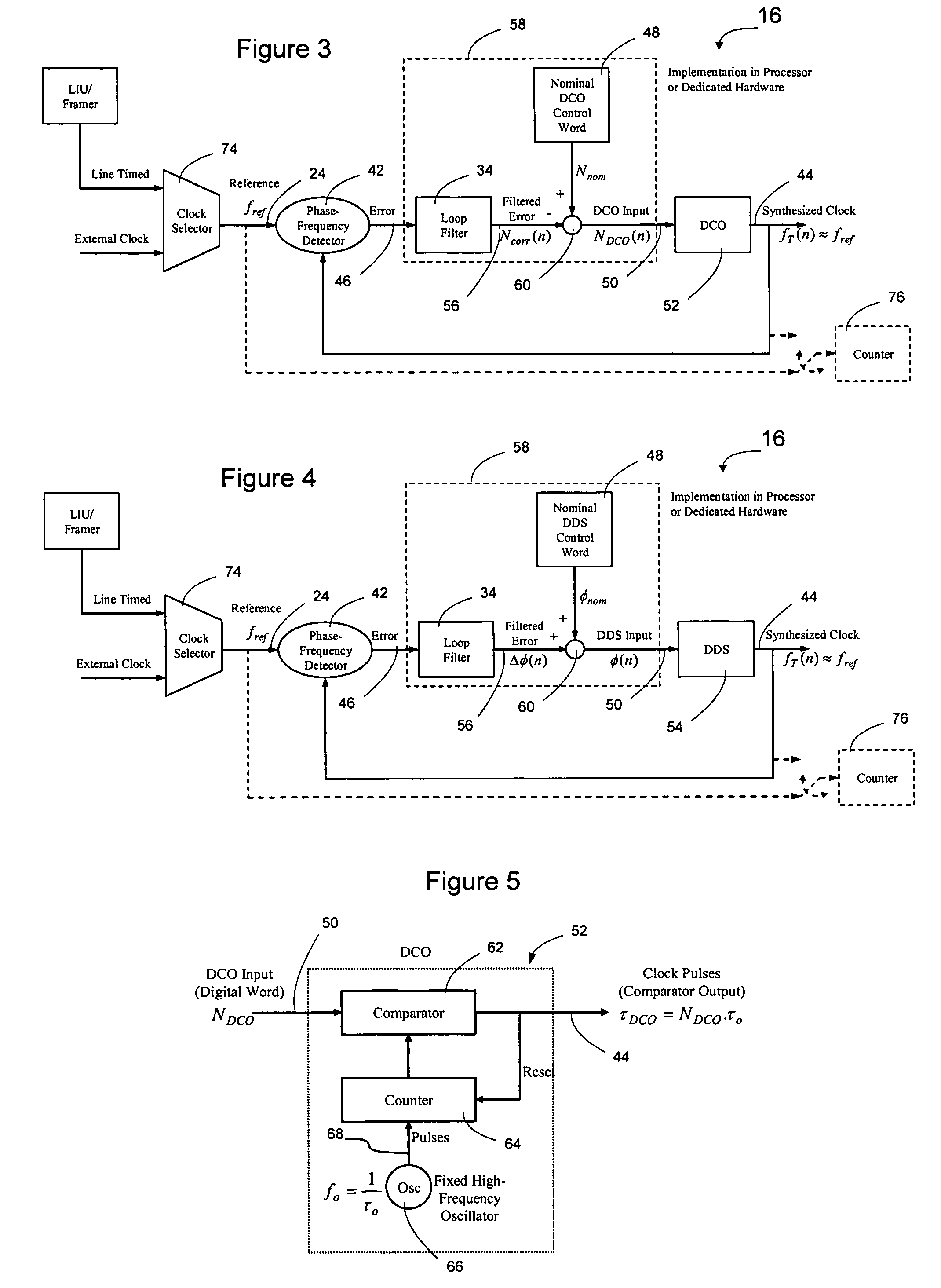

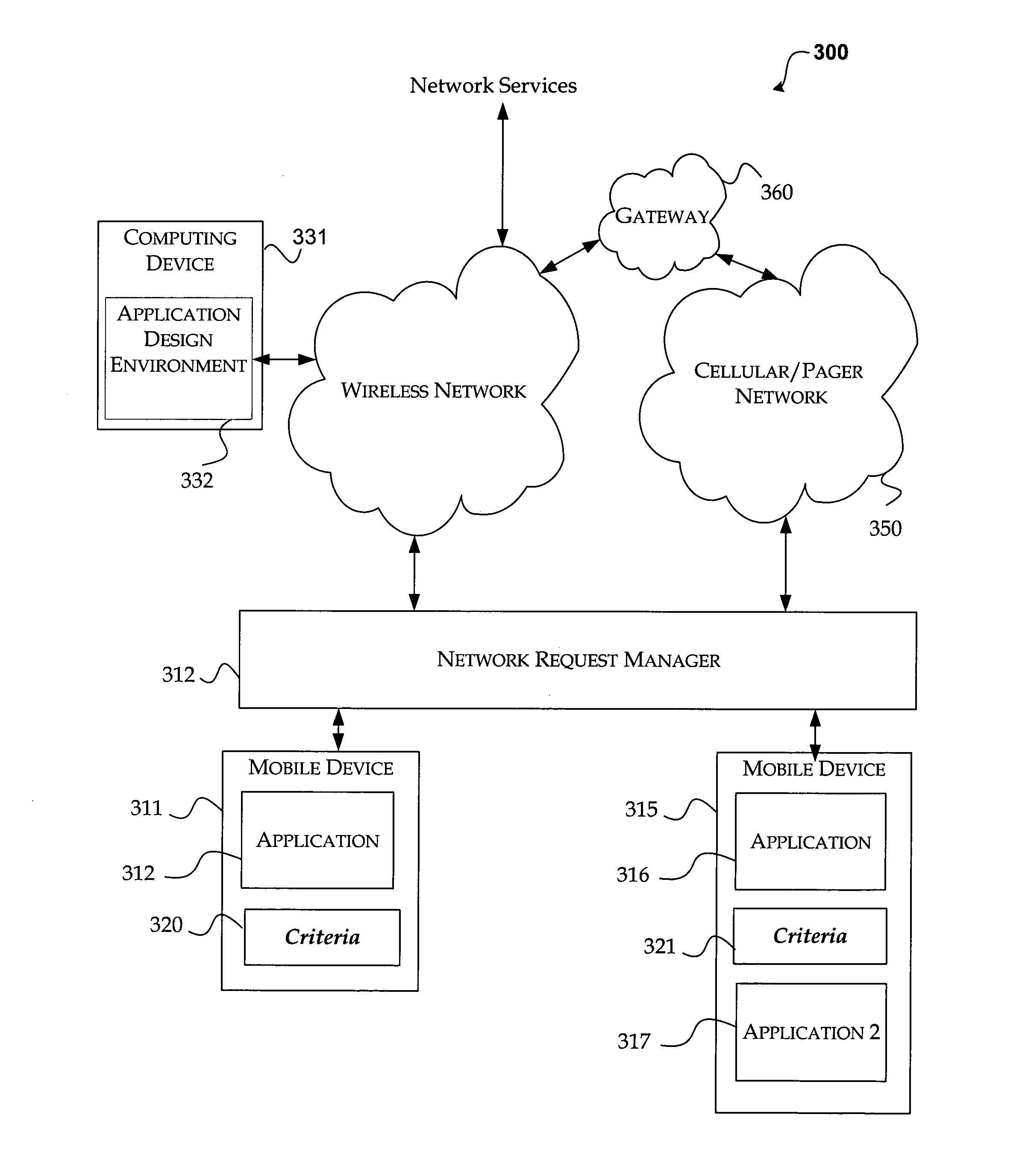

Network elements may be synchronized over an asynchronous network by implementing a master clock as an all digital PLL that includes a Digitally Controlled Frequency Selector (DCFS), the output frequency of which may be directly controlled through the input of a control word. The PLL causes the control word input to the master DCFS to be adjusted to cause the output of the master DCFS to lock onto a reference frequency. Information associated with the control word is transmitted from the master clock to the slave clocks which are also implemented as DCFSs. By using the transmitted information to recreate the master control word, the slaves may be made to assume the same state as the master DCFS without requiring the slaves to be implemented as PLLs. The DCFS may be formed as a digitally controlled oscillator (DCO) or as a Direct Digital Synthesizer (DDS).

Owner:CIENA

Audio communications using devices with different capabilities

InactiveUS20060041616A1Facilitates distributed collaborationCompact integrationMultiple digital computer combinationsOffice automationComputer hardwareWide area

Owner:PRAGMATUS AV

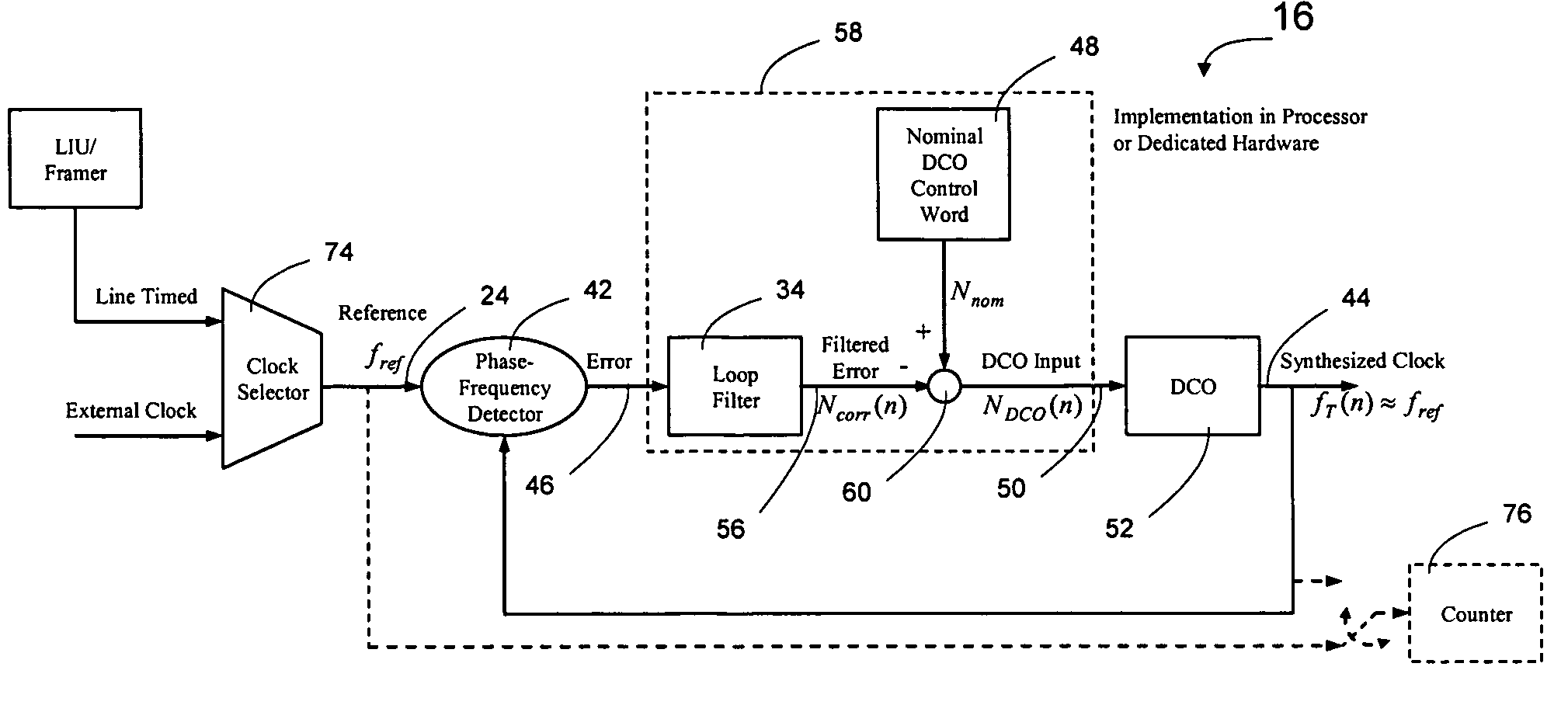

Clock reconstruction for time division multiplexed traffic transported over asynchronous ethernet networks

A clock reconstruction mechanism for synchronous TDM communications traffic transported over asynchronous networks such as Ethernet networks. The invention is applicable to edge switches in Metropolitan Area Networks (MANs) that transport legacy TDM traffic using a Circuit Emulation Services (CES) module whereby TDM traffic is encapsulated and transported across the Ethernet network where it is de-encapsulated and clocked out to the destination. The mechanism encapsulates the input TDM data stream into Ethernet packets and inserts a network timestamp within the packet. At the destination CES, a local timestamp is generated for each received packet as it is received. The network timestamp is extracted and input along with the local timestamp to a Digital Time Locked Loop (DTLL) which is operative to accurately reconstruct the original transmit TDM clock. The filter in the DTLL performs a Least Squares Regression (LSR) algorithm and Infinite Impulse Response (IIR) filter algorithm to generate a clock control signal for adjusting the clock generated.

Owner:VENTURE LENDING & LEASING III +1

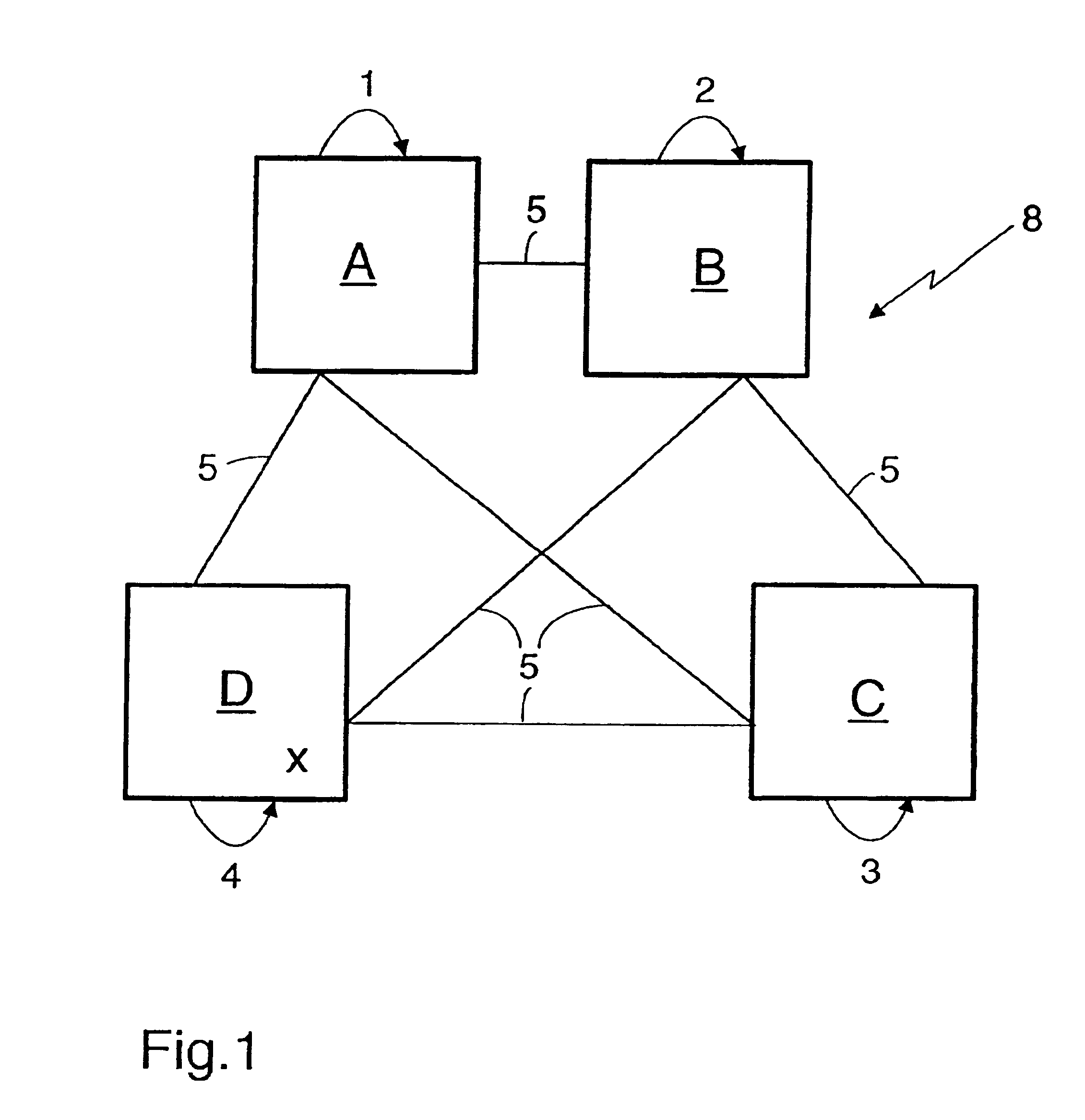

Agreement and atomic broadcast in asynchronous networks

InactiveUS20020129087A1Reduce the numberSmall sizeSpecial service provision for substationUser identity/authority verificationAsynchronous networkAtomic broadcast

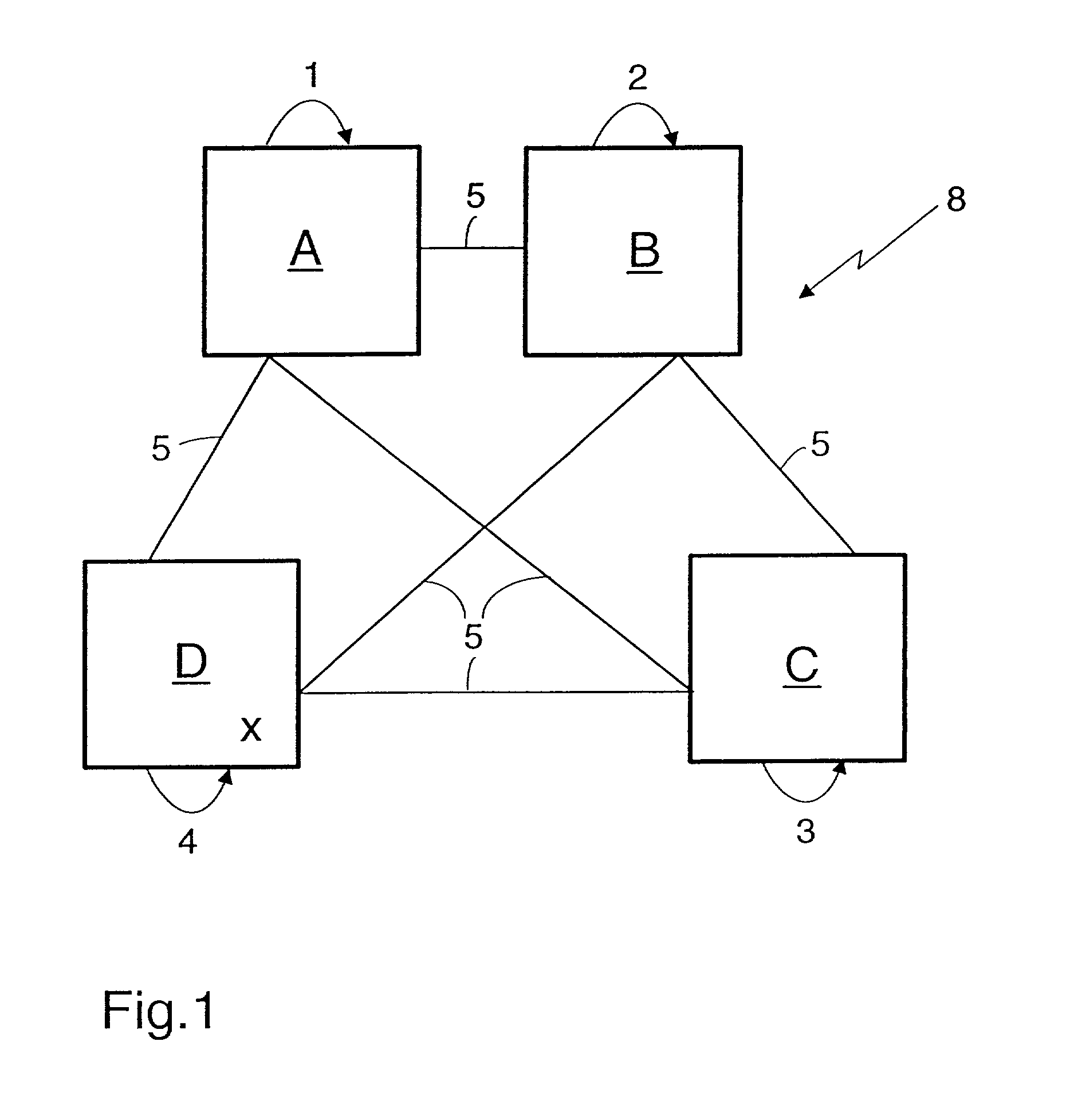

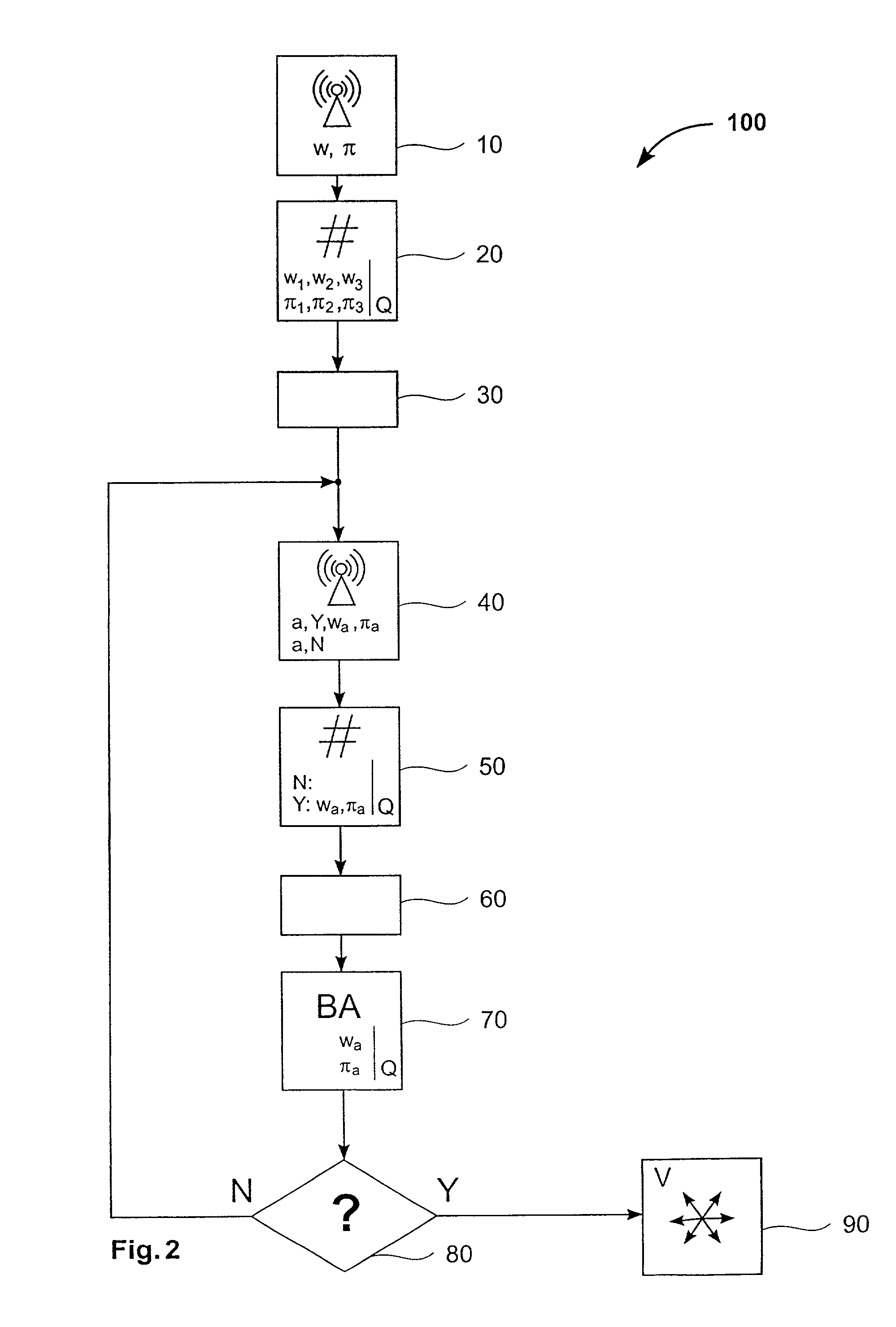

Methods and apparatus for achieving agreement among participating network devices in an asynchronous network for deciding on a common value is disclosed, whereby the common value is validated by a justification and both together satisfy a predetermined predicate. Moreover, a method for reliably broadcasting messages in an order within the asynchronous network is described. Up to one third or more of the participating network devices might be faulty in arbitrary ways.

Owner:IBM CORP

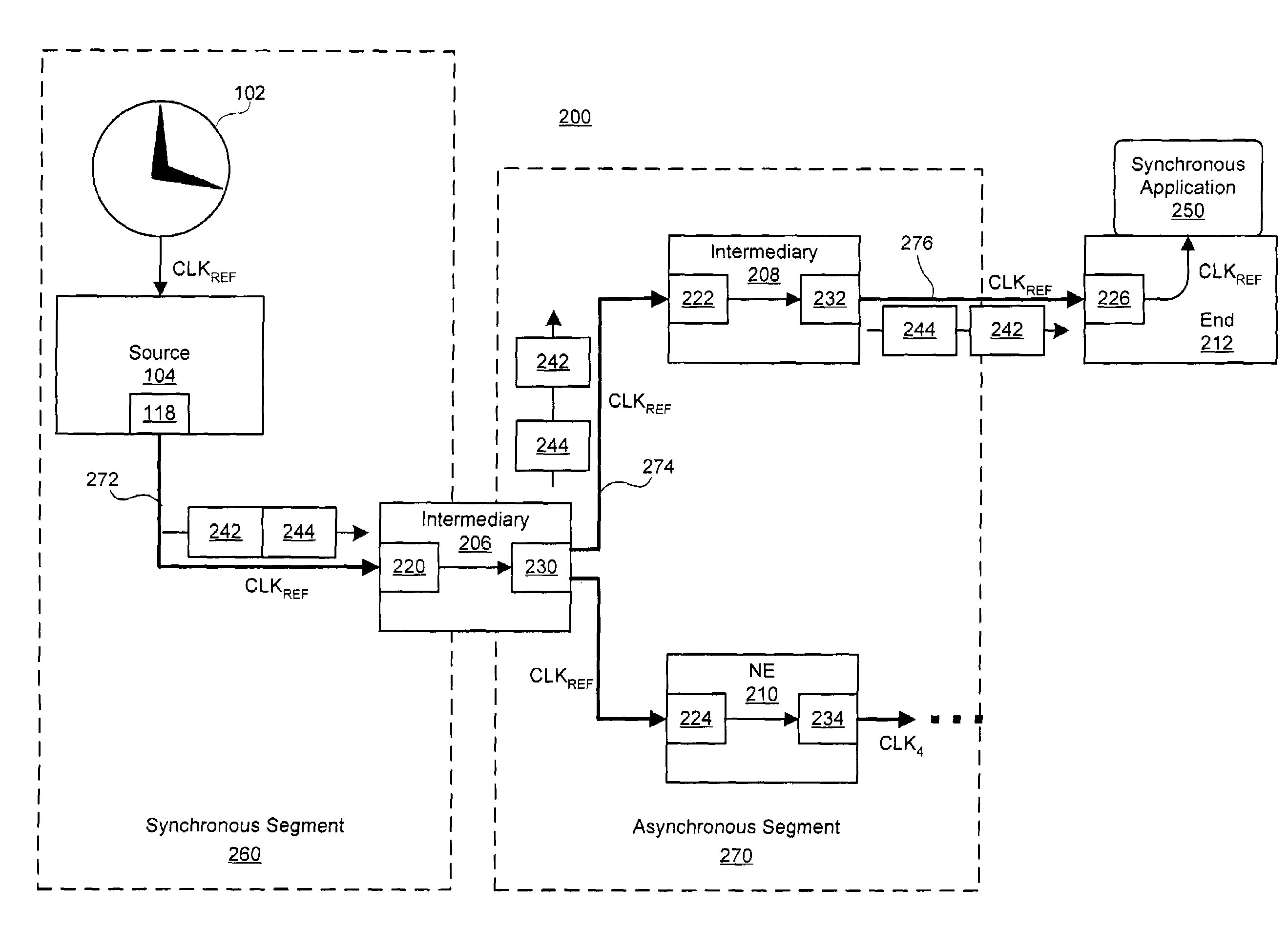

Method and system for link-based clock synchronization in asynchronous networks

InactiveUS7483450B1Guaranteed maximum utilizationTime-division multiplexSynchronising arrangementAsynchronous networkPhysical layer

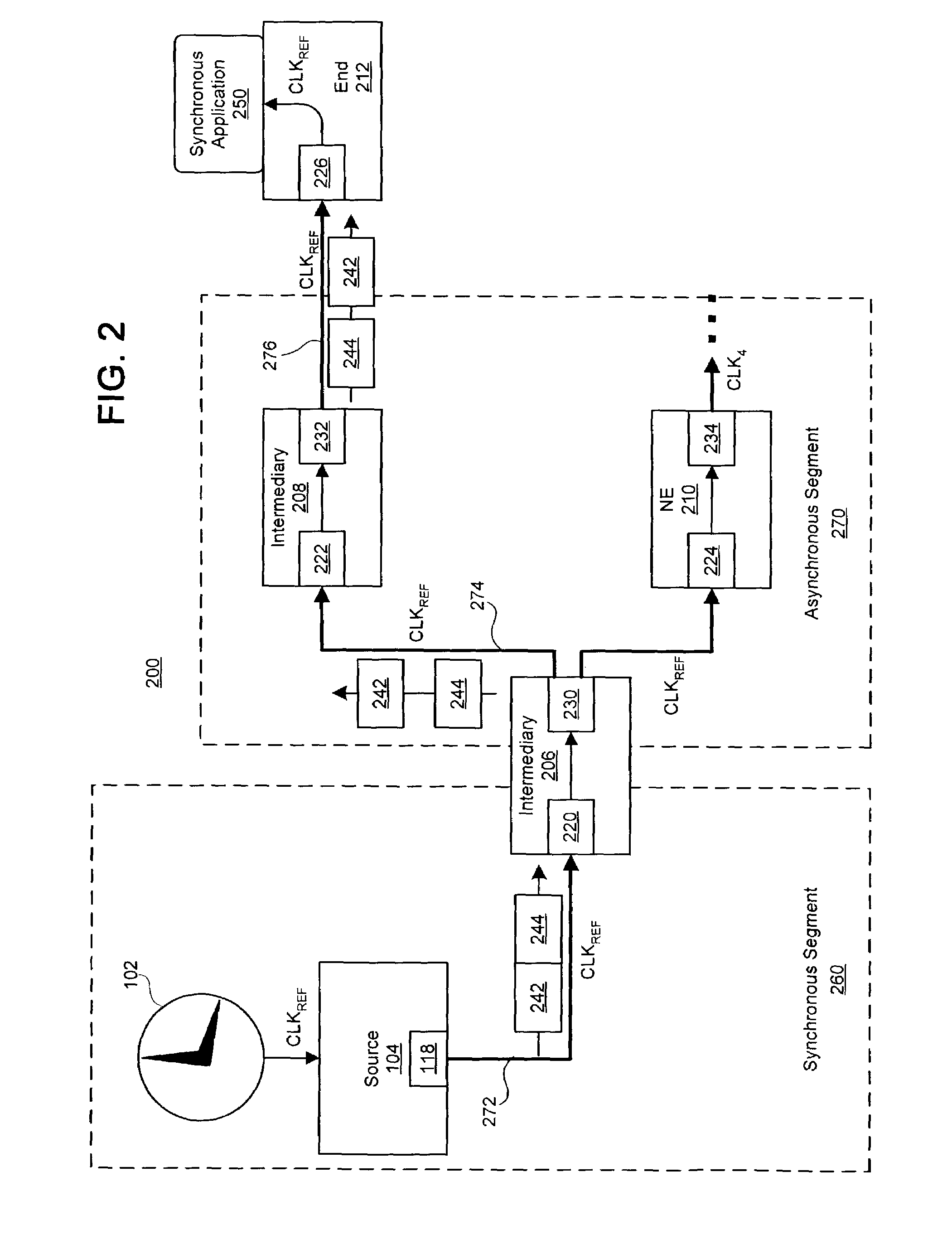

A system and method for clock synchronization in a network having one or more asynchronous data links is provided. A clock signal is propagated through, at the physical layer, a sequence of network devices linking a source network device to a destination network device of the network. Each asynchronous data link between the source network device and the destination network device is adapted to receive an incoming clock signal from the previous network device and then provide a clock signal synchronized to the received clock signal to the next network device of the sequence. At the same time, each network device of an asynchronous segment of the network can continue to transmit packets of data asynchronously. By locking the link-based frequency on a per link bases, the receiver clocks located at the edge of a network can be tied directly to a primary source located in the core network.

Owner:RPX CLEARINGHOUSE

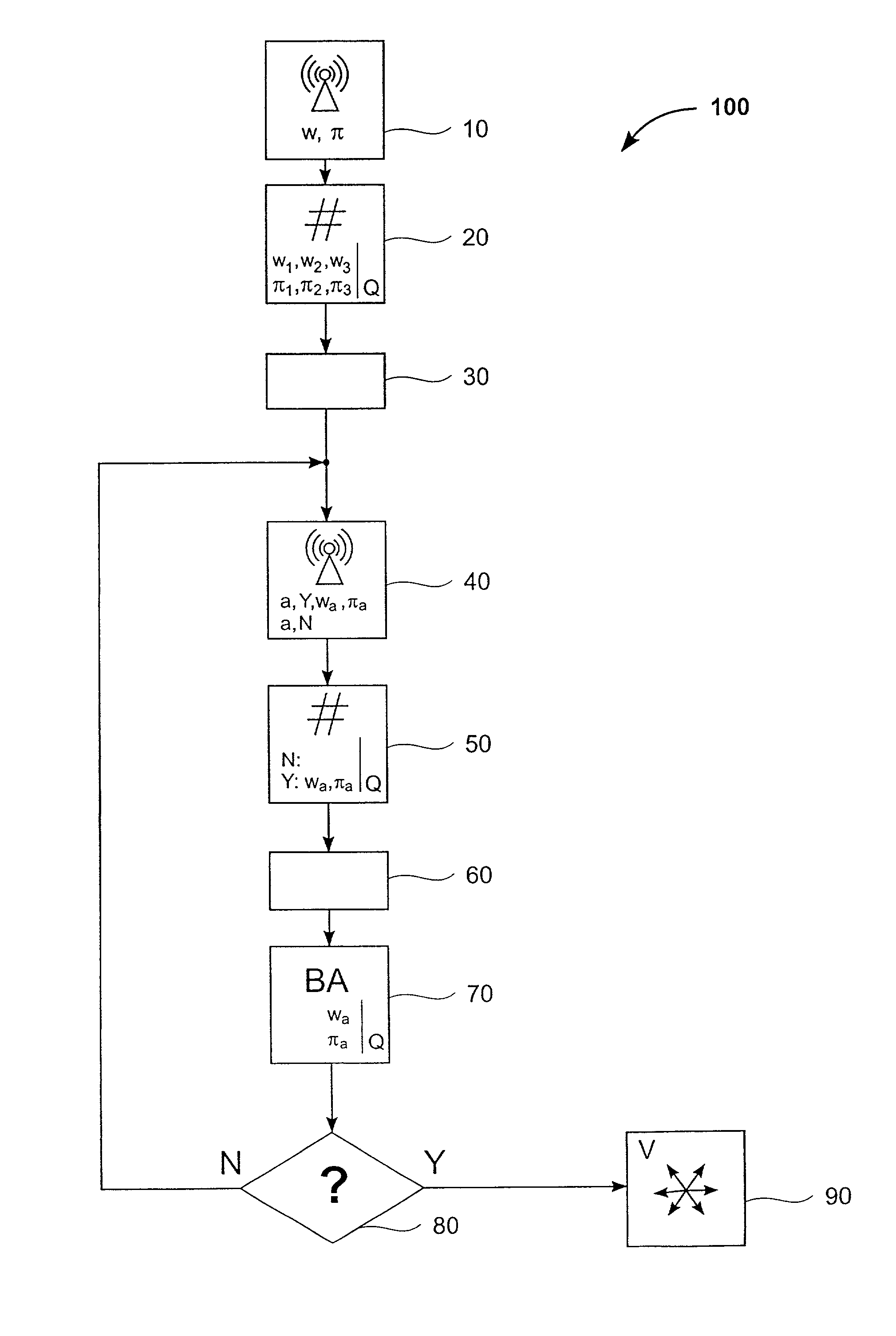

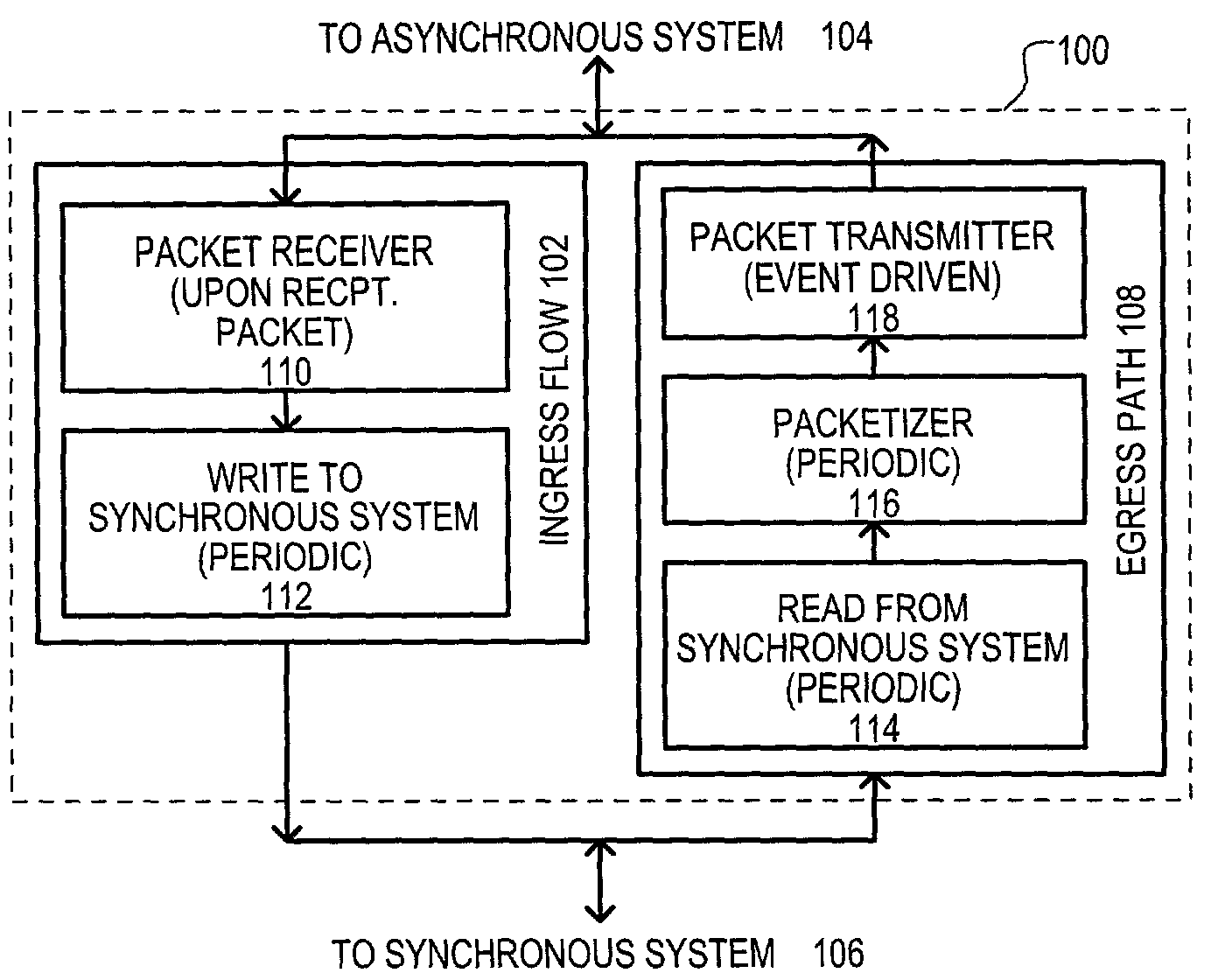

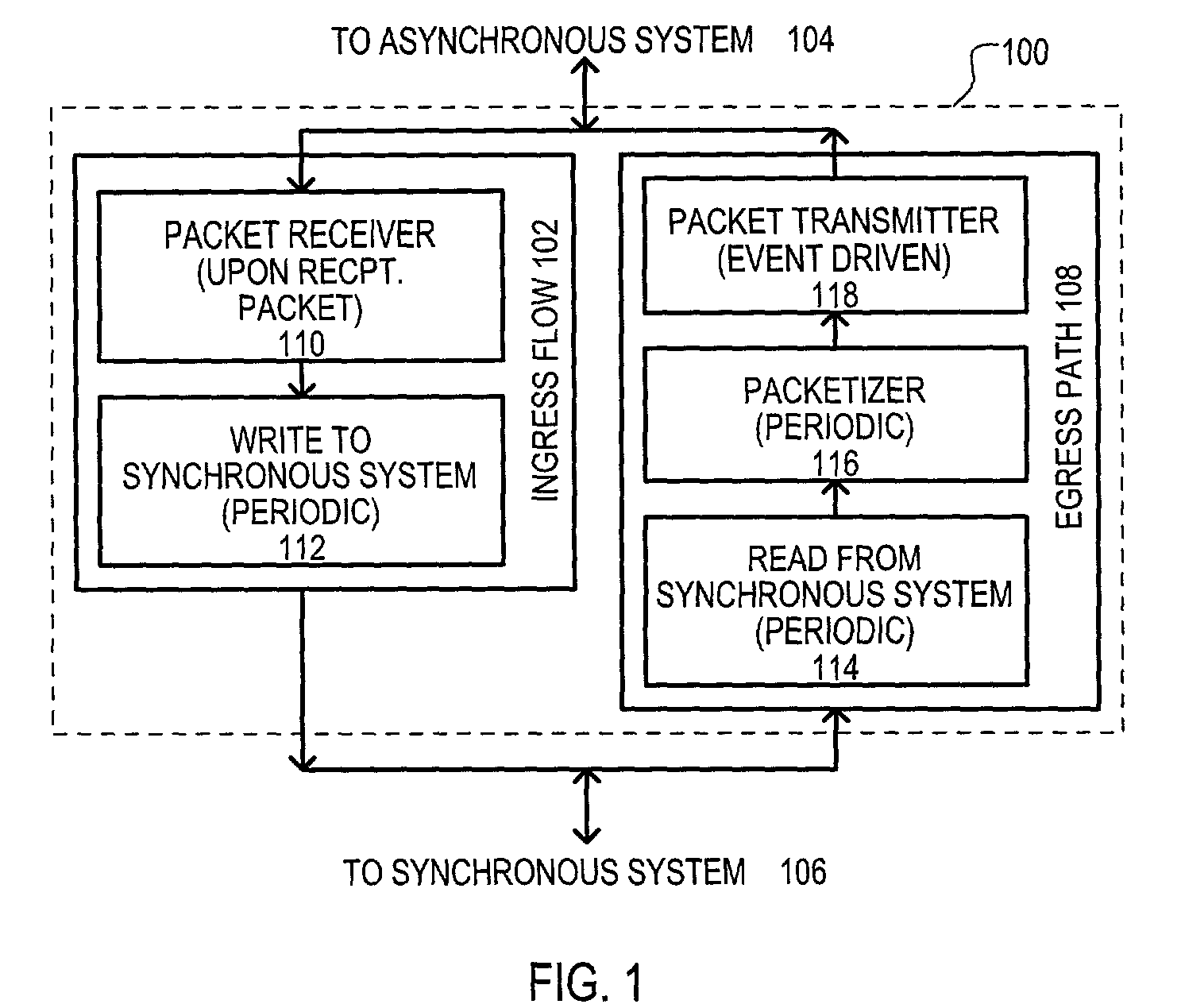

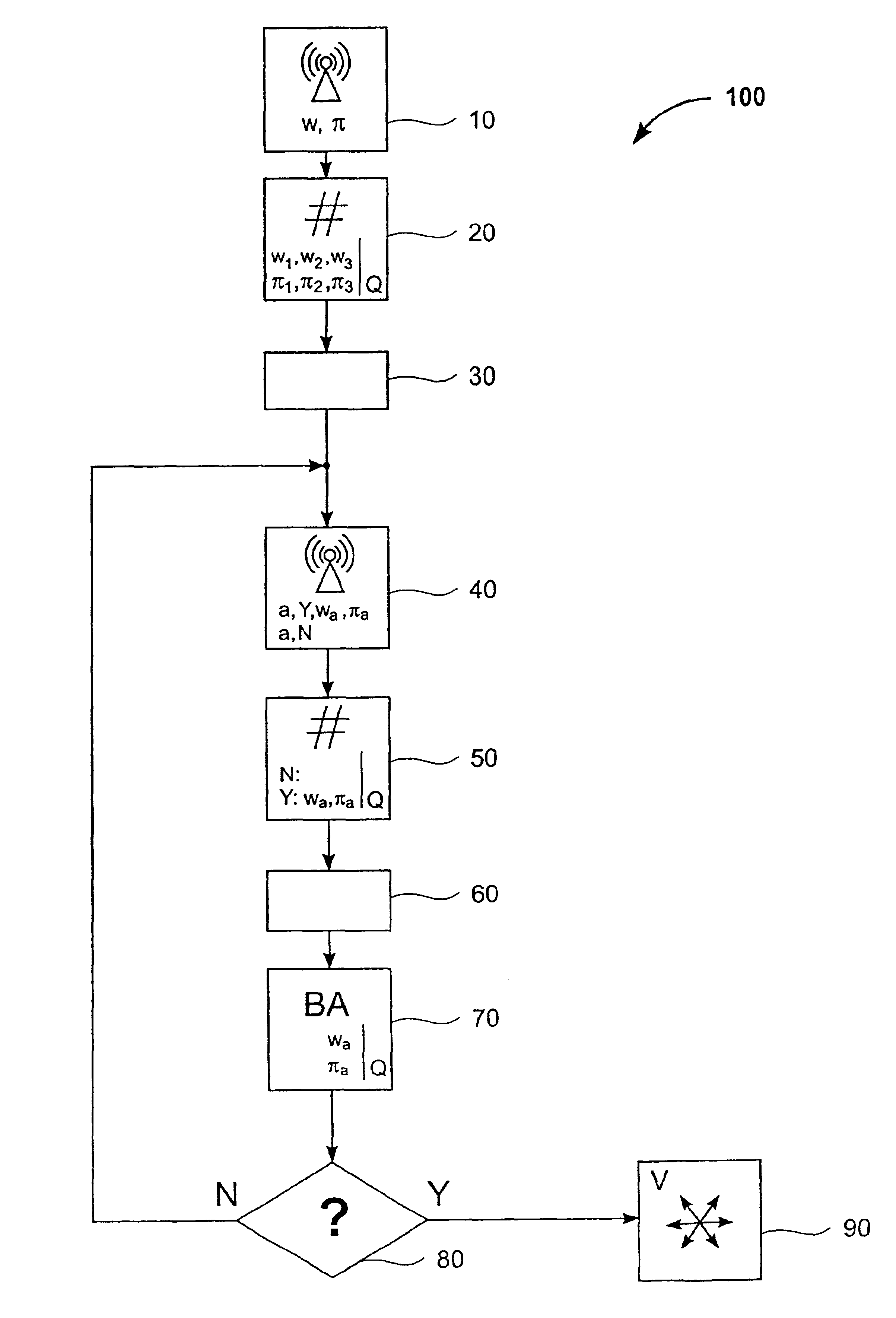

Media flow method for transferring real-time data between asynchronous and synchronous networks

InactiveUS7126957B1Time-division multiplexData switching by path configurationReal-time dataSynchronous motor

A system for transmitting real-time data between an asynchronous network (104) and a synchronous network (106) is disclosed. A method (100) may include an ingress path (102) for transmitting data from an asynchronous system (104) to a synchronous system (106), and an egress path (108) for transmitting data from a synchronous system (106) to an asynchronous system (104). An ingress path (102) may include a packet receiver (110) and write to synchronous system (112) steps. An egress path (108) may include read from synchronous system (114), packetizer (116), and packet transmitter (118) steps.

Owner:UTSTARCOM INC

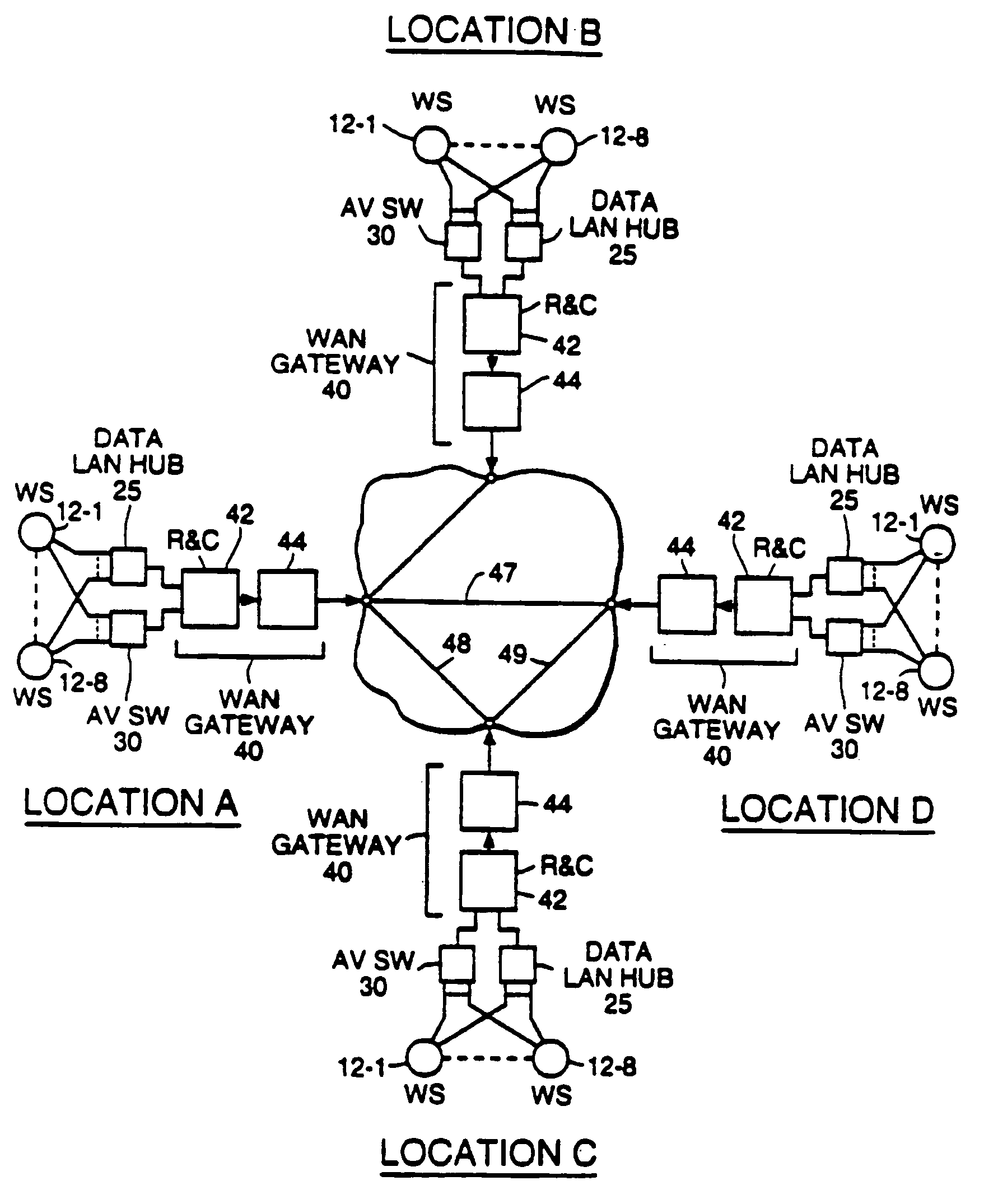

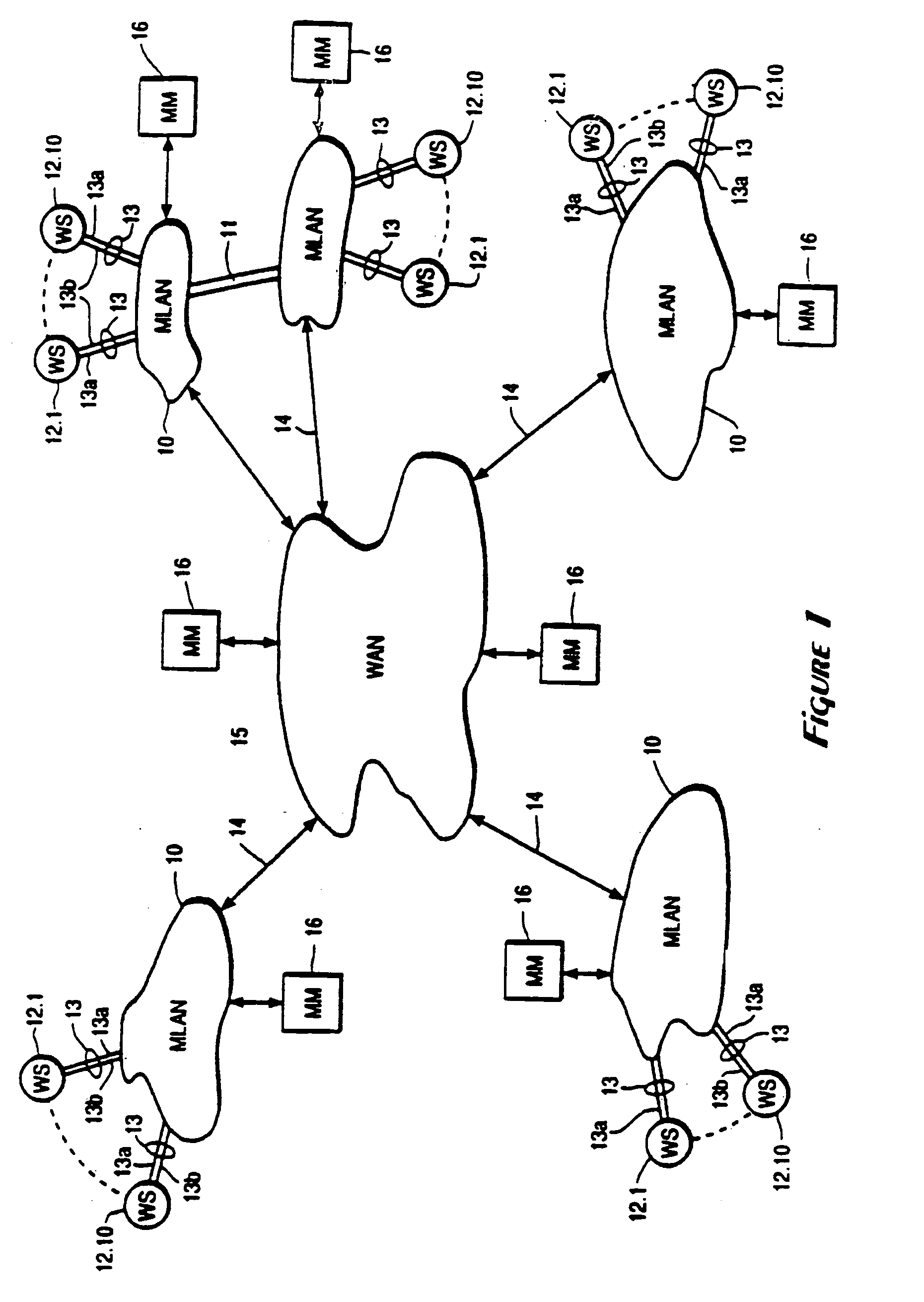

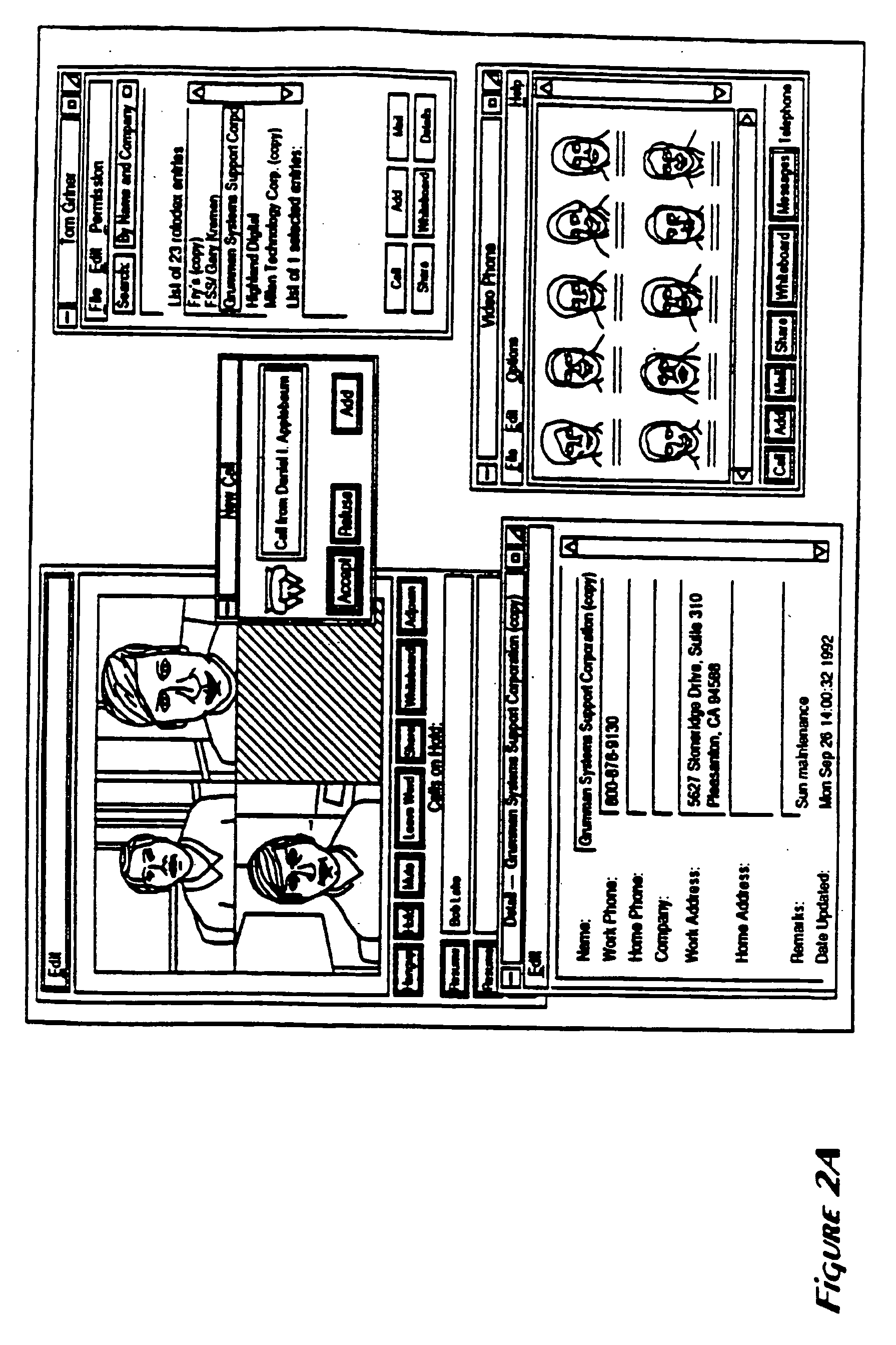

Asynchronous network audio/visual collaboration system

ActiveUS7613773B2Television conference systemsAnalogue secracy/subscription systemsAsynchronous networkWorkstation

A method and a system for synchronizing audio / video messages and message-related information stored in a workstation with audio / video messages and message-related information stored in a server. A copy of the message-related information stored in the workstation is transferred to the server. The workstation identifies workstation messages that have not been transferred from the workstation to the server. A copy of the identified messages are transferred to the server. The server identifies messages in the server that have not been transferred to the workstation. The server transfers to the workstation the messages identified by the server. The server merges the message-related information transferred to it by the workstation and transfers a copy of the merged message-related information to the workstation.

Owner:RENESSELAER POLYTECHNIC INST

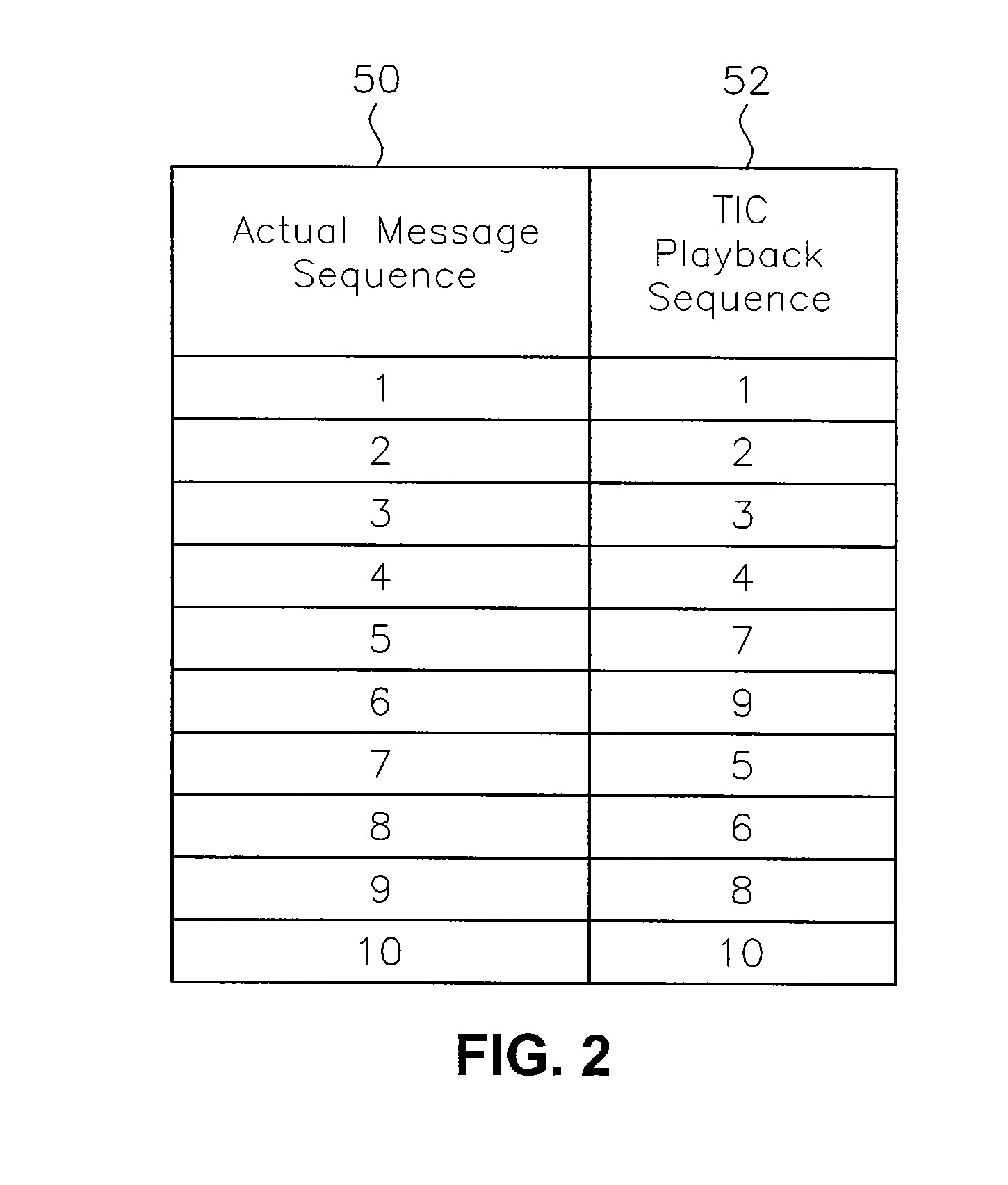

Clock synchronization and distribution over a legacy optical Ethernet network

InactiveUS7649910B1Time-division multiplexElectromagnetic transmissionData streamAsynchronous network

A novel clock method and synchronization mechanism for recovering and distributing a centralized clock source synchronously over legacy asynchronous network devices such as legacy optical Ethernet devices that do not support synchronous Ethernet. An external device functions transparently to provide legacy optical Ethernet devices a clock synchronization and distribution mechanism. The external devices implement a clock conversion scheme whereby multiple clocks having diverse rates are converted to clock signals all having a common rate. One of the converted clocks is selected and all downstream clock signals are then derived from this clock. A high quality clock source located anywhere on the network is distributed throughout the network thus turning an asynchronous Ethernet network into a synchronous Ethernet network. Synchronous TDM data streams can then be easily transported over the Ethernet network.

Owner:NOKIA SIEMENS NETWORKS ETHERNET SOLUTIONS +1

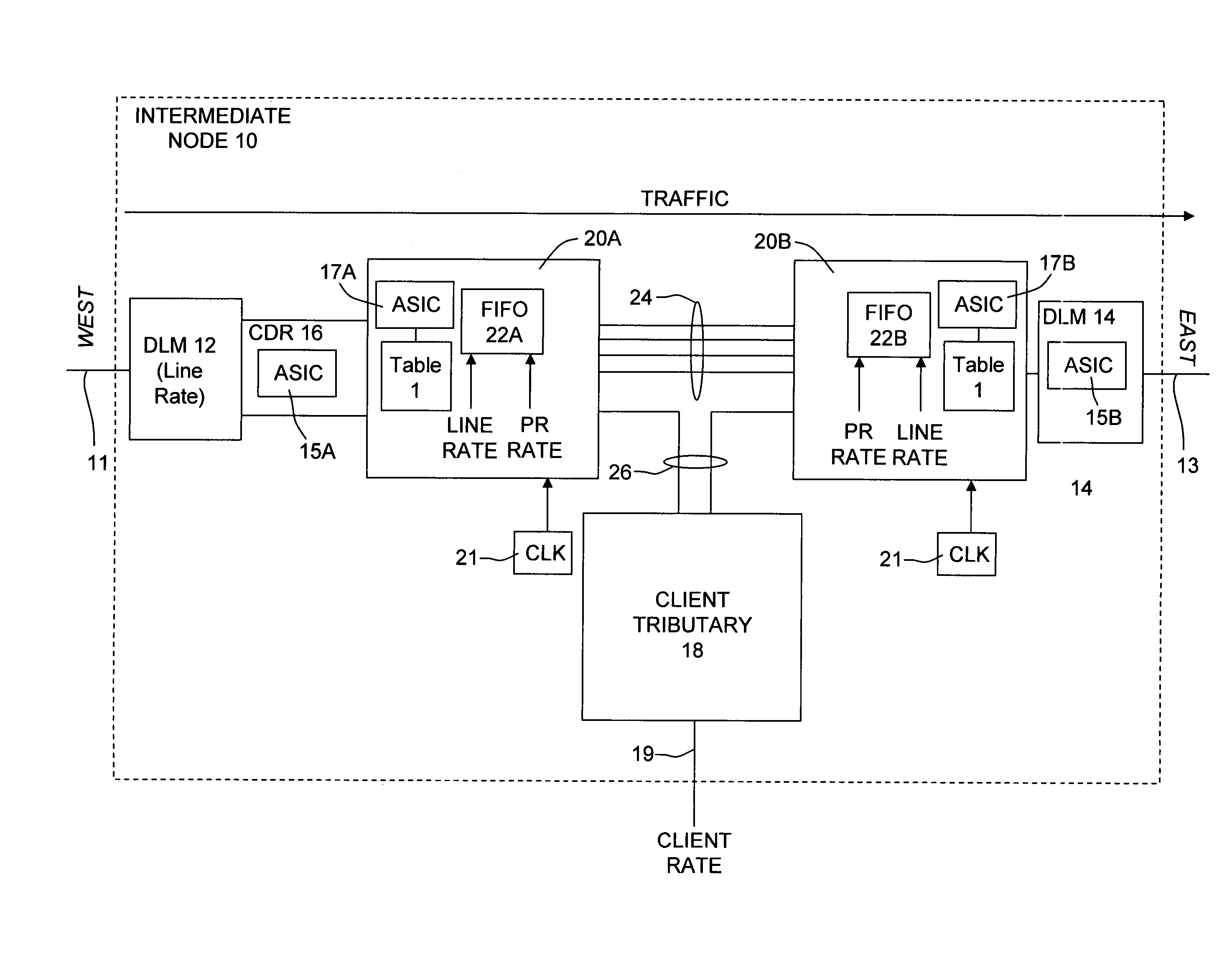

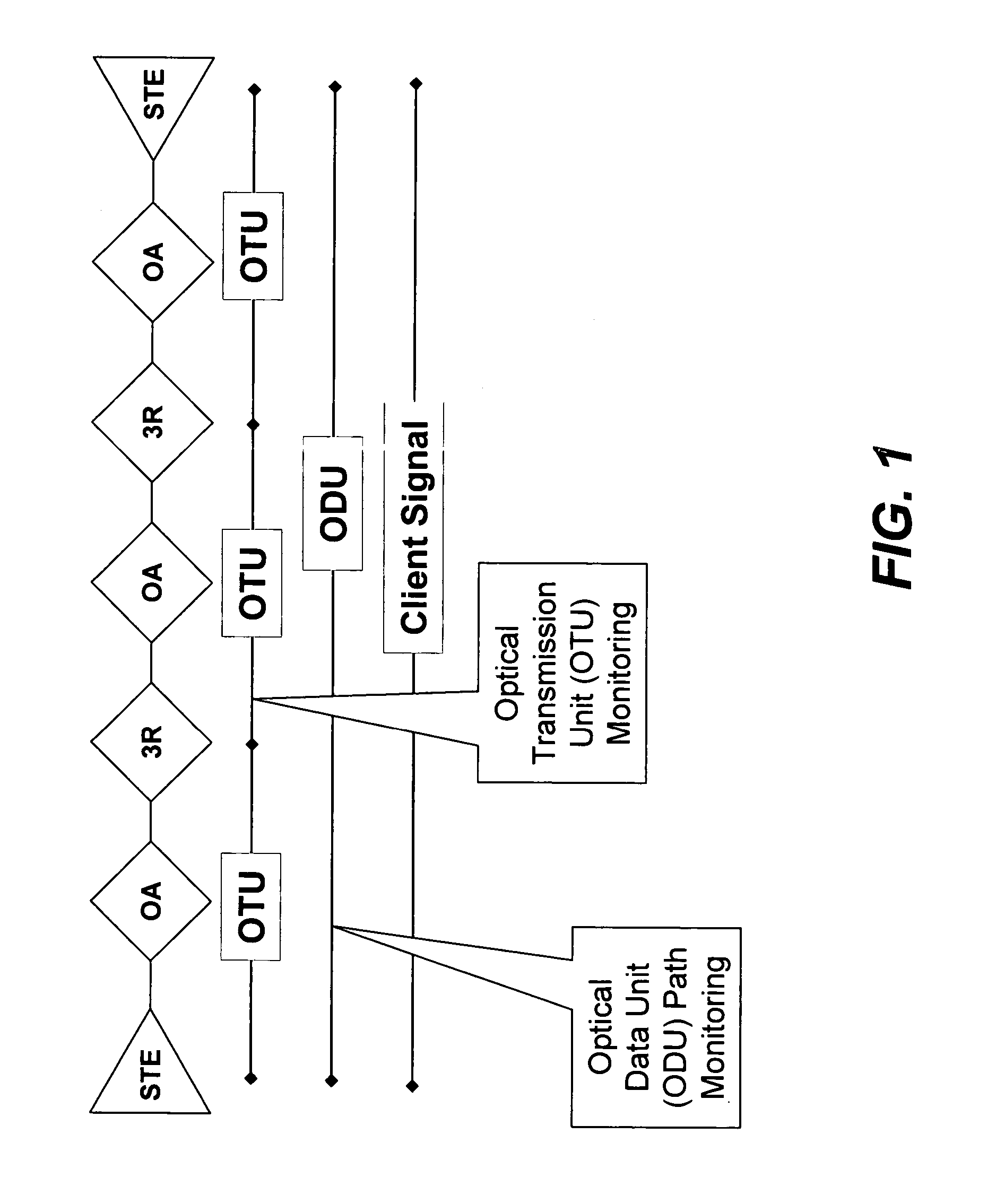

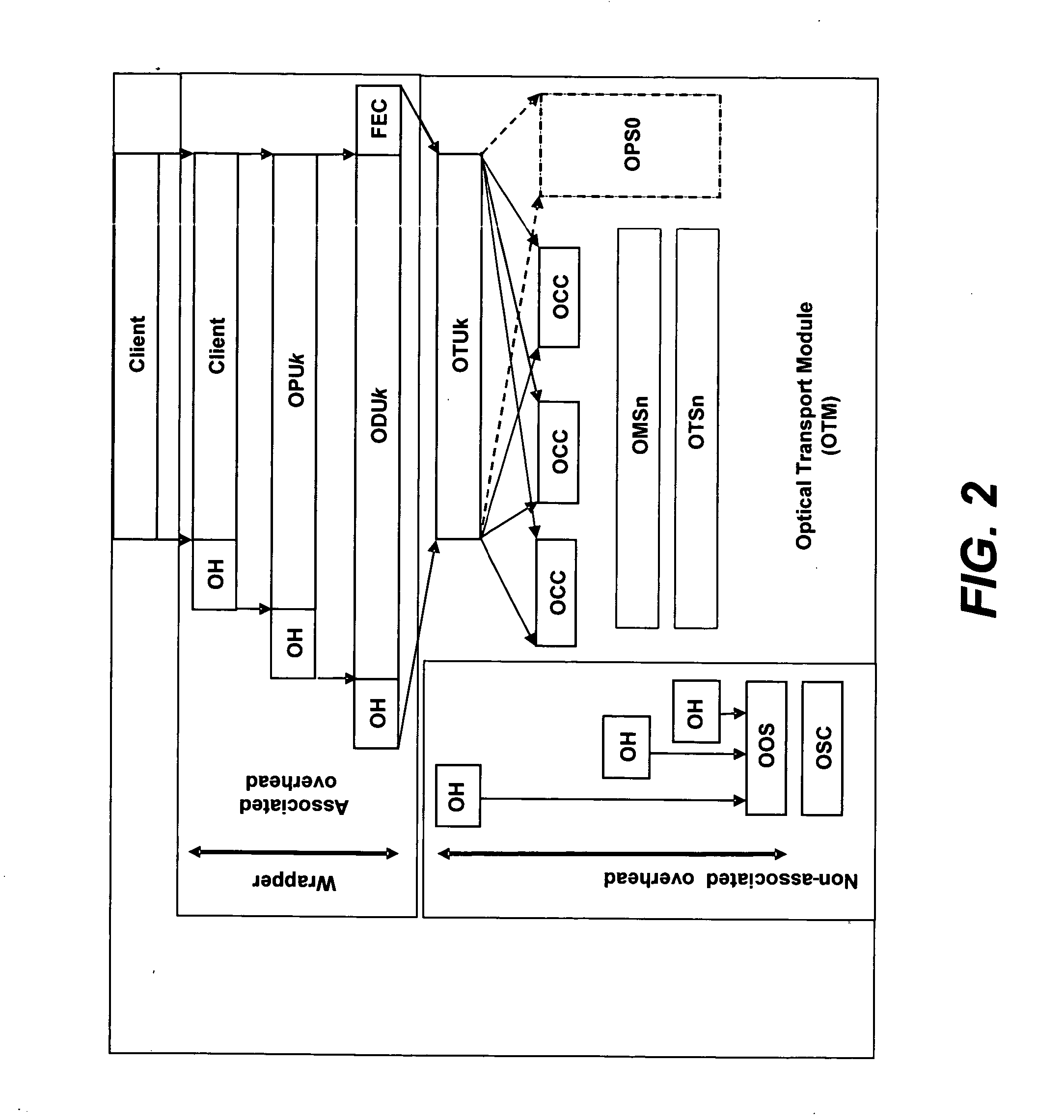

Optical transmission network with asynchronous mapping and demapping and digital wrapper frame for the same

ActiveUS7286487B2Reduce manufacturing costLow costError preventionFrequency-division multiplex detailsTransmission protocolLine rate

An optical transmission network is inherently asynchronous due to the utilization of a variable overhead ratio (V-OHR). The network architecture makes extensive use of OEO regeneration, i.e., deals with any electronic reconditioning to correct for transmission impairments, such as, for example, FEC encoding, decoding and re-encoding, signal reshaping, retiming as well as signal regeneration. The optical transmission network includes a plesiochronous clocking system with intermediate nodes designed to operate asynchronously with a single local frequency clock without complicated network synchronization schemes employing high cost clocking devices such as phase locked loop (PLL) control with crystal oscillators and other expensive system components. The asynchronous network operation provides for asynchronous remapping or remapping of any client signal utilizing any type of transmission protocol where the line side rate or frequency is always the same frequency for the payload signal and the local frequency at an intermediate node is set to a local reference clock in accordance with the payload type and its overhead ratio, i.e., the overhead ratio is varied to meet the desired difference between the line rate or frequency and the desired client signal payload rate or frequency for the particular client signal payload type.

Owner:INFINERA CORP

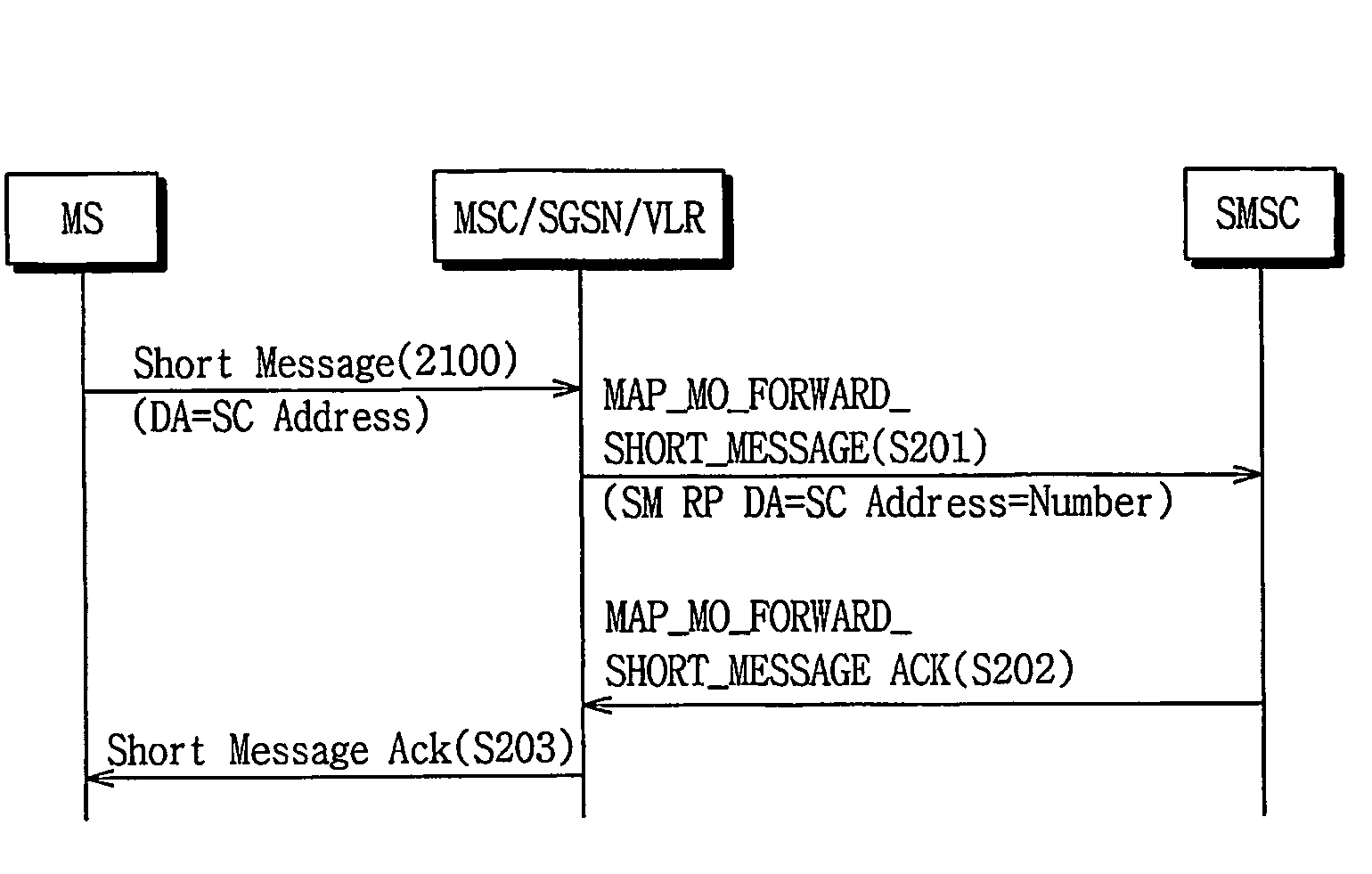

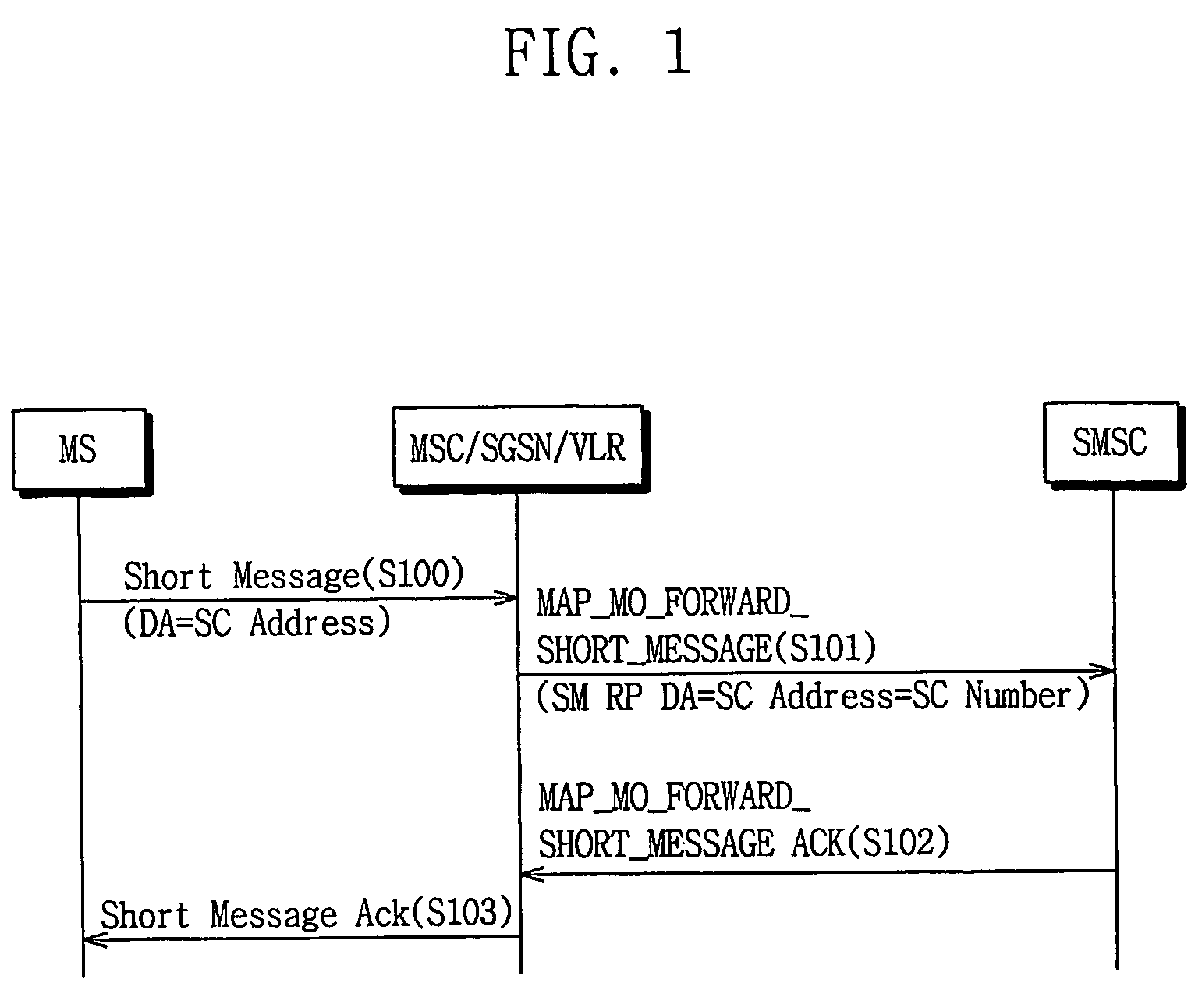

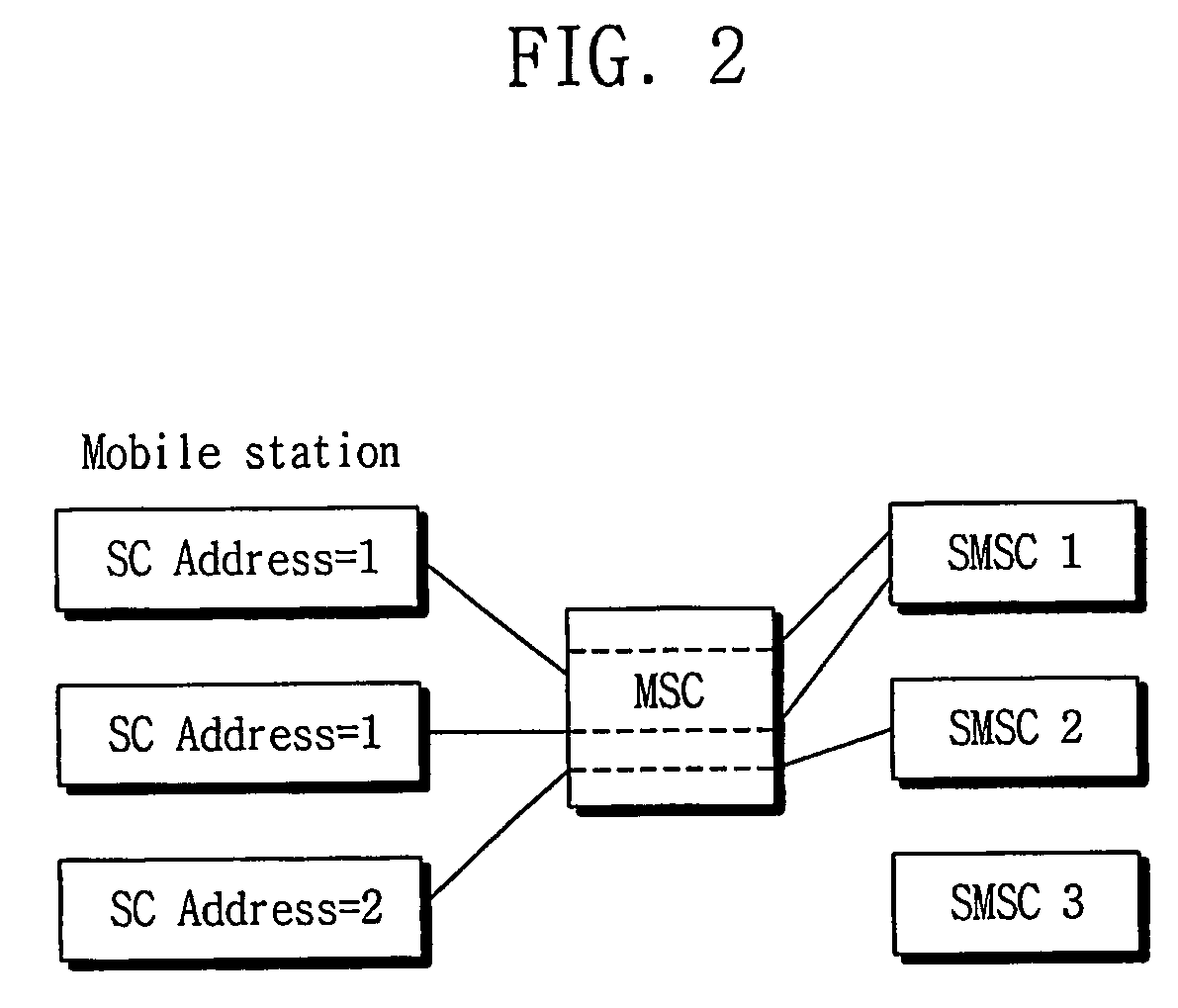

Method for processing address of short message service center in IMT-2000 asynchronous network

InactiveUS7221952B2Efficient use ofNetwork traffic/resource managementSubstation equipmentAsynchronous networkMessage processing

The present invention relates to a method for processing an address of a short message service center in a WCDMA network, including: a load centralization confirmation step where an operation control unit receives short message processing states from each short message service center, confirms load centralization states of each short message service center, and generates an operation message; a path setup step where a mobile switching center receives a short message from a mobile station, and sets up a transmission path of the short message according to the operation message; and an optimal transmission step where the mobile switching center transmits the short message from the mobile station to the corresponding short message service center through the transmission path according to the result of the path setup step. When a lot of messages are centralized to a specific short message service center due to call habits of subscribers, some subscribers of the short message service center arc distributed to another short message service center, and thus service center reception ability is predictable. It is also possible to actively cope with civil appeals and troubles.

Owner:SK TELECOM CO LTD

Satellite (GPS) assisted clock apparatus, circuits, systems and processes for cellular terminals on asynchronous networks

ActiveUS8249616B2Fixed lengthRadio transmissionSatellite radio beaconingAsynchronous networkComputer terminal

A wireless circuit (1100, 1190) for tracking an incoming signal and for use in a network (2000) having handover from one part (Cell A) of the network to another part (Cell B). The wireless circuit includes a processor (CE 1100) responsive to the incoming signal, the processor (CE 1100) operable to generate pulse edges representing network-based receiver synchronization instances (RSIs), and a timekeeping circuitry (2420, 2430, 2450) including an oscillator circuitry (2162), the timekeeping circuitry (2420, 2430) operable to maintain a set of counter circuitries (2422-2428) including a counter circuitry (2422) operable to maintain at least one network time component based on the RSIs and another counter circuitry (2428) operable at least during handover and during loss of network coverage for maintaining at least one internal time component (NC) based on the oscillator circuitry (2162), the set of counter circuitries (2422-2428) operable to account for elapsing time substantially gaplessly and substantially without overlap between the time components during a composite of network coverage, loss of network coverage and handover, and the timekeeping circuitry further including a time generator (2450) for combining the time components from the set of counter circuitries (2422-2428) to generate an approximate absolute time (SGTB). Other electronic circuits, positioning systems, methods of operation, and processes of manufacture are also disclosed and claimed.

Owner:TEXAS INSTR INC

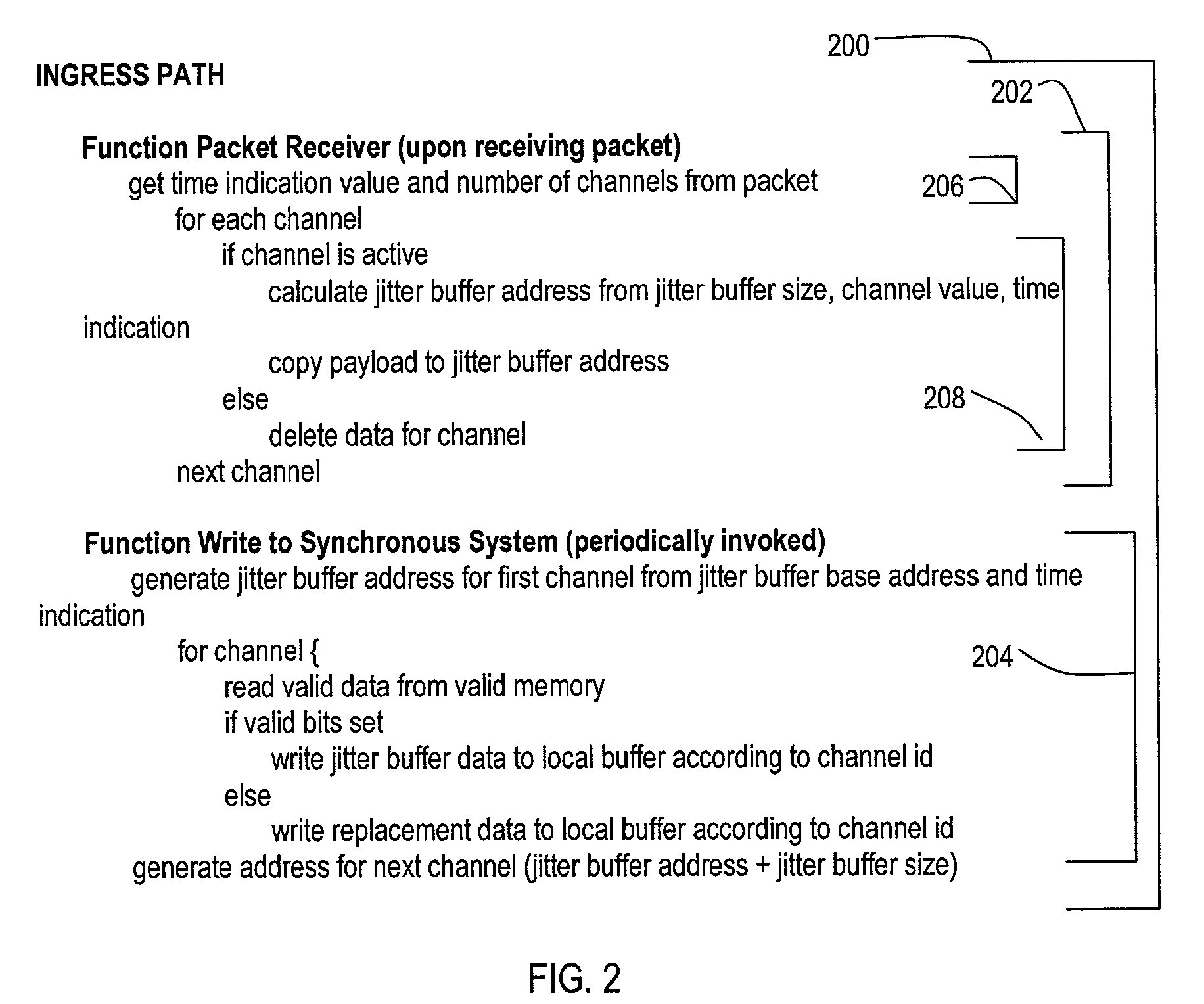

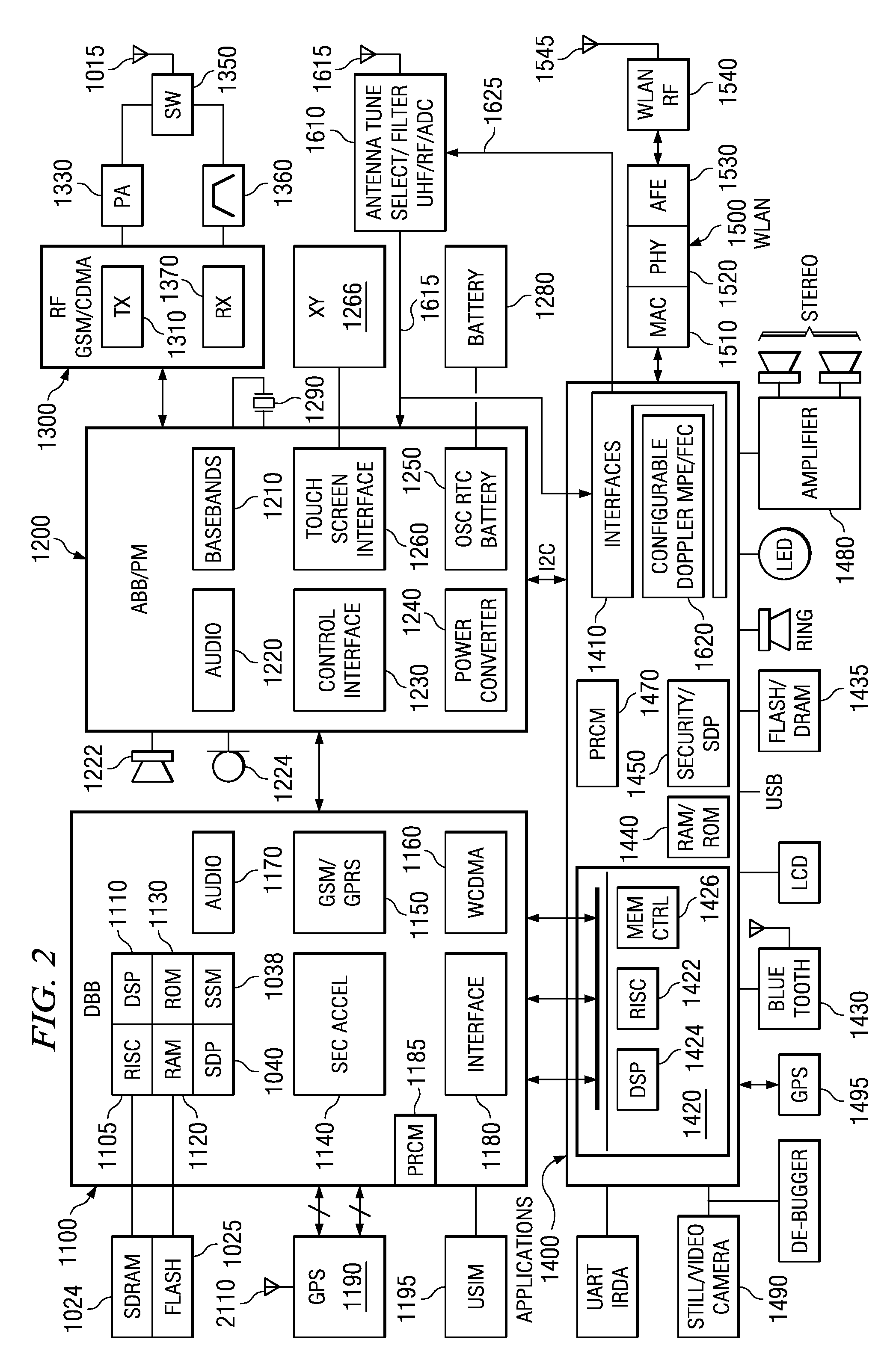

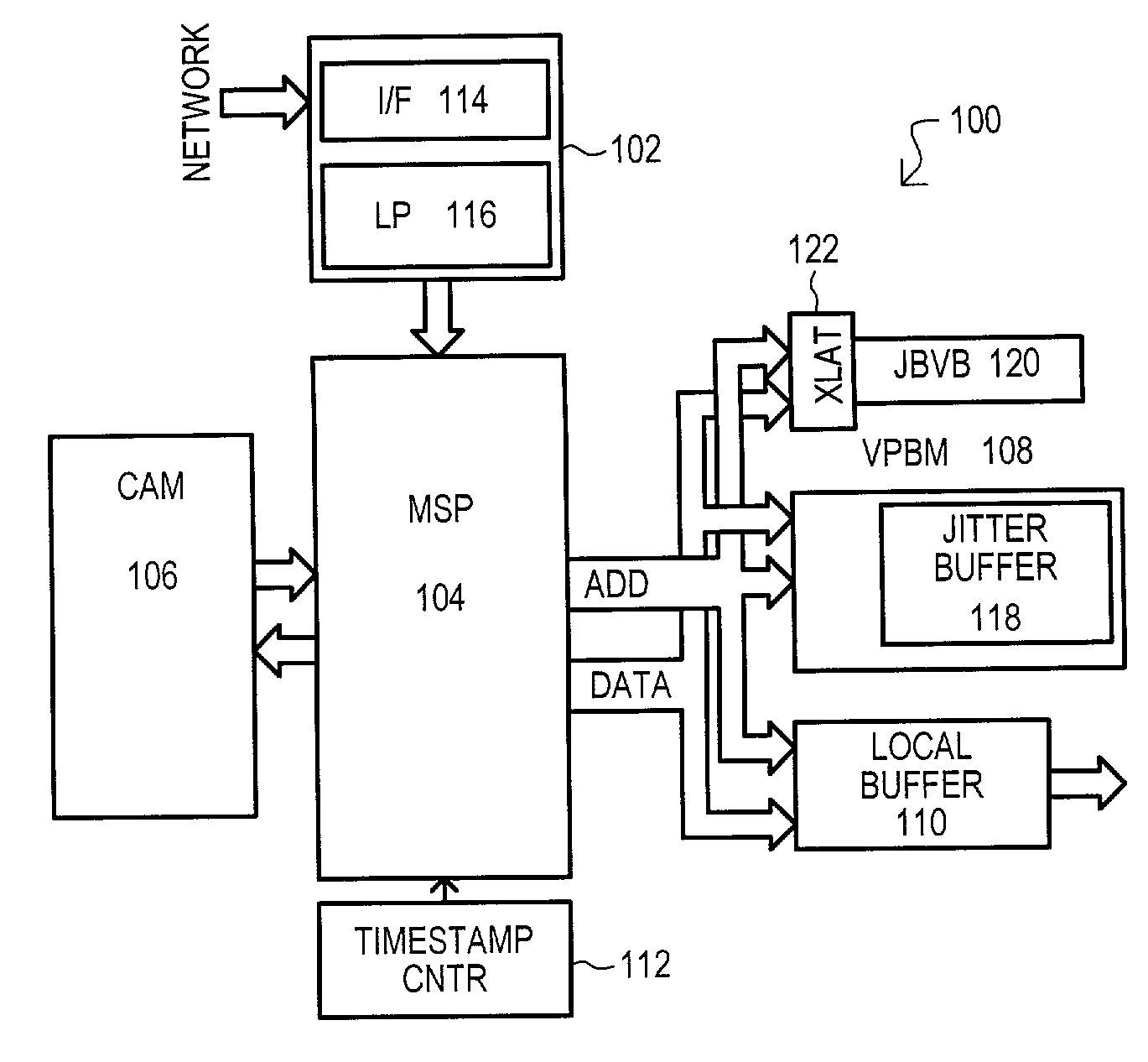

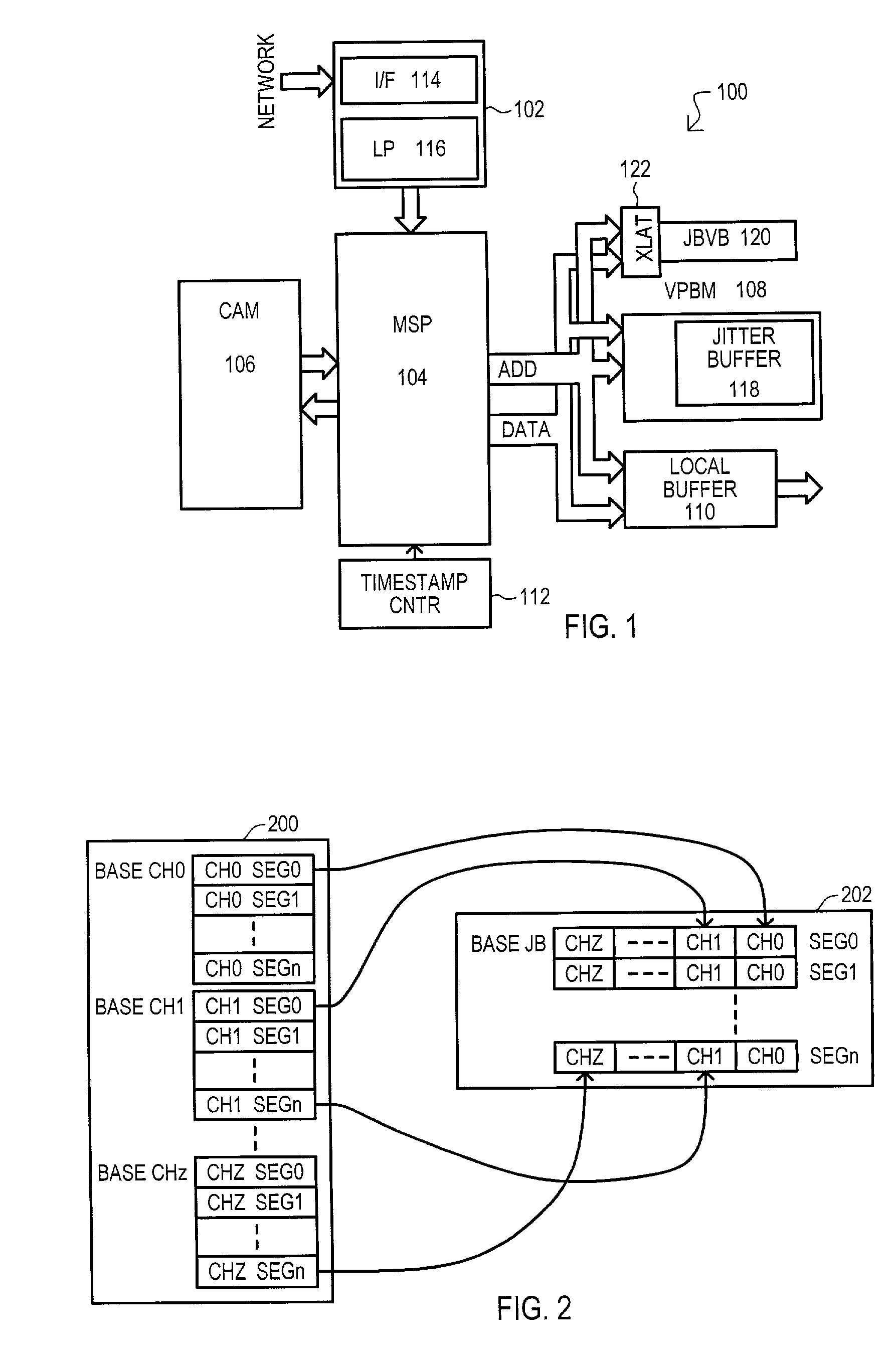

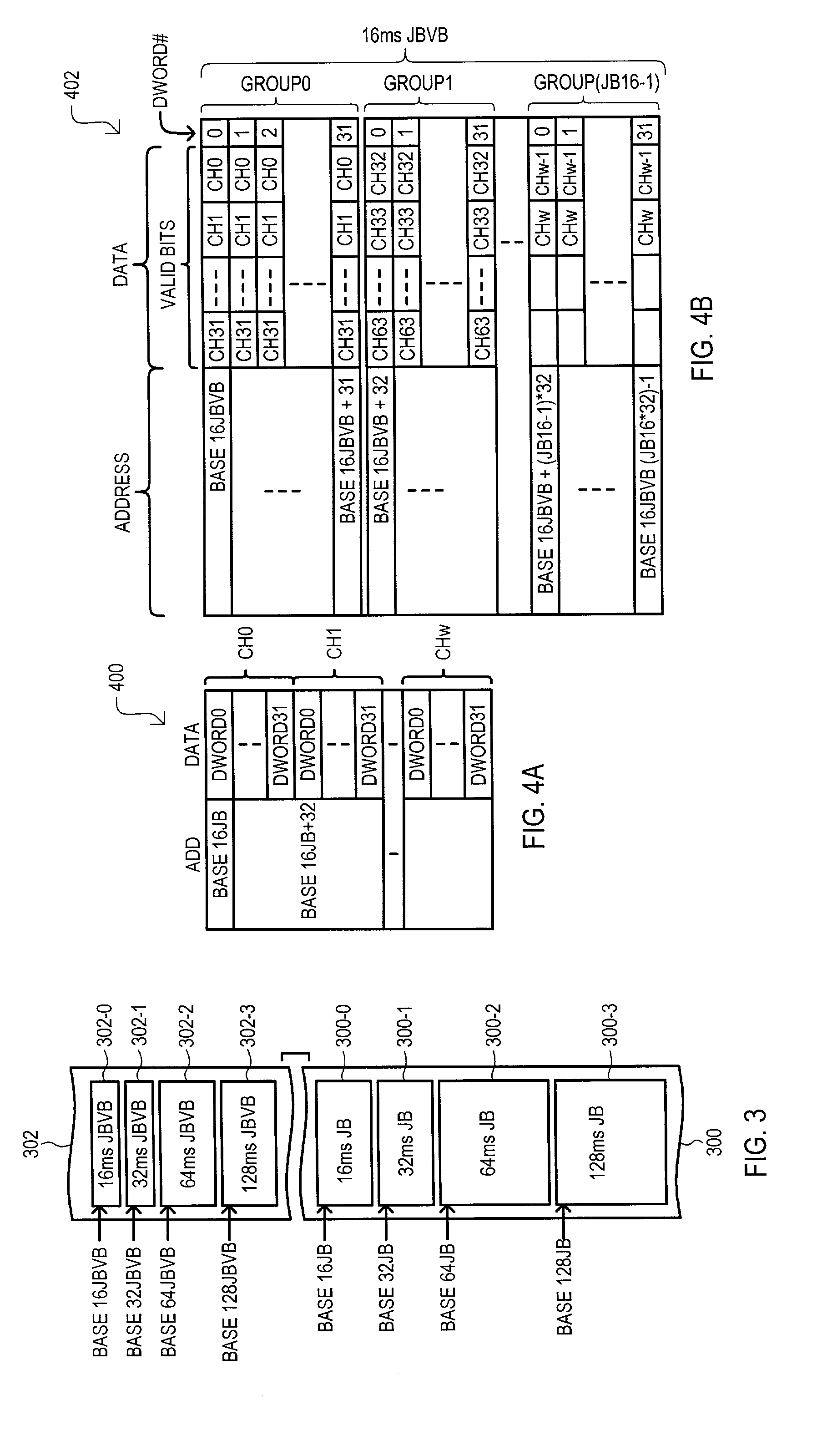

Jitter buffer state management system for data transmitted between synchronous and asynchronous data networks

A system (100) for receiving data from an asynchronous network and transmitting such data onto a synchronous network includes a voice packet buffer memory system (108) with a jitter buffer (118) having groups of entries storing data for voice channels and jitter buffer valid bit (JBVB) memory (120) for status of a particular entry for multiple jitter buffer groups. Writing or reading data from a jitter buffer entry sets a corresponding JBVB memory bit to a valid or invalid state respectively. Jitter buffer data may be read with a corresponding state memory bit. If a corresponding JBVB memory bit is valid, data from a jitter buffer (118) may be provided as an output. If a corresponding JBVB memory bit is invalid, a loss recovery algorithm may compensate for such invalid jitter buffer data.

Owner:UTSTARCOM INC +1

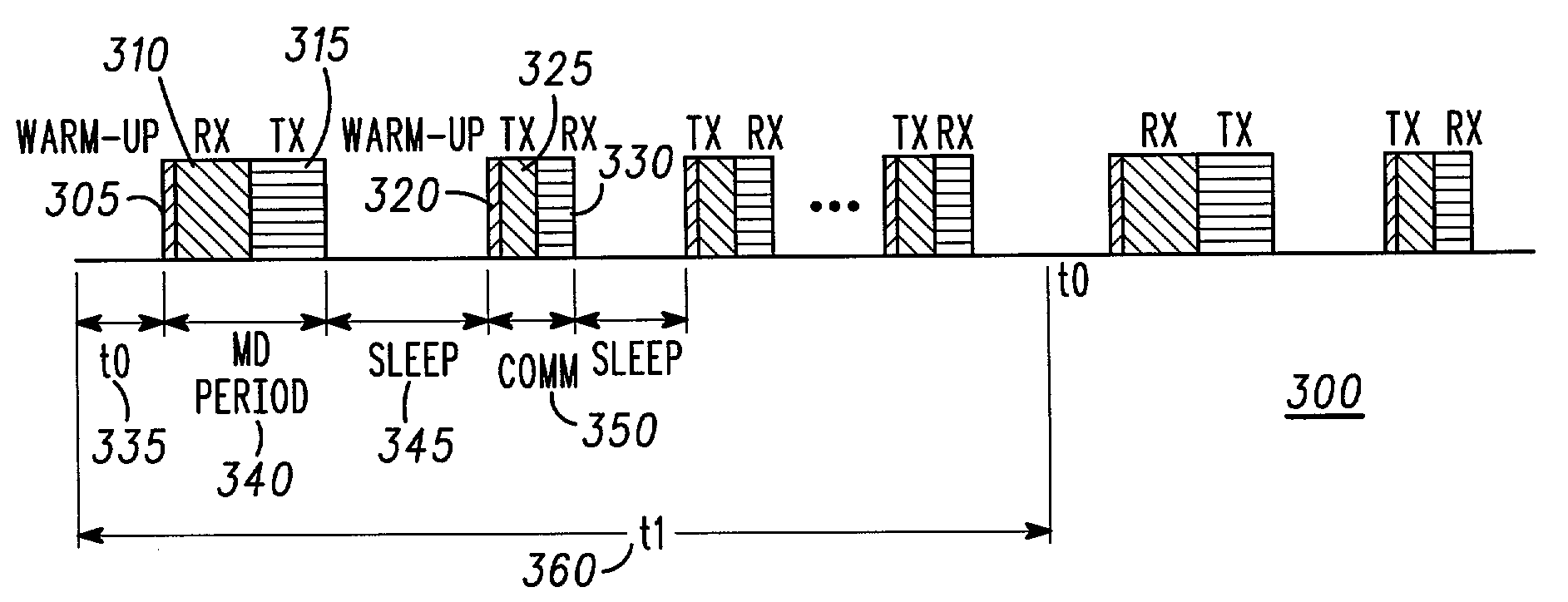

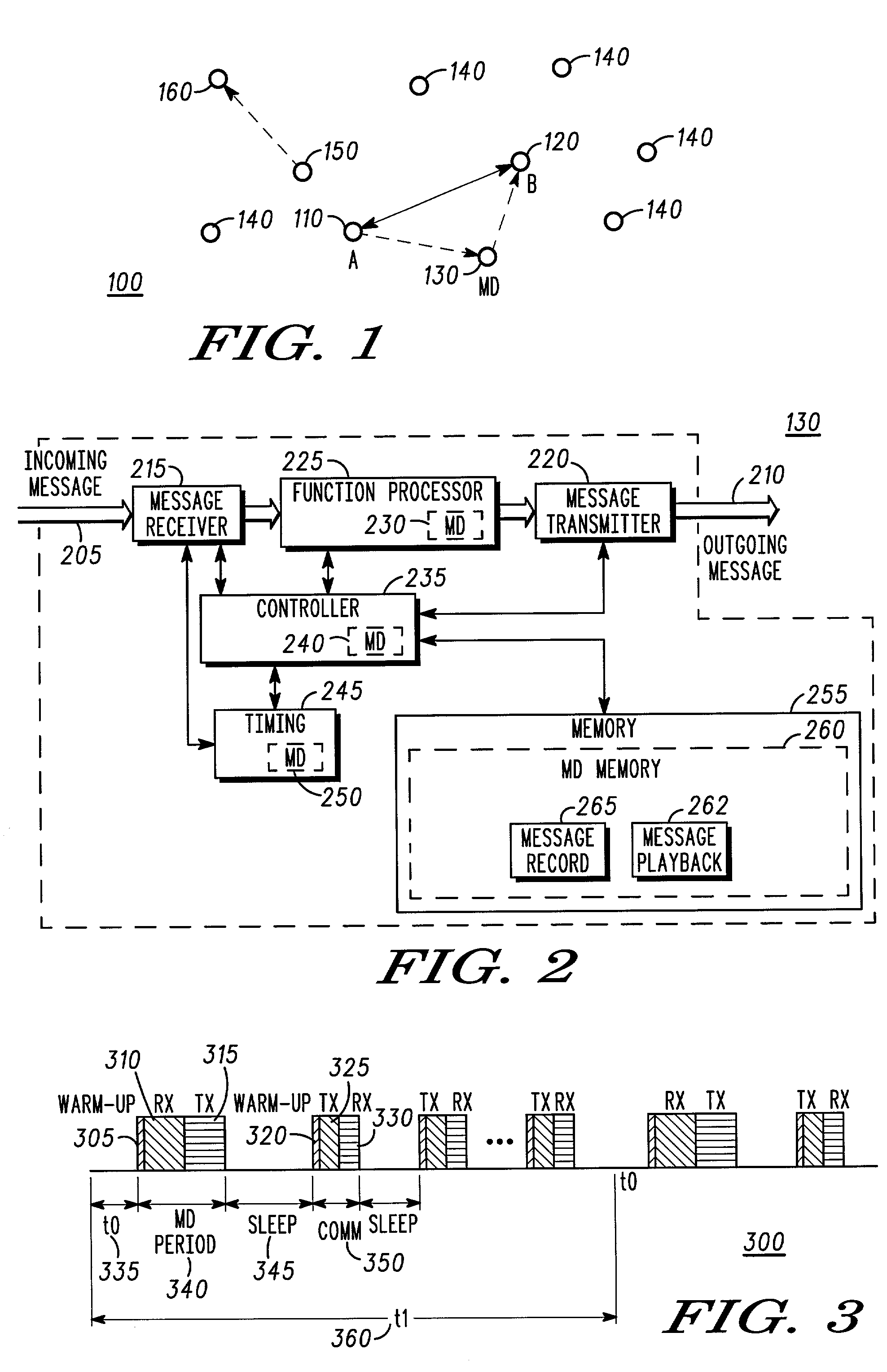

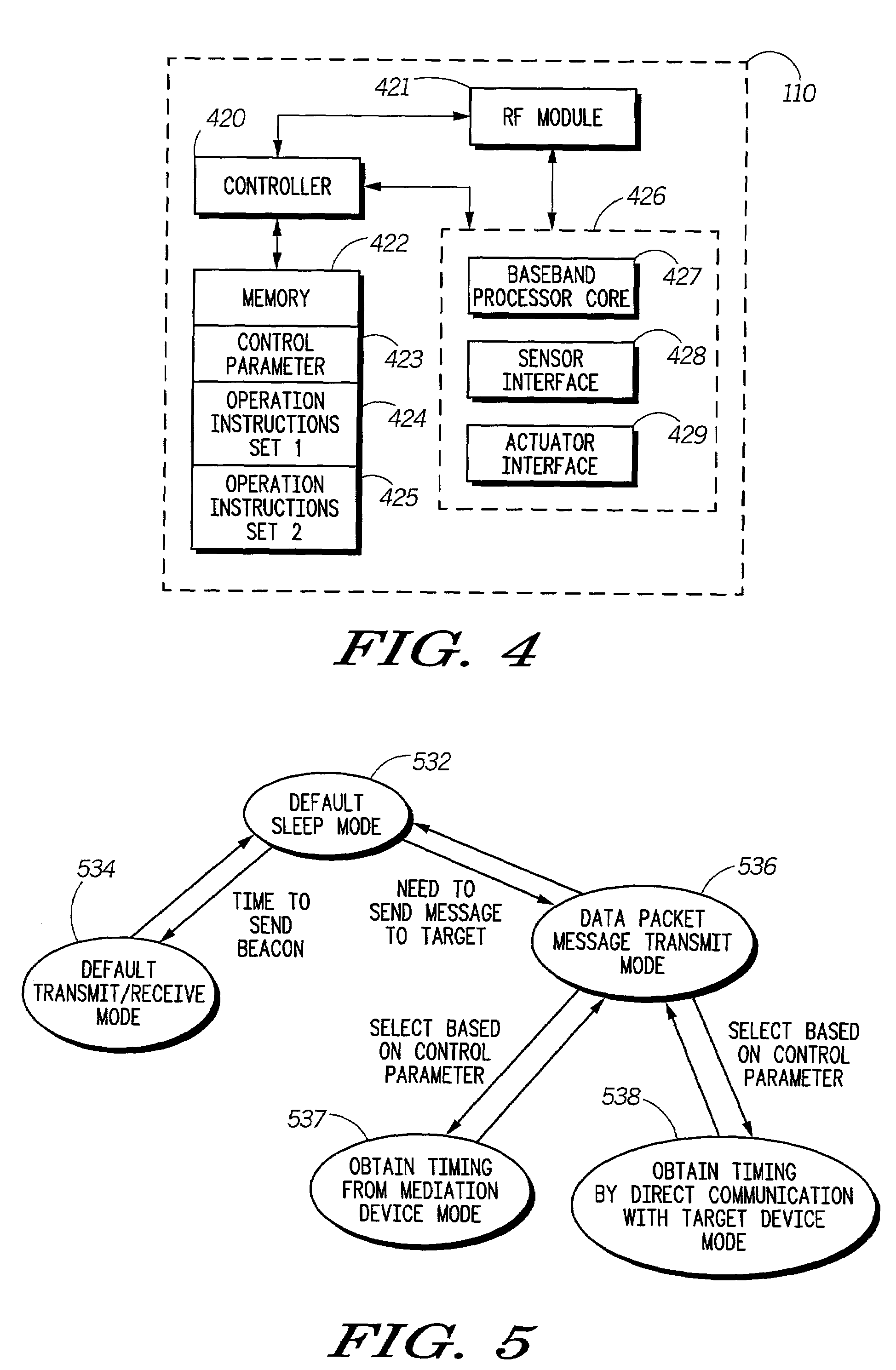

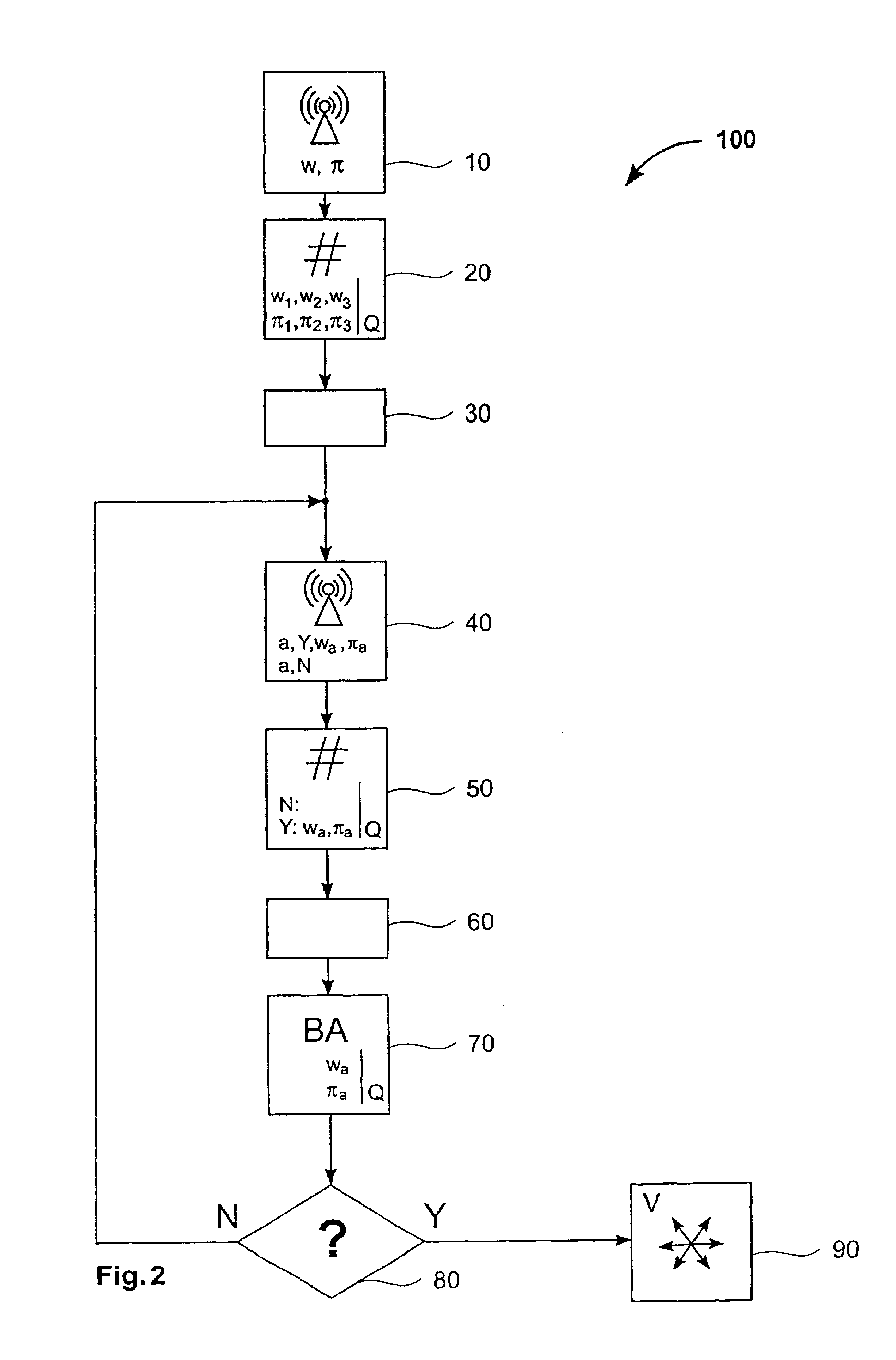

System and method for asynchronous communications employing direct and indirect access protocols

A communication access protocol improves the accessibility of devices operating on an asynchronous network (100), while supporting reduced power consumption. The network (100) includes a mediation device (130) for facilitating communications among network devices. Generally, each network device periodically transmits beacon signals to advertise its presence, and listens for communication signals targeted at the network device (532, 534). A device initiating communication with another operates in one of at least two operating modes in order to establish communications (536, 537, 538). In one mode, the initiating device communicates with the mediation device in order to derive timing information for the other device (537). In another mode, the initiating device listens to receive beacon signals directly from the target device in order to synchronize communications with the device (538). The selection of one of the two operating modes depends on a control parameter established for the initiating device, which in one embodiment is dependent on the urgency of communication, a maximum number of retries for using the mediation device, or the like.

Owner:ARRIS ENTERPRISES LLC

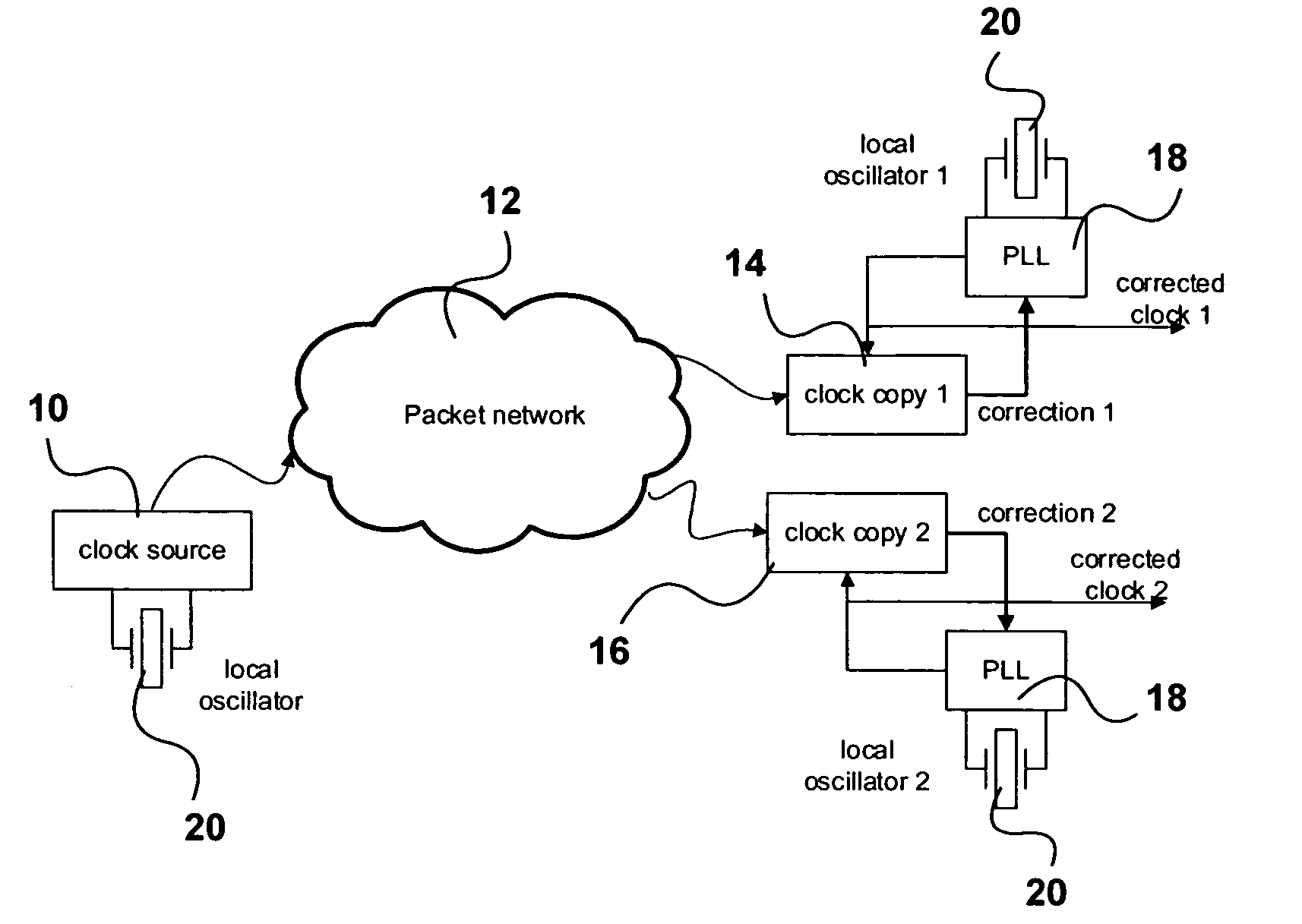

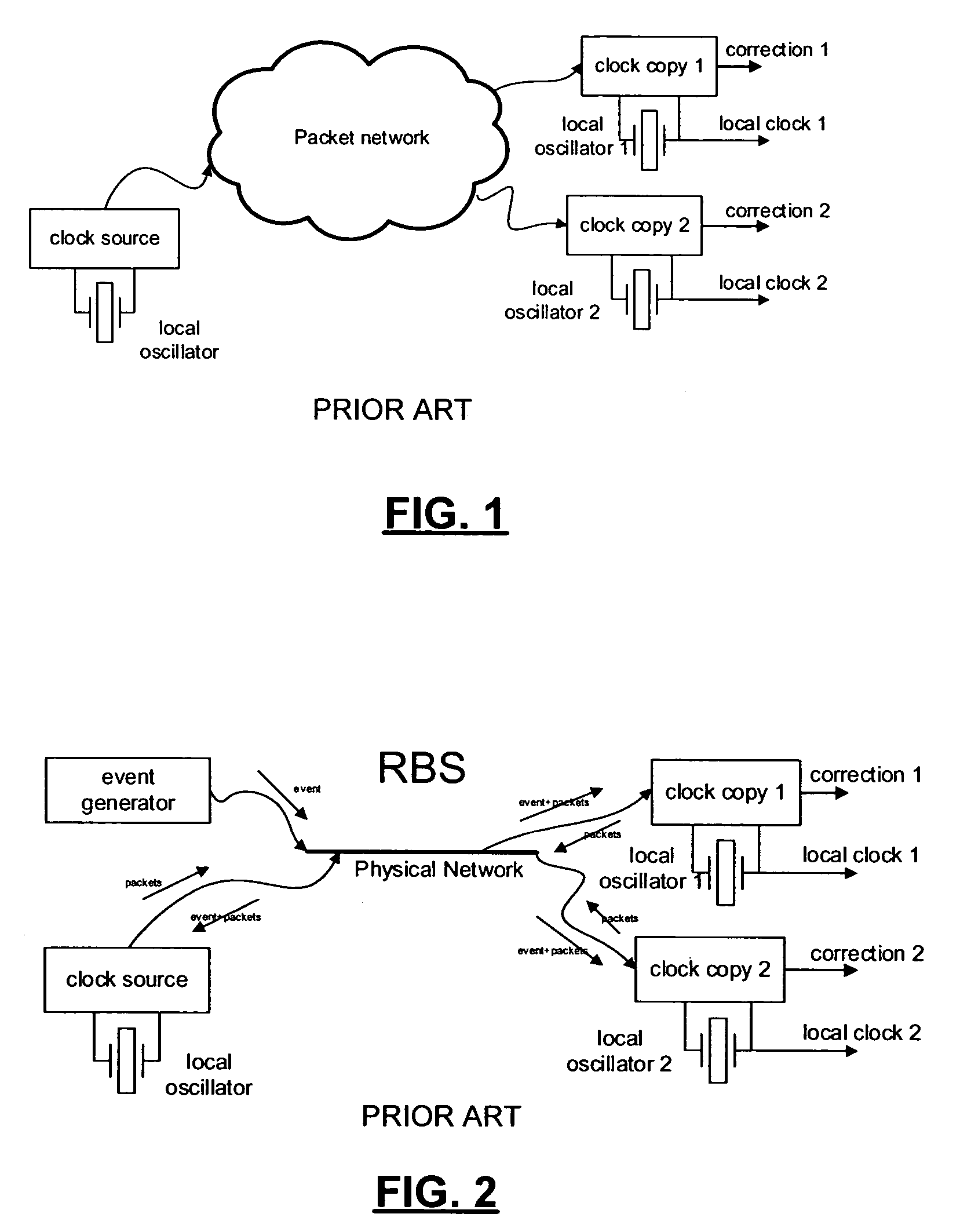

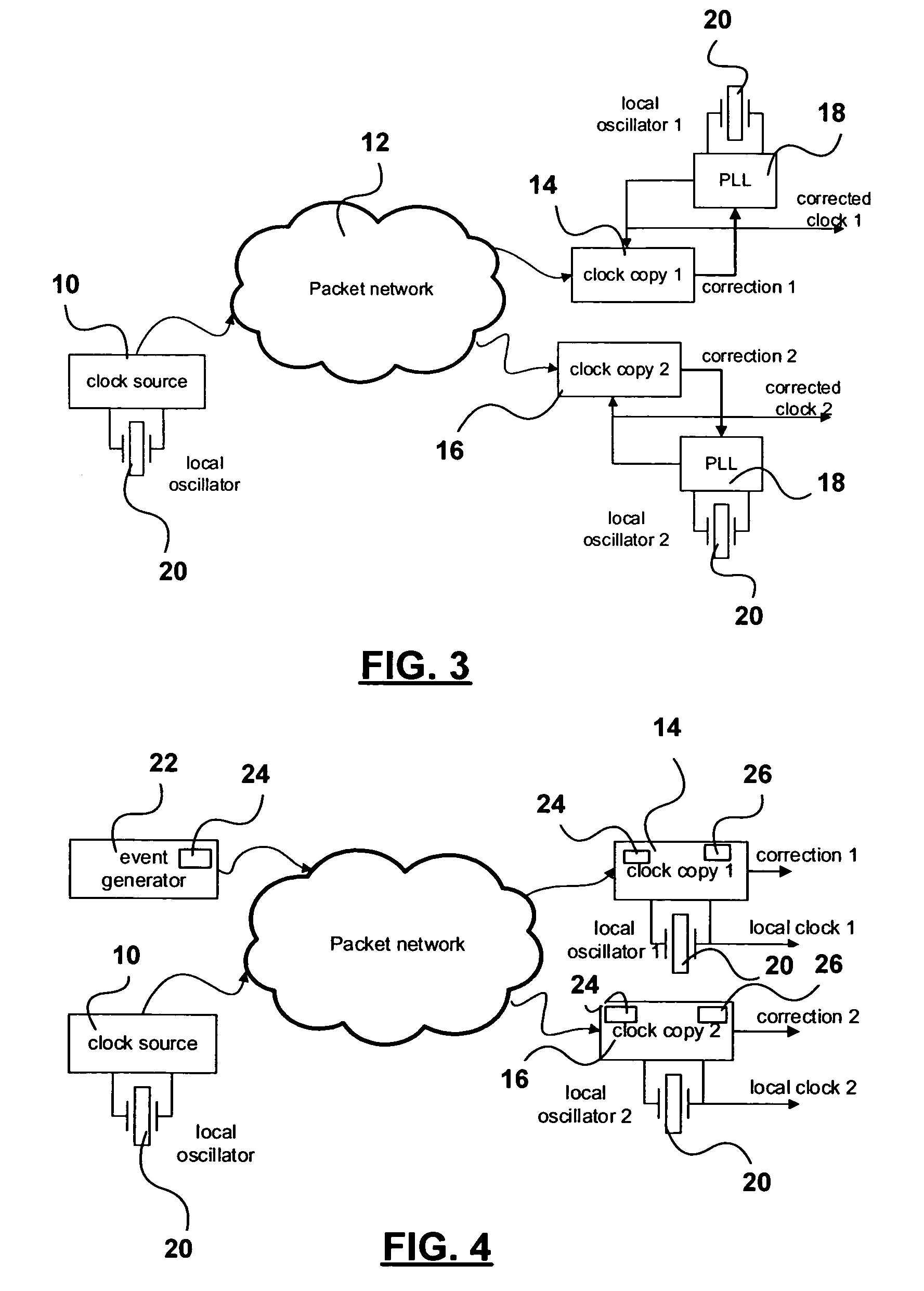

Alignment of clock domains in packet networks

ActiveUS7315546B2Low costAvoid misunderstandingTime-division multiplexData switching by path configurationTime informationPacket generator

Disclosed is a method and apparatus for aligning clock domains over an asynchronous network between a source controlled by a first clock and a destination controlled by a second clock. The predicted delay is estimated for transmitting packets between a source and destination over the network. The time-stamped synchronization packets are sent to the destination, each time-stamped synchronization packet carries timing information based on a master clock at the source. A set of synchronization packets are received at the destination to create a set of data points, and the set of data points is weighted so that synchronization packets exhibiting a delay further from the expected delay are accorded less weight than synchronization packets exhibiting a delay closer to the expected delay. The expected delay is updated to create a current delay estimate based on the set of data points taking into account the different weighting of the data points. These steps are continually repeated on new sets of data points created from newly received synchronization packets using the current delay estimate for the expected delay. And a clock domain at the destination is continually aligned with a clock domain at the source based on the current delay estimate for packets traversing the network between the source and destination.

Owner:ZARLINK SEMICON LTD

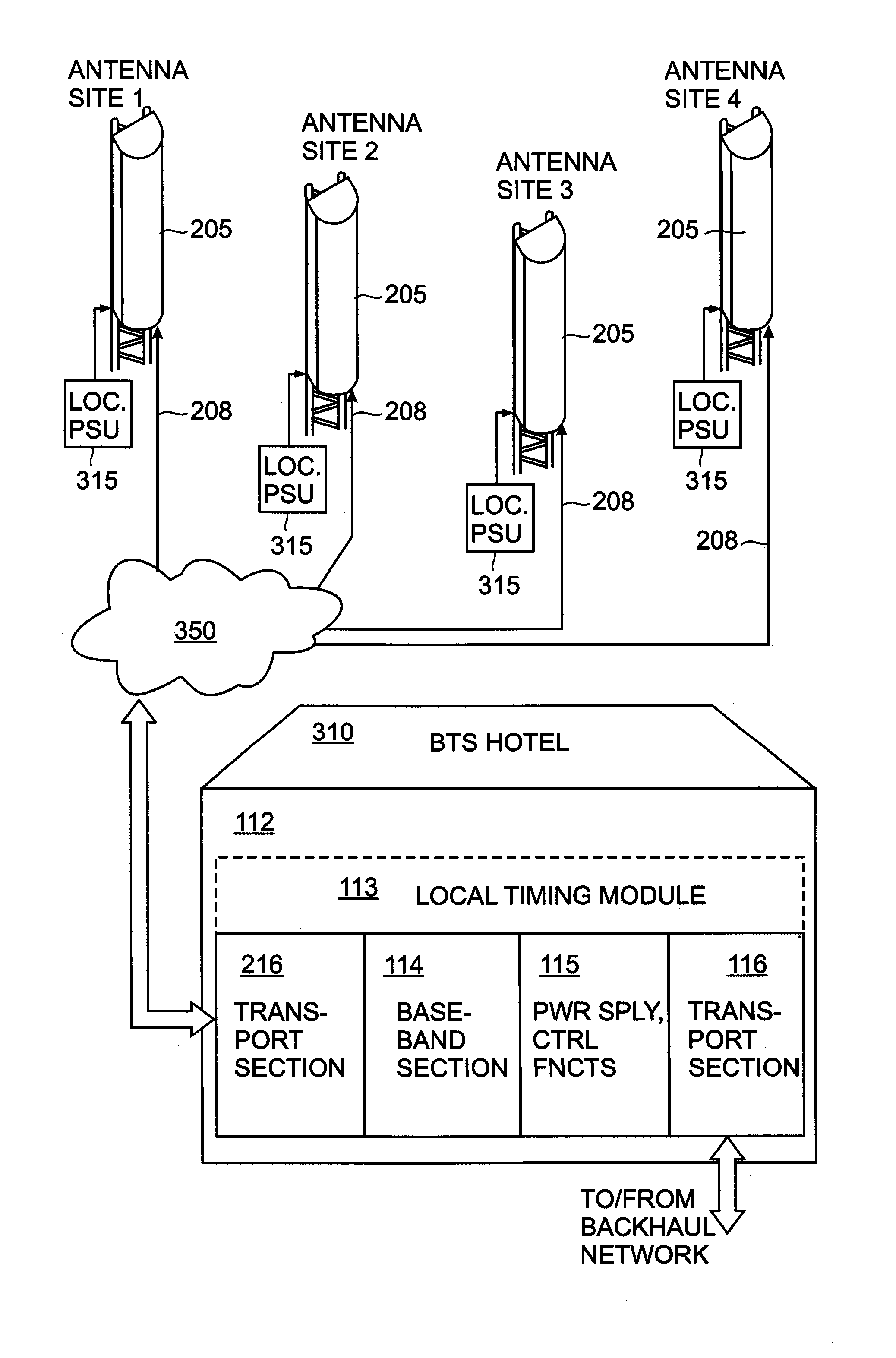

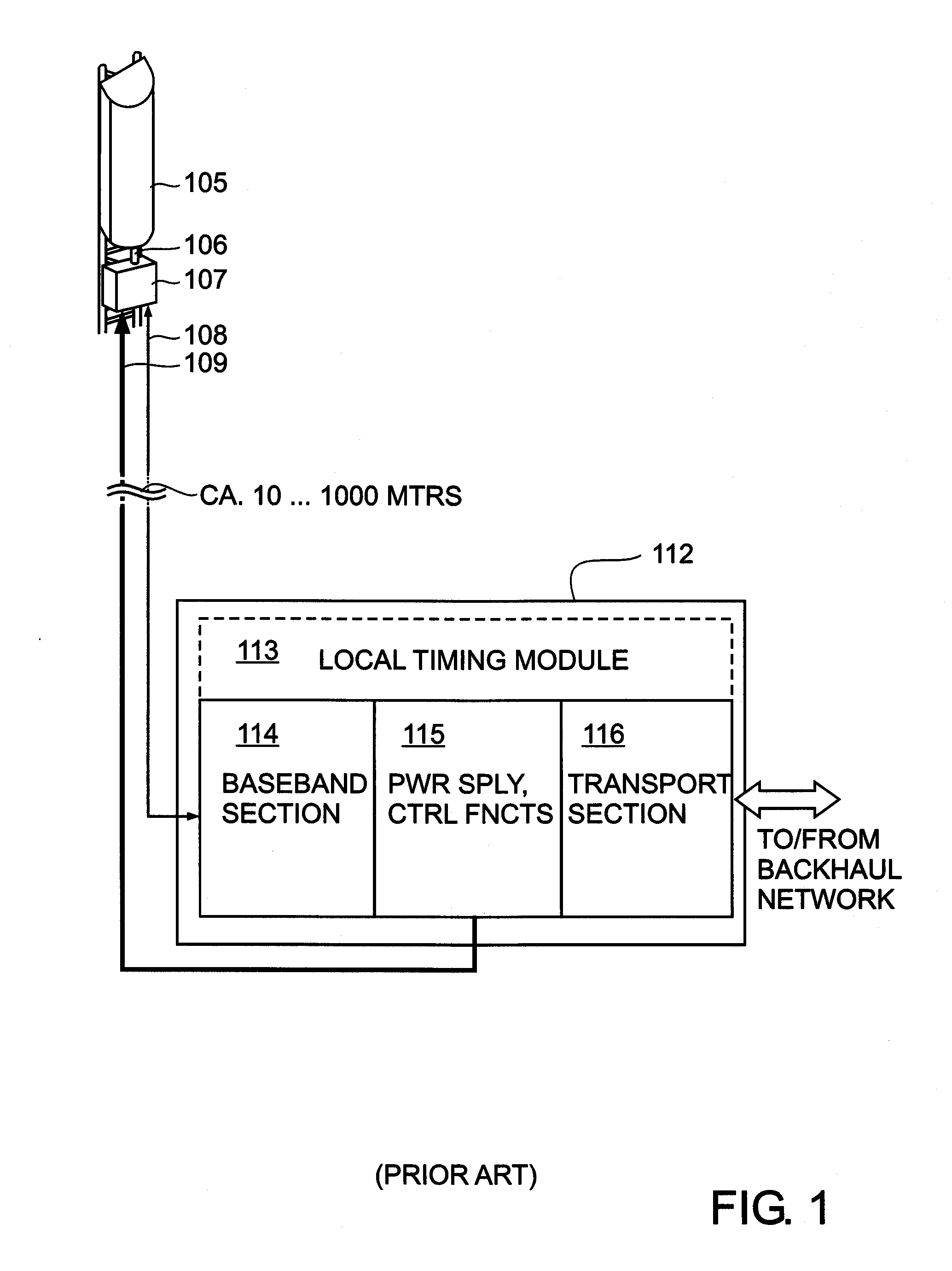

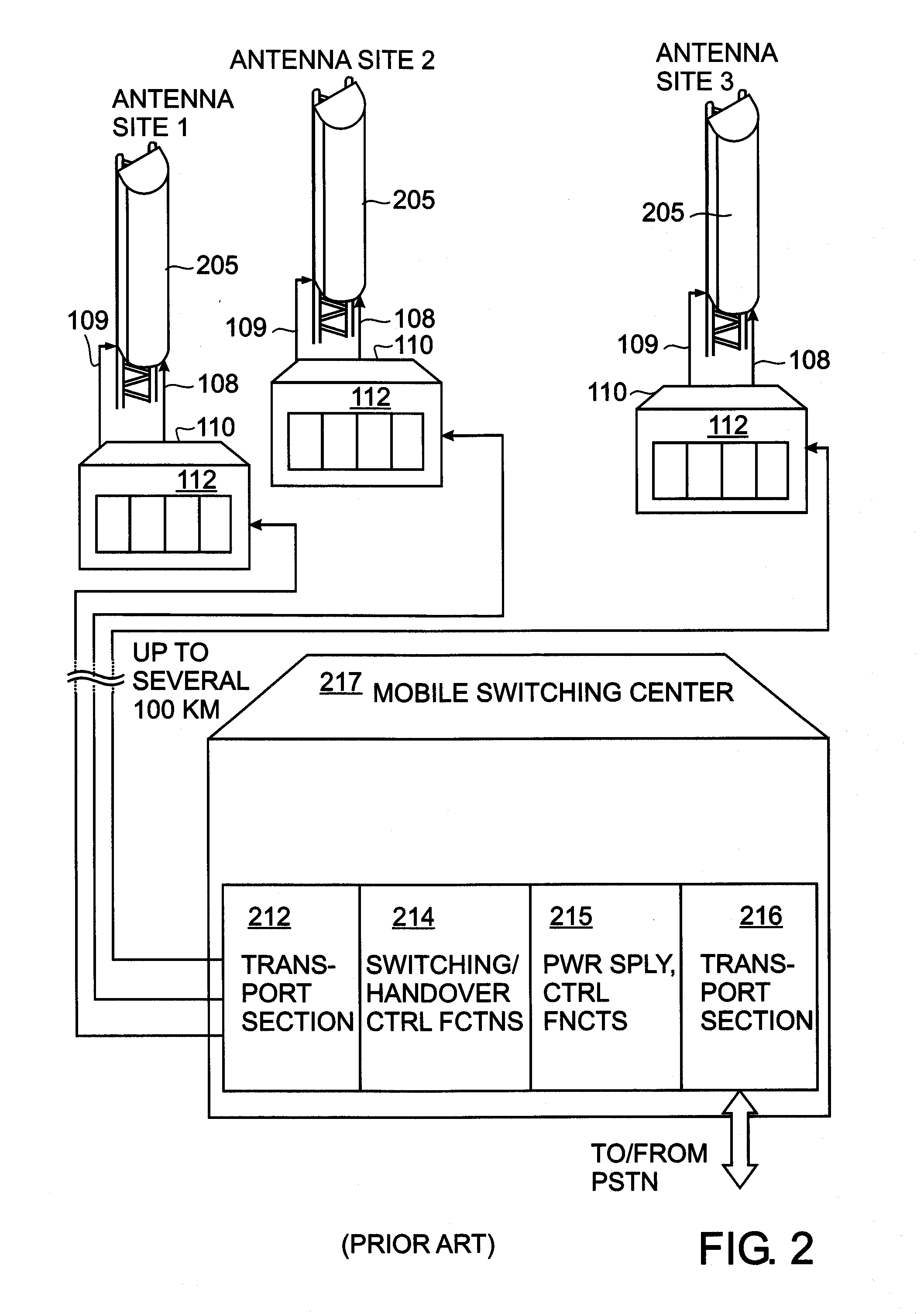

Remote radio head

InactiveUS20110310881A1Avoid congestionOptimize timingTime-division multiplexSynchronising arrangementAsynchronous networkComputer science

A remote radio head is disclosed that comprises an interface for connecting the remote radio head to a base station via an asynchronous packet network, an absolute time reference source for (time-)synchronising a signal transceived by the remote radio head. A corresponding method for transmitting a transmit signal at a remote radio head comprises: receiving a data packet at an interface connecting the remote radio head to a base station via an asynchronous network, processing the data packet to form the transmit signal, determining an absolute time reference by means of an absolute time reference source local to the remote radio head, and transmitting the transmit signal in an absolute time-synchronised manner with respect to the absolute time reference. A method for receiving a receive signal at a remote radio head is also disclosed.

Owner:UBIDYNE

Agreement and atomic broadcast in asynchronous networks

InactiveUS6931431B2Rapid terminationReduce the possibilitySpecial service provision for substationUser identity/authority verificationComputer networkAsynchronous network

Methods and apparatus for achieving agreement among participating network devices in an asynchronous network for deciding on a common value is disclosed, whereby the common value is validated by a justification and both together satisfy a predetermined predicate. Moreover, a method for reliably broadcasting messages in an order within the asynchronous network is described. Up to one third or more of the participating network devices might be faulty in arbitrary ways.

Owner:INT BUSINESS MASCH CORP

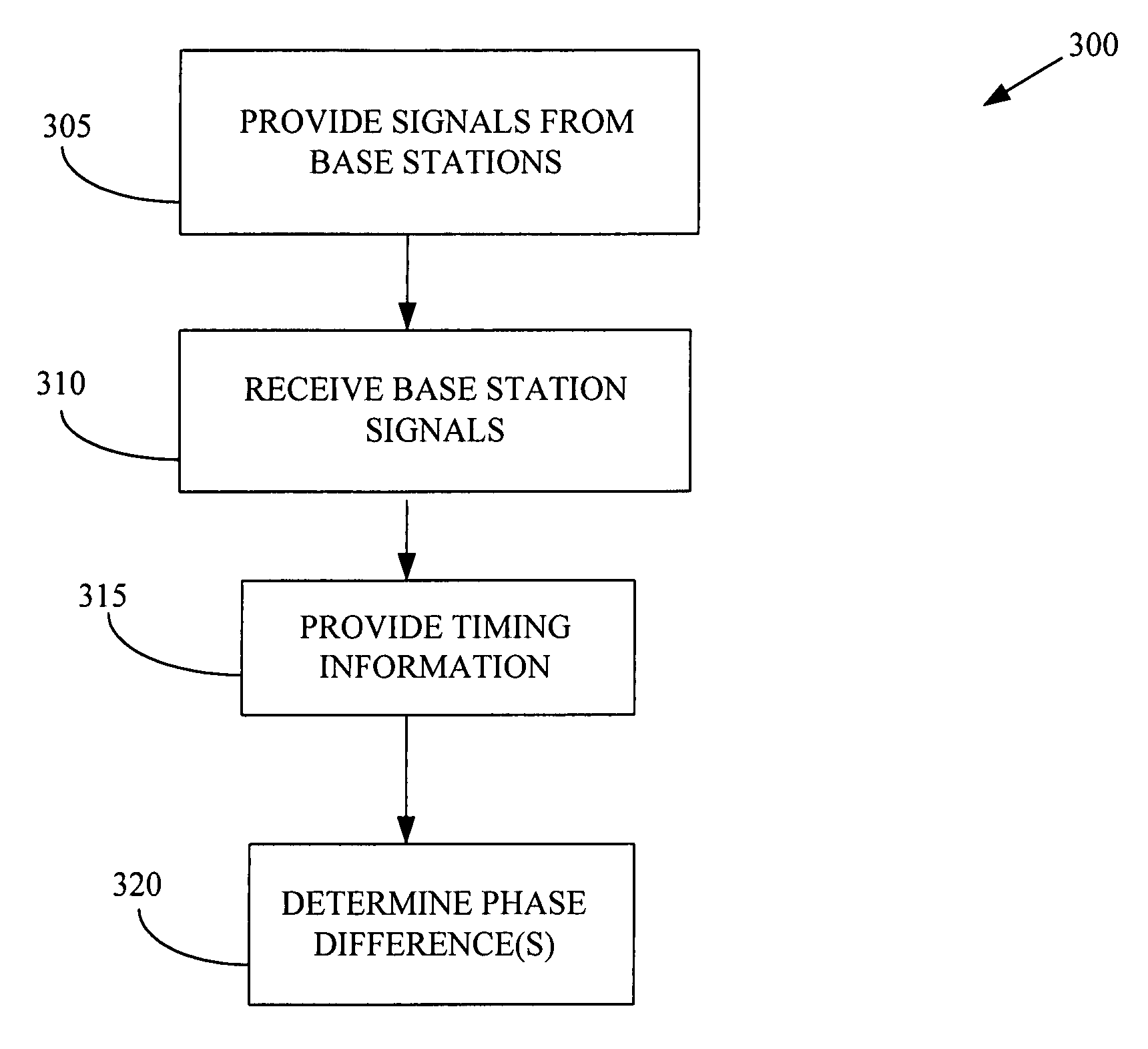

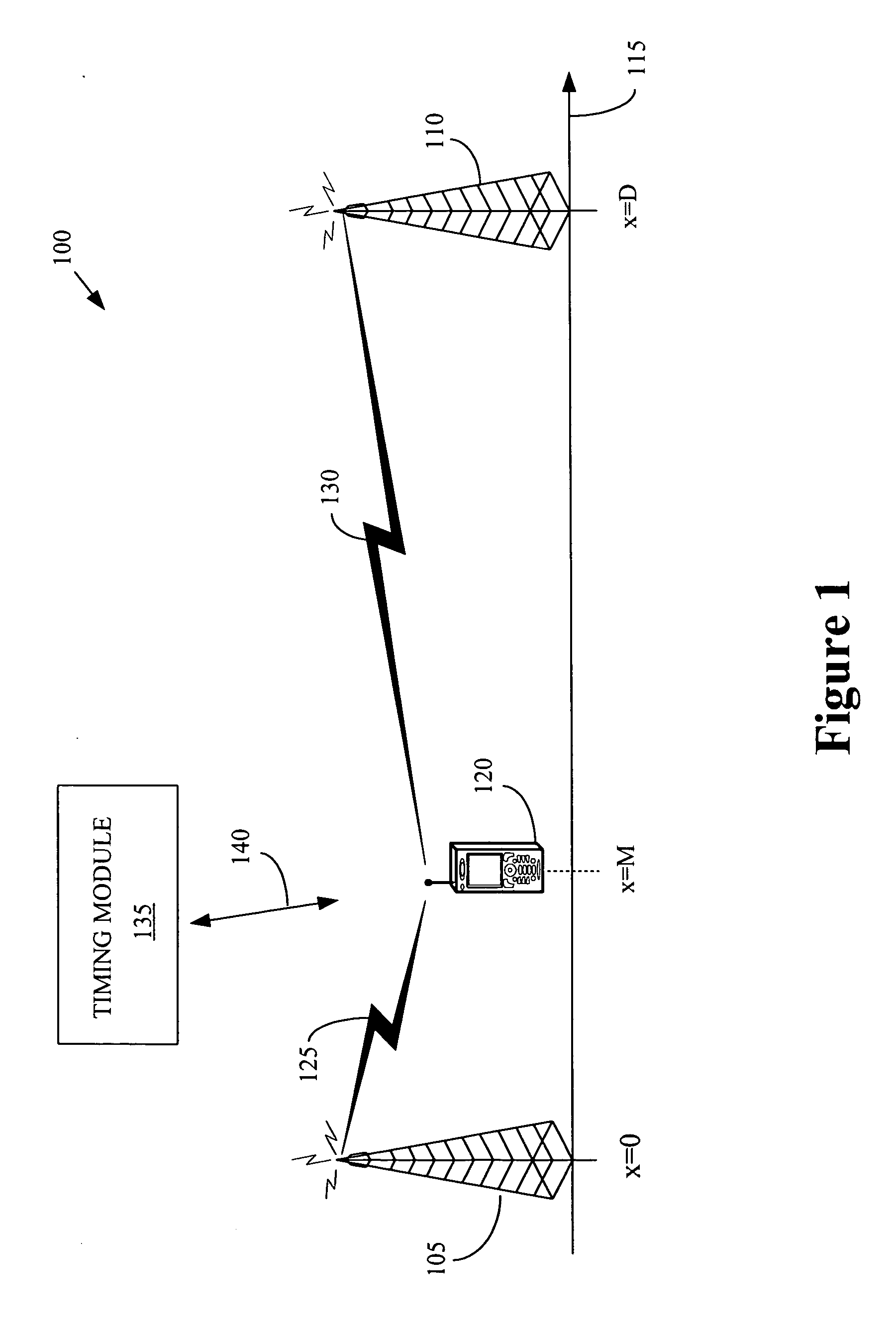

Evaluating base station timing in an asynchronous network

InactiveUS20060239391A1Well formedSynchronisation arrangementSynchronising arrangementTime informationPhase difference

The present invention provides a method of wireless communication with at least one mobile unit and at least two base stations. The method includes determining a phase difference between at least two timing signals associated with said at least two base stations based upon timing information provided by said at least one mobile unit from at least one known location.

Owner:LUCENT TECH INC

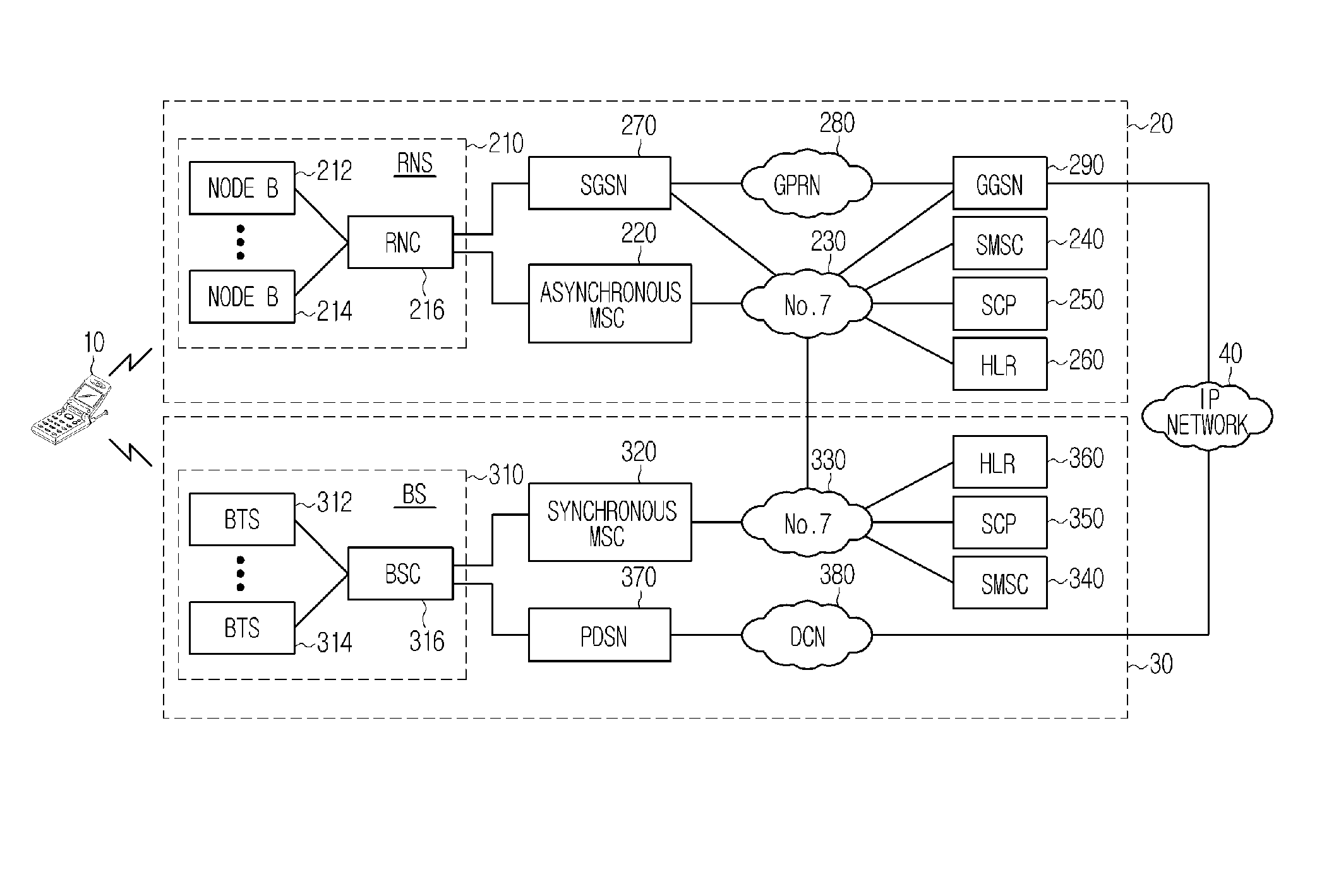

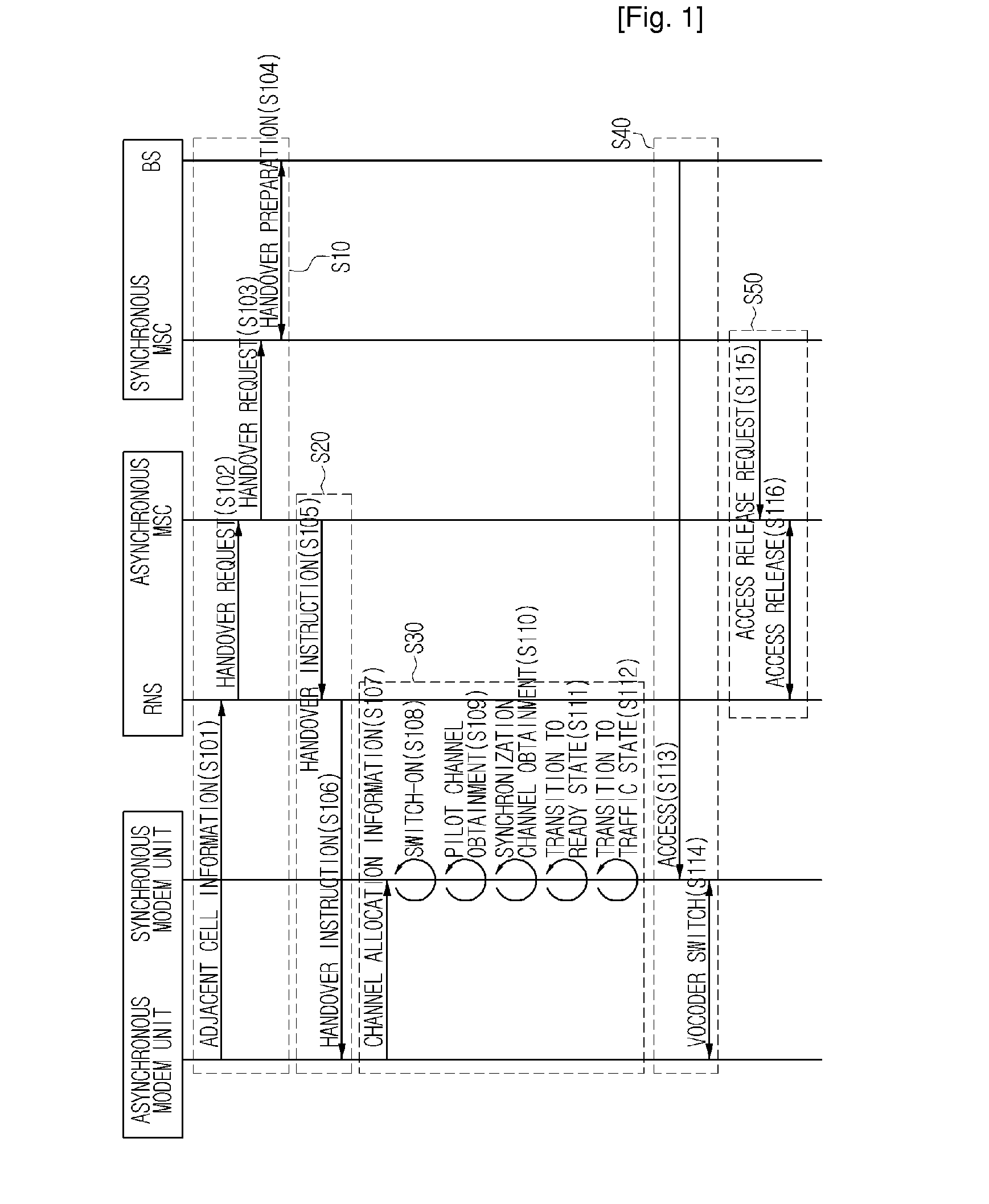

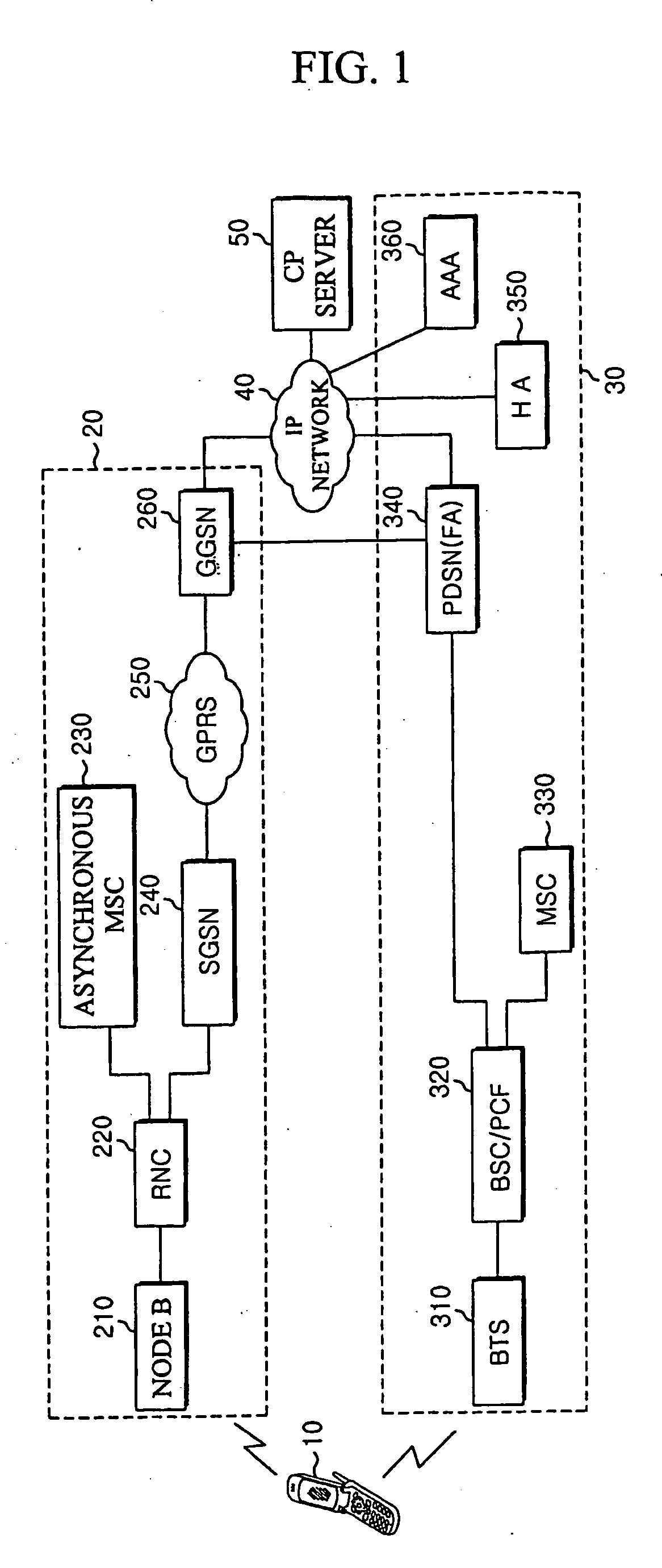

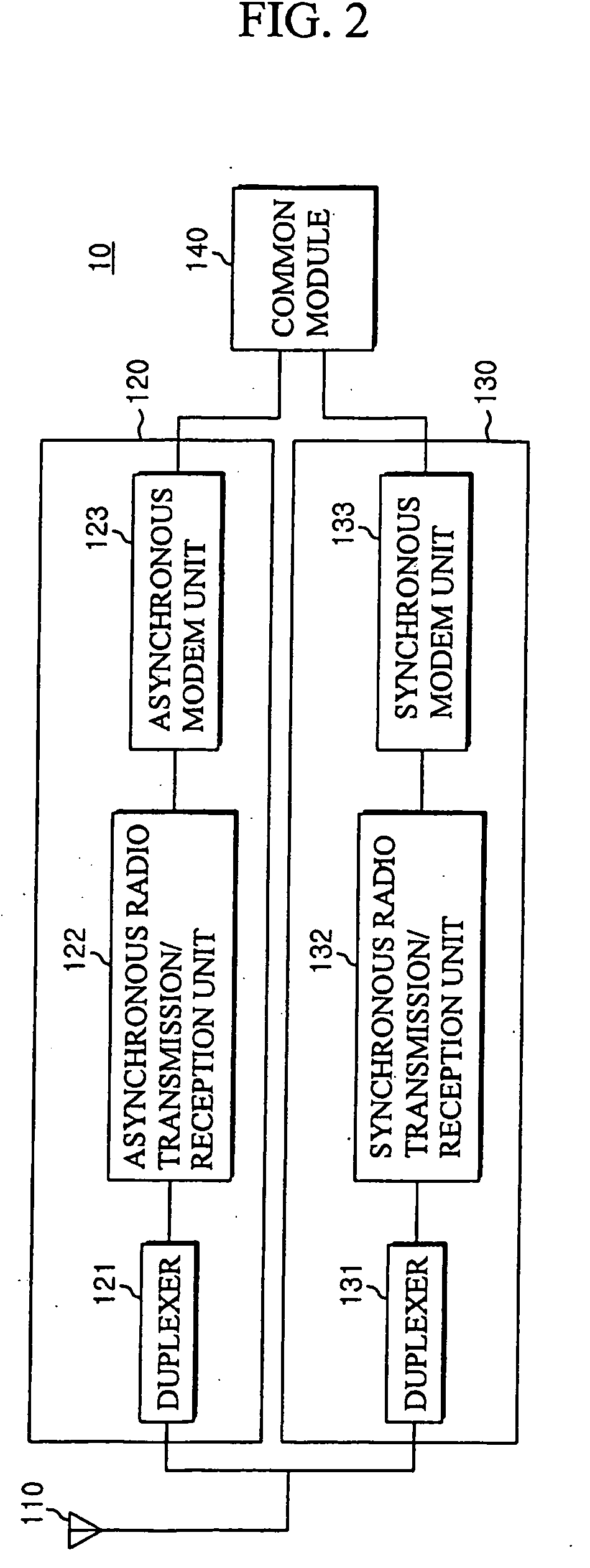

Handover Method for Mixed Mobile Communication System of Asynchronous Network and Synchronous Network

InactiveUS20080219212A1Increase success rateReduce power consumptionRadio/inductive link selection arrangementsRadio transmission for post communicationModem deviceAsynchronous network

A method for improving a success rate of handover in a mobile communication system in which an asynchronous network and a synchronous network are mixed is disclosed. The method comprises the steps of: an asynchronous system instructing an asynchronous modem of a mobile station to initiate a synchronous modem according to a handover request, the handover request that is generated from the mobile station when intensions of a forwarding and receiving signals between the mobile station and a node B of the asynchronous system are less than a predetermined intension; the asynchronous system determining a cell for the handover and instructing the mobile station to handover a synchronous system; the asynchronous modem requesting the synchronous modem to receiving a current communication according to a handover request of the asynchronous system to the asynchronous modem; the mobile station accessing the synchronous system; and the asynchronous releasing the communication with the mobile station.

Owner:SK TELECOM CO LTD

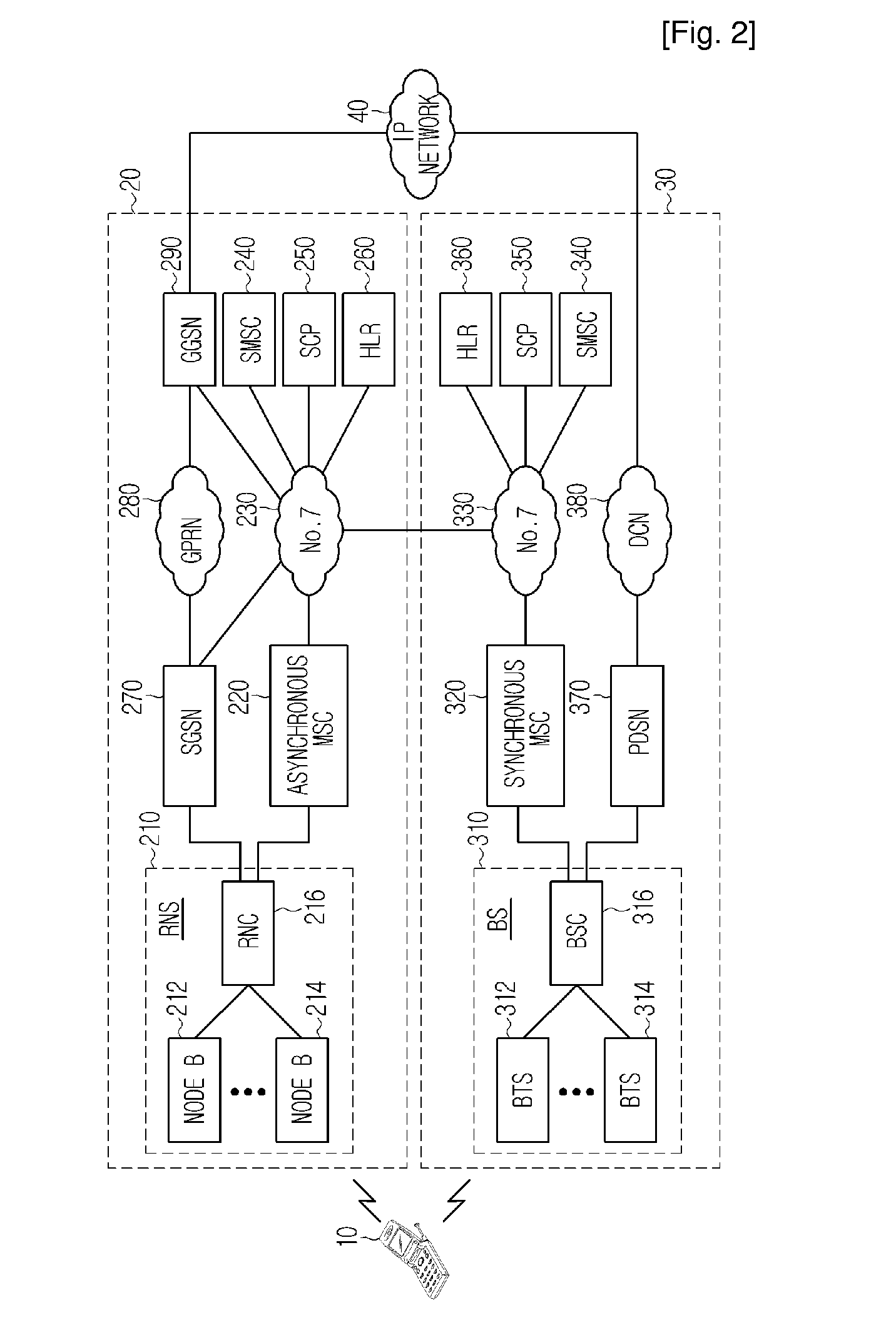

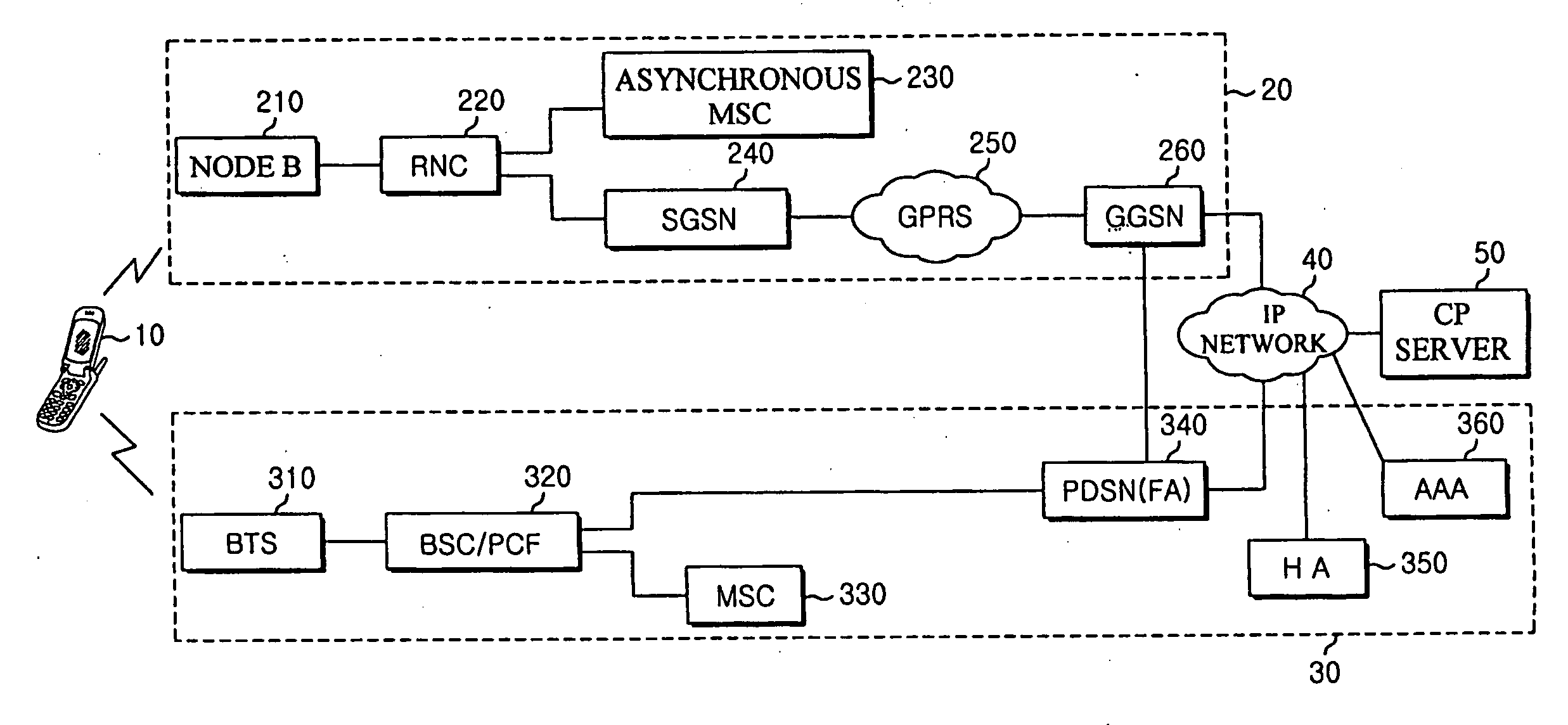

System for packet data service in the mixed network of asynchronous communication network and synchronous communication network and hand-over method thereof

InactiveUS20090190549A1Avoid service interruptionTime-division multiplexRadio transmission for post communicationPacket data serving nodeMix network

Disclosed herein is a mobile communication terminal and handover method therefor. In the mobile communication system, a Gateway GPRS Support Node (GGSN) of the asynchronous network is connected to a Packet Data Service Node (PDSN) of the synchronous network. Accordingly, as a mobile communication terminal, using packet data service in the asynchronous mobile communication system, moves into an area of a synchronous mobile communication system, the synchronous mobile communication system sets control signals and traffic to transmit packet data in response to a request from the asynchronous mobile communication system. Further, if forward and reverse channels are assigned between the mobile communication terminal and the synchronous mobile communication system, call setup is performed to provide the packet data service, and then a node B of the asynchronous mobile communication system releases the connection to the mobile communication terminal.

Owner:SK TELECOM CO LTD

Method and apparatus for synchronizing clock timing between network elements

Network elements may be synchronized over an asynchronous network by implementing a master clock as an all digital PLL that includes a Digitally Controlled Frequency Selector (DCFS), the output frequency of which may be directly controlled through the input of a control word. The PLL causes the control word input to the master DCFS to be adjusted to cause the output of the master DCFS to lock onto a reference frequency. Information associated with the control word is transmitted from the master clock to the slave clocks which are also implemented as DCFSs. By using the transmitted information to recreate the master control word, the slaves may be made to assume the same state as the master DCFS without requiring the slaves to be implemented as PLLs. The DCFS may be formed as a digitally controlled oscillator (DCO) or as a Direct Digital Synthesizer (DDS).

Owner:CIENA

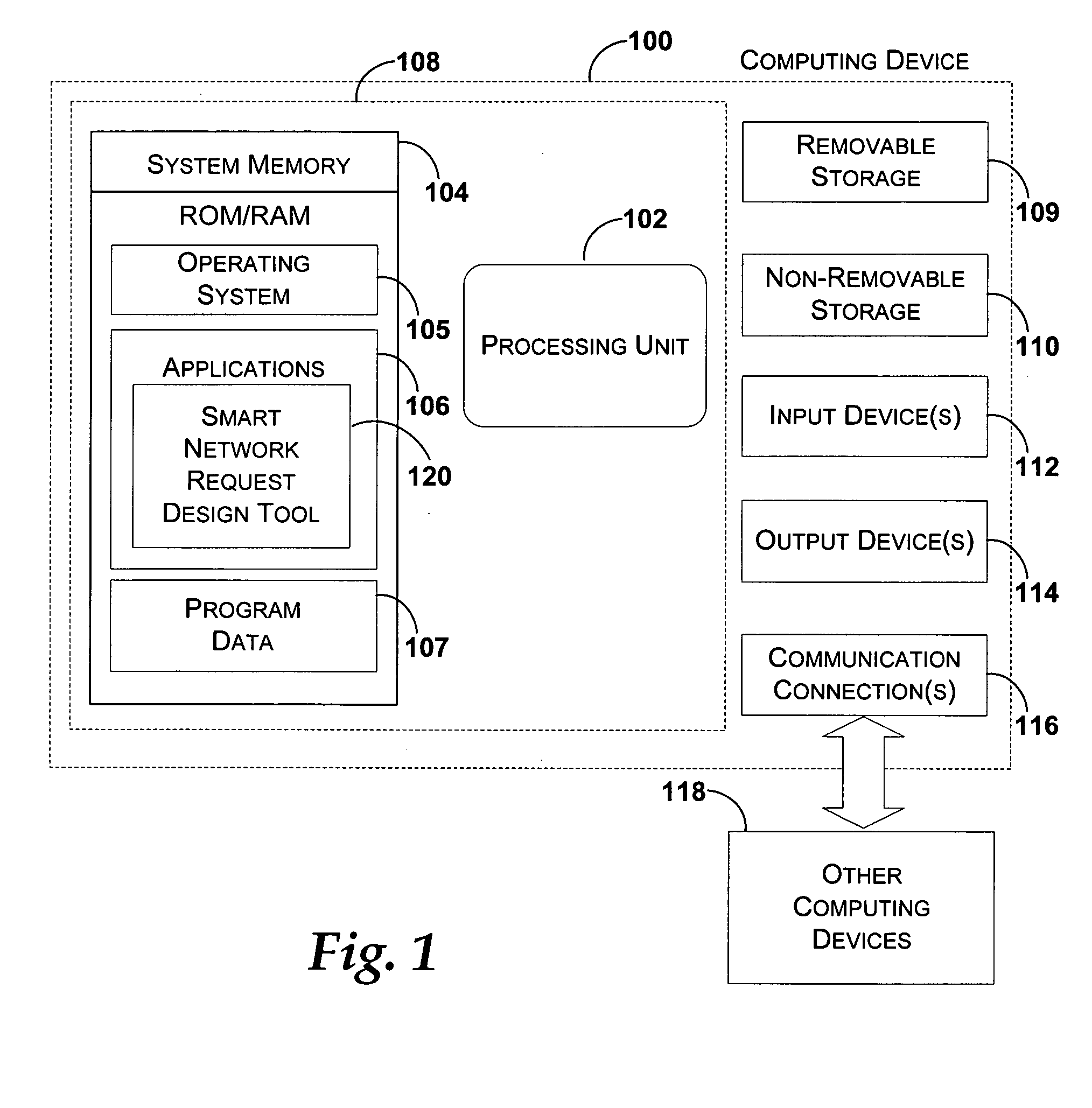

System and method for applying flexible attributes to execute asynchronous network requests

ActiveUS20060184675A1Simple processNetwork traffic/resource managementMultiple digital computer combinationsGraphicsGraphical user interface

Flexible attributes are attached to network requests that may be executed asynchronously. Any number of criteria may be attached to network requests. The requests are queued until the associated criteria are satisfied. Once the criteria are satisfied, the request is executed. Applications that make the requests are provided with simple success and failure notifications that they can respond to with various logic. Any type of criteria may be attached to a request. The criteria may be associated with the requests at design time of the application using a graphical user interface.

Owner:MICROSOFT TECH LICENSING LLC

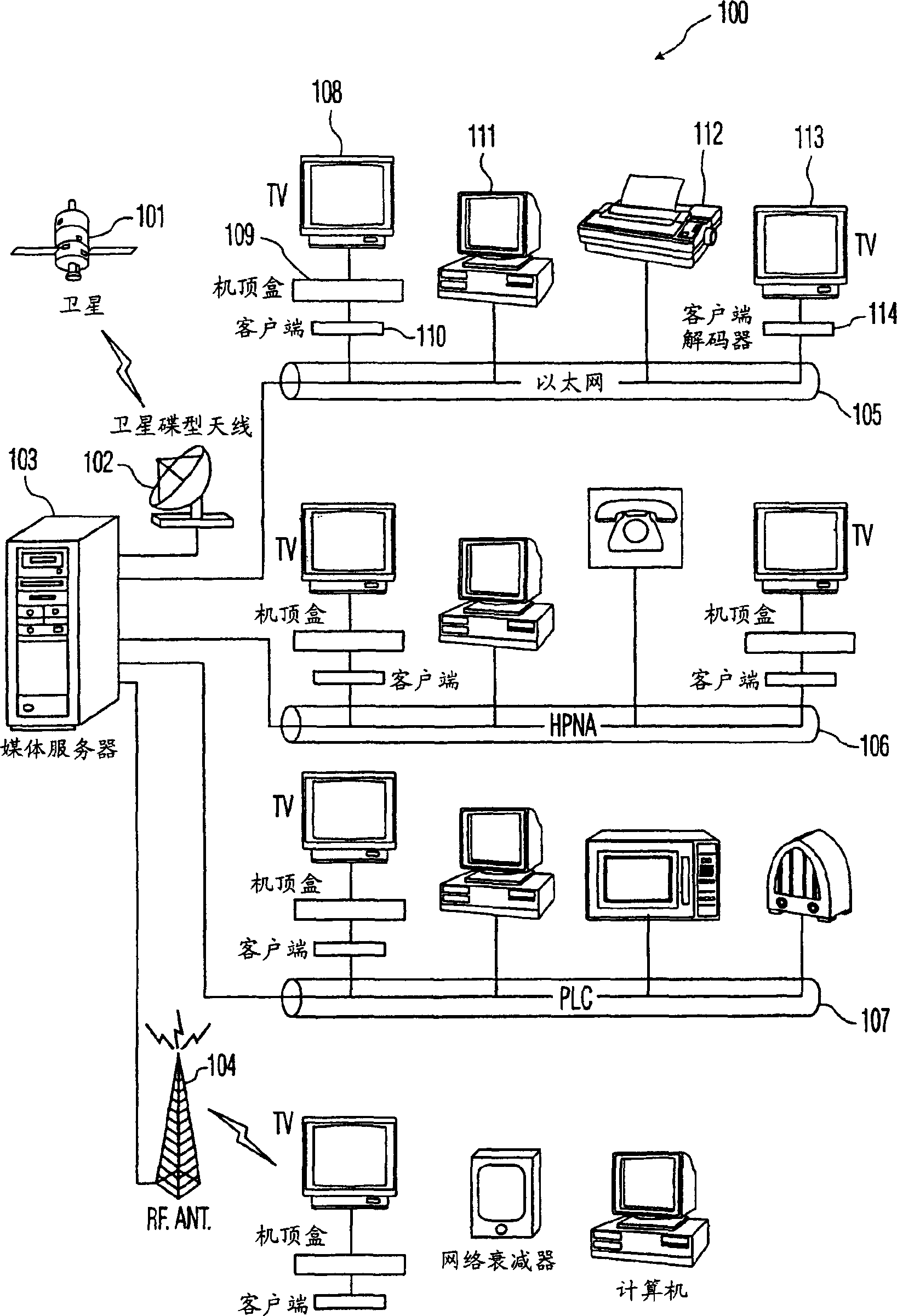

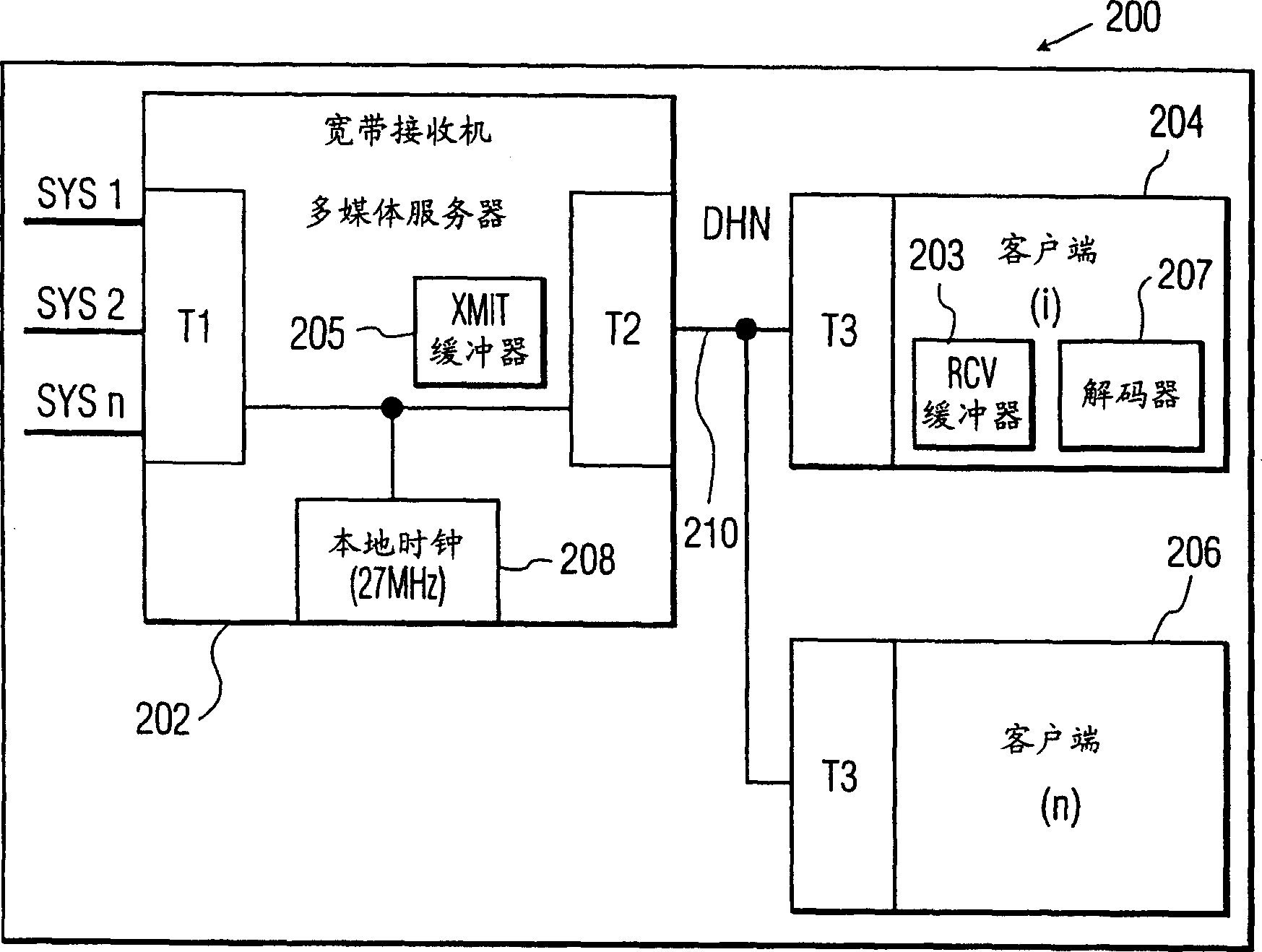

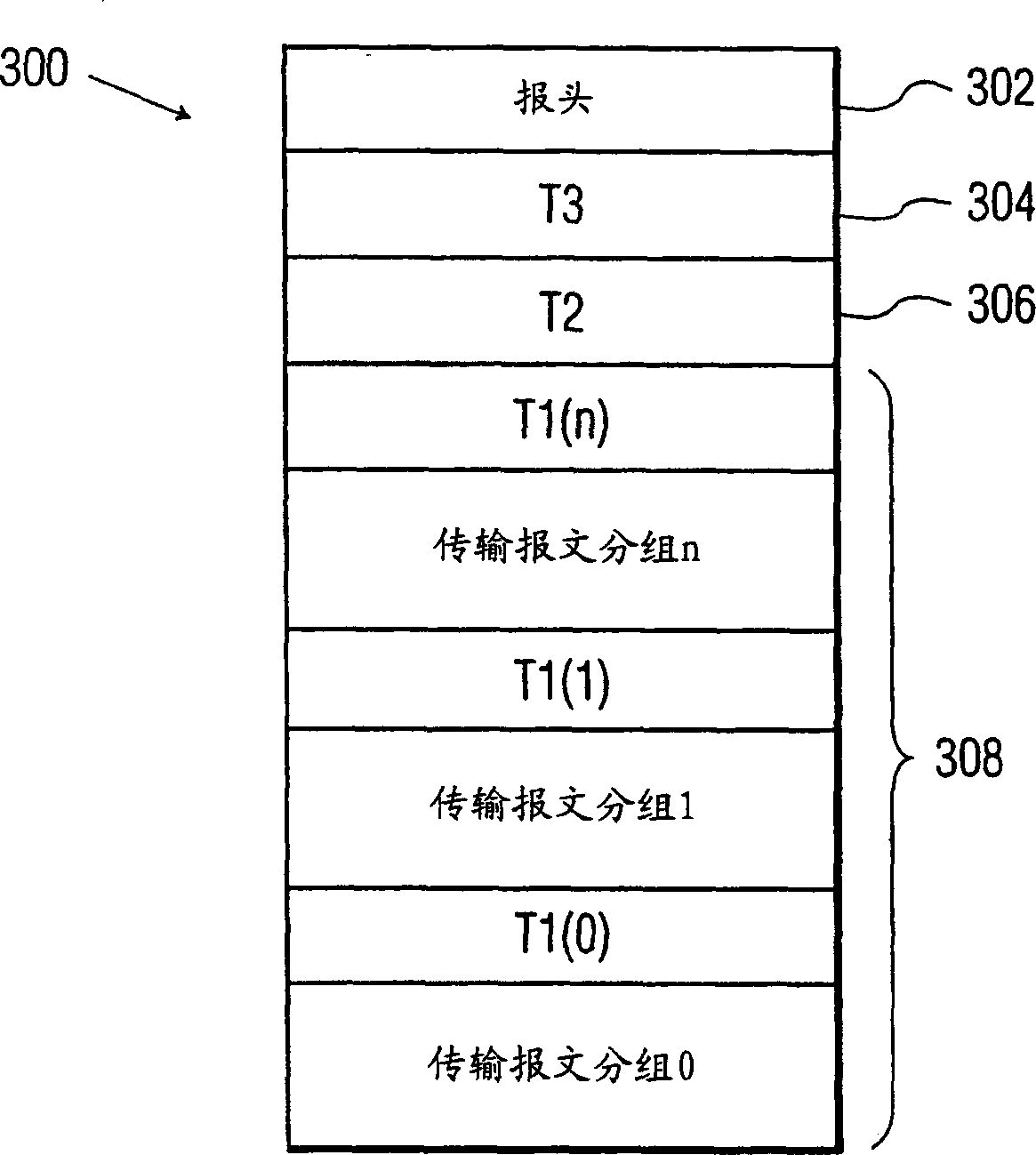

Multimedia jitter removal in an asynchronous digital home network

InactiveCN1522510ATime-division multiplexData switching by path configurationData streamPhysical layer

A method and an apparatus using a system level clocking scheme to remove jitter from multi-media packets distributed over an asynchronous network, in particular an Ethernet network. The present invention overcomes the problems associated with jitter introduced in an Ethernet network by using various time stamps to synchronize a client device clock to a headend clock and to control the data flow in the client device to match the rate that the data is received by a broadband receiver coupled to the headend. A first time stamp is prepended to the transport packets when the packets are received from the headend. A second time stamp is placed in the data frame when the data frame is placed on the network. A third time stamp is placed in the data frame when the data frame is received from the network. The second and third time stamps are used for clock synchronization and the first time stamp is used for data flow control. According to the present invention, the time stamps are added at the physical layer so that the time stamps correspond to the actual time the data packets are placed onto and received from the asynchronous network.

Owner:THOMSON LICENSING SA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com