Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

8054results about "Conductive pattern formation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

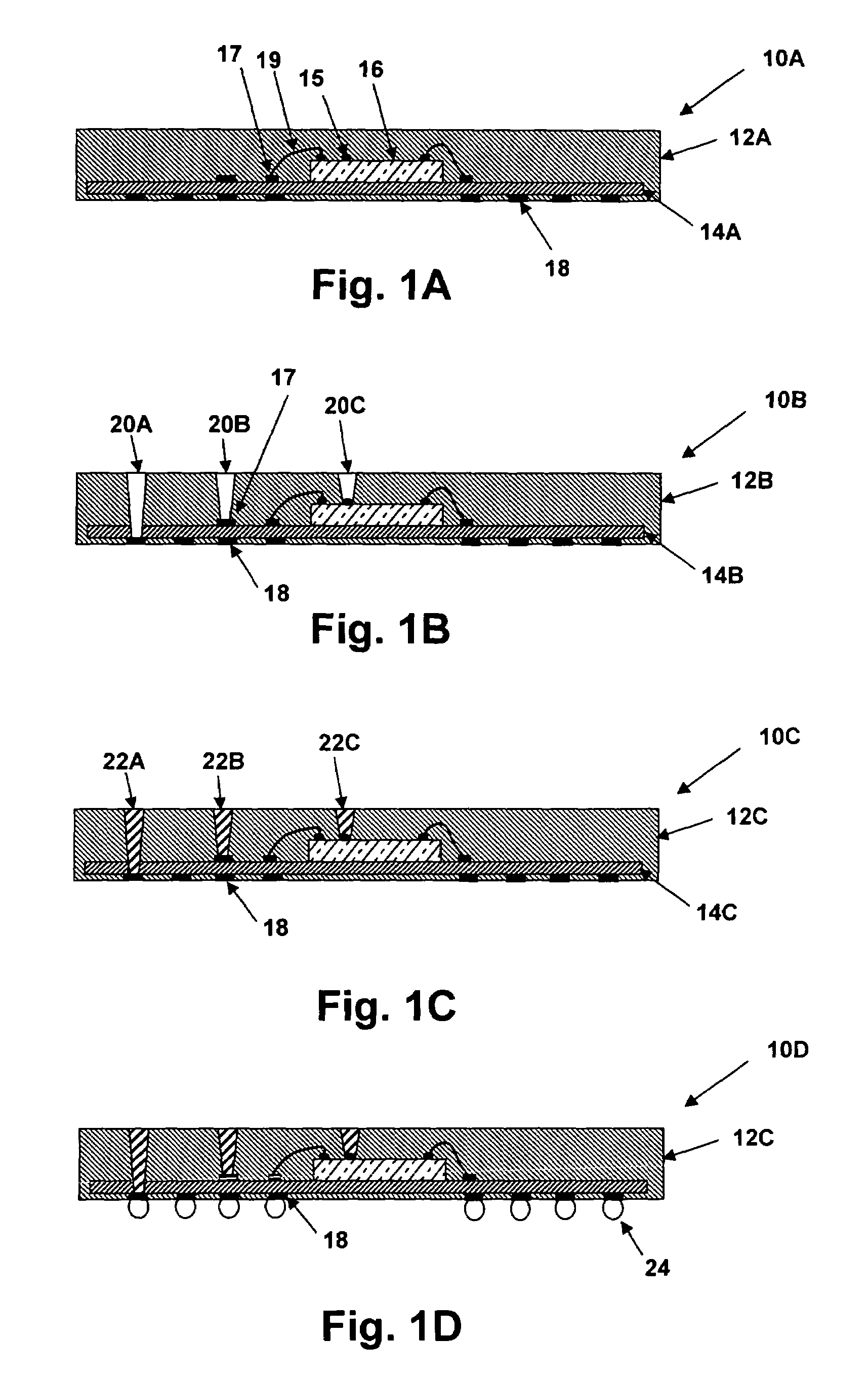

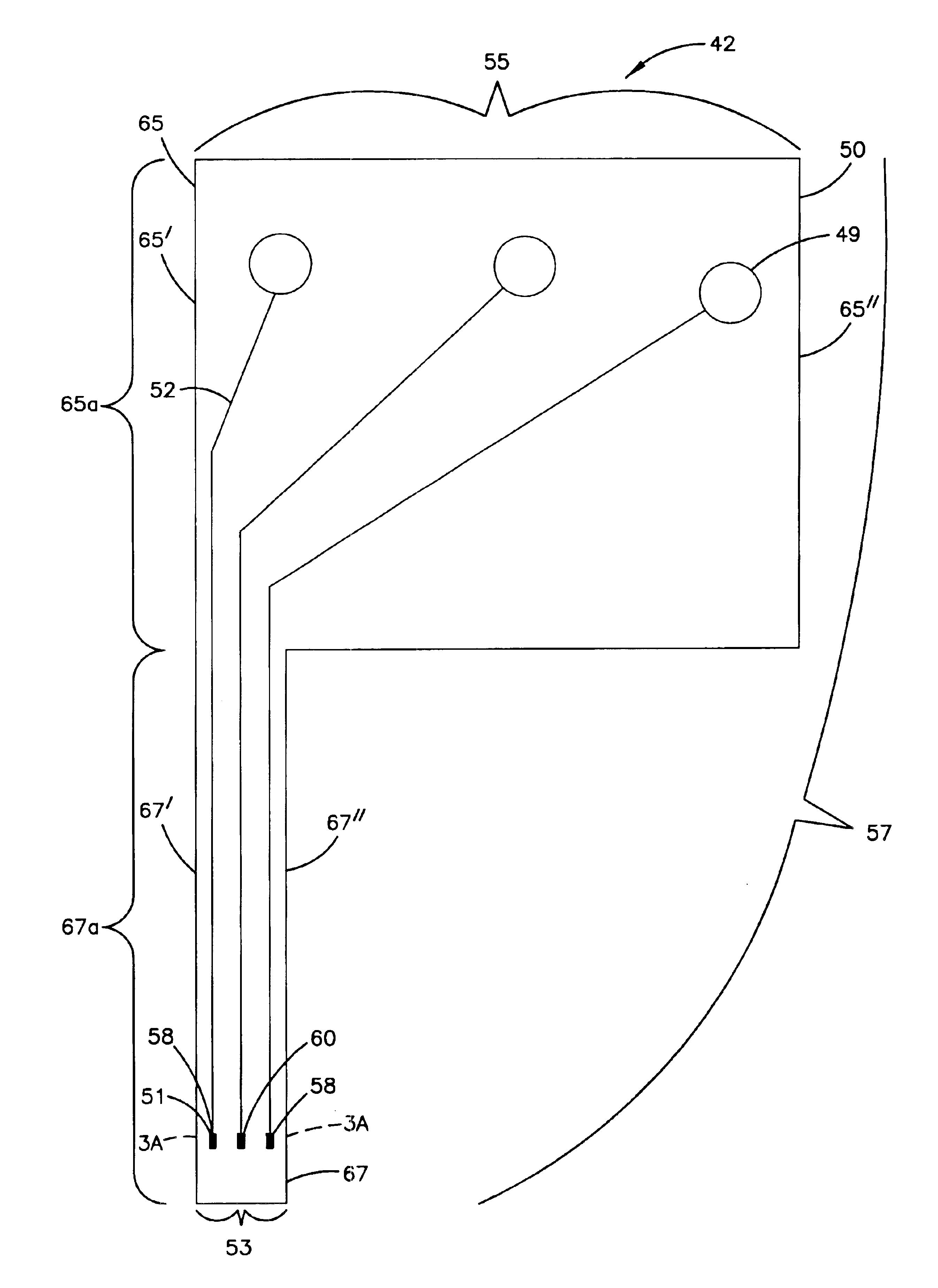

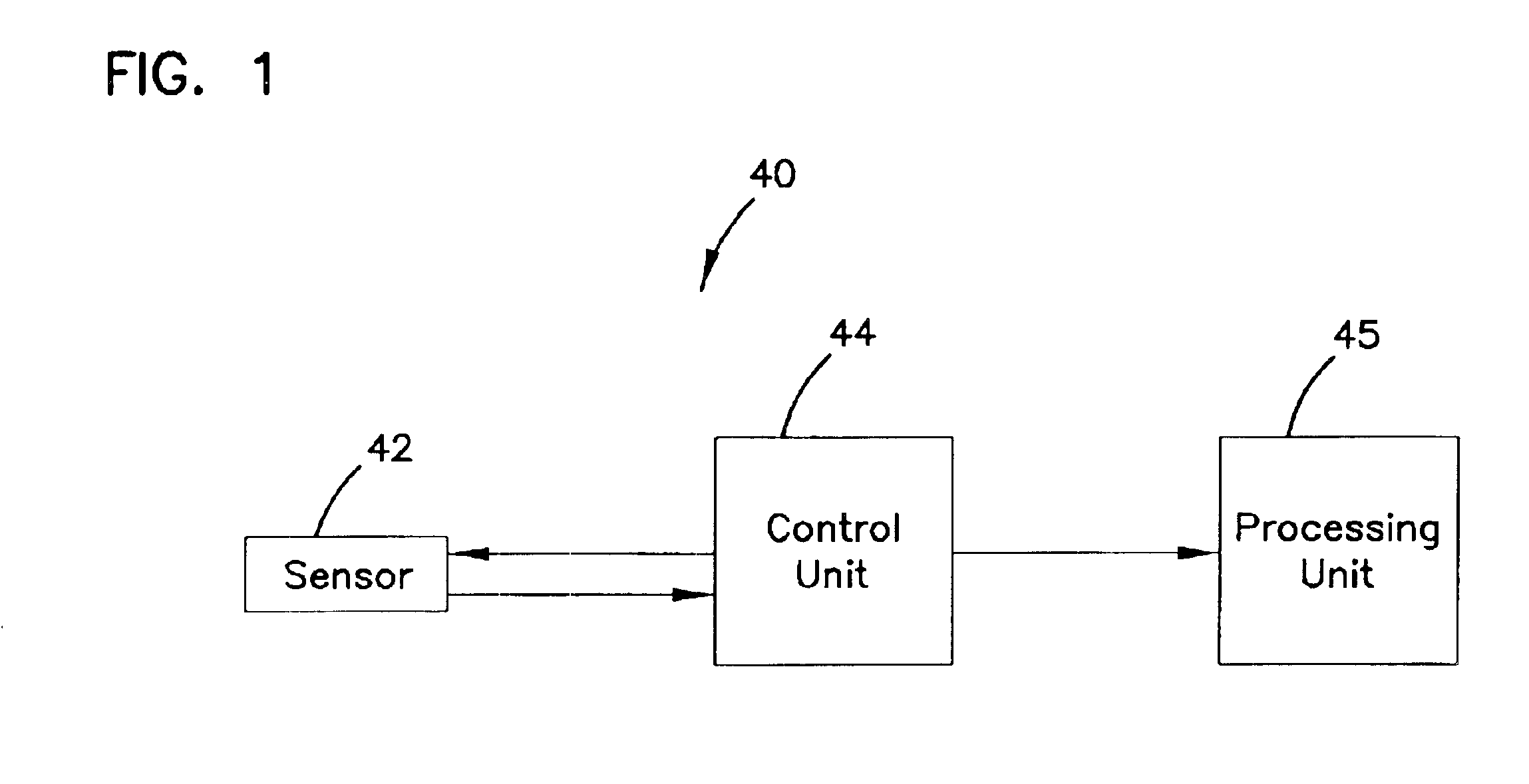

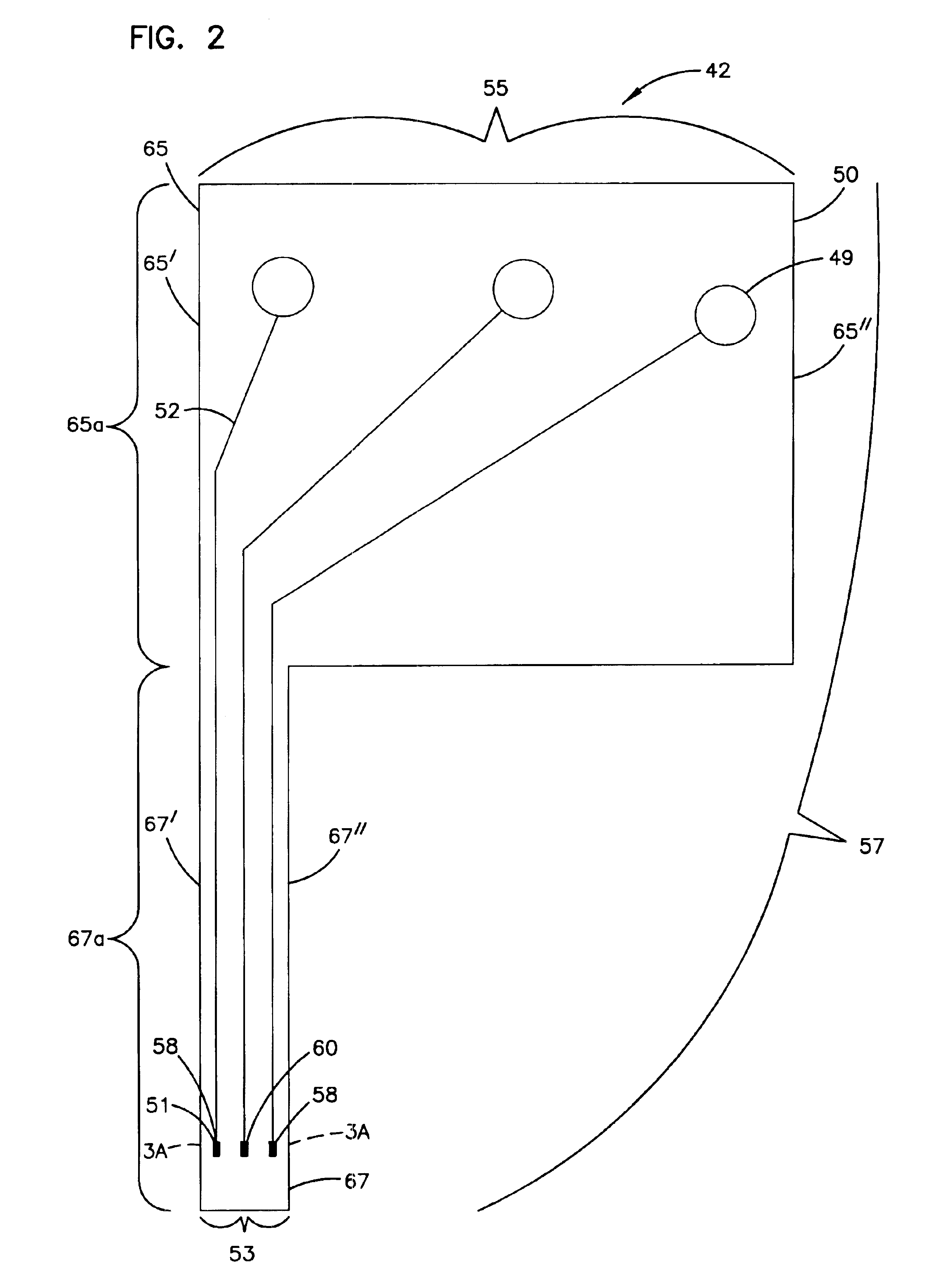

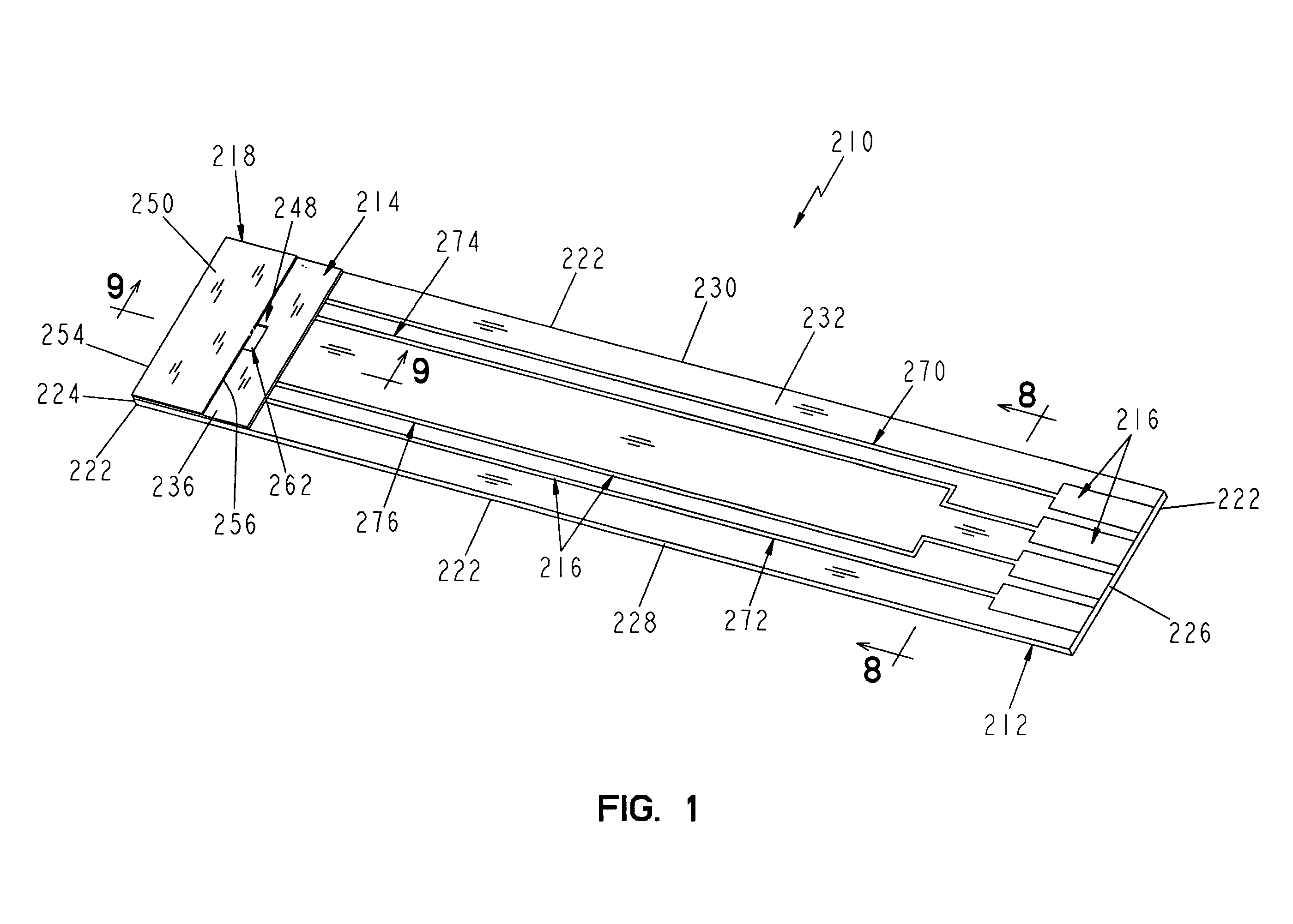

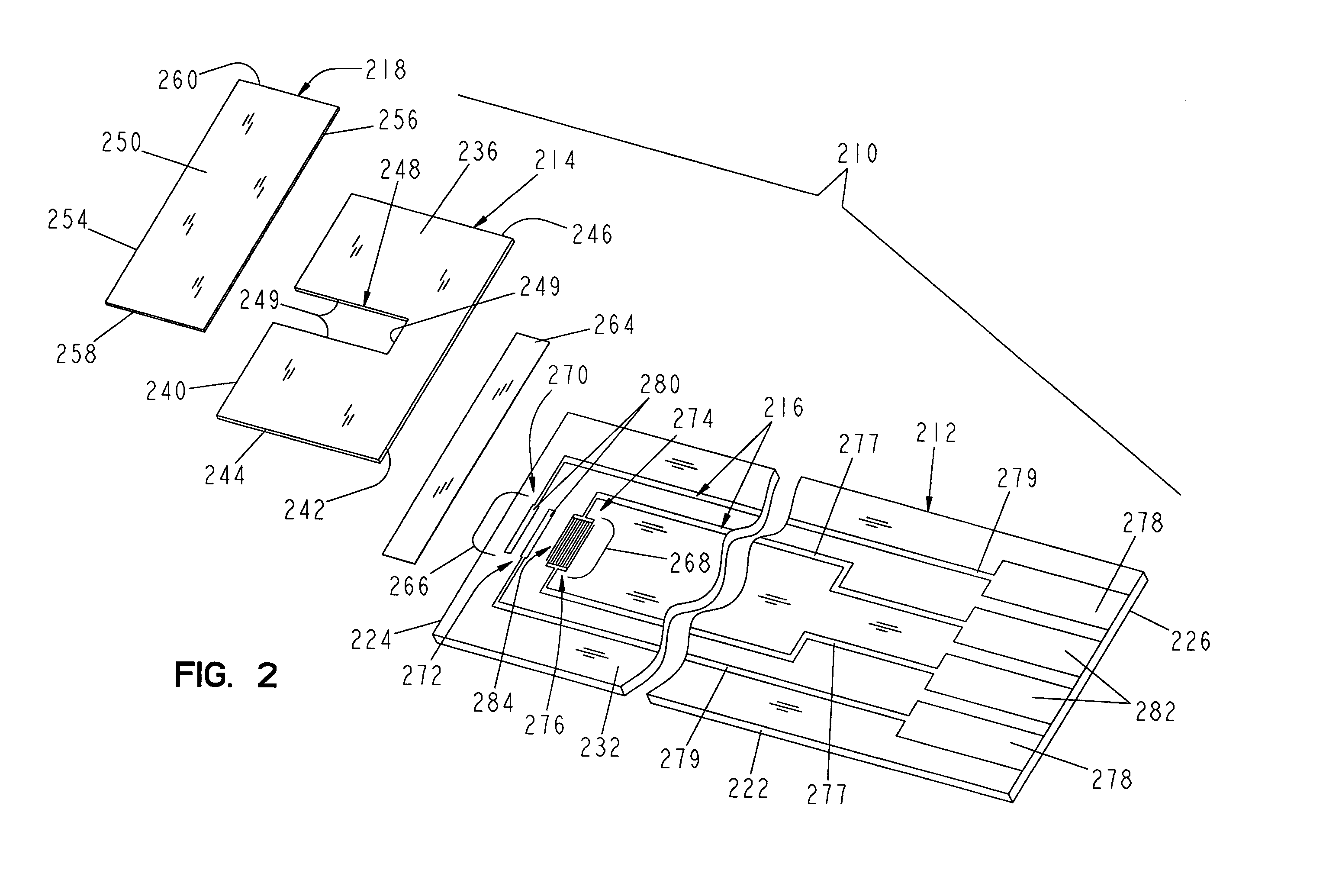

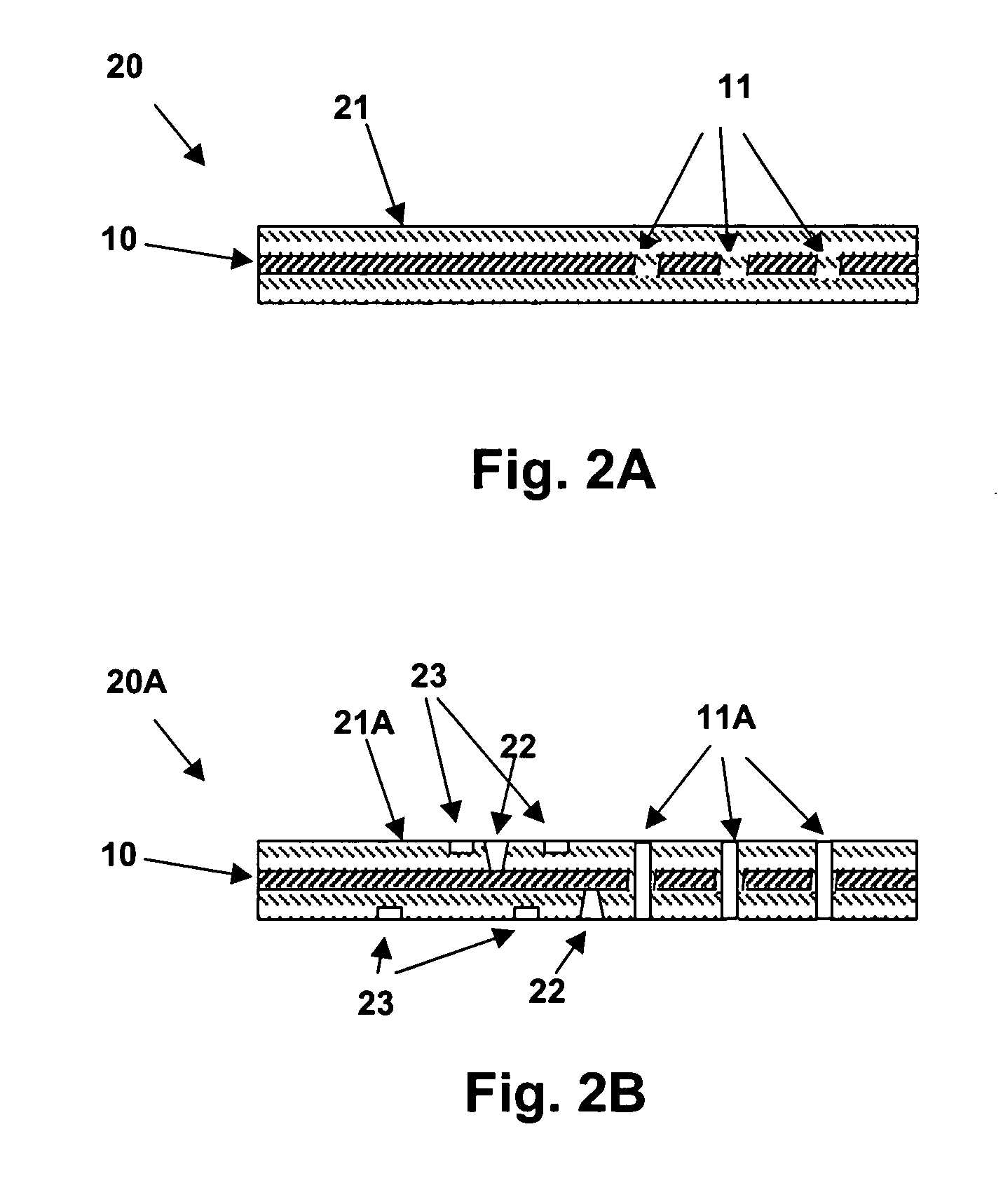

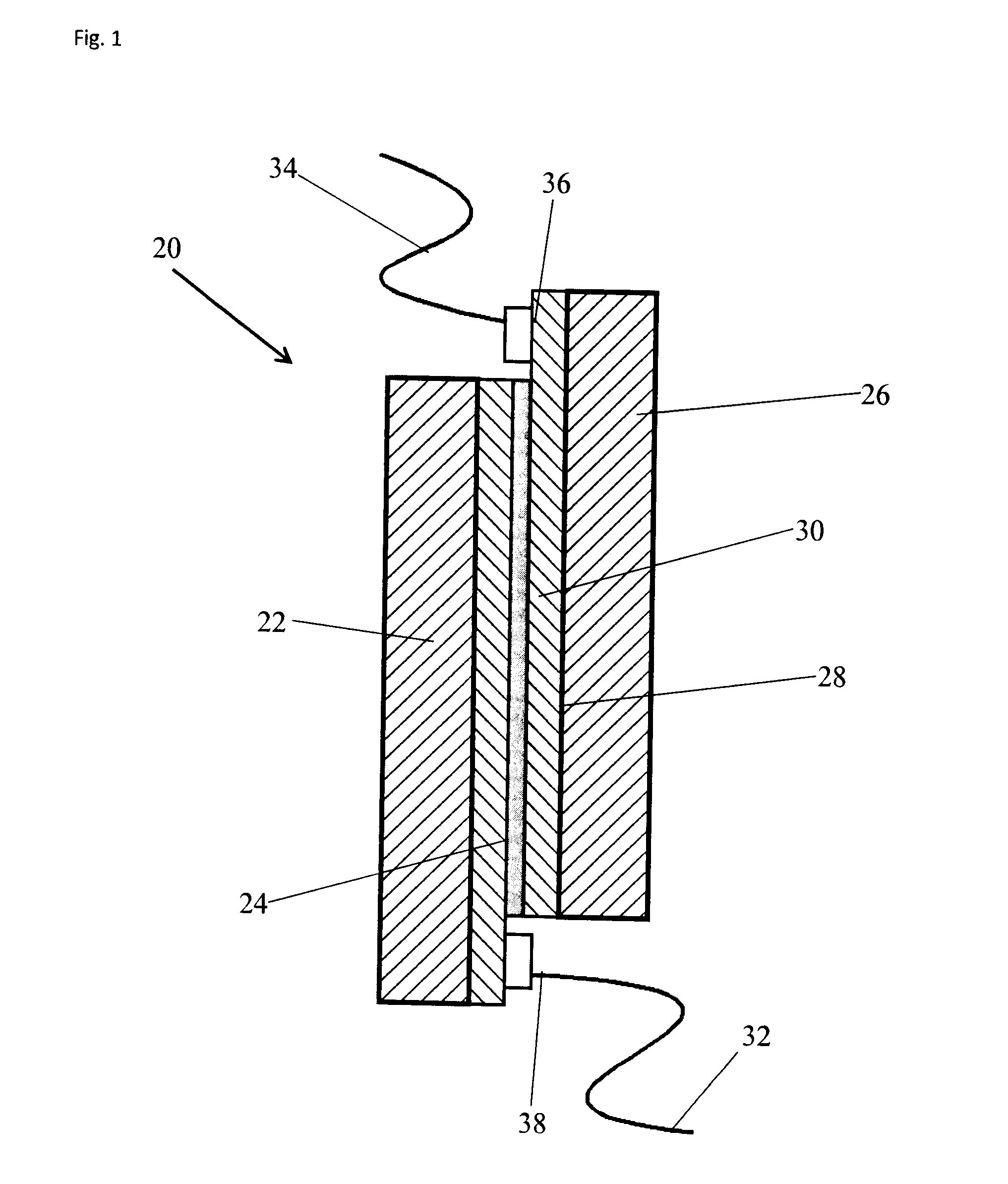

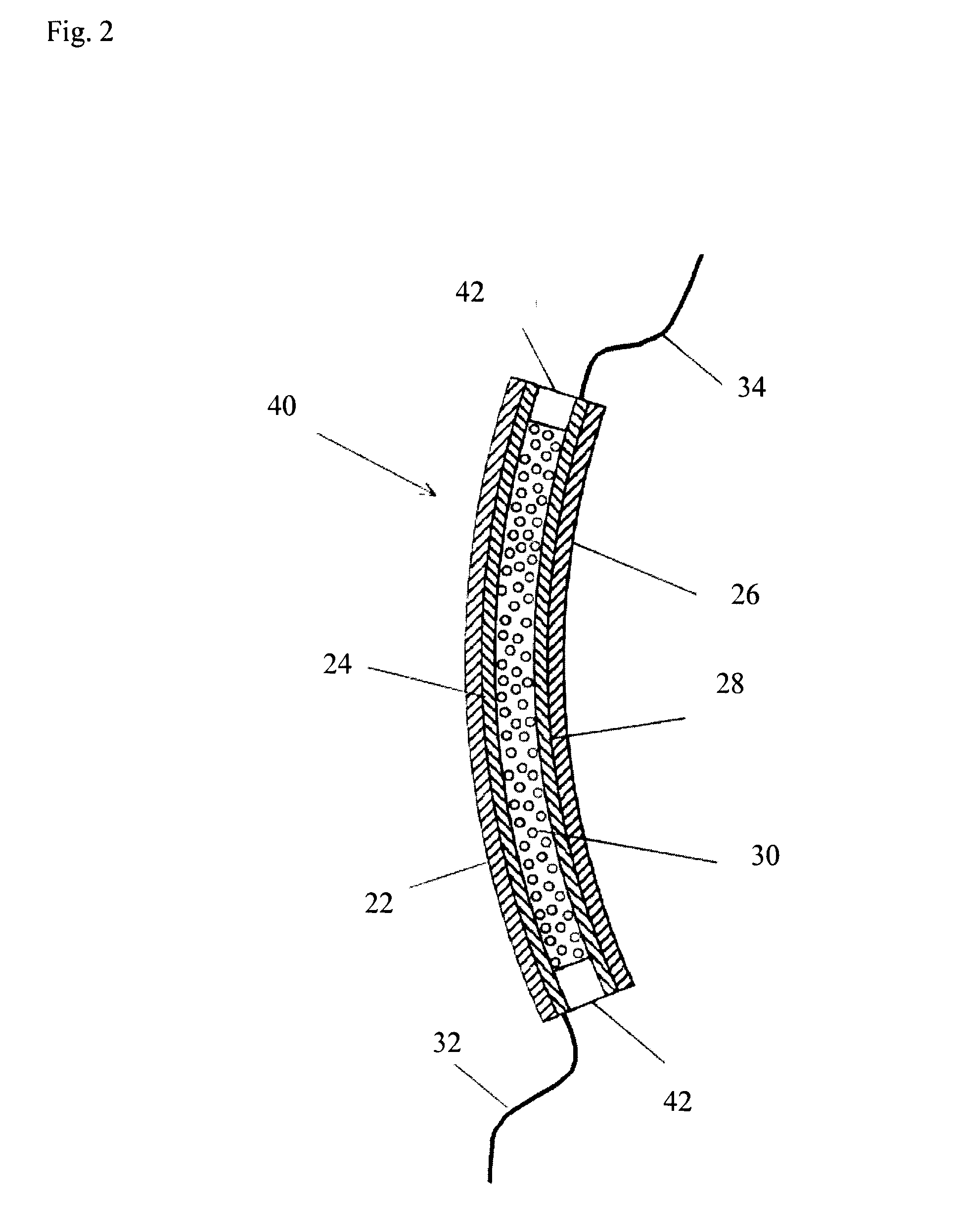

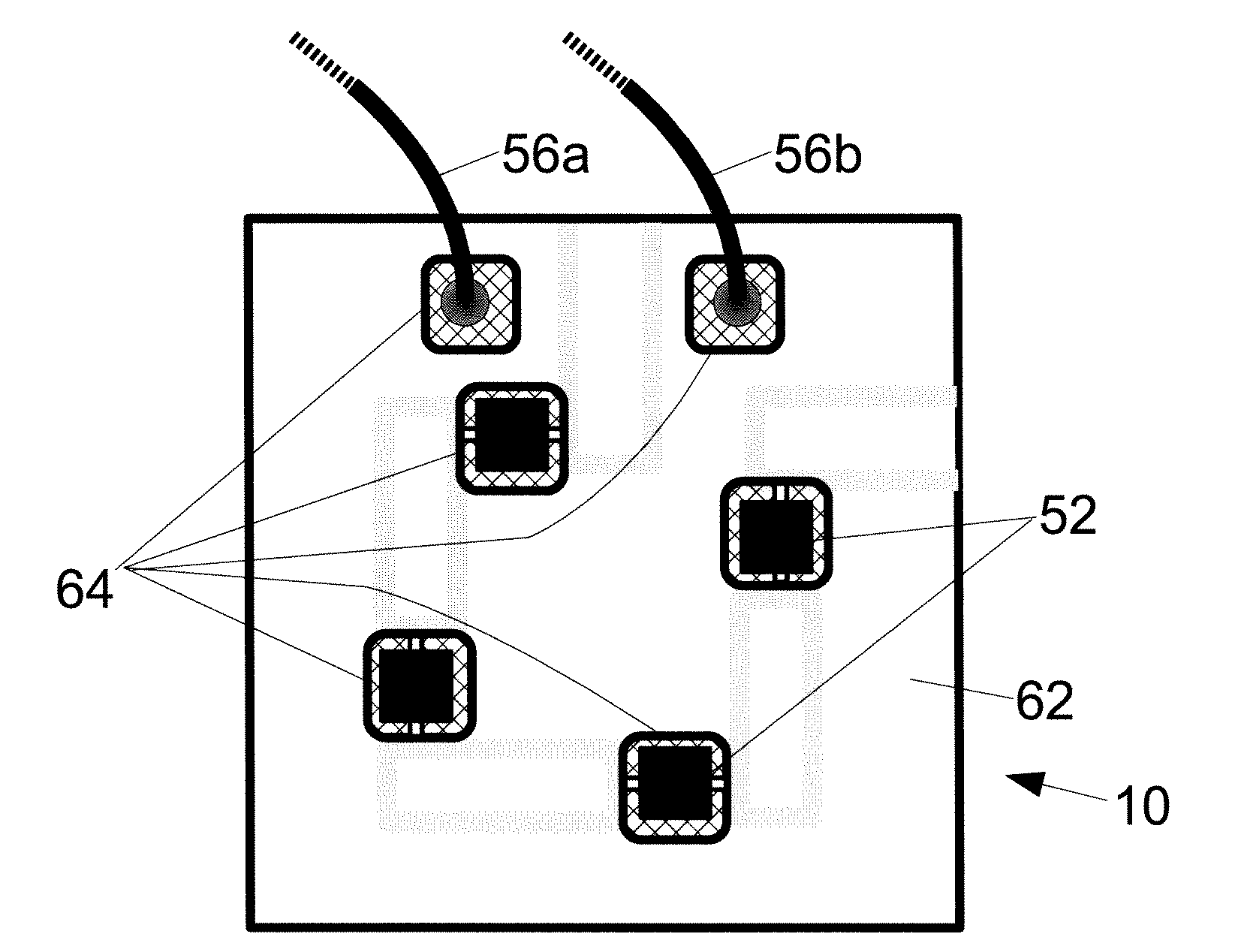

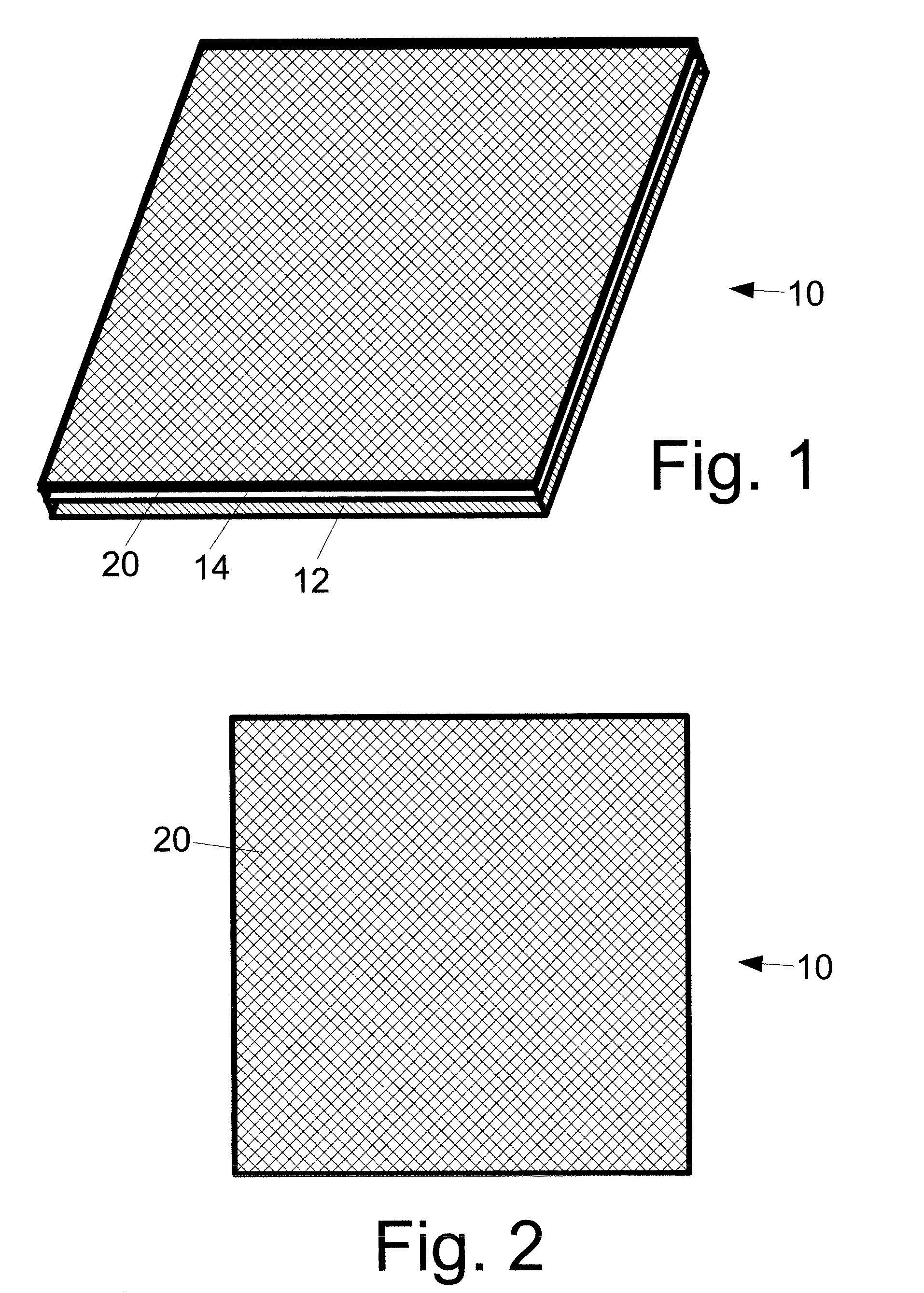

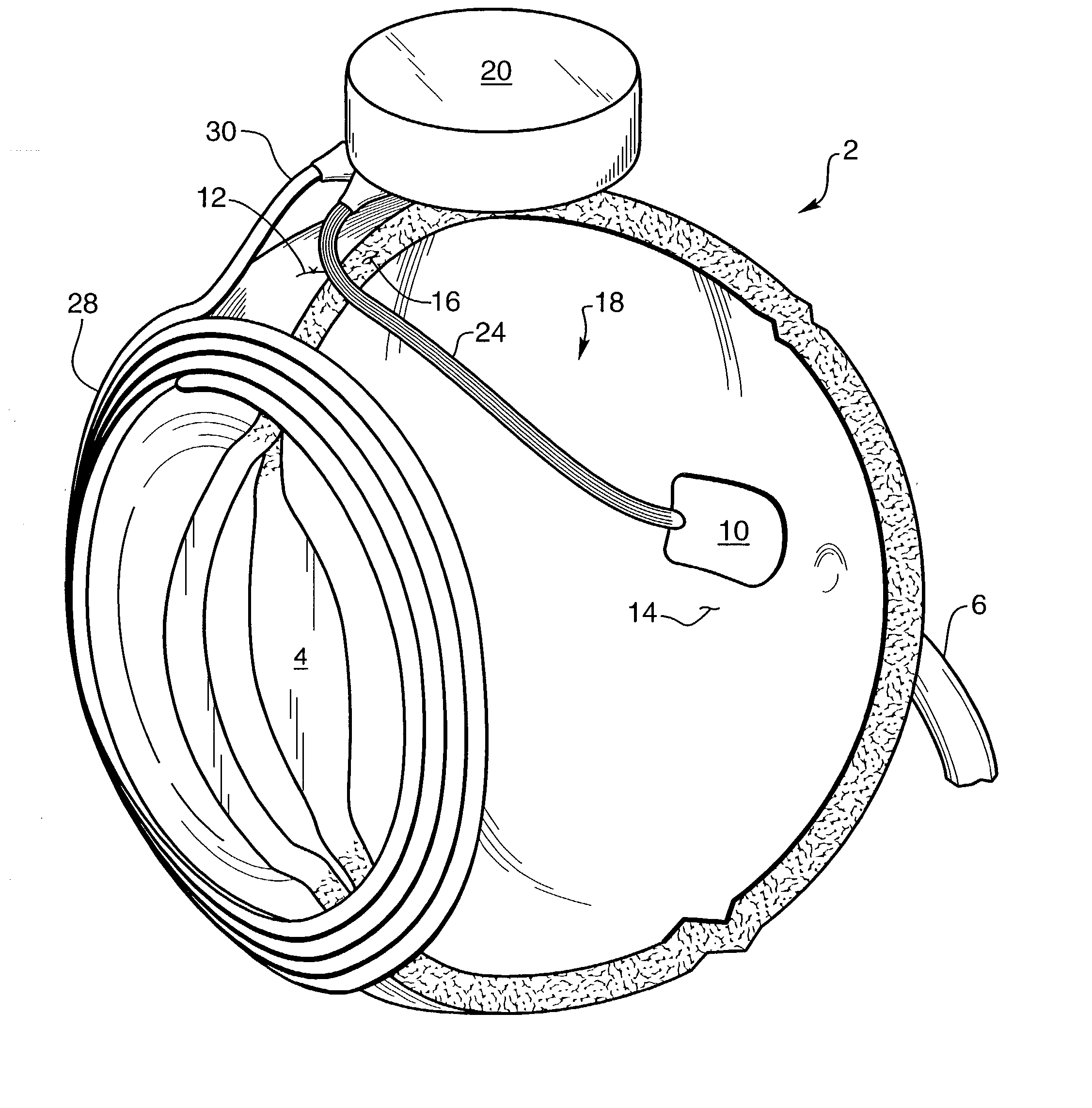

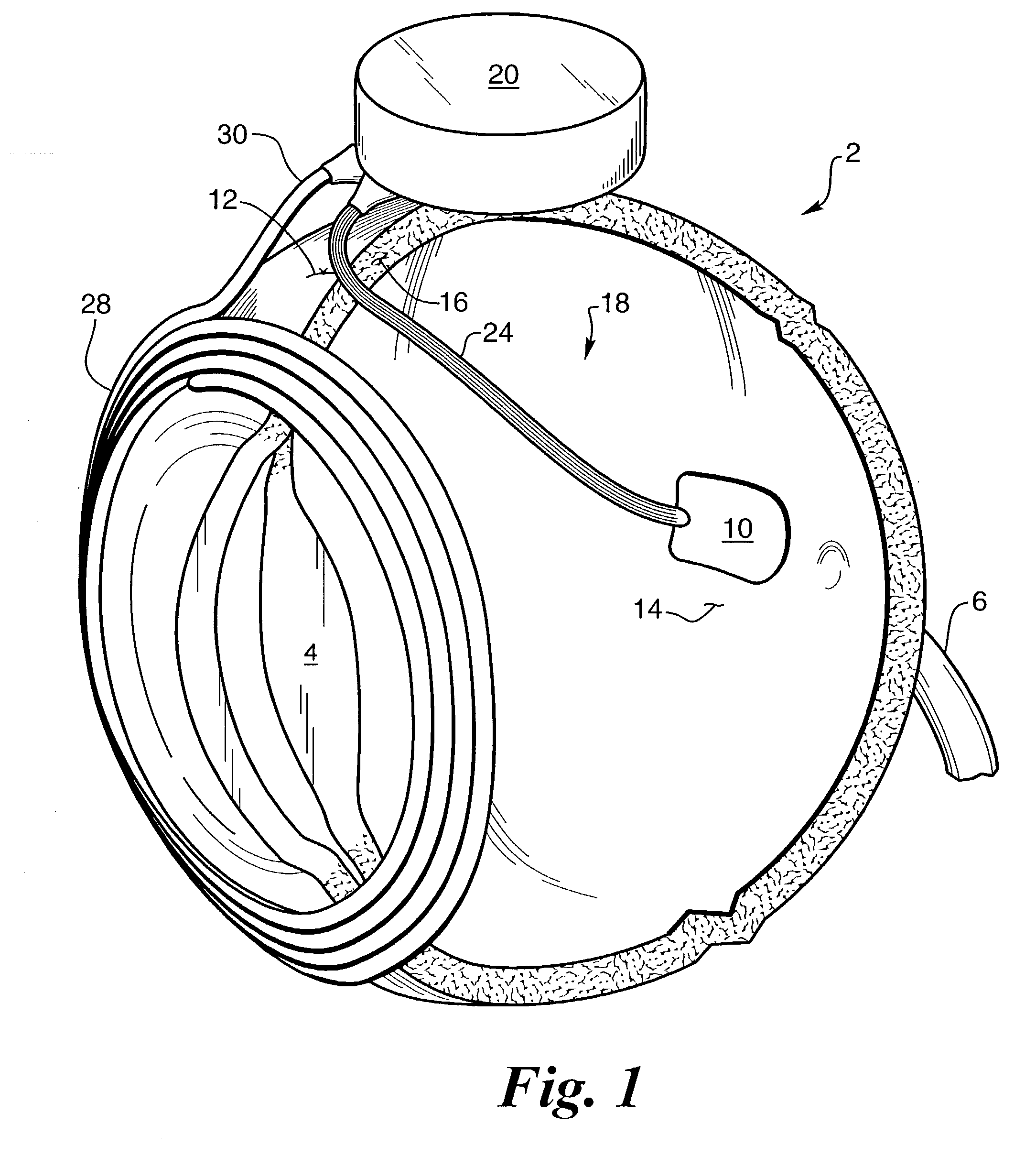

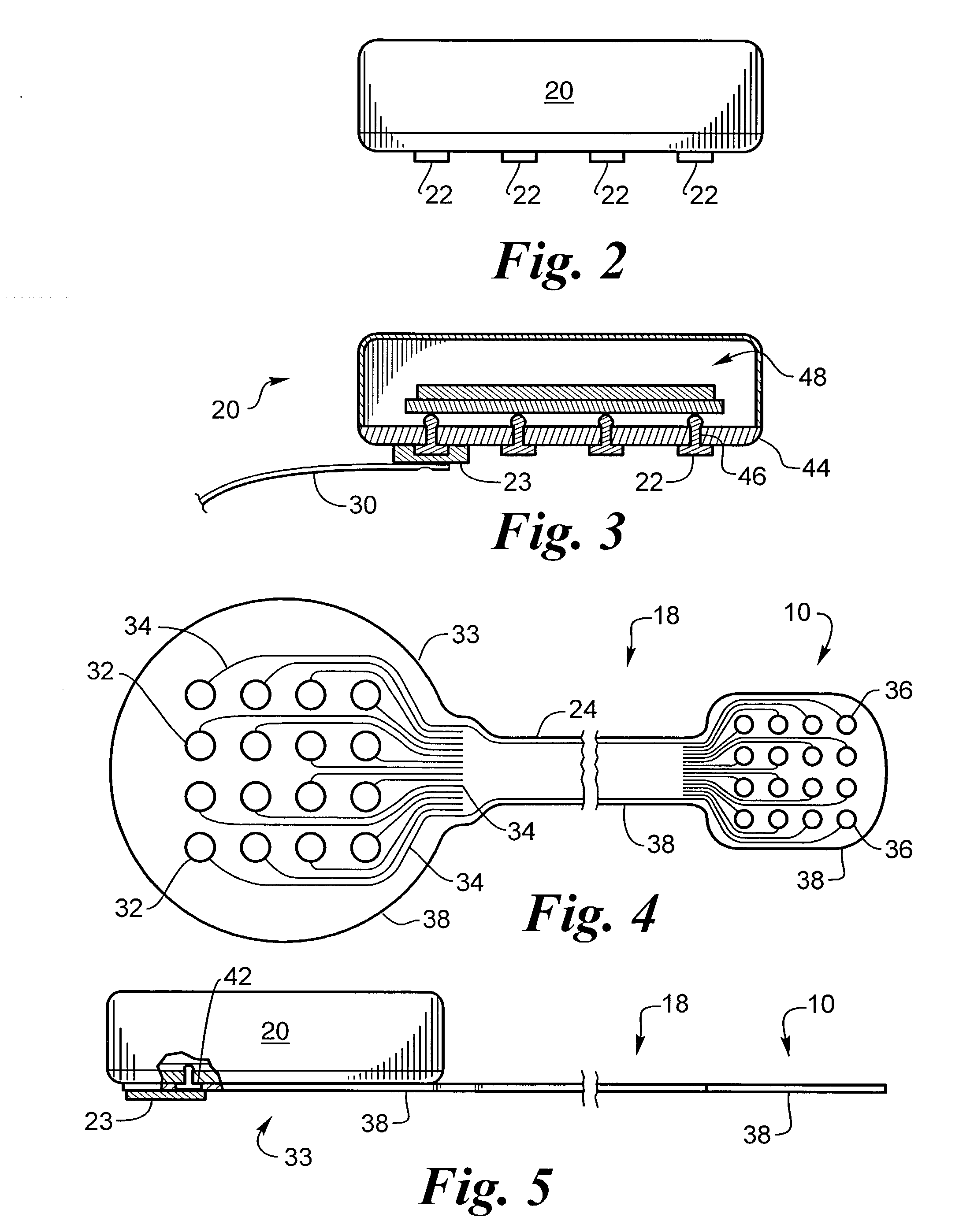

Flex circuit shielded optical sensor

InactiveUS6985764B2Cross-talk/noise/interference reductionColor/spectral properties measurementsPhotovoltaic detectorsPhotodetector

A flex circuit optical sensor has an integrated Faraday shield. A conductive trace layer disposed on a substrate is used to form a conductive grid which shields the face of a photodetector. A conductive ink layer is formed on a substrate side opposite the trace layer. The back and sides of the detector are shielded by flex circuit flaps that have the conductive ink layer but substantially exclude the trace layer so as to fold over and closely adhere to the detector body. The shielded substrate flaps advantageously eliminate a separate detector shield, which is typically fabricated with an etched copper part that must be attached to a flex circuit before mounting the detector.

Owner:JPMORGAN CHASE BANK NA

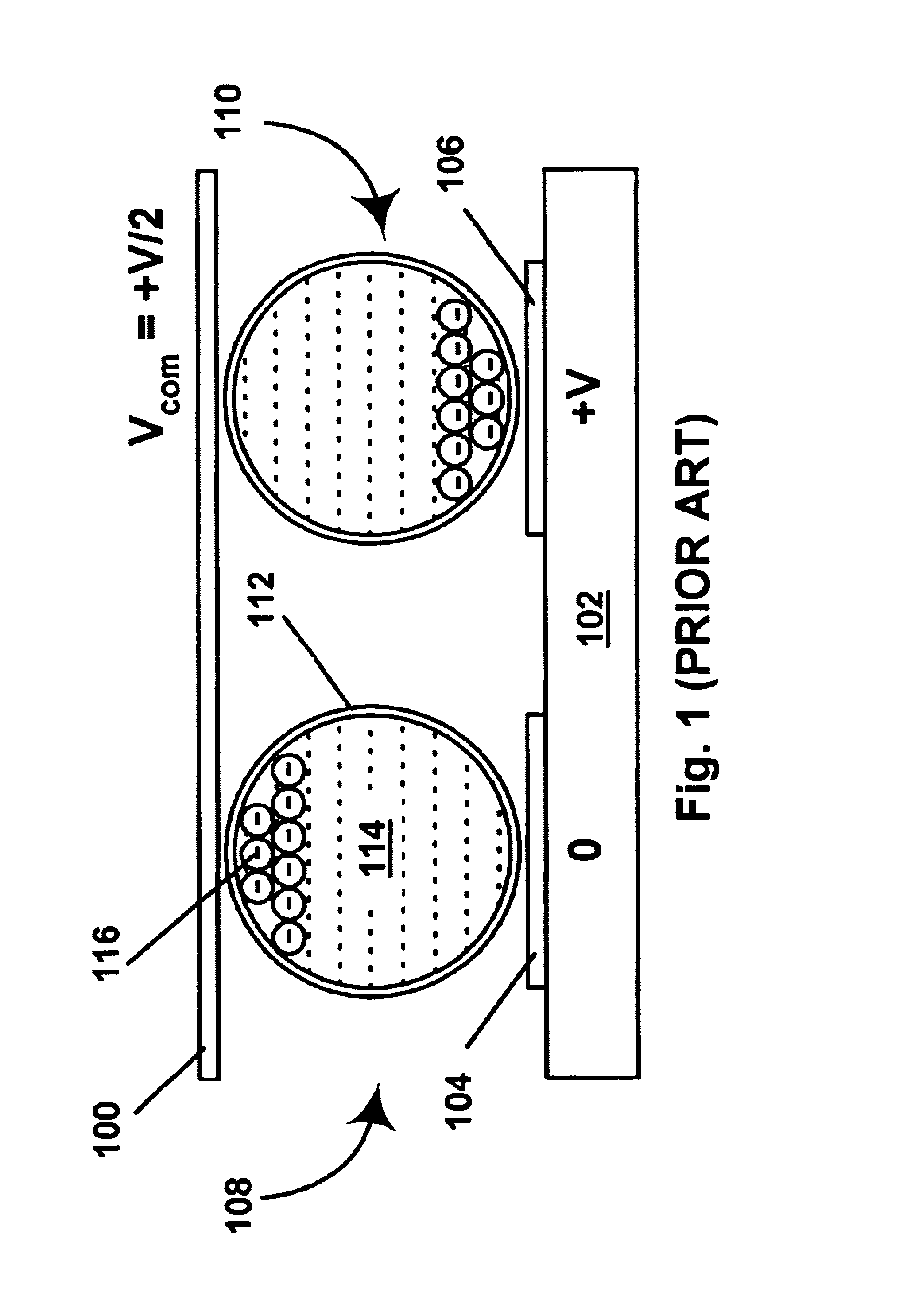

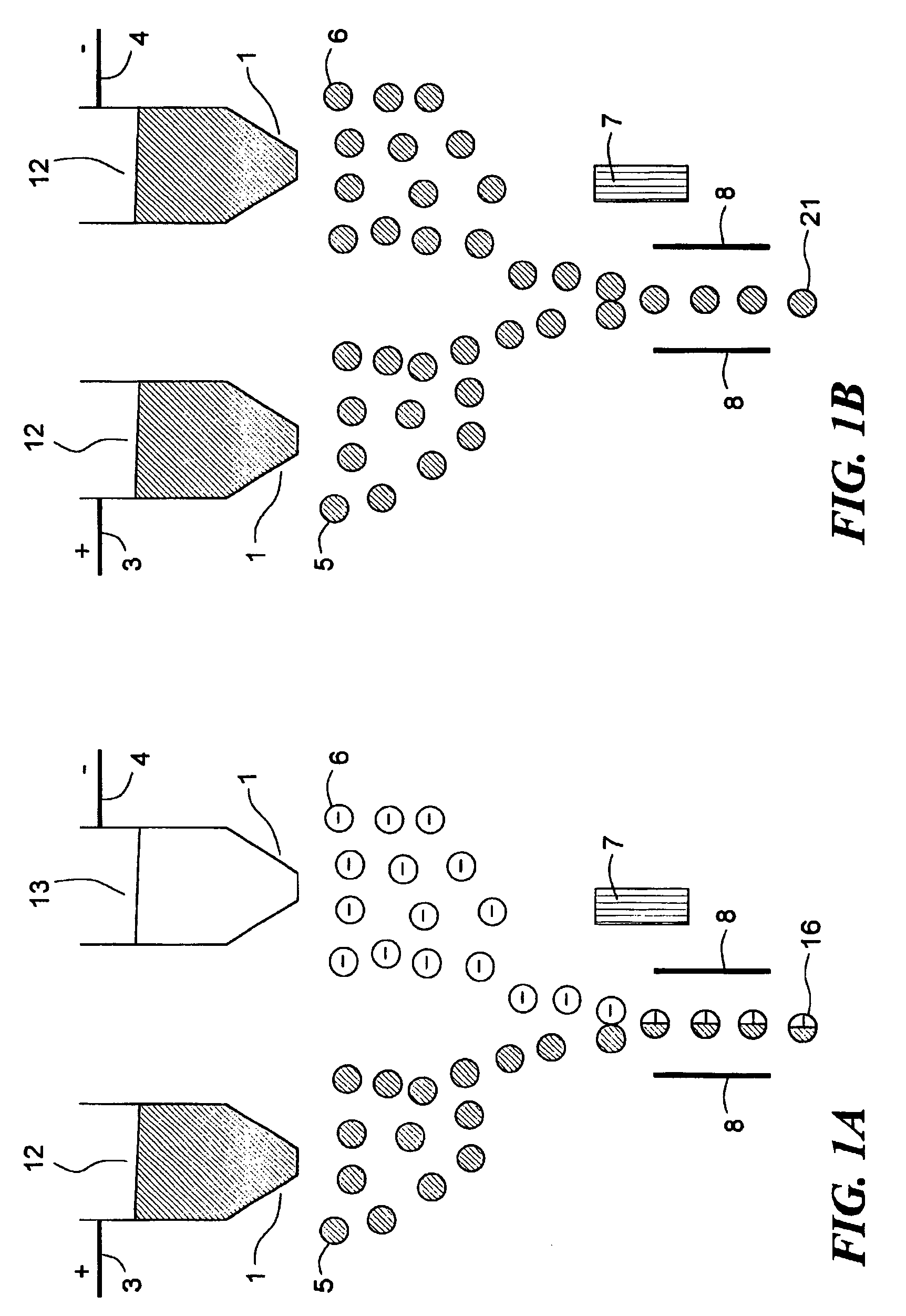

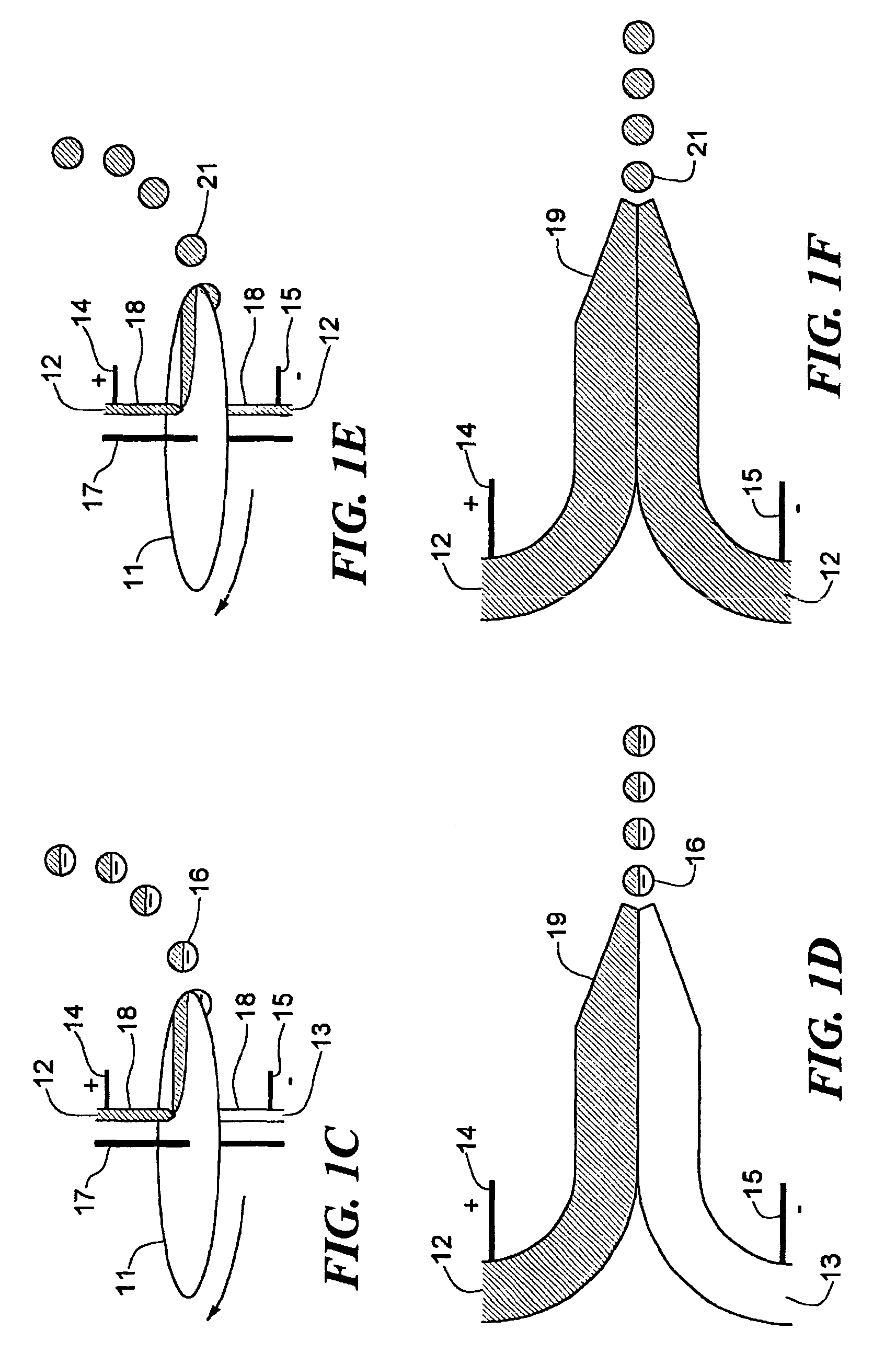

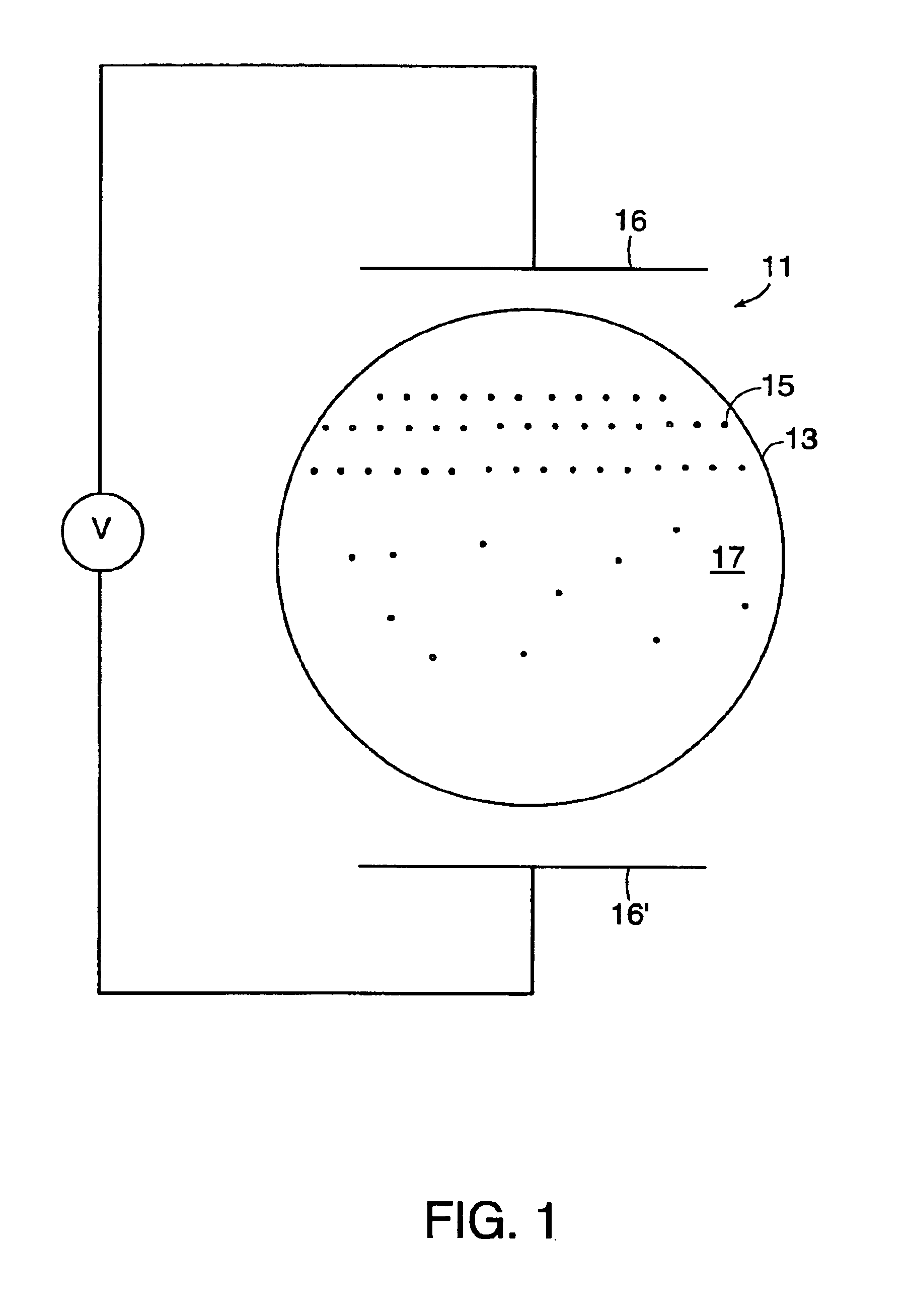

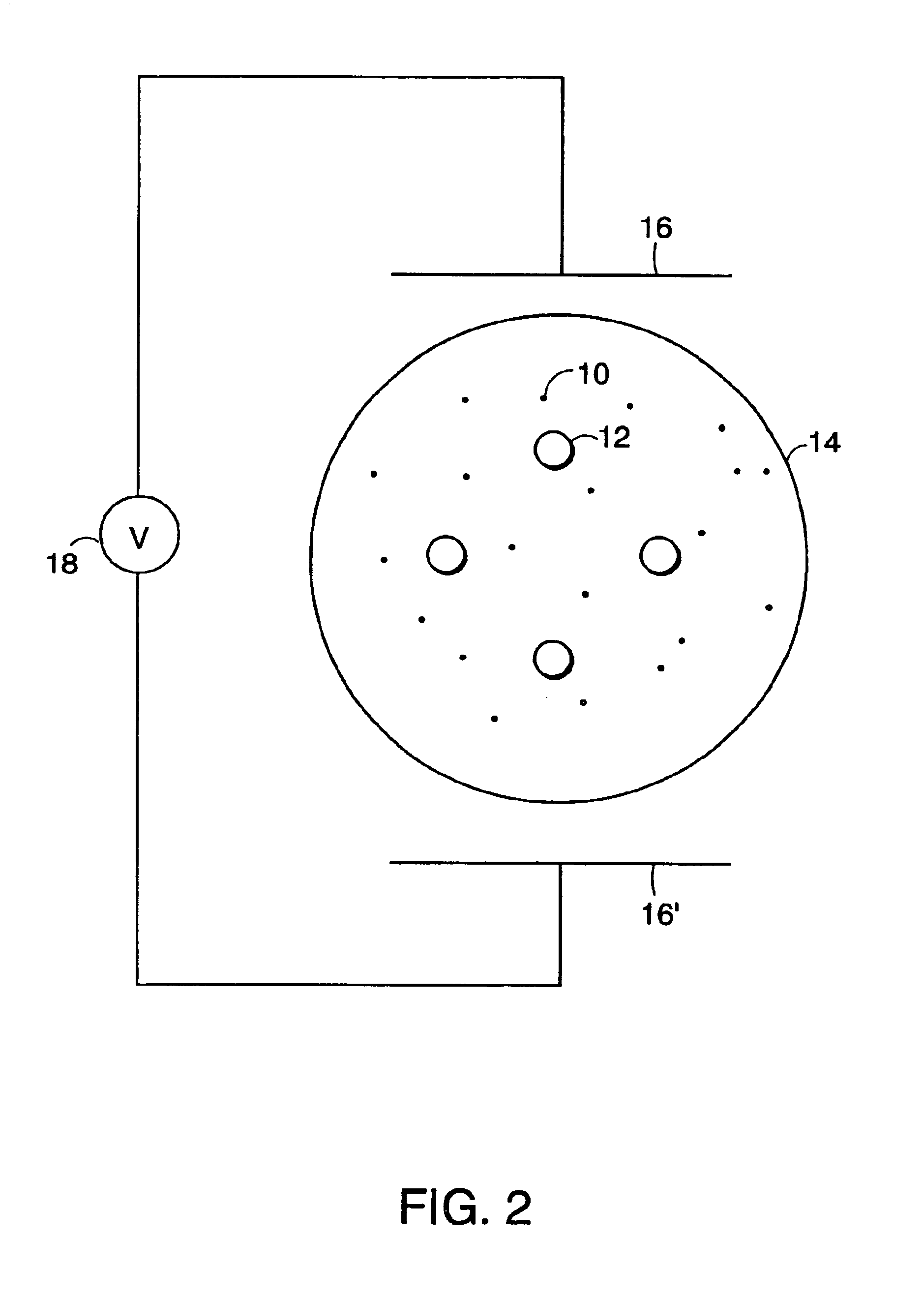

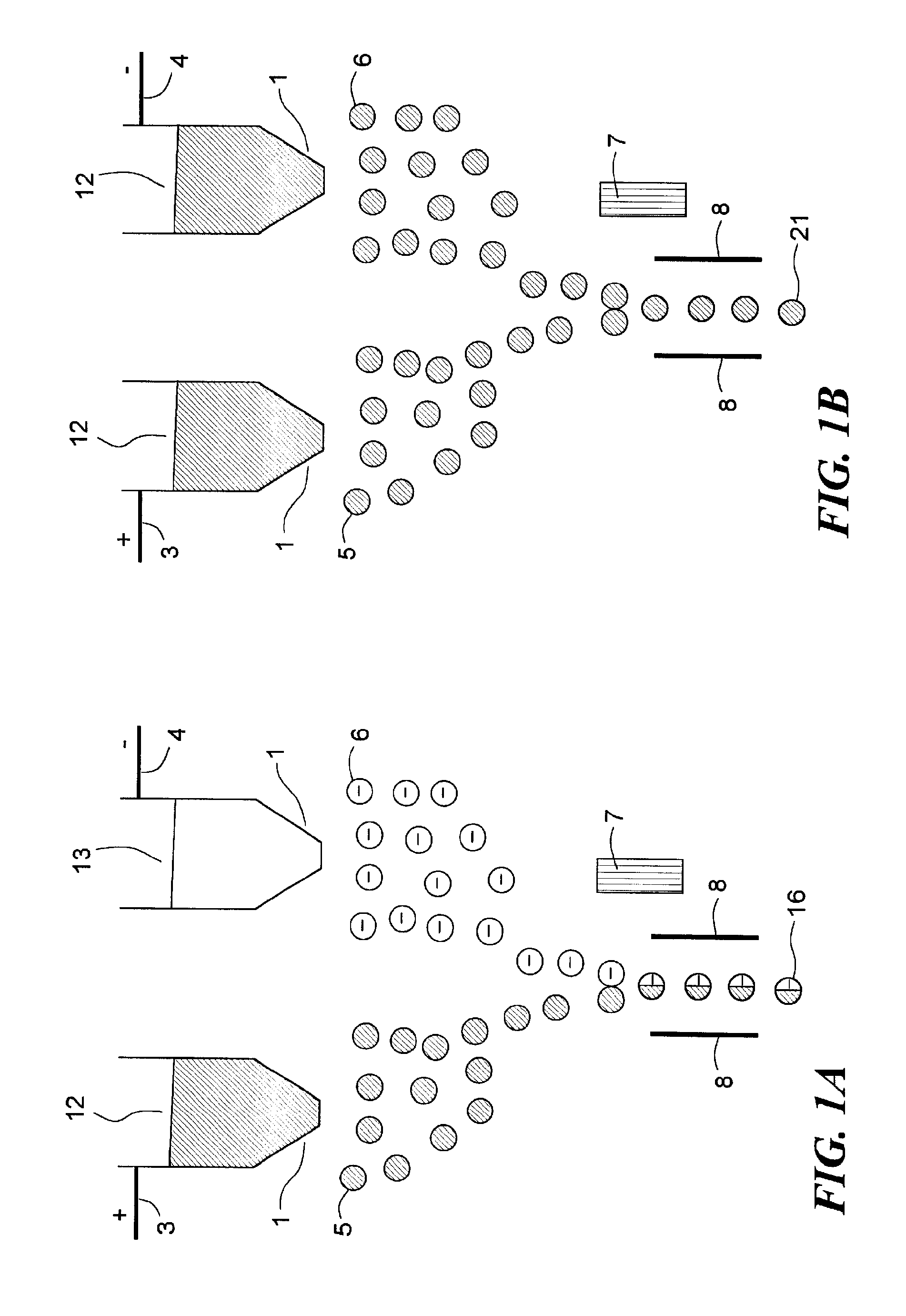

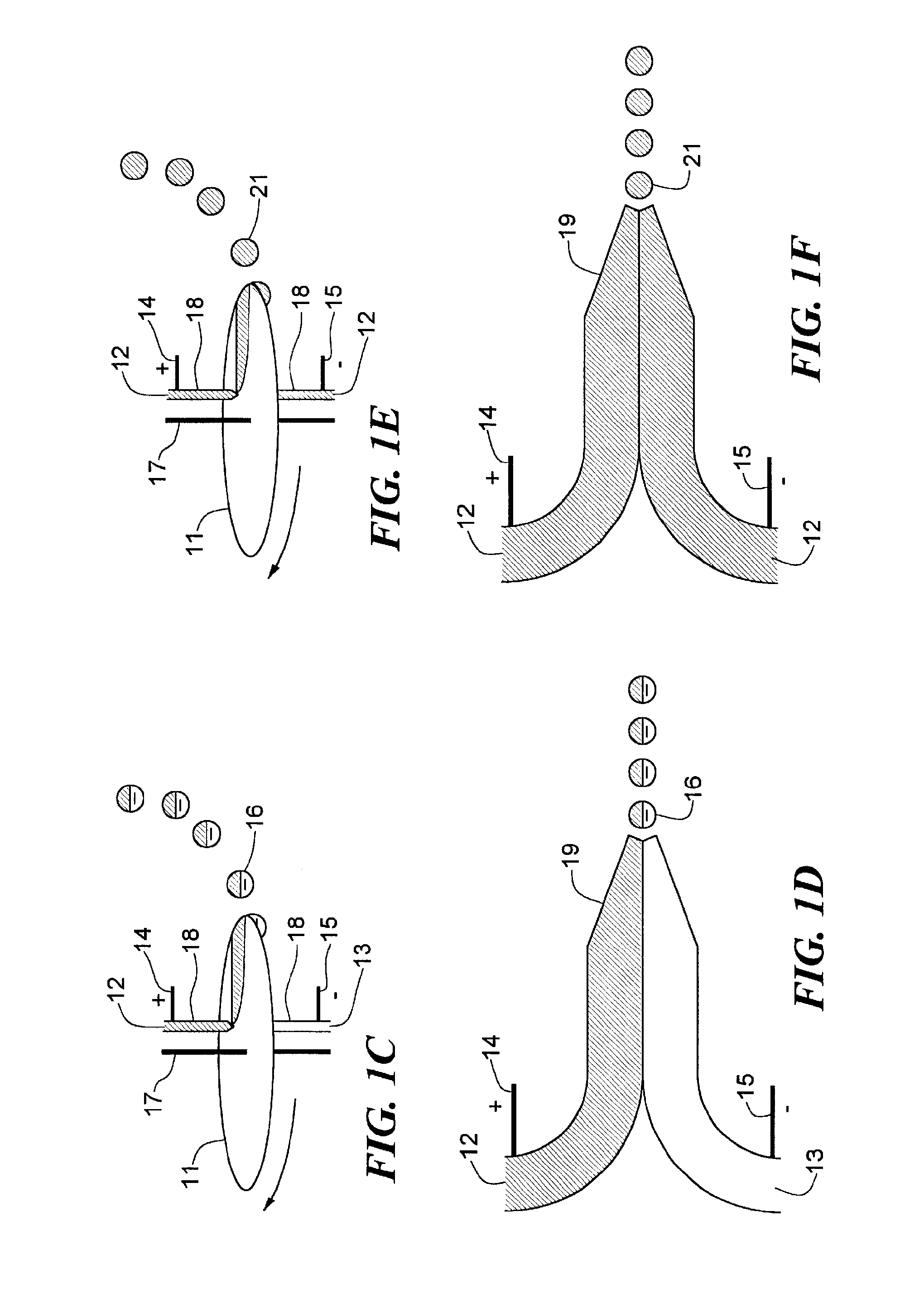

Electrophoretic displays using nanoparticles

InactiveUS6721083B2Less wavelengthIncrease volumeMechanical clocksSolid-state devicesChemical compoundElectrophoresis

Owner:E INK CORPORATION

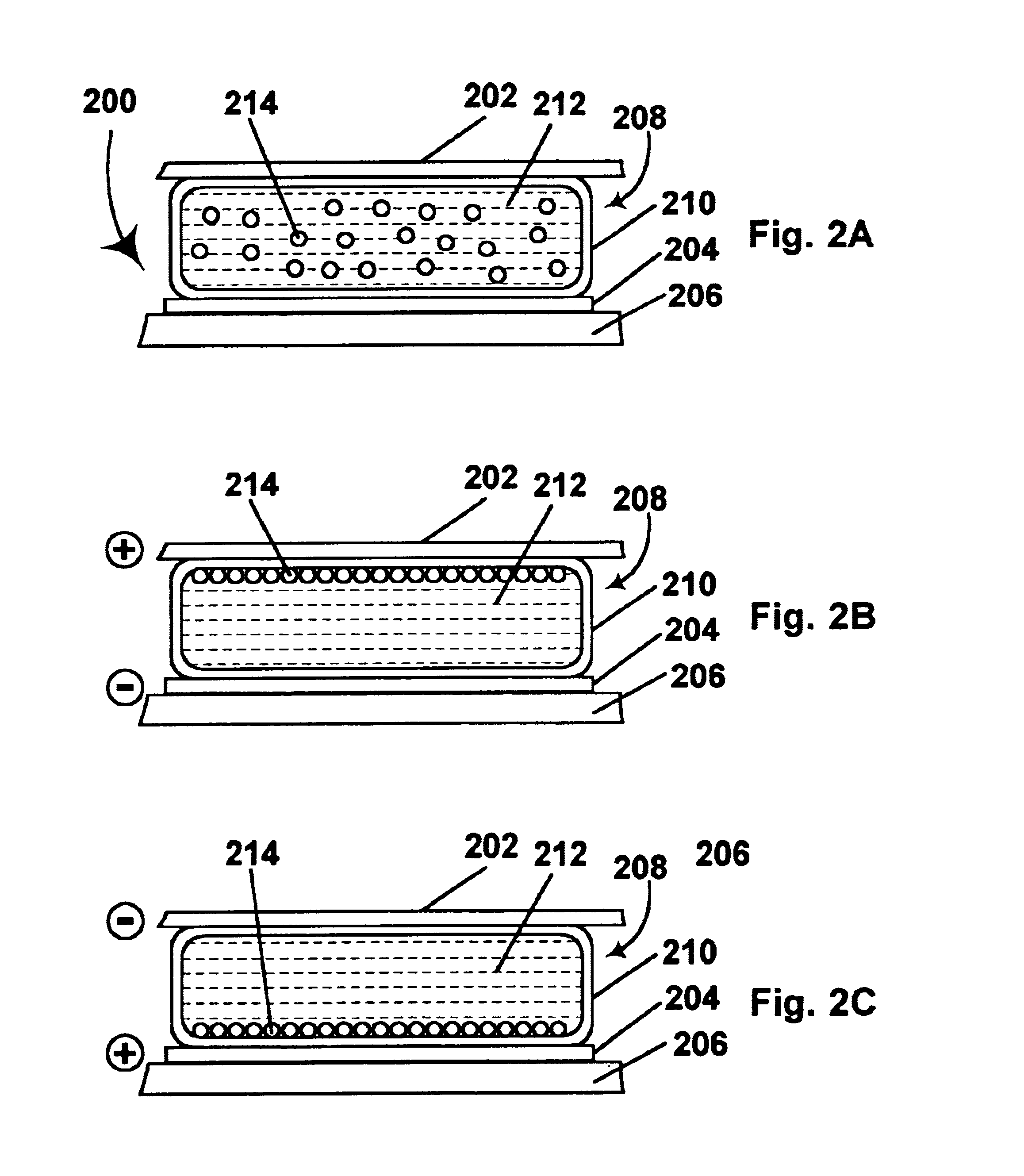

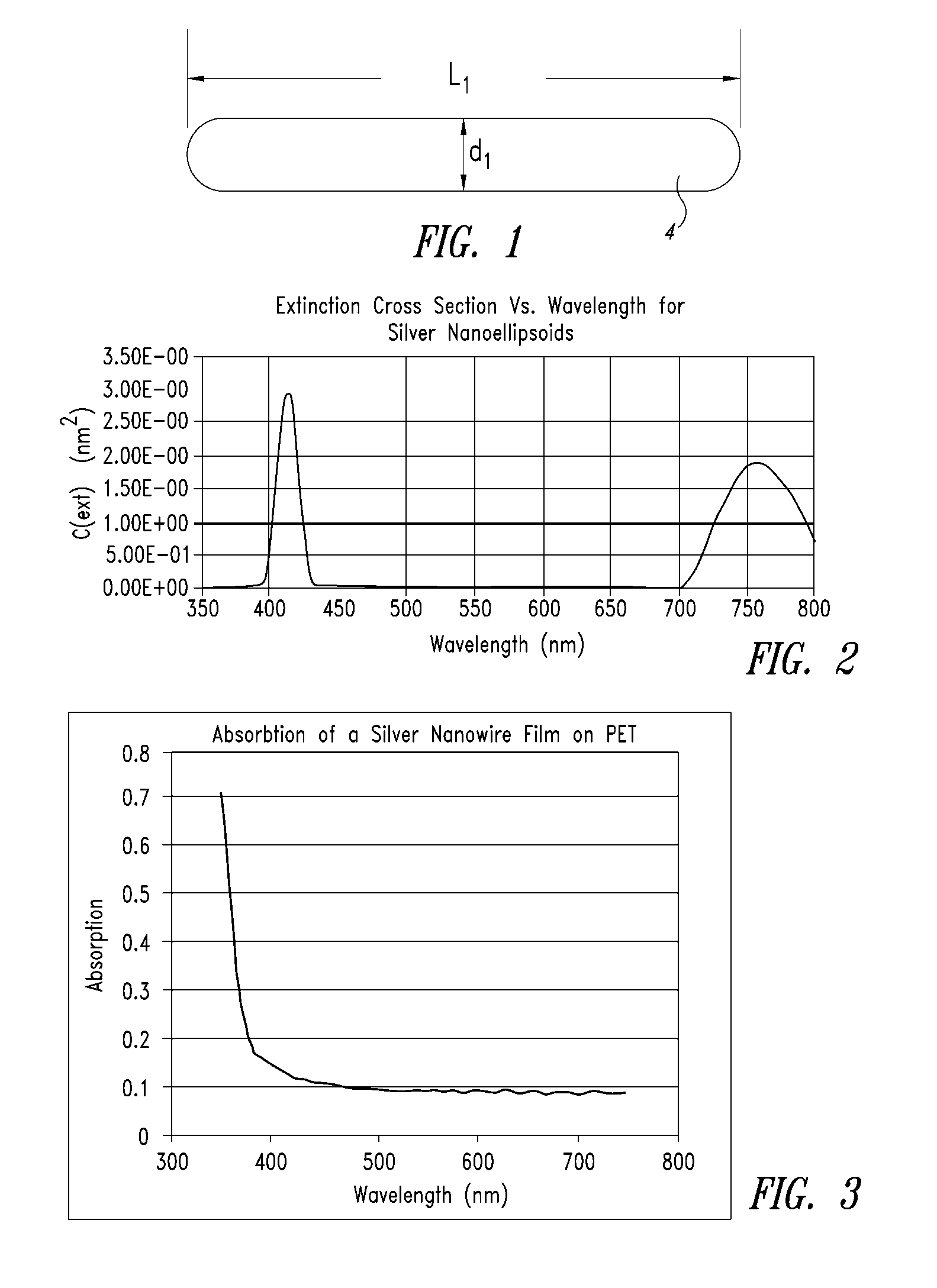

Nanowire-based transparent conductors and applications thereof

A transparent conductor including a conductive layer coated on a substrate is described. More specifically, the conductive layer comprises a network of nanowires that may be embedded in a matrix. The conductive layer is optically clear, patternable and is suitable as a transparent electrode in visual display devices such as touch screens, liquid crystal displays, plasma display panels and the like.

Owner:CHAMP GREAT INTL

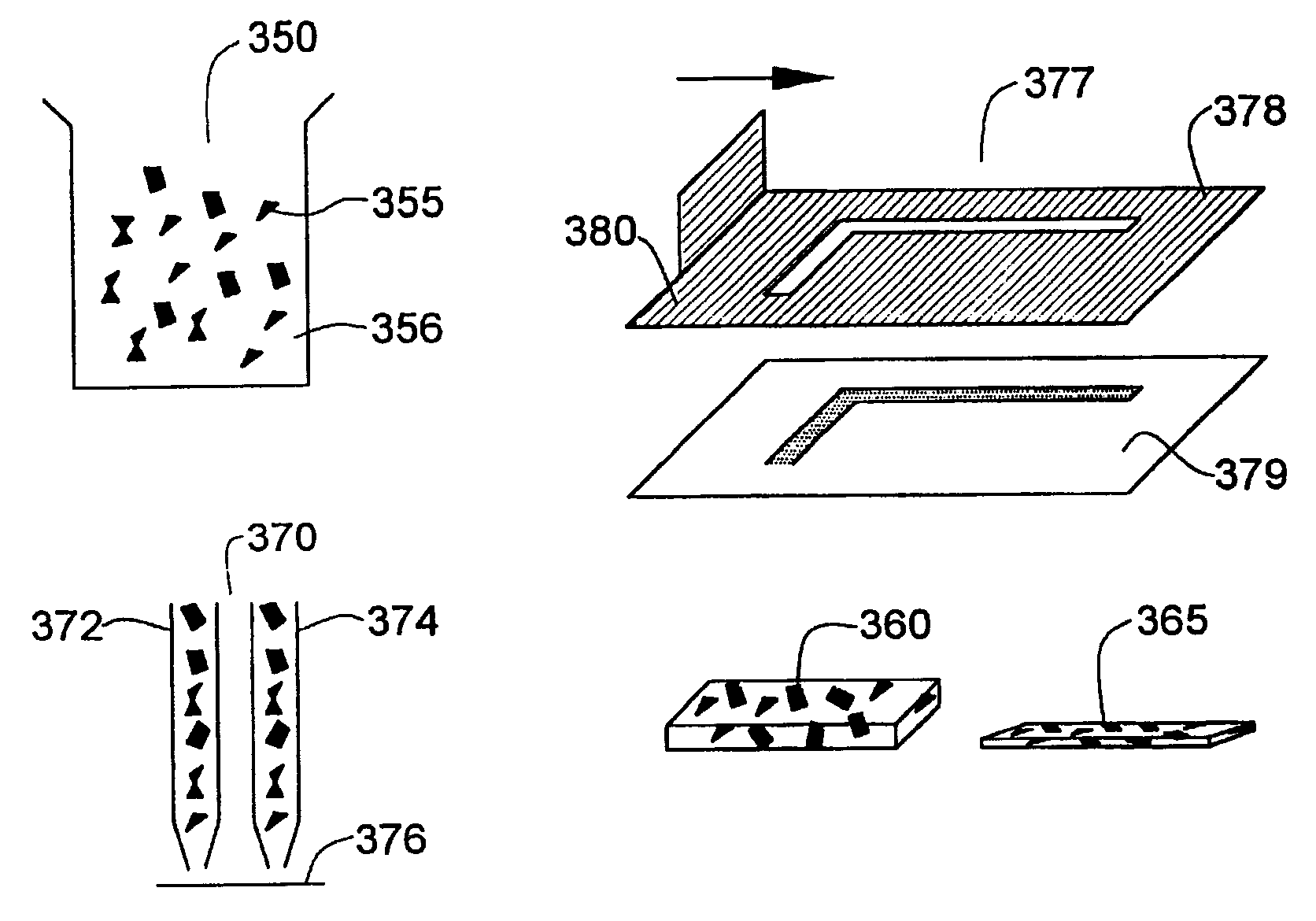

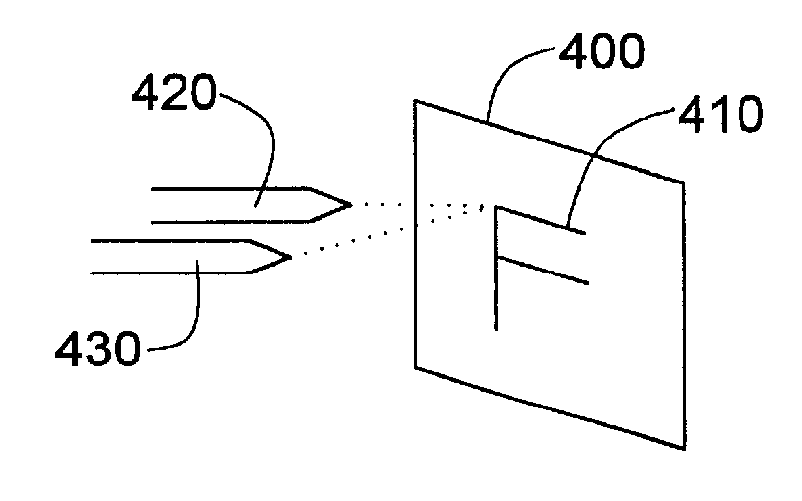

Precision spray processes for direct write electronic components

InactiveUS6251488B1Keep for a long timeIncrease probabilityMolten spray coatingVacuum evaporation coatingElectrical resistance and conductanceElectronic component

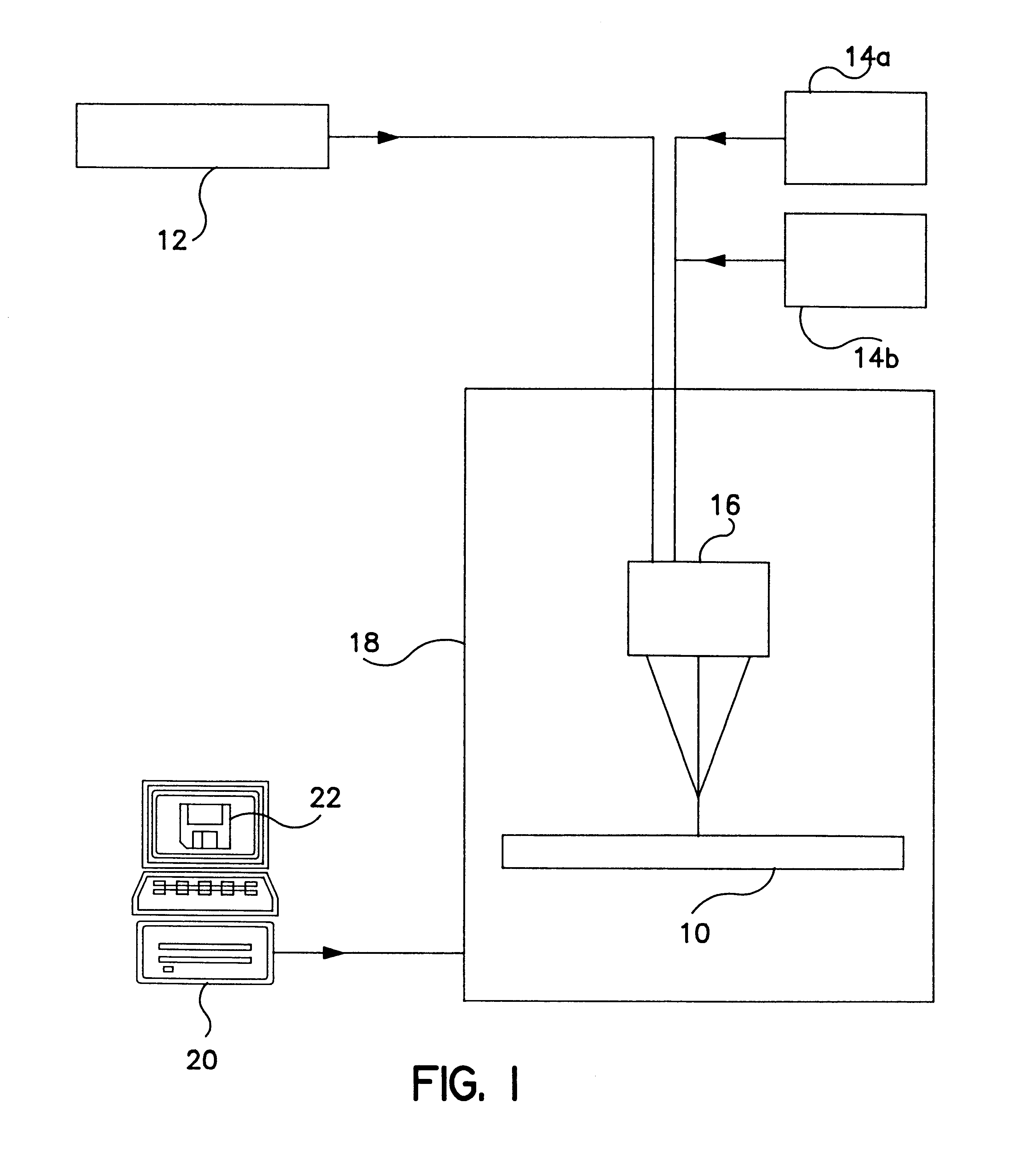

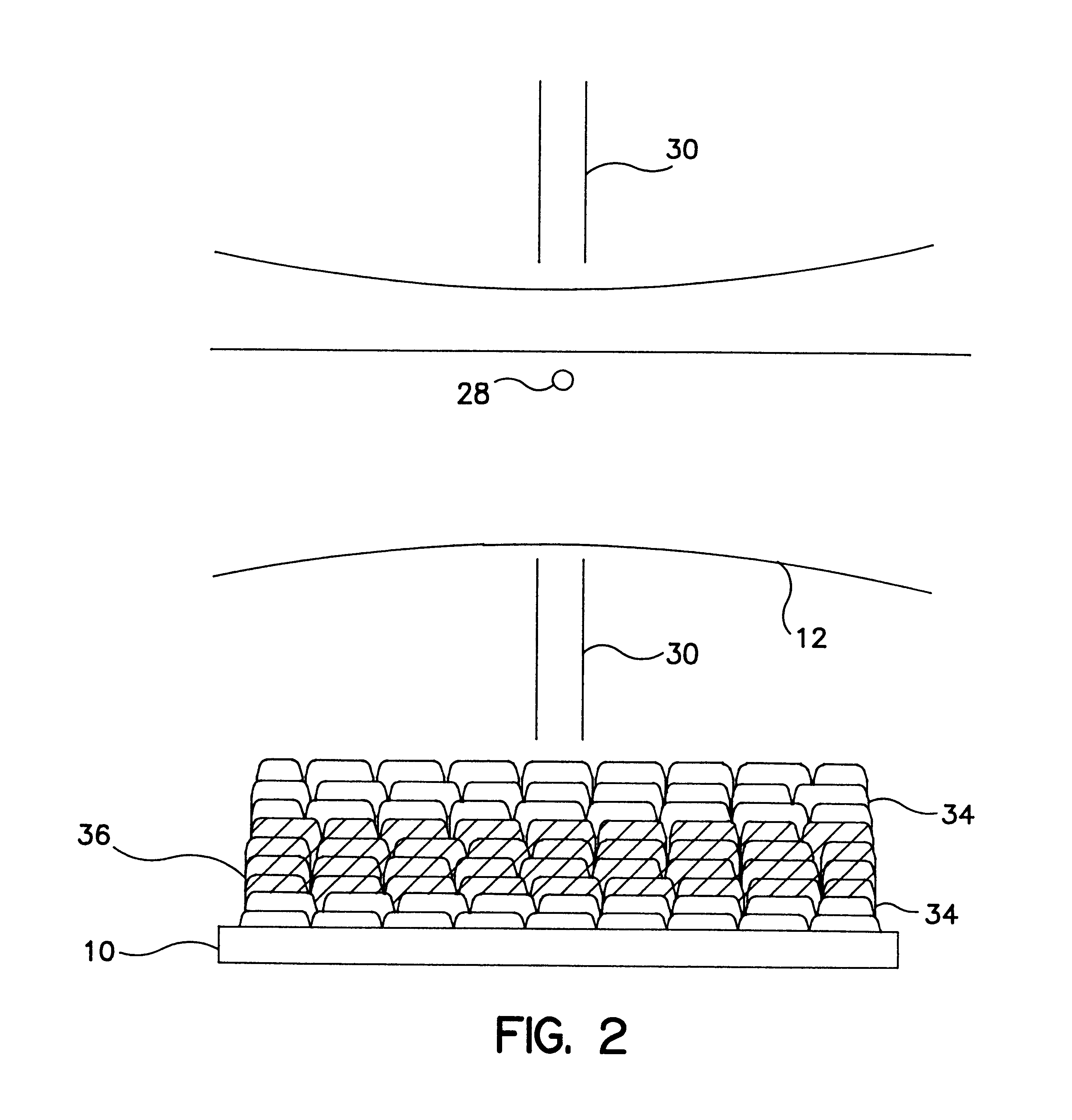

This invention combines the precision spray process with in-flight laser treatment in order to produce direct write electronic components. In addition to these components, the process can lay down lines of conductive, inductive, and resistive materials. This development has the potential to change the approach to electronics packaging. This process is revolutionary in that components can be directly produced on small structures, thus removing the need for printed circuit boards.

Owner:OPTOMEC DESIGN CO

Method and apparatus for 3D interconnect

ActiveUS8076237B2Improve adhesionInhibited DiffusionSemiconductor/solid-state device detailsPrinted circuit aspectsConductive materialsEngineering

The present invention discloses methods for depositing a material, particularly a conductive material, in cavities of a substrate and forming bonding contacts or pads thereon. An intracavity structure may be utilized in conjunction with embodiments of the present invention to provide efficient filling of diverse cavities within the substrate. Also provided are embodiments for interconnection structures using filled cavities, along with electrically conductive or reactive structures which may include capacitors fabricated within a substrate.

Owner:ASM NUTOOL

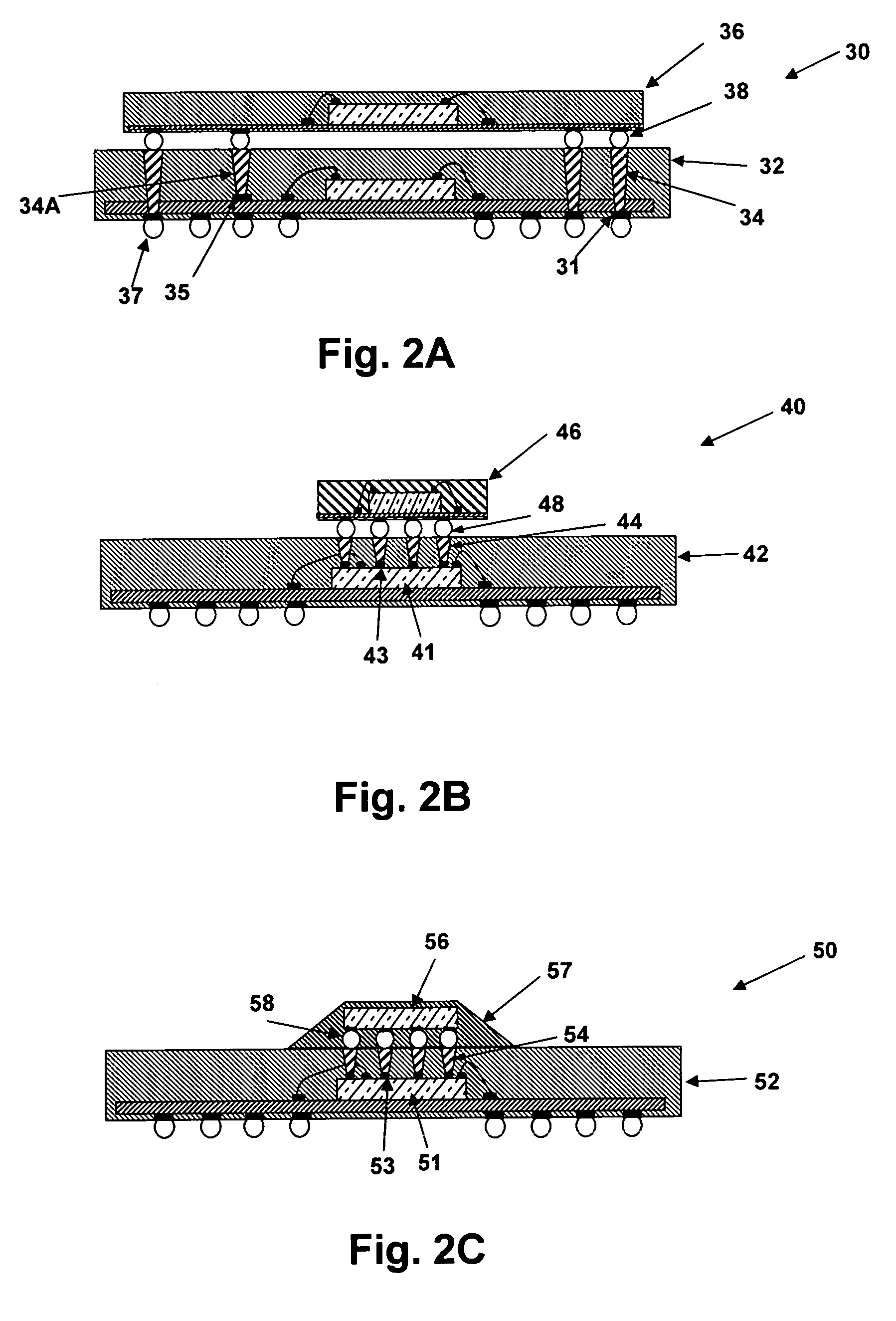

Method of manufacturing a semiconductor package

InactiveUS7185426B1Printed circuit assemblingSemiconductor/solid-state device detailsElectrical conductorSemiconductor package

A semiconductor package including top-surface terminals for mounting another semiconductor package provides a three-dimensional circuit configuration that can provide removable connection of existing grid-array packages having a standard design. A semiconductor die is mounted on an electrically connected to a circuit substrate having terminals disposed on a bottom side for connection to an external system. The die and substrate are encapsulated and vias are laser-ablated or otherwise formed through the encapsulation to terminals on the top surface of the substrate that provide a grid array mounting lands to which another grid array semiconductor package may be mounted. The bottom side of the vias may terminate and electrically connect to terminals on the substrate, terminals on the bottom of the semiconductor package (through terminals) or terminals on the top of the semiconductor die. The vias may be plated, paste-filled, filled with a low melting point alloy and may have a conical profile for improved plating performance.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

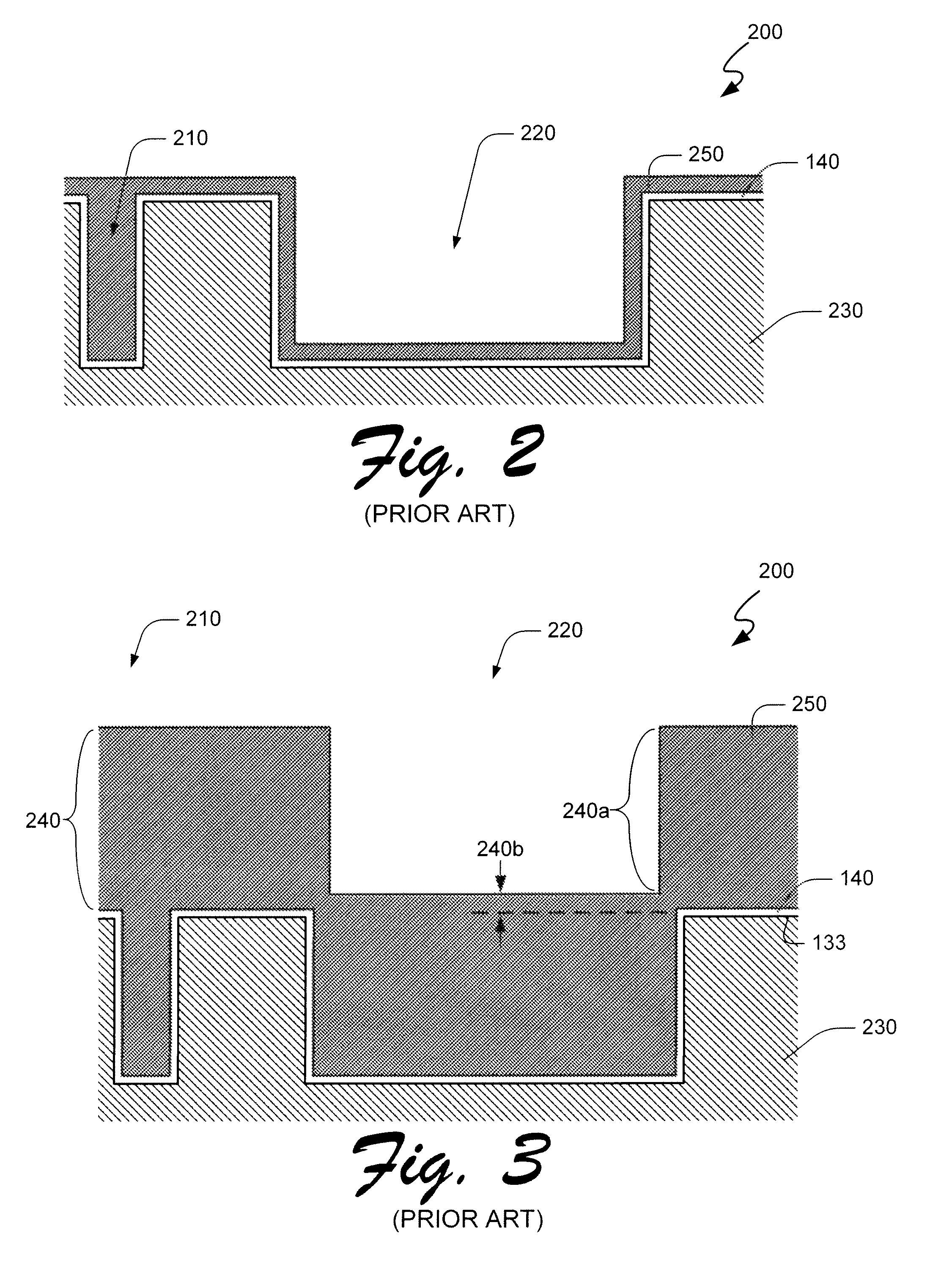

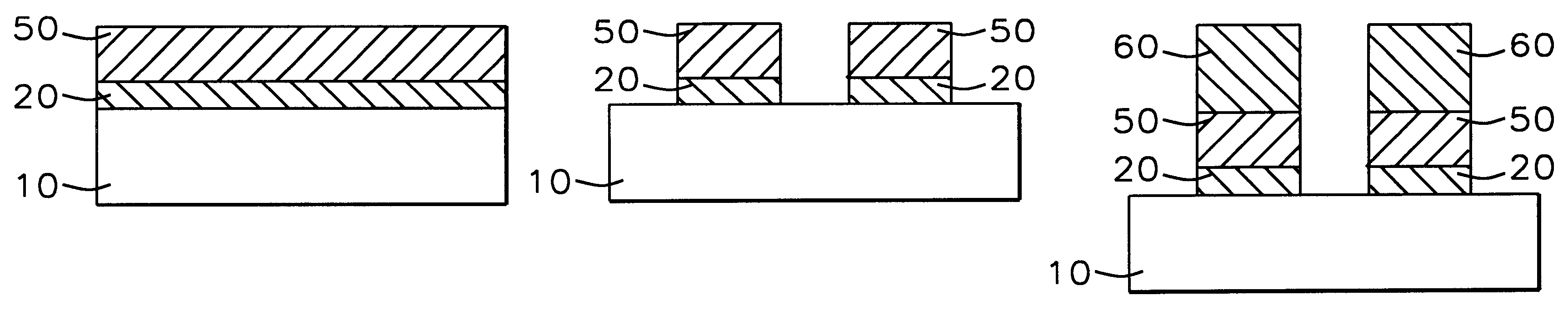

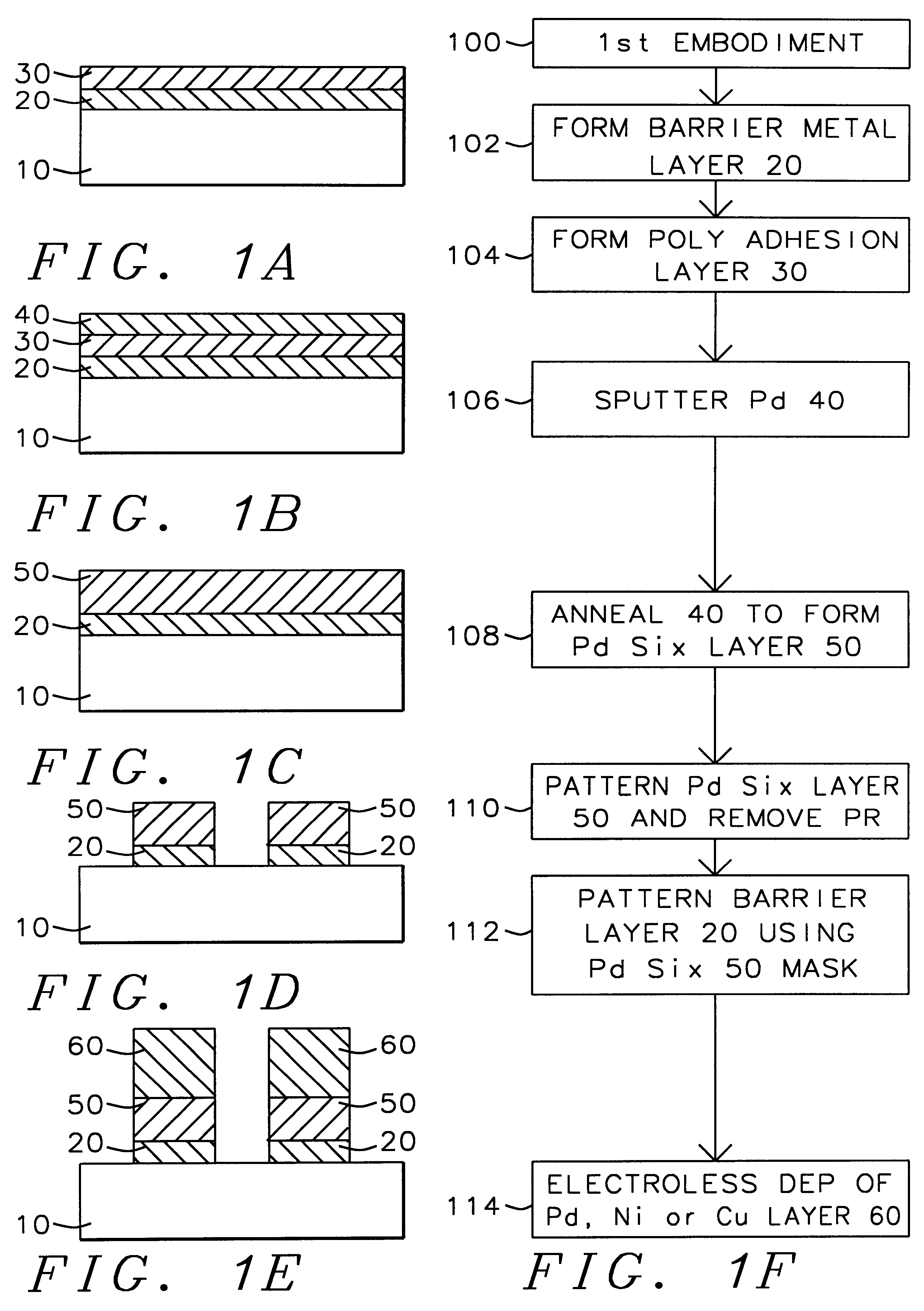

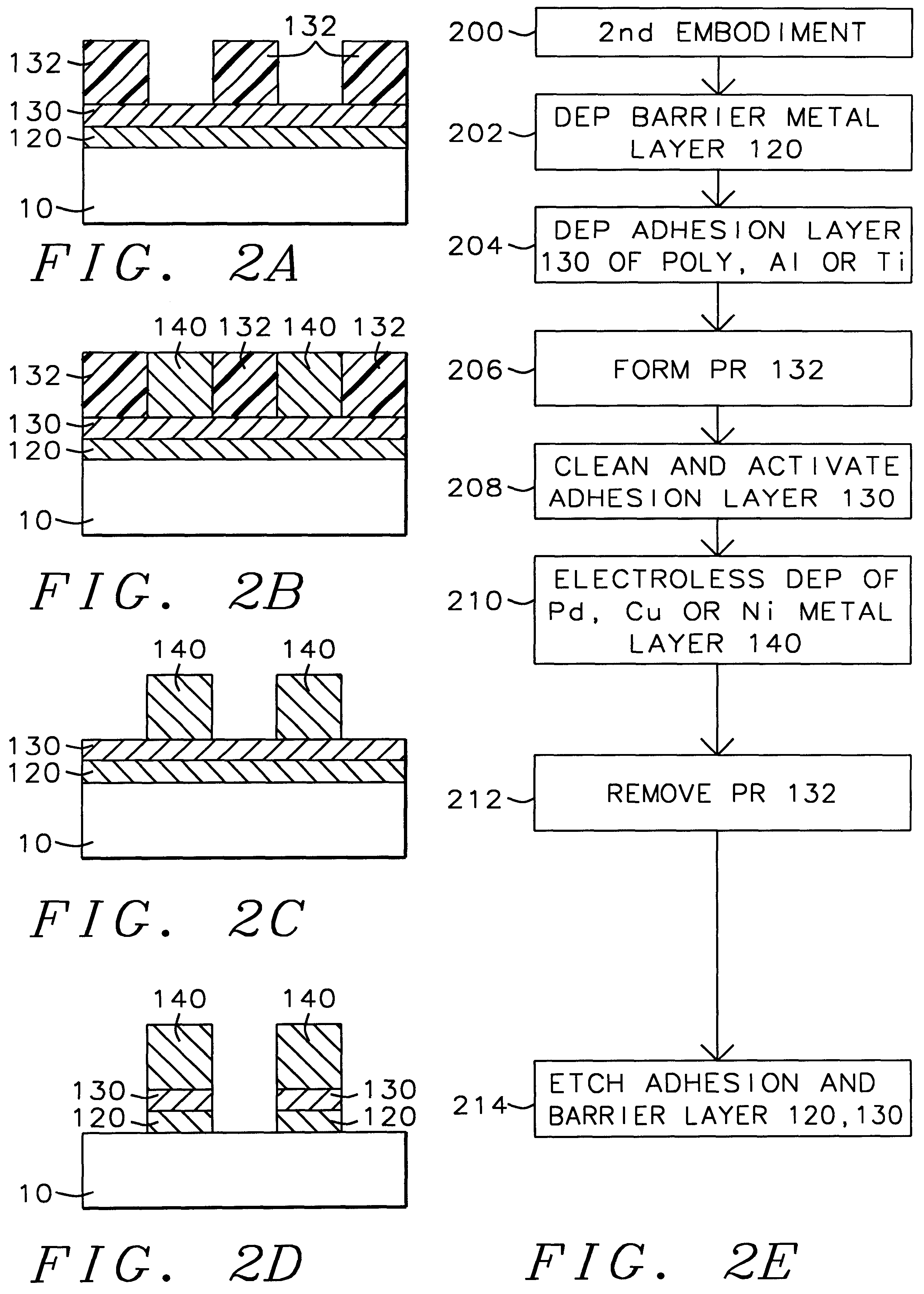

Method of electroless plating copper on nitride barrier

InactiveUS6436816B1Insulating substrate metal adhesion improvementSolid-state devicesCopper platingElectroless deposition

A method with three embodiments of manufacturing metal lines and solder bumps using electroless deposition techniques. The first embodiment uses a PdSix seed layer 50 for electroless deposition. The PdSix layer 50 does not require activation. A metal line is formed on a barrier layer 20 and an adhesion layer 30. A Palladium silicide seed layer 50 is then formed and patterned. Ni, Pd or Cu is electroless deposited over the Palladium silicide layer 50 to form a metal line. The second embodiment selectively electrolessly deposits metal 140 over an Adhesion layer 130 composed of Poly Si, Al, or Ti. A photoresist pattern 132 is formed over the adhesion layer. A metal layer 140 of Cu or Ni is electrolessly deposited over the adhesion layer. The photoresist layer 132 is removed and the exposed portion of the adhesion layer 130 and the underlying barrier metal layer 120 are etched thereby forming a metal line. The third embodiment electroless deposits metal over a metal barrier layer that is roughen by chemical mechanical polishing. A solder bump is formed using an electroless deposition of Cu or Ni by: depositing an Al layer 220 and a barrier metal layer 230 over a substrate 10. The barrier layer 230 is polished and activated. Next, the aluminum layer 220 and the barrier metal layer 230 are patterned. A metal layer 240 is electroless deposited. Next a solder bump 250 is formed over the electroless metal layer 240.

Owner:TAIWAN SEMICON MFG CO LTD

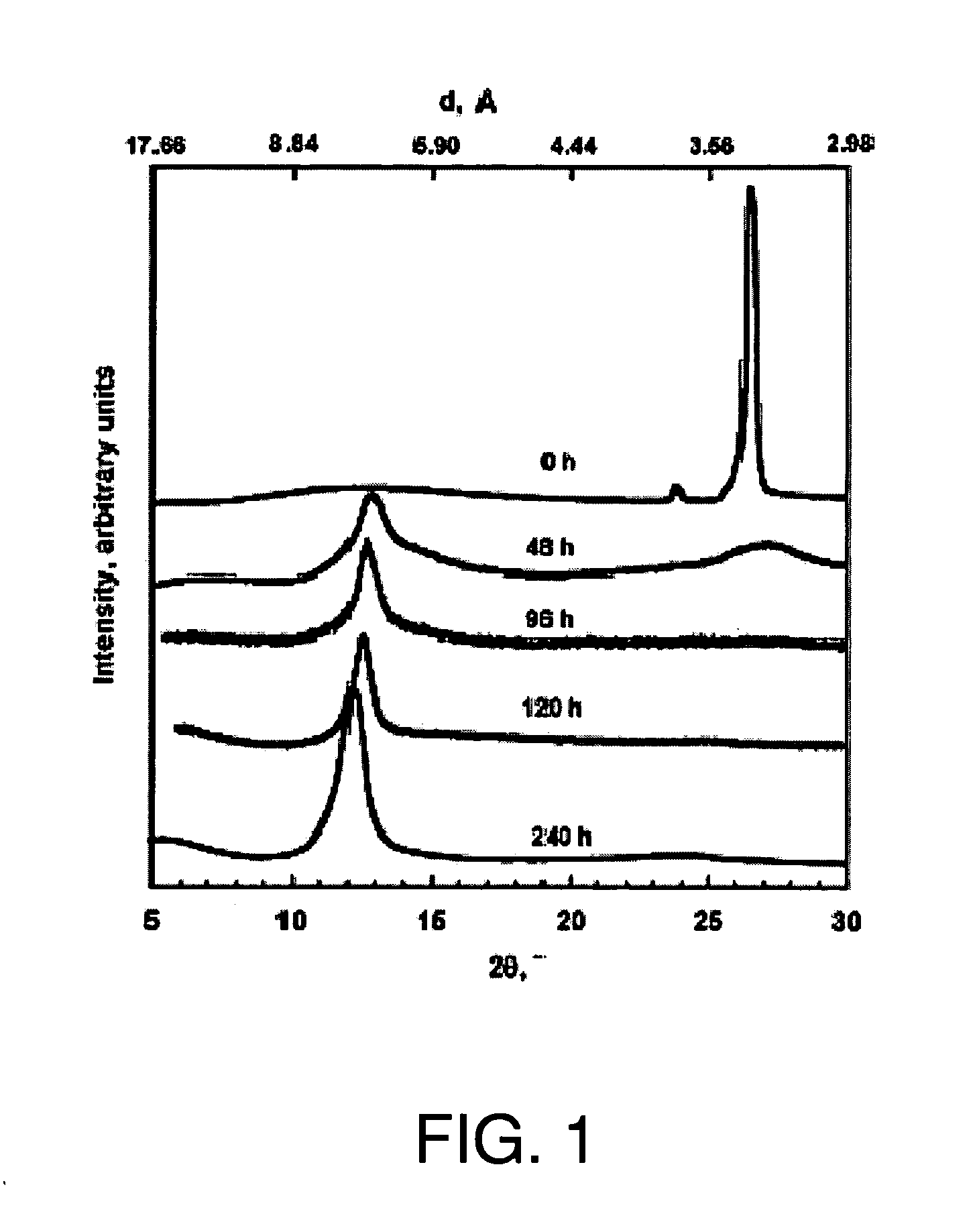

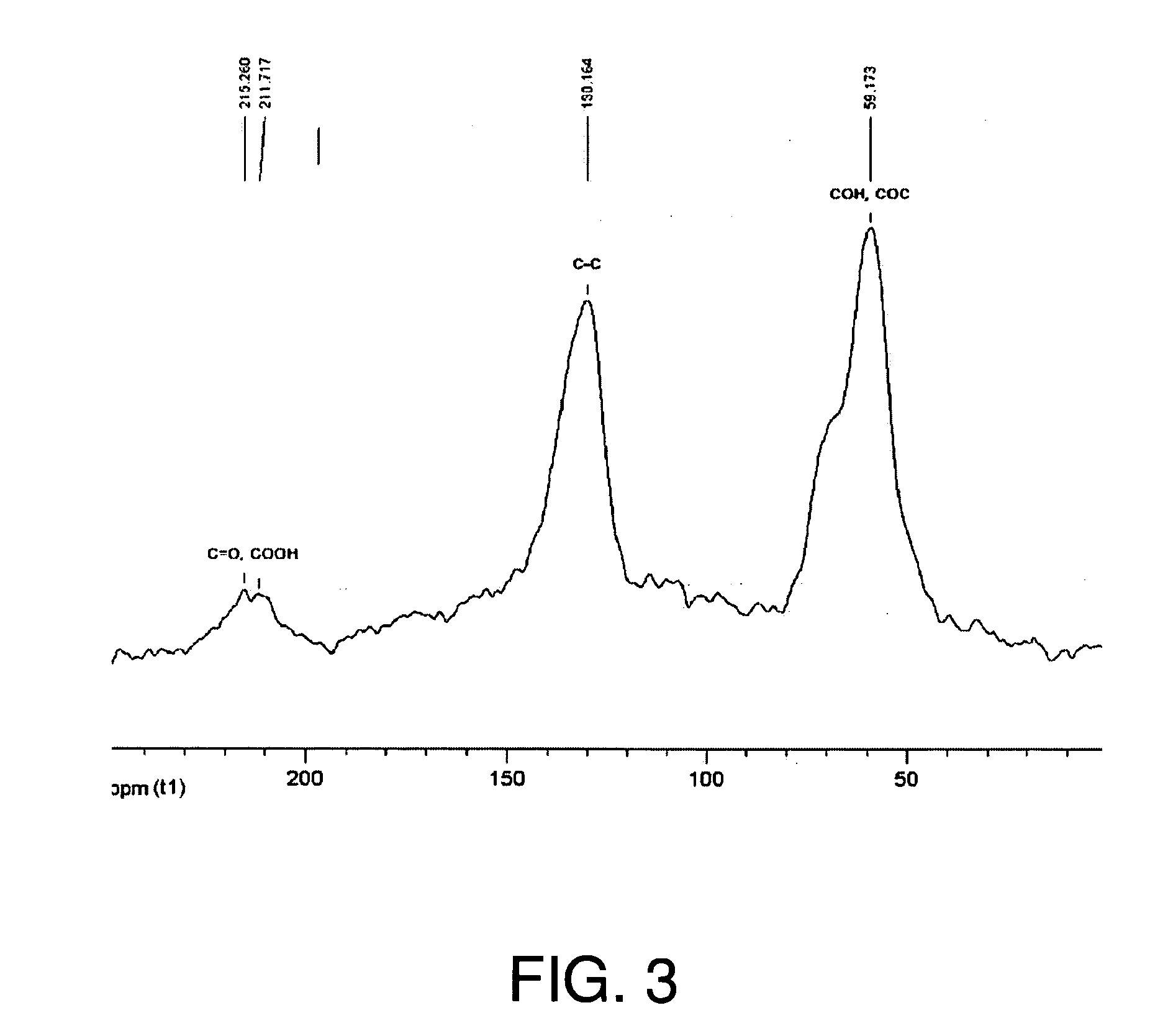

Thermally exfoliated graphite oxide

ActiveUS20070092432A1Improve diffusion barrier propertyHigh aspect ratioMaterial nanotechnologyGraphiteX-rayMaterials science

A modified graphite oxide material contains a thermally exfoliated graphite oxide with a surface area of from about 300 m2 / g to 2600 m2 / g, wherein the thermally exfoliated graphite oxide displays no signature of the original graphite and / or graphite oxide, as determined by X-ray diffraction.

Owner:THE TRUSTEES FOR PRINCETON UNIV

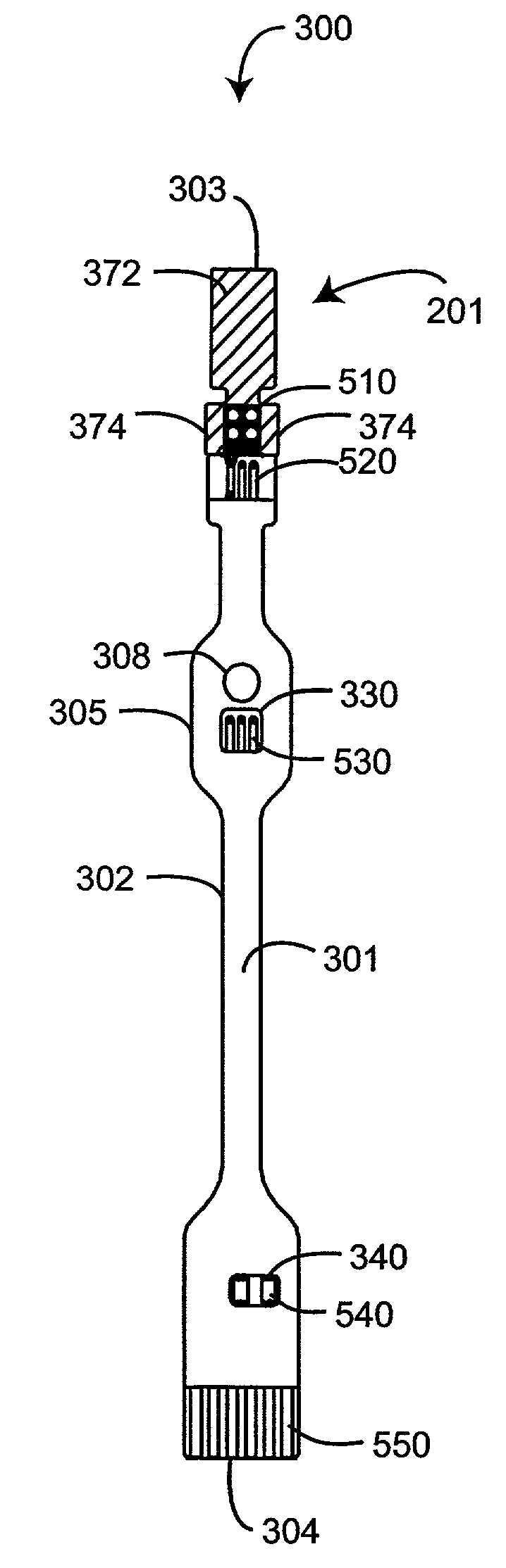

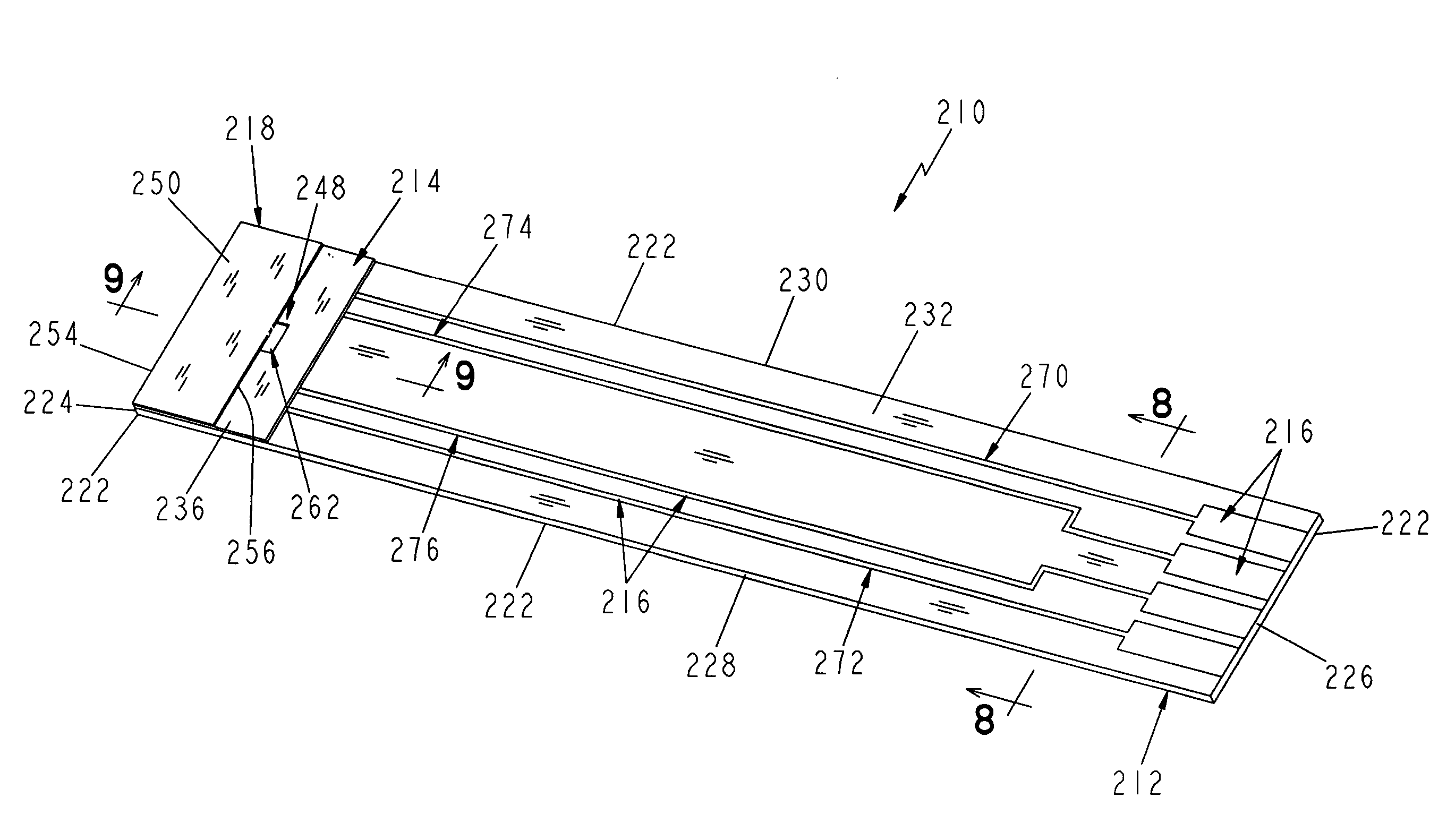

Method of making a transcutaneous electrochemical sensor

InactiveUS6973706B2Efficient productionWave amplification devicesDecorative surface effectsEngineeringConductive materials

A process for the manufacture of small sensors with reproducible surfaces, including electrochemical sensors. One process includes fanning channels in the surface of a substrate and disposing a conductive material in the channels to form an electrode. The conductive material can also be formed on the substrate by other impact and non-impact methods. In a preferred embodiment, the method includes cutting the substrate to form a sensor having a connector portion and a transcutaneous portion, the two portions having edges that define one continuous straight line.

Owner:THERASENSE

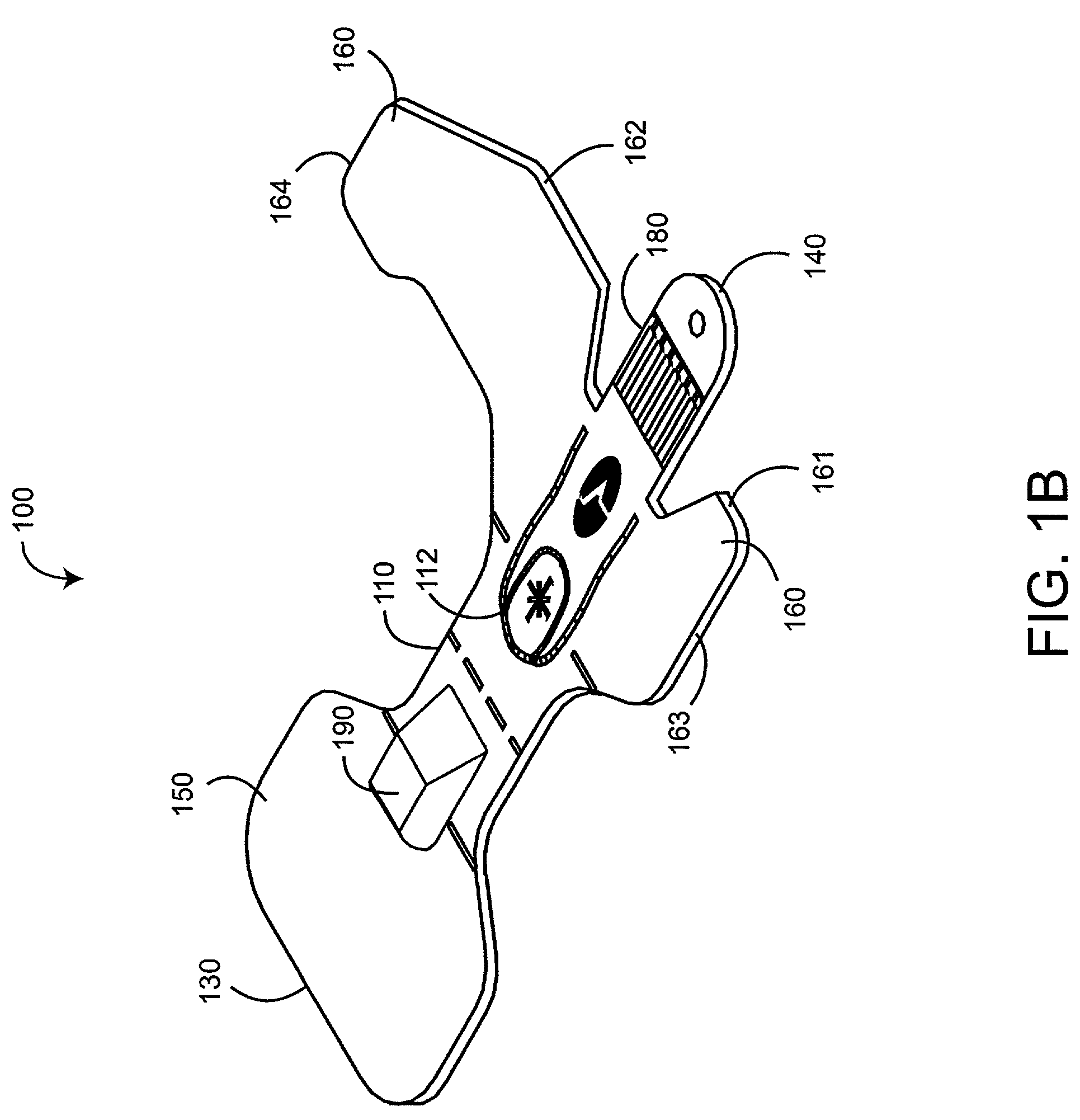

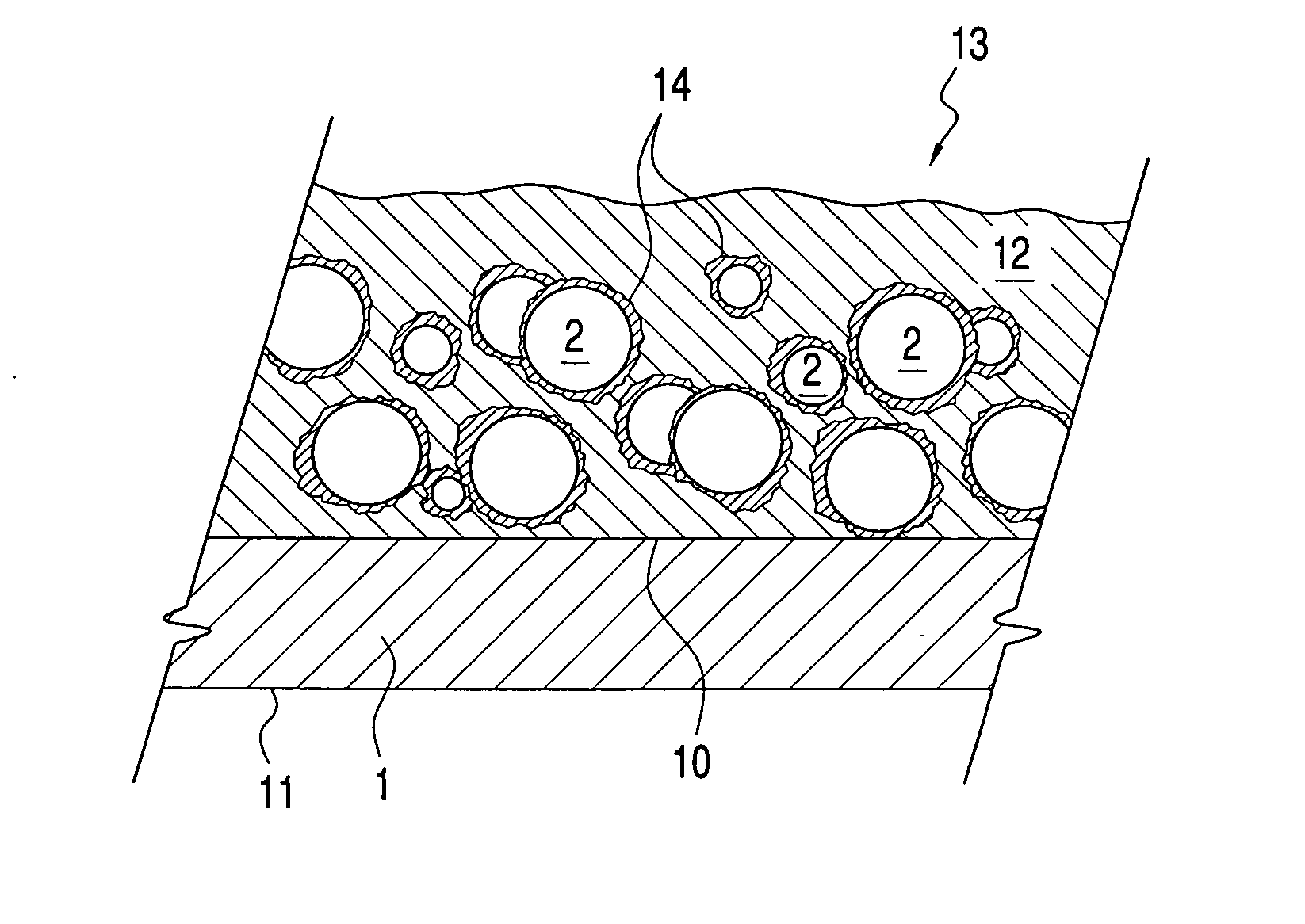

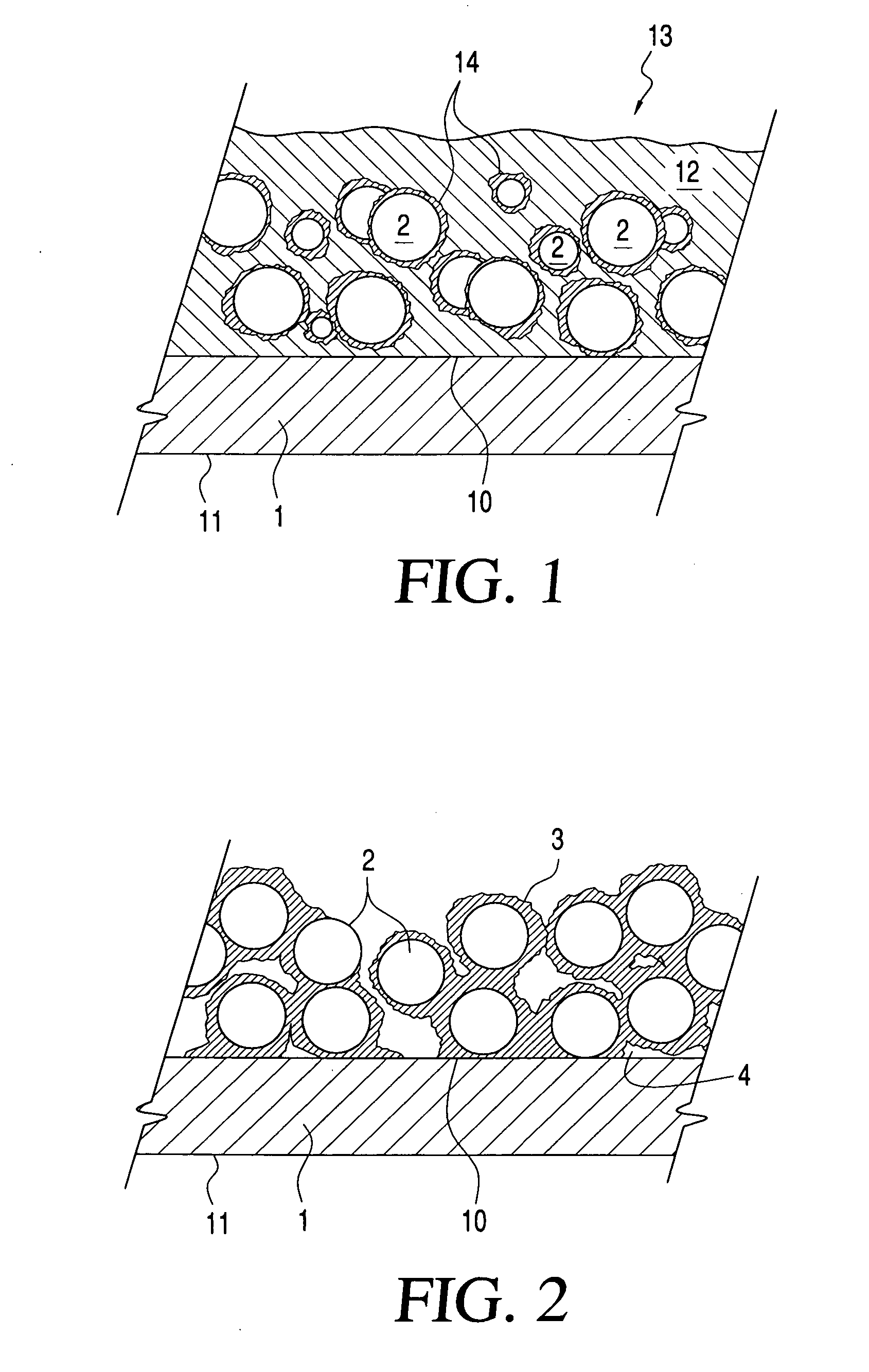

Method of making a biosensor

InactiveUS7073246B2Immobilised enzymesBioreactor/fermenter combinationsConductive materialsEngineering

A method of making a biosensor is provided. The biosensor includes an electrically conductive material on a base and electrode patterns formed on the base, the patterns having different feature sizes. The conductive material is partially removed from the base using broad field laser ablation so that less than 90% of the conductive material remains on the base and that the electrode pattern has an edge extending between two points. A standard deviation of the edge from a line extending between two points is less than about 6 μm.

Owner:ROCHE DIABETES CARE INC +1

Printable electrical conductors

An electrical conductor formed from one or more metallic inks. The electrical conductor comprises a network of interconnected metallic nodes. Each node comprises a metallic composition, e.g., one or more metals or alloys. The network defines a plurality of pores having an average pore volume of less than about 10,000,000 nm3. The electrical conductors advantageously have a high degree of conductivity, e.g., a resistivity of not greater than about 10× the resistivity of the (bulk) metallic composition, which forms the individual nodes.

Owner:CABOT CORP

Electronically addressable microencapsulated ink and display thereof

InactiveUS7148128B2Inexpensive displayInking apparatusMechanical clocksSemiconductor materialsDisplay device

We describe a system of electronically active inks which may include electronically addressable contrast media, conductors, insulators, resistors, semiconductive materials, magnetic materials, spin materials, piezoelectric materials, optoelectronic, thermoelectric or radio frequency materials. We further describe a printing system capable of laying down said materials in a definite pattern. Such a system may be used for instance to: print a flat panel display complete with onboard drive logic; print a working logic circuit onto any of a large class of substrates; print an electrostatic or piezoelectric motor with onboard logic and feedback or print a working radio transmitter or receiver.

Owner:E INK CORPORATION

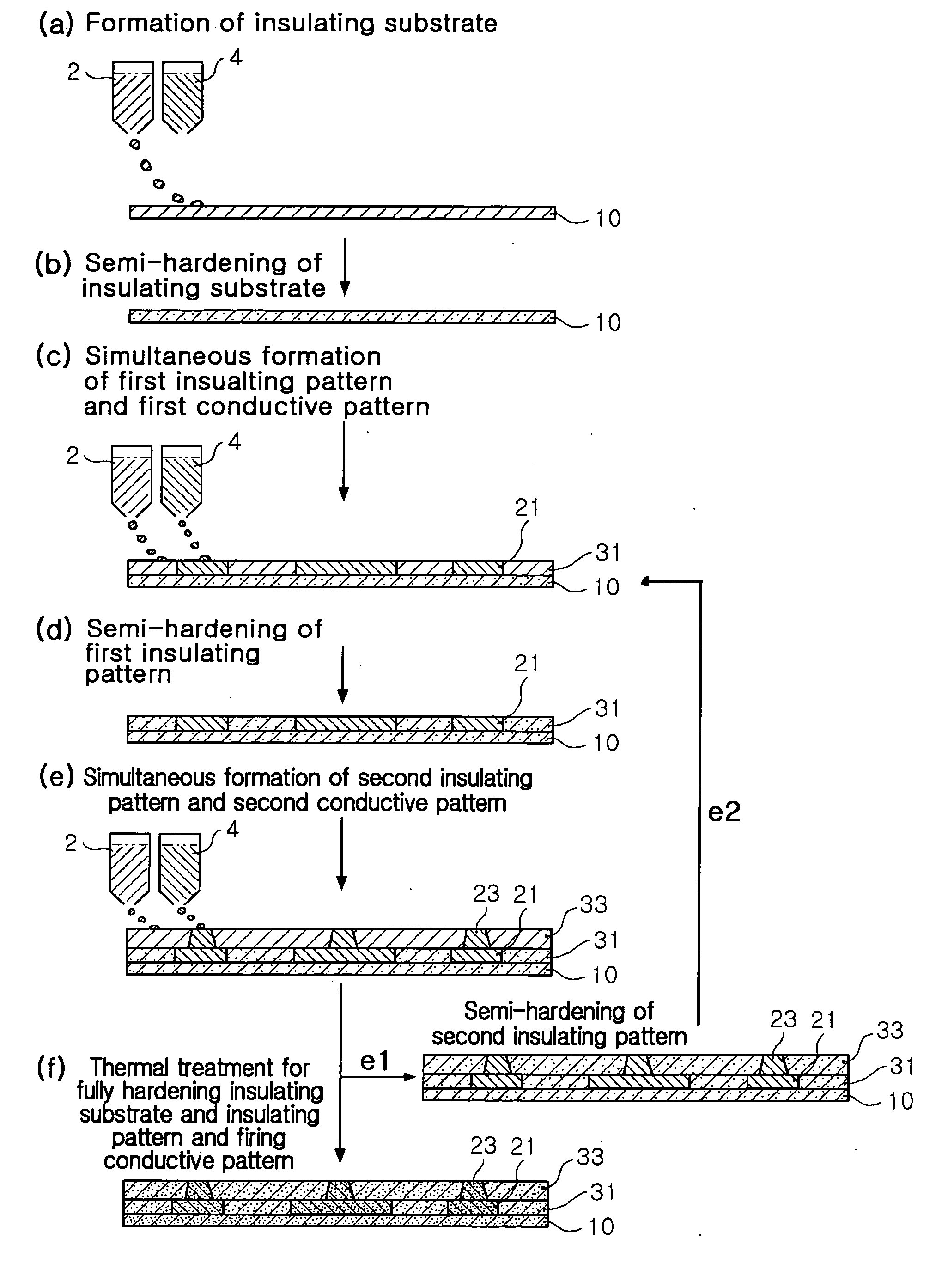

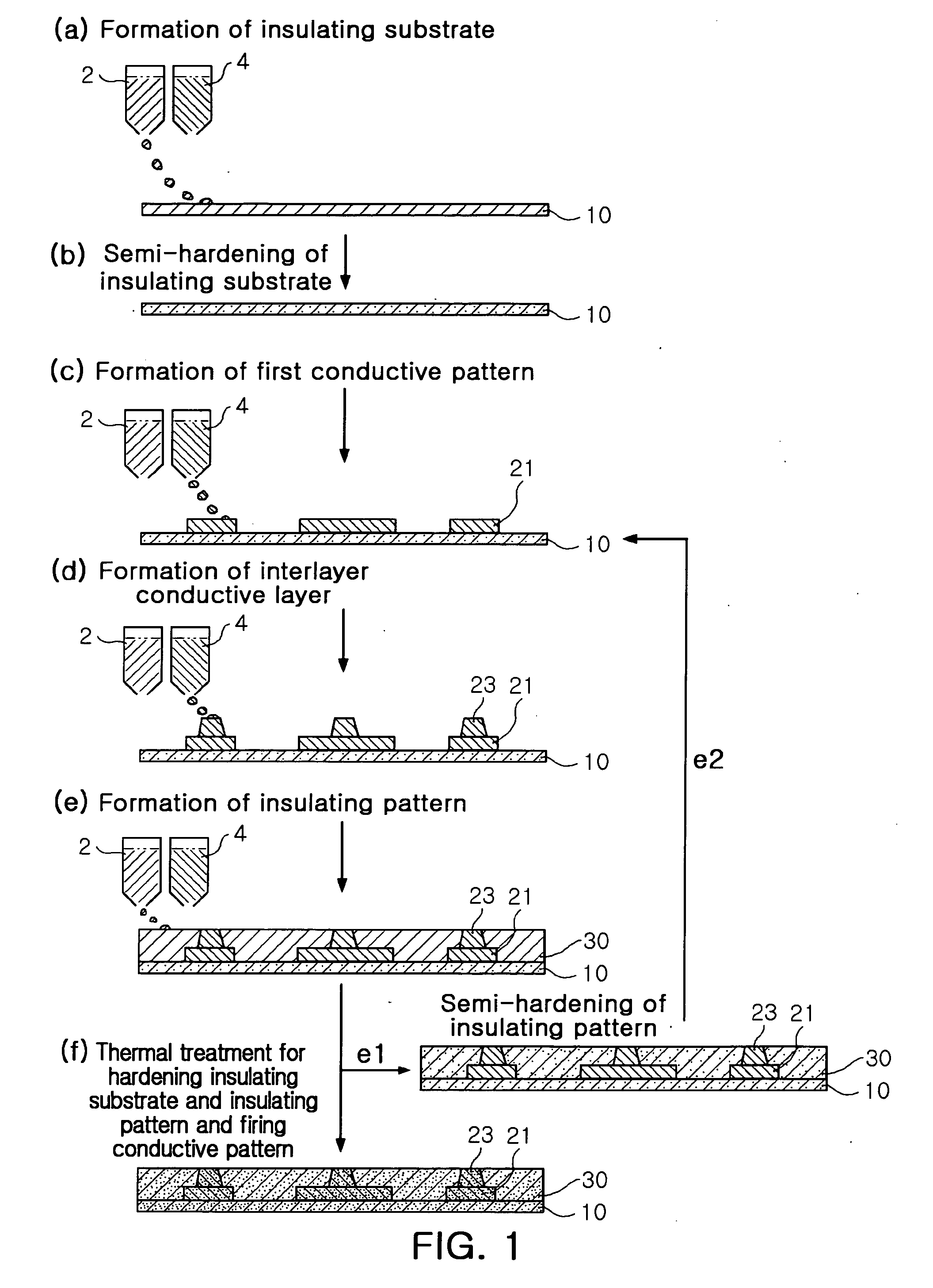

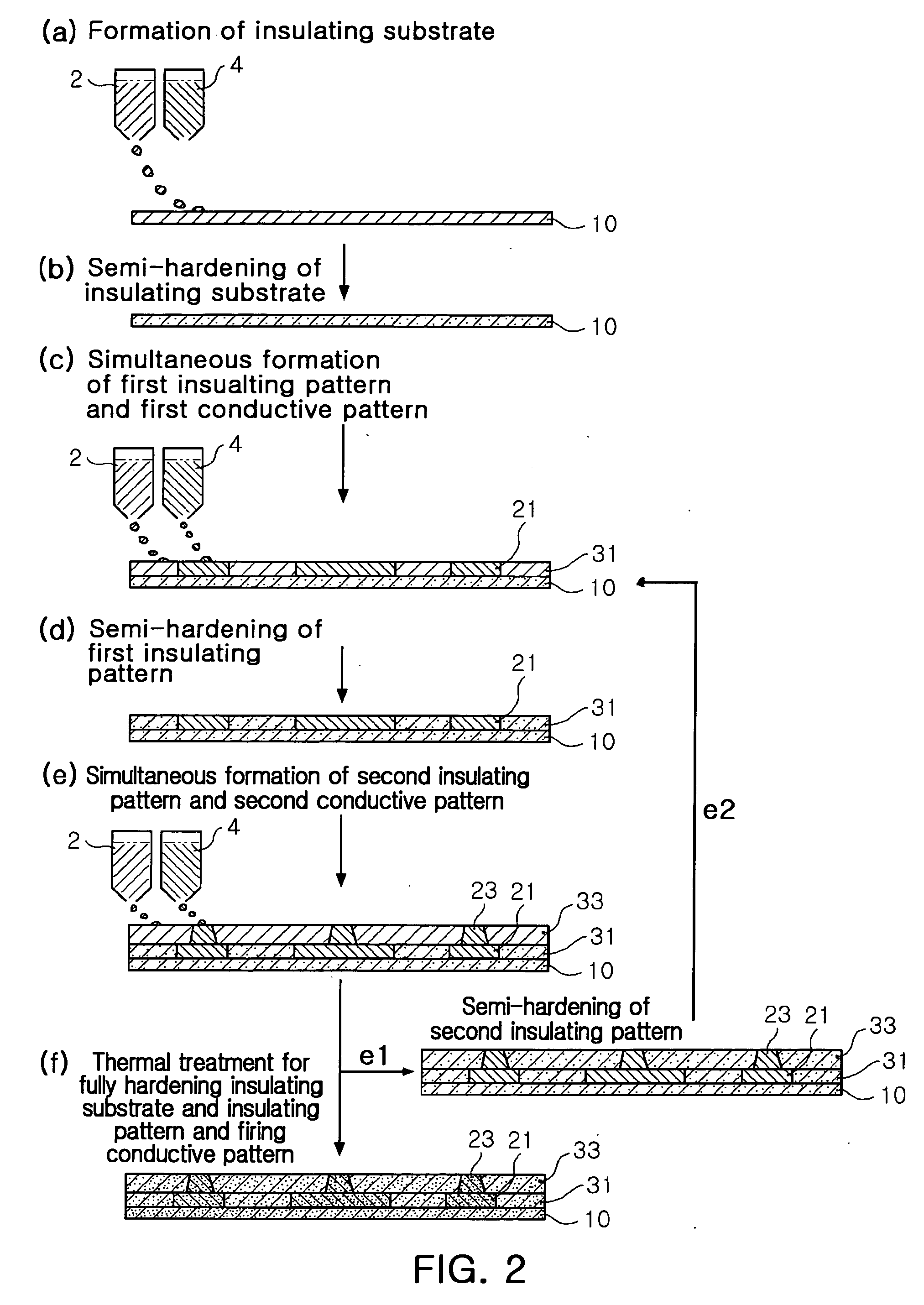

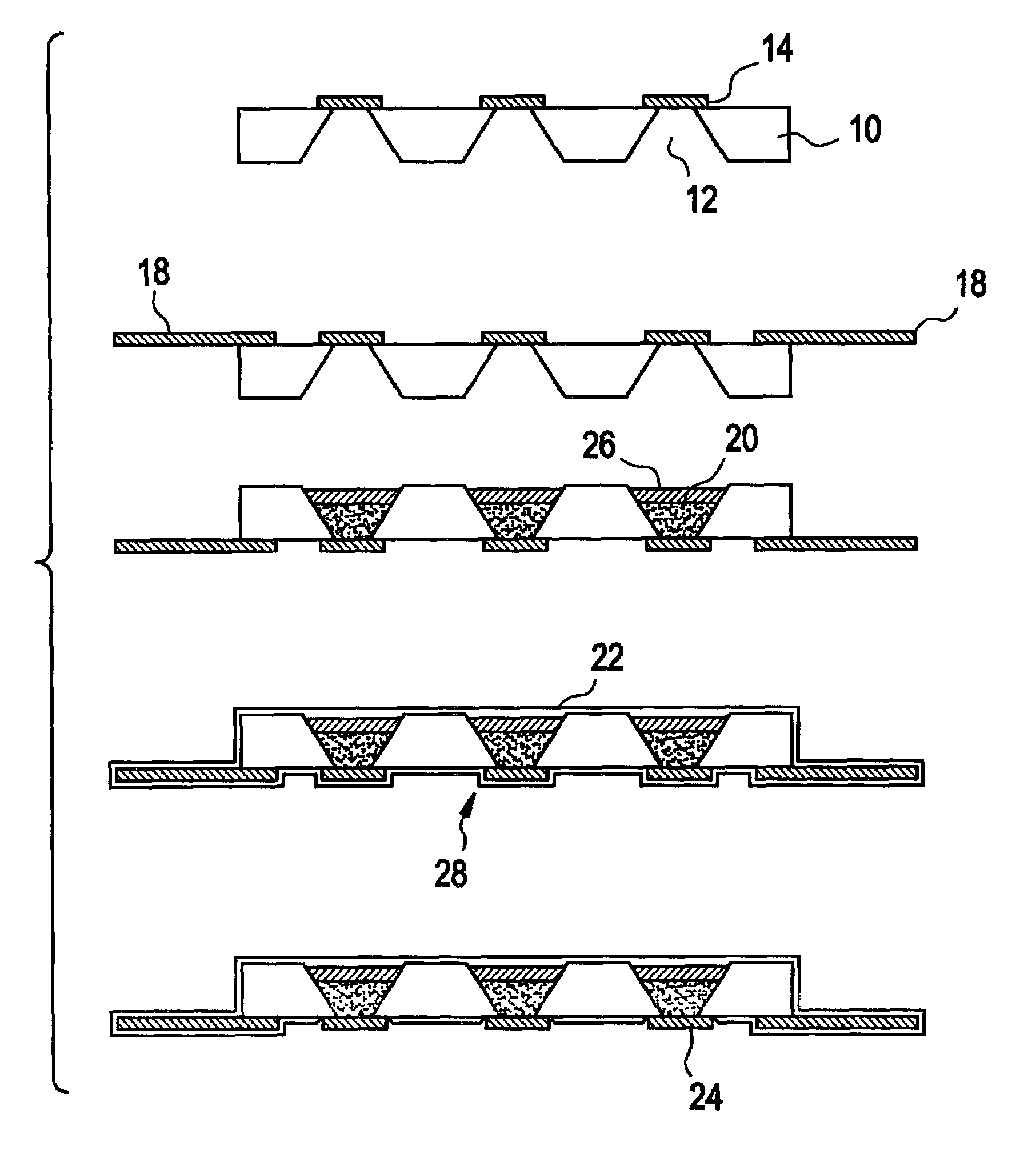

Printed wiring board and method for manufacturing the same

InactiveUS20070128855A1High peel strengthPeel strengthAdditive manufacturing apparatusPrinted circuit aspectsTwo stepThermal treatment

Provided is a method for manufacturing a printed wiring board, which can enhance the peel strength between an insulating layer and a conductive pattern by a two-step process, that is, a semi-hardening and full-hardening of the insulating layer. In the method for manufacturing the printed wiring board having one or more layers of a conductive pattern and an insulating pattern, an insulating pattern is formed on an insulating substrate, and at least one of the insulating substrate and the insulating pattern is semi-hardened. A conductive pattern is formed on the insulating substrate and / or the insulating pattern, thereby providing a stack structure. Then, a thermal treatment is performed on the stack structure to fully harden the semi-hardened insulating substrate and / or insulating pattern, and the conductive pattern is fired.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

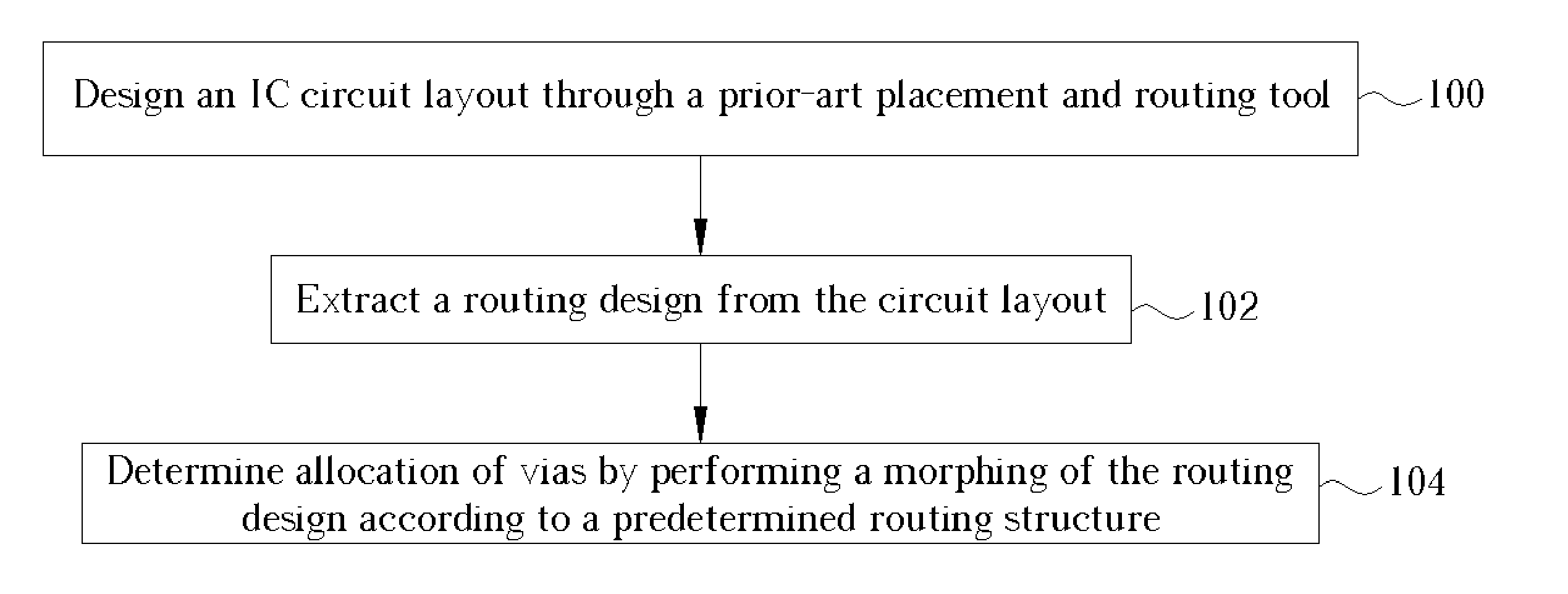

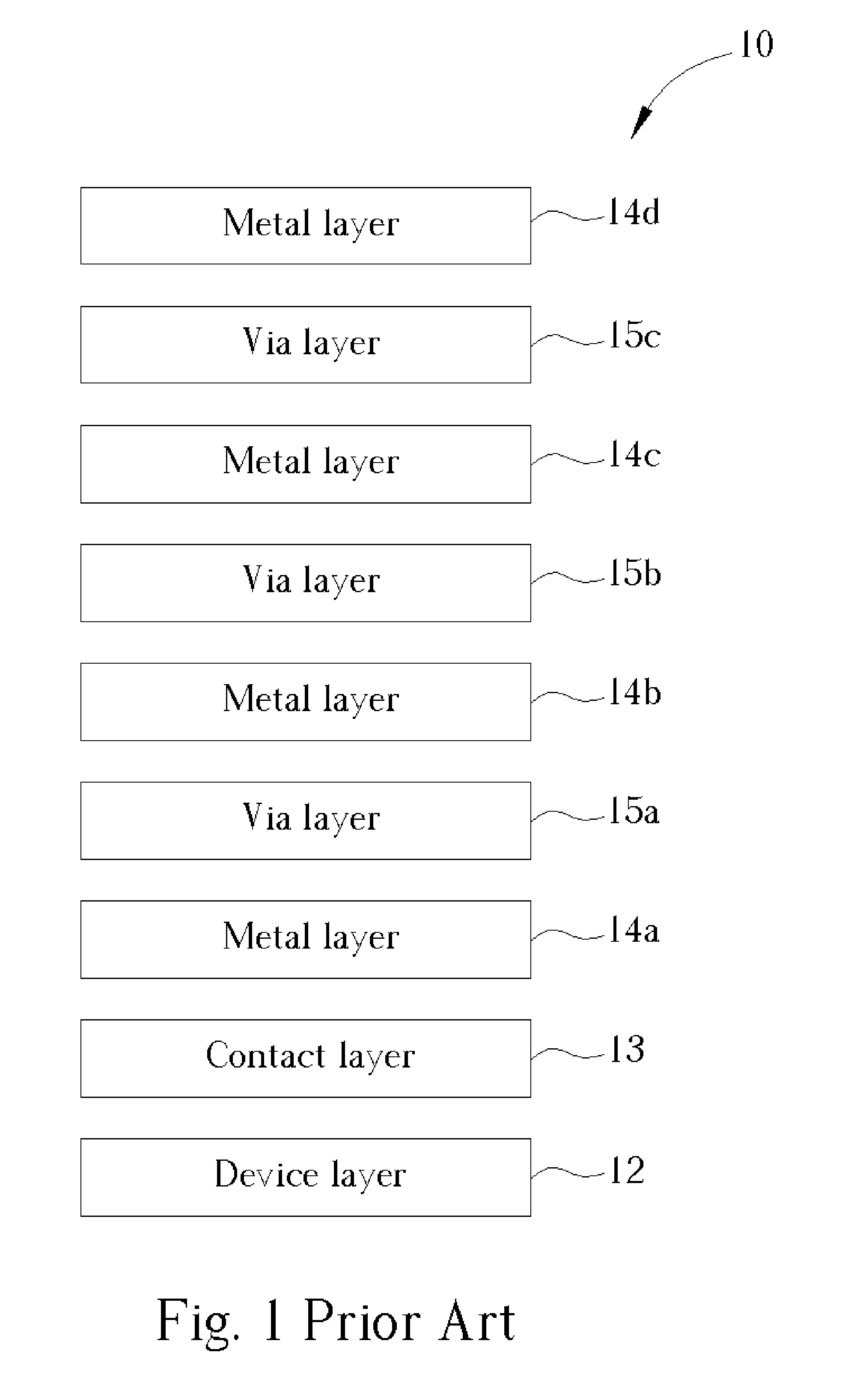

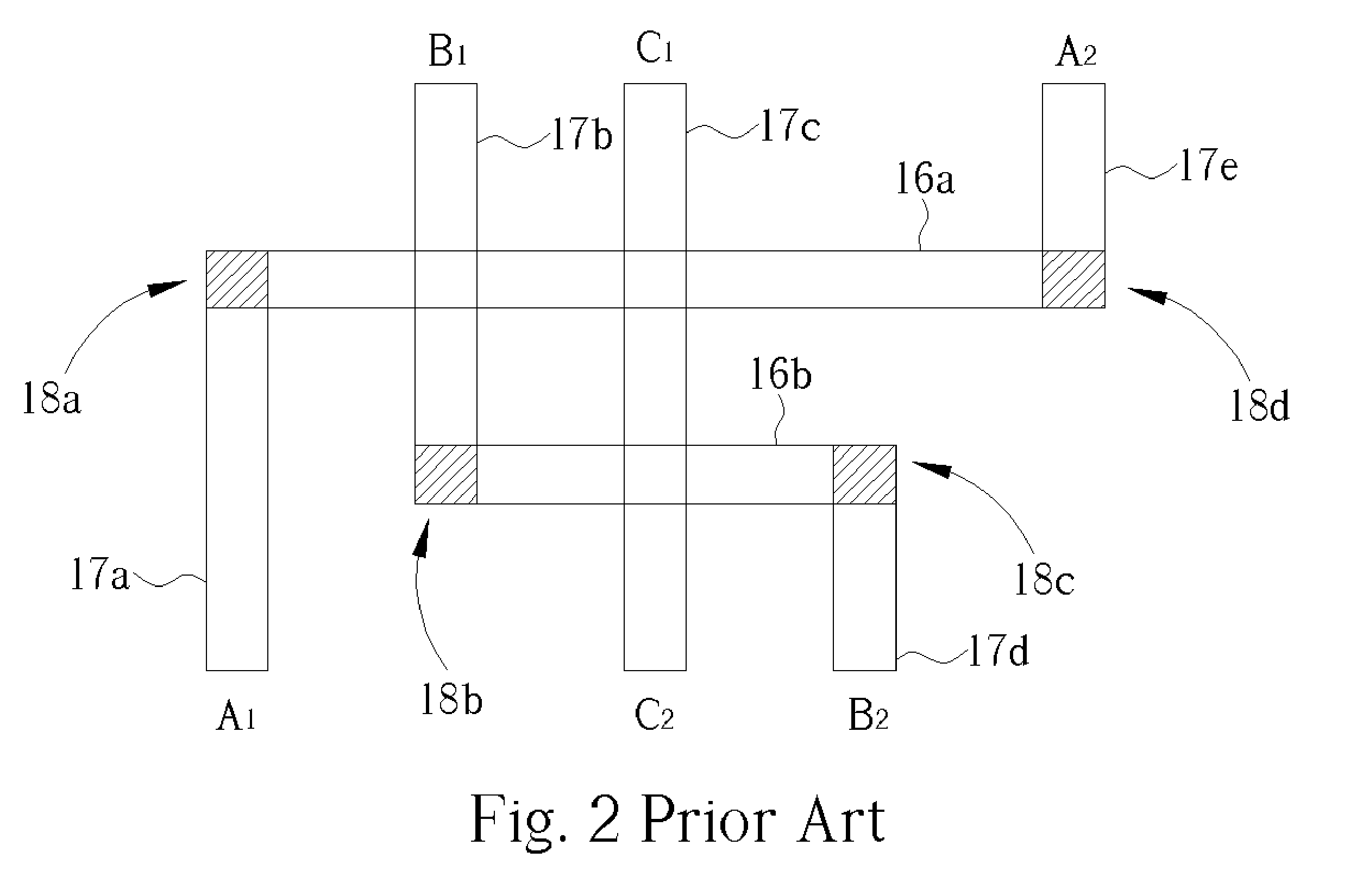

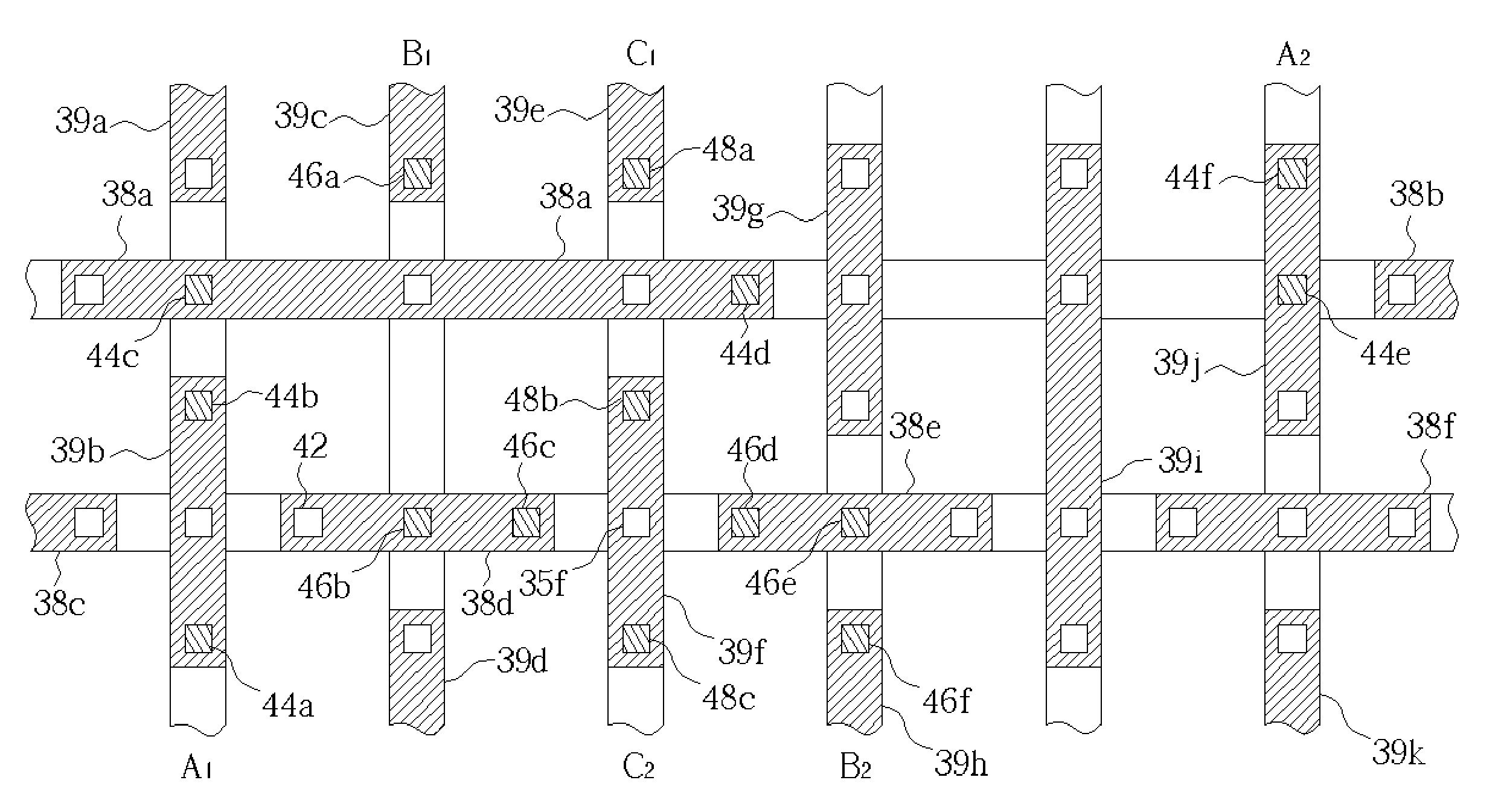

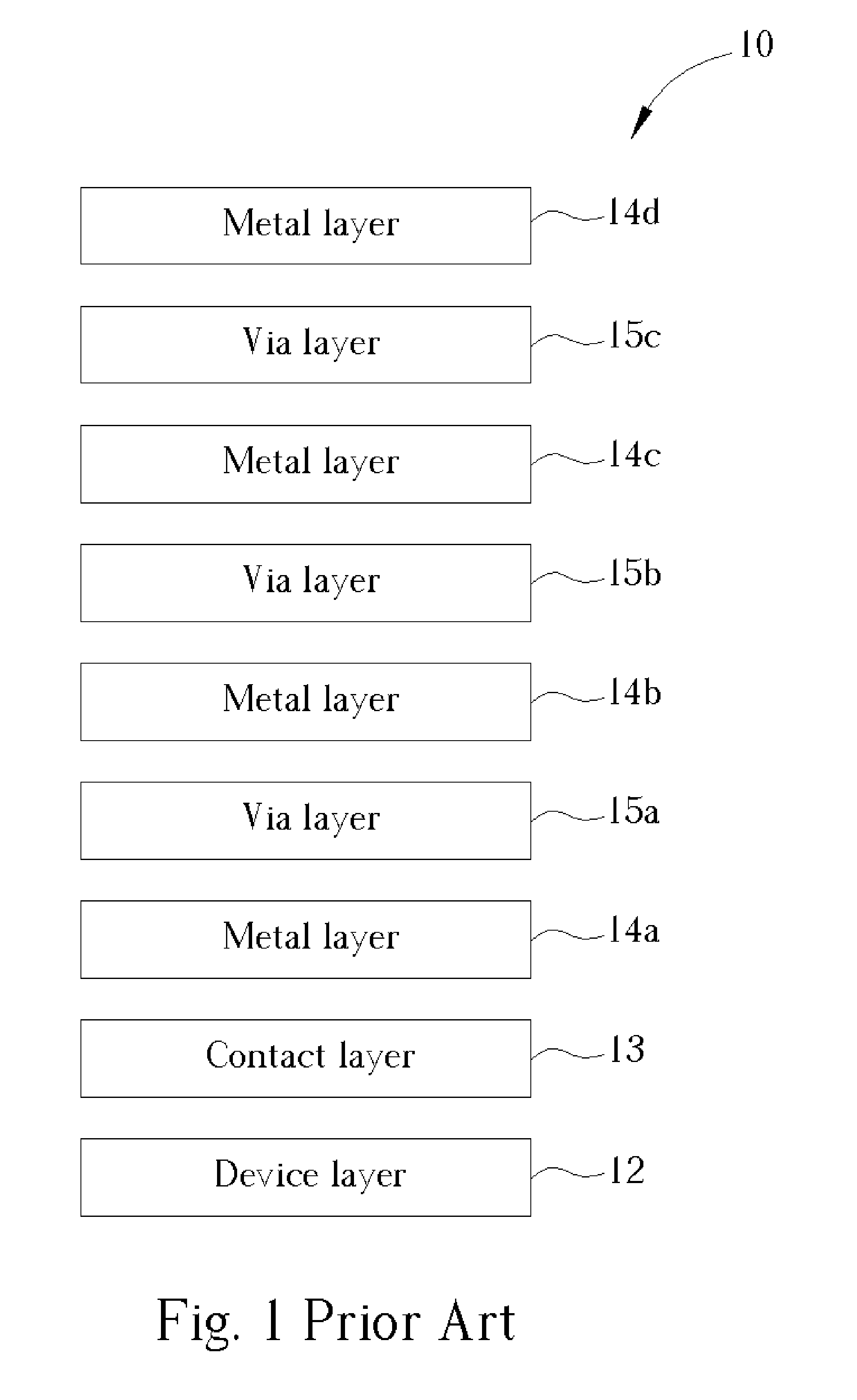

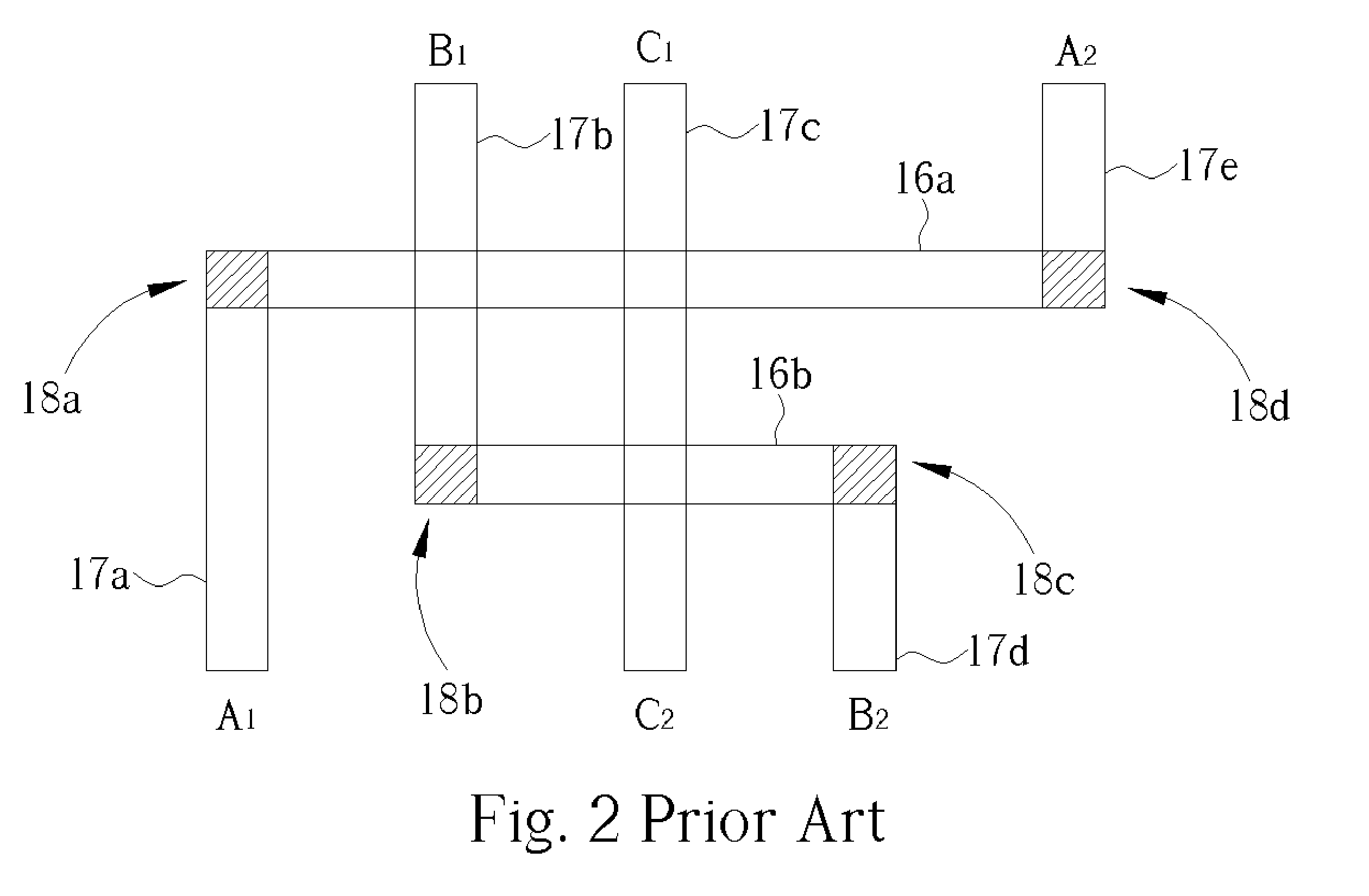

Method for programming a routing layout design through one via layer

ActiveUS20050055828A1Avoid feesPrinted circuit assemblingLine/current collector detailsComputer science

A method for programming a routing layout design through one via layer includes forming a plurality of metal traces on a first routing layer and a second routing layer, and positioning a plurality of vias within a via layer disposed between the first and second routing layers for connecting the metal traces on the first and second routing layers according to a first current route defined by a predetermined circuit layout design to connect a first node and a second node so as to establish a second current route equivalent to the first current route.

Owner:FARADAY TECH CORP

Conductor track structures and method for production thereof

InactiveUS7060421B2Simple structureProduced simply and reliablyPhotomechanical apparatusLiquid/solution decomposition chemical coatingElectrical conductorSpinel

Conductive tracks disposed on an electrically non-conductive support material by depositing a metallized layer on metal nuclei produced by using electromagnetic radiation to break up electrically non-conductive metal compounds dispersed in the support material, and a method for producing them. The electrically non-conductive metal compounds are insoluble spinel-based inorganic oxides which are thermally stable and are stable in acidic or alkaline metallization baths, and which are higher oxides with a spinel structure, and which remain unchanged in non-irradiated areas. The spinel-based inorganic oxides used are heat resistant and remain stable after being subjected to soldering temperatures. The conductor tracks are reliably and easily produced and adhere strongly to the support.

Owner:PAPST MOTOREN GMBH & CO KG

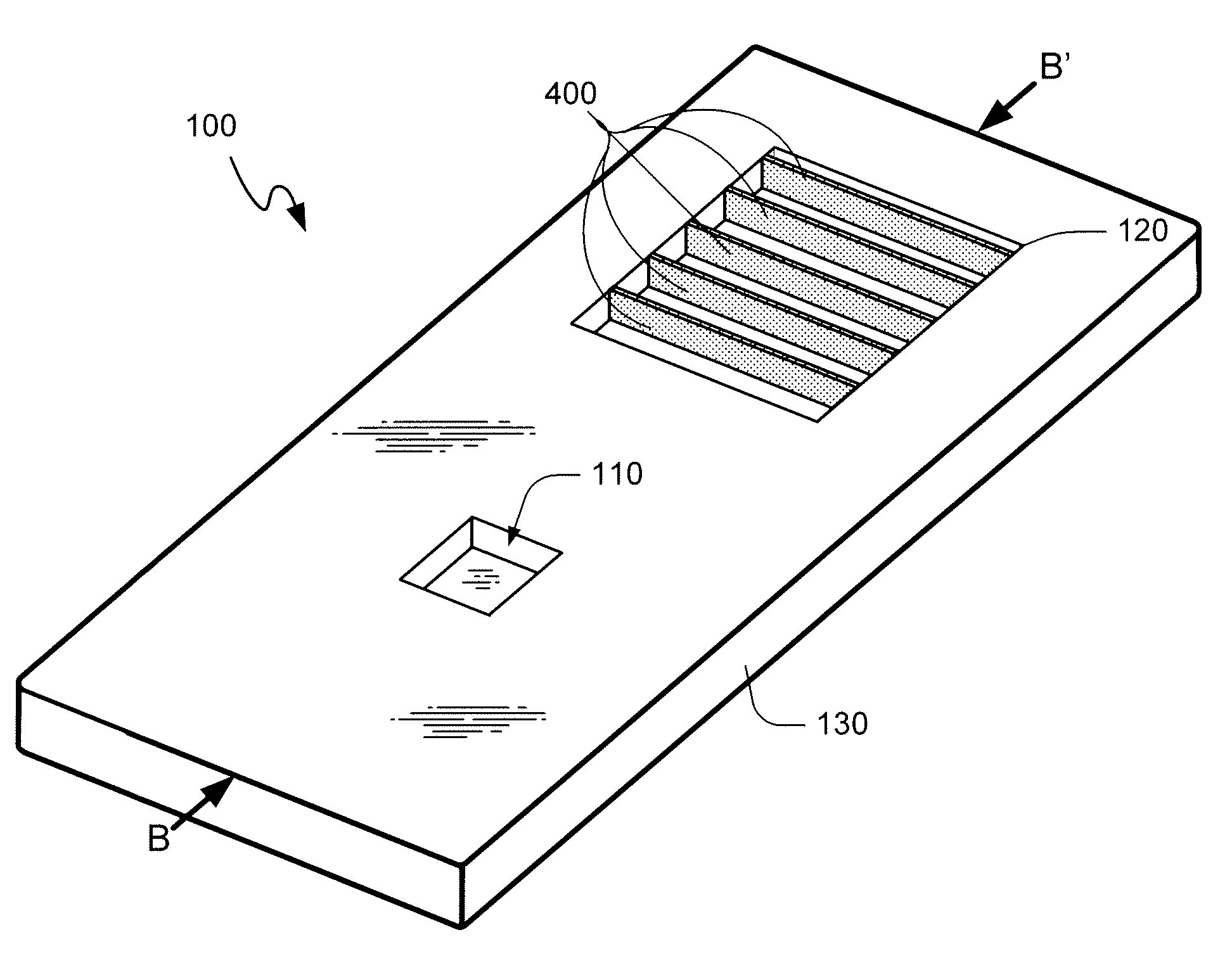

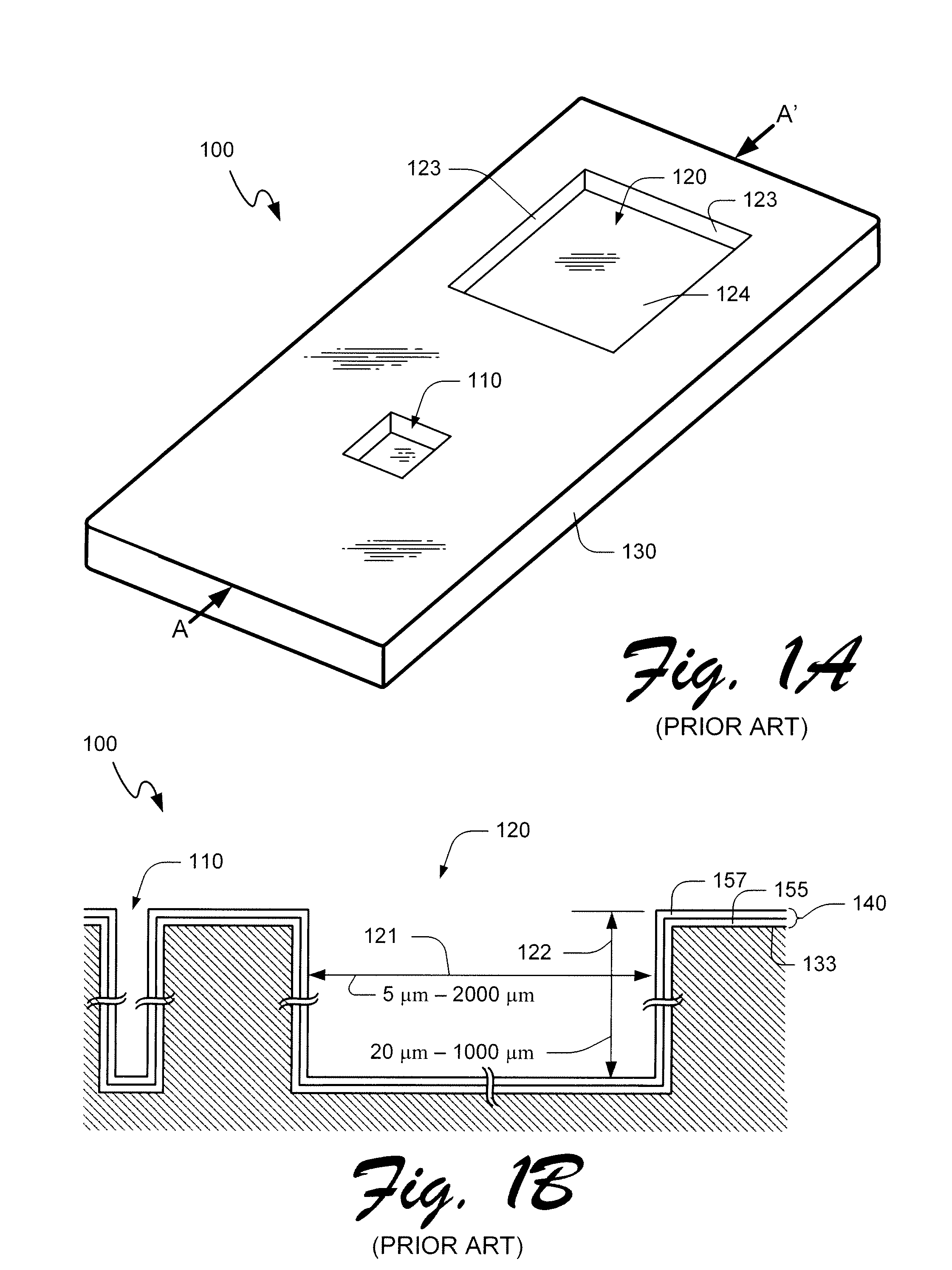

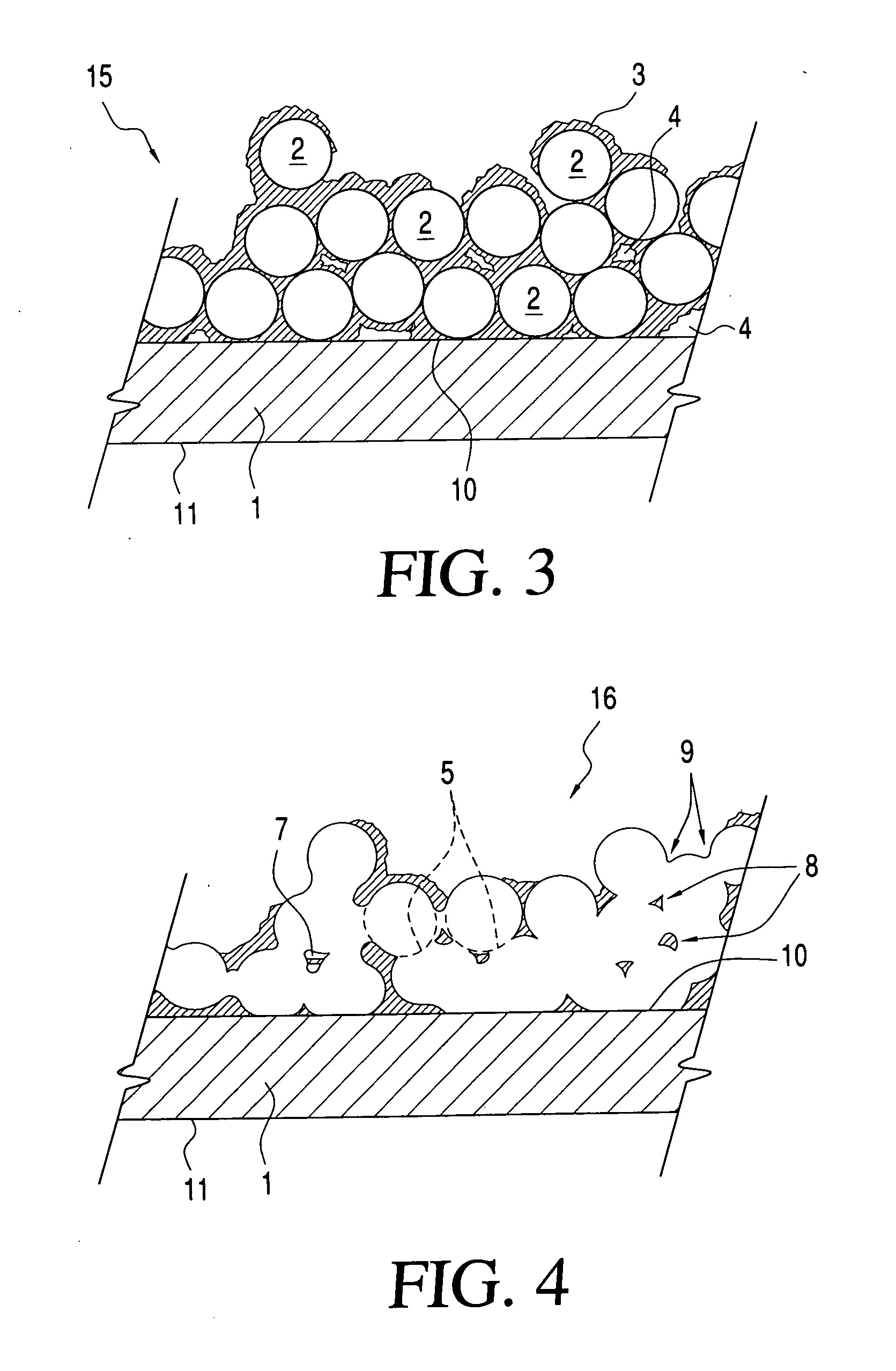

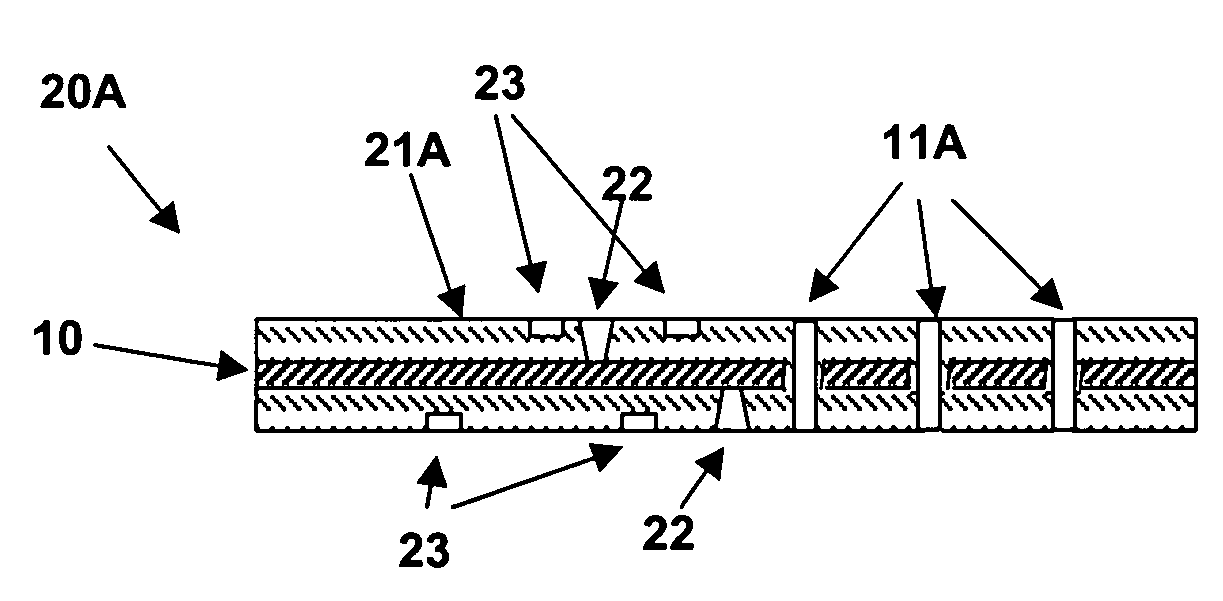

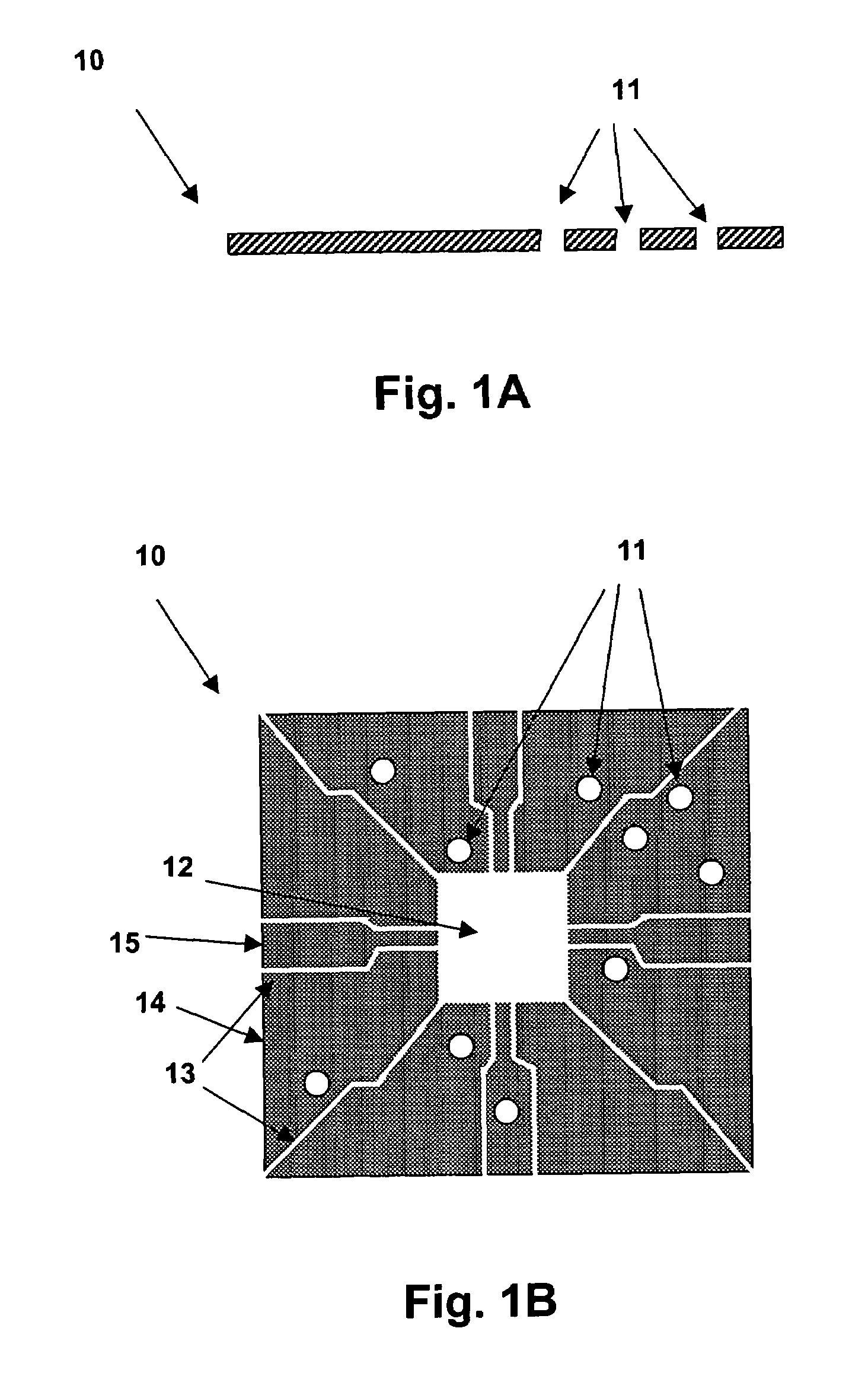

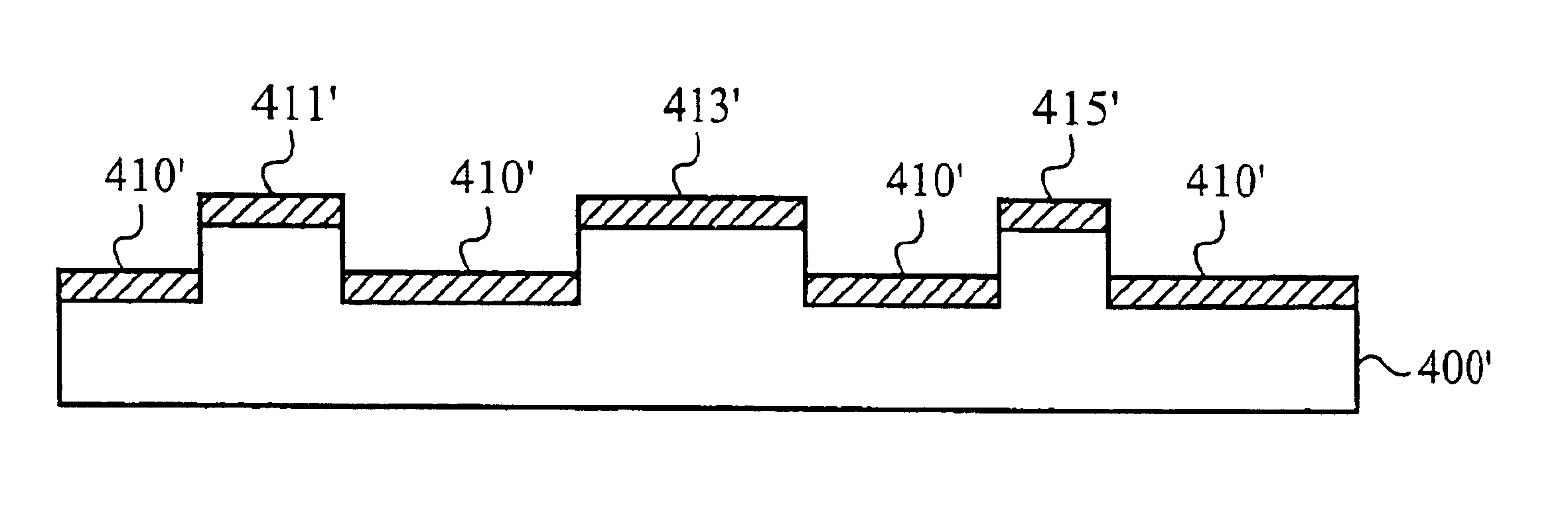

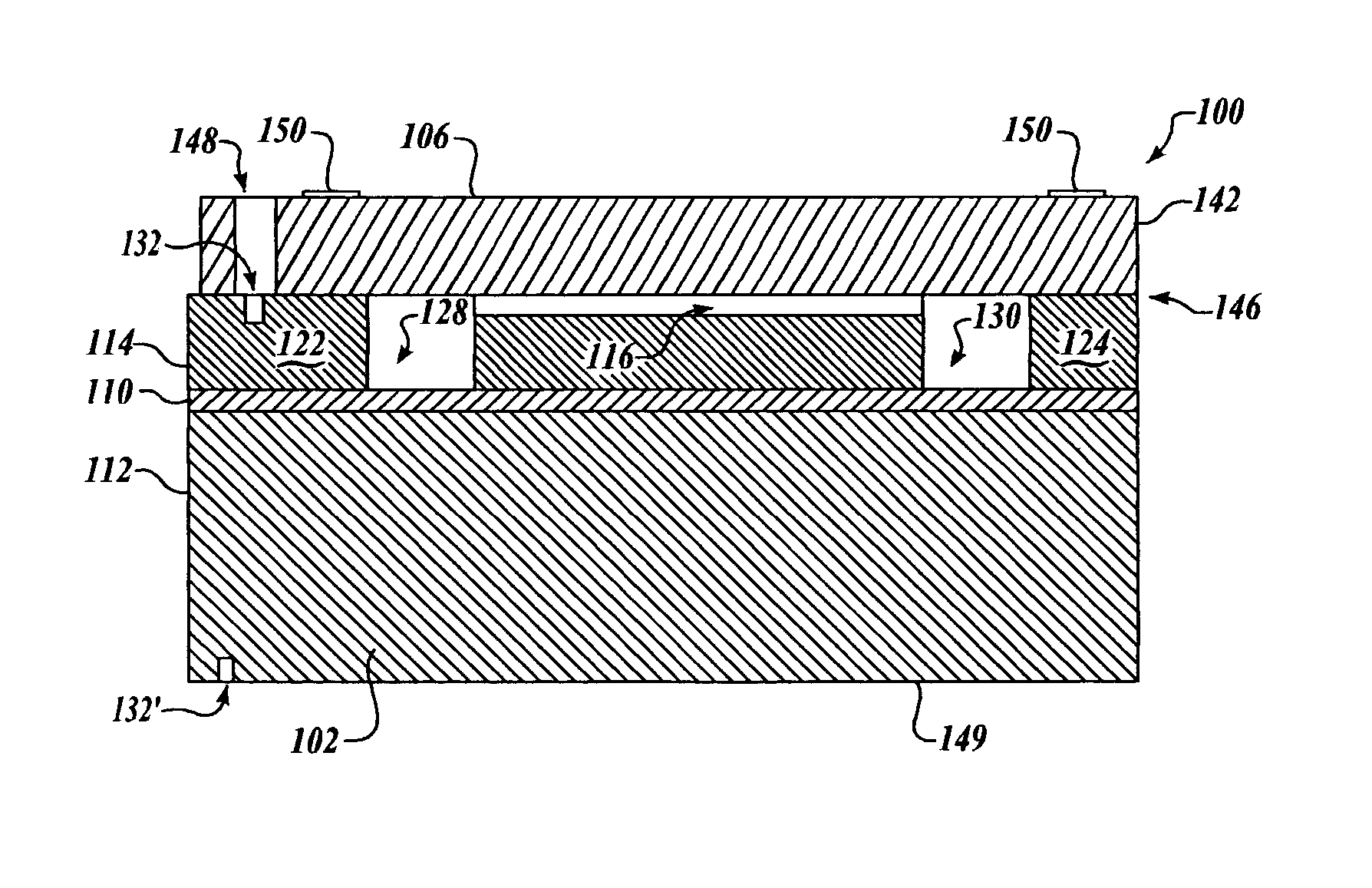

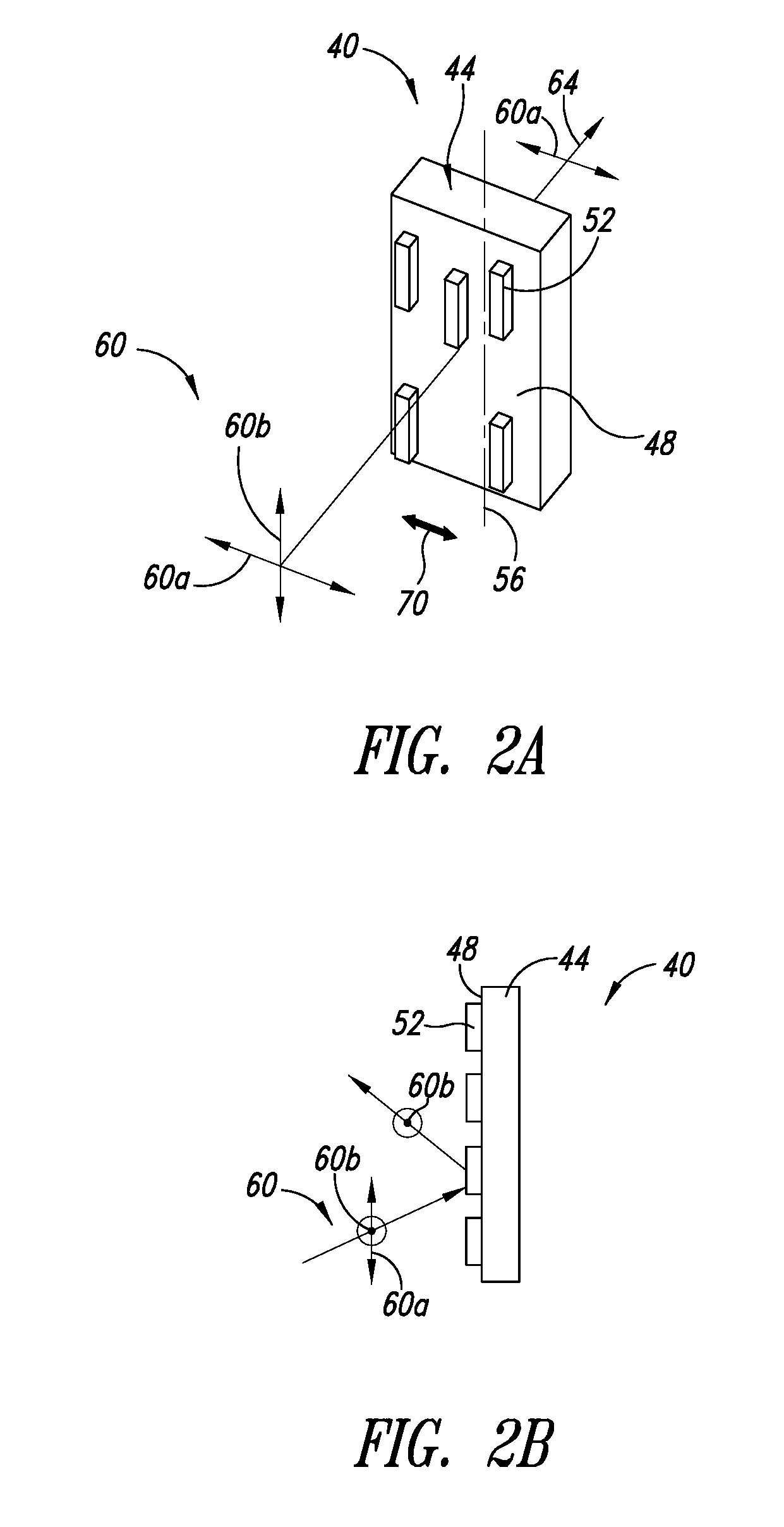

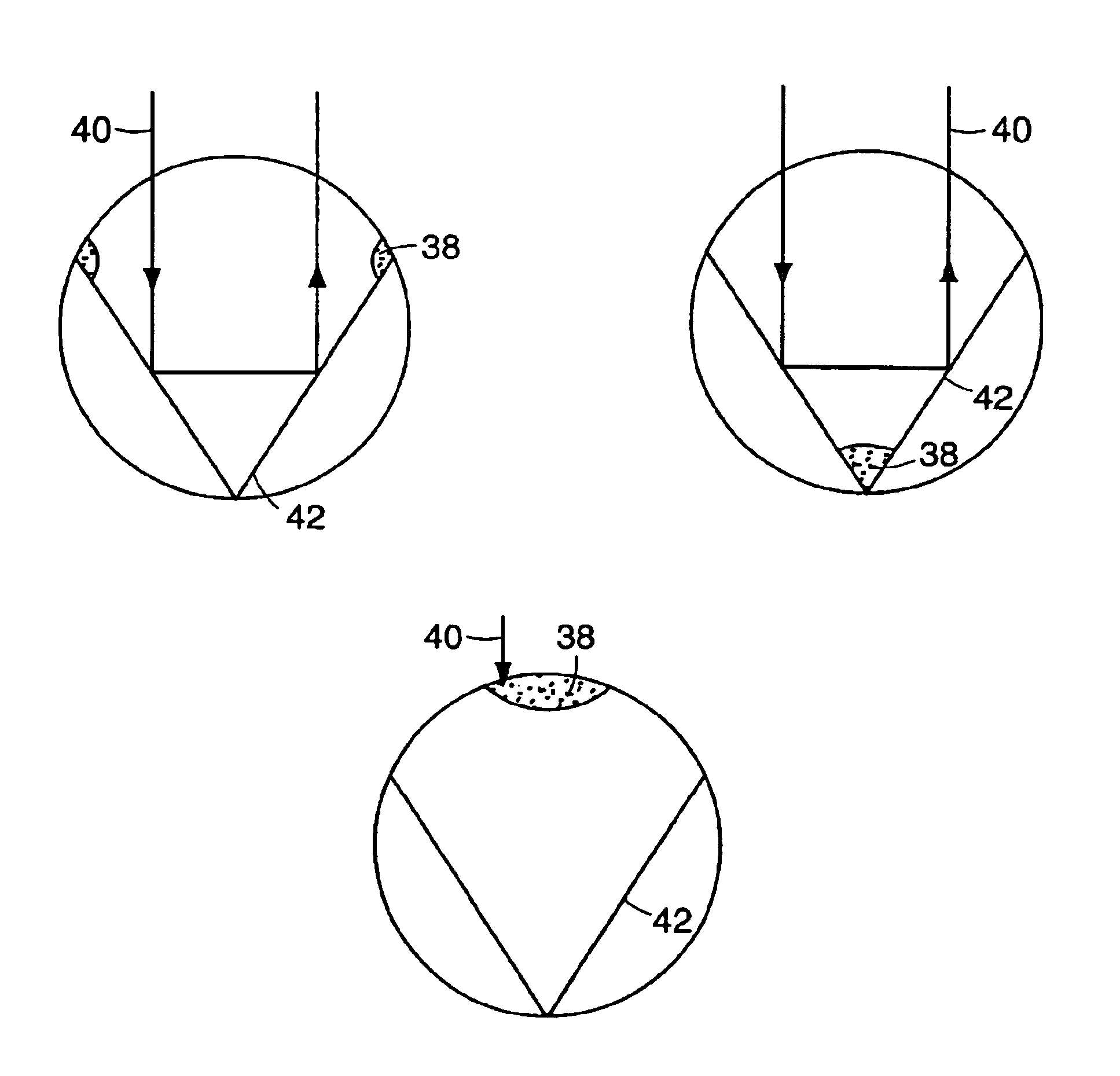

Integrated circuit substrate having laser-embedded conductive patterns and method therefor

InactiveUS6930256B1Printed electric component incorporationSemiconductor/solid-state device detailsScreen printingHigh density

An integrated circuit substrate having laser-embedded conductive patterns provides a high-density mounting and interconnect structure for integrated circuits. Conductive patterns within channels on the substrate provide interconnects that are isolated by the channel sides. A dielectric material is injection-molded or laminated over a metal layer that is punched or etched. The metal layer can provide one or more power planes within the substrate. A laser is used to ablate channels on the surfaces of the outer dielectric layer for the conductive patterns. The conductive patterns are electroplated or paste screen-printed and an etchant-resistive material is applied. Finally, a plating material can be added to exposed surfaces of the conductive patterns. An integrated circuit die and external terminals can then be attached to the substrate, providing an integrated circuit having a high-density interconnect.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

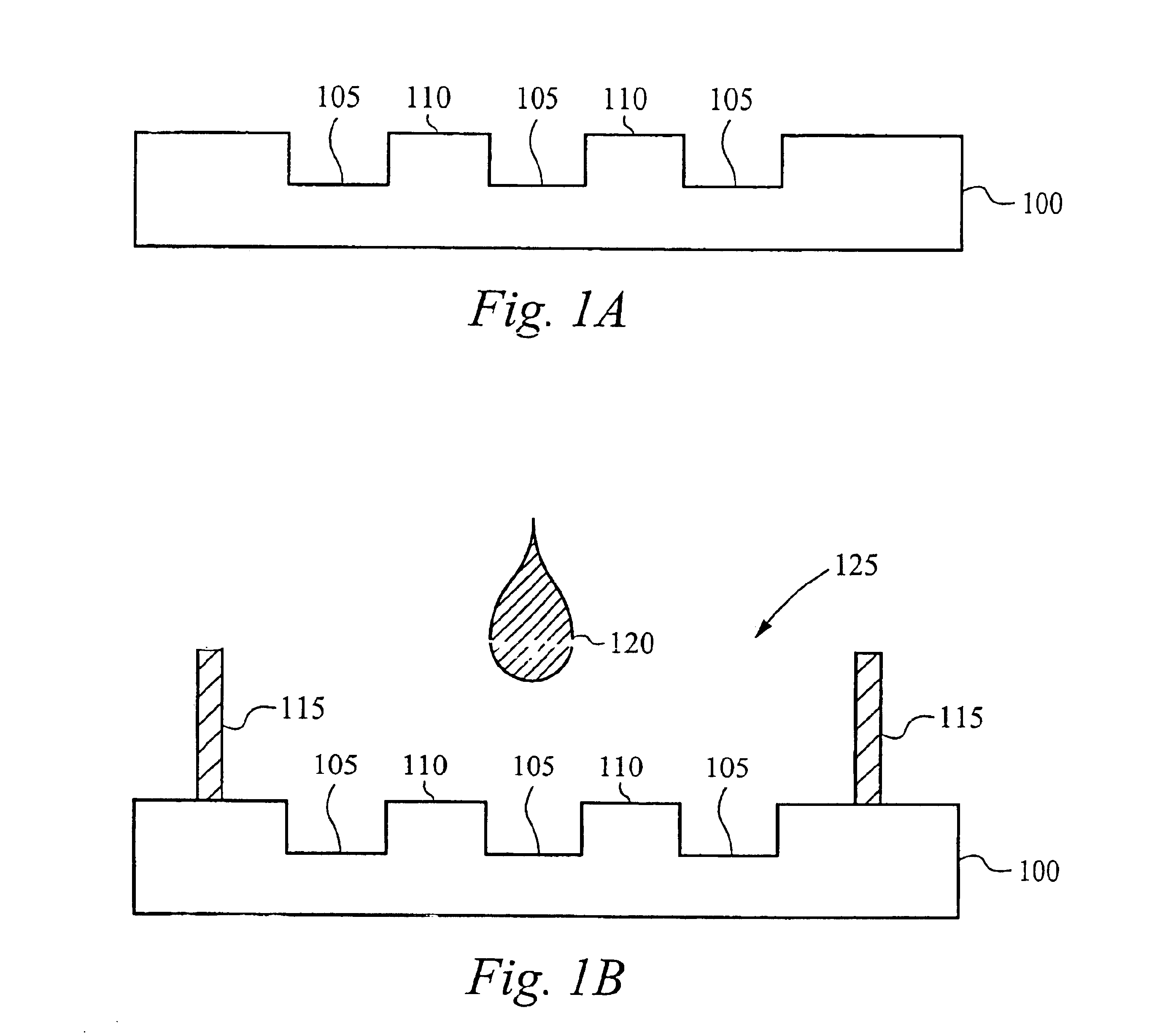

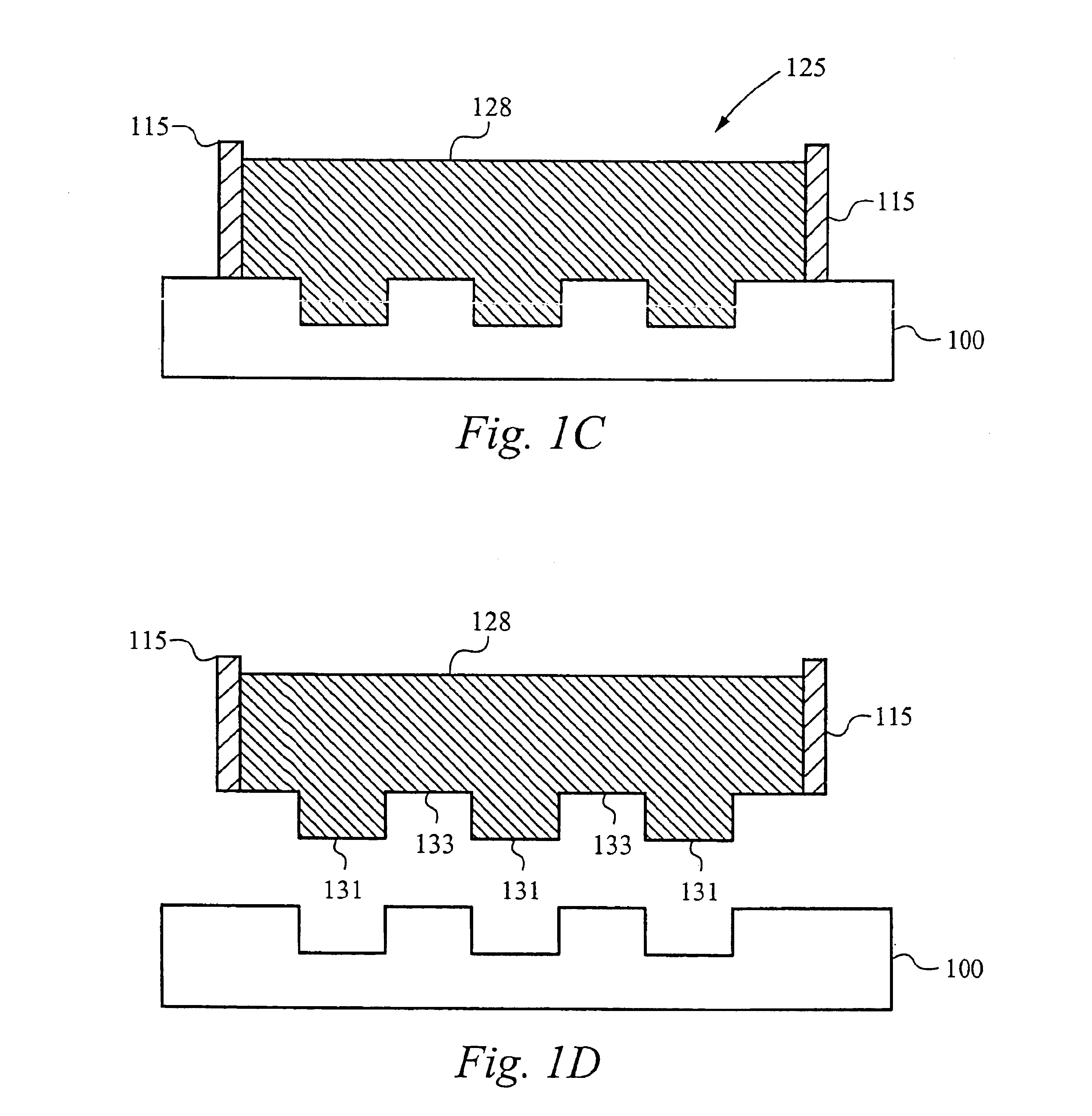

Contact print methods

InactiveUS6957608B1High definitionImprove printing effectMechanical working/deformationSolid-state devicesContact printSolvent

A method of and device for controlled printing using liquid embossing techniques is disclosed. In accordance with the embodiments of the invention a stamp comprises a differentiated embossing surface with protruding and recessed surfaces to enhance the ability of the stamp to selectively displace liquid ink from a print surface and / or remove solvent from the liquid in a soft curing process. A stamp with differentiated surfaces is fabricated by selectively coating, or otherwise treating the protruding features, the recessed features, or a combination thereof, such that the surface energies and / or wettability of the protruding surfaces and the recessed surfaces are differentiated.

Owner:KOVIO

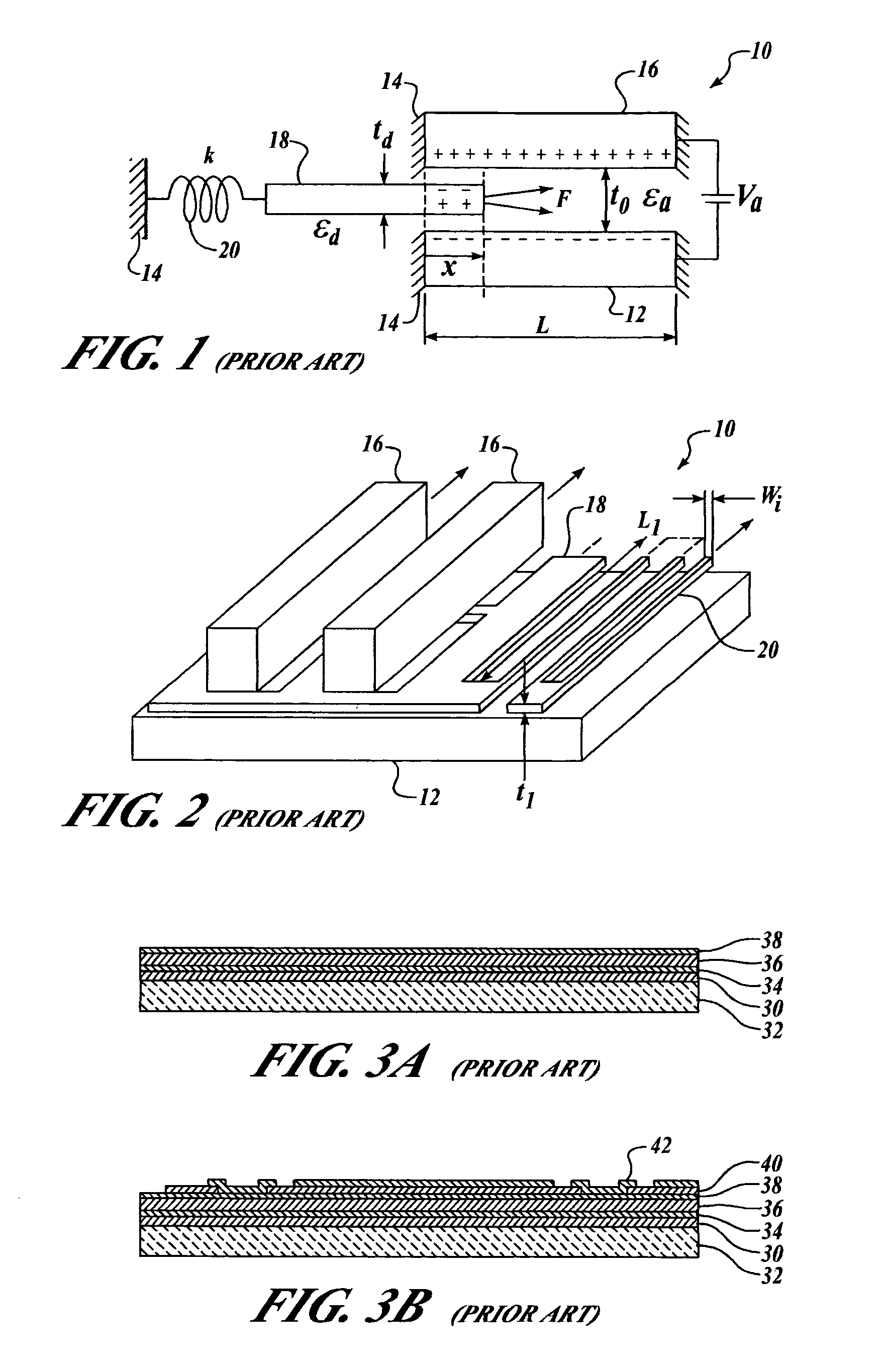

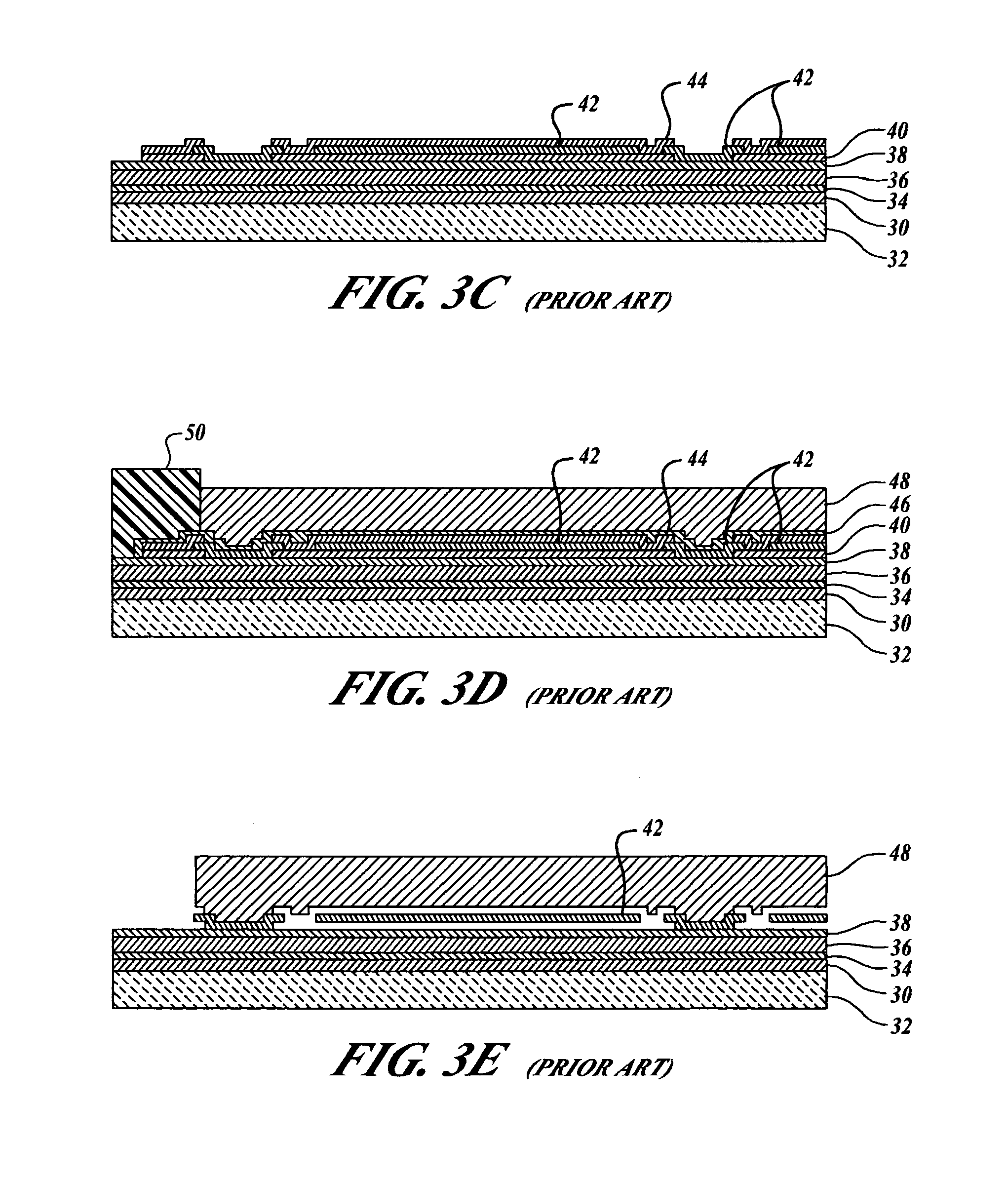

Method of manufacturing vibrating micromechanical structures

A method for fabrication of single crystal silicon micromechanical resonators using a two-wafer process, including either a Silicon-on-insulator (SOI) or insulating base and resonator wafers, wherein resonator anchors, a capacitive air gap, isolation trenches, and alignment marks are micromachined in an active layer of the base wafer; the active layer of the resonator wafer is bonded directly to the active layer of the base wafer; the handle and dielectric layers of the resonator wafer are removed; viewing windows are opened in the active layer of the resonator wafer; masking the single crystal silicon semiconductor material active layer of the resonator wafer with photoresist material; a single crystal silicon resonator is machined in the active layer of the resonator wafer using silicon dry etch micromachining technology; and the photoresist material is subsequently dry stripped.

Owner:HONEYWELL INT INC

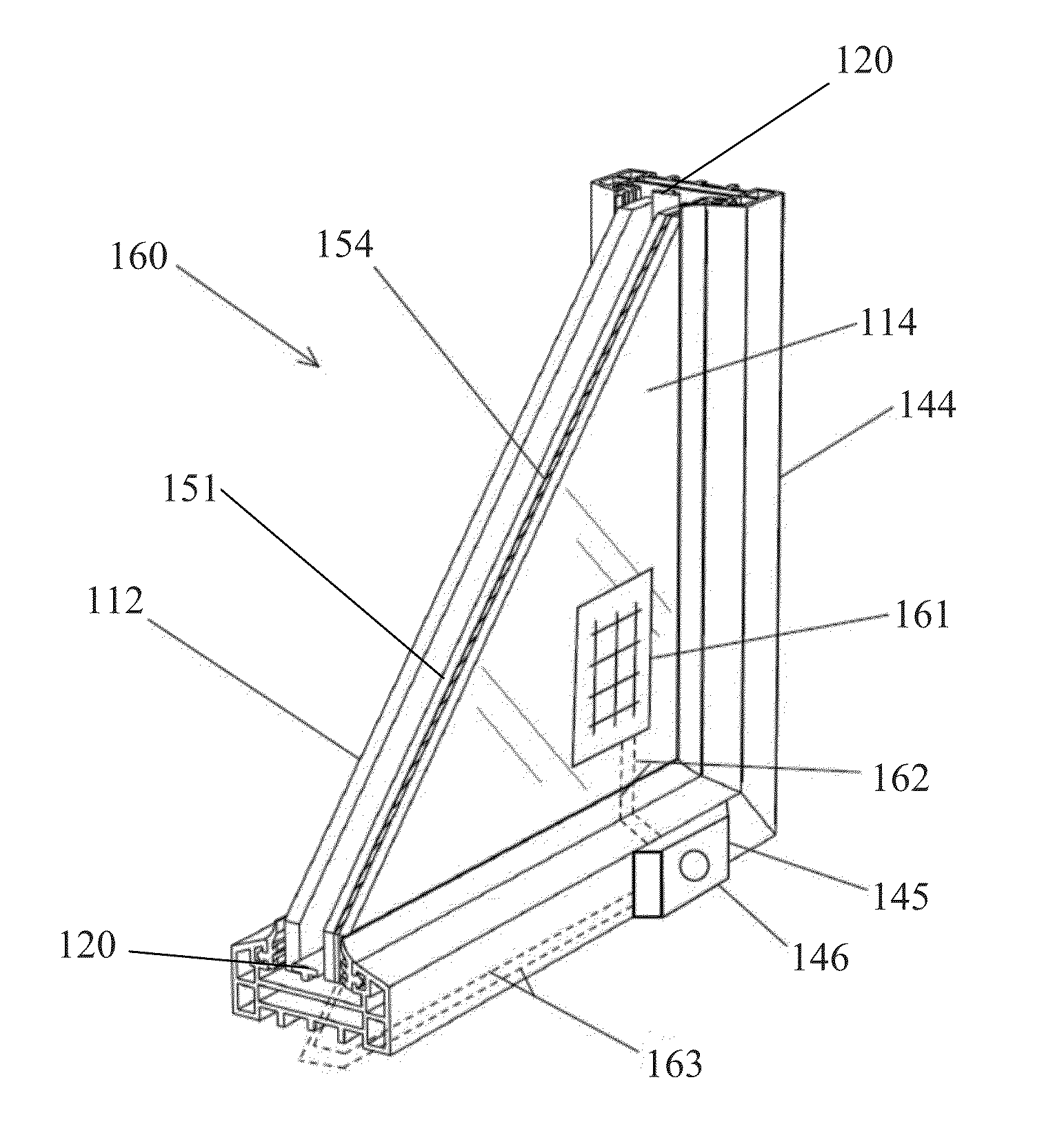

Variable transmittance optical devices

ActiveUS20130278989A1Reduce solar heat gainReduce cooling loadAntiglare equipmentStatic indicating devicesThermal energyElectricity

A self-powered variable transmittance optical device, such as a smart window or other device, and associated method are provided. The device comprises one or more transparent substrates, with a switching material disposed thereon or therebetween. The switching material may be a hybrid photochromic / electrochromic material capable of transitioning from a first transmittance state to a second transmittance state with application of electricity, and from second state to first state due to another stimulus, such as UV radiation. Electrodes are coupled to the switching material for applying electricity. An electrical system provides for controllable application of the electricity, and may store energy. Energy is provided by an energy-harvesting power source such as a solar cell or other photovoltaic source, or array thereof, or another device for harvesting vibrational or thermal energy. Energy harvesting, energy storage capacity and / or switching material may be configured to provide at least a predetermined level of device operability.

Owner:SOLUTIA CANADA INC

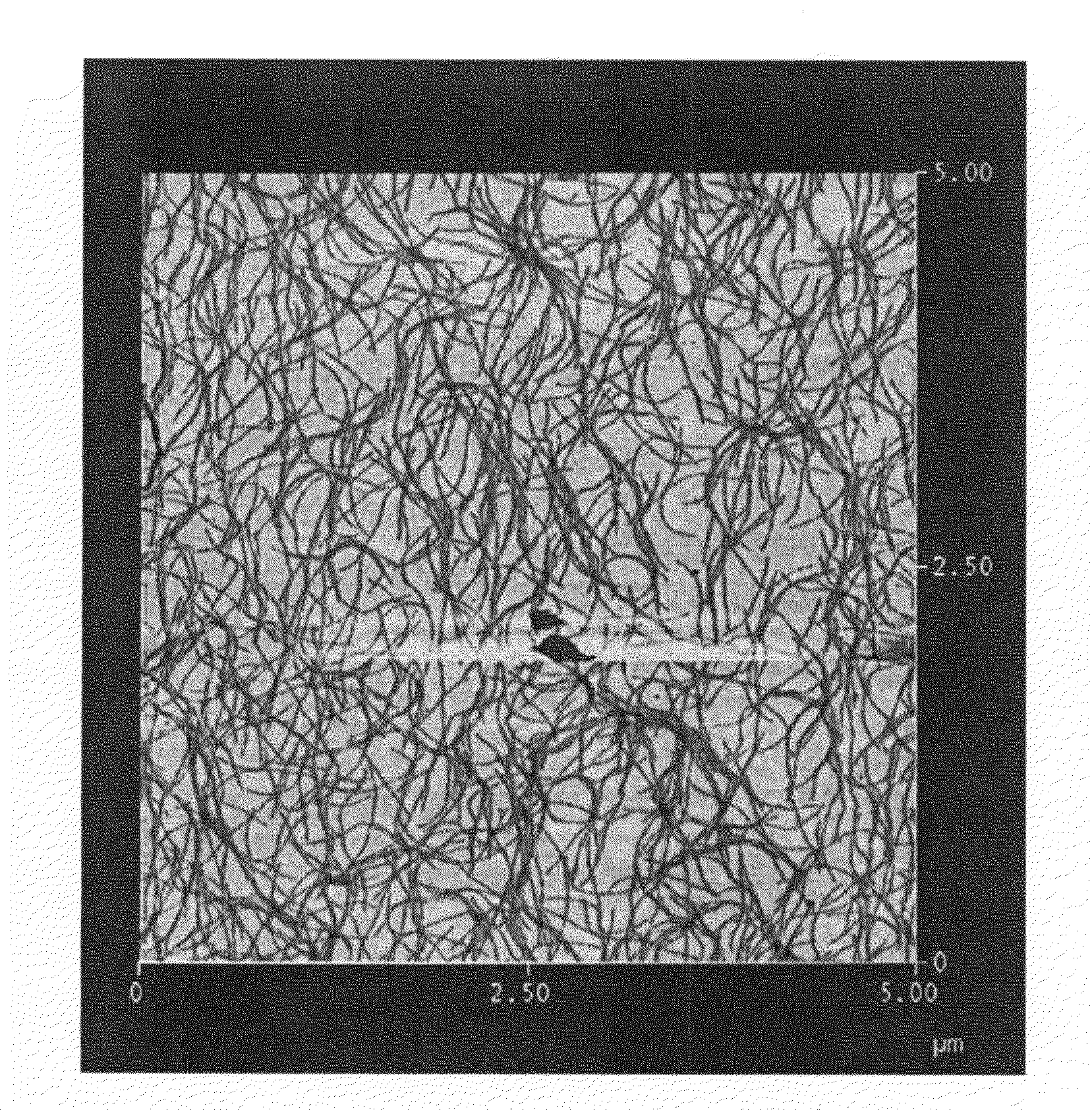

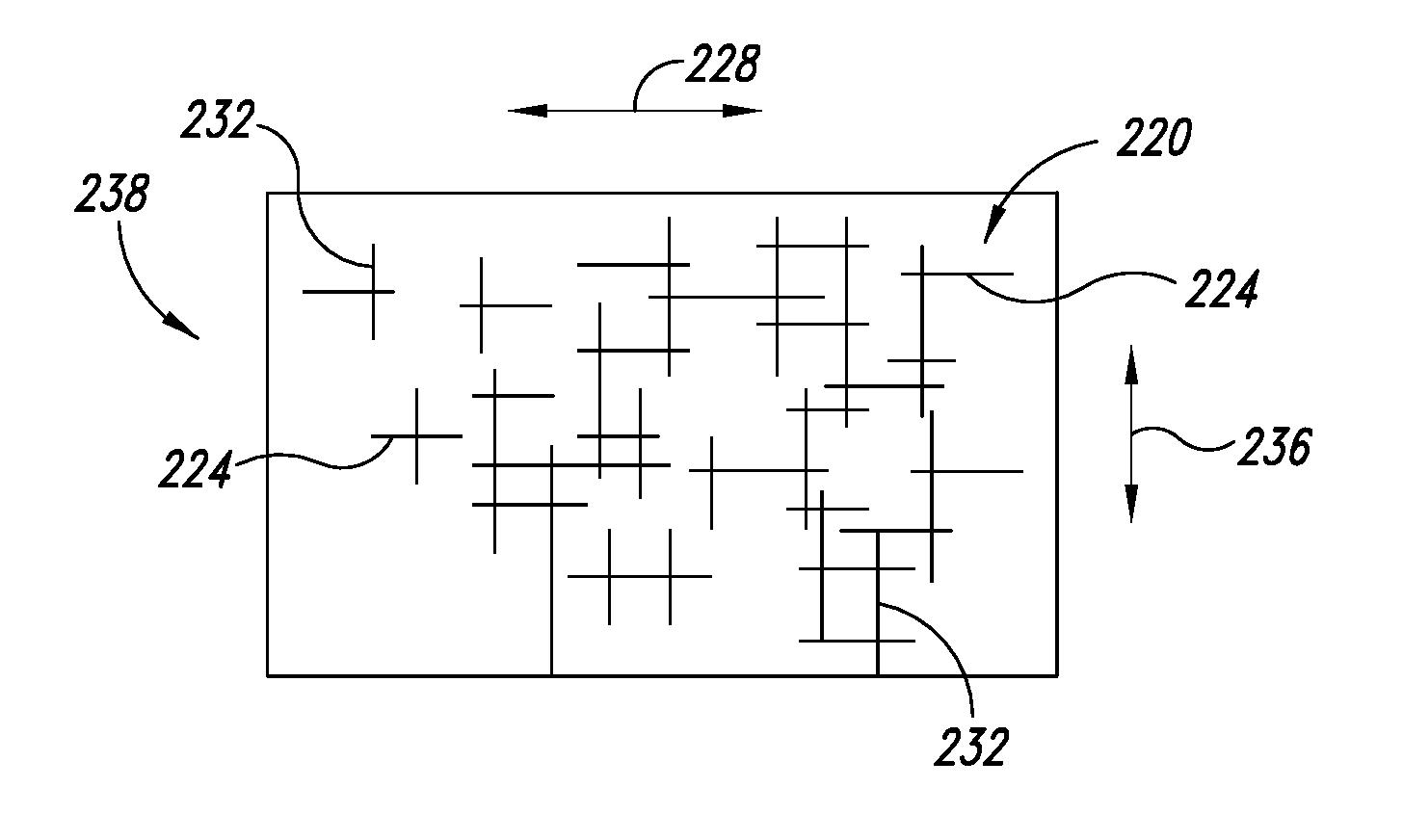

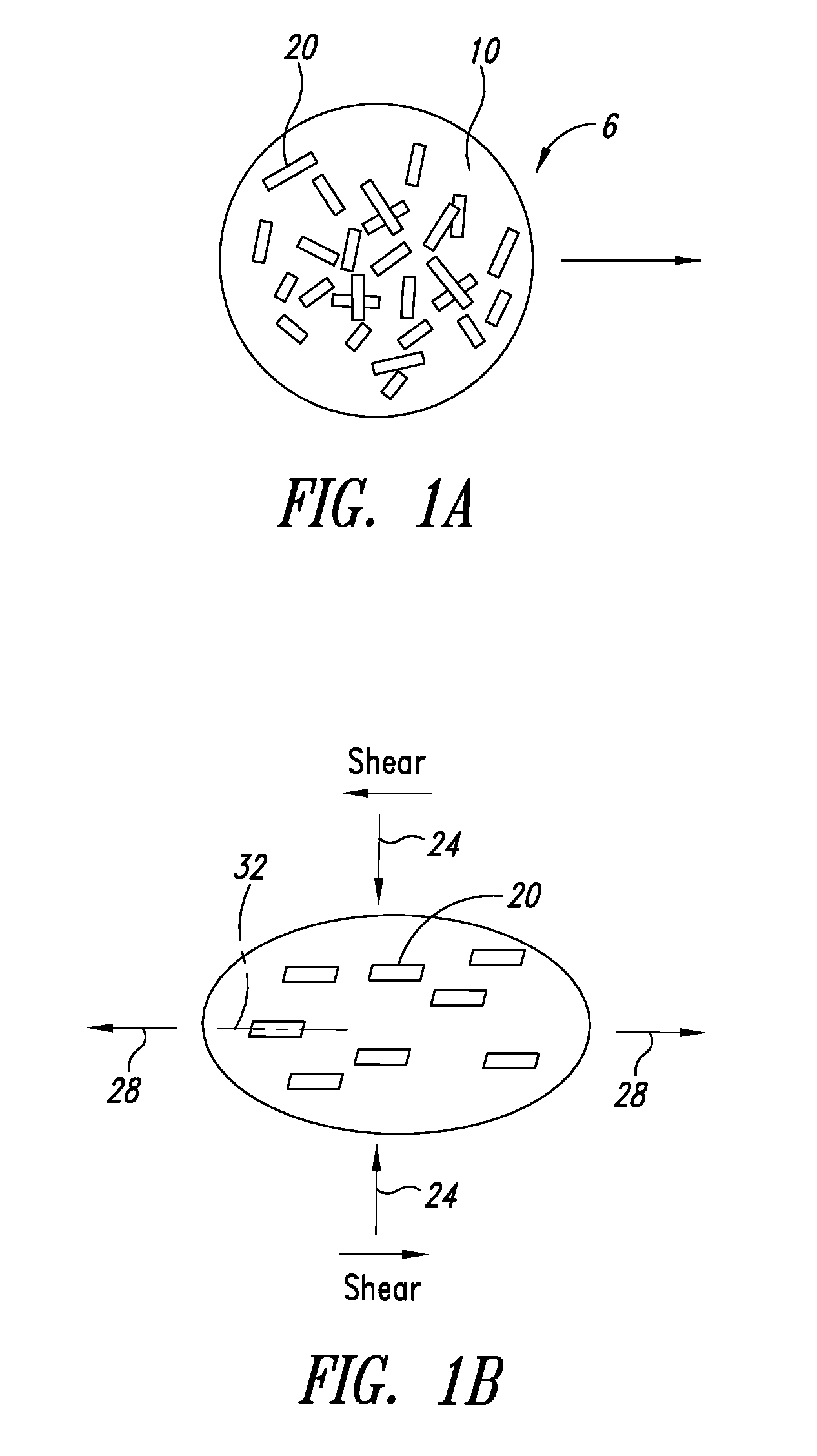

Functional films formed by highly oriented deposition of nanowires

InactiveUS20090052029A1Reduce manufacturing costIncreased durabilityMaterial nanotechnologyNon-insulated conductorsNanowireNanometre

Optical films formed by deposition of highly oriented nanowires and methods of aligning suspended nanowires in a desired direction by flow-induced shear force are described.

Owner:CAMBRIOS TECH +1

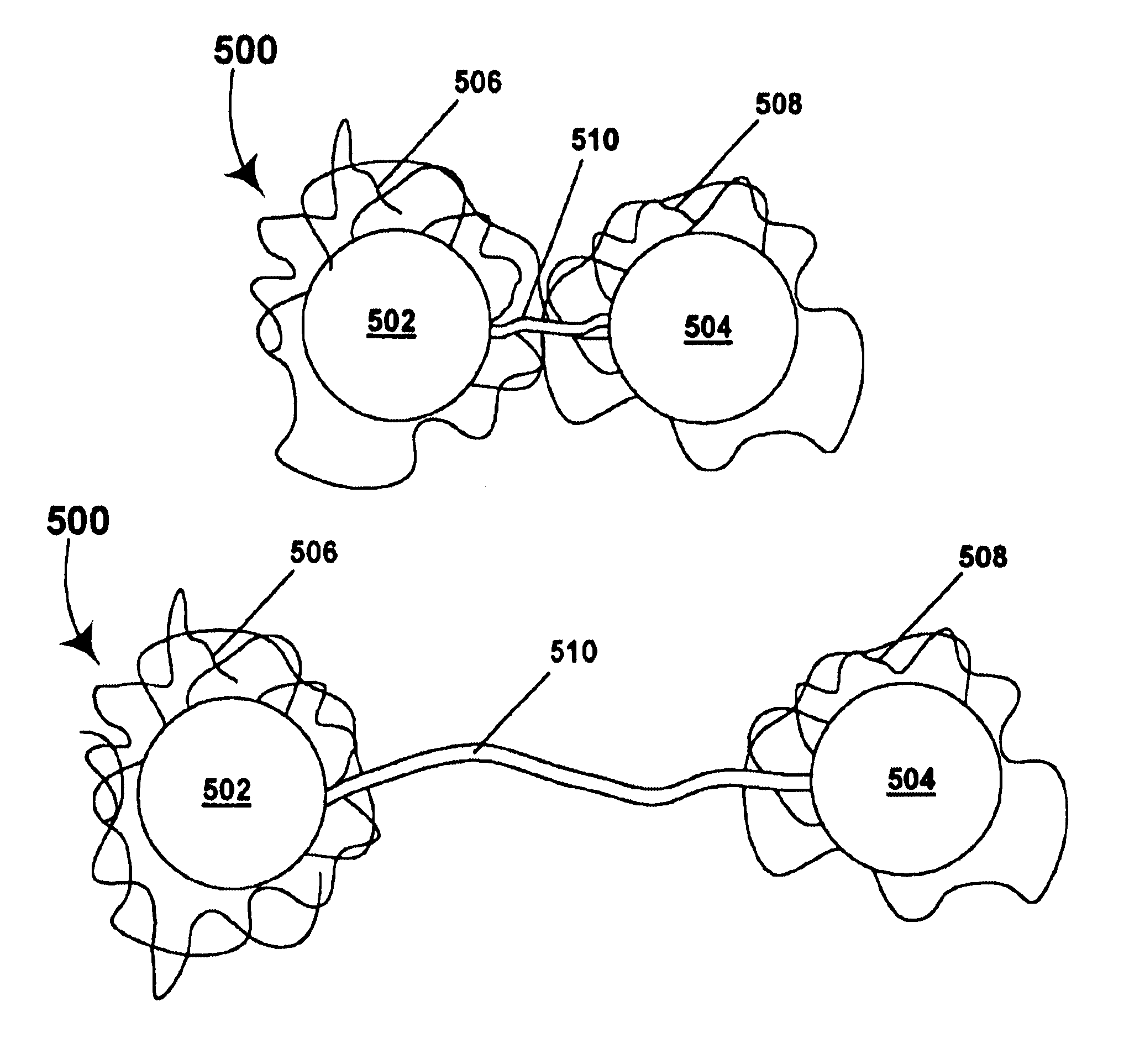

Retroreflective electrophoretic displays and materials for making the same

InactiveUS7071913B2High level controlDisorientingMechanical clocksStatic indicating devicesCelluloseOptical property

Disclosed herein are novel electrophoretic displays and materials useful in fabricating such displays. In particular, novel encapsulated displays are disclosed. Particles encapsulated therein are dispersed within a suspending, or electrophoretic, fluid. This fluid may be a mixture of two or more fluids or may be a single fluid. The displays may further comprise particles dispersed in a suspending fluid, wherein the particles contain a liquid. In either case, the suspending fluid may have a density or refractive index substantially matched to that of the particles dispersed therein. Finally, also disclosed herein are electro-osmotic displays. These displays comprise at least one capsule containing either a cellulosic or gel-like internal phase and a liquid phase, or containing two or more immiscible fluids. Application of electric fields to any of the electrophoretic displays described herein affects an optical property of the display.

Owner:E INK CORPORATION

Electronically addressable microencapsulated ink and display thereof

InactiveUS20070052757A1Inexpensive displayMechanical clocksVisual indicationsElectrical conductorSemiconductor materials

A system of electronically active inks is described which may include electronically addressable contrast media, conductors, insulators, resistors, semiconductive materials, magnetic materials, spin materials, piezoelectric materials, optoelectronic, thermoelectric or radio frequency materials. We further describe a printing system capable of laying down said materials in a definite pattern. Such a system may be used for instance to: print a flat panel display complete with onboard drive logic; print a working logic circuit onto any of a large class of substrates; print an electrostatic or piezoelectric motor with onboard logic and feedback or print a working radio transmitter or receiver.

Owner:E INK CORPORATION

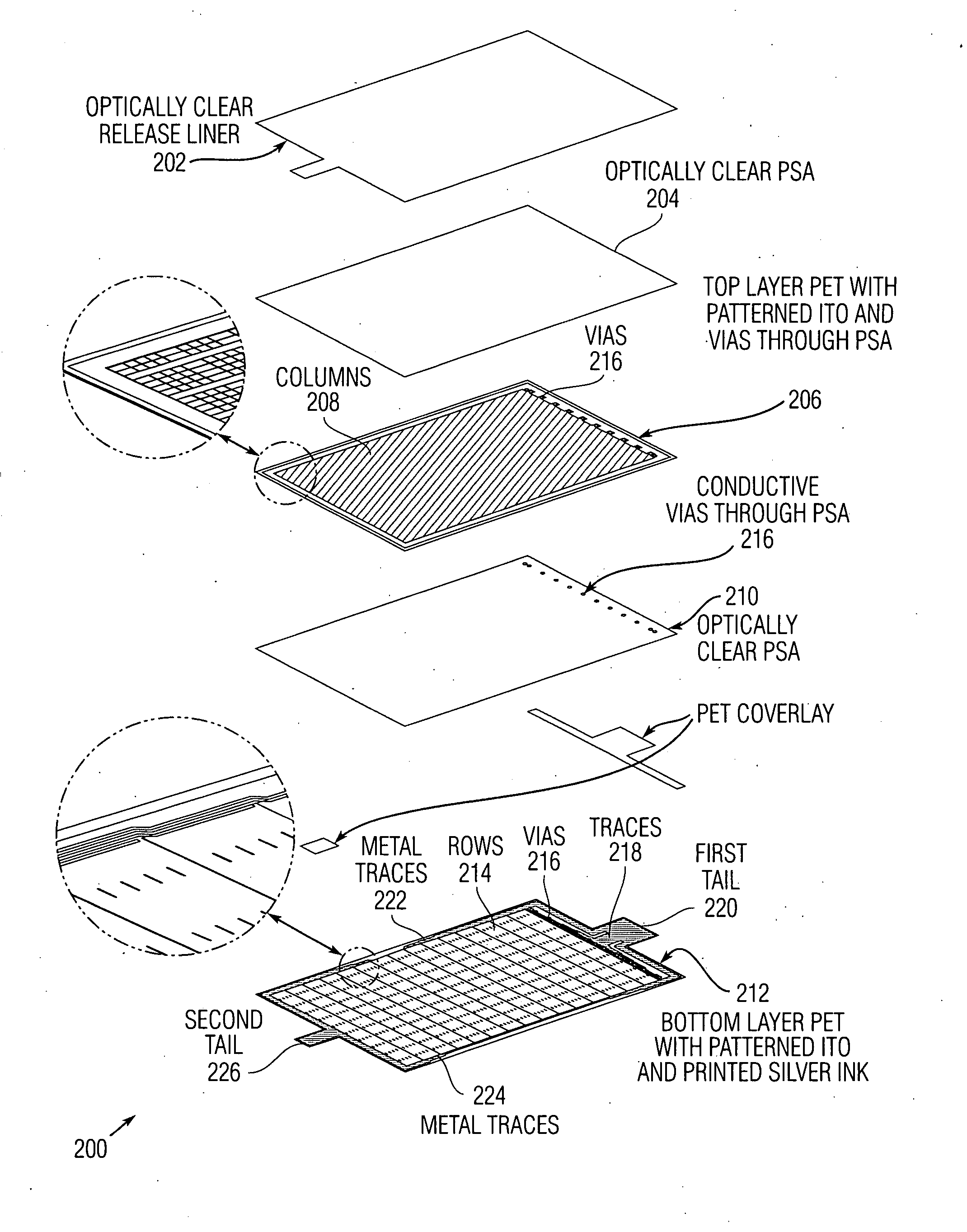

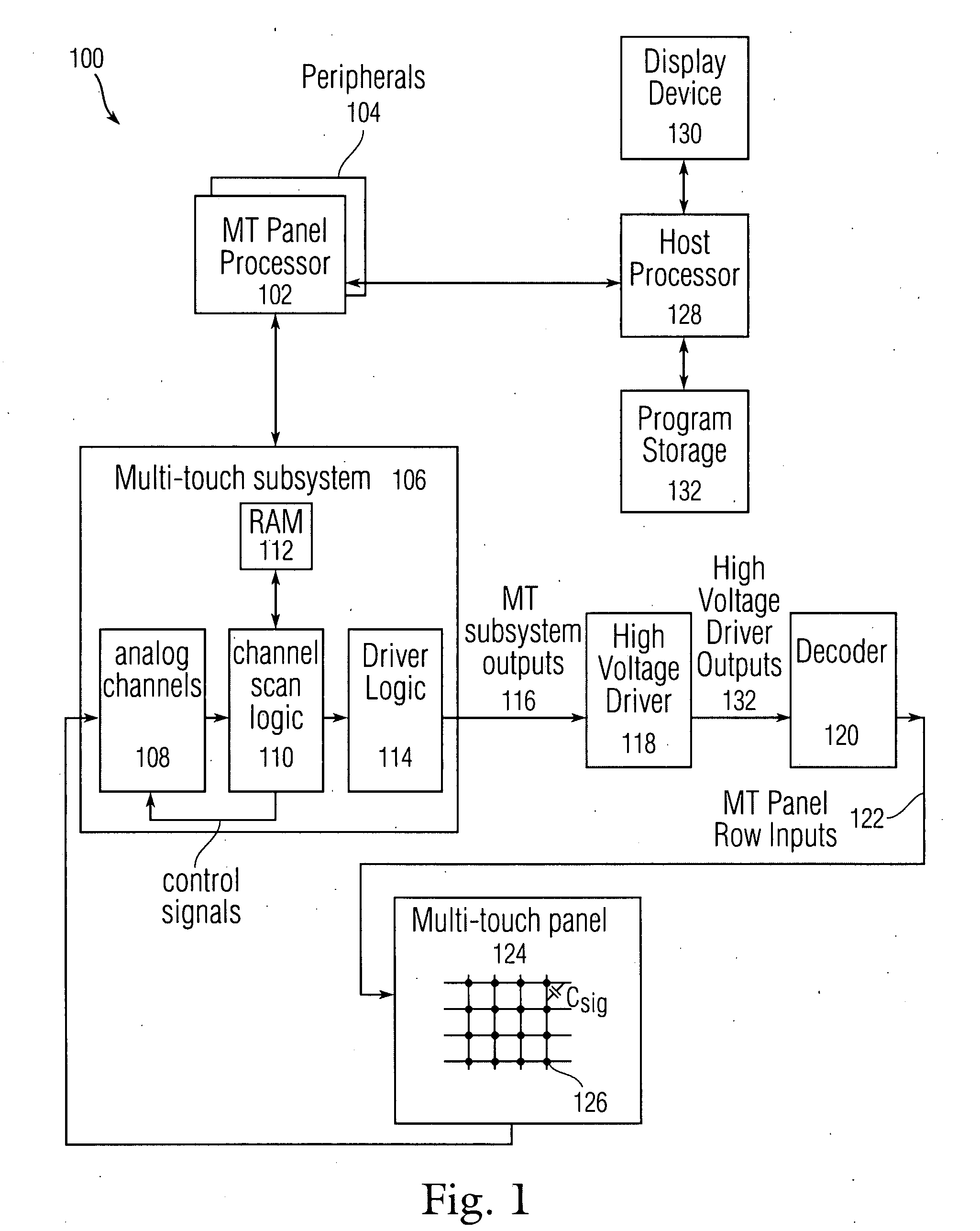

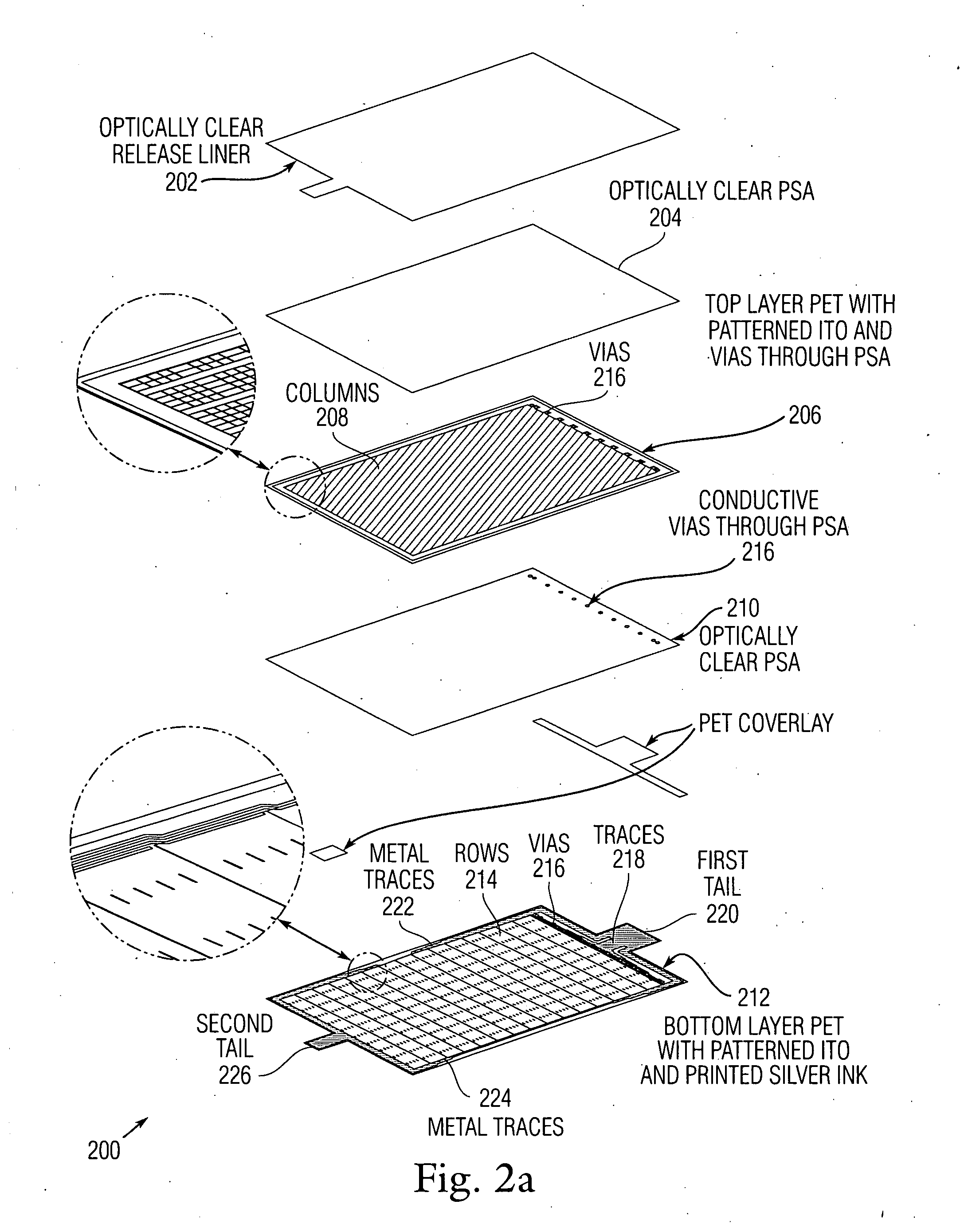

Pet-based touch pad

ActiveUS20080143683A1Avoid less flexibilityMinimized in sizeTransparent dielectricsConductive pattern formationAdhesiveEngineering

A space-efficient substantially transparent mutual capacitance touch sensor panel can be created by forming columns made of a substantially transparent conductive material on one side of a first substantially transparent substrate, forming rows made of the substantially transparent conductive material on one side of a second substantially transparent substrate, adhering the two substrates together with a substantially transparent adhesive, bringing column connections down to the second substrate using vias, and routing both the column and row connections to a single connection area on the second substrate. In addition, in some embodiments some of the row connections can be routed to a second connection area on the second substrate to minimize the size of the sensor panel.

Owner:APPLE INC

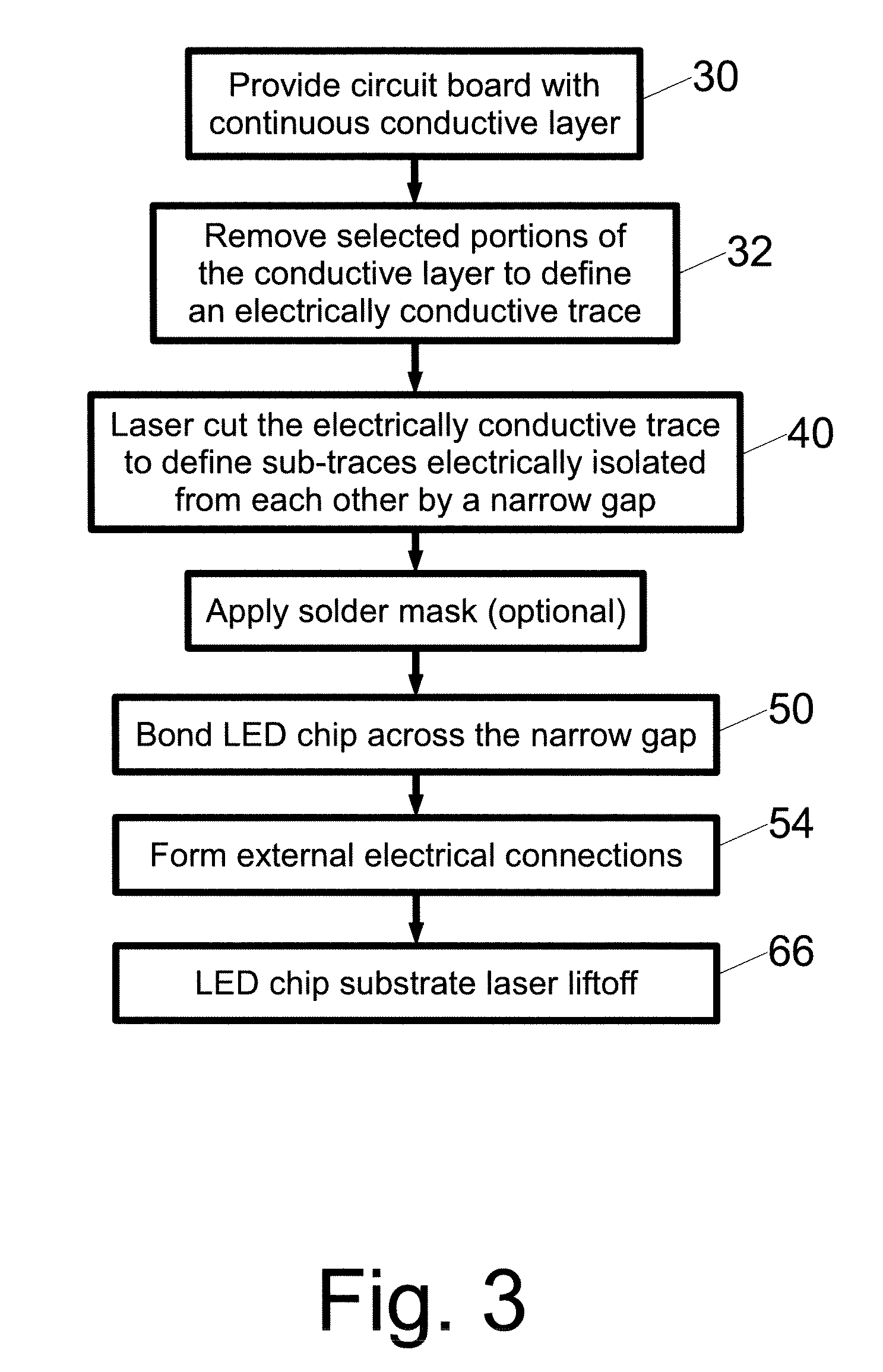

Circuit board for direct flip chip attachment

InactiveUS20090212317A1Semiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageLaser cutting

A packaging method comprises: forming a circuit board by forming a substantially continuous conductive layer on an insulating board and removing selected portions of the continuous conductive layer to define an electrically conductive trace; laser cutting the electrically conductive trace to define sub-traces electrically isolated from each other by a laser-cut gap formed by the laser cutting; and bonding a light emitting diode (LED) chip to the circuit board across or adjacent to the laser-cut gap, the bonding including operatively electrically connecting an electrode of the LED chip to one of the sub-traces without using an interposed submount. A semiconductor package comprises an LED chip flip-chip bonded to sub-traces of an electrically conductive trace of a circuit board, the sub-traces being electrically isolated from each other by a narrow gap of less than or about 100 microns.

Owner:LUMINATION

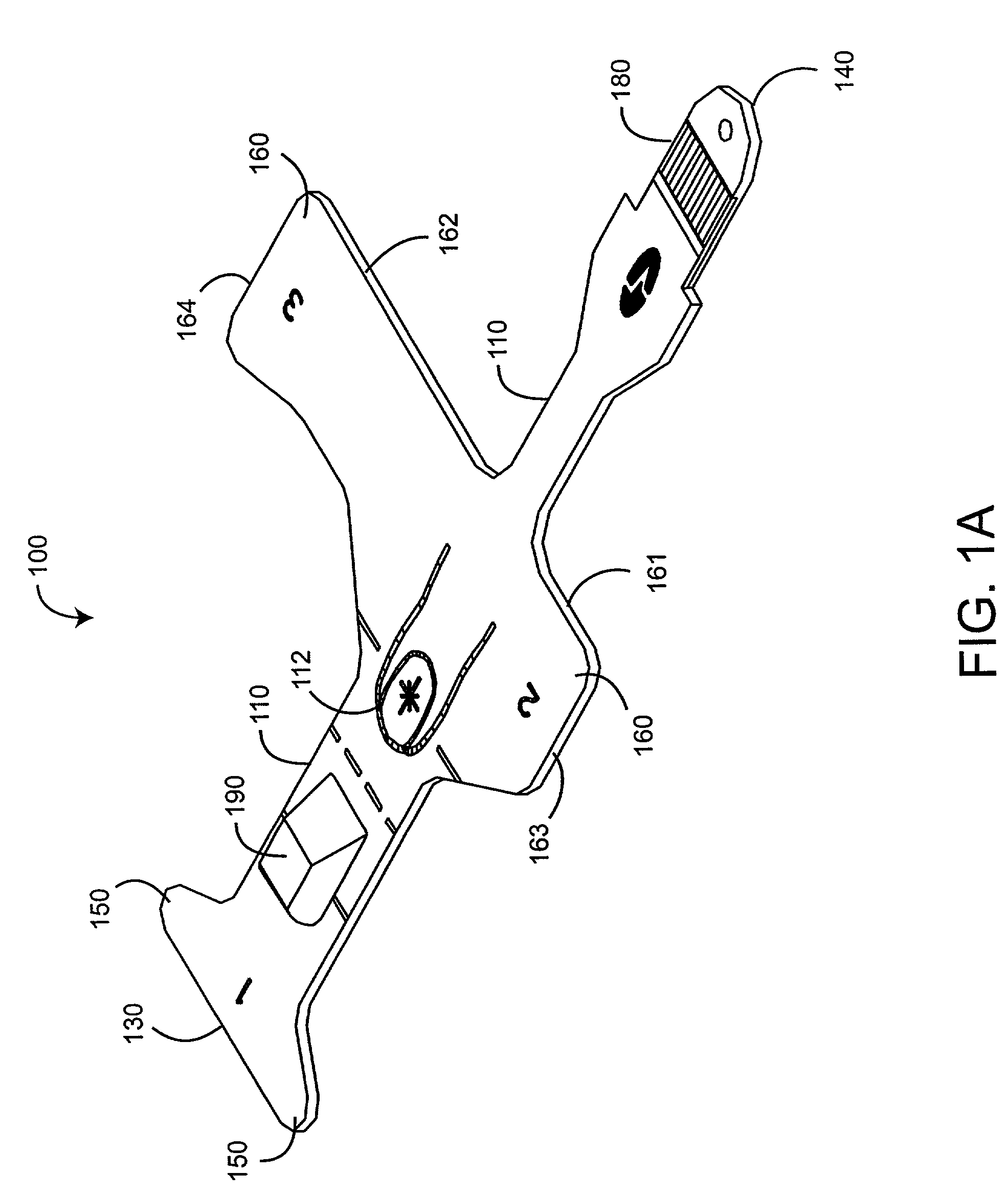

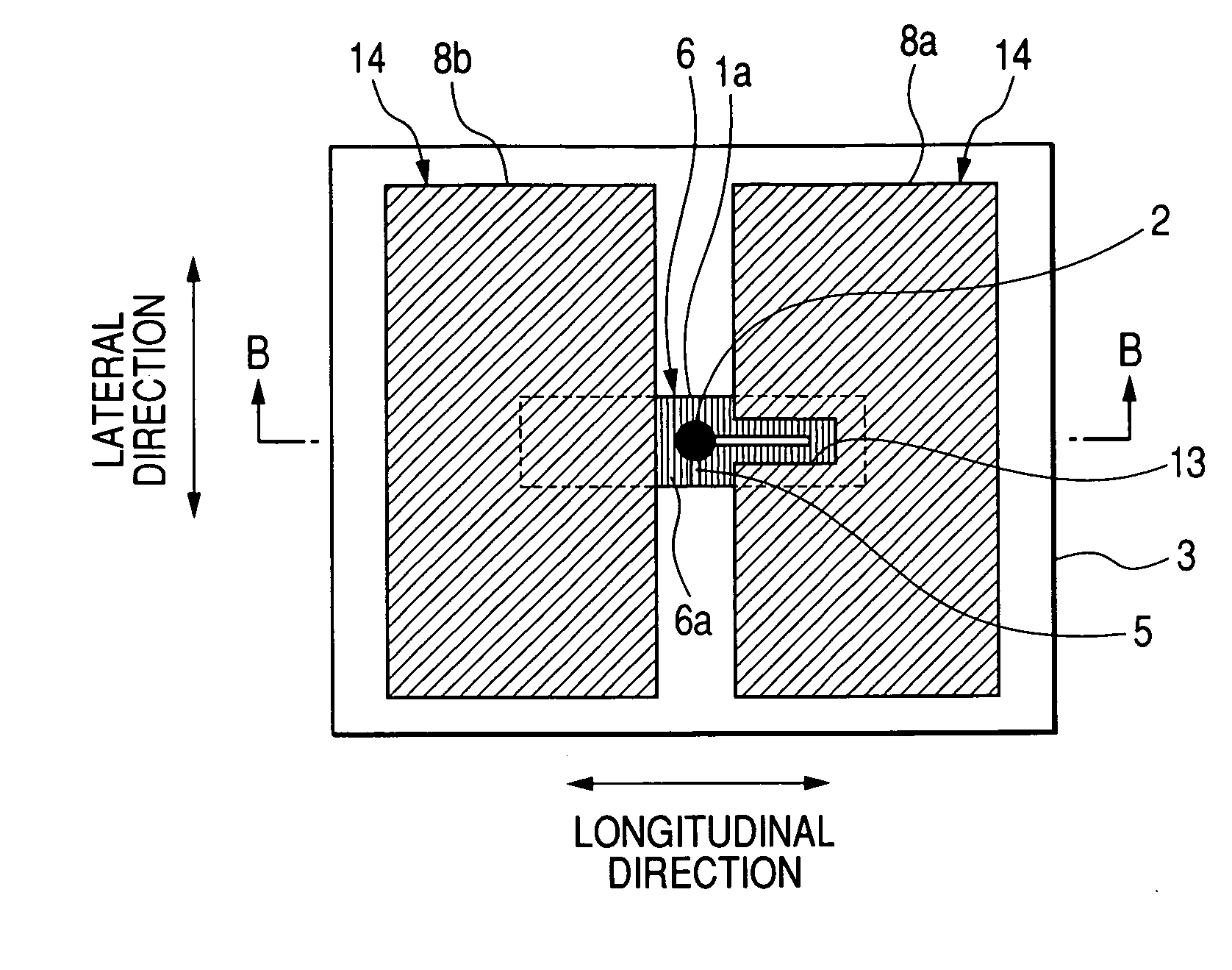

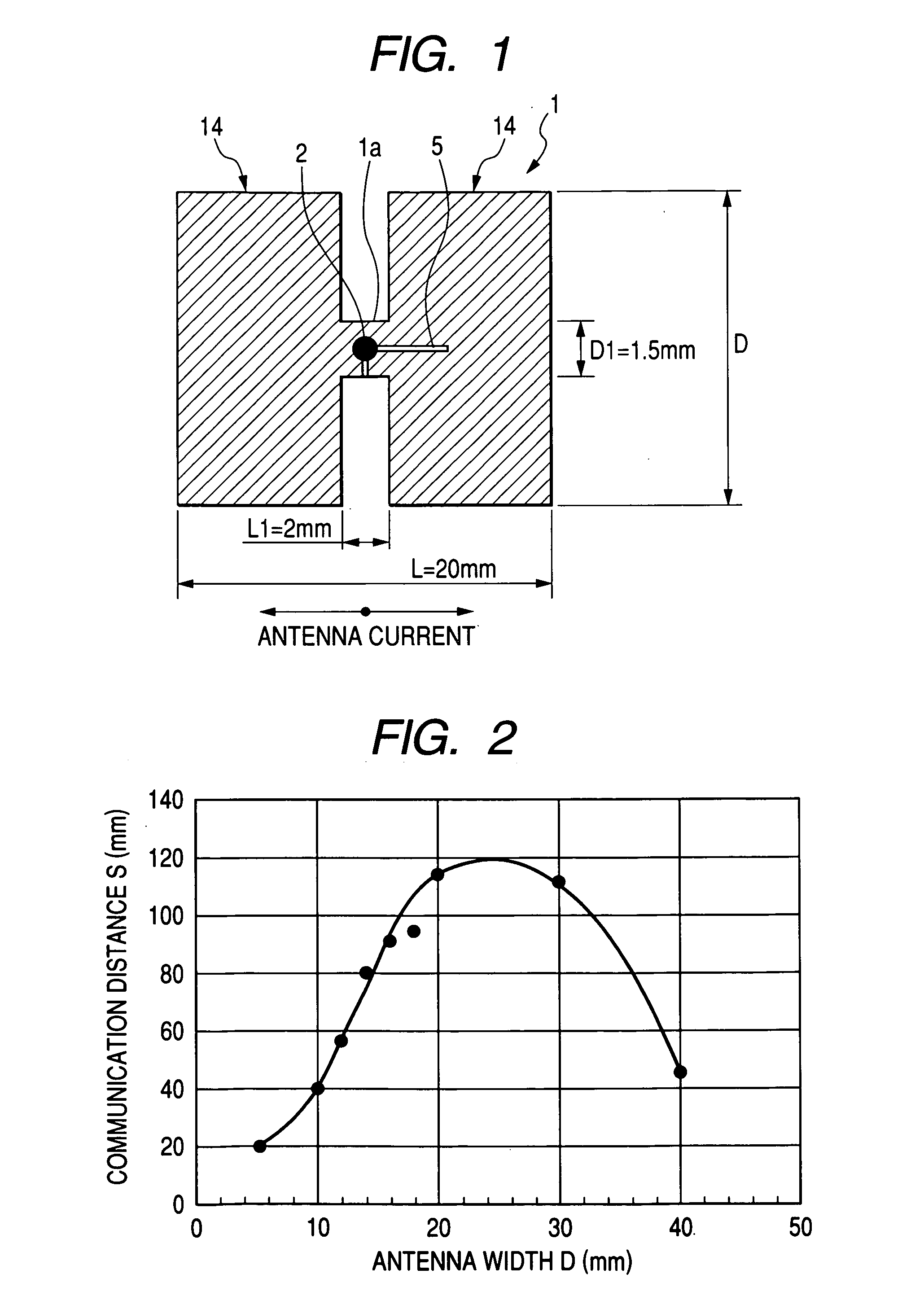

Radio frequency IC tag and method for manufacturing the same

InactiveUS20050275539A1Maximum antenna efficiencyReduces efficiency of antennaAntenna supports/mountingsSemiconductor/solid-state device detailsRadio frequencyElectric power

A radio frequency IC tag and a manufacturing method for the same includes an IC chip on which information is stored, and an antenna for transmitting the information that is stored on the IC chip. In the antenna, a power-feeding part on which the IC chip is mounted extends along a direction in which an electric current flows. Radiation parts are formed so that the width of the radiation parts becomes wider than that of the power-feeding part with respect to the longitudinal axis of the power-feeding part. The radiation parts extend from the power-feeding part, at both sides thereof, along the direction in which the electric current flows.

Owner:HITACHI LTD

Printable conductive features and processes for making same

InactiveUS20060001726A1Conductive materialLiquid/solution decomposition chemical coatingReducing agentMetal

Processes for forming conductive features from one or more inks and conductive features formed from the processes. In one aspect, the process includes a step of applying a first ink comprising a metal precursor to at least a portion of a first substrate to form an at least partially coated substrate. In a second step, the first ink is contacted with a reducing agent, optionally derived from a second ink, under conditions effective to reduce the metal in the metal precursor to its elemental form.

Owner:CABOT CORP

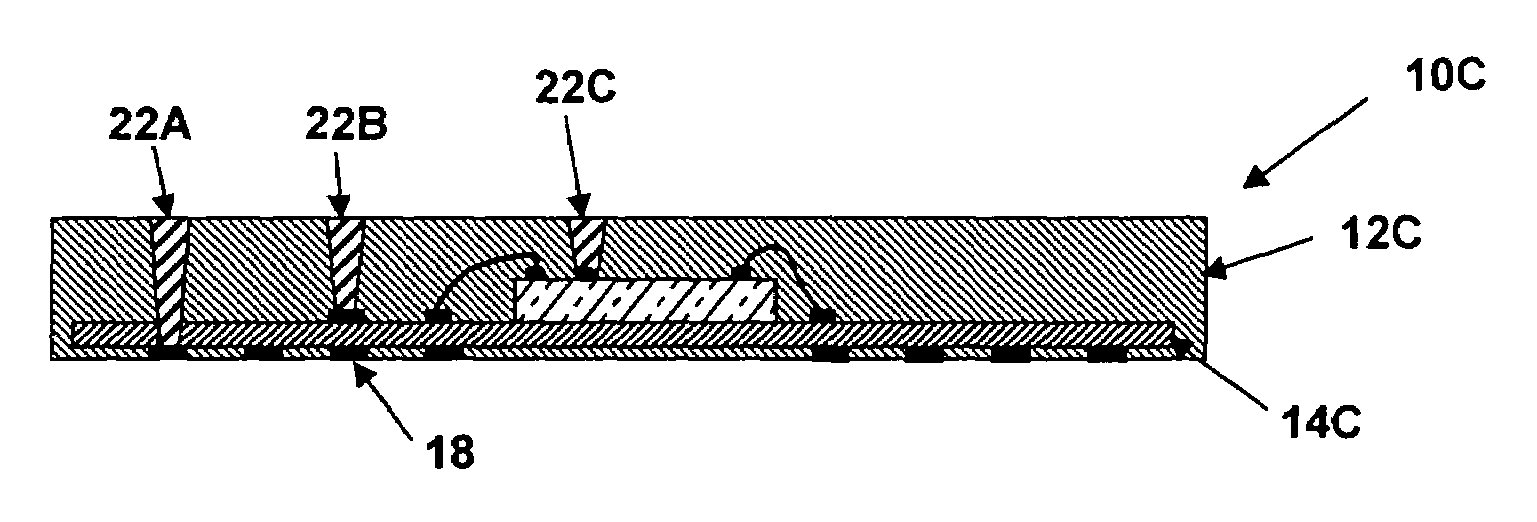

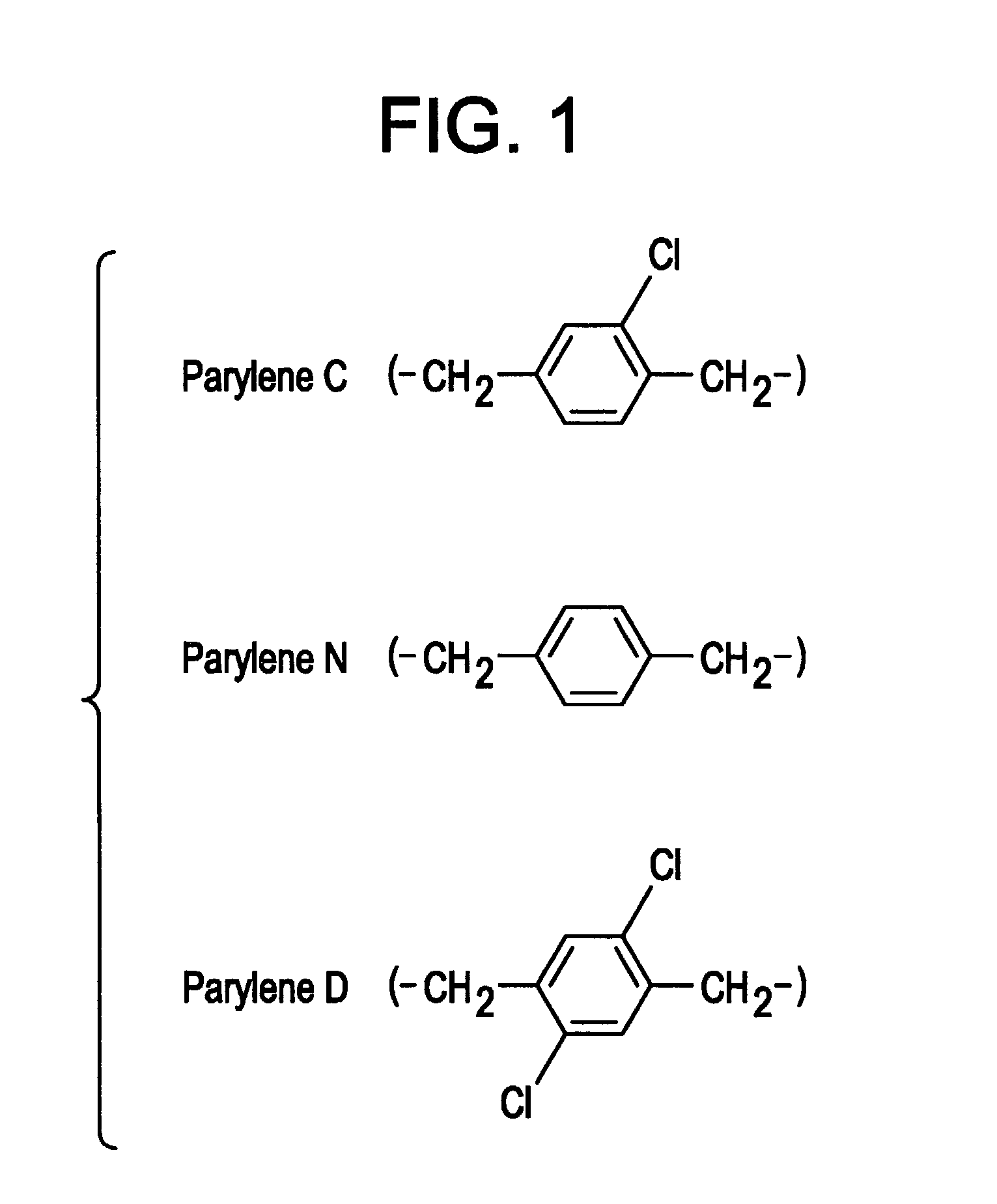

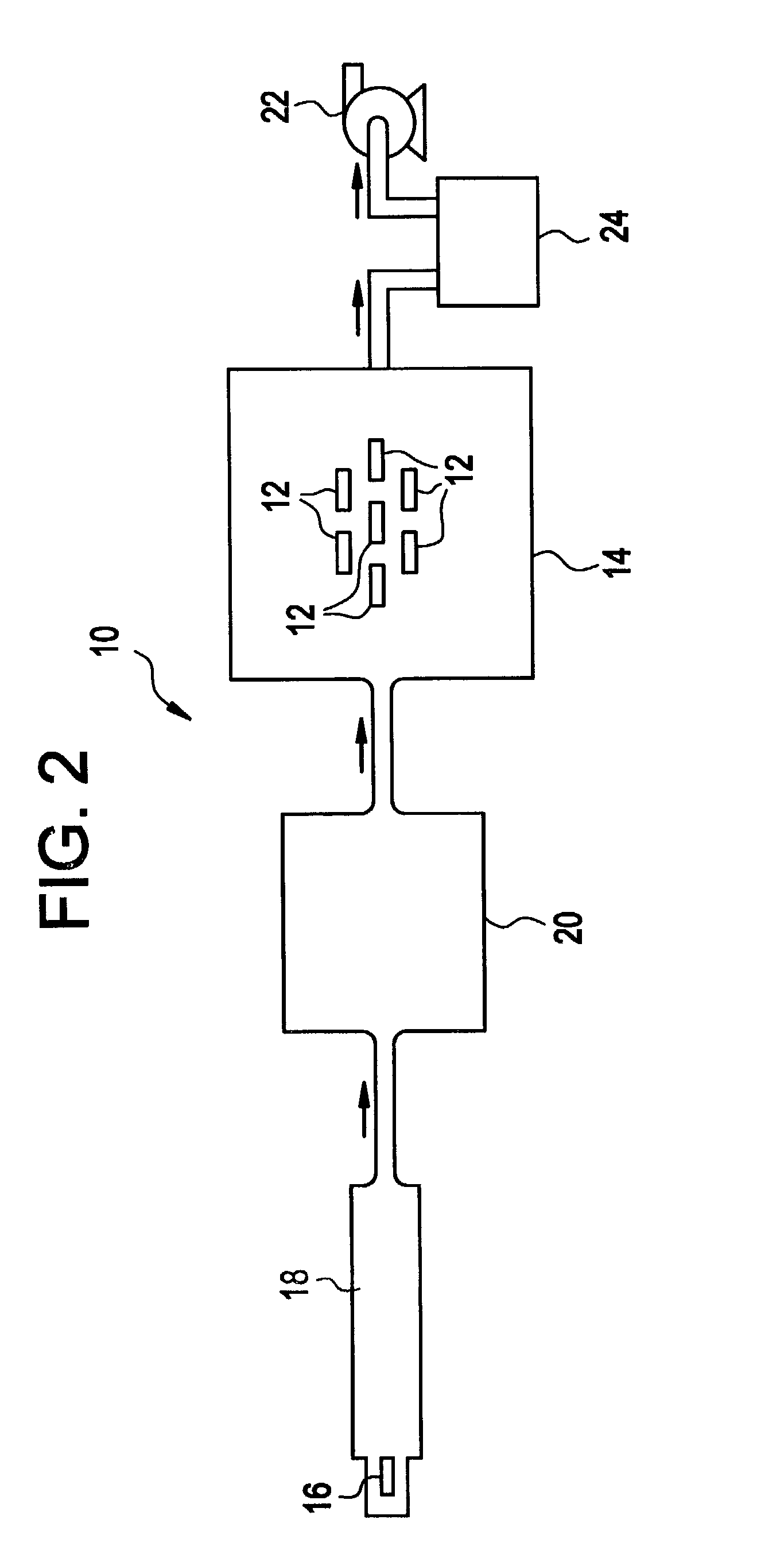

Methods for conformal coating and sealing microchip reservoir devices

InactiveUS6973718B2Reduce adverse reactionsPrinted circuit assemblingLiquid surface applicatorsParyleneGas phase

Methods are provided for conformally coating microchip devices and for sealing reservoirs containing molecules or devices in a microchip device. One method comprises (i) providing a substrate having a plurality of reservoirs having reservoir openings in need of sealing; (ii) loading reservoir contents comprising molecules, a secondary device, or both, into the reservoirs; and (iii) applying a conformal coating barrier layer, such as a vapor depositable polymeric material, e.g., parylene, onto the reservoir contents over at least the reservoir openings to seal the reservoir openings. Another method comprises vapor depositing a conformal coating material onto a microchip device having at least two reservoirs and reservoir caps positioned over molecules or devices stored in the reservoirs, and providing that the conformal coating does not coat or is removed from the reservoir caps.

Owner:MICROCHIPS INC

Method for programming a routing layout design through one via layer

A method for programming a routing layout design through one via layer includes forming a plurality of metal traces on a first routing layer and a second routing layer, and positioning a plurality of vias within a via layer disposed between the first and second routing layers for connecting the metal traces on the first and second routing layers according to a first current route defined by a predetermined circuit layout design to connect a first node and a second node so as to establish a second current route equivalent to the first current route.

Owner:FARADAY TECH CORP

Biocompatible bonding method and electronics package suitable for implantation

ActiveUS20030233134A1Uniform propertySemiconductor/solid-state device detailsSolid-state devicesFlexible circuitsHermetic seal

The invention is directed to a method of bonding a hermetically sealed electronics package to an electrode or a flexible circuit and the resulting electronics package, that is suitable for implantation in living tissue, such as for a retinal or cortical electrode array to enable restoration of sight to certain non-sighted individuals. The hermetically sealed electronics package is directly bonded to the flex circuit or electrode by electroplating a biocompatible material, such as platinum or gold, effectively forming a plated rivet-shaped connection, which bonds the flex circuit to the electronics package. The resulting electronic device is biocompatible and is suitable for long-term implantation in living tissue.

Owner:CORTIGENT INC +1

Ink-jet inks containing metal nanoparticles

ActiveUS20050078158A1Slow sedimentation rateLow and viscosity gradeMeasurement apparatus componentsConductive materialWater basedNanometre

Compositions for use in ink jet printing onto a substrate comprising a water based dispersion including metallic nanoparticles and appropriate stabilizers. Also disclosed are methods for the production of said compositions and methods for their use in ink jet printing onto suitable substrates.

Owner:YISSUM RES DEV CO OF THE HEBREWUNIVERSITY OF JERUSALEM LTD

Popular searches

Sensors Measuring/recording heart/pulse rate Blood characterising devices Printed circuit non-printed electric components association Semiconductor devices Semiconductor/solid-state device manufacturing Time-pieces with integrated devices Microballoon preparation Colloidal chemistry details Metallic pattern materials

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com