Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

31results about How to "Increase circuit speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

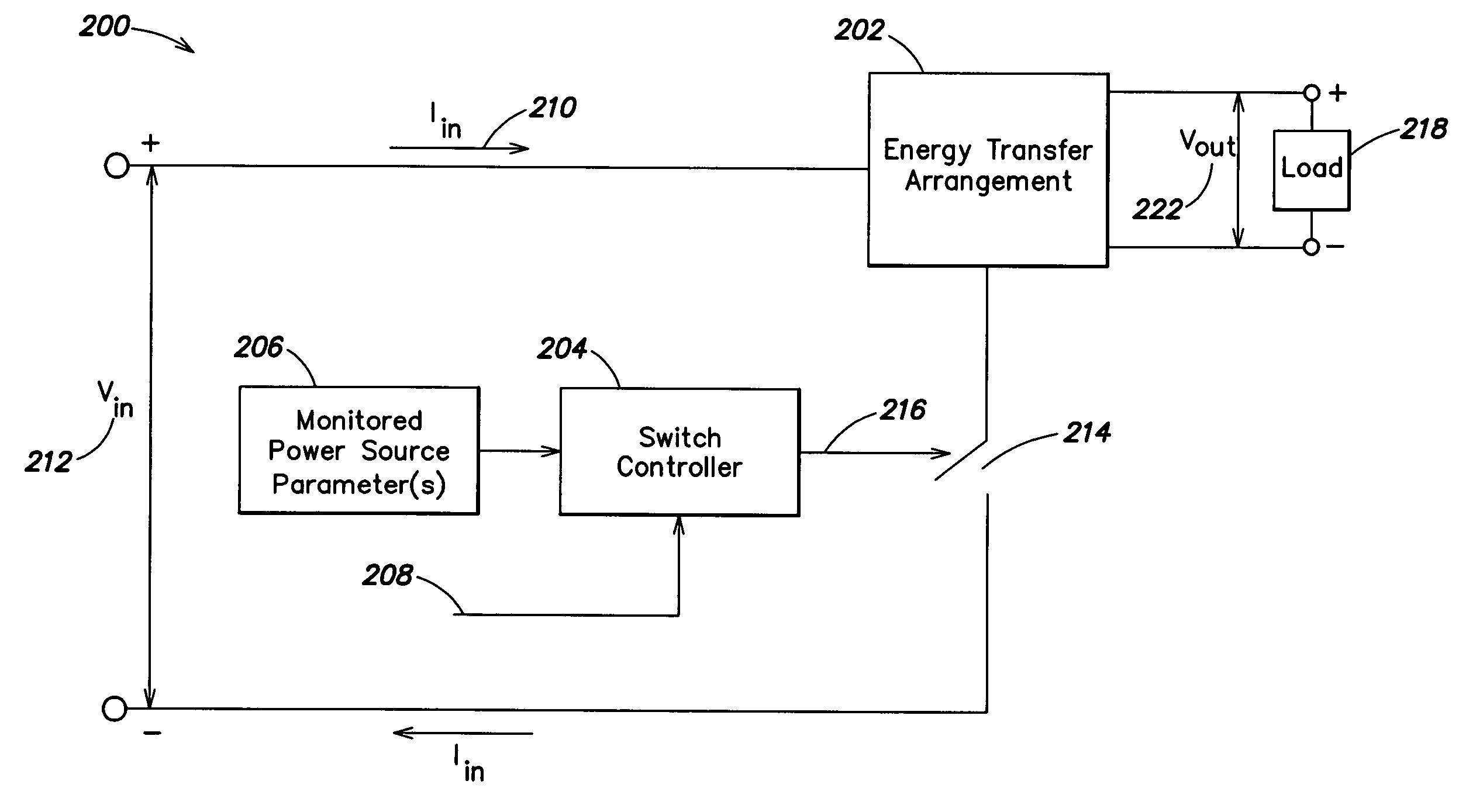

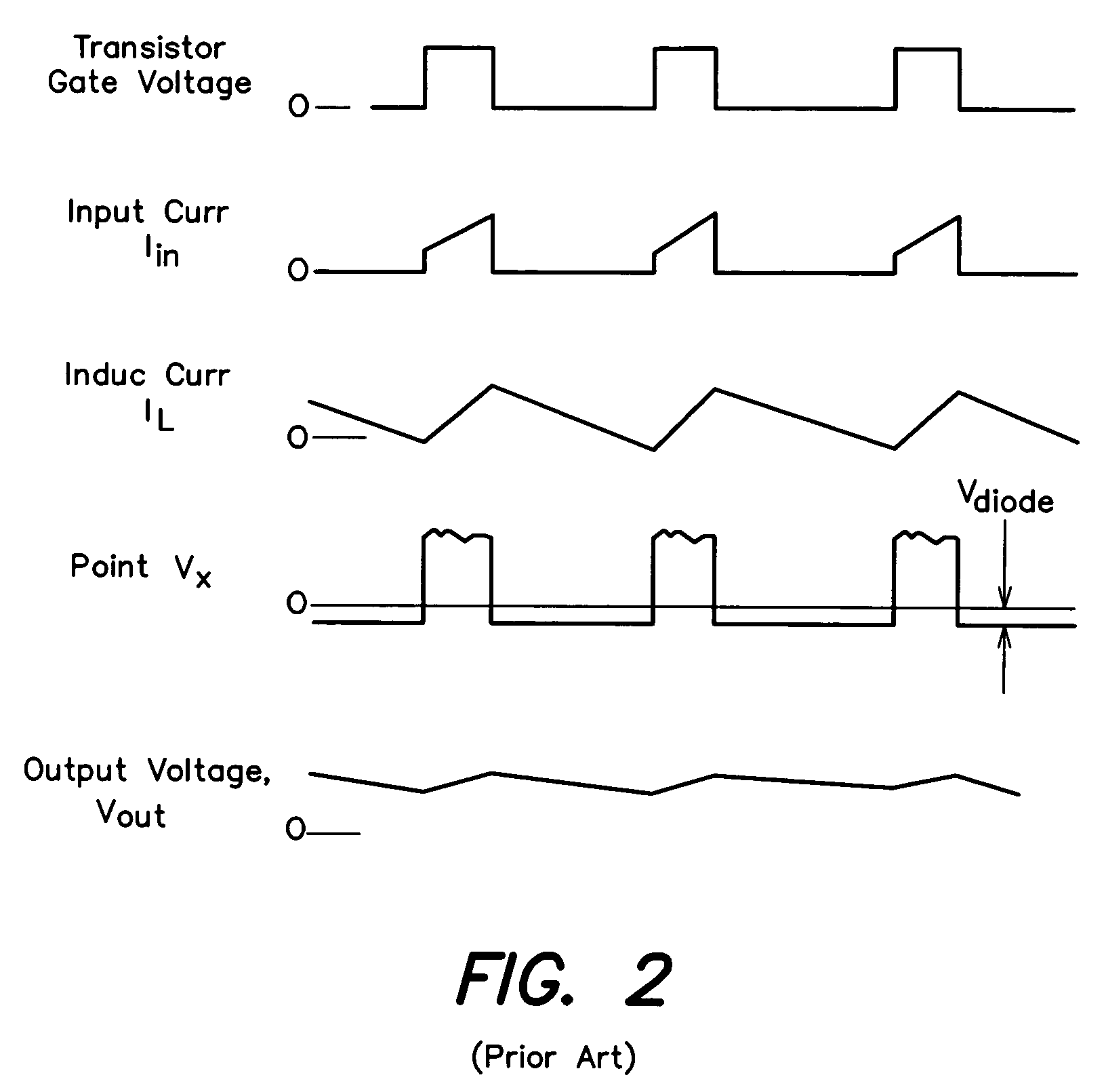

LED power control methods and apparatus

ActiveUS7256554B2Improve power efficiencyReduce functional redundancyEfficient power electronics conversionElectroluminescent light sourcesDc dc converterLight equipment

Methods and apparatus for providing and controlling power to loads including one or more LEDs. In one example, a controlled predetermined power is provided to a load without requiring any feedback information from the load (i.e., without monitoring a load voltage and / or load current). In another example, a “feed-forward” power driver for an LED-based light source combines the functionality of a DC-DC converter and a light source controller, and is configured to control the intensity of light generated by the light source based on modulating the average power delivered to the light source in a given time period, without monitoring and / or regulating the voltage or current provided to the light source. In various examples, significantly streamlined circuits having fewer components, higher overall power efficiencies, and smaller space requirements are realized. Based on various power driver configurations, lighting apparatus incorporating one or more power drivers for one or more LED-based loads may be implemented, and multiple such lighting apparatus may be coupled together to form a lighting network in which operating power is efficiently provided throughout the network.

Owner:SIGNIFY NORTH AMERICA CORP

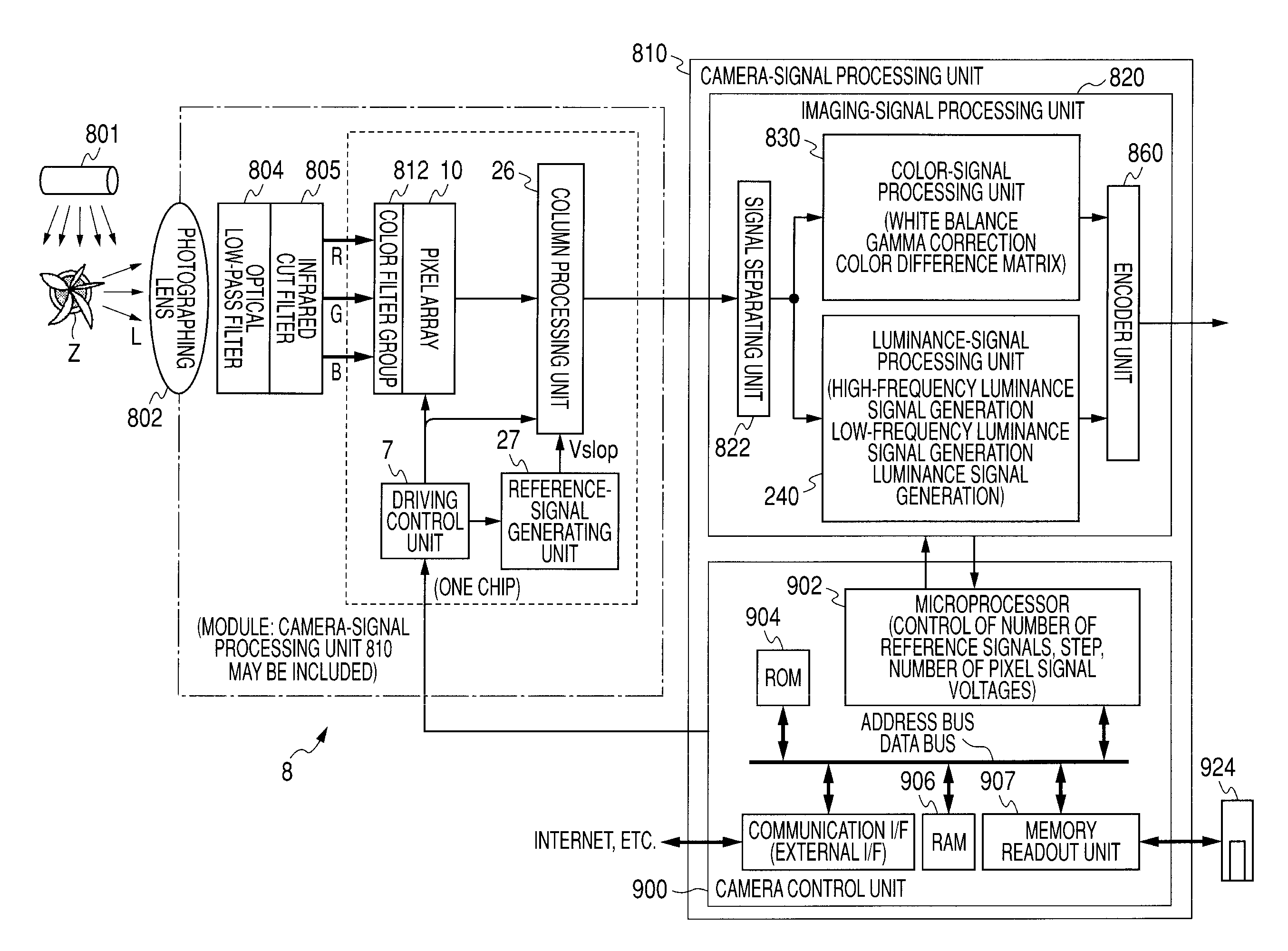

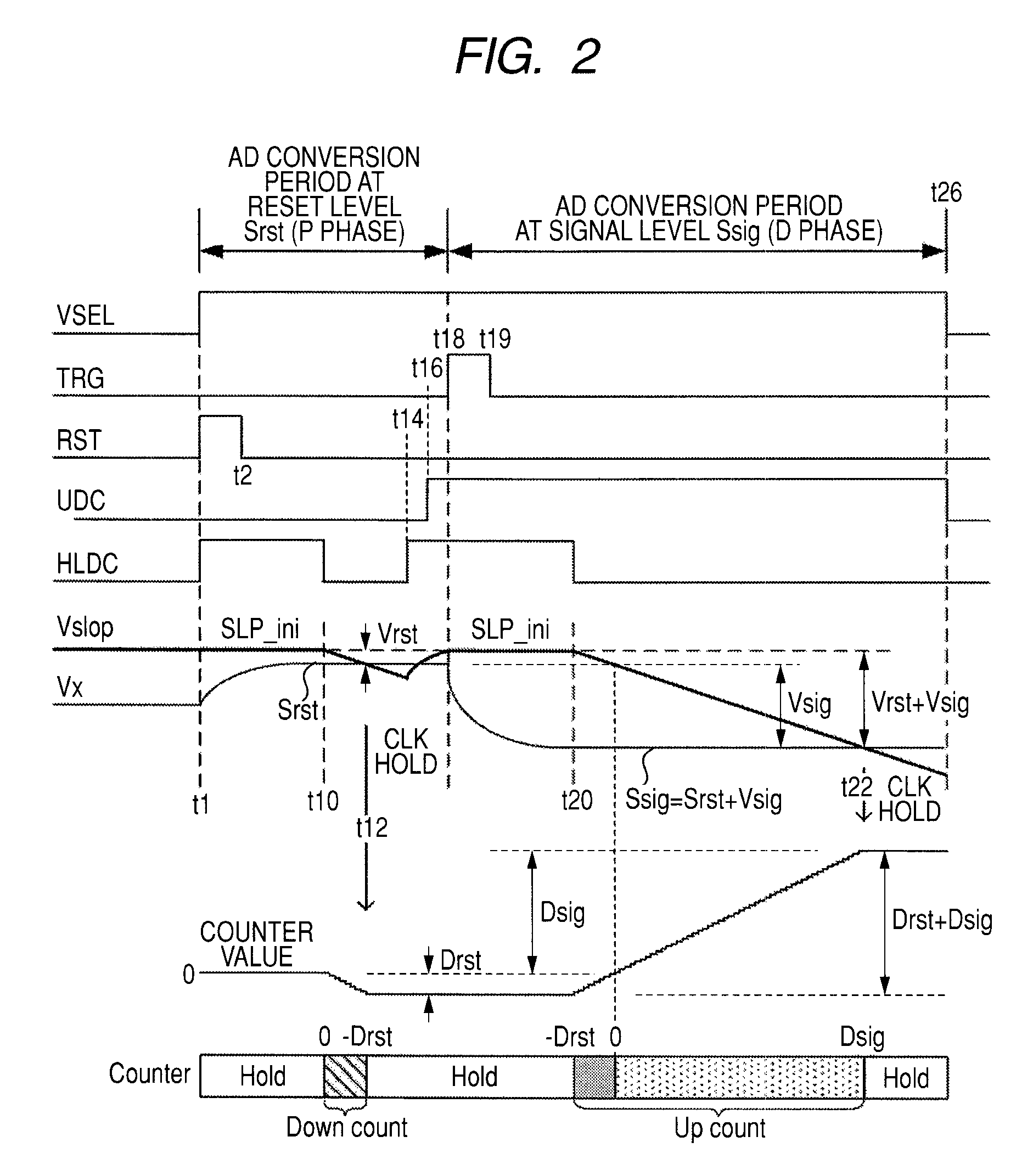

Solid-state imaging device and imaging apparatus

InactiveUS20080192127A1Reduce comparison processing timeIncrease speedAnalogue/digital conversionTelevision system detailsDigital dataComputer science

A solid-state imaging device includes a reference-signal generating unit that generates plural kinds of reference signals for converting an analog pixel signal into digital data, a reference-signal selecting unit that selects any one of the plural kinds of reference signals, a comparing unit that compares the pixel signal and the selected reference signal, and a count unit that performs count processing in parallel with comparison processing in the comparing unit and stores a count value at a point when the comparison processing is completed. The count unit decides digital data of the pixel signal in a 1 LSB step by storing a count value at a point when the comparison processing is completed for any one of the plural kinds of reference signals and correcting the stored count value on the basis of results of the comparison processing for respective remaining reference signals of the plural kinds of reference signals.

Owner:SONY CORP

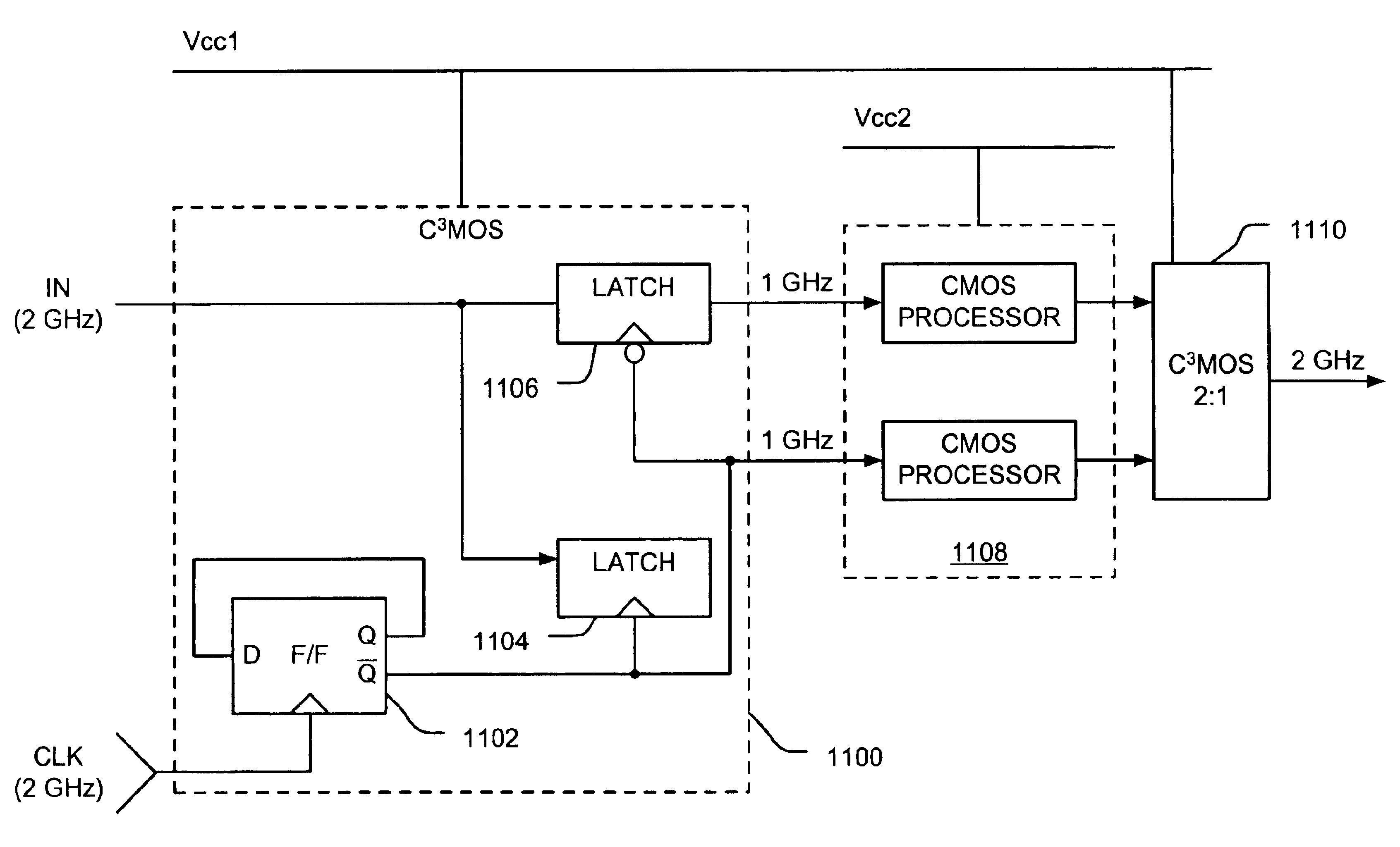

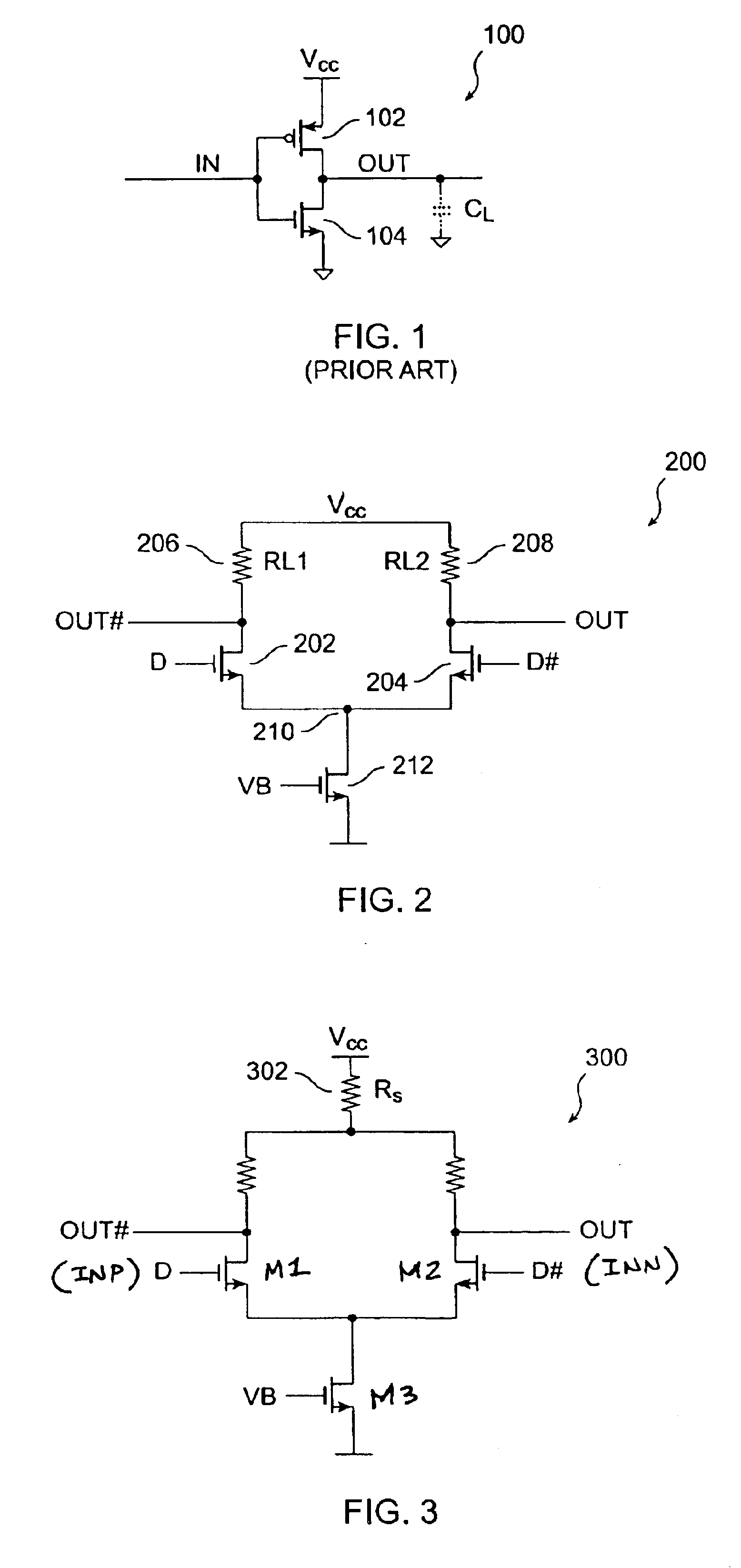

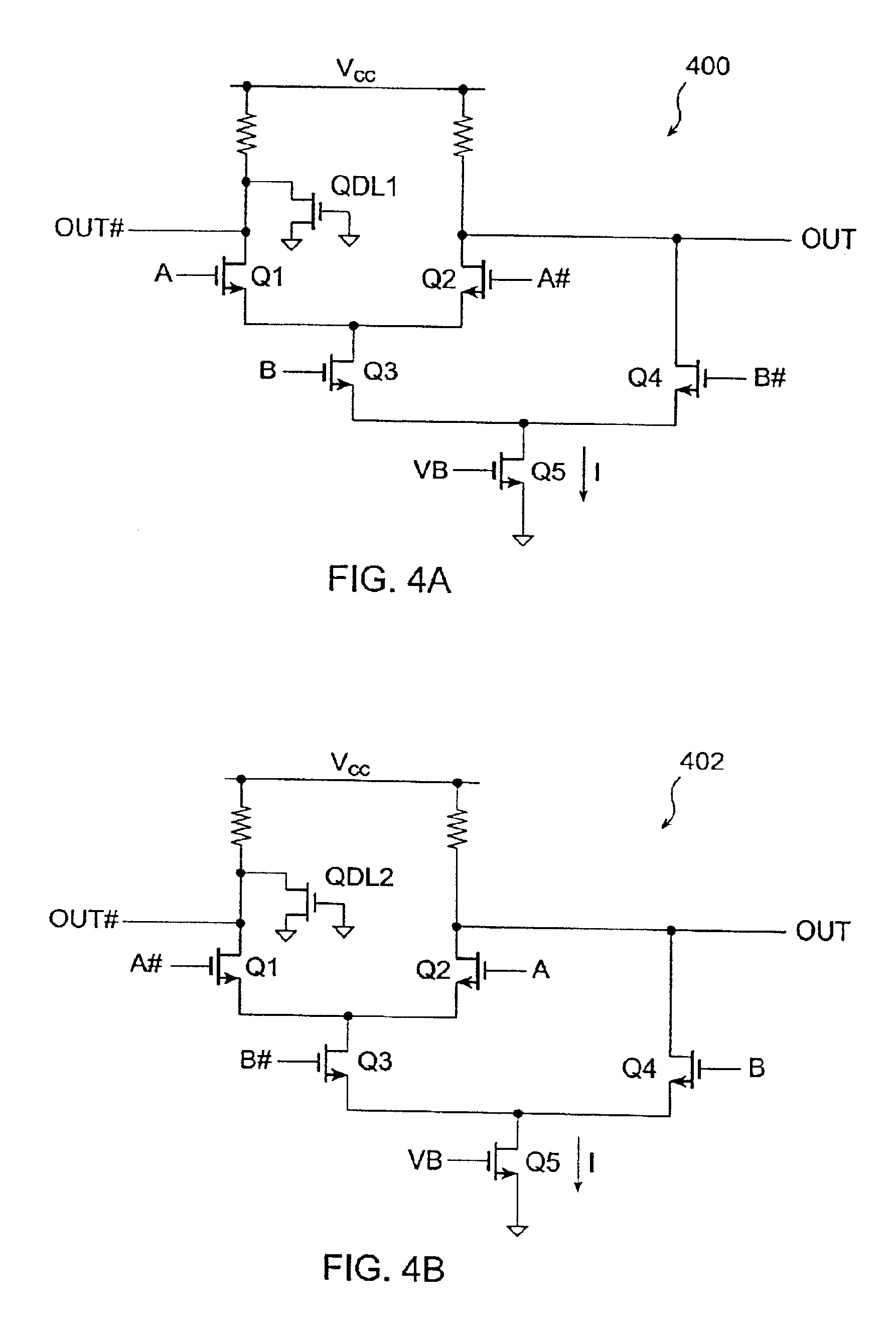

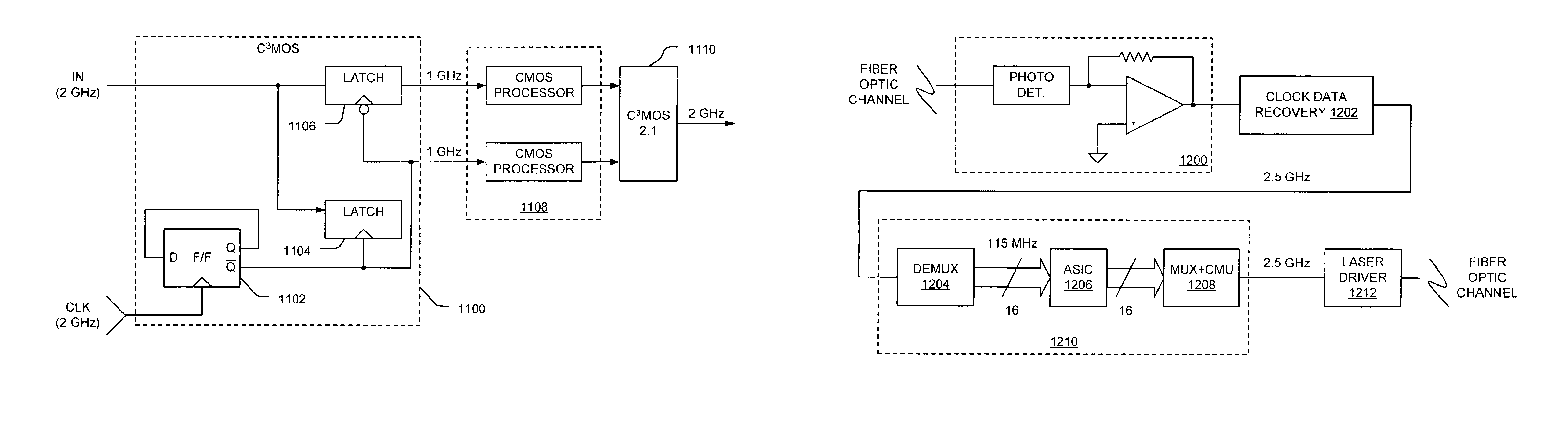

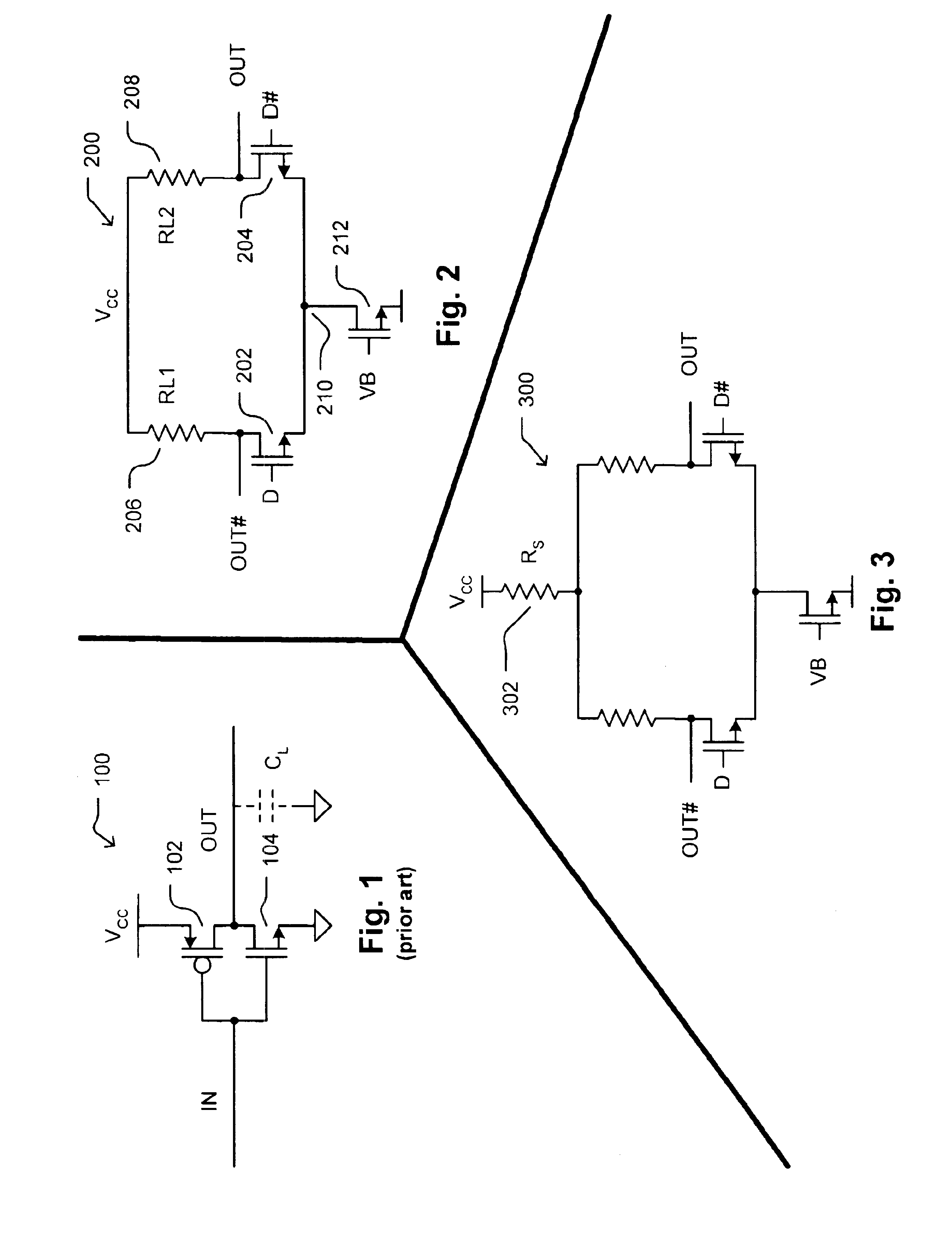

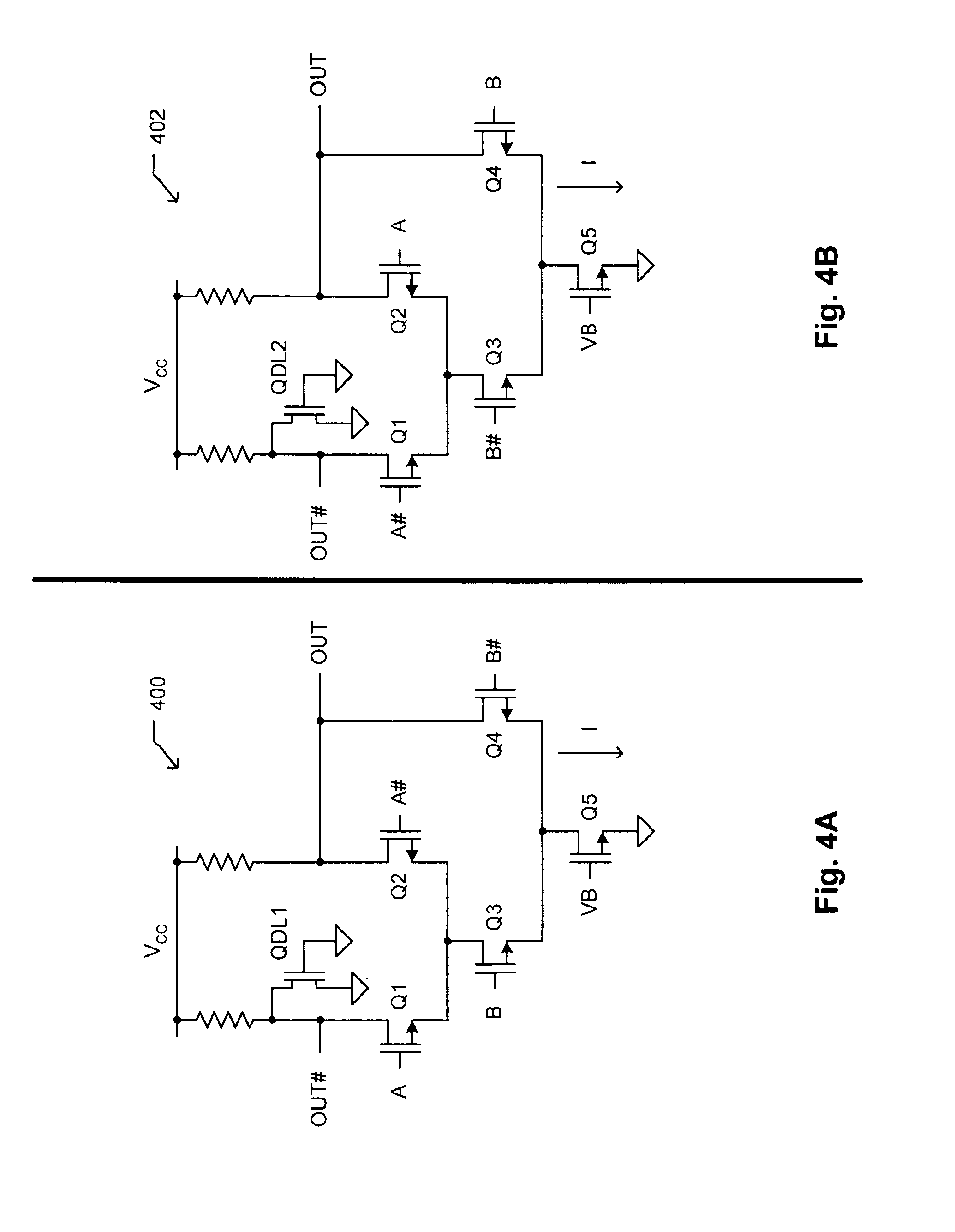

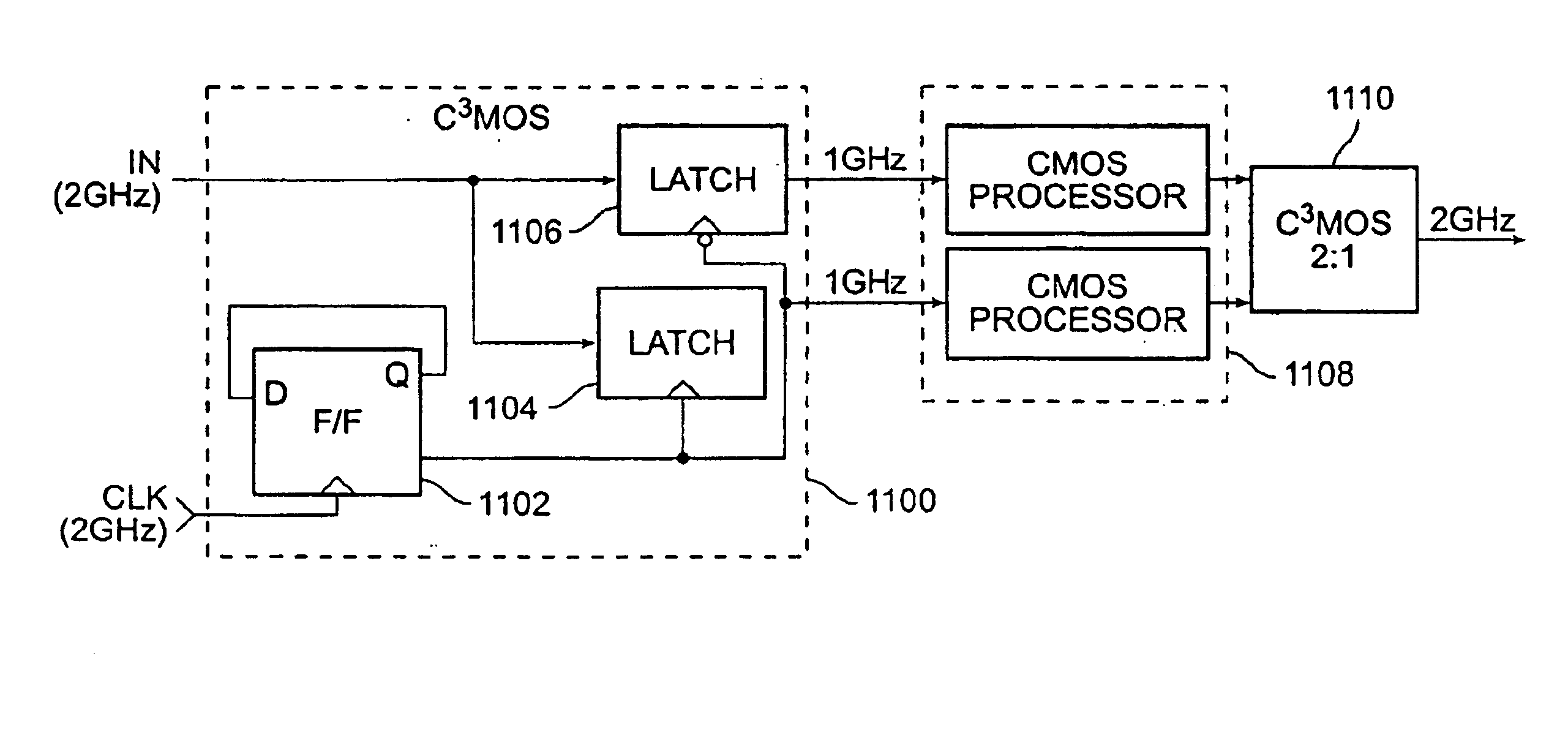

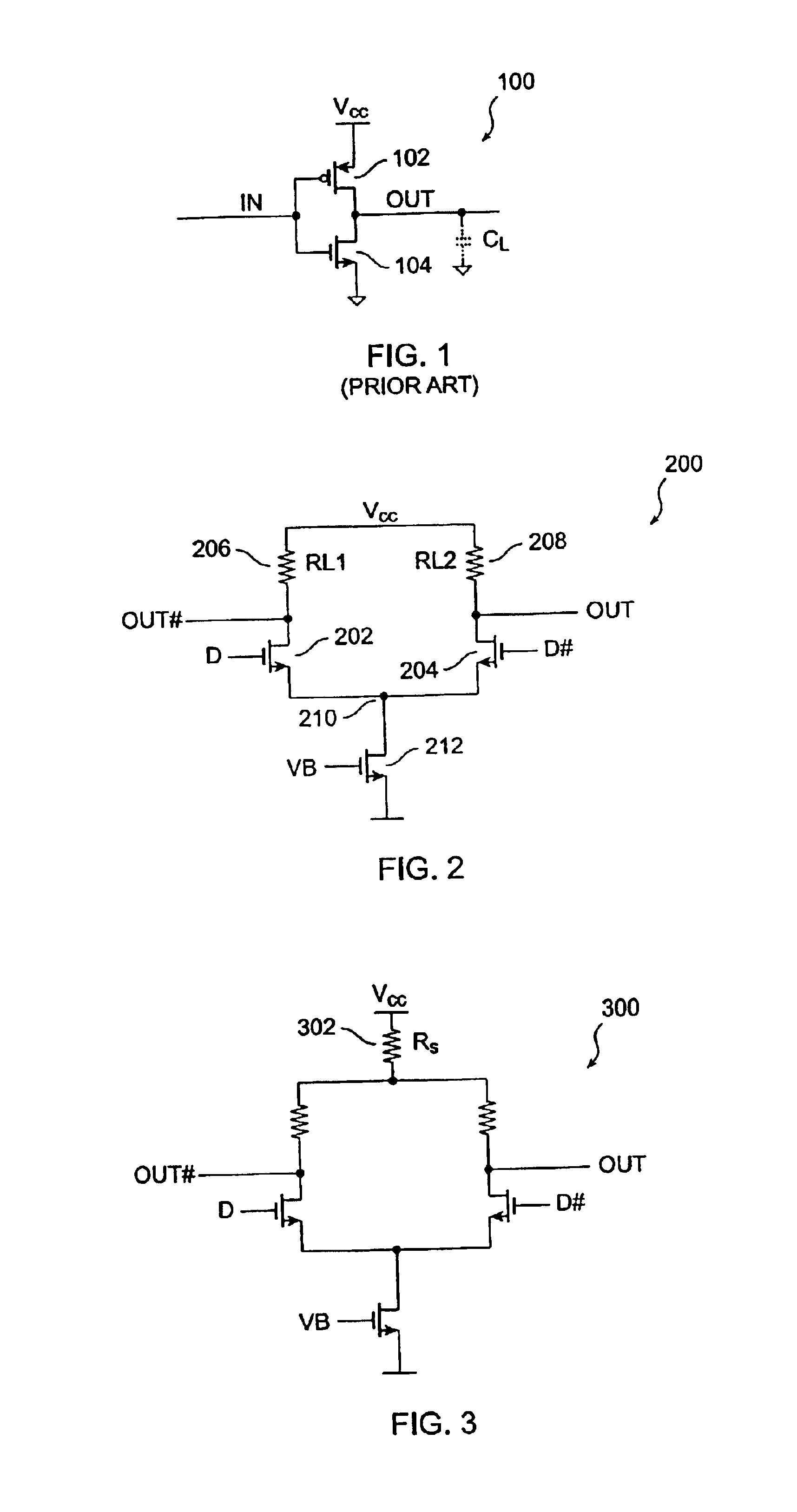

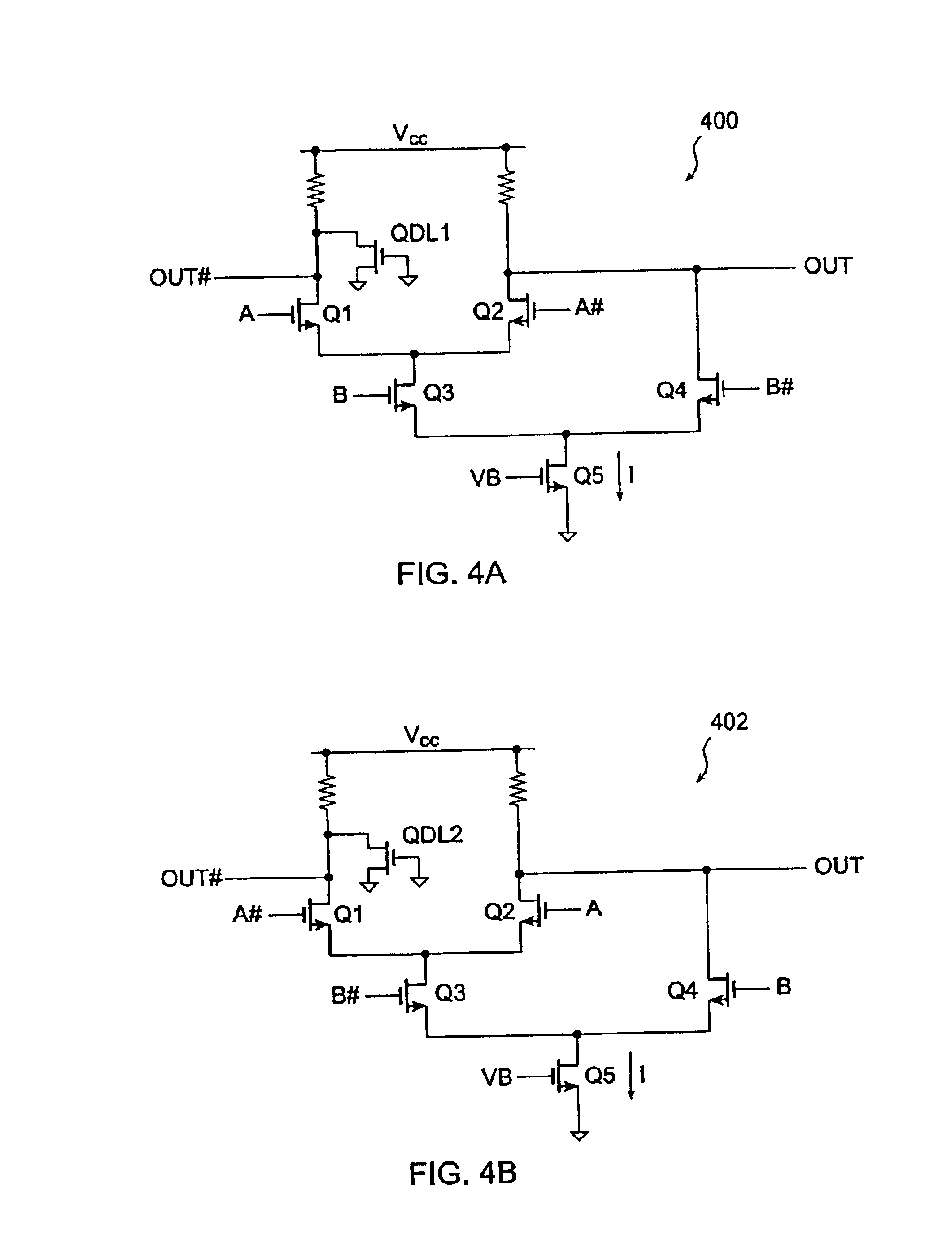

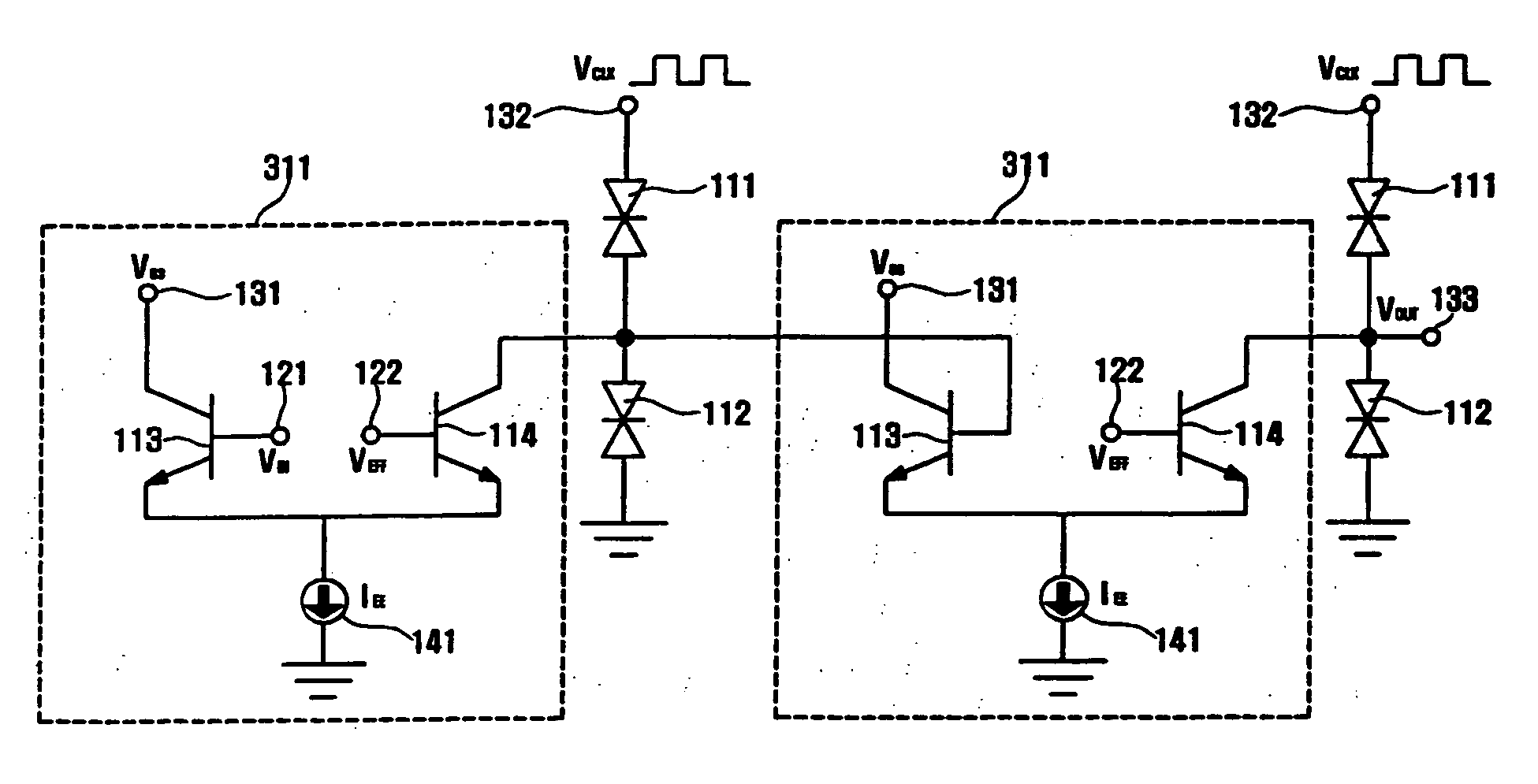

Current-controlled CMOS circuit using higher voltage supply in low voltage CMOS process

InactiveUS6911855B2Speed maximizationDissipates static currentElectronic switchingElectric pulse generatorTransceiverEngineering

Various circuit techniques for implementing ultra high speed circuits use current-controlled CMOS (C3MOS) logic fabricated in conventional CMOS process technology. An entire family of logic elements including inverter / buffers, level shifters, NAND, NOR, XOR gates, latches, flip-flops and the like are implemented using C3MOS techniques. Optimum balance between power consumption and speed for each circuit application is achieve by combining high speed C3MOS logic with low power conventional CMOS logic. The combined C3MOS / CMOS logic allows greater integration of circuits such as high speed transceivers used in fiber optic communication systems. The C3MOS structure enables the use of a power supply voltage that may be larger than the voltage required by the CMOS fabrication process, further enhancing the performance of the circuit.

Owner:AVAGO TECH INT SALES PTE LTD

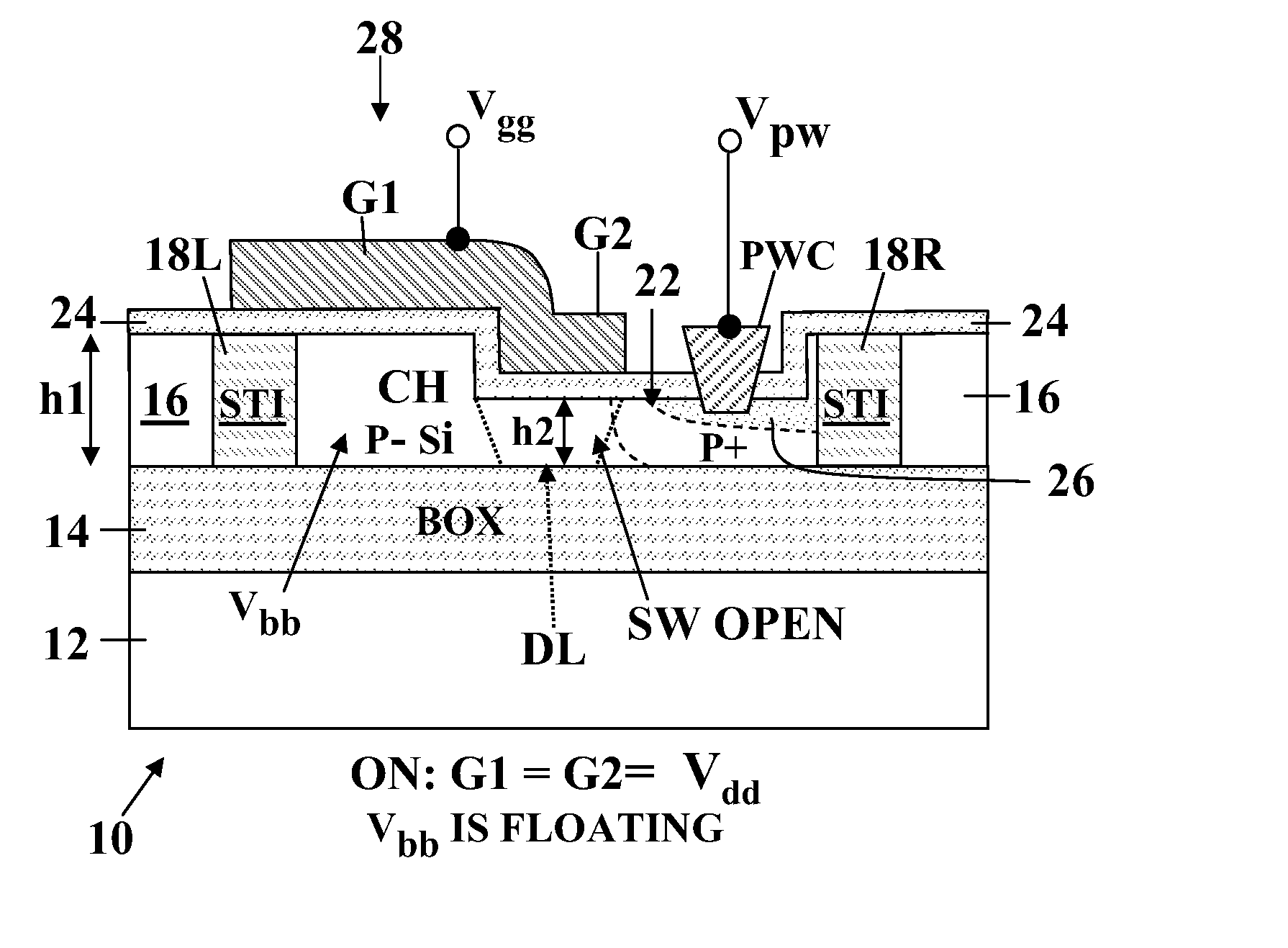

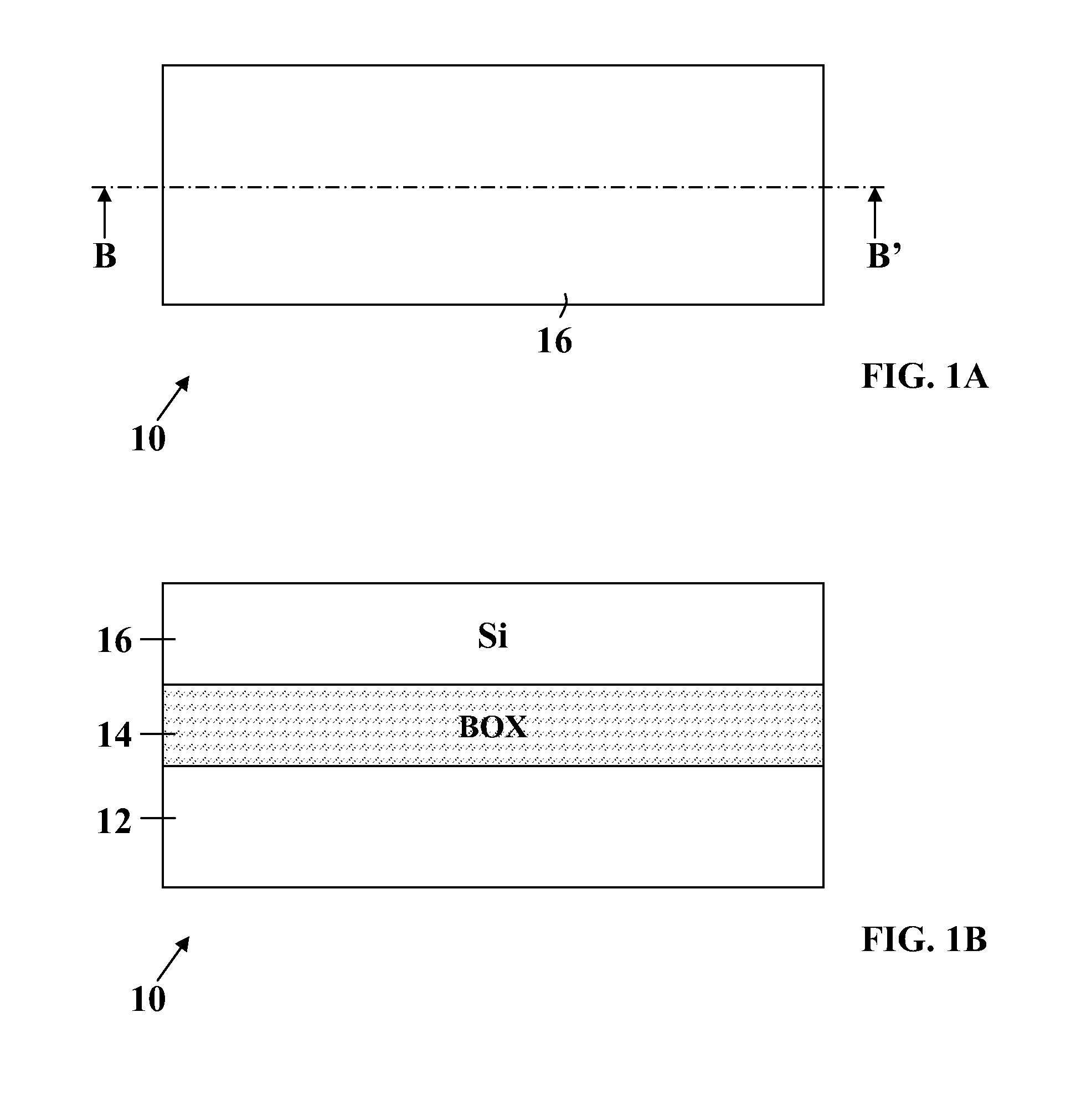

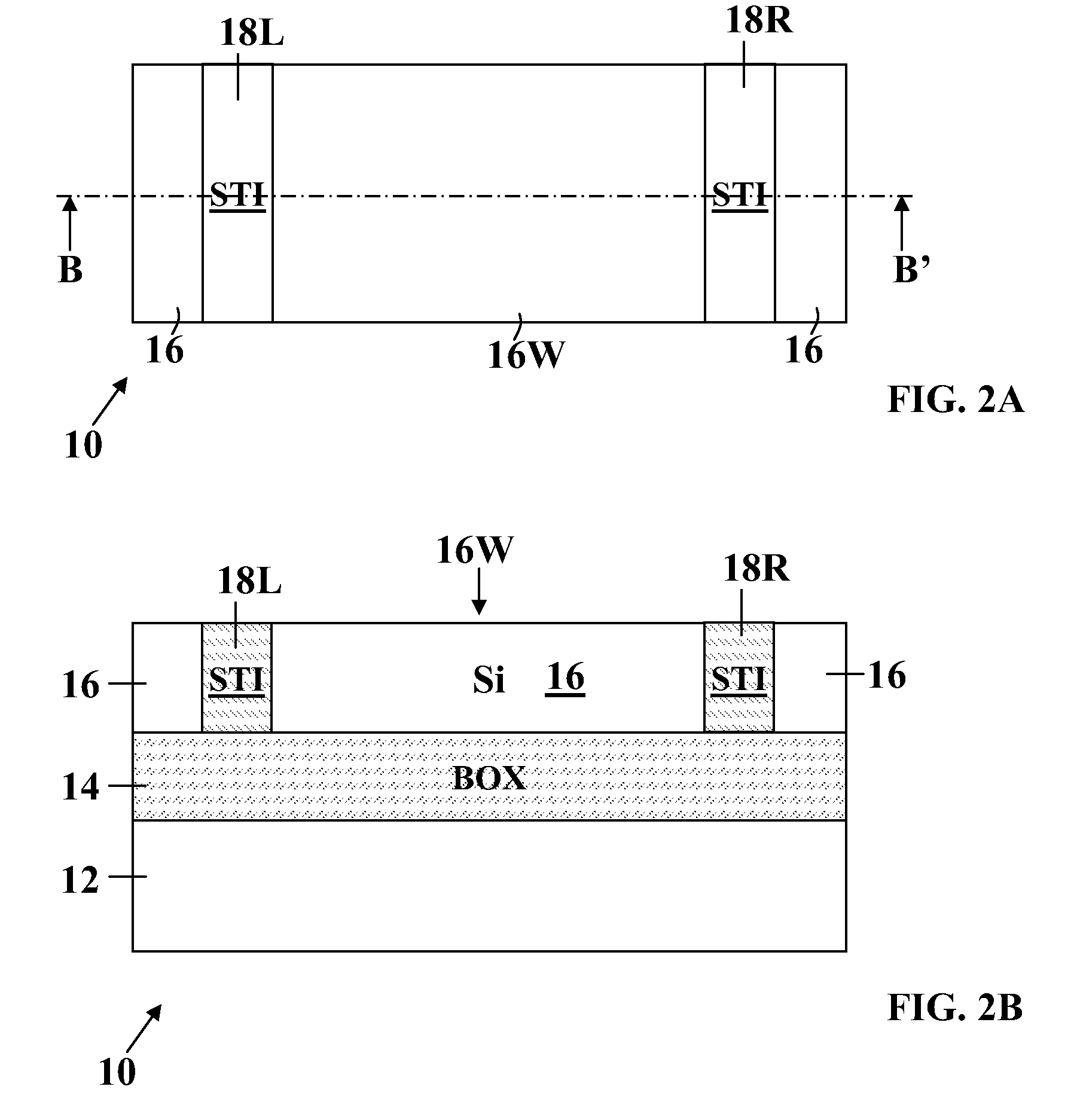

Soi mosfet device with adjustable threshold voltage

InactiveUS20080191788A1Increase circuit speedLimit leakage currentSemiconductor/solid-state device manufacturingElectric variable regulationMOSFETGate dielectric

An SOI semiconductor device includes a silicon semiconductor layer divided into an FET region with source, channel, and drain regions therein formed on a BOX layer, with a switch region next to the FET region; and a contact region next to the switch region distal from the FET region. The FET region has a greater thickness than the switch region. A conformal gate dielectric layer covers the FET region and the switch. A dual function gate electrode formed over the gate dielectric layer includes an FET portion above the FET region and an auxiliary gate portion extending therefrom above the switch region. A contact is formed reaching through the gate dielectric layer into electrical and mechanical contact with the contact region. The switch varies the depth of the depletion region to open and close current flow between the channel of the FET device and the contact region to suppress subthreshold leakage current.

Owner:IBM CORP

Current-controlled CMOS circuit using higher voltage supply in low voltage CMOS process

InactiveUS6982583B2Speed maximizationIncrease circuit speedExclusive-OR circuitsMultiple input and output pulse circuitsTransceiverHigh voltage

Various circuit techniques for implementing ultra high speed circuits use current-controlled CMOS (C3MOS) logic fabricated in conventional CMOS process technology. An entire family of logic elements including inverter / buffers, level shifters, NAND, NOR, XOR gates, latches, flip-flops and the like are implemented using C3MOS techniques. Optimum balance between power consumption and speed for each circuit application is achieve by combining high speed C3MOS logic with low power conventional CMOS logic. The combined C3MOS / CMOS logic allows greater integration of circuits such as high speed transceivers used in fiber optic communication systems. The C3MOS structure enables the use of a power supply voltage that may be larger than the voltage required by the CMOS fabrication process, further enhancing the performance of the circuit.

Owner:AVAGO TECH INT SALES PTE LTD

Current-controlled CMOS circuit using higher voltage supply in low voltage CMOS process

InactiveUS6897697B2Speed maximizationDissipates static currentExclusive-OR circuitsElectronic switchingTransceiverEngineering

Various circuit techniques for implementing ultra high speed circuits use current-controlled CMOS (C3MOS) logic fabricated in conventional CMOS process technology. An entire family of logic elements including inverter / buffers, level shifters, NAND, NOR, XOR gates, latches, flip-flops and the like are implemented using C3MOS techniques. Optimum balance between power consumption and speed for each circuit application is achieve by combining high speed C3MOS logic with low power conventional CMOS logic. The combined C3MOS / CMOS logic allows greater integration of circuits such as high speed transceivers used in fiber optic communication systems. The C3MOS structure enables the use of a power supply voltage that may be larger than the voltage required by the CMOS fabrication process, further enhancing the performance of the circuit.

Owner:AVAGO TECH INT SALES PTE LTD

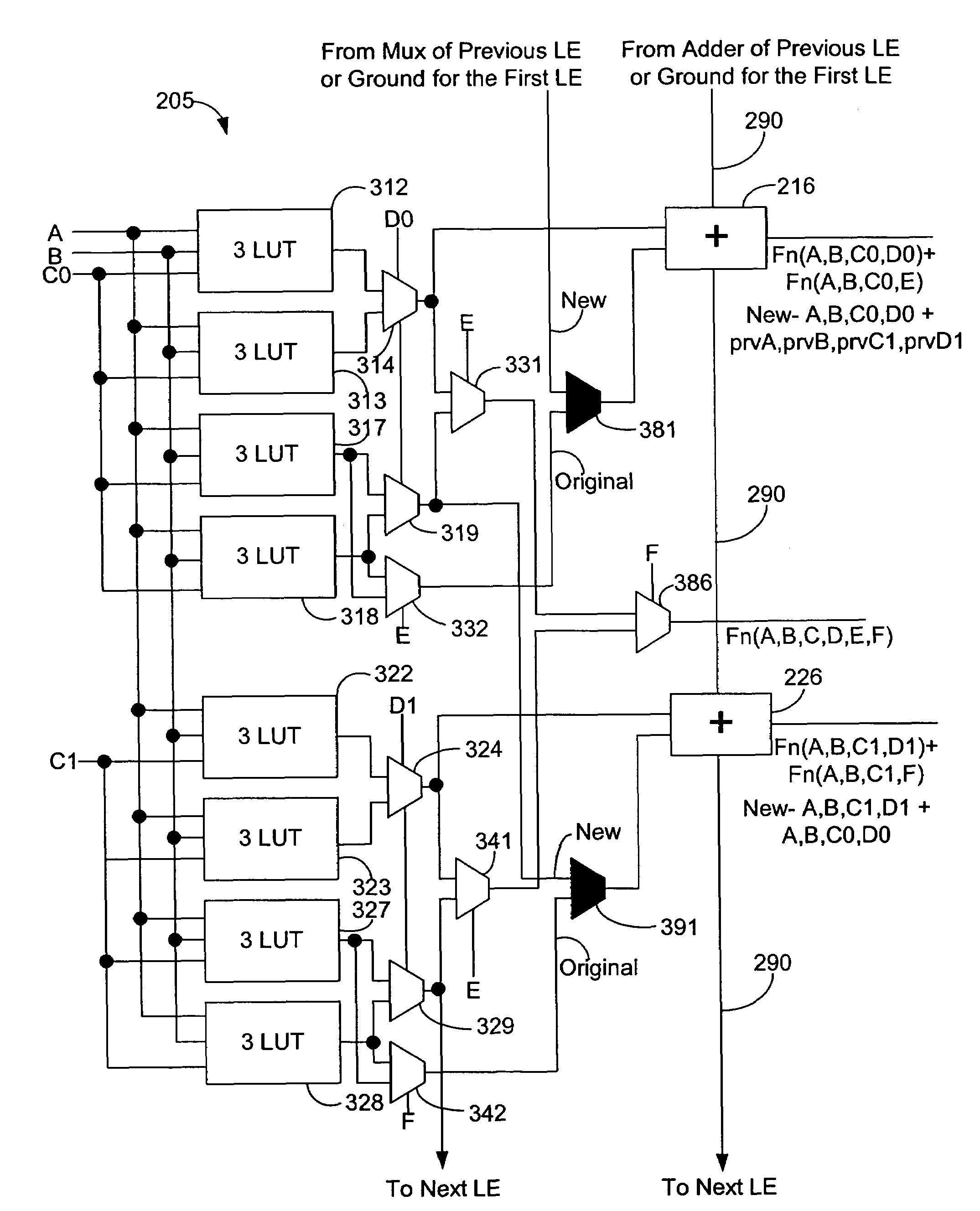

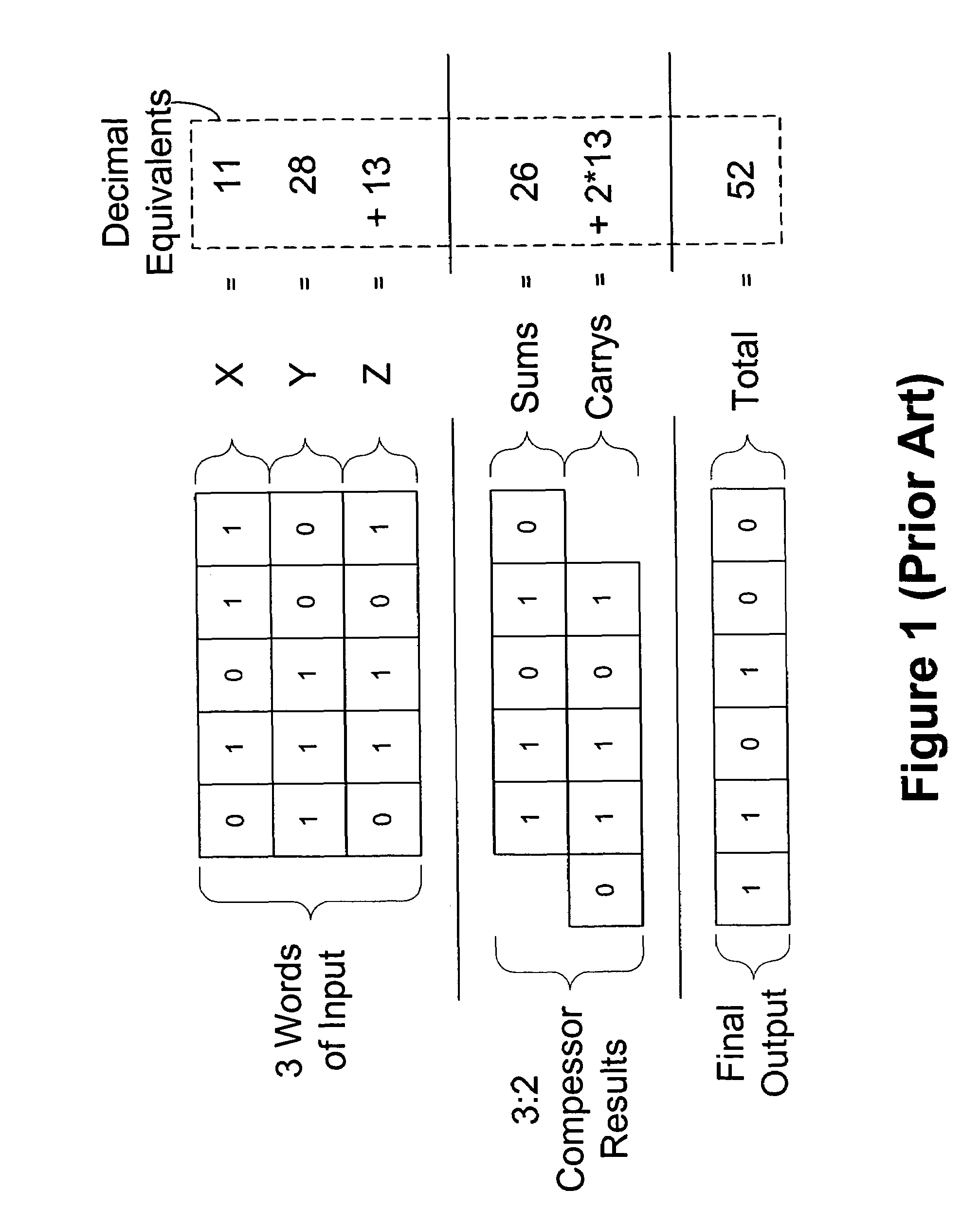

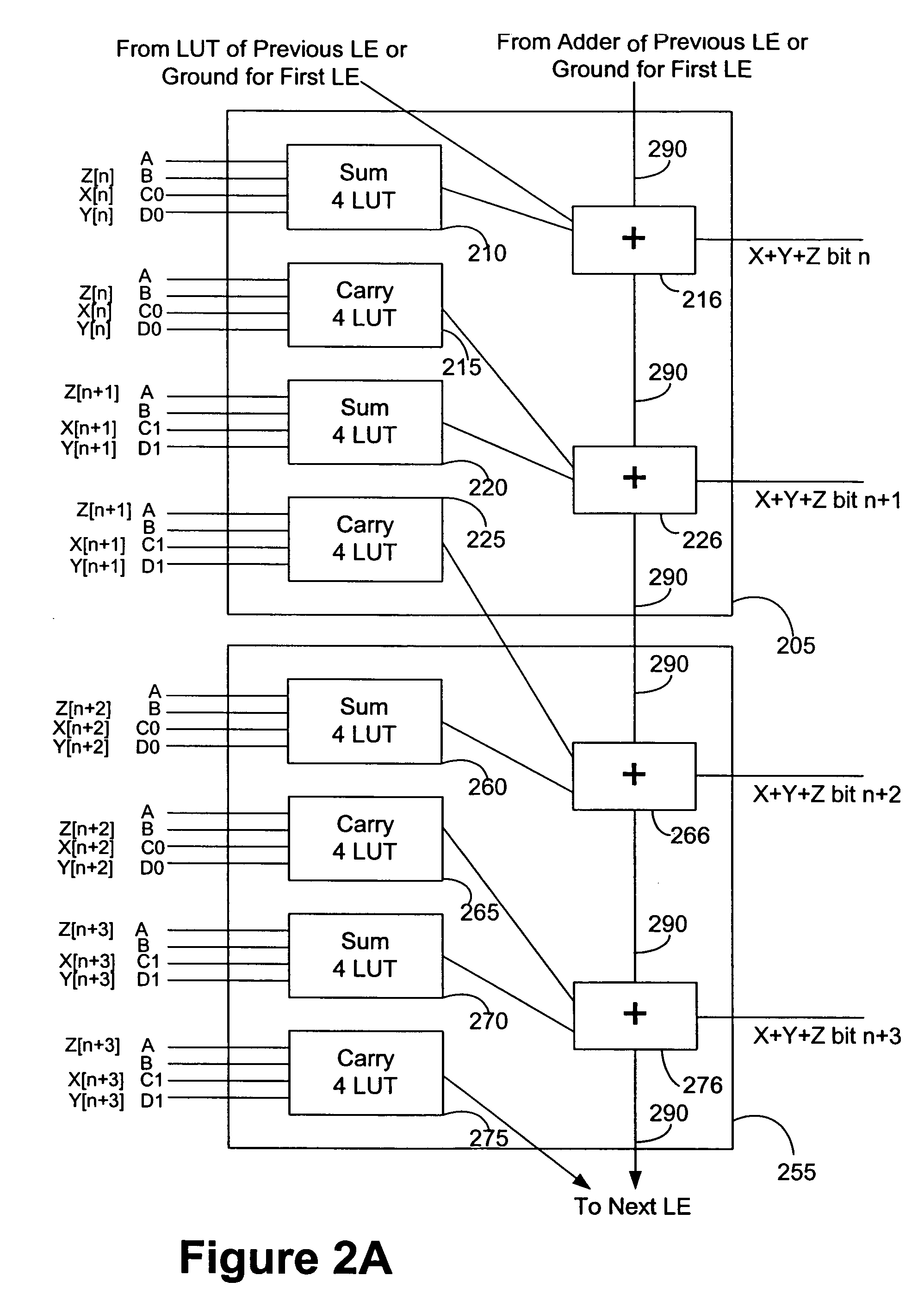

Logic cell supporting addition of three binary words

InactiveUS7565388B1Increase circuit speedShorten the counting processComputation using non-contact making devicesLogic circuitsLogic cellTheoretical computer science

Logic circuits that support the addition of three binary numbers using hardwired adders are described. In one embodiment, this is accomplished by using a 3:2 compressor (i.e., a Carry Save Adder method), using hardwired adders to add the sums and carrys produced by the 3:2 compression, and sharing carrys data calculated in one logic element (“LE”) with the following LE. In such an embodiment, with the exception of the first and last LEs in a logic array block (“LAB”), each LE in effect lends one look-up table (“LUT”) to the LE below (i.e., the following LE) and borrows one LUT from the LE above (i.e., the previous LE). The LUT being lent or borrowed is one that implements the carry function in the 3:2 compressor model. In another aspect, an embodiment of the present invention provides LEs that include selectors to select signals corresponding to the addition of three binary numbers mode.

Owner:ALTERA CORP

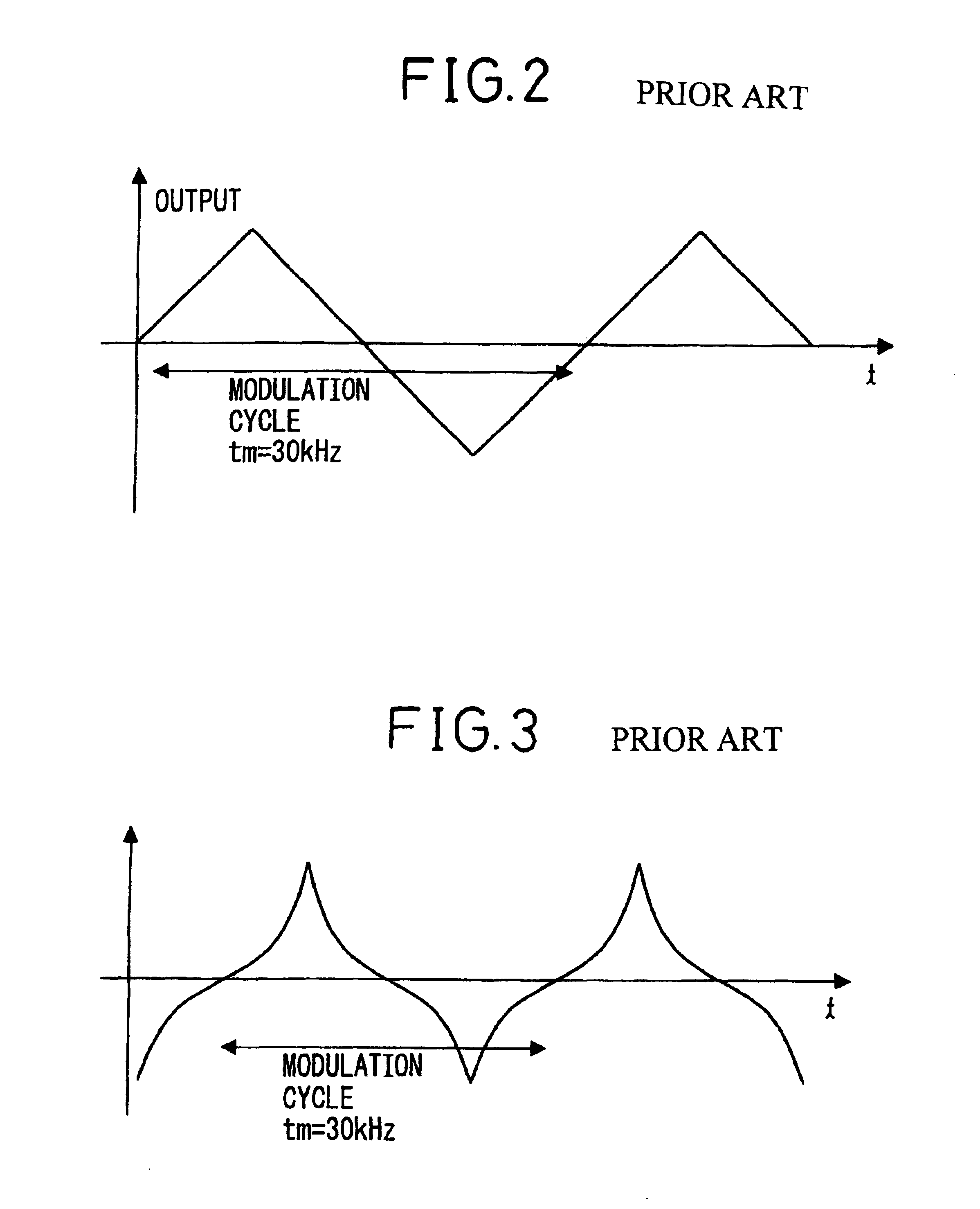

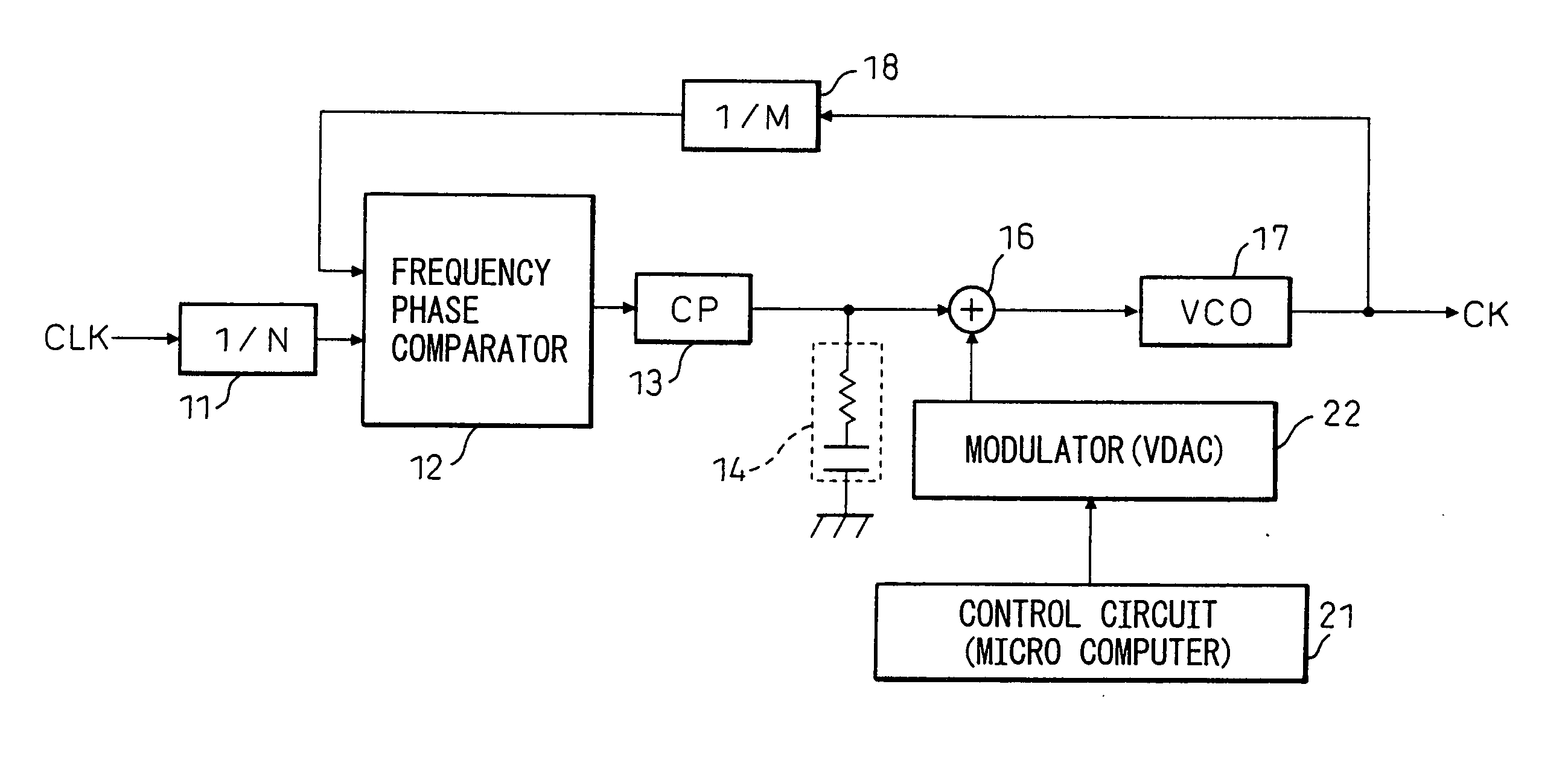

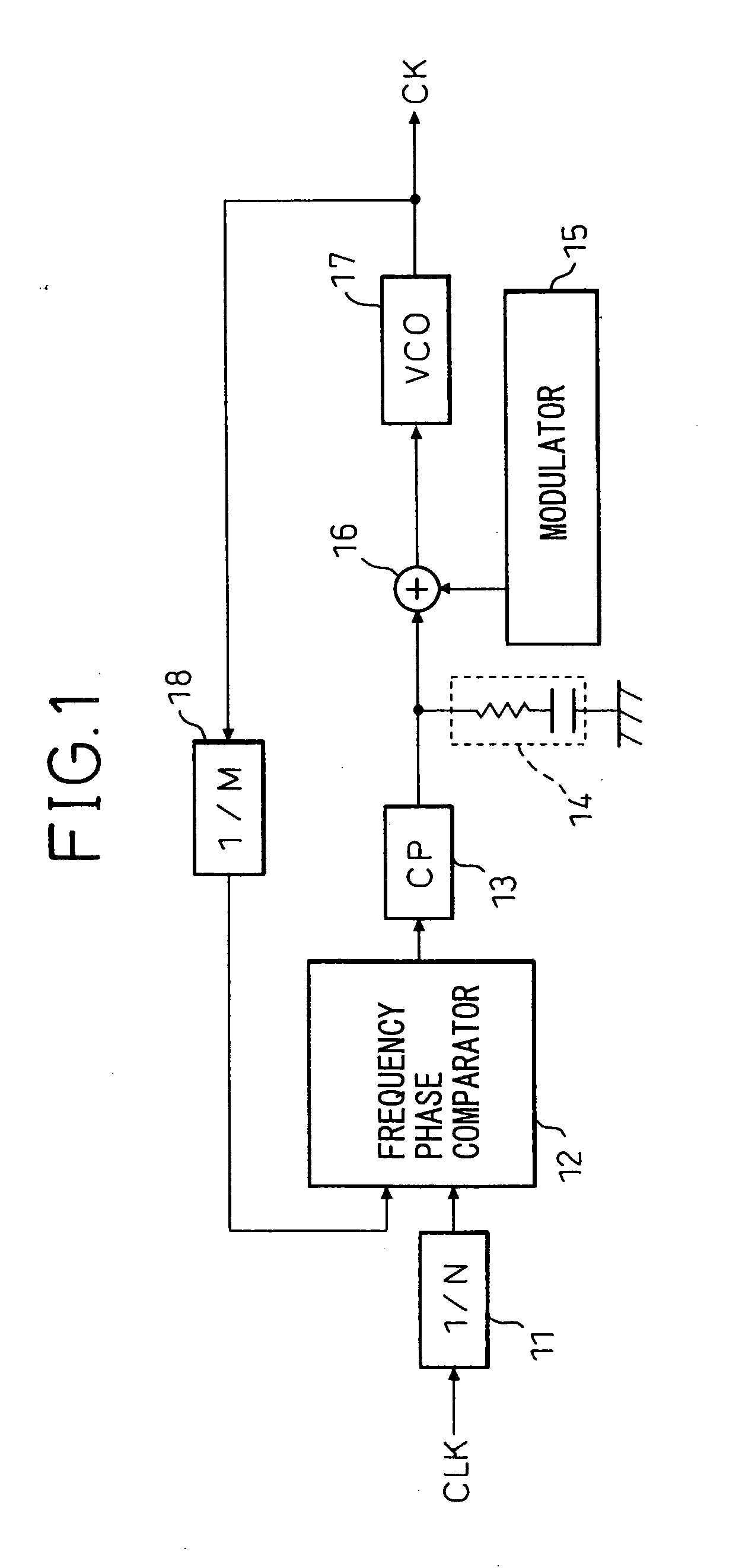

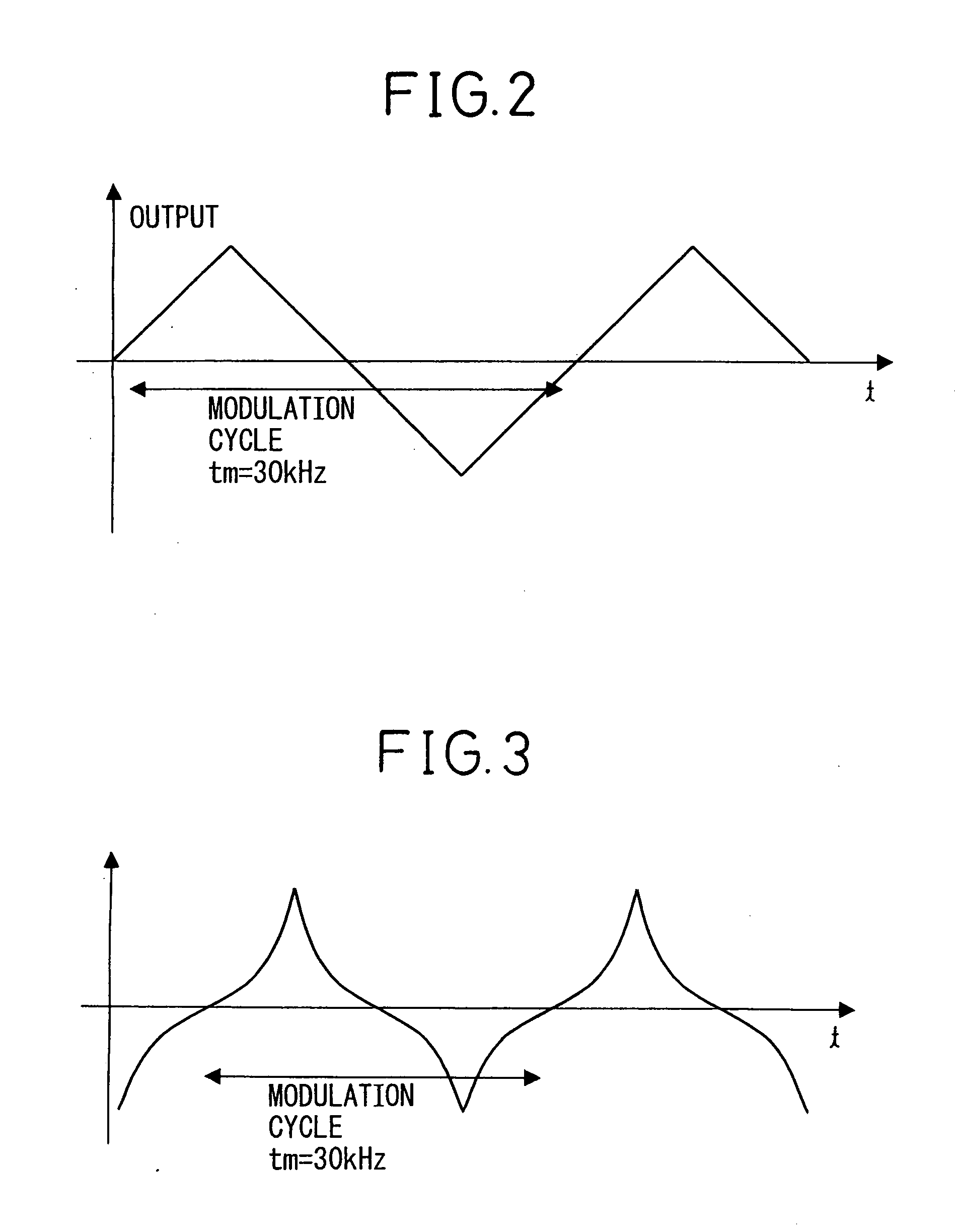

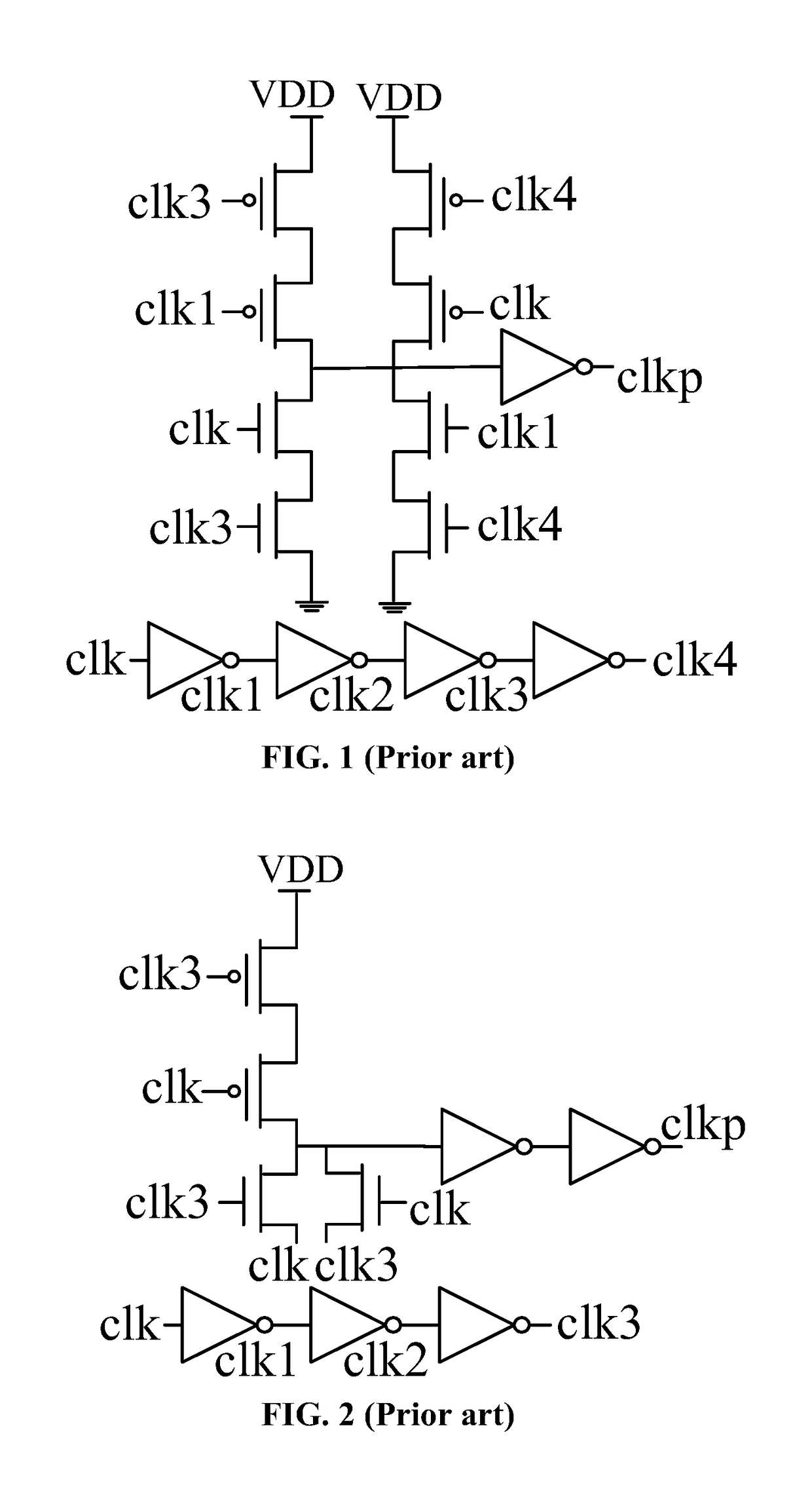

Spread spectrum clock generation circuit, jitter generation circuit and semiconductor device

ActiveUS6975148B2Reduce radiated noiseIncrease circuit speedElectric signal transmission systemsPulse automatic controlDevice materialCurrent controlled oscillator

A spread spectrum clock generation circuit capable of further reducing the electromagnetic wave radiation with a simple configuration has been disclosed and, particularly in a spread spectrum clock generation circuit using a current control oscillator (ICO), a differential signal to which a spread spectrum modulation signal, the period or amplitude of which changes, is added is generated, and the differential signal is applied to the ICO and a clock is generated.

Owner:MONTEREY RES LLC

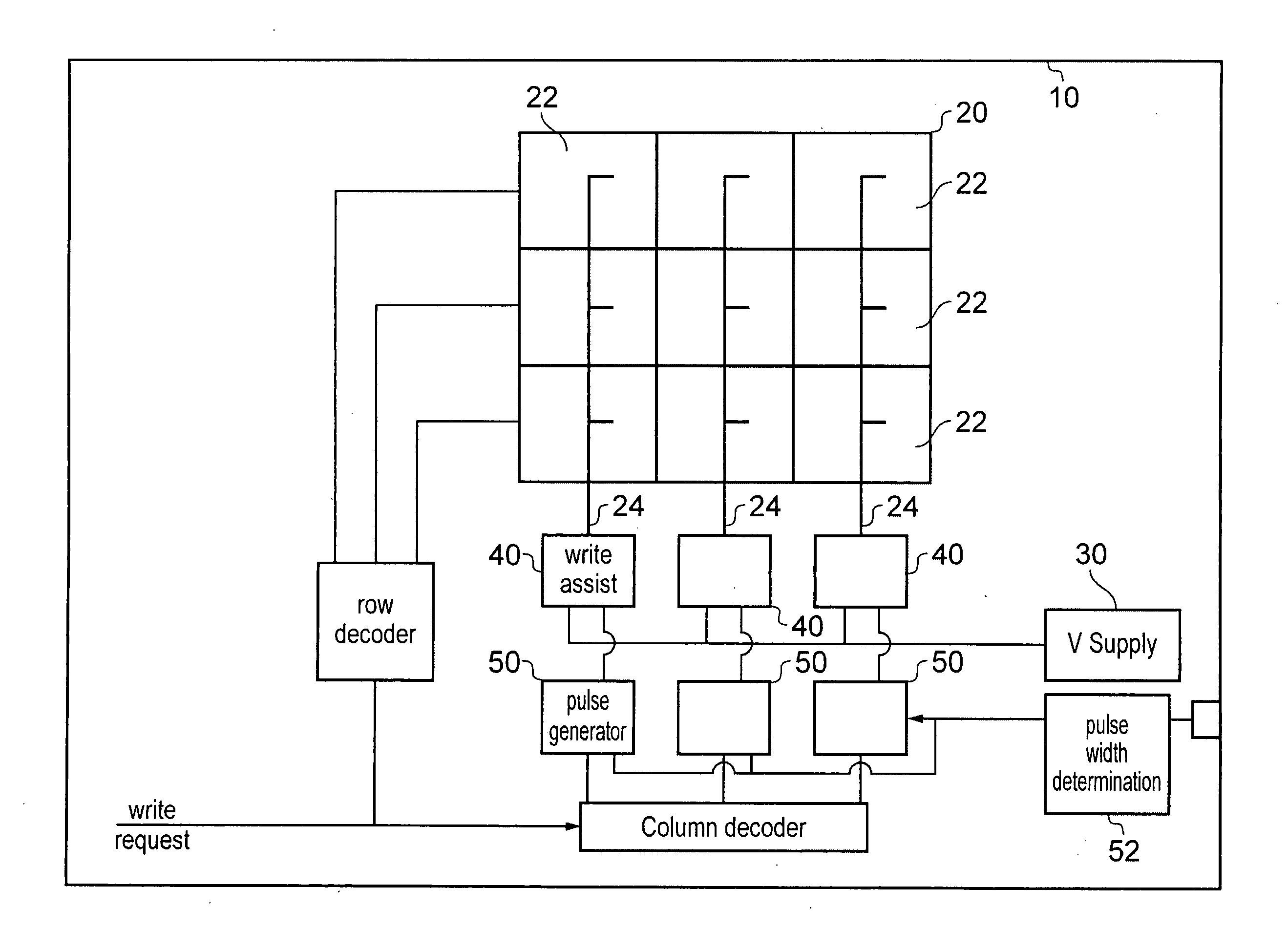

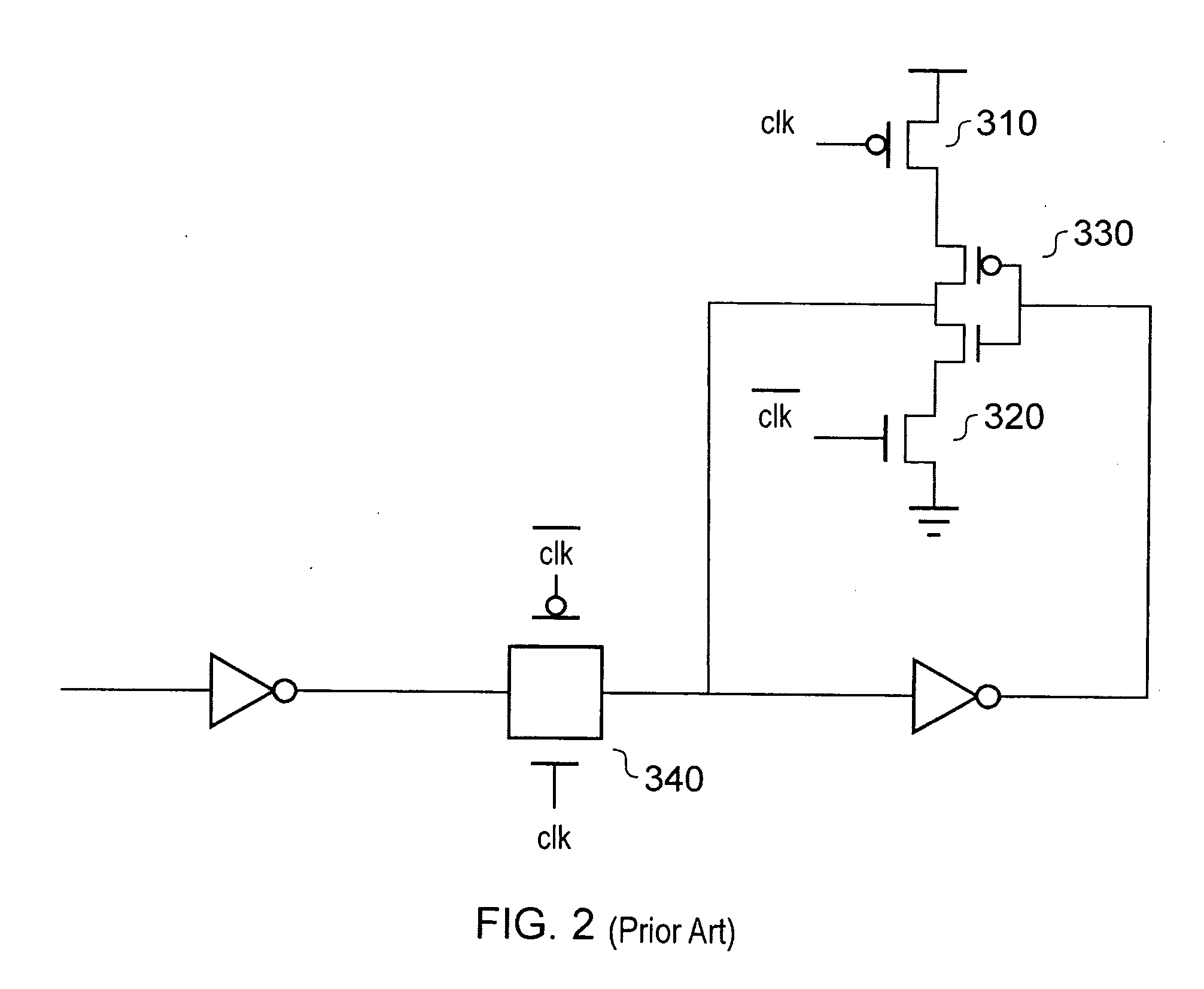

Assisting write operations to data storage cells

A data store and method of storing data is disclosed that comprises: an input for receiving a data value; at least one storage cell comprising: a feedback loop for storing the data value; an output for outputting the stored data value; the feedback loop receiving a higher voltage and a lower voltage as power supply, the data store further comprising: a voltage supply for powering the data store, the voltage supply outputting a high voltage level and a low voltage level; write assist circuitry arranged between the voltage supply and the at least one storage cell, the write assist circuitry being responsive to a pulse signal to provide a discharge path between the high voltage level and a lower voltage level and thereby generate a reduced internal voltage level from the high voltage level for a period dependent on a width of the pulse signal, the reduced internal voltage level being lower than the high voltage level, such that when powered the feedback loop receives the reduced internal voltage level as the higher voltage for a period determined by the pulse width and the high voltage level at other times; and pulse signal generation circuitry for generating said pulse signal.

Owner:ARM LTD

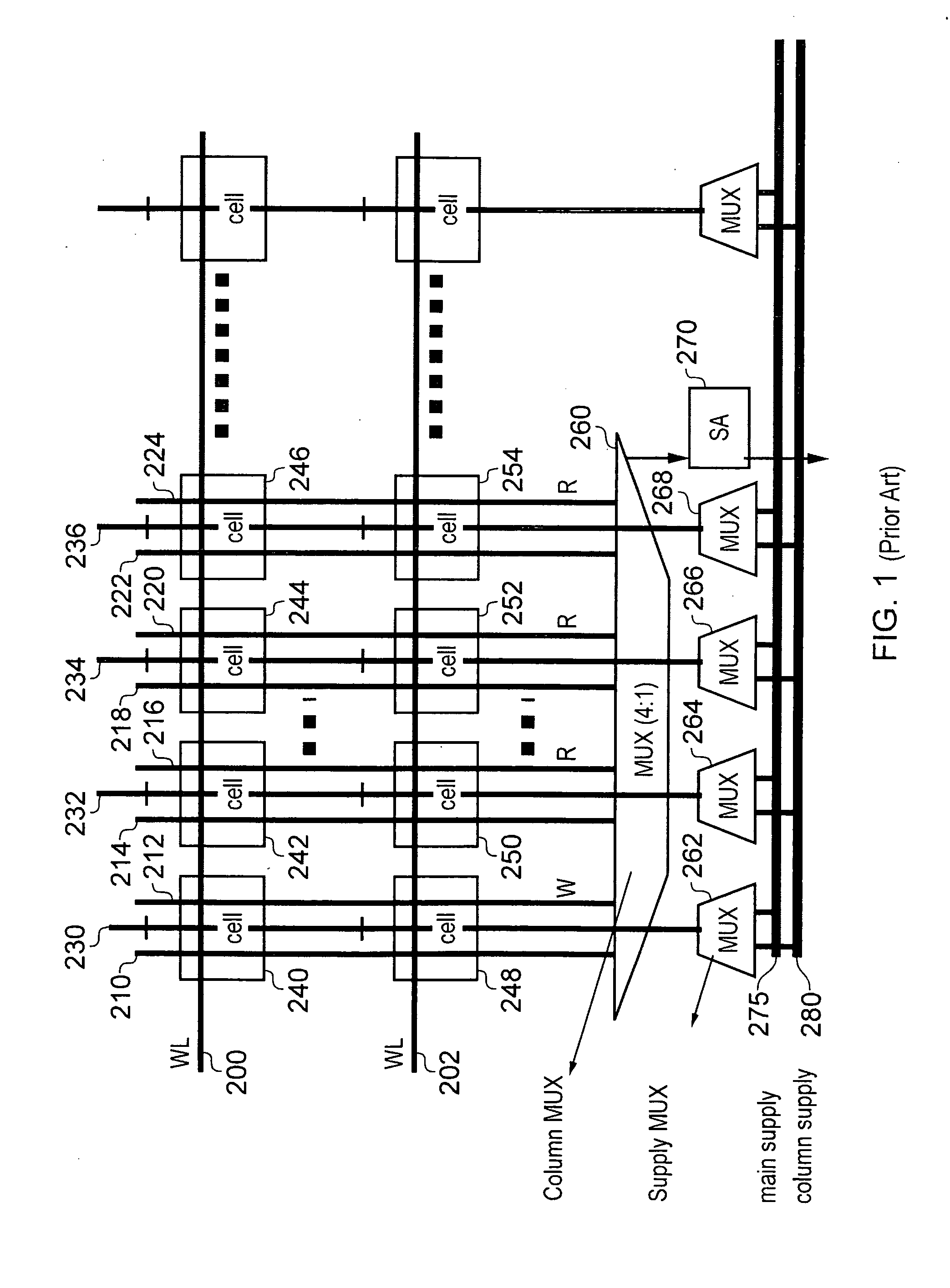

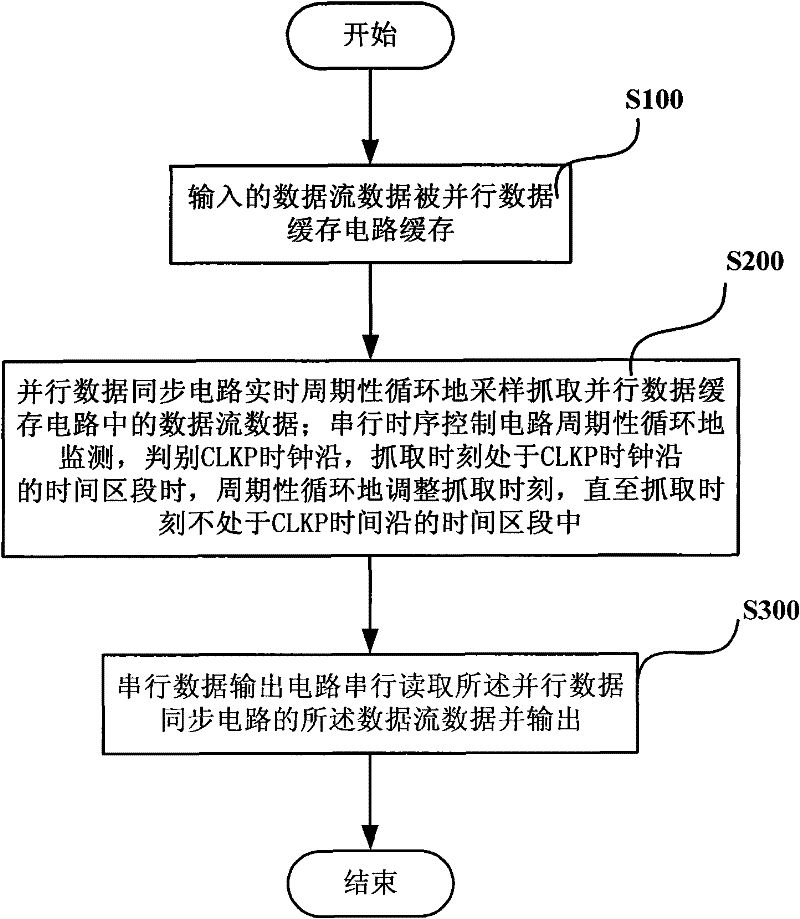

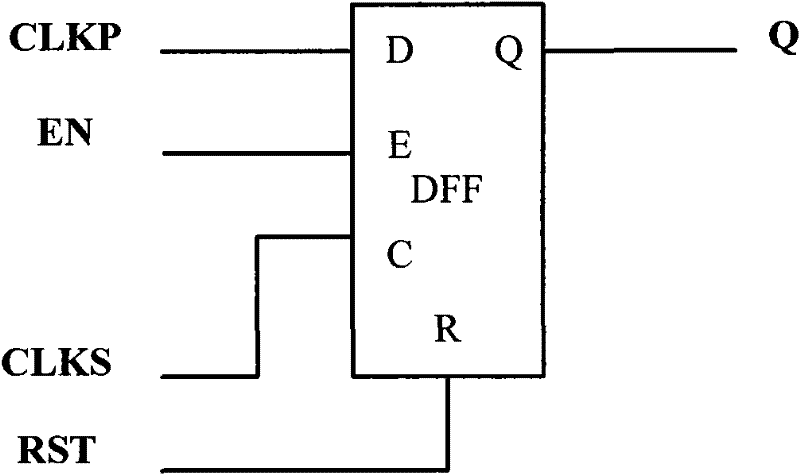

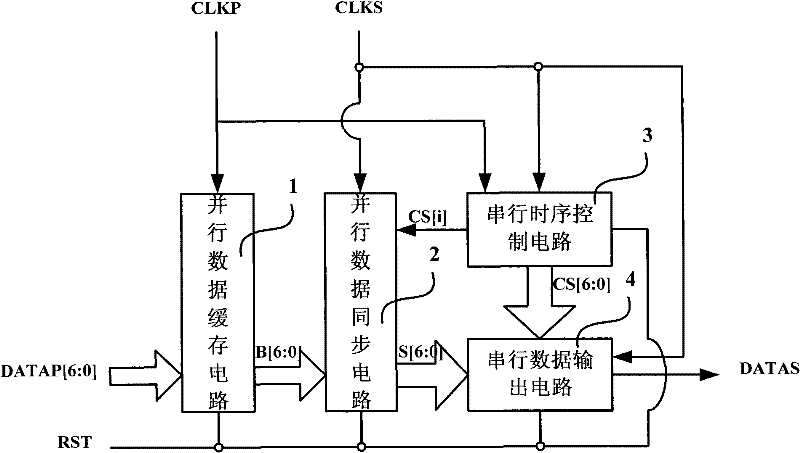

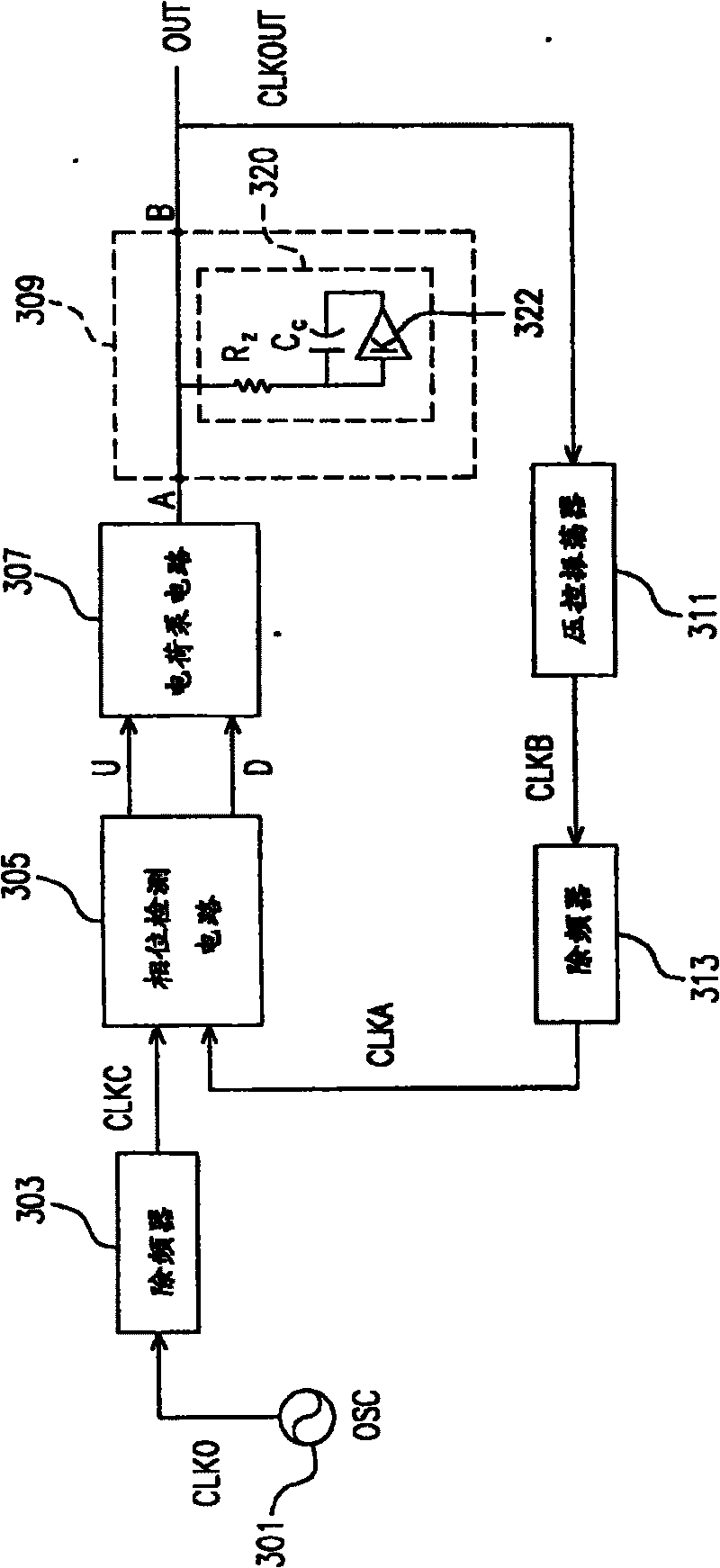

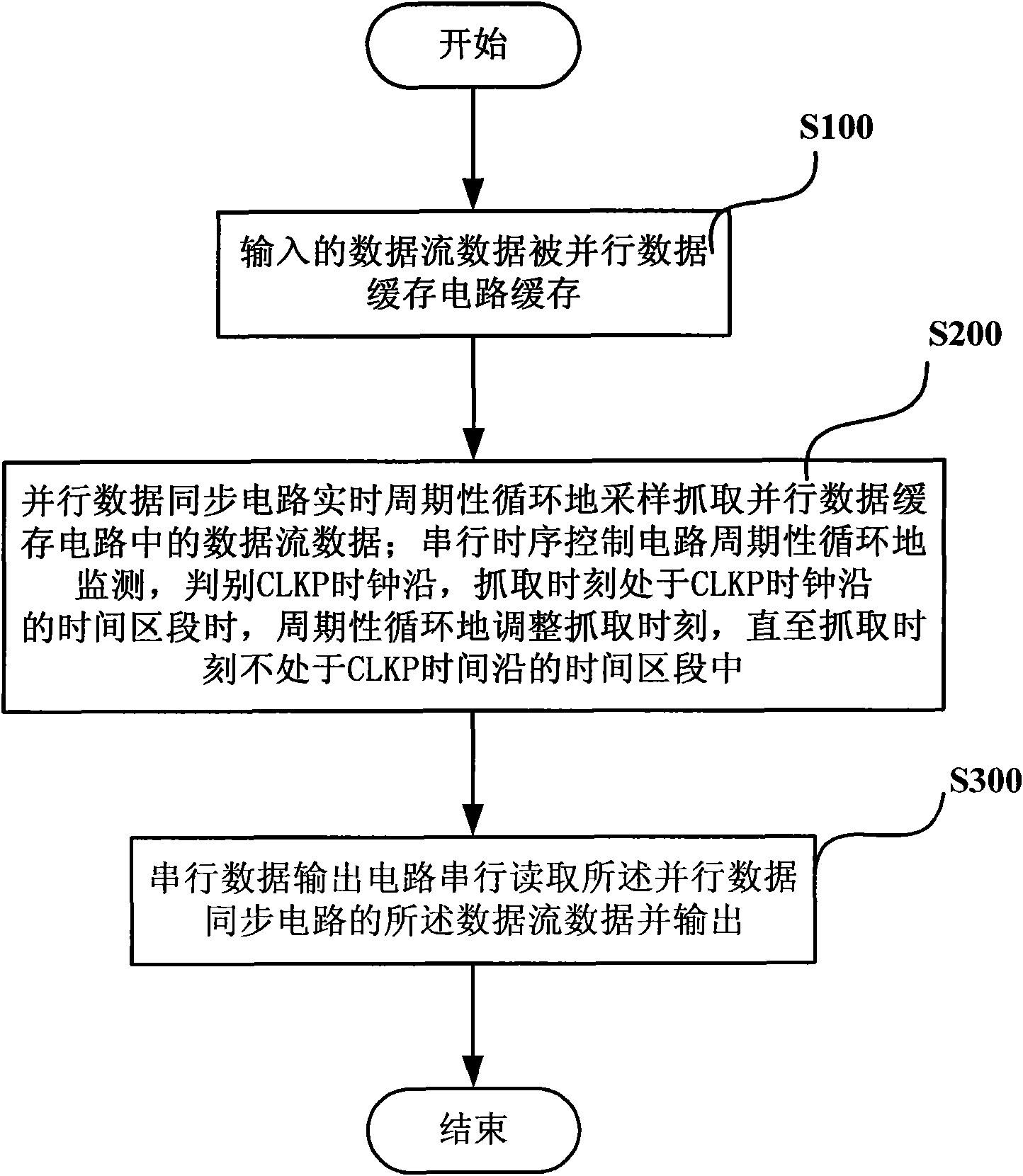

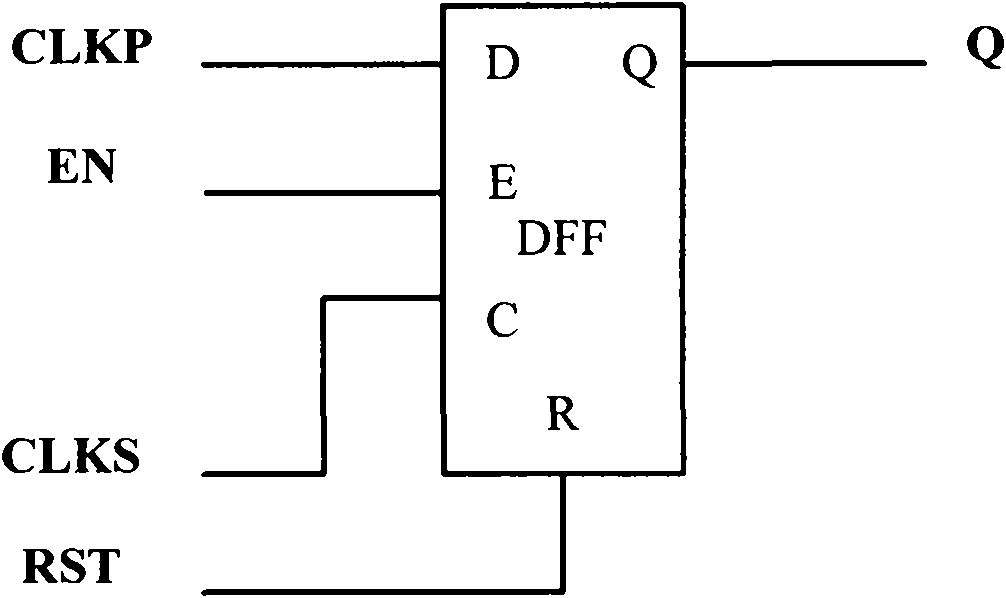

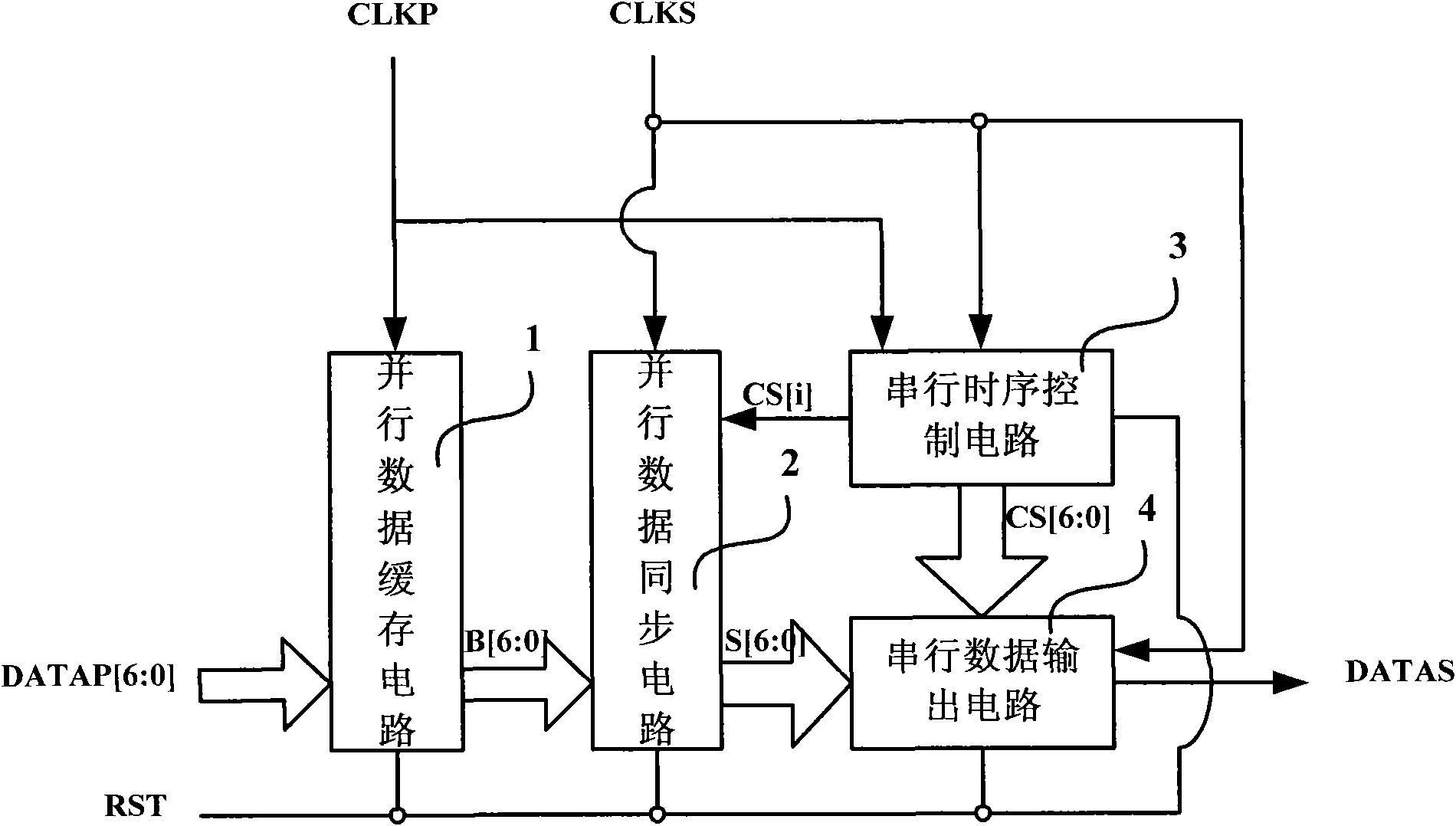

Real-time conversion transmission method and device of parallel-series data stream for cross asynchronous clock domain

ActiveCN102447477AIncrease circuit speedTimely and accurate timing security issuesParallel/series conversionData synchronizationTime domain

The invention discloses a real-time conversion transmission method and device of parallel-series data stream for cross asynchronous clock domain, comprising a parallel data synchronizer, which is used for capturing the data stream periodically in real time and storing into the parallel data synchronizer under the control of a serial clock CLKS which is synchronous to output device of serial data and an enabling controlling signal CS sent out by serial timing controller which is synchronous to clock CLKP; the serial timing controller, monitoring clock CLKP periodically in the clock domain of clock CLKS, distinguishing indeterminate state of clock CLKP, the indeterminate state being a time domain zone of a data transmission zone; when distinguishing that the capturing moment is in a time zone of the data transmission zone of clock CLKP, the serial timing controller cyclically adjusts capturing moment until the capturing moment is in the time zone of determined state of clock CLKP, the determined state being the time zone besides the data transmission zone; the output device of serial data, reading the data stream of parallel data synchronizer and output serially under the control of the serial timing controller. The invention is characterized by being simple and reliable, good practicability and being in favor of applying in the large scale integrated circuit.

Owner:ALLWINNER TECH CO LTD

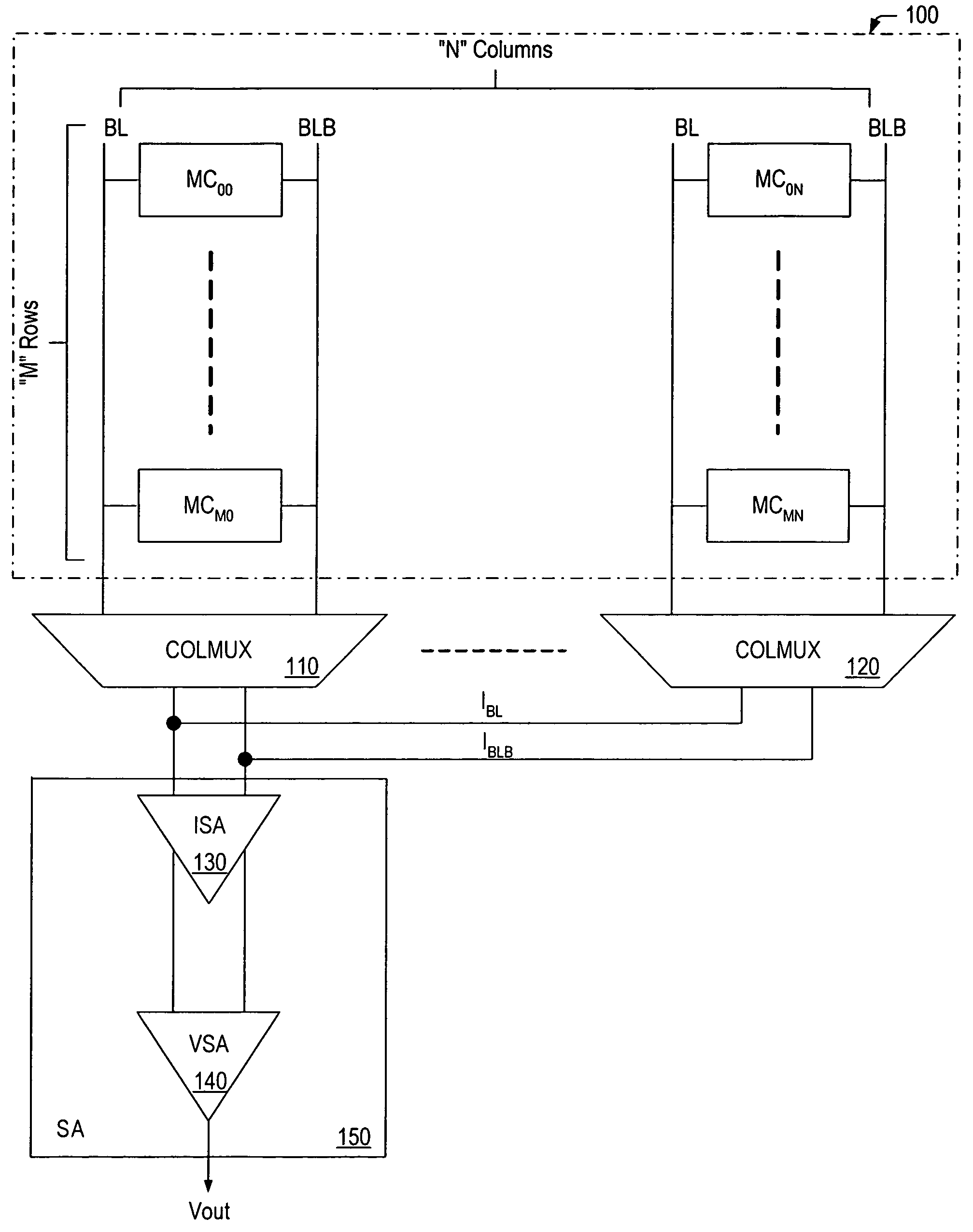

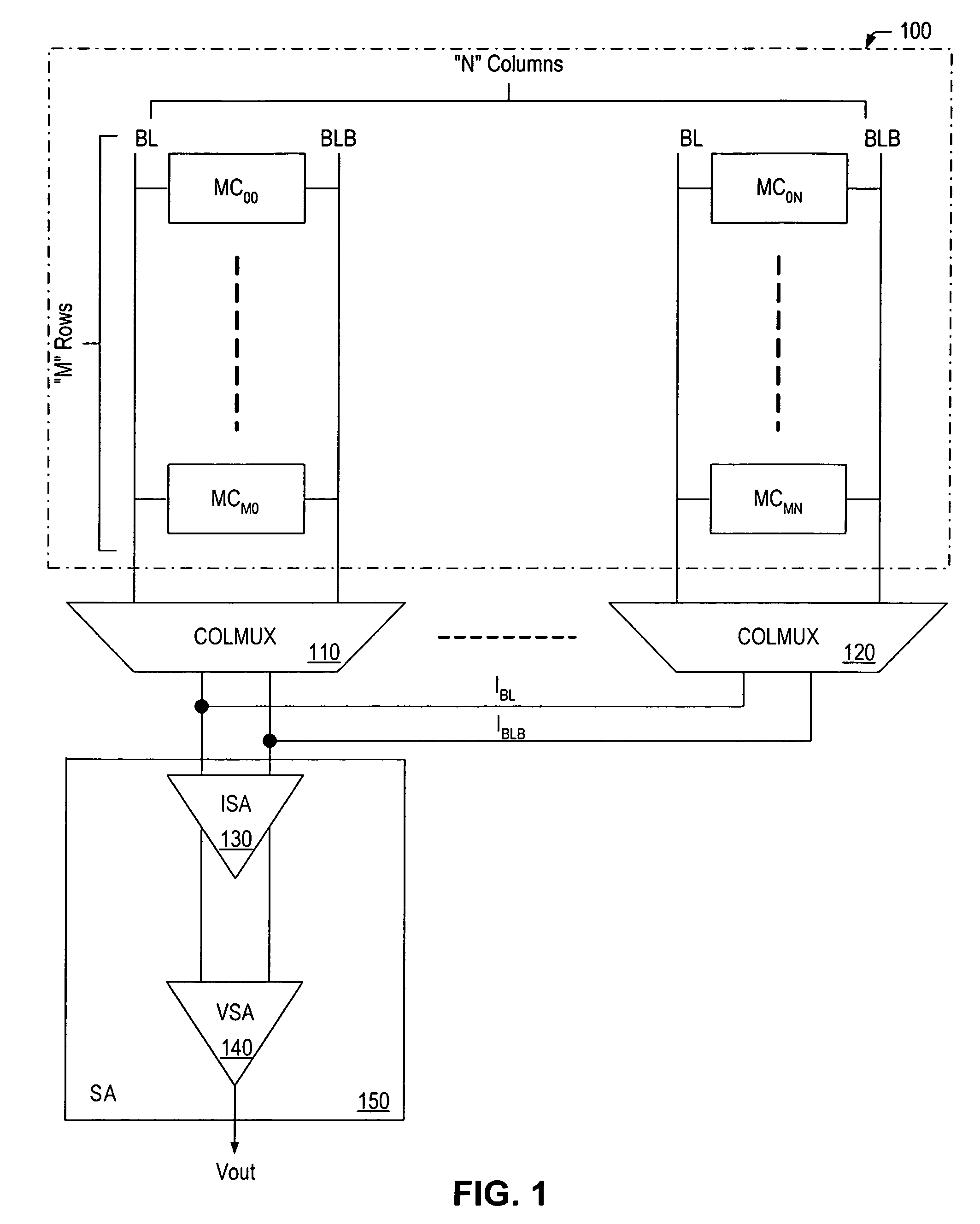

Memory device, current sense amplifier, and method of operating the same

InactiveUS7616513B1Improving mismatch toleranceImprove circuit stabilityRead-only memoriesDigital storageAudio power amplifierTime segment

A memory device, current sense amplifier and method of operating the same are disclosed herein. In accordance with one embodiment, the current sense amplifier circuit may include a pair of cross-coupled transistors, a pair of output nodes and a first pair of load transistors. The pair of cross-coupled transistors may be coupled for receiving a pair of differential currents and for generating a pair of differential voltages, which may then be supplied to the pair of output nodes. The first pair of load transistors may have mutually-connected gate terminals, mutually-connected drain terminals, and a source terminal coupled to a different one of the output nodes. In a unique aspect of the invention, an equalization transistor may coupled between the pair of output nodes for equalizing the pair of differential voltages for a predetermined amount of time at the beginning of a sense cycle. As such, the equalization transistor may be added to prevent the current sense amplifier circuit from generating erroneous results during the predetermined time period.

Owner:MONTEREY RES LLC

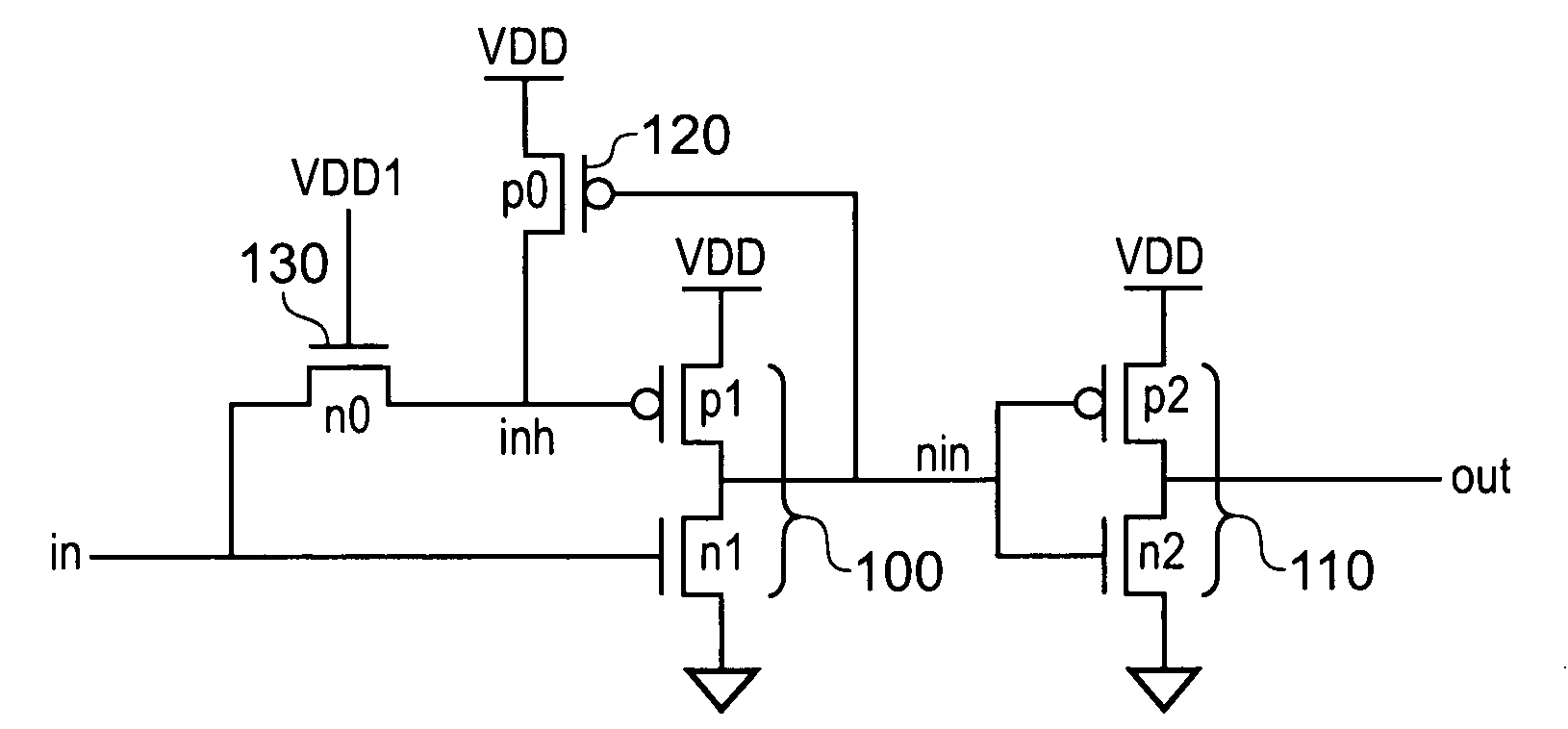

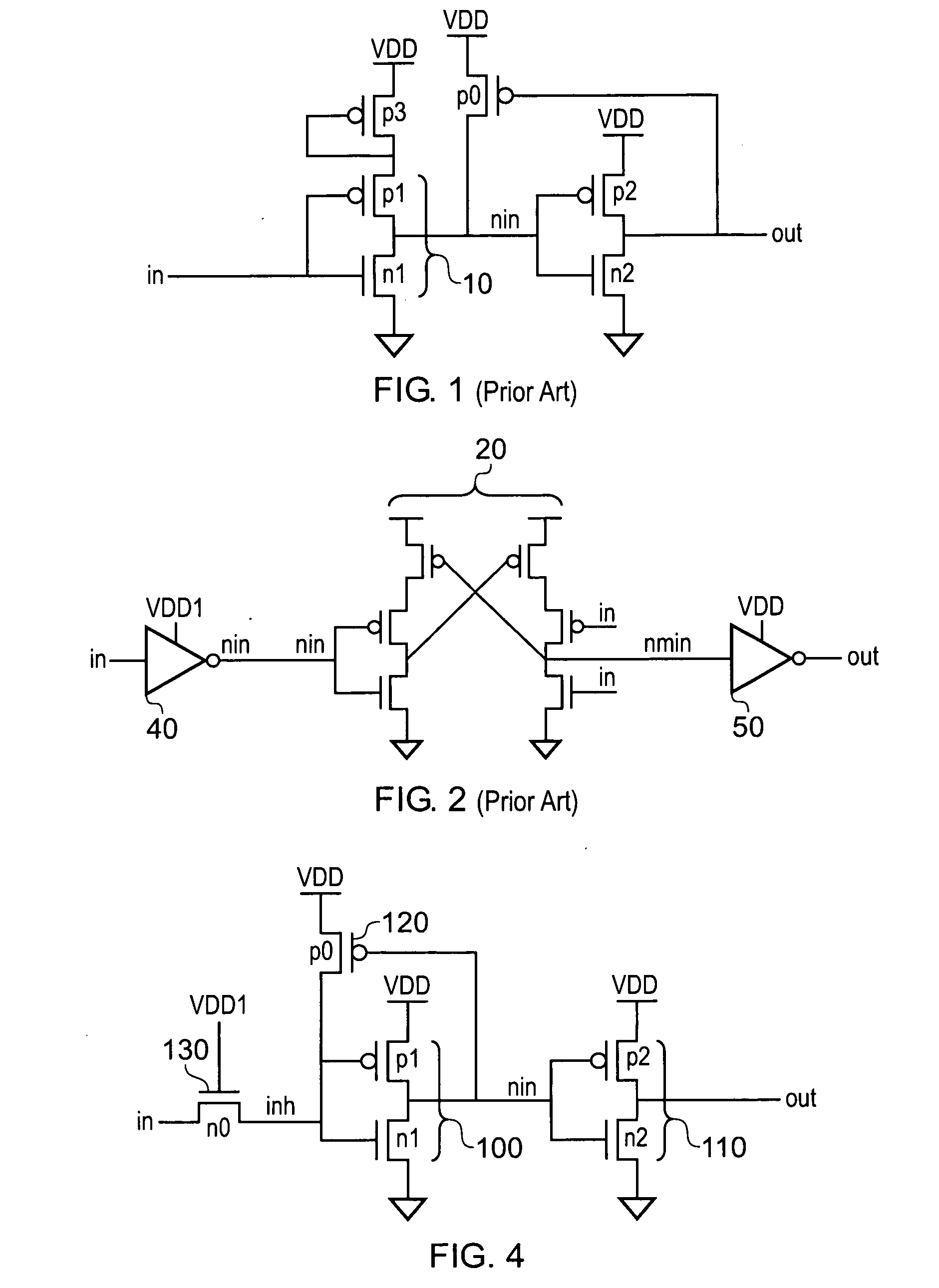

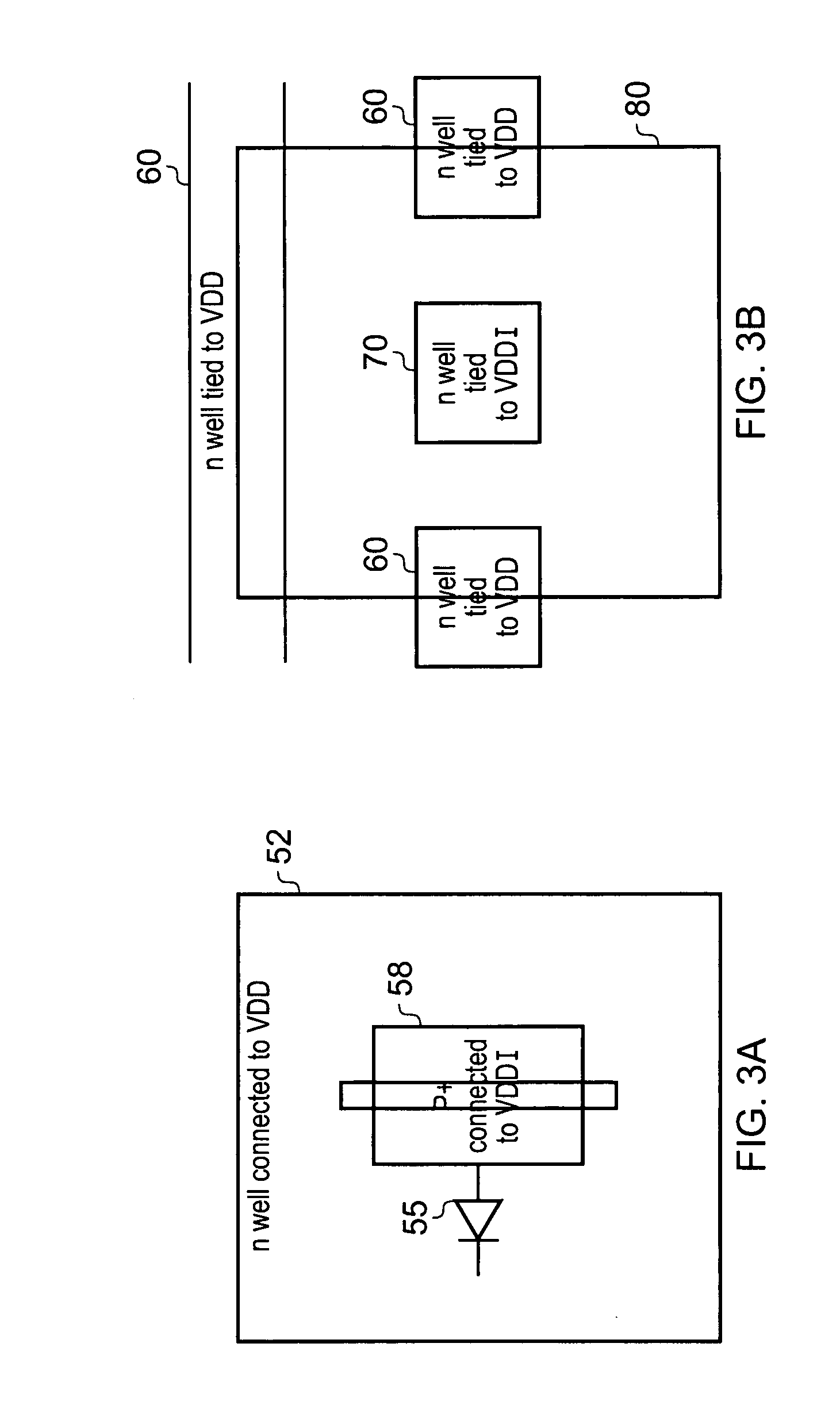

Shifting of a voltage level between different voltage level domains

InactiveUS20090108904A1Reduce outputSave leakage currentPower reduction by control/clock signalPulse automatic controlEngineeringVoltage source

A voltage level shifter for receiving a digital signal from a first voltage domain and converting said signal to a digital signal in a second voltage domain is disclosed. The voltage level shifter comprises: an input for receiving said digital signal from said first voltage domain; a device connected to said input of said voltage level shifter for receiving said digital signal from said first voltage domain and for outputting a digital signal in said second voltage domain, said device being powered by said second voltage domain; a first switching device arranged to connect a high level voltage source of said second domain to an input of said device in response to said input digital signal having a high level and to isolate said high level voltage source of said second domain from said input of said device in response to said input digital signal having a low level; and a second switching device arranged between said voltage level shifter input and said input of said device for inhibiting current flow from said high level voltage source of said second domain to said voltage level shifter input in response to a high level signal at said voltage level shifter input and for allowing current flow in both directions between said voltage level shifter input and said input of said device in response to said voltage level shifter input having a low level signal.

Owner:ARM LTD

Spread spectrum clock generation circuit, jitter generation circuit and semiconductor device

ActiveUS20050285641A1Low costLarge scaleElectric signal transmission systemsPulse automatic controlDevice materialCurrent controlled oscillator

Owner:MONTEREY RES LLC

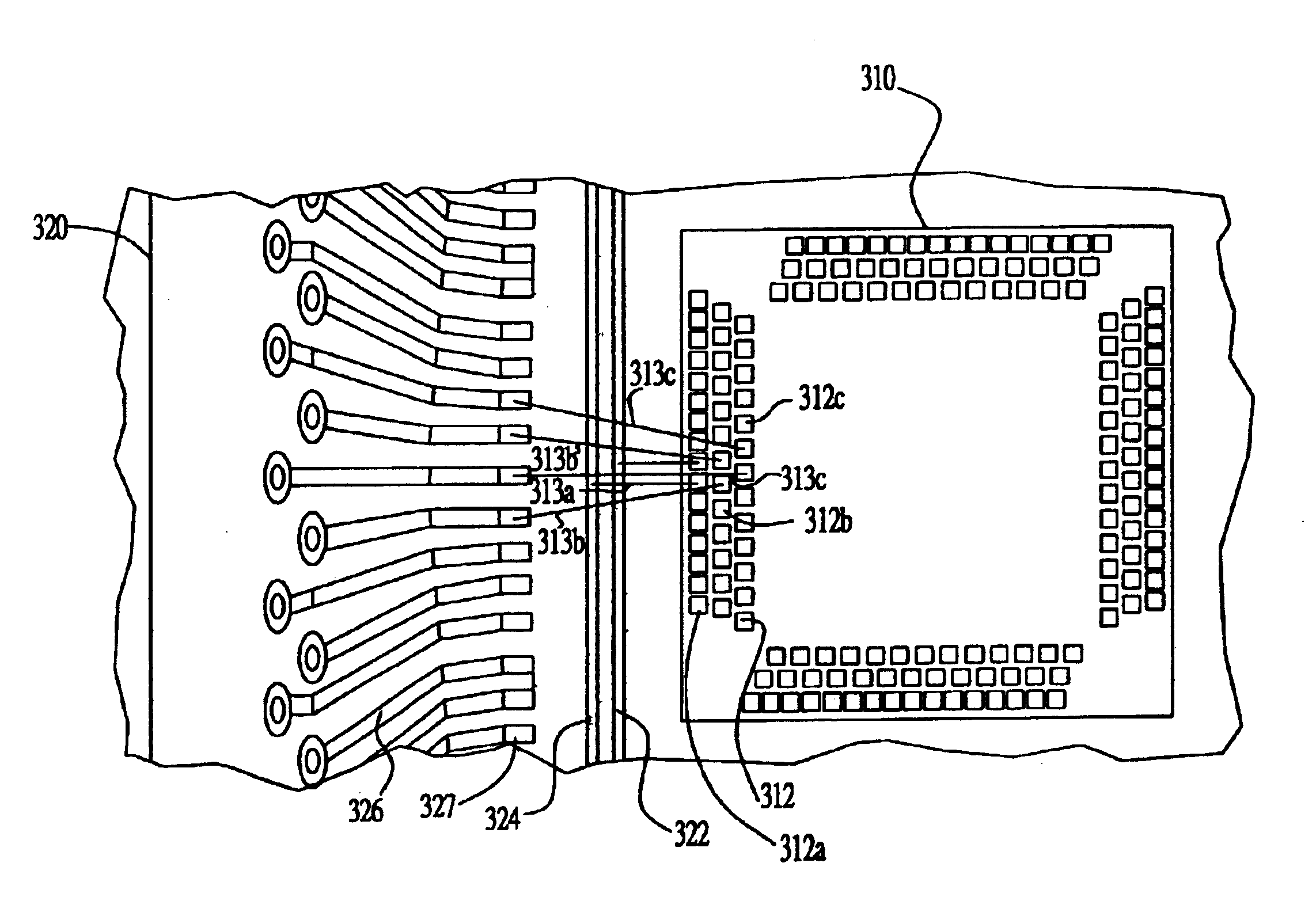

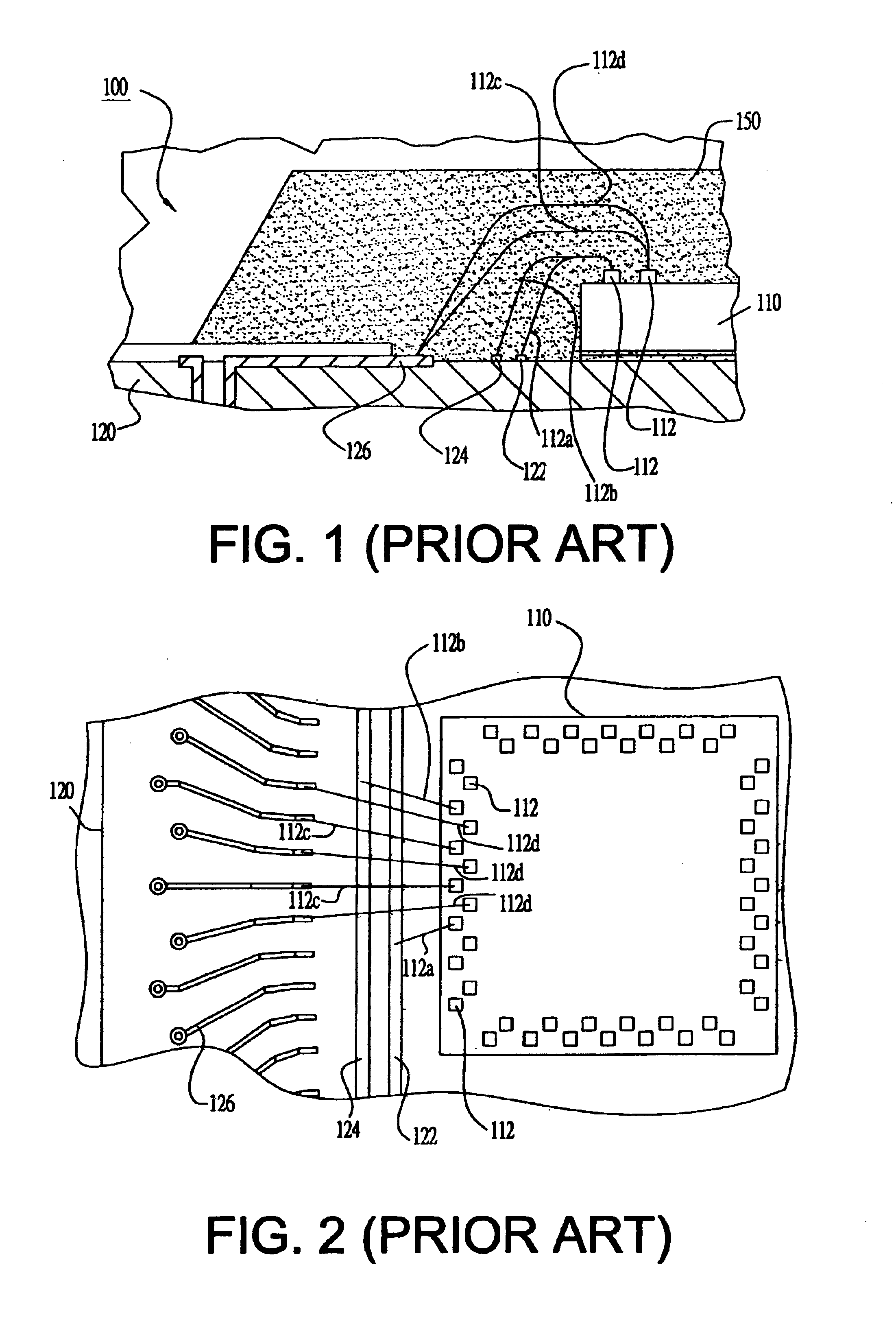

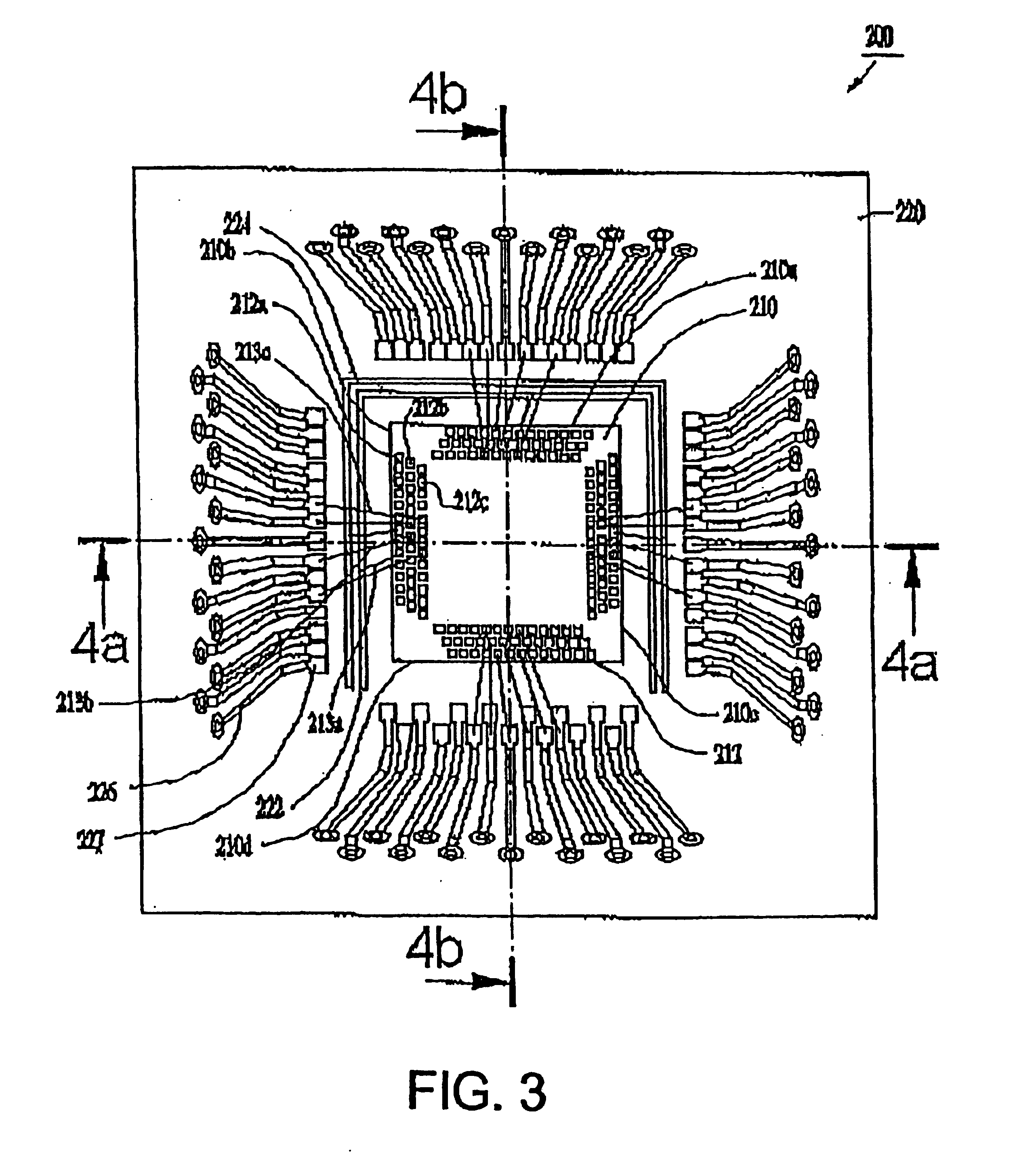

Ball grid array package

InactiveUS6921981B2Convenient ArrangementImprove the level ofSemiconductor/solid-state device detailsSolid-state devicesEngineeringBall grid array

A BGA package comprises a chip with an array pad design disposed on the top surface of a substrate. The chip has a plurality of bonding pads located about the periphery thereof. The bonding pads of the chip are positioned in three rows, an inner row, a middle row, and an outer row along the sides of the chip. All of the power supply pads and ground pads are adjacent to one another and designed in the outer row of the bonding pads, and the I / O pads are designed in the outer row, the middle row and the inner row of the bonding pads. The outer row, middle row, and the inner row of the bonding pads are electrically connected to the substrate through three tiers of bonding wires with different loop height, respectively.

Owner:ADVANCED SEMICON ENG INC

Solid-state imaging device and apparatus with an increased speed of analog to digital conversion

InactiveUS8063960B2Improve processing speedIncrease in speed of AD conversionAnalogue/digital conversionTelevision system detailsDigital dataComputer science

A solid-state imaging device includes a reference-signal generating unit that generates plural kinds of reference signals for converting an analog pixel signal into digital data, a reference-signal selecting unit that selects any one of the plural kinds of reference signals, a comparing unit that compares the pixel signal and the selected reference signal, and a count unit that performs count processing in parallel with comparison processing in the comparing unit and stores a count value at a point when the comparison processing is completed. The count unit decides digital data of the pixel signal in a 1 LSB step by storing a count value at a point when the comparison processing is completed for any one of the plural kinds of reference signals and correcting the stored count value on the basis of results of the comparison processing for respective remaining reference signals of the plural kinds of reference signals.

Owner:SONY CORP

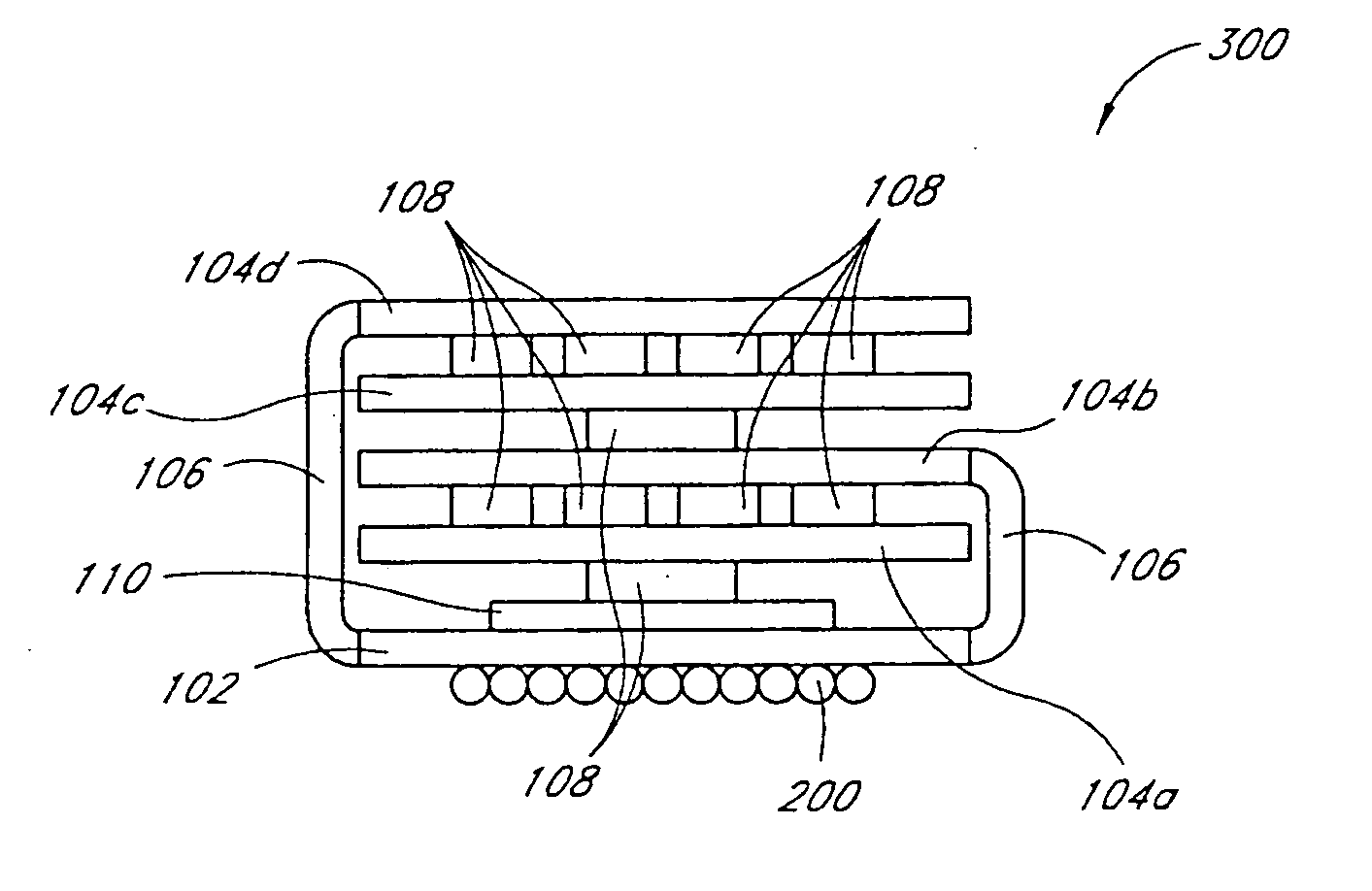

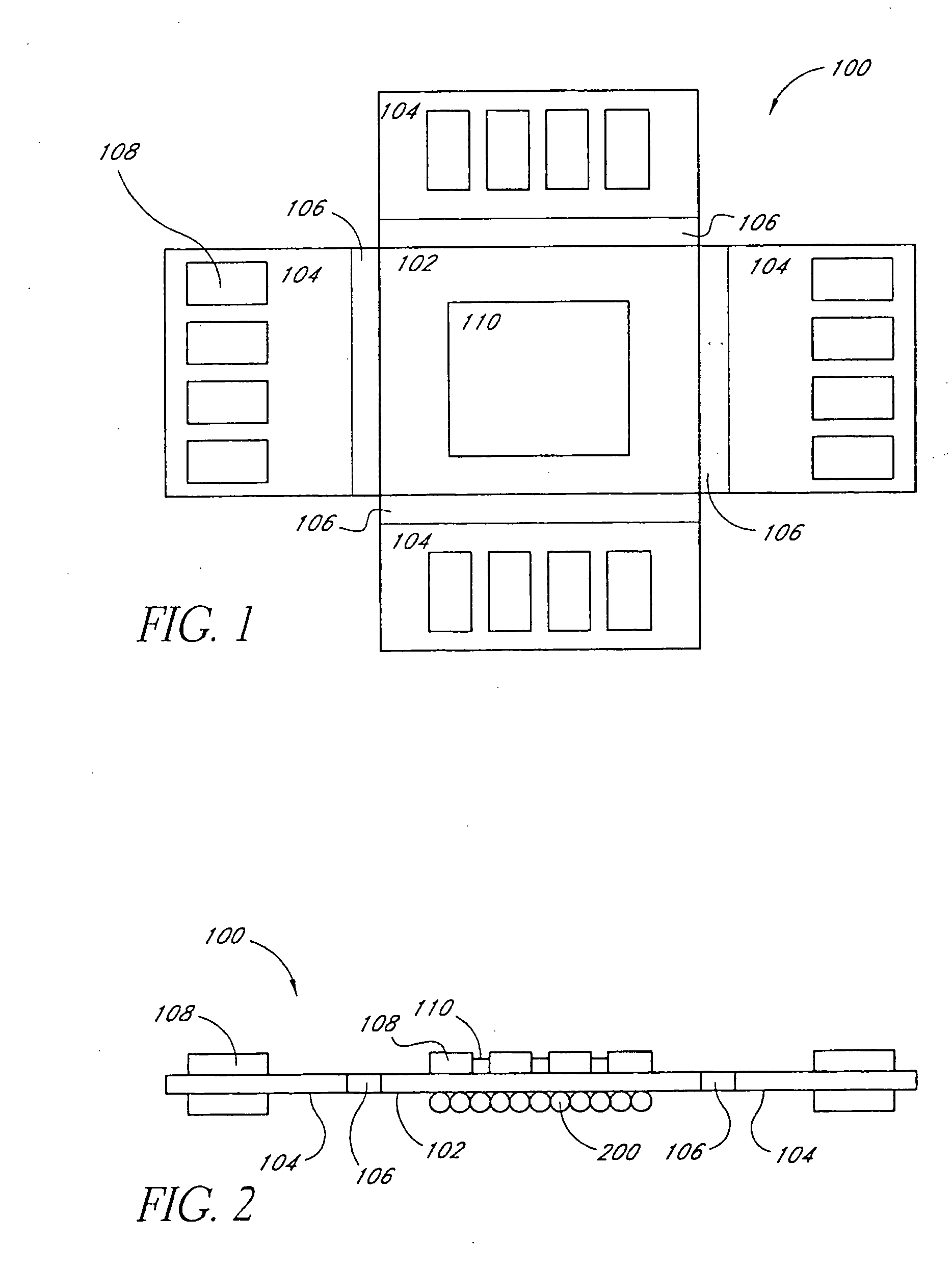

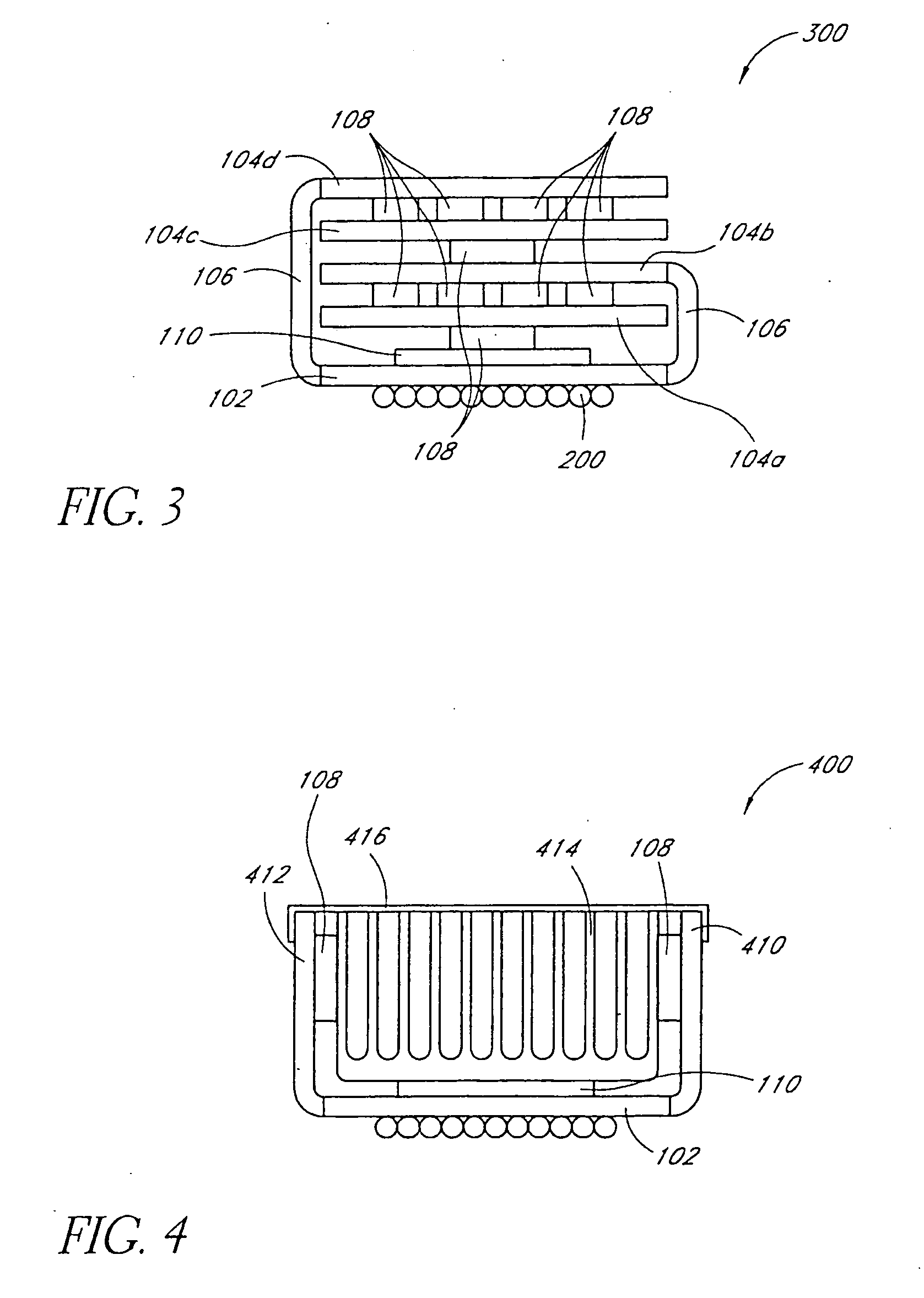

Processor/memory module with foldable substrate

InactiveUS20060209515A1Save spaceHigh densitySemiconductor/solid-state device detailsSolid-state devicesComputer moduleEngineering

A packaging approach reduces the overall footprint for interconnecting multiple semiconductor devices. In an embodiment, a processor mounts onto the center of a substrate with flexible appendages and memory components mount to the flexible appendages. The appendages fold over the processor to produce a processor / memory module. The processor / memory module occupies less area on the main printed circuit board than the laterally interconnected processor and memory devices would occupy.

Owner:MOSHAYEDI MARK

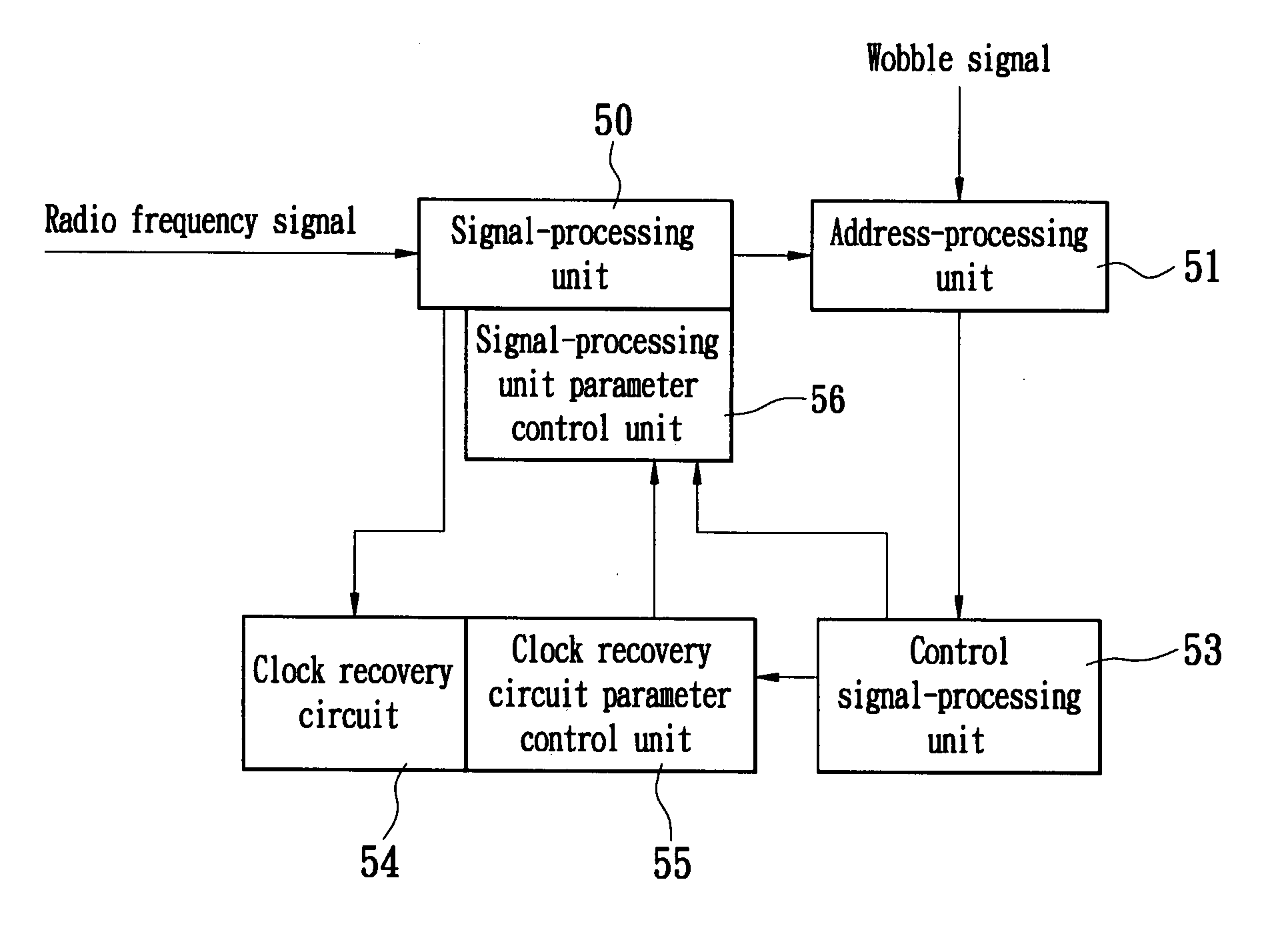

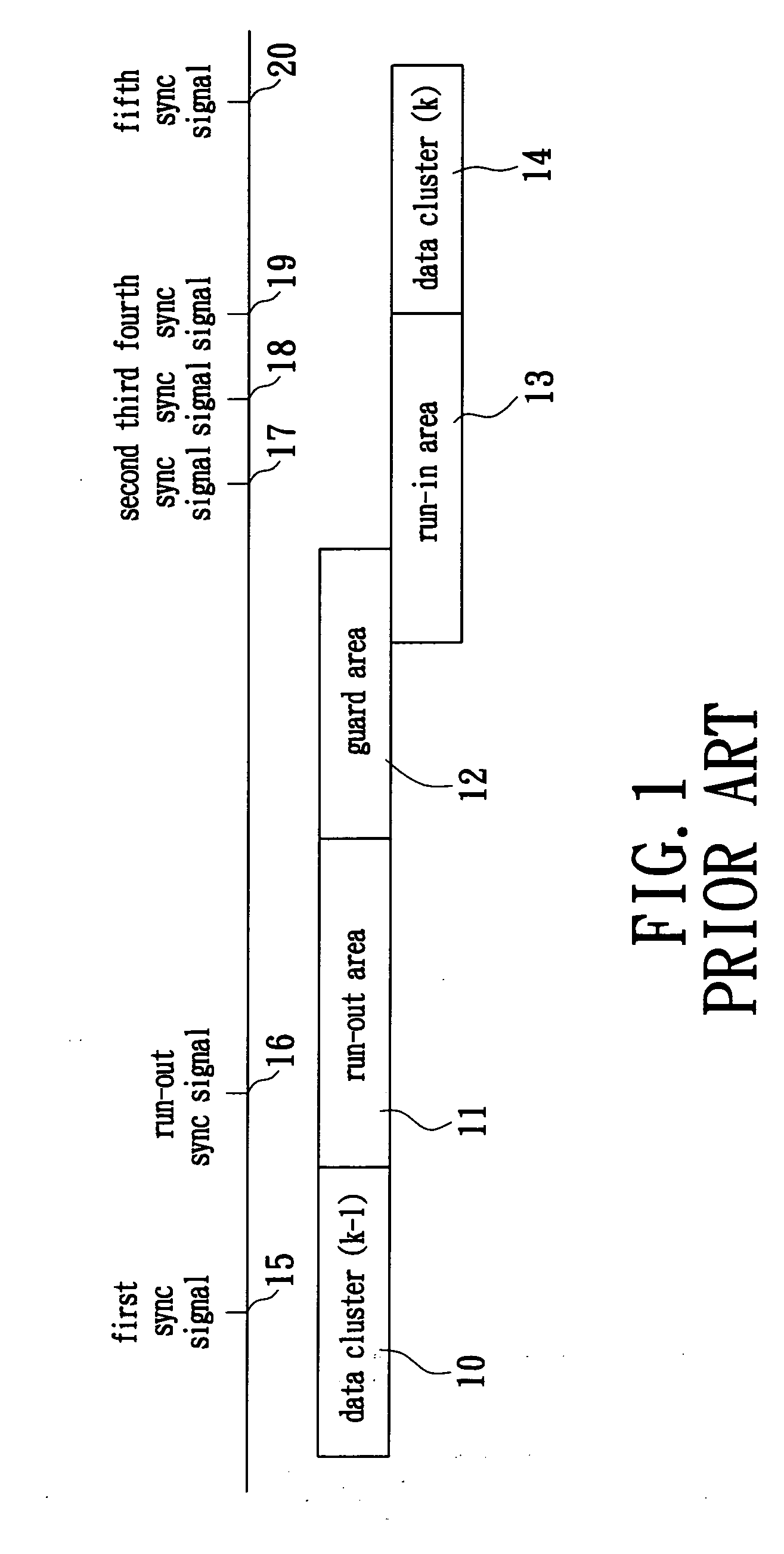

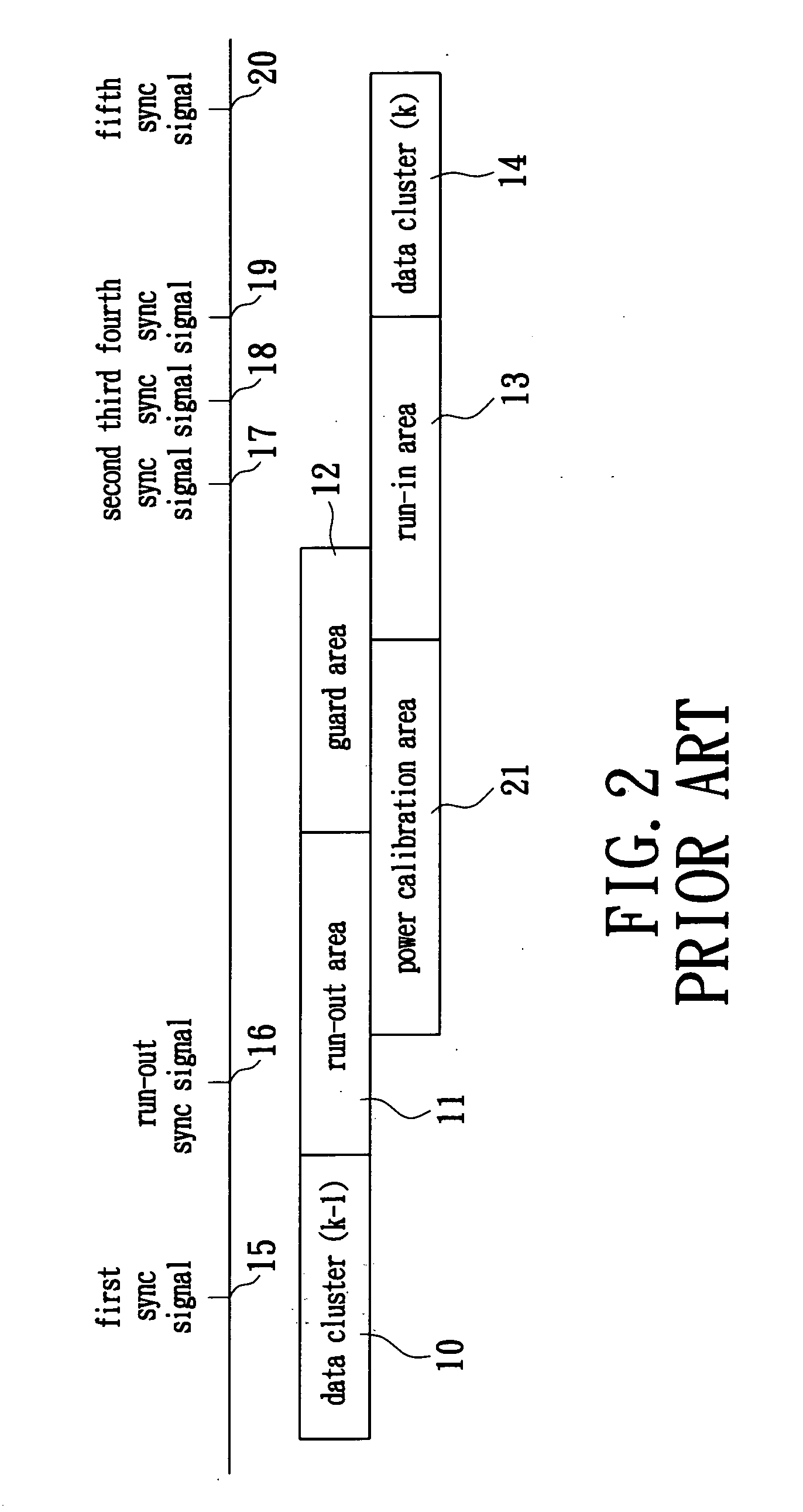

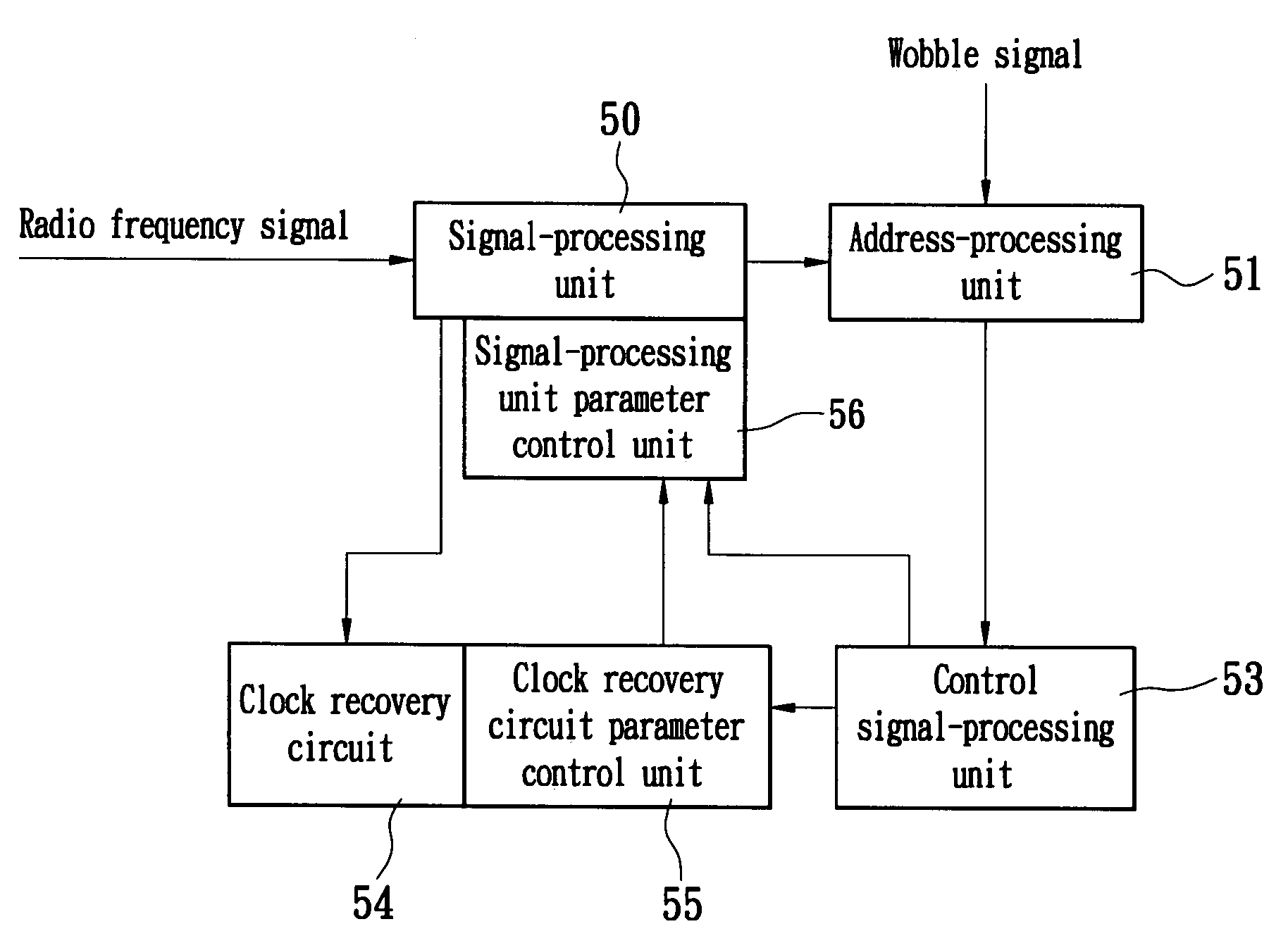

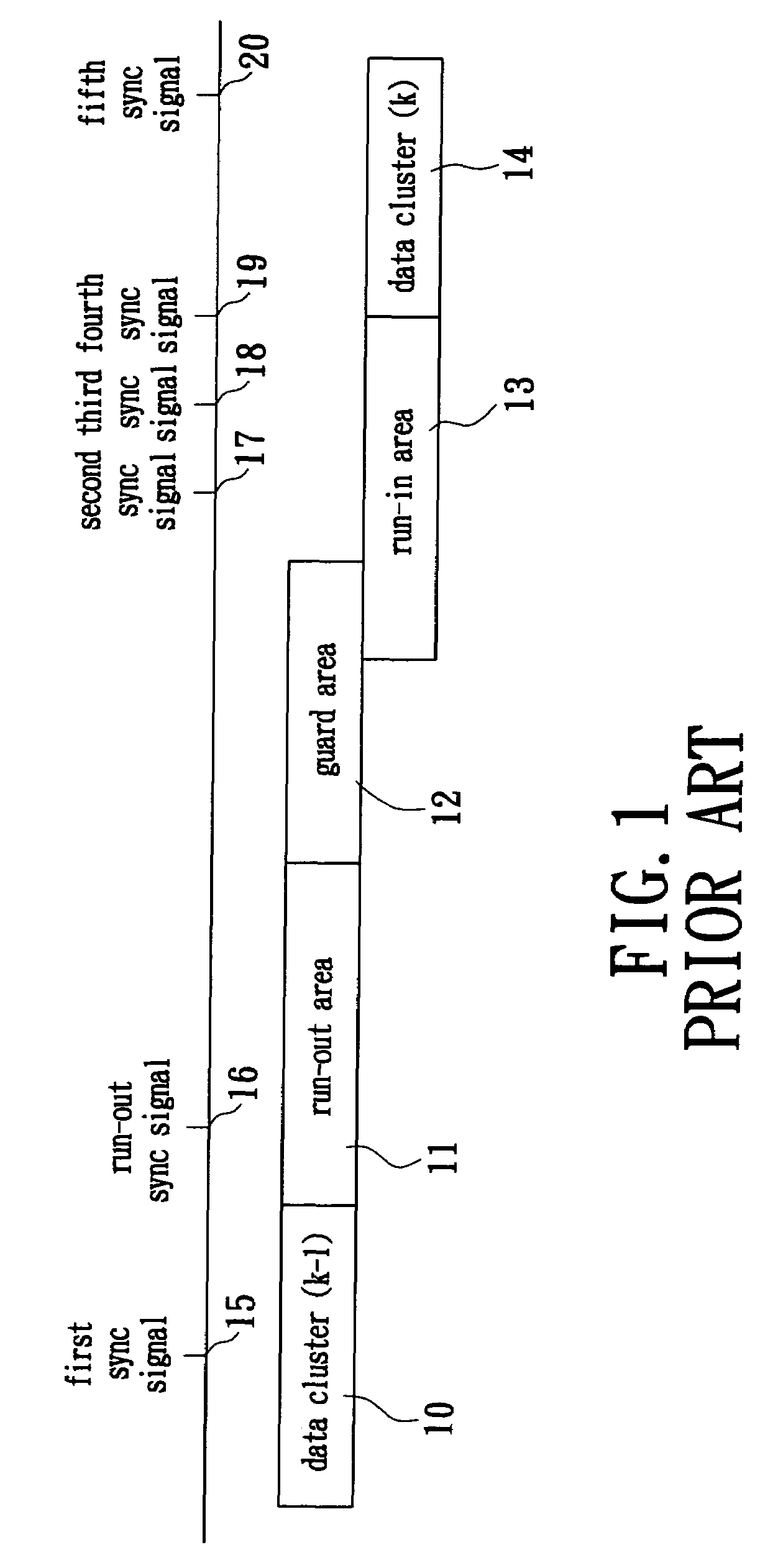

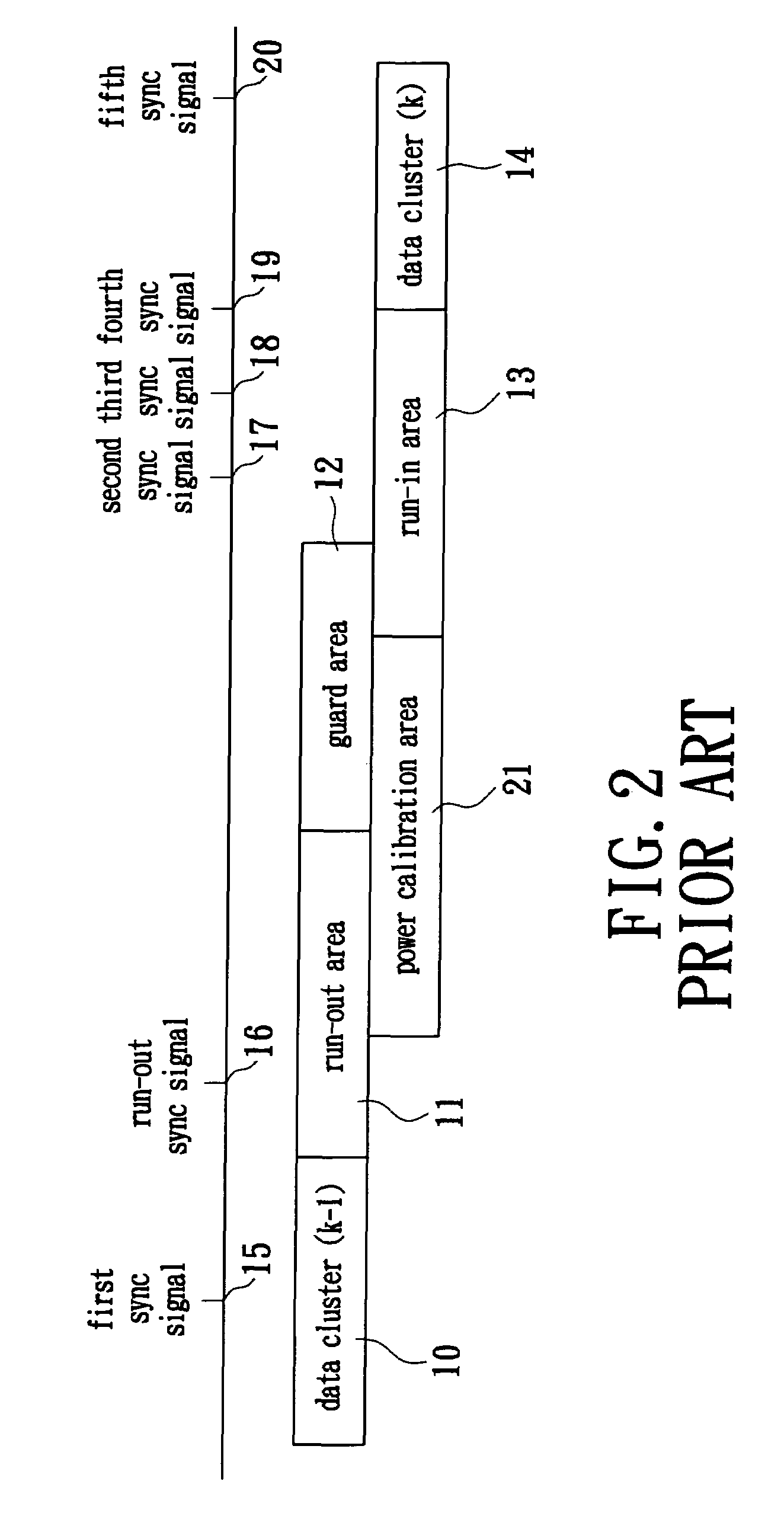

Apparatus for controlling discrete data in disk overwrite area or power calibration area

InactiveUS20070140081A1Increase convergent speed of circuitEnhanced control signalModification of read/write signalsFilamentary/web record carriersData controlControl signal

An apparatus for controlling discrete data in a disk overwrite area or a power calibration area comprises a signal-processing unit, an address-processing unit, a control signal-processing unit, a clock recovery circuit, a signal-processing unit parameter control unit, and a clock recovery circuit parameter control unit, wherein the control signal-processing unit uses a message produced by a data on the disc to determine the control signals such as hold, load, or increasing bandwidth for holding, loading, and increasing the bandwidth of the parameters for processing the related circuits (such as the circuit of the signal-processing unit or the clock recovery circuit) of the discrete data produced between the two data clusters, so as to increase the convergent speed of the circuits for assuring the accuracy of reading data.

Owner:MEDIATEK INC

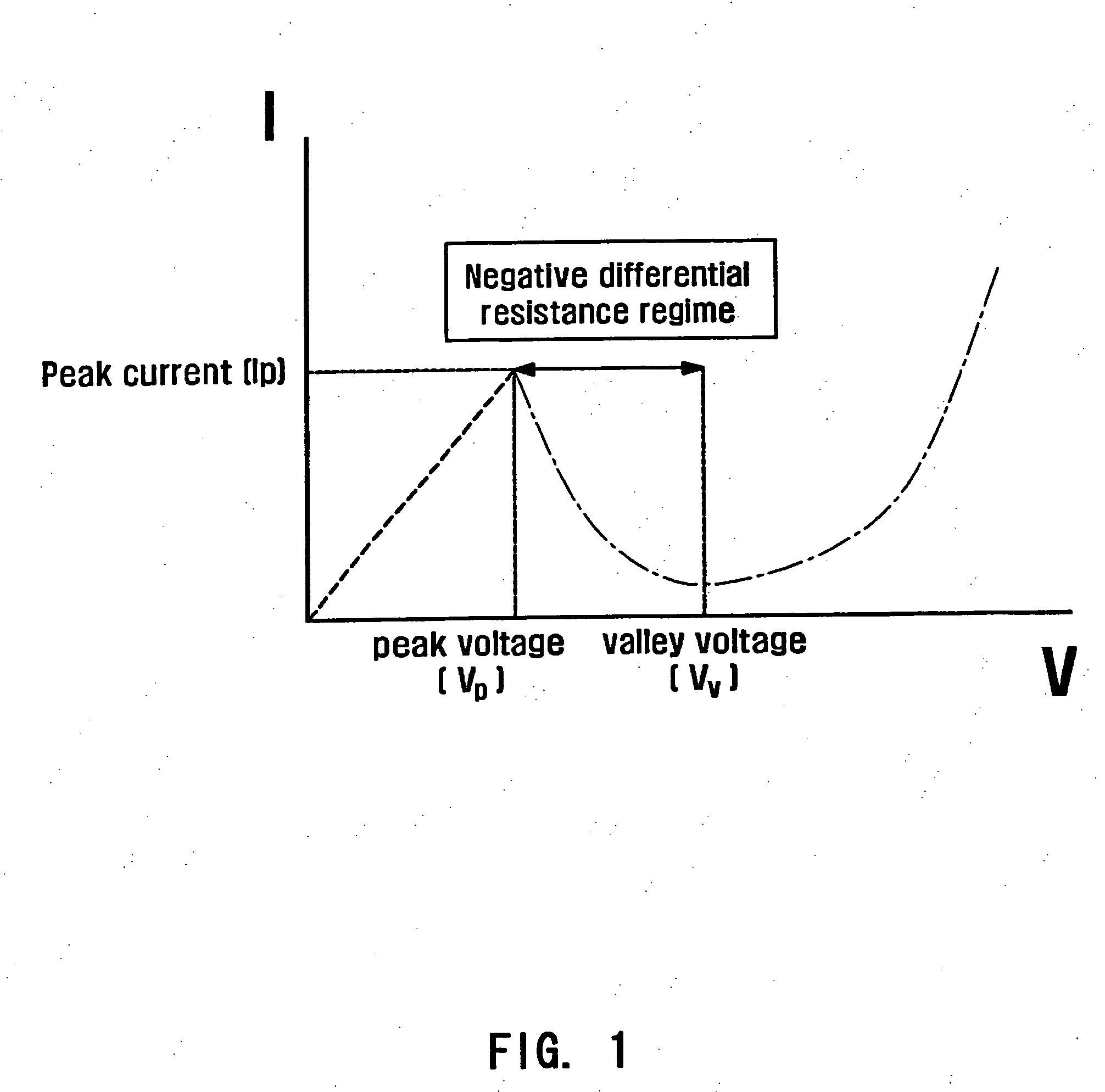

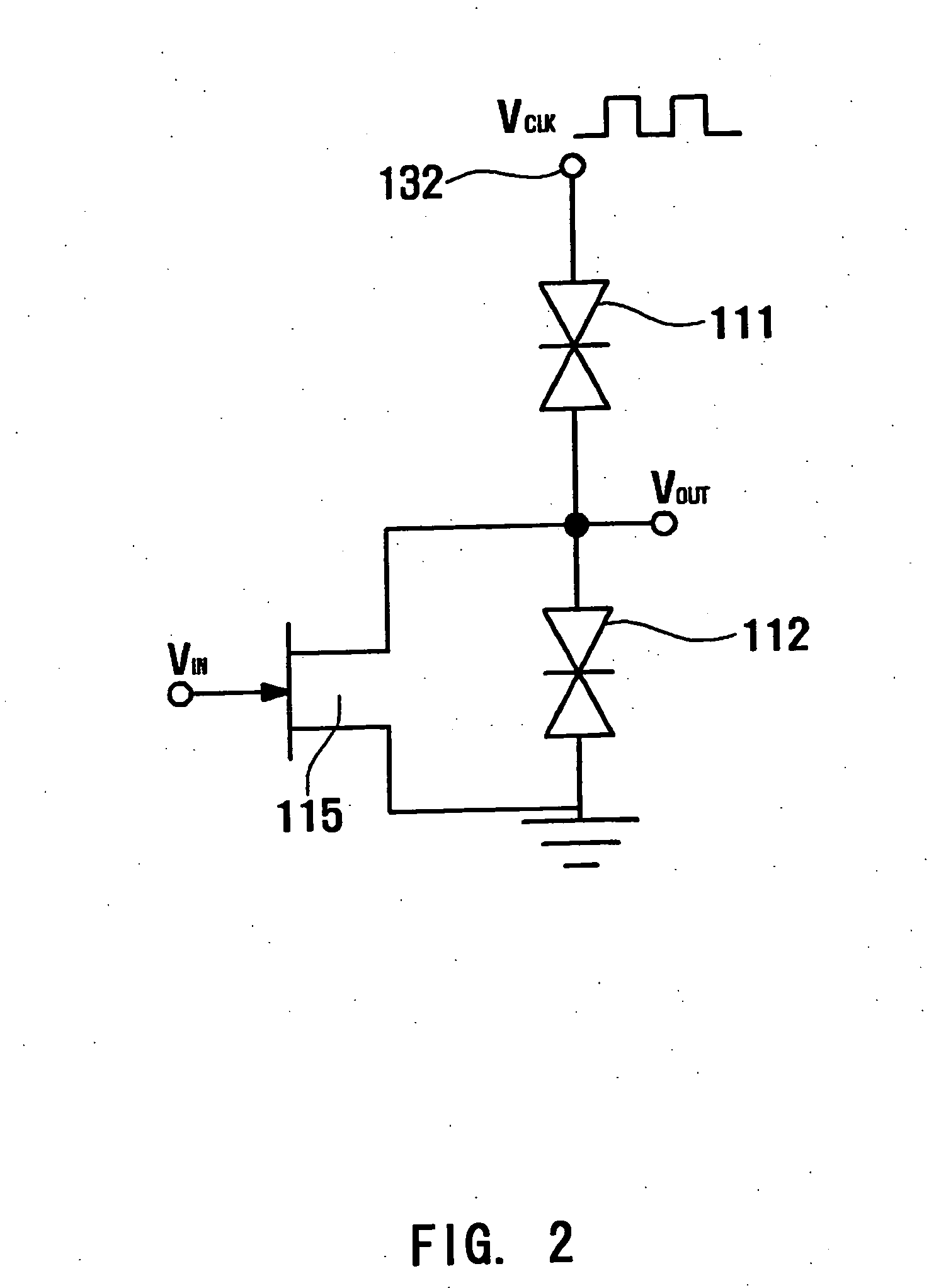

Tunneling diode logic IC using CML-type input driving circuit configuration and monostable bistable transition logic element (MOBILE)

InactiveUS20060132168A1Improve compatibilityIncrease circuit speedLogic circuits characterised by logic functionNanoinformaticsDriver circuitTunnel diode

The present invention relates to CML(Current Mode Logic)-type input driving method and tunneling diode logic using MOBILE(Monostable Nistable transition Logic Element) configuration, as kinds of very high-speed digital logic circuits. The objectives of the present invention are to improve the disadvantage of MOBILE circuit configuration that is an existing tunneling diode logic, and at the same time provide new MOBILE based logic functions. Wherein, the difficulty for input voltage adjustment is resolved by replacing the input part with a CML input driving gate, and speed problem due to transistor is resolved. Moreover, a plurality of logic functions such as inverted return-to-zero D flip-flop, non-inverted return-to-zero D flip-flop, return-to-zero OR gate, return-to-zero D flip-flop generating differential output, and optical flip-flop are implemented.

Owner:KOREA ADVANCED INST OF SCI & TECH

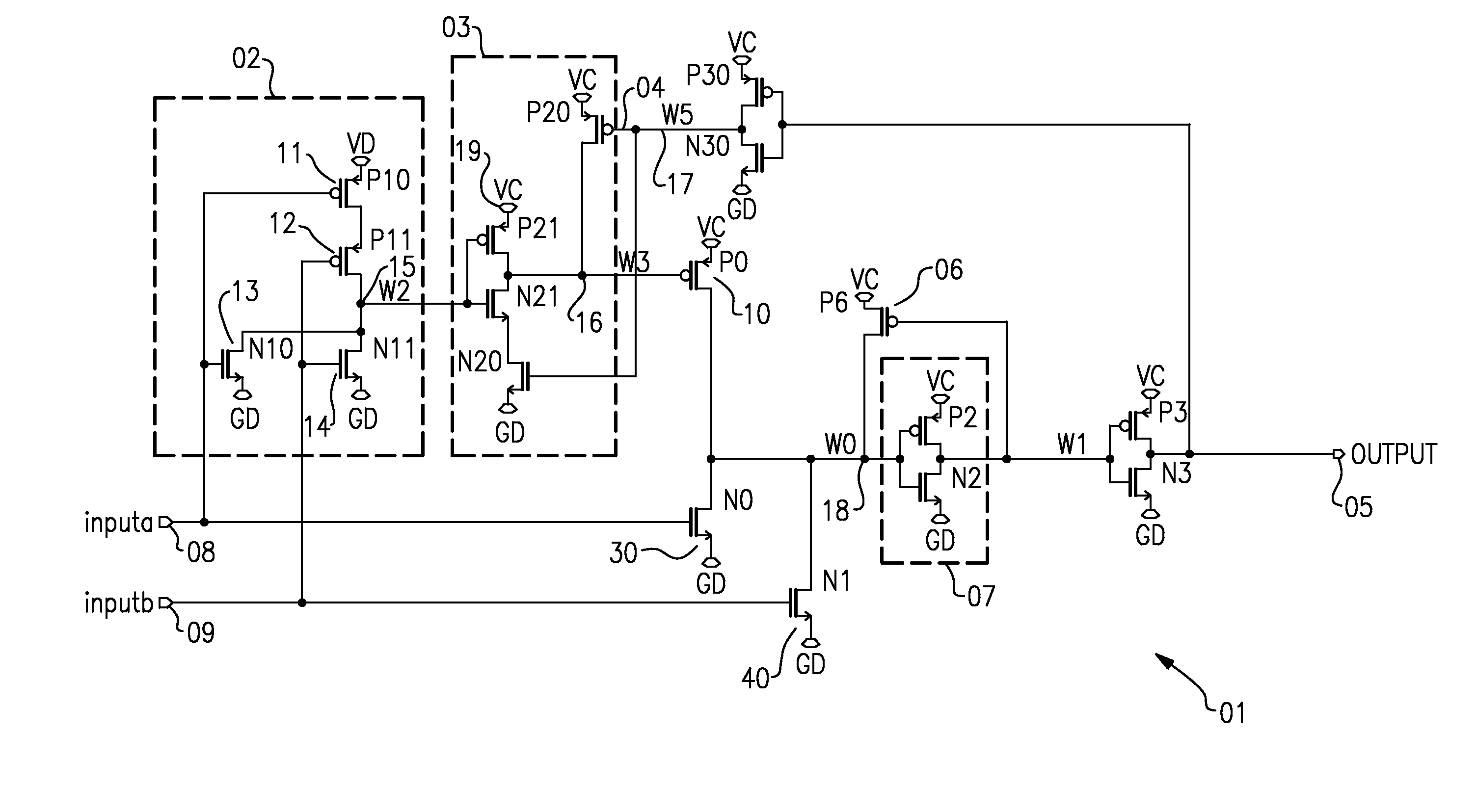

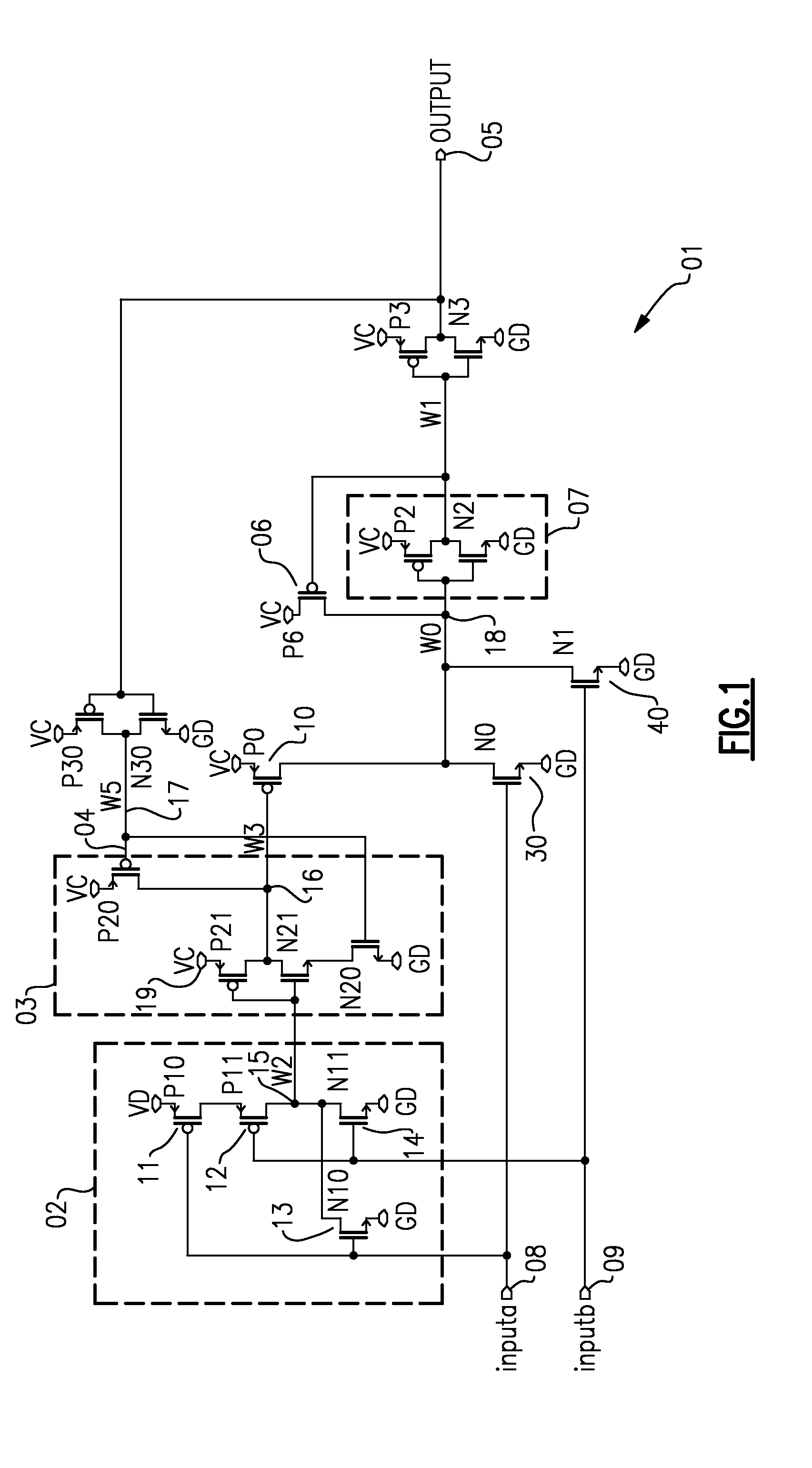

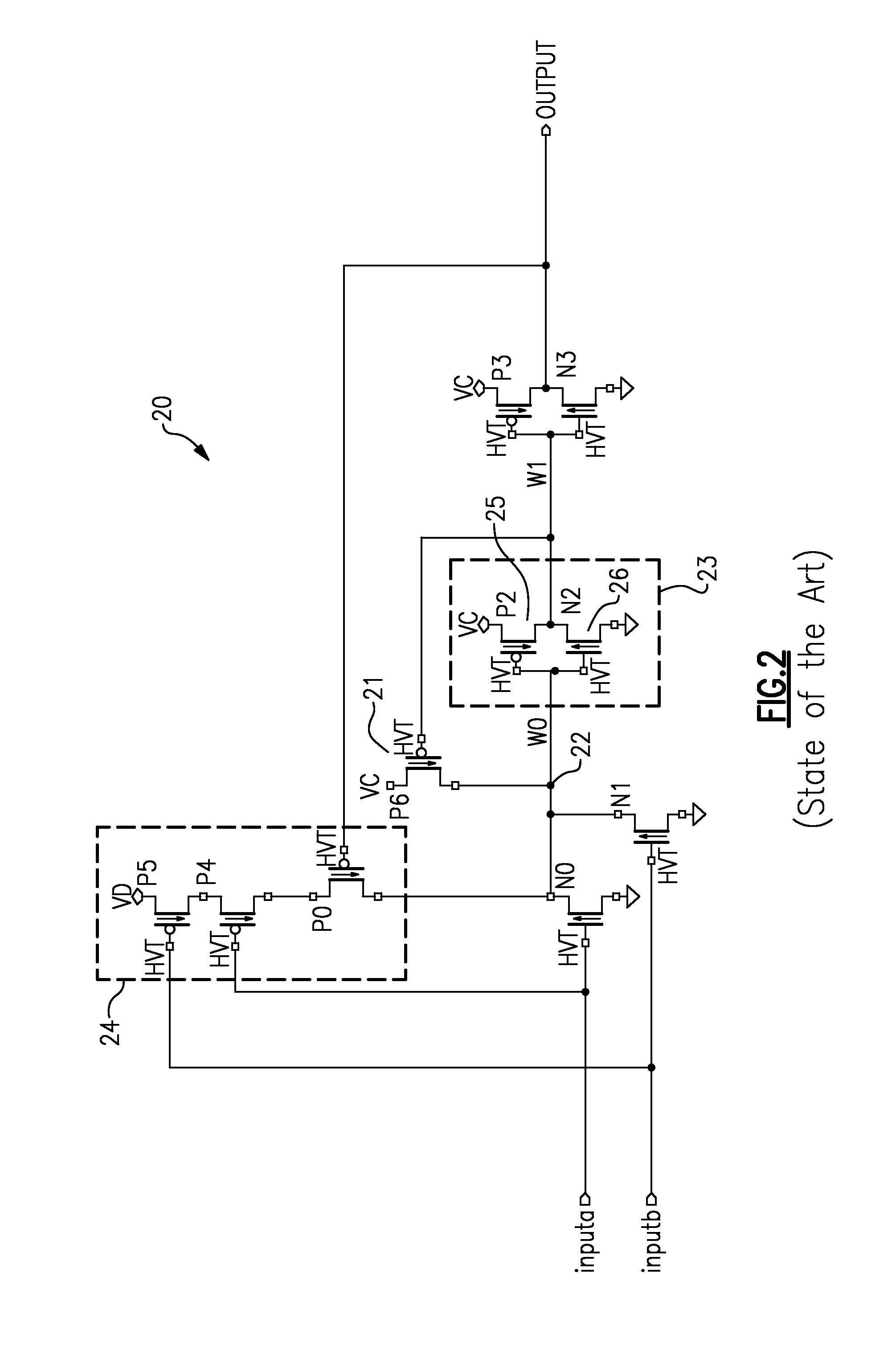

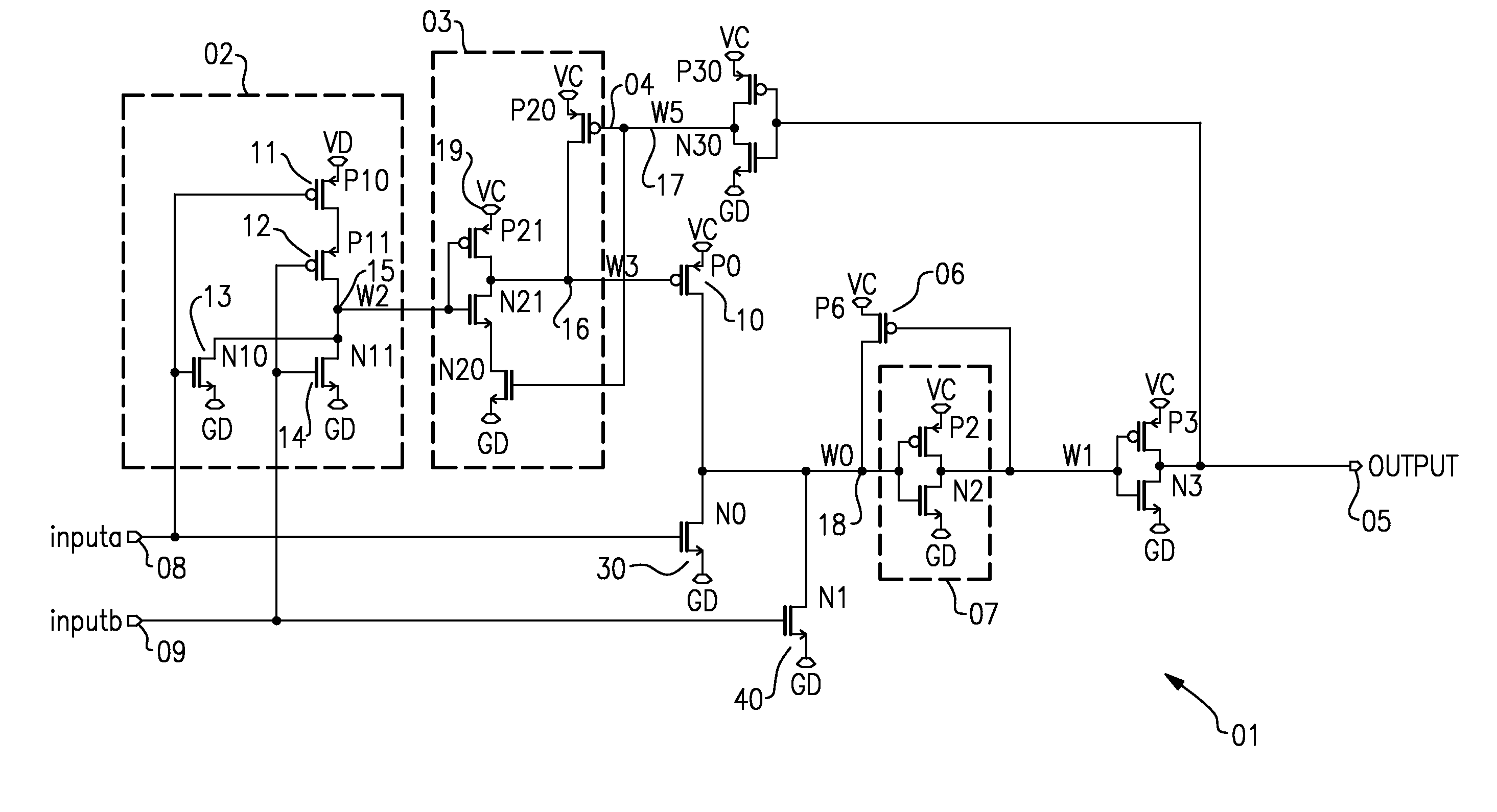

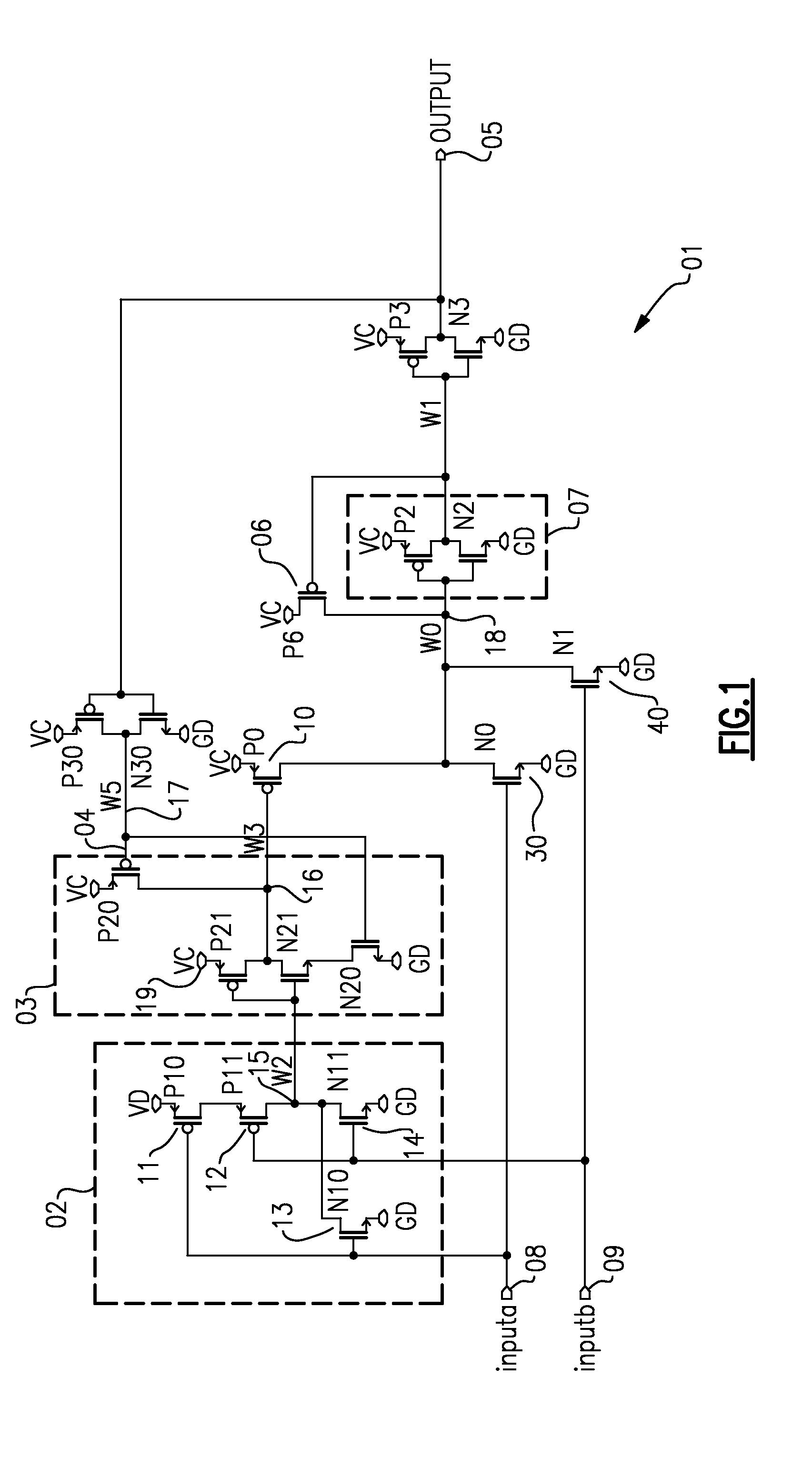

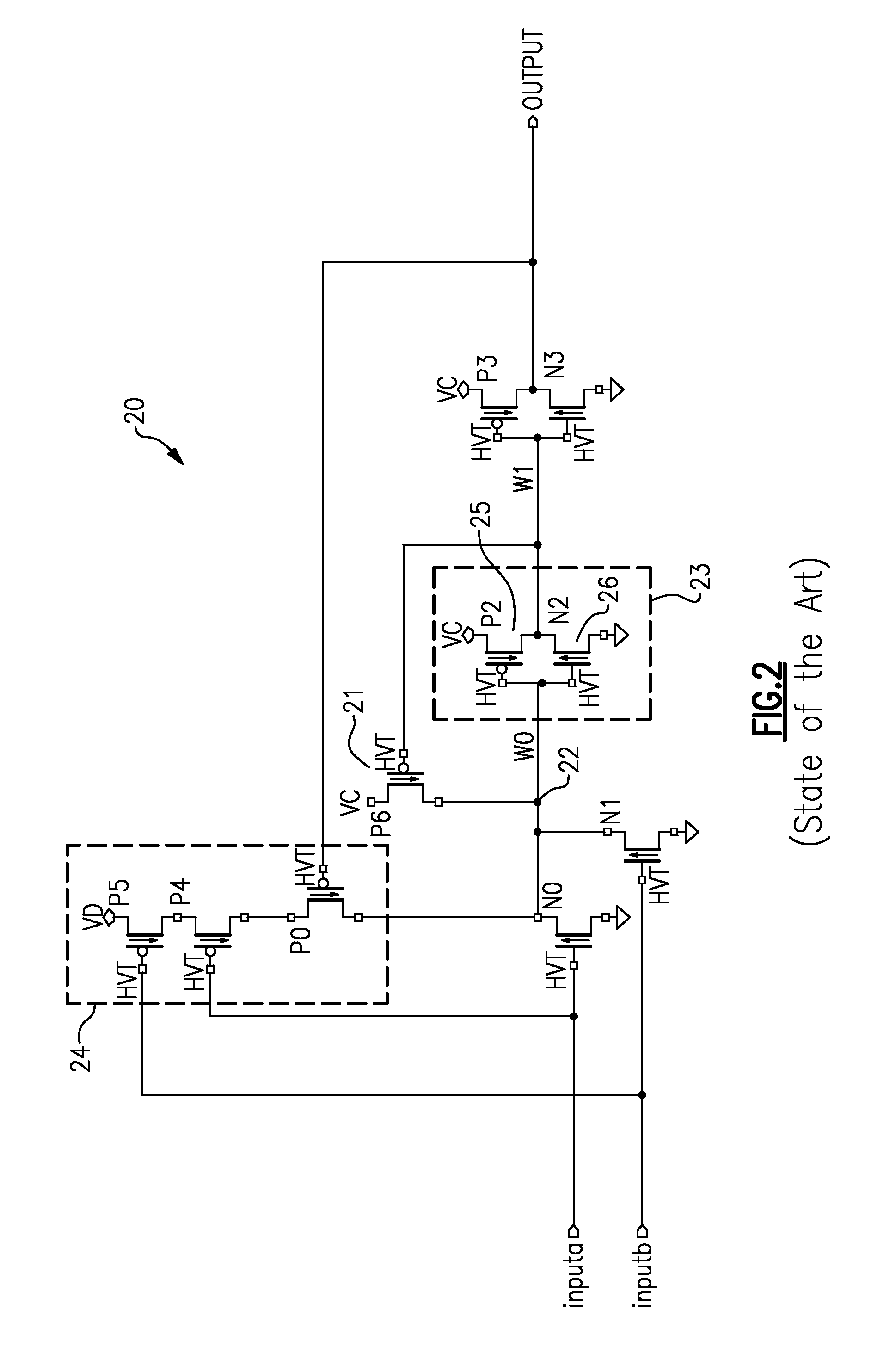

Circuit Combining Level Shift Function with Gated Reset

InactiveUS20090058465A1Simplify logic functionsReduce in quantityPower reduction in field effect transistorsLogic circuits coupling/interface using field-effect transistorsLow voltageEngineering

A circuit (01) combining level shift function with gated reset is described, performing a simple logic function with inputs supplied from a lower voltage (VD) and a drive out at its output (05) with a higher voltage (VC). Said circuit (01) comprises a gated reset scheme plus devices (10, 30, 40) for logic function.

Owner:IBM CORP

Apparatus for controlling discrete data in disk overwrite area or power calibration area

InactiveUS7885154B2Increase convergent speed of circuitIncrease speedModification of read/write signalsFilamentary/web record carriersControl signalClock recovery

An apparatus for controlling discrete data in a disk overwrite area or a power calibration area comprises a signal-processing unit, an address-processing unit, a control signal-processing unit, a clock recovery circuit, a signal-processing unit parameter control unit, and a clock recovery circuit parameter control unit, wherein the control signal-processing unit uses a message produced by a data on the disc to determine the control signals such as hold, load, or increasing bandwidth for holding, loading, and increasing the bandwidth of the parameters for processing the related circuits (such as the circuit of the signal-processing unit or the clock recovery circuit) of the discrete data produced between the two data clusters, so as to increase the convergent speed of the circuits for assuring the accuracy of reading data.

Owner:MEDIATEK INC

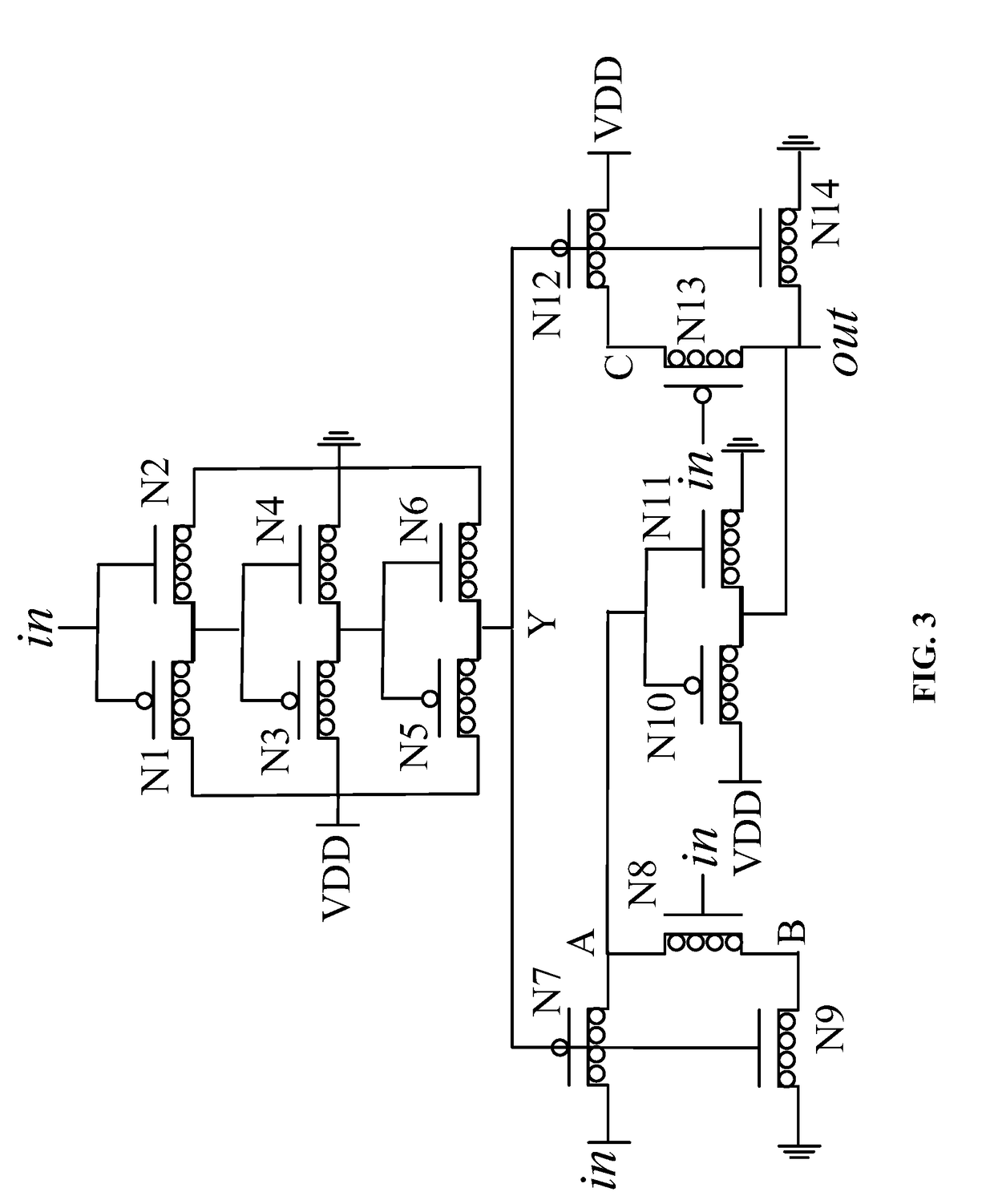

Carbon nanotube field effect transistor-based pulse generator

ActiveUS20170117881A1Minimum input-output time delayEliminating short circuit power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingCarbon nanotube field-effect transistorPhysics

A CNFET based pulse generator, including a first Carbon Nanotube Field Effect Transistor (CNFET), a second CNFET, a third CNFET, a fourth CNFET, a fifth CNFET, a sixth CNFET, a seventh CNFET, an eighth CNFET, a ninth CNFET, a tenth CNFET, an eleventh CNFET, a twelfth CNFET, a thirteenth CNFET, and a fourteenth CNFET. The first CNFET, the third CNFET, the fifth CNFET, the seventh CNFET, the tenth CNFET, the twelfth CNFET, and the thirteenth CNFET are P-type CNFETs. The second CNFET, the fourth CNFET, the sixth CNFET, the eighth CNFET, the ninth CNFET, the eleventh CNFET, and the fourteenth CNFET are N-type CNFETs.

Owner:NINGBO UNIV

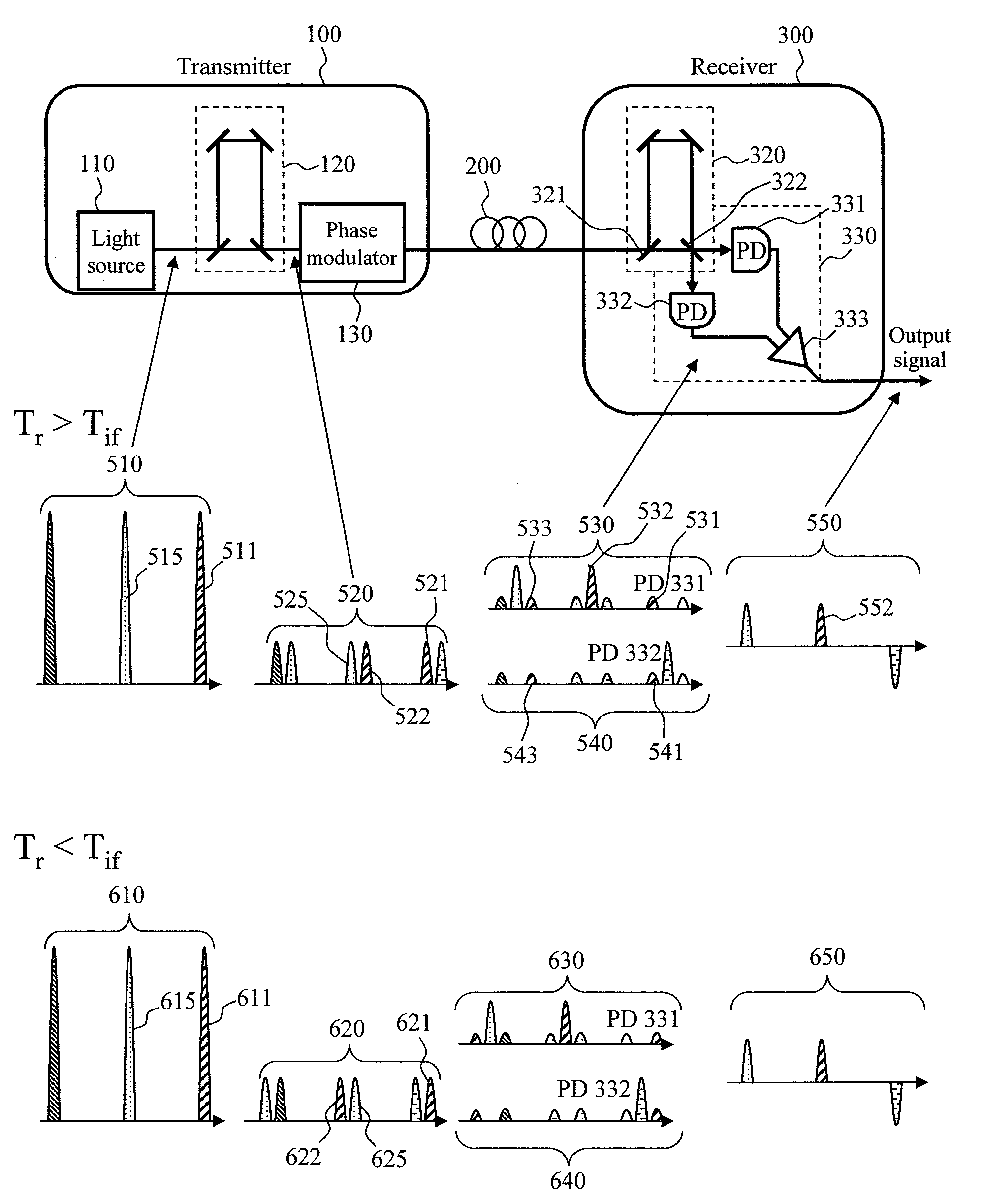

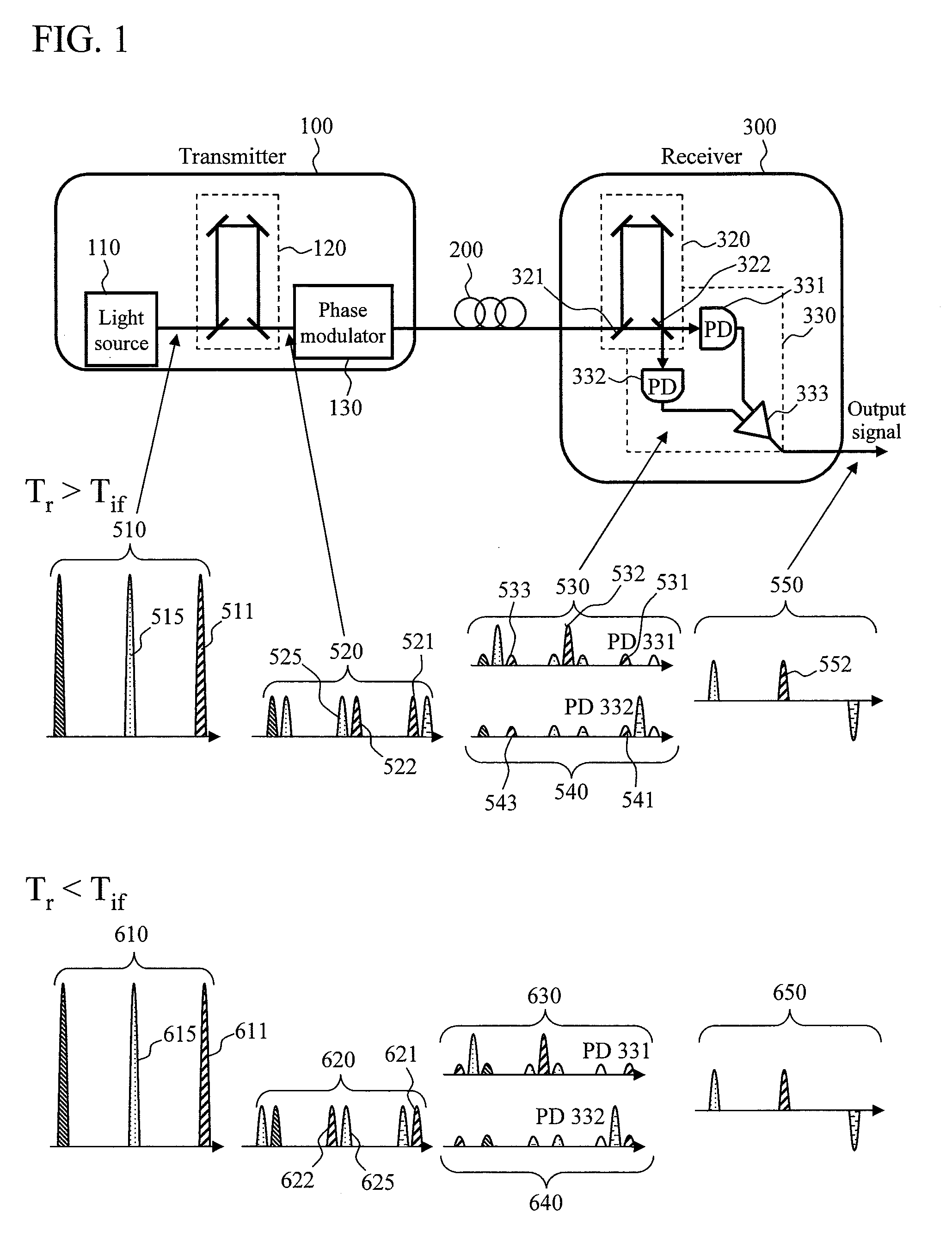

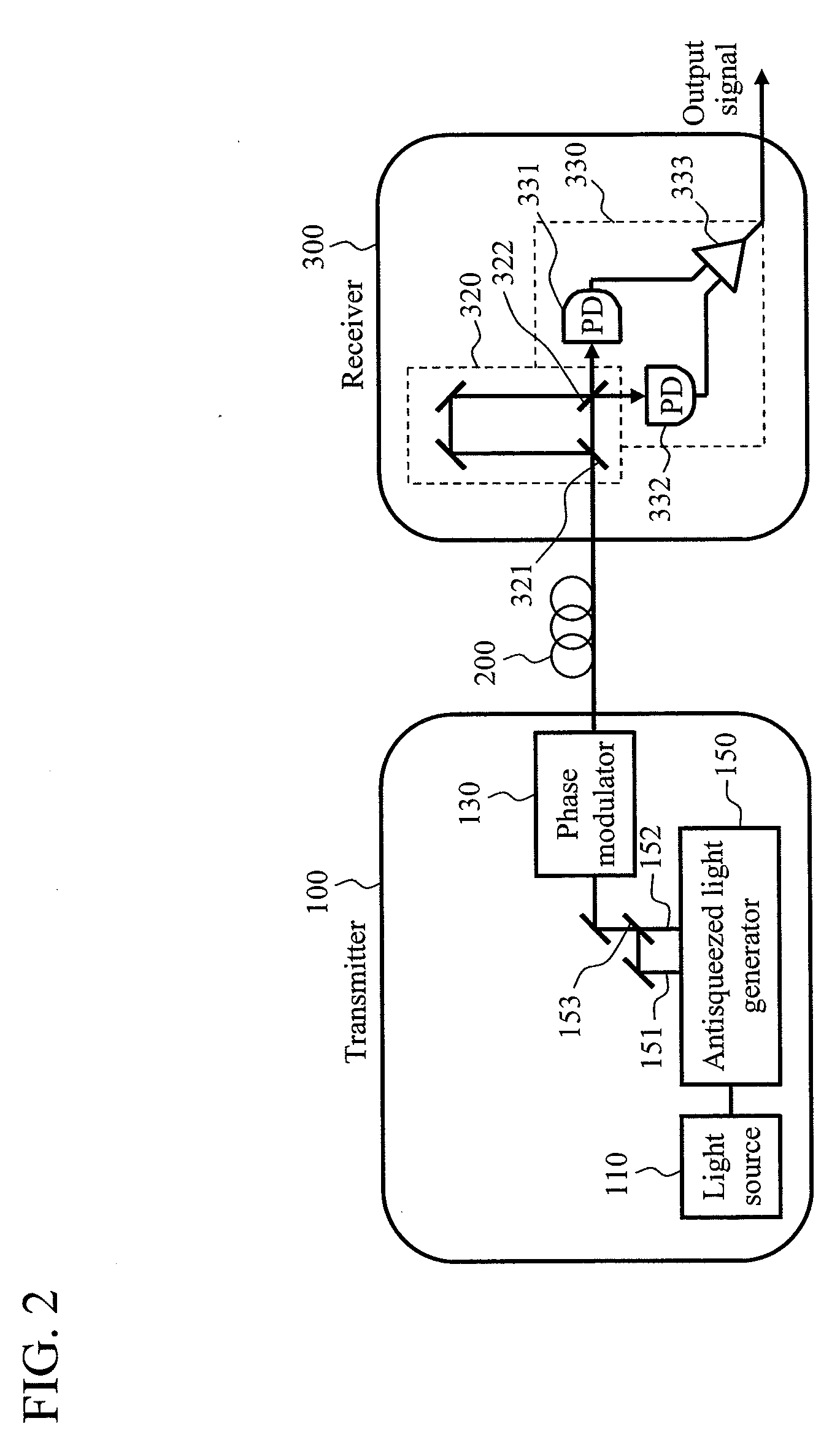

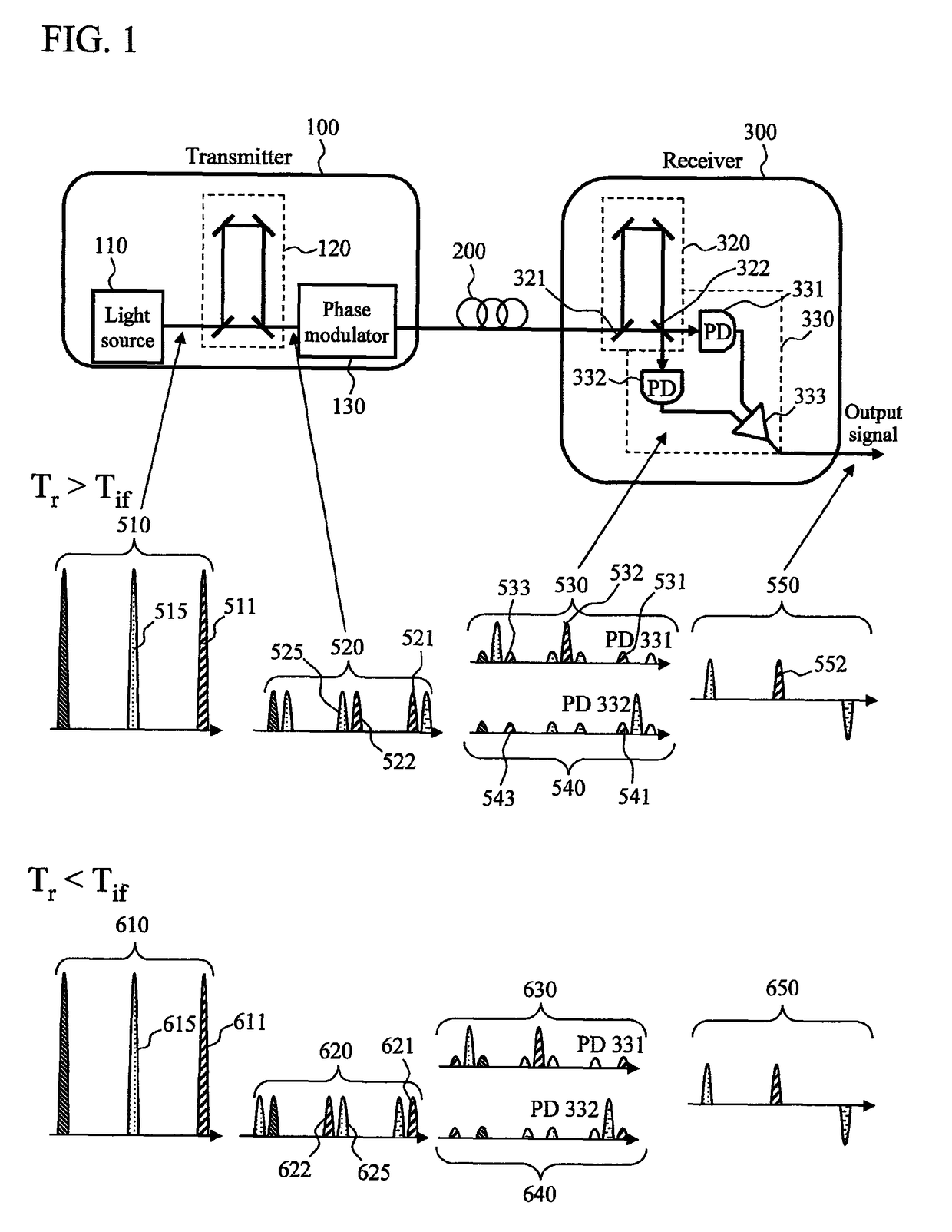

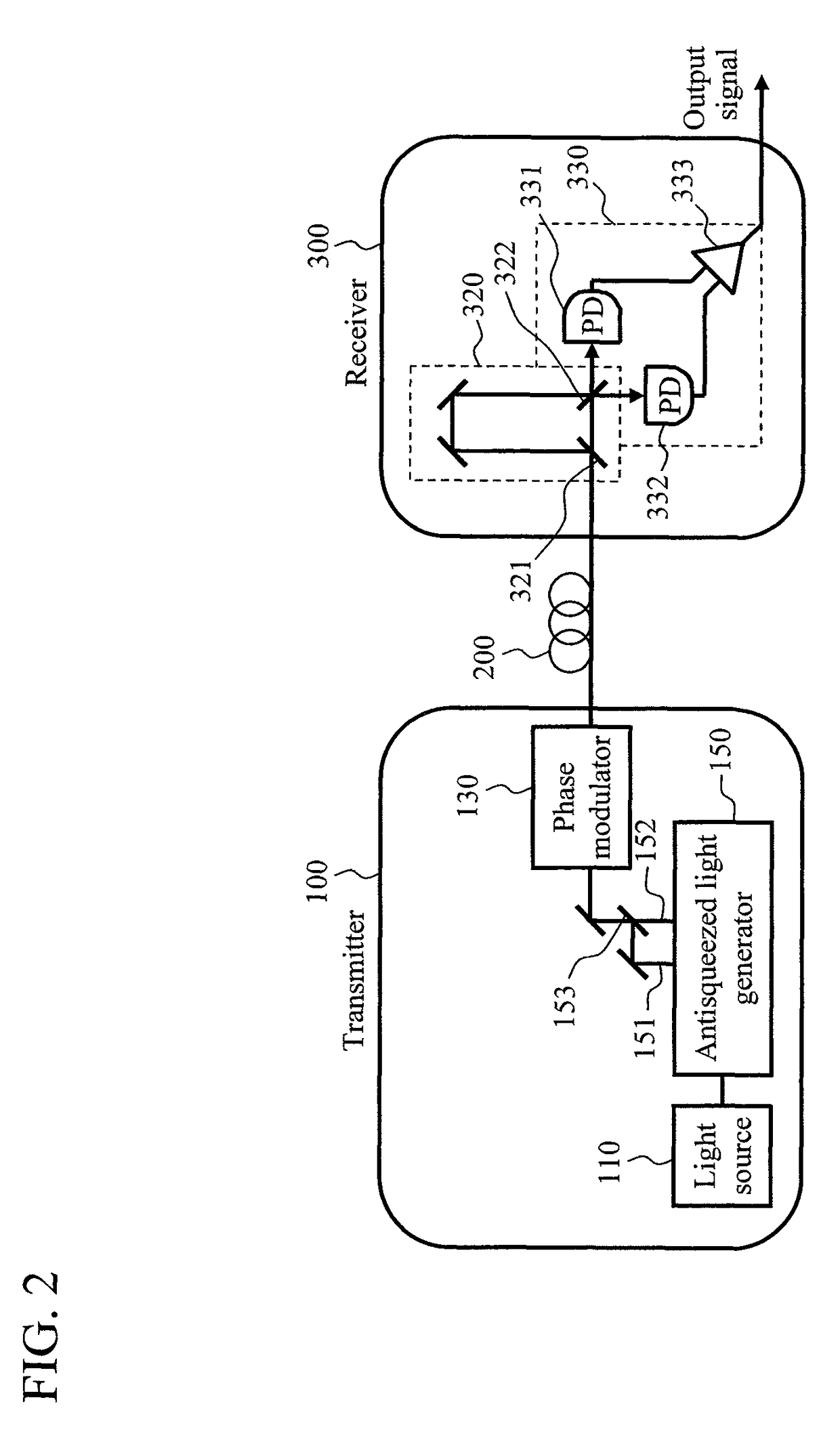

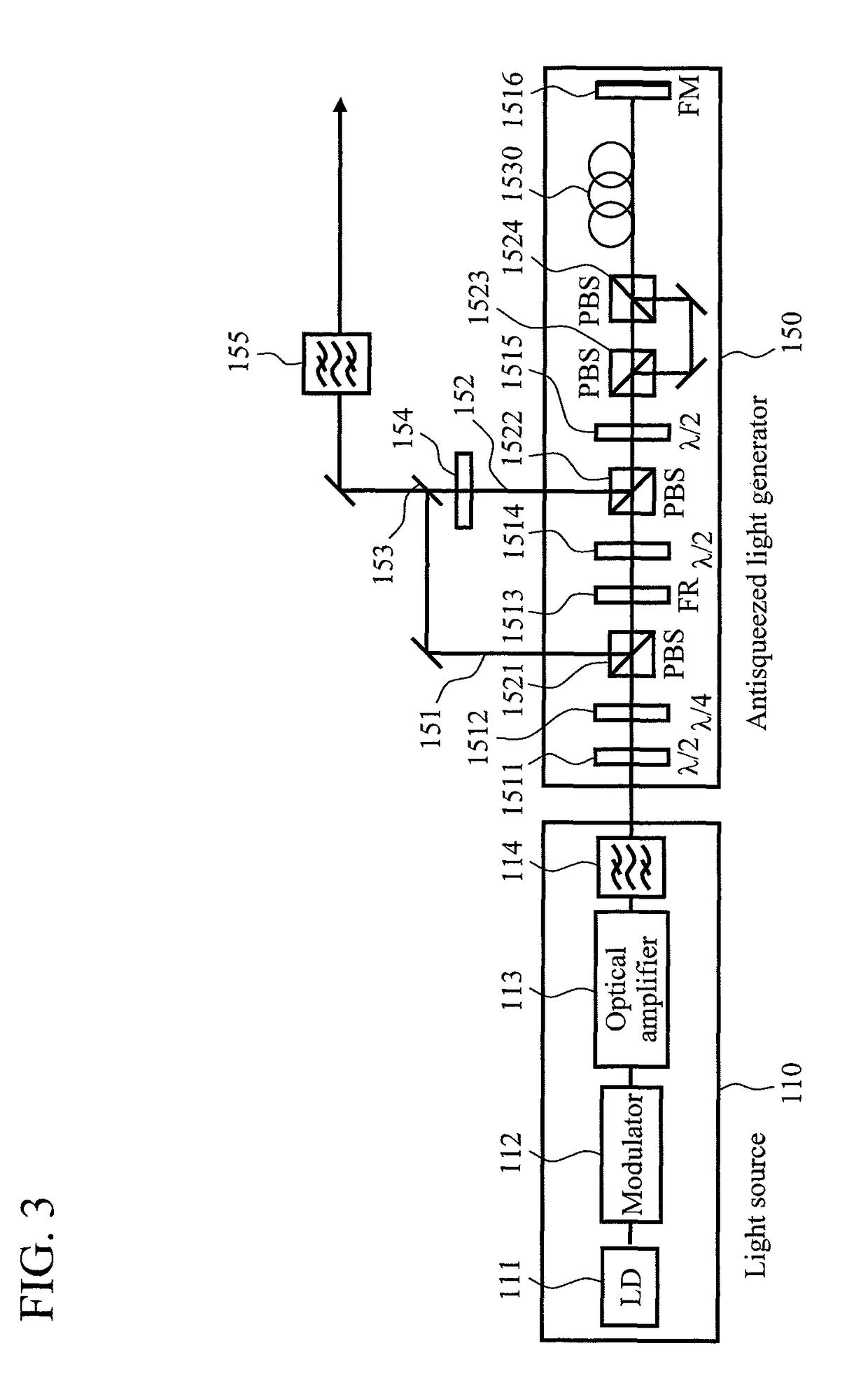

Optical transmitting and receiving system

InactiveUS20090052905A1Simple processImprove processing speedSecret communicationElectromagnetic transmission optical aspectsPhysicsDual pulse

Signals can be superimposed on optical phase even when low-coherency light is used, and a bit rate and a signal coding format similar to those used in ordinary optical communications can be used. A transmitter includes an asymmetric interferometer or an antisqueezed light generator to convert a train of single pulses into a train of dual pulses. A receiver also includes an asymmetric interferometer that provides the same delay time as that between the dual pulses. The receiver allows pulses originating in the same light source to interfere, so that signals can be superimposed on the phase even when a low-coherency light source is used. The delay time (optical path length difference) provided in the asymmetric interferometer is set to be longer than half the period of the pulses outputted from the optical pulse source. In the transmitter, two pulses are modulated as a unit, one of the two pulses being the rear pulse of a pair of dual pulses and the other pulse being the front pulse of the next pair of dual pulses. In the receiver, a balanced detector receives the modulated pulses, and the balanced detector only outputs interference pulses but does not output non-interference pulses.

Owner:HITACHI LTD

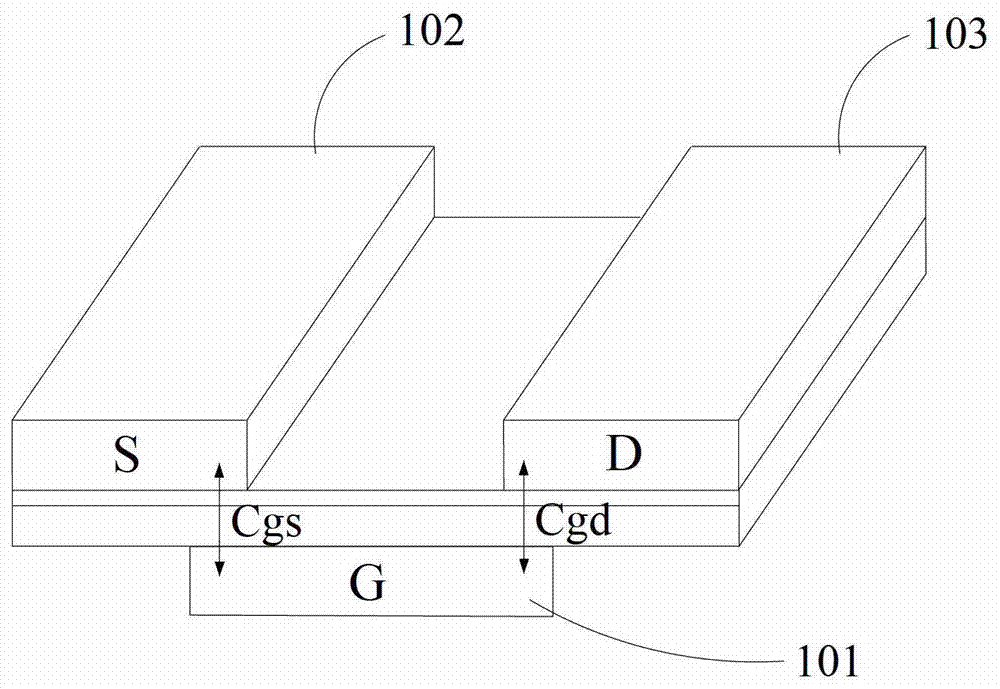

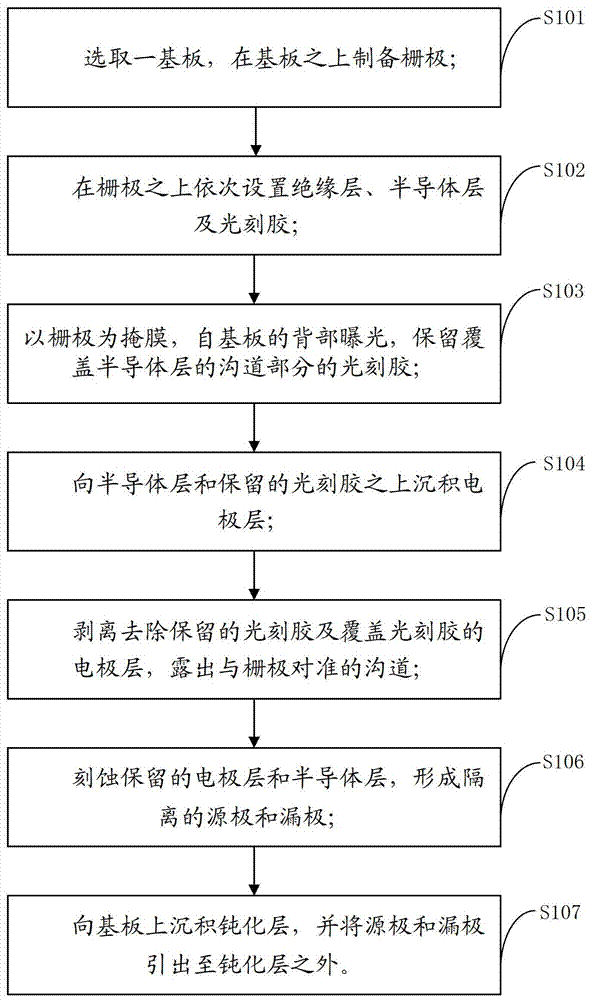

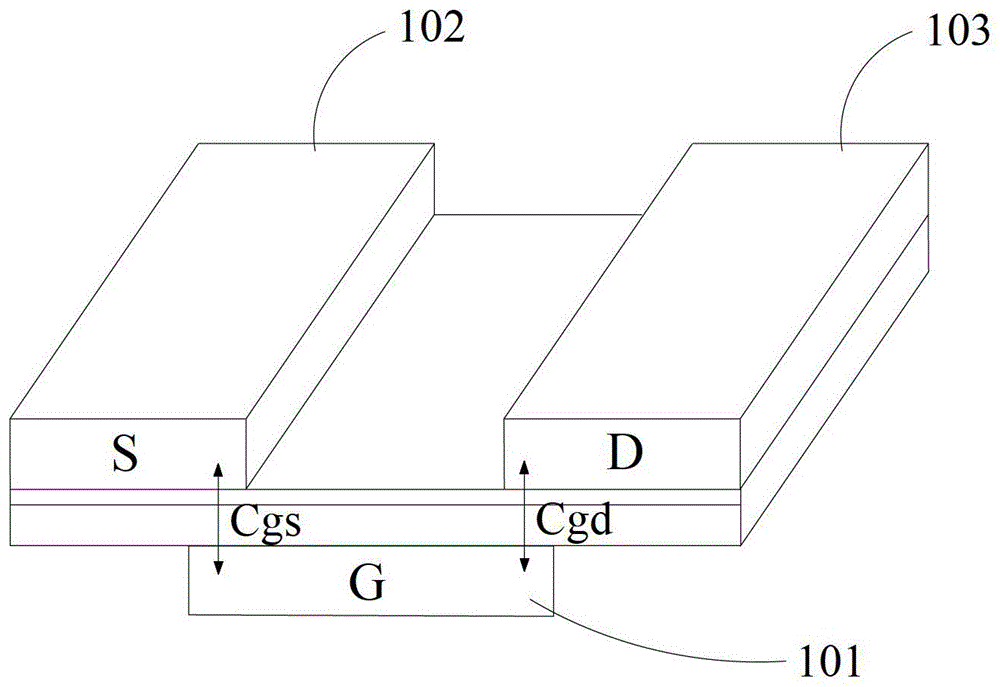

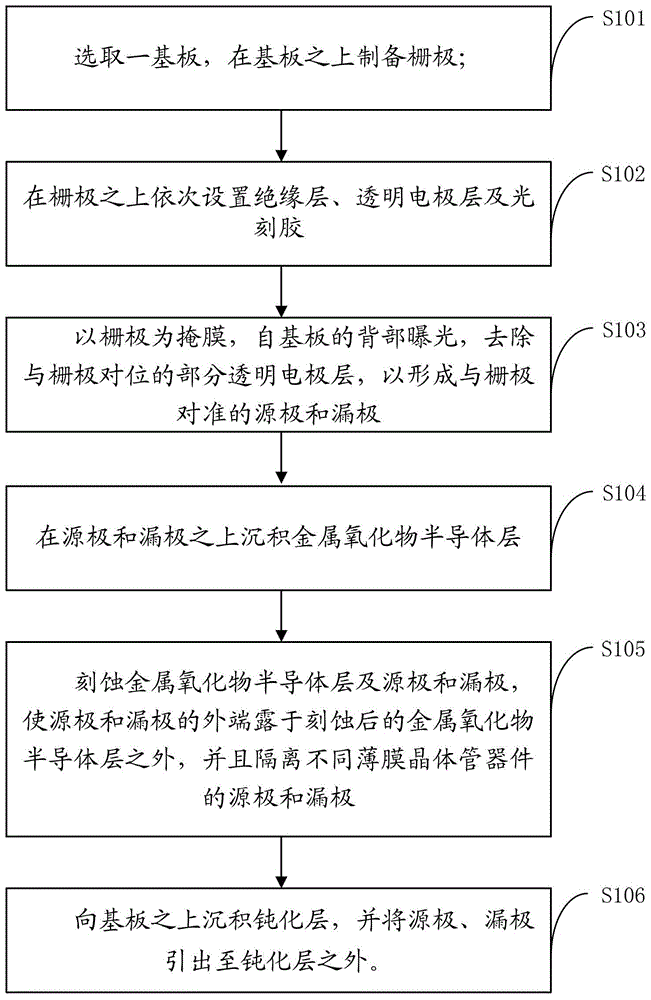

A kind of metal oxide TFT device and manufacturing method

InactiveCN104040693BImprove performanceEasy to controlTransistorSolid-state devicesParasitic capacitanceEngineering

The present invention is applicable to the technical field of electronic devices, and provides a method for manufacturing a metal oxide TFT device, comprising selecting a substrate and preparing a gate on the substrate; sequentially disposing an insulating layer, a semiconductor layer and a photoresist on the gate; The gate is a mask, which is exposed from the back of the substrate, and the photoresist covering the channel part of the semiconductor layer is retained; the electrode layer is deposited on the semiconductor layer and the photoresist; the photoresist and the electrode layer covering the photoresist are peeled off to expose channel; etch the electrode layer and semiconductor layer to form an isolated source and drain; deposit a passivation layer to lead out the source and drain. In the present invention, the gate is used as a mask to realize self-alignment through back exposure and photoresist stripping, the process is simple and the alignment accuracy is high, the parasitic capacitance is weakened, the performance of the device is improved, and no etching barrier layer is required. The process is simplified, the bad influence of the etching barrier layer on the semiconductor channel is avoided, and the alignment of the mask plate is no longer a key alignment requirement, thereby reducing the manufacturing difficulty.

Owner:SHENZHEN ROYOLE TECH CO LTD

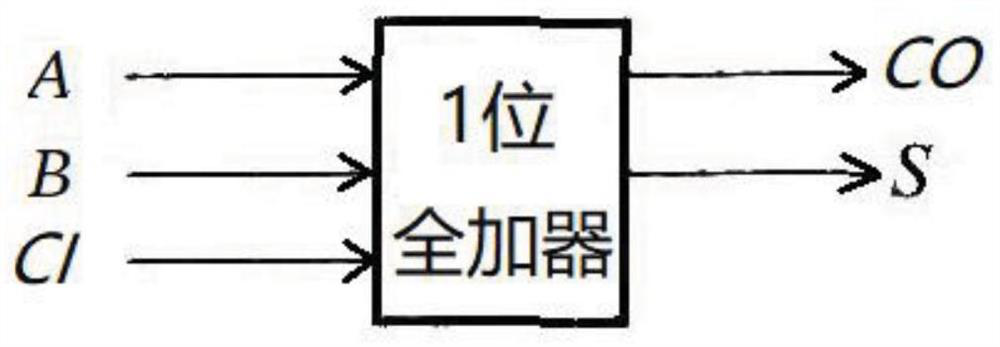

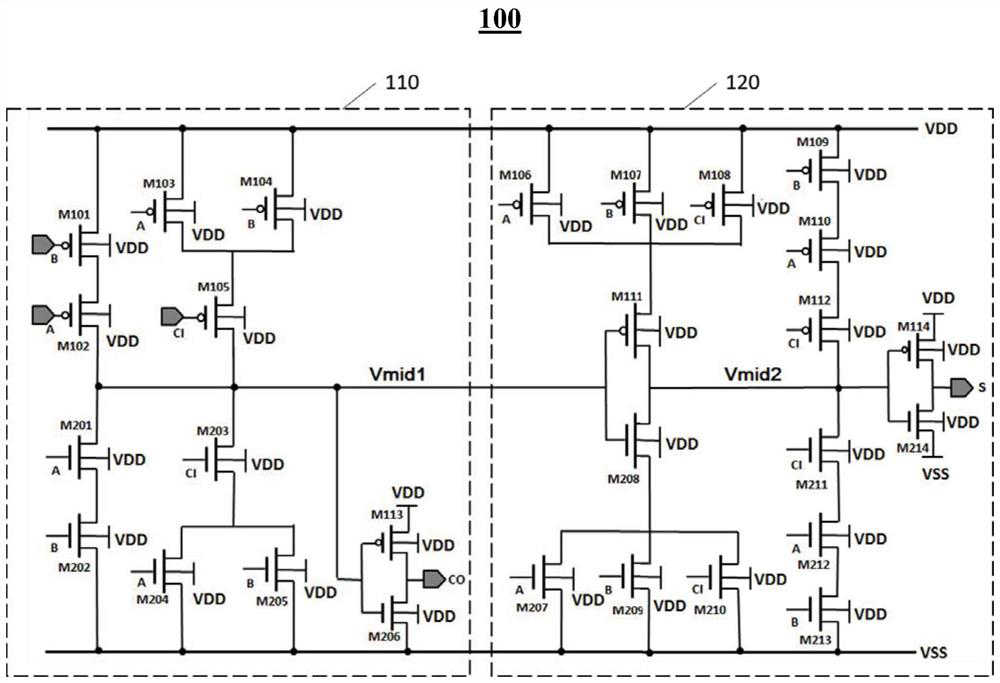

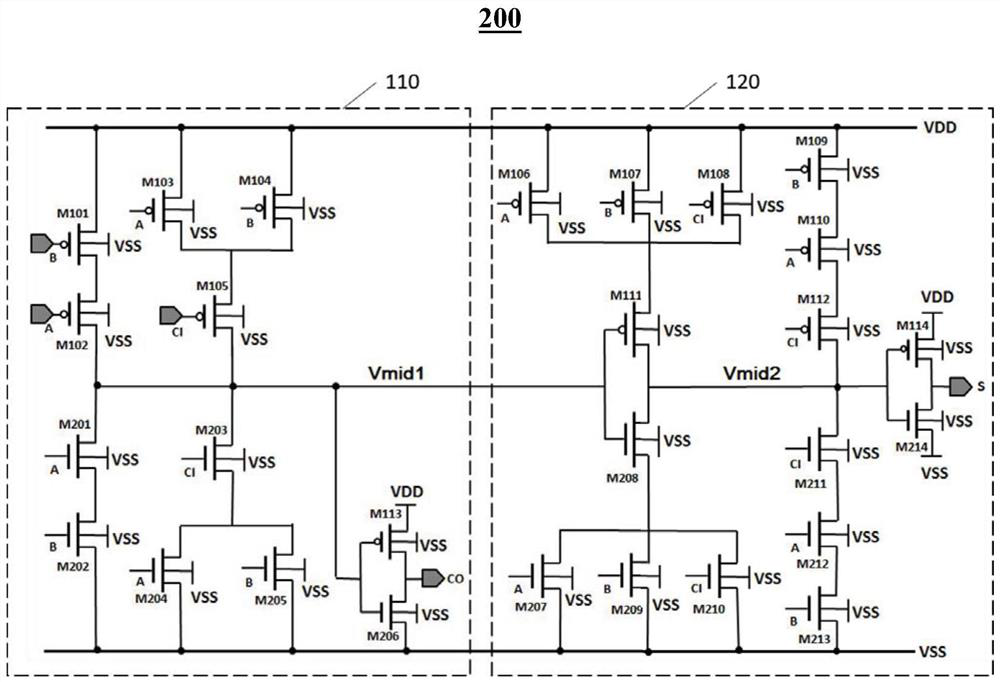

CMOS full adder and multi-bit full adder

PendingCN112118005ADecrease riseIncrease circuit speedLogic circuits characterised by logic functionTelecommunicationsCMOS

The invention discloses a CMOS full adder. The CMOS full adder comprises more than one PMOS field effect transistor, more than one NMOS field effect transistor and a connecting circuit. The connectingcircuit is used for connecting the more than one PMOS field effect transistor and the more than one NMOS field effect transistor. The connecting circuit is configured to reduce a threshold voltage ofat least one of the more than one PMOS field effect transistor and the more than one NMOS field effect transistor. The invention further discloses a multi-bit full adder. The multi-bit full adder comprises a plurality of CMOS full adders. The CMOS full adder and the multi-bit full adder can effectively reduce the ascending, descending and propagation delay conditions of the device, thereby improving the circuit speed.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Circuit combining level shift function with gated reset

InactiveUS7755394B2Simplify logic functionsReduce in quantityPower reduction in field effect transistorsLogic circuit coupling/interface arrangementsLow voltageHigh voltage

Owner:INT BUSINESS MASCH CORP

Optical transmitting and receiving system

InactiveUS8121489B2Improve processing speedSimple signal processingSecret communicationElectromagnetic transmission optical aspectsOptical communicationOptical path length

Signals can be superimposed on optical phase even when low-coherency light is used, and a bit rate and a signal coding format similar to those used in ordinary optical communications can be used. A transmitter includes an asymmetric interferometer or an antisqueezed light generator to convert a train of single pulses into a train of dual pulses. A receiver also includes an asymmetric interferometer that provides the same delay time as that between the dual pulses. The receiver allows pulses originating in the same light source to interfere, so that signals can be superimposed on the phase even when a low-coherency light source is used. The delay time (optical path length difference) provided in the asymmetric interferometer is set to be longer than half the period of the pulses outputted from the optical pulse source. In the transmitter, two pulses are modulated as a unit, one of the two pulses being the rear pulse of a pair of dual pulses and the other pulse being the front pulse of the next pair of dual pulses. In the receiver, a balanced detector receives the modulated pulses, and the balanced detector only outputs interference pulses but does not output non-interference pulses.

Owner:HITACHI LTD

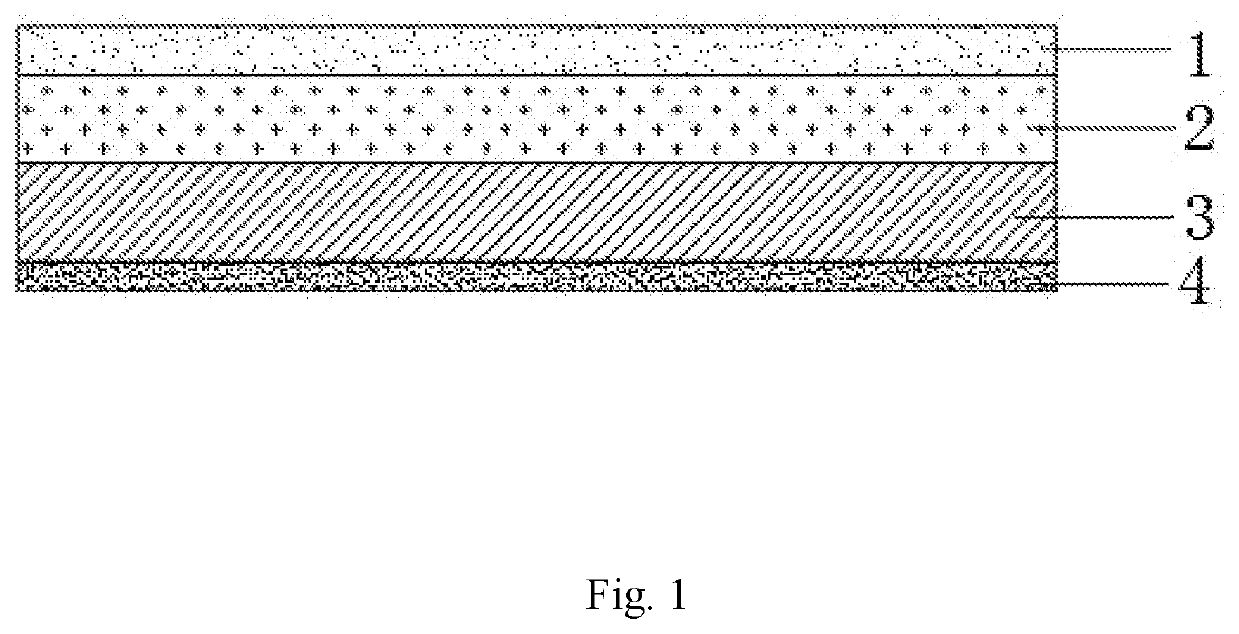

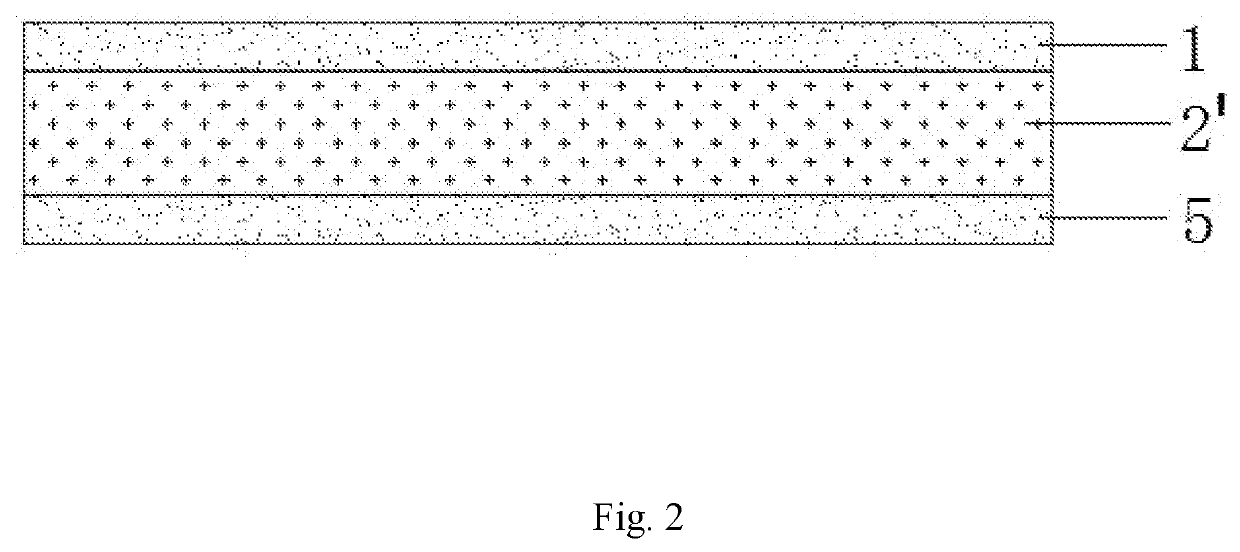

Method for preparing novel material layer structure of circuit board and article thereof

PendingUS20220272845A1Simple manufacturing processIncrease circuit speedLight absorption dielectricsDielectric materialsAdhesiveThin membrane

The present invention discloses a method for preparing a novel material layer structure of a circuit board, comprising the steps of: (1) combining a film with a copper layer to form an FCCL single-sided board; (2) applying a semi-cured functional material layer on a back side of the film of the FCCL single-sided board, wherein the semi-cured functional material layer is an MPI film, an LCP film, a TFP film, a PTFE film, a copper ion migration resistant film, an LDK high-frequency functional adhesive, a copper ion migration resistant adhesive, or a mixture of the LDK high-frequency functional adhesive and the copper ion migration resistant adhesive to form a novel material layer structure for a circuit board. An article prepared by performing the above methods is also disclosed. The prepared novel material layer structure of the circuit board has high-frequency characteristics and / or copper ion migration resistance, and can be used as an integral structure. In the circuit board manufacturing process, it can be manufactured as the circuit board manufacturing material to be different circuit board structures, which brings great convenience for subsequent circuit board manufacturing and simplifies the manufacturing process.

Owner:LI LONGKAI

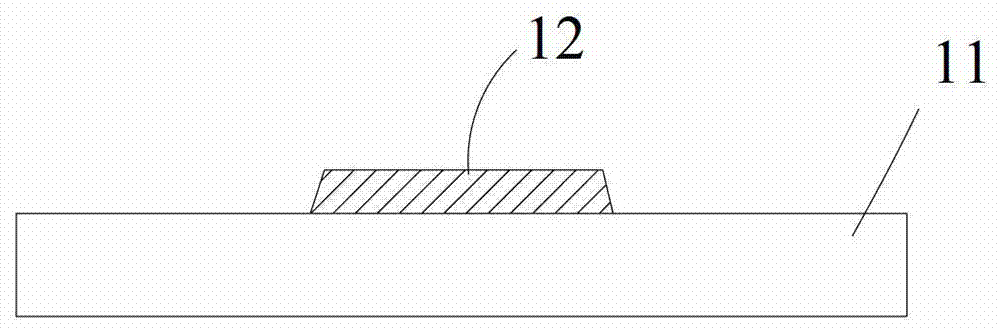

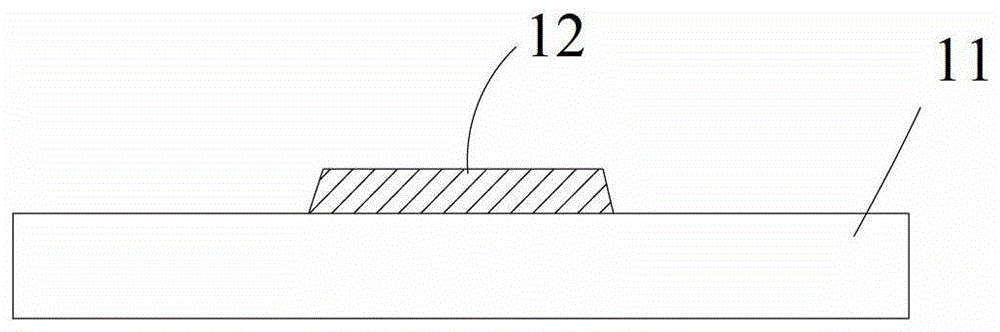

Self-aligned metal oxide thin film transistor device and manufacturing method

ActiveCN104040683BMinimizeEasy to controlTransistorSolid-state devicesComing outElectrical conductor

Provided is a method for producing a self-aligned metal oxide thin-film transistor (TFT) component, which comprises: selecting a substrate (11), and preparing a gate electrode (12) on the substrate (11); arranging an insulation layer (13), a transparent electrode layer (14) and photoresist (15) in sequence on the gate electrode (12); using the gate electrode (12) as a mask, and exposing from a back of the substrate (11) to form source and drain electrodes (141, 142) that are aligned with the gate electrode (12); depositing a metal oxide semiconductor layer (17) on the transparent electrode layer (14); etching the semiconductor layer (17) and the source and drain electrodes (141, 142) to make outer ends of the source and drain electrodes (141, 142) come out of the metal oxide semiconductor layer; depositing a passivation layer (18), and leading out the source and drain electrodes (141, 142). The component uses a transparent conductor as an electrode layer, uses a bottom gate as a mask to perform back exposure, and etches the source and drain electrodes, which implements self-alignment between the source and drain electrodes and the gate electrode, effectively reduces parasitic capacitance, and improves component performance. The component is in a bottom gate and bottom contact structure. No etching blocking layer needs to be fabricated, simplifying a process, reducing usage of photolithographic masks, improving efficiency, and improving electrical characteristics of the component.

Owner:SHENZHEN ROYOLE TECH CO LTD

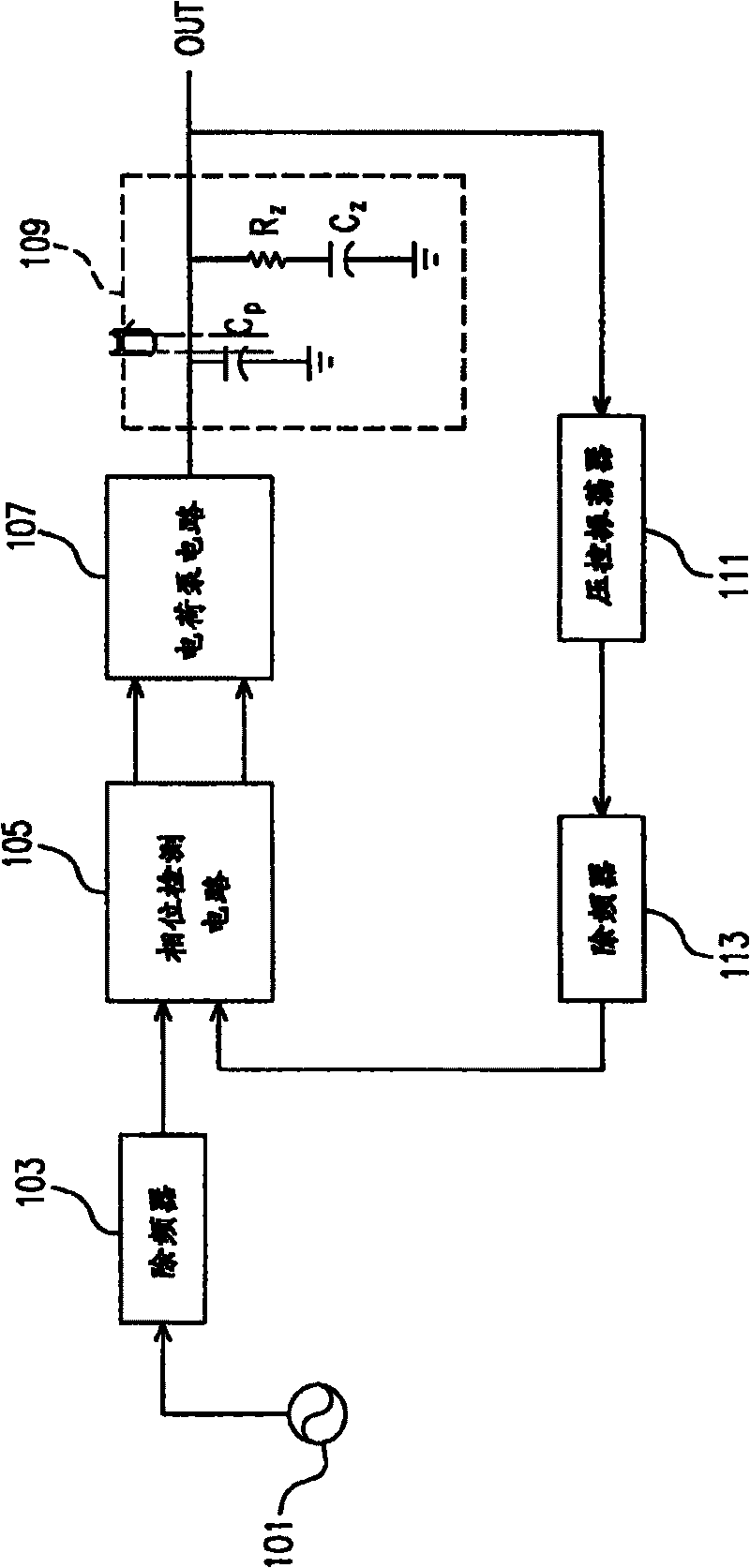

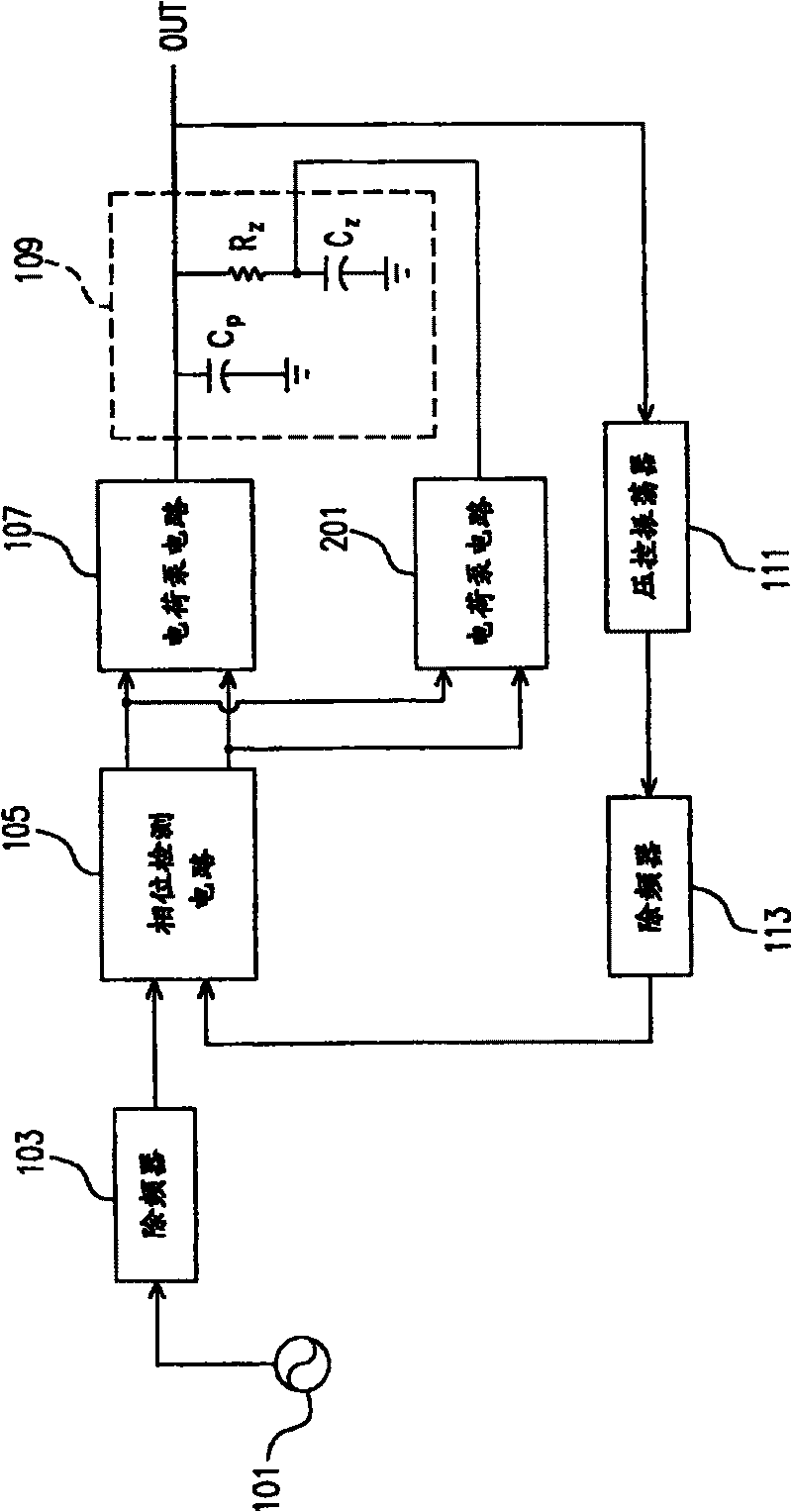

Phase lock loop and loop filter therefor

This invention relates to a phase-lock loop and its applied loop filter including a first resistor, a first capacitor and an amplifier with a specific gain value, among which, the amplifier has an input end coupled to the input and output ends of the loop filter by the first resistor, the amplifier has an output end coupled to the input end of the amplifier via the first capacitor.

Owner:VIA TECH INC

Real-time conversion transmission method and device of parallel-series data stream for cross asynchronous clock domain

ActiveCN102447477BIncrease circuit speedTimely and accurate timing security issuesParallel/series conversionData synchronizationTime domain

The invention discloses a real-time conversion transmission method and device of parallel-series data stream for cross asynchronous clock domain, comprising a parallel data synchronizer, which is used for capturing the data stream periodically in real time and storing into the parallel data synchronizer under the control of a serial clock CLKS which is synchronous to output device of serial data and an enabling controlling signal CS sent out by serial timing controller which is synchronous to clock CLKP; the serial timing controller, monitoring clock CLKP periodically in the clock domain of clock CLKS, distinguishing indeterminate state of clock CLKP, the indeterminate state being a time domain zone of a data transmission zone; when distinguishing that the capturing moment is in a time zone of the data transmission zone of clock CLKP, the serial timing controller cyclically adjusts capturing moment until the capturing moment is in the time zone of determined state of clock CLKP, the determined state being the time zone besides the data transmission zone; the output device of serial data, reading the data stream of parallel data synchronizer and output serially under the control of the serial timing controller. The invention is characterized by being simple and reliable, good practicability and being in favor of applying in the large scale integrated circuit.

Owner:ALLWINNER TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com