Real-time conversion transmission method and device of parallel-series data stream for cross asynchronous clock domain

A technology of asynchronous clock and transmission method, applied in the direction of parallel/serial conversion, code conversion, electrical components, etc., can solve the problems of increased power consumption, complex circuit structure, unfavorable digital-analog hybrid design, high-speed circuit application, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

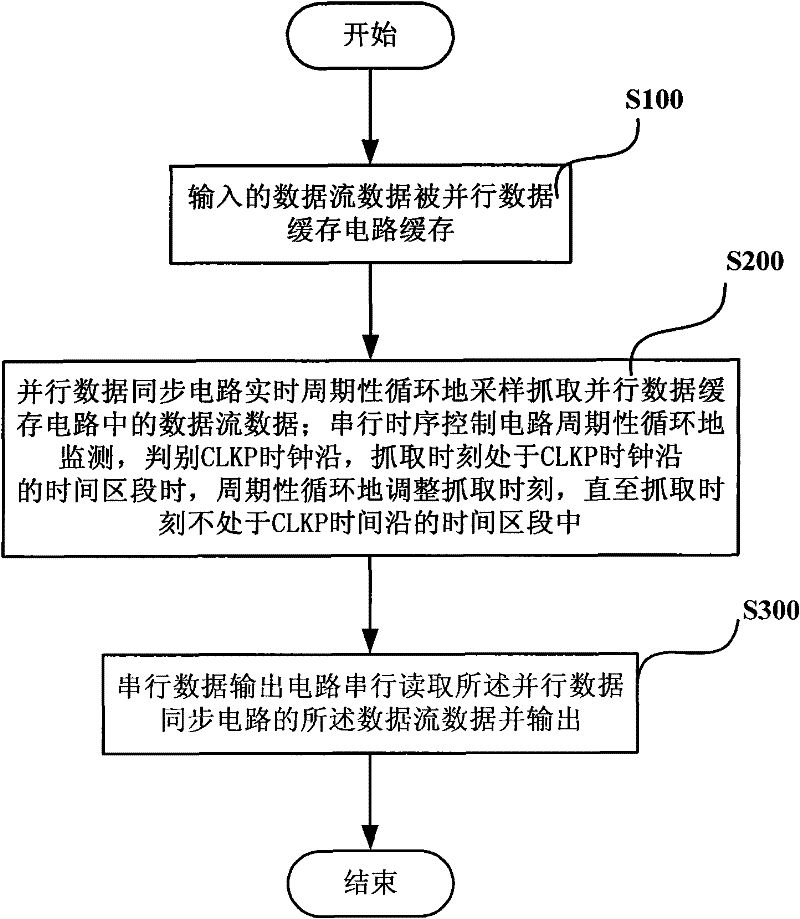

[0102] The real-time conversion and transmission method of the parallel-serial data stream across the asynchronous clock domain in the embodiment of the present invention, such as figure 1 shown, including the following steps:

[0103] Step S100, the input data stream is buffered by a parallel data buffer controlled by a parallel clock signal CLKP synchronized with it;

[0104] Step S200, the parallel data synchronizer 2 synchronized with the serial clock signal CLKS is under the control of the serial clock signal CLKS synchronized with the serial data exporter 4 and the enable control signal CS issued by the serial timing controller 3 , by connecting the first data bus of the parallel data buffer 1 and the parallel data synchronizer 2, the data in the parallel data buffer 1 is periodically sampled and captured in real time and stored in the parallel data synchronizer 2;

[0105] The frequency of the serial clock signal CLKS is N times the frequency of the parallel clock sign...

Embodiment 2

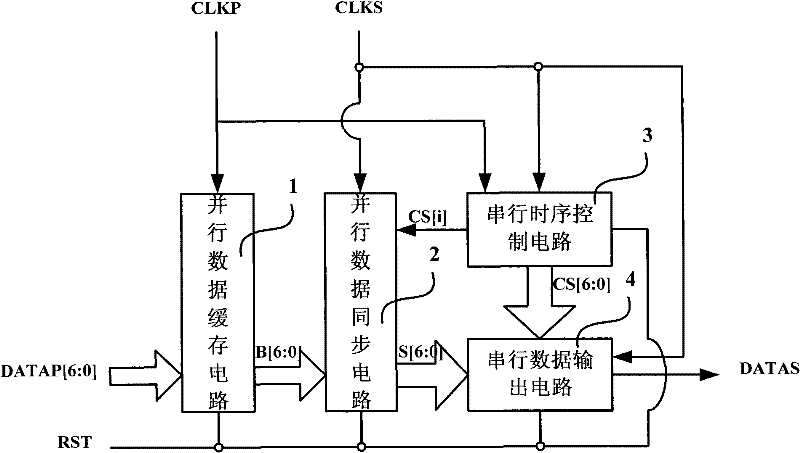

[0129] Such as image 3 As shown, the device for real-time conversion and transmission of parallel-to-serial data streams across asynchronous clock domains according to the embodiment of the present invention includes a parallel data buffer 1, a parallel data synchronizer 2, a serial timing controller 3 and a serial data output device 4;

[0130] The parallel data buffer 1 and the parallel data synchronizer 2 are connected by a first data bus (parallel data bus) identical to the parallel data bit width;

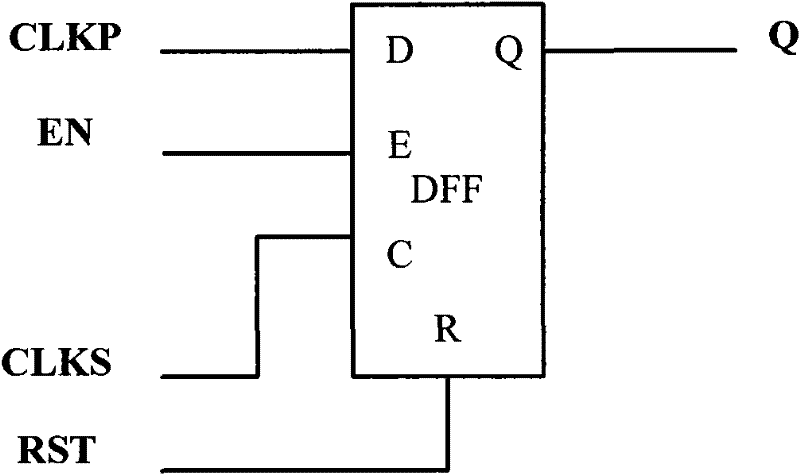

[0131] The parallel data synchronizer 2 is connected to the serial timing controller 3 through a control bus having the same bit width as the parallel data;

[0132] The parallel data synchronizer 2 and the serial data exporter 4 are connected through a second data bus having the same bit width as the serial data;

[0133] As a possible implementation manner, the parallel clock signal CLKP and the serial clock signal CLKS in the embodiment of the present invention may be res...

Embodiment 3

[0219] Taking a device for real-time conversion and transmission of parallel-serial data streams across asynchronous clock domains in an LVDS interface circuit for driving flat panel displays as an example, the device for real-time conversion and transmission of parallel-serial data streams across asynchronous clock domains of the present invention will be further described in detail.

[0220] Such as image 3 As shown, in this embodiment, taking the real-time conversion and transmission device of the parallel-serial data stream across the asynchronous clock domain in the LVDS interface circuit driving the panel display as an example, the real-time conversion of the parallel-serial data stream across the asynchronous clock domain in the embodiment of the present invention However, it should be noted that the device for real-time conversion and transmission of parallel-to-serial data streams across asynchronous clock domains of the present invention is also applicable to other v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com