Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

182 results about "Cmos fabrication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

CMOS fabrication process. The front-end-of-line (FEOL) is the first portion of IC fabrication where the individual devices (transistors, capacitors, resistors, etc.) are patterned in the semiconductor. FEOL generally covers everything up to (but not including) the deposition of metal interconnect layers.

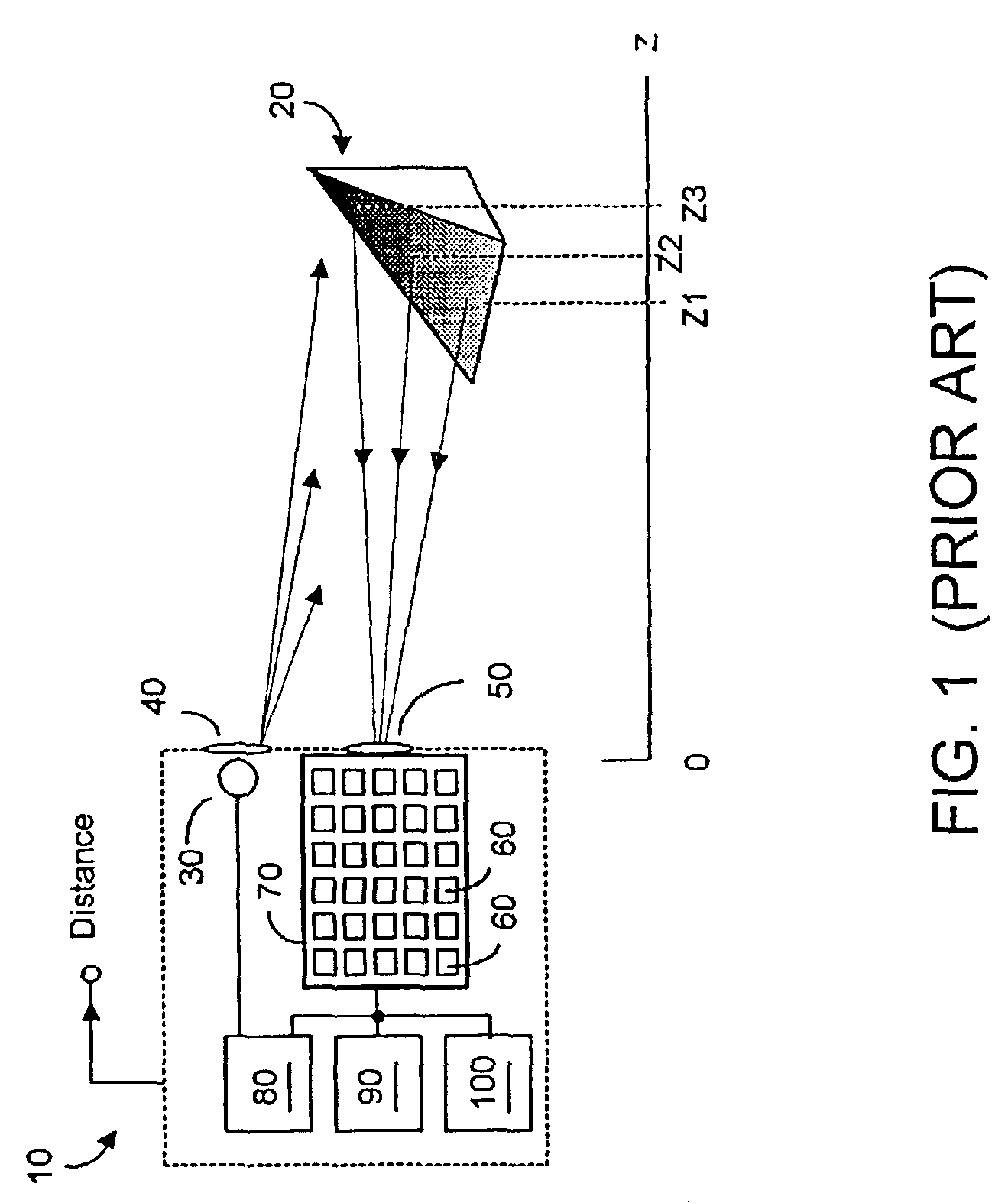

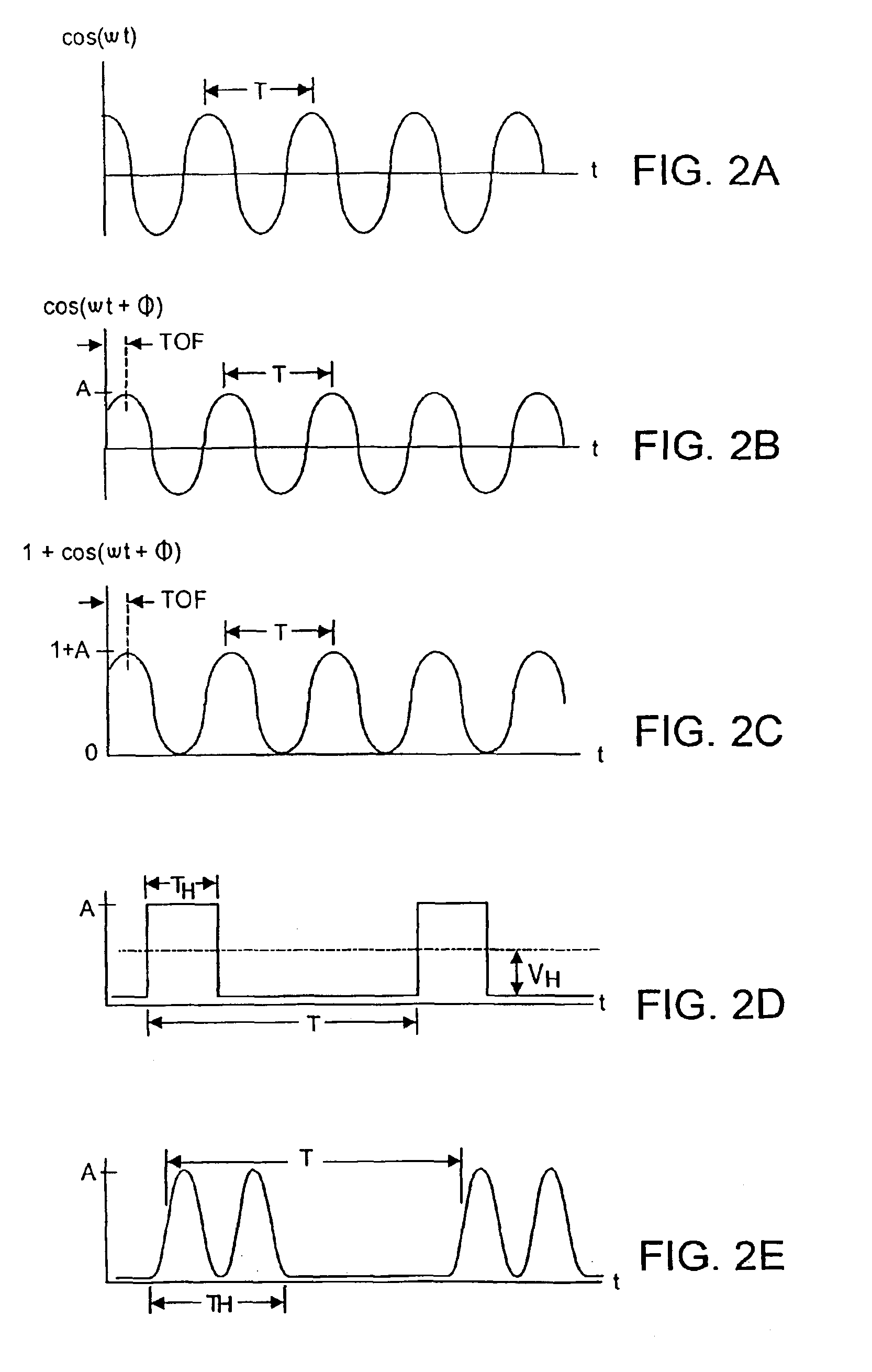

Methods and devices for charge management for three-dimensional sensing

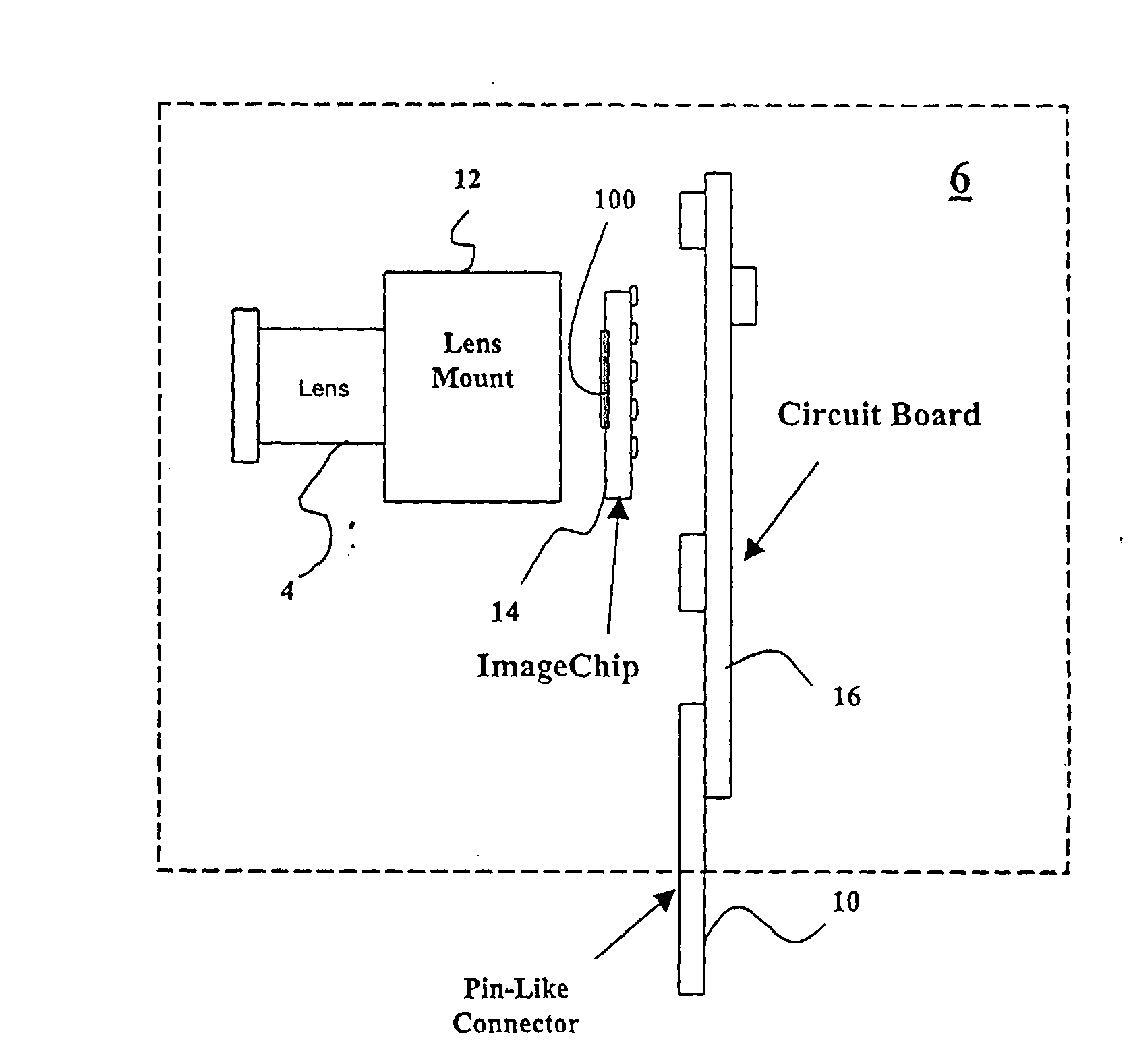

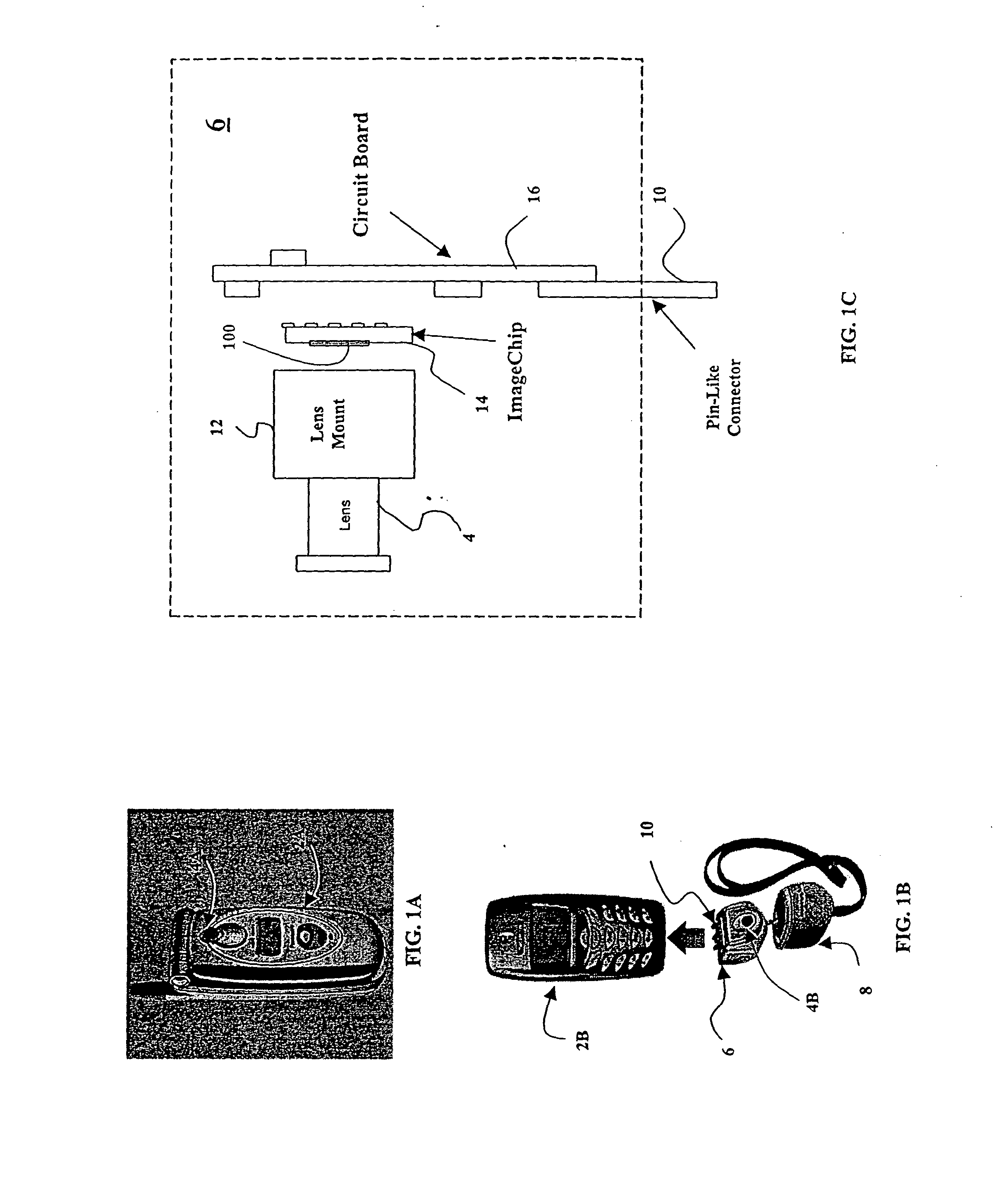

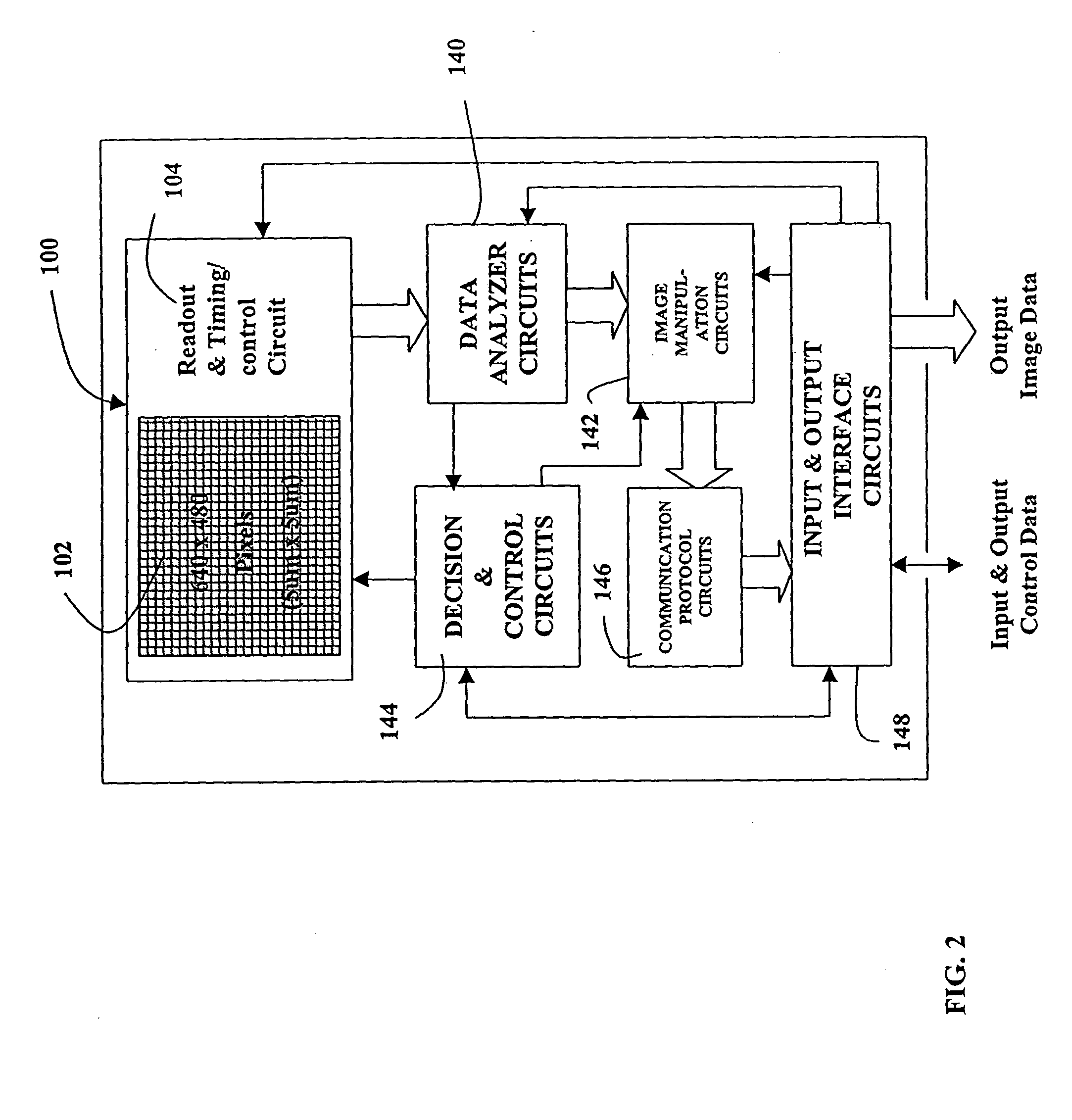

InactiveUS6906793B2Minimal overheadEffective coloringTelevision system detailsOptical rangefindersCMOSHigh frequency modulation

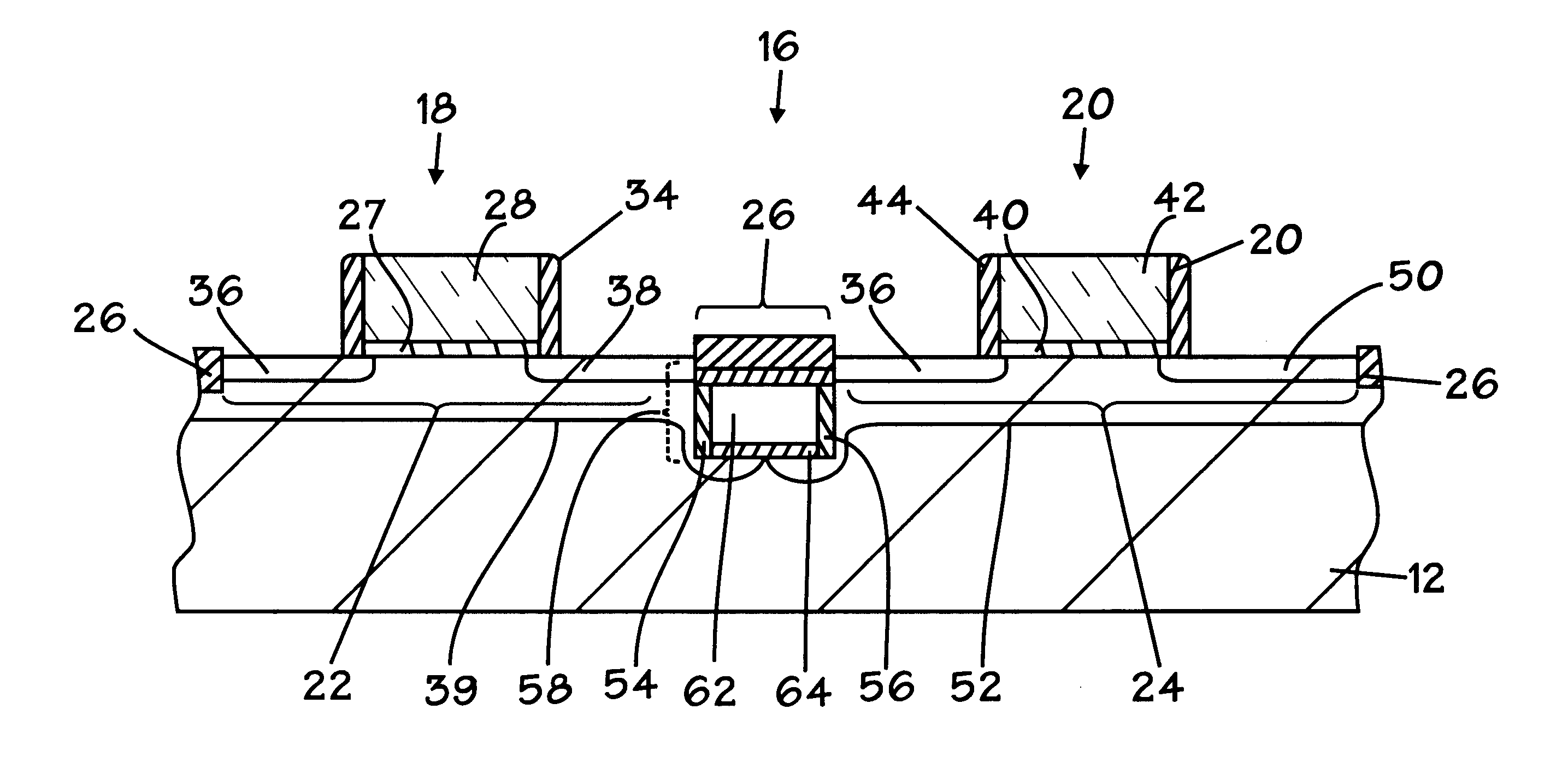

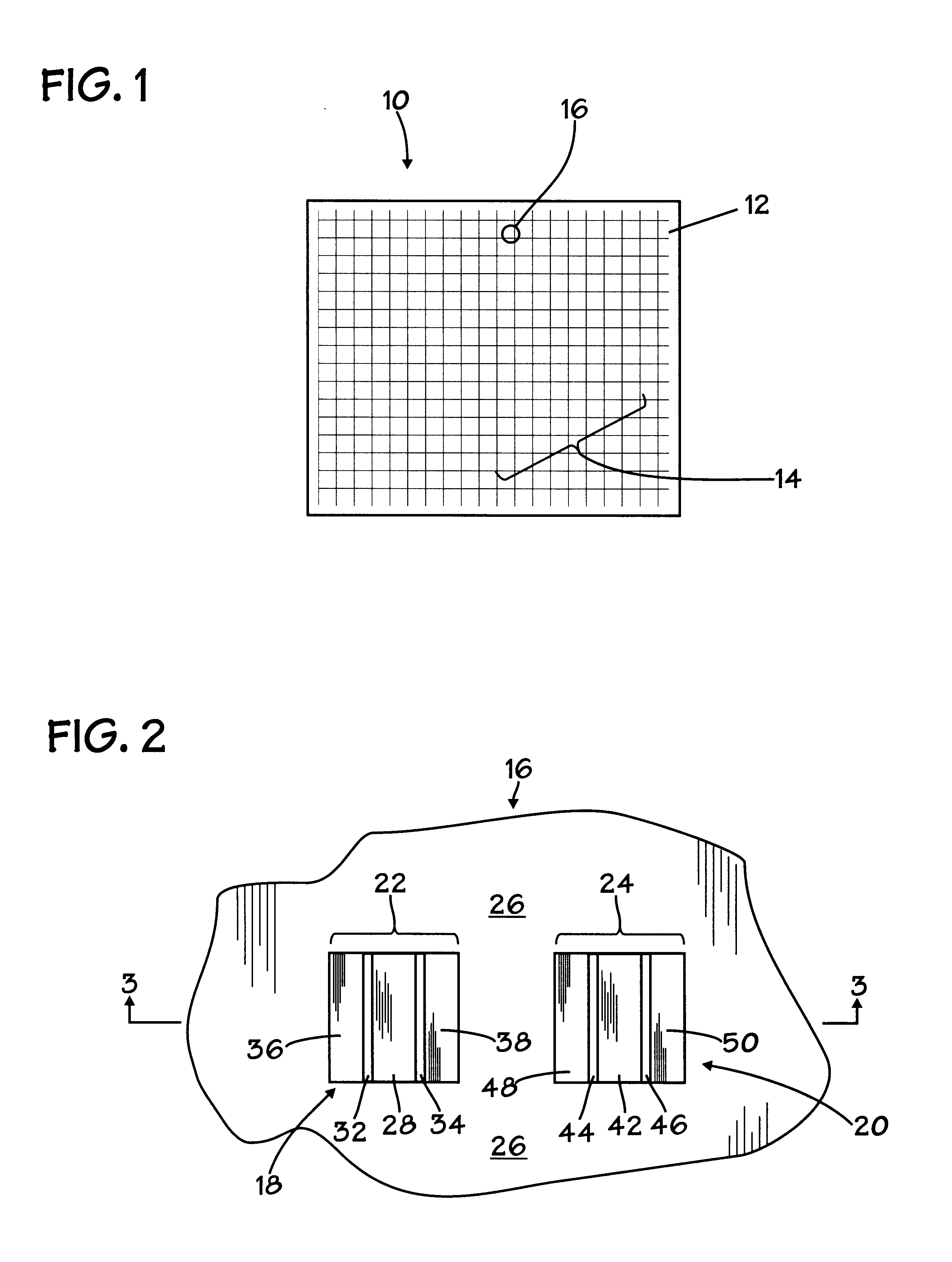

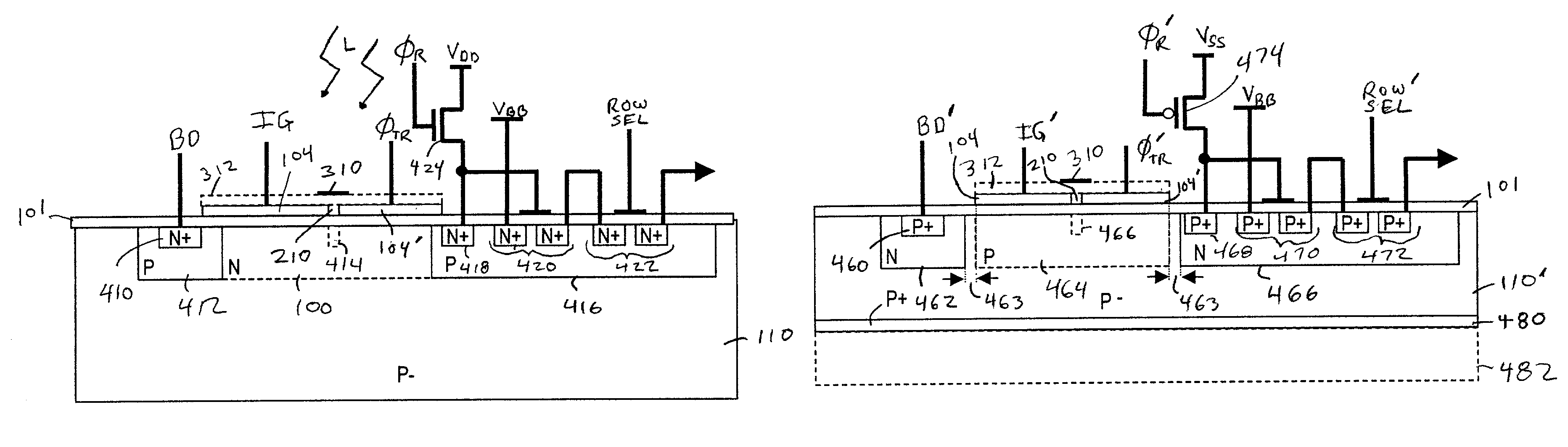

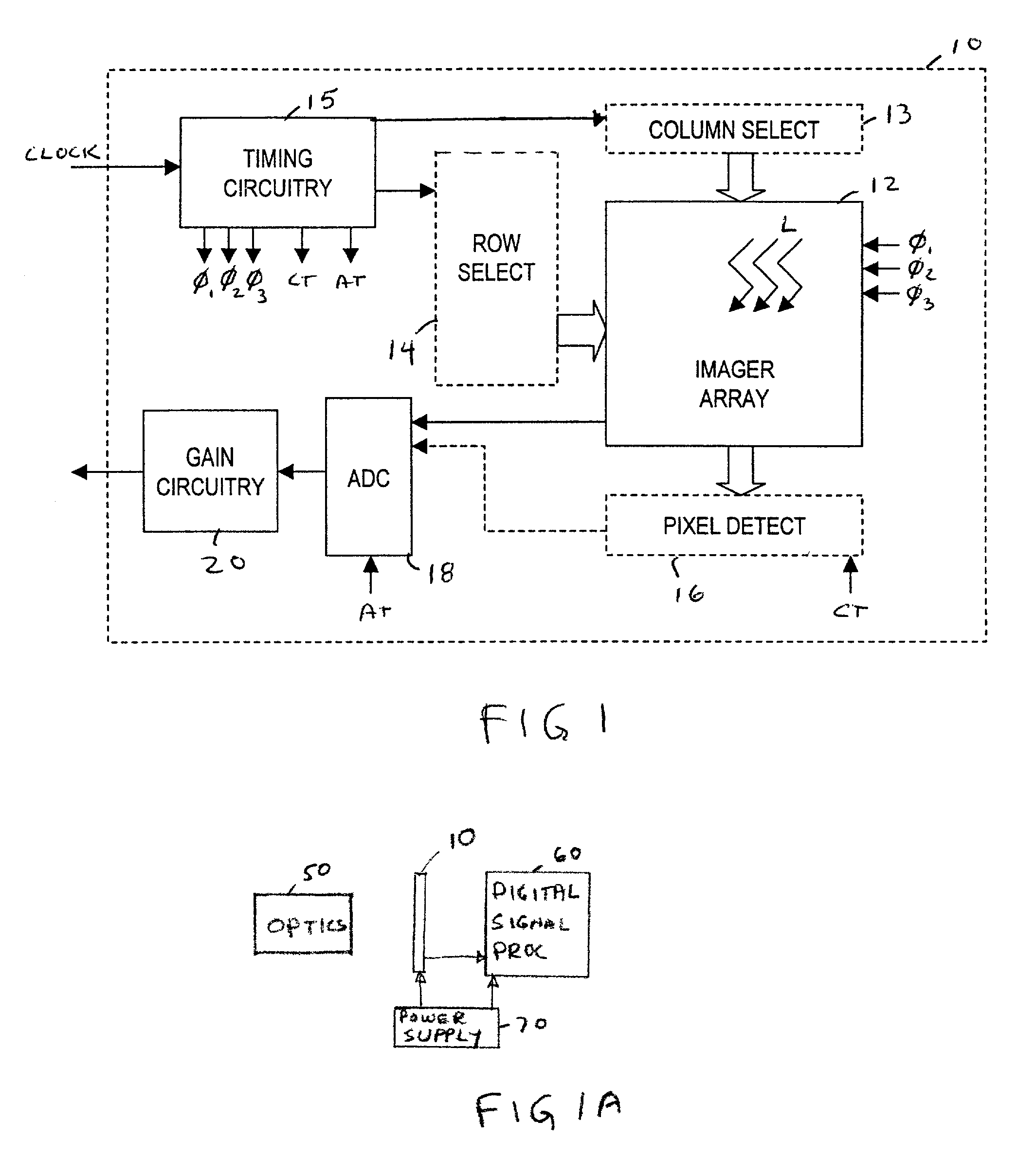

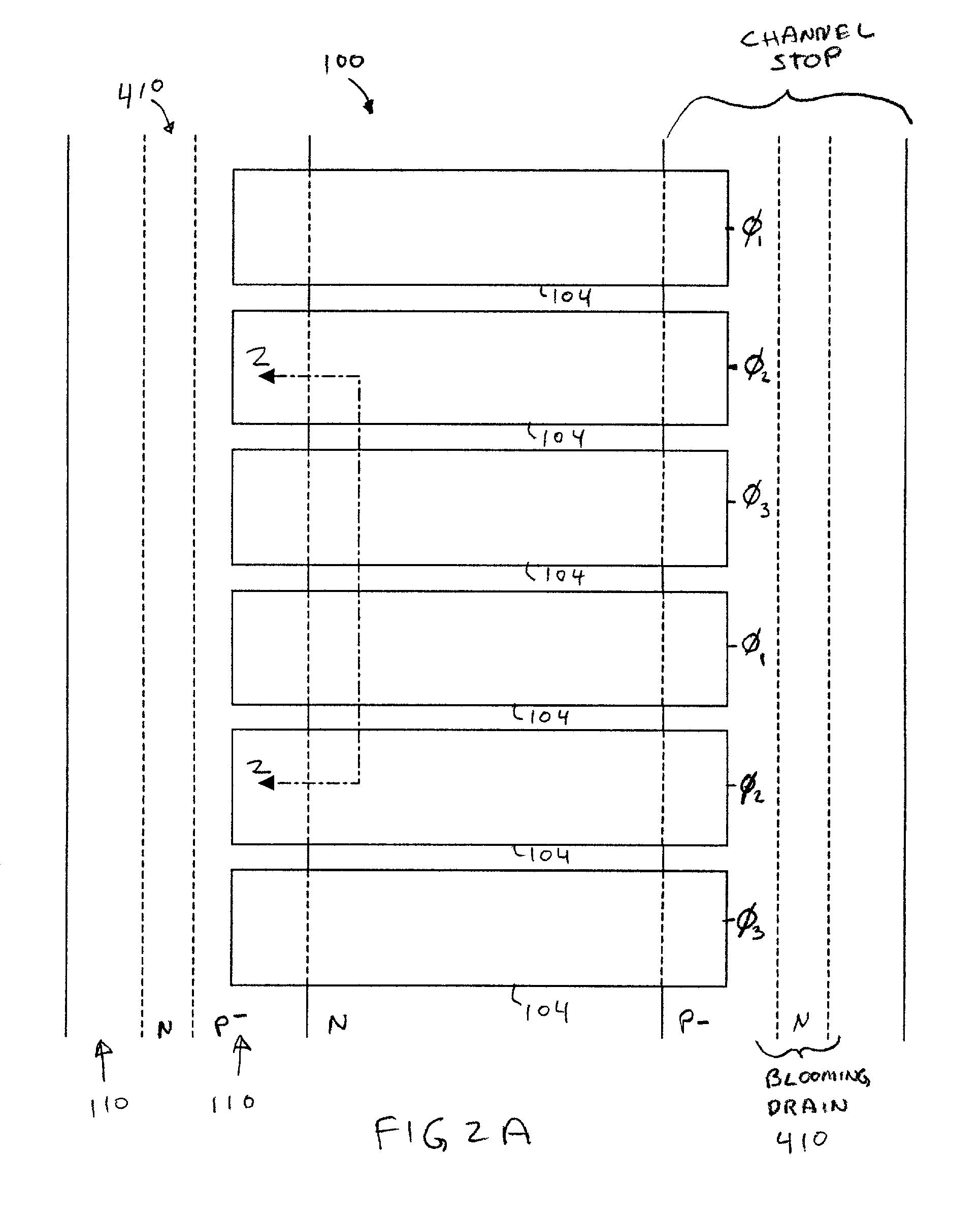

Structures and methods for three-dimensional image sensing using high frequency modulation includes CMOS-implementable sensor structures using differential charge transfer, including such sensors enabling rapid horizontal and slower vertical dimension local charge collection. Wavelength response of such sensors can be altered dynamically by varying gate potentials. Methods for producing such sensor structures on conventional CMOS fabrication facilities include use of “rich” instructions to command the fabrication process to optimize image sensor rather than digital or analog ICs. One detector structure has closely spaced-apart, elongated finger-like structures that rapidly collect charge in the spaced-apart direction and then move collected charge less rapidly in the elongated direction. Detector response is substantially independent of the collection rate in the elongated direction.

Owner:MICROSOFT TECH LICENSING LLC

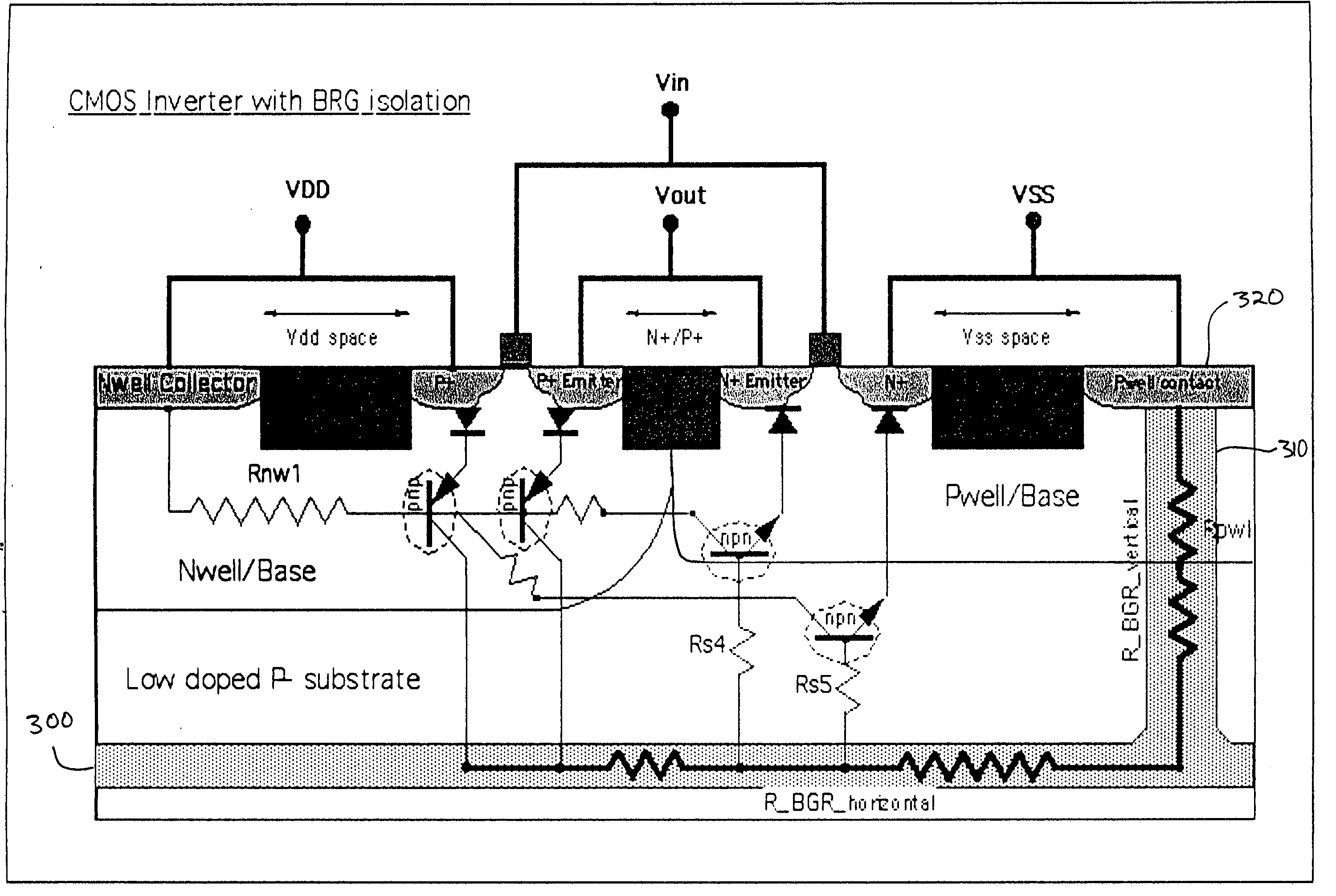

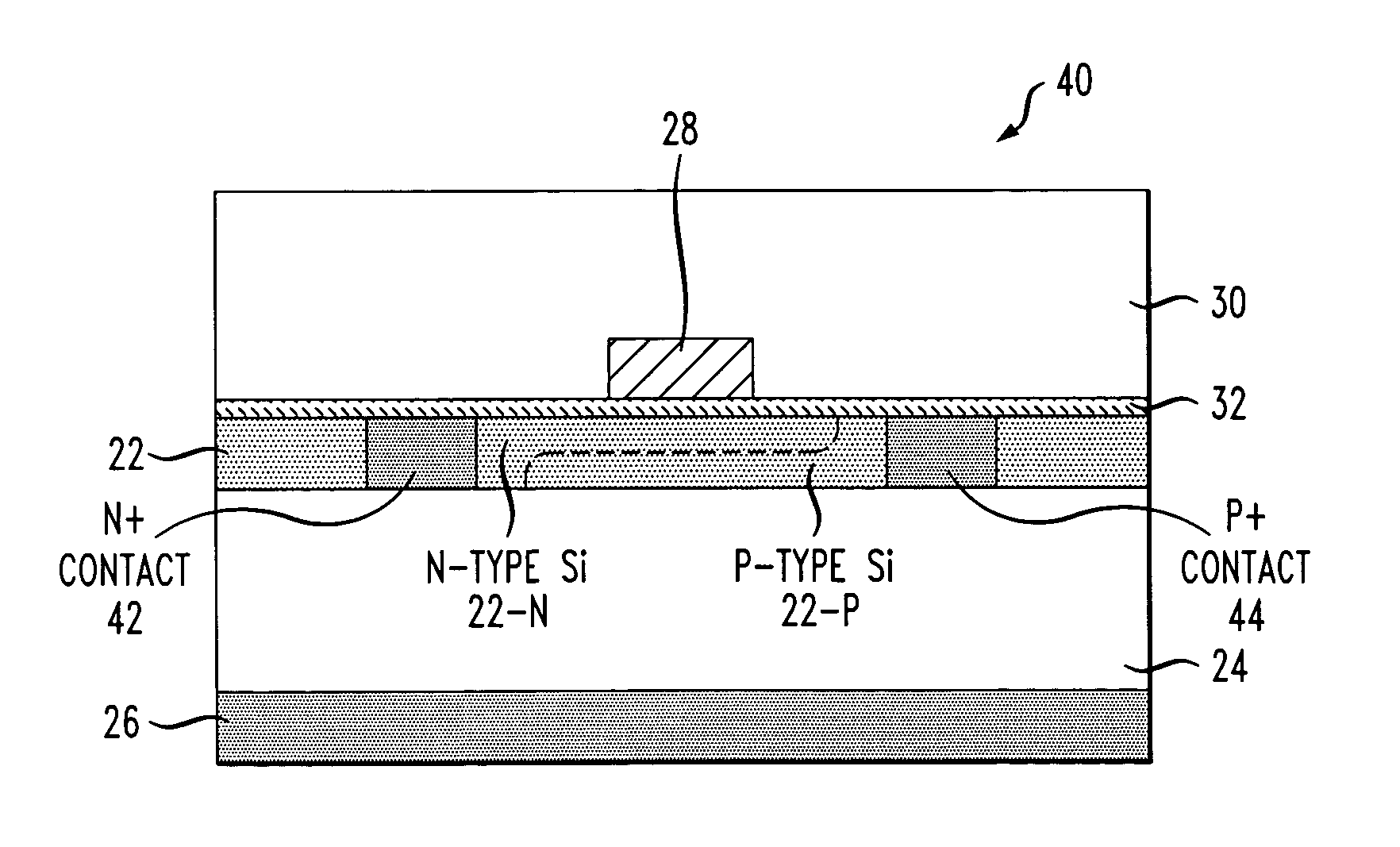

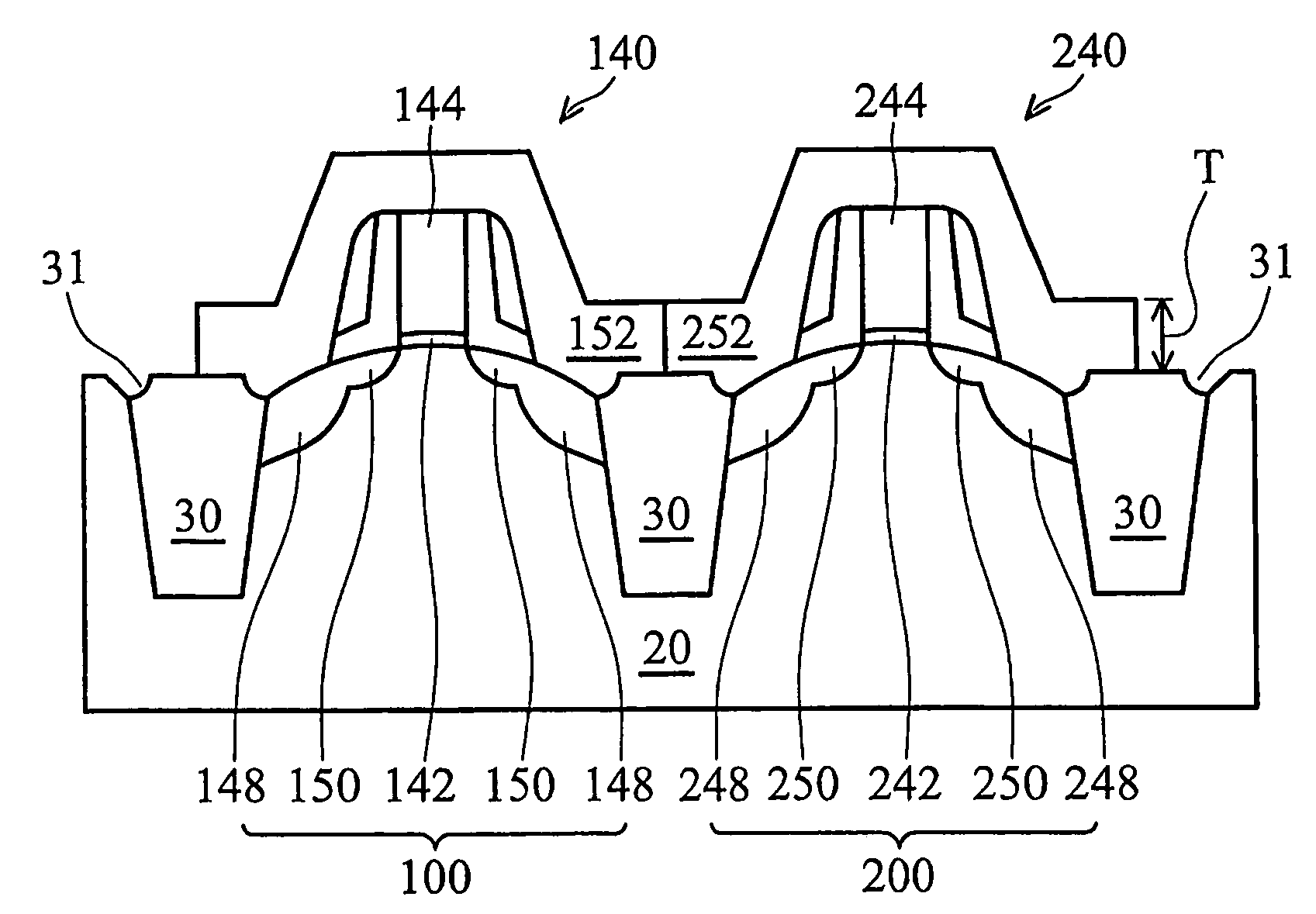

Buried guard ring and radiation hardened isolation structures and fabrication methods

ActiveUS20050179093A1Reduce and eliminate detrimental effectLow costTransistorSemiconductor/solid-state device detailsManufacturing technologyDevice material

Semiconductor devices can be fabricated using conventional designs and process but including specialized structures to reduce or eliminate detrimental effects caused by various forms of radiation. Such semiconductor devices can include the one or more parasitic isolation devices and / or buried guard ring structures disclosed in the present application. The introduction of design and / or process steps to accommodate these novel structures is compatible with conventional CMOS fabrication processes, and can therefore be accomplished at relatively low cost and with relative simplicity.

Owner:SILICON SPACE TECH

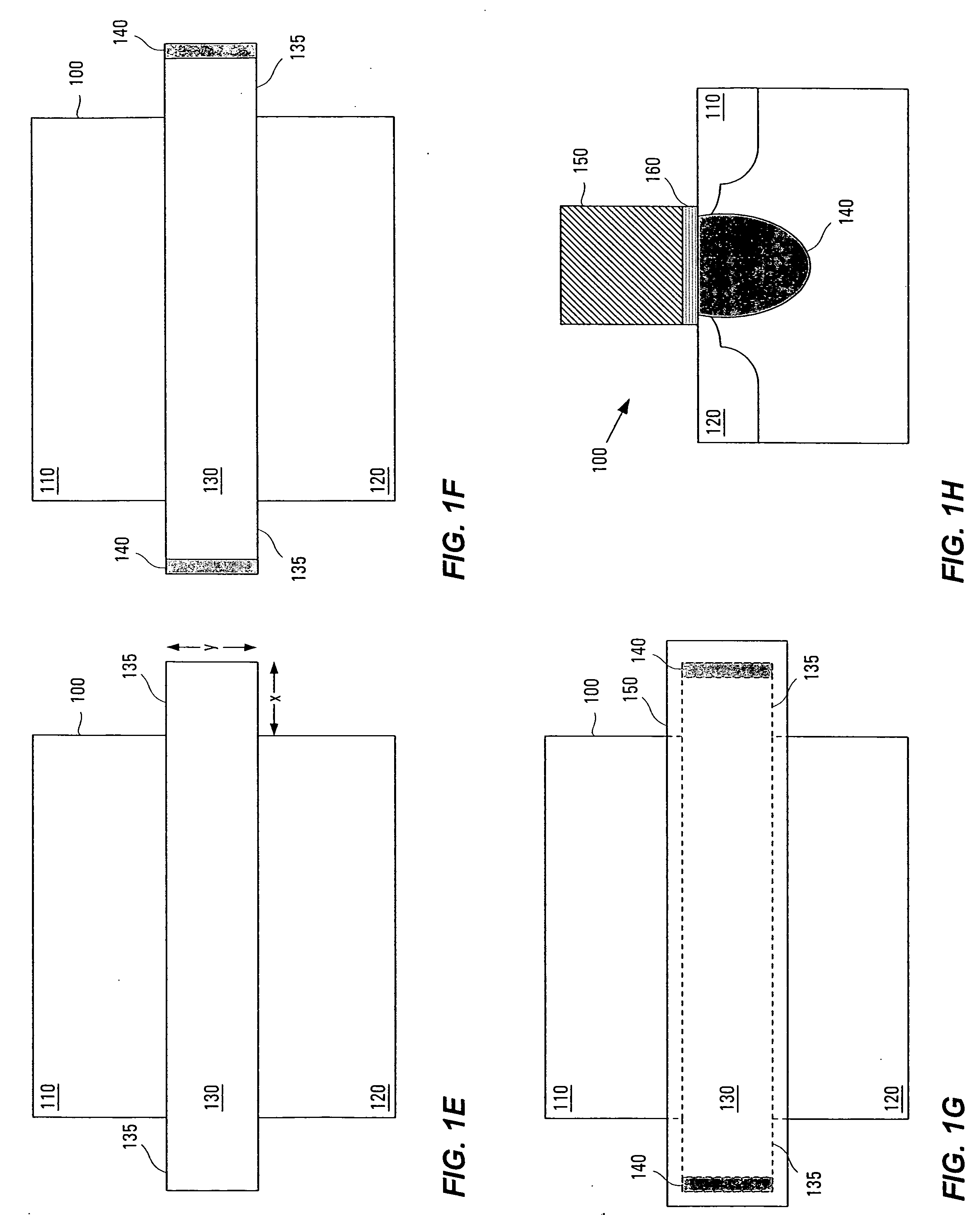

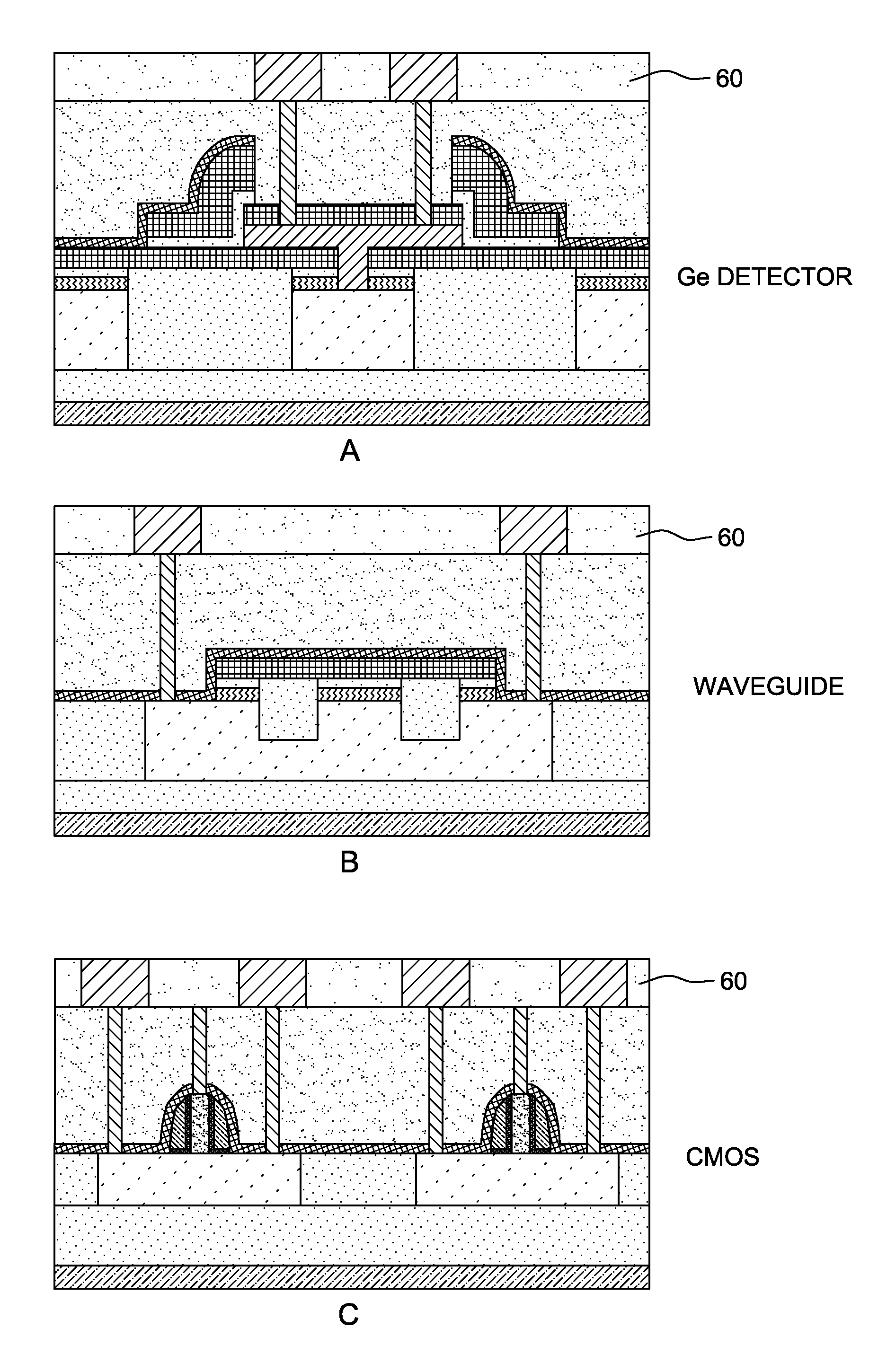

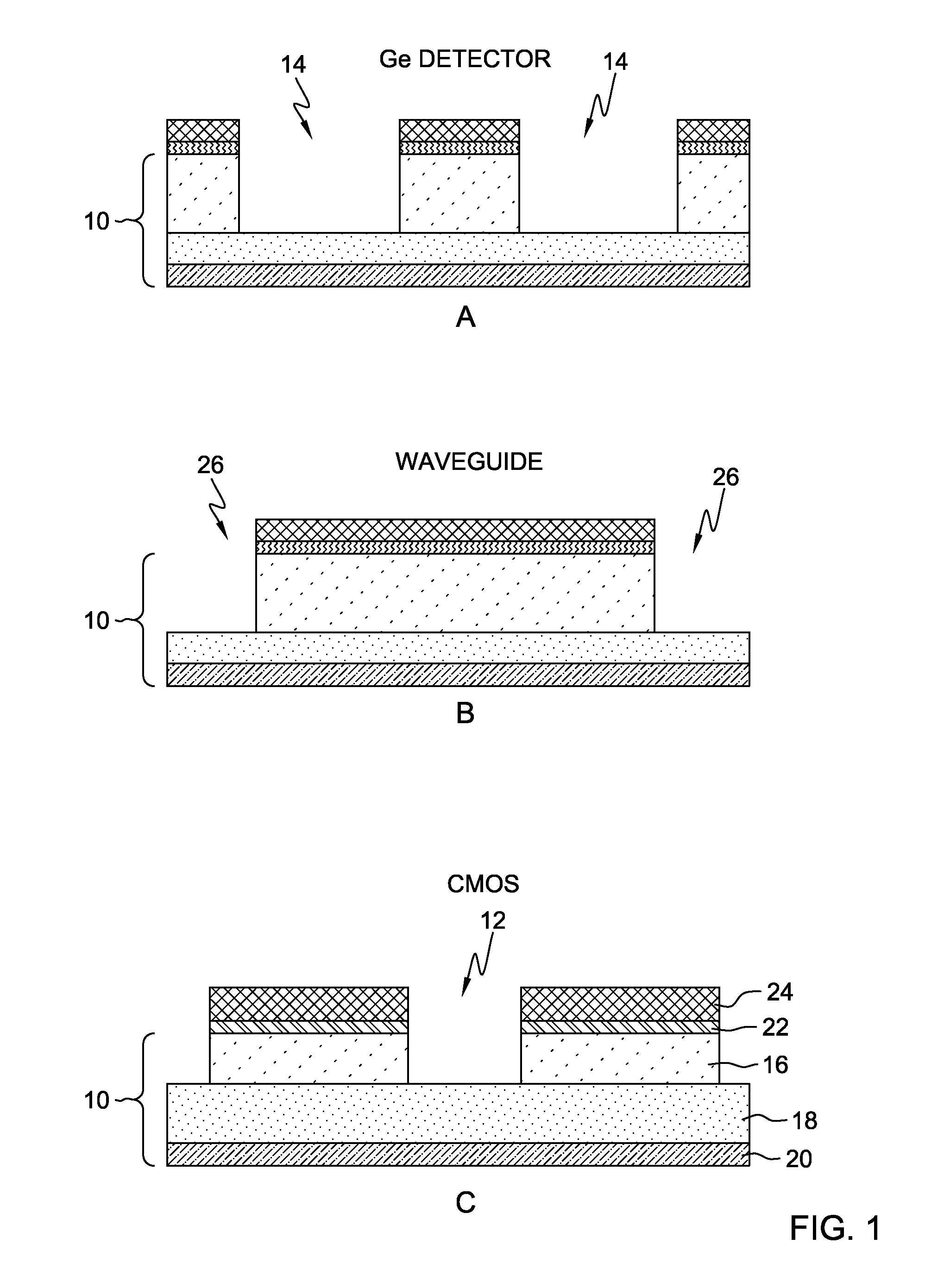

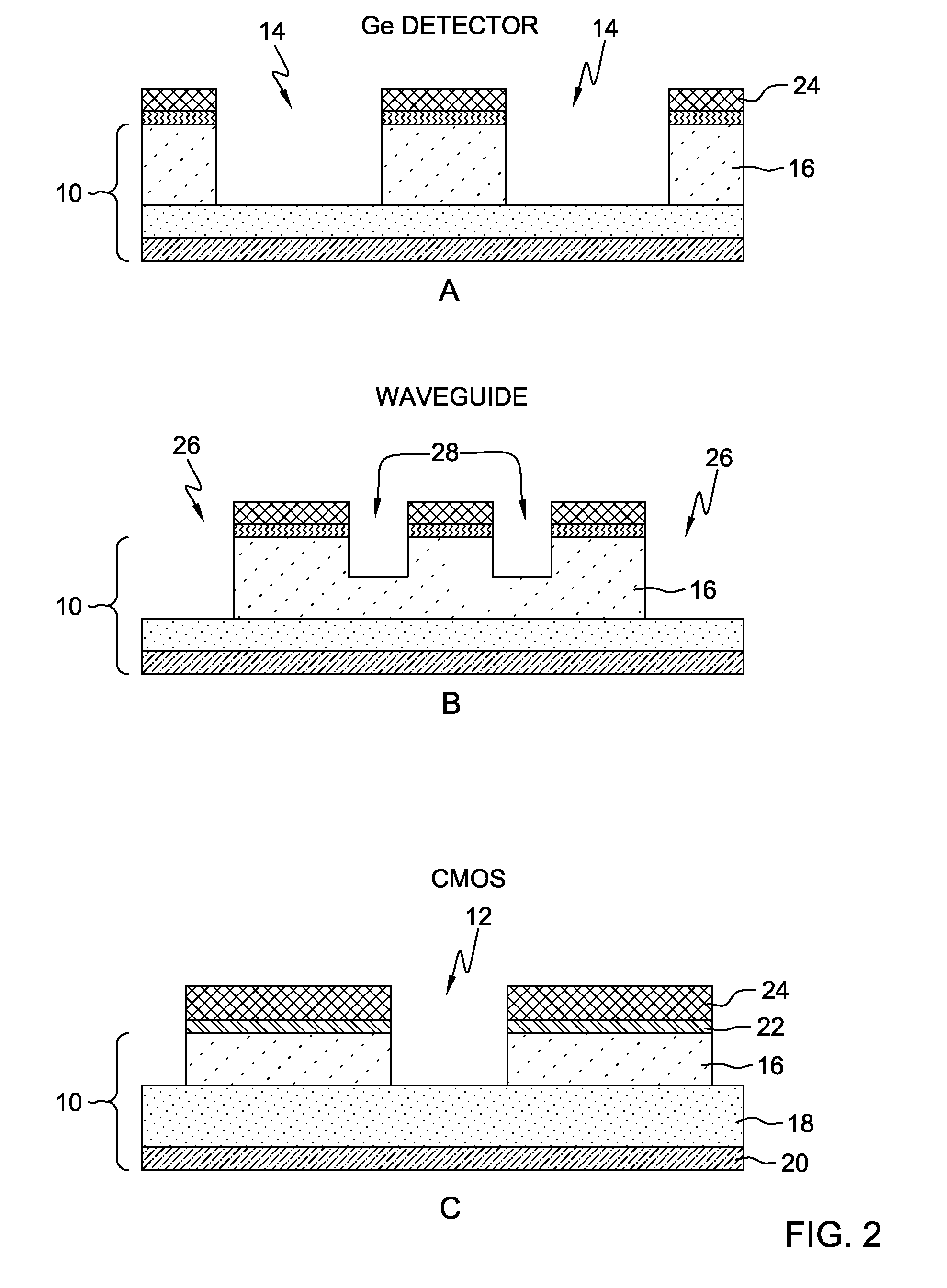

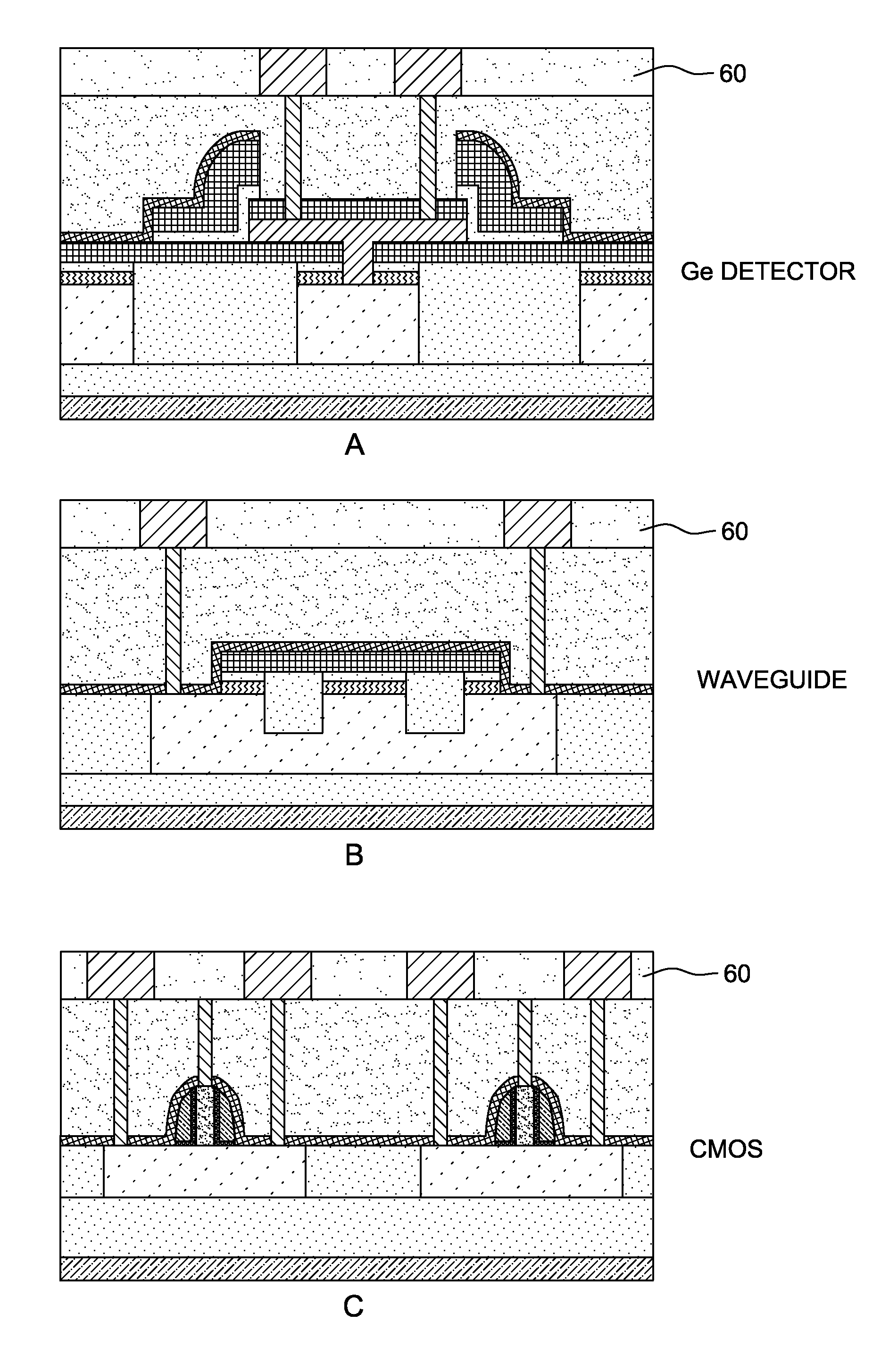

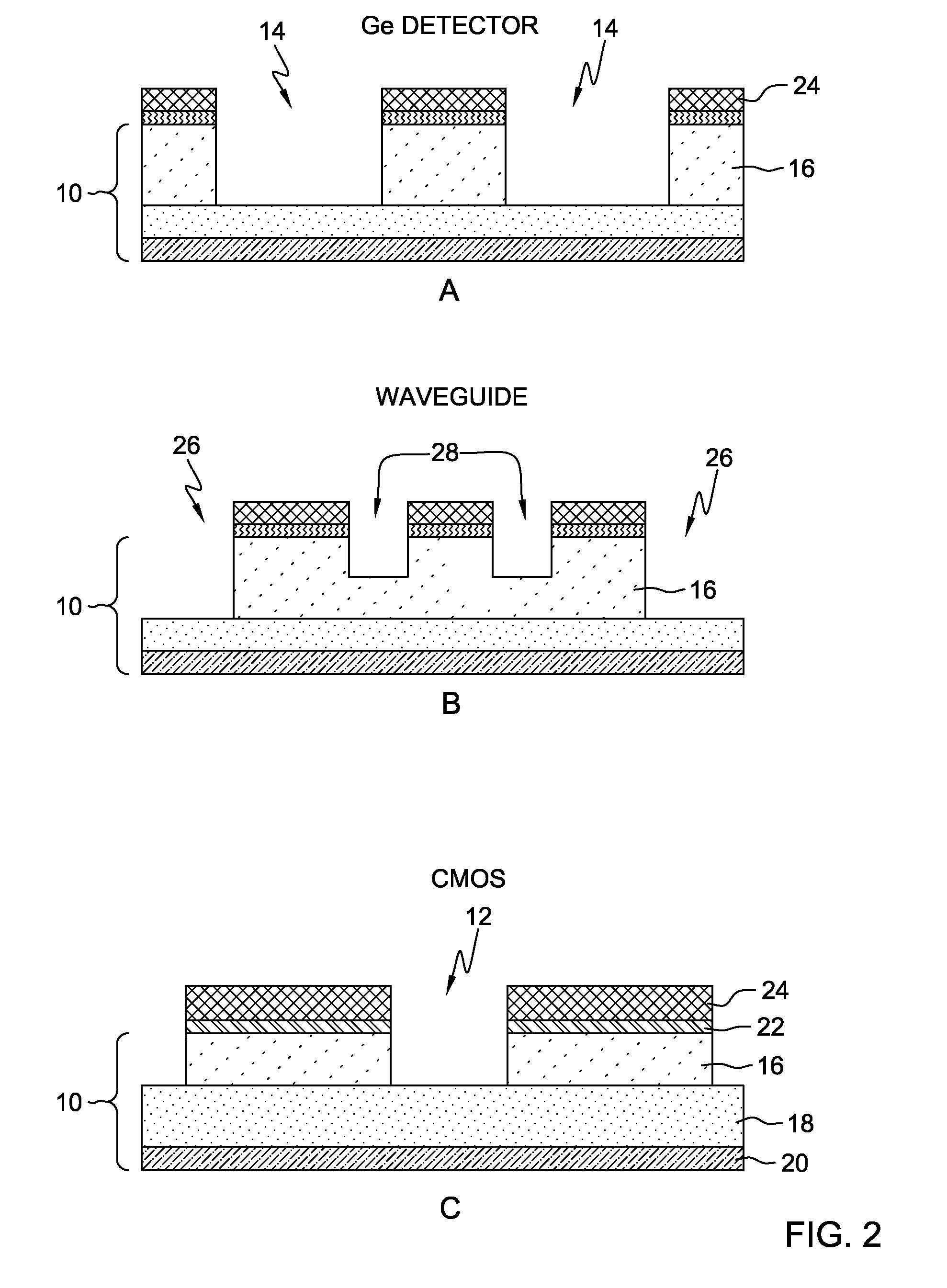

Fabricating photonics devices fully integrated into a CMOS manufacturing process

ActiveUS20120129302A1Lower resistanceSemiconductor/solid-state device manufacturingOptical light guidesCMOSPhotodetector

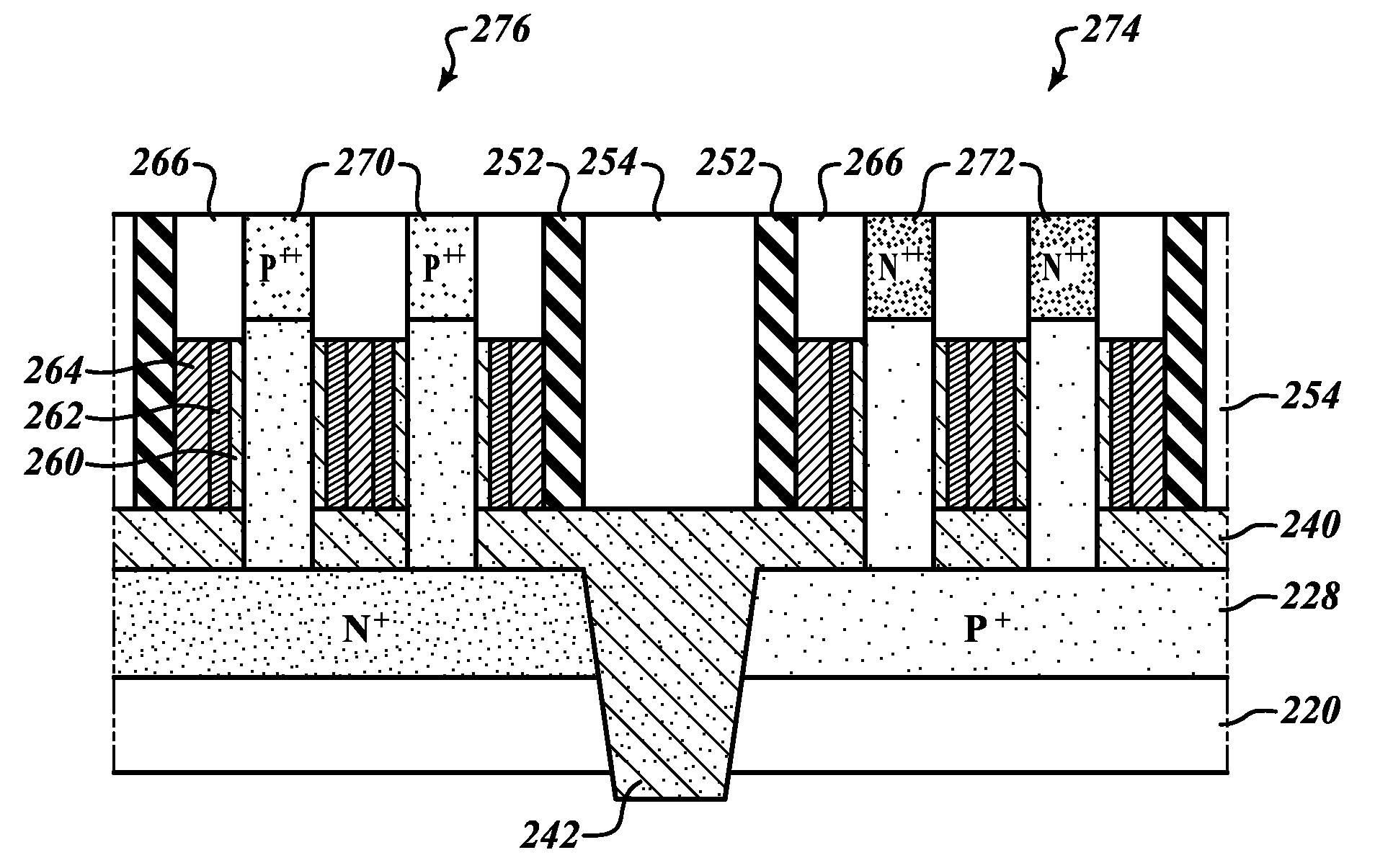

Disclosed are process enhancements to fully integrate the processing of a photonics device into a CMOS manufacturing process flow. A CMOS wafer may be divided into different portions. One of the portions is for the CMOS devices and one or more other portions are for the photonics devices. The photonics devices include a ridged waveguide and a germanium photodetector. The germanium photodetector may utilize a seeded crystallization from melt process so there is more flexibility in the processing of the germanium photodetector.

Owner:GLOBALFOUNDRIES US INC

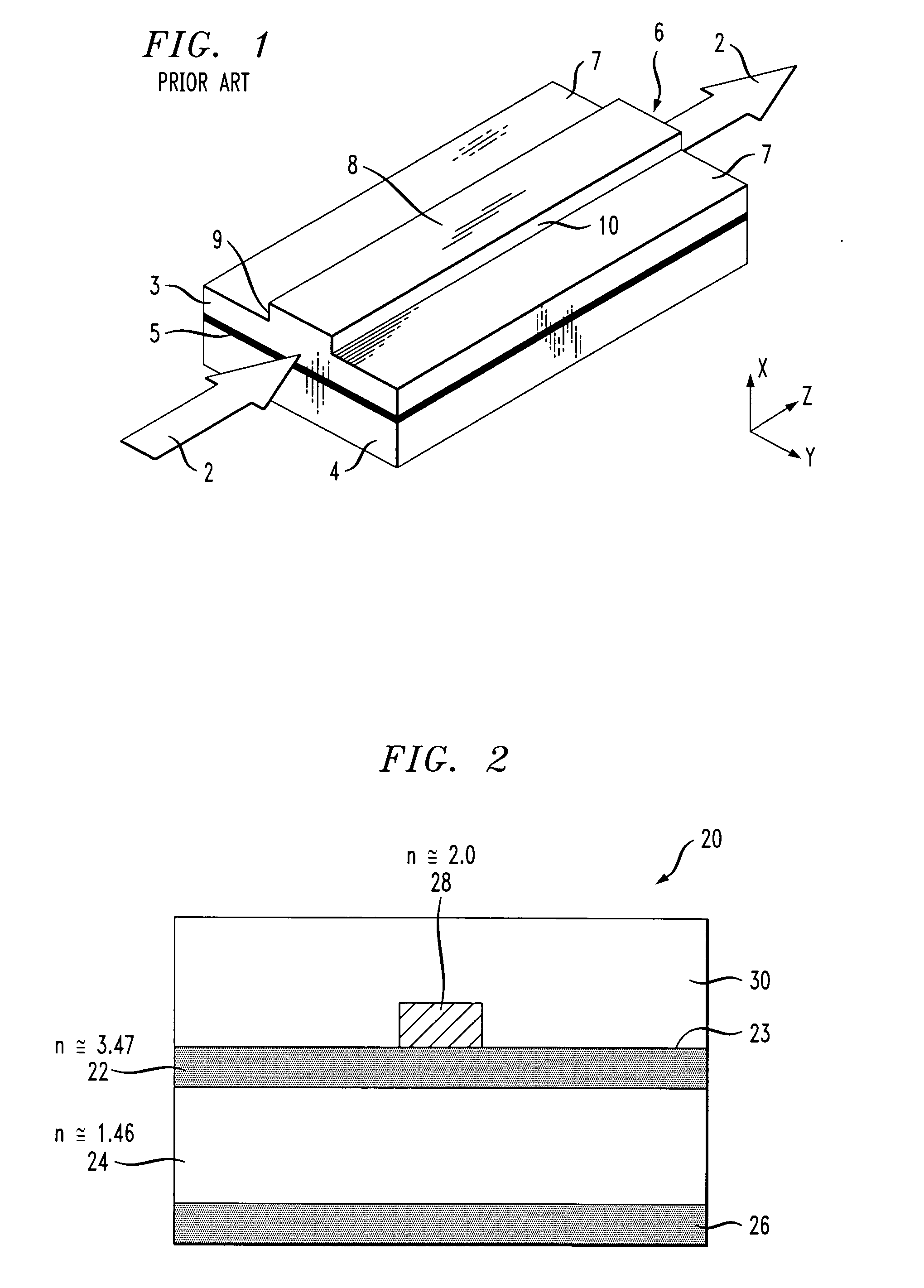

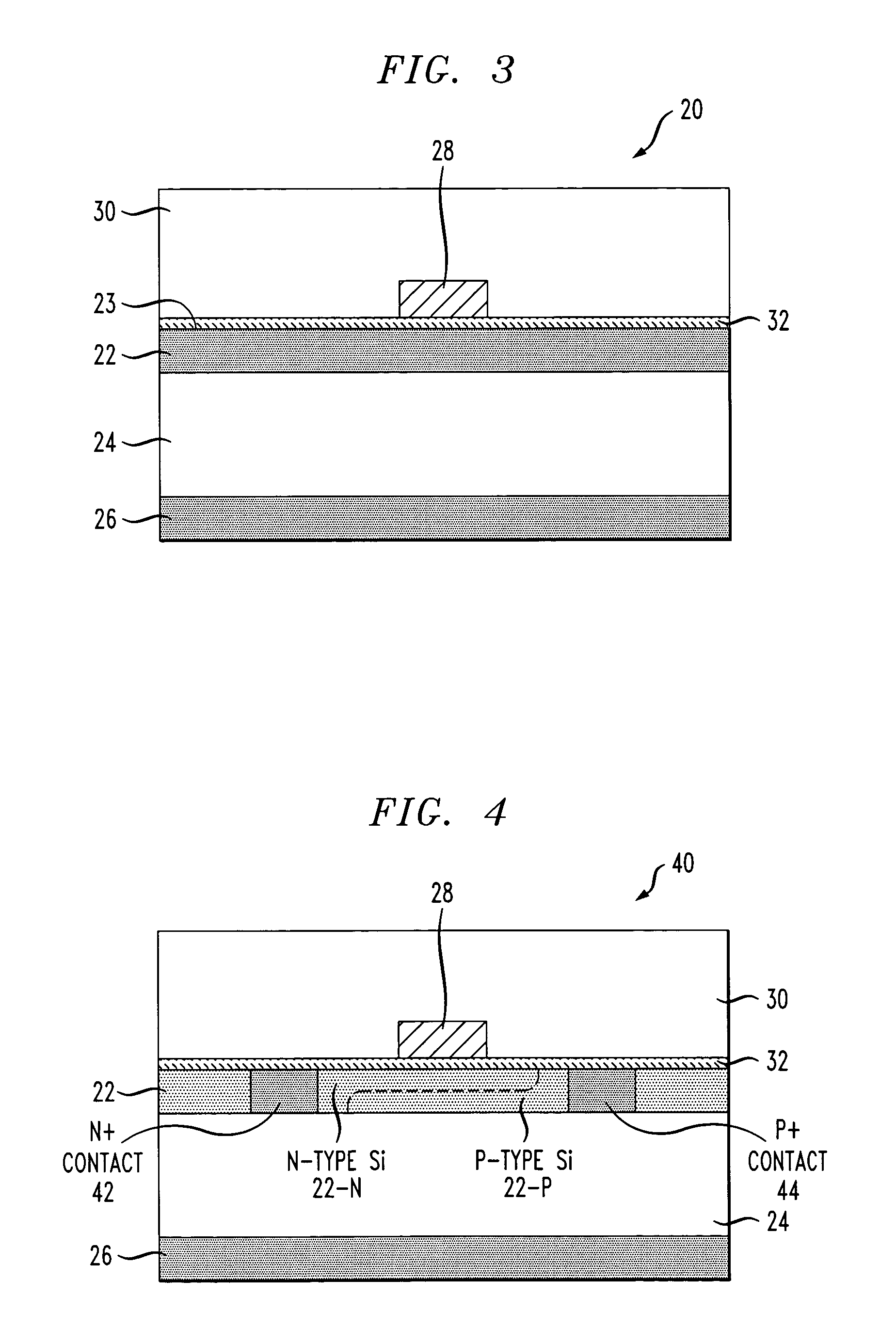

CMOS-compatible integration of silicon-based optical devices with electronic devices

ActiveUS6968110B2Reduce the possibilityReduce yieldTransistorCladded optical fibreCMOSElectrical devices

A conventional CMOS fabrication technique is used to integrate the formation of passive optical devices and active electro-optic devices with standard CMOS electrical devices on a common SOI structure. The electrical devices and optical devices share the same surface SOI layer (a relatively thin, single crystal silicon layer), with various required semiconductor layers then formed over the SOI layer. In some instances, a set of process steps may be used to simultaneously form regions in both electrical and optical devices. Advantageously, the same metallization process is used to provide electrical connections to the electrical devices and the active electro-optic devices.

Owner:CISCO TECH INC

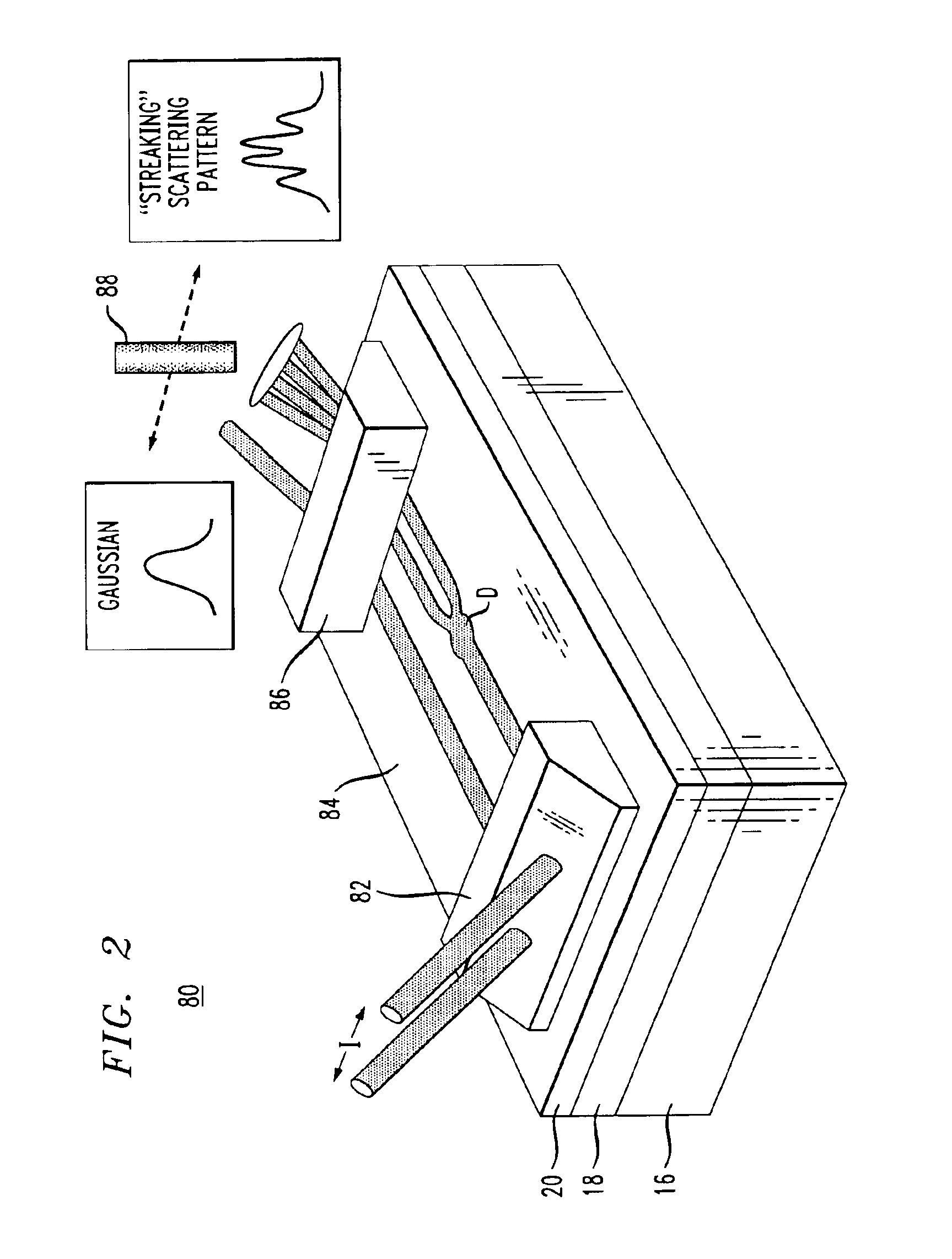

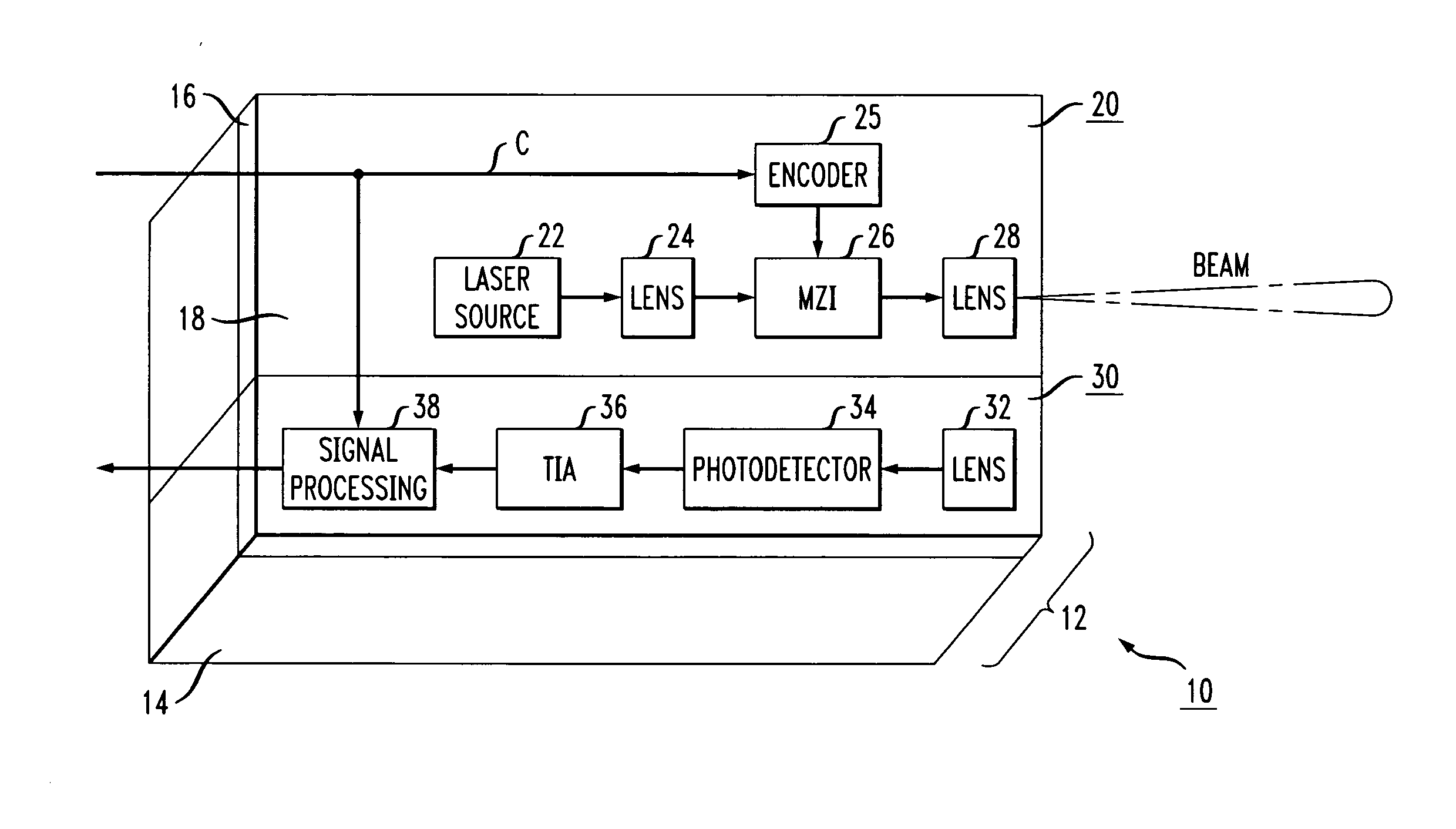

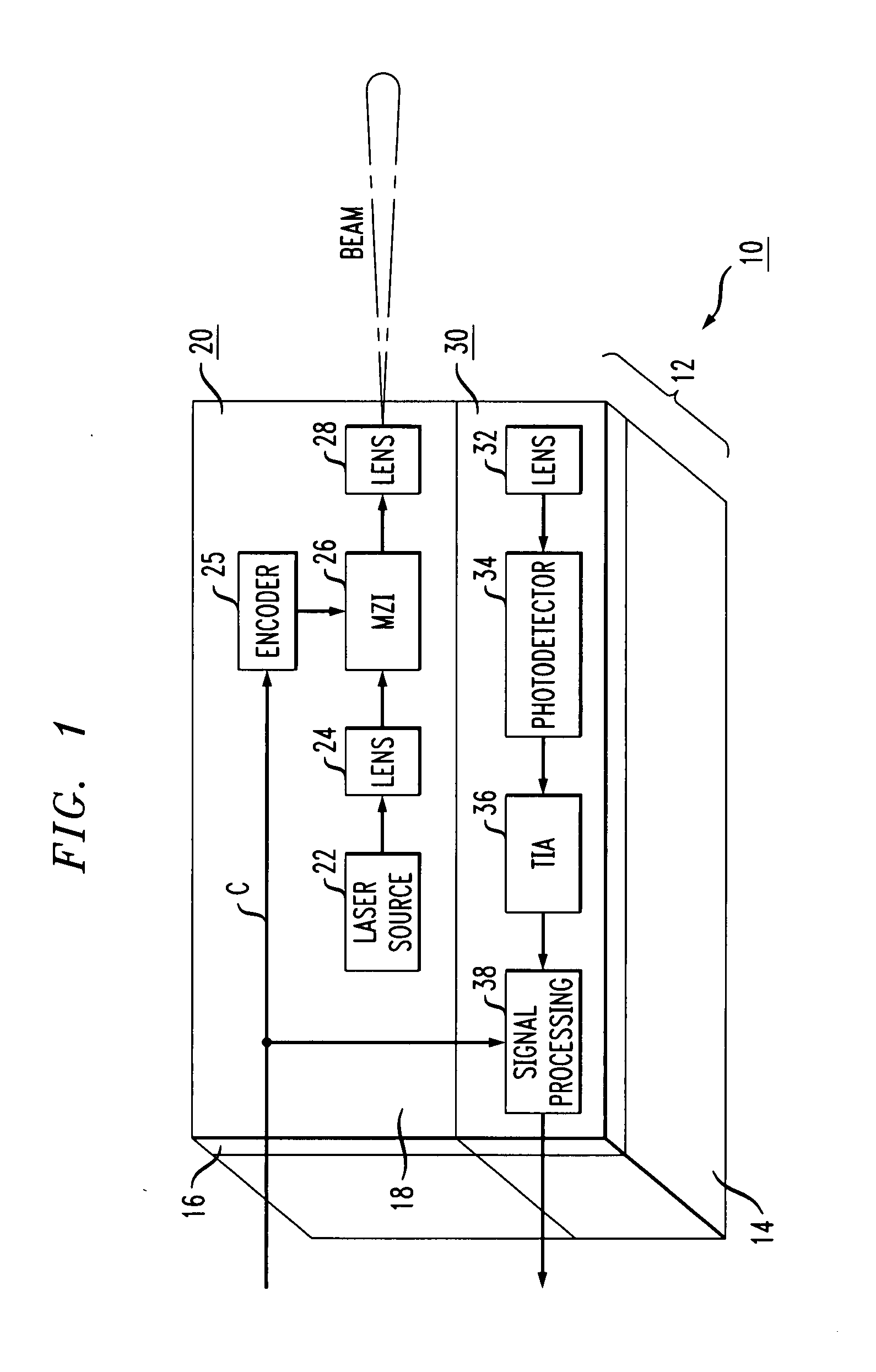

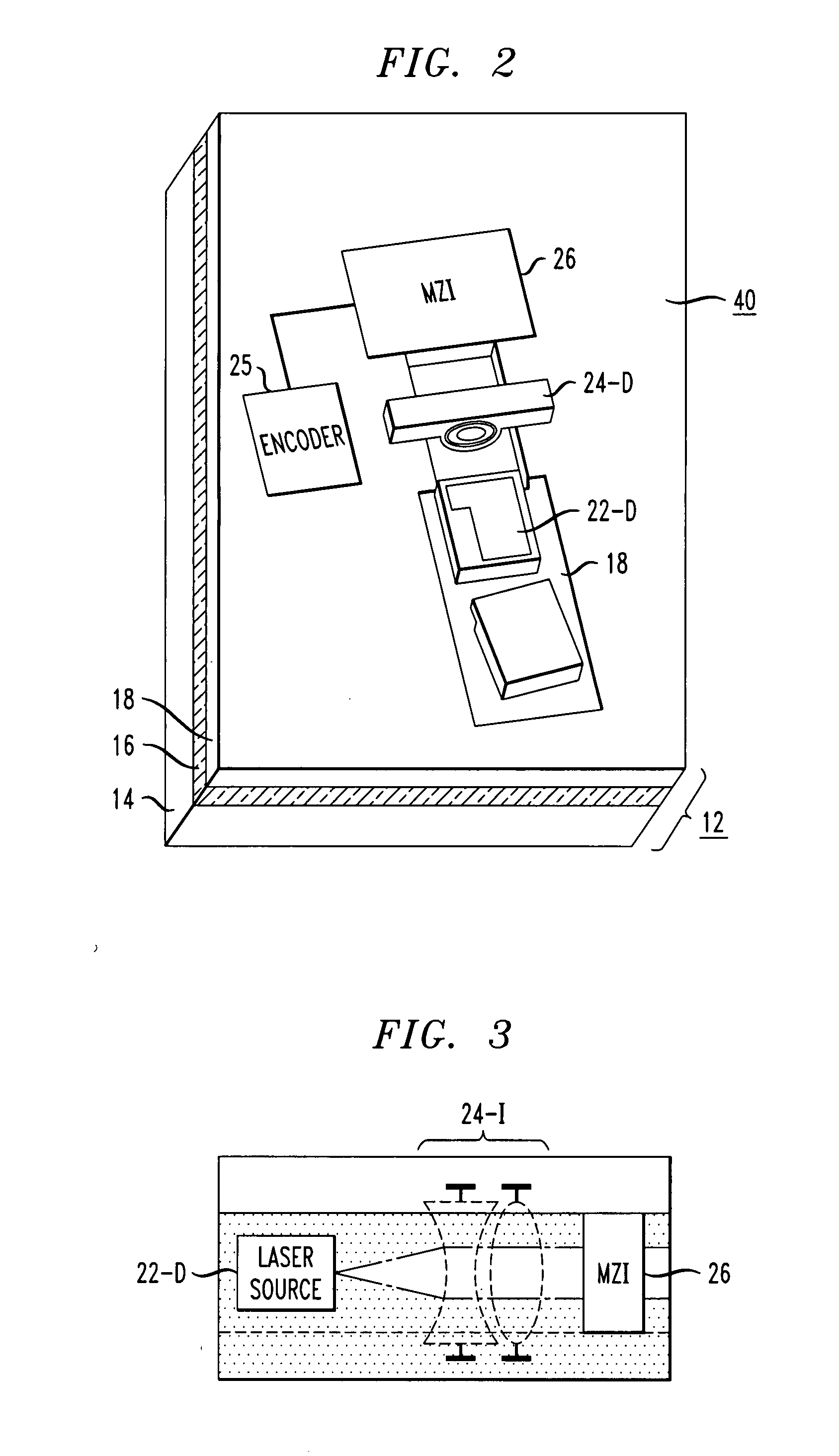

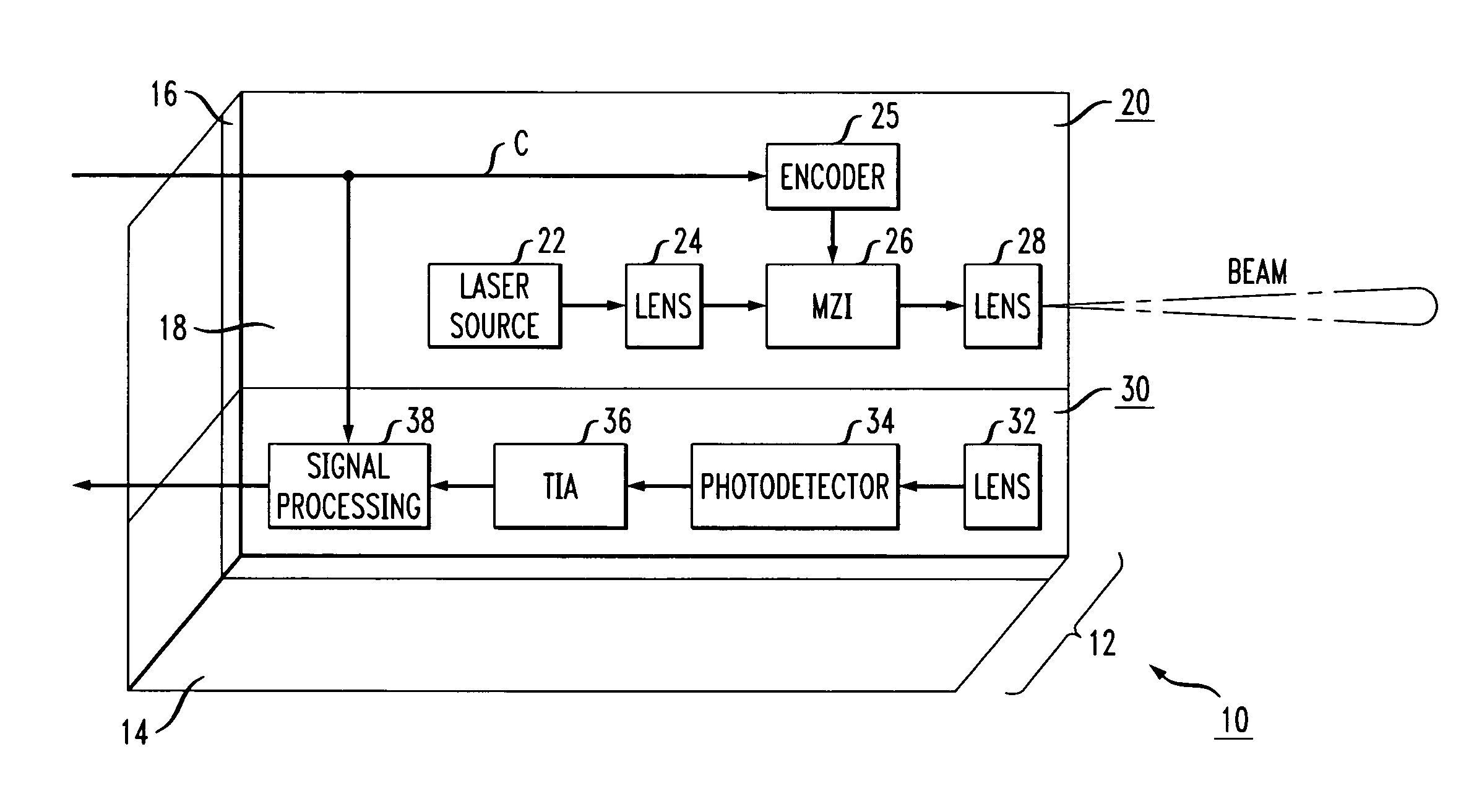

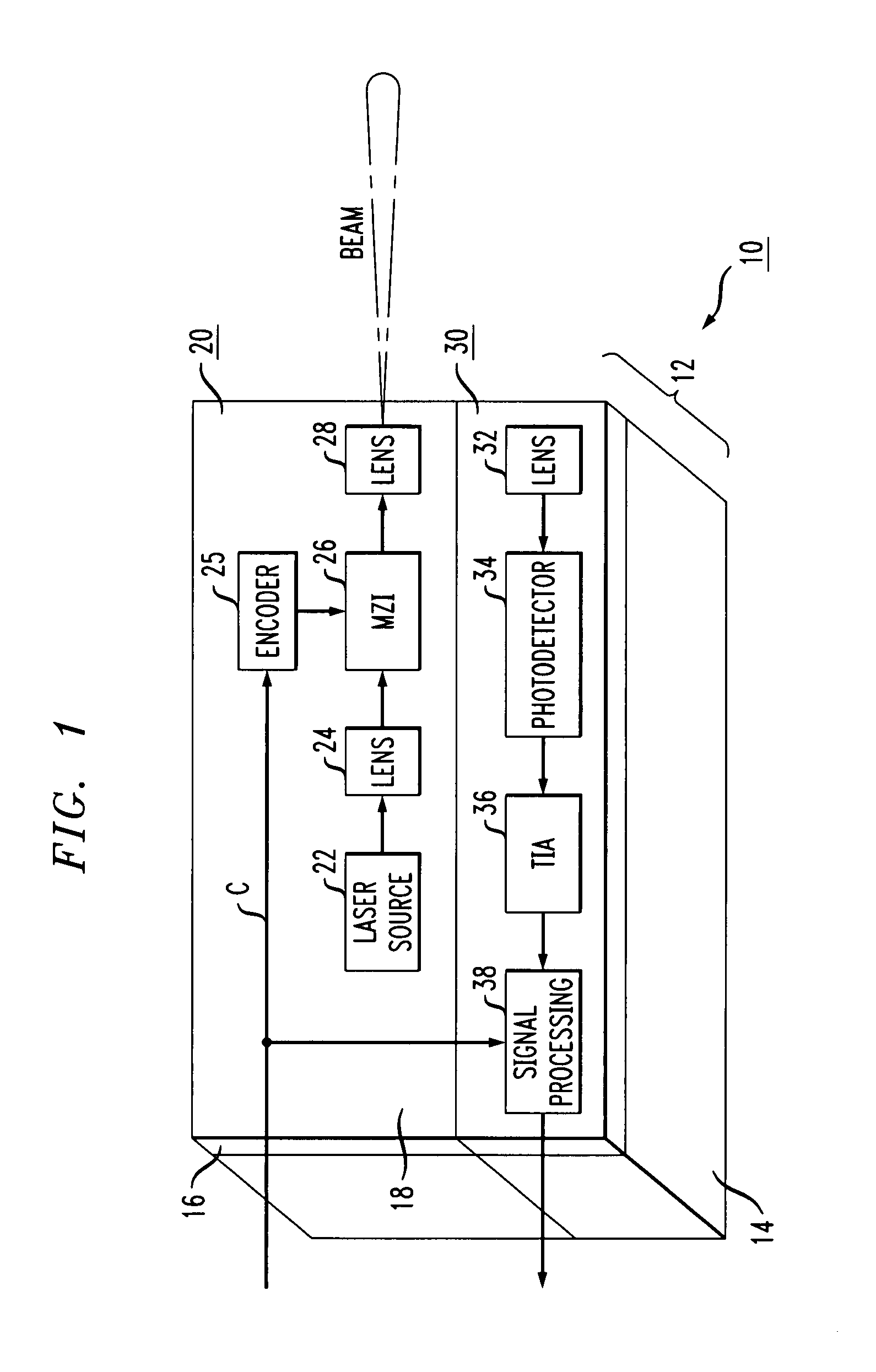

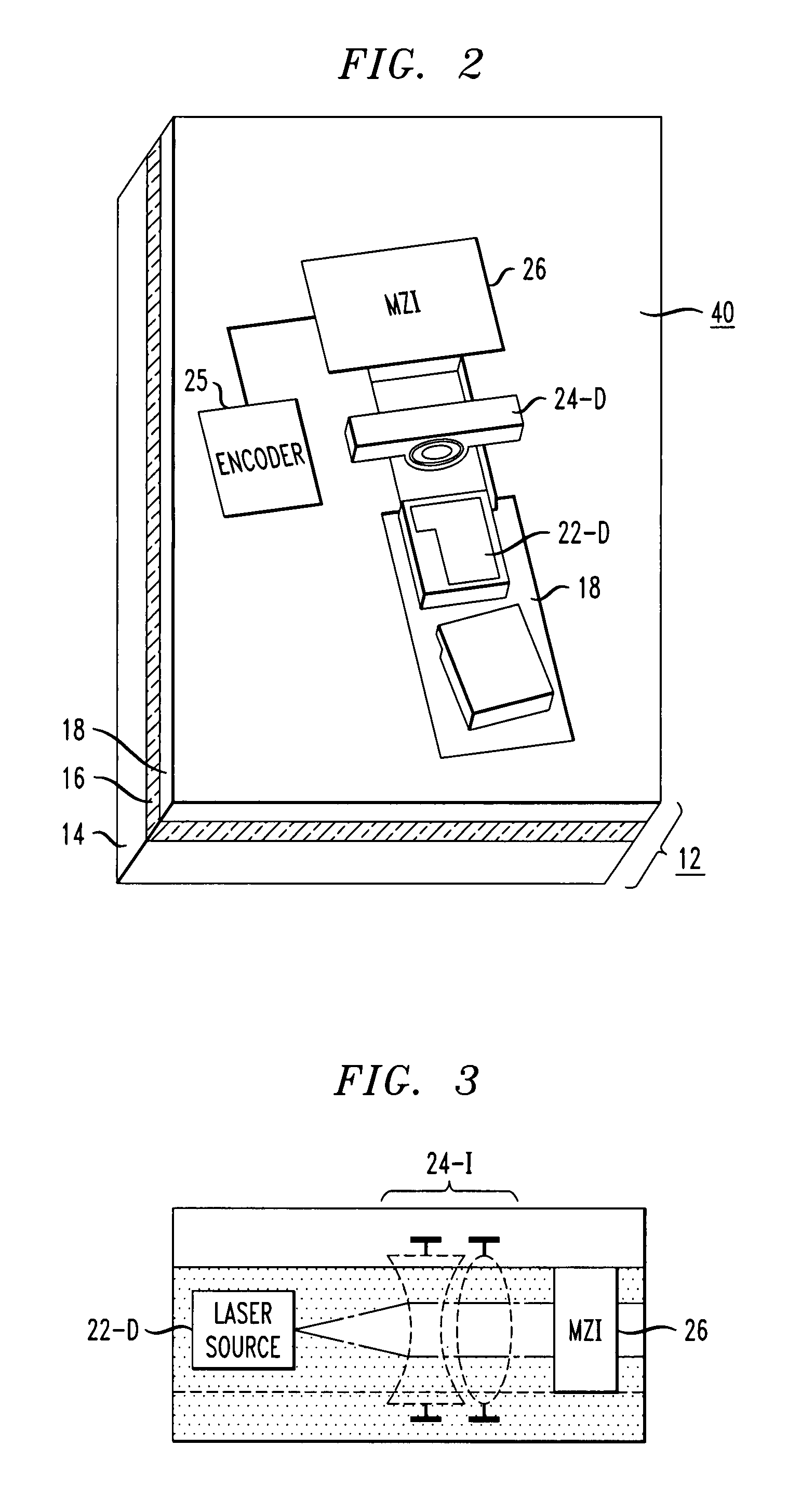

LIDAR system utilizing SOI-based opto-electronic components

ActiveUS20100271614A1Low costImprove reliabilityOptical rangefindersSolid-state devicesOpto electronicCmos fabrication

A compact, integrated LIDAR system utilizes SOI-based opto-electronic components to provide for lower cost and higher reliability as compared to current LIDAR systems. Preferably, an SOI-based LIDAR transmitter and an SOI-based LIDAR receiver (both optical components and electrical components) are integrated within a single module. The various optical and electrical components are formed utilizing portions of the SOI layer and applying well-known CMOS fabrication processes (e.g., patterning, etching, doping), including the formation of additional layer(s) over the SOI layer to provide the required devices. A laser source itself is attached to the SOI arrangement and coupled through an integrated modulation device (such as a Mach-Zehnder interferometer, i.e., MZI) to provide the scanning laser output signal (the scan controlled by, for example, an electrical (encoder) input to the input to the MZI). The return, reflected optical signal is received by a photodetector integrated within the SOI arrangement, where it is thereafter converted into an electrical signal and subjected to various types of signal processing to perform the desired type(s) of signal characterization / signature analysis.

Owner:CISCO TECH INC

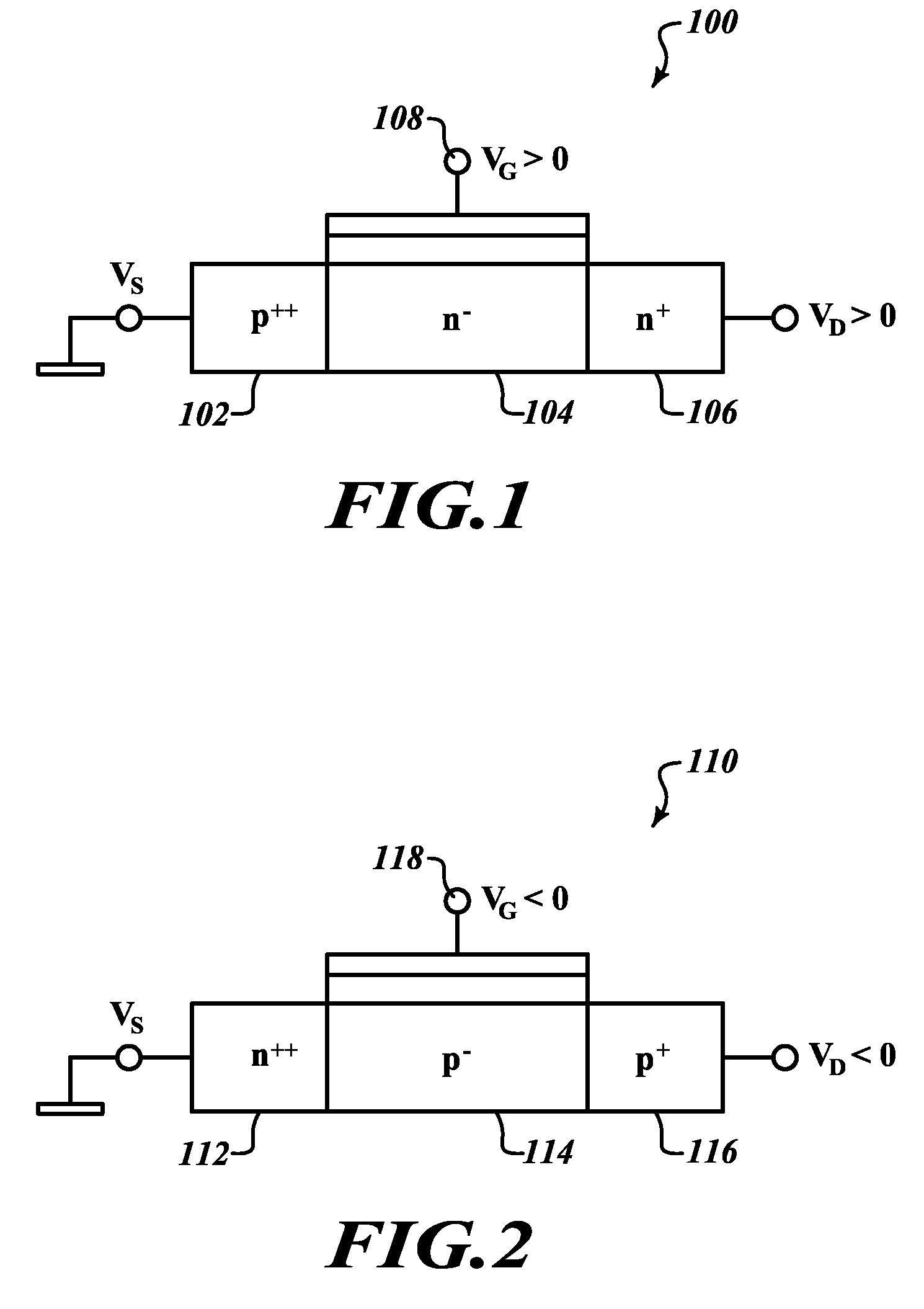

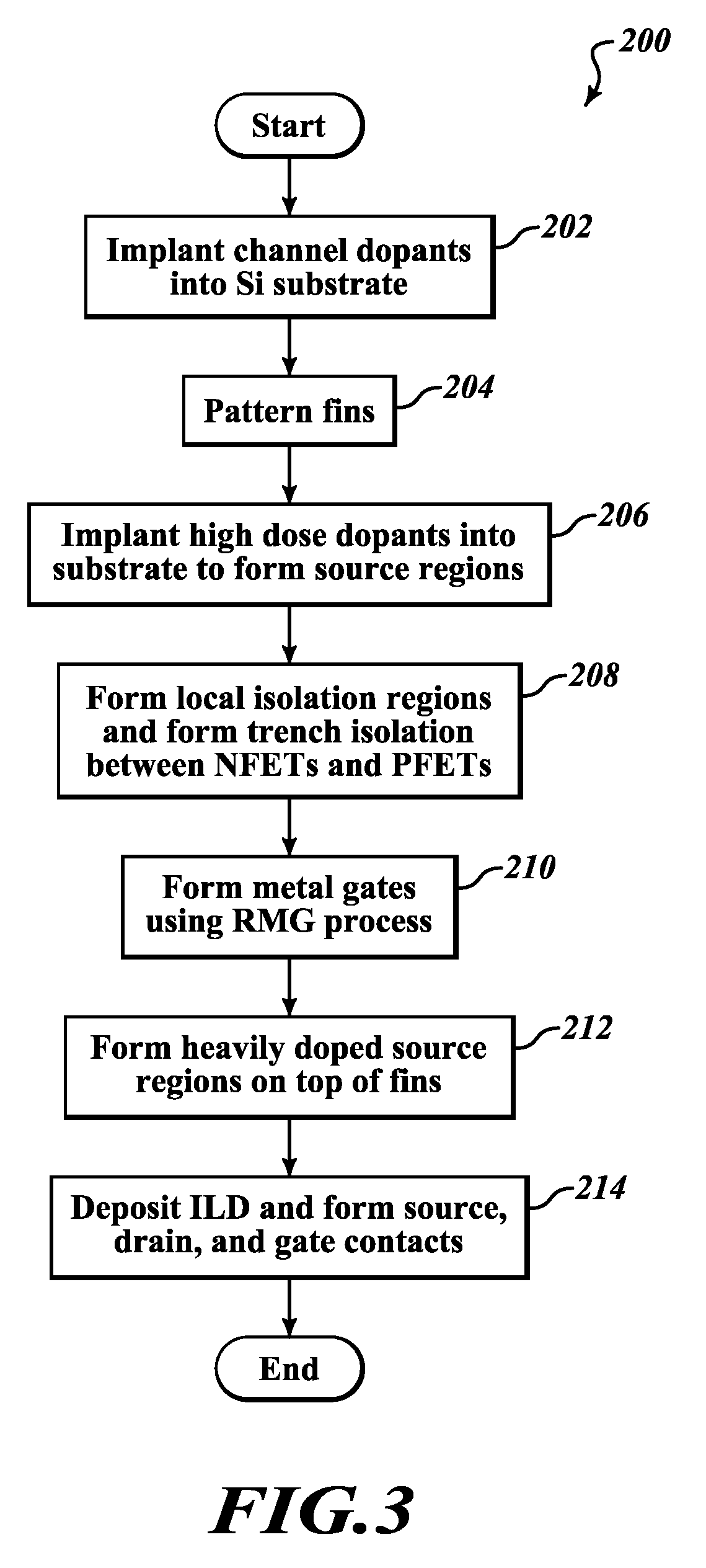

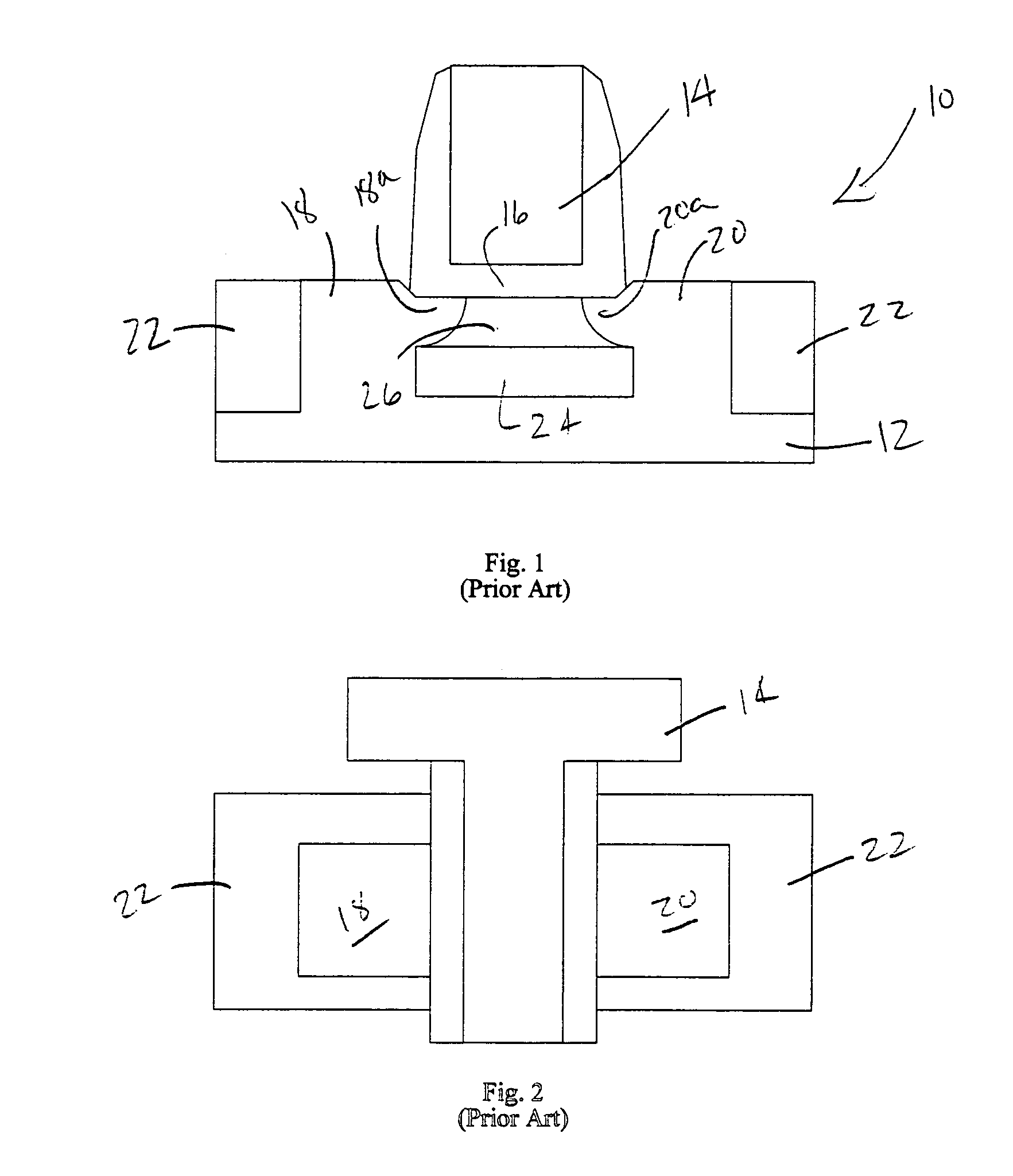

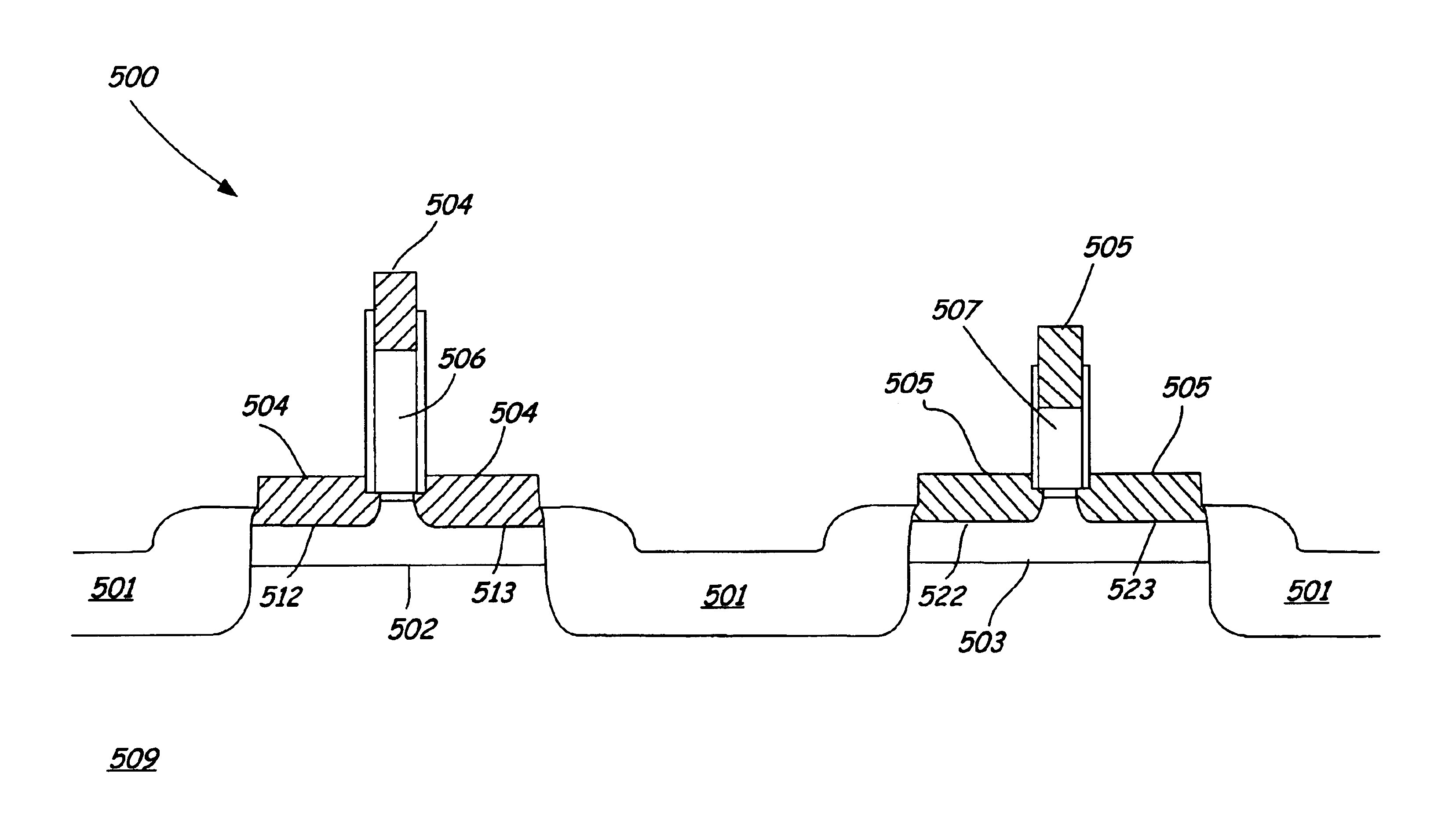

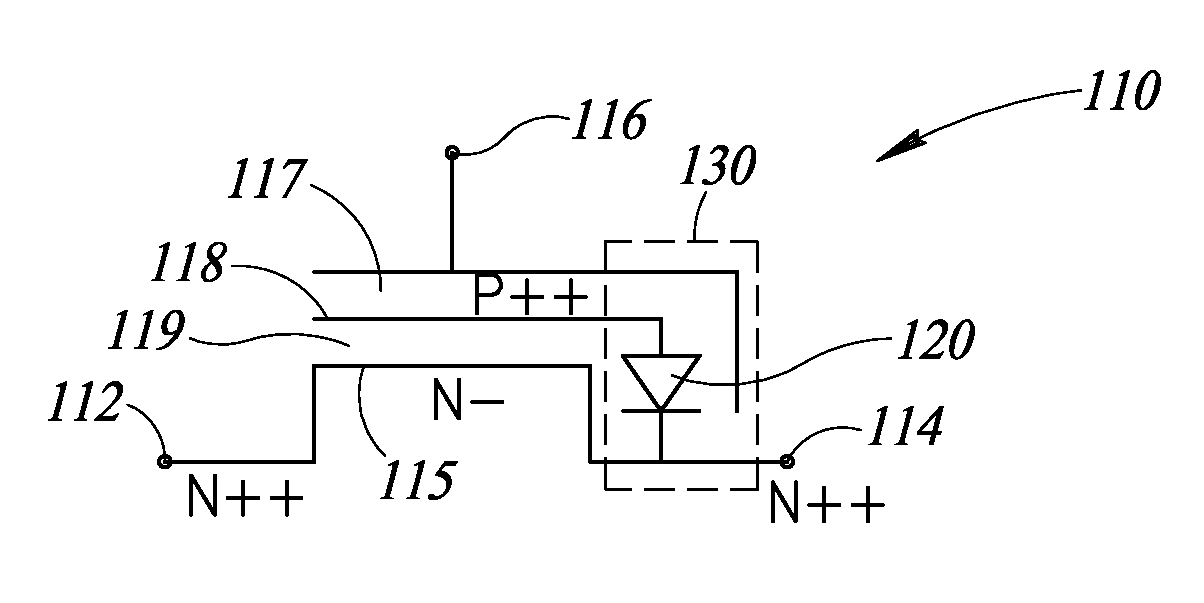

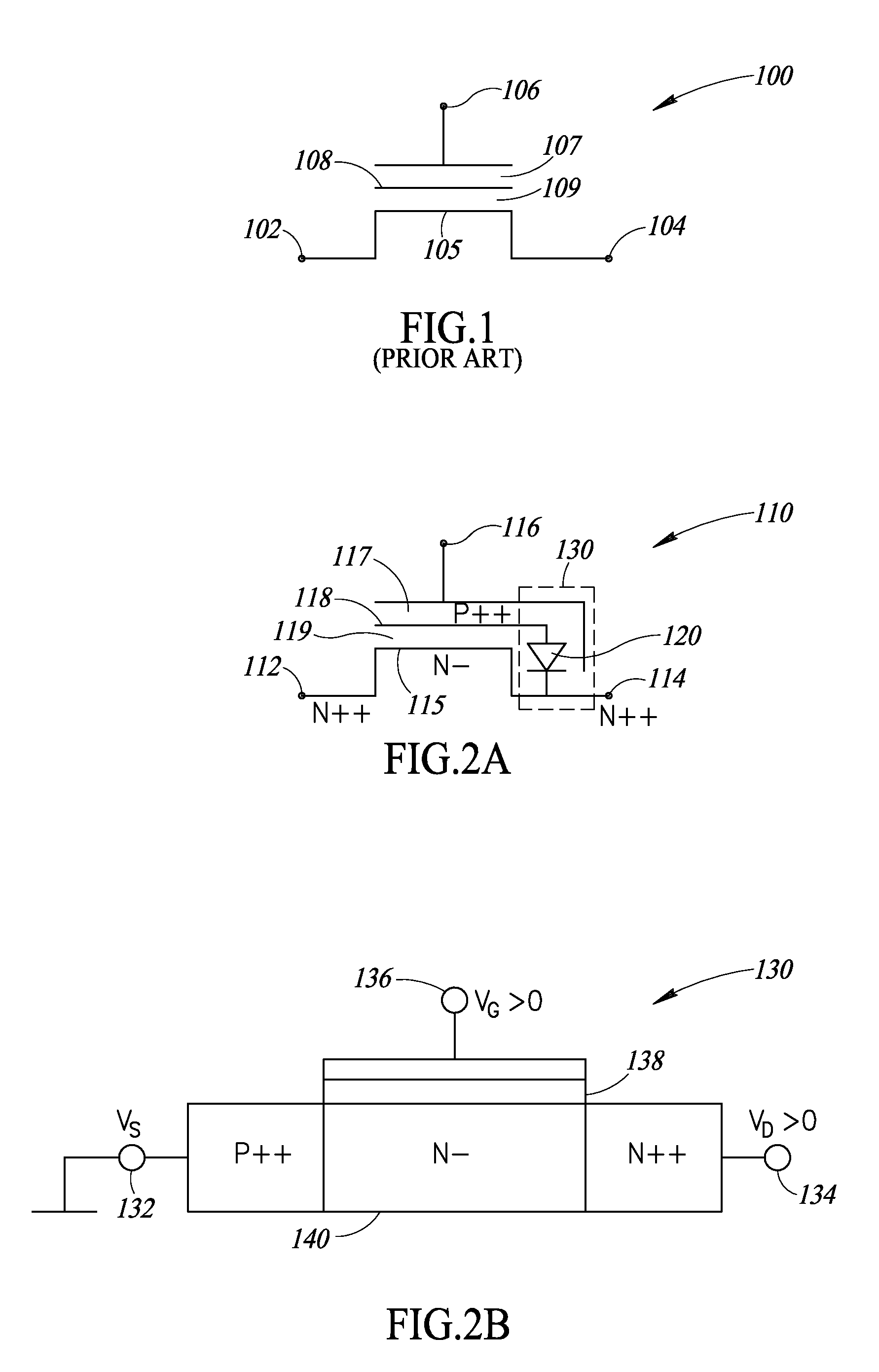

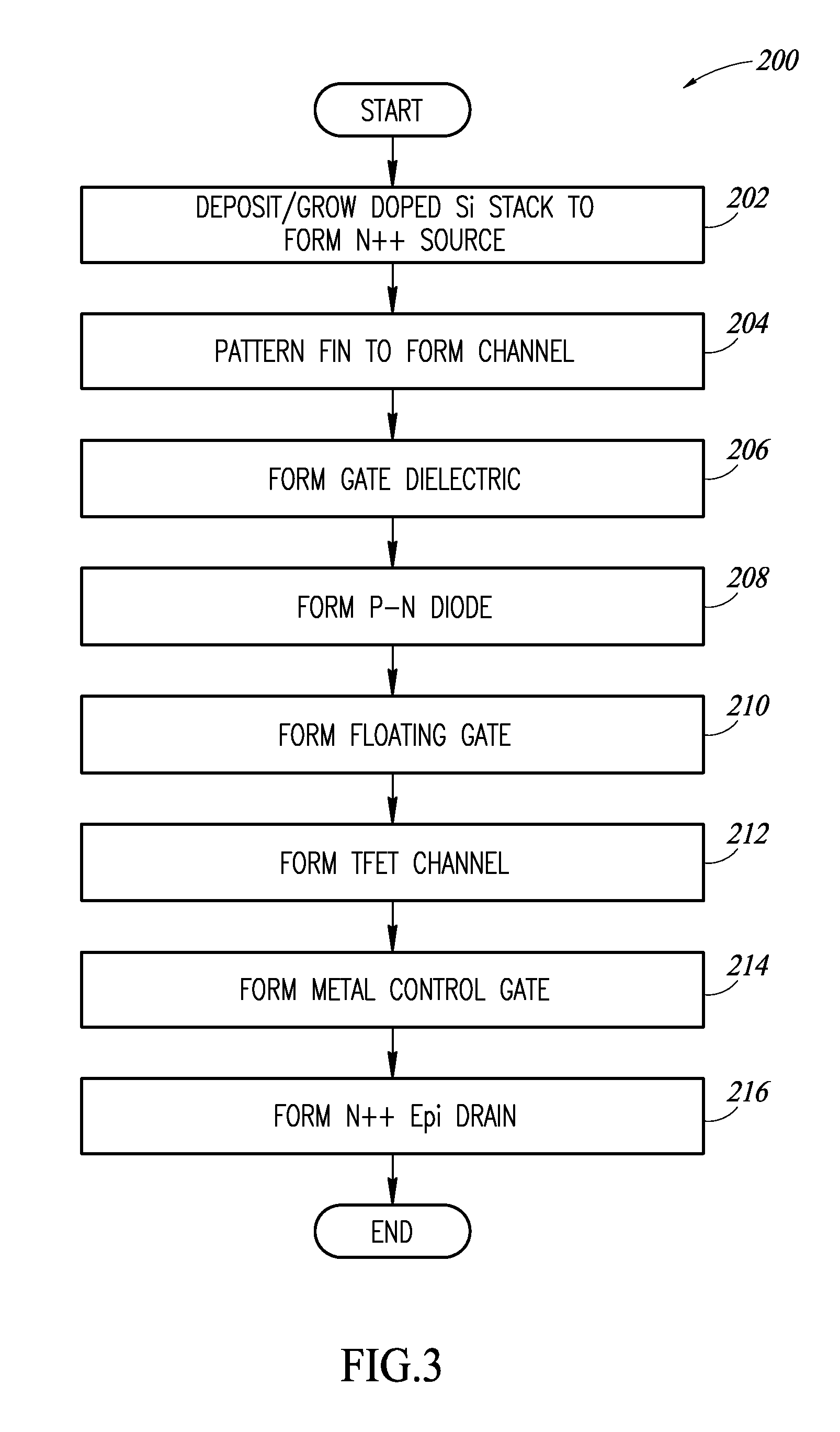

Vertical tunneling finfet

ActiveUS20160293756A1Increase current densityTransistorSemiconductor/solid-state device manufacturingHigh current densityCMOS

A tunneling transistor is implemented in silicon, using a FinFET device architecture. The tunneling FinFET has a non-planar, vertical, structure that extends out from the surface of a doped drain formed in a silicon substrate. The vertical structure includes a lightly doped fin defined by a subtractive etch process, and a heavily-doped source formed on top of the fin by epitaxial growth. The drain and channel have similar polarity, which is opposite that of the source. A gate abuts the channel region, capacitively controlling current flow through the channel from opposite sides. Source, drain, and gate terminals are all electrically accessible via front side contacts formed after completion of the device. Fabrication of the tunneling FinFET is compatible with conventional CMOS manufacturing processes, including replacement metal gate and self-aligned contact processes. Low-power operation allows the tunneling FinFET to provide a high current density compared with conventional planar devices.

Owner:STMICROELECTRONICS SRL

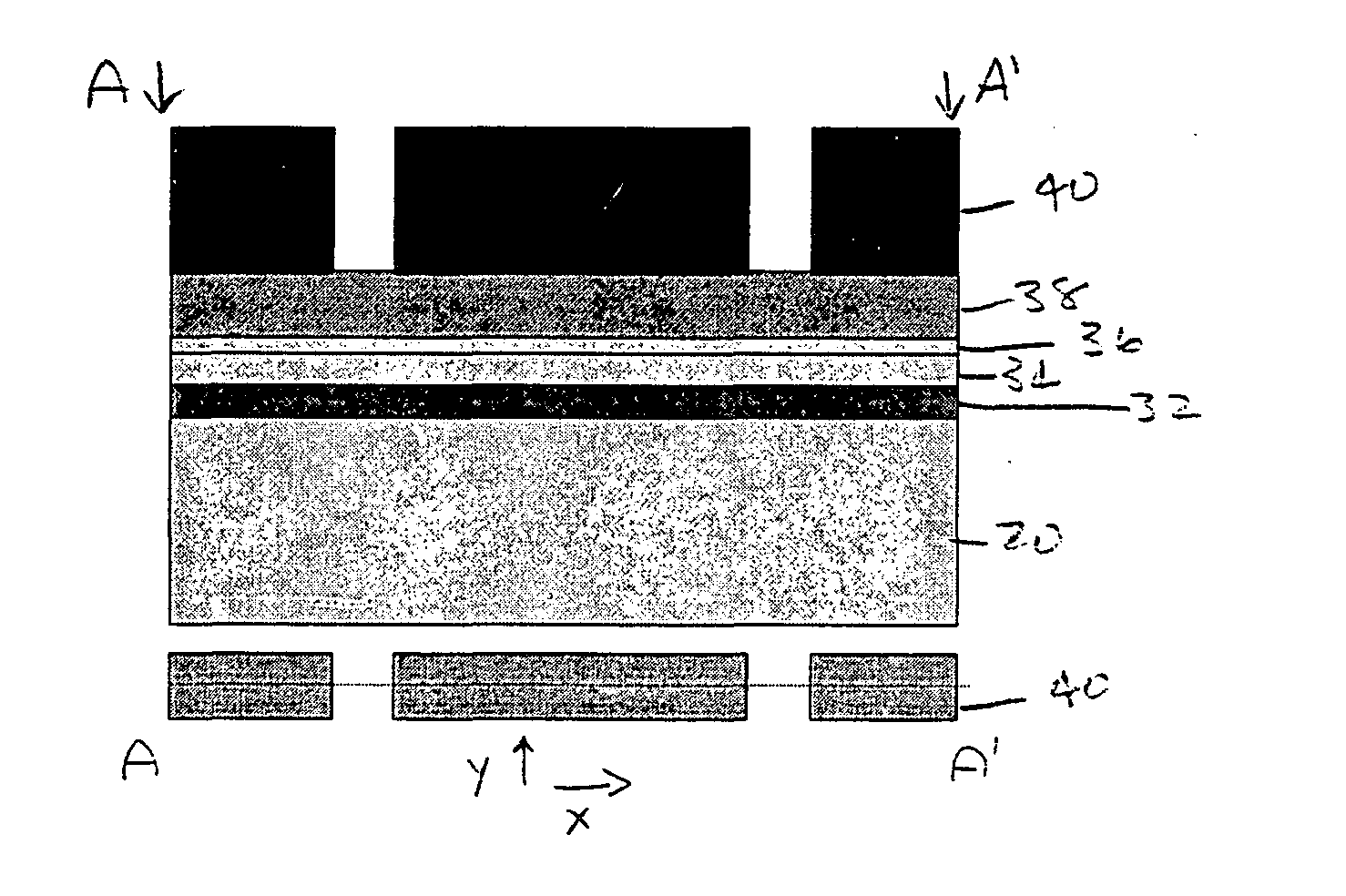

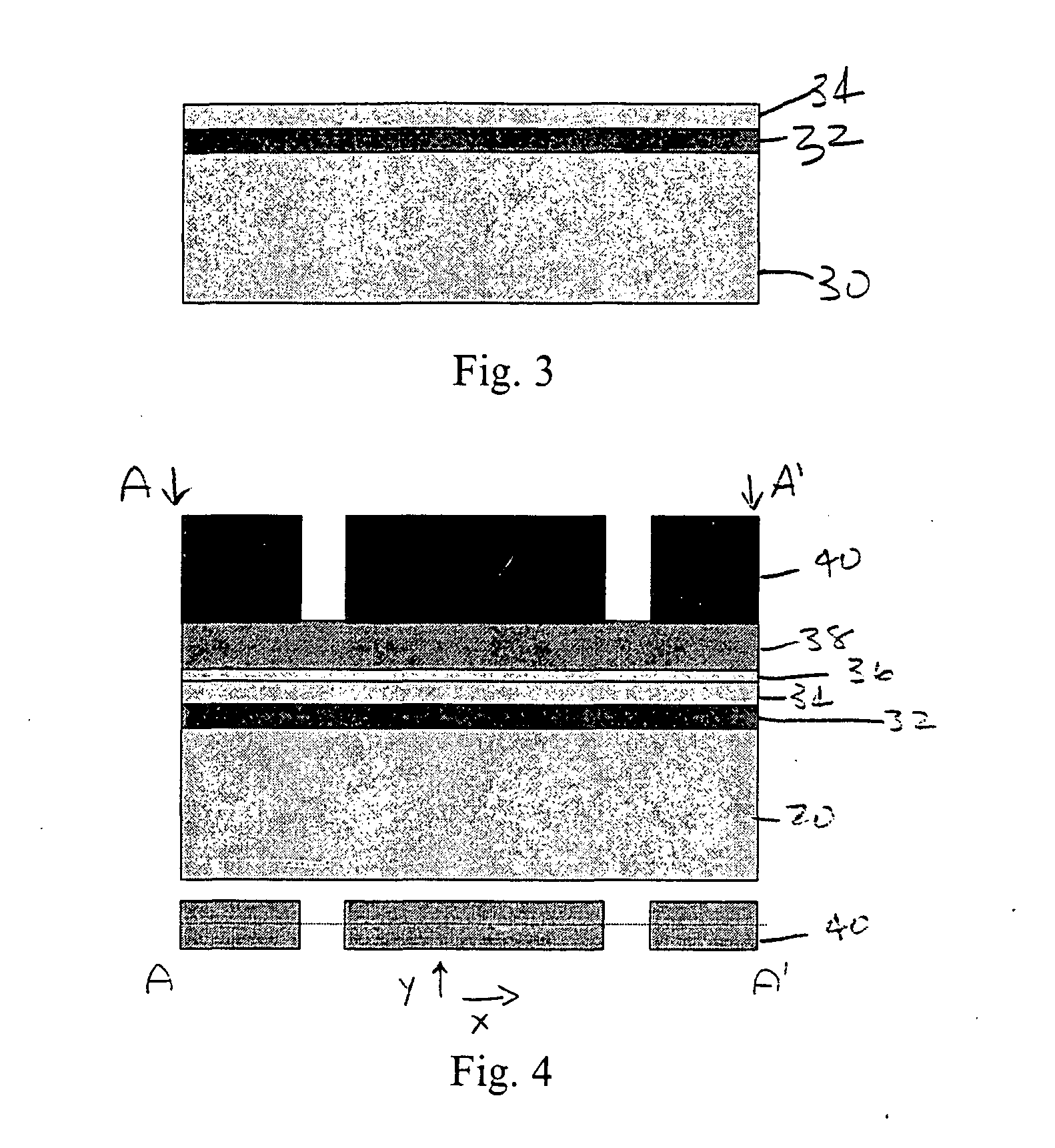

Photoconductor on active pixel image sensor

InactiveUS20040036010A1Low costMass productionTelevision system detailsTelevision system scanning detailsSemiconductor materialsSpectral response

A MOS or CMOS based photoconductor on active pixel image sensor. Thin layers of semi-conductor material, doped to PIN or NIP photoconducting layers, located above MOS and / or CMOS pixel circuits produce an array of layered photodiodes. Positive and negative charges produced in the layered photodiodes are collected and stored as electrical charges in the MOS and / or CMOS pixel circuits. The present invention also provides additional MOS or CMOS circuits for reading out the charges and for converting the charges into images. With the layered photodiode of each pixel fabricated as continuous layers of charge generating material on top of the MOS and / or CMOS pixel circuits, extremely small pixels are possible with almost 100 percent packing factors. MOS and CMOS fabrication techniques permit sensor fabrication at very low costs. In preferred embodiments all of the sensor circuits are incorporated on or in a single crystalline substrate along with the sensor pixel circuits. Techniques are disclosed for tailoring the spectral response of the sensor for particular applications.

Owner:E PHOCUS

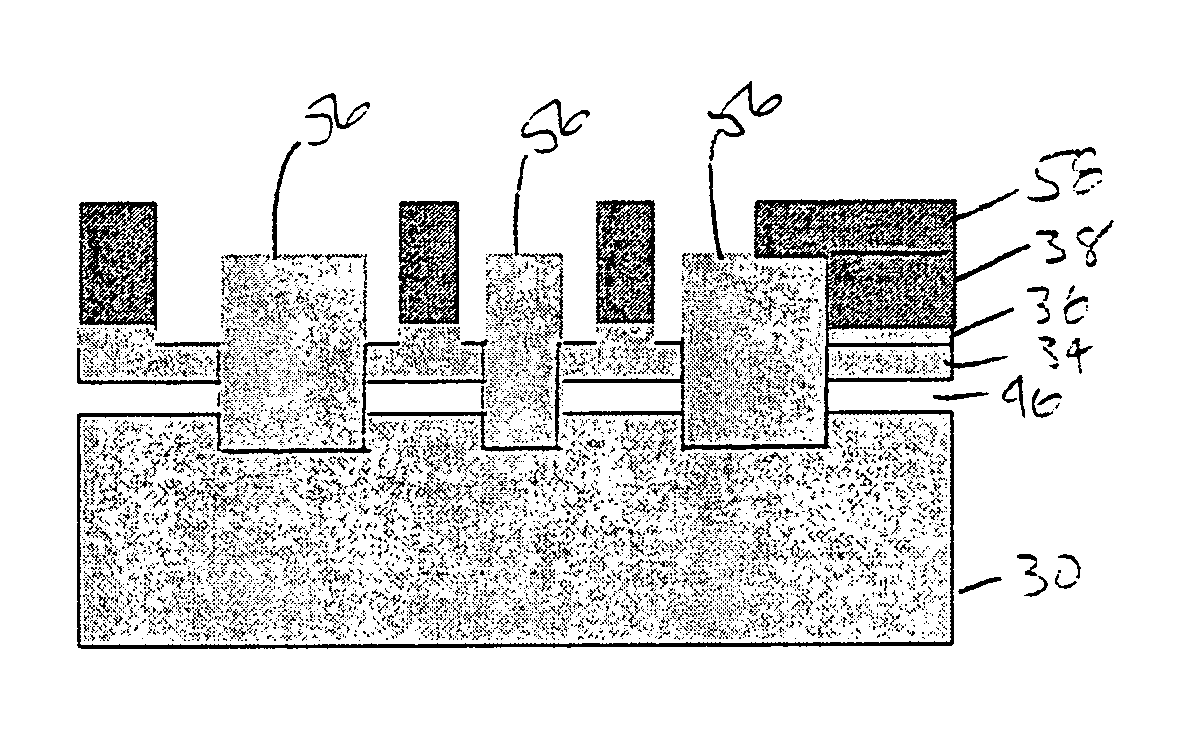

Method of making air gap isolation by making a lateral EPI bridge for low K isolation advanced CMOS fabrication

InactiveUS6268637B1Semiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

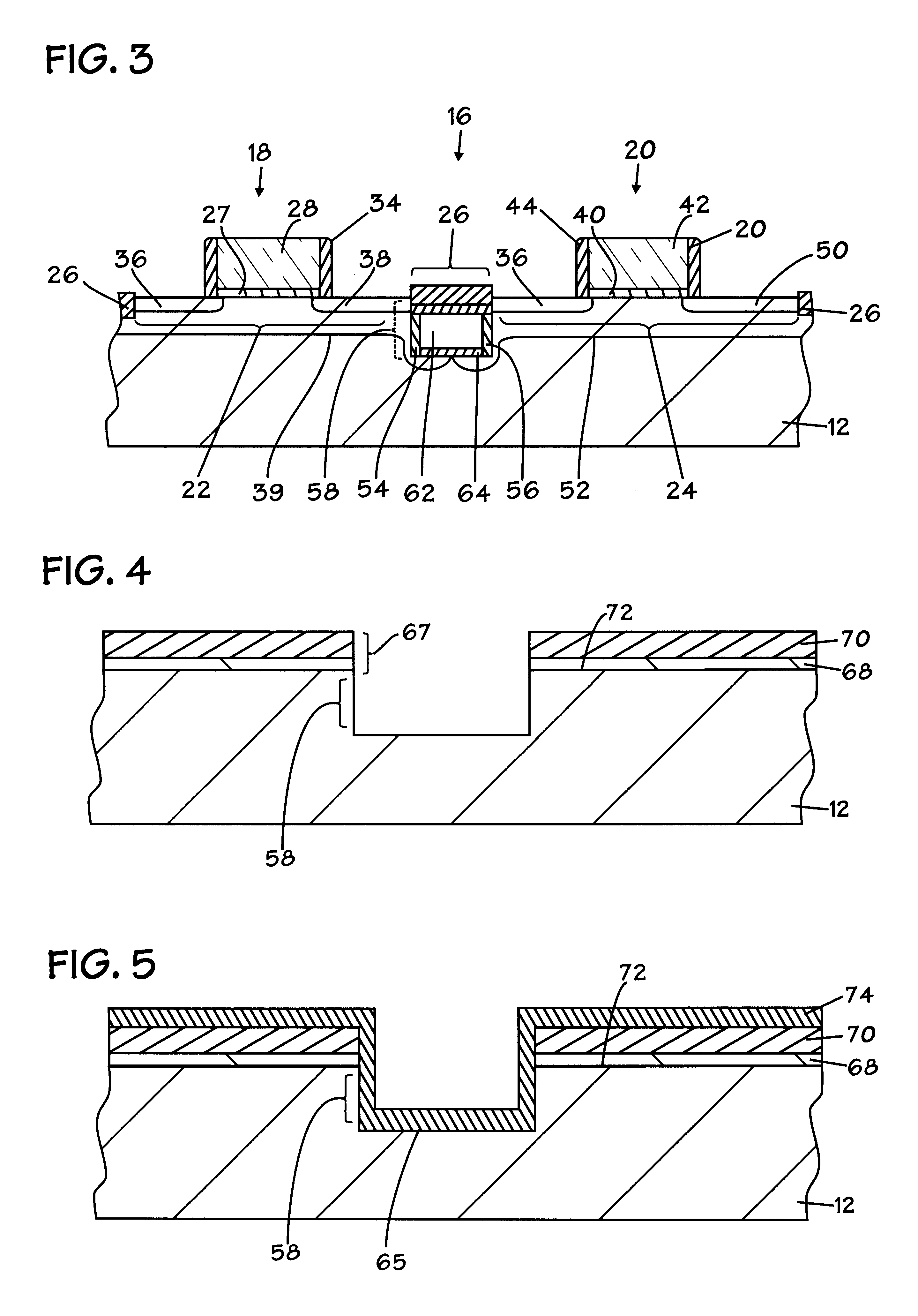

An isolation structure and a method of making the same are provided. In one aspect, the method includes the steps of forming a trench in a substrate and forming a first insulating sidewall in the trench and a second insulating in the trench in spaced-apart relation to the first insulating sidewall. A bridge layer is formed between the first and the second sidewalls. The bridge layer, the first and second sidewalls, and the substrate define an air gap in the trench. The isolation structure exhibits a low capacitance in a narrow structure. Scaling is enhanced and the potential for parasitic leakage current due to non-planarity is reduced.

Owner:GLOBALFOUNDRIES INC

Buried guard ring and radiation hardened isolation structures and fabrication methods

ActiveUS7304354B2Reduce and eliminate effectLow costTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

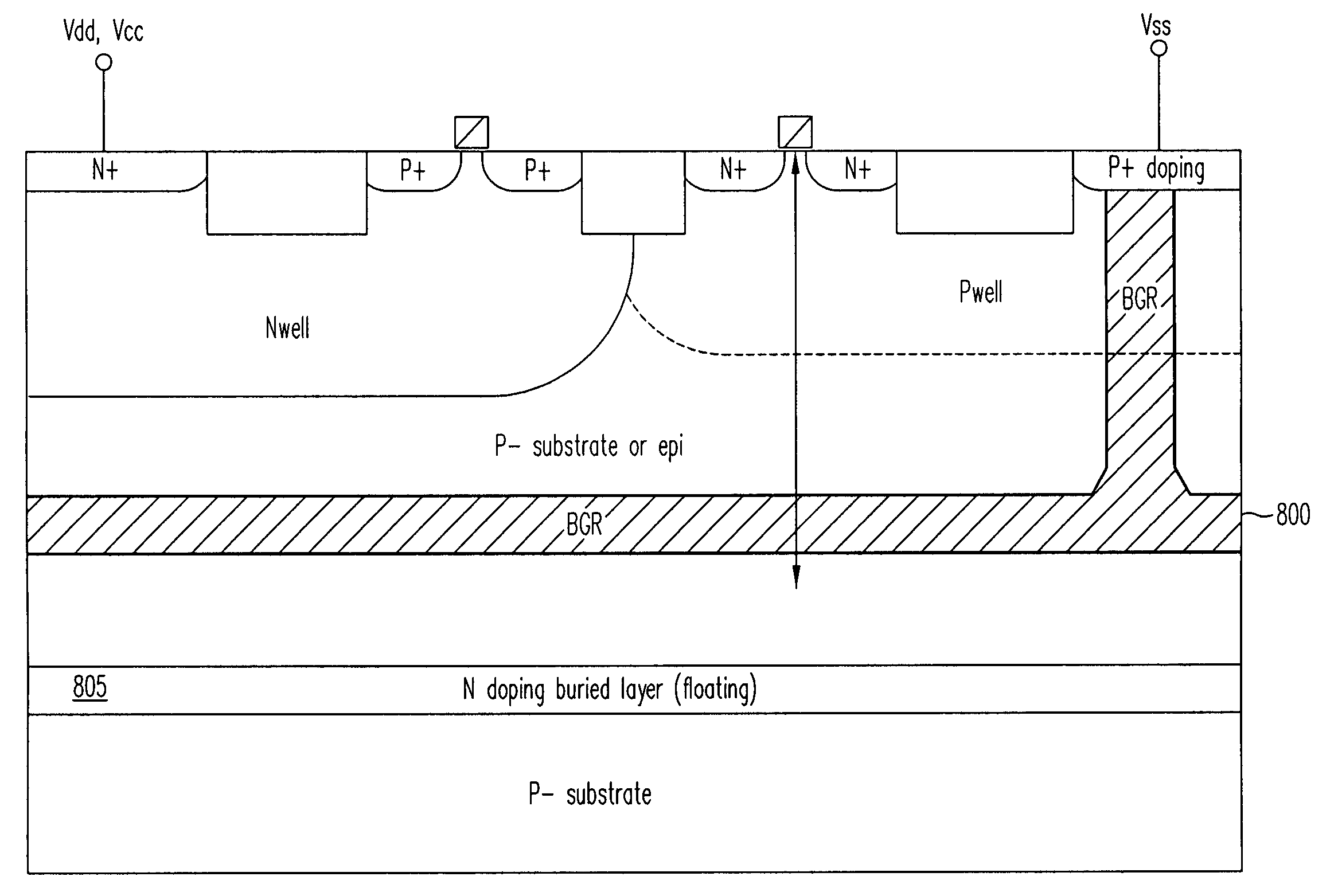

Semiconductor devices can be fabricated using conventional designs and process but including specialized structures to reduce or eliminate detrimental effects caused by various forms of radiation. Such semiconductor devices can include the one or more parasitic isolation devices and / or buried guard ring structures disclosed in the present application. The introduction of design and / or process steps to accommodate these novel structures is compatible with conventional CMOS fabrication processes, and can therefore be accomplished at relatively low cost and with relative simplicity.

Owner:SILICON SPACE TECH

LIDAR system utilizing SOI-based opto-electronic components

ActiveUS7936448B2Low costImprove reliabilityOptical rangefindersSolid-state devicesPhotodetectorMach–Zehnder interferometer

Owner:CISCO TECH INC

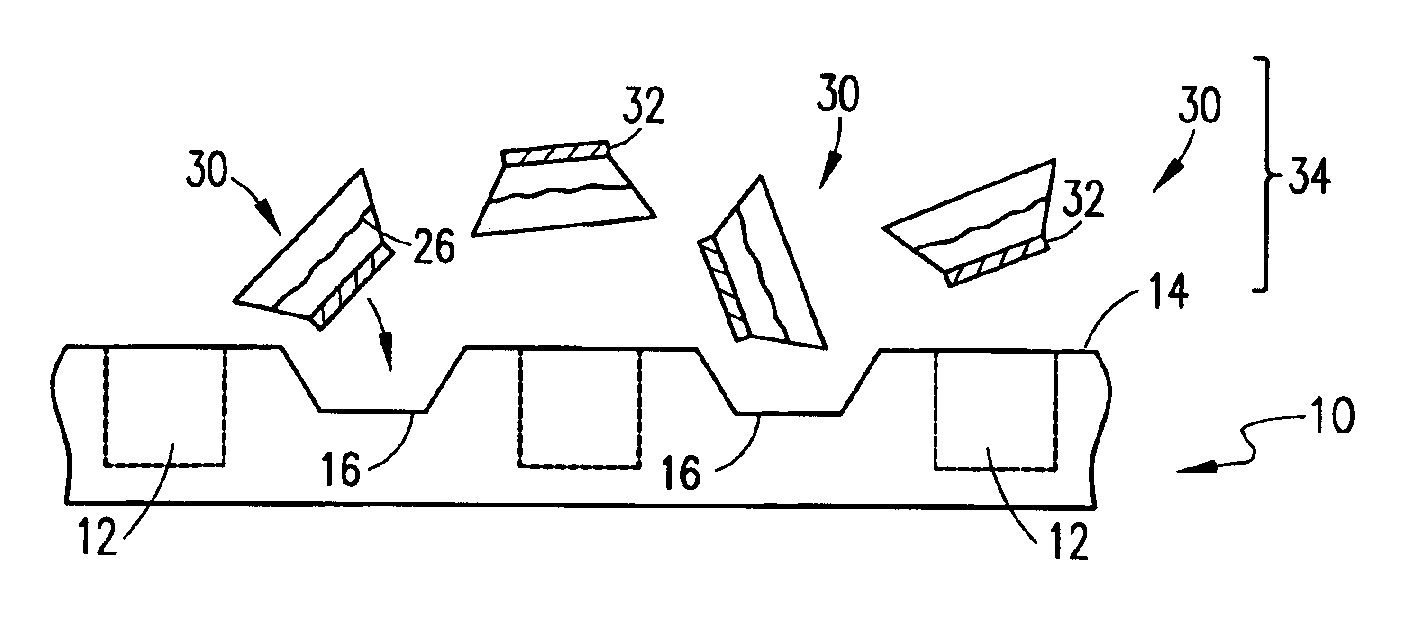

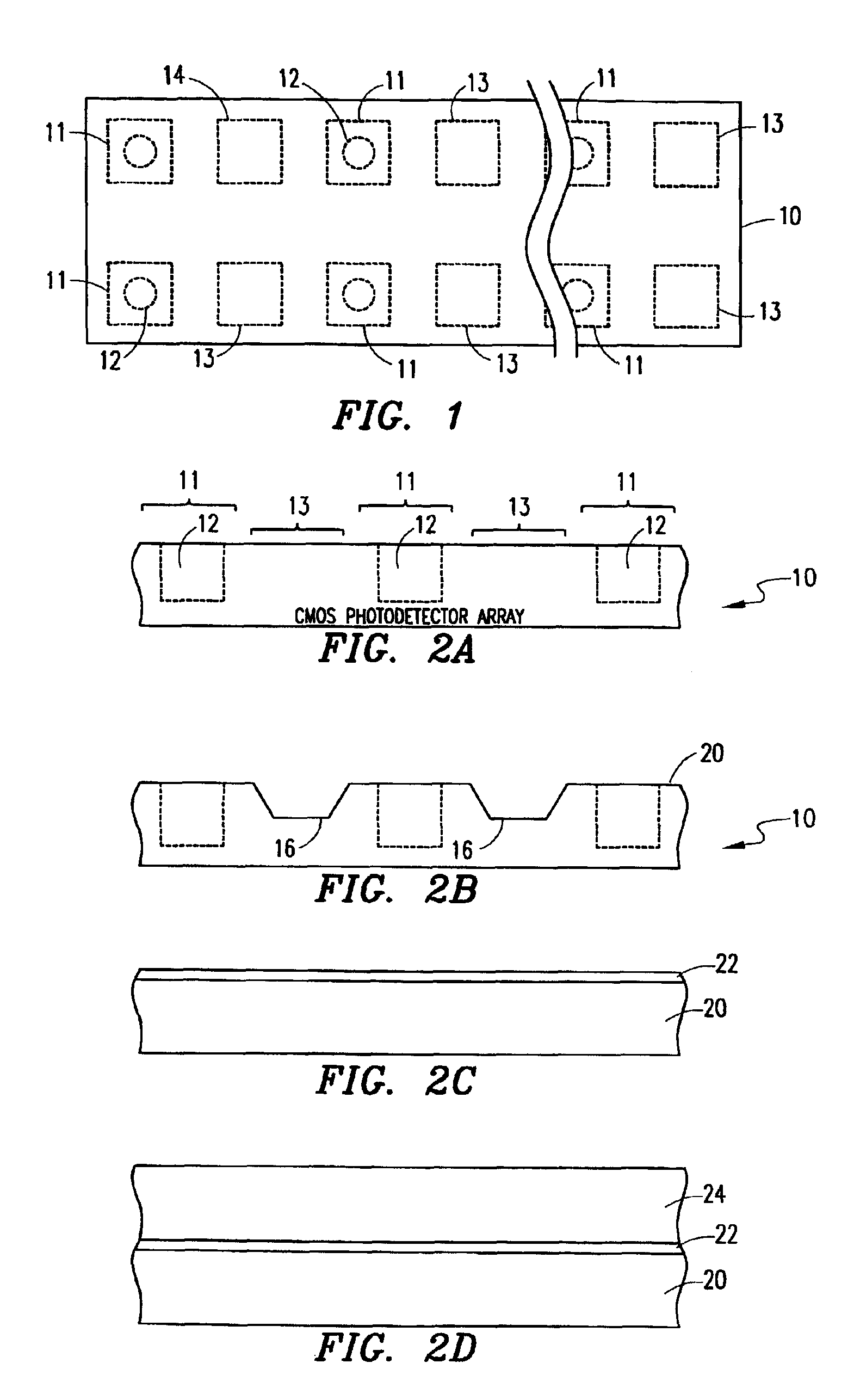

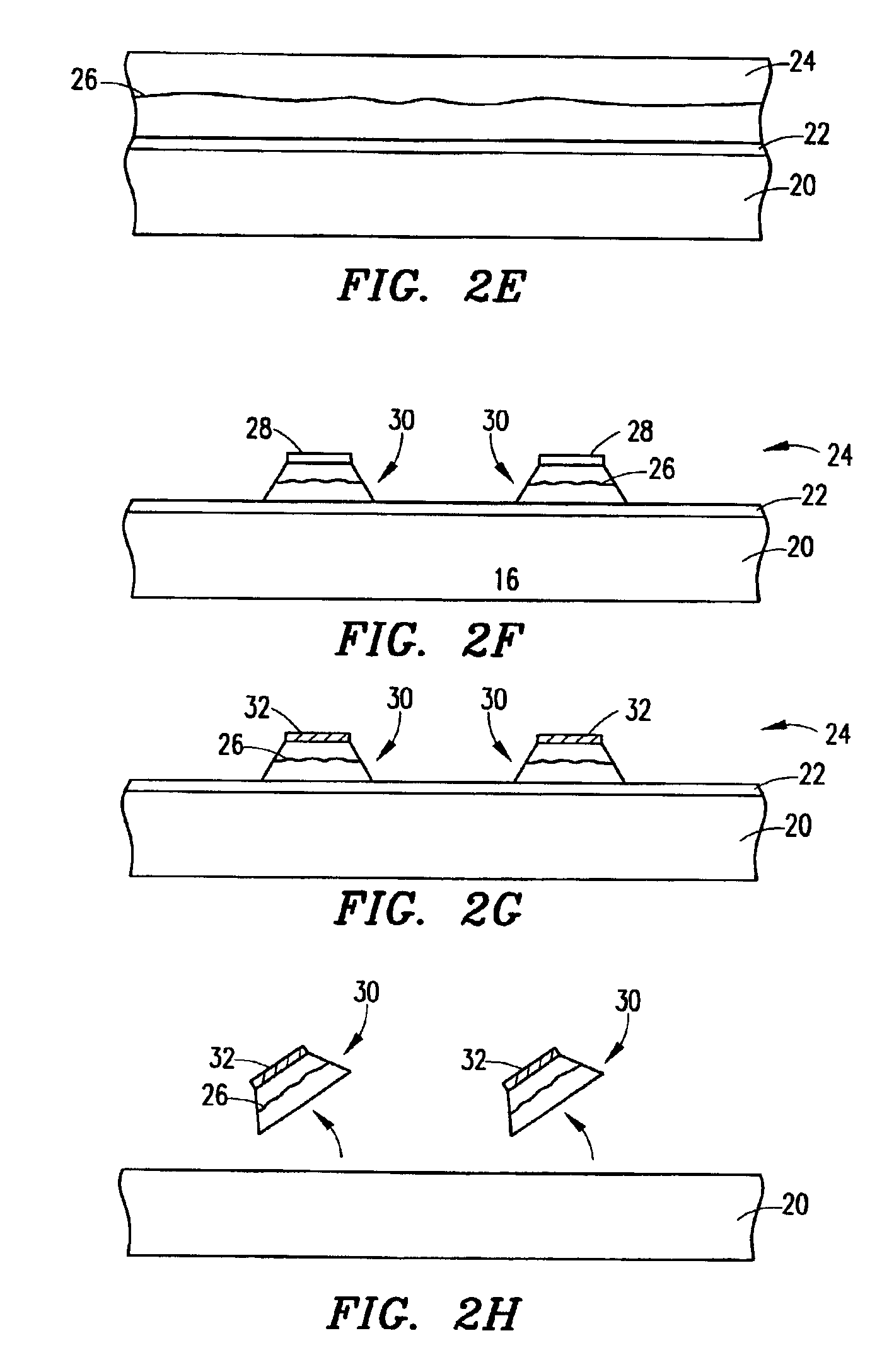

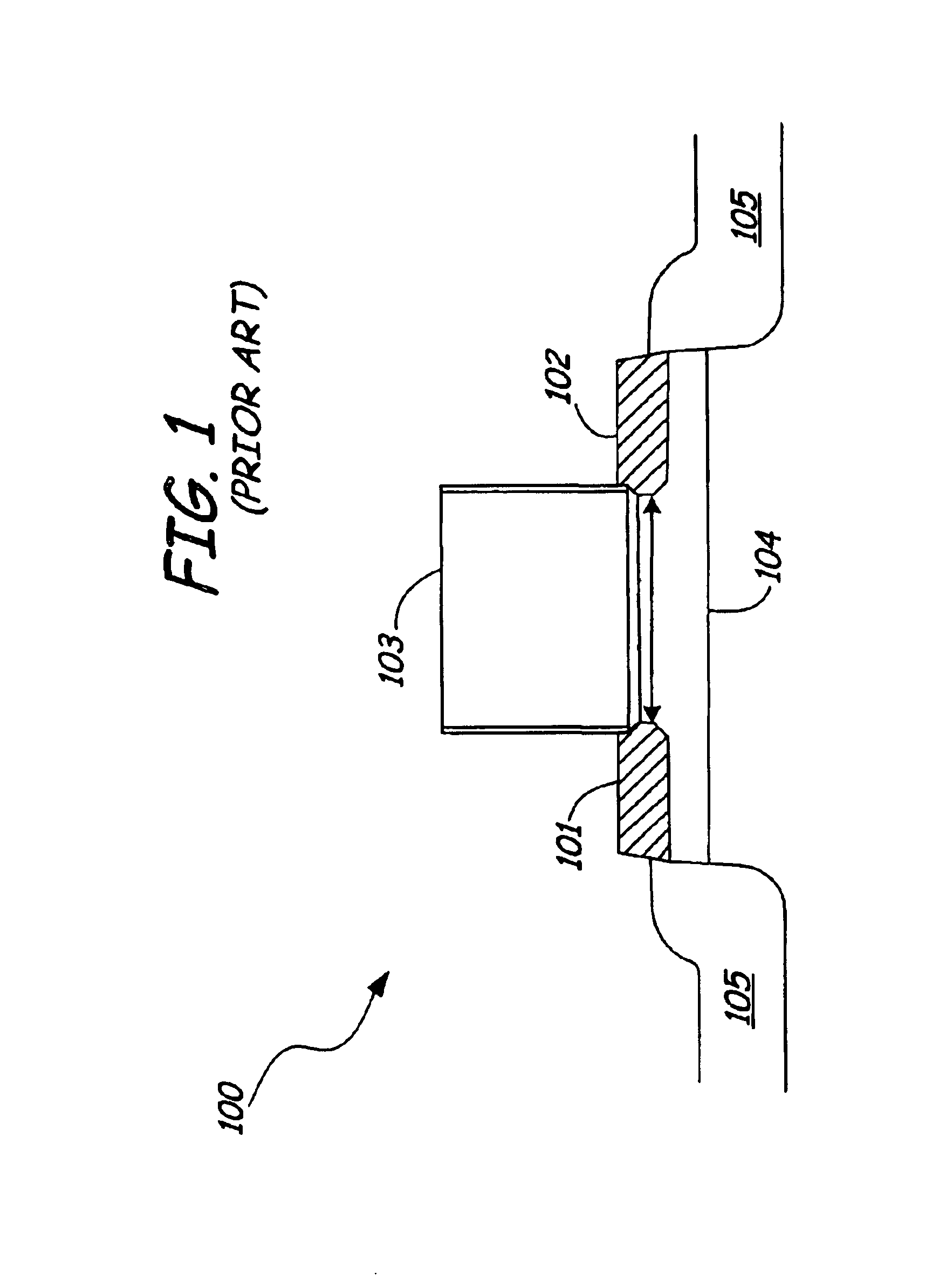

Optical excitation/detection device and method for making same using fluidic self-assembly techniques

The disclosure is directed toward an optical excitation / detection device that includes an arrayed plurality of photodetectors and separately formed photoemitters, as well as a method for making such a device. A CMOS fabricated photodetector array including a plurality of individual photoreceptors is selectively etched back between photoreceptor locations to reveal a plurality of recessed regions having a certain geographic profile. A plurality of semiconductor blocks, each having light emitting capability and each having a certain geometric profile that is complementary in size and shape to the certain geometric profile of the recessed regions, are separately fabricated. These blocks are included within a fluid to form a slurry. The slurry is then flowed over the CMOS fabricated photodetector array in accordance with a fluidic self-assembly technique, and the included semiconductor blocks are individually deposited within each of the plurality of recessed regions in the CMOS fabricated photodetector array. The deposited blocks are then attached within the recessed regions to form the optical excitation / detection device from an arrayed plurality of photodetectors and separately formed photoemitters.

Owner:SANOFI AVENTIS DEUT GMBH

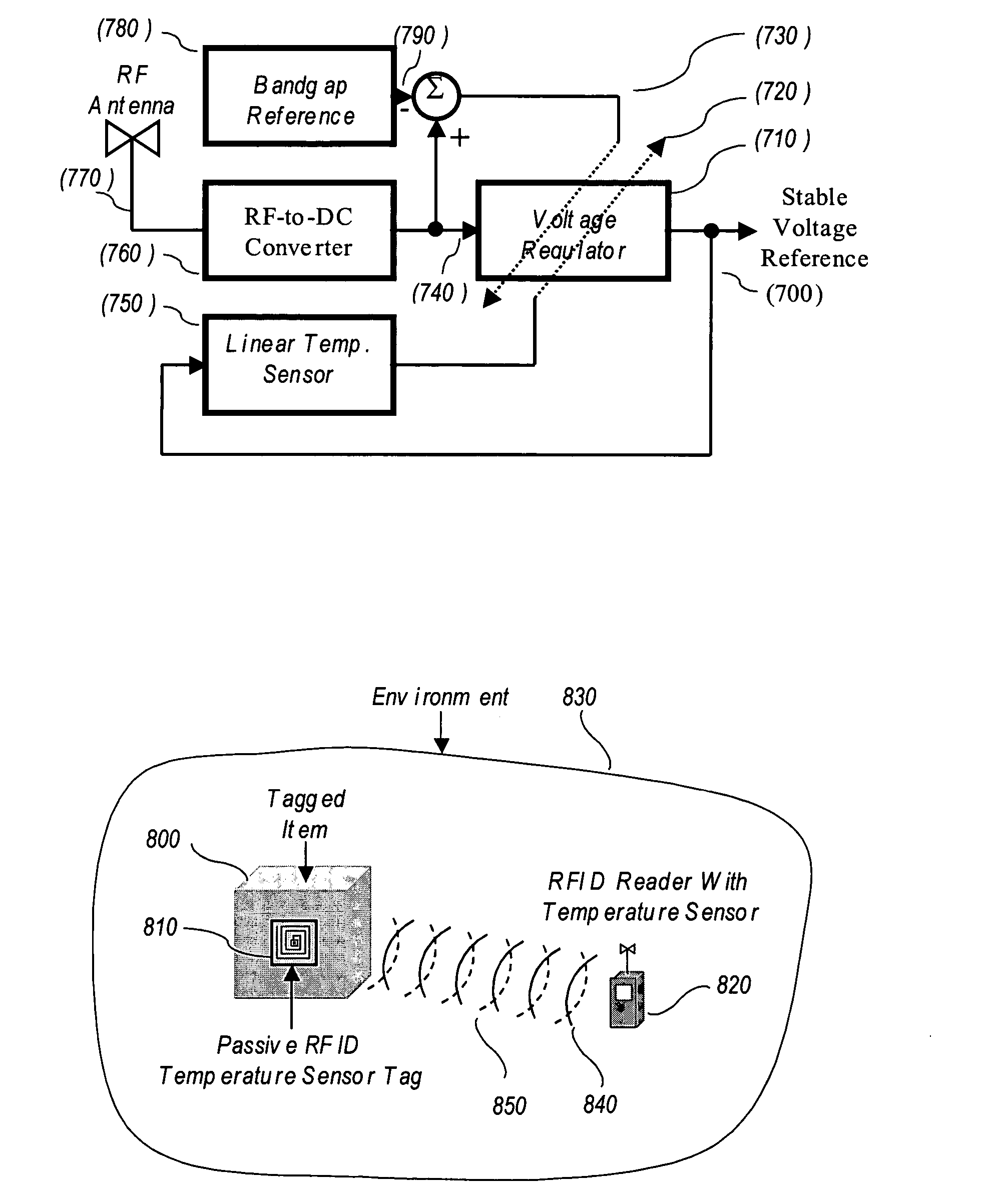

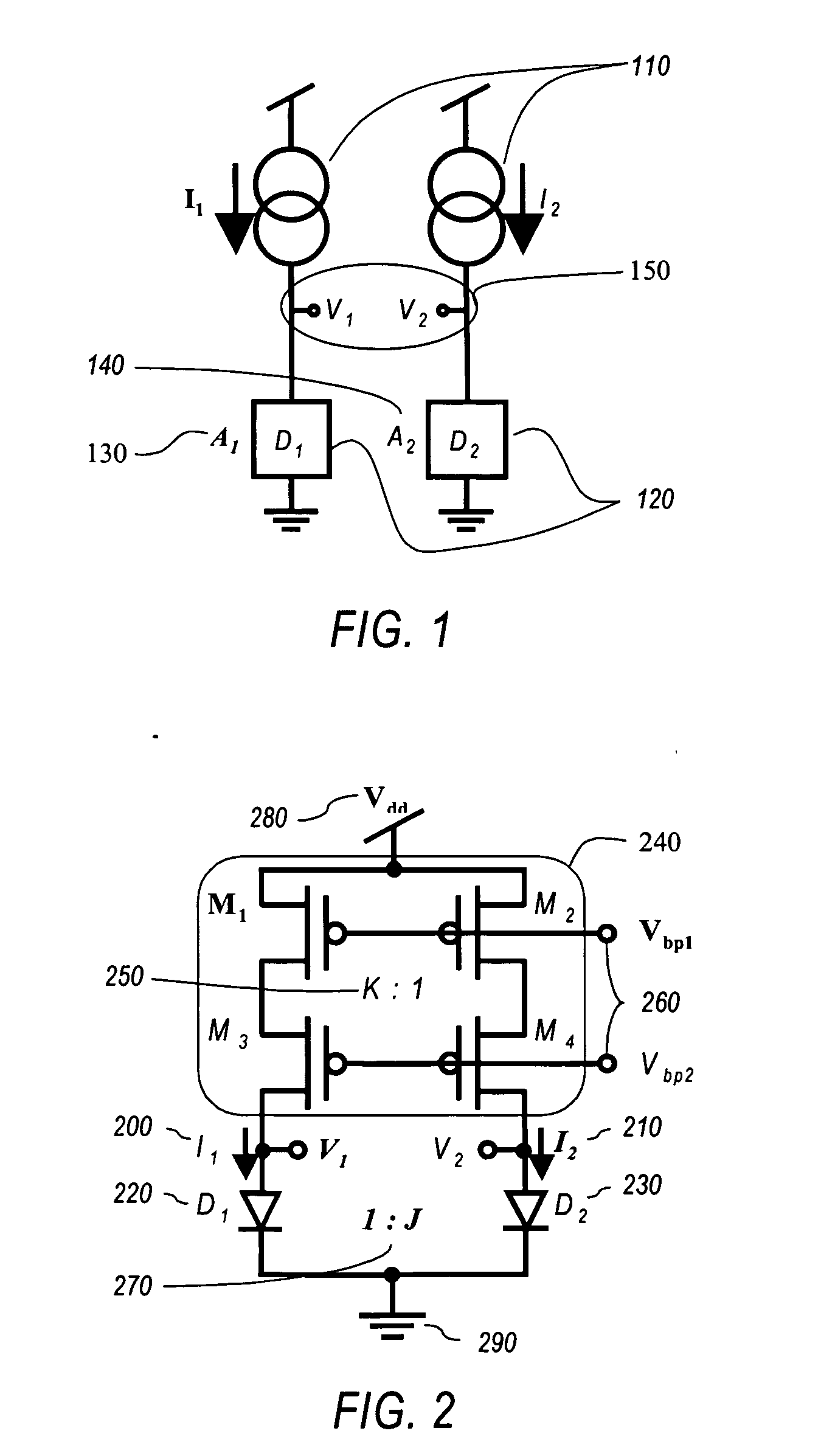

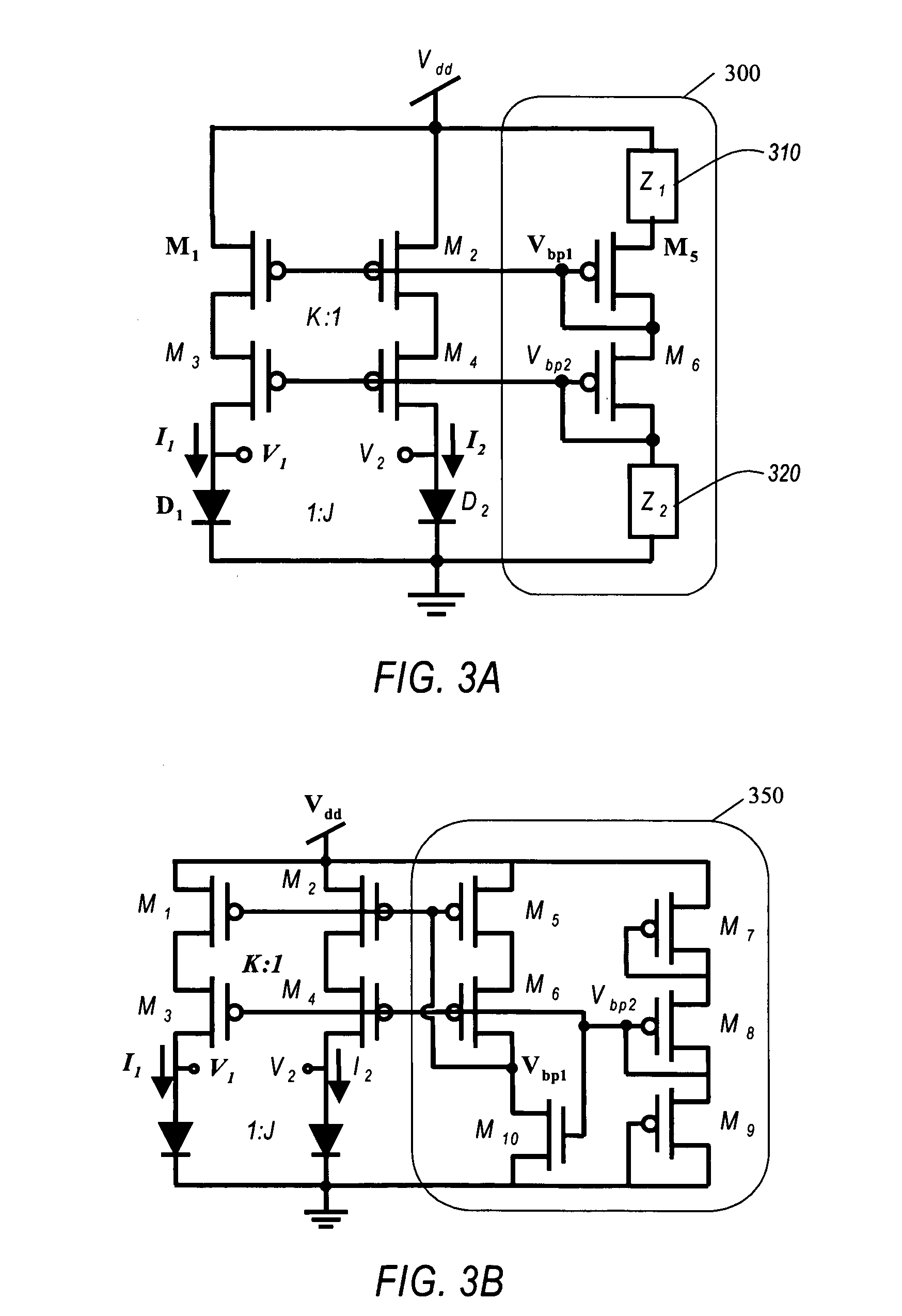

One point calibration integrated temperature sensor for wireless radio frequency applications

ActiveUS20060202821A1Removal costAdditional chip surface areaVehicle testingInflated body pressure measurementLine sensorManufacturing technology

A low power analog linear temperature sensor integrateable with digital and / or analog circuits in CMOS fabrication processes. The sensor is accurately calibrateable at a single temperature that yields a linear relationship between measured differential voltage and temperature over a wide variety of temperature ranges. The sensor provides stable voltage and current references that are essential for wireless sensor platforms. There are many applications where sensors require stable voltage / current references and the physics of the sensor's transduction mechanisms are themselves temperature dependent. Wireless platforms such as, but not limited to, passive RFID tags with the addition of on- or off-chip sensors provide a low cost solution for a variety of low cost sensor applications.

Owner:ALTIVERA

Ultra low-loss CMOS compatible silicon waveguides

InactiveUS20060133754A1Reduce lossReduce light lossOptical waveguide light guideNon-linear opticsBand shapeScattering loss

A low loss optical waveguiding structure for silicon-on-insulator (SOI)-based arrangements utilizes a tri-material configuration including a rib / strip waveguide formed of a material with a refractive index less than silicon, but greater than the refractive index of the underlying insulating material. In one arrangement, silicon nitirde may be used. The index mismatch between the silicon surface layer (the SOI layer) and the rib / strip waveguide results in a majority of the optical energy remaining within the SOI layer, thus reducing scattering losses from the rib / strip structure (while the rib / strip allows for guiding along a desired signal path to be followed). Further, since silicon nitirde is an amorphous material without a grain structure, this will also reduce scattering losses. Advantageously, the use of silicon nitride allows for conventional CMOS fabrication processes to be used in forming both passive and active devices.

Owner:CISCO TECH INC +1

Fabrication of silicon-on-nothing (SON) MOSFET fabrication using selective etching of Si1-xGex layer

A method for fabrication of silicon-on-nothing (SON) MOSFET using selective etching of Si1−xGex layer, includes preparing a silicon substrate; growing an epitaxial Si1−xGex layer on the silicon substrate; growing an epitaxial thin top silicon layer on the epitaxial Si1−xGex layer; trench etching of the top silicon and Si1−xGex, into the silicon substrate to form a first trench; selectively etching the Si1−xGex layer to remove substantially all of the Si1−xGex to form an air gap; depositing a layer of SiO2 by CVD to fill the first trench; trench etching to from a second trench; selectively etching the remaining Si1−xGex layer; depositing a second layer of SiO2 by CVD to fill the second trench, thereby decoupling a source, a drain and a channel from the substrate; and completing the structure by state-of-the-art CMOS fabrication techniques.

Owner:SHARP KK

Radiation hardened isolation structures and fabrication methods

ActiveUS20070141794A1Reduce and eliminate effectLow costTransistorSolid-state devicesManufacturing technologyDevice material

Semiconductor devices can be fabricated using conventional designs and process but including specialized structures to reduce or eliminate detrimental effects caused by various forms of radiation. Such semiconductor devices can include one or more parasitic isolation devices and / or buried layer structures disclosed in the present application. The introduction of design and / or process steps to accommodate these novel structures is compatible with conventional CMOS fabrication processes, and can therefore be accomplished at relatively low cost and with relative simplicity.

Owner:SILICON SPACE TECH

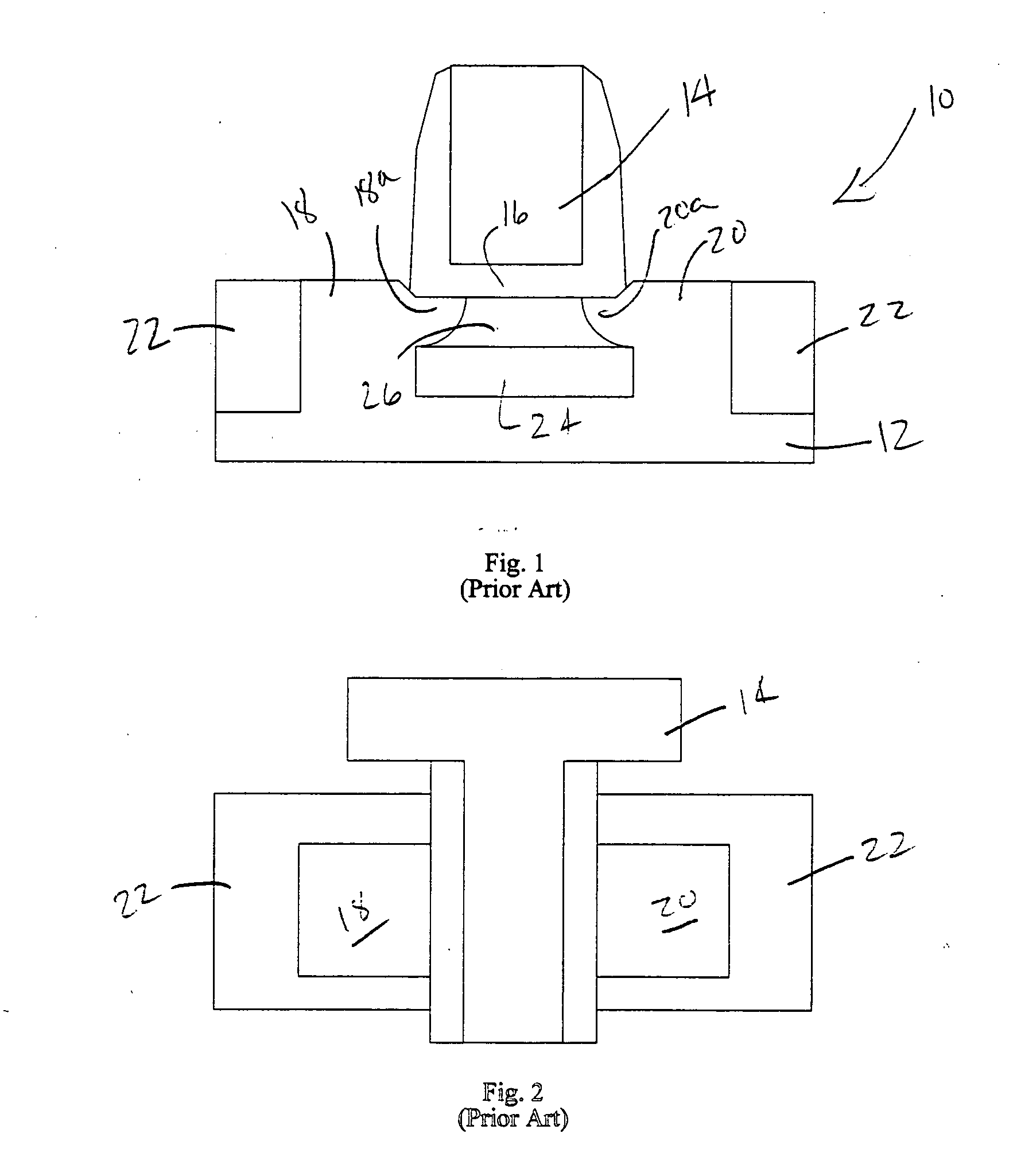

CCD imager constructed with CMOS fabrication techniques and back illuminated imager with improved light capture

An optical sensor circuit for generating signals corresponding to received photoelectrons is formed on a single monolithic substrate and includes a charge coupled device (CCD) array. The array is formed of a plurality of pixels constructed by a standard CMOS process. Each pixel is formed of at least one charge well of minority carriers and a gate oxide layer overlaying the at least one charge well. At least two spaced gate electrodes corresponding in position to the at least two charge wells overlays the gate oxide layer. The space between adjacent electrodes defines a gap to transfer charge between adjacent ones of at the least two spaced gate electrodes and the gap is stabilized. A back-illuminated imager is also described in which photocarriers are diverted from devices integrated with the pixel by a PN junction formed in the pixel structure.

Owner:SRI INTERNATIONAL

Fabricating photonics devices fully integrated into a CMOS manufacturing process

ActiveUS8633067B2Lower resistanceSolid-state devicesSemiconductor/solid-state device manufacturingCMOSPhotodetector

Disclosed are process enhancements to fully integrate the processing of a photonics device into a CMOS manufacturing process flow. A CMOS wafer may be divided into different portions. One of the portions is for the CMOS devices and one or more other portions are for the photonics devices. The photonics devices include a ridged waveguide and a germanium photodetector. The germanium photodetector may utilize a seeded crystallization from melt process so there is more flexibility in the processing of the germanium photodetector.

Owner:GLOBALFOUNDRIES US INC

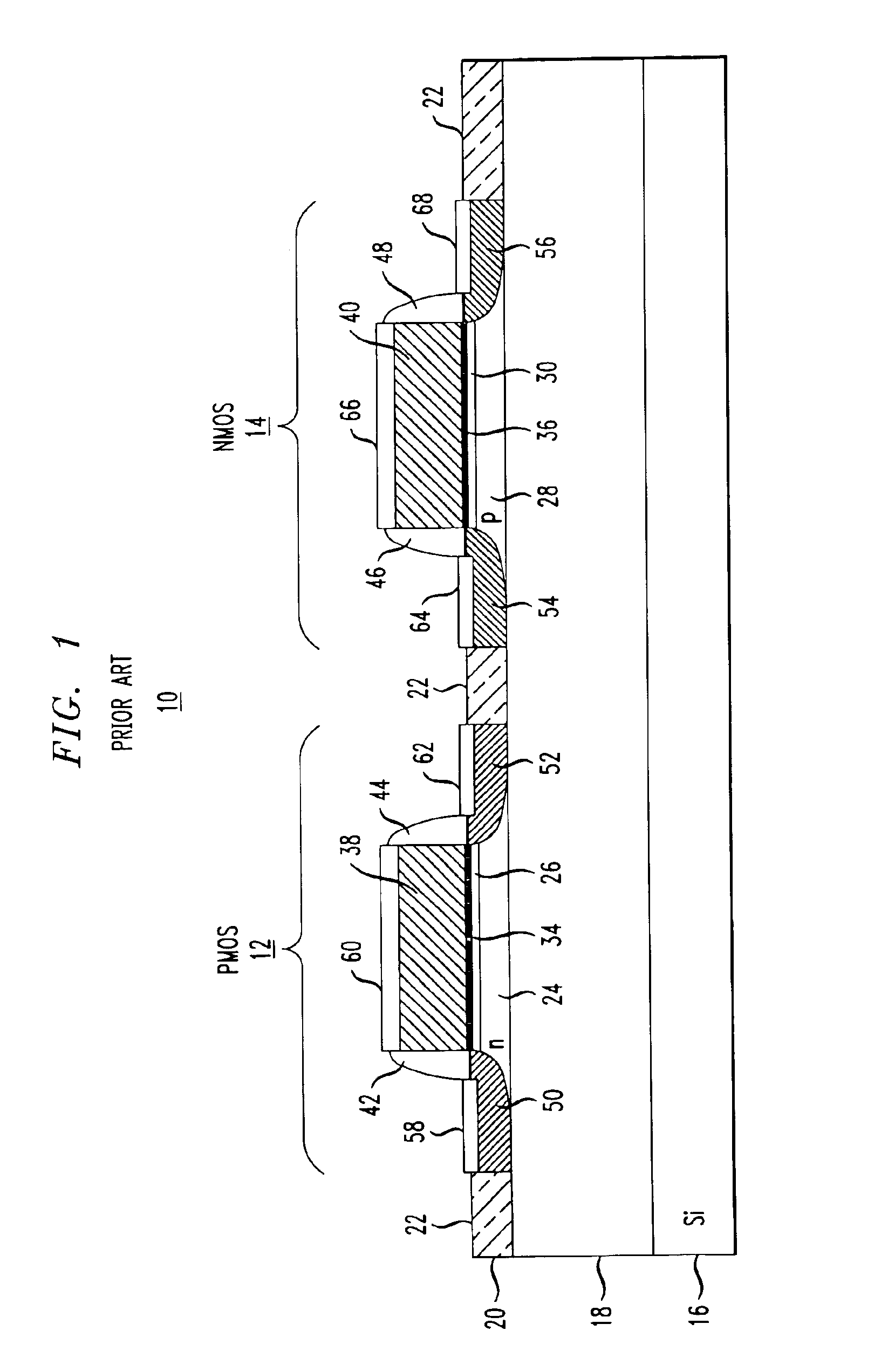

Schottky barrier CMOS fabrication method

InactiveUS6974737B2Inhibition formationTransistorSemiconductor/solid-state device manufacturingSalicideCMOS

A CMOS device and method of fabrication are disclosed. The present invention utilizes Schottky barrier contacts for source and / or drain contact fabrication within the context of a CMOS device and CMOS integrated circuits, to eliminate the requirement for halo / pocket implants, shallow source / drain extensions to control short channel effects, well implant steps, and complex device isolation steps. Additionally, the present invention eliminates the parasitic bipolar gain associated with CMOS device operation, reduces manufacturing costs, tightens control of device performance parameters, and provides for superior device characteristics as compared to the prior art. The present invention, in one embodiment, uses a silicide exclusion mask process to form the dual silicide Schottky barrier source and / or drain contact for the complimentary PMOS and NMOS devices forming the CMOS device.

Owner:AVOLARE 2 LLC

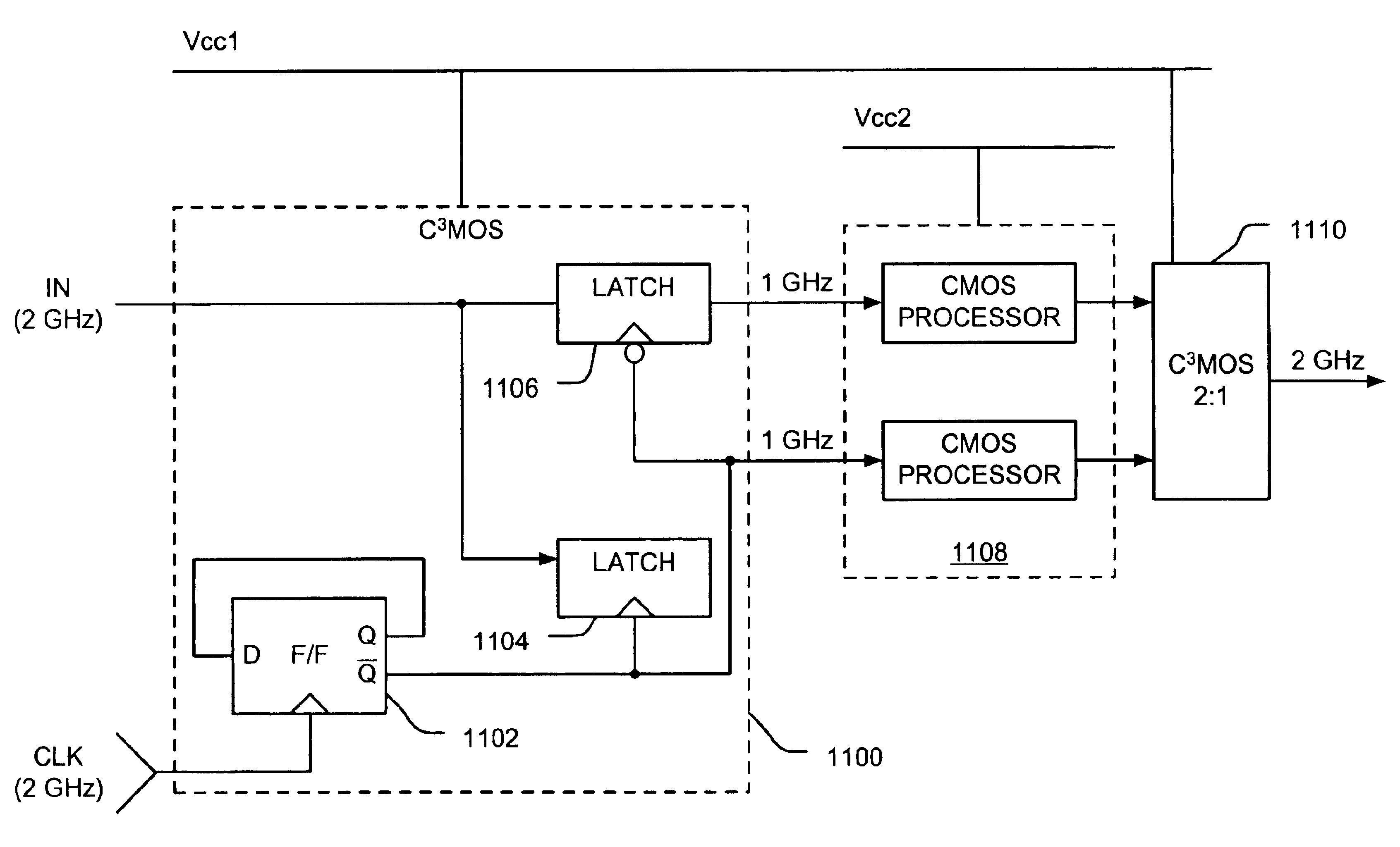

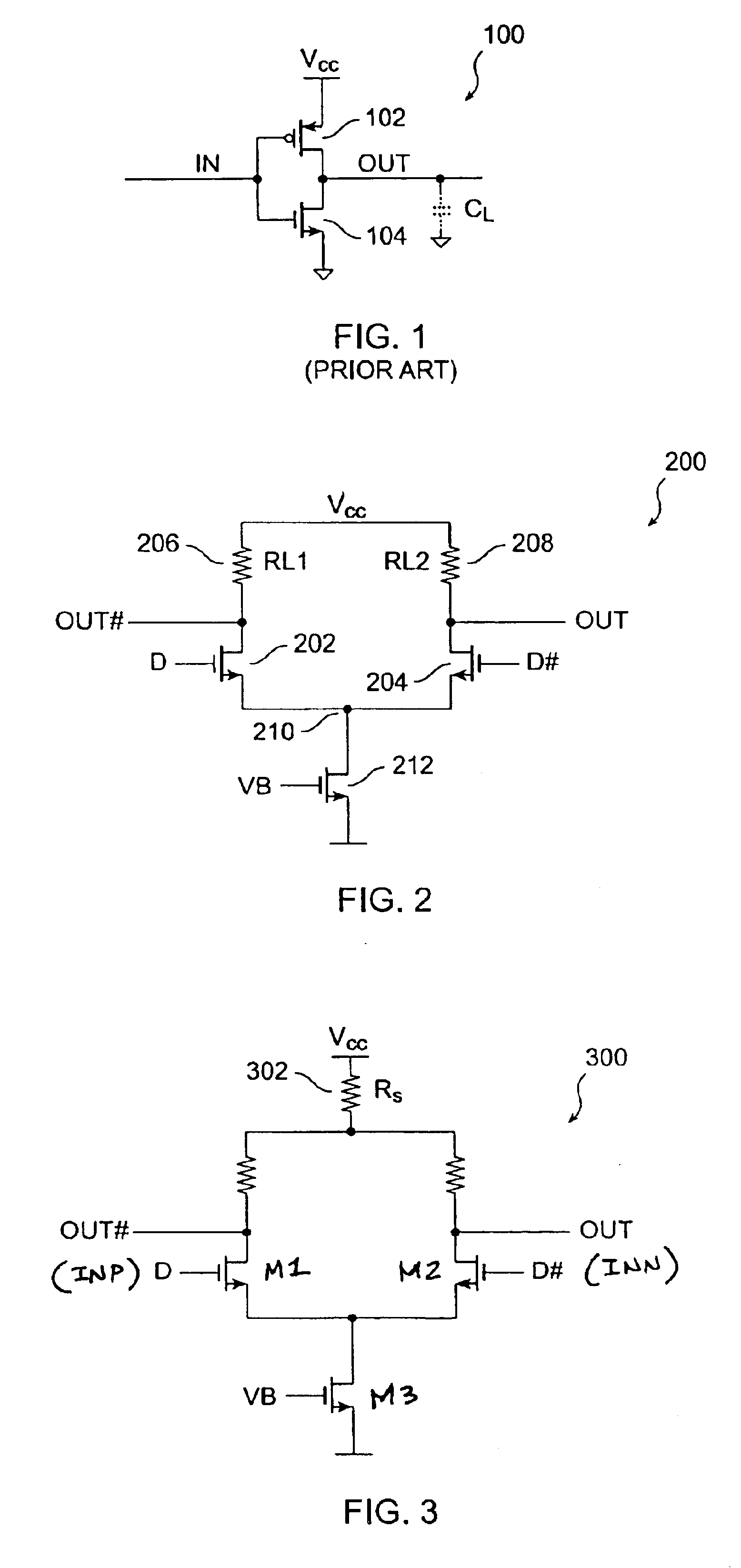

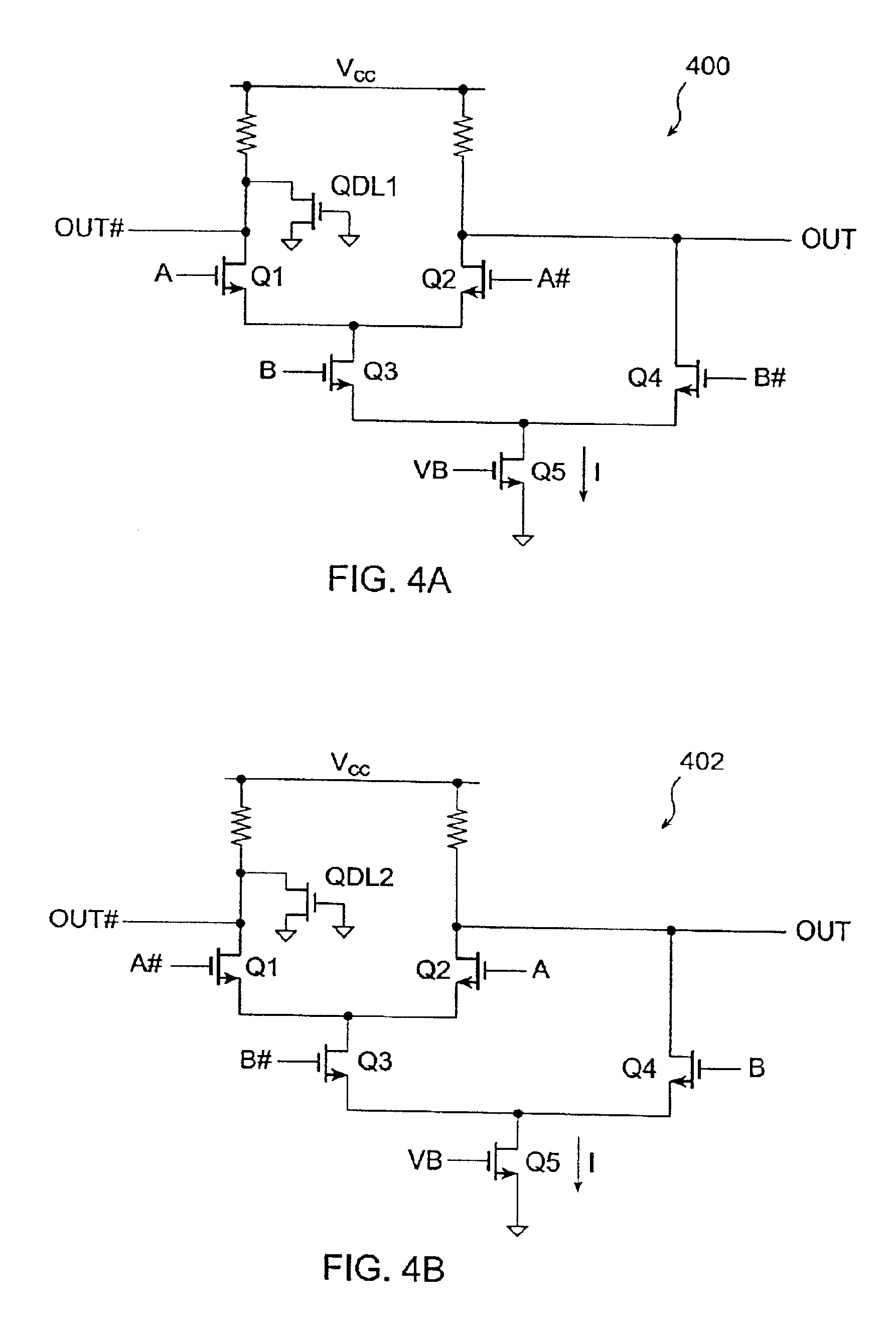

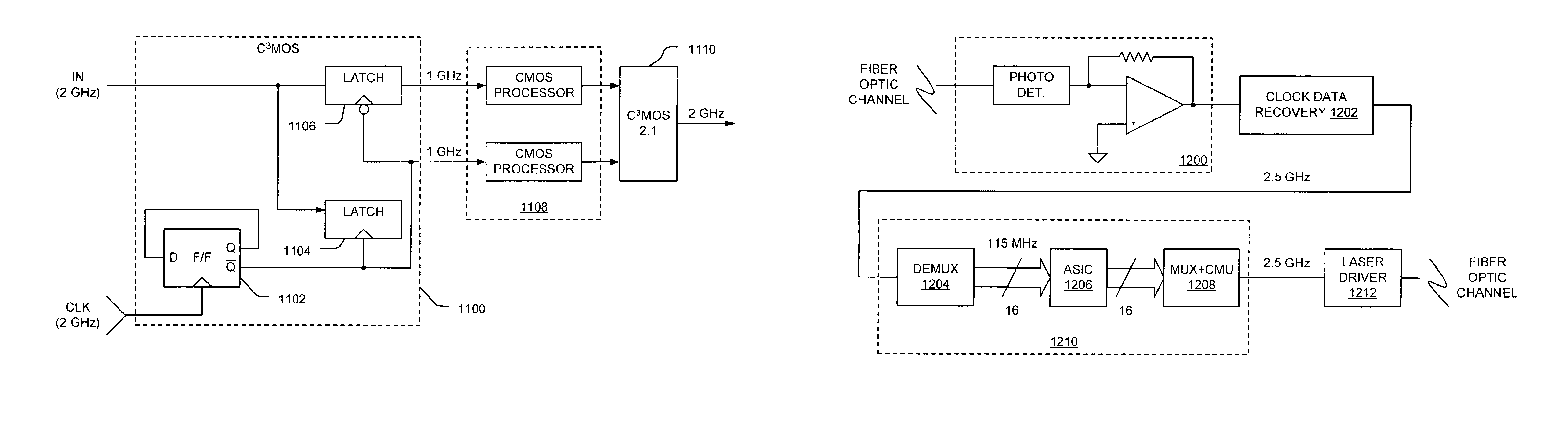

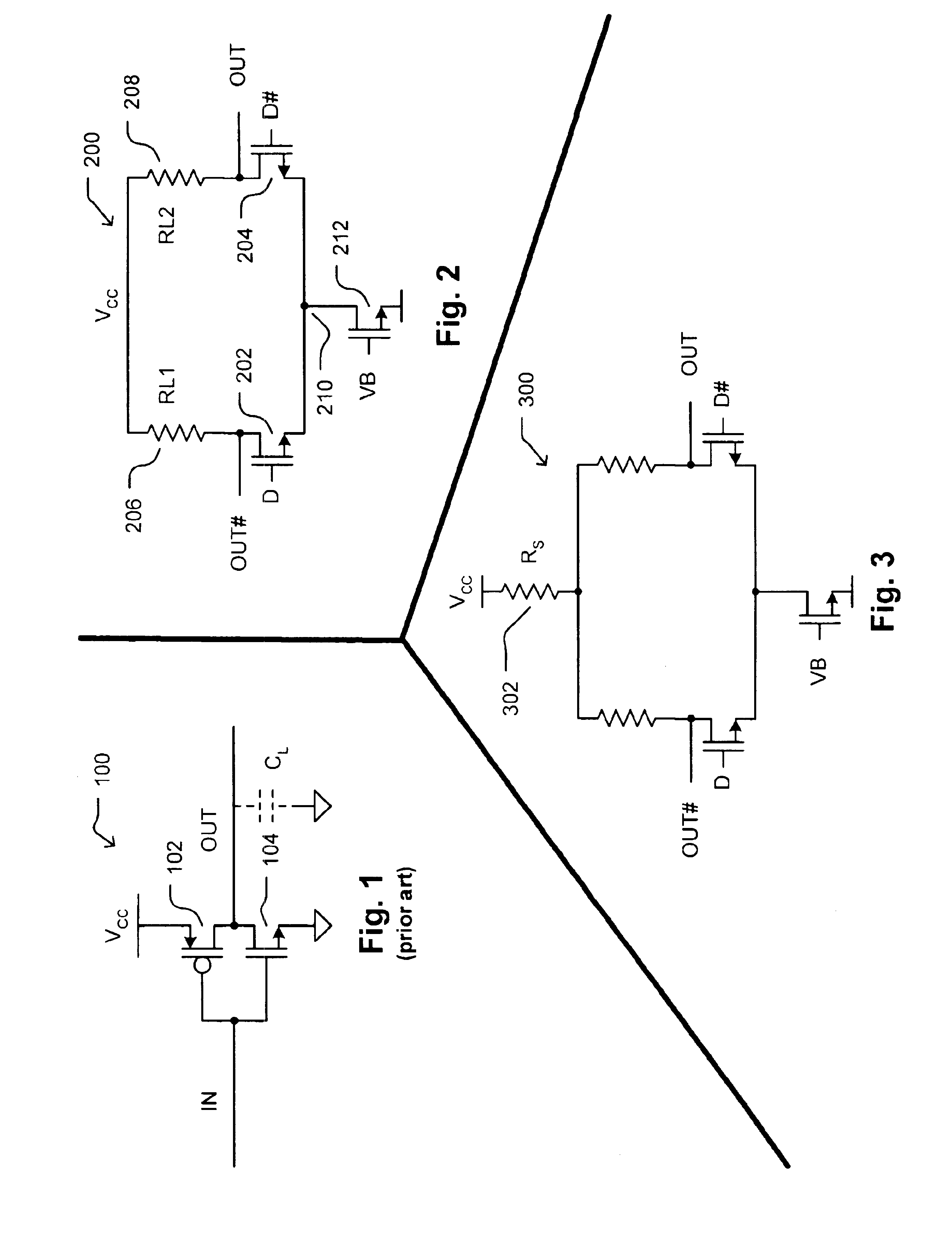

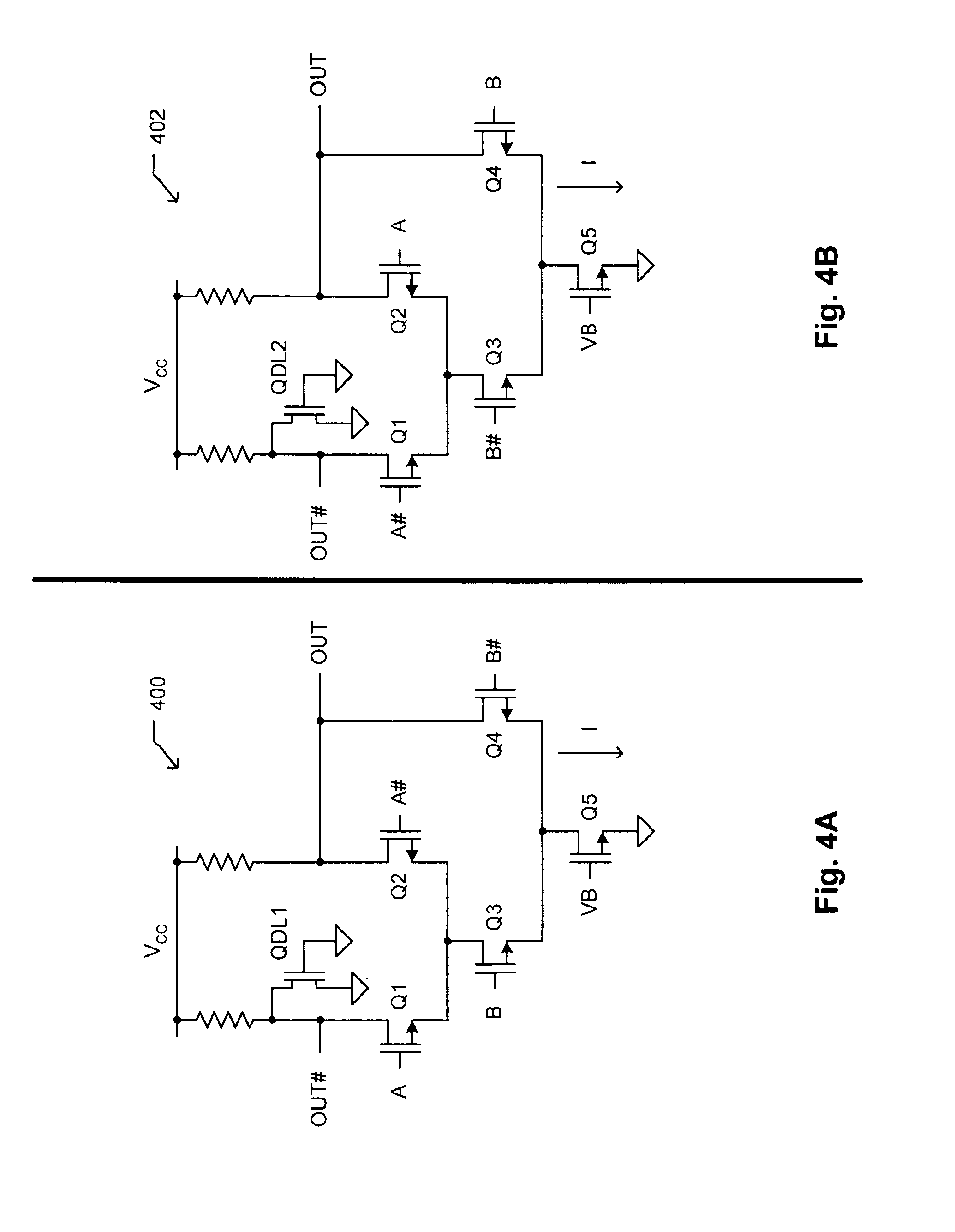

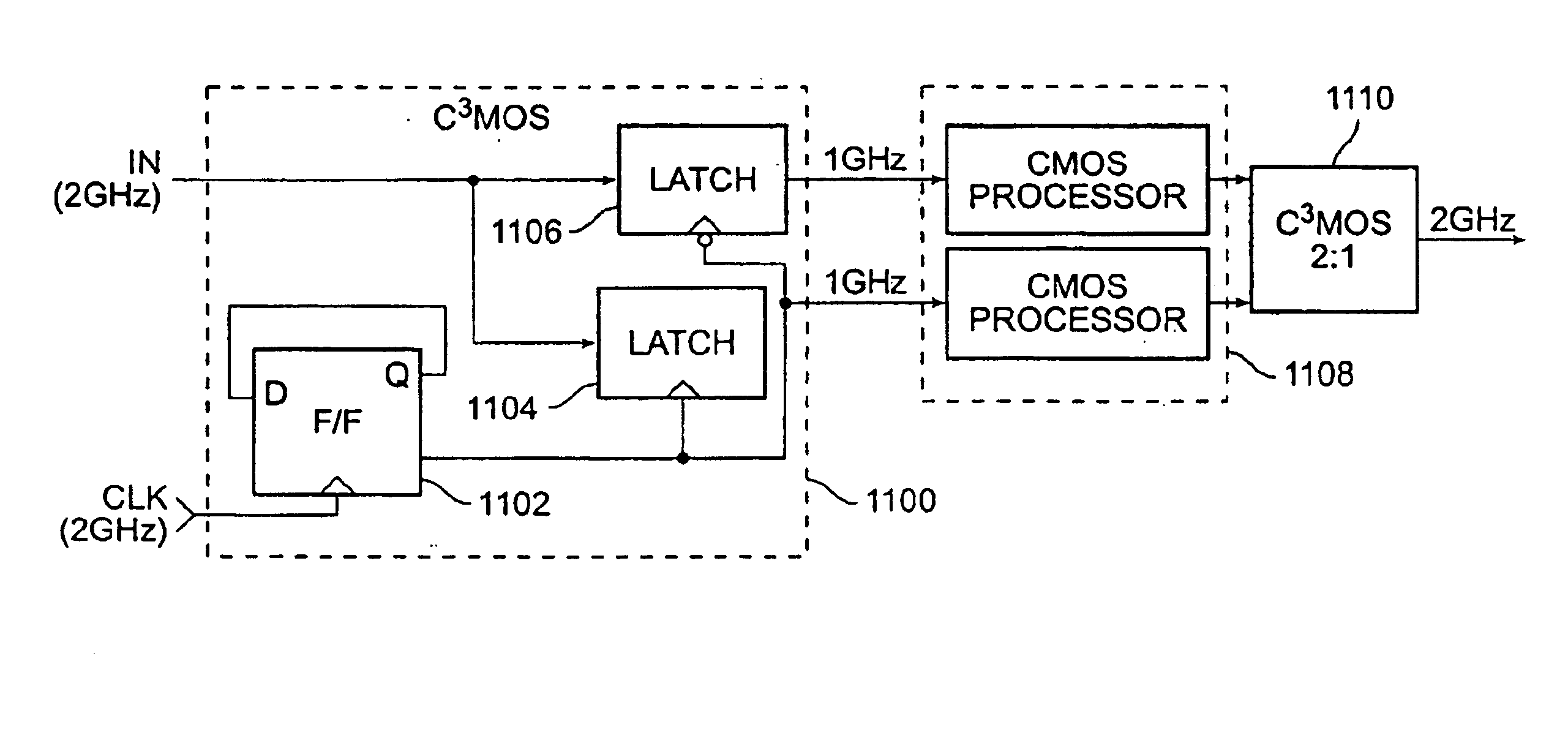

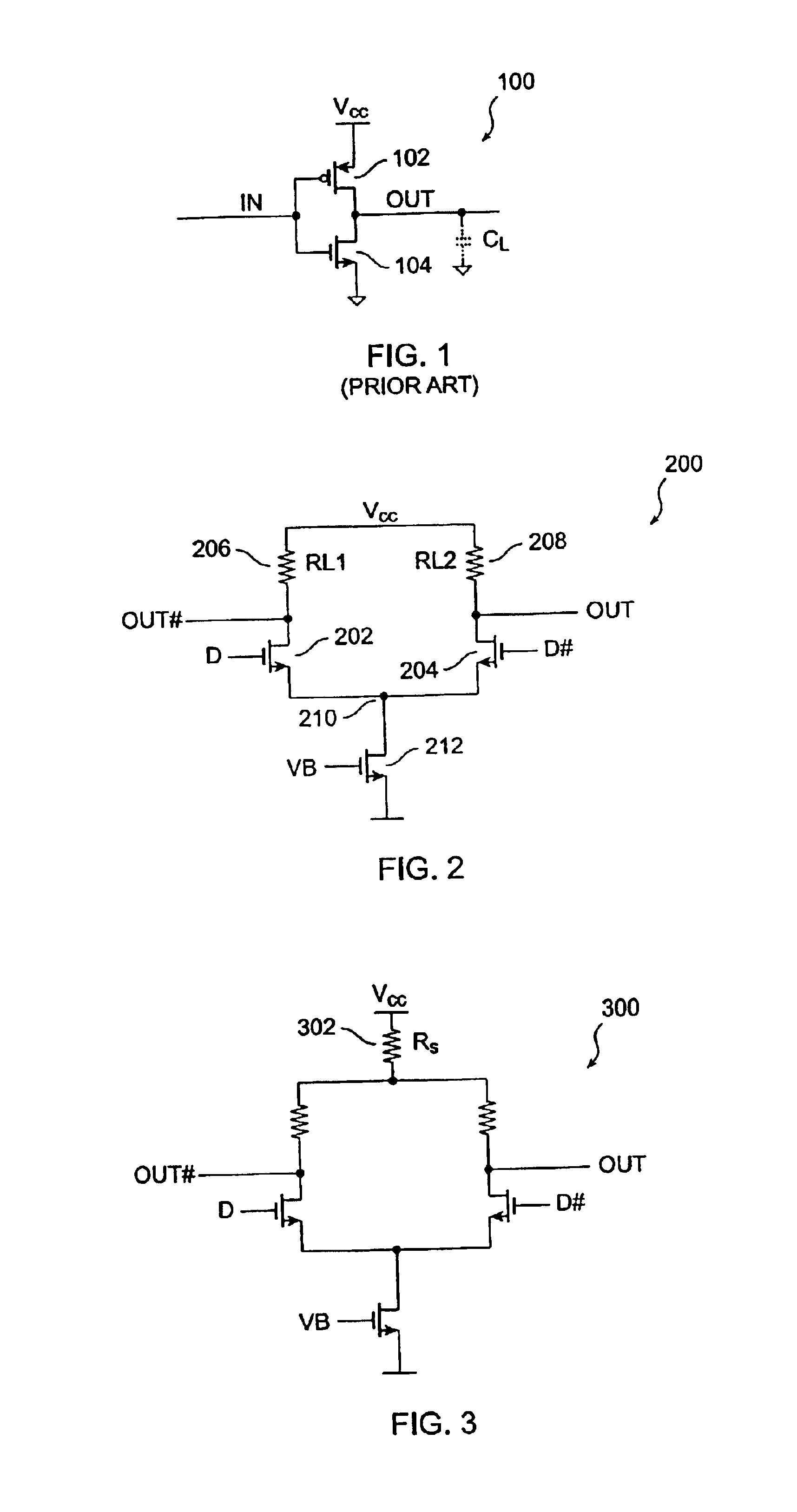

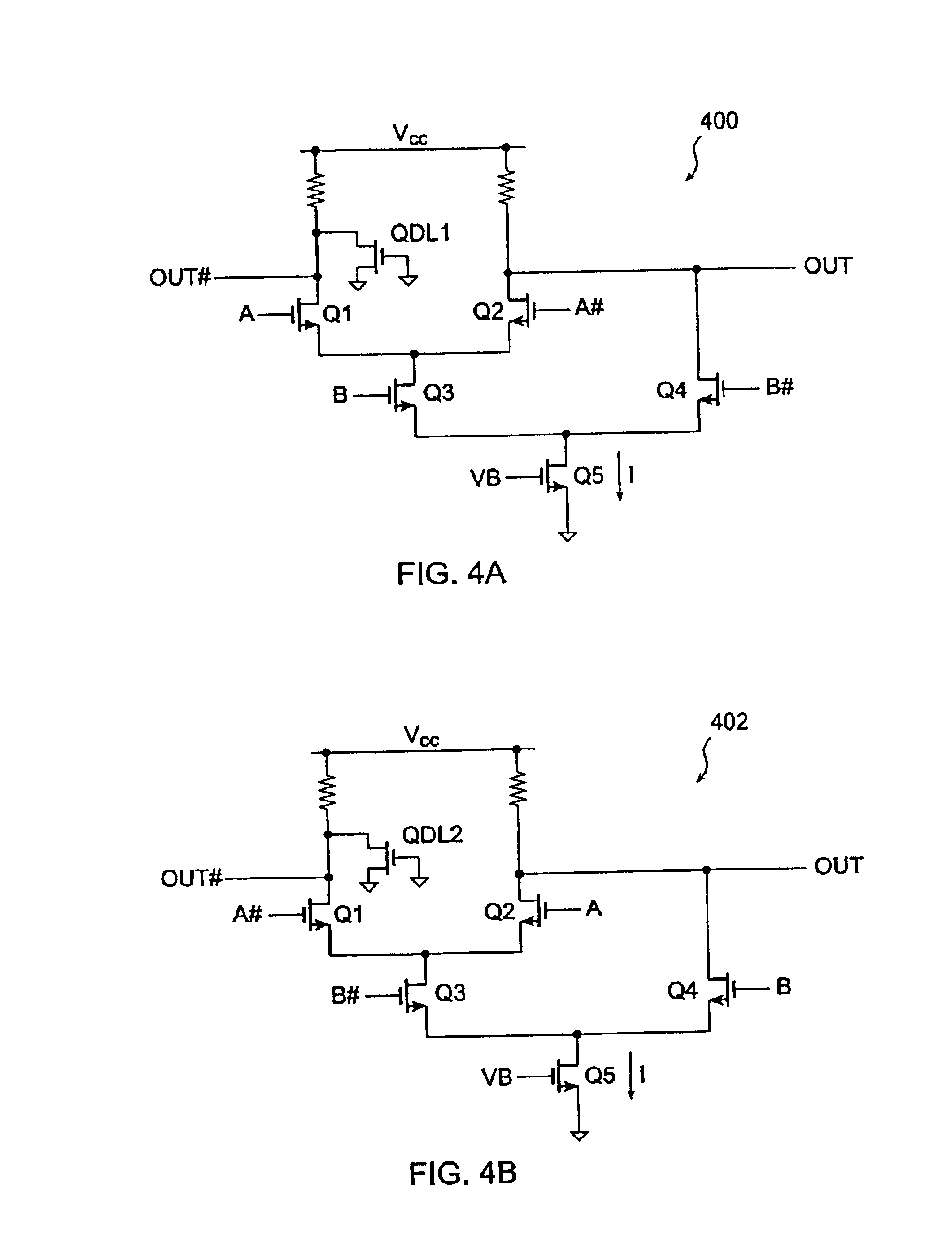

Current-controlled CMOS circuit using higher voltage supply in low voltage CMOS process

InactiveUS6911855B2Speed maximizationDissipates static currentElectronic switchingElectric pulse generatorTransceiverEngineering

Various circuit techniques for implementing ultra high speed circuits use current-controlled CMOS (C3MOS) logic fabricated in conventional CMOS process technology. An entire family of logic elements including inverter / buffers, level shifters, NAND, NOR, XOR gates, latches, flip-flops and the like are implemented using C3MOS techniques. Optimum balance between power consumption and speed for each circuit application is achieve by combining high speed C3MOS logic with low power conventional CMOS logic. The combined C3MOS / CMOS logic allows greater integration of circuits such as high speed transceivers used in fiber optic communication systems. The C3MOS structure enables the use of a power supply voltage that may be larger than the voltage required by the CMOS fabrication process, further enhancing the performance of the circuit.

Owner:AVAGO TECH INT SALES PTE LTD

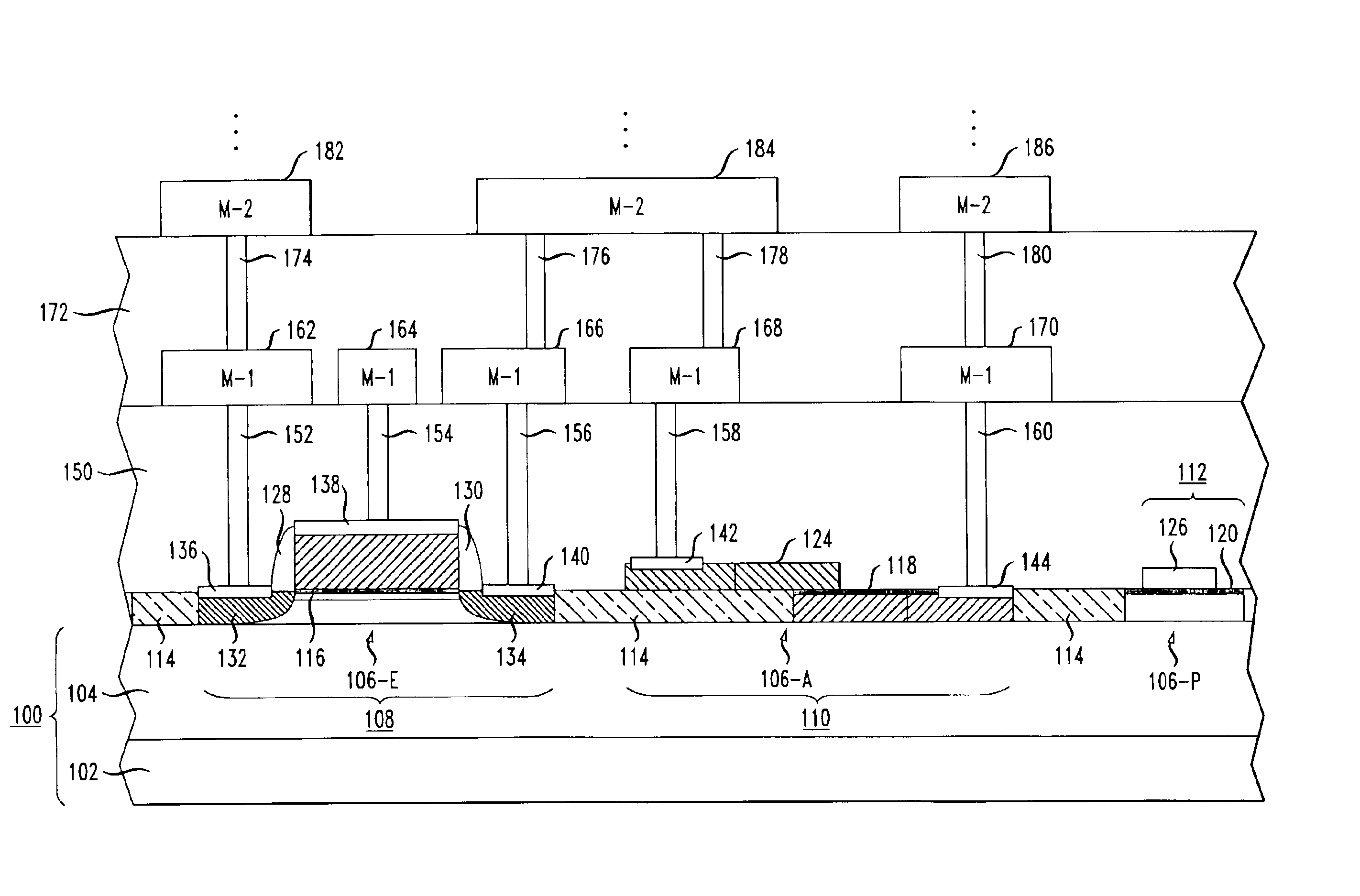

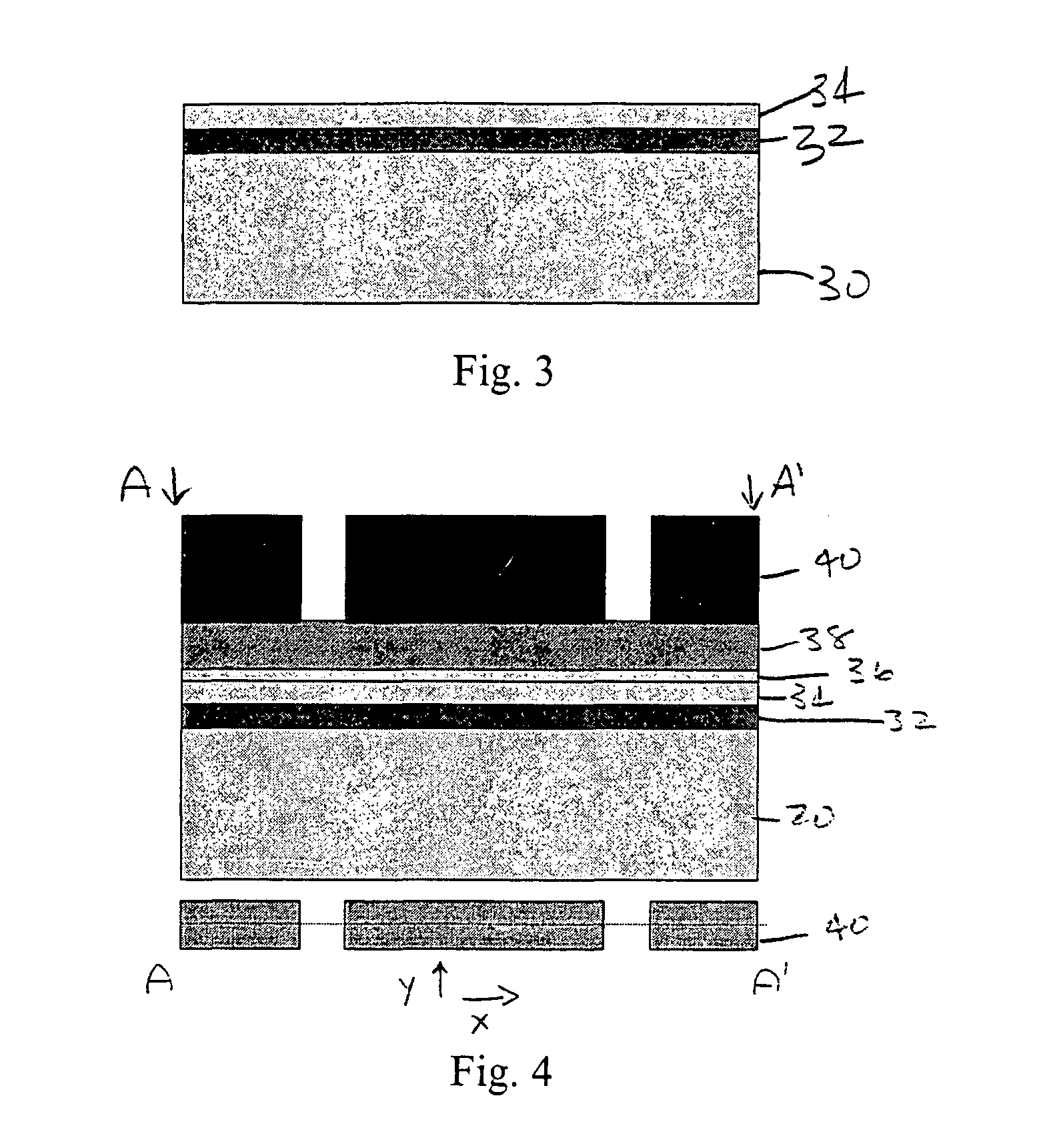

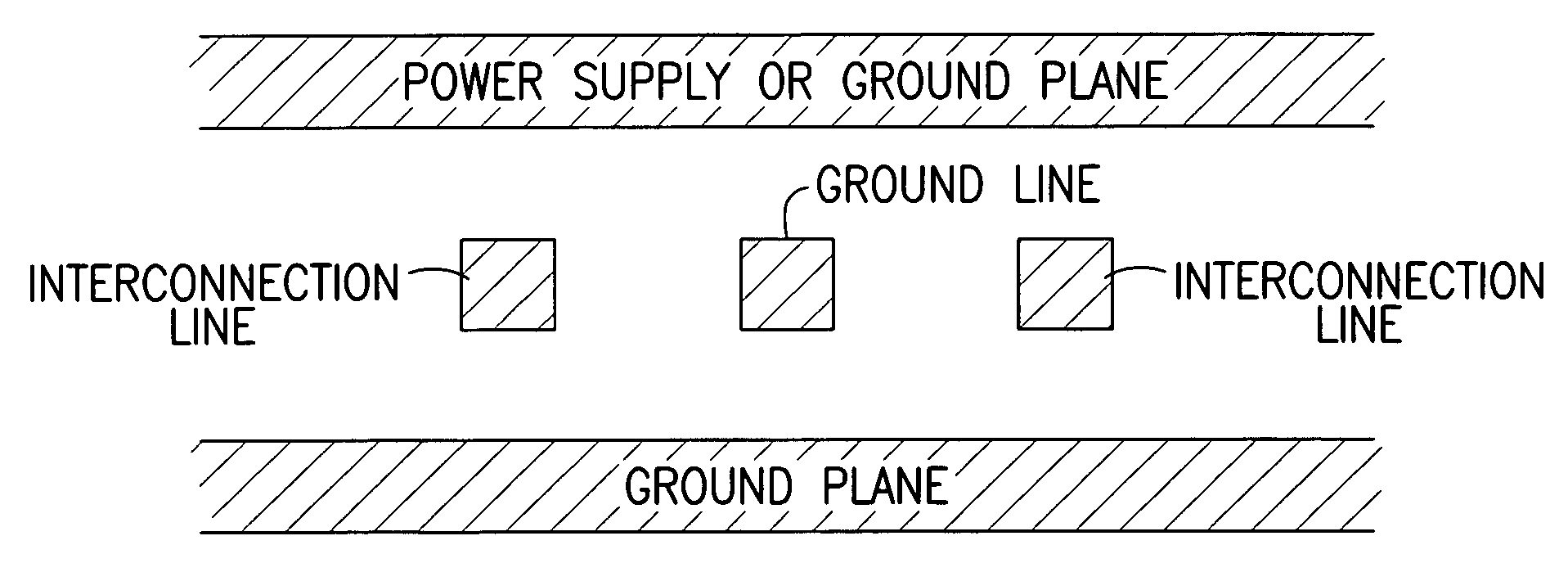

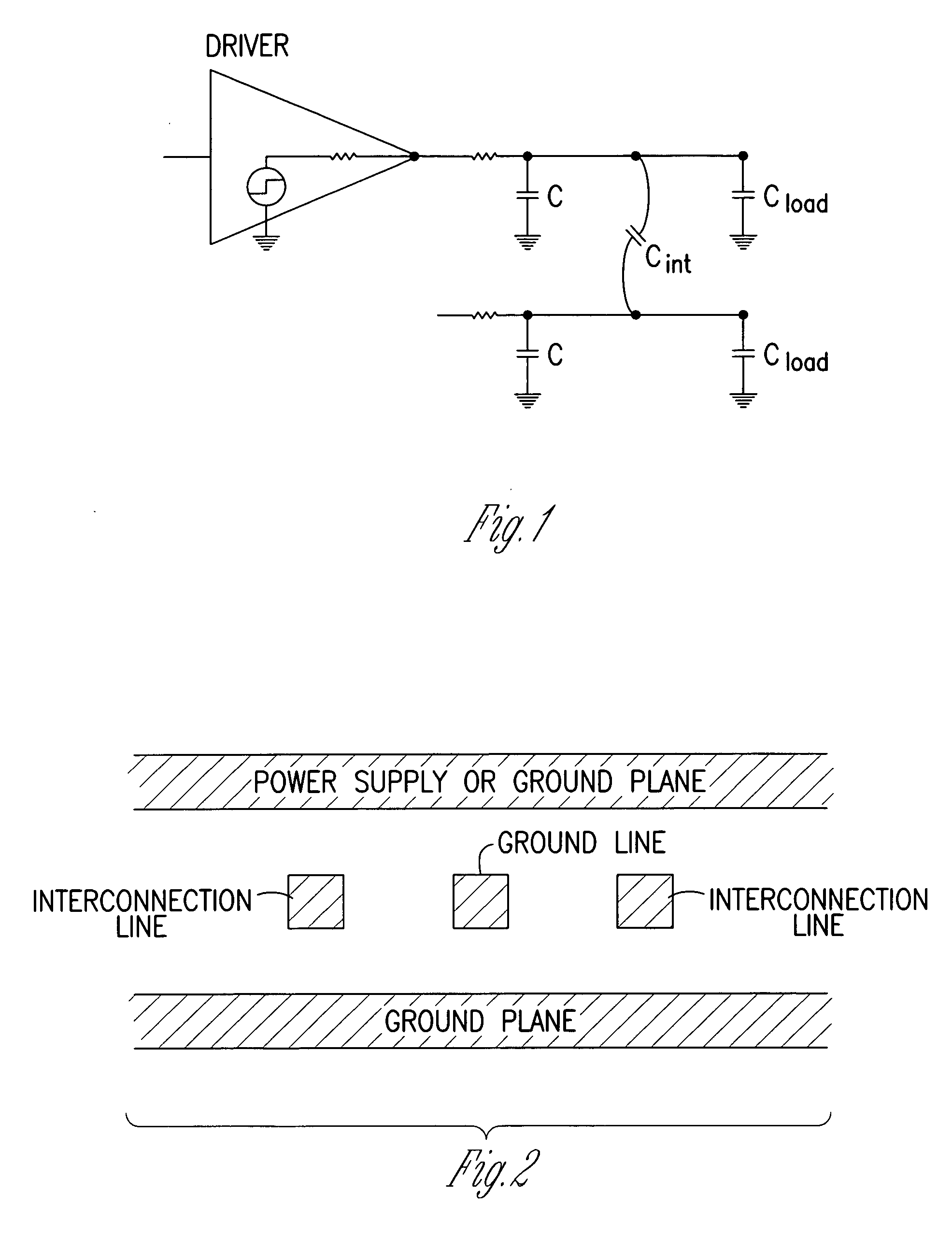

Capacitive techniques to reduce noise in high speed interconnections

InactiveUS20050023650A1Reduce noiseReduce signal delaySemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

Improved methods and structures are provided using capacitive techniques to reduce noise in high speed interconnections, such as in CMOS integrated circuits. The present invention offers an improved signal to noise ration. The present invention provides for the fabrication of improved transmission lines for silicon-based integrated circuits using conventional CMOS fabrication techniques. Embodiments of a method for forming transmission lines in an integrated circuit include forming a first layer of electrically conductive material on a substrate. The method includes forming a first layer of insulating material on the first layer of the electrically conductive material. The first layer has a thickness of less than 1.0 micrometers (μm). A transmission line is formed on the first layer of insulating material. The transmission line has a thickness and a width of approximately 1.0 micrometers. A second layer of insulating material is formed on the transmission line. And, a second layer of electrically conductive material is formed on the second layer of insulating material.

Owner:MICRON TECH INC

Fabrication of silicon-on-nothing (SON) MOSFET fabrication using selective etching of Si1-xGex layer

A method for fabrication of silicon-on-nothing (SON) MOSFET using selective etching of Si1-xGex layer, includes preparing a silicon substrate; growing an epitaxial Si1-xGex layer on the silicon substrate; growing an epitaxial thin top silicon layer on the epitaxial Si1-xGex layer; trench etching of the top silicon and Si1-xGex, into the silicon substrate to form a first trench; selectively etching the Si1-xGex layer to remove substantially all of the Si1-xGex to form an air gap; depositing a layer of SiO2 by CVD to fill the first trench; trench etching to from a second trench; selectively etching the remaining Si1-xGex layer; depositing a second layer of SiO2 by CVD to fill the second trench, thereby decoupling a source, a drain and a channel from the substrate; and completing the structure by state-of-the-art CMOS fabrication techniques.

Owner:SHARP KK

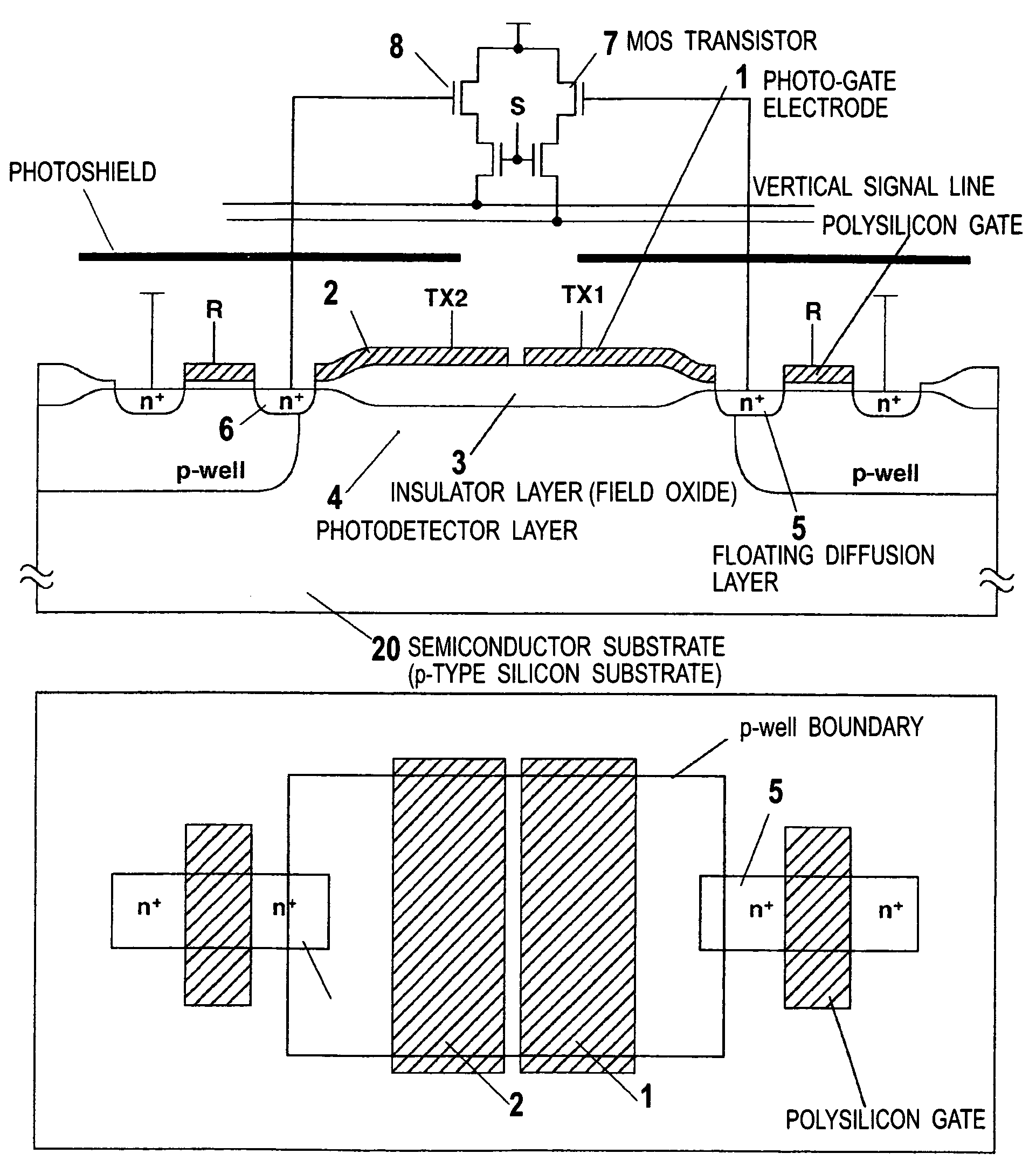

Time-of-light flight type distance sensor

InactiveUS7671391B2Maximum performanceLow costTelevision system detailsOptical rangefindersPhotodetectorFloating diffusion

A lower cost range-finding image sensor based upon measurement of reflection time of light with reduced fabrication processes compared to standard CMOS manufacturing procedures. An oxide film is formed on a silicon substrate, and two photo-gate electrodes for charge-transfer are provided on the oxide film. Floating diffusion layers for taking charges out from a photodetector layer are provided at the ends of the oxide film, and on the outside thereof are provided a gate electrode for resetting and a diffusion layer for providing a reset voltage.

Owner:NAT UNIV CORP SHIZUOKA UNIV

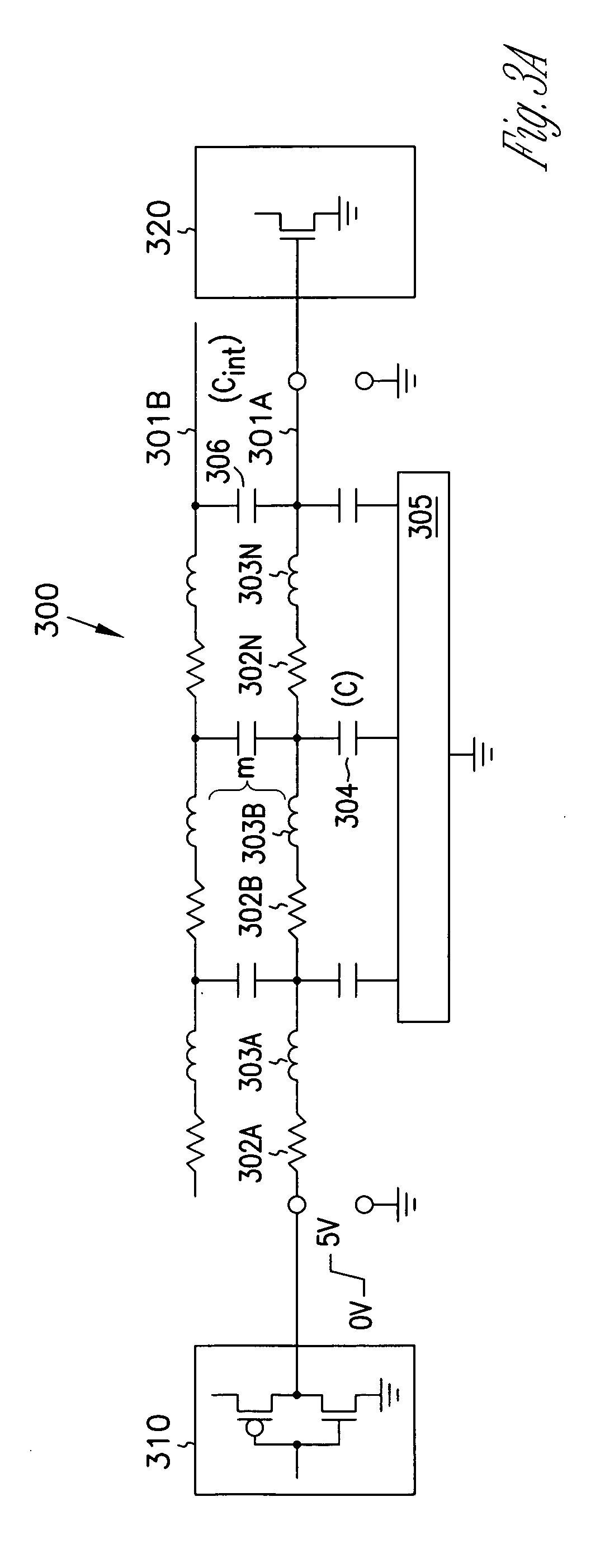

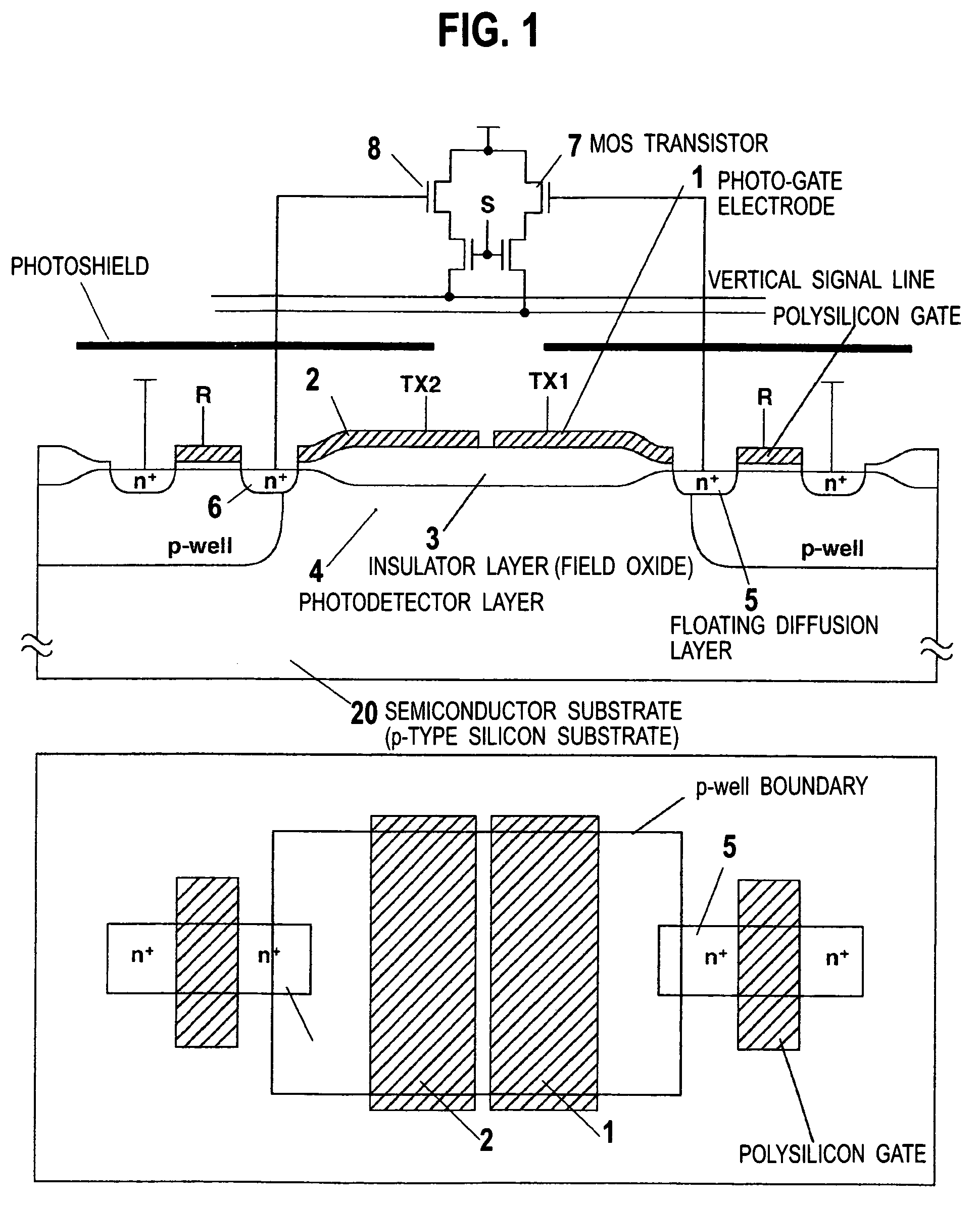

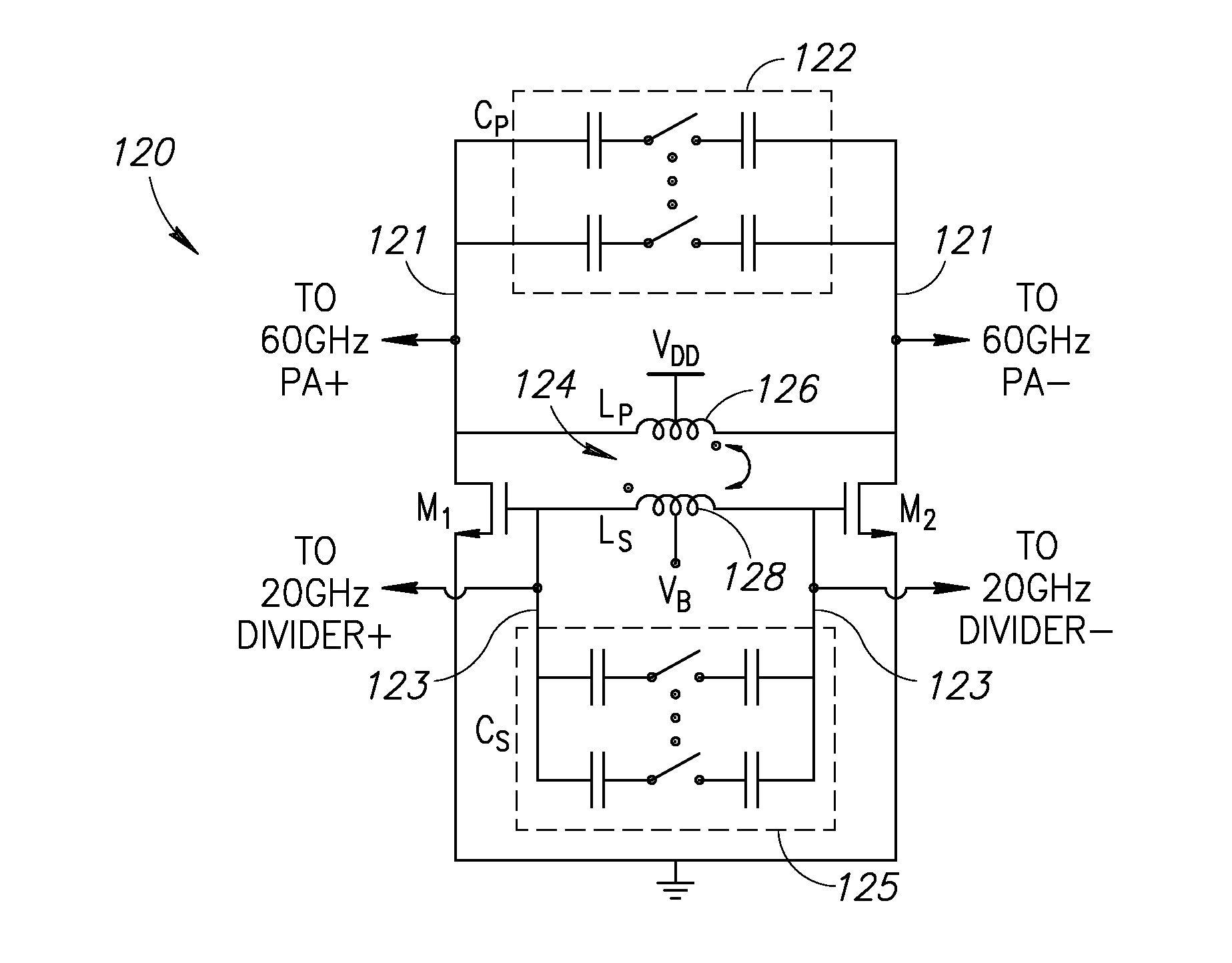

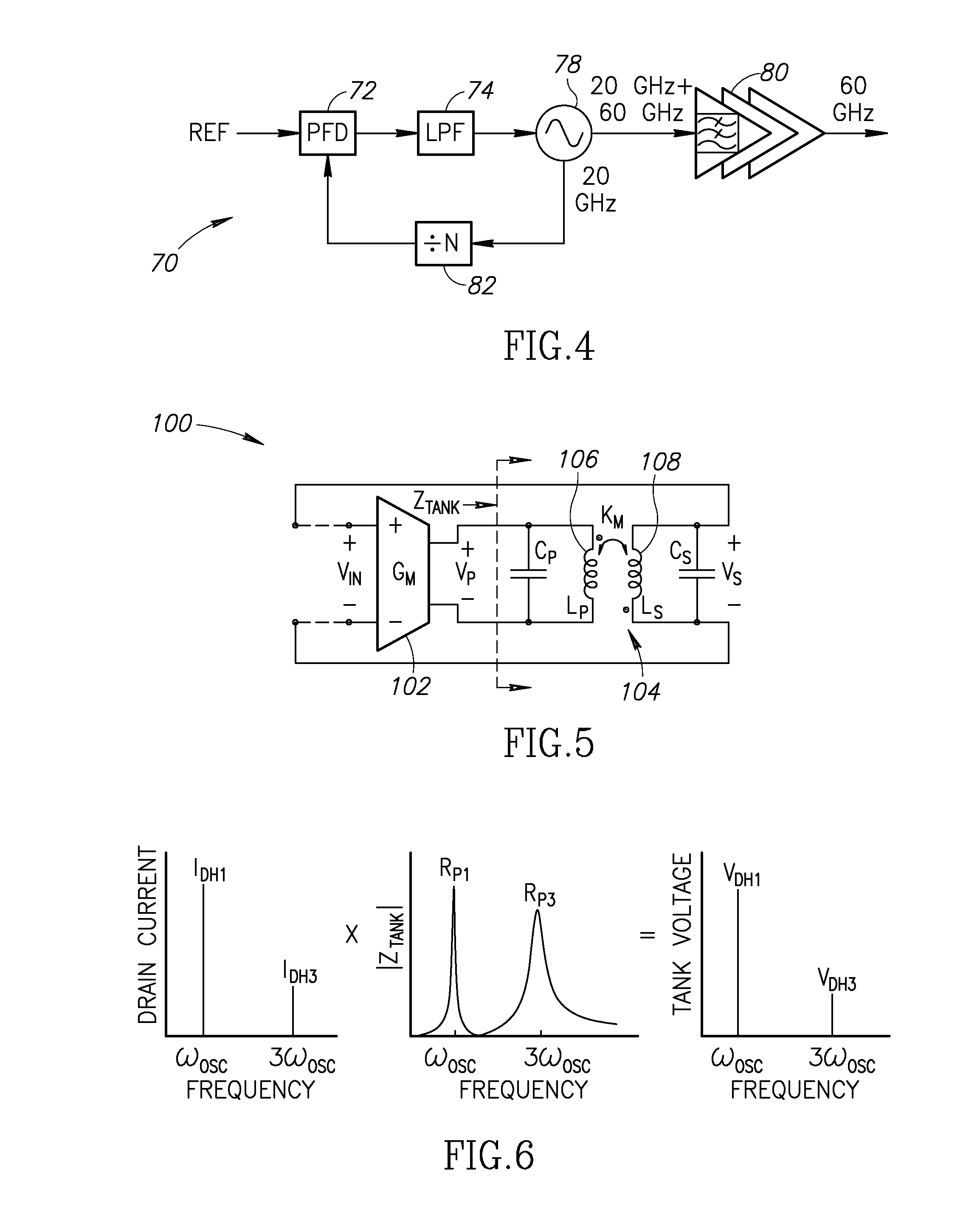

60 GHz Frequency Generator Incorporating Third Harmonic Boost And Extraction

ActiveUS20160099681A1Improve efficiencyImprove noiseResonant circuit tuningPulse automatic controlCMOSDBc

A novel and useful 60 GHz frequency generator based on a third harmonic extraction technique which improves system level efficiency and performance. The frequency generator employs a third harmonic boosting technique to increase the third harmonic at the output of the oscillator. The oscillator generates both ˜20 GHz fundamental and a significant amount of the third harmonic at ˜60 GHz and avoids the need for a frequency divider operating at 60 GHz. The undesired fundamental harmonic at ˜20 GHz is rejected by the good fundamental HRR inherent in the oscillator buffer stage while the ˜60 GHz component is amplified to the output. The fundamental harmonic is further suppressed by an active cancellation by properly combining the two outputs. The oscillator fabricated in 40 nm CMOS exhibits a phase noise of −100 dBc / Hz at 1 MHz offset from a 60 GHz carrier and have a tuning range of 25%.

Owner:SHORT CIRCUIT TECH LLC

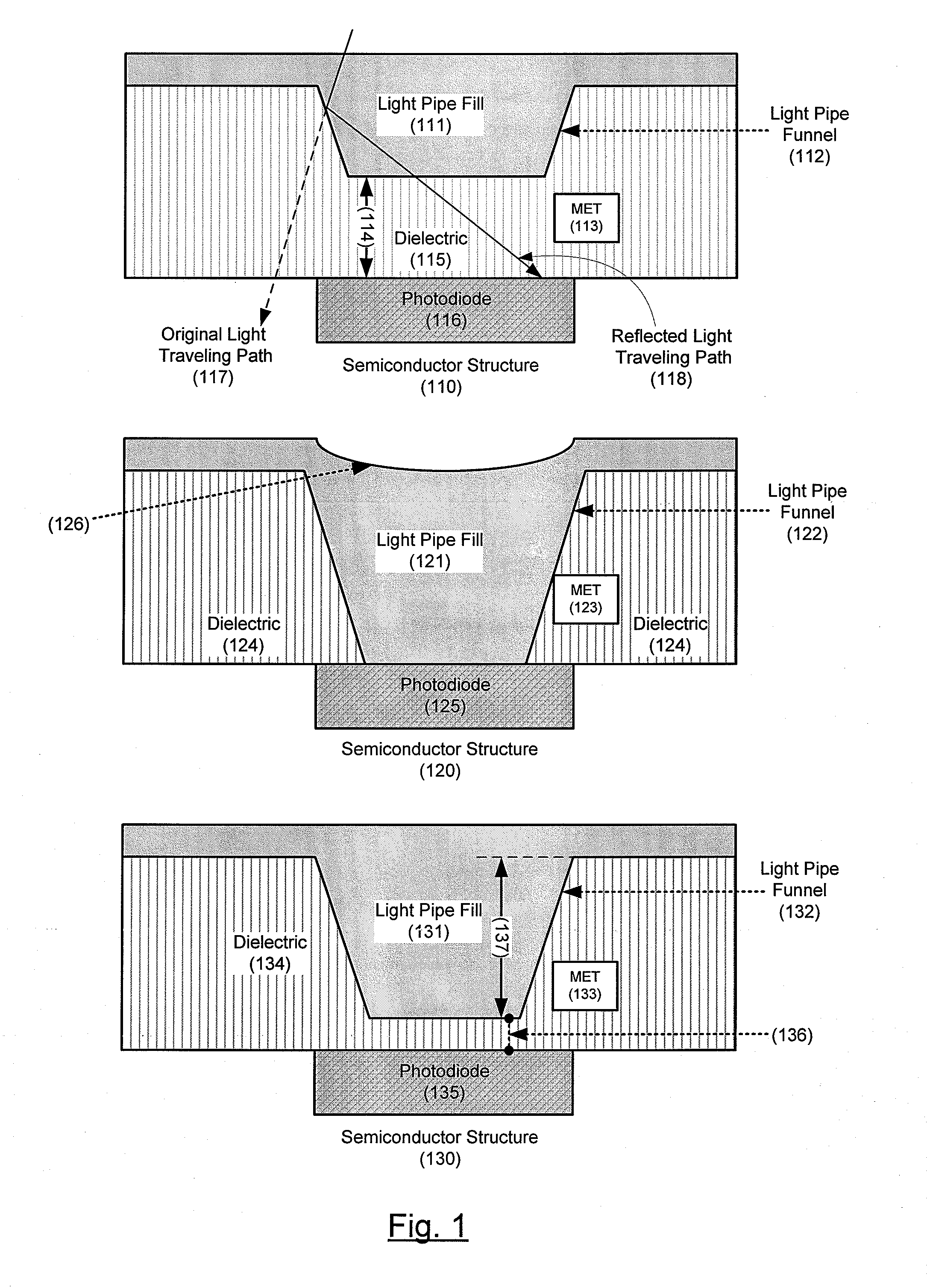

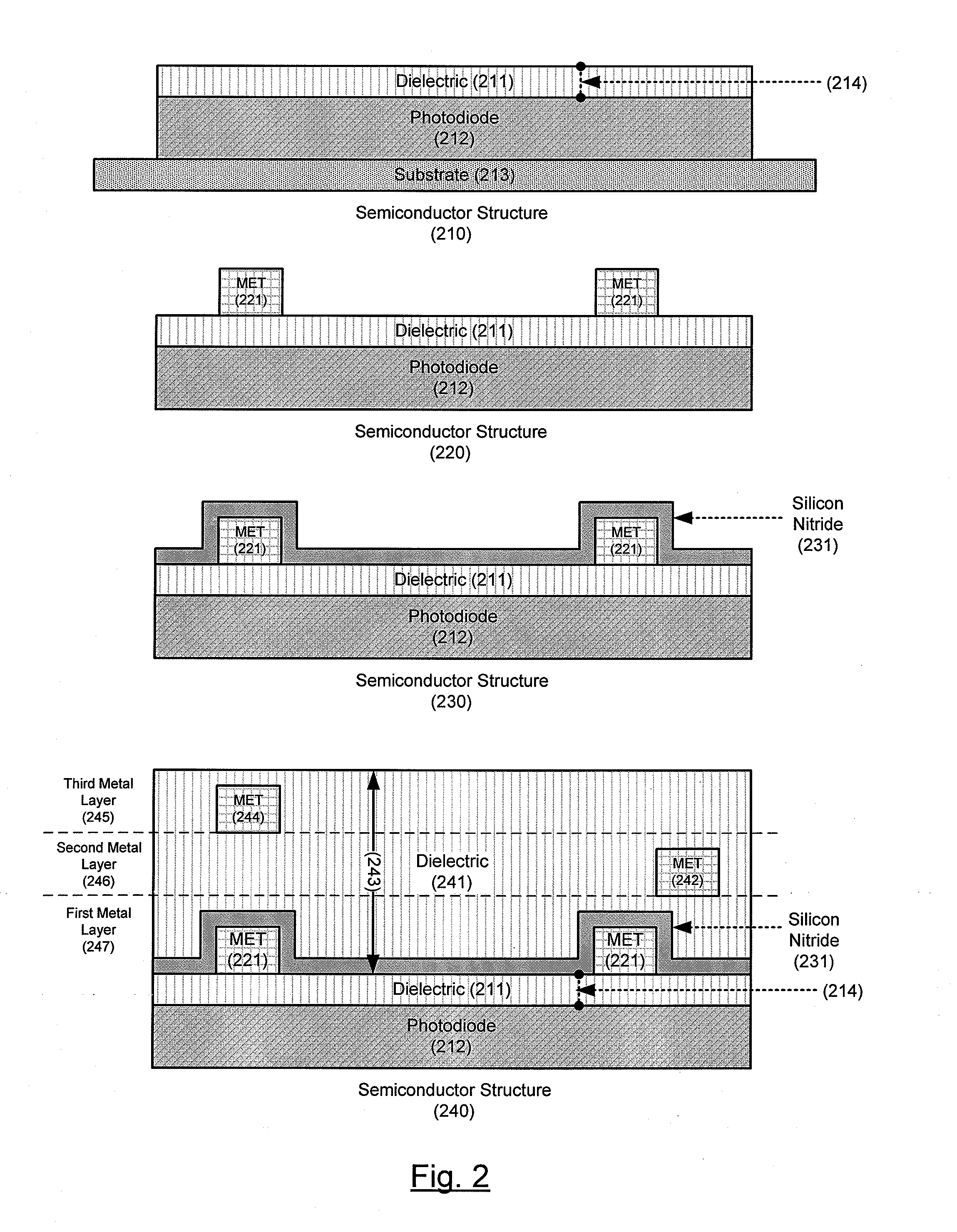

Light pipe etch control for CMOS fabrication

ActiveUS20110316106A1Solid-state devicesSemiconductor/solid-state device manufacturingEtchingSemiconductor structure

In accordance with at least some embodiments of the present disclosure, a process for fabricating a light pipe (LP) is described. The process may be configured to construct a semiconductor structure having an etch-stop layer above a photodiode region and a first dielectric layer above the etch-stop layer. The process may be configured to etch a LP funnel through the first dielectric layer. And the process may be further configured to stop the etching of the LP funnel upon reaching and removing of the etch-stop layer.

Owner:HIMAX IMAGING LIMITED

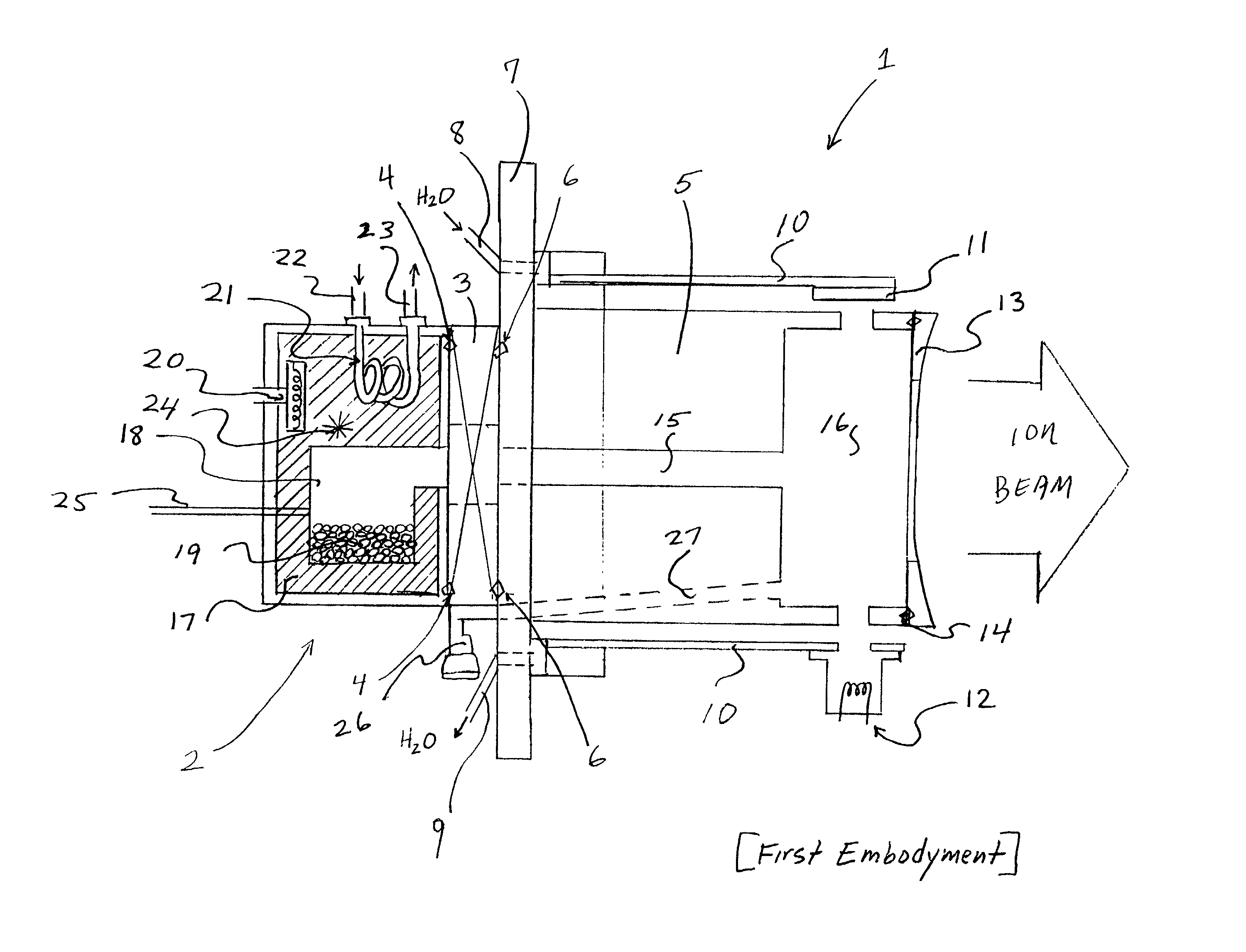

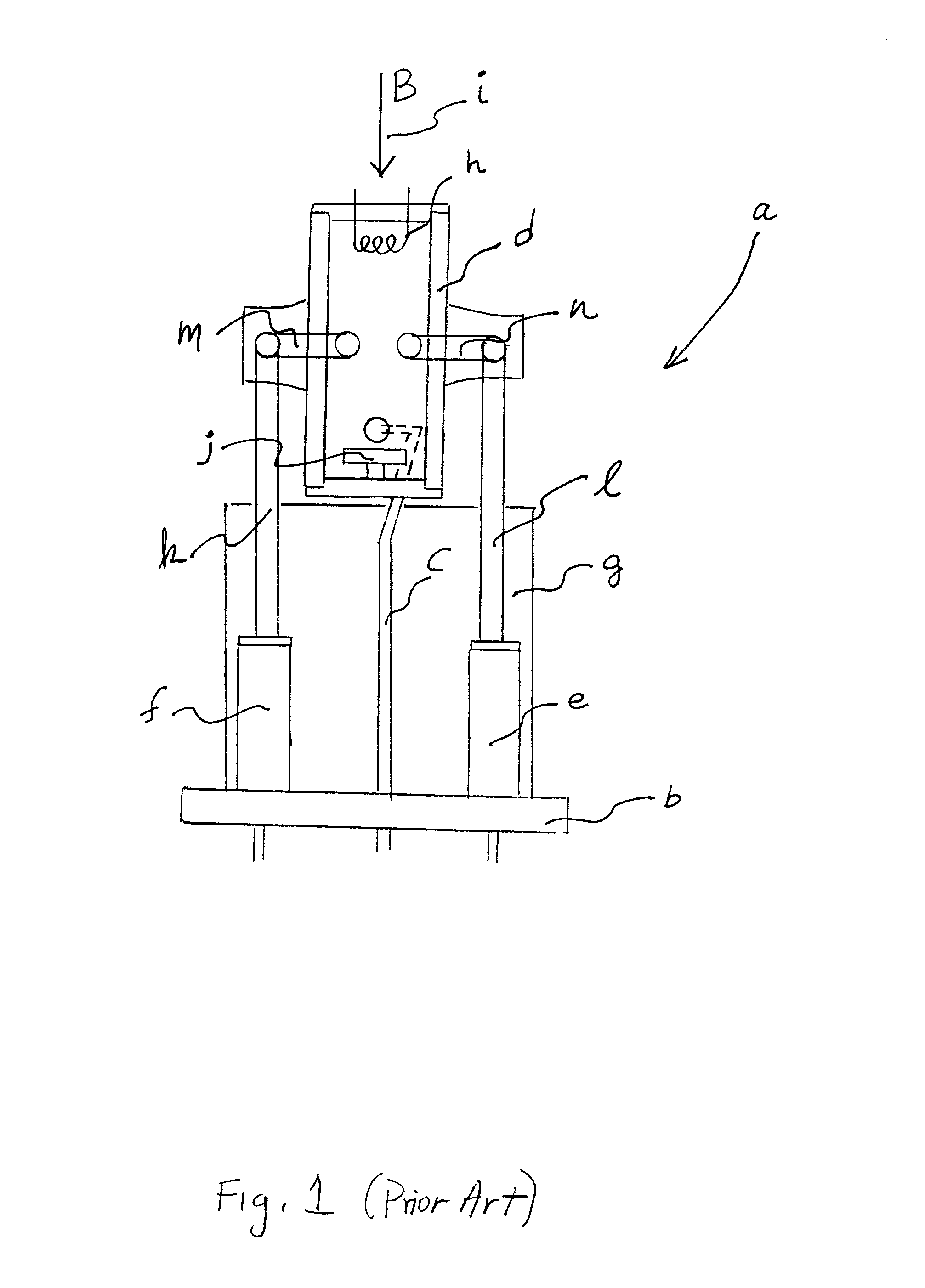

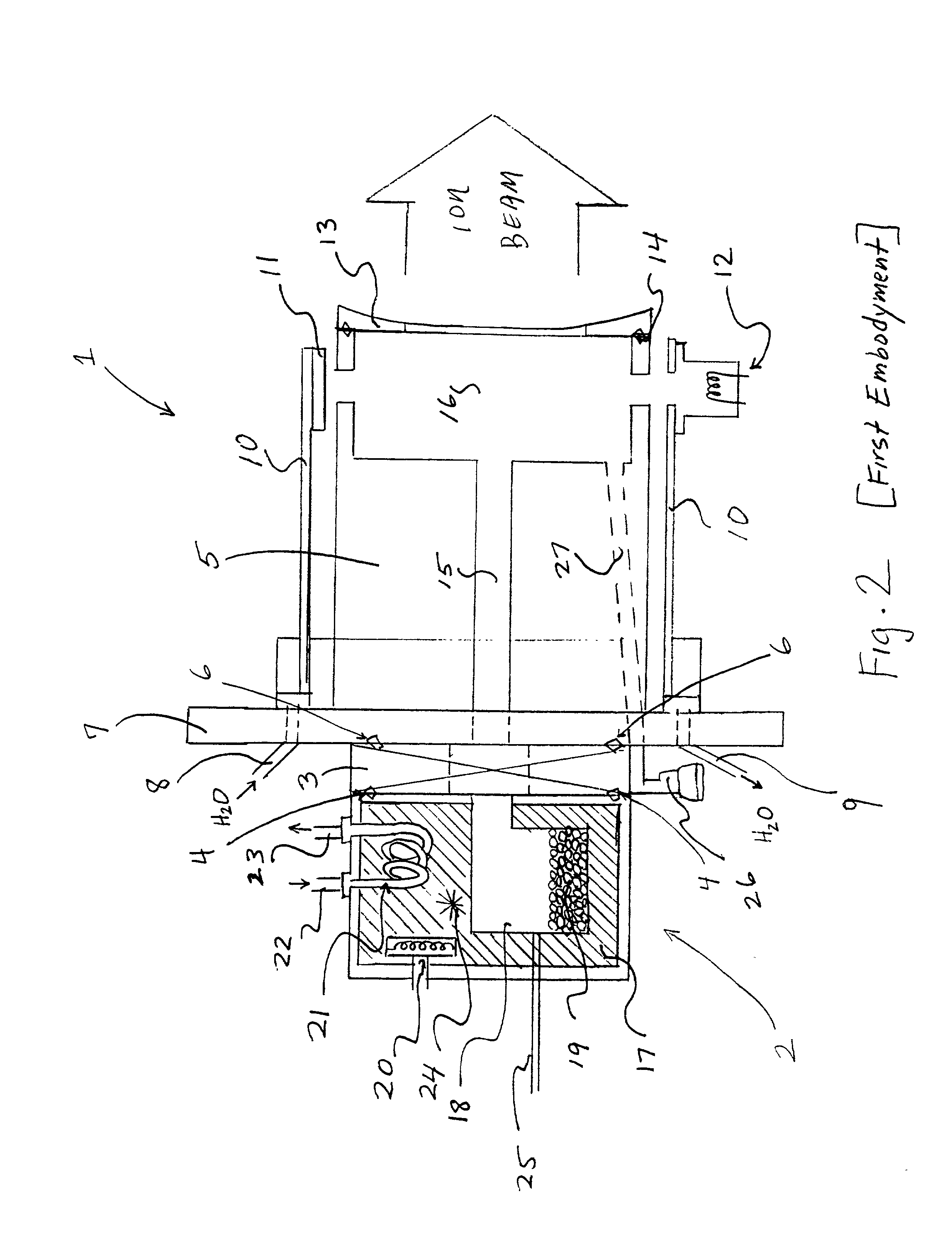

Electron beam ion source with integral low-temperature vaporizer

InactiveUS20020070672A1Maximizes conductanceMinimizes conductanceElectric discharge tubesSemiconductor/solid-state device manufacturingHigh energy beamIon implantation

An ion source for ion implantation system and a method of ion implantation employs a controlled broad, directional electron beam to ionize process gas or vapor, such as decaborane, within an ionization volume by primary electron impact, in CMOS manufacturing and the like. Isolation of the electron gun for producing the energetic electron beam and of the beam dump to which the energetic beam is directed, as well as use of the thermally conductive members for cooling the ionization chamber and the vaporizer, enable use with large molecular species such as decaborane, and other materials which are unstable with temperature. Electron optics systems, facilitate focusing of electrons from an emitting surface to effectively ionize a desired volume of the gas or vapor that is located adjacent the extraction aperture. The components enable retrofit into ion implanters that have used other types of ion sources. Demountable vaporizers, and numerous other important features, realize economies in construction and operation. Achievement of production-worthy operation in respect of very shallow implants is realized.

Owner:SEMEQUIP

Current-controlled CMOS circuit using higher voltage supply in low voltage CMOS process

InactiveUS6982583B2Speed maximizationIncrease circuit speedExclusive-OR circuitsMultiple input and output pulse circuitsTransceiverHigh voltage

Various circuit techniques for implementing ultra high speed circuits use current-controlled CMOS (C3MOS) logic fabricated in conventional CMOS process technology. An entire family of logic elements including inverter / buffers, level shifters, NAND, NOR, XOR gates, latches, flip-flops and the like are implemented using C3MOS techniques. Optimum balance between power consumption and speed for each circuit application is achieve by combining high speed C3MOS logic with low power conventional CMOS logic. The combined C3MOS / CMOS logic allows greater integration of circuits such as high speed transceivers used in fiber optic communication systems. The C3MOS structure enables the use of a power supply voltage that may be larger than the voltage required by the CMOS fabrication process, further enhancing the performance of the circuit.

Owner:AVAGO TECH INT SALES PTE LTD

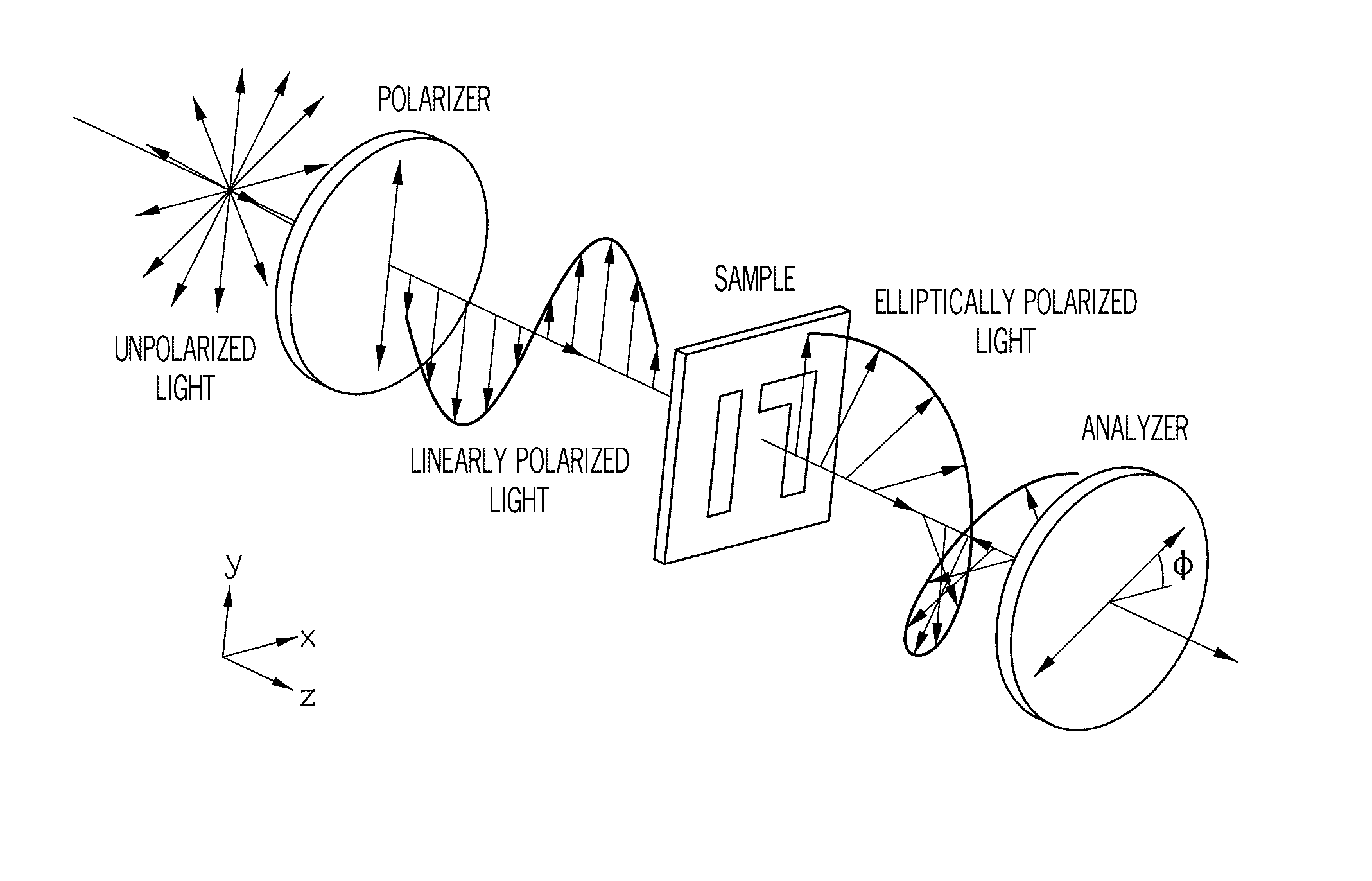

Tag with a non-metallic metasurface that converts incident light into elliptically or circularly polarized light regardless of polarization state of the incident light

InactiveUS20160341859A1Polarising elementsNanoopticsThermionic emissionCircularly polarized radiation

An optical device for generating narrow-band circularly and elliptically polarized radiation, either by conversion from externally incident light or through thermal emission of heated objects. The optical device includes a metasurface comprised of unit cells, where each unit cell contains structural elements or features that break two mirror inversion symmetries of the unit cell and couple bright and dark resonances. In this manner, the optical device emits circularly polarized radiation that does not exhibit a preference for right-hand circularly polarized light or left-hand circularly polarized light incident upon it. As a result, multiple of such optical devices with different unit cell sizes, geometries and dimensions of the intra-cell elements may be implemented as a tag that thermally emits different states of circularly polarized radiation confined to multiple spectrally-narrow bands. Since the optical device can be fabricated in CMOS, the tag can be used for preventing / identifying tampering with genuine electronic components.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

Current-controlled CMOS circuit using higher voltage supply in low voltage CMOS process

InactiveUS6897697B2Speed maximizationDissipates static currentExclusive-OR circuitsElectronic switchingTransceiverEngineering

Various circuit techniques for implementing ultra high speed circuits use current-controlled CMOS (C3MOS) logic fabricated in conventional CMOS process technology. An entire family of logic elements including inverter / buffers, level shifters, NAND, NOR, XOR gates, latches, flip-flops and the like are implemented using C3MOS techniques. Optimum balance between power consumption and speed for each circuit application is achieve by combining high speed C3MOS logic with low power conventional CMOS logic. The combined C3MOS / CMOS logic allows greater integration of circuits such as high speed transceivers used in fiber optic communication systems. The C3MOS structure enables the use of a power supply voltage that may be larger than the voltage required by the CMOS fabrication process, further enhancing the performance of the circuit.

Owner:AVAGO TECH INT SALES PTE LTD

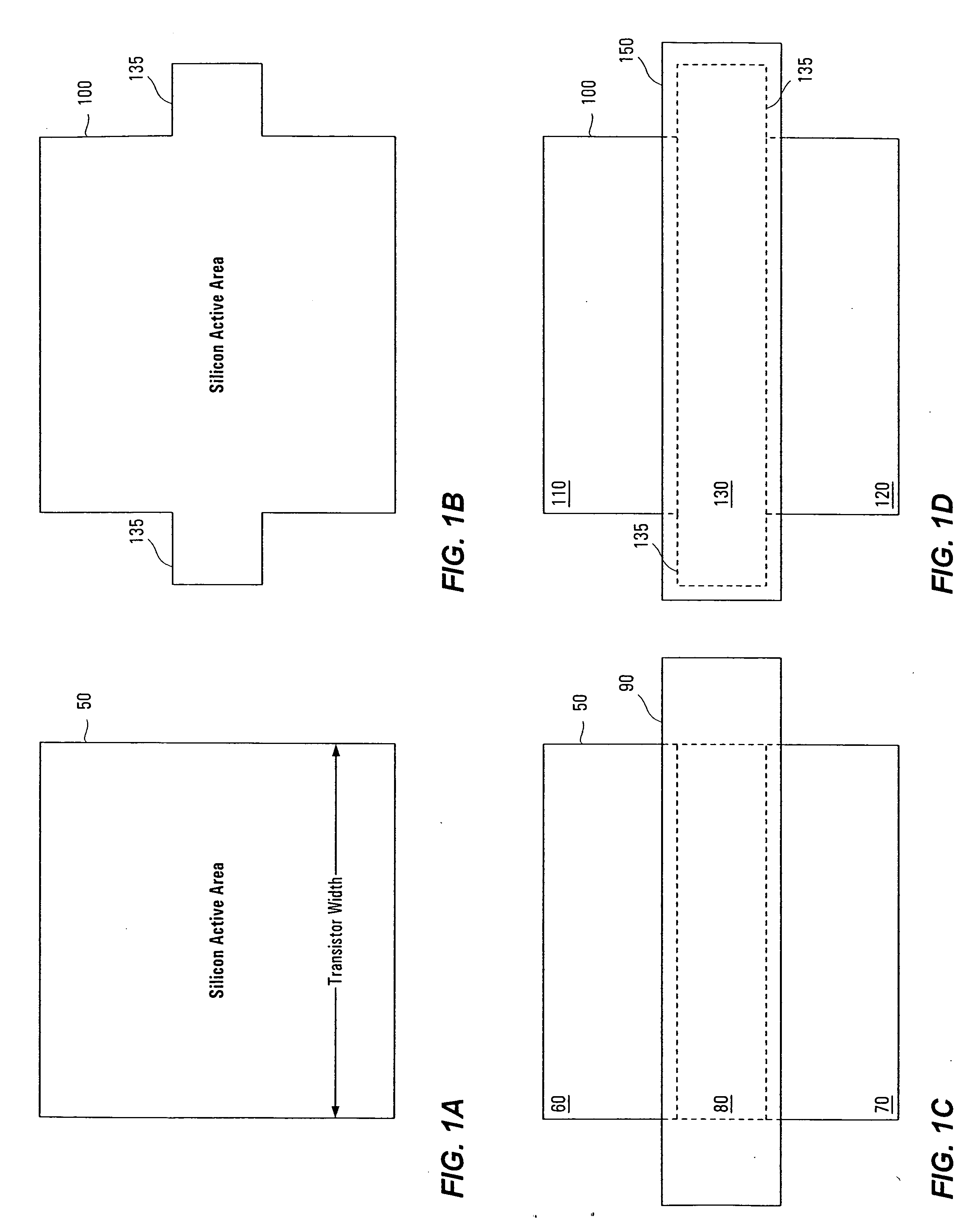

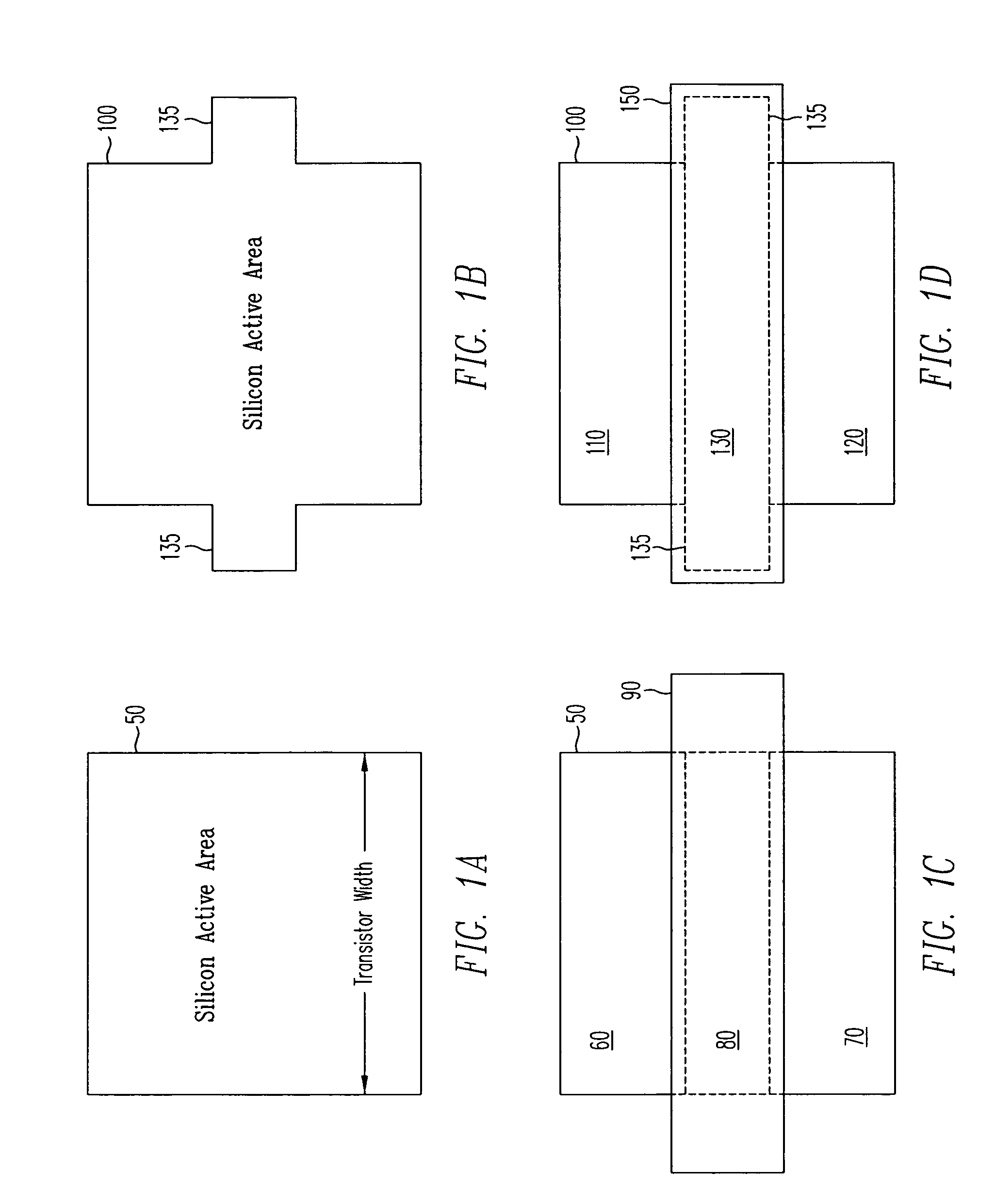

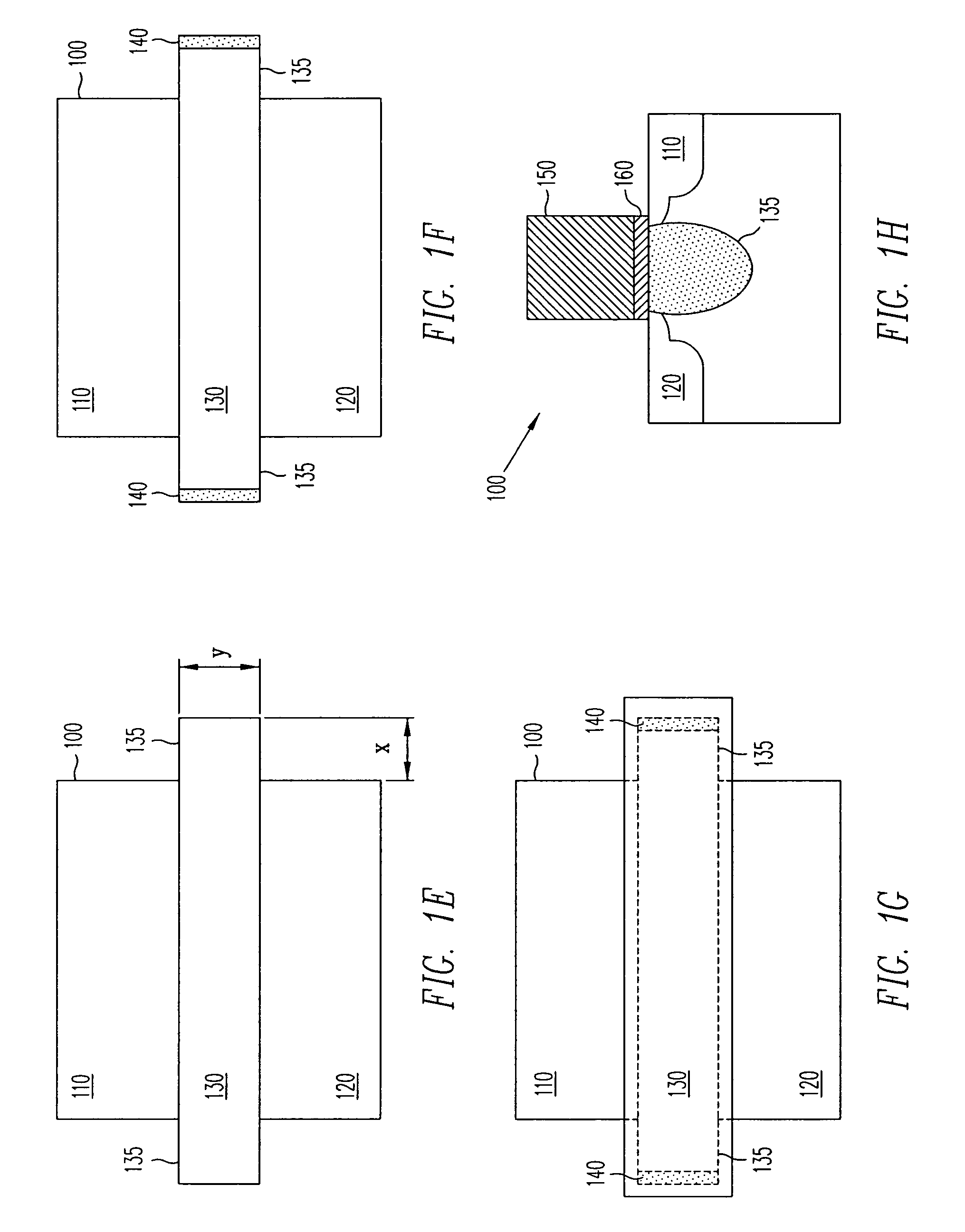

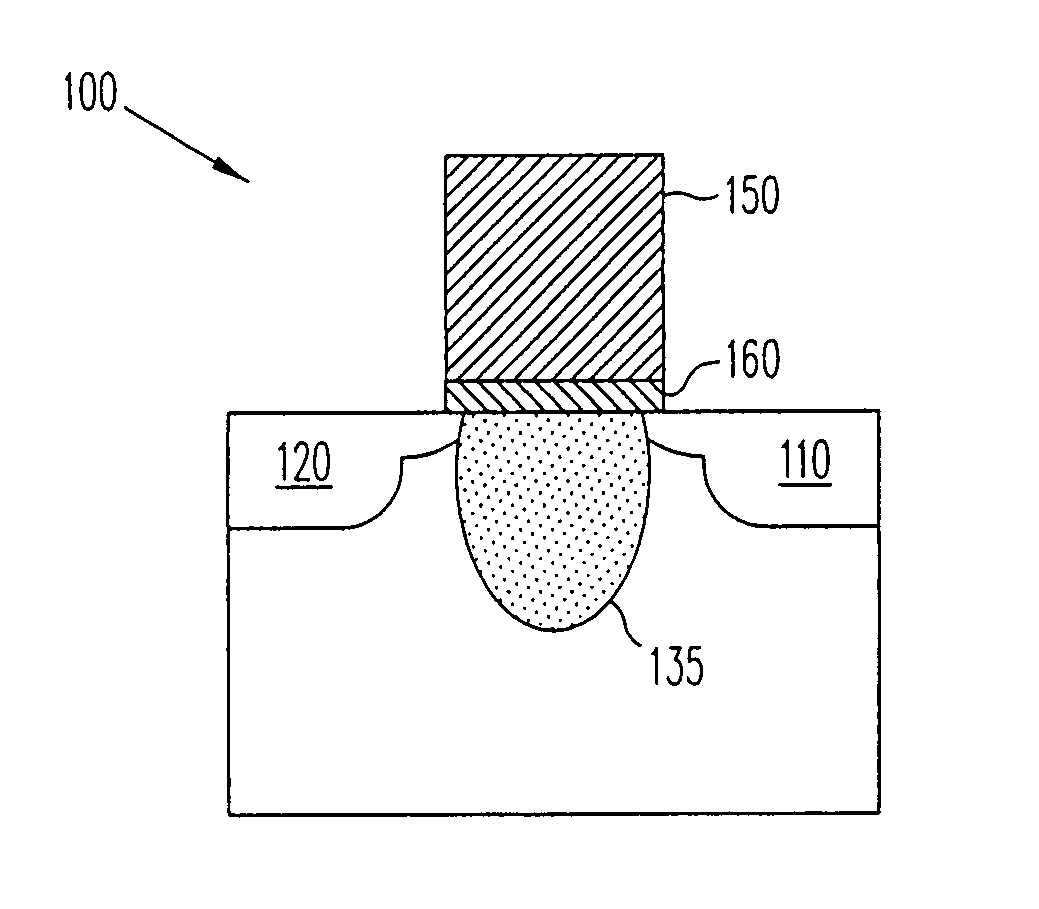

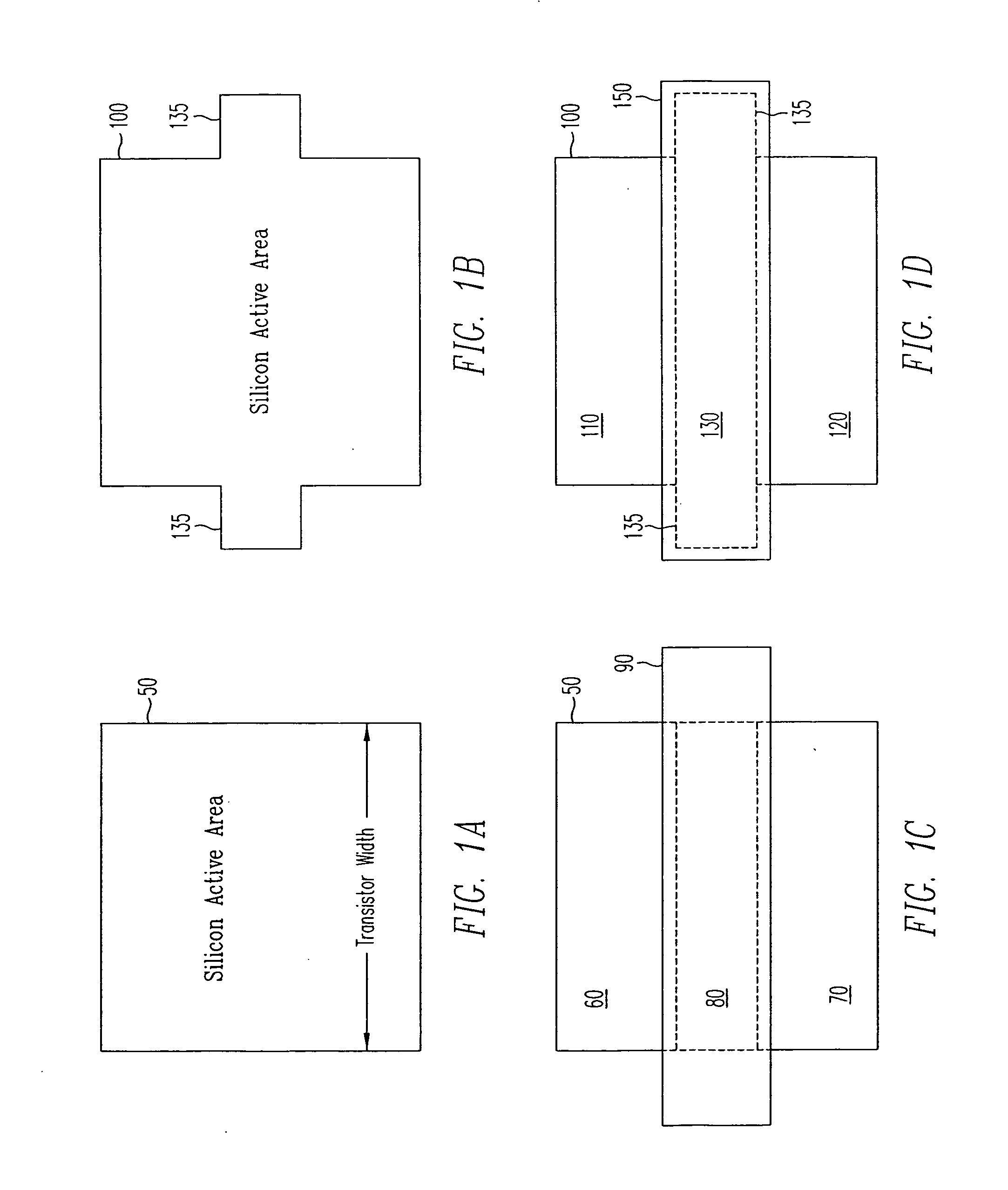

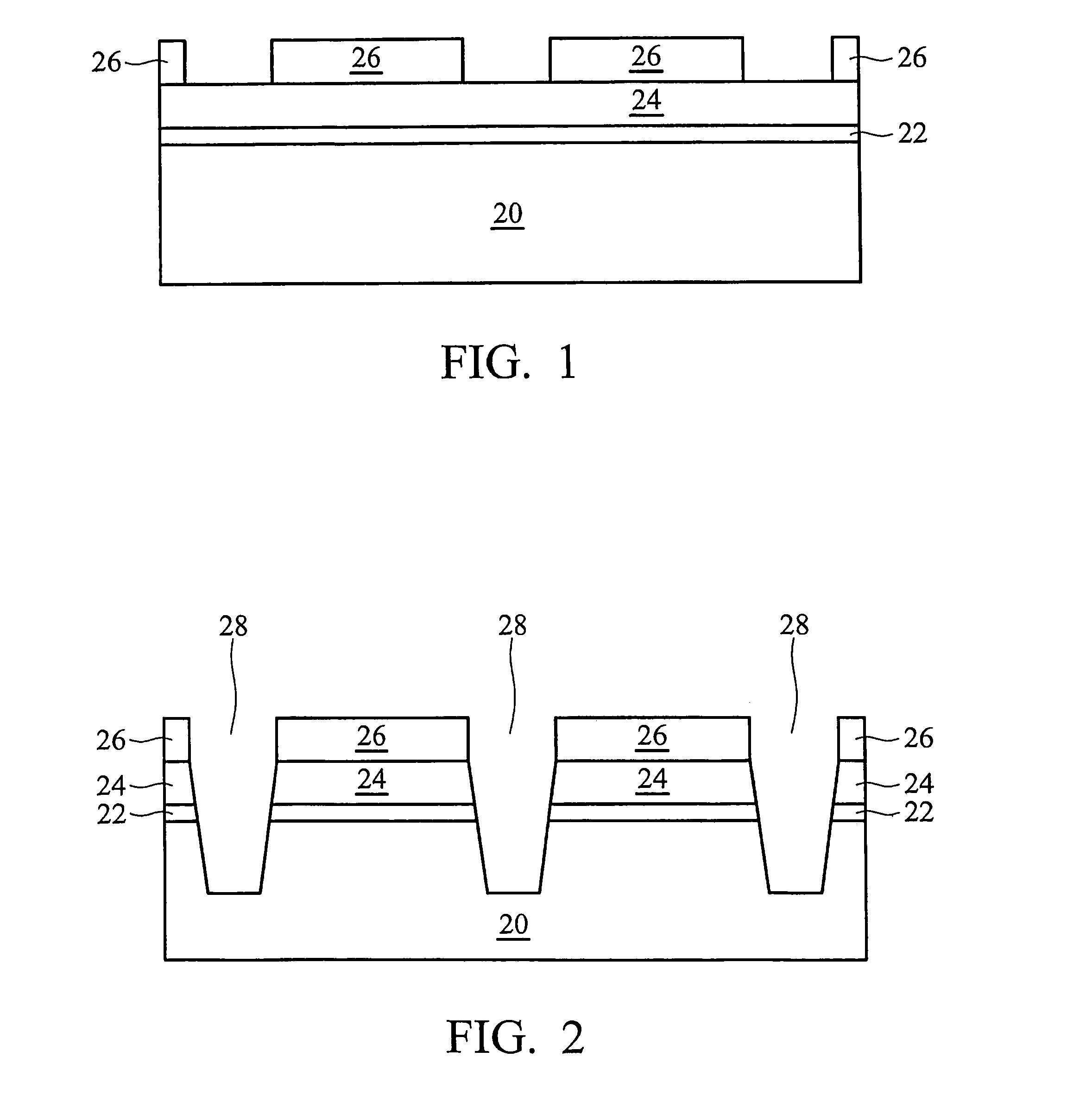

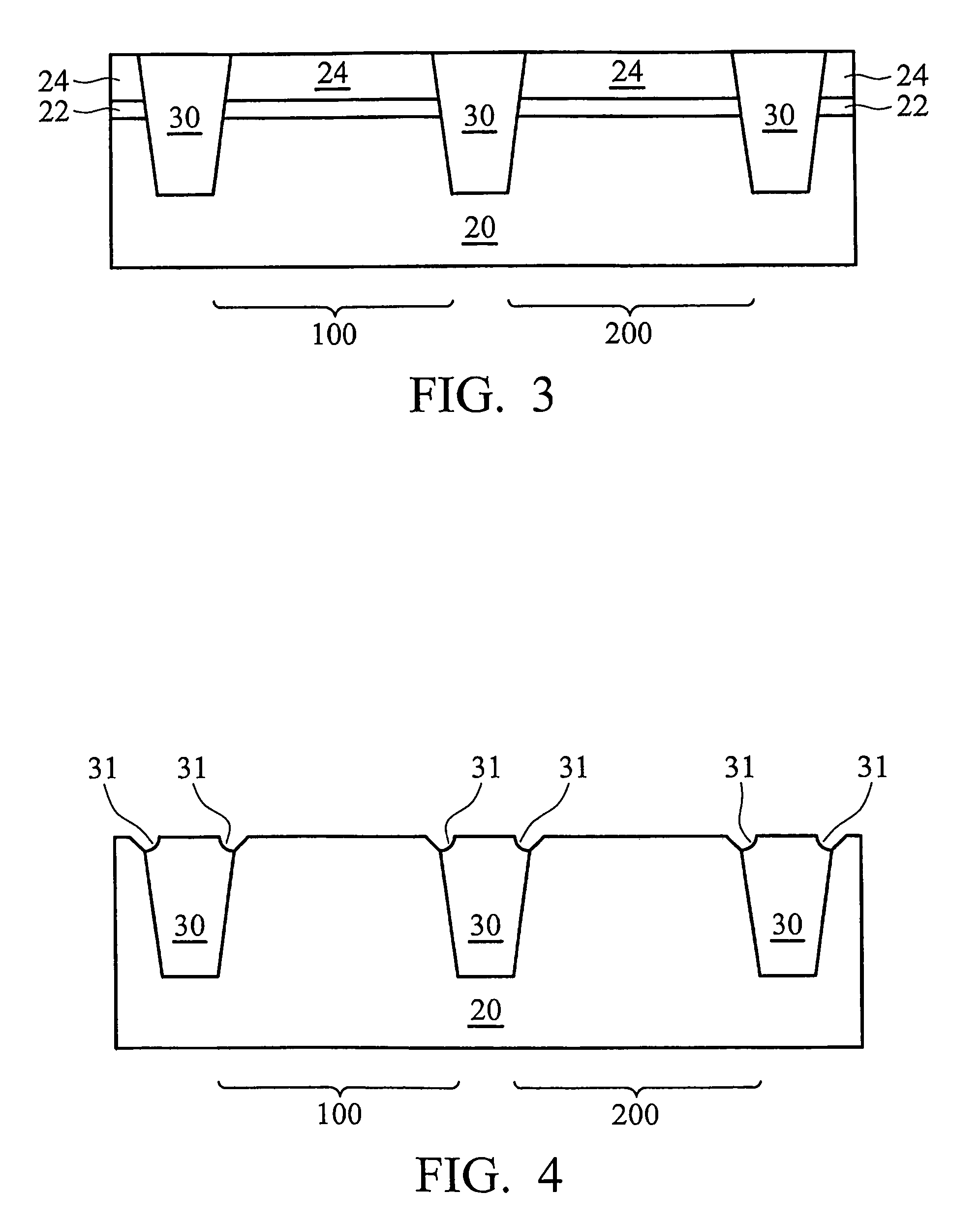

Diffusion topography engineering for high performance CMOS fabrication

ActiveUS7355262B2Increase pressureImprove device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenSemiconductor structure

Semiconductor structures are formed using diffusion topography engineering (DTE). A preferred method includes providing a semiconductor substrate, forming trench isolation regions that define a diffusion region, performing a DTE in a hydrogen-containing ambient on the semiconductor substrate, and forming a MOS device in the diffusion region. The DTE causes silicon migration, forming a rounded or a T-shaped surface of the diffusion regions. The method may further include recessing a portion of the diffusion region before performing the DTE. The diffusion region has a slanted surface after performing the DTE.

Owner:TAIWAN SEMICON MFG CO LTD

Semi-floating gate fet

A semi-floating gate transistor is implemented as a vertical FET built on a silicon substrate, wherein the source, drain, and channel are vertically aligned, on top of one another. Current flow between the source and the drain is influenced by a control gate and a semi-floating gate. Front side contacts can be made to each one of the source, drain, and control gate terminals of the vertical semi-floating gate transistor. The vertical semi-floating gate FET further includes a vertical tunneling FET and a vertical diode. Fabrication of the vertical semi-floating gate FET is compatible with conventional CMOS manufacturing processes, including a replacement metal gate process. Low-power operation allows the vertical semi-floating gate FET to provide a high current density compared with conventional planar devices.

Owner:STMICROELECTRONICS SRL

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com