Vertical double-diffused metal oxide semiconductor field effect transistor having semi-insulating polysilicon layer

A technology of semi-insulating polysilicon and oxide semiconductors, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., and can solve the problems of increased conduction loss of devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

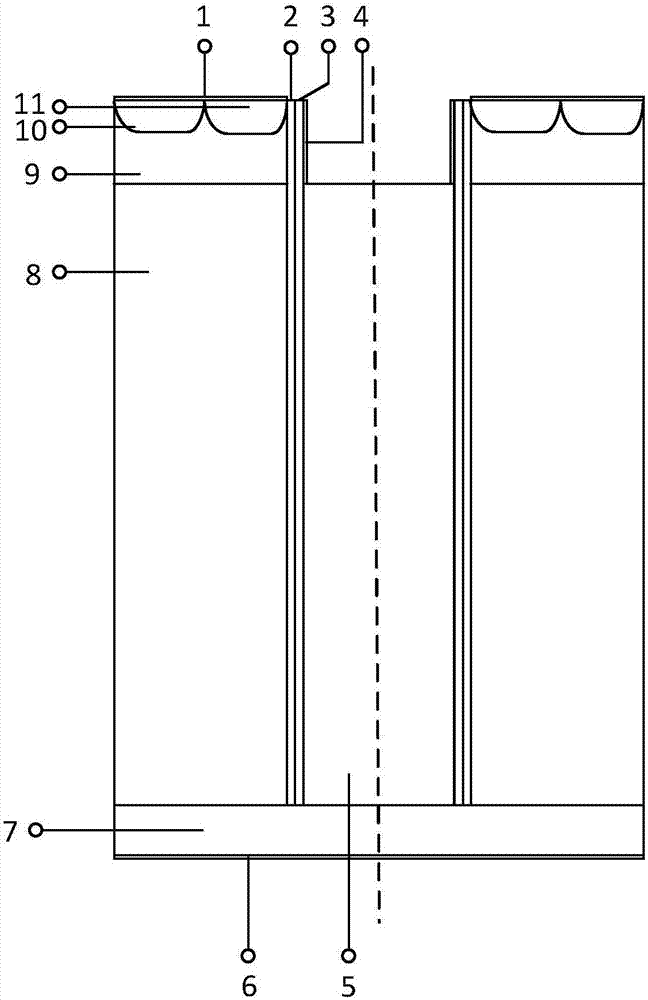

[0044] Such as figure 1 As shown, the vertical double-diffused metal oxide semiconductor field effect transistor with a semi-insulating polysilicon layer includes:

[0045] Substrate drain region 7 of semiconductor material with a doping concentration of 1×10 13 cm -3 ~1×10 15 cm -3 ;

[0046] A drift region 8 formed by an epitaxial layer on the substrate;

[0047] a base region 9 formed by doping on the drift region;

[0048] Etching a trench on the base region, the trench goes down through the drift region to the substrate drain region;

[0049] The gate insulating layer 2 formed on the side wall of the trench has a thickness of 0.02-0.1 μm;

[0050] Oxygen-doped semi-insulating polysilicon layer 3 deposited outside the gate insulating layer; the thickness of the semi-insulating polysilicon layer is 0.2-1.5 μm; the oxygen-doped ratio of the semi-insulating polysilicon layer is 15%-35%, and its corresponding resistivity for 10 9 ~10 11 Ω cm;

[0051] Depositing an ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com