Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

76results about How to "Small line width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

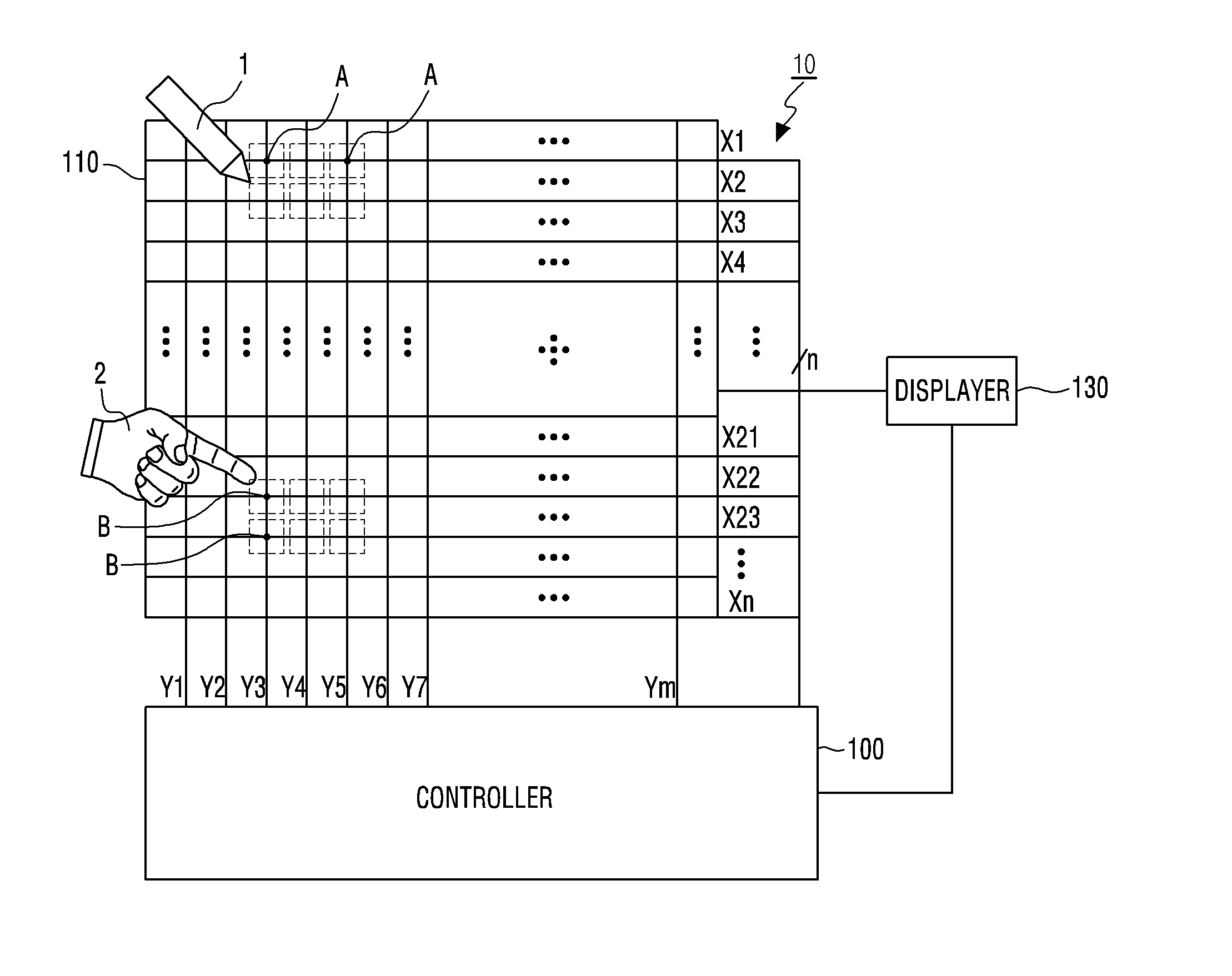

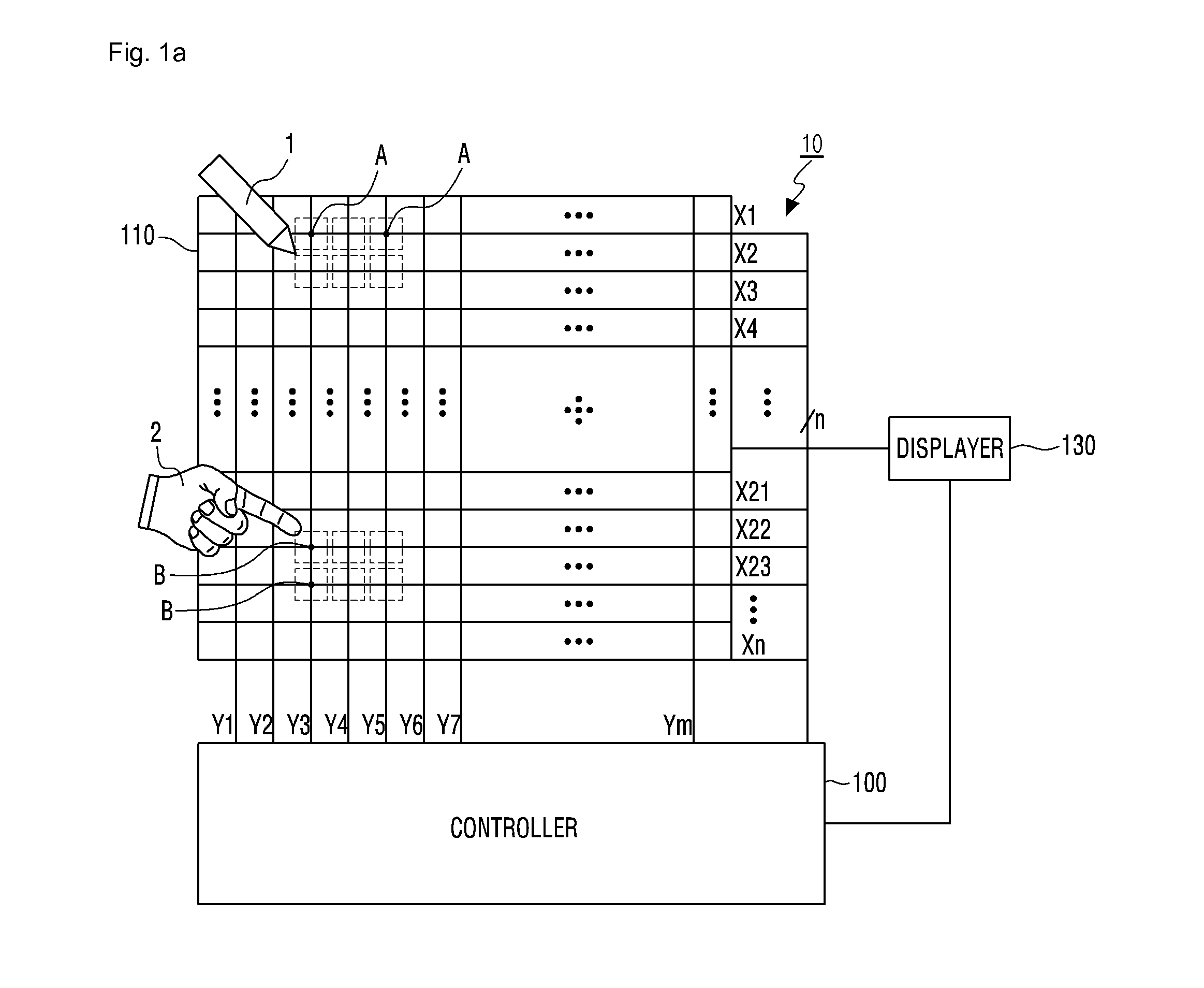

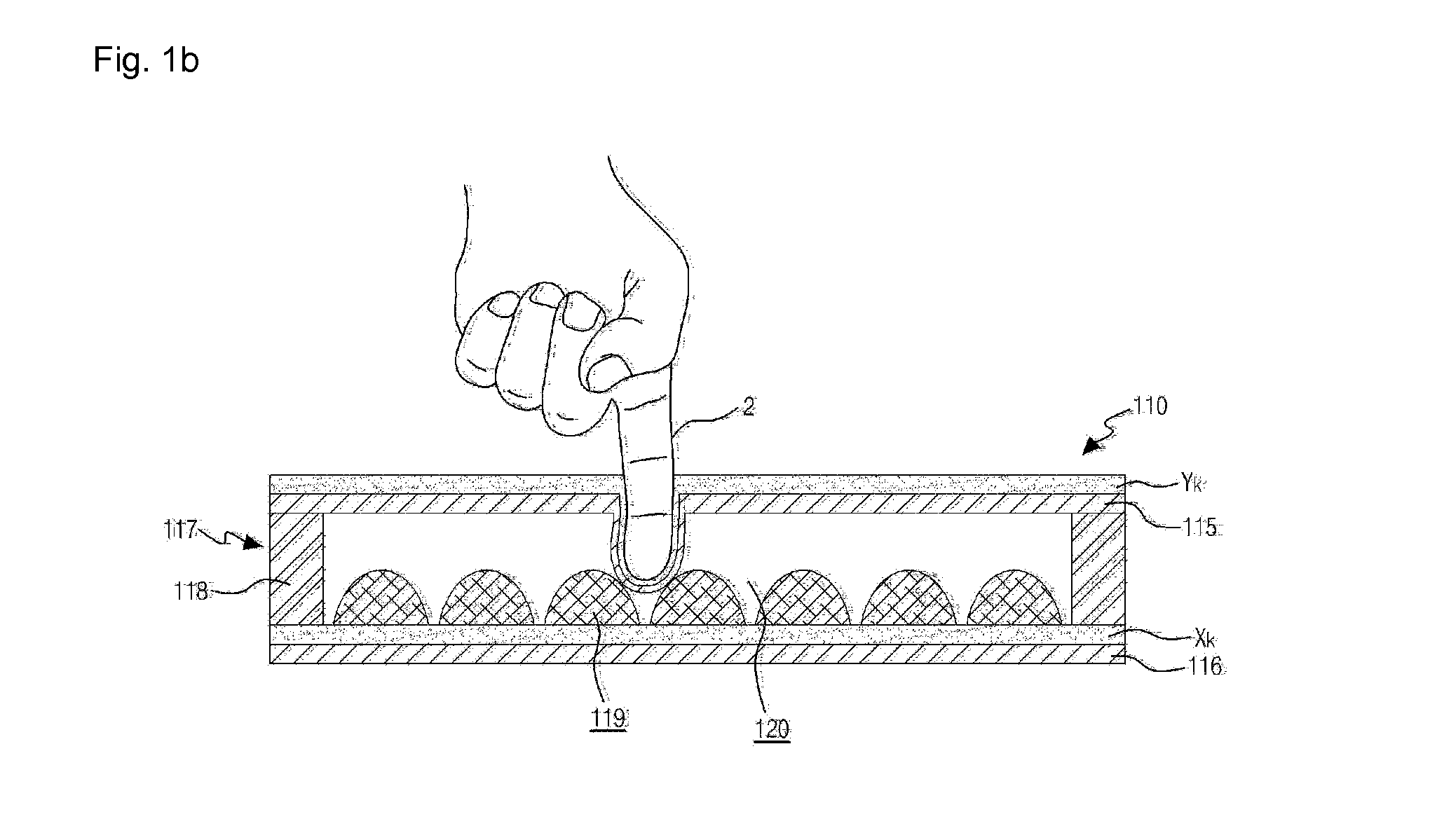

Touch screen contoller and method for controlling thereof

ActiveUS20150160778A1Small line widthShorter lengthInput/output processes for data processingTouch panelDisplay device

A touch panel control device may be provided that includes: a touch panel which generates at least one touch signal in response to a touch of an object; a displayer; and a controller which performs a first touch action mode in which the change of the touch position of the object is displayed on the displayer by a line in response to the object which has touched the touch panel, and performs a second touch action mode in which, in response to the position change of the object which corresponds to the position of the line displayed on the displayer, it is to carry out at least one of the removal of at least a portion of the line displayed on the displayer and the change of the color coordinate of the line. Also, a method for controlling the touch panel may be also provided.

Owner:HIDEEP

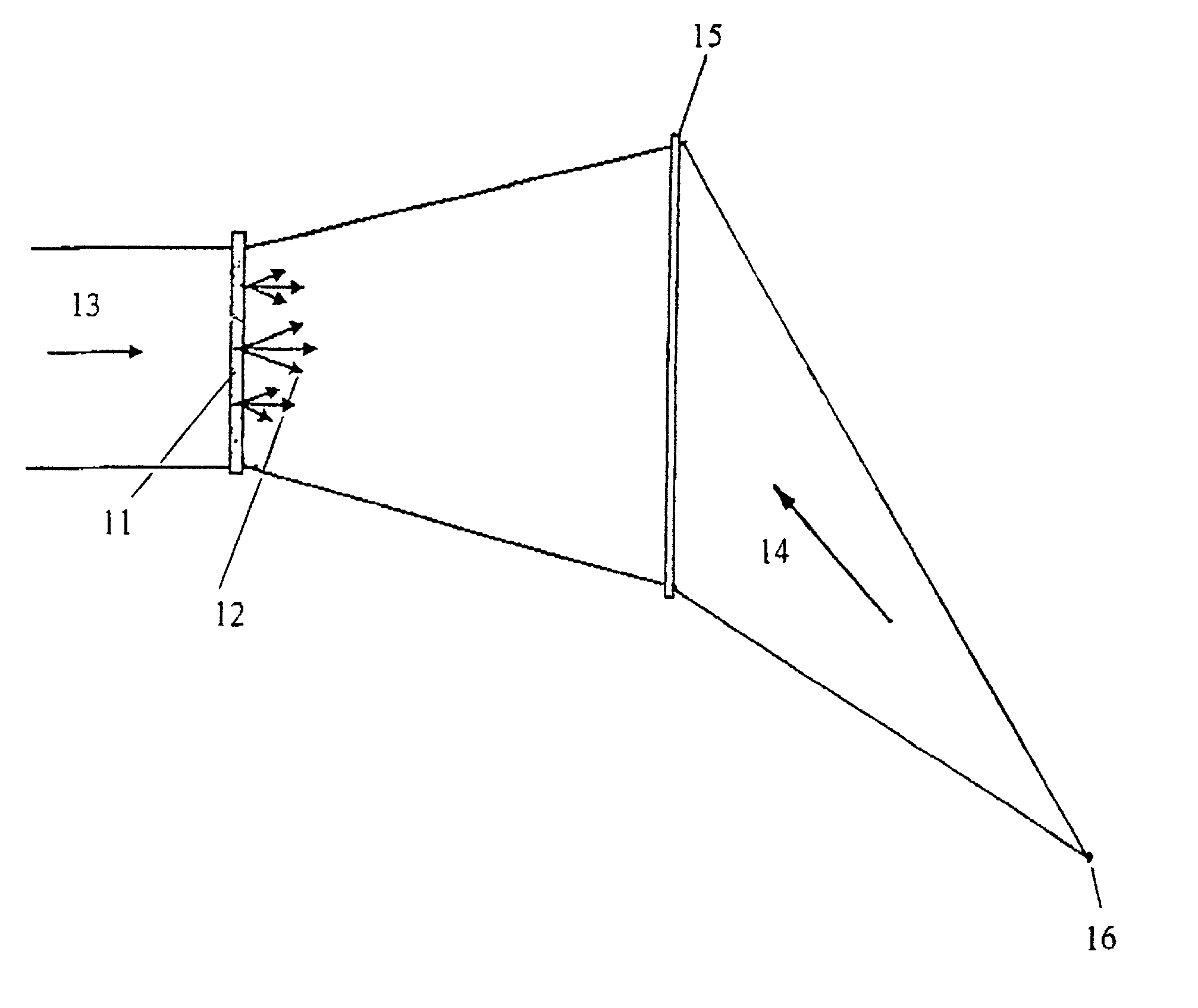

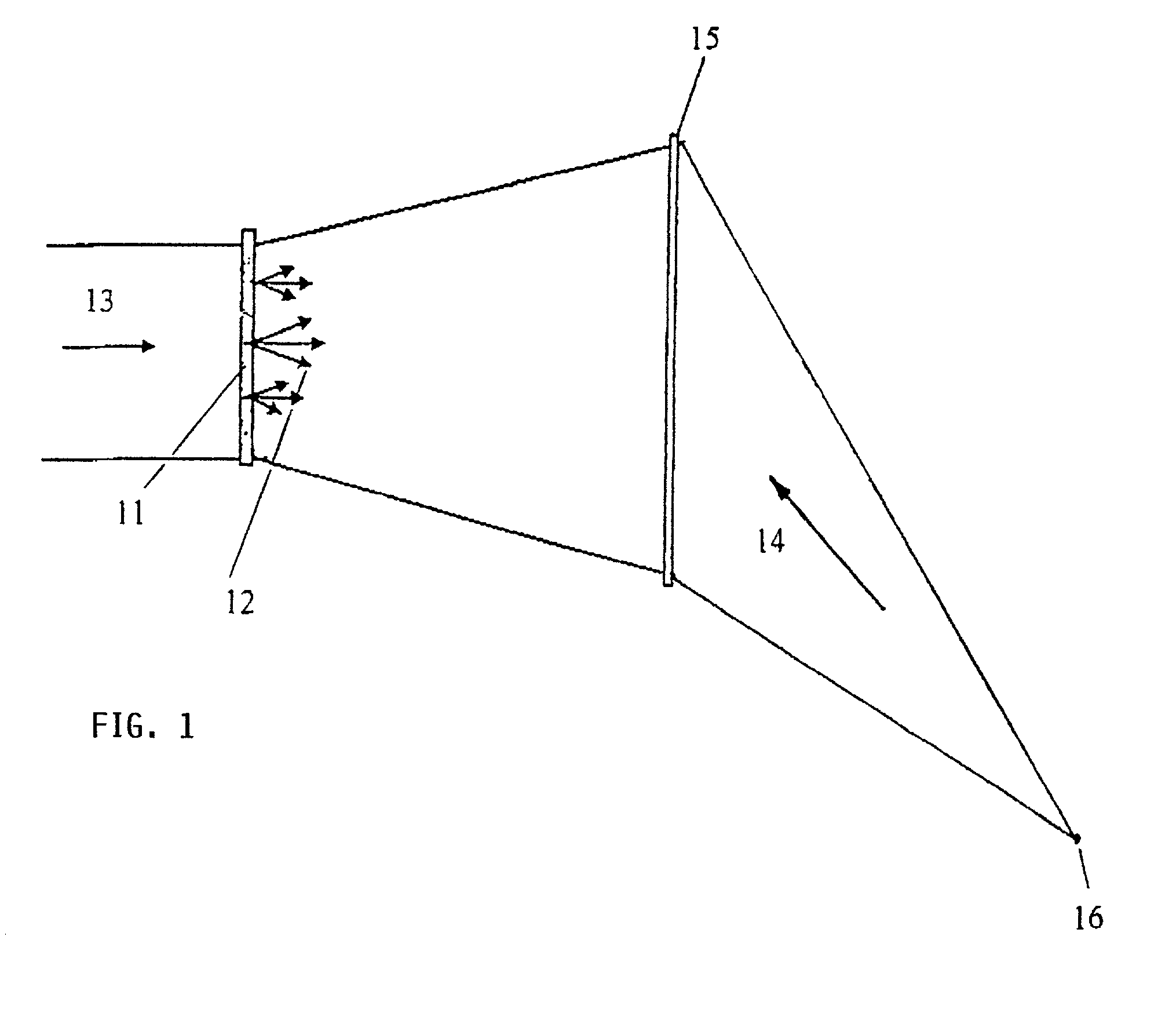

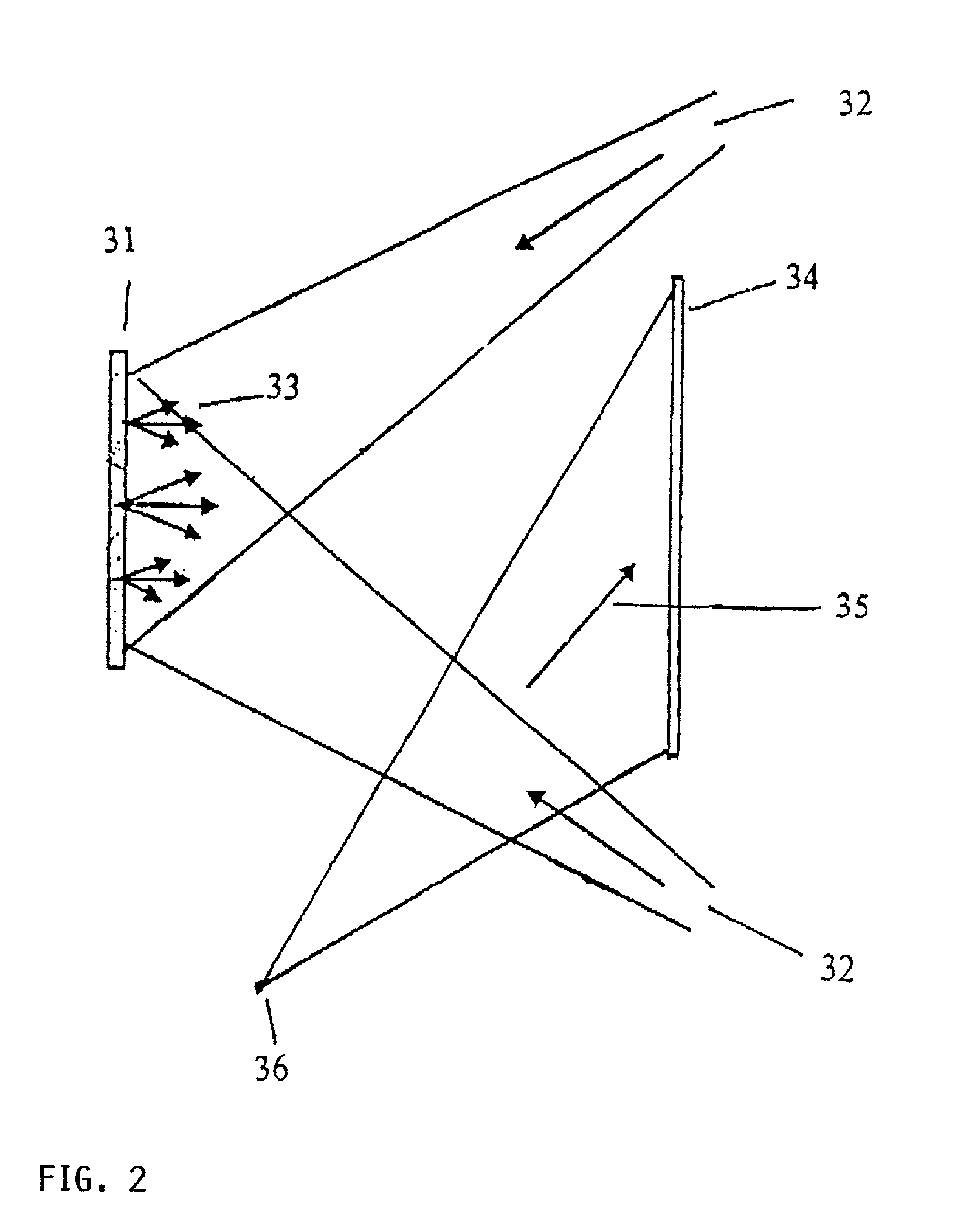

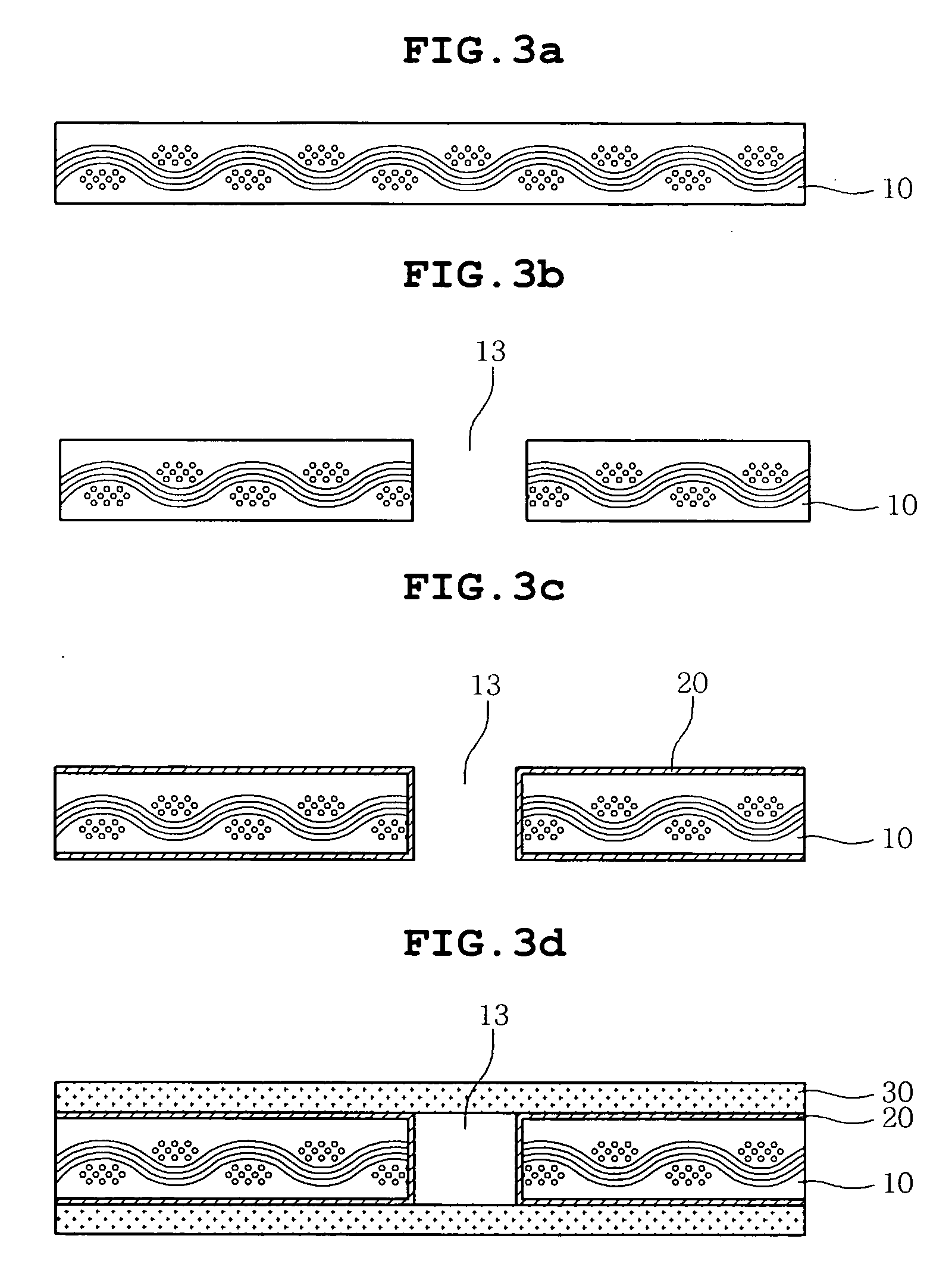

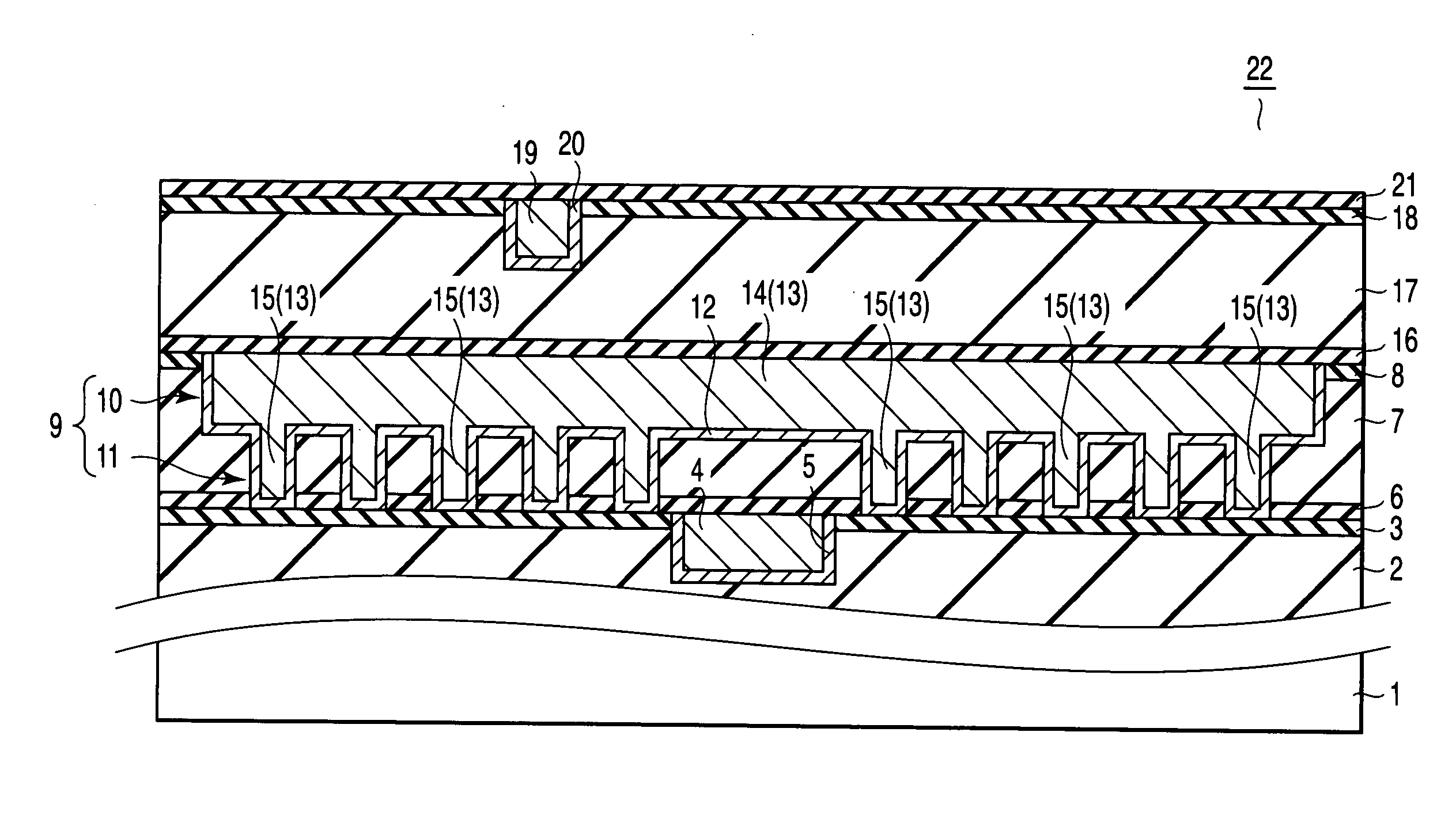

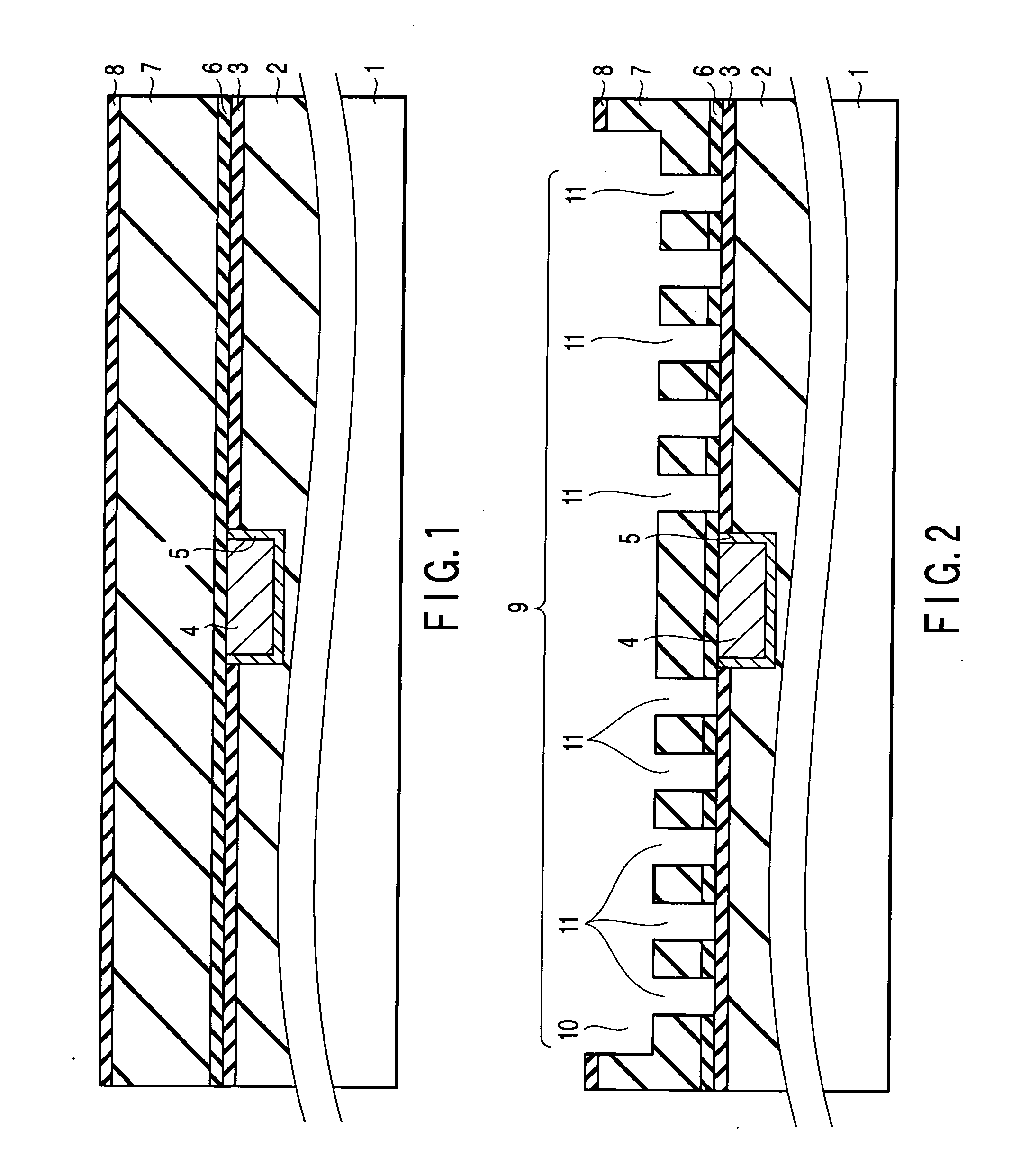

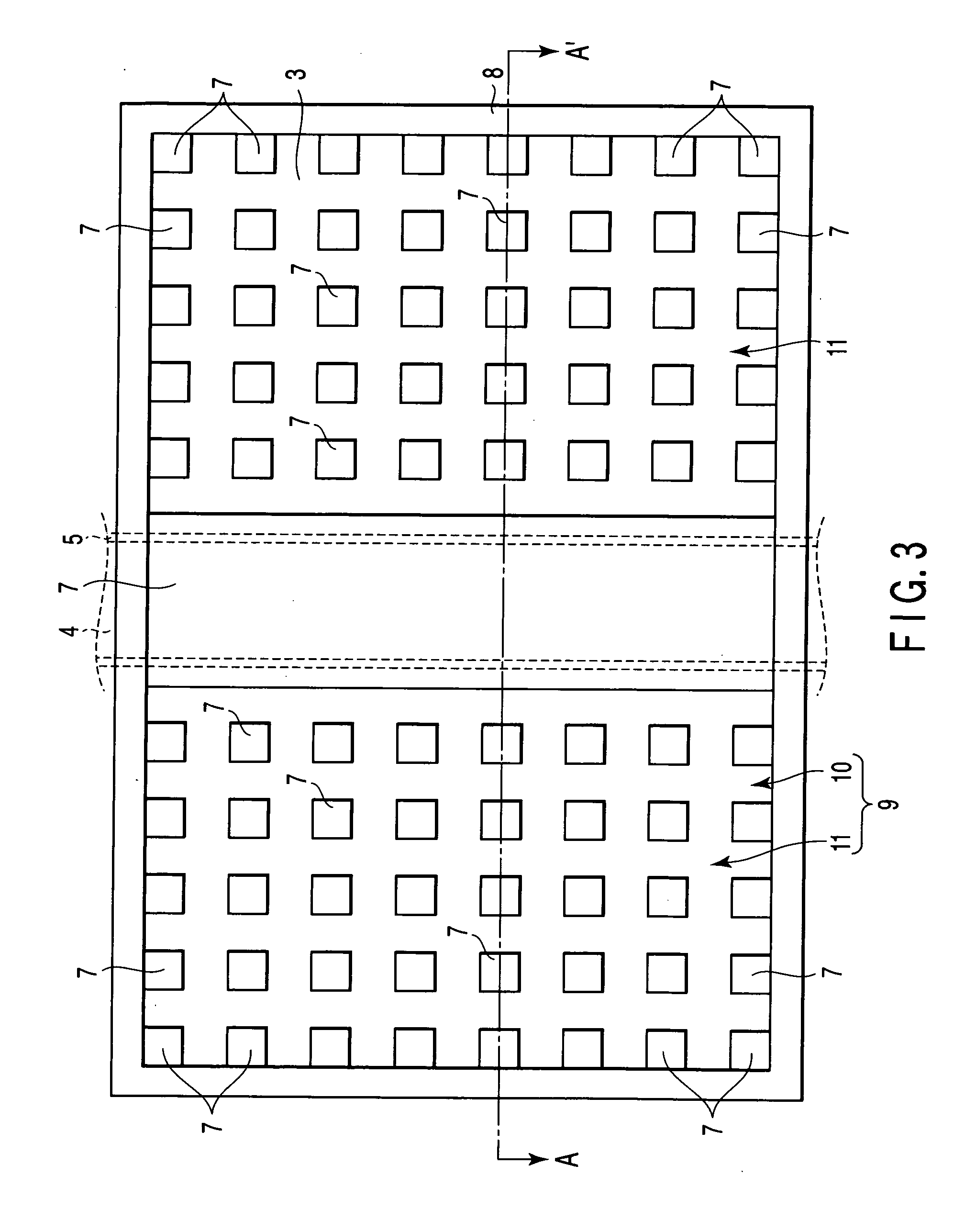

Holographic display screen and method for producing the screen

InactiveUS20020154349A1Large viewing angleFulfil requirementsVehicle componentsOptical elementsHolographic screenPhase grating

A transparent holographic display screen for laser projection of at least one or more monochromatic wavelengths, is constructed to selectively diffuse an incident narrow-band laser beam at a predetermined solid angle and simultaneously to pass wide-band ambient light unobstructed through the display screen. The transparent holographic display screen has at least one holographic volume phase grating which is optically coupled to or integrated with a transparent carrier plate. The holographic display screen with its volume grating is produced by illuminating a real screen as an object into a primary hologram and recording a real holographic image of said real screen into a secondary hologram.

Owner:EADS DEUT GMBH

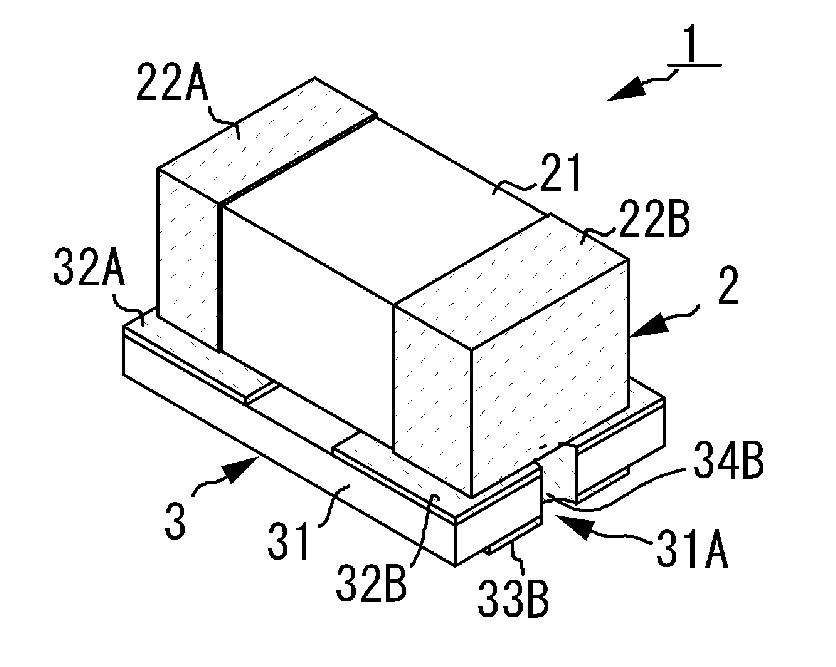

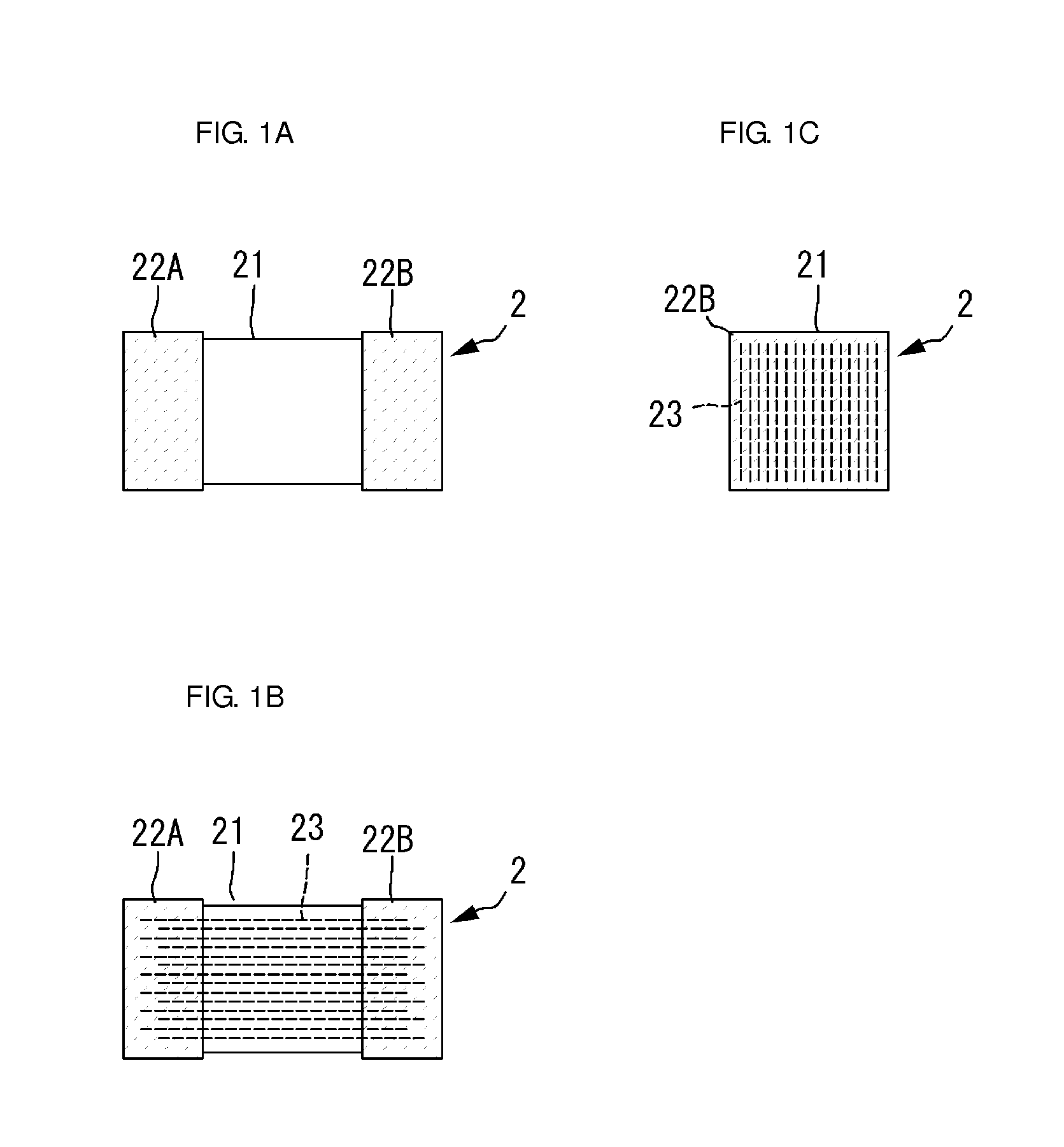

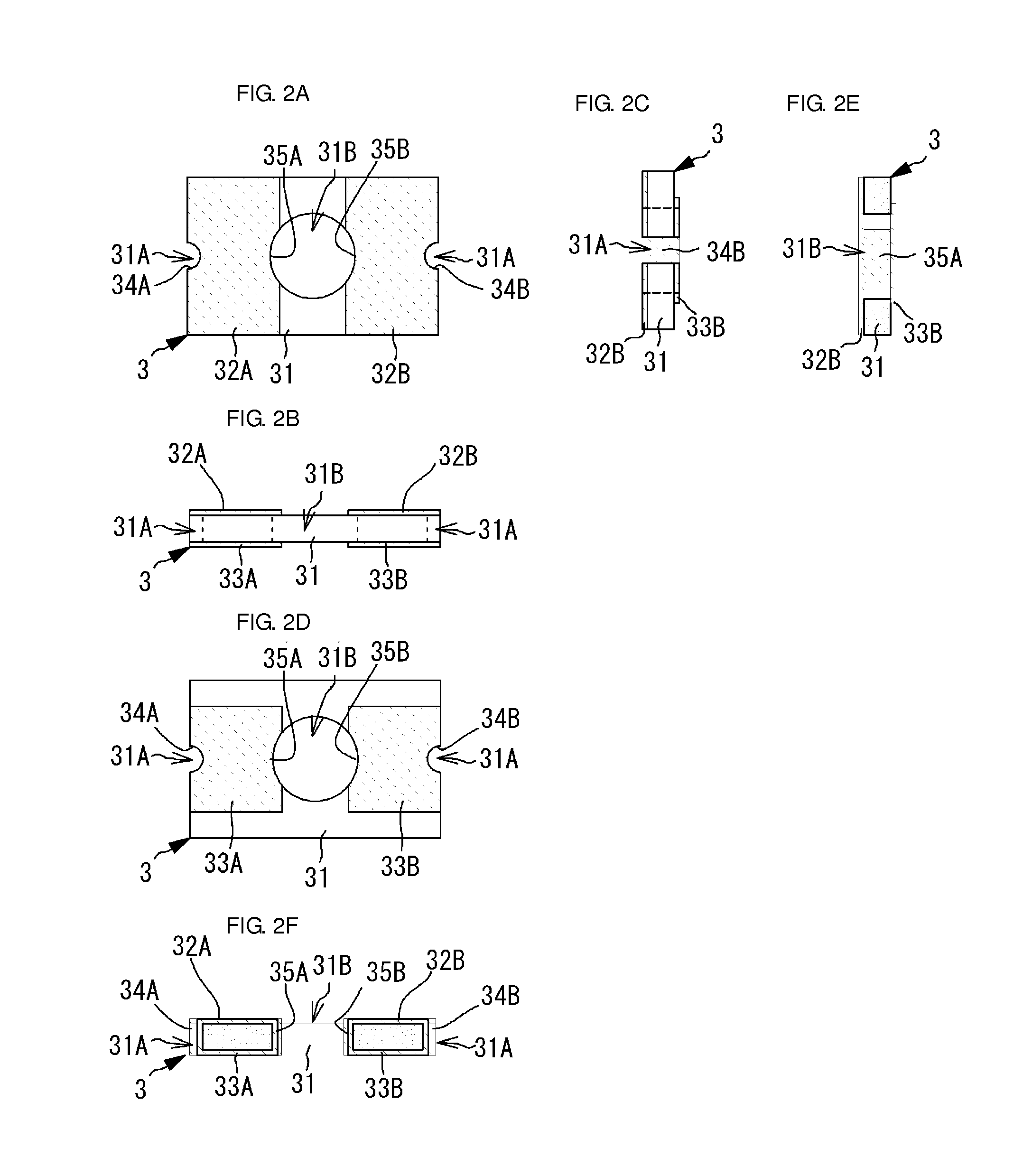

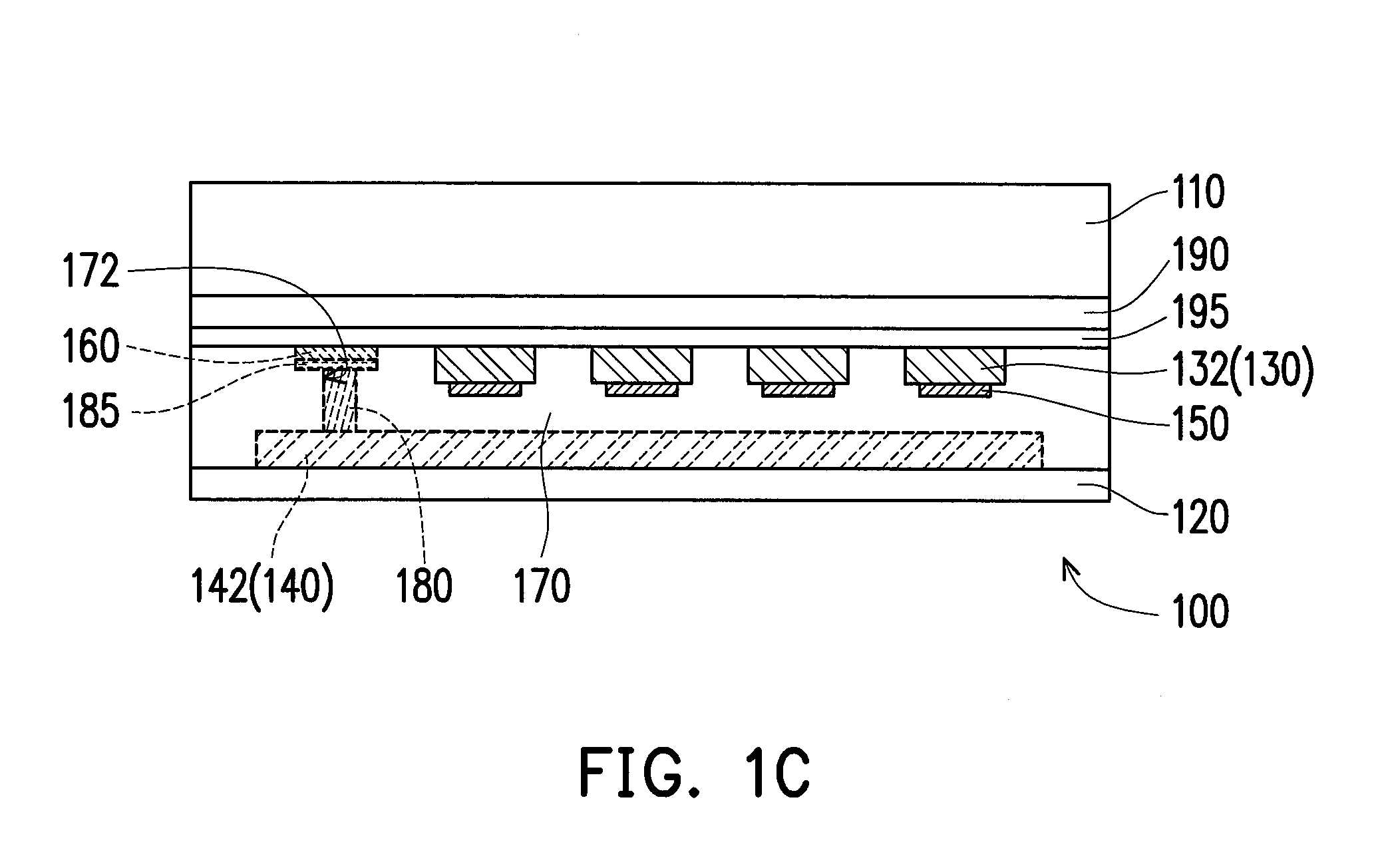

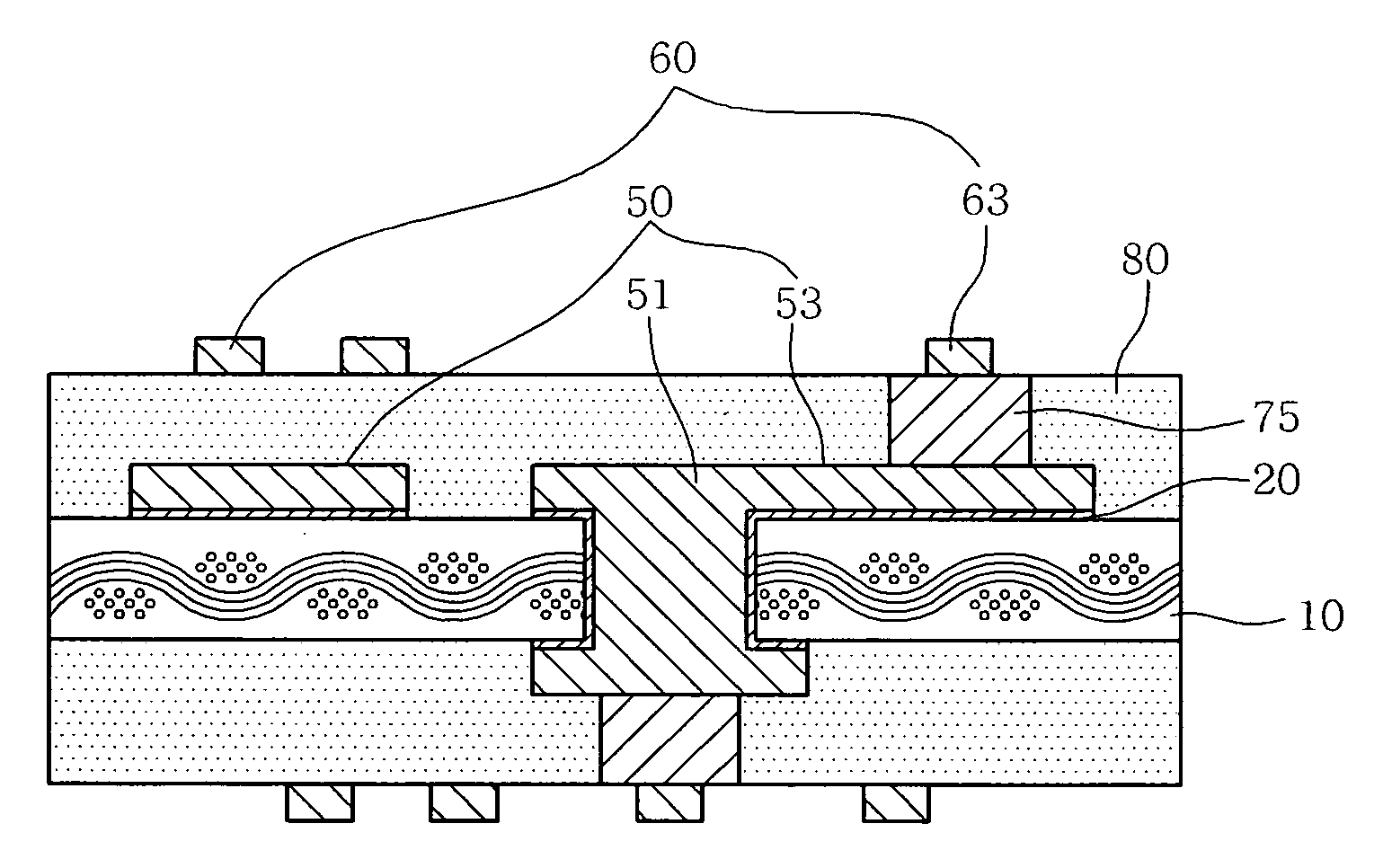

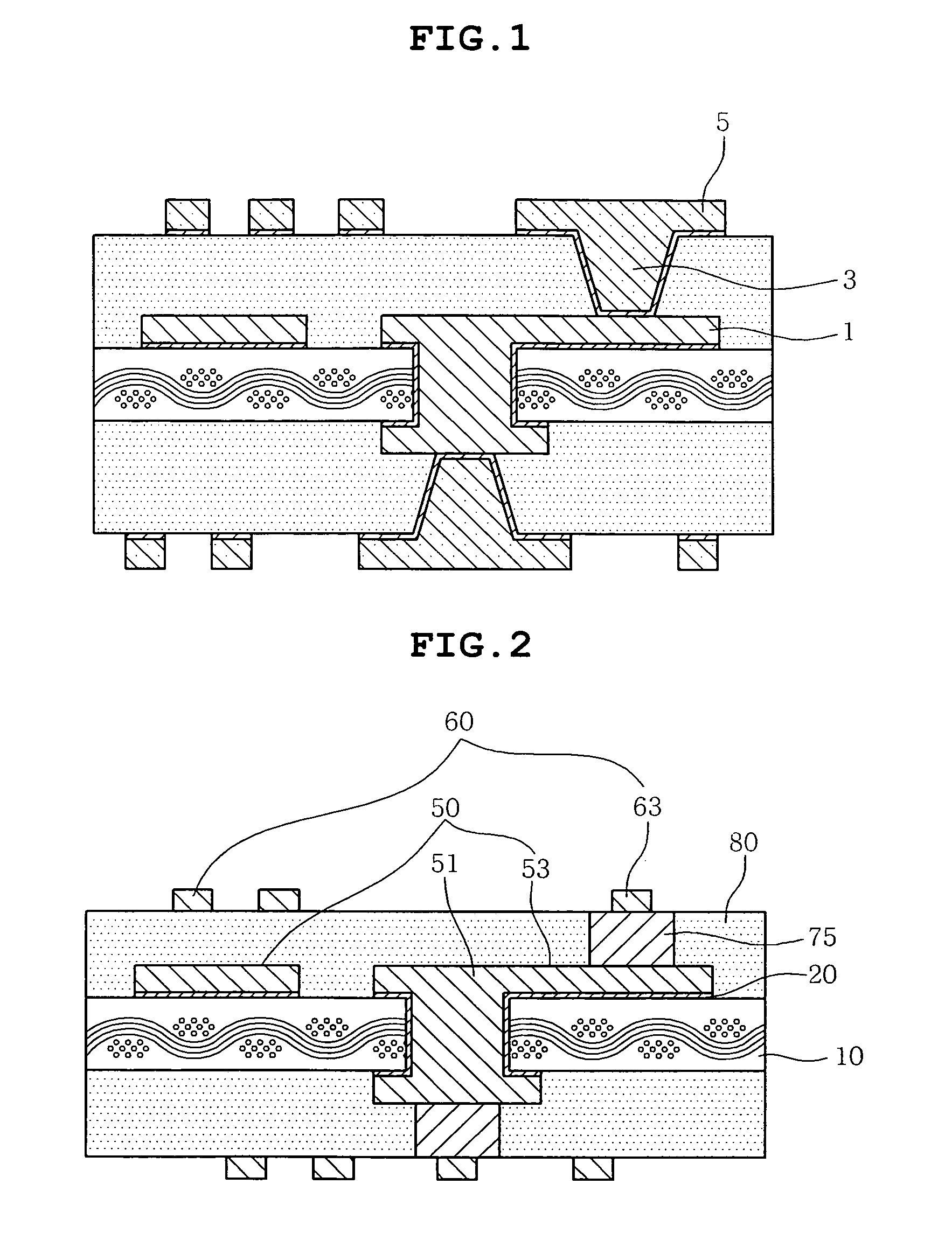

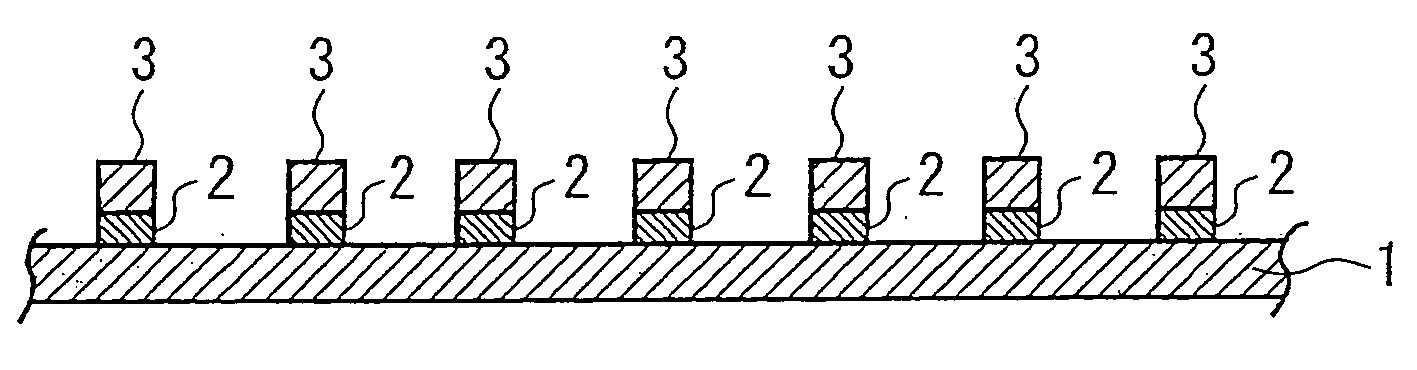

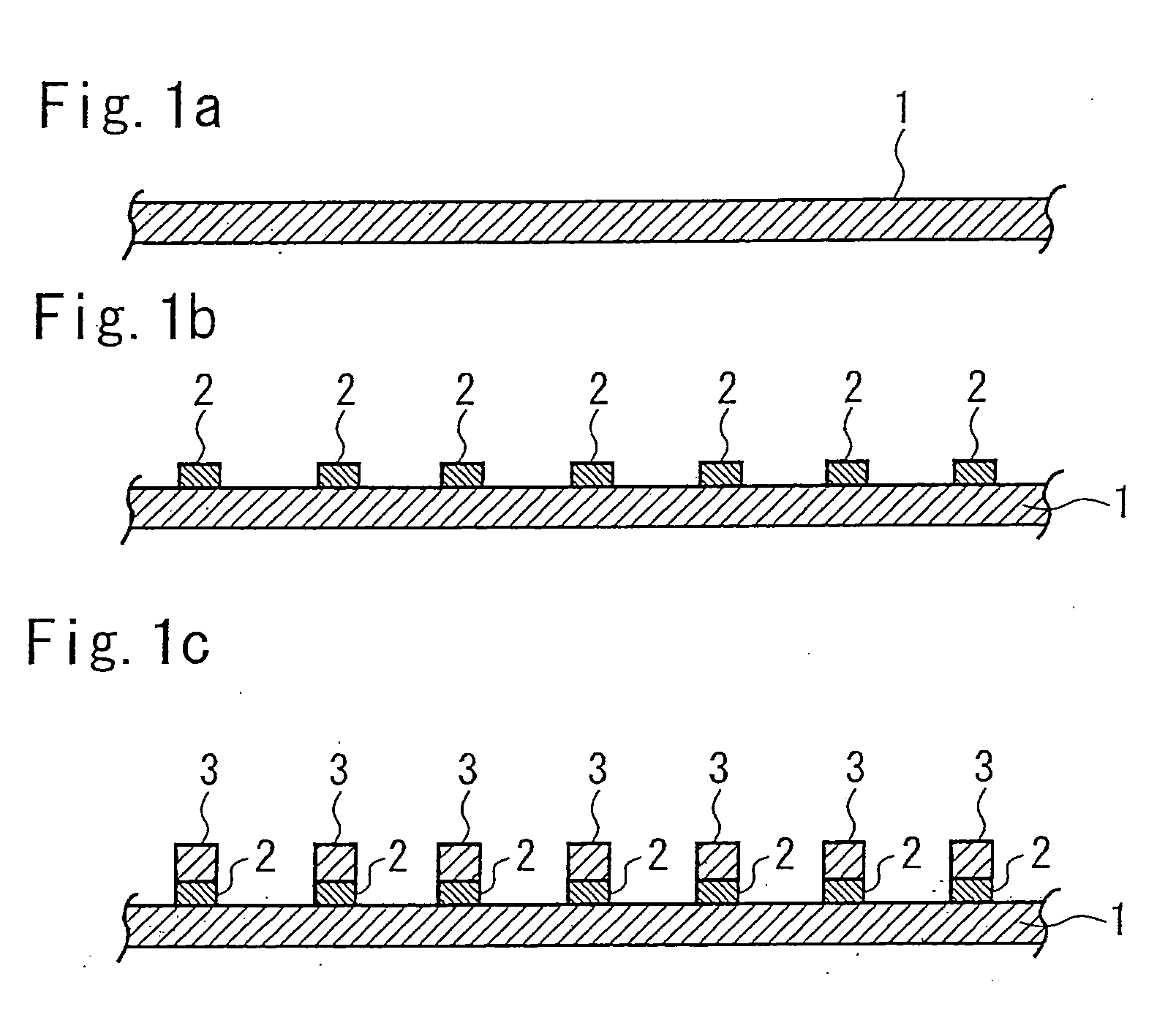

Chip-component structure

ActiveUS20130329389A1Small line widthReduce the amount requiredAnti-noise capacitorsFeed-through capacitorsInterposerEngineering

A chip-component structure includes an interposer on which a multilayer capacitor is mounted. The interposer includes component connecting electrodes, external connection electrodes, side electrodes, and in-hole electrodes. The component connecting electrodes and the external connection electrodes are electrically connected by the side electrodes and the in-hole electrodes. Outer electrodes of the capacitor are joined to the component connecting electrodes.

Owner:MURATA MFG CO LTD

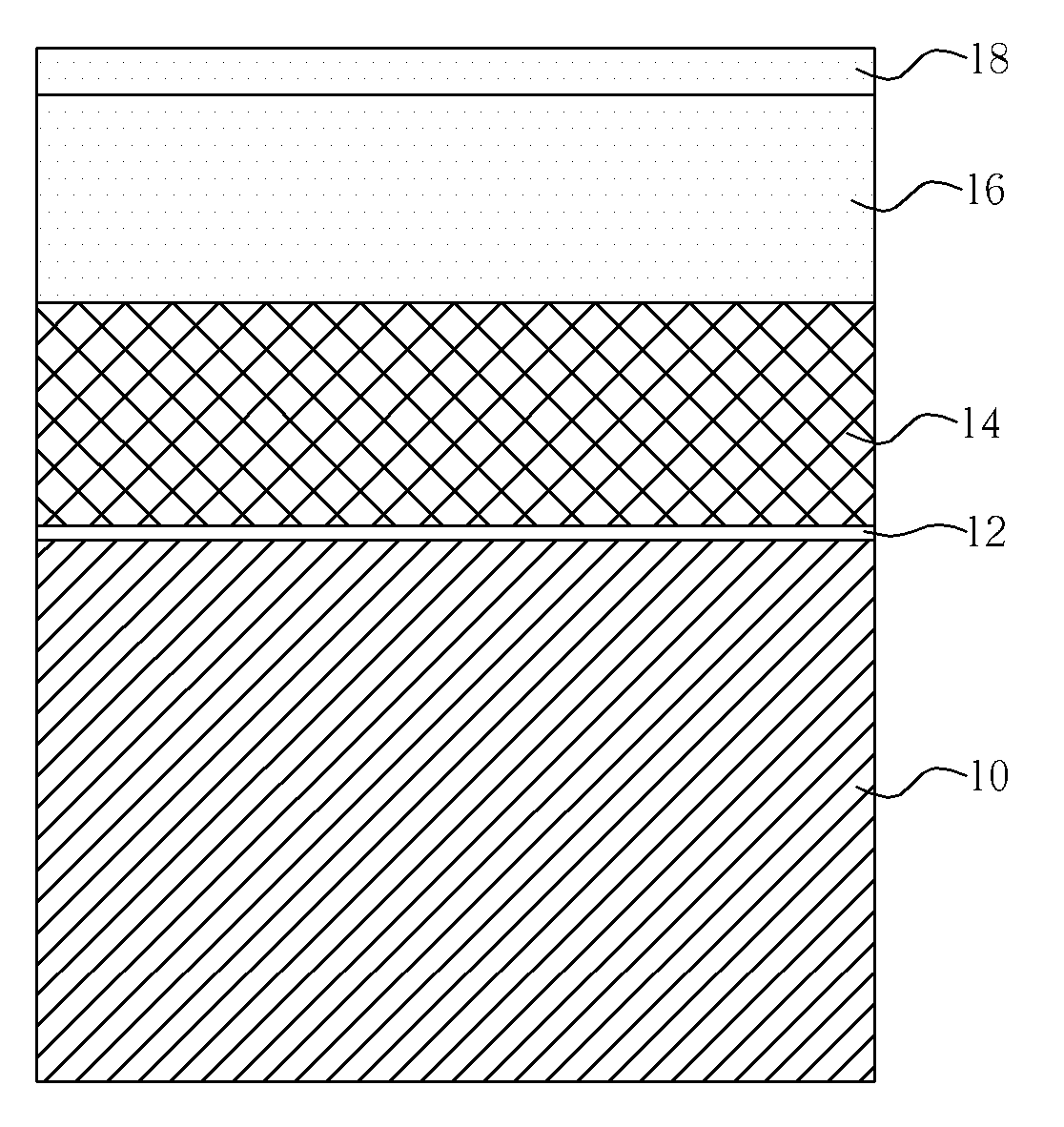

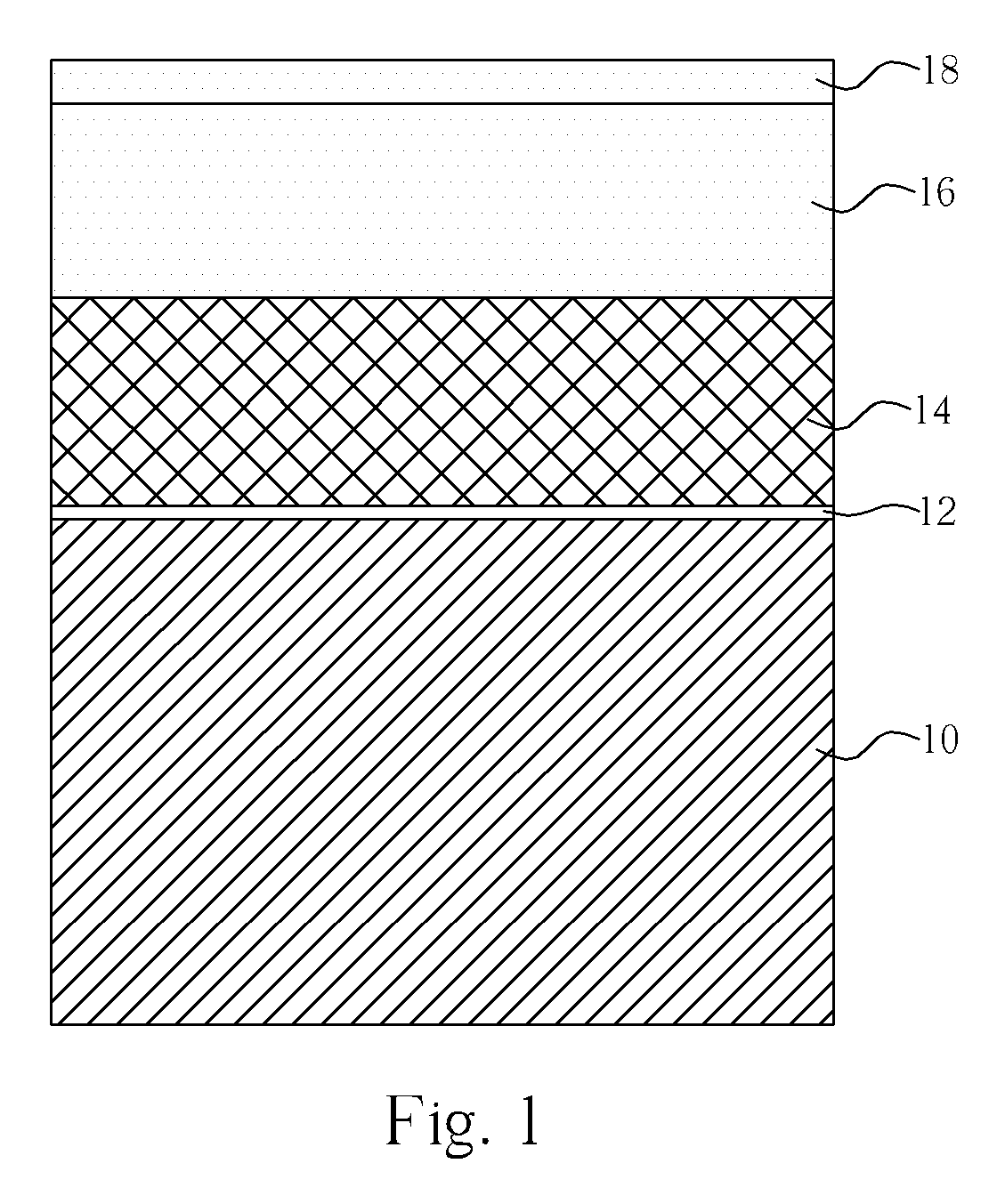

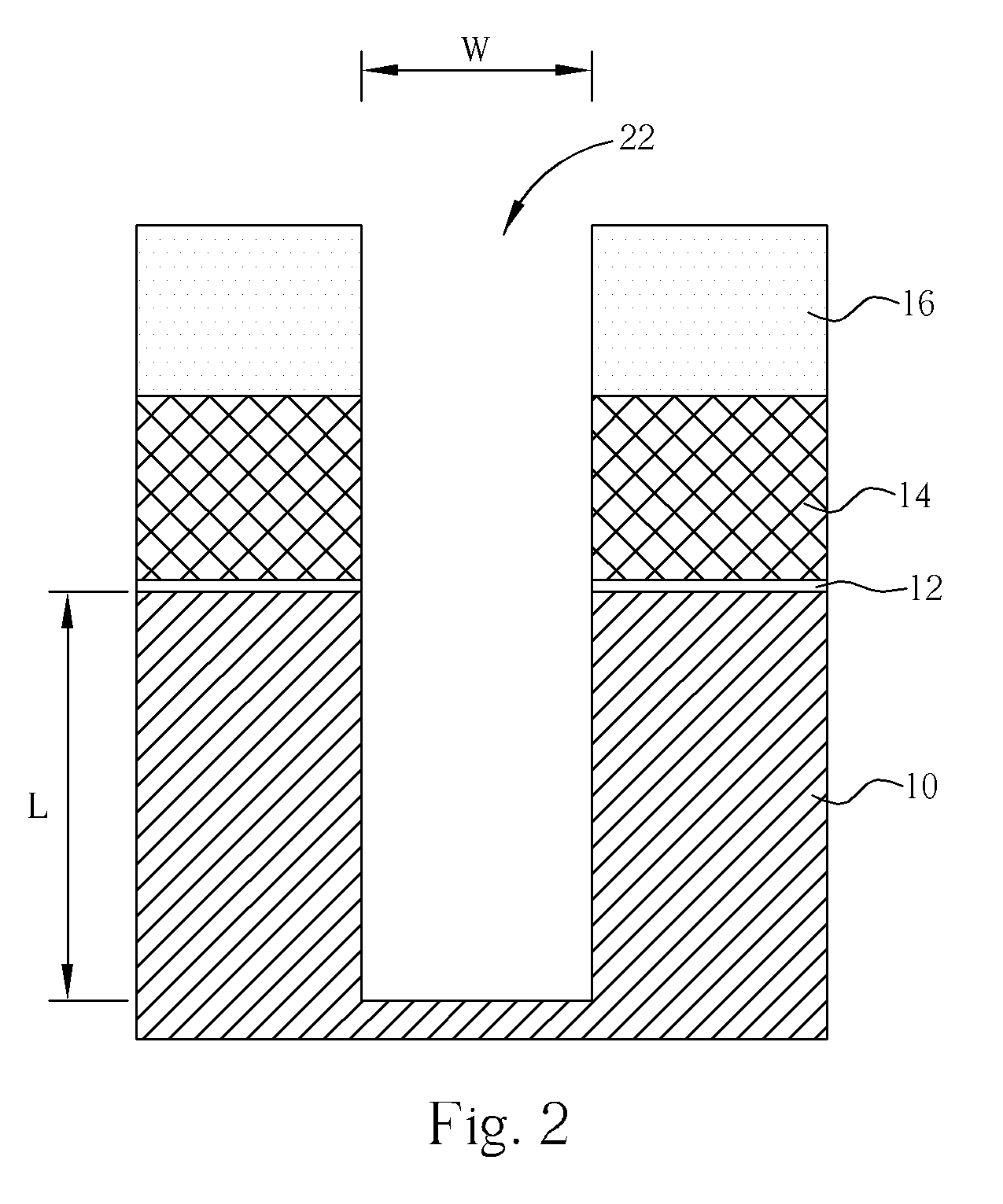

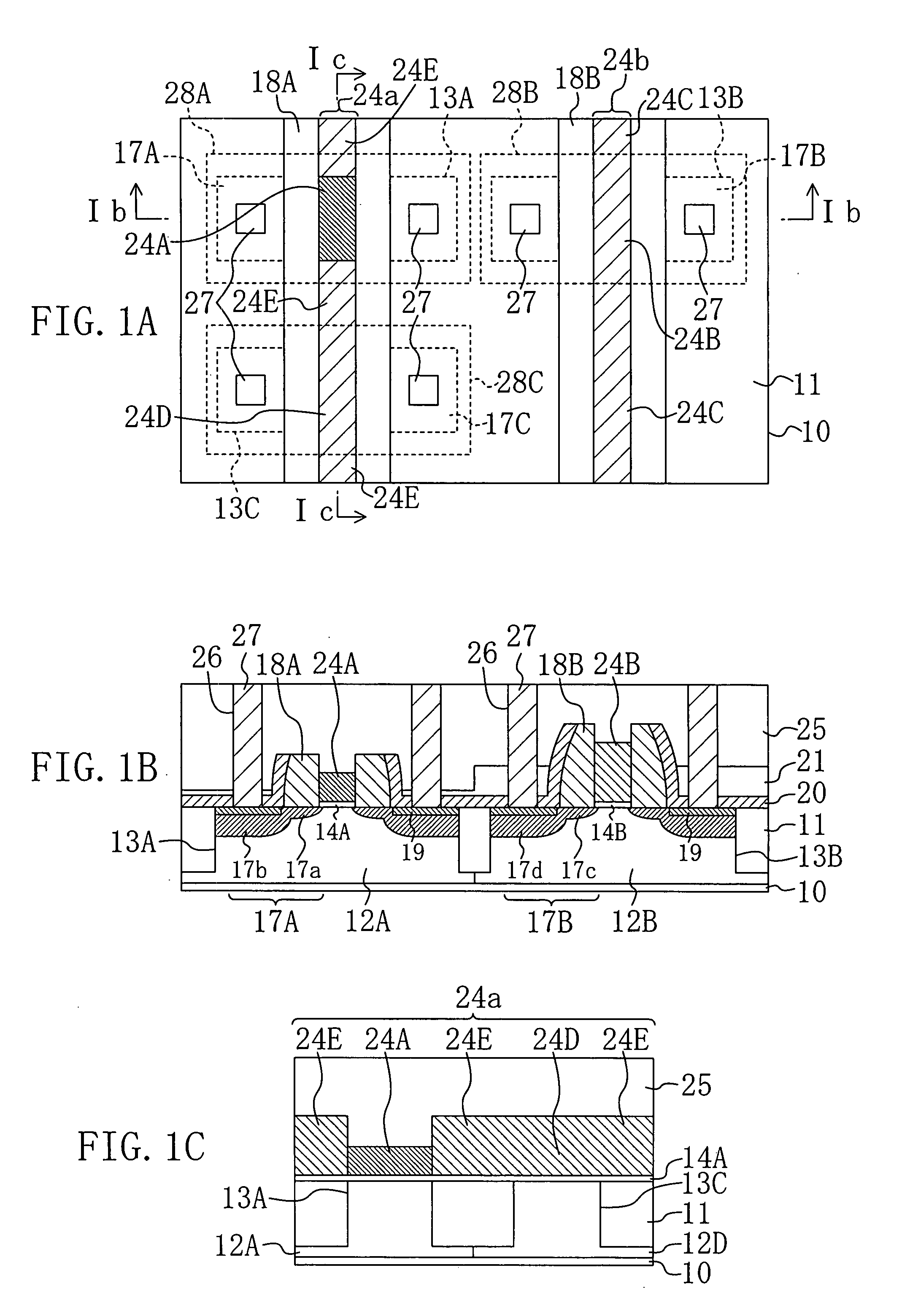

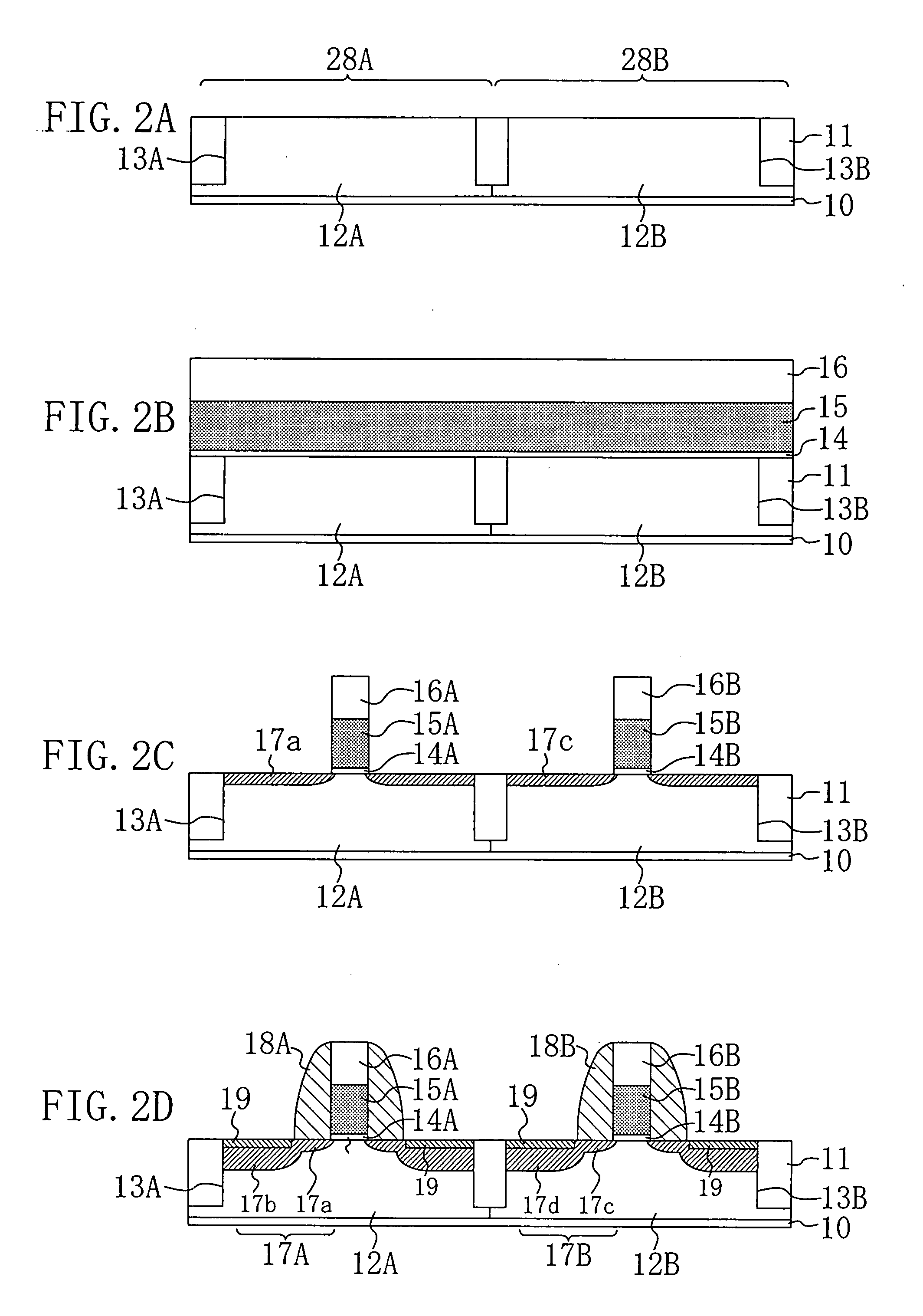

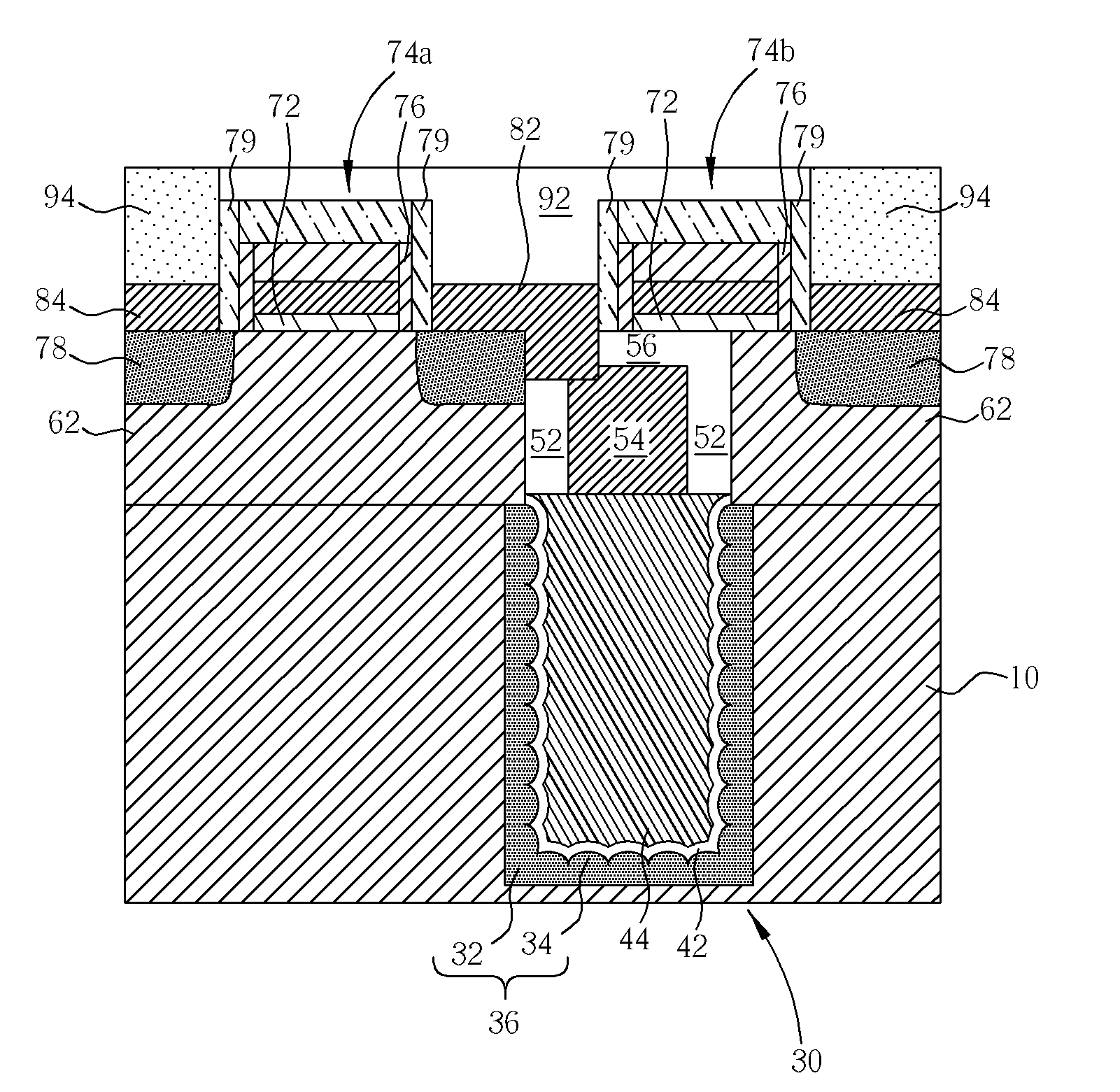

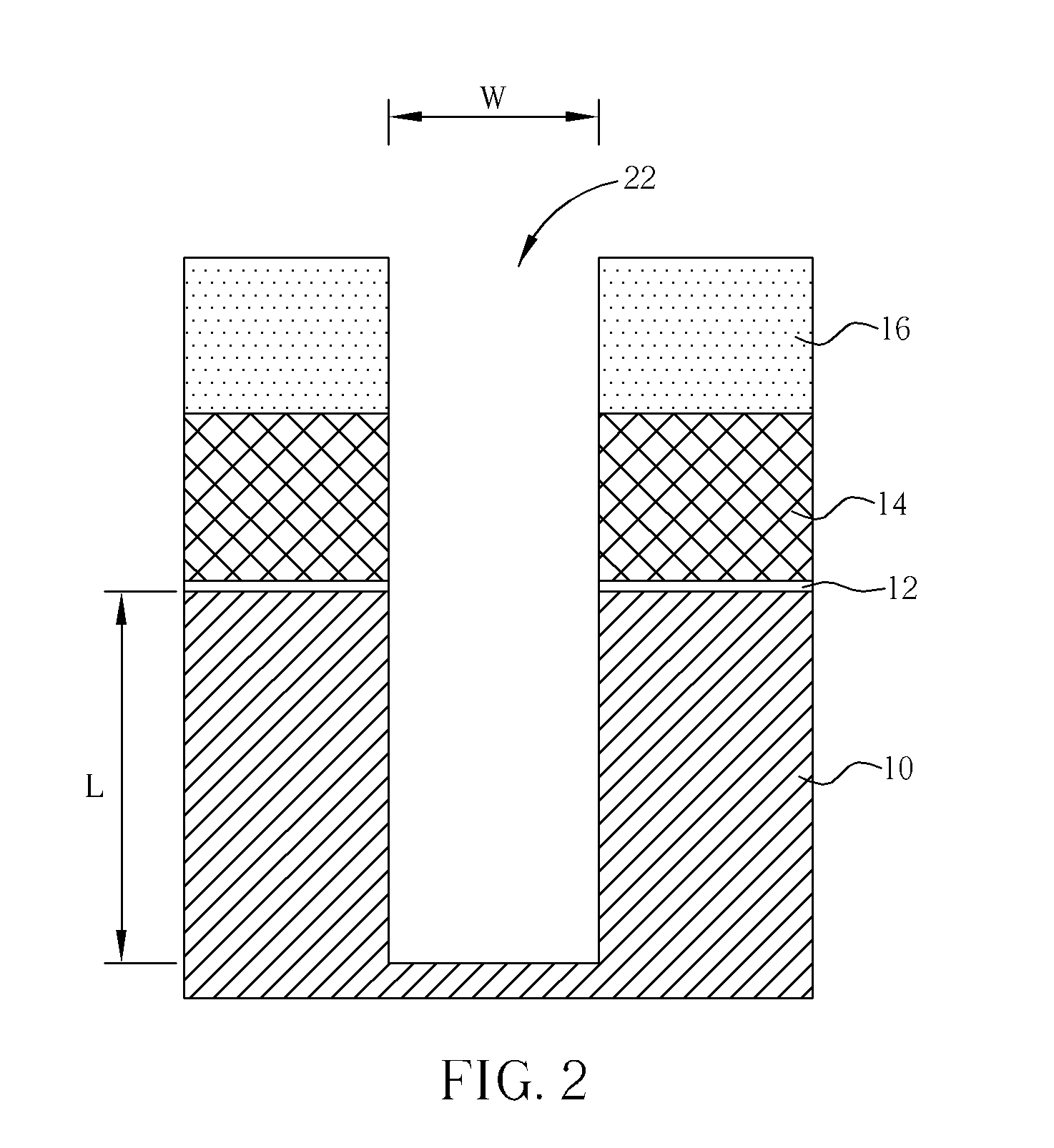

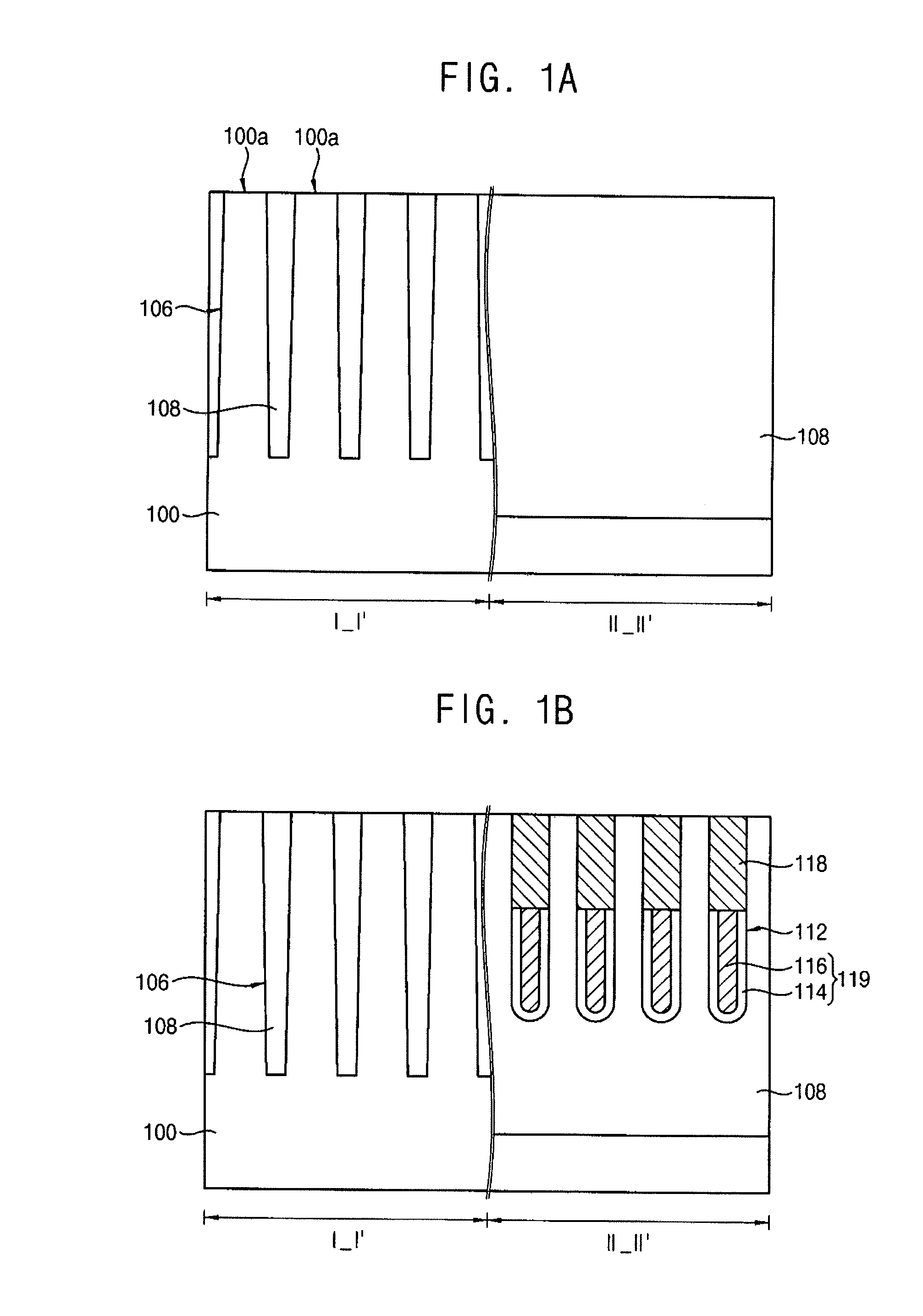

Method of fabricating a trench capacitor having increased capacitance

InactiveUS20070045699A1Increase capacitanceSmall line widthTransistorSolid-state devicesCapacitanceElectrical conductor

The present invention pertains to a method of fabricating a trench capacitor having increased capacitance. To tackle a difficult problem of etching deeper trenches having very high aspect ratio, an epitaxial silicon growth process is employed in the fabrication of next-generation trench DRAM devices. A large-capacitance trench capacitor is first fabricated in the silicon substrate. An epitaxial silicon layer is then grown on the silicon substrate. Active areas, shallow trench isolation regions, and gate conductors are formed on / in the epitaxial silicon layer.

Owner:AVAYA INC

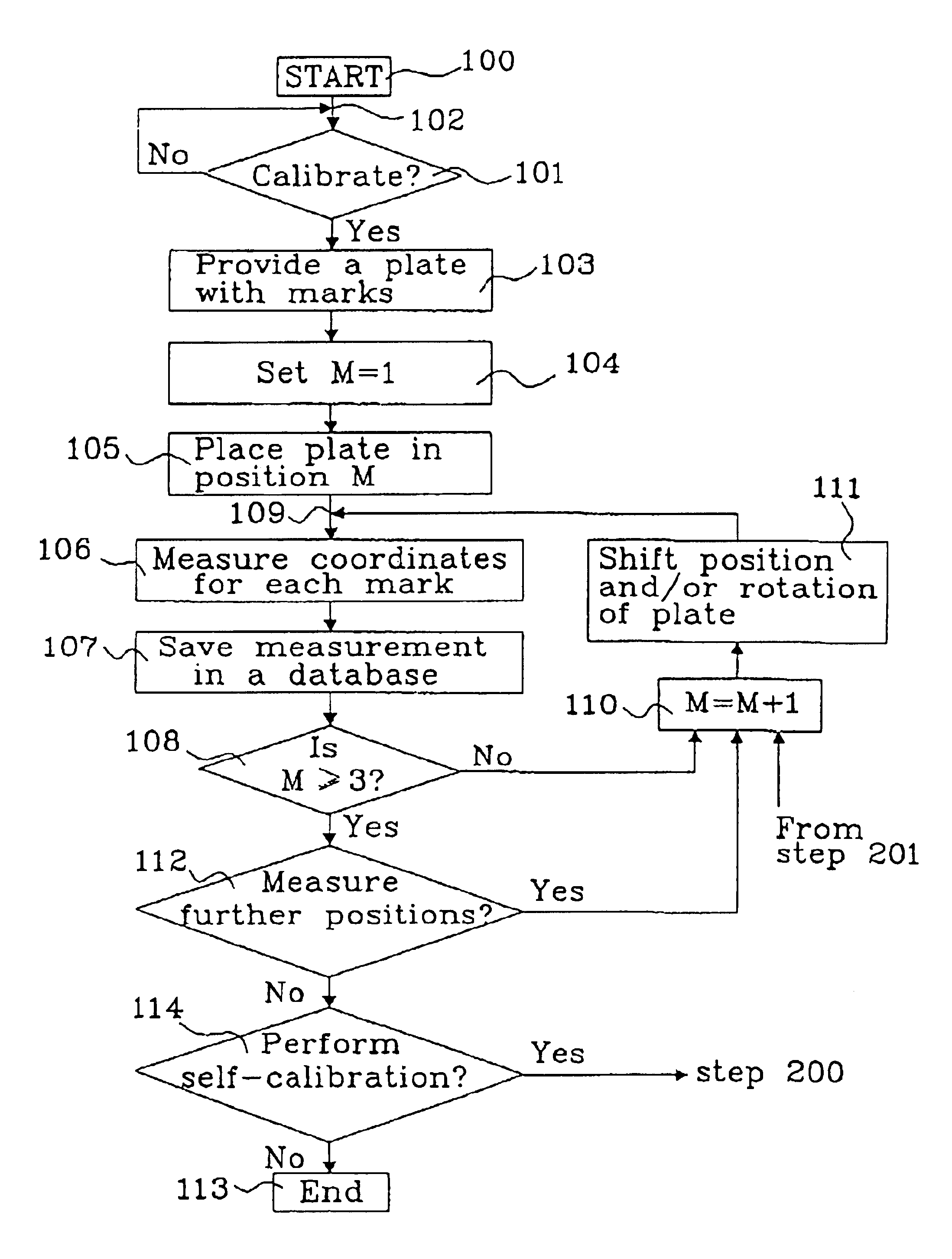

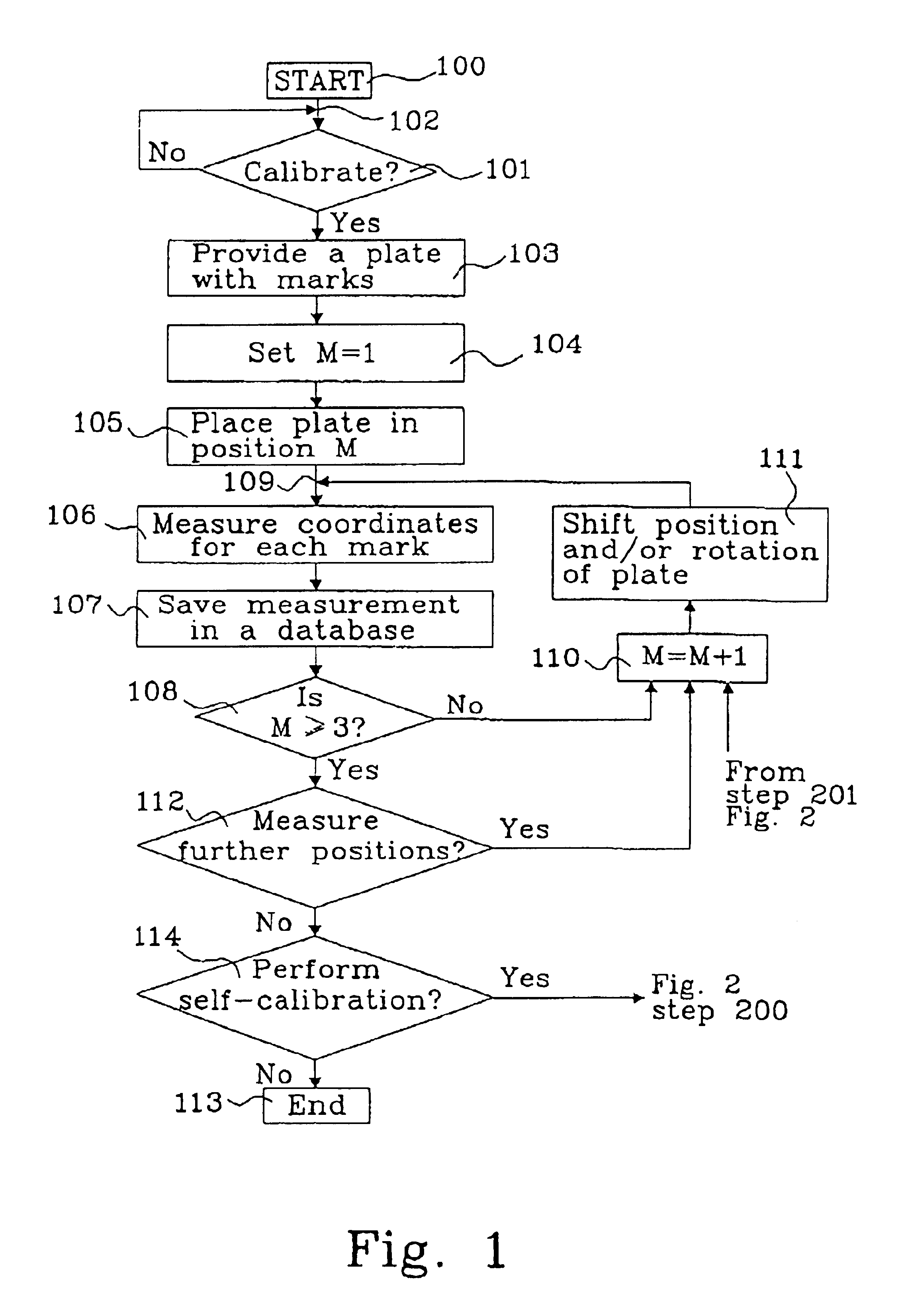

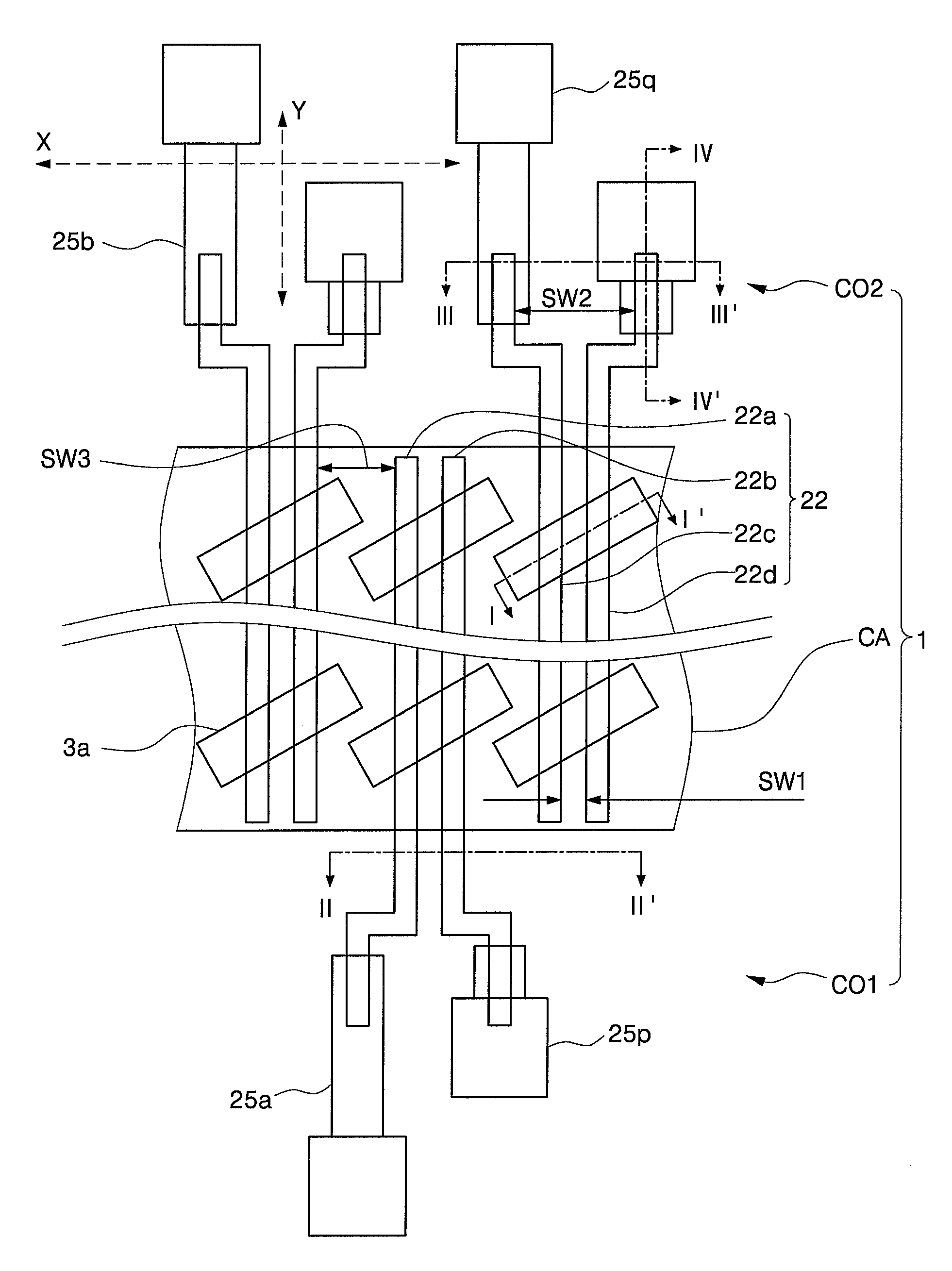

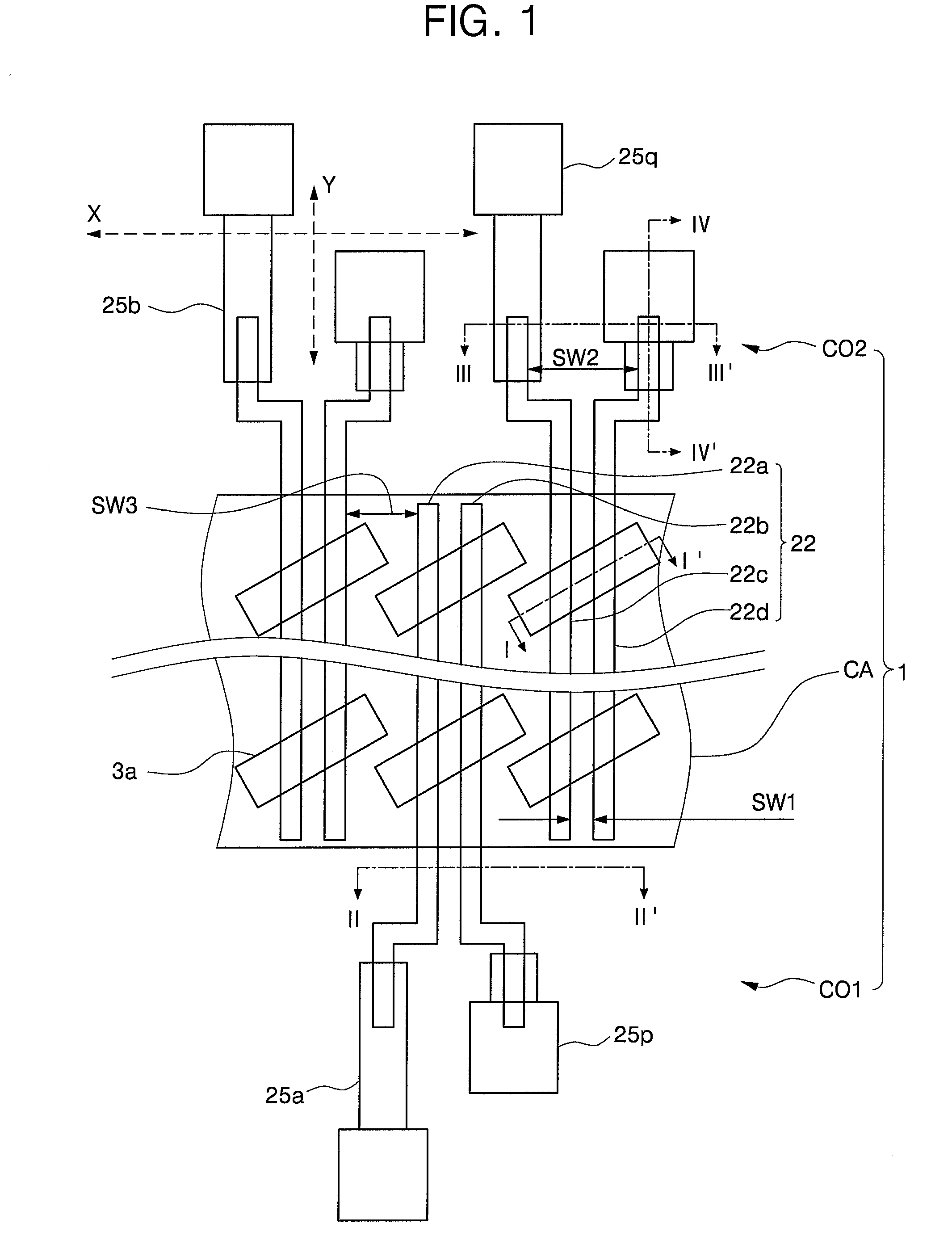

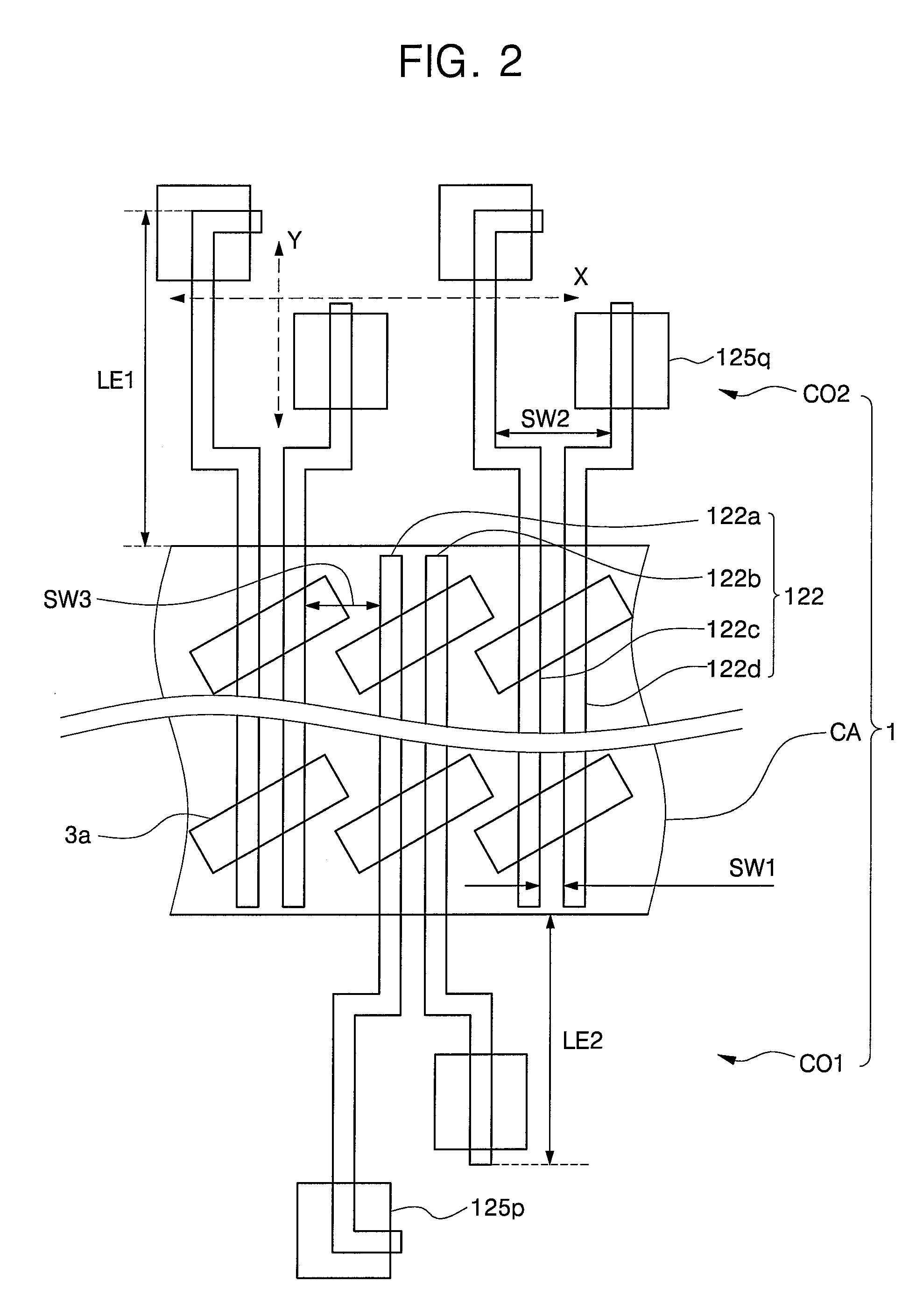

Method for calibration of a metrology stage

InactiveUS6948254B2Raise the possibilitySmall line widthUsing electrical meansPhotomechanical exposure apparatusMetrologyEngineering

The present invention relates to a method for calibrating a metrology stage in at least two dimensions using an artefact plate having marks forming a pattern, comprising the steps of: placing the artefact plate on the metrology stage in at least three positions, assuming the geometrical properties of the metrology stage and the artefact plate, and the positions of the artefact plate for each measurement, forming a model predicting the measurements of the artefact plate, measuring the marks by the metrology stage, and inverting said model to improve the assumptions on metrology stage and artefact plate.

Owner:MICRONIC LASER SYST AB

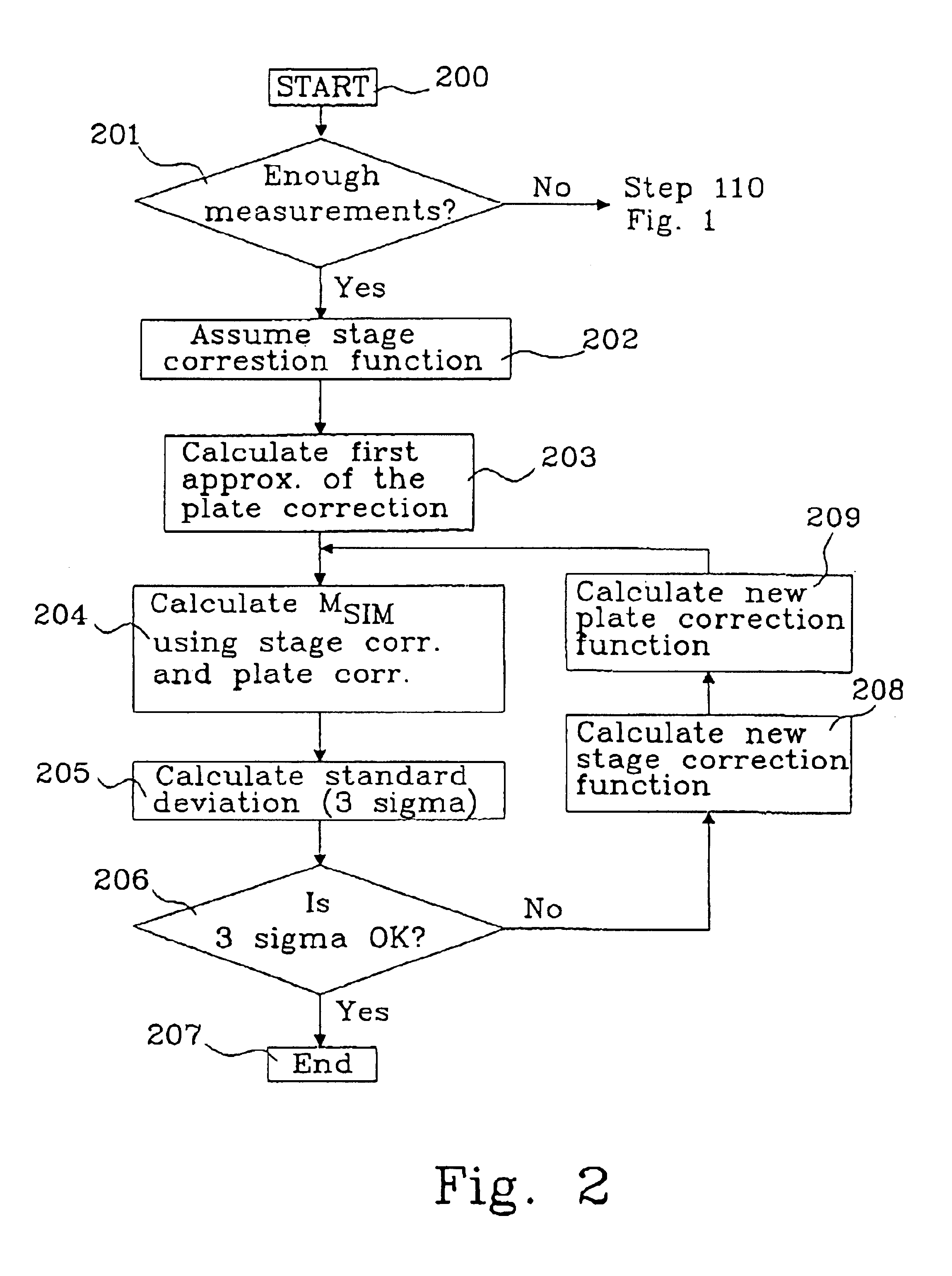

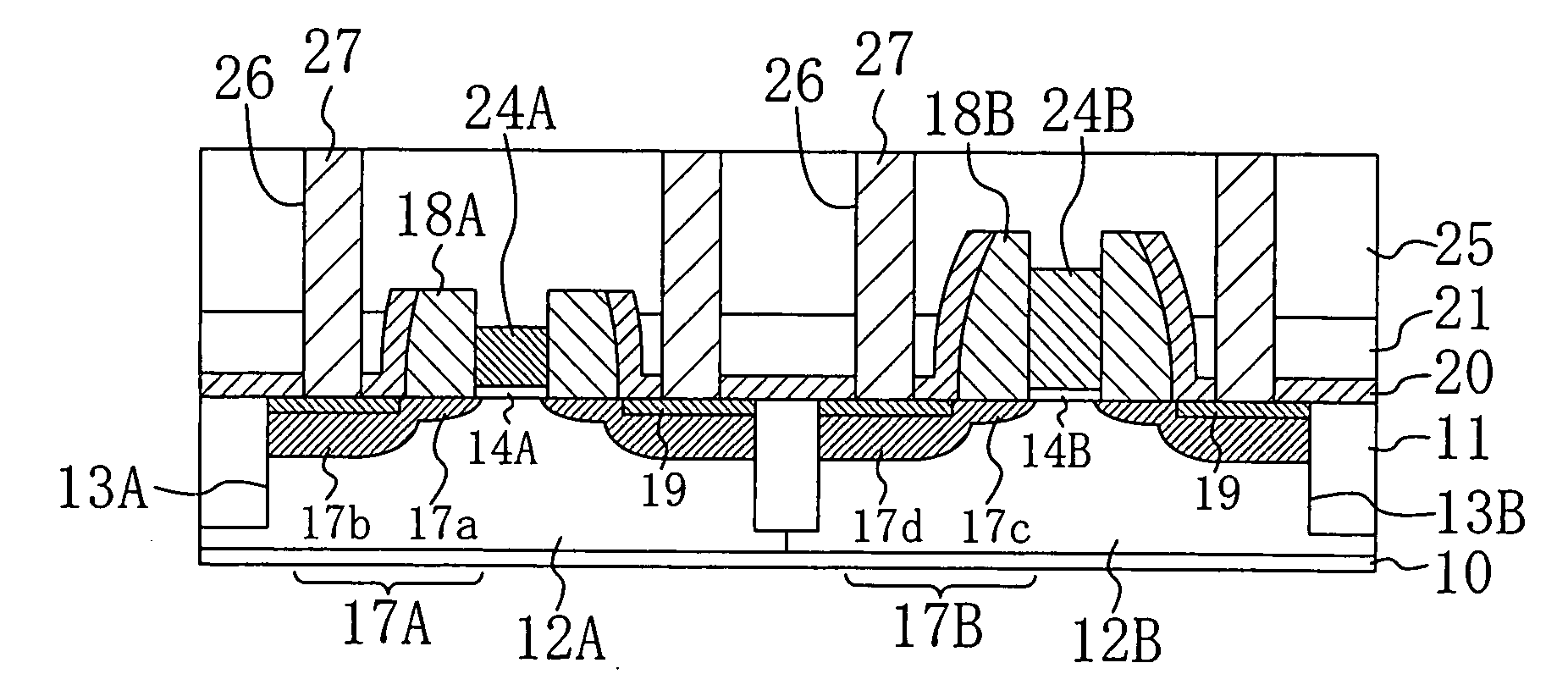

Semiconductor device and method for fabricating the same

InactiveUS20080128825A1Reduce thicknessLower interconnect resistanceTransistorSemiconductor/solid-state device manufacturingSiliconSemiconductor

A p-type MIS transistor includes a first gate insulating film formed on a first active region; and a first fully silicided gate pattern that is obtained by fully siliciding a silicon film, is formed to extend over the first active region with the first gate insulating film sandwiched therebetween, and includes a first fully silicided gate electrode provided on the first active region and a first fully silicided gate line provided on the isolation region. The first fully silicided gate pattern includes, along a gate width direction, a portion having a first thickness and including the first fully silicided gate electrode and portions each having a second thickness larger than the first thickness and respectively disposed on both sides of the portion having the first thickness.

Owner:PANASONIC CORP

Touch panel and manufacturing method thereof and touch display panel

InactiveUS20140015767A1Small line widthNarrow line width effectElectric switchesSelector switchesAdhesiveConductive materials

A touch panel including a first and a second substrates, a first and a second sensing electrode layers, plural first lines, plural second lines, a conductive material layer and a shielding layer is provided. The first and the second sensing electrode layers are respectively disposed on the first and the second substrates and located in a sensing region. The first and the second lines are disposed on the first substrate and located in a periphery region. The first lines connect to the first sensing electrode layer. The optical adhesive layer encapsulates the first and the second sensing electrode layers and the first and the second lines. The optical adhesive layer has an opening. The conductive material layer is disposed inside the opening. The second lines connect to the second sensing electrode layer via the conductive material layer. The shielding layer is located above the first and the second lines.

Owner:E INK HLDG INC

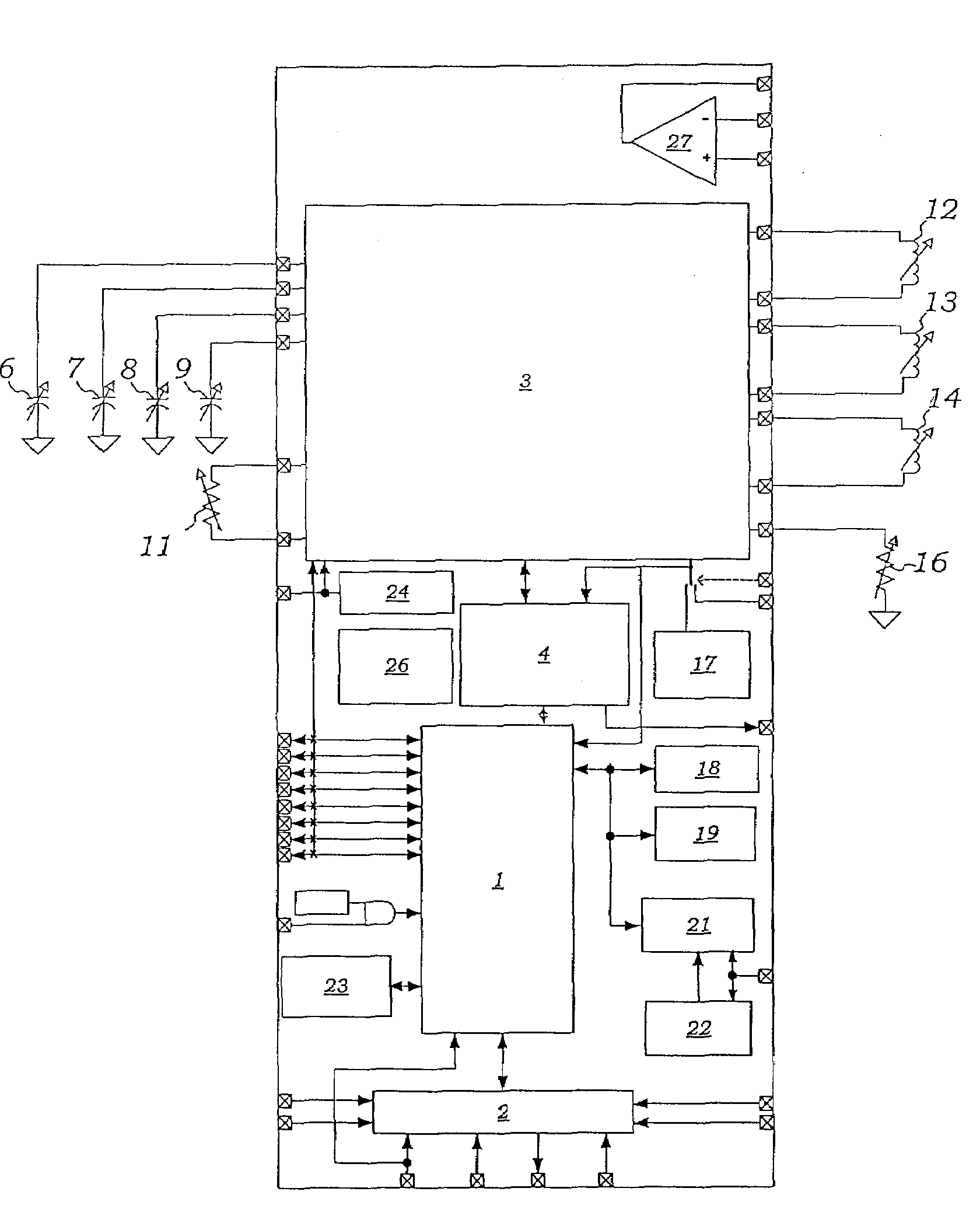

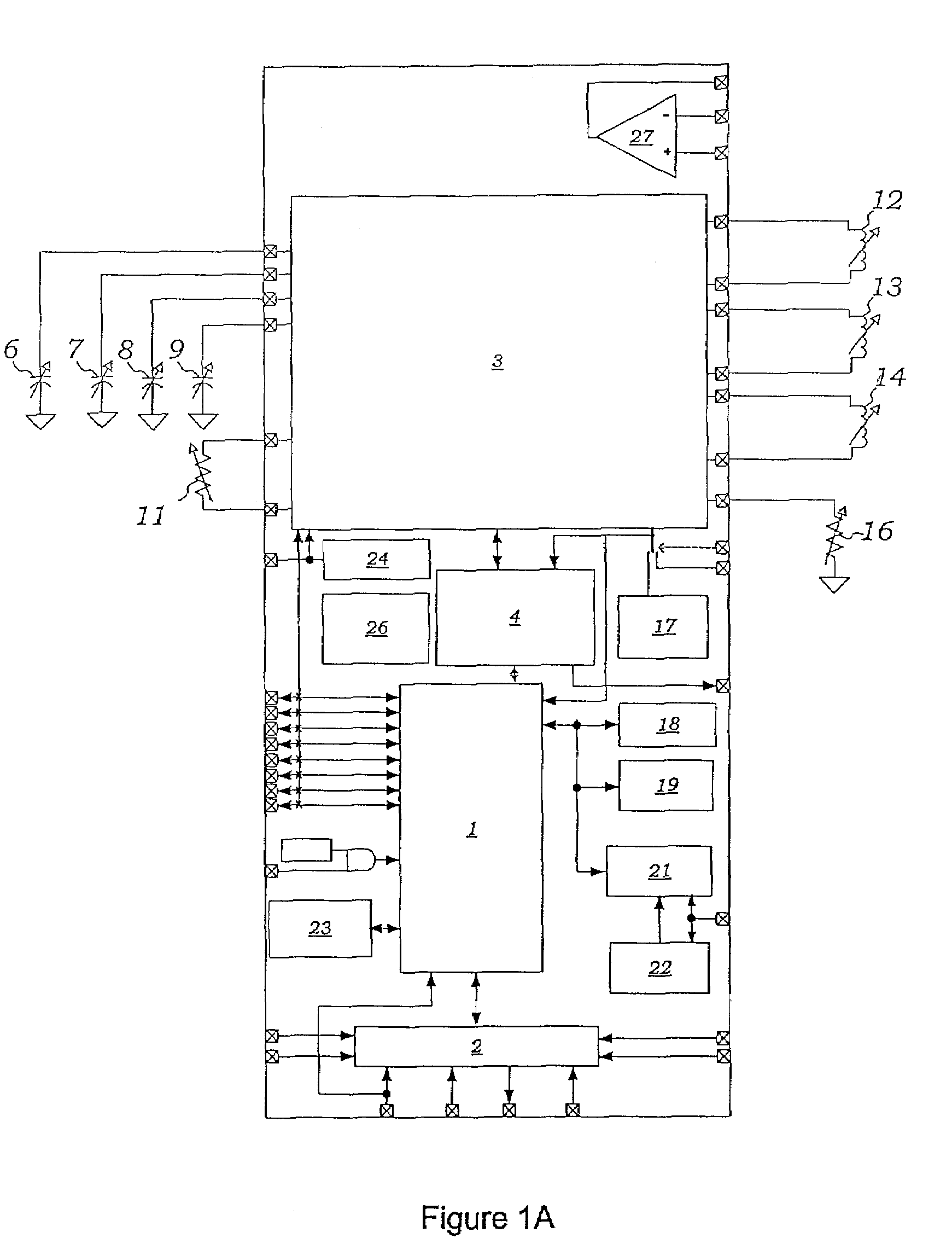

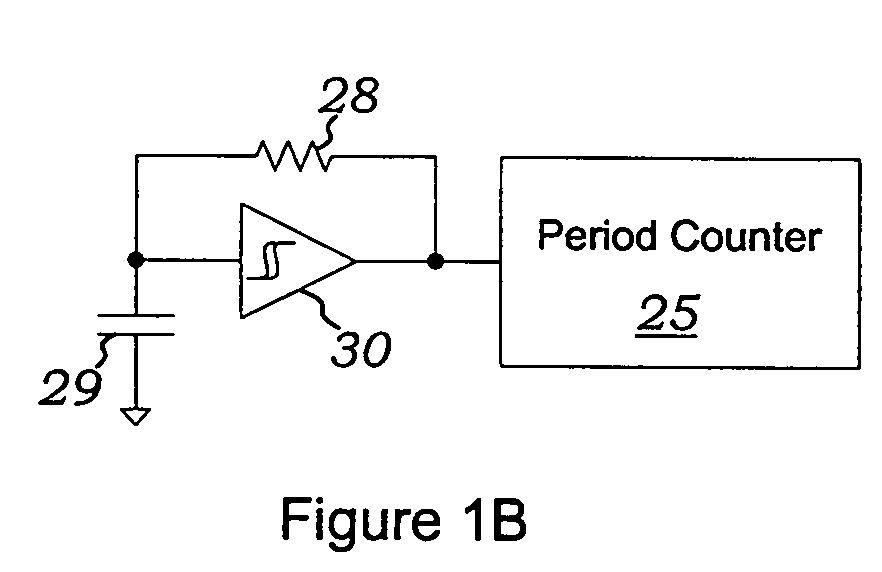

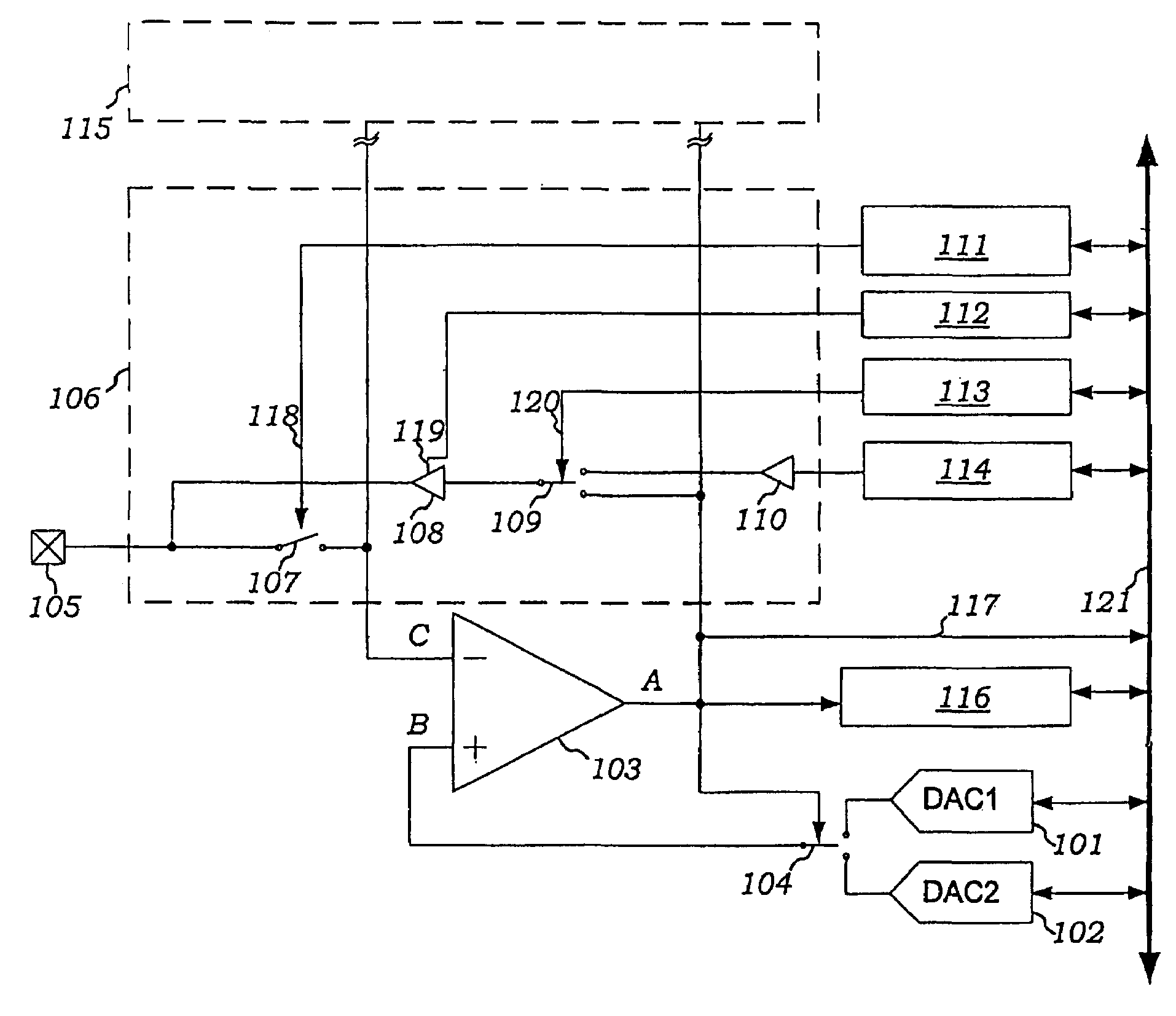

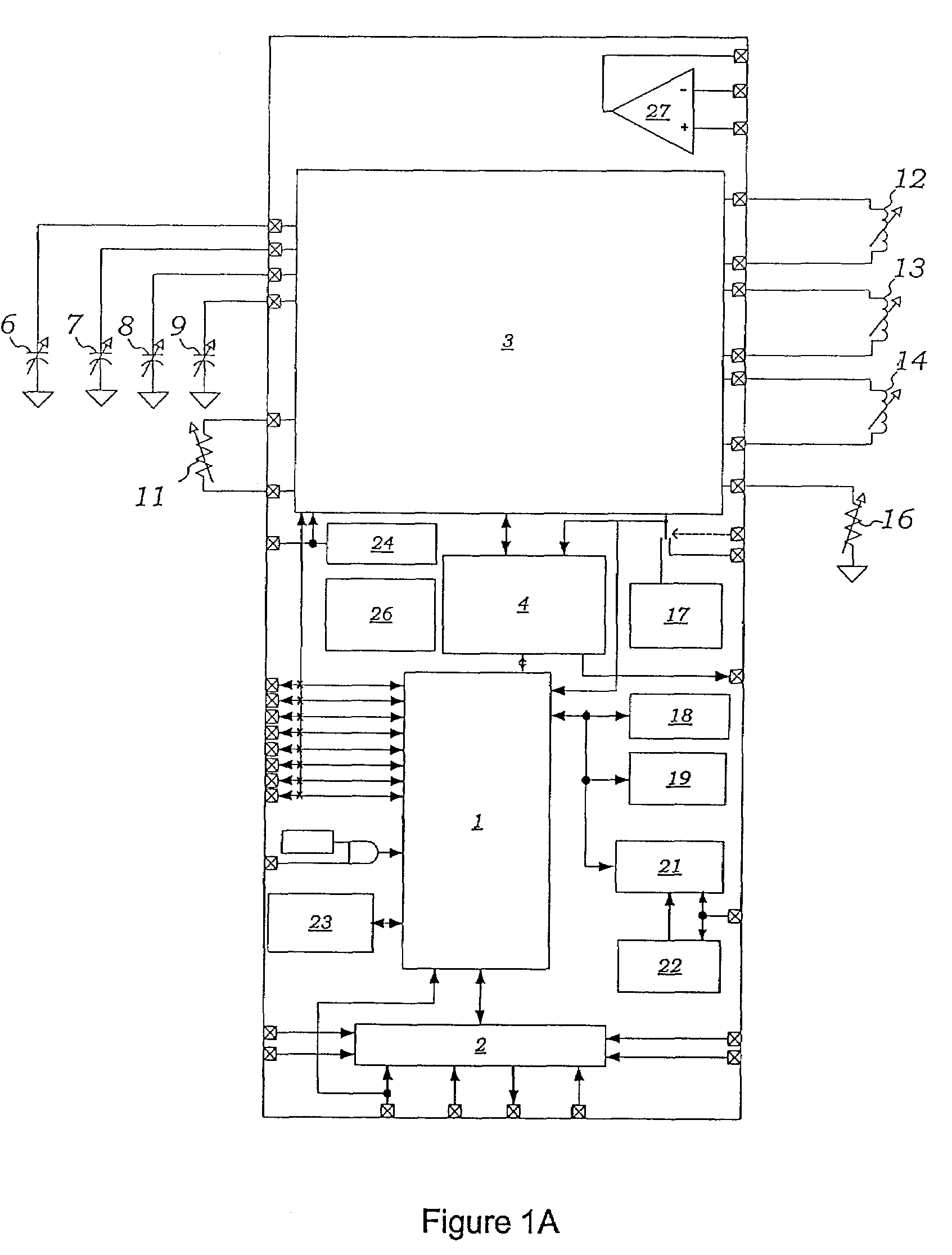

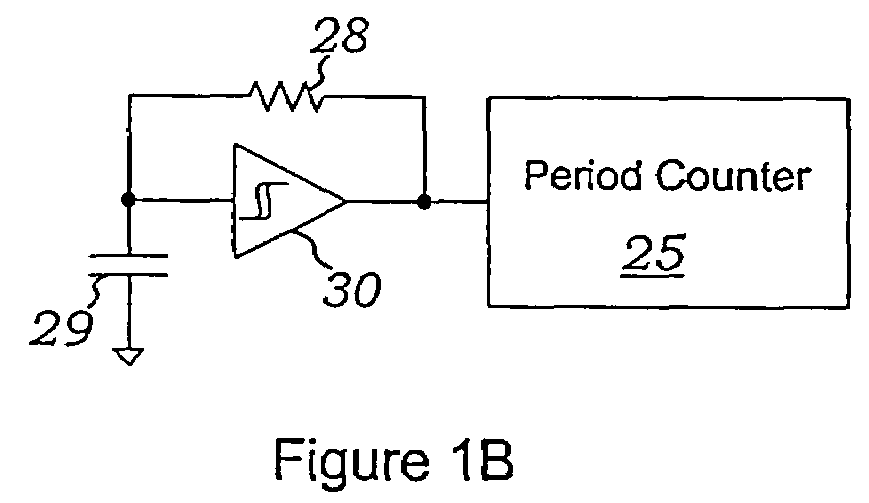

Method for signal extraction in a universal sensor IC

InactiveUS7285964B1Low costIncrease power consumptionResistance/reactance/impedenceMultiple sensorCombined use

A apparatus and method for creating a universally usable and configurable sensor platform which is used in conjunction with various sensor and sensing elements to sense and measure environmental conditions which incorporates inputs from multiple sensors 6-9 and 12-14. The apparatus incorporates an oscillator 3 which provides a signal whose frequency varies according to the inputs from sensors 6-9 and 12-14 in combination with a microprocessor 1. A cordic block 61 allows for supplemental calculations of trigonometric operations and functions. An output unit 2 converts the signals received from microprocessor 1 into a variety of serial protocols.

Owner:SENSOR PLATFORMS

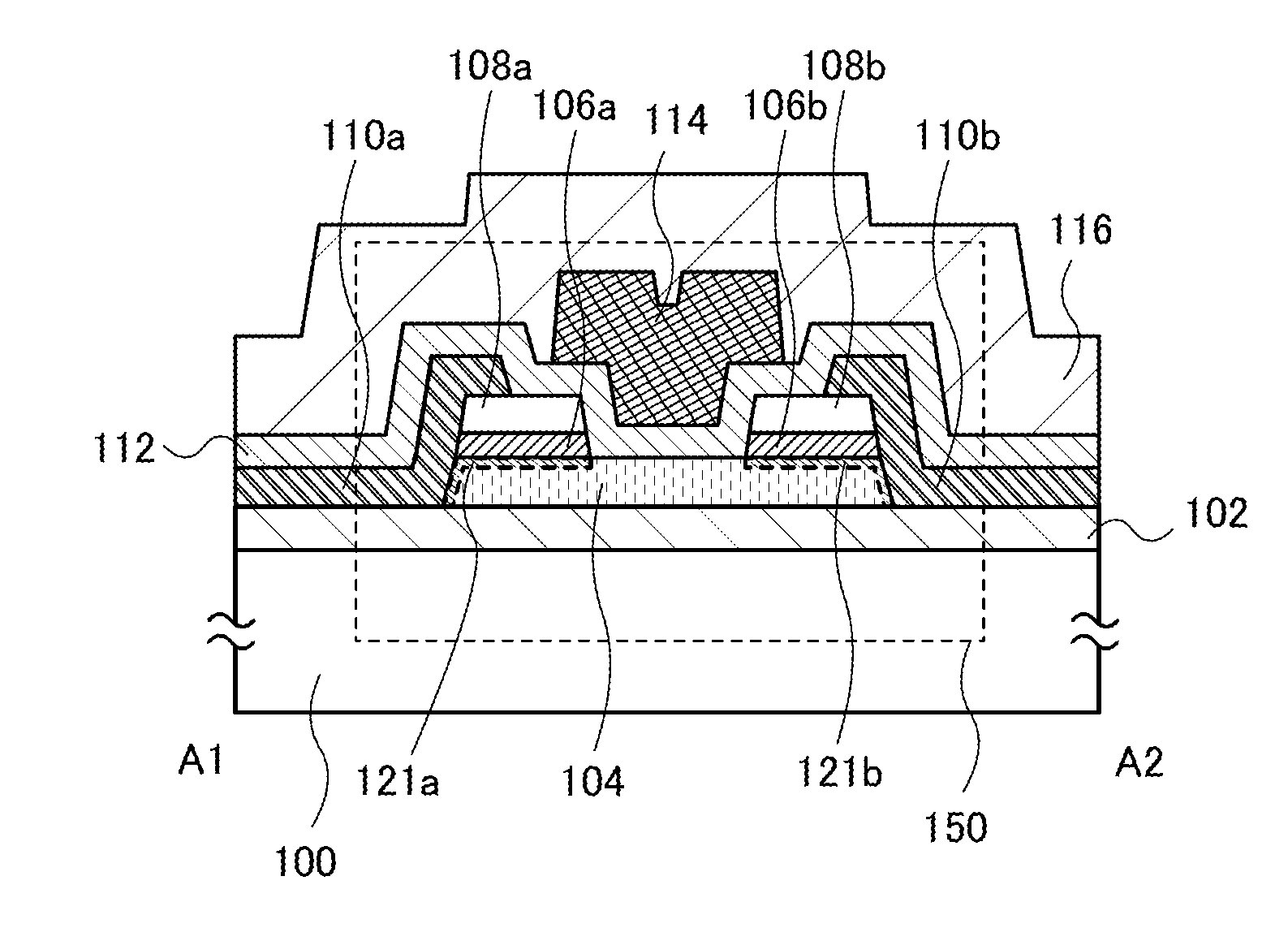

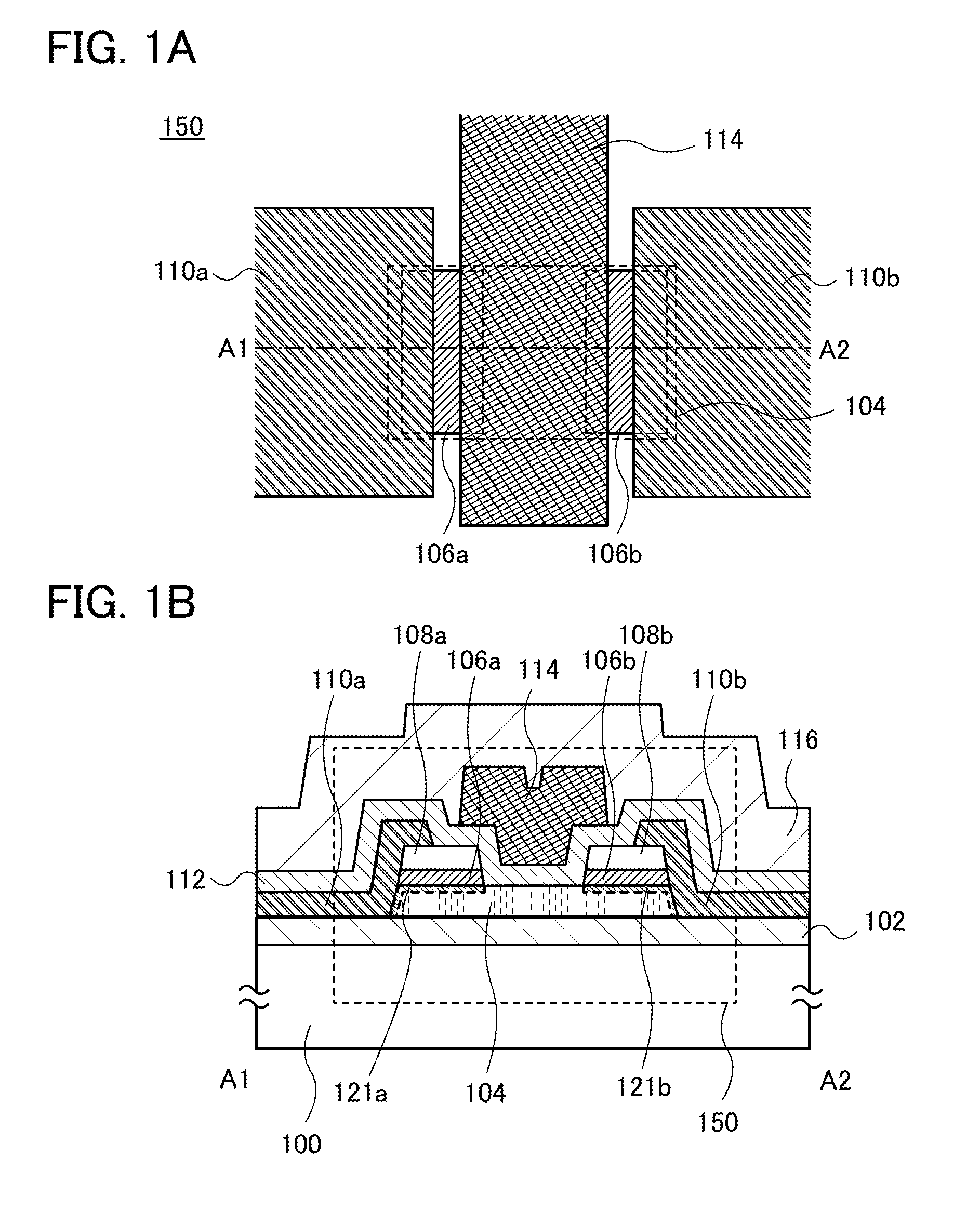

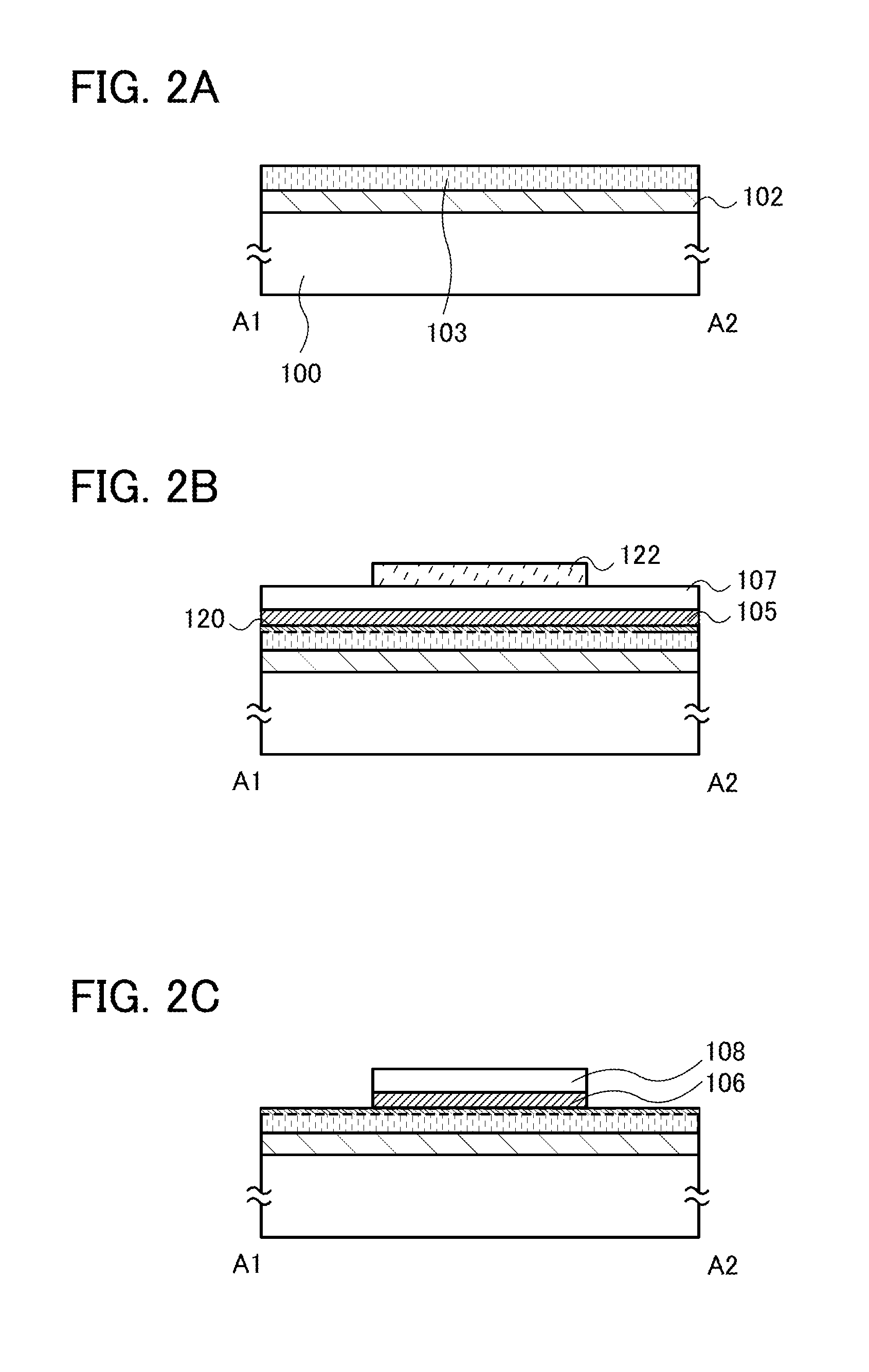

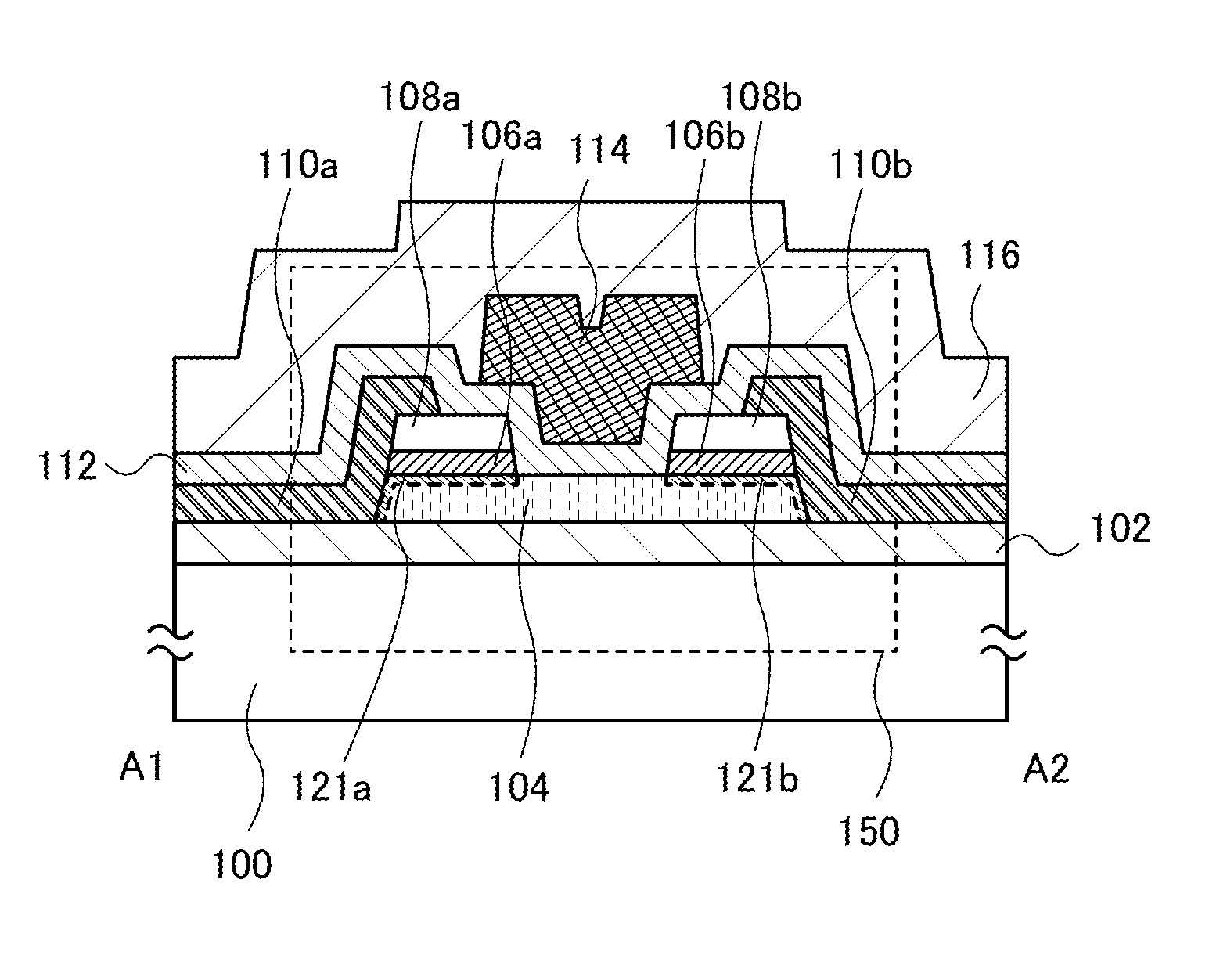

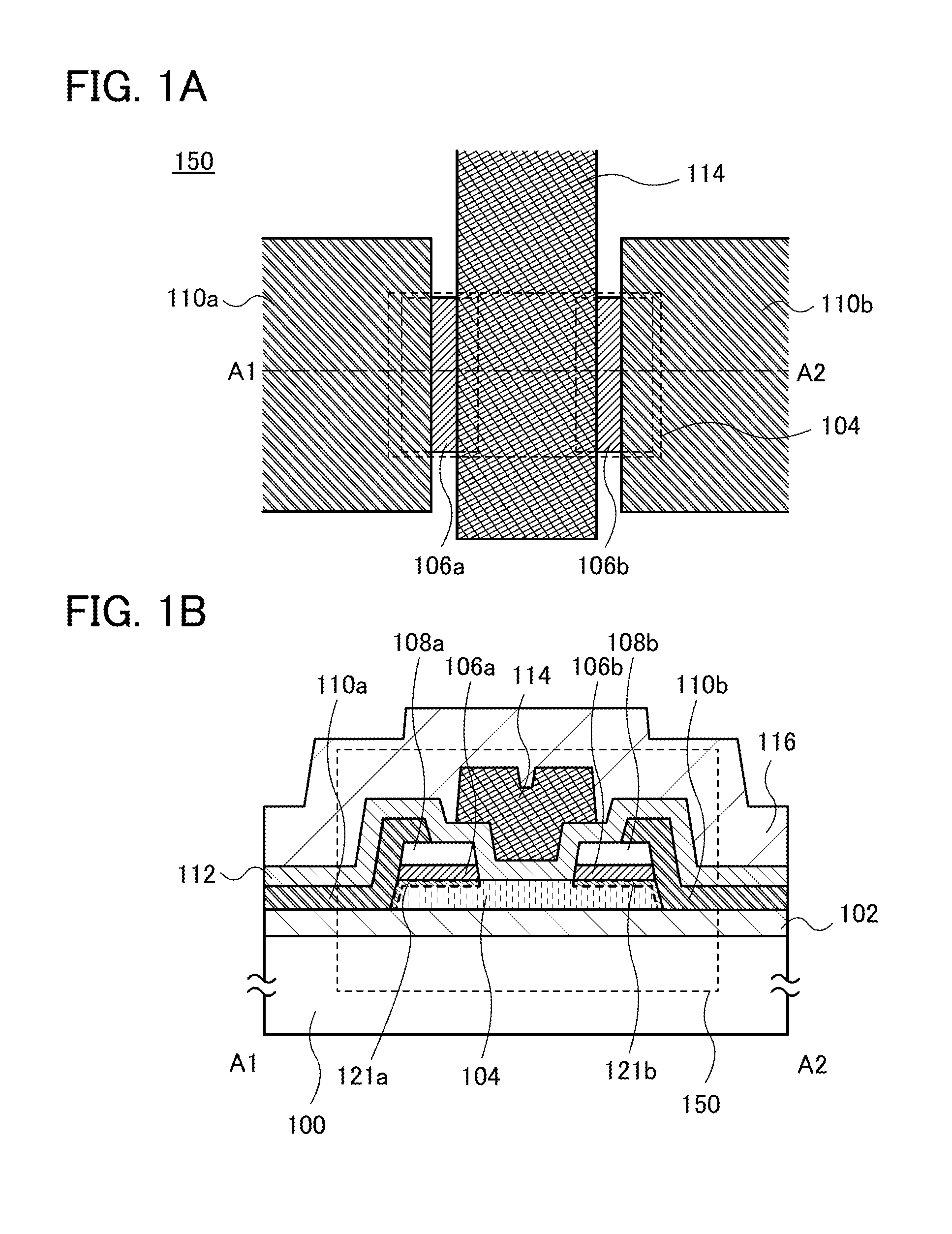

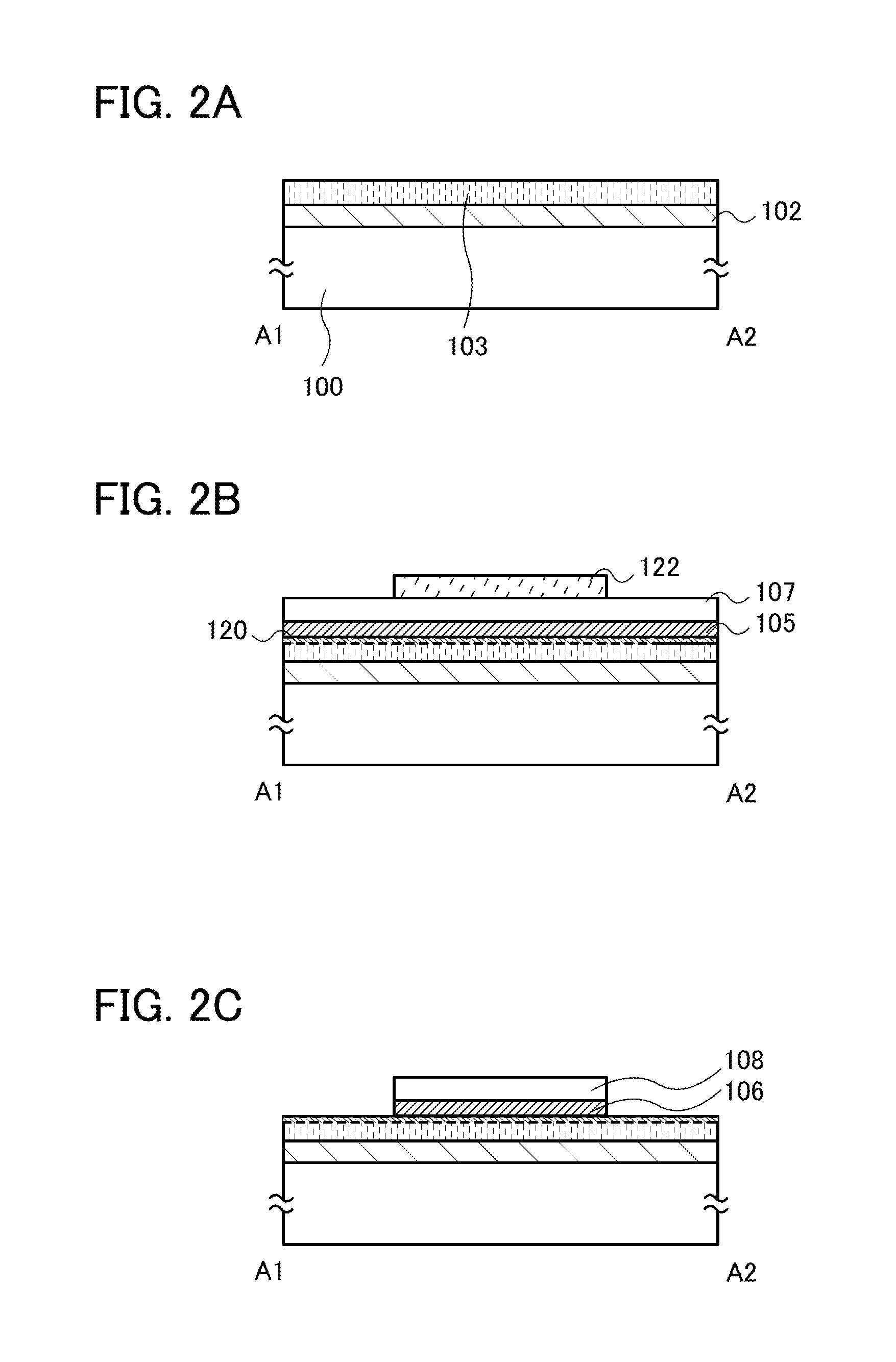

Semiconductor device and manufacturing method thereof

ActiveUS20140264323A1High electrical characteristicHigh yieldTransistorSolid-state devicesOxide semiconductorOxide

When an oxide semiconductor film is microfabricated, with the use of a hard mask, unevenness of a side surface of the oxide semiconductor film can be suppressed. Specifically, a semiconductor device comprises an oxide semiconductor film over an insulating surface; a first hard mask and a second hard mask over the oxide semiconductor film; a source electrode over the oxide semiconductor film and the first hard mask; a drain electrode over the oxide semiconductor film and the second hard mask; a gate insulating film over the source electrode and the drain electrode; and a gate electrode overlapping with the gate insulating film and the oxide semiconductor film, and the first and second hard masks have conductivity.

Owner:SEMICON ENERGY LAB CO LTD

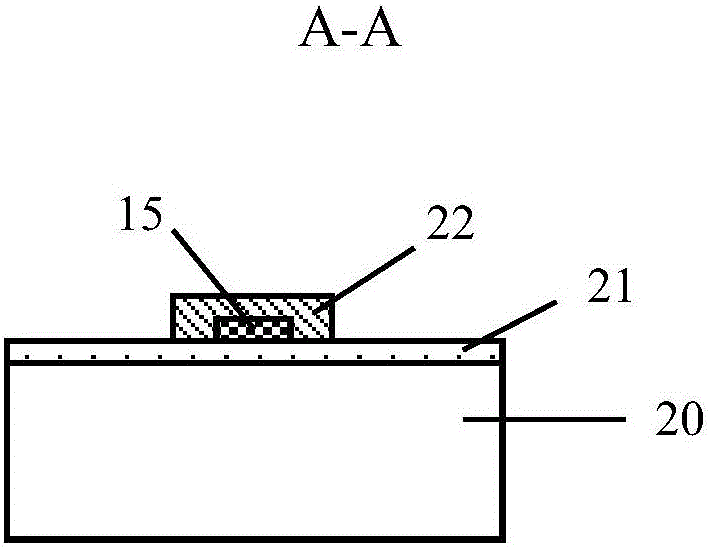

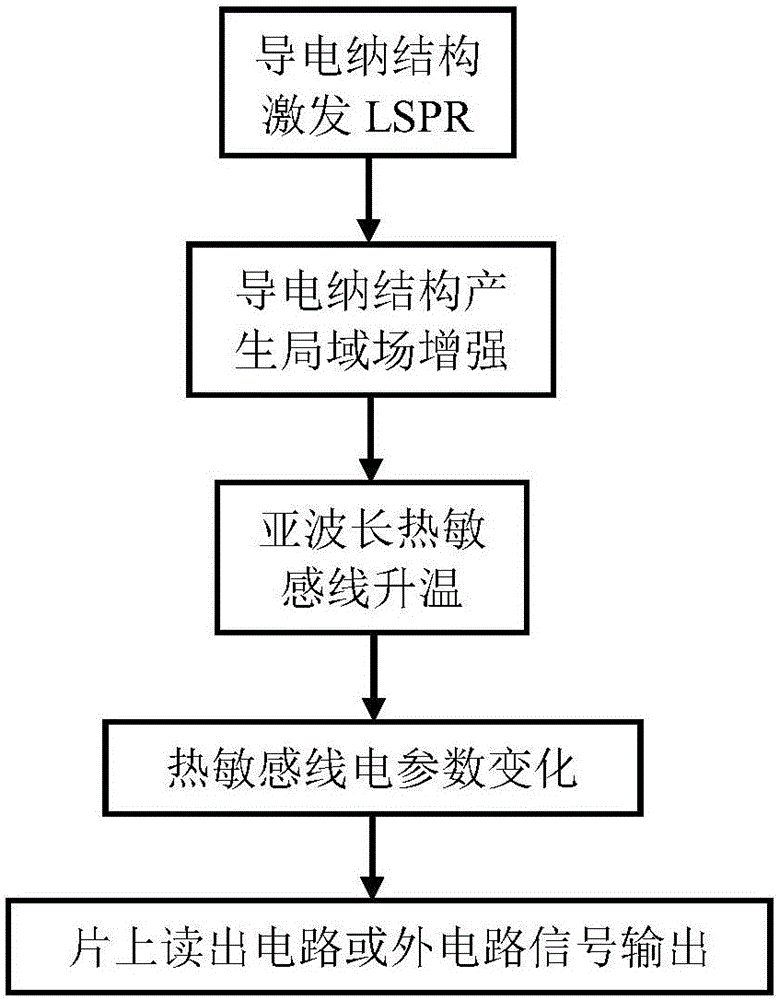

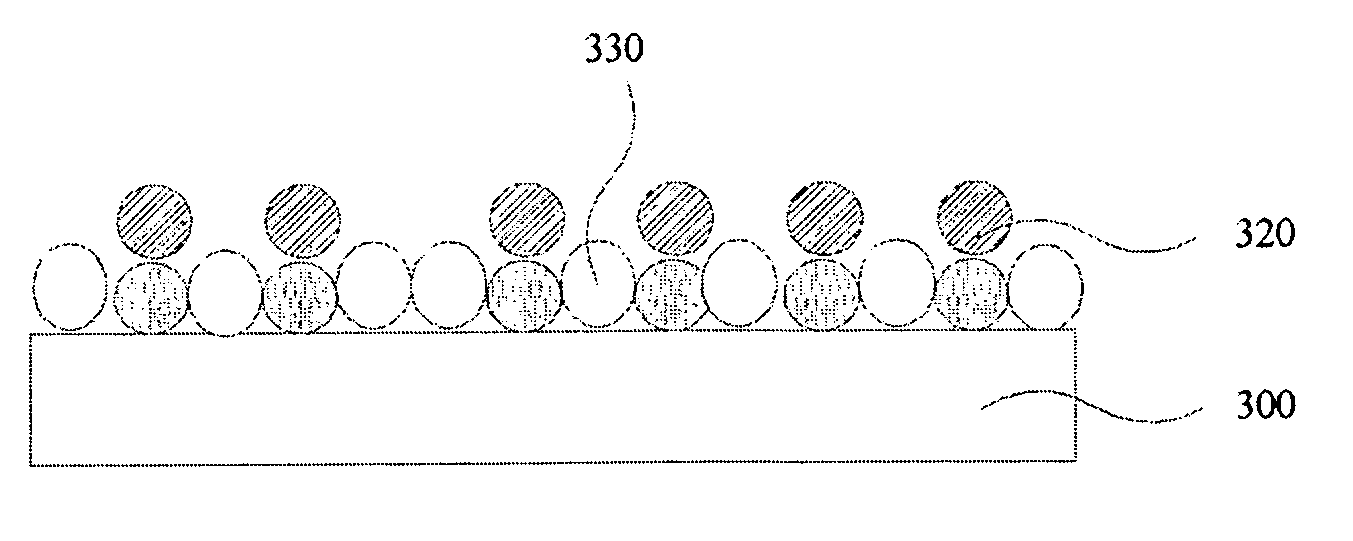

Short wave optical thermal detector and focal plane array device thereof

ActiveCN105977335ASimple structureStructural parameter optimizationSolid-state devicesRadiation controlled devicesElectromagnetic radiationFocal Plane Arrays

The invention discloses a short wave optical thermal detector and a focal plane array device thereof. The short wave optical thermal detector includes an electrode, an electric contact, a photo-thermal detection structure and a substrate. Two ends of the electrode are connected with the electric contact and the photo-thermal detection structure respectively. The photo-thermal detection structure includes heat reactive lines and conducting Na particles capable of generating local surface Plasmon resonance. When electromagnetic radiation of a specific wavelength acts on the conducting Na particles, local surface Plasmon resonance is generated, os that hot spots are formed. Therefore, temperature rise of the heat reactive lines is caused and electric parameter change is caused, and detection of specific electromagnetic radiation by the detector is realized. Through adjusting geometric parameters of the conducting Na particles and combining the conducting Na particles of different parameters, selective spectrum radiation detection and multi-waveband radiation detection are realized. The optical thermal detector provided by the invention is simple in structure and the low cost short wave optical (ultraviolet, visible light and near infrared) waveband detector and the focal plane array device thereof are realized.

Owner:WUHAN IND INST FOR OPTOELECTRONICS

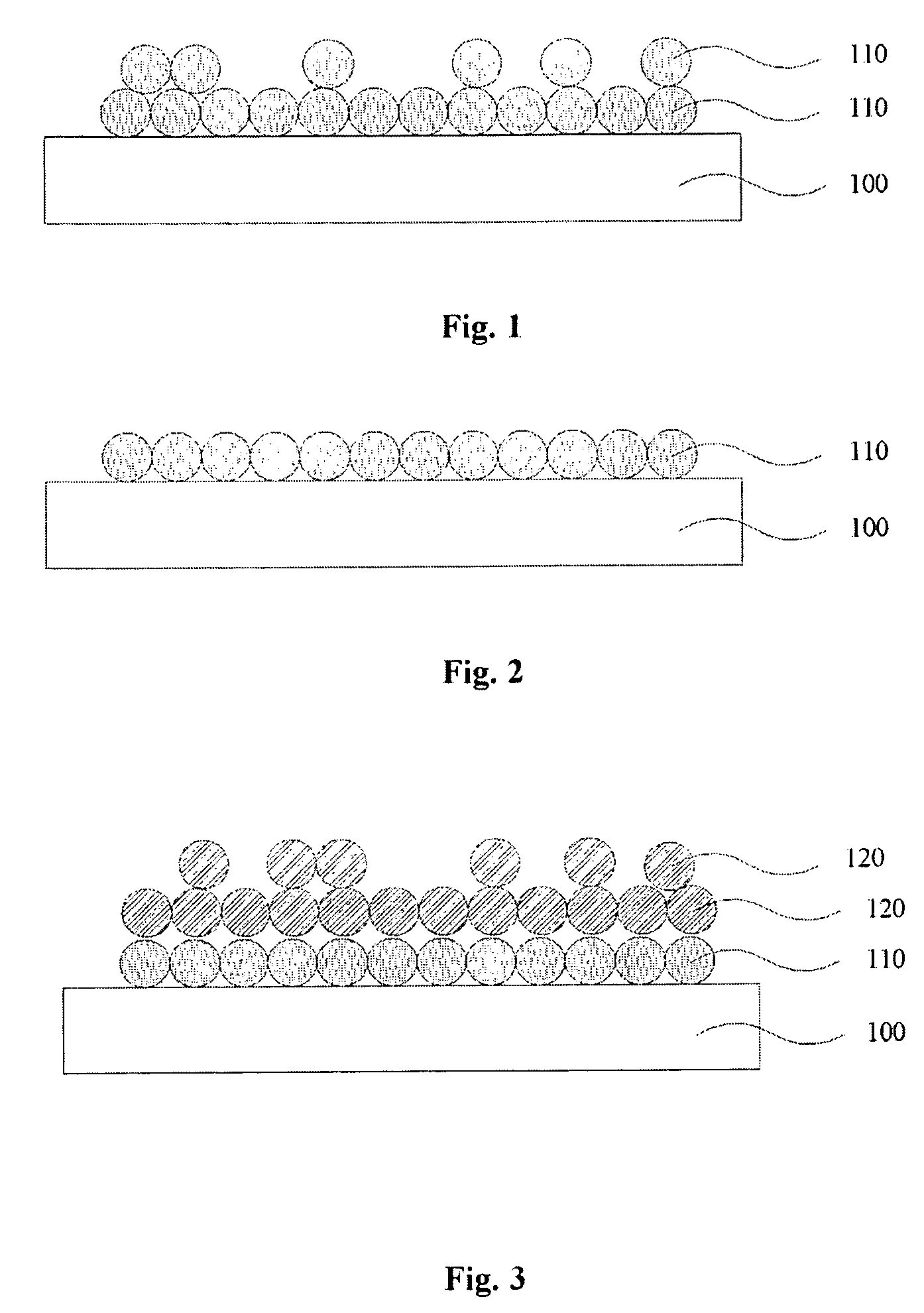

Method for applying a metal on a substrate

InactiveUS20090205853A1Maintain good propertiesImprove signal integrityPretreated surfacesRecord information storageMetal coatingElectrical conductor

There is disclosed a method for applying a first metal on a substrate, which method comprises the steps a) producing polymers on the surface of said substrate, said polymers comprising carboxylic groups and adsorbed ions of at least one second metal, said ions being adsorbed at a pH above 7, b) reducing said ions to the second metal and c) depositing said first metal on the reduced ions of said second metal. The invention further comprises objects manufactured according to the method. Advantages of the present invention include improved adhesion of the metal coating, possibility to coat many difficult materials. The process is suitable for large-scale and continuous production and it will reduce the waste of metal. Circuits manufactured according to the invention display improved signal integrity. Also there is the possibility to manufacture circuits which are built up sequentially with several layers of conductors in distinct patterns. It is also possible to manufacture of circuits with a very small line width.

Owner:LINEA TERGI

Printed circuit board and method of manufacturing the same

InactiveUS20090260868A1High-density circuit patternSmall line widthStacked resist layersPrinted circuit aspectsElectrical connectionEngineering

The printed circuit board includes the via formed with the electroplating layer unlike a conventional via formed with an electroless plating layer and an electroplating layer and having a cylindrical shape, and thus exhibits good interlayer electrical connection and high reliability of physical contact upon thermal stress caused by the variance in physical properties of material depending on changes in temperature. The via has no upper land, and thus a fine circuit pattern of the circuit layer can be formed on the via.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Semiconductor device

InactiveUS20070007618A1Small line widthImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor

There is disclosed a semiconductor device comprising a plurality of inter-level dielectric films which are stacked and provided in plural layers above a substrate, at least one first conductor which is provided in at least one inter-level dielectric film of the stacked inter-level dielectric films, and a plurality of second conductors which are provided in the inter-level dielectric film in which the first conductor is provided and which are connected to the lower surface of the first conductor and which are extended along the downward direction from the first conductor and further extended along a first direction and a second direction perpendicular to the first direction in such a manner as to be spaced apart from each other to form a lattice shape.

Owner:KK TOSHIBA

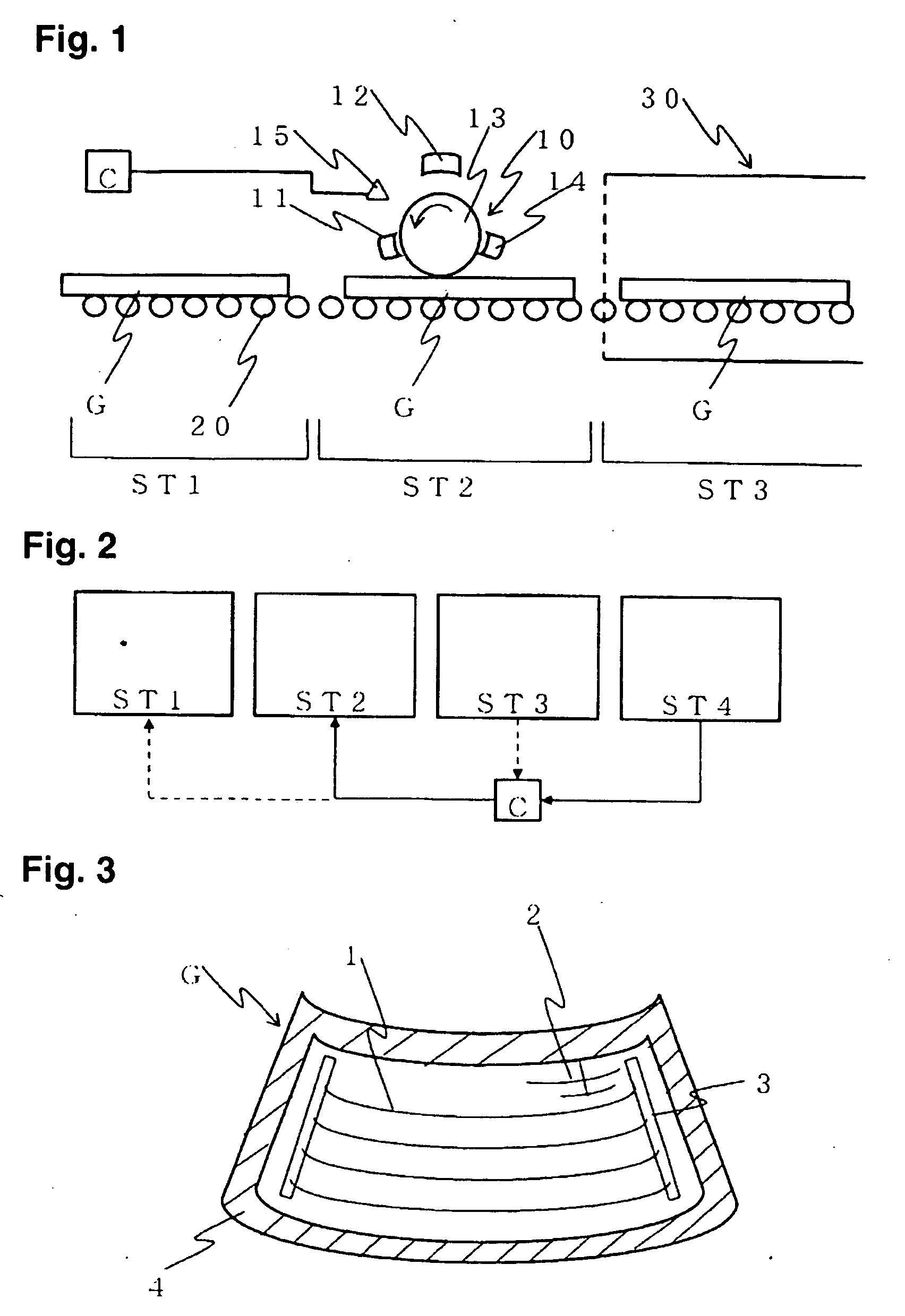

Electromagnetic-shielding transparent window member and method for producing the same

ActiveUS20050178569A1Low costFew stepsMagnetic/electric field screeningVacuum evaporation coatingElectromagnetic shieldingResin coating

A method for producing an electromagnetic-shielding transparent window member including a transparent film and a patterned conductor disposed thereon includes the steps of applying a resin coating material containing a catalyst for electroless plating to the transparent film to form a patterned resin having the same pattern as the patterned conductor to be formed; and depositing a conductive material only on the patterned resin by electroless plating to form the patterned conductor.

Owner:BRIDGESTONE CORP

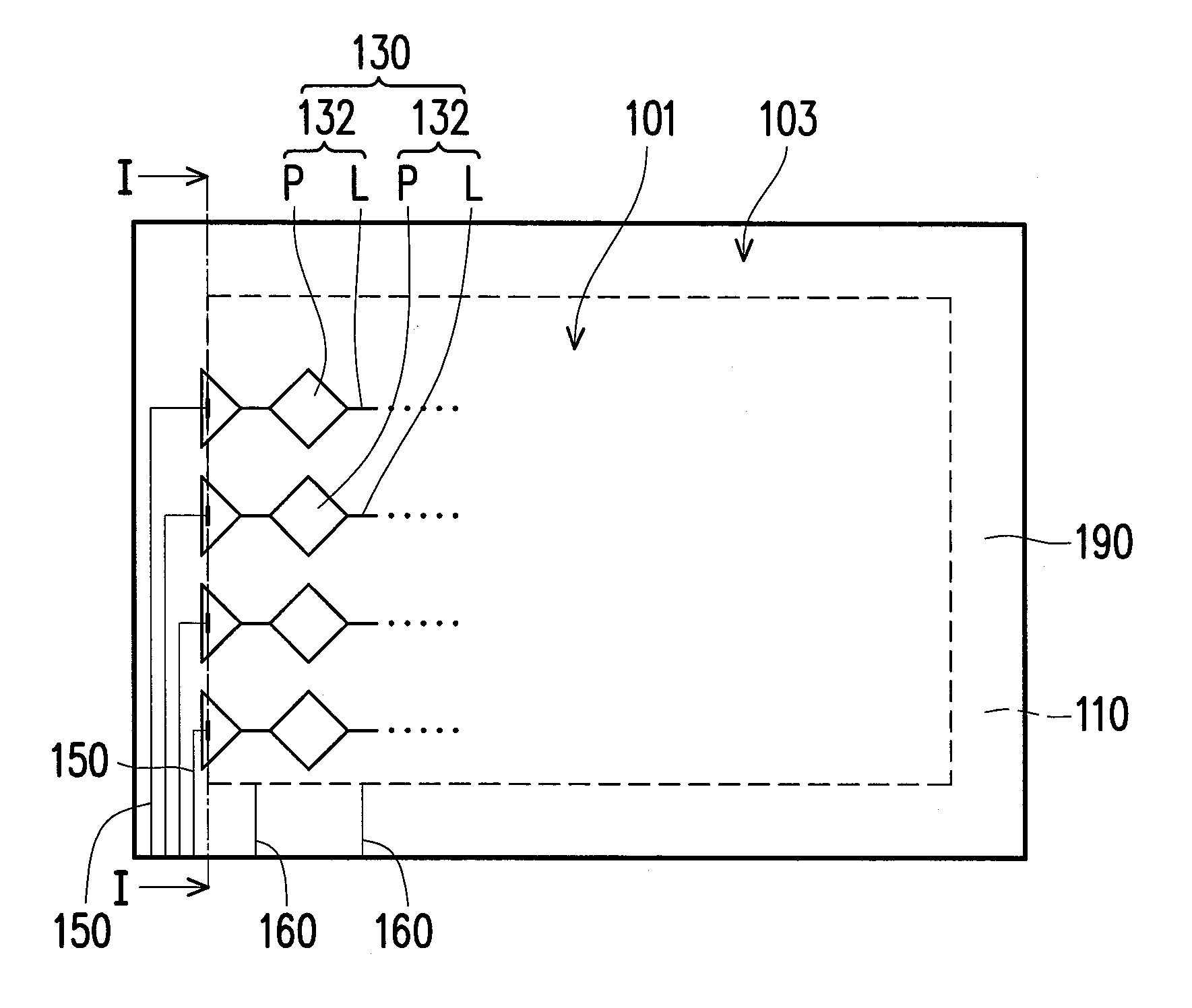

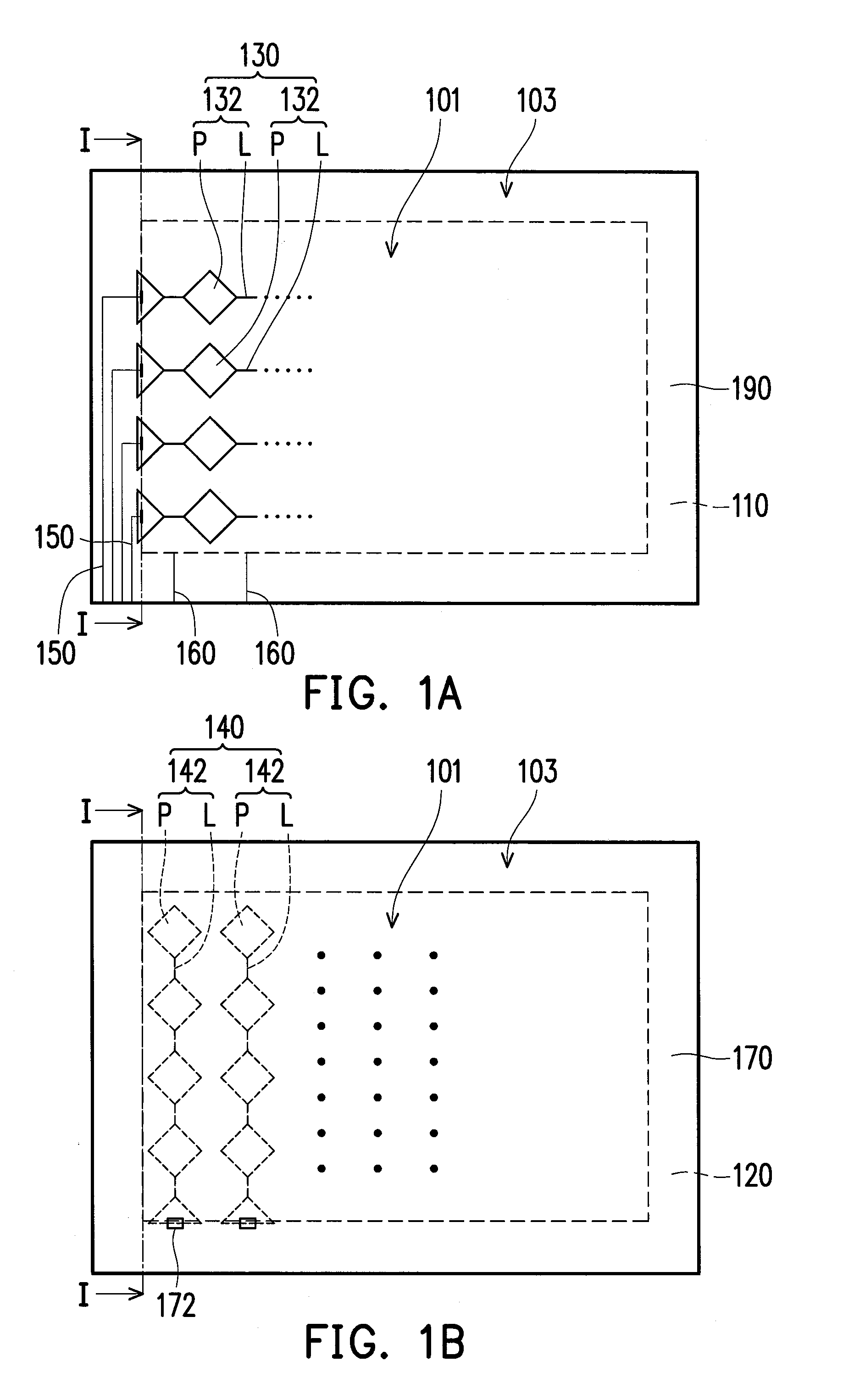

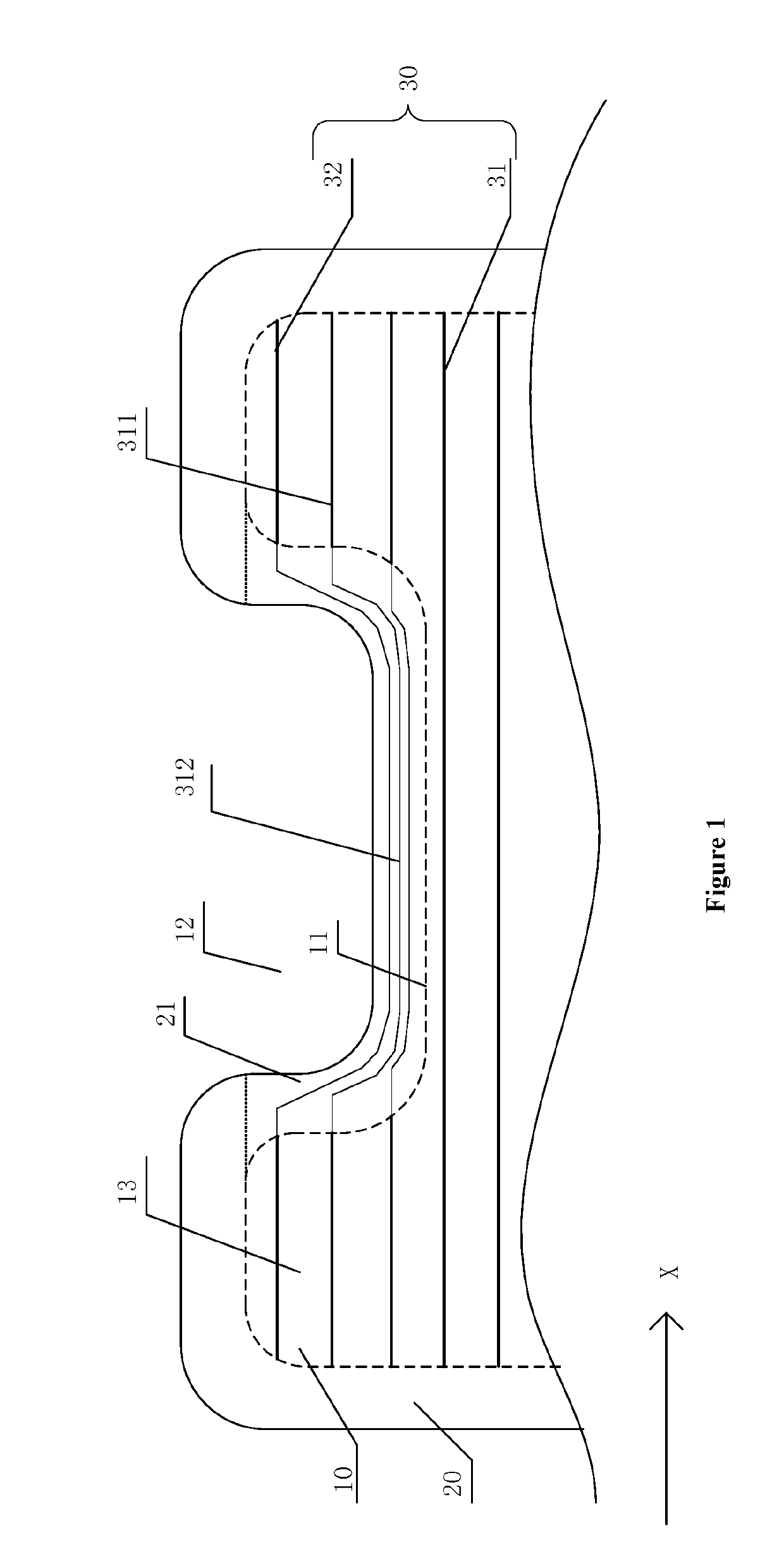

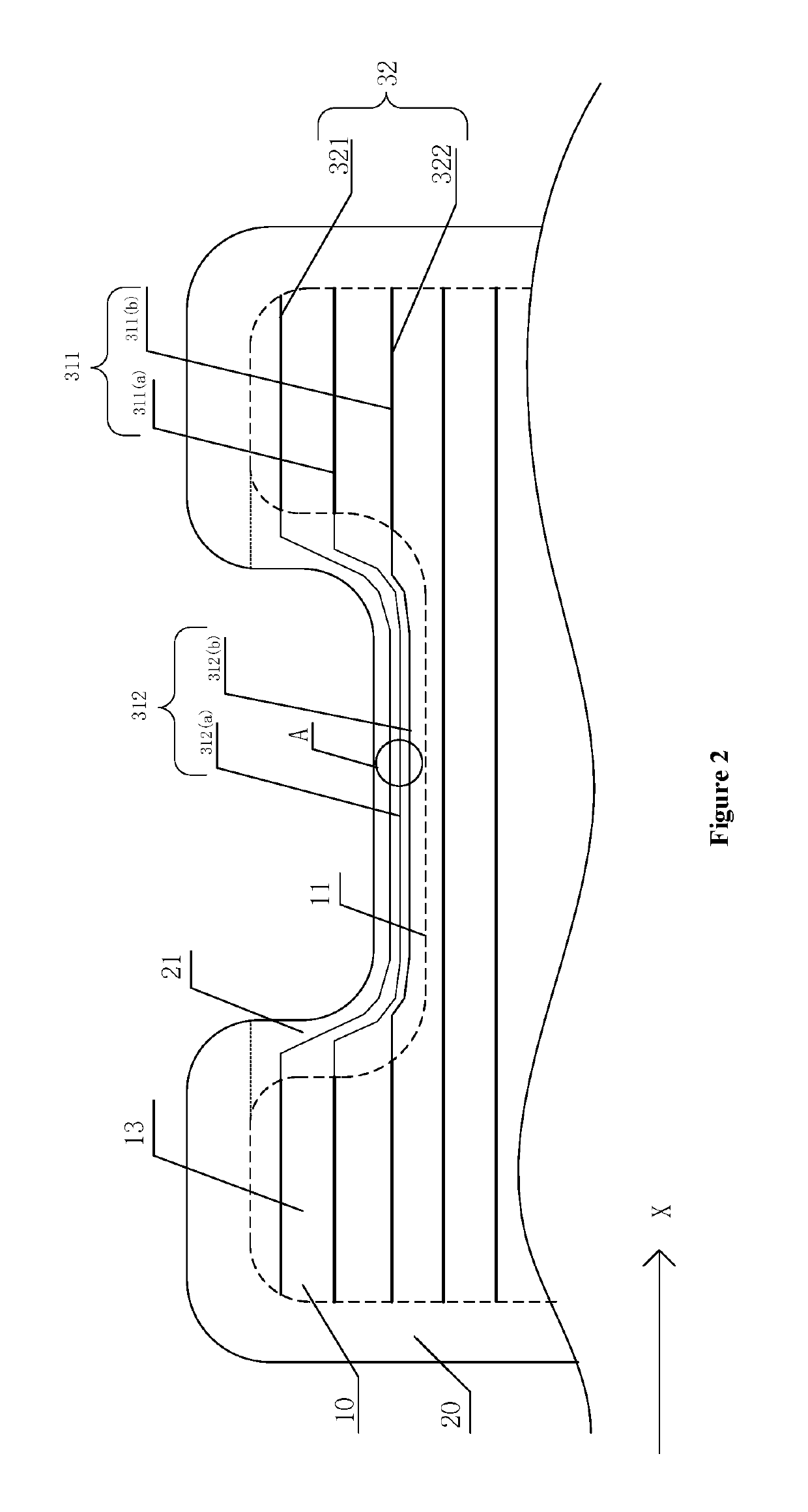

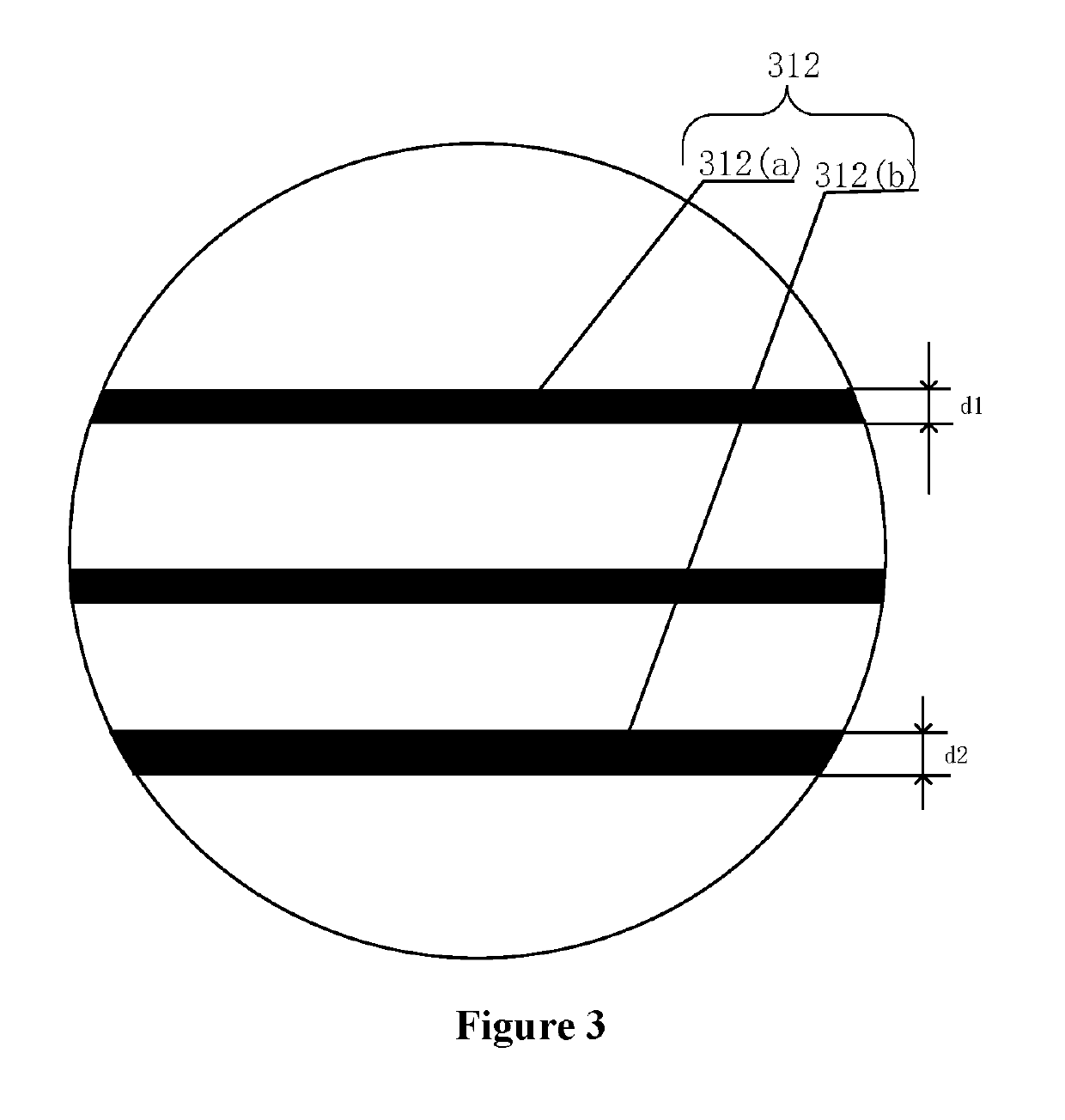

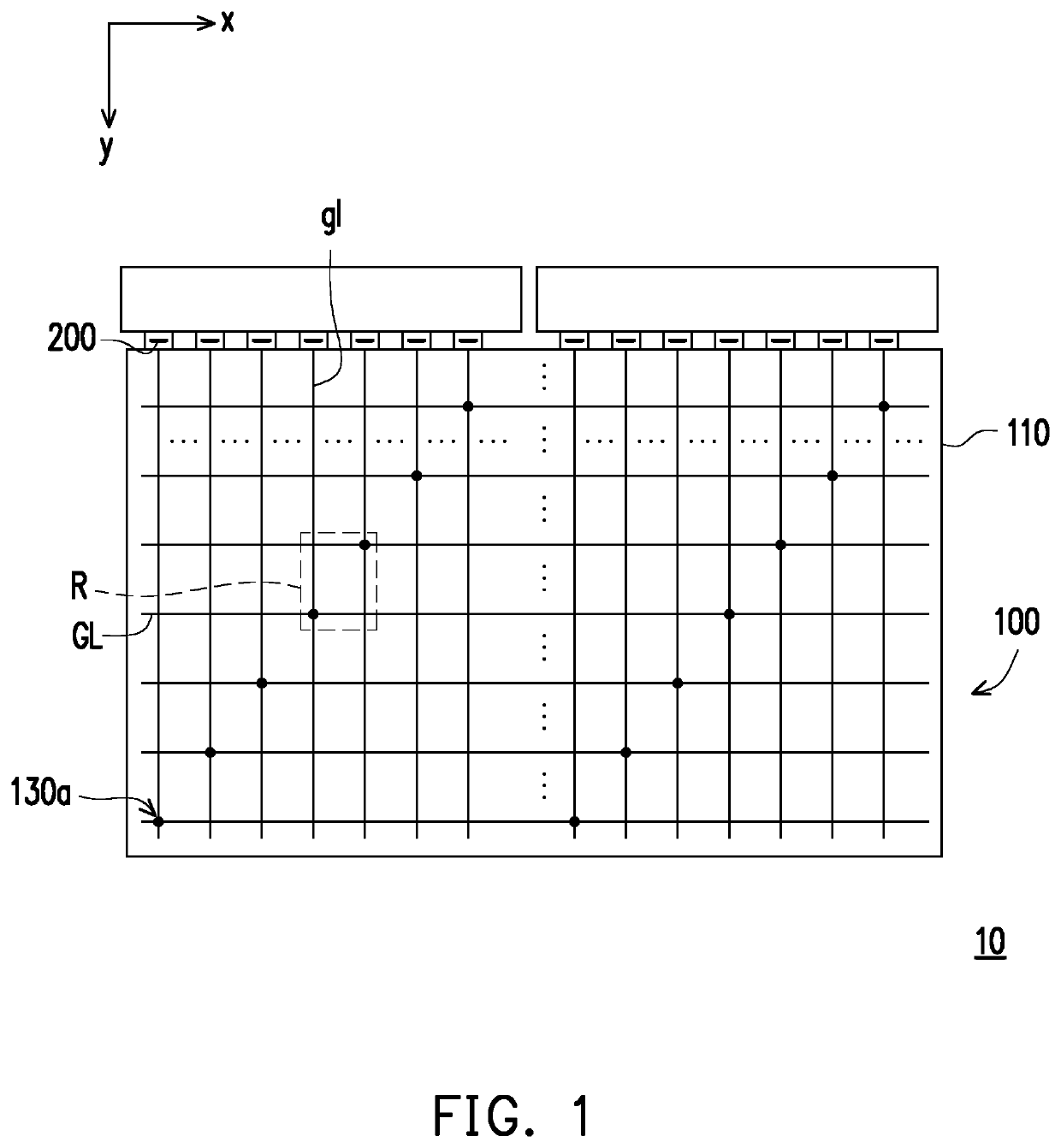

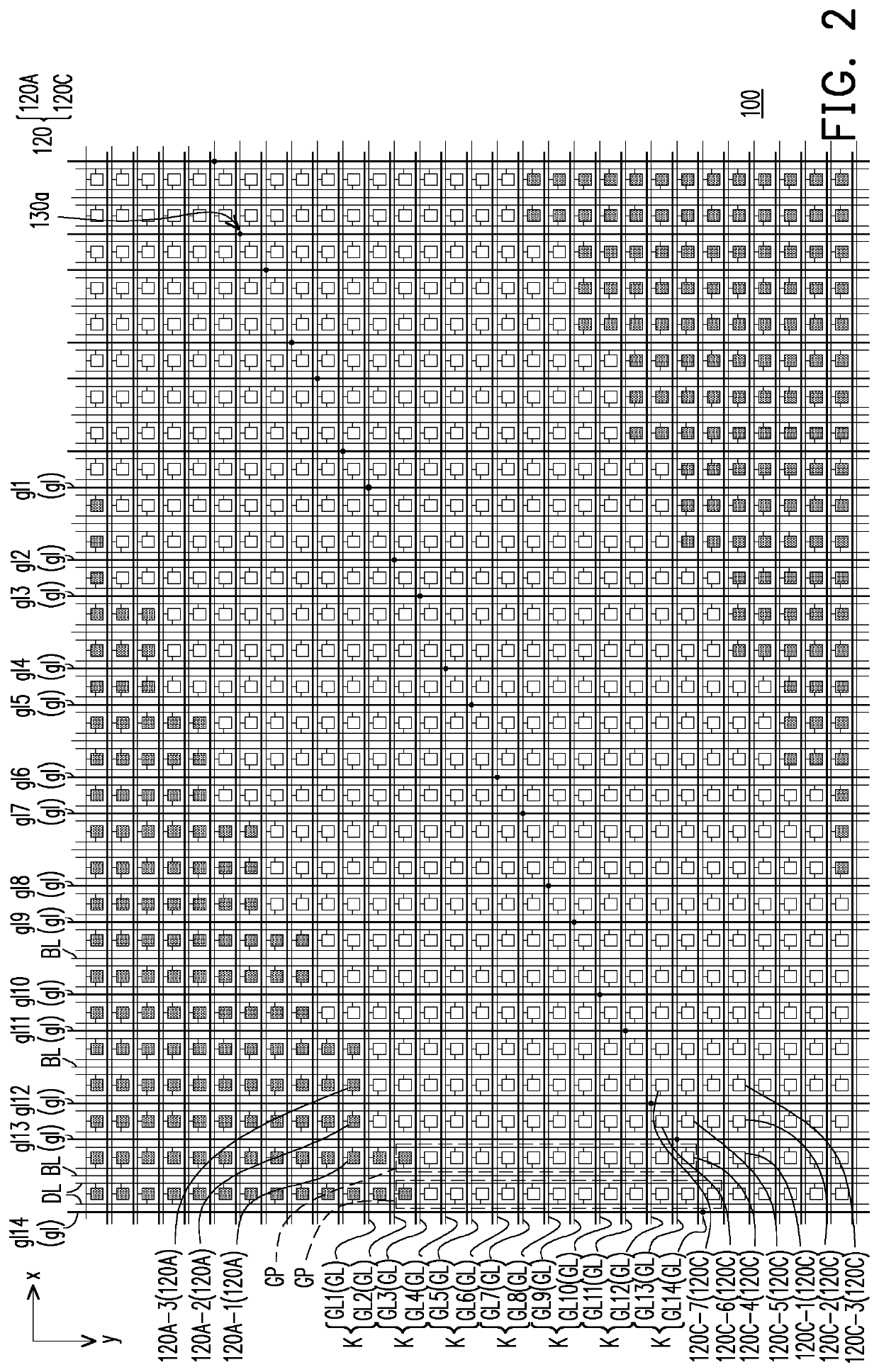

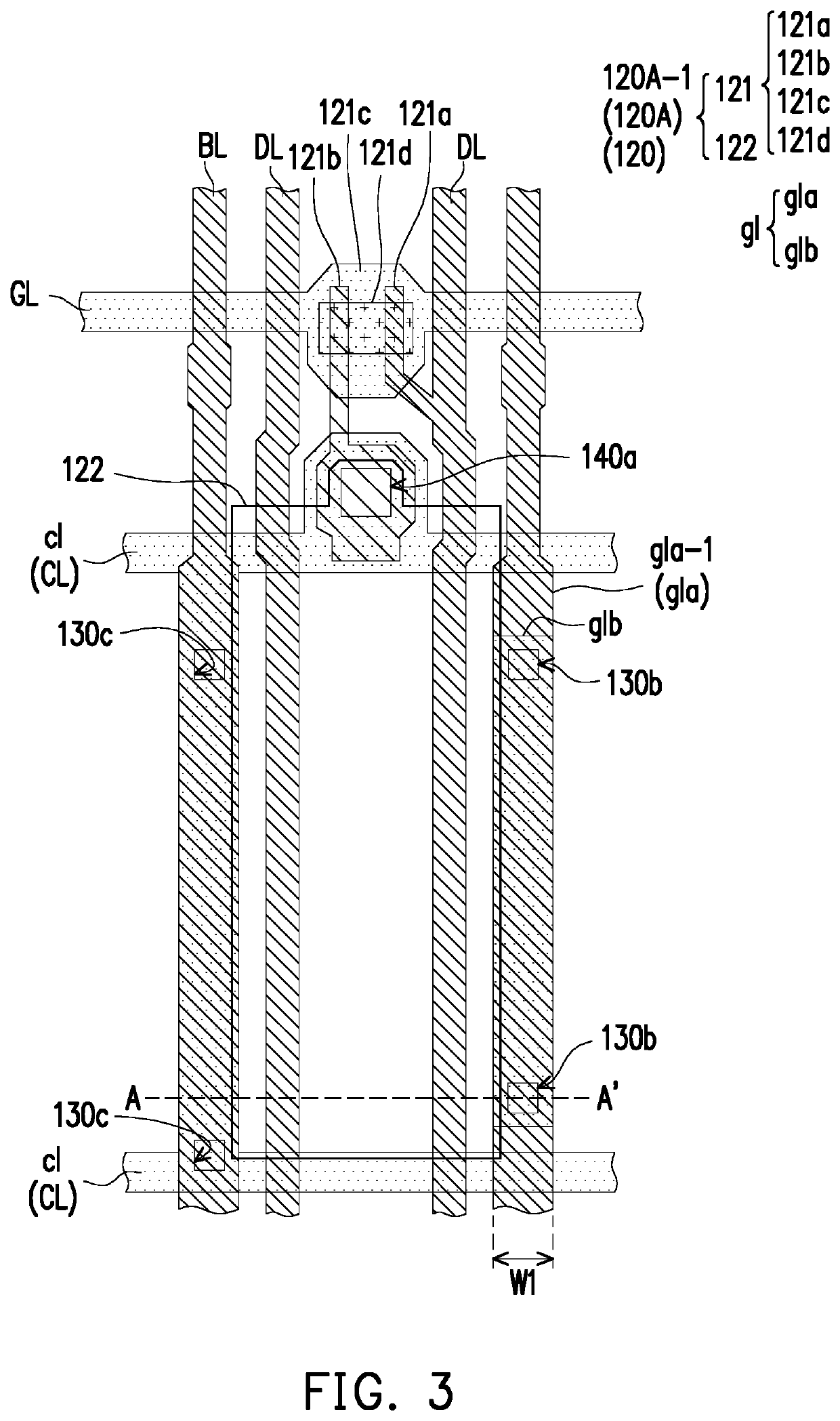

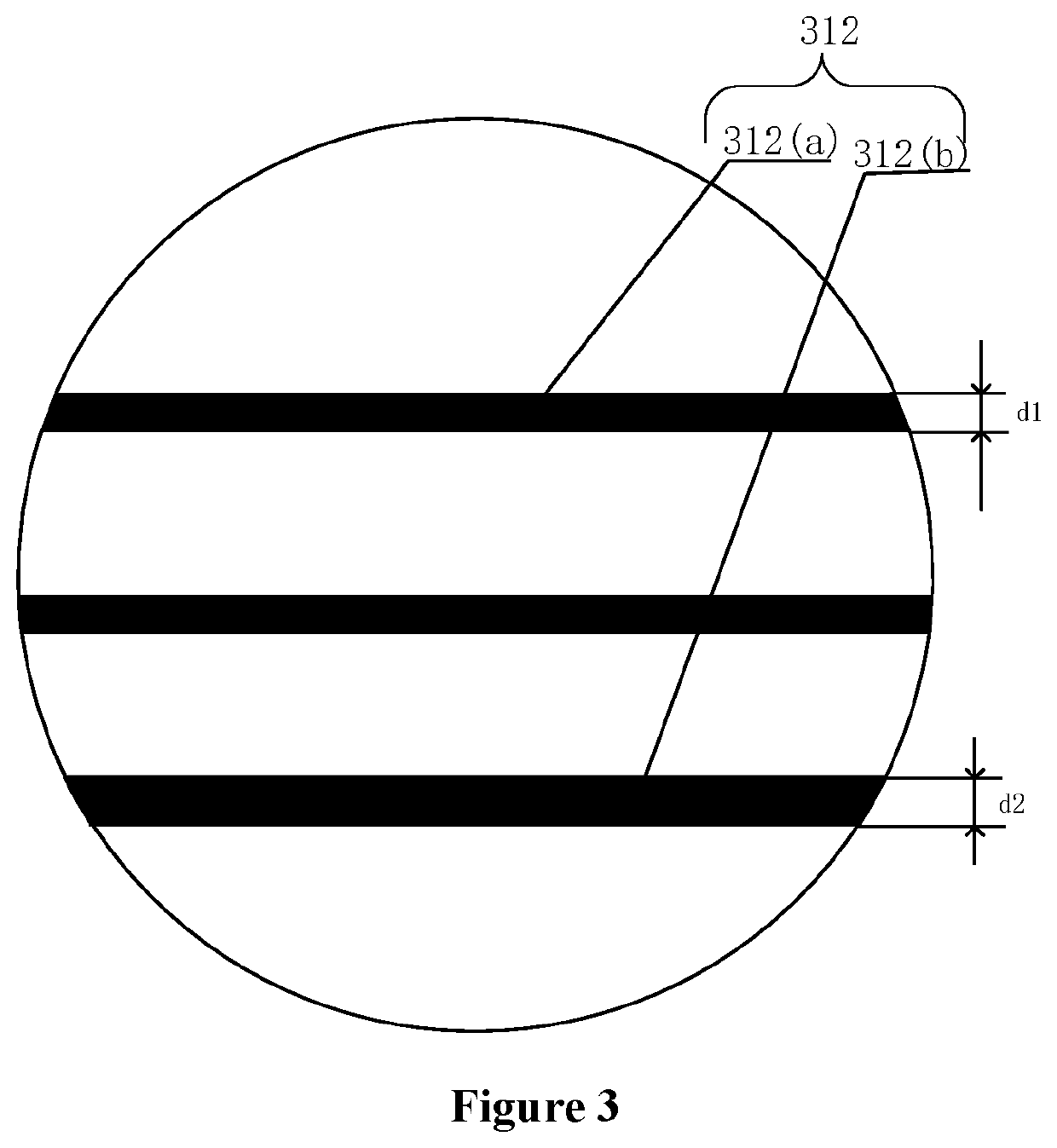

Array substrate, display panel, and display device thereof

ActiveUS20190304999A1Improve display uniformityImprove the display effectStatic indicating devicesSolid-state devicesLine widthDisplay device

An array substrate, a display panel, and a display device are provided. The array substrate includes a display region and a non-display region surrounding the display region. The array substrate also includes a plurality of gate lines. The plurality of gate lines include a plurality of regular gate lines and at least one irregular gate line. The plurality of regular gate lines are disposed in the display region and extended along a first direction. The at least one irregular gate line includes at least one first trace portion and a second trace portion electrically connected to each other. The at least one first trace portion has a same line width as a regular gate line of the plurality of regular gate lines, and the second trace portion has a line width smaller than the at least one first trace portion.

Owner:SHANGHAI AVIC OPTOELECTRONICS

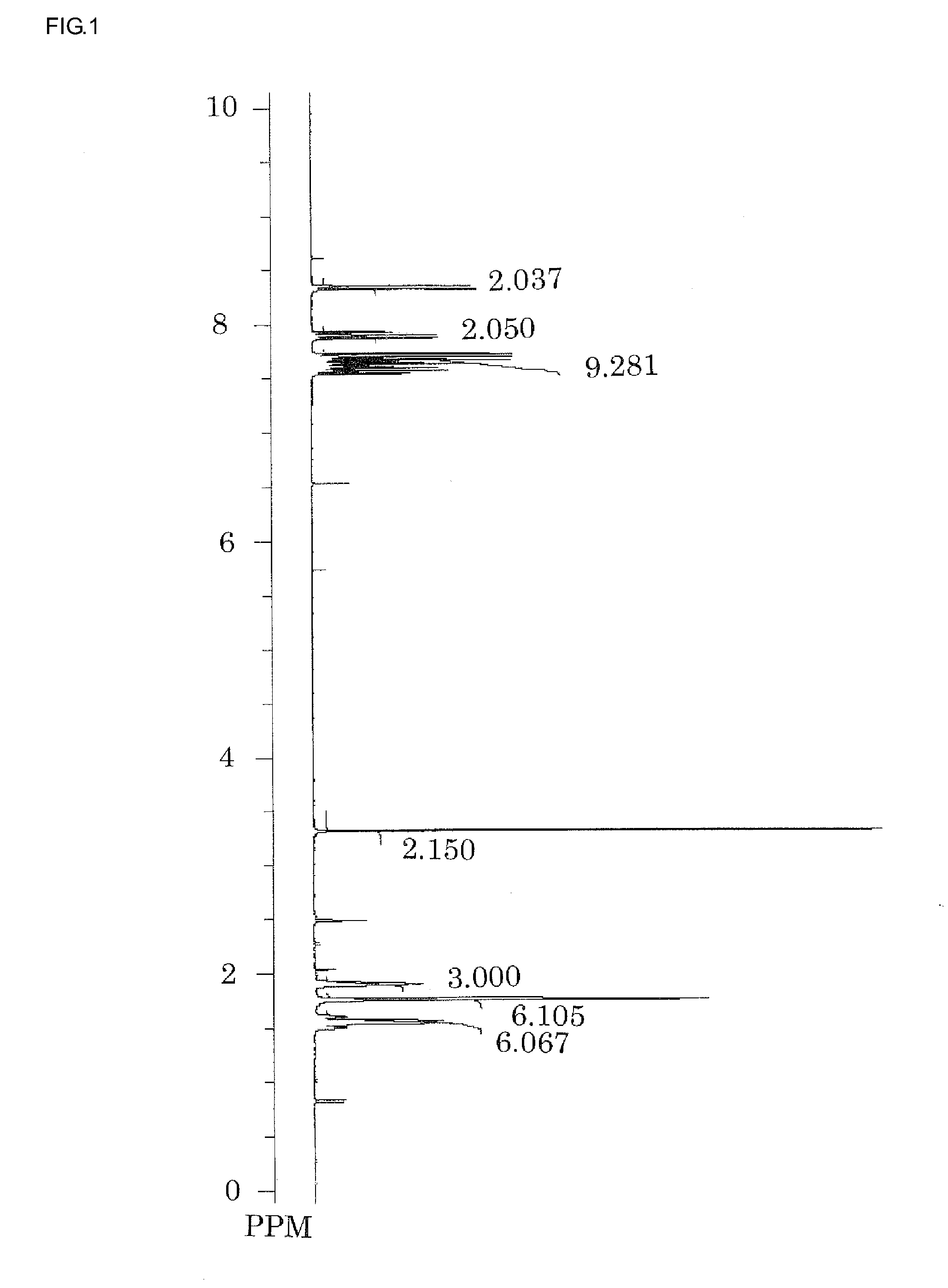

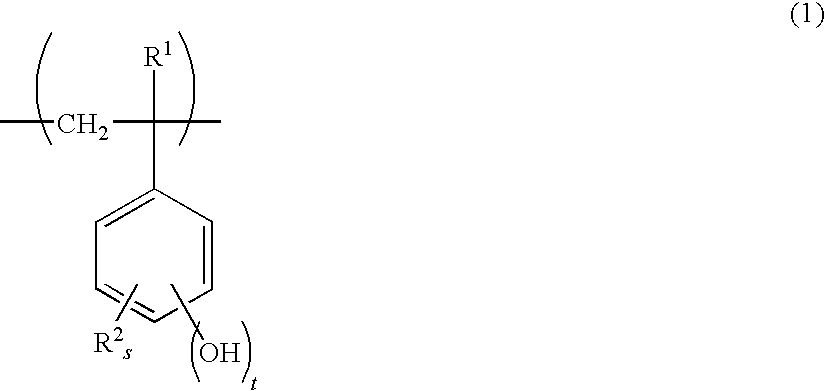

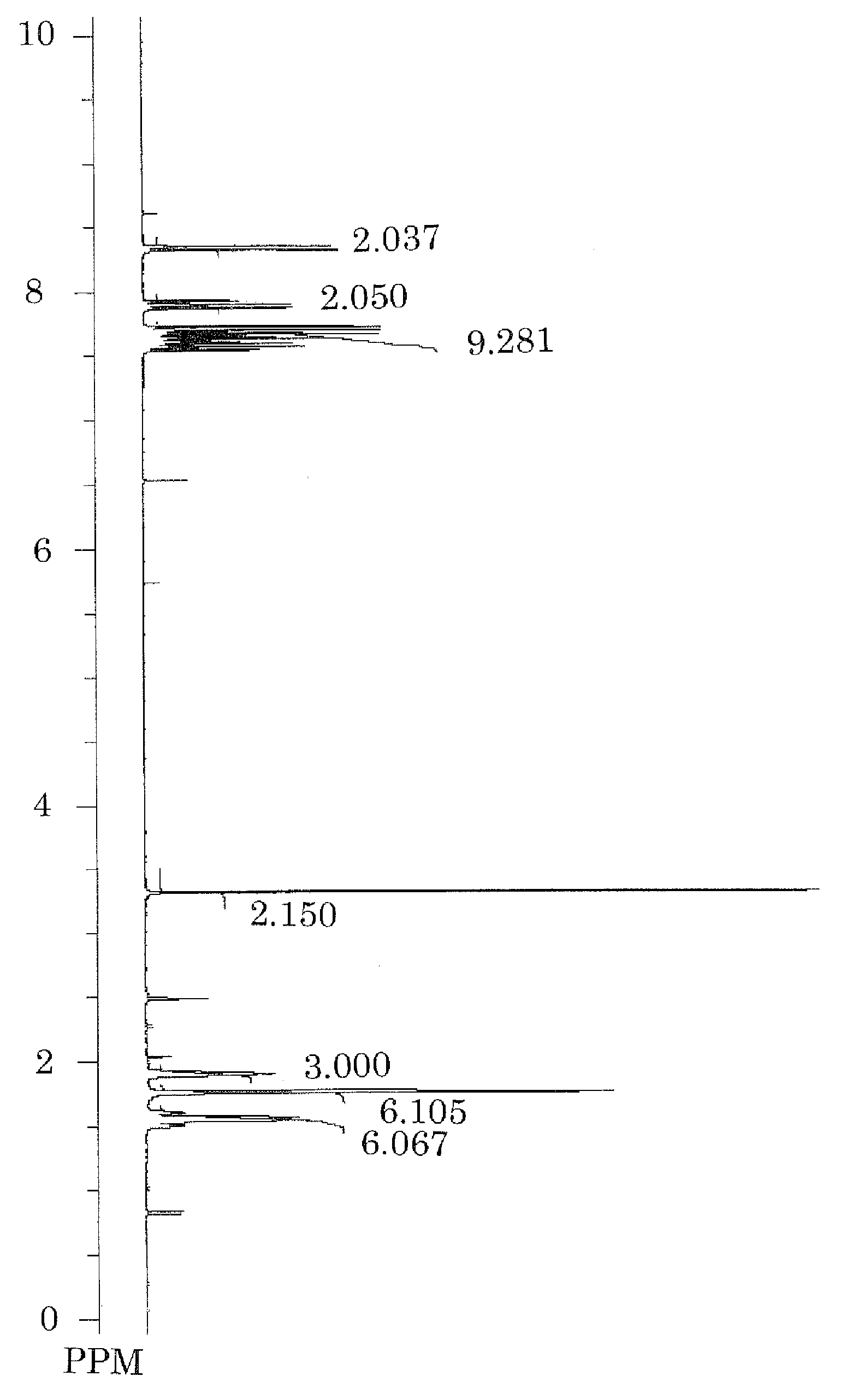

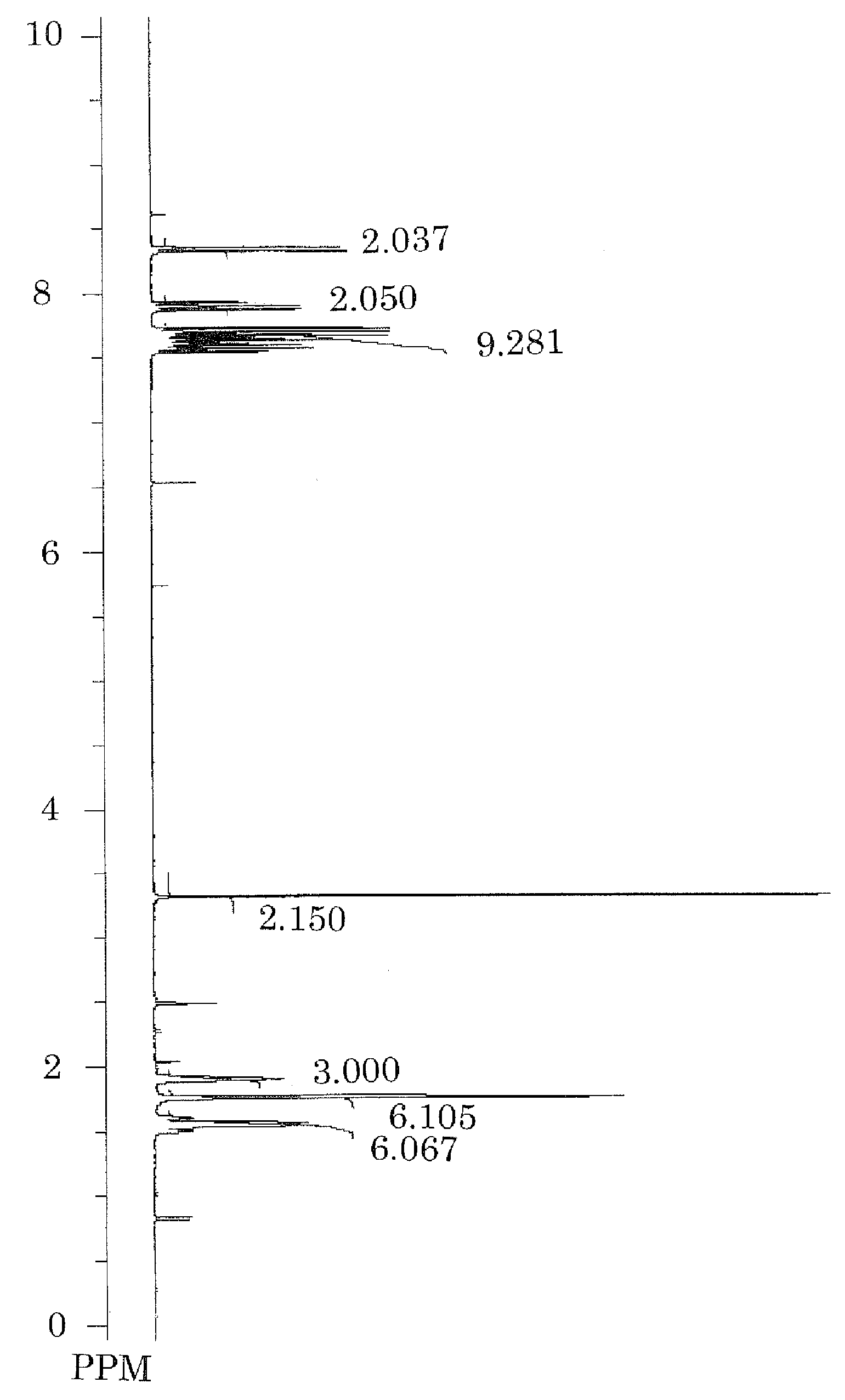

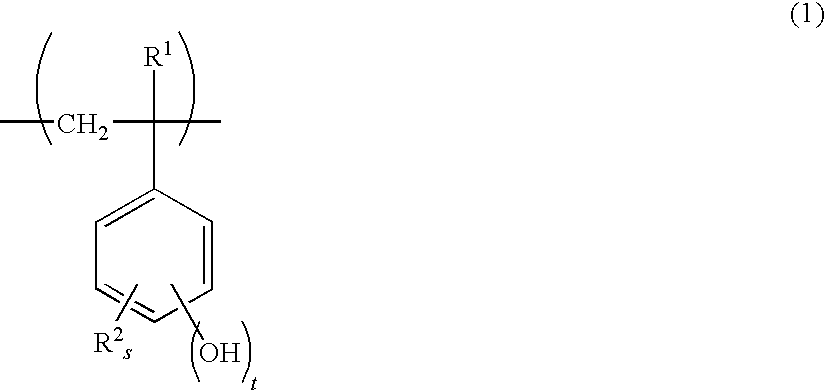

Chemically-amplified positive resist composition and patterning process thereof

ActiveUS20100009286A1Good solubilityLittle variancePhotosensitive materialsRadiation applicationsResistOrganic solvent

There is disclosed a chemically-amplified positive resist composition comprising, as main components, (A) a base polymer, which contains one or more kinds of a monomer unit represented by the following general formula (1) and the like, and is an alkali-insoluble polymer whose hydroxyl group is partly protected by an acetal group while alkali-soluble when deprotected by an acid catalyst, (B) a sulfonium salt containing a sulfonate anion, (C) a basic component, and (D) an organic solvent. In a lithography technology by a photo resist, an extremely high temporal stability is necessary. In addition, it must give a good pattern profile not dependent on a substrate and have a high resolution power. There can be provided a chemically-amplified positive resist composition which can solve these problems simultaneously, a resist patterning process using the same, and a method for producing a photo mask blank.

Owner:SHIN ETSU CHEM IND CO LTD

Semiconductor device and manufacturing method thereof

ActiveUS9437744B2Run at high speedReduce power consumptionTransistorSolid-state devicesSemiconductorSemiconductor device

When an oxide semiconductor film is microfabricated, with the use of a hard mask, unevenness of a side surface of the oxide semiconductor film can be suppressed. Specifically, a semiconductor device comprises an oxide semiconductor film over an insulating surface; a first hard mask and a second hard mask over the oxide semiconductor film; a source electrode over the oxide semiconductor film and the first hard mask; a drain electrode over the oxide semiconductor film and the second hard mask; a gate insulating film over the source electrode and the drain electrode; and a gate electrode overlapping with the gate insulating film and the oxide semiconductor film, and the first and second hard masks have conductivity.

Owner:SEMICON ENERGY LAB CO LTD

Method for signal extraction in a universal sensor IC

InactiveUS7307411B1Low costIncrease power consumptionAmplifier modifications to reduce noise influenceResistance/reactance/impedenceCombined useMultiple sensor

A apparatus and method for creating a universally usable and configurable sensor platform which is used in conjunction with various sensor and sensing elements to sense and measure environmental conditions which incorporates inputs from multiple sensors 6-9 and 12-14. The apparatus incorporates an oscillator 3 which provides a signal whose frequency varies according to the inputs from sensors 6-9 and 12-14 in combination with a microprocessor 1. A cordic block 61 allows for supplemental calculations of trigonometric operations and functions. An output unit 2 converts the signals received from microprocessor 1 into a variety of serial protocols.

Owner:SENSOR PLATFORMS

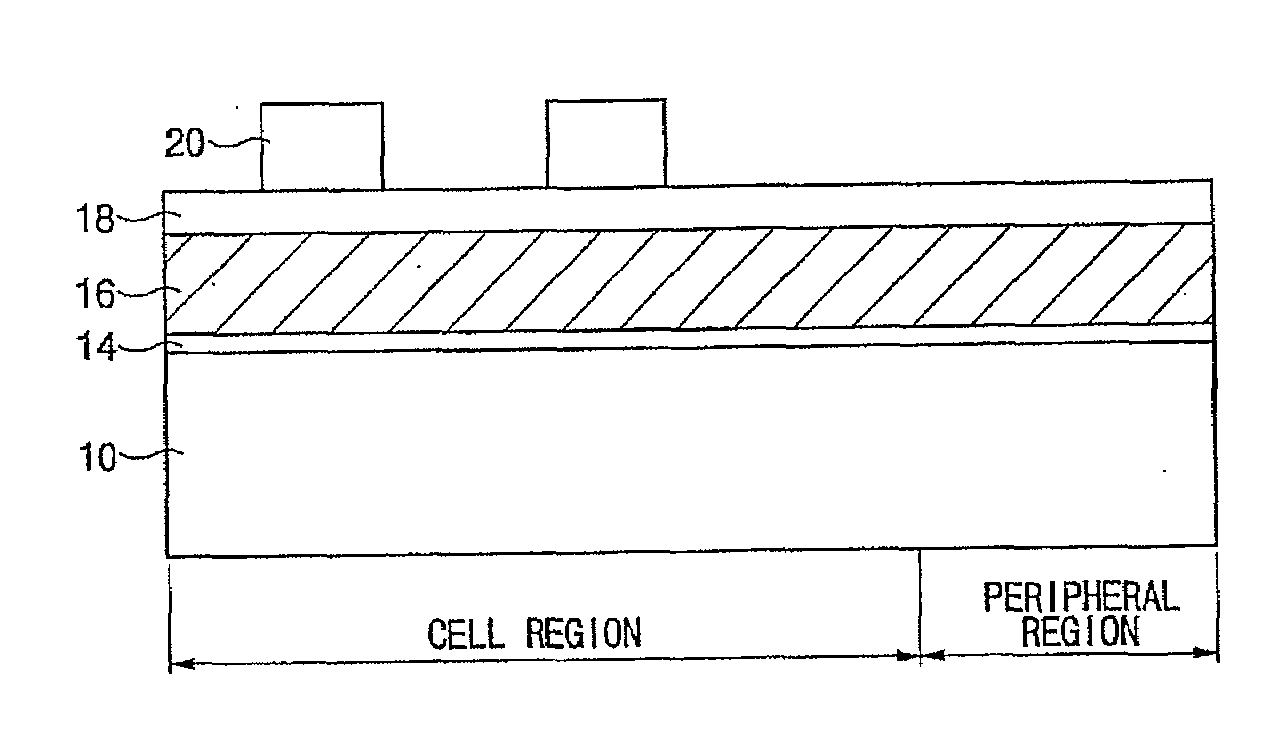

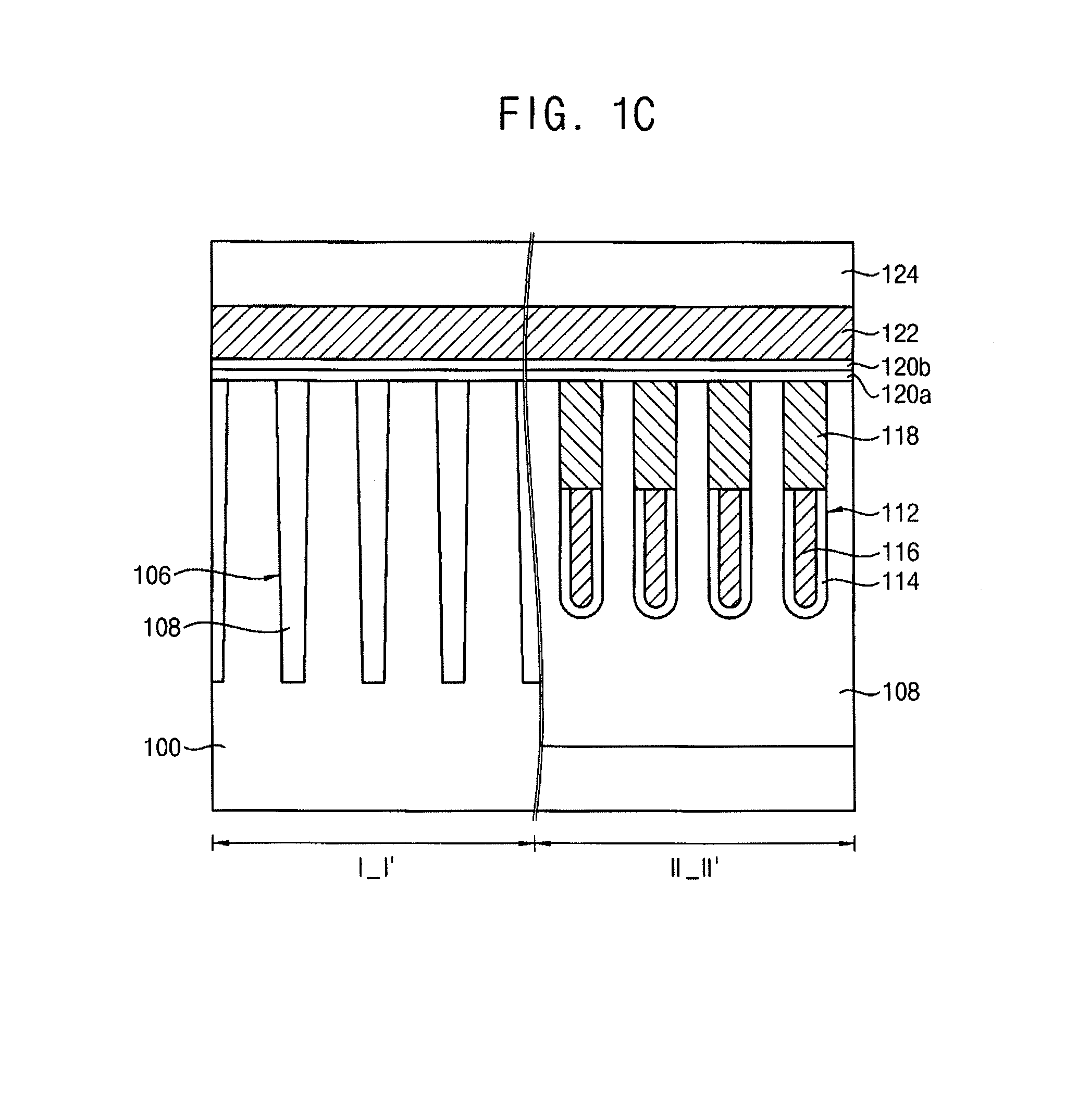

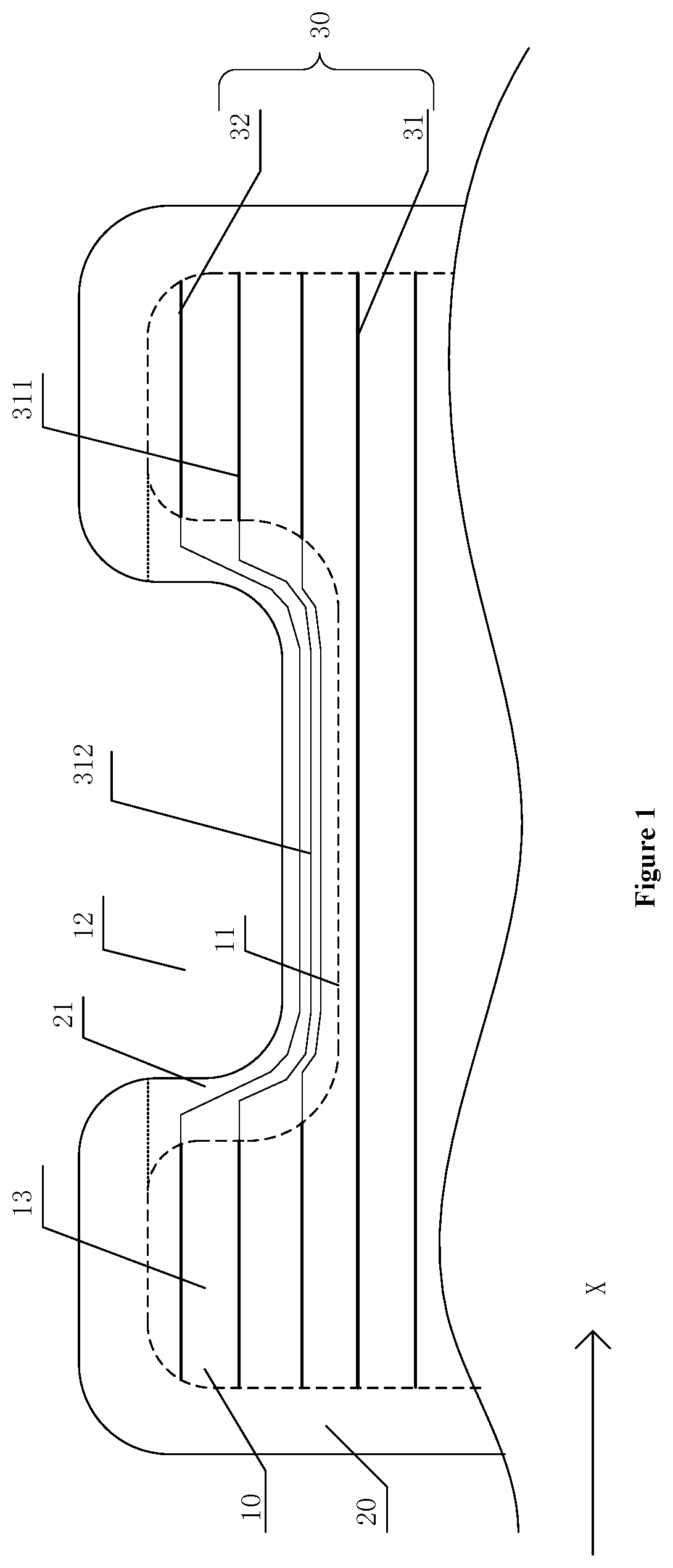

Semiconductor device including conductive lines with fine line width and method of fabricating the same

ActiveUS20080203587A1Small line widthSemiconductor/solid-state device detailsSolid-state devicesFine lineLithography process

A semiconductor device comprises a semiconductor substrate including a first core region and a second core region between which a cell array region is interposed, a first conductive line and a second conductive line extending to the first core region across the cell array region, and a third conductive line and a fourth conductive line extending to the second core region across the cell array region, wherein a line width of the first through fourth conductive lines is smaller than a resolution limit in a lithography process.

Owner:SAMSUNG ELECTRONICS CO LTD

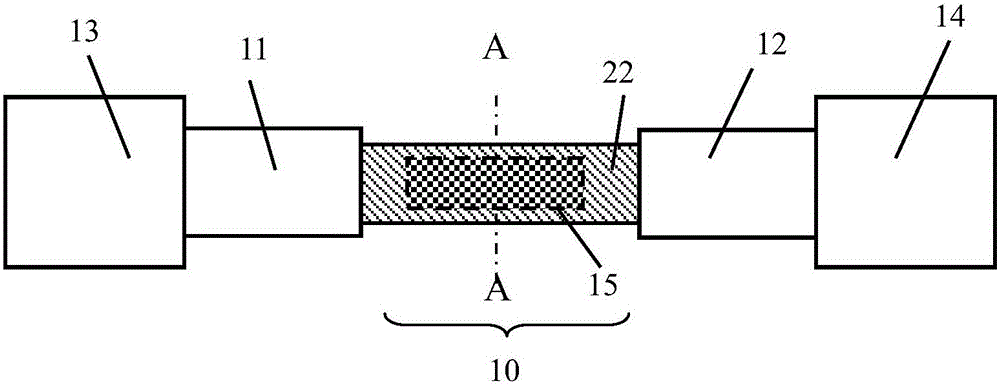

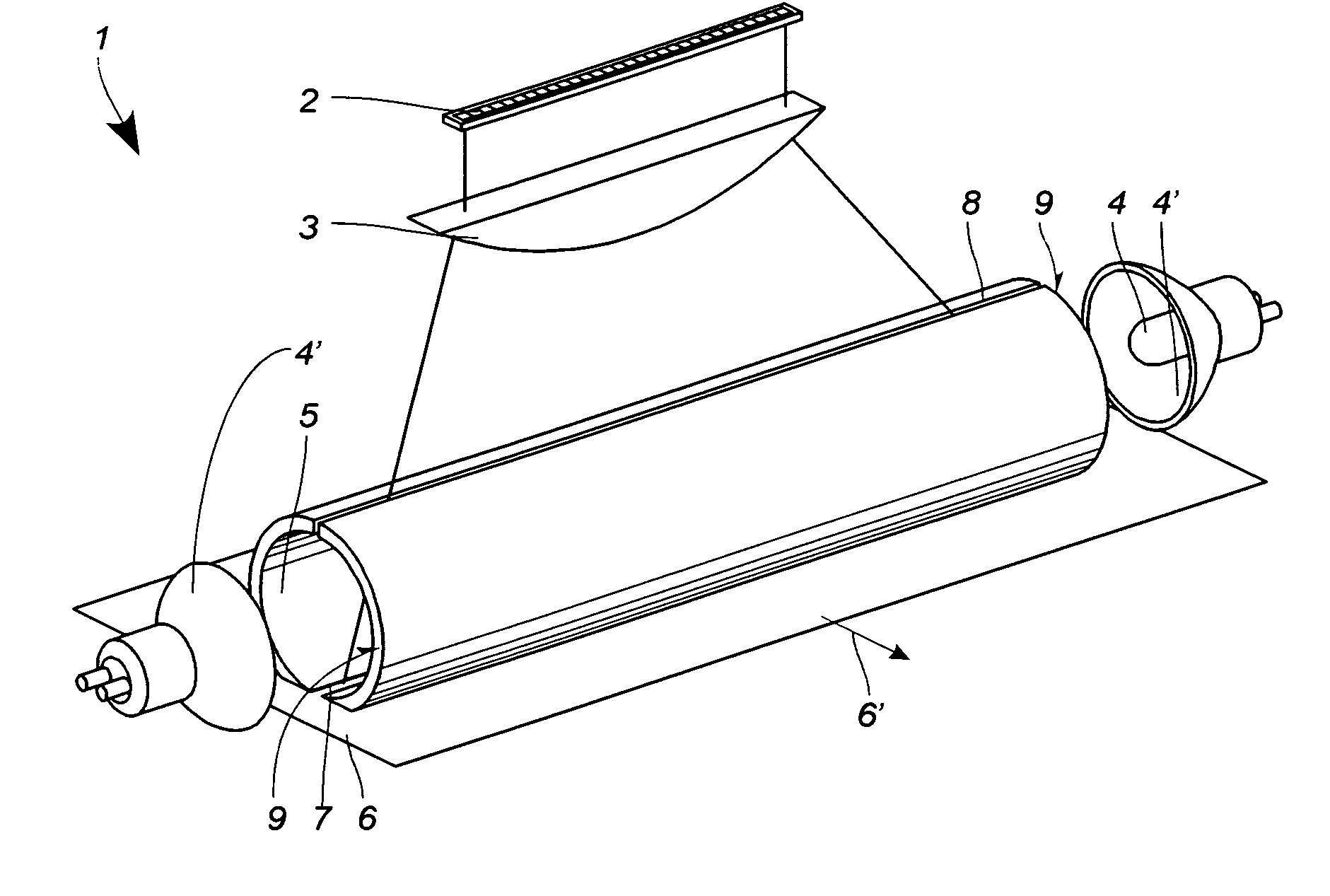

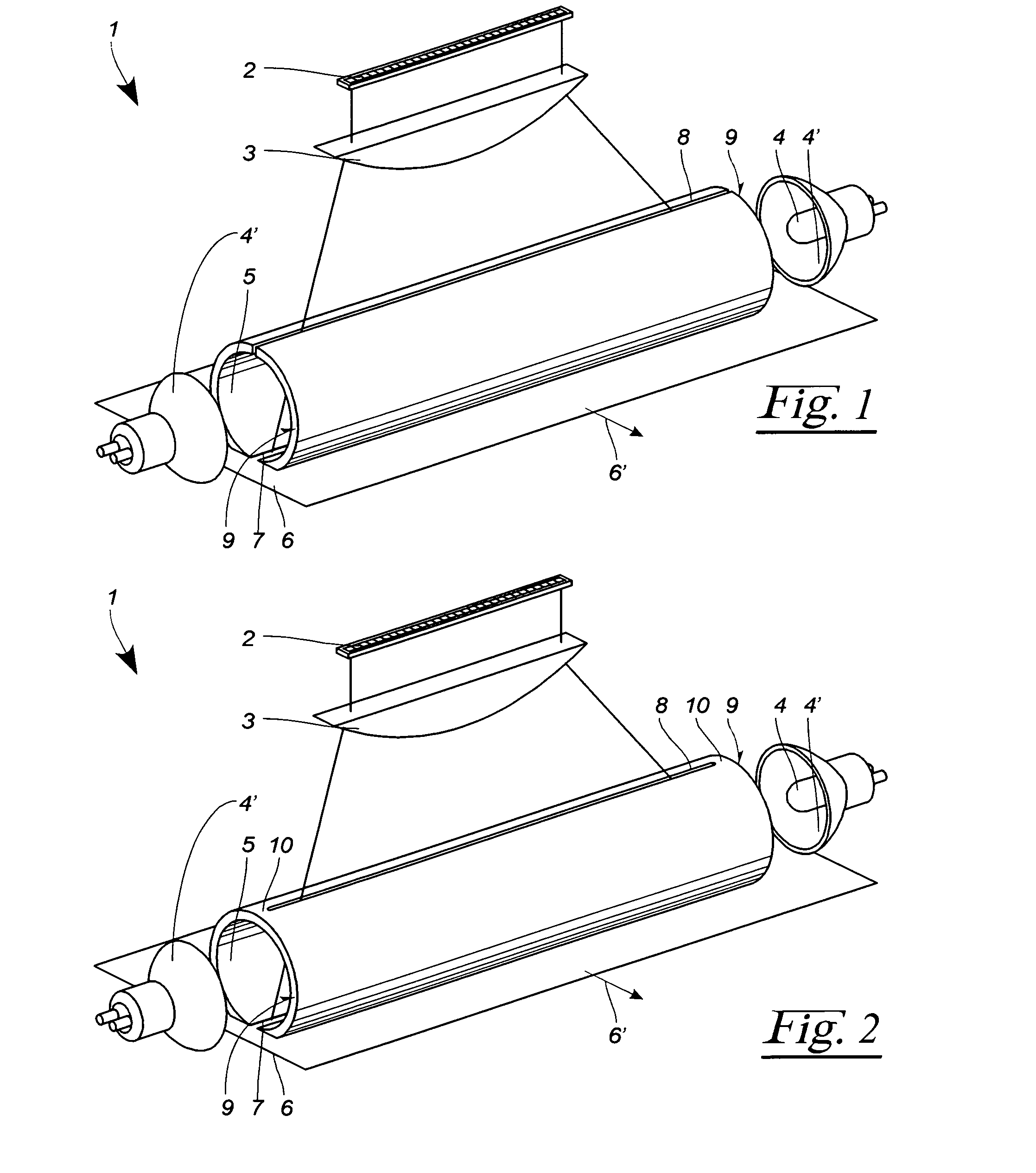

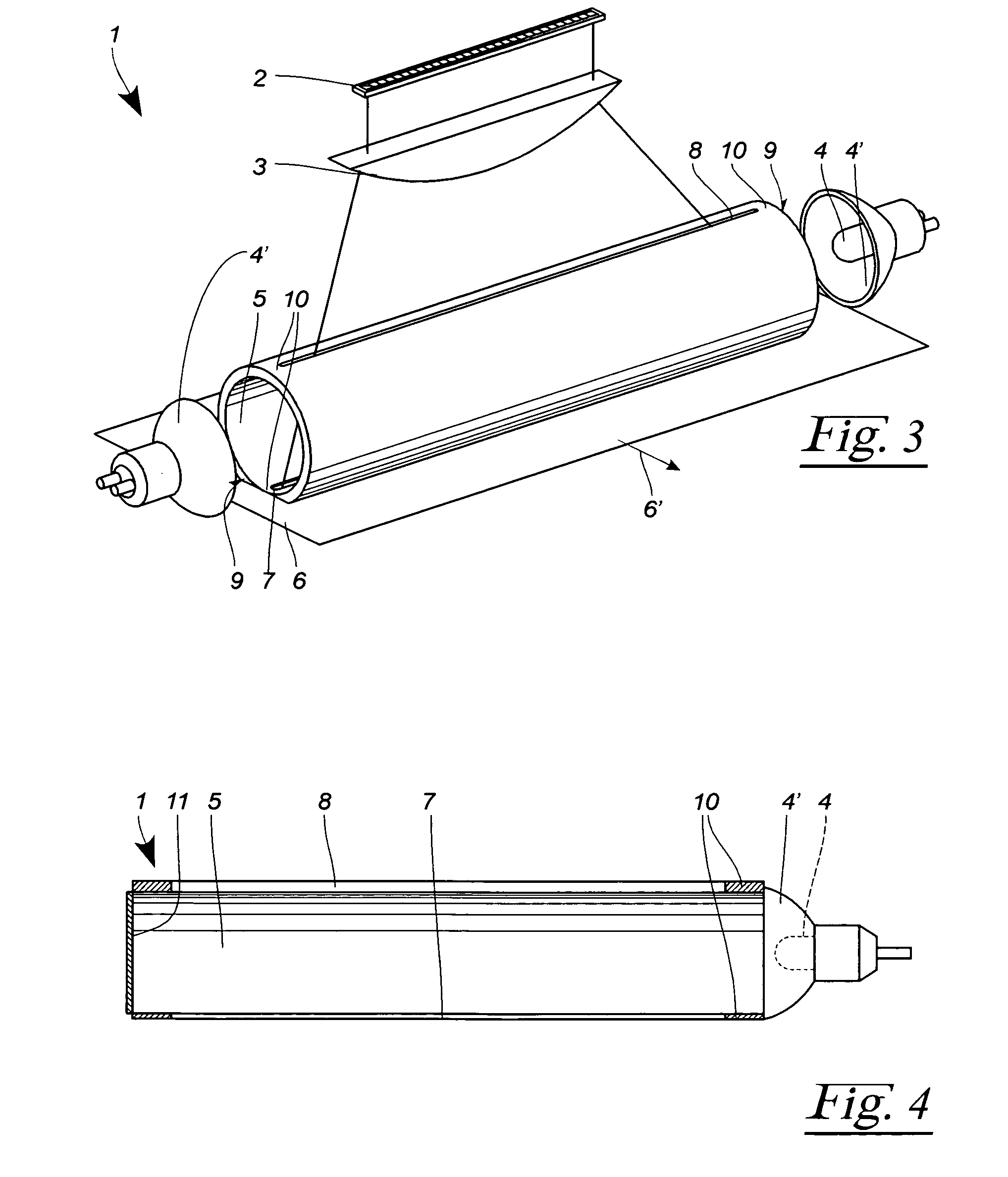

Apparatus for linear illumination of a moving product web

ActiveUS7784975B2High possible luminanceIncrease brightnessPoint-like light sourcePortable electric lightingOptoelectronicsHigh luminance

An apparatus (1) serves for linear illumination of a moving product web (6), the apparatus (1) having at least one light source (4) emitting light. In order to achieve high luminance in a linear subregion of the product web (6), at least a portion of the light emitted by the light source (4) is reflected towards the product web (6) by at least one tubular reflector (5). The tubular reflector (5) in this case has at least one light exit slit (7) which is assigned to the product web (6). Moreover, the tubular reflector has at least one observation slit (8) which lies opposite the light exit slit (7). The illuminated product web (6) can be observed through this observation slit (8) by means of a line camera (2).

Owner:ADVANCED VISION TECH

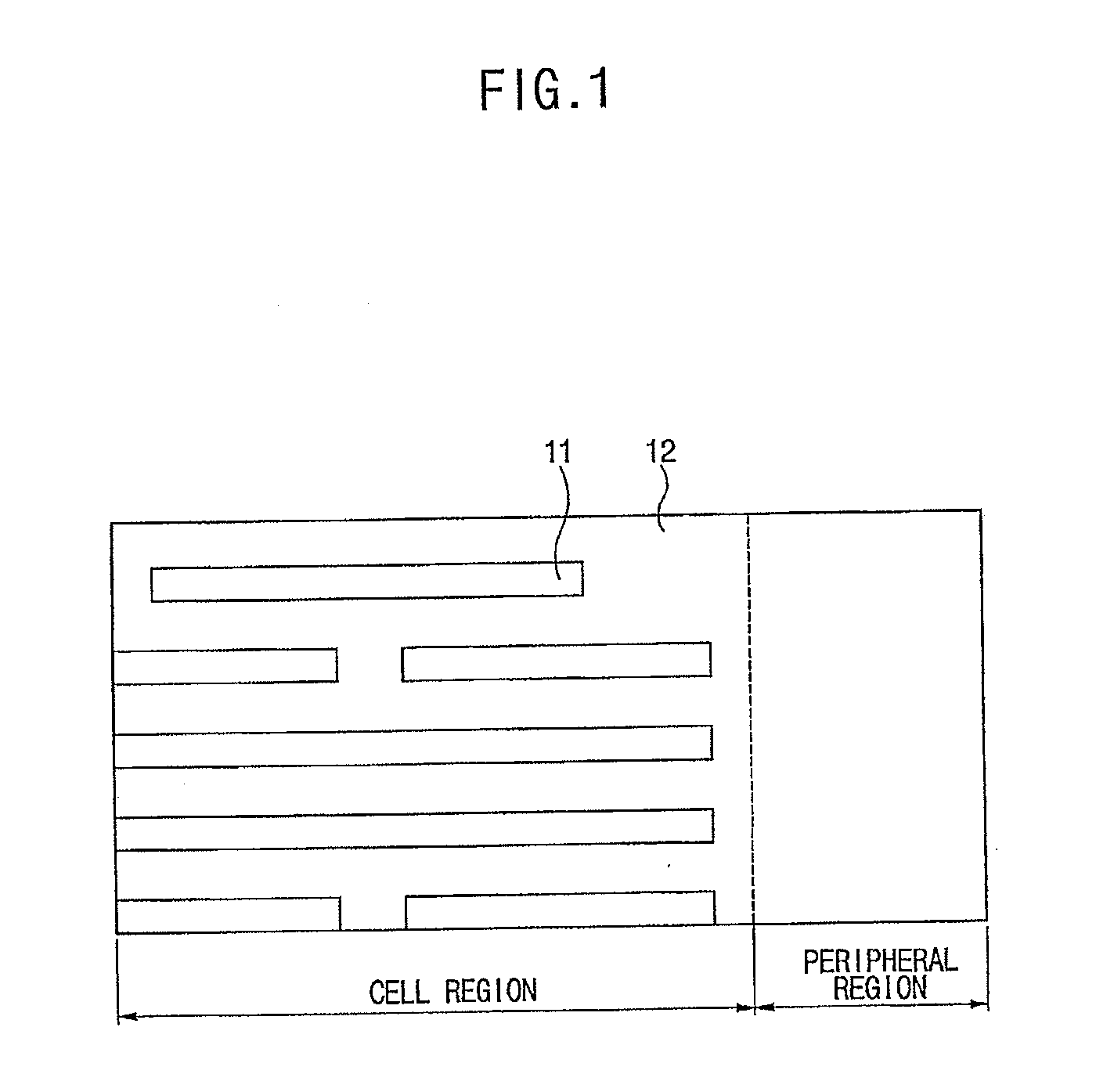

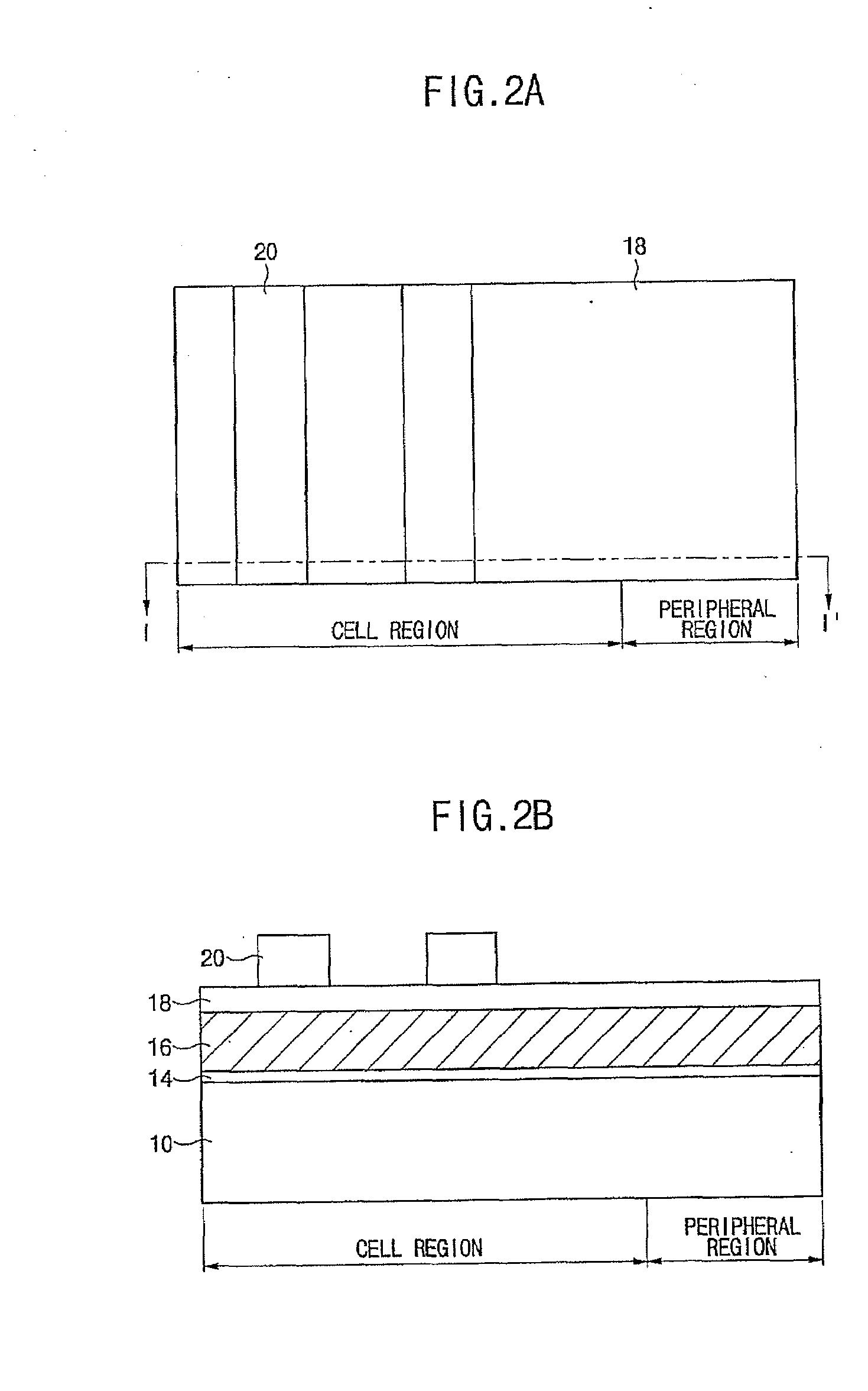

Method of forming a pattern in a semiconductor device and method of forming a gate using the same

ActiveUS20080261156A1Well formedDifferent line widthSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusDevice materialCell region

A method of forming a pattern in a semiconductor device is described. A substrate divided into cell and peripheral regions is provided, and an object layer is formed on a substrate. A buffer pattern is formed on the object layer in the cell region along a first direction. A spacer is formed along a sidewall of the buffer pattern in the cell region, and a hard mask layer remains on the object layer in the peripheral region. The buffer layer is removed, and the spacer is separated along a second direction different from the first direction, thereby forming a cell hard mask pattern. A peripheral hard mask pattern is formed in the peripheral region. A minute pattern is formed using the cell and peripheral hard mask patterns in the substrate. Therefore, a line width variation or an edge line roughness due to the photolithography process is minimized.

Owner:SAMSUNG ELECTRONICS CO LTD

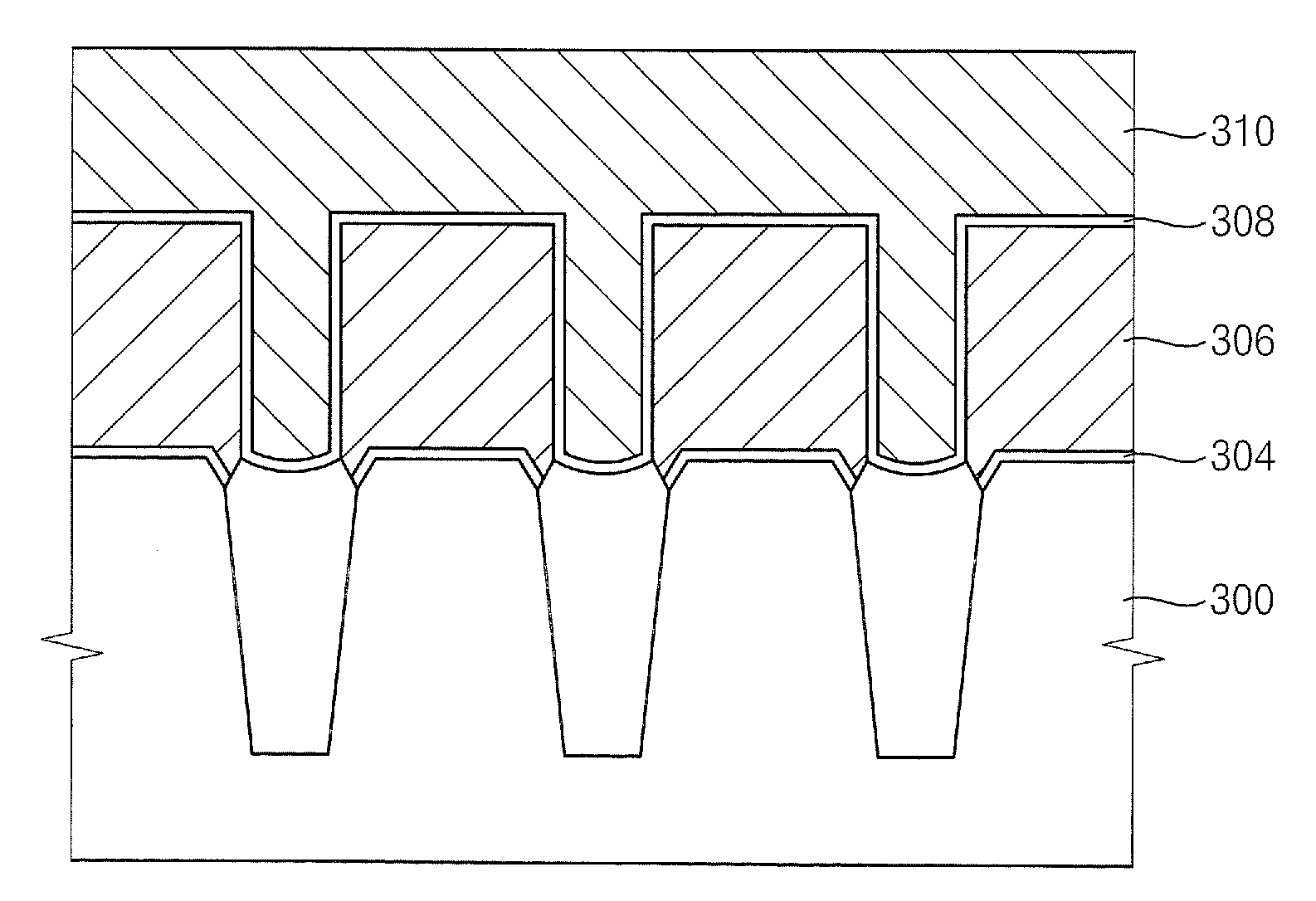

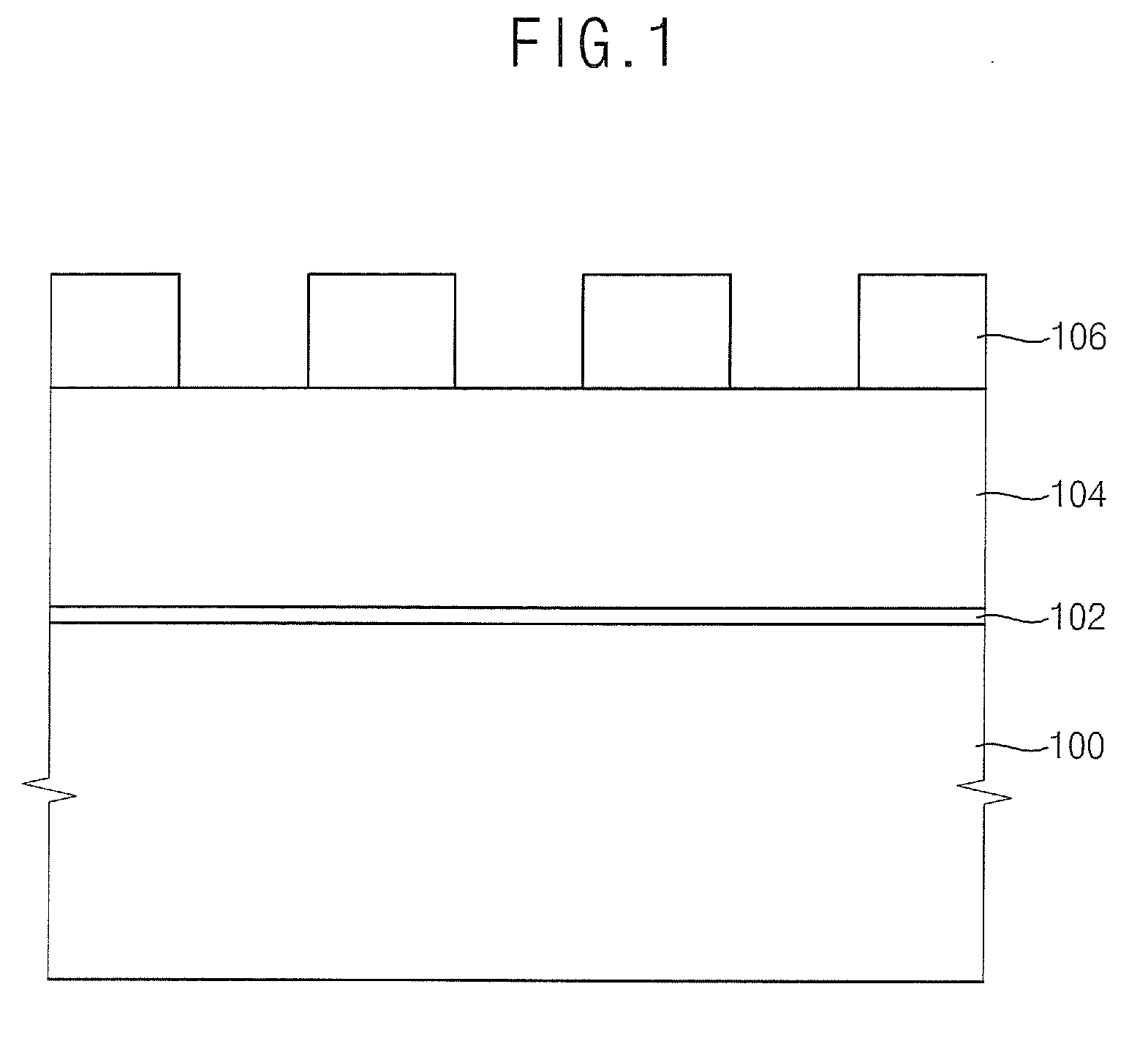

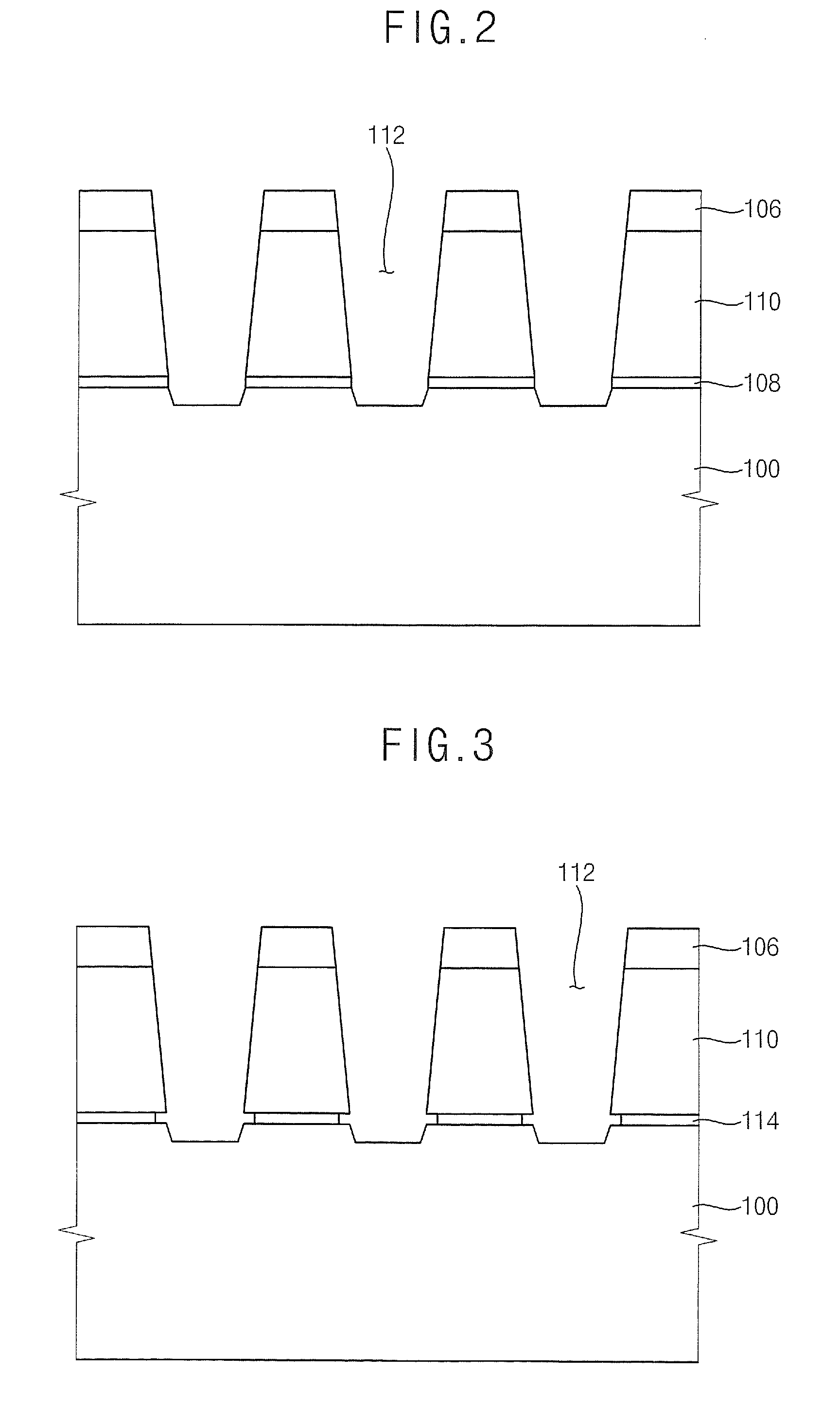

Trench Isolation Methods, Methods of Forming Gate Structures Using the Trench Isolation Methods and Methods of Fabricating Non-Volatile Memory Devices Using the Trench Isolation Methods

InactiveUS20080044981A1Small line widthSemiconductor/solid-state device manufacturingLine widthEngineering

Methods of fabricating semiconductor devices including forming a mask pattern on a semiconductor substrate are provided. The mask pattern defines a first opening that at least partially exposes the semiconductor substrate and includes a pad oxide layer and a nitride layer pattern on the pad oxide layer pattern. The nitride layer has a line width substantially larger than the pad oxide layer pattern. A second opening that is connected to the first opening is formed by at least partially removing a portion of the semiconductor substrate exposed through the first opening. The second opening has a sidewall that has a first inclination angle and at least partially exposing the semiconductor substrate. A trench connected to the second opening is formed by etching a portion of the semiconductor substrate exposed through the second opening using the mask pattern as an etch mask. The trench is substantially narrower than the second opening and has a sidewall that has a second inclination angle that is substantially larger than the first inclination angle.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of fabricating a trench capacitor having increased capacitance

InactiveUS20080142862A1Small line widthIncrease capacitanceTransistorSolid-state devicesCapacitanceElectrical conductor

The present invention pertains to a method of fabricating a trench capacitor having increased capacitance. To tackle a difficult problem of etching deeper trenches having very high aspect ratio, an epitaxial silicon growth process is employed in the fabrication of next-generation trench DRAM devices. A large-capacitance trench capacitor is first fabricated in the silicon substrate. An epitaxial silicon layer is then grown on the silicon substrate. Active areas, shallow trench isolation regions, and gate conductors are formed on / in the epitaxial silicon layer.

Owner:NAN YA TECH

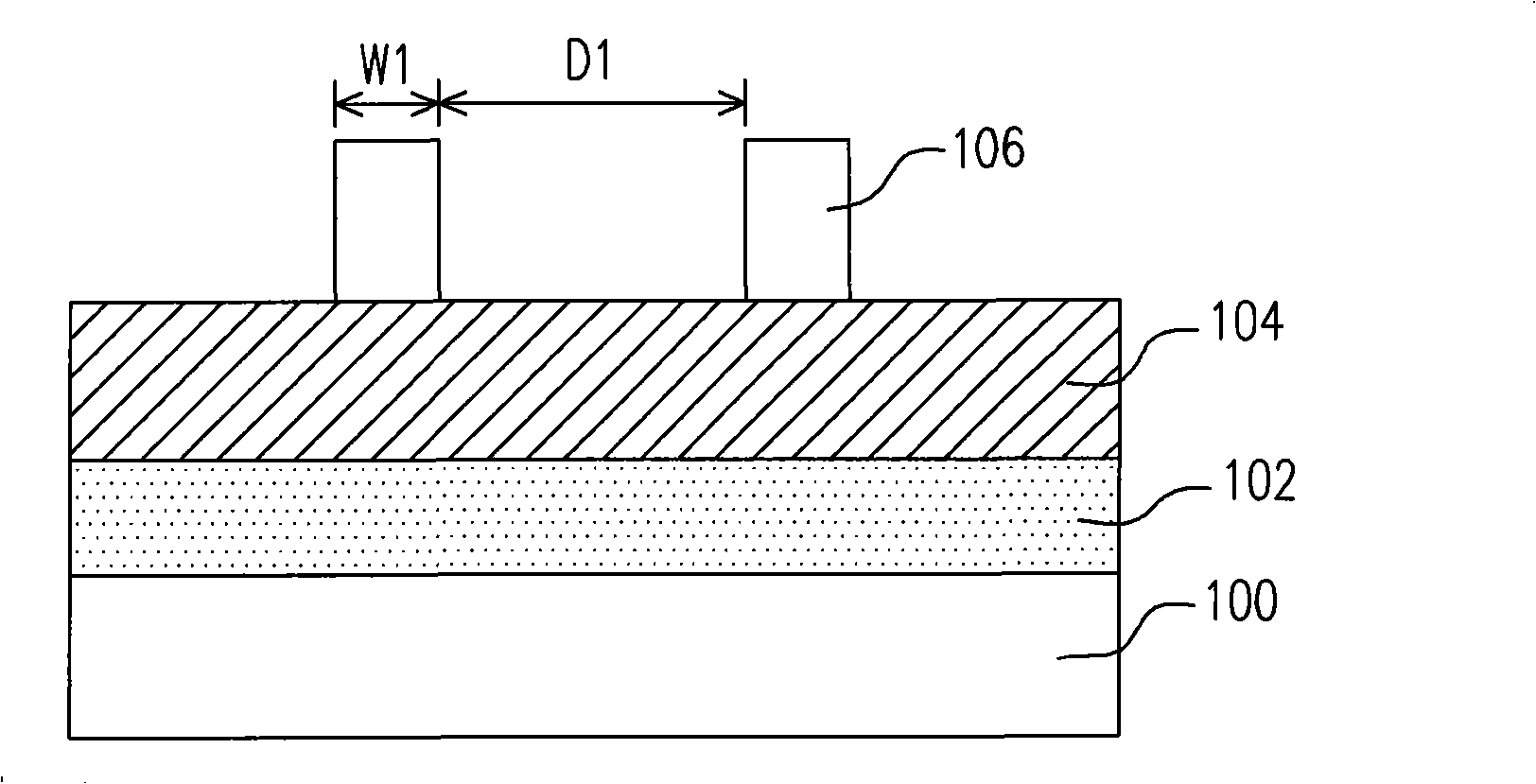

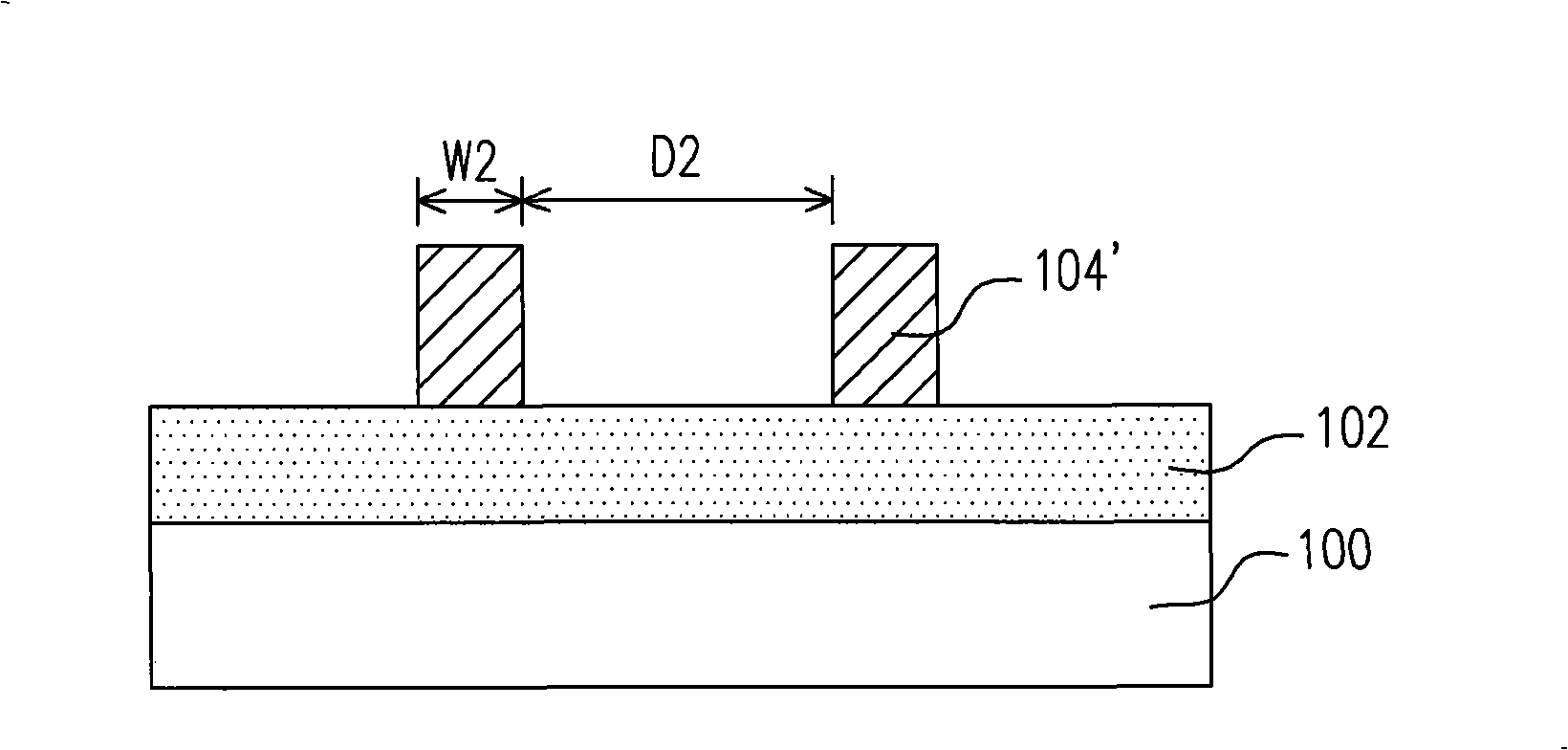

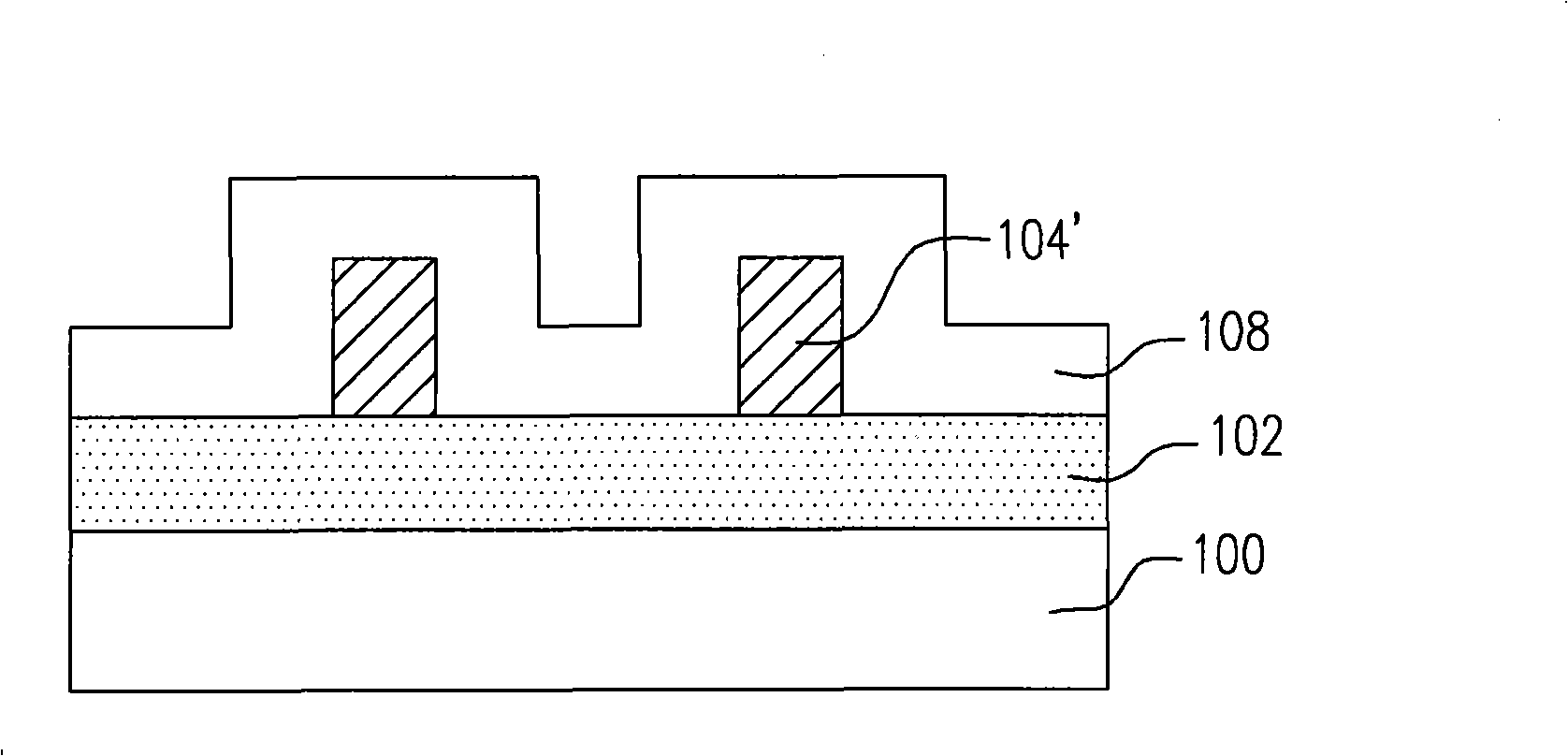

Method for forming graphic pattern

ActiveCN101345190AHighly integratedSmall line widthSemiconductor/solid-state device manufacturingBiomedical engineeringHard mask

The invention provides a forming method of a pattern, comprising the steps as follows: firstly, a material layer is provided; a patterned hard mask layer is formed on the material layer; subsequently, a clearance wall is respectively formed on the side wall of the patterned hard mask layer; subsequently, the patterned hard mask layer is removed and an opening is formed between the two adjacent clearance walls; subsequently, the clearance wall is used as the mask so as to remove a part of material layer, thus forming a patterned material layer.

Owner:MACRONIX INT CO LTD

Pixel array substrate and driving method thereof

ActiveUS20200272010A1Small line widthStatic indicating devicesSolid-state devicesActive componentEngineering

A pixel array substrate including a substrate, data lines, gate lines, pixels, and transfer lines is provided. The data lines are disposed on the substrate and arranged in a first direction. The gate lines are disposed on the substrate and arranged in a second direction interlaced with the first direction. The pixels are disposed on the substrate, each of which includes an active device electrically connected to one of the data lines and one of the gate lines and a pixel electrode electrically connected to the active device. The transfer lines are arranged in the first direction and electrically connected to the gate lines, respectively. The pixels include first pixels. In a top view of the pixel array substrate, at least one of the pixel electrodes of the first pixels is partially overlapped with one of the transfer lines. A driving method of a pixel array substrate is also provided.

Owner:AU OPTRONICS CORP

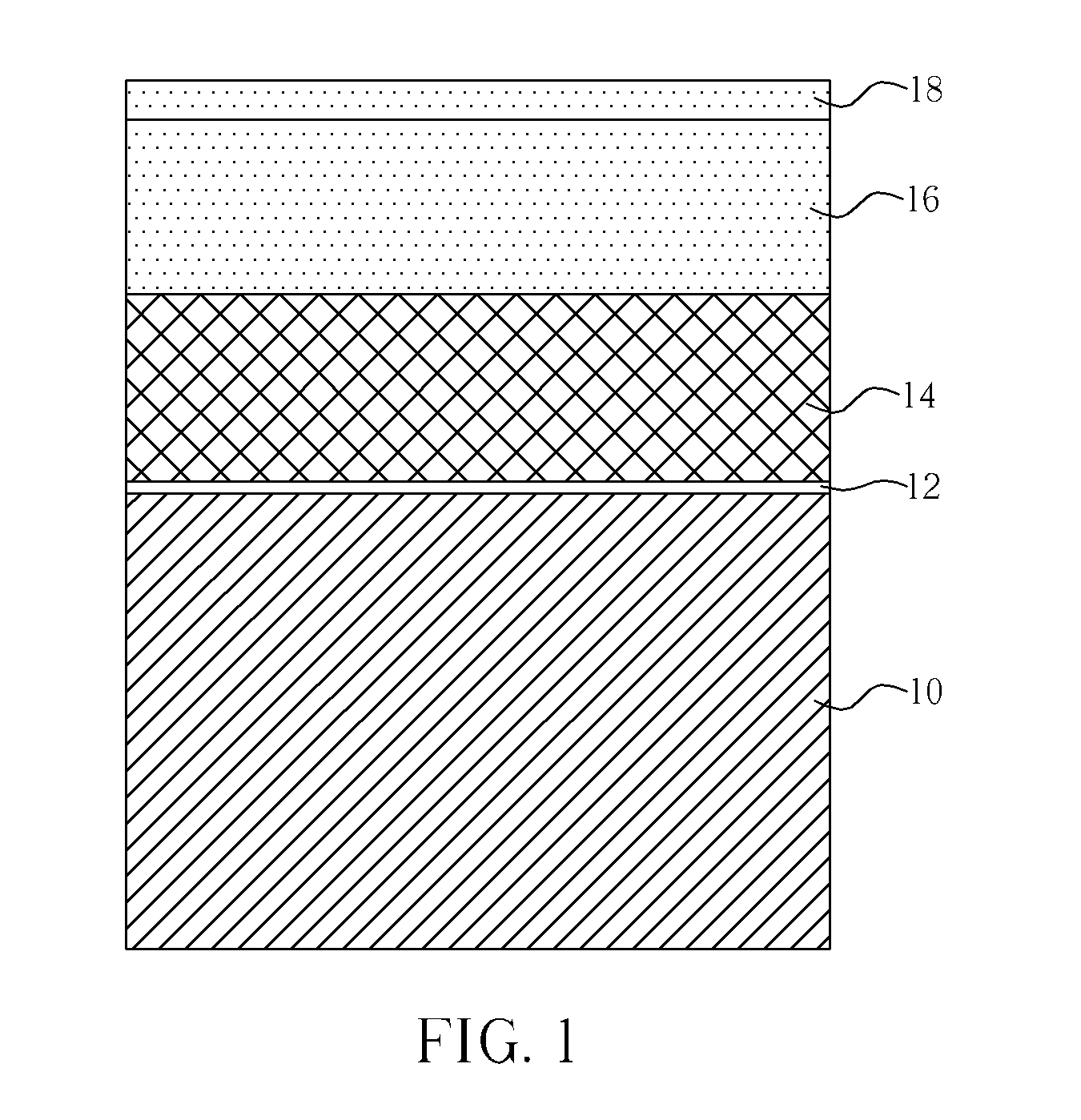

Atomic layer deposition method and semiconductor device formed by the same

ActiveUS8273639B2Reduce flow rateHigh densitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingAtomic layer depositionSemiconductor

Disclosed are atomic layer deposition method and a semiconductor device including the atomic layer, including the steps: placing a semiconductor substrate in an atomic layer deposition chamber; feeding a first precursor gas to the semiconductor substrate within the chamber to form a first discrete monolayer on the semiconductor substrate; feeding an inert purge gas to the semiconductor substrate within the chamber to remove the first precursor gas which has not formed the first discrete monolayer on the semiconductor substrate; feeding a second precursor gas to the chamber to react with the first precursor gas which has formed the first discrete monolayer, forming a discrete atomic size islands; and feeding an inert purge gas to the semiconductor substrate within the chamber to remove the second precursor gas which has not reacted with the first precursor gas and byproducts produced by the reaction between the first and the second precursor gases.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Chemically-amplified positive resist composition and patterning process thereof

ActiveUS8202677B2Improve responseReduced responsePhotosensitive materialsRadiation applicationsResistLithographic artist

There is disclosed a chemically-amplified positive resist composition comprising, as main components, (A) a base polymer, which contains one or more kinds of a monomer unit represented by the following general formula (1) and the like, and is an alkali-insoluble polymer whose hydroxyl group is partly protected by an acetal group while alkali-soluble when deprotected by an acid catalyst, (B) a sulfonium salt containing a sulfonate anion, (C) a basic component, and (D) an organic solvent. In a lithography technology by a photo resist, an extremely high temporal stability is necessary. In addition, it must give a good pattern profile not dependent on a substrate and have a high resolution power. There can be provided a chemically-amplified positive resist composition which can solve these problems simultaneously, a resist patterning process using the same, and a method for producing a photo mask blank.

Owner:SHIN ETSU CHEM CO LTD

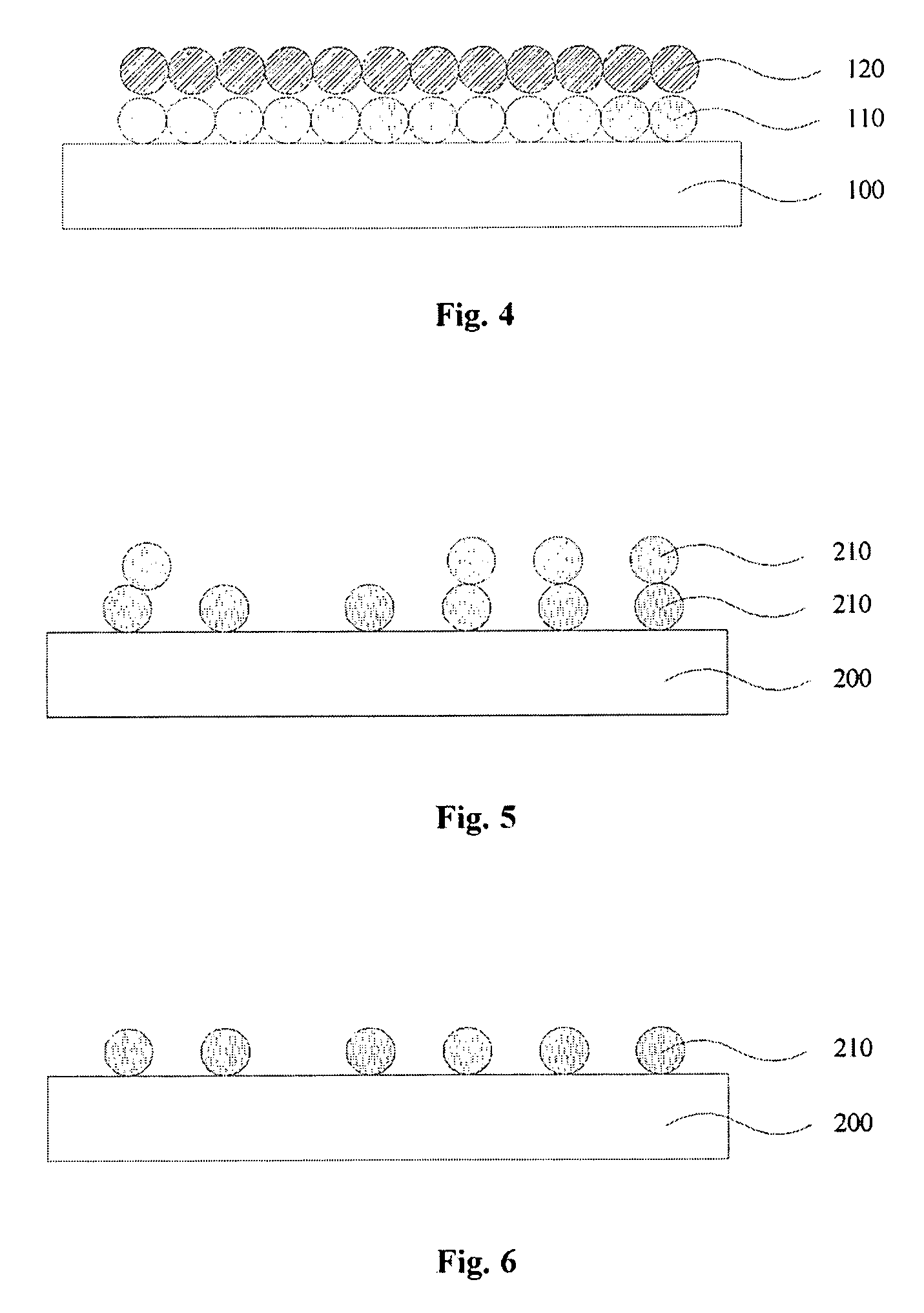

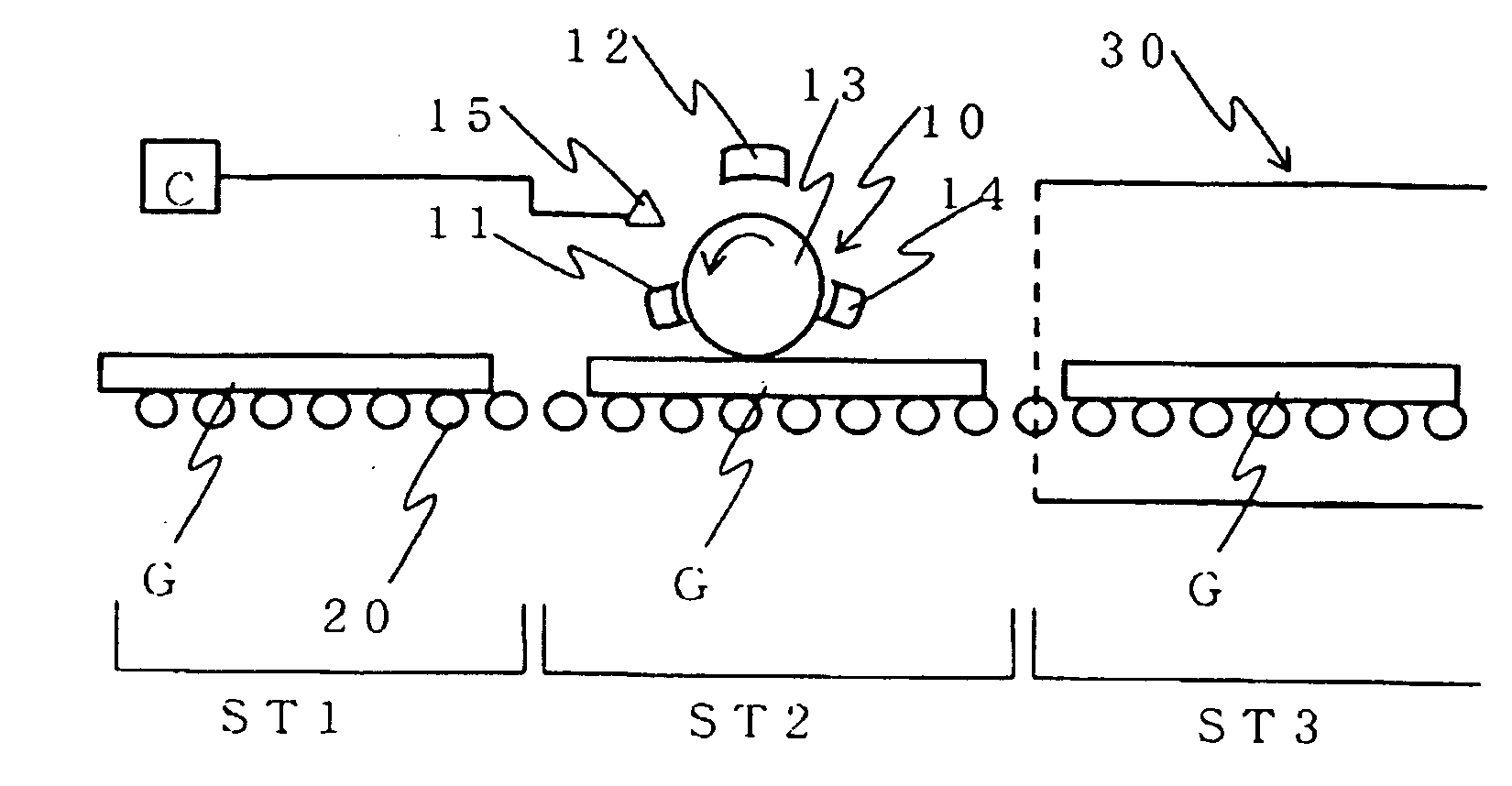

Method for producing a glass plate with a conductive printed wire and glass plate with a conductive printed wire

InactiveUS20090095512A1Improve adhesionImprove electrical performanceWindowsConductive layers on insulating-supportsSurface roughnessGlass sheet

Provided is a process for producing a glass plate with a conductive printed wire, which does not require a screen plate for each model, facilitates adjustments for desired heat generation performance or antenna performance, has an excellent adhesion to a glass plate surface, and minimizes surface roughness.The process for producing a glass plate with a conductive printed wire is characterized in that a laminate comprising a layer obtained by electro printing a first conductive toner having a number standard average particle size (D50) of 10 μm<D50≦50 μm and a layer obtained by electro printing a second conductive toner having a particle size (D50) of 5 μm≦D50≦10 μm is formed on a surface of a glass plate and the glass plate is heated to fire the toners to thereby form a conductive printed wire having a predetermined pattern on the surface of the glass plate.

Owner:ASAHI GLASS CO LTD

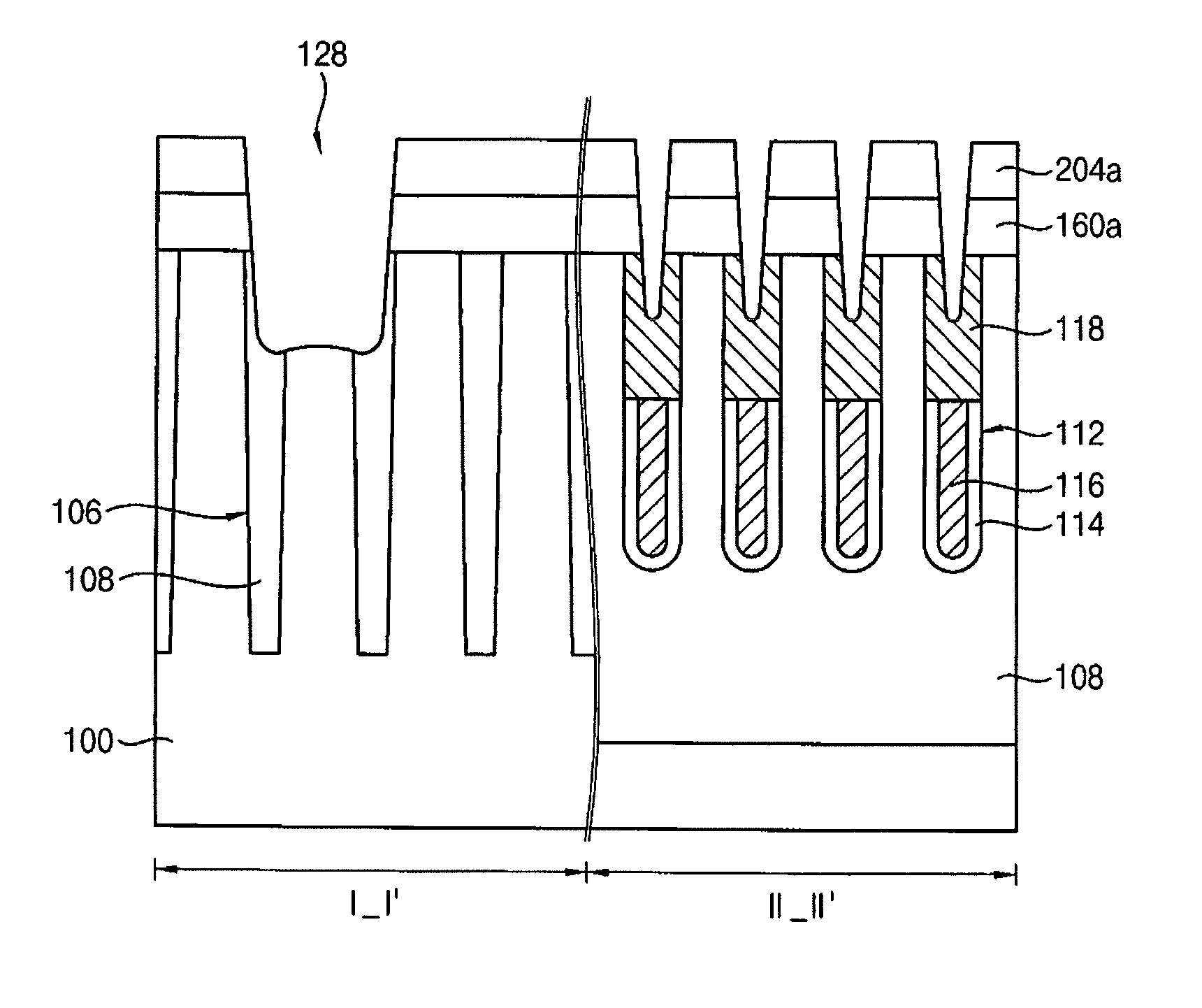

Methods for fabricating a semiconductor device

A method for fabricating a semiconductor device includes forming a device isolation layer pattern on a substrate to form an active region, the active region including a first contact forming region at a center p of the active region and second and third contact forming regions at edges of the active region, forming an insulating layer and a first conductive layer on the substrate, forming a mask pattern having an isolated shape on the first conductive layer, etching the first conductive layer and the insulating layer to expose the active region of the first contact forming region by using the mask pattern, to form an opening portion between pillar structures, forming a second conductive layer in the opening, and patterning the second conductive layer and the first preliminary conductive layer pattern to form a wiring structure contacting the first contact forming region and having an extended line shape.

Owner:SAMSUNG ELECTRONICS CO LTD

Array substrate, display panel, and display device thereof

ActiveUS10644038B2Improve display uniformityImprove the display effectStatic indicating devicesSolid-state devicesDisplay deviceComputational physics

Owner:SHANGHAI AVIC OPTOELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com