Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

160 results about "Semiconductor wafer fabrication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor wafer fabrication is defined as process for production of photonic and electrical circuits which include LEDs, RF (radio frequency) amplifiers, and, optical computer components.

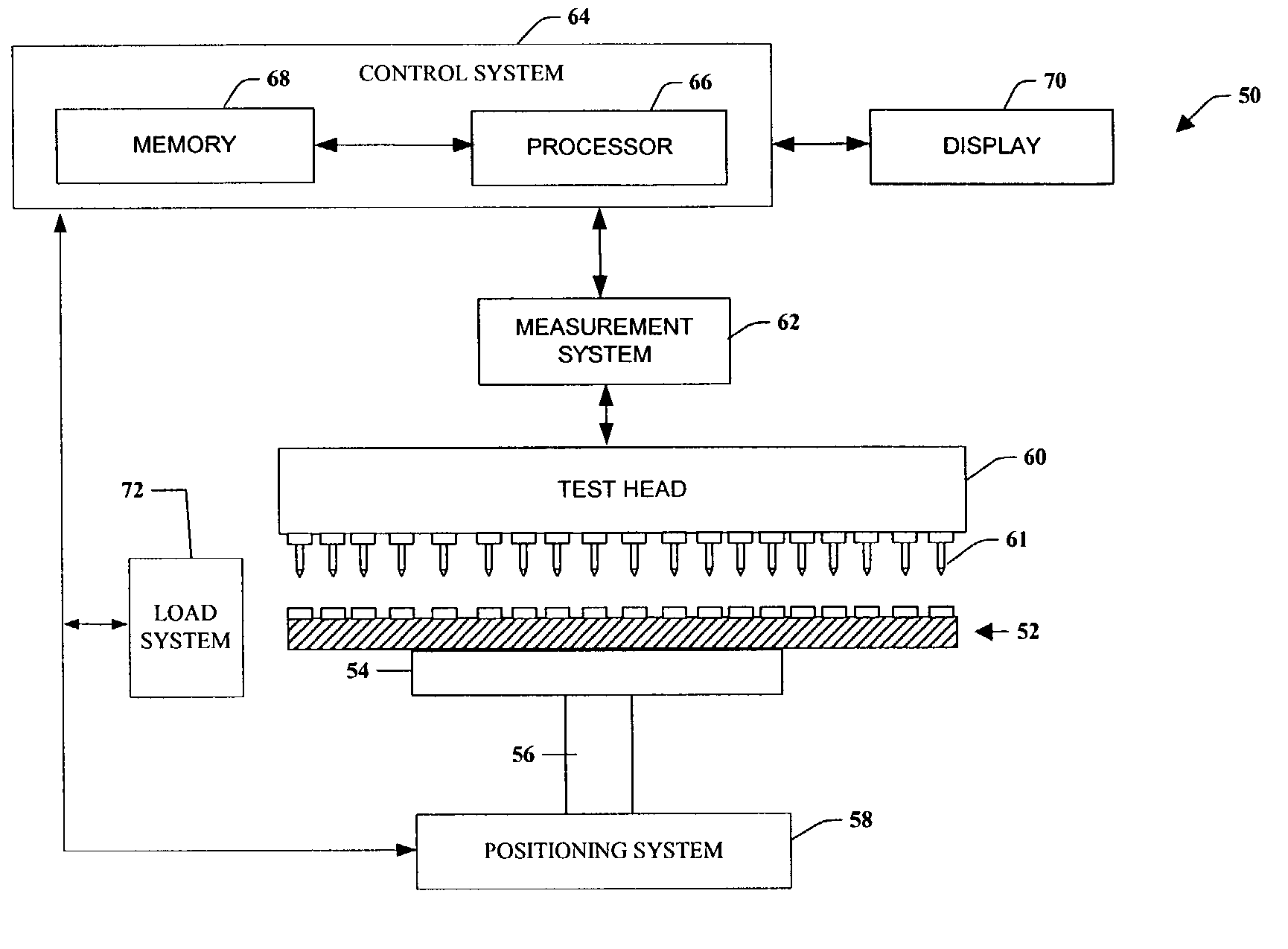

Method and system for semiconductor wafer fabrication process real-time in-situ interactive supervision

InactiveUS6363294B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingWafer fabricationEngineering

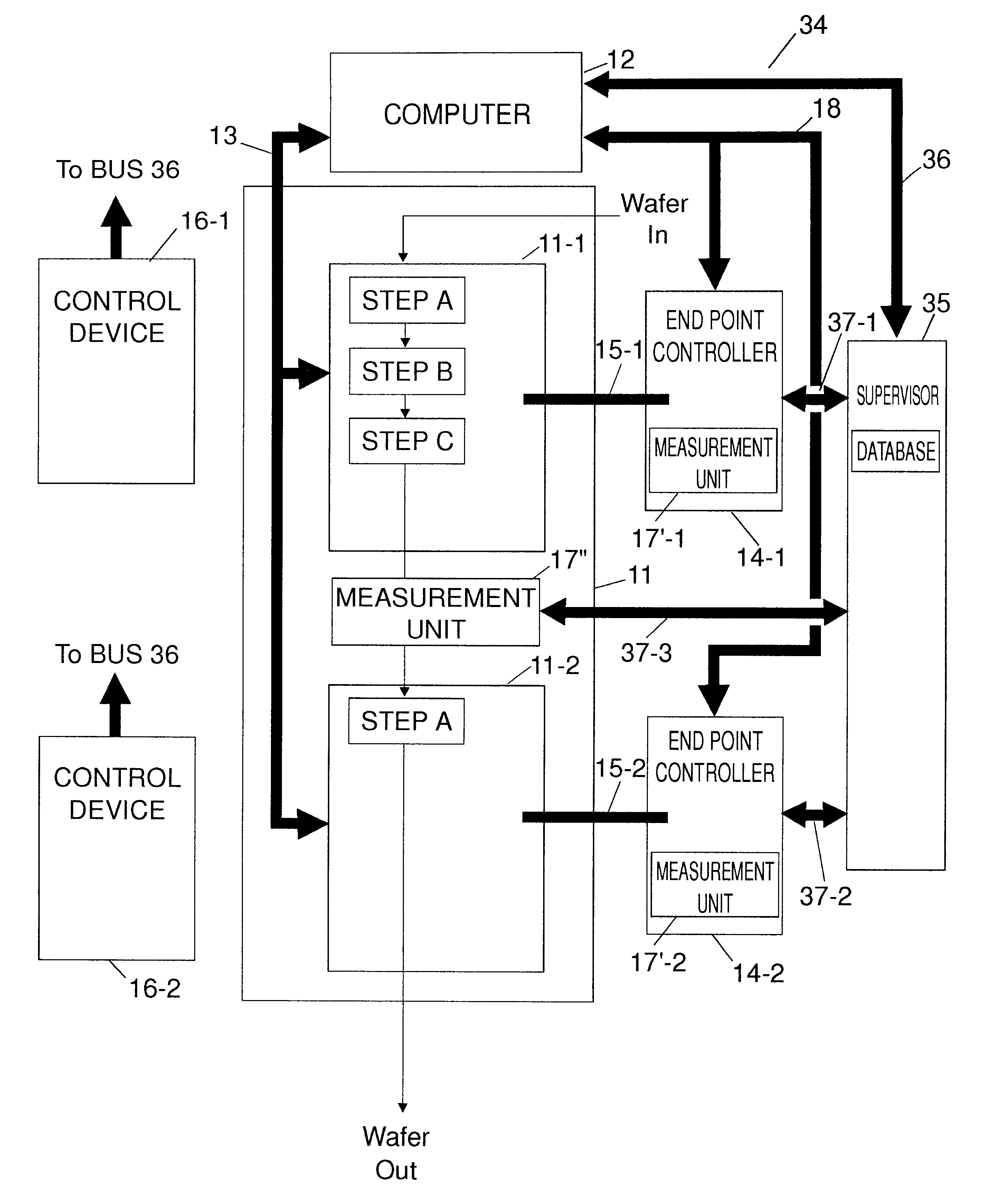

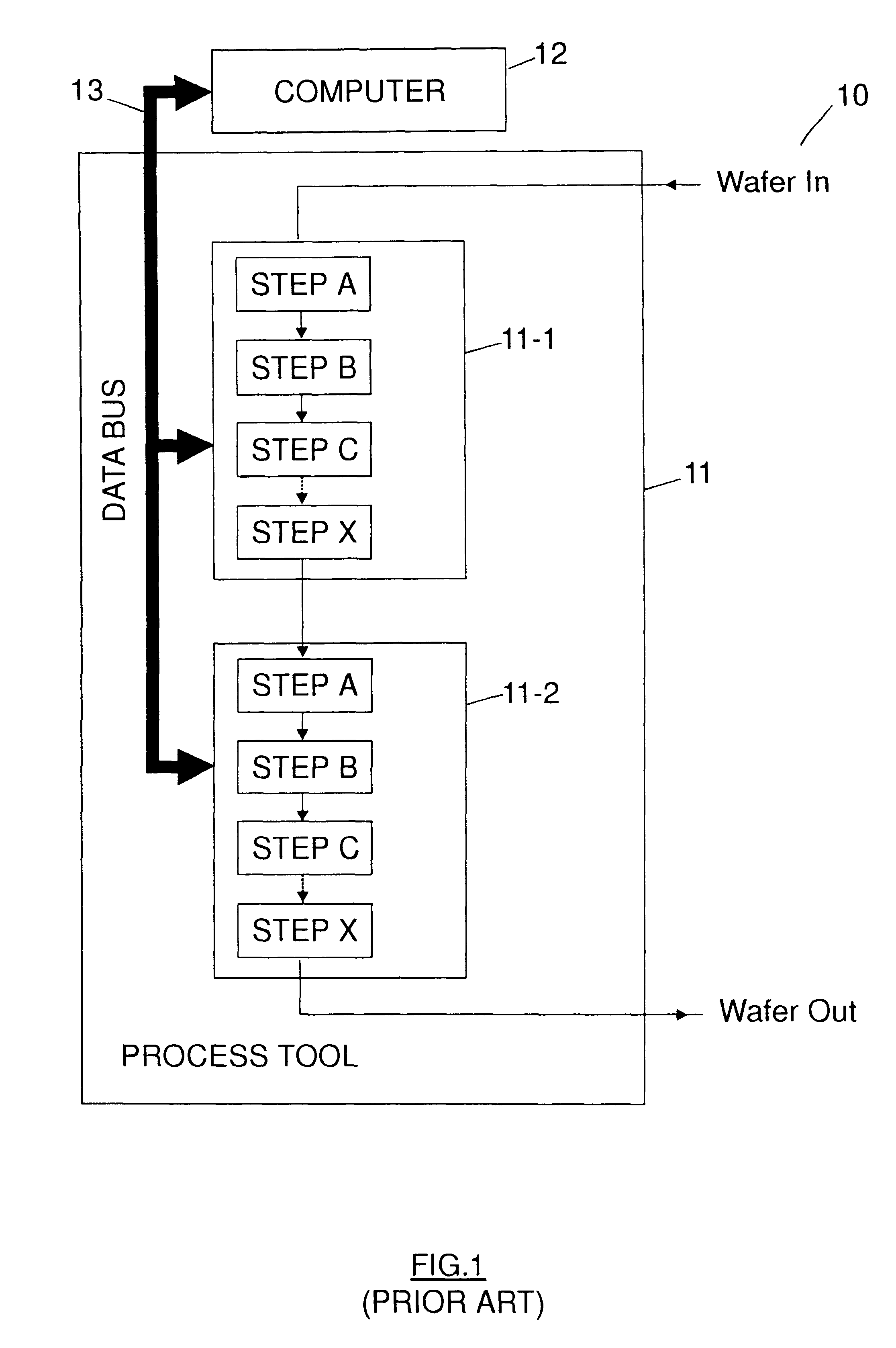

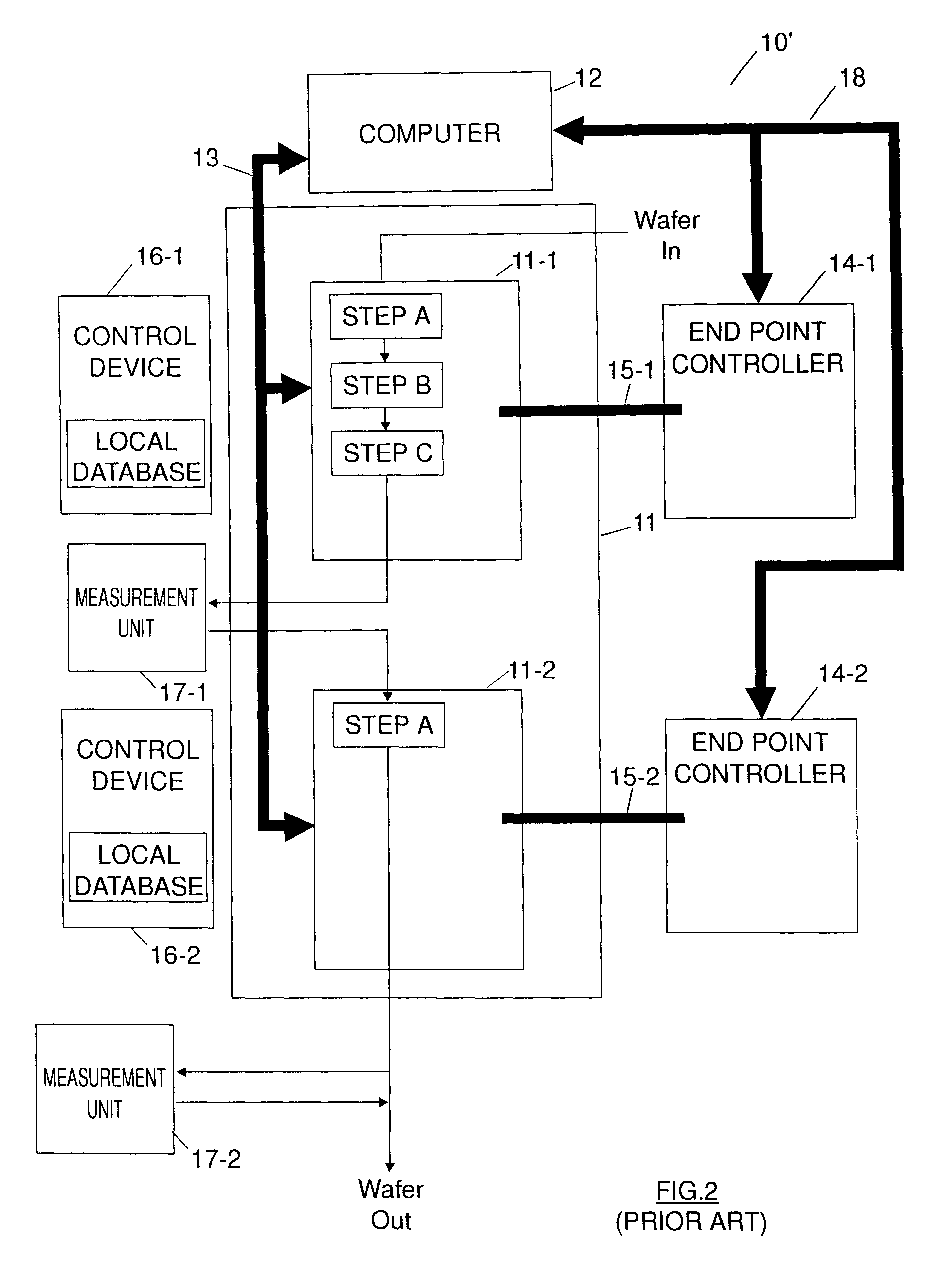

Method and system for real-time in-situ interactive supervision of a step performed in a tool during semiconductor wafer fabrication process. The system includes a tool and the computer attached thereto, an end point detection controller, a database and a supervisor to supervise the whole wafer processing for that step. The controller is used to monitor a key process parameter of the step and is adapted to perform in-situ measurements. The database contains the evolution of said process parameter in normal operating conditions and in all the identified deviations. It further contains the history of the wafer until this step and a reference to the batch and process names for this step and the wafer identification number. At the end of the step, the important process parameters and any alert code are stored in the database to up-date the wafer history. This technique allows a total clusterized wafer fabrication process and prevents wafer rejection.

Owner:IBM CORP

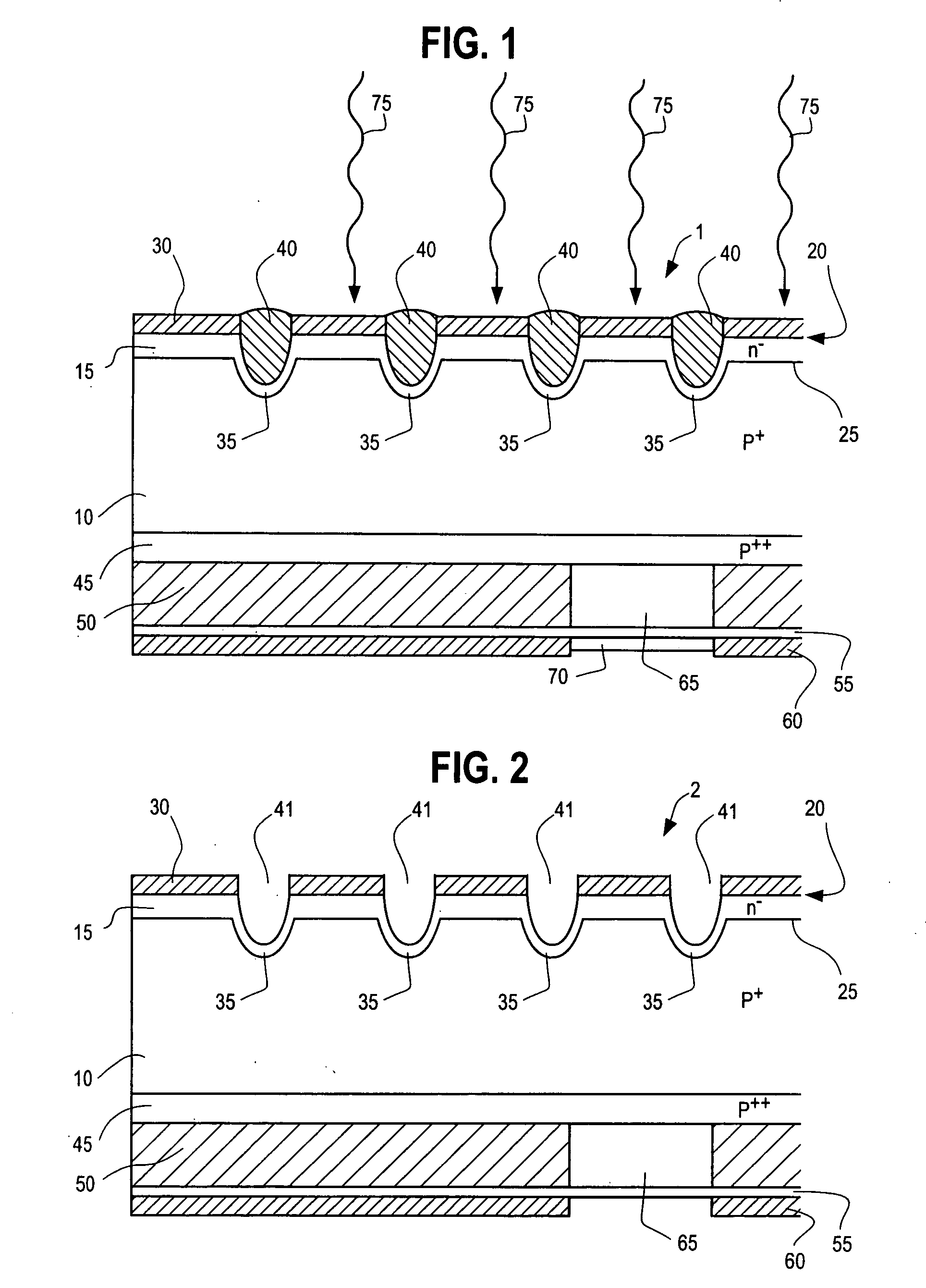

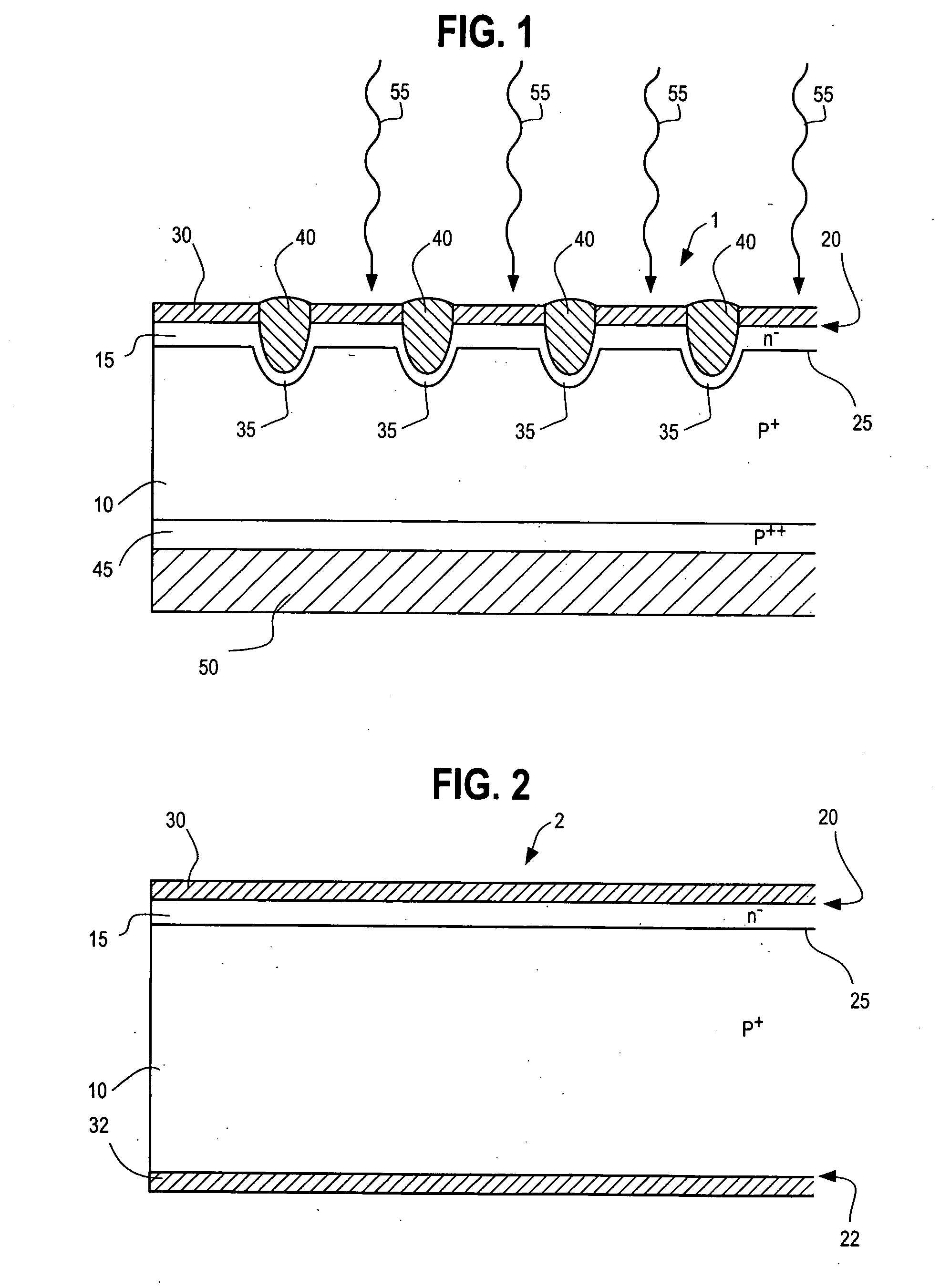

Process for manufacturing photovoltaic cells

InactiveUS20050268963A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationBack surface fieldEngineering

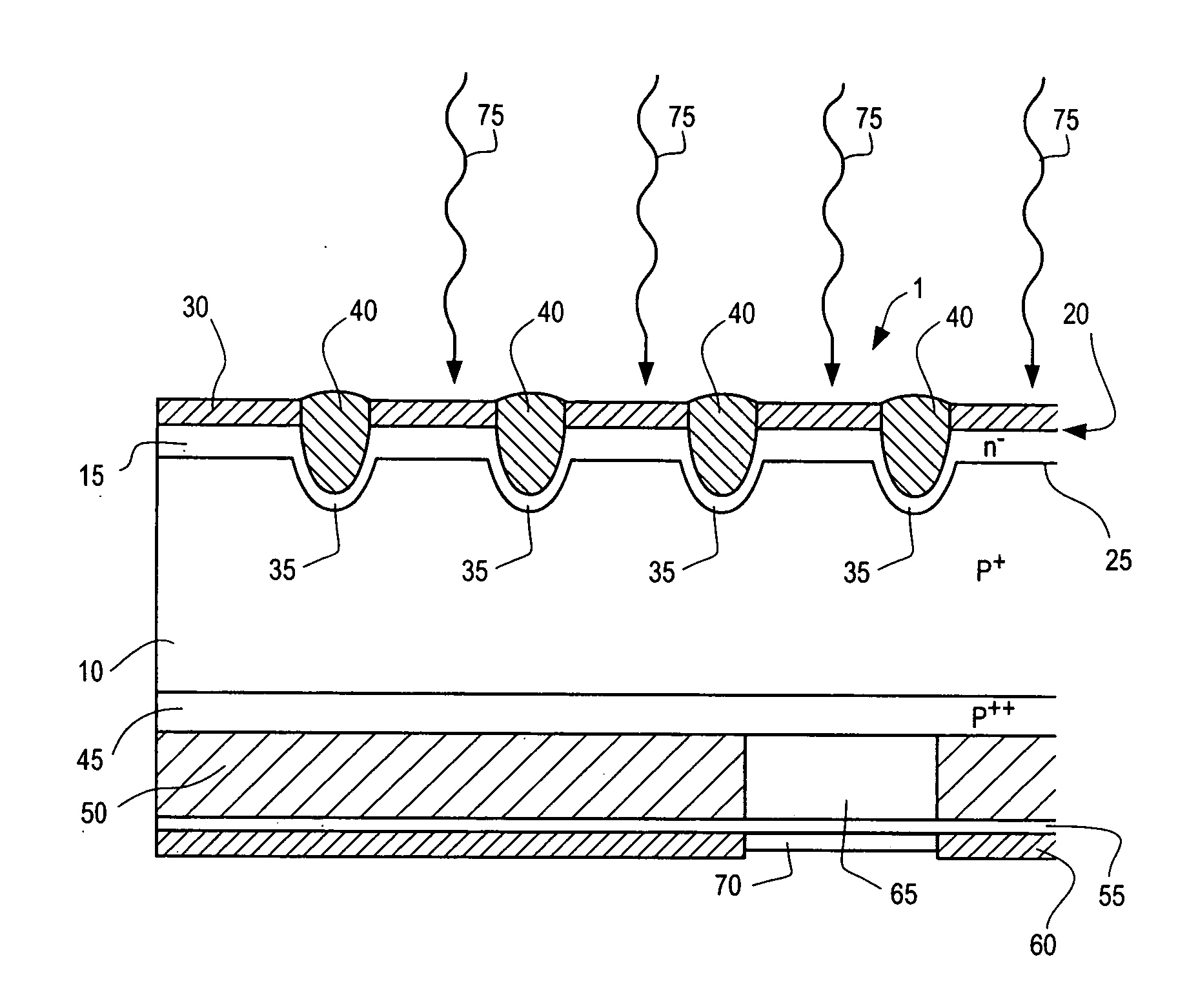

A process for making a photovoltaic cell using a semiconductor wafer doped with a first dopant, the wafer comprising a front surface and a back surface, the process comprising the steps of forming a first layer on the front surface of the wafer, the first layer comprising a second dopant of a conductivity type opposite the first dopant; depositing a surface coating on the front surface over the first layer; forming grooves in the front surface after depositing the surface coating thereon; adding a second dopant to the grooves; depositing a doping material on the back surface; treating the wafer having the doping material deposited thereon to form a back surface field, masking at least a portion of the back surface of the wafer after the treating; and adding a conductive material to the grooves to form an electrical contact.

Owner:BP CORP NORTH AMERICA INC

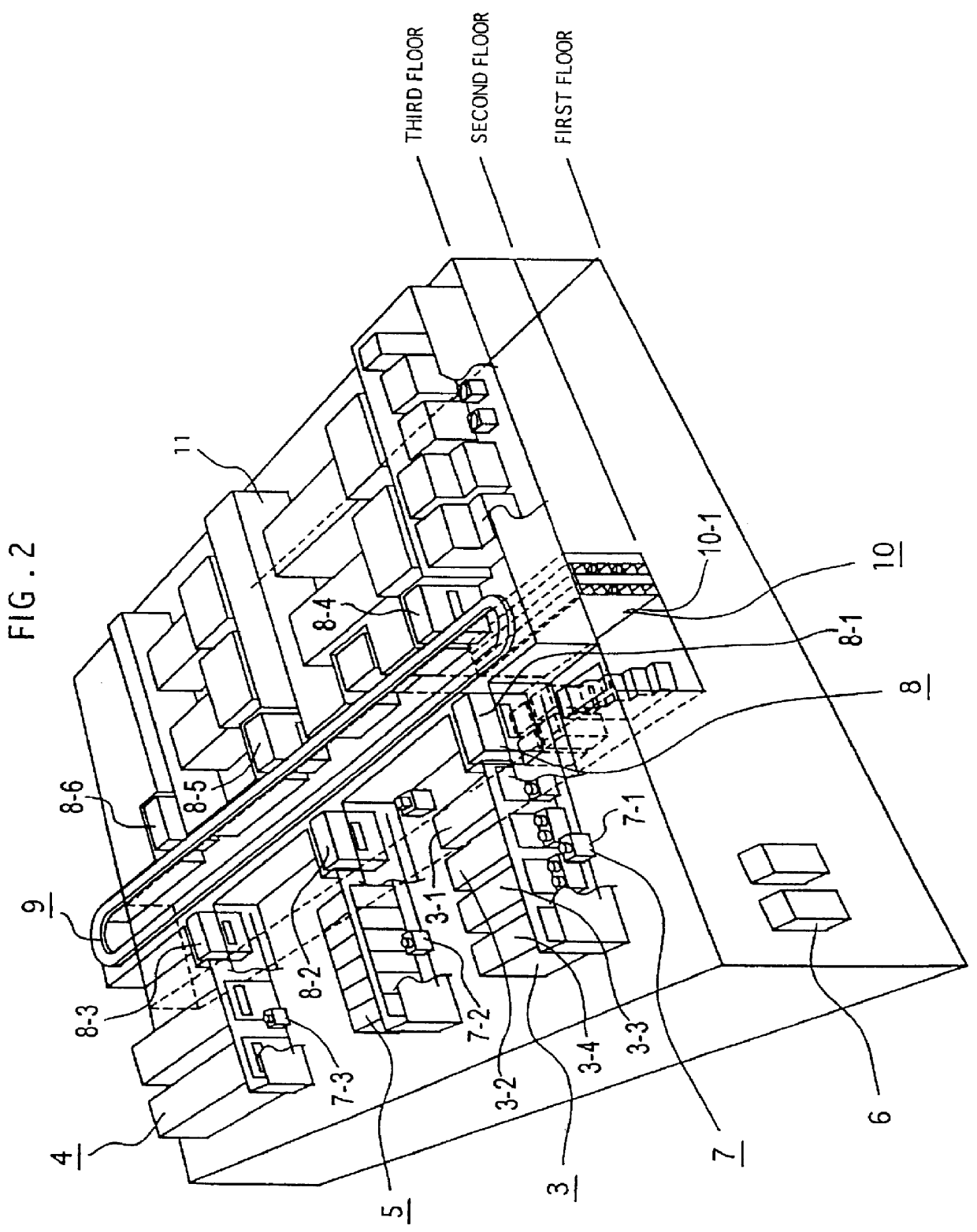

Method and apparatus for controlling semiconductor wafer fabrication equipment based on a remaining process time applicable to the processors

InactiveUS6134482ASemiconductor/solid-state device manufacturingCharge manipulationSemiconductor wafer fabricationSemiconductor

Semiconductor wafer fabrication equipment comprising a selecting device for selecting semiconductor wafers destined to a processor on the basis of a remaining process time applicable to that processor in the equipment, a transporting device for transporting the selected semiconductor wafers to the processor, another selecting device for selecting a processor or a storage device constituting a transport destination to which to transport processed semiconductor wafers, and another transporting device for transporting the semiconductor wafers to the destination processor or storage device in accordance with a transport control changeover code read from the processors and storage devices of the equipment.

Owner:MITSUBISHI ELECTRIC CORP

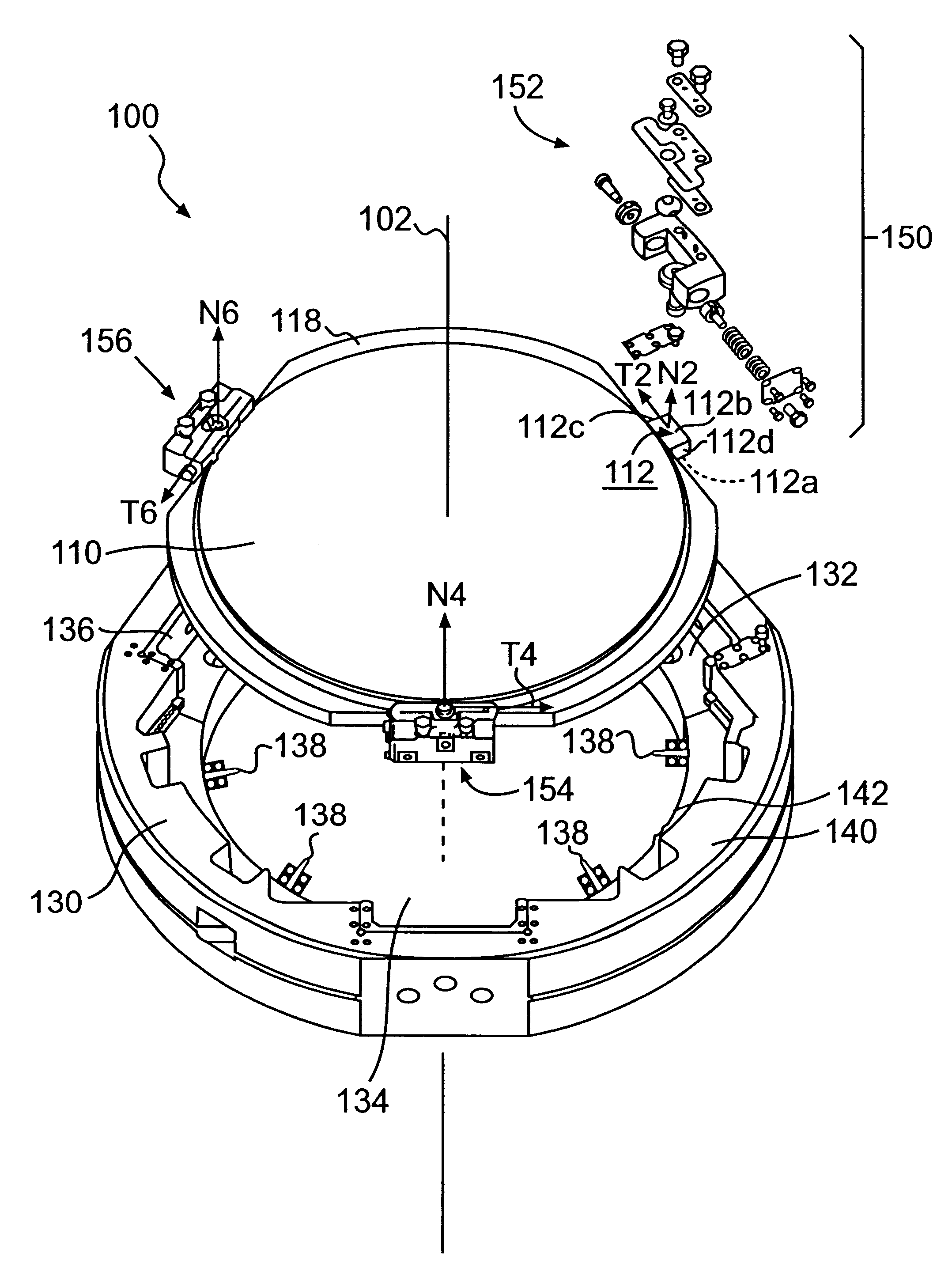

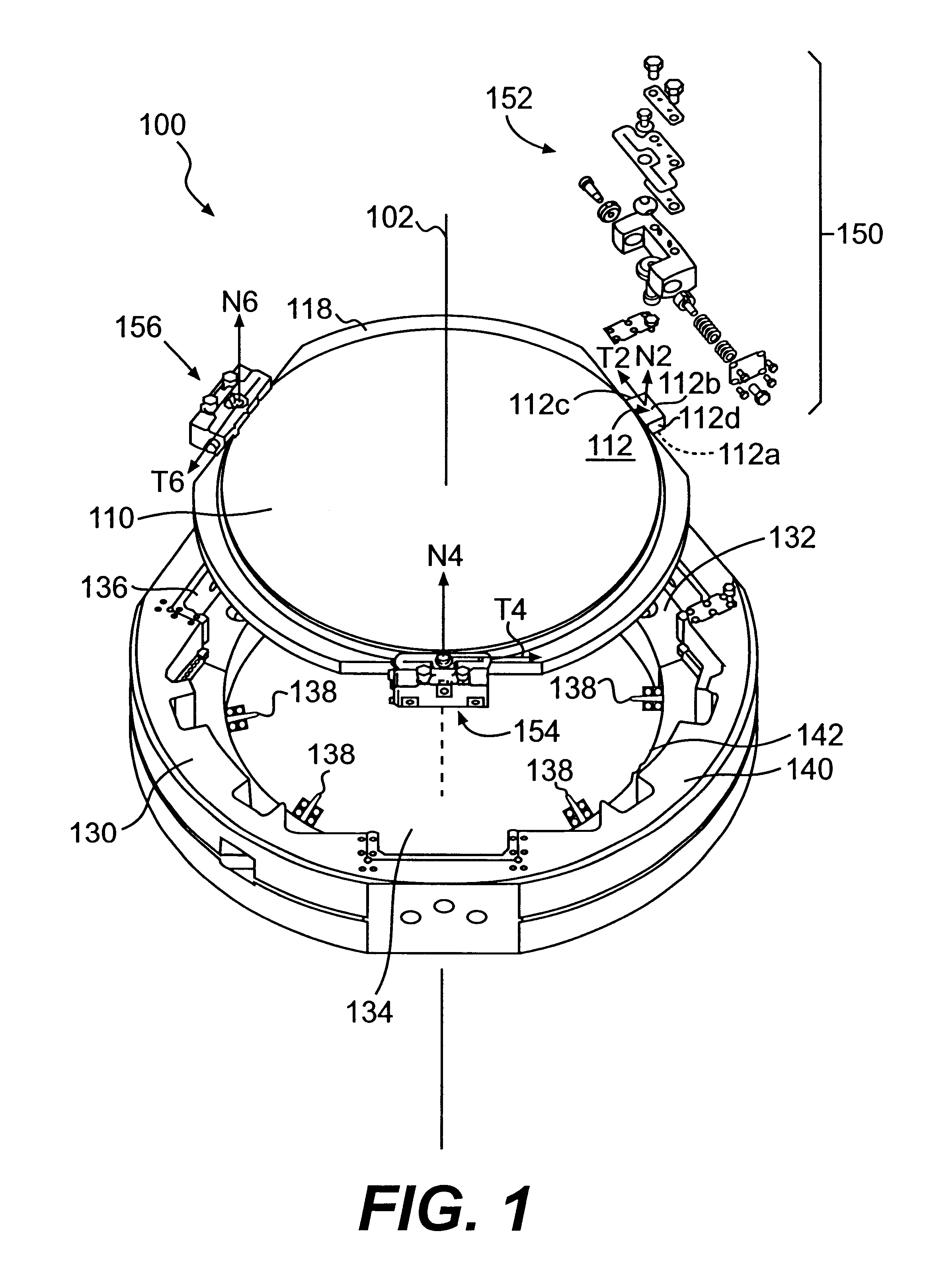

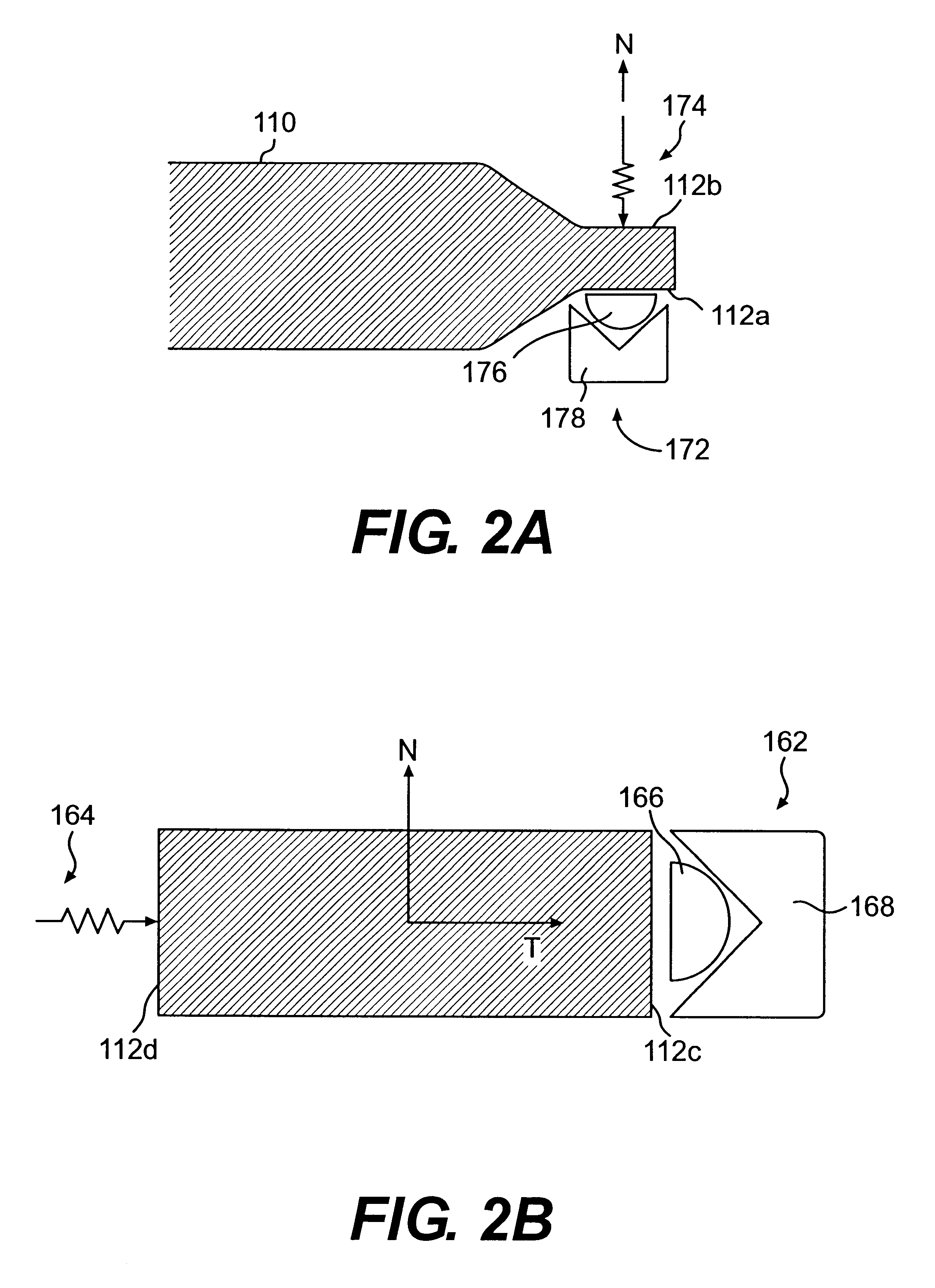

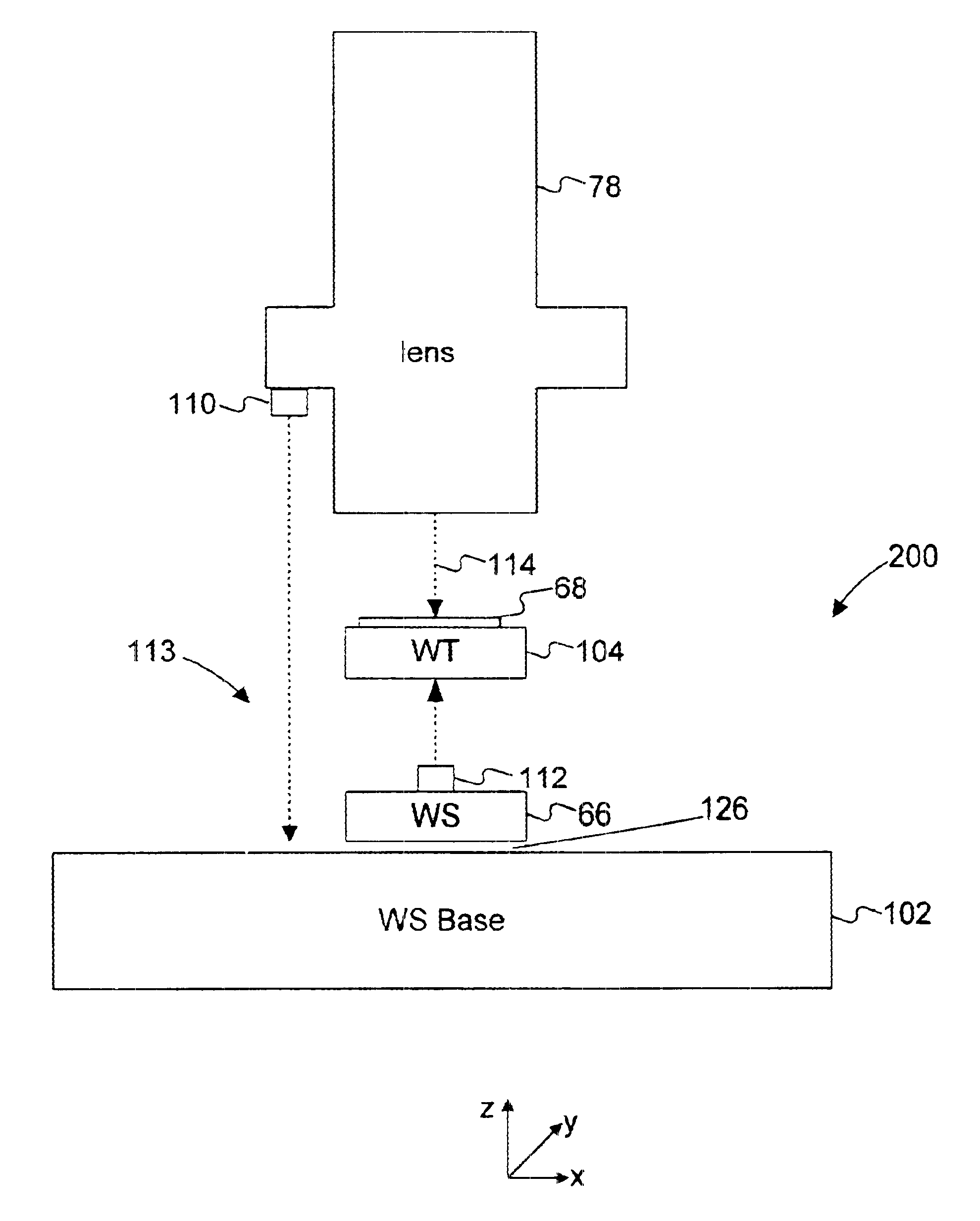

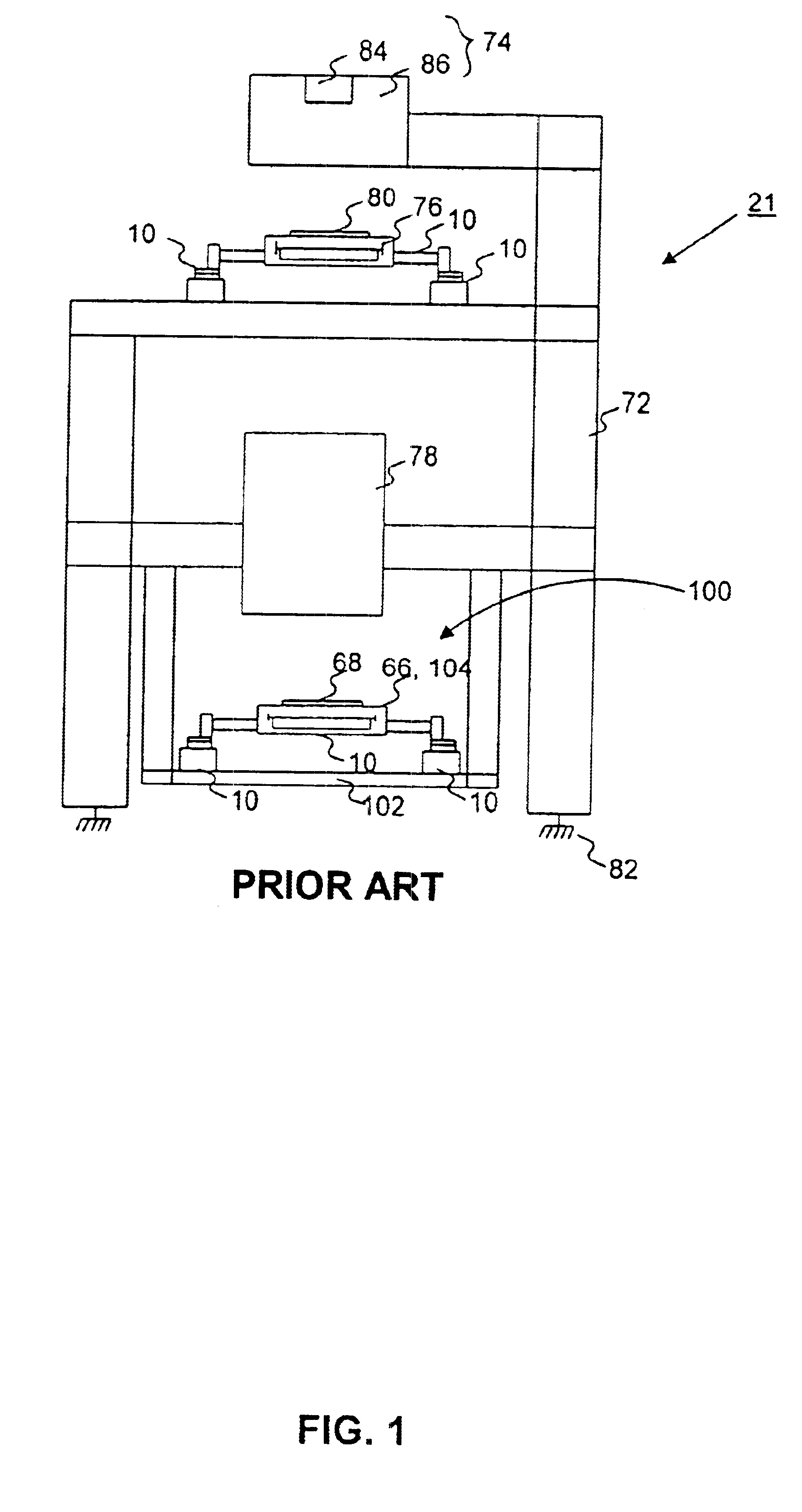

Kinematic optical mounting

InactiveUS6400516B1Semiconductor/solid-state device manufacturingPhotomechanical exposure apparatusKinematicsOptical mount

An optical mounting assembly, such as a lens cell assembly, method for making a lens cell assembly, and method for supporting a lens in the lens cell assembly are provided to kinematically mount an optical element to an optical holder. The optical mounting assembly includes an optical element having a plurality of mounting pads distributed around an outer circumference of the optical element, and an optical holder having a corresponding plurality of clamping brackets distributed around an inner circumference of the optical holder. The optical holder supports or constrains movement of the optical element at points of contact between the plurality of mounting pads and the corresponding plurality of clamping brackets both in a normal direction parallel to the optical axis of the assembly and in a tangential direction of the corresponding mounting pad. When the optical element has three mounting pads and the optical holder constrains the optical element at corresponding three clamping brackets, the optical element is constrained in six degrees of freedom, three in the normal direction and another three in the tangential direction at the corresponding mounting pads. The optical mounting assembly of this invention can be used in combination with a projection lens assembly in a semiconductor wafer manufacturing process.

Owner:NIKON CORP

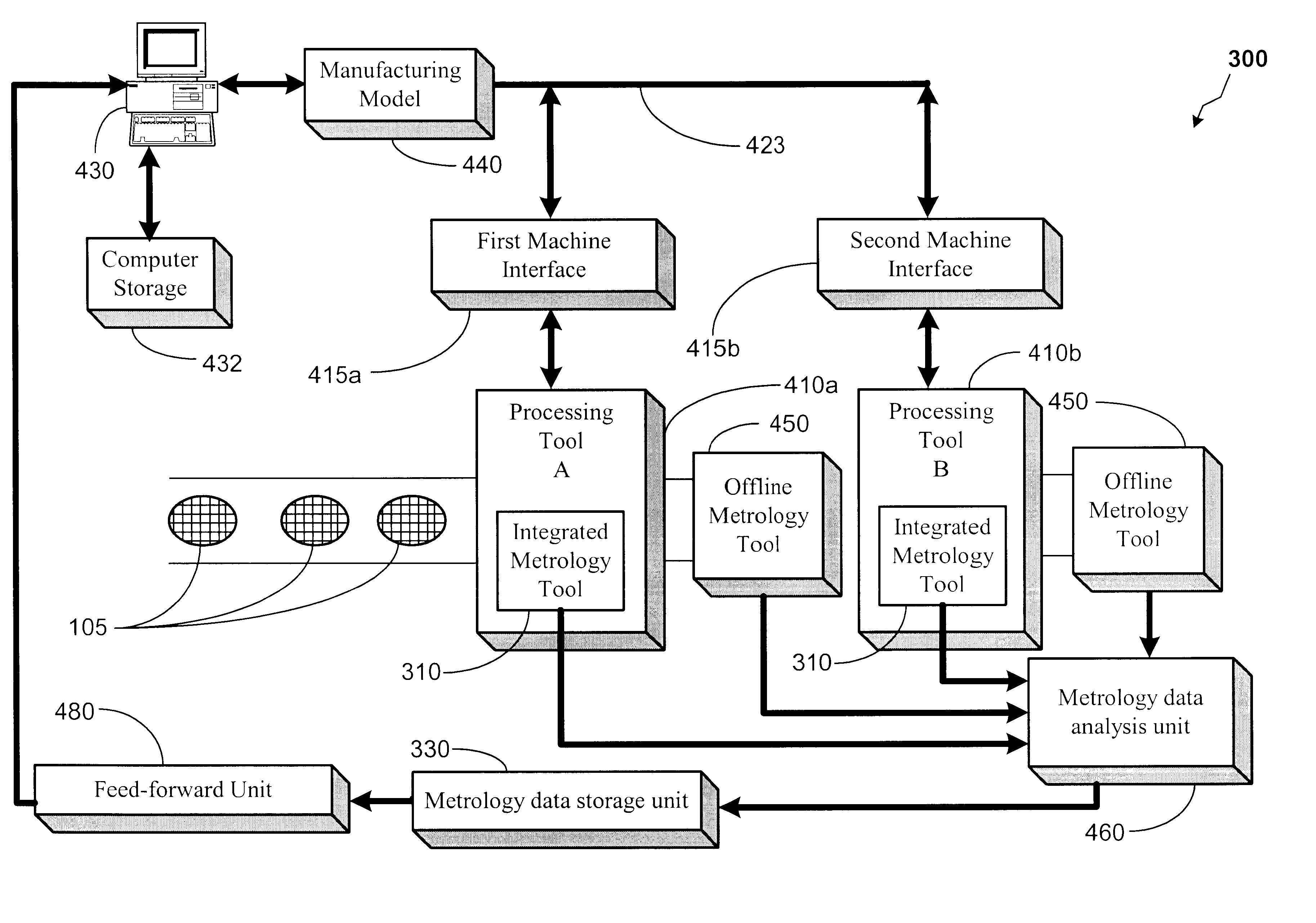

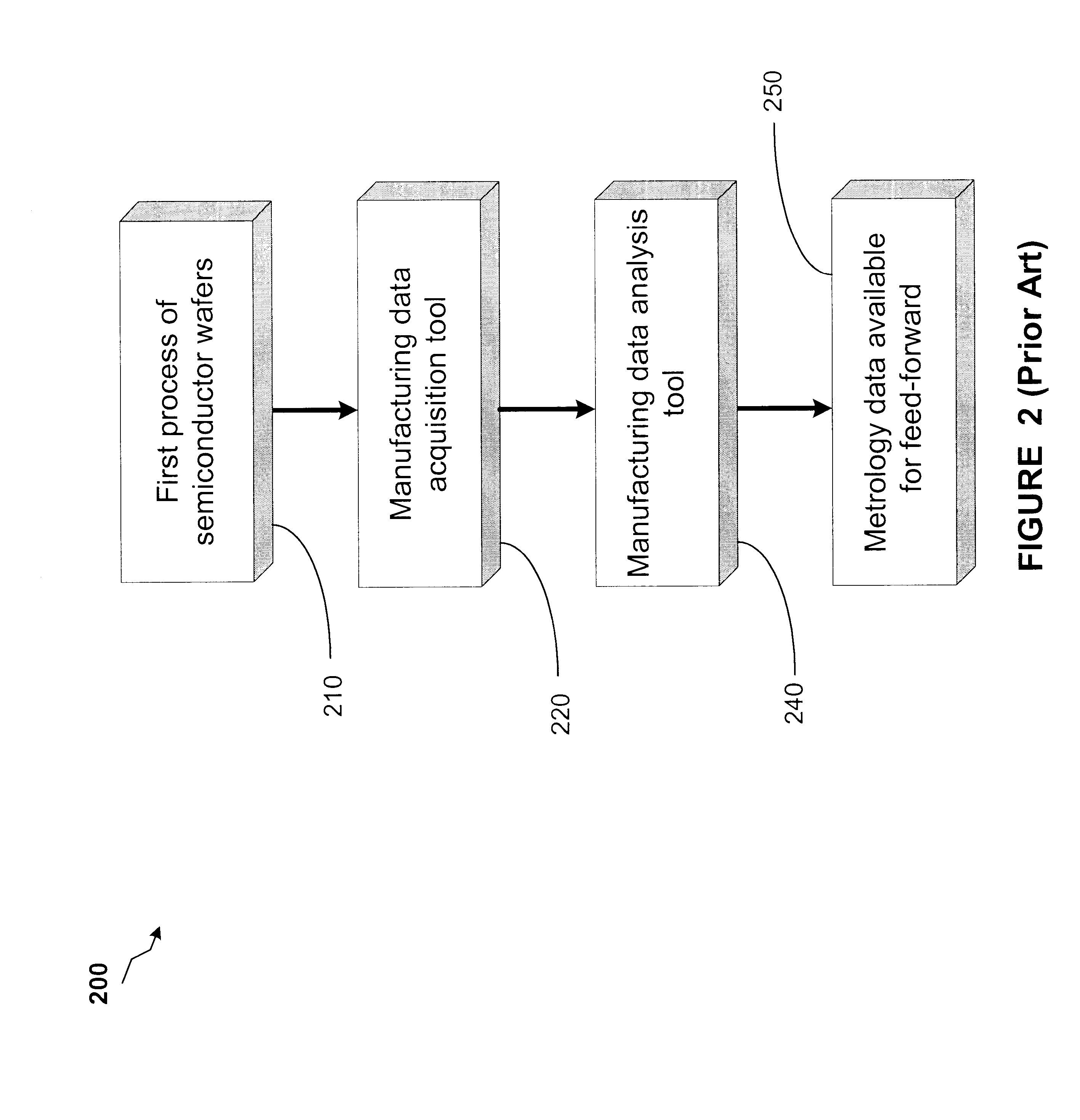

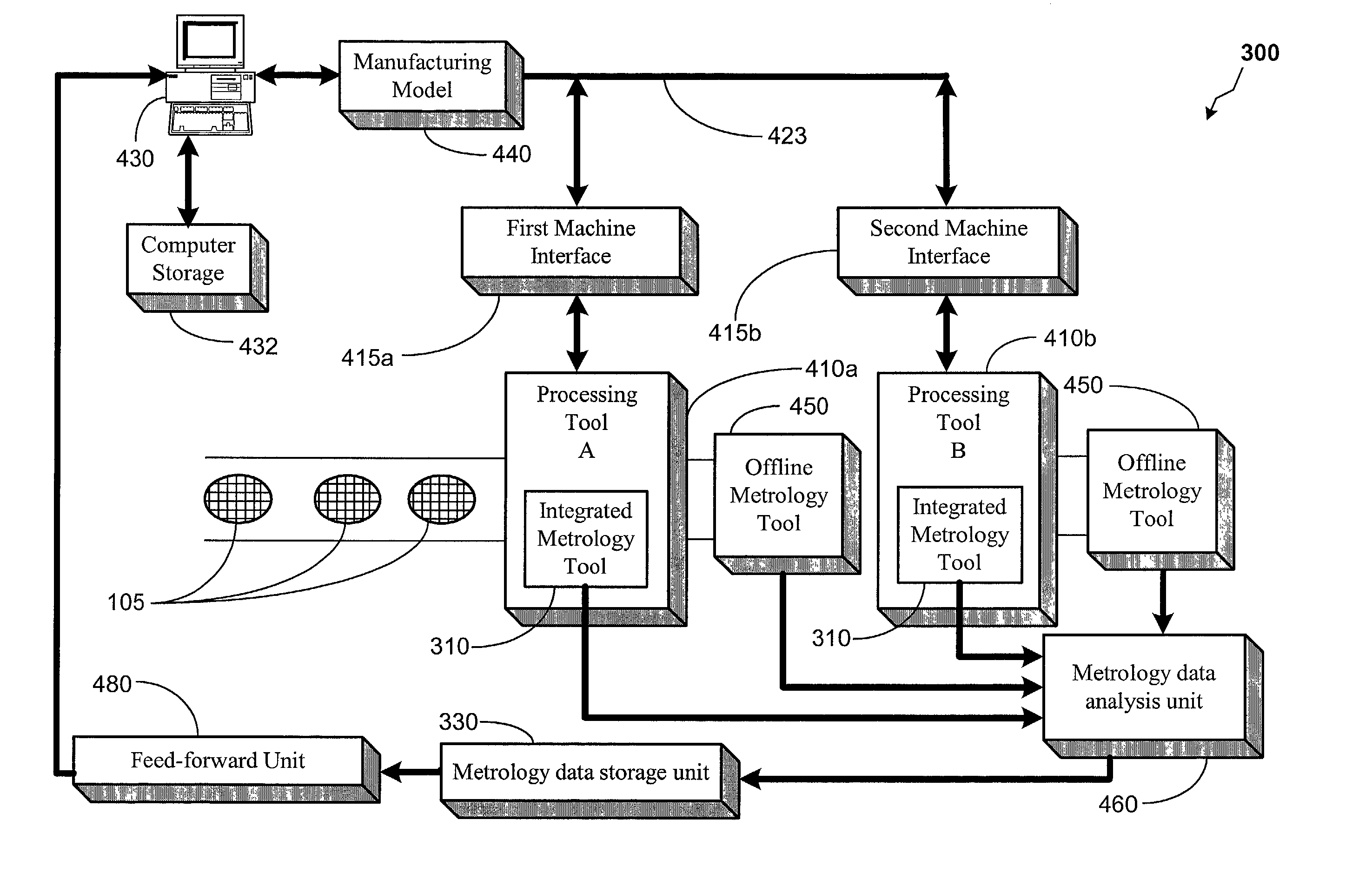

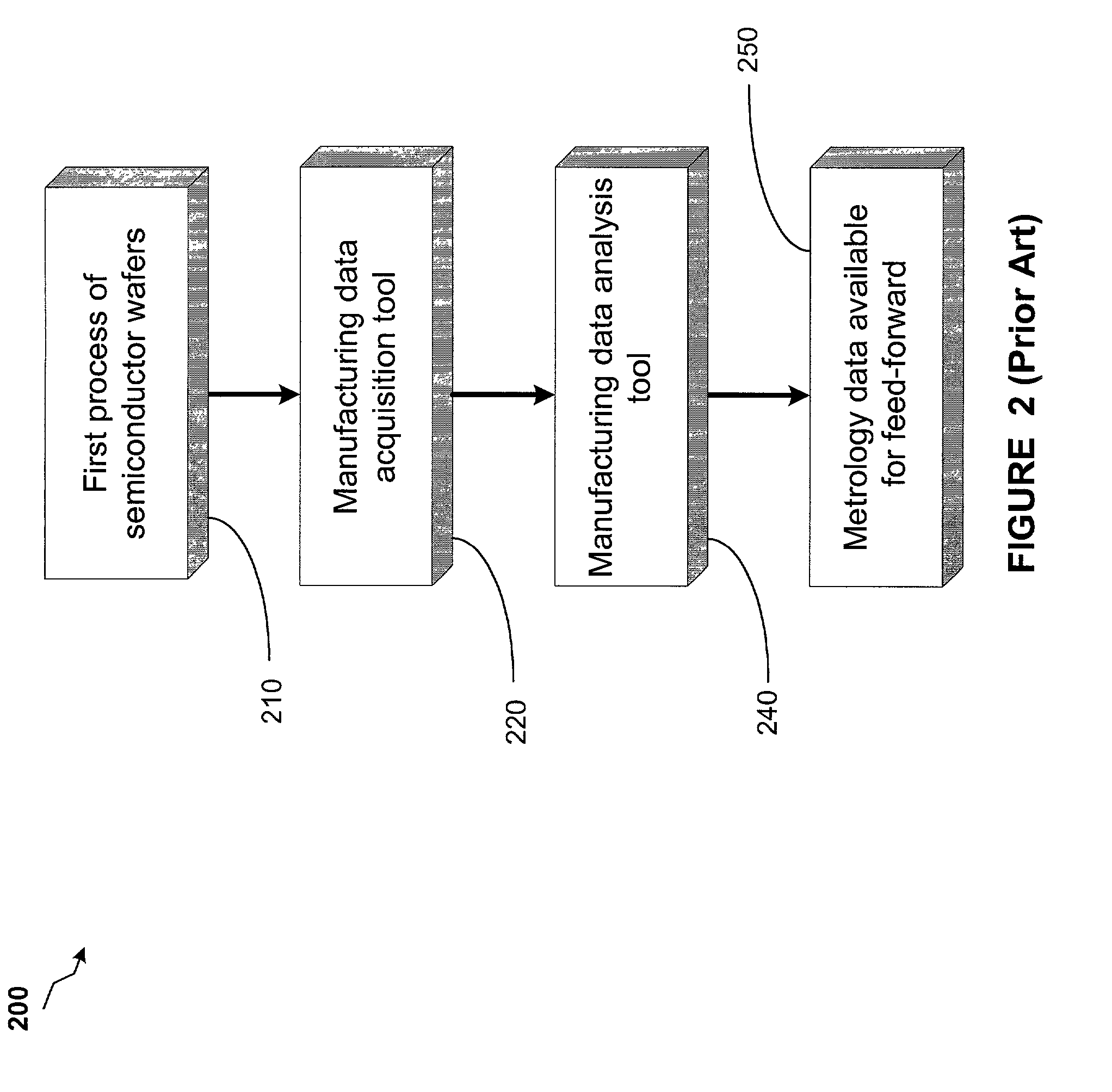

Method and apparatus for utilizing integrated metrology data as feed-forward data

InactiveUS6708075B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingMetrologySemiconductor wafer fabrication

A method and an apparatus for performing feed-forward correction during semiconductor wafer manufacturing. A first process on a semiconductor wafer is performed. Integrated metrology data related to the first process of the semiconductor wafer is acquired. An integrated metrology feed-forward process is performed based upon the integrated metrology data, the integrated metrology feed-forward process comprising identifying at least one error on the semiconductor wafer based upon the integrated metrology data related to the first process of the semiconductor wafer and performing an adjustment process to a second process to be performed on the wafer to compensate for the error. The second process on the semiconductor wafer is performed based upon the adjustment process.

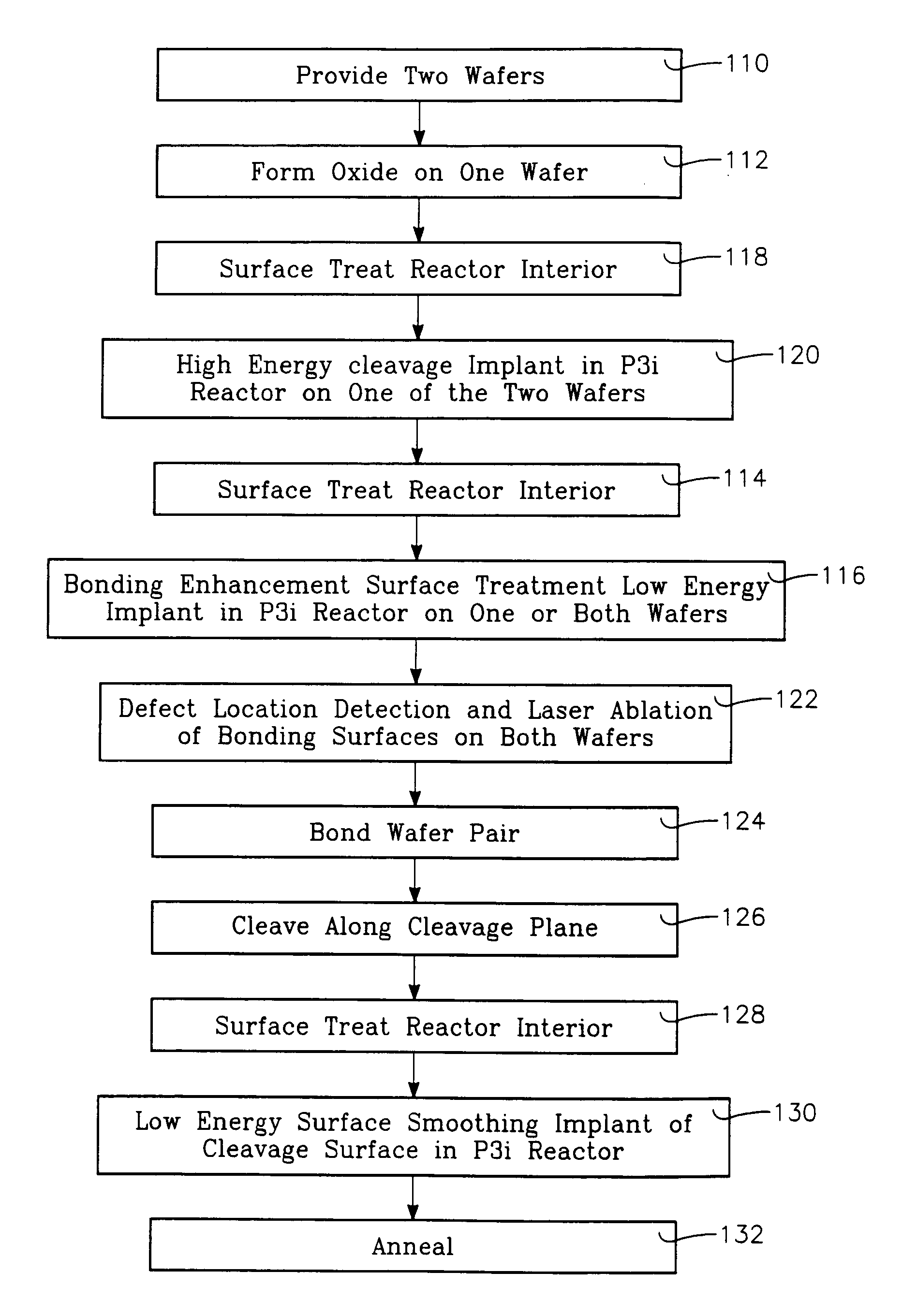

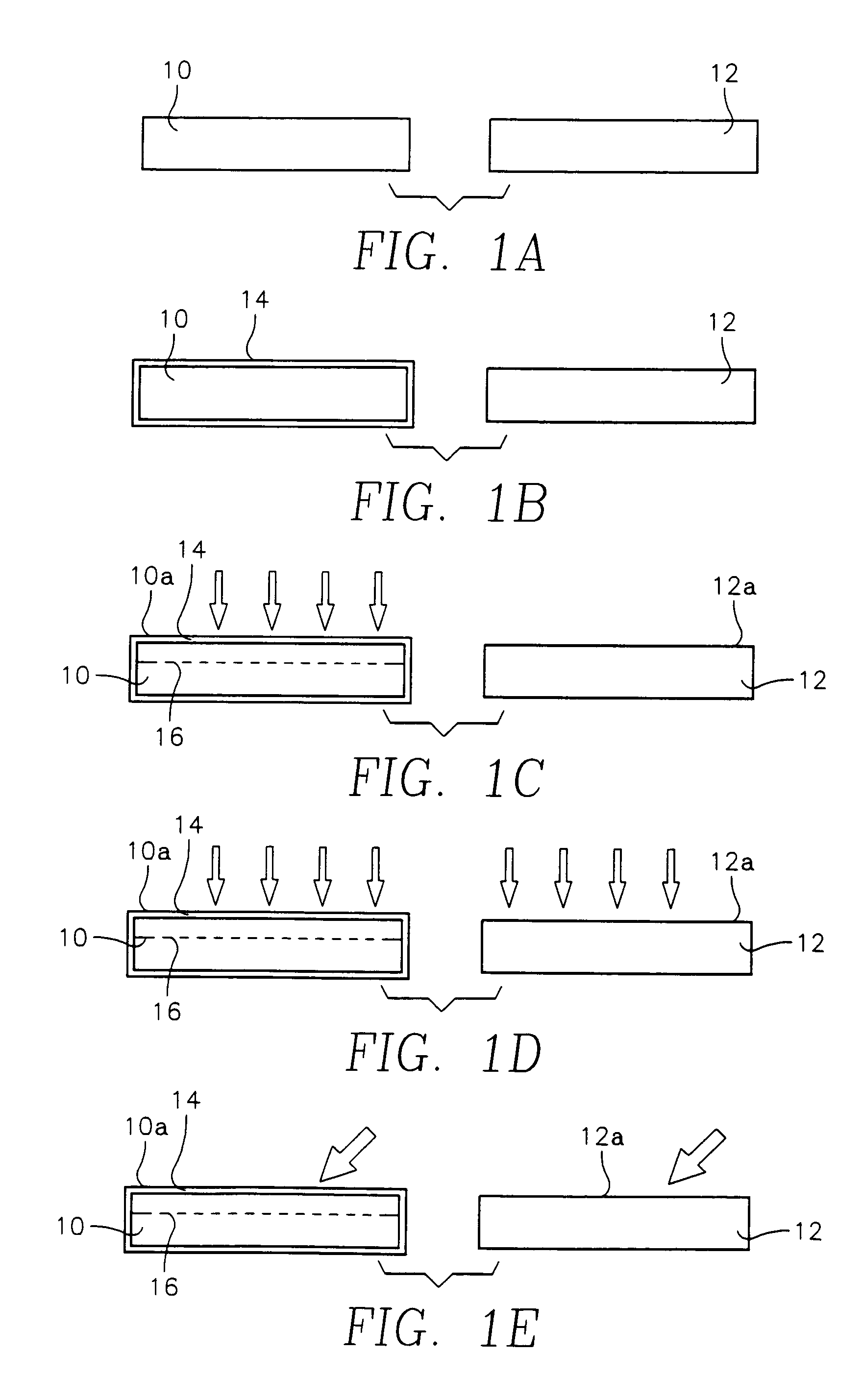

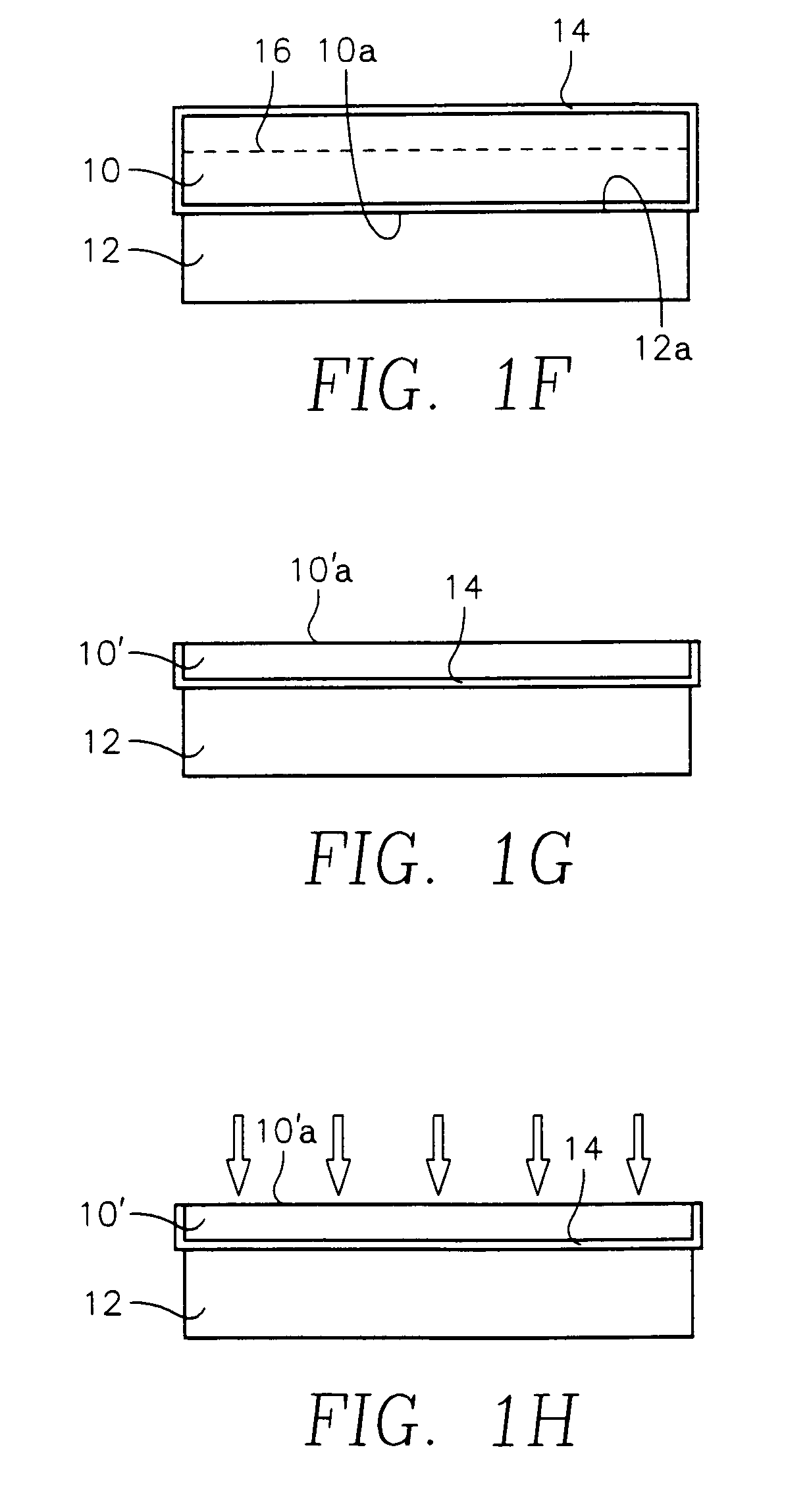

Silicon-on-insulator wafer transfer method using surface activation plasma immersion ion implantation for wafer-to-wafer adhesion enhancement

InactiveUS7183177B2TransistorElectric discharge tubesSemiconductor structurePlasma-immersion ion implantation

Owner:APPLIED MATERIALS INC

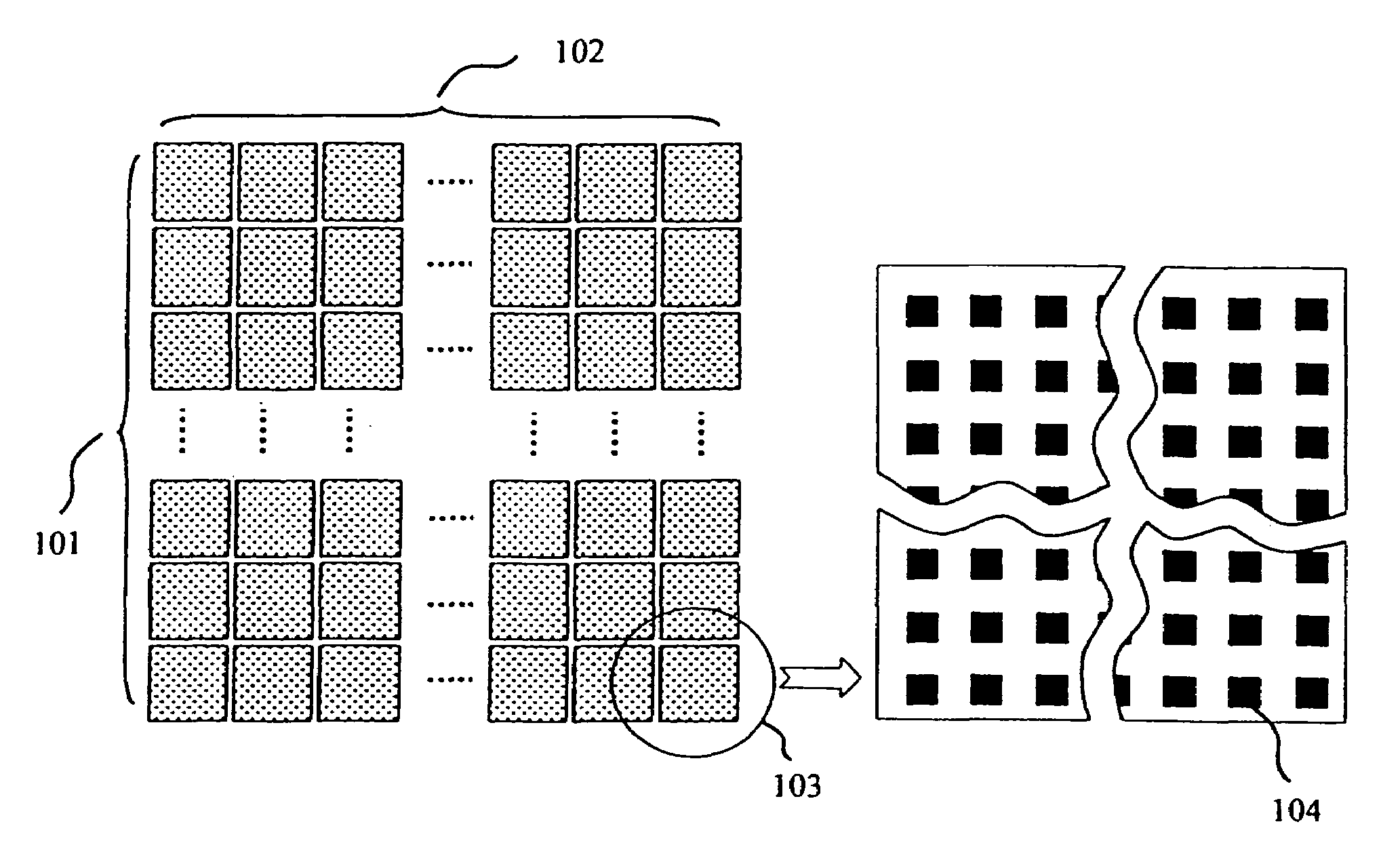

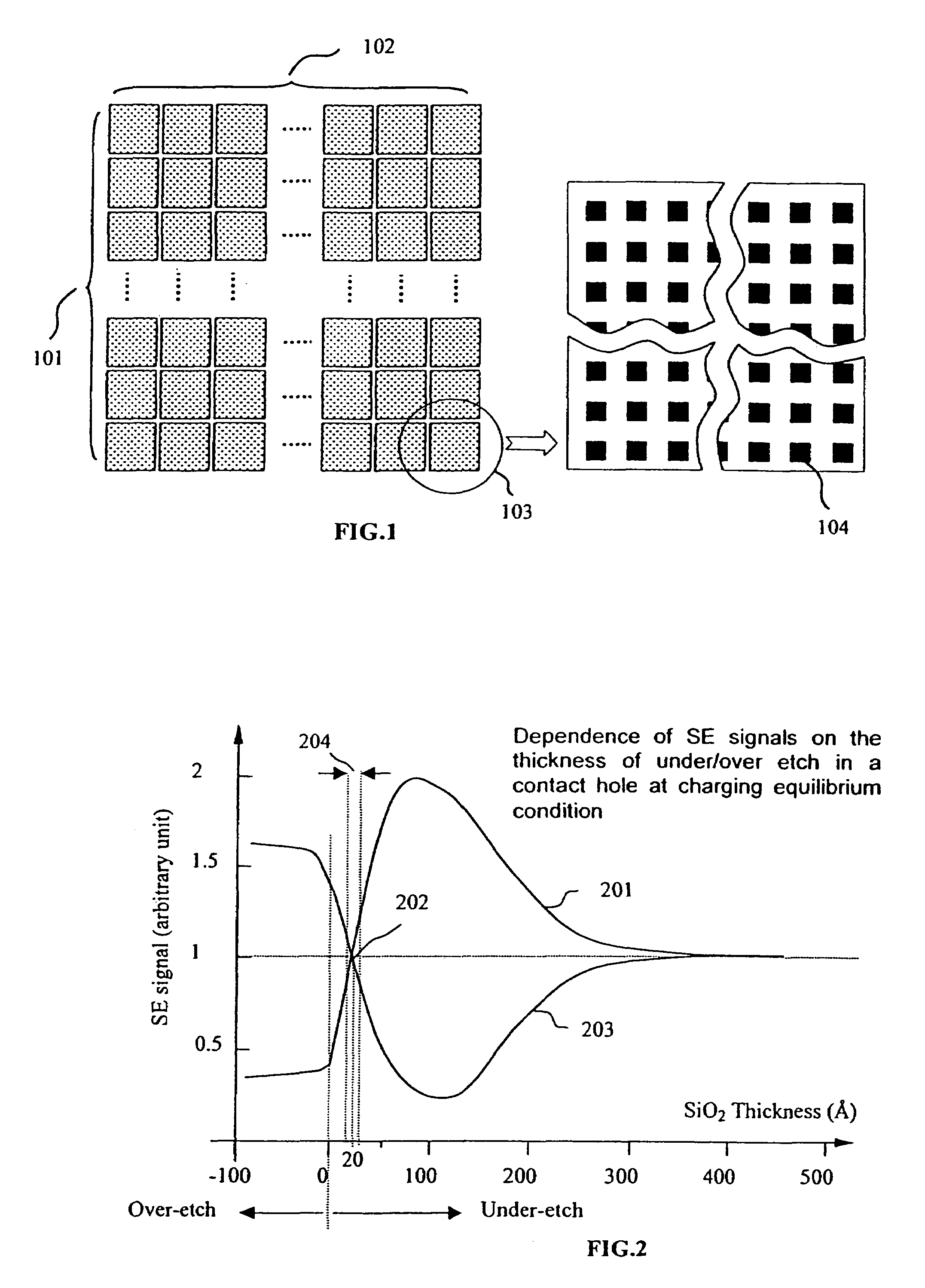

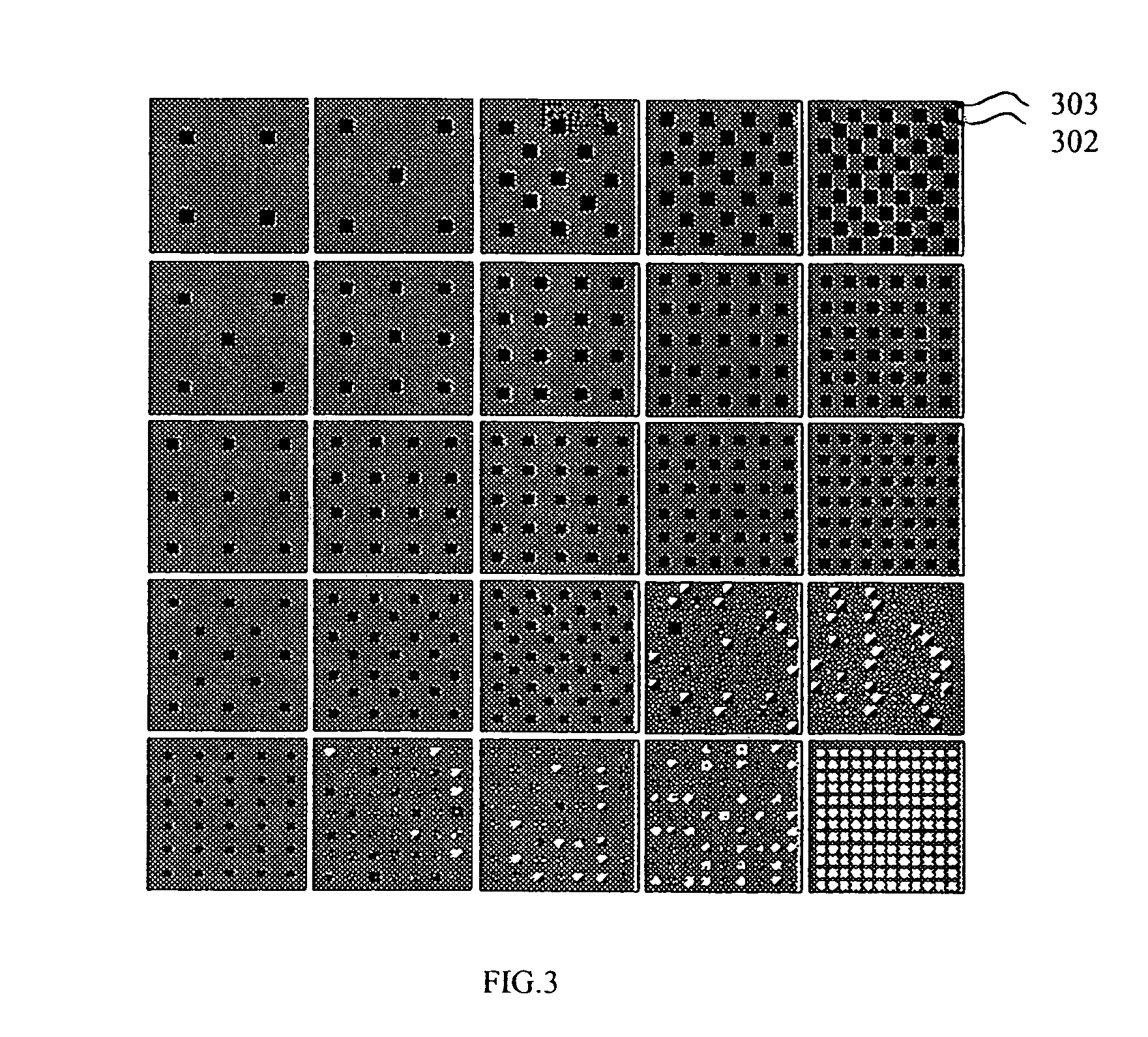

Method for in-line monitoring of via/contact holes etch process based on test structures in semiconductor wafer manufacturing

InactiveUS7105436B2Reduce contactSemiconductor/solid-state device testing/measurementVacuum gauge using ionisation effectsImaging processingEngineering

Owner:HERMES MICROVISION TAIWAN +2

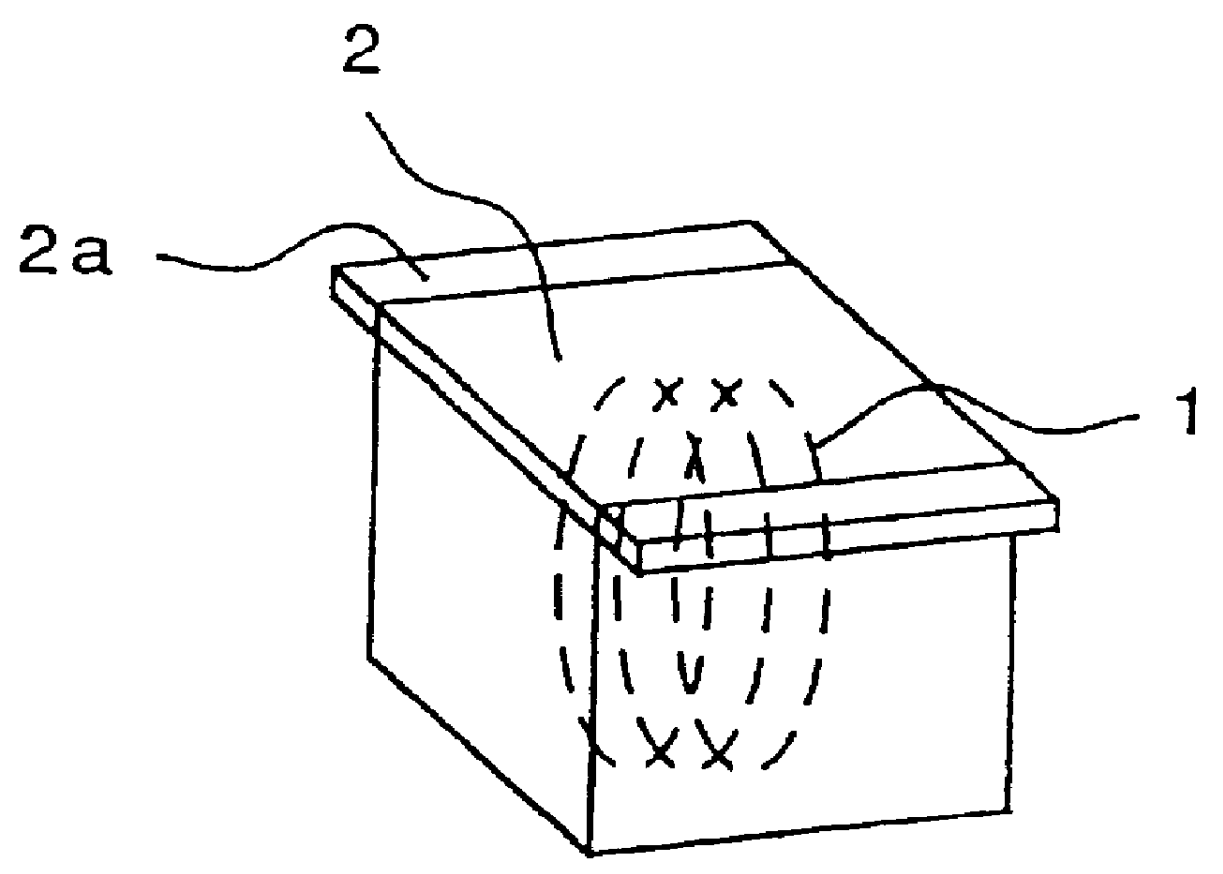

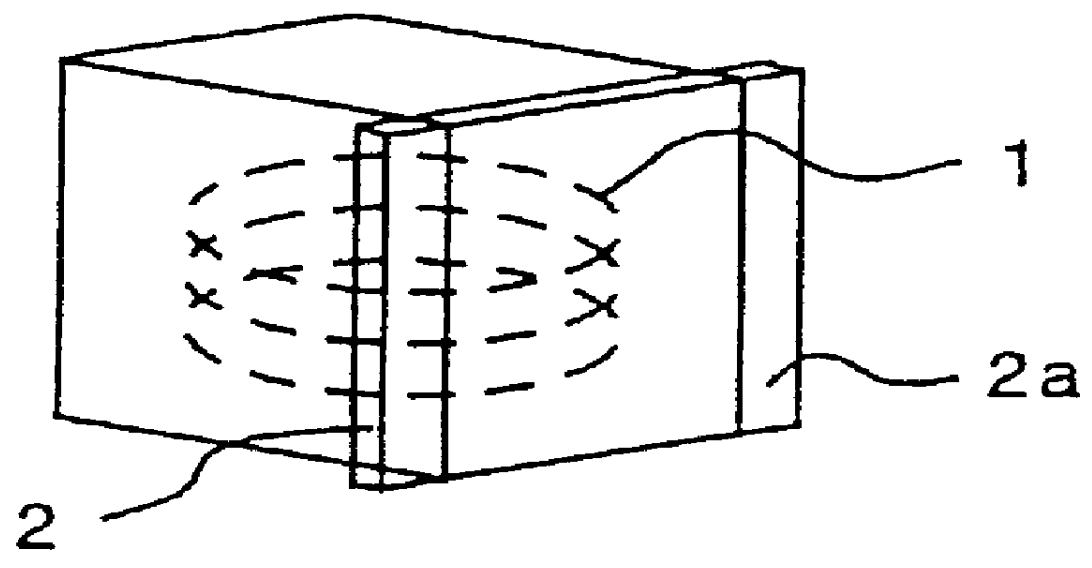

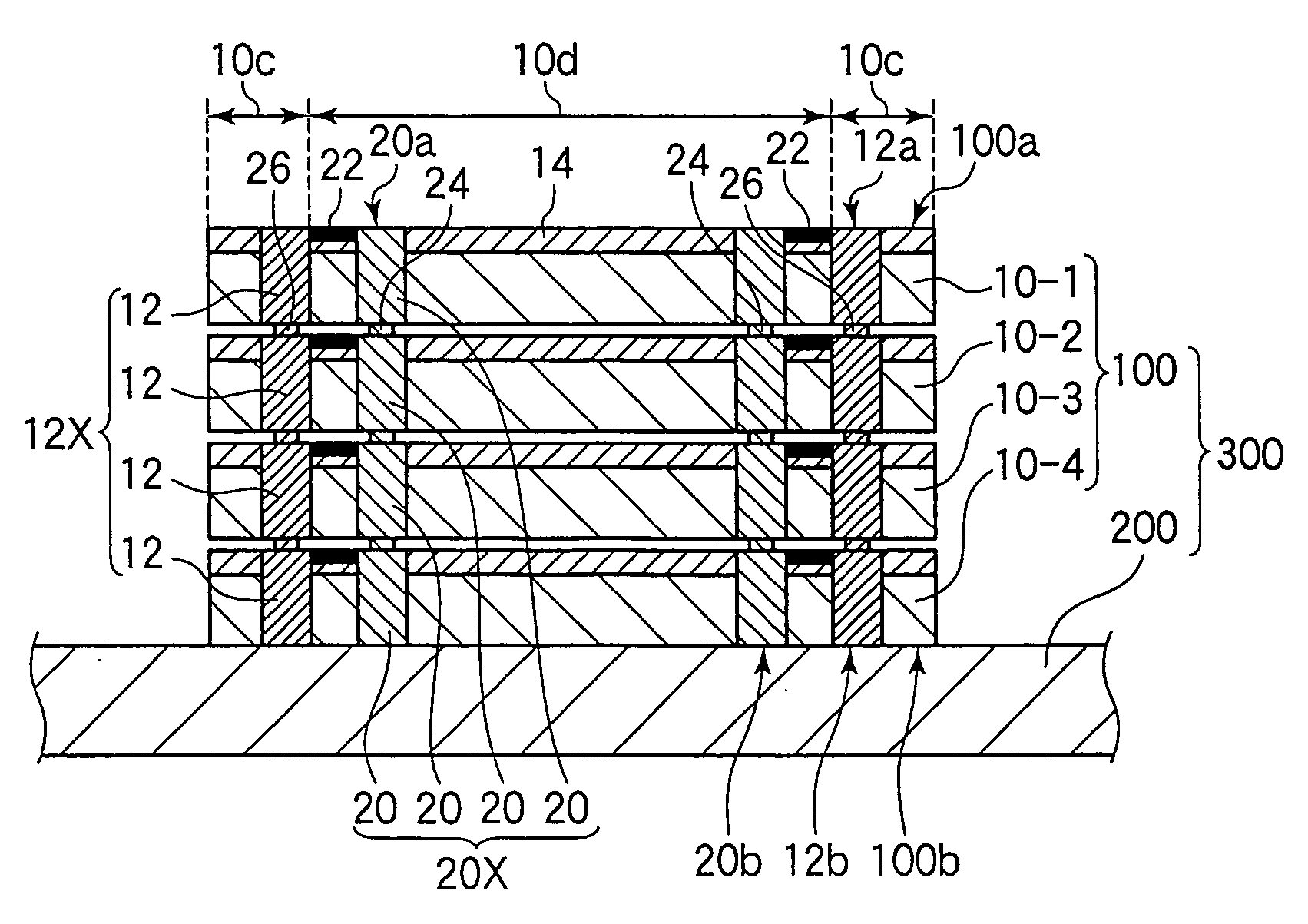

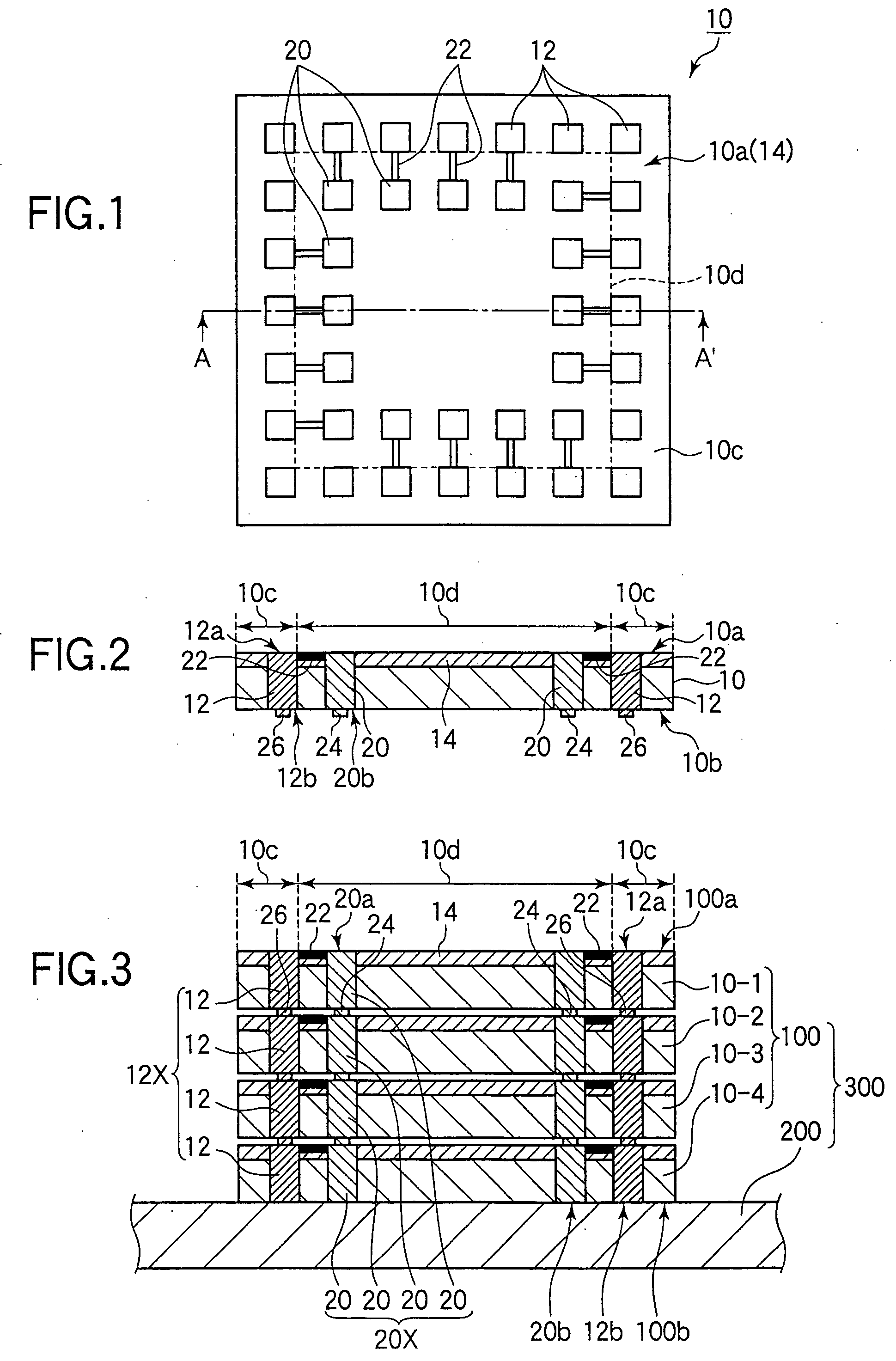

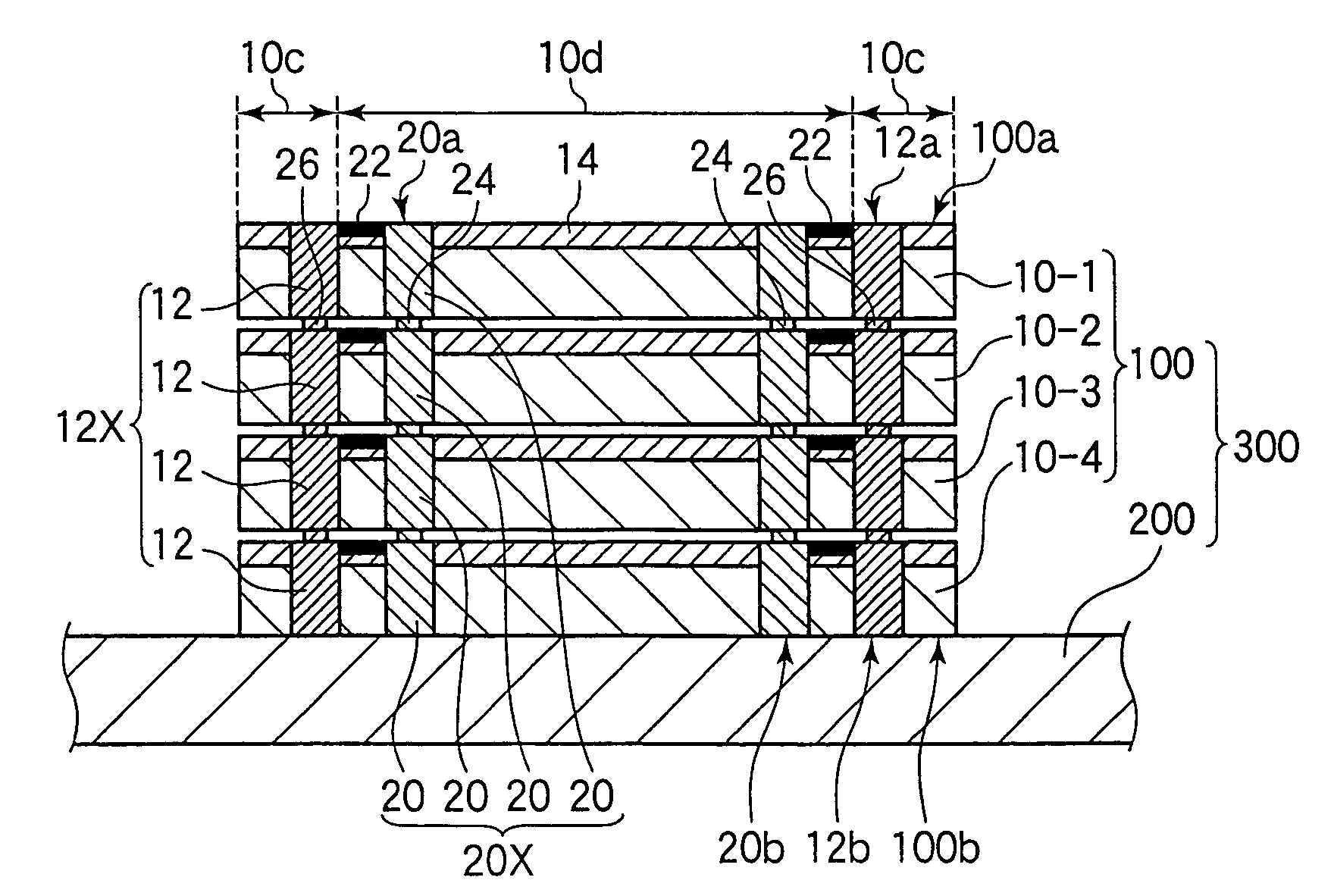

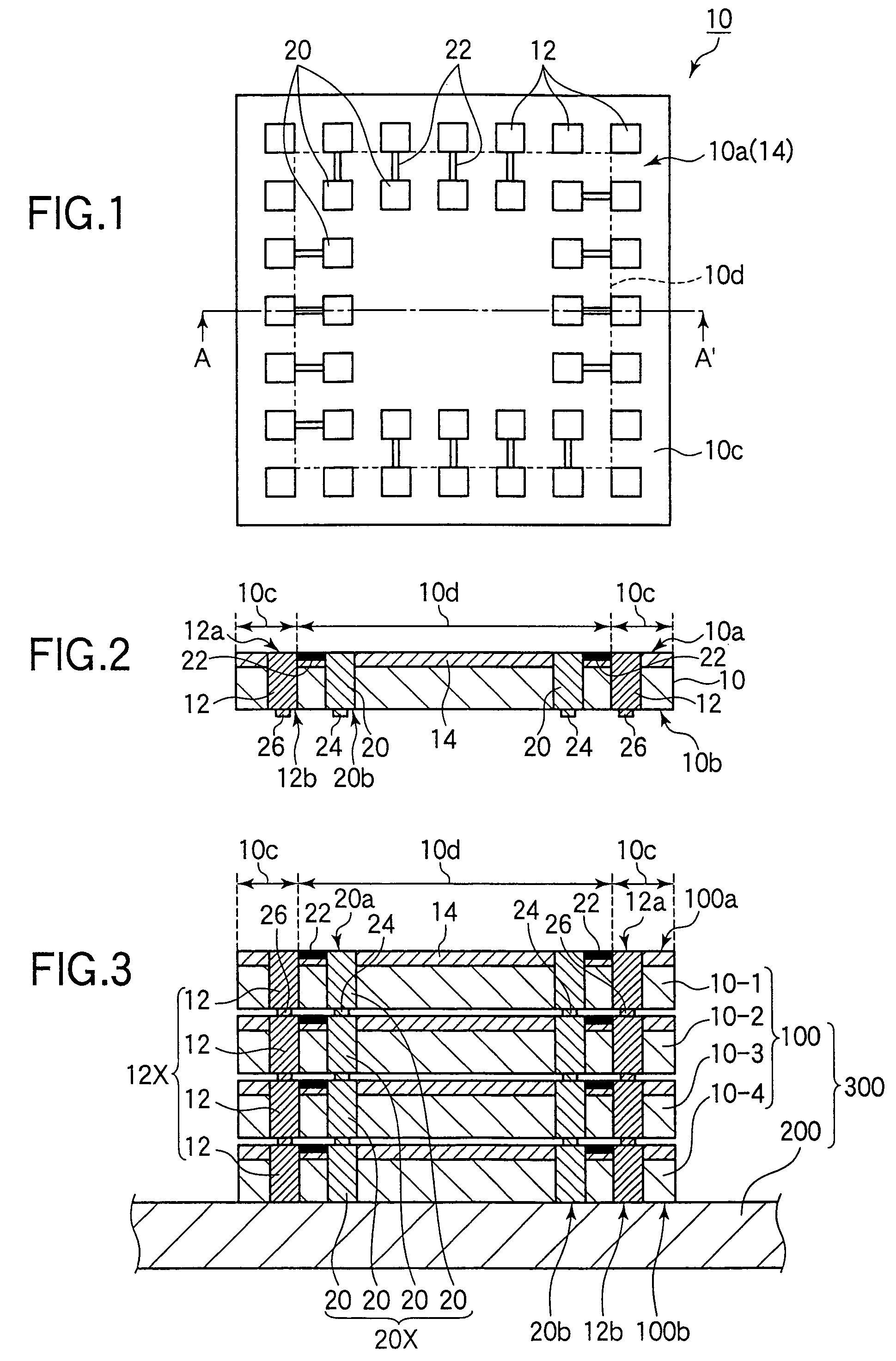

Semiconductor device, stacked structure, and manufacturing method

ActiveUS20060197181A1Improve cooling effectImprove packaging efficiencySemiconductor/solid-state device detailsSolid-state devicesDevice materialWafer dicing

An array of electrically conductive members, formed around the edges of a semiconductor device or chip, penetrate from one major surface of the device to the other major surface. In an area located inward of this array, a multiplicity of thermally conductive members also penetrate from one major surface to the other major surface. The semiconductor device can be manufactured from a semiconductor wafer by creating holes that penetrate partway through the wafer, filling the holes with metal to form the electrically conductive members and thermally conductive members, and then grinding the lower surface of the wafer to expose the ends of the electrically conductive members and thermally conductive members before dicing the wafer into chips. The thermally conductive members improve heat dissipation performance when semiconductor chips of this type are combined into a stacked multichip package.

Owner:TAIWAN SEMICON MFG CO LTD

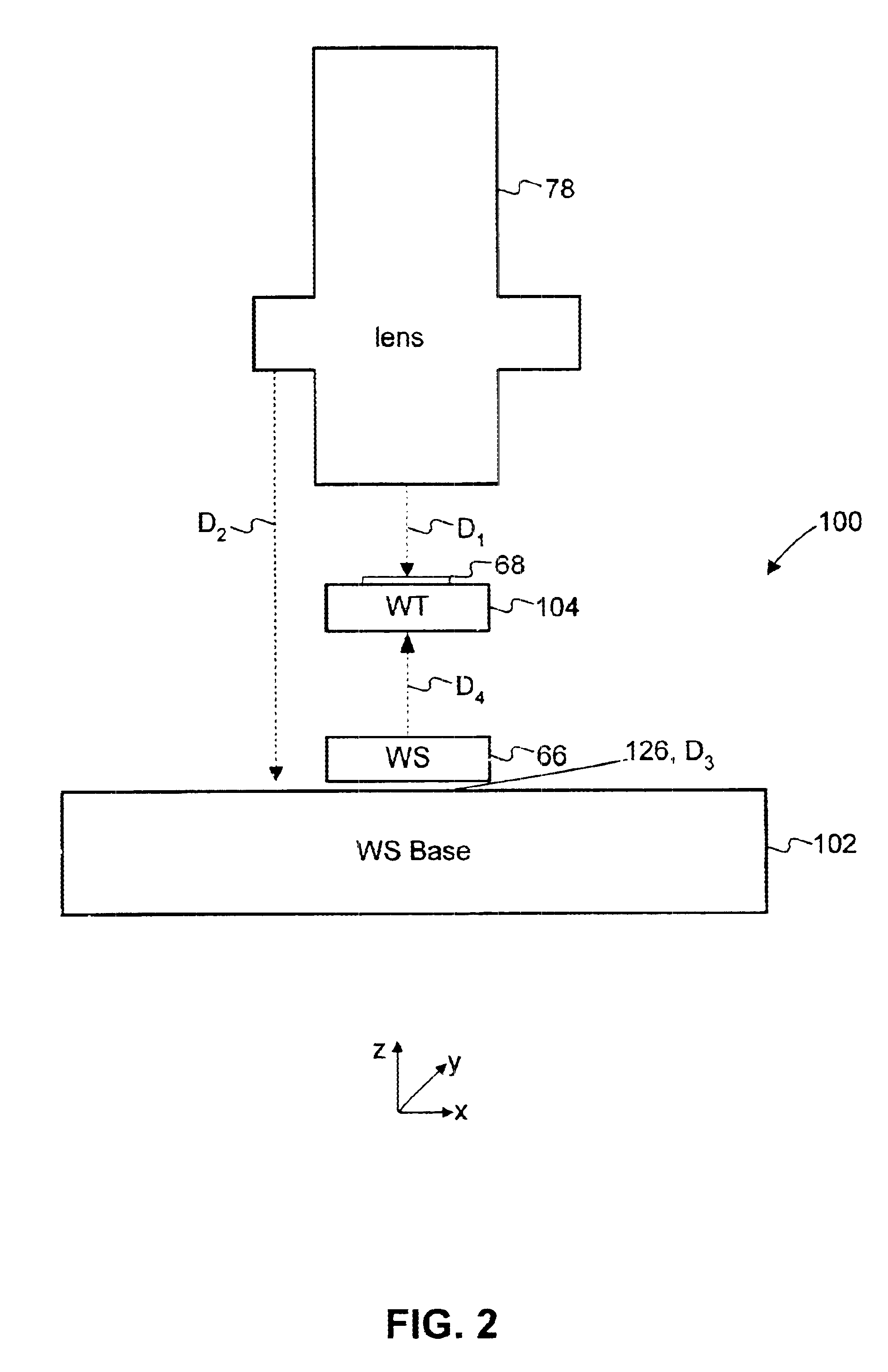

Wafer stage assembly, servo control system, and method for operating the same

A wafer stage assembly, wafer table servo control system, and method for operating the same, are provided for use in combination with a projection lens assembly in a semiconductor wafer manufacturing process. The wafer stage assembly includes a wafer stage base supporting a wafer stage to position the semiconductor wafer, a wafer table connected to the wafer stage to support the wafer, a plurality of sensors, and an actuator. The sensors include a first sensor to determine a position of an exposure point on the wafer relative to the projection lens assembly, and a second sensor to determine a position of a focal point of the projection lens assembly relative to the exposure point. To increase focusing properties of the projection lens assembly, in response to the determined positions of the exposure point and the focal point, the actuator moves the wafer table so that the exposure point substantially coincides with the focal point. The wafer table servo control system is provided to operate the wafer stage assembly. The servo control system includes a first sensor controller to generate a first position signal of an exposure point on the wafer table relative to a projection lens assembly, and a second sensor controller to generate a second position signal of a focal point of the projection lens assembly relative to the exposure point. The servo control system also includes a wafer table controller to determine and generate a correction force corresponding to the first and second position signals. The correction force is then exerted onto the wafer table to bring the exposure point to substantially coincide with the focal point.

Owner:NIKON CORP

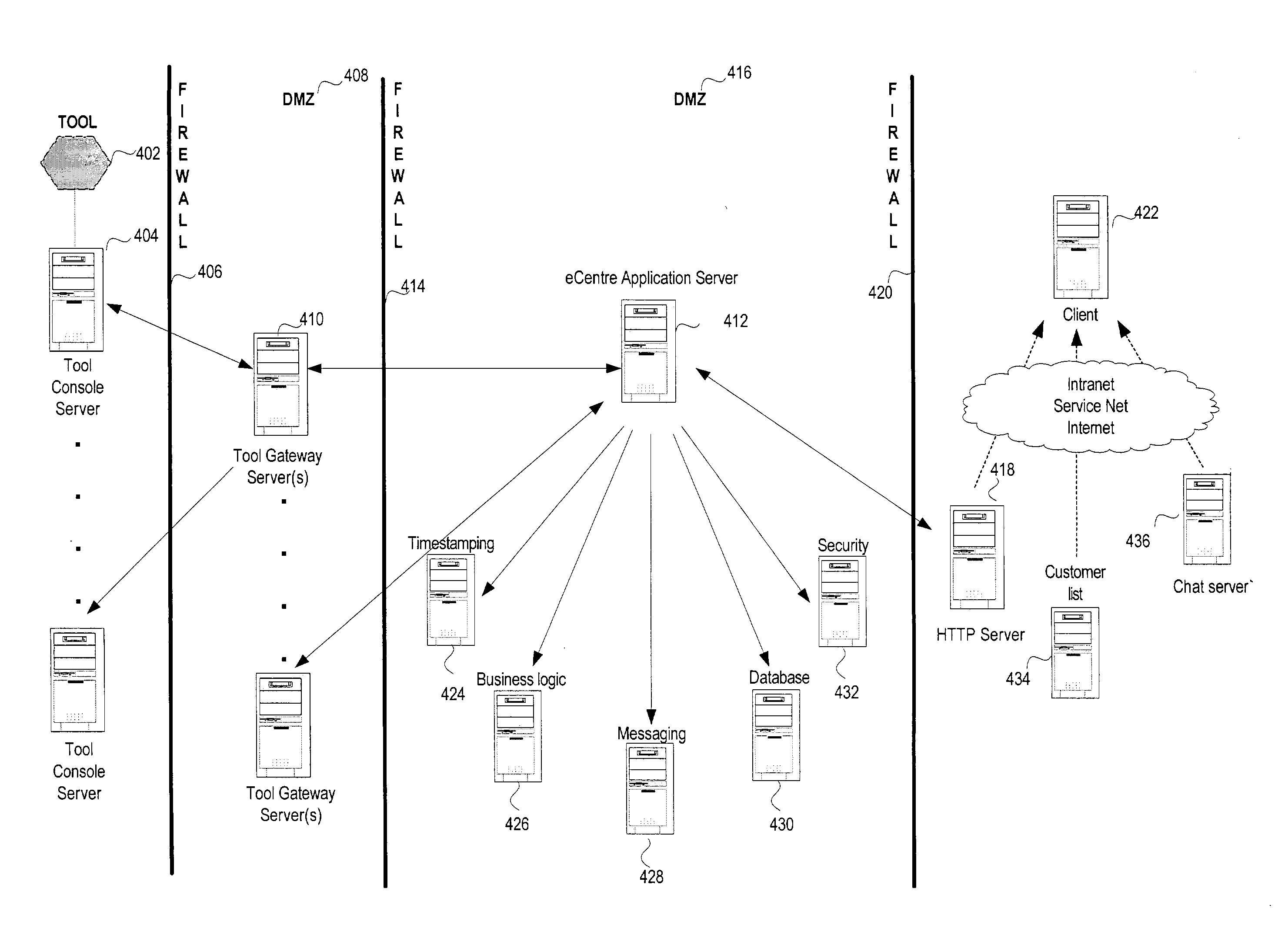

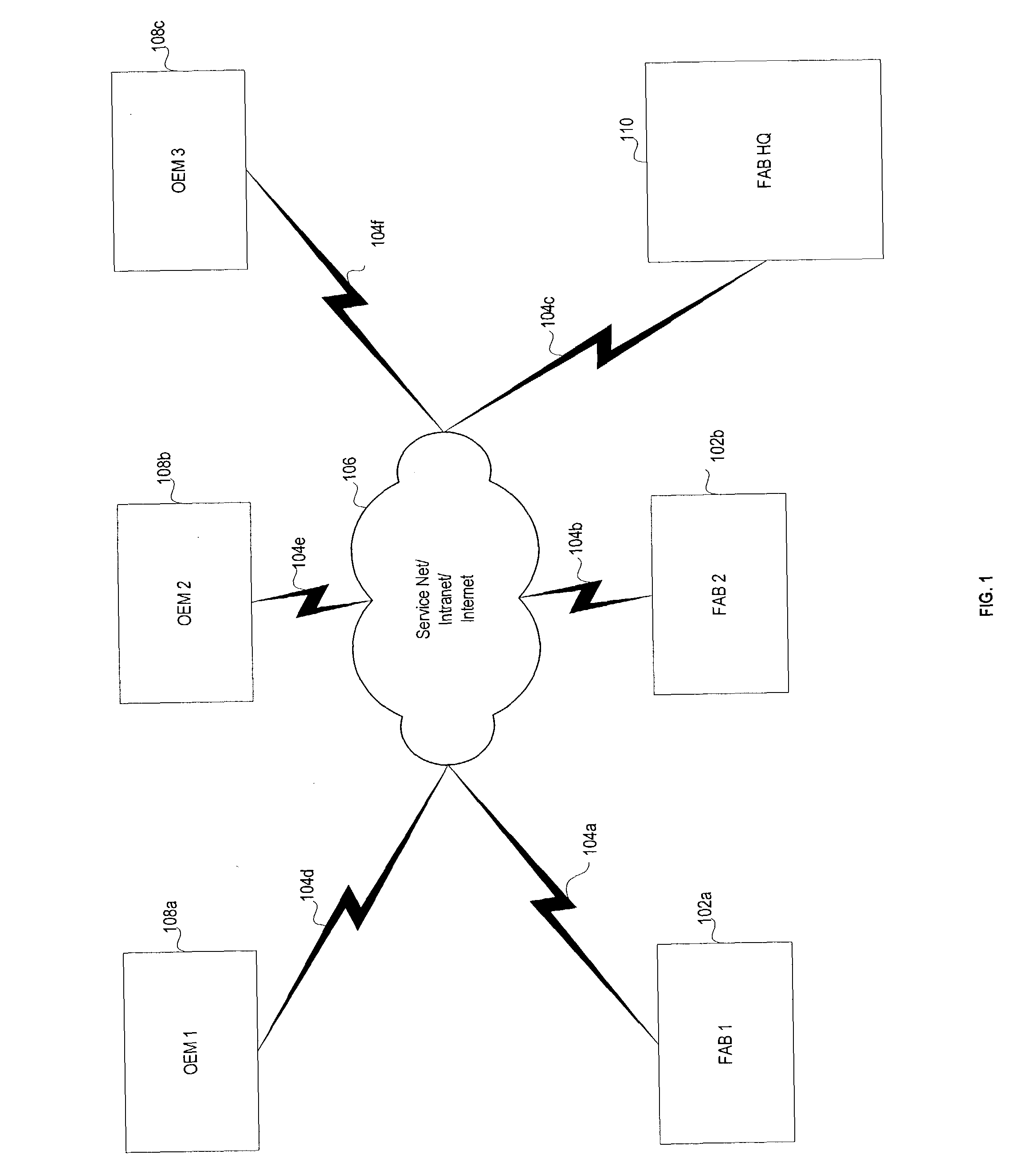

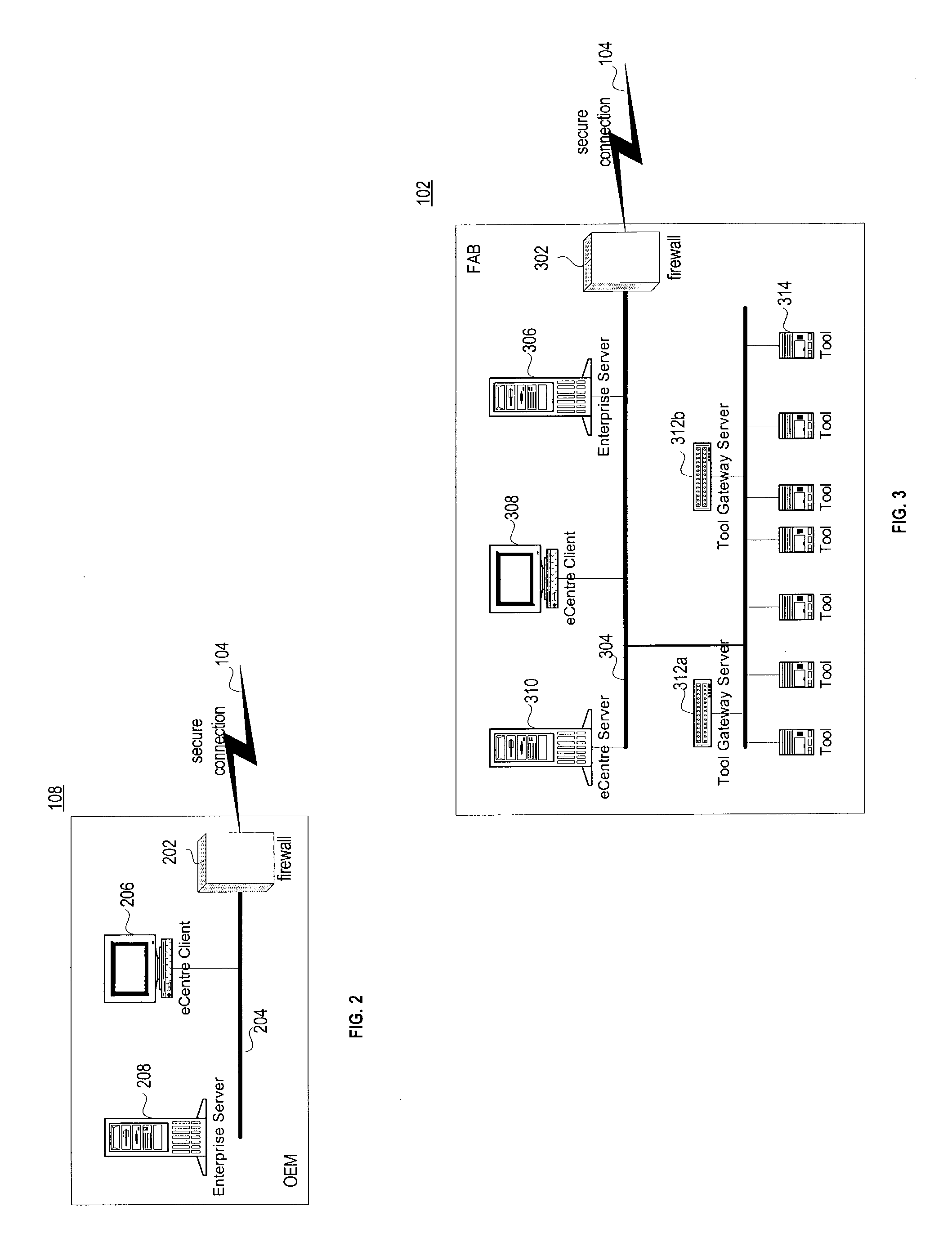

Data brokering system for integrated remote tool access, data collection, and control

InactiveUS20030208448A1Detecting faulty hardware by remote testElectric testing/monitoringSemiconductor wafer fabricationData harvesting

A data brokering system for semiconductor wafer data is presented that comprises: a FAB having at least one automated semiconductor wafer manufacturing tool; a plurality of OEMs, coupled to the FAB via a secure service net; means for providing data about a semiconductor wafer manufactured by the tool to one of the OEMs without revealing information about the tool; and means for collecting fees based on characteristics of the provided data.

Owner:ILS TECH INC

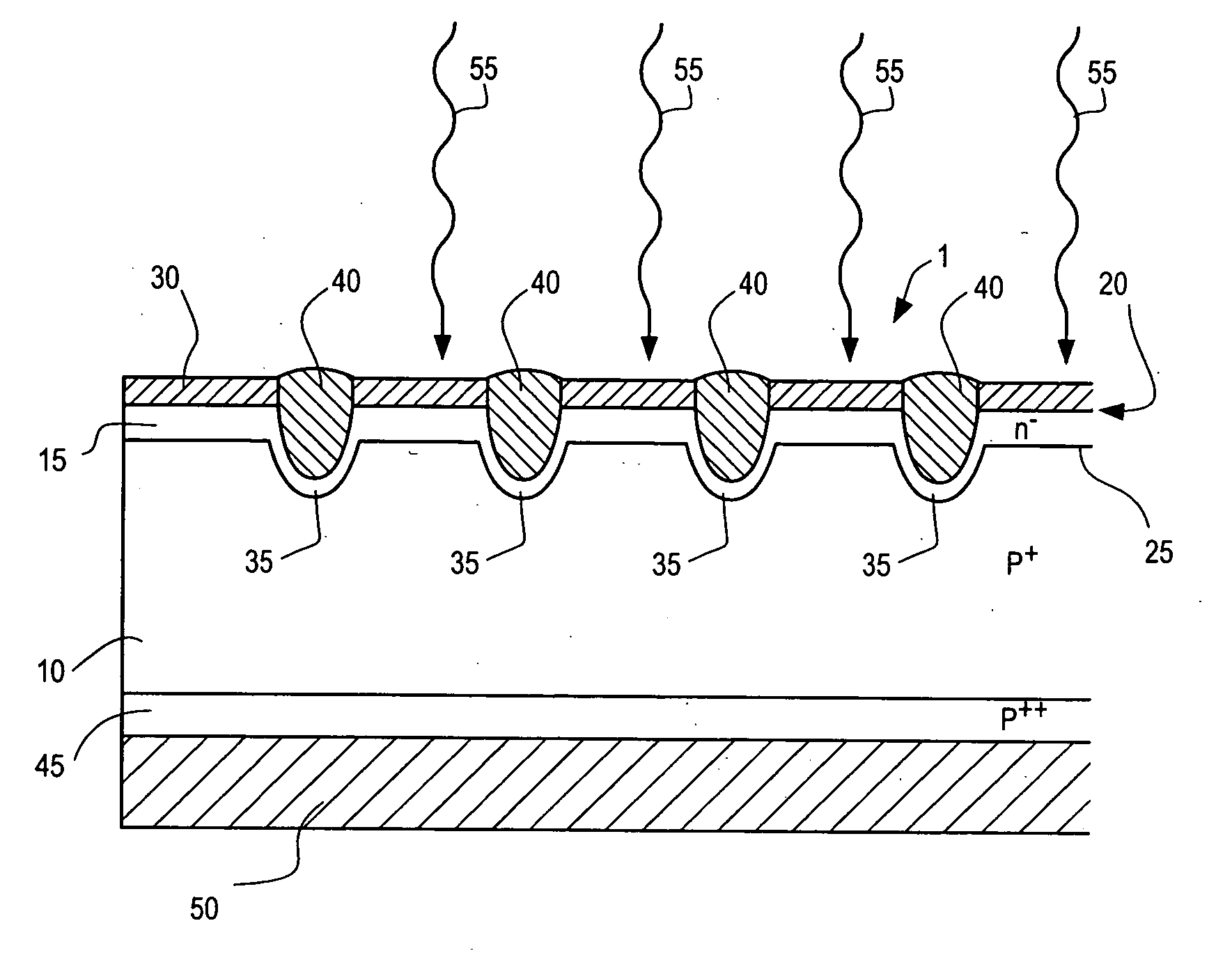

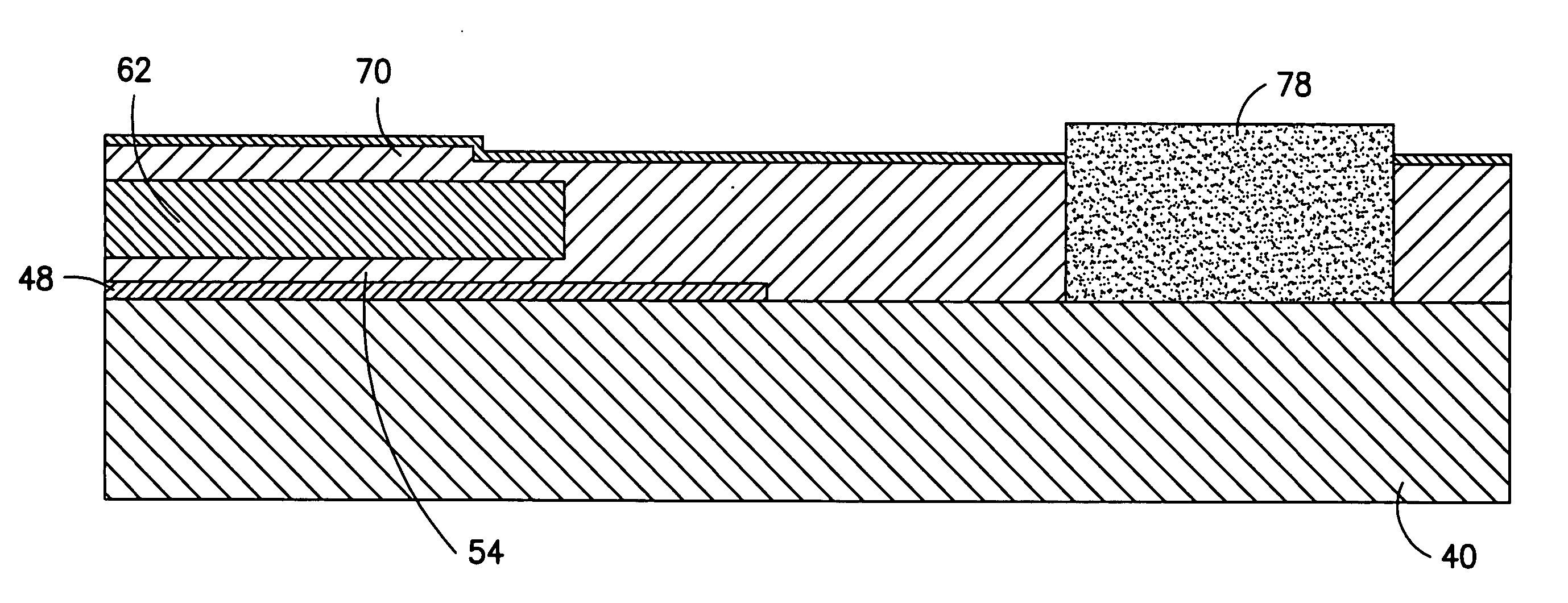

Process for manufacturing photovoltaic cells

InactiveUS20050189013A1Final product manufactureSemiconductor/solid-state device manufacturingDopantConductive materials

A process for making a photovoltaic cell using a semiconductor wafer doped with a first dopant and having a front surface and a back surface, the process comprising the steps of forming a first layer on the front surface of the wafer, the first layer comprising a second dopant of a conductivity type opposite the first dopant; depositing a surface coating on the back surface; forming grooves in the front surface; adding dopant to the groove of a conductivity type opposite the first dopant subsequent to depositing the surface coating on the back surface; removing the surface coating from the back surface after adding dopant to the grooves; forming a back contact over the back surface after removal of the surface coating; and adding conductive material to the grooves.

Owner:BP CORP NORTH AMERICA INC

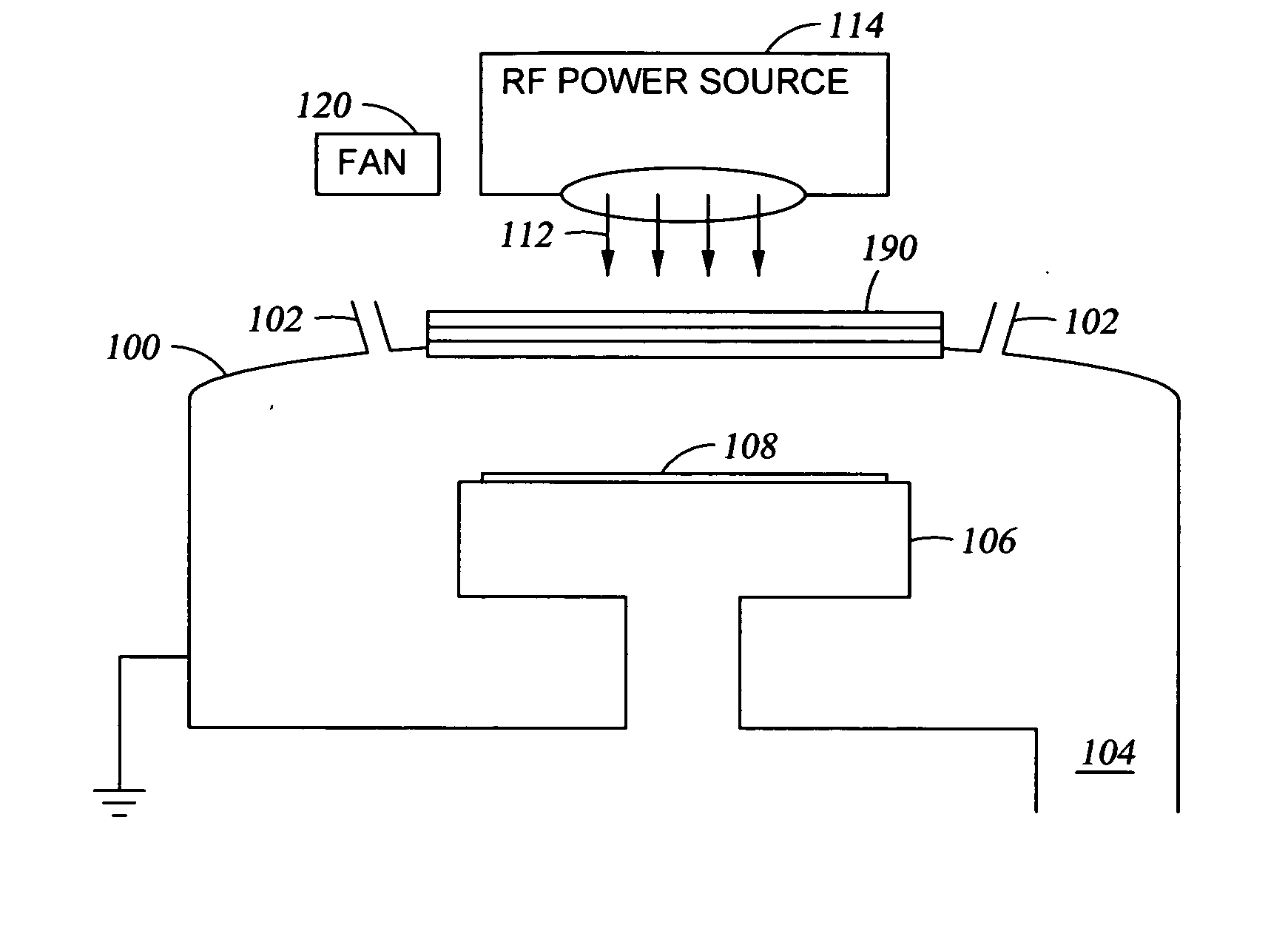

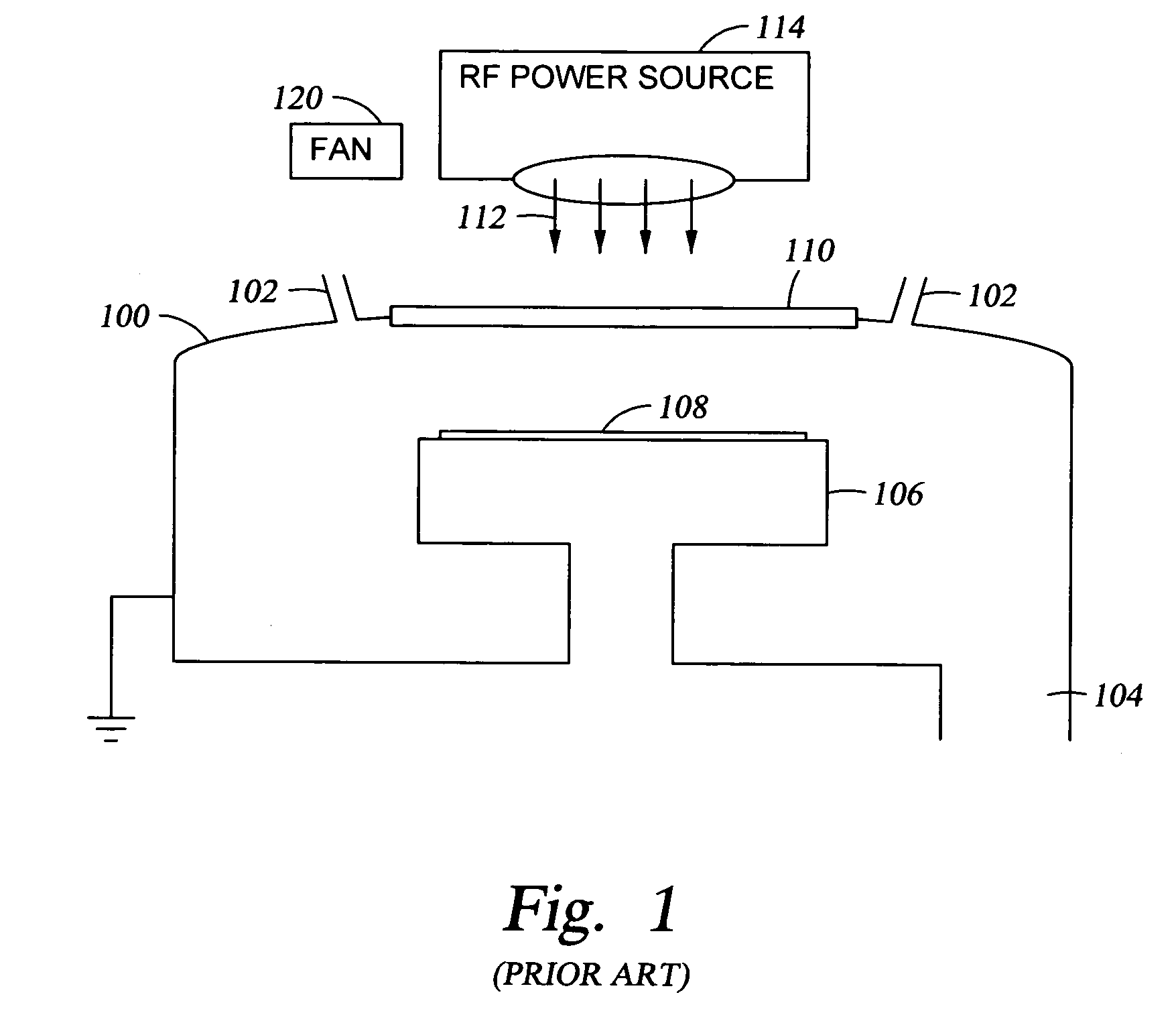

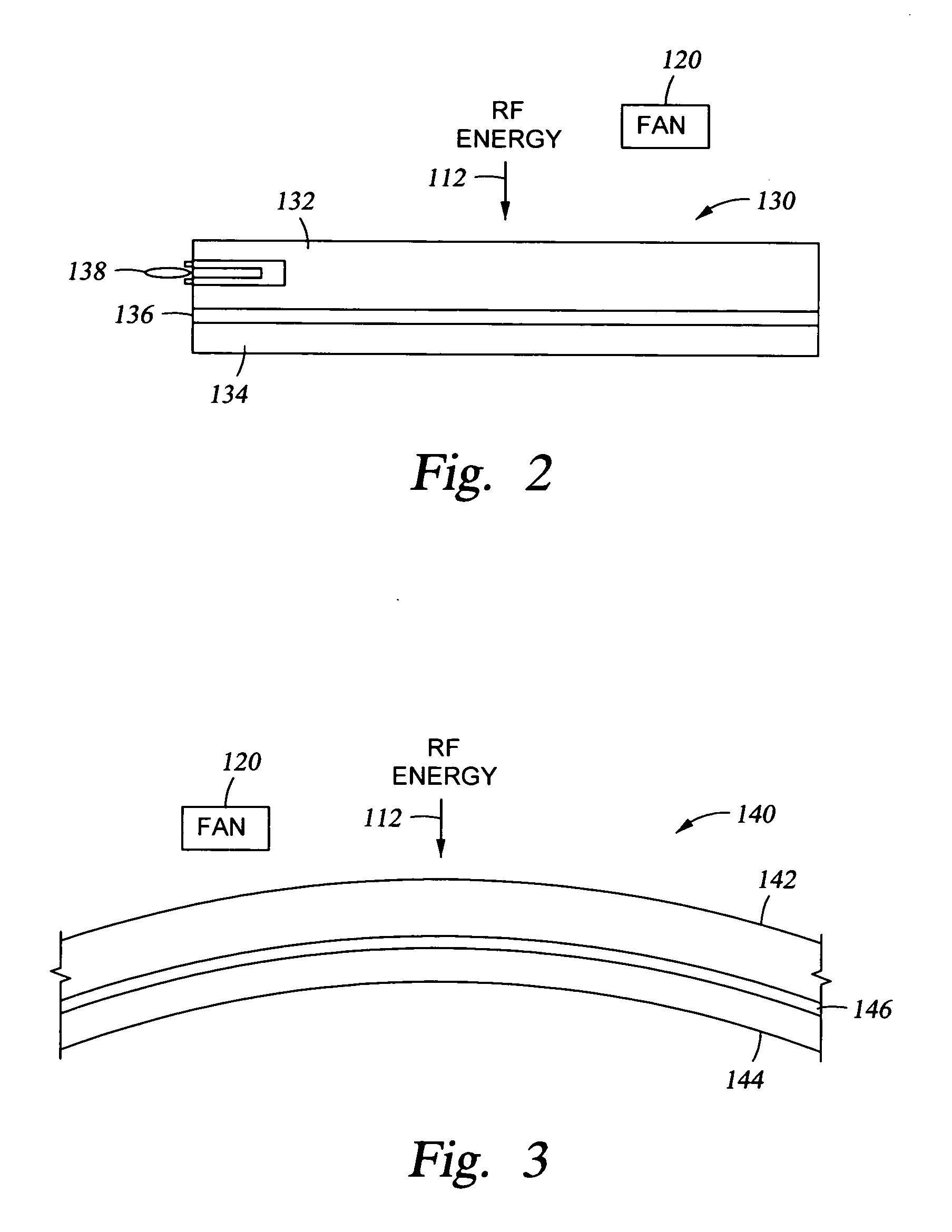

Bonded multi-layer RF window

InactiveUS20070079936A1Adequate plasma-resistant propertyImprove thermal conductivityElectric discharge tubesLaminationChemical reactionWafering

A bonded multi-layer RF window may include an external layer of dielectric material having desired thermal properties, an internal layer of dielectric material exposed to plasma inside a reaction chamber, and an intermediate layer of bonding material between the external layer and the internal layer. Heat produced by the chemical reaction inside the chamber and by the transmission of RF energy through the window may be conducted from the internal layer to the external layer, which may be cooled during a semiconductor wafer manufacturing process. A bonded multi-layer RF window may include cooling conduits for circulating coolant to facilitate cooling of the internal layer; additionally or alternatively, gas distribution conduits and gas injection apertures may be included for delivering one or more process gases into a reaction chamber. A system including a plasma reaction chamber may employ the inventive bonded multi-layer RF window.

Owner:APPLIED MATERIALS INC

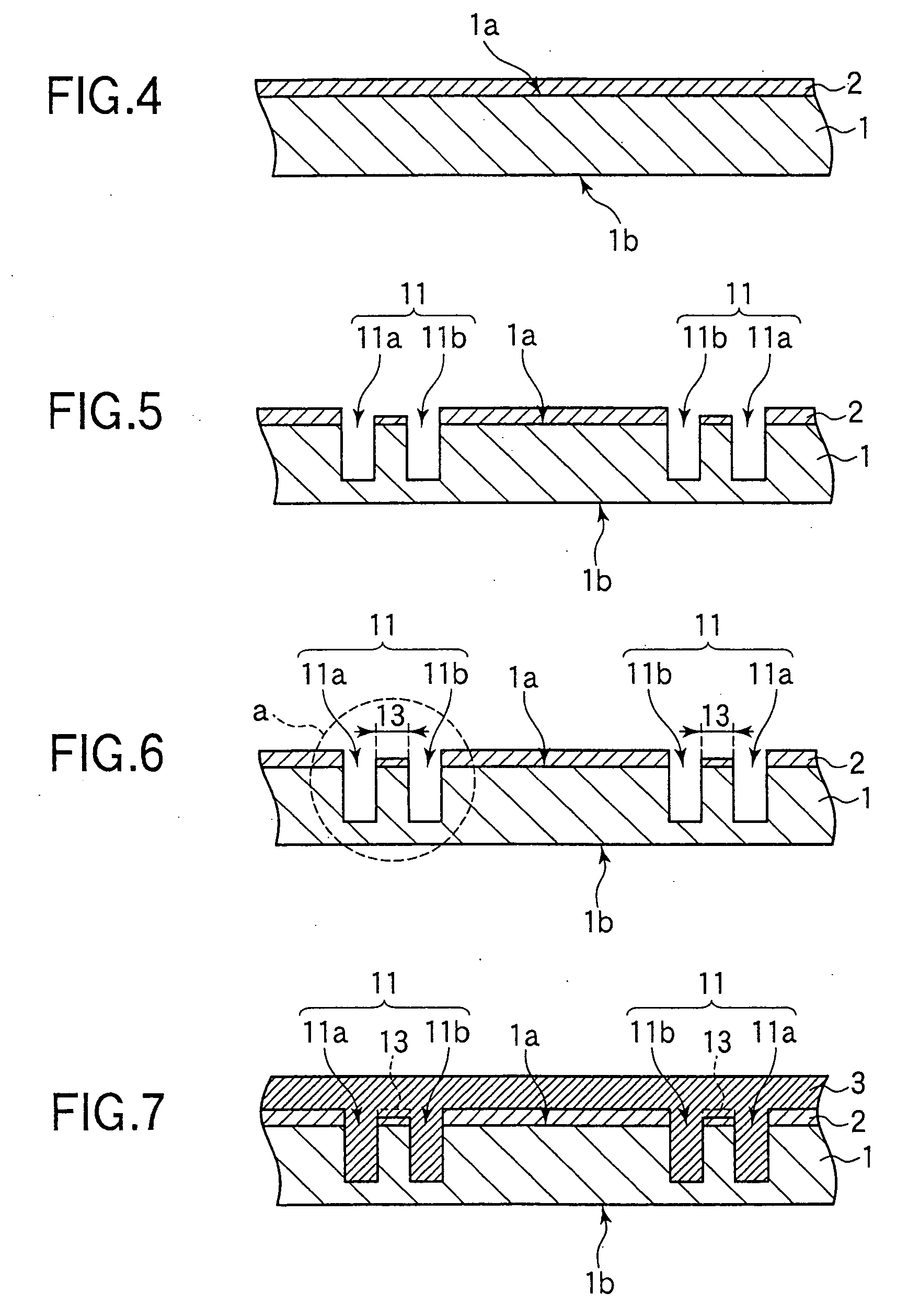

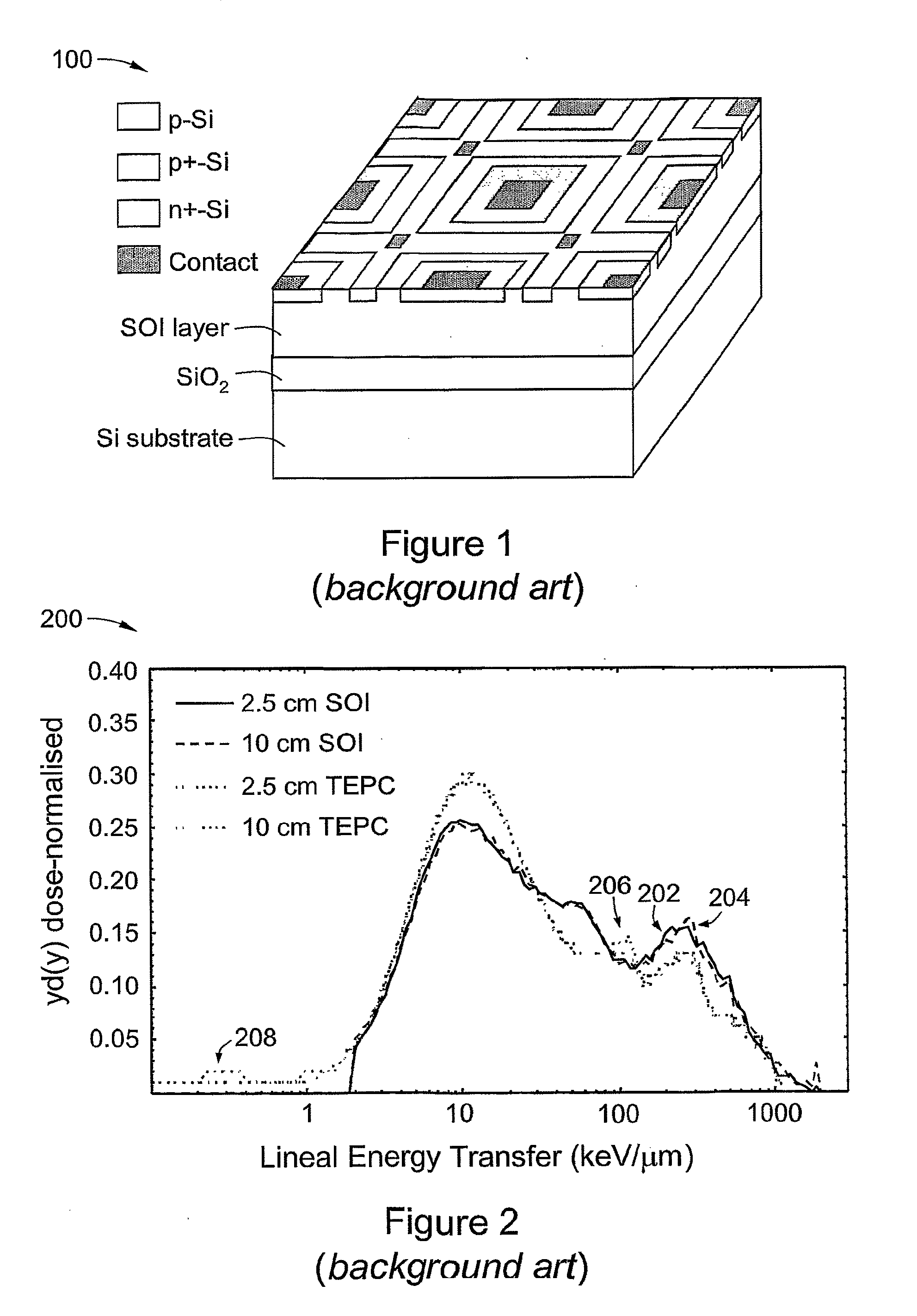

Method and apparatus for tissue equivalent solid state microdosimetry

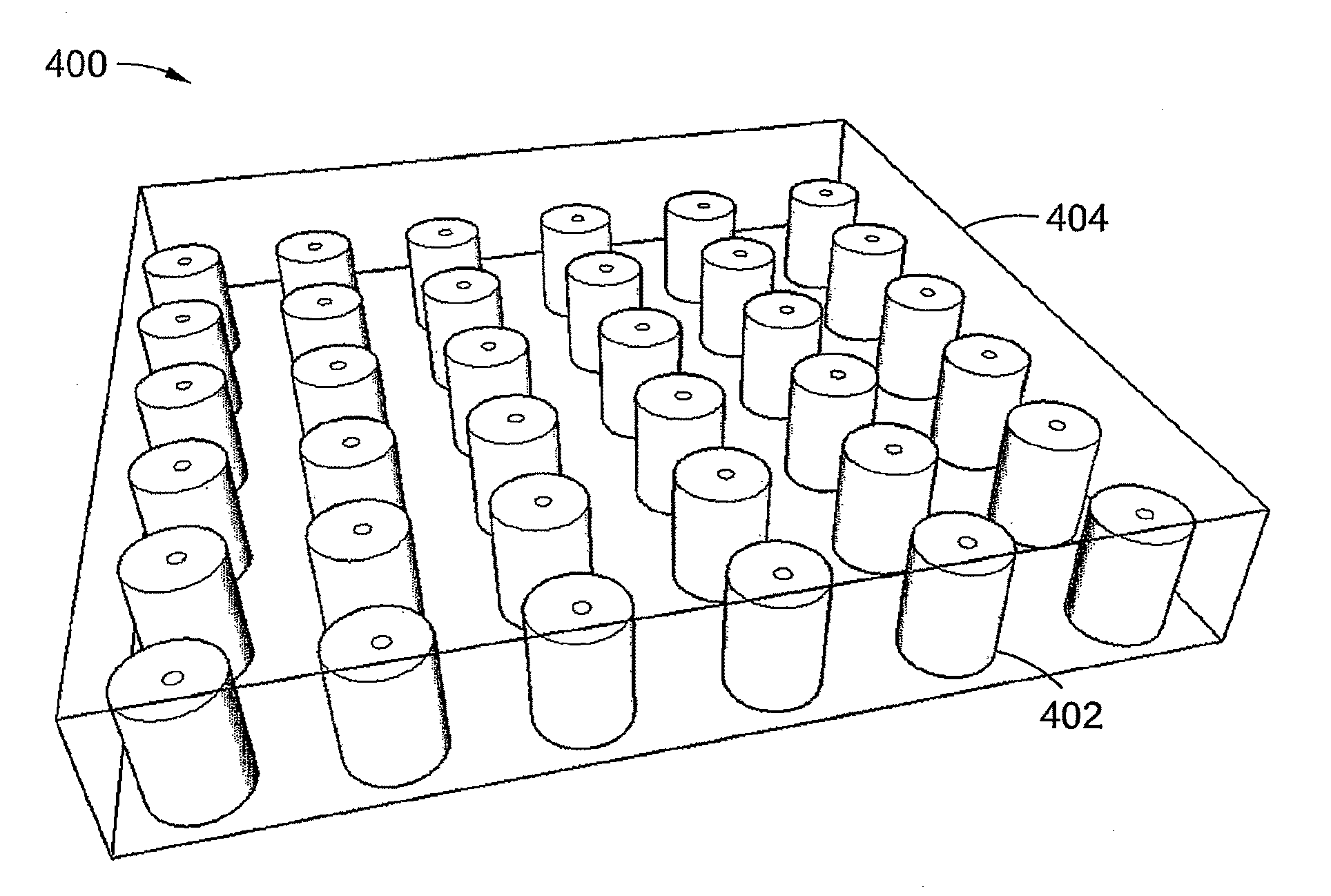

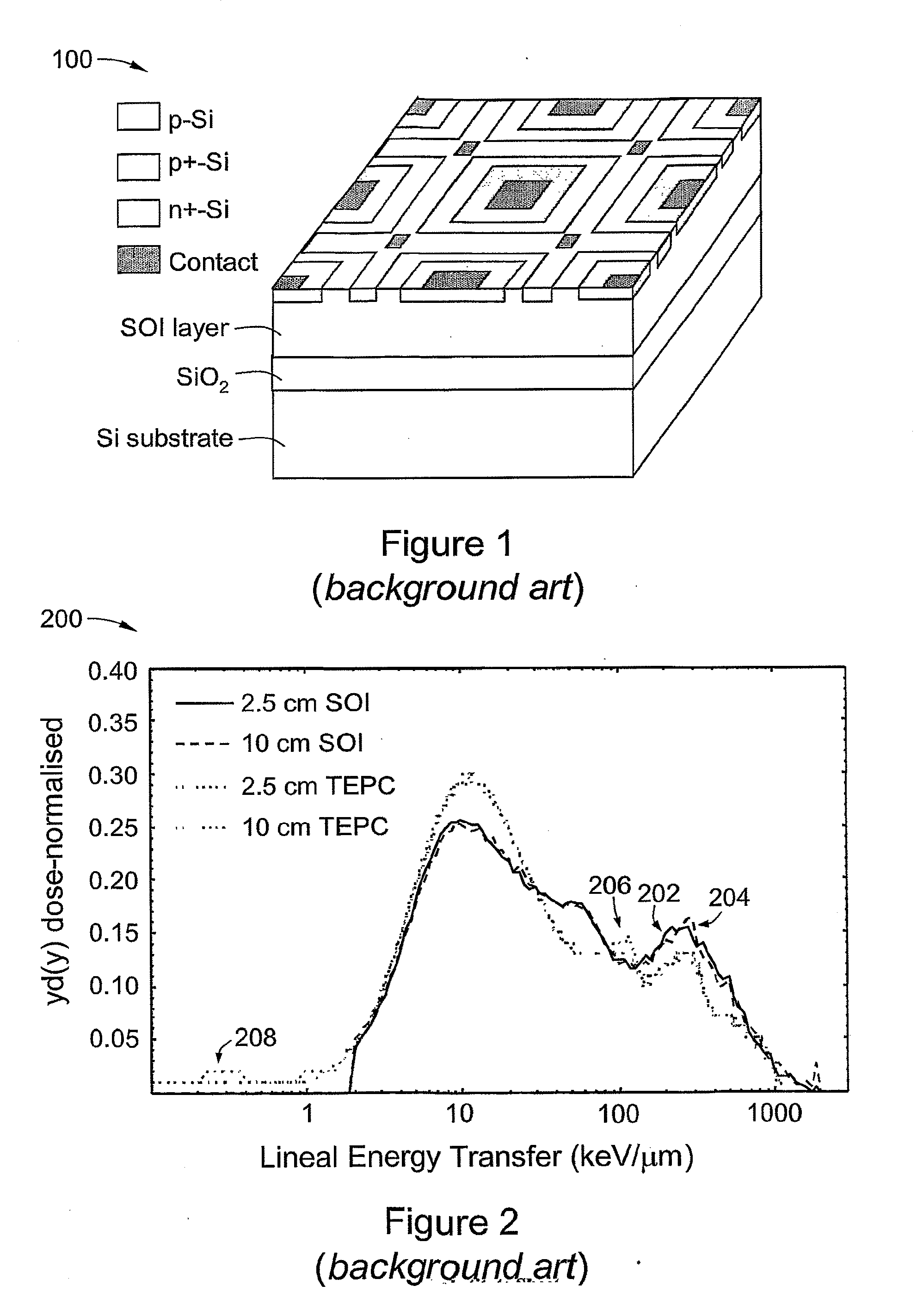

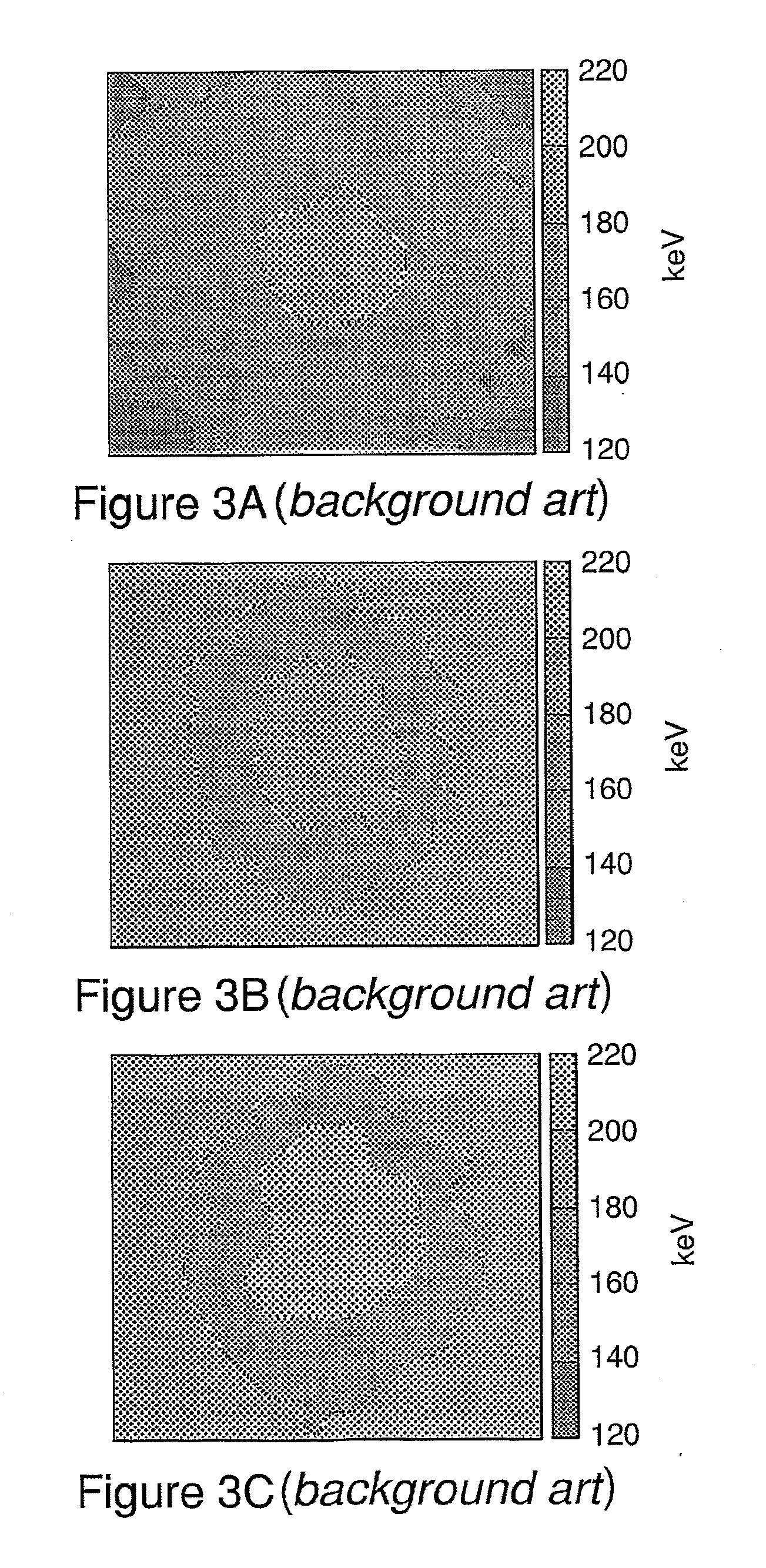

ActiveUS8421022B2Little noiseReduce errorsX-ray/infra-red processesDosimetersSemiconductor detectorP–n junction

A microdosimeter, comprising an array of three-dimensional p-n junction semiconductor detectors, each providing a sensitive volume-target and a tissue equivalent medium for generating secondary charged particles. The array is manufactured from a semiconductor on insulator wafer and the detectors are located to detect secondary charged particles generated in the tissue equivalent medium.

Owner:UNIV OF WOLLONGONG

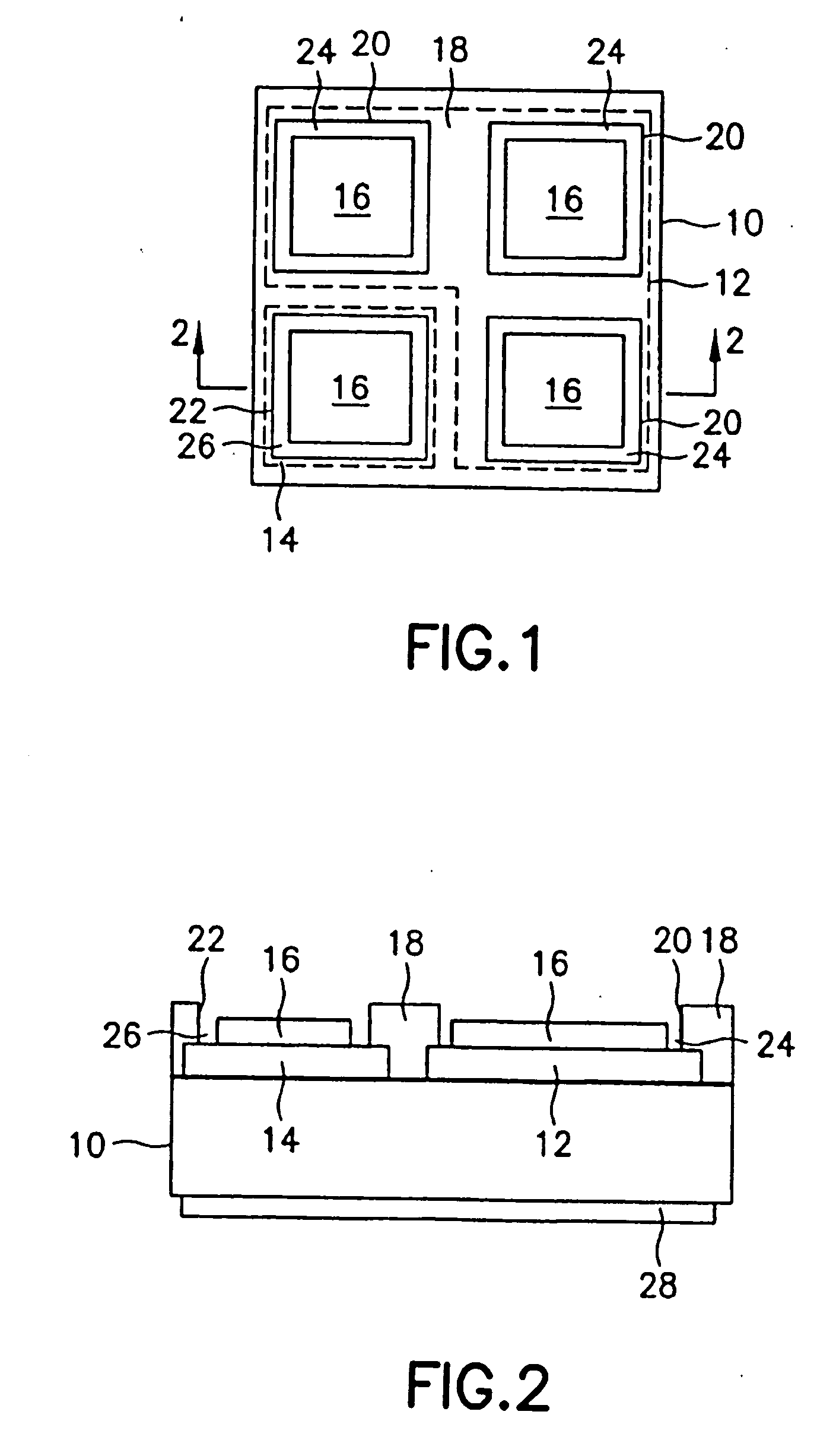

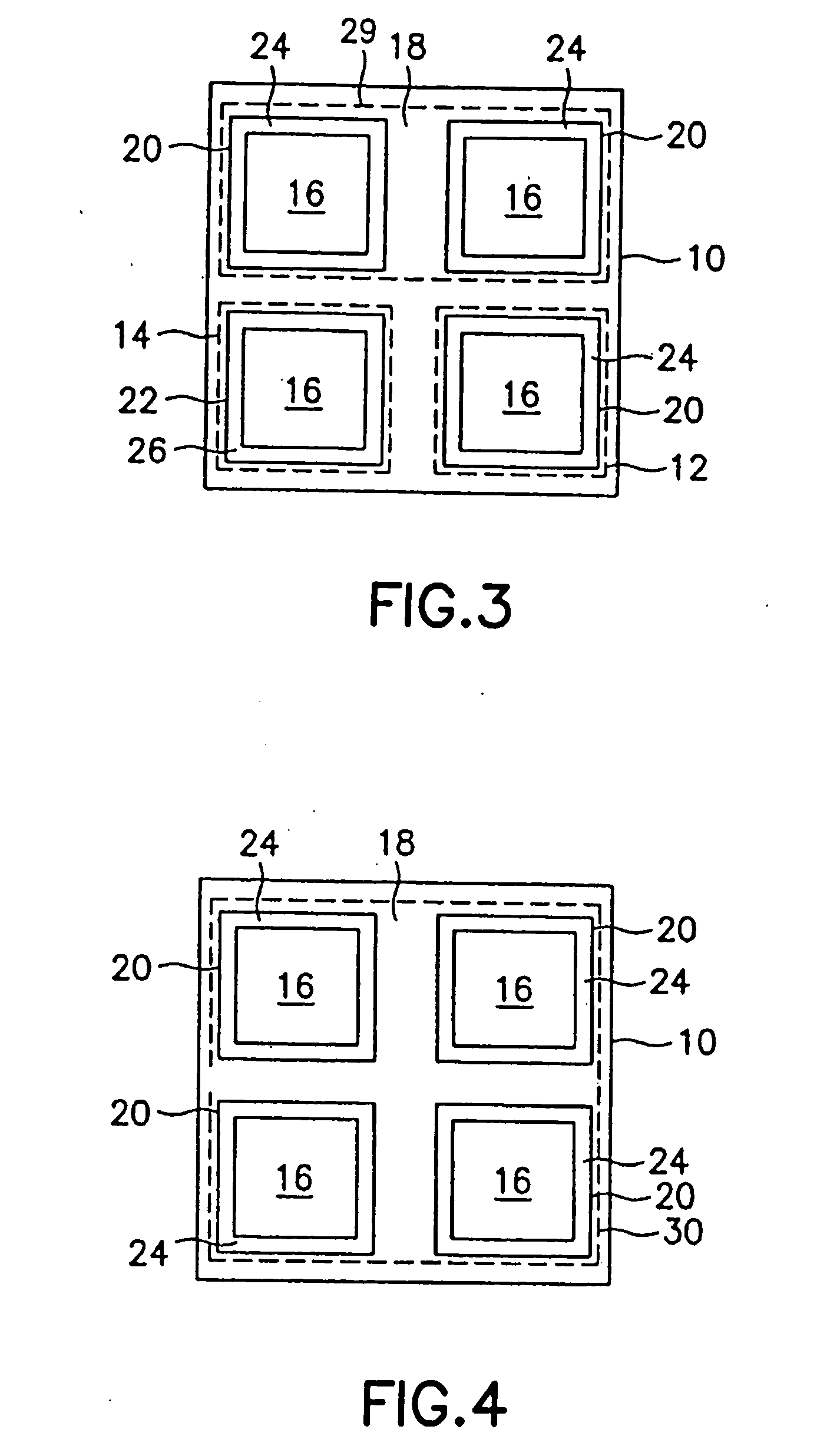

Semiconductor package fabrication

ActiveUS20060205112A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package fabrication method in which drop on demand deposition of a drop on demand depositable material is used to prepare one component or a plurality of components of a semiconductor package or multi-chip module.

Owner:INFINEON TECH AMERICAS CORP

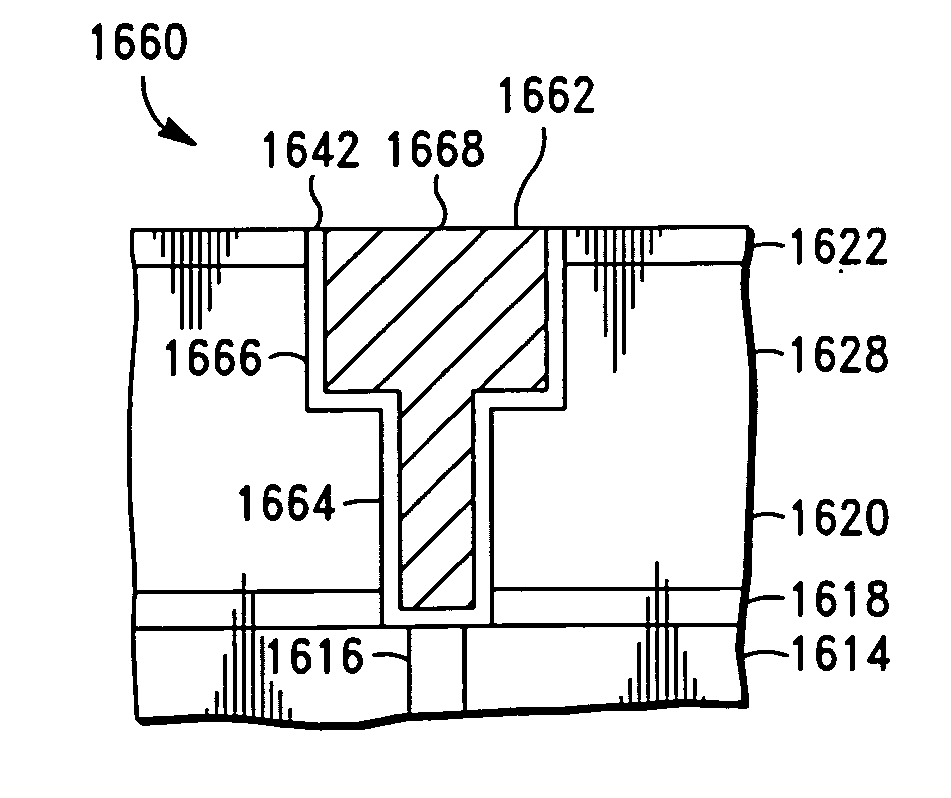

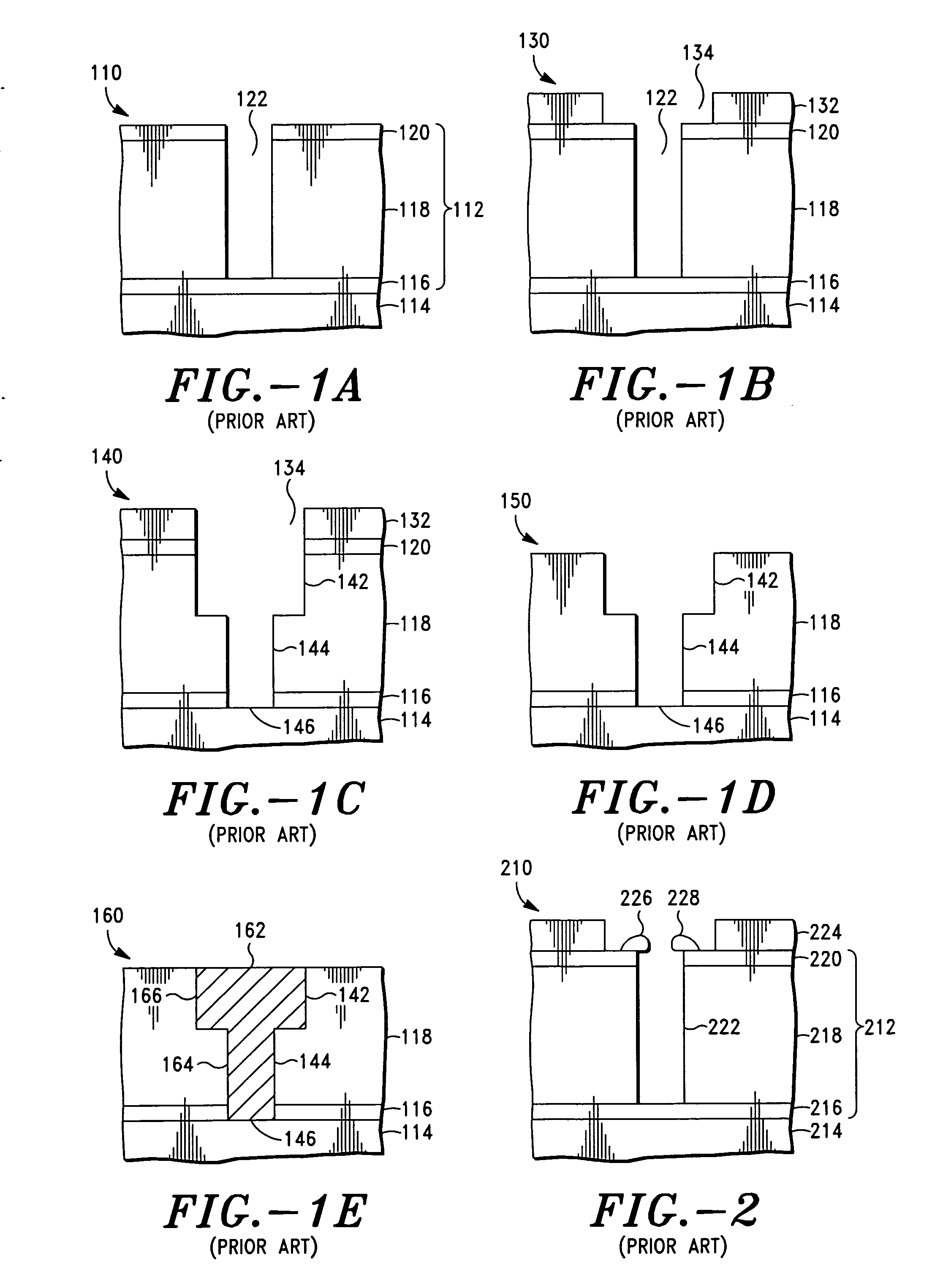

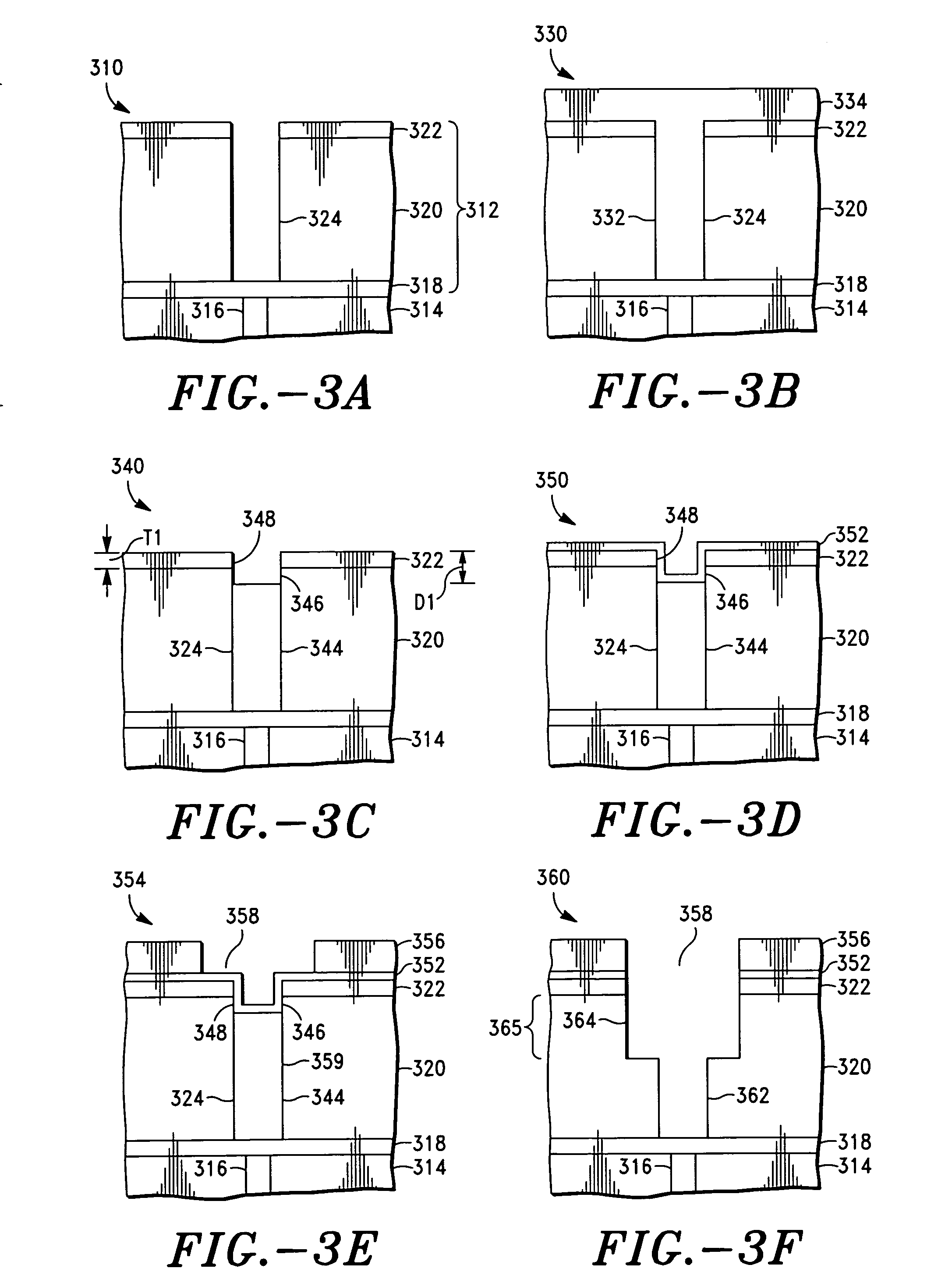

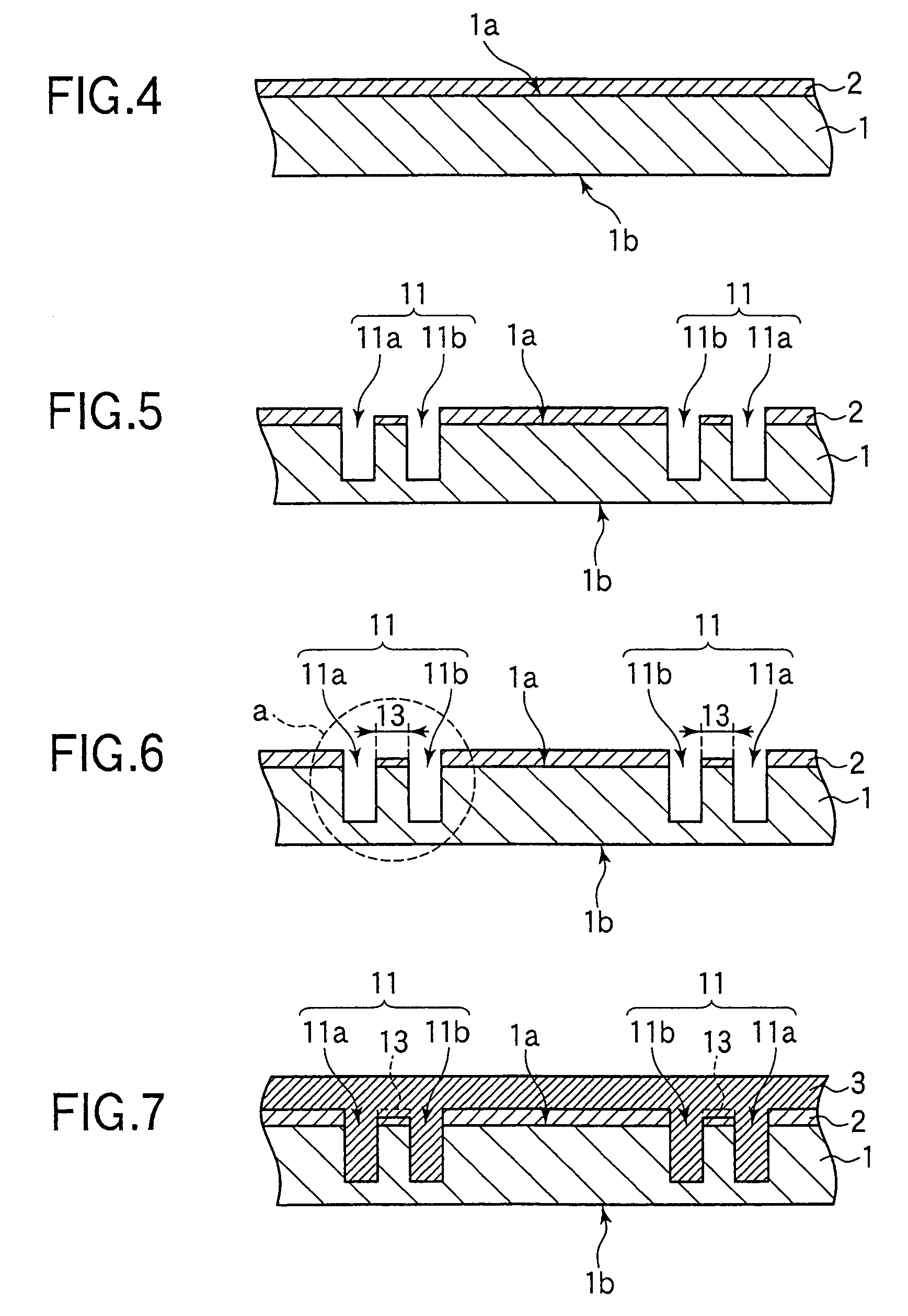

Integrated circuit fabricating techniques employing sacrificial liners

InactiveUS20070082477A1Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor wafer fabricationPhotoresist

The present invention provides techniques for fabricating integrated circuit structures in semiconductor wafer fabrication. A via hole is prepared in a dielectric stack having a bottom via etch stop layer. The via hole is not extended through the via etch stop layer at this stage of the process. The via hole is partly filled with a sacrificial via fill such that a recess without sacrificial via fill is formed in the top portion of the via hole. A substantially conformal sacrificial layer is deposited on the top surface of the dielectric stack and in the recess. Then, a photoresist layer is deposited on the sacrificial fill. A trench etch mask overlaying the via hole, is developed in the photoresist layer. This mask is etched through the sacrificial layer that is formed on the top surface of the dielectric stack as well as through the sacrificial fill and sacrificial layer that is present in the via hole. Additionally, the mask is employed for etching a trench partly through the dielectric layer thereby forming a trench and an underlying via hole. The via hole is then extended through the via etch stop layer. Subsequently, the photoresist layer and the sacrificial layer are removed from the top surface of the dielectric stack resulting in a trench and underlying via hole that is suitable for fabricating a dual damascene structure. Alternatively, a recess can be formed by depositing a substantially conformal sacrificial layer on the top surface of the dielectric stack and in the via hole to form a lined via hole. The lined via hole is then partly filled with a sacrificial via fill such that a recess without sacrificial via fill is formed in the top portion of the lined via hole. Next, a photoresist layer is deposited in the recess and on the sacrificial liner that is deposited on the top surface of the dielectric stack.

Owner:APPLIED MATERIALS INC

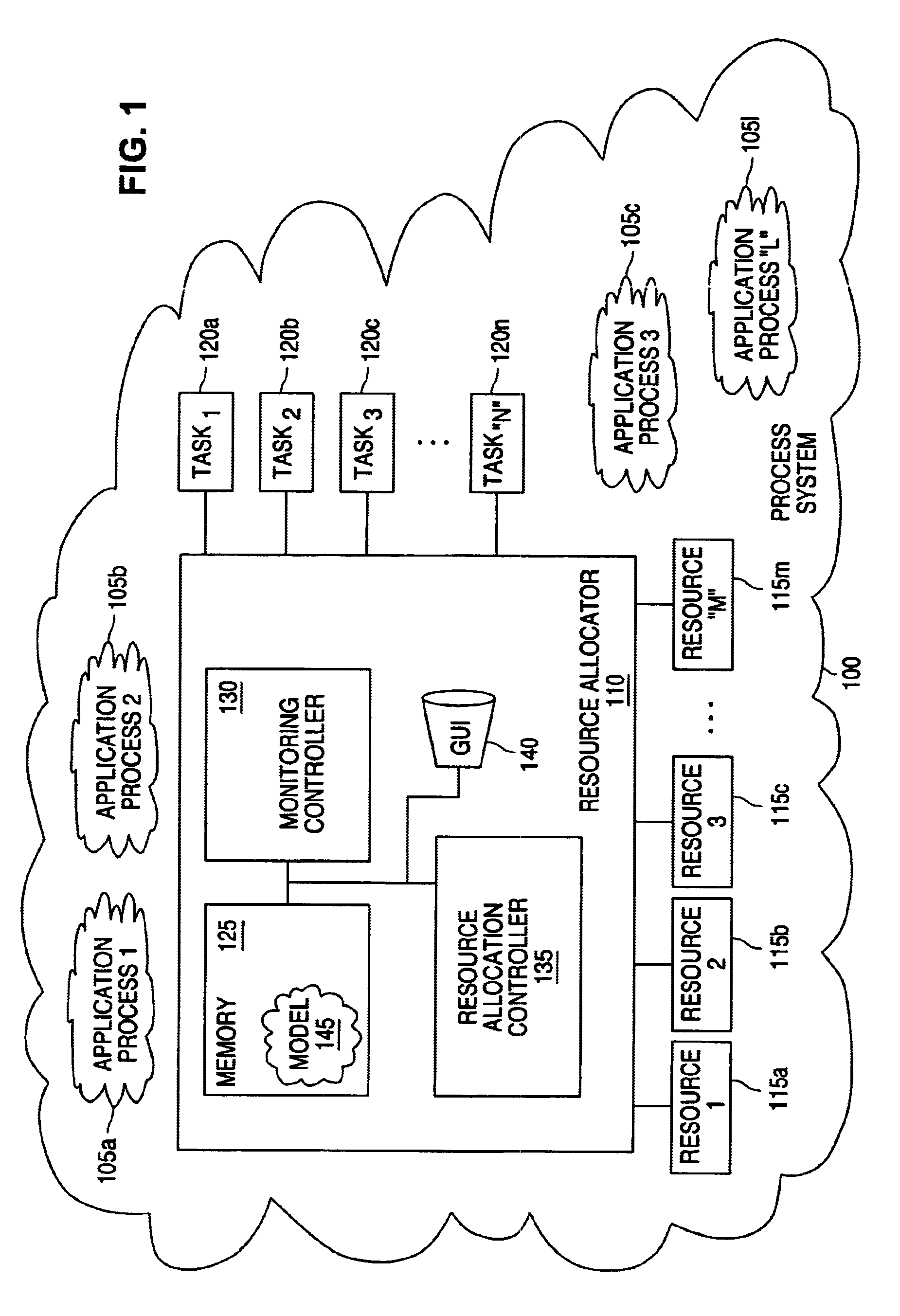

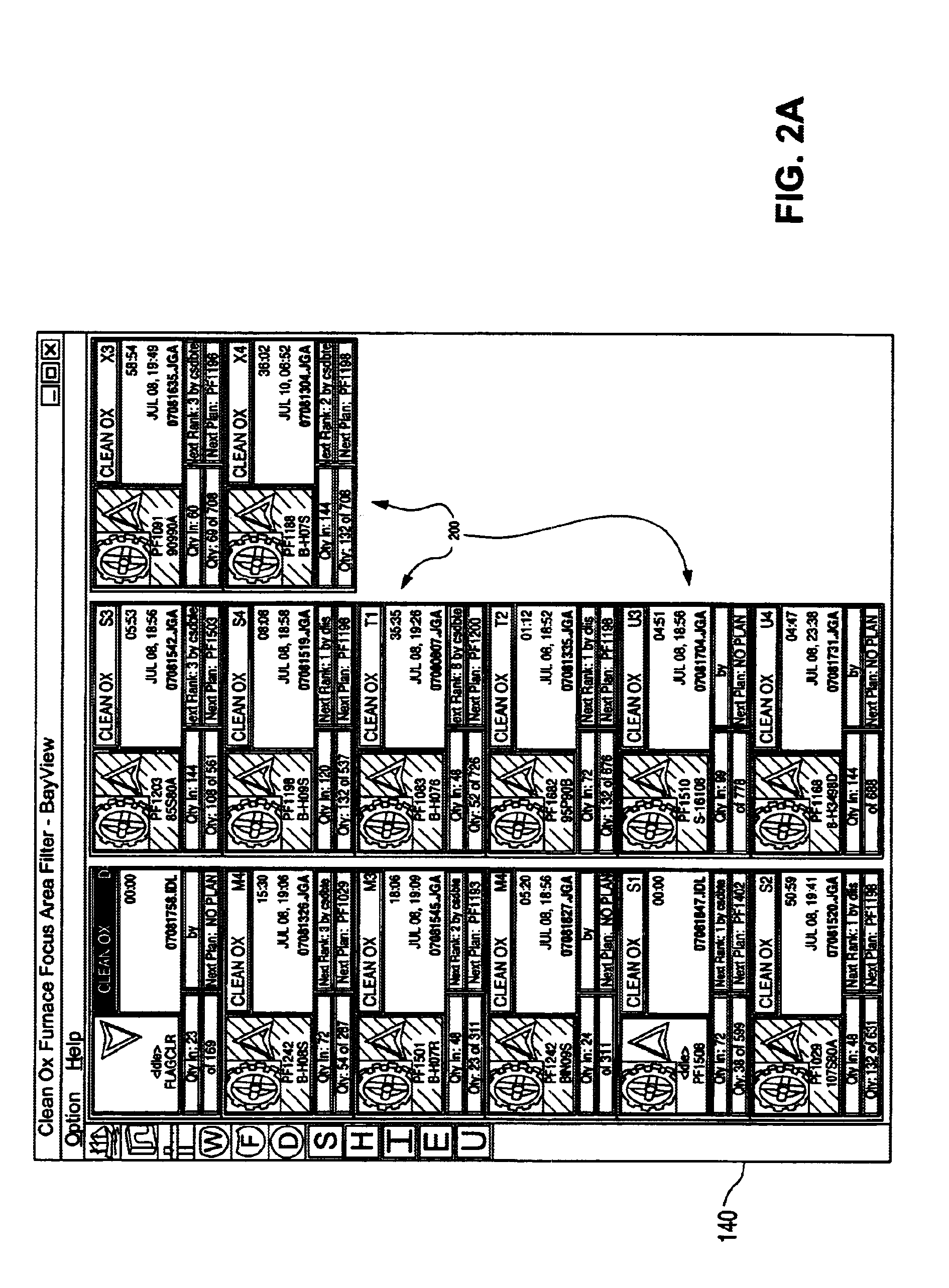

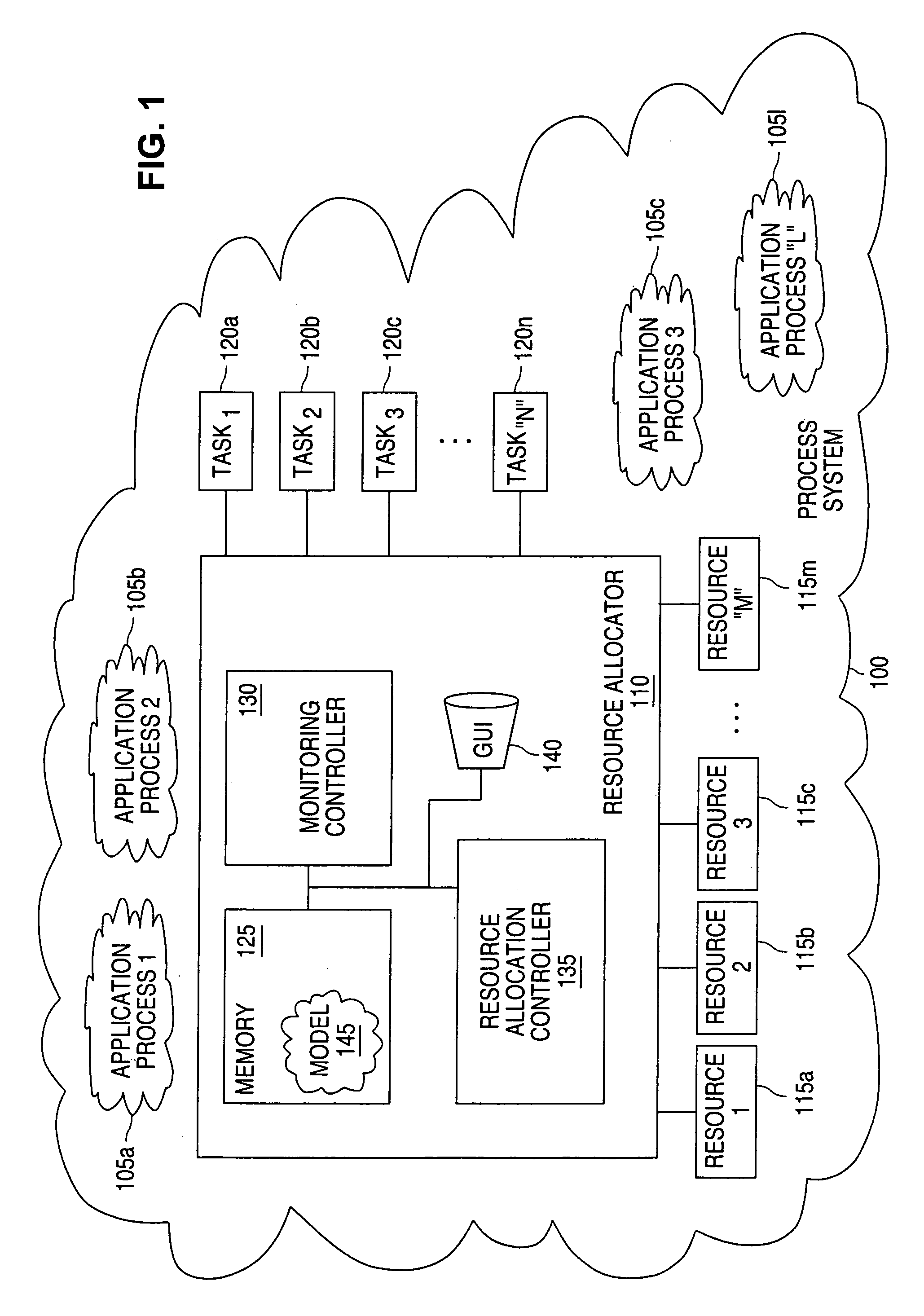

Graphical user interface for allocating multi-function resources in semiconductor wafer fabrication and method of operation

A system and method is disclosed for allocating multi-function resources among a plurality of tasks within a process system in semiconductor wafer fabrication. A resource allocator allocates multi-function resources among tasks within a process system that executes at least one application process. The resource allocator comprises a monitoring controller, model of the process system, a resource allocation controller, and a graphical user interface. The graphical user interface transforms process system information of the resource allocator into an audio-visual format to enable supervisory interaction. In one embodiment the graphical user interface provides information to reduce load conflict among multiple furnaces in semiconductor wafer fabrication.

Owner:NAT SEMICON CORP

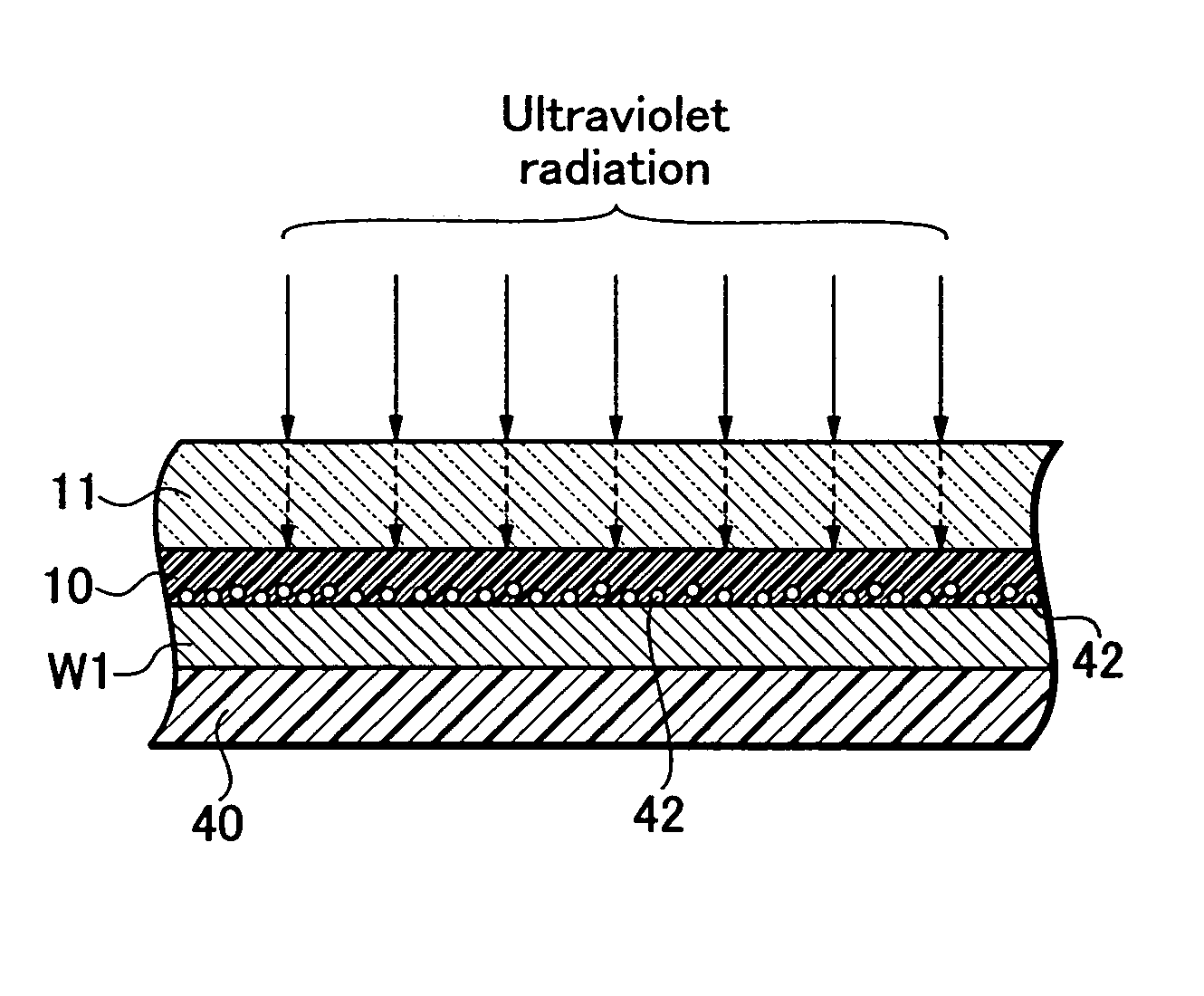

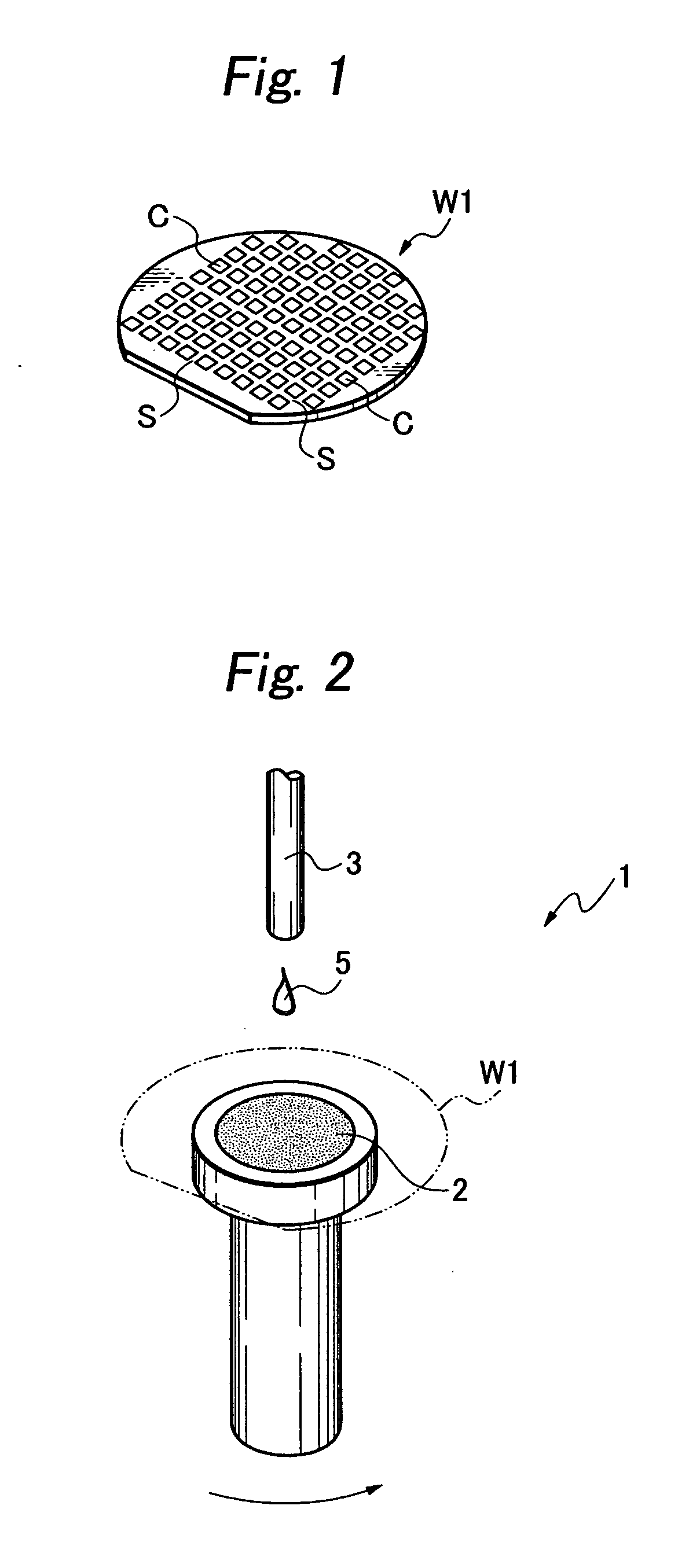

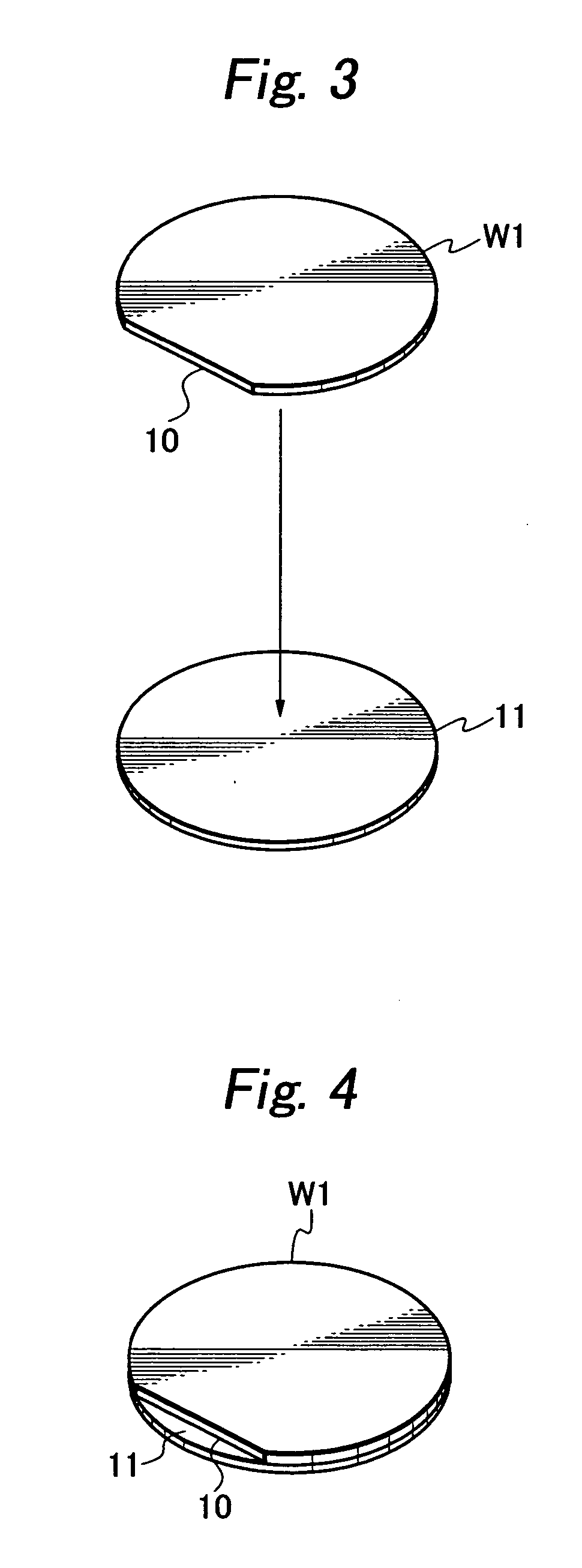

Method for manufacturing semiconductor chip

InactiveUS20040192012A1Reduce adhesionSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor chipEngineering

In manufacturing thinned semiconductor chips by grinding a semiconductor wafer supported on a rigid support substrate, in order to remove semiconductor wafer or semiconductor chips from the support substrate without damage to the semiconductor wafer or semiconductor chips, a semiconductor wafer at its surface is bonded on a light-transmissive support substrate through an adhesive layer having an adhesion force to reduce upon exposed to light radiation, thereby exposing the back surface of the semiconductor wafer. A tape is bonded to the backside of the semiconductor wafer integrated with the support substrate of after grinding, wherein the tape is supported at the periphery. Before or after bonding of the tape, light radiation is applied to the adhesive layer at a side close to the support substrate to reduce the adhesion force in the adhesion layer. Thereafter, the support substrate and adhesive layer is removed from the surface of the semiconductor wafer, leaving the semiconductor wafer held by the tape and frame. The semiconductor wafer supported by the tape and frame is cut at streets into individual semiconductor chips.

Owner:KANSAI PAINT CO LTD +1

Method and apparatus for utilizing integrated metrology data as feed-forward data

InactiveUS20030097198A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingMetrologyEngineering

A method and an apparatus for performing feed-forward correction during semiconductor wafer manufacturing. A first process on a semiconductor wafer is performed. Integrated metrology data related to the first process of the semiconductor wafer is acquired. An integrated metrology feed-forward process is performed based upon the integrated metrology data, the integrated metrology feed-forward process comprising identifying at least one error on the semiconductor wafer based upon the integrated metrology data related to the first process of the semiconductor wafer and performing an adjustment process to a second process to be performed on the wafer to compensate for the error. The second process on the semiconductor wafer is performed based upon the adjustment process.

Owner:GLOBALFOUNDRIES US INC

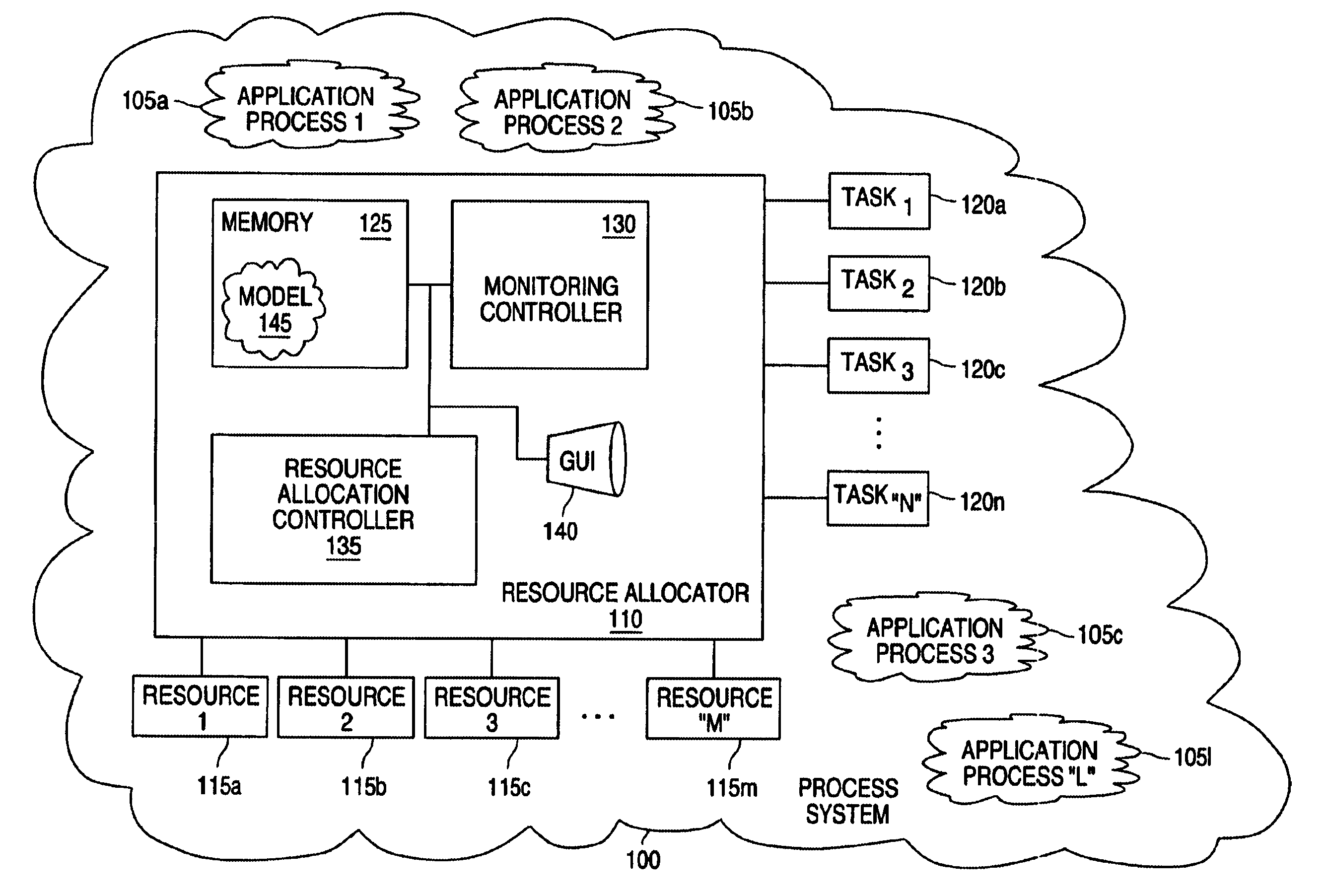

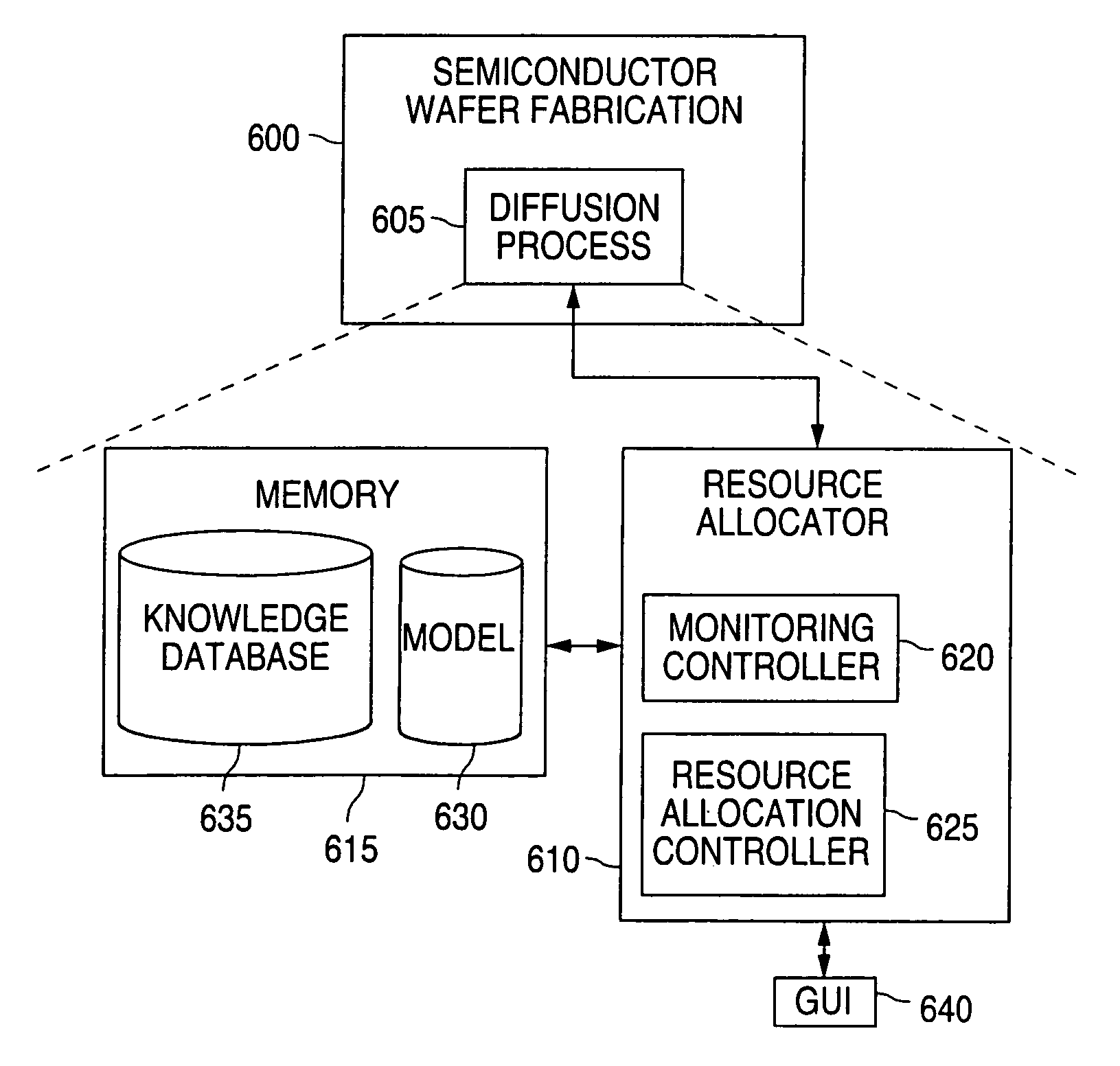

System and method for allocating multi-function resources for a wetdeck process in semiconductor wafer fabrication

InactiveUS7184850B1Efficient executionProgramme controlComputer controlProcess systemsApplication software

A system and method is disclosed for allocating multi-function resources among a plurality of tasks within a wetdeck process in semiconductor wafer fabrication. A resource allocator allocates multi-function resources among tasks within a process system that executes at least one application process. The resource allocator comprises a monitoring controller, model of the process system and a resource allocation controller. The monitoring controller monitors measurable characteristics associated with the executing application process, multi-function resources and tasks. The model represents the multi-function resources and the tasks, and defines relationships among them. The resource allocation controller operates the model in response to the monitored measurable characteristics and allocates ones of the multi-function resources among ones of the tasks to efficiently execute the wetdeck process of the semiconductor wafer fabrication process.

Owner:NAT SEMICON CORP

Method and apparatus for tissue equivalent solid state microdosimetry

ActiveUS20100090118A1Accurate observationLittle noiseX-ray/infra-red processesDosimetersSemiconductor detectorP–n junction

A microdosimeter, comprising an array of three-dimensional p-n junction semiconductor detectors, each providing a sensitive volume-target and a tissue equivalent medium for generating secondary charged particles. The array is manufactured from a semiconductor on insulator wafer and the detectors are located to detect secondary charged particles generated in the tissue equivalent medium.

Owner:UNIV OF WOLLONGONG

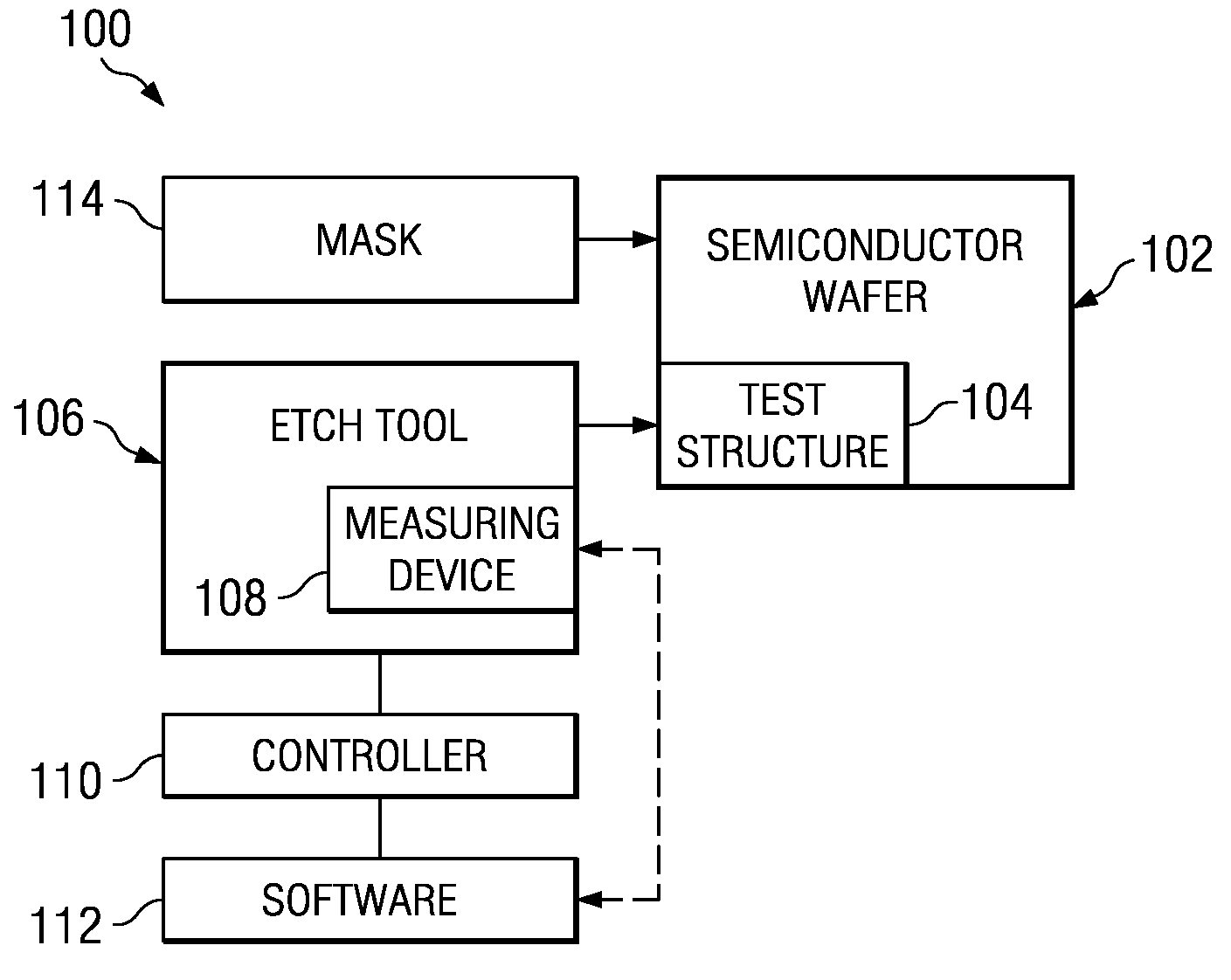

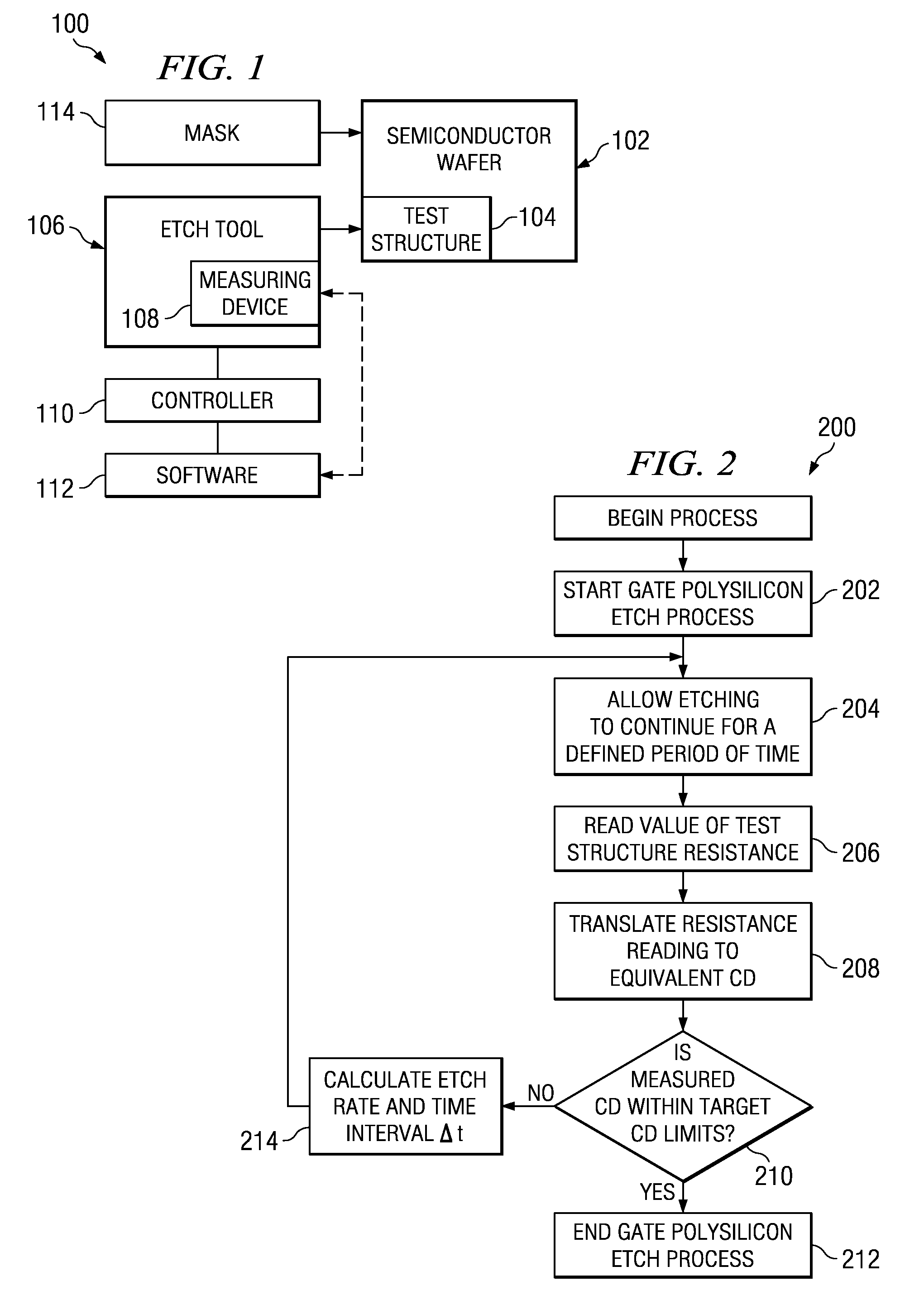

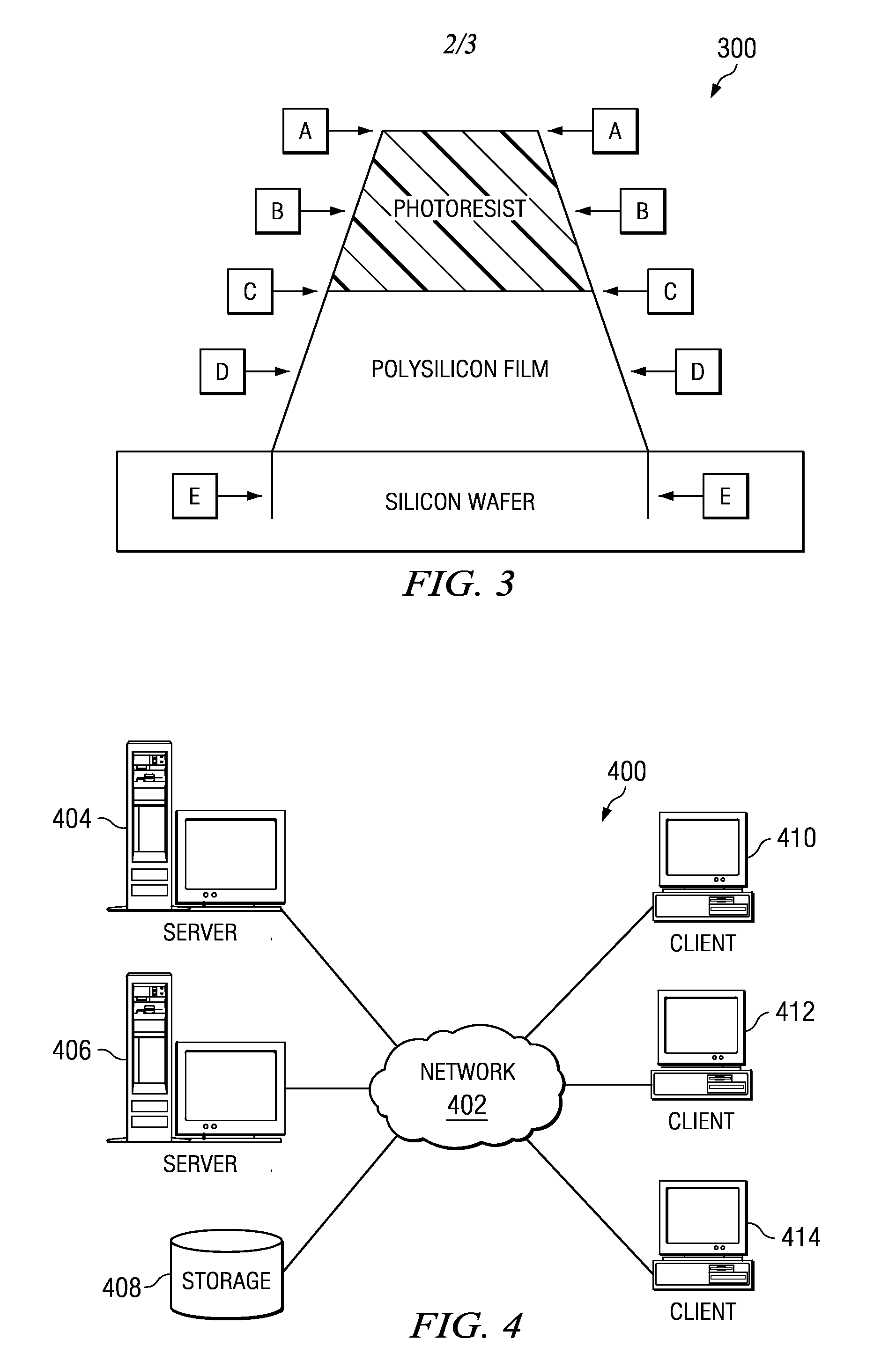

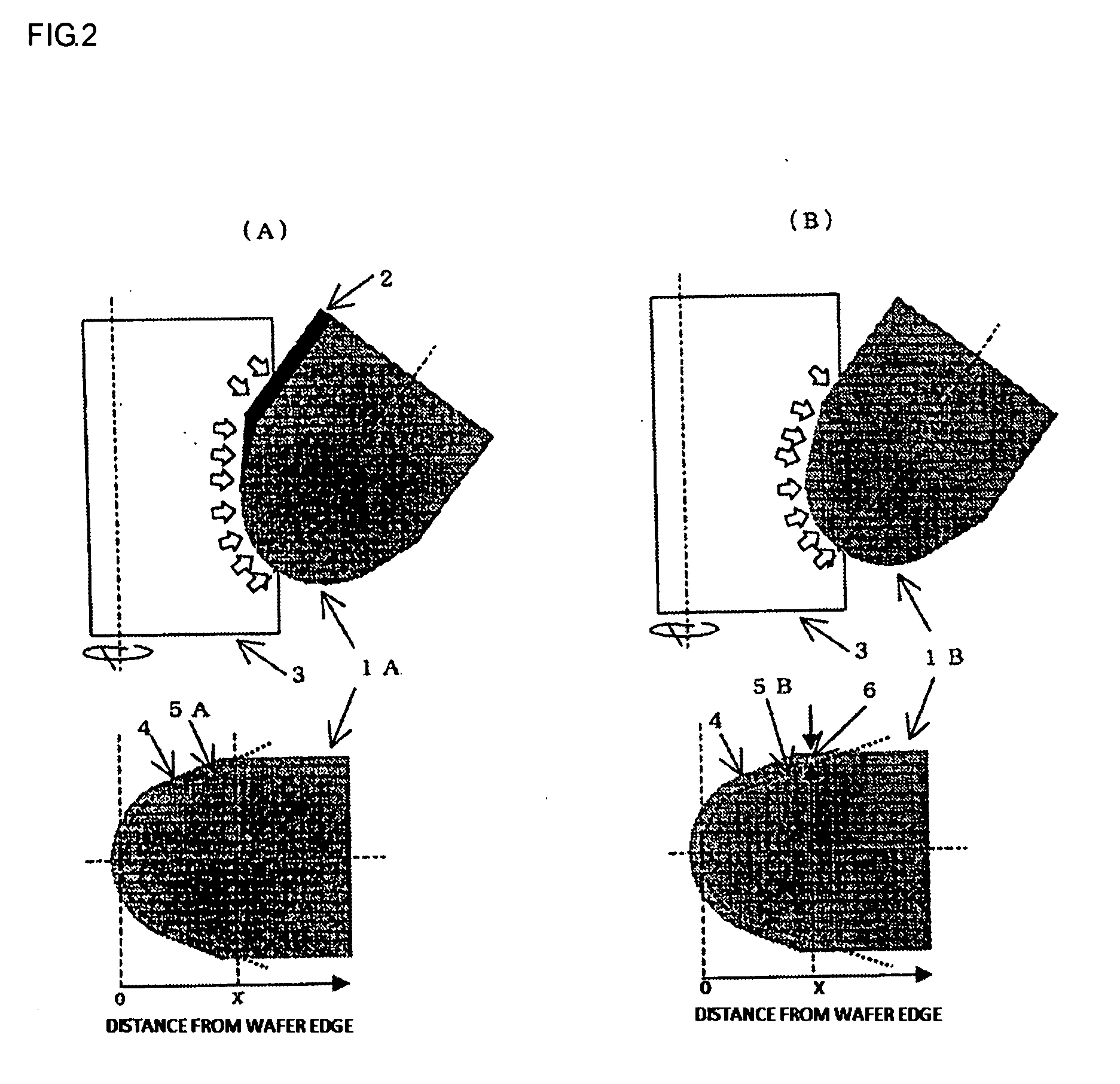

Control of Critical Dimensions of Etched Structures on Semiconductor Wafers

InactiveUS20080185103A1Semiconductor/solid-state device testing/measurementSolid-state devicesMonitoring and controlEngineering

A system for real-time monitoring and control of critical dimensions during semiconductor wafer fabrication is provided. The system measures structures in situ, that is, as they are being etched onto a wafer layer.

Owner:IBM CORP

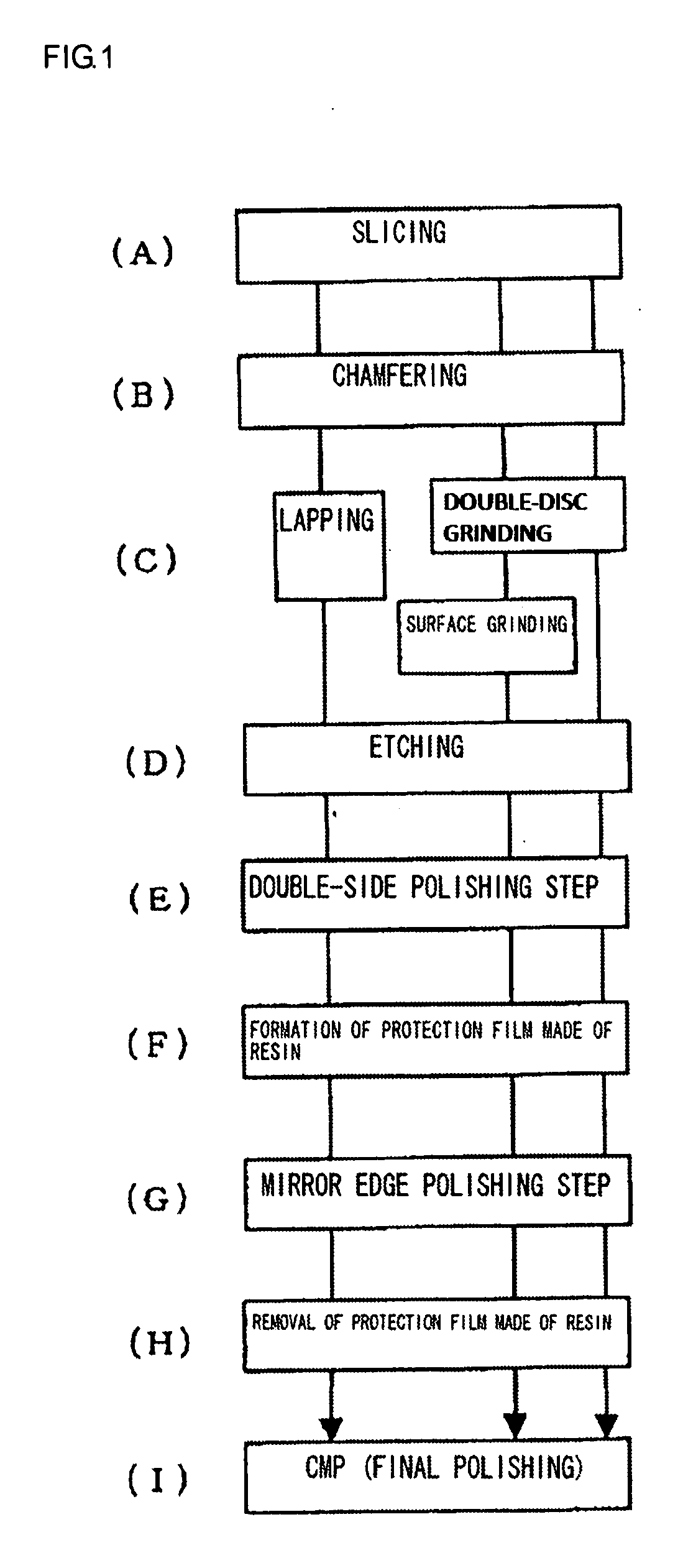

Semiconductor Wafer Fabricating Method and Semiconductor Wafer Mirror Edge Polishing Method

InactiveUS20080113510A1Low costExcessively polishedEdge grinding machinesSemiconductor/solid-state device manufacturingEdge surfaceEngineering

There is provided a semiconductor wafer fabricating method comprising at least: a double-side polishing step of mirror-polishing a front surface and a back surface of a semiconductor wafer; and a mirror edge polishing step of mirror-polishing a chamfered part of the double-side-polished semiconductor wafer, wherein a protection film made of a resin which suppresses polishing is formed on the front surface or both the front and back surfaces of the semiconductor wafer after the double-side polishing step, then the mirror edge polishing step is carried out, and thereafter the protection film made of a resin is removed. As a result, it is possible to provide a step of eliminating an increase in a cost due to, e.g., a facility investment or an increase in the number of steps as much as possible, removing a scratch or an impression on an edge surface of the chamfered part of the semiconductor wafer, and suppressing excessive polishing caused when a polishing pad enters a main surface of the wafer at the mirror edge polishing step of mirror-polishing the chamfered part of the wafer, thereby preventing a wafer outer peripheral shape, especially an edge roll-off from being degraded.

Owner:SHIN-ETSU HANDOTAI CO LTD

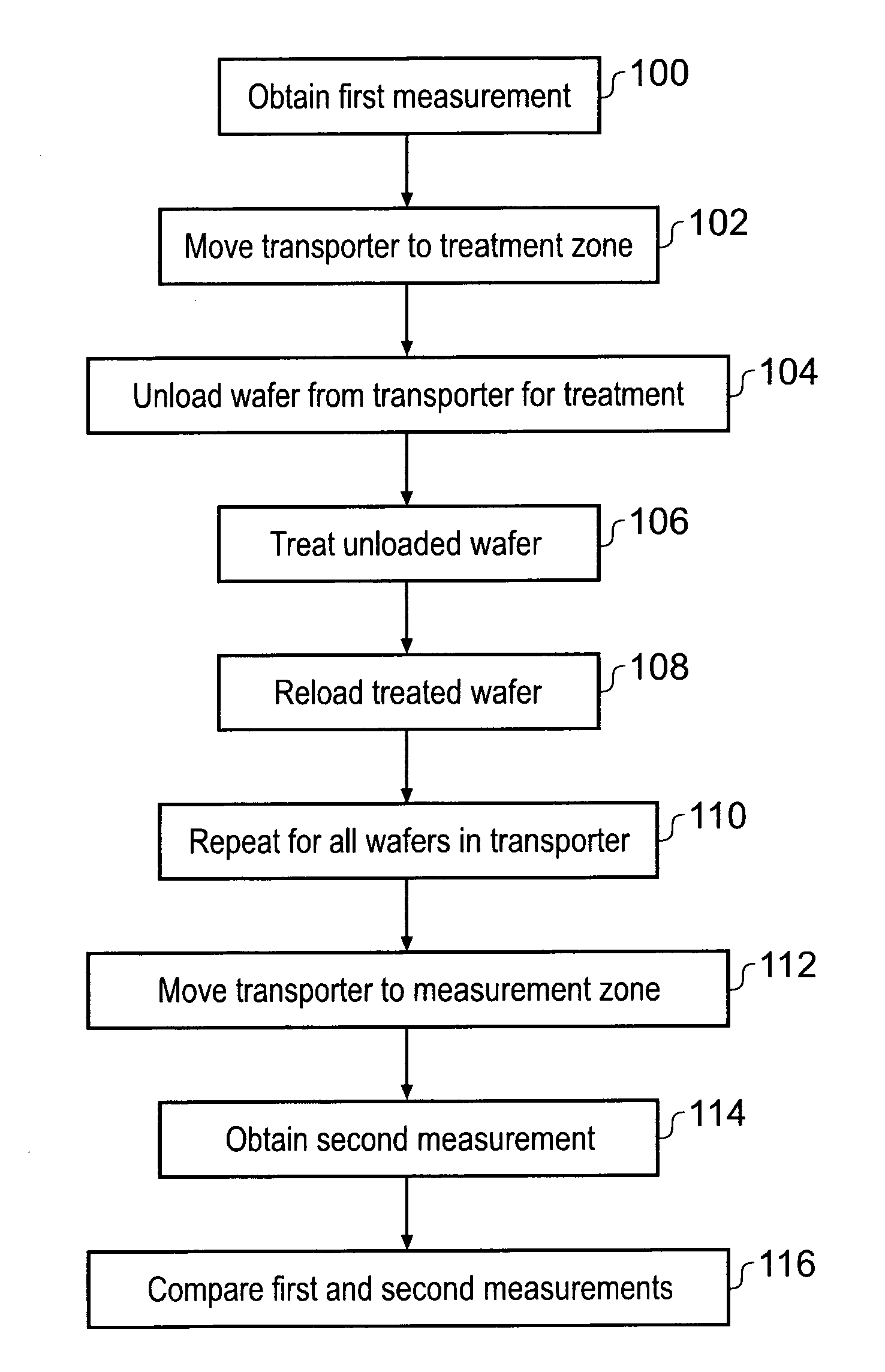

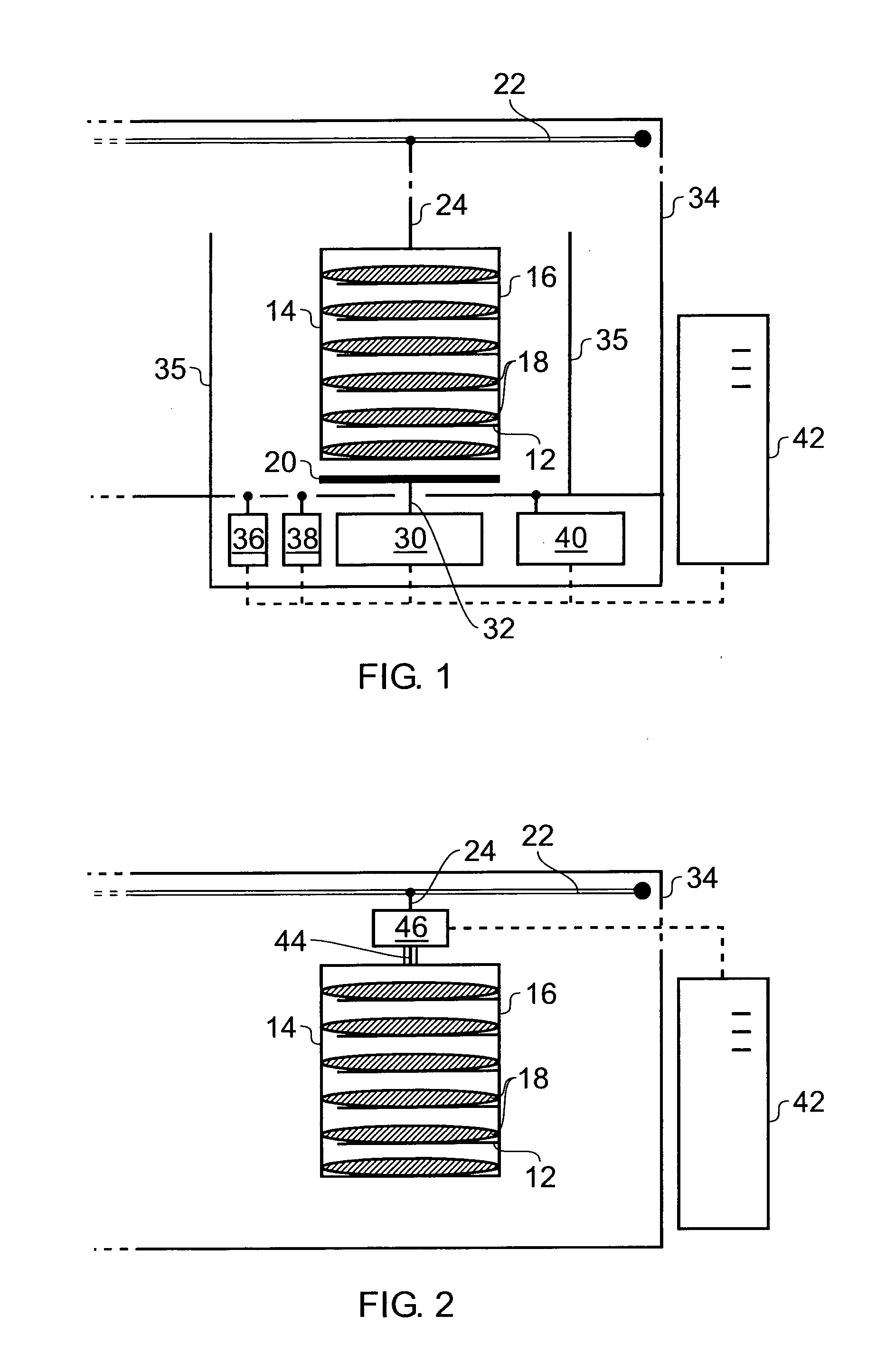

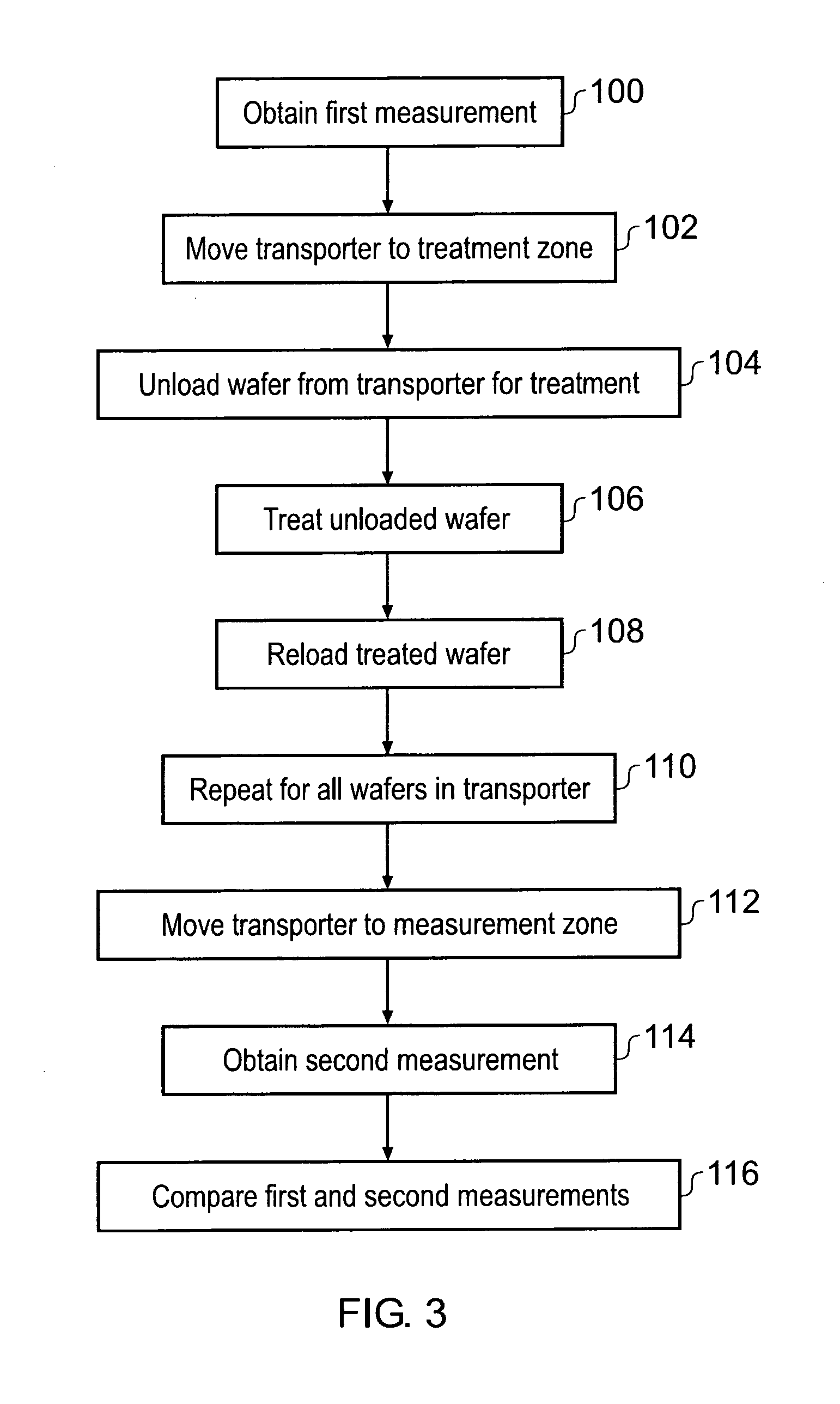

Semiconductor Wafer Monitoring Apparatus and Method

InactiveUS20110015773A1Improve efficiencyImprove throughputSemiconductor/solid-state device manufacturingSpecial data processing applicationsMetrologyEngineering

Metrology methods and apparatus for semiconductor wafer fabrication in which data for metrology is obtained by detecting a measurable property of a monitored entity, which is either (i) a wafer transporter (e.g. a FOUP) loaded with one or more wafers to be monitored, or (ii) a plurality of wafers. Performing metrology measurements on a loaded wafer transporter enables the step of extracting wafer (s) from the transporter for metrology measurements to be omitted. Moreover, metrology measurement may be obtained while transporting the wafer (s) between treatment locations. By considering a plurality of wafers as a unit, a single measurement representing a combination of individual wafer responses is obtained. All wafers contribute to the metrology measurement without the need to perform individual wafer measurements.

Owner:METRYX

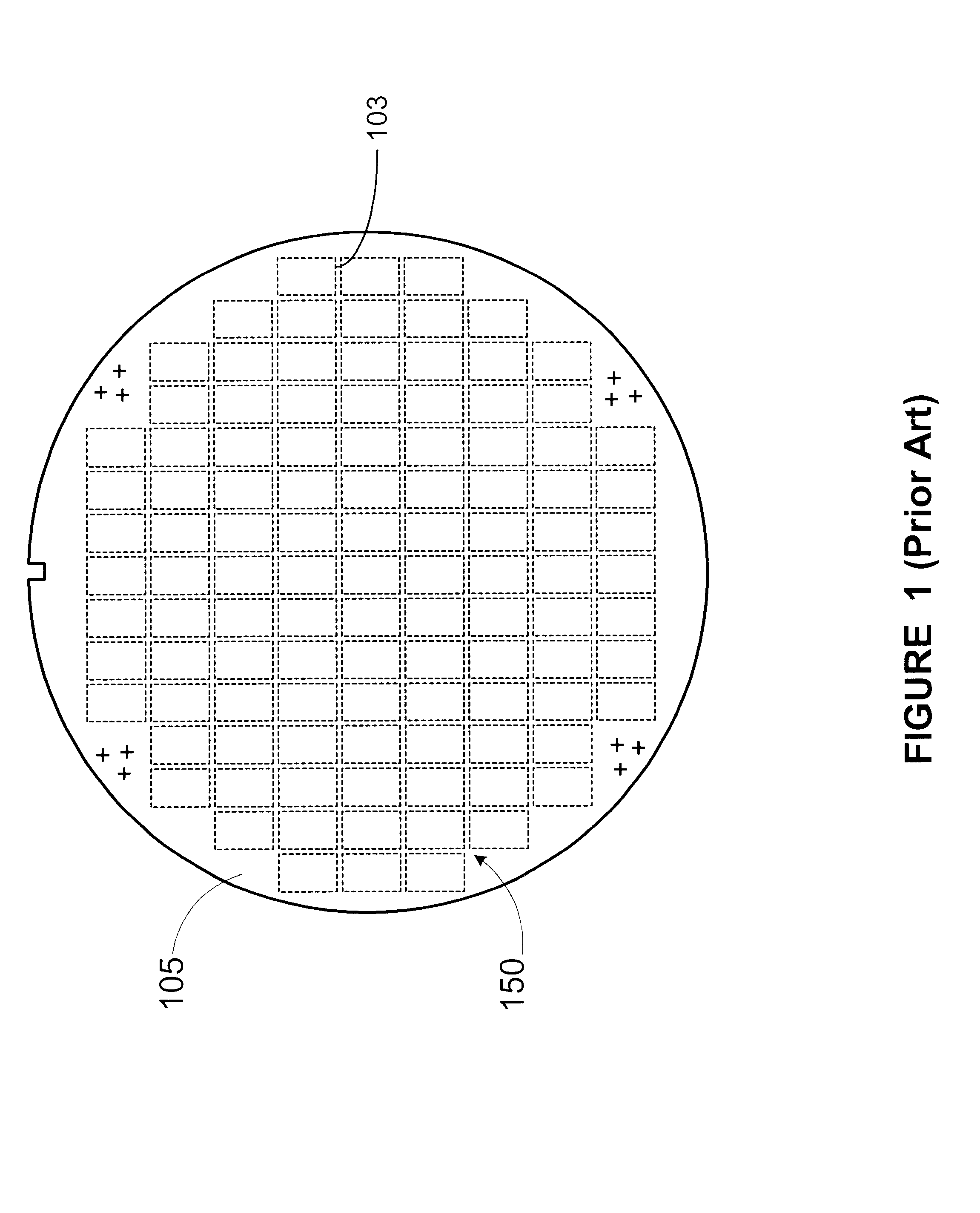

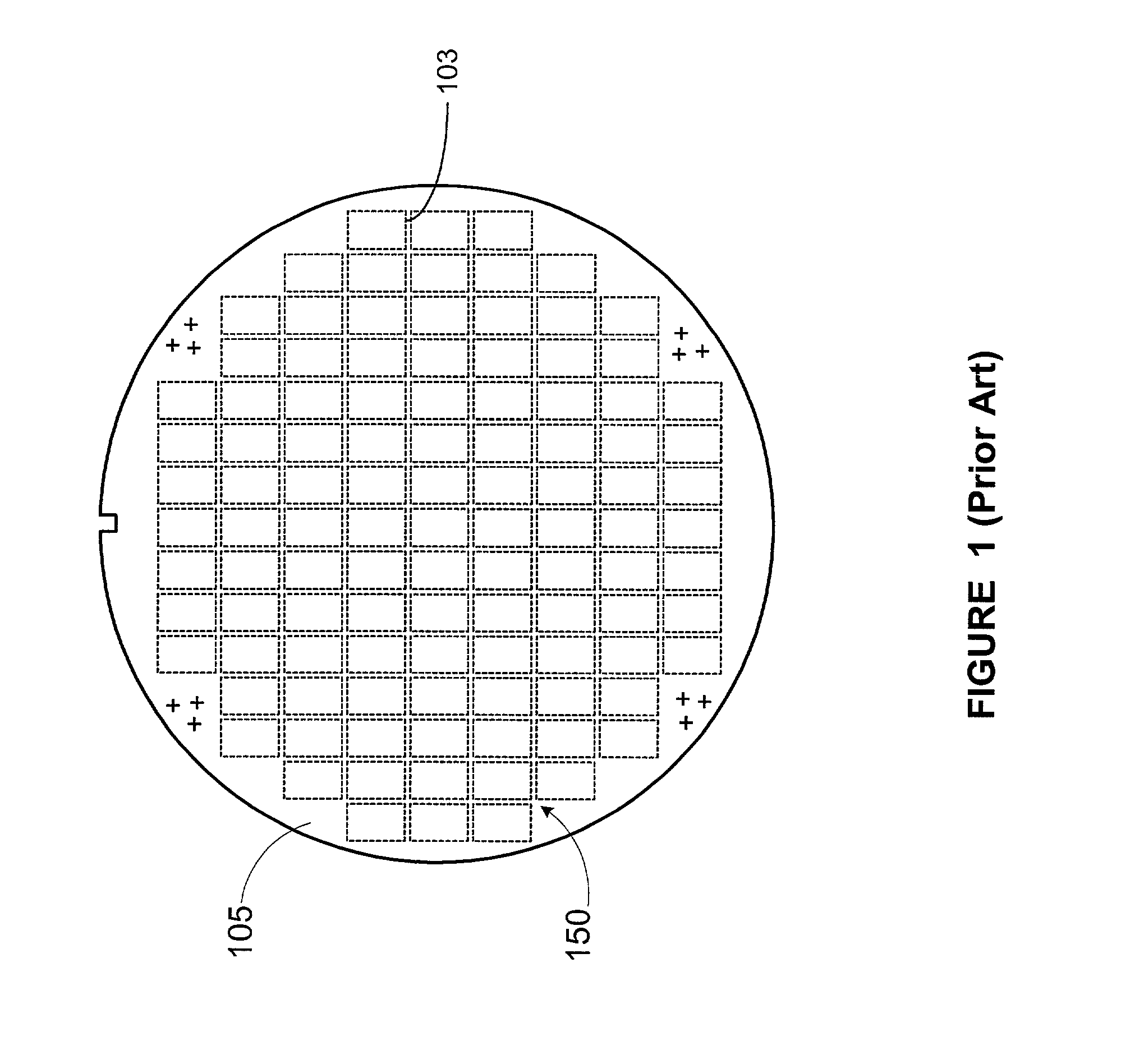

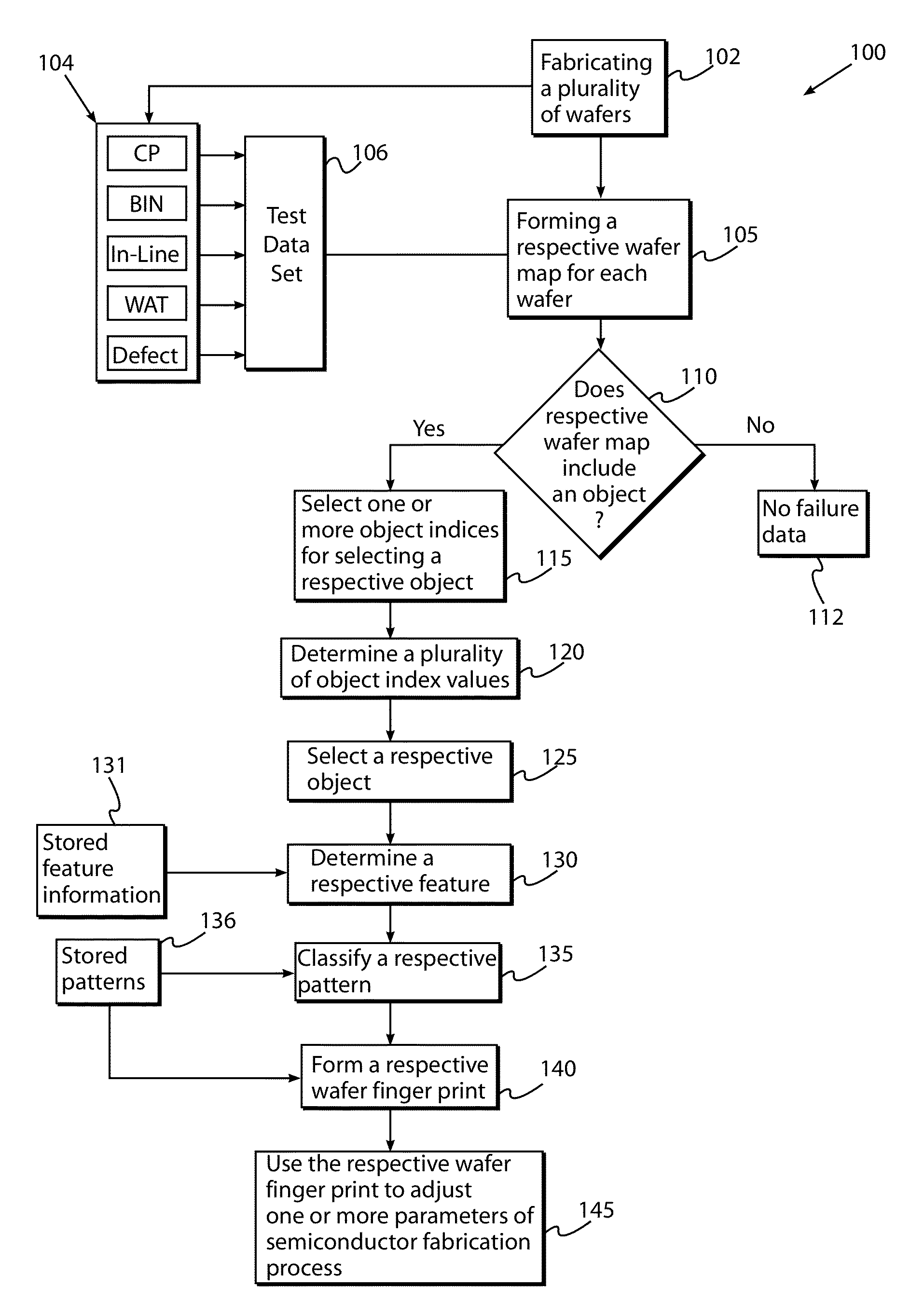

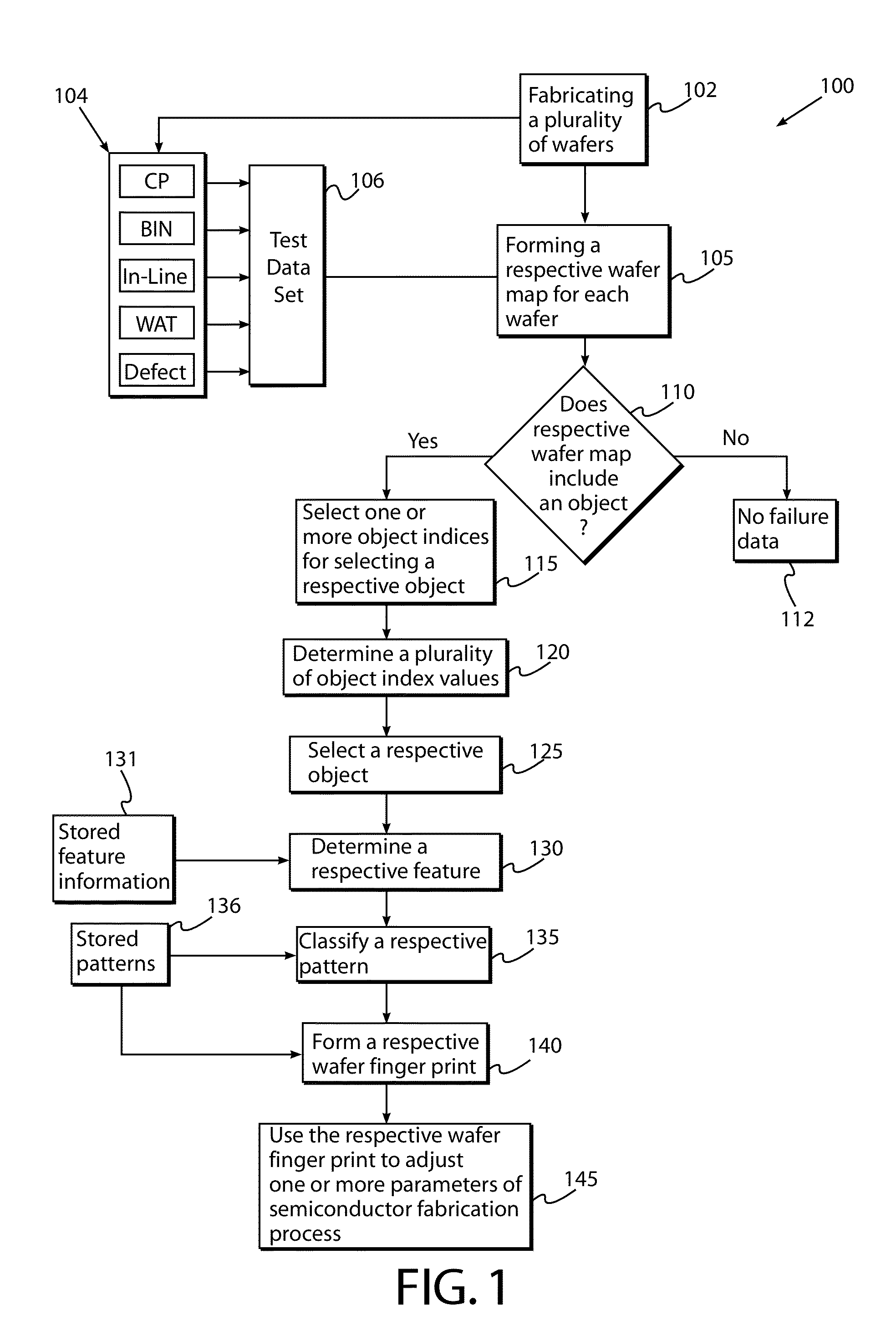

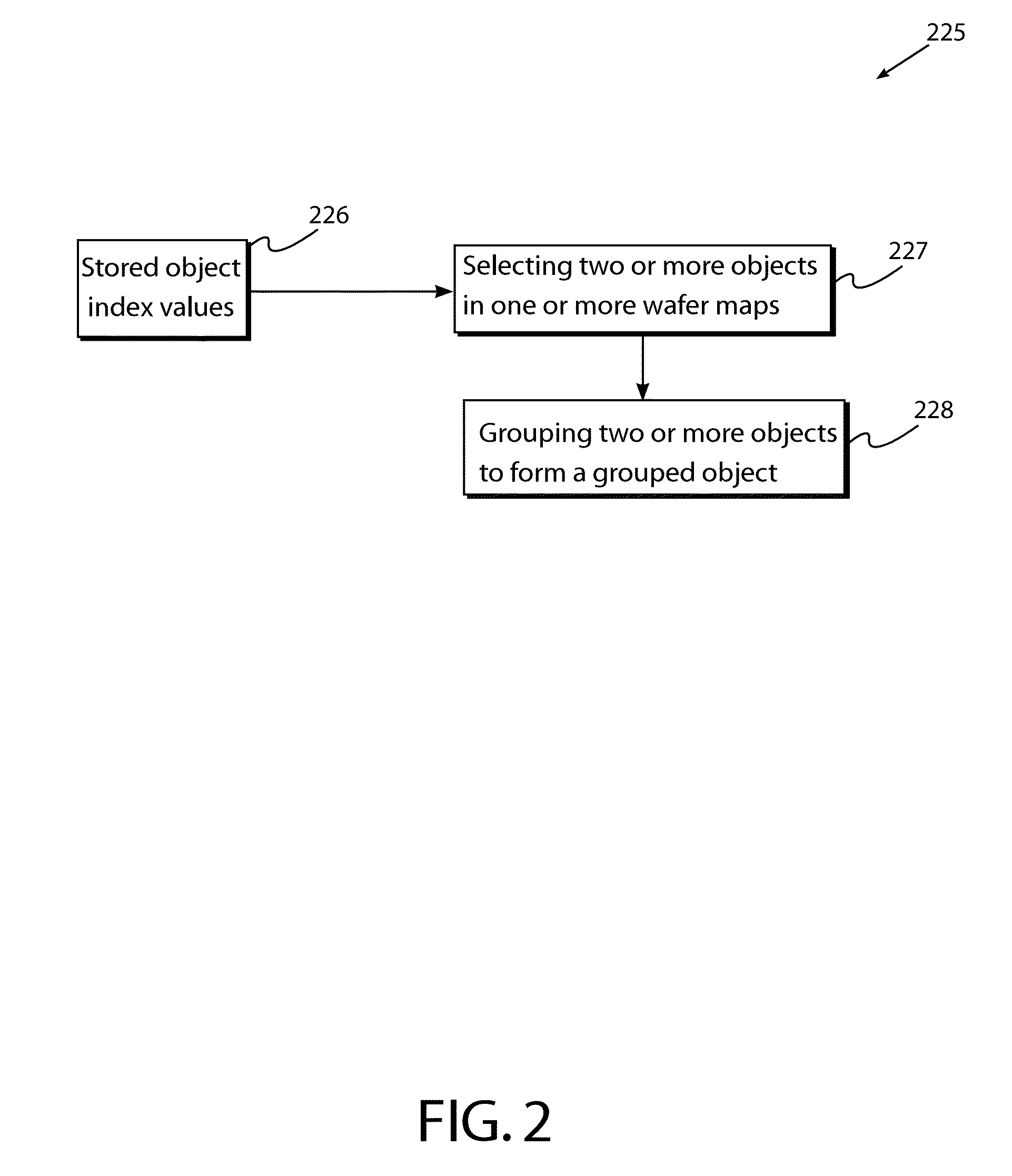

Systems and methods of automatically detecting failure patterns for semiconductor wafer fabrication processes

ActiveUS20130288403A1Semiconductor/solid-state device testing/measurementSolid-state devicesData setEngineering

A system and method of automatically detecting failure patterns for a semiconductor wafer process is provided. The method includes receiving a test data set collected from testing a plurality of semiconductor wafers, forming a respective wafer map for each of the wafers, determining whether each respective wafer map comprises one or more respective objects, selecting the wafer maps that are determined to comprise one or more respective objects, selecting one or more object indices for selecting a respective object in each respective selected wafer map, determining a plurality of object index values in each respective selected wafer map, selecting an object in each respective selected wafer map, determining a respective feature in each of the respective selected wafer, classifying a respective pattern for each of the respective selected wafer maps and using the respective wafer fingerprints to adjust one or more parameters of the semiconductor fabrication process.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor device, stacked structure, and manufacturing method

ActiveUS7649249B2Improve cooling effectImprove packaging efficiencySemiconductor/solid-state device detailsSolid-state devicesWafer dicingSemiconductor chip

An array of electrically conductive members, formed around the edges of a semiconductor device or chip, penetrate from one major surface of the device to the other major surface. In an area located inward of this array, a multiplicity of thermally conductive members also penetrate from one major surface to the other major surface. The semiconductor device can be manufactured from a semiconductor wafer by creating holes that penetrate partway through the wafer, filling the holes with metal to form the electrically conductive members and thermally conductive members, and then grinding the lower surface of the wafer to expose the ends of the electrically conductive members and thermally conductive members before dicing the wafer into chips. The thermally conductive members improve heat dissipation performance when semiconductor chips of this type are combined into a stacked multichip package.

Owner:TAIWAN SEMICON MFG CO LTD

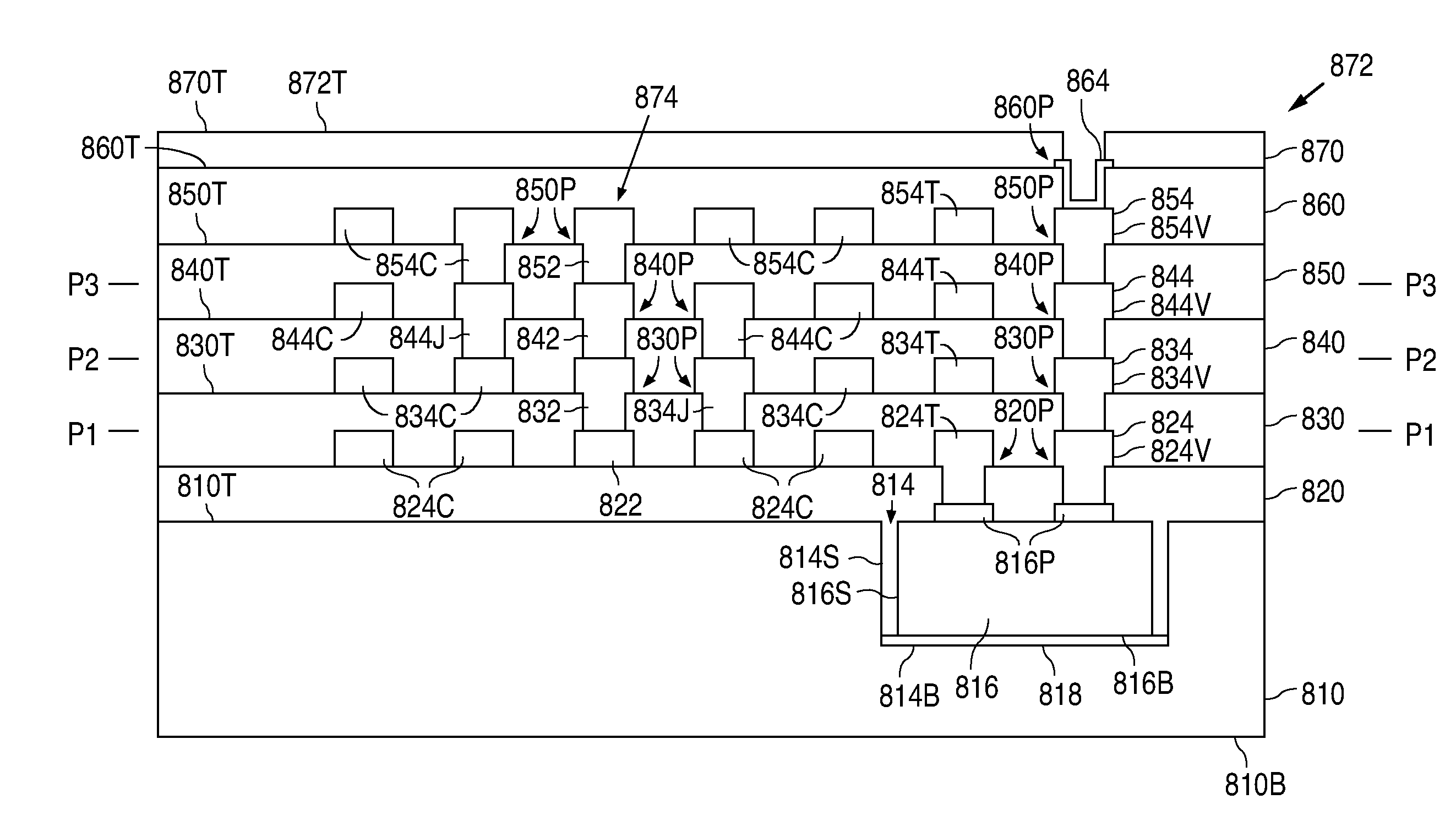

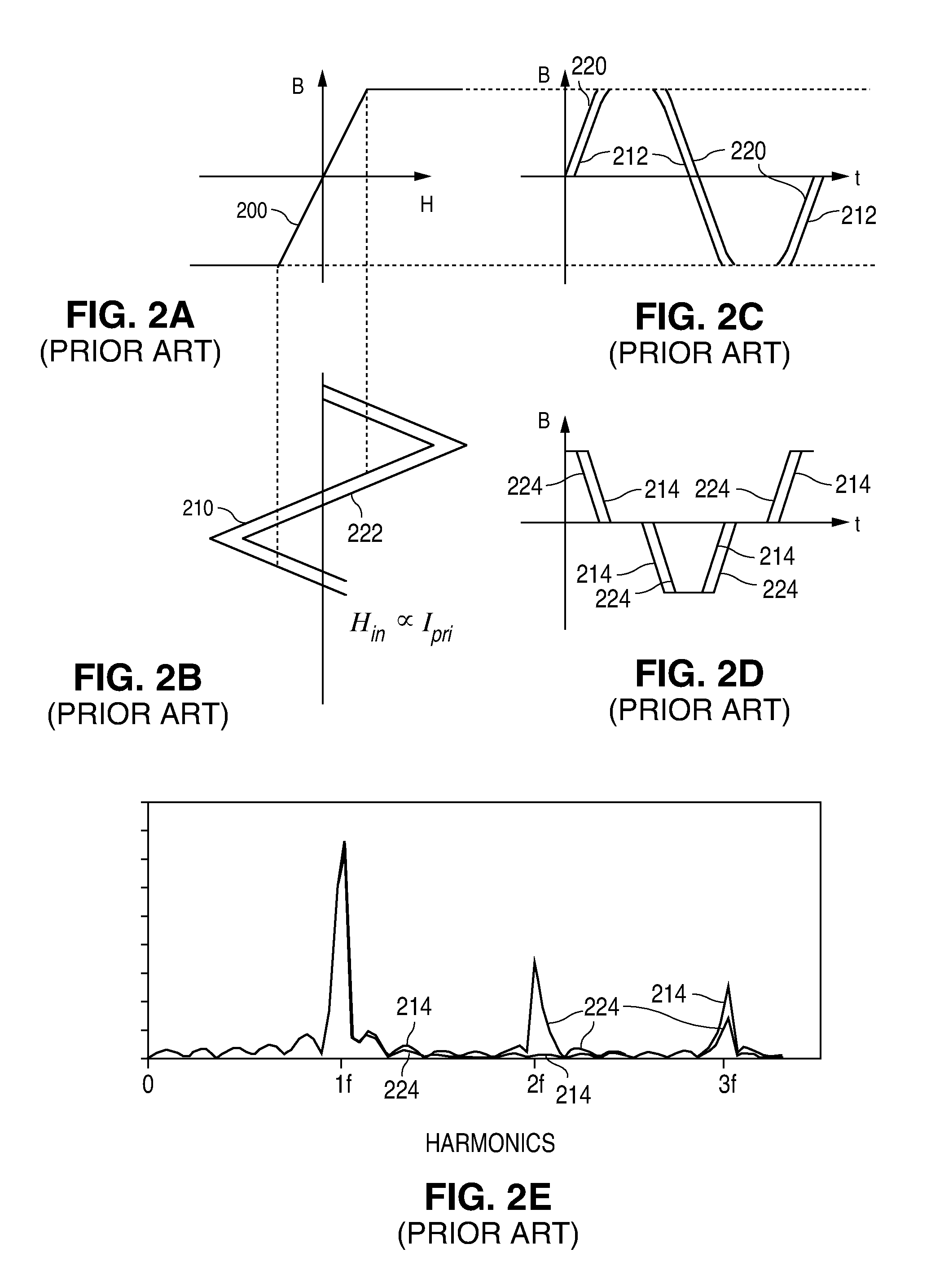

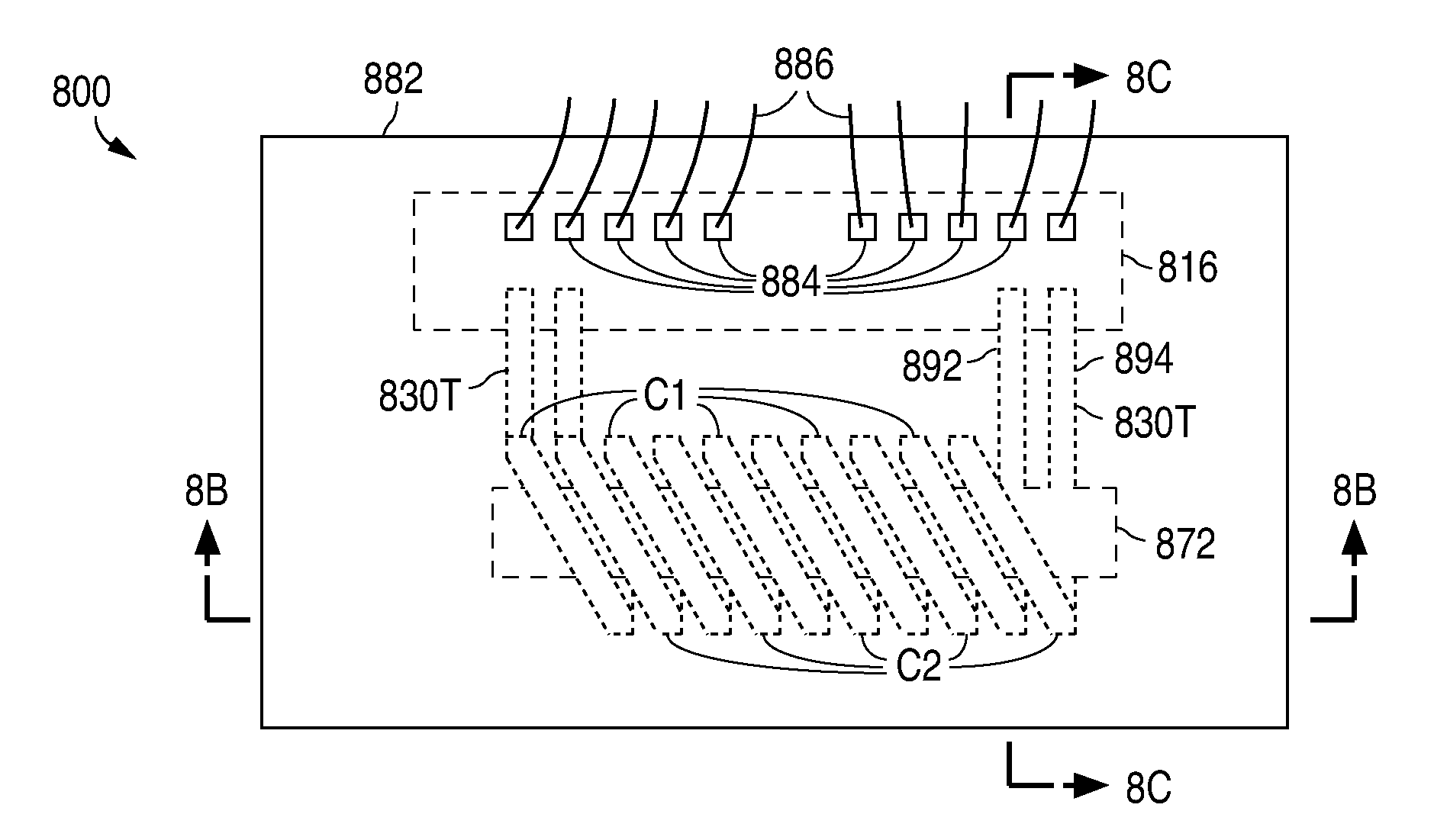

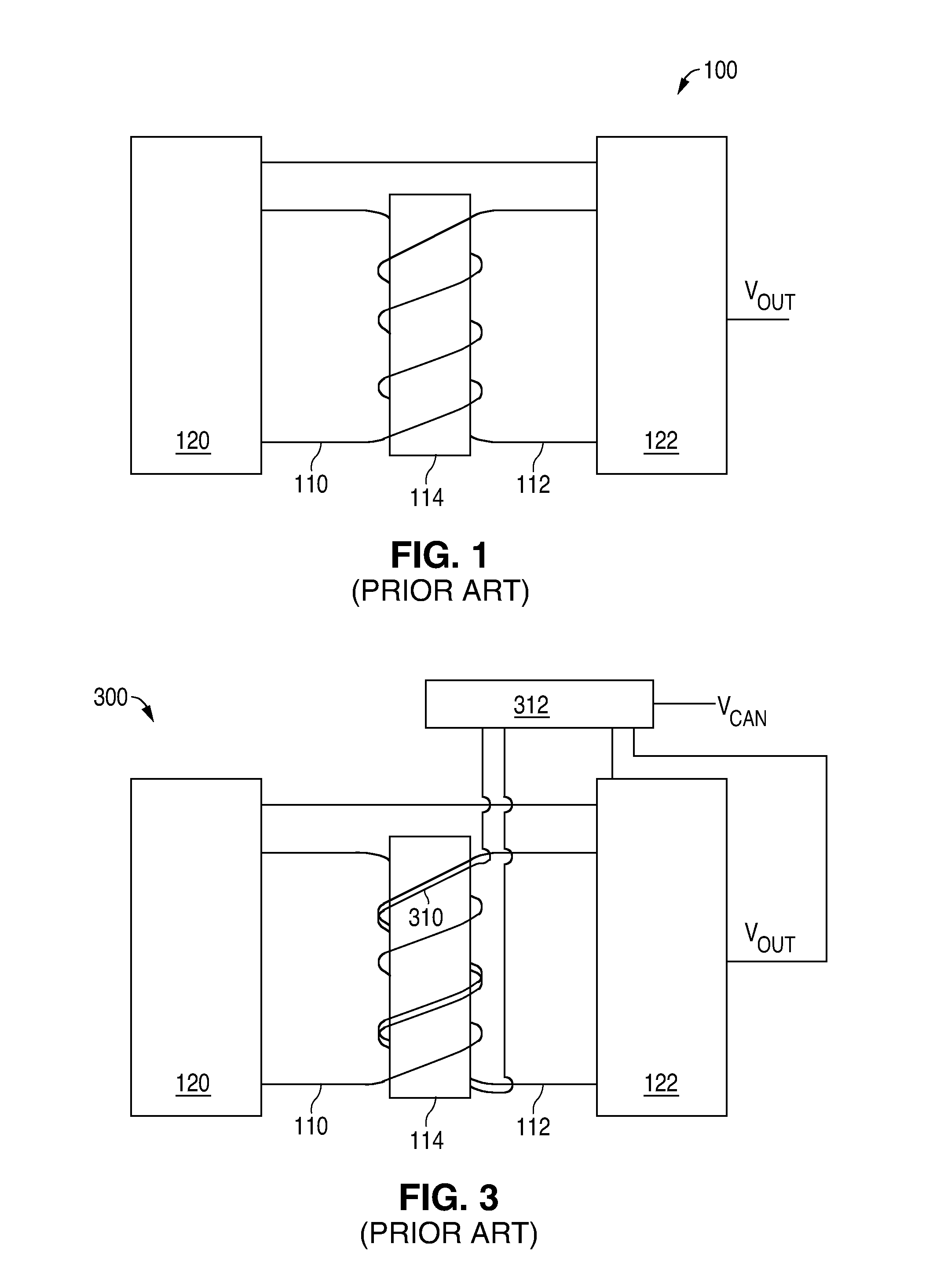

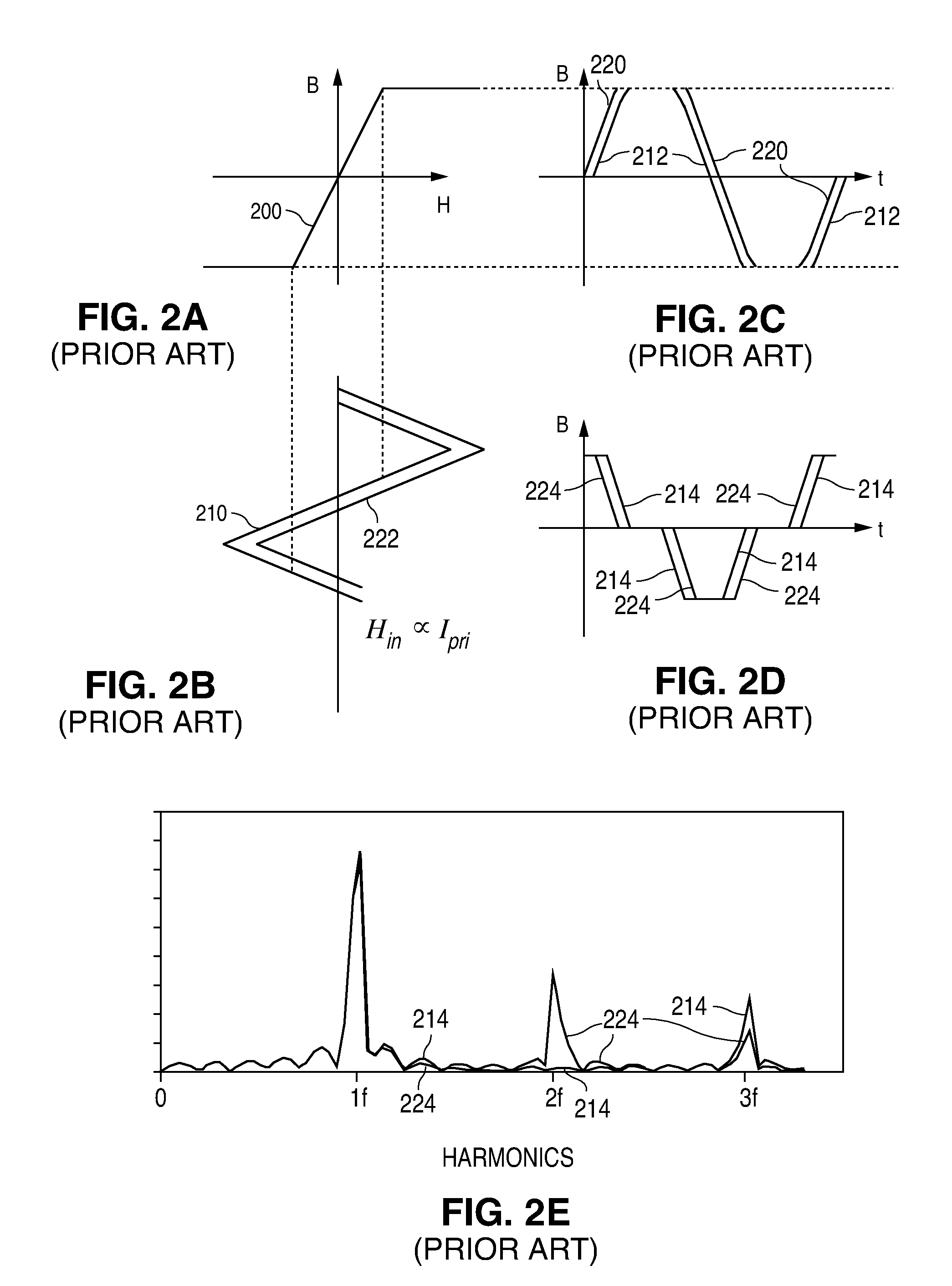

Z-Axis Semiconductor Fluxgate Magnetometer

ActiveUS20130099334A1Semiconductor/solid-state device detailsMagnetic field measurement using flux-gate principleEngineeringSemiconductor wafer fabrication

A z-axis fluxgate magnetometer is formed in a semiconductor wafer fabrication sequence, which significantly reduces the size and cost of the fluxgate magnetometer. The semiconductor wafer fabrication sequence forms a vertical magnetic core structure, a first wire structure wound around the magnetic core structure, and a second wire structure wound around the magnetic core structure.

Owner:TEXAS INSTR INC

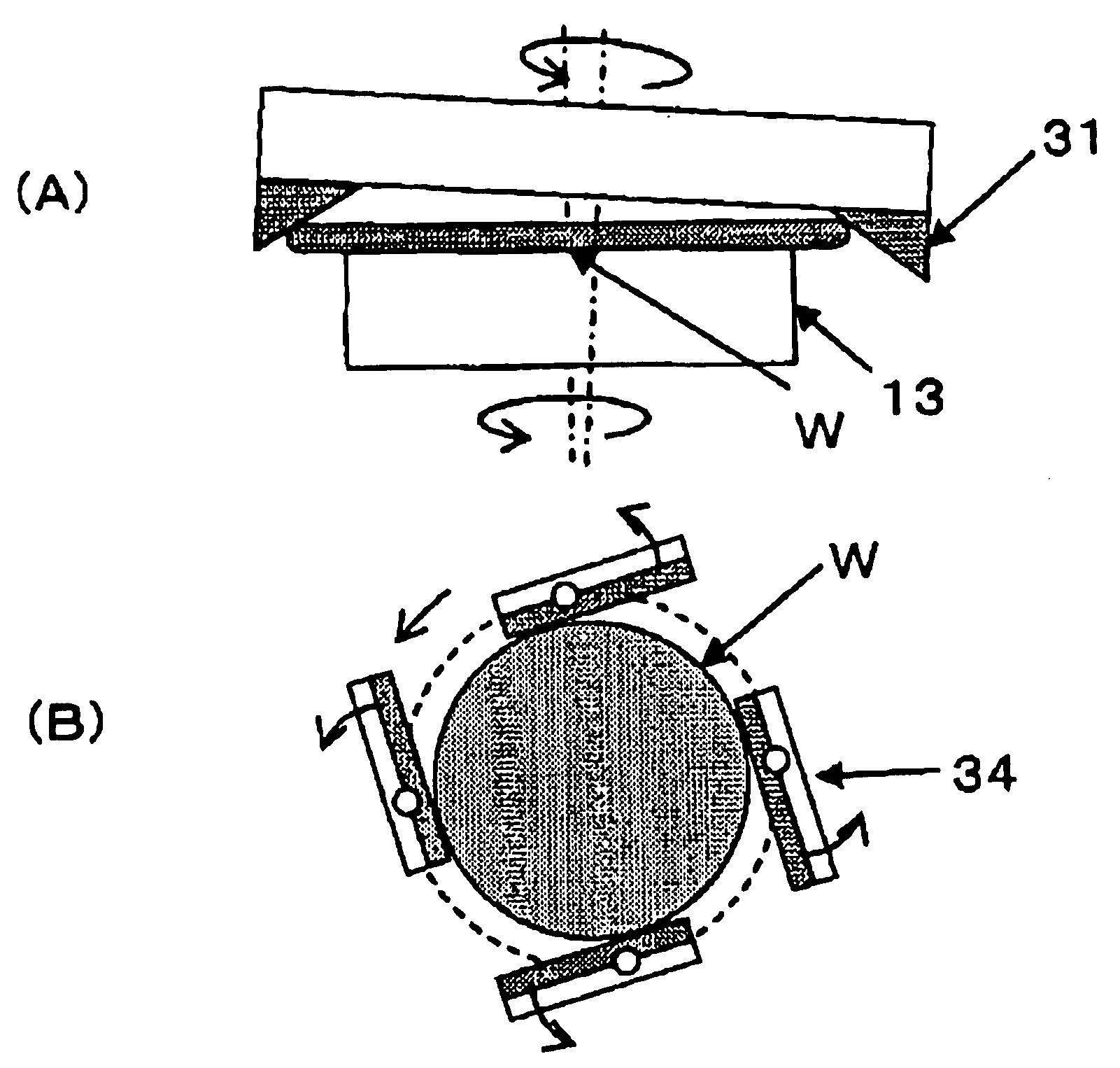

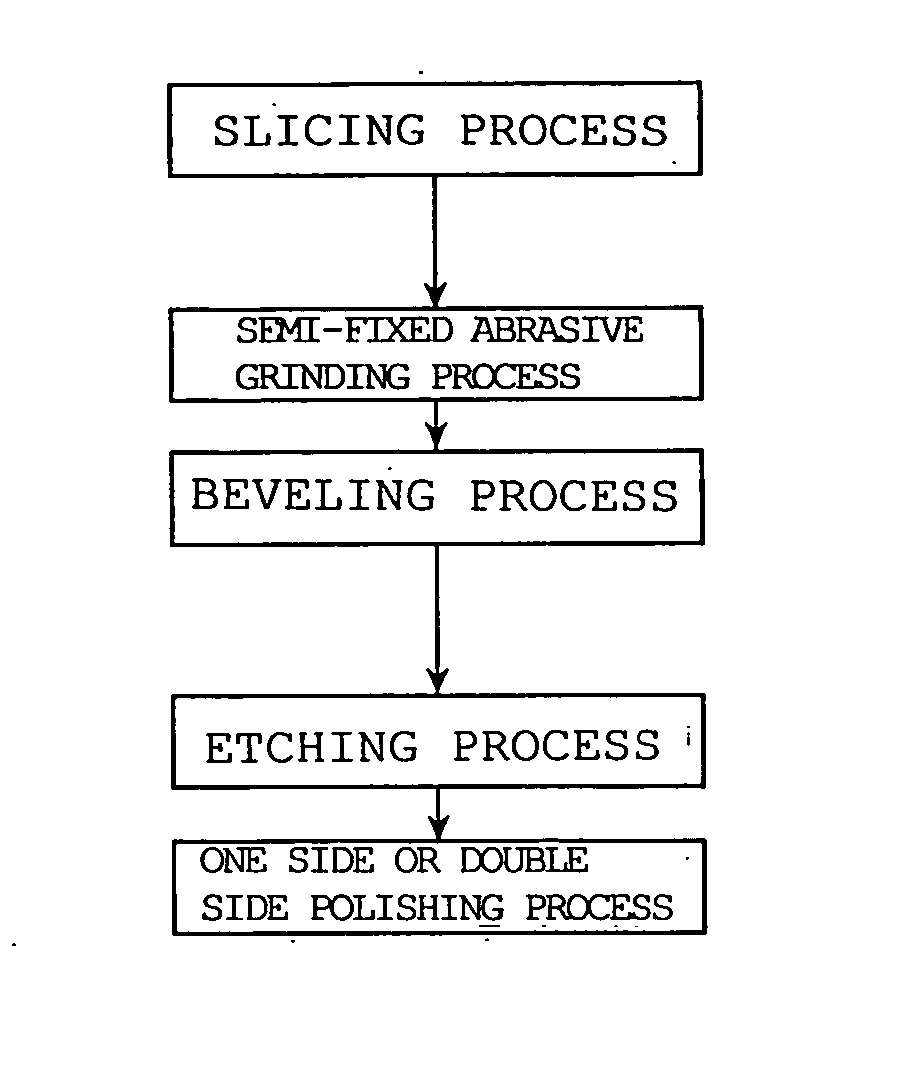

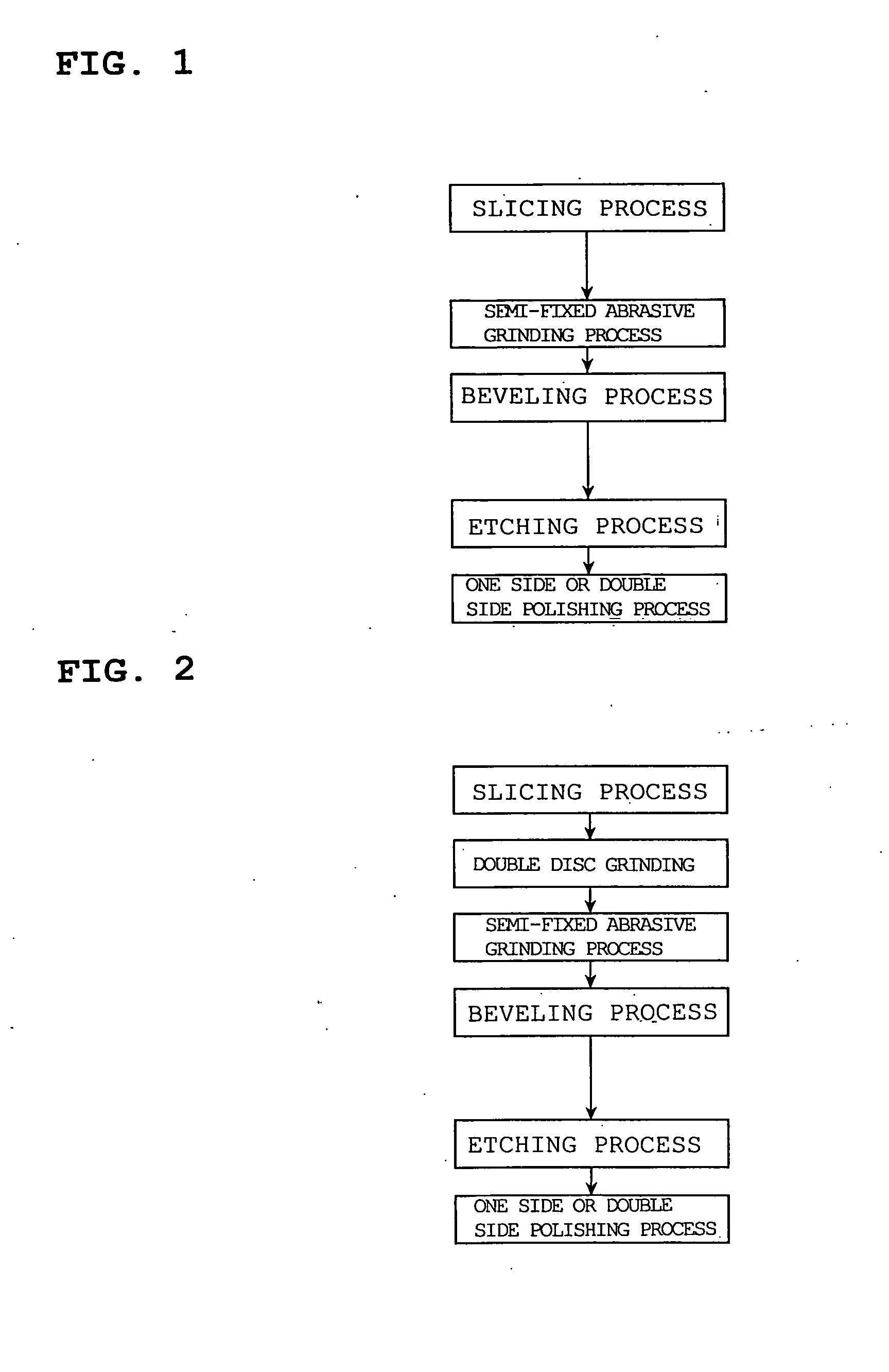

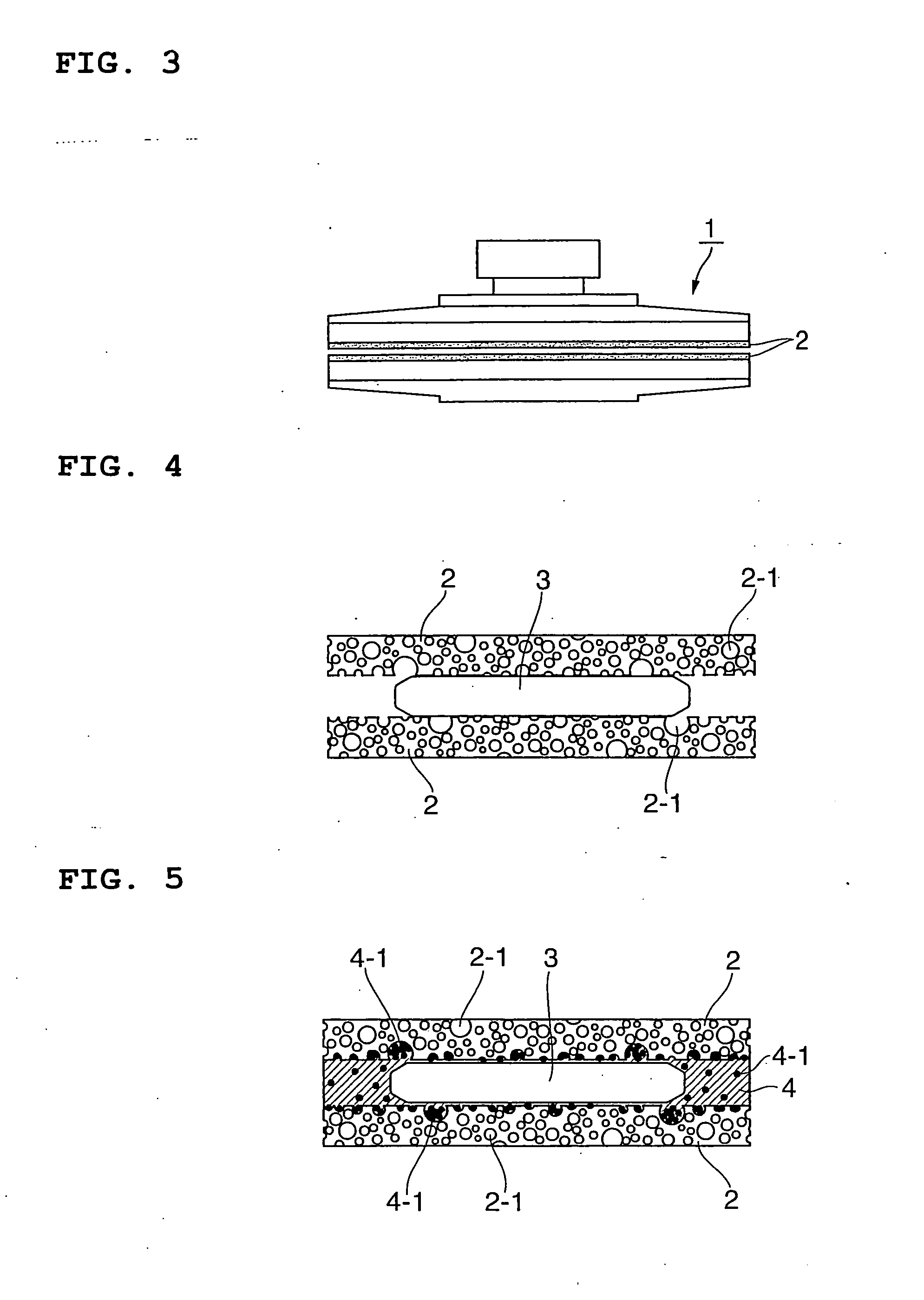

Production method for semiconductor wafer

InactiveUS20070023395A1Simplify the manufacturing processBetter finished surfaceEdge grinding machinesDecorative surface effectsEngineeringSemiconductor wafer fabrication

A production method for a semiconductor wafer is provided in which semi-fixed abrasive grain grinding with free abrasive grains reduces minute surface undulations generated by wire saw slicing or double disc grinding as well as simplifying conventional semiconductor wafer fabrication process steps. A production method for a semiconductor wafer characterized by conducting a slicing process, then a beveling process, an etching process, and a one side or double side polishing process, wherein a semi-fixed abrasive grinding process using a porous polishing pad and free abrasive grains is conducted after the slicing process.

Owner:SUMCO CORP

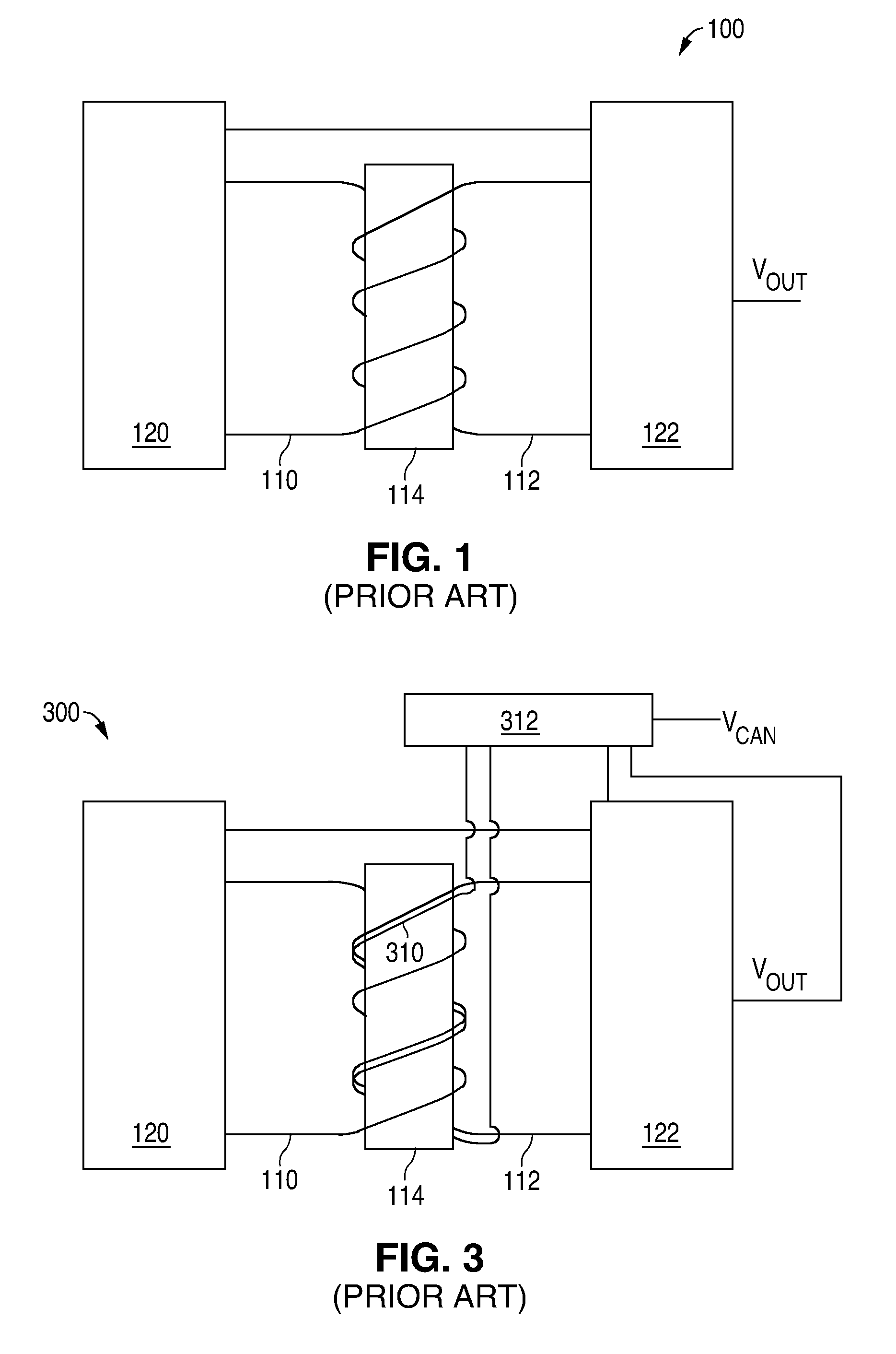

Semiconductor Fluxgate Magnetometer

ActiveUS20130049749A1Magnetic field measurement using flux-gate principleSemiconductor/solid-state device manufacturingSemiconductor wafer fabricationSemiconductor

A fluxgate magnetometer is formed in a semiconductor wafer fabrication sequence, which significantly reduces the size and cost of the fluxgate magnetometer. The semiconductor wafer fabrication sequence attaches a die, which has drive and sense circuits, to the bottom surface of a cavity formed in a larger structure, and forms drive and sense coils around a magnetic core structure on the top surface of the larger structure.

Owner:NAT SEMICON CORP

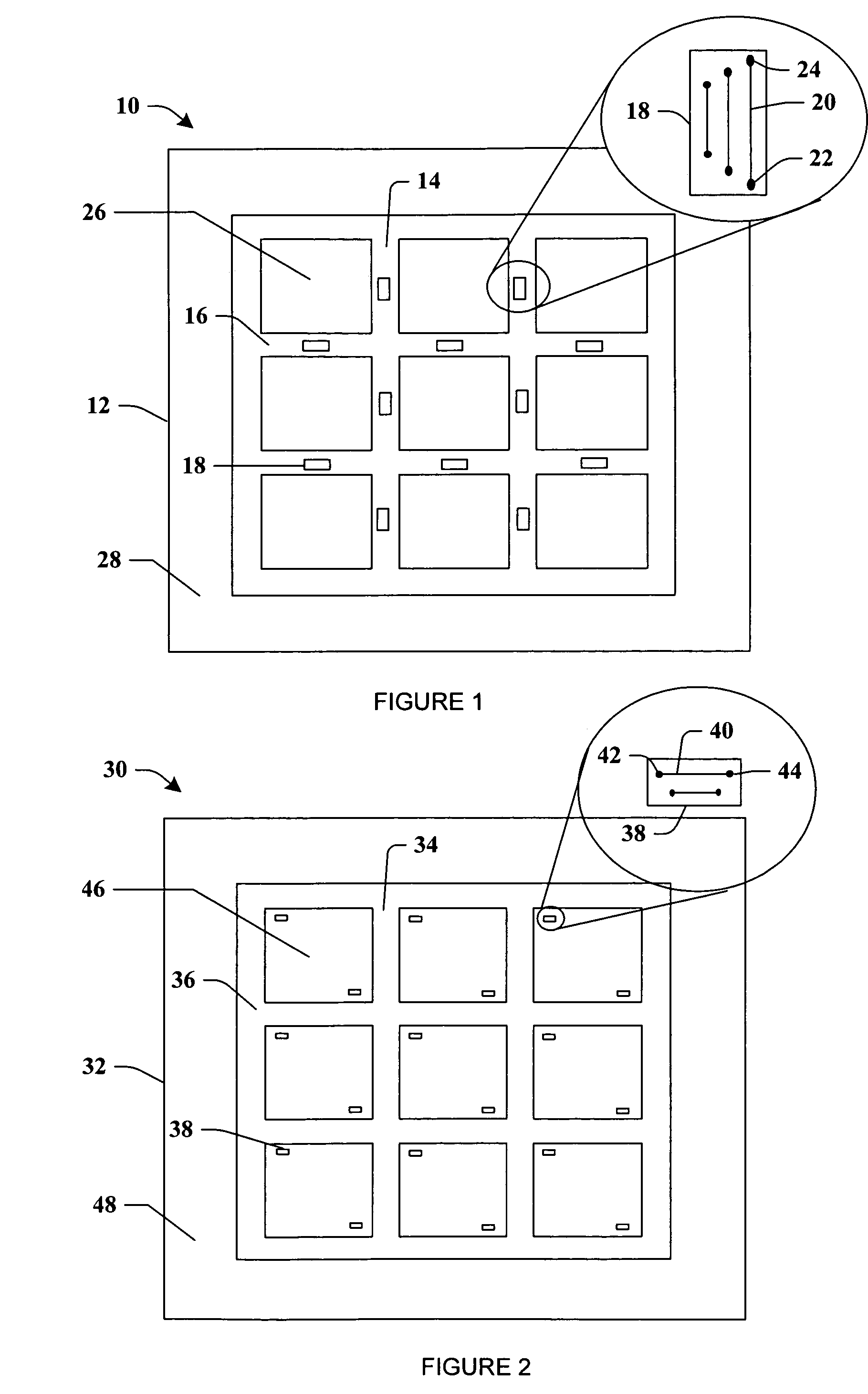

Electrical critical dimension measurement and defect detection for reticle fabrication

InactiveUS6972576B1Well formedAvoid wasting spaceSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceElectricityEngineering

A system for testing a reticle used in semiconductor wafer fabrication is provided. The system includes a reticle that has an opaque metal layer over a translucent substrate. The reticle includes one or more test features containing probe points operable for electrical contact. The system includes a reticle test system that is capable of applying a voltage to the probe points, measuring the resulting current, calculating the corresponding resistance of the test features, and determining the critical dimensions of the test features. The system is also capable of determining defects based on the resistance measurements. The critical dimension information and defect information can then be used to refine the processes used in the fabrication of subsequent reticles.

Owner:GLOBALFOUNDRIES INC

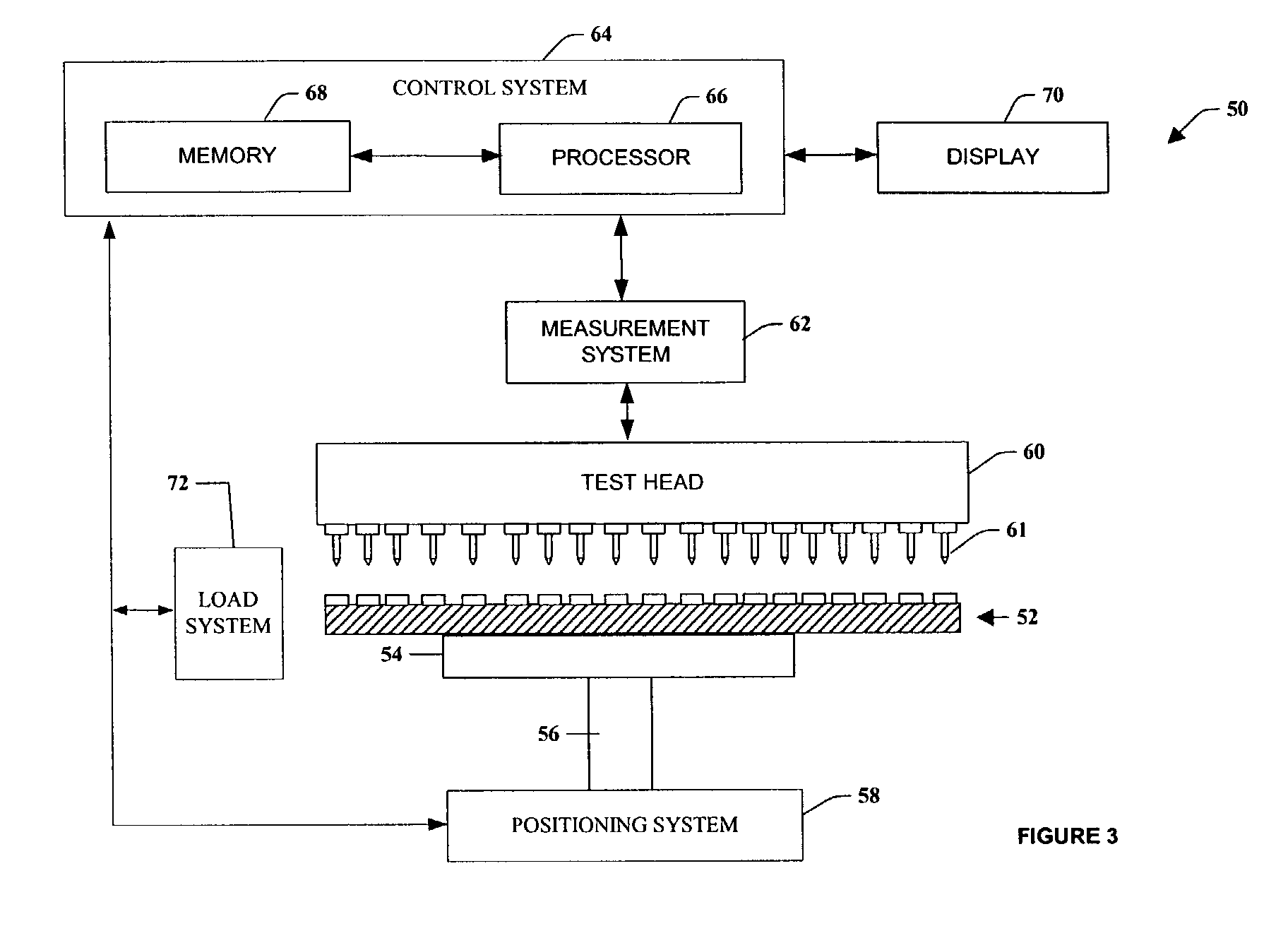

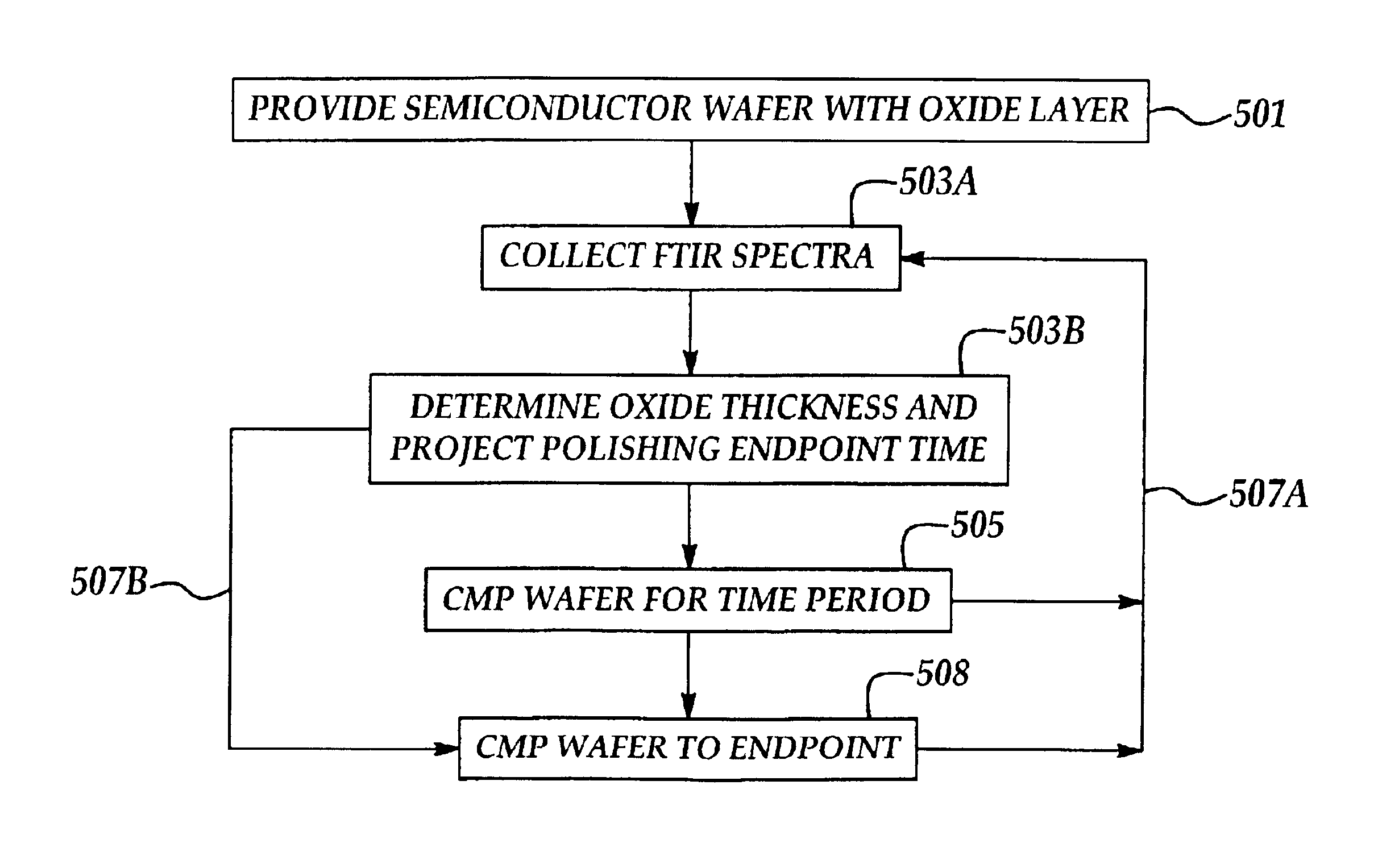

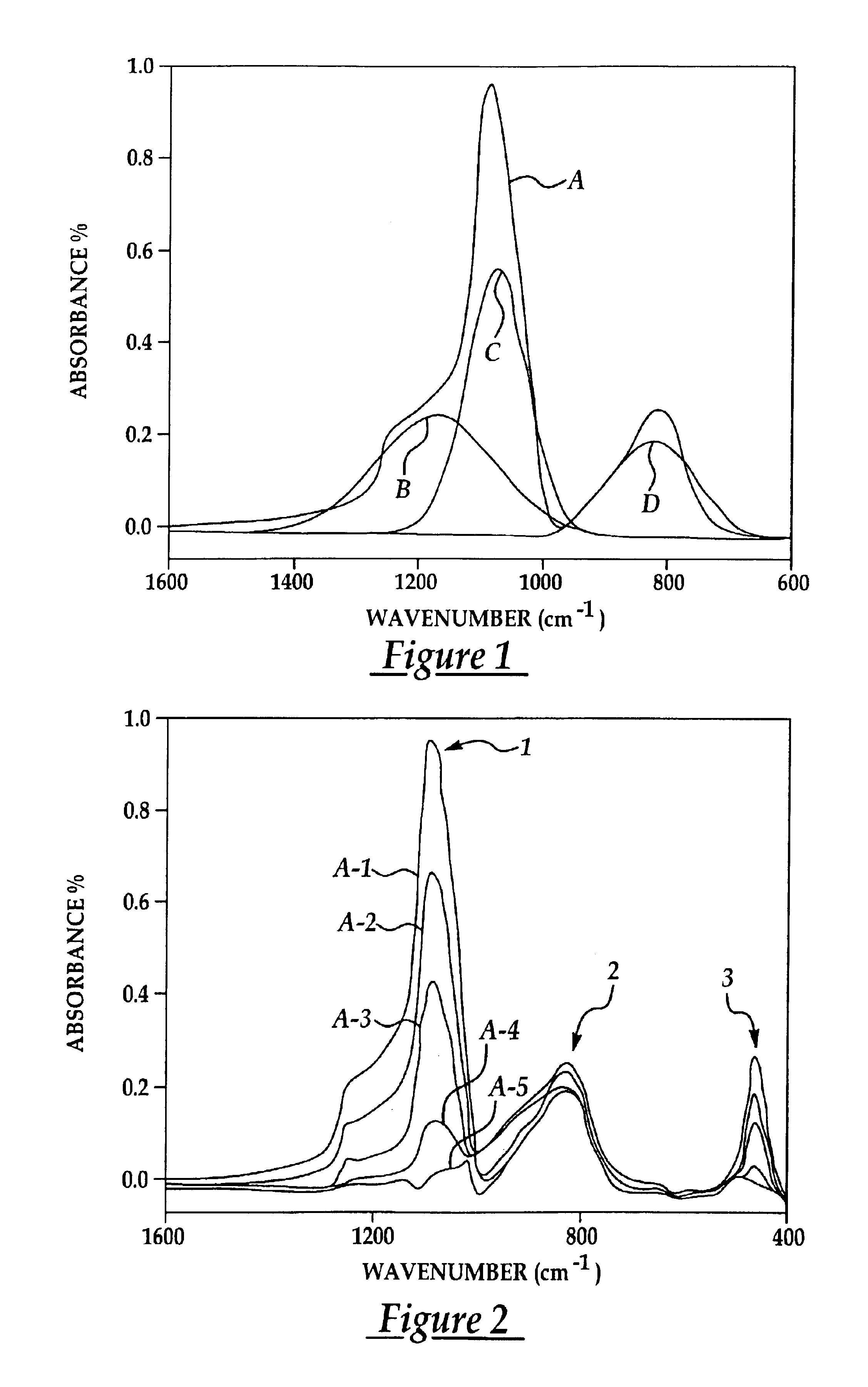

Method to measure oxide thickness by FTIR to improve an in-line CMP endpoint determination

A method for determining a material layer thickness transmissive to infrared (IR) energy in a semiconductor wafer manufacturing process including providing at least one semiconductor wafer comprising an IR transmissive layer; passing IR energy through the IR transmissive layer to produce at least one Fourier transform infrared (FTIR) spectrum; and, determining an amount of the IR transmissive layer present according to an amount of IR energy absorbed by a predetermined contributing characteristic vibrational mode portion of the FTIR spectrum.

Owner:TAIWAN SEMICON MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com