Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

765 results about "Wafer dicing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

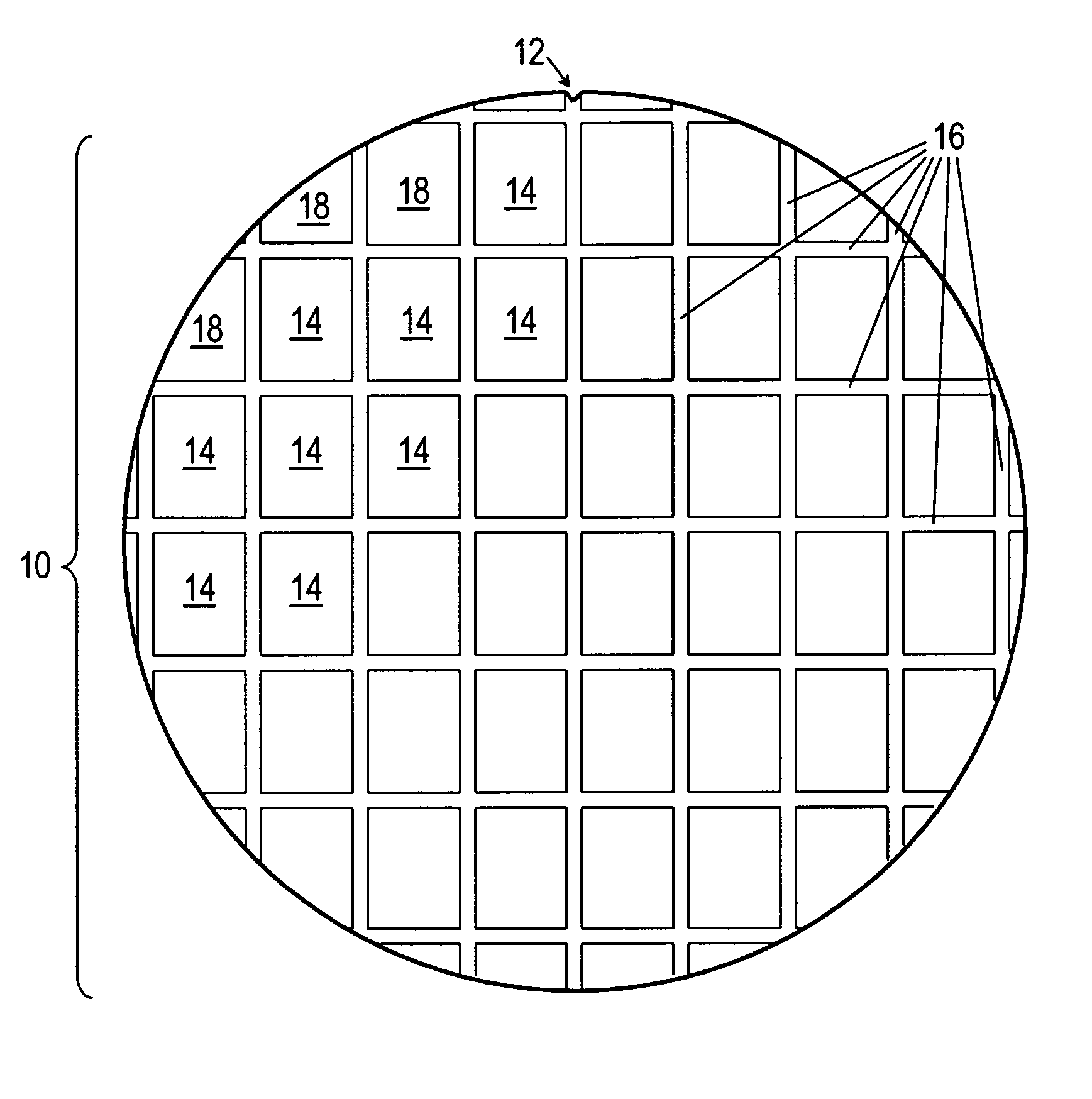

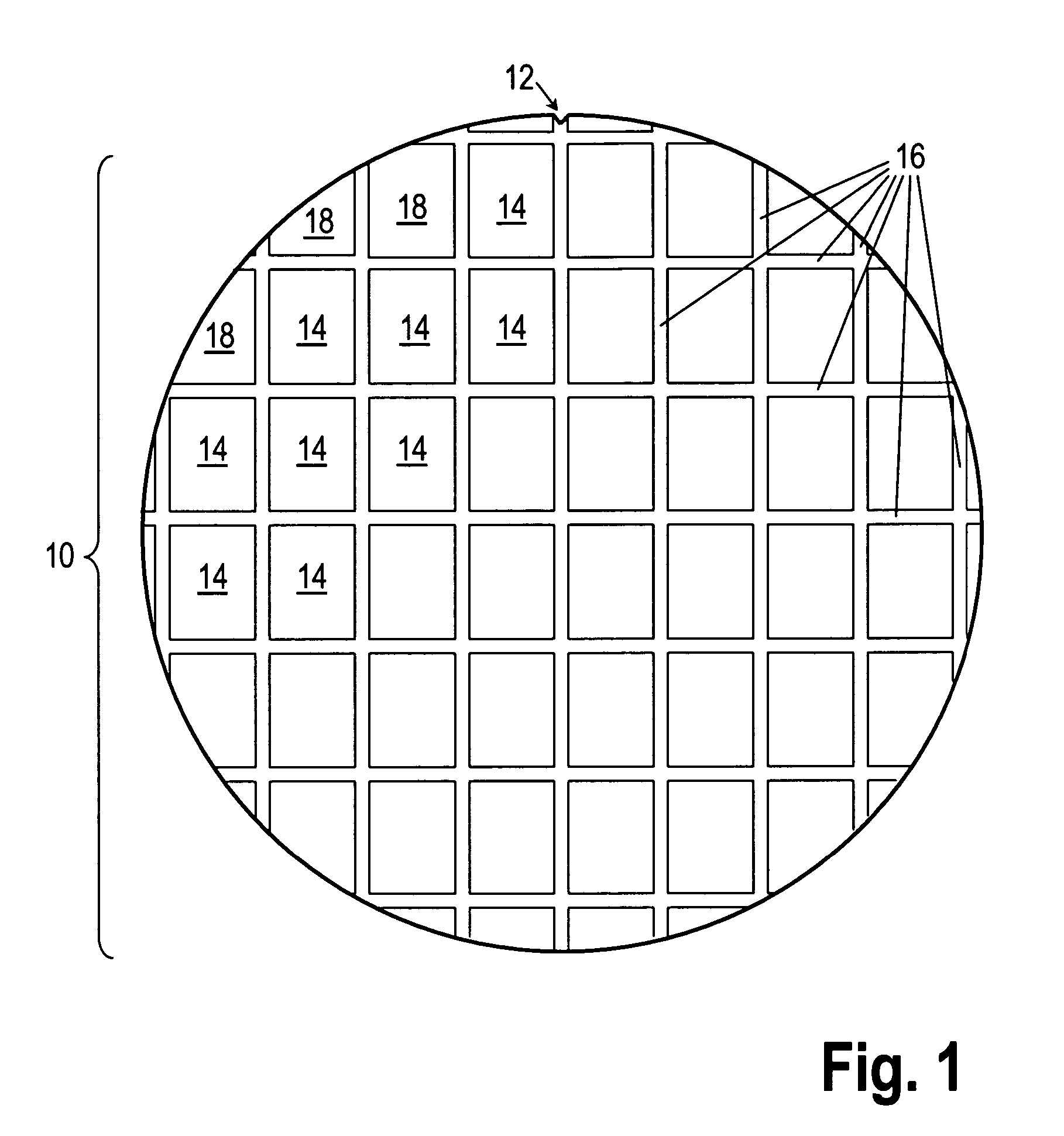

In the context of manufacturing integrated circuits, wafer dicing is the process by which die are separated from a wafer of semiconductor following the processing of the wafer. The dicing process can involve scribing and breaking, mechanical sawing (normally with a machine called a dicing saw) or laser cutting. All methods are typically automated to ensure precision and accuracy. Following the dicing process the individual silicon chips are encapsulated into chip carriers which are then suitable for use in building electronic devices such as computers, etc.

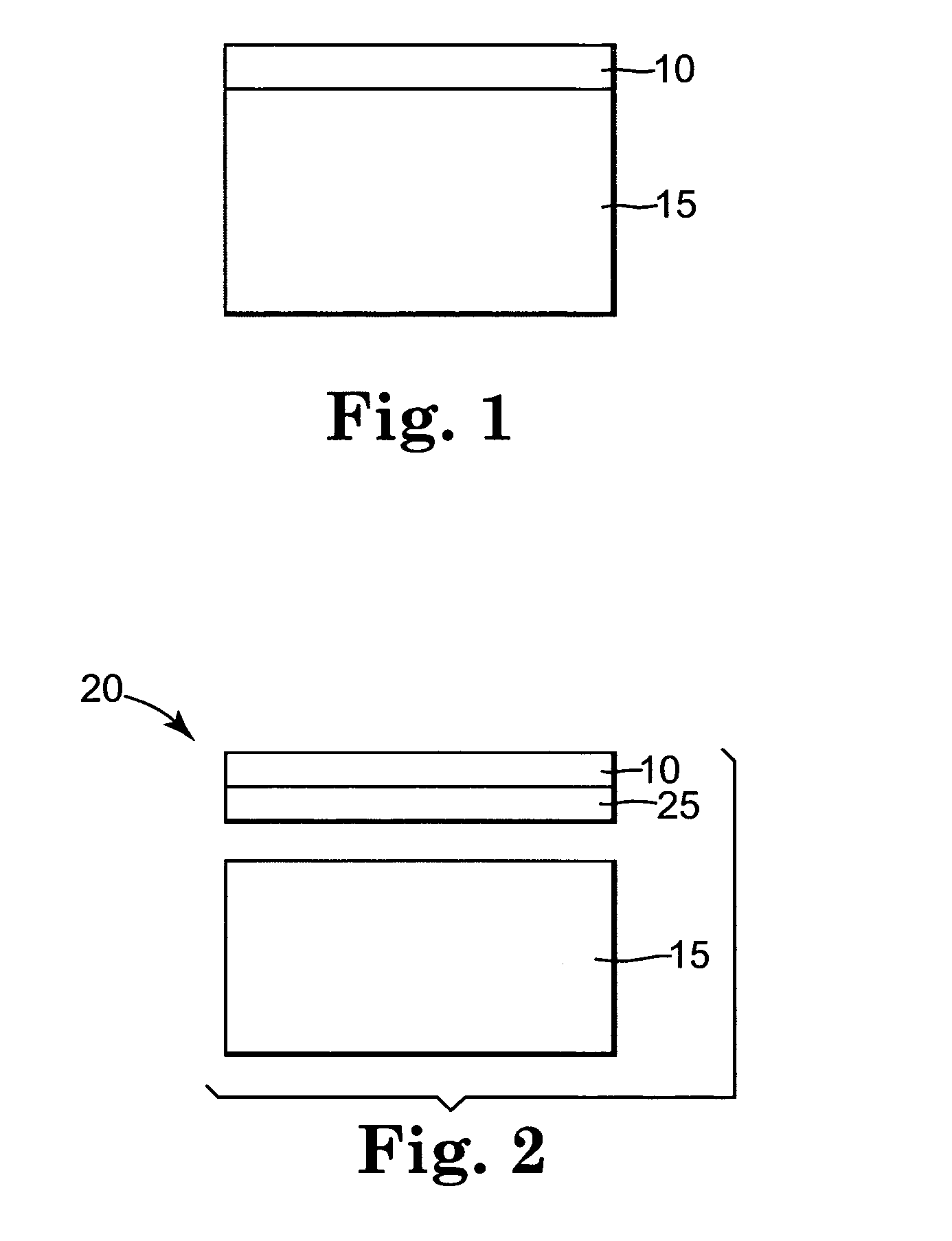

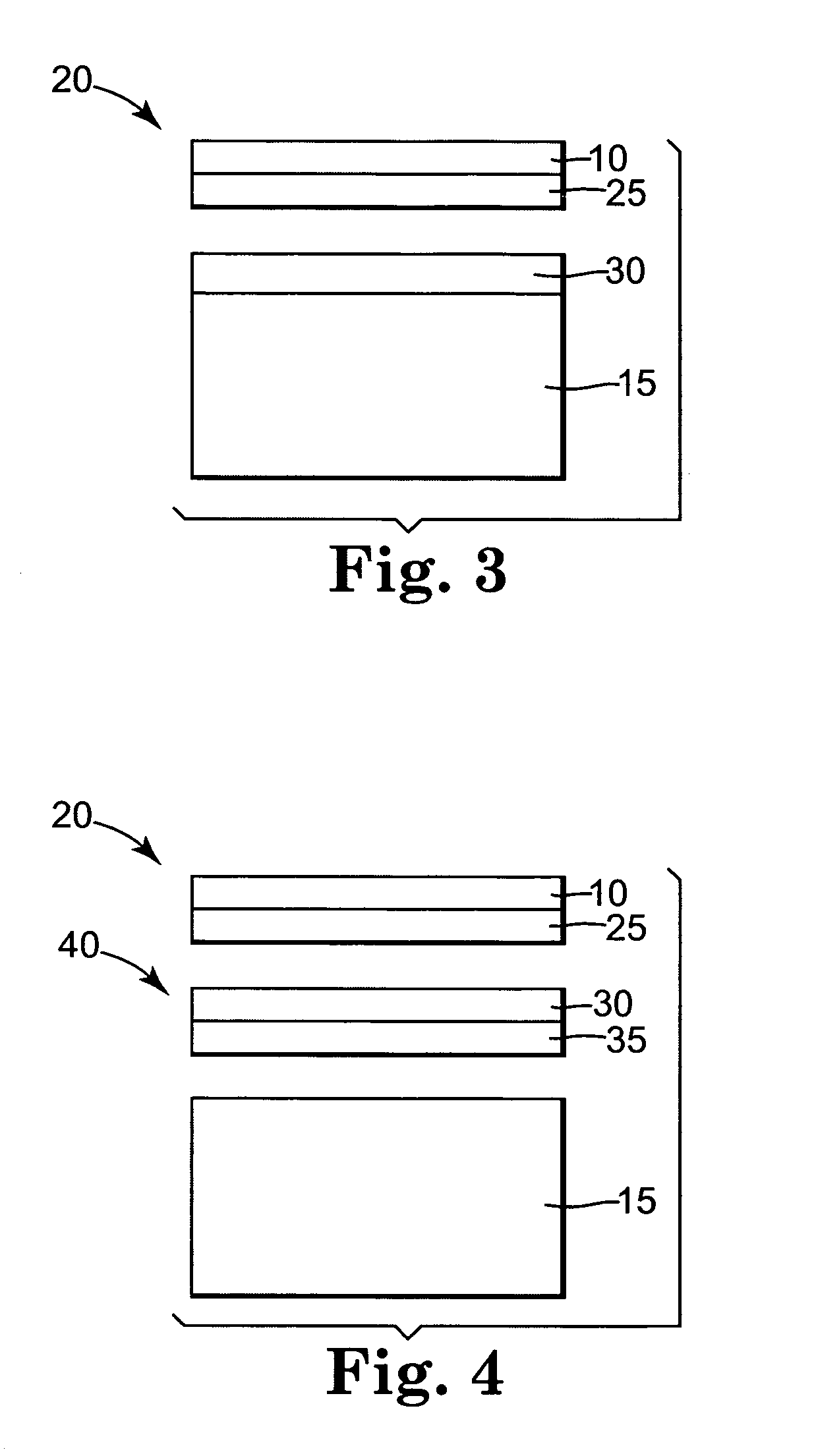

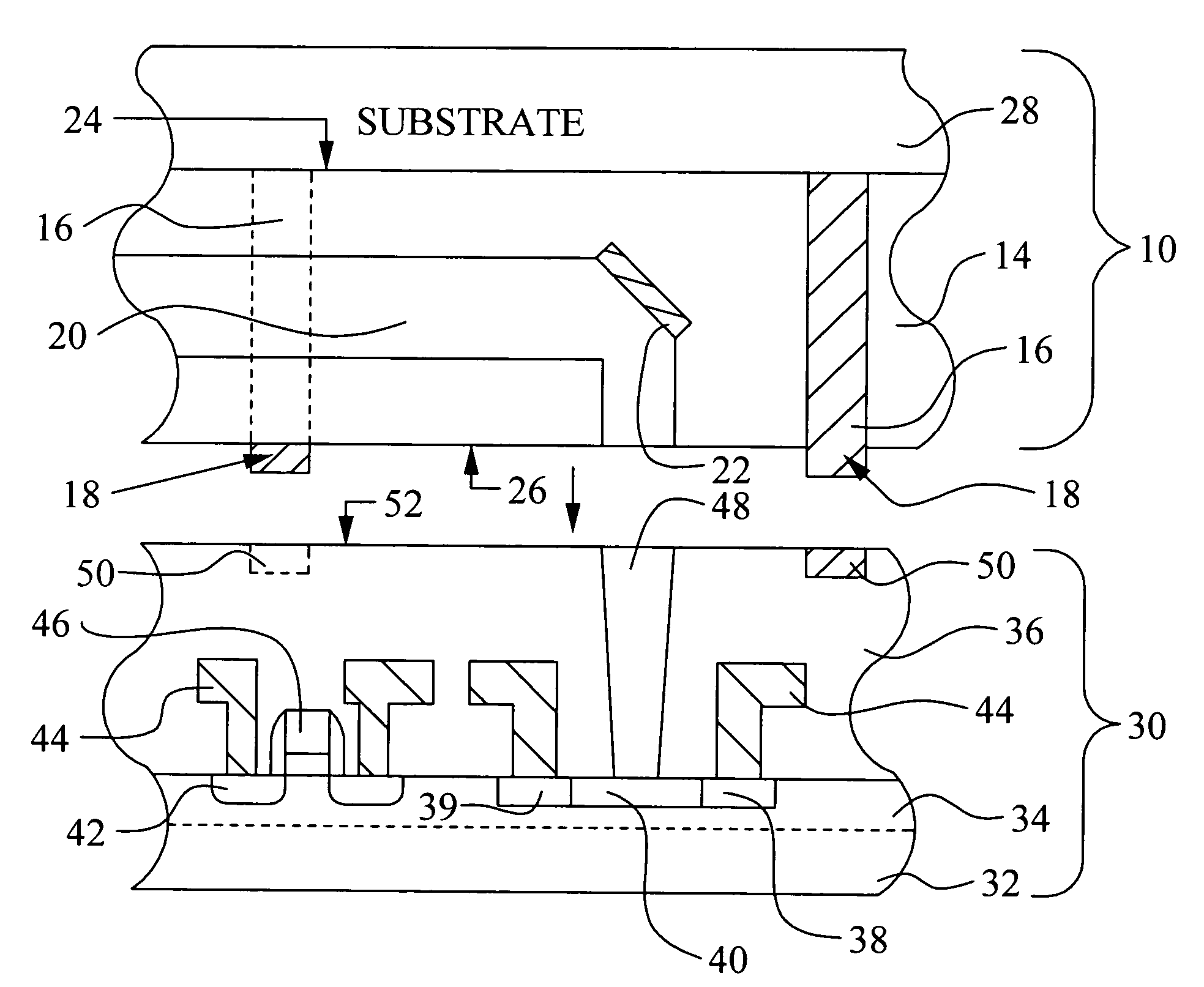

Wafer bonding of thinned electronic materials and circuits to high performance substrates

InactiveUS20040009649A1Material nanotechnologySemiconductor/solid-state device detailsWafer dicingEngineering

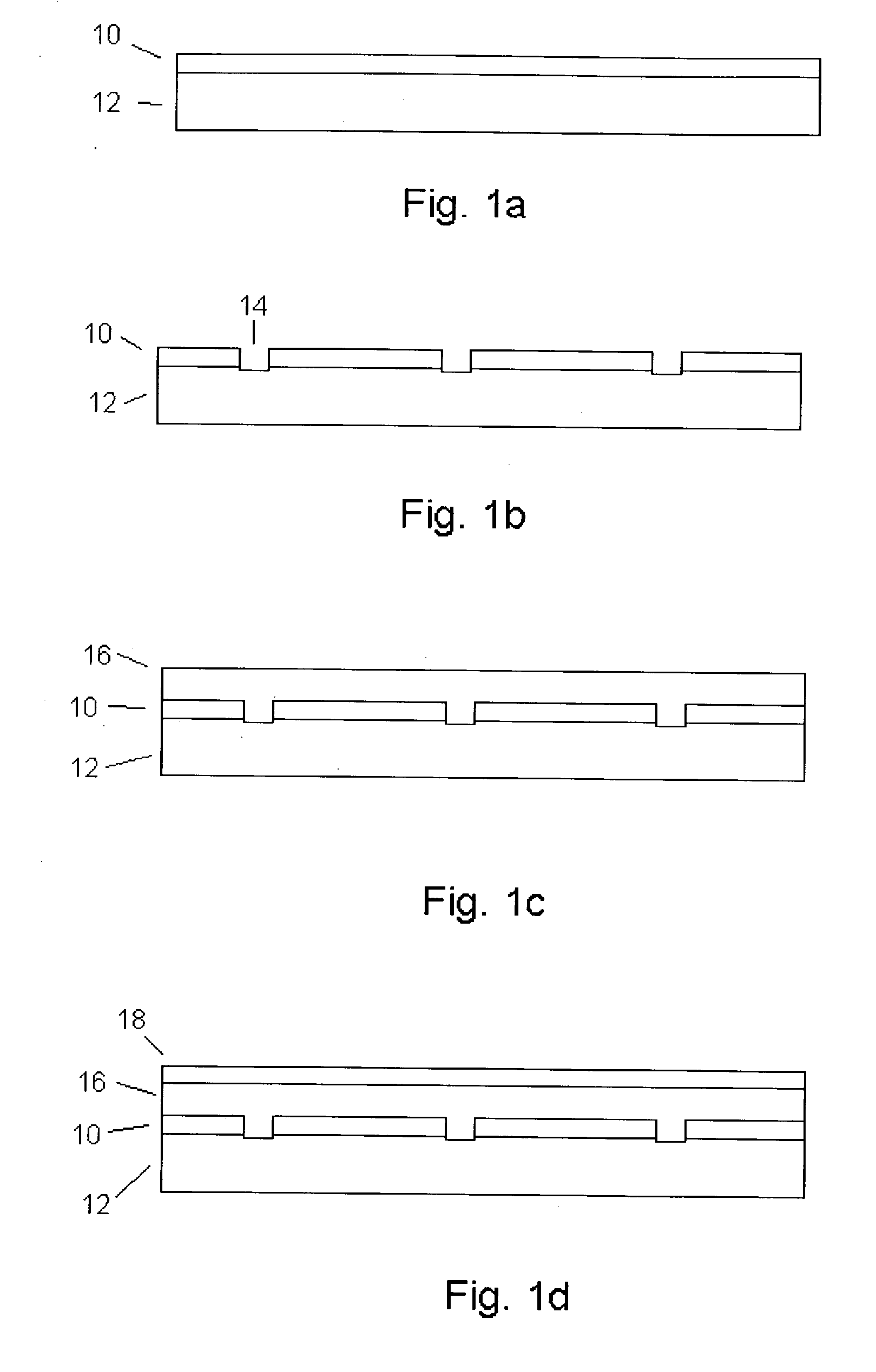

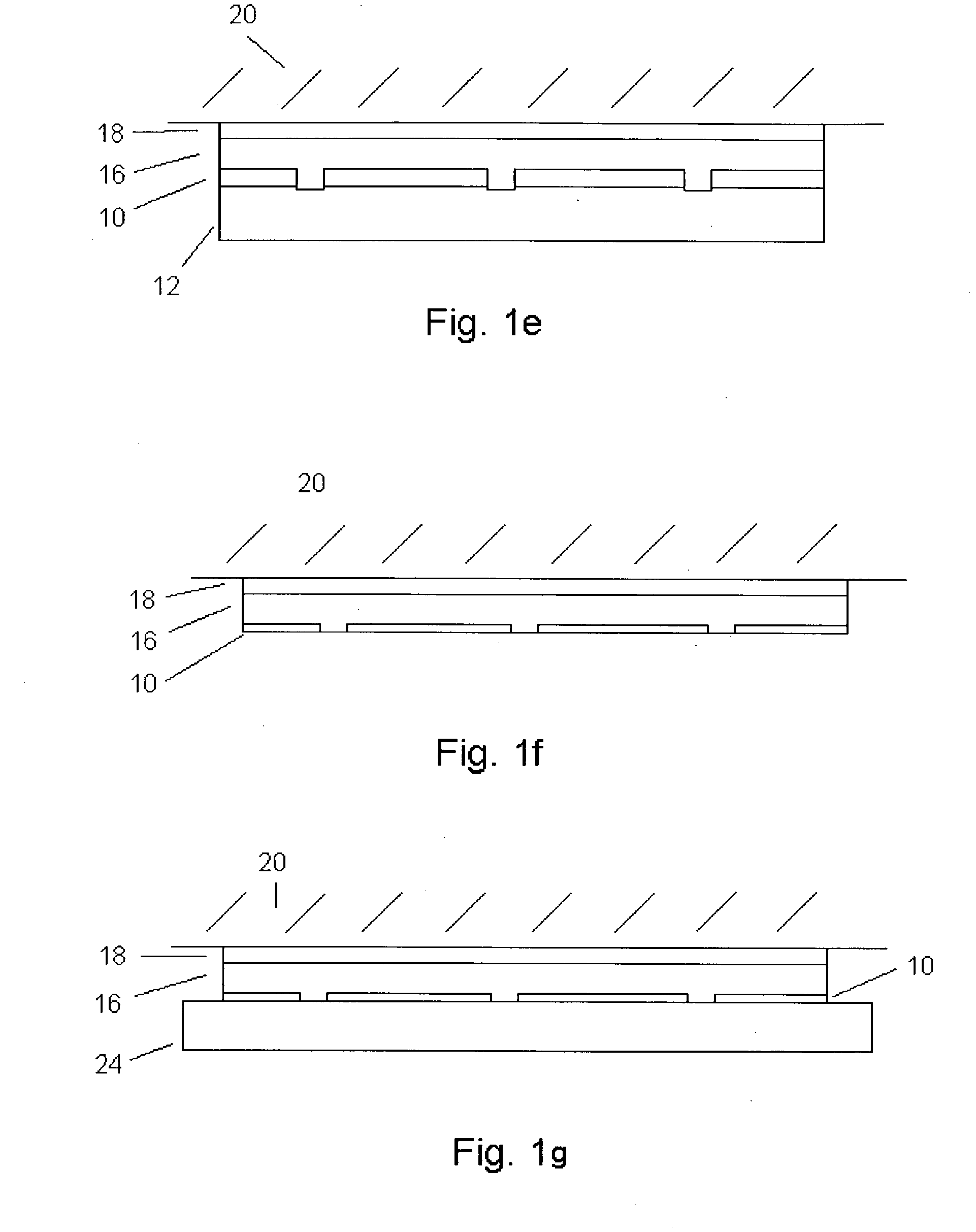

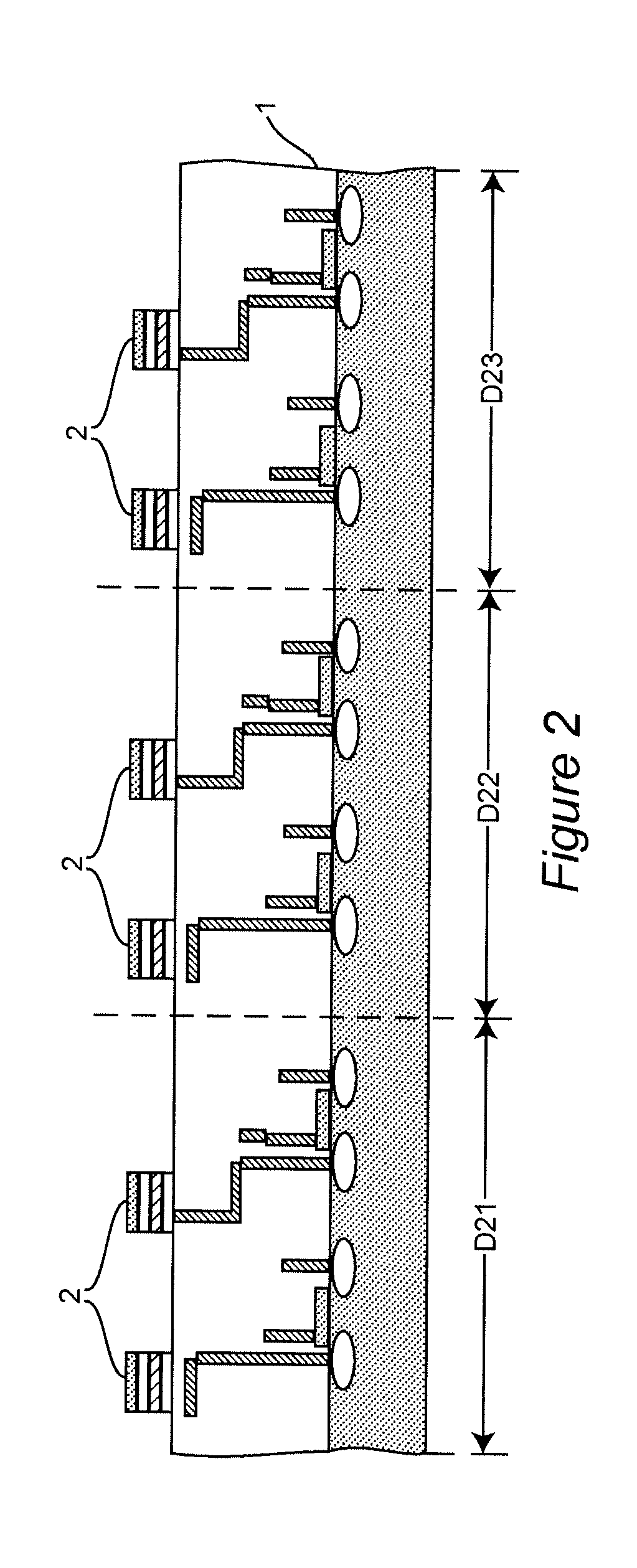

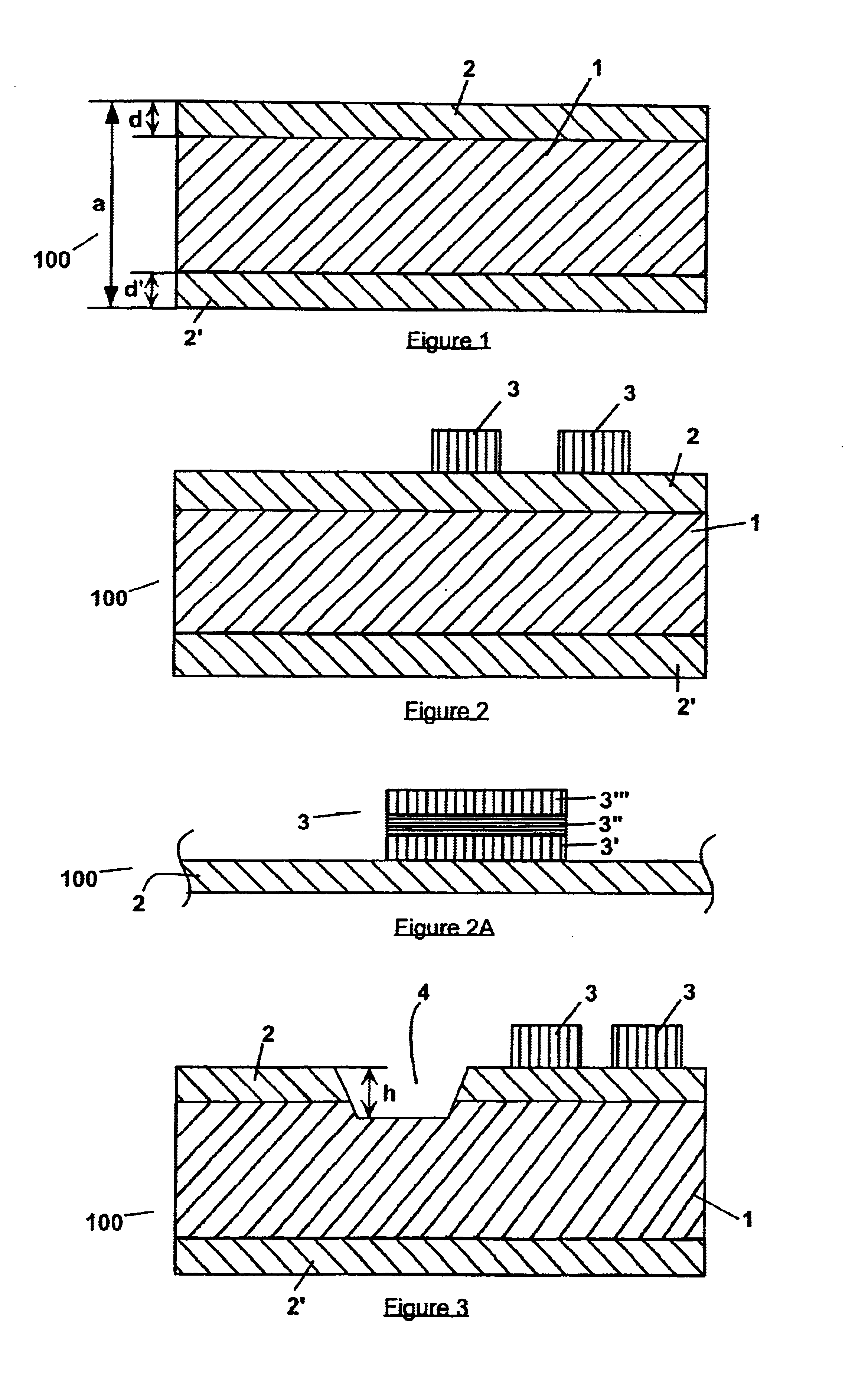

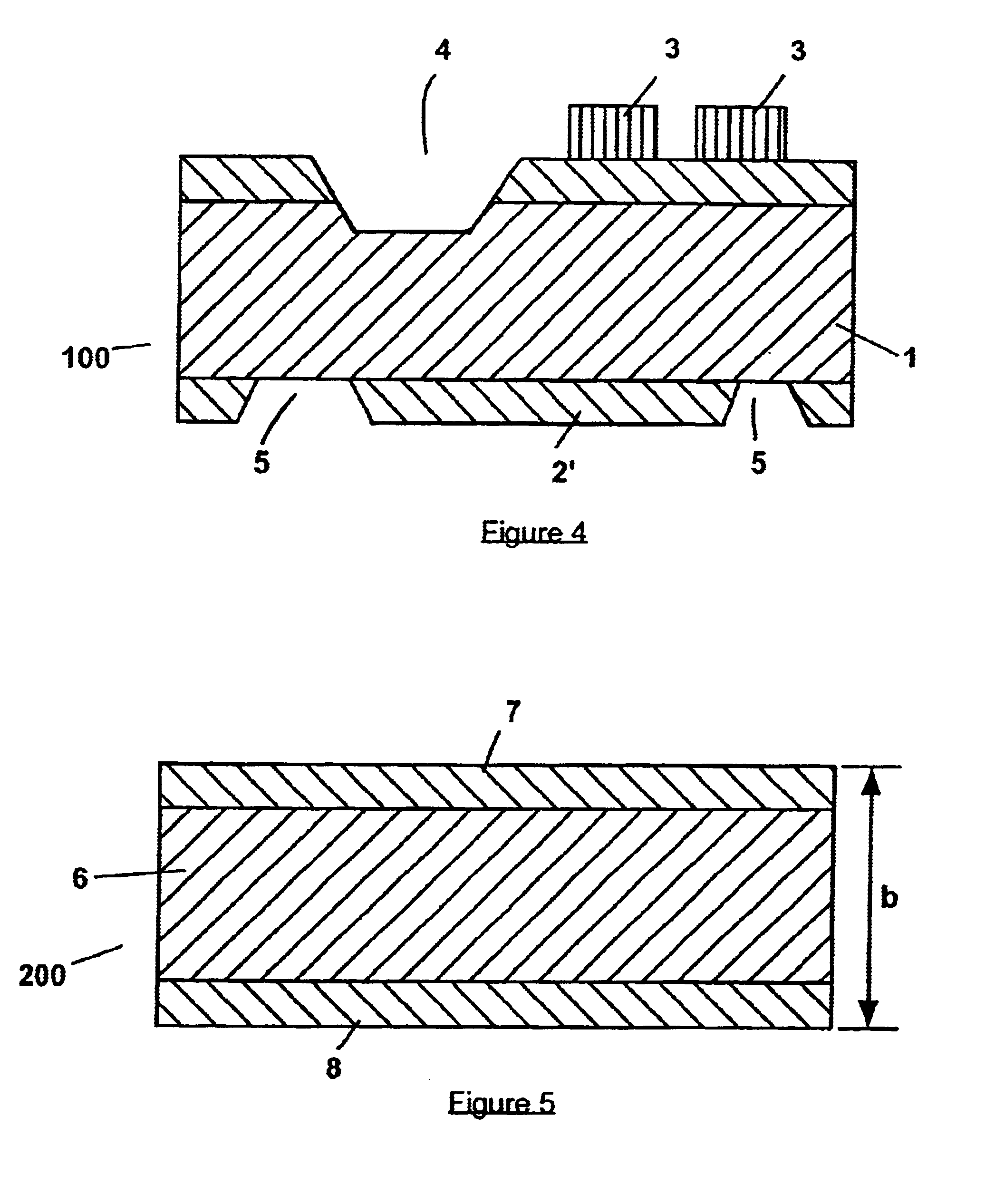

A method of bonding a wafer to a substrate comprising the steps of: providing a wafer having a front surface and a back surface; attaching the front surface of the wafer to a support; thinning the wafer from the back surface; bonding the back surface of the wafer to a substrate using a thin bonding technique; and removing the support from the front surface of the wafer. A circuit comprising: a substrate; and a wafer; wherein the wafer is at most about 50 microns thick; wherein the wafer has a front surface comprising features; and wherein the wafer has a back surface bonded to the substrate using a thin bonding technique.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

Storage structure with cleaved layer

InactiveUS6967149B2Solid-state devicesSemiconductor/solid-state device manufacturingWafer dicingSingle crystal

Owner:HEWLETT PACKARD DEV CO LP

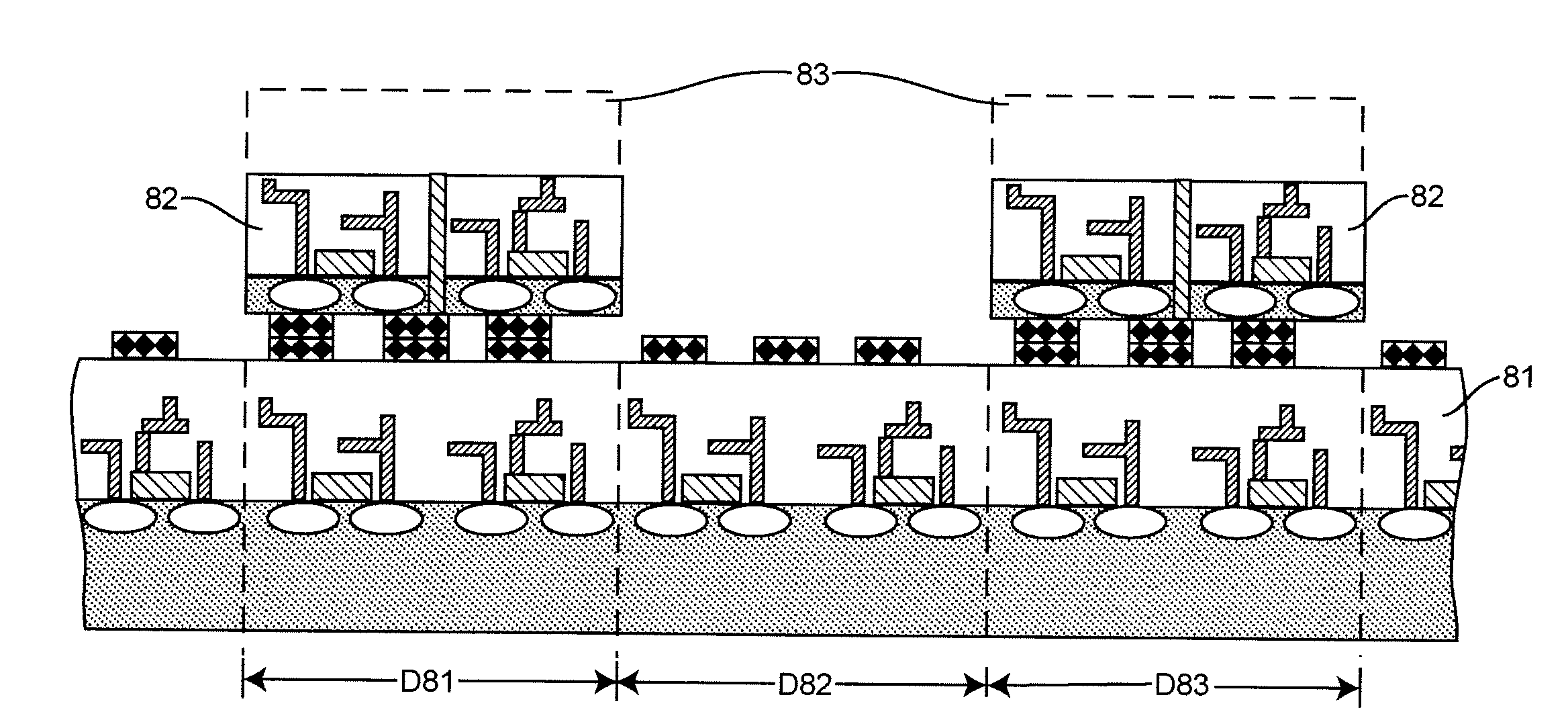

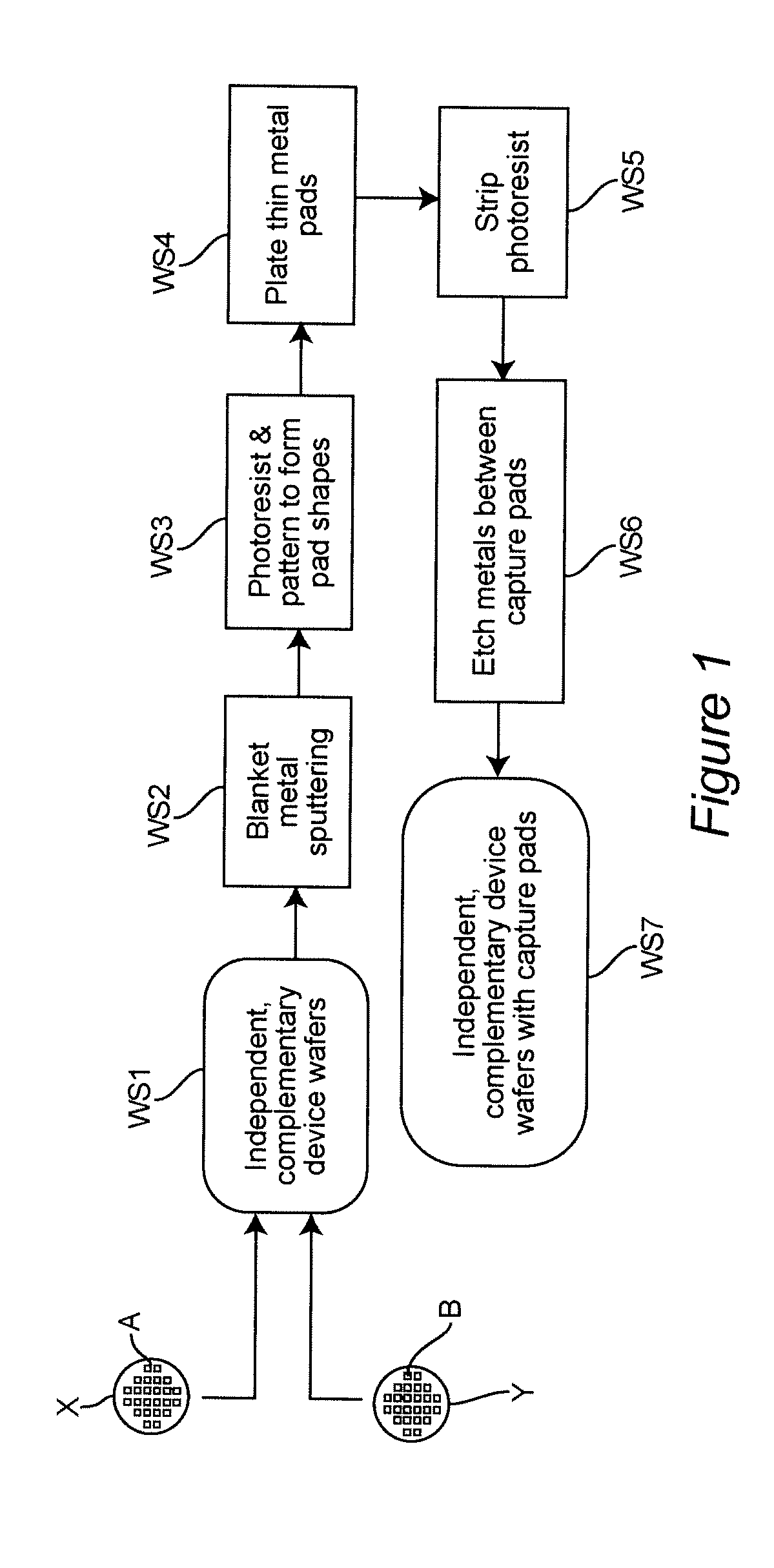

Method and Structure for Optimizing Yield of 3-D Chip Manufacture

ActiveUS20080142959A1Maximize frequencyLow costSemiconductor/solid-state device detailsSolid-state devicesThin metalEtching

The process begins with separate device wafers having complimentary chips. Thin metal capture pads, having a preferred thickness of about 10 microns so that substantial pressure may be applied during processing without damaging capture pads, are deposited on both device wafers, which are then tested and mapped for good chip sites. A handle wafer is attached to one device wafer, which can then be thinned to improve via etching and filling. Capture pads are removed and replaced after thinning. The device wafer with handle wafer is diced, and good chips with attached portions of the diced handle wafer are positioned and bonded to the good chip sites of the other device wafer, and the handle wafer portions are removed. The device wafer having known good 3-D chips then undergoes final processing.

Owner:INT BUSINESS MASCH CORP

Wafer dicing using femtosecond-based laser and plasma etch

ActiveUS20110312157A1Electric discharge tubesSemiconductor/solid-state device detailsWafer dicingEngineering

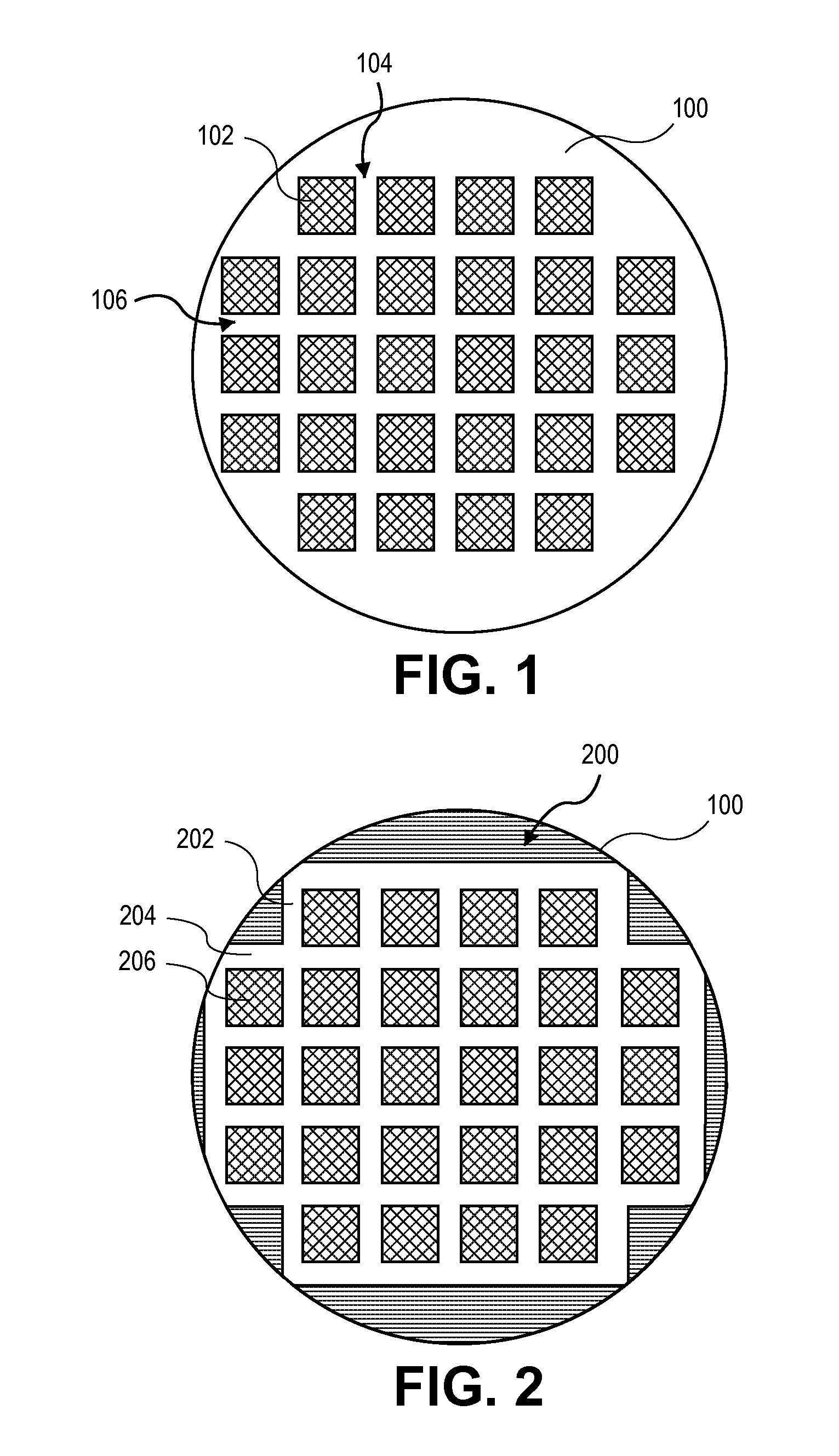

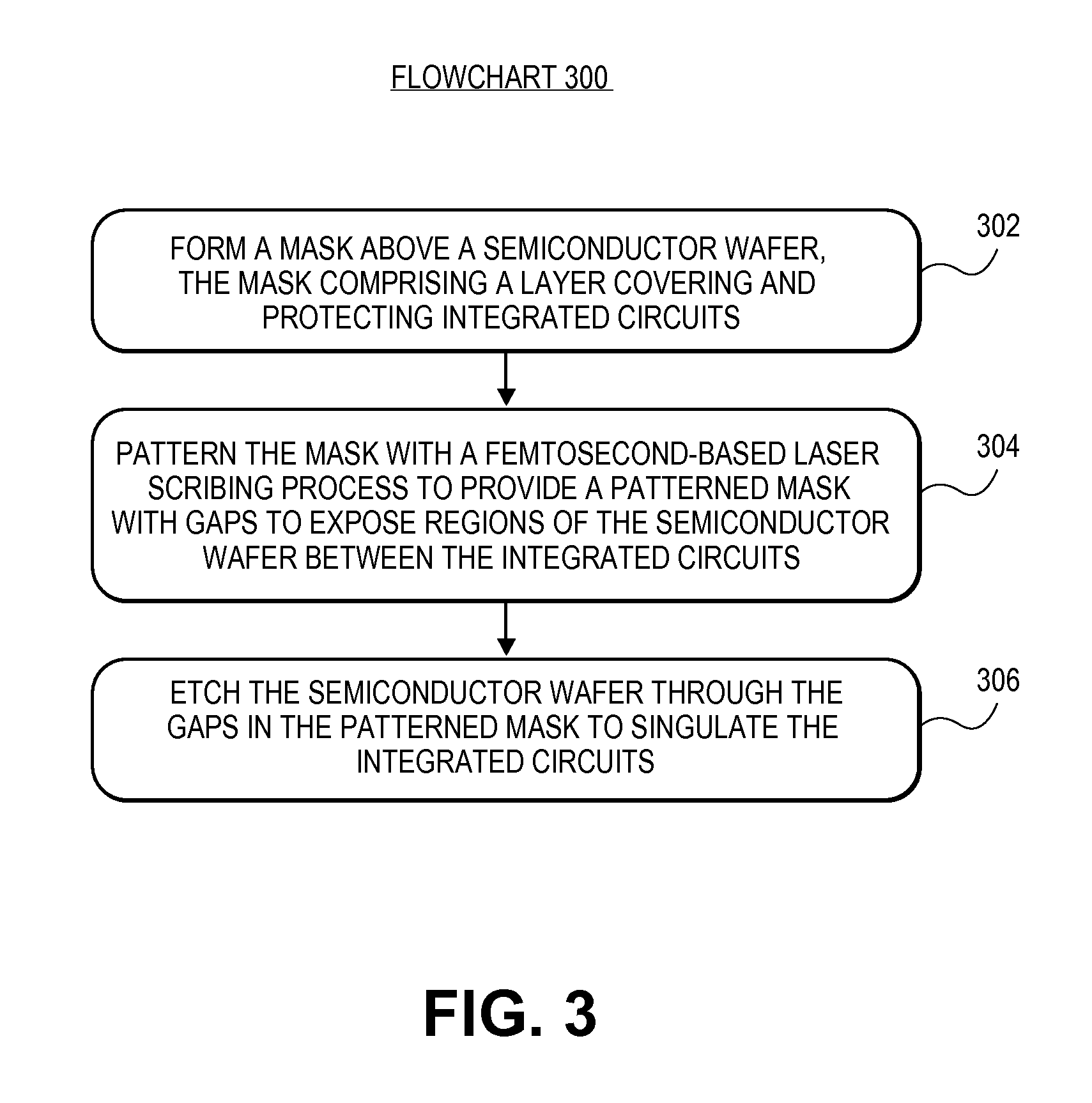

Methods of dicing semiconductor wafers, each wafer having a plurality of integrated circuits, are described. A method includes forming a mask above the semiconductor wafer. The mask is composed of a layer covering and protecting the integrated circuits. The mask is patterned with a femtosecond-based laser scribing process to provide a patterned mask with gaps. The patterning exposes regions of the semiconductor wafer between the integrated circuits. The semiconductor wafer is then etched through the gaps in the patterned mask to singulate the integrated circuits.

Owner:APPLIED MATERIALS INC

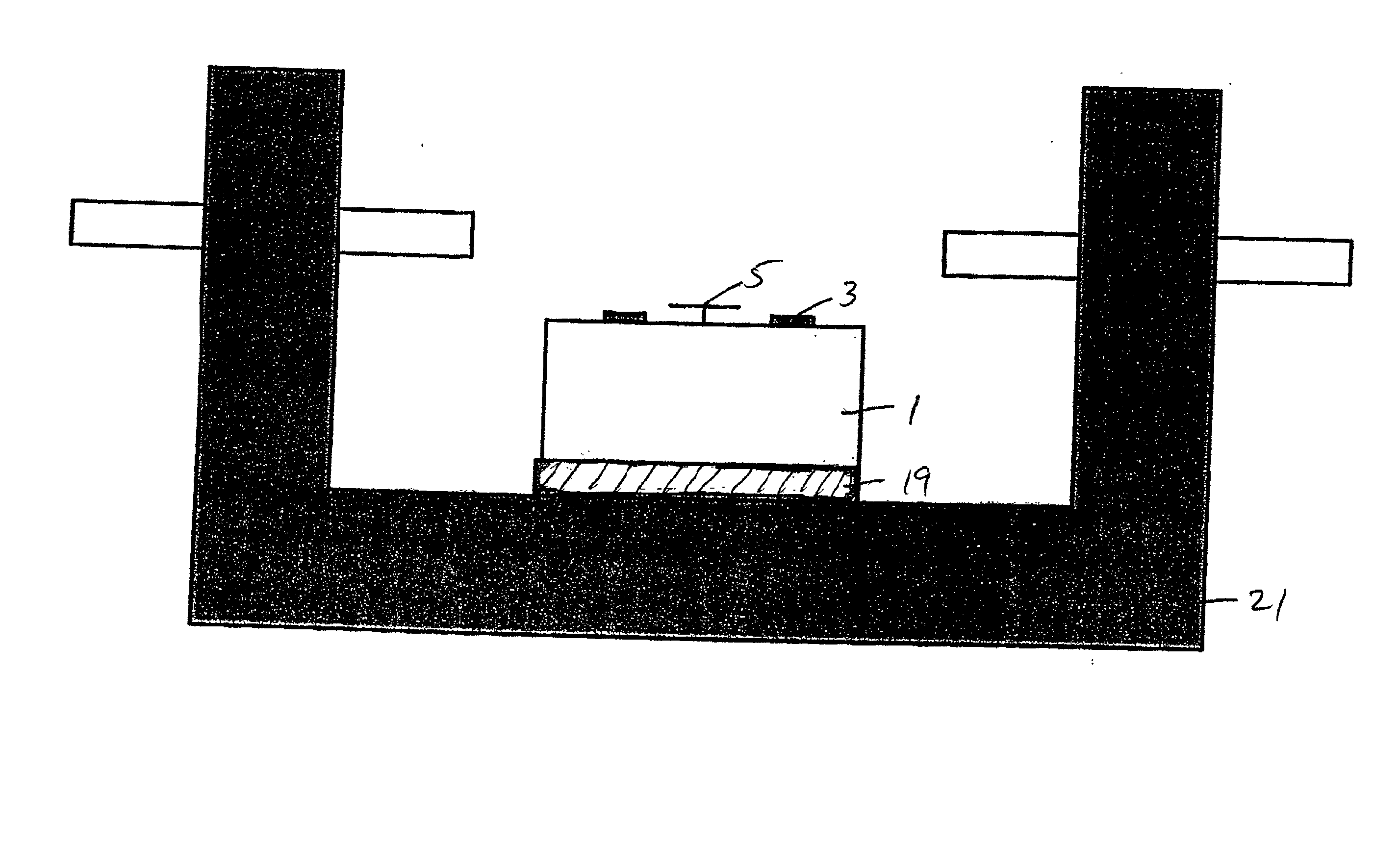

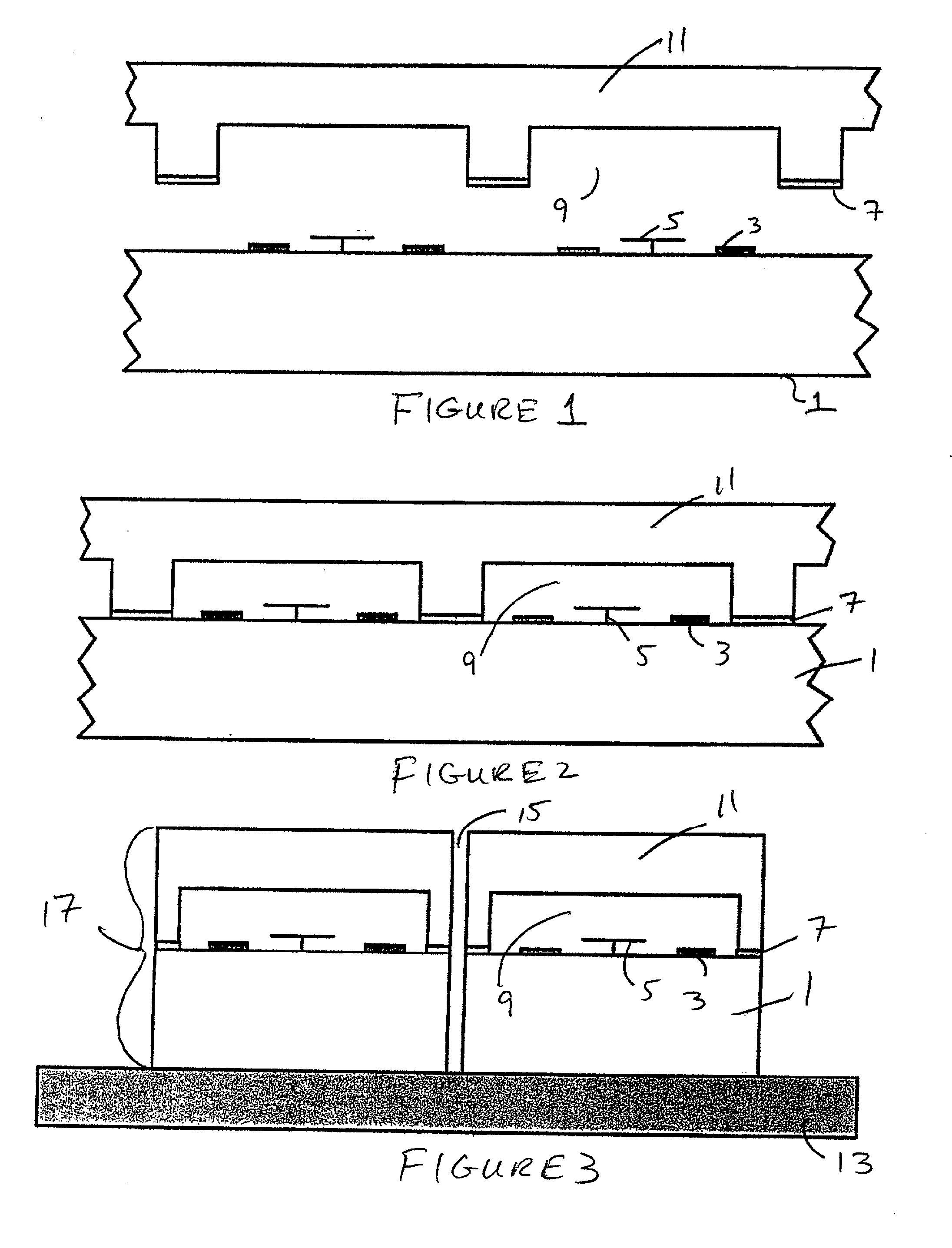

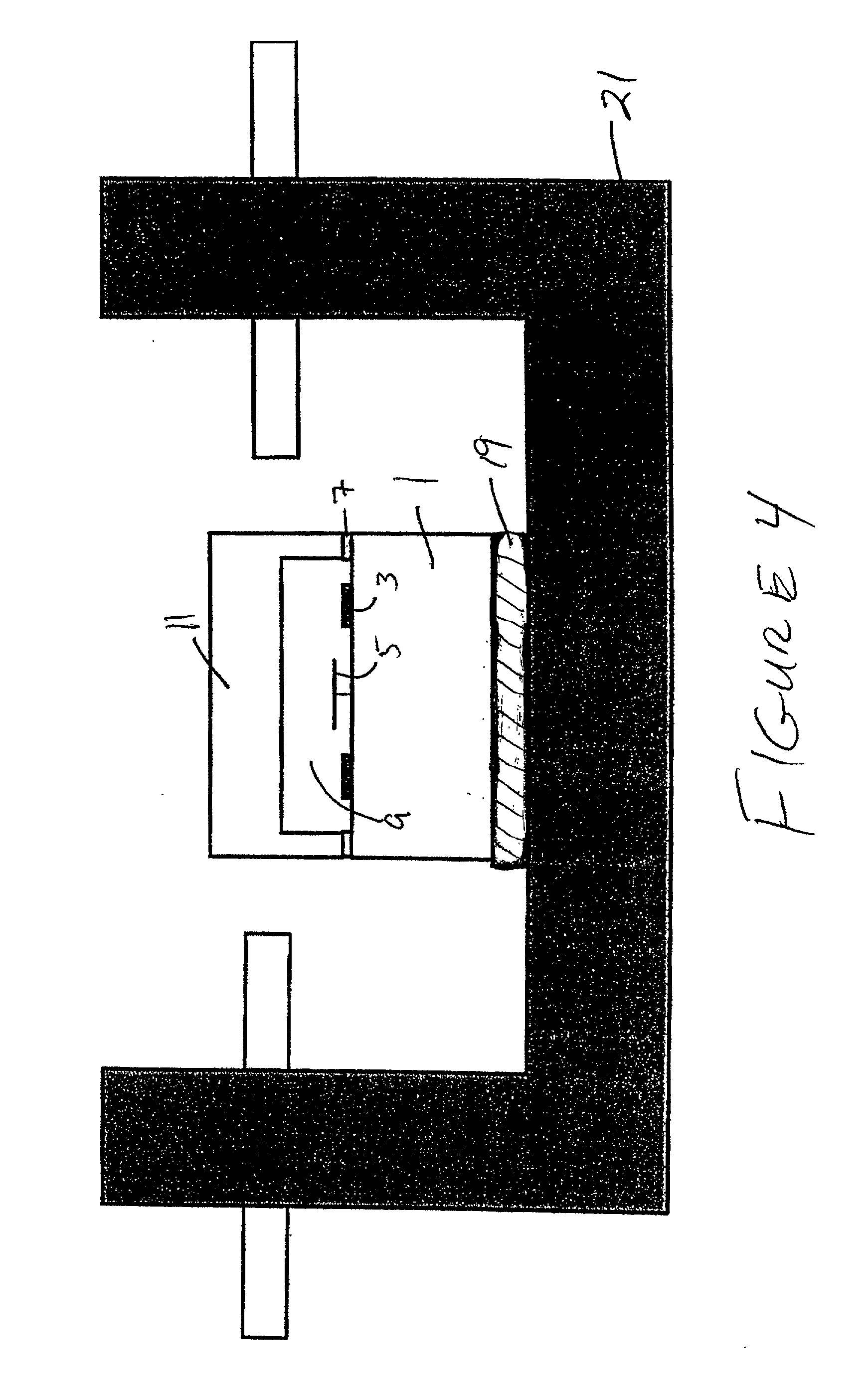

Method and device for protecting micro electromechanical systems structures during dicing of a wafer

InactiveUS20020076848A1Prevent electrostatically induced damageAvoid damageDecorative surface effectsSolid-state devicesSystem structureEngineering

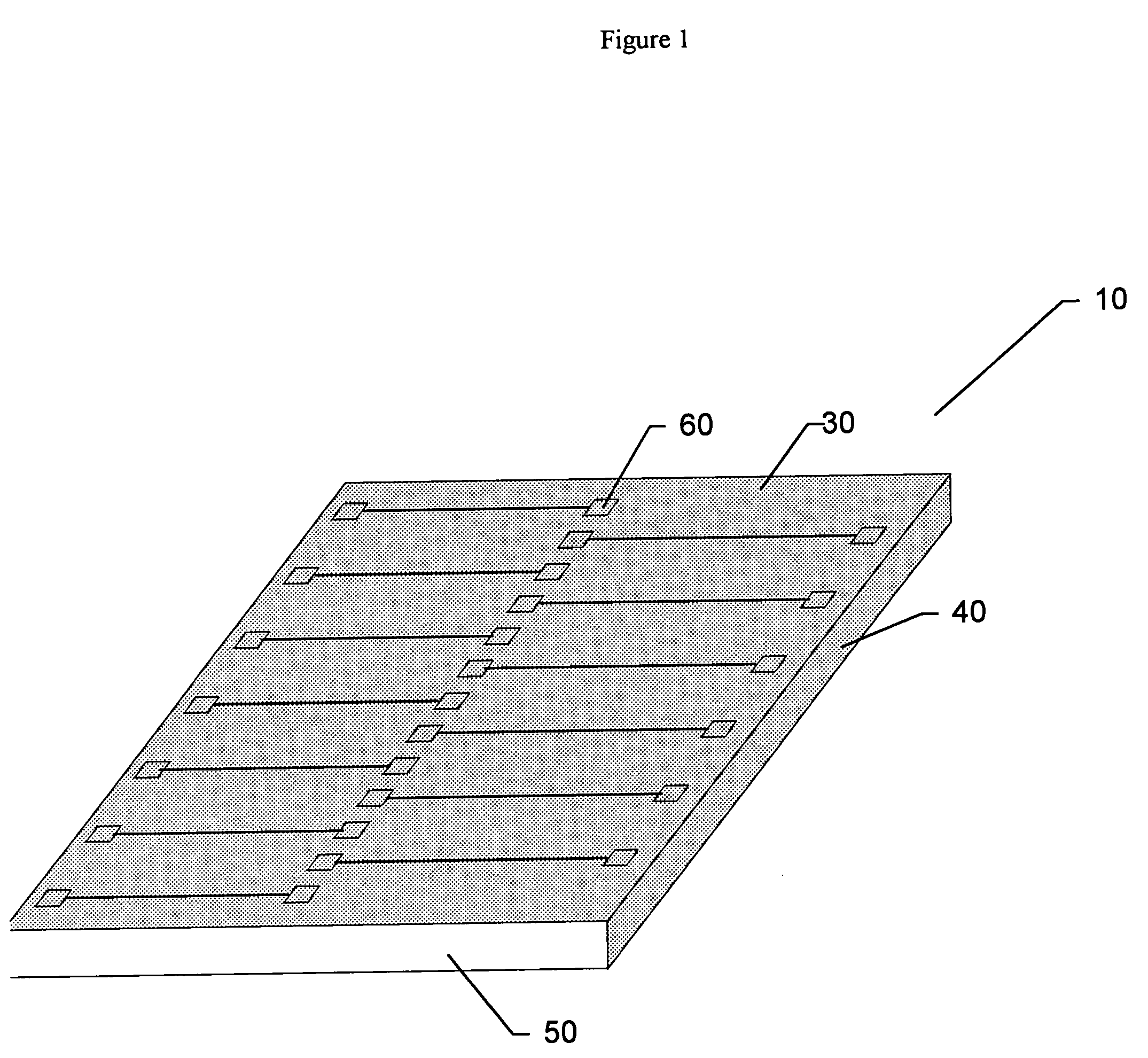

A wafer cap protects micro electromechanical system ("MEMS") structures during a dicing of a MEMS wafer to produce individual MEMS dies. A MEMS wafer is prepared having a plurality of MEMS structure sites thereon. Upon the MEMS wafer, the wafer cap is mounted to produce a laminated MEMS wafer. The wafer cap is recessed in areas corresponding to locations of the MEMS structure sites on the MEMS wafer. The capped MEMS wafer can be diced into a plurality of MEMS dies without causing damage to or contaminating the MEMS die.

Owner:ANALOG DEVICES INC

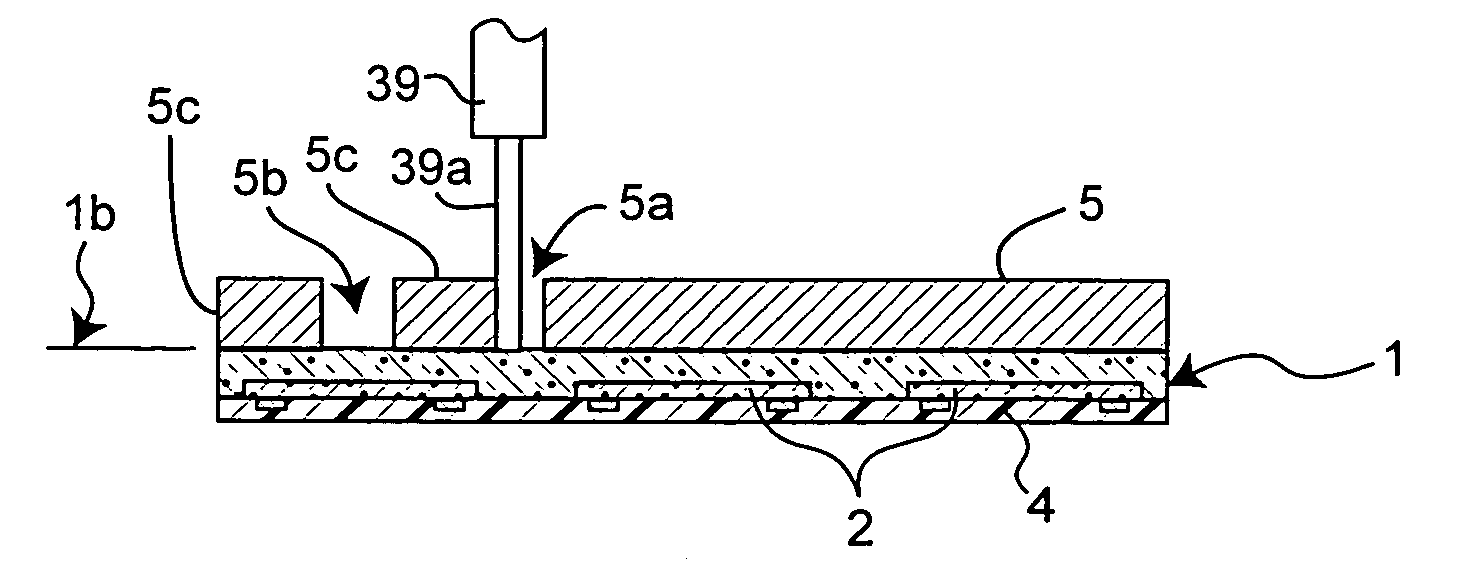

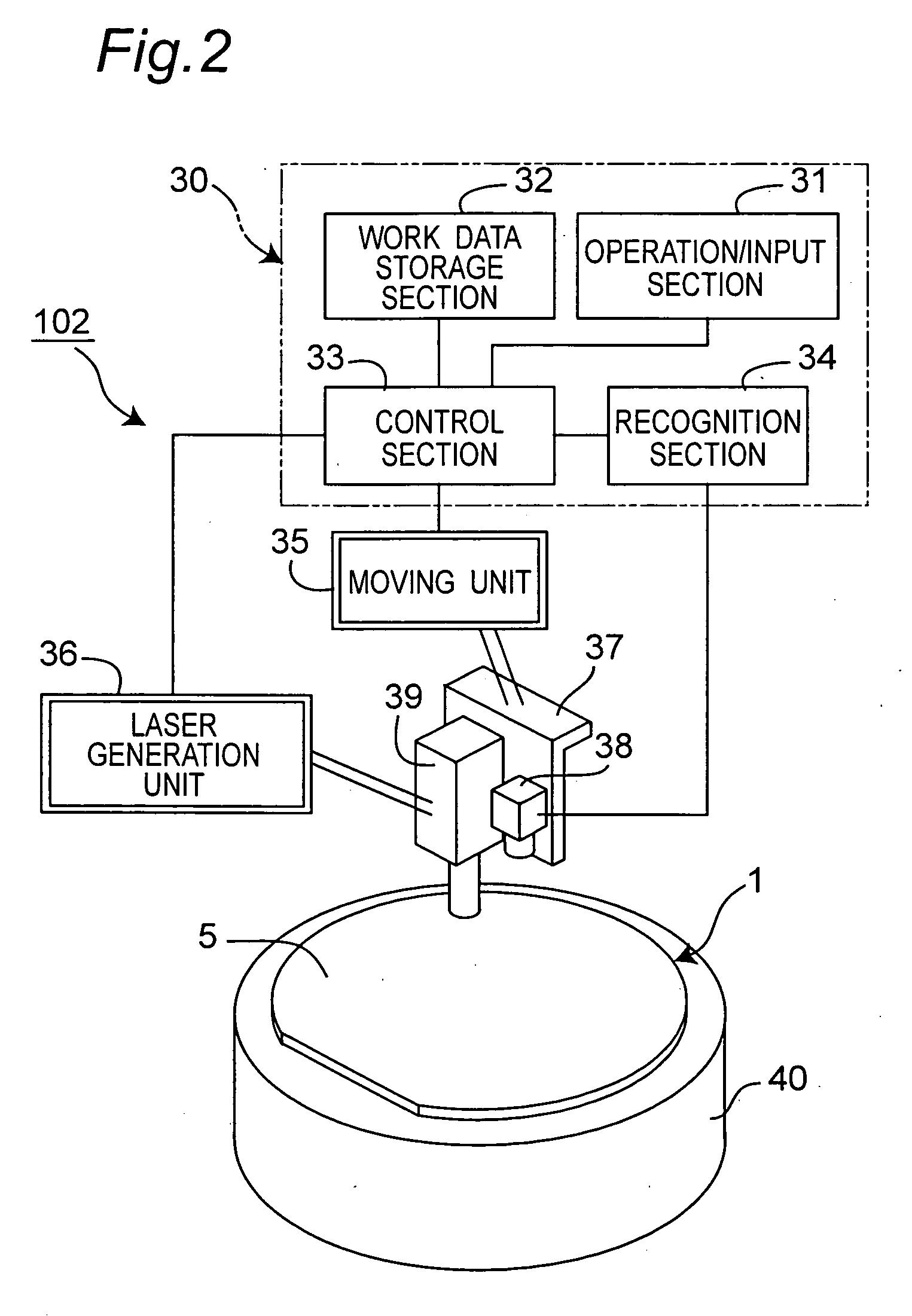

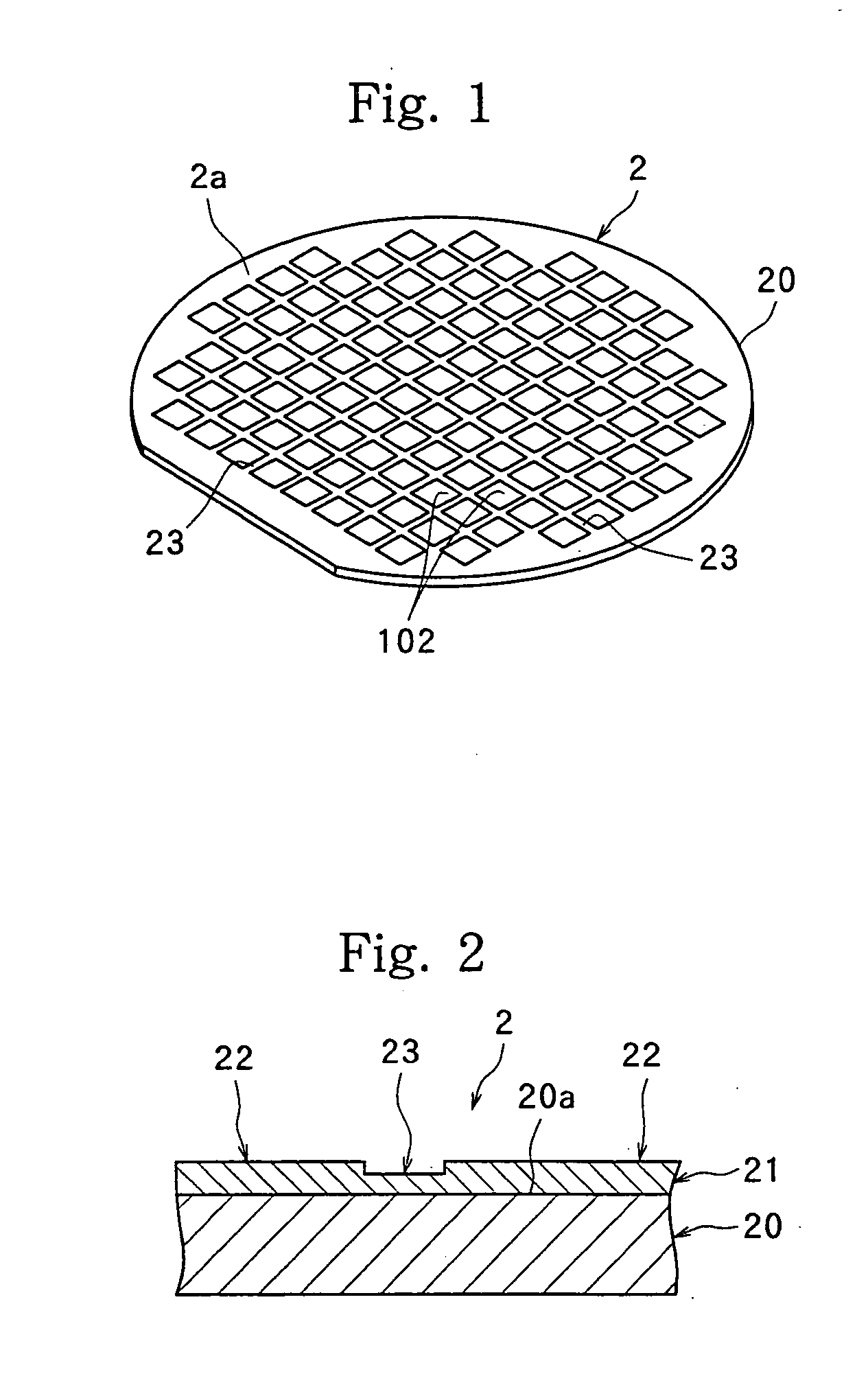

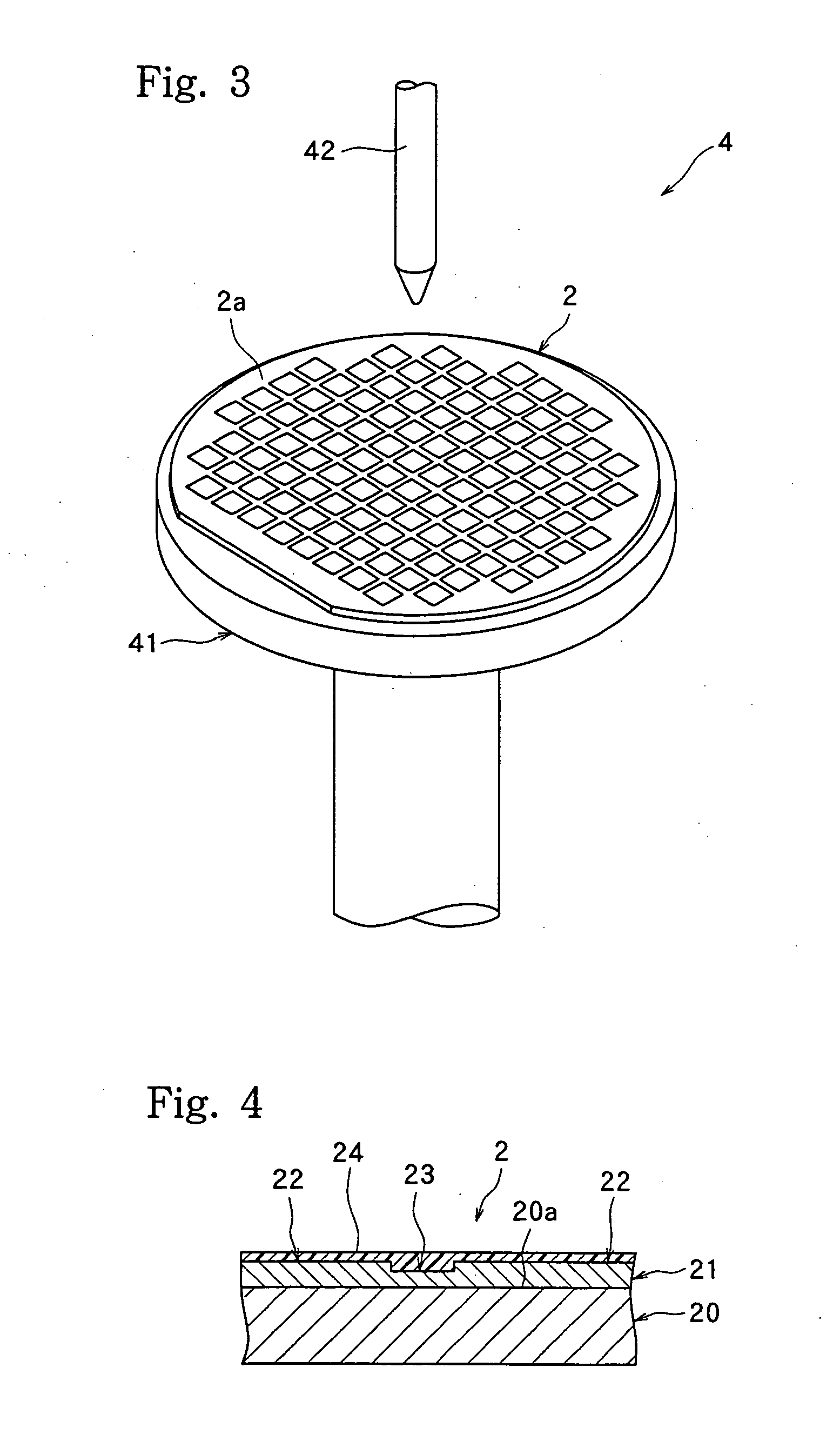

Manufacturing method for semiconductor devices, and formation apparatus for semiconductor wafer dicing masks

ActiveUS7629228B2Avoid quality lossSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsWafer dicingEngineering

On a mask placement-side surface of a semiconductor wafer in which a plurality of semiconductor devices are formed, a mask is placed, while dicing lines for dicing the semiconductor wafer into the respective separate semiconductor devices are defined and a surface of a flawed semiconductor device among the respective semiconductor devices is partially exposed, and then plasma etching is applied to the mask placement-side surface of the semiconductor wafer so as to dice the semiconductor wafer into the respective semiconductor devices along the defined dicing lines, and an exposed portion of the flawed semiconductor device is removed so as to form a removed portion as a flawed semiconductor device distinguishing mark.

Owner:PANASONIC CORP

Manufacturing method for semiconductor devices, and formation apparatus for semiconductor wafer dicing masks

ActiveUS20060024924A1Maintain consistencyQuality improvementSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsWafer dicingEngineering

On a mask placement-side surface of a semiconductor wafer in which a plurality of semiconductor devices are formed, a mask is placed, while dicing lines for dicing the semiconductor wafer into the respective separate semiconductor devices are defined and a surface of a flawed semiconductor device among the respective semiconductor devices is partially exposed, and then plasma etching is applied to the mask placement-side surface of the semiconductor wafer so as to dice the semiconductor wafer into the respective semiconductor devices along the defined dicing lines, and an exposed portion of the flawed semiconductor device is removed so as to form a removed portion as a flawed semiconductor device distinguishing mark.

Owner:PANASONIC CORP

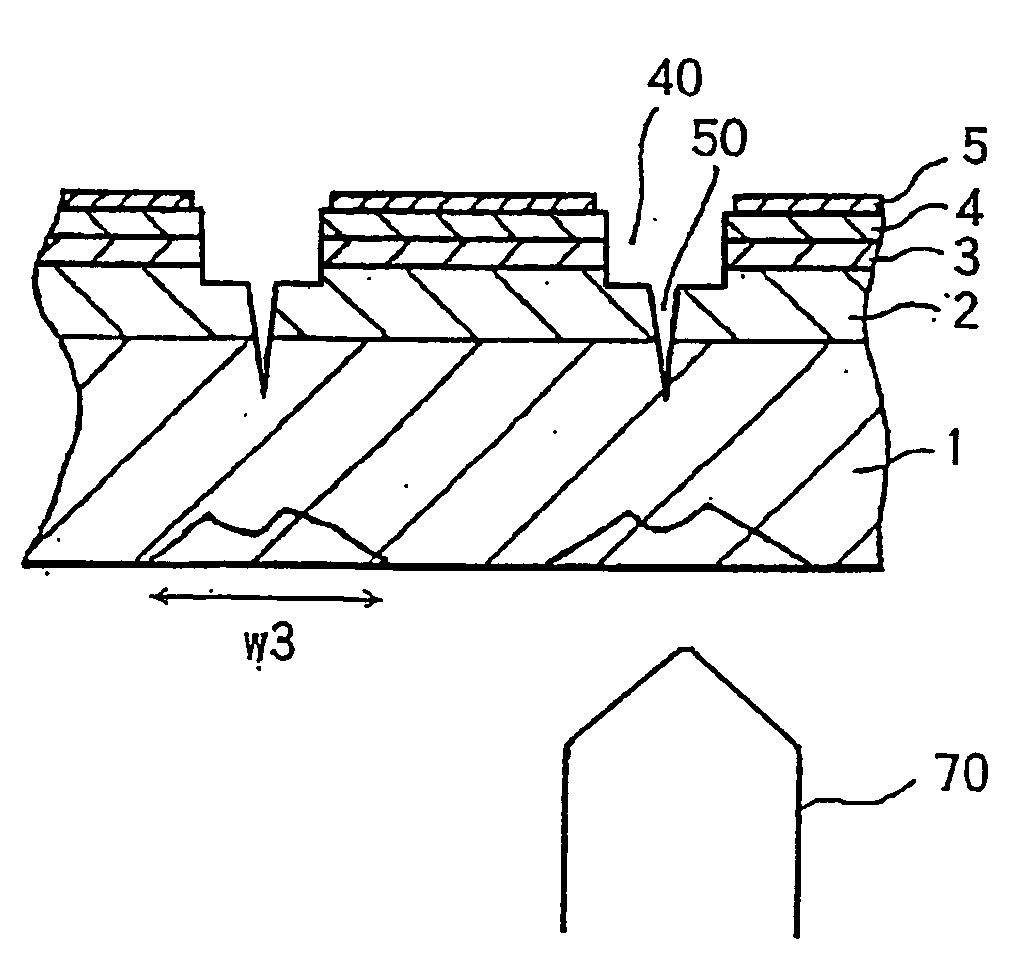

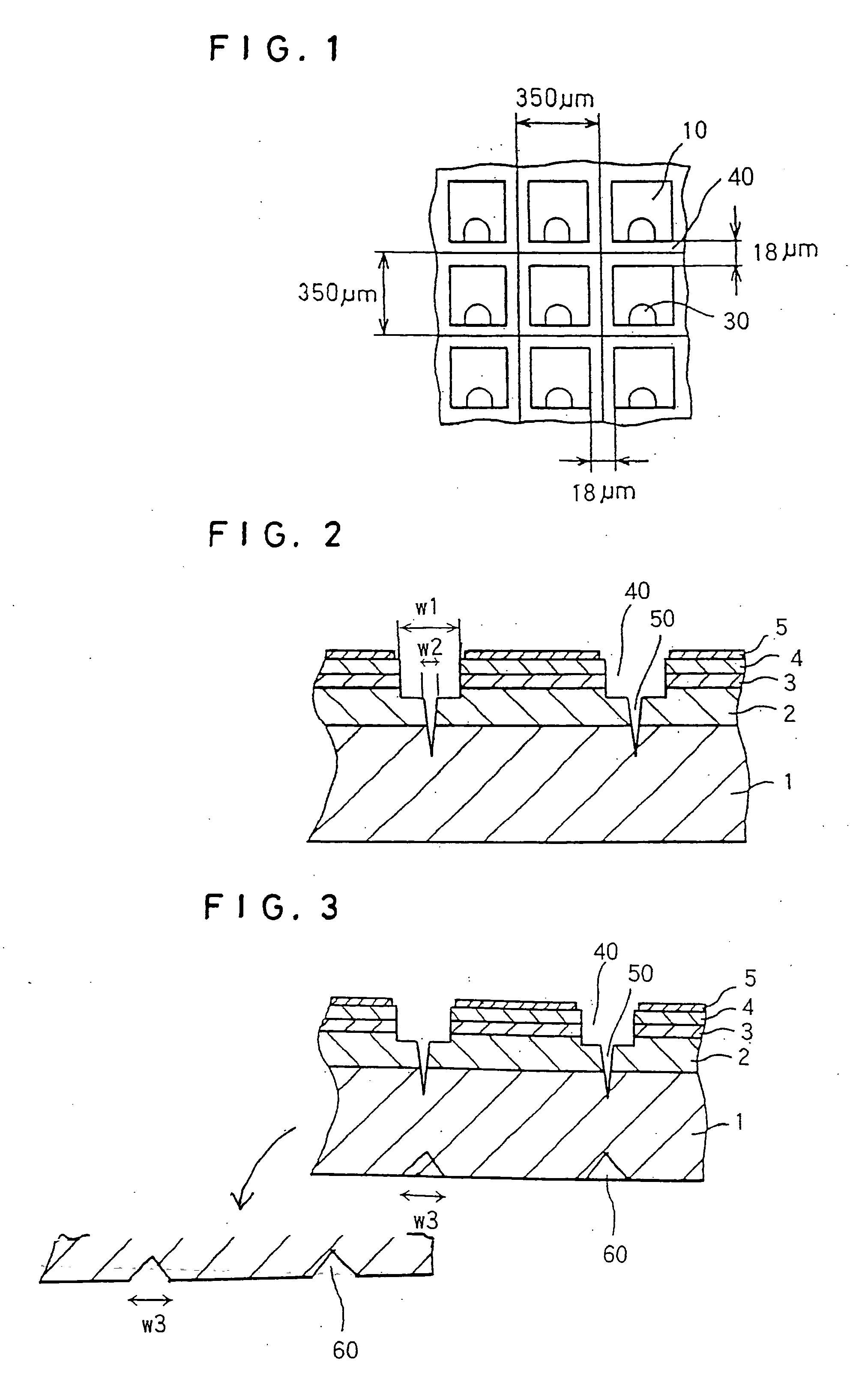

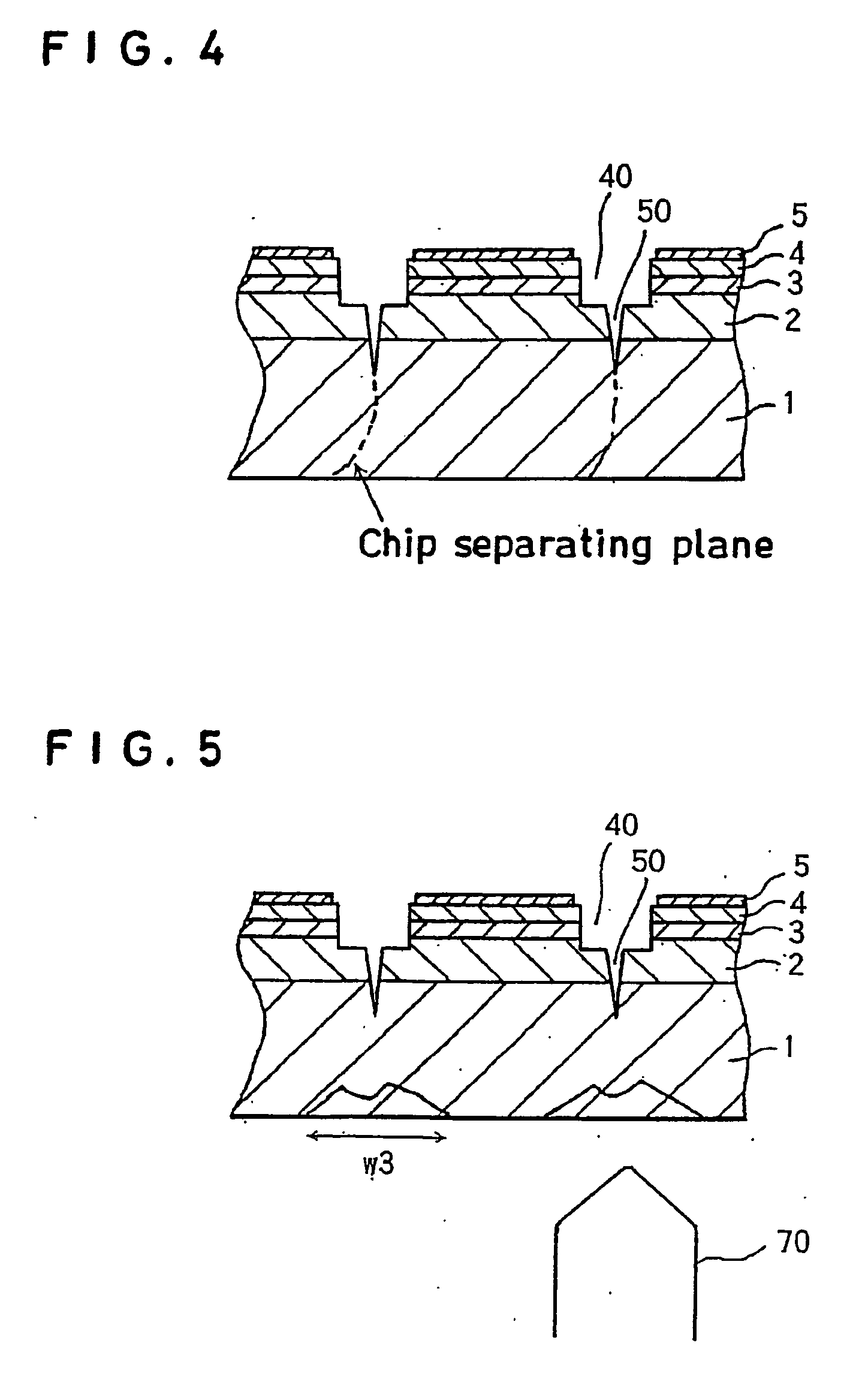

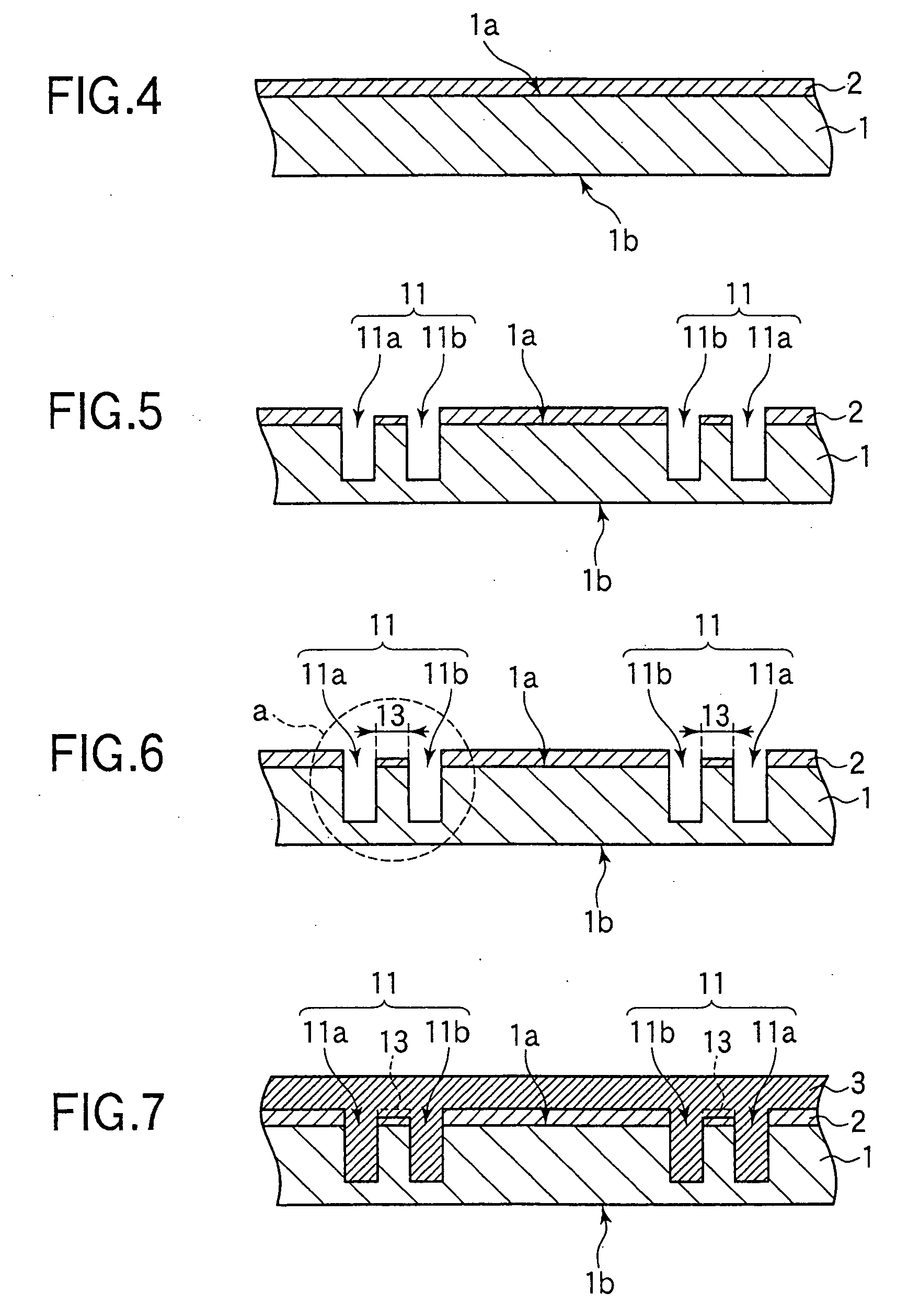

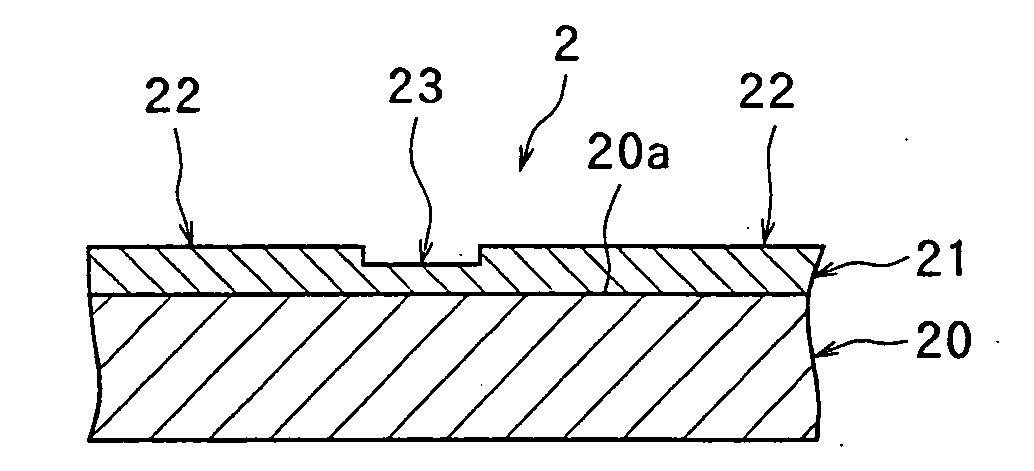

Method for Fabrication of Semiconductor Light-Emitting Device and the Device Fabricated by the Method

ActiveUS20080121906A1Semiconductor/solid-state device manufacturingWelding/soldering/cutting articlesWafer dicingSemiconductor package

A method for producing a semiconductor light-emitting device includes stacking at least a first conductive type semiconductor layer (2), an active layer (3) and a second conductive type semiconductor layer (4) on a substrate (1) to form a wafer, then forming on a side of growth surfaces of the semiconductor layers first trenches (40) exposing the first conductive type semiconductor layer, further forming second trenches (50) reaching the substrate from above the first trenches by using a laser beam, subsequently forming third trenches (60) from the substrate at the positions corresponding to the second trenches, and finally cutting the wafer into chips. The produced semiconductor chips provide an enhanced efficiency of extracting emitted light even when the end faces thereof are smooth surfaces and they allow the semiconductor layer to be cut without distorting the end faces of the chips.

Owner:TOYODA GOSEI CO LTD

Method for packaging a microelectronic device using on-die bond pad expansion

InactiveUS7071024B2Semiconductor/solid-state device detailsSolid-state devicesWafer dicingDie bonding

Expanded bond pads are formed over a passivation layer on a semiconductor wafer before the wafer is diced into individual circuit chips. After dicing, the individual chips are packaged by fixing each chip within a package core and building up one or more metallization layers on the resulting assembly. In at least one embodiment, a high melting temperature (lead free) alternative bump metallurgy (ABM) form of controlled collapse chip connect (C4) processing is used to form relatively wide conducting platforms over the bond pads on the wafer.

Owner:INTEL CORP

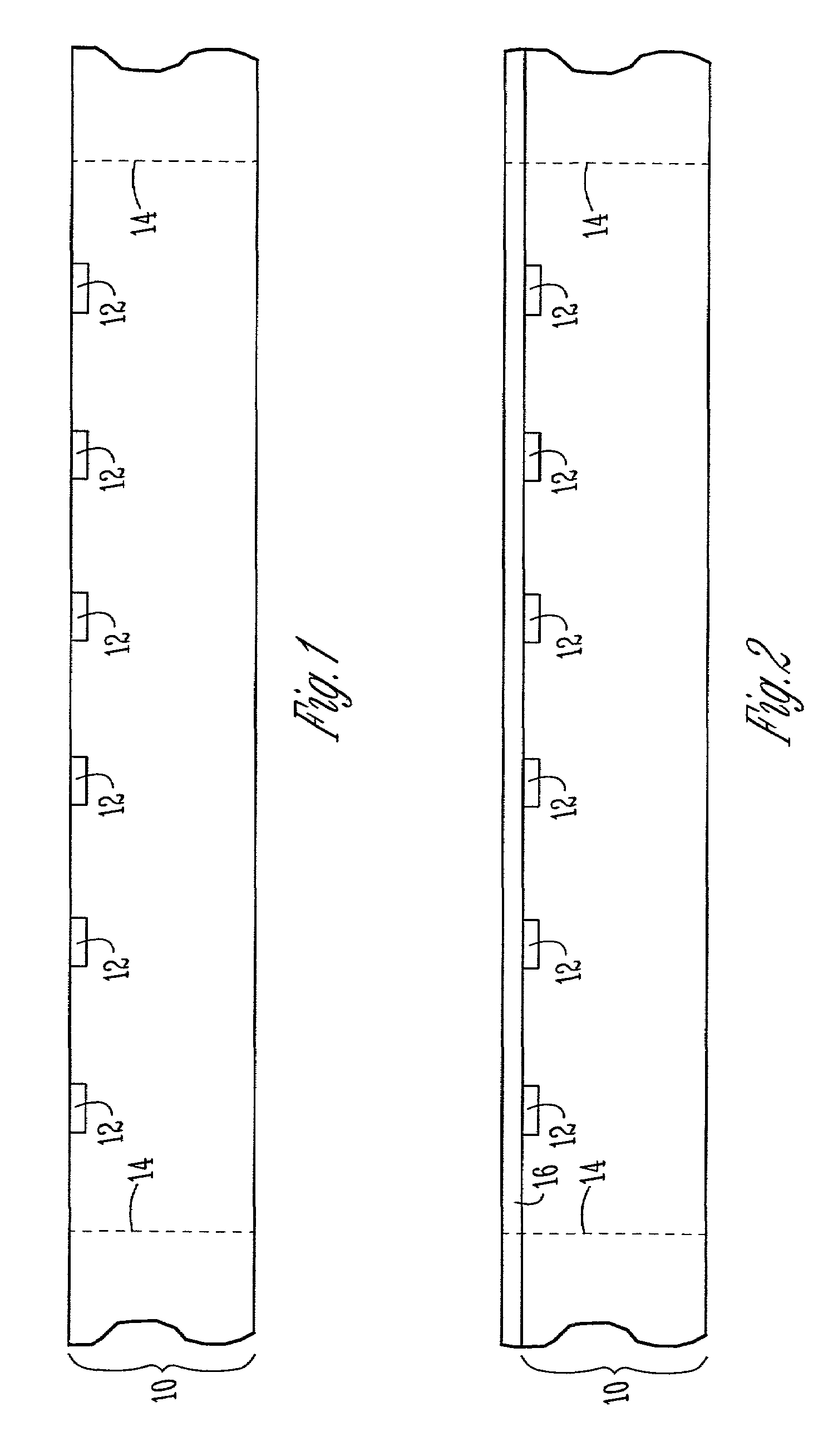

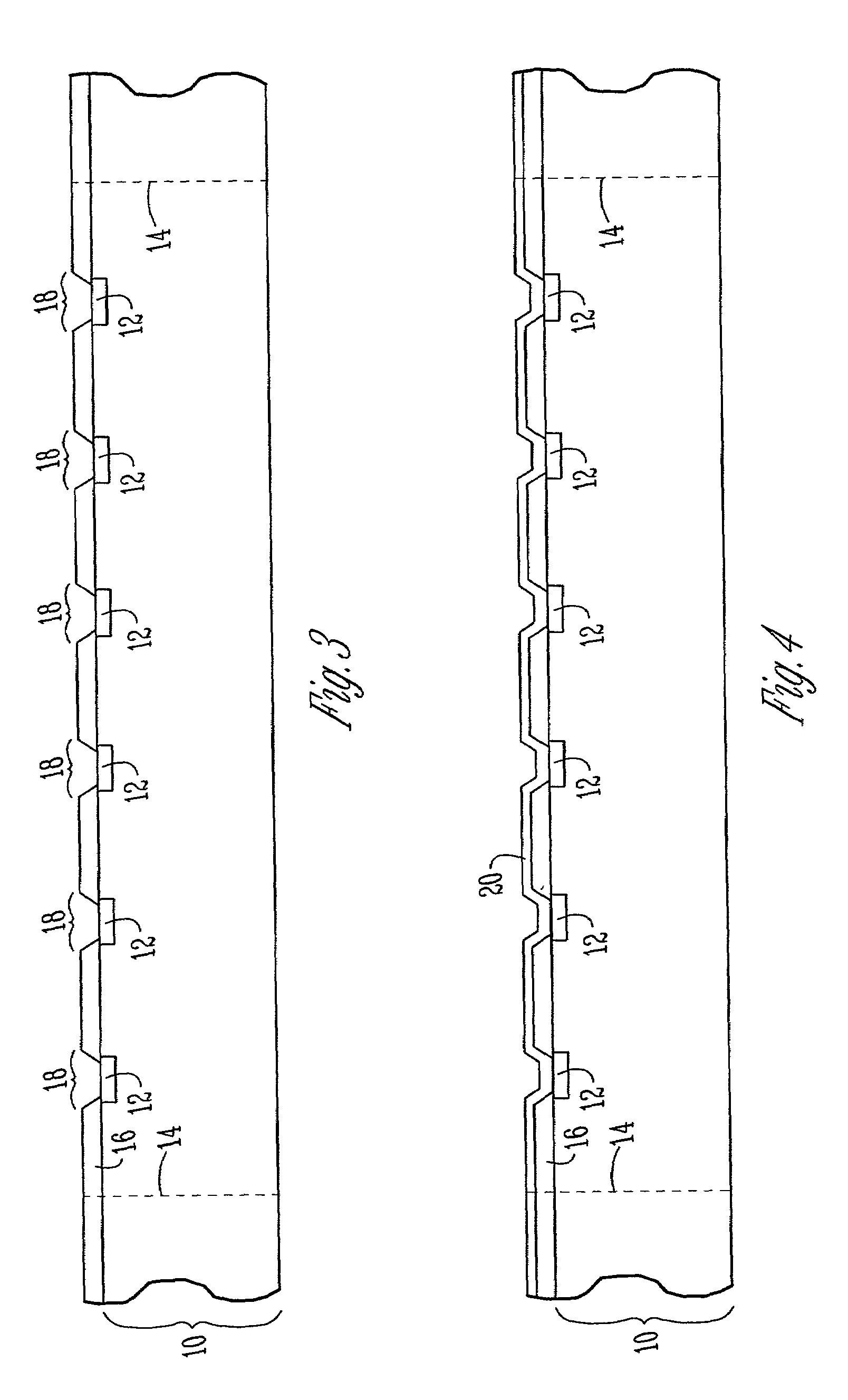

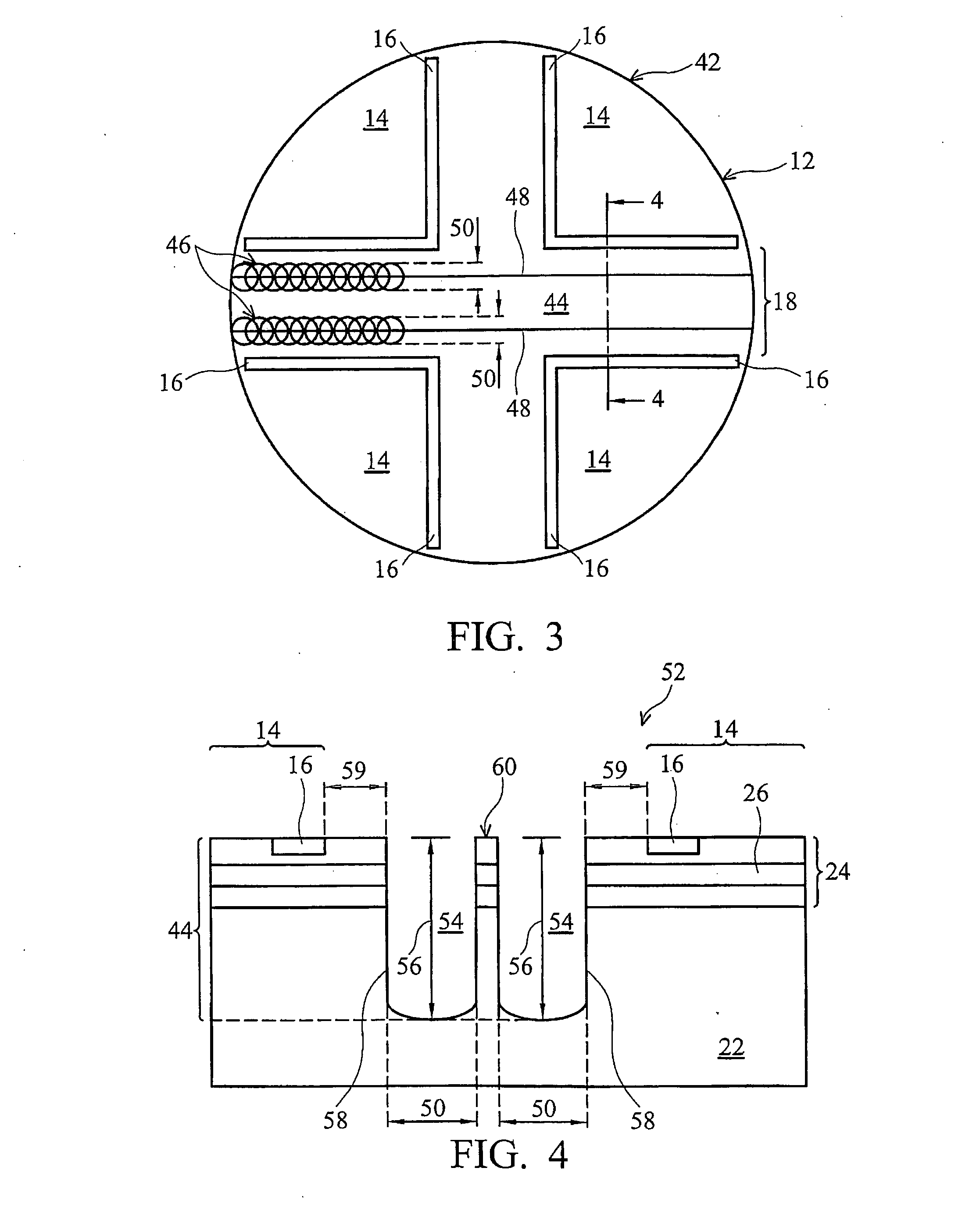

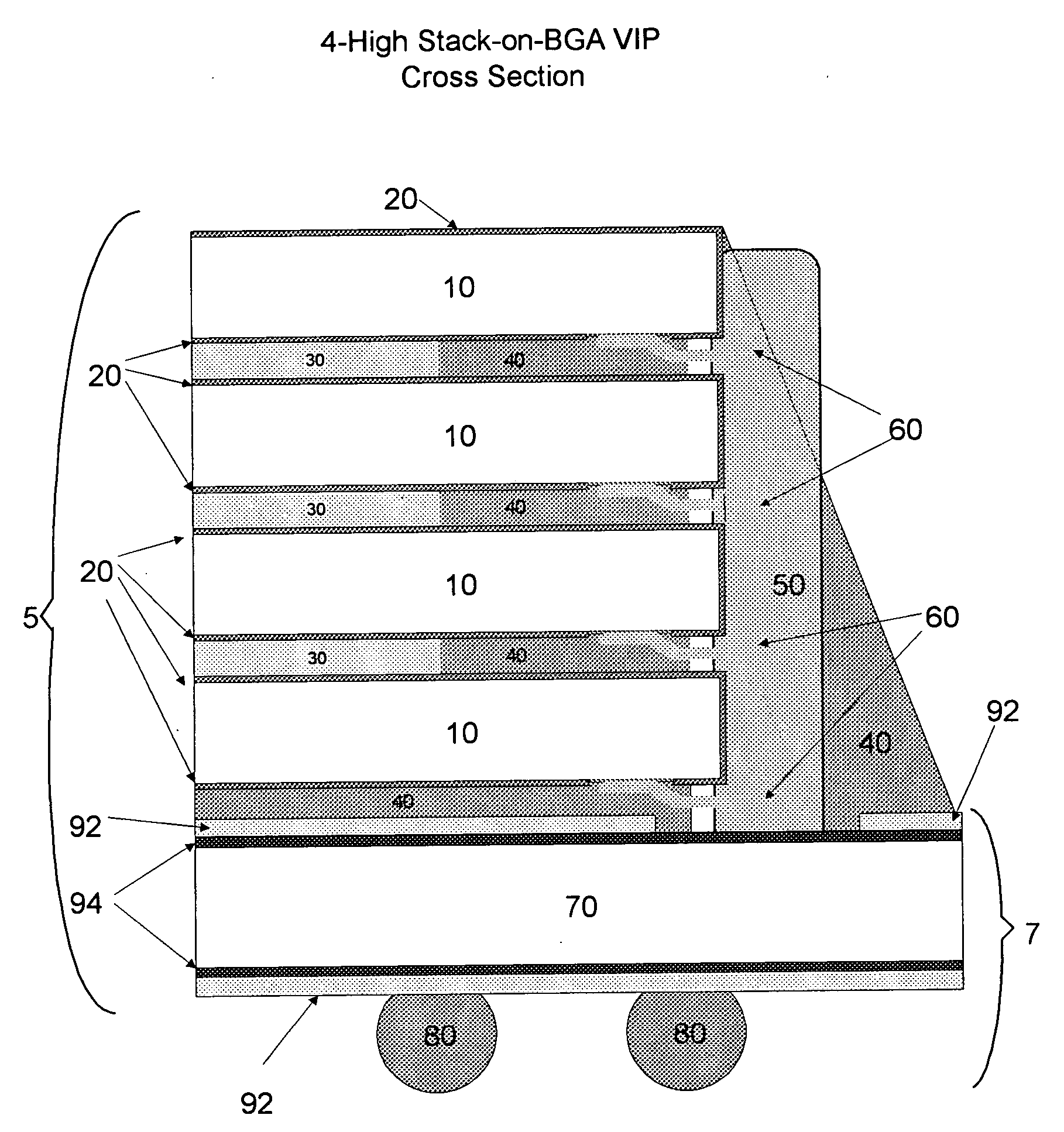

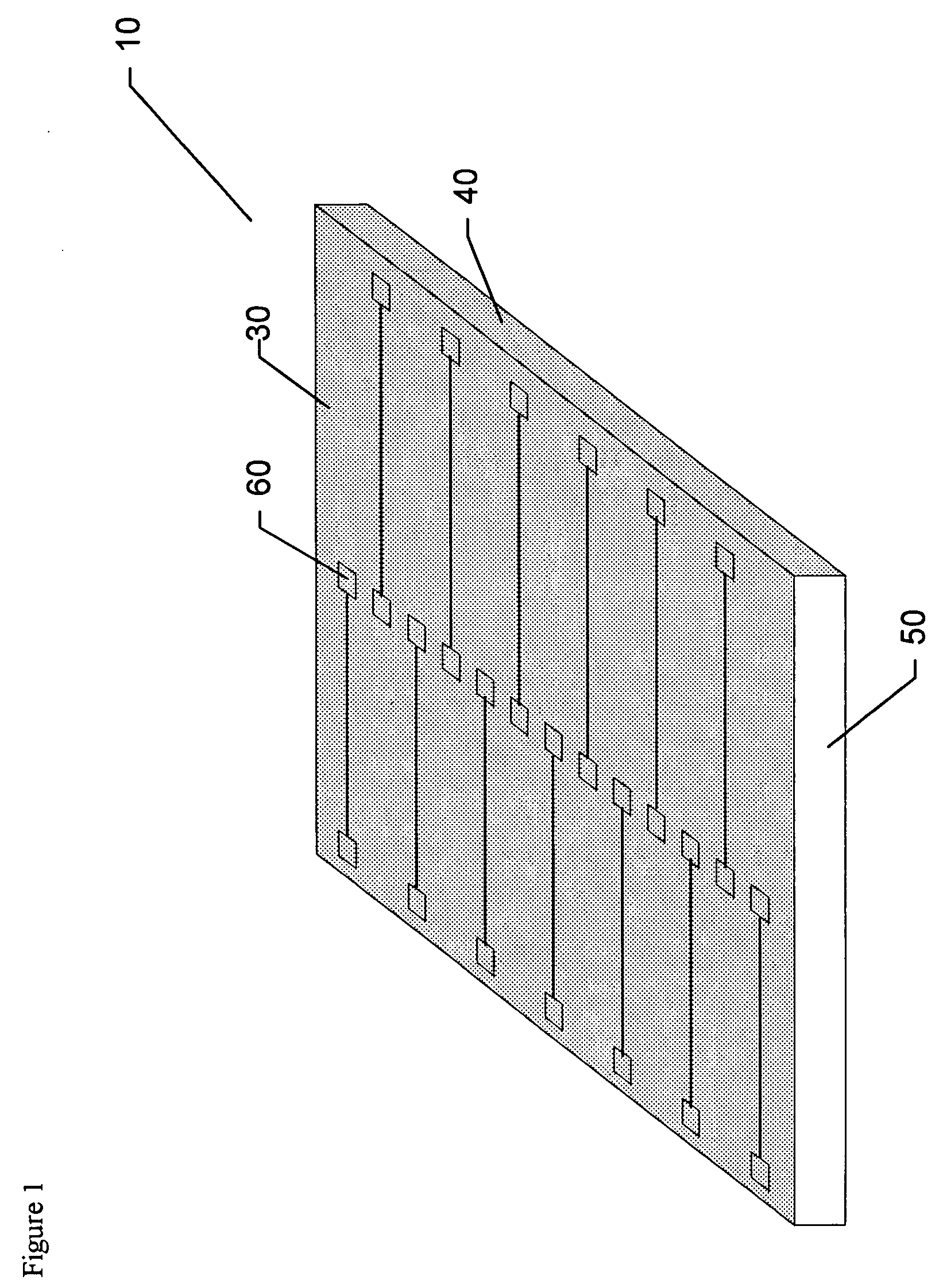

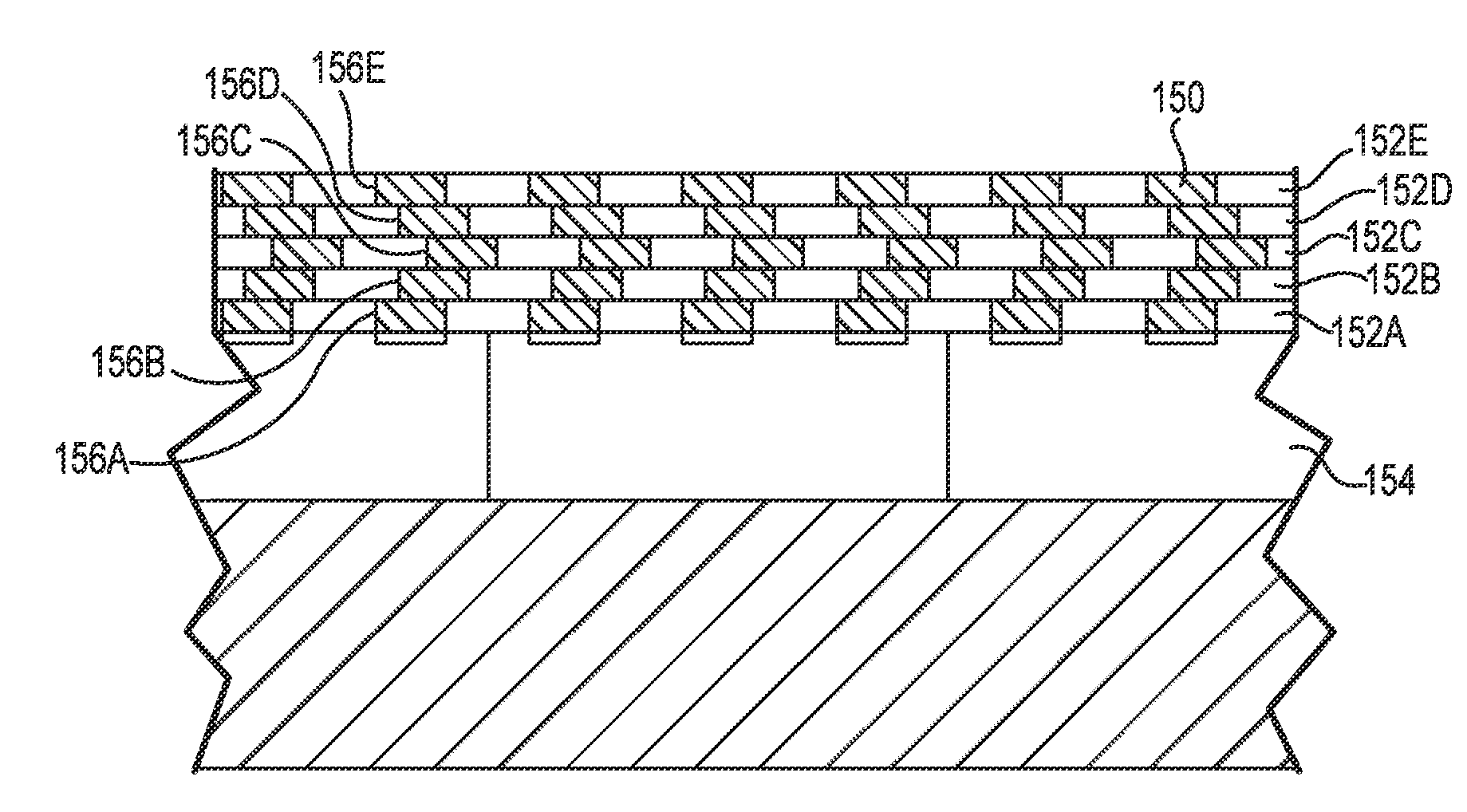

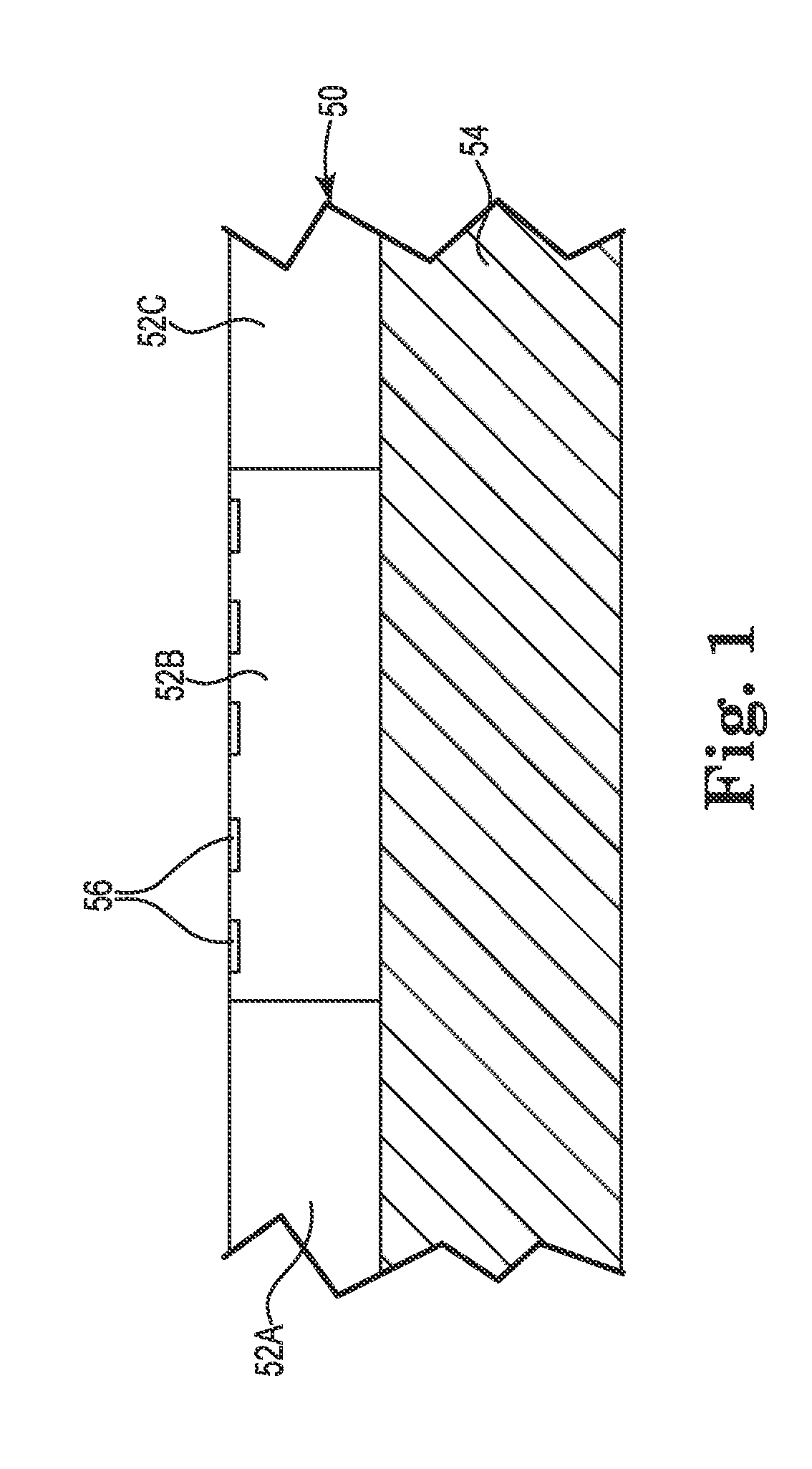

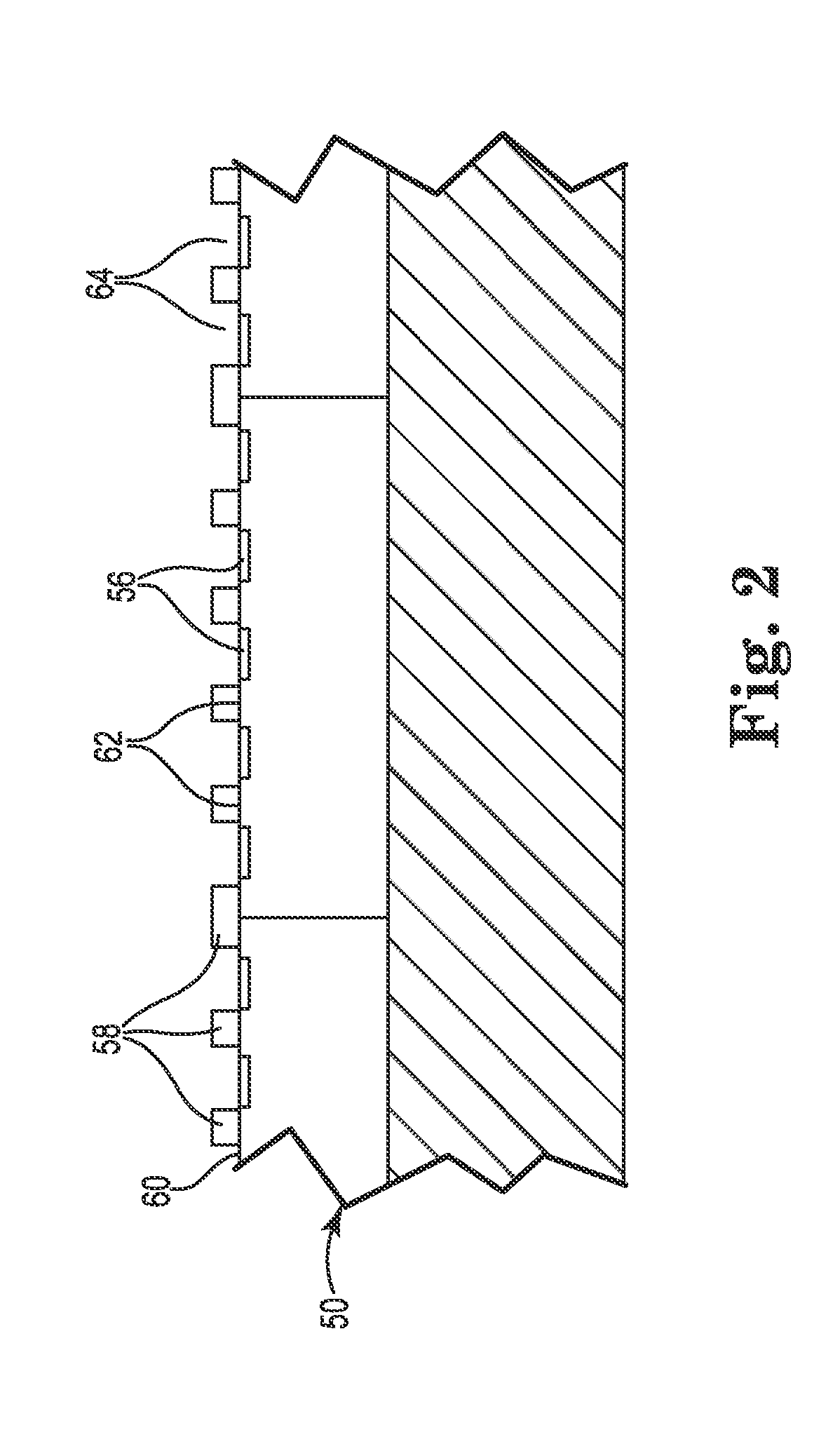

Micropede stacked die component assembly

InactiveUS20050258530A1Simple methodSemiconductor/solid-state device detailsSolid-state devicesEpoxyWafer dicing

The present invention provides an apparatus for vertically interconnecting semiconductor die, integrated circuit die, or multiple die segments. Metal rerouting interconnects which extend to one or more sides of the die or segment can be optionally added to the die or multi die segment to provide edge bonding pads upon the surface of the die for external electrical connection points. After the metal rerouting interconnect has been added to the die on the wafer, the wafer is optionally thinned and each die or multiple die segment is singulated from the wafer by cutting or other appropriate singulation method. After the die or multiple die segments are singulated or cut from the wafer, insulation is applied to all surfaces of the die or multiple die segments, openings are made in the insulation above the desired electrical connection pads, and the die or multiple die segments are placed on top of one another to form a stack. Vertically adjacent segments in the stack are electrically interconnected by attaching a short flexible bond wire or bond ribbon to the exposed electrical connection pad at the peripheral edges of the die which protrudes horizontally from the die and applying electrically conductive polymer, or epoxy, filaments or lines to one or more sides of the stack.

Owner:INVENSAS CORP

Semiconductor-dielectric-semiconductor device structure fabricated by wafer bonding

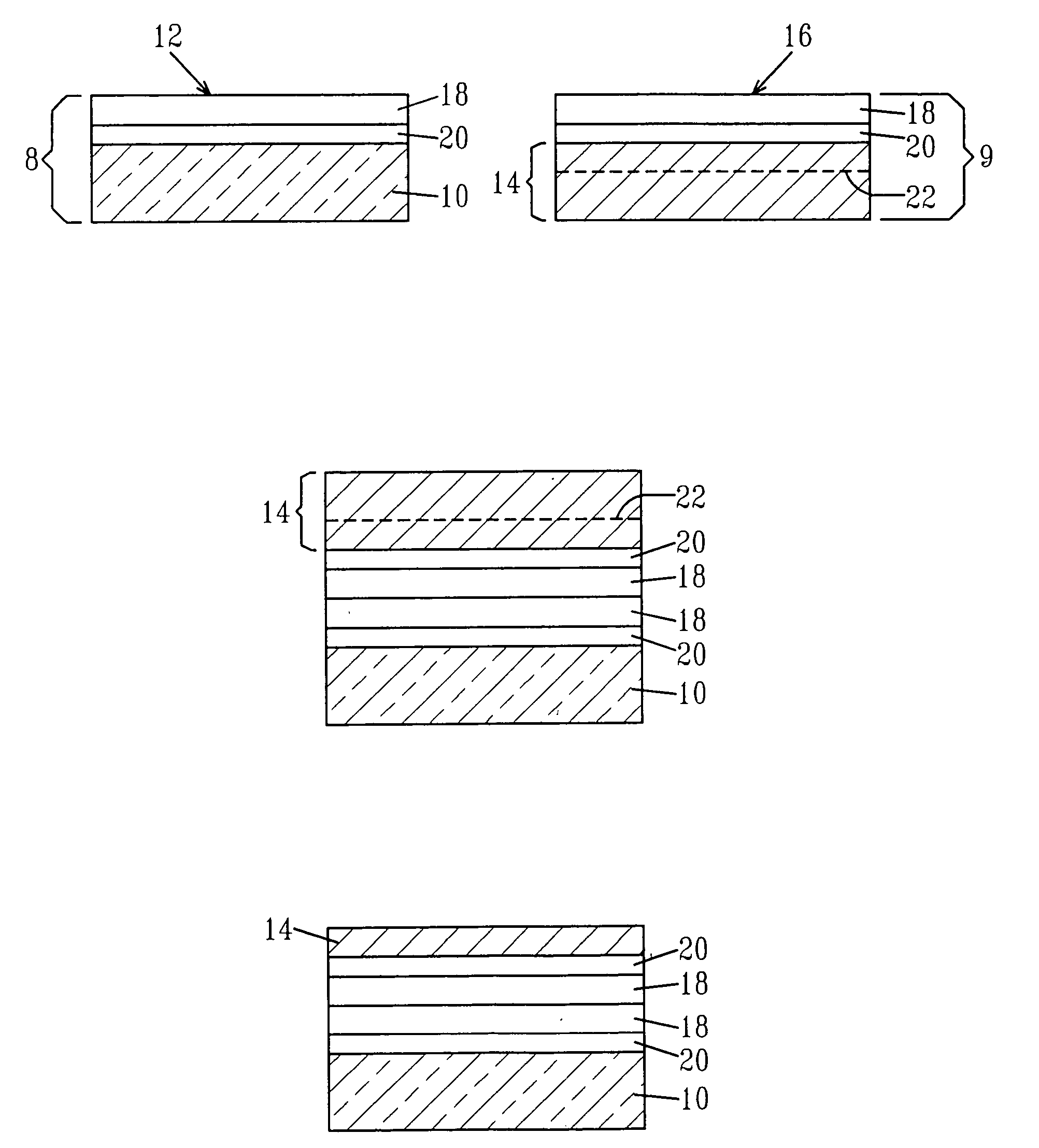

InactiveUS20060035450A1Easy to controlEnsure qualitySemiconductor/solid-state device manufacturingSemiconductor devicesDielectricWafer dicing

A method of forming a gate stack for semiconductor electronic devices utilizing wafer bonding of at least one structure containing a high-k dielectric material is provided. The method of the present invention includes a step of first selecting a first and second structure having a major surface respectively. In accordance with the present invention, at least one, or both, of the first and second structures includes at least a high-k dielectric material. Next, the major surfaces of the first and second structures are bonded together to provide a bonded structure containing at least the high-k dielectric material of a gate stack.

Owner:ELPIS TECH INC

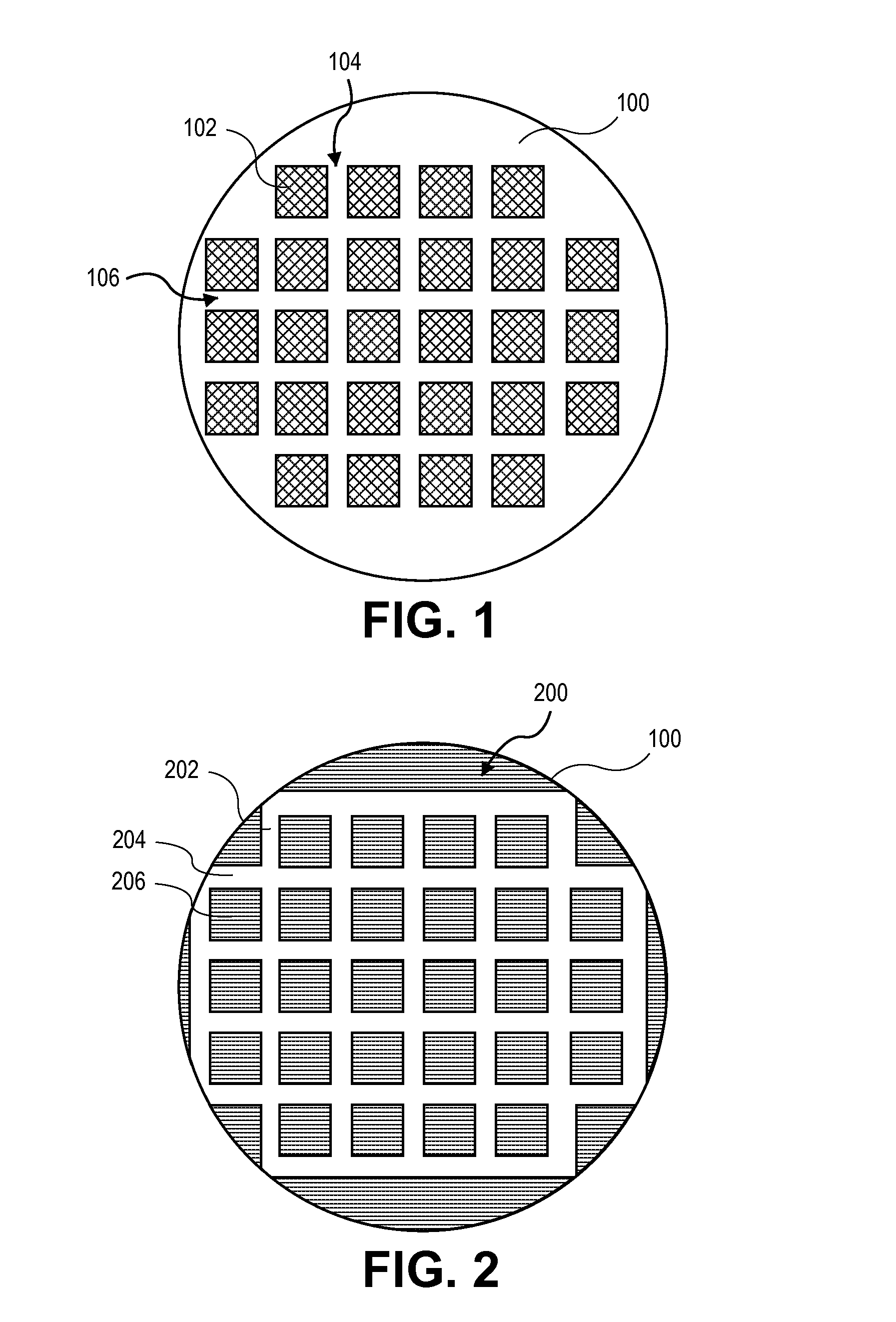

Hybrid laser and plasma etch wafer dicing using substrate carrier

ActiveUS20120322239A1Solid-state devicesSemiconductor/solid-state device manufacturingWafer dicingLaser scribing

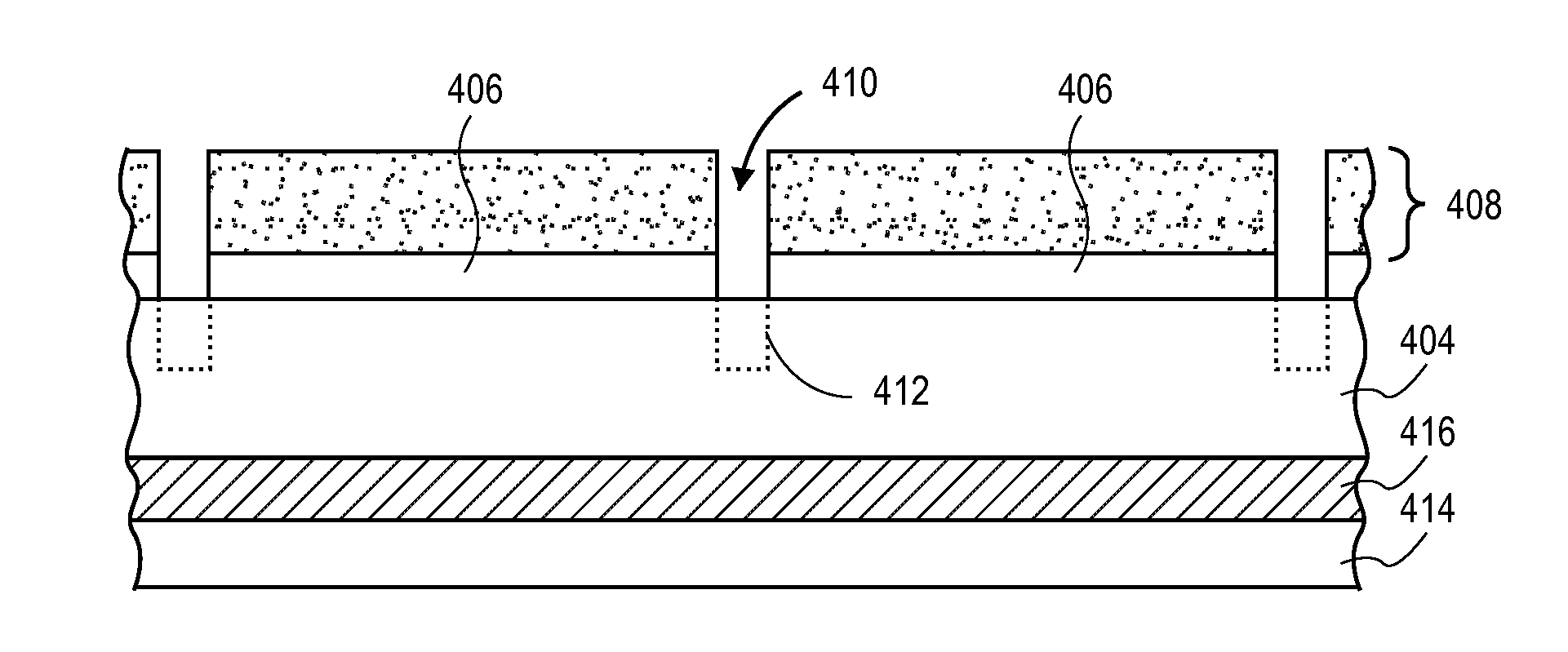

Methods of dicing semiconductor wafers, each wafer having a plurality of integrated circuits, are described. A method includes forming a mask above the semiconductor wafer, the mask composed of a layer covering and protecting the integrated circuits. The semiconductor wafer is supported by a substrate carrier. The mask is then patterned with a laser scribing process to provide a patterned mask with gaps, exposing regions of the semiconductor wafer between the integrated circuits. The semiconductor wafer is then etched through the gaps in the patterned mask to singulate the integrated circuits while supported by the substrate carrier.

Owner:APPLIED MATERIALS INC

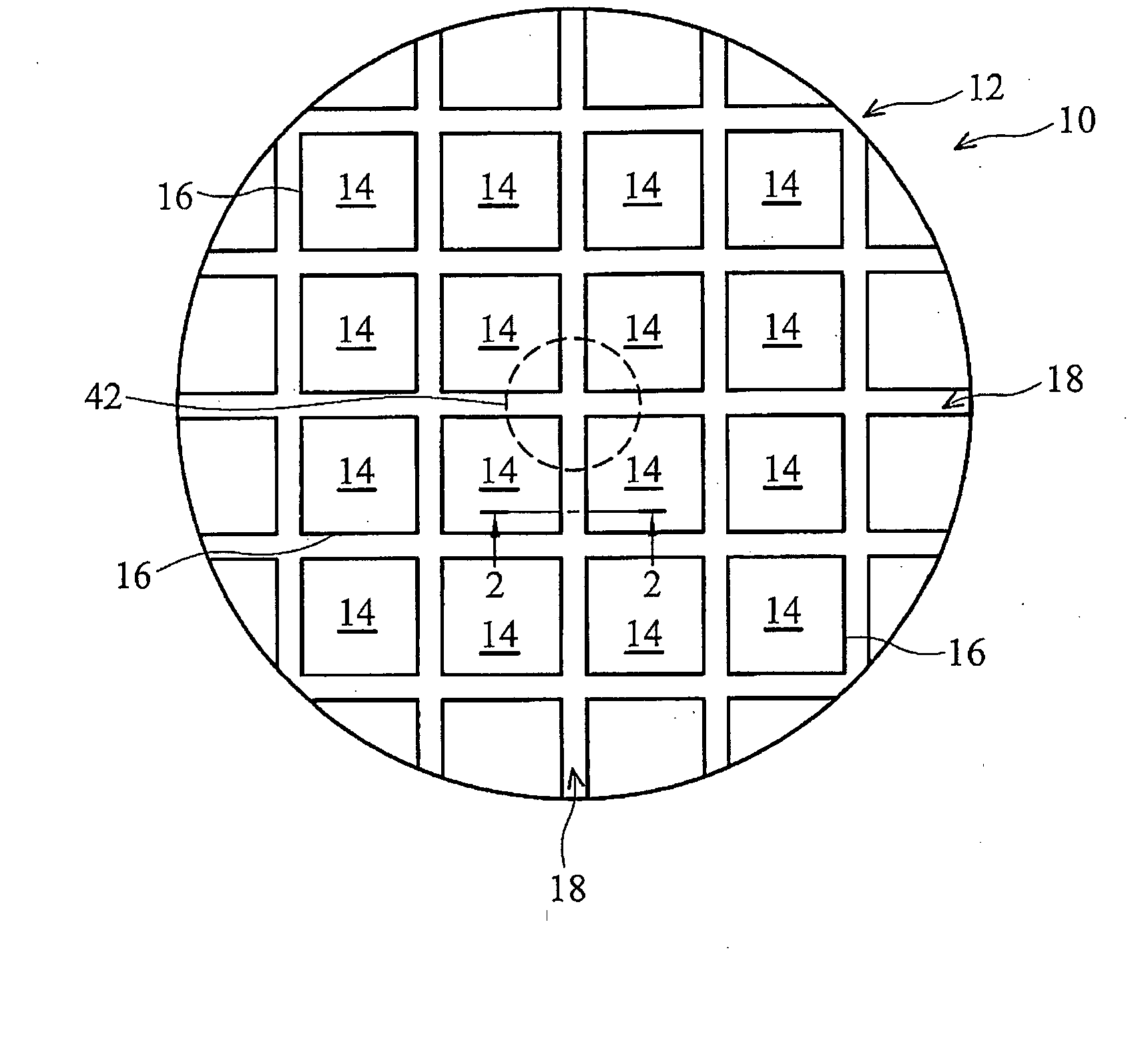

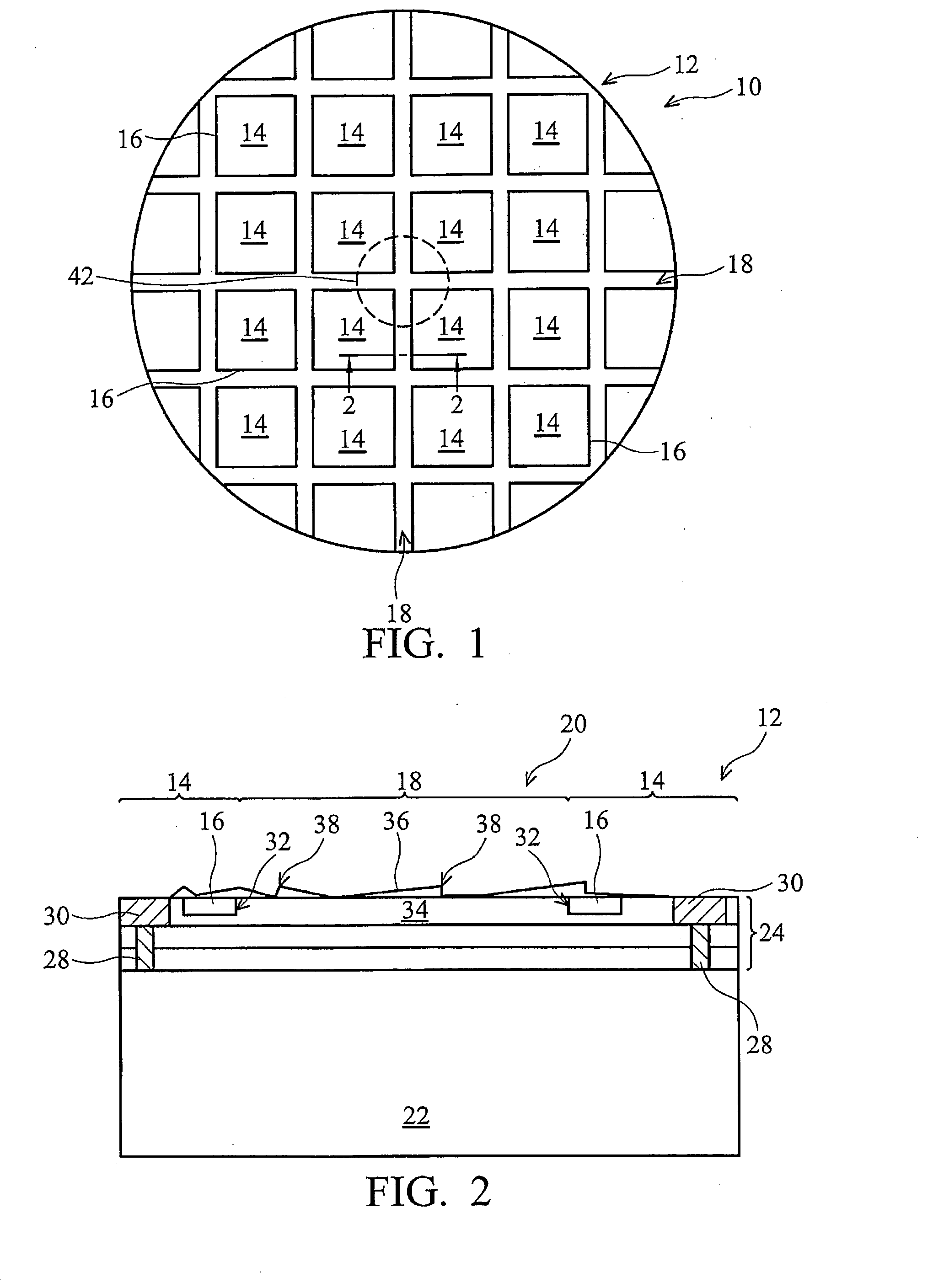

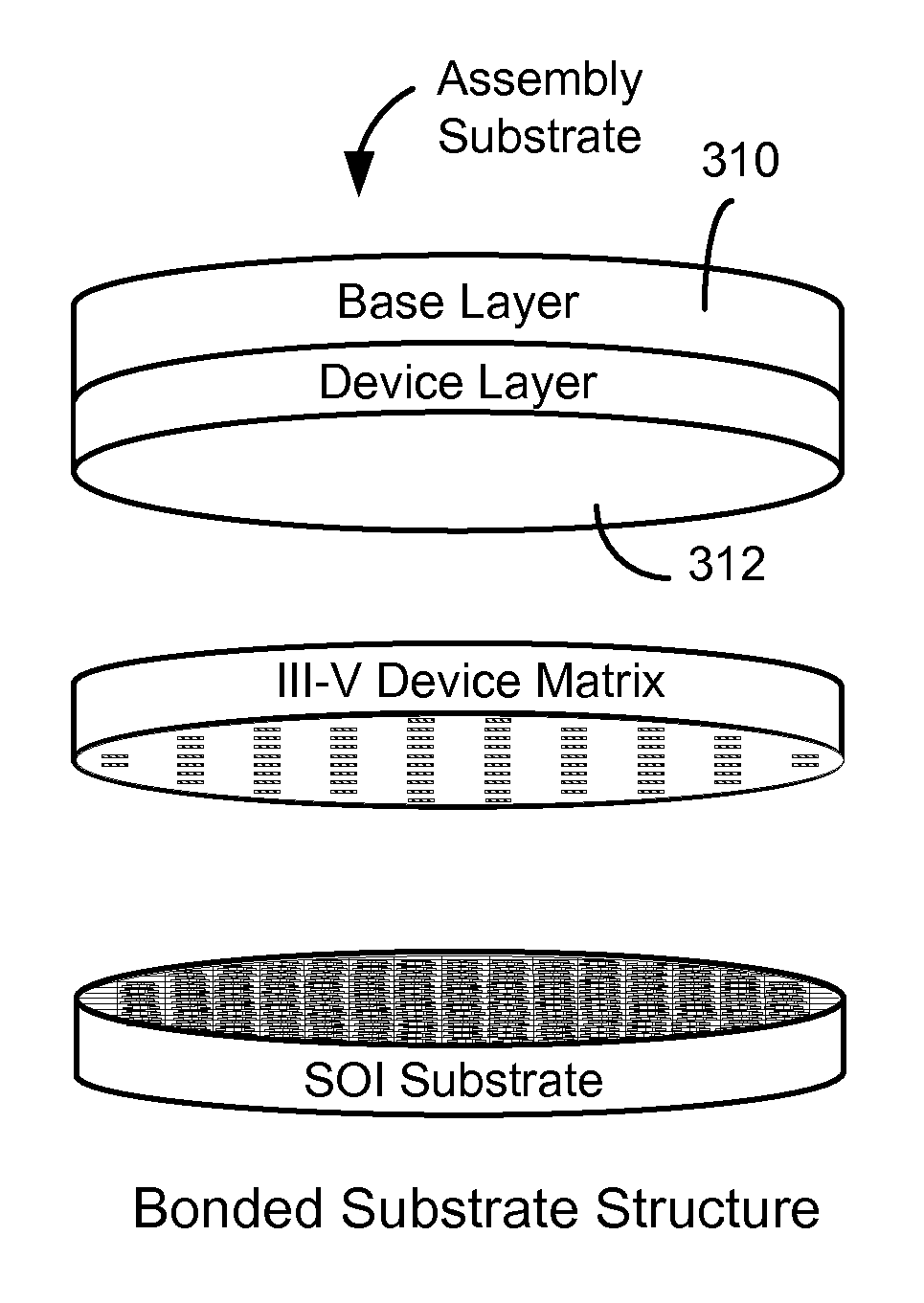

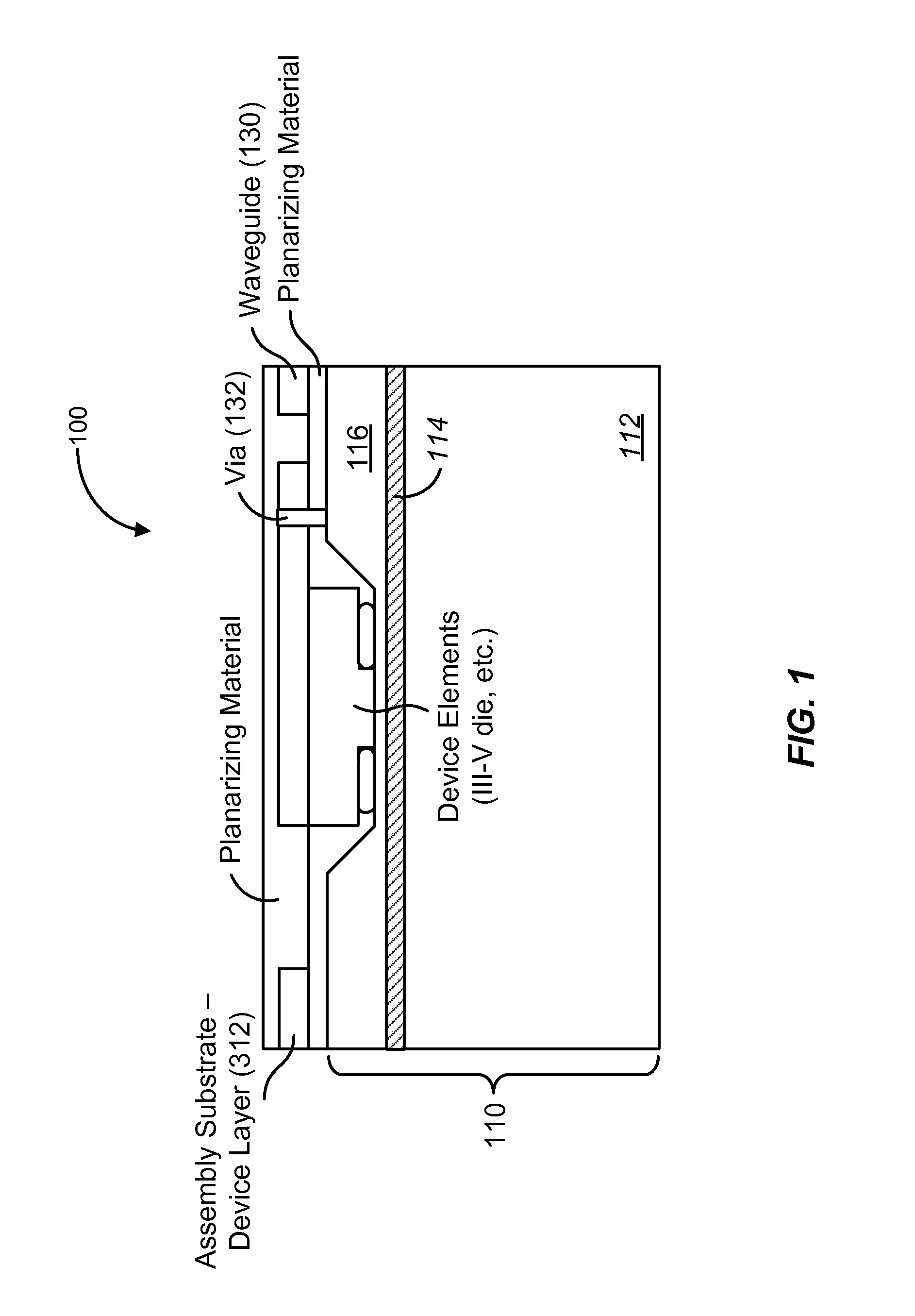

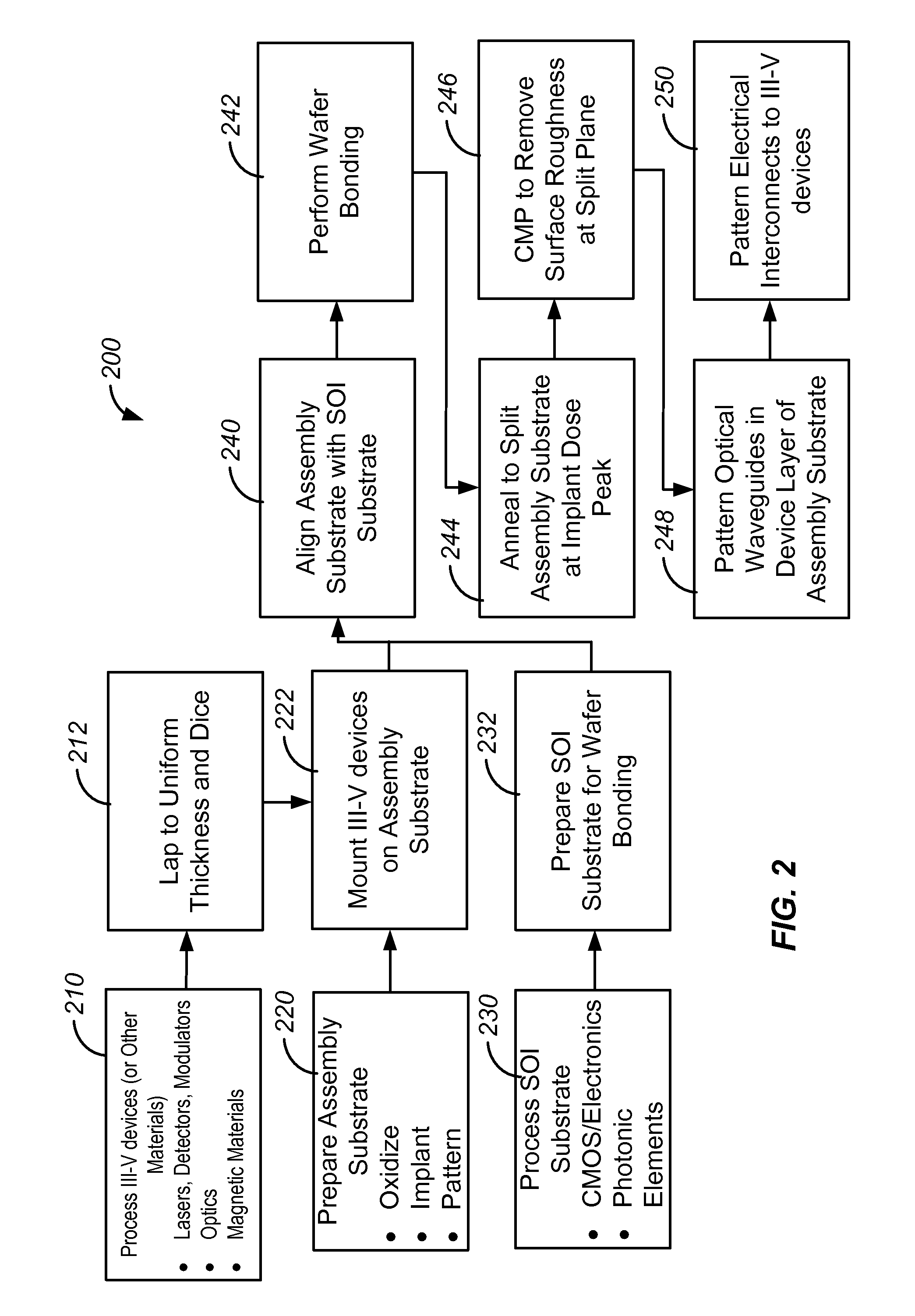

Method and system for template assisted wafer bonding

ActiveUS8222084B2Alignment toleranceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureWafer dicing

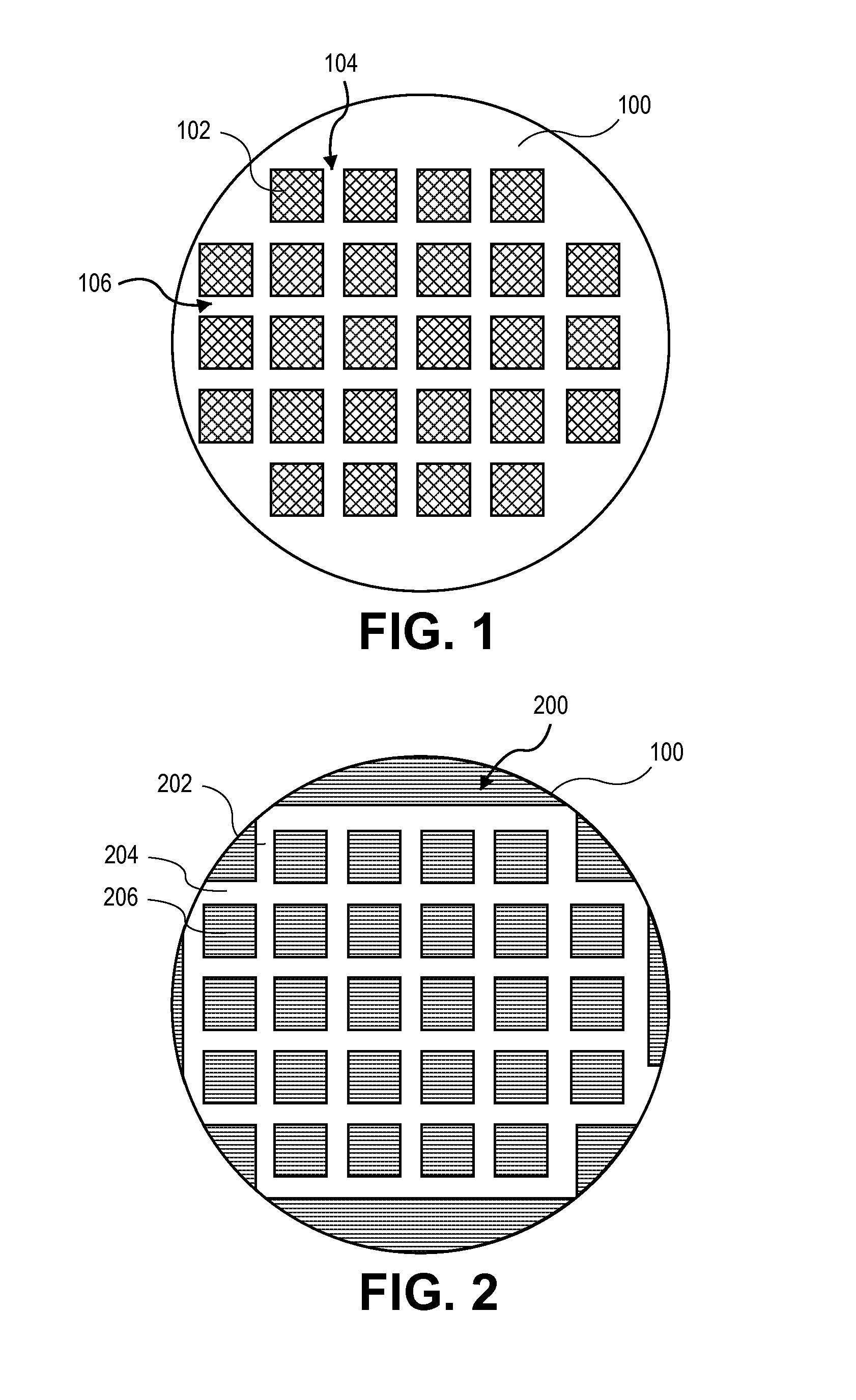

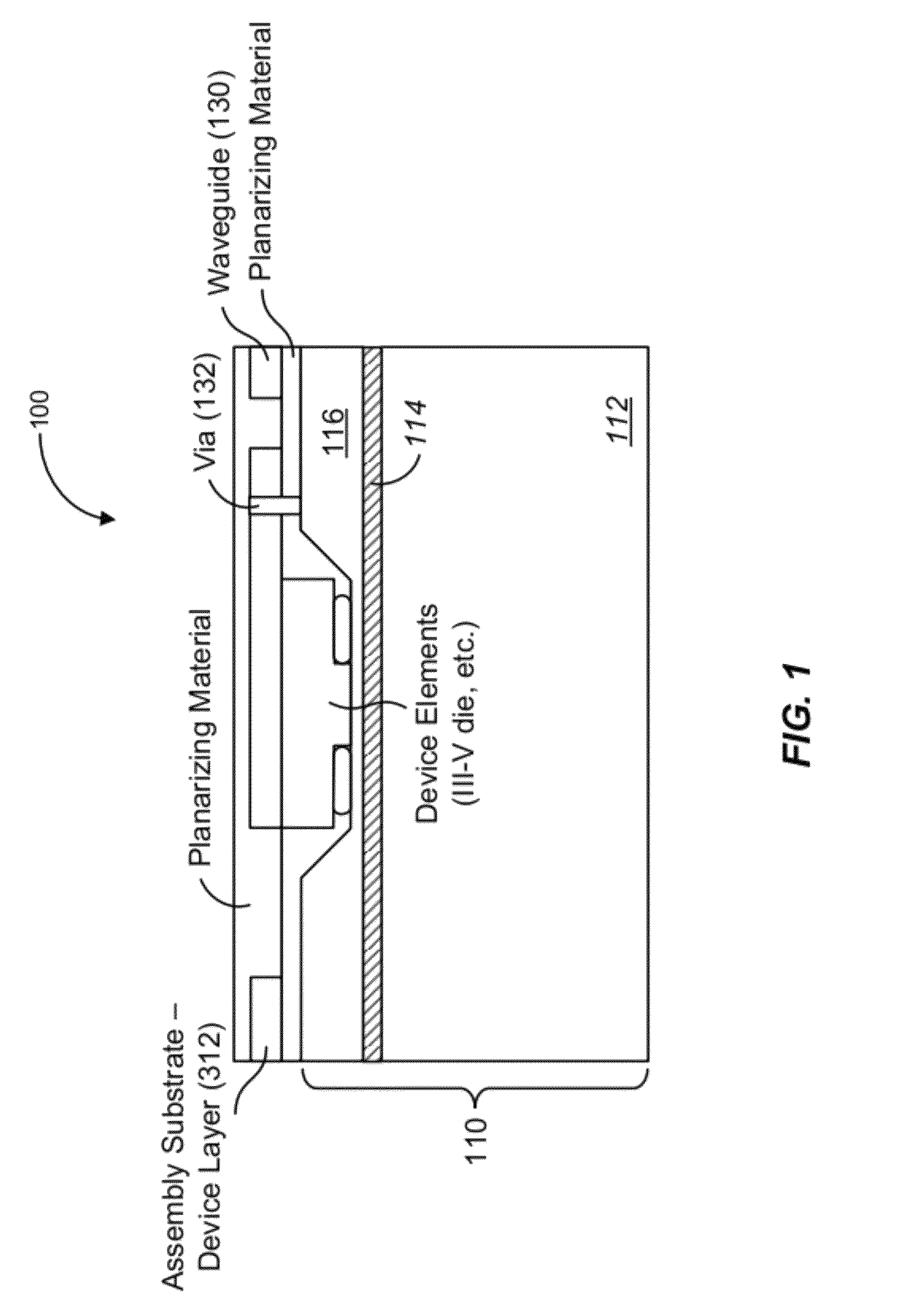

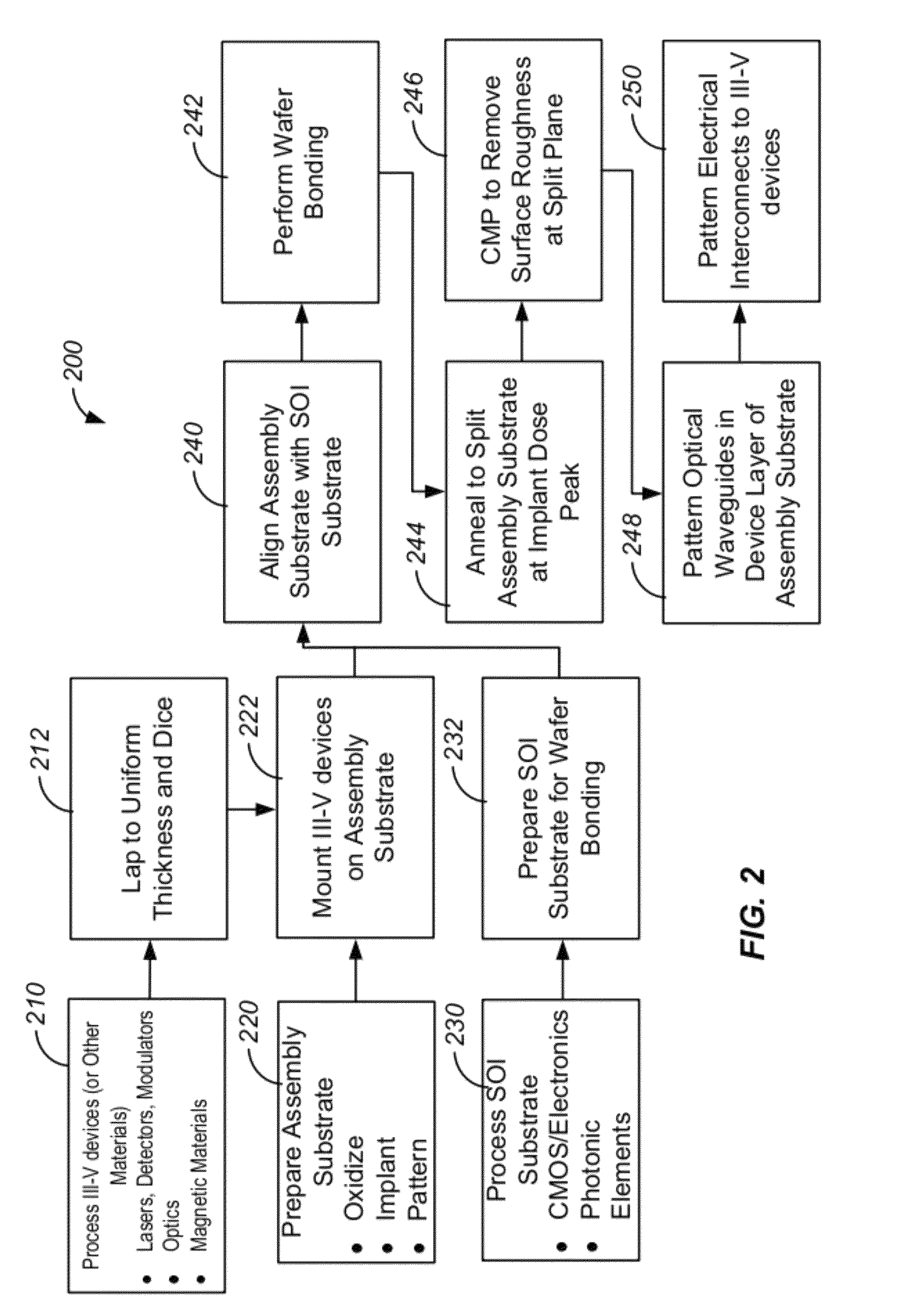

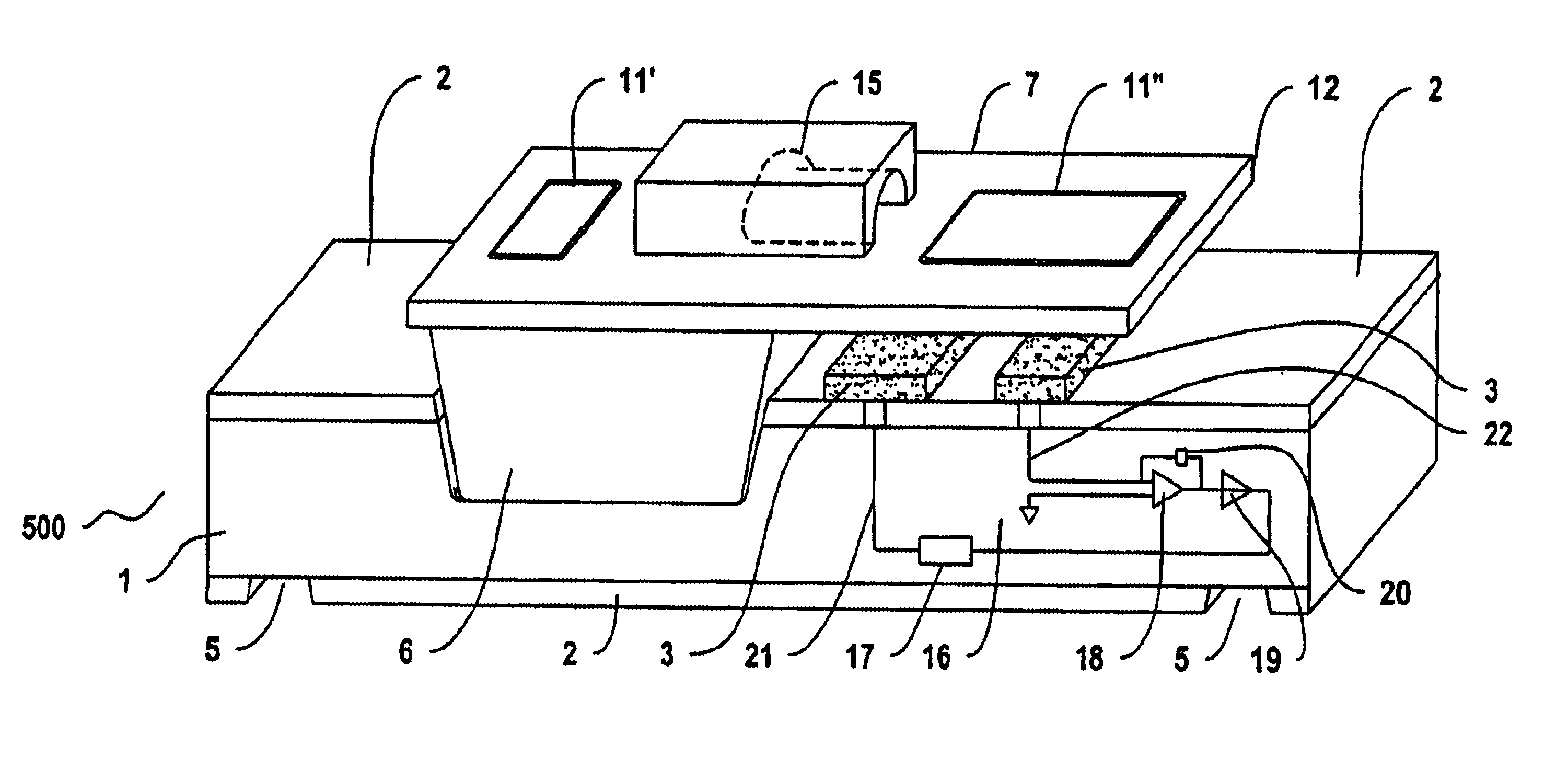

A method of fabricating a composite semiconductor structure includes providing an SOI substrate including a plurality of silicon-based devices and providing a compound semiconductor substrate including a plurality of photonic devices. The method also includes dicing the compound semiconductor substrate to provide a plurality of photonic dies. Each die includes one or more of the plurality of photonics devices. The method further includes providing an assembly substrate, mounting the plurality of photonic dies on predetermined portions of the assembly substrate, aligning the SOI substrate and the assembly substrate, joining the SOI substrate and the assembly substrate to form a composite substrate structure, and removing at least a portion of the assembly substrate from the composite substrate structure.

Owner:SKORPIOS TECH

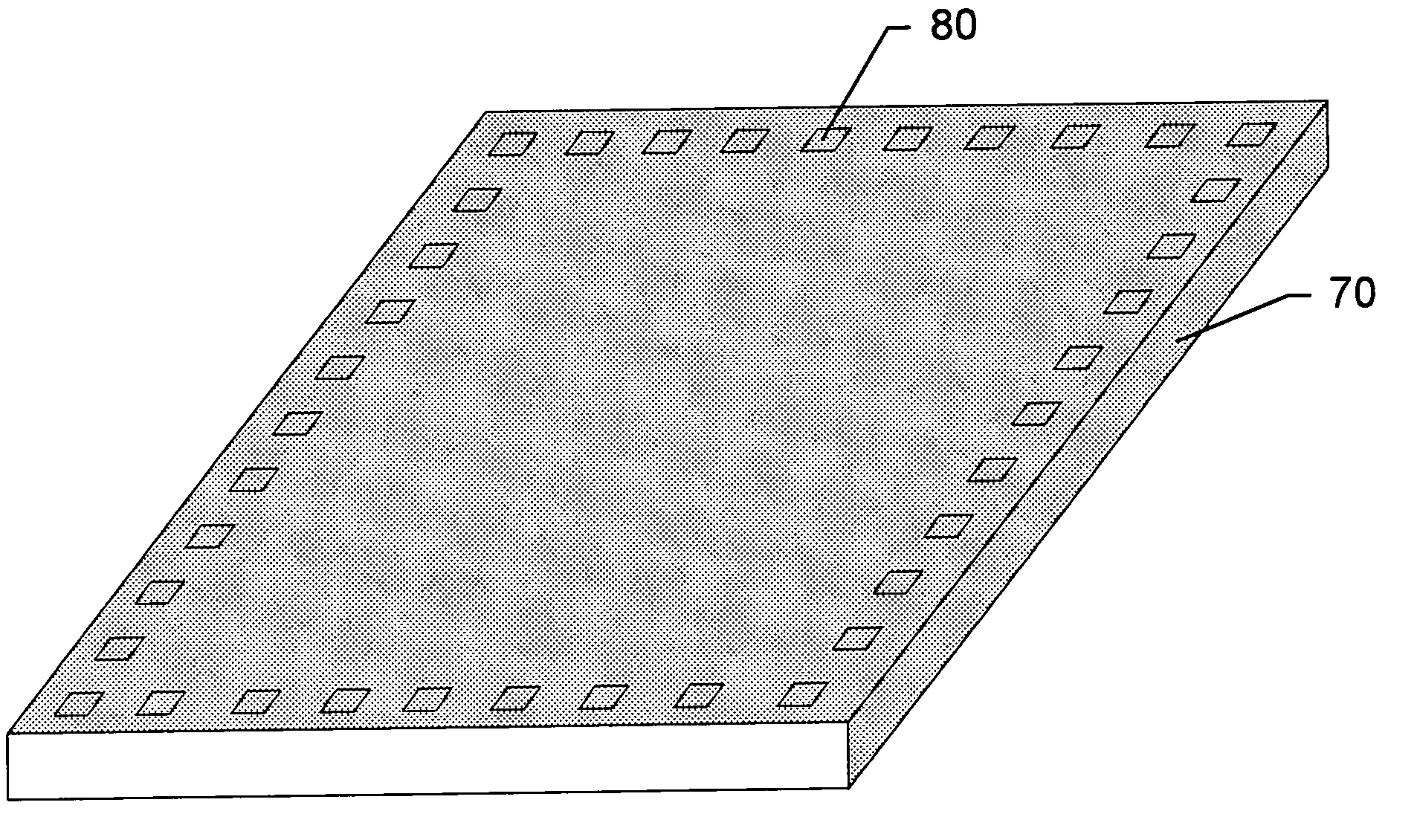

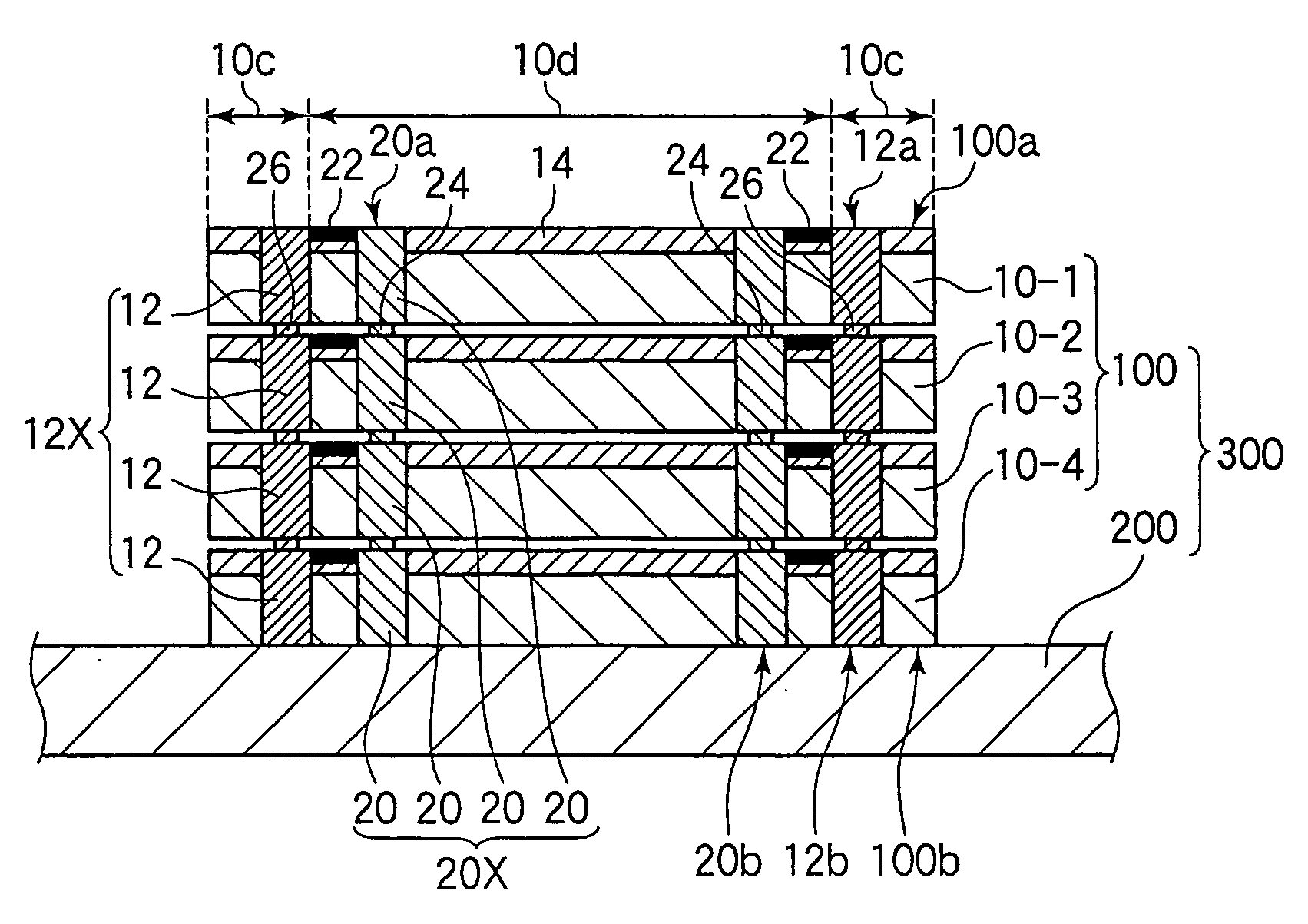

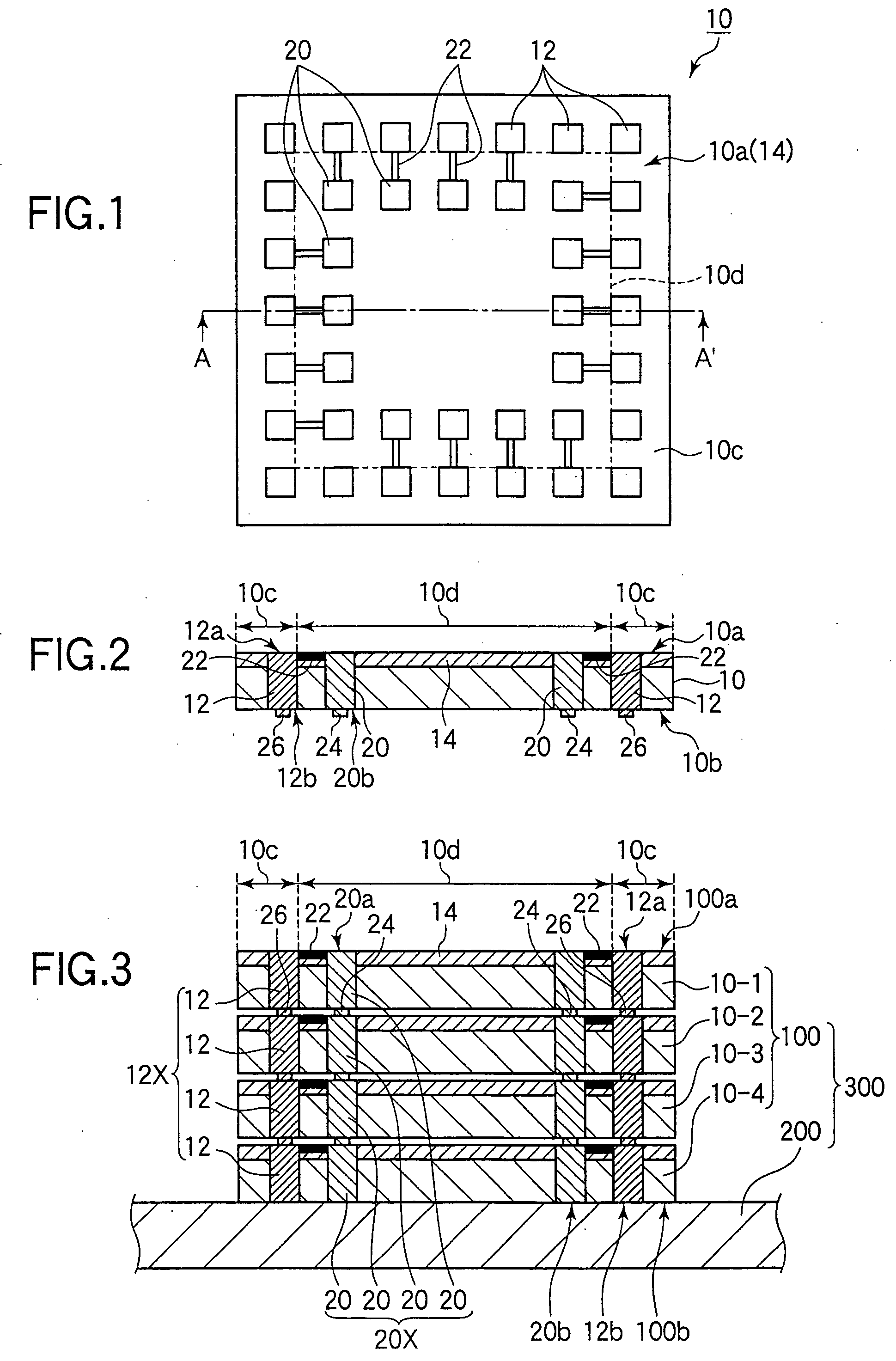

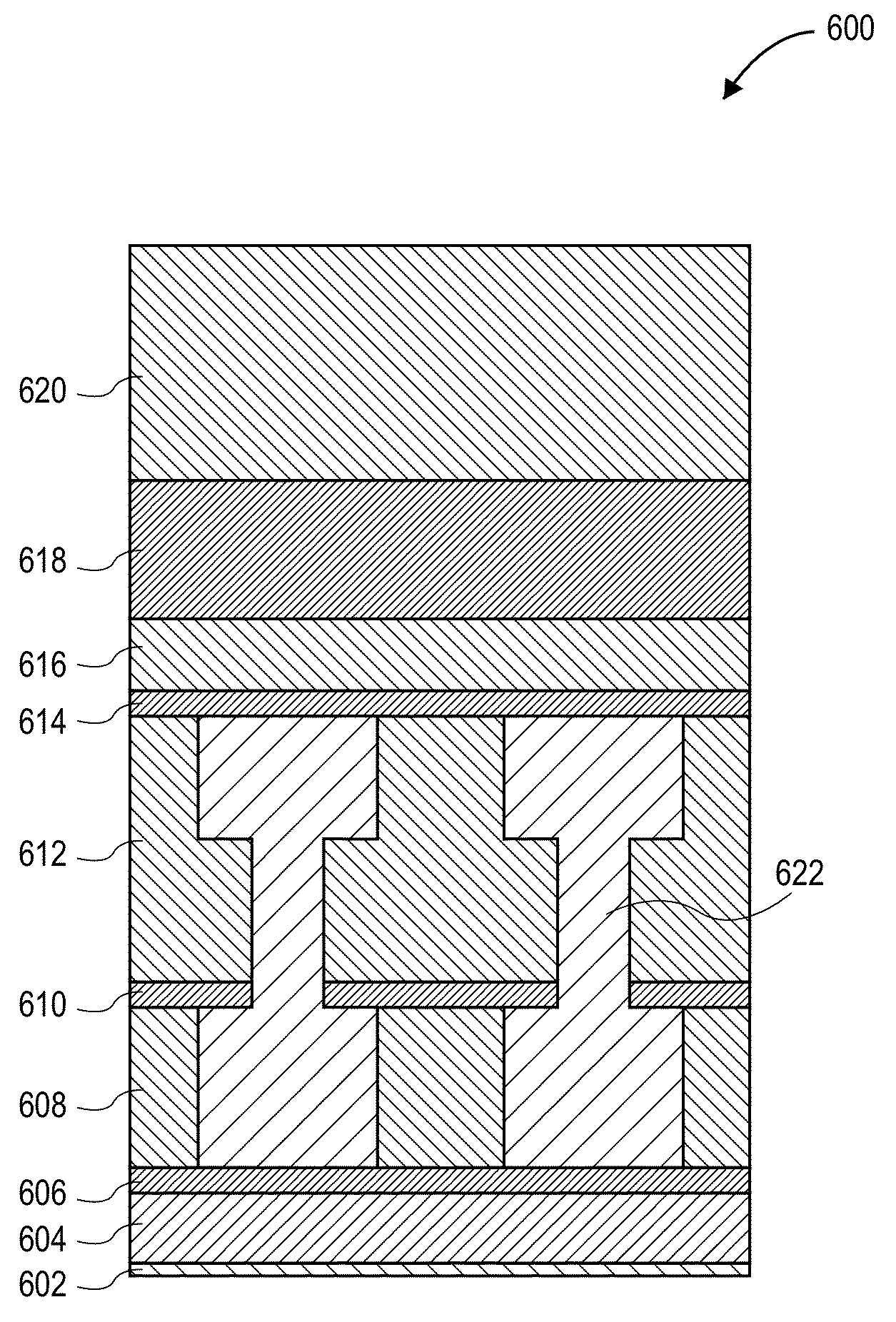

Semiconductor device, stacked structure, and manufacturing method

ActiveUS20060197181A1Improve cooling effectImprove packaging efficiencySemiconductor/solid-state device detailsSolid-state devicesDevice materialWafer dicing

An array of electrically conductive members, formed around the edges of a semiconductor device or chip, penetrate from one major surface of the device to the other major surface. In an area located inward of this array, a multiplicity of thermally conductive members also penetrate from one major surface to the other major surface. The semiconductor device can be manufactured from a semiconductor wafer by creating holes that penetrate partway through the wafer, filling the holes with metal to form the electrically conductive members and thermally conductive members, and then grinding the lower surface of the wafer to expose the ends of the electrically conductive members and thermally conductive members before dicing the wafer into chips. The thermally conductive members improve heat dissipation performance when semiconductor chips of this type are combined into a stacked multichip package.

Owner:TAIWAN SEMICON MFG CO LTD

Method of cutting integrated circuit chips from wafer by ablating with laser and cutting with saw blade

ActiveUS20060189099A1Different surface textureEliminate and significantly reduce numberSolid-state devicesSemiconductor/solid-state device manufacturingWaferingWafer dicing

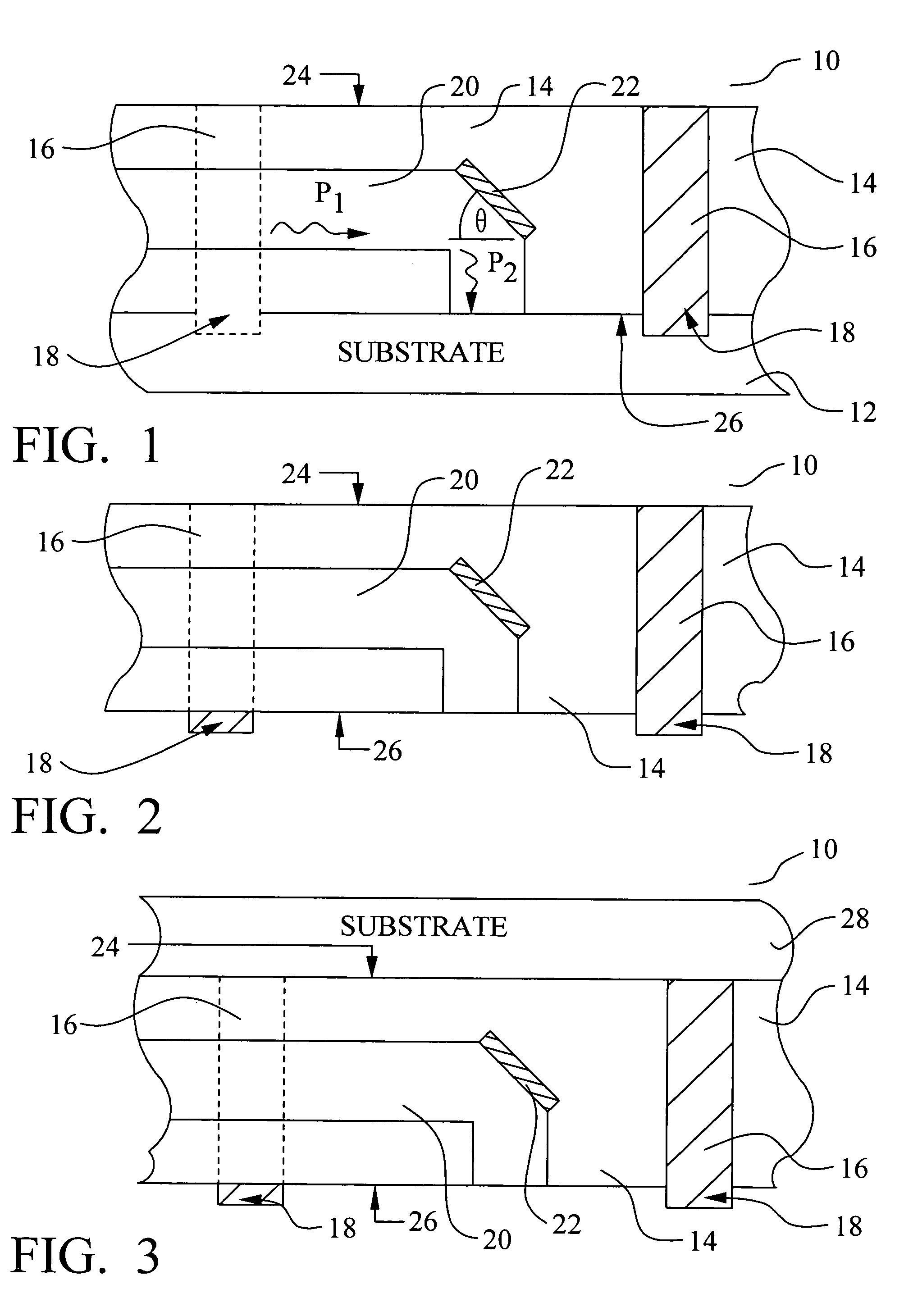

A method of cutting an integrated circuit chip from a wafer having a plurality of integrated circuit chips is provided. An upper portion of the wafer is ablated using two laser beams to form two substantially parallel trenches that extend into the wafer from a top surface of the wafer through intermetal dielectric layers and at least partially into a substrate of the wafer. After the ablating to form the two trenches, cutting through the wafer between outer sidewalls of the two laser-ablated trenches with a saw blade is performed. A width between the outer sidewalls of the two laser-ablated trenches is greater than a cutting width of the saw blade. This may be particularly useful in lead-free packaging applications and / or applications where the intermetal dielectric layers use low-k dielectric materials, for example.

Owner:TAIWAN SEMICON MFG CO LTD

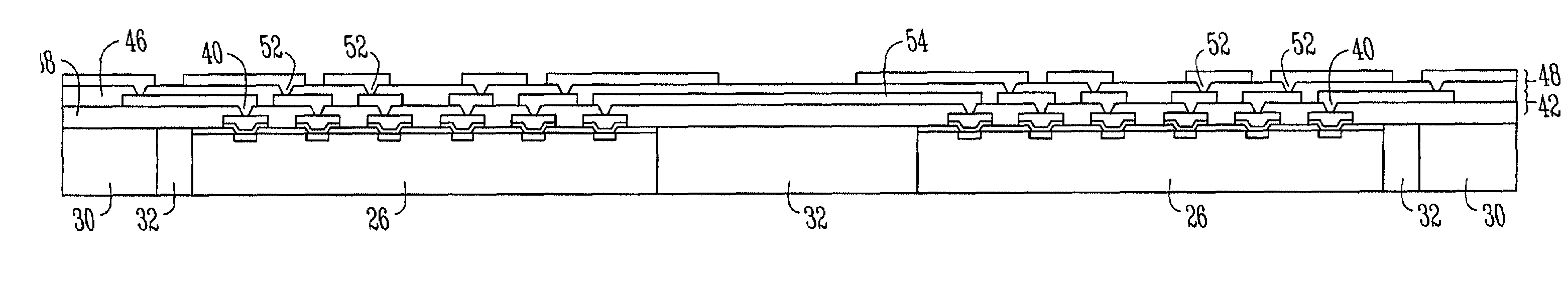

Stacked die BGA or LGA component assembly

InactiveUS20050230802A1Simple methodSemiconductor/solid-state device detailsSolid-state devicesEpoxyWafer dicing

The present invention provides an apparatus for vertically interconnecting semiconductor die, integrated circuit die, or multiple die segments. Metal rerouting interconnects which extend to one or more sides of the die or segment can be optionally added to the die or multi die segment to provide edge bonding pads upon the surface of the die for external electrical connection points. After the metal rerouting interconnect has been added to the die on the wafer, the wafer is optionally thinned and each die or multiple die segment is singulated from the wafer by cutting or other appropriate singulation method. After the die or multiple die segments are singulated or cut from the wafer, insulation is applied to all surfaces of the die or multiple die segments, openings are made in the insulation above the desired electrical connection pads, and the die or multiple die segments are placed on top of one another to form a stack. Vertically adjacent segments in the stack are electrically interconnected by attaching a short flexible bond wire or bond ribbon to the exposed electrical connection pad at the peripheral edges of the die which protrudes horizontally from the die and applying electrically conductive polymer, or epoxy, filaments or lines to one or more sides of the stack.

Owner:INVENSAS CORP

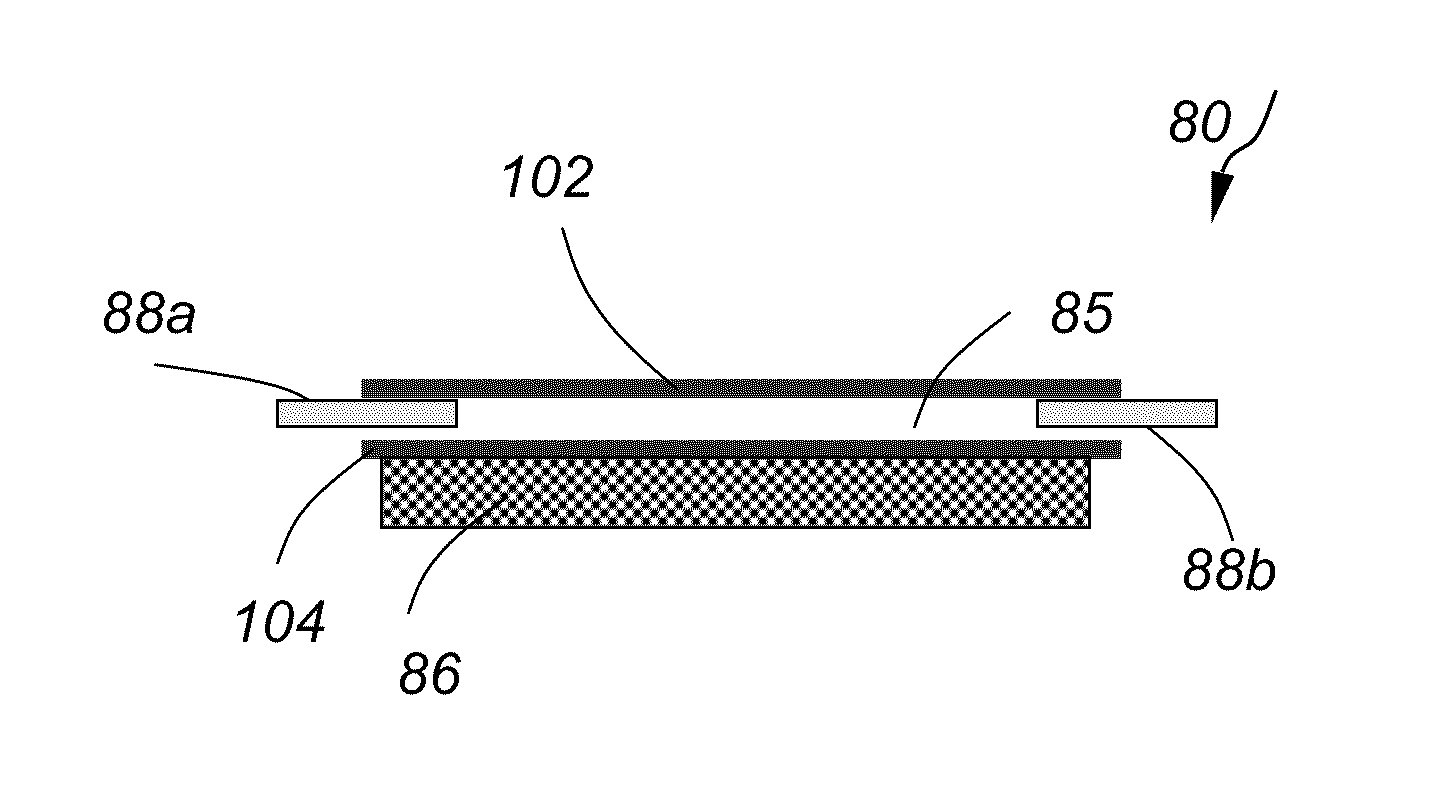

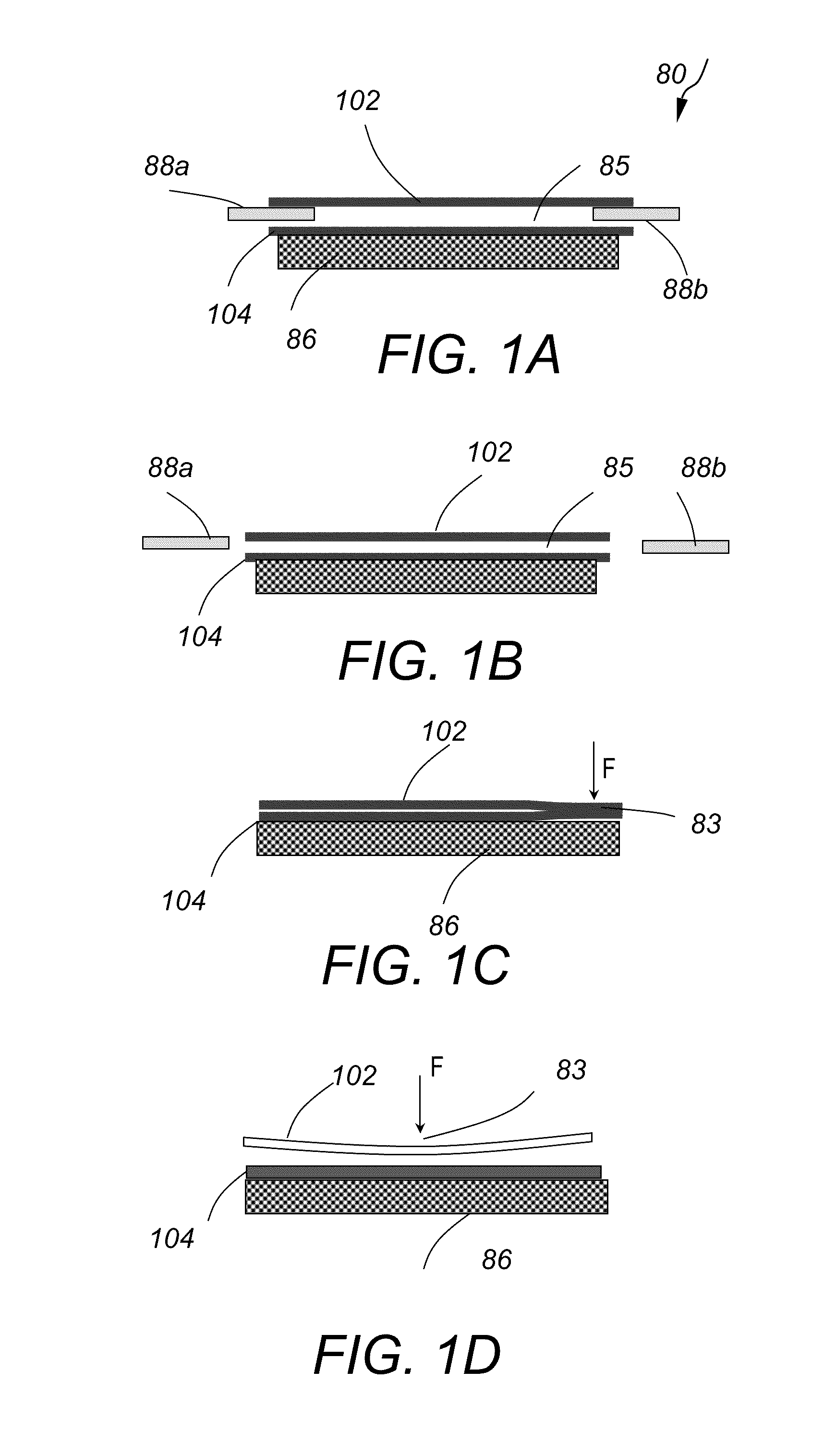

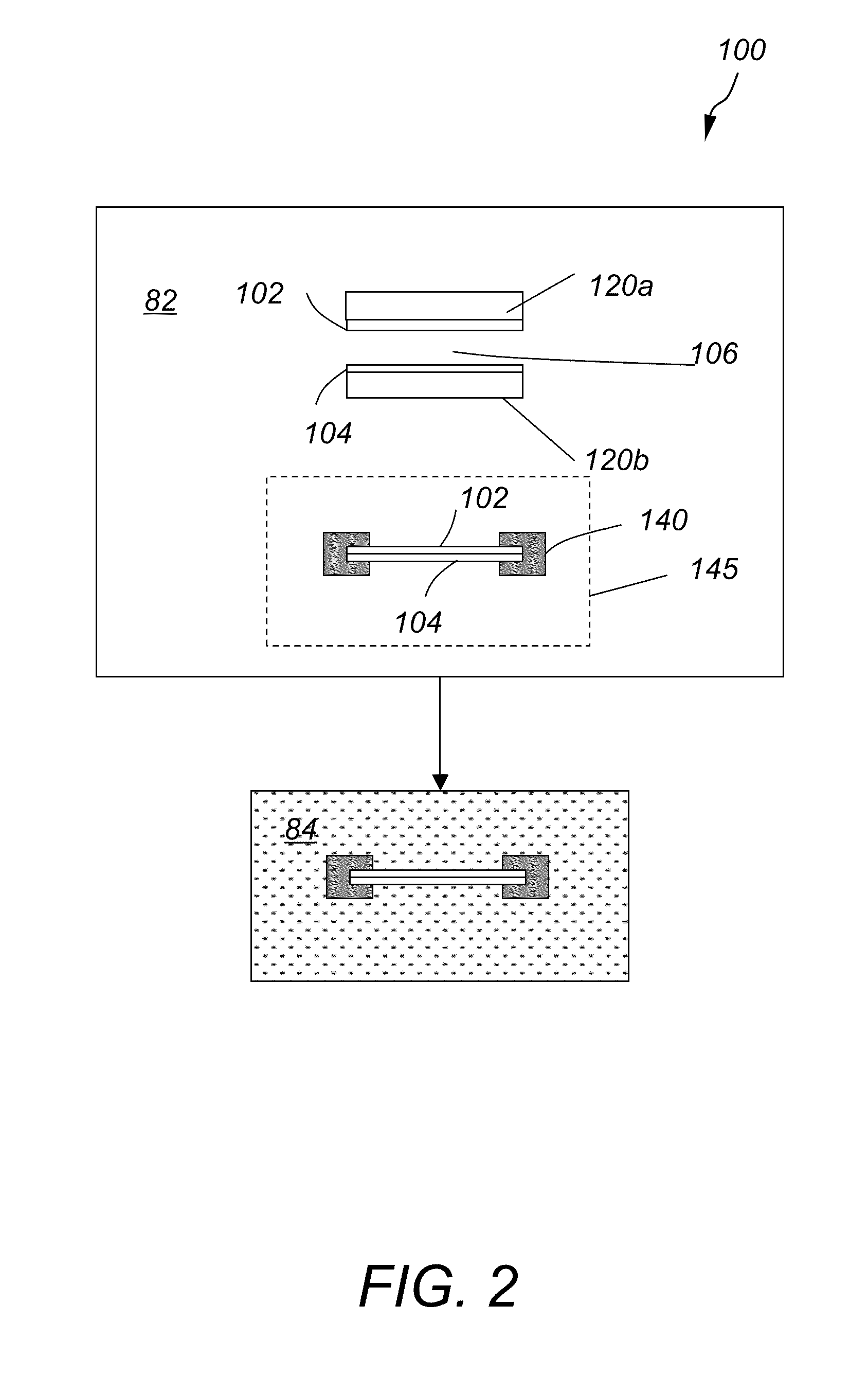

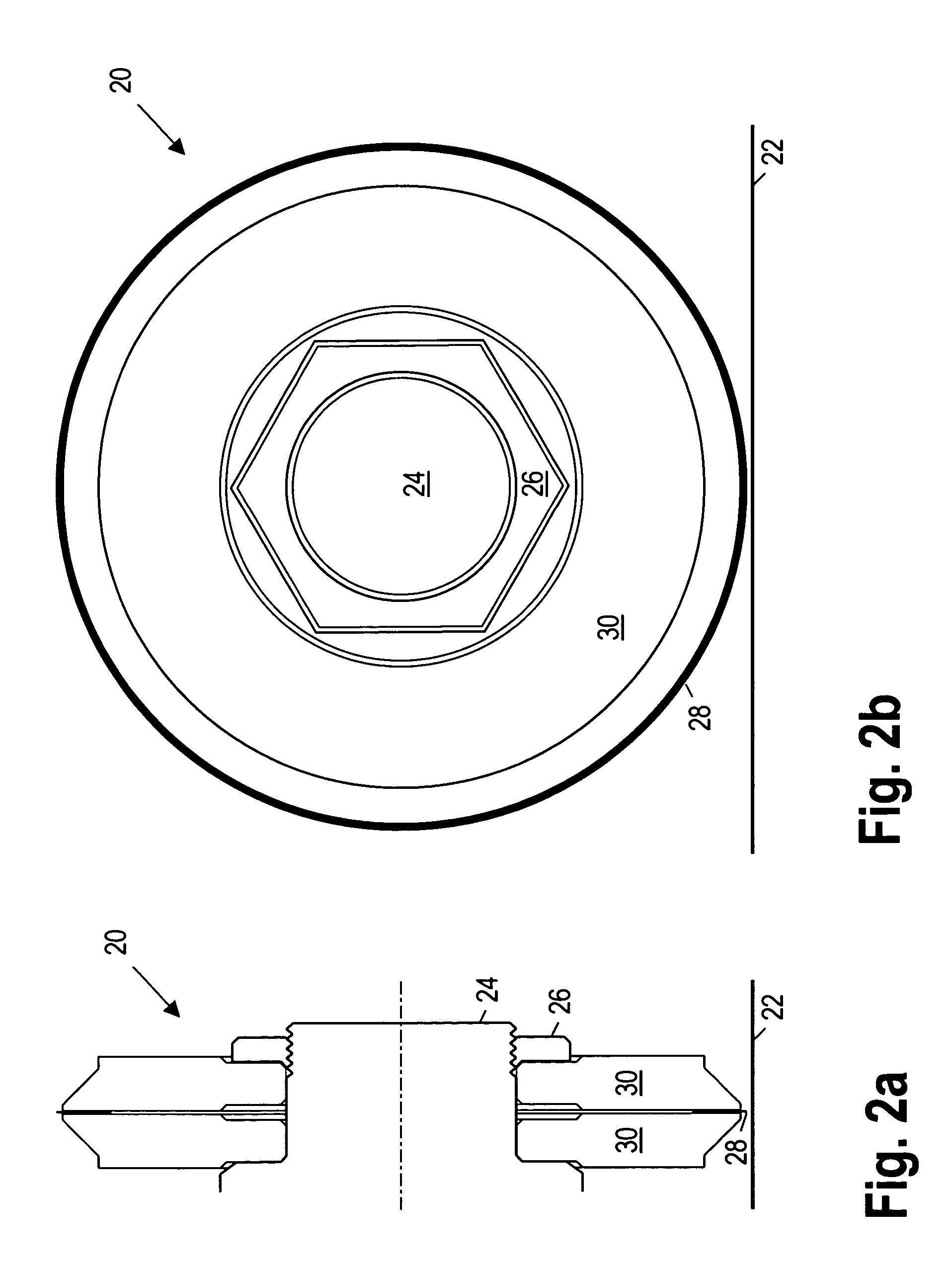

Method and apparatus for wafer bonding with enhanced wafer mating

ActiveUS20100122762A1Reduce pressureAccuracy in alignmentPrinted circuit assemblingMechanical working/deformationWafer dicingEngineering

An improved wafer-to-wafer bonding method includes aligning an upper and a lower wafer and initiating a bond at a single point by applying pressure to a single point of the upper wafer via the flow of pressurized gas through a port terminating at the single point. The bond-front propagates radially across the aligned oppositely oriented wafer surfaces at a set radial velocity rate bringing the two wafer surfaces into full atomic contact by controlling the gas pressure and / or controlling the velocity of the motion of the lower wafer up toward the upper wafer.

Owner:SUSS MICRO TEC LITHOGRAPHY

Method for reducing stress concentrations on a semiconductor wafer by surface laser treatment

ActiveUS20050003633A1Reduce stress concentrationReduced area of stress concentrationSolid-state devicesSemiconductor/solid-state device manufacturingStress concentrationWafer dicing

A method for treating an area of a semiconductor wafer surface with a laser for reducing stress concentrations is disclosed. The wafer treatment method discloses treating an area of a wafer surface with a laser beam, wherein the treated area is ablated or melted by the beam and re-solidifies into a more planar profile, thereby reducing areas of stress concentration and stress risers that contribute to cracking and chipping during wafer singulation. Preferably, the treated area has a width less than that of a scribe street, but wider than the kerf created by a wafer dicing blade. Consequently, when the wafer is singulated, the dicing blade will preferably saw through treated areas only. It will be understood that the method of the preferred embodiments may be used to treat other areas of stress concentration and surface discontinuities on the wafer, as desired.

Owner:TEXAS INSTR INC

Method and system for template assisted wafer bonding

ActiveUS20120149148A1Increase costRelaxing alignment toleranceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureWafer dicing

A method of fabricating a composite semiconductor structure includes providing an SOI substrate including a plurality of silicon-based devices and providing a compound semiconductor substrate including a plurality of photonic devices. The method also includes dicing the compound semiconductor substrate to provide a plurality of photonic dies. Each die includes one or more of the plurality of photonics devices. The method further includes providing an assembly substrate, mounting the plurality of photonic dies on predetermined portions of the assembly substrate, aligning the SOI substrate and the assembly substrate, joining the SOI substrate and the assembly substrate to form a composite substrate structure, and removing at least a portion of the assembly substrate from the composite substrate structure.

Owner:SKORPIOS TECH

Pressure sensitive adhesive sheet for wafer sticking

InactiveUS20010019766A1Avoid vibrationMinimize chipSolid-state devicesSemiconductor/solid-state device manufacturingPlasticizerPolyvinyl chloride

A pressure sensitive adhesive sheet for wafer sticking, comprising a base of polyvinyl chloride containing a plasticizer and, superimposed thereon, an energy radiation curable pressure sensitive adhesive layer, the energy radiation curable pressure sensitive adhesive layer, before exposure to energy radiation, having an elastic modulus ranging from 4.0x104 to 5.0x106 Pa at 50° C. The use of this pressure sensitive adhesive sheet for wafer sticking enables inhibiting the vibration of wafer at the time of dicing of the wafer so that chipping of the wafer can be minimized.

Owner:LINTEC CORP

Protective film agent for laser dicing and wafer processing method using the protective film agent

InactiveUS20060105544A1Improve adhesionEffectively preventing deposition of debrisSemiconductor/solid-state device manufacturingRadiation-absorbing paintsUltravioletWafer dicing

A protective film agent for laser dicing according to the present invention comprises a solution having, dissolved therein, a water-soluble resin and at least one laser light absorber selected from the group consisting of a water-soluble dye, a water-soluble coloring matter, and a water-soluble ultraviolet absorber. The protective film agent is coated on a surface of a wafer, which is to be processed, and is then dried to form a protective film. Laser dicing through the protective film produces chips from the wafer. As a result, deposition of debris can be effectively prevented on the entire face of the chips, including their peripheral edge portions.

Owner:TOKYO OHKA KOGYO CO LTD +1

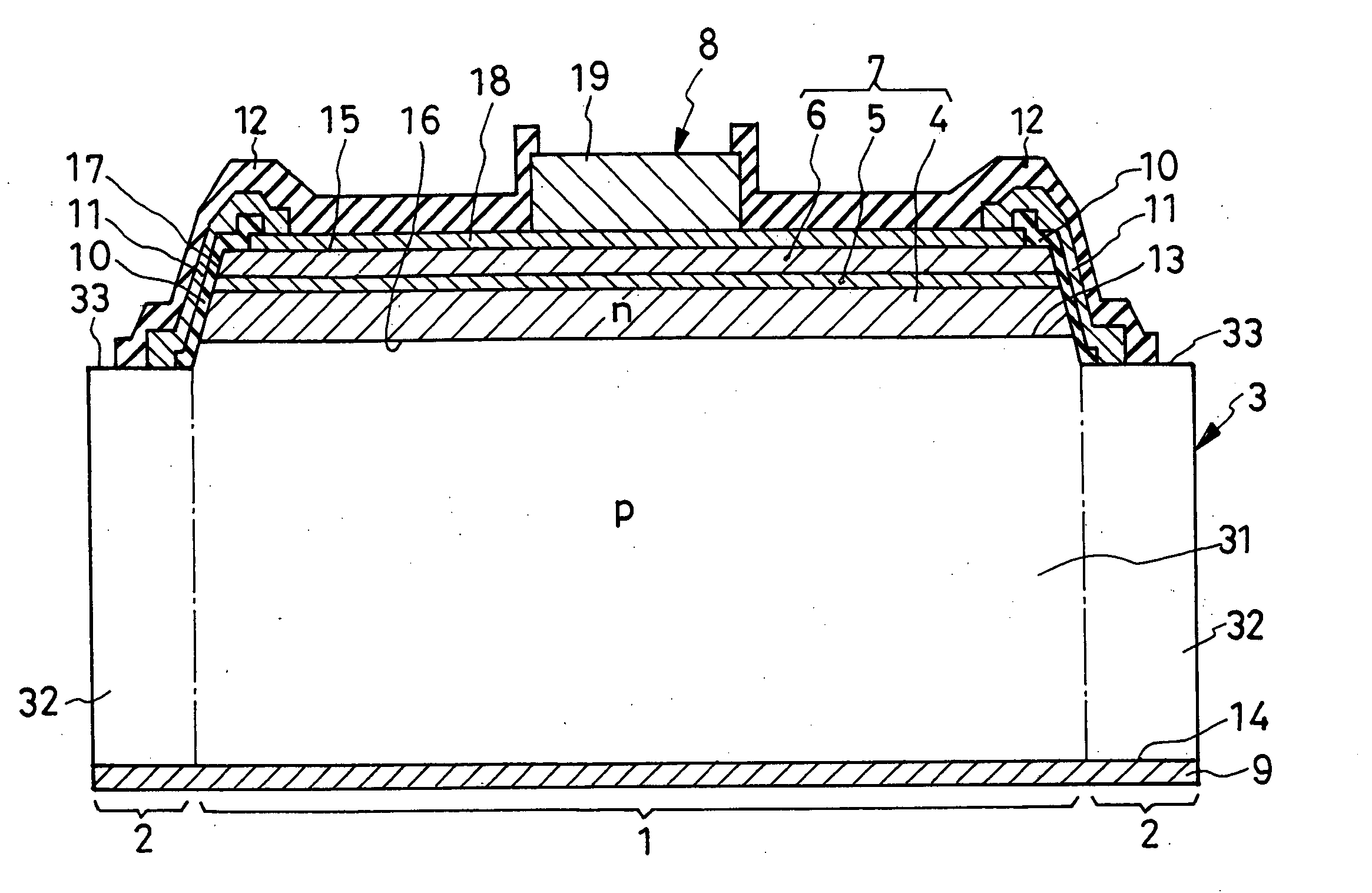

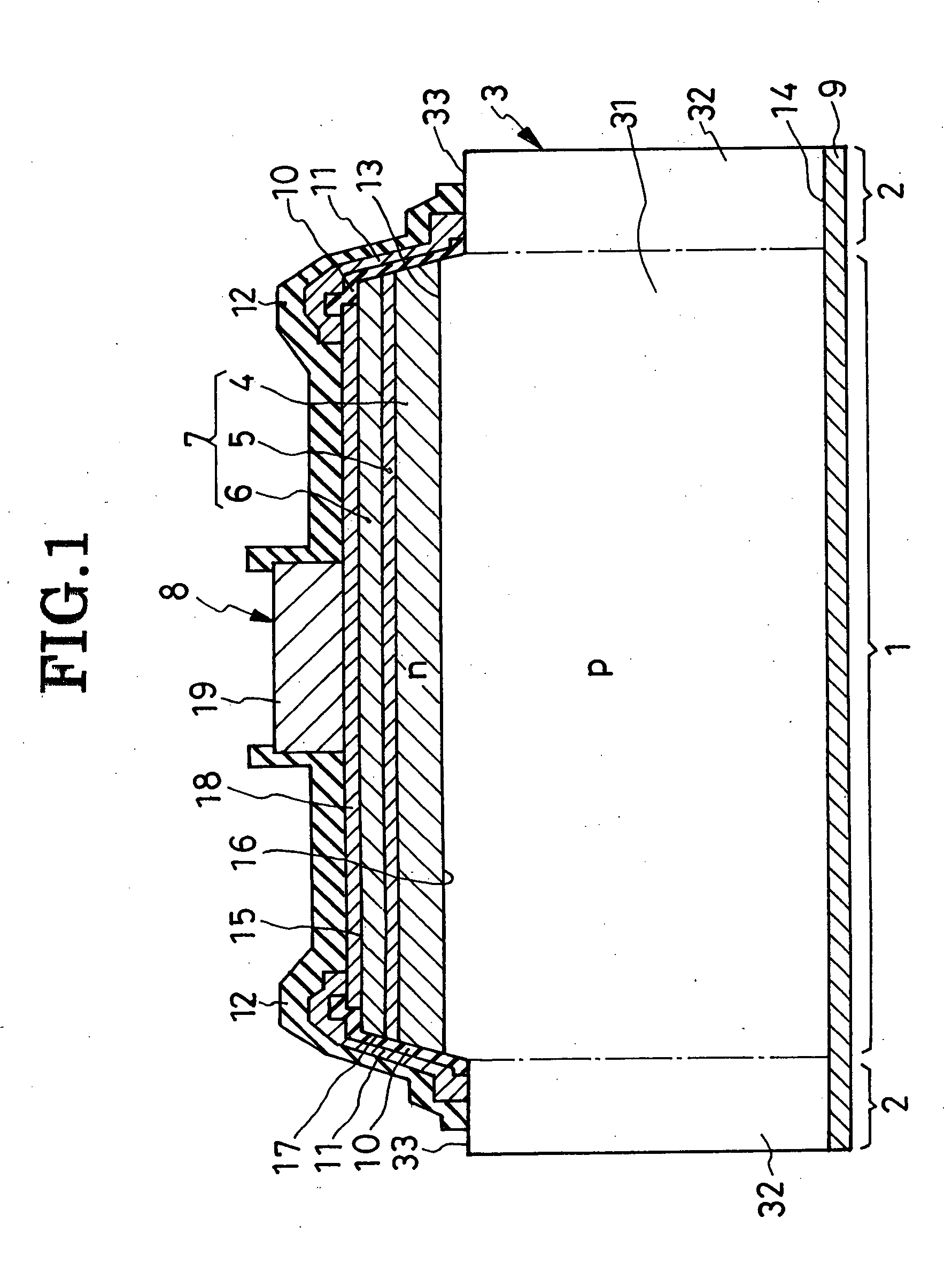

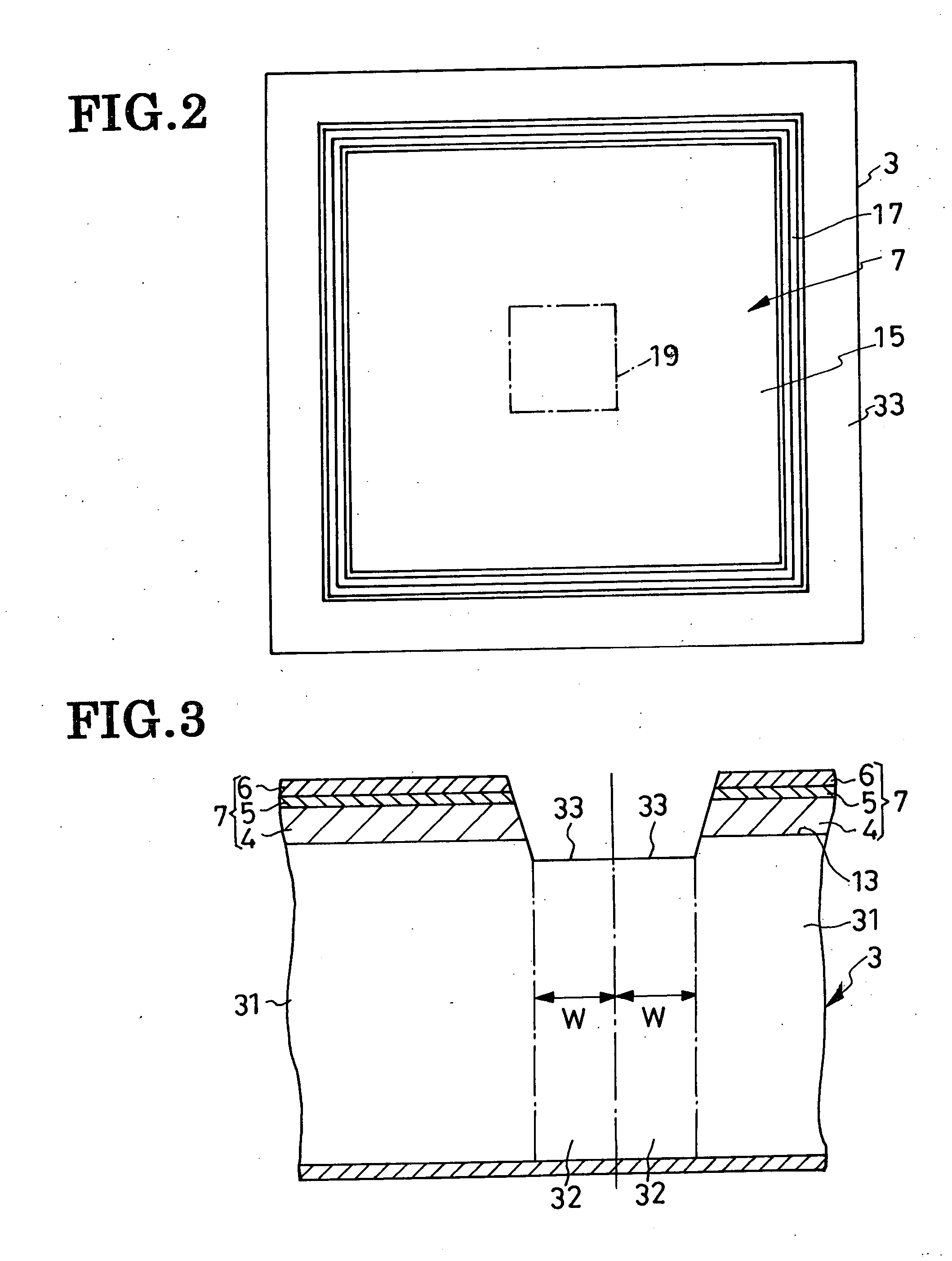

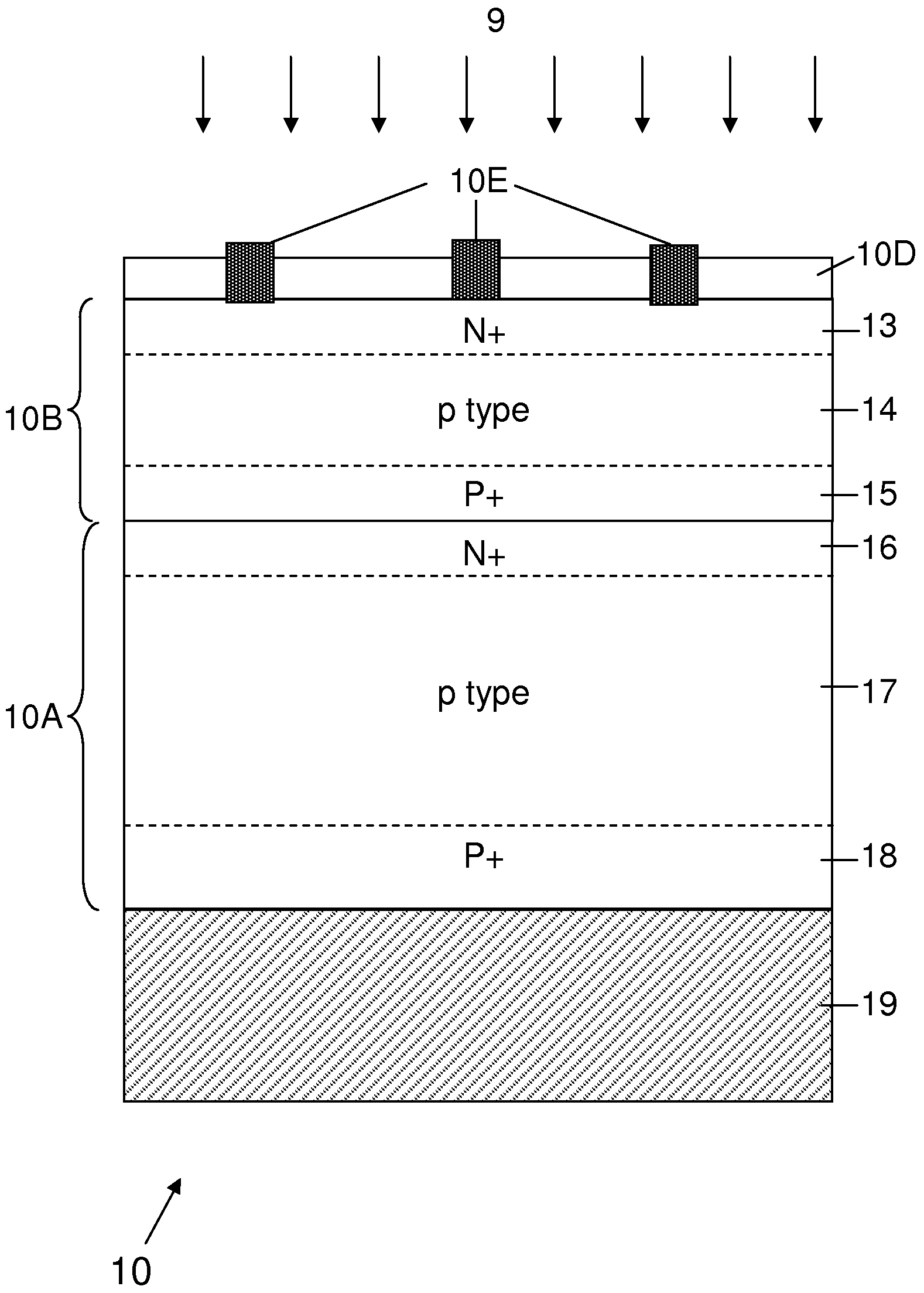

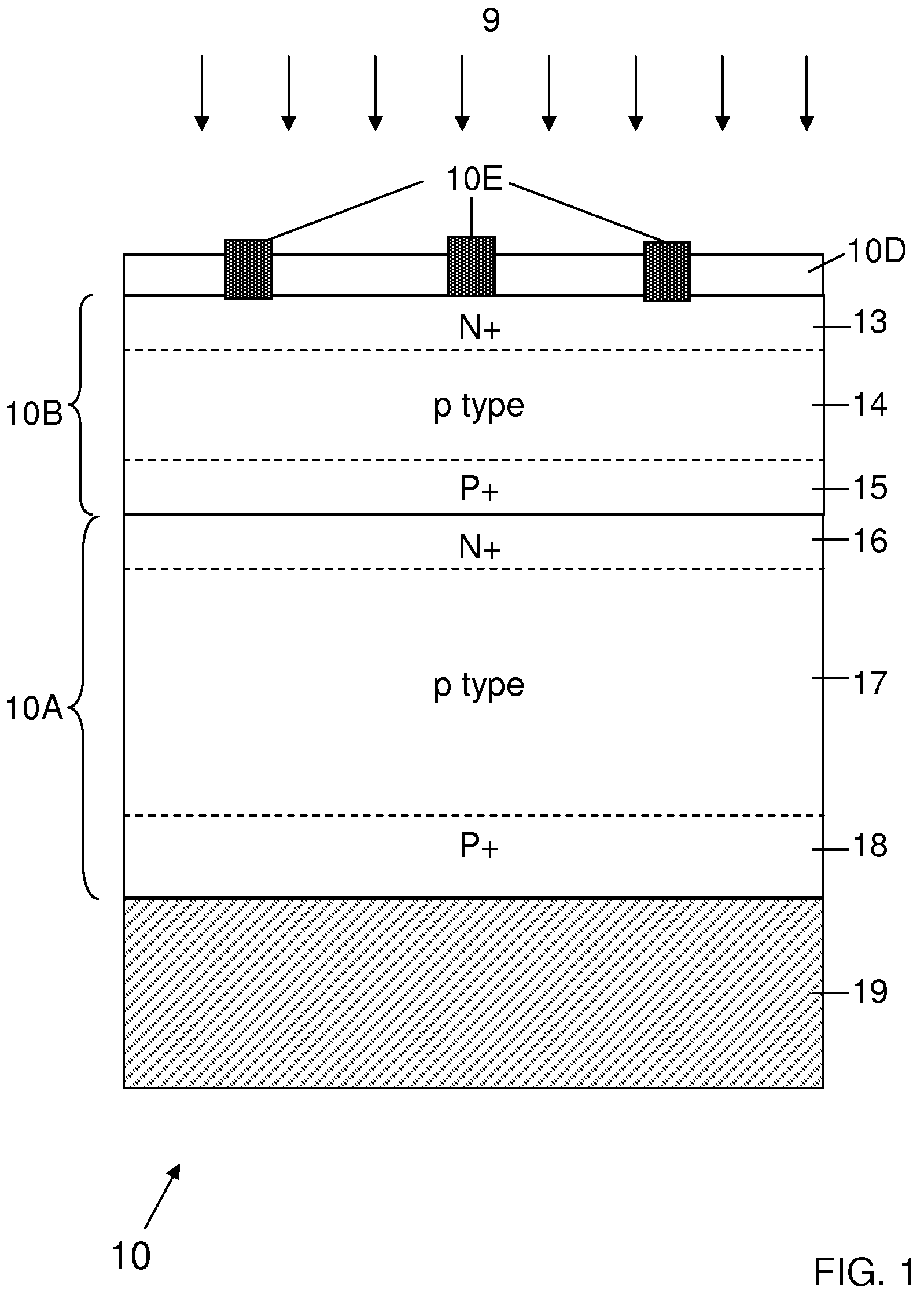

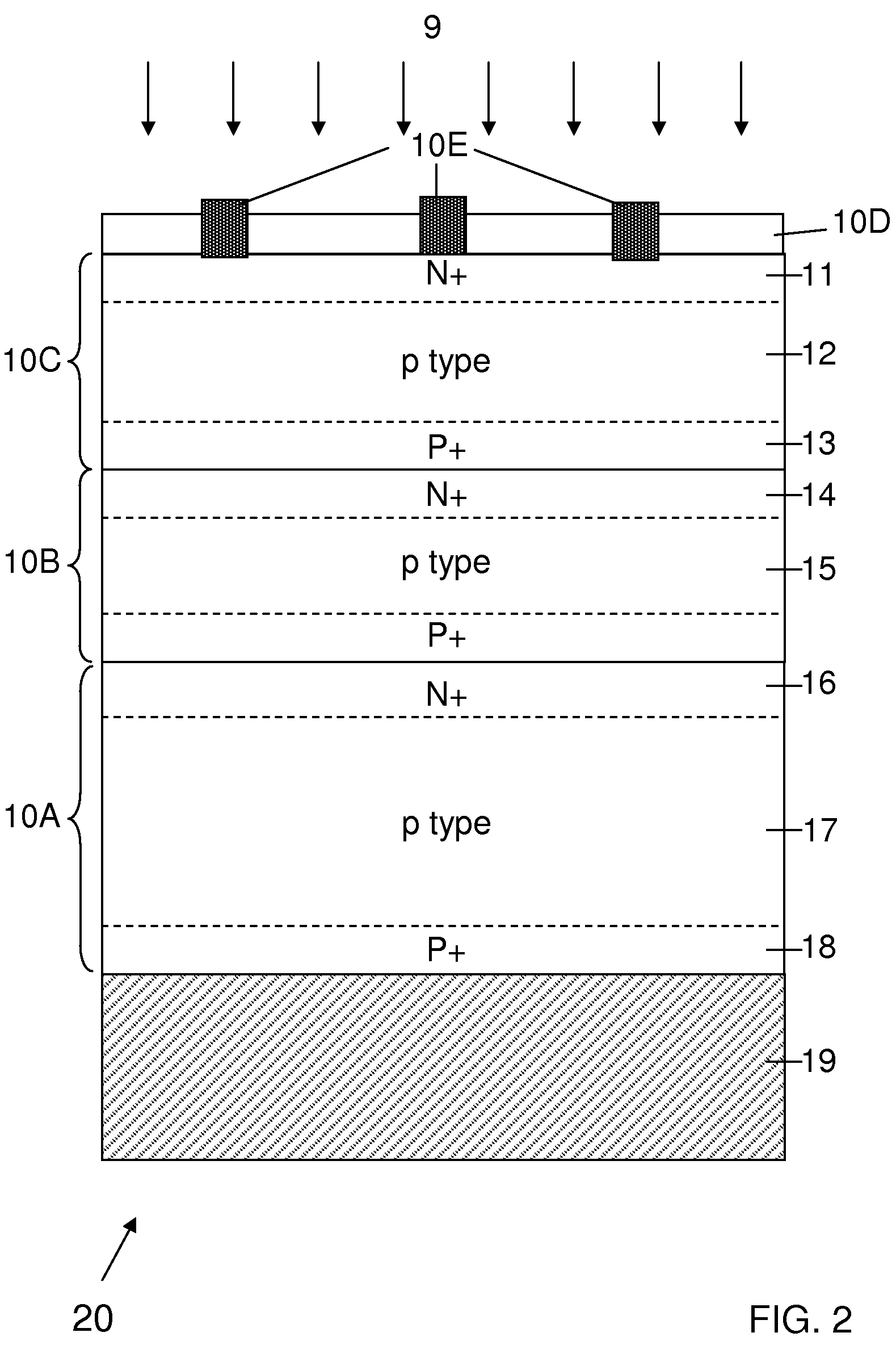

Overvoltage-protected light-emitting semiconductor device

ActiveUS20060181828A1Simpler and more compactLess-expensive constructionSemiconductor/solid-state device detailsSolid-state devicesOvervoltageDevice material

An LED incorporating an overvoltage protector with a minimum of space requirement. The LED itself comprises a p-type semiconductor substrate, a light-generating semiconductor region grown epitaxially thereon, a first electrode on the light-generating semiconductor region, and a second electrode on the underside of the substrate. The standard method of LED fabrication is such that the substrate is notionally divisible into a main portion in register with the overlying light-generating semiconductor region and, surrounding the main portion, a tubular marginal portion needed for dicing the wafer into individual squares or dice. The overvoltage protector comprises an n-type semiconductor film formed on the marginal portion of the substrate and held against the side surfaces of the light-generating semiconductor region via an insulating film. Creating a pn junction with the marginal portion of the p-type substrate, the n-type semiconductor film provides an overvoltage protector diode which is electrically connected reversely in parallel with the LED. Various other embodiments are disclosed.

Owner:SANKEN ELECTRIC CO LTD

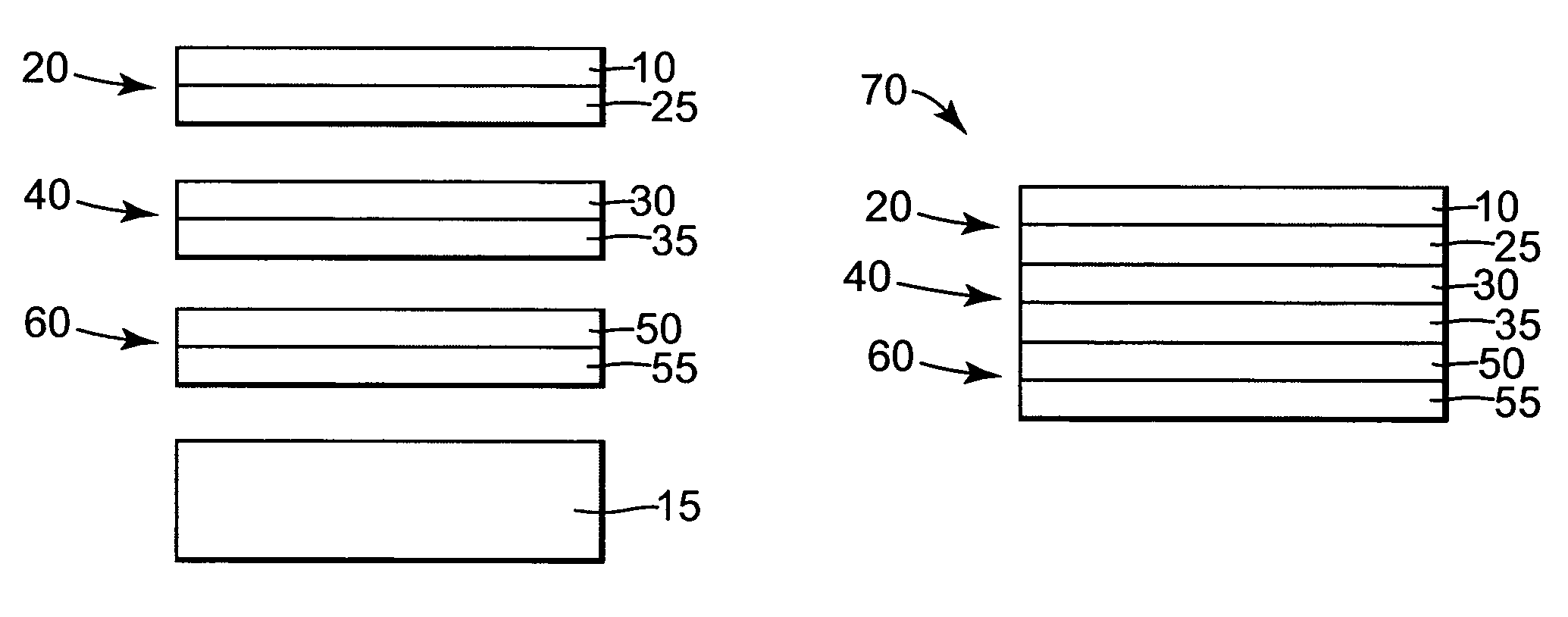

Tandem nanofilm solar cells joined by wafer bonding

An energy conversion device comprises at least two thin film photovoltaic cells fabricated separately and joined by wafer bonding. The cells are arranged in a hierarchical stack of decreasing order of their energy bandgap from top to bottom. Each of the thin film cells has a thickness in the range from about 0.5 μm to about 10 μm. The photovoltaic cell stack is mounted upon a thick substrate composed of a material selected from silicon, glass, quartz, silica, alumina, ceramic, metal, graphite, and plastic. Each of the interfaces between the cells comprises a structure selected from a tunnel junction, a heterojunction, a transparent conducting oxide, and an alloying metal grid; and the top surface and / or the lower surface of the energy conversion device may contain light-trapping means.

Owner:IBM CORP

Semiconductor die terminal

InactiveUS20120049342A1Function increaseImprove performanceSemiconductor/solid-state device detailsSolid-state devicesPresent methodWafer dicing

A method of making semiconductor die terminals and a semiconductor device with die terminals made according to the present method. At least a first mask layer is selectively printed on at least a portion of a wafer containing a plurality of the semiconductor devices to create first recesses aligned with electrical terminals on the semiconductor devices. A conductive material is deposited in a plurality of the first recesses to form die terminals on the semiconductor devices. The first mask layer is removed to expose the die terminals, and the wafer is diced into a plurality of discrete semiconductor devices.

Owner:HSIO TECH

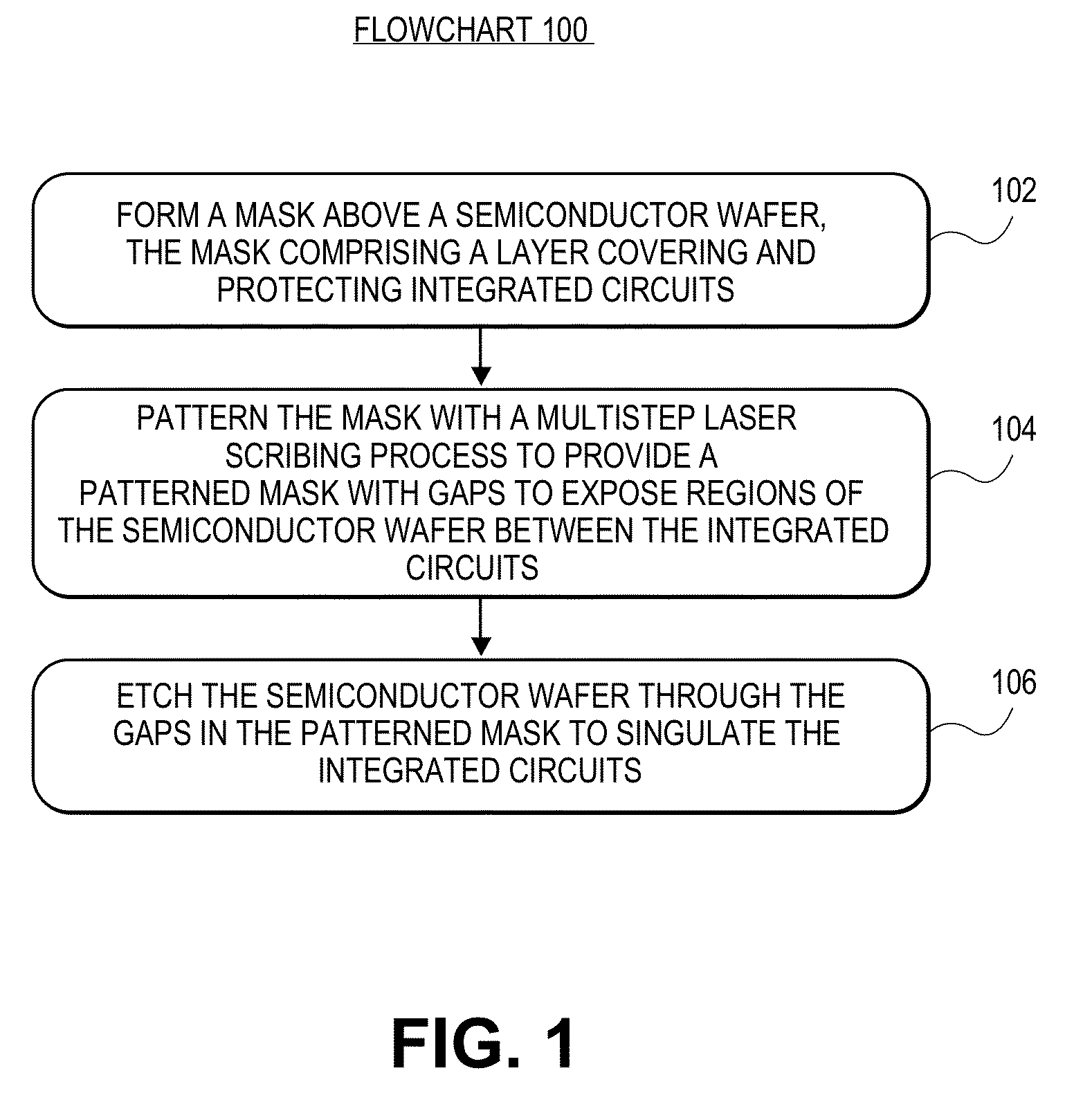

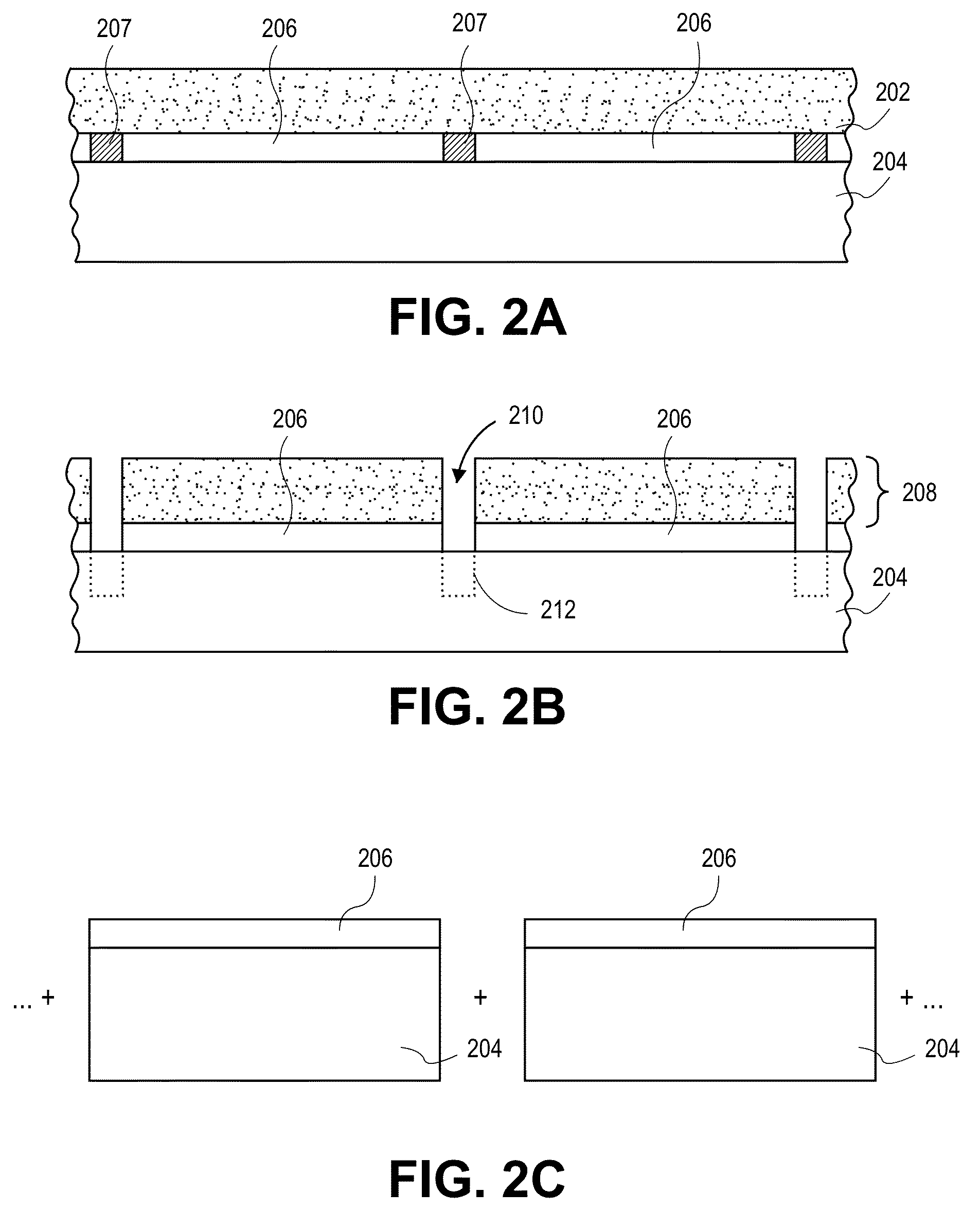

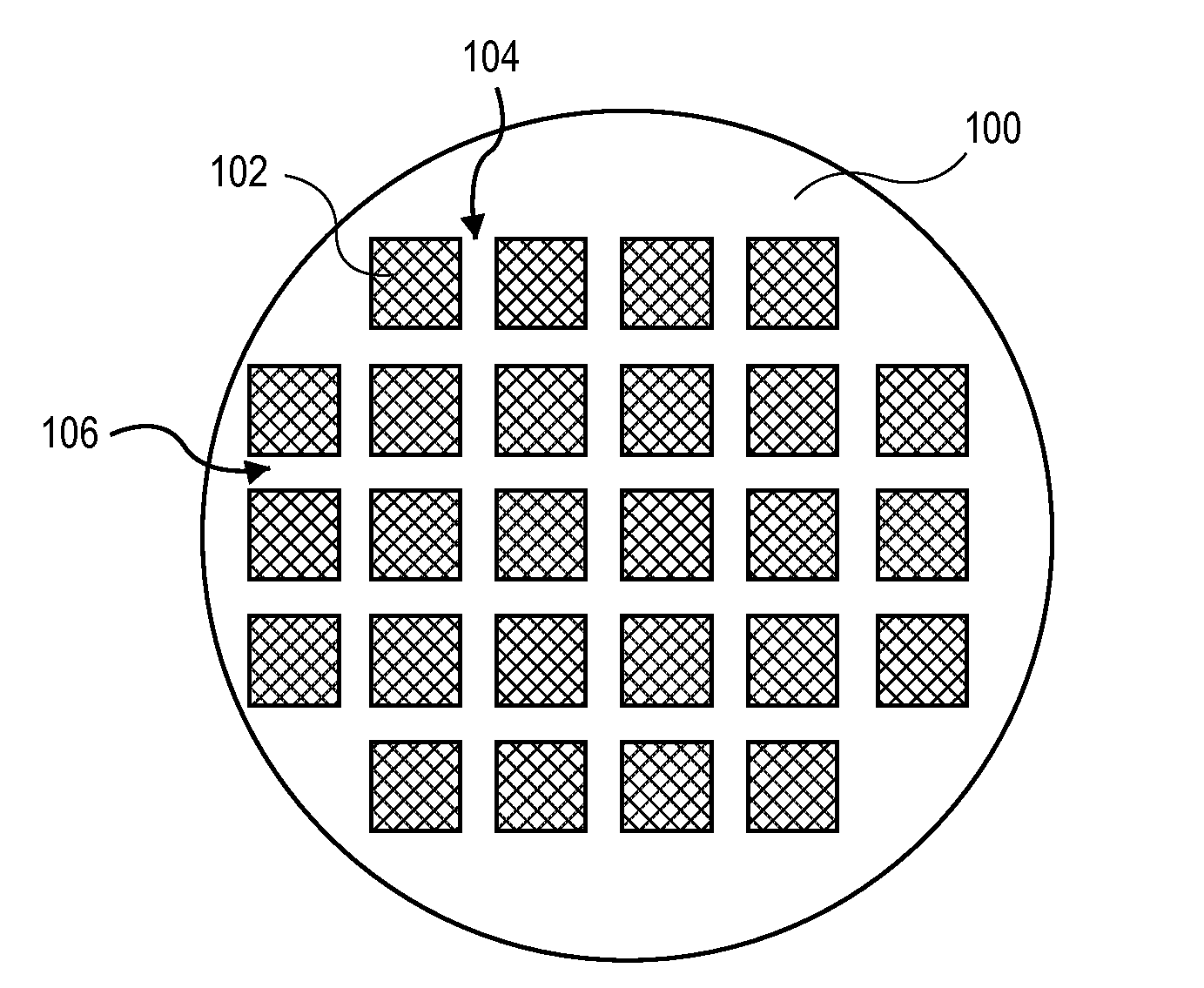

Wafer dicing using hybrid multi-step laser scribing process with plasma etch

ActiveUS20130267076A1Semiconductor/solid-state device manufacturingWelding/soldering/cutting articlesWafer dicingLaser scribing

Methods of dicing semiconductor wafers, each wafer having a plurality of integrated circuits, are described. A method includes forming a mask above the semiconductor wafer. The mask is composed of a layer covering and protecting the integrated circuits. The mask is patterned with a multi-step laser scribing process to provide a patterned mask with gaps. The patterning exposes regions of the semiconductor wafer between the integrated circuits. The semiconductor wafer is then etched through the gaps in the patterned mask to singulate the integrated circuits.

Owner:APPLIED MATERIALS INC

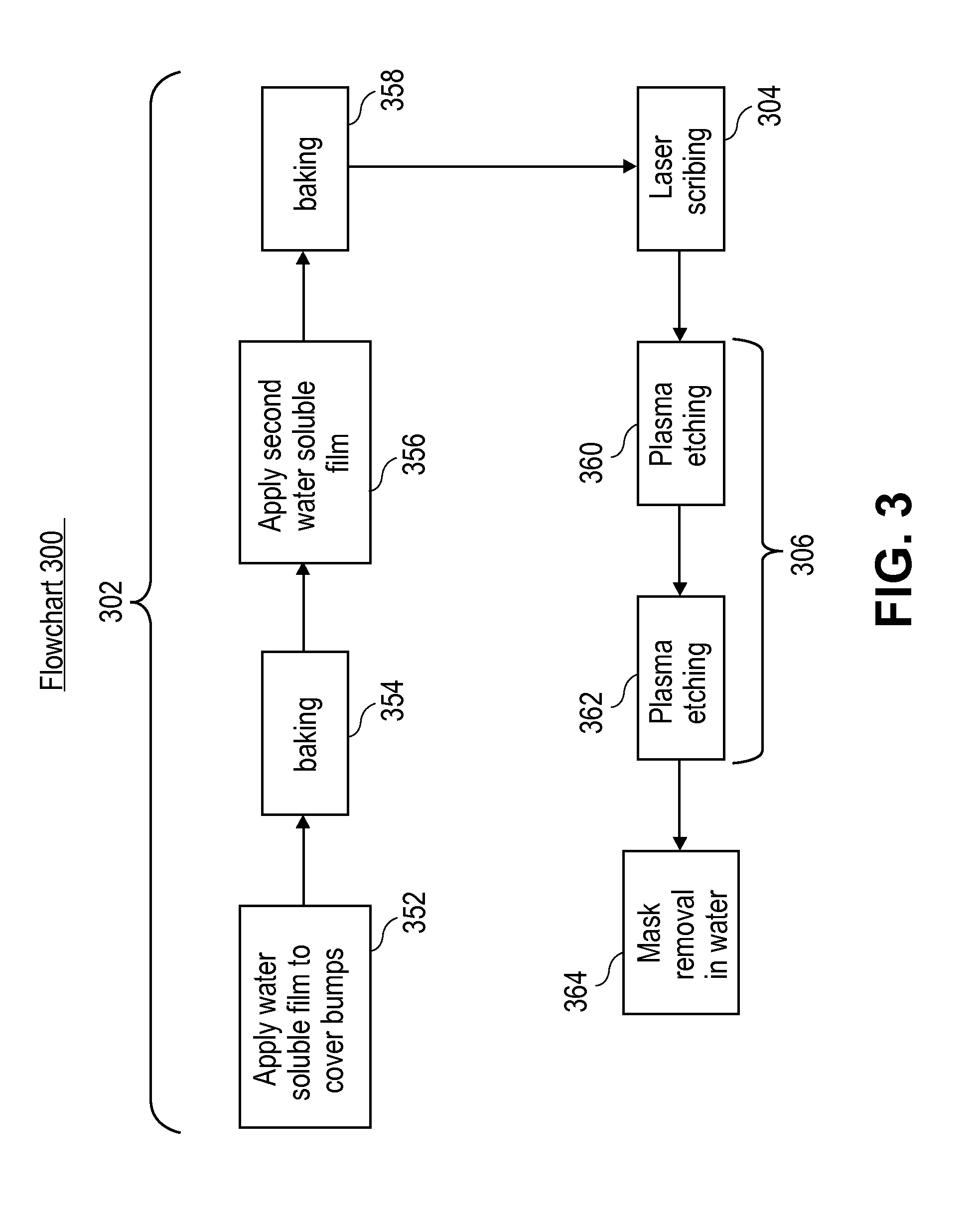

Method of coating water soluble mask for laser scribing and plasma etch

Methods of using a hybrid mask composed of a first water soluble film layer and a second water-soluble layer for wafer dicing using laser scribing and plasma etch described. In an example, a method of dicing a semiconductor wafer having a plurality of integrated circuits involves forming a hybrid mask above the semiconductor wafer. The hybrid mask is composed of a first water-soluble layer disposed on the integrated circuits, and a second water-soluble layer disposed on the first water-soluble layer. The method also involves patterning the hybrid mask with a laser scribing process to provide a patterned hybrid mask with gaps, exposing regions of the semiconductor wafer between the integrated circuits. The method also involves etching the semiconductor wafer through the gaps in the patterned hybrid mask to singulate the integrated circuits.

Owner:APPLIED MATERIALS INC

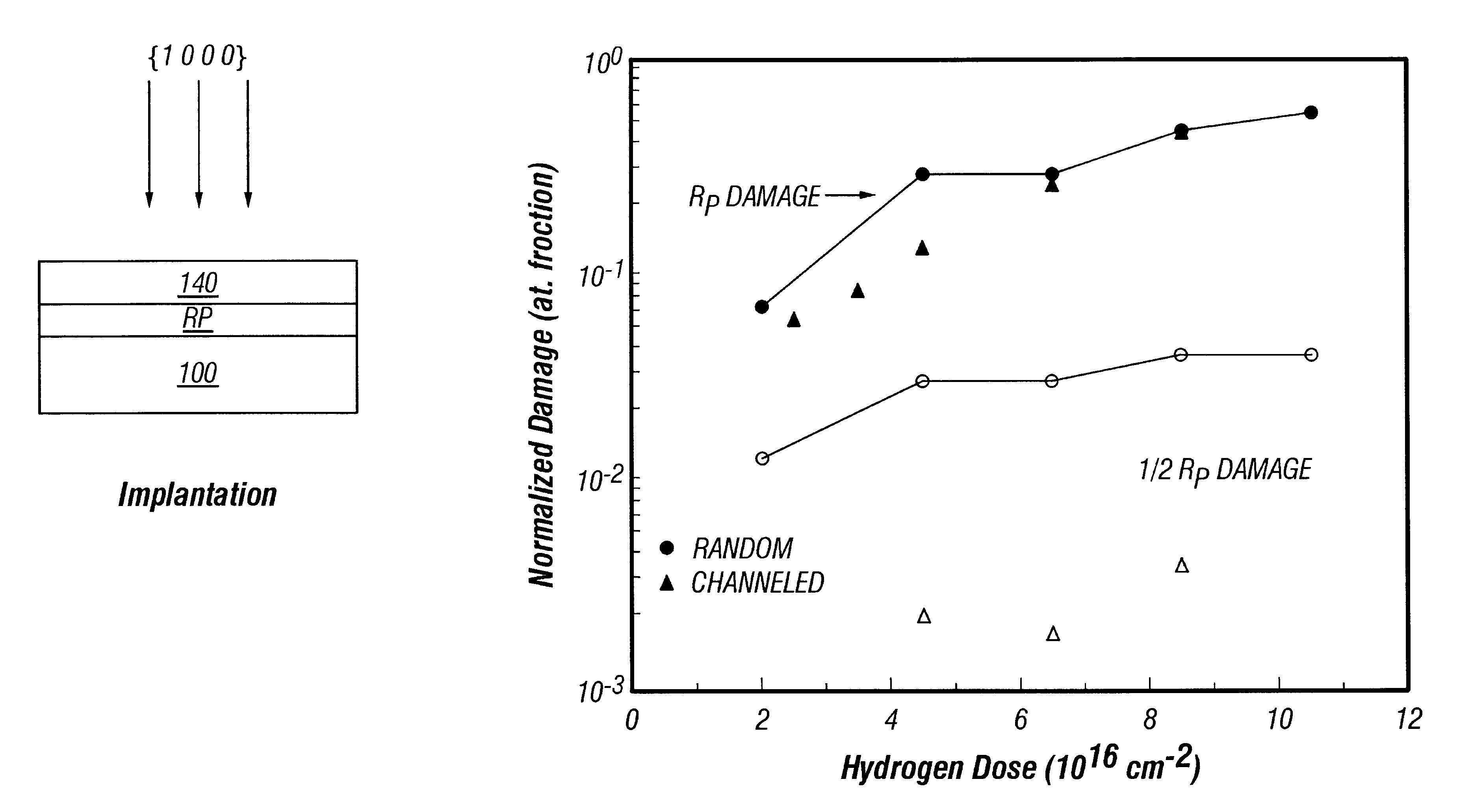

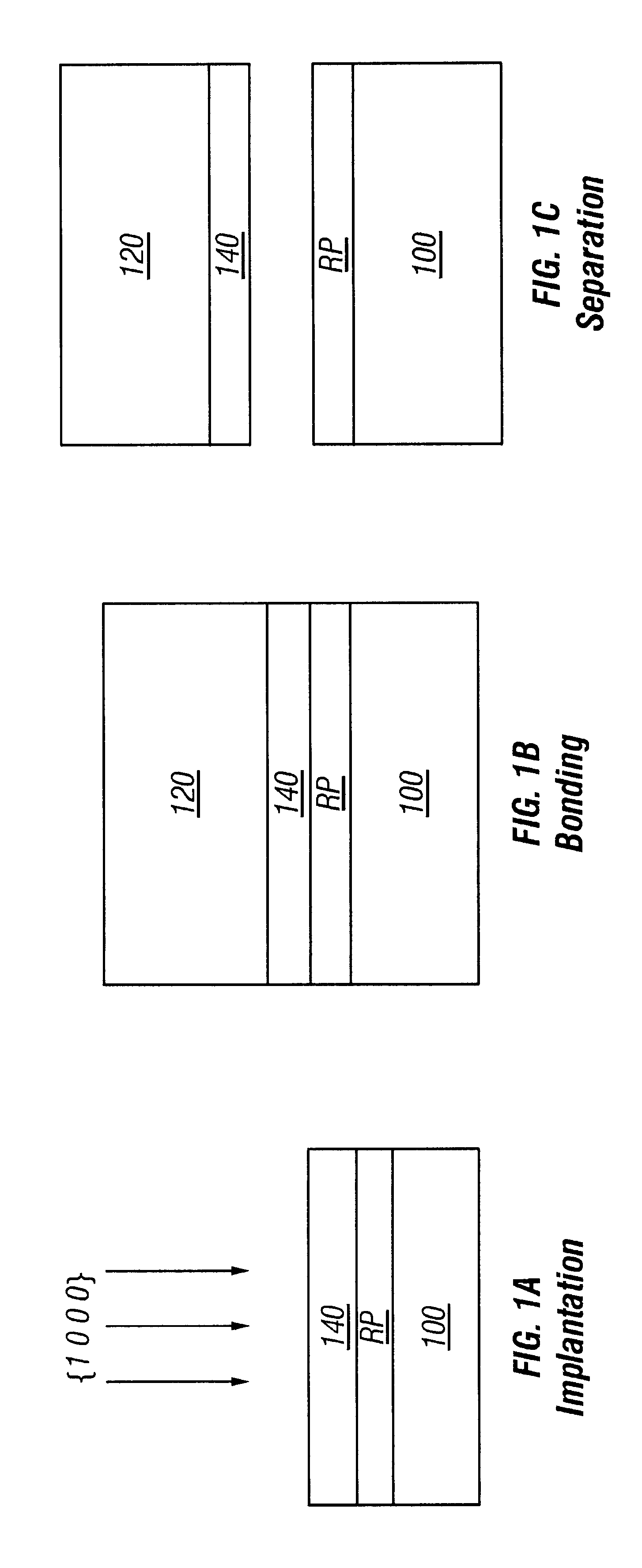

Method for transfer of thin-film of silicon carbide via implantation and wafer bonding

Systems and methods are described for transfer of a thin-film via implantation, wafer bonding, and separation. A method for transfer of a thin-film, includes: implanting a source crystal with ions along a crystallographic channel and at a temperature of at least approximately 200° C. to i) form a strained region and ii) define the thin-film; then bonding a surface of the thin-film to a target wafer; and then separating a) the target wafer and the thin-film from b) a remainder of the source crystal along the strained region. The systems and methods provide advantages because the electrical carriers in the crystal, and consequently the thin-film, are not deactivated and the quality of the transferred thin-film is improved.

Owner:LOCKHEED MARTIN ENERGY SYST INC +1

VLSI-photonic heterogeneous integration by wafer bonding

InactiveUS7203387B2Improve performanceSemiconductor/solid-state device manufacturingCoupling light guidesPhotonicsWafer dicing

A new method to form a VLSI-photonic heterogeneous system device is achieved. The method comprises providing an optical substrate comprising at least one passive optical component formed therein. An electronic substrate is provided comprising at least one active electronic component formed therein. A plurality of metal pillars are formed through the optical substrate and protruding out a first surface of the optical substrate. A plurality of metal pads are formed on a first surface of the electronic substrate. The optical substrate and the electronic substrate are bonding together by a method further comprising aligning the first surfaces of the optical and electronic substrates such that the protruding metal pillars contact the metal pads. The optical and electronic substrates are then thermally treated such that the metal pillars bond to the metal pads.

Owner:AGENCY FOR SCI TECH & RES

Method of fabrication of a micro-channel based integrated sensor for chemical and biological materials

InactiveUS6933164B2High selectivityReduce laborMaterial analysis using sonic/ultrasonic/infrasonic wavesFixed microstructural devicesContact padWafer dicing

Owner:HRL LAB

Semiconductor processing

InactiveUS20050272225A1Increase usable surface areaConstant gapMetal-working apparatusSemiconductor/solid-state device manufacturingWafer dicingMechanical engineering

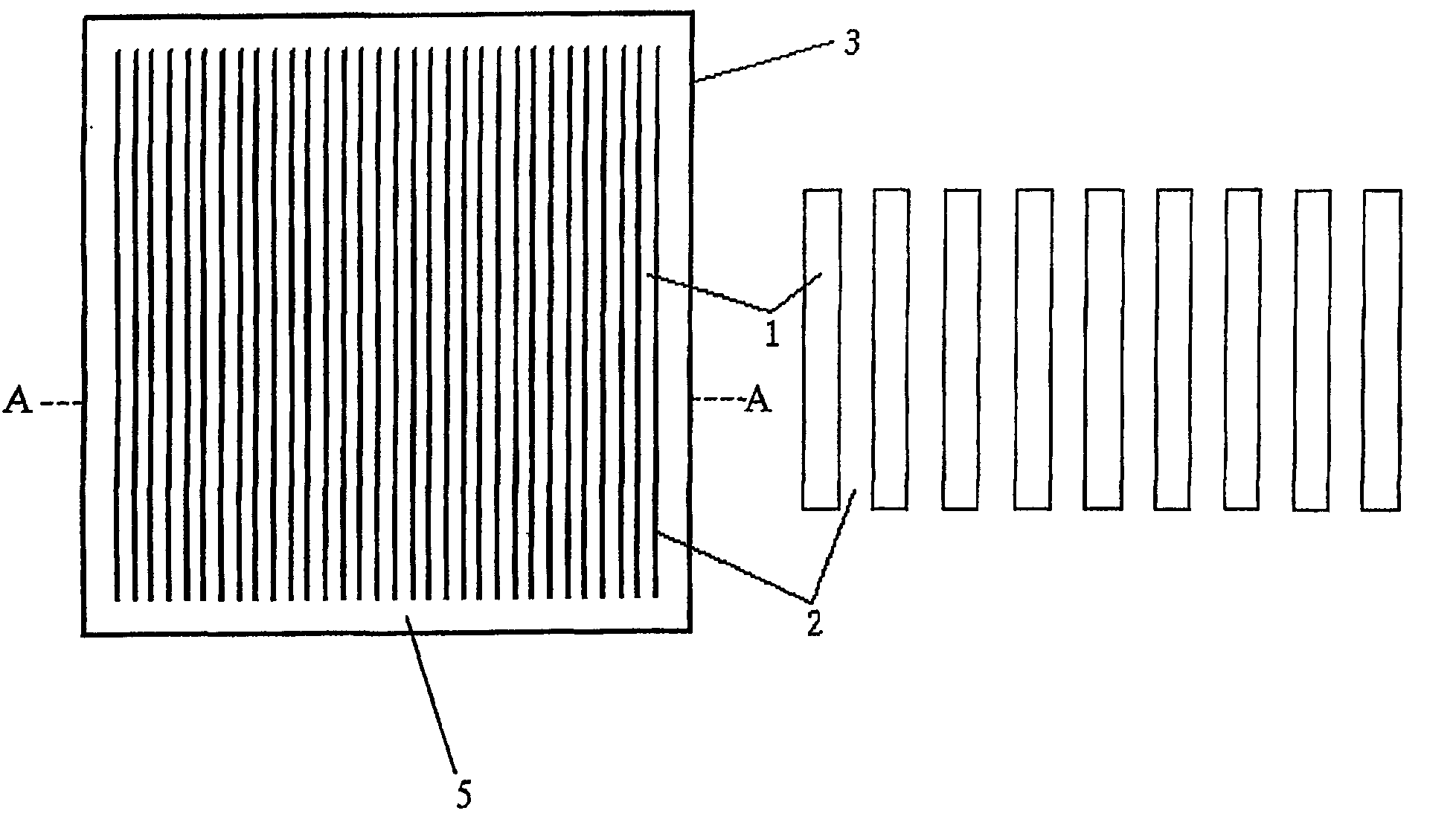

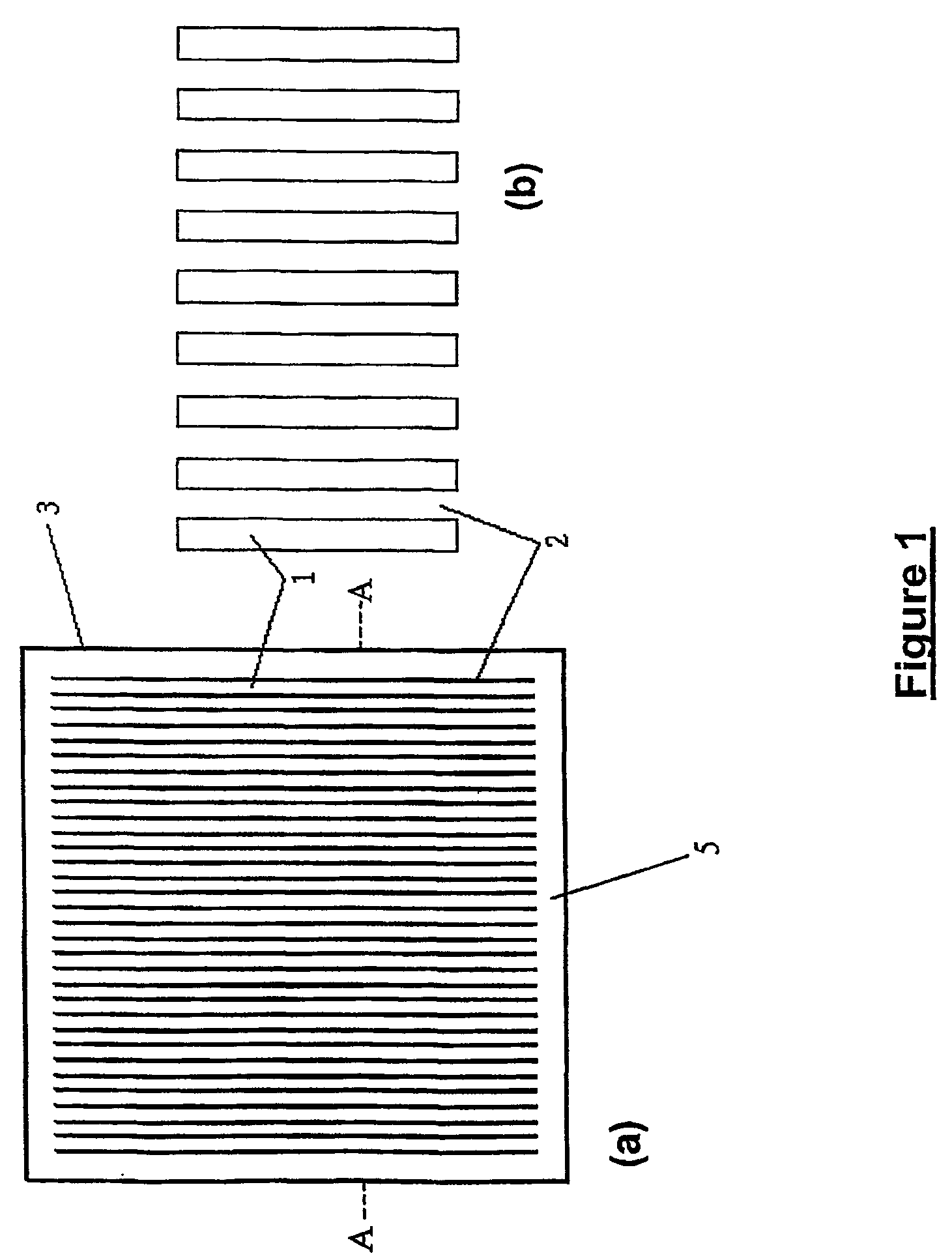

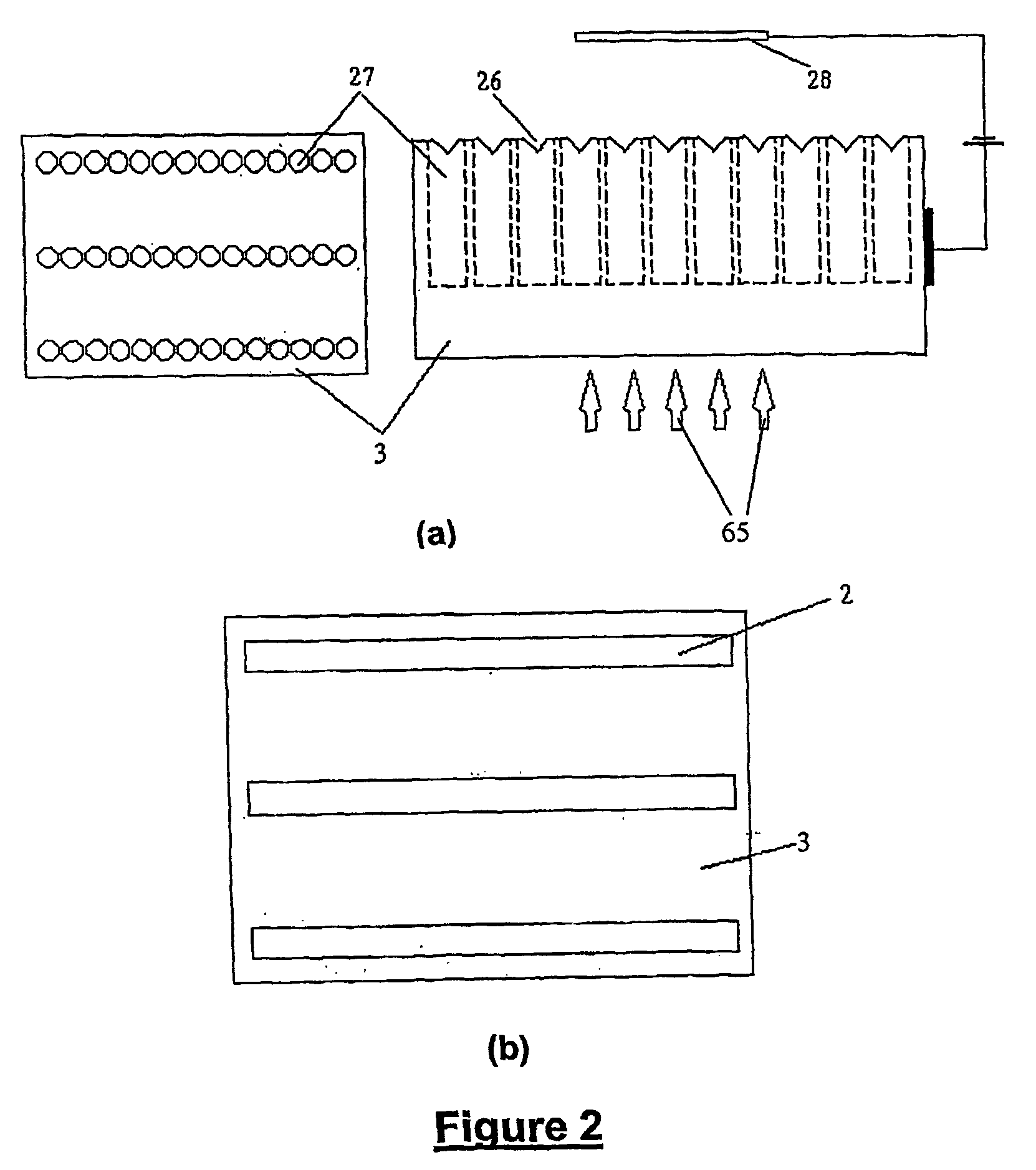

The invention provides a method for increasing the usable surface area of a semiconductor wafer having a substantially planar surface and a thickness dimension at right angles to said substantially planar surface, the method including the steps of selecting a strip thickness for division of the wafer into a plurality of strips, selecting a technique for cutting the wafer into the strips at an angle to the substantially planar surface, in which the combined strip thickness and width of wafer removed by the cutting is less than the thickness of the wafer, cutting the wafer into strips using the selected technique and separating the strips from each other.

Owner:AUSTRALIEN NAT UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com