Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

348 results about "Wafer fabrication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

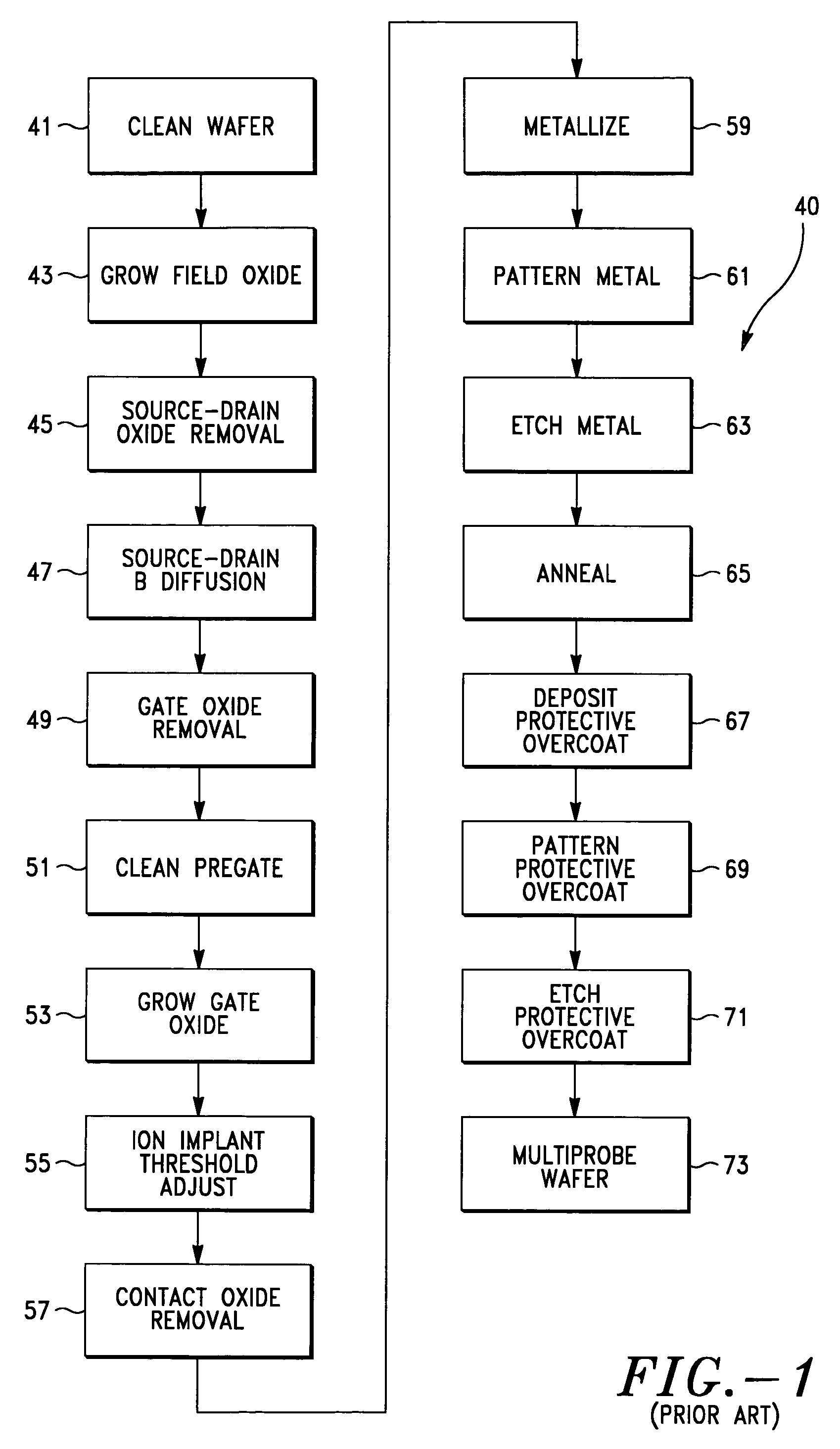

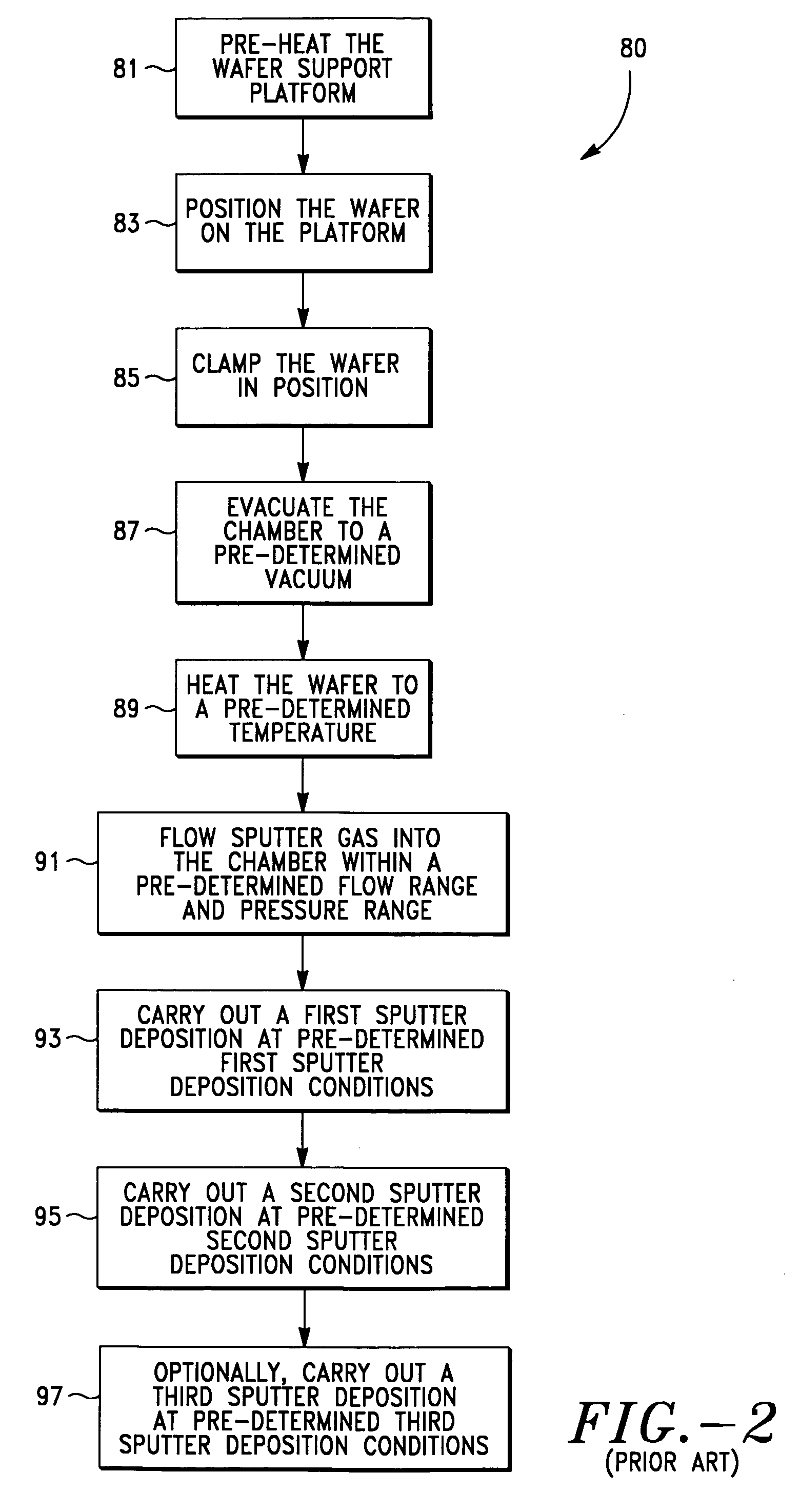

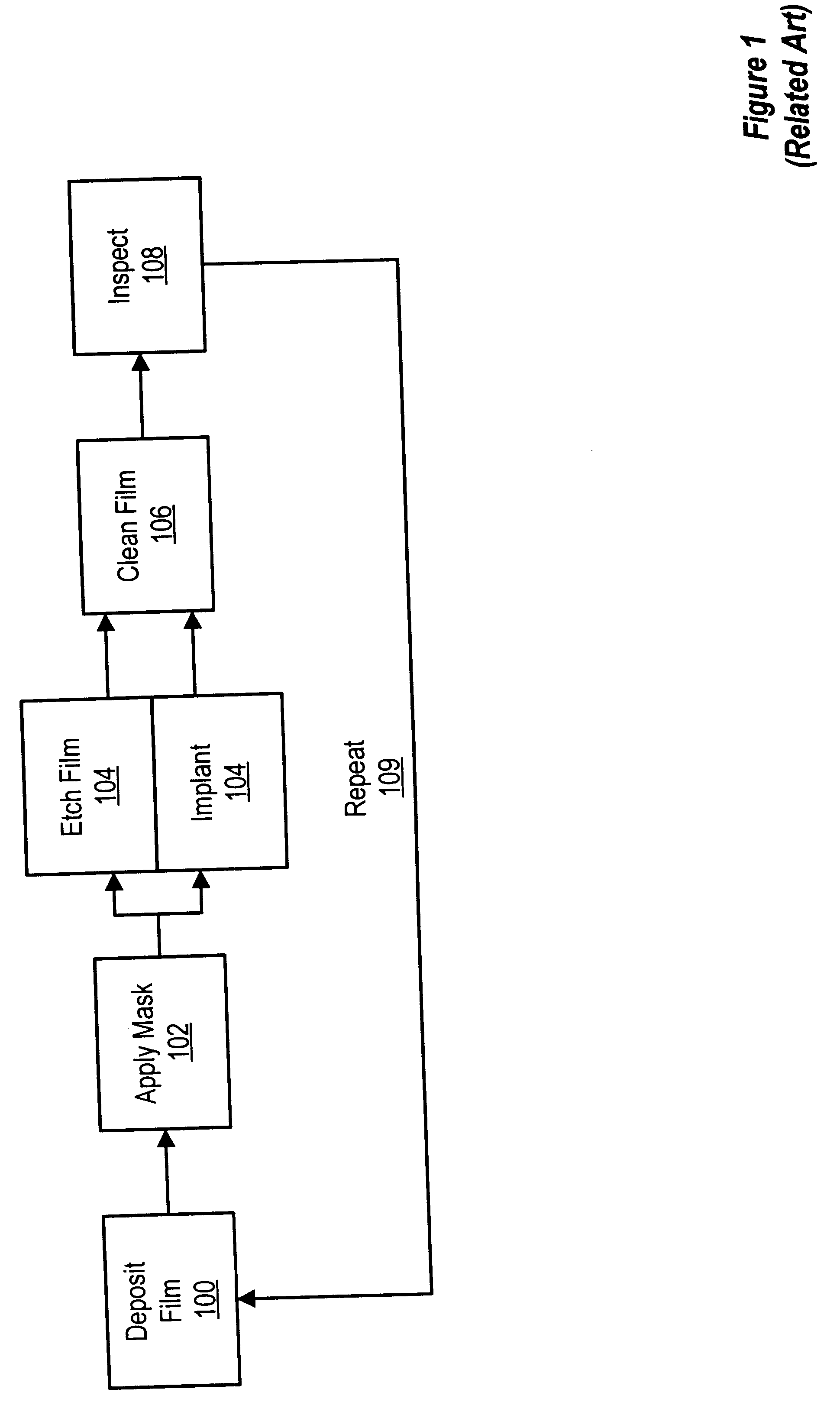

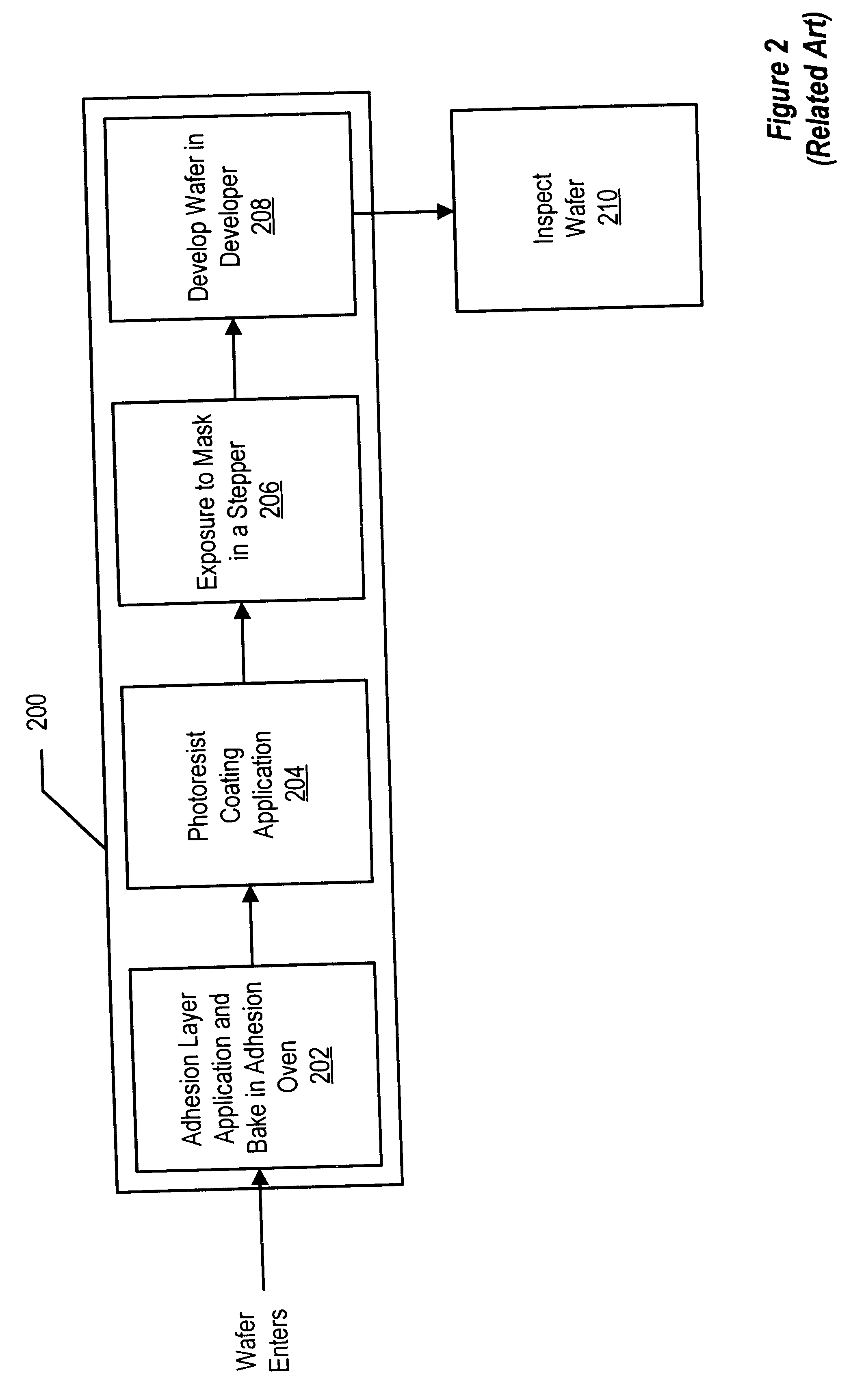

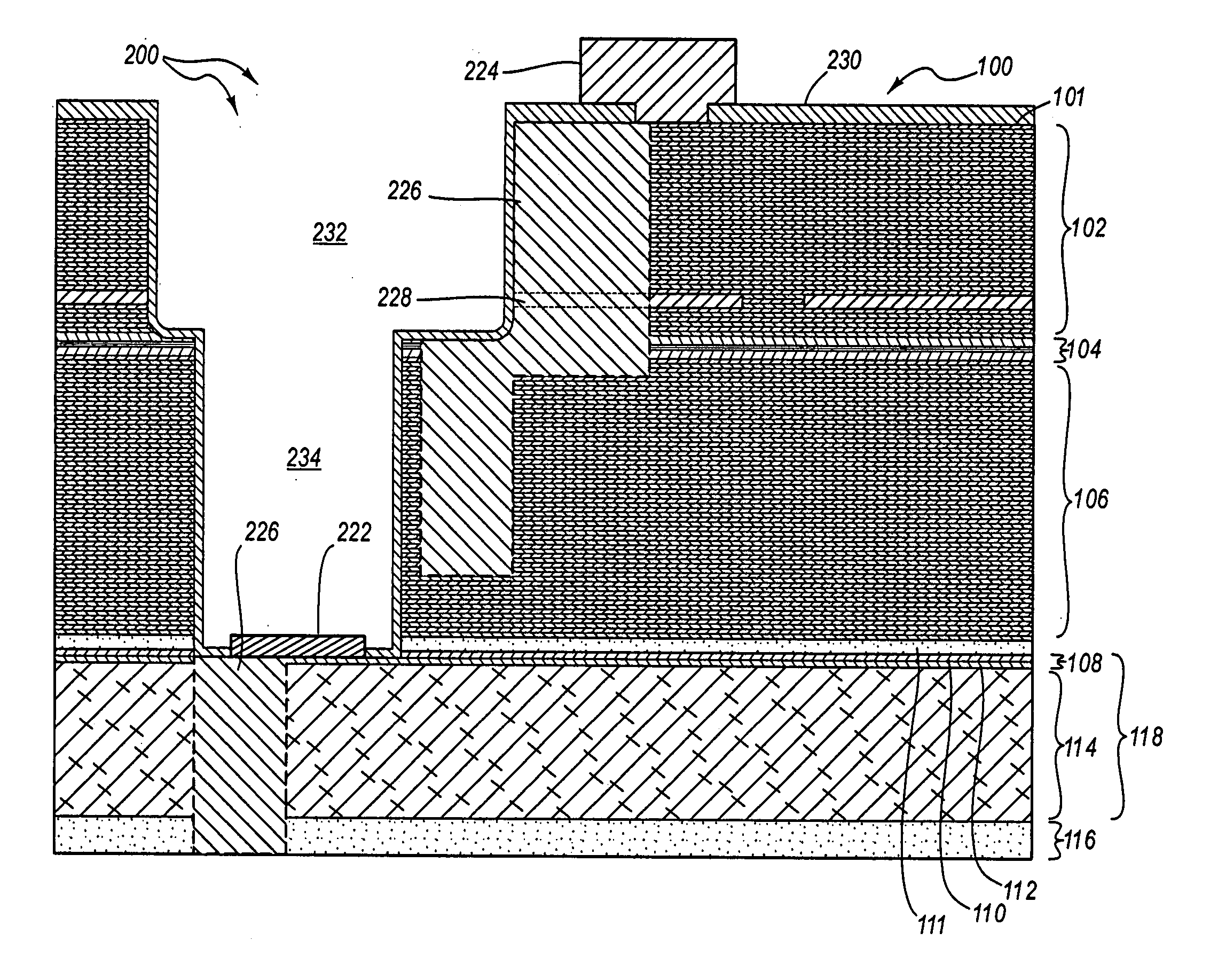

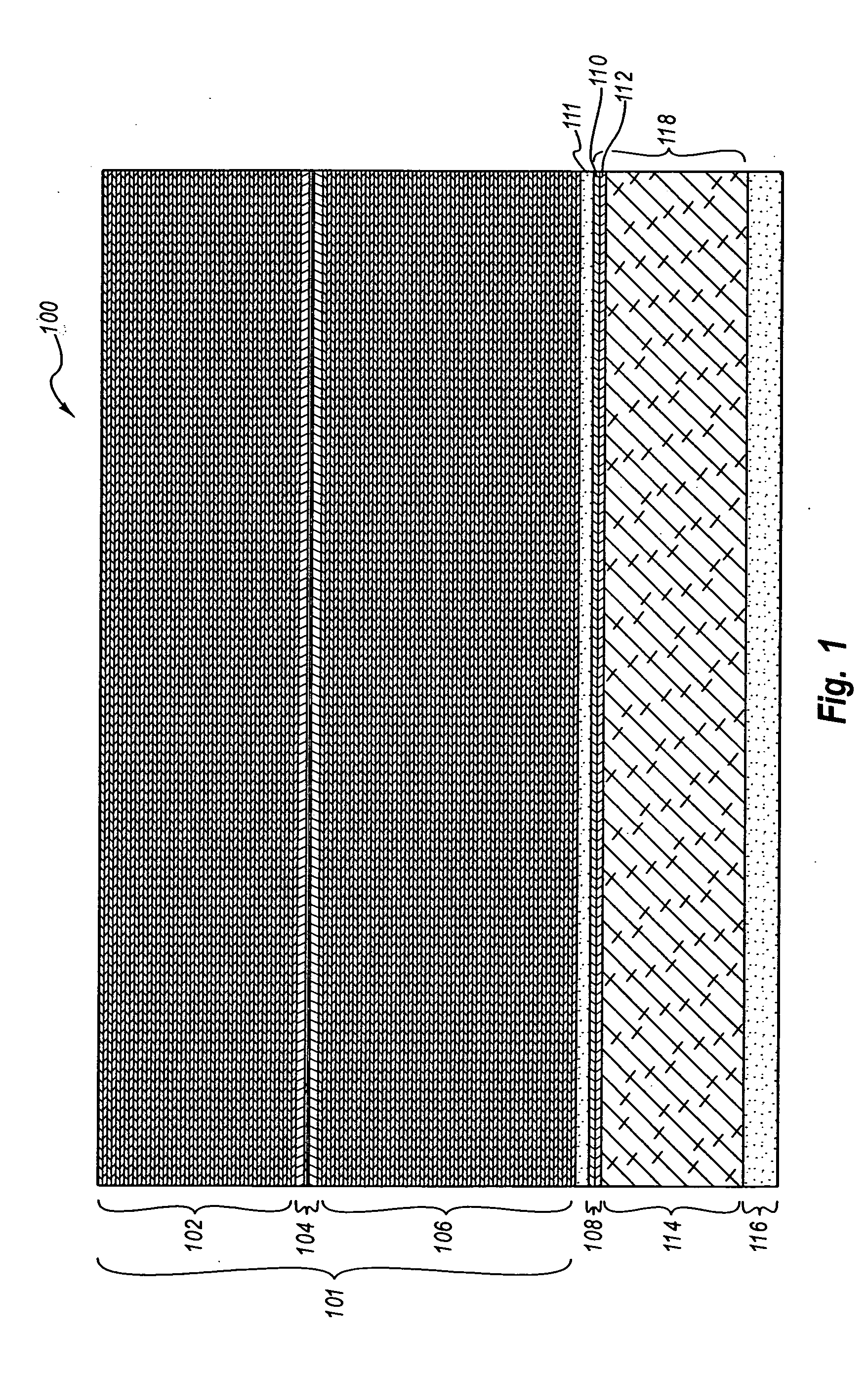

Wafer fabrication is a procedure composed of many repeated sequential processes to produce complete electrical or photonic circuits on semiconductor wafers. Examples include production of radio frequency (RF) amplifiers, LEDs, optical computer components, and CPUs for computers. Wafer fabrication is used to build components with the necessary electrical structures.

Method and system for semiconductor wafer fabrication process real-time in-situ interactive supervision

InactiveUS6363294B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingWafer fabricationEngineering

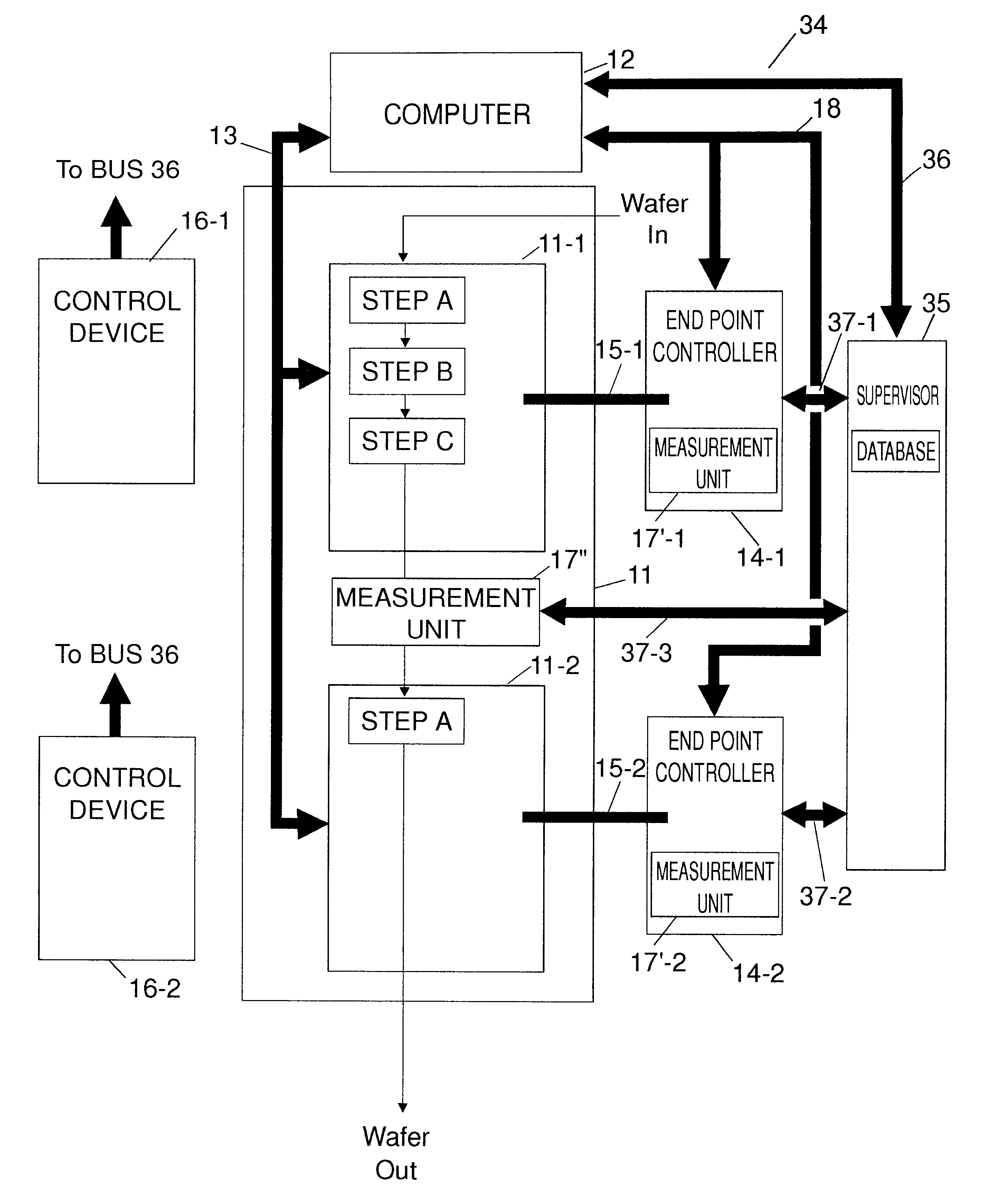

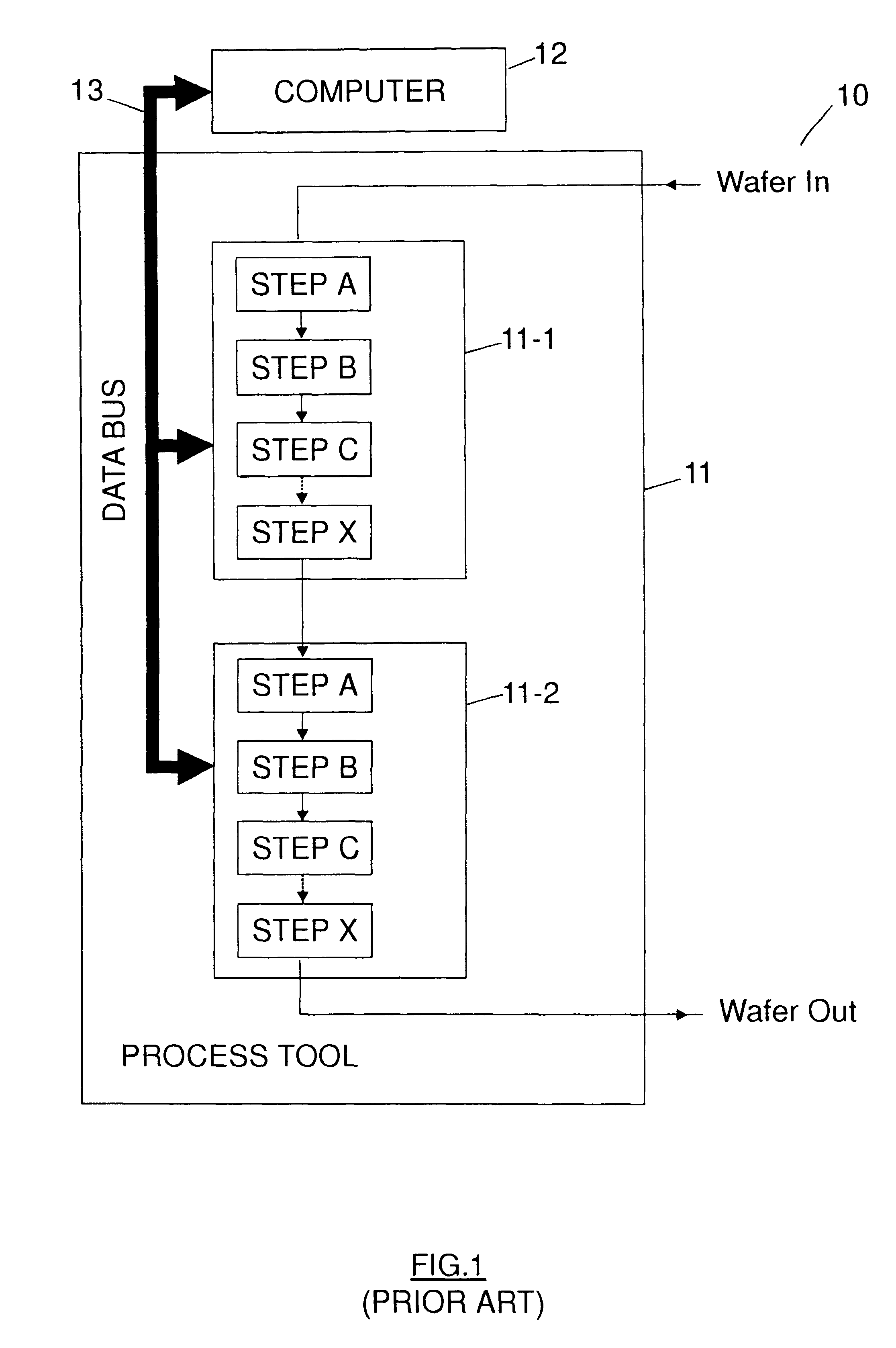

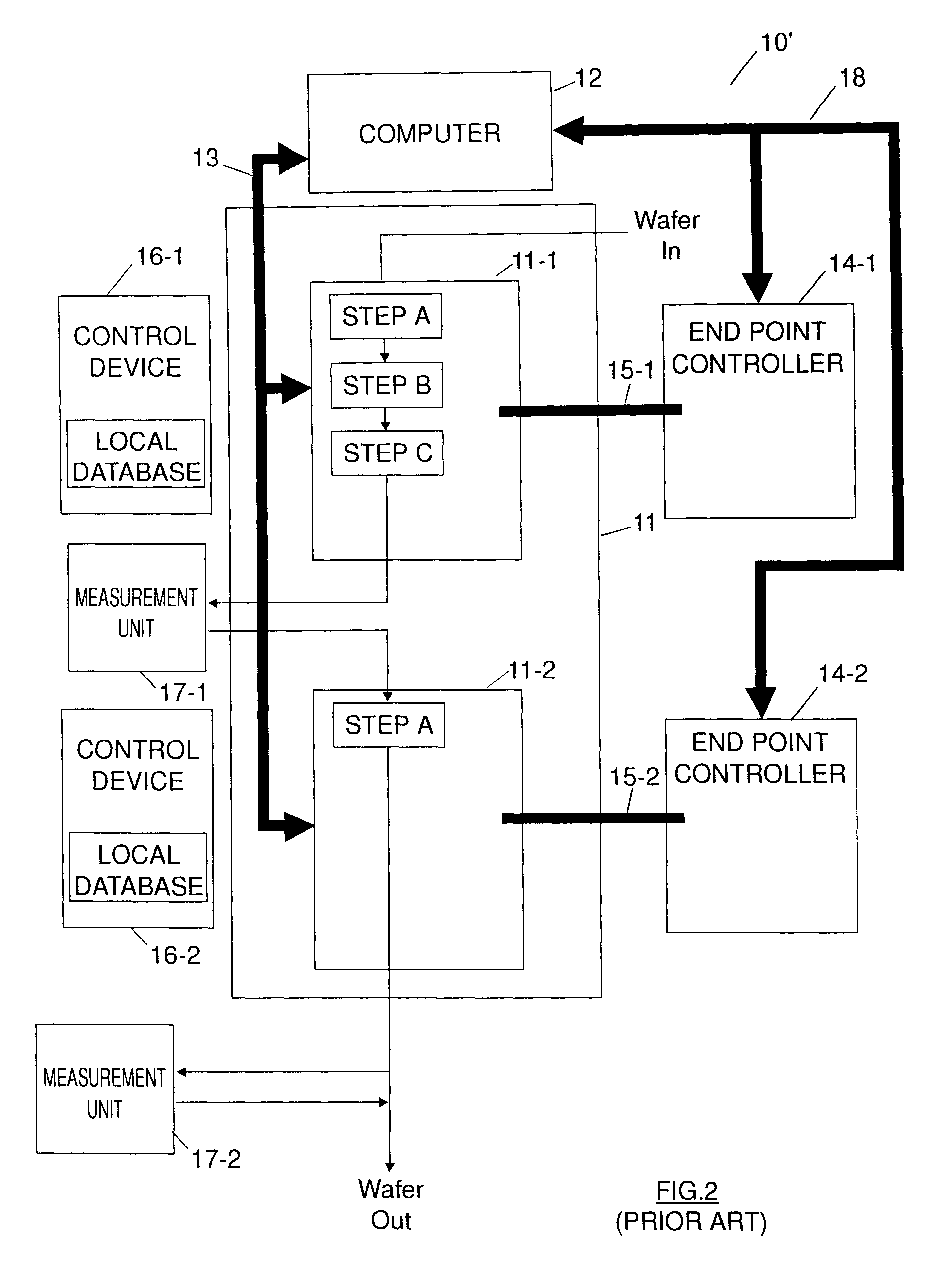

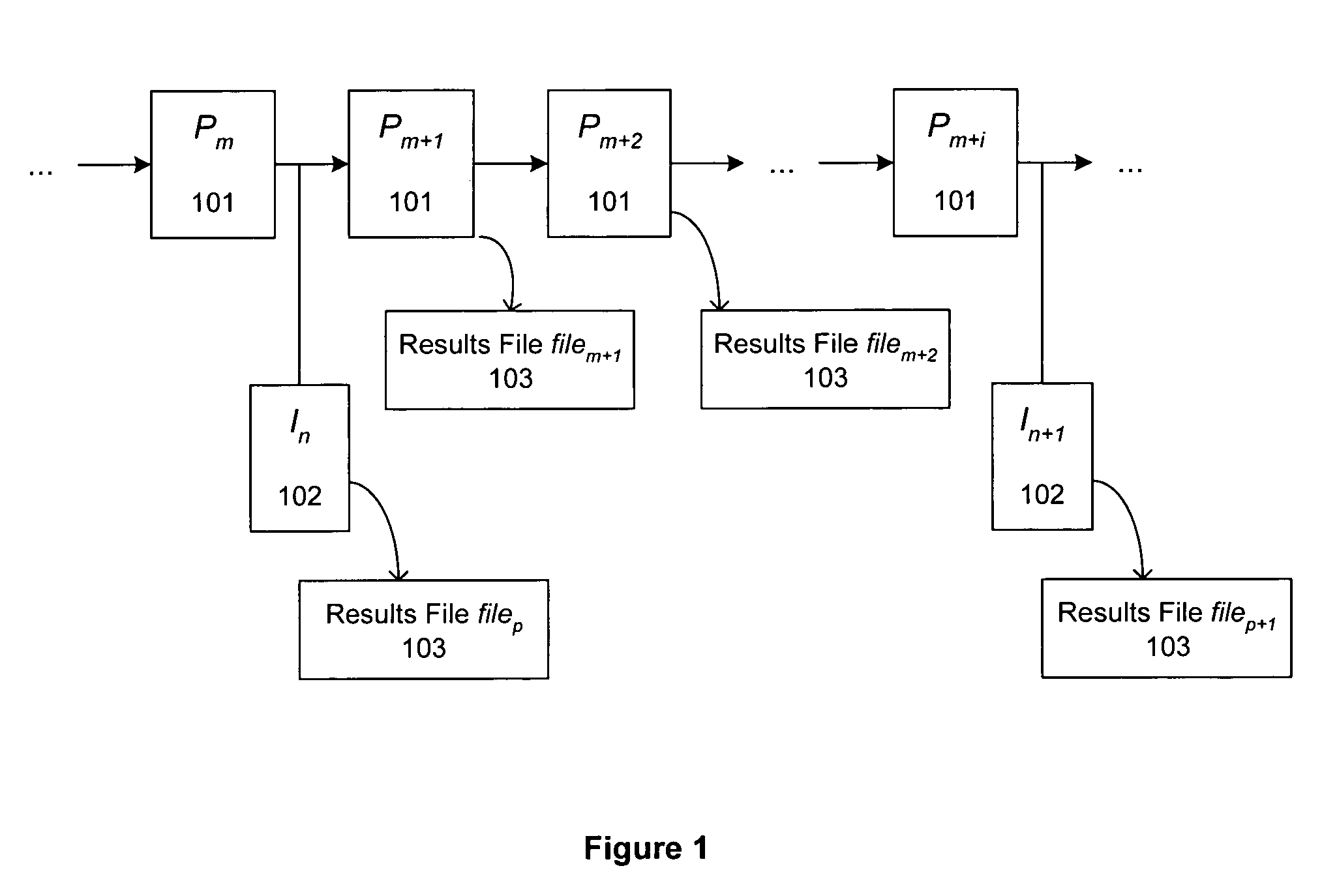

Method and system for real-time in-situ interactive supervision of a step performed in a tool during semiconductor wafer fabrication process. The system includes a tool and the computer attached thereto, an end point detection controller, a database and a supervisor to supervise the whole wafer processing for that step. The controller is used to monitor a key process parameter of the step and is adapted to perform in-situ measurements. The database contains the evolution of said process parameter in normal operating conditions and in all the identified deviations. It further contains the history of the wafer until this step and a reference to the batch and process names for this step and the wafer identification number. At the end of the step, the important process parameters and any alert code are stored in the database to up-date the wafer history. This technique allows a total clusterized wafer fabrication process and prevents wafer rejection.

Owner:IBM CORP

Wafer fabrication data acquisition and management systems

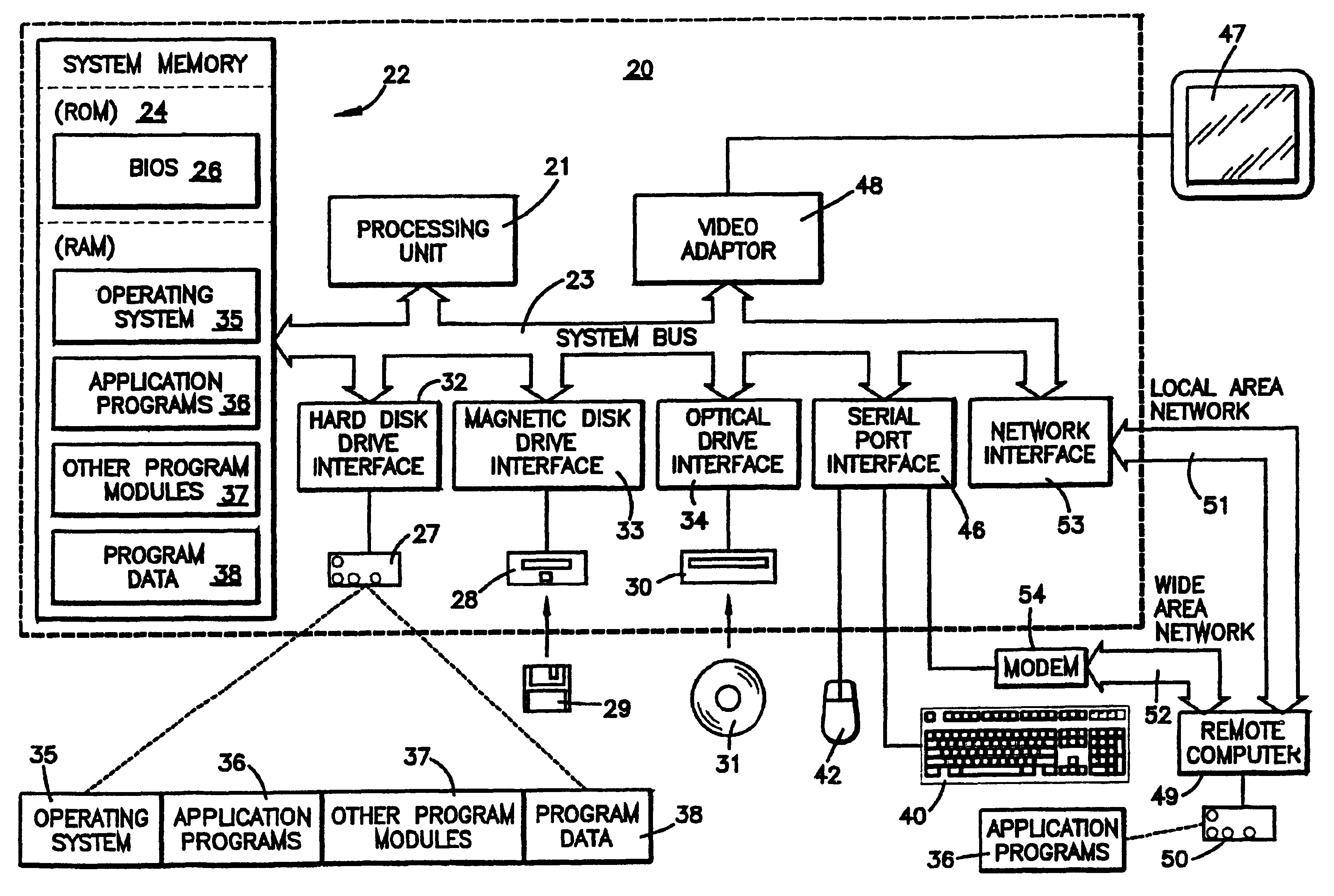

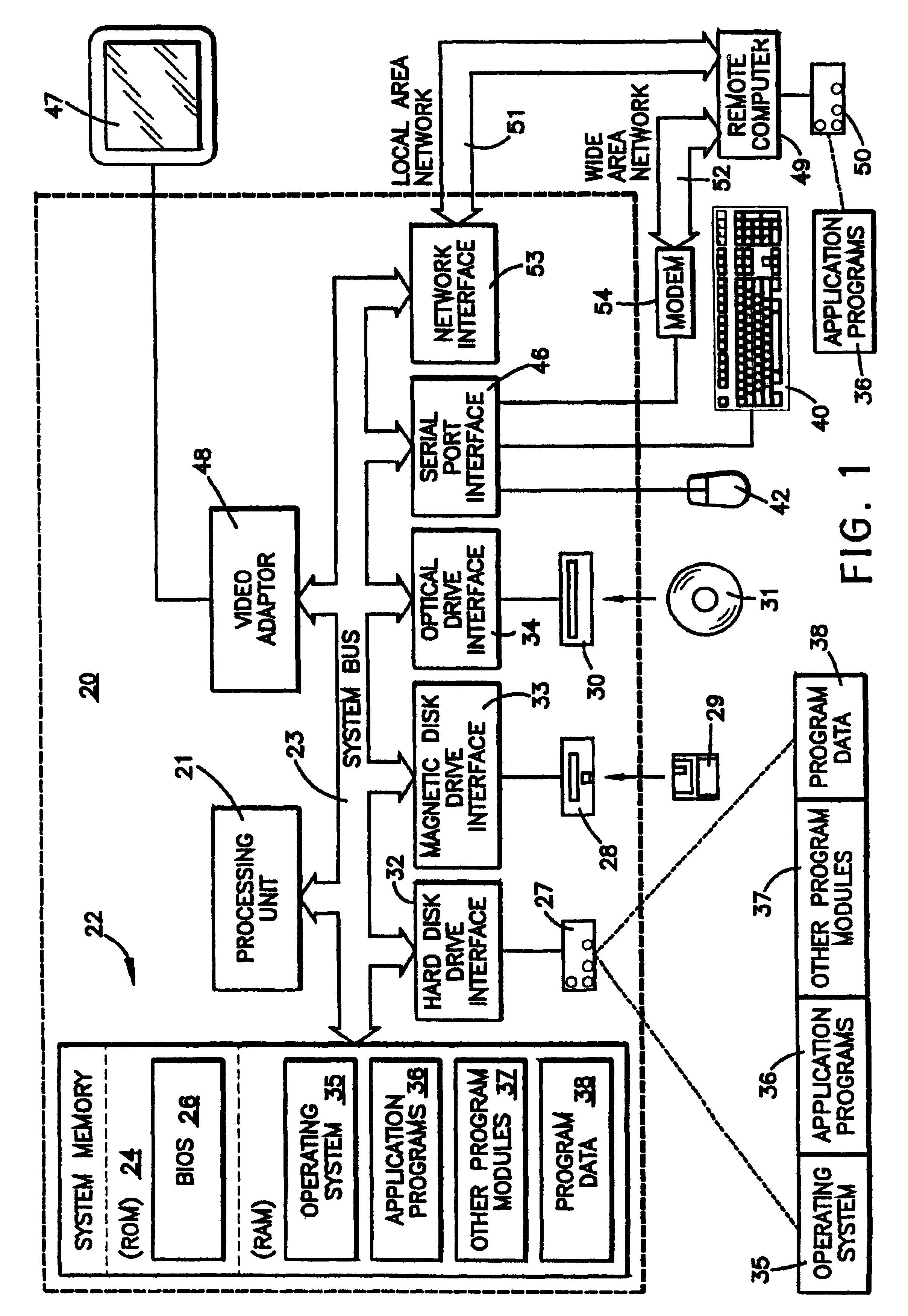

InactiveUS6952656B1Improve data transfer performanceIncrease costResistance/reactance/impedenceComputer controlWafer fabricationData acquisition

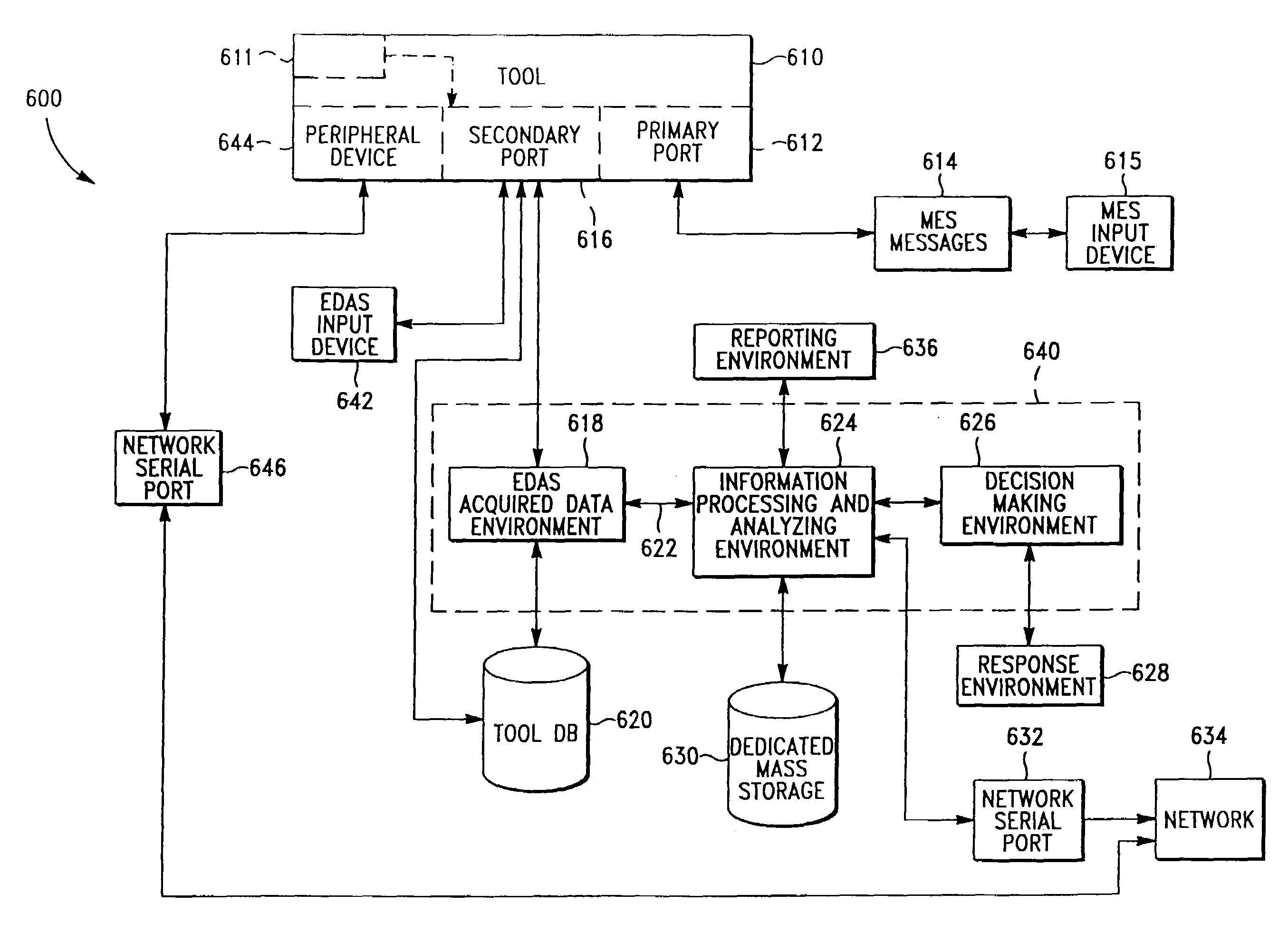

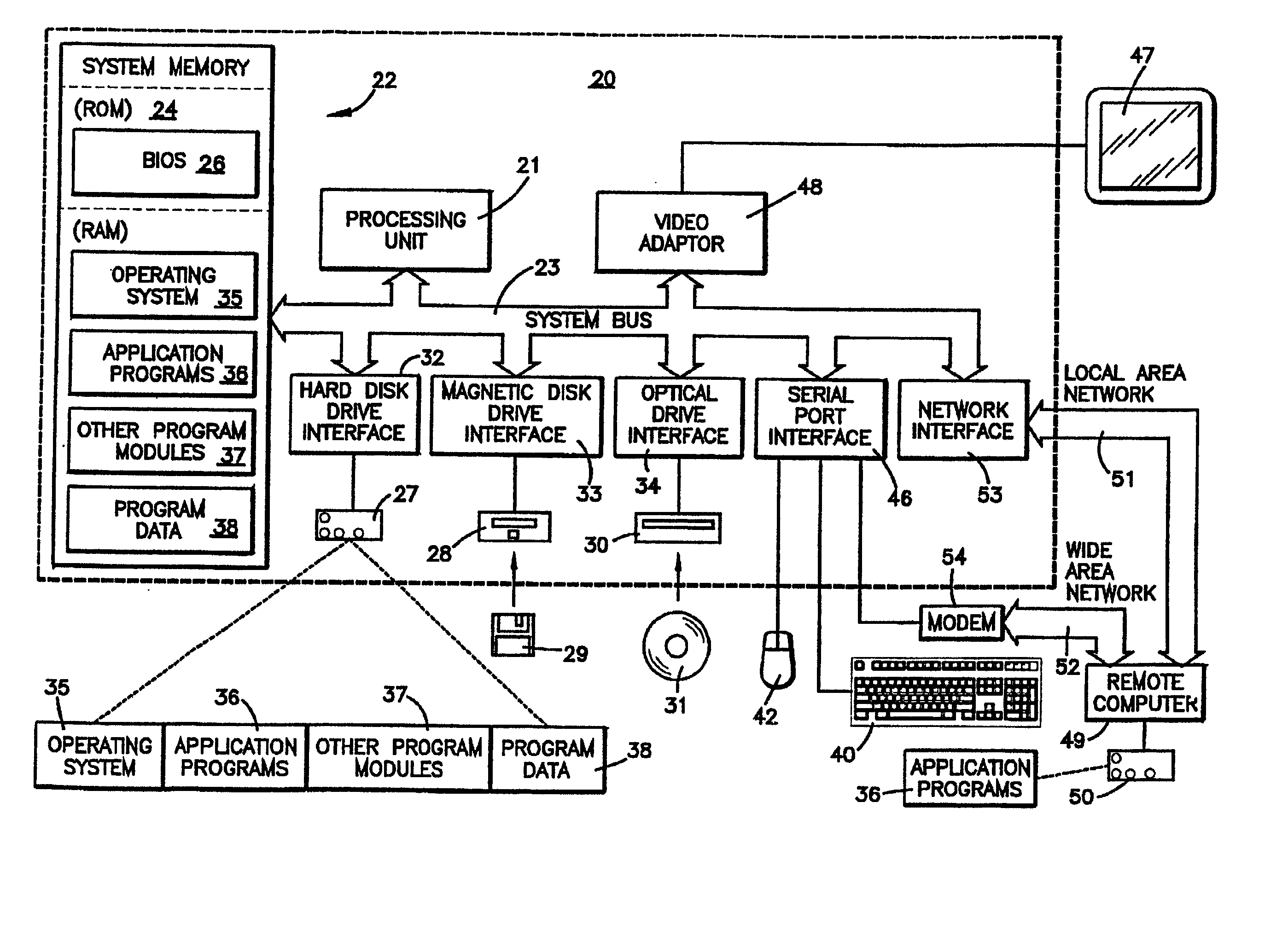

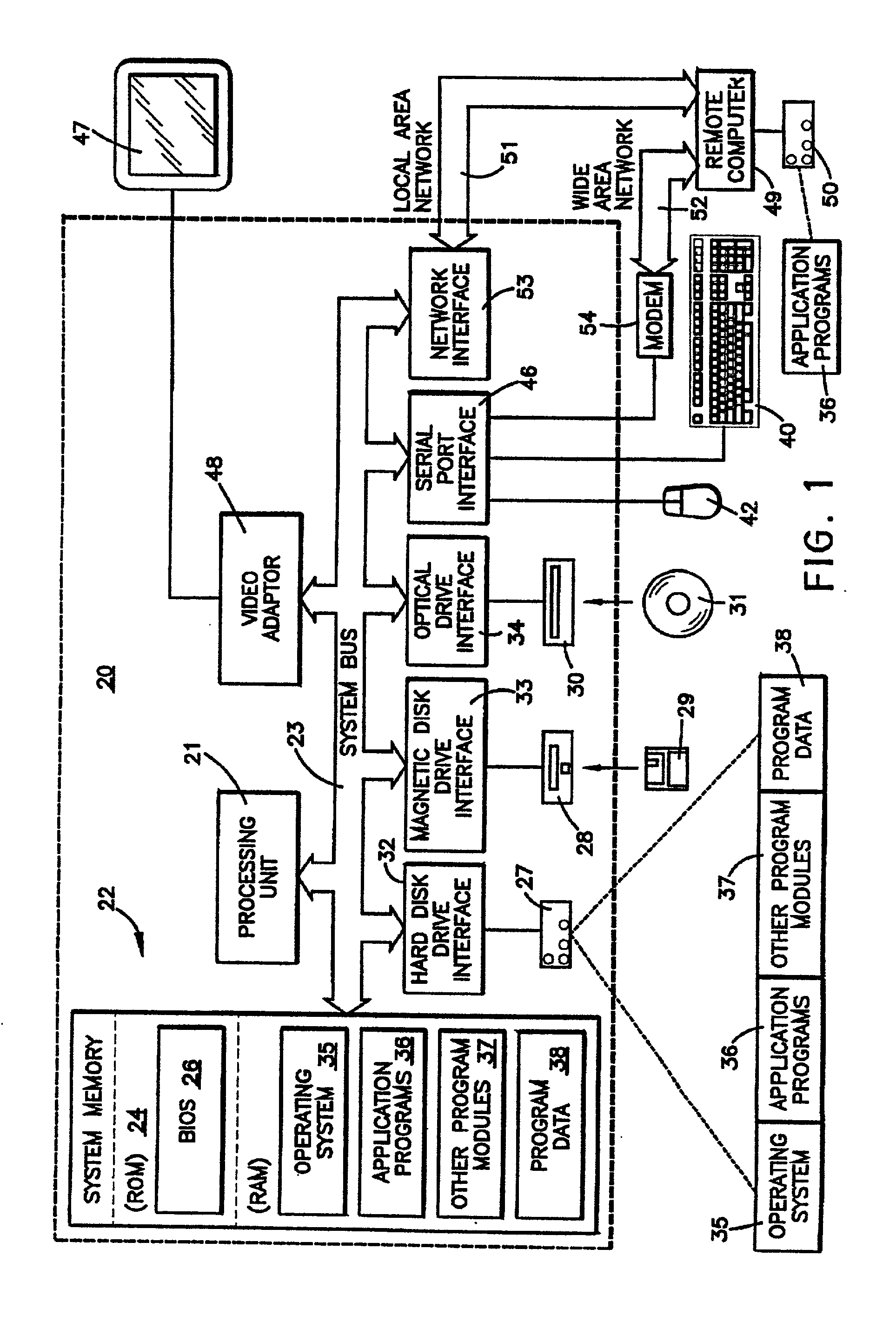

The present invention provides a semiconductor processing device (800) including a tool (802) having one or more sensors, a primary data communication port (804) and a secondary data communication port (806). A sensor data acquisition subsystem (808) acquires sensor data from the tool via the secondary port (806). The data acquisition subsystem (808) acquires MES operation messages via the primary port (804). Sensor data are communicated to a sensor processing unit (828) of a sensor data processing subsystem (810). The sensor processing unit (828) processes and analyzes the sensor data. Additionally, the processing unit (828) can be adapted for making product or processing related decisions, for example activating an alarm if the process is not operating within control limits. In another embodiment, the present invention provides a method and apparatus for processing data from a wafer fab facility (1000) including a plurality of tools (1004–1010) each having a primary data communication port (1012–1018) and a secondary data communication port (1042–1048).

Owner:APPLIED MATERIALS INC

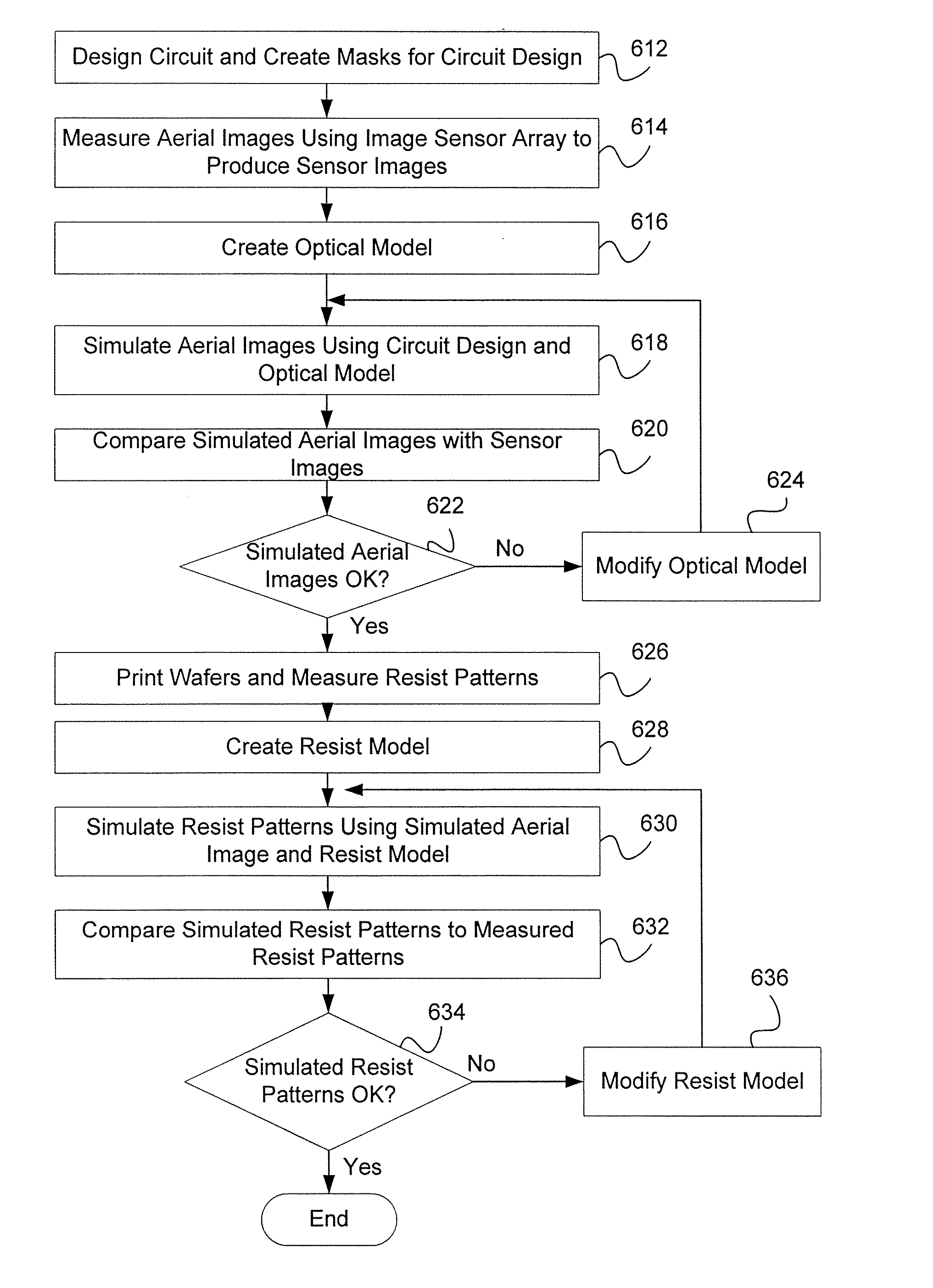

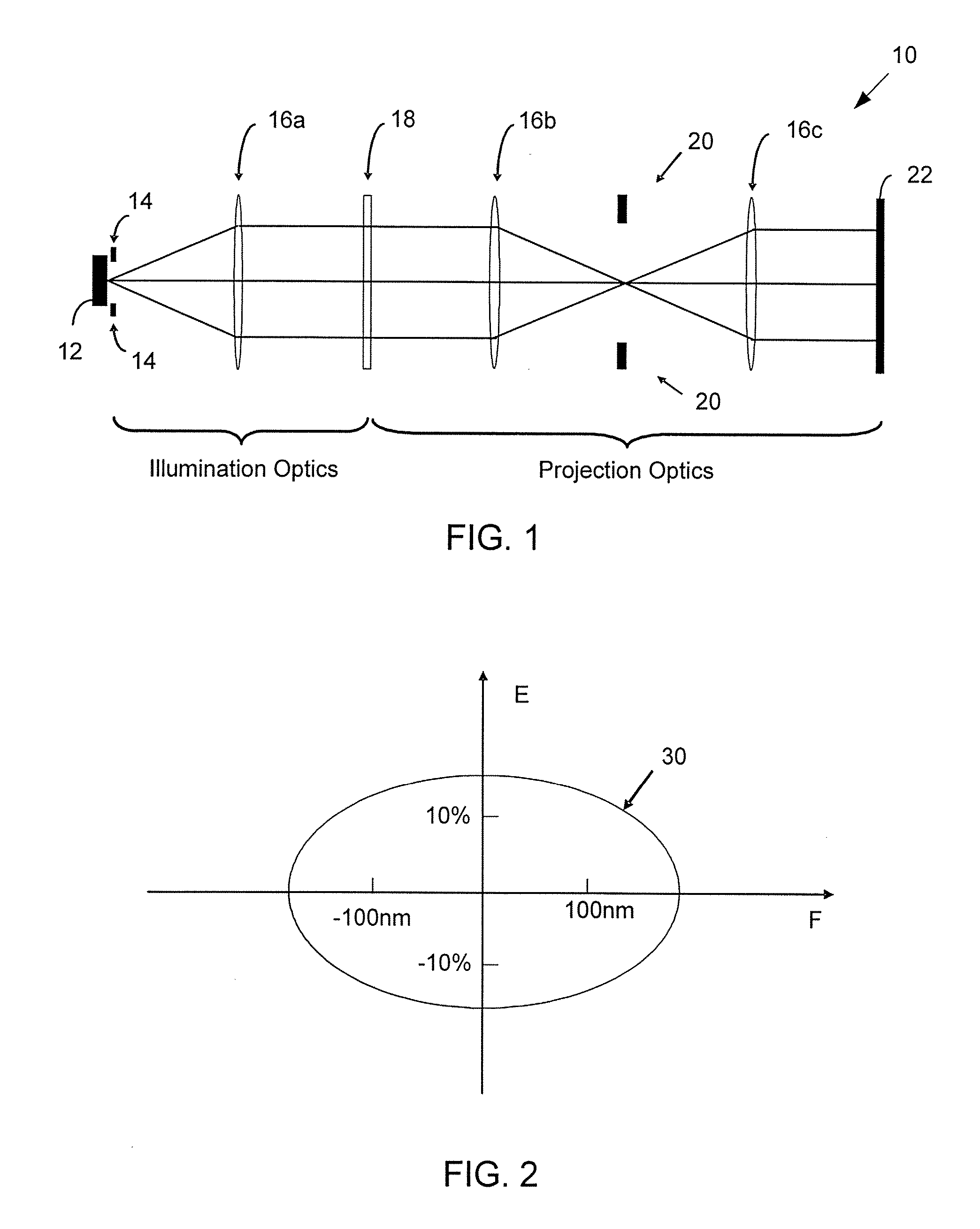

Method for lithography model calibration

ActiveUS20070032896A1Easy CalibrationImprove predictabilityPhotomechanical apparatusCalibration apparatusLithography processLithographic artist

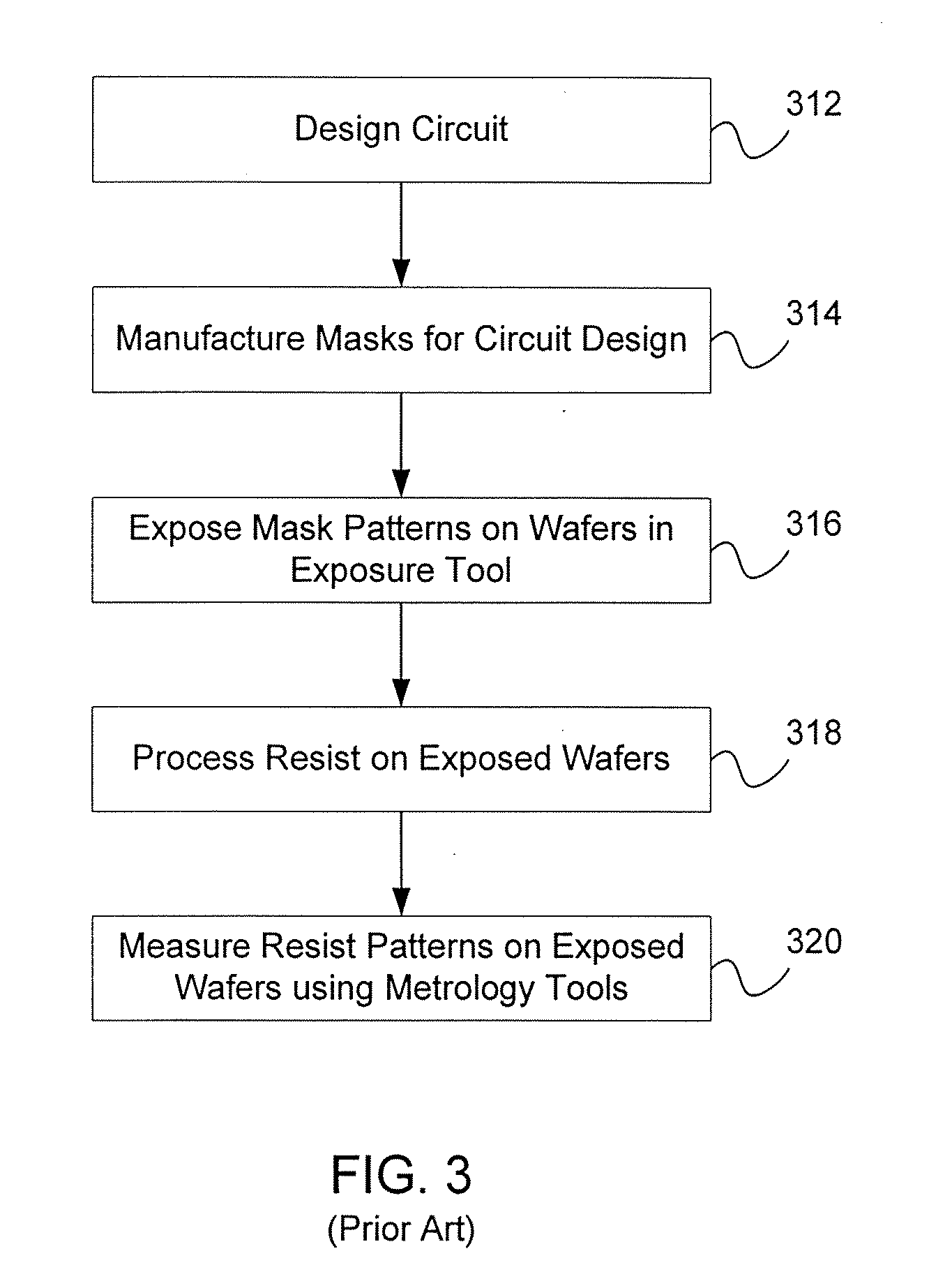

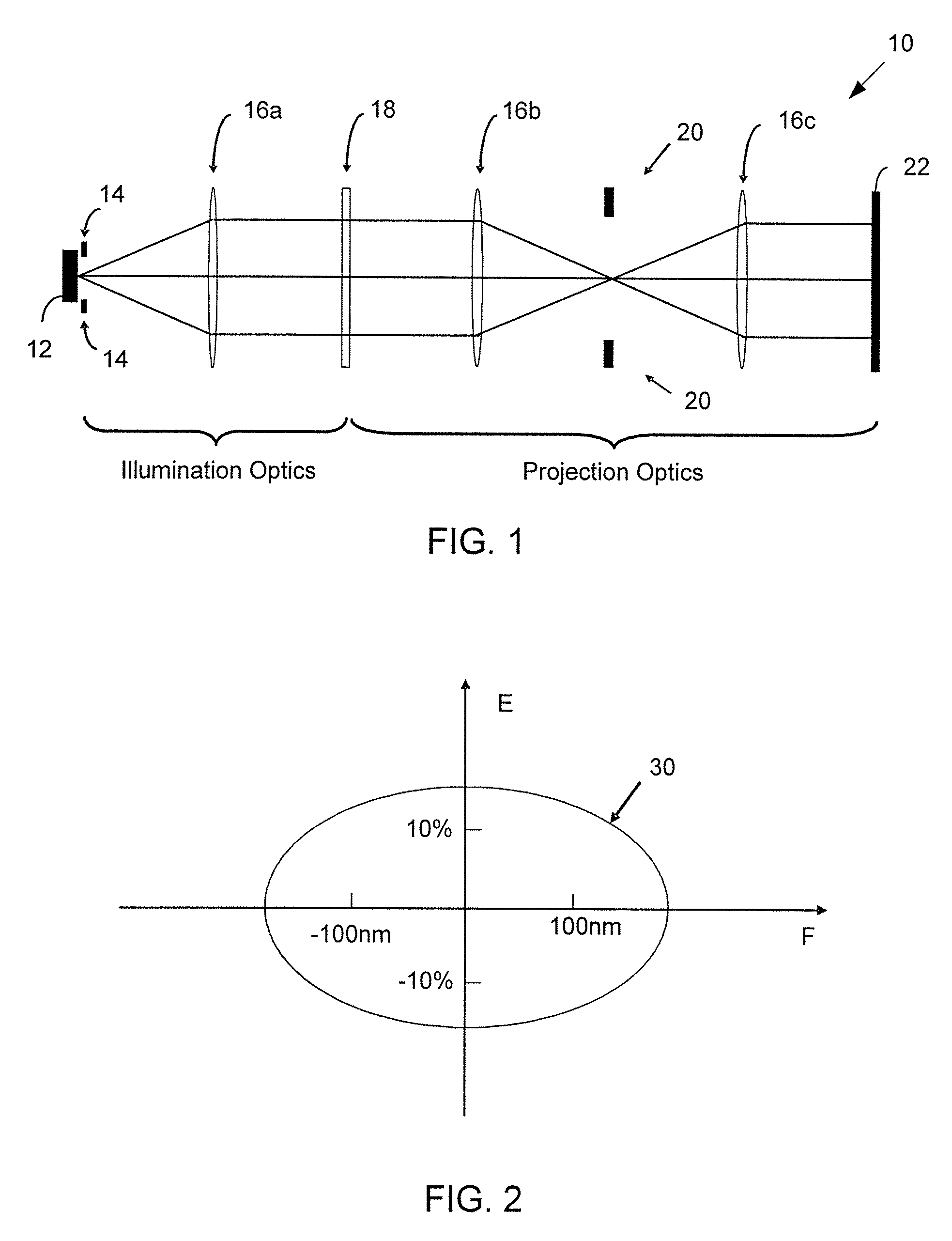

A method for separately calibrating an optical model and a resist model of lithography process using information derived from in-situ aerial image measurements to improve the calibration of both the optical model and the resist model components of the lithography simulation model. Aerial images produced by an exposure tool are measured using an image sensor array loaded into the exposure tool. Multiple embodiments of measuring aerial image information and using the measured aerial image information to calibrate the optical model and the resist model are disclosed. The method of the invention creates more accurate and separable optical and resist models, leading to better predictability of the pattern transfer process from mask to wafer, more accurate verification of circuit patterns and how they will actually print in production, and more accurate model-based process control in the wafer fabrication facility.

Owner:ASML NETHERLANDS BV

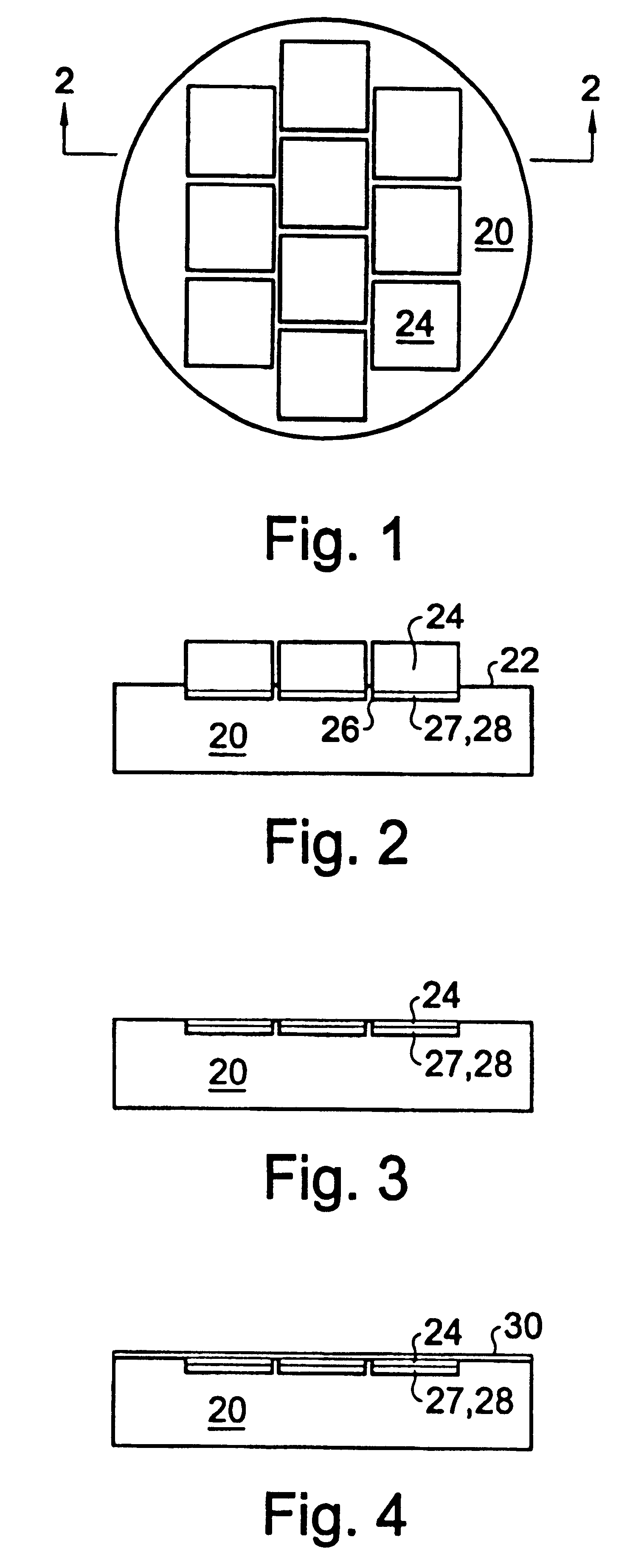

Semiconductor light emitting device, light emitting module and lighting apparatus

ActiveUS20060180818A1Reduce color unevennessImprove manufacturing productivityPlanar light sourcesLight source combinationsLight equipmentLed array

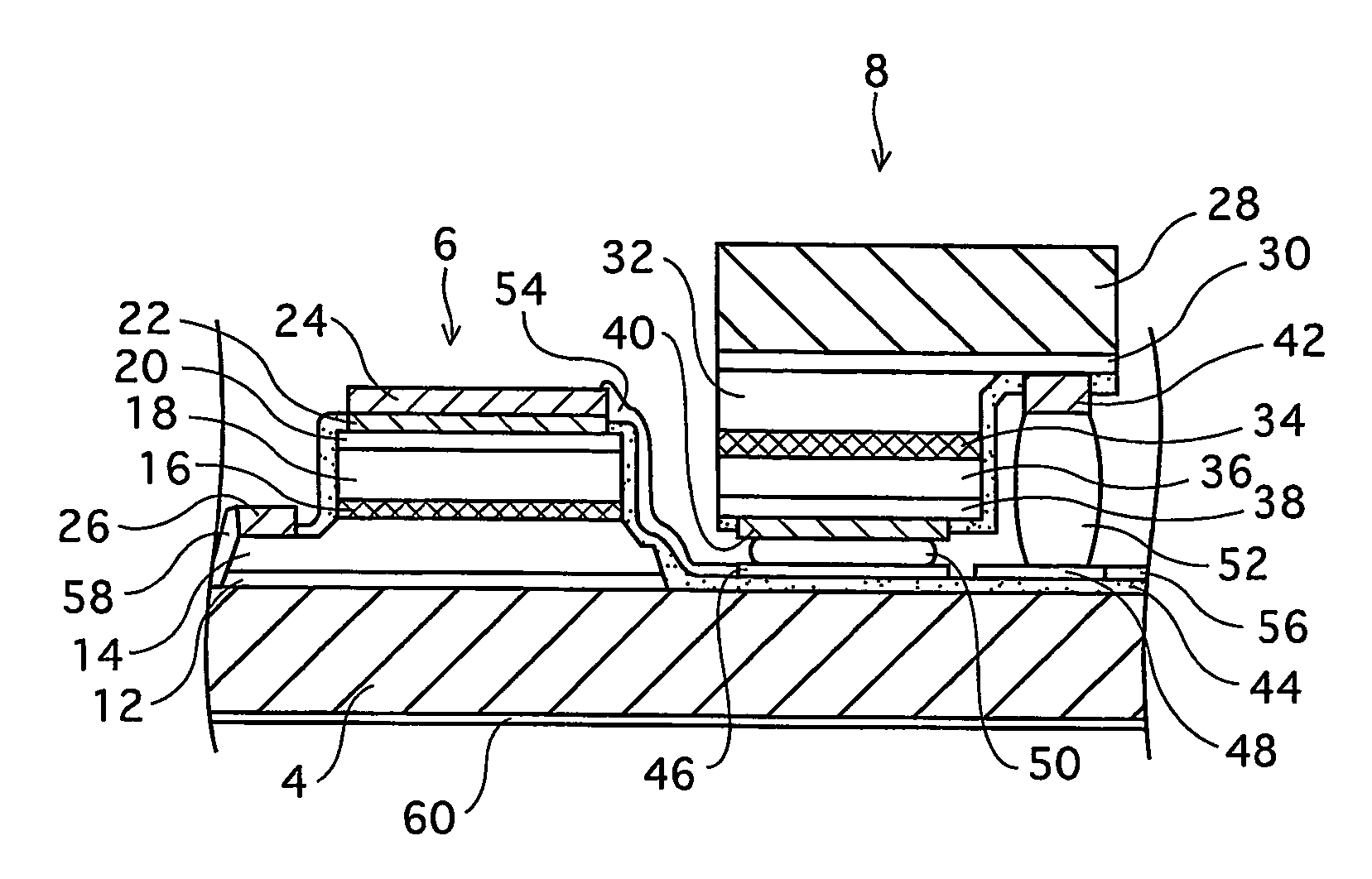

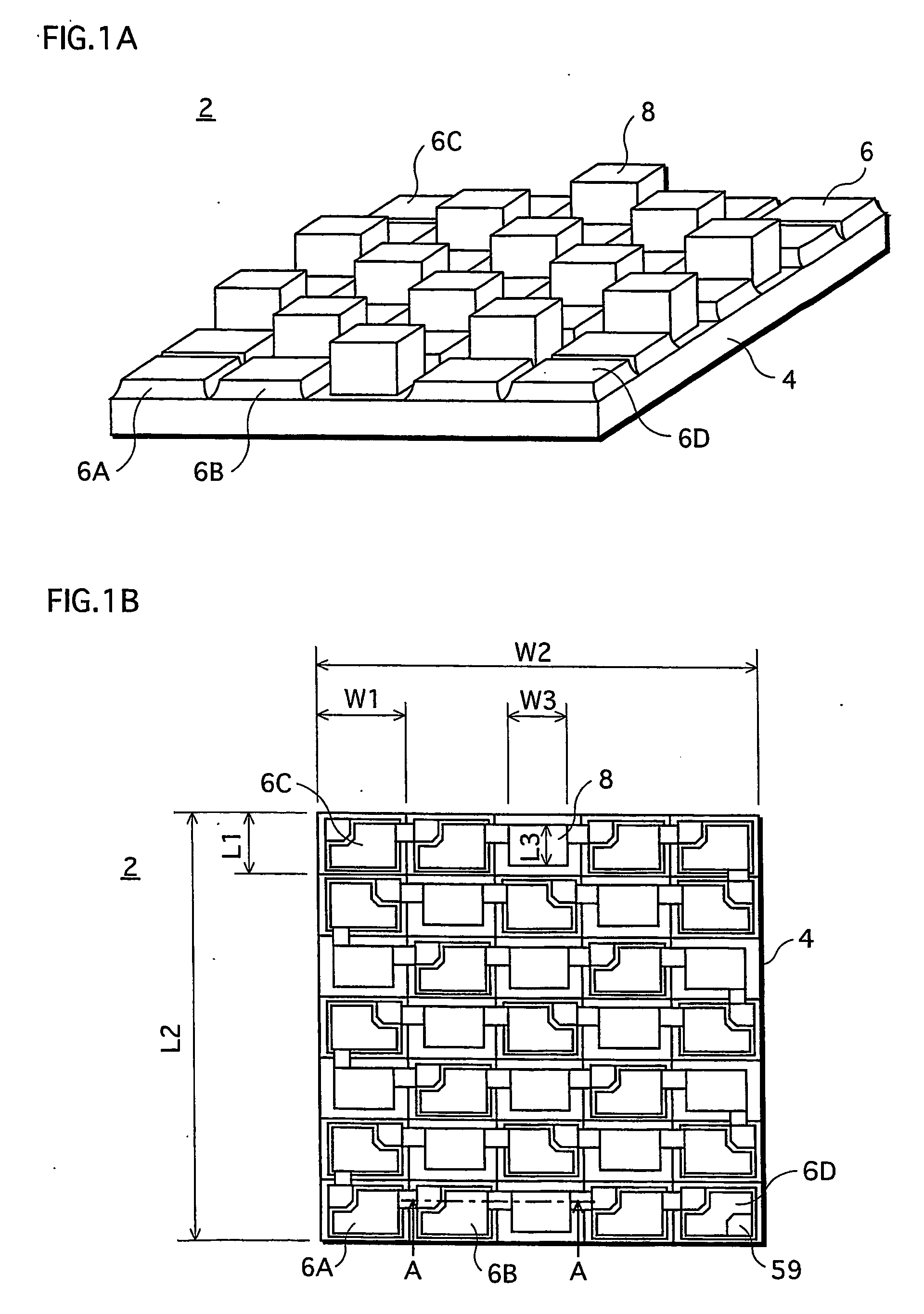

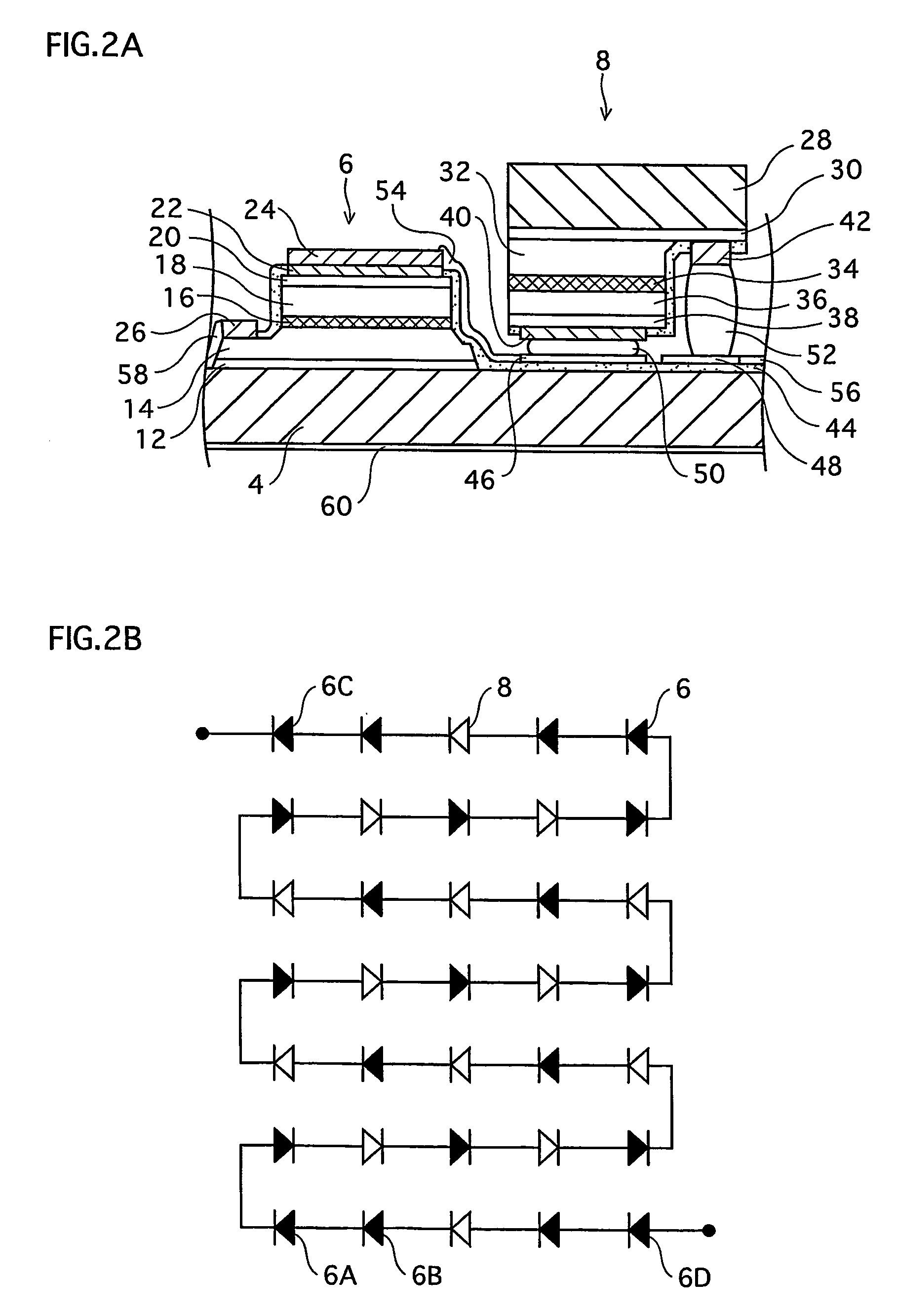

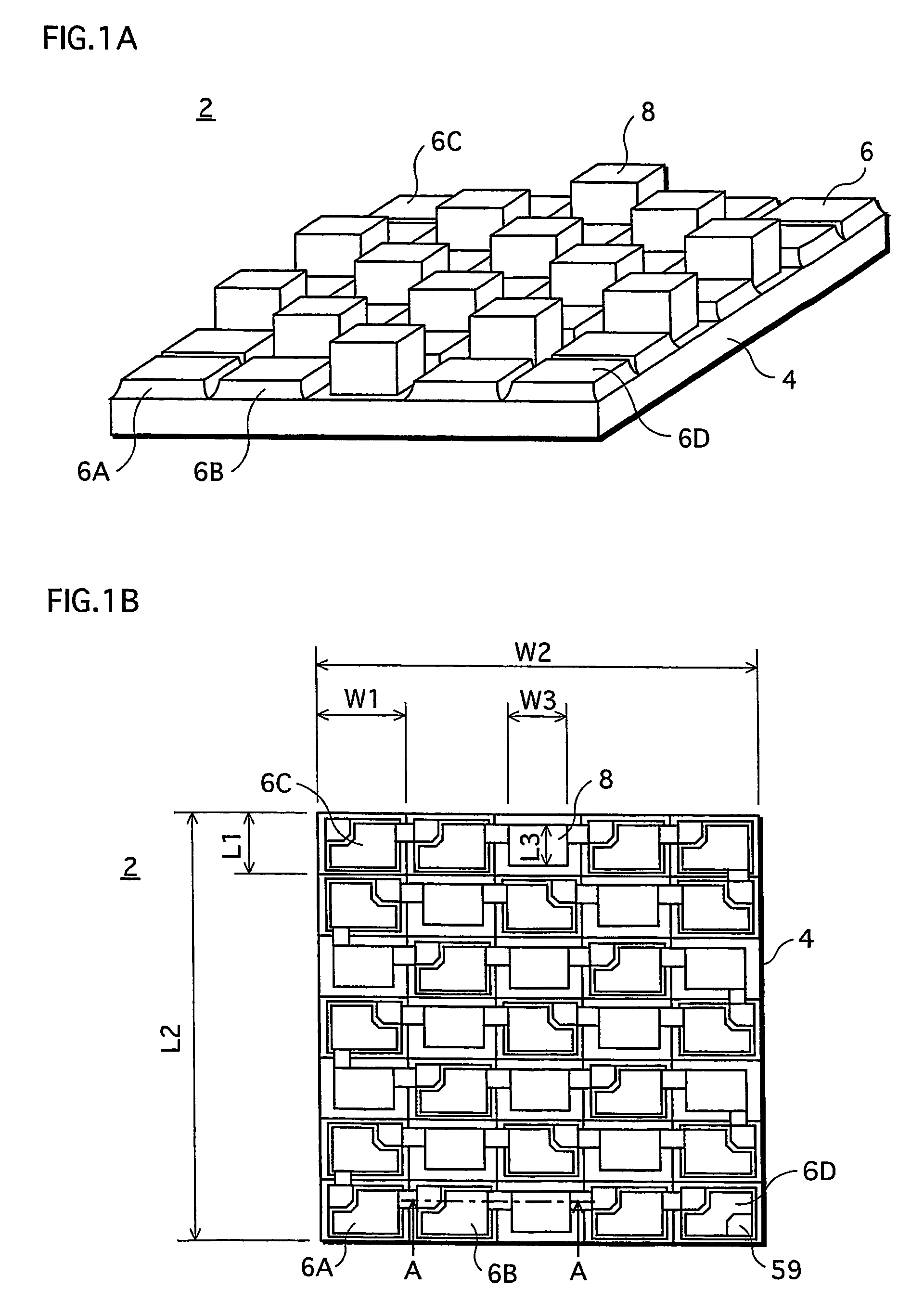

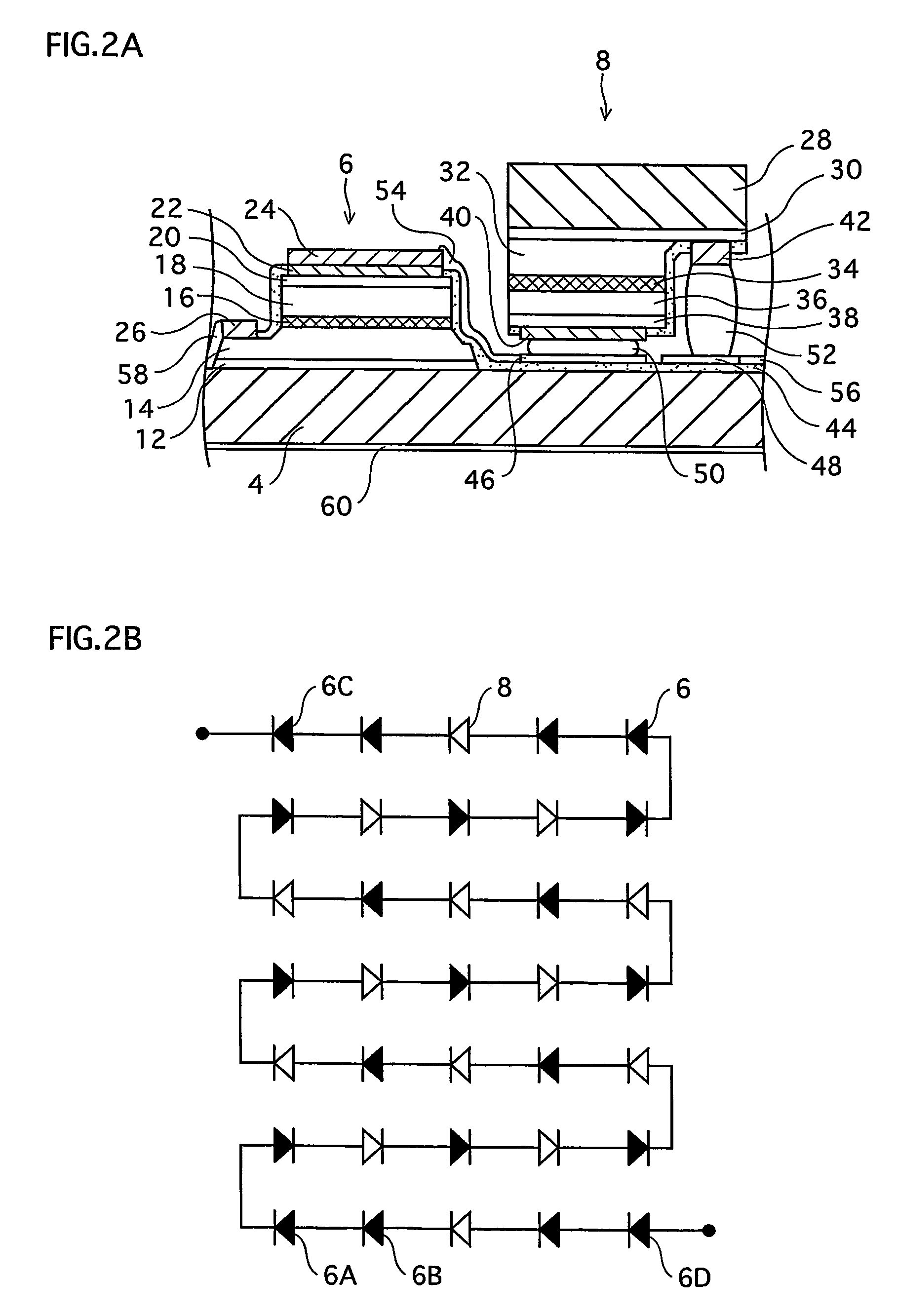

An LED array chip (2) includes blue LEDs (6) and red LEDs (8). The blue LEDs (6) are formed by epitaxial growth on an SiC substrate (4). Bonding pads (46 and 48) are formed on the SiC substrate (4) in a wafer fabrication process. The red LEDs (8) are separately manufactured from the blue LEDs (6), and flip-chip mounted on the bonding pads (46 and 48) formed on the SiC substrate.

Owner:PANASONIC CORP

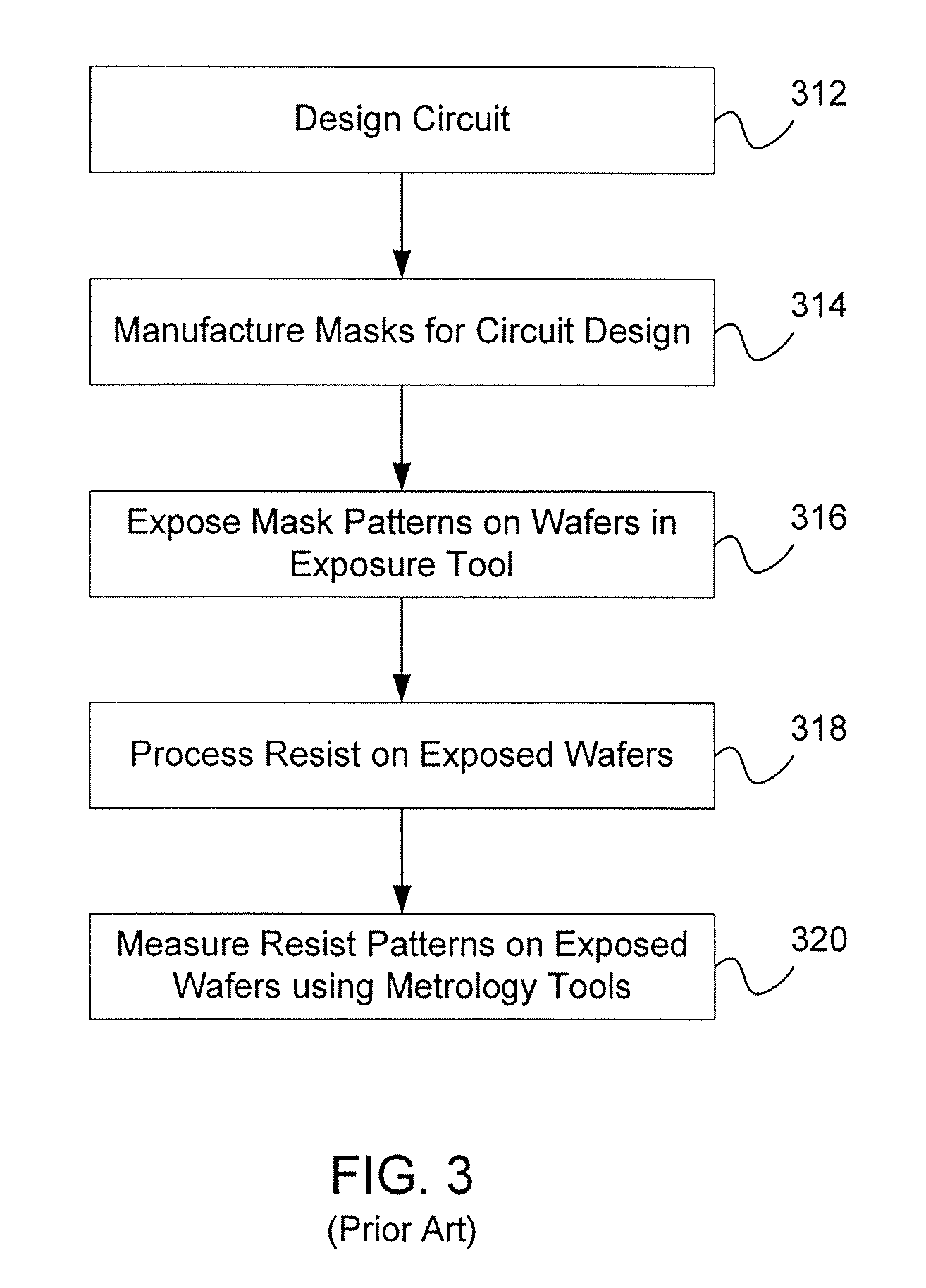

Computer-implemented methods, processors, and systems for creating a wafer fabrication process

InactiveUS20060161452A1Market predictionsDetecting faulty computer hardwareWafer fabricationEngineering

Computer-implemented methods, processors, and systems for creating a wafer fabrication process are provided. One computer-implemented method includes determining individual error budgets for different parameters of the wafer fabrication process based on an overall error budget for the wafer fabrication process and simulated images that illustrate how reticle design data will be printed on a wafer at different values of the different parameters. The method also includes creating the wafer fabrication process based on the overall error budget and the individual error budgets.

Owner:KLA TENCOR TECH CORP

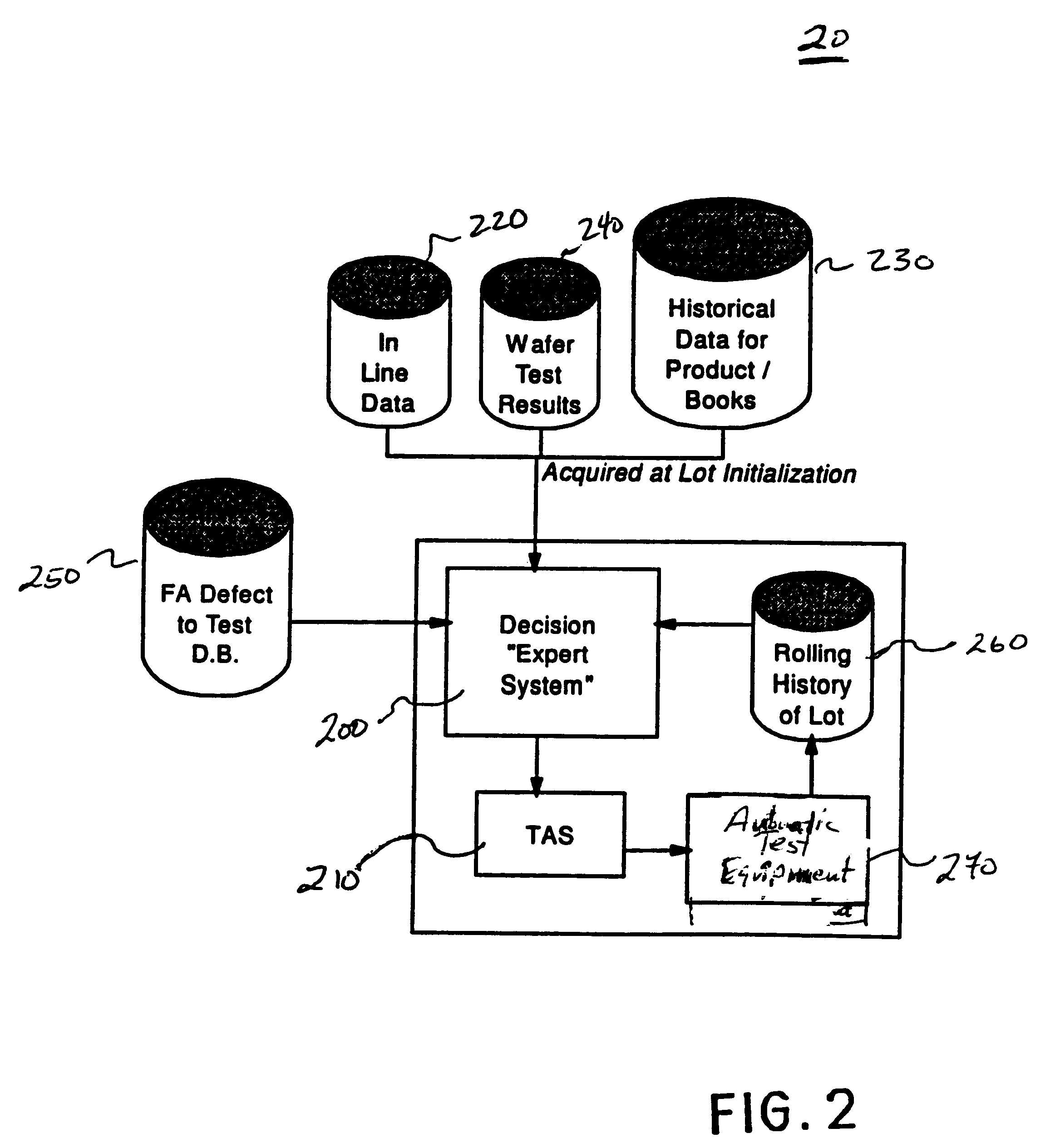

Method for test optimization using historical and actual fabrication test data

InactiveUS6618682B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingQuality levelWafer fabrication

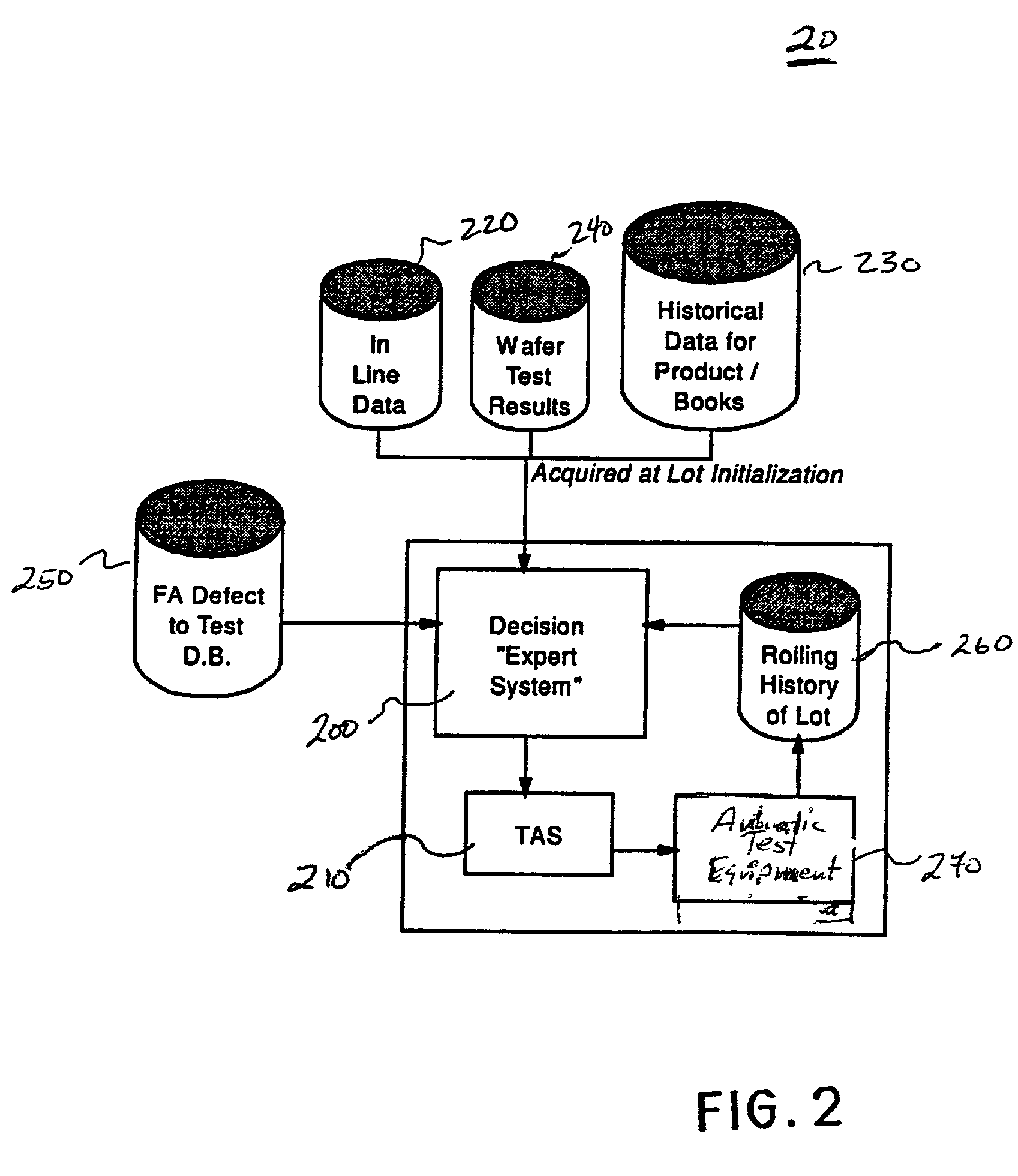

A method and system are provided that minimize wafer or package level test time without adversely impacting yields in downstream manufacturing processes or degrading outgoing quality levels. The method provides optimization by determining, a priority, the most effective set of tests for a given lot or wafer. The invention implements a method using a processor-based system involving the integration of multiple sources of data that include: historical and realtime, product specific and lot specific, from wafer fabrication data (i.e., process measurements, defect inspections, and parametric testing), product qualification test results, physical failure analysis results and manufacturing functional test results. These various forms of data are used to determine an optimal set of tests to run using a test application sequence, on a given product to optimize test time with minimum risk to yield or product quality.

Owner:CADENCE DESIGN SYST INC

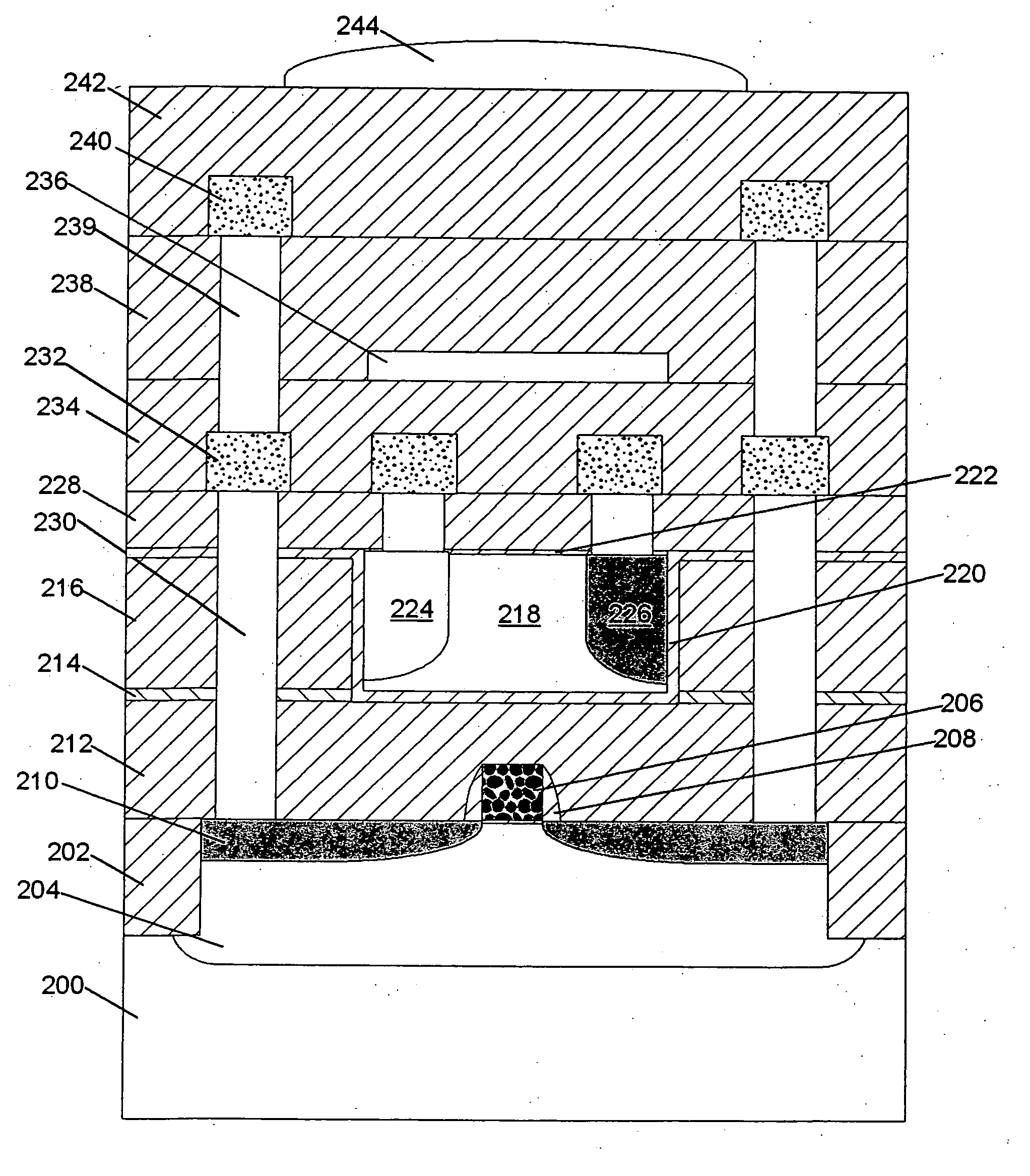

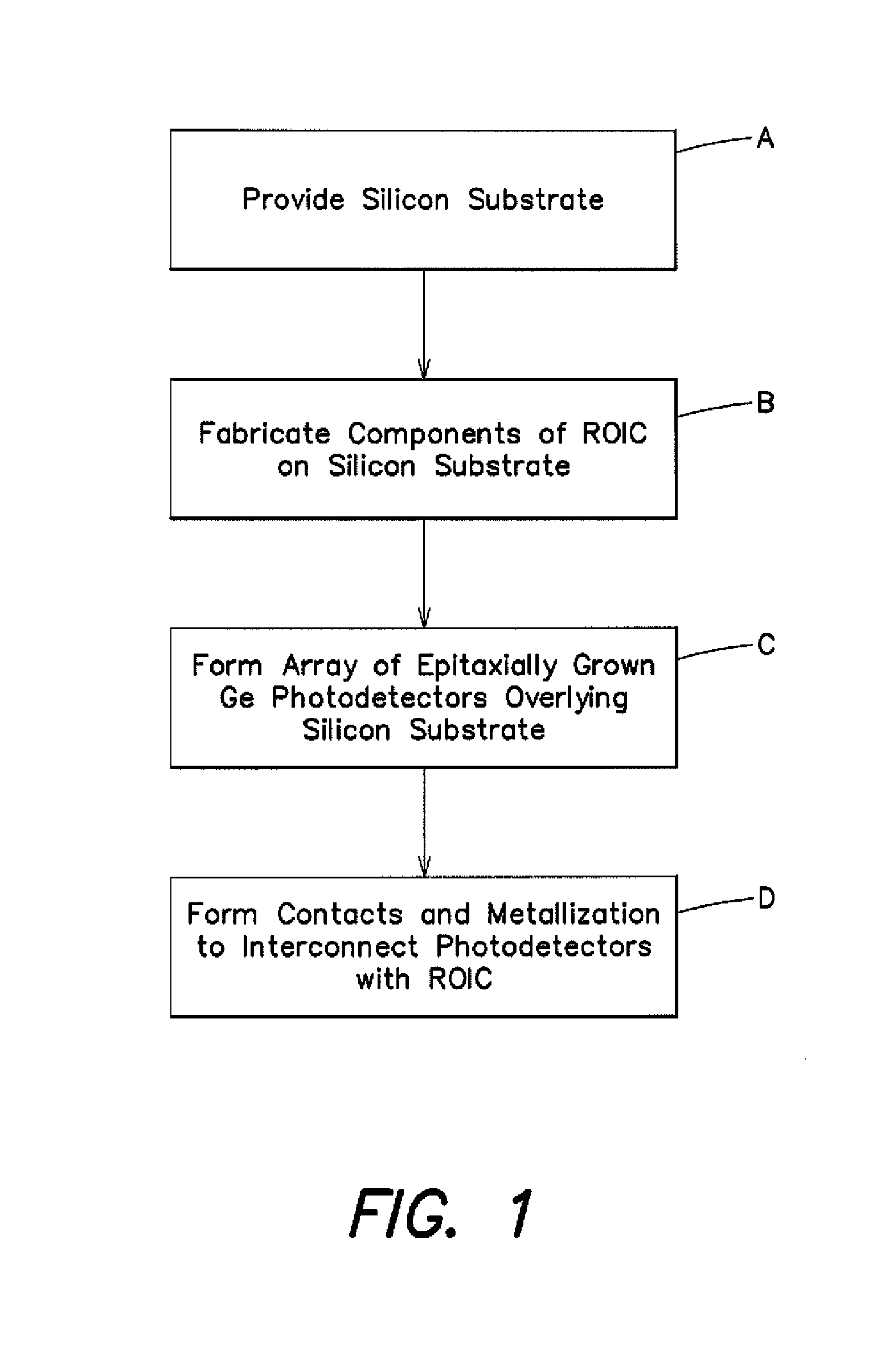

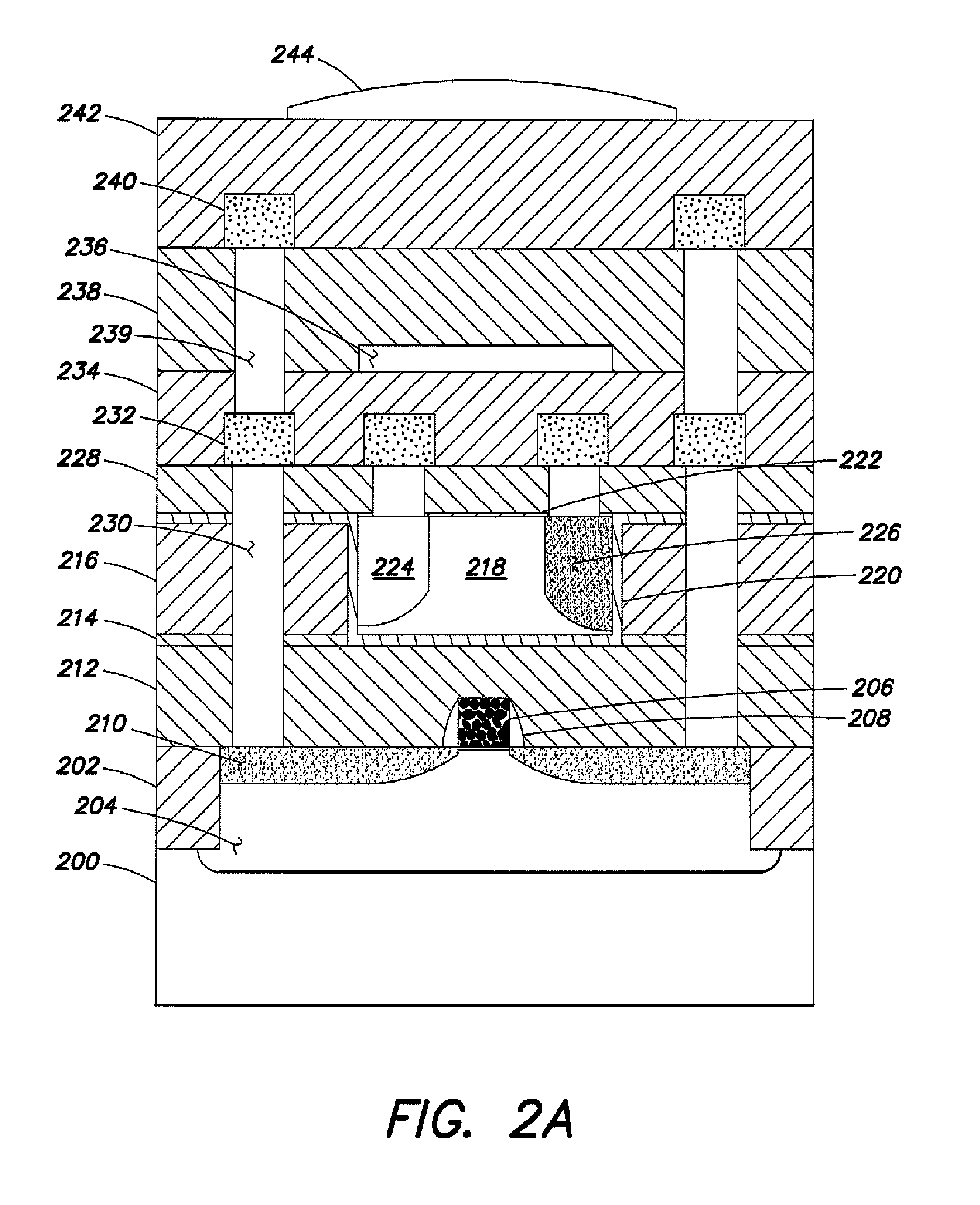

Image sensor comprising isolated germanium photodetectors integrated with a silicon substrate and silicon circuitry

ActiveUS20050205954A1Minimizes signal degradationAcceleration measurement using interia forcesSolid-state devicesPhotovoltaic detectorsPhotodetector

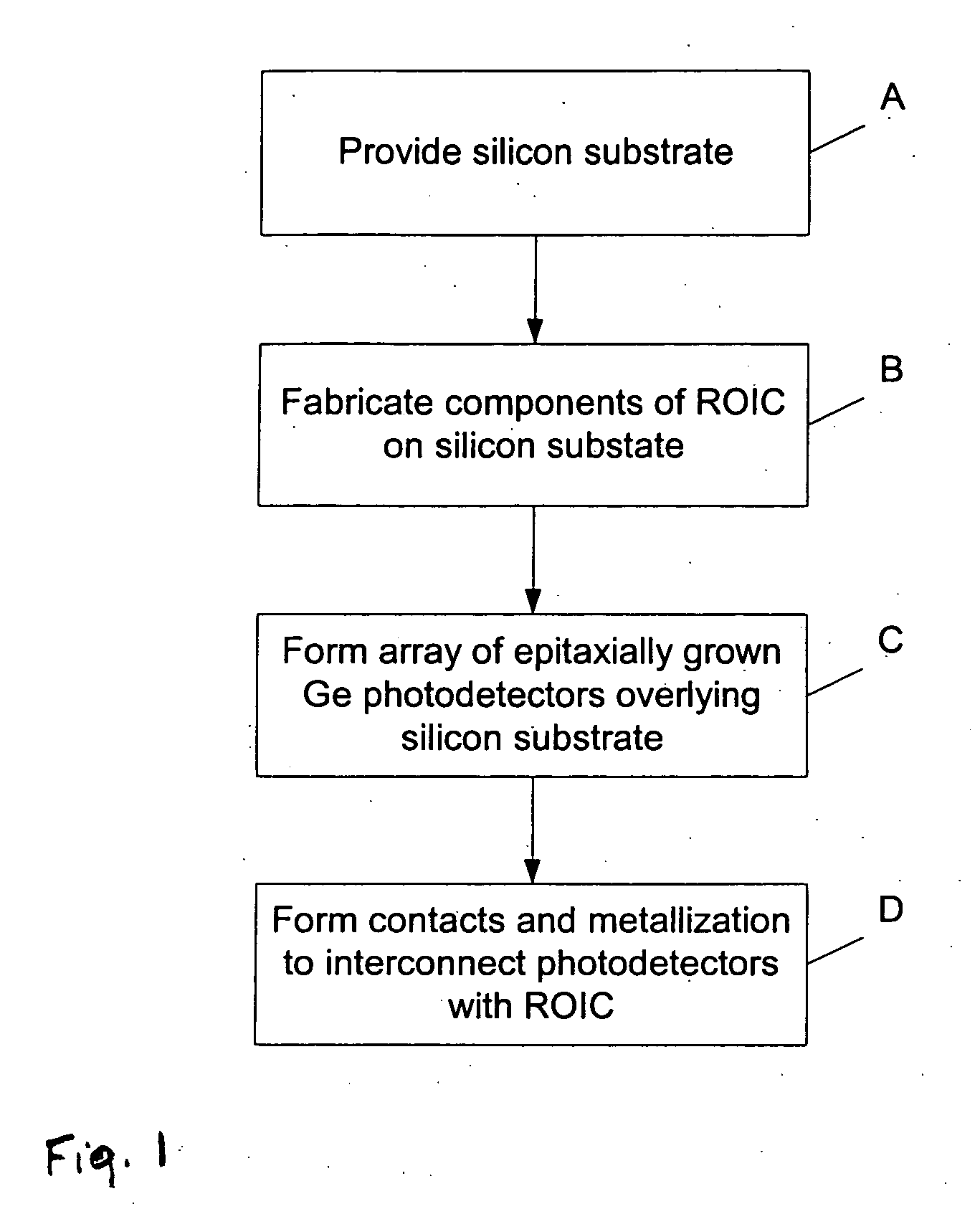

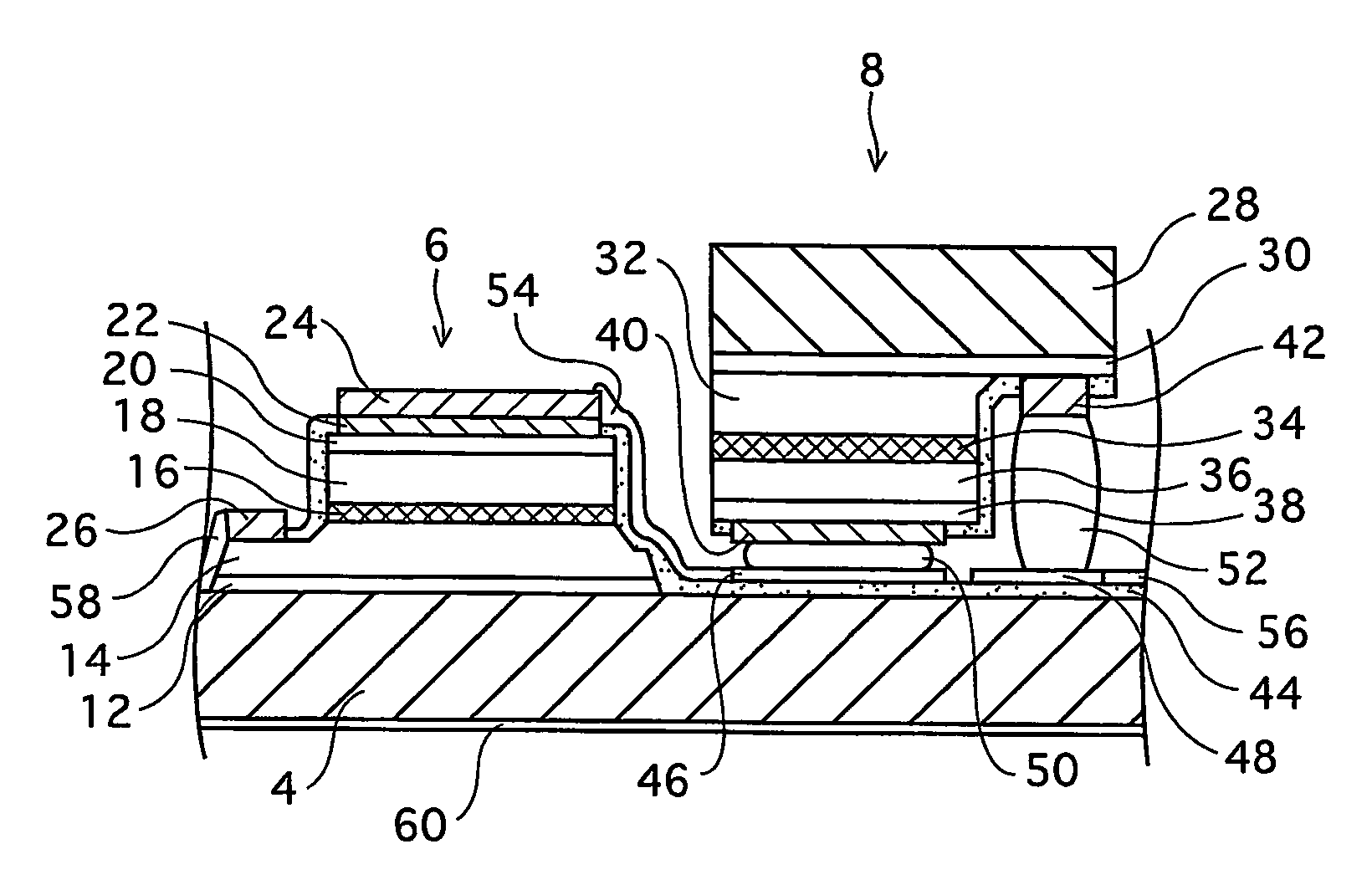

In accordance with the invention, an improved image sensor comprises an array of germanium photosensitive elements integrated with a silicon substrate and integrated with silicon readout circuits. The silicon transistors are formed first on a silicon substrate, using well known silicon wafer fabrication techniques. The germanium elements are subsequently formed overlying the silicon by epitaxial growth. The germanium elements are advantageously grown within surface openings of a dielectric cladding. Wafer fabrication techniques are applied to the elements to form isolated germanium photodiodes. Since temperatures needed for germanium processing are lower than those for silicon processing, the formation of the germanium devices need not affect the previously formed silicon devices. Insulating and metallic layers are then deposited and patterned to interconnect the silicon devices and to connect the germanium devices to the silicon circuits. The germanium elements are thus integrated to the silicon by epitaxial growth and integrated to the silicon circuitry by common metal layers.

Owner:INFRARED NEWCO

Semiconductor light emitting device, light emitting module and lighting apparatus

ActiveUS7473934B2Reduce color unevennessImprove manufacturing productivityPlanar light sourcesLight source combinationsLight equipmentLed array

An LED array chip (2) includes blue LEDs (6) and red LEDs (8). The blue LEDs (6) are formed by epitaxial growth on an SiC substrate (4). Bonding pads (46 and 48) are formed on the SiC substrate (4) in a wafer fabrication process. The red LEDs (8) are separately manufactured from the blue LEDs (6), and flip-chip mounted on the bonding pads (46 and 48) formed on the SiC substrate.

Owner:PANASONIC CORP

Method for test optimization using historical and actual fabrication test data

InactiveUS20020155628A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingQuality levelWafer fabrication

A method and system are provided that minimize wafer or package level test time without adversely impacting yields in downstream manufacturing processes or degrading outgoing quality levels. The method provides optimization by determining, a priority, the most effective set of tests for a given lot or wafer. The invention implements a method using a processor-based system involving the integration of multiple sources of data that include: historical and realtime, product specific and lot specific, from wafer fabrication data (i.e., process measurements, defect inspections, and parametric testing), product qualification test results, physical failure analysis results and manufacturing functional test results. These various forms of data are used to determine an optimal set of tests to run using a test application sequence, on a given product to optimize test time with minimum risk to yield or product quality.

Owner:CADENCE DESIGN SYST INC

Method for lithography model calibration

ActiveUS7488933B2More accurate and separable optical and resist modelsImprove predictabilityPhotomechanical apparatusCalibration apparatusLithography processWafer fabrication

A method for separately calibrating an optical model and a resist model of lithography process using information derived from in-situ aerial image measurements to improve the calibration of both the optical model and the resist model components of the lithography simulation model. Aerial images produced by an exposure tool are measured using an image sensor array loaded into the exposure tool. Multiple embodiments of measuring aerial image information and using the measured aerial image information to calibrate the optical model and the resist model are disclosed. The method of the invention creates more accurate and separable optical and resist models, leading to better predictability of the pattern transfer process from mask to wafer, more accurate verification of circuit patterns and how they will actually print in production, and more accurate model-based process control in the wafer fabrication facility.

Owner:ASML NETHERLANDS BV

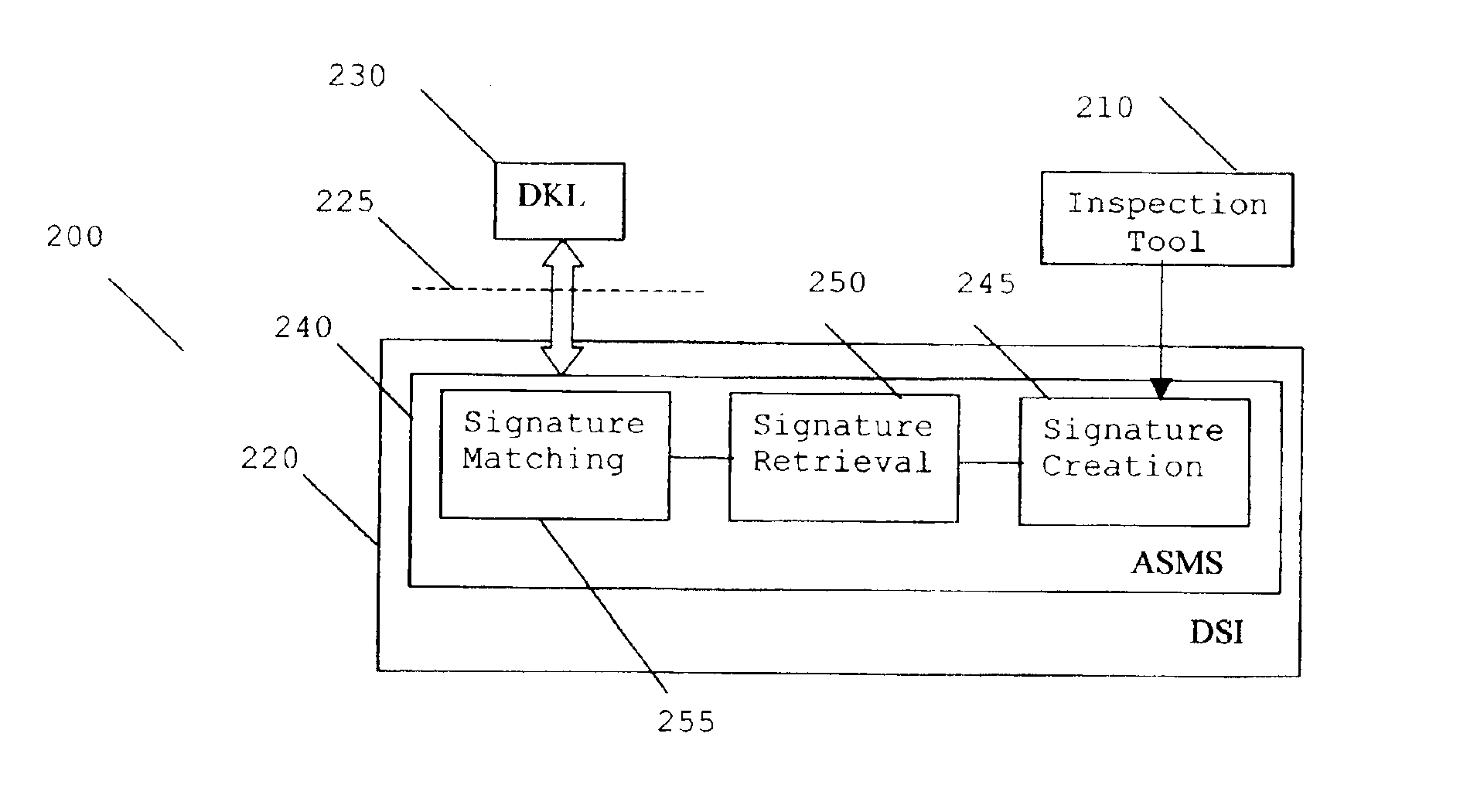

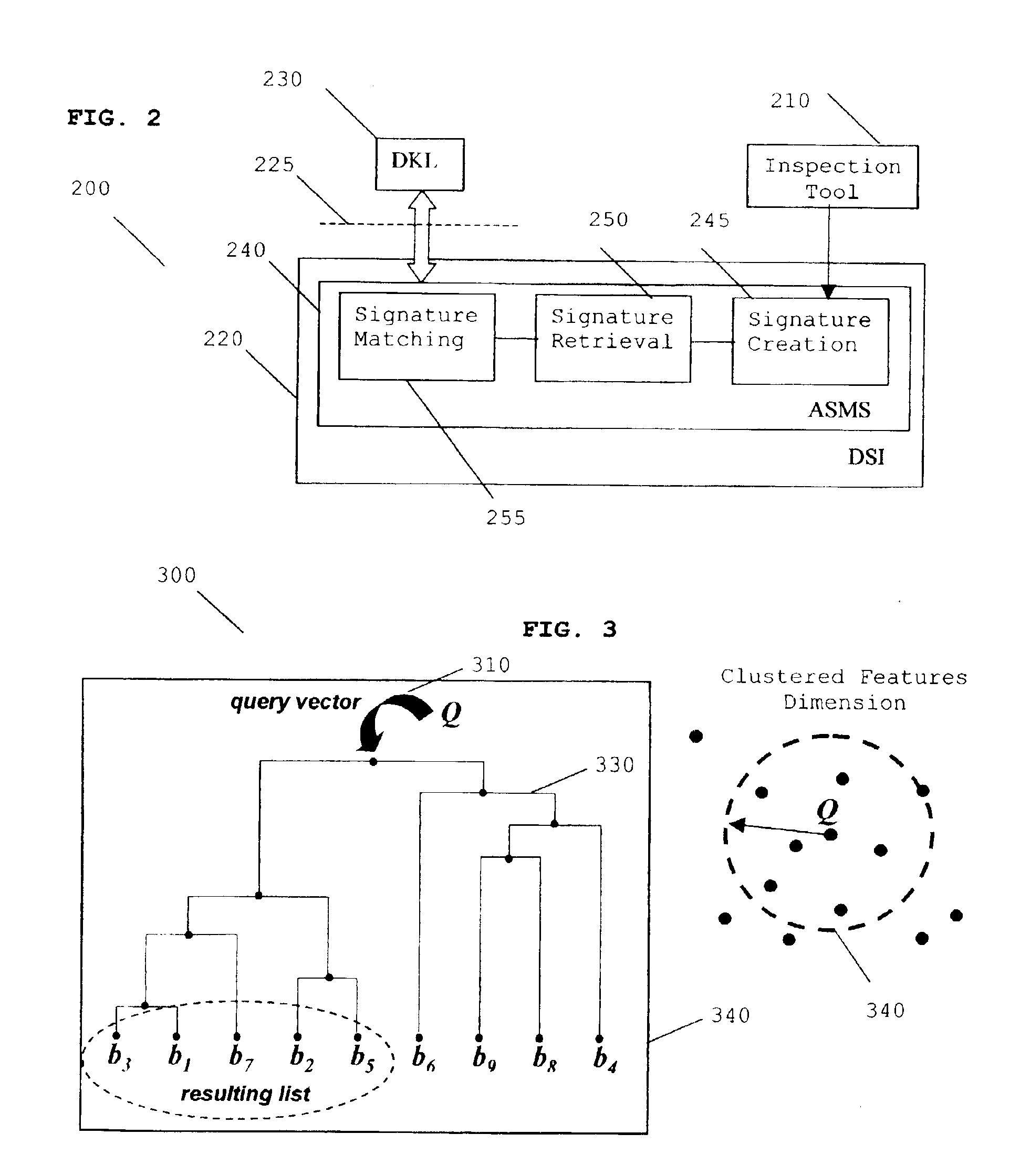

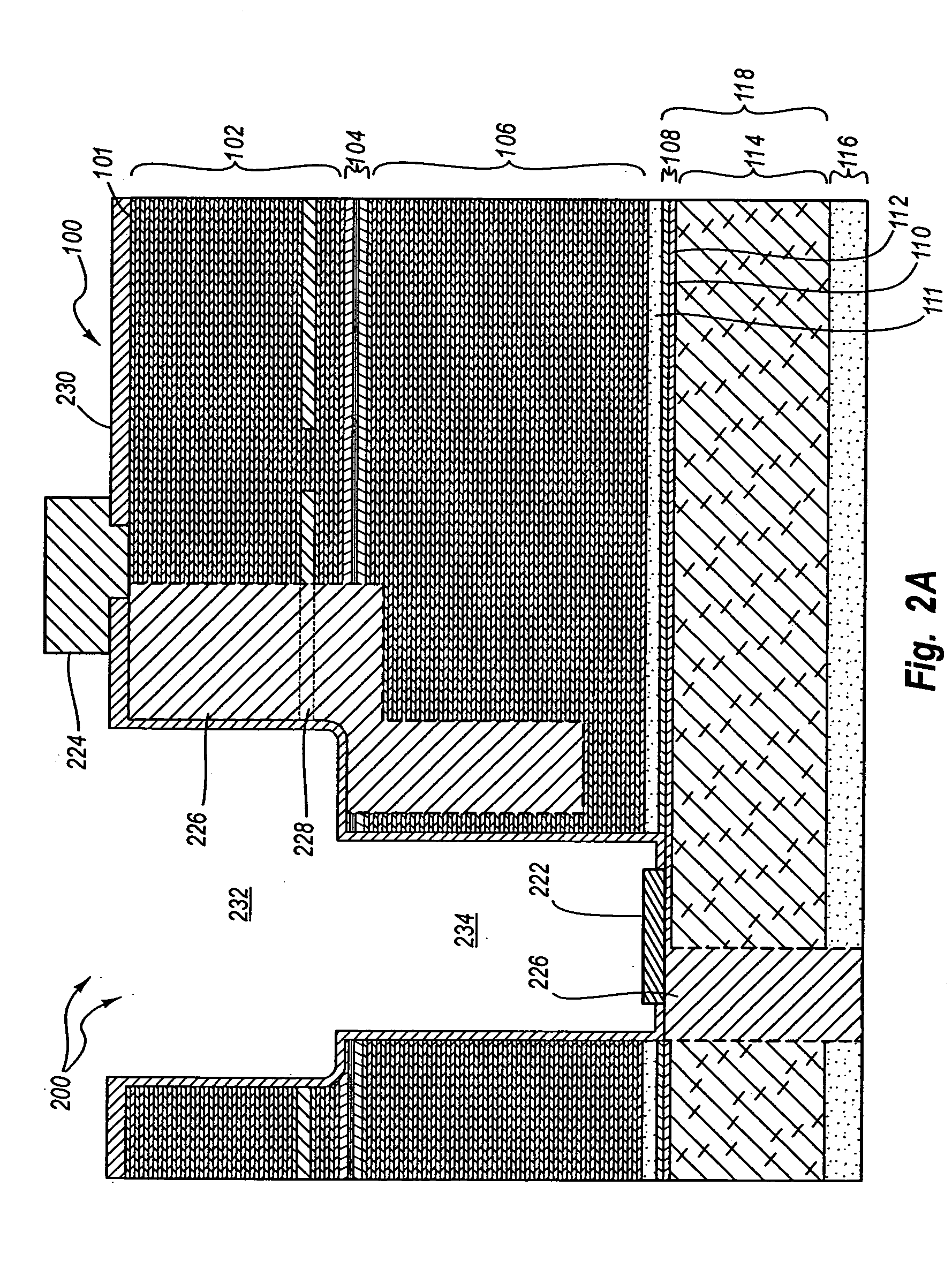

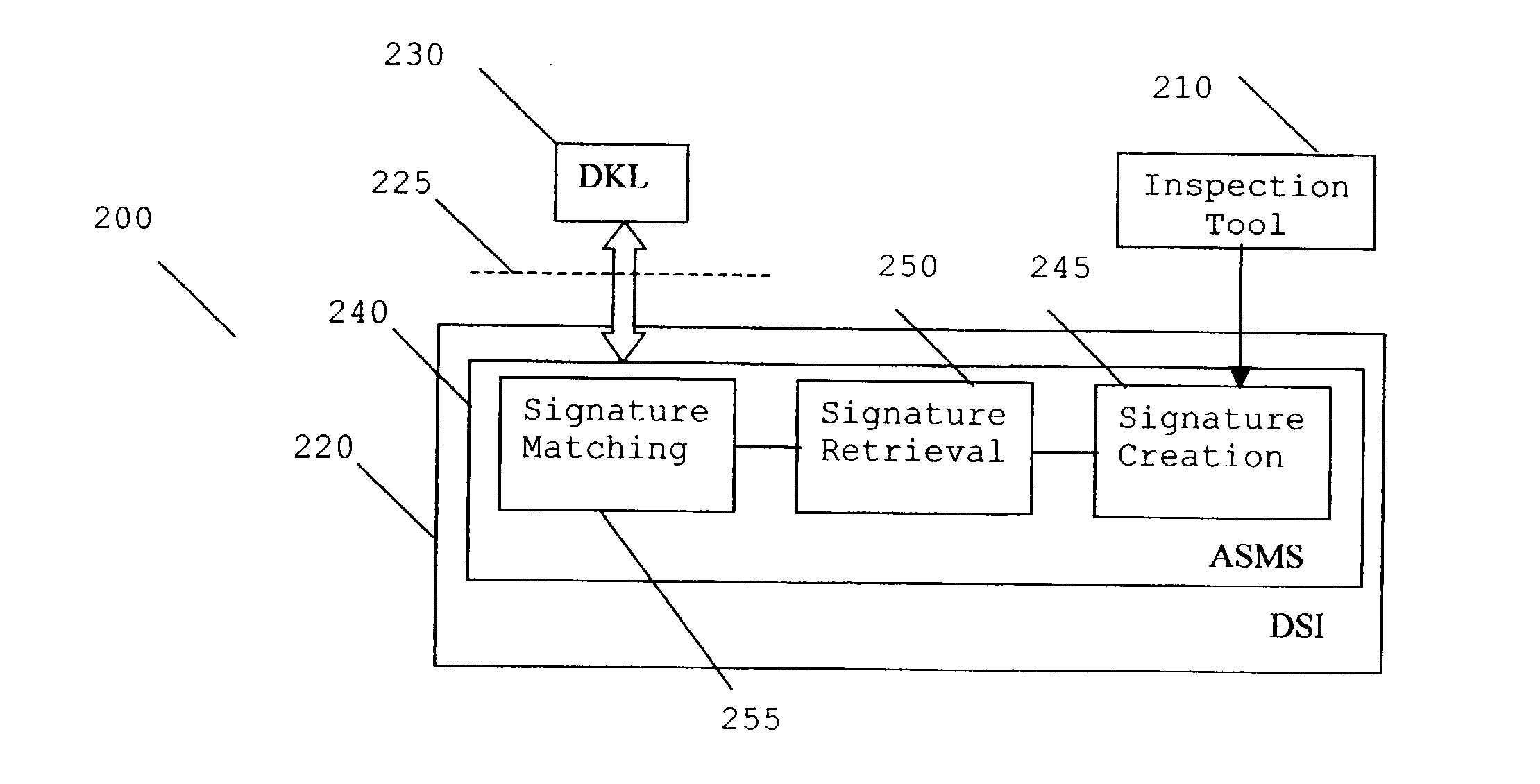

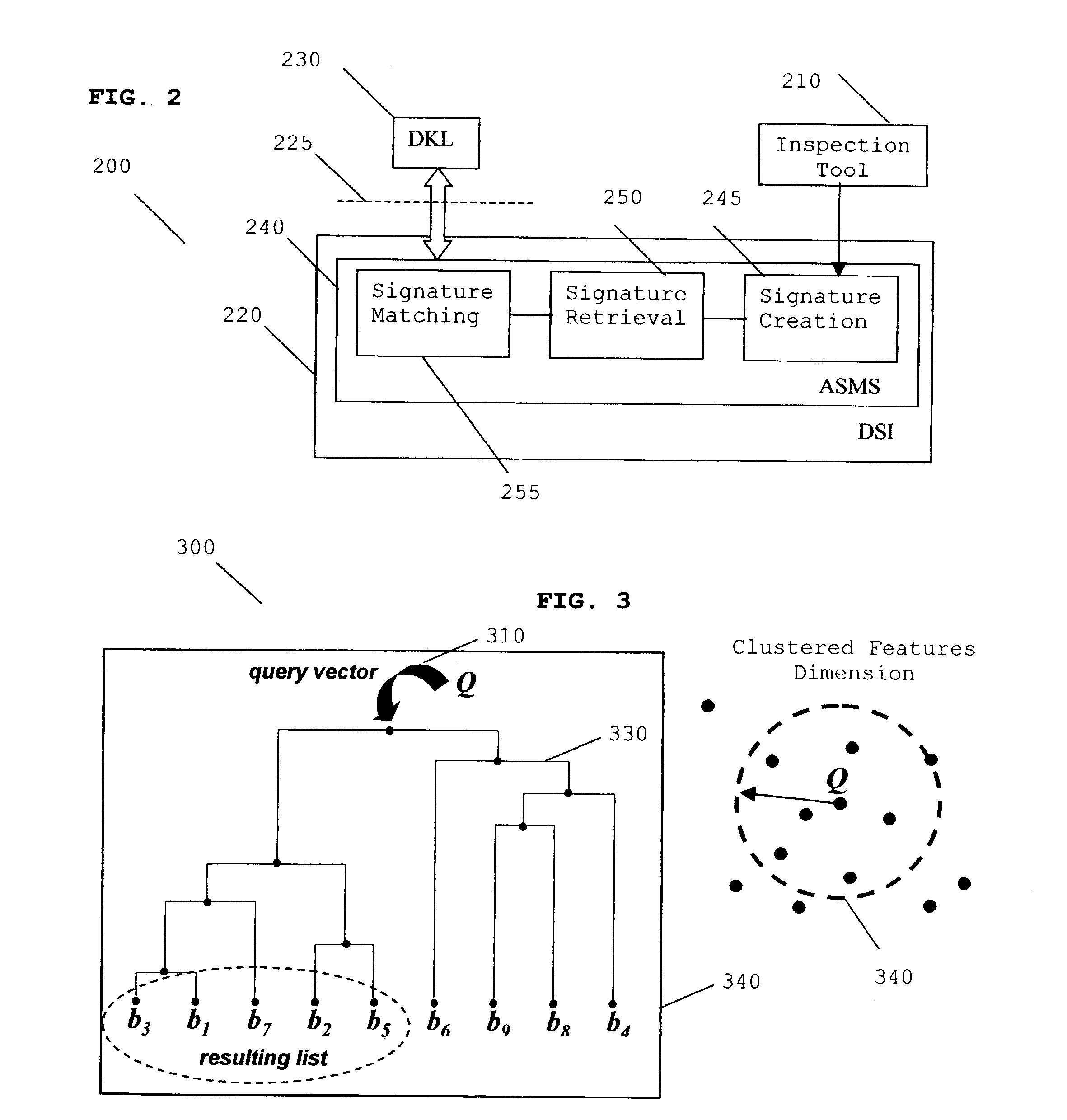

System to identify a wafer manufacturing problem and method therefor

InactiveUS6885977B2Semiconductor/solid-state device testing/measurementNuclear monitoringRoot causeComputer science

A method (400) for determining a response to a wafer manufacturing process problem includes the steps of generating a wafer map signature (406) containing defect attributes to be identified and retrieving (410) one or more wafer map signatures from a database. The wafer map signature to be identified is matched (414) with the one or more wafer map signatures from the database in order to help find a root cause of a defect in a wafer manufacturing process.This provides at least the advantage that a signature matching capability allows an Operator to more accurately identify a root manufacturing cause of a wafer defect. Furthermore, instant feedback to the wafer manufacturing process can be provided to facilitate rapid correction of manufacturing errors.

Owner:APPLIED MATERIALS INC

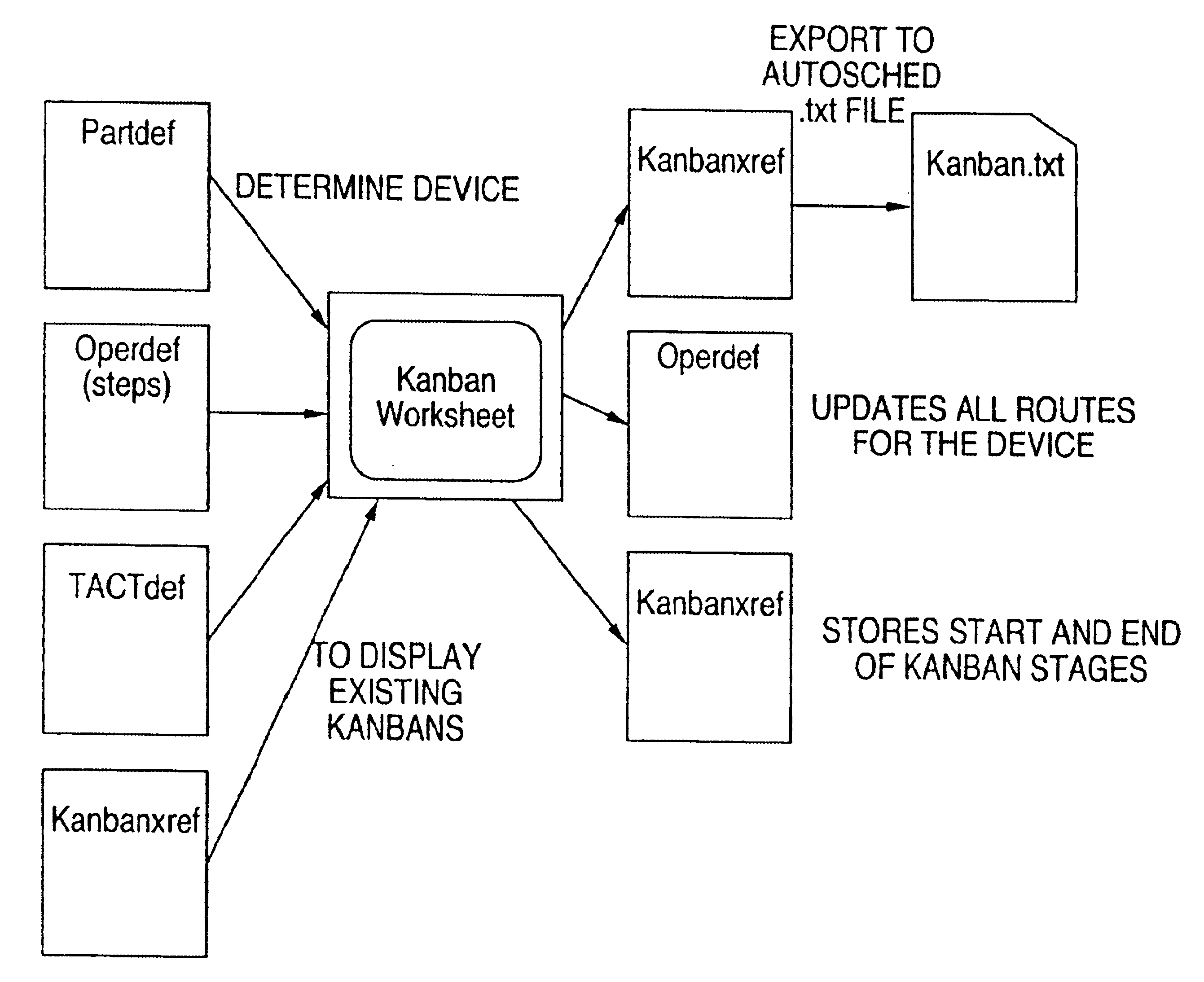

Integrated wafer fabrication production characterization and scheduling system

InactiveUS6889178B1Technology managementTotal factory controlManufacture execution systemWafer fabrication

An integrated wafer fab production scheduling and simulation system incorporates a manufacturing execution system with a scheduling system based on simulation. The integrated system provides manufacturers with a simulation tool integrated with the manufacturing execution system to evaluate proposed production control logic as a practical alternative to expensive experimentation on an actual production system. Furthermore, simulation models are used to create short-term dispatch schedules to steer daily manufacturing operations towards planned performance goals. Innovative features include integration of preventive maintenance scheduling, Kanban based WIP control, an integrated time standard database, and real time lot move updates.

Owner:SONY CORP +1

Image sensor comprising isolated germanium photodetectors integrated with a silicon substrate and silicon circuitry

ActiveUS7453129B2Minimizes signal degradationAcceleration measurement using interia forcesSolid-state devicesPhotovoltaic detectorsManufacturing technology

In accordance with the invention, an improved image sensor comprises an array of germanium photosensitive elements integrated with a silicon substrate and integrated with silicon readout circuits. The silicon transistors are formed first on a silicon substrate, using well known silicon wafer fabrication techniques. The germanium elements are subsequently formed overlying the silicon by epitaxial growth. The germanium elements are advantageously grown within surface openings of a dielectric cladding. Wafer fabrication techniques are applied to the elements to form isolated germanium photodiodes. Since temperatures needed for germanium processing are lower than those for silicon processing, the formation of the germanium devices need not affect the previously formed silicon devices. Insulating and metallic layers are then deposited and patterned to interconnect the silicon devices and to connect the germanium devices to the silicon circuits. The germanium elements are thus integrated to the silicon by epitaxial growth and integrated to the silicon circuitry by common metal layers.

Owner:INFRARED NEWCO +1

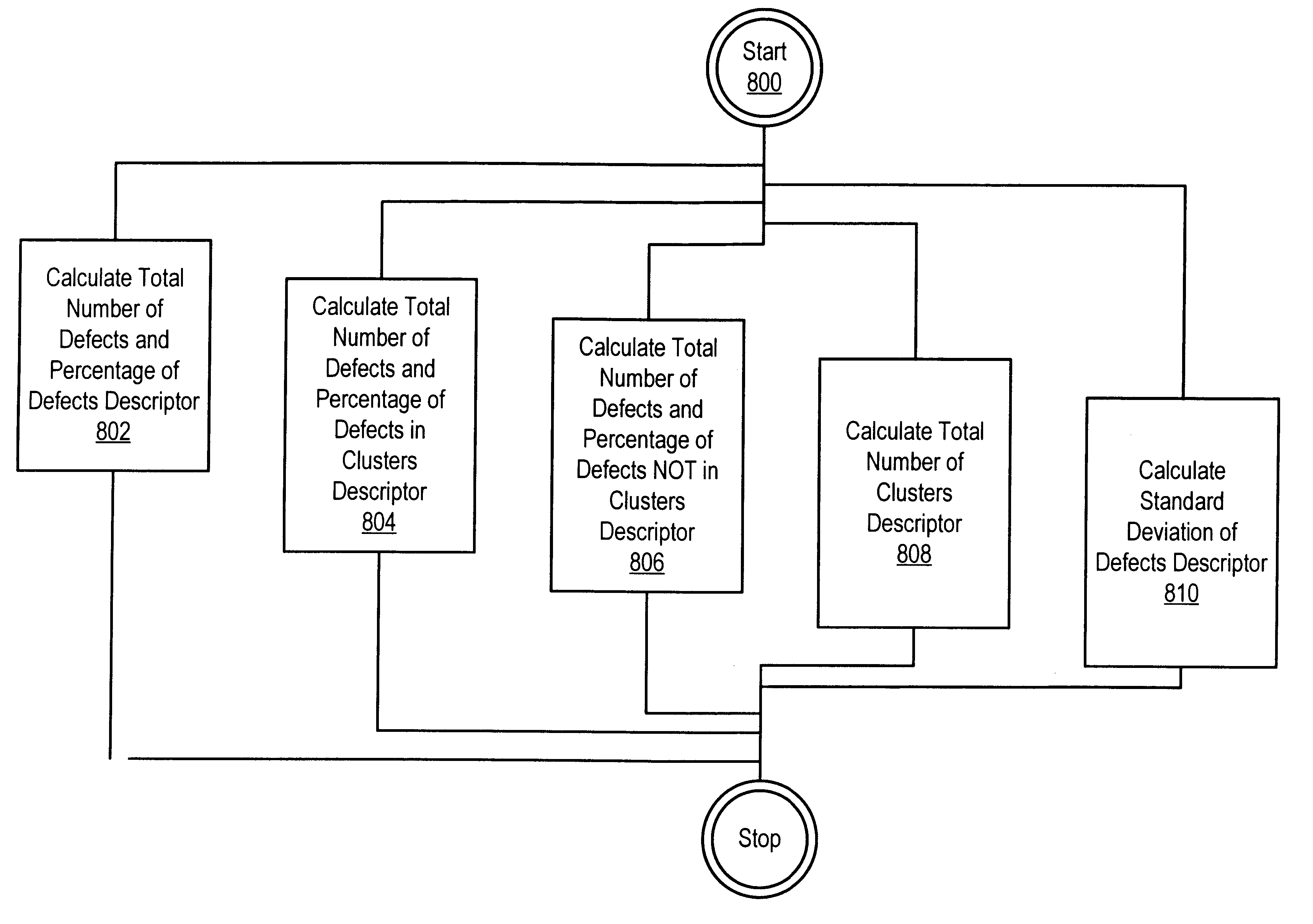

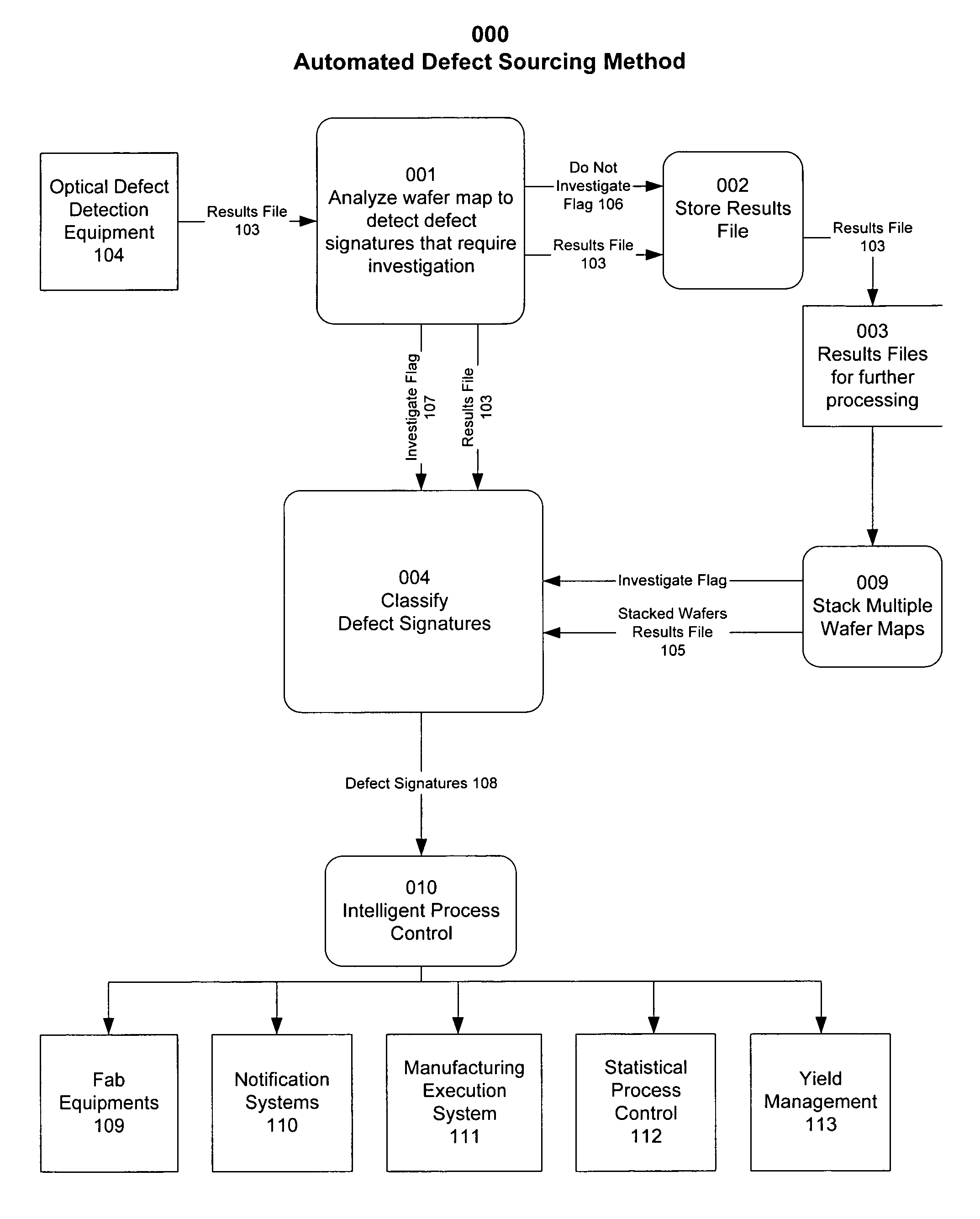

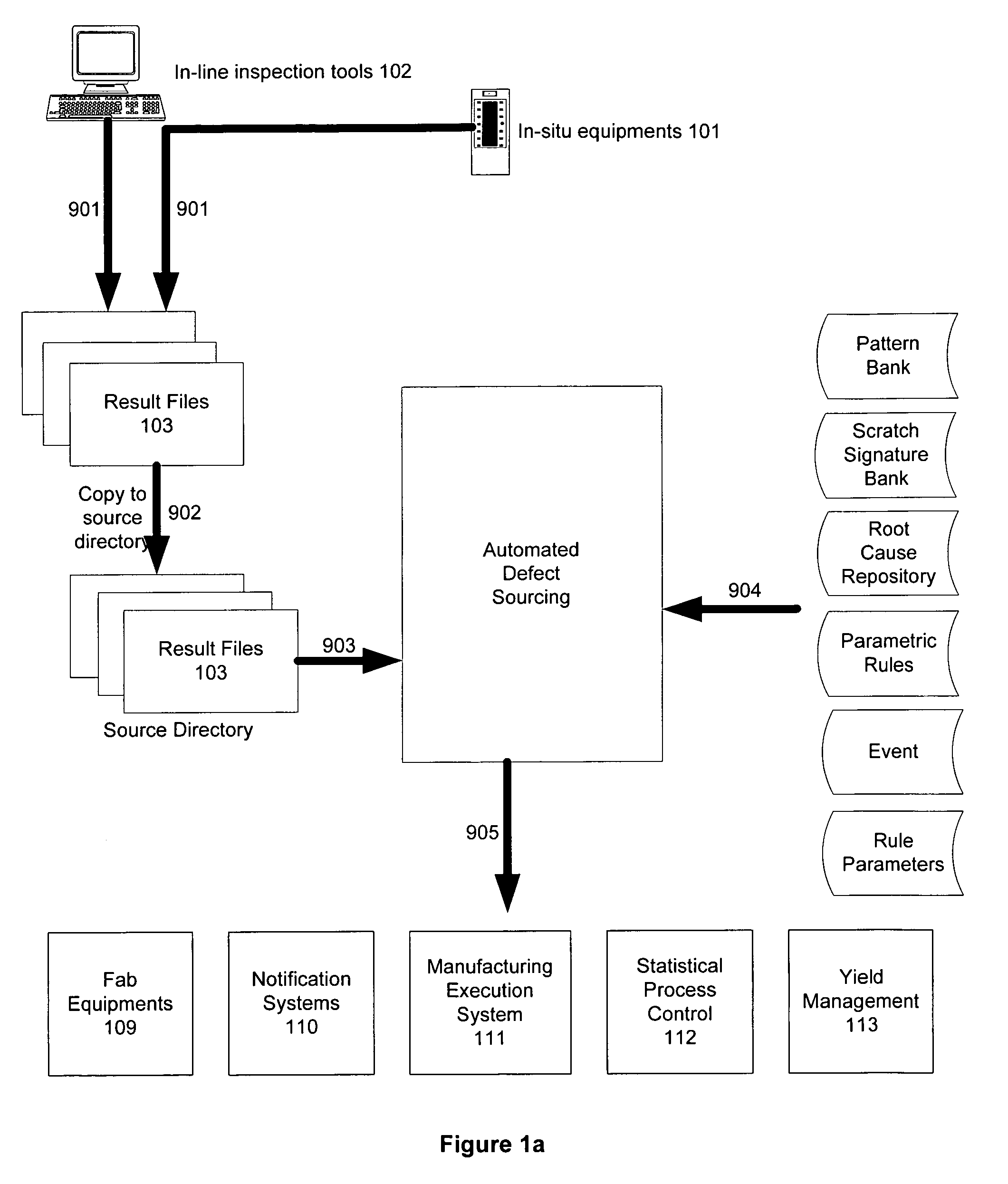

Automatic defect source classification

InactiveUS6507933B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingWafer fabricationQuality control

A method and system for use in wafer fabrication quality control. The method and system make quantitative a qualitative integrated circuit wafer defect signature. In response to the quantitativize wafer fabrication defect signature, the method and system identify at least one cause of the defect signature.

Owner:GLOBALFOUNDRIES INC

Light emitting device with an integrated monitor photodiode

InactiveUS20050286593A1Increased susceptibilityLaser detailsSemiconductor lasersVertical-cavity surface-emitting laserTunnel diode

A monolithically formed laser and photodiode. The monolithically formed laser and photodiode includes a Vertical Cavity Surface Emitting Laser (VCSEL) that includes a first PN junction. The first PN junction includes a first p layer and a first n layer. A tunnel diode is connected to the VCSEL both physically and electronically through a wafer fabrication process. A photodiode is connected to the tunnel diode. The photodiode is connected to the tunnel diode by physical and electronic connections. The tunnel diode and photodiode may share some common layers. The tunnel diode includes a second PN junction. The monolithically formed laser and photodiode allow for an integrated structure with diode biasing flexibility including the use of a single supply to bias both the laser and photodiodes.

Owner:II VI DELAWARE INC

System to identify a wafer manufacturing problem and method therefor

InactiveUS20040122859A1Semiconductor/solid-state device testing/measurementDigital data processing detailsRoot causeComputer science

A method (400) for determining a response to a wafer manufacturing process problem includes the steps of generating a wafer map signature (406) containing defect attributes to be identified and retrieving (410) one or more wafer map signatures from a database. The wafer map signature to be identified is matched (414) with the one or more wafer map signatures from the database in order to help find a root cause of a defect in a wafer manufacturing process. This provides at least the advantage that a signature matching capability allows an Operator to more accurately identify a root manufacturing cause of a wafer defect. Furthermore, instant feedback to the wafer manufacturing process can be provided to facilitate rapid correction of manufacturing errors.

Owner:APPLIED MATERIALS INC

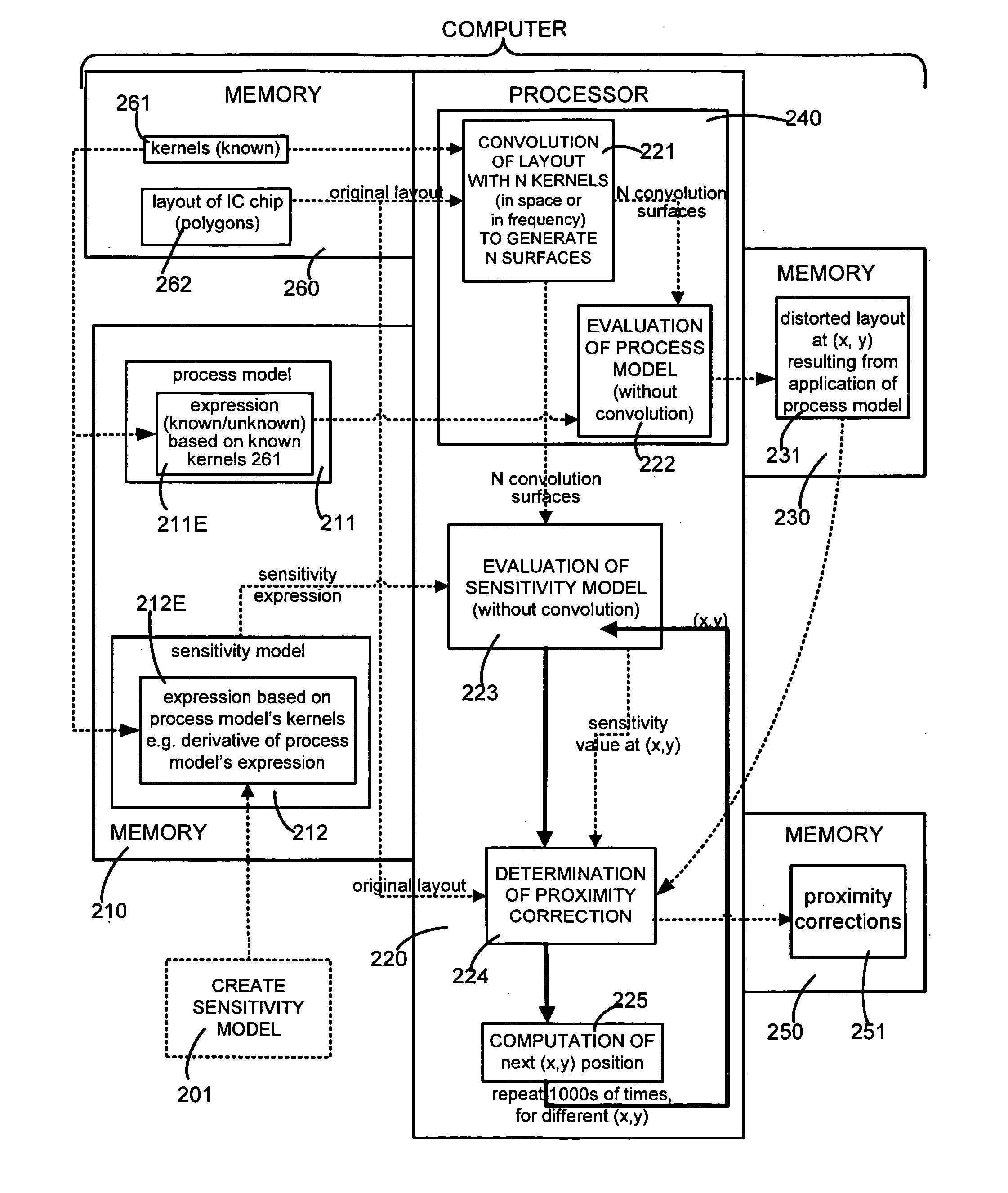

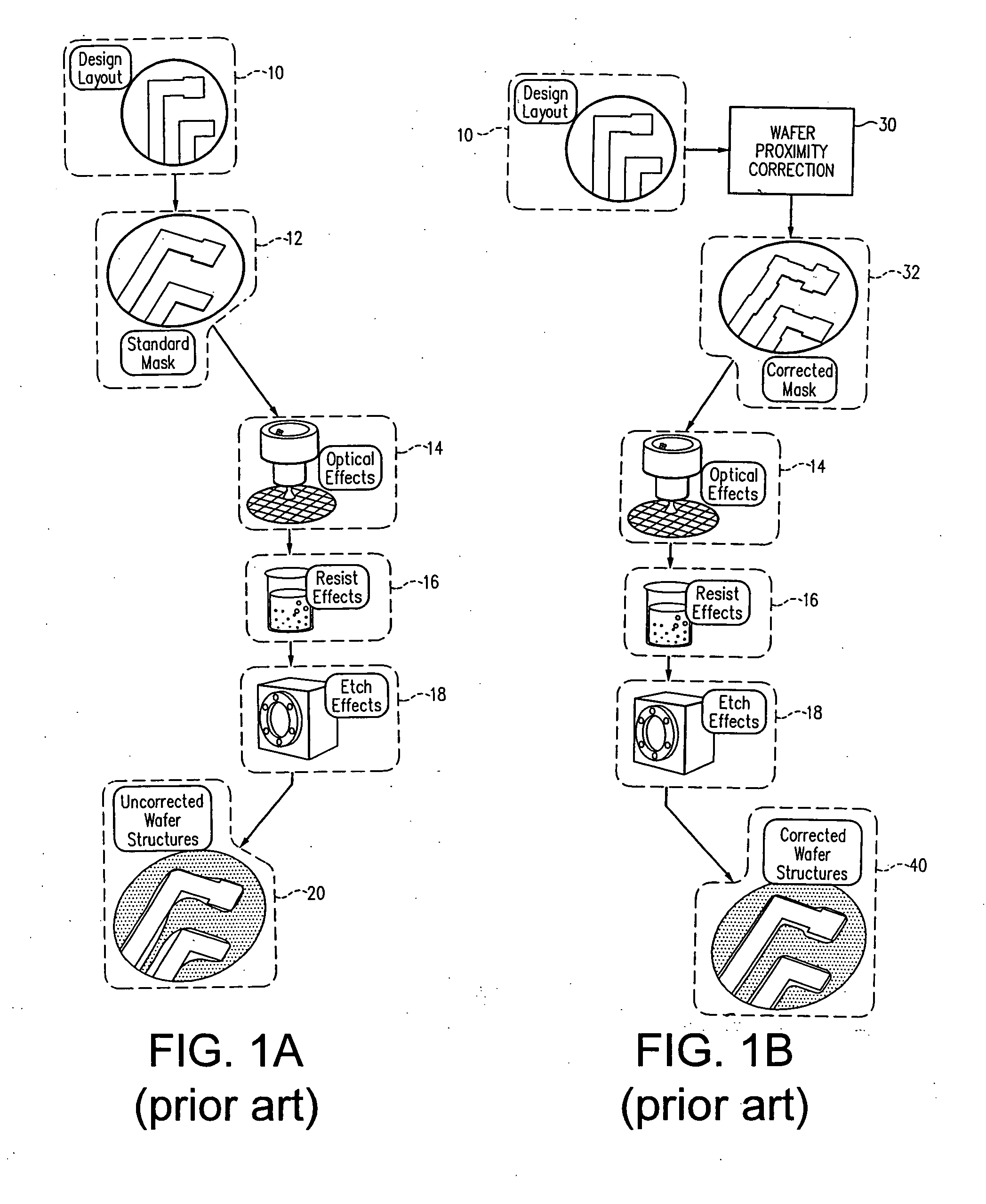

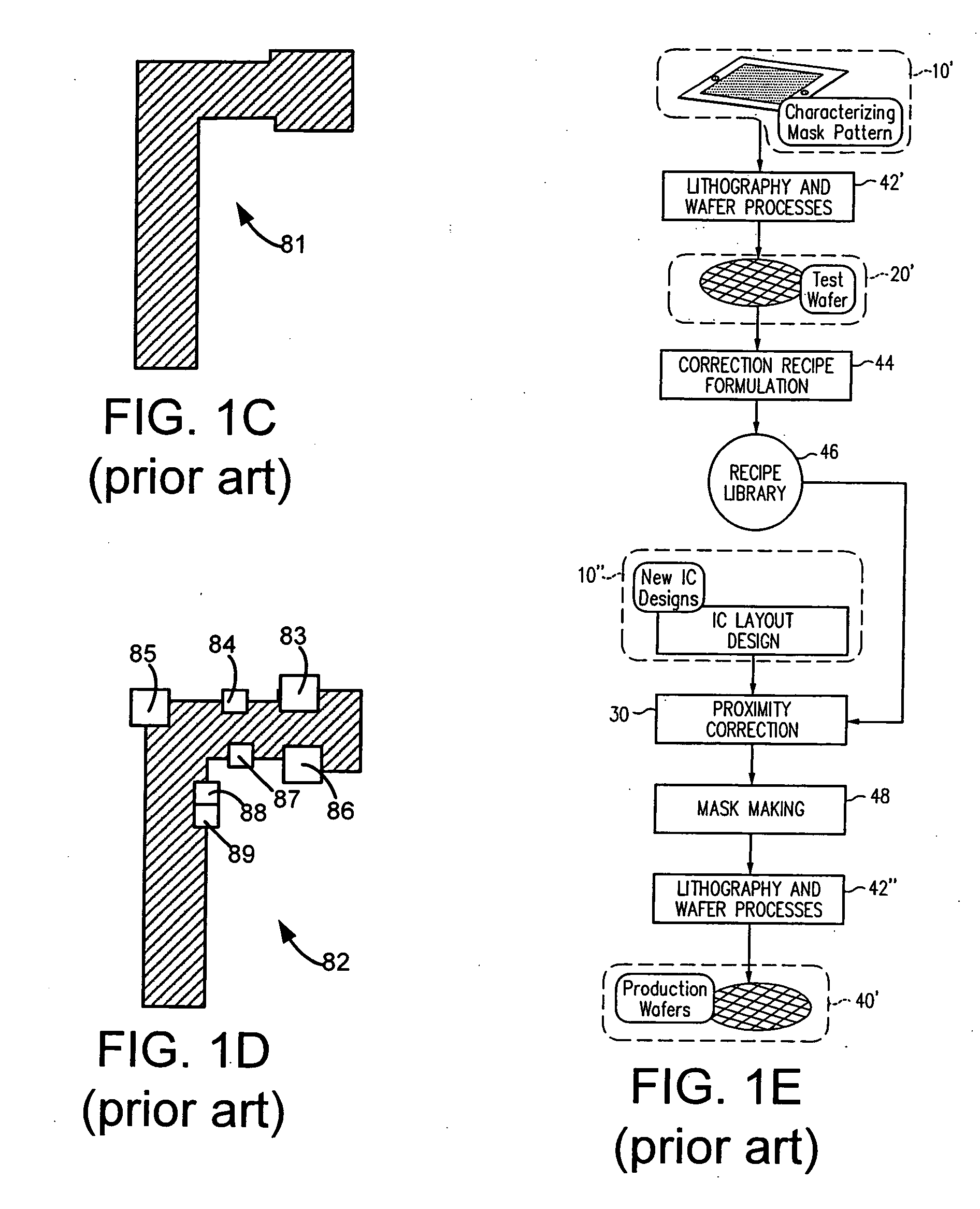

Model of sensitivity of a simulated layout to a change in original layout, and use of model in proximity correction

ActiveUS20070101310A1Simple calculationReduce memory requirementsPhotomechanical apparatusCAD circuit designSpatial functionAlgorithm

A memory is encoded with a model of sensitivity of a distorted layout generated by simulation of a wafer fabrication process, with respect to a change in an original layout that is input to the simulation. The sensitivity model comprises an expression of convolution of the original layout with spatial functions (“kernels”) that are identical to kernels of a process model used in the simulation. A difference between the distorted layout and the original layout is computed, and the difference is divided by a sensitivity value which is obtained directly by evaluating the kemel-based sensitivity model, and the result is used to identify a proximity correction (such as serif size or contour movement) to be made to the original layout. Use of a sensitivity model based on a process model's kernels eliminates a second application of the process model to evaluate sensitivity, thereby to reduce memory and computation requirements.

Owner:SYNOPSYS INC

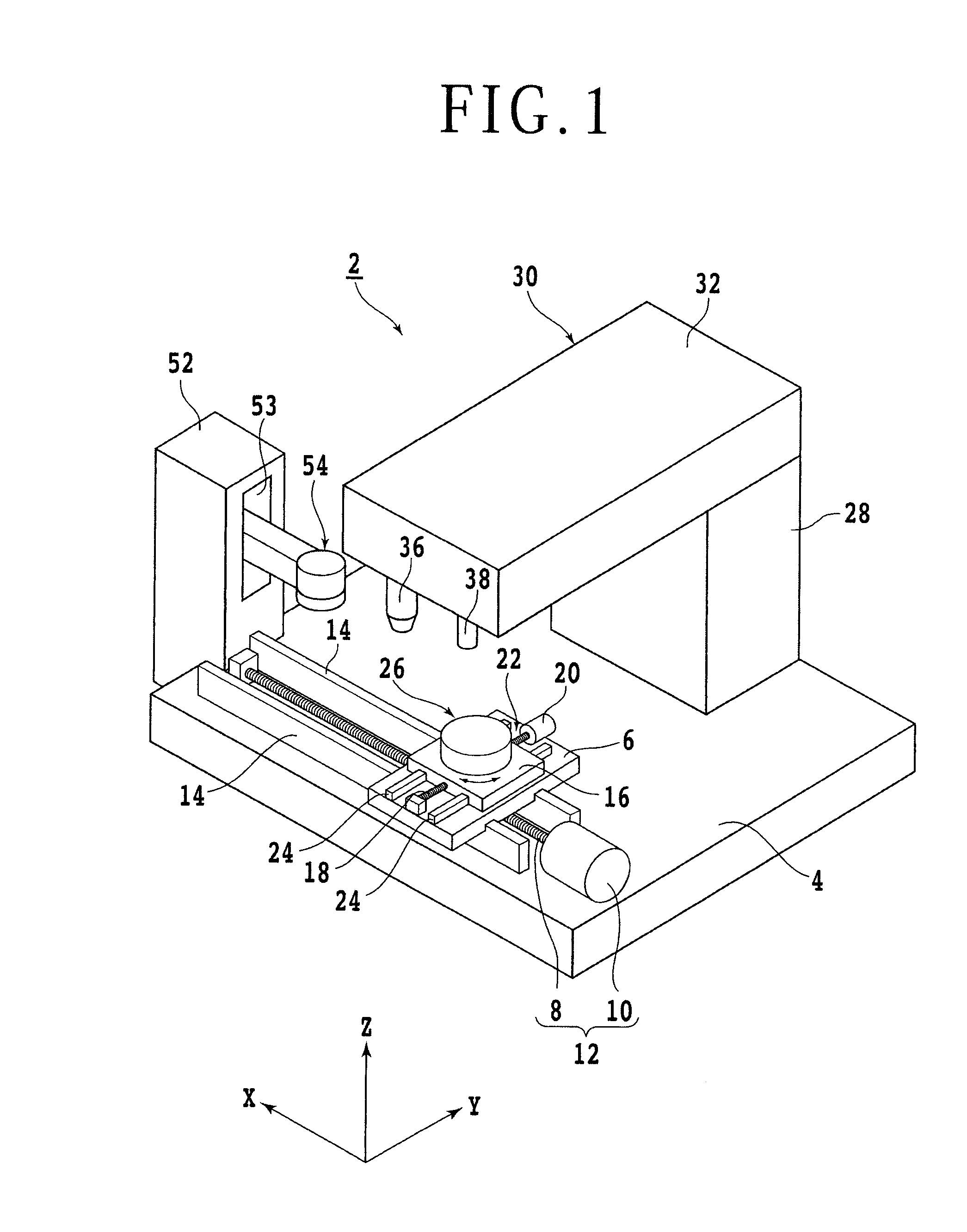

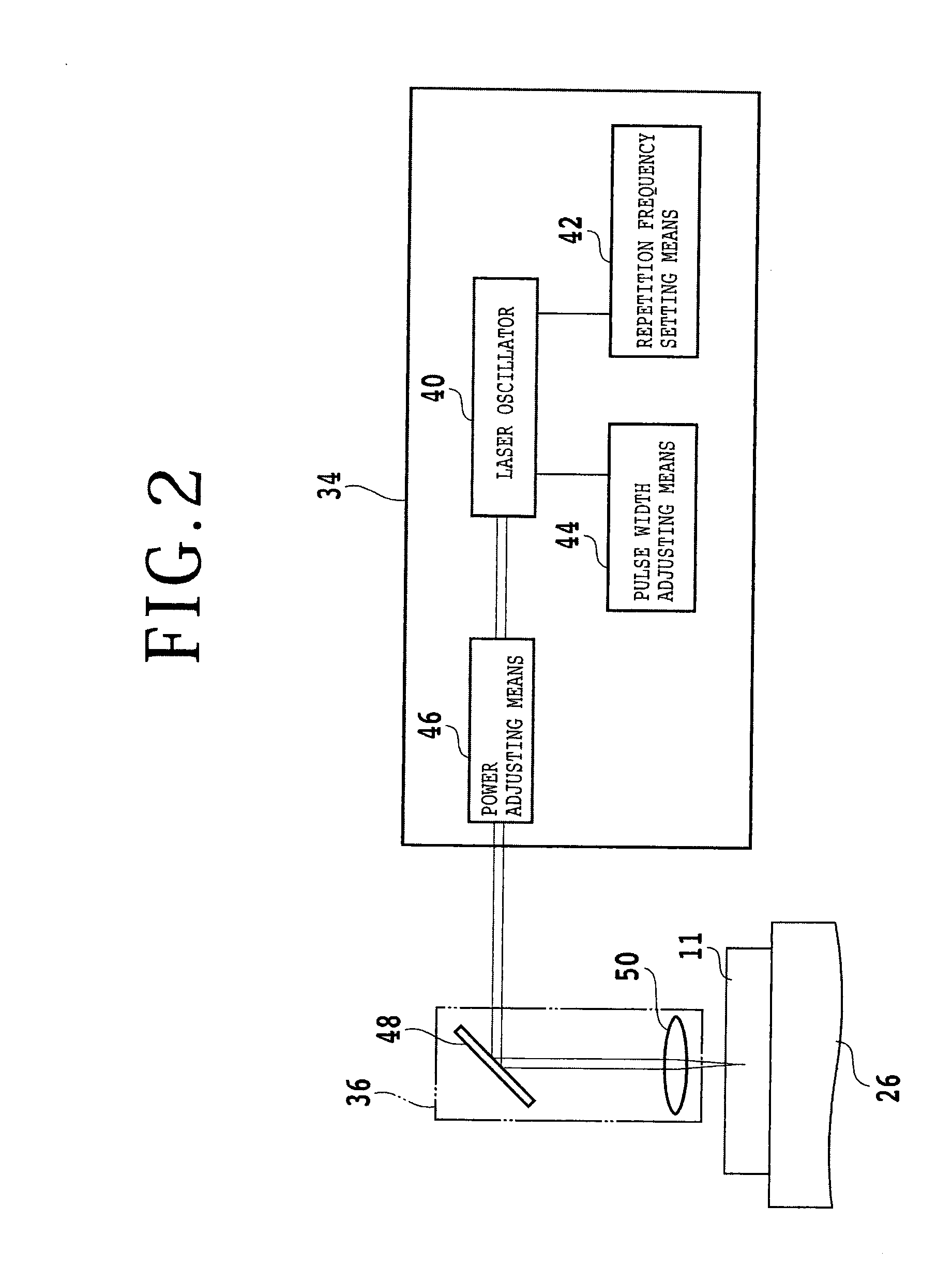

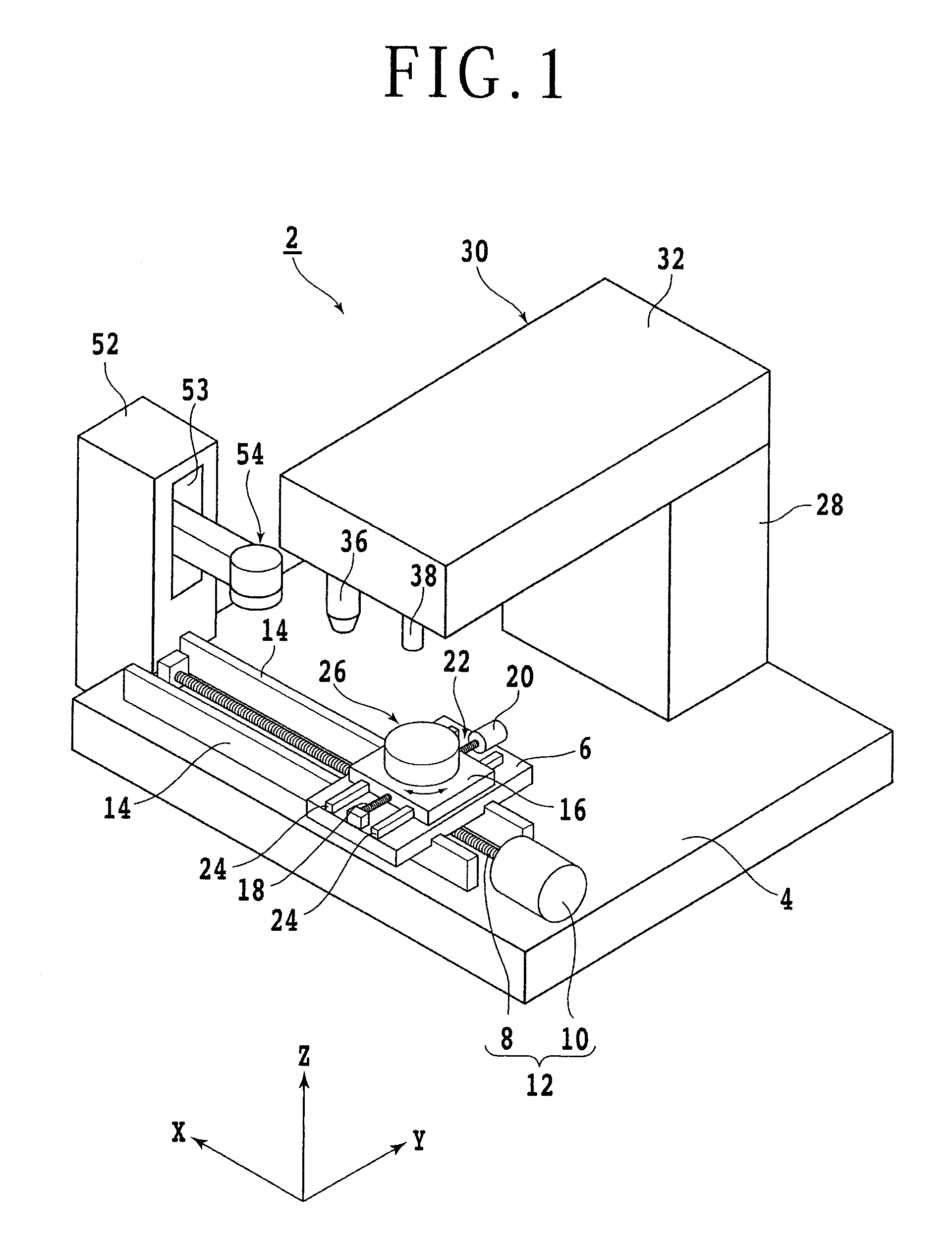

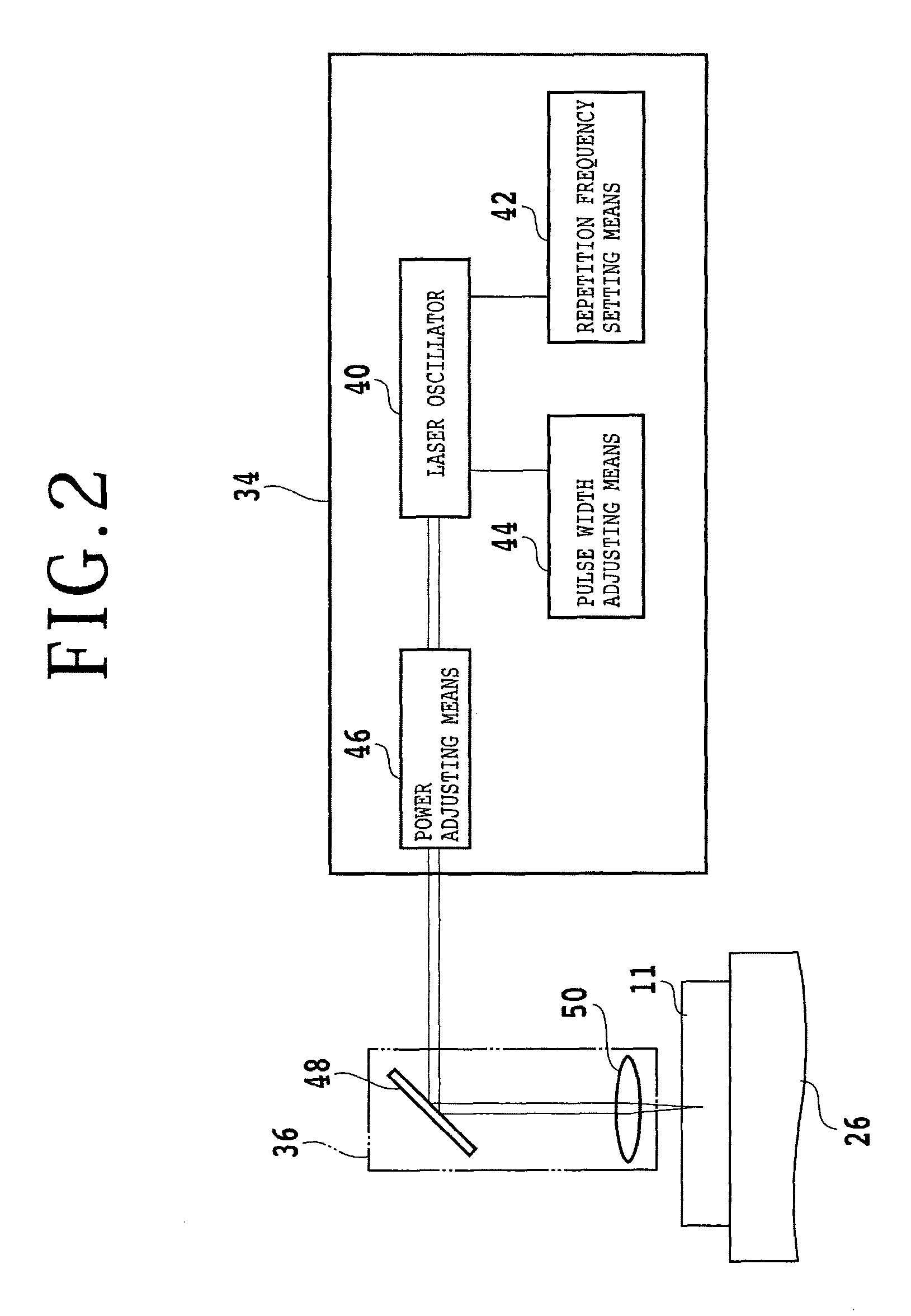

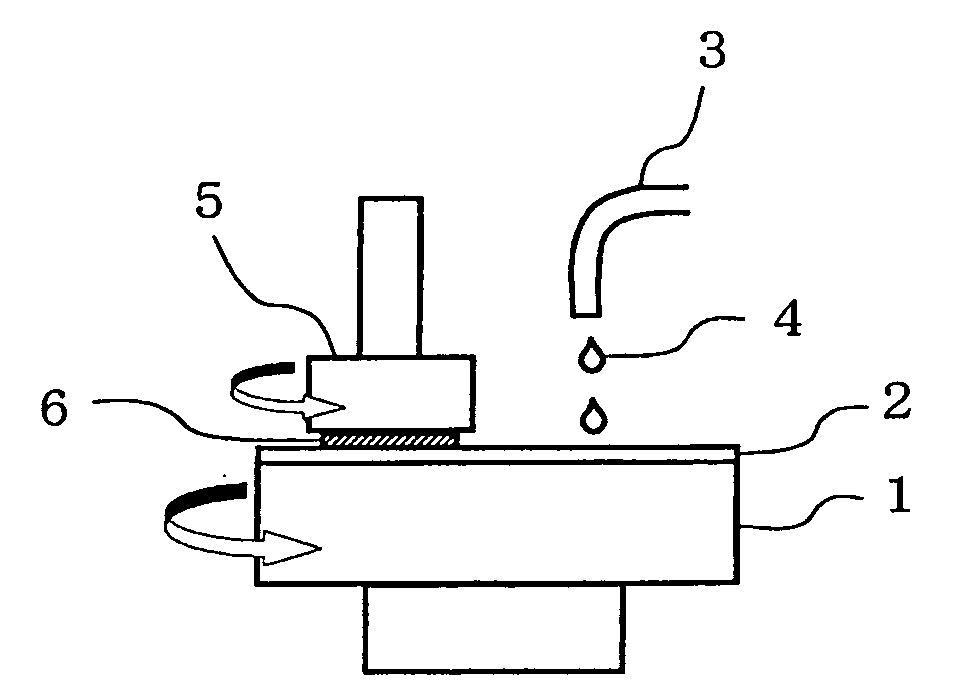

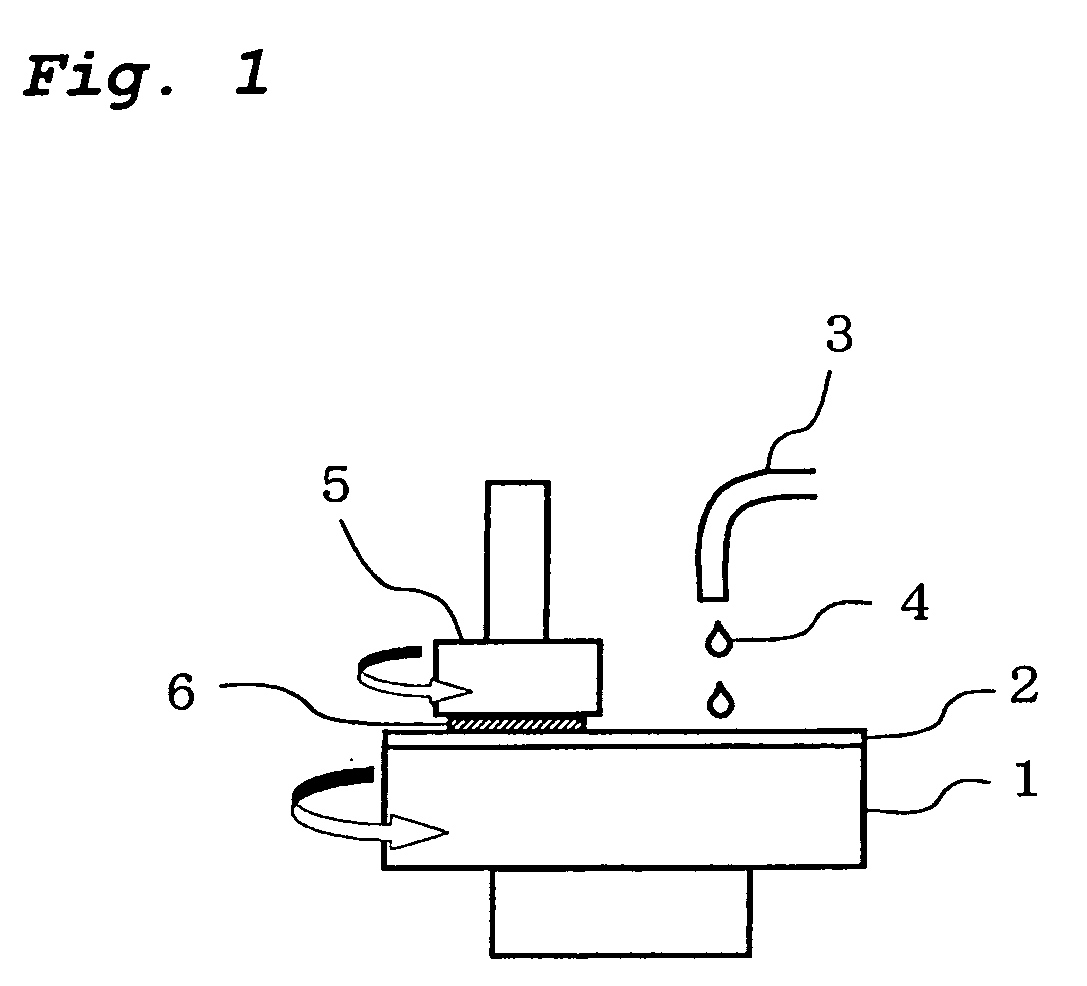

Wafer producing method

ActiveUS20160158881A1Easy to separateImprove productivityPolycrystalline material growthAfter-treatment detailsLight beamWafer fabrication

A wafer producing method for producing a hexagonal single crystal wafer from a hexagonal single crystal ingot includes a separation start point forming step of setting the focal point of a laser beam inside the ingot at a predetermined depth from the upper surface of the ingot, which depth corresponds to the thickness of the wafer to be produced, and next applying the laser beam to the upper surface of the ingot while relatively moving the focal point and the ingot to thereby form a modified layer parallel to the upper surface of the ingot and cracks extending from the modified layer, thus forming a separation start point. In the separation start point forming step, the laser beam is applied to the ingot plural times with the focal point of the laser beam set at the modified layer previously formed, thereby separating the cracks from the modified layer.

Owner:DISCO CORP

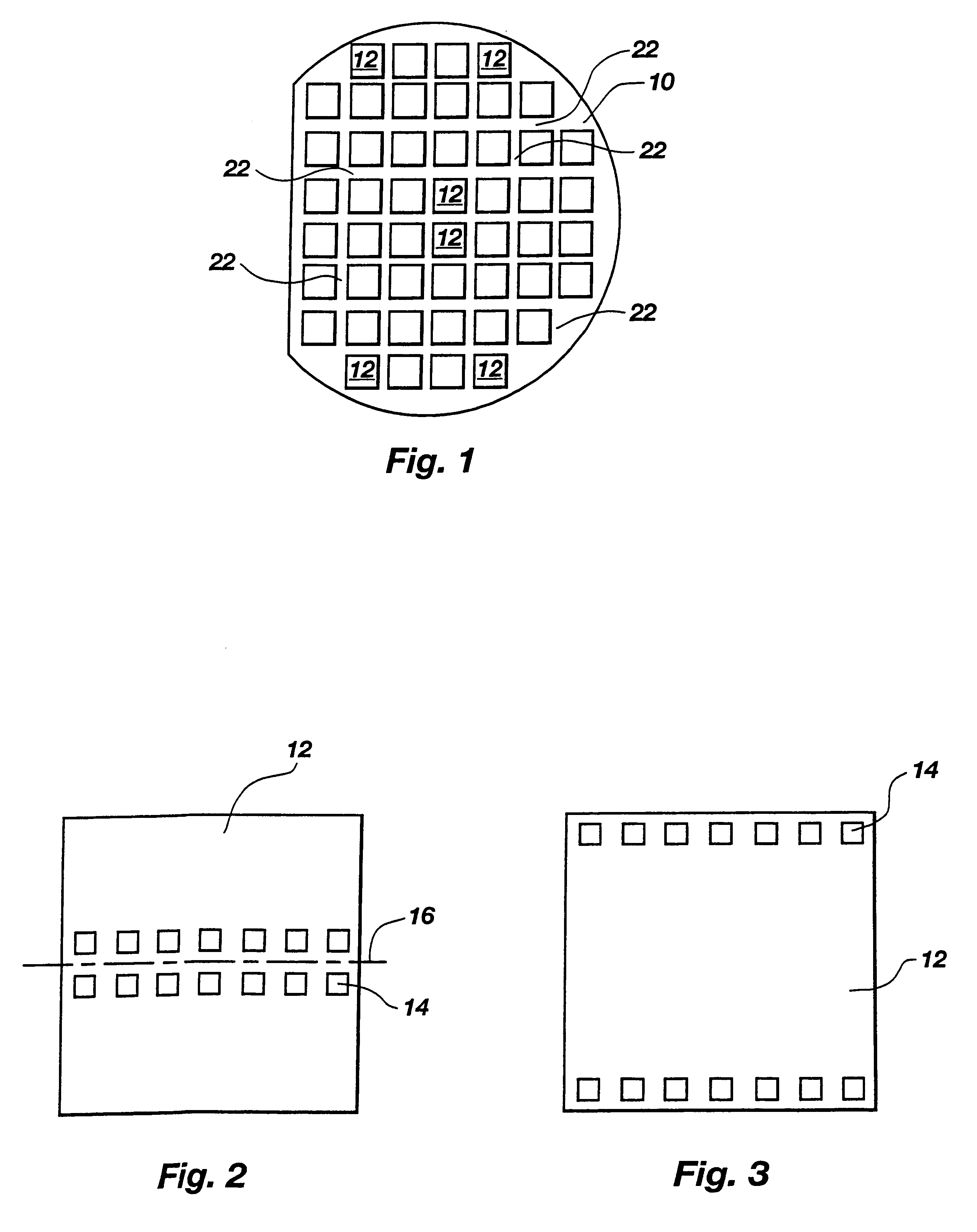

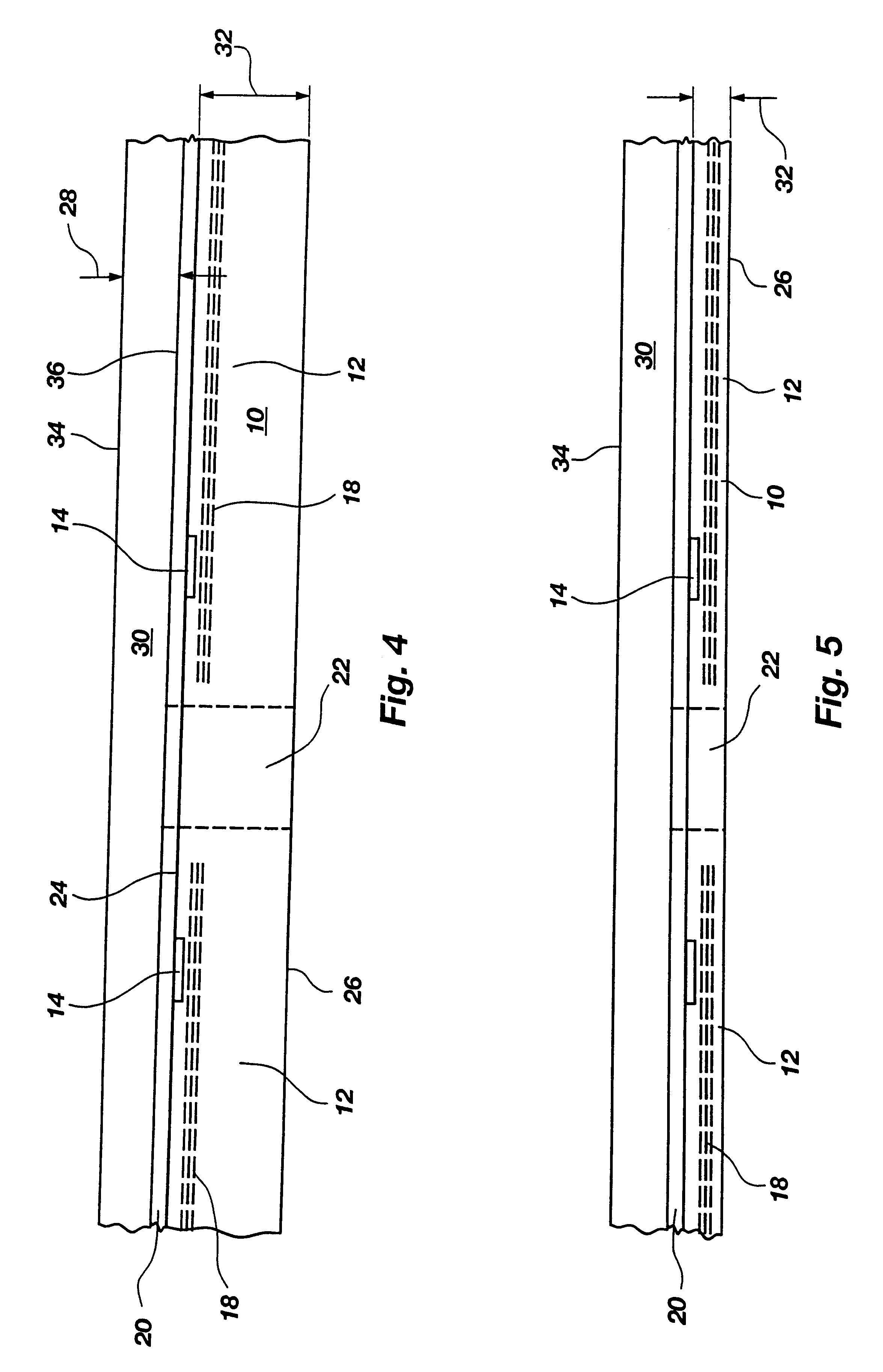

Wafer level fabrication and assembly of chip scale packages

InactiveUS6284573B1Semiconductor/solid-state device detailsSolid-state devicesWafer fabricationEngineering

A method for producing integrated circuit devices comprises the steps of forming and packaging such devices at the wafer scale including forming a plurality of chip circuits with bond pads, adhesively fixing a plate of glass to the active surface of the wafer, slicing the wafer, applying a sealant layer to the backside of the wafer, forming contact holes through the upper glass plate, metallizing the glass plate and singulating the individual chips. Use of etchable glass for the package and palladium for metallization provides an advantageous construction method.

Owner:ROUND ROCK RES LLC

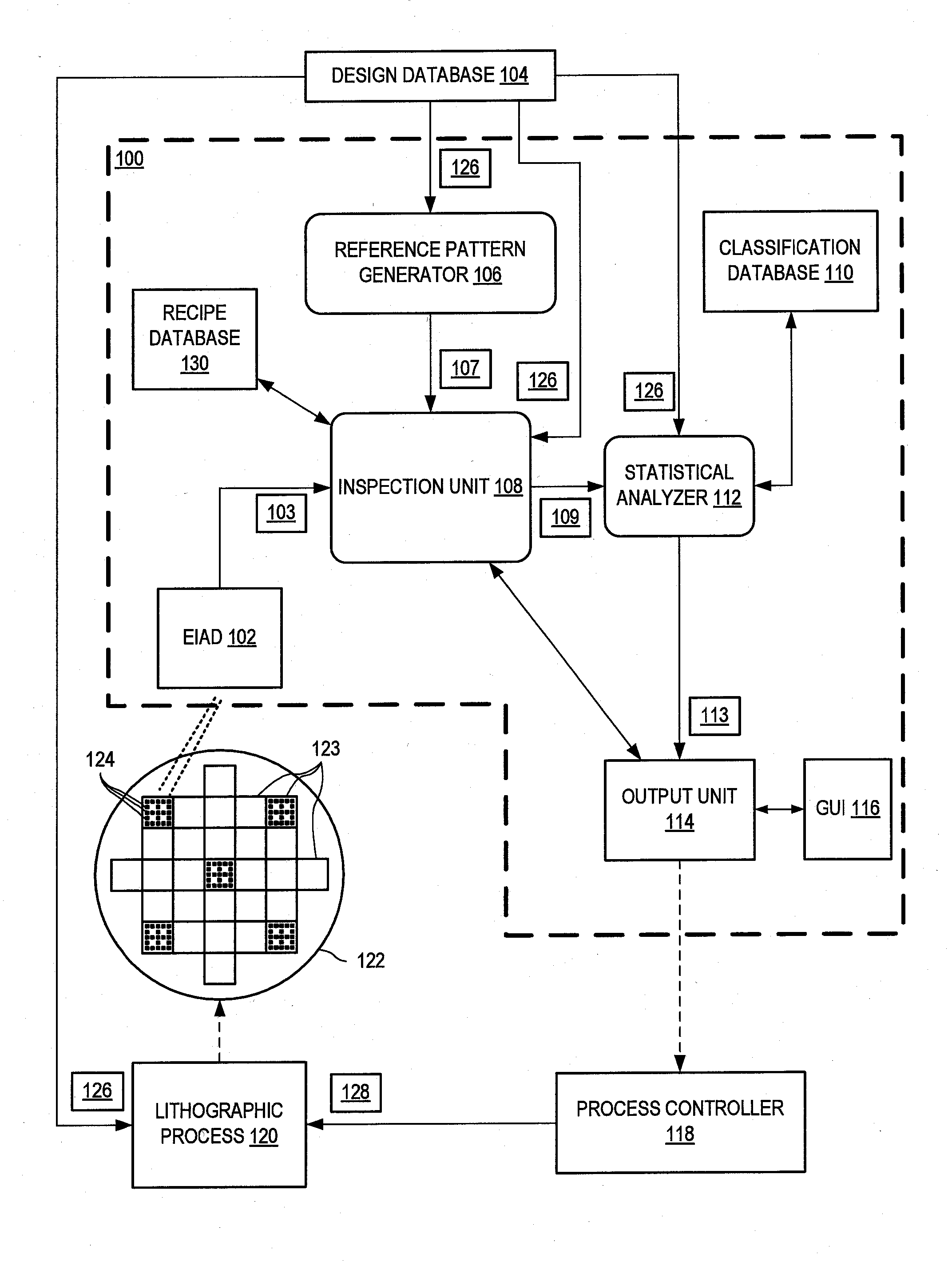

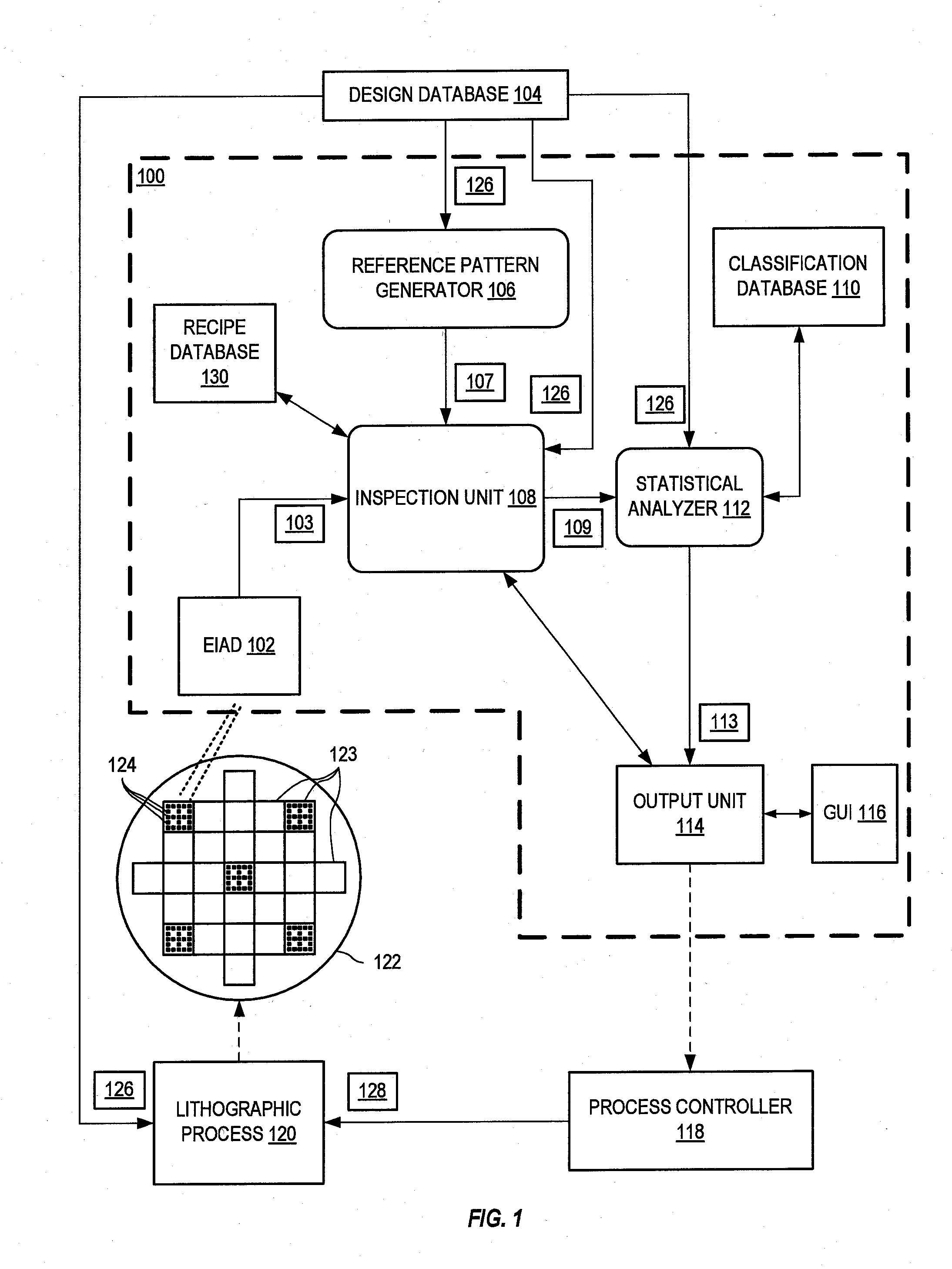

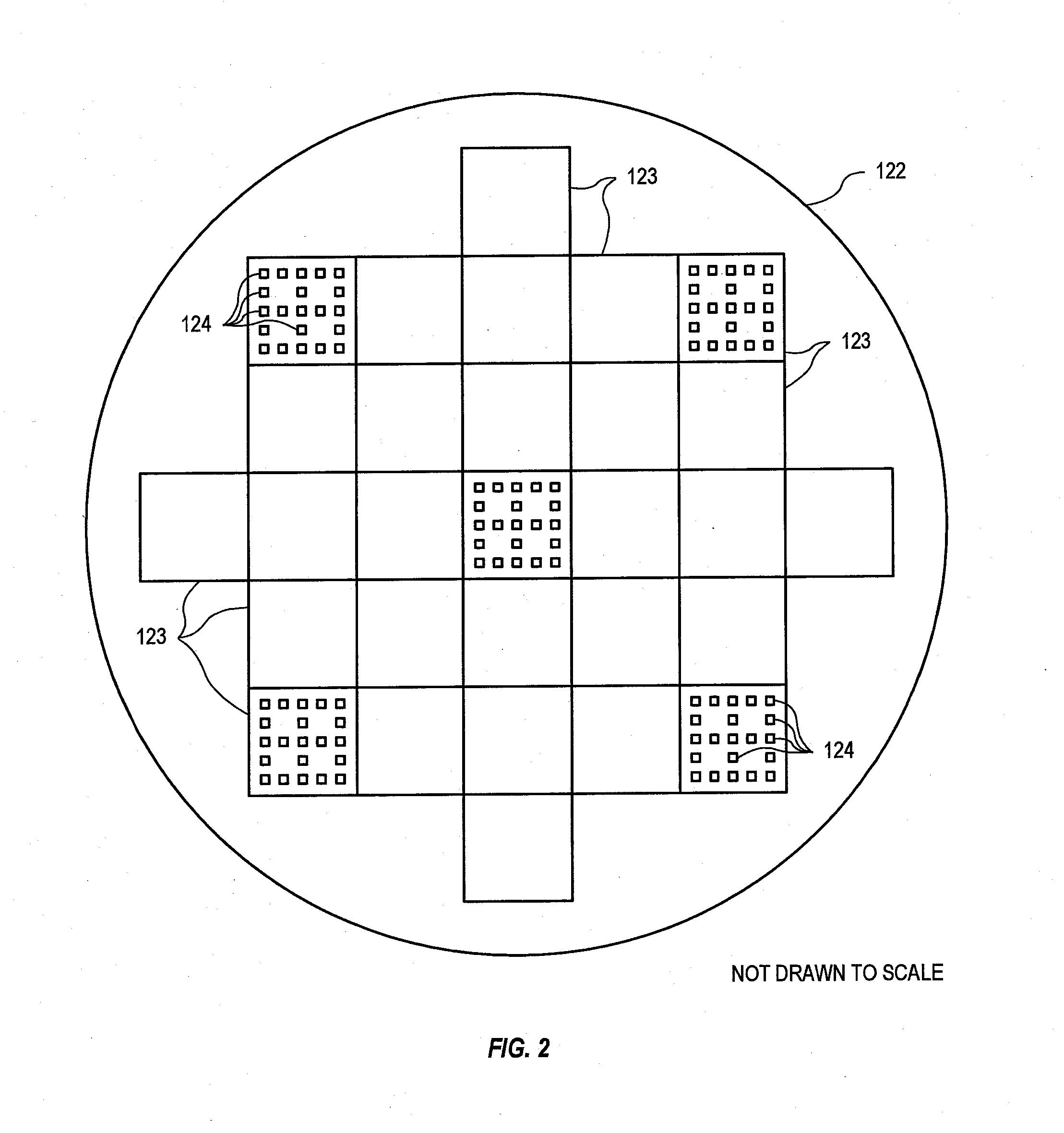

Defect And Critical Dimension Analysis Systems And Methods For A Semiconductor Lithographic Process

Apparatus and method evaluate a wafer fabrication process for forming patterns on a wafer based upon design data. Within a recipe database, two or more inspection regions are defined on the wafer for analysis. Patterns within each of the inspection regions are automatically selected based upon tendency for measurement variation resulting from variation in the fabrication process. For each inspection region, at least one image of patterns within the inspection region is captured, a reference pattern, represented by one or both of (a) one or more line segments and (b) one or more curves, is automatically generated from the design data. An inspection unit detects edges within each of the images and registers the image with the reference pattern. One or more measurements are determined from the edges for each of the selected patterns and are processed within a statistical analyzer to form statistical information associated with the fabrication process.

Owner:TASMIT INC

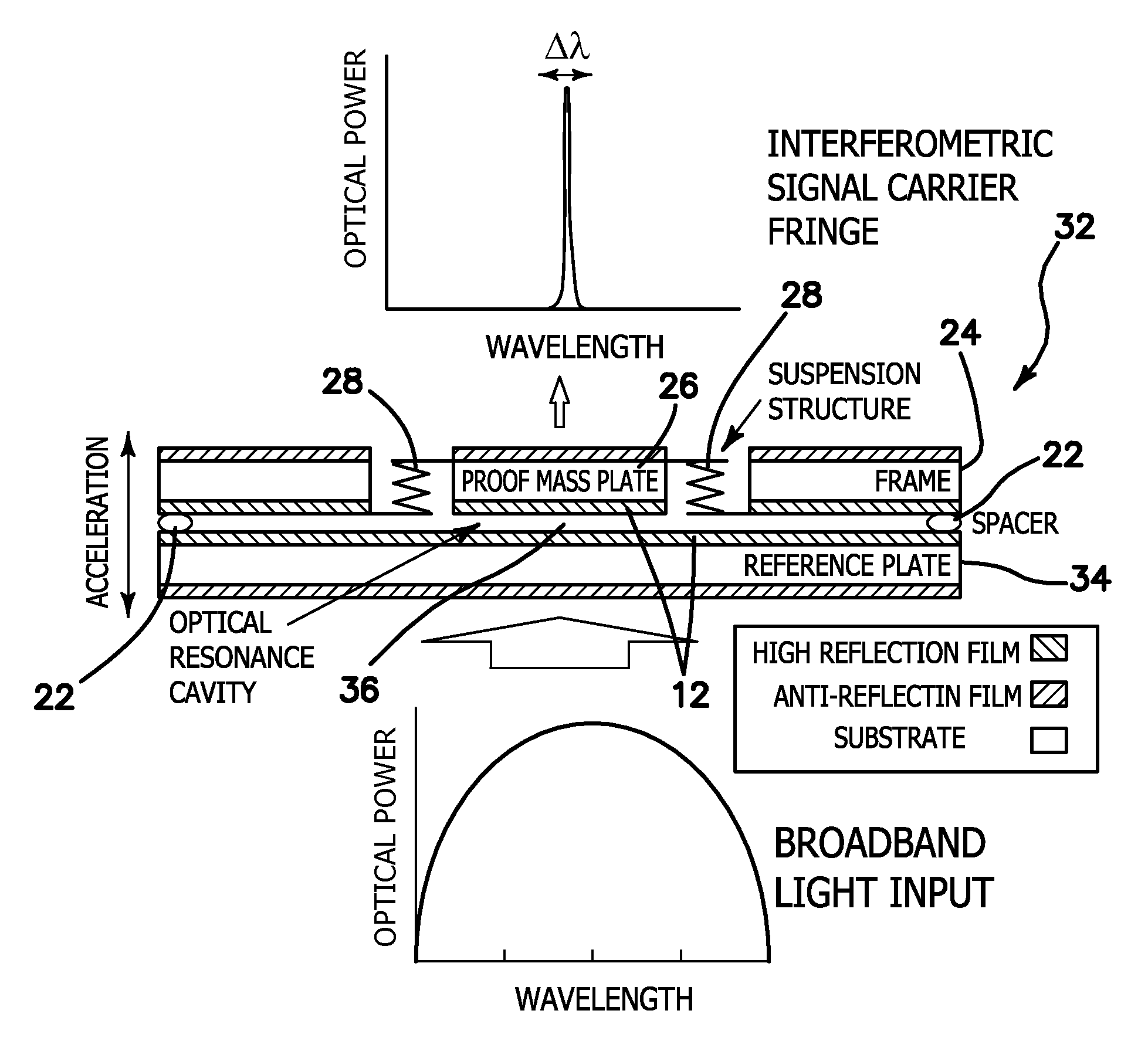

Single wafer fabrication process for wavelength dependent reflectance for linear optical serialization of accelerometers

ActiveUS20100046002A1Easy to manufactureHigh resolutionAcceleration measurement using interia forcesSubsonic/sonic/ultrasonic wave measurementMultiplexingAccelerometer

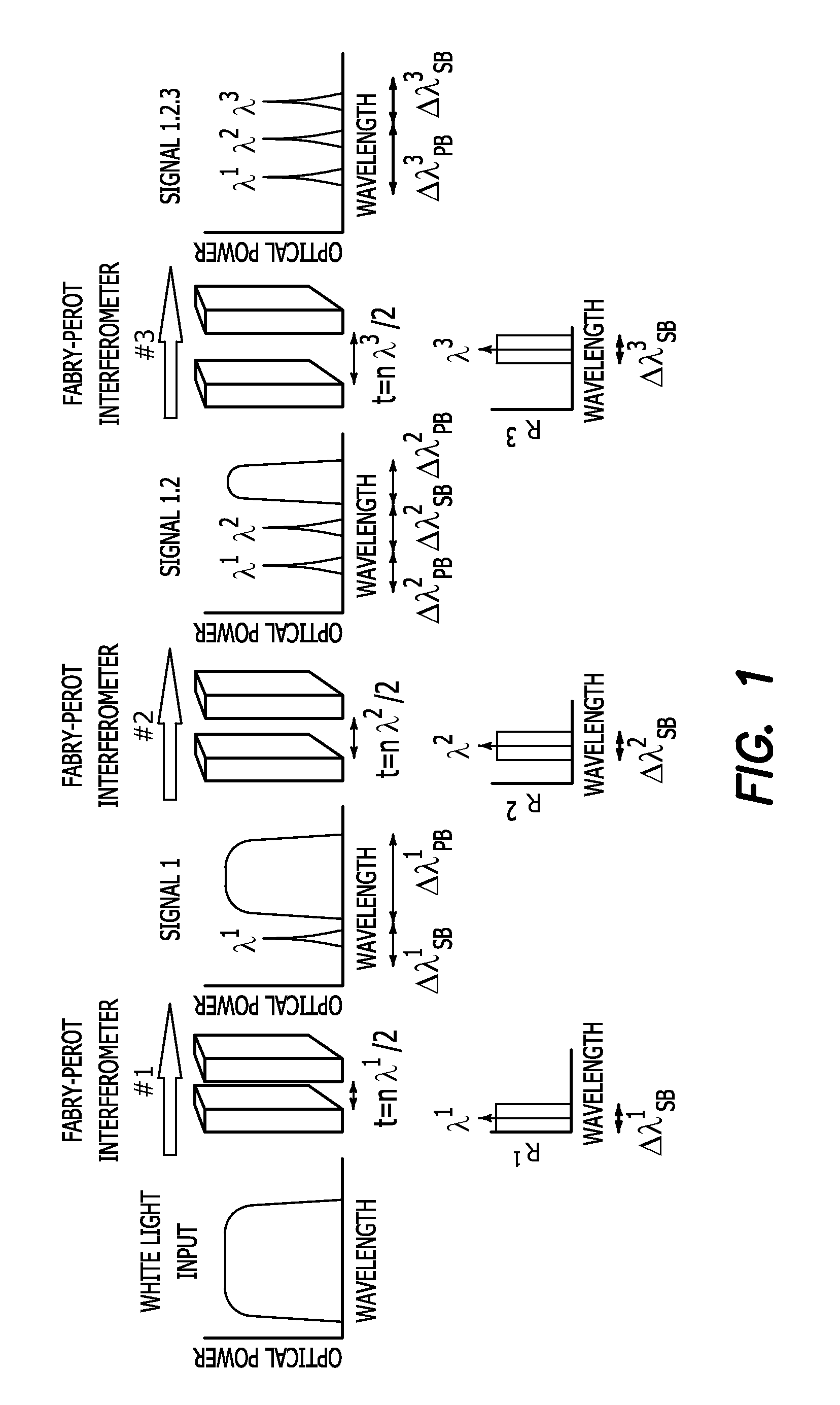

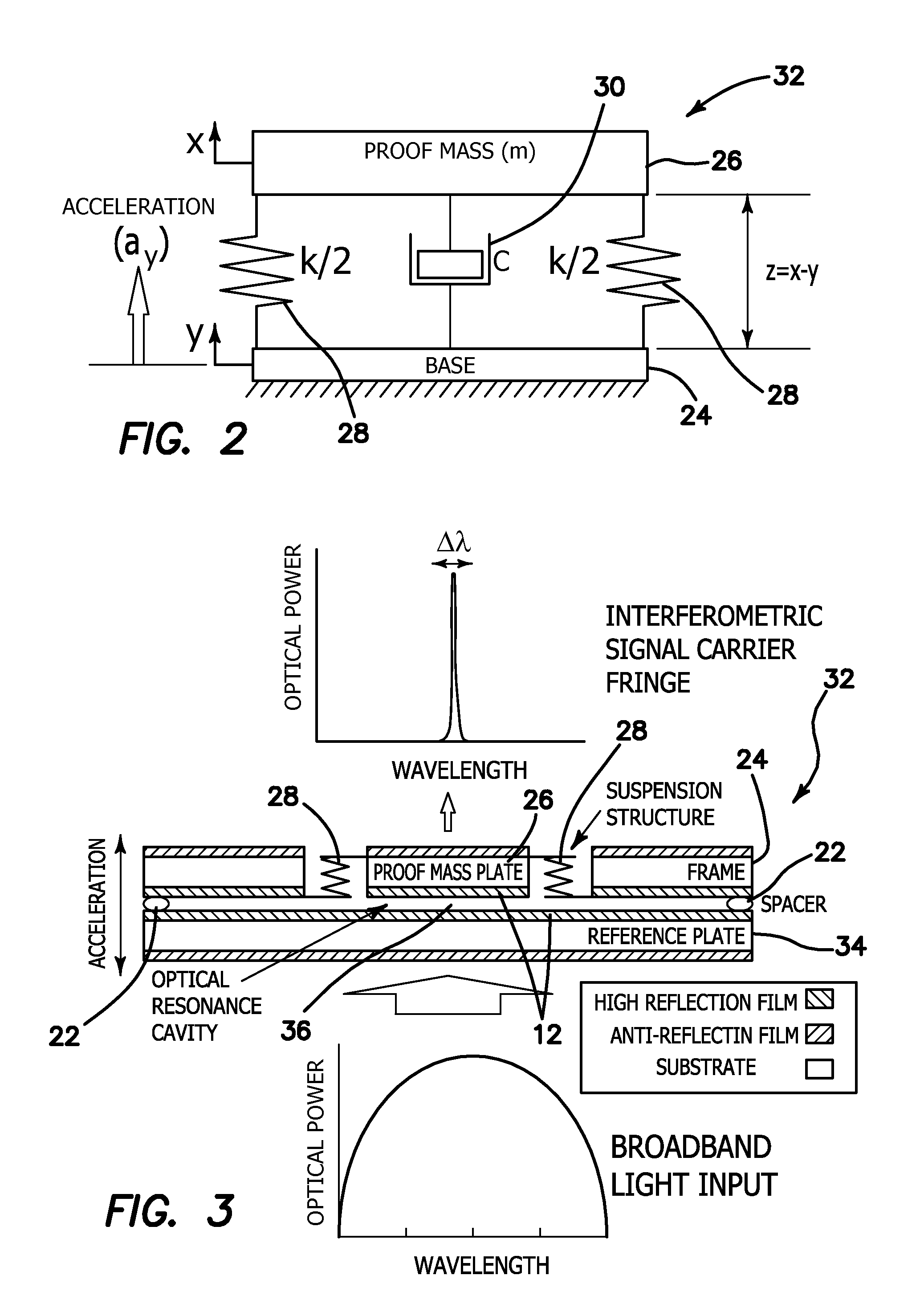

A plurality of Fabry-Perot interferometric sensors are optically coupled in series with each other to form an ordered optical series. Each Fabry-Perot interferometric sensor has a unique signalband and a passband. Each Fabry-Perot interferometric sensor has its unique signalband within the passbands of all of the next higher ordered Fabry-Perot interferometric sensors in the optical series so that a corresponding unique fringe signal from each of the Fabry-Perot interferometric sensors is a multiplexed output from the optical series.

Owner:RGT UNIV OF CALIFORNIA

Scheduling method in silicon chip working process

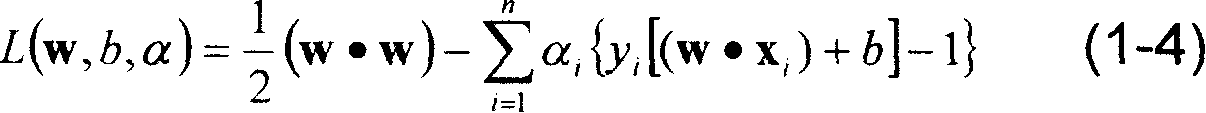

ActiveCN101179043AAvoid idlingIncrease profitSemiconductor/solid-state device manufacturingTotal factory controlSupport vector machineIdle time

The invention discloses a scheduling method in wafer fabrication which is used for scheduling operation sequence of a plurality of processing procedures of processing equipment of a plurality of silicon wafers. The method takes the processing procedure as a unit for scheduling. The processing procedure refers to a processing step of any silicon wafer in any chamber flow field in a process task: firstly, performing queue sequencing of a plurality of processing procedures according to utilization situation of the chamber flow field, then performing downstream processing in turn according to the queue. When performing the queue sequencing, applying multi-class support vector machine to sort according to the chamber flow field preparation time, switch time, idle time after performance of process and relative emergency degree of every working procedure. The utilization rate of chamber flow field is high, the average processing time is short and production efficiency is high. The scheduling method is mainly applicable to the processing procedures of silicon wafer processing equipment and can also be applied to mobilize processing operations of other equipment.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

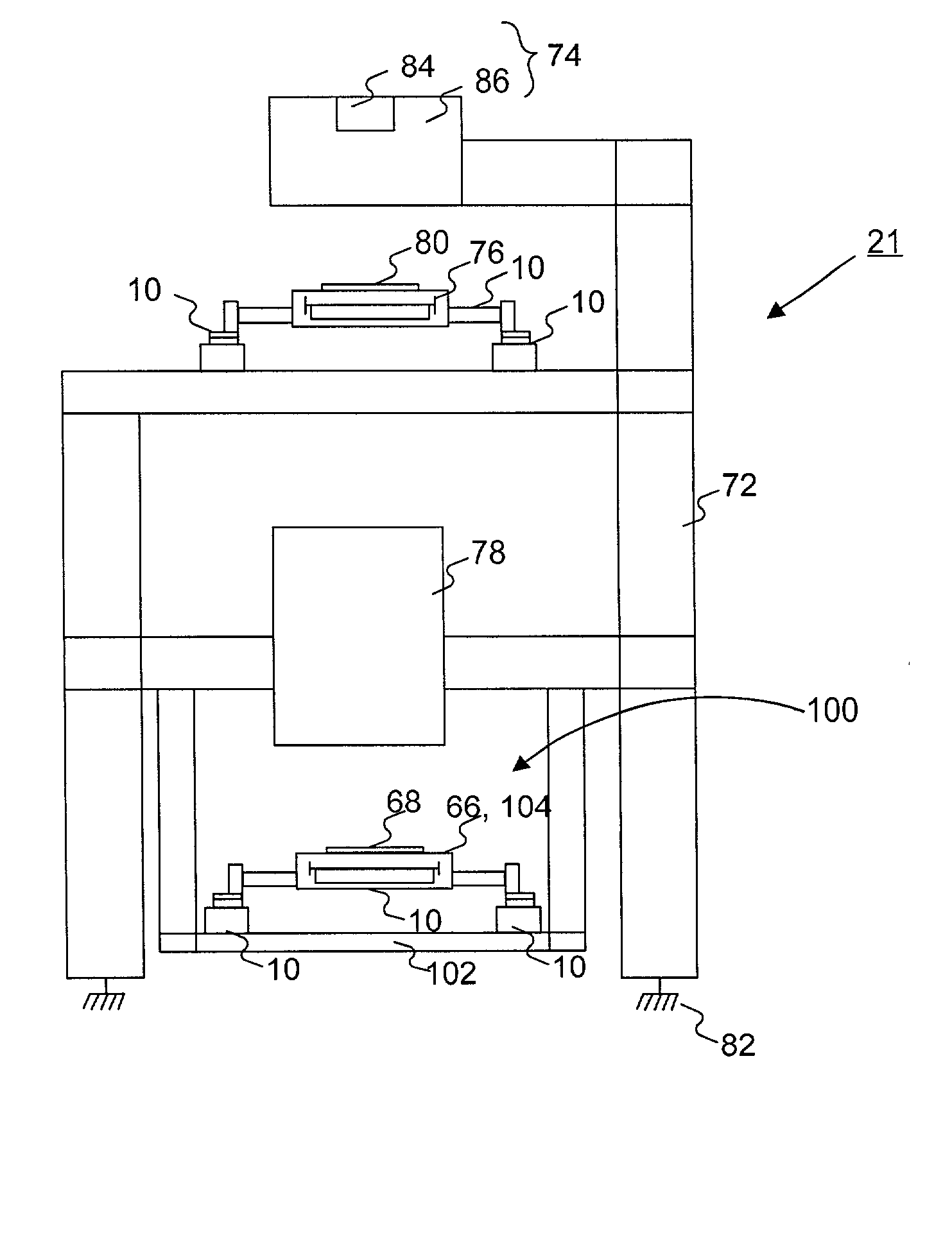

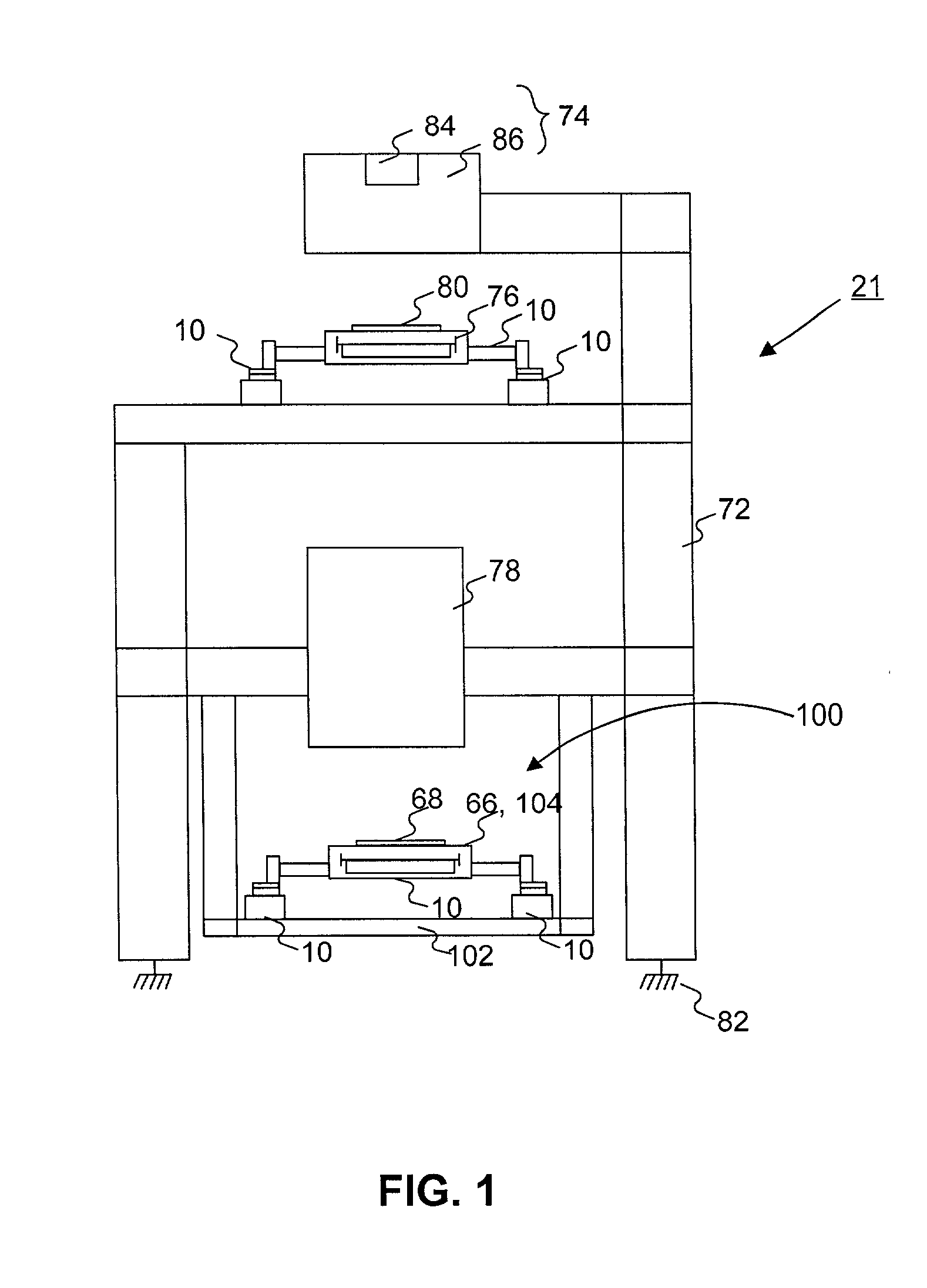

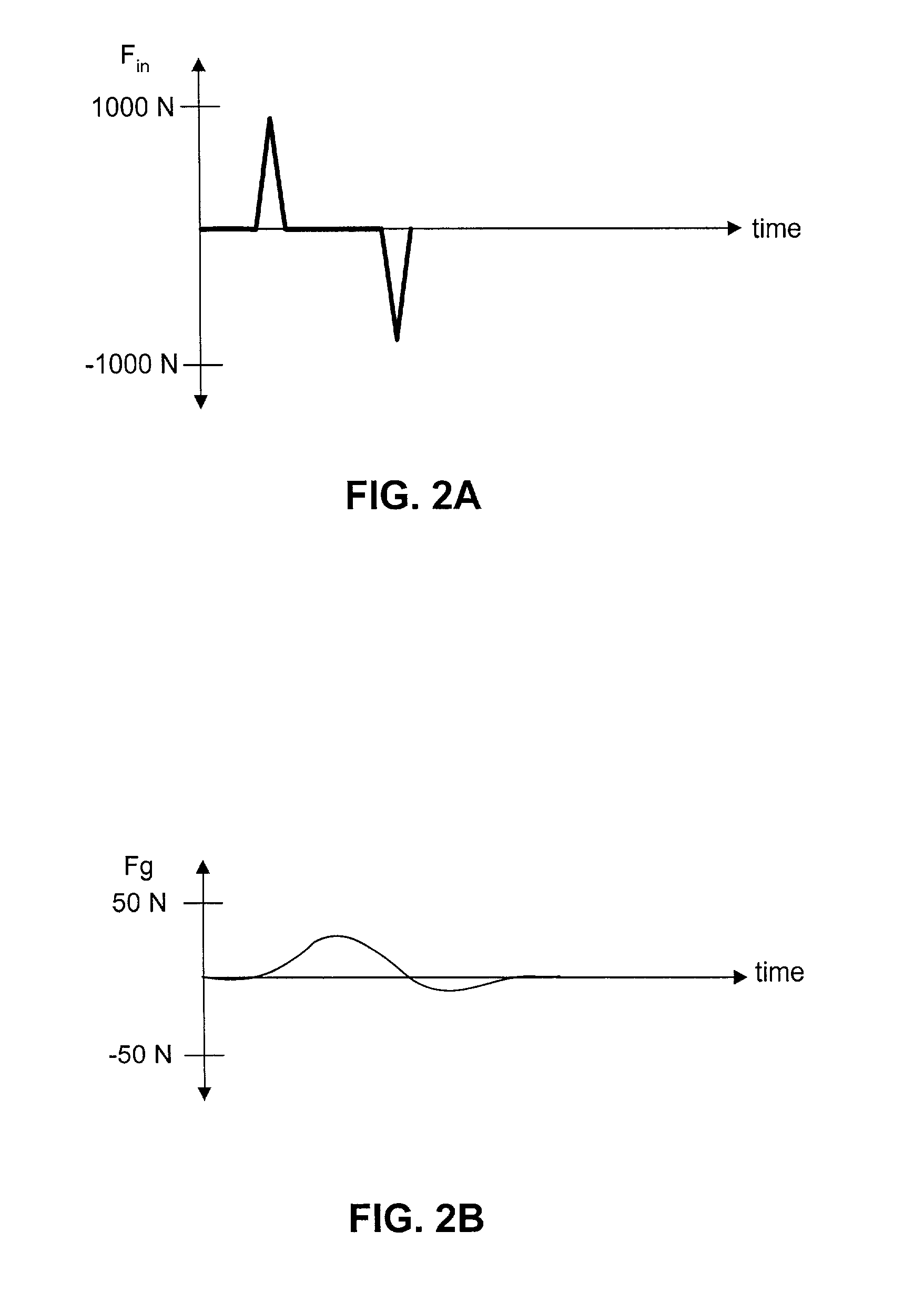

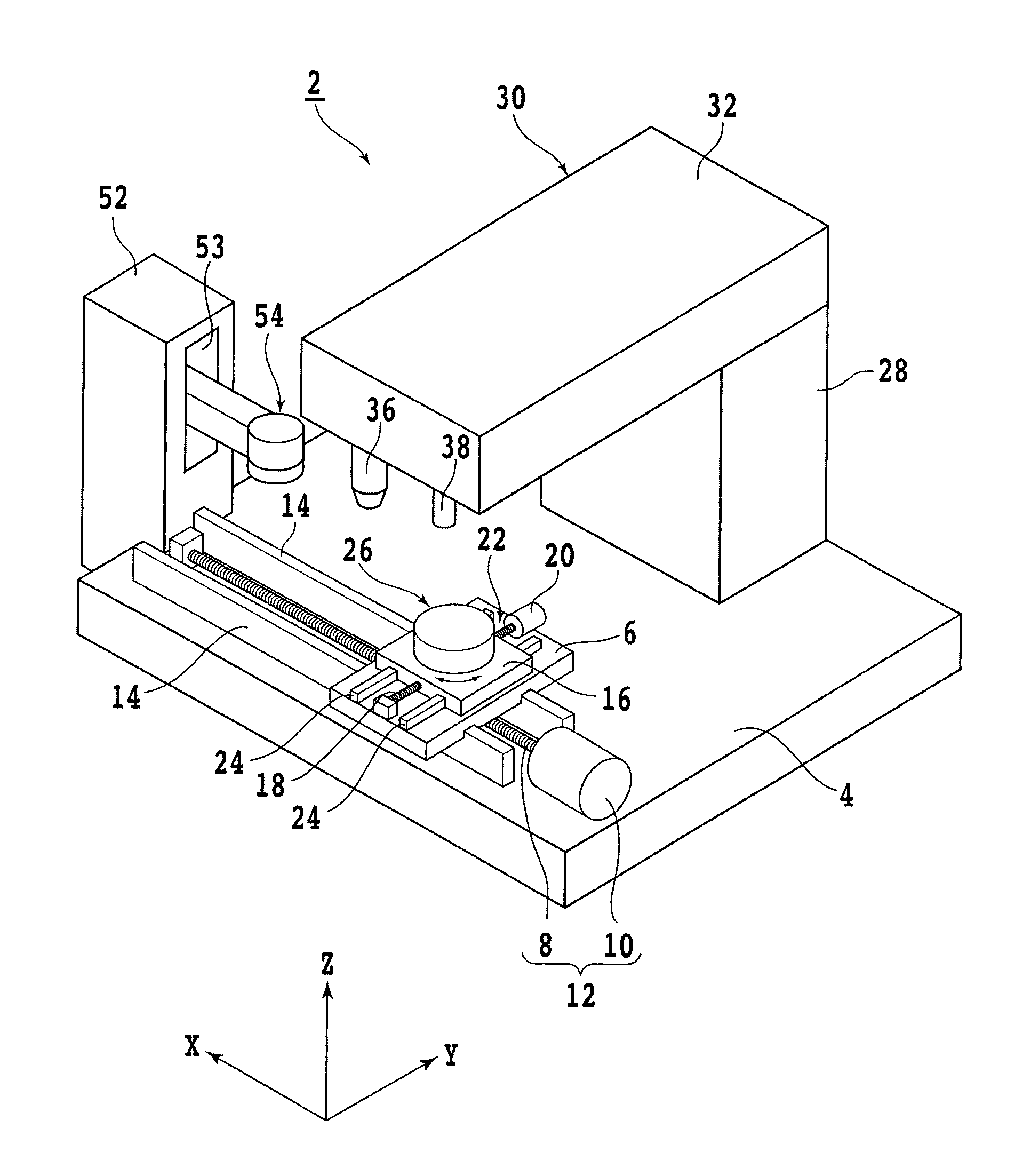

Reaction mass for a stage device

InactiveUS20020093637A1Electric controllersIgnition automatic controlSupporting systemControl system

A stage assembly and support system are provided to stabilize a stage base, such as a wafer stage base or a reticle stage base, minimizing forces transmitted from the stage assembly to a stationary surface, such as the ground, and thereby preventing vibration of other parts or systems in a wafer manufacturing process. Depending of the applicable photolithography system, a reticle stage and / or a wafer stage are accelerated in response to a wafer manufacturing control system to position the semiconductor substrates. The jerking motions of the reticle stage and / or wafer stage cause reaction forces acting on the reticle stage base and / or wafer stage base. The reaction forces induce vibration to the stationary surface and surrounding parts of the photolithography system. The wafer stage assembly and support system according to this invention allow the reticle stage base and / or wafer stage base to move relative the stationary surface. The base, acting as a massive reaction mass, stores a kinetic energy from the reaction force and gradually dissipates such energy by applying small forces to the reaction mass. The stage assembly and support system according to this invention are also capable of canceling any disturbance forces acting on the base.

Owner:NIKON CORP

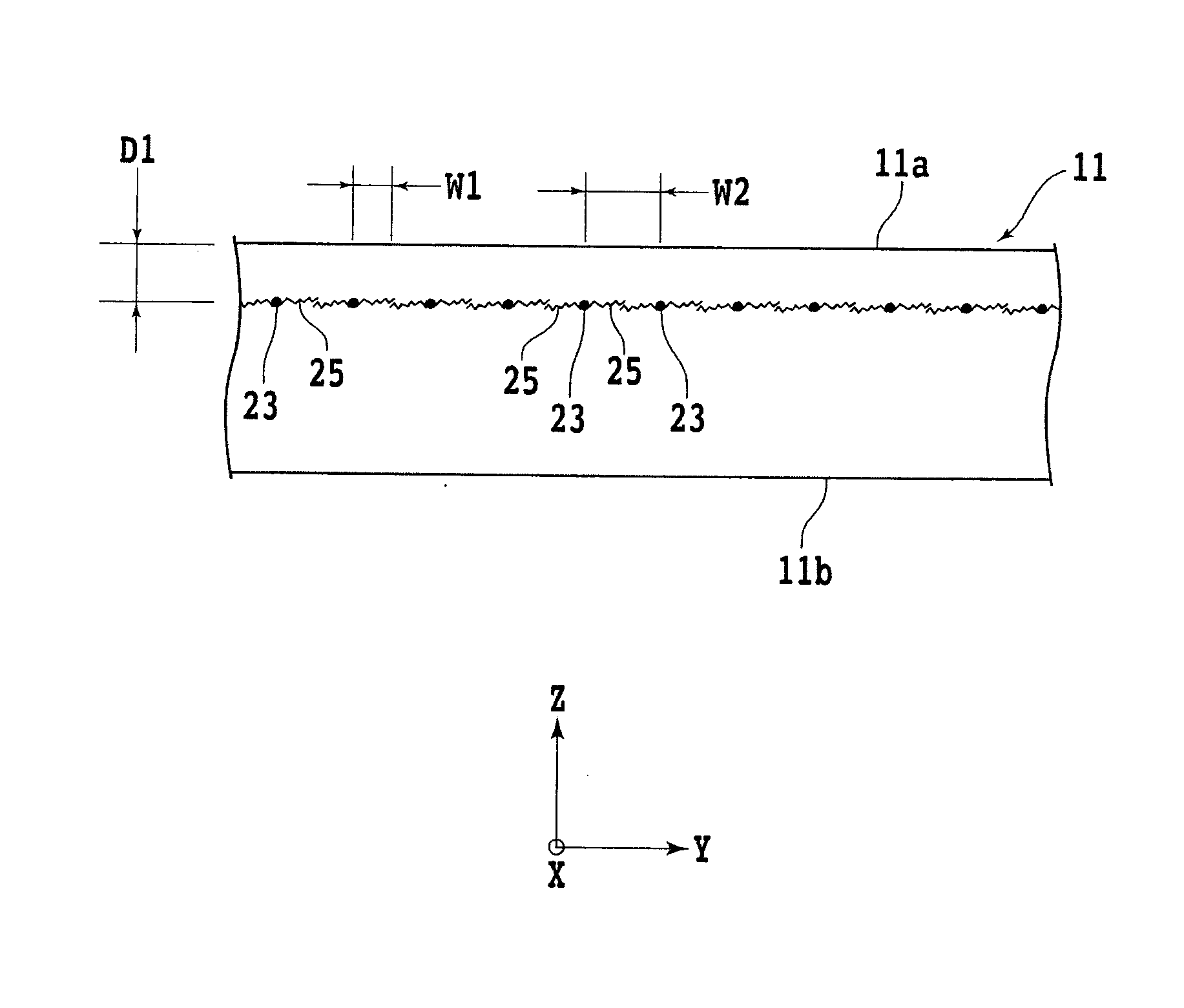

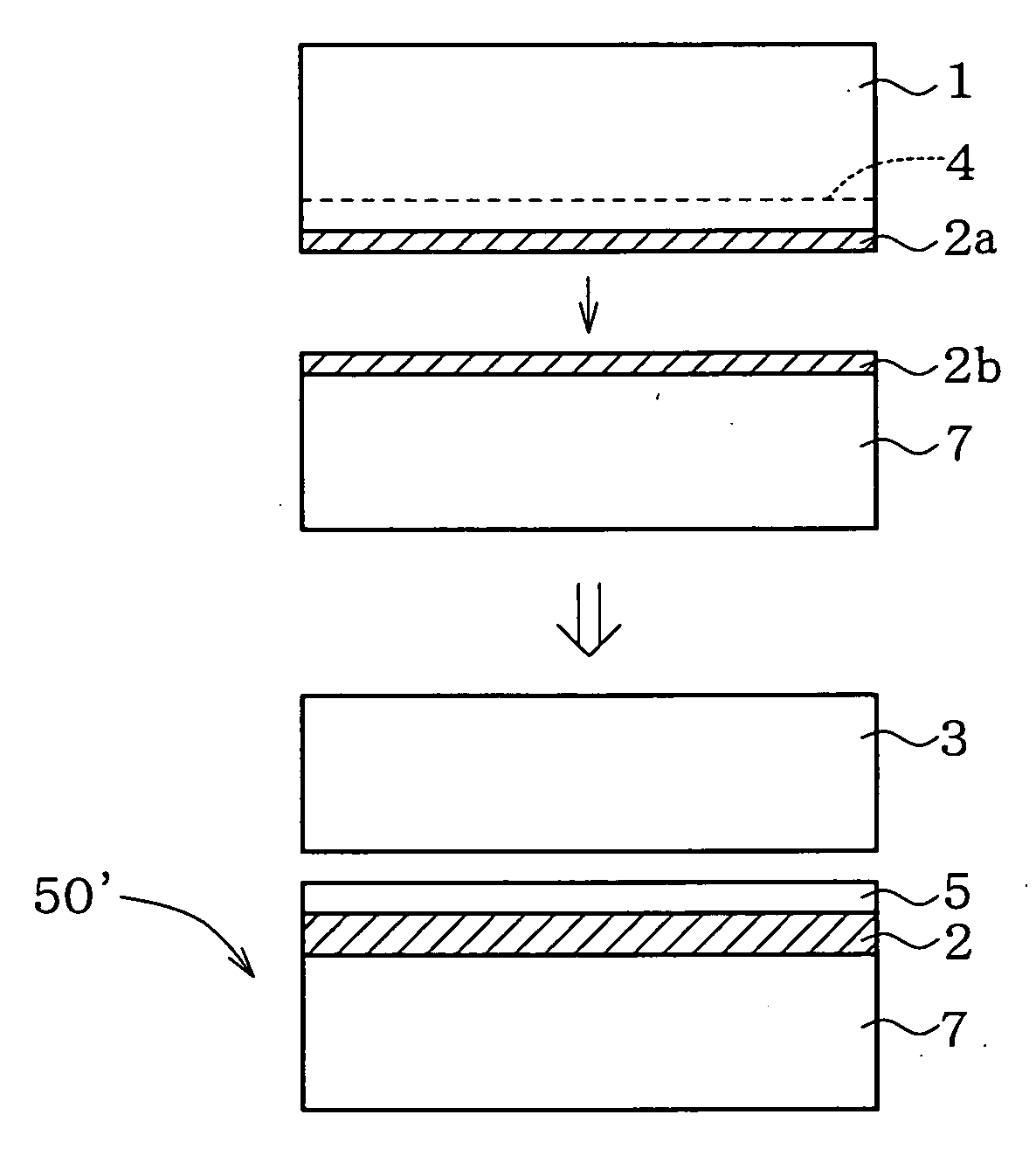

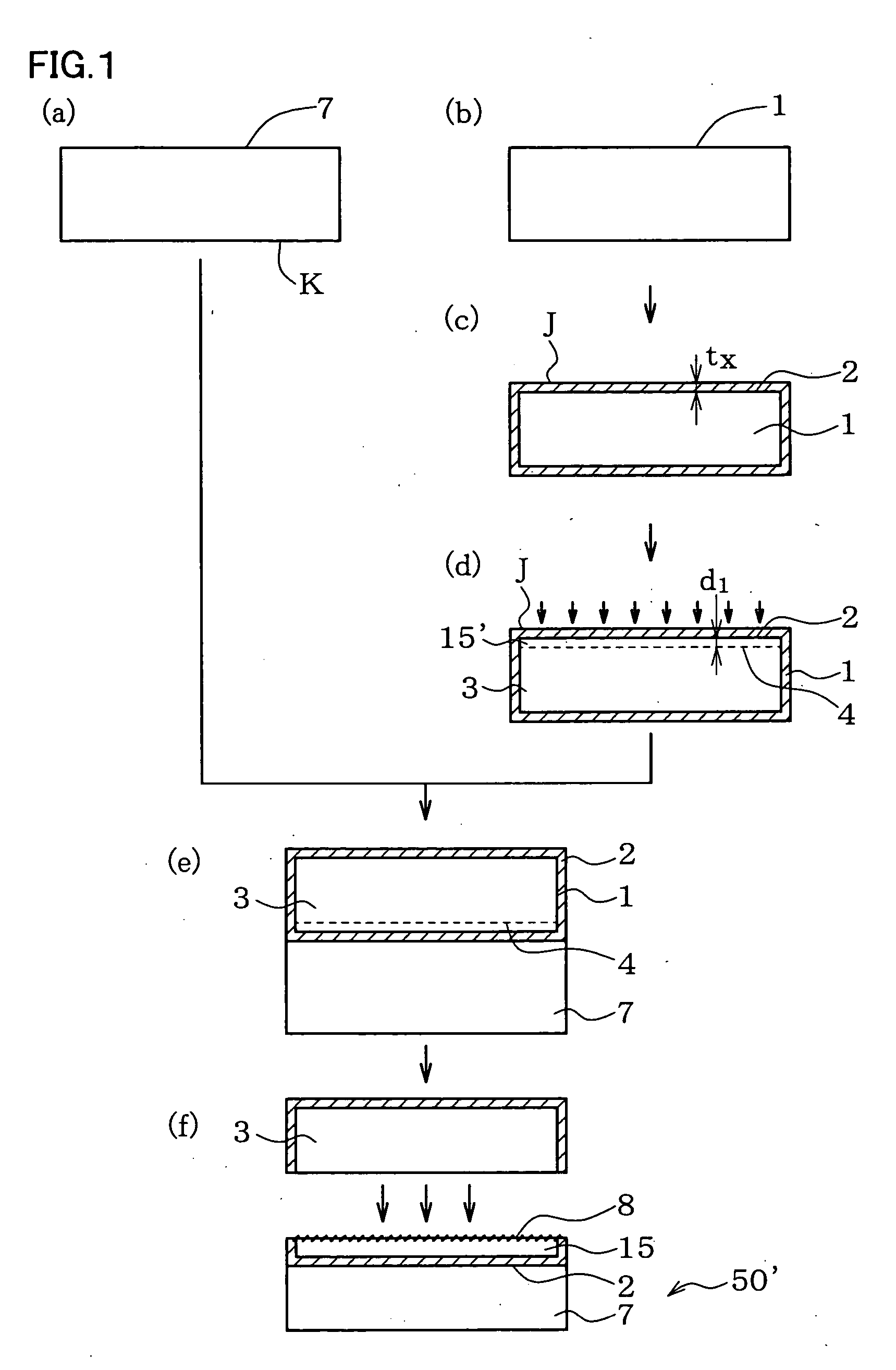

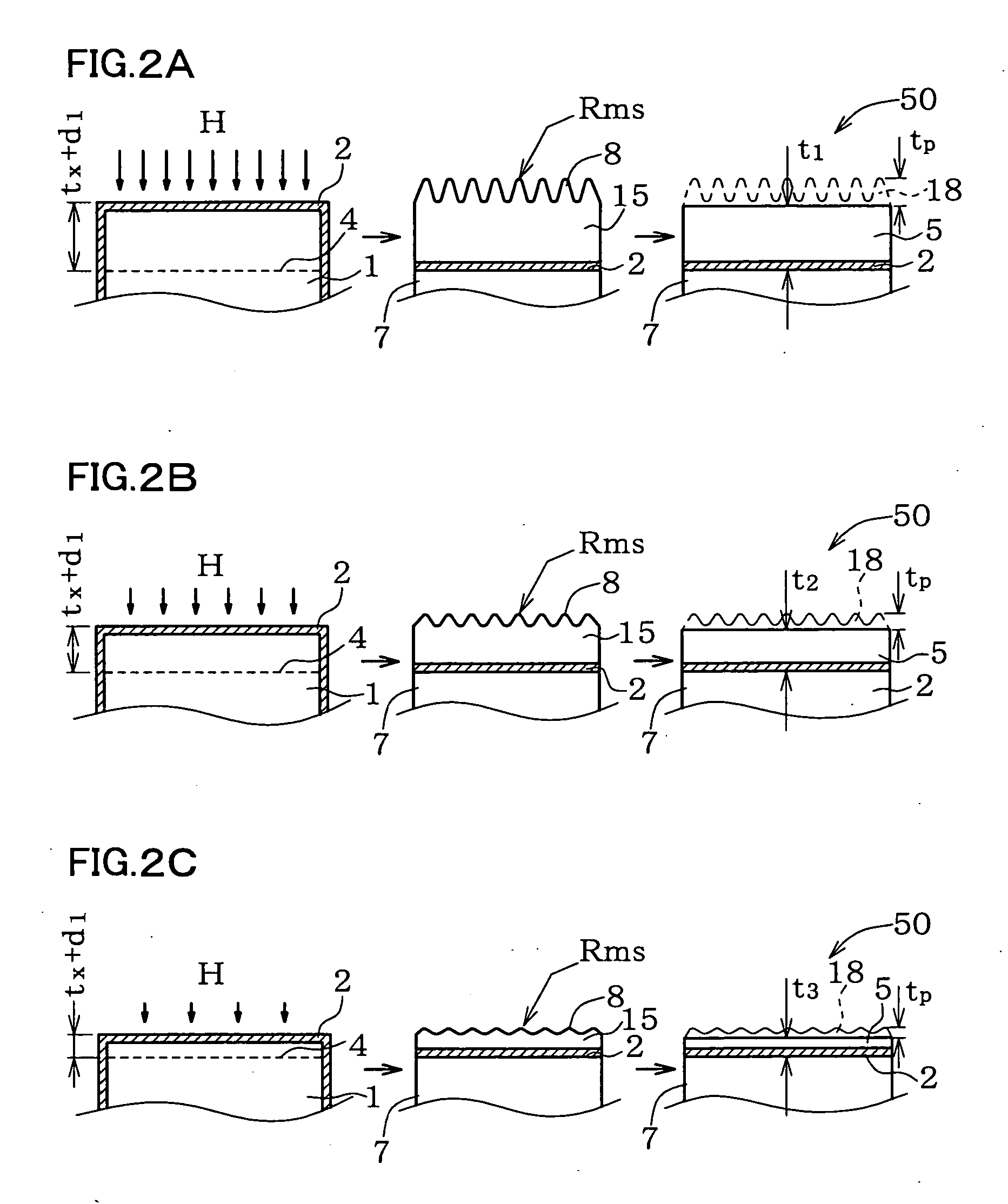

Soi wafer manufacturing method

ActiveUS20060040469A1Reduce roughnessImprove uniformitySolid-state devicesSemiconductor/solid-state device manufacturingWaferingSurface roughness

In order to adjust thickness of a bonded silicon single crystal film 15 depending of thickness of an SOI layer 5 to be obtained, depth of formation d1+tx of a separatory ion implanted layer 4, measured from a first main surface J, in the separatory ion implanted layer formation step is adjusted through energy of the ion implantation. Dose of the ion implantation is set smaller as the depth of formation measured from the first main surface J becomes smaller. A smaller dose results in a smaller surface roughness of the separation surface, and makes it possible to reduce polishing stock removal of the separation surface of the bonded silicon single crystal film in the planarization step. Uniformity in the thickness of the SOI layer can consequently be improved even for the case where a thin SOI layer has to be formed. The present invention is therefore successful in providing a method of fabricating an SOI wafer capable of suppressing variations in the intra-wafer and inter-wafer uniformity of the thickness of the SOI layer to a sufficiently low level, even for the case where a required level of the thickness of the SOI layer is extremely small.

Owner:SHIN-ETSU HANDOTAI CO LTD

Automated sourcing of substrate microfabrication defects using defects signatures

InactiveUS7229845B1Data processing applicationsSemiconductor/solid-state device testing/measurementWaferingAlgorithm

Automated defect sourcing system identifies root-causes of yield excursion due to contamination, process faults, equipment failure and / or handling in timely manner and provides accurate timely feedback to address and contain the sources of yield excursion. A signature bank stores known wafer surface manufacturing defects as defect signatures. The signature of a manufacturing defect pattern is associated with a type of equipment or process, and used to source the manufacturing defects and to provide process control for changing and / or stopping yield excursion during fabrication. A defect signature recognition engine matches wafer defects against the signature bank during wafer fabrication. Once the defect signature is detected during fabrication, handling and / or disposing the root-cause of the corresponding defect is facilitated using messages according to an event handling database. Optionally, a real-time process control for wafer fabrication is provided.

Owner:SIGLAZ +1

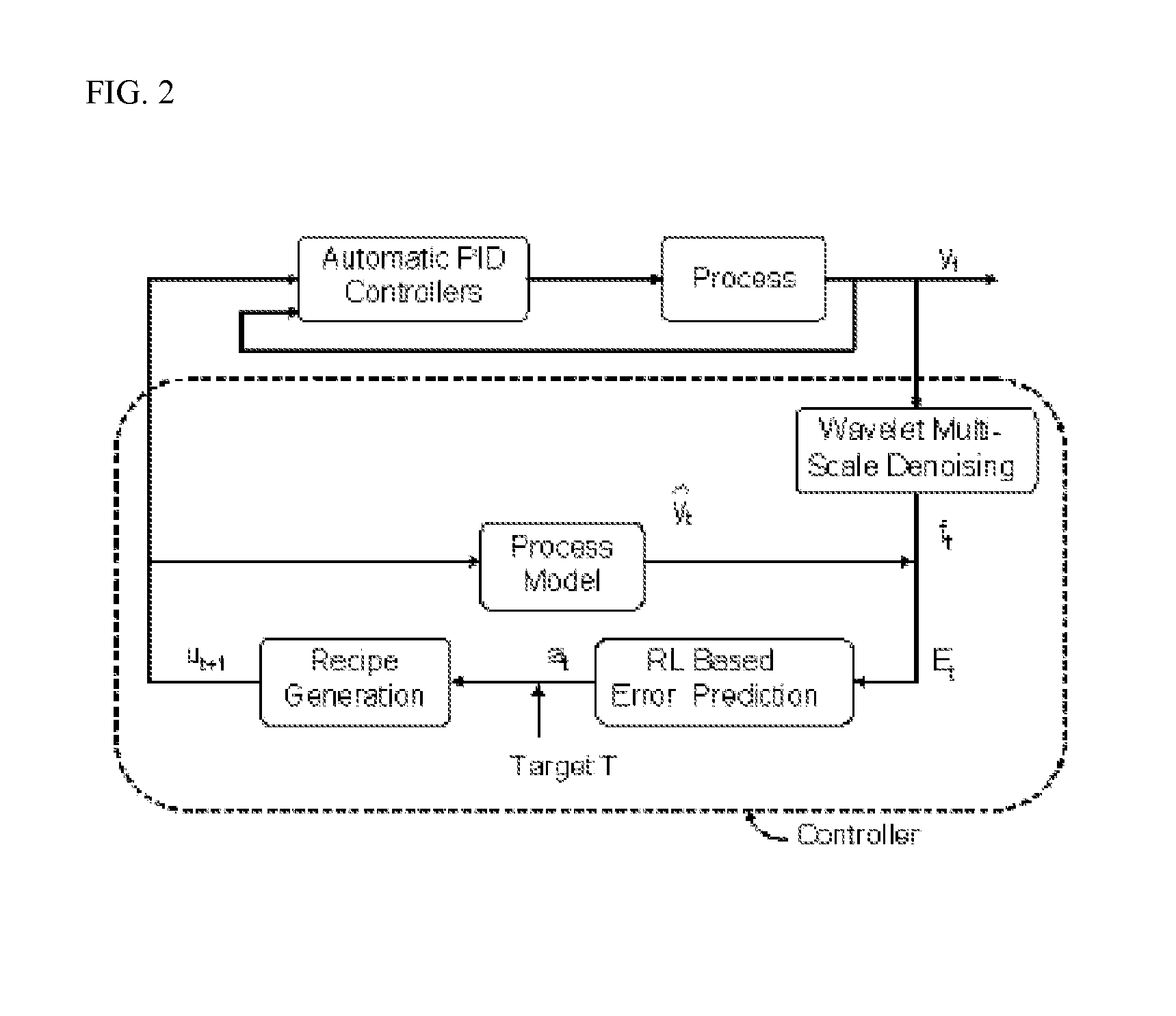

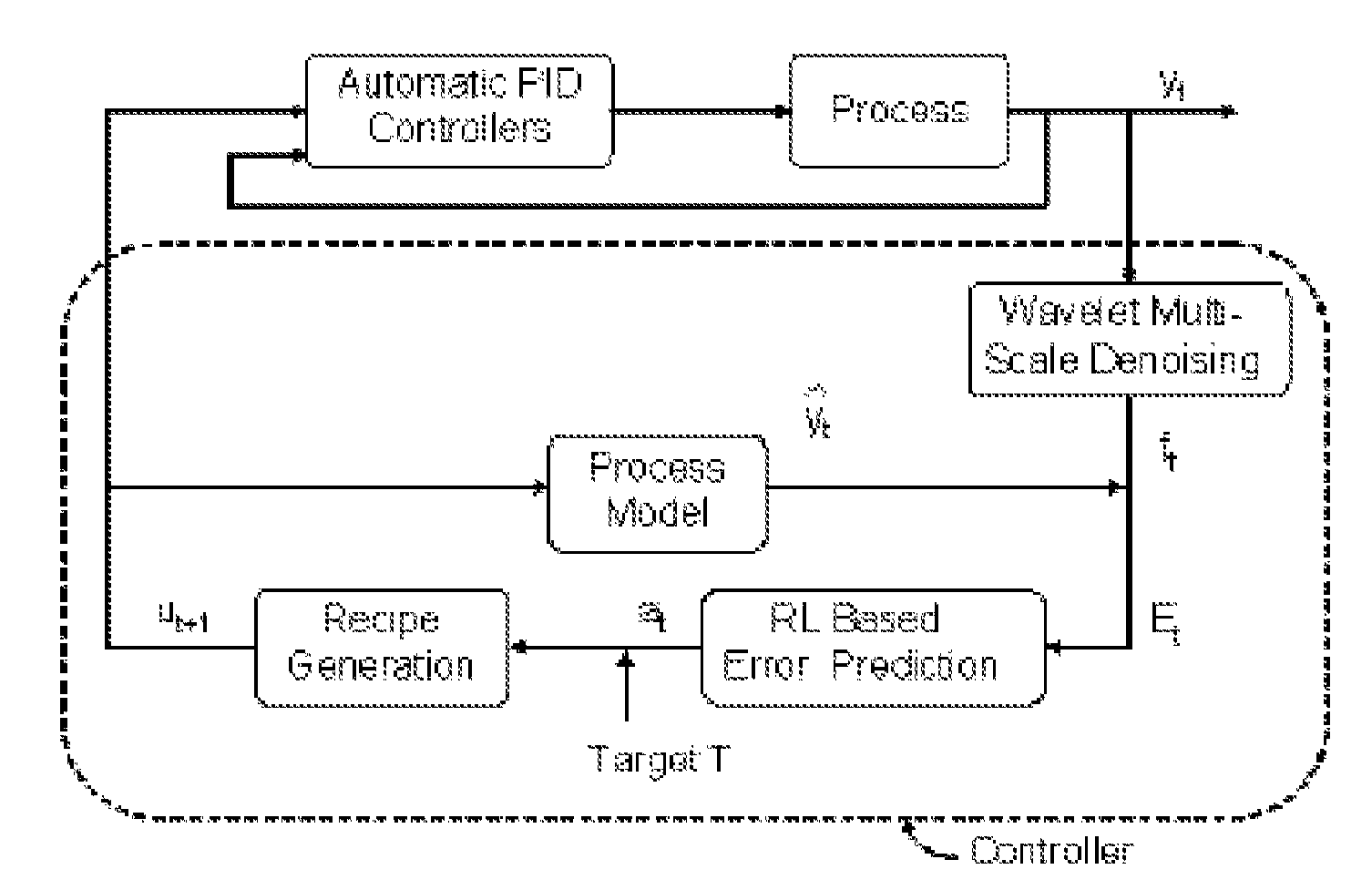

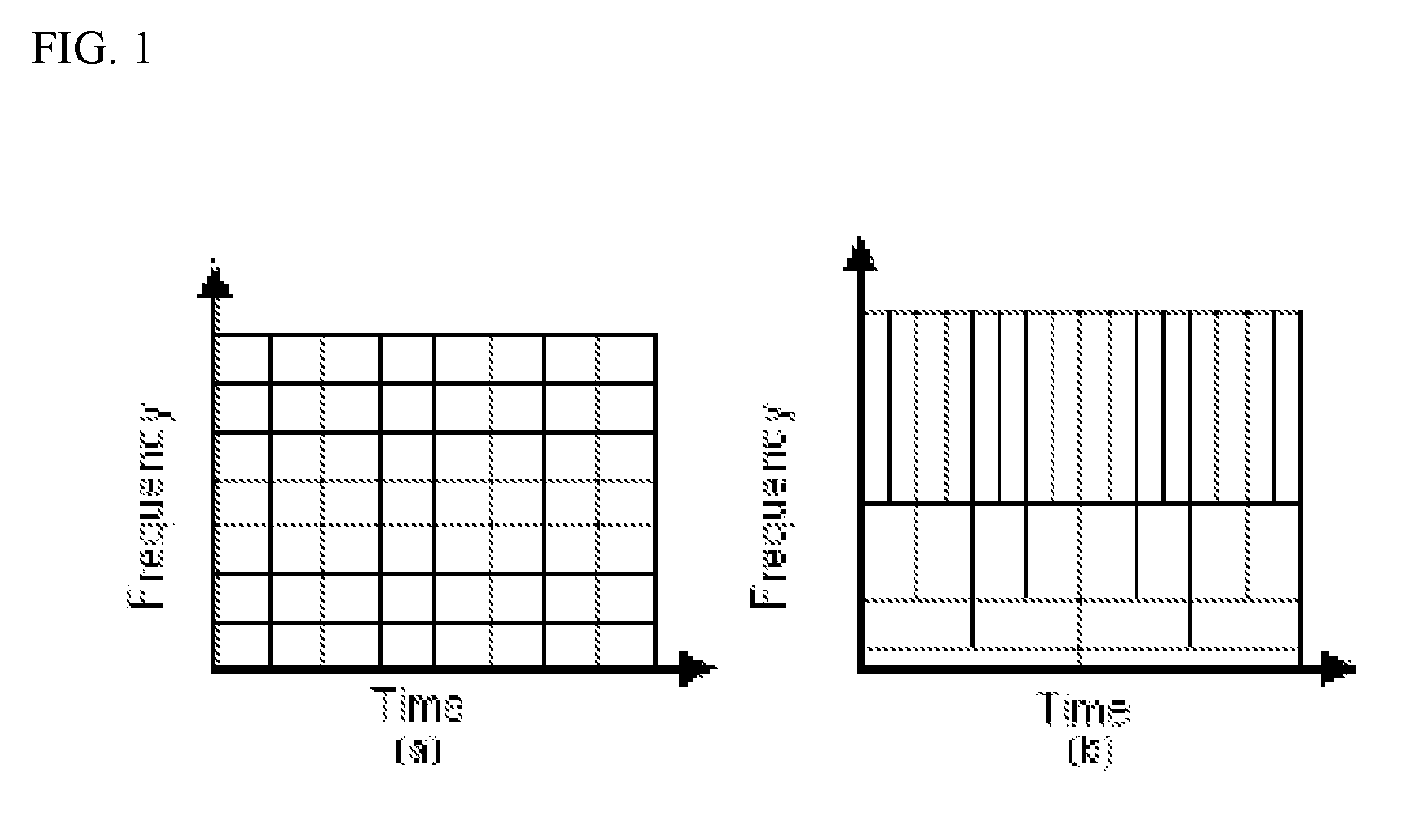

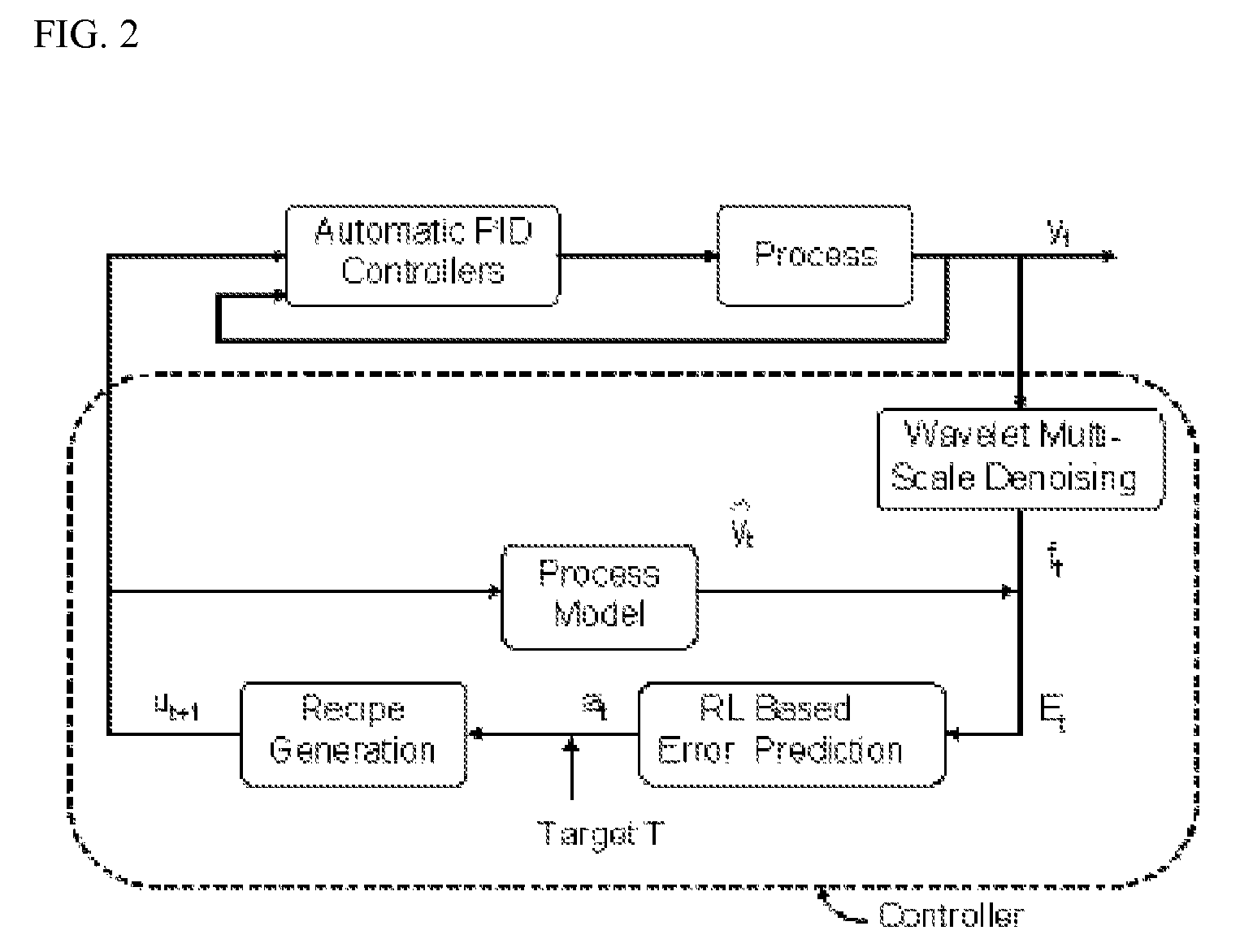

System for Multiresolution Analysis Assisted Reinforcement Learning Approach to Run-By-Run Control

InactiveUS20070260346A1Fast convergenceReduce varianceIgnition automatic controlControllers with particular characteristicsMultiresolution analysisControl system

A new multiresolution analysis (wavelet) assisted reinforcement learning (RL) based control strategy that can effectively deal with both multiscale disturbances in processes and the lack of process models. The application of wavelet aided RL based controller represents a paradigm shift in the control of large scale stochastic dynamic systems of which the control problem is a subset. The control strategy is termed a WRL-RbR controller. The WRL-RbR controller is tested on a multiple-input-multiple-output (MIMO) Chemical Mechanical Planarization (CMP) process of wafer fabrication for which process model is available. Results show that the RL controller outperforms EWMA based controllers for low autocorrelation. The new controller also performs quite well for strongly autocorrelated processes for which the EWMA controllers are known to fail. Convergence analysis of the new breed of WRL-RbR controller is presented. Further enhancement of the controller to deal with model free processes and for inputs coming from spatially distributed environments are also addressed.

Owner:UNIV OF SOUTH FLORIDA

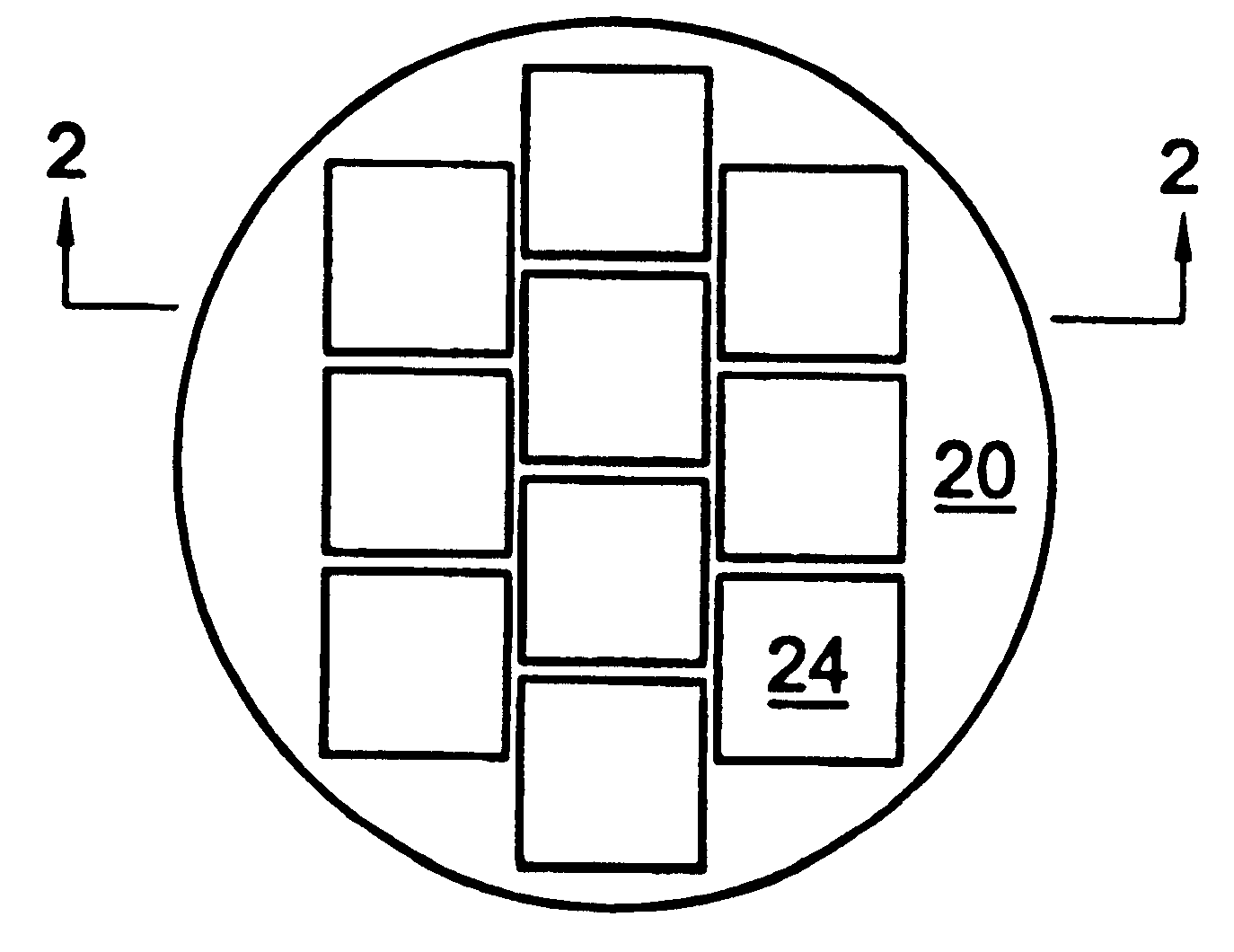

Discrete wafer array process

InactiveUS6248646B1High temperature resistanceGreat ruggednessSolid-state devicesSemiconductor/solid-state device manufacturingWaferingCompound (substance)

A method of preparing small wafers for compatibility with conventional large wafer fabrication equipment comprising the following steps: indenting a face of a large wafer to form an array of depressions thereon, each depression sized to matingly accept a lower portion of a small wafer; applying a bonding medium to an exterior side of the depressions on the indented face of the large wafer; matingly fitting the small wafers into the depressions so that the small wafers are positioned in an array on the large wafer; and, removing the top portion of the small wafers standing out of the depressions by chemical mechanical polishing so that the remaining portions of the small wafers then have a uniform thickness generally equal to the depth of the indentations in the large wafer. A preferred aspect of this invention provides for a method as above wherein the small wafer is SiC and the large wafer is made from an amorphous substance which comprises SiC or aluminum nitride.

Owner:OKOJIE ROBERT S

Wafer producing method

ActiveUS9517530B2Efficient productionEasy to separatePolycrystalline material growthSemiconductor/solid-state device manufacturingWafer fabricationSingle crystal

Owner:DISCO CORP

System for multiresolution analysis assisted reinforcement learning approach to run-by-run control

InactiveUS7672739B2Fast convergenceReduce varianceIgnition automatic controlControllers with particular characteristicsMultiresolution analysisWafer fabrication

A new multiresolution analysis (wavelet) assisted reinforcement learning (RL) based control strategy that can effectively deal with both multiscale disturbances in processes and the lack of process models. The application of wavelet aided RL based controller represents a paradigm shift in the control of large scale stochastic dynamic systems of which the control problem is a subset. The control strategy is termed a WRL-RbR controller. The WRL-RbR controller is tested on a multiple-input-multiple-output (MIMO) Chemical Mechanical Planarization (CMP) process of wafer fabrication for which process model is available. Results show that the RL controller outperforms EWMA based controllers for low autocorrelation. The new controller also performs quite well for strongly autocorrelated processes for which the EWMA controllers are known to fail. Convergence analysis of the new breed of WRL-RbR controller is presented. Further enhancement of the controller to deal with model free processes and for inputs coming from spatially distributed environments are also addressed.

Owner:UNIV OF SOUTH FLORIDA

Polishing Composition for CMP and device wafer producing method using the same

InactiveUS20090104778A1Reduce and minimize and eliminate scratchReducing and minimizing and surface scratchOther chemical processesSemiconductor/solid-state device manufacturingGlycerol DerivativesAcyl group

Disclosed is a polishing composition for CMP which contains a polyglycerol derivative (A) represented by following Formula (1):RO—(C3H6O2)n—H (1)wherein R represents one selected from a hydroxyl-substituted or unsubstituted alkyl group having one to eighteen carbon atoms, a hydroxyl-substituted or unsubstituted alkenyl or alkapolyenyl group having two to eighteen carbon atoms, an acyl group having two to twenty-four carbon atoms, and hydrogen atom; and “n” denotes an average degree of polymerization of glycerol units and is an integer of 2 to 40; an abrasive (B); and water.

Owner:DAICEL CHEM IND LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com