Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

519 results about "High memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

High memory is the part of physical memory in a computer which is not directly mapped by the page tables of its operating system kernel. The phrase is also sometimes used as shorthand for the High Memory Area, which is a different concept entirely.

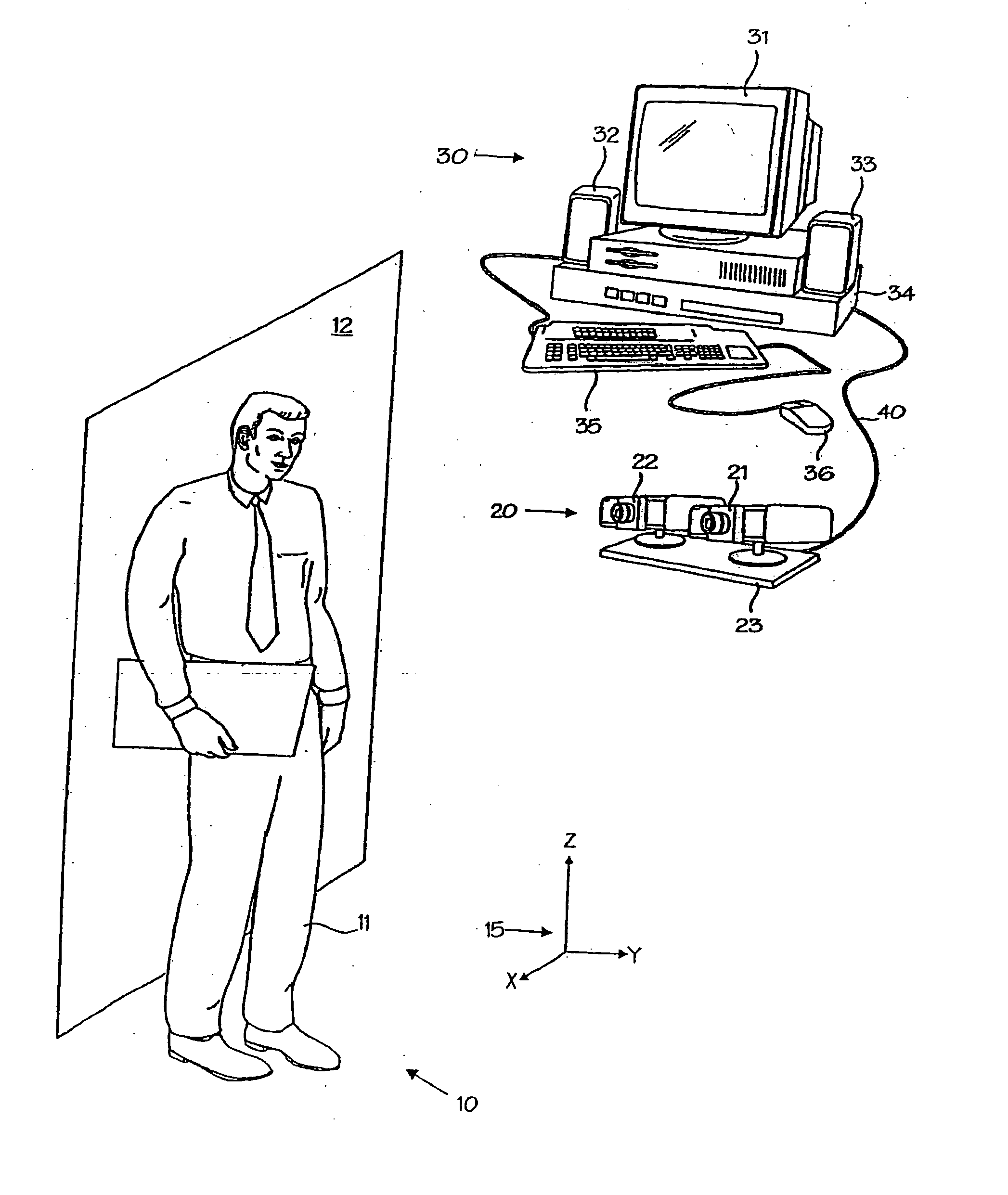

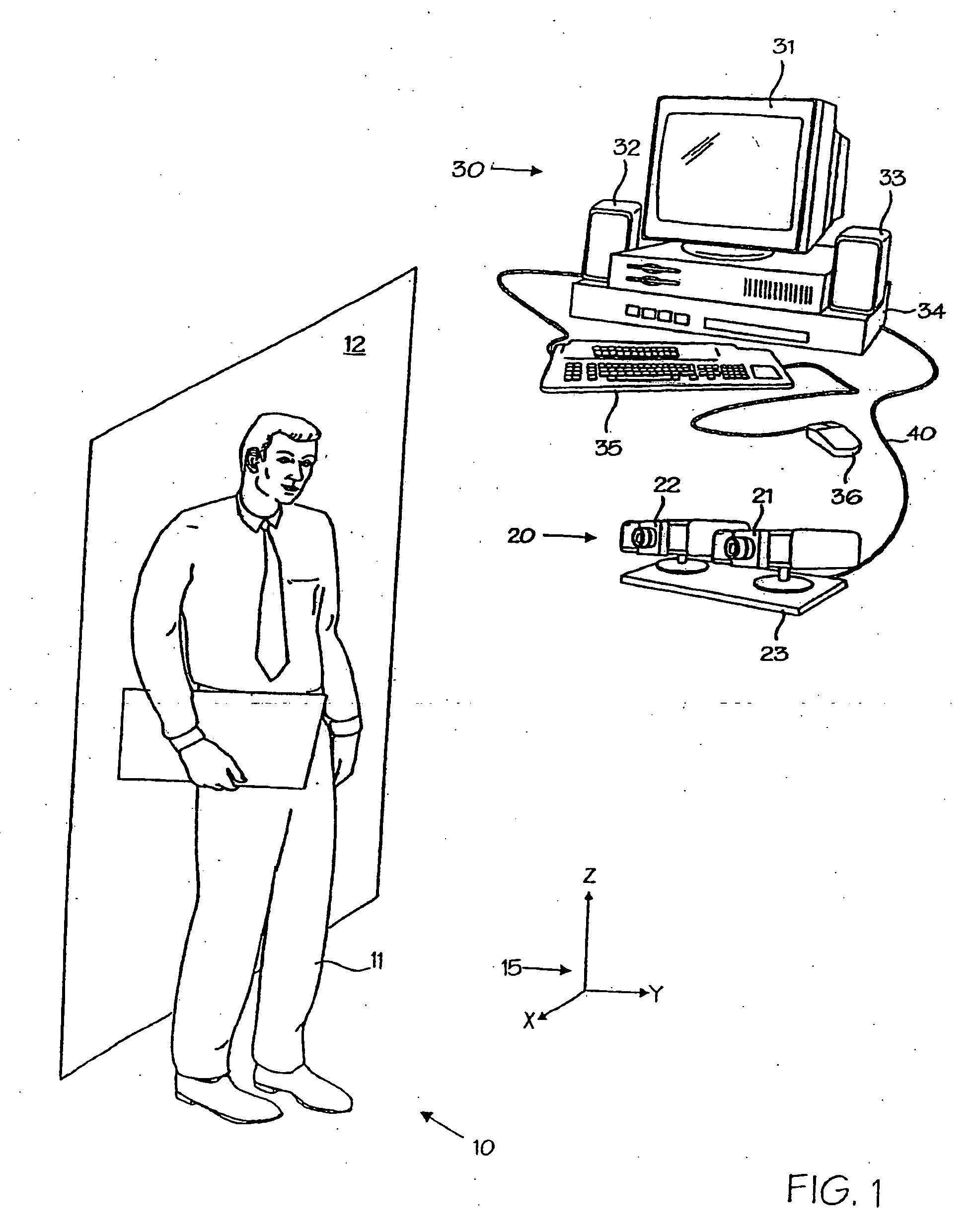

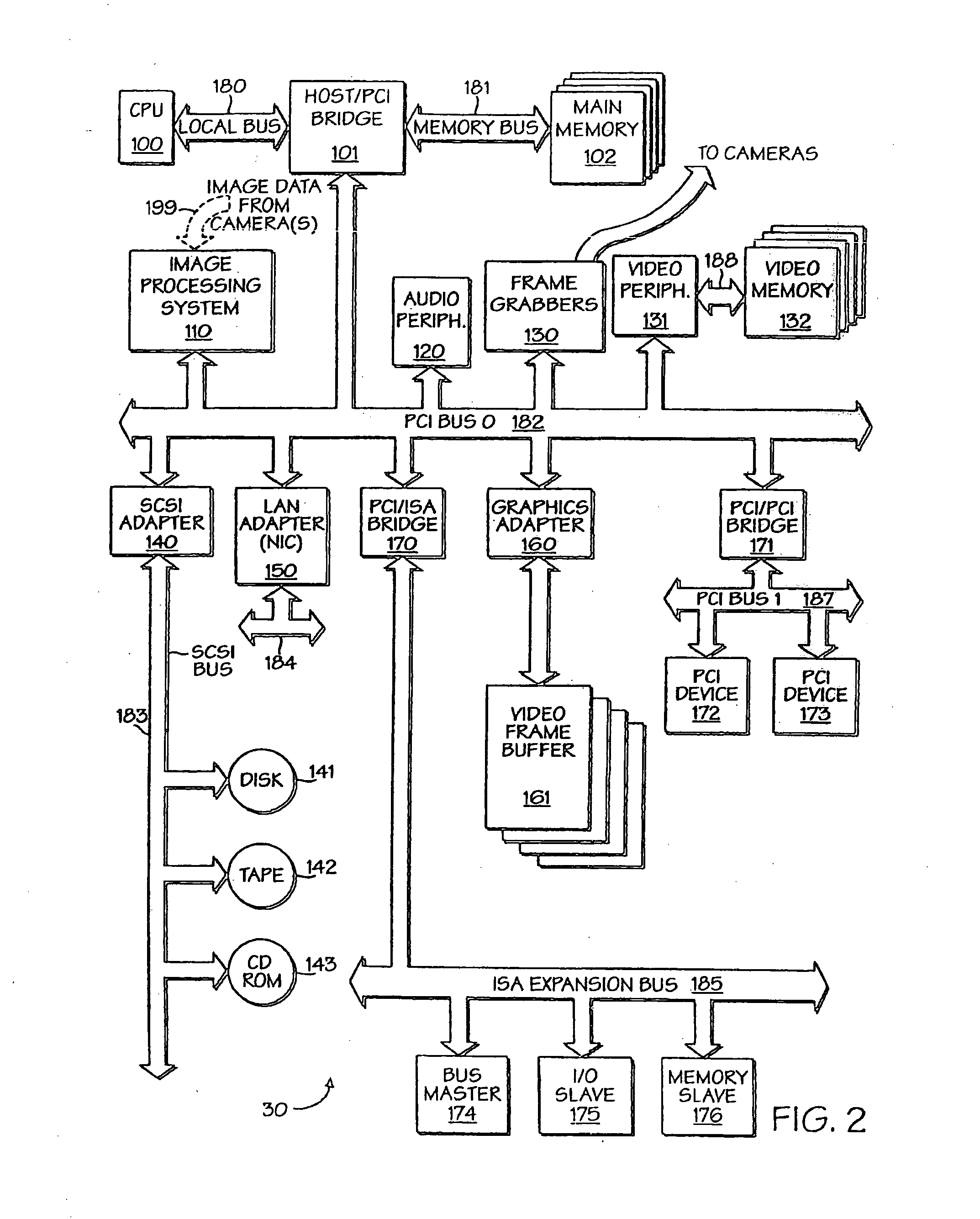

Data processing system and method

InactiveUS6215898B1Reduce overheadHigh sensitivityImage enhancementImage analysisStatic random-access memoryHigh memory

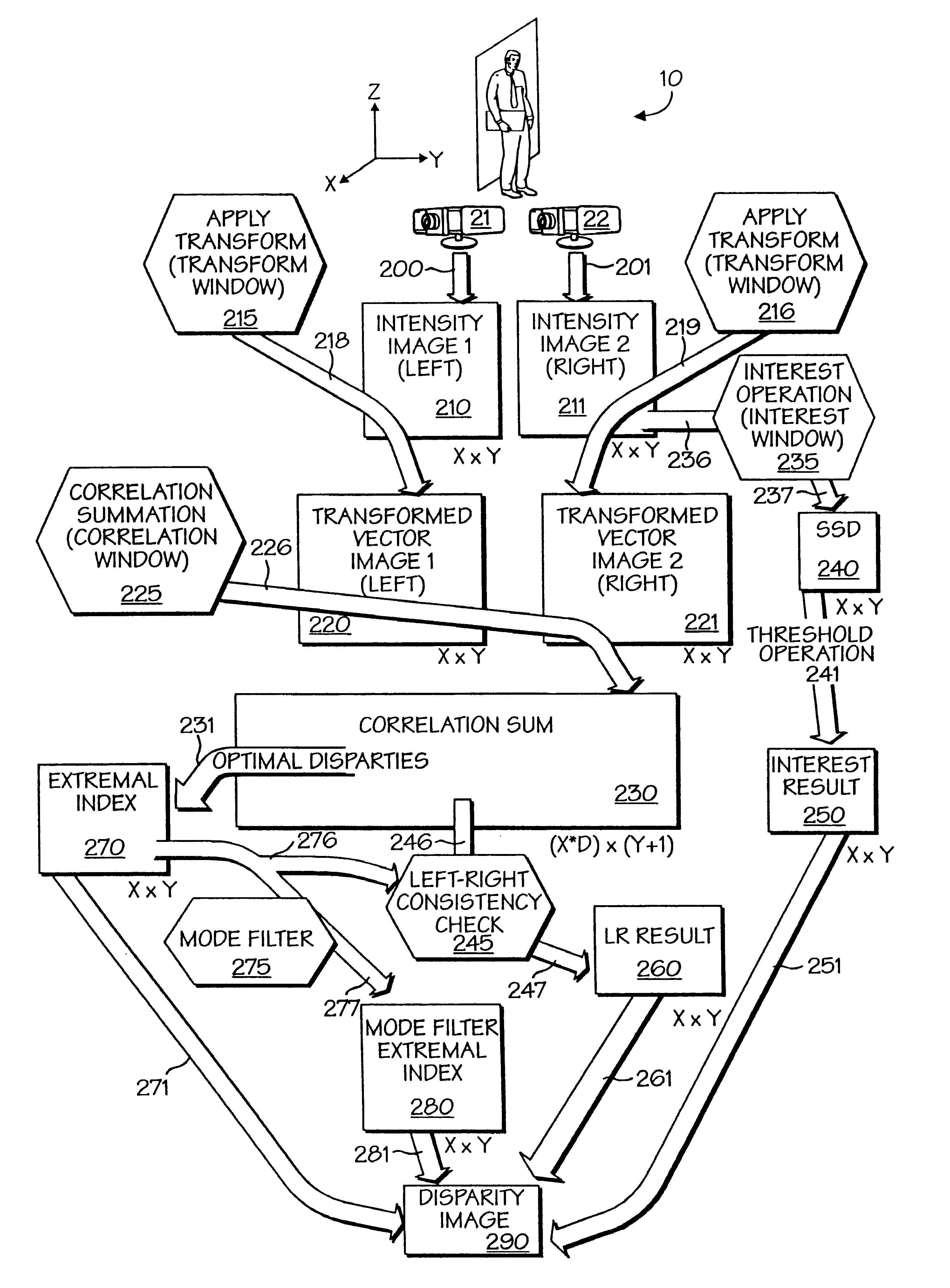

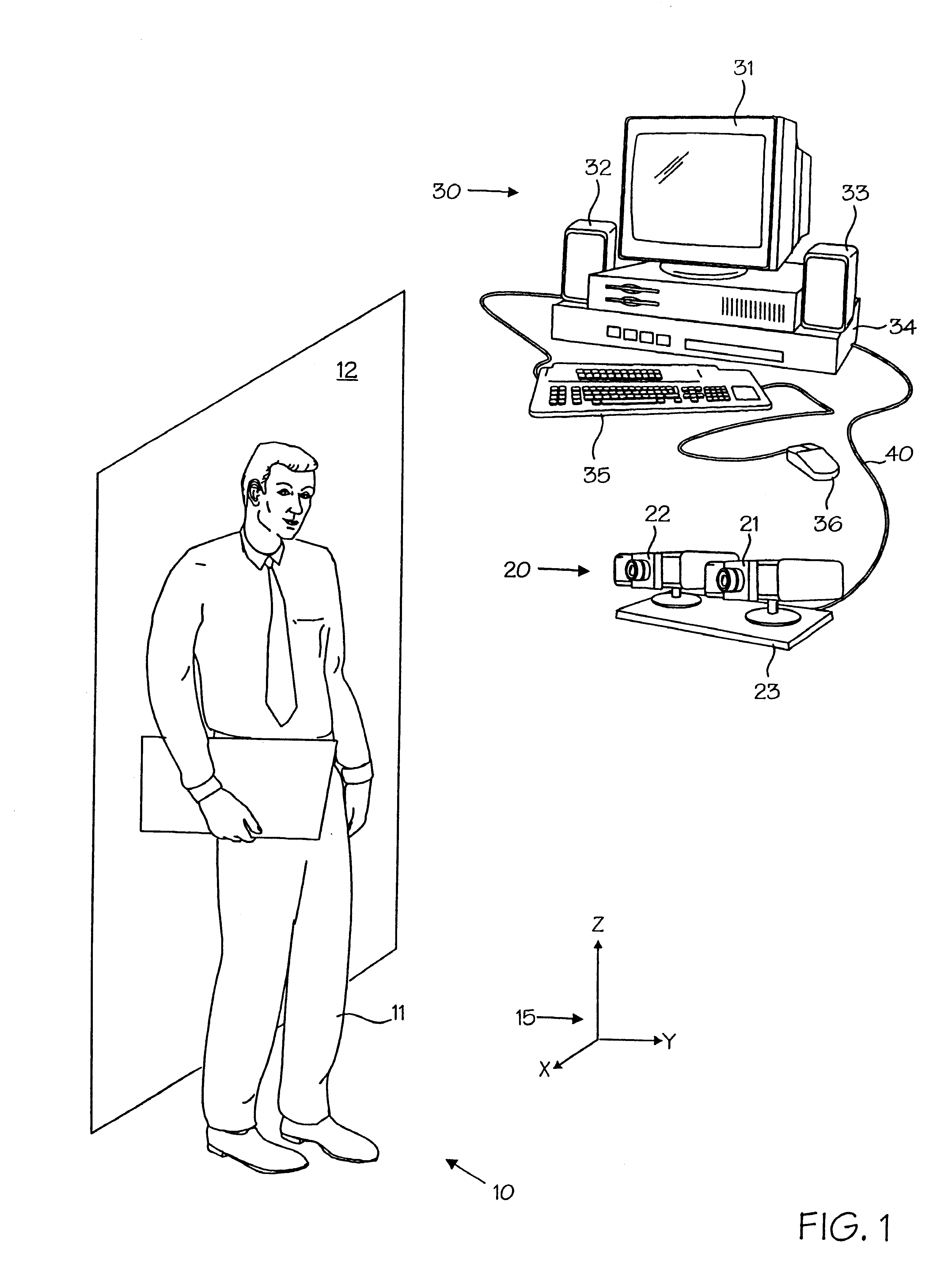

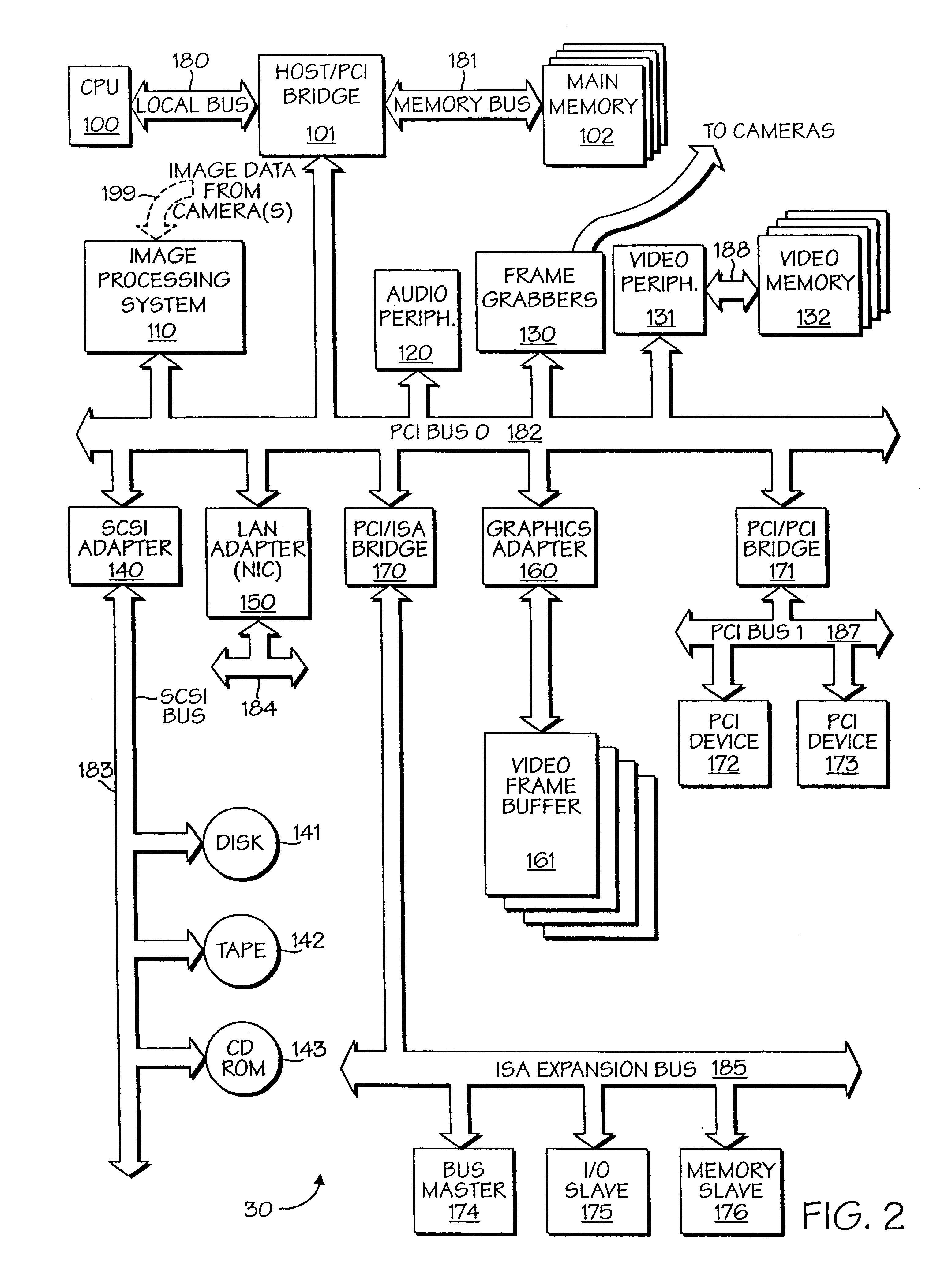

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP

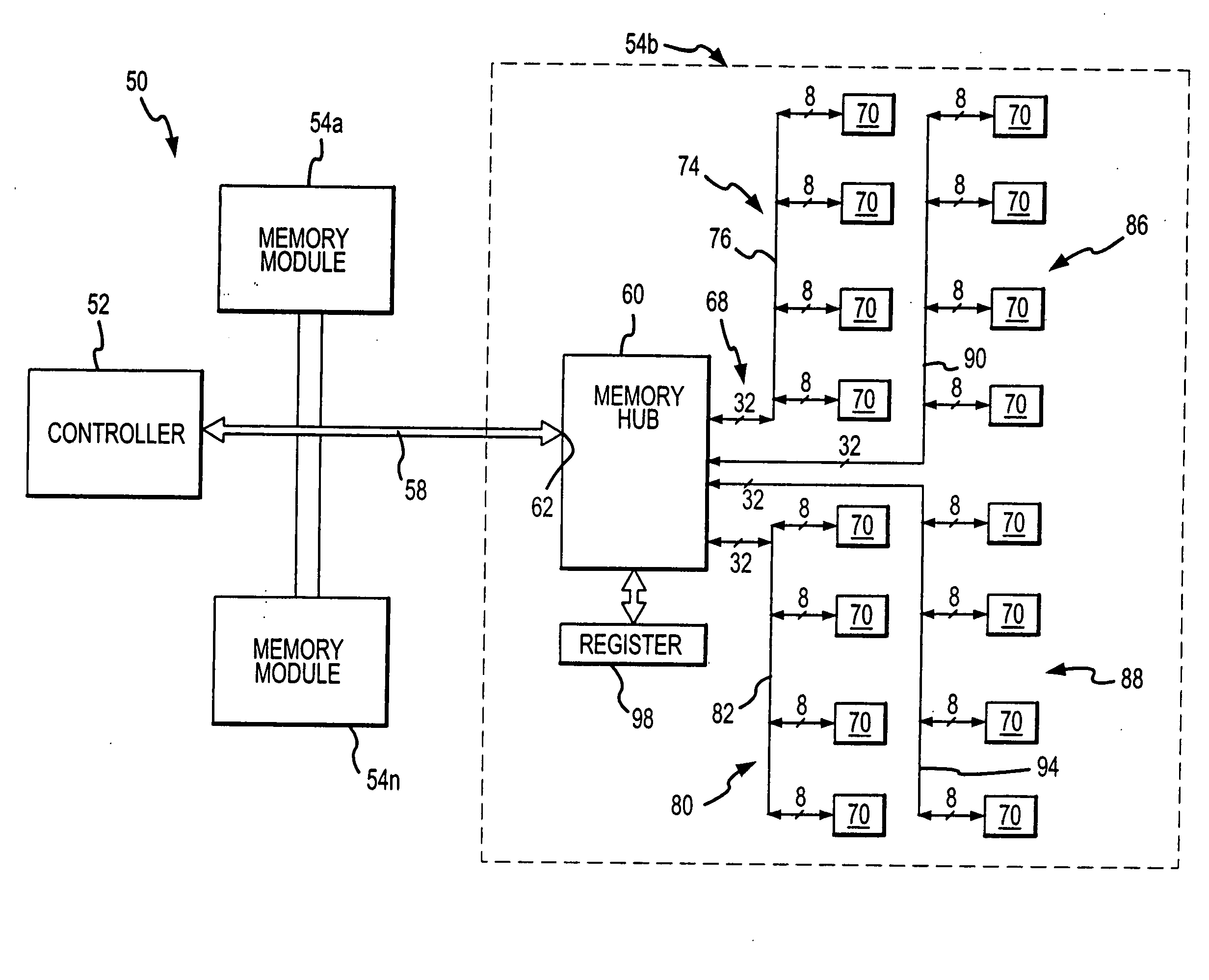

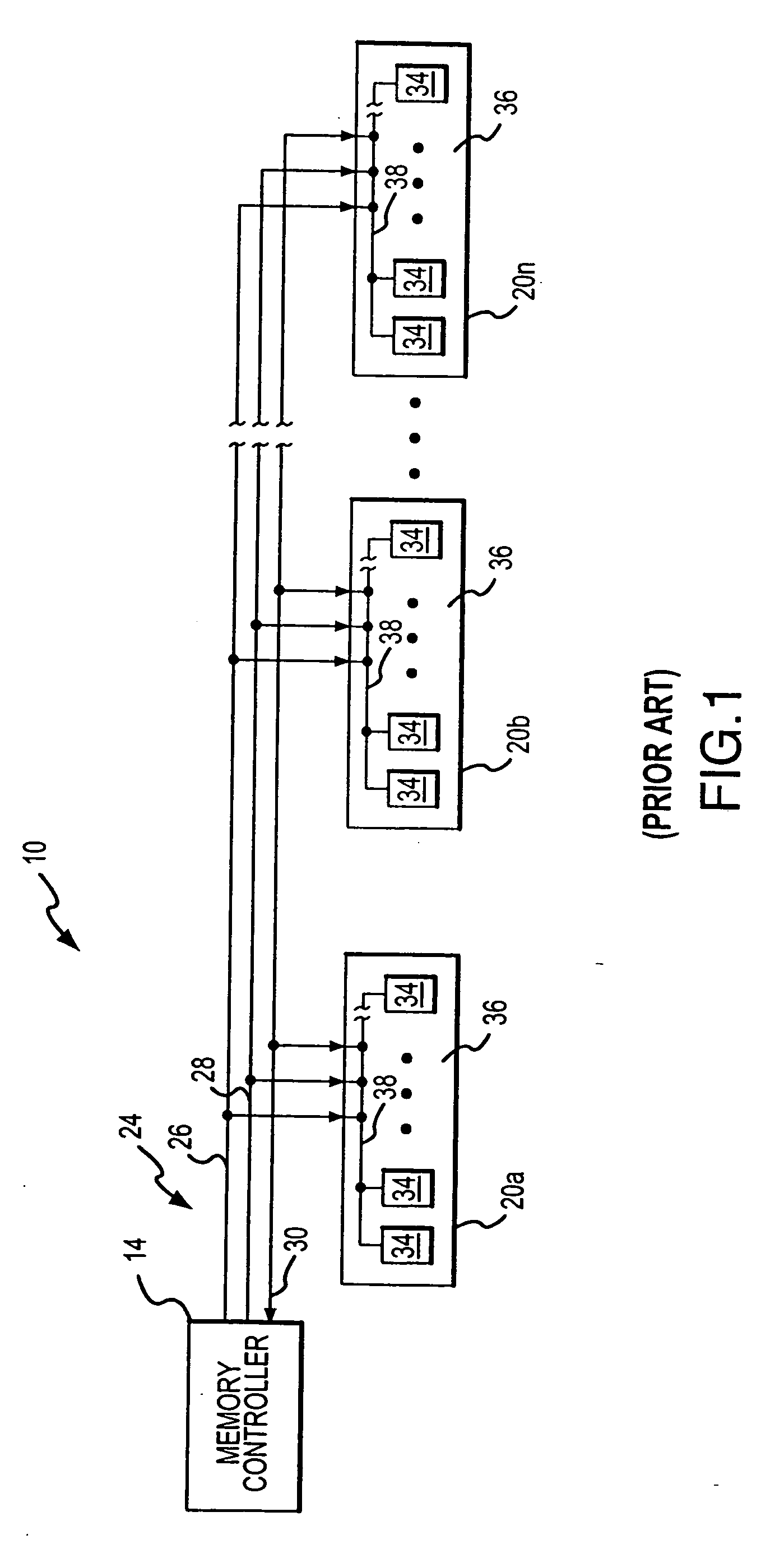

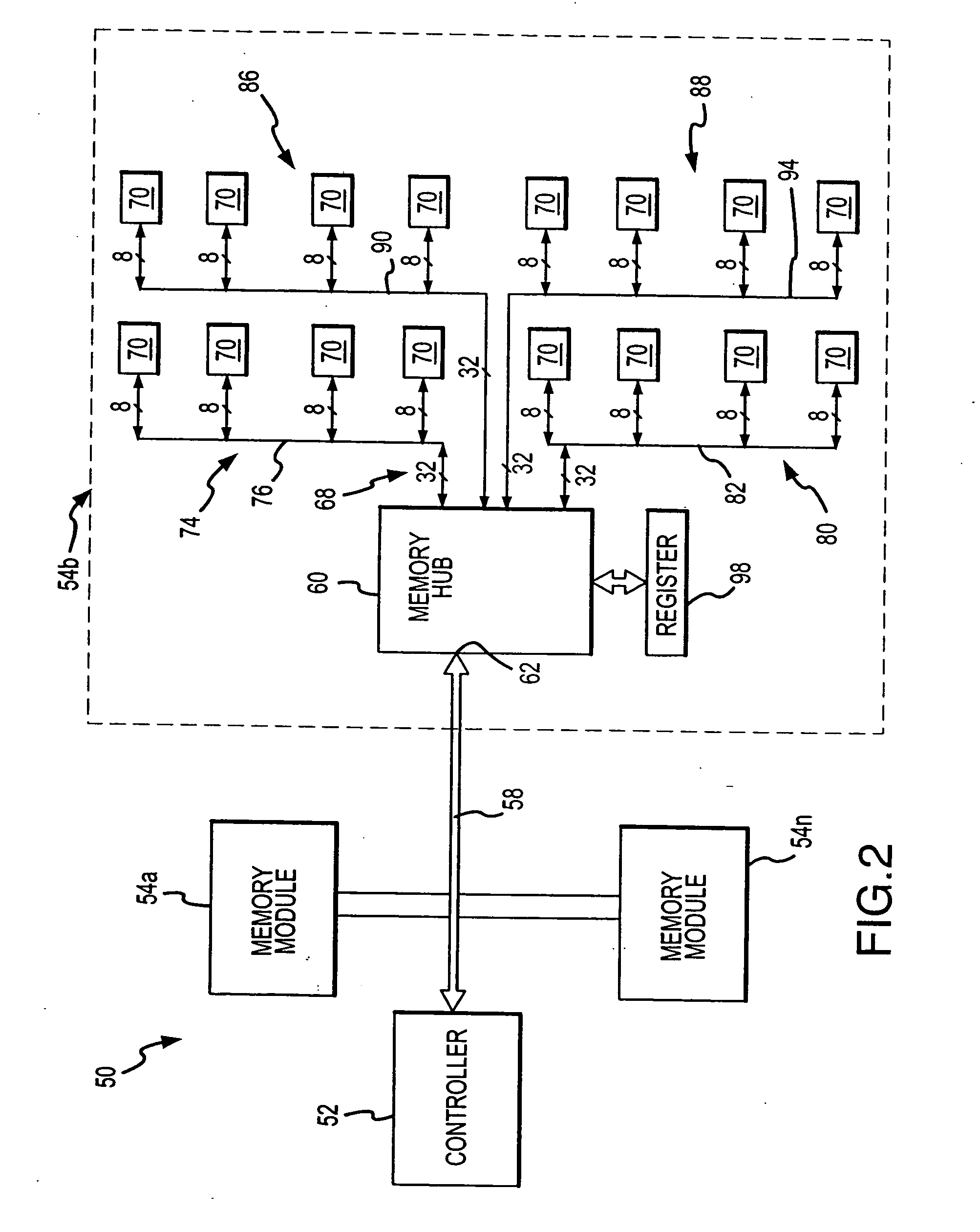

Reconfigurable memory module and method

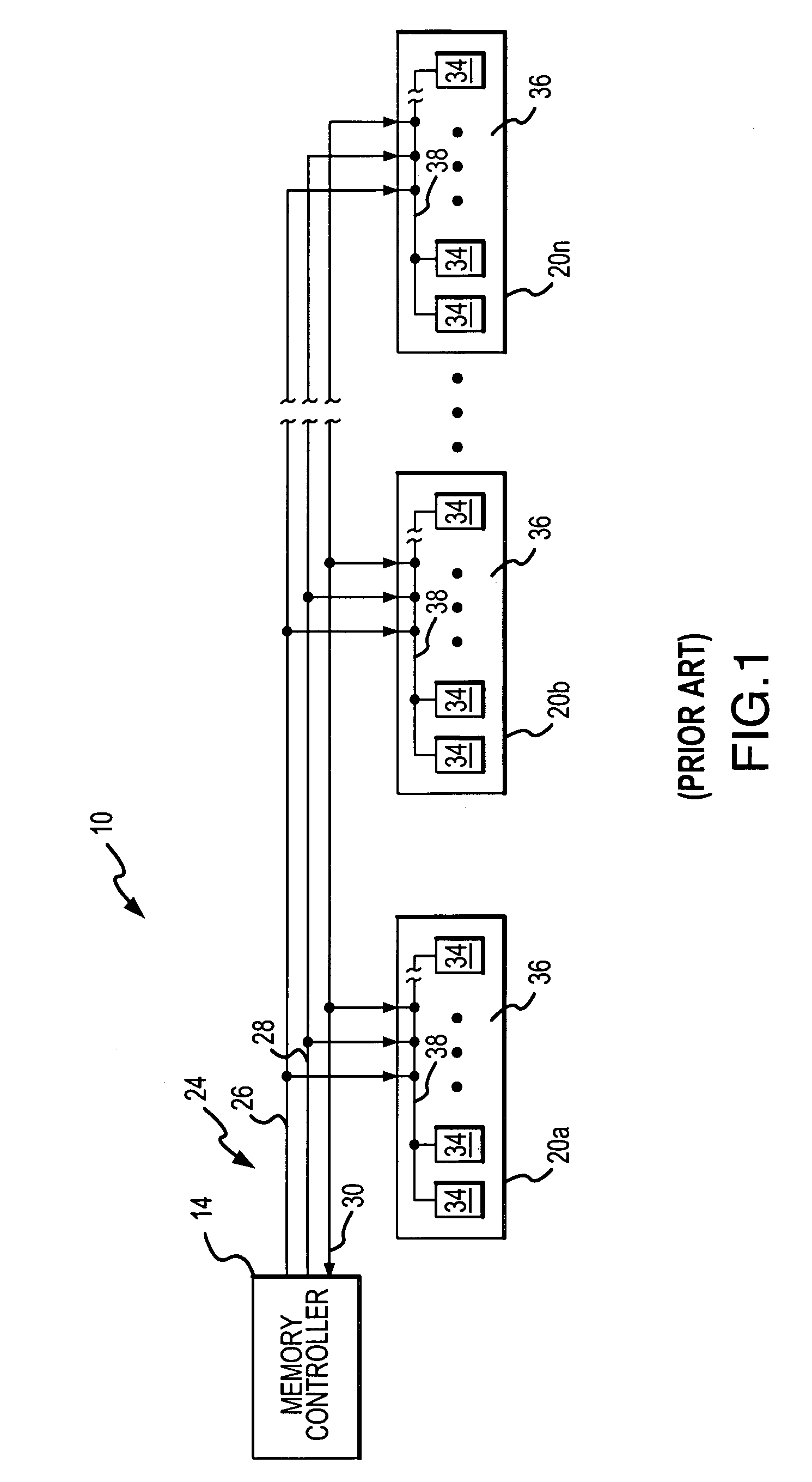

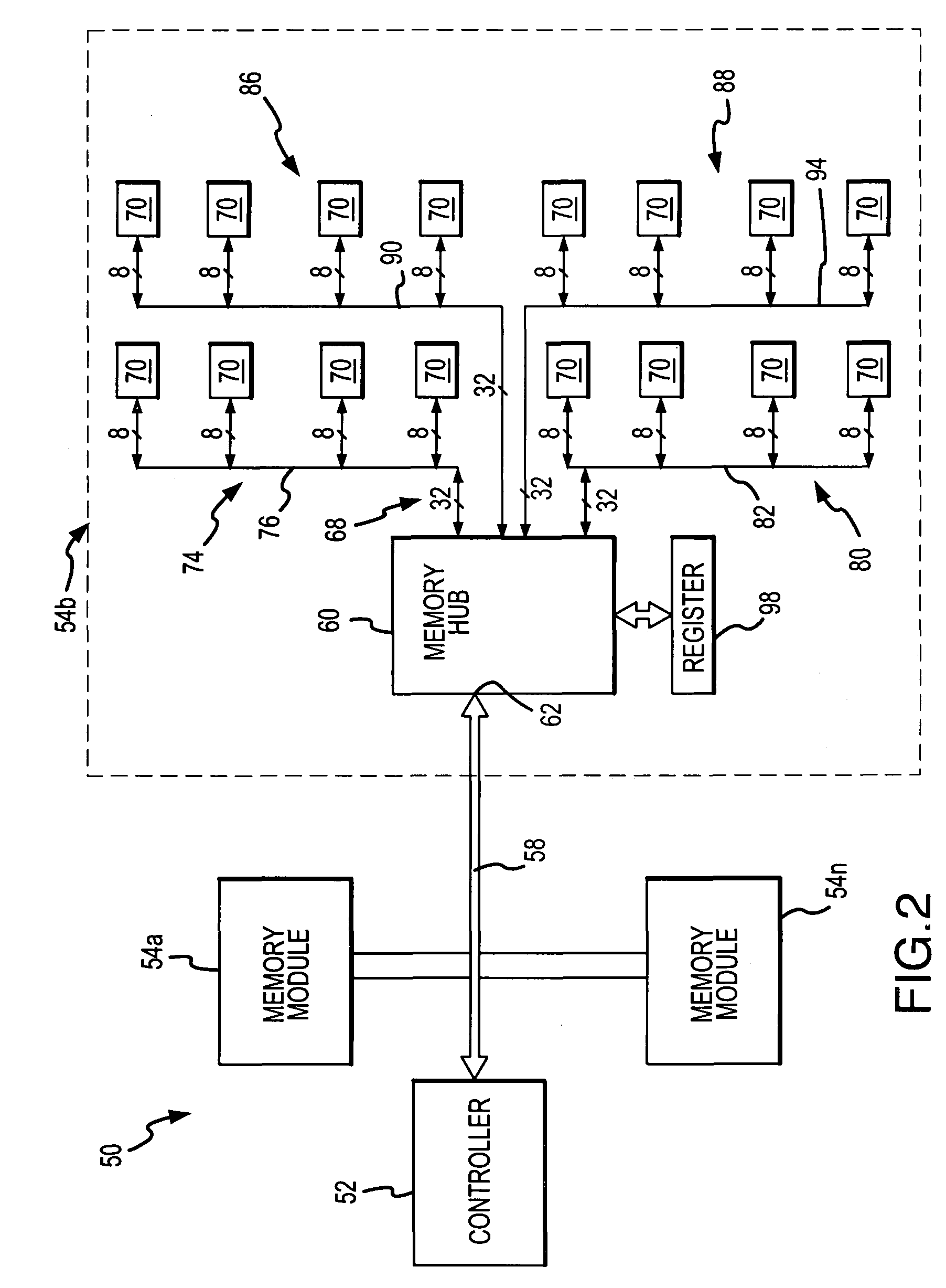

InactiveUS7120727B2High bandwidthMemory adressing/allocation/relocationHigh bandwidthComputerized system

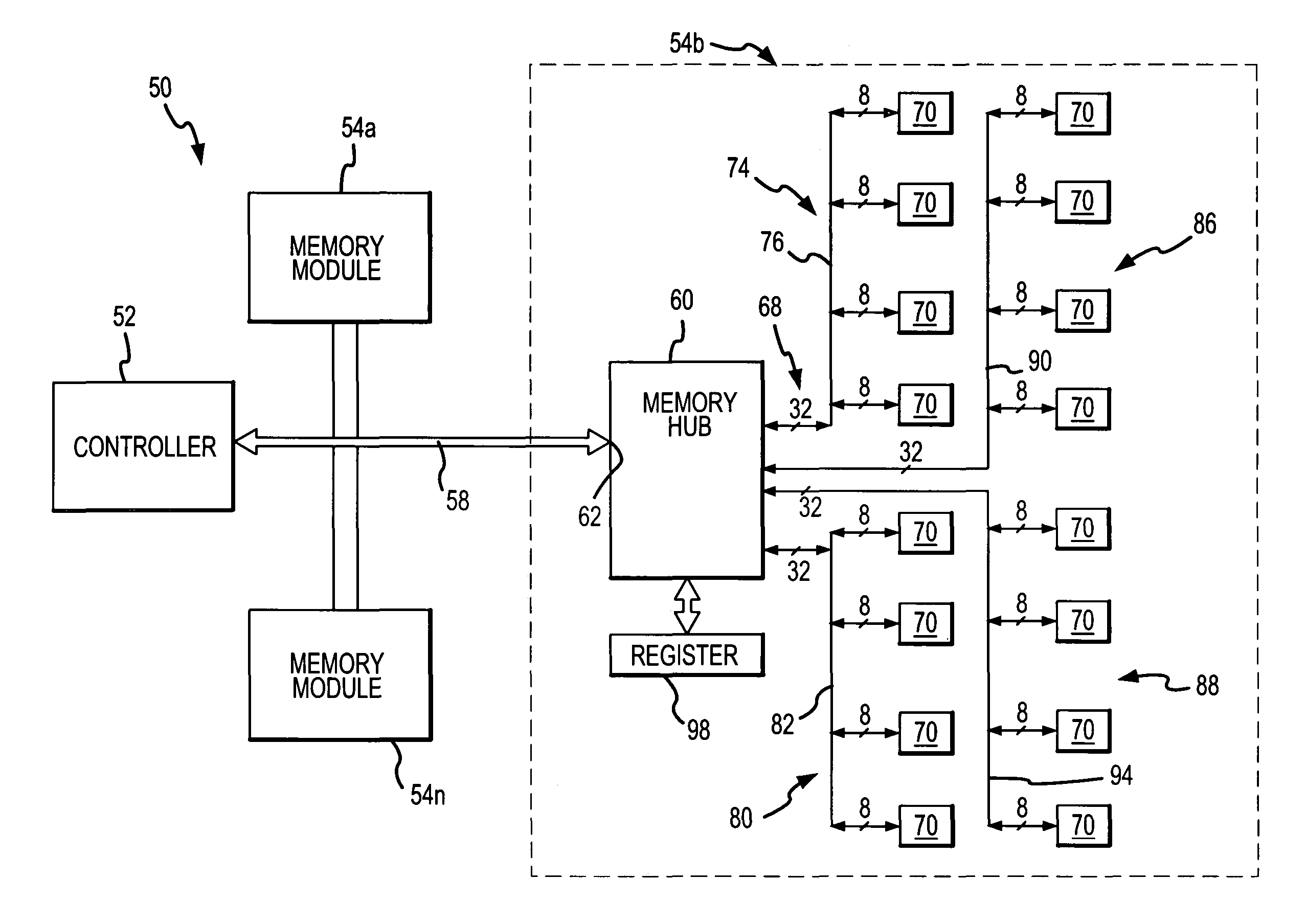

A computer system includes a controller coupled to a plurality of memory modules each of which includes a memory hub and a plurality of memory devices divided into a plurality of ranks. The memory hub is operable to configure the memory module to simultaneously address any number of ranks to operate in a high bandwidth mode, a high memory depth mode, or any combination of such modes.

Owner:ROUND ROCK RES LLC

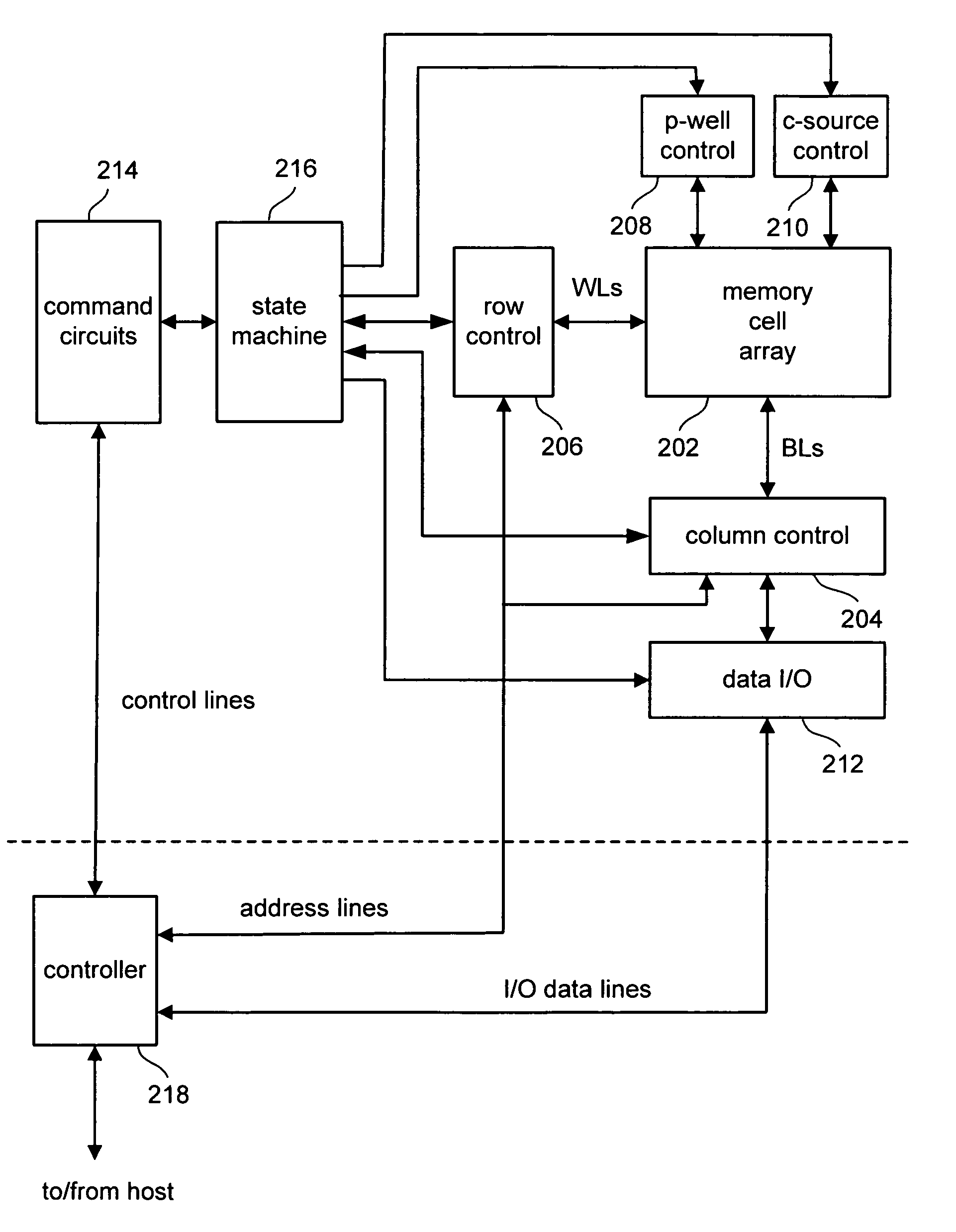

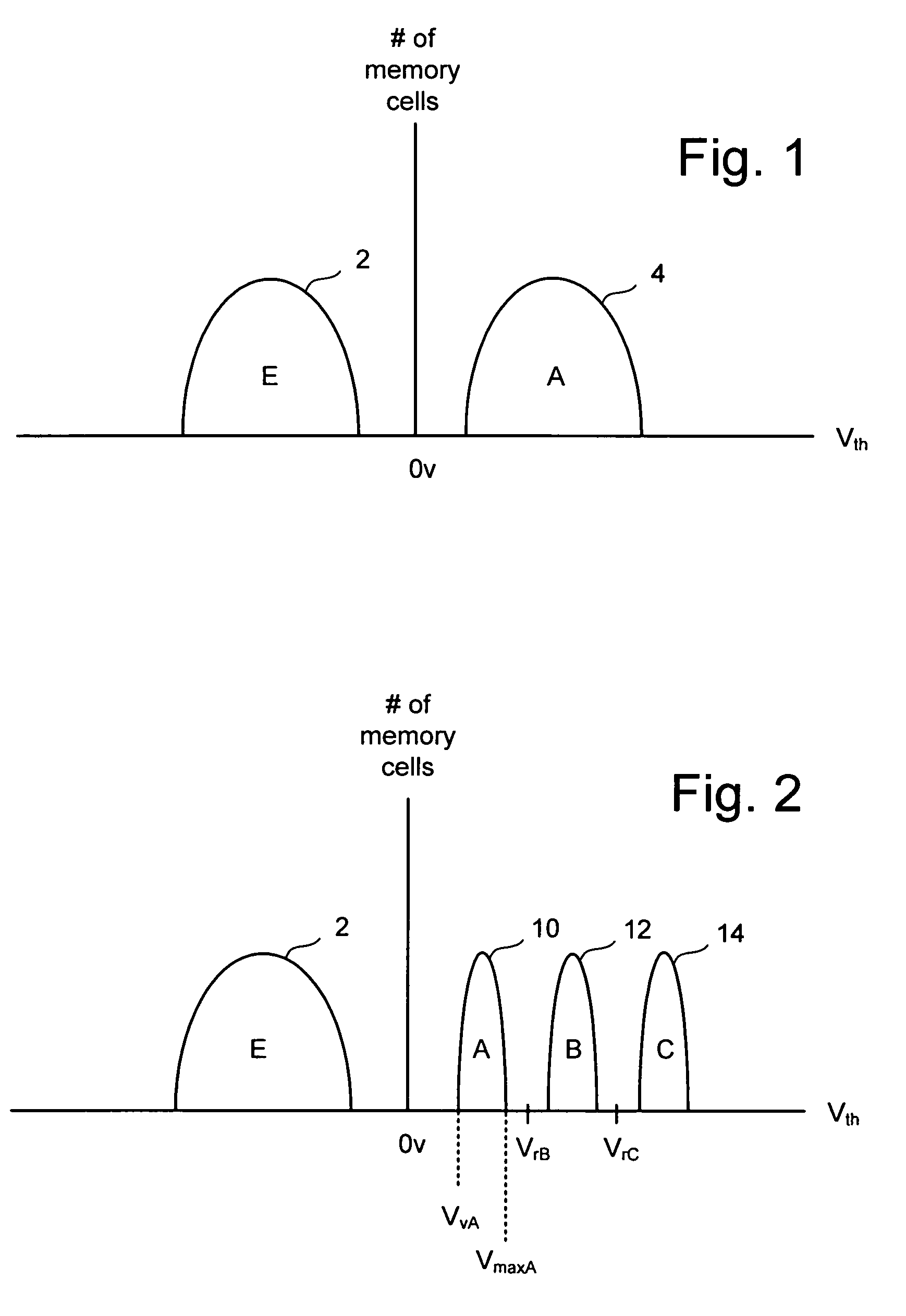

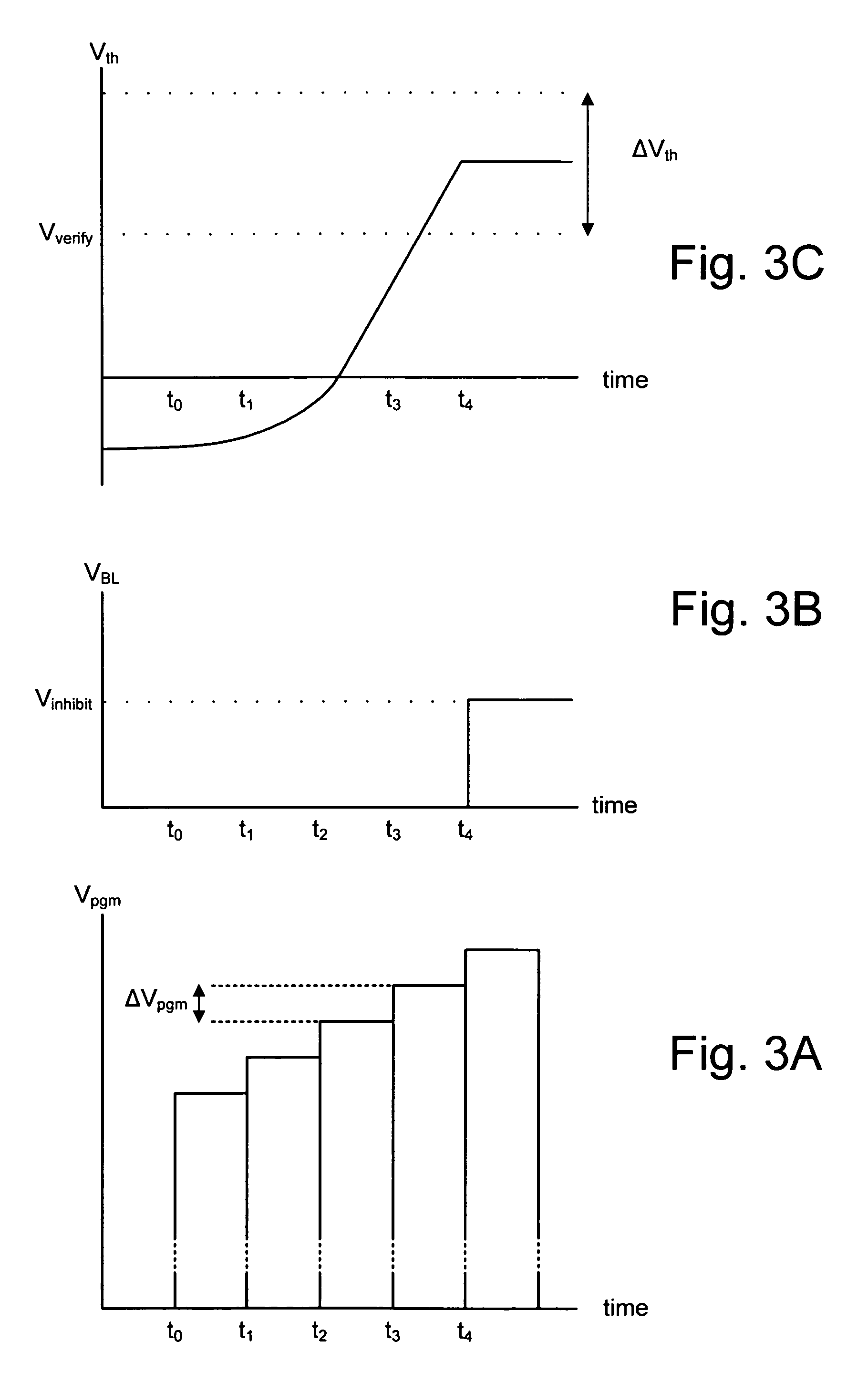

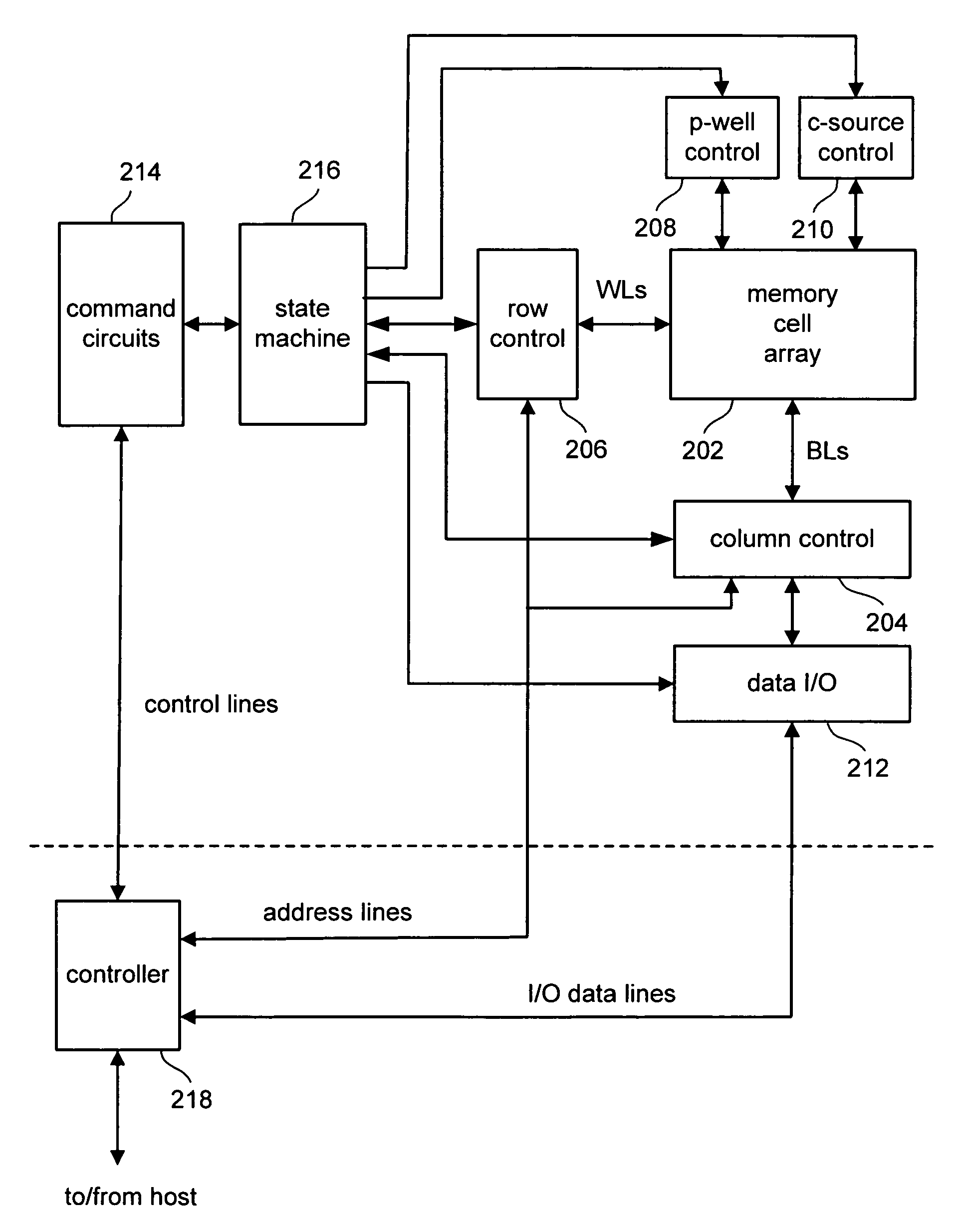

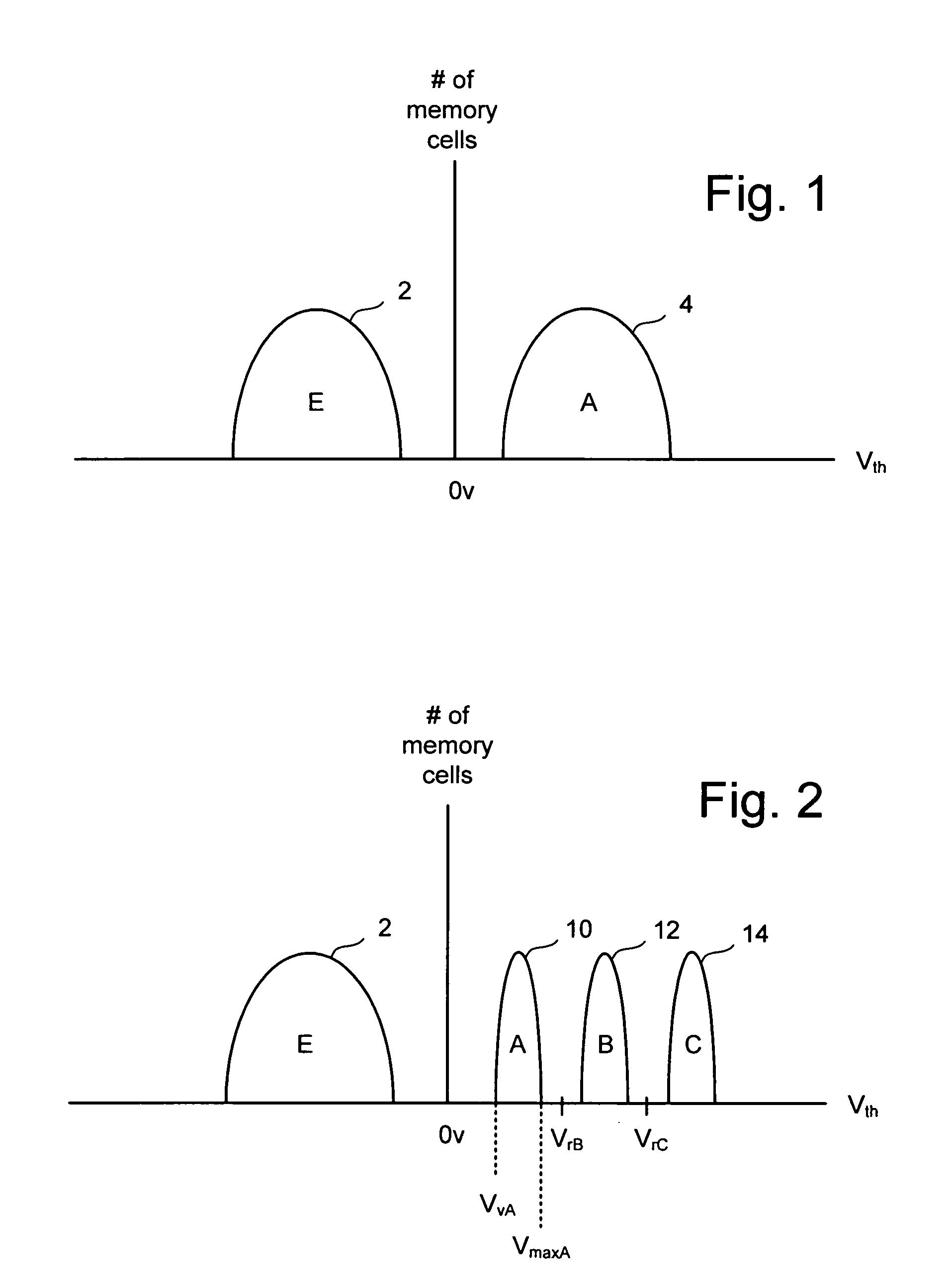

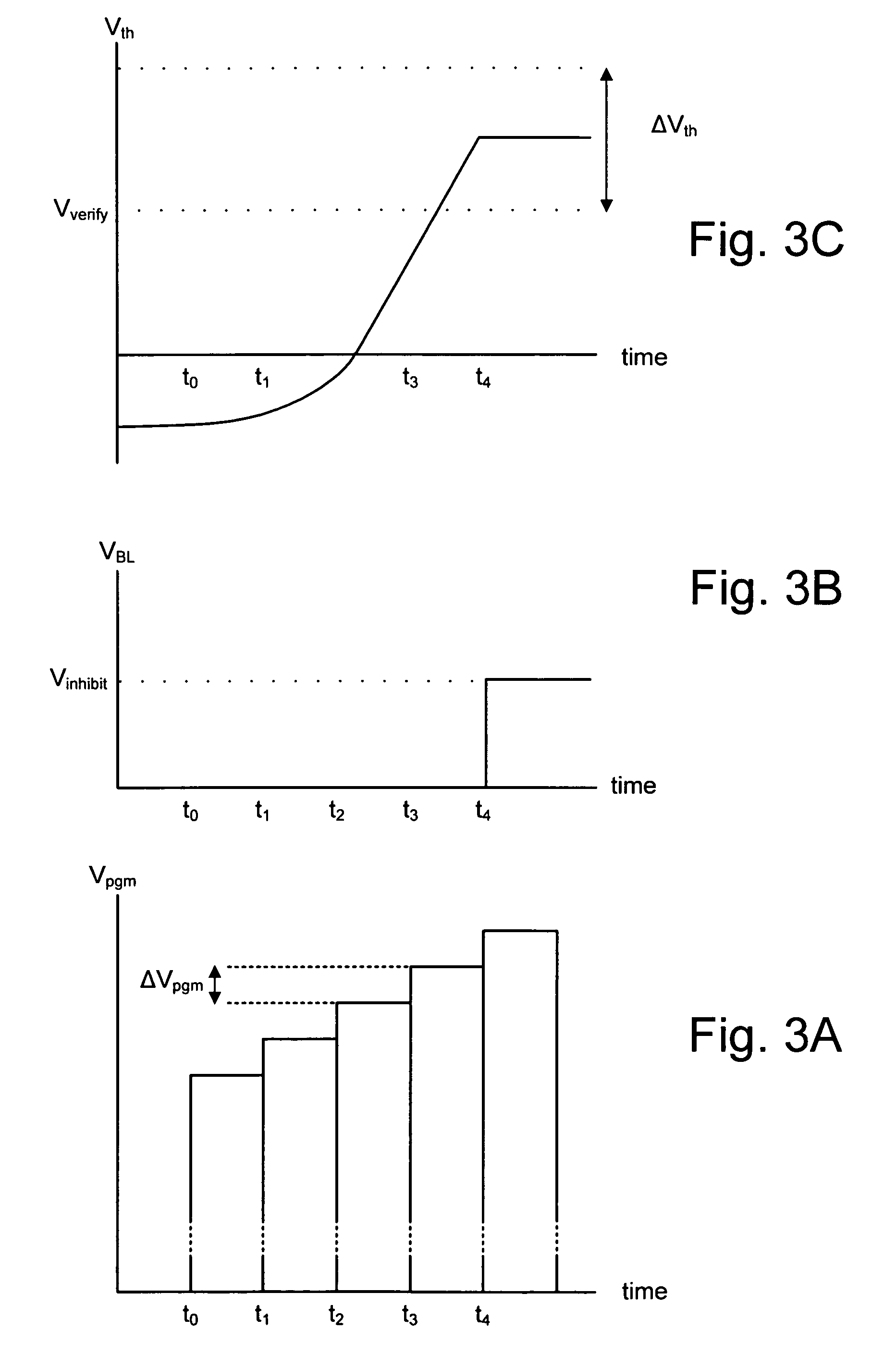

Faster programming of higher level states in multi-level cell flash memory

A program voltage signal implemented as a series of increasing program voltage pulses is applied to a set of non-volatile storage elements. Different increment values can be used when programming memory cells to different memory states. A smaller increment value can be used when programming memory cells to lower threshold voltage memory states and a larger increment value used when programming memory cells to higher threshold voltage memory states such as the highest memory state in an implementation. When non-volatile storage elements of a set are programmed to different memory states under simultaneous application of a single program voltage signal, programming can be monitored to determine when lower state programming is complete. The increment value can then be increased to complete programming to the highest memory state. Coarse / fine programming methodology can be incorporated for the highest memory state when the increment value is increased to maintain the threshold distribution within a reasonable range.

Owner:SANDISK TECH LLC

Data processing system and method

InactiveUS20060013473A1Eliminate informationImage enhancementImage analysisStatic random-access memoryHigh memory

A powerful, scaleable, and reconfigurable image processing system and method of processing data therein is described. This general purpose, reconfigurable engine with toroidal topology, distributed memory, and wide bandwidth I / O are capable of solving real applications at real-time speeds. The reconfigurable image processing system can be optimized to efficiently perform specialized computations, such as real-time video and audio processing. This reconfigurable image processing system provides high performance via high computational density, high memory bandwidth, and high I / O bandwidth. Generally, the reconfigurable image processing system and its control structure include a homogeneous array of 16 field programmable gate arrays (FPGA) and 16 static random access memories (SRAM) arranged in a partial torus configuration. The reconfigurable image processing system also includes a PCI bus interface chip, a clock control chip, and a datapath chip. It can be implemented in a single board. It receives data from its external environment, computes correspondence, and uses the results of the correspondence computations for various post-processing industrial applications. The reconfigurable image processing system determines correspondence by using non-parametric local transforms followed by correlation. These non-parametric local transforms include the census and rank transforms. Other embodiments involve a combination of correspondence, rectification, a left-right consistency check, and the application of an interest operator.

Owner:INTEL CORP

Faster programming of higher level states in multi-level cell flash memory

ActiveUS20060120165A1Shorten programming timeRead-only memoriesDigital storageVoltage pulseHigh memory

A program voltage signal implemented as a series of increasing program voltage pulses is applied to a set of non-volatile storage elements. Different increment values can be used when programming memory cells to different memory states. A smaller increment value can be used when programming memory cells to lower threshold voltage memory states and a larger increment value used when programming memory cells to higher threshold voltage memory states such as the highest memory state in an implementation. When non-volatile storage elements of a set are programmed to different memory states under simultaneous application of a single program voltage signal, programming can be monitored to determine when lower state programming is complete. The increment value can then be increased to complete programming to the highest memory state. Coarse / fine programming methodology can be incorporated for the highest memory state when the increment value is increased to maintain the threshold distribution within a reasonable range.

Owner:SANDISK TECH LLC

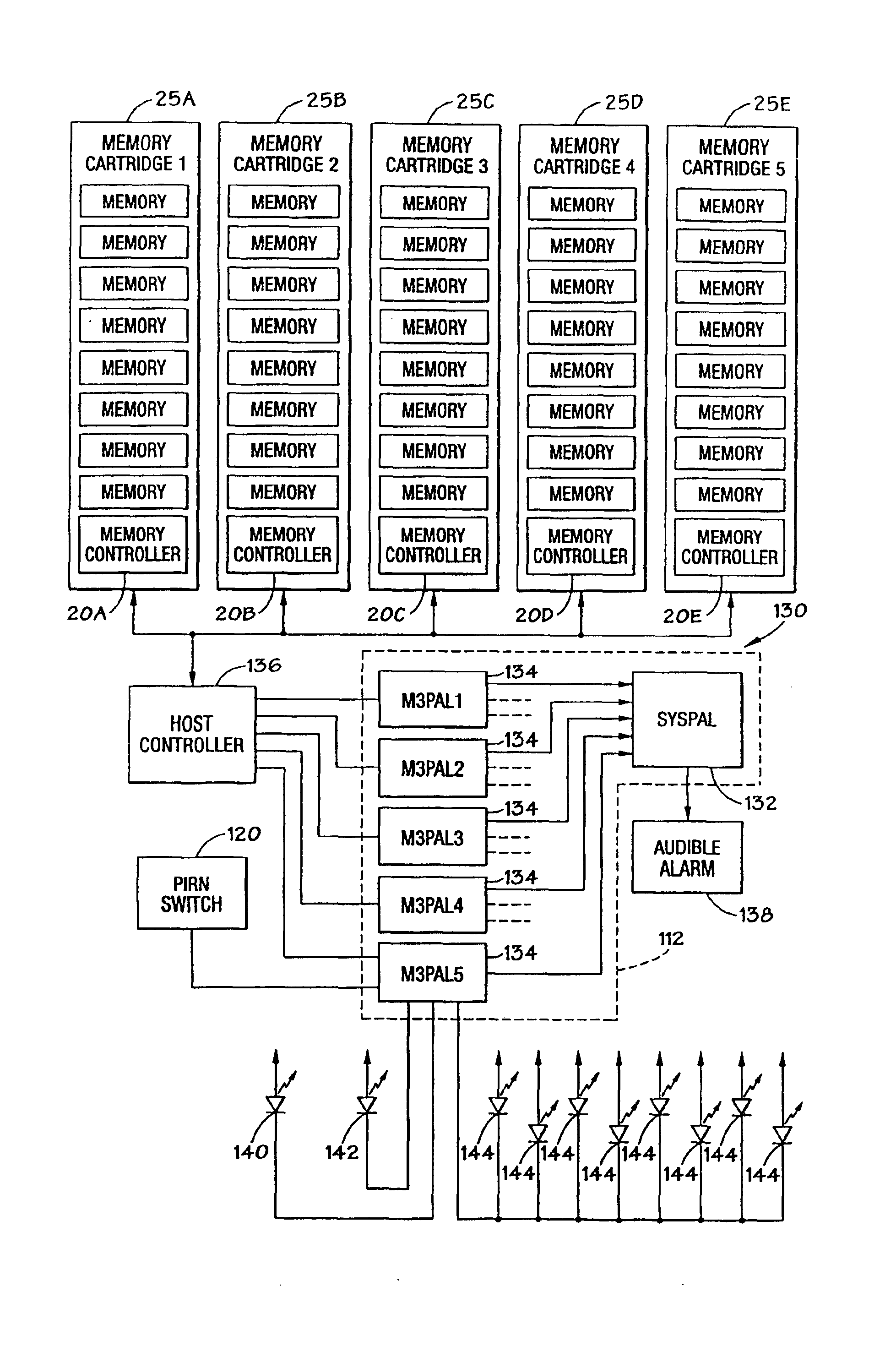

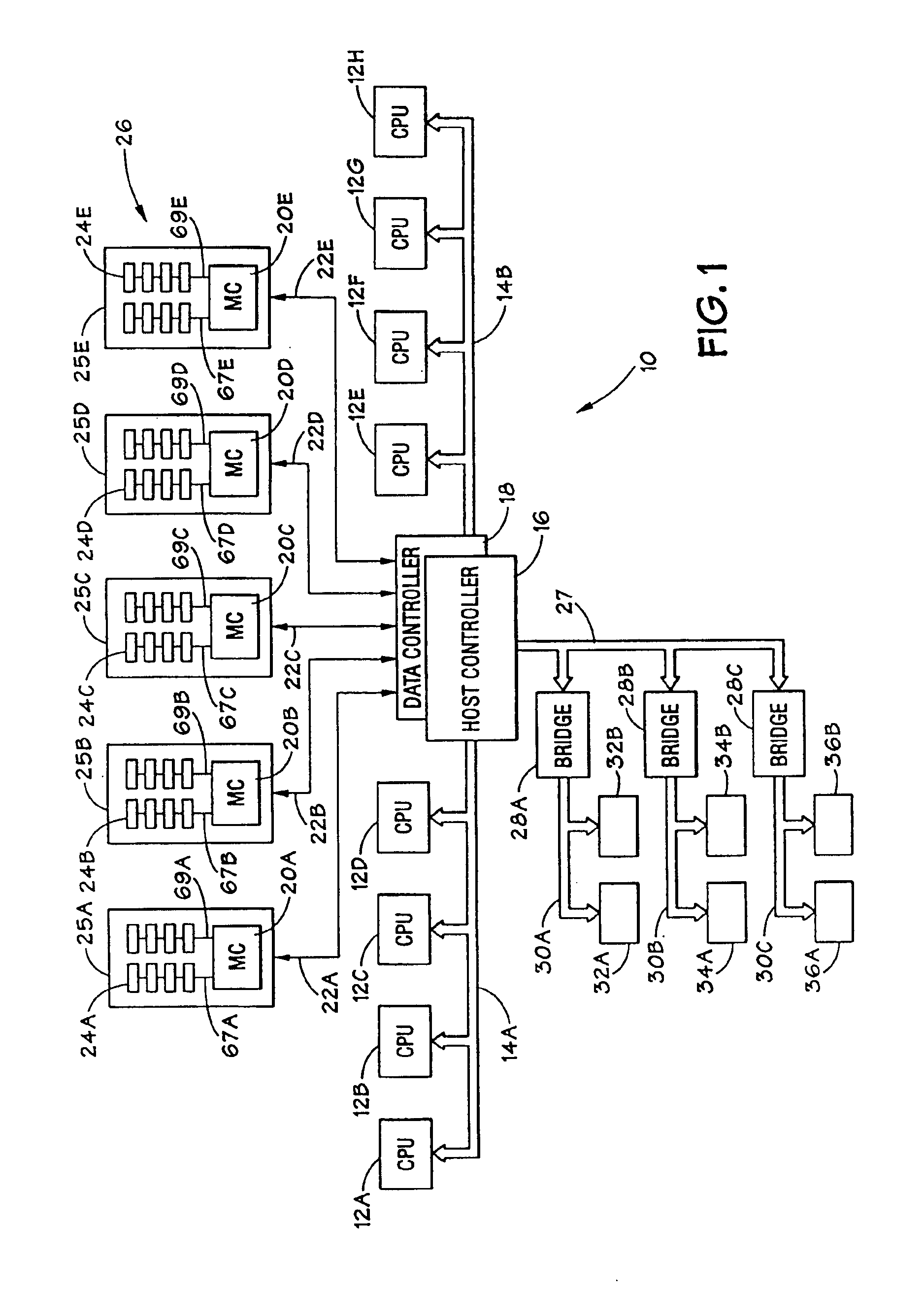

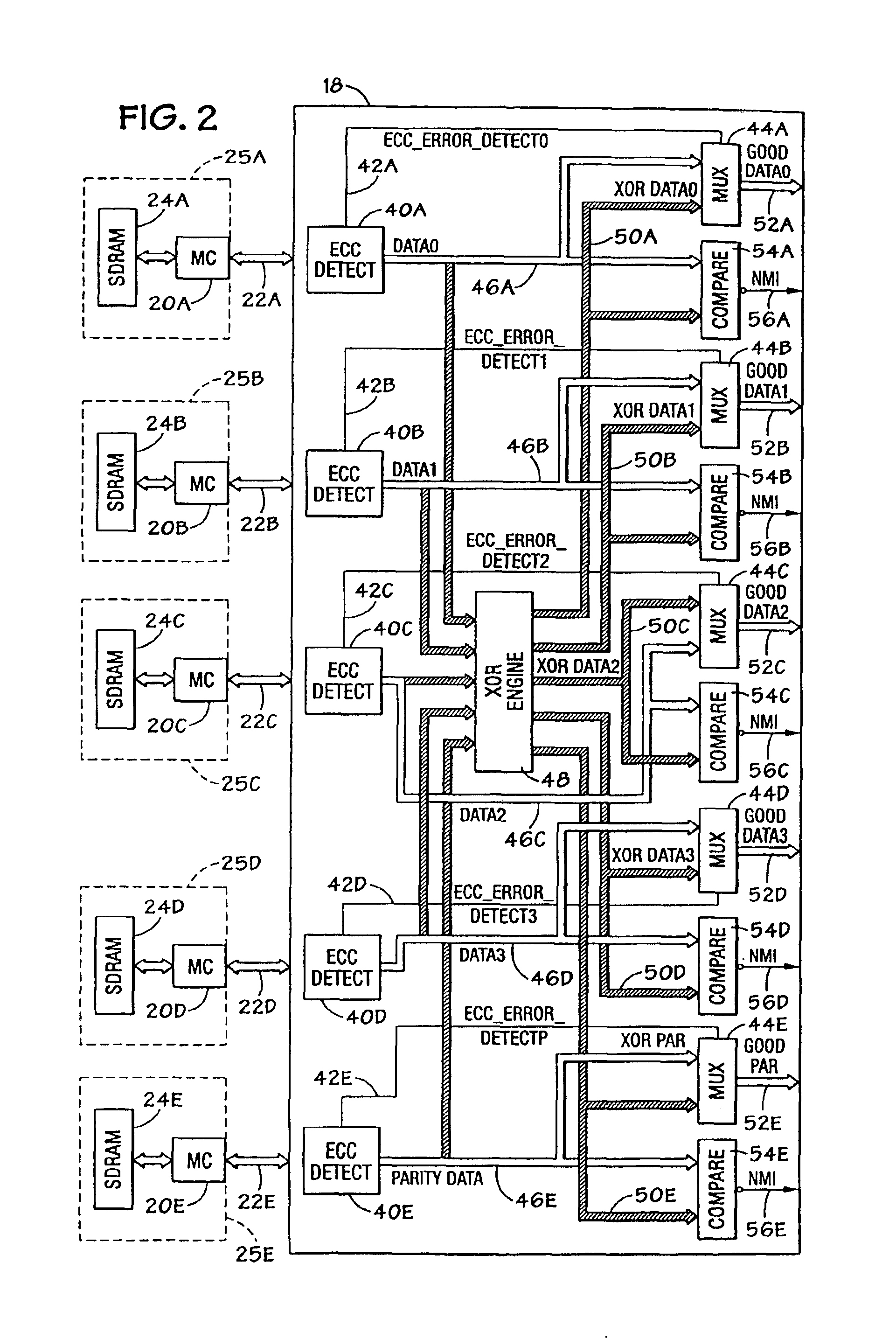

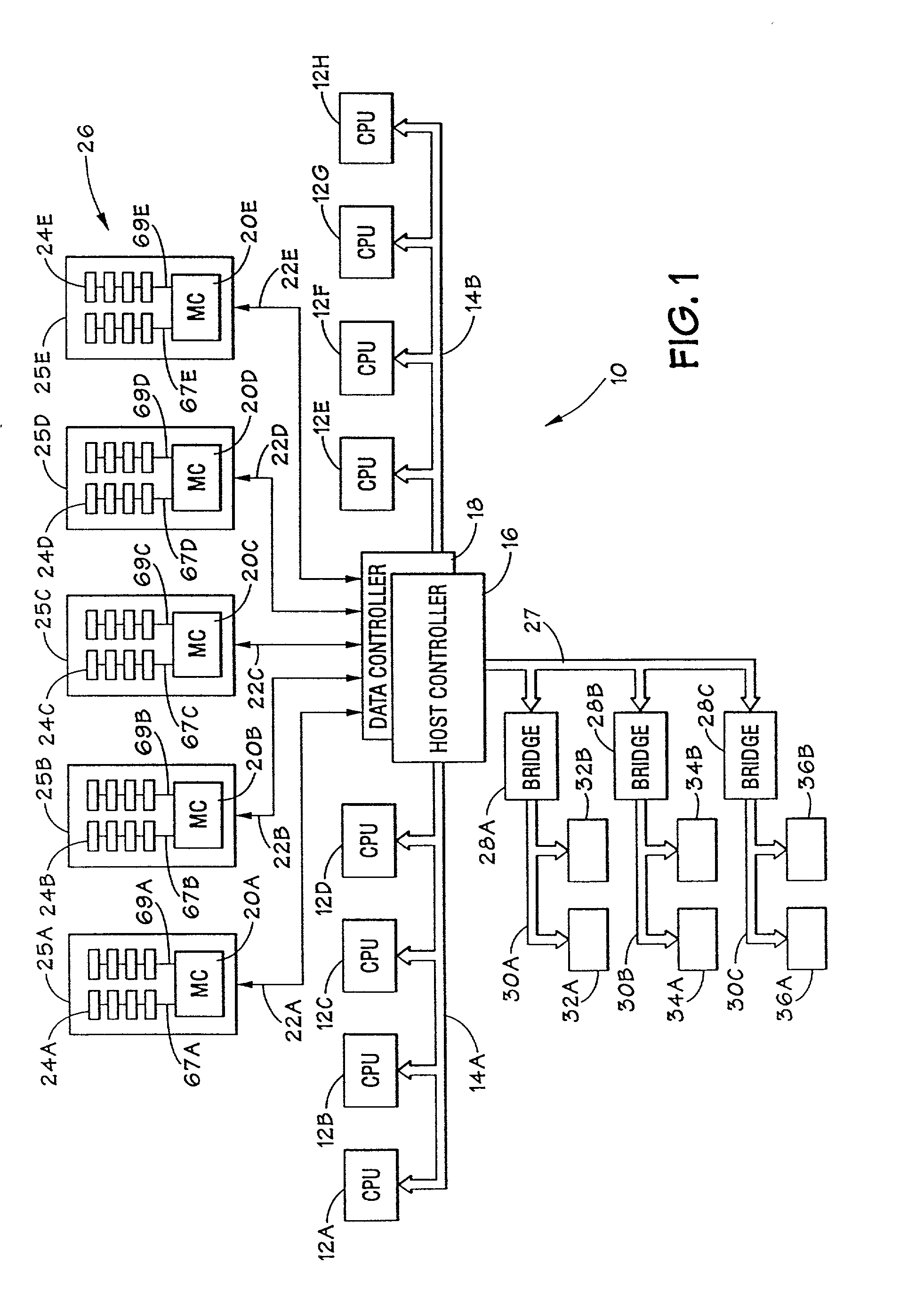

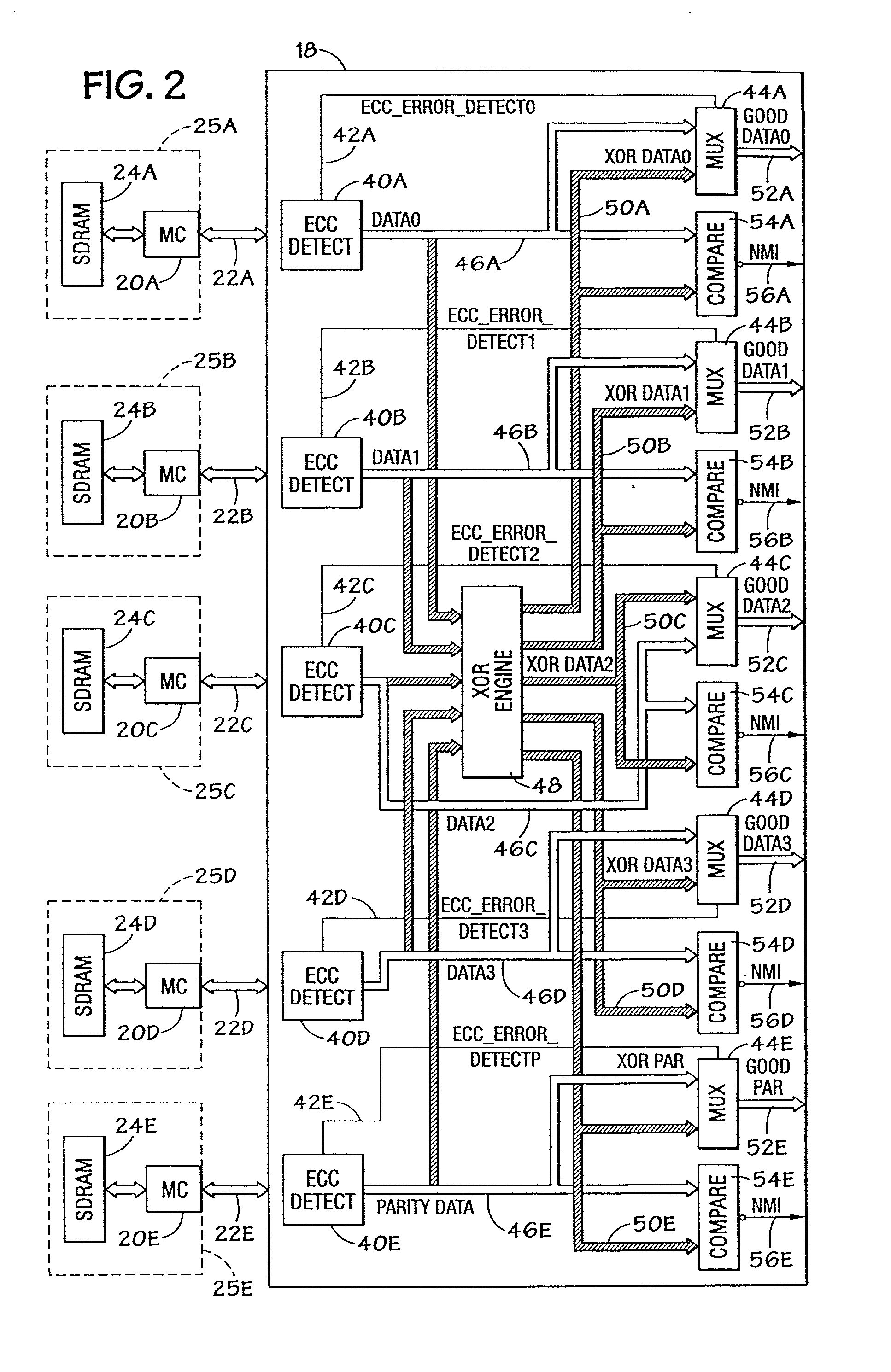

Hot-upgrade/hot-add memory

InactiveUS6854070B2Component plug-in assemblagesRedundant data error correctionParallel computingComputerized system

A method of adding memory capacity to a computer system. The computer system comprises a redundant memory system including a plurality of memory cartridges. By powering-down a memory cartridge, adding an additional memory module to the memory cartridge, and powering-up the memory cartridge for each memory cartridge in the system, the system can transition from a redundant mode of operation to a non-redundant mode of operation for each power-down, thus allowing the computer system to remain functional during the addition of the memory module. Alternatively, memory cartridges with higher memory capacity than those currently present in the computer system can be used to replace existing memory cartridges in the computer system, using the same techniques.

Owner:HEWLETT PACKARD DEV CO LP

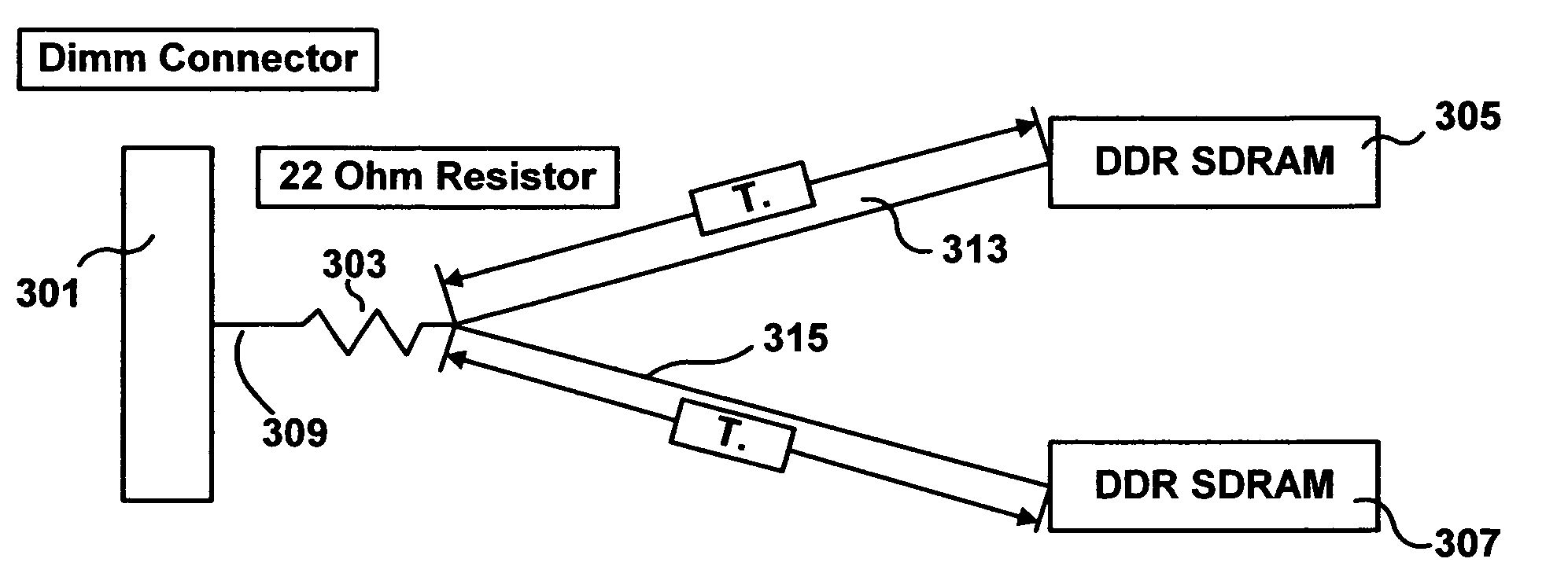

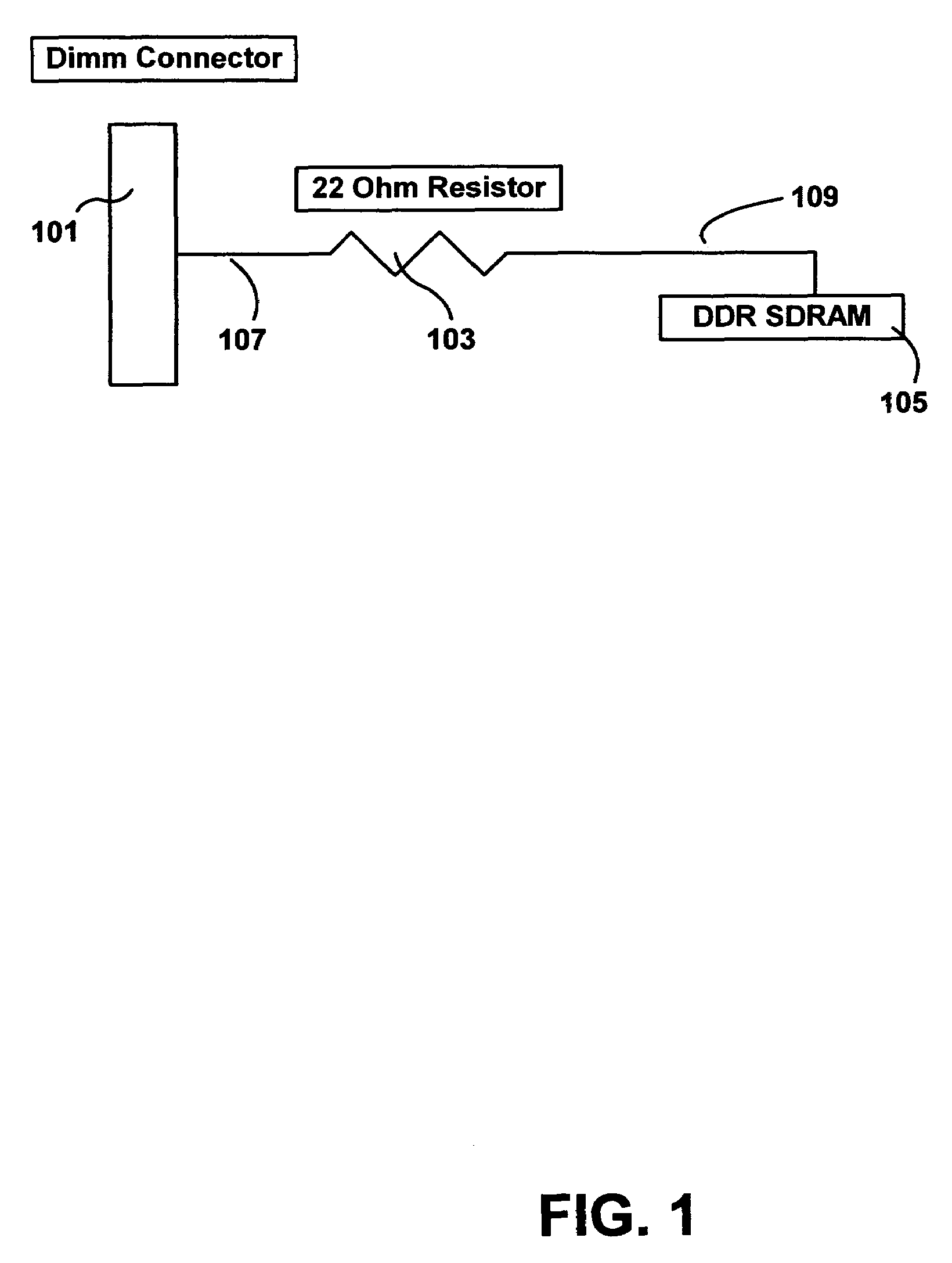

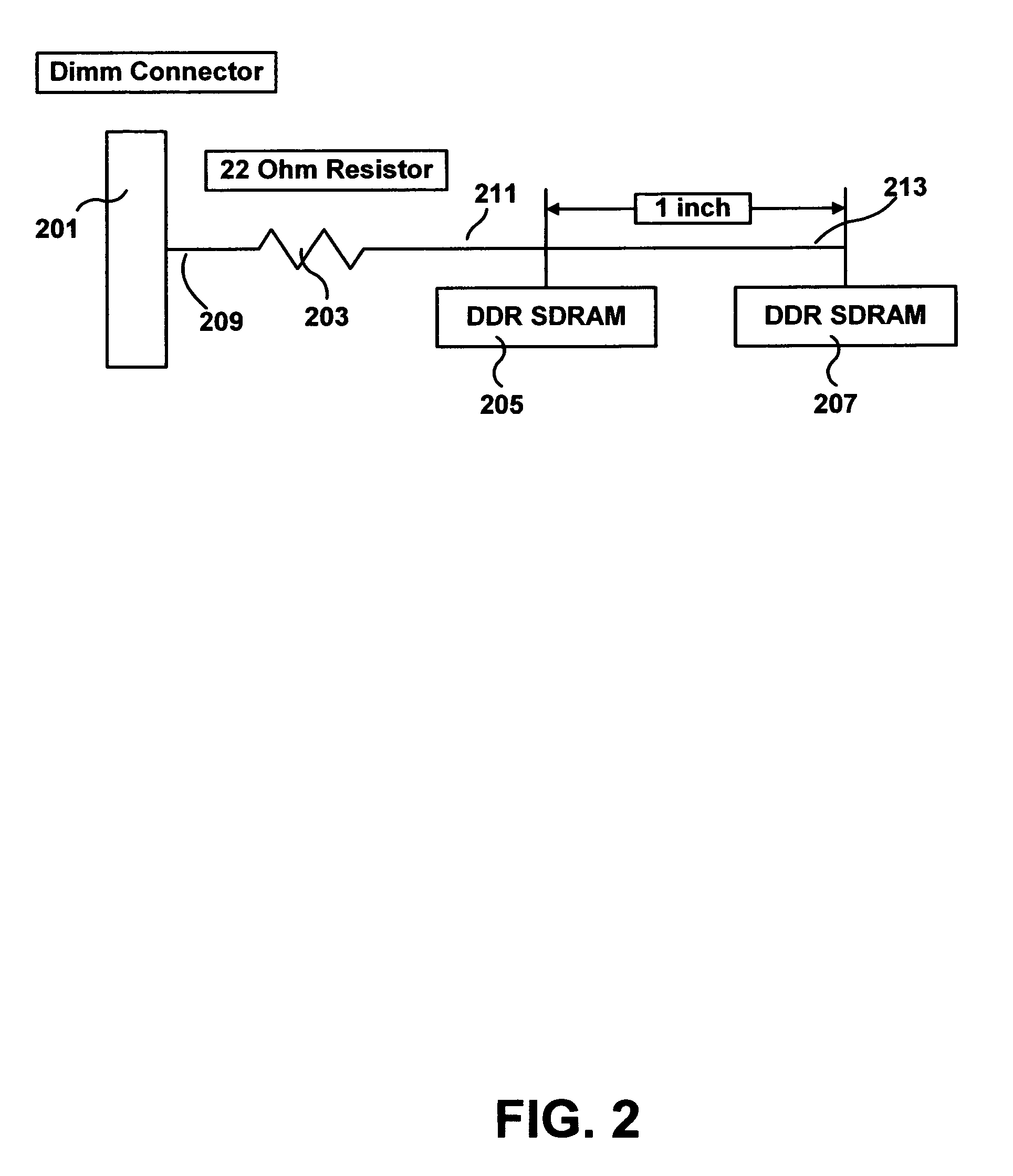

Double-high memory system compatible with termination schemes for single-high memory systems

ActiveUS7054179B2Static storagePrinted circuits structural associationsParallel computingHigh memory

A double-high memory system compatible with termination schemes for single-high memory systems. The system includes an interface for input and output of data. A plurality of memory units is configured in two rows. A transmission line couples the plurality of memory units and the interface. The double-high memory system is provided in a non-stacked arrangement.

Owner:SK HYNIX INC

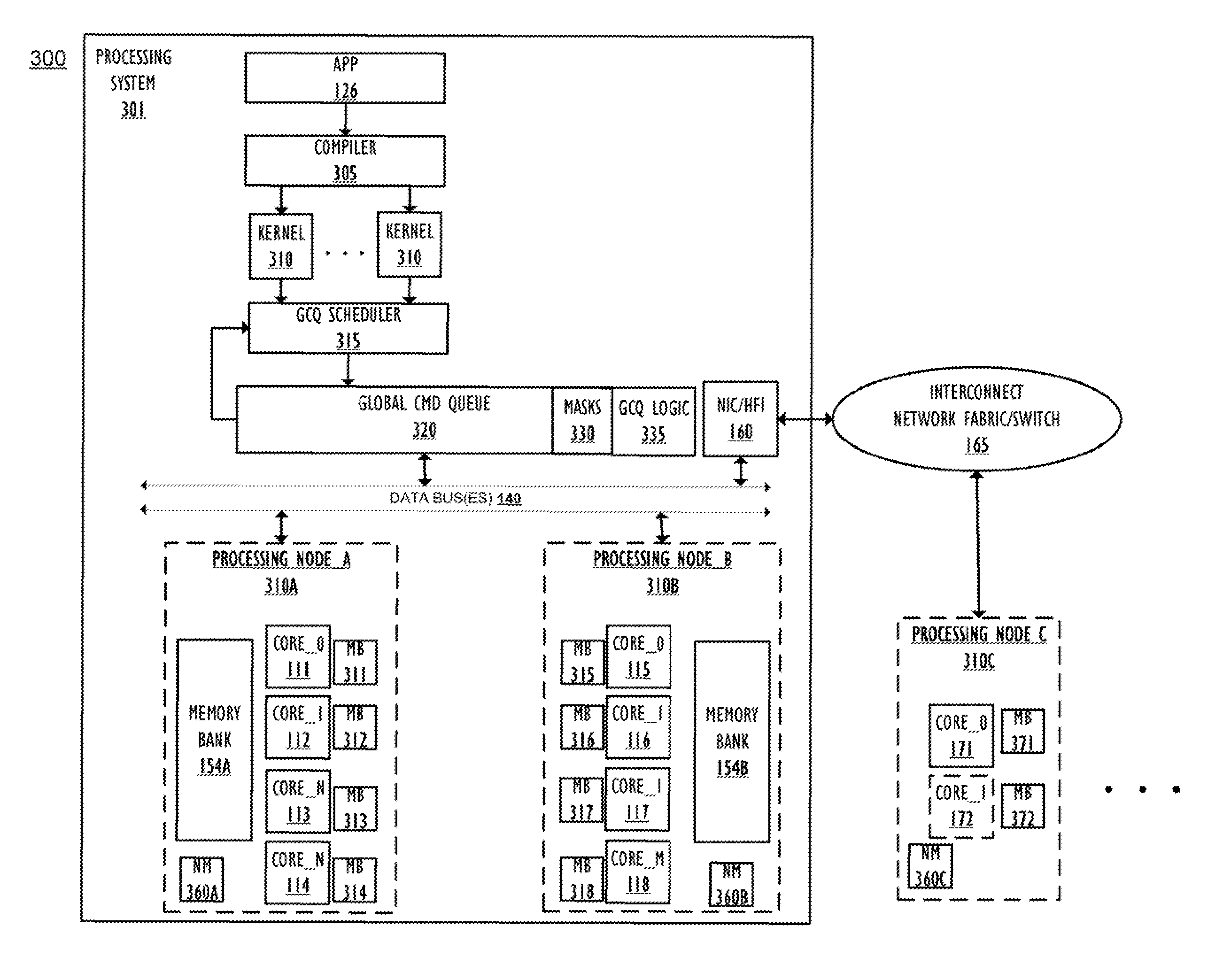

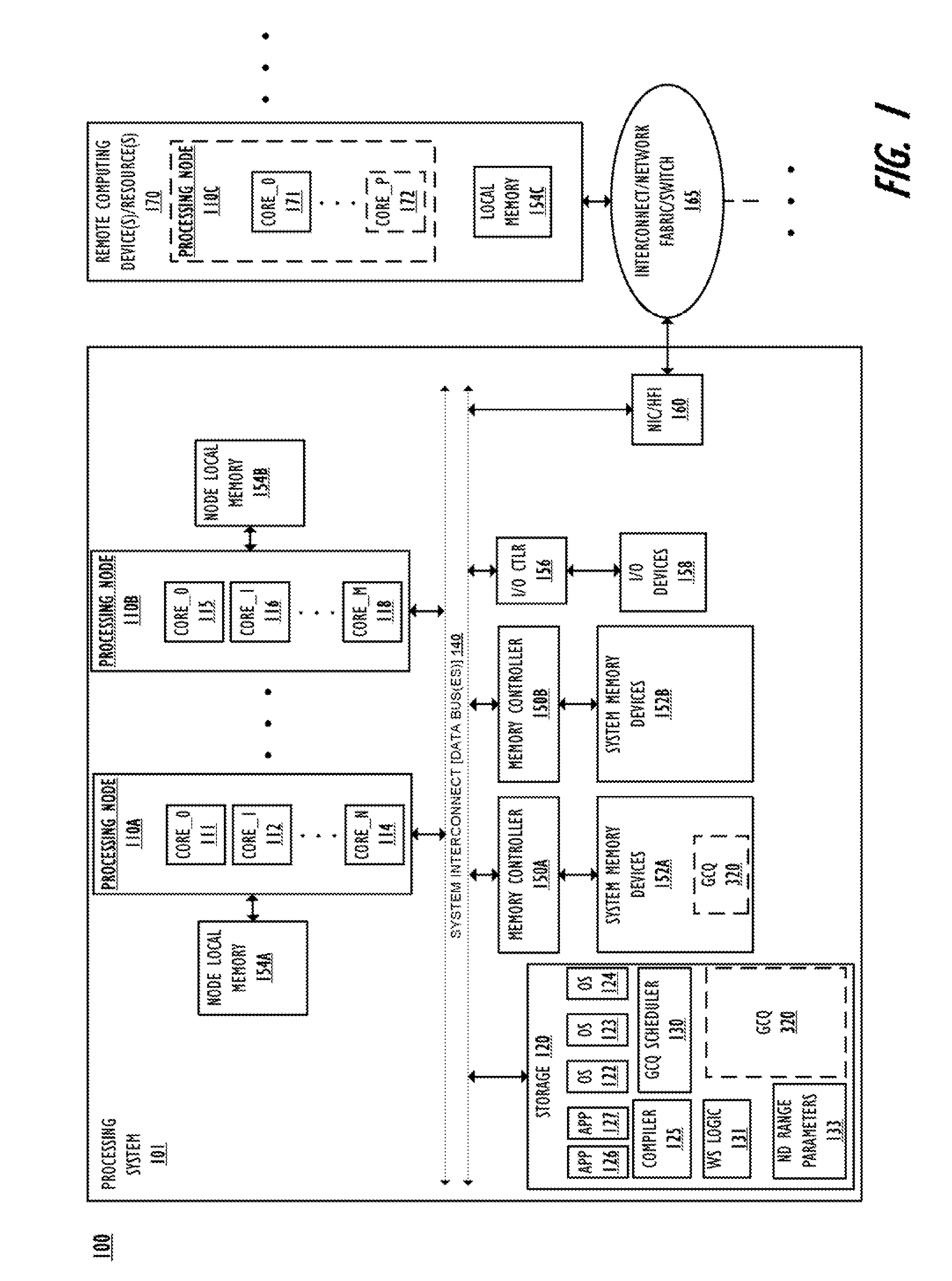

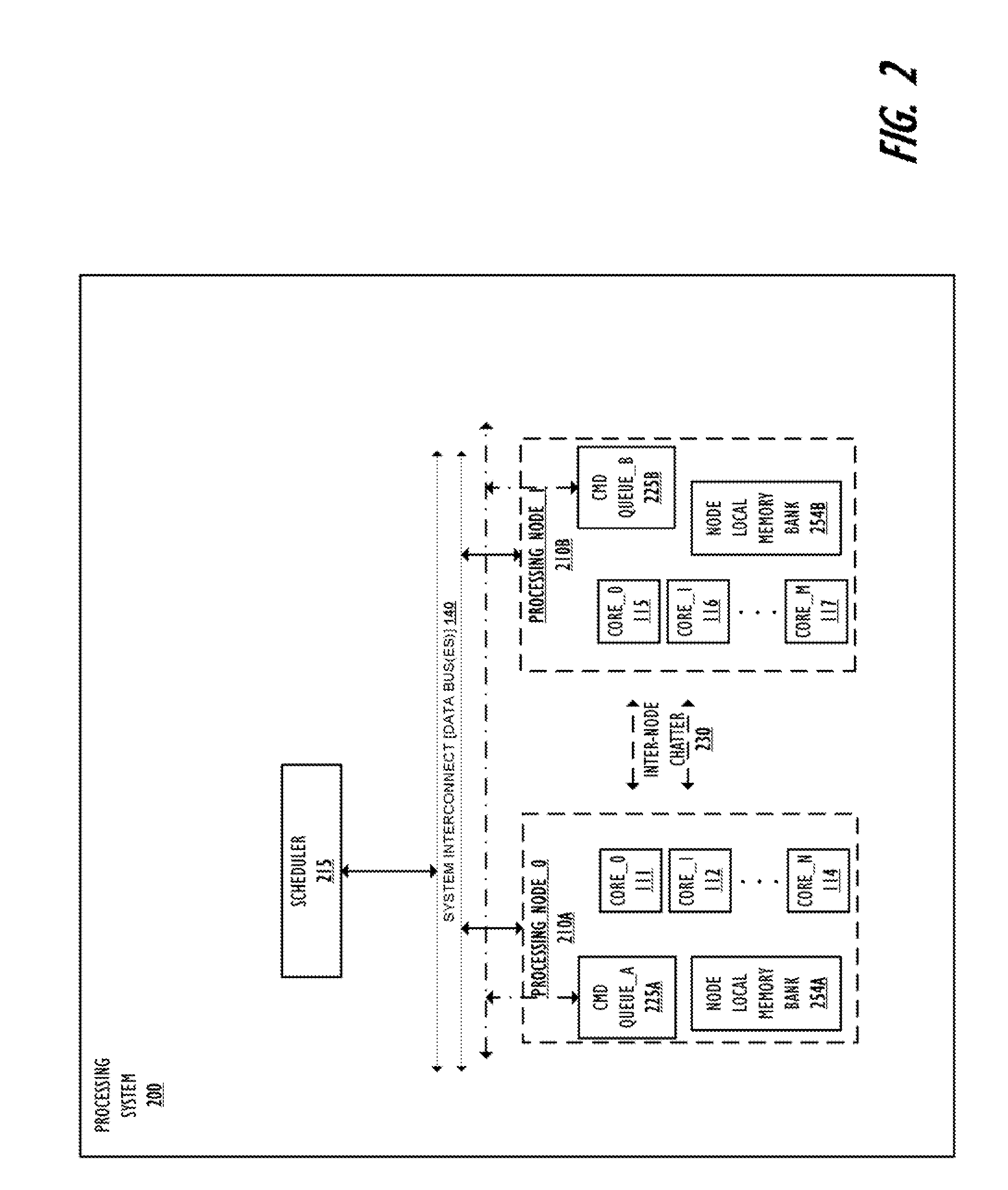

Method to reduce queue synchronization of multiple work items in a system with high memory latency between processing nodes

InactiveUS20110161976A1High access latencyEfficient dispatch/completionResource allocationProgram synchronisationParallel computingEngineering

A method efficiently dispatches / completes a work element within a multi-node, data processing system that has a global command queue (GCQ) and at least one high latency node. The method comprises: at the high latency processor node, work scheduling logic establishing a local command / work queue (LCQ) in which multiple work items for execution by local processing units can be staged prior to execution; a first local processing unit retrieving via a work request a larger chunk size of work than can be completed in a normal work completion / execution cycle by the local processing unit; storing the larger chunk size of work retrieved in a local command / work queue (LCQ); enabling the first local processing unit to locally schedule and complete portions of the work stored within the LCQ; and transmitting a next work request to the GCQ only when all the work within the LCQ has been dispatched by the local processing units.

Owner:IBM CORP

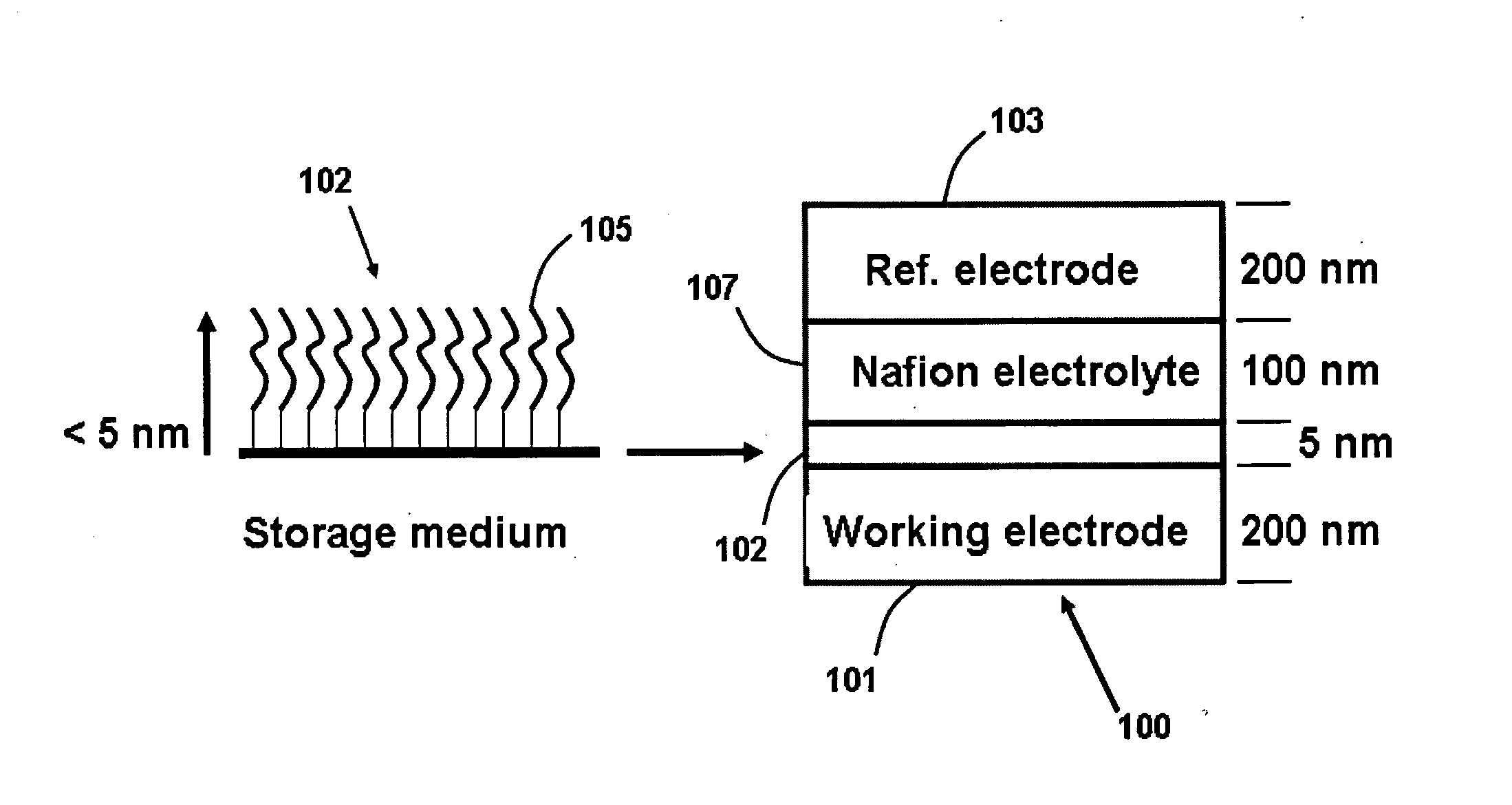

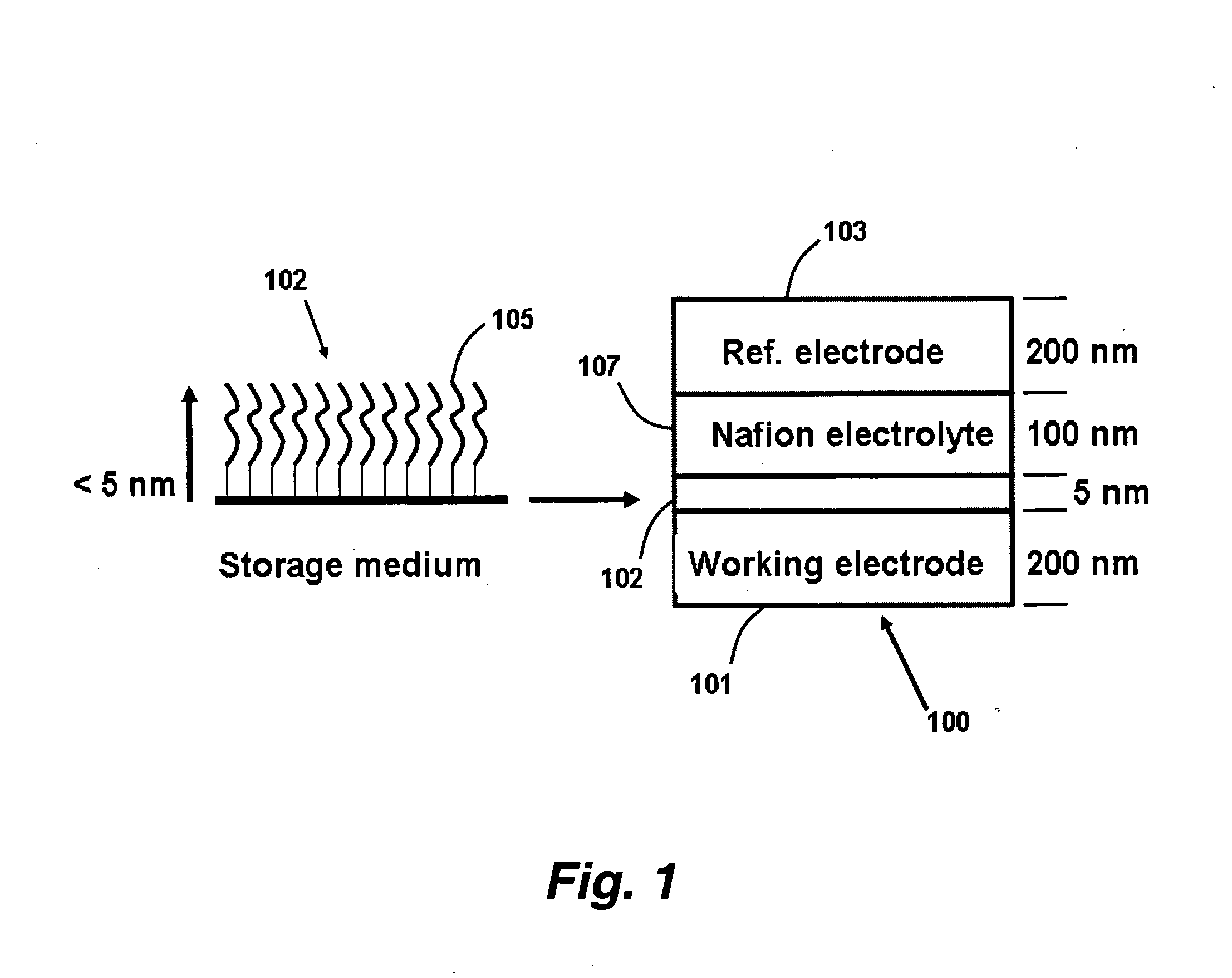

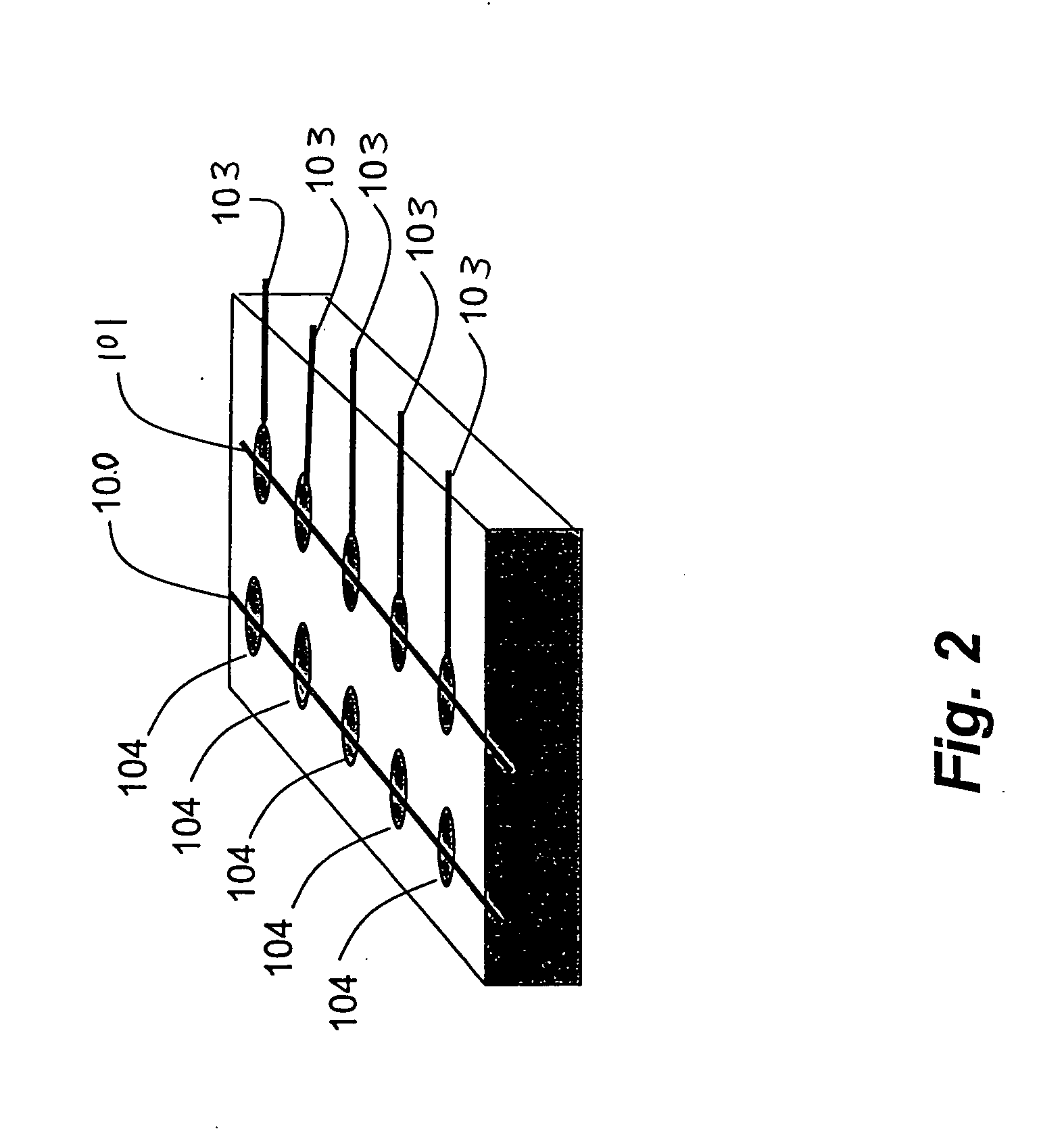

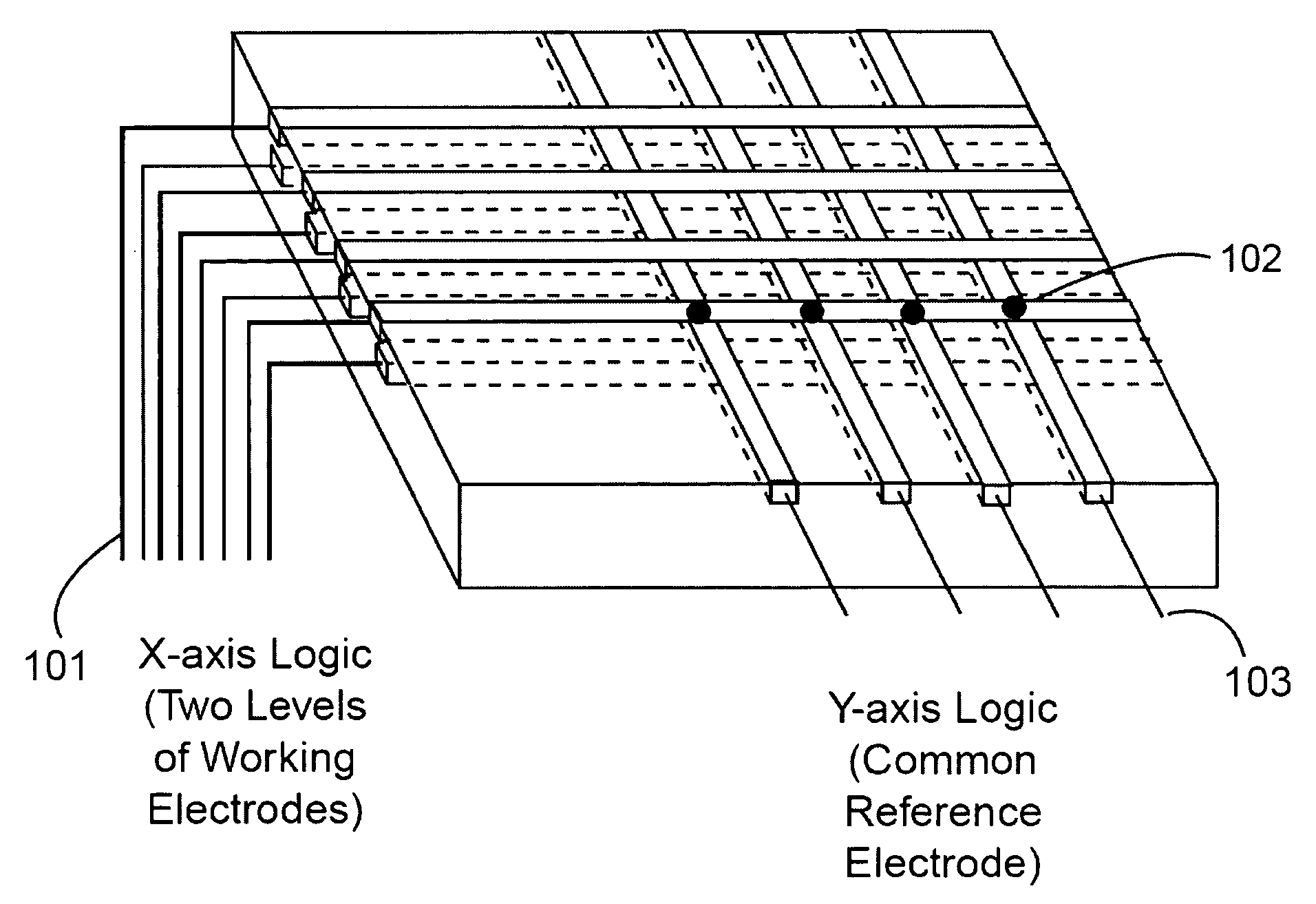

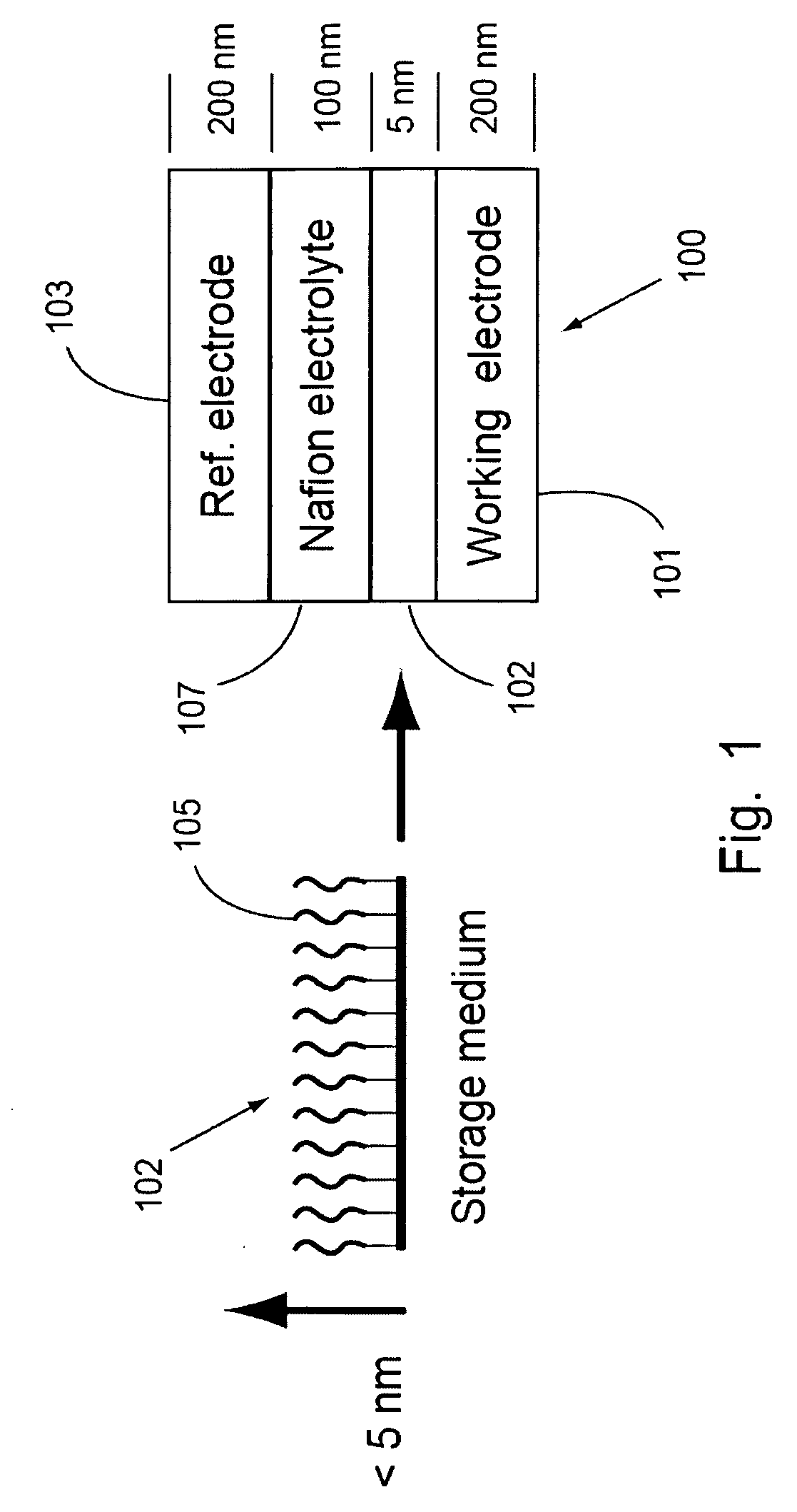

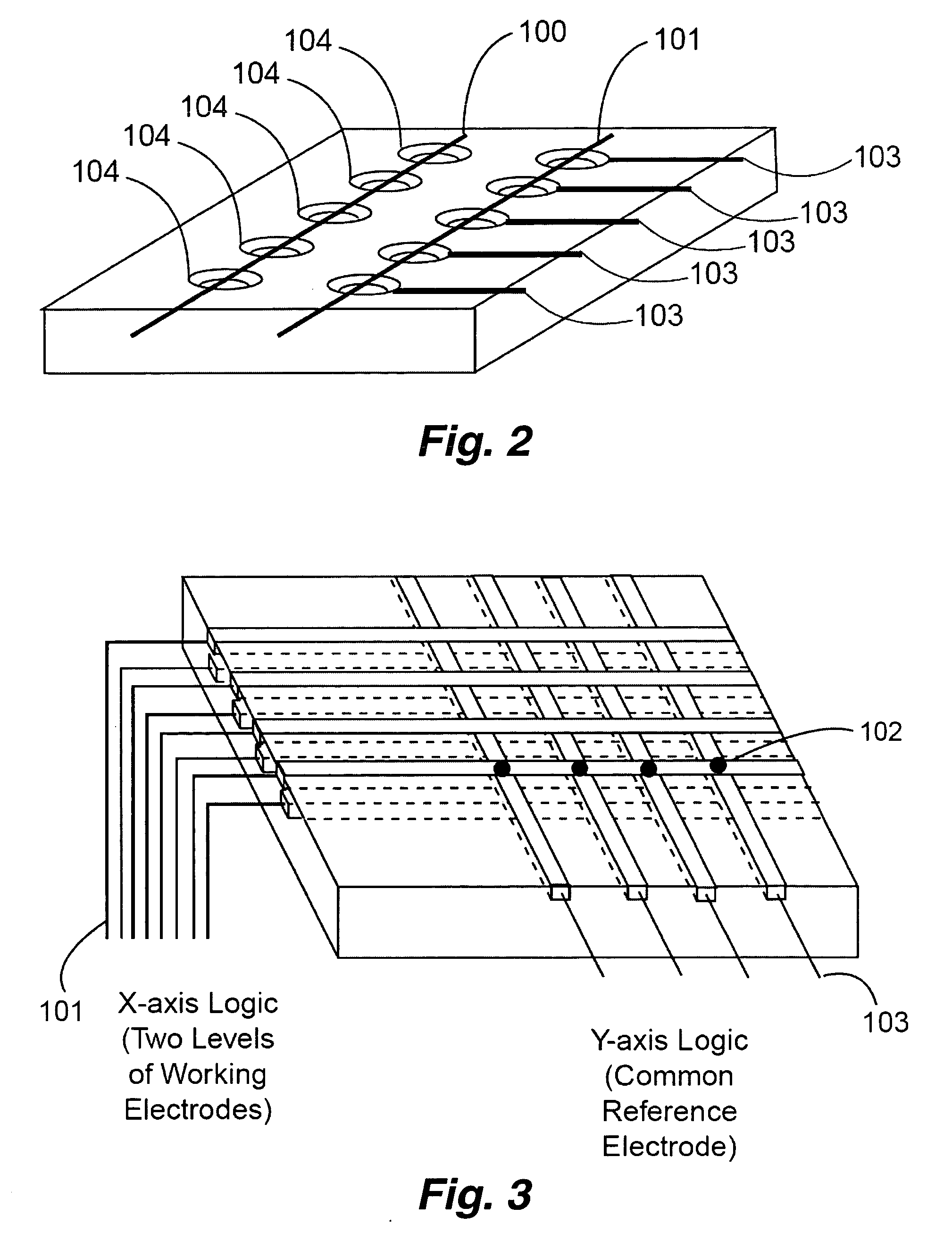

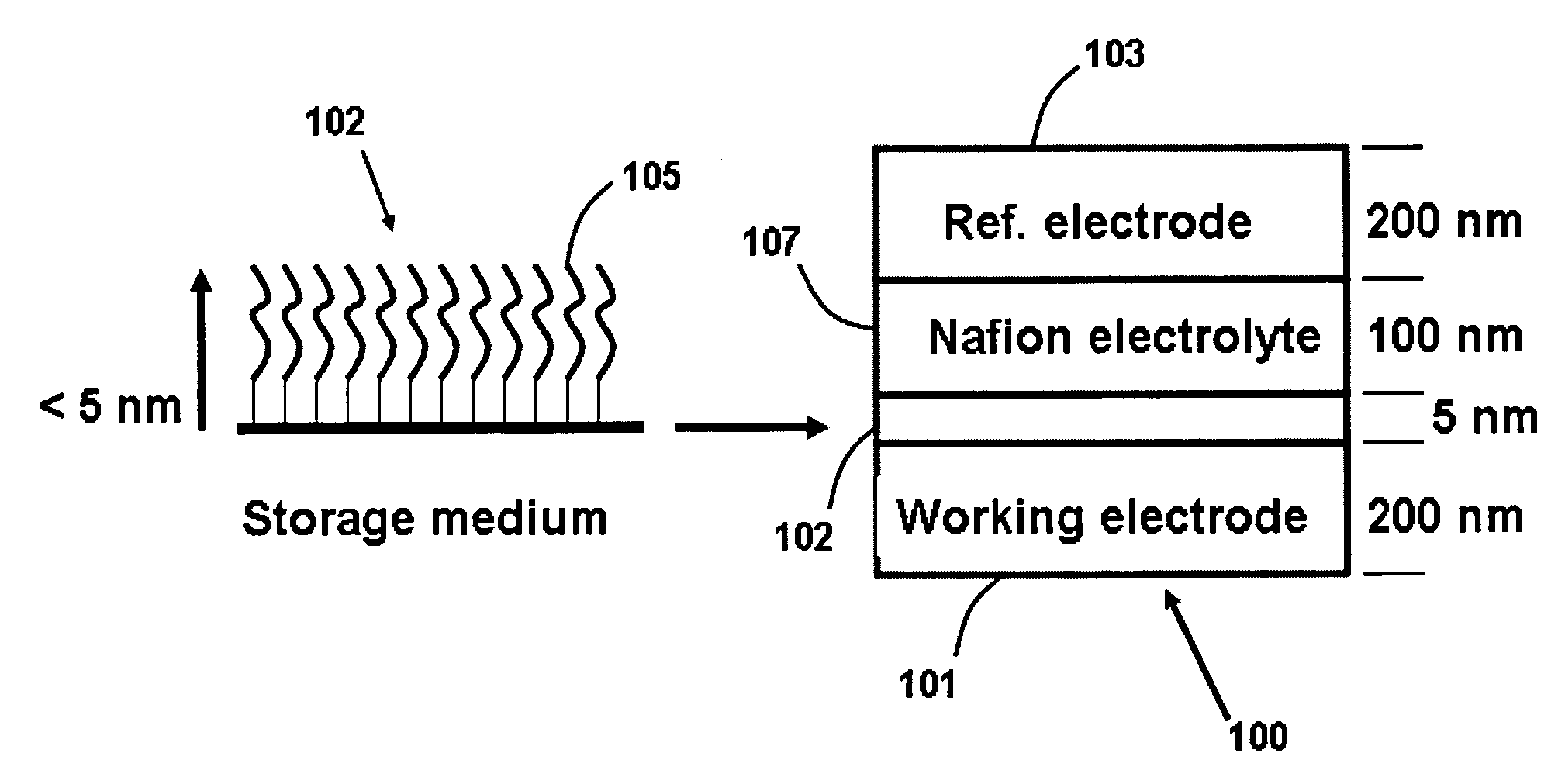

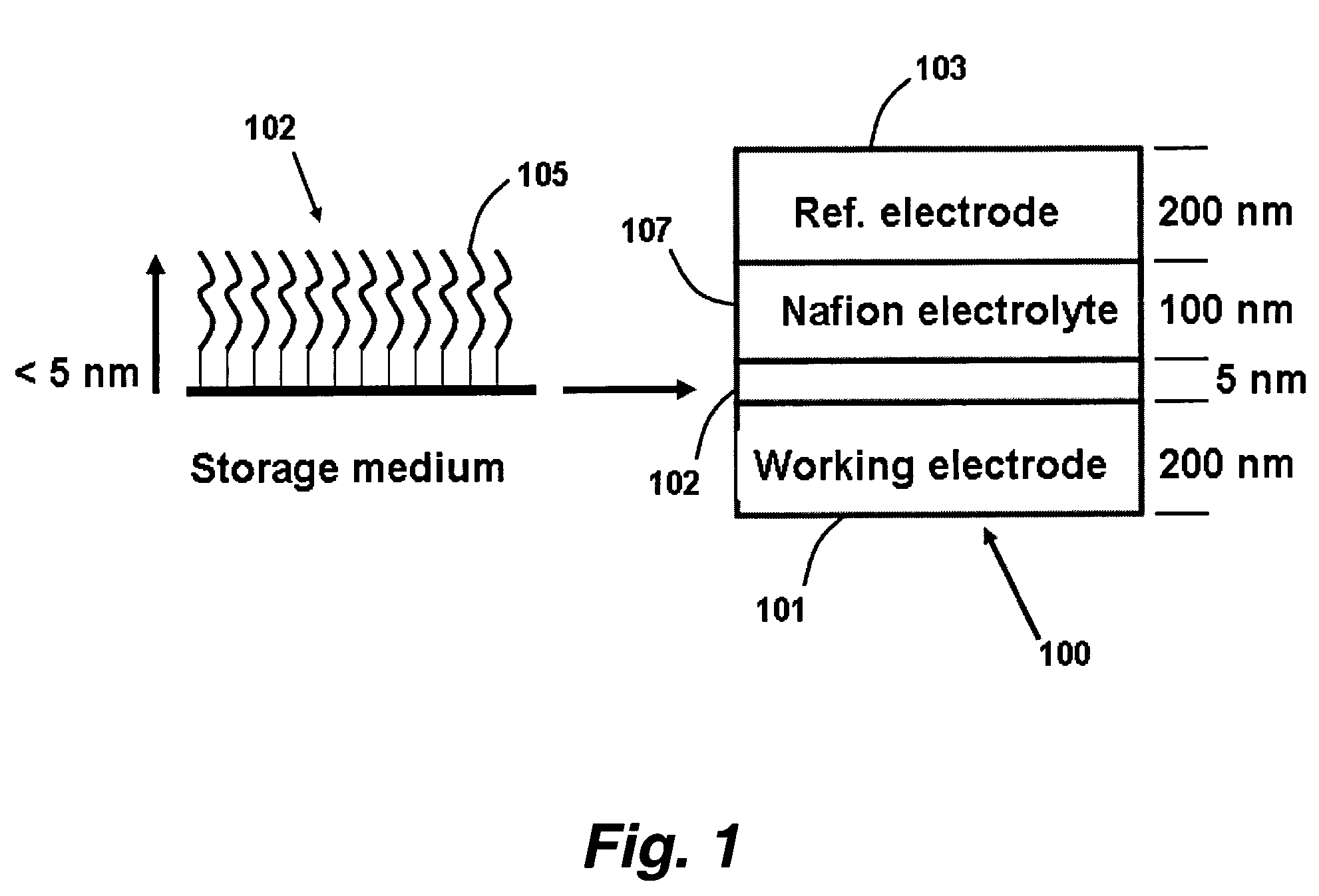

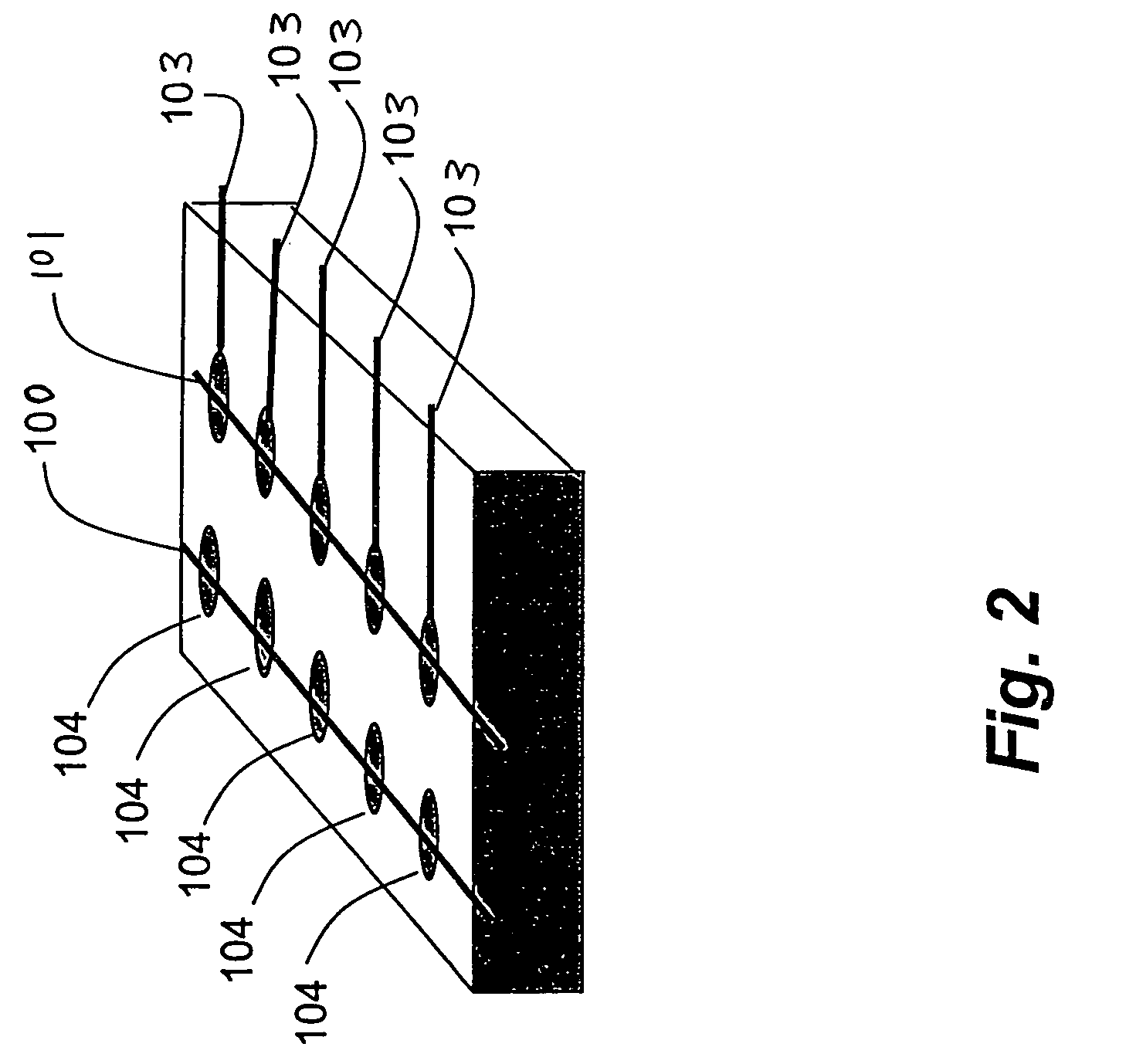

High density non-volatile memory device

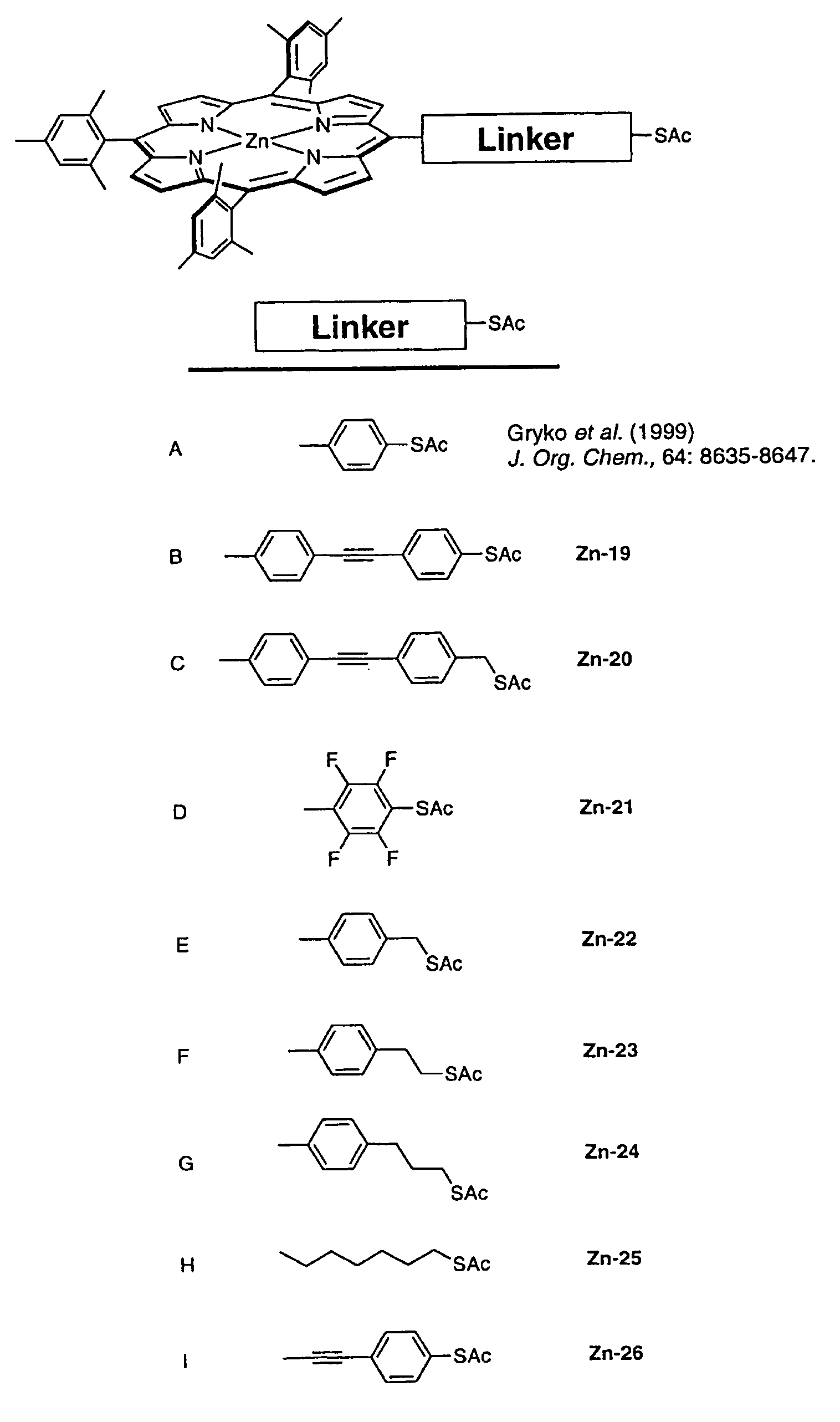

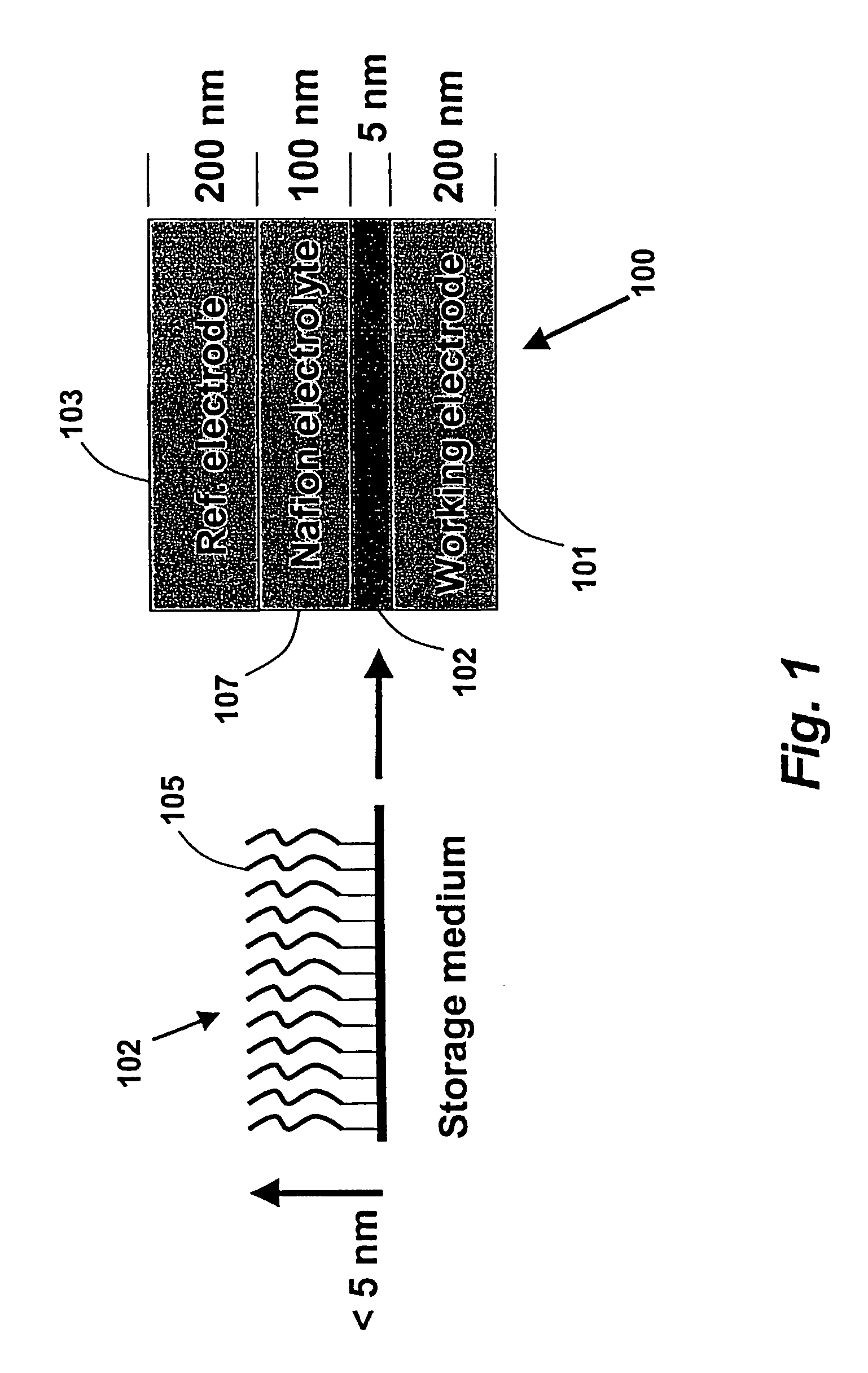

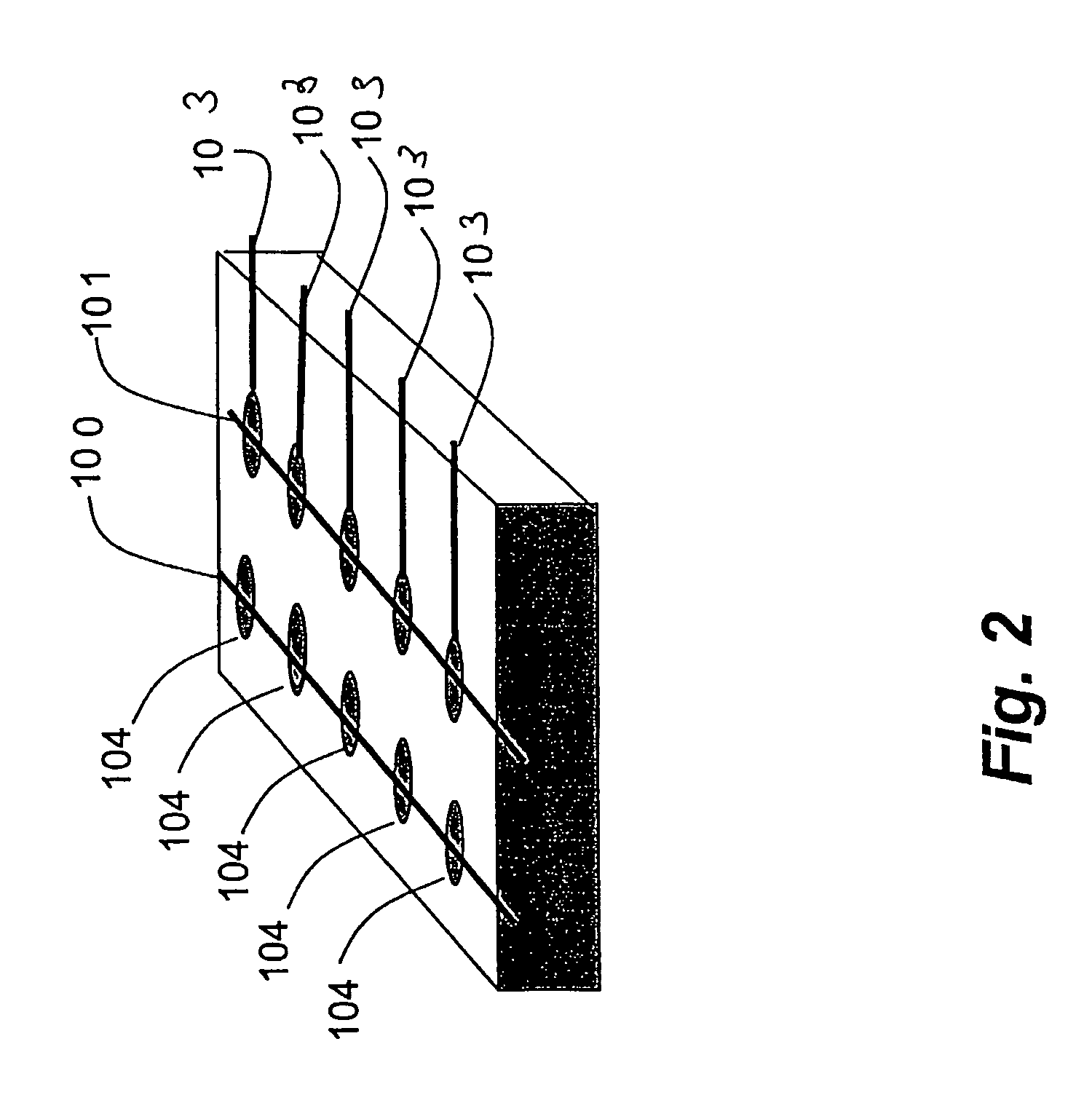

InactiveUS20050041494A1Suitable mechanical propertyPrevent charge leakageNanoinformaticsSolid-state devicesChemical synthesisFault tolerance

This invention provides novel high density memory devices that are electrically addressable permitting effective reading and writing, that provide a high memory density (e.g., 1015 bits / cm3), that provide a high degree of fault tolerance, and that are amenable to efficient chemical synthesis and chip fabrication. The devices are intrinsically latchable, defect tolerant, and support destructive or non-destructive read cycles. In a preferred embodiment, the device comprises a fixed electrode electrically coupled to a storage medium having a multiplicity of different and distinguishable oxidation states wherein data is stored in said oxidation states by the addition or withdrawal of one or more electrons from said storage medium via the electrically coupled electrode.

Owner:NORTH CAROLINA STATE UNIV +1

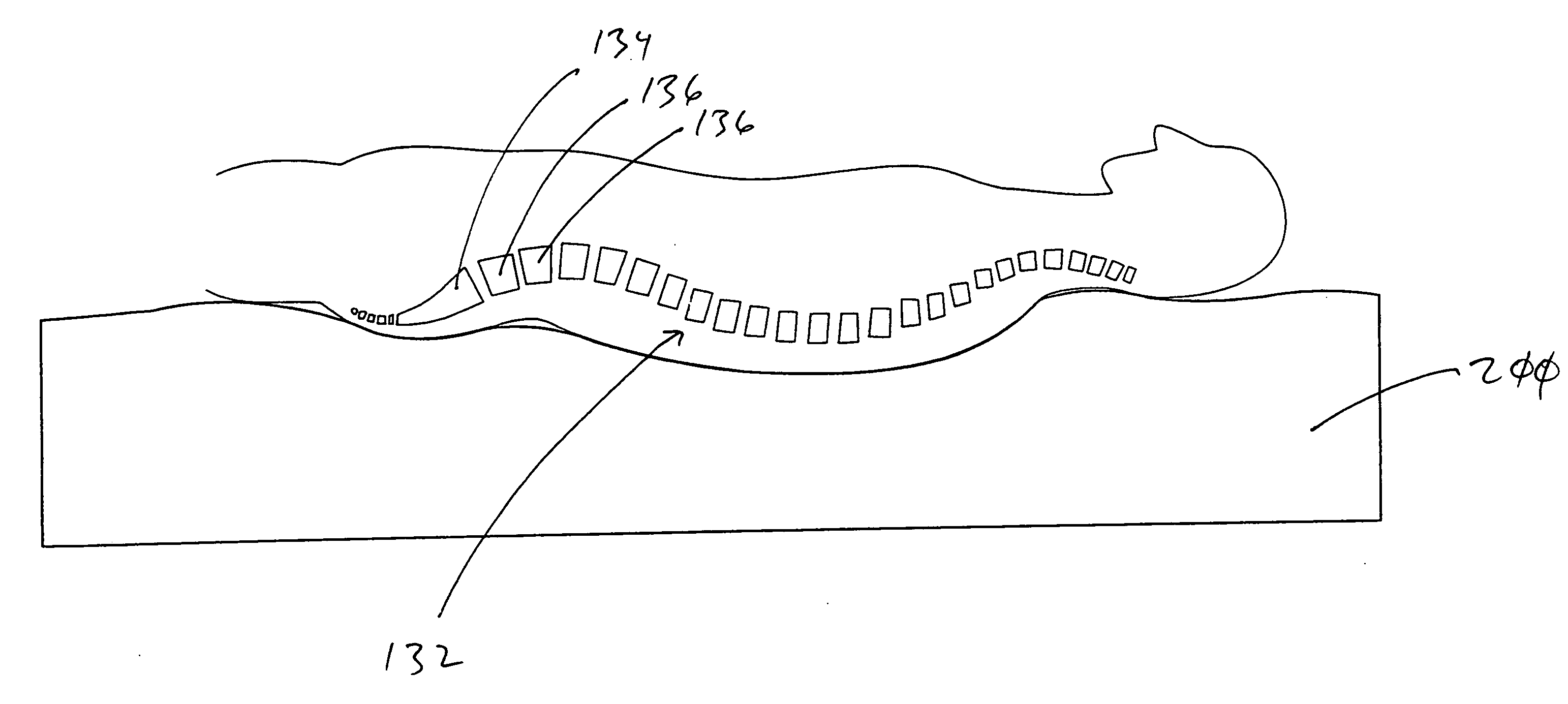

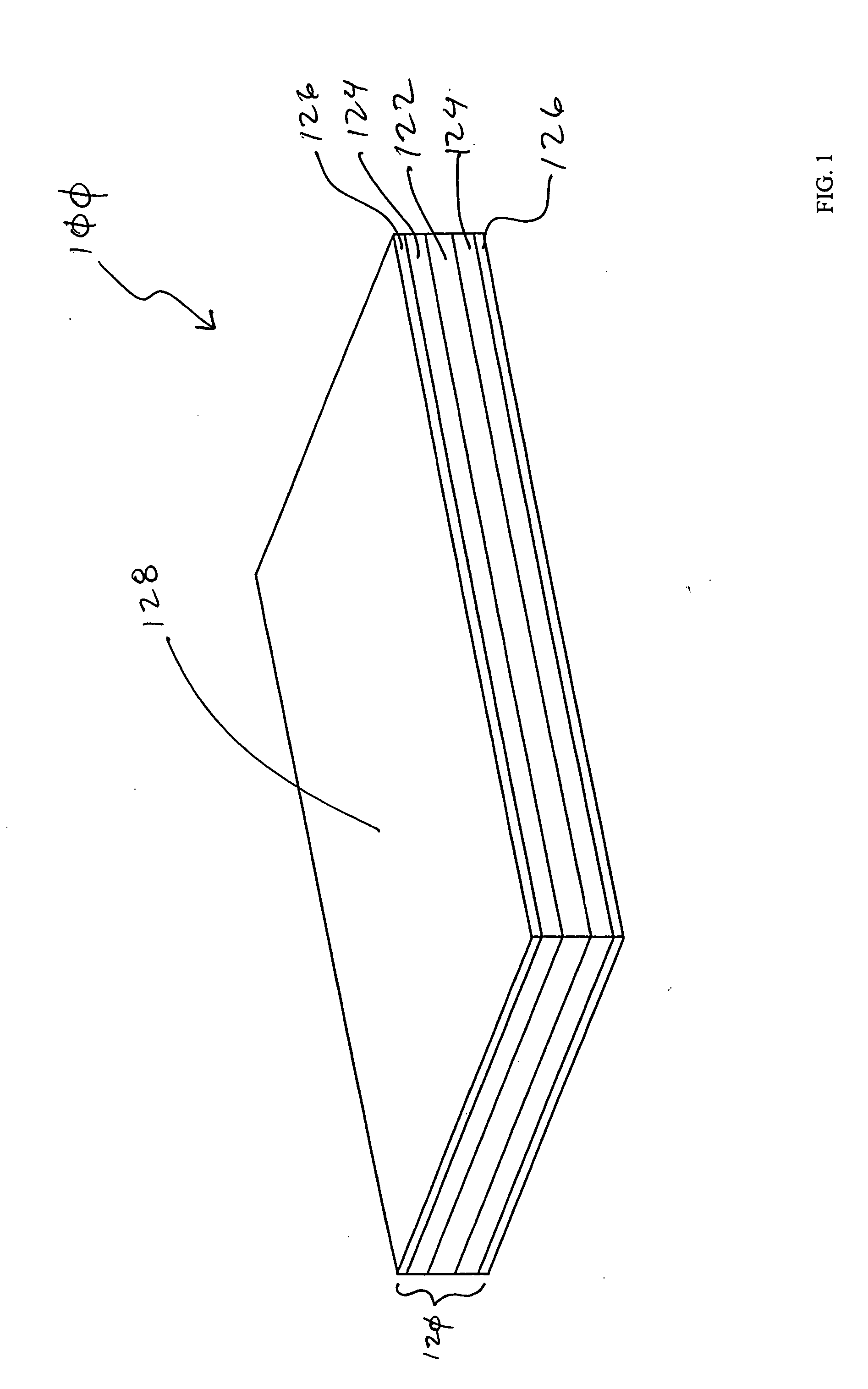

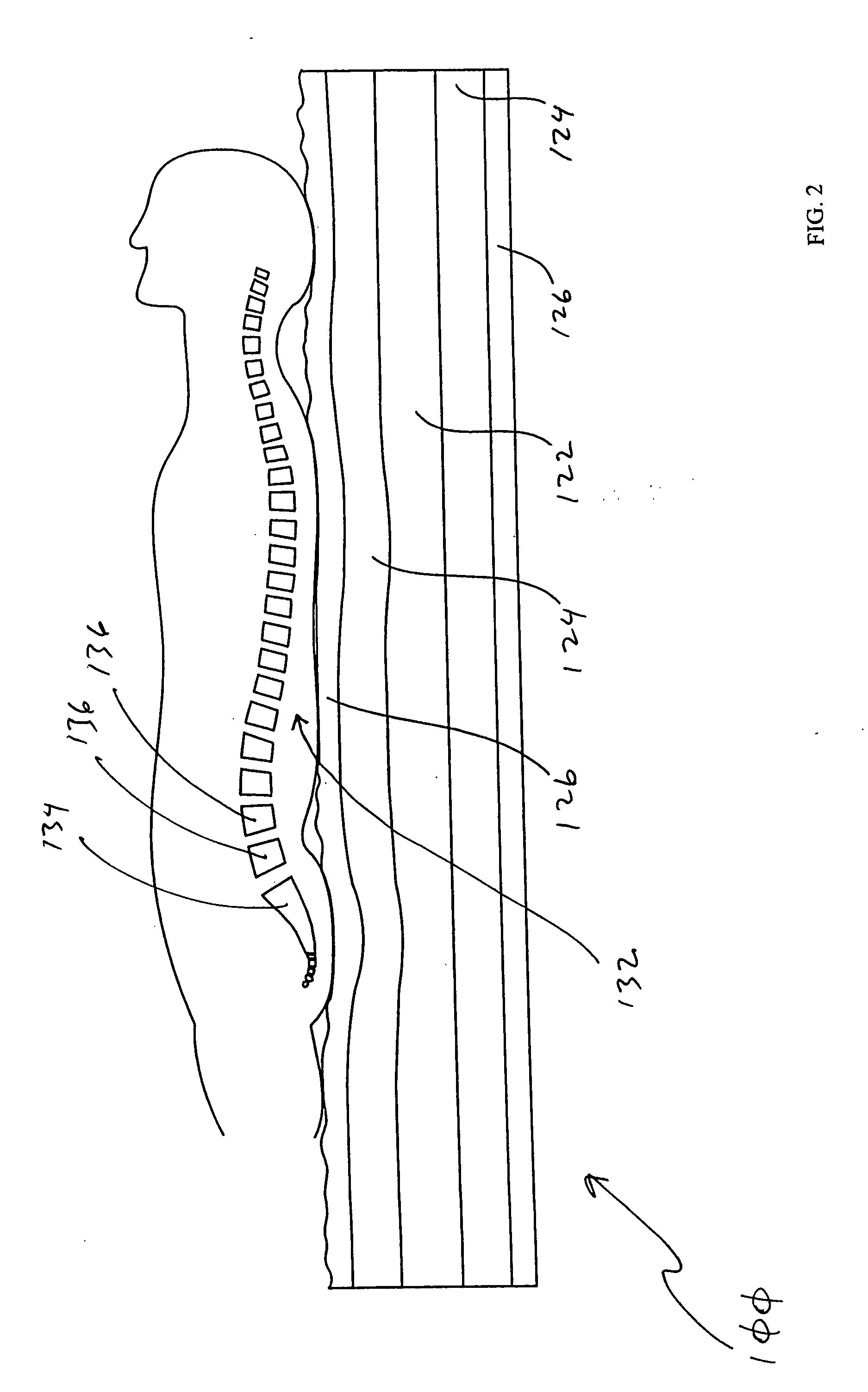

Spinal tension and pressure relieving body support apparatus

InactiveUS20080010751A1Improve abilitiesPromote blood circulationStuffed mattressesSpring mattressesMuscle tissueInter layer

A therapeutic support apparatus comprises multiple layers of foam having different densities and memories. The support apparatus comfortably supports the weight of a user while minimizing pressure points between the user and the support apparatus. Each foam layer has a unique density and memory based upon the type of tissue the layer is intended to support. A relatively low-memory outer foam layer made from latex non-viscoelastic foam substantially supports skin and subcutaneous tissue. A relatively high-density and medium-memory intermediate layer made from polyurethane foam supports muscle tissue. A relatively high-density and high-high memory core layer made from polyurethane foam supports the spine. In combination, these layers minimize hyperextension and promote blood circulation and comfort while the support apparatus is used by a user positioned in a supine, recumbent, or sideways-lying position.

Owner:MEDINNOVATIONS INT

Reconfigurable memory module and method

A computer system includes a controller coupled to a plurality of memory modules each of which includes a memory hub and a plurality of memory devices divided into a plurality of ranks. The memory hub is operable to configure the memory module to simultaneously address any number of ranks to operate in a high bandwidth mode, a high memory depth mode, or any combination of such modes.

Owner:ROUND ROCK RES LLC

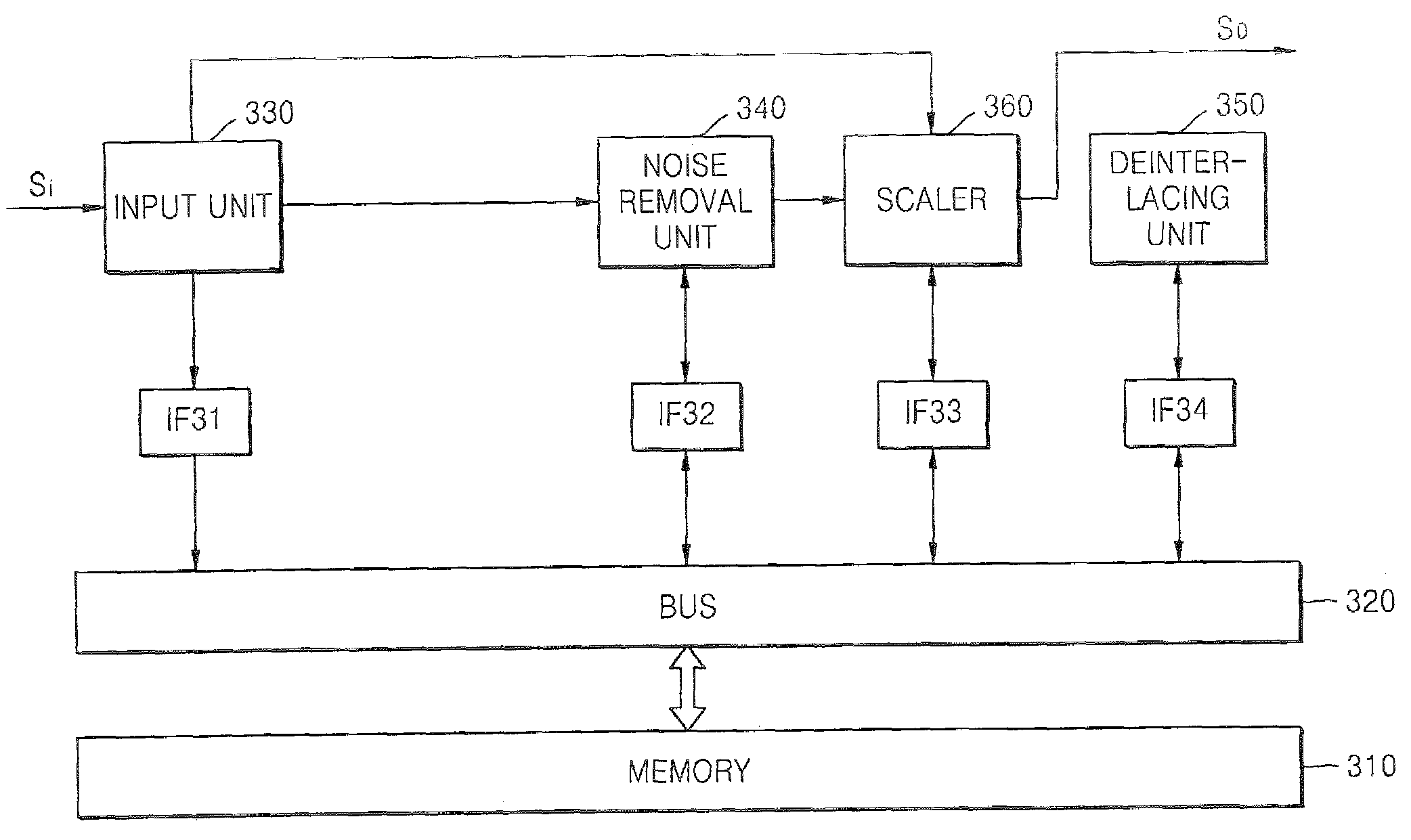

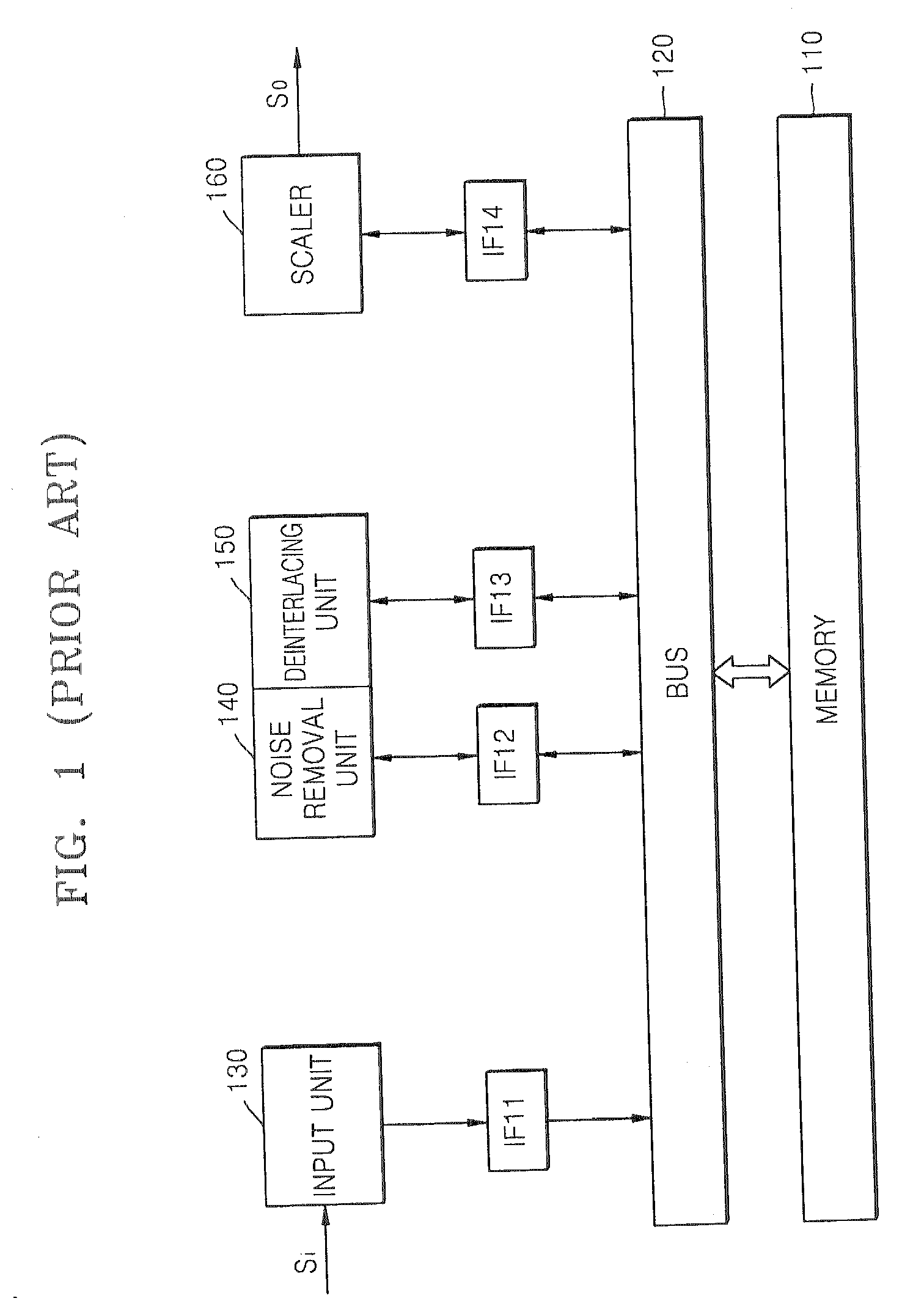

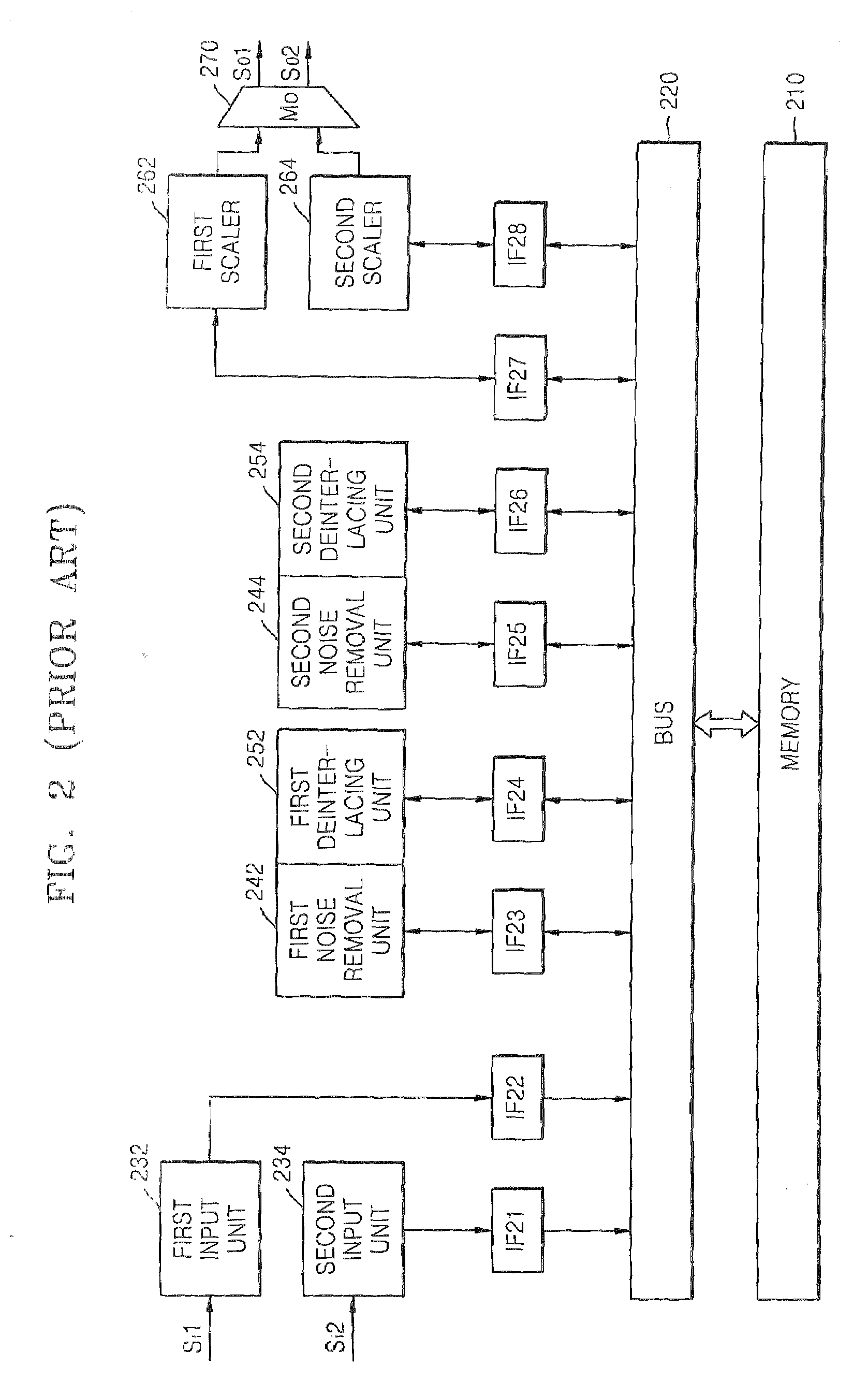

Apparatus and method for processing image signal without requiring high memory bandwidth

ActiveUS20070159642A1Reduce image sizeTelevision system detailsDigitally marking record carriersControl signalNoise removal

An image signal processor for processing an input image signal to output an output image signal includes an input unit receiving the input image signal, a noise removal unit removing noise from the input image signal, and a scaler reducing, maintaining or magnifying the image size of the input image signal. The scaler directly receives the input image signal from the input unit or the noise removal unit in response to a route control signal, reduces the image size of the input image signal when the image size of the input image signal is larger than the image size of the output image signal and stores the image signal with a reduced image size in a memory. The scaler maintains or magnifies the image size of the image signal stored in the memory and outputs the image signal with a maintained or magnified image size as the output image signal.

Owner:SAMSUNG ELECTRONICS CO LTD

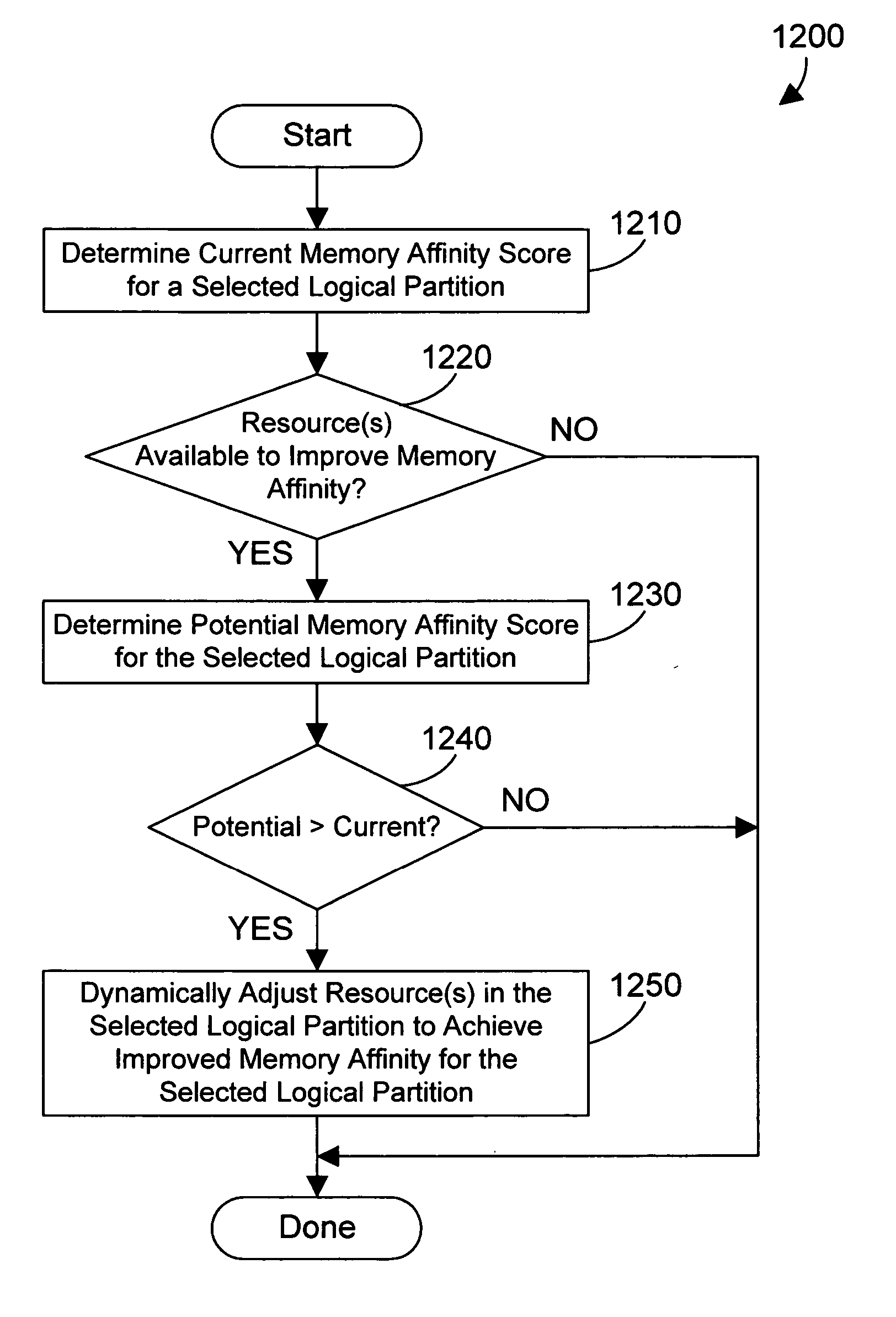

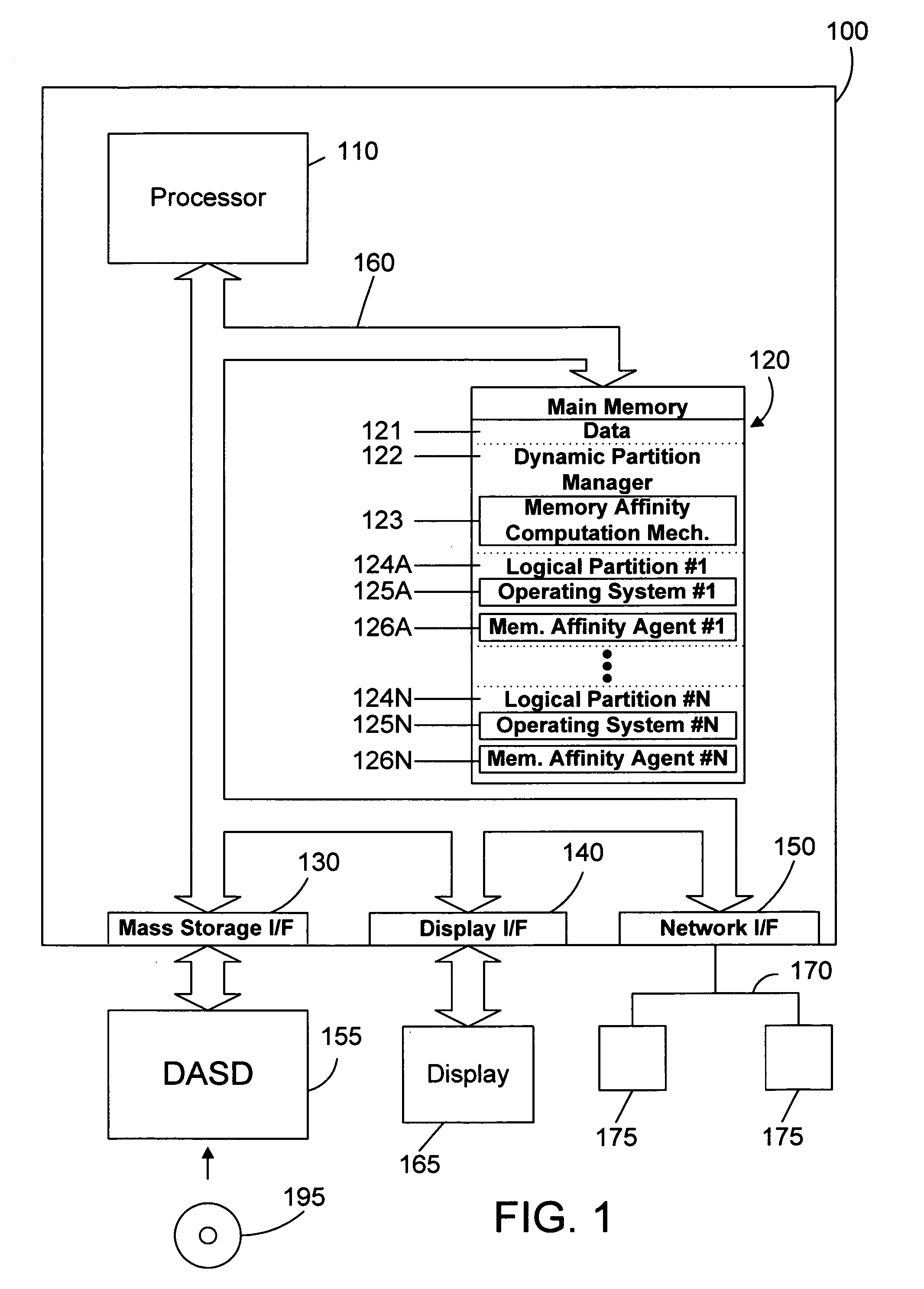

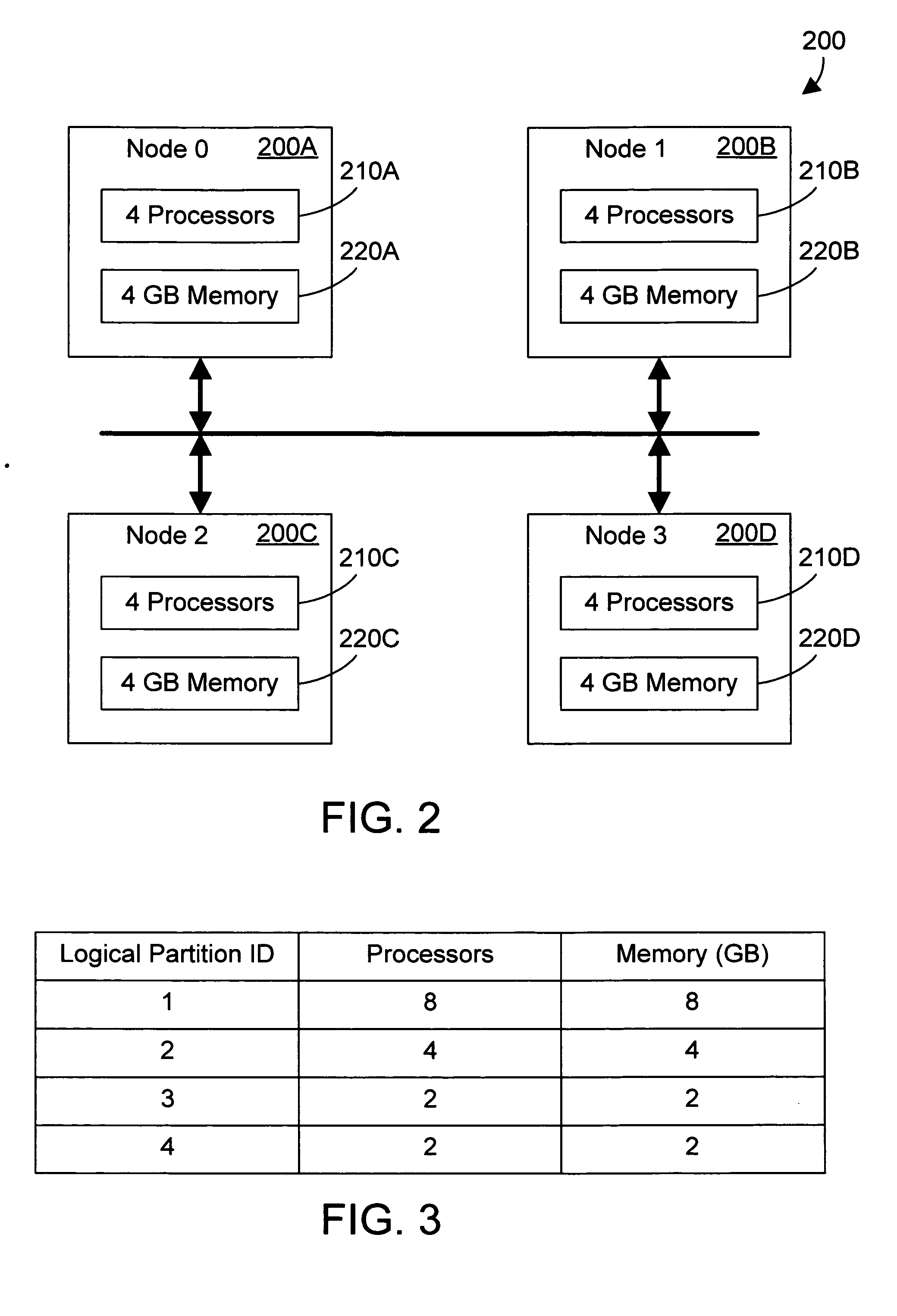

Apparatus and method for dynamically improving memory affinity of logical partitions

InactiveUS20070168635A1Improve memory affinityHigh affinityProgram controlMemory systemsTheoretical computer scienceTerm memory

In a computer system that includes multiple nodes and multiple logical partitions, a dynamic partition manager computes current memory affinity and potential memory affinity at the request of a logical partition to help the logical partition determine whether a reallocation of resources between nodes may improve memory affinity for the logical partition. If so, the logical partition requests reallocation of resources by the dynamic partition manager so memory affinity for the logical partition is improved.

Owner:IBM CORP

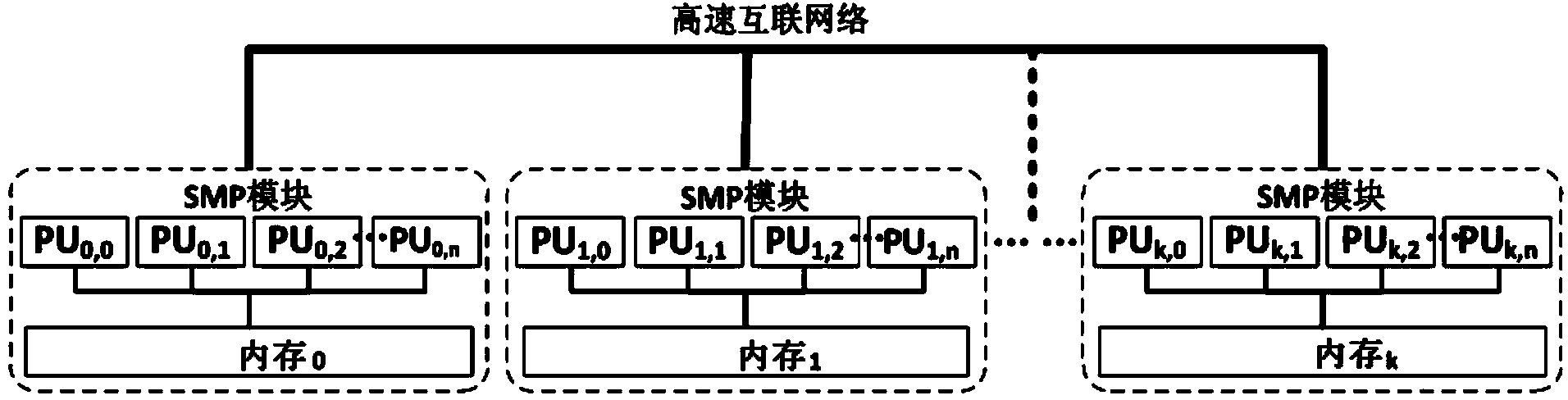

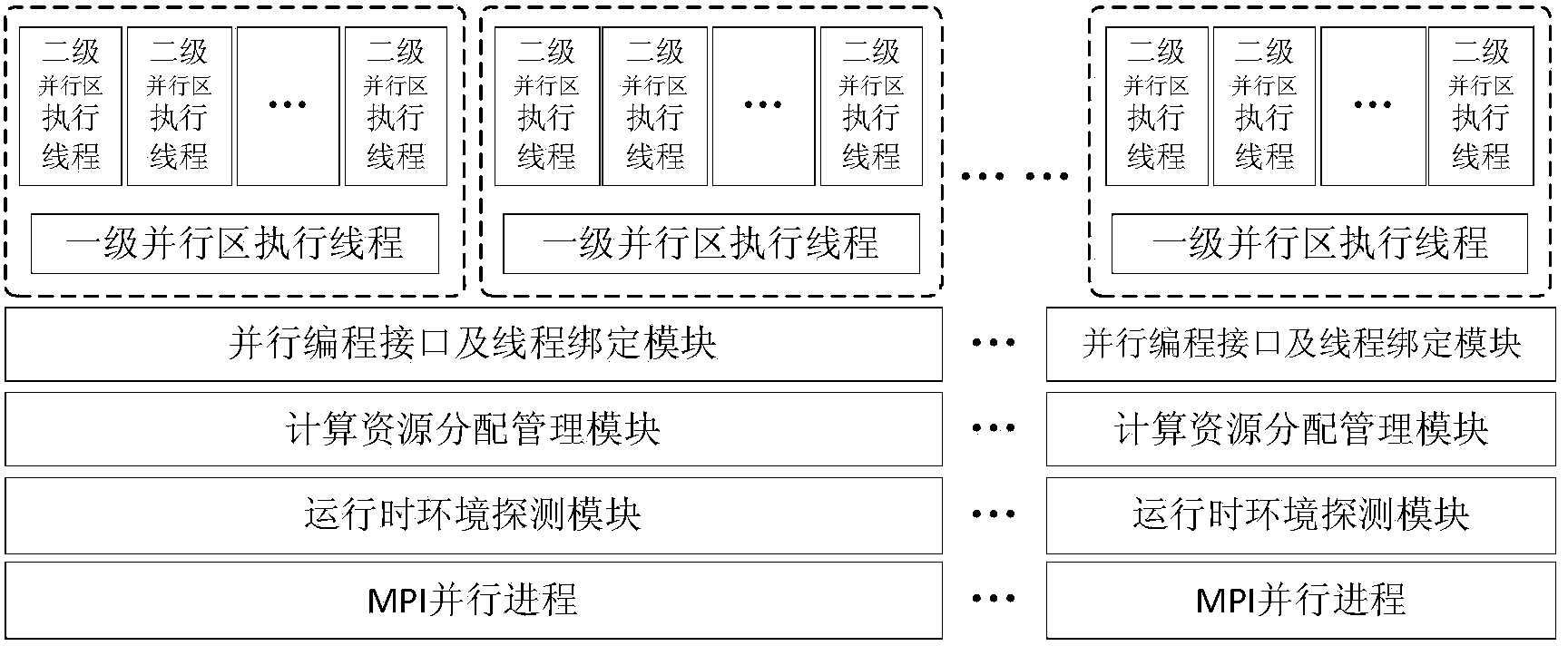

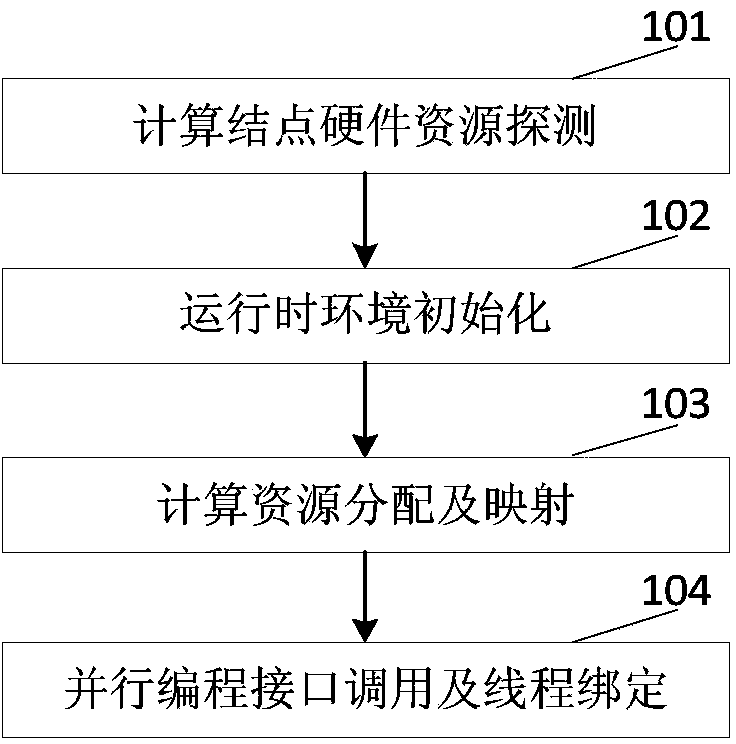

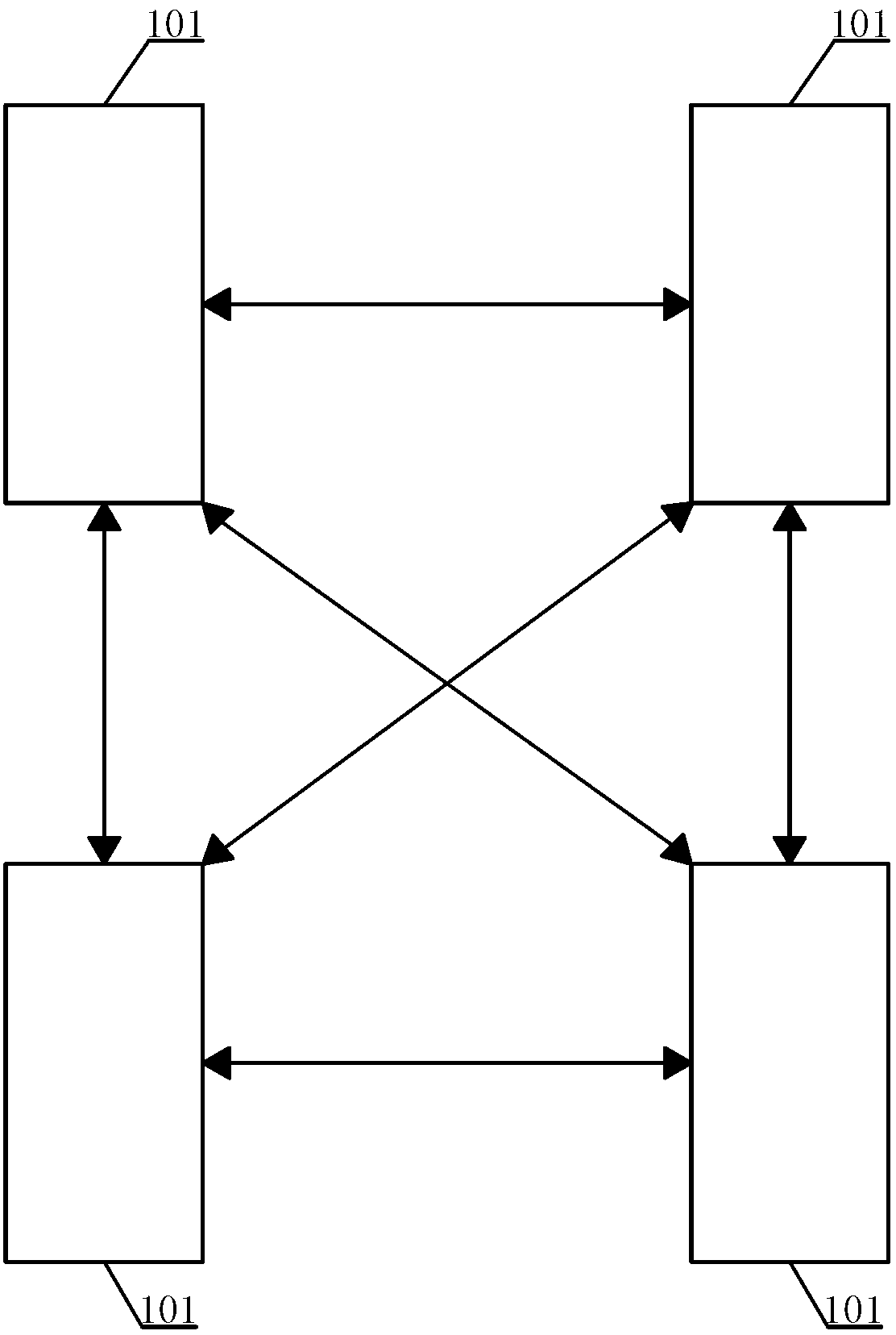

Thread for high-performance computer NUMA perception and memory resource optimizing method and system

ActiveCN104375899ASolve the problem of excessive granularity of memory managementSolve fine-grained memory access requirementsResource allocationComputer architecturePerformance computing

The invention discloses a thread for high-performance computer NUMA perception and a memory resource optimizing method and system. The system comprises a runtime environment detection module used for detecting hardware resources and the number of parallel processes of a calculation node, a calculation resource distribution and management module used for distributing calculation resources for parallel processes and building the mapping between the parallel processes and the thread and a processor core and physical memory, a parallel programming interface, and a thread binding module which is used for providing the parallel programming interface, obtaining a binding position mask of the thread according to mapping relations and binding the executing thread to a corresponding CPU core. The invention further discloses a multi-thread memory manager for NUMA perception and a multi-thread memory management method of the multi-thread memory manager. The manager comprises a DSM memory management module and an SMP module memory pool which manage SMP modules which the MPI processes belong to and memory distributing and releasing in the single SMP module respectively, the system calling frequency of the memory operation can be reduced, the memory management performance is improved, remote site memory access behaviors of application programs are reduced, and the performance of the application programs is improved.

Owner:INST OF APPLIED PHYSICS & COMPUTATIONAL MATHEMATICS

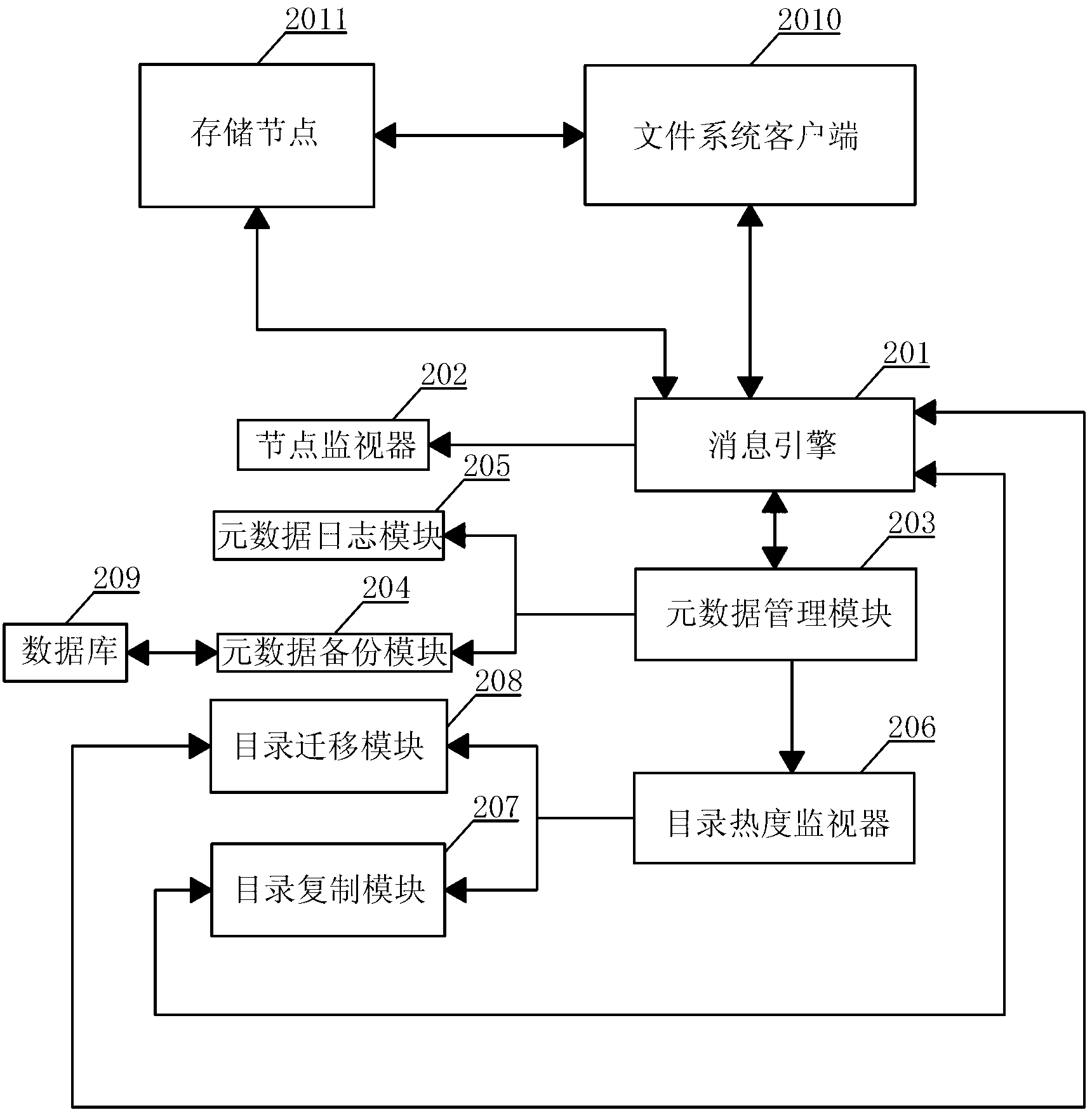

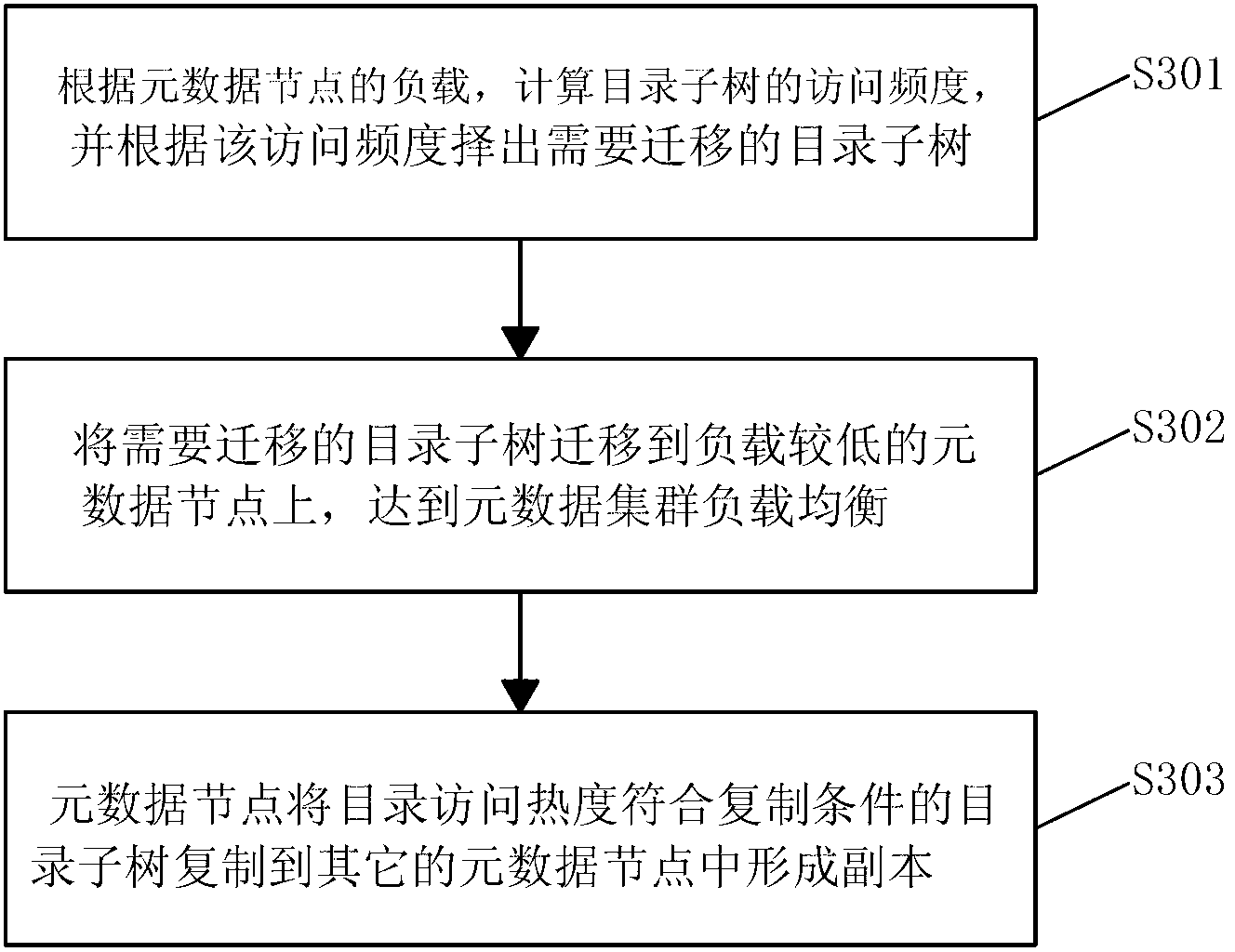

System and method for metadata management

InactiveCN103279568AImprove usabilityIncrease storage capacityHardware monitoringSpecial data processing applicationsDistributed File SystemMetadata management

The invention discloses a system and a method for metadata management. The system comprises a message engine, a node monitor, a metadata management module, a metadata backup module, a directory heat monitor, a directory replication module and a directory migration module. Metadata of the system are distributed in nodes of a metadata cluster instead of a single capacity limited in memory capacity, so that the memory capacity can be expanded horizontally; a dynamic distribution policy is adopted in the distribution of the metadata, so that high availability and high memory capacity of a distributed file system required in enterprise application environment and high expansibility of the memory capacity and access performance are improved.

Owner:WUXI UNIS STORAGE SYST

High density memory device

InactiveUS20060209587A1Easy constructionEasy to manufactureMaterial nanotechnologyNanoinformaticsFault toleranceChemical synthesis

Owner:RGT UNIV OF CALIFORNIA +1

Hot-upgrade/hot-add memory

InactiveUS20020010875A1Memory loss protectionComponent plug-in assemblagesParallel computingComputerized system

A method of adding memory capacity to a computer system. The computer system comprises a redundant memory system including a plurality of memory cartridges. By powering-down a memory cartridge, adding an additional memory module to the memory cartridge, and powering-up the memory cartridge for each memory cartridge in the system, the system can transition from a redundant mode of operation to a non-redundant mode of operation for each power-down, thus allowing the computer system to remain functional during the addition of the memory module. Alternatively, memory cartridges with higher memory capacity than those currently present in the computer system can be used to replace existing memory cartridges in the computer system, using the same techniques.

Owner:HEWLETT PACKARD DEV CO LP

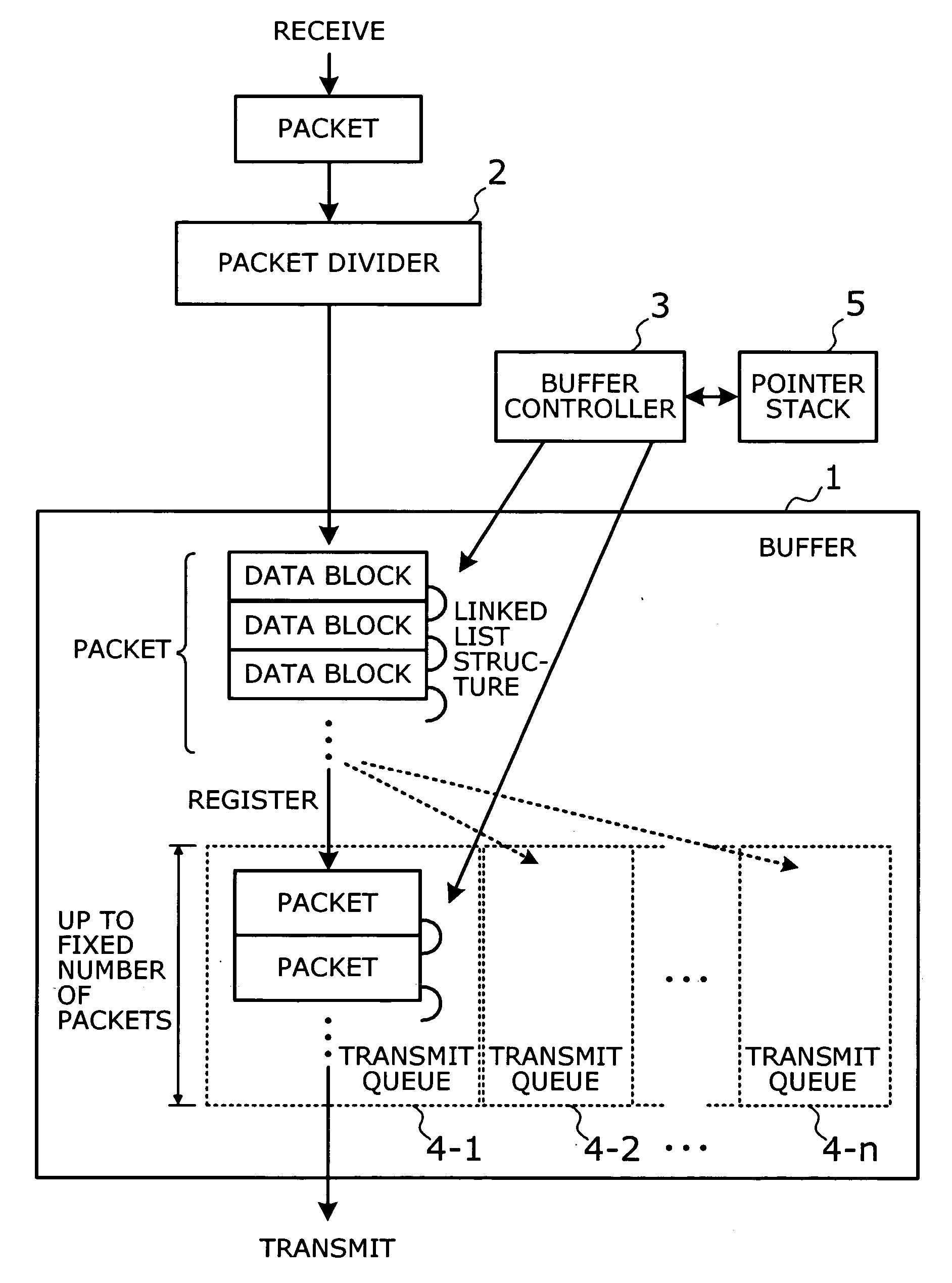

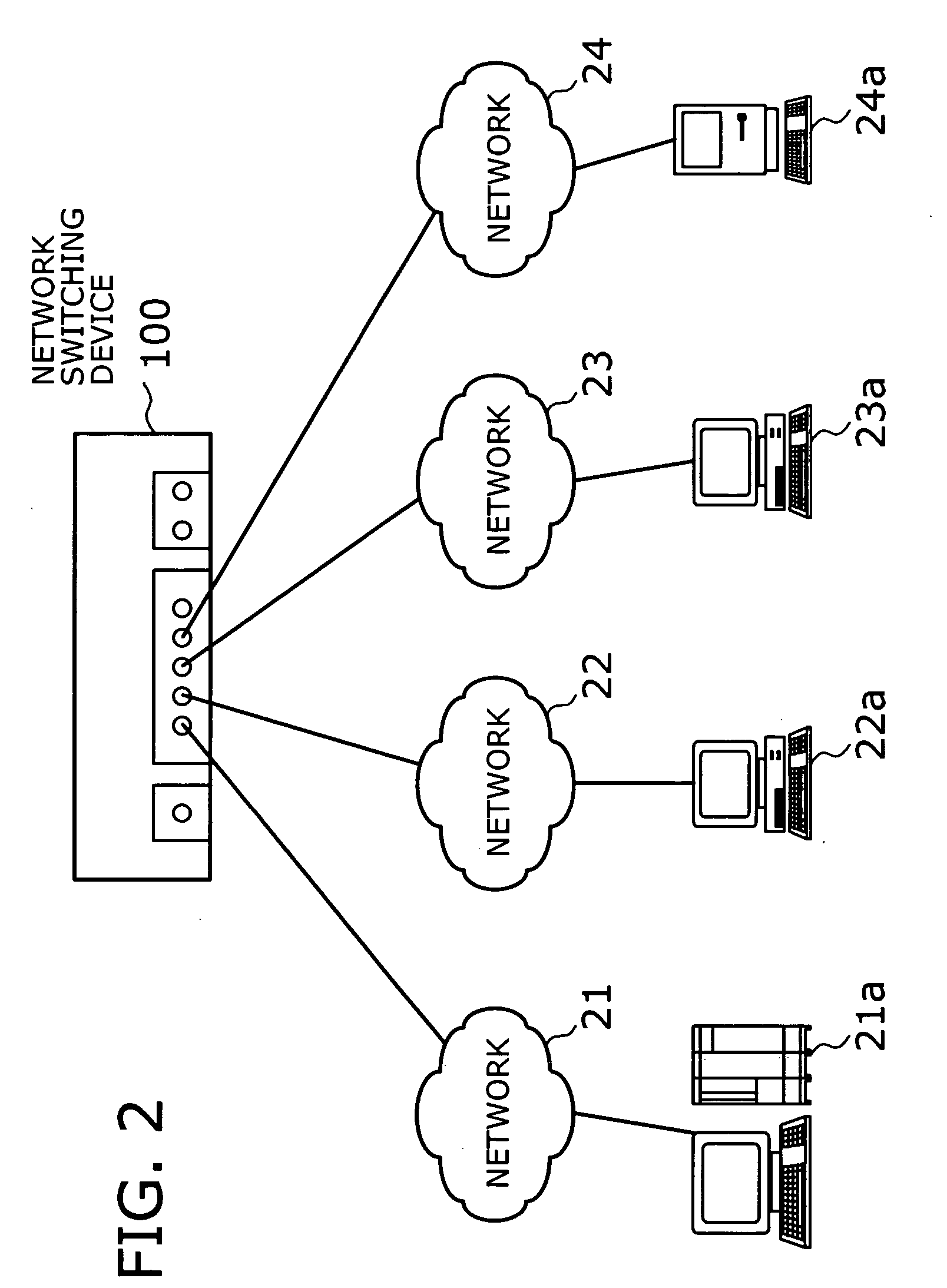

Network switching device and method using shared buffer

InactiveUS20050163141A1Improve efficiencyImprove memory usageData switching by path configurationElectric digital data processingComputer hardwareNetwork packet

A network switching device that prevents its shared buffer from suffering a blocking problem, while achieving a higher memory use efficiency in buffering variable-length packets. Every received packet is divided into one or more fixed-length data blocks and supplied to the buffer. Under the control of a buffer controller, a transmit queue is created to store up to a fixed number of data blocks for each different destination network, and the data blocks written in the buffer are registered with a transmit queue corresponding to a given destination. The linkage between data blocks in each packet, as well as the linkage between packets in each transmit queue, is managed as a linked list structure based on the locations of data blocks in the buffer.

Owner:SOCIONEXT INC

High density molecular memory device

InactiveUS7061791B2Suitable mechanical propertyPrevent charge leakageNanoinformaticsSolid-state devicesFault toleranceChemical synthesis

This invention provides novel high density memory devices that are electrically addressable permitting effective reading and writing, that provide a high memory density (e.g., 1015 bits / cm3), that provide a high degree of fault tolerance, and that are amenable to efficient chemical synthesis and chip fabrication. The devices are intrinsically latchable, defect tolerant, and support destructive or non-destructive read cycles. In a preferred embodiment, the device comprises a fixed electrode electrically coupled to a storage medium having a multiplicity of different and distinguishable oxidation states wherein data is stored in said oxidation states by the addition or withdrawal of one or more electrons from said storage medium via the electrically coupled electrode.

Owner:NORTH CAROLINA STATE UNIV +1

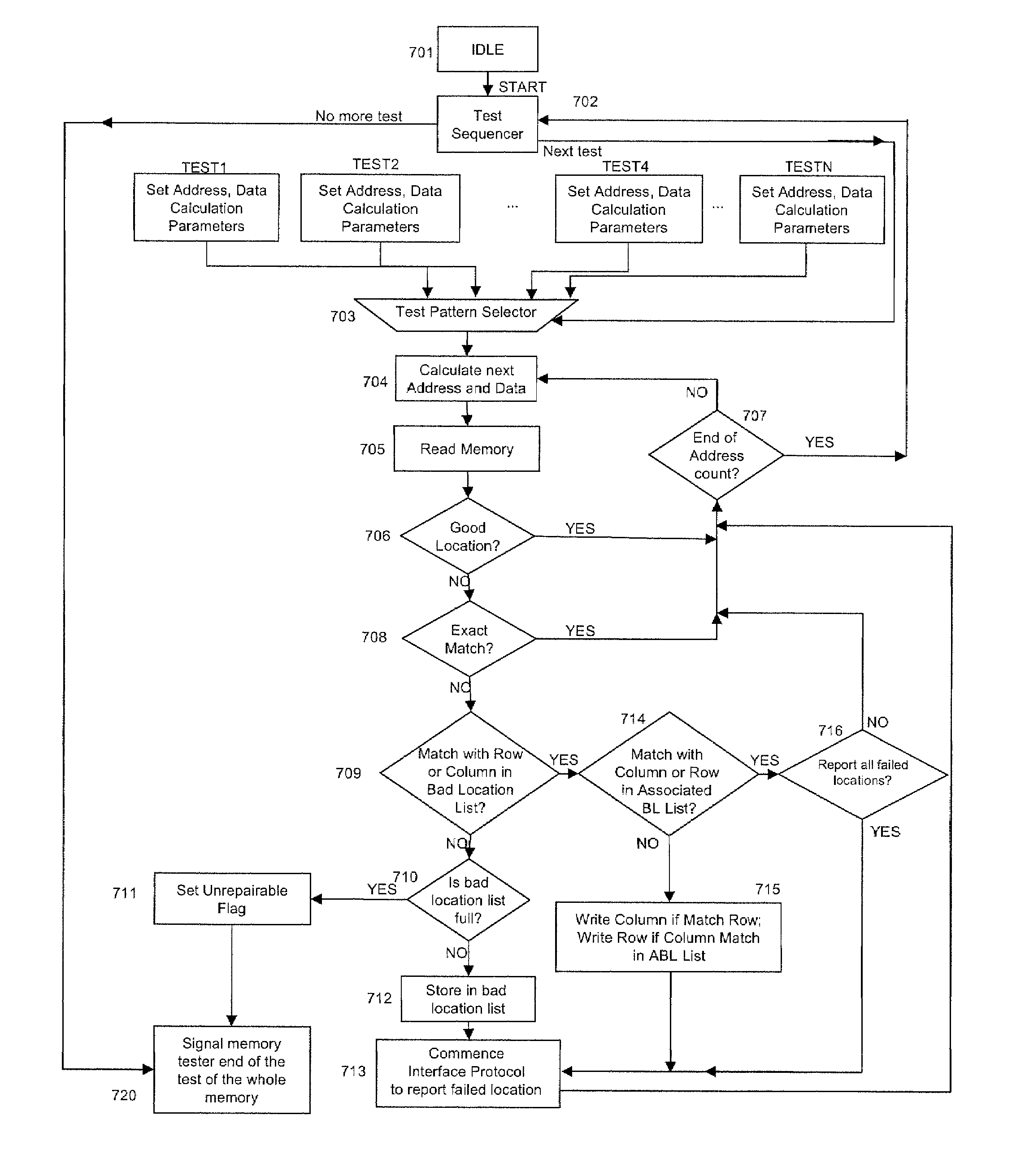

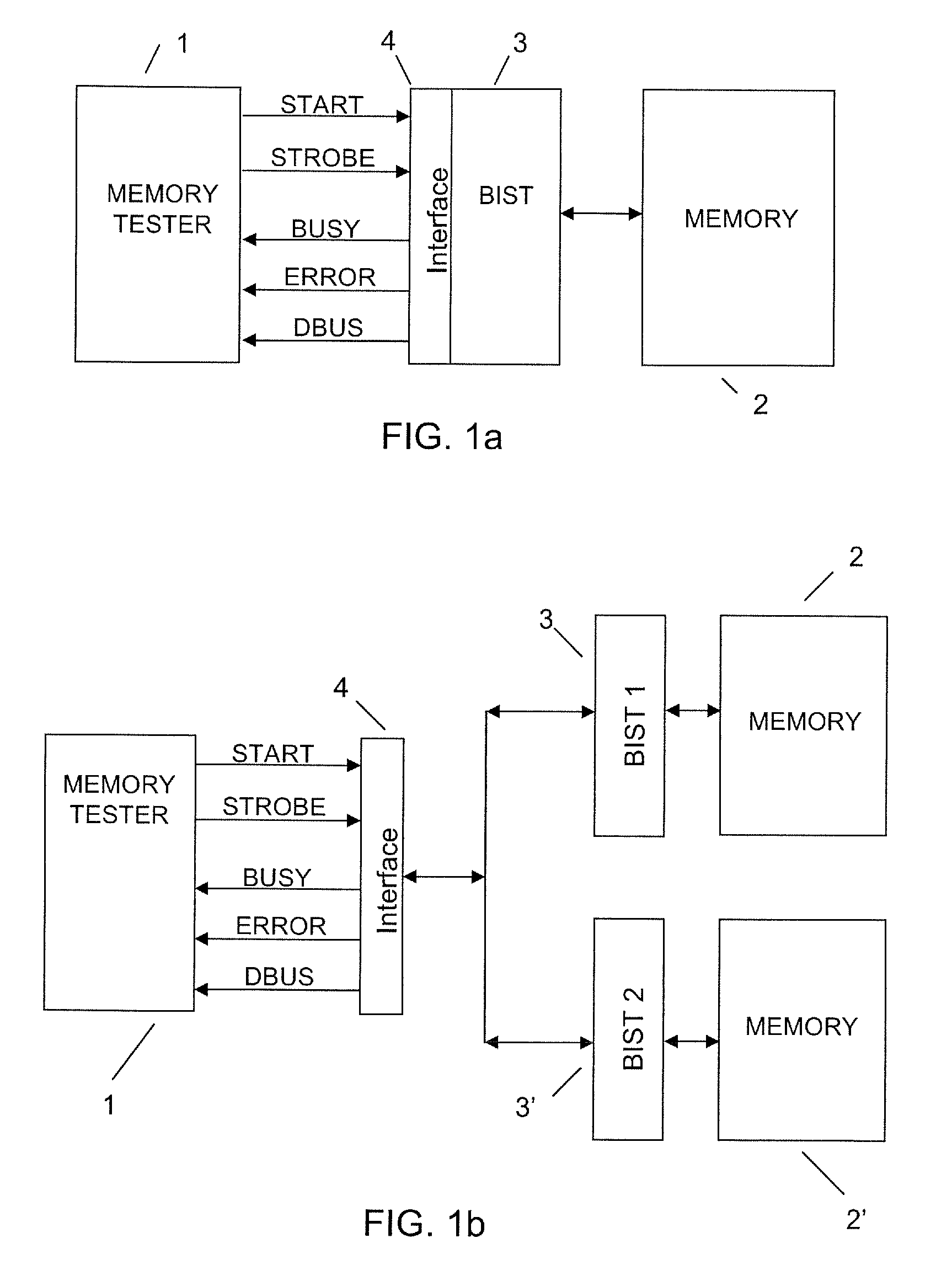

Method and system for memory testing and test data reporting during memory testing

ActiveUS7734966B1Reduced pin countNarrow interfaceElectronic circuit testingError detection/correctionAnalysis dataHigh memory

The present invention provides a method and system for improving memory testing efficiency, raising the speed of memory testing, detecting memory failures occurring at the memory operating frequency, and reducing data reported for redundancy repair analysis. The memory testing system includes a first memory tester extracting failed memory location information from the memory at a higher memory operating frequency, an external memory tester receiving failed memory location information at a lower memory tester frequency, and an interface between the first memory tester and the external memory tester. The memory testing method uses data strobes at the memory tester frequency to clock out failed memory location information obtained at the higher memory operating frequency. In addition, the inventive method reports only enough information to the external memory tester for it to determine row, column and single bit failures repairable with the available redundant resources. The present invention further provides a redundant resource allocation system, which uses a bad location list and an associated bad location list to classify failed memory locations according to a predetermined priority sequence, and allocates redundant resources to repair the failed memory locations according to the priority sequence.

Owner:MARVELL ASIA PTE LTD

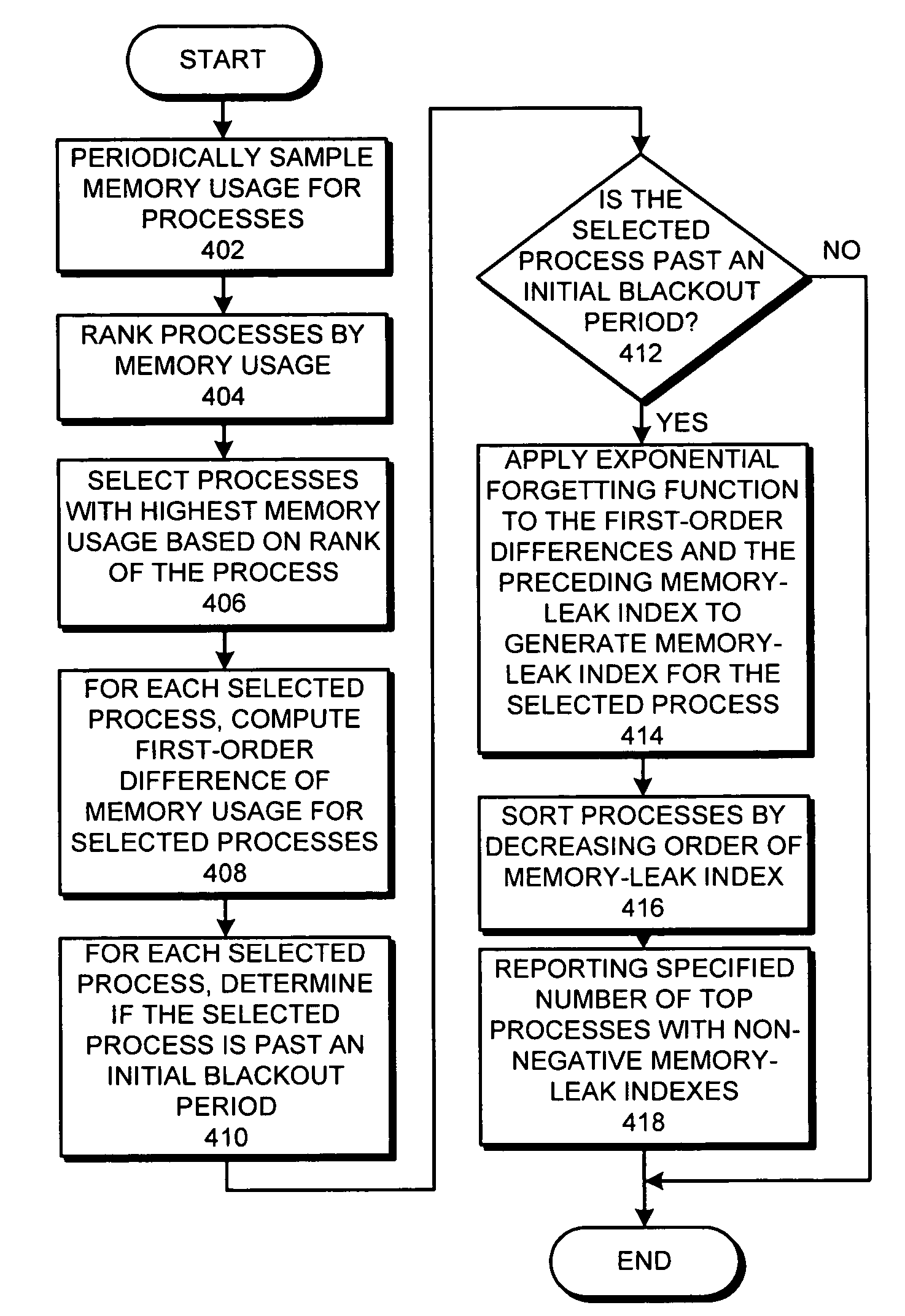

Method and apparatus for detecting memory leaks in computer systems

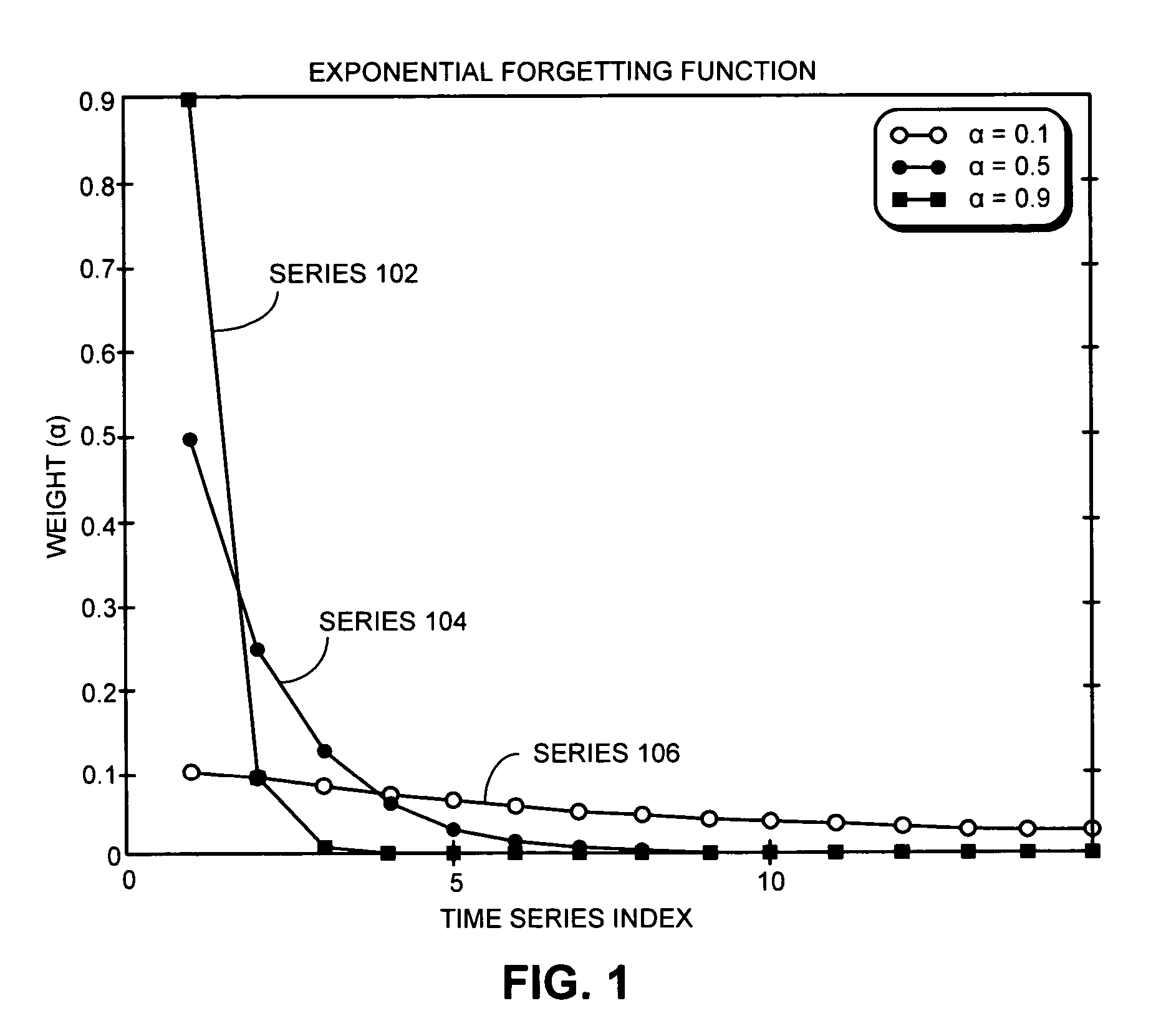

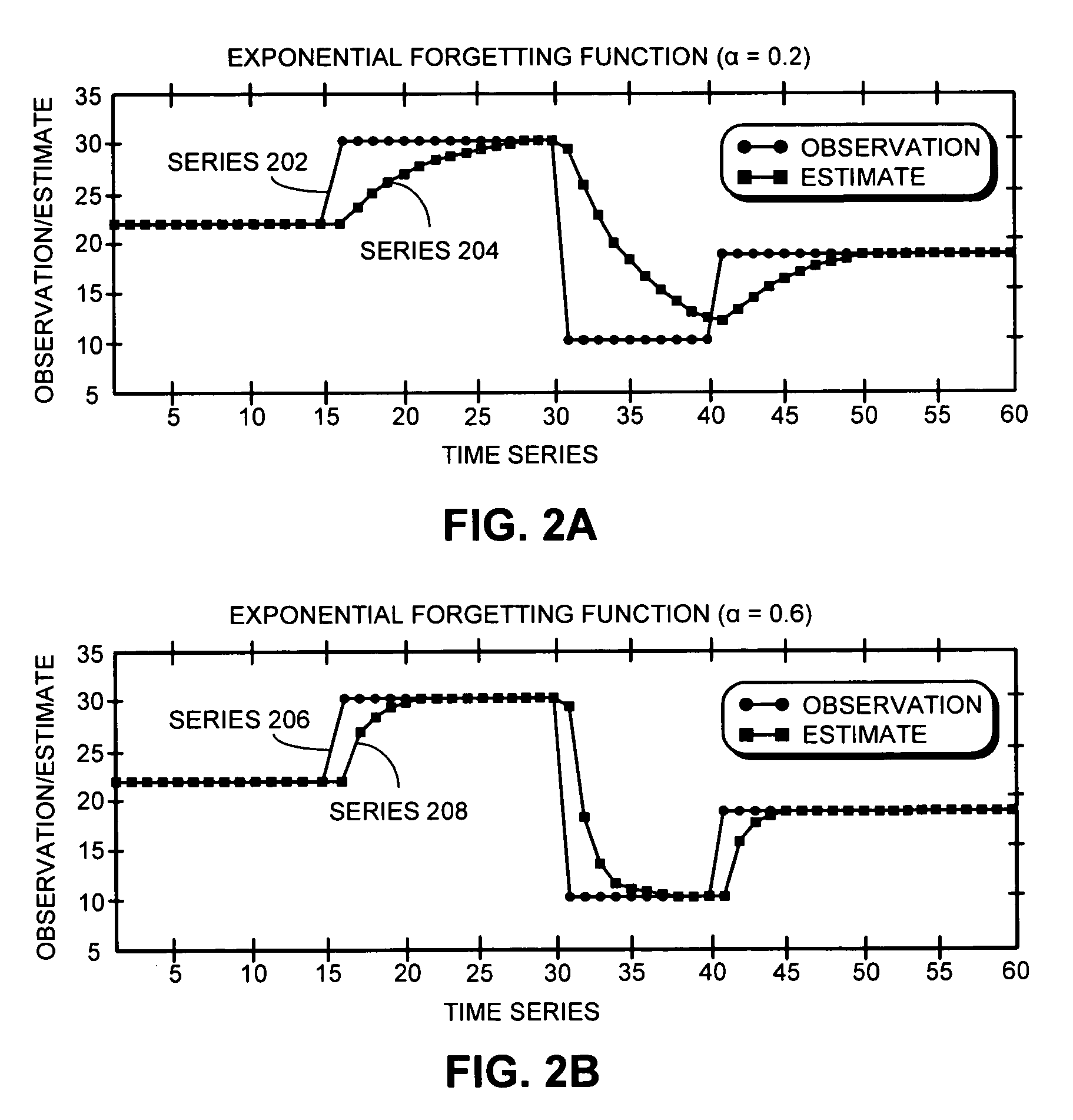

ActiveUS7716648B2Discard past memory usage values more quicklyDiscard past memory usage valuesError detection/correctionSpecific program execution arrangementsRankingComputerized system

A system that identifies processes with a memory leak in a computer system. During operation, the system periodically samples memory usage for processes running on the computer system. The system then ranks the processes by memory usage and selects a specified number of processes with highest memory usage based on the ranking. For each selected process, the system computes a first-order difference of memory usage by taking a difference between the memory usage at a current sampling time and the memory usage at an immediately preceding sampling time. The system then generates a memory-leak index based on the first-order difference and a preceding memory-leak index computed at the immediately preceding sampling time.

Owner:ORACLE INT CORP

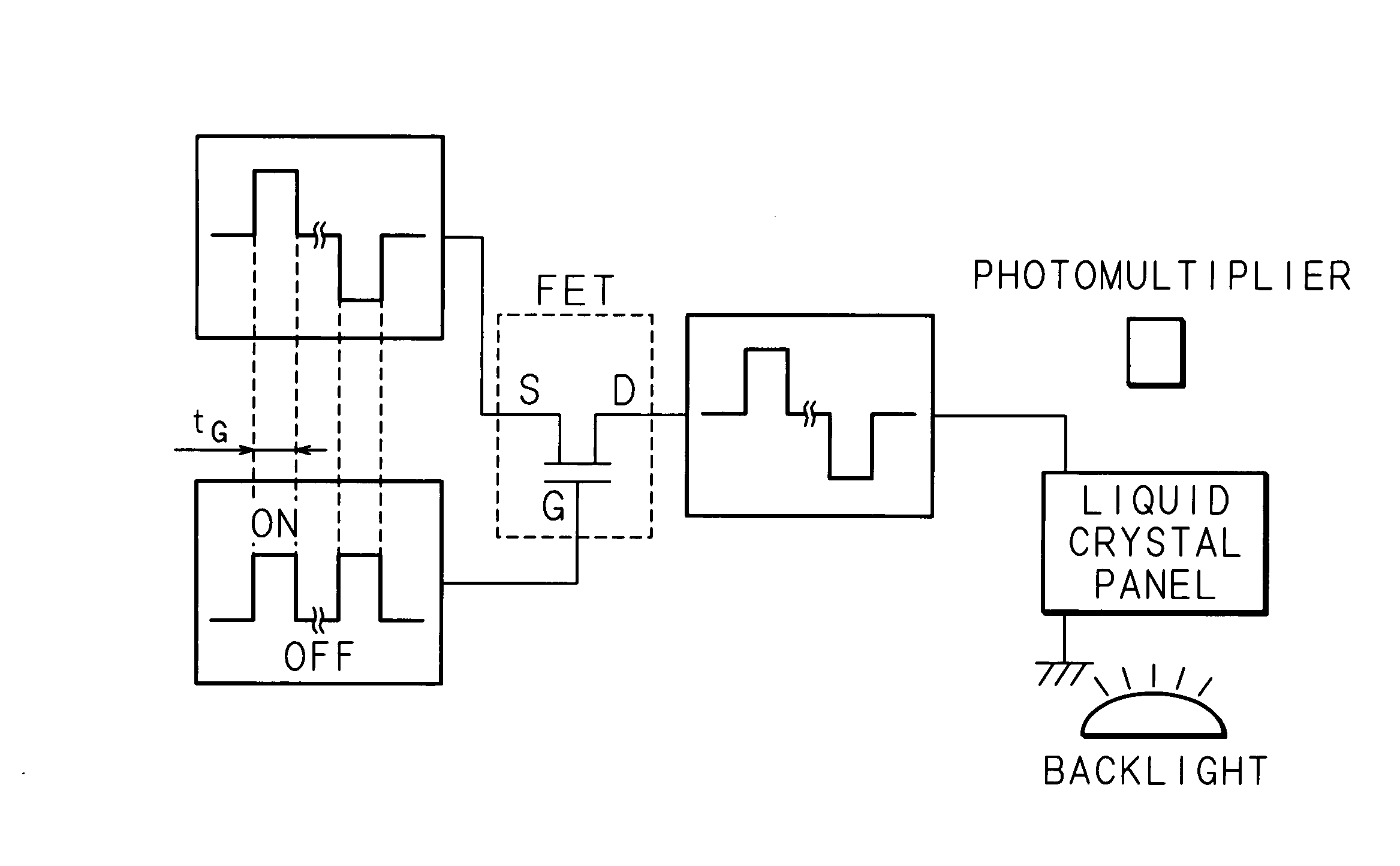

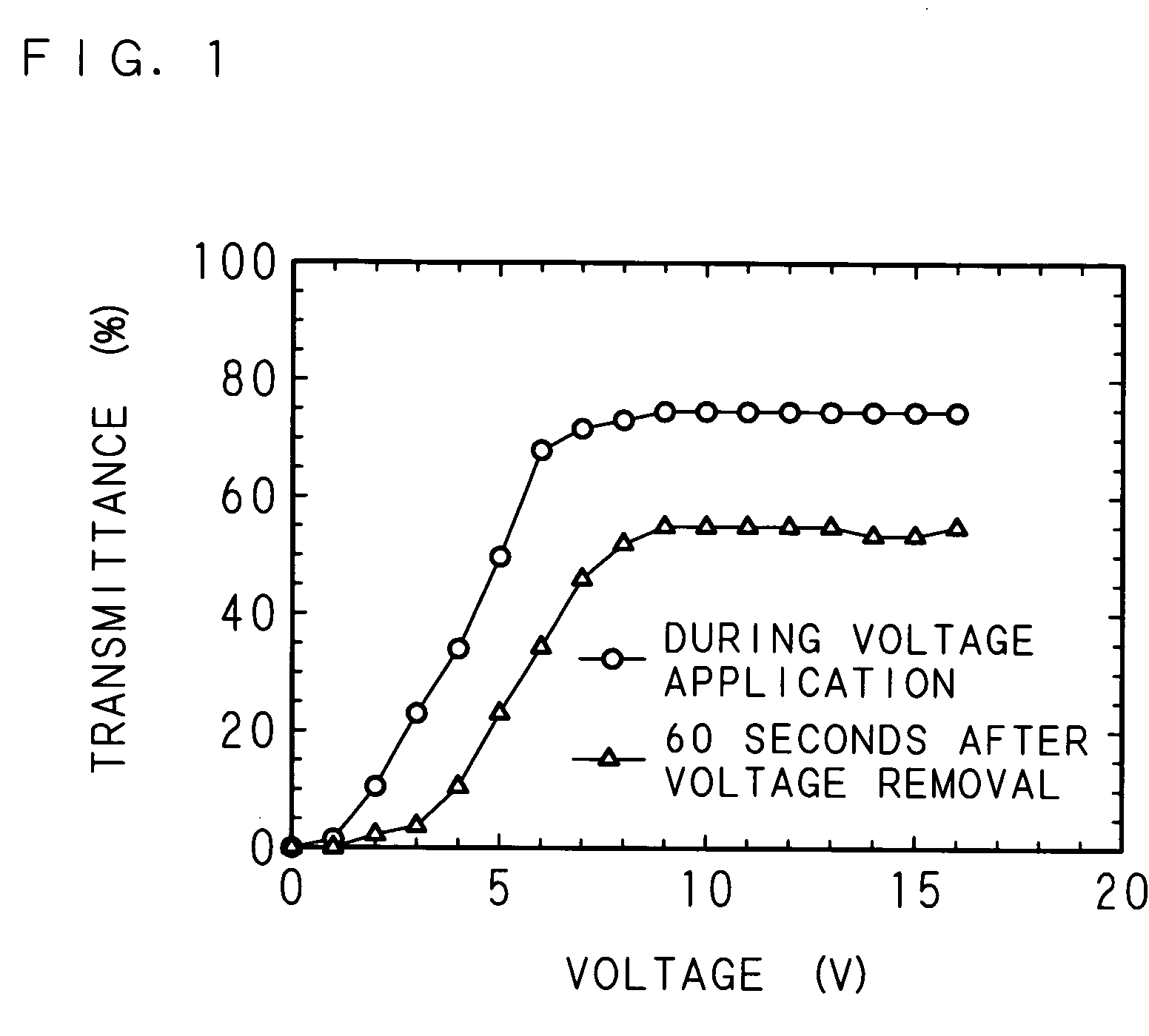

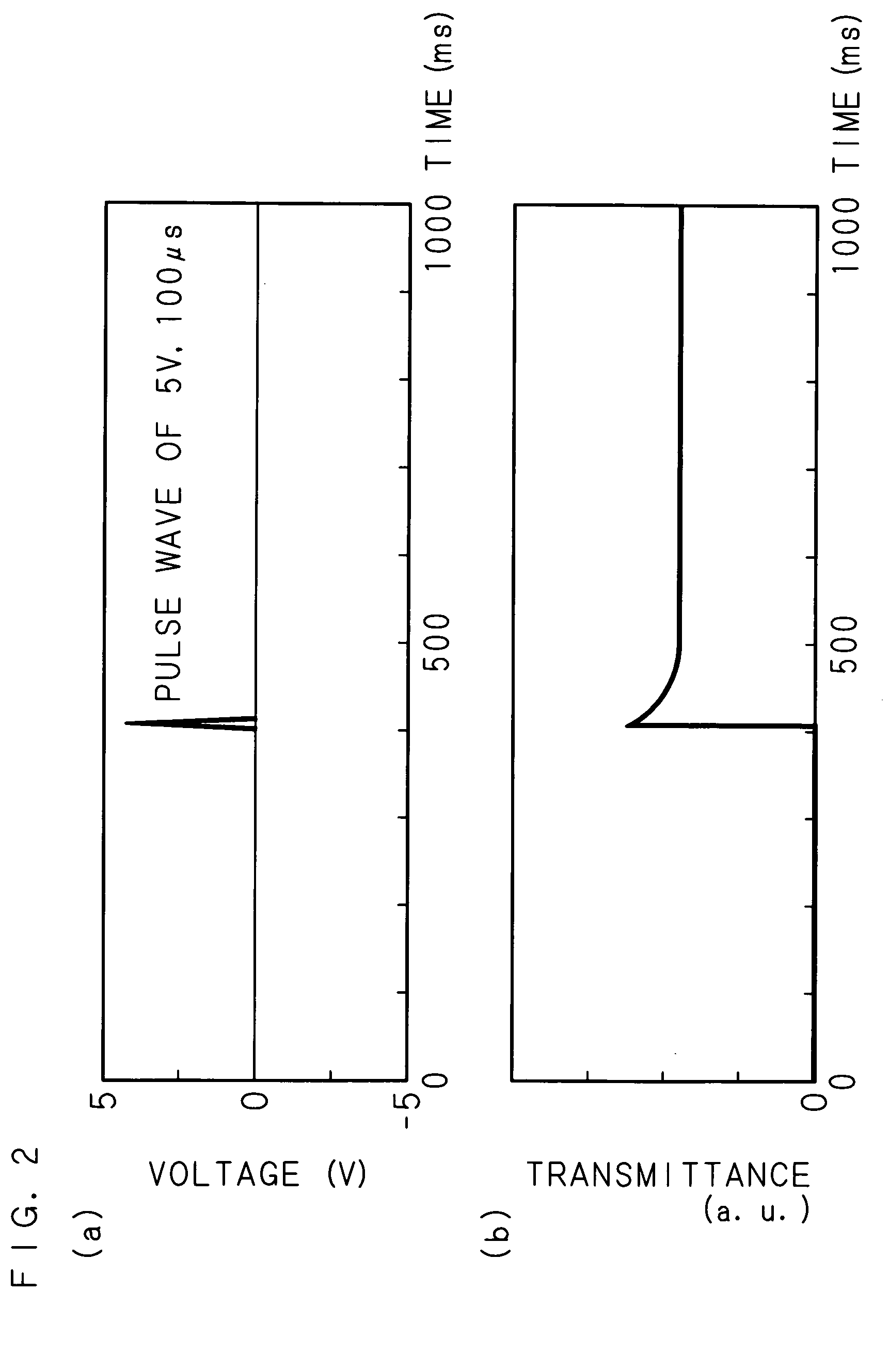

Liquid crystal display device

InactiveUS20060092122A1Reduce power consumptionAdequate responseStatic indicating devicesLiquid-crystal displayHigh memory

A voltage corresponding to desired image data is applied to a ferroelectric liquid crystal having a spontaneous polarization at a predetermined cycle to rewrite the displayed image (period A), and then, all voltages applied to the ferroelectric liquid crystal are removed (timing C) to retain the displayed image before the removal (period B). A gate selection period (voltage application period to the ferroelectric liquid crystal) t2 before stopping the voltage application is set longer than a gate selection period (voltage application period to the ferroelectric liquid crystal) t1 in the normal display. Increasing the voltage application period to the ferroelectric liquid crystal provides a sufficient response of the liquid crystal during the gate selection period, thereby realizing high memory ability.

Owner:FUJITSU LTD

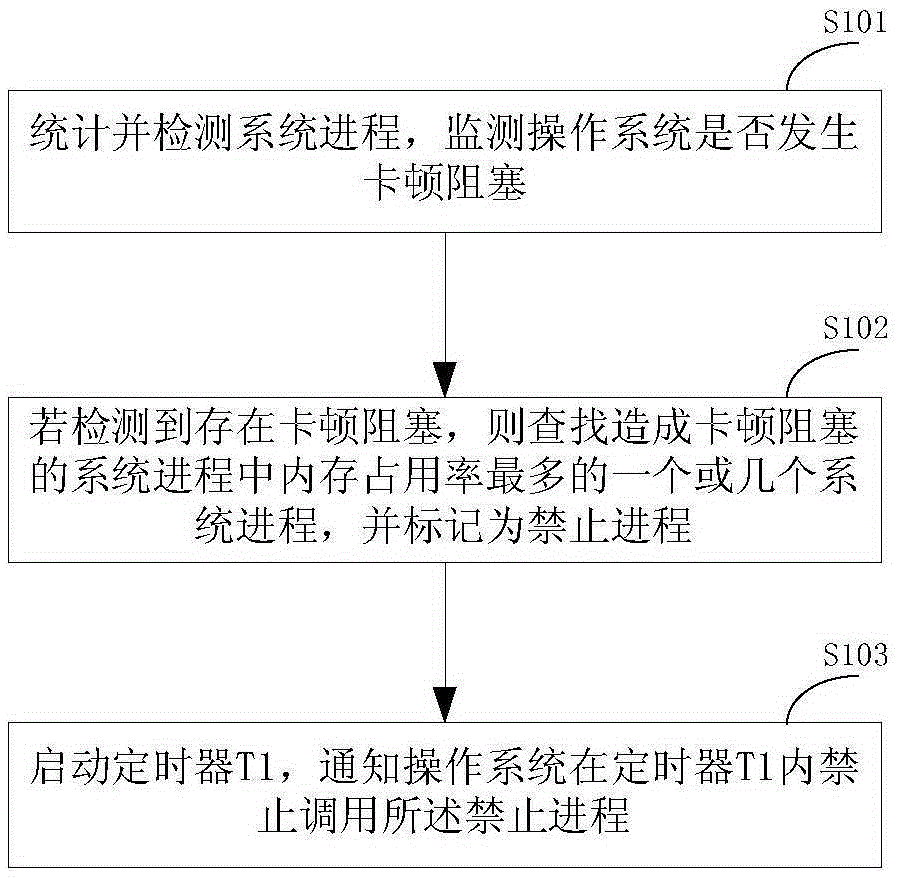

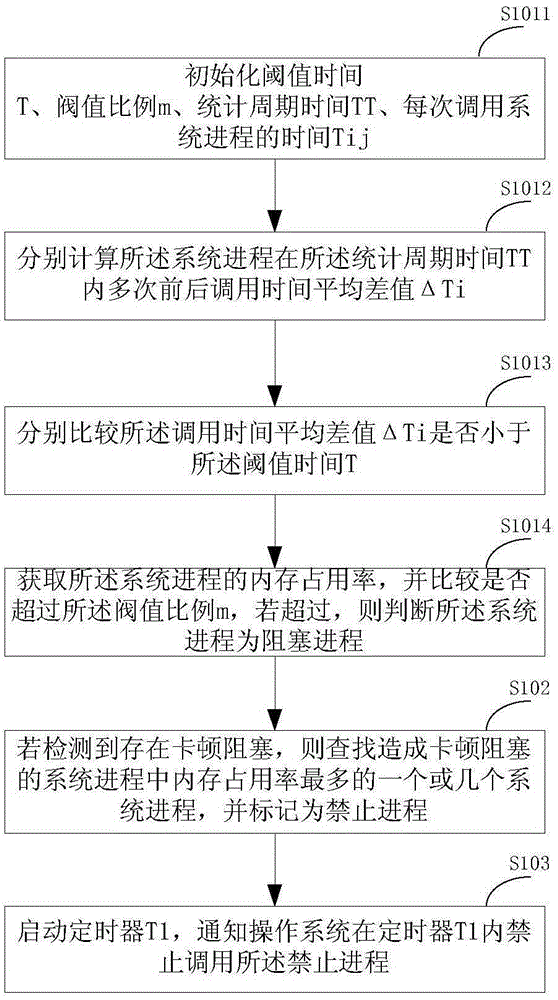

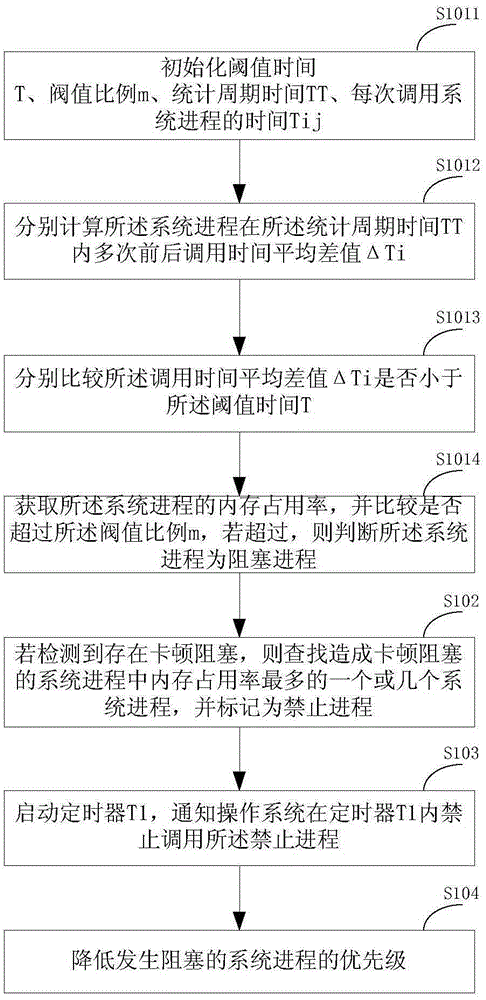

Restoration method and apparatus for jamming caused by system process runtime exception and mobile terminal

ActiveCN105302637AReduce CatonReduce stagnationProgram initiation/switchingFault responseOperational systemMemory footprint

The invention discloses a restoration method and apparatus for jamming caused by a system process runtime exception and a mobile terminal. The method specifically comprises: performing statistics and detection on system processes, and monitoring whether an operation system is jammed or not; if detecting that the operation system is jammed, searching for one or more system processes with the highest memory occupation rate in the system processes causing the jamming, and marking the searched system process as a forbidden process; starting a timer T1 for notifying the operation system to forbid the calling of the forbidden process in the timer T1; and lowering the priority of the system process causing the jamming. With the restoration method, the system jamming can be automatically detected; and by starting the timer T1 for notifying the operation system to forbid the calling of the forbidden process in the timer T1, and lowering the priority of the system process causing the jamming, the jamming and unsmooth phenomena of the operation system are reduced, the operation experience of users is improved, and the smooth operation of the mobile terminal is enjoyed.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

High density non-volatile memory device

InactiveUS7042755B1Suitable mechanical propertyPrevent charge leakageMaterial nanotechnologyNanoinformaticsFault toleranceChemical synthesis

This invention provides novel high density memory devices (FIG. 3) that are electrically addressable permitting effective reading and writing, that provide a high memory density (102), that provide a high degree of fault tolerance, and that are amenable to efficient chemical synthesis and chip fabrication. The devices arc intrinsically latchable, defect tolerant, and support destructive or non-destructive read cycles. In a preferred embodiment, the device comprises a fixed electrode electrically coupled to a storage medium having a multiplicity of different and distinguishable oxidation states wherein data is stored in said oxidation states by the addition or withdrawal of one or more electrons from said storage medium via the electrically coupled electrode.

Owner:NORTH CAROLINA STATE UNIV +1

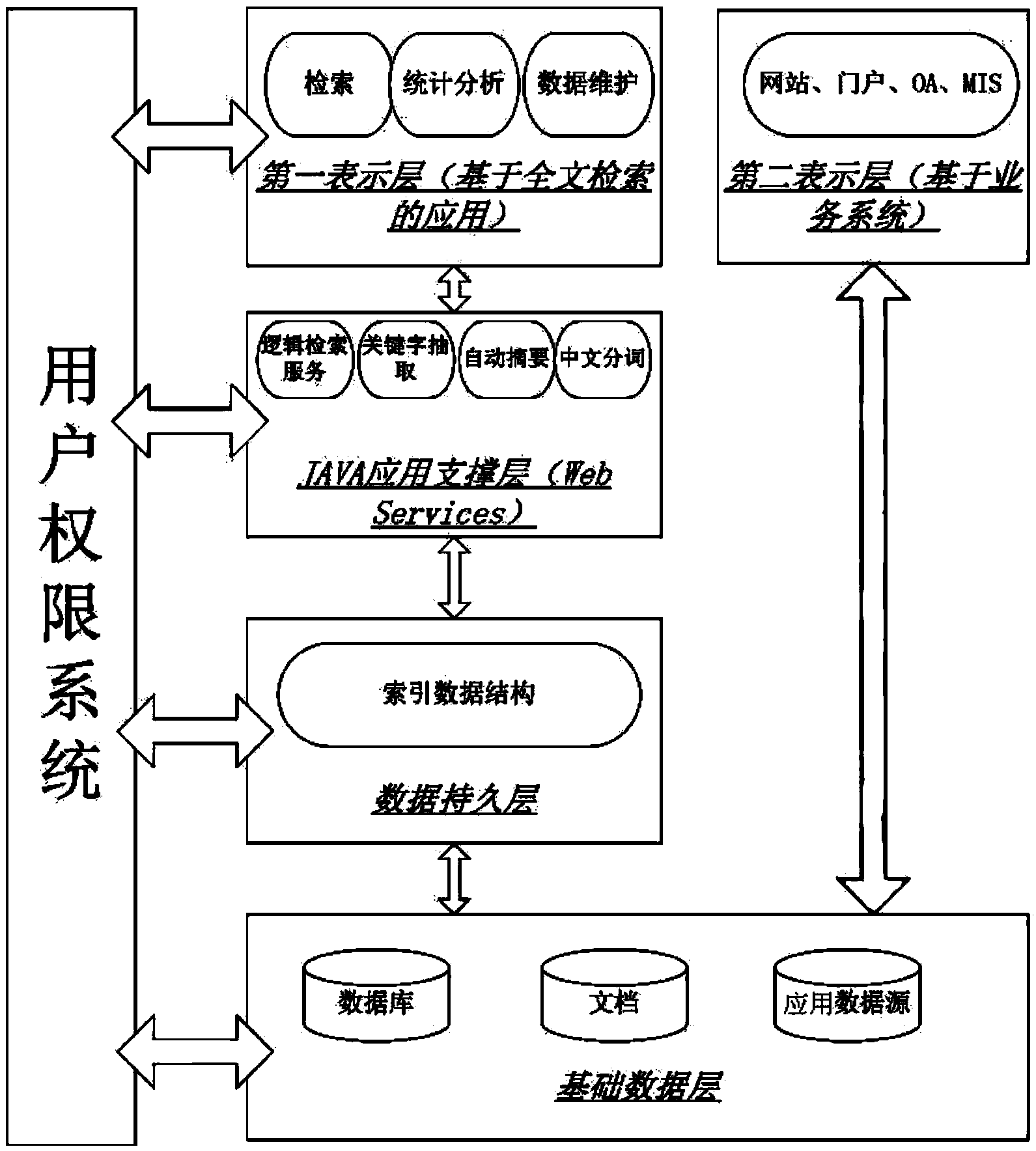

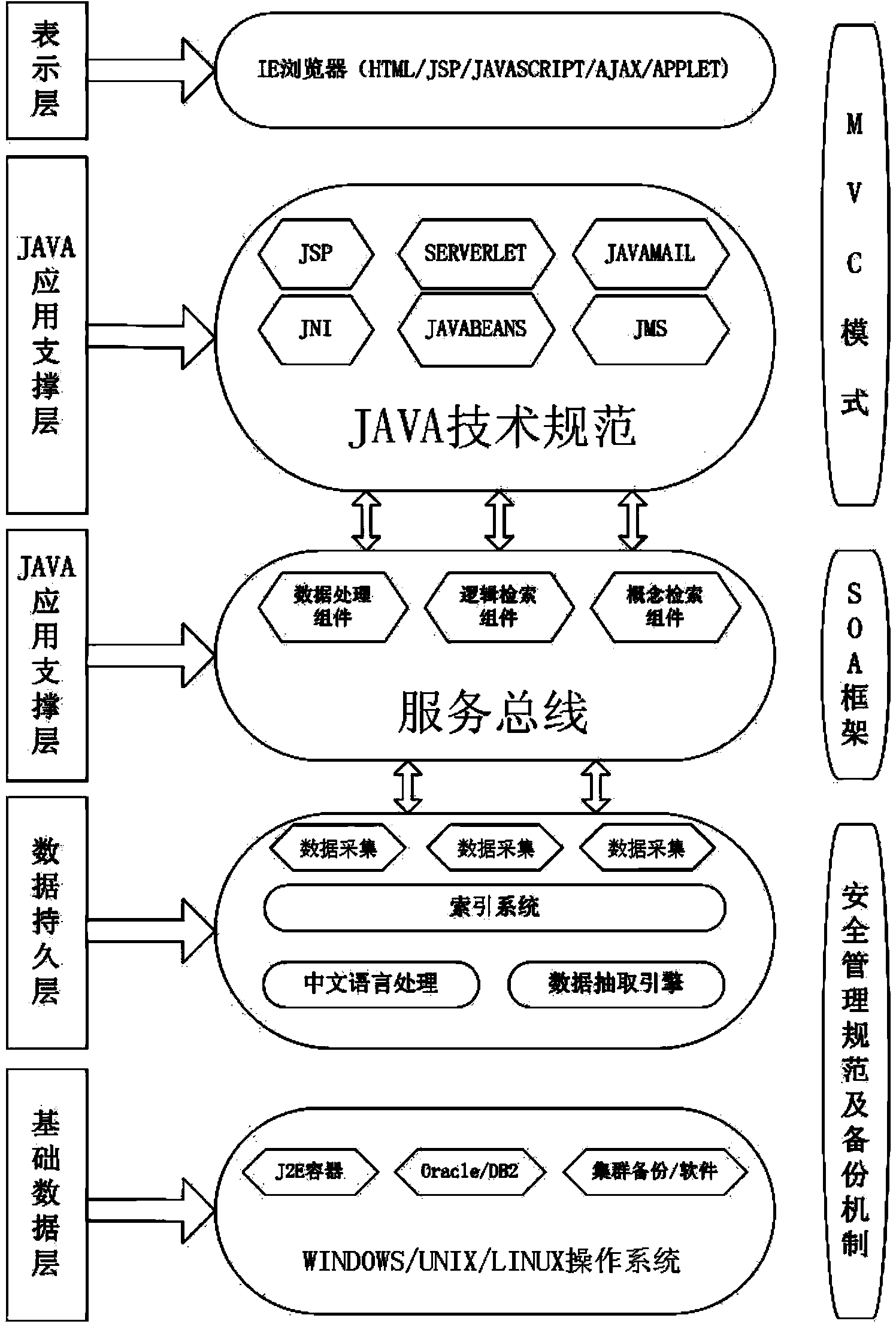

Cloud search platform

InactiveCN103412933ASearch results are accurateImprove reliabilitySpecial data processing applicationsLow delayHigh memory

The invention discloses a cloud search platform. The cloud search platform comprises a user authority system and a second presentation layer. The cloud search platform is characterized by further comprising a basic data layer, a data persistence layer, a JAVA application support layer and a first persistence layer which sequentially perform bidirectional data communication, wherein the user authority system performs bidirectional data communication with the basic data layer, the data persistence layer, the JAVA application support layer and the first persistence layer respectively; and the second persistence layer performs bidirectional data communication with the basic data layer. The cloud search platform provided by the invention has the characteristics of all-directional search, high reliability, high memory space, low delay and the like; and a cloud search platform which is more advanced, easy to use, and fast in response and analysis speeds is provided for enterprises or governments.

Owner:南京物联网应用研究院有限公司

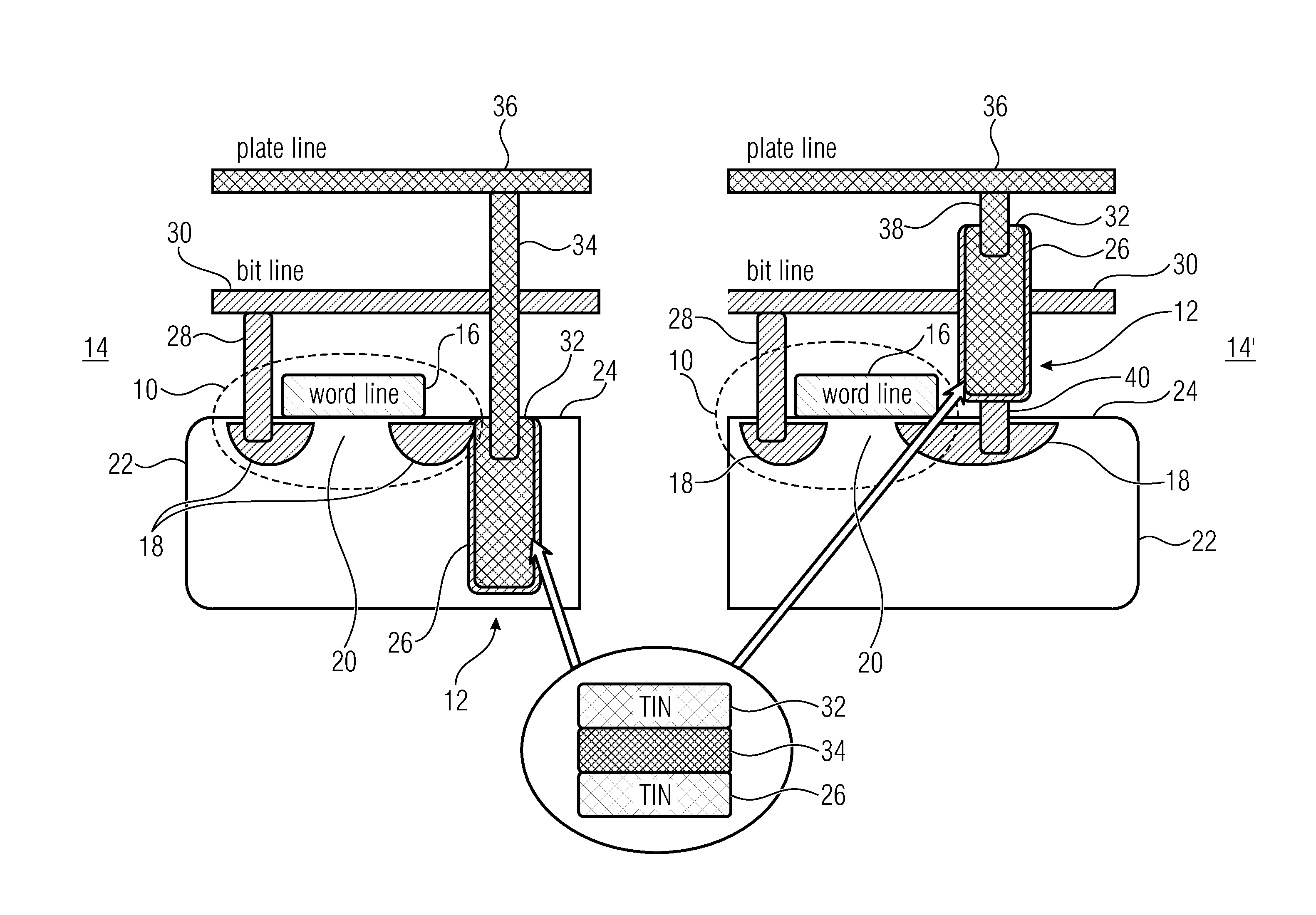

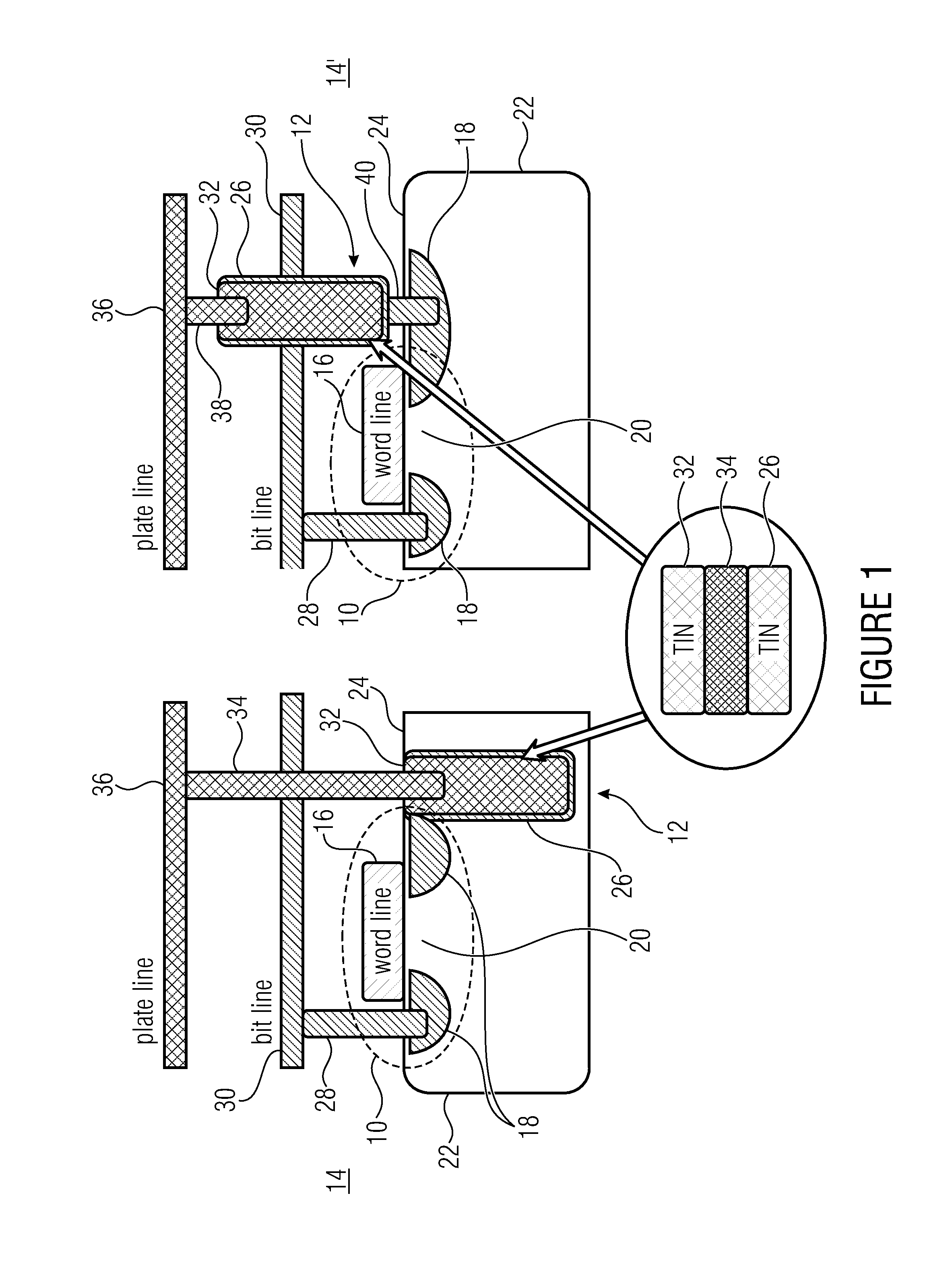

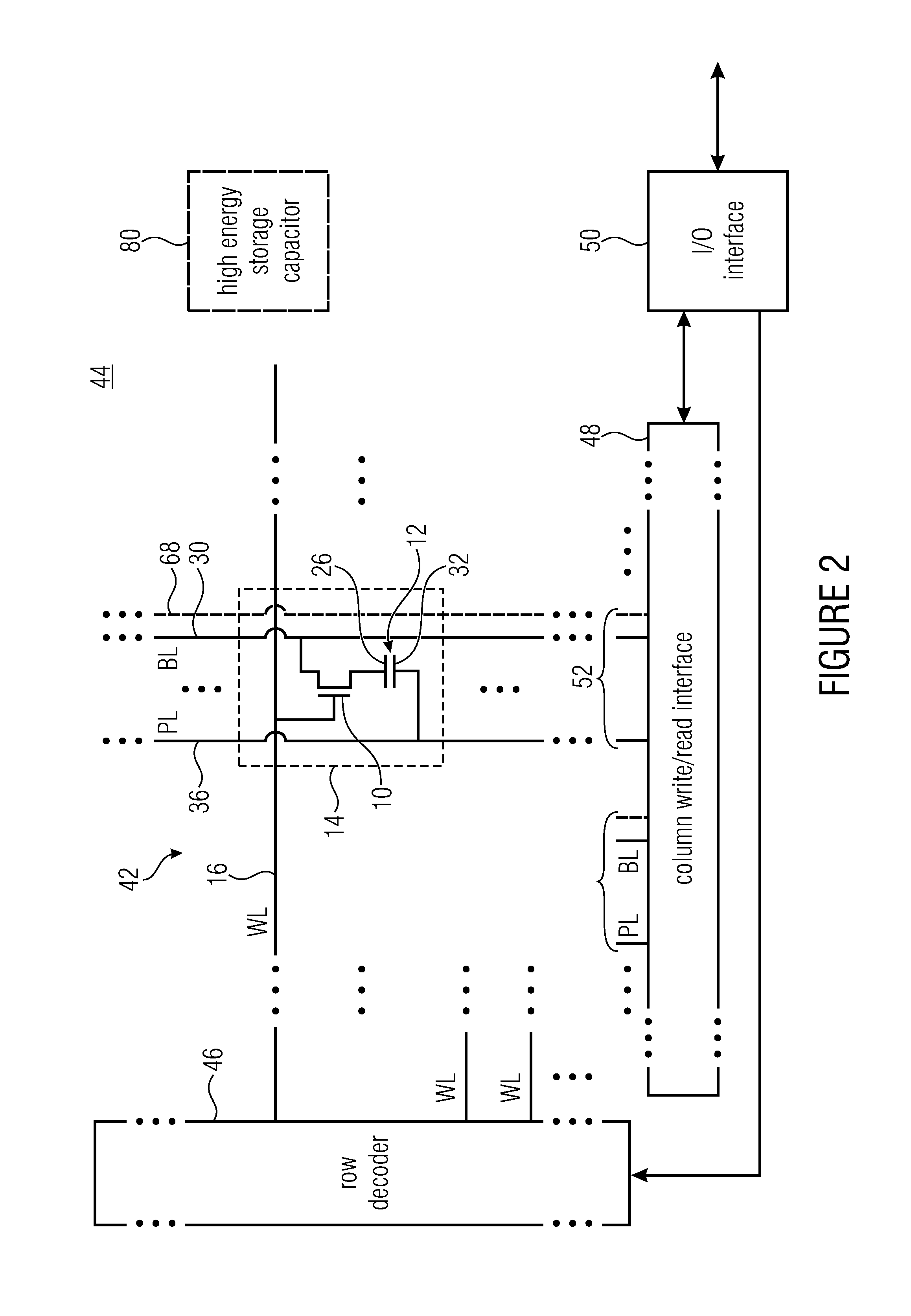

Memory cell

ActiveUS20150162063A1Long memory enduranceEasy to manufactureDigital storageComputer hardwareHigh memory

Nonvolatile storage with long memory endurance having the advantages of easy manufacturability is obtained by using a memory cell having an information storage element including a ferroelectric material, and operating the memory cell in a volatile operating mode and a nonvolatile operating mode. The option of operating the memory cell in the volatile operating mode enables the associated advantages of high memory speed at long endurance, wherein, however, the option of operating the memory cell in the nonvolatile operating mode can bridge gaps in the power supply.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

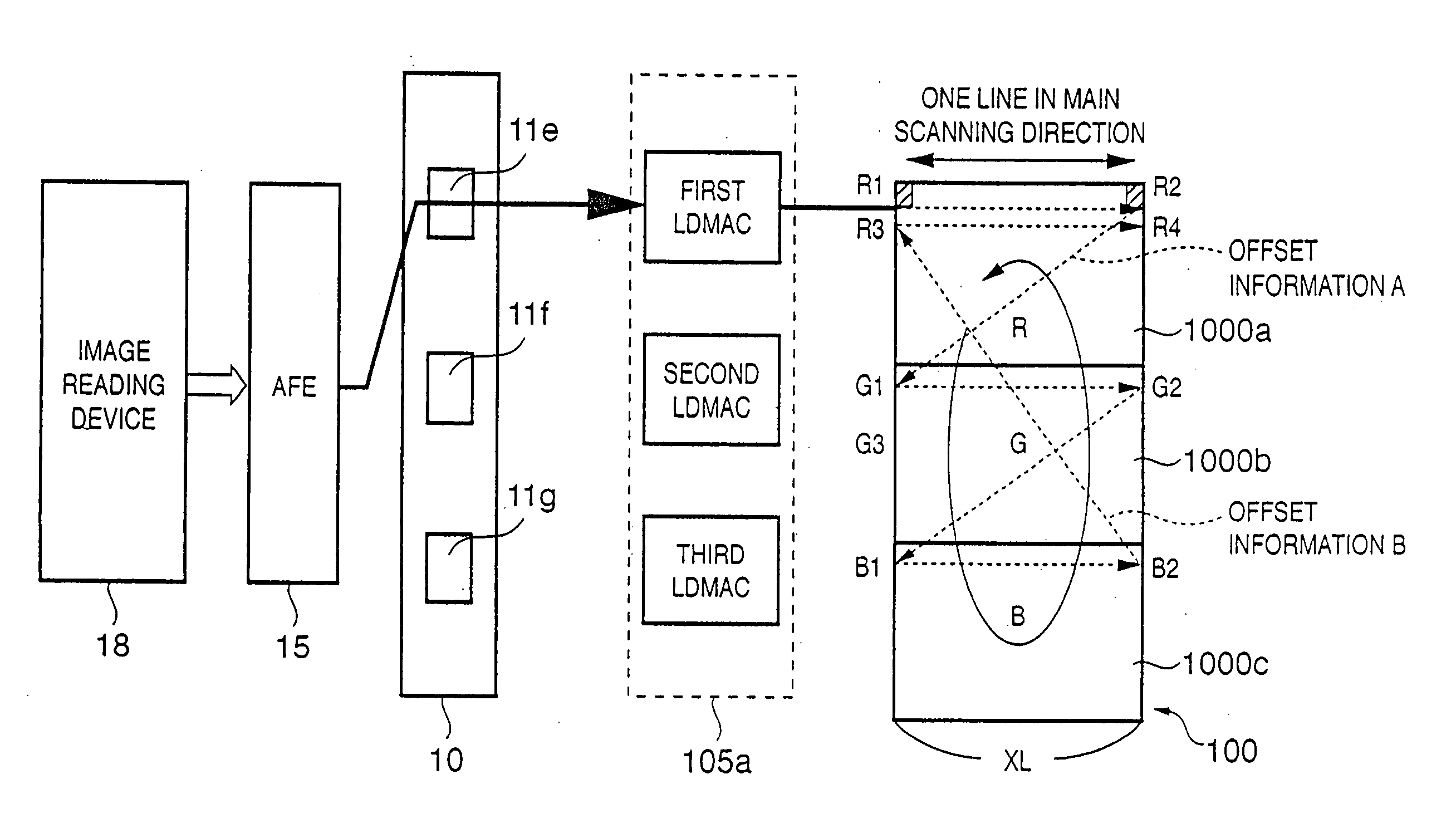

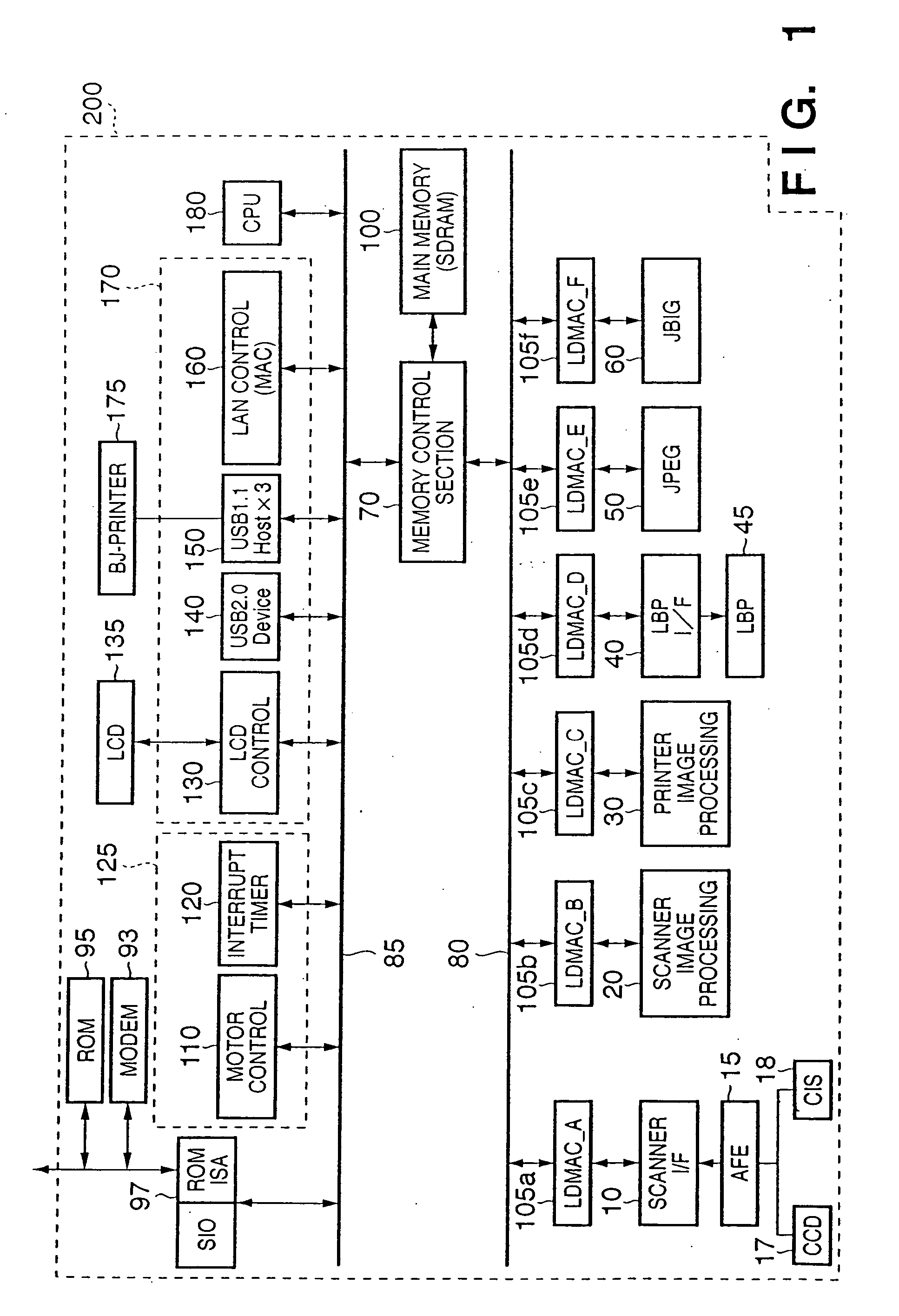

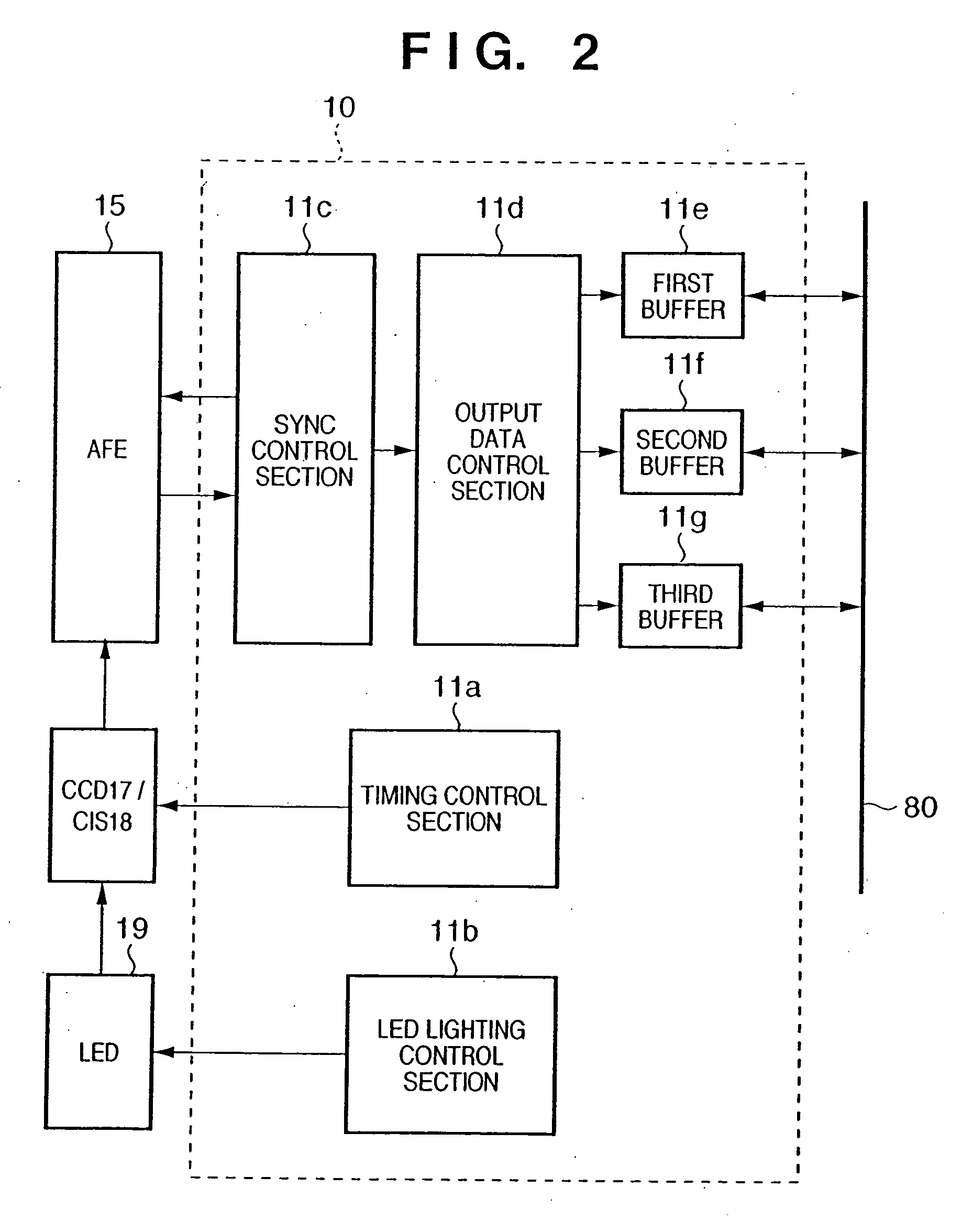

Image processing apparatus and image processing method

InactiveUS20060256120A1Memory adressing/allocation/relocationDigital computer detailsImaging processingComputer graphics (images)

To provide an image processing technique compatible with both a CCD and a CIS, which controls storage of image data read by each device in a memory and the read of the stored data for each rectangular area to obtain a high memory efficiency, an image processing apparatus includes a memory area control section which sets, for image data bitmapped on a first memory, a rectangular area divided in a main scanning direction and sub-scanning direction, an address generation section which generates address information to read out image data corresponding to the rectangular area in correspondence with the set rectangular area, a memory control section which reads out the image data corresponding to the rectangular area and DMA-transfers the image data to a second memory in accordance with the generated address information, and an image processing section which executes image processing for each rectangular area of the DMA-transferred data by using the second memory.

Owner:CANON KK

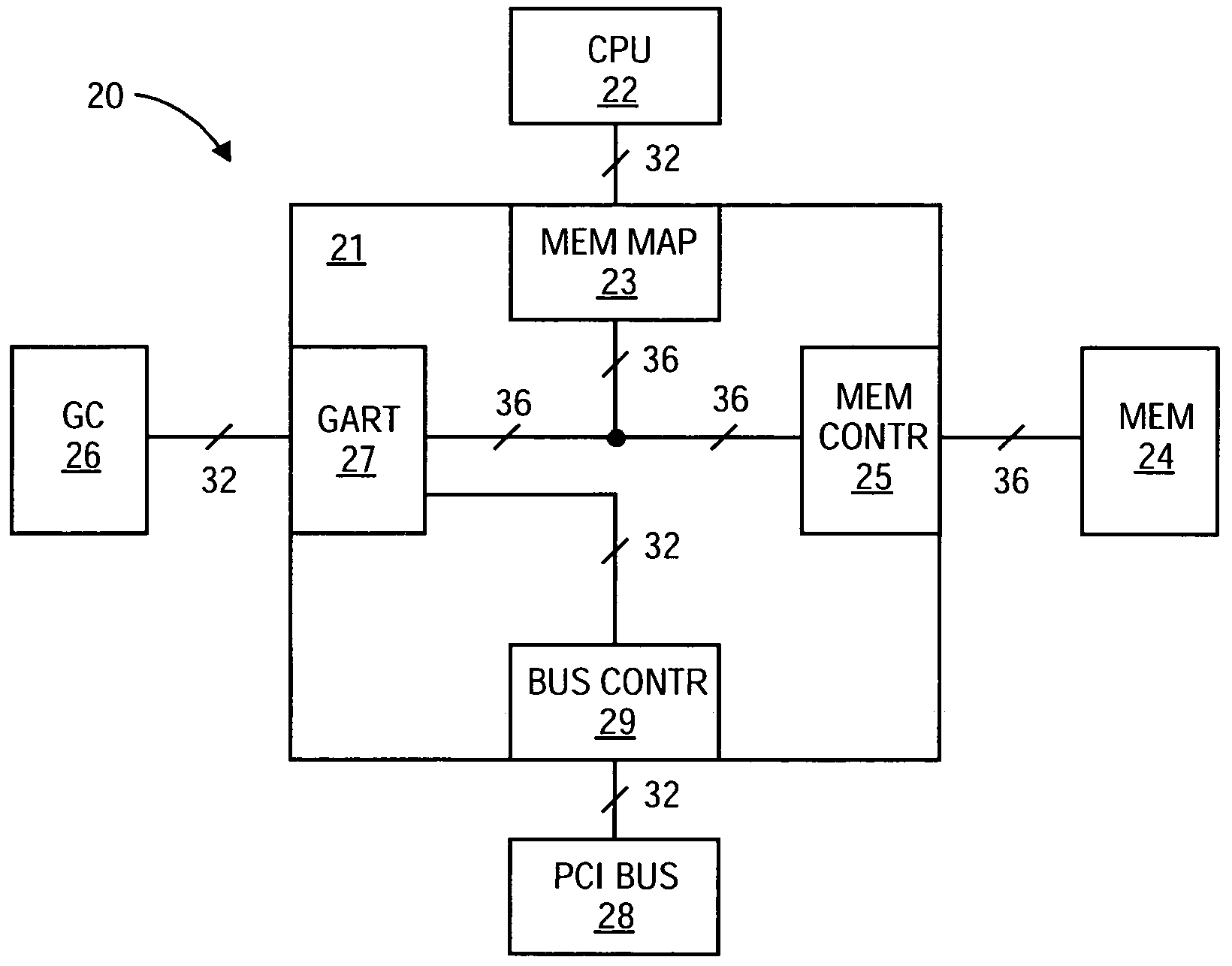

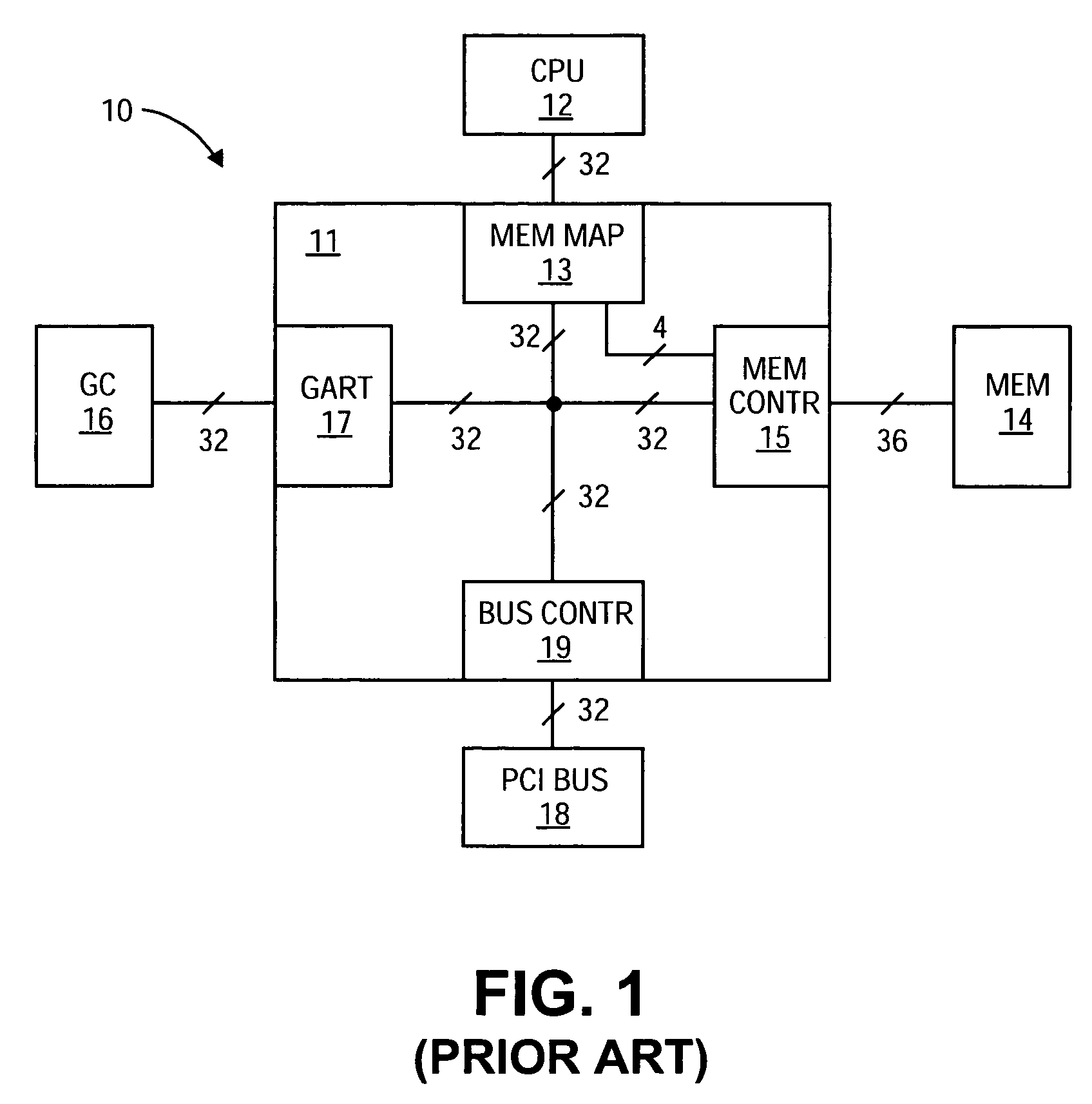

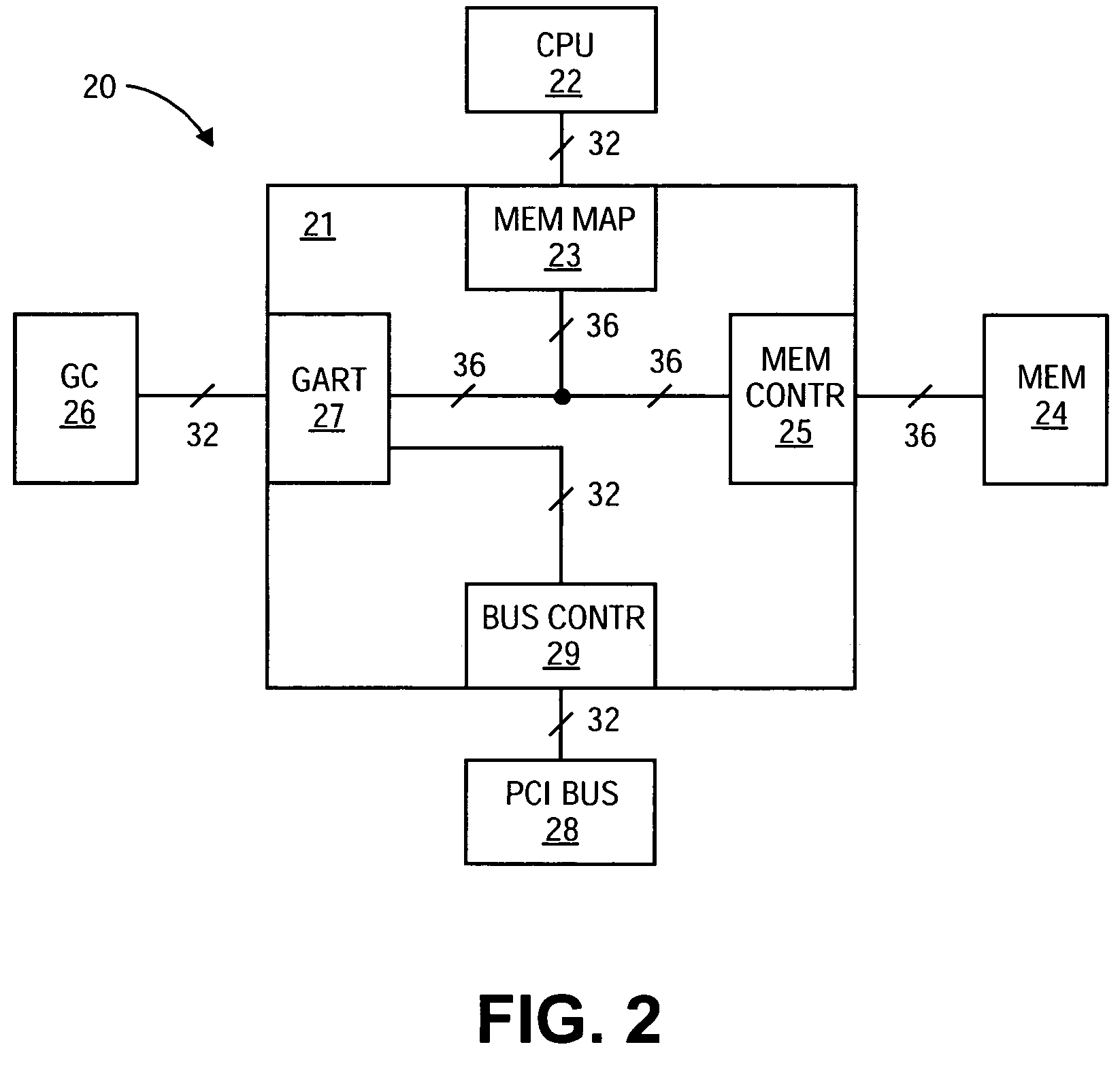

Remapping I/O device addresses into high memory using GART

An address translation apparatus and method that can convert a limited-range memory address from a peripheral device to an expanded-range memory address on the fly. The invention can expand the limited address capability of a peripheral bus, such as a PCI bus with a 4 GB address range, to a much larger address capability, such as a 64 GB address range. This conversion can be performed on the fly by hardware, so that no appreciable delay in transfer time is created. The conversion can be performed by adding features to a conventional graphics controller interface, thus minimizing the impact on circuit complexity and system cost.

Owner:INTEL CORP

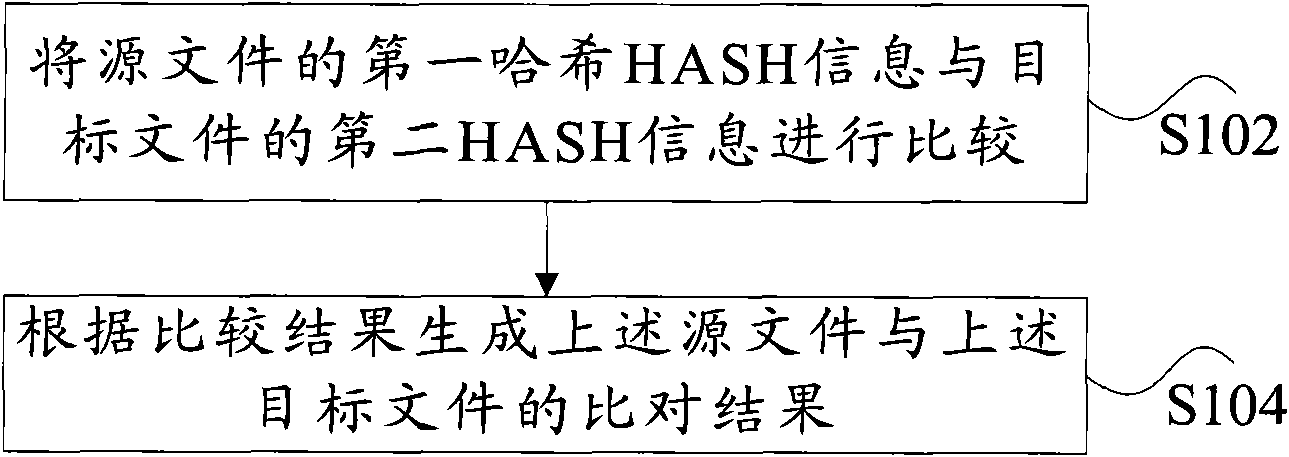

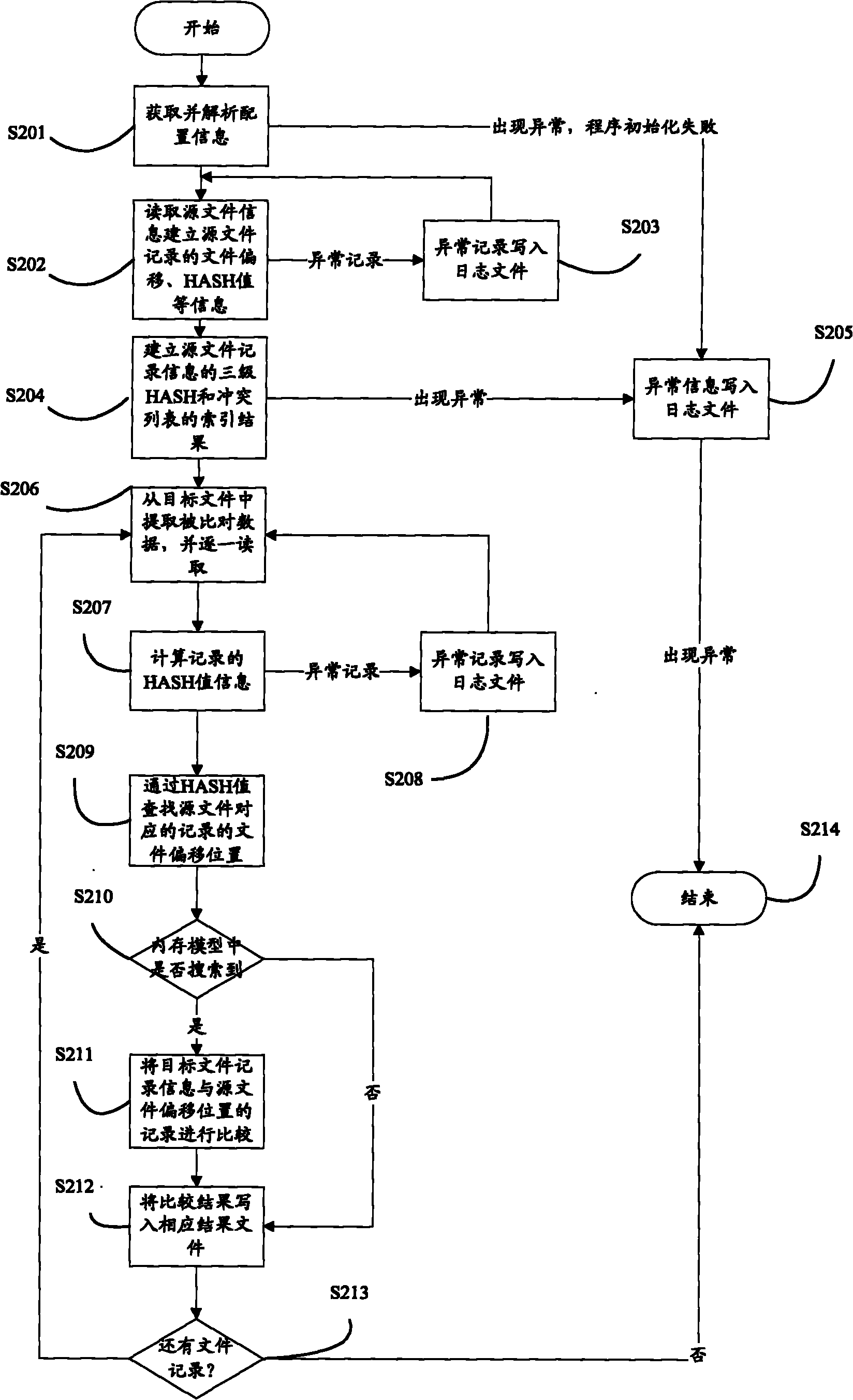

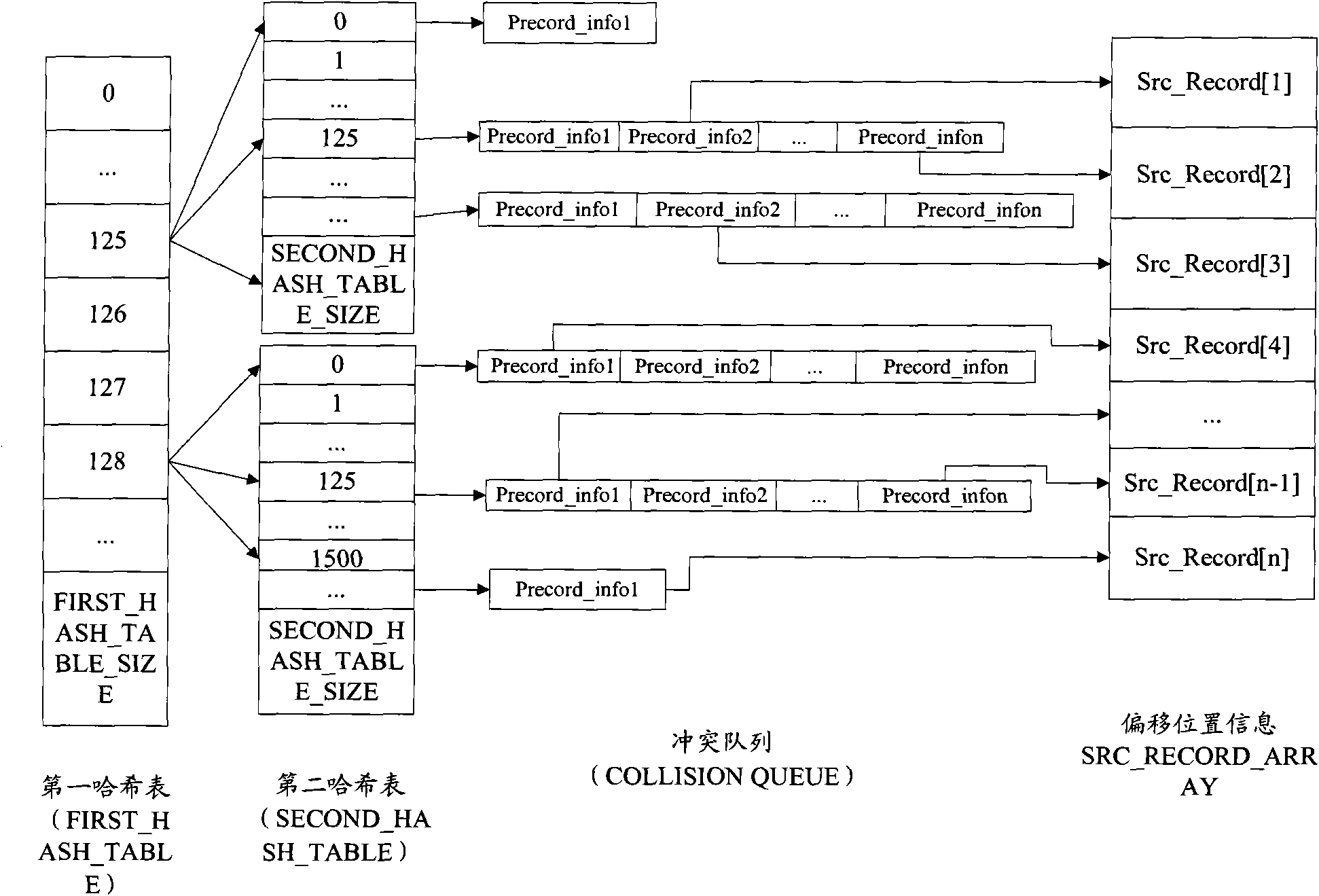

Data comparison method and device

InactiveCN101957858ASolve the problem of high memory usageReduced execution timeDigital data information retrievalSpecial data processing applicationsOccupancy rateMemory footprint

The invention discloses a data comparison method and a device. The method comprises the steps of: comparing the first HASH information of a source file with the second HASH information of a target file; and creating a comparison result of the source file and the target file on the basis of a comparison result. The invention solves the problem of higher memory occupancy rate caused by a data comparison method in the prior art, and achieves the effects of reducing execution time and enhancing processing efficiency.

Owner:ZTE CORP

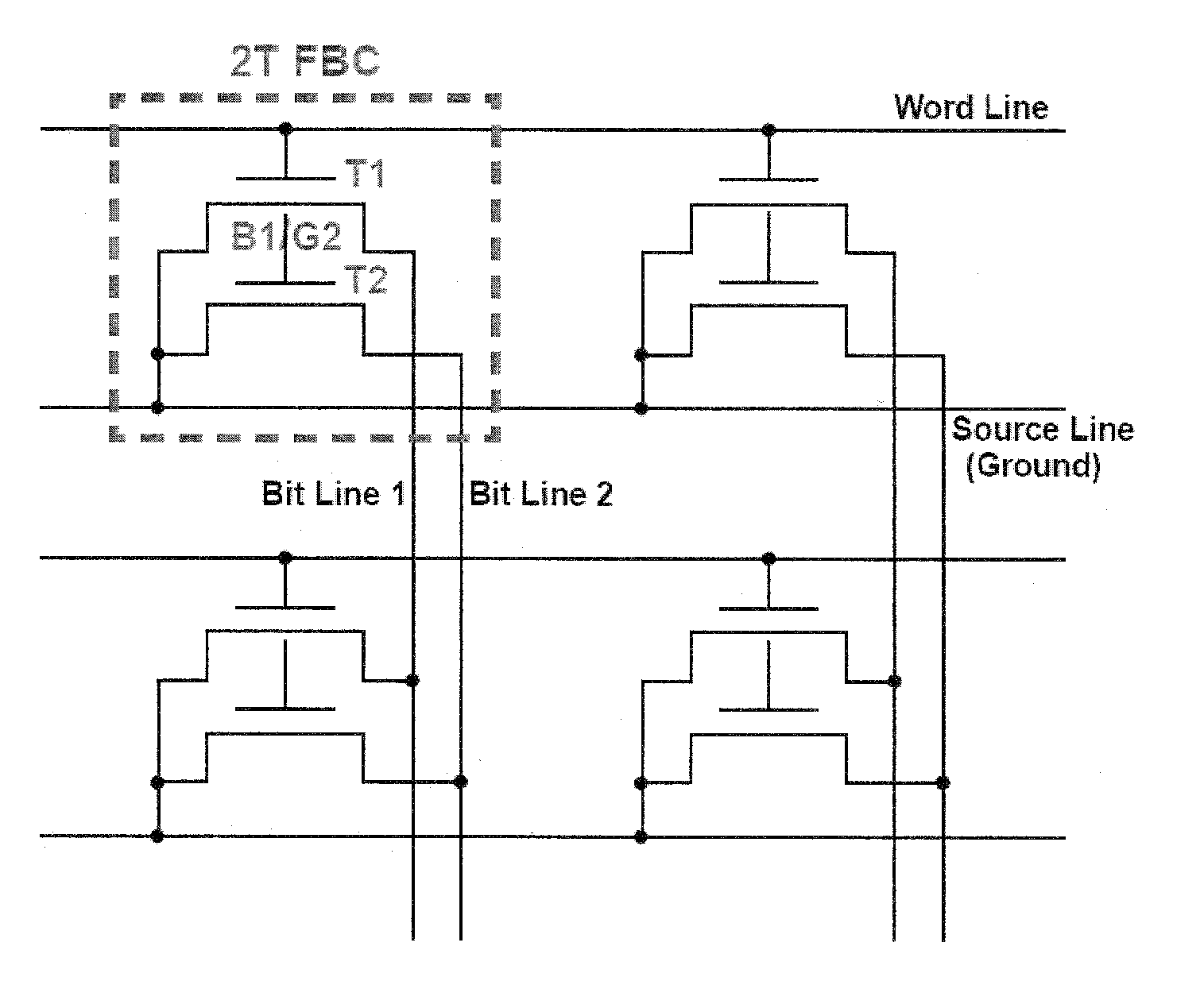

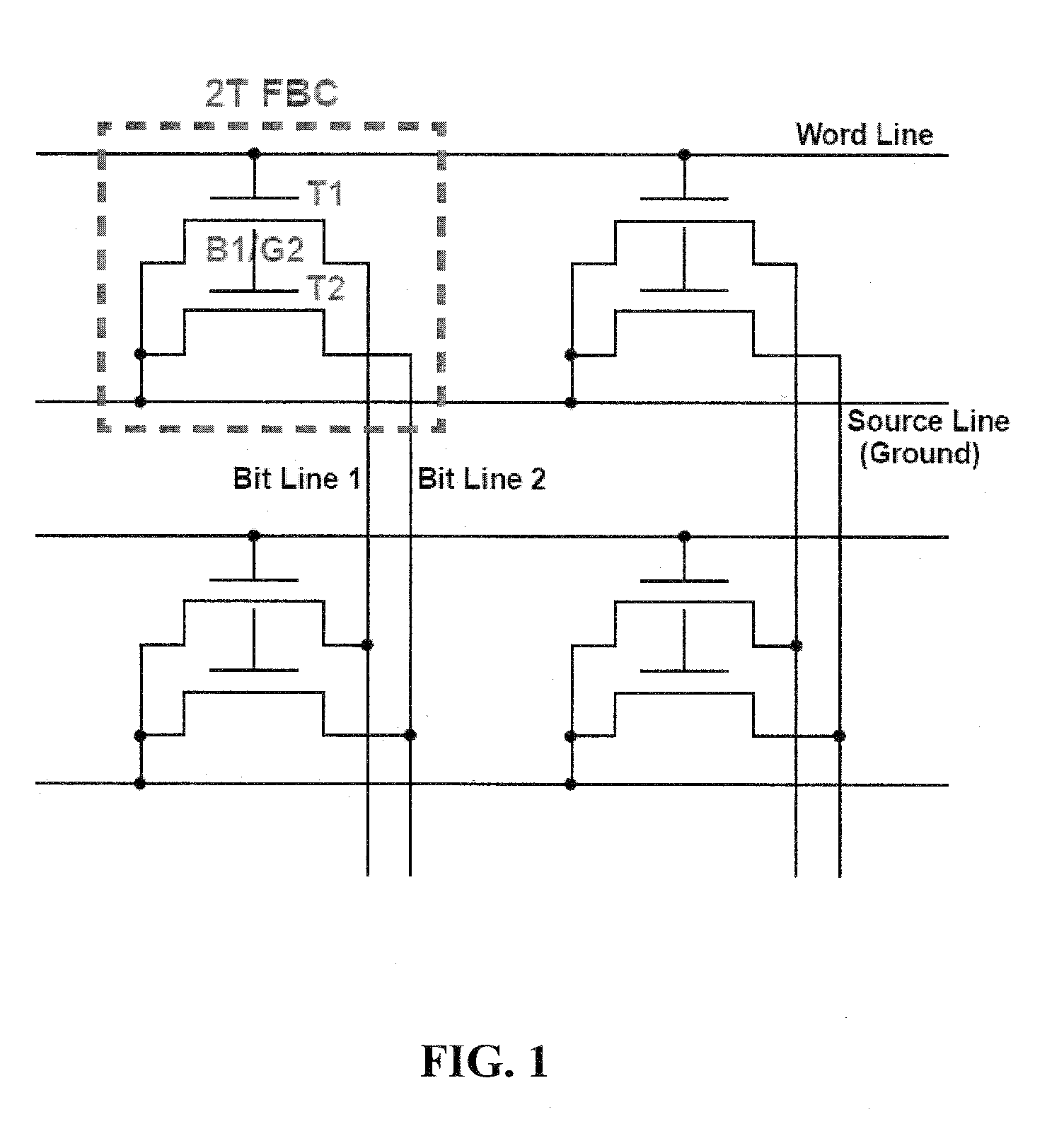

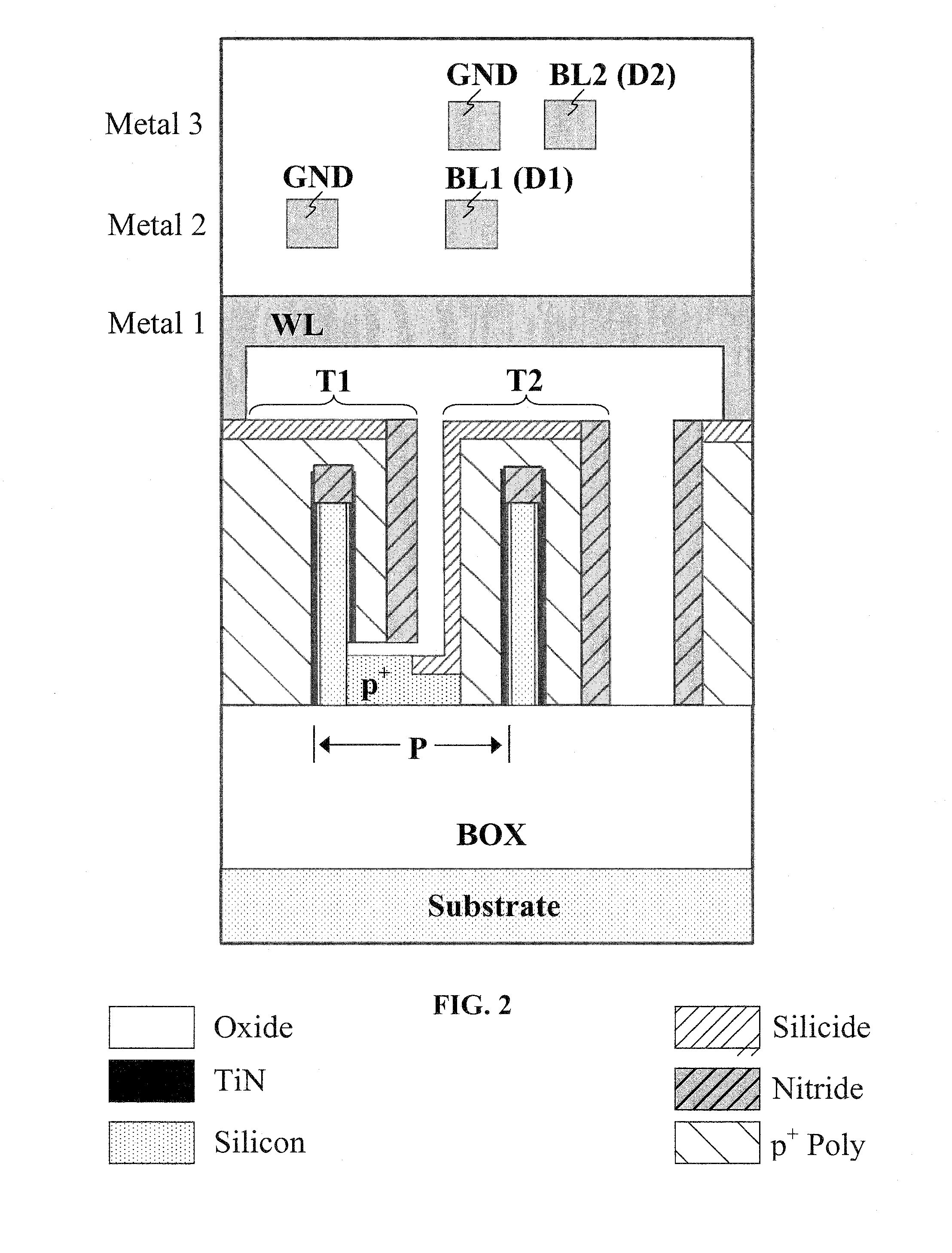

Two-Transistor Floating-Body Dynamic Memory Cell

InactiveUS20100329043A1Improve performanceImprove scalabilityTransistorSolid-state devicesHigh memoryBody dynamics

Embodiments relate to a two-transistor (2T) floating-body cell (FBC) for embedded-DRAM applications. Further embodiments pertain to a floating-body / gate cell (FBGC), which yields reduction in power dissipation, in addition to better signal margin, longer data retention, and higher memory density.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com