Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

71 results about "Memory tester" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Memory testers are specialized test equipment used to test and verify memory modules.

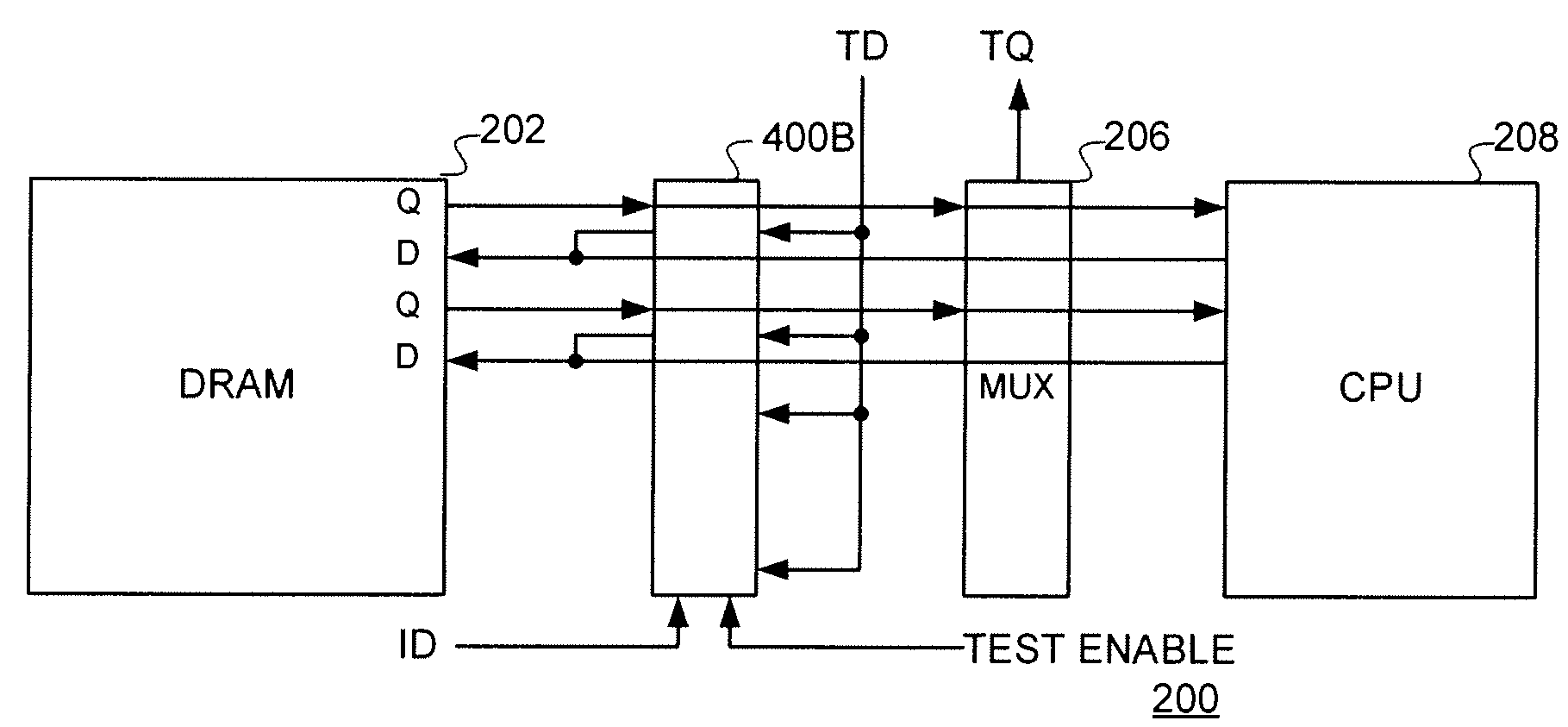

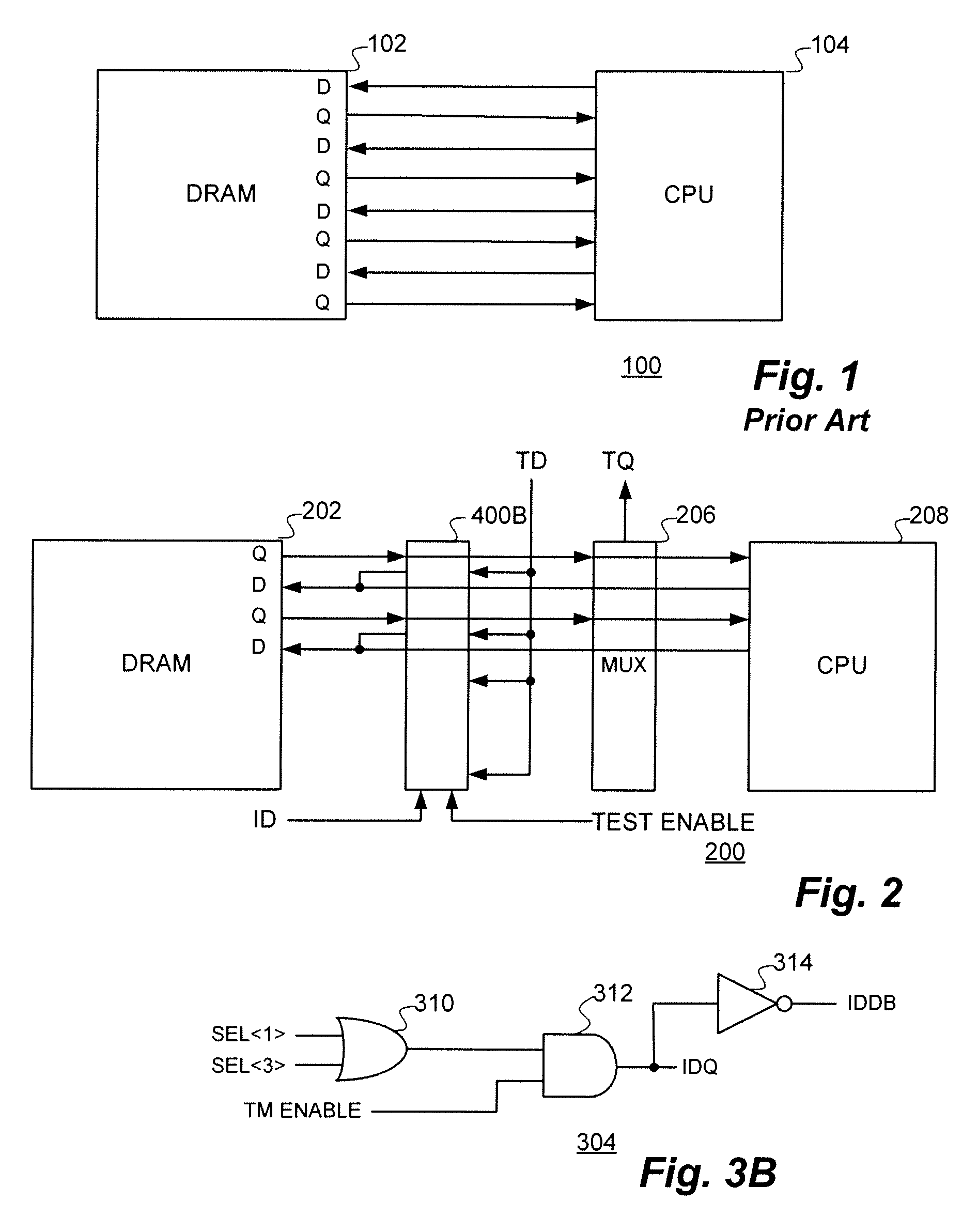

Captured synchronous DRAM fails in a working environment

InactiveUS6467053B1Minimize degradationError detection/correctionComponent plug-in assemblagesLength variationDram memory

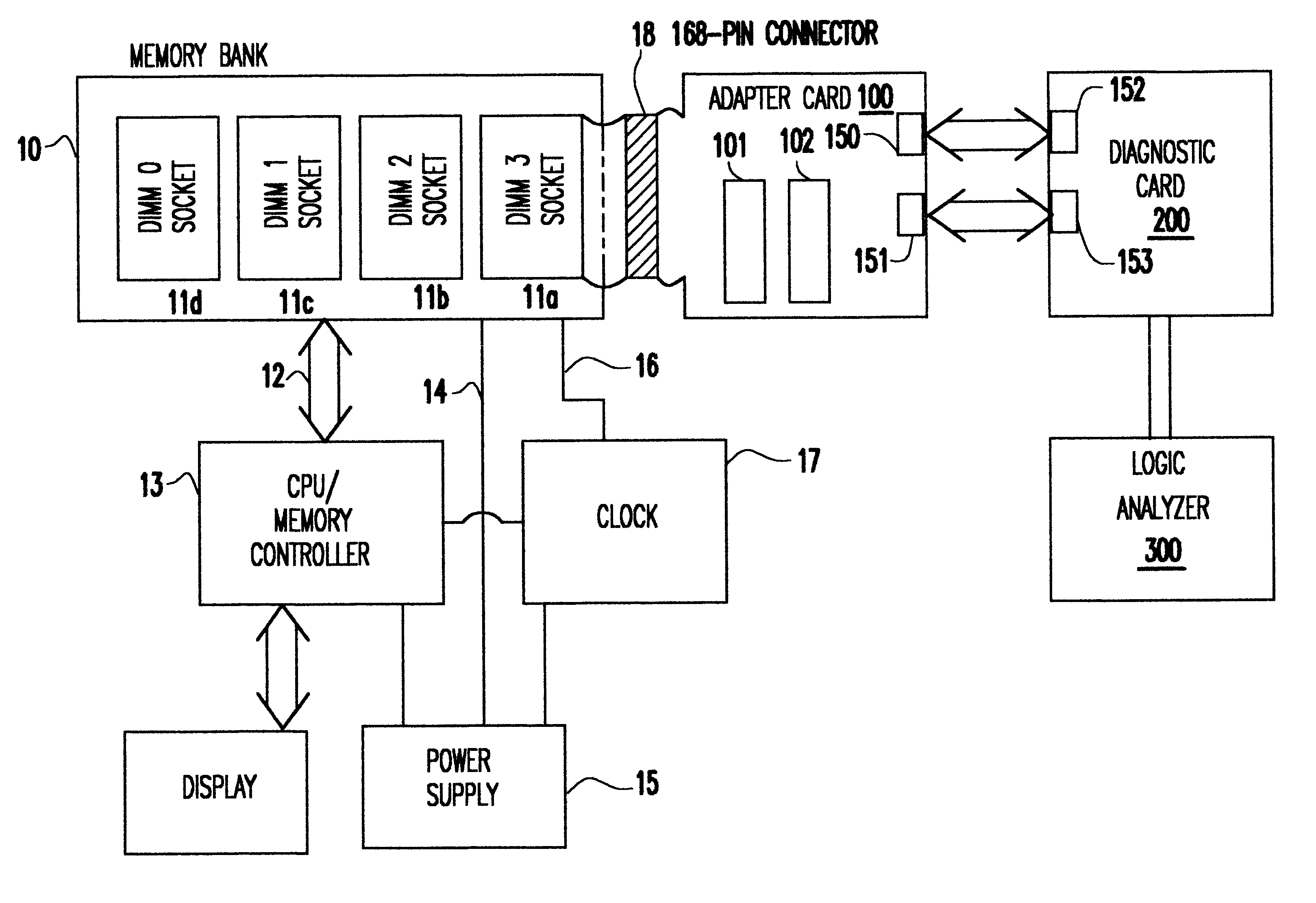

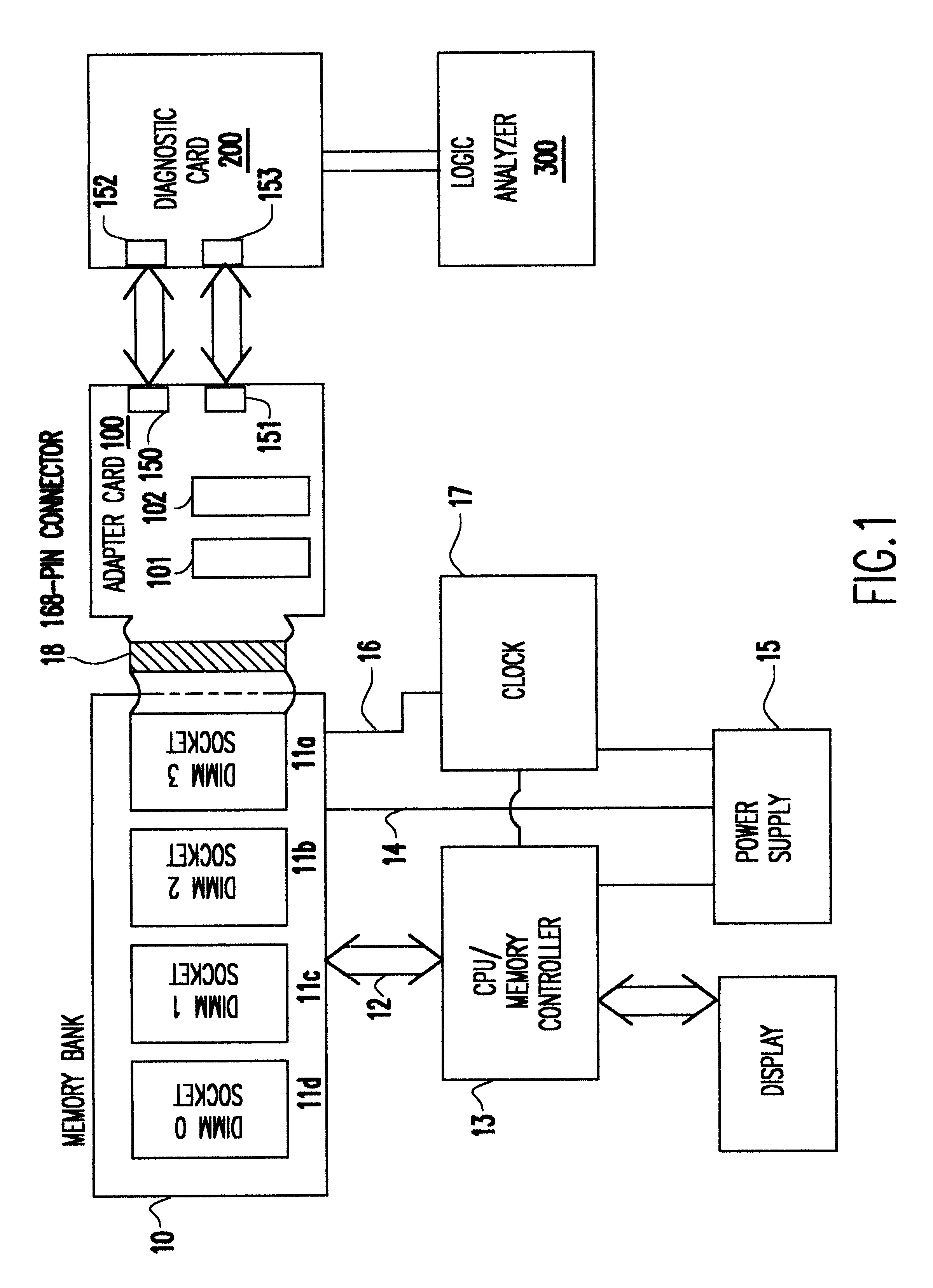

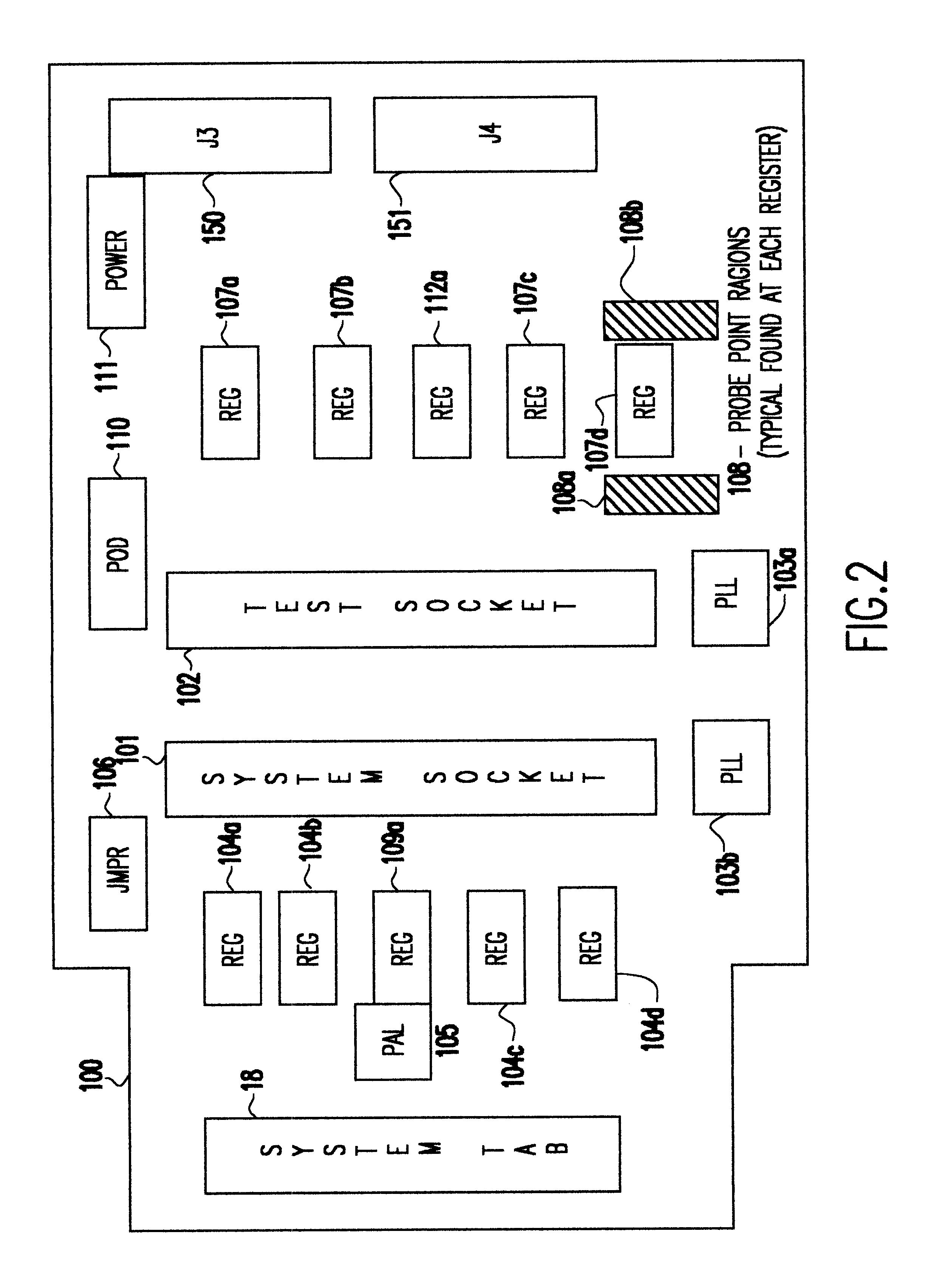

A Synchronous DRAM memory test assembly that converts a normal PC or Workstation with a synchronous bus into a memory tester. The test assembly may be split into two segments: a diagnostic card and an adapter card to limit mechanical load on the system socket as well as permit varying form factors. This test assembly architecture supports memory bus speeds of 66 MHz and above, and provides easy access for a logic analyzer. The test assembly supports Registered and Unbuffered Synchronous DRAM products. The test assembly permits good and questionable synchronous modules to be compared using an external logic analyzer. It permits resolution of in-system fails that occur uniquely in system environments and may be otherwise difficult or impossible to replicate. The test assembly re-drives the system clocks with a phase lock loop (PLL) buffer to a memory module socket on the test assembly to permit timing adjustments to minimize the degradation to the system's memory bus timings due to the additional wire length and loading. The test assembly is programmable to adjust to varying bus timings such as: CAS (column address strobe) Latencies and Burst Length variations. It is designed with Field Programmable Gate Arrays (FPGAs) to allow for changes internally without modifying the test assembly.

Owner:GLOBALFOUNDRIES INC

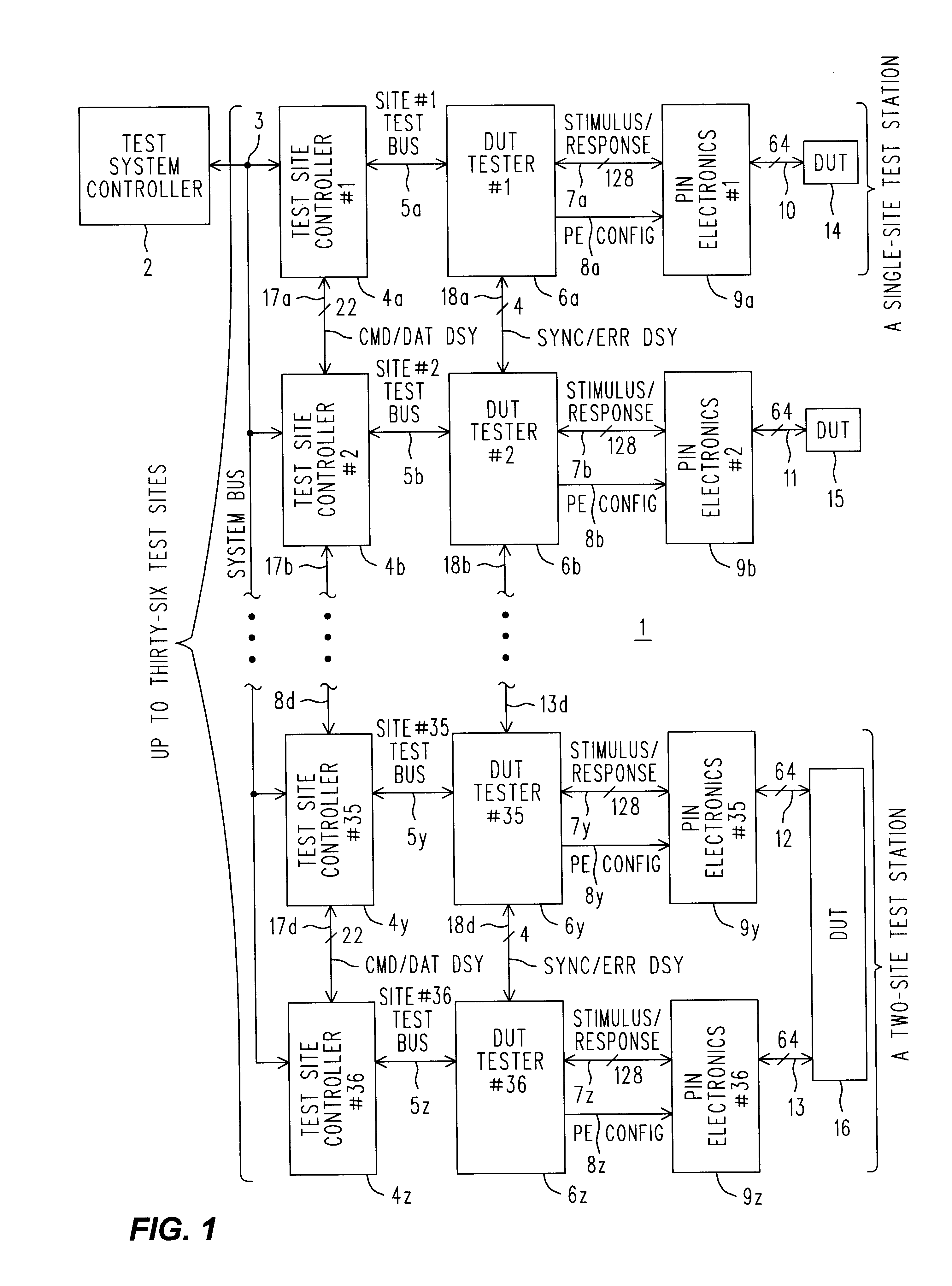

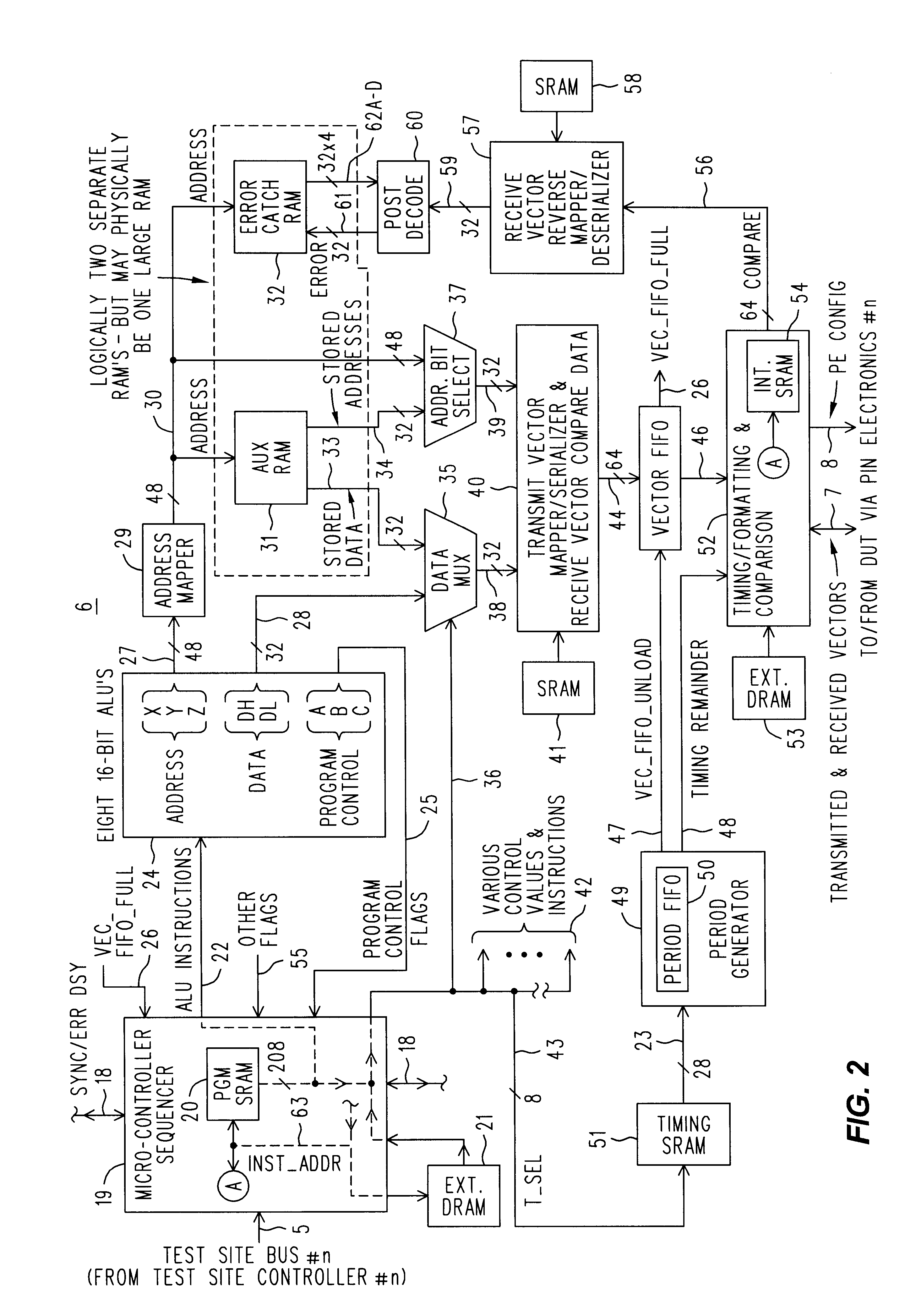

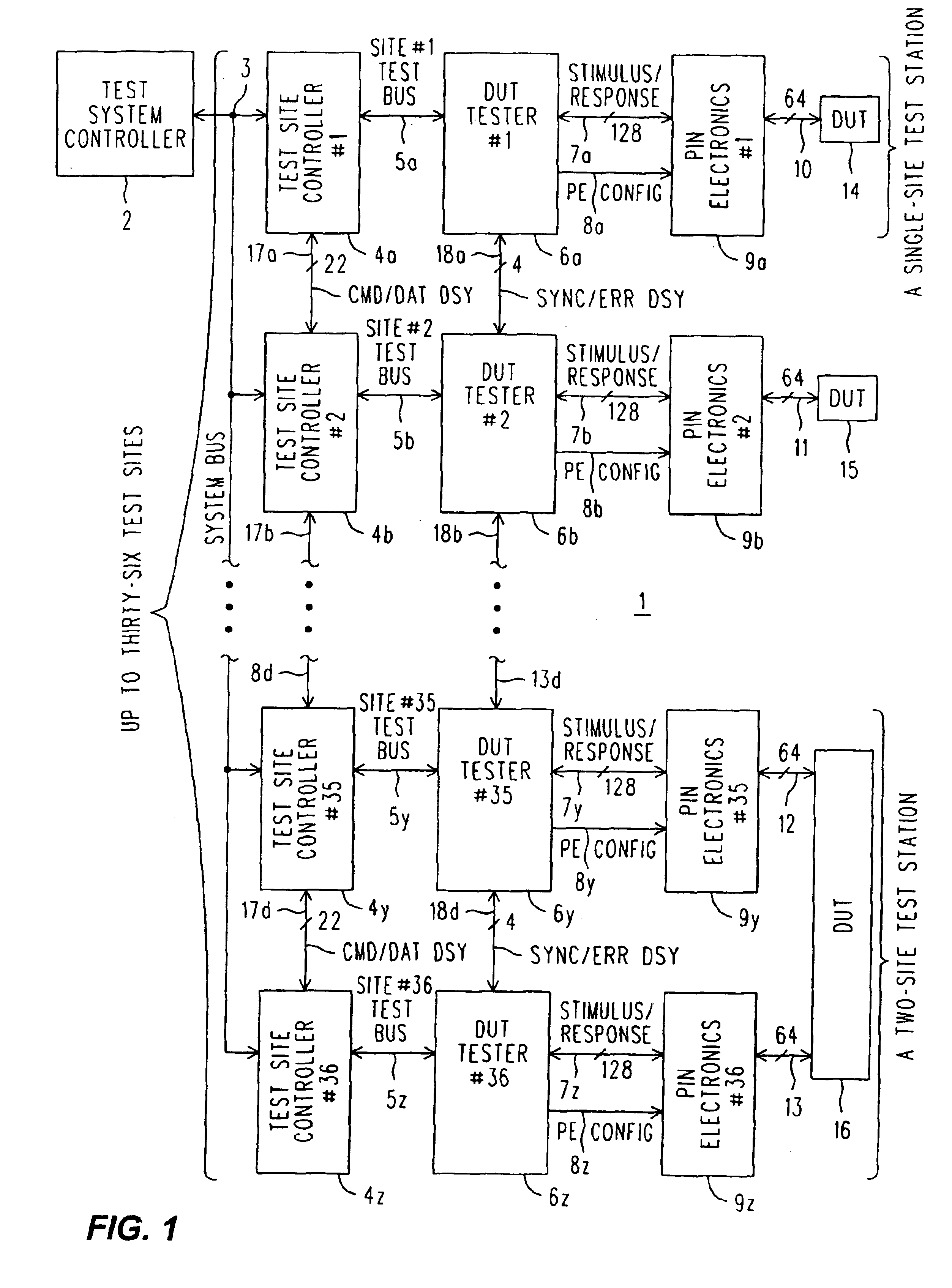

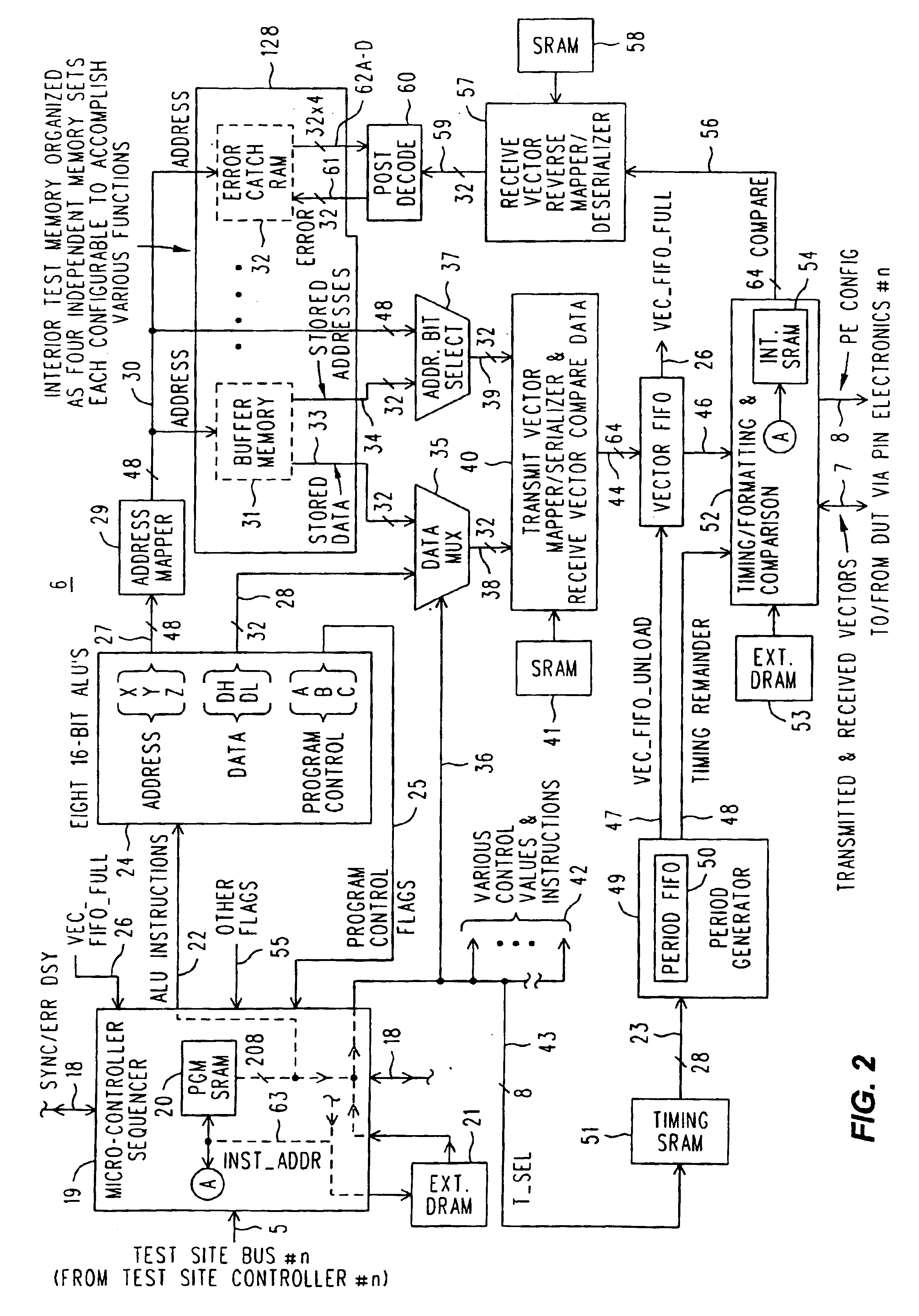

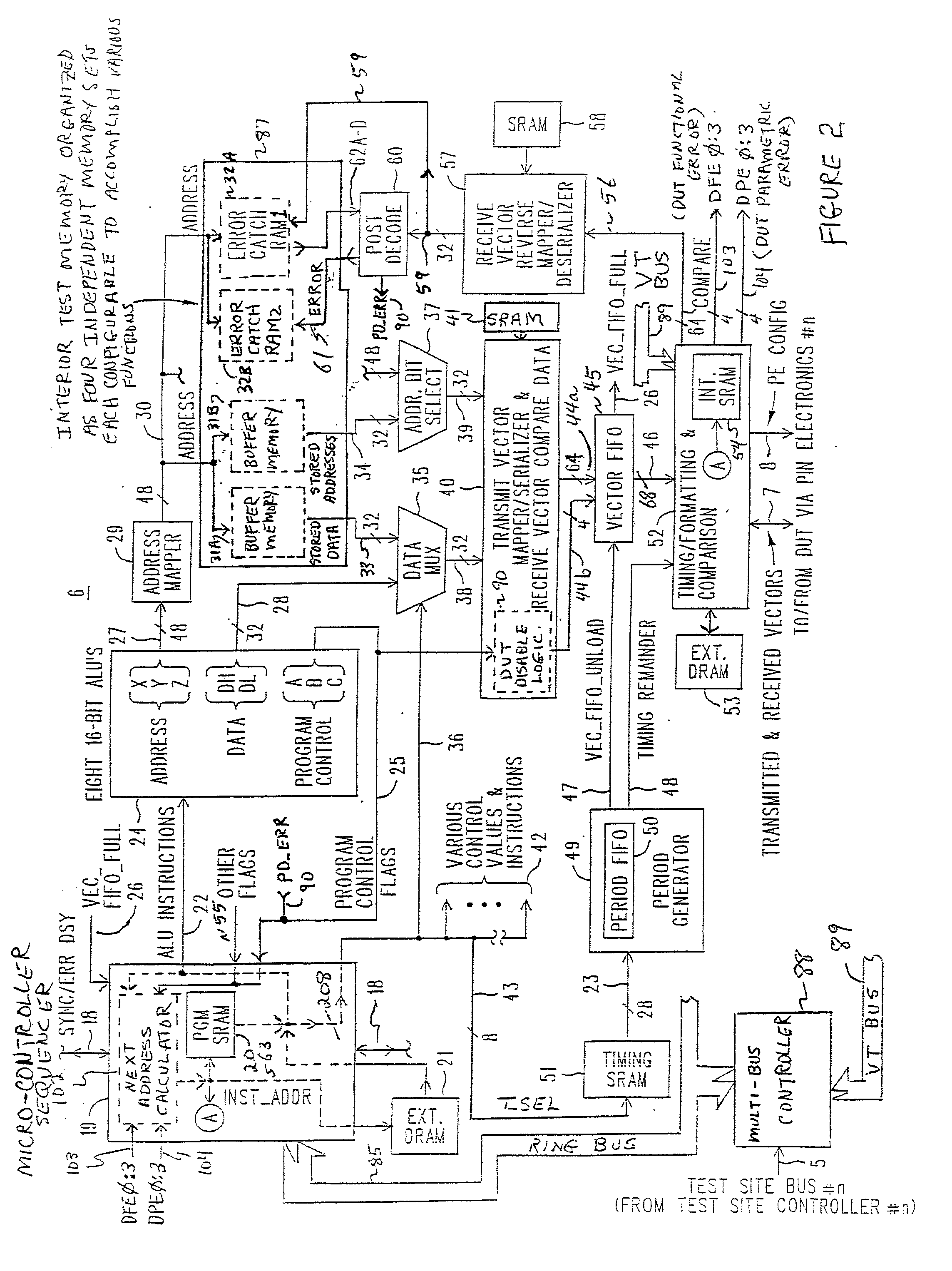

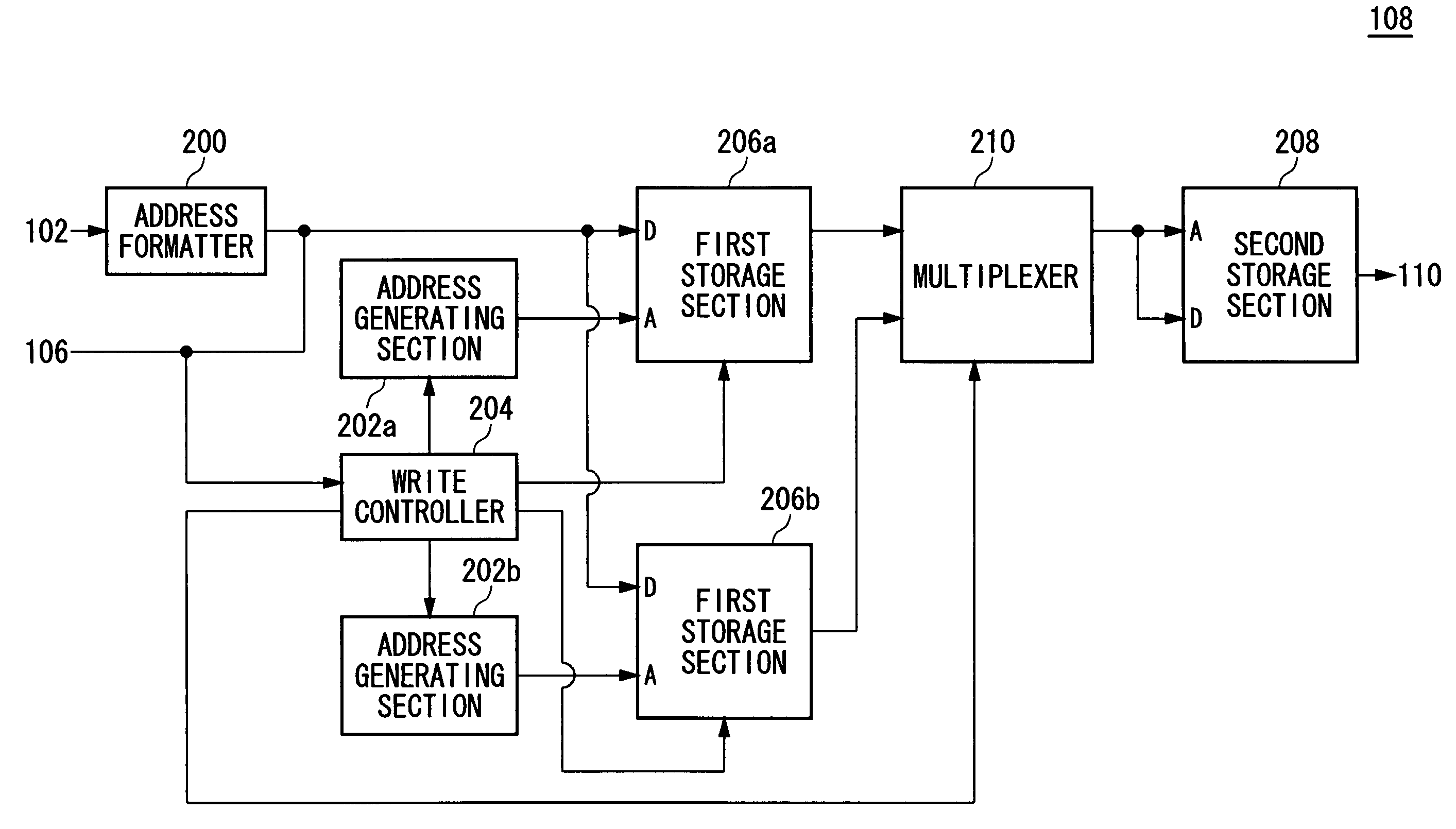

Error catch RAM for memory tester has SDRAM memory sets configurable for size and speed

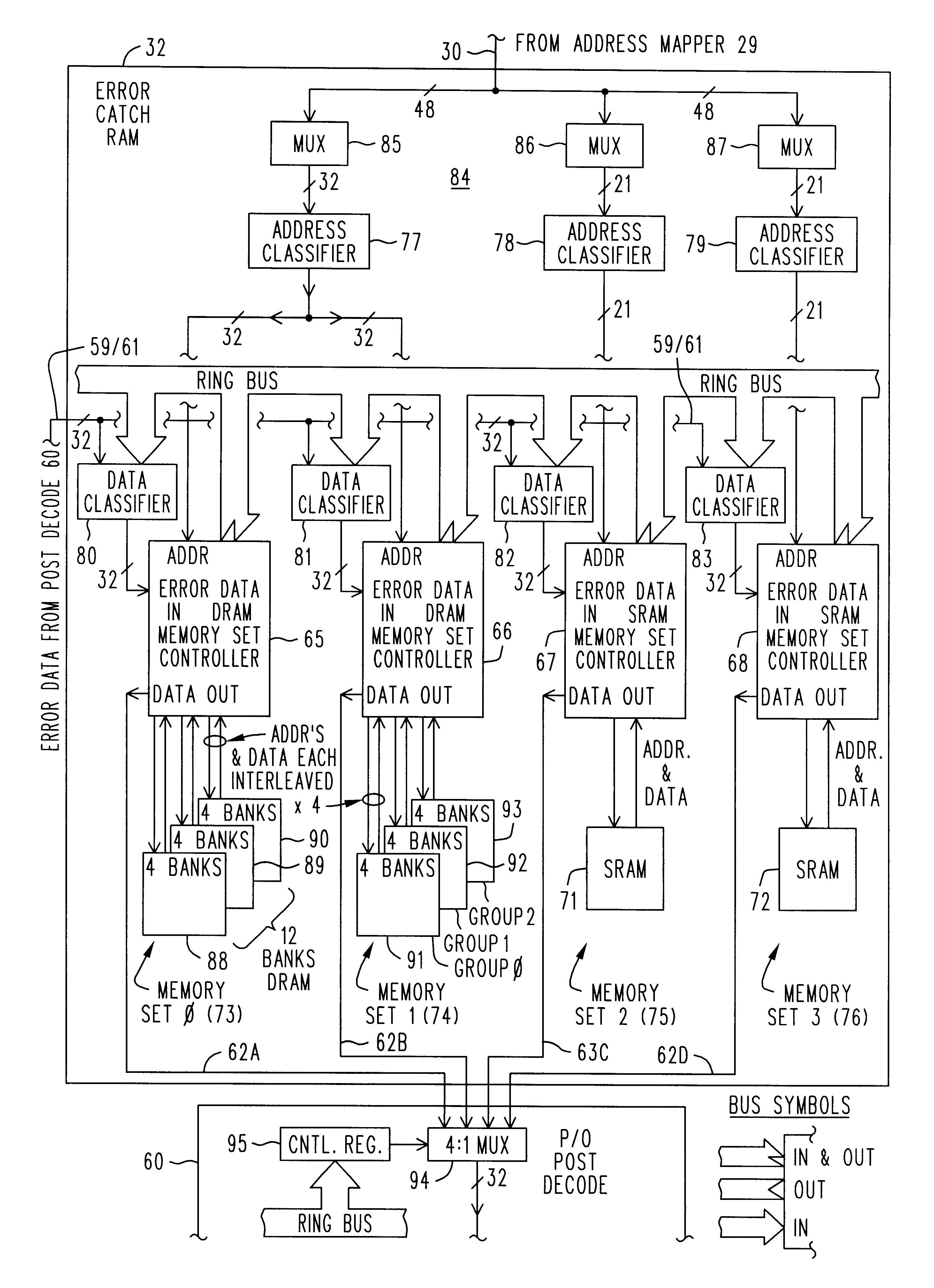

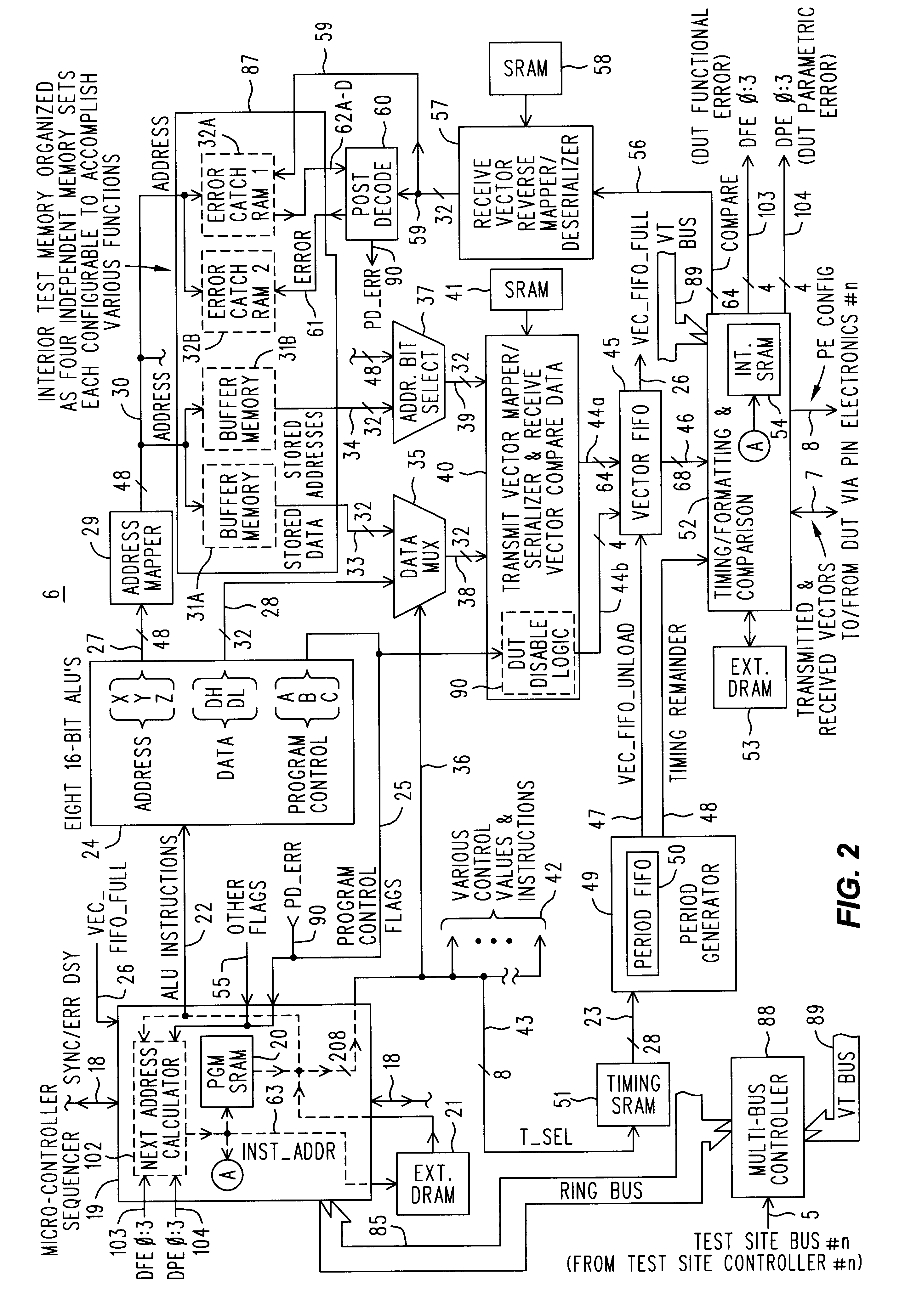

DRAM speed of operation in an Error Catch RAM can be increased by a combination of interleaving signals for different Banks of memory in a Group thereof and multiplexing between those Groups of Banks. A three-way multiplexing between three Groups of four Banks each, combined with a flexible four-fold interleaving scheme for signals to a Group produces an increase in speed approaching a factor of twelve, while requiring only three memory busses. Each of the twelve Banks represents the entire available address space, and any individual write cycle might access any one of the twelve Banks. A utility mechanism composes results for all twelve Banks during a read cycle at an address into a unified result. There is a mechanism to track of the integrity of the composed results, as further write operations can produce the need for another composing step. There are four Memory Sets, two are "internal" SRAM's and two are "external" DRAM's. The SRAM's are integral parts of VLSI circuits, while the DRAM's are individual packaged parts adjacent that VLSI. The amount of DRAM is optional. For DRAM memory sets the multiplexing and interleaving mode allows full random access at speeds of up to 100 MHz. For speeds will not exceed 33 MHz, the DRAM's can be configured to provide three times the depth in return for the lower speed by removing the multiplexing between Groups in favor of just interleaving upon one larger Group; Bank enable bits that were used as part of the multiplexing can now be used as regular address bits to increase the size of the address space of the one Group that remains. If the testing to the DUT fits the "linear" mode of access, a twelve-fold increase in memory depth is available, even when the DUT is tested at the highest speed the tester can operate at. This eliminates the interleaving scheme in favor of addressing within a single Bank at a time. Another reconfiguration is to combine the external memory sets into one memory set that has twice the depth of either uncombined set, regardless of other (i.e., the speed related) modes of operation.

Owner:VERIGY PTE

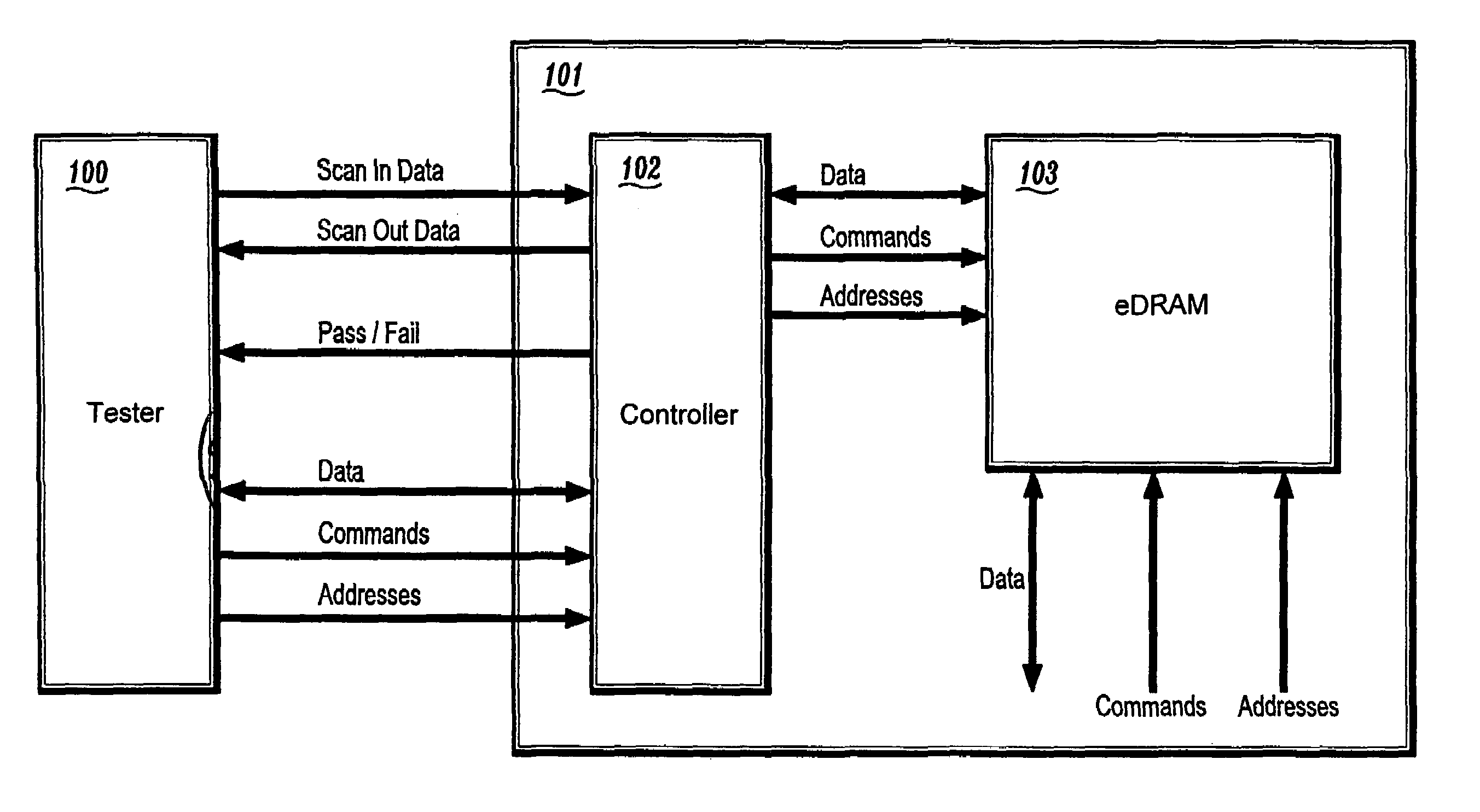

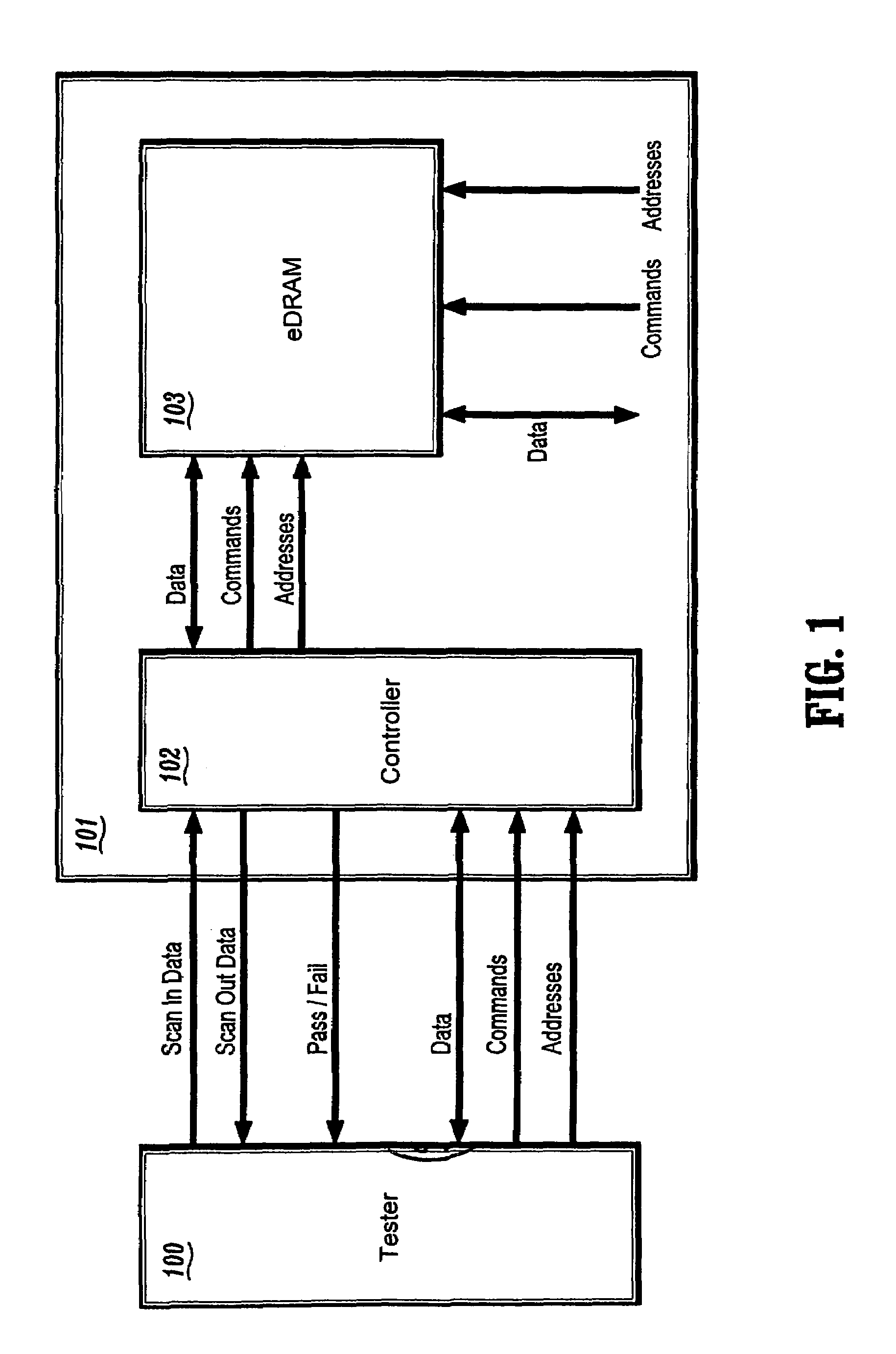

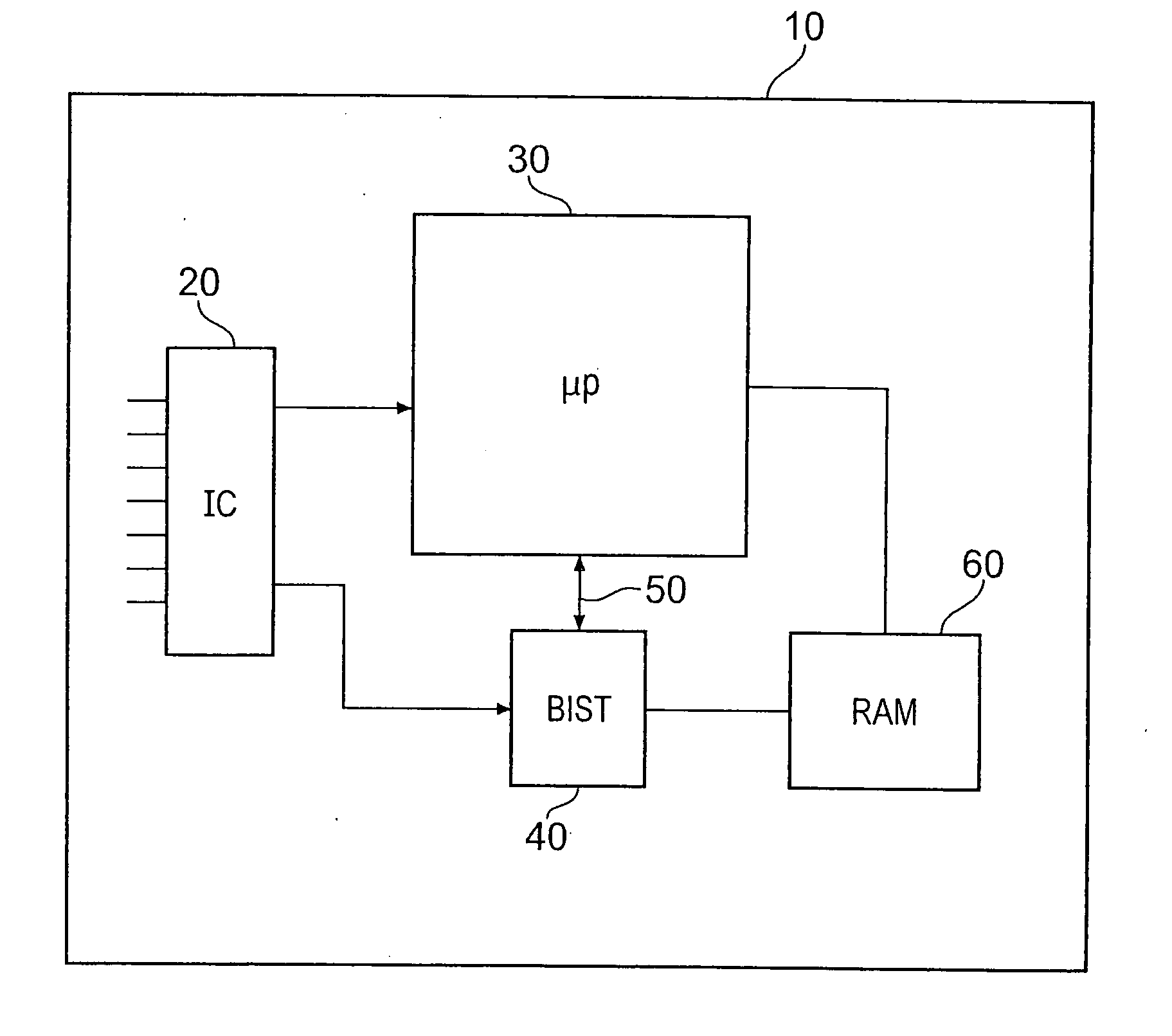

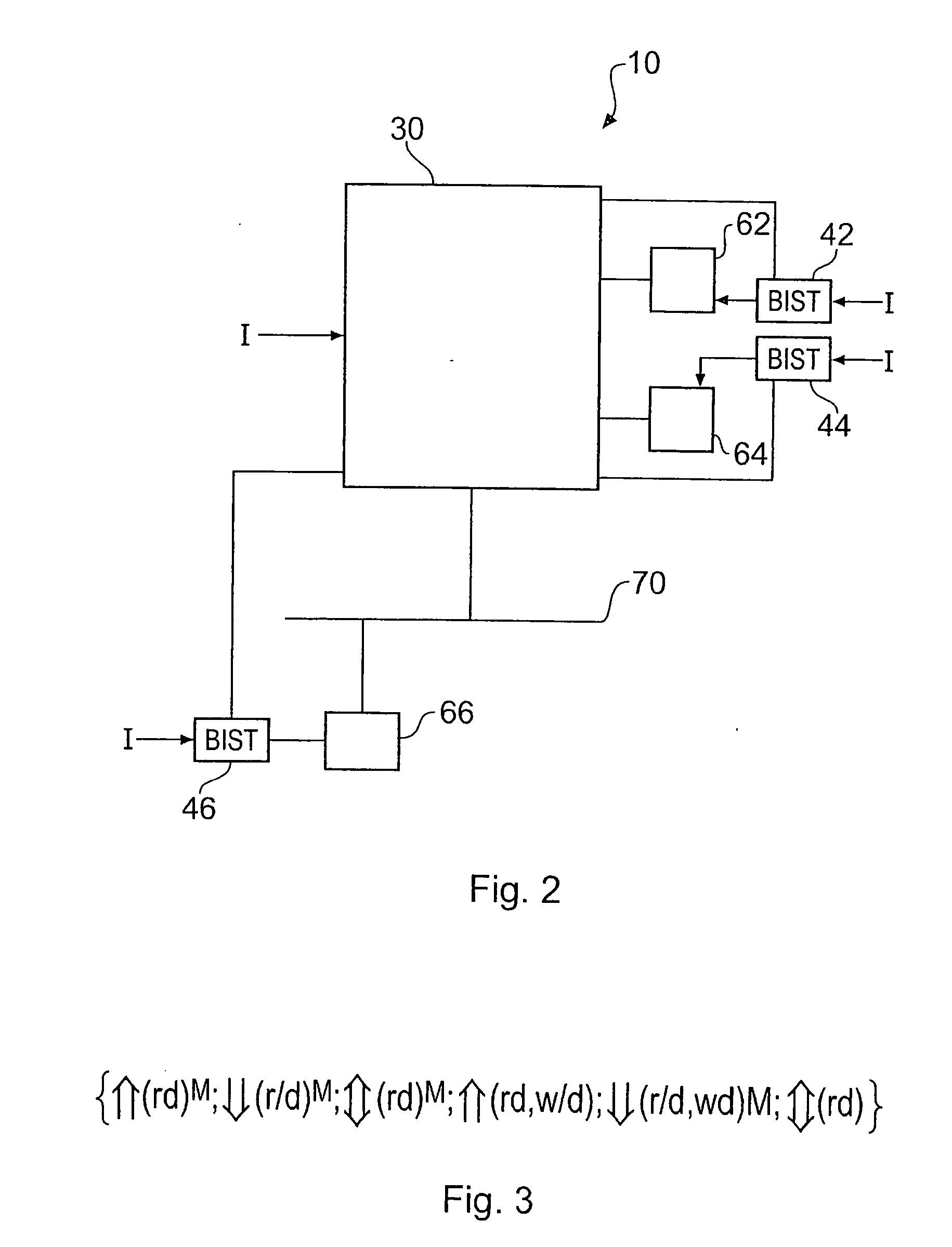

Circuit and method for testing embedded DRAM circuits through direct access mode

A circuit and method for testing an eDRAM through a test controller with direct access (DA) mode logic is provided. The circuit and method of the present invention allows the testing of eDRAMs with a conventional memory tester. The present invention provides a semiconductor device including an embedded dynamic random access memory (eDRAM) for storing data, the eDram including a plurality of memory cells, and a test controller for testing the plurality of memory cells to determine if the cells are defective, the test controller including built-in self-test (BIST) logic circuitry for performing tests and for interfacing to a logic tester, and direct access mode logic circuitry for interfacing the eDRAM with an external memory tester. The test controller further comprises a multiplexer for multiplexing data, commands, and addresses from the BIST logic circuitry and the direct access mode logic circuitry to the eDRAM.

Owner:POLARIS INNOVATIONS LTD

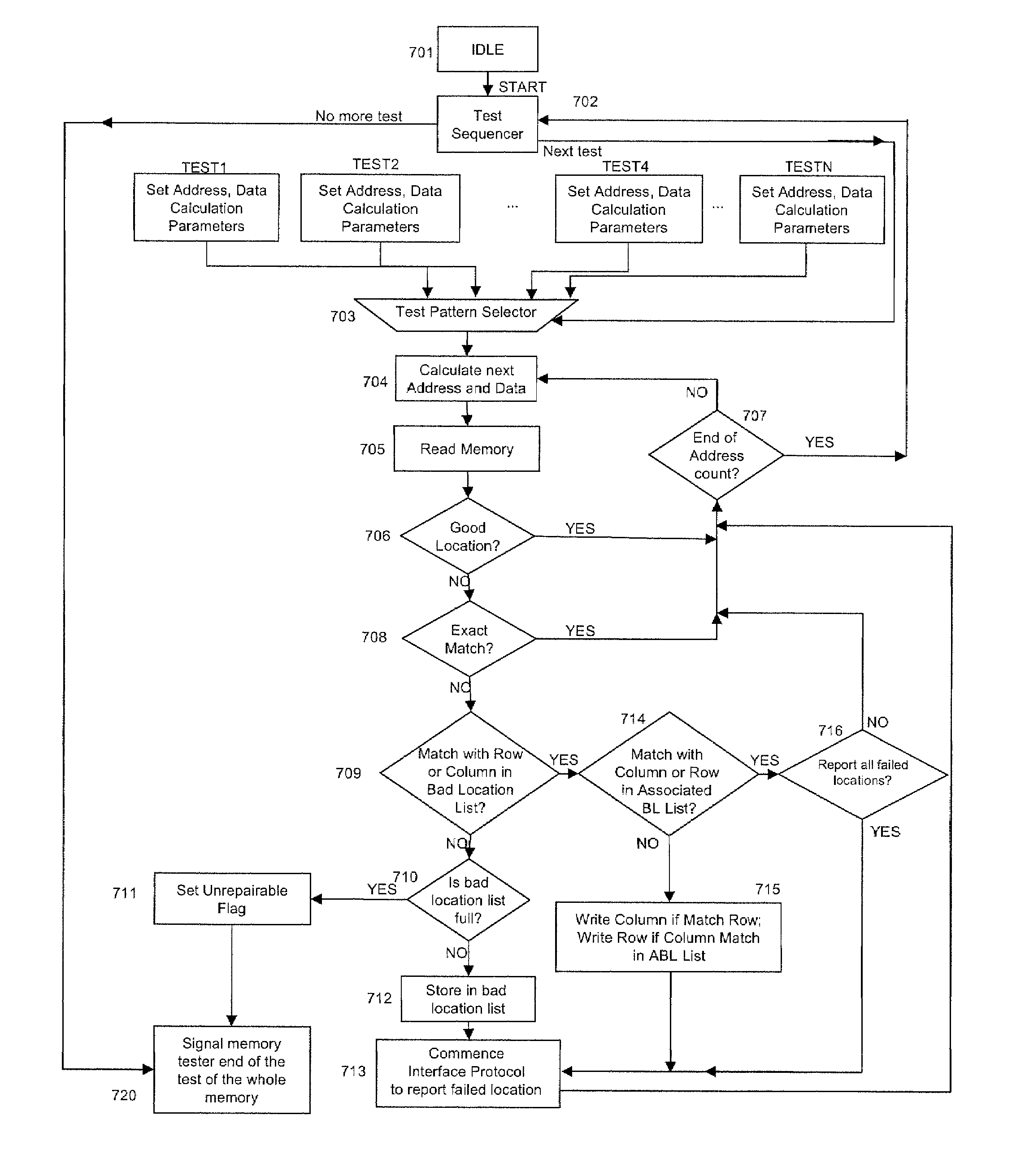

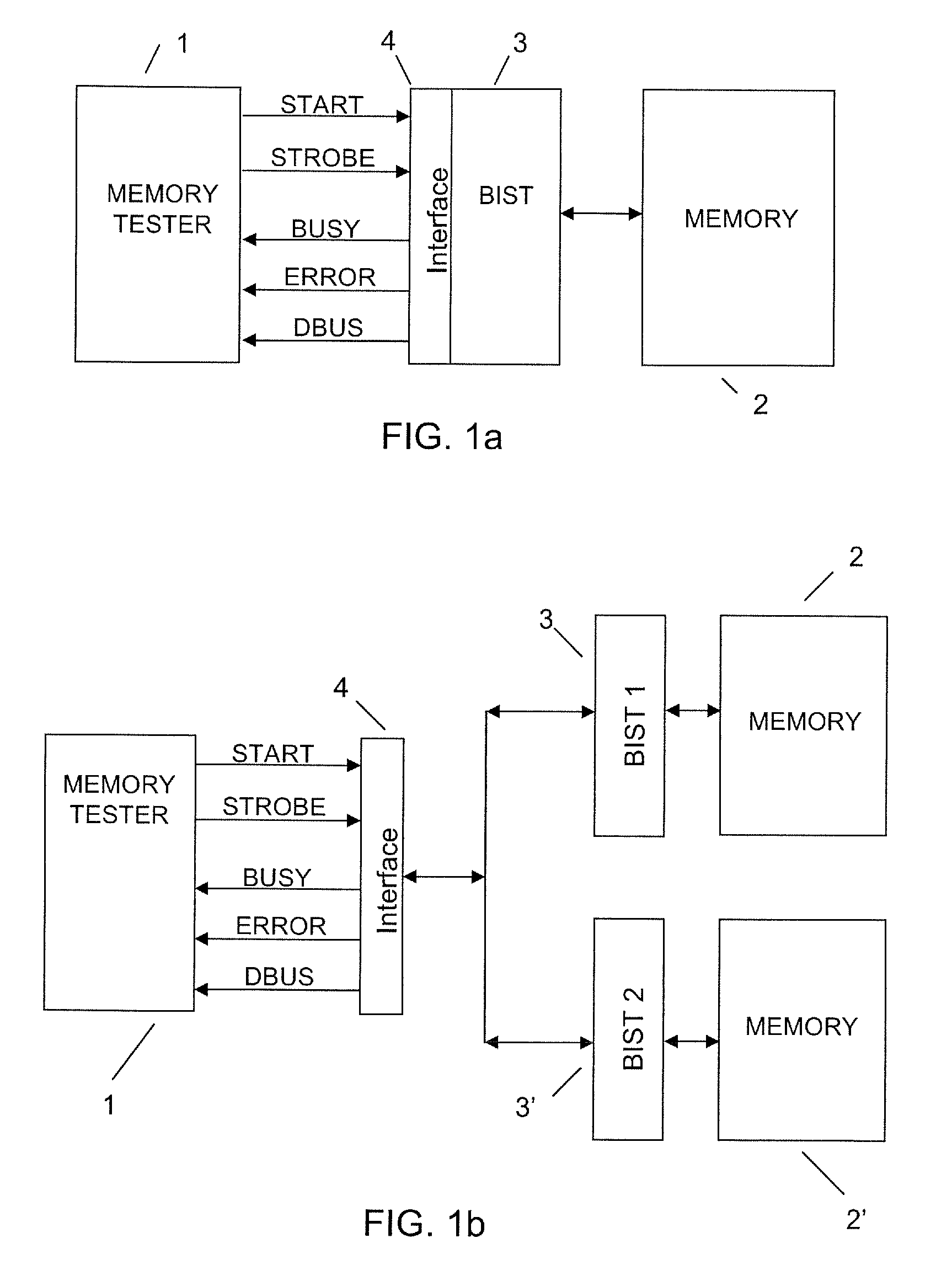

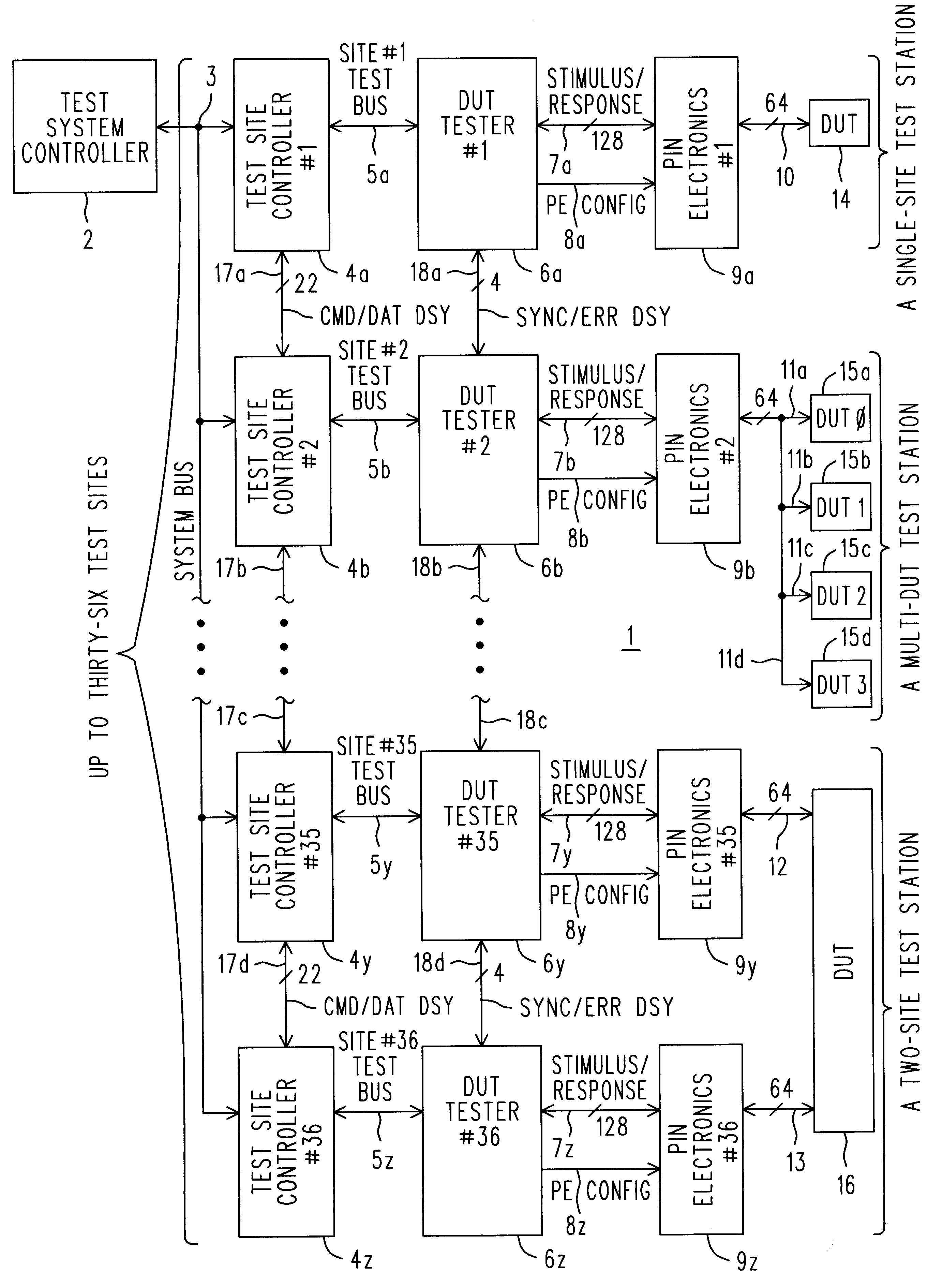

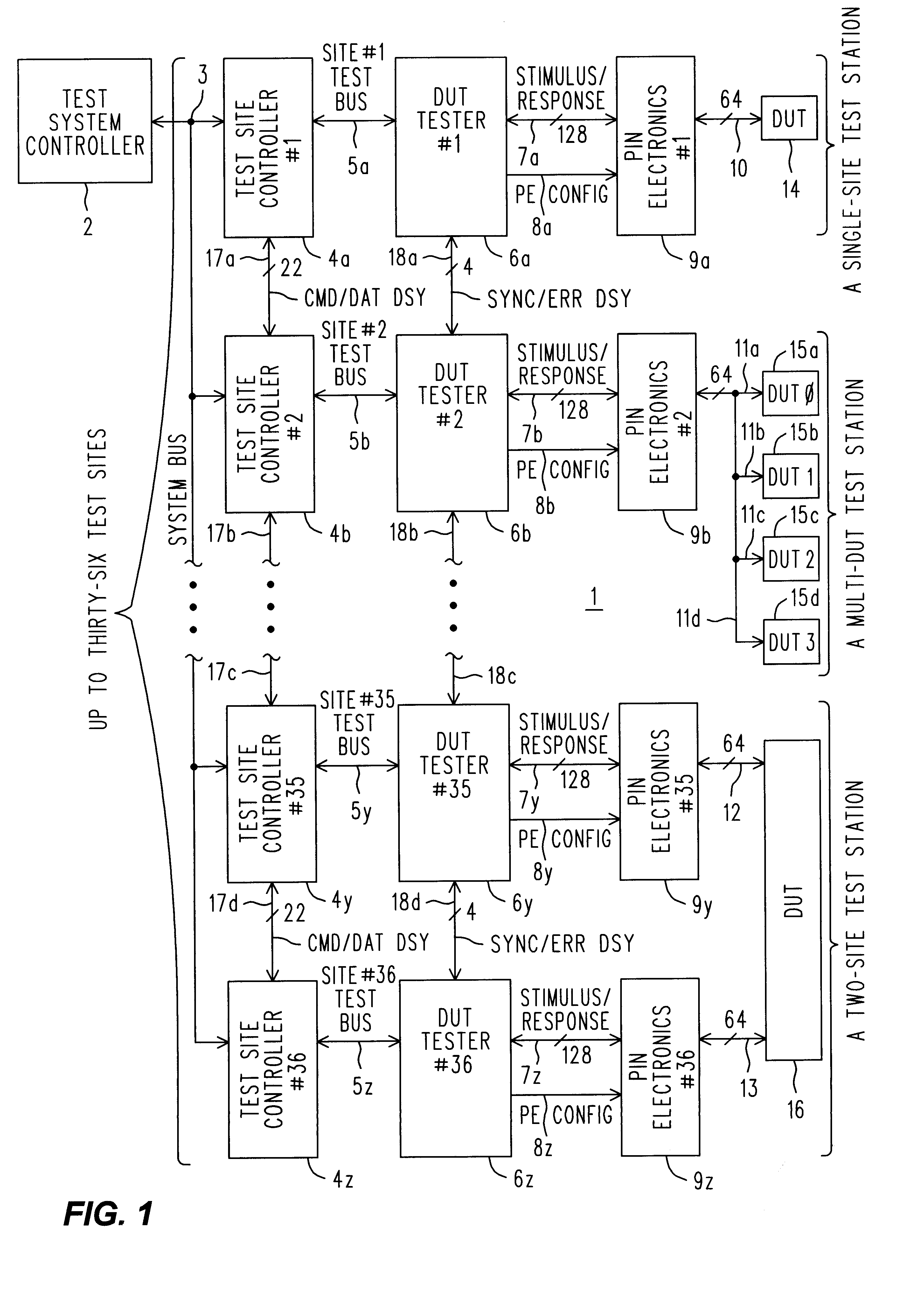

Method and system for memory testing and test data reporting during memory testing

ActiveUS7734966B1Reduced pin countNarrow interfaceElectronic circuit testingError detection/correctionAnalysis dataHigh memory

The present invention provides a method and system for improving memory testing efficiency, raising the speed of memory testing, detecting memory failures occurring at the memory operating frequency, and reducing data reported for redundancy repair analysis. The memory testing system includes a first memory tester extracting failed memory location information from the memory at a higher memory operating frequency, an external memory tester receiving failed memory location information at a lower memory tester frequency, and an interface between the first memory tester and the external memory tester. The memory testing method uses data strobes at the memory tester frequency to clock out failed memory location information obtained at the higher memory operating frequency. In addition, the inventive method reports only enough information to the external memory tester for it to determine row, column and single bit failures repairable with the available redundant resources. The present invention further provides a redundant resource allocation system, which uses a bad location list and an associated bad location list to classify failed memory locations according to a predetermined priority sequence, and allocates redundant resources to repair the failed memory locations according to the priority sequence.

Owner:MARVELL ASIA PTE LTD

Memory tester has memory sets configurable for use as error catch RAM, Tag RAM's, buffer memories and stimulus log RAM

InactiveUS6851076B1Fast and easy to controlAggravating and wastefulElectronic circuit testingStatic storageMemory testerHost machine

The various functions that are desirable for interior test memory within a memory tester are implemented in Memory Sets each serving as the host for one or sometimes more of such functions. For certain classes of testing a portion of interior test memory can be used as a Stimulus Log RAM that operates as an ideal DUT to create the correct conditions that are to exist in an actual DUT after testing. The actual part can then be tested, while the expected receive vectors are taken from the Stimulus Log RAM, and the comparison results sent to an ECR, Tag RAM's, etc., as usual. In this way the test program does not have to create or contain within itself the particular receive vectors that are the expected response from the applied stimulus.

Owner:ADVANTEST CORP

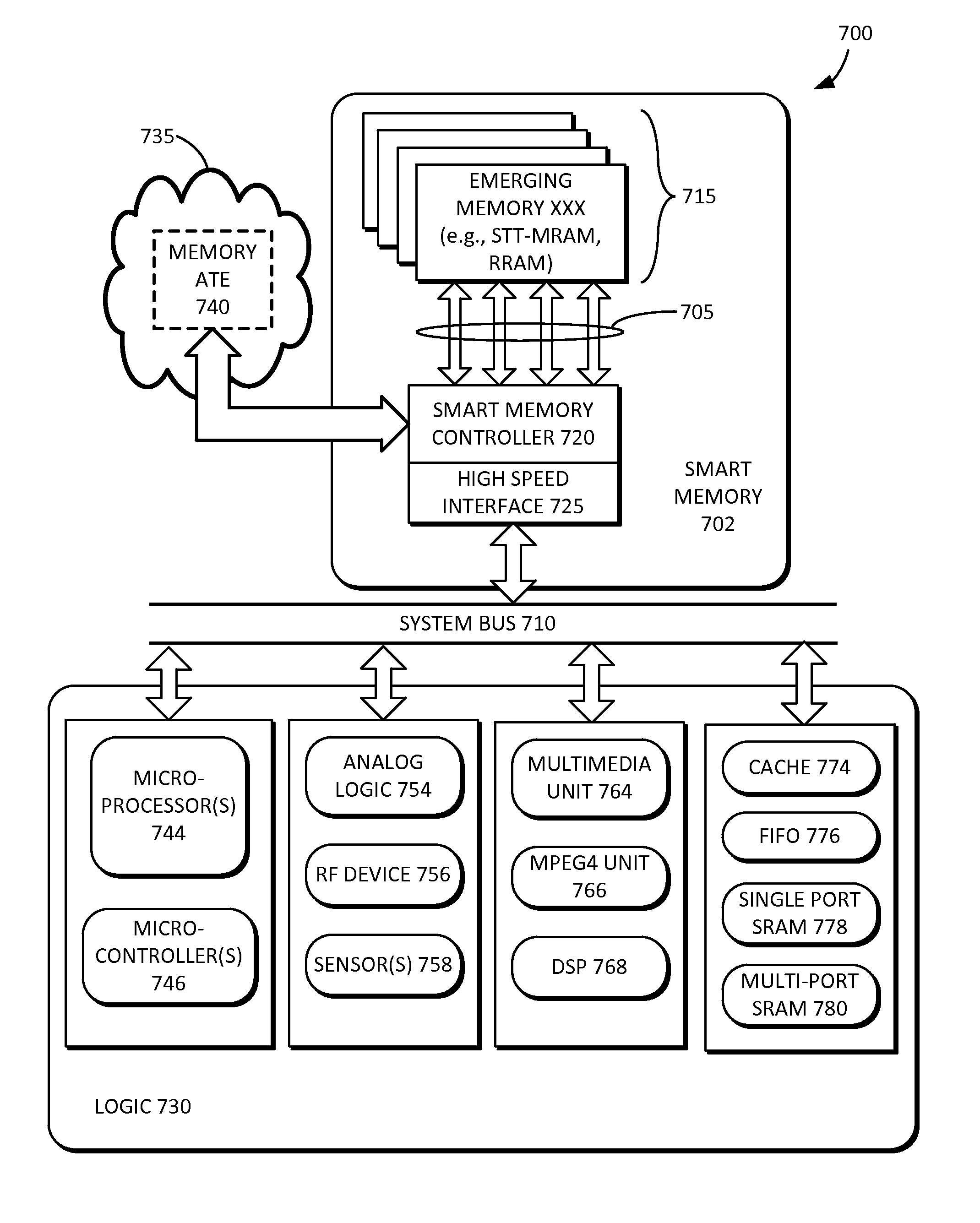

Architecture and method for remote memory system diagnostic and optimization

InactiveUS20130212207A1Easy diagnosisPromote repairDigital computer detailsComputer security arrangementsSpecific testSmart memory

A smart memory system preferably includes a memory including one or more memory chips and a smart memory controller. The smart memory controller includes a transmitter communicatively coupled to the cloud. The transmitter securely transmits a product identification (ID) associated with the memory to the cloud. A cloud-based data center receives and stores the product ID and related information associated with the memory. A smart memory tester receives a product specific test program from the cloud-based data center. The smart memory tester may remotely test the memory via the cloud in accordance with the product specific test program. The information stored in the cloud-based data center can be accessed anywhere in the world by authorized personnel. Repair solutions can be remotely determined based on the test results and the diagnostic information. The repair solutions are transmitted to the smart memory controller, which repairs the memory.

Owner:SAMSUNG ELECTRONICS CO LTD

Apparatus for testing memories with redundant storage elements

InactiveUS6862703B2Valid choiceQuantity minimizationError detection/correctionStatic storageMemory testerRandom access memory

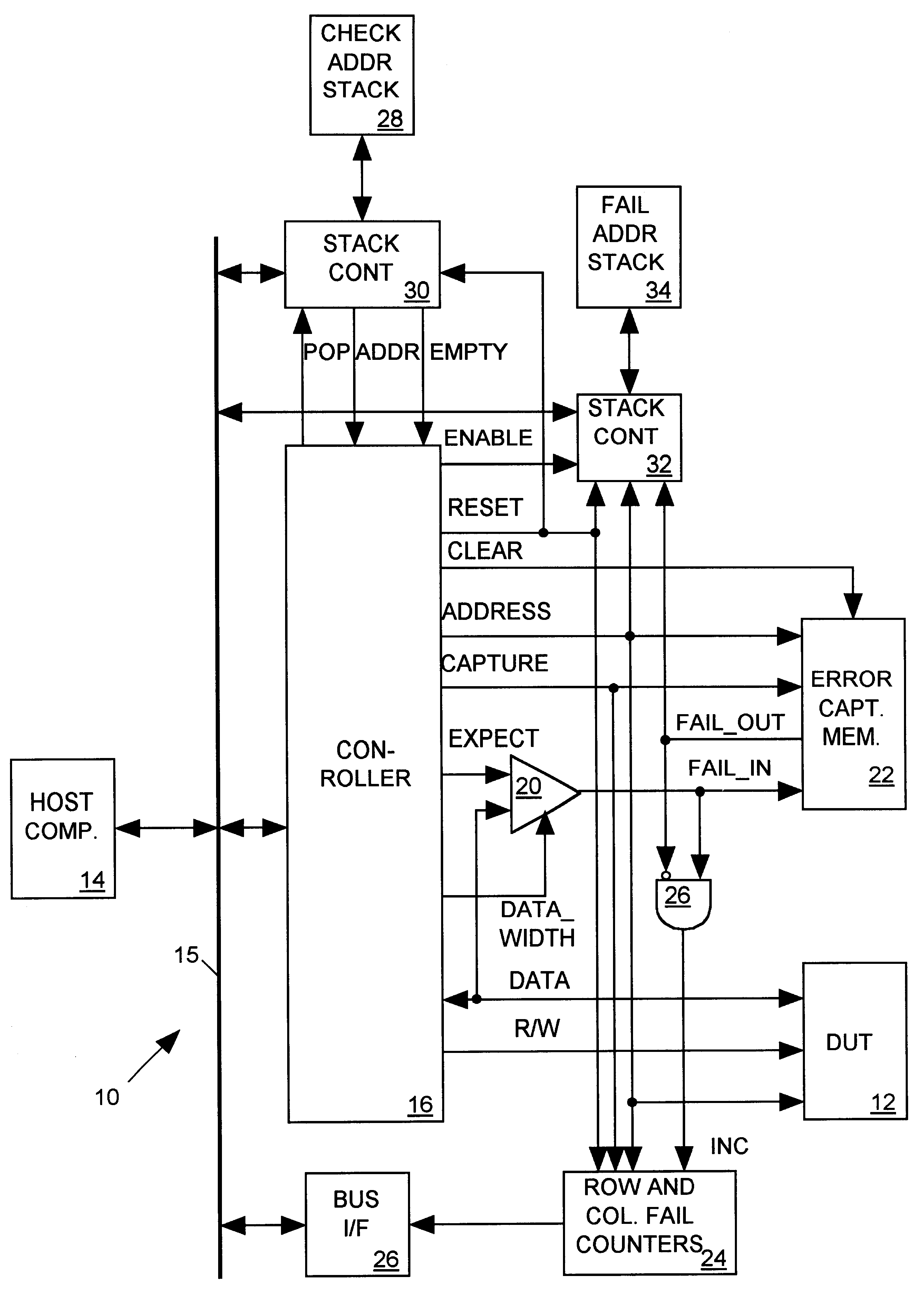

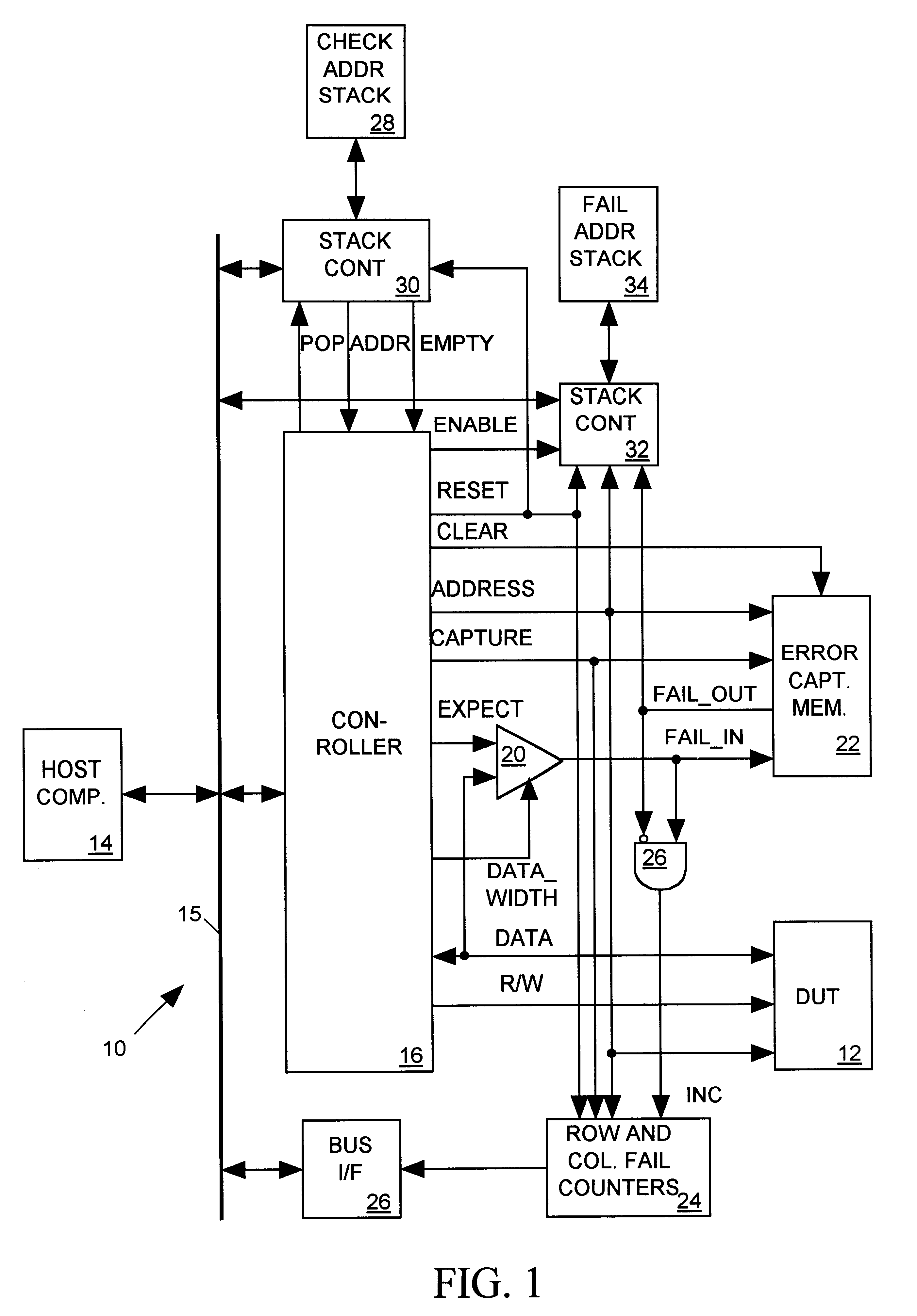

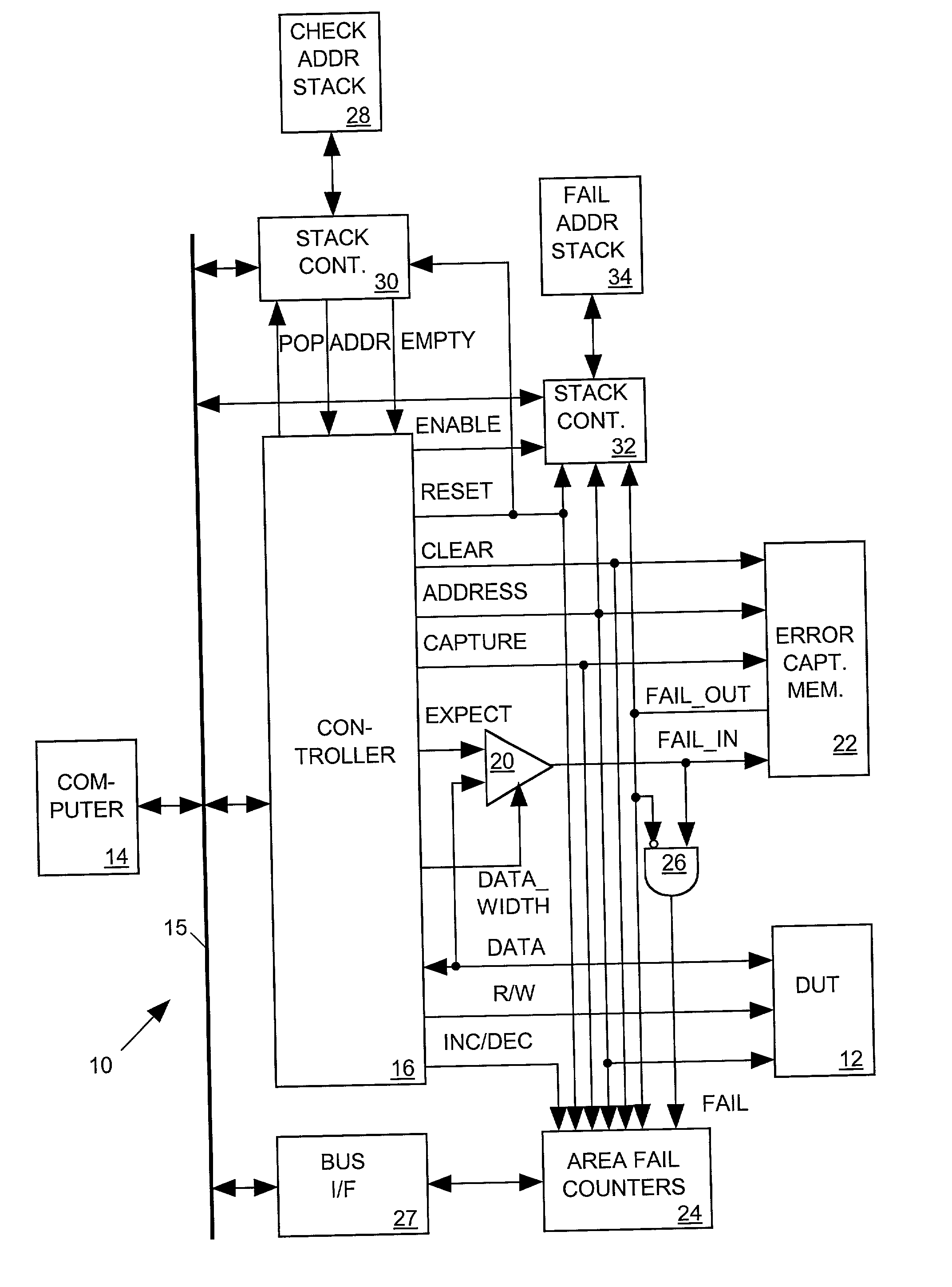

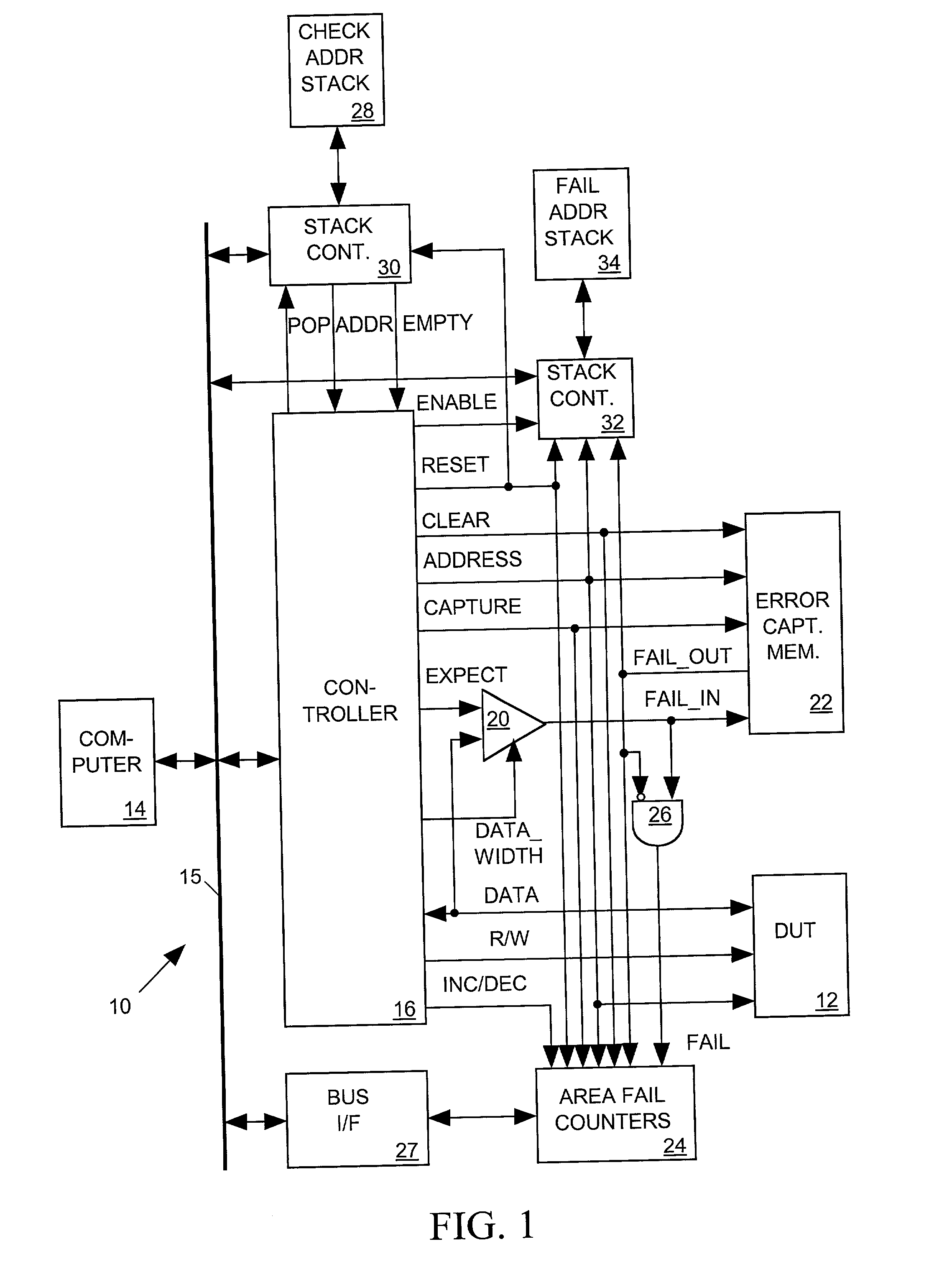

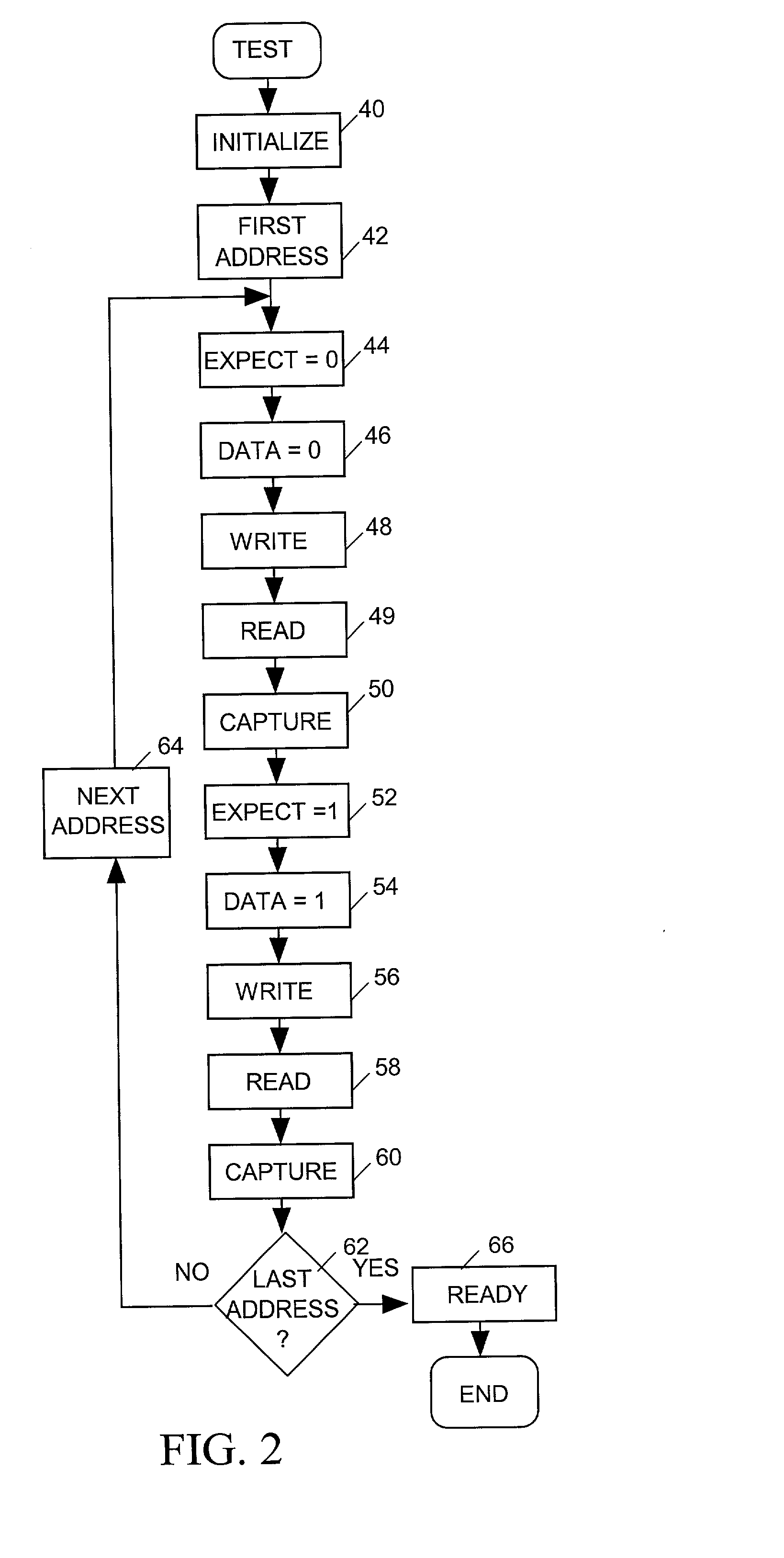

A memory tester tests a random access memory device under test (DUT) comprising addressable rows and columns of memory cells, and provides a computer with enough information to determine how to efficiently allocate spare rows and columns for replacing rows and columns containing defective memory cells. During a test the memory tester writes a “fail” bit into each address of an error capture memory (ECM) to indicate whether a correspondingly addressed memory cell of the DUT is defective. The tester also includes a set of programmable area fail counters, each for counting of the number of memory cells within a separately selected area of the memory's address space. After the test, the computer processes the counts to determine whether it needs to allocate the spare rows and columns and, in some cases, to determine how to allocate the spare rows and columns. When it cannot allocate spare rows and columns on the basis of the counts alone, the computer commands the tester to read the fail bits in selected areas of the ECM's address space to determine the addresses of the defective memory cells and to supply those addresses to the computer to enable it to determine how to allocate spare rows and columns.

Owner:CREDENCE SYSTEMS

Algorithmically programmable memory tester with history FIFO's that aid in error analysis and recovery

InactiveUS6574764B2Increase overheadDigital circuit testingMarginal checkingMemory testerTester device

The problem is to branch back to an appropriate location within a memory tester test program, and also restore its state of algorithmic control, when an error associated therewith occurs later in time at the DUT. Owing to delays in pipelines connecting the program execution environment to the DUT and back again. These delays allow the program to arbitrarily advance beyond where the stimulus was given. The arbitrary advance makes it difficult to determine the exact circumstances that were associated with the error. A branch based on the error signal can restart a section of the test program, but it is likely only a template needing further test algorithm control information that varies dynamically as the test program executes. The solution is to equip the memory tester with History FIFO's whose depths are adjusted to account for the sum of the delays of the pipelines, relative to the location of that History FIFO. When the error flag is generated the desired program location and state information is present at the bottom of an appropriate History FIFO.

Owner:ADVANTEST CORP

Apparatus for testing memories with redundant storage elements

InactiveUS6256757B1Provide quicklyElectronic circuit testingError detection/correctionMemory testerRandom access memory

A memory tester tests a random access memory device under test (DUT) comprising addressable rows and columns of memory cells, and provides a host computer with enough information to determine how to efficiently allocate spare rows and columns for replacing rows and columns containing defective memory cells. During a test the memory tester writes a bit into each address of an error capture memory (ECM) to indicate whether a correspondingly addressed memory cell of the DUT is defective. The tester also counts of the number of memory cells of each row and column that are defective. After the test the counts are supplied to the host computer. When the host computer is unable to determine how to allocate the spare rows and columns from the counts alone, it requests the tester to process the data in the ECM to determine and supply the host computer with addresses of the defective memory cells.

Owner:CREDENCE SYSTEMS

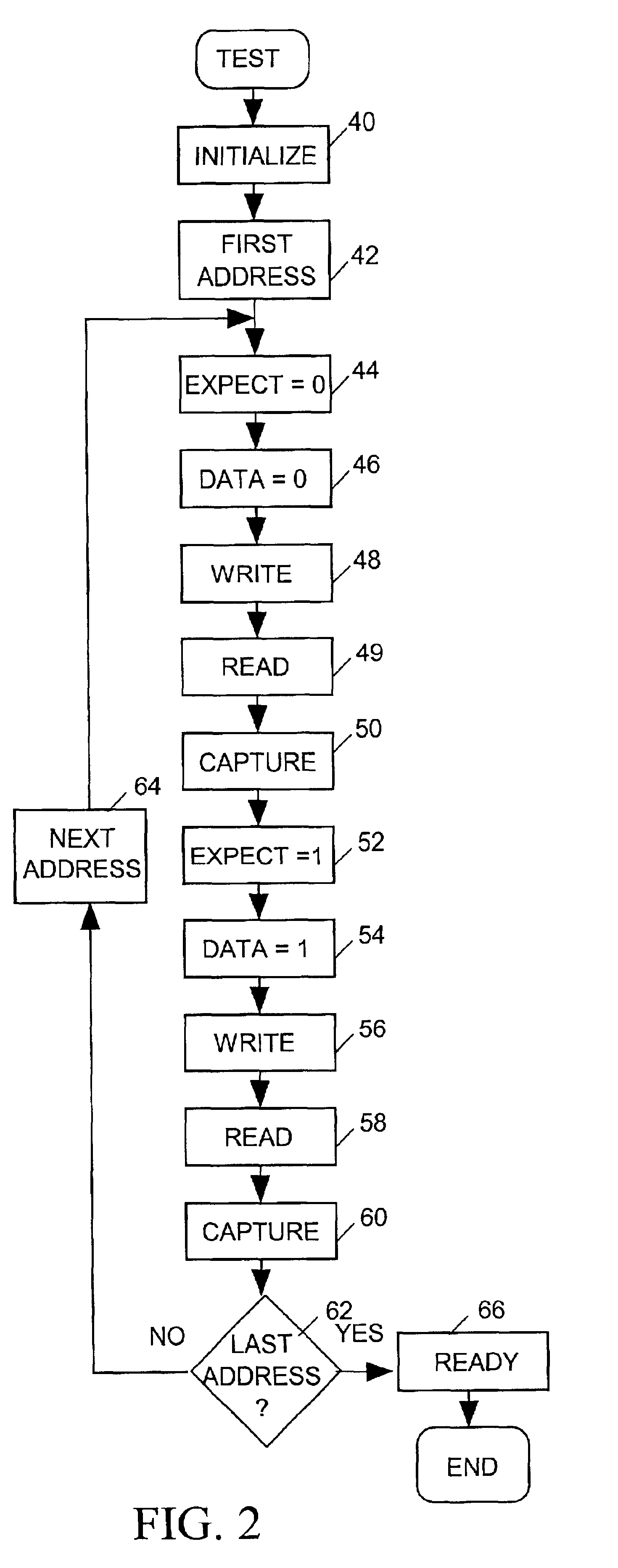

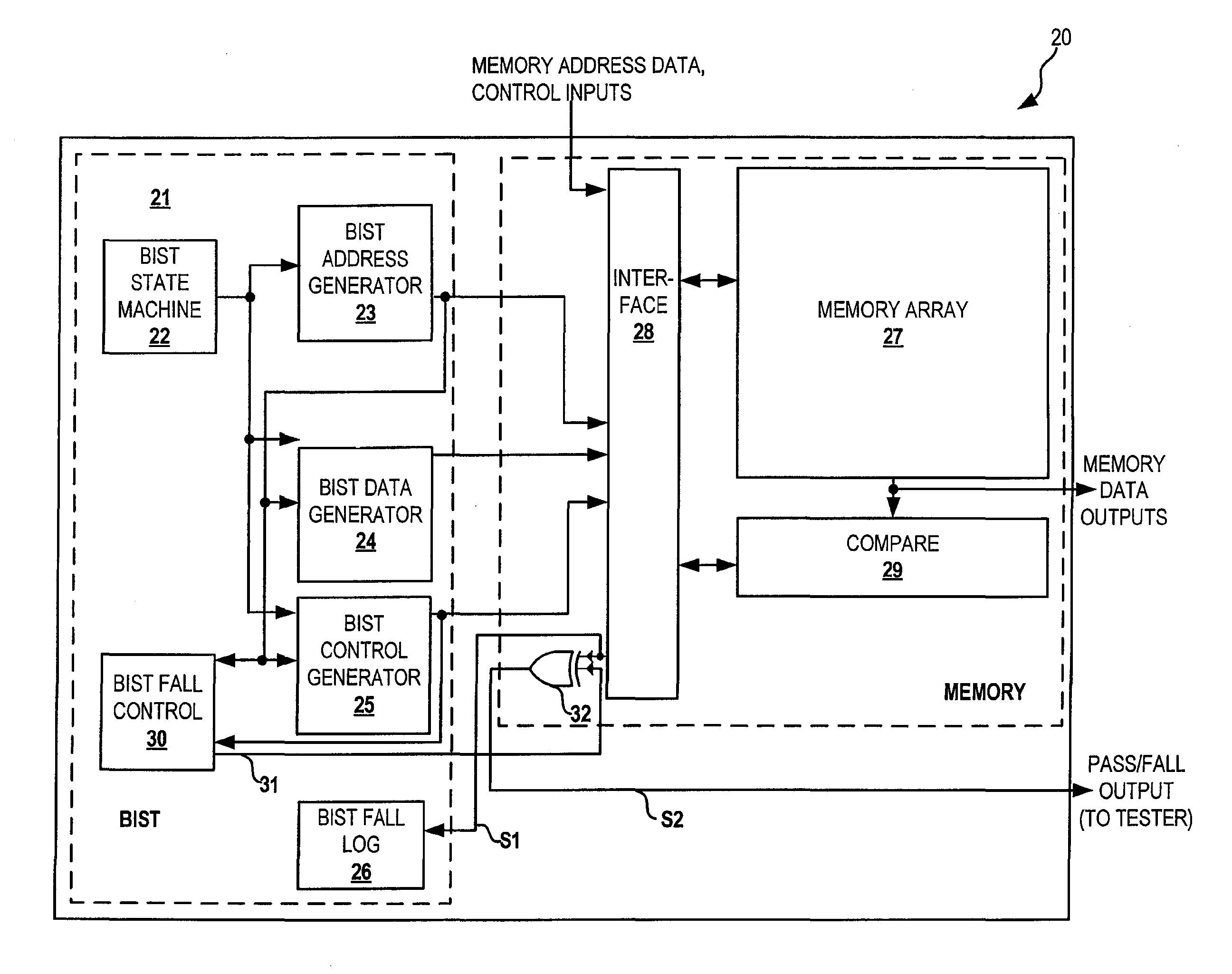

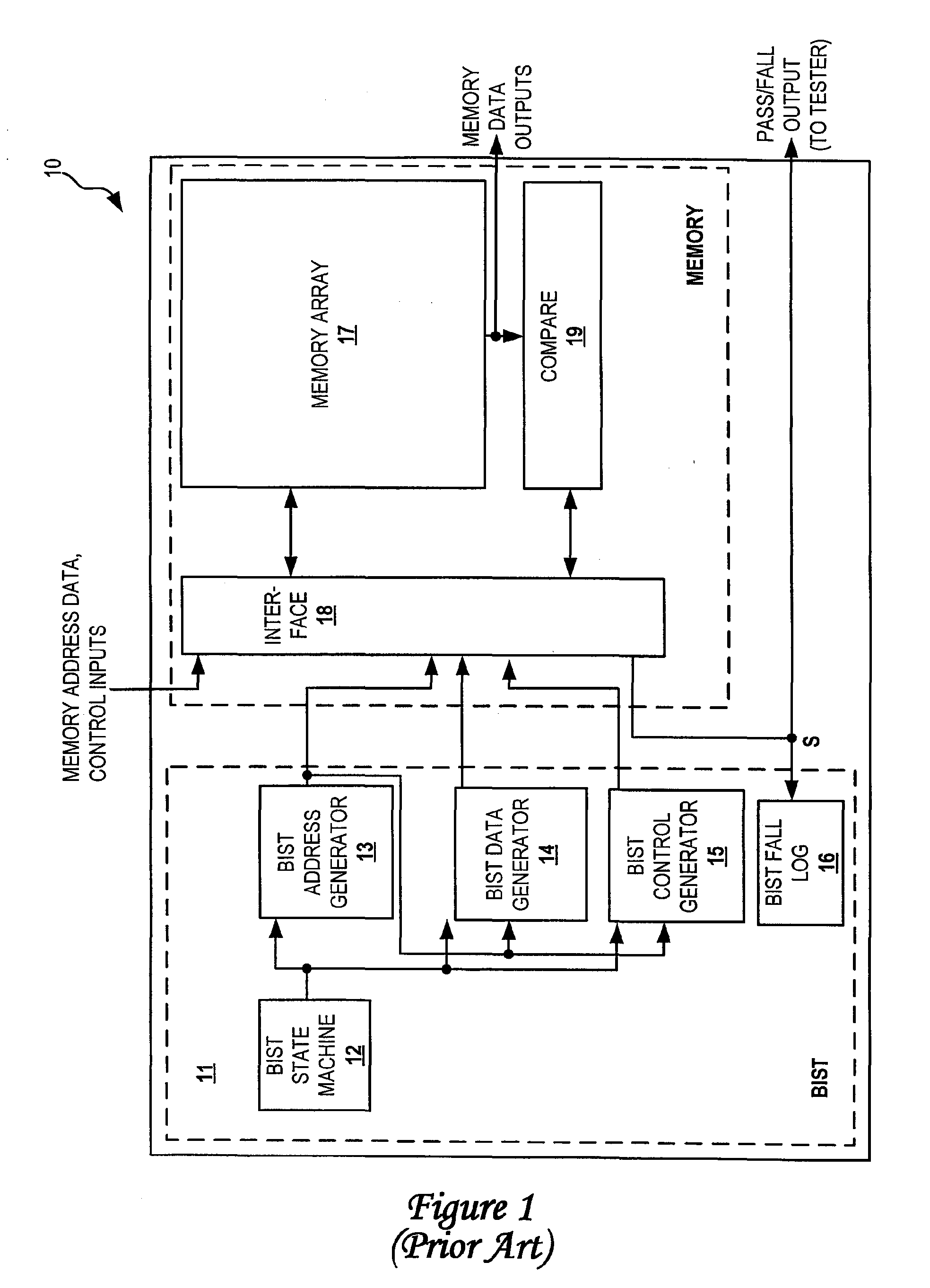

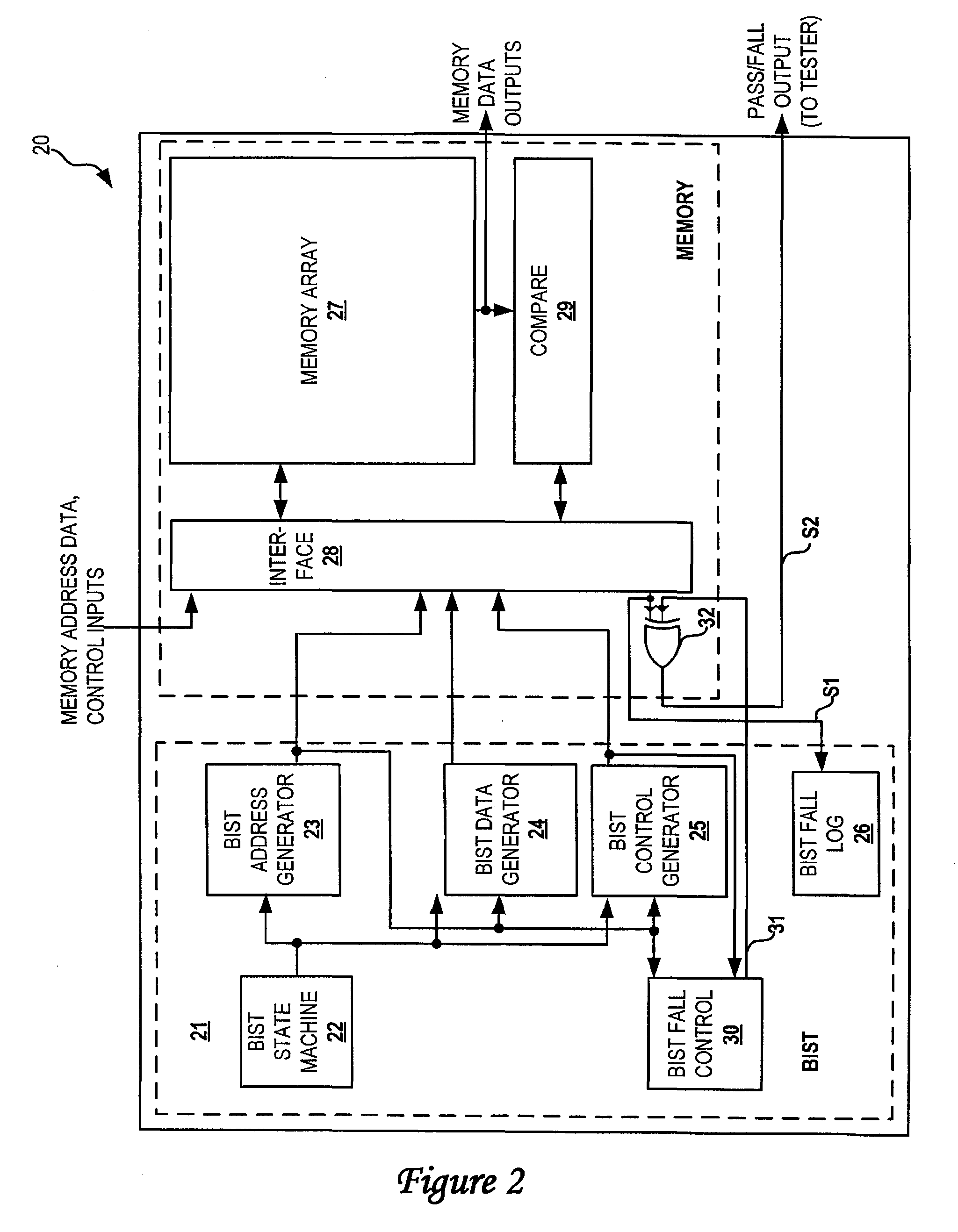

Method and apparatus for verifying memory testing software

ActiveUS20060190788A1Verify accuracyElectronic circuit testingError detection/correctionMemory faultsParallel computing

A method for verifying the accuracy of memory testing software is disclosed. A built-in self test (BIST) fail control function is utilized to generate multiple simulated memory fails at various predetermined locations within a memory array of a memory device. The memory array is then tested by a memory tester. Afterwards, a bit fail map is generated by the logical-to-physical mapping software based on all the memory fails indicated by the memory tester. The bit fail map provides all the fail memory locations derived by the logical-to-physical mapping software. The fail memory locations derived by the logical-to-physical mapping software are then compared to the predetermined memory locations to verify the accuracy of the logical-to-physical mapping software.

Owner:MARVELL ASIA PTE LTD

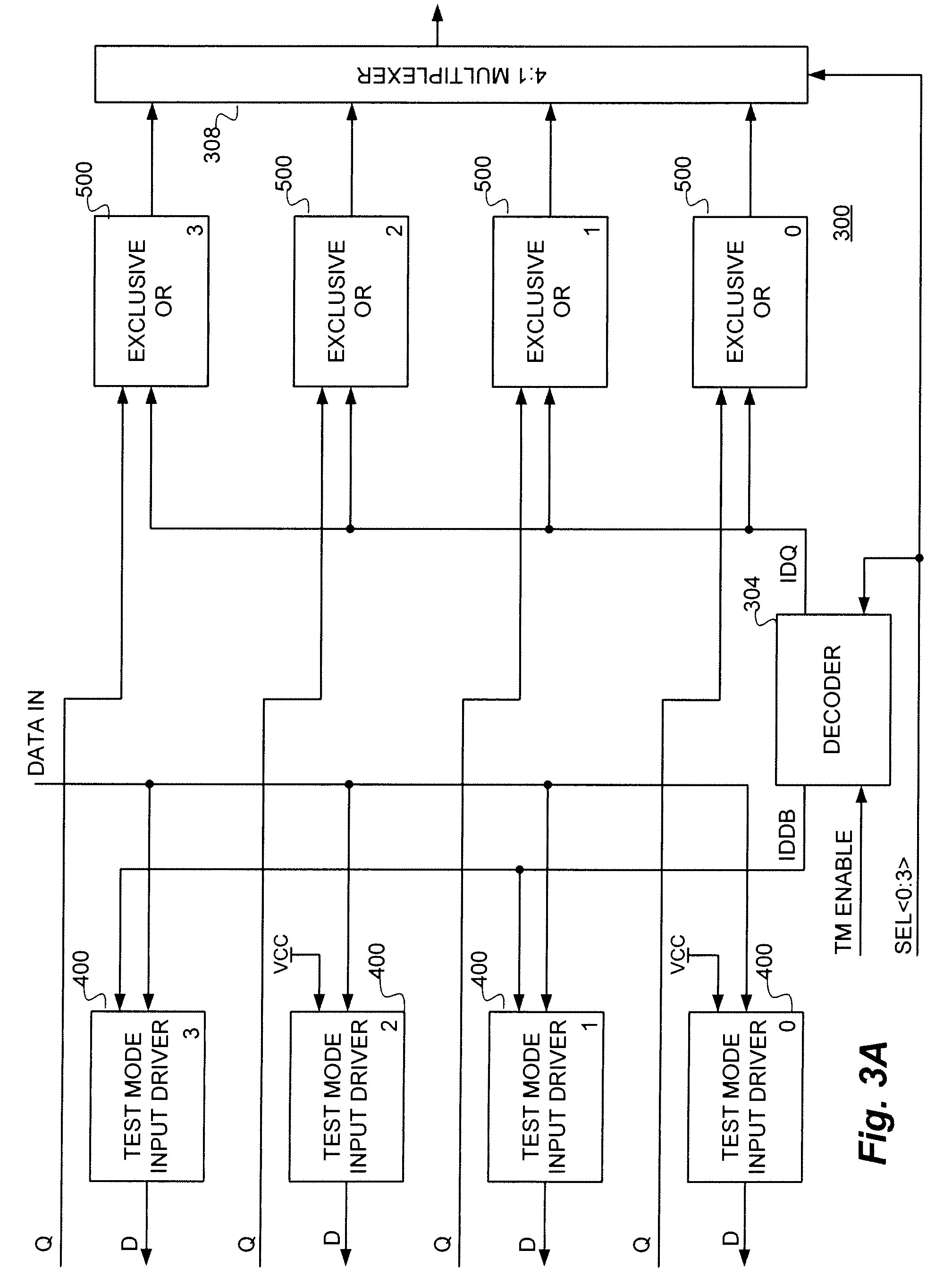

Data inversion register technique for integrated circuit memory testing

ActiveUS7631233B2Maximize probabilityReduce in quantityError preventionElectronic circuit testingMemory testerProcessor register

A data inversion register technique for integrated circuit memory testing in which data input signals are selectively inverted in a predetermined pattern to maximize the probability of identifying failures during testing. In accordance with the technique of the present invention, on predetermined input / outputs (I / Os,) data inputs may be inverted to create a desired test pattern (such as data stripes) which are “worst case” for I / O circuitry or column stripes which are “worst case” for memory arrays. A circuit in accordance with the technique of the present invention then matches the pattern for the data out path, inverting the appropriate data outputs to obtain the expected tester data. In this way, the test mode is transparent to any memory tester.

Owner:INVENSAS CORP

Memory tester uses arbitrary dynamic mappings to serialize vectors into transmitted sub-vectors and de-serialize received sub-vectors into vectors

InactiveUS7076714B2Solve the real problemElectronic circuit testingError detection/correctionTheoretical computer scienceProgramming constructs

The problem of sequentially “squeezing” small fields of data in a larger data path in and out of a memory device can be solved in an algorithmically driven memory tester by defining sub-vectors to represent data in the small field, where a sequence of sub-vectors represents the data that would be represented by a full sized vector if such a full sized vector could be applied to the DUT. A programming construct in the programming language of the algorithmically driven memory tester allows sub-vectors to be defined, as well as an arbitrary mapping that each is to have. The arbitrary mapping is not static, but changes dynamically as different sub-vectors are encountered. Arbitrary dynamic mappings change as sub-vectors are processed, and may include the notion that, during the activity for a sub-vector, this (or these) bit(s) of a vector do not (presently) map to any pin at all of the DUT. The arbitrary dynamic mapping is implemented by a collection of MUX's configured by data stored ahead of time in an SRAM, in accordance with what defining program constructs are encountered by the compiler as it processes the test program. A dynamic reverse mapper, also a collection of MUX's similarly controlled by an SRAM, serves as a de-serializer that assembles a sequence of received sub-vectors into a final received full-sized vector.

Owner:ADVANTEST CORP

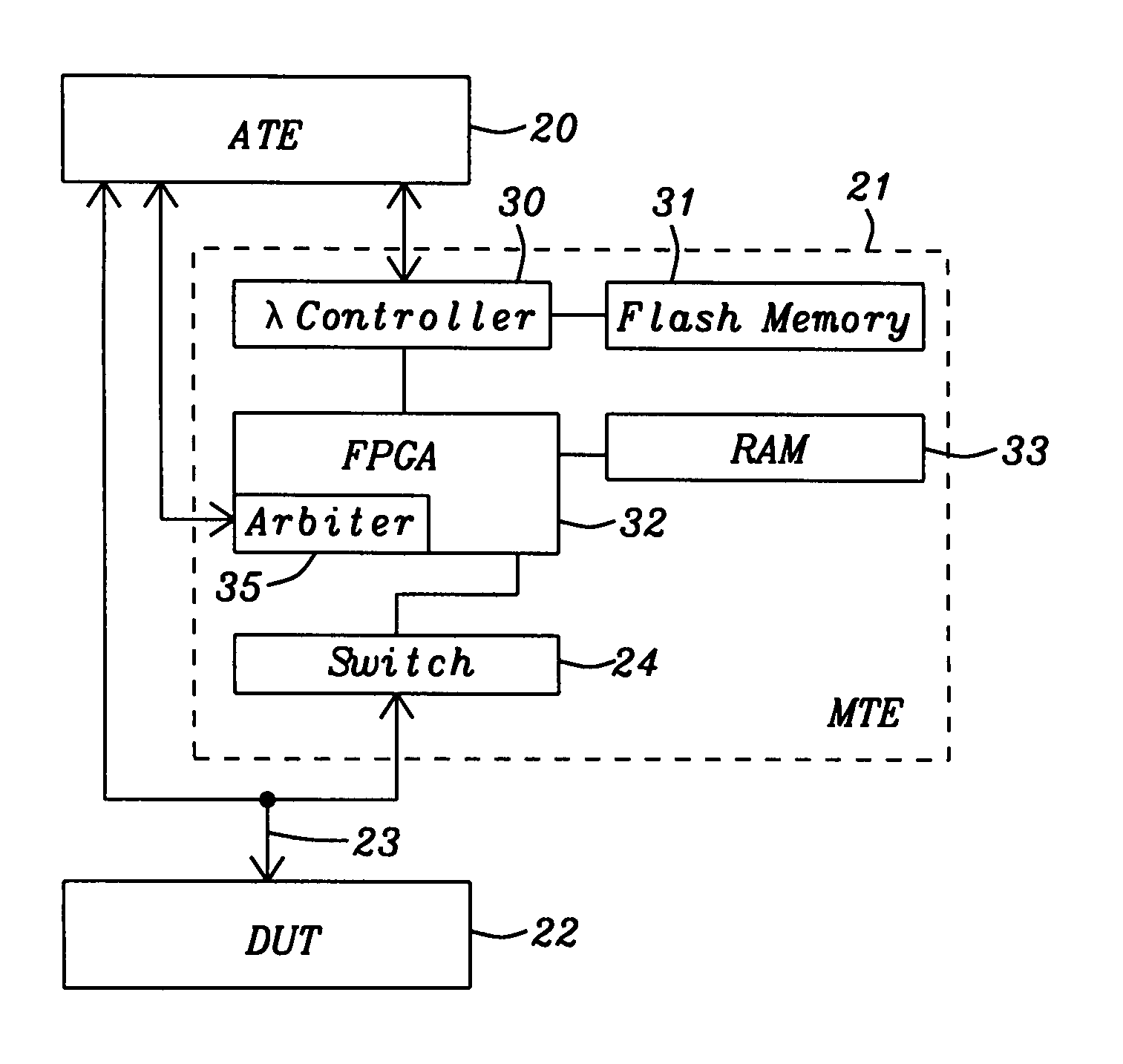

Memory test engine

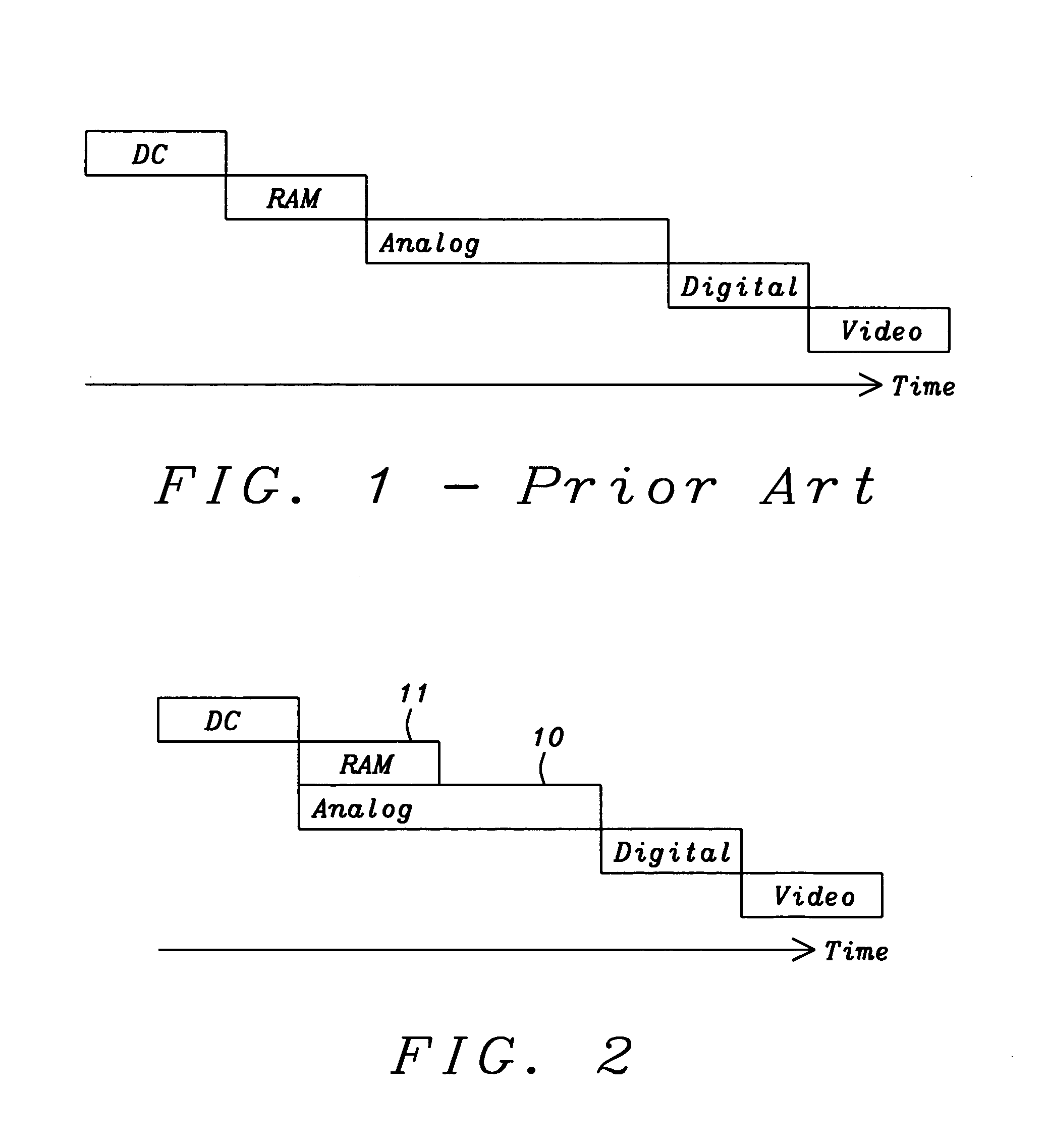

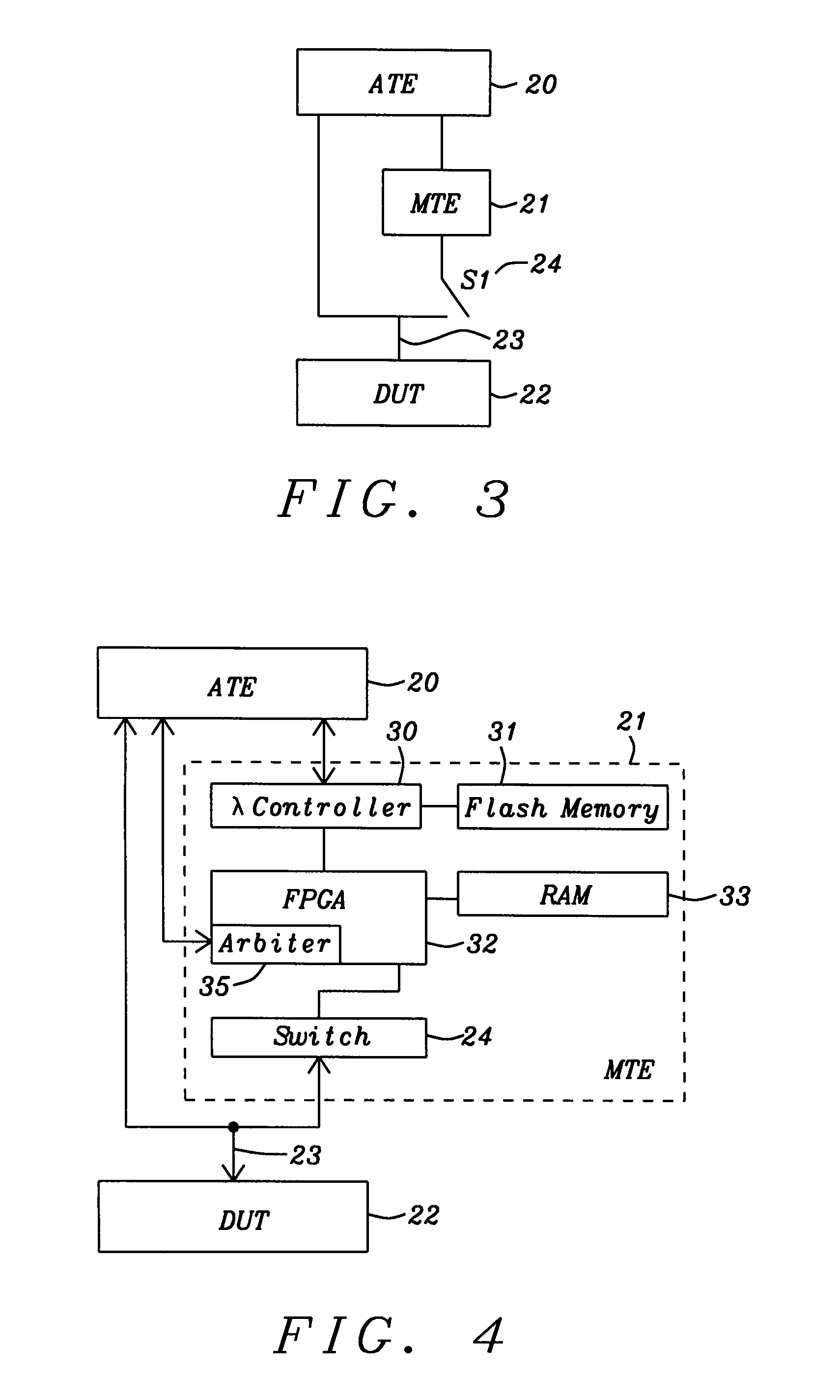

InactiveUS20070271059A1Avoid interferenceShorten test timeResistance/reactance/impedenceElectronic circuit testingMemory testerTester device

A memory test engine performs memory tests on an embedded memory located in a device under test (DUT) simultaneous to analog tests performed by an automatic tester. The automatic tester provides coded information to the memory test engine, which includes a description of the embedded memory within the DUT. The memory test engine operates autonomous to the automatic tester; apply addresses, data and control and comparing results of the memory test to expected values. The automatic tester and the memory test engine use the same DUT data bus; and therefore, arbitrate the use of the bus of the DUT.

Owner:DIALOG SEMICONDUCTOR GMBH

Algorithmically programmable memory tester with history FIFO's that aid in ERROR analysis and recovery

The problem is to branch back to an appropriate location within a memory tester test program, and also restore its state of algorithmic control, when an error associated therewith occurs later in time at the DUT. Owing to delays in pipelines connecting the program execution environment to the DUT and back again. These delays allow the program to arbitrarily advance beyond where the stimulus was given. The arbitrary advance makes it difficult to determine the exact circumstances that were associated with the error. A branch based on the error signal can restart a section of the test program, but it is likely only a template needing further test algorithm control information that varies dynamically as the test program executes. The solution is to equip the memory tester with History FIFO's whose depths are adjusted to account for the sum of the delays of the pipelines, relative to the location of that History FIFO. When the error flag is generated the desired program location and state information is present at the bottom of an appropriate History FIFO. This is also readily applicable when the test program uses an ALU to generate its own DUT stimuli, as well as to the case when the test program / ALU addresses an intermediate Buffer Memory whose contents are central to the nature of the testing the DUT is to undergo. The first is an ALU History FIFO, while the second is a Buffer Memory History FIFO. There can also be ECR History FIFO's. There is a mechanism to track system re-configuration as it occurs and adjust the depths of the various History FIFO's according to resulting pipeline depth. There is a mechanism to freeze the contents of a History FIFO upon the generation of an error. A History FIFO can be extended to allow a branching instruction in the test program to not prematurely respond to an error flag sooner than the pipeline delay needed for that error flag's value to be determined by a cause located within the test program.

Owner:ADVANTEST CORP

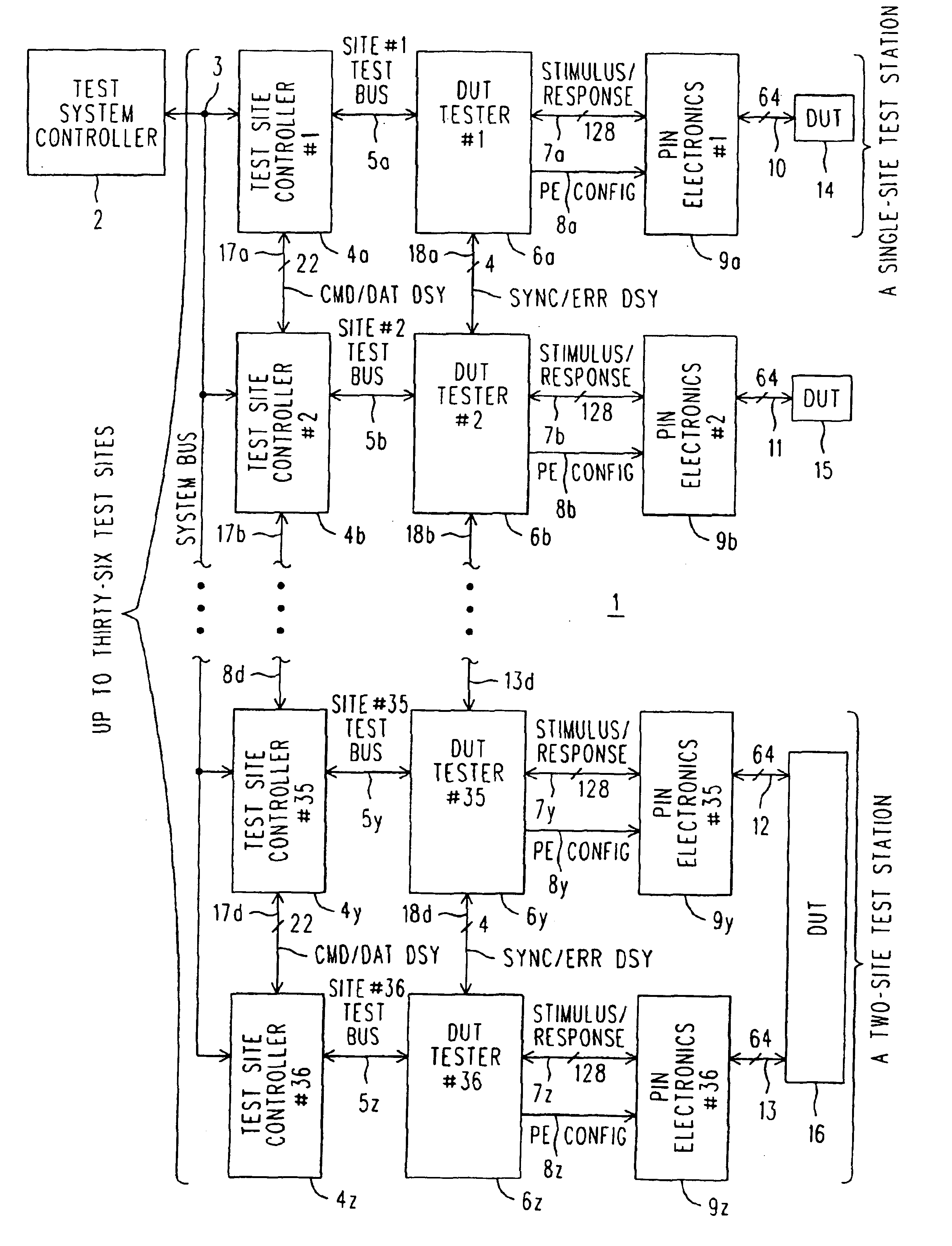

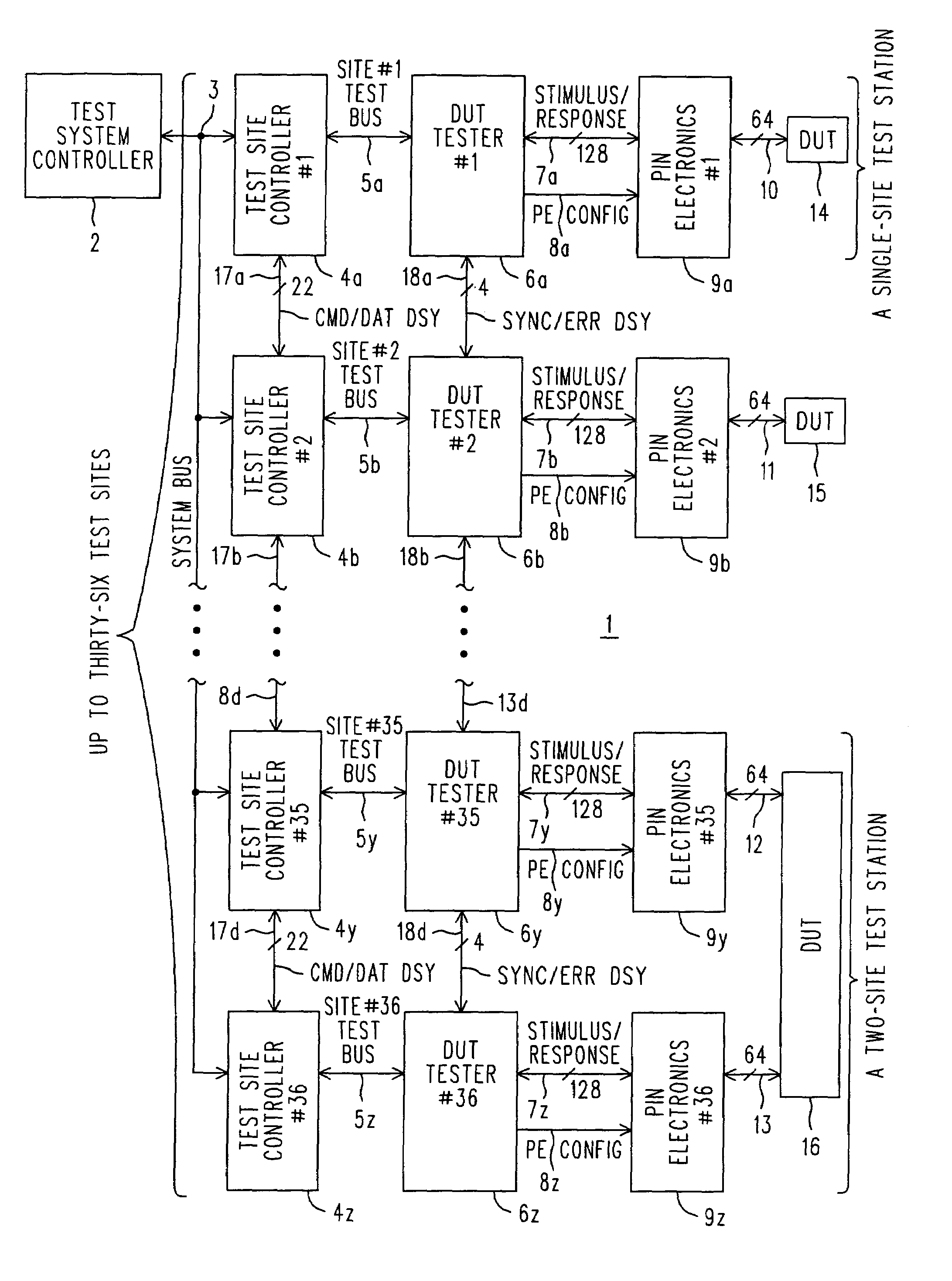

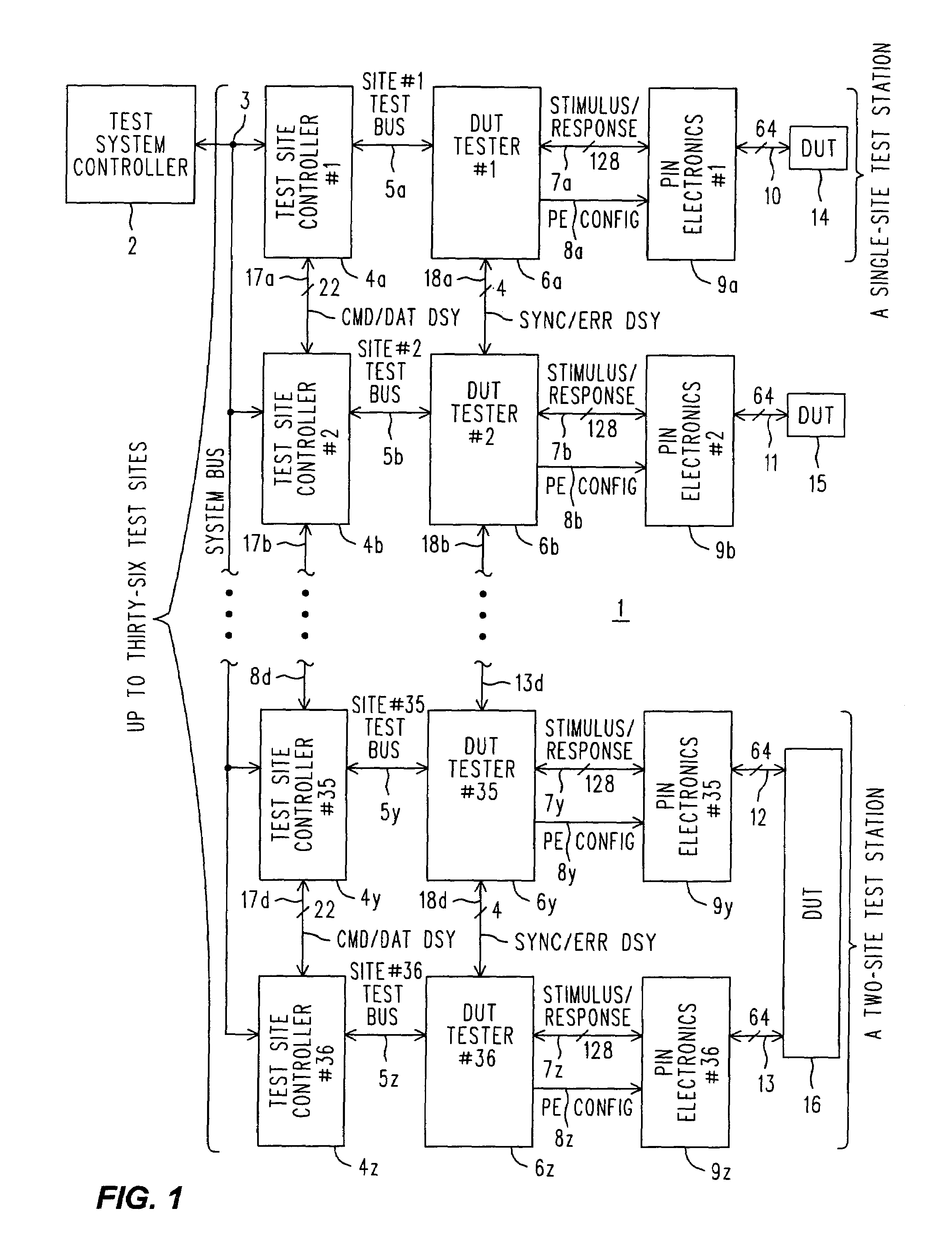

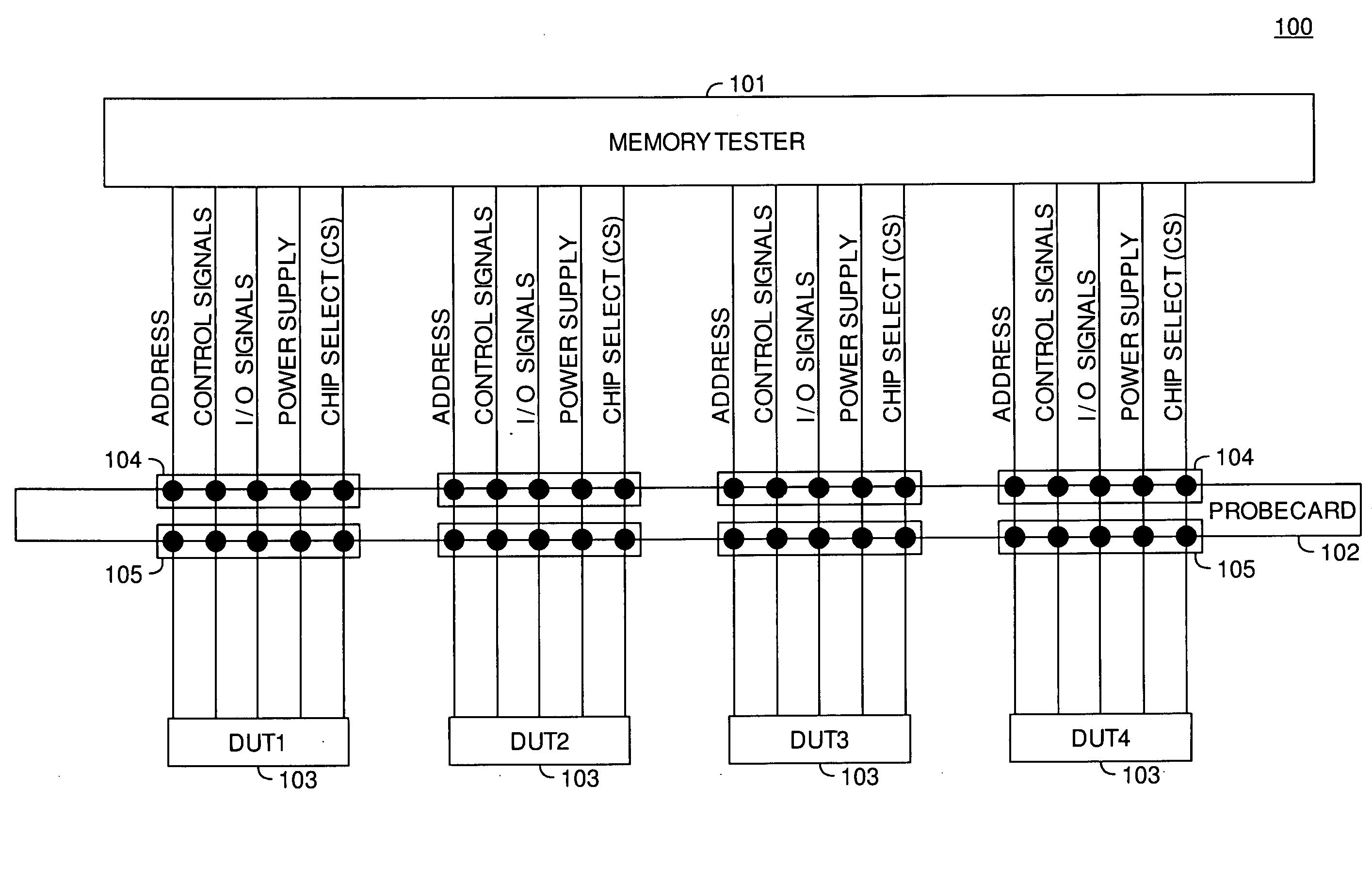

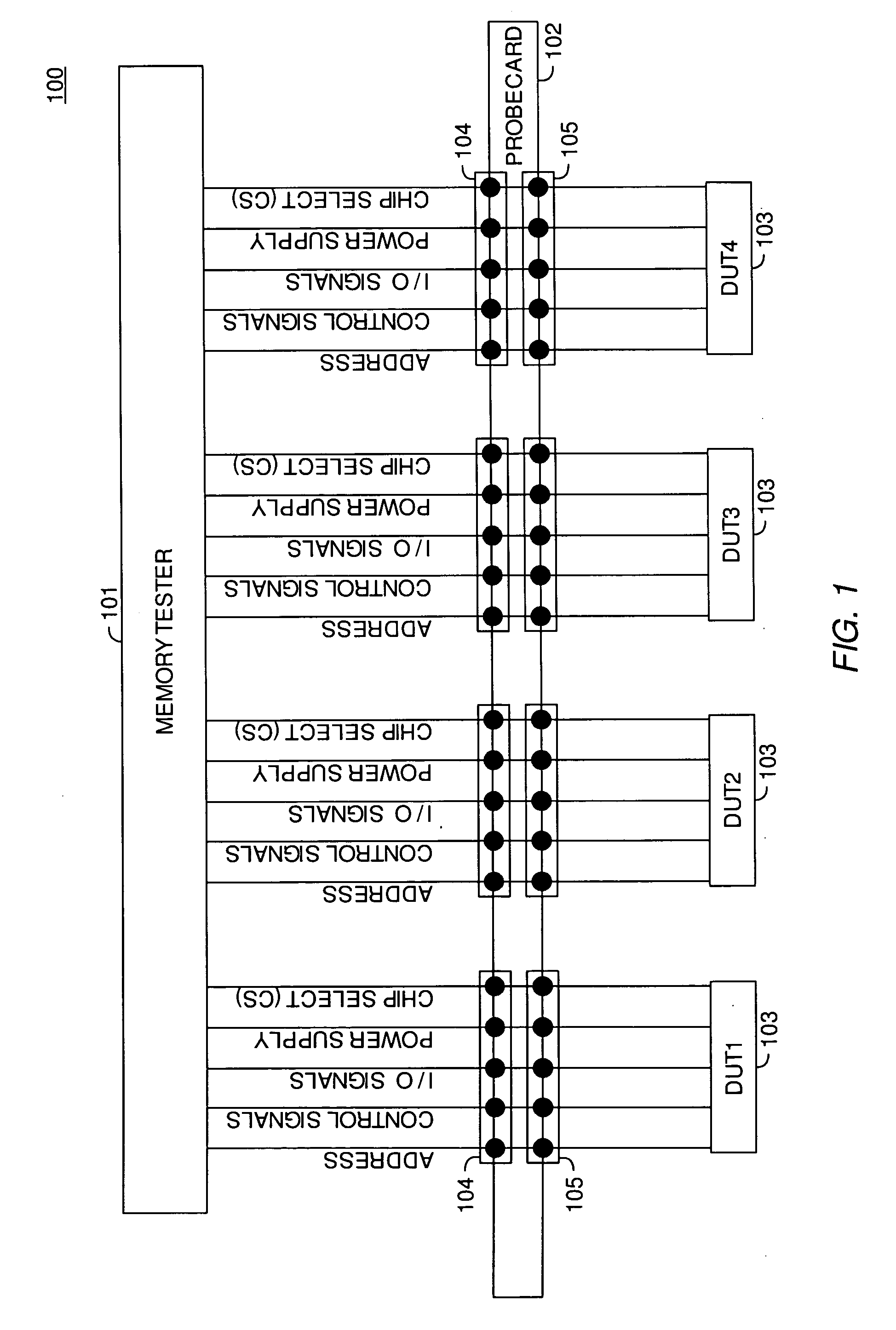

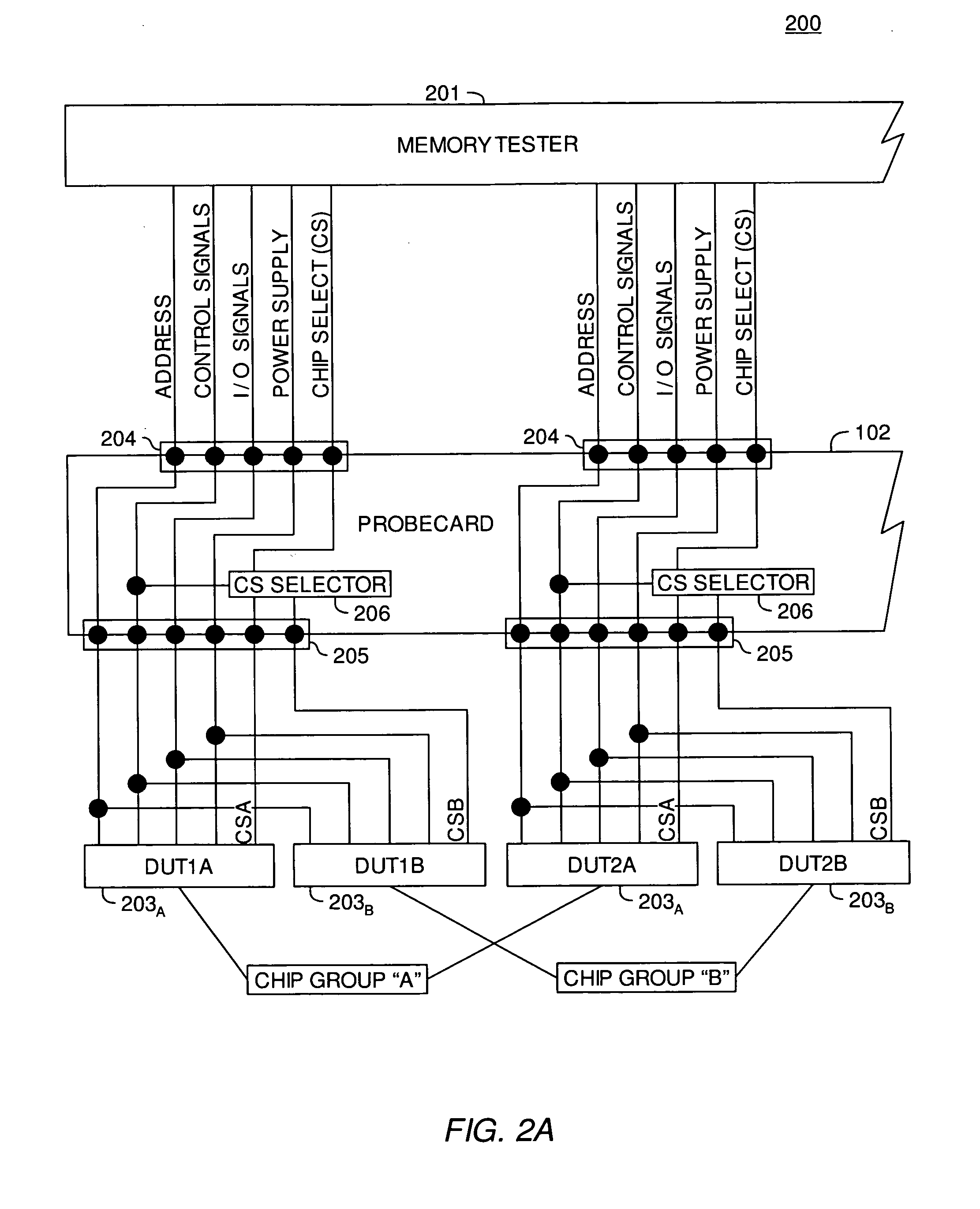

Test parallelism increase by tester controllable switching of chip select groups

InactiveUS20070165469A1Improve parallelismImprove the level ofElectrical testingDigital storageProbe cardMemory tester

Embodiments of the invention generally provide methods and systems for increasing the level of parallelism in testing memory devices. A set of test signals provided by a memory tester may be shared by two or more devices under test. A chip selector may be used to select at least one or all the devices sharing a given set of test signals. By sharing test signals between multiple devices, the level of parallel testing may be increased without increasing the pin count and complexity of memory testers and probe cards.

Owner:POLARIS INNOVATIONS

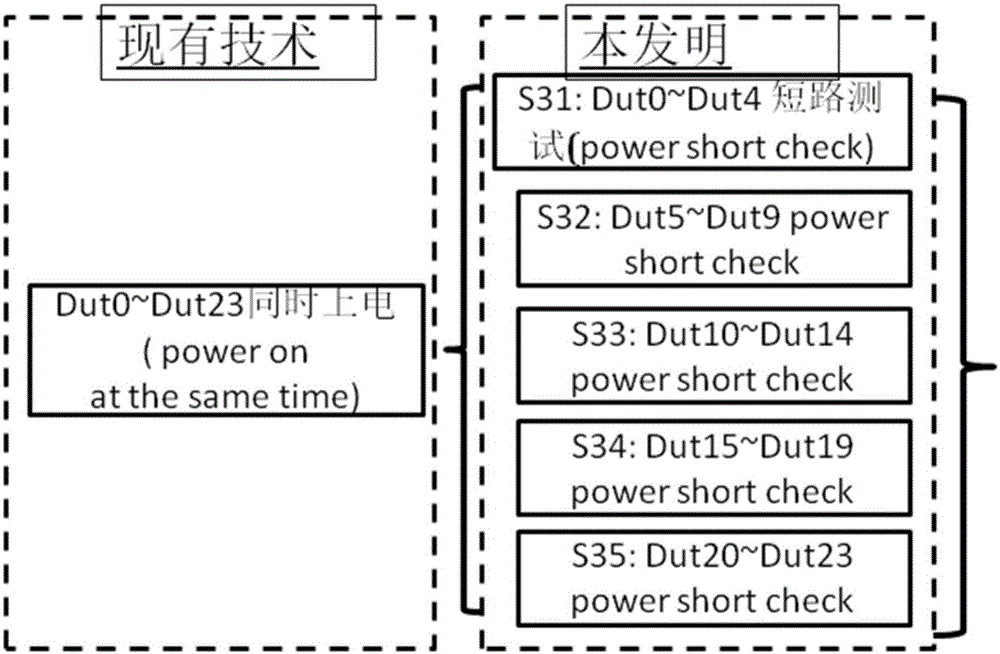

Memory wafer test method and memory tester

ActiveCN105070320AAvoid large leakage current damageAvoid damageStatic storageMemory chipShort-circuit test

The invention provides a memory wafer test method and a memory tester. According to the test method, before wafer probing such as function test is performed, firstly, a simultaneous-test memory chip on a wafer is subjected to grouping short-circuit test; whether the wafer fails or not is judged; the memory tester only starts after the wafer passes the short-circuit test; and the wafer probing is performed, so that the condition that a probe card and the like can be damaged by heavy leakage current of a failed wafer when the tester is directly used for probing on the failed wafer is avoided; meanwhile, a damaged chip can be found and removed as early as possible; the average test time of the wafer test is reduced; and the test cost is reduced. The memory tester provided by the invention is additionally provided with a grouping management unit; the grouping management unit can perform probe grouping on the probe card; and pins of a tested memory chip in the group are grounded for short-circuit test, so that the tester can be protected, and the condition that the probe card and the like can be damaged by great leakage current of the failed wafer when the tester is directly used for probing on the failed wafer is avoided.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

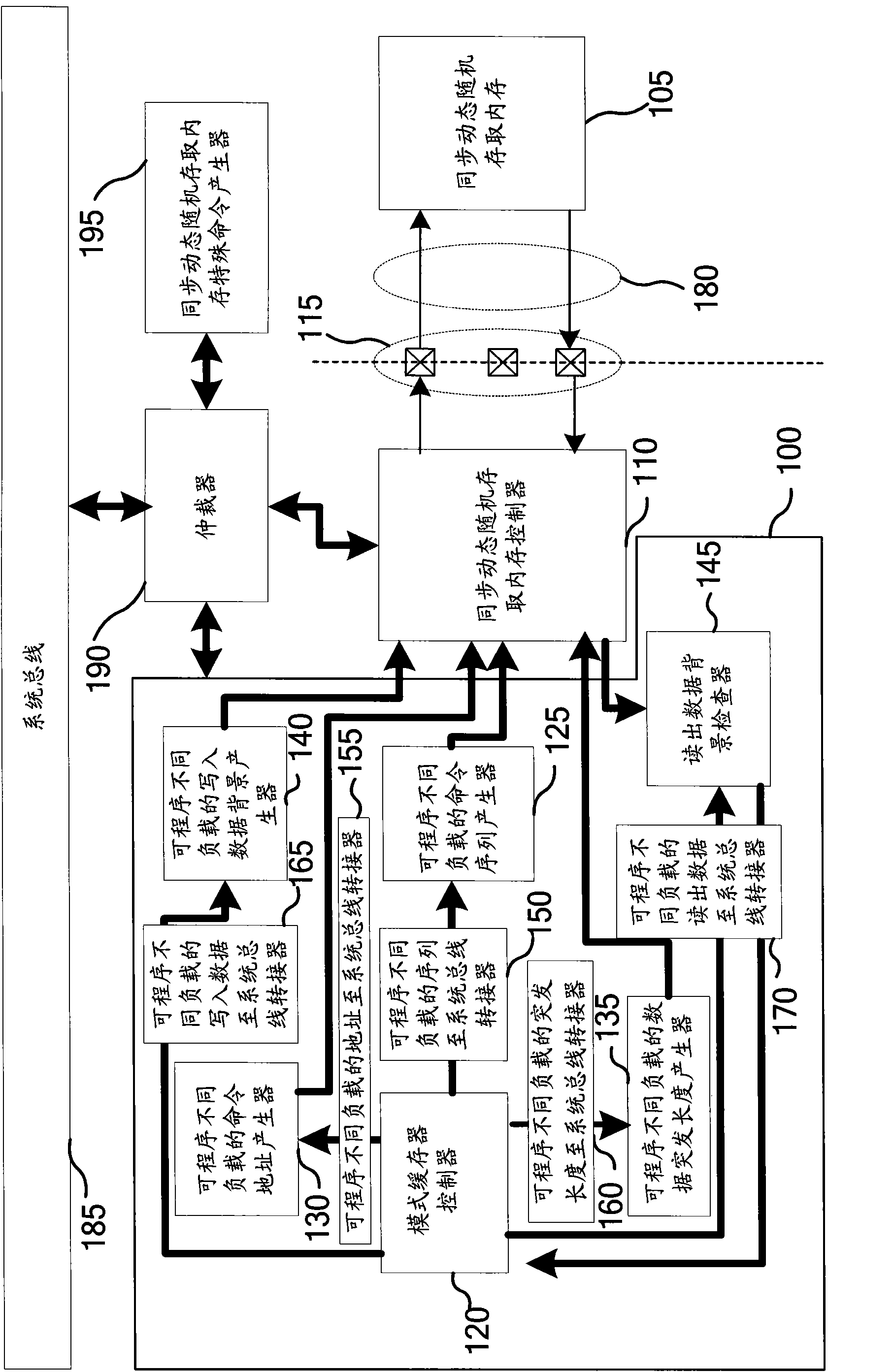

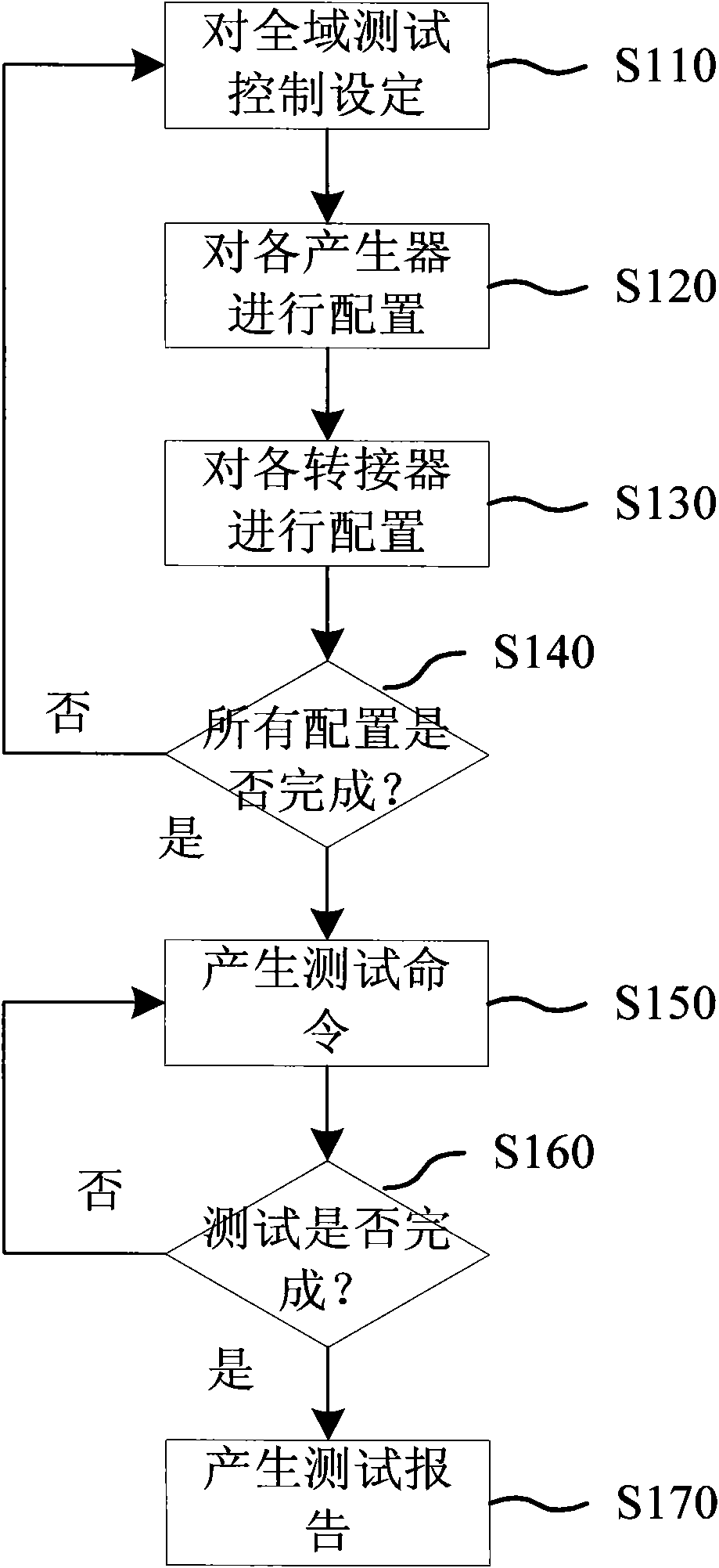

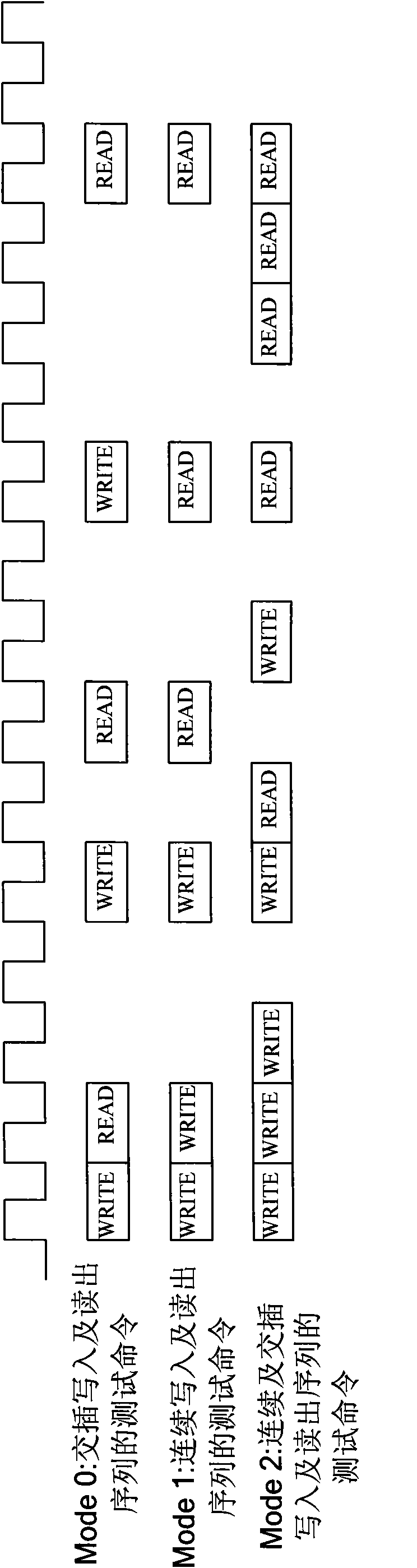

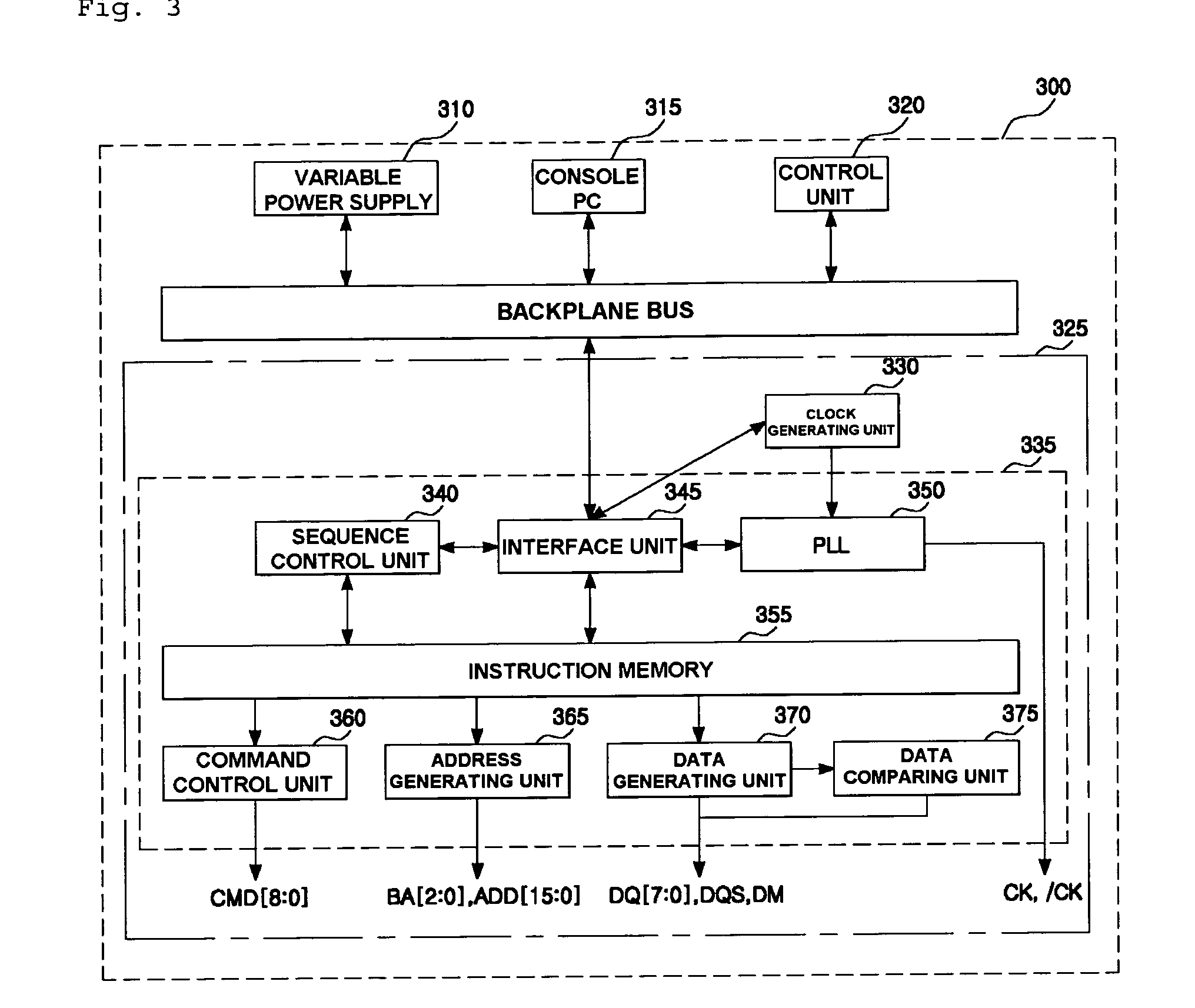

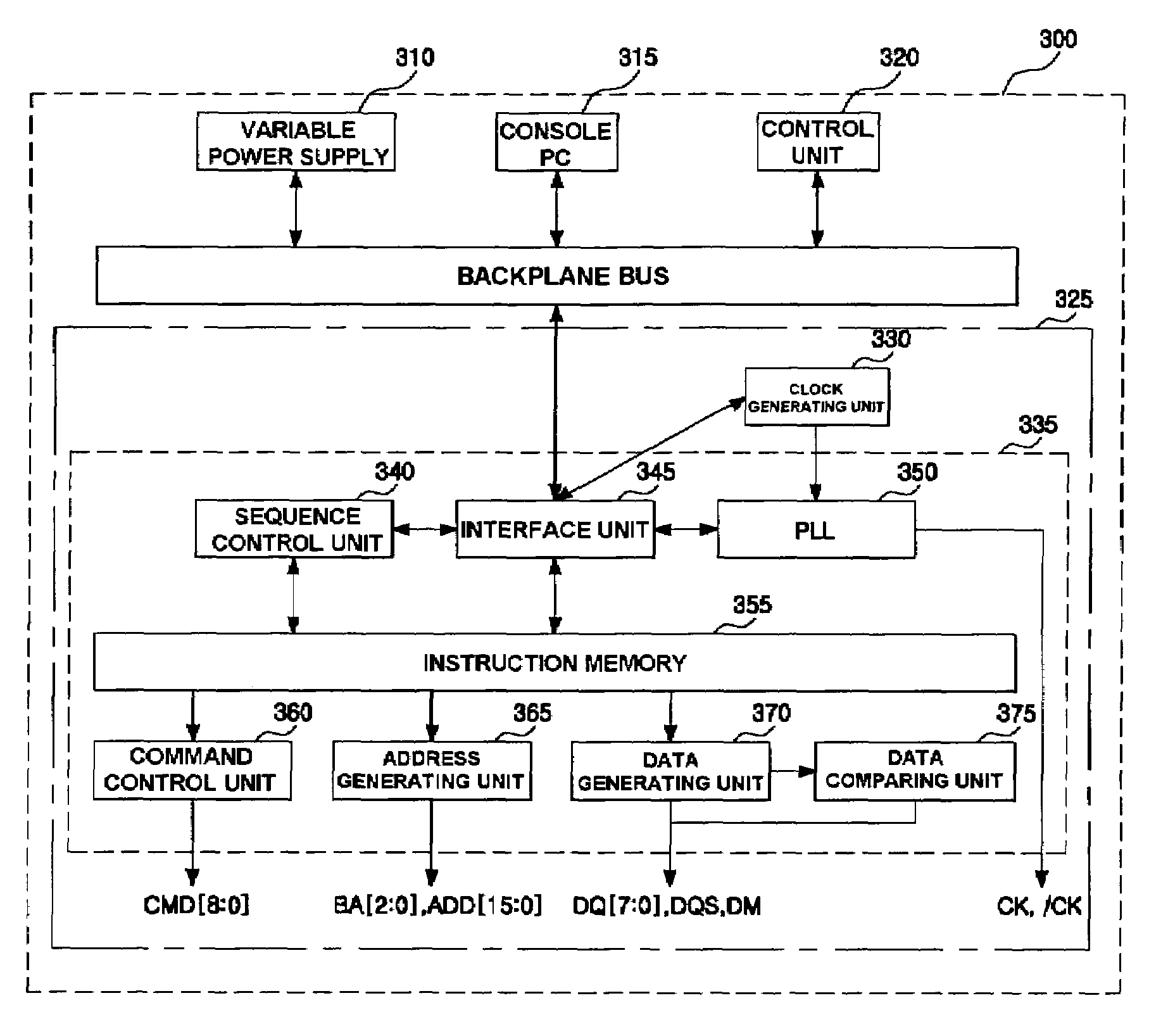

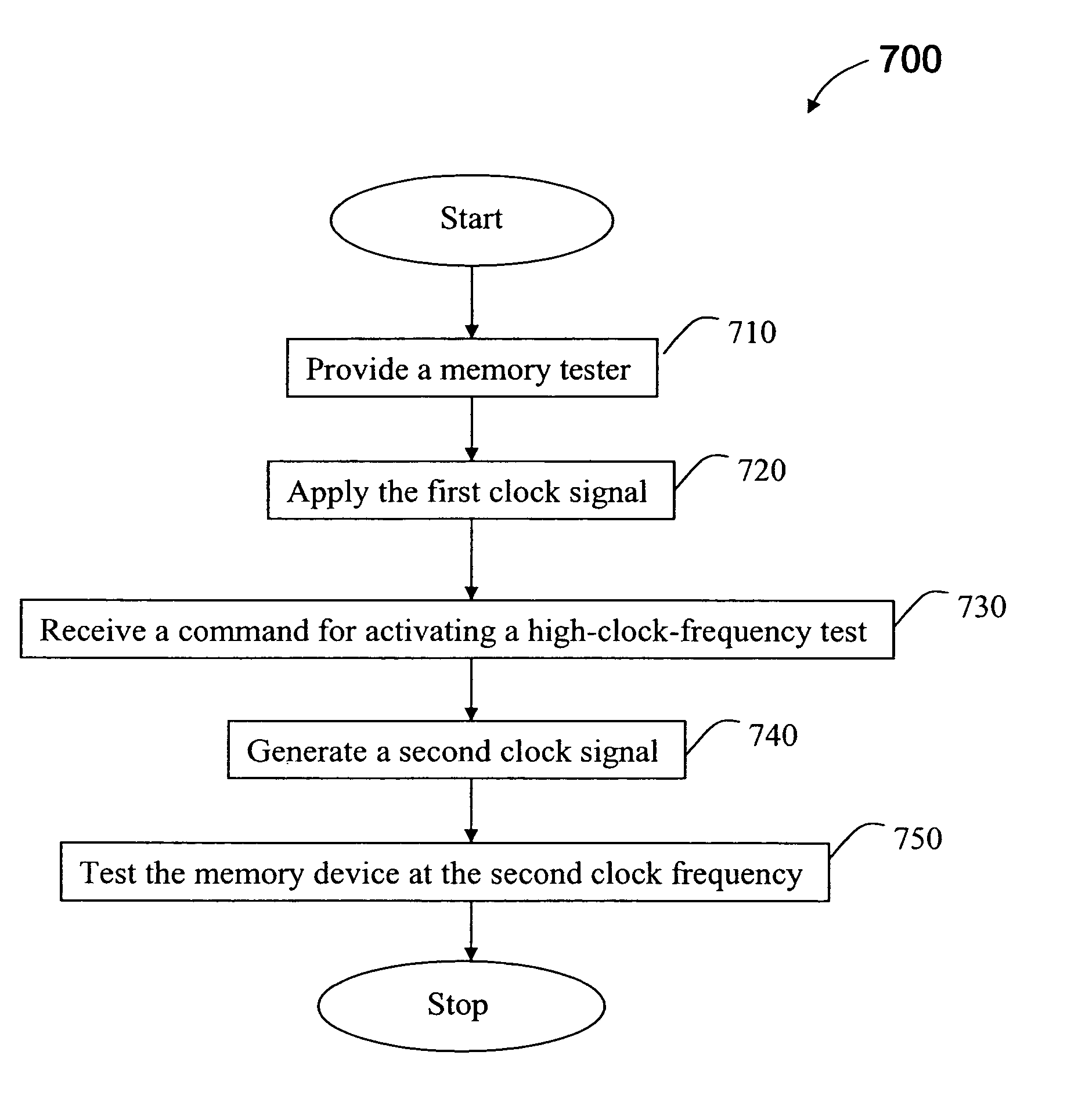

Memory test system

InactiveCN101916593AImprove trustworthinessSolve test problemsStatic storageHigh speed memoryTest sample

The invention provides a memory test system, which can solve a test problem caused by a high-speed memory interface and a synchronous dynamic random access memory (SDRAM). Each hardware mode in the memory test system can be set independently so as to combine into diversity of test samples, which can execute programmable test of difficult loads, practical example test and write-in feedback test. Simultaneously the write-in feedback test of the memory test system can independently test a memory controller, so that the system can test a memory controller which is embedded into an integrated circuit without communicating with an entity SDRAM. In addition, in a validation stage of the integrated circuit, the technology of the invention can be used for analyzing and distinguishing whether a problem point is in or out of the integrated circuit, and testing a write-in command and a read-out command.

Owner:SUNPLUS TECH CO LTD

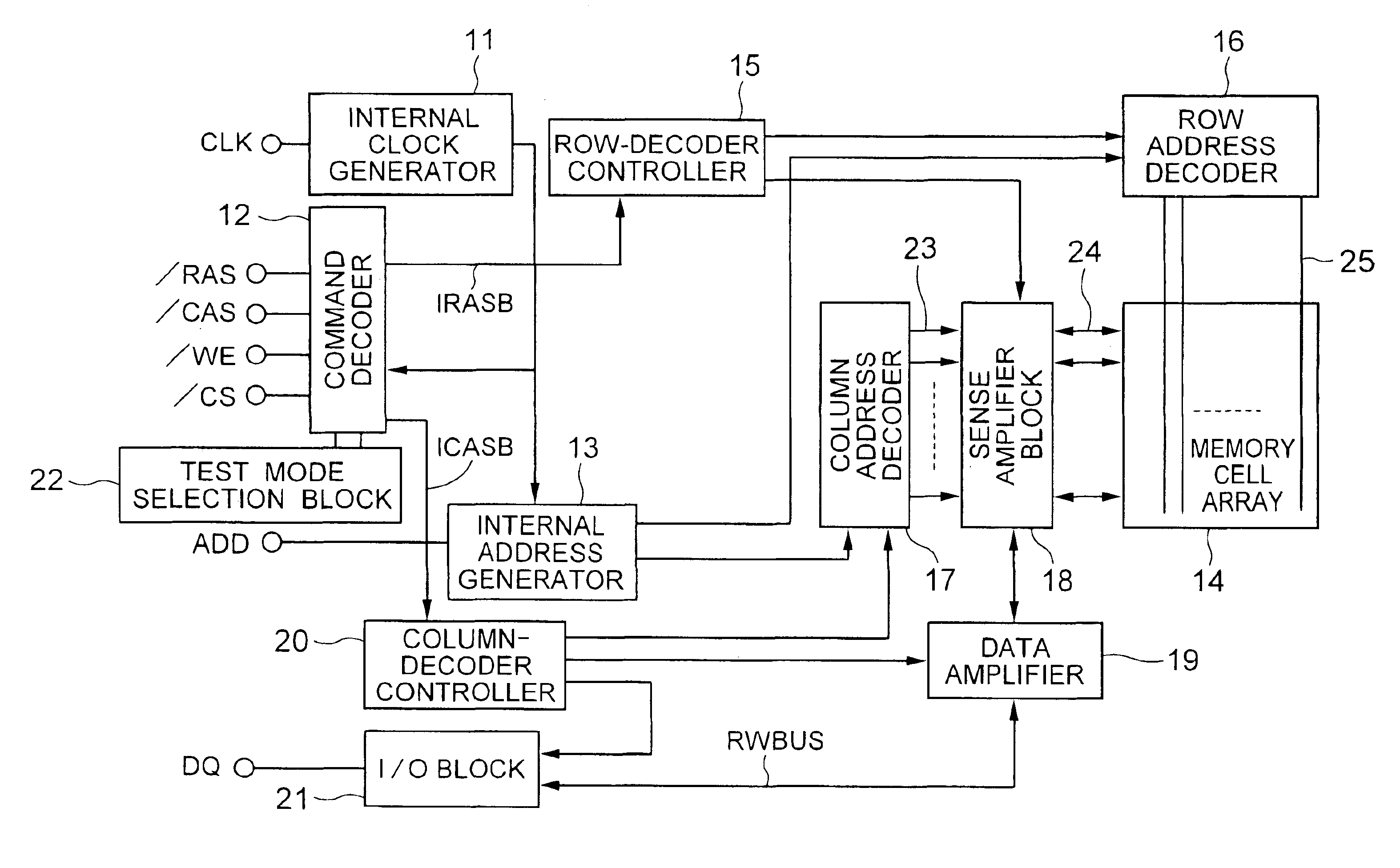

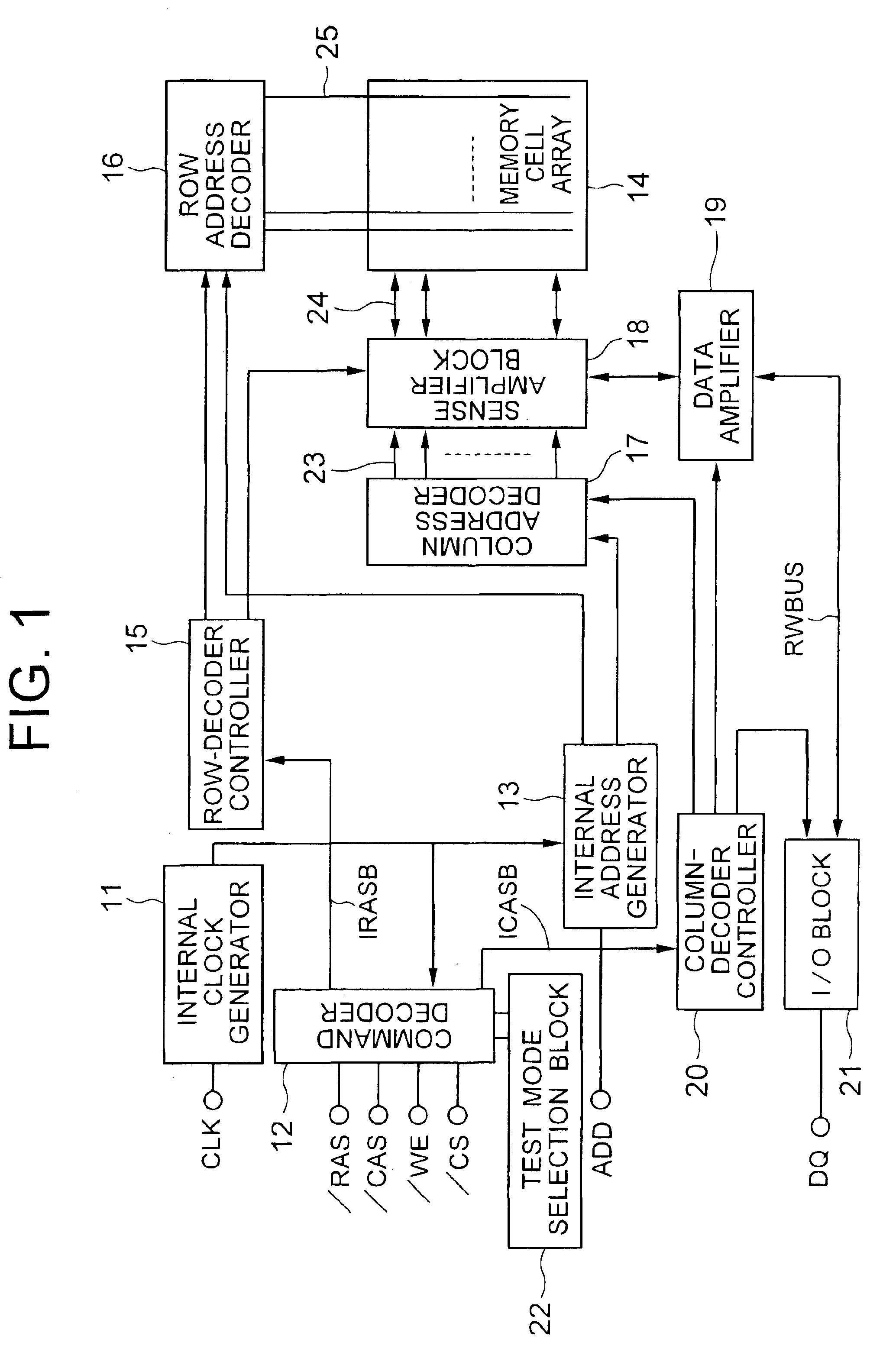

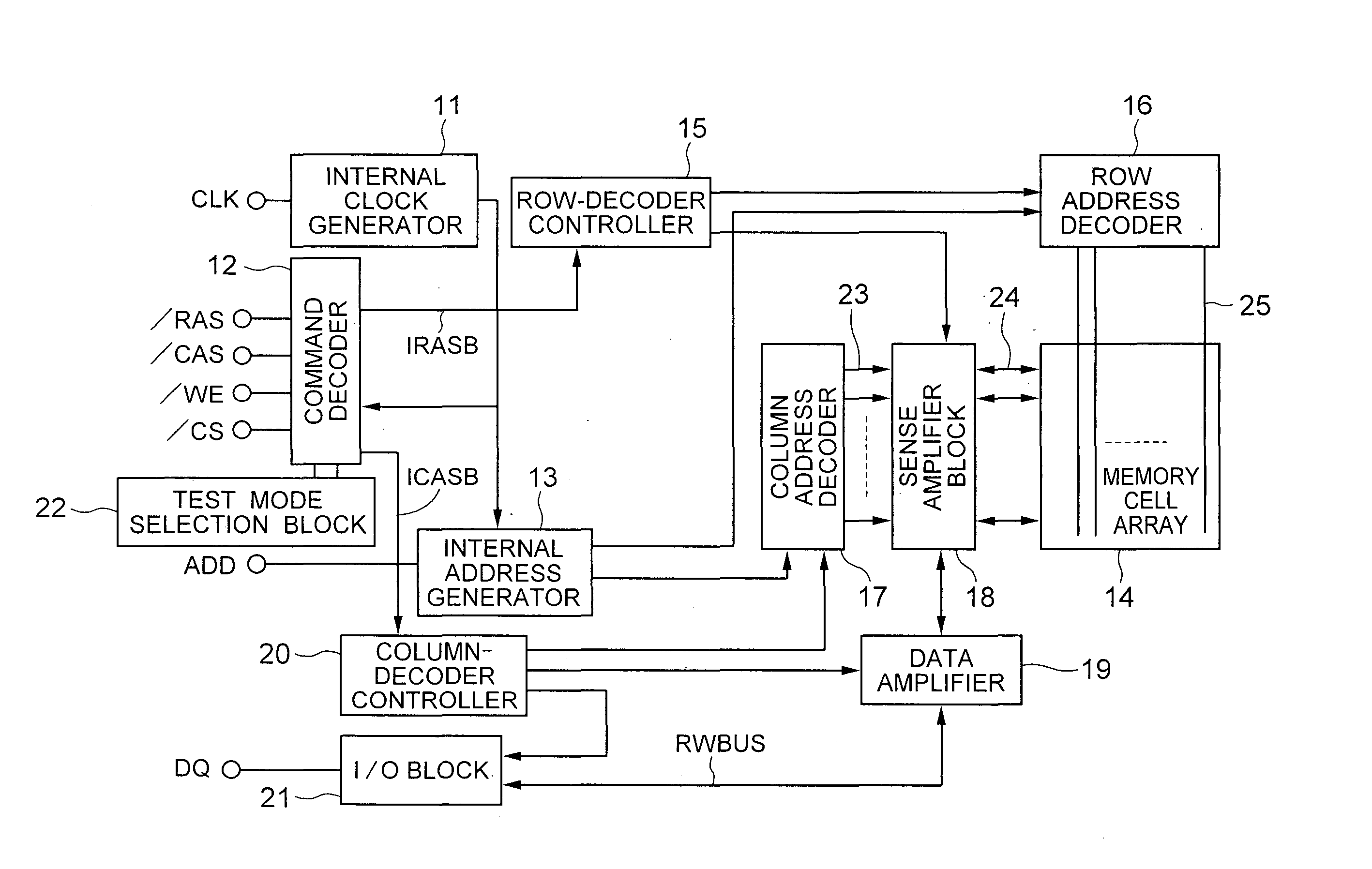

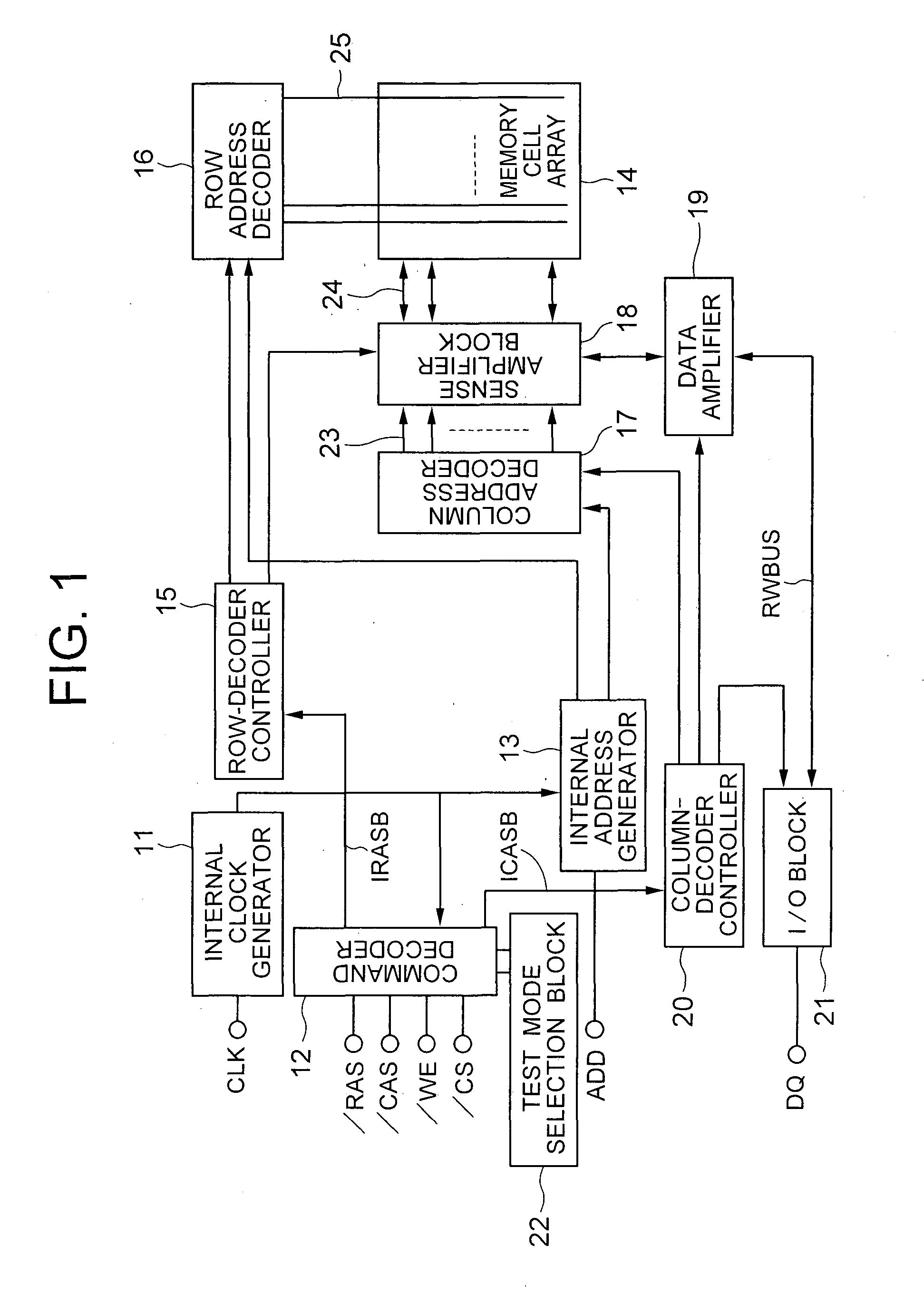

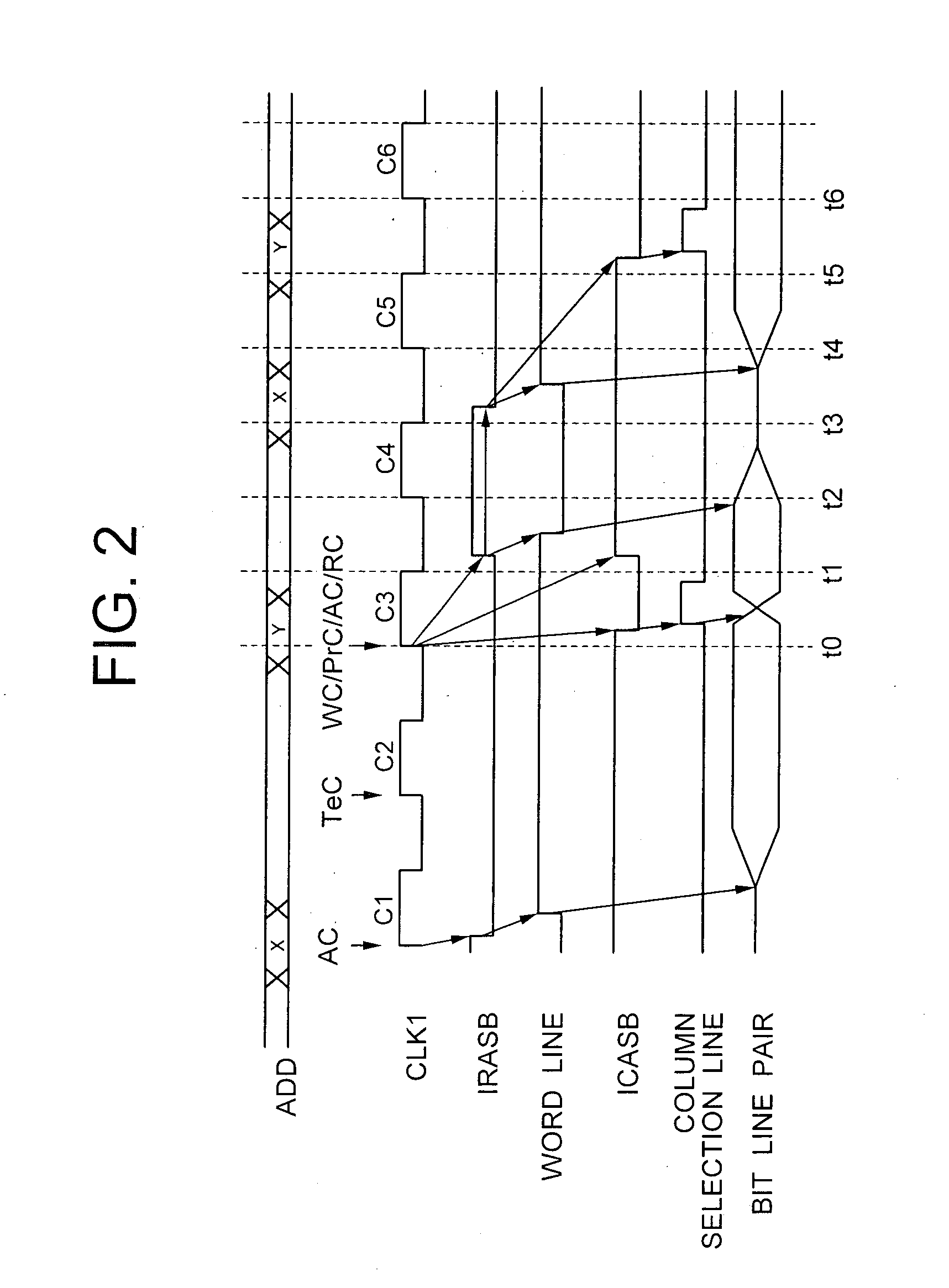

Synchronous semiconductor memory device having a desired-speed test mode

InactiveUS6868020B2Without increasing the time length needed for the memory testElectronic circuit testingDigital storageLow speedMemory tester

A synchronous DRAM has a test mode wherein a specified external signal is input to a command decoder of the DRAM. The command decoder generates a plurality of internal commands including activating signal for selecting a word line, write signal, precharge signal, another activating signal and read signal at consecutive timings which do not depend on an external clock signal. A low-speed memory tester can be used for testing the high-speed synchronous DRAM.

Owner:LONGITUDE SEMICON S A R L

Synchronous semiconductor memory device having a desired-speed test mode

A synchronous DRAM has a test mode wherein a specified external signal is input to a command decoder of the DRAM. The command decoder generates a plurality of internal commands including activating signal for selecting a word line, write signal, precharge signal, another activating signal and read signal at consecutive timings which do not depend on an external clock signal. A low-speed memory tester can be used for testing the high-speed synchronous DRAM.

Owner:LONGITUDE SEMICON S A R L

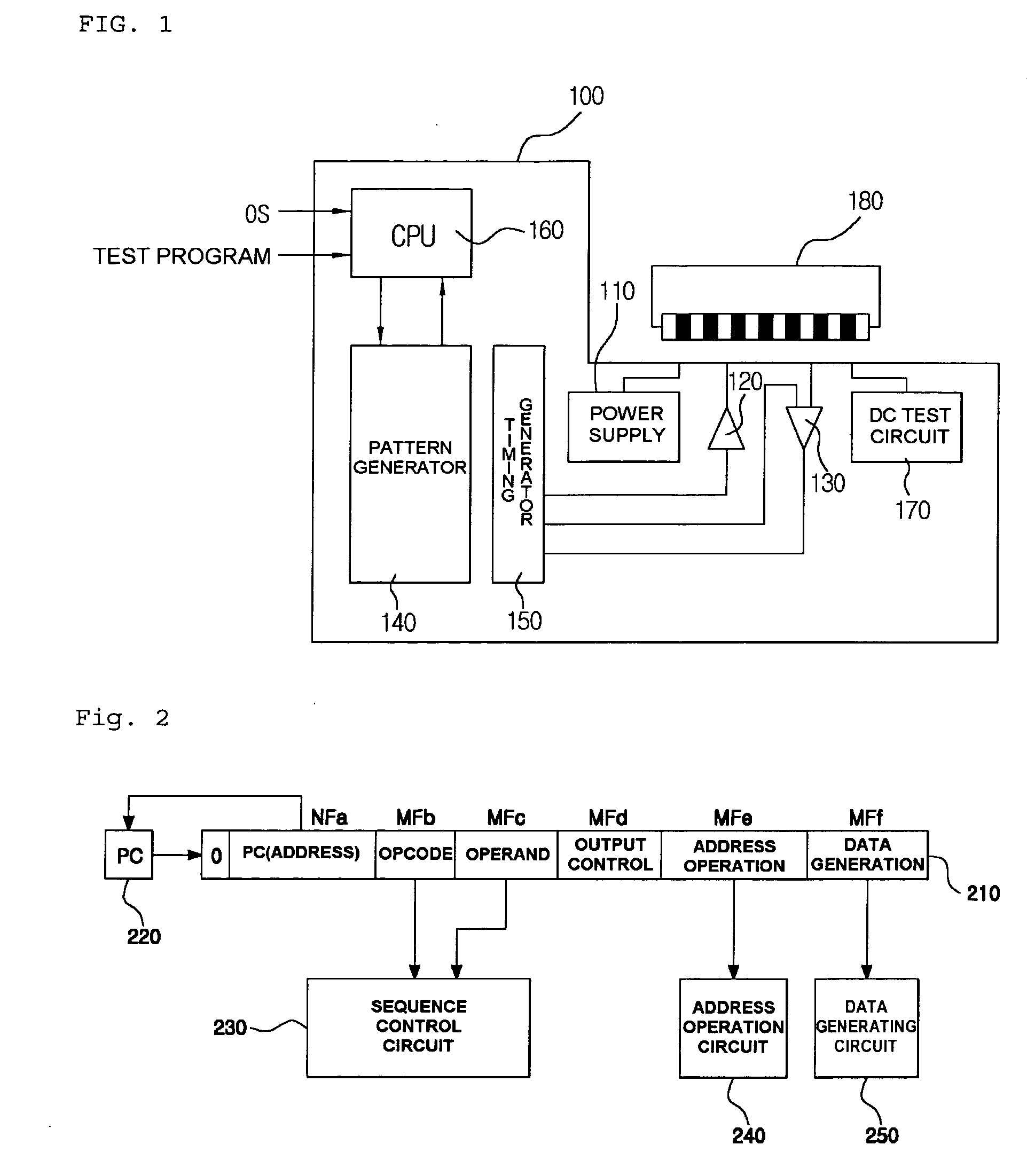

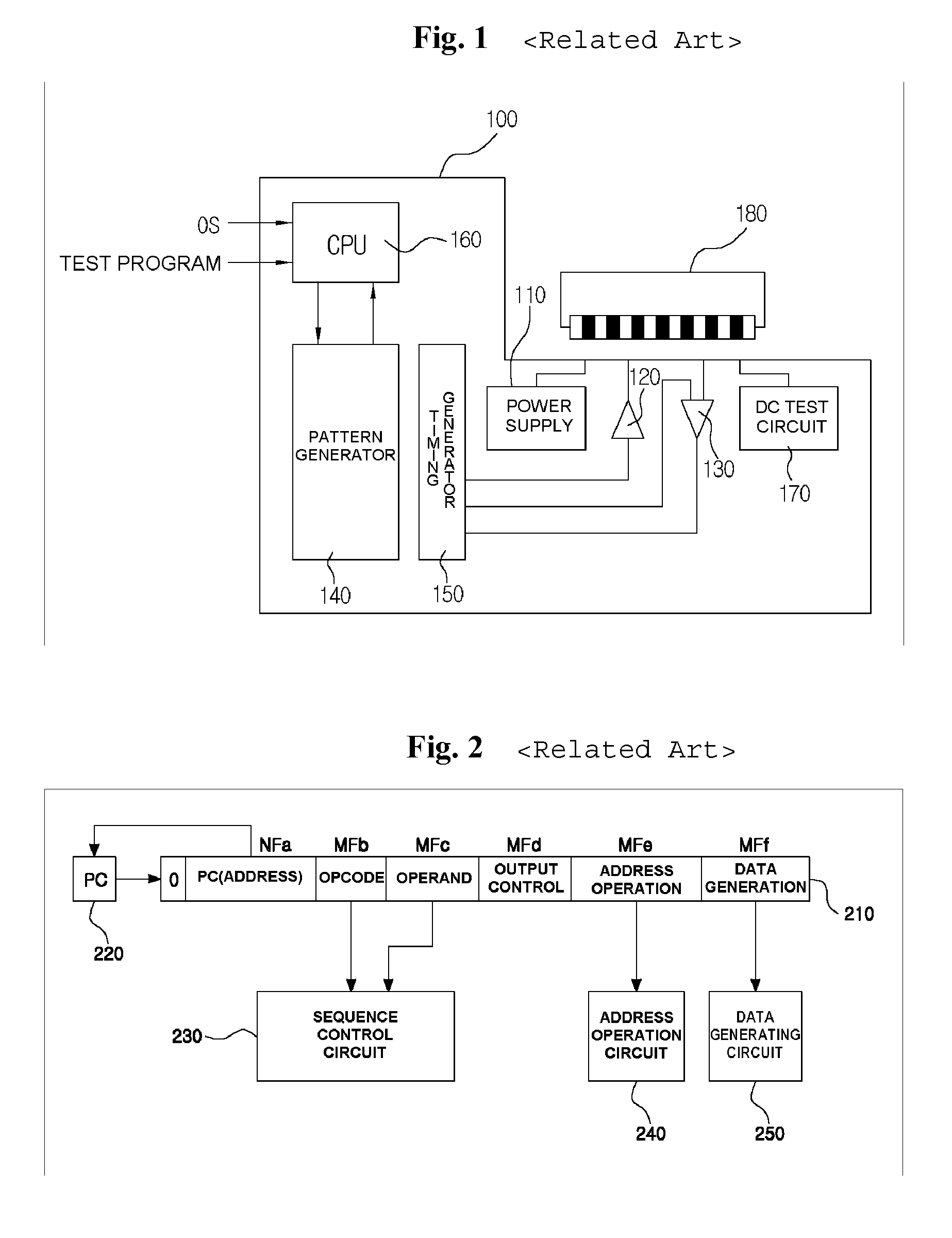

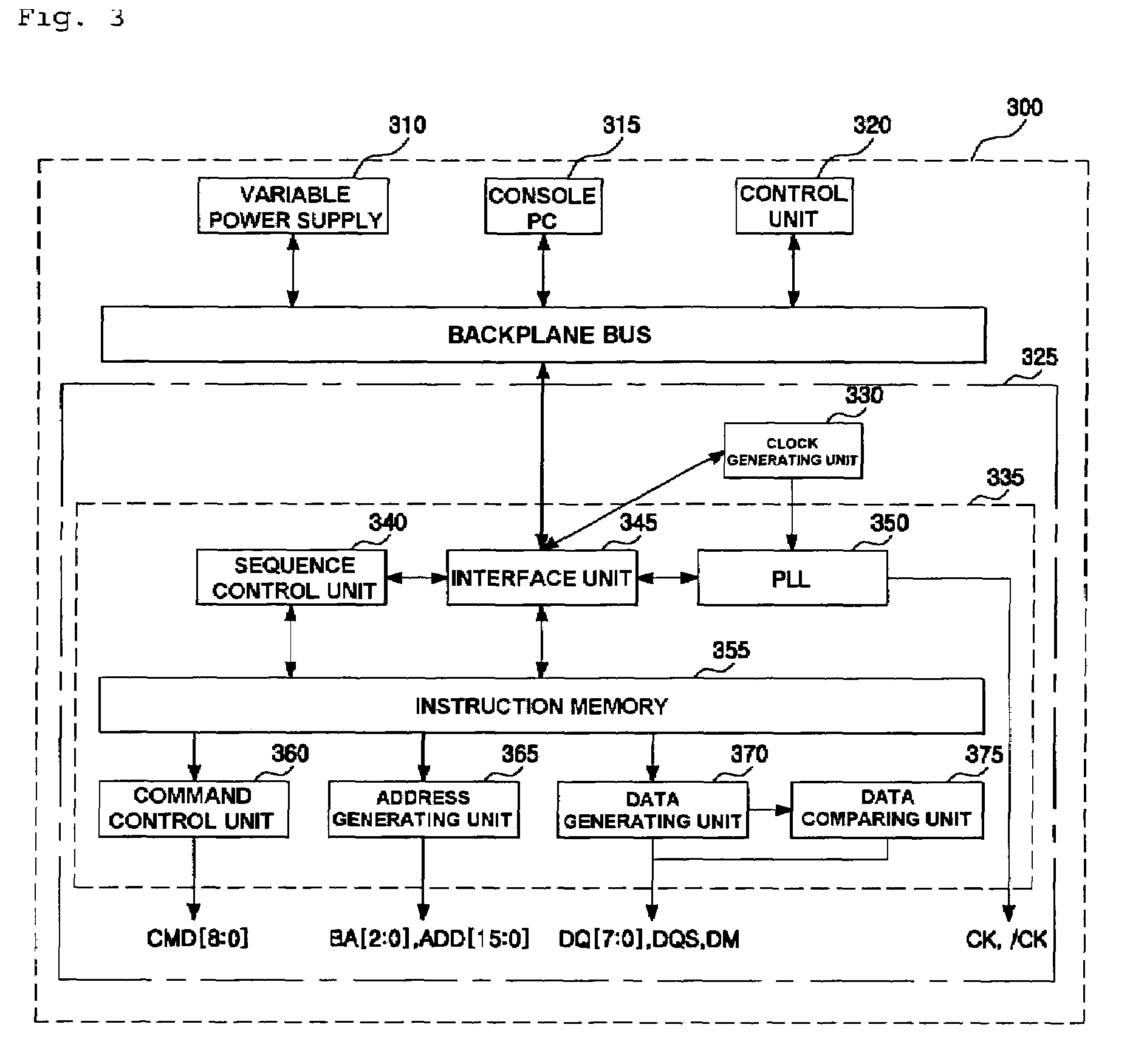

Algorithm pattern generator for testing a memory device and memory tester using the same

Disclosed is an algorithm pattern generator for testing a memory device. It has a configuration which can optimize a configuration of a memory tester including an address scrambling and a data scrambling in the memory tester for carrying out a test at a memory device module level or a component level.

Owner:UNITEST

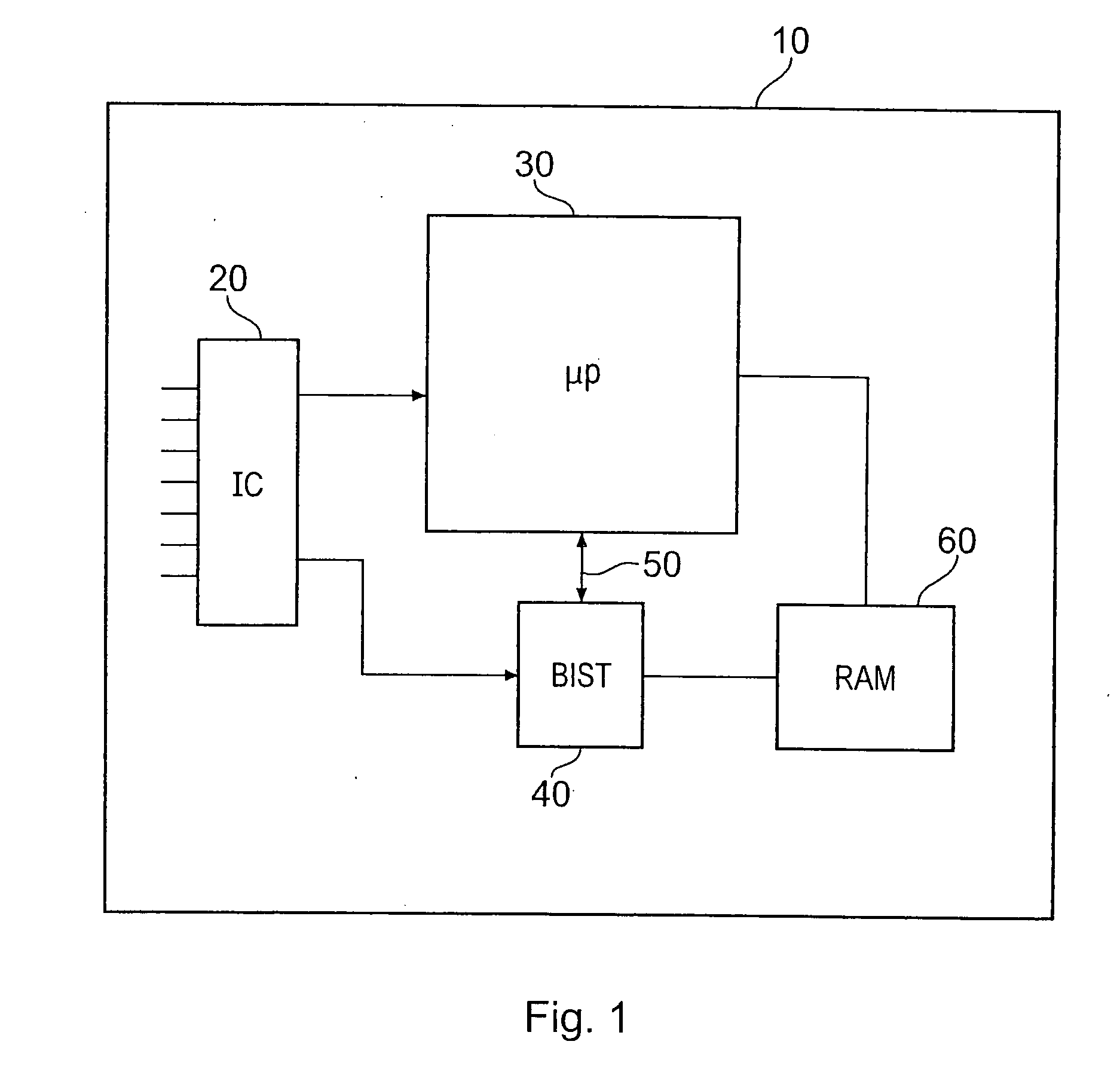

Memory testing

ActiveUS20080010567A1Shorten the timePotential latencyElectronic circuit testingFunctional testingProcess logicMemory tester

This application discloses a data processing apparatus comprising: at least one memory; processing logic operable to perform data processing operations on data and operable to access said at least one memory; and memory testing logic operable to perform a transparent algorithm testing routine on said at least one memory, said data processing apparatus impeding said processing logic from accessing said at least one memory while said memory testing logic is performing said testing routine; wherein said processing logic and said memory testing logic are operable to detect a system event, said memory testing logic being operable when performing said testing routine to respond to detection of said system event by stopping said testing routine and restoring said at least one memory to an initial state, said initial state being a state it was in immediately prior to commencement of said testing routine, whereupon said data processing apparatus is operable to allow said processing logic to access said at least one memory.

Owner:ARM LTD

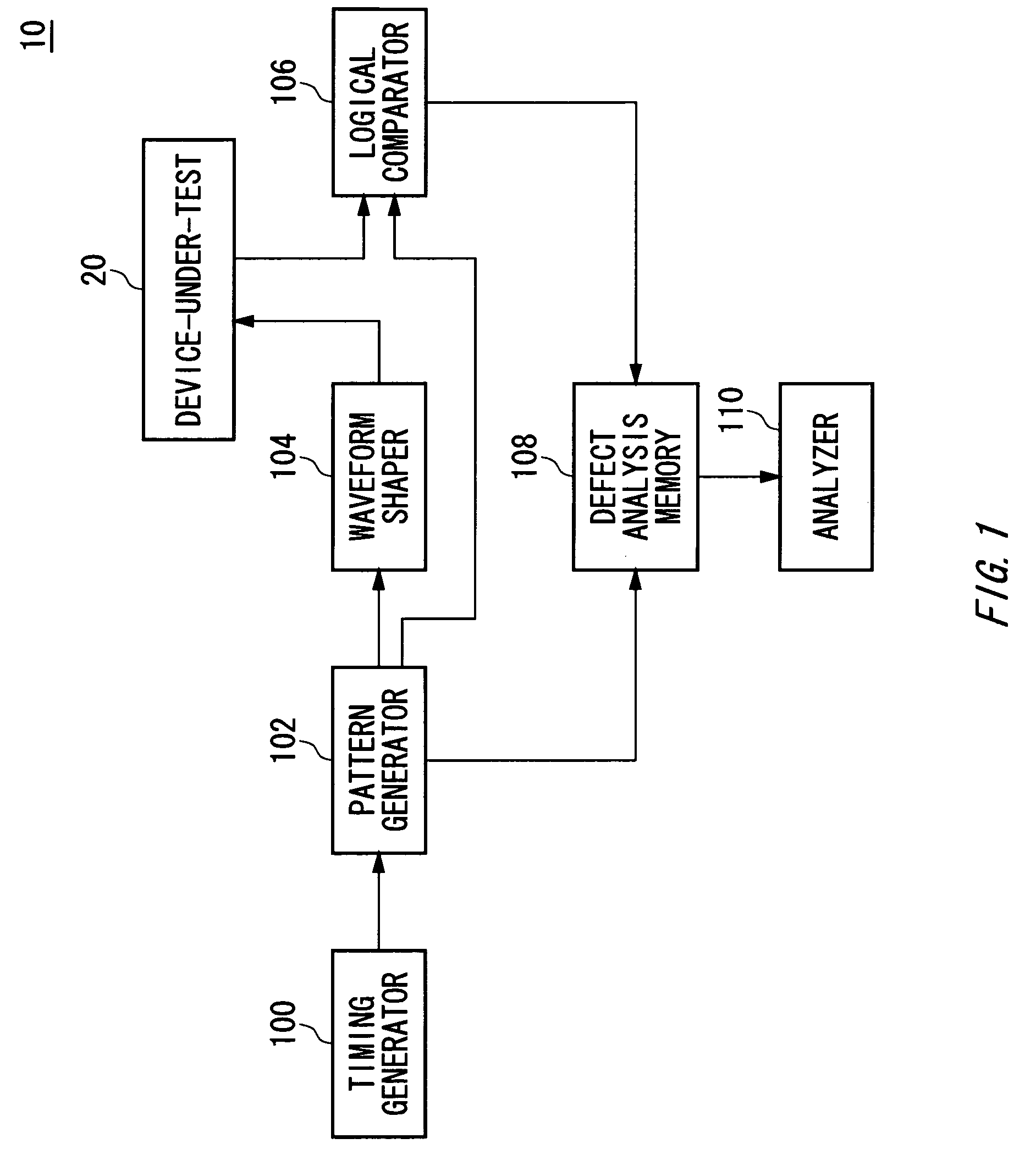

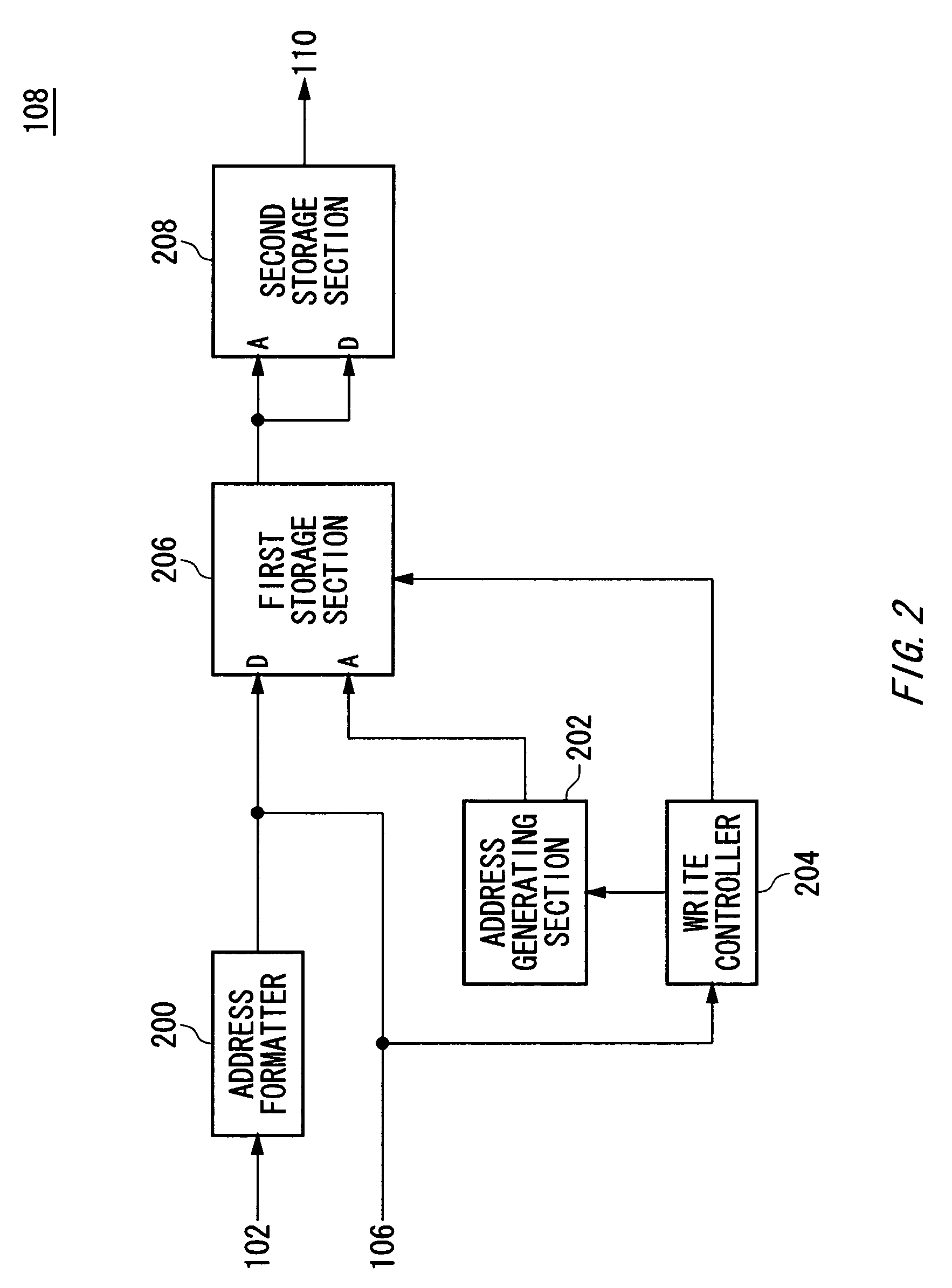

Memory tester having defect analysis memory with two storage sections

A test apparatus for testing a device-under-test includes: a pattern generator configured to generate an address signal, a test signal, and an expected value signal; a logical comparator configured to compare an output signal outputted from the device-under-test with the expected value signal. The logical comparator generates a fail signal when the output signal is different from the expected value signal; and a failure analysis memory configured to receive the address signal from the pattern generator and to receive the fail signal from the logical comparator. The failure analysis memory includes: a first storage section configured to store a fail address value that corresponds to the fail signal and a fail data value included in the fail signal as a set of data; and a second storage section configured to read the set of data from the first storage section and to store the fail data value.

Owner:ADVANTEST CORP

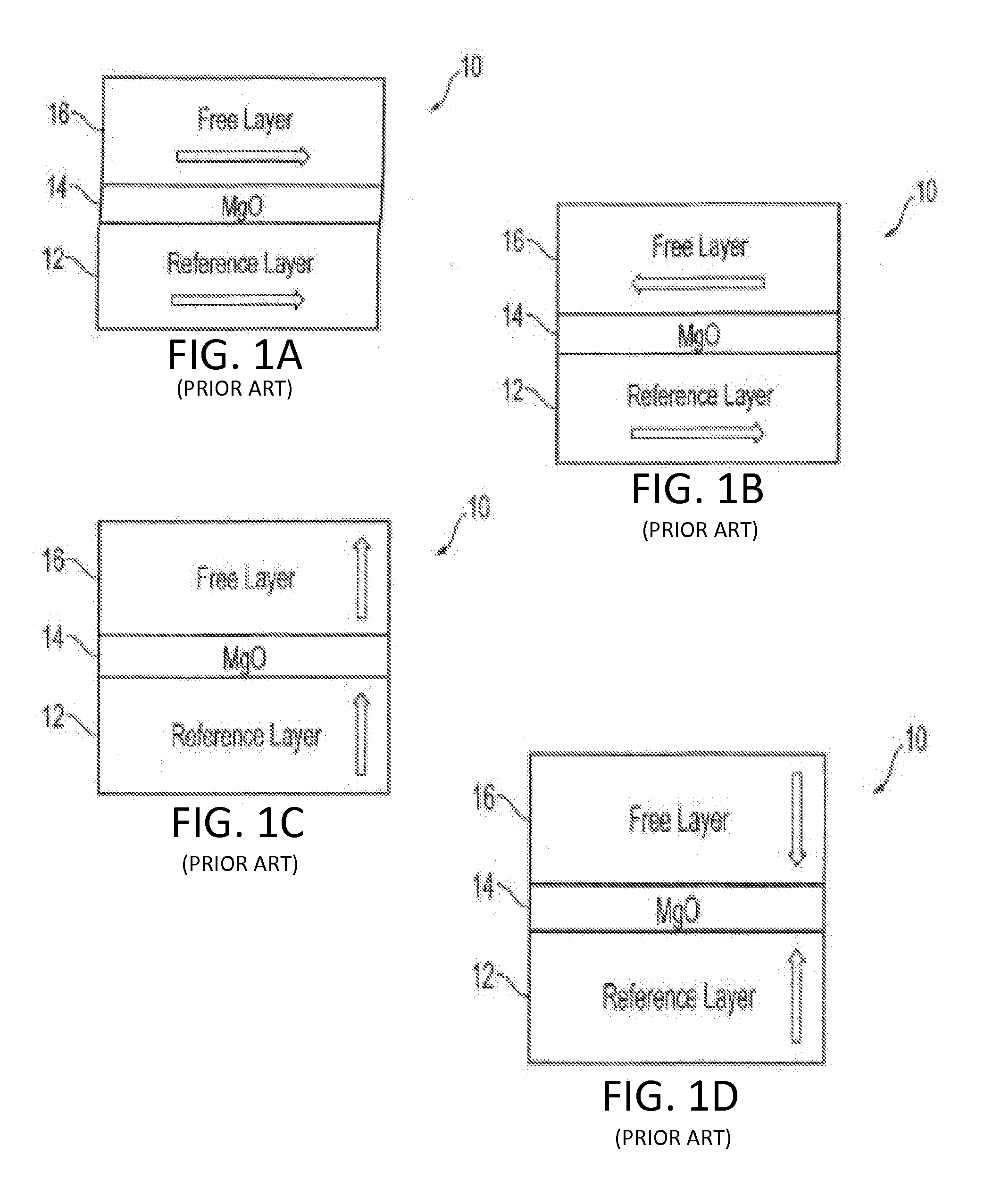

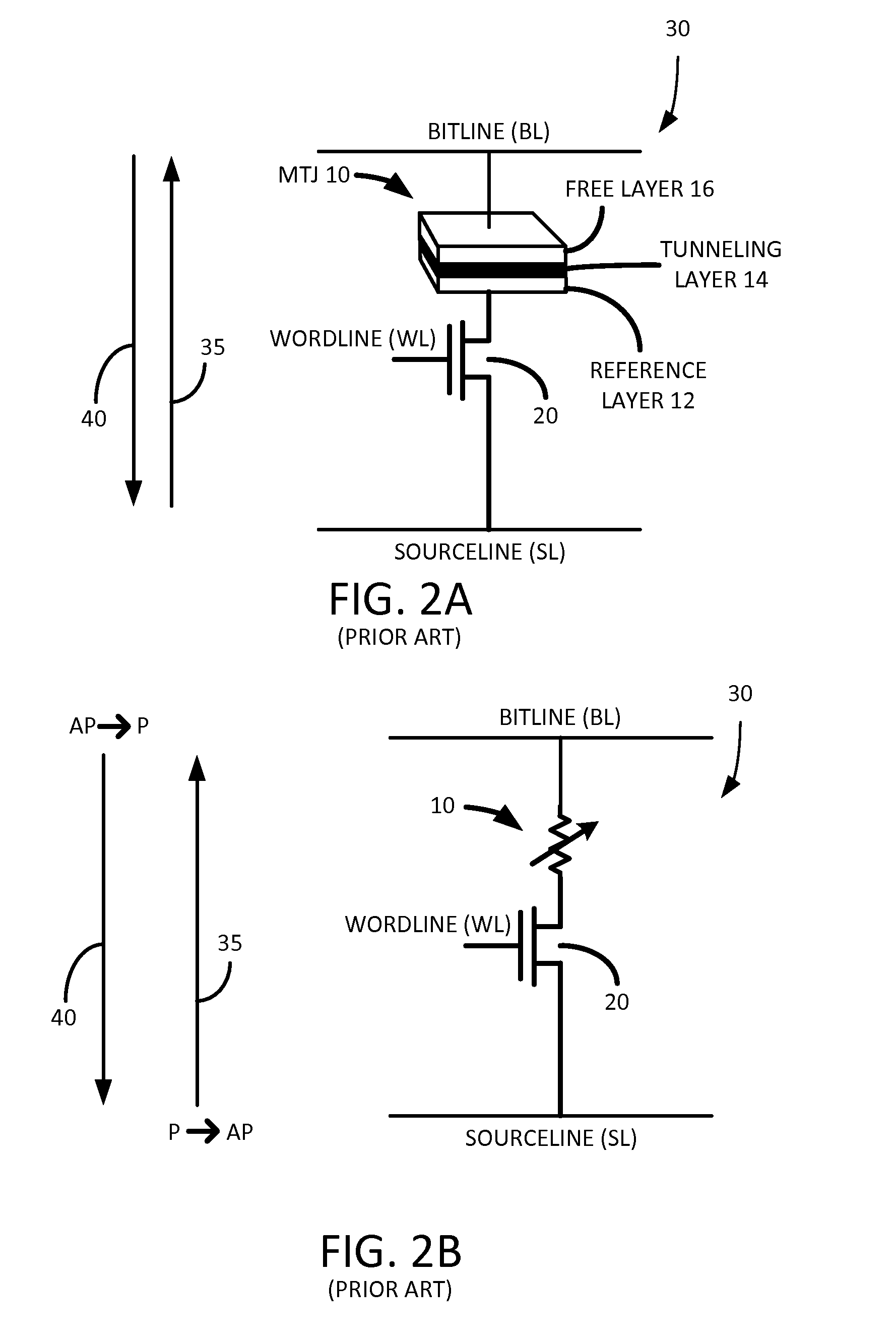

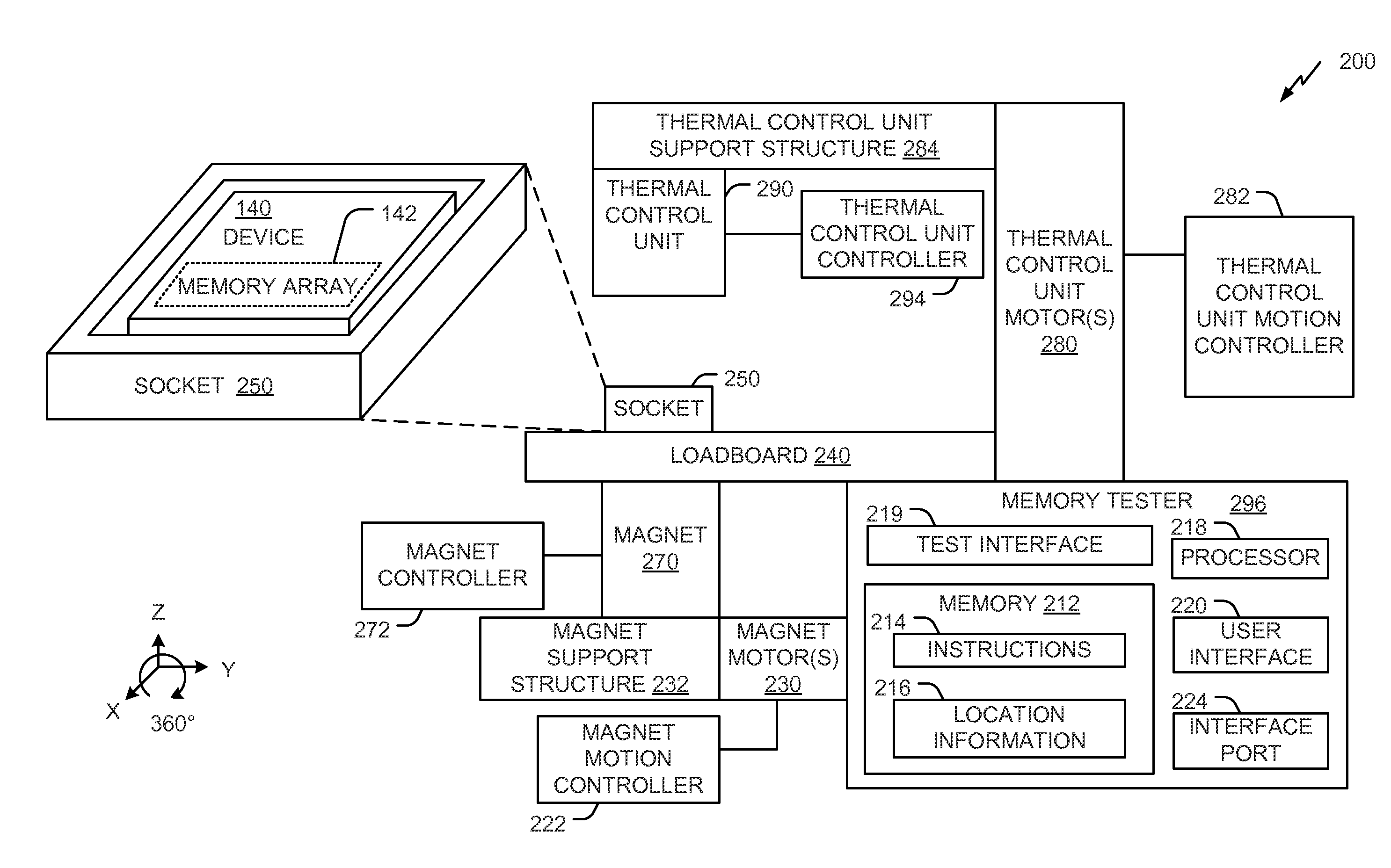

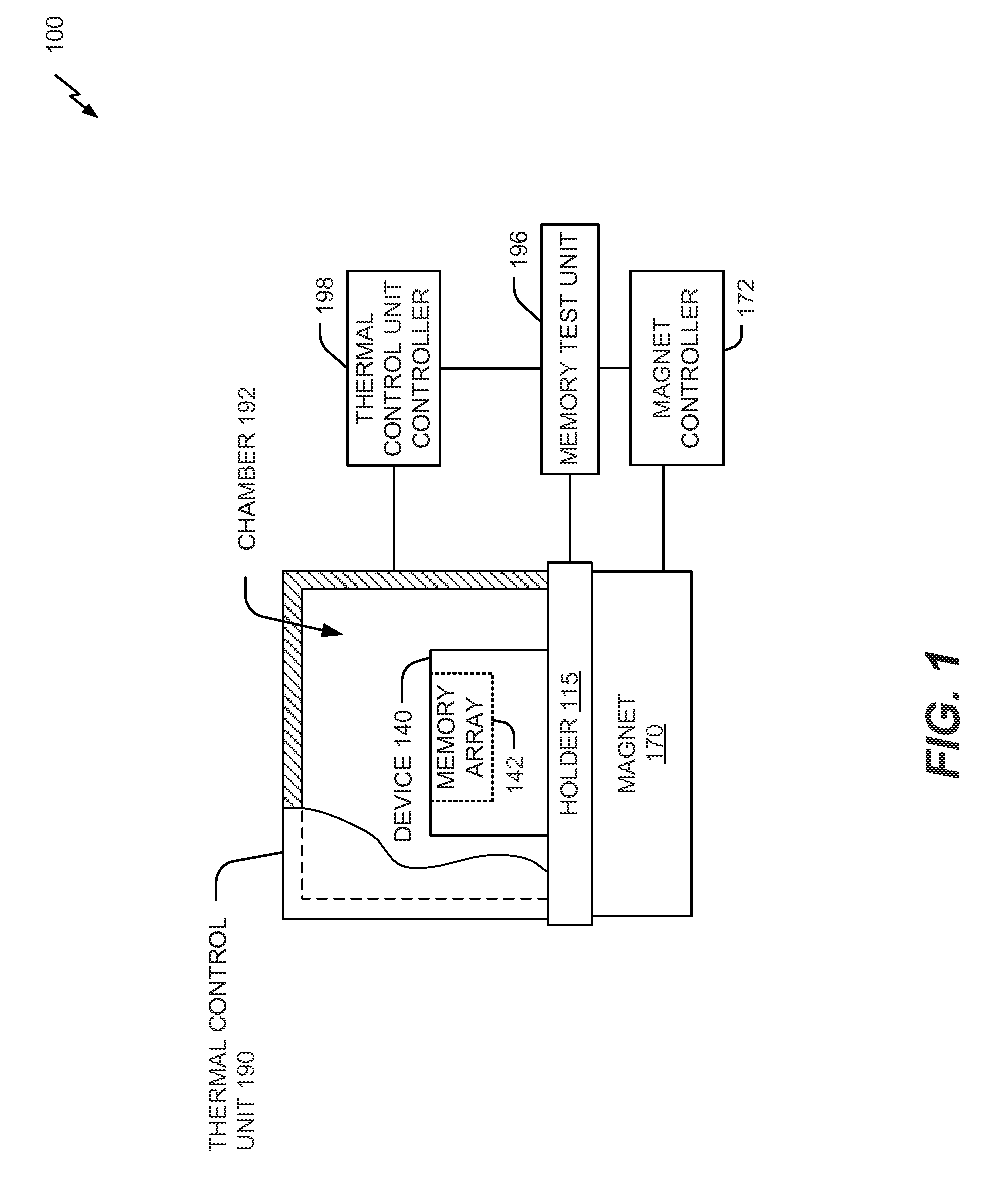

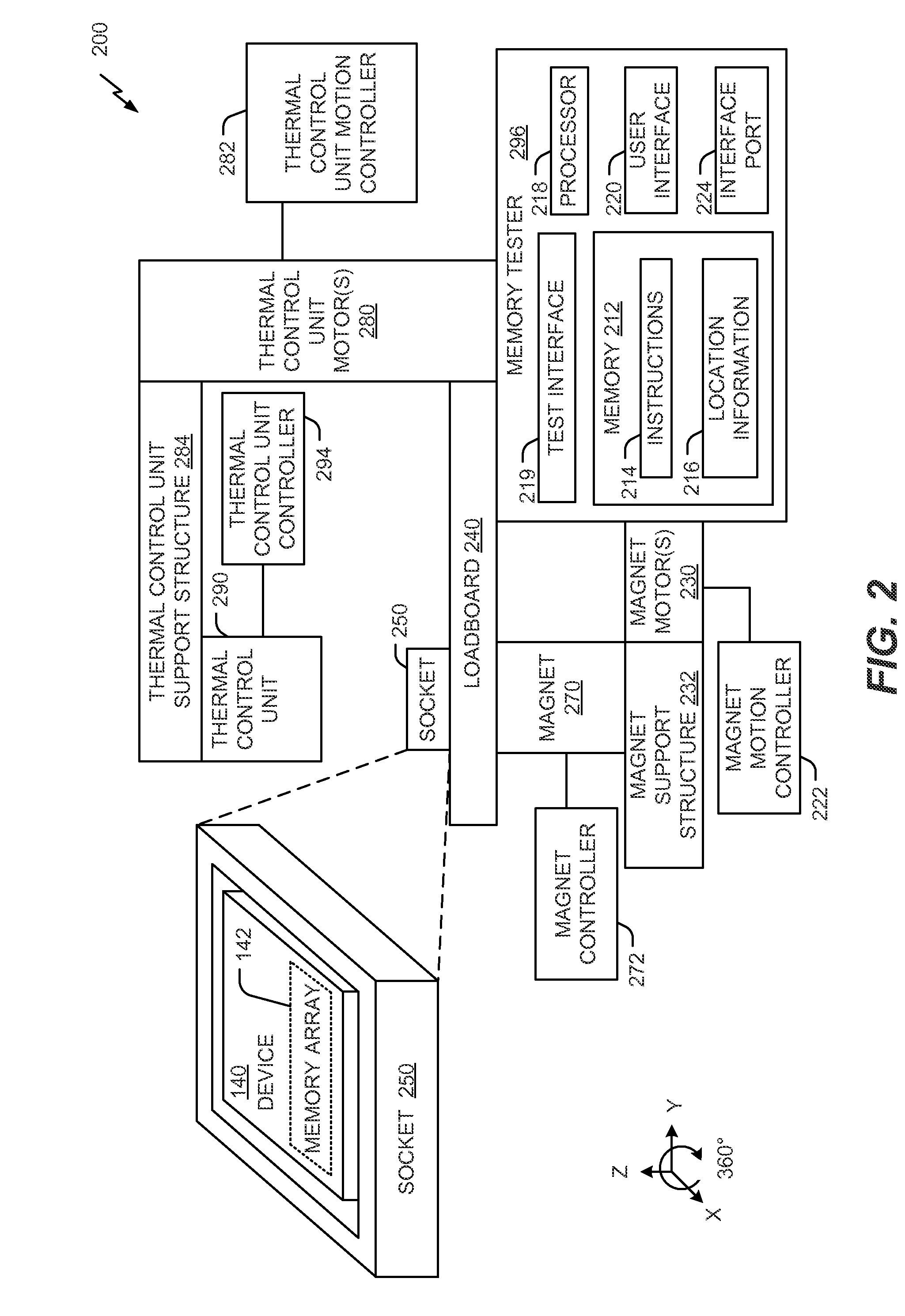

Magnetic automatic test equipment (ATE) memory tester device and method employing temperature control

ActiveUS20140254251A1Improve MRAM designSimple designDigital storageTemperature controlAutomatic test equipment

In a particular embodiment, a method includes controlling a temperature within a chamber while applying a magnetic field. A device including a memory array is located in the chamber. The method includes applying a magnetic field to the memory array and testing the memory array during application of the magnetic field to the memory array at a target temperature.

Owner:QUALCOMM INC

Apparatus for testing memories with redundant storage elements

A memory tester tests a random access memory device under test (DUT) comprising addressable rows and columns of memory cells, and provides a computer with enough information to determine how to efficiently allocate spare rows and columns for replacing rows and columns containing defective memory cells. During a test the memory tester writes a "fail" bit into each address of an error capture memory (ECM) to indicate whether a correspondingly addressed memory cell of the DUT is defective. The tester also includes a set of programmable area fail counters, each for counting of the number of memory cells within a separately selected area of the memory's address space. After the test, the computer processes the counts to determine whether it needs to allocate the spare rows and columns and, in some cases, to determine how to allocate the spare rows and columns. When it cannot allocate spare rows and columns on the basis of the counts alone, the computer commands the tester to read the fail bits in selected areas of the ECM's address space to determine the addresses of the defective memory cells and to supply those addresses to the computer to enable it to determine how to allocate spare rows and columns.

Owner:CREDENCE SYSTEMS

Algorithm pattern generator for testing a memory device and memory tester using the same

ActiveUS7302623B2Electronic circuit testingError detection/correctionMemory testerPattern generation

Disclosed is an algorithm pattern generator for testing a memory device. It has a configuration which can optimize a configuration of a memory tester including an address scrambling and a data scrambling in the memory tester for carrying out a test at a memory device module level or a component level.

Owner:UNITEST

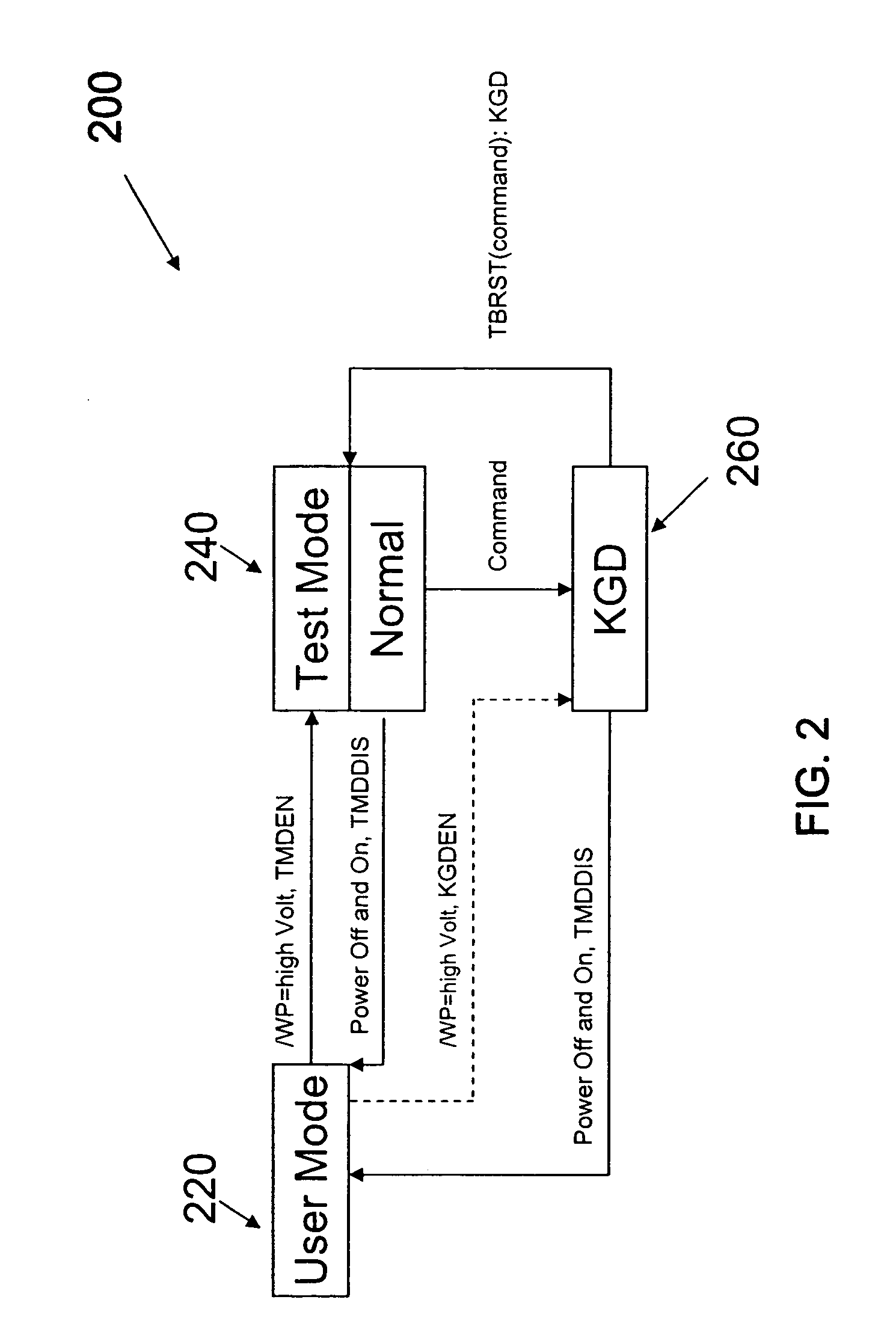

Clock frequency doubler method and apparatus for serial flash testing

Method and apparatus for memory device testing at a higher clock rate than the clock rate provided by a memory tester. The method includes providing a memory tester capable of generating a first clock signal characterized by a first clock frequency, and applying the first clock signal to the memory device. The method also includes receiving a command for activating a high-clock-frequency test mode. The method generates a second clock signal in the memory device in response to the first clock signal. The second clock signal is characterized by a second clock frequency which is higher than the first clock frequency. The method then tests the memory device at the second clock frequency. In a specific embodiment, the method is applied to a serial flash memory device. The invention can also be applied to testing and operating other memory devices or systems that include synchronized circuits.

Owner:WINBOND ELECTRONICS CORP

Clock frequency doubler method and apparatus for serial flash testing

Method and apparatus for memory device testing at a higher clock rate than the clock rate provided by a memory tester. The method includes providing a memory tester capable of generating a first clock signal characterized by a first clock frequency, and applying the first clock signal to the memory device. The method also includes receiving a command for activating a high-clock-frequency test mode. The method generates a second clock signal in the memory device in response to the first clock signal. The second clock signal is characterized by a second clock frequency which is higher than the first clock frequency. The method then tests the memory device at the second clock frequency. In a specific embodiment, the method is applied to a serial flash memory device. The invention can also be applied to testing and operating other memory devices or systems that include synchronized circuits.

Owner:WINBOND ELECTRONICS CORP

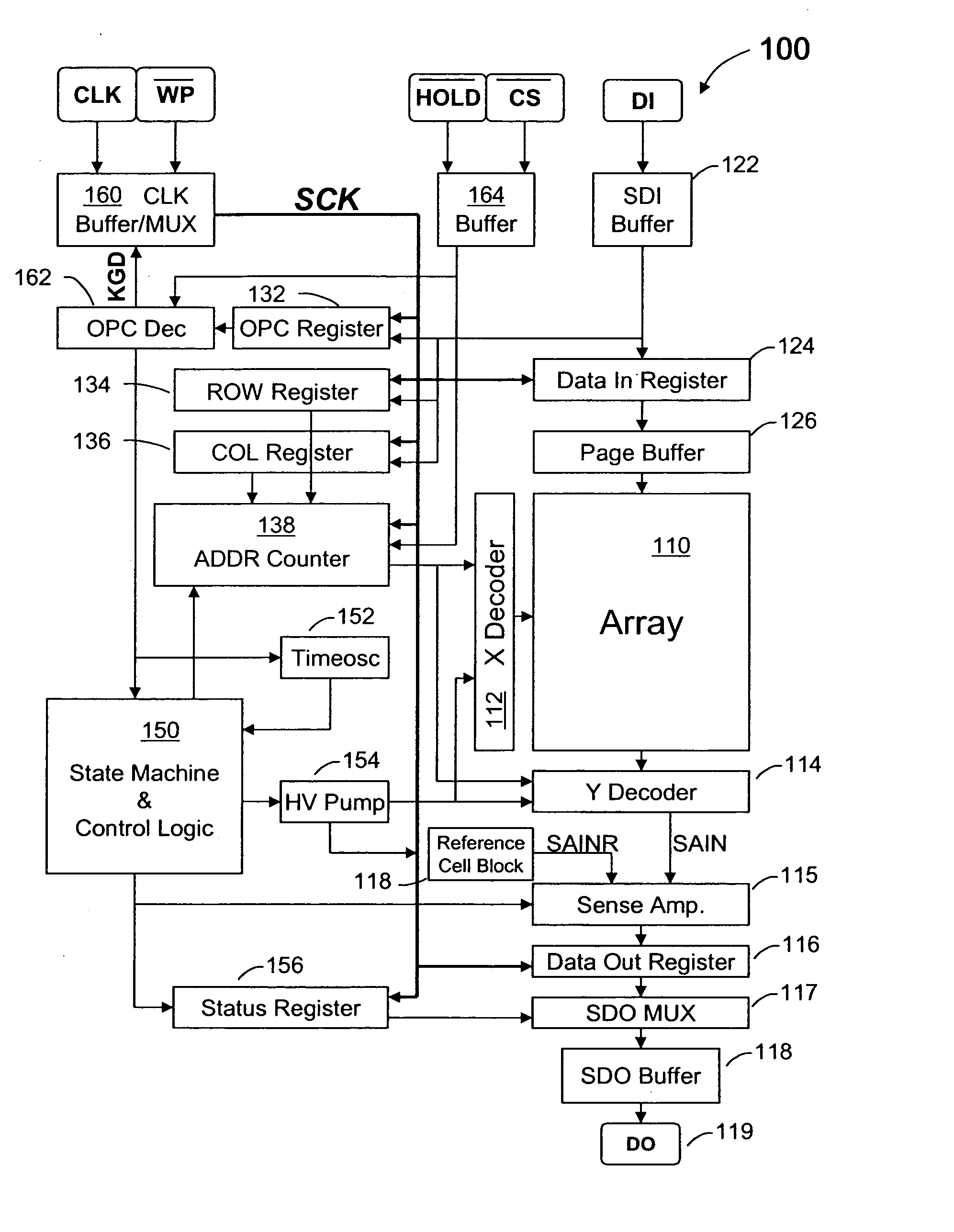

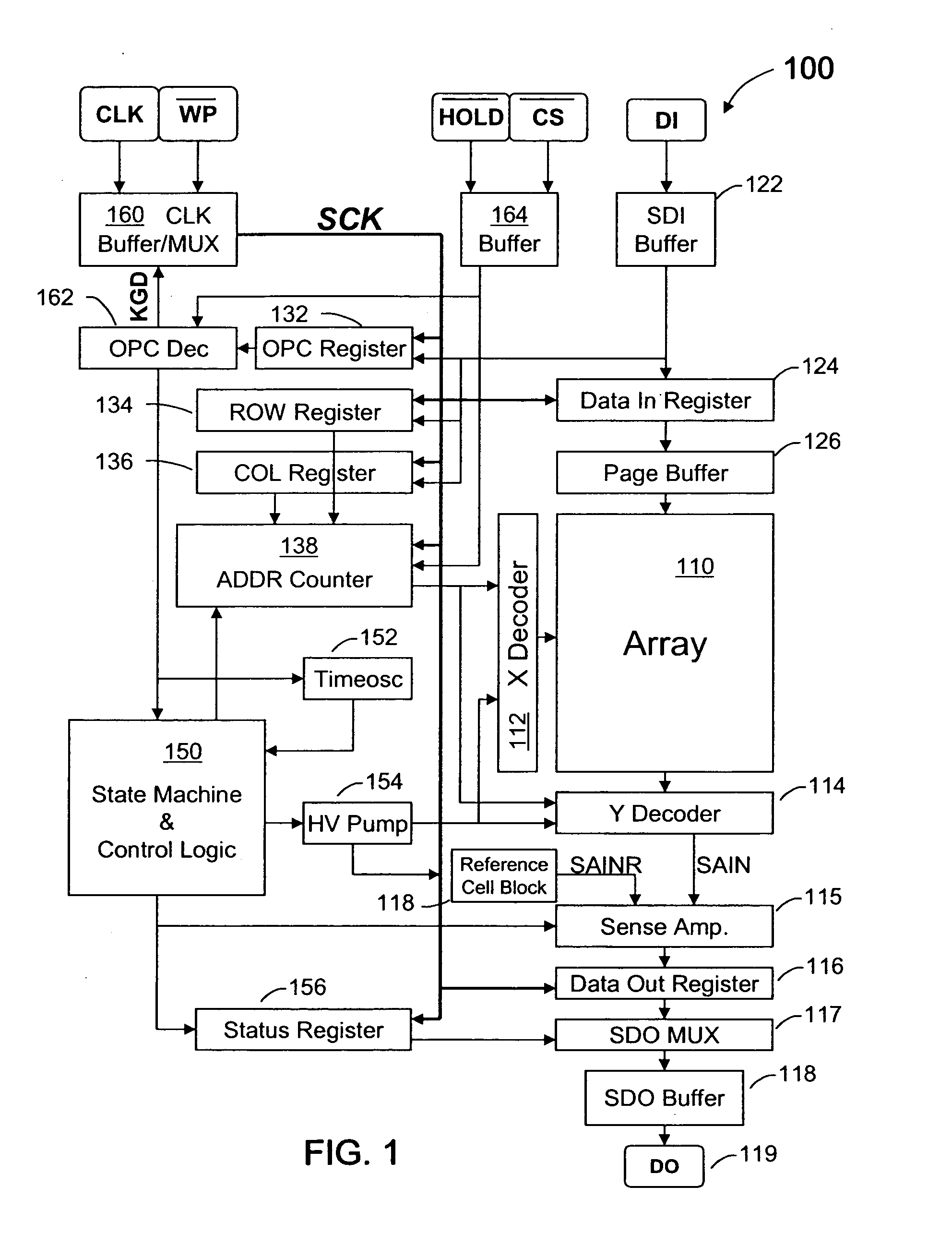

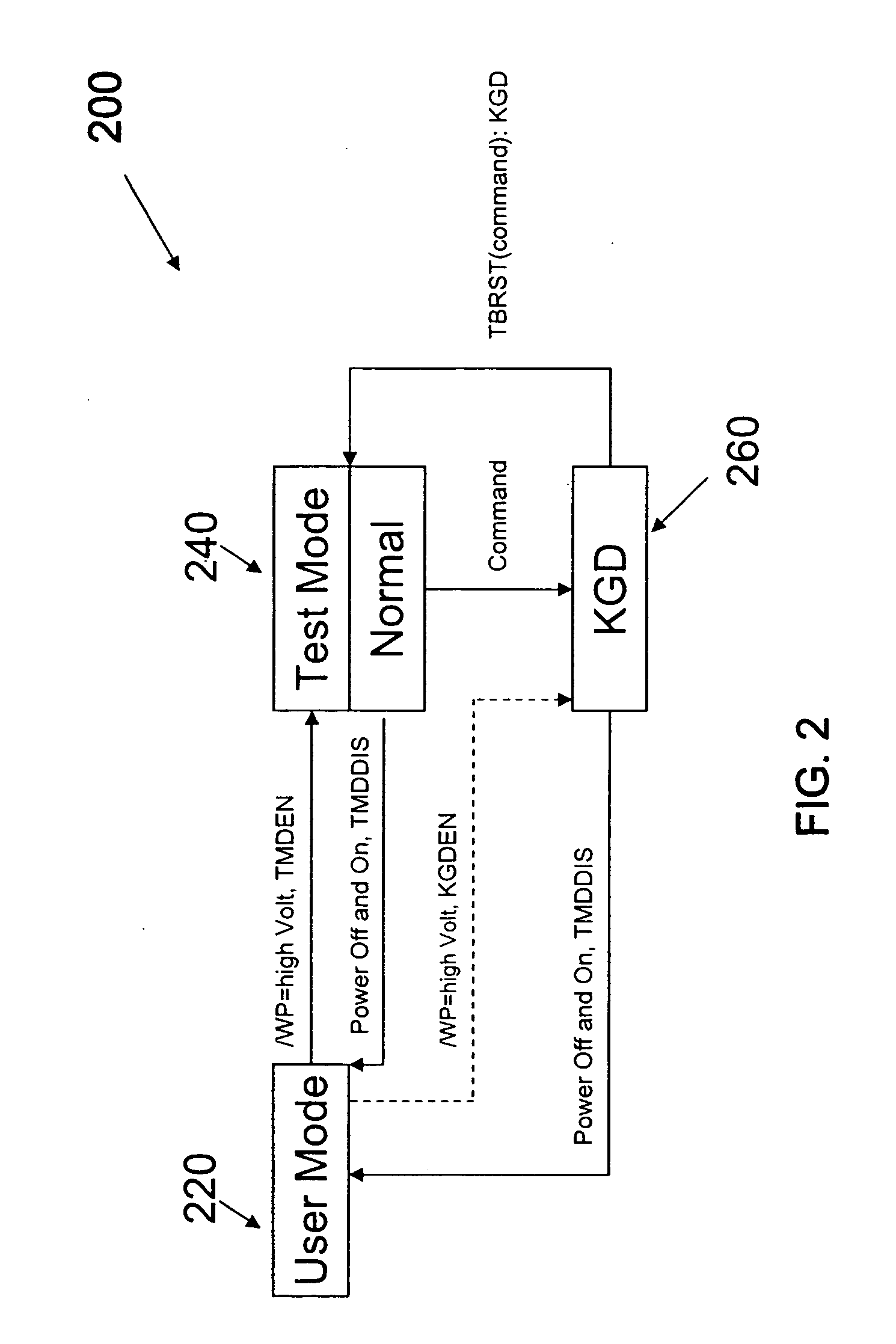

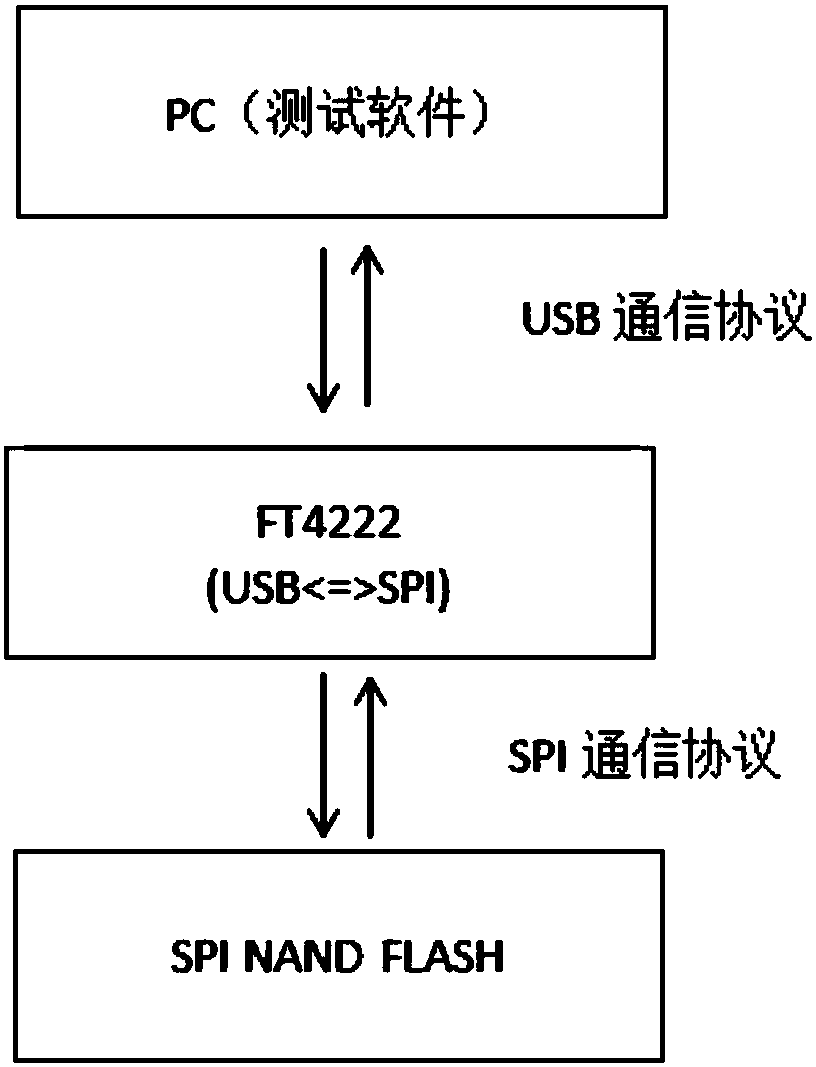

SPI flash memory test system and method based on FT4222

The invention discloses a SPI flash memory test system and a method based on FT4222. According to the SPI flash memory test method, calling of FT4222 chip equipment in a debugging tool is carried outbased on test statements input by testers, configuration of test conditions is carried out based on SPI NAND Flash modules of different parameters, and at last, loading of the test statements into theFT4222 chip modules is carried out so as to realize test of the SPI NAND Flash module. The method is capable of testing simple SPI NAND Flash reading, writing, and erasuring, and realizing BurnIn test (stability test), and achieving special test purposes via modifying test software program codes.

Owner:NANJING HEYANGTEK CO LTD

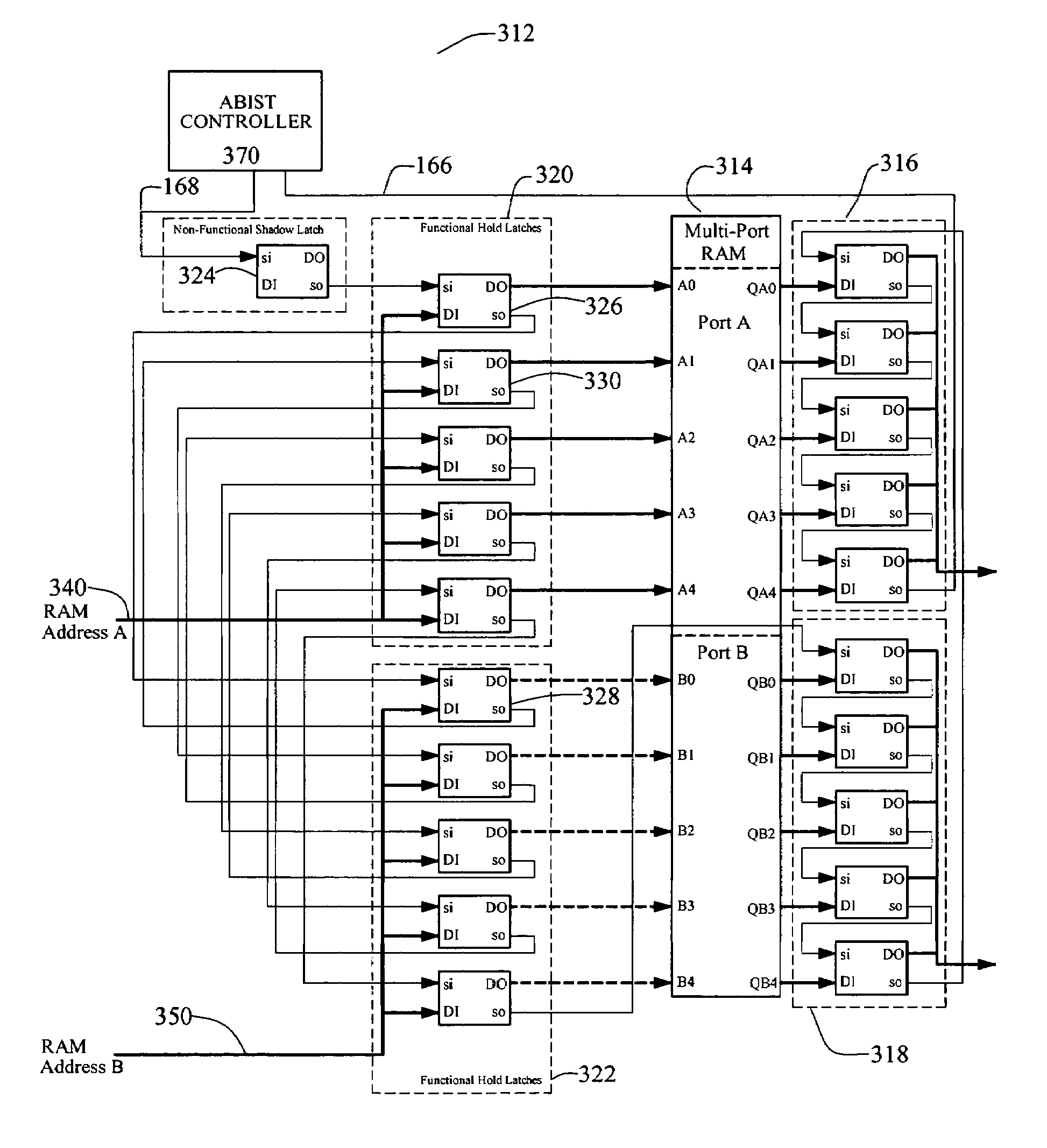

Scanned memory testing of multi-port memory arrays

Owner:INT BUSINESS MASCH CORP

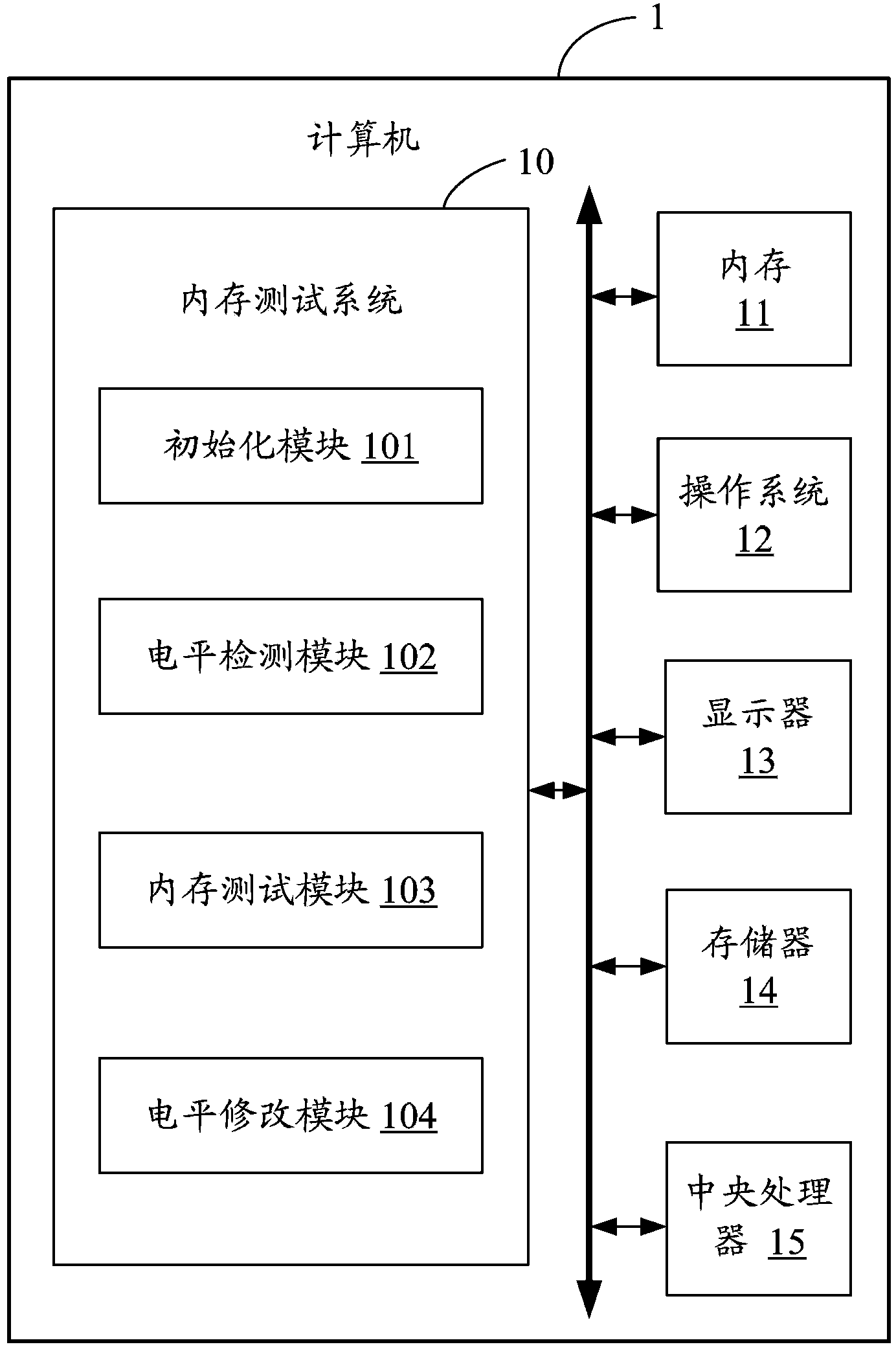

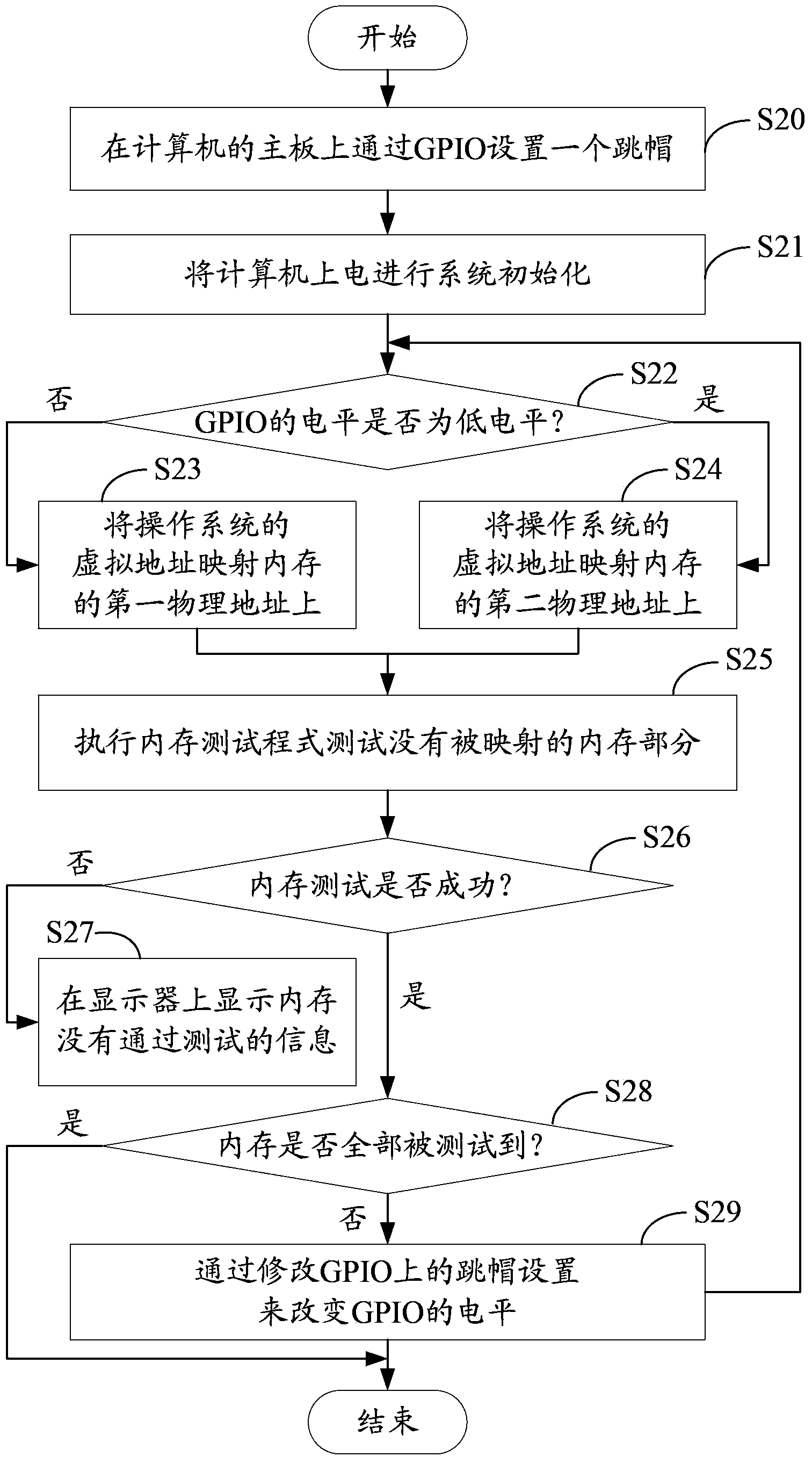

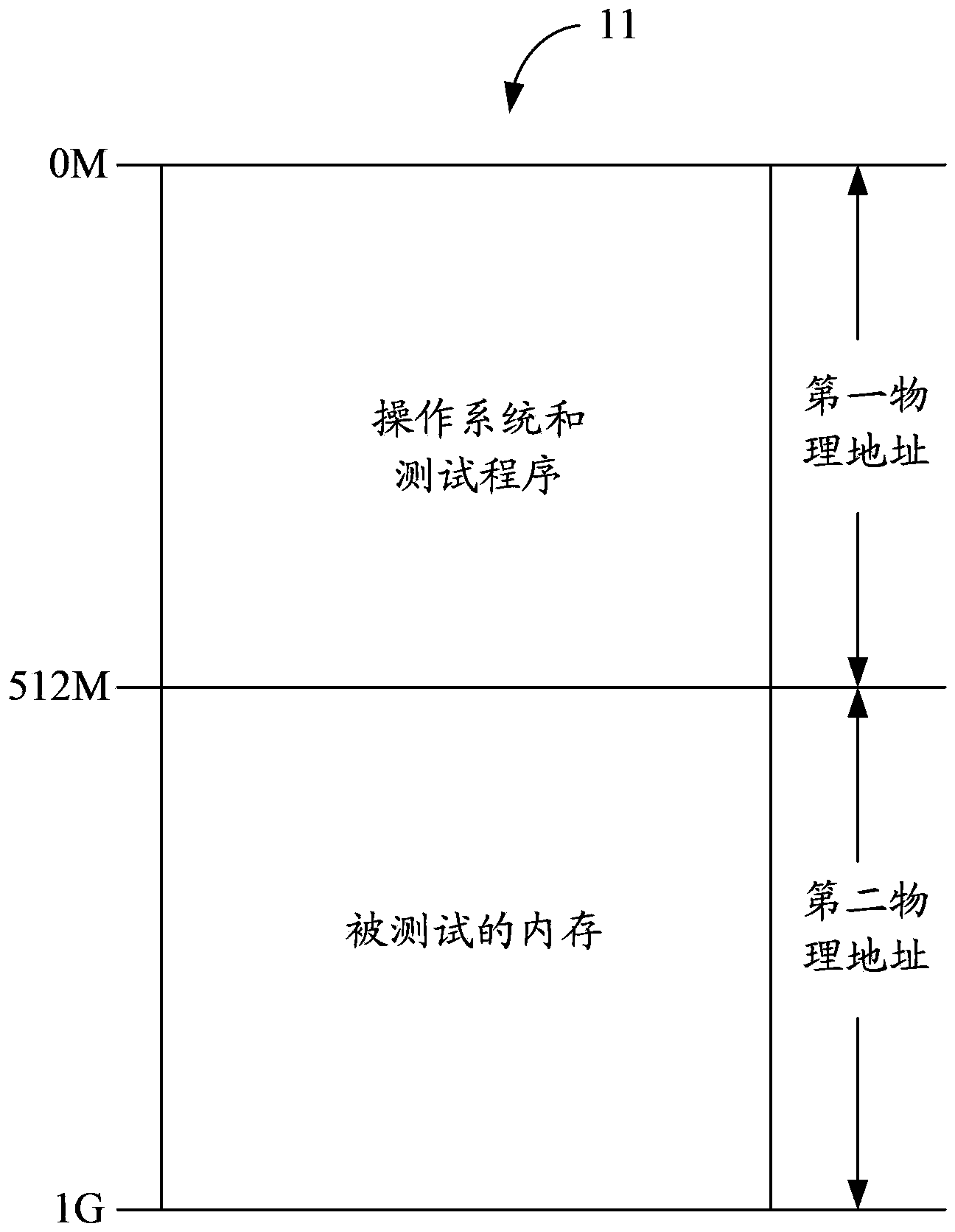

Memory test system and method

The invention discloses a memory test system and a memory test method which are applied to a computer which comprises a memory and an operation system. The method comprises the following steps: setting a jumper cap on the main board of the computer through GPIO and powering up the computer to carry out system initialization; detecting whether the level of the GPIO on the main board is low level; when the level of the GPIO is high level, mapping the virtual address used by the operation system on the first physical address of the memory; when the level of the GPIO is low level, mapping then virtual address used by the operation system on the second physical address of the memory; executing the memory test program to test the memory part which is not mapped; detecting whether the memory is completely tested; when the memory is not completely tested, changing the level of the GPIO through the changing of the jumper cap setting on the GPIO. Through the memory test system and method, the virtual address used by the operation system can be mapped to different physical memory addresses so as to integrally test the whole physical memory of the computer.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com