Memory wafer test method and memory tester

A technology for memory testing and wafer testing, which is applied in the field of memory wafer testing methods and memory testing machines, can solve problems such as damaged probe cards and damaged probe cards of testing machines, so as to save testing cost and time, avoid large Effect of Leakage Current Damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] In order to make the purpose and features of the present invention more obvious and understandable, the specific implementation of the present invention will be further described below in conjunction with the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments.

[0036] Please refer to figure 1 , the present invention proposes a memory wafer testing method, comprising:

[0037] S1, connecting a wafer containing a plurality of memory chips under test through the probe card of the memory tester, so as to realize the physical and electrical connection between the memory tester and each memory chip under test on the wafer;

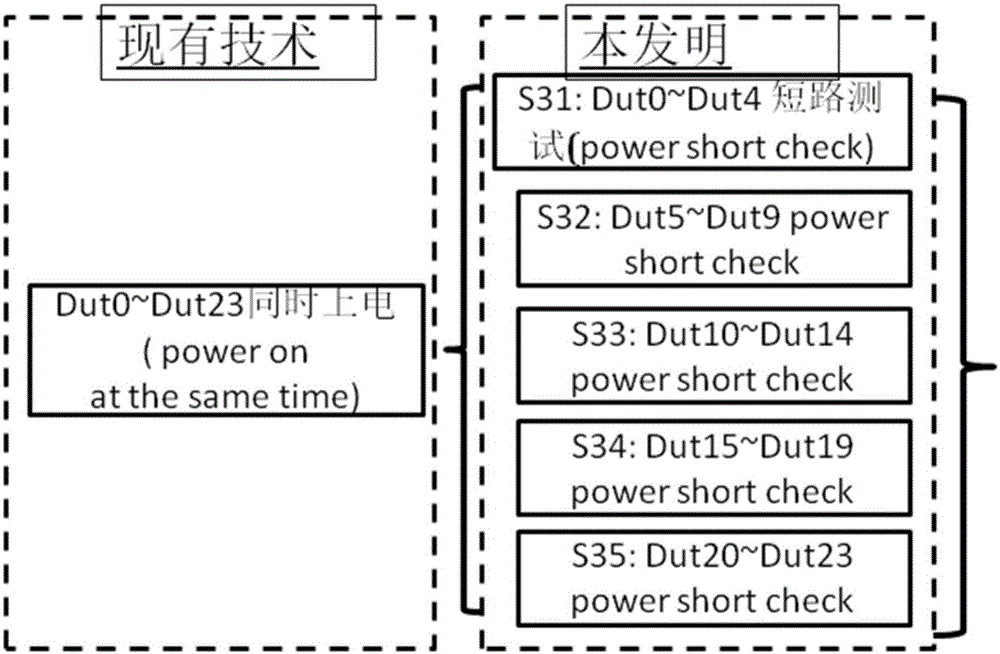

[0038] S2, grouping the test probes of the probe card, so as to group all the memory chips under test;

[0039] S3, using the precision measurement unit of the memory testing machine to perform a group short-circuit test on the memory chips on the wafer accor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com