Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

671 results about "Wafer testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Wafer testing is a step performed during semiconductor device fabrication. During this step, performed before a wafer is sent to die preparation, all individual integrated circuits that are present on the wafer are tested for functional defects by applying special test patterns to them. The wafer testing is performed by a piece of test equipment called a wafer prober. The process of wafer testing can be referred to in several ways: Wafer Final Test (WFT), Electronic Die Sort (EDS) and Circuit Probe (CP) are probably the most common.

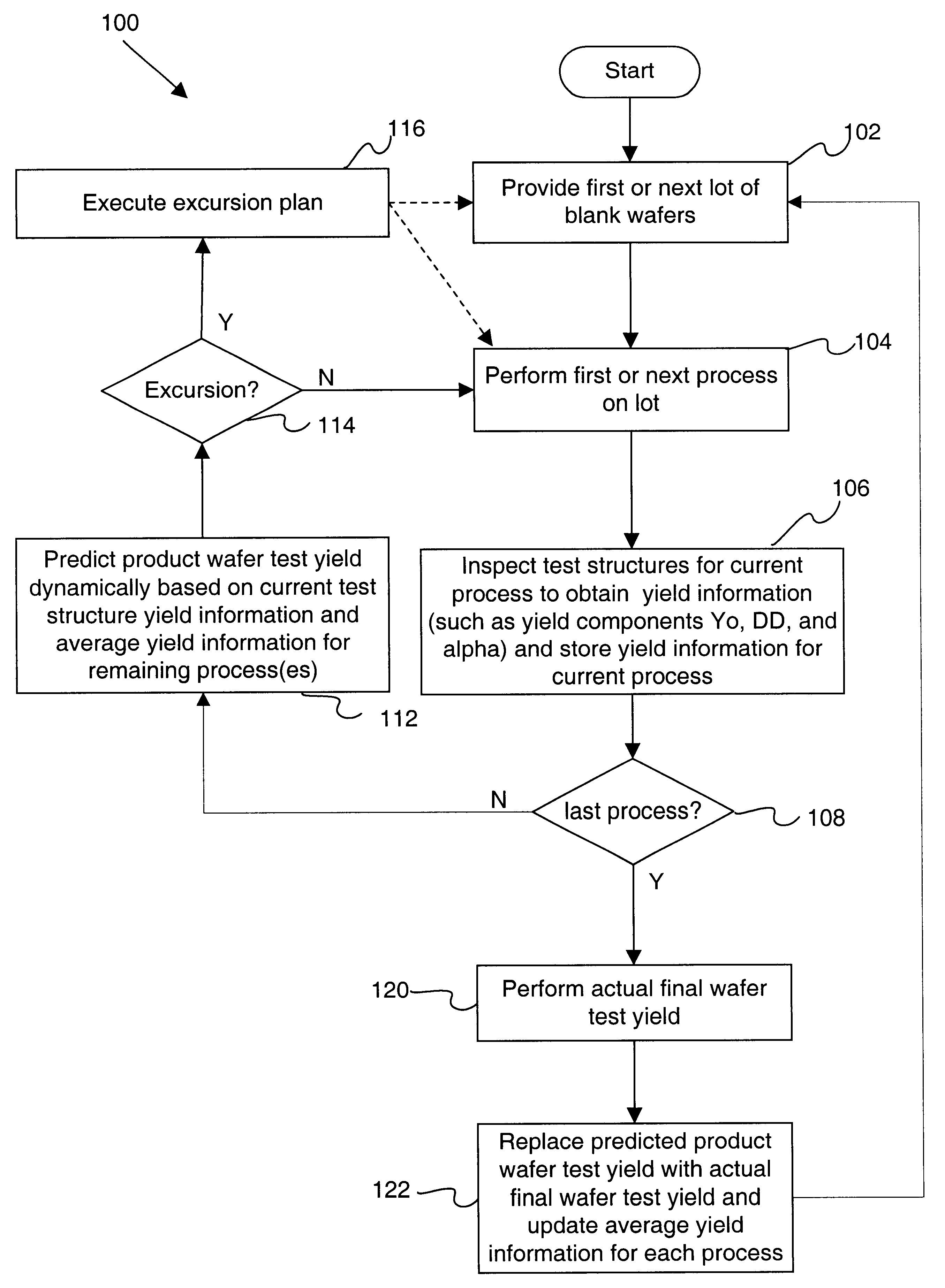

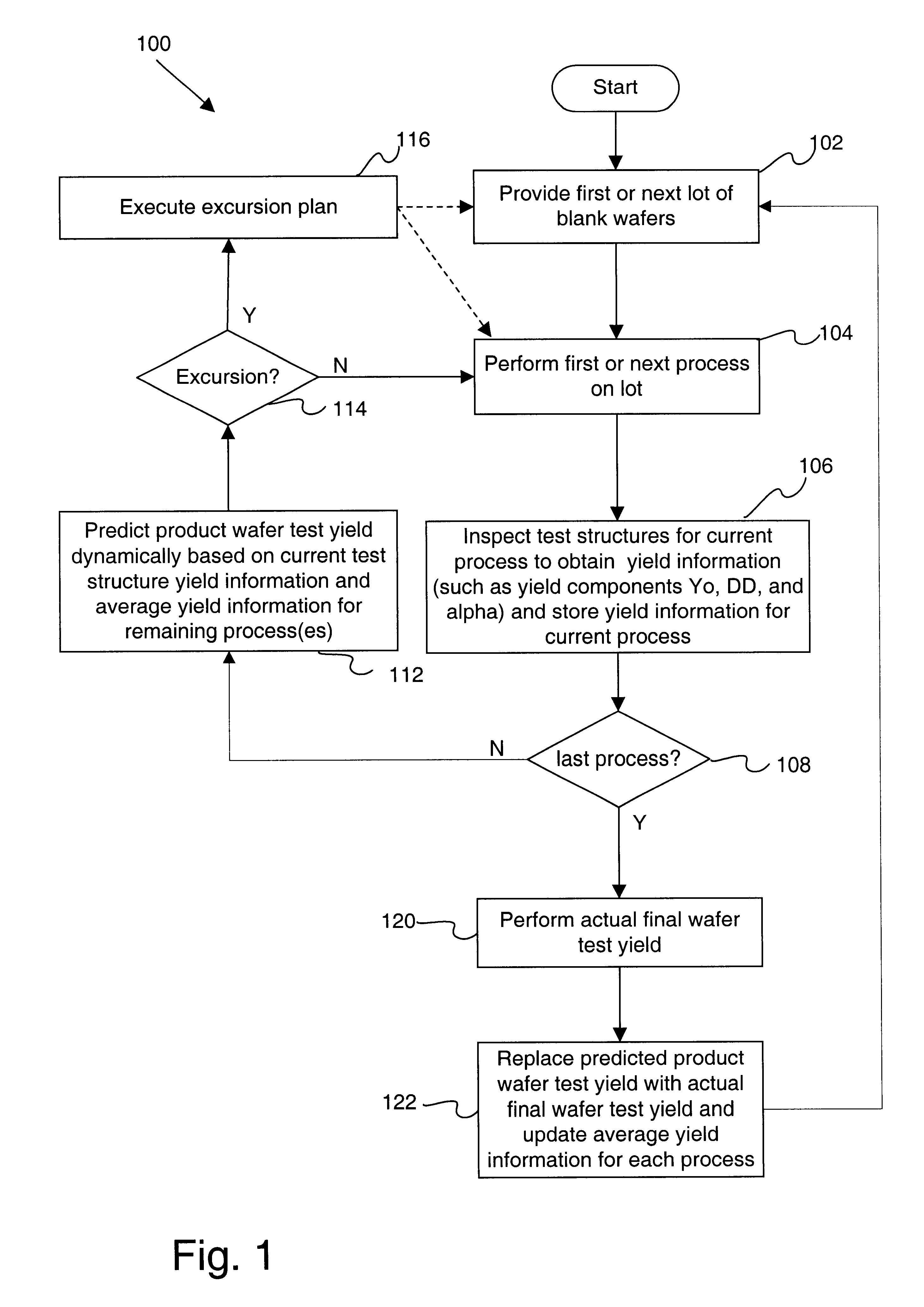

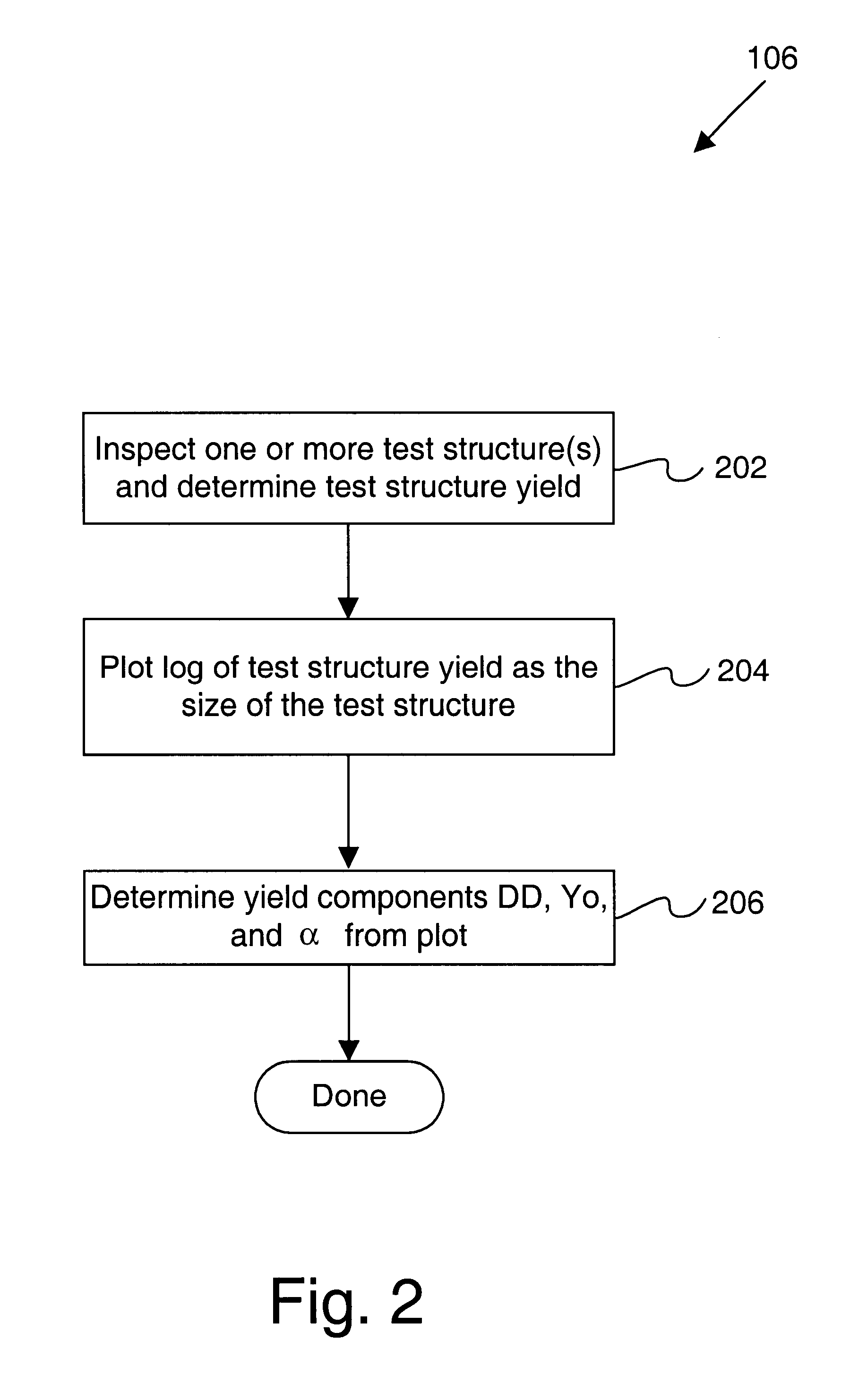

Methods and systems for predicting IC chip yield

InactiveUS6751519B1Semiconductor/solid-state device testing/measurementNuclear monitoringProcess engineeringReliability engineering

Disclosed are methods and apparatus for efficiently managing IC chip yield learning. In general terms, as each wafer lot moves through fabrication, yield information is obtained from each set of test structures for a particular process or defect mechanism. The nature of the yield information is such that it may be used directly or indirectly to predict product wafer test yield. In one implementation, the yield information includes a systematic yield (Y.sub.0), a defect density (DD), and a defect clustering factor (.alpha.) determined based on the inspected test structure's yield. A running average of the yield information for each process or defect mechanism is maintained as each wafer lot is processed. As a particular wafer lot moves through the various processes, a product wafer-sort test yield may be predicted at any stage in the fabrication process based on the running-average yield information maintained for previously fabricated wafer lots.

Owner:KLA TENCOR TECH CORP

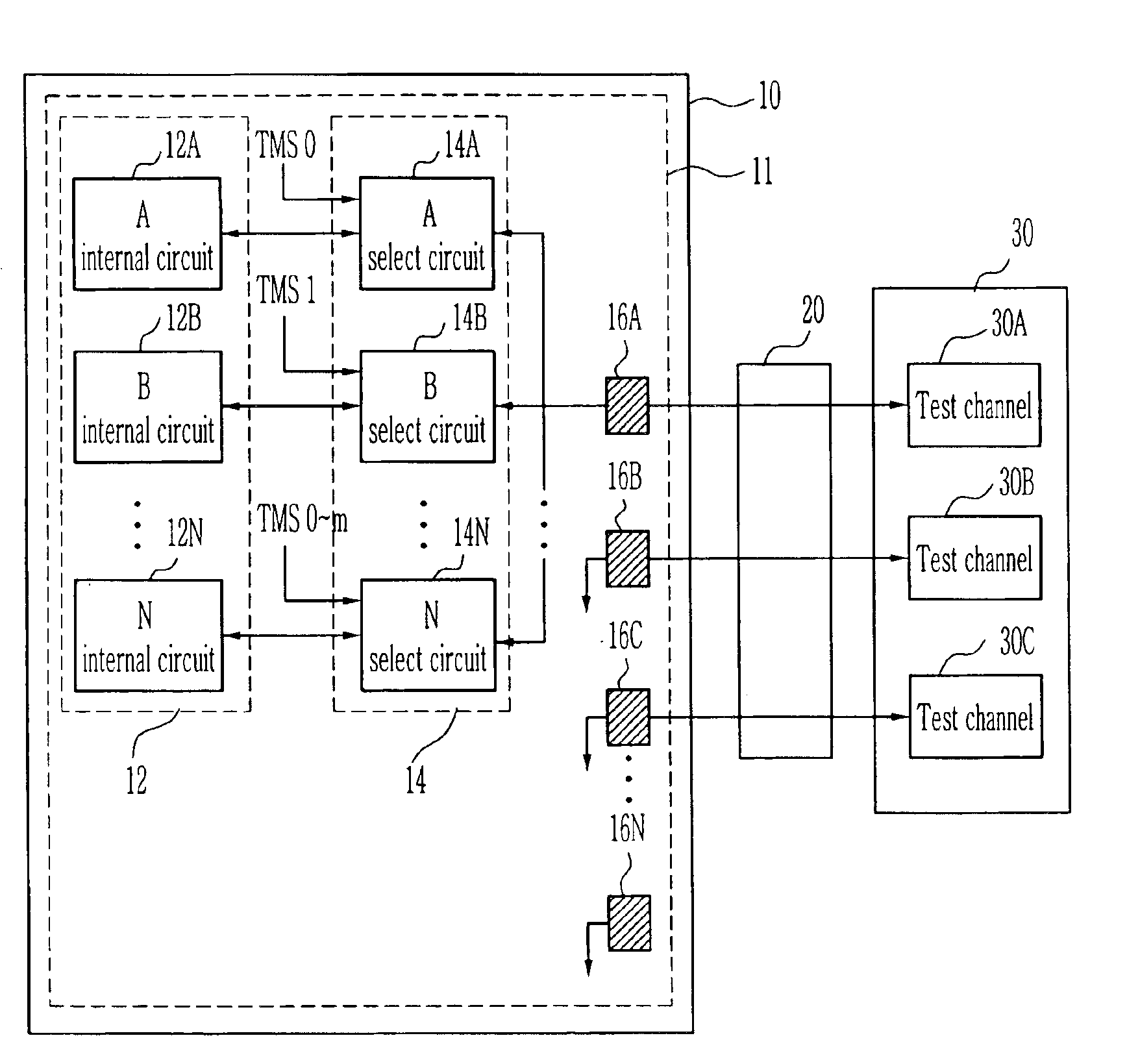

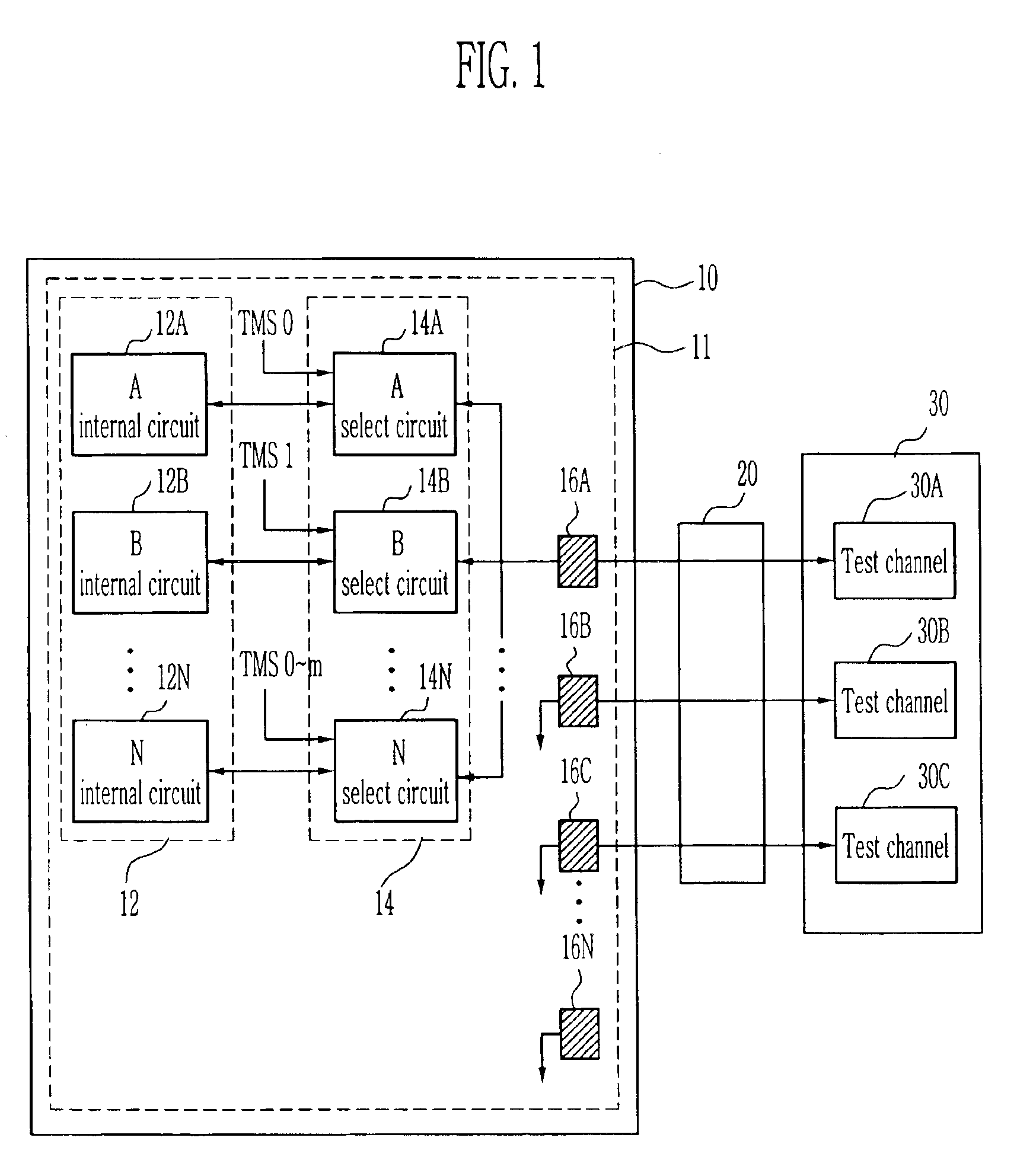

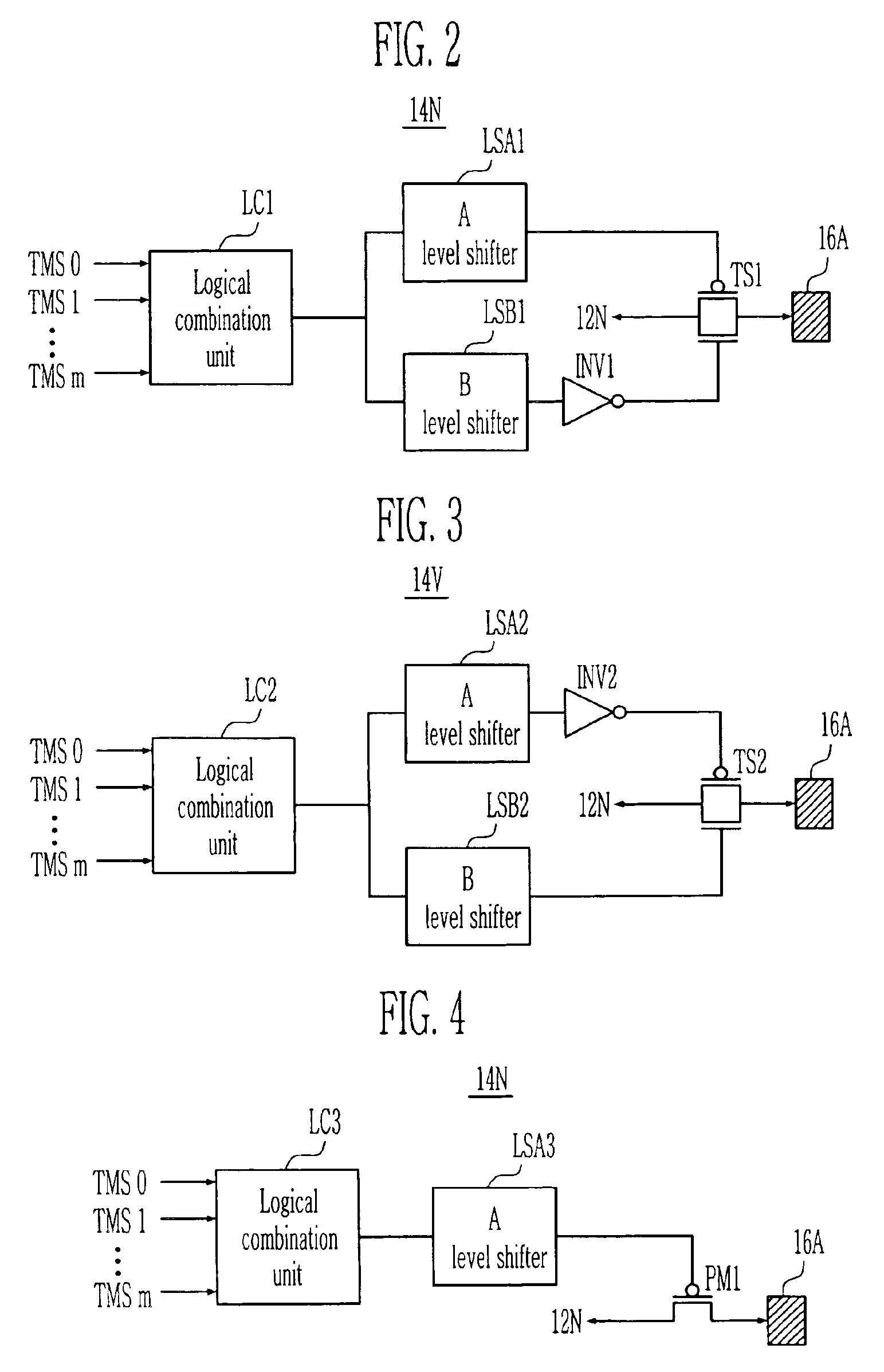

Semiconductor device for reducing the number of probing pad used during wafer test and method for testing the same

The present invention relates to a semiconductor device and a method for testing the same capable of reducing the number of probing pads used during wafer test. The semiconductor device includes a select circuit connected between a plurality of internal circuits to be tested and a single probing pad, for transmitting test signals inputted from the probing pads to any one of the plurality of the internal circuits according to a test mode signal generated in a wafer test mode. It is possible to reduce the number of the probing pads in the integrated circuit used for connection to a probe for contact of a probe card during wafer test. It is therefore possible to reduce test time.

Owner:SK HYNIX INC

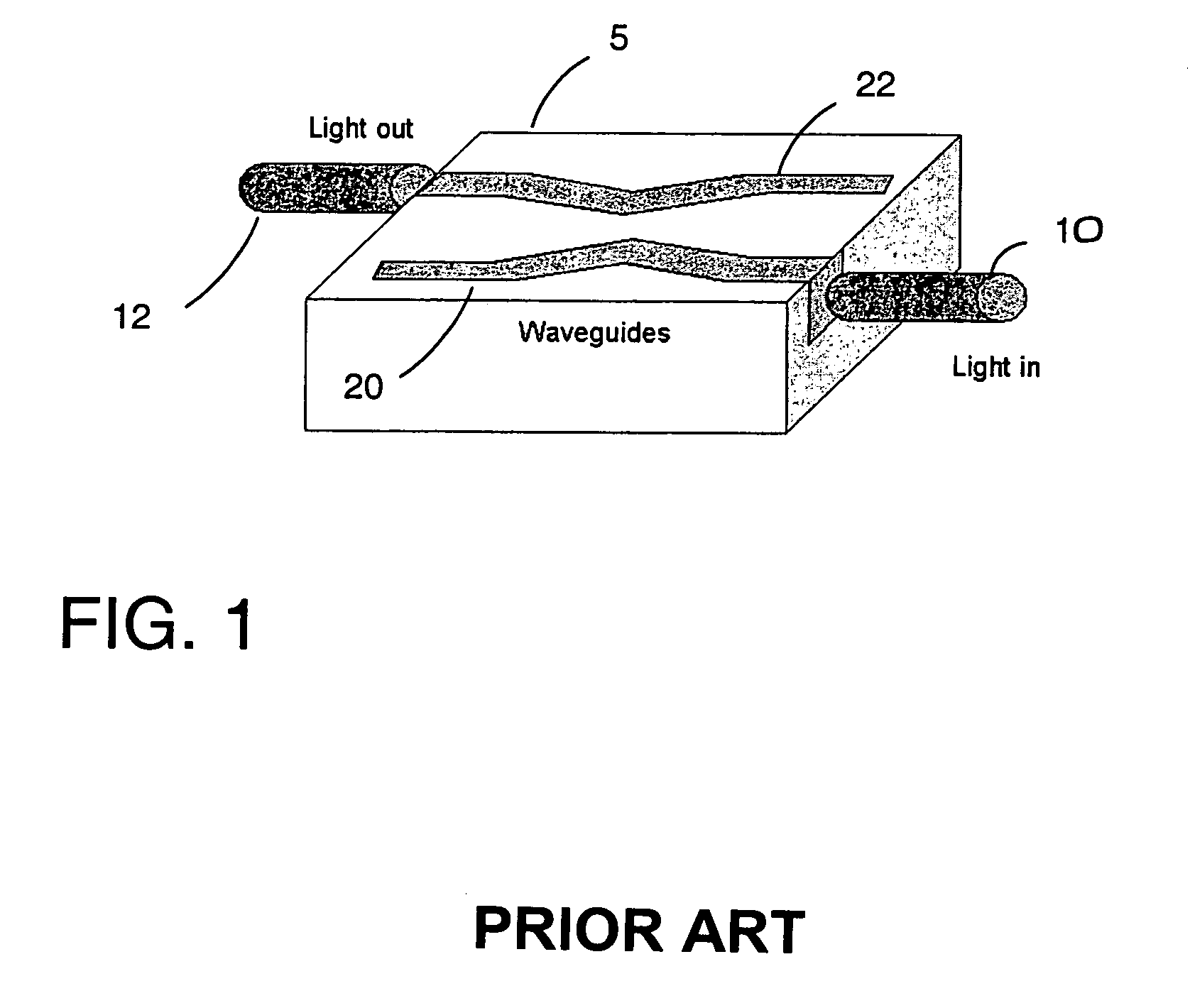

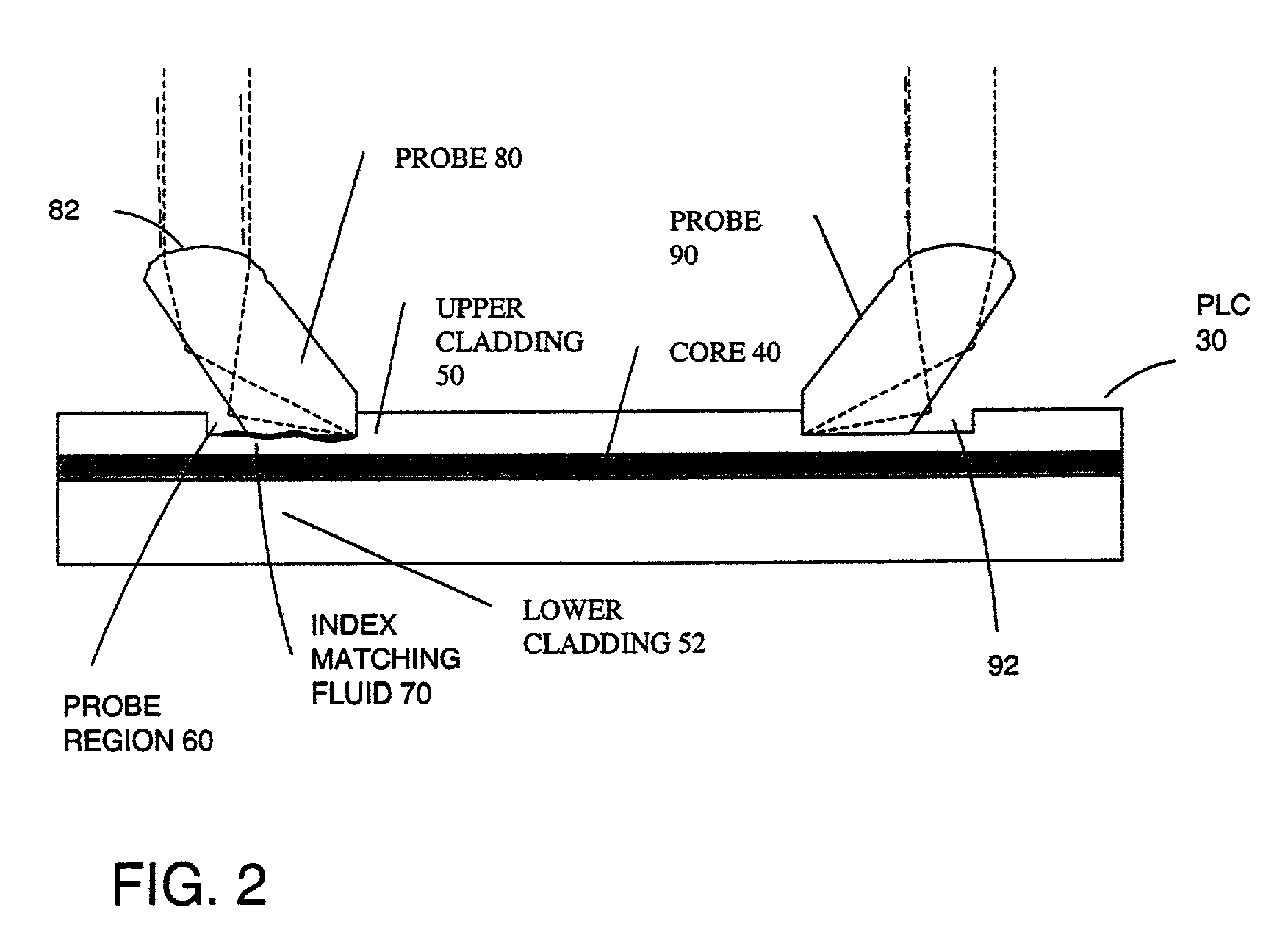

Optical probe for wafer testing

A first optical probe is used to test a planar lightwave circuit. In one embodiment, a second probe is used in combination with the first probe to test the planar lightwave circuit by sending and receiving a light beam through the planar lightwave circuit.

Owner:INTEL CORP

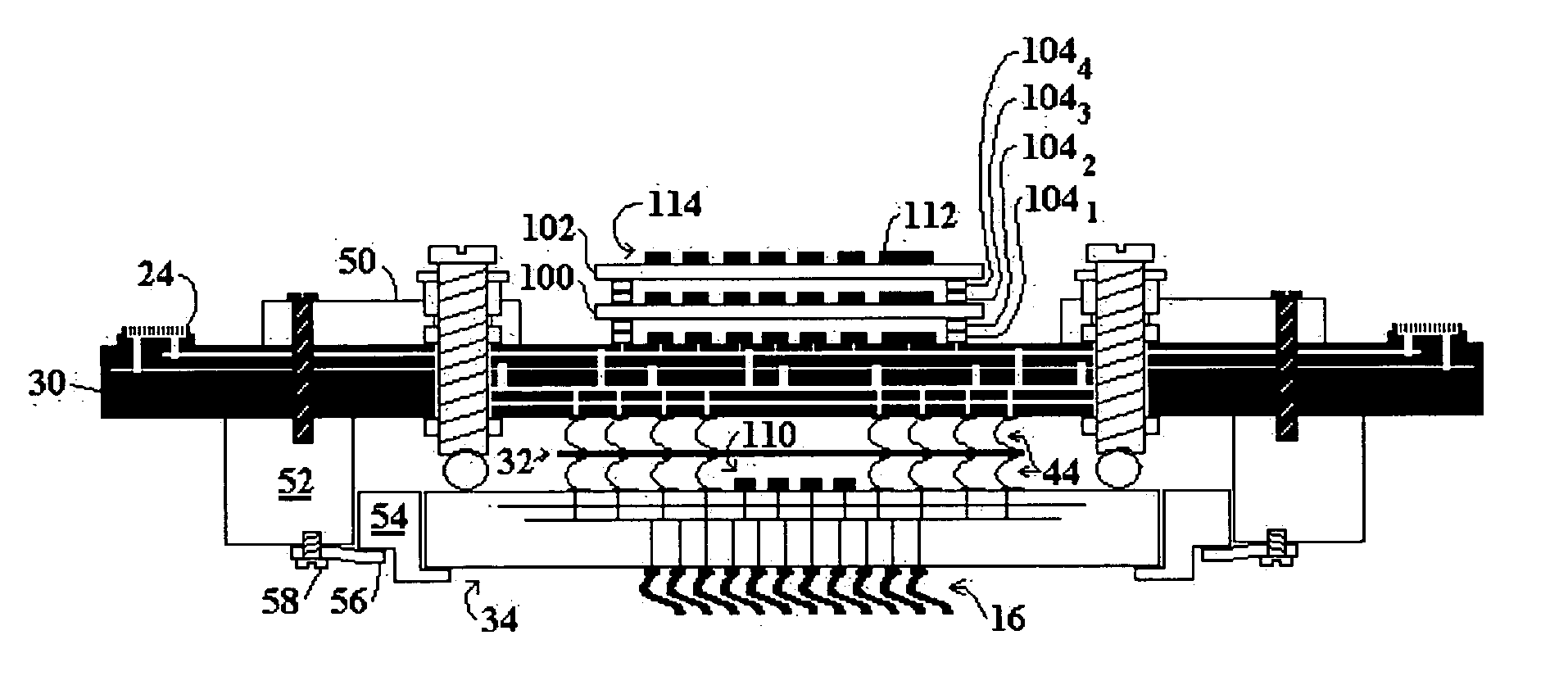

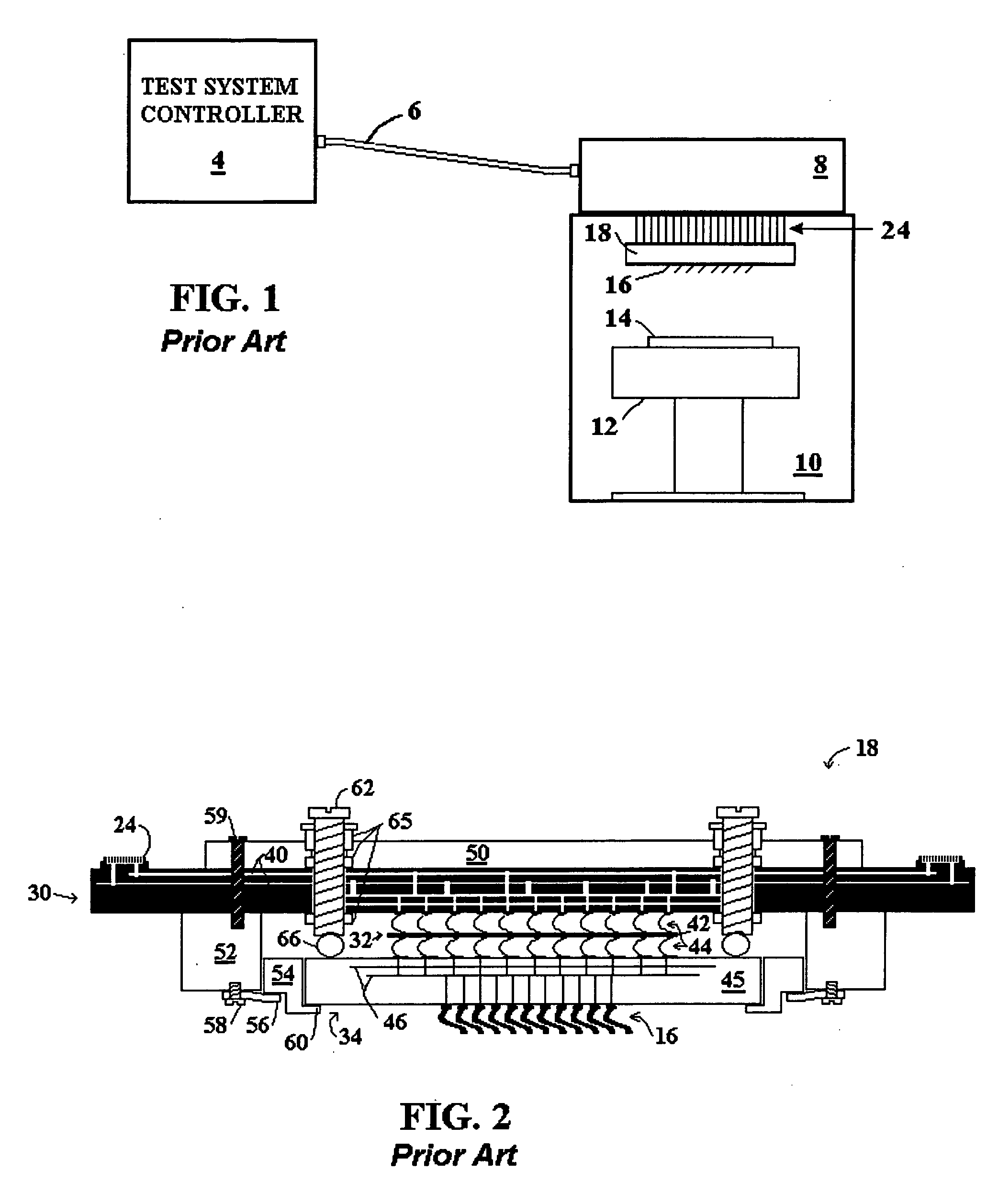

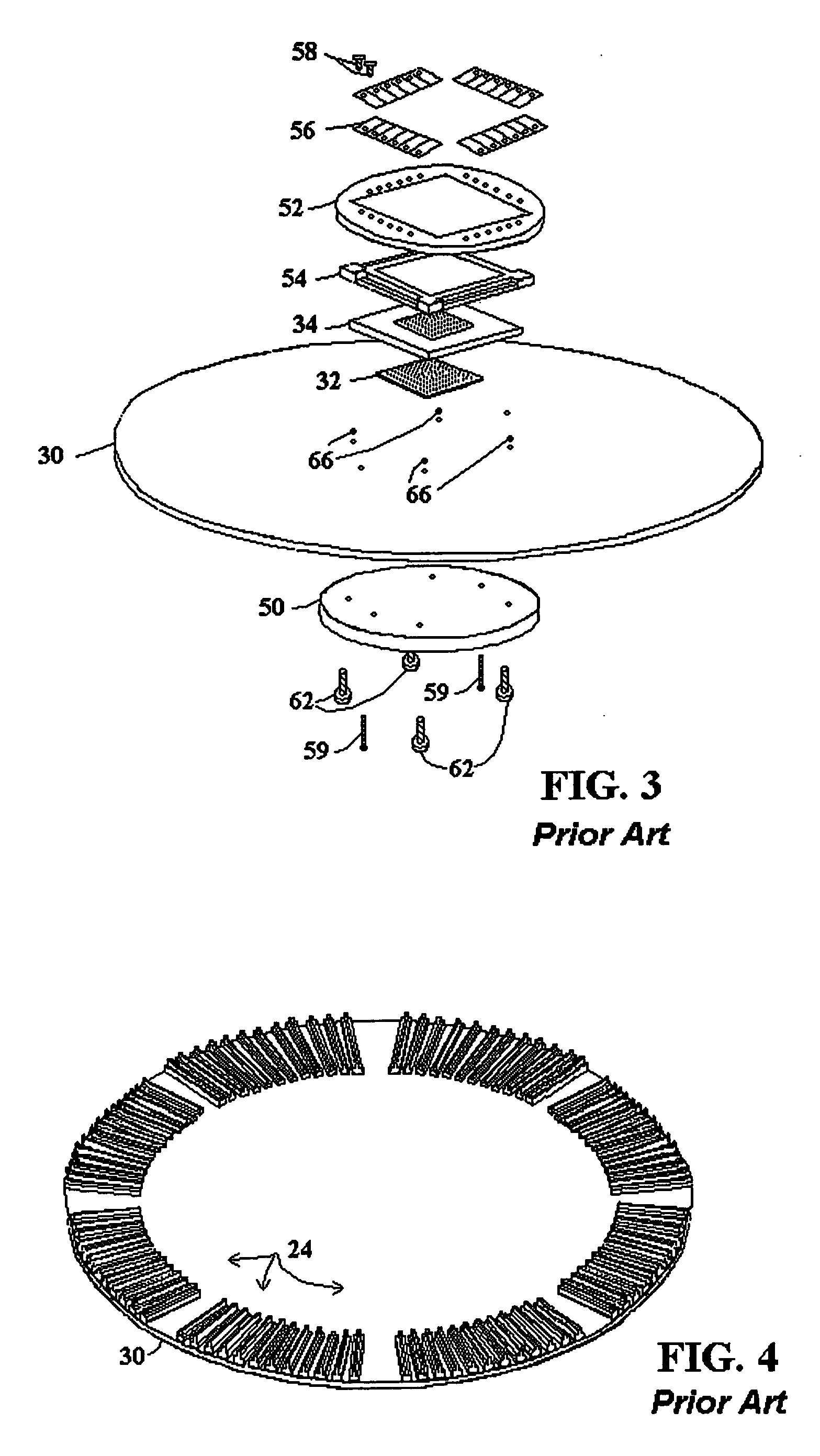

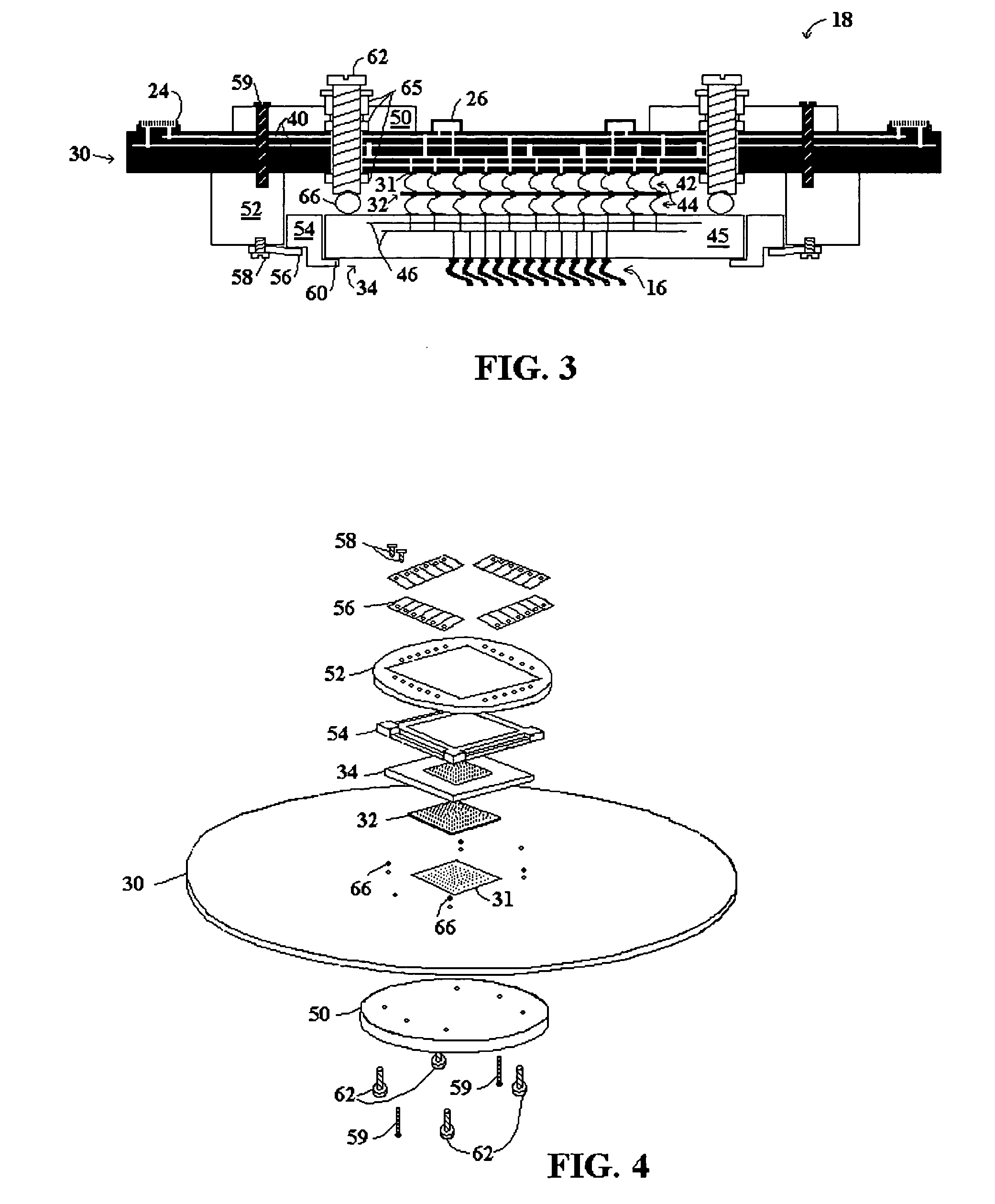

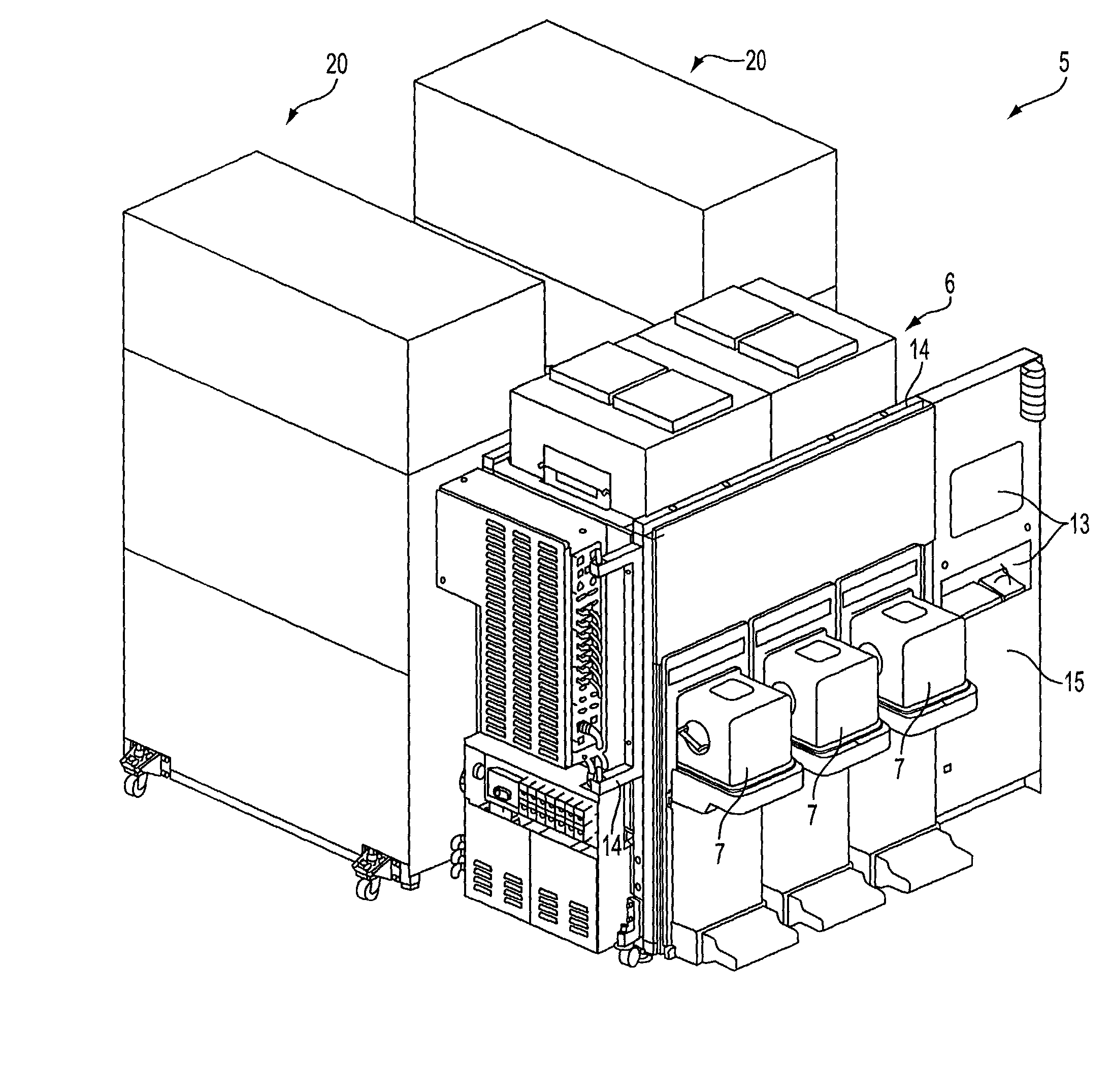

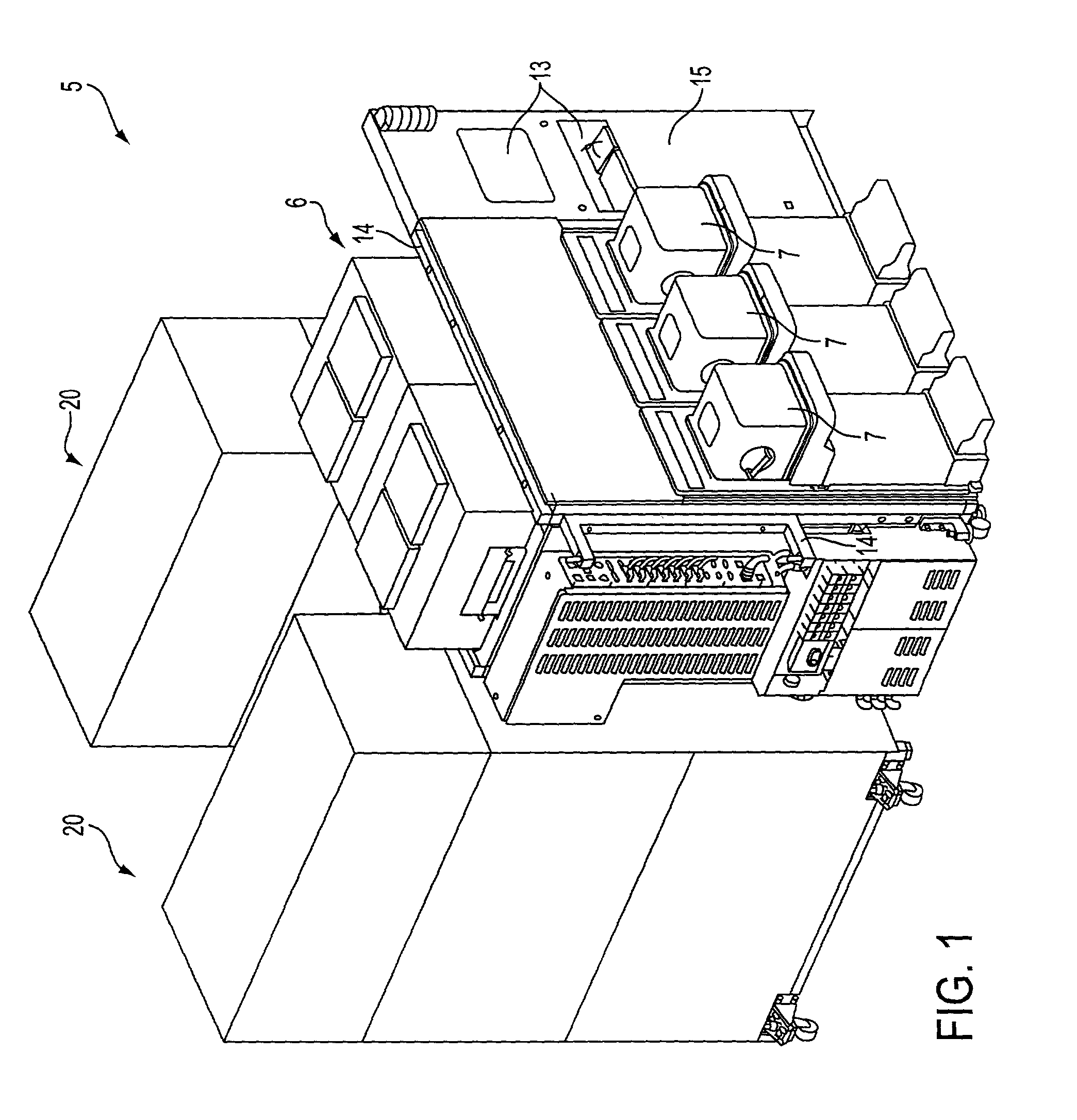

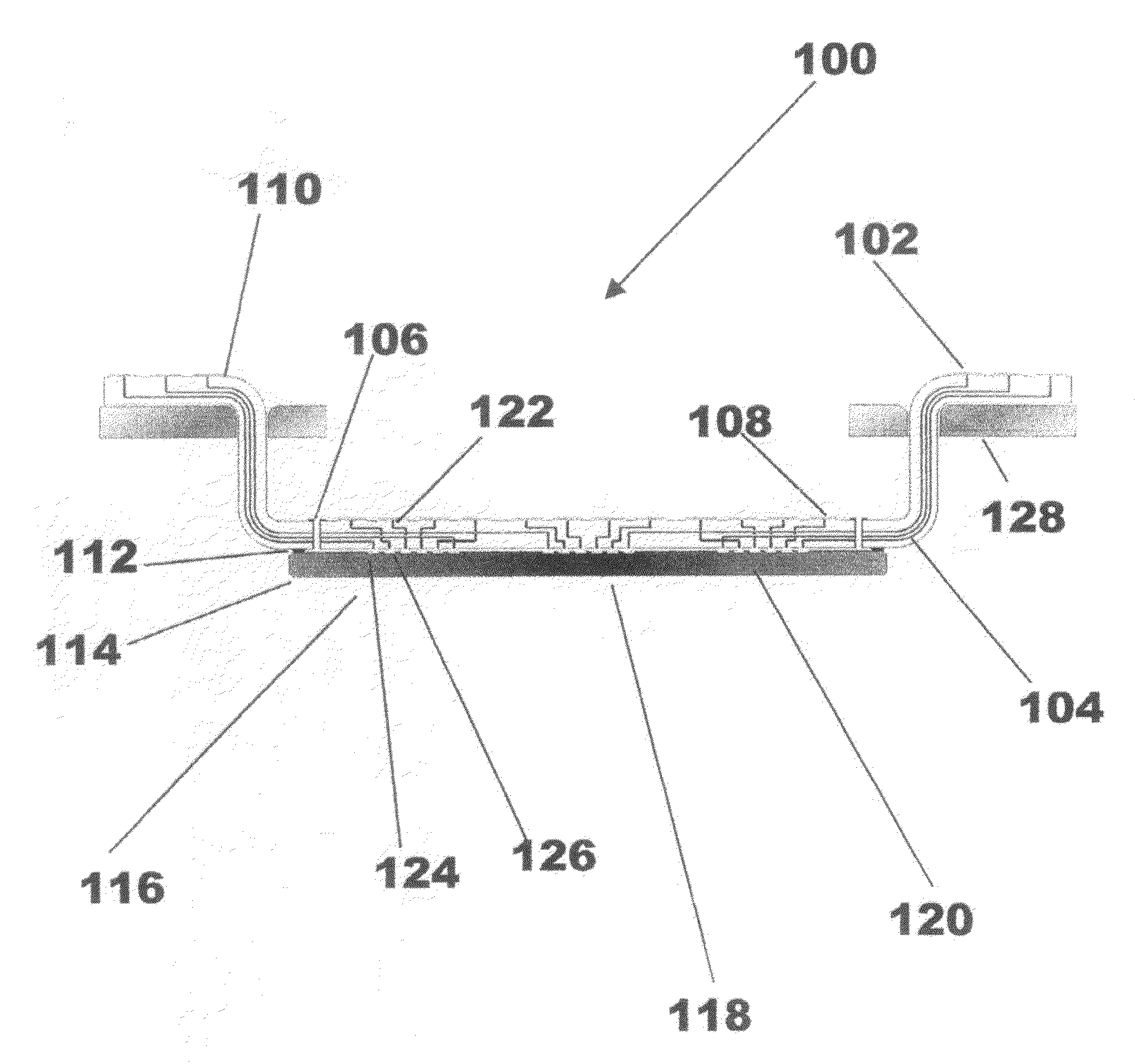

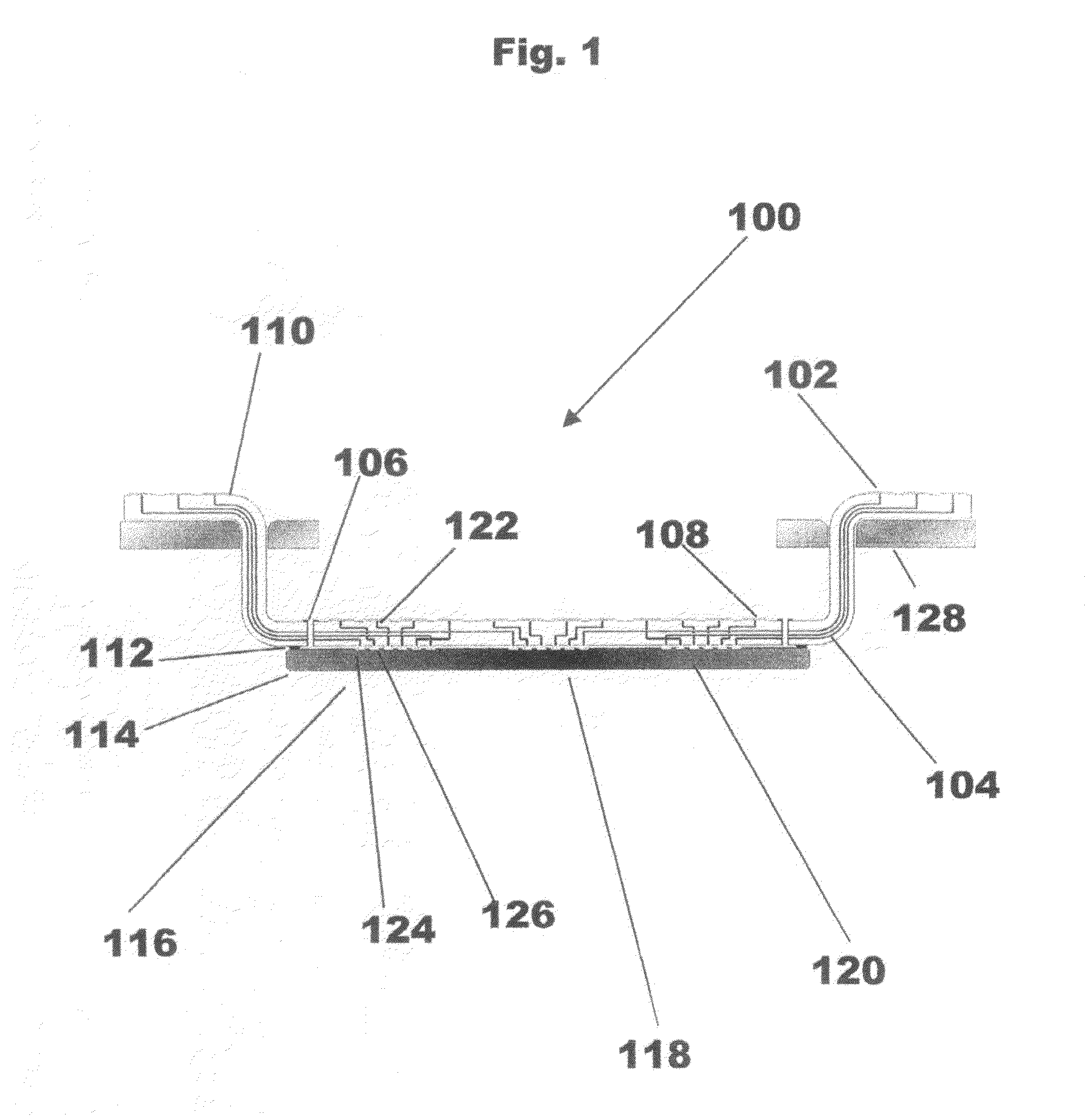

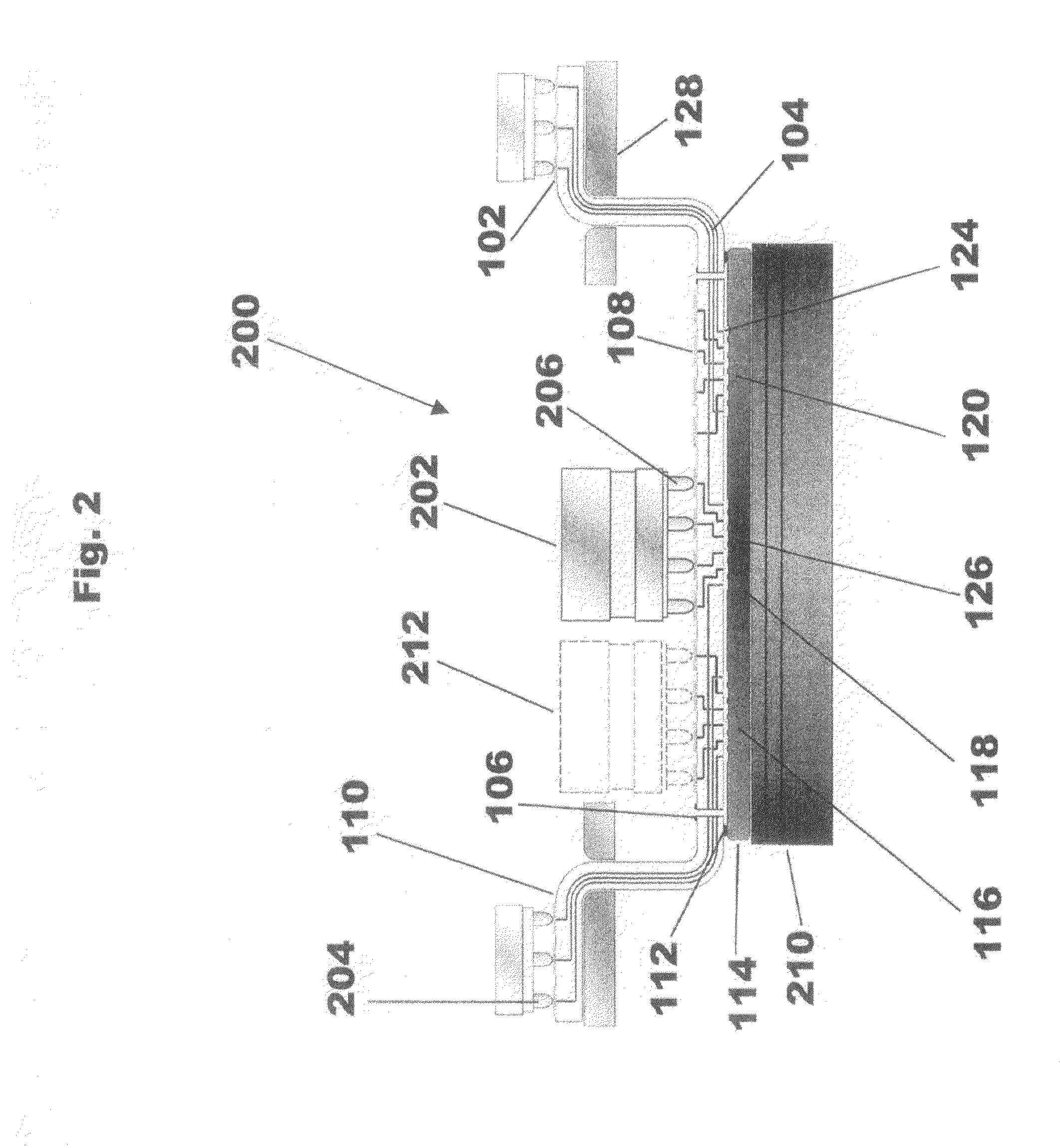

Intelligent probe card architecture

ActiveUS20050237073A1Digital circuit testingOverload protection arrangementsElectrical resistance and conductanceProbe card

A probe card for a wafer test system is provided with a number of on board features enabling fan out of a test system controller channel to test multiple DUTs on a wafer, while limiting undesirable effects of fan out on test results. On board features of the probe card include one or more of the following: (a) DUT signal isolation provided by placing resistors in series with each DUT input to isolate failed DUTs; (b) DUT power isolation provided by switches, current limiters, or regulators in series with each DUT power pin to isolate the power supply from failed DUTs; (c) self test provided using an on board micro-controller or FPGA; (d) stacked daughter cards provided as part of the probe card to accommodate the additional on board test circuitry; and (e) use of a interface bus between a base PCB and daughter cards of the probe card, or the test system controller to minimize the number of interface wires between the base PCB and daughter cards or between the base PCB and the test system controller.

Owner:FORMFACTOR INC

Programmable devices to route signals on probe cards

InactiveUS20060170435A1Great switching densityLong life cycleSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsProbe cardTest engineer

A probe card of a wafer test system includes one or more programmable ICs, such as FPGAs, to provide routing from individual test signal channels to one of multiple probes. The programmable ICs can be placed on a base PCB of the probe card, or on a daughtercard attached to the probe card. With programmability, the PCB can be used to switch limited test system channels away from unused probes. Programmability further enables a single probe card to more effectively test devices having the same pad array, but having different pin-outs for different device options. Reprogrammability also allows test engineers to re-program as they are debugging a test program. Because the programmable IC typically includes buffers that introduce an unknown delay, in one embodiment measurement of the delay is accomplished by first programming the programmable IC to provide a loop back path to the test system so that buffer delay can be measured, and then reprogramming the programmable IC now with a known delay to connect to a device being tested.

Owner:FORMFACTOR INC

Semiconductor wafer processing system with vertically-stacked process chambers and single-axis dual-wafer transfer system

InactiveUS20020033136A1Optimize vertical orientation and layoutReduce system footprintSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusTransfer systemComputer module

A semiconductor wafer processing system including a multi-chamber module having vertically-stacked semiconductor wafer process chambers and a loadlock chamber dedicated to each semiconductor wafer process chamber. Each process chamber includes a chuck for holding a wafer during wafer processing. The multi-chamber modules may be oriented in a linear array. The system further includes an apparatus having a dual-wafer single-axis transfer arm including a monolithic arm pivotally mounted within said loadlock chamber about a single pivot axis. The apparatus is adapted to carry two wafers, one unprocessed and one processed, simultaneously between the loadlock chamber and the process chamber. A method utilizing the disclosed system is also provided.

Owner:AVIZA TECHNOLOGY INC

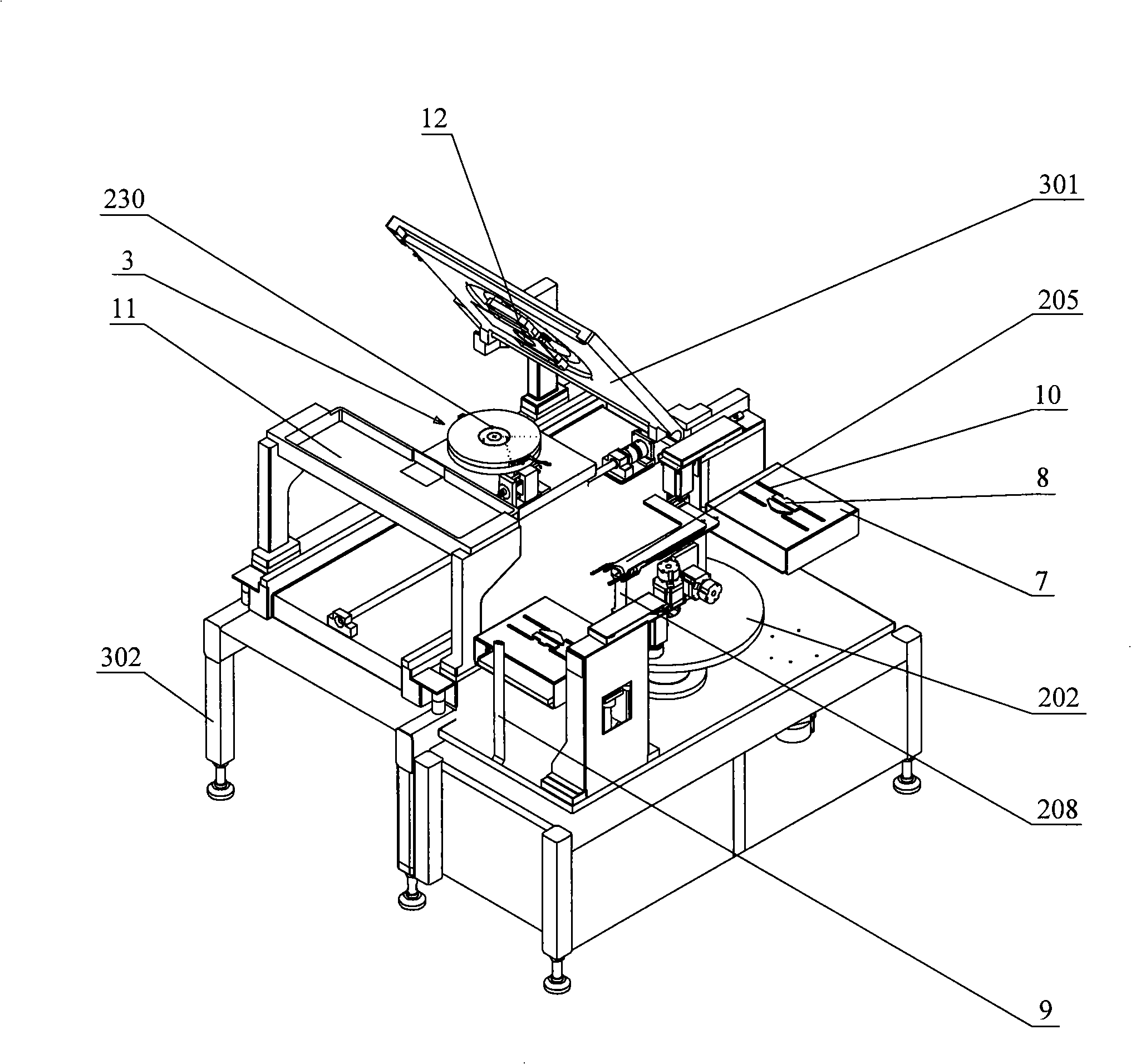

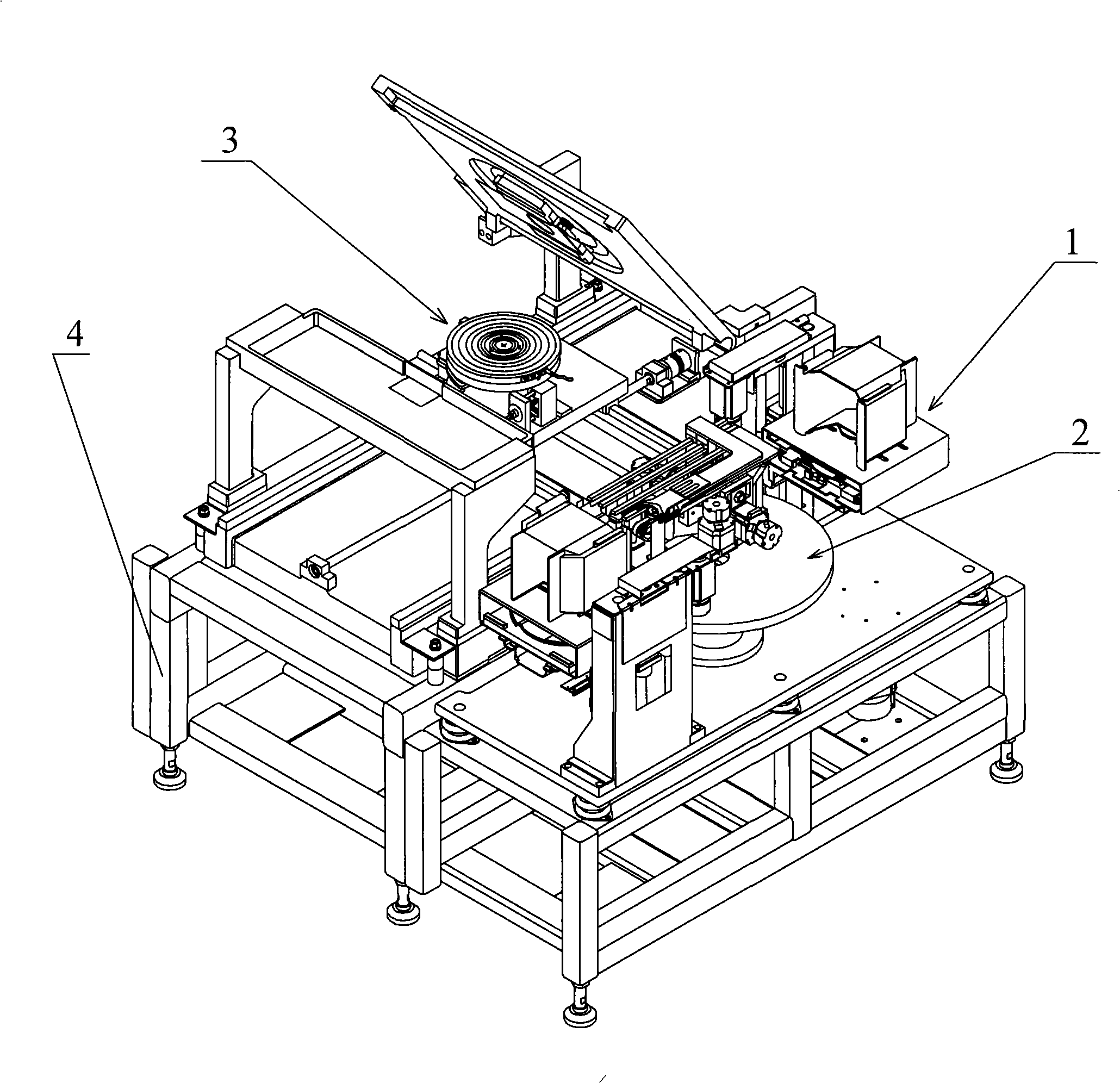

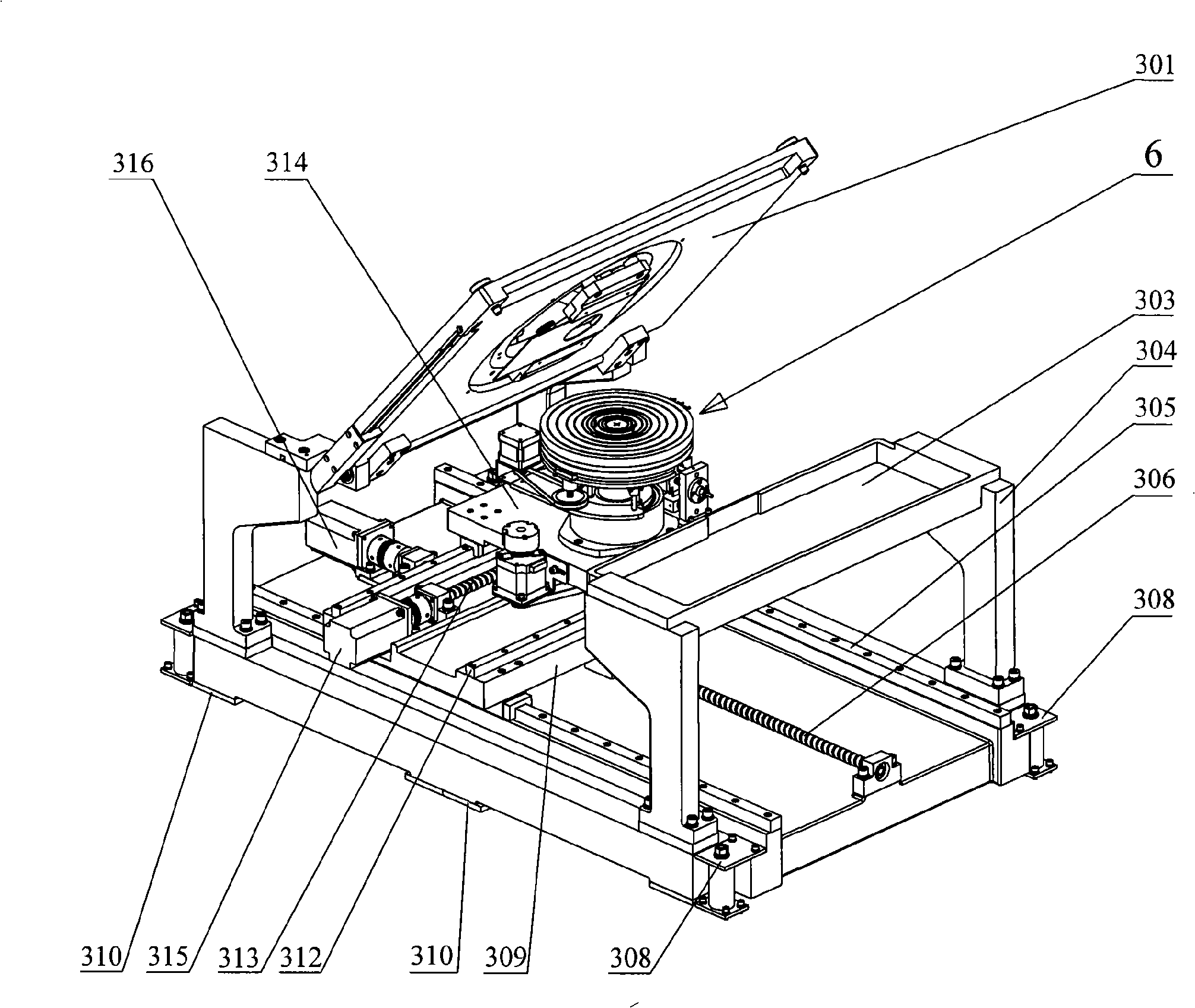

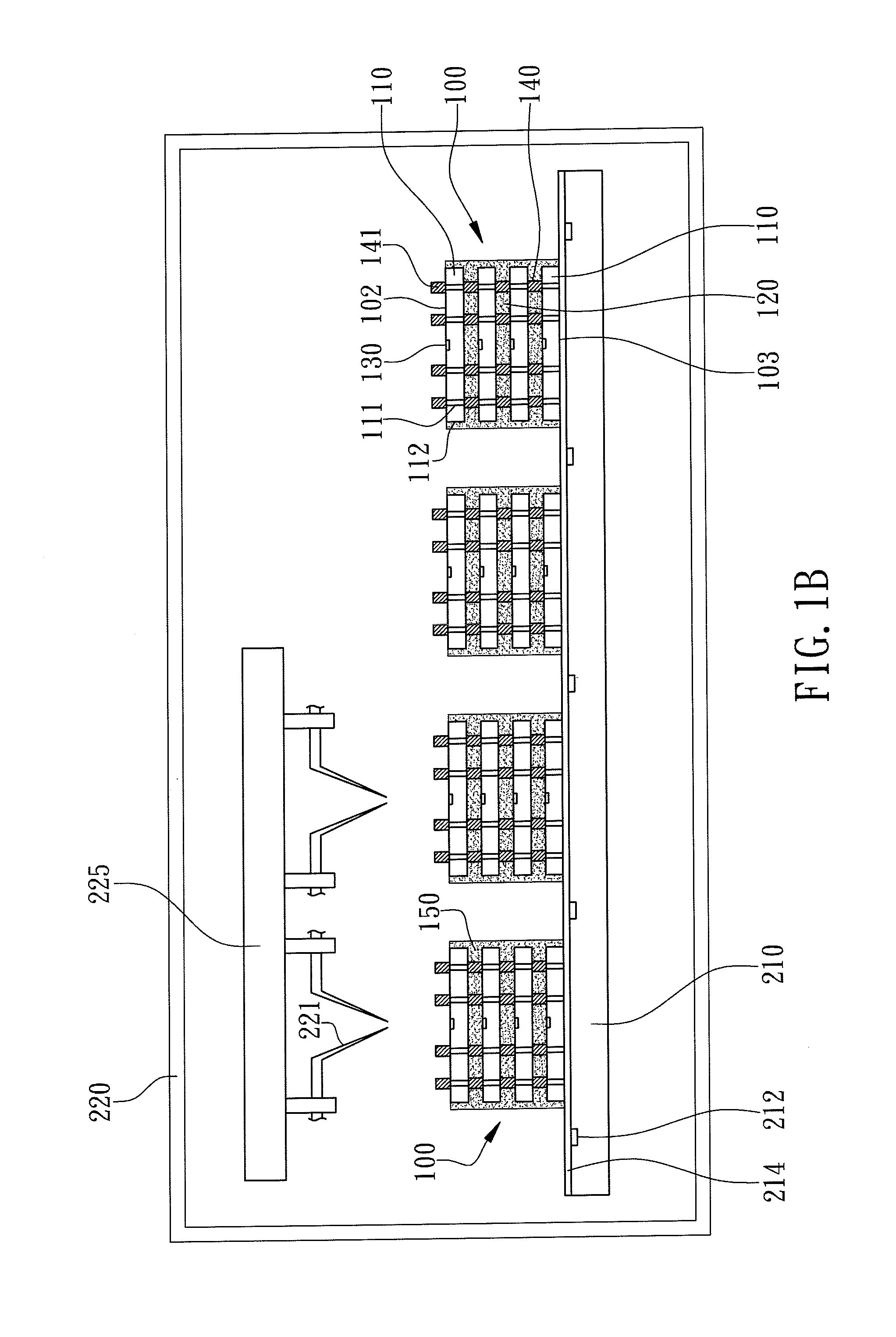

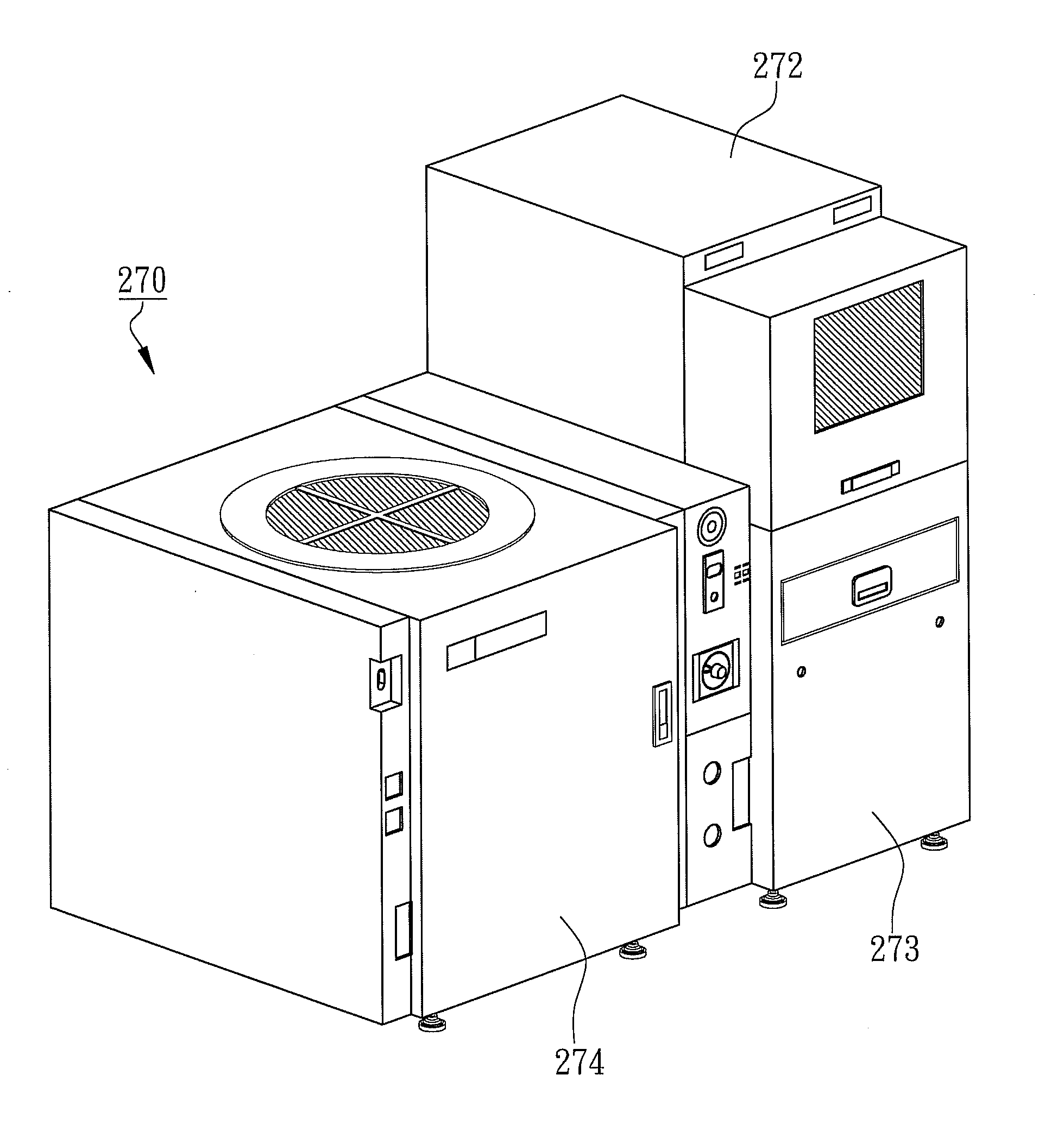

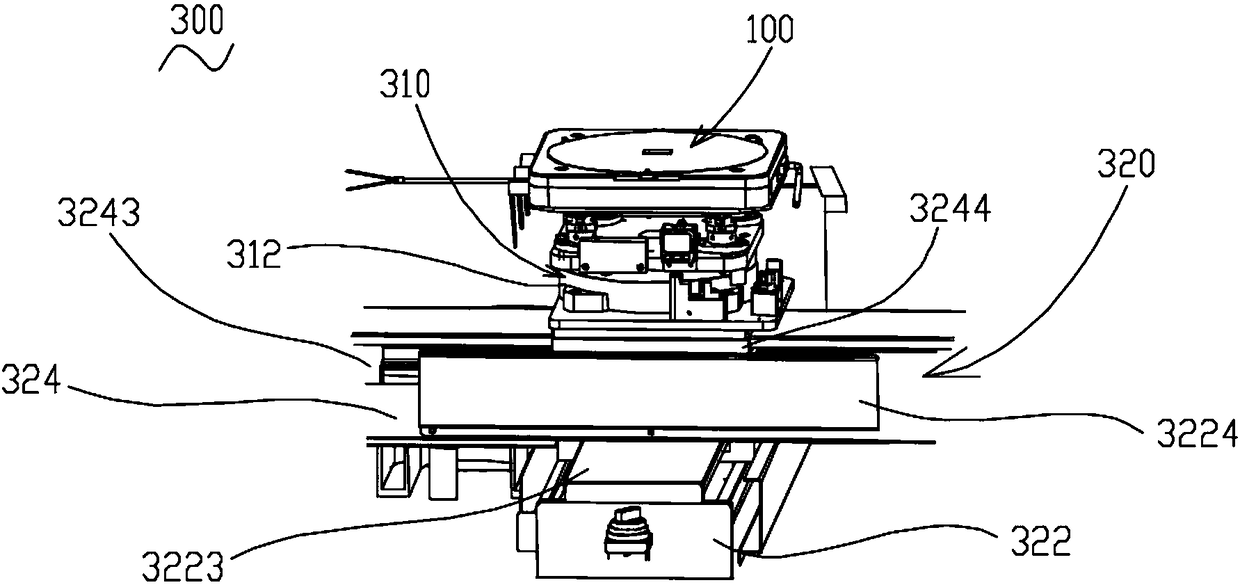

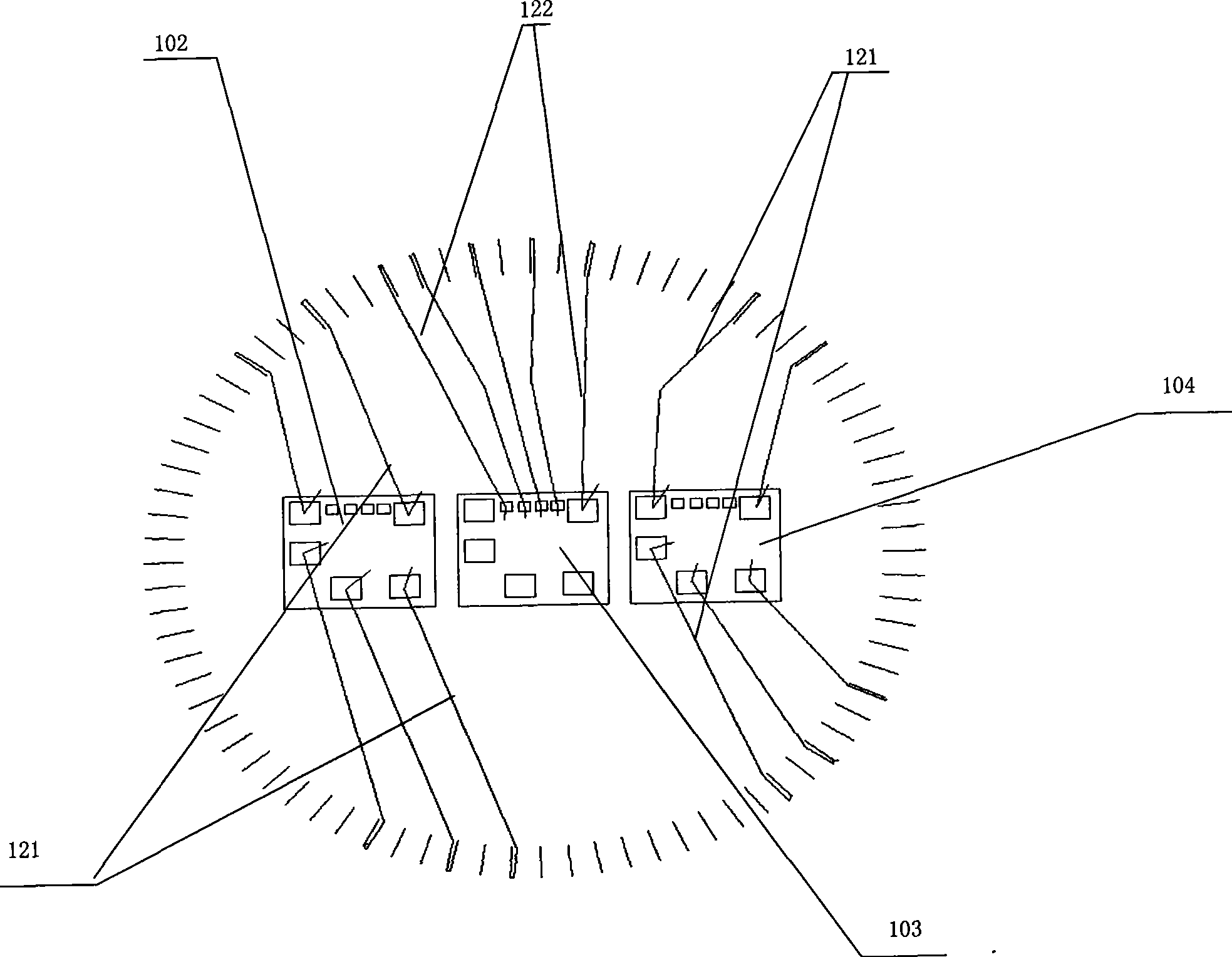

Full-automatic wafer test method and equipment accomplishing the method

InactiveCN101261306AThe method is efficientHigh degree of automationSemiconductor/solid-state device testing/measurementElectronic circuit testingTest platformWafer testing

The invention discloses a full automatic wafer test method and a device to realize the test method. The method includes the following steps: scanning a spool box, drawing chips, rough adjusting, sending the chips, accuracy alignment, testing and replacing the wafer. The device to realize the full automatic wafer test method consists of a chip placing and counting device arranged on a stander, a wafer transmission device arranged on a stander at one side of the chip placing and counting device, and a wafer test platform device arranged at one side of the wafer transmission device and matched with the transmission device. The method has the advantages of high efficiency, low test cost, high automation and accurate test result.

Owner:无锡市易控系统工程有限公司

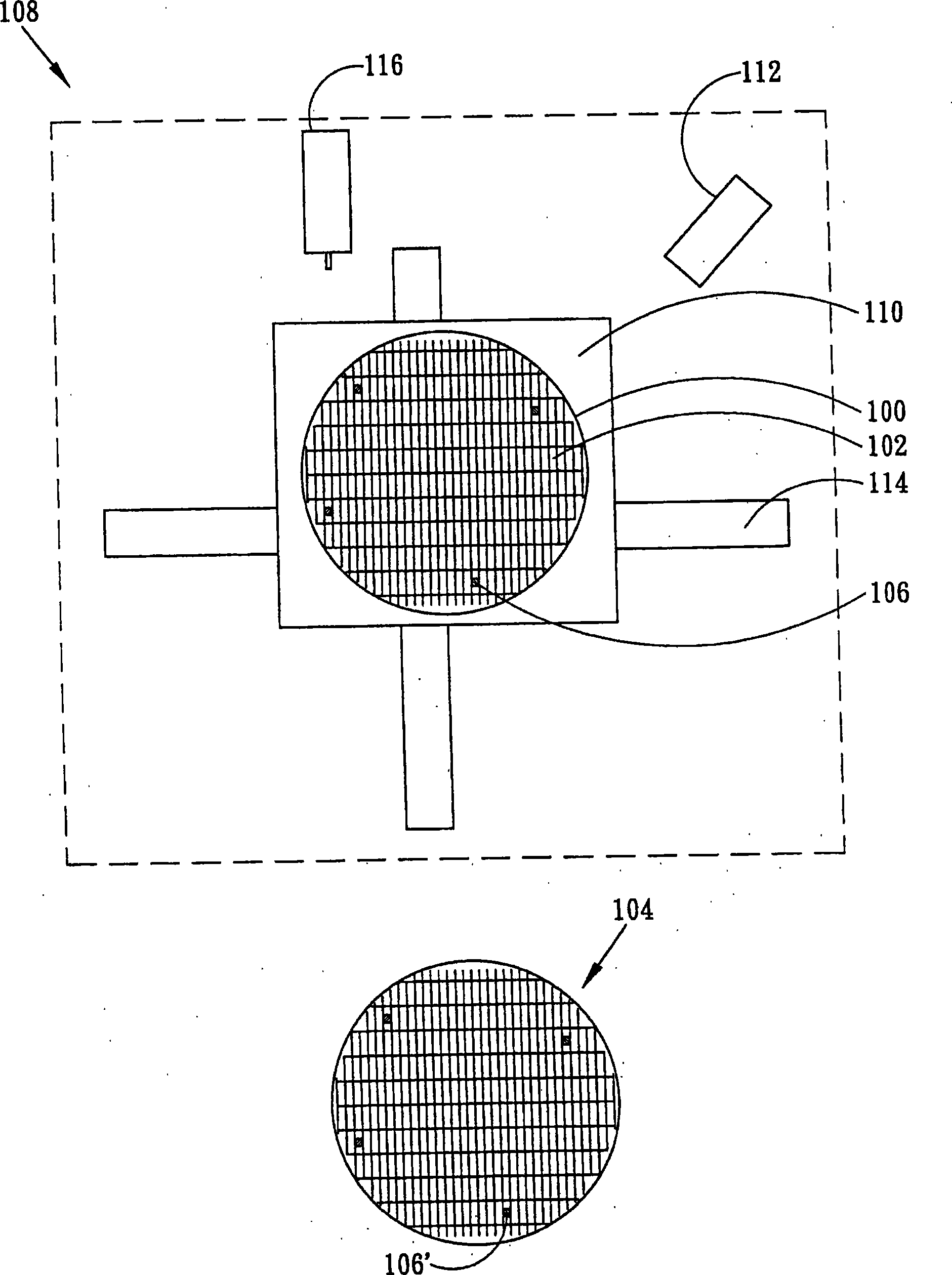

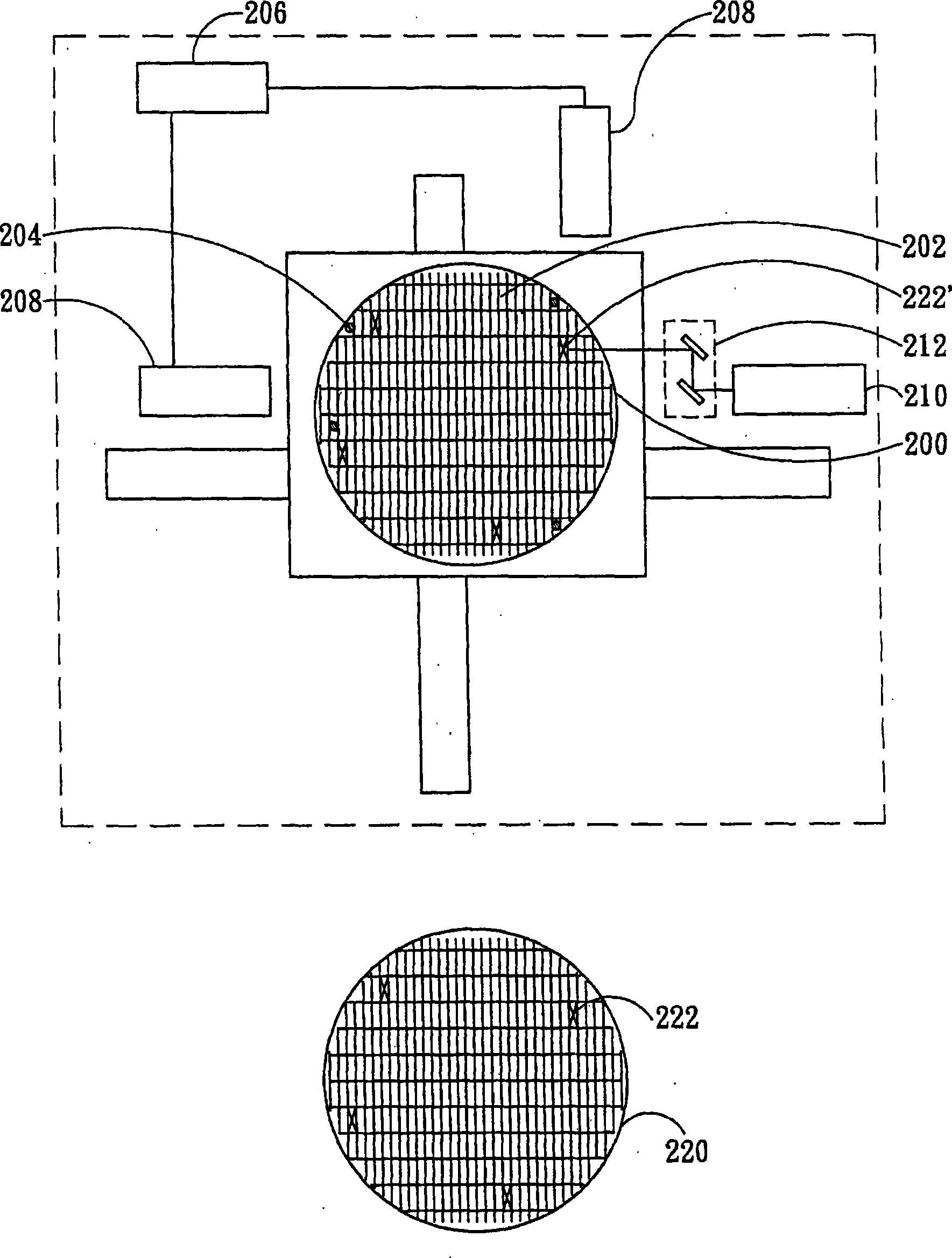

Method for marking wafer, method for marking poor product crystal grain, method for wafer contraposition, and wafer test machine

InactiveCN101369516ASave spaceReduce the number of machinesSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingPermanent markerEngineering

The invention provides a method for marking a wafer, which comprises providing a wafer having at least two reference marks, wherein a surface of the wafer comprises a plurality of crystal grains, at the same time, detecting the reference marks of the wafer to perform a wafer alignment, and marking the wafer by a laser. In addition, the invention can be suitable for marking the crystal grains of the wafer (for example, throwout crystal grains), comparing to the prior art of marking the throwout crystal grains by ink, has advantages of less wafer pollution, operation time, workshop space and permanent marker, is easier to reconstruct by the existing wafer tester or ink machine platform.

Owner:KING YUAN ELECTRONICS

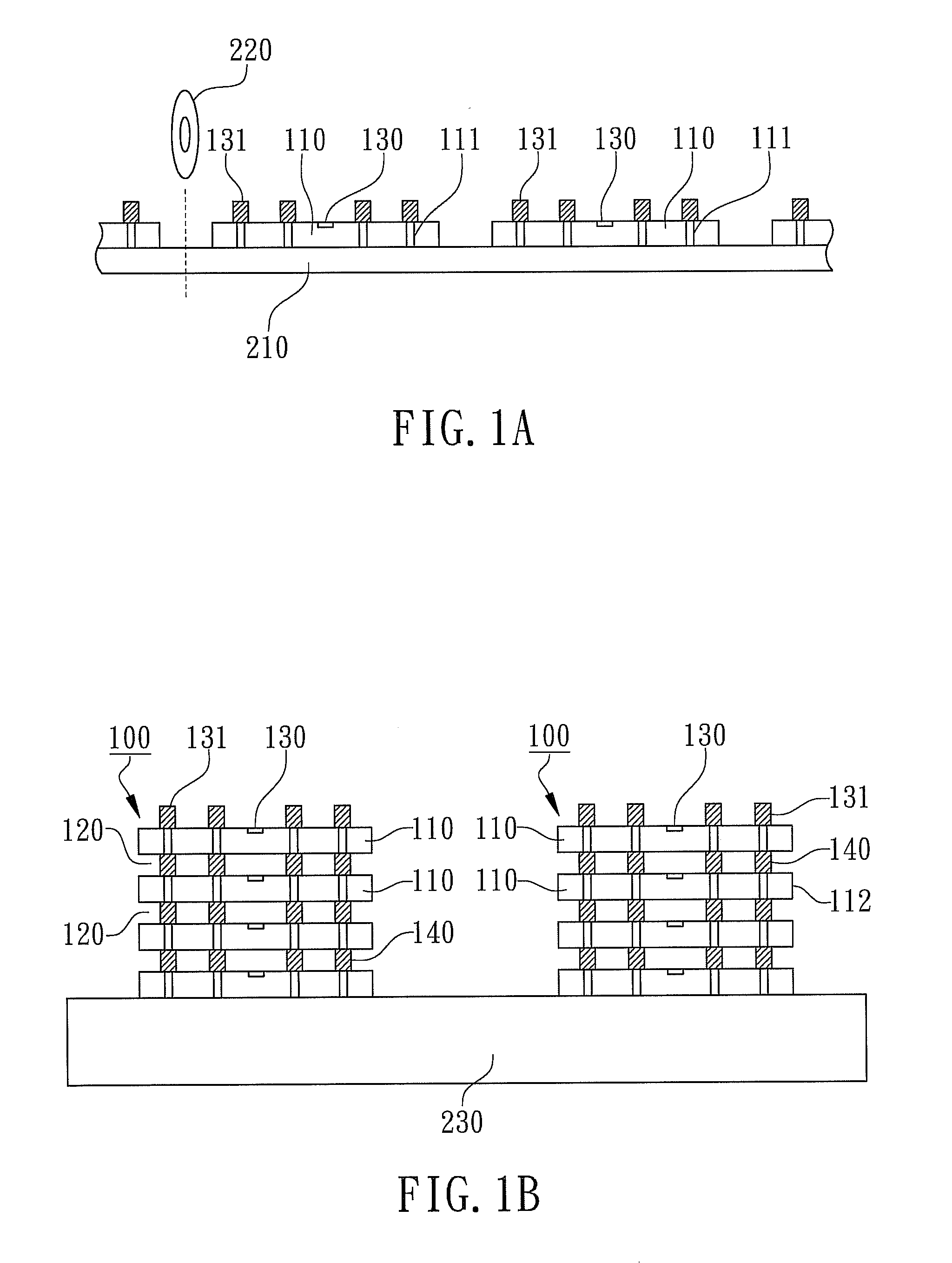

Method for wafer-level testing diced multi-chip stacked packages

InactiveUS20140051189A1Reduce test costsSemiconductor/solid-state device testing/measurementSolid-state devicesAdhesiveElectrical connection

Disclosed is a method for wafer-level testing a plurality of diced multi-chip stacked packages. Each package includes a plurality of chips with vertically electrical connections such as TSVs. Next, according to a die-on-wafer array arrangement, the multi-chip stacked packages are fixed on a transparent reconstructed wafer by a photo-sensitive adhesive, and the packages are located within the component-bonding area of the wafer. Then, the transparent reconstructed wafer carrying the multi-chip stacked packages can be loaded into a wafer tester for probing. Accordingly, the wafer testing probers in the wafer tester can be utilized to probe the testing electrodes of the stacked packages so that it is easy to integrate this wafer-level testing method especially into TSV packaging processes.

Owner:POWERTECH TECHNOLOGY

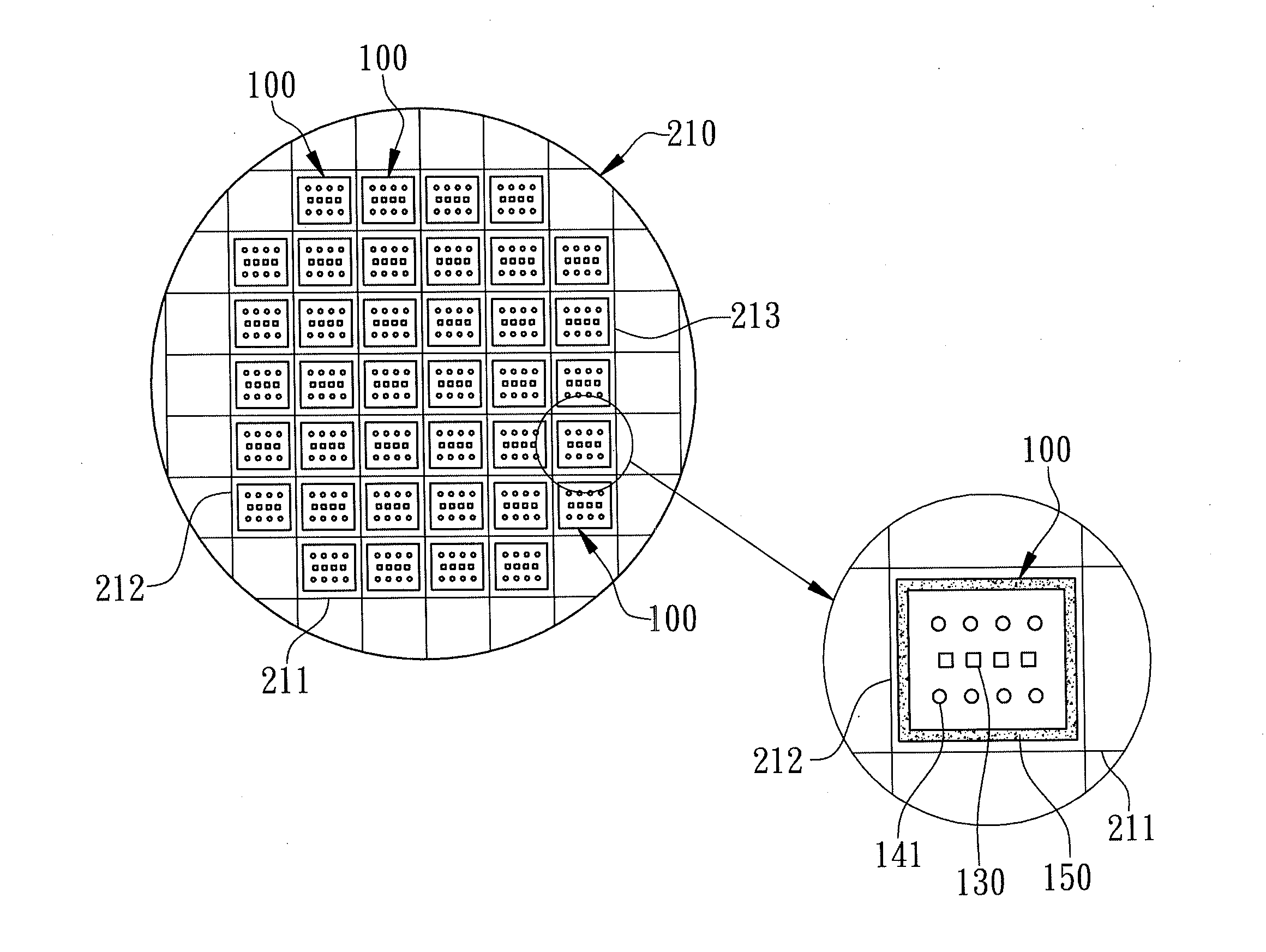

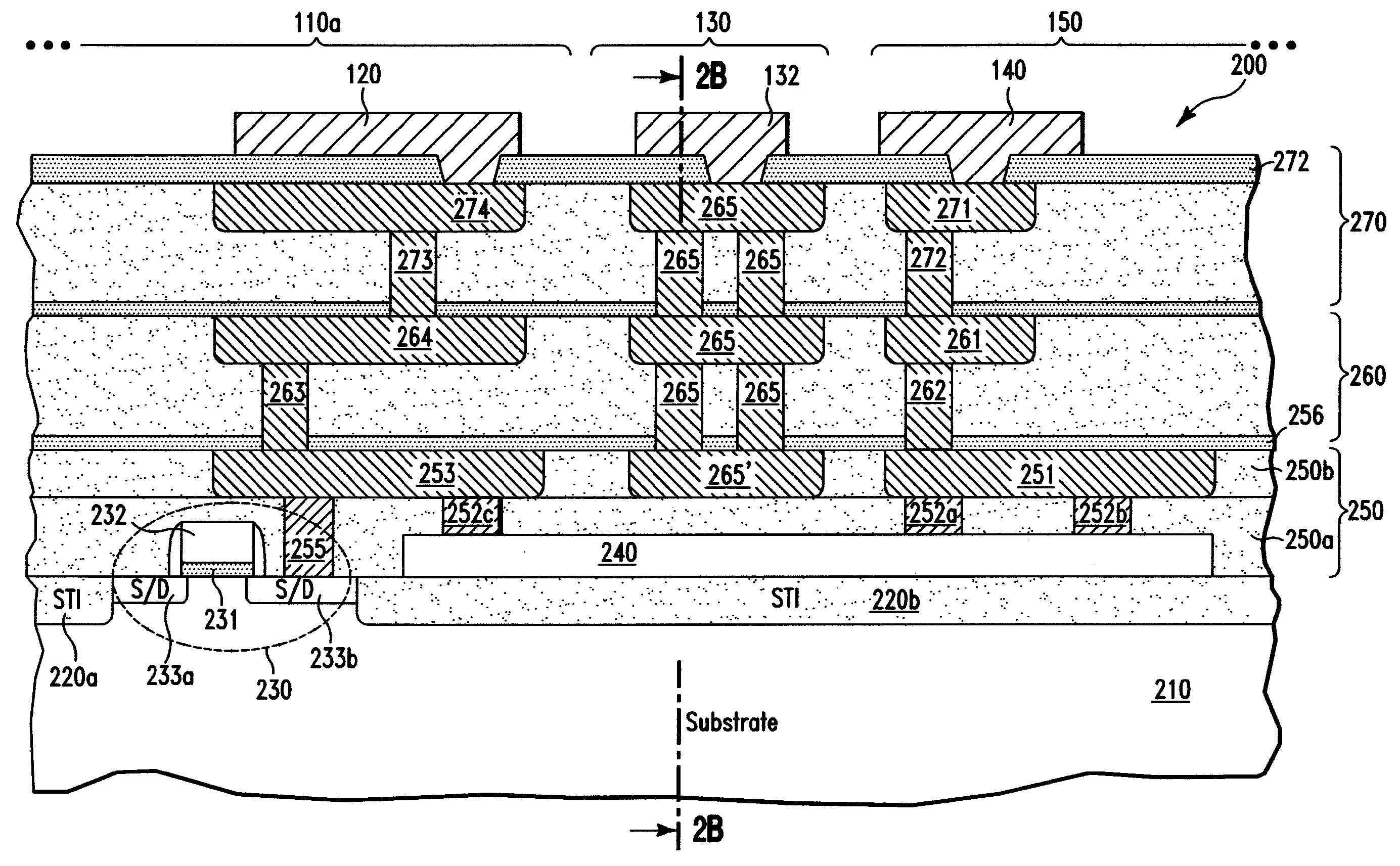

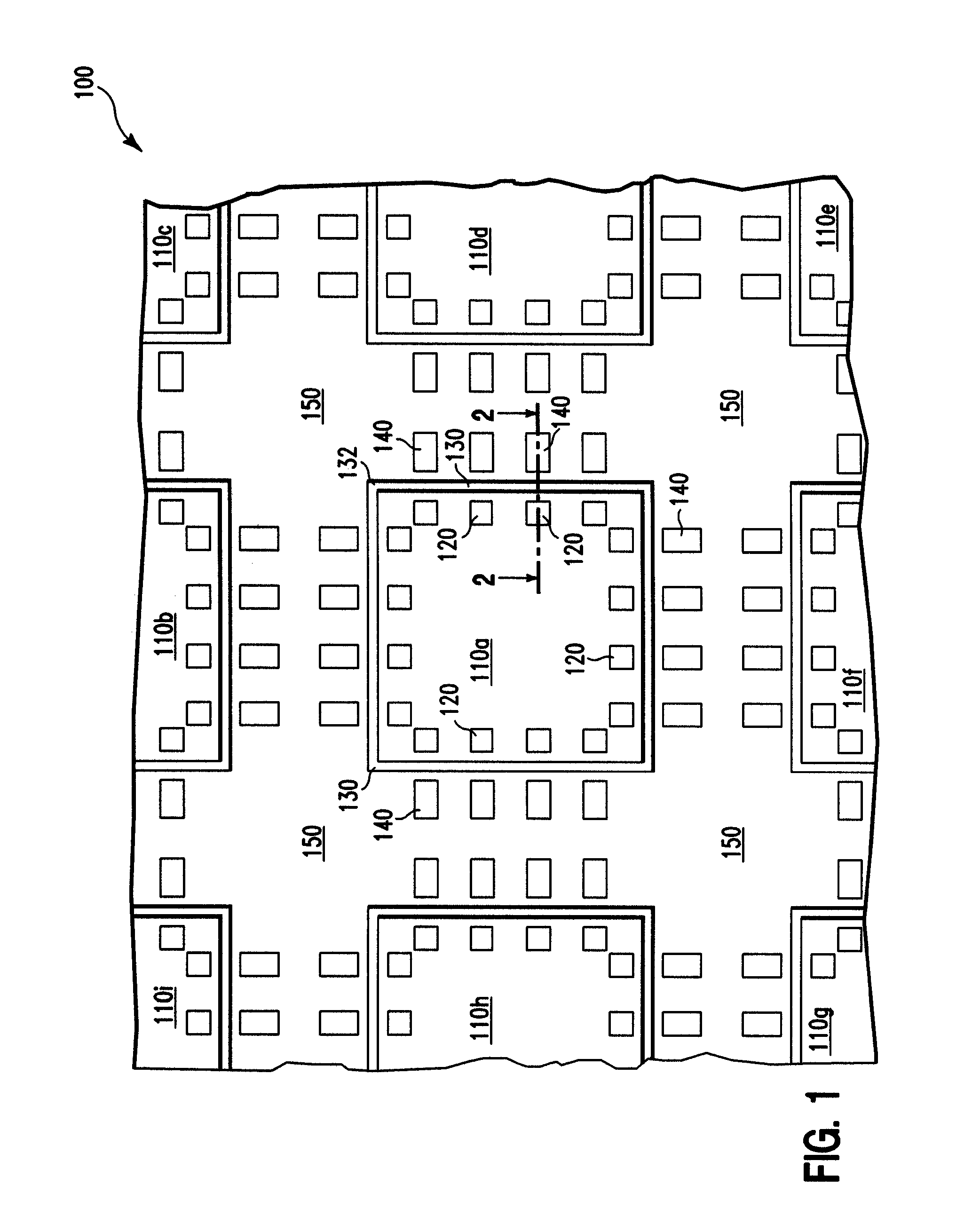

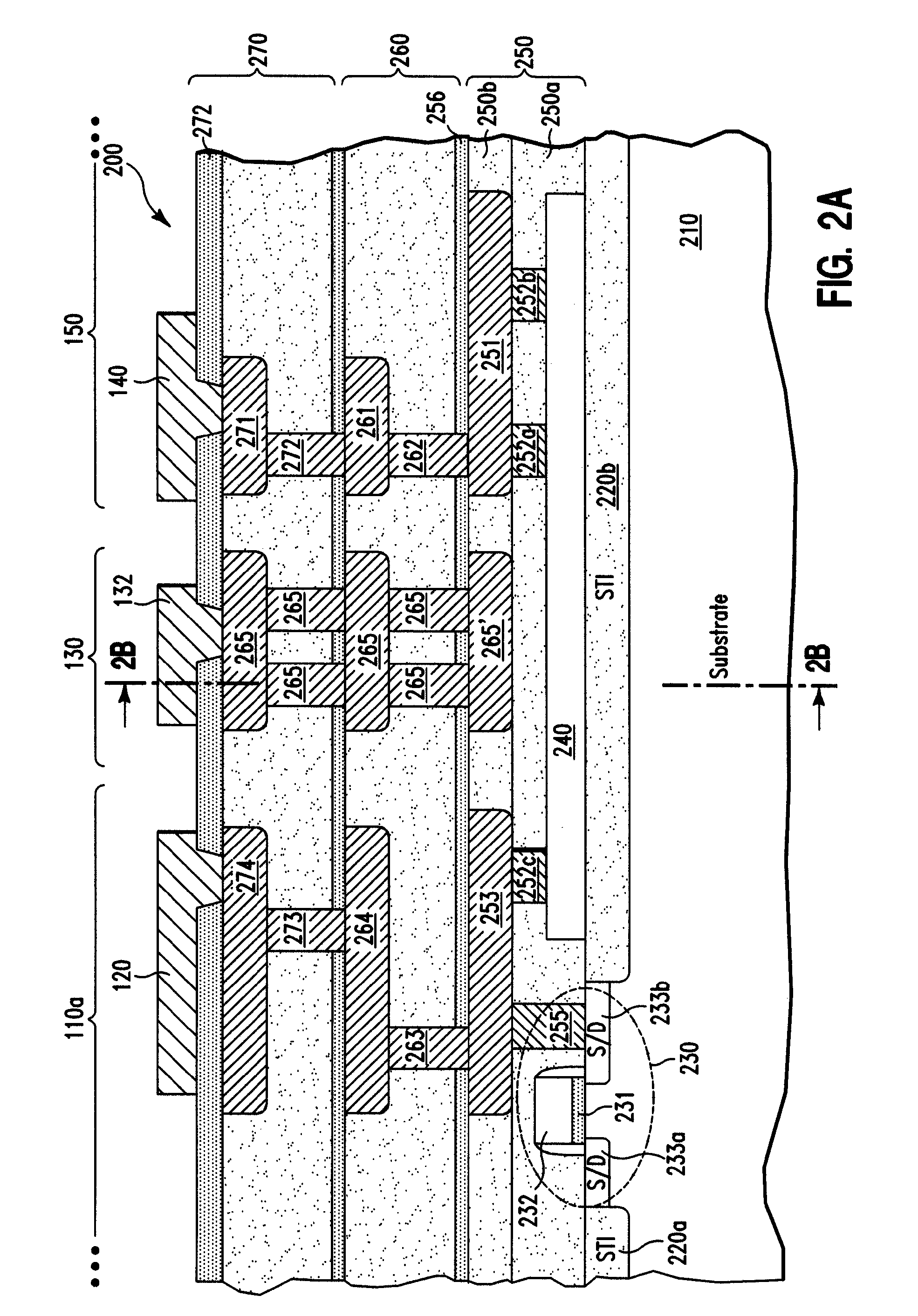

Probing pads in kerf area for wafer testing

InactiveUS7482675B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical connectionEngineering

A structure and a method for forming the same. The structure includes (a) a substrate having a top substrate surface; (b) an integrated circuit on the top substrate surface, wherein the integrated circuit includes a bond pad electrically connected to a transistor of the integrated circuit; (c) a protection ring on the top substrate surface and on a perimeter of the integrated circuit; (c) a kerf region on the top substrate surface, wherein the protection ring is sandwiched between and physically isolates the integrated circuit and the kerf region, wherein the kerf region includes a probe pad electrically connected to the bond pad, and wherein the kerf region is adapted to be destroyed by chip dicing without damaging the integrated circuit and the protection ring.

Owner:GLOBALFOUNDRIES INC

Optical Wafer and Die Probe Testing

InactiveUS20140363905A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingOptical testEngineering

An optical die probe wafer testing circuit arrangement and associated testing methodology are described for mounting a production test die (157) and surrounding scribe grid (156) to a test head (155) which is positioned over a wafer (160) in alignment with a die under test (163) and surrounding scribe grid (161, 165), such that one or more optical deflection mirrors (152, 154) in the test head scribe grid (156) are aligned with one or more optical deflection mirrors (162, 164) in the scribe grid (161, 165) for the die under test (163) to enable optical die probe testing on the die under test (163) by directing a first optical test signal (158) from the production test die (157), through the first and second optical deflection mirrors (e.g., 152, 162) and to the first die.

Owner:NXP USA INC

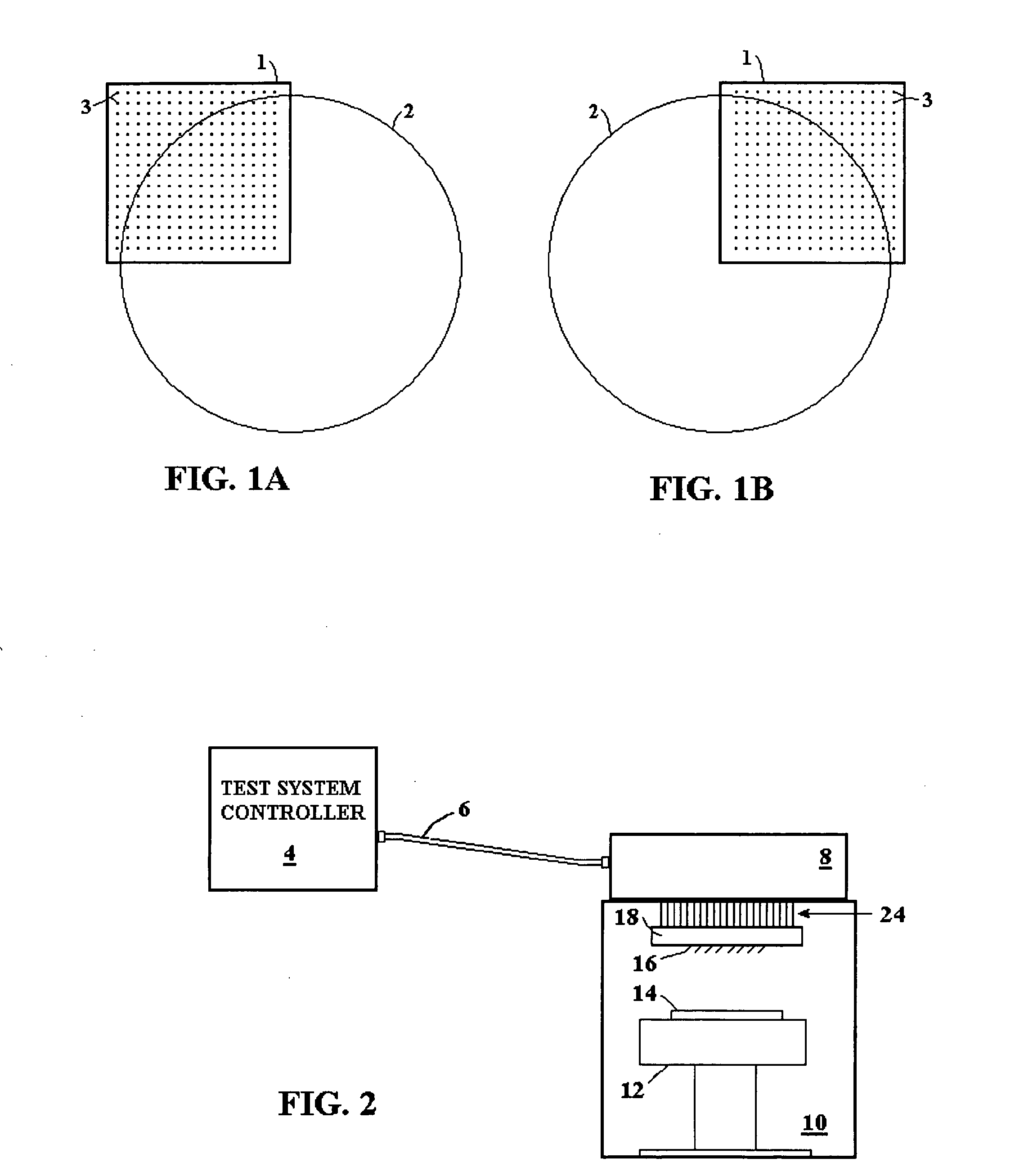

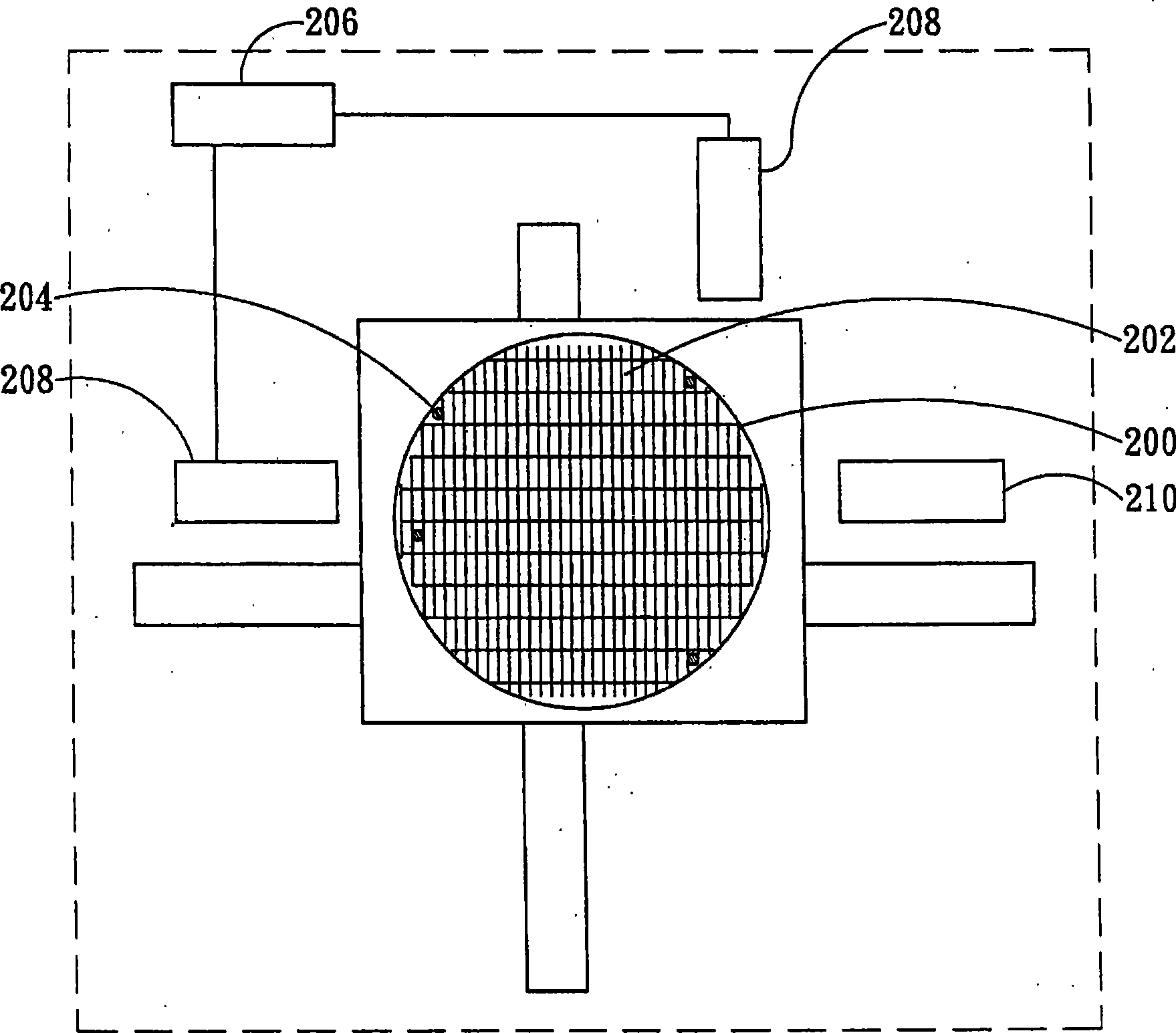

Methods for multi-modal wafer testing using edge-extended wafer translator

ActiveUS7456643B2Electrical measurement instrument detailsIndividual semiconductor device testingEngineeringIntegrated circuit

Access to integrated circuits of a wafer for concurrently performing two or more types of testing, is provided by bringing a wafer and an edge-extended wafer translator into an attached state. The edge-extended wafer translator having wafer-side contact terminals and inquiry-side contact terminals disposed thereon, a first set of wafer-side contact terminals being electrically coupled to a first set of inquiry-side contact terminals, and a second set of wafer-side contact terminals being electrically coupled to a second set of inquiry-side contact terminals. The edge-extended wafer translator having a central portion generally coextensive with the attached wafer, and an edge-extended portion extending beyond the boundary generally defined by the outer circumferential edge of the wafer. A first set of pads of at least one integrated circuit is electrically coupled to the first set of wafer-side contact terminals, and a second set of pads of the integrated circuit is electrically coupled to the second set of wafer-side contact terminals. The edge-extended wafer translator may be shaped such that its edge-extended portion is not coplanar with the central portion thereof.

Owner:SHANGHAI CARSON SEMICON CO LTD

Method for testing multi-chip stacked packages

InactiveUS20130076384A1Easy to integrateReduce in quantityElectronic circuit testingAdhesive beltEngineering

Disclosed is a method for testing multi-chip stacked packages. Initially, one or more substrate-less chip cubes are provided, each consisting of a plurality of chips such as chips stacked together having vertically connected with TSV's where there is a stacked gap between two adjacent chips. Next, the substrate-less chip cubes are adhered onto an adhesive tape where the adhesive tape is attached inside an opening of a tape carrier. Then, a filling encapsulant is formed on the adhesive tape to completely fill the chip stacked gaps. Next, the tape carrier is fixed on a wafer testing carrier in a manner to allow the substrate-less chip cubes to be loaded into a wafer tester without releasing from the adhesive tape. Accordingly, the probers of the wafer tester can be utilized to probe testing electrodes of the substrate-less chip cubes so that it is easy to integrate this testing method in TSV fabrication processes.

Owner:POWERTECH TECHNOLOGY

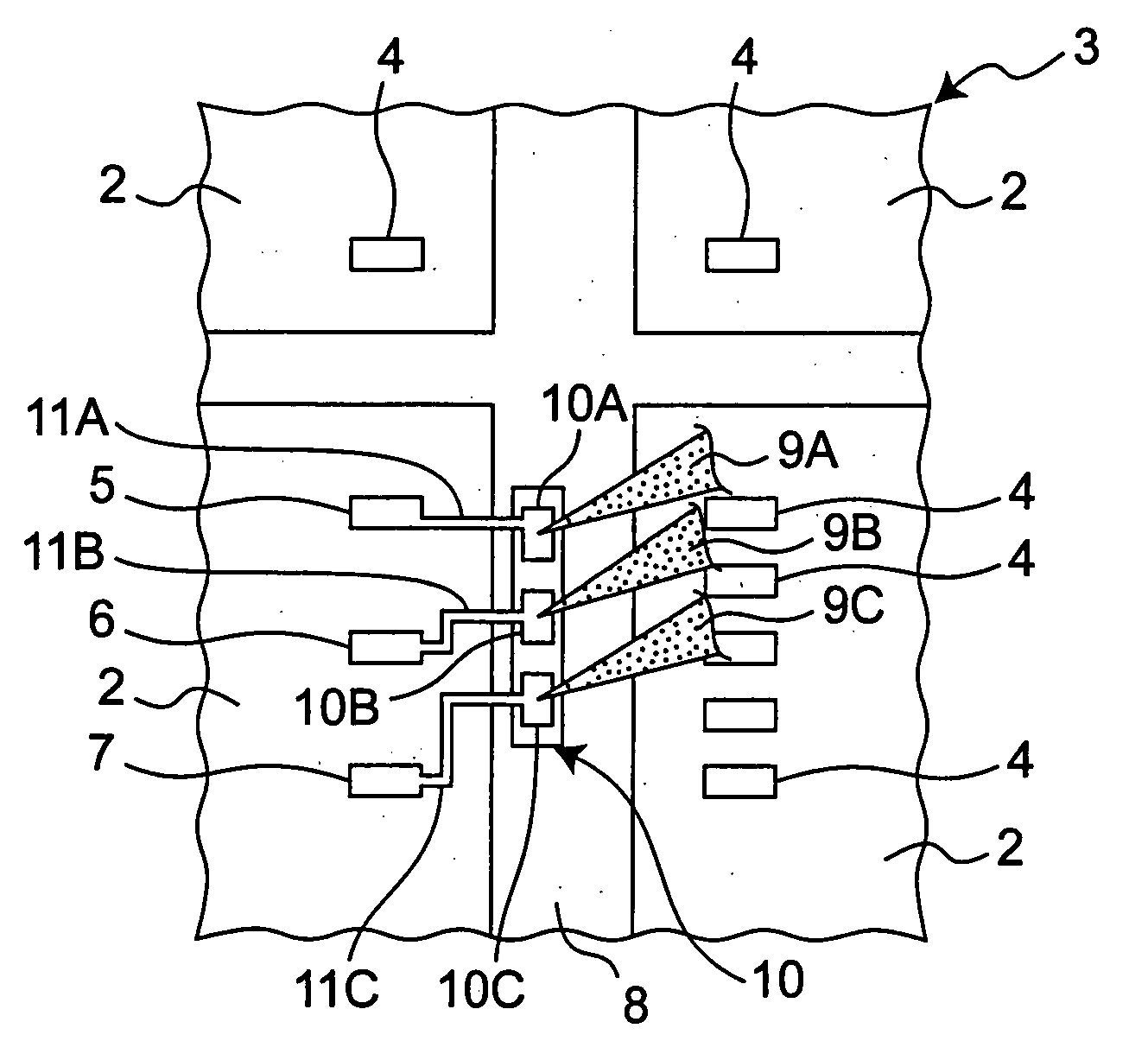

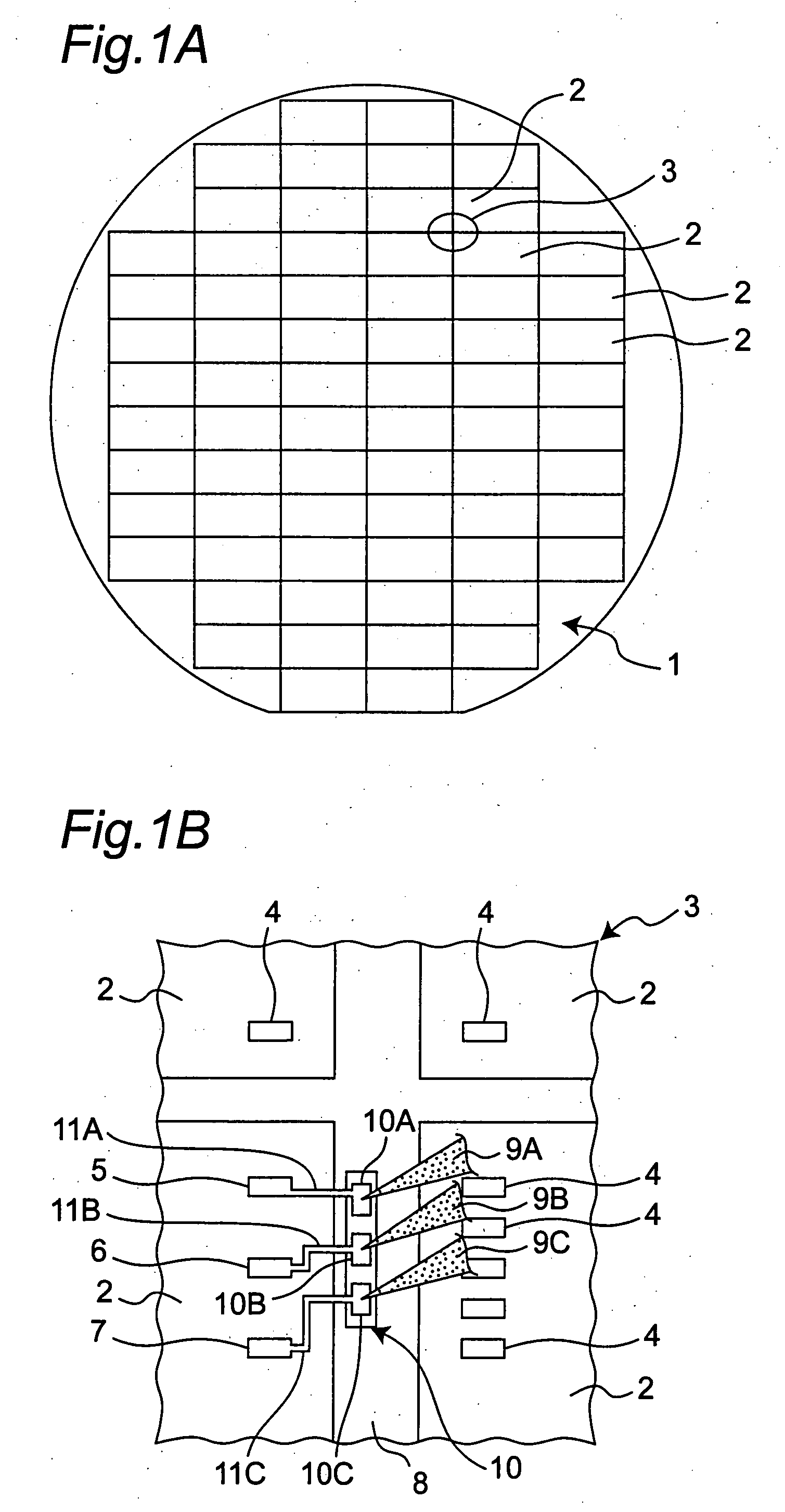

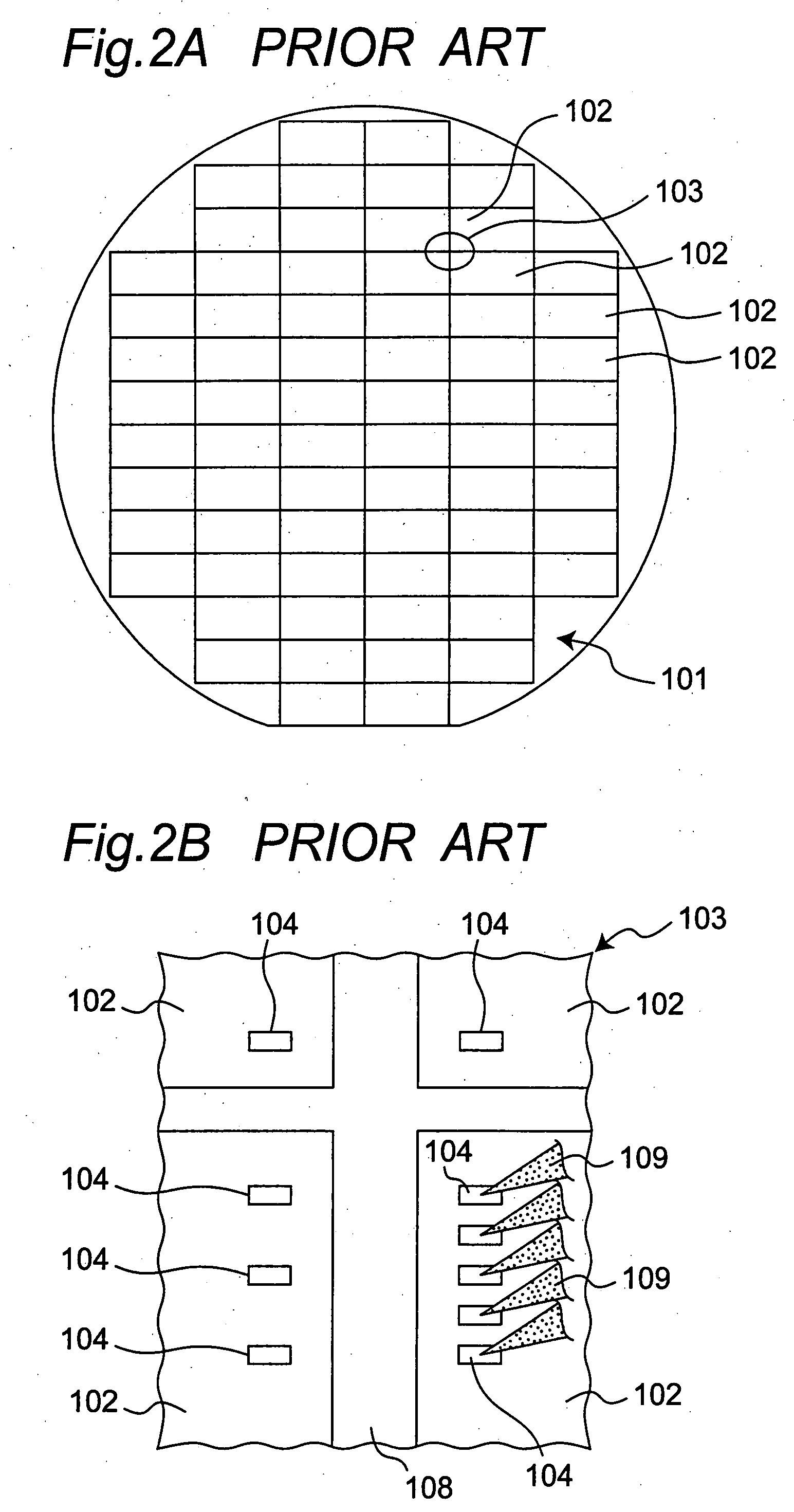

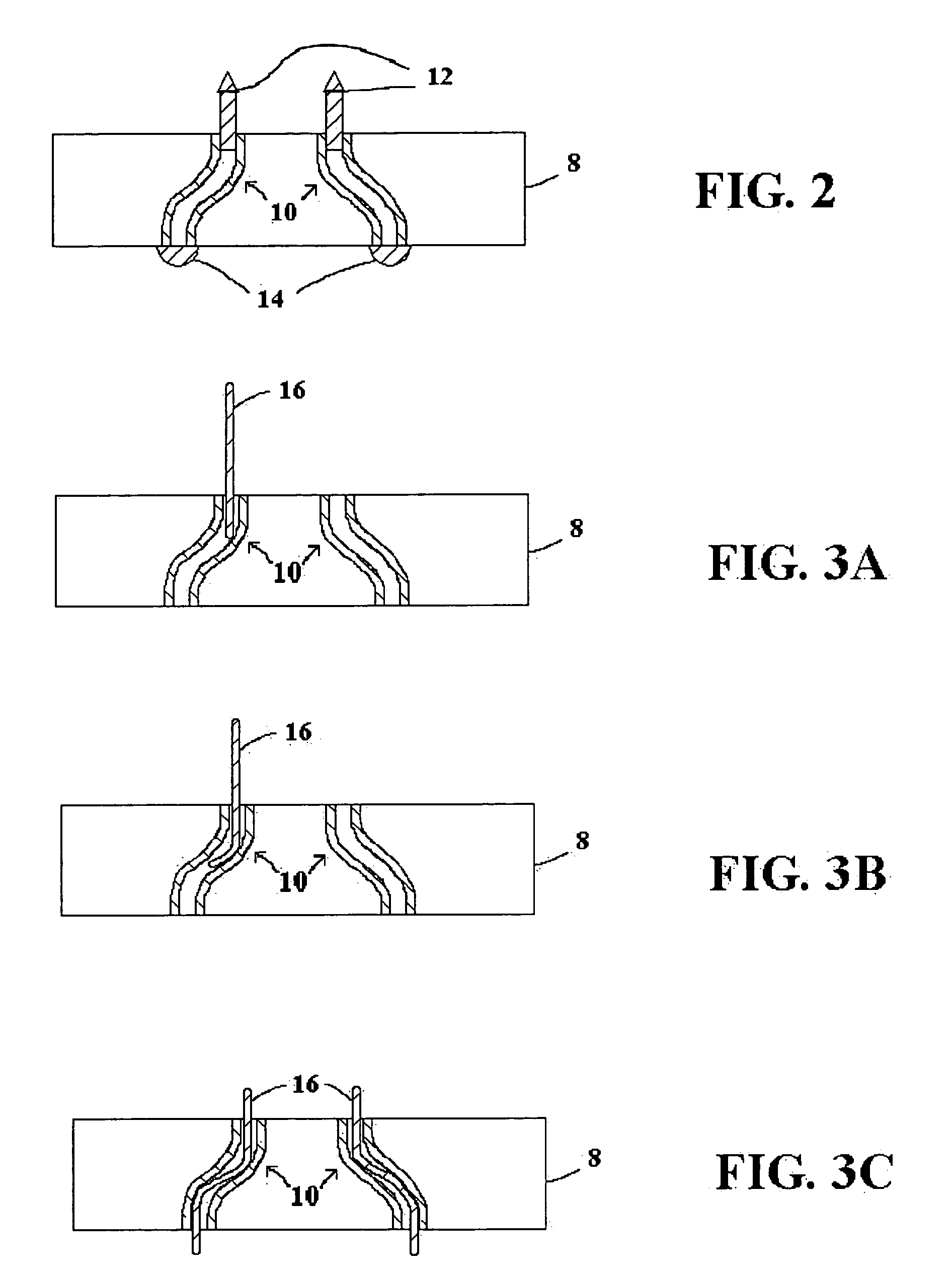

Wafer and semiconductor device testing method

InactiveUS20080017856A1Reduce in quantityReduce contactSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsProbe cardDevice material

At least three pads 10A, 10B, 10C are provided on a scribe line 8 located adjacent to a chip region 2. The three pads are a power pad 10A connected to a power potential portion 5 in the chip region 2, a grounding pad 10B connected to a ground potential portion 6 in the chip region 2, and a switchover pad 10C that is connected to a semiconductor device 7 in the chip region 2 and switches the operating state of the semiconductor device 7 between a normal operating state and a standby state. During a wafer test, contact pins 9A, 9B, 9C of a probe card are brought in contact with the three pads 10A, 10B, 10C, respectively.

Owner:SHARP KK

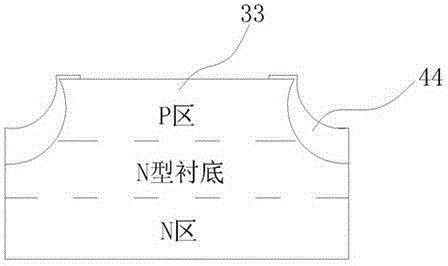

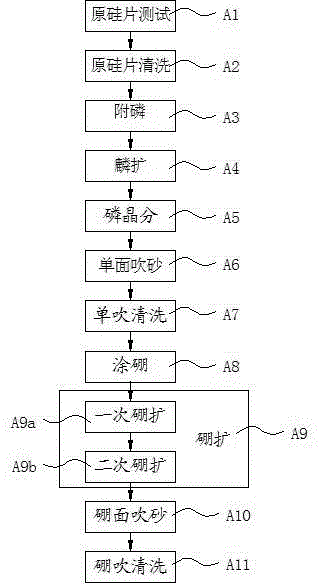

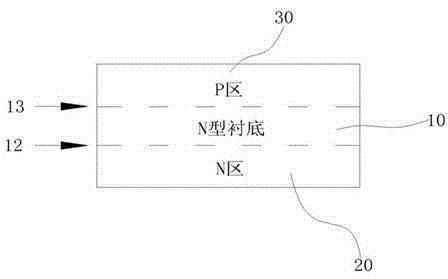

Manufacturing process of transient voltage suppression diode chip

ActiveCN103606521AStress reliefReduce defectsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotoresist

The invention discloses a manufacturing process of a transient voltage suppression diode chip. The manufacturing process of the transient voltage suppression diode chip includes two production processes: a diffusion process and a GPP process. The steps of the diffusion process include original silicon wafer testing, original silicon wafer washing, phosphorus attachment, phosphorus diffusion, phosphorus wafer separation, single side sand blasting, single blasting washing, boron coating, boron diffusion, boron wafer separation, boron side sand blasting, and boron blasting washing, wherein the step of boron diffusion comprises primary boron diffusion and secondary boron diffusion; and the steps of the GPP process sequentially include oxidation, primary photoetching, groove etching, photoresist sintering, groove washing, SIPOS passive film formation, glassivation, secondary photoetching, surface etching, and nickel-gold plating. The manufacturing process of the transient voltage suppression diode chip in the invention reduces defects of the chip, enables voltage distribution to be relatively concentrated, and reduces reverse leakage current at the same time.

Owner:南通康芯半导体科技有限公司

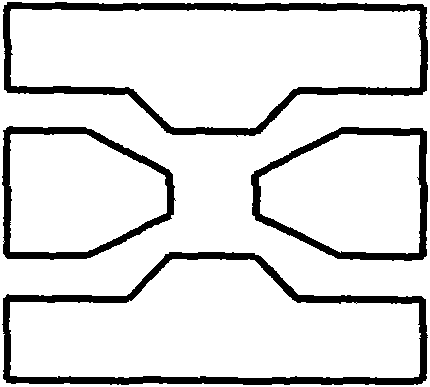

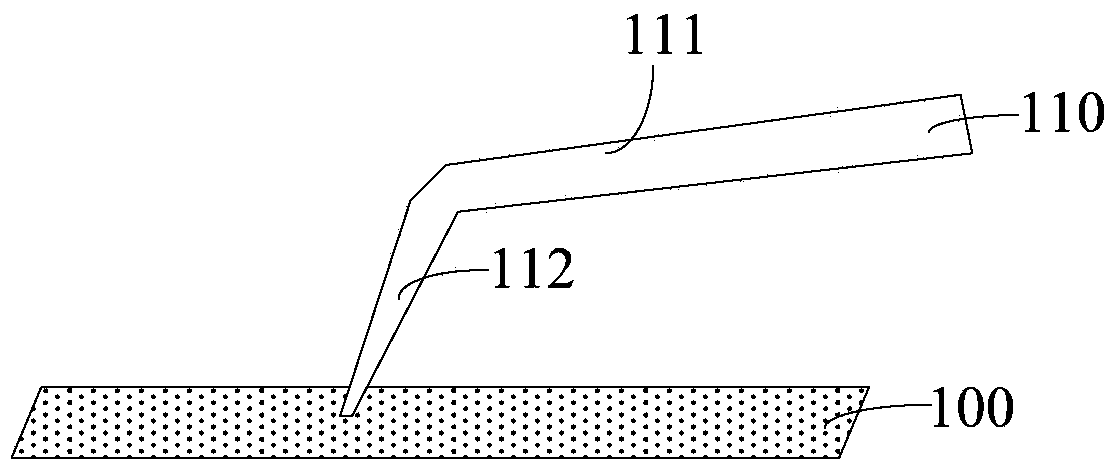

Probe of cantilever probe card

InactiveUS20090212807A1Reduce cleaning frequencyExtended run timeElectrical measurement instrument detailsElectrical testingEpoxyProbe card

A probe of a cantilever probe card (Epoxy probe card) is disclosed. The probe has a tip and a surface region extended from the tip of the probe about 5-10 mil is coated with a nano-film of high electro-conductive nanomaterial. The thickness of the nano-film is about 1-20 nm. Through the coating process, the nano-film coated on the probe of the cantilever probe card can efficiently provide the excellent advantages of no-clean, stable electro-conductivity, minimum overdrive force and longer usage lifetime for the probe of cantilever probe card. Accordingly, the yield of wafer testing can be improved and the frequency of cleaning the probe can be decreased. Furthermore, the total testing cost can be reduced.

Owner:IPWORKS TECH CORP

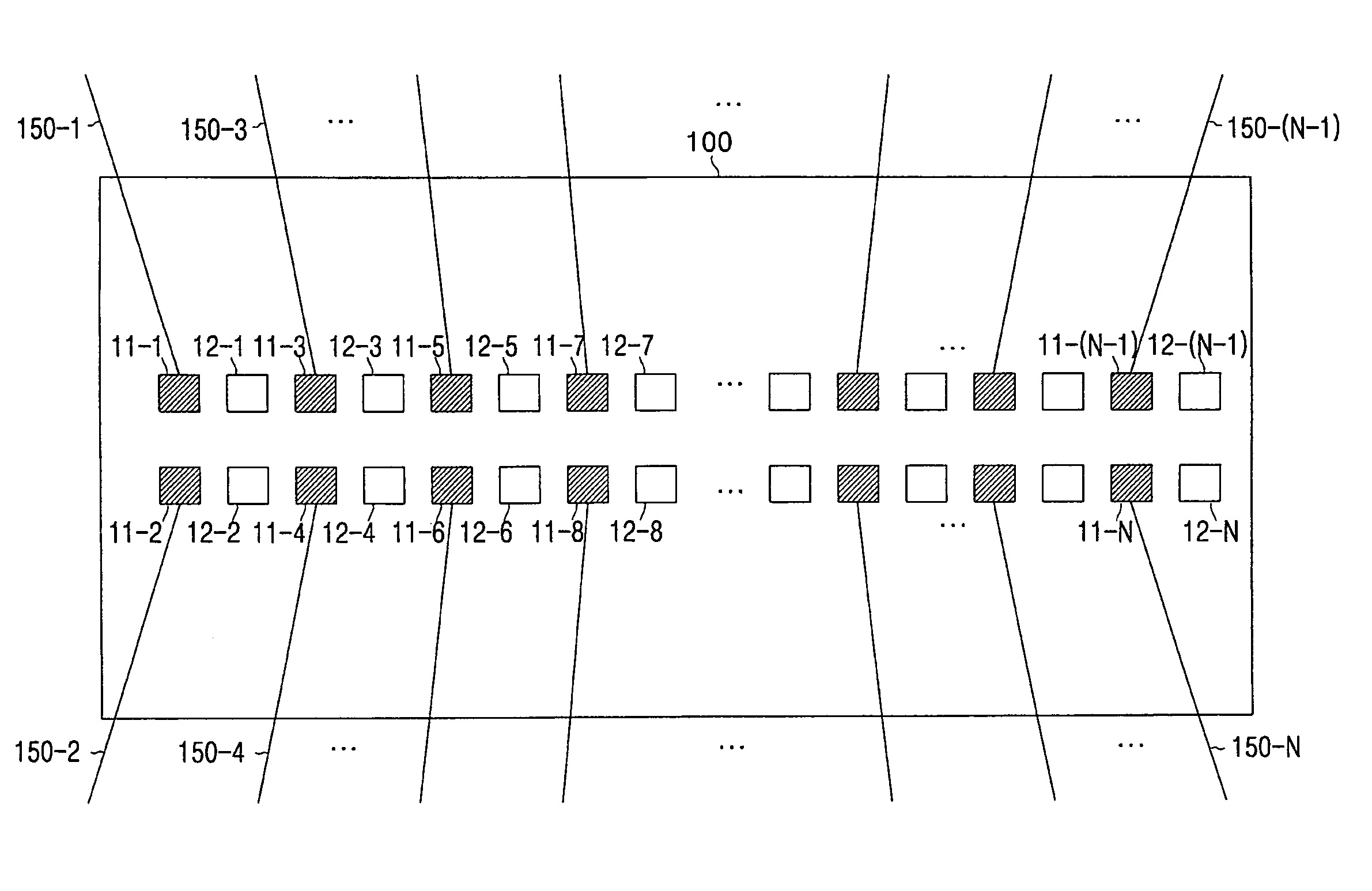

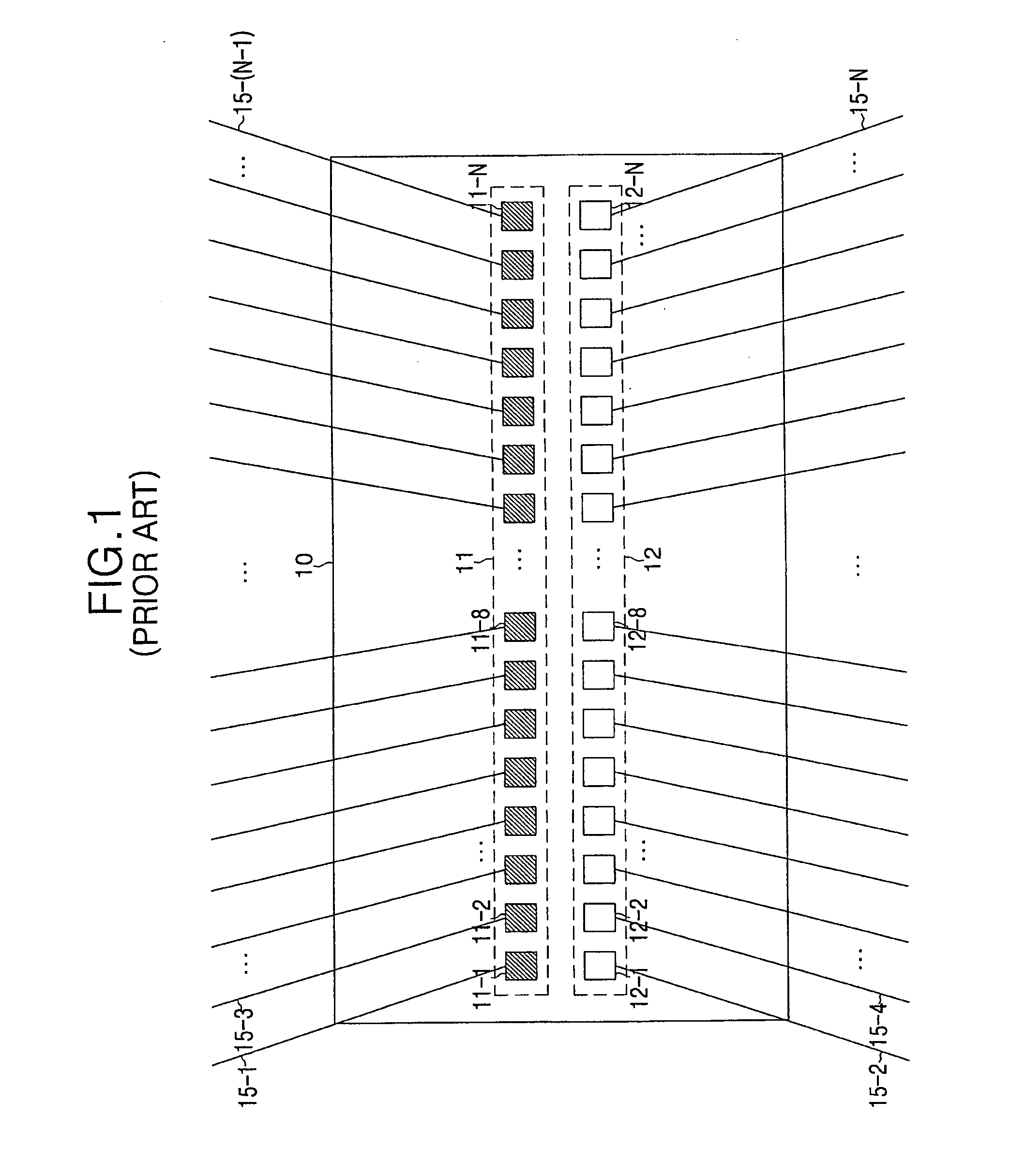

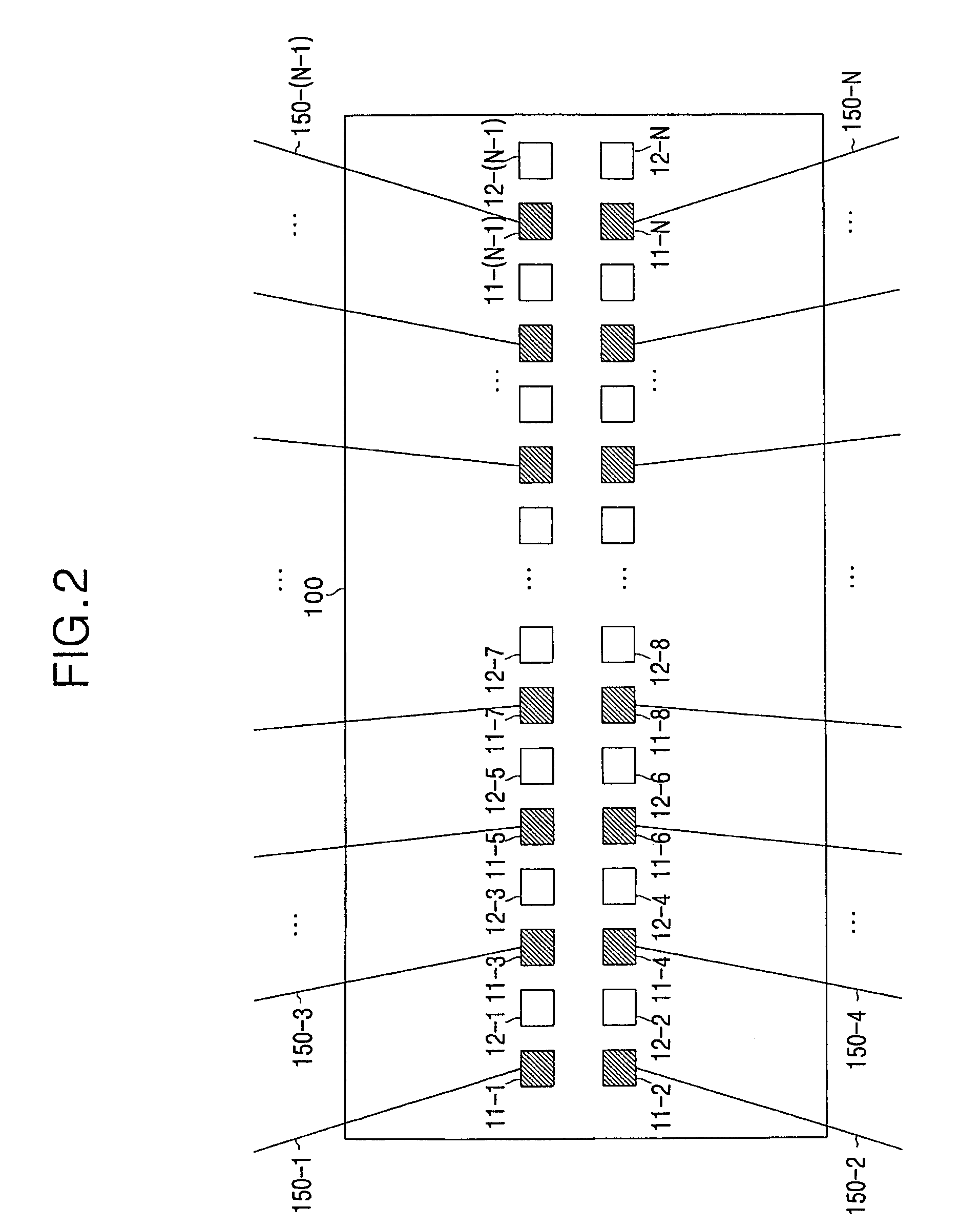

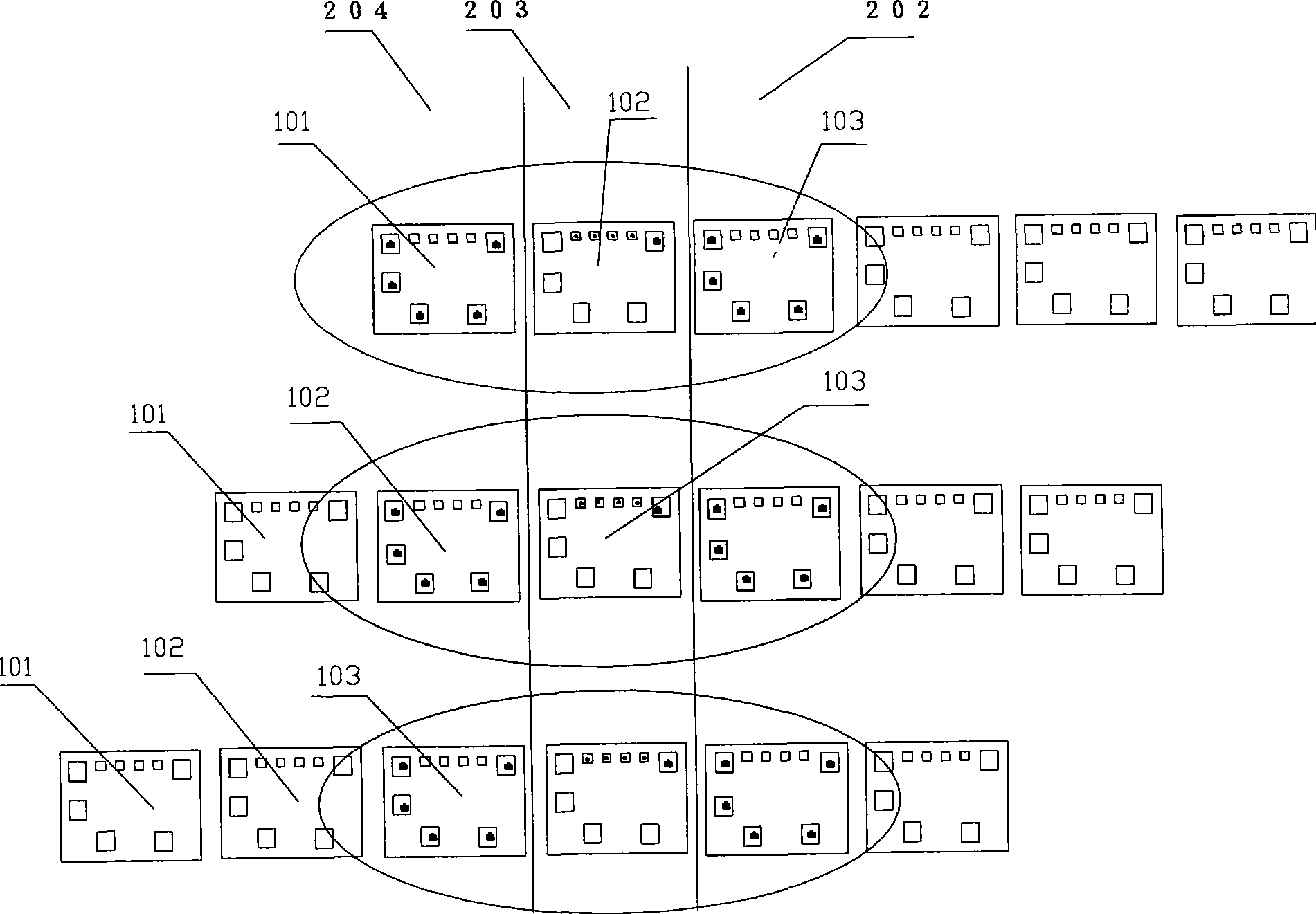

Semiconductor memory device and test method thereof

ActiveUS20080175080A1Minimize the numberSemiconductor/solid-state device testing/measurementSolid-state devicesContact testProbe card

Provided are a semiconductor memory device and a test method thereof. The semiconductor memory device includes: a die in which a plurality of internal circuits are integrated; a plurality of first and second channel pads having a first pad size and a first pad pitch, disposed in an alternating manner in a straight line at a center part of the die, and divided into a plurality of parallel rows, wherein the plurality of first and second channel pads are configured to selectively contact test probes in an alternating manner to receive an external wafer test signal and to output a signal generated by the plurality of internal circuits to the exterior. Therefore, it is possible to perform a test using plural channel pads during a wafer test of the semiconductor memory device using a plurality of probes of a probe card without incorrect contacts or non-contact with adjacent pads.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods for making vertical electric feed through structures usable to form removable substrate tiles in a wafer test system

InactiveUS20050108875A1Easily attachableEasily detachablePrinted circuit assemblingLine/current collector detailsConvertersTransformer

Methods are provided for making vertical feed through electrical connection structures in a substrate or tile. The vertical feed throughs are configured to make the tile attachable and detachable as a layer between other substrates. For example, the tile with vertical feedthroughs can form an easily detachable space transformer tile in a wafer test system. The vertical feed through paths are formed with one end of each feed through hole permanently encapsulating a first electrical contact, and a second end supporting another pluggable and unpluggable electrical probe contact. Decoupling capacitors can be further plugged into holes formed in close proximity to the vertical feed through holes to increase performance of the decoupling capacitor.

Owner:FORMFACTOR INC

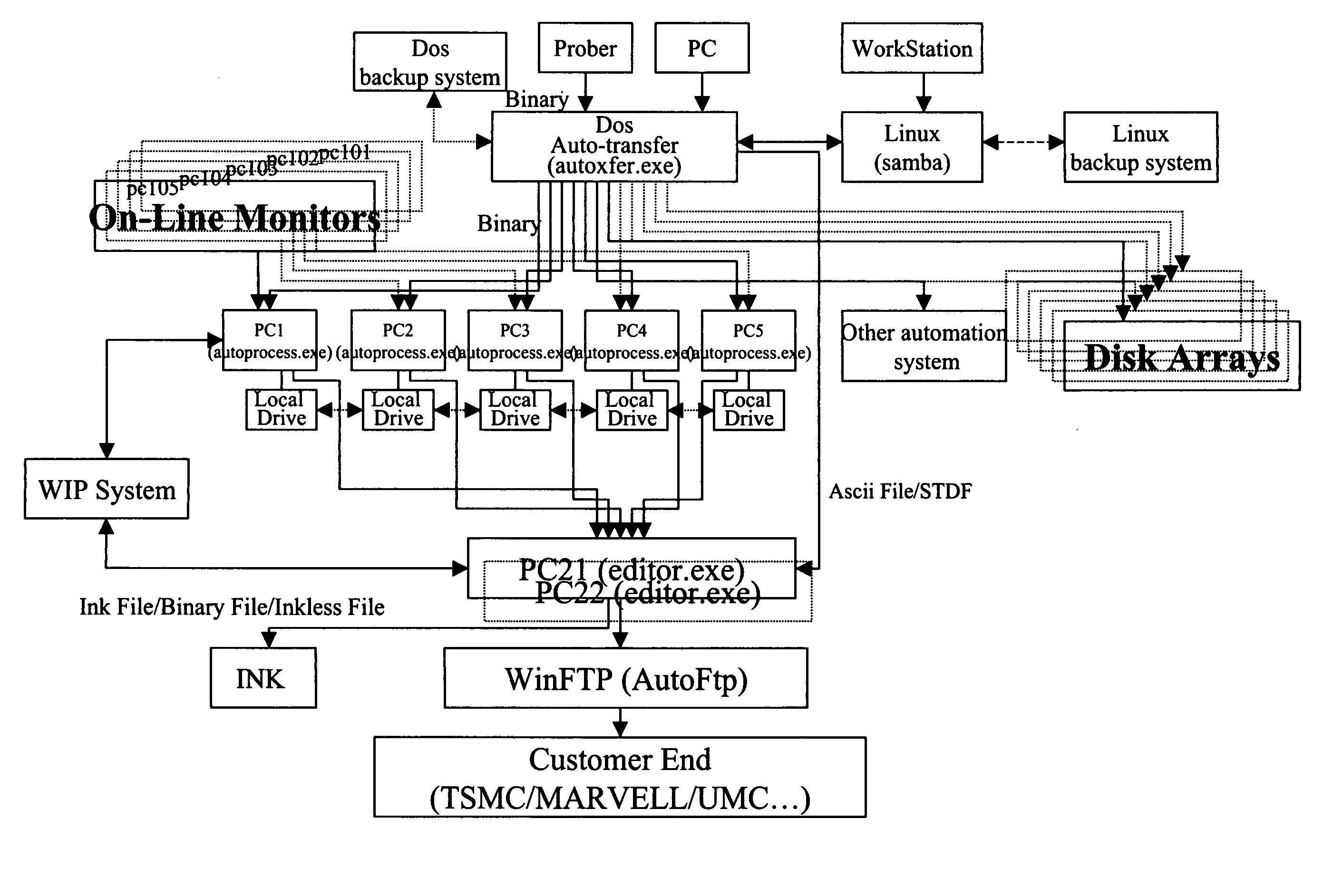

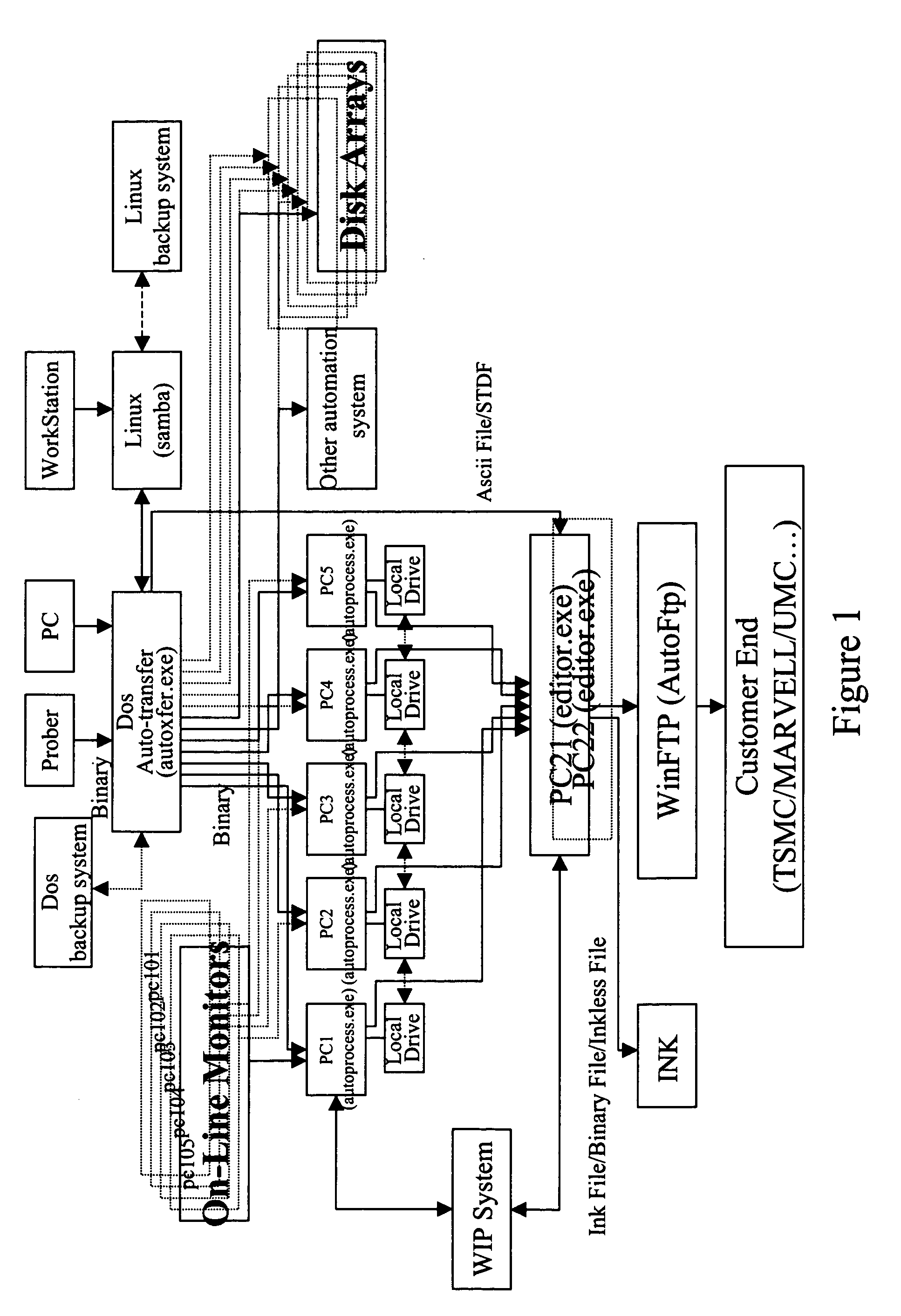

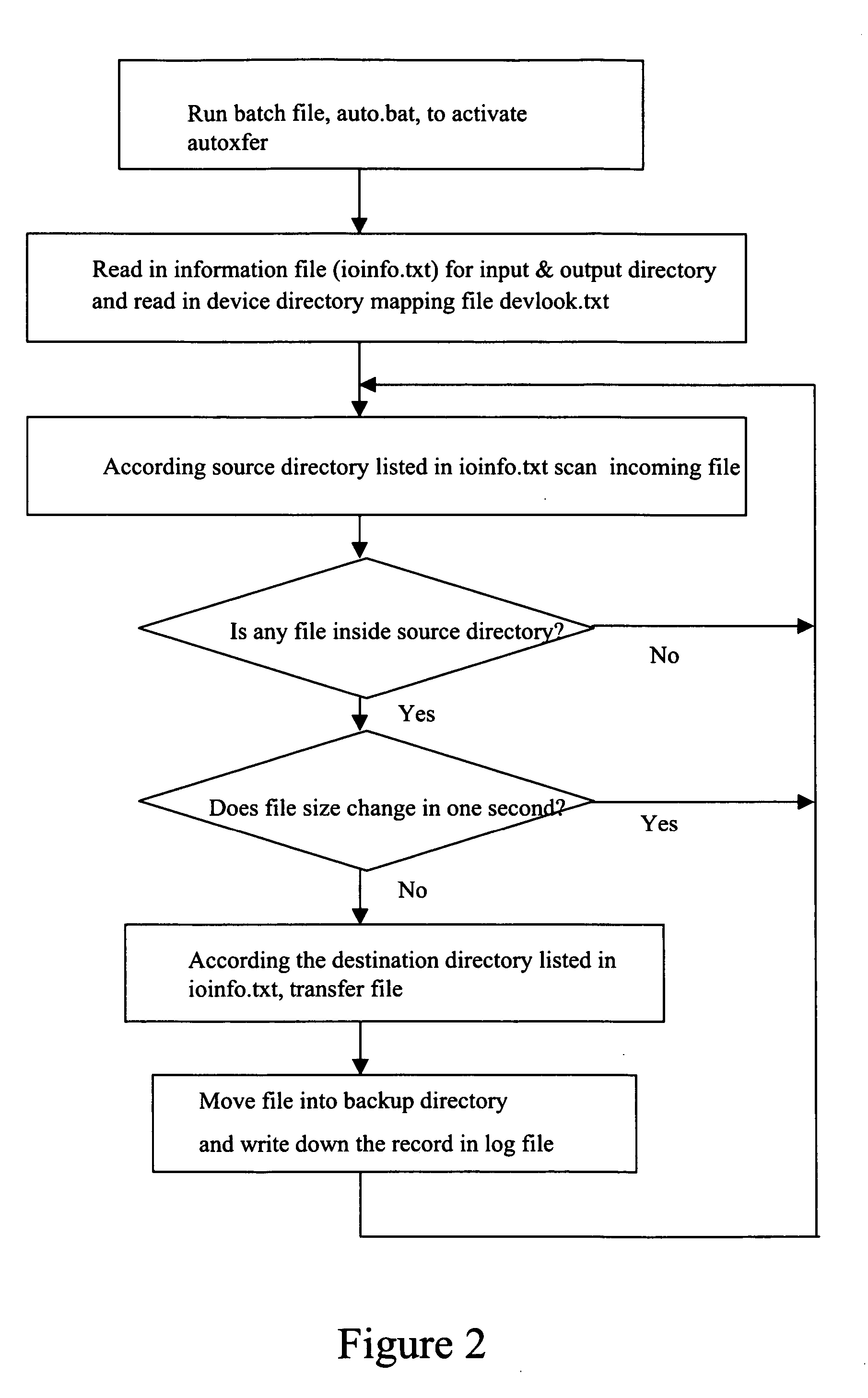

Universal and integrated wafer testing real-time monitoring software system and its open system architecture

InactiveUS20060036394A1Shorten cycle timeRisk minimizationElectrical testingStructural/machines measurementProduction lineDrive mapping

A wafer testing real-time monitoring software system and its unique open software architecture which achieves real-time monitoring of wafer test results and on-line changing of externally hooked software to satisfy customer needs without changing its main program. The software structure receives and processes binary files from different probers and converts these into readable ASCII files. The system consists of four software programs that can operate independently. These programs are an automatic transfer program, a program which converts wafer test results from a binary file to an ASCII file, a program which receives the ASCII files and performs wafer map editing, and an auto-ftp program which automatically scans data and sends data to remote locations. Additionally, multiple workstations can process data from probers simultaneously. The on-line monitor on a production line can see production results from multiple major workstations through the network drive and drive mapping functions.

Owner:CHEN WEN LING +1

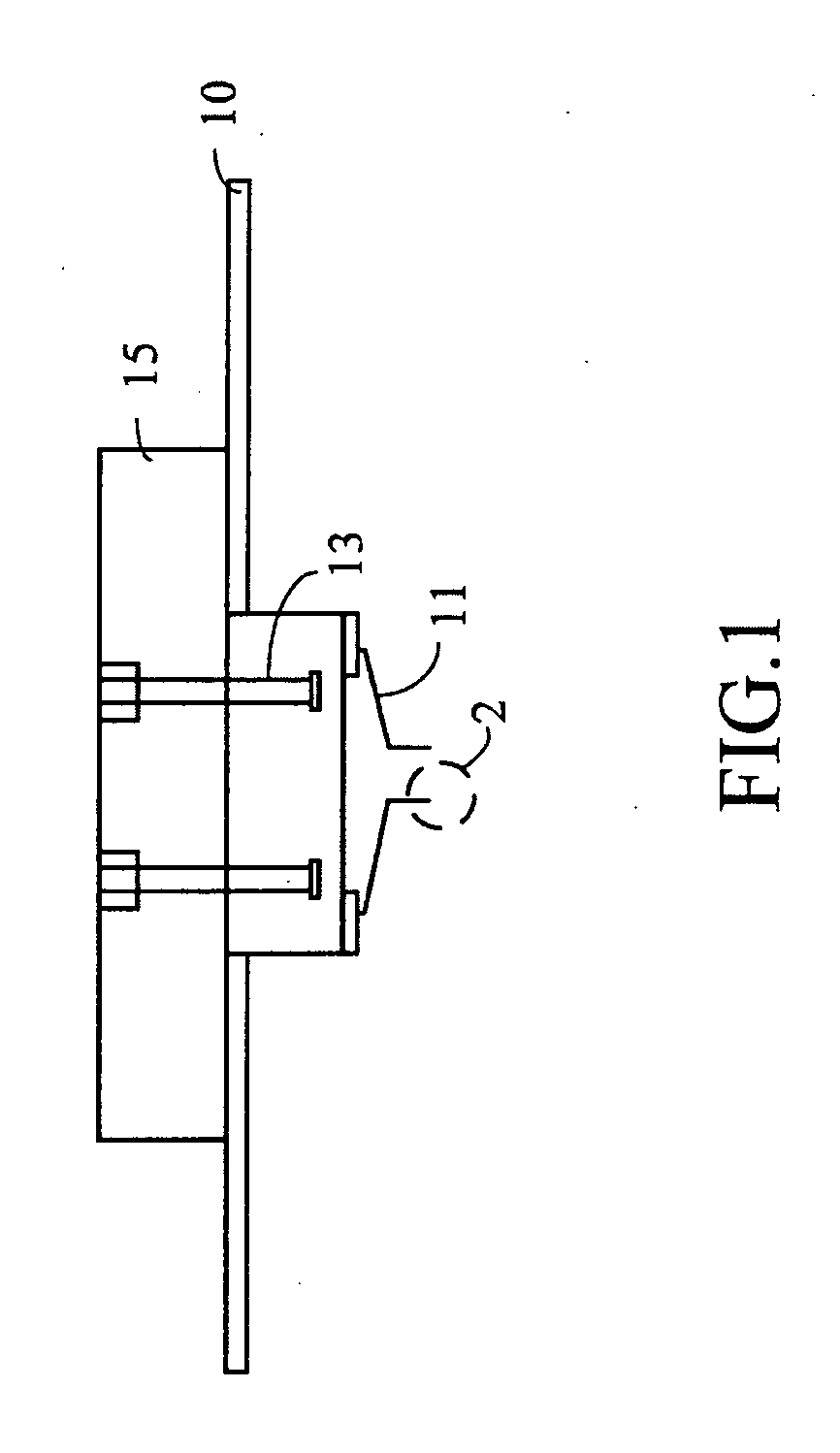

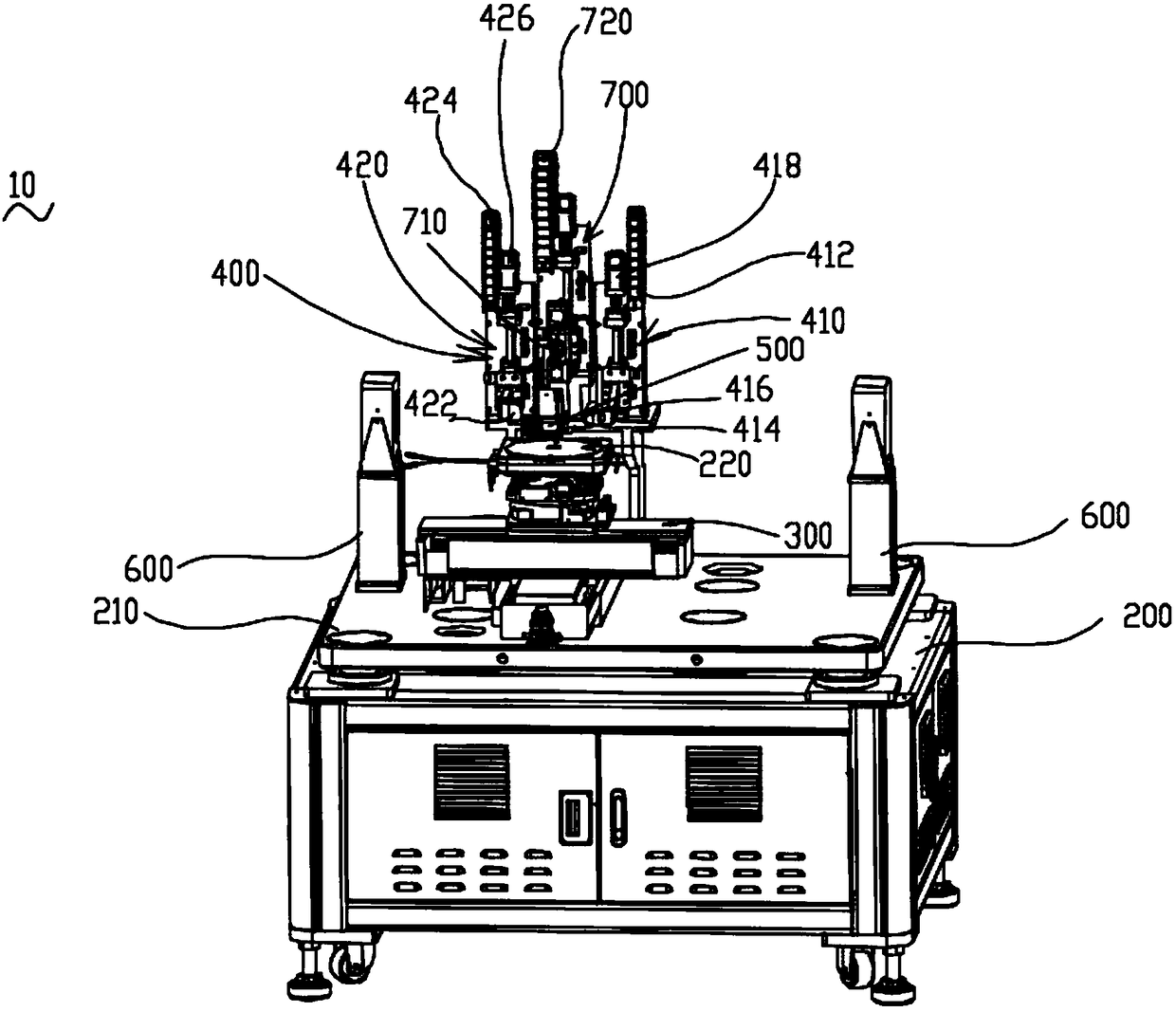

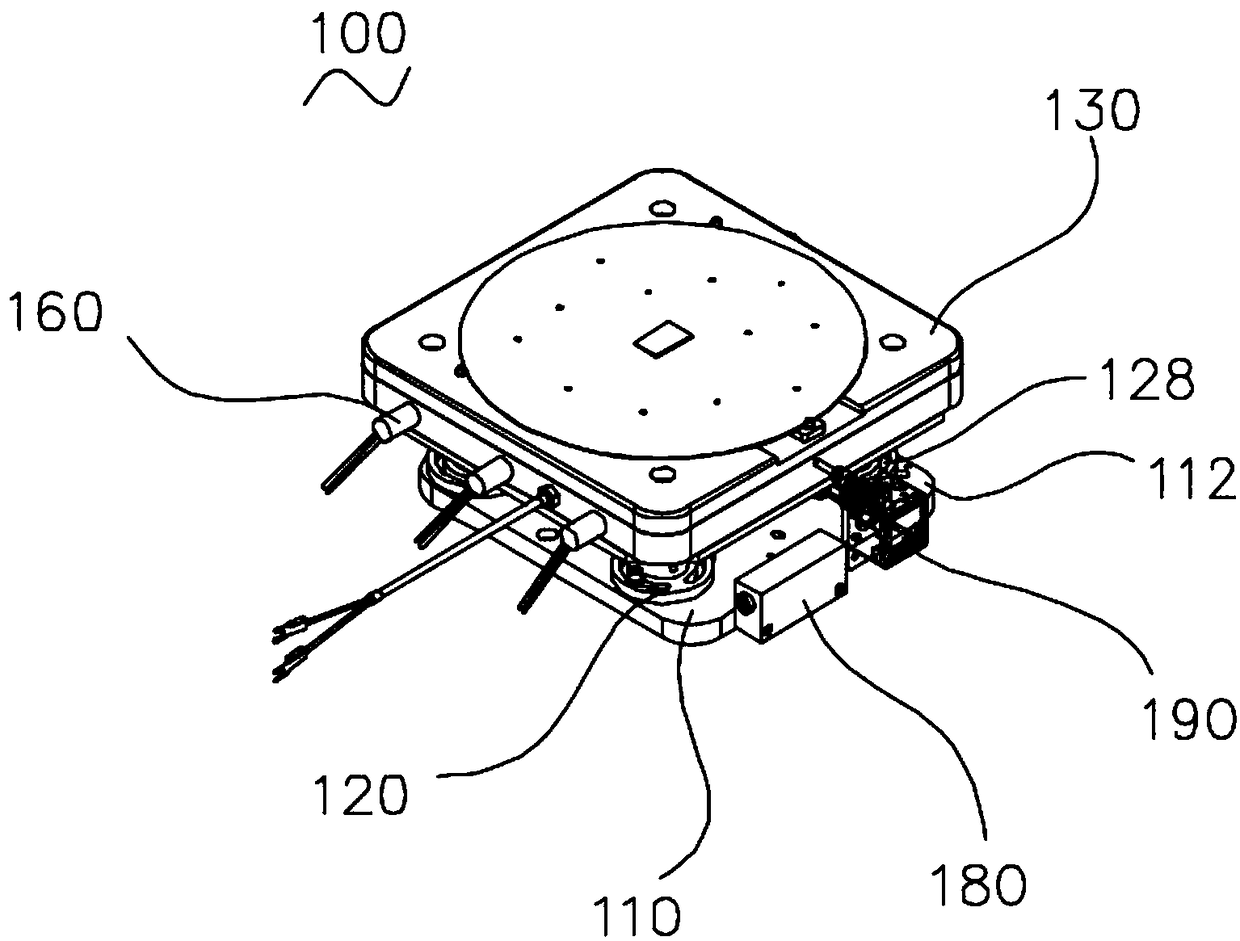

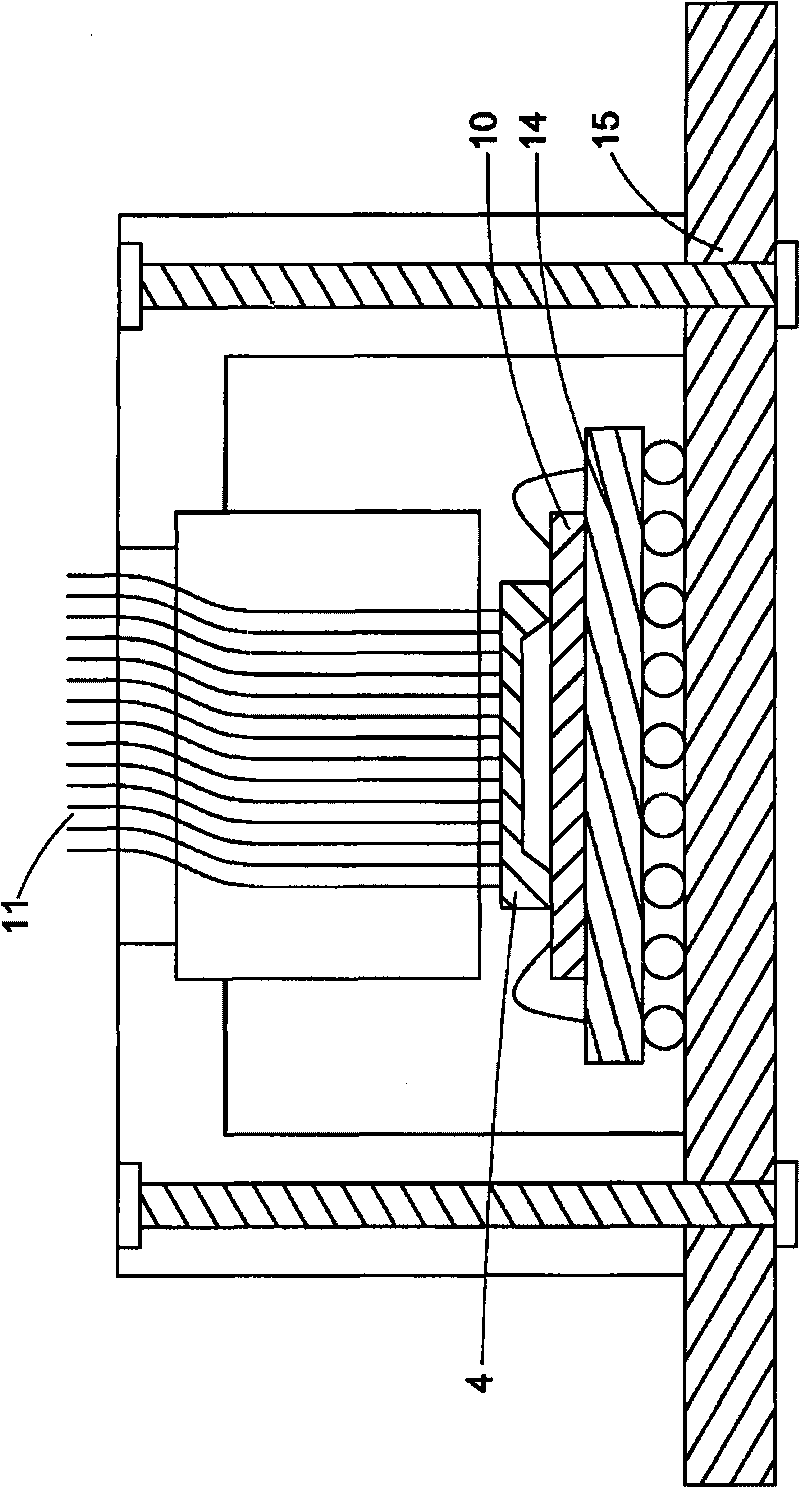

Automatic wafer testing machine

PendingCN108493124AFully automatedFast testSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingTest efficiencyTest station

The invention relates to an automatic wafer testing machine used for fixing and testing a chip located on a wafer. The automatic wafer testing machine comprises a machine, an angle adjustment mechanism, a wafer test positioning device, a test component and a controller. The machine is provided with a test station. The angle adjustment mechanism comprises a rotation component and a translation component. The wafer test positioning device is installed on the surface of the angle adjustment mechanism, wherein the surface faces away from an installation surface. The angle adjustment mechanism candrive the wafer test positioning device to rotate or translate so as to drive the chip to move to the test station. The test component is used for carrying out performance detection on the chip located at the test station. The controller, the angle adjustment mechanism and the test component are connected in a communication connection mode. The controller is used for sending trigger signals to theangle adjustment mechanism and the test component respectively so as to trigger the angle adjustment mechanism and the test component. The automatic wafer testing machine has characteristics that a test speed is fast and test efficiency is high.

Owner:SHENZHEN JPT OPTO ELECTRONICS CO LTD

Micro-wave on-wafer testing method based on unknown material substrate

ActiveCN101634672AAvoid measurement errorsAvoid error accumulationResistance/reactance/impedenceMicrowaveField analysis

The invention relates to an on-wafer testing method for a micro-wave element based on an unknown material substrate. The method comprises the following steps: firstly, a TRL calibration part, an open circuit resonator and an element to be measured which are suitable for micro-wave on-wafer testing are prepared on a substrate; secondly, a micro-wave on-wafer testing system is calibrated by using a TRL calibration method; thirdly, resonation point of the open circuit resonator is tested by the calibrated micro-wave on-wafer testing system; fourthly, effective dielectric constant and transmission line impedance of the substrate are calculated according to a measured resonation point; fifthly, an S parameter of the element to be measured is measured, and reference impedance of the S parameter is the impedance obtained in the last step; and finally, a reference S parameter with 50 omega impedance is acquired by adopting a method of S parameter impedance conversion. The method has the advantages that the system impedance of the TRL calibration part can be calculated through testing the open circuit resonator; the method combined with standard TRL calibration not only can carry out on-wafer testing on the micro-wave element under the condition that the characteristic of a material is unknown, but also can be combined with a method of field analysis to calculate the real characteristic of the material.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

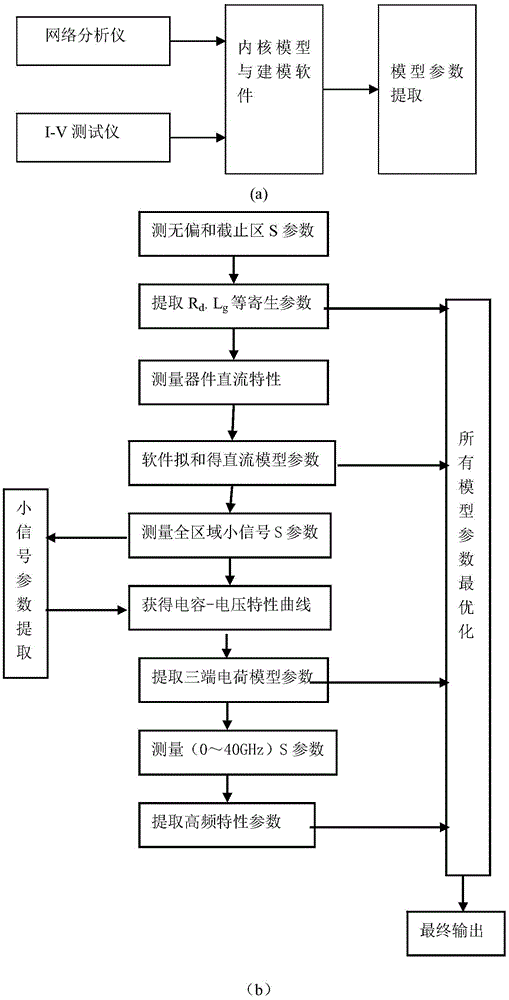

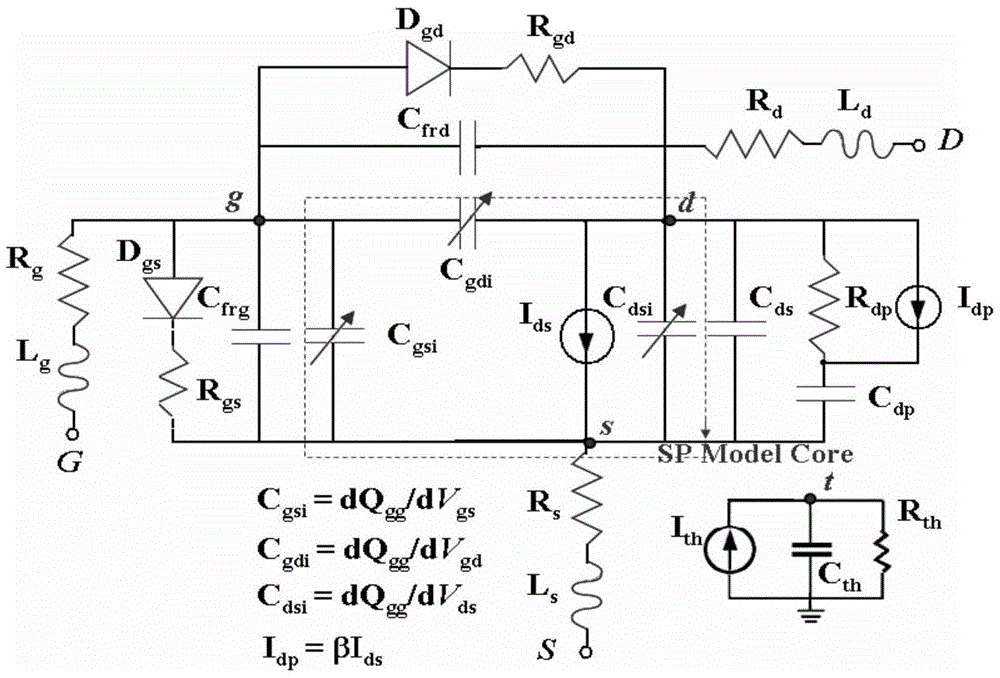

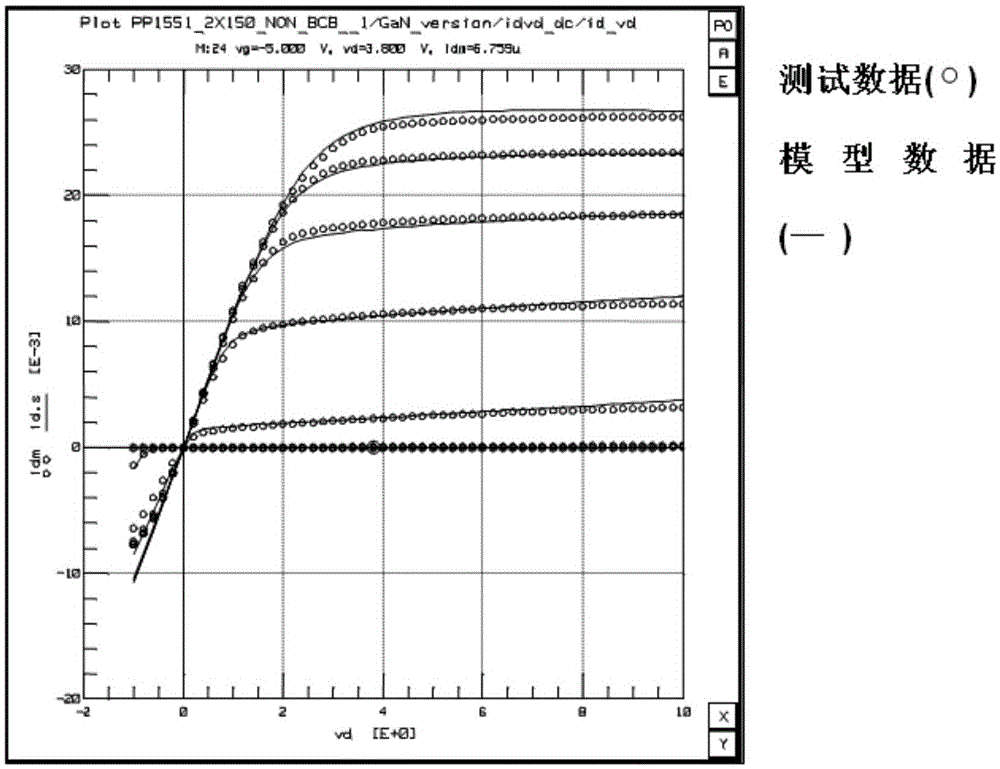

Modelling method for surface potential basis intensive model of III-V group HEMT (High Electron Mobility Transistor)

ActiveCN105468828ASolve the physics problem of quantum effect processingSolve the problem of difficult glueCAD circuit designSpecial data processing applicationsCapacitancePhysical model

The invention discloses a modelling method for a surface potential basis intensive model of an III-V group HEMT (High Electron Mobility Transistor). The method comprises the following steps of firstly, establishing an intrinsic structure model and an extrinsic structure model of the III-V group HEMT, combining a physical structure and a behavior mechanism of a device to construct a topological structure, and then embedding the established models into a commercial EDA (Electronic Design Automation) tool; secondly, carrying out on-wafer testing on an actual depletion device to obtain various performance test data of the device; and lastly, verifying the intensive model. The model solves the problems that the existing current and charge equations of the device cannot integrate, the segment points are discontinuous and the equations cannot be used for nonlinear circuit simulation; through a method for solving a surface potential source equation to deduce model current and charge / capacitance equations, a physical problem for quantum effect processing and a numerical algorithm problem caused by simultaneous self-consistent solution of a classic carrier transport equation and a new effect in the existing physical model are solved; and furthermore, a computational formula for volume charge density is deducted again, so that a problem of difficulty in gluing in a charge model is solved.

Owner:HANGZHOU DIANZI UNIV

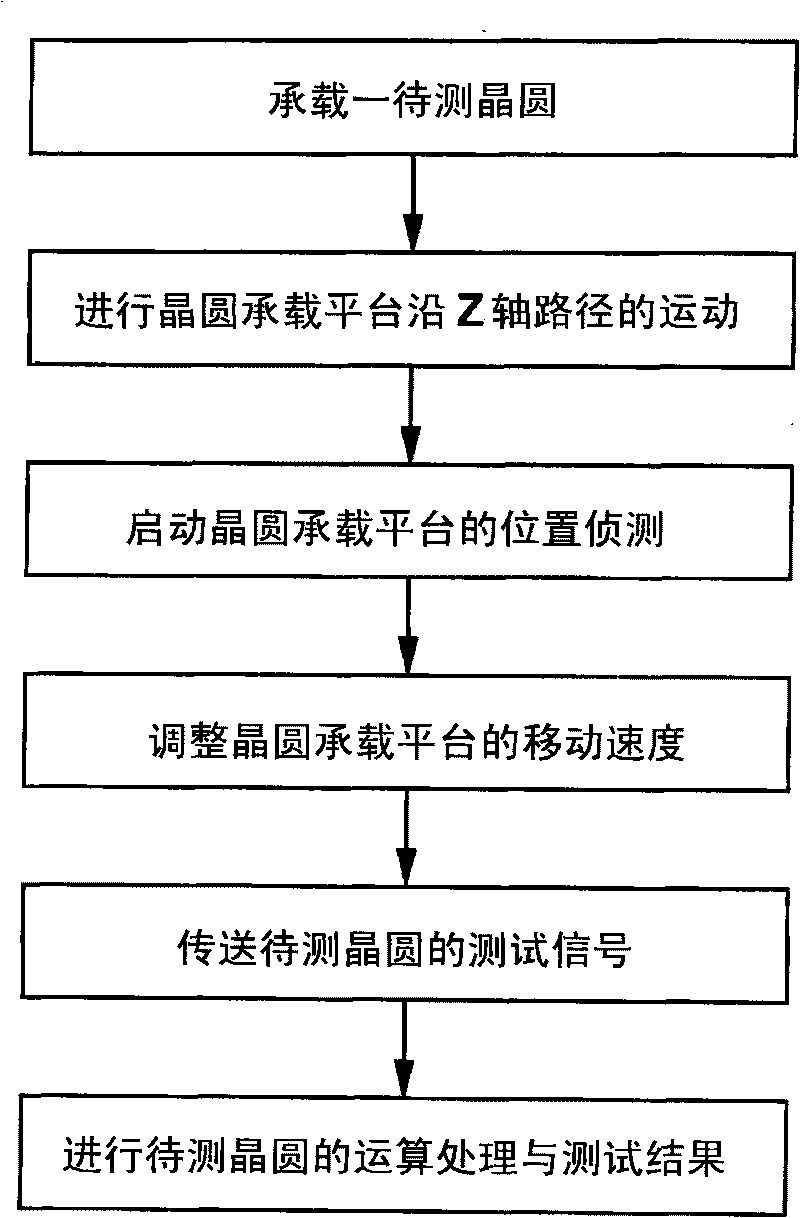

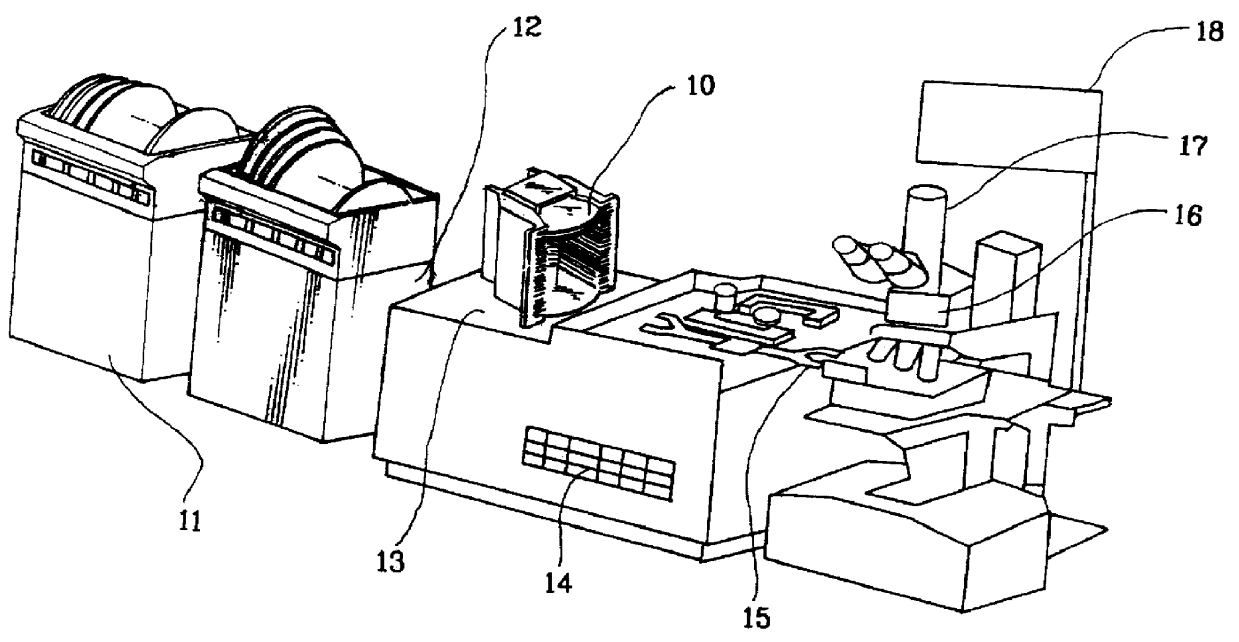

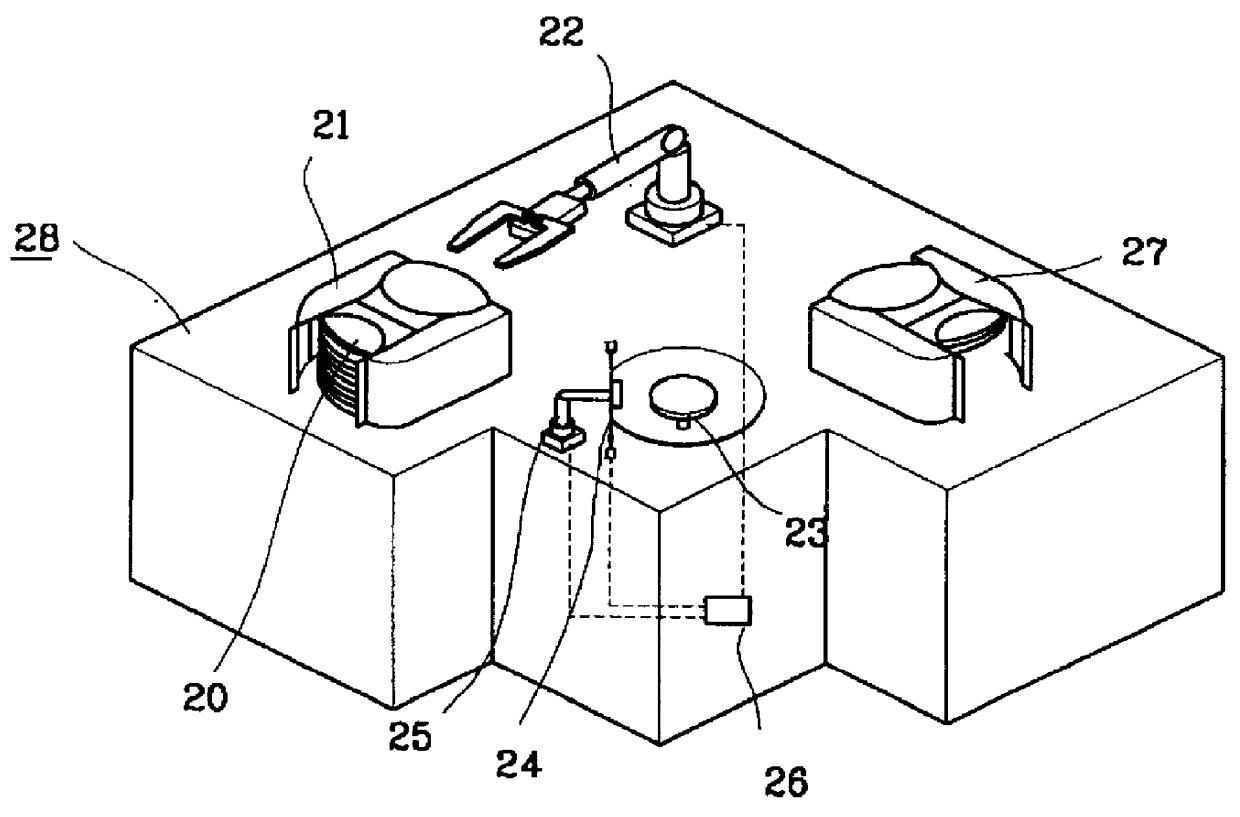

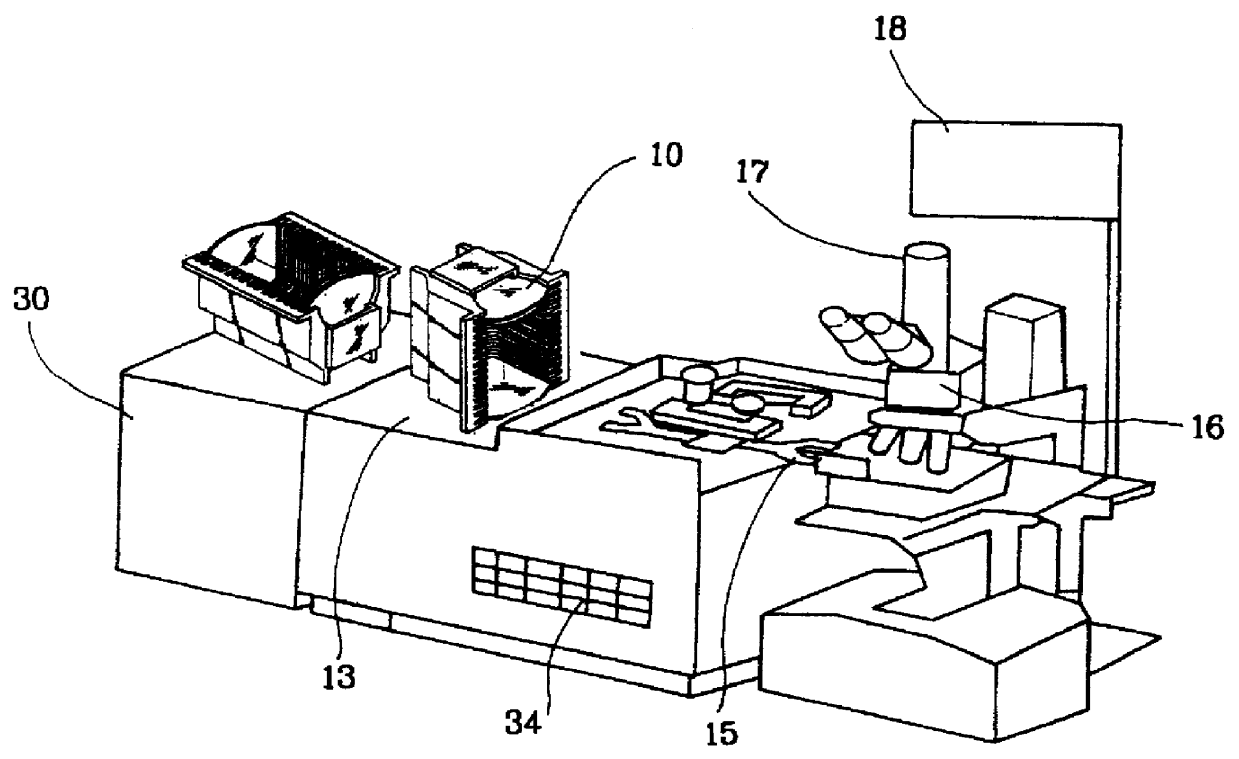

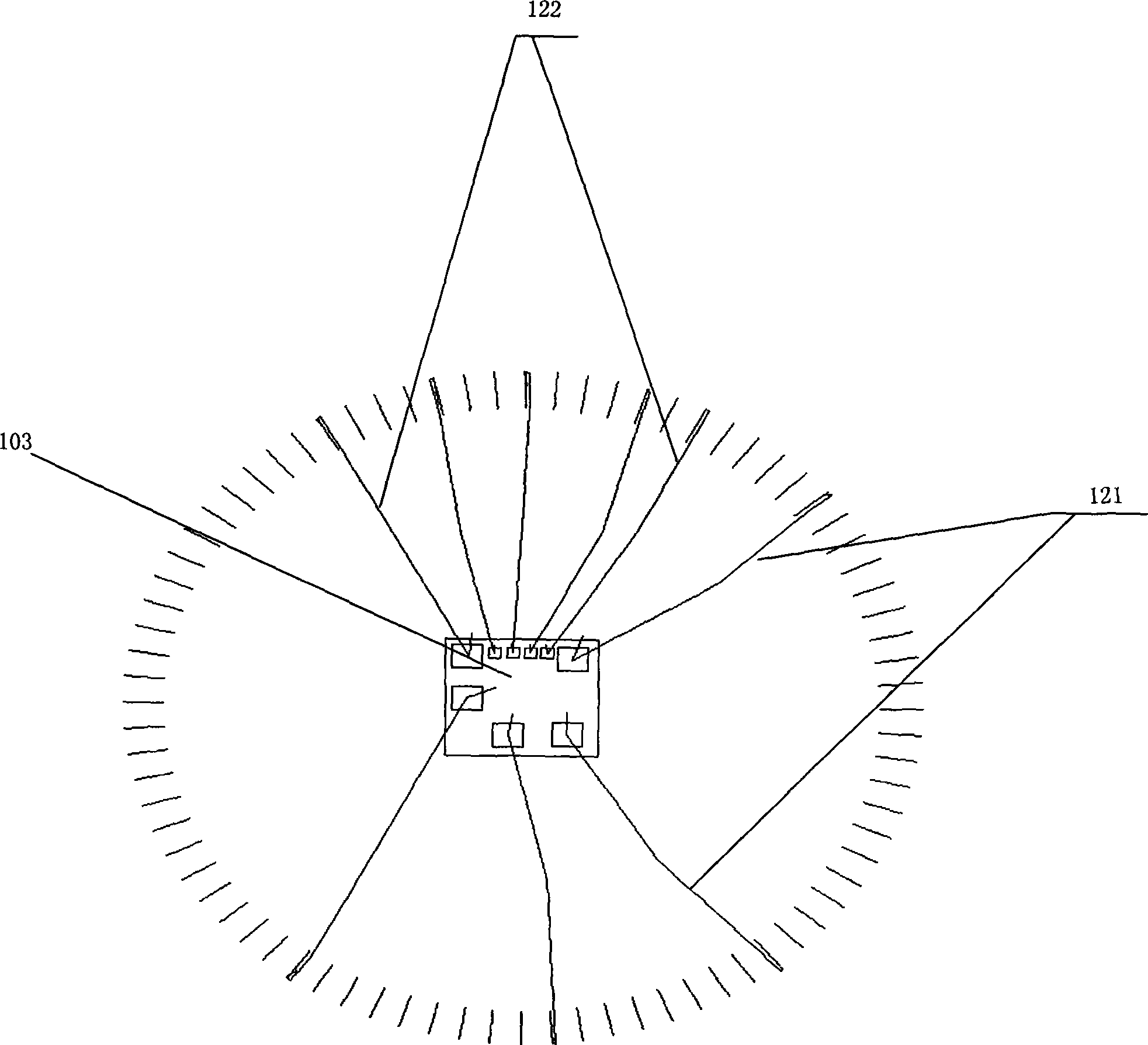

Wafer tester and testing method thereof

InactiveCN101738573AAvoid destructionReach micro contactElectrical measurement instrument detailsIndividual semiconductor device testingProbe cardContact mode

The invention provides a wafer tester and a testing method thereof. The wafer tester comprises a wafer bearing platform, a probe card, a plurality of converters, a testing carrier plate, a test board and a feedback device, wherein the wafer bearing platform provides movement of three axes of X, Y and Z so as to bear a wafer to be tested; the probe card comprises a plurality of probes for testing the wafer to be tested of the wafer bearing platform; the plurality of the converters are arranged on a Z-axis path of the wafer bearing platform moving towards the probe card respectively; when each converter detects that the wafer bearing platform displaces along the Z axis, a displacement electronic signal is output to the feedback device; the feedback device receives the displacement electronic signal so as to adjust a moving speed of the wafer bearing platform along the Z axis and further make the wafer on the wafer bearing platform contact the probes of the probe card in a micro-contact mode, which can avoid that the probes of the probe card directly damage a micro-circuit of the wafer caused by an inappropriate Z-axis speed.

Owner:KING YUAN ELECTRONICS

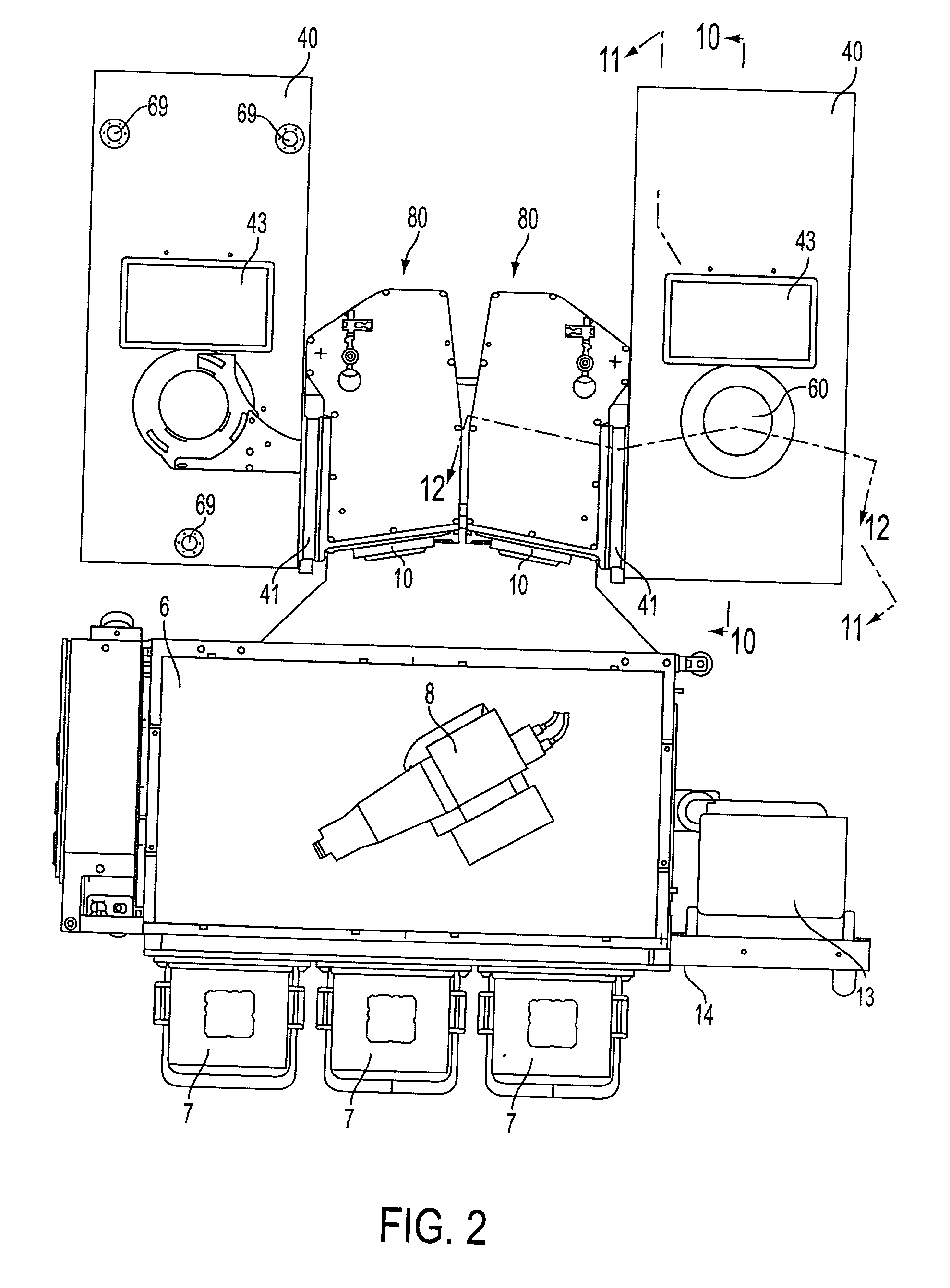

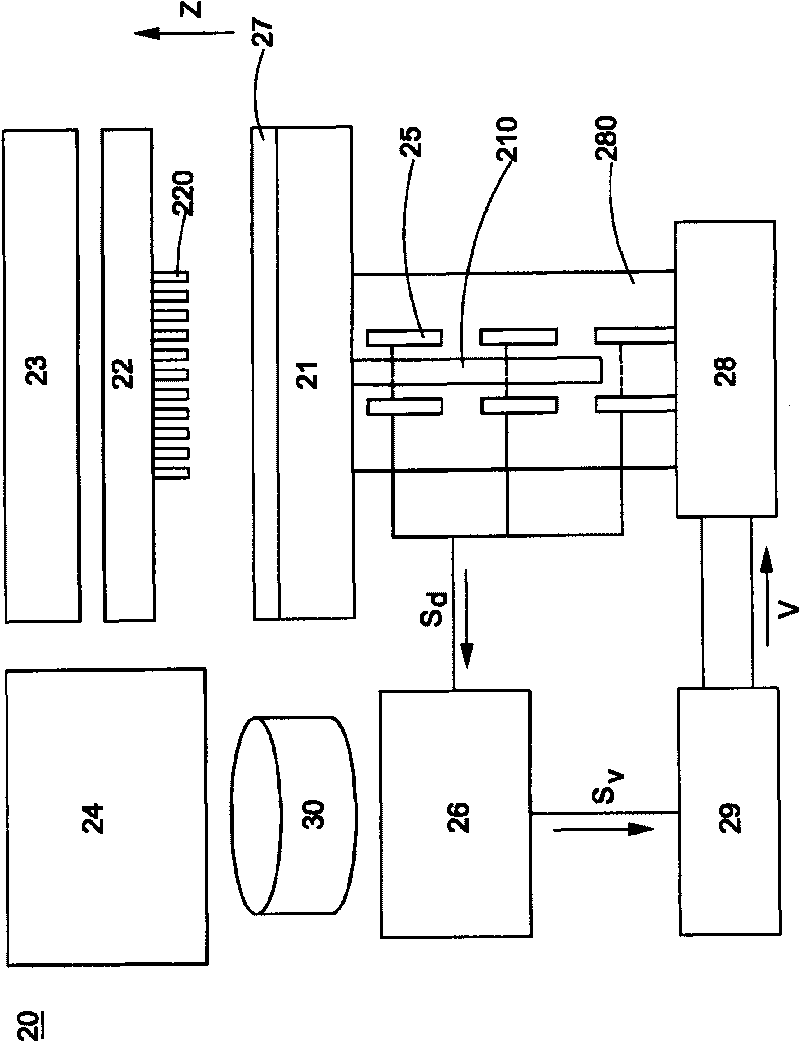

Semiconductor wafer testing apparatus with a combined wafer alignment/wafer recognition station

InactiveUS6027301ASemiconductor/solid-state device testing/measurementElectronic circuit testingEngineeringCycle time

A semiconductor wafer testing apparatus has a work table on which a carrier containing semiconductor wafers to be checked is placed. The work table is equipped for combined wafer alignment and wafer code recognition while the wafers remain in their carrier in one position on the work table. The alignment is accomplished with a wafer flat zone aligner which has a pair of roller pins each coming in contact with circumferences of the wafers being stacked in the carrier through an open lower part of the carrier and an opening in the table. The wafer code recognition is accomplished with an optical character recognizer that moves up and down and forward and backward with respect to the carrier, and interposes between the wafers in the carrier so as to read out codes which are on each wafer. This combined automated work station helps prevent contamination of the wafers by an operator or by unnecessary handling of the wafers, and also reduces cycle time for the entire inspection process.

Owner:SAMSUNG ELECTRONICS CO LTD

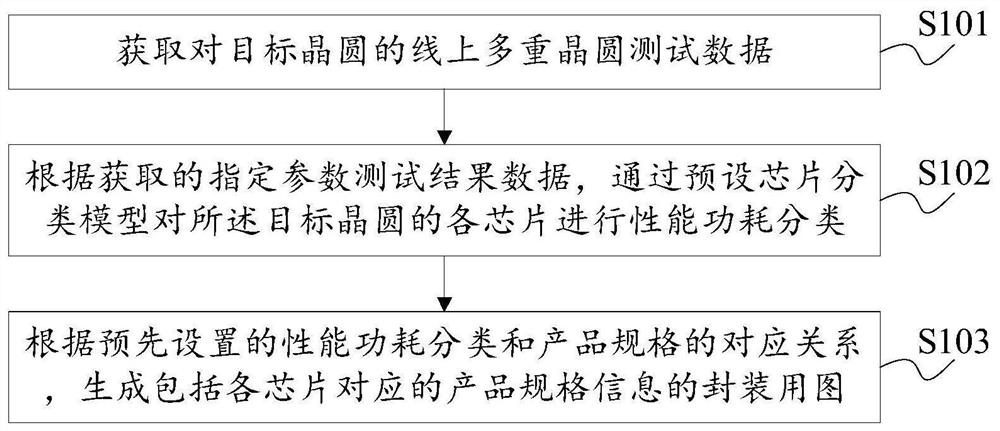

Wafer test classification method and system

ActiveCN112382582ASave change timeControllable ratioSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingComputer scienceReliability engineering

The embodiment of the invention discloses a wafer test classification method and system, belongs to the technical field of chips, and the method comprises the steps: obtaining the online multi-wafer test data of a target wafer before a packaging step, wherein the test data comprises specified parameter test result data of the target wafer under different temperature and voltage test conditions; performing performance power consumption classification on each chip of the target wafer through a preset chip classification model according to the acquired specified parameter test result data; and generating a packaging graph including product specification information corresponding to each chip according to a preset corresponding relationship between the performance power consumption classification and the product specification. According to the invention, offline chip performance analysis and classification can be carried out according to wafer test parameters, thereby achieving the purposes of improving the performance level of a final device, meeting the requirements of product specifications with different performance and power consumption, and improving the productivity of actual products.

Owner:HYGON INFORMATION TECH CO LTD

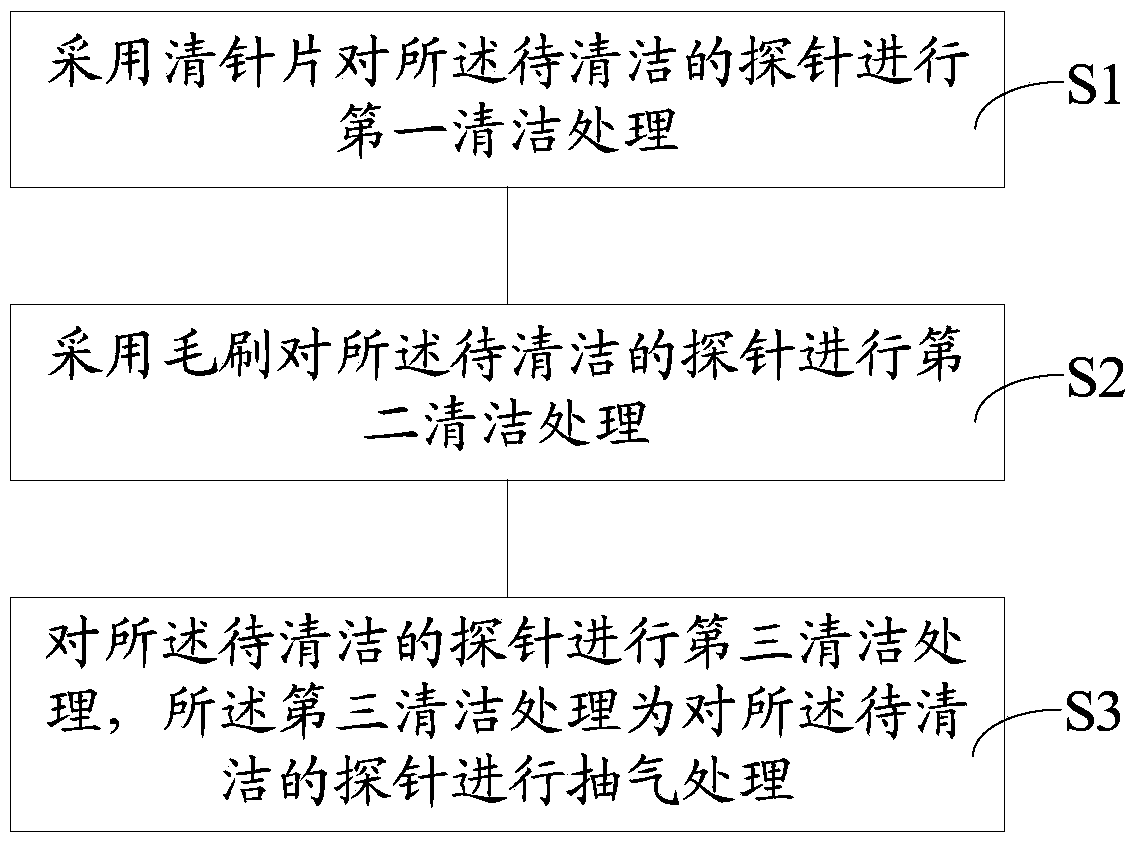

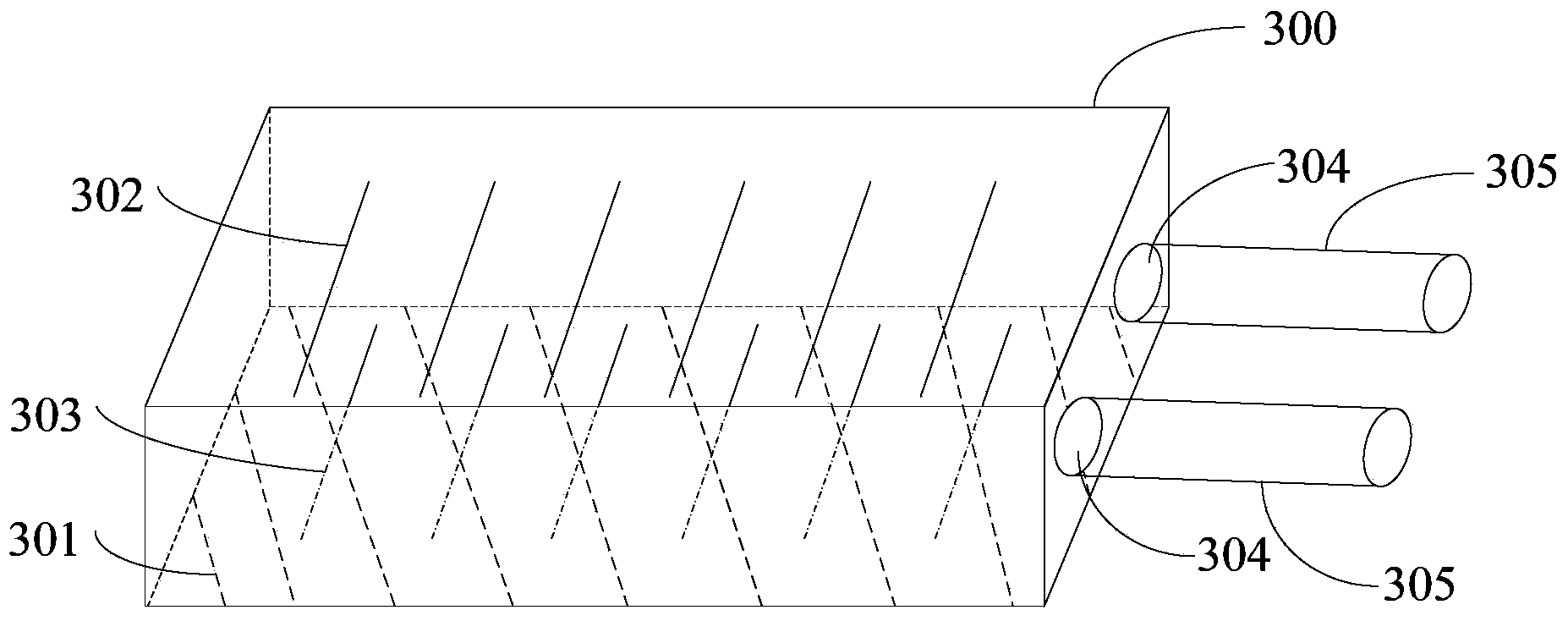

Probe cleaning method and probe cleaning device

ActiveCN103878150AImprove reliabilityImprove accuracyDirt cleaningCleaning using toolsCleaning methodsBiomedical engineering

The invention provides a probe cleaning method and a probe cleaning device. The probe cleaning method comprises the steps of providing a probe to be cleaned, adopting a probe cleaning piece to primarily clean the probe to be cleaned, adopting a brush to secondarily clean the probe to be cleaned, thirdly cleaning the probe to be cleaned, namely extracting air of the probe to be cleaned in the third cleaning process, and carrying out the first cleaning process, the second cleaning process and the third cleaning process at the same time. According to the probe cleaning method and the probe cleaning device, probe cleaning efficiency is improved, impurity removing ability is enhanced, probe cleaning time is shortened, accuracy and reliability of wafer testing results are improved, wafer testing time is shortened, and production efficiency is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

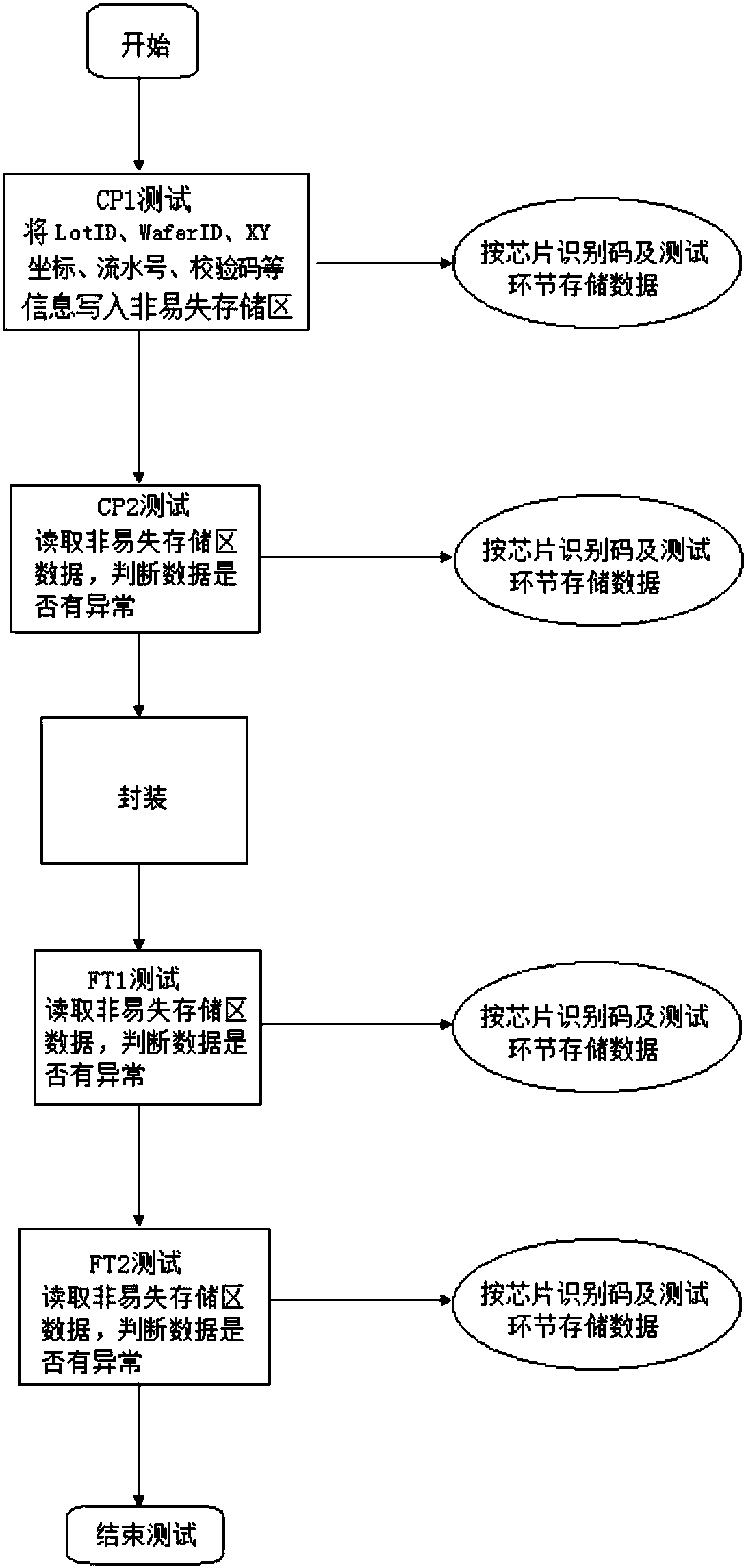

Whole-process traceable semiconductor test data recording method

ActiveCN107808831AAccurate acquisitionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsData recordingSemiconductor

The invention relates to a whole-process traceable semiconductor test data recording method. The unique identification code of each chip is written into a non-volatile memory area of the chip. Data iswritten into a database by taking the unique identification codes and test links as data index information. Through the identification codes and the test links, all test data can be indexed in the database, data generated in the whole test process can be tracked, and the change of the data can be monitored. For the same chip, data during wafer test and data of finished product test after packaging can be seen, and the data of each test link can be quickly and accurately obtained, so that the engineer can analyze the process data and screen out final qualified chips.

Owner:SINO IC TECH

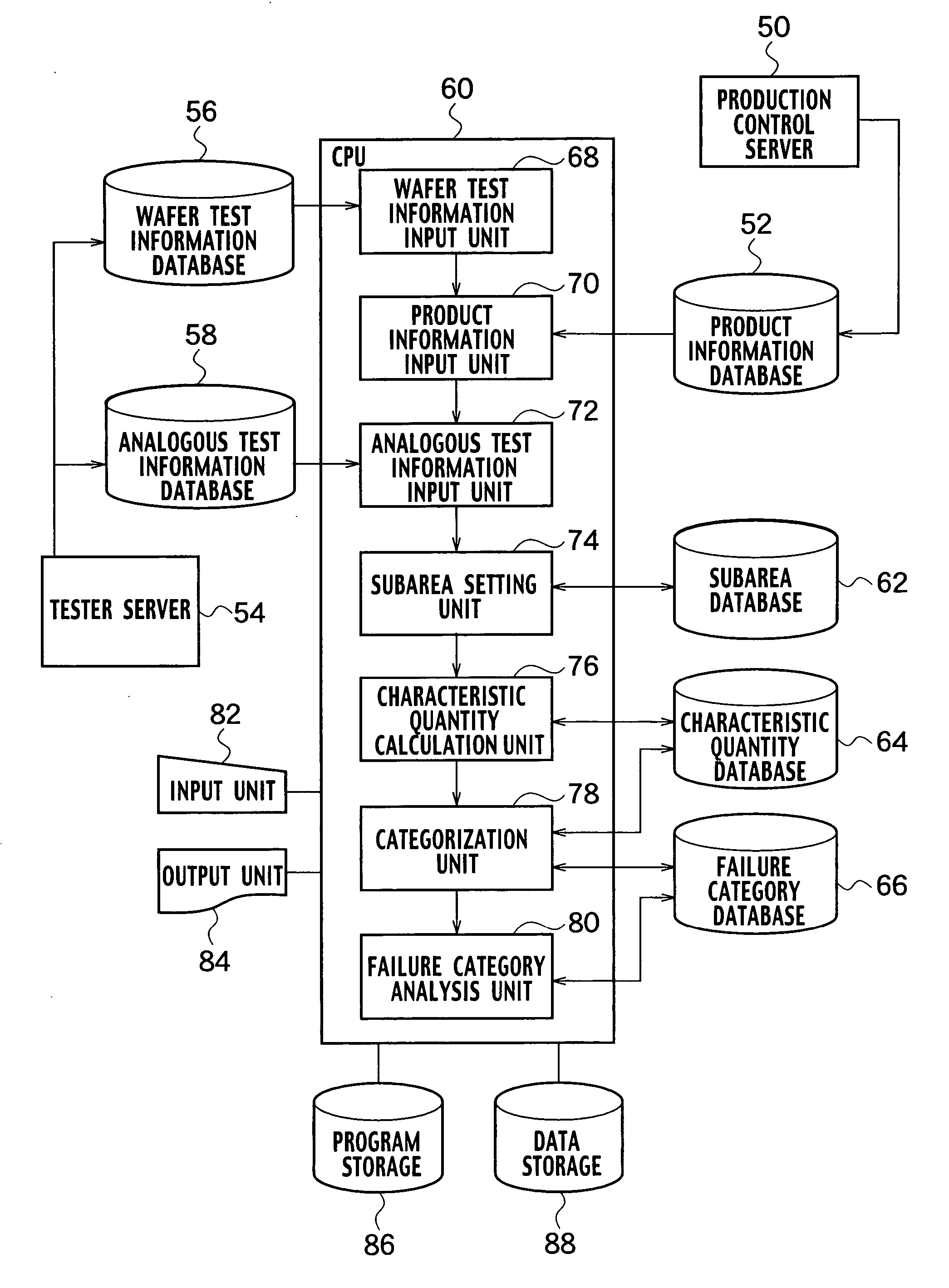

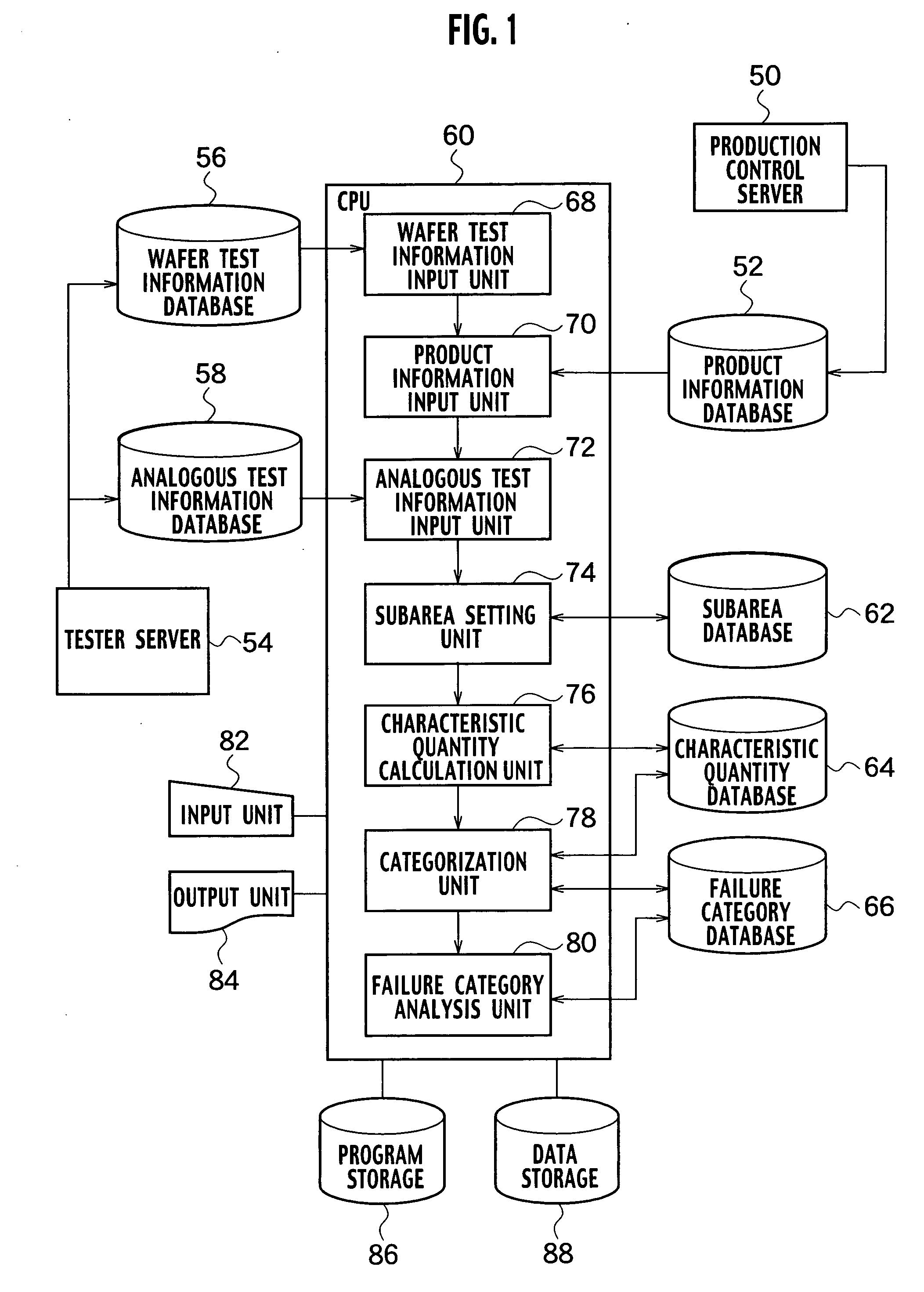

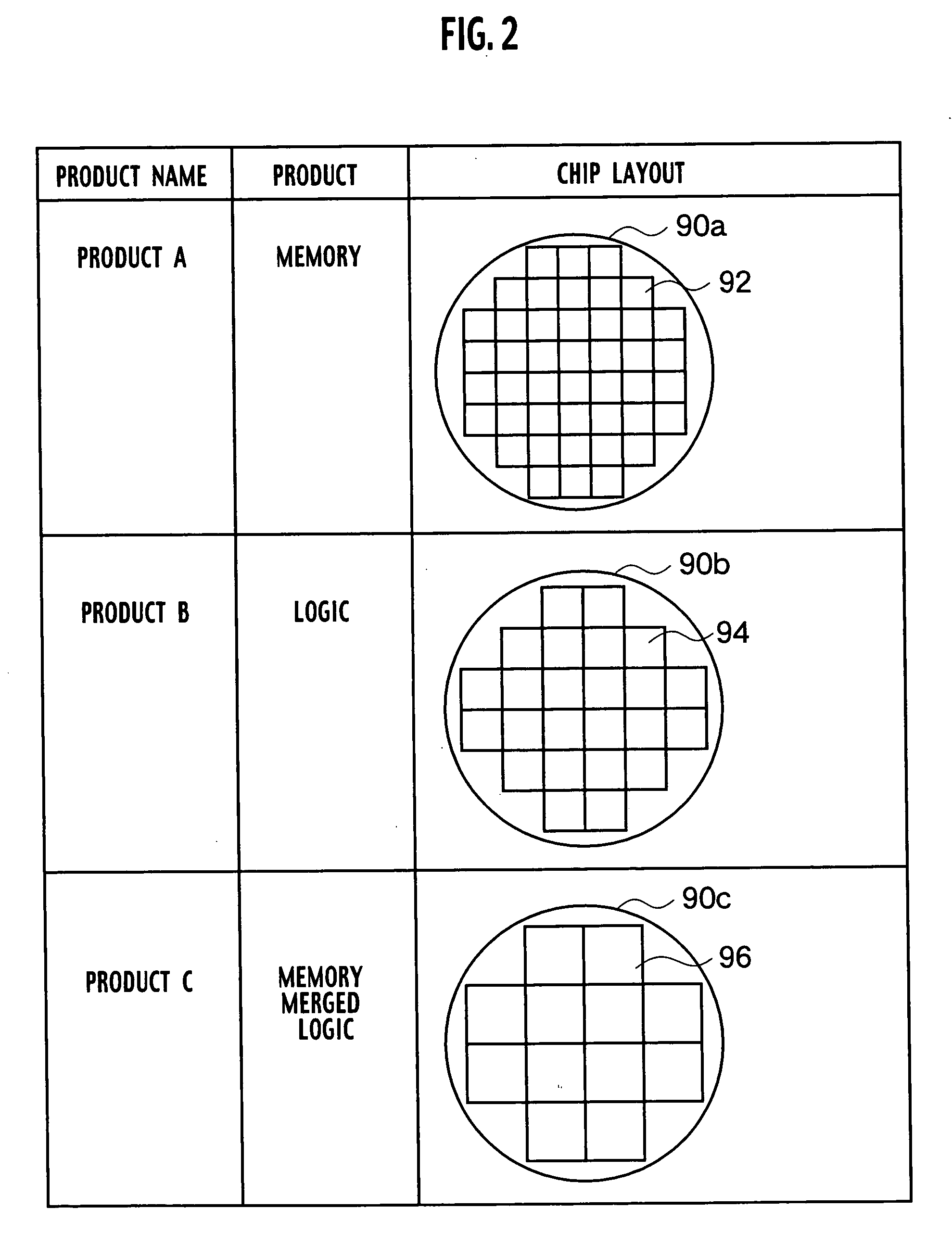

Failure detection system, failure detection method, and computer program product

InactiveUS20050102591A1Semiconductor/solid-state device testing/measurementElectronic circuit testingCorrelation coefficientElectricity

A failure detection system includes a wafer test information input unit which acquires pass / fail maps for wafers for a plurality of types of semiconductor devices, displaying failure chip areas based on results of electrical tests performed on chips; an analogous test information input unit which classifies the electrical tests into analogous electrical tests with regard to analogous failures among the semiconductor devices; a subarea setting unit which assigns subareas common to the types of semiconductor devices on a wafer surface; a characteristic quantity calculation unit which statistically calculates characteristic quantities based on a number of the failure chip areas included in the subareas for each analogous electrical test; and a categorization unit which obtains correlation coefficients between the characteristic quantities corresponding to the subareas, and classifies clustering failure patterns of the failure chip areas into categories by comparing the correlation coefficients with a threshold.

Owner:KK TOSHIBA

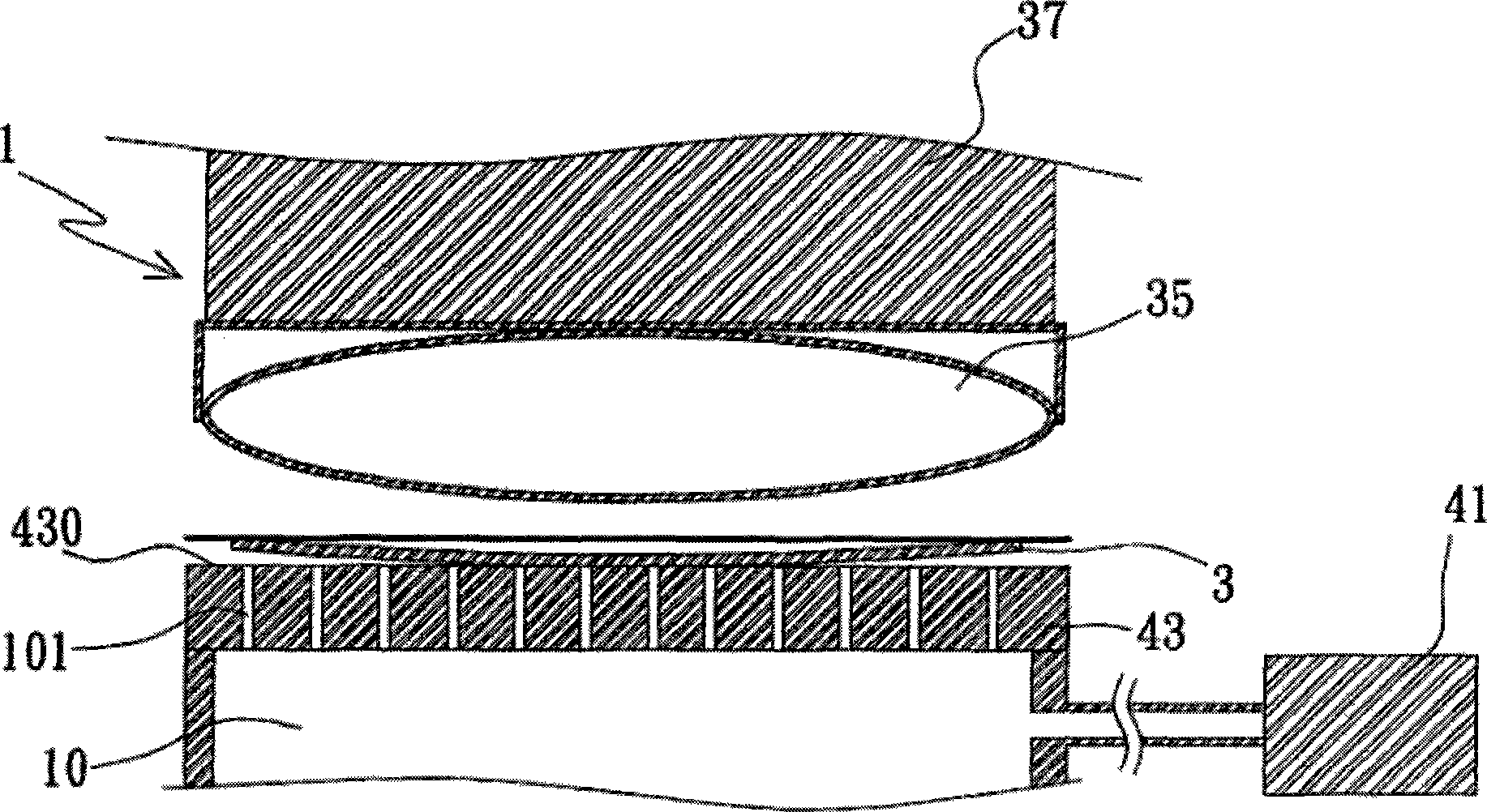

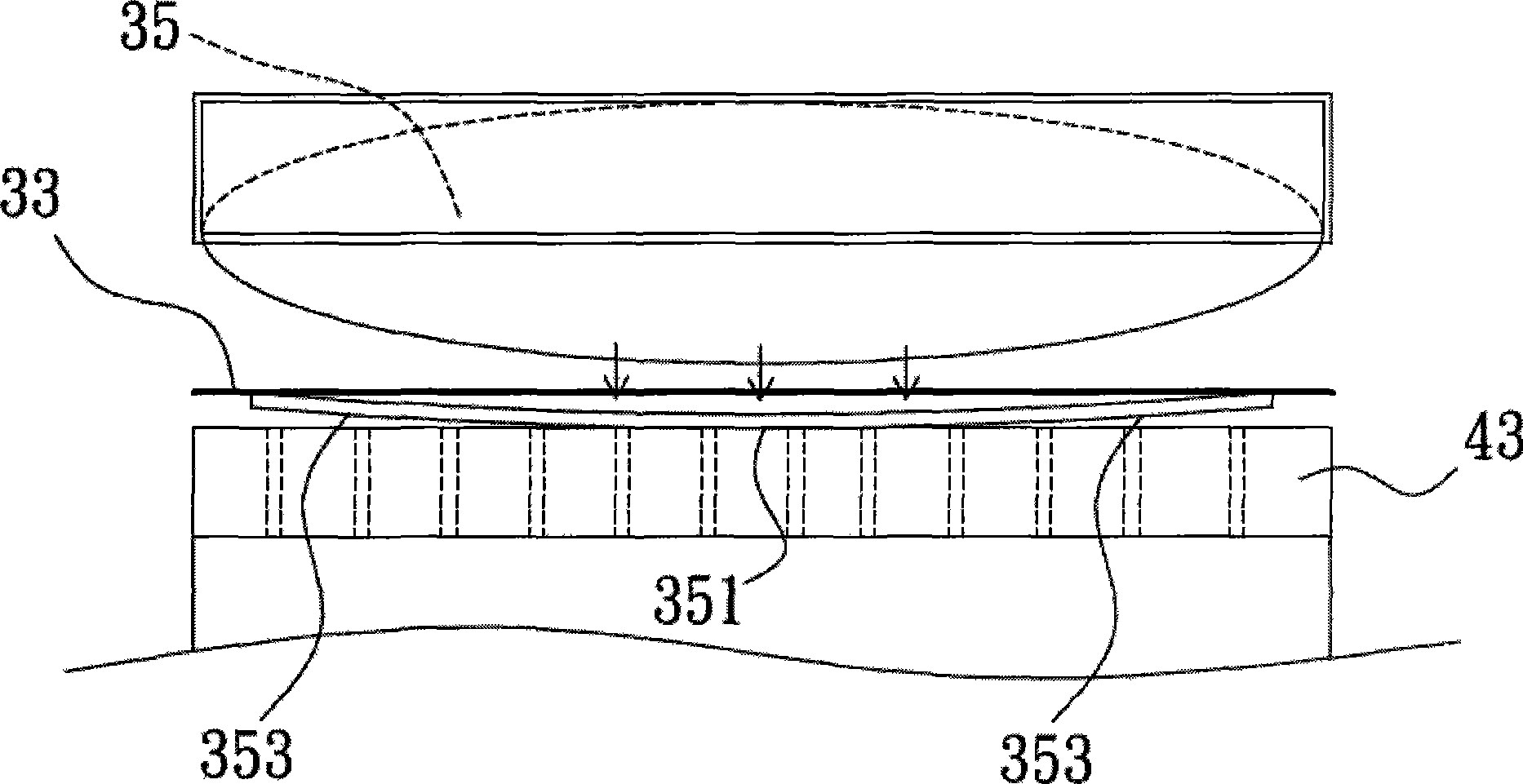

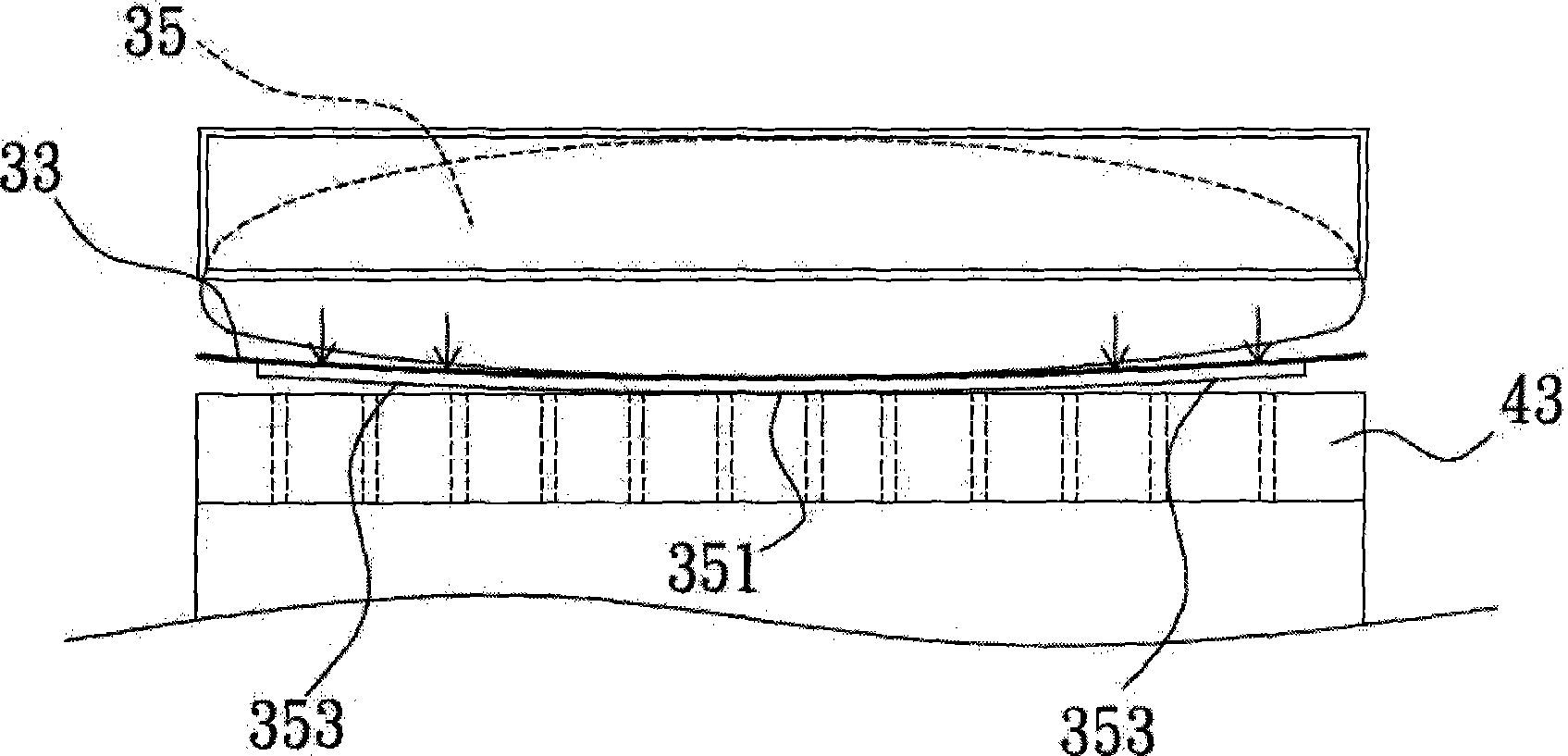

Fixing/releasing auxiliary device for a wafer detection platform, the wafer detection platform and method therefor

InactiveCN101393885AEasy to measure correctlyAvoid damageSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingOperation modeEngineering

The invention discloses a fixing / releasing auxiliary device for wafer testing equipment, the testing equipment and a method thereof. The invention aims to help the testing equipment test a wafer to be tested, which is placed on the bearing surface of the bearing device of the testing equipment, by solving the problem that the uneven surface of the wafer stops the wafer from being successfully absorbed and fixed by air-pores on the bearing device. The method comprises the following steps: a set of mobile units are used for steadily pressing downwards a flexible material, so that the central part of the material, which is thicker than the peripheral part of the material, can come into contact with the central part of the wafer to be tested much earlier; and then the material is gradually pressed downwards so as to gradually flatten the whole piece of the wafer-the central part first and then the peripheral part-on the bearing surface. The invention provides an automatic operation mode, but also prevents the wafer to be tested from being broken or poor contact in the course of pressing, thereby enhancing the output yield and the output rate.

Owner:CHROMA ELECTRONICS SHENZHEN

Test method for asynchronously repairing and adjusting silicon wafer with anti-interference

ActiveCN101510520AAvoid interferenceImprove test accuracySemiconductor/solid-state device testing/measurementElectronic circuit testingProbe cardEngineering

The invention provides a test method of an anti-interference asynchronous trimming wafer, wherein, a probe card is used for testing and trimming a chip on the wafer. Two probes which are a test probe and a fuse probe are arranged on the probe card. The method includes the following steps: step one, the initial value of the chip before a fuse is trimmed is tested; step two, the fuse is trimmed; step three, the final trimming result after the fuse is trimmed is tested. In the three steps, only one probe is adopted to be in contact with the chip for each time. The chip to be tested is only in contact with the test probe and is not in contact with the fuse probe in step one and step three when the relevant parameter values of the chip to be tested are measured, thereby avoiding the interference of the fuse probe in the testing of the chip so as to greatly improve the measuring accuracy of the initial value.

Owner:SINO IC TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com