Test method for asynchronously repairing and adjusting silicon wafer with anti-interference

A wafer testing and trimming technology, applied in electronic circuit testing, semiconductor/solid-state device testing/measurement, etc., which can solve problems such as interference and increase chip interference.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The preferred embodiments of the present invention are given below in conjunction with the accompanying drawings to describe the technical solution of the present invention in detail.

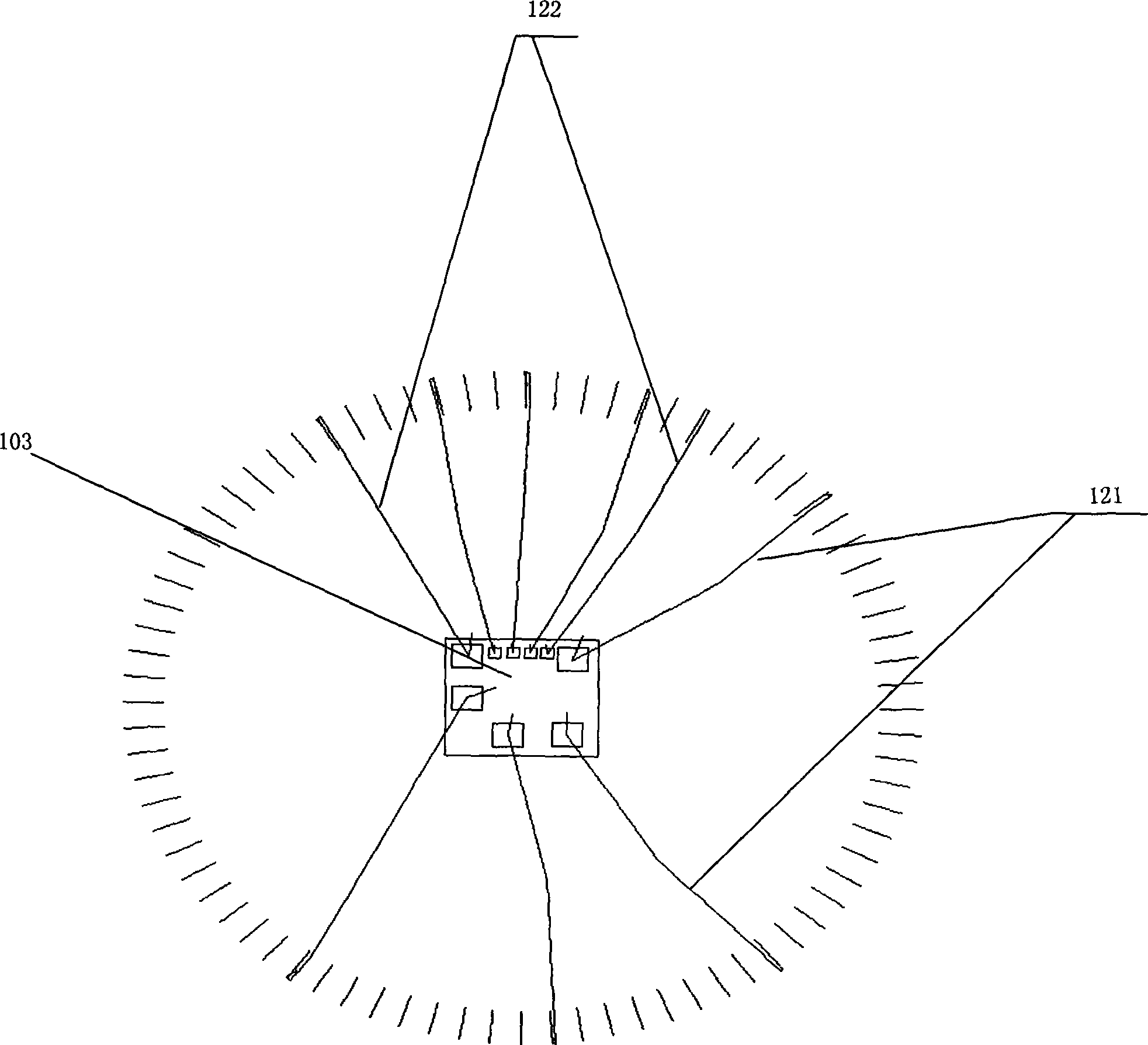

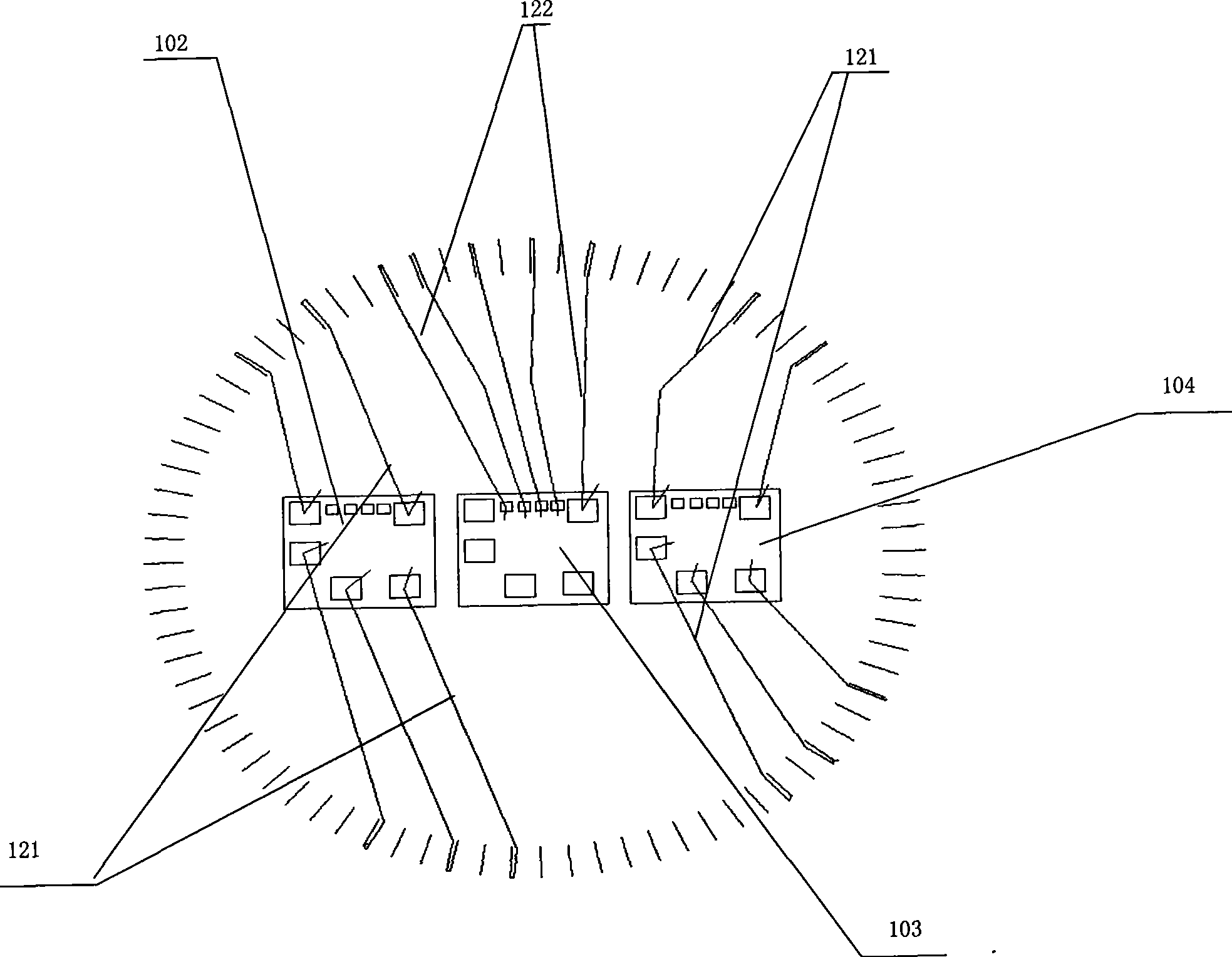

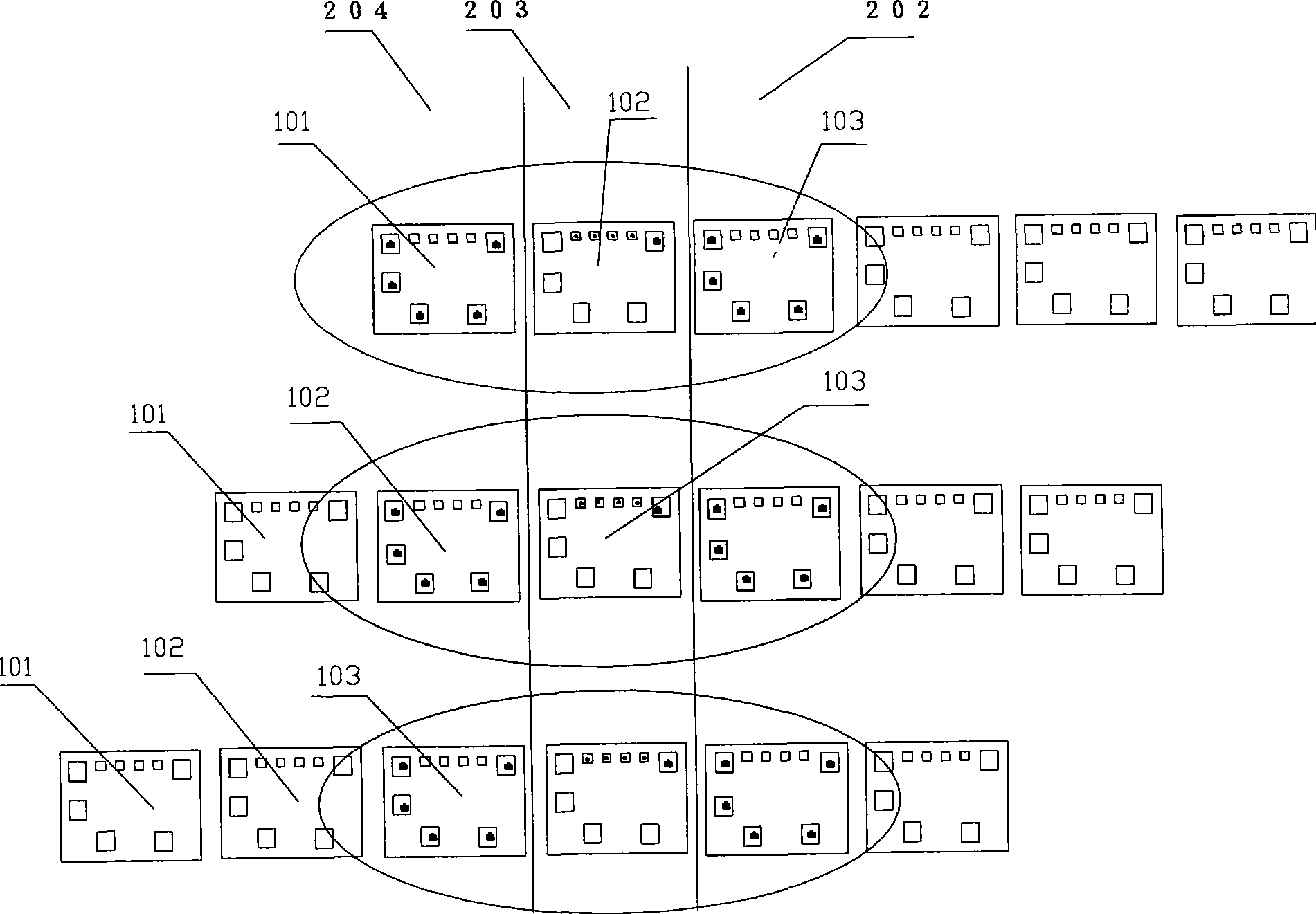

[0023] figure 2 It is an enlarged schematic diagram of the corresponding positions of the fuse probe 122 and the test probe 121 on the adjacent chips 102, 103, 104 on the wafer when the probe card 10 of the present utility model is used for wafer testing. The wire probes are only in contact with the corresponding contacts on the chip 103, and the two groups of test probes are respectively in contact with the test probe contacts on the chip 102 and the chip 104. It can be seen that the fuse probe 122 and the test probe 121 are in the same step. Corresponding to different chips, when testing a certain chip, there will be no interference caused by the fuse probe 122 and the test probe 121 being in contact with the chip at the same time.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com