Nano-wire field effect transistor, method for manufacturing the transistor, and integrated circuit including the transistor

a technology of nanowire field and transistor, which is applied in the direction of nanotechnology, electrical apparatus, semiconductor devices, etc., can solve the problems of less than 1% of inefficient power consumption due to leakage current rather than operating power increase, difficult to perfectly suppress leakage current increase and sub-threshold slope, and improve the variation in size and characteristics. , the effect of superior size reproducibility and uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

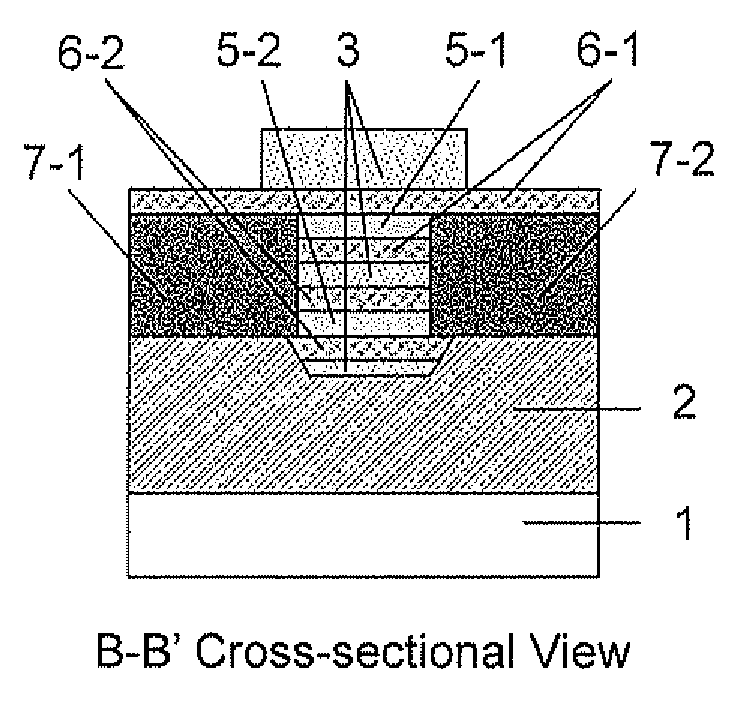

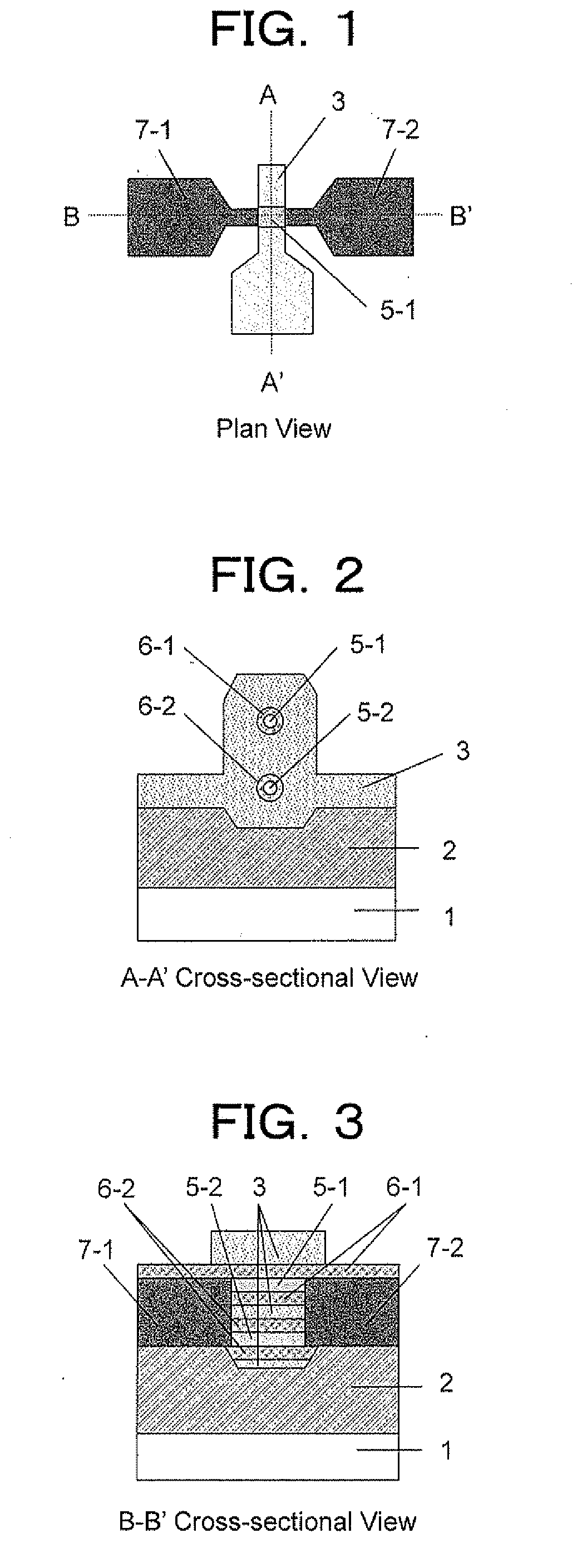

[0063]FIGS. 1, 2 and 3 show a first embodiment in accordance with the present invention. FIG. 1 is a plan view of a nano-wire field effect transistor in accordance with the present invention, the transistor having a pair of nano-wires each having a circular cross-section shape and being arranged one above the other formed on a (100) SOI substrate. FIG. 2 is an A-A′ cross-sectional view thereof, and FIG. 3 is a B-B′ cross-sectional view thereof. In FIGS. 1 to 3, numeral reference 1 denotes a substrate, 2 denotes a buried oxide film, 3 denotes a gate electrode, 5-1 and 5-2 denote nano-wares each having a circular cross-section shape and simultaneously formed one above the other. 6-1 and 6-2 are gate insulator films, and 7-1 and 7-2 are a source region and a drain region, respectively.

[0064]FIGS. 4 to 19 show an example of a fabrication process of the nano-wire field effect transistor having a pair of nano-wires each having a circular cross-section shape and being arranged one above th...

second embodiment

[0074]FIGS. 20, 21 and 22 show the second embodiment of the present invention. FIG. 20 shows a plan view of a nano-wire field effect transistor in accordance with the present invention. In this figure, a plurality of pairs of nano-wires each having a circular cross-section shape arranged one above the other are arranged in parallel. FIG. 21 shows an A-A′ cross-sectional view thereof, and FIG. 22 shows a B-B′ cross-sectional view thereof. In FIGS. 20 to 22, numeral reference 1 denotes a substrate, 2 denotes a buried oxide film, 3 denotes a gate electrode, 5-5, 5-6, 5-7, 5-8, 5-9, and 5-10 denote nano-wires each having a circular cross-section shape, 6-5, 6-6, 6-7, 6-8, 6-9, and 6-10 denote gate insulator films, and 7-1 and 7-2 denote source-drain regions.

[0075]A fabrication process of the second embodiment is basically same as that of the first embodiment. A different point is that in the electron beam lithography process in the above paragraph 0016, a pattern of the nano-wire is for...

third embodiment

[0076]FIGS. 23, 24, and 25 show the third embodiment of the present invention. FIG. 23 shows a plan view of an integrated circuit in accordance with the present invention. In this figure, a nano-wire field effect transistor including a pair of nano-wires each having a circular cross-section shape arranged one above the other is used as a PMOS, whereas a nano-wire field effect transistor with a nano-wire having a circular cross-section shape where the upper nano-wire a circular cross-section shape is removed by an etching is used as an NMOS. FIG. 24 shows an A1-A1′ and A2-A2′ cross-sectional views thereof, and FIG. 25 shows a B-B′ cross-sectional view thereof.

[0077]In FIGS. 23 to 25, numeral reference 1 denotes a substrate, 2 denotes a buried oxide film, 3 denotes a gate electrode, 5-1, 5-2, and 5-4 are nano-wires each having a circular cross-section shape, 6-1, 6-2, 6-3, and 6-4 denote gate insulator films, and 7-1, 7-2, 7-3, and 7-4 denote source-drain regions.

[0078]A fabrication p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com