Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "High frequency performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

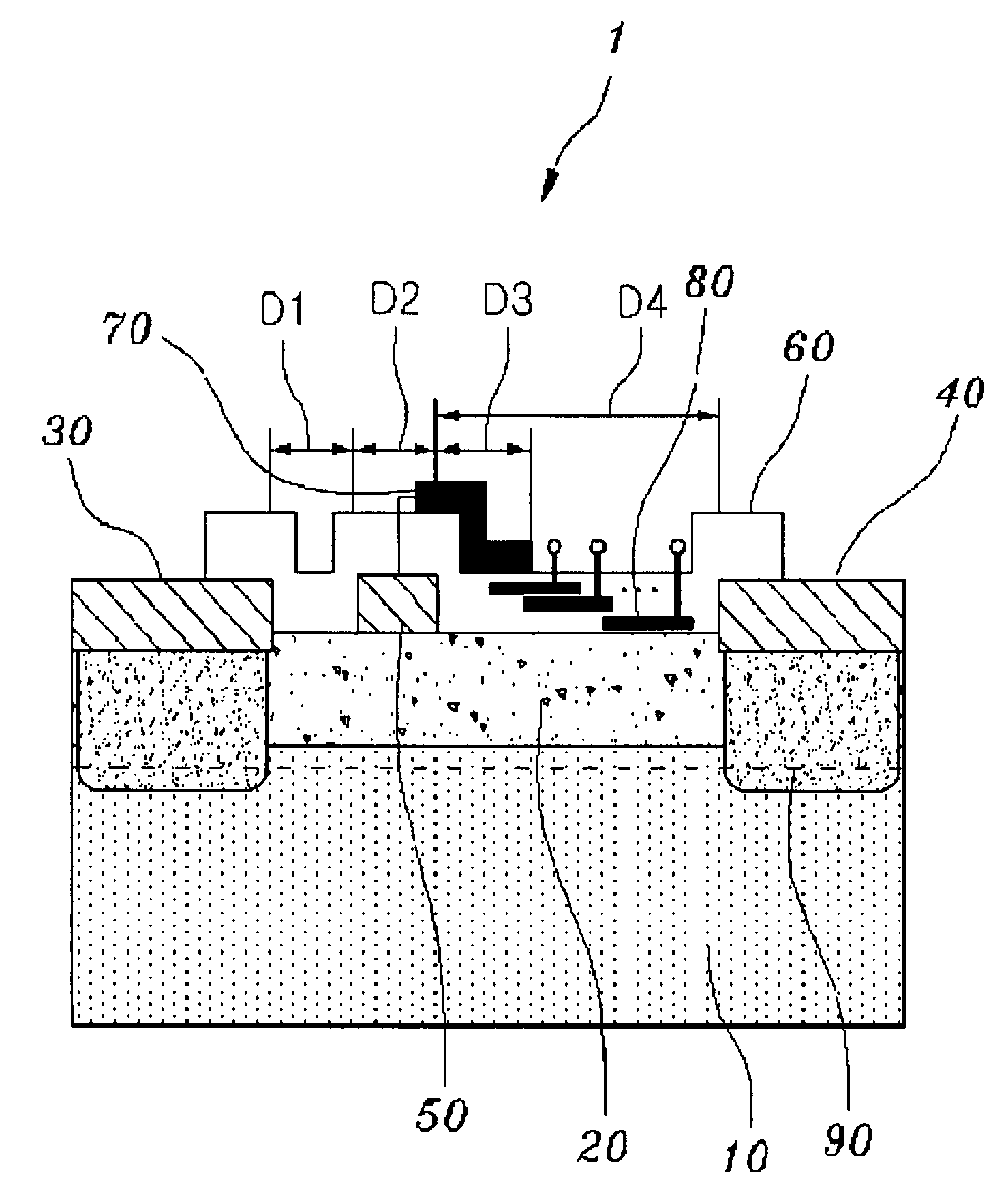

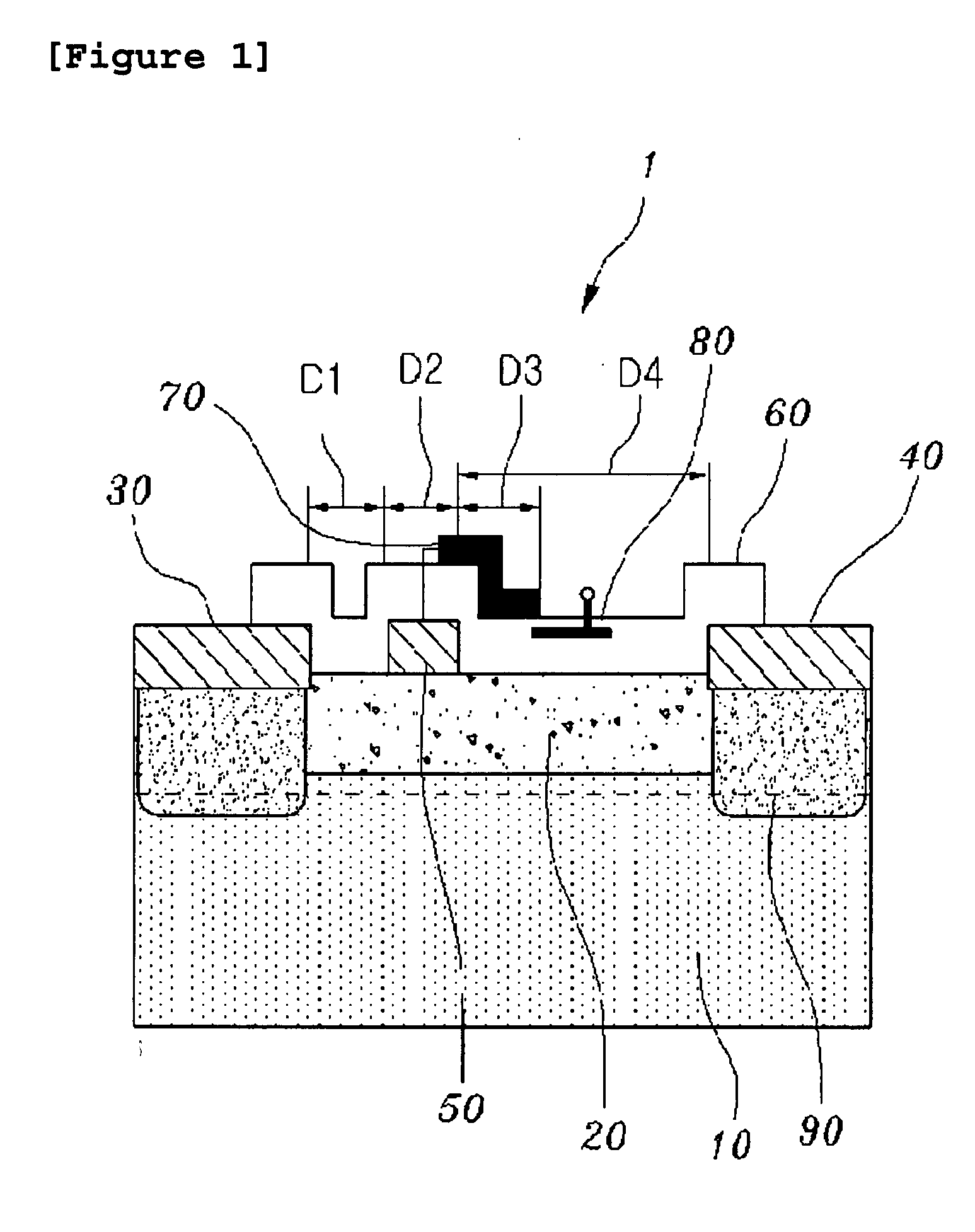

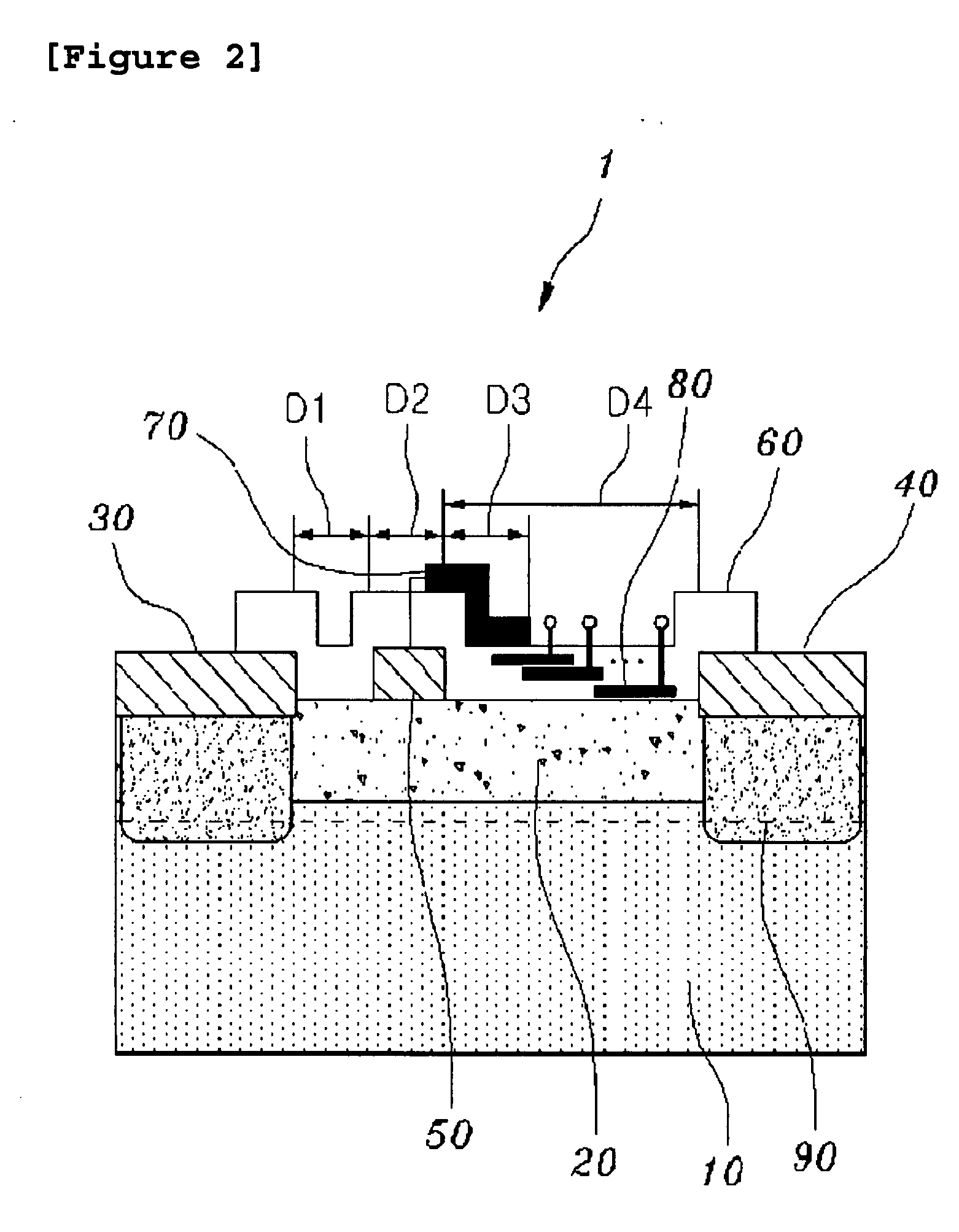

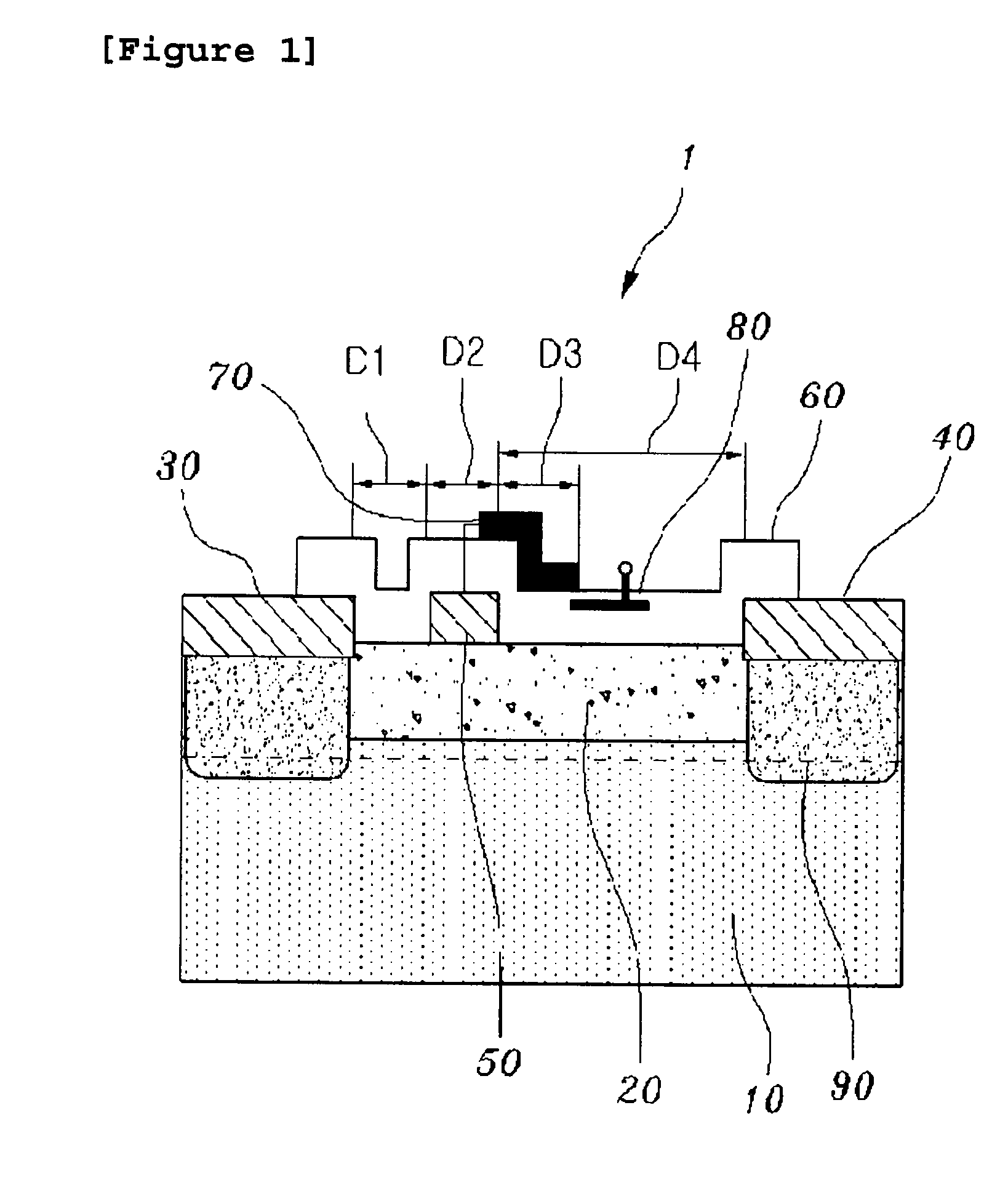

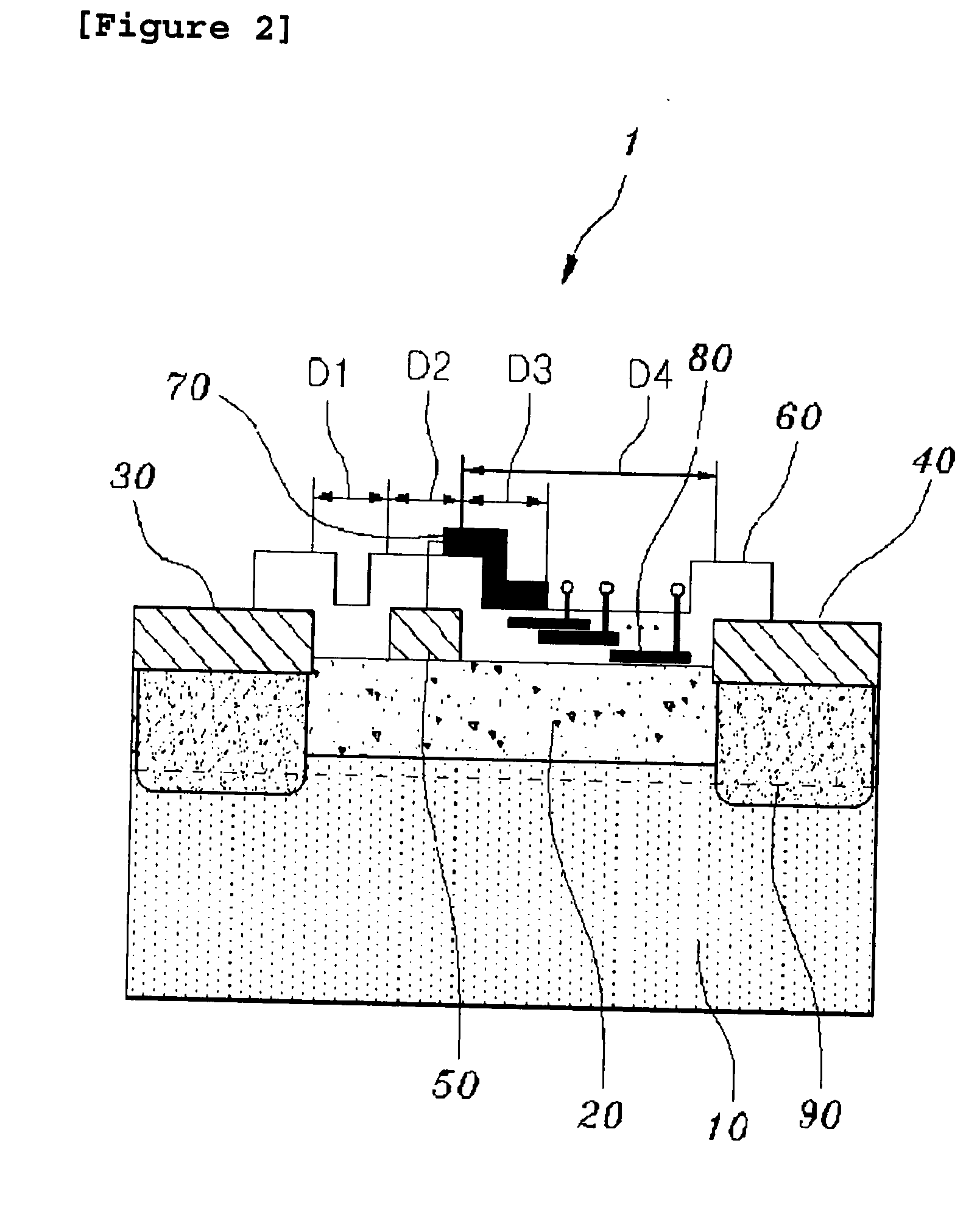

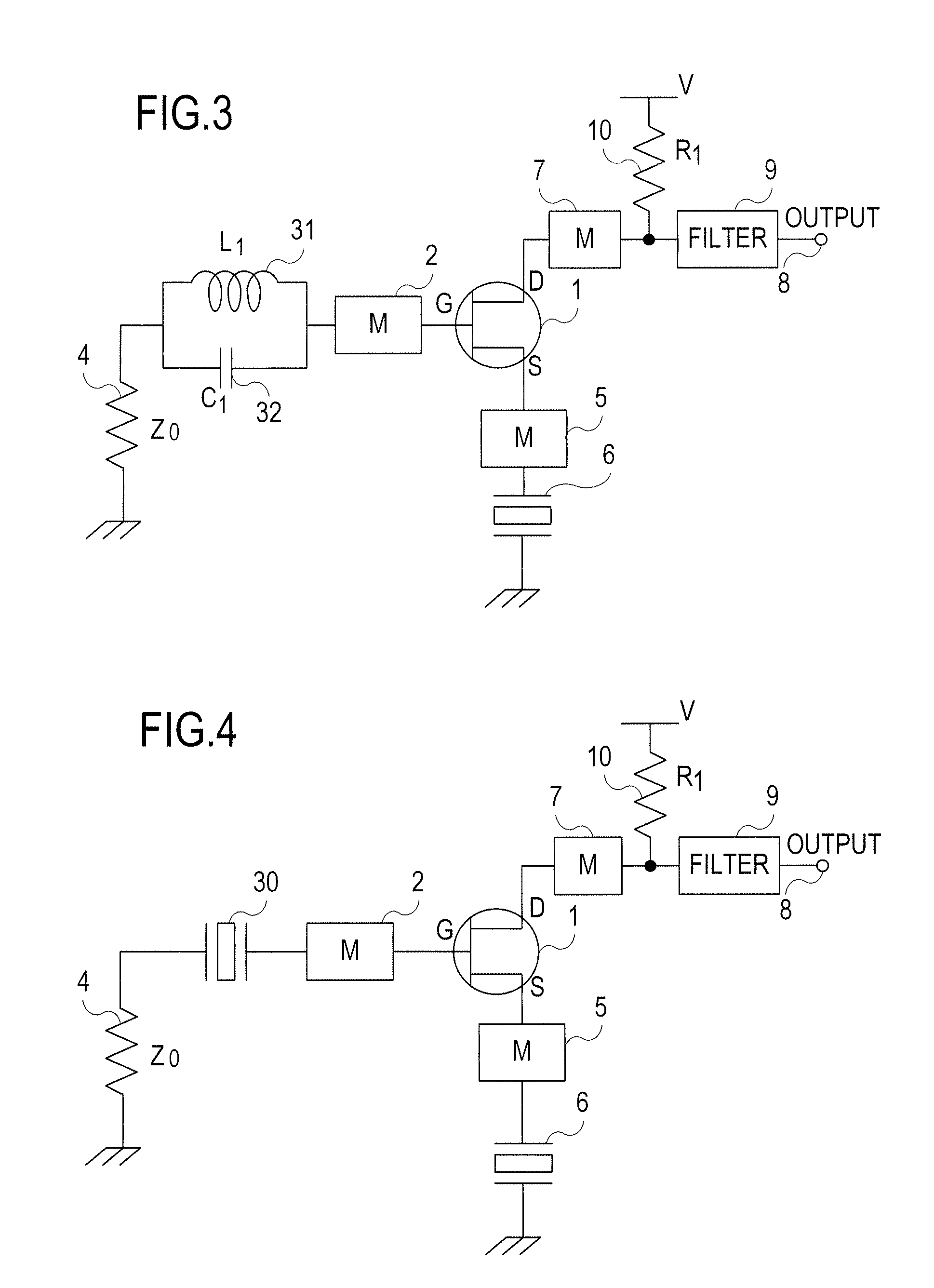

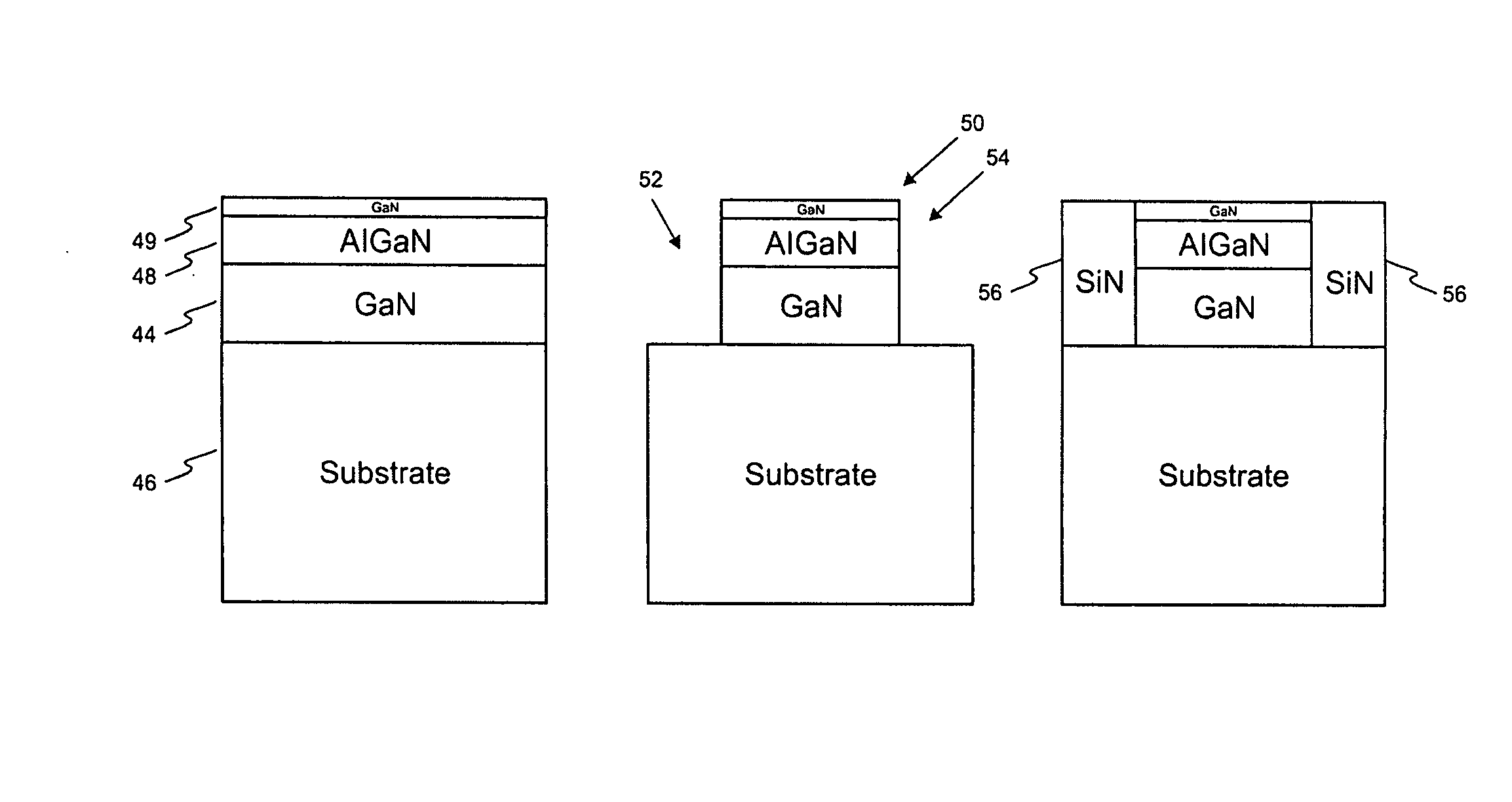

Gallium nitride high electron mobility transistor having inner field-plate for high power applications

InactiveUS20080073670A1Reduce peak valueHigh frequency performanceSemiconductor devicesPhysicsCapacitance

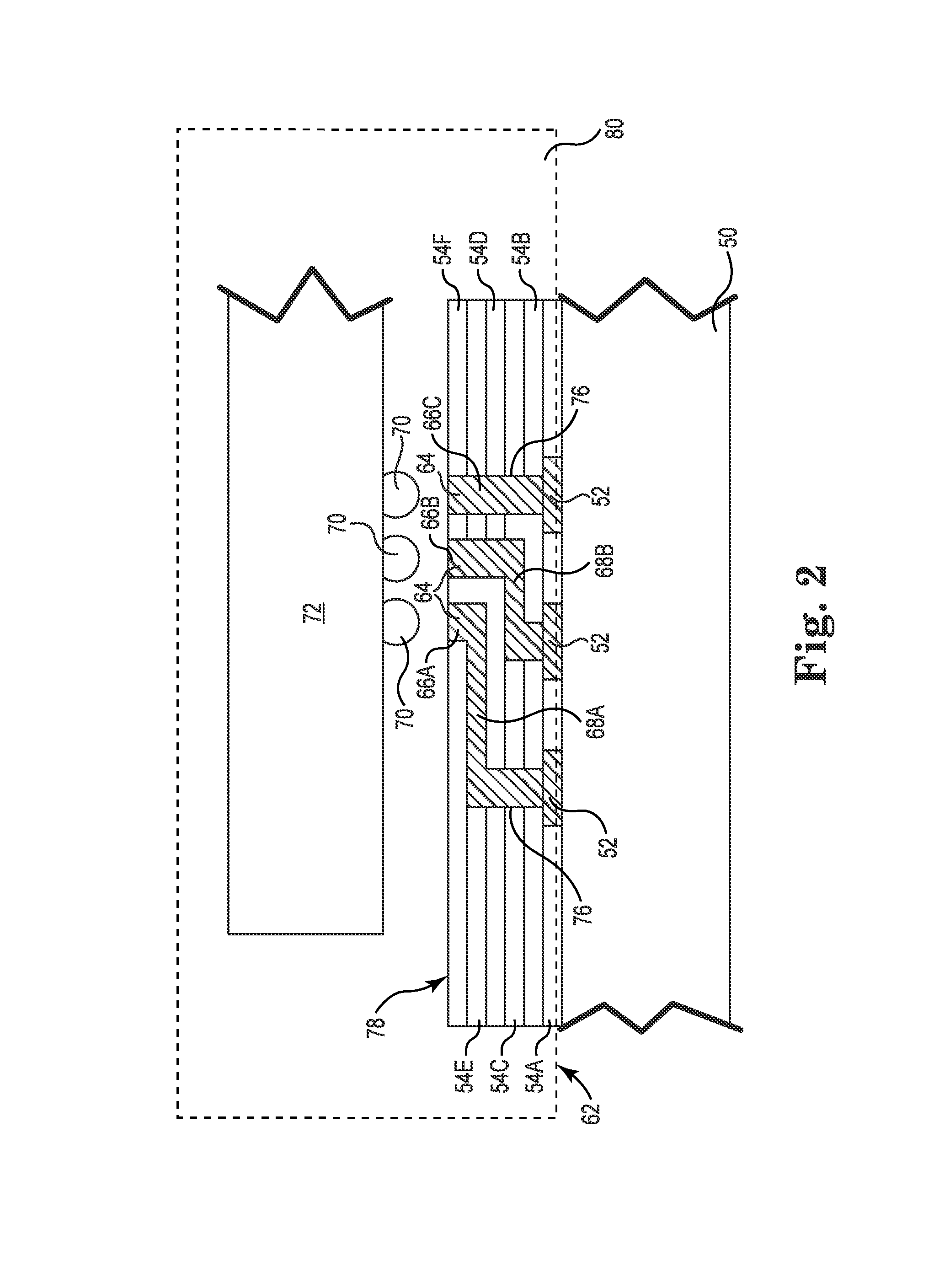

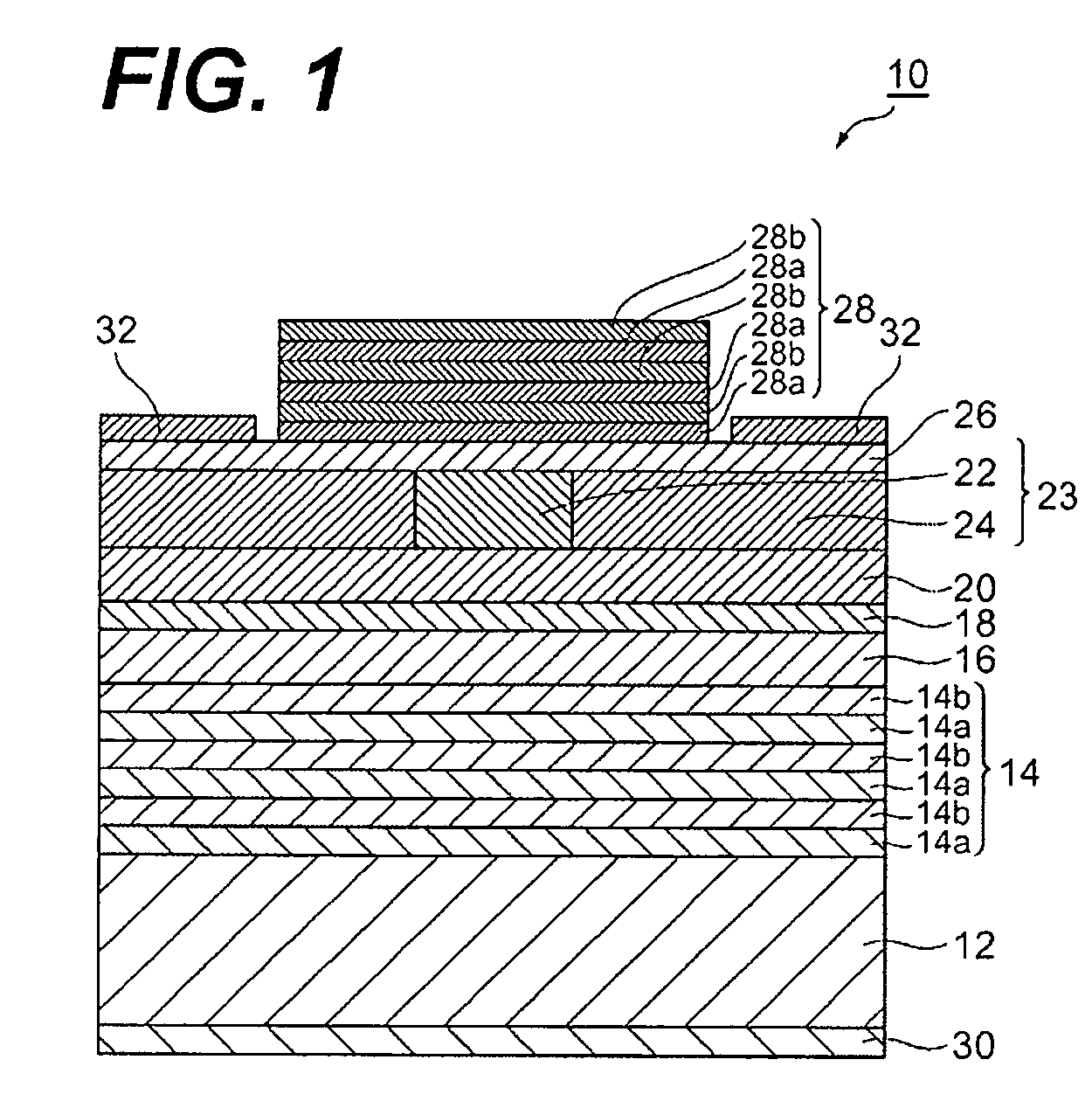

A gallium nitride high electron mobility transistor, in which an inner field-plate is disposed between the gate and drain of the high electron mobility transistor, so that an electric field is distributed between gate and drain regions to reduce a peak value and to reduce gate leakage current while maintaining high frequency performance, thus obtaining a high breakdown voltage, reducing the capacitance between the gate and the drain attributable to a shielding effect, and improving linearity and high power and high frequency characteristics through variation in the input voltage of the inner field-plate. The gallium-nitride high electron mobility transistor includes a gallium nitride buffer layer. An aluminum gallium-nitride barrier layer is formed on the buffer layer. A source electrode is placed on the barrier layer. A drain electrode is placed on the barrier layer to be spaced apart from the source electrode. A gate electrode is placed on a top of the barrier layer to be spaced apart from the source electrode and the drain electrode. A dielectric layer is deposited on the top of the barrier layer. An electric field electrode is formed on the dielectric layer located on the gate electrode. An inner field-plate is formed in the dielectric layer to be spaced apart from the gate electrode and the drain electrode.

Owner:KOREA ADVANCED INST OF SCI & TECH

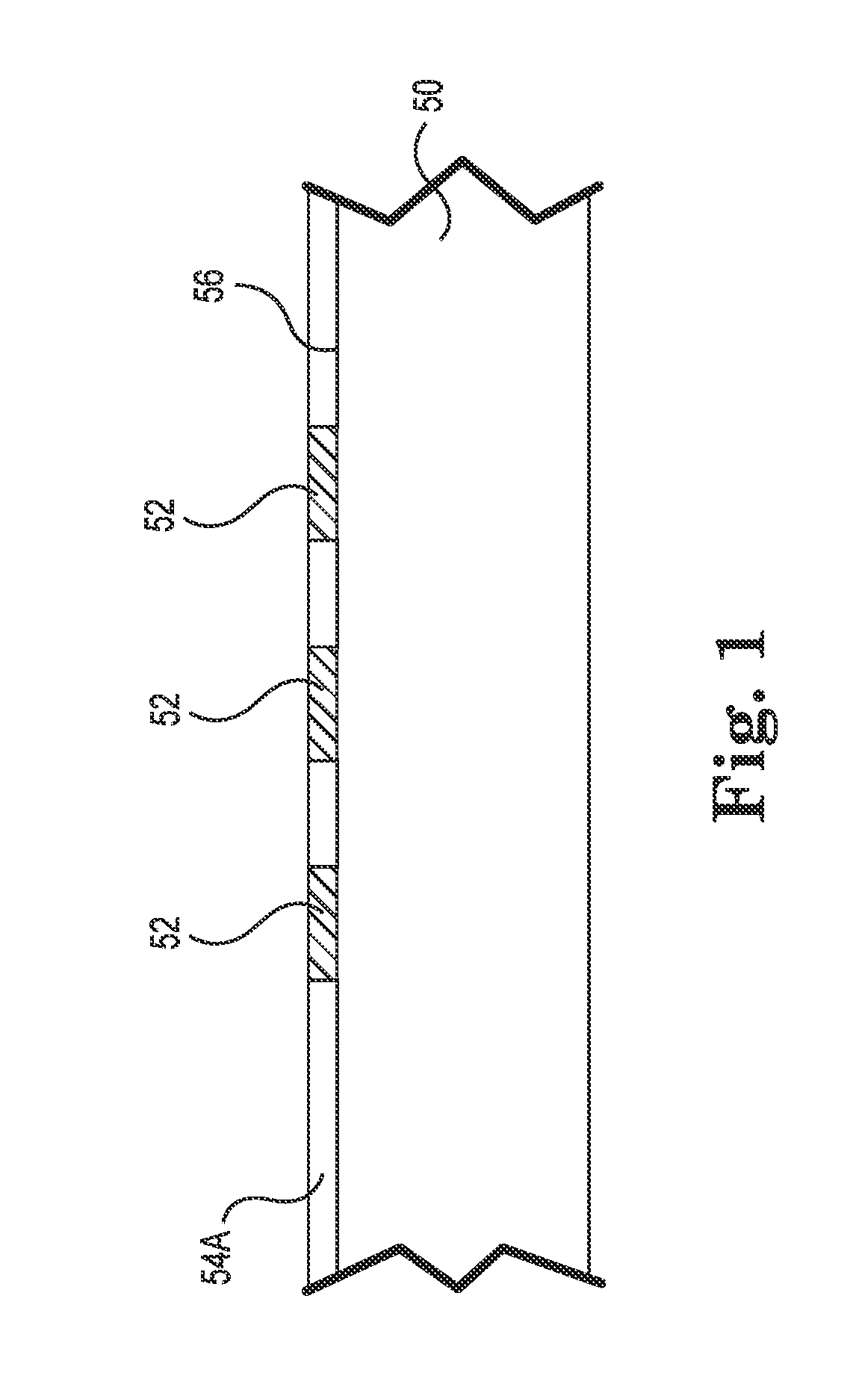

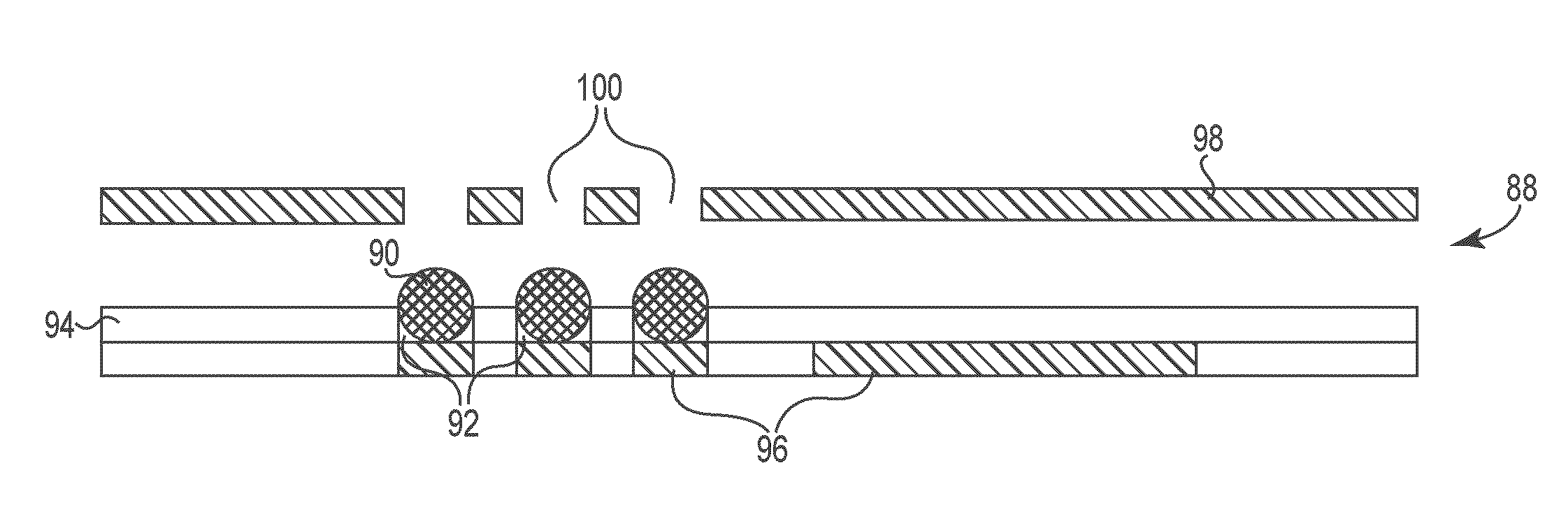

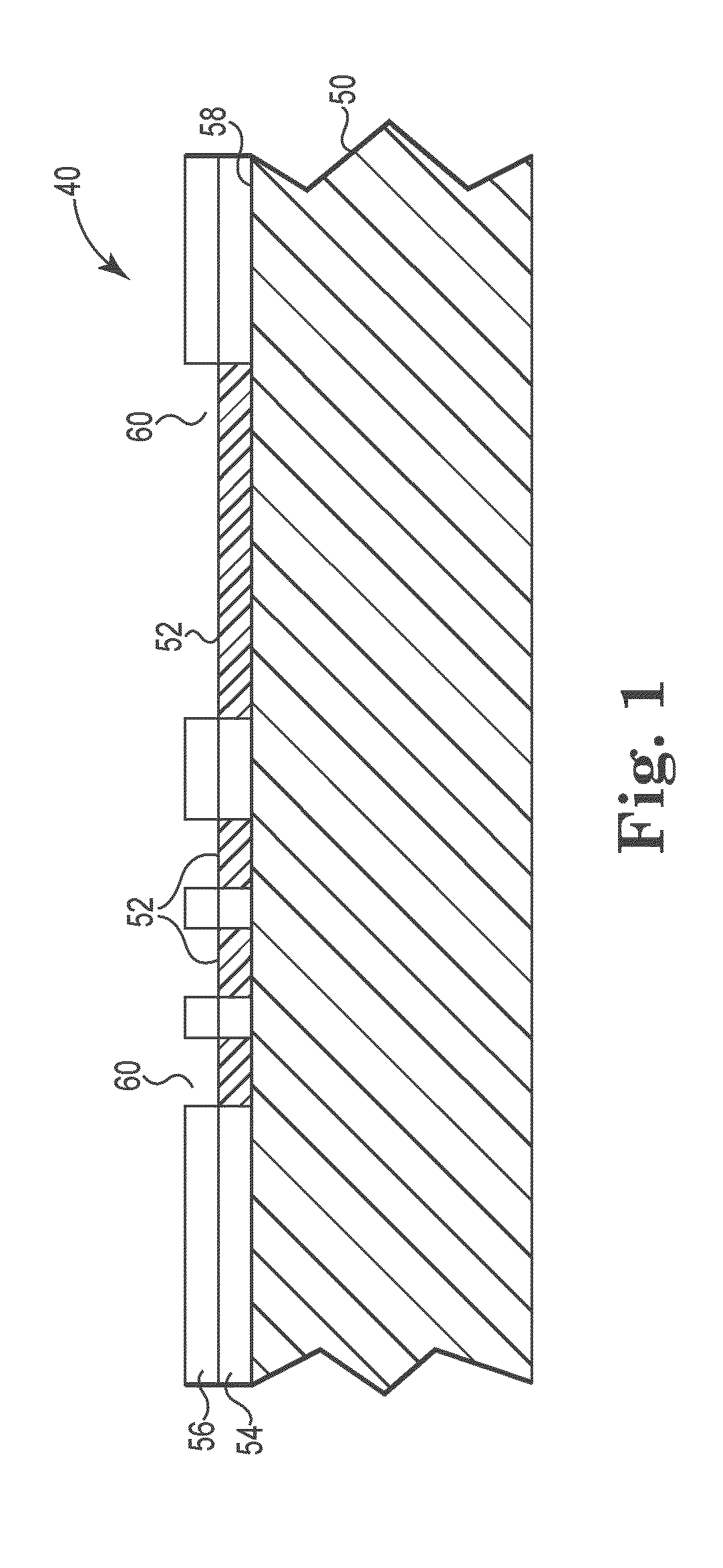

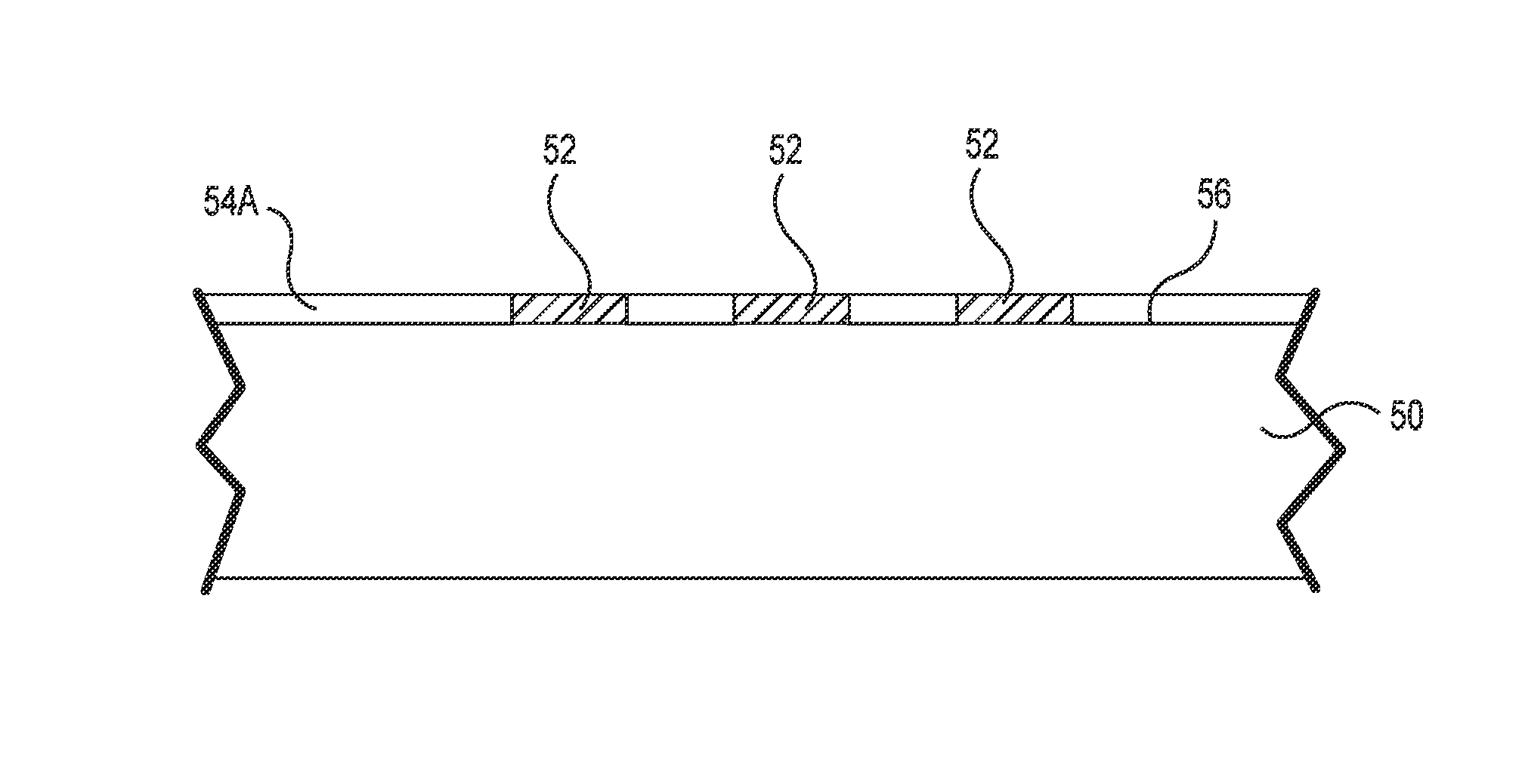

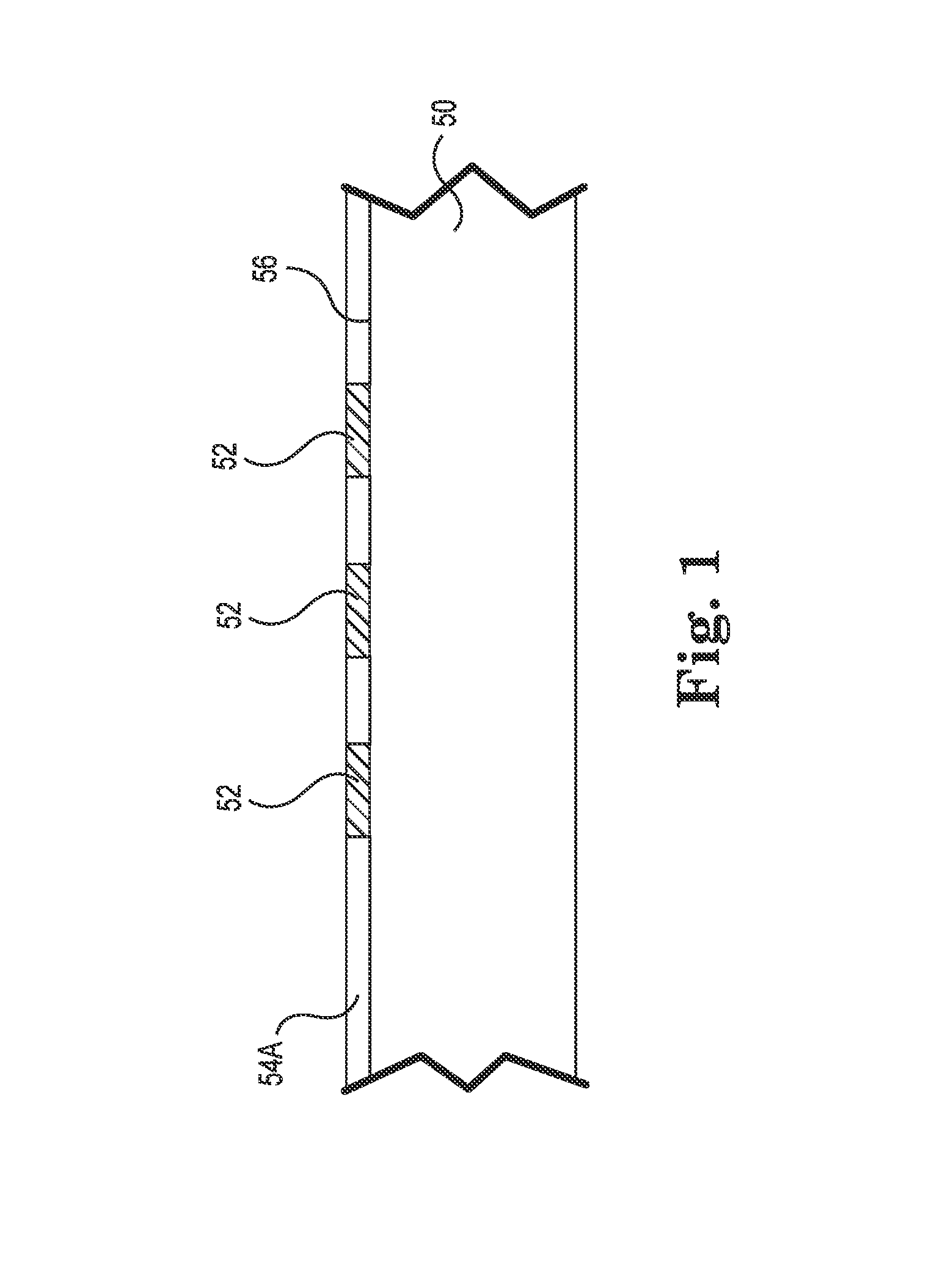

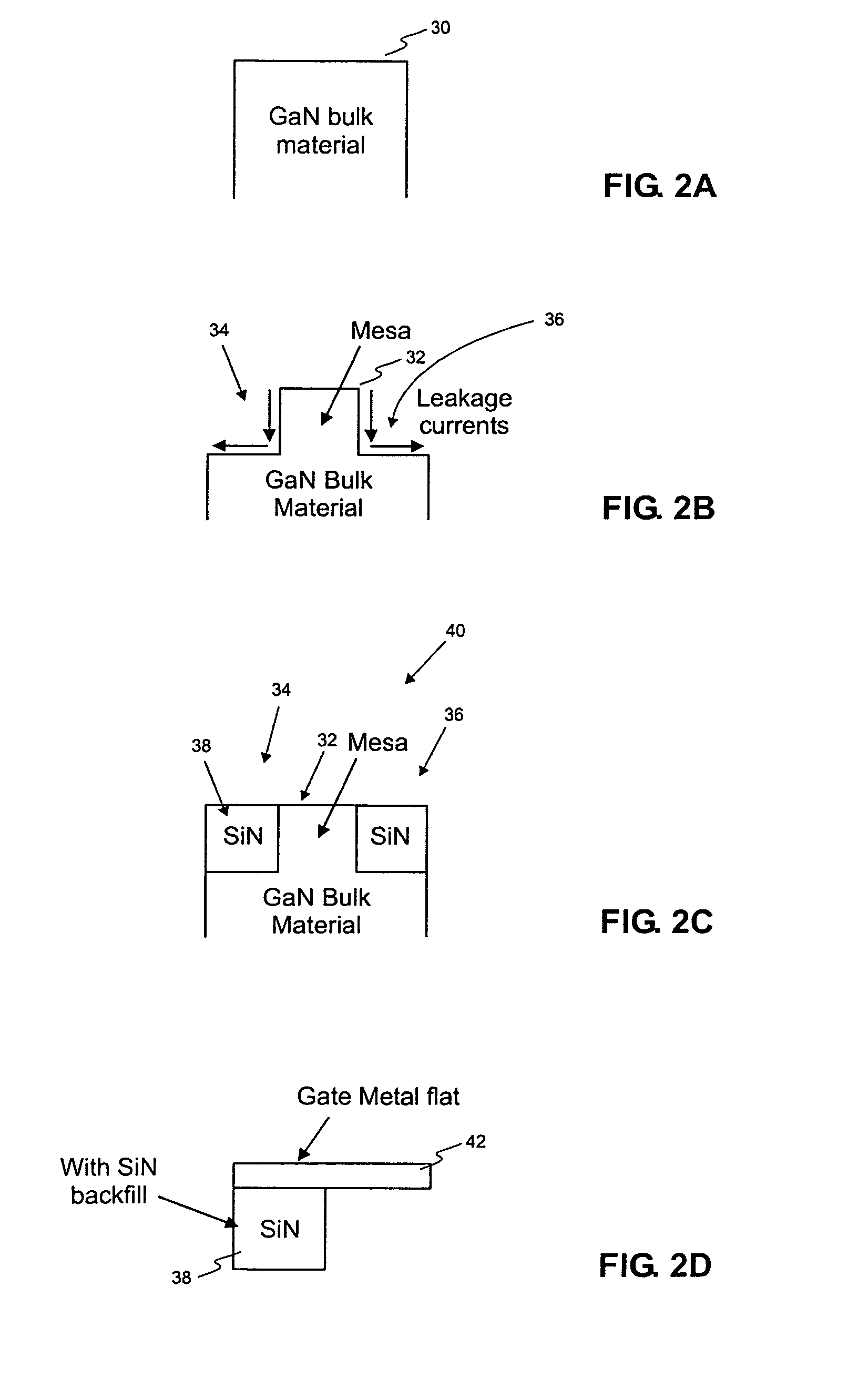

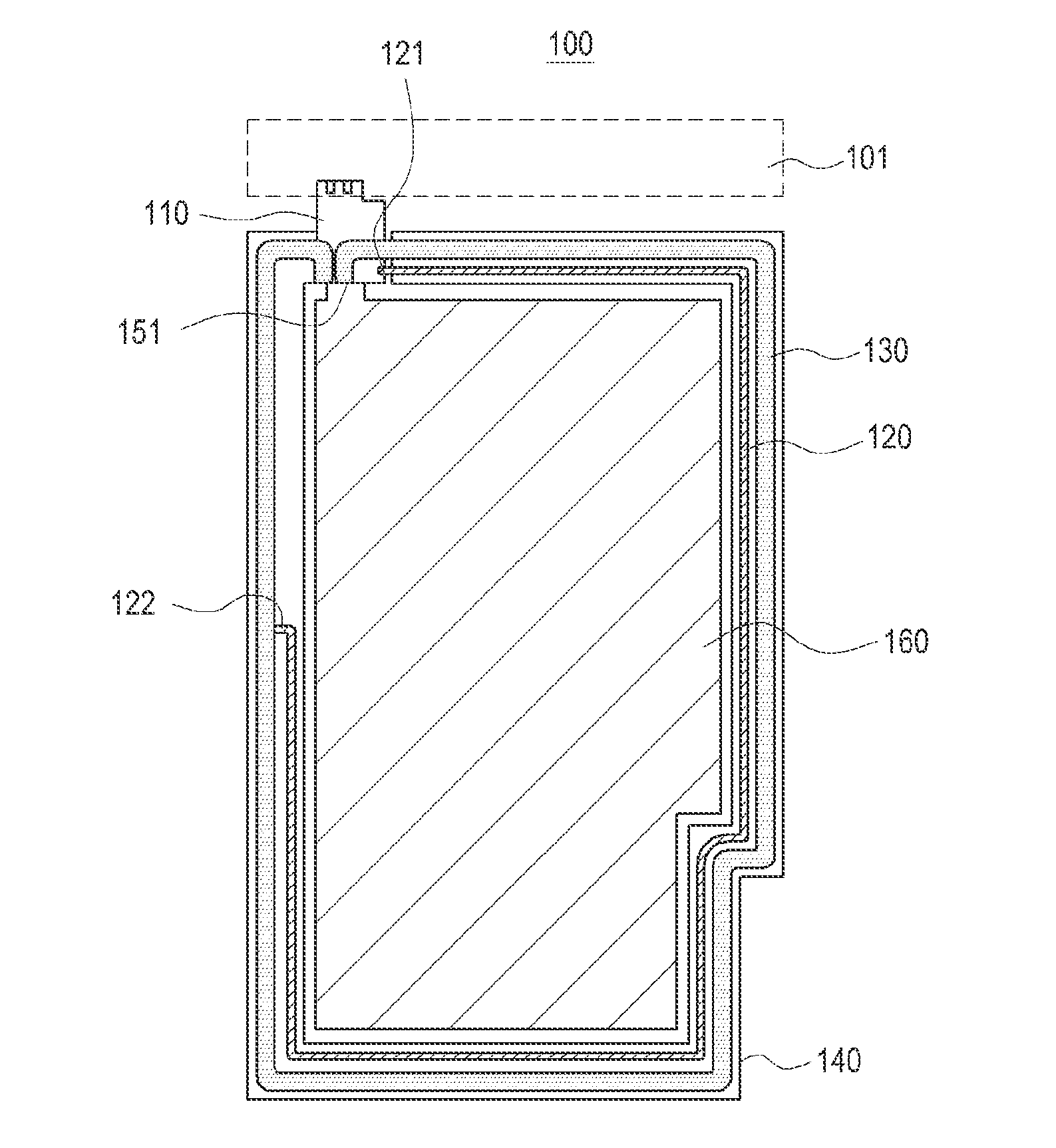

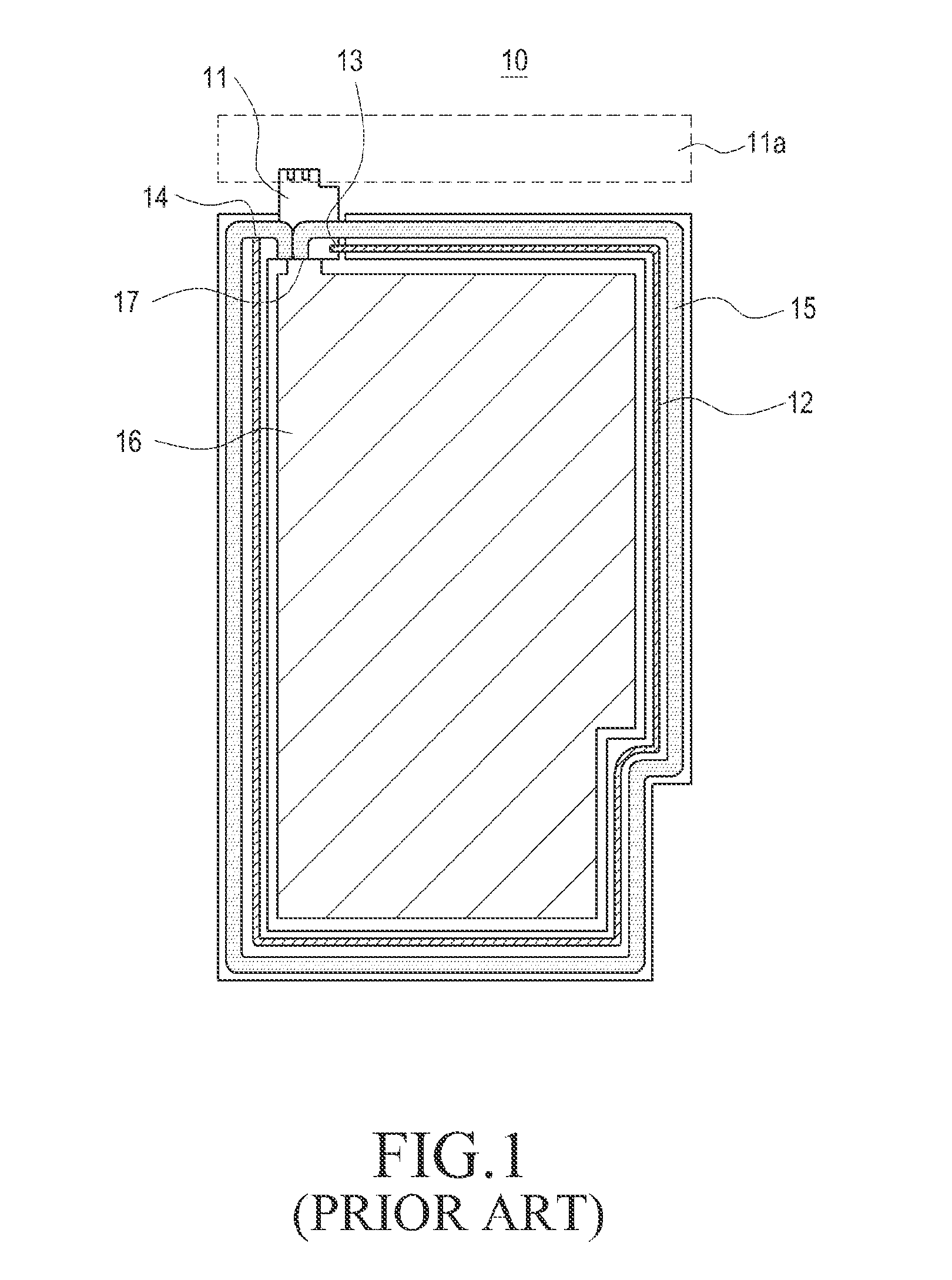

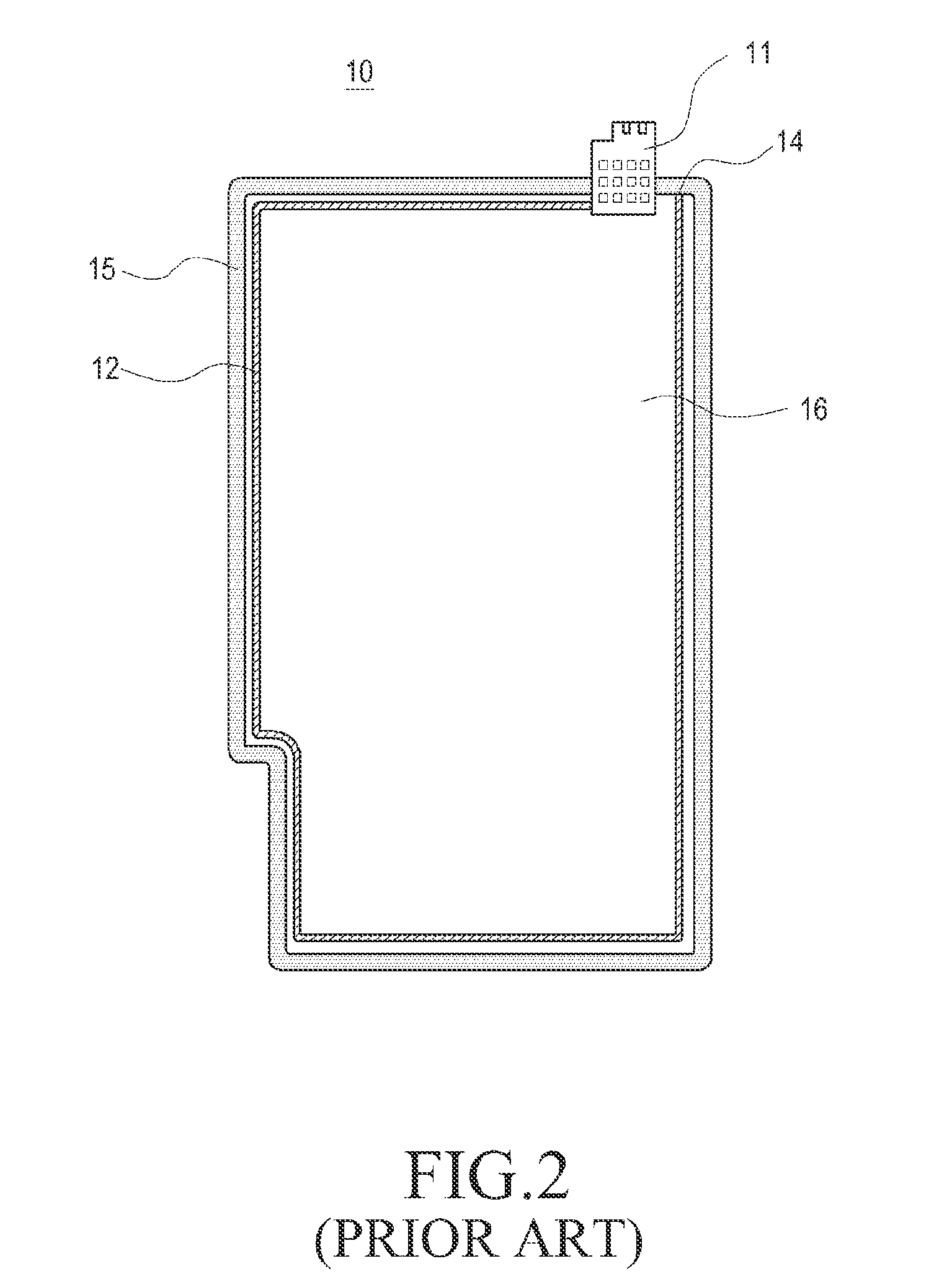

Compliant printed circuit area array semiconductor device package

ActiveUS20120061846A1Low production costImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesRoad surfaceIc devices

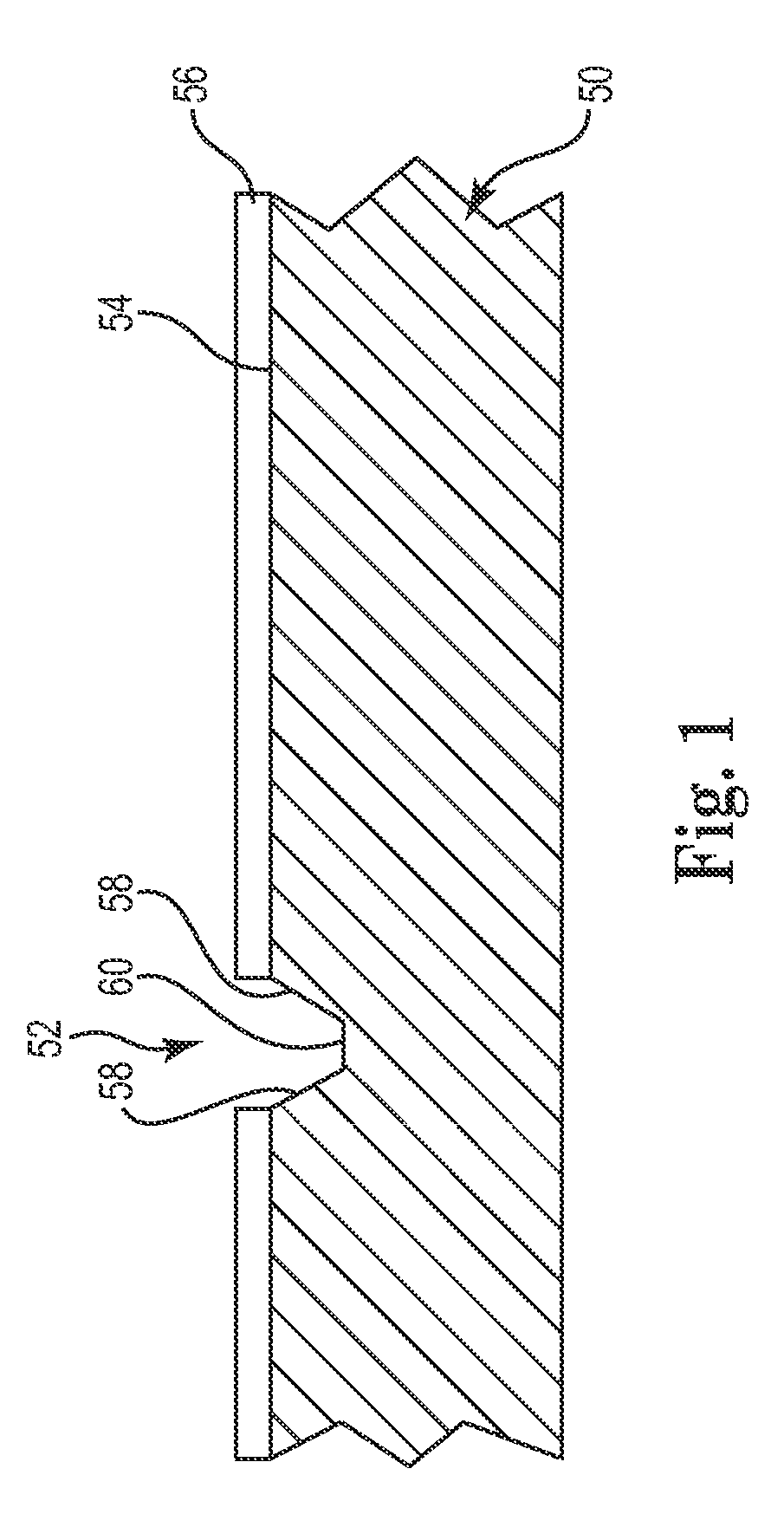

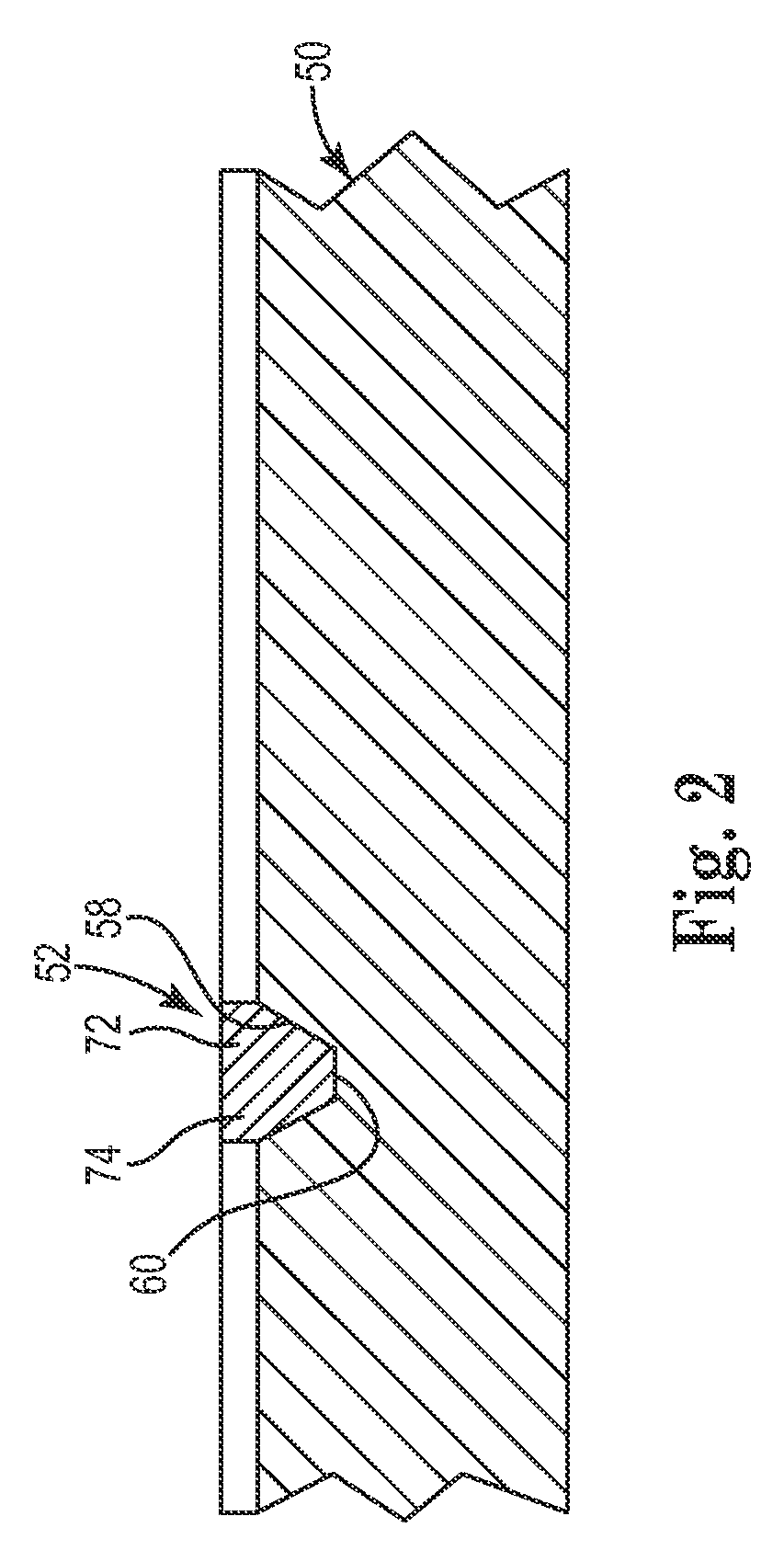

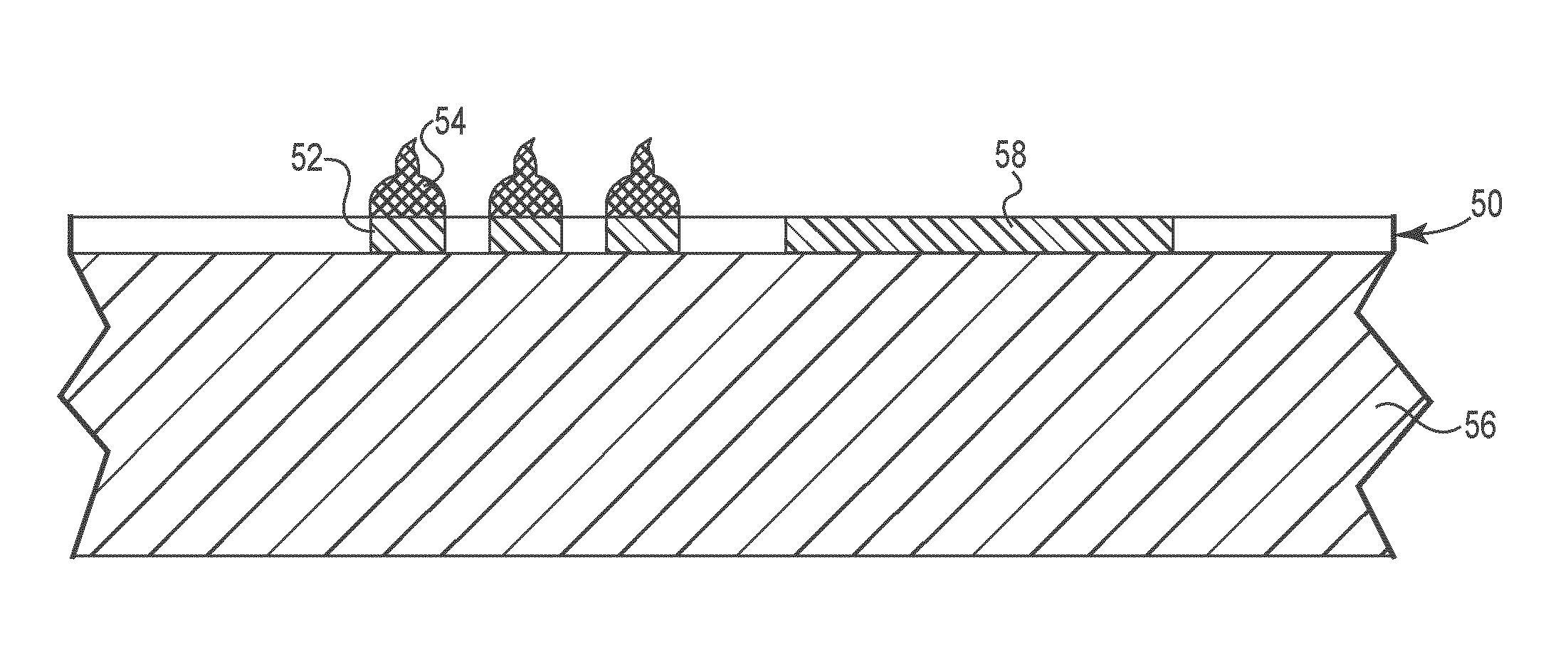

An integrated circuit (IC) package for an IC device, and a method of making the same. The IC package includes an interconnect assembly with at least one printed compliant layer, a plurality of first contact members located along a first major surface, a plurality of second contact members located along a second major surface, and a plurality of printed conductive traces electrically coupling a plurality of the first and second contact members. The compliant layer is positioned to bias at least the first contact members against terminals on the IC device. Packaging substantially surrounds the IC device and the interconnect assembly. The second contact members are accessible from outside the packaging.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV +1

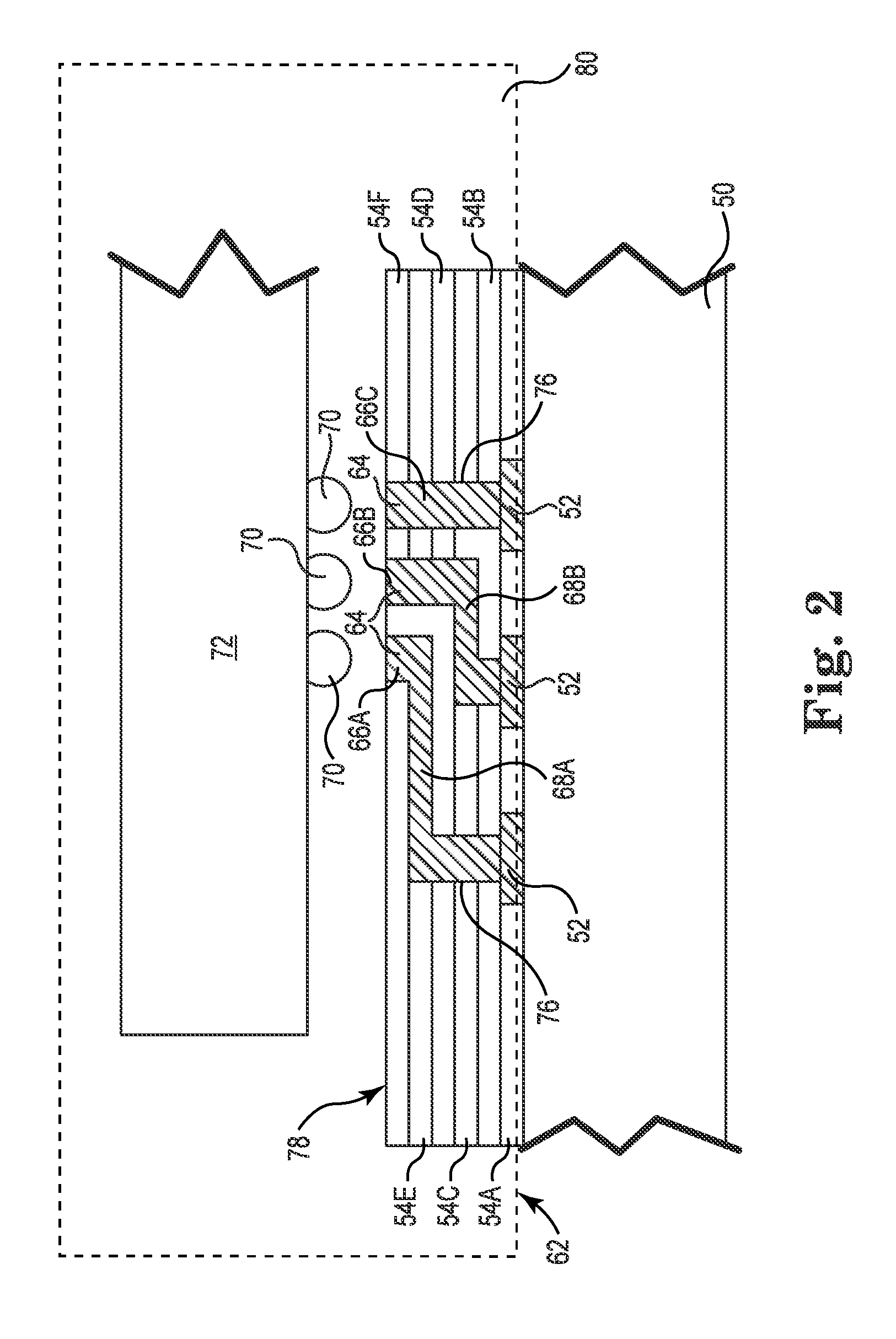

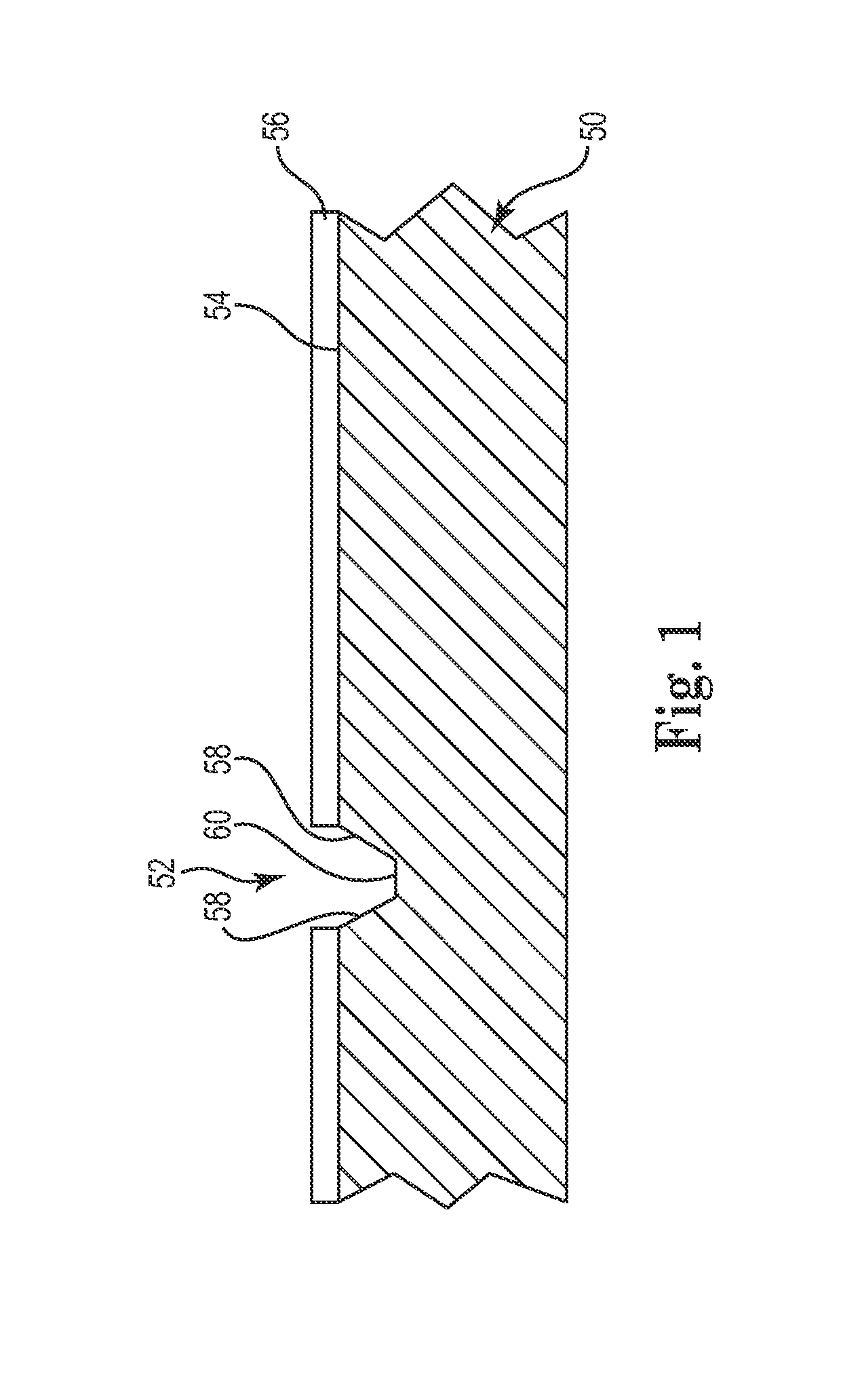

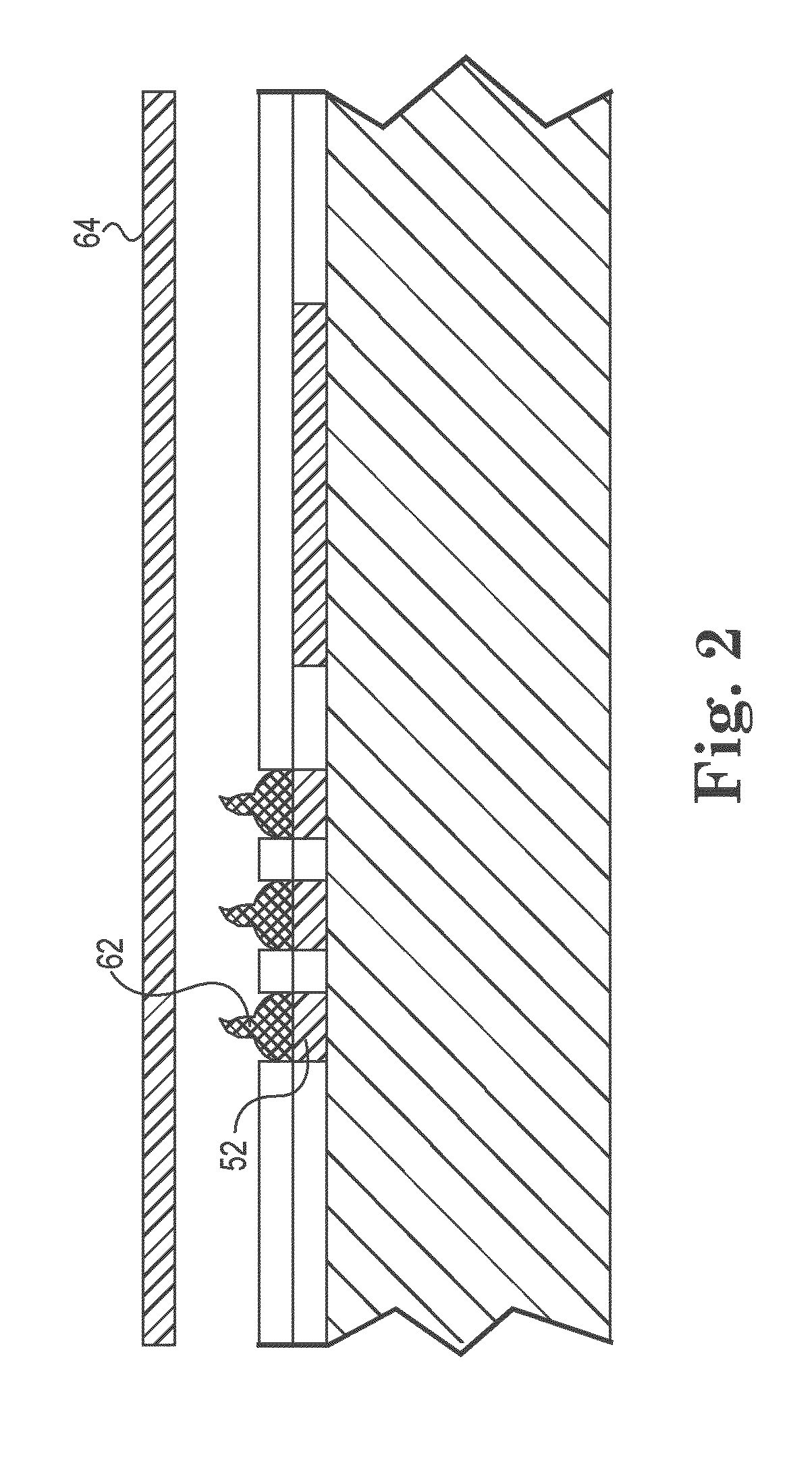

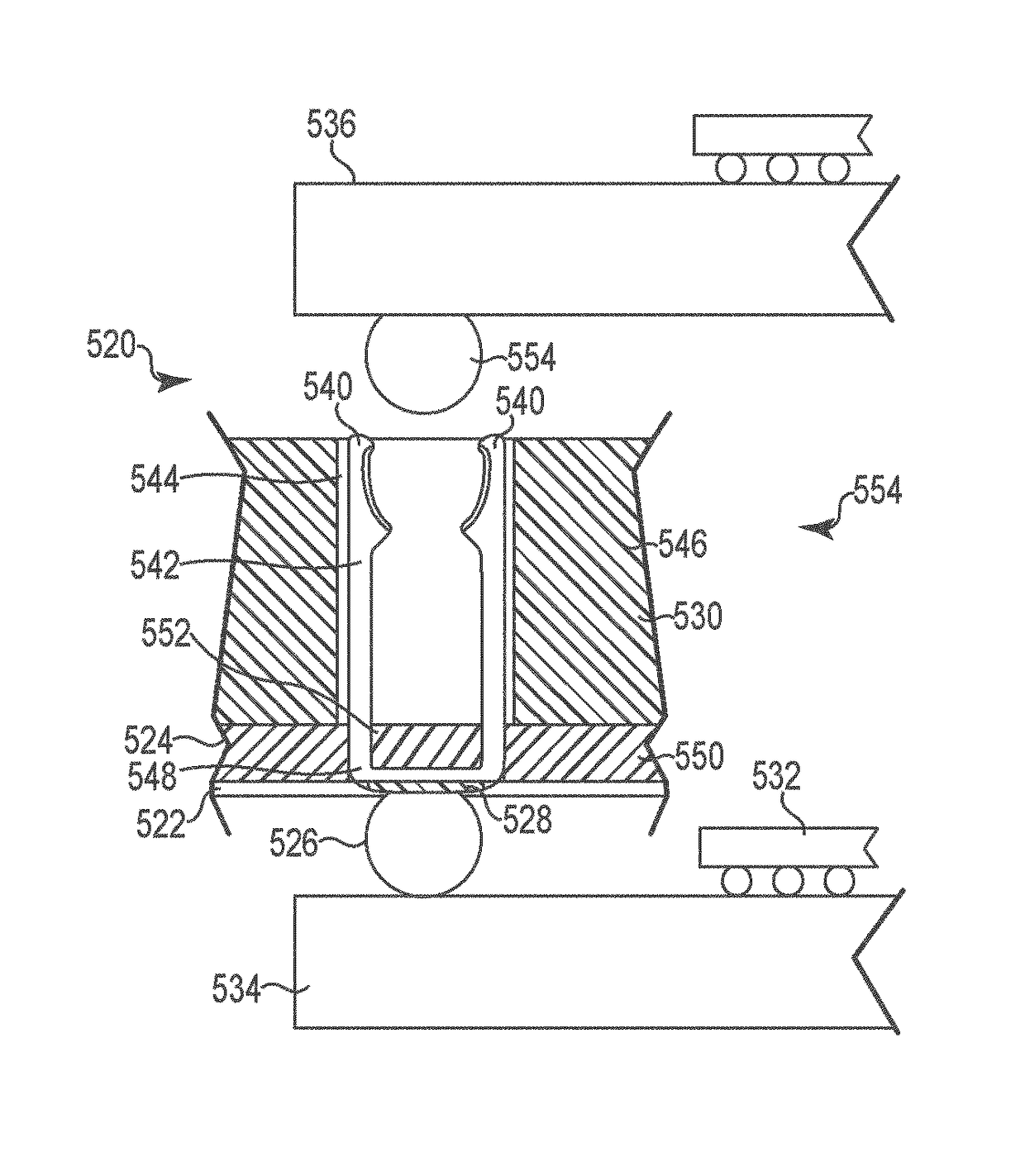

Compliant wafer level probe assembly

ActiveUS20120068727A1Electrical performance be enhanceLow costLine/current collector detailsElectronic circuit testingTest stationElectrical devices

A probe assembly that acts as a temporary interconnect between terminals on a circuit member and a test station. The probe assembly can include a base layer of a dielectric material printed onto a surface of a fixture. The surface of the fixture can have a plurality of cavities. A plurality of discrete contact members can be formed in the plurality of cavities in the fixture and coupled to the base layer. A plurality of conductive traces can be printed onto an exposed surface of the base layer and electrically coupled with proximal ends of one or more of the discrete contact members. A compliant layer can be deposited over the conductive traces and the proximal ends of the contact members. A protective layer can be deposited on the compliant layer such that when the probe assembly is removed from the fixture the distal ends of the contact members contact terminals on the circuit member and the conductive traces electrically couple the circuit member to a test station. Electrical devices on the probe assembly can communicate with the test station to provide adaptive testing.

Owner:HSIO TECH

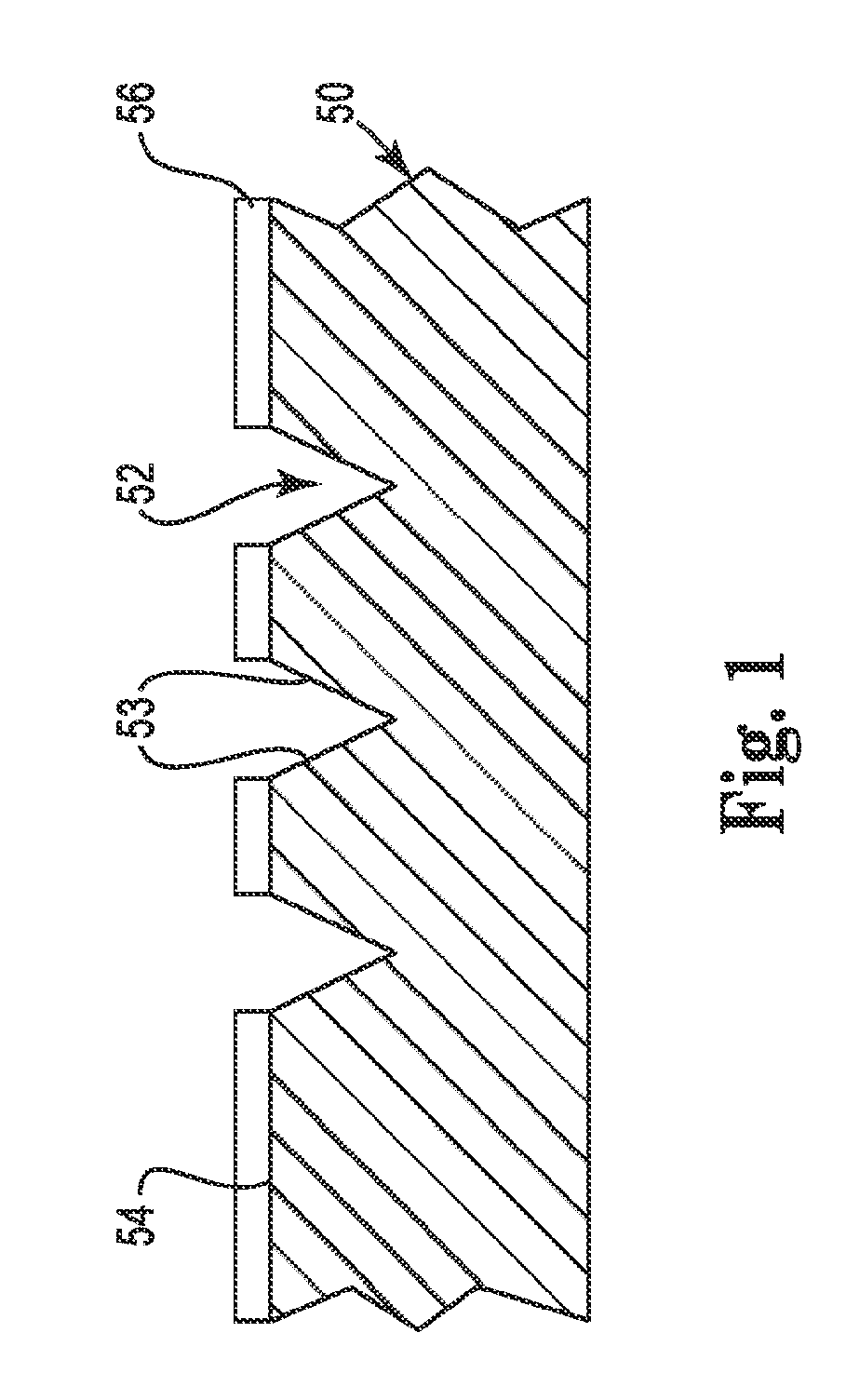

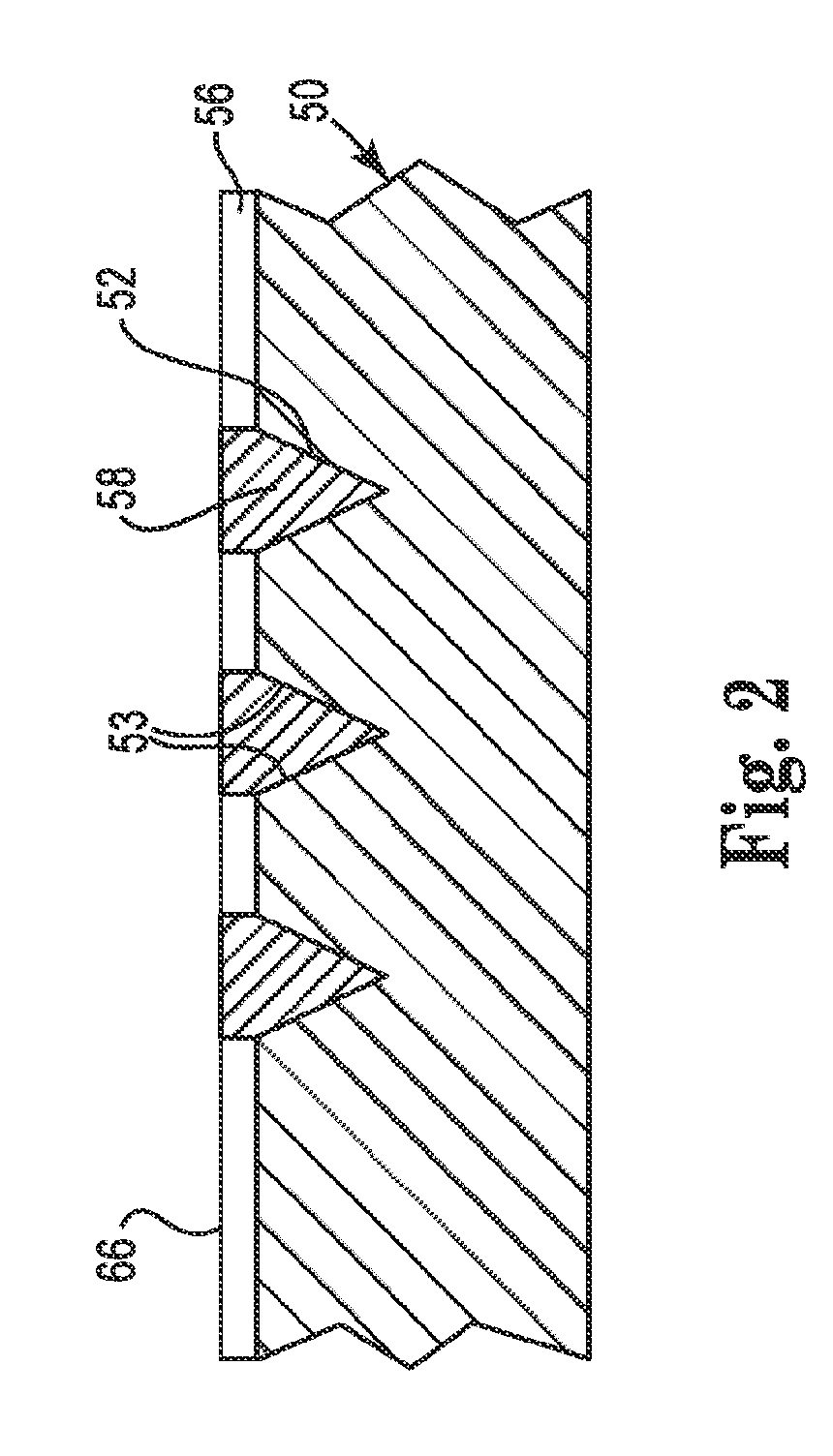

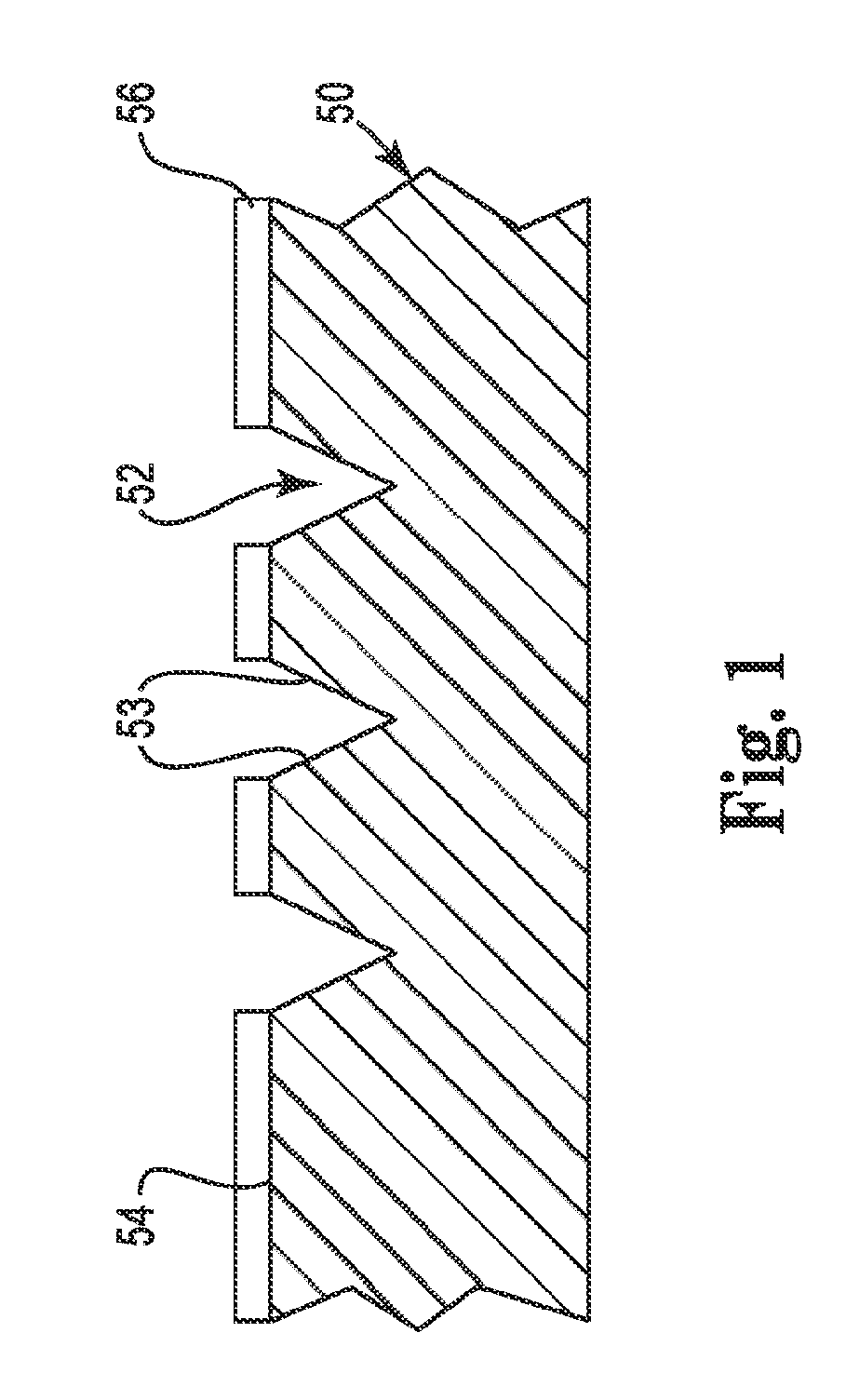

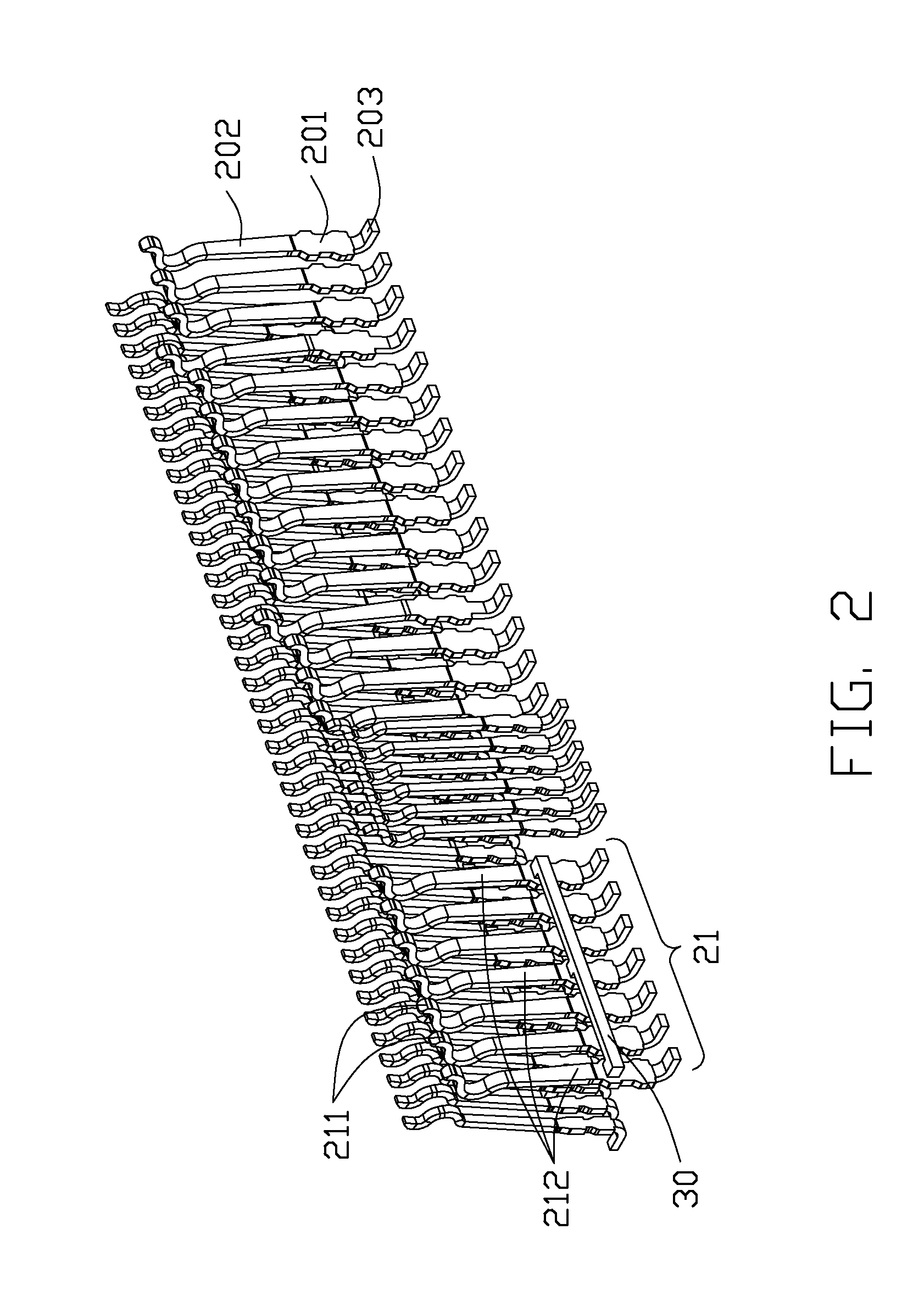

Compliant printed circuit peripheral lead semiconductor test socket

ActiveUS20120049877A1Low production costSolution to short lifeElectrically conductive connectionsElectrical measurement instrument detailsElectricityContact pad

A test socket that provides a temporary interconnect between terminals on an integrated circuit (IC) device and contact pads on a test printed circuit board (PCB). The test socket includes a compliant printed circuit and a socket housing. The compliant printed circuit includes at least one compliant layer, a plurality of first contact members located along a first major surface, a plurality of second contact members located along a second major surface, and a plurality of conductive traces electrically coupling the first and second contact members. The compliant layer is positioned to bias the first contact members against the terminals on the IC device and the second contact members against contact pads on the test PCB. The socket housing is coupled to the compliant printed circuit so the first contact members are positioned in a recess of the socket housing sized to receive the IC device.

Owner:HSIO TECH

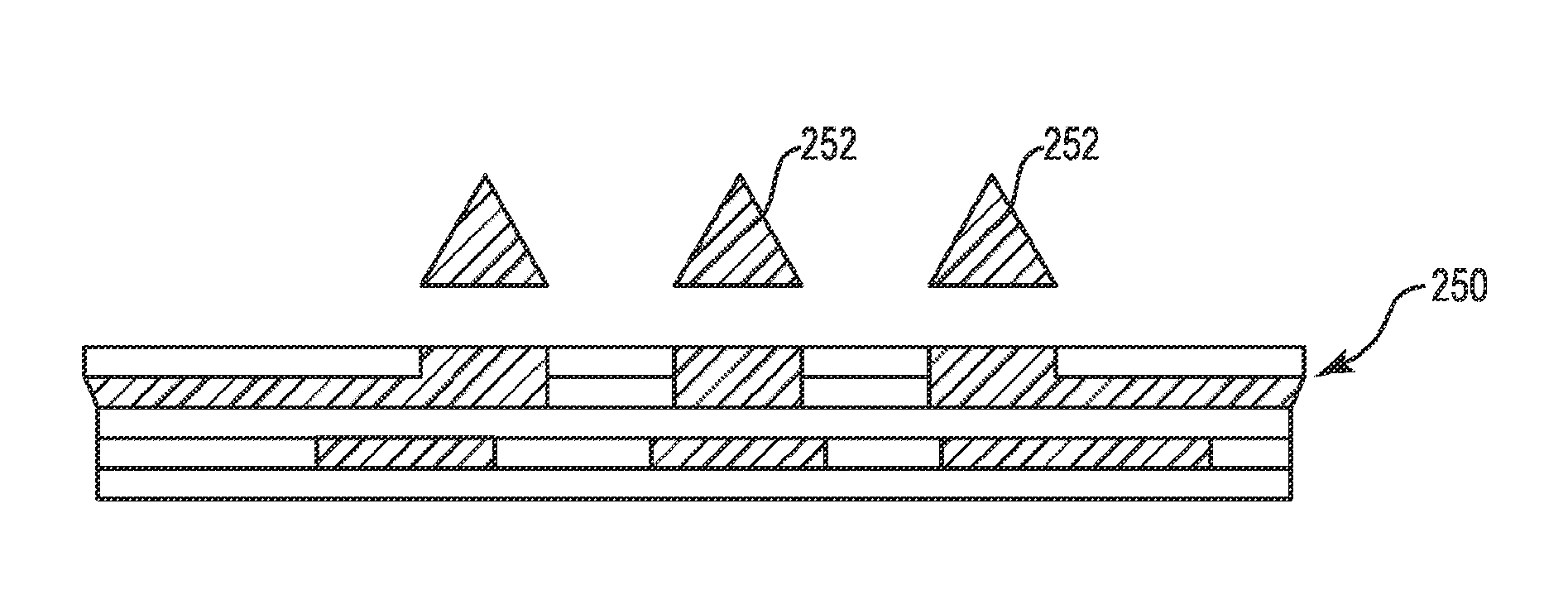

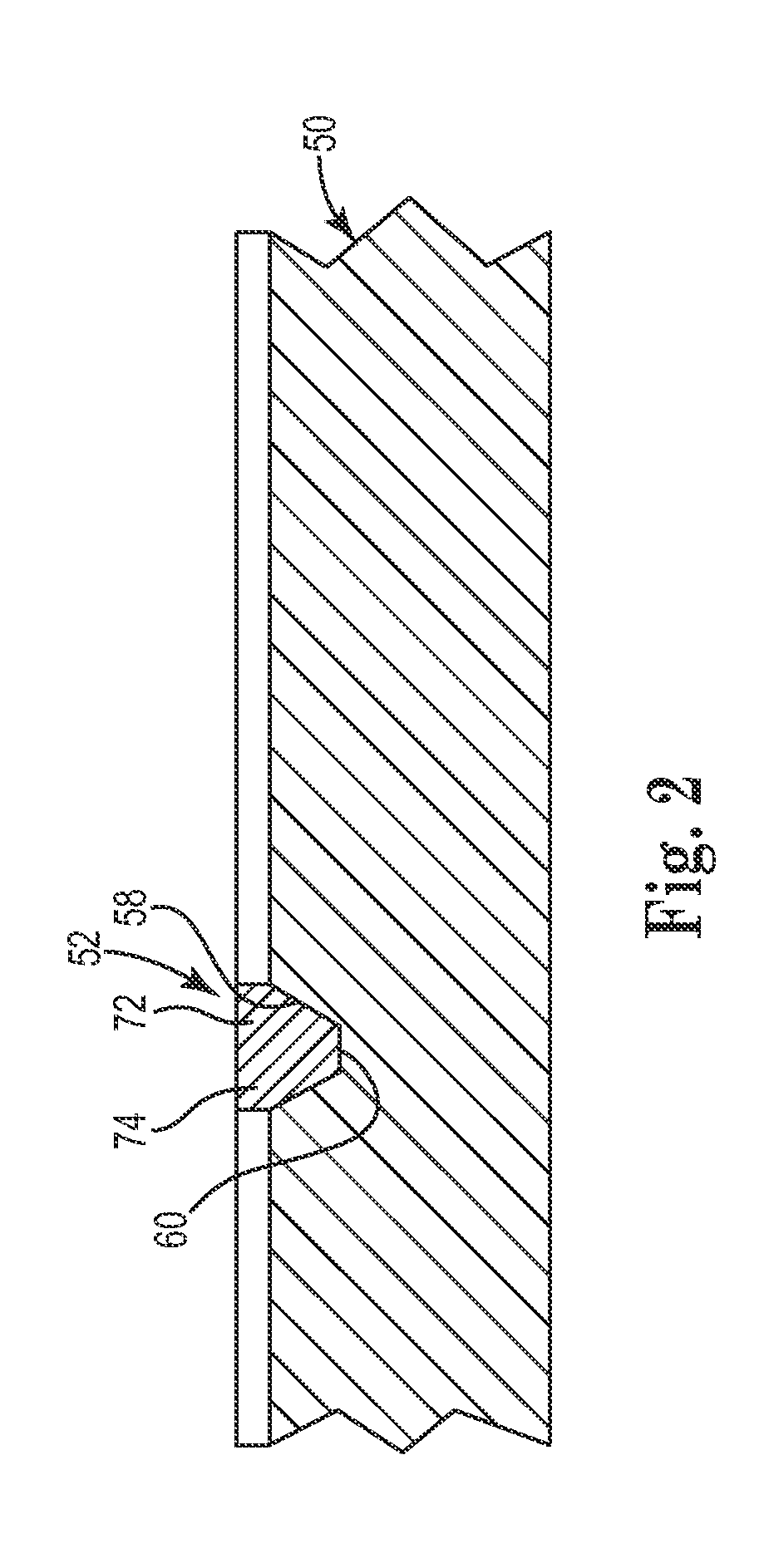

Bumped semiconductor wafer or die level electrical interconnect

InactiveUS20120182035A1Improve electrical performanceMonitor performanceContactless circuit testingTest stationSemiconductor

A probe assembly that acts as a temporary interconnect between terminals on an IC device and a test station. The probe assembly includes a plurality of stud bumps arranged on a first surface of a substrate in a configuration corresponding to the terminal on the IC device. The stud bumps include a shape adapted to temporarily couple with the terminals on the IC device. A plurality of conductive traces on the substrate electrically couple the stud bumps with the test station.

Owner:HSIO TECH

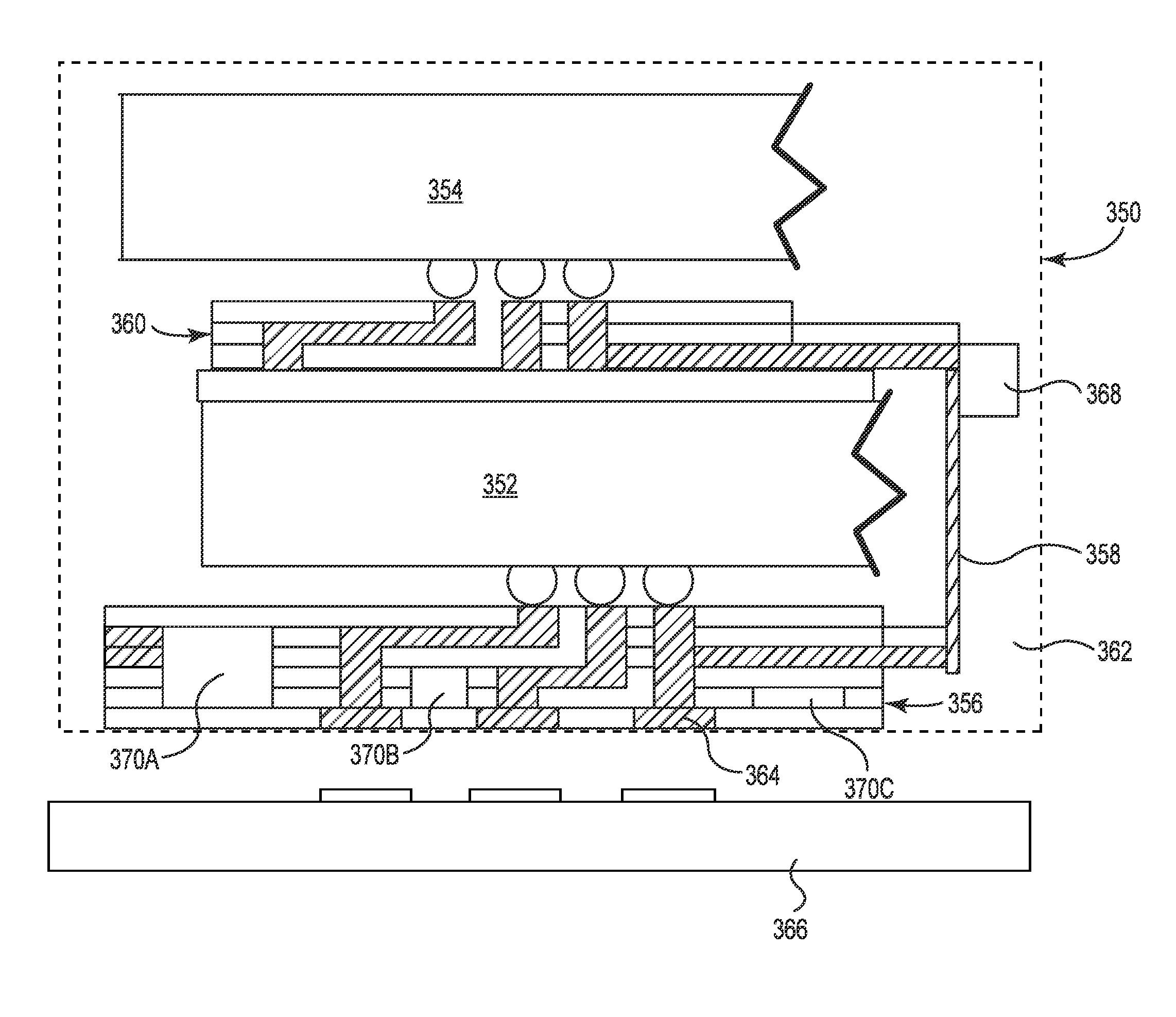

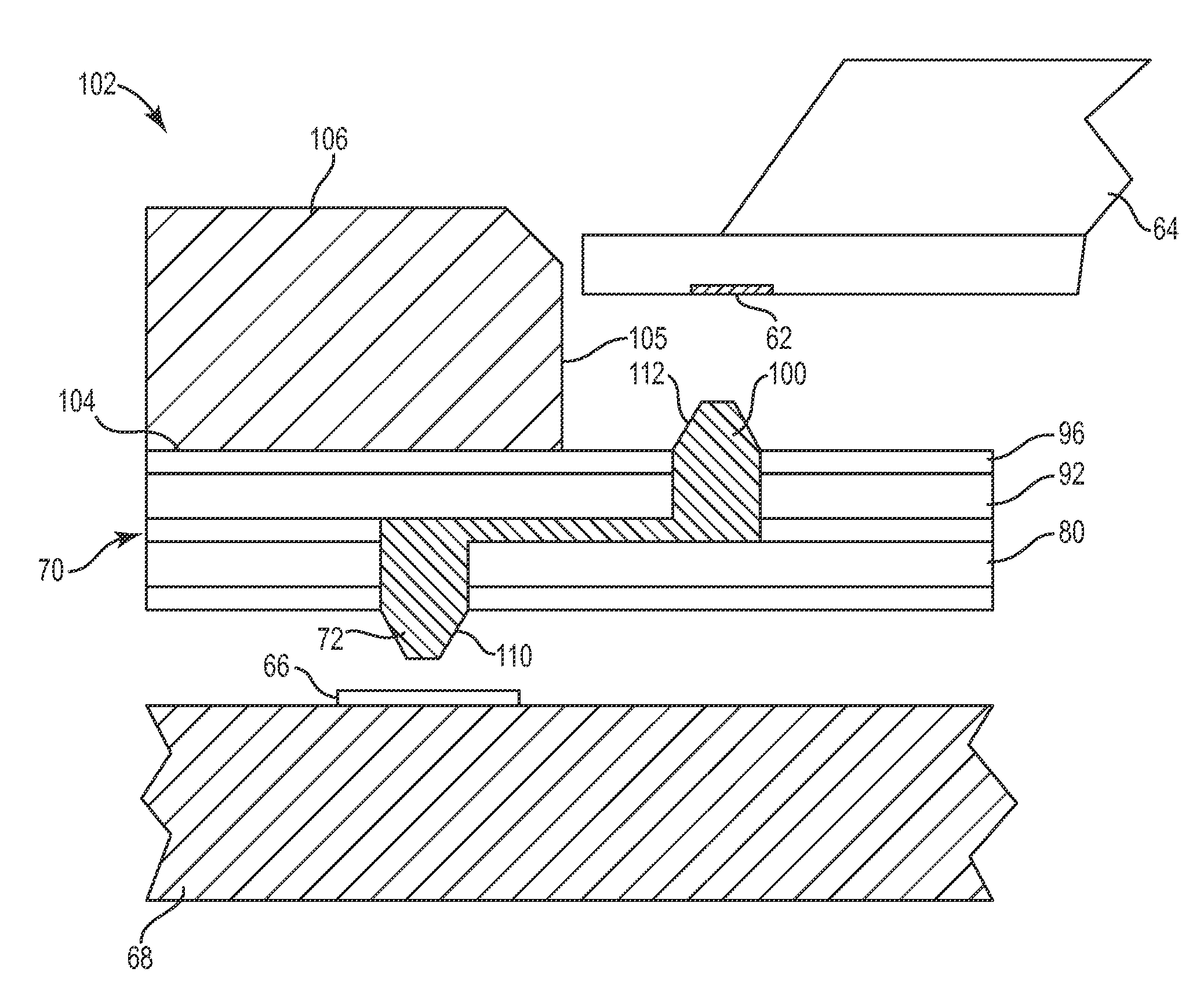

Area array semiconductor device package interconnect structure with optional package-to-package or flexible circuit to package connection

ActiveUS20120161317A1Alleviate environmental issuesImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

An area array integrated circuit (IC) package for an IC device. The IC package includes a first substrate with conductive traces electrically coupled to the IC device. An interconnect assembly having a first surface is mechanically coupled to the first substrate. The interconnect assembly includes a plurality of contact members electrically coupled to the conductive traces on the first substrate. A second substrate is mechanically coupled to a second surface of the interconnect assembly so that the first substrate, the interconnect assembly, and the second substrate substantially surround the IC device. The second substrate includes conductive traces that are electrically coupled to the contact members in the interconnect assembly.

Owner:HSIO TECH

Compliant wafer level probe assembly

ActiveUS8803539B2Low costHigh-frequency performanceLine/current collector detailsElectronic circuit testingElectrical devicesTest station

A probe assembly that acts as a temporary interconnect between terminals on a circuit member and a test station. The probe assembly can include a base layer of a dielectric material printed onto a surface of a fixture. The surface of the fixture can have a plurality of cavities. A plurality of discrete contact members can be formed in the plurality of cavities in the fixture and coupled to the base layer. A plurality of conductive traces can be printed onto an exposed surface of the base layer and electrically coupled with proximal ends of one or more of the discrete contact members. A compliant layer can be deposited over the conductive traces and the proximal ends of the contact members. A protective layer can be deposited on the compliant layer such that when the probe assembly is removed from the fixture the distal ends of the contact members contact terminals on the circuit member and the conductive traces electrically couple the circuit member to a test station. Electrical devices on the probe assembly can communicate with the test station to provide adaptive testing.

Owner:HSIO TECH

Method of making a compliant printed circuit peripheral lead semiconductor test socket

ActiveUS8789272B2Low production costSolution to short lifePrinted circuit assemblingElectrically conductive connectionsContact padEngineering

A test socket that provides a temporary interconnect between terminals on an integrated circuit (IC) device and contact pads on a test printed circuit board (PCB). The test socket includes a compliant printed circuit and a socket housing. The compliant printed circuit includes at least one compliant layer, a plurality of first contact members located along a first major surface, a plurality of second contact members located along a second major surface, and a plurality of conductive traces electrically coupling the first and second contact members. The compliant layer is positioned to bias the first contact members against the terminals on the IC device and the second contact members against contact pads on the test PCB. The socket housing is coupled to the compliant printed circuit so the first contact members are positioned in a recess of the socket housing sized to receive the IC device.

Owner:HSIO TECH

Bumped semiconductor wafer or die level electrical interconnect

InactiveUS8988093B2Low costHigh-frequency performanceElectrical measurement instrument detailsContactless circuit testingIc devicesTest station

Owner:HSIO TECH

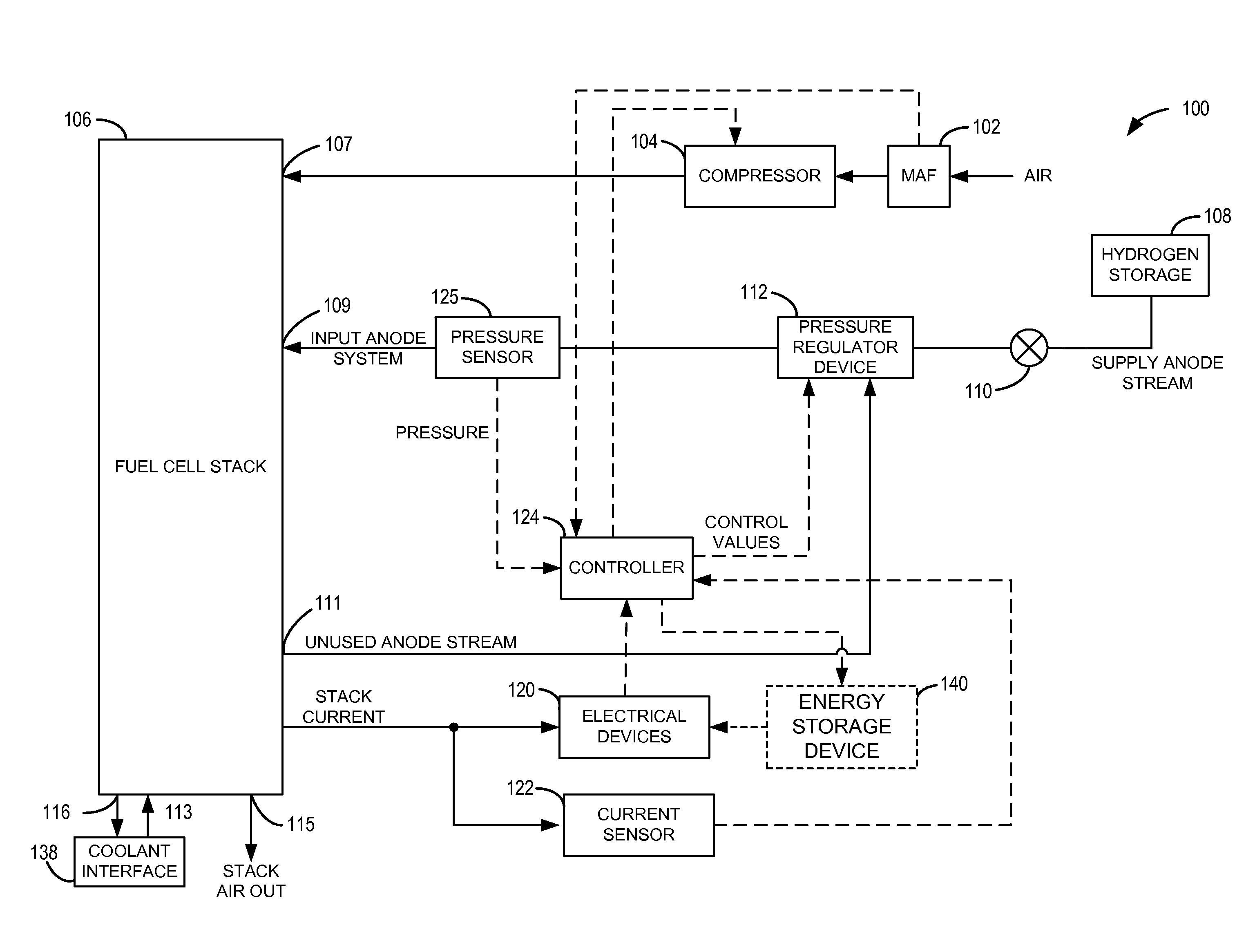

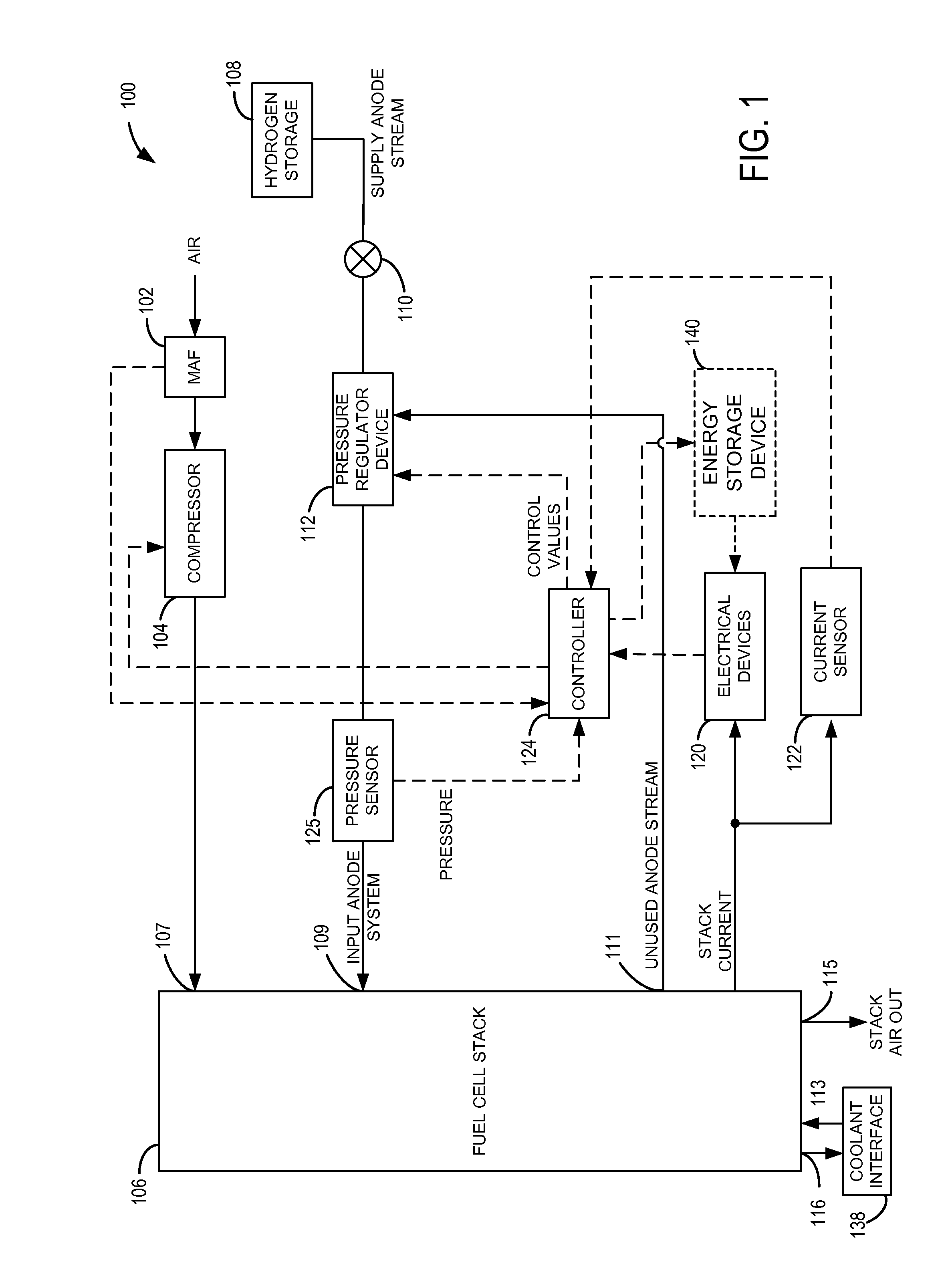

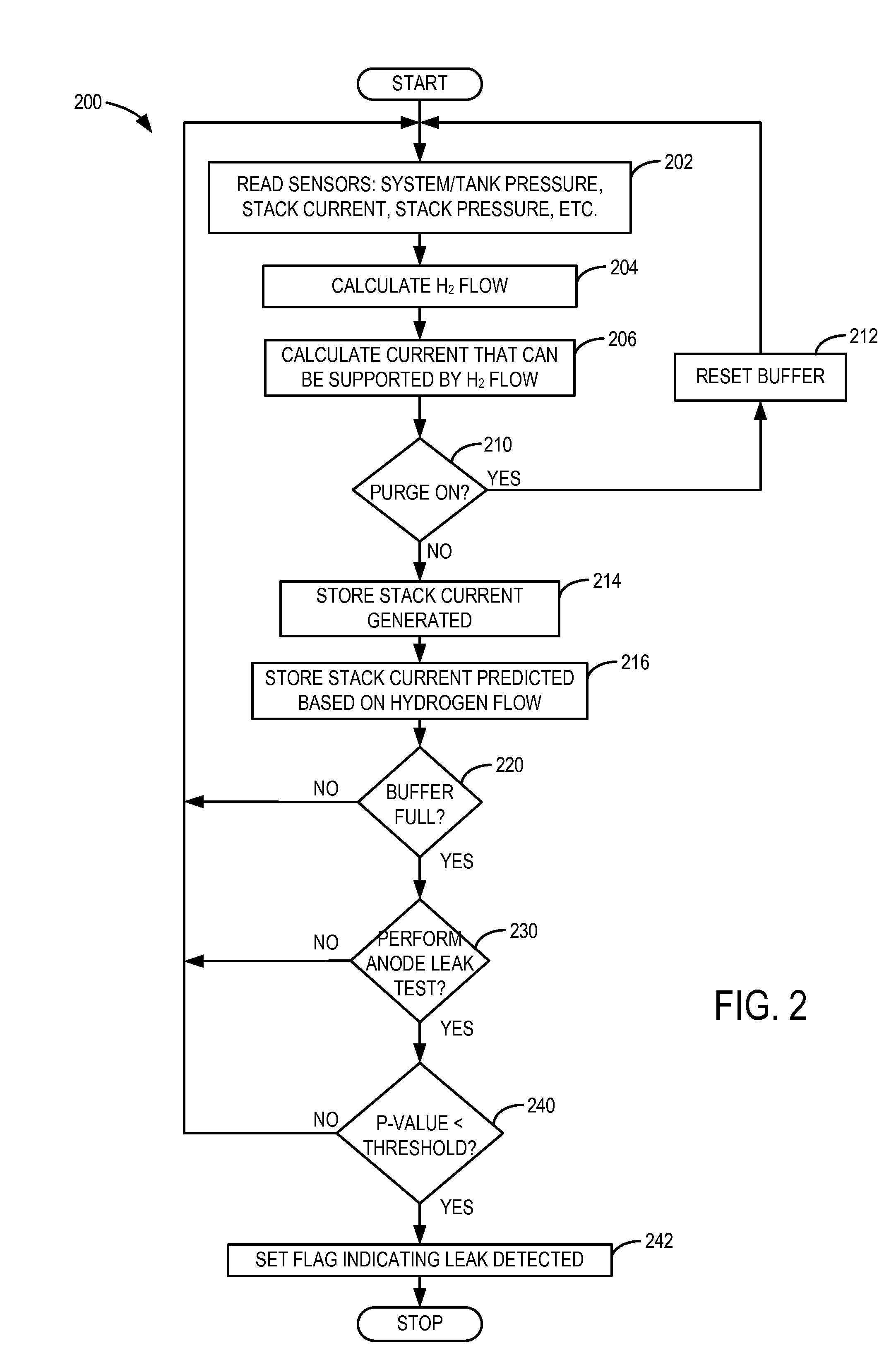

Methods for determining anode integrity during fuel cell vehicle operation

ActiveUS20160172696A1High frequencyIncreases vehicle costFuel cell auxillariesMotive system fuel cellsHydrogenFuel cells

A system and methods are provided for testing anode integrity during vehicle operation. In one example described, the system and methods allow for anode leak tests during vehicle operation based on a flow of hydrogen into a fuel cell, the flow of hydrogen into the fuel cell maintaining the vehicle power while the leak test is performed. The methods further allow for operational adjustments responsive to the leak test, which may include controlling the vehicle power to manage vehicle operations in the presence of a hydrogen leak in some instances.

Owner:FORD GLOBAL TECH LLC

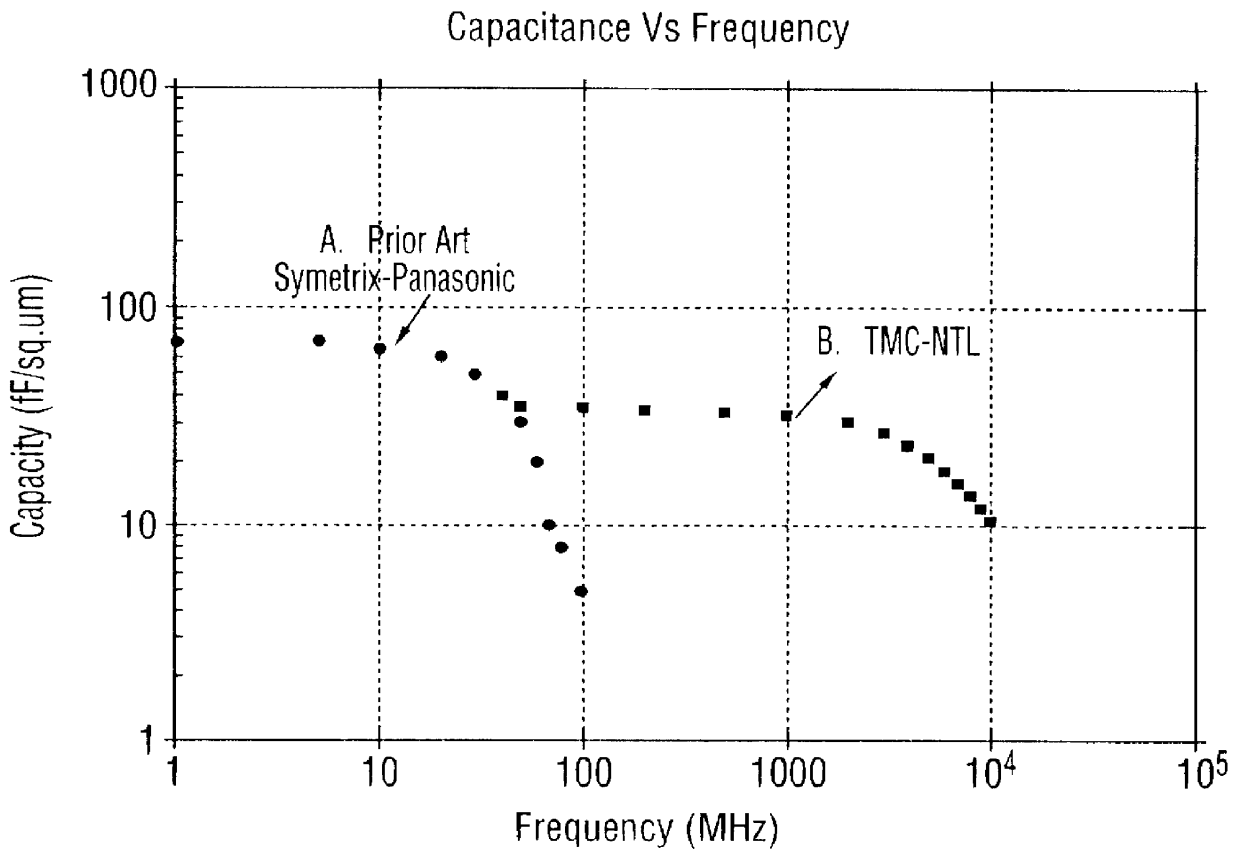

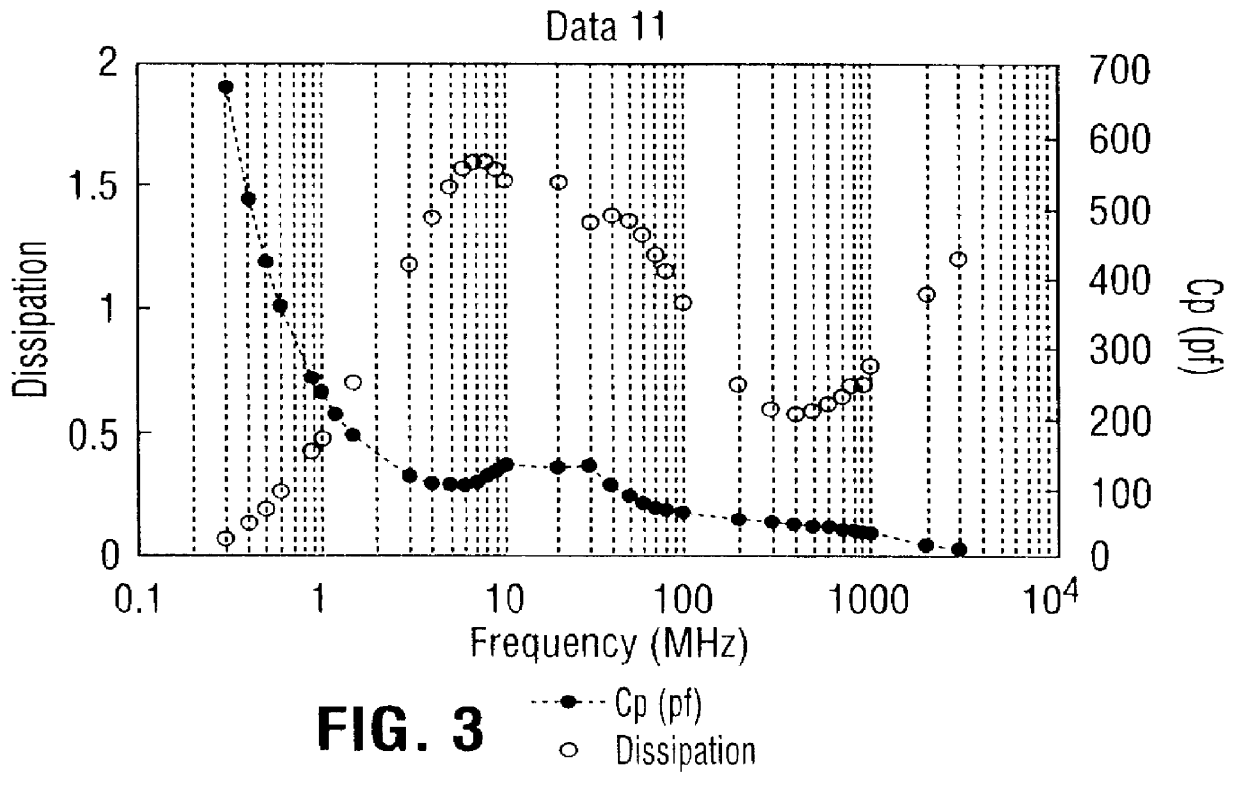

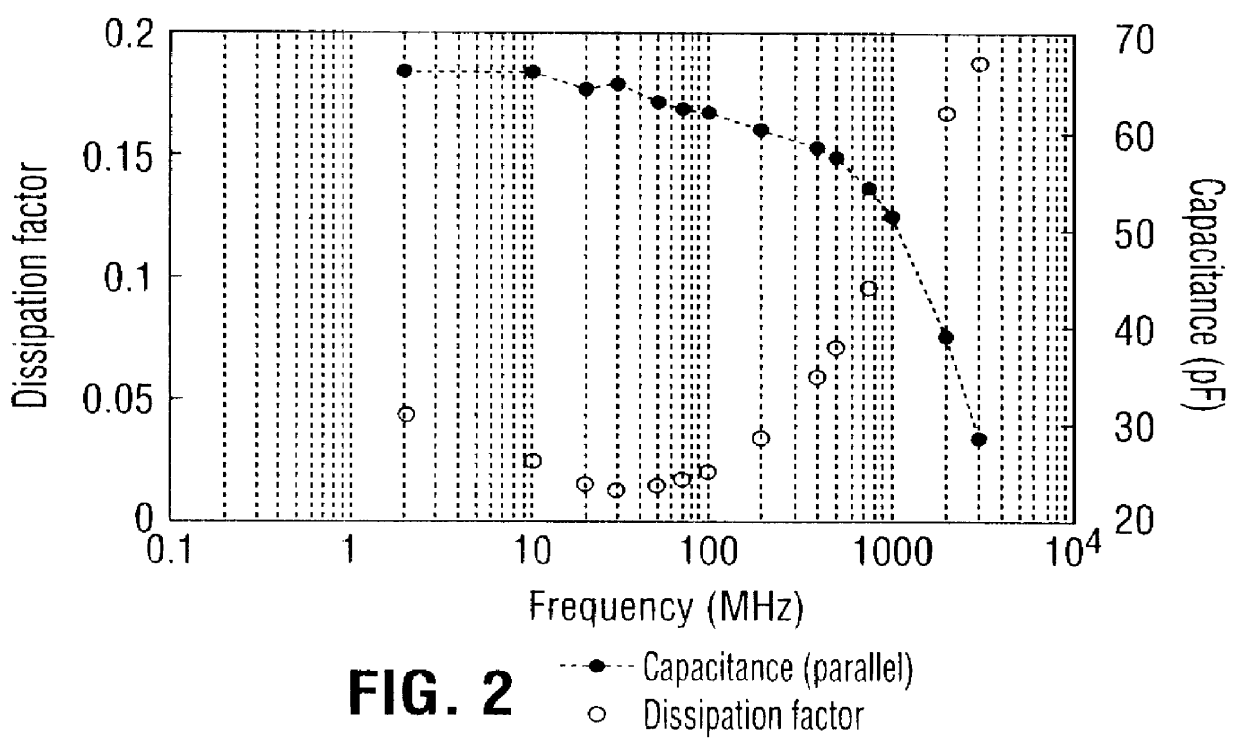

Ferroelectric dielectric for integrated circuit applications at microwave frequencies

InactiveUS6146905AReduce decreaseAvoids and reduces problemSemiconductor/solid-state device manufacturingCapacitor with voltage varied dielectricLead zirconate titanateWater vapor

A ferroelectric dielectric for microwave applications is provided comprising a polycrystalline perovskite phase of lead zirconate titanate dielectric material. Small grain size material is provided by a low temperature process, by a rapid thermal annealing process. A layer of amorphous ferroelectric precursor material is deposited and annealed in an oxygen containing atmosphere in the presence of water vapor, preferably with the addition of a few percent of ozone, and at a temperature of less than 500.degree. C. Advantageously, the method provides for formation of a ferroelectric material comprising lead zirconate titanate with a grain size less than 20 nm, with low film stress, high dielectric constant and low leakage current, which has excellent ferroelectric characteristics up to 10 GHz. This material has applications for capacitors, as filters, decoupling, coupling, and bypass elements and also for high frequency surface acoustic wave devices.

Owner:NORTEL NETWORKS LTD

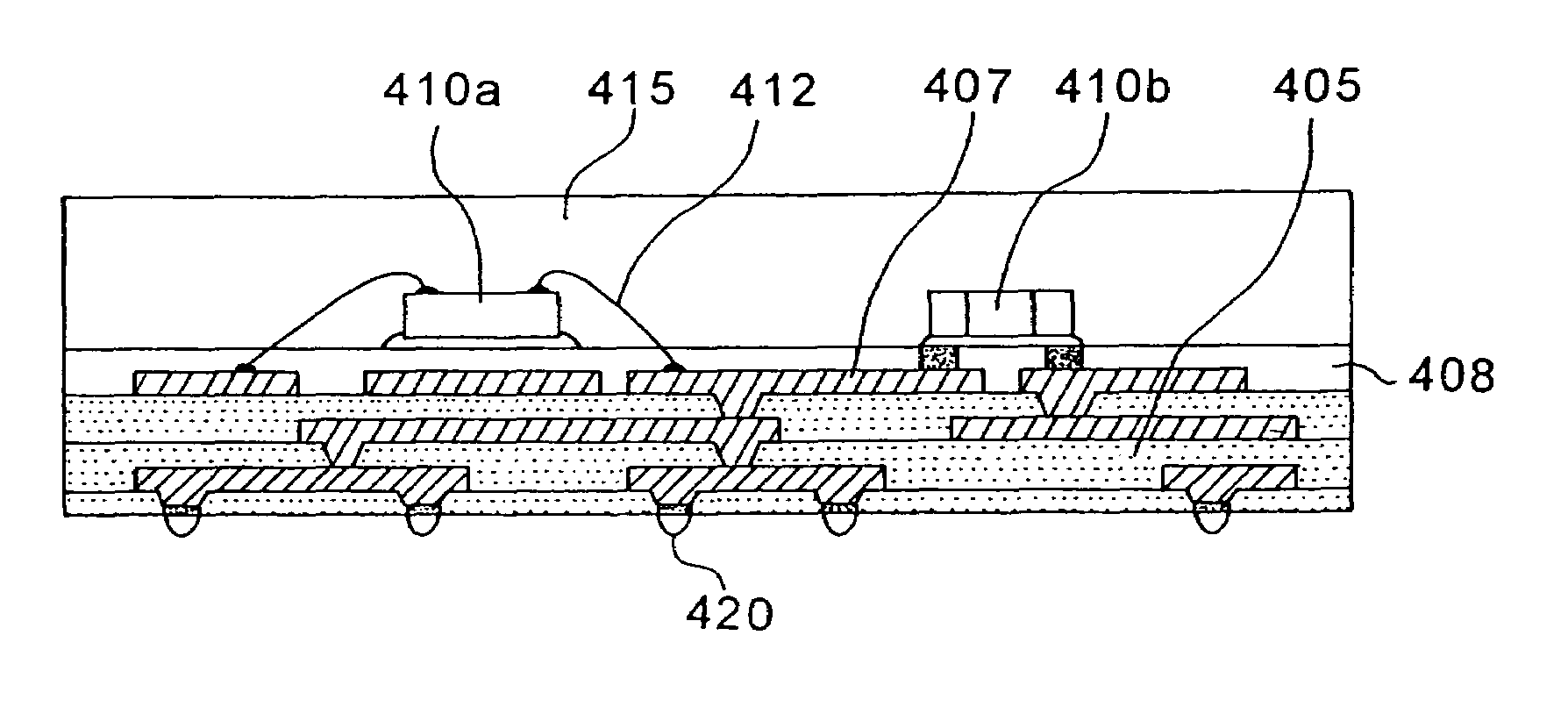

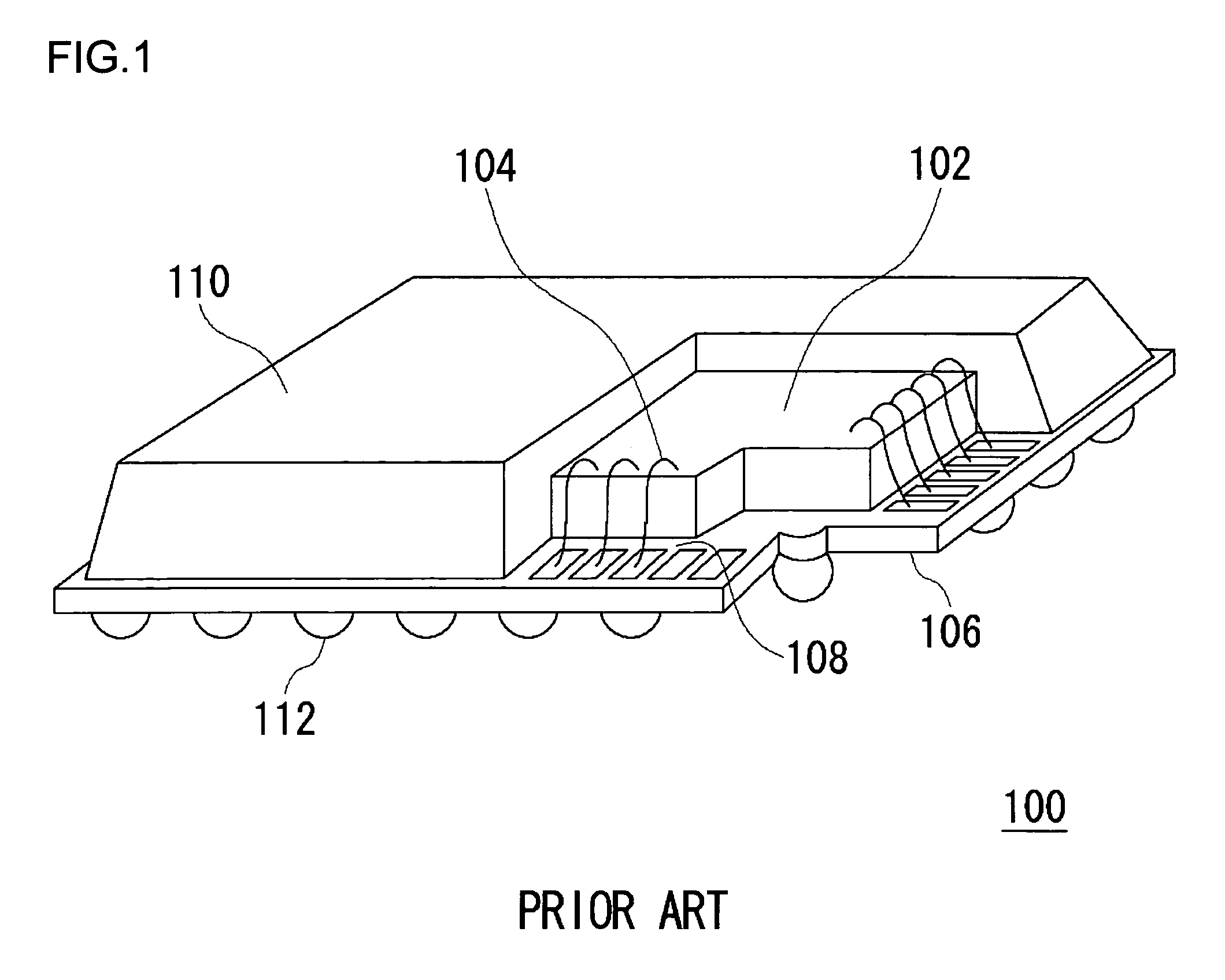

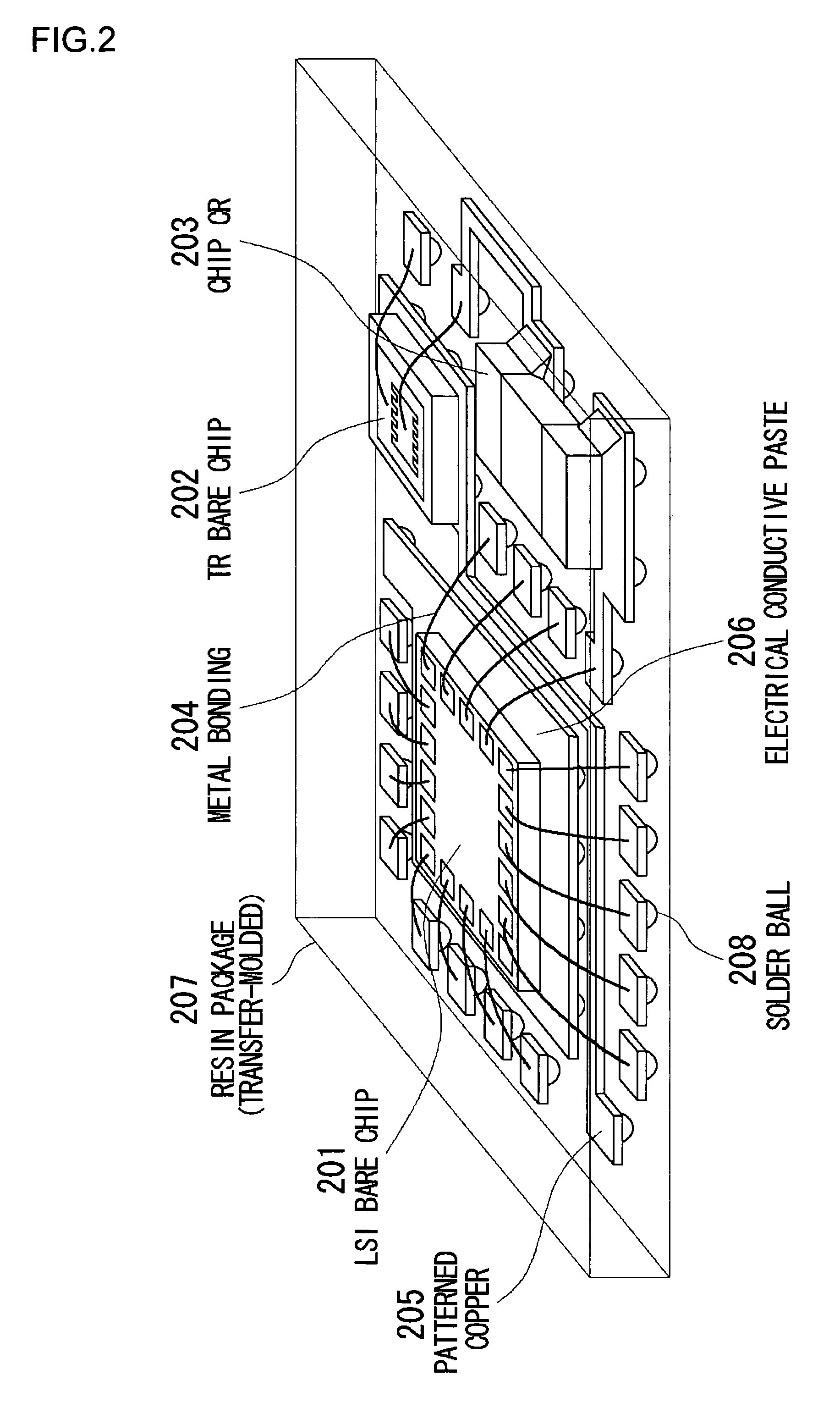

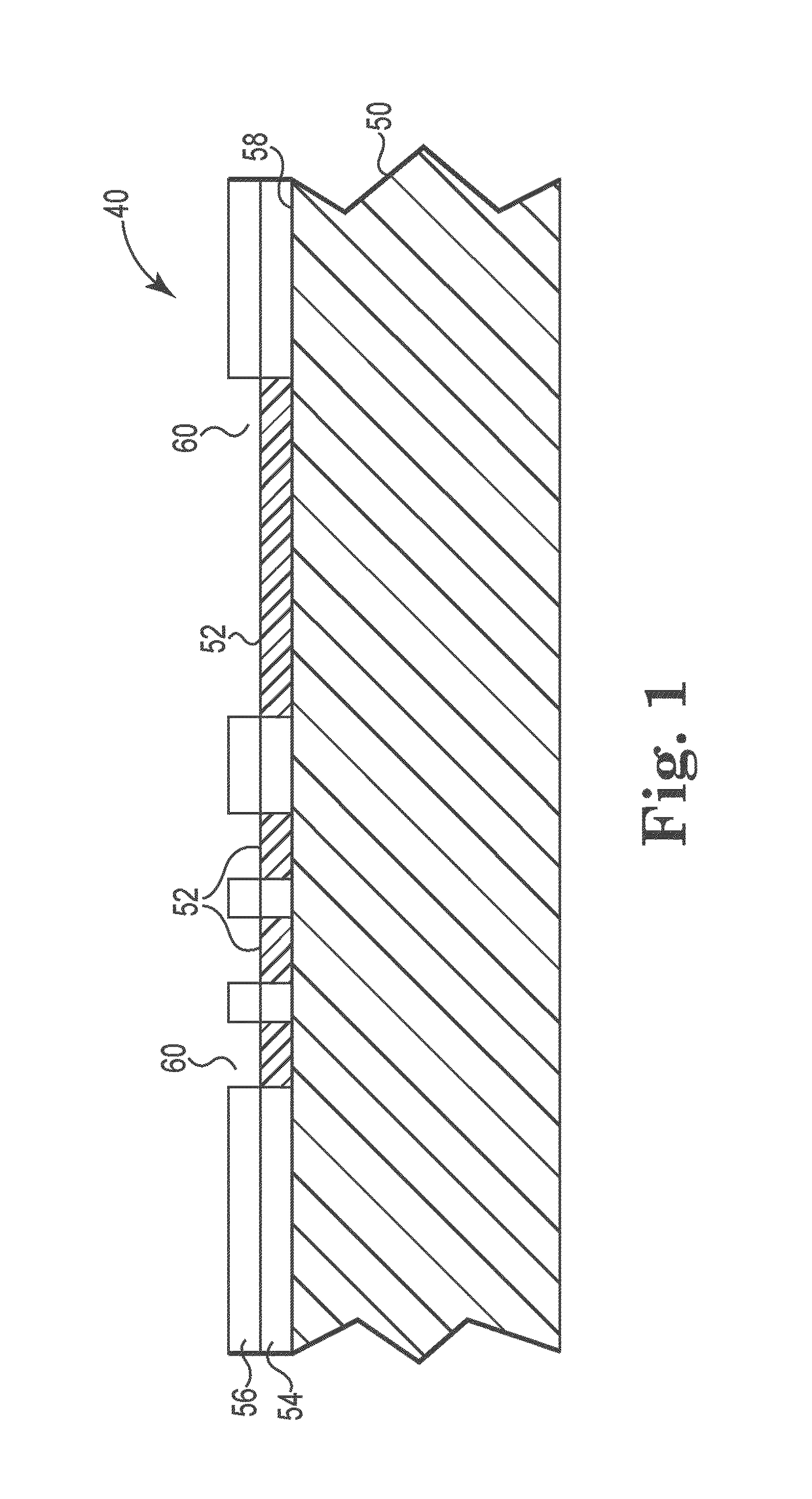

Semiconductor device, method for manufacturing same and thin plate interconnect line member

ActiveUS7301228B2Improve process controllabilityImprove adhesivenessSemiconductor/solid-state device detailsSolid-state devicesDielectric lossEngineering

The present invention provides a low-profile and light-weight semiconductor device having improved product reliability and higher frequency performance. A multi-layer interconnect line structure is disposed just under circuit devices 410a and 410b. An Interlayer insulating film 405 that composes a part of the multi-layer interconnect line structure is formed of a material having a relative dielectric constant within a range from 1.0 to 3.7, and a dielectric loss tangent within a range from 0.0001 to 0.02.

Owner:SEMICON COMPONENTS IND LLC

Gallium nitride high electron mobility transistor having inner field-plate for high power applications

InactiveUS20090261384A1Reduce the valueReduce leakage currentTransistorCapacitanceGate leakage current

A gallium nitride high electron mobility transistor, in which an inner field-plate is disposed between the gate and drain of the high electron mobility transistor, so that an electric field is distributed between gate and drain regions to reduce a peak value and to reduce gate leakage current while maintaining high frequency performance, thus obtaining a high breakdown voltage, reducing the capacitance between the gate and the drain attributable to a shielding effect, and improving linearity and high power and high frequency characteristics through variation in the input voltage of the inner field-plate.

Owner:KOREA ADVANCED INST OF SCI & TECH

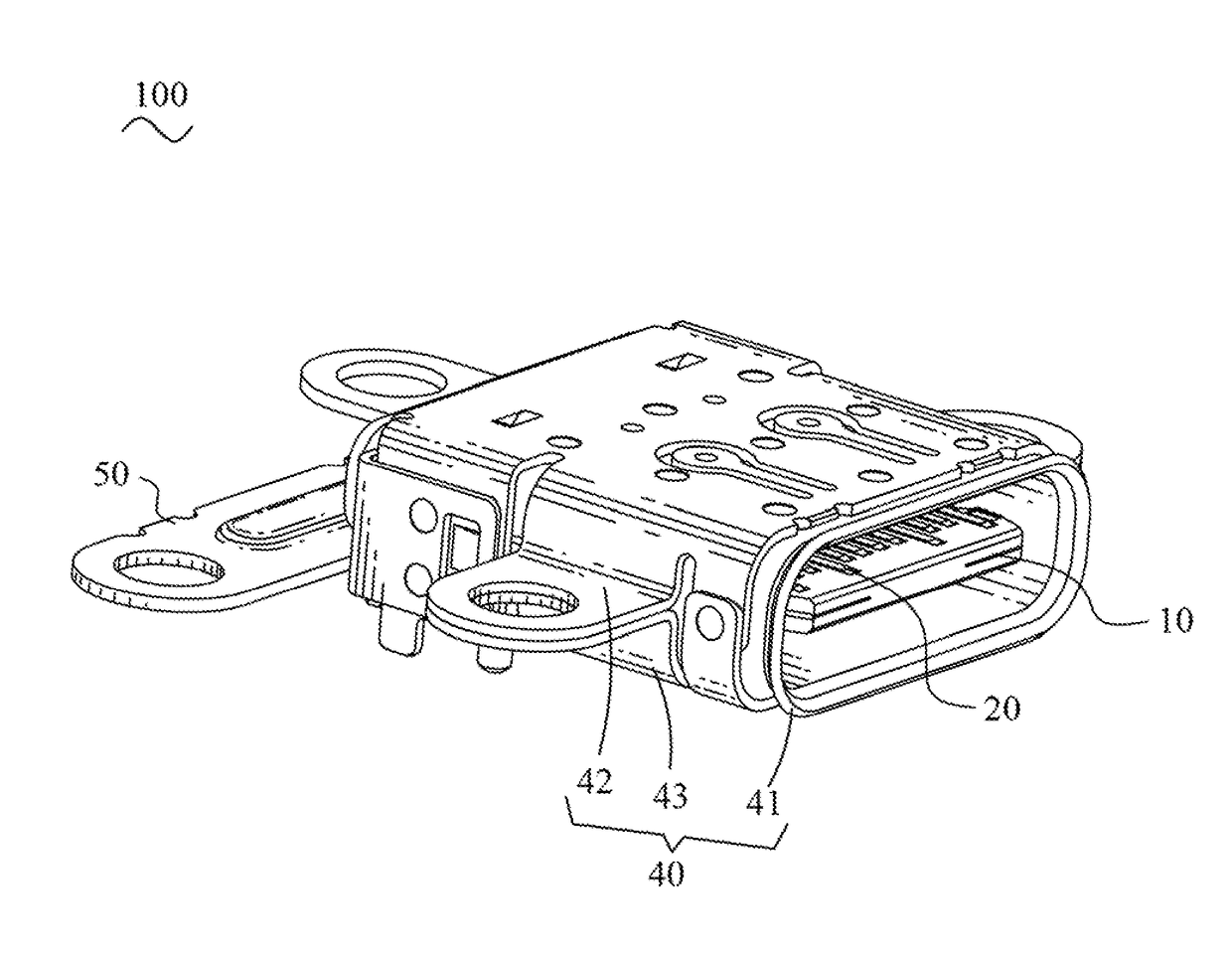

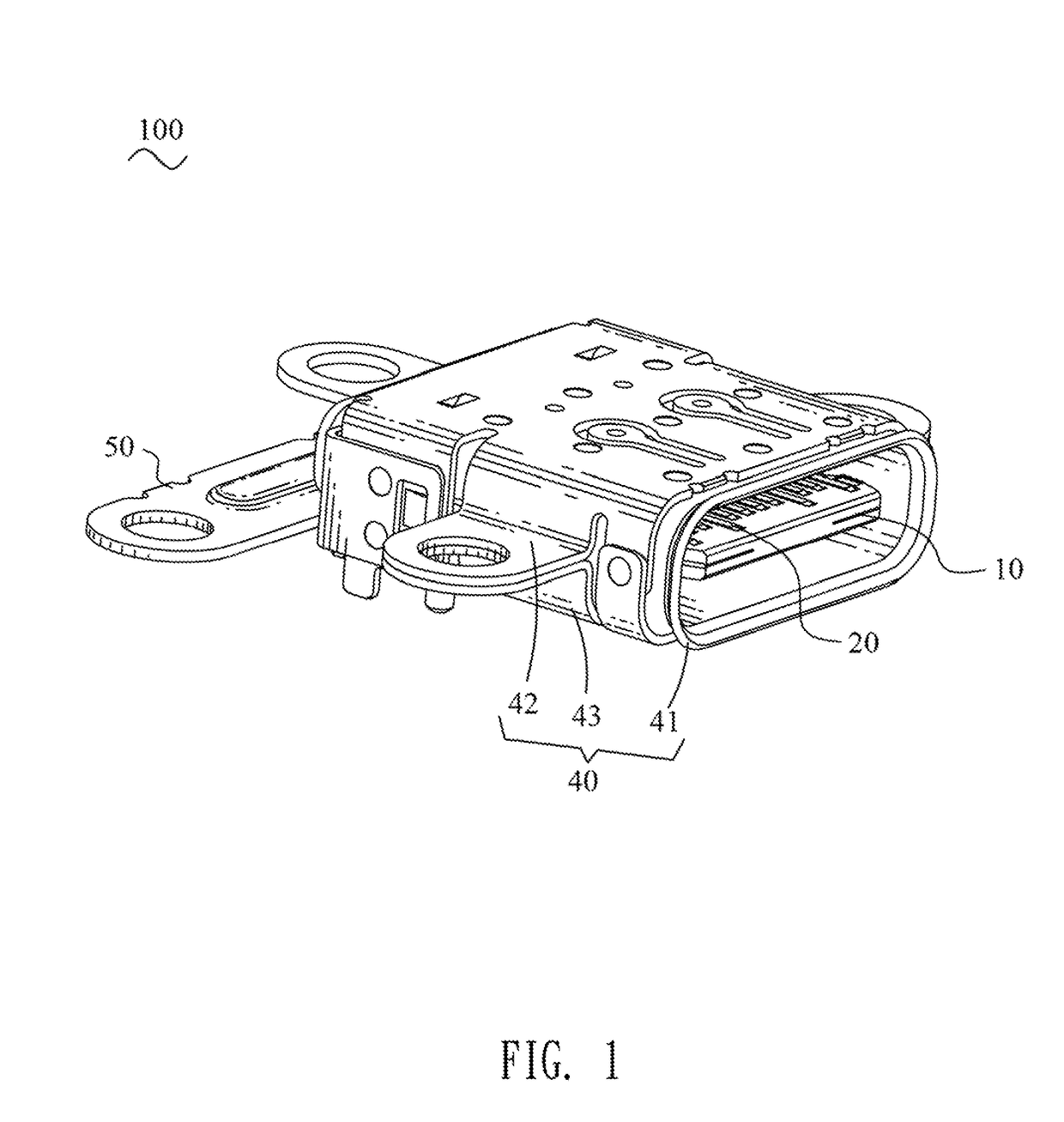

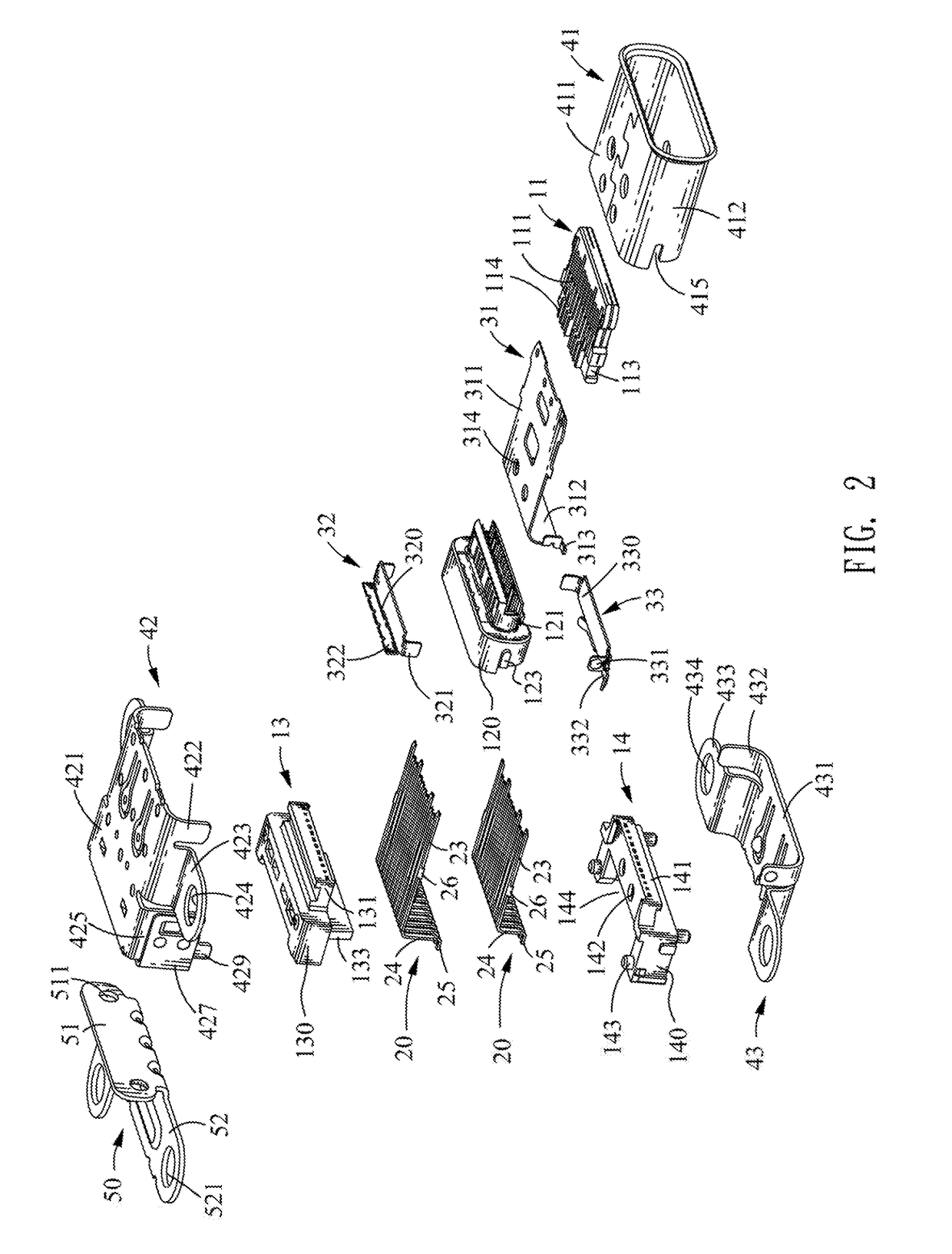

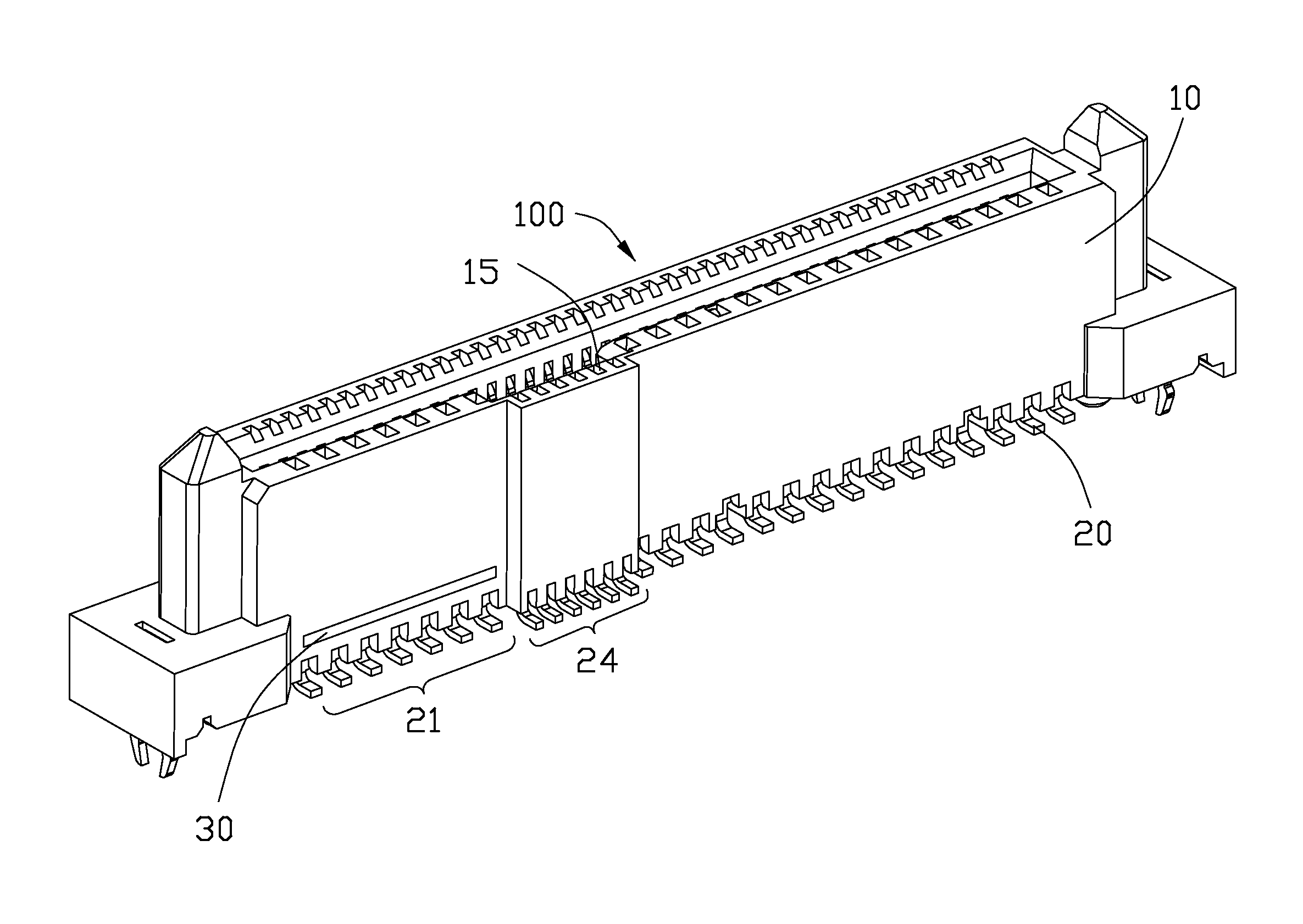

Electrical connector

ActiveUS9653850B1Improve high-frequency performanceHigh frequency performanceTwo-part coupling devicesCoupling protective earth/shielding arrangementsEngineeringElectrical and Electronics engineering

An electrical connector includes an insulating assembly, terminals, an inner shielding assembly and an outer shielding assembly. The insulating assembly has a tongue board at a front. The terminals are insert molded the insulating assembly and are divided into an upper row and a lower row with contacts portions located at a top side and a bottom side of the tongue board. Outmost two of the upper row of terminals and outmost two of the lower row of terminals are grounding terminals, outsides of rears of the contact portions of the grounding terminals form touch portions. The inner shielding assembly includes an upper shielding piece and a lower shielding piece located to a rear of the tongue board. The outer shielding assembly includes a shielding sleeve sleeving and spaced from the tongue board, the shielding sleeve contacts with at least one of the upper shielding piece and the lower shielding piece.

Owner:CHENG UEI PRECISION IND CO LTD

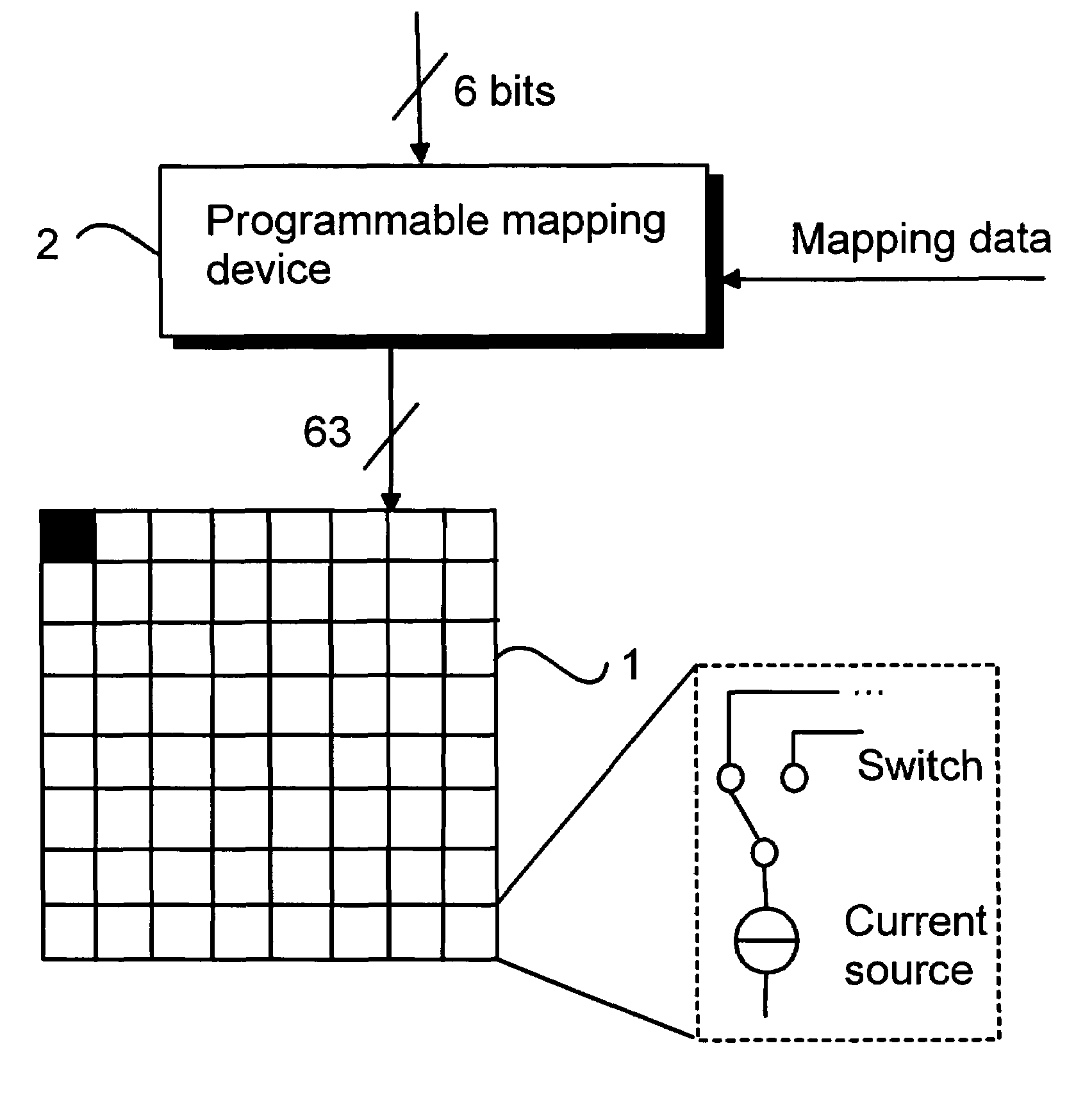

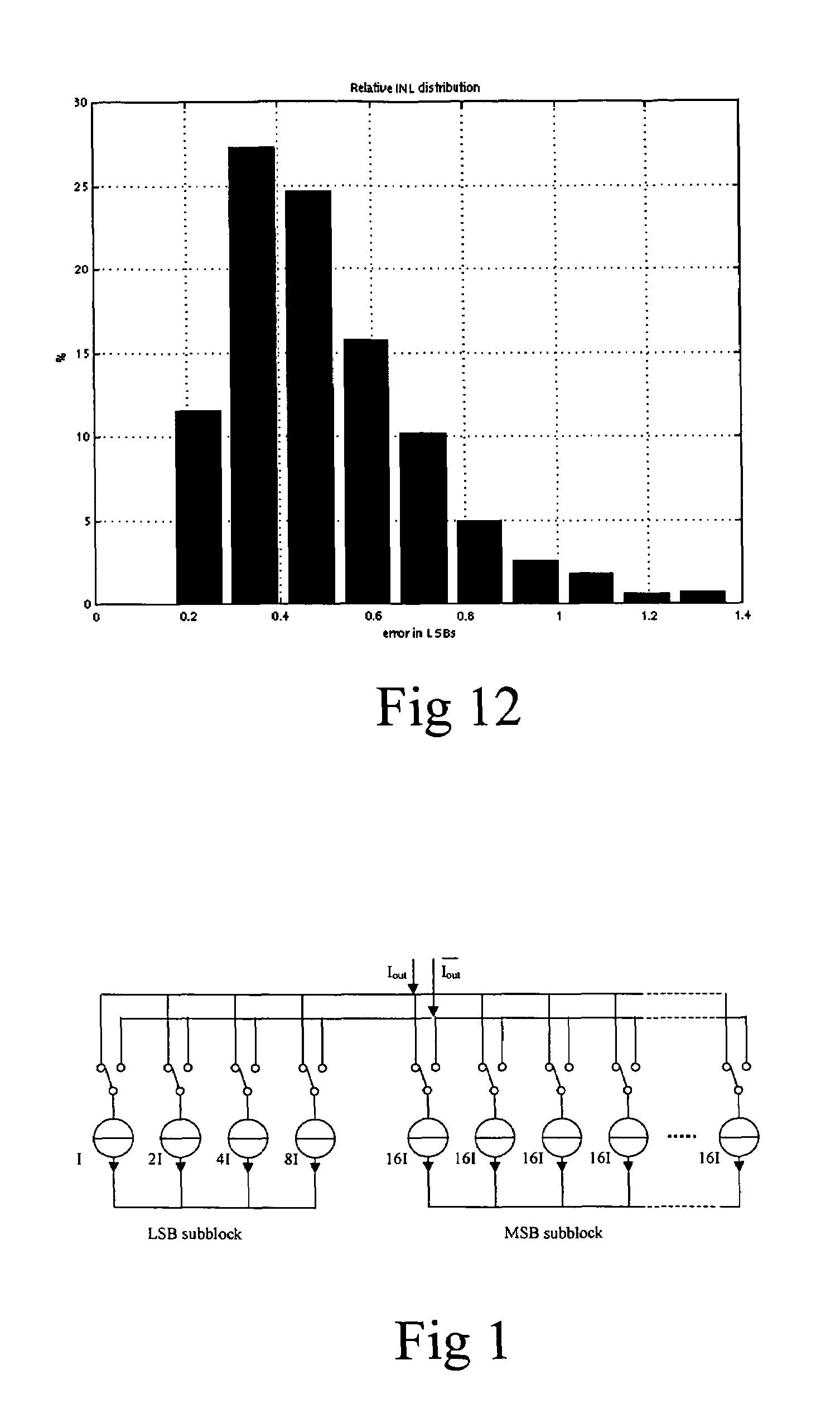

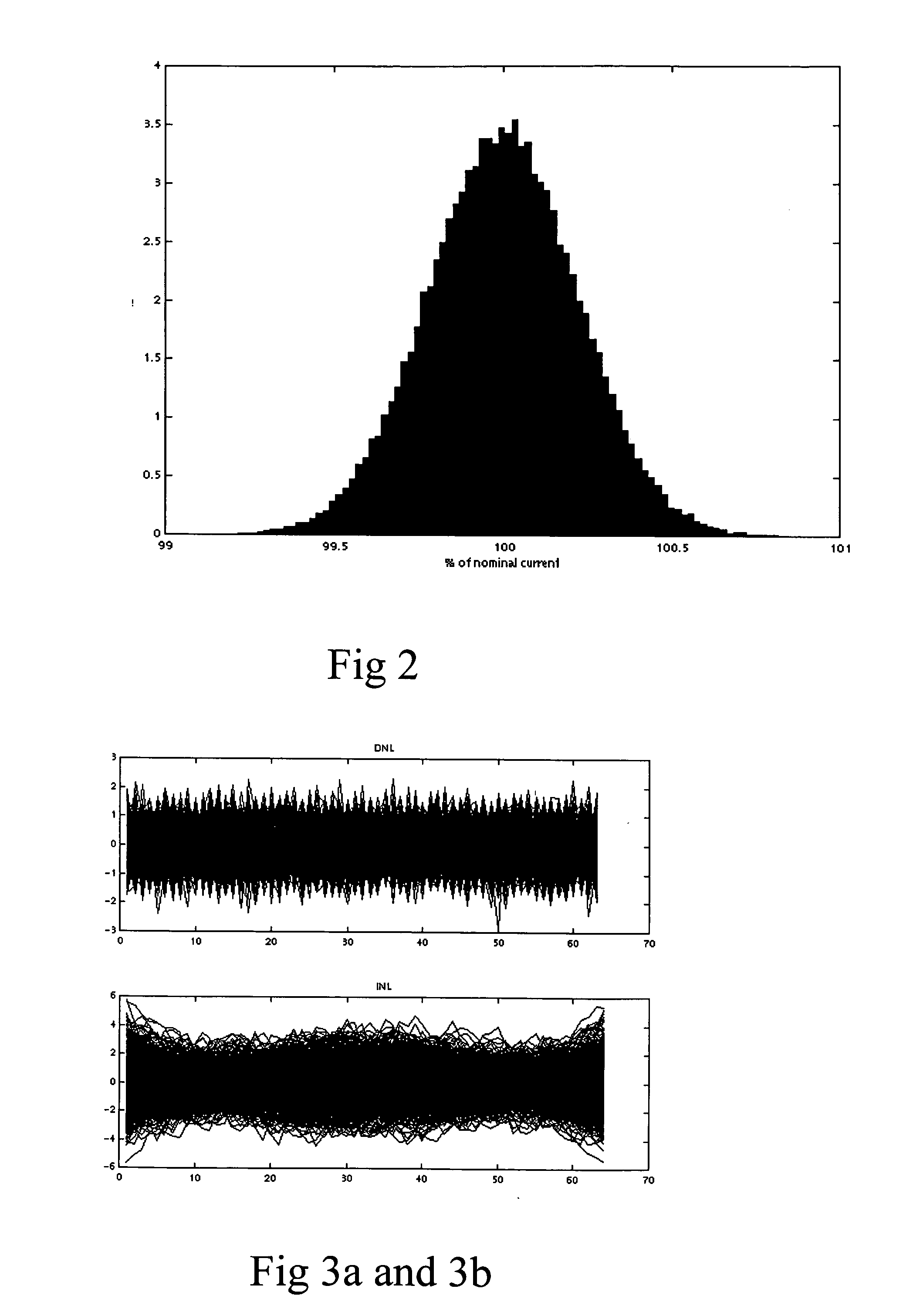

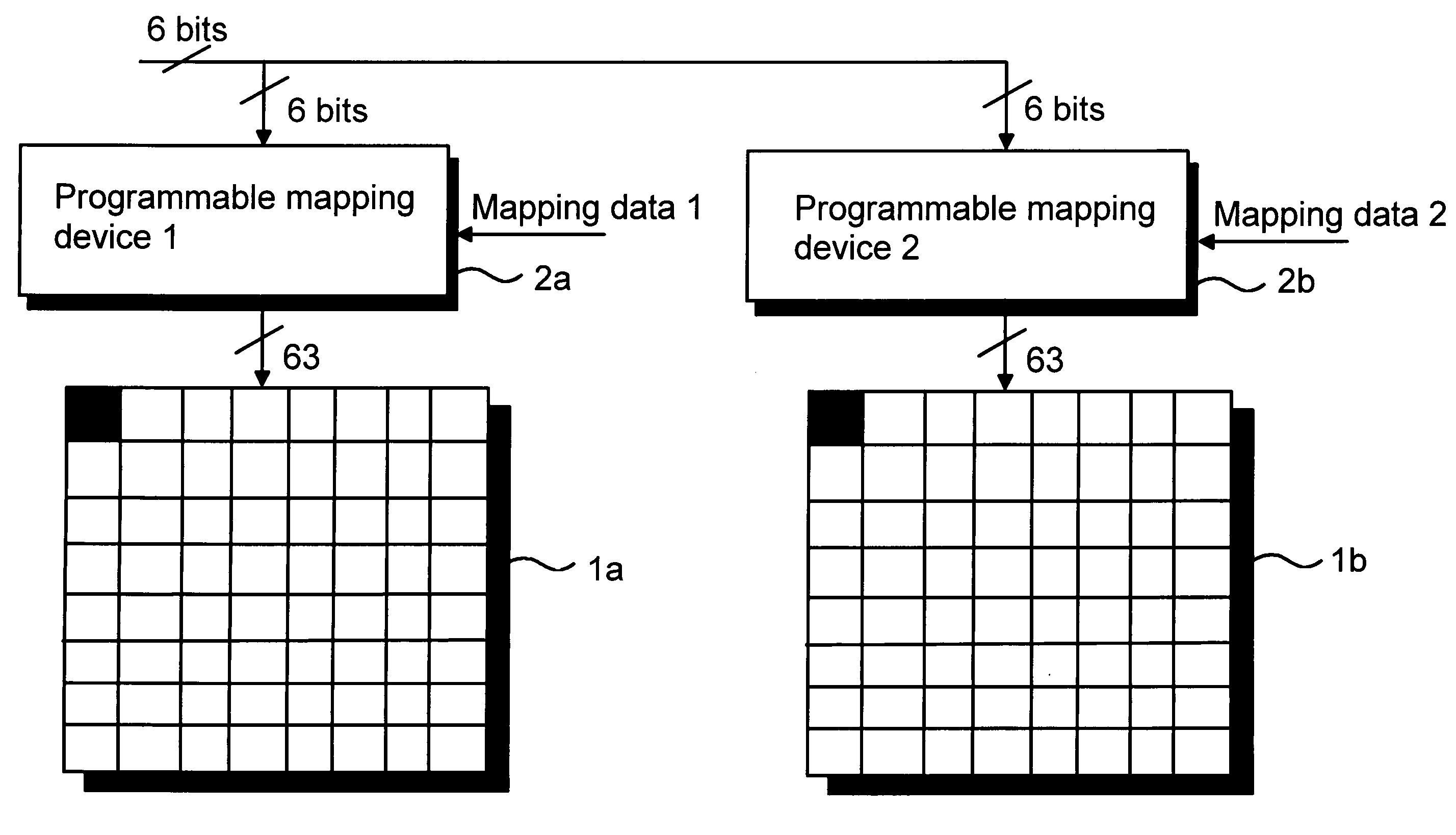

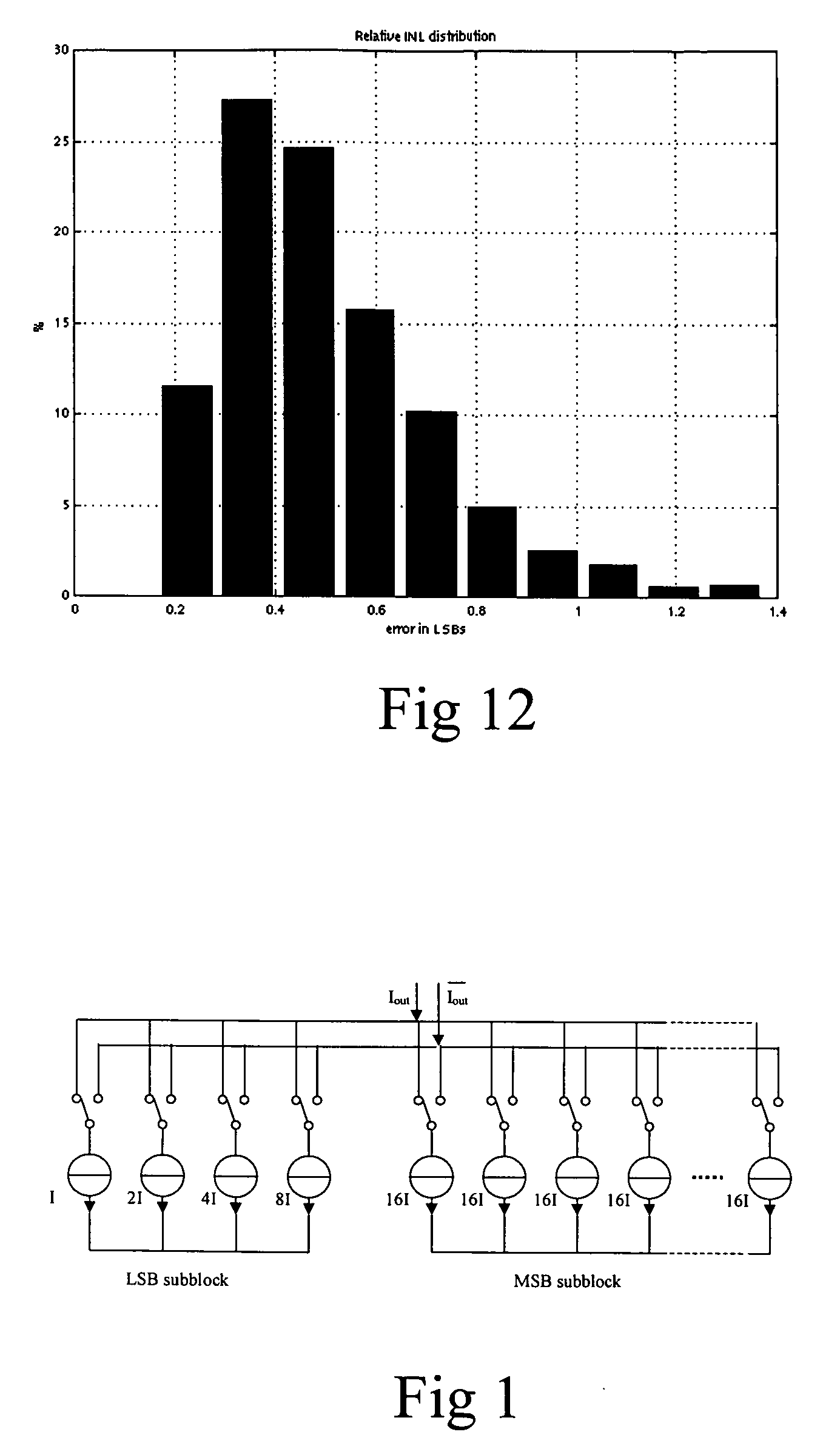

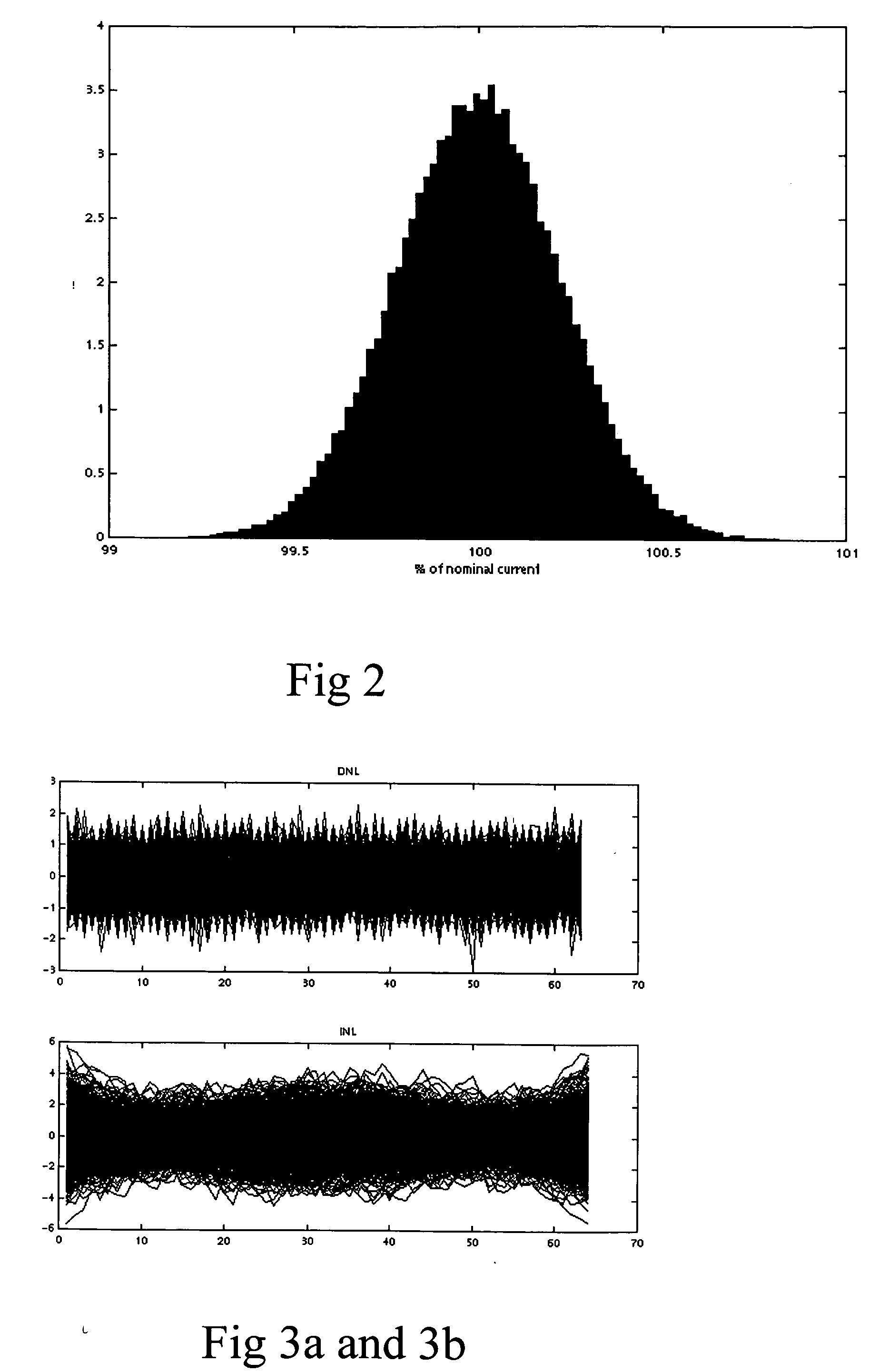

Method for calibrating a digital-to-analog converter and a digital-to-analog converter

InactiveUS7026967B2The solution result is accurateError minimizationElectric signal transmission systemsDigital-analogue convertorsEngineeringAnalog signal

The invention describes a method for digitally calibrating a segmented current-steering D / A-converter. One embodiment of the present invention is a 14-bit DAC, where 6 MSB's are converted with two unweighted current source array. Further, in this invention a new method for organising the switching order based on the analysed data of mismatch of the current sources is presented. A programmable mapping device is used instead of the fixed thermometer decoding before the switch array. Using this programmable mapping device the switching order of the current switches can be selected optimally so that the error in the resulting analog signal is minimised. The switching order is programmed to the mapping device on the basis of the calibration method according to the present invention. The inventive amendment is aimed at processing errors which cause poor matching inside the component itself. This amendment is done by rearranging unweighted unity current switches into a more optimum order.

Owner:VIVO MOBILE COMM CO LTD

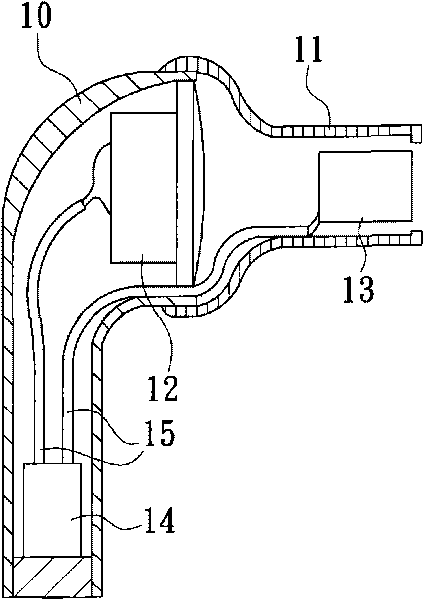

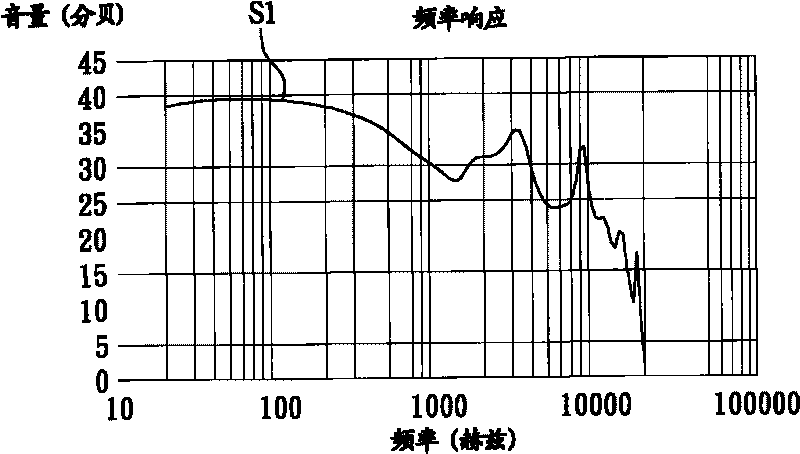

Noise-suppressing earphone

InactiveCN101742373AChange the level of connectivityReduce distanceEarpiece/earphone attachmentsSound producing devicesEngineeringHeadphones

The invention relates to a noise-suppressing earphone, which comprises an earphone body, a loudspeaker, a microphone and a signal processor, wherein the earphone body has a chamber and a sound-transmitting tube; the loudspeaker and the microphone are both arranged in the chamber; sound signals are provided by the loudspeaker and outputted by the sound-transmitting tube; the microphone is positioned beside the loudspeaker and receives the sound signals in the chamber; the signal processor is electrically connected with the loudspeaker and the microphone at the same time; the signal processor provides electric signals for the loudspeaker so as to be converted into the sound signals; the microphone converted the received sound signals into the electric signals so as to be transmitted to the signal processor; and aiming at the part of the sound signals which is defined as noise, the signal processor outputs reverse-phase signals added to the loudspeaker.

Owner:MERRY ELECTRONICS CO LTD

Method for calibrating a digital-to-analog converter and a digital-to-analog converter

InactiveUS20050052297A1Less effectThe solution result is accurateElectric signal transmission systemsDigital-analogue convertorsThermometerDigital-to-analog converter

The invention describes a method for digitally calibrating a segmented current-steering D / A-converter. One embodiment of the present invention is a 14-bit DAC, where 6 MSB's are converted with two unweighted current source array. Further, in this invention a new method for organising the switching order based on the analysed data of mismatch of the current sources is presented. A programmable mapping device is used instead of the fixed thermometer decoding before the switch array. Using this programmable mapping device the switching order of the current switches can be selected optimally so that the error in the resulting analog signal is minimised. The switching order is programmed to the mapping device on the basis of the calibration method according to the present invention. The inventive amendment is aimed at processing errors which cause poor matching inside the component itself. This amendment is done by rearranging unweighted unity current switches into a more optimum order.

Owner:VIVO MOBILE COMM CO LTD

Compliant printed circuit area array semiconductor device package

ActiveUS9054097B2Low production costImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesRoad surfaceEngineering

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV +1

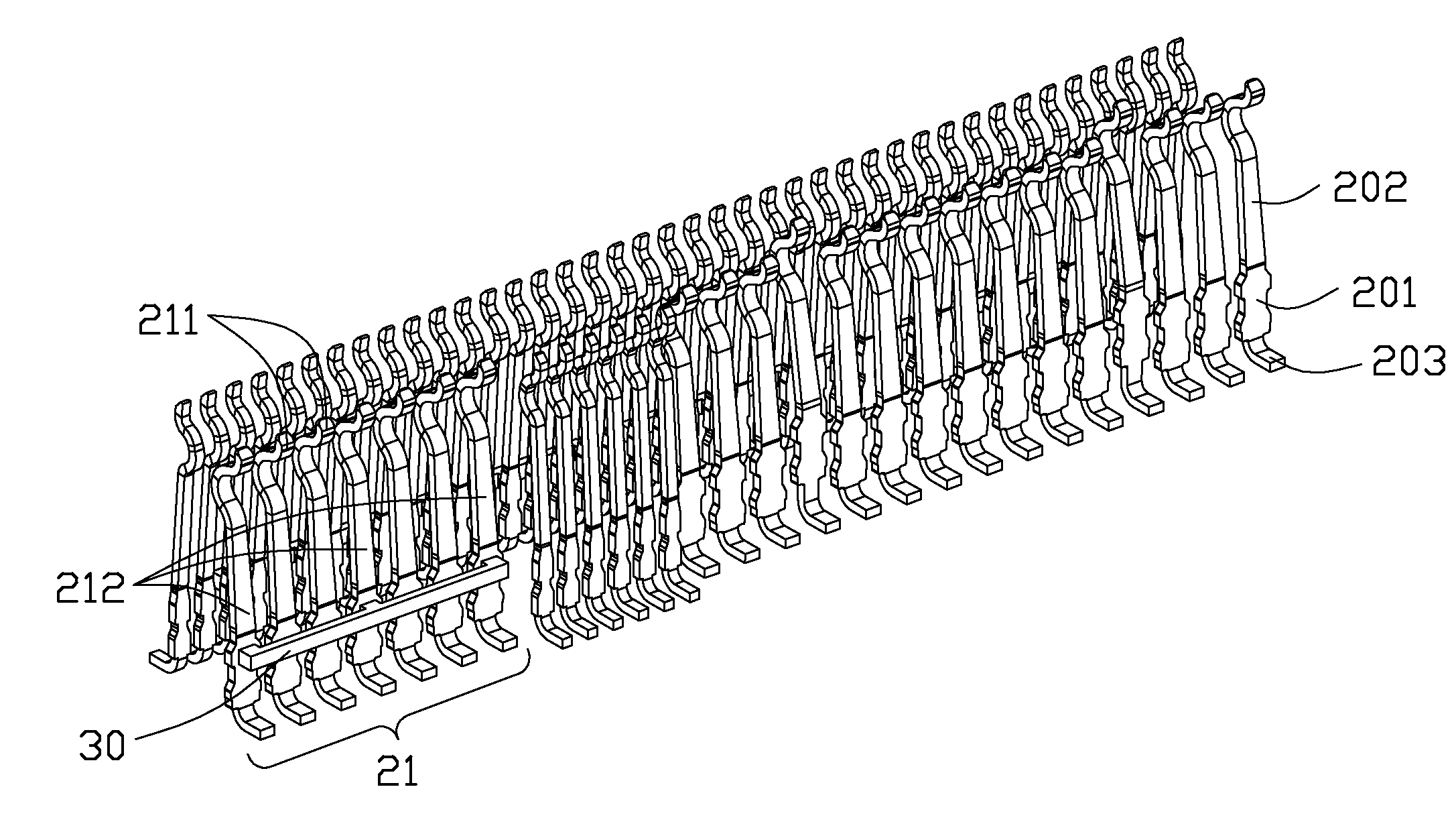

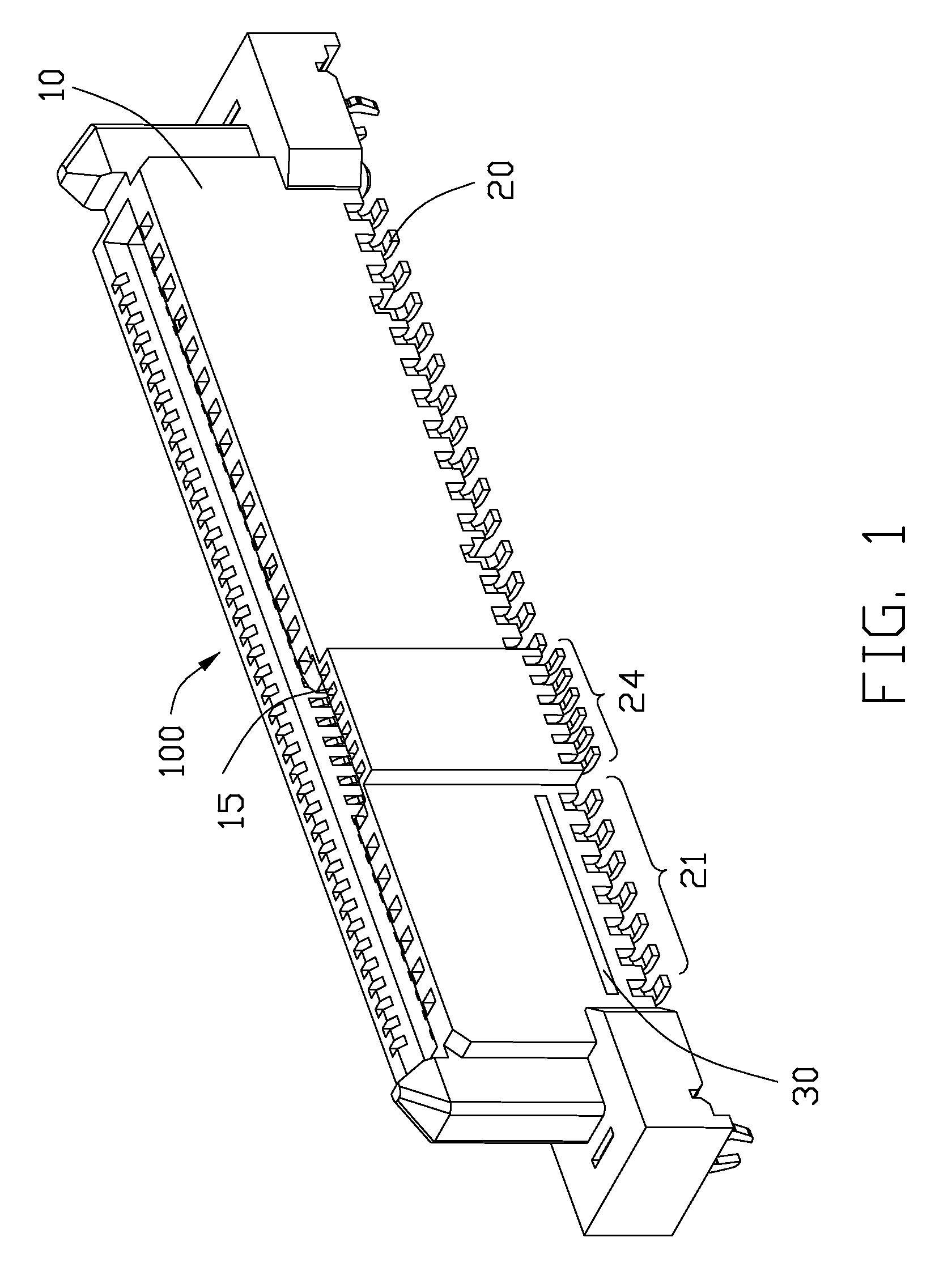

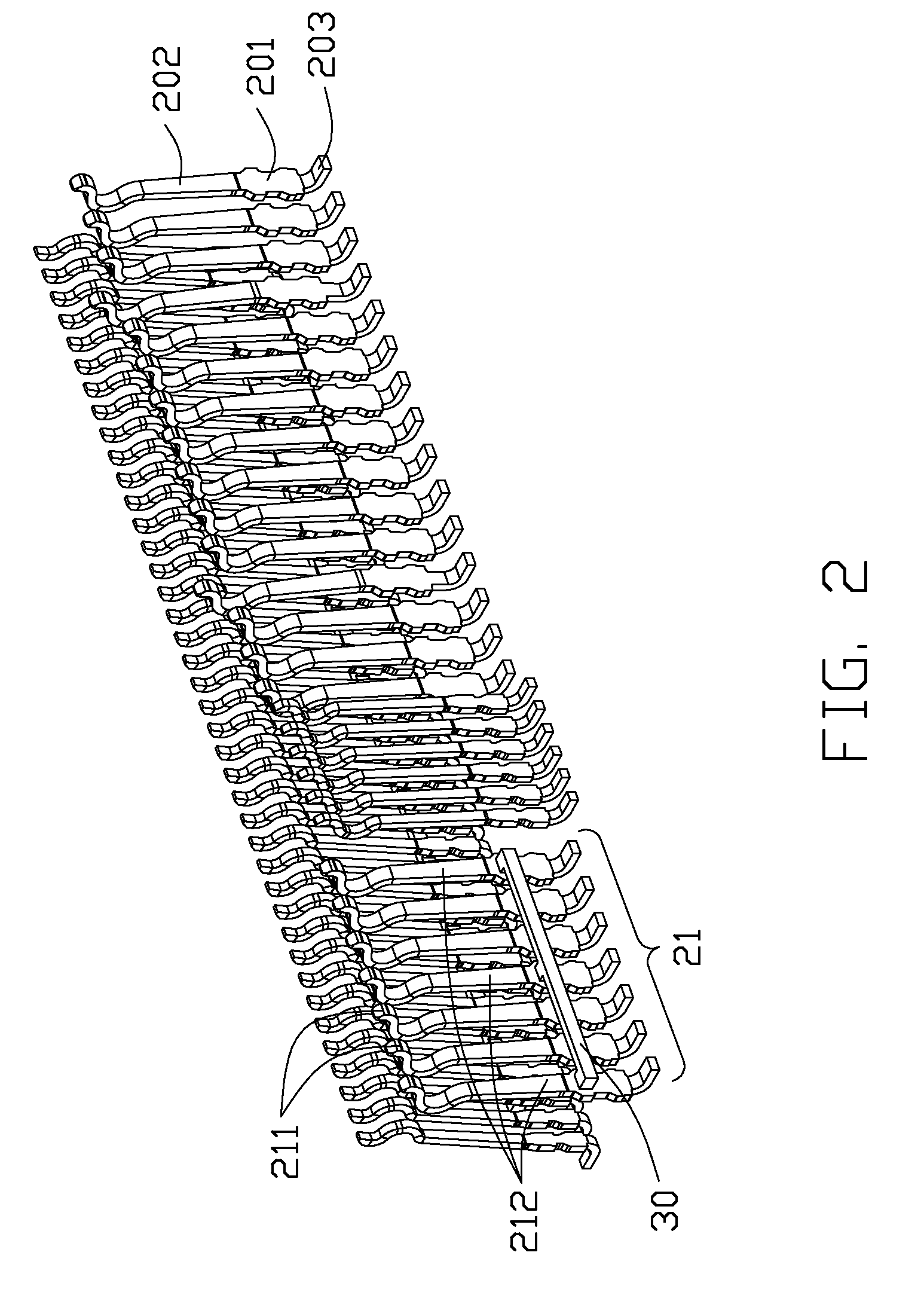

Electrical connector having better high-frequency performance

ActiveUS9281589B2Improve performanceImprove stabilityElectrically conductive adhesive connectionsTwo-part coupling devicesElectricityAdhesive

An electrical connector includes an insulative housing and a plurality of conductive terminals fixed in the insulative housing. The conductive terminals includes a first terminal group, the first terminal group includes a plurality of signal terminals and a plurality of grounding terminals. The insulative housing defines a cured conductive adhesive, the cured conductive adhesive makes the grounding terminals of the first terminal group shorted to each other.

Owner:FOXCONN INTERCONNECT TECH LTD

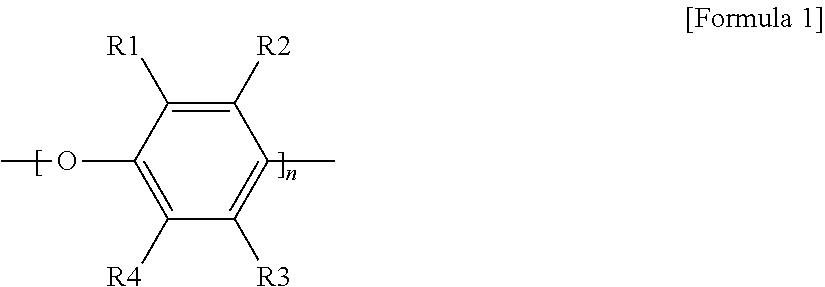

Resin composition, metal foil provided with resin layer, metal clad laminate, and printed wiring board

ActiveUS20150140296A1Improve high frequency performanceImprove electrical performanceDielectric materialsSynthetic resin layered productsSolubilityMetal foil

An object of the present invention is to provide a resin composition which enables formation of a resin layer having excellent electrical performance including high frequency performance and appropriate solubility with desmear solution required on a material used in manufacturing of a printed wiring board.To achieve the object, the resin composition used for constituting a resin layer on a metal layer surface of a laminate includes a polyphenylene ether compound and 10 parts by mass to 100 parts by mass of a styrene-butadiene block copolymer and 0.1 parts by mass to 100 parts by mass of a component promoting solubility with desmear solution against 100 parts by mass of the polyphenylene ether compound.

Owner:MITSUI MINING & SMELTING CO LTD

Videolaryngostroboscope

InactiveUS7654952B2Accurate checkIncrease probabilityBronchoscopesLaryngoscopesLarynxComputer science

An innovative one-piece videolaryngostroboscope that provides slow motion visualization and detailed analysis of the vocal cords movements, which are imperceptible to the naked eye due, by means of a video camera with stroboscopic; said apparatus is used to perform examinations in patients, aiming to assess the incidence of larynx cancer. The invention including a processor base; an optics tube with a built-in light sources, a built-in video camera; a microphone, an auxiliary pedal and software.

Owner:OTT CIRO TIMOTEO

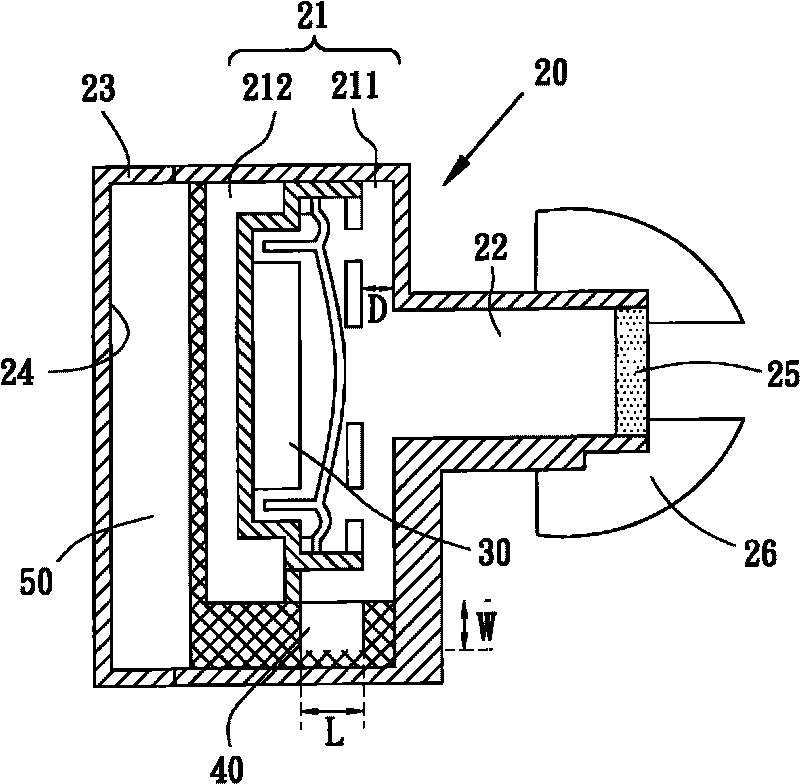

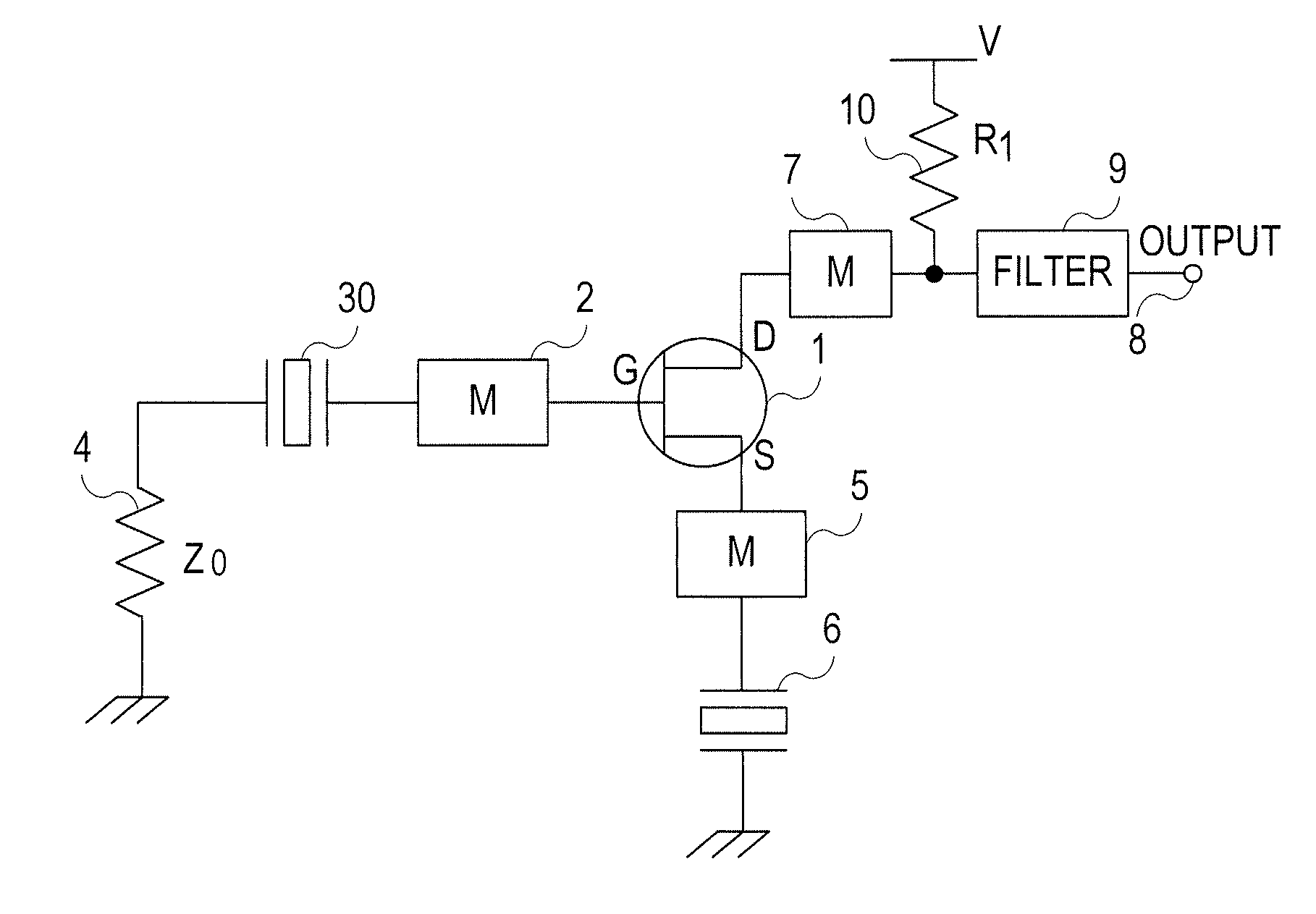

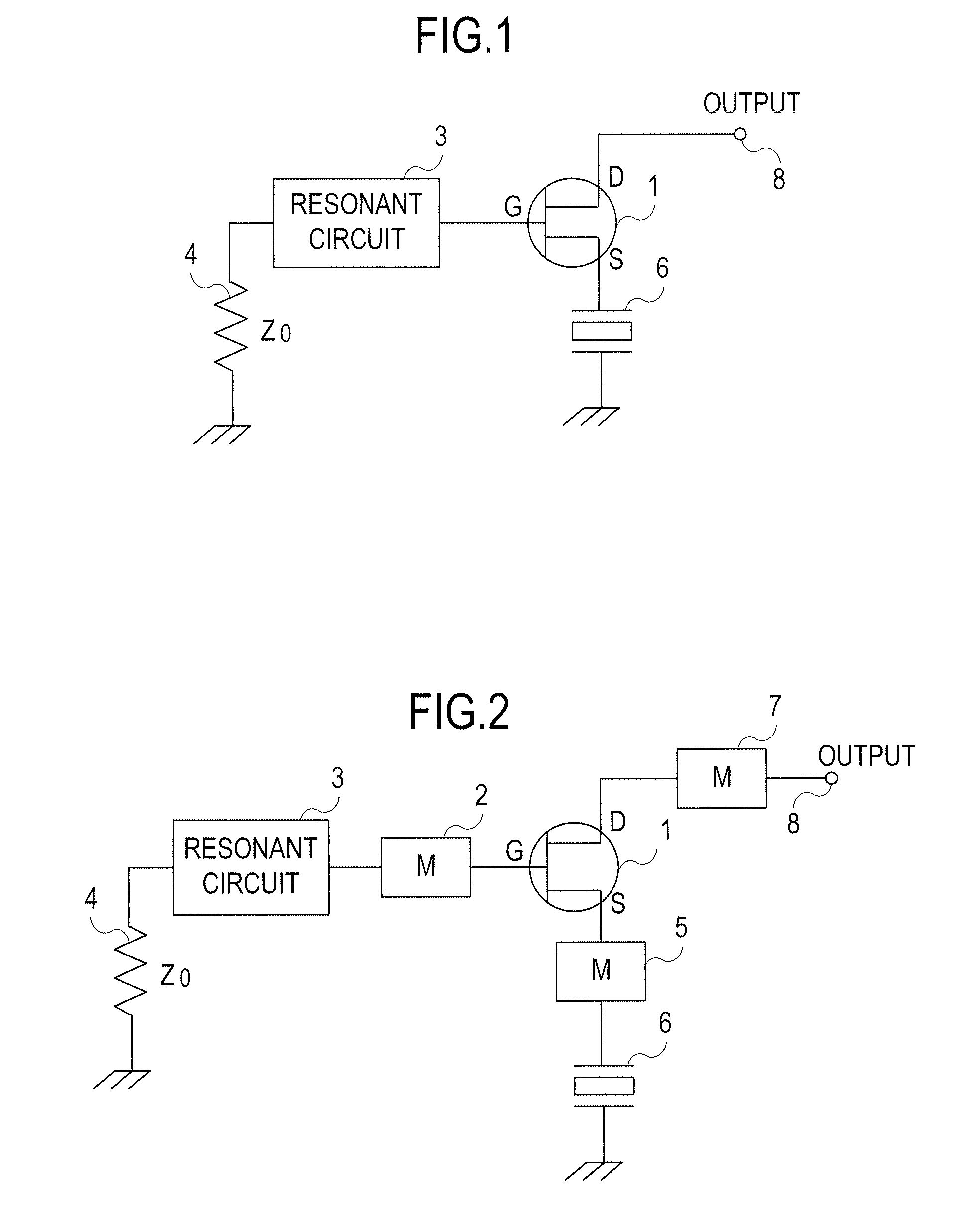

Piezoelectric oscillator

InactiveUS8669821B2High-frequency performanceEarly stabilization of frequencyApparatus using electrochemical resonatorsElectric pulse generatorFrequency stabilizationResonance

Provided is a piezoelectric oscillator to attain high-frequency performance and frequency stabilization with the use of reflection characteristics of a reflective element. A piezoelectric oscillator is configured such that: a resonant circuit is connected to a gate of a field effect transistor; an output terminal is connected to a drain and a power supply voltage V is applied to the drain; a piezoelectric resonator is connected to a source, as a reflective element; and a resonance frequency of the resonant circuit and an oscillation frequency of the piezoelectric resonator as a reflective element are set to substantially the same frequency, and further, the piezoelectric oscillator may be configured such that a first matching circuit is provided between the resonant circuit and the gate, a second matching circuit is provided between the drain and the output terminal, and a third matching circuit is provided between the source and the reflective element.

Owner:NIHON DEMPA KOGYO CO LTD

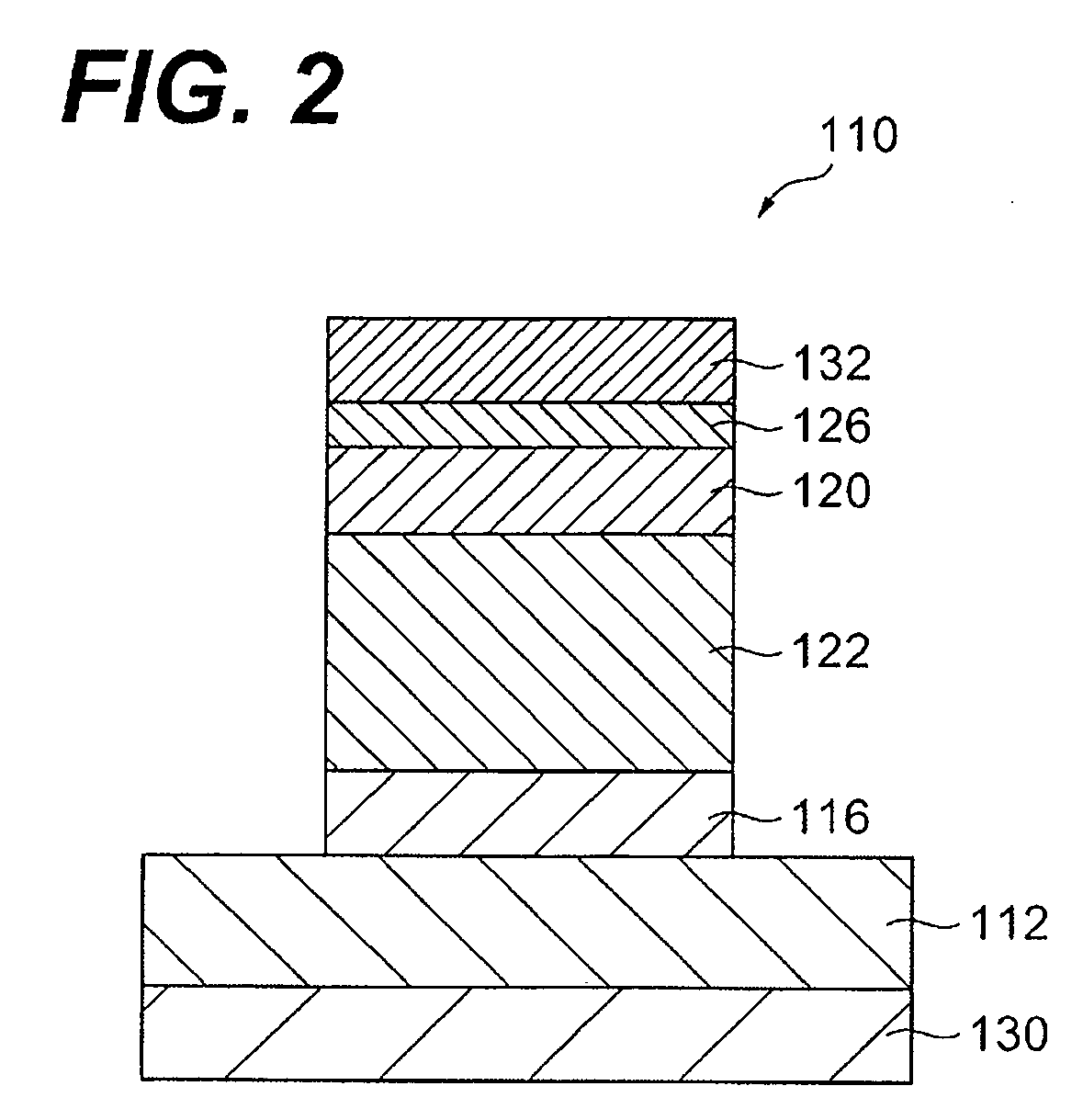

Semiconductor light-emitting device with a surface emitting type

InactiveUS20090116526A1Increase flexibilityImprove design flexibilityLaser detailsSemiconductor/solid-state device manufacturingParasitic capacitanceHigh resistivity

A structure of an optical device with the surface emitting type and a method to form the optical device are disclosed, where the optical device is able to operate in high frequencies. The device provides a lower DBR structure, an active layer, a current injection layer, a current blocking layer, and an upper DBR structure on a GaAs substrate. The current blocking layer, horizontally putting the current injection layer therebetween, are an un-doped GaInP grown at a temperature between 500 to 600° C. and an un-doped AlGaInP grown at a temperature between 500 to 650° C. Because the un-doped current blocking layer shows the high resistivity for both electrons and holes, the parasitic capacitance in the current blocking layer becomes small.

Owner:SUMITOMO ELECTRIC IND LTD

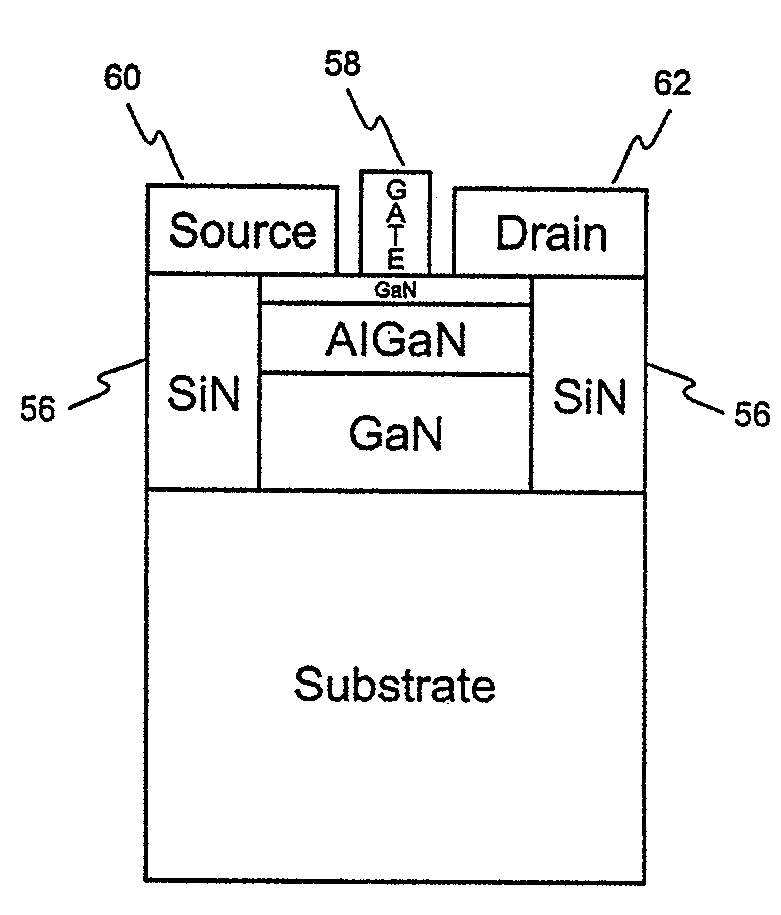

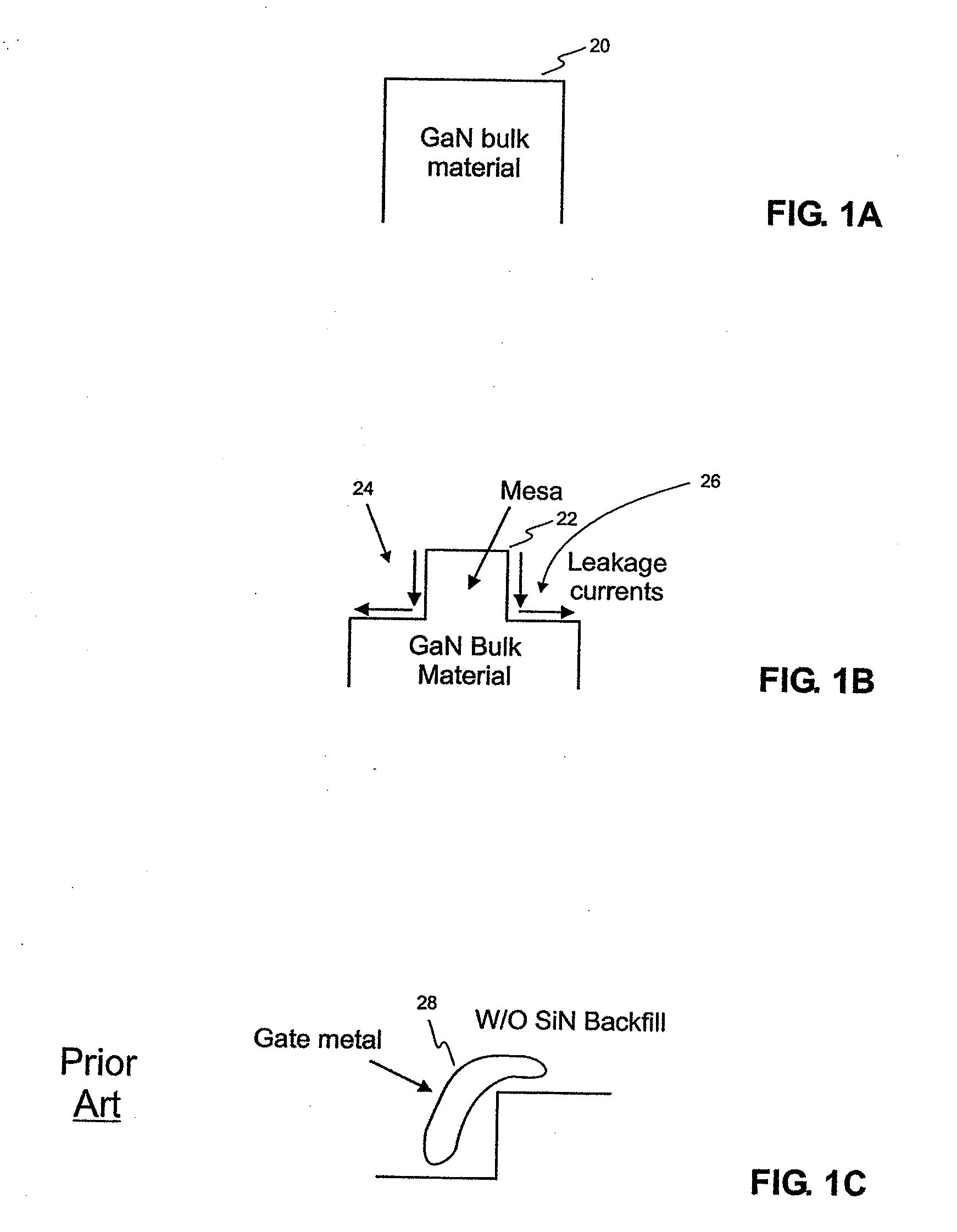

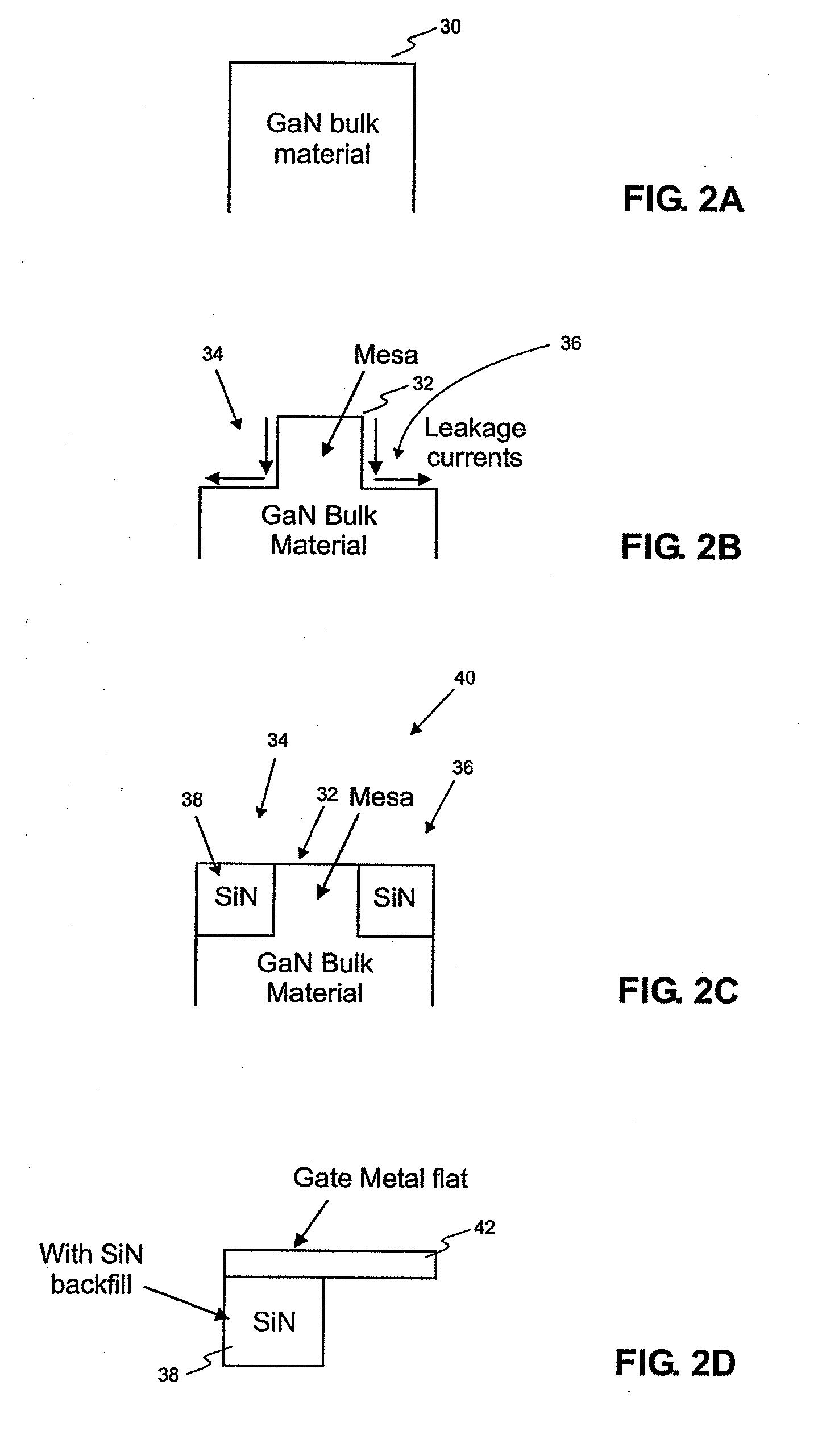

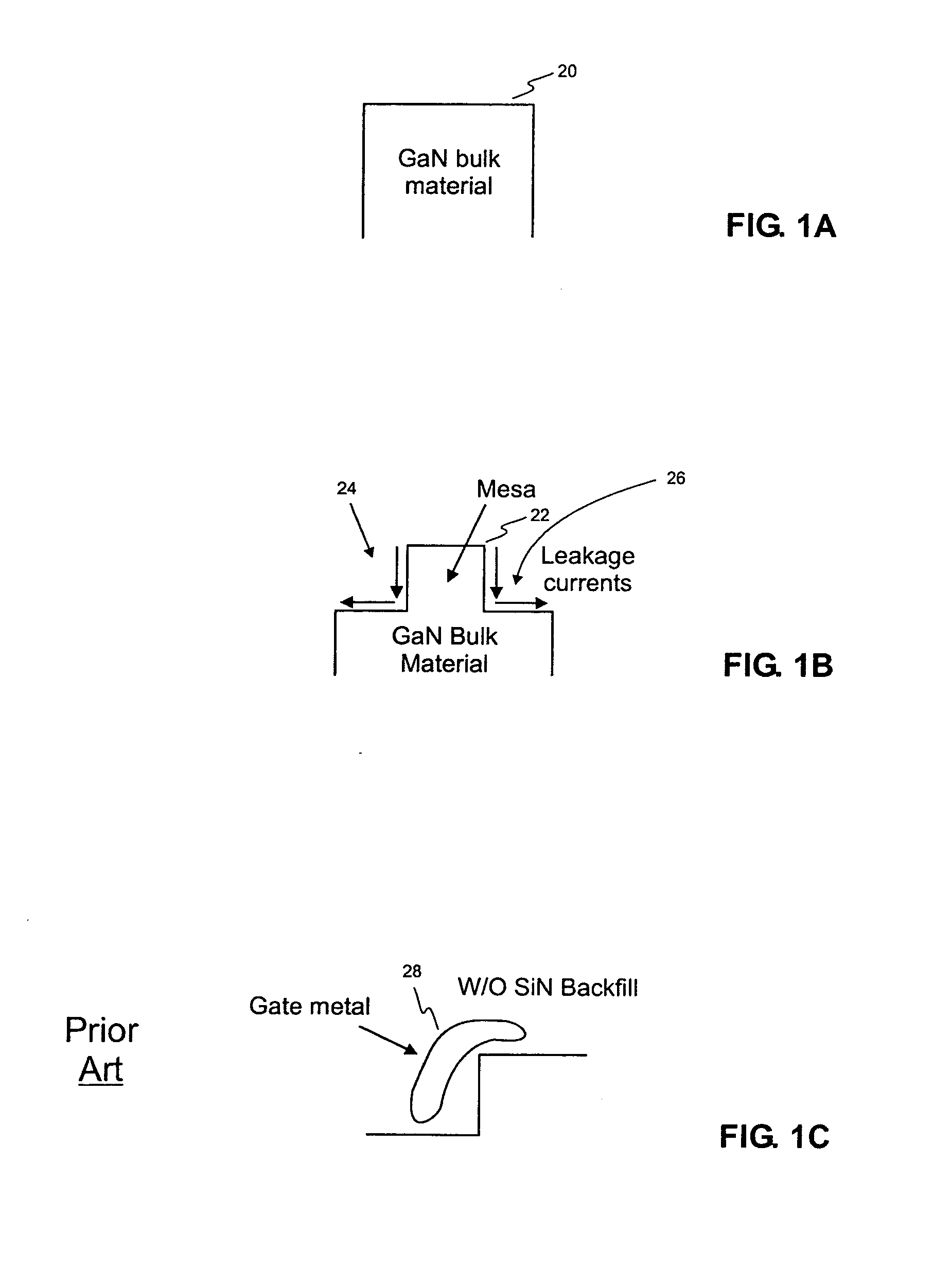

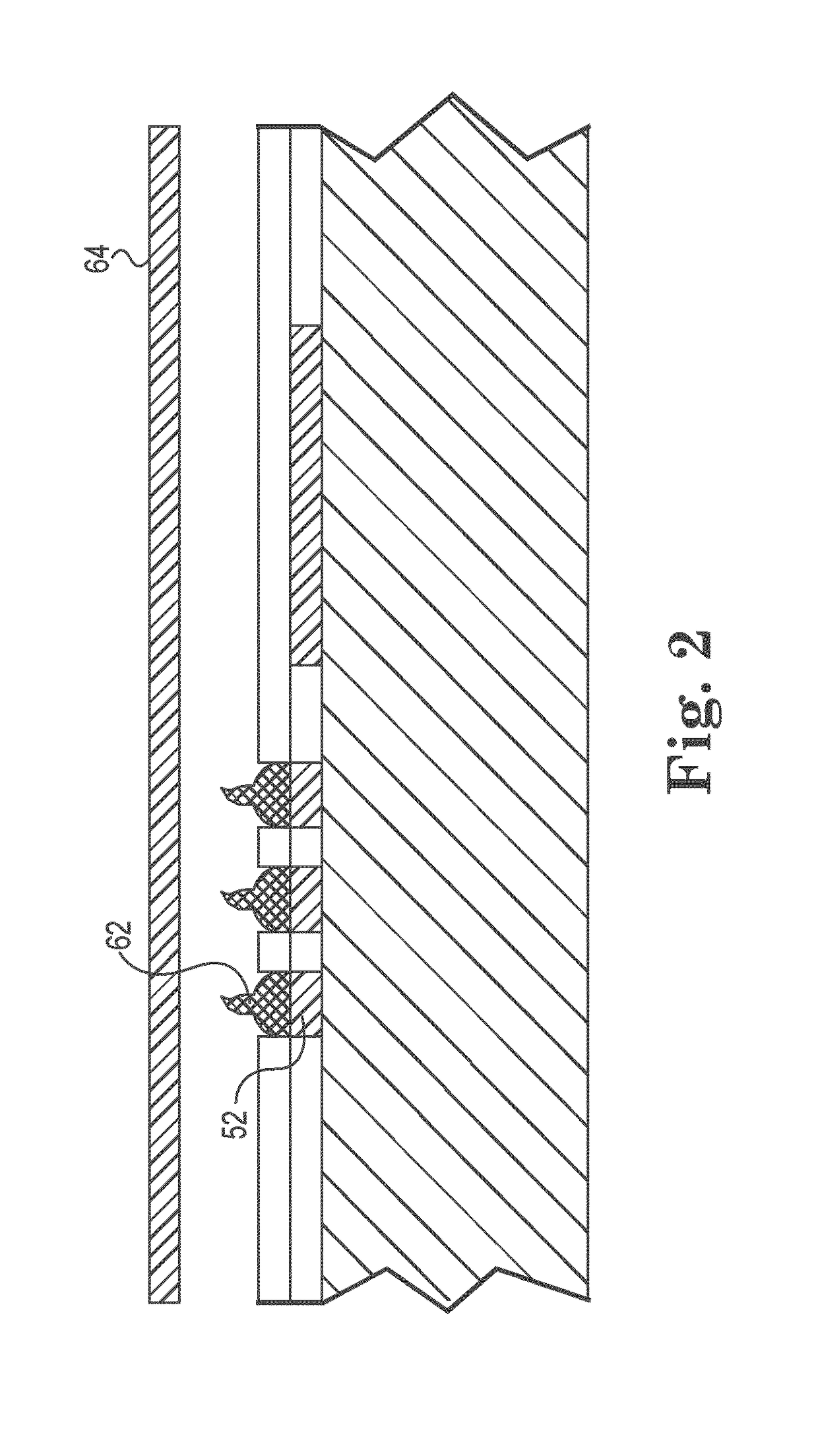

LEAKAGE BARRIER FOR GaN BASED HEMT ACTIVE DEVICE

ActiveUS20080153215A1Obviates problemReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate leakage currentDrain current

An improved HEMT formed from a GaN material system is disclosed which has reduced gate leakage current relative to known GaN based HEMTs and eliminates the problem of current constrictions resulting from deposition of the gate metal over the step discontinuities formed over the gate mesa. The HEMT device is formed from a GaN material system. One or more GaN based materials are layered and etched to form a gate mesa with step discontinuities defining source and drain regions. In order to reduce the leakage current, the step discontinuities are back-filled with an insulating material, such as silicon nitride (SiN), forming a flat surface relative to the source and drain regions, to enable to the gate metal to lay flat. By back-filling the source and drain regions with an insulating material, leakage currents between the gate and source and the gate and drain are greatly reduced. In addition, current constrictions resulting from the deposition of the gate metal over a step discontinuity are virtually eliminated.

Owner:NORTHROP GRUMMAN SYST CORP

Electrical connector having better high-frequency performance

ActiveUS20150200503A1Improve performanceImprove stabilityElectrically conductive adhesive connectionsTwo-part coupling devicesElectricityAdhesive

An electrical connector includes an insulative housing and a plurality of conductive terminals fixed in the insulative housing. The conductive terminals includes a first terminal group, the first terminal group includes a plurality of signal terminals and a plurality of grounding terminals. The insulative housing defines a cured conductive adhesive, the cured conductive adhesive makes the grounding terminals of the first terminal group shorted to each other.

Owner:FOXCONN INTERCONNECT TECHNOLOGY LIMITED

Leakage barrier for GaN based HEMT active device

ActiveUS20070218611A1Obviates problemReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate leakage currentCurrent limiting

An improved HEMT formed from a GaN material system is disclosed which has reduced gate leakage current relative to known GaN based HEMTs and eliminates the problem of current constrictions resulting from deposition of the gate metal over the step discontinuities formed over the gate mesa. The HEMT device is formed from a GaN material system. One or more GaN based materials are layered and etched to form a gate mesa with step discontinuities defining source and drain regions. In order to reduce the leakage current, the step discontinuities are back-filled with an insulating material, such as silicon nitride (SiN), forming a flat surface relative to the source and drain regions, to enable to the gate metal to lay flat. By back-filling the source and drain regions with an insulating material, leakage currents between the gate and source and the gate and drain are greatly reduced. In addition, current constrictions resulting from the deposition of the gate metal over a step discontinuity are virtually eliminated.

Owner:NORTHROP GRUMMAN SYST CORP

Area array semiconductor device package interconnect structure with optional package-to-package or flexible circuit to package connection

ActiveUS9613841B2Improve interconnect reliabilityHigh-frequency performancePrinted circuit assemblingSemiconductor/solid-state device detailsFlexible circuitsIc devices

Owner:HSIO TECH

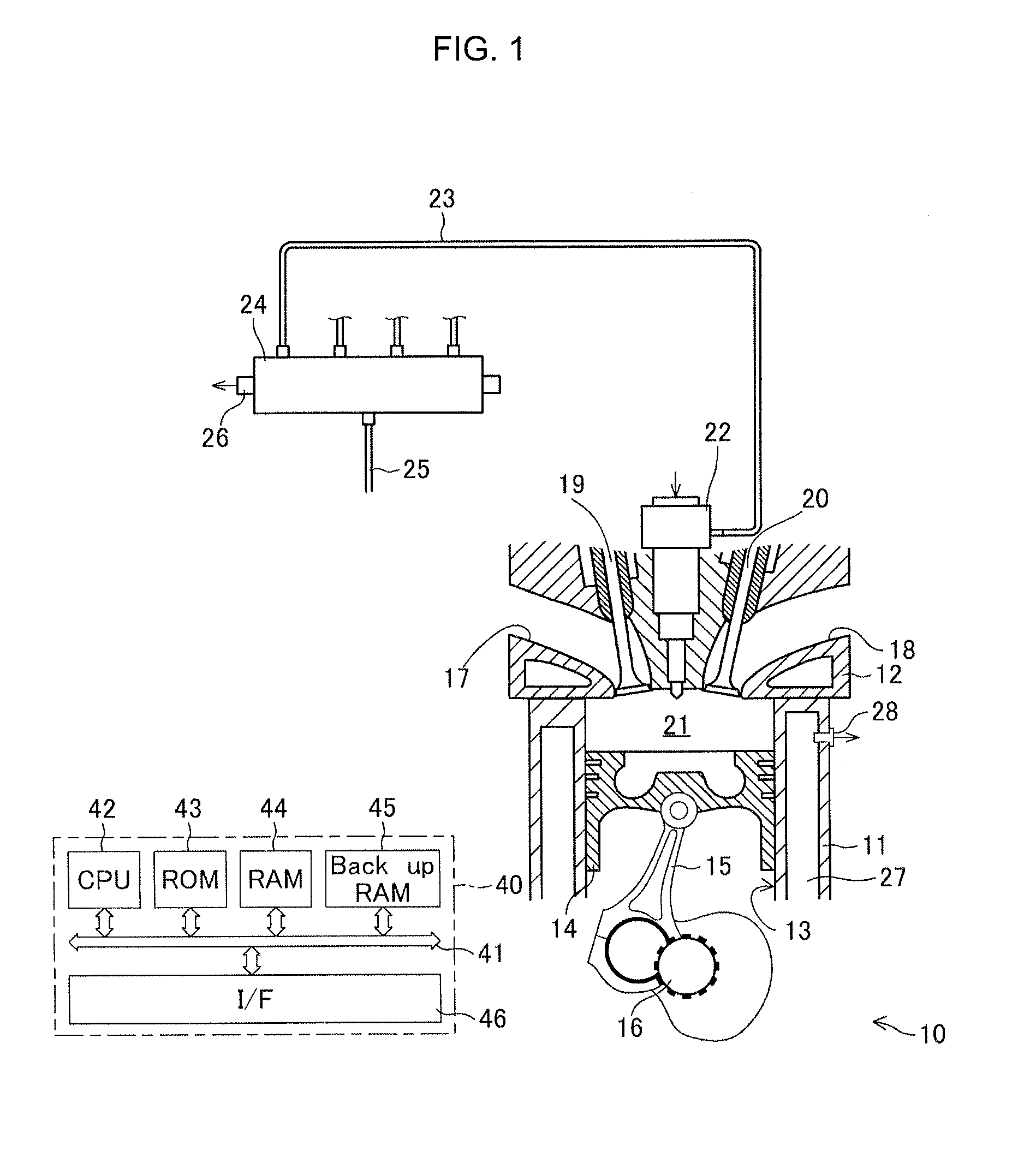

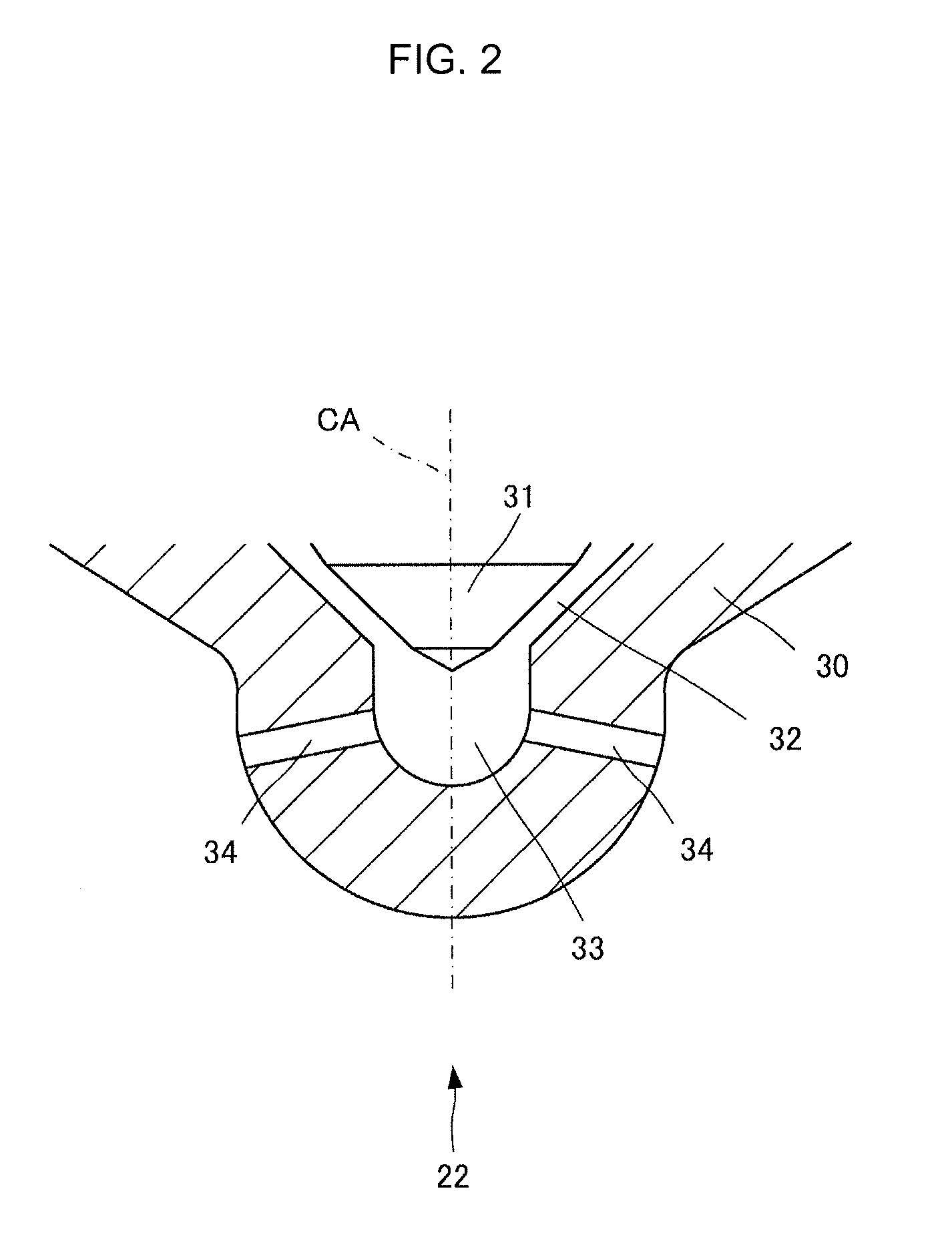

Deposit amount estimation device of engine

ActiveUS8869605B2Easy to understandLittle has been producedInternal-combustion engine testingElectrical controlFuel injectionInjector

The invention relates to a deposit amount estimation device for estimating a deposit amount by calculating an amount of a deposit on an injection hole wall face of a fuel injector (22). An increment judgment of whether an actual fuel injection amount is larger than the required fuel injection amount corresponding thereto when a fuel injection command value corresponding to a required fuel injection amount smaller than a predetermined amount is given to the fuel injector, is performed, and when it is judged that the actual fuel injection amount is larger than the required fuel injection amount corresponding thereto by the increment judgment, the deposit amount is estimated on the basis of the difference between the actual fuel injection amount and the required fuel injection amount corresponding thereto.

Owner:TOYOTA JIDOSHA KK

Cordless charging apparatus

InactiveUS20140017998A1Minimizing electromagnetic interferenceProcess stabilityNear-field transmissionBatteries circuit arrangementsResonatorEngineering

A cordless charging apparatus is provided. The cordless charging apparatus includes a cordless power reception resonator including a feeding connector for electric feeding, and a ground connector for grounding. The ground connector is spaced apart from a connection terminal connecting the cordless power reception resonator to a circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

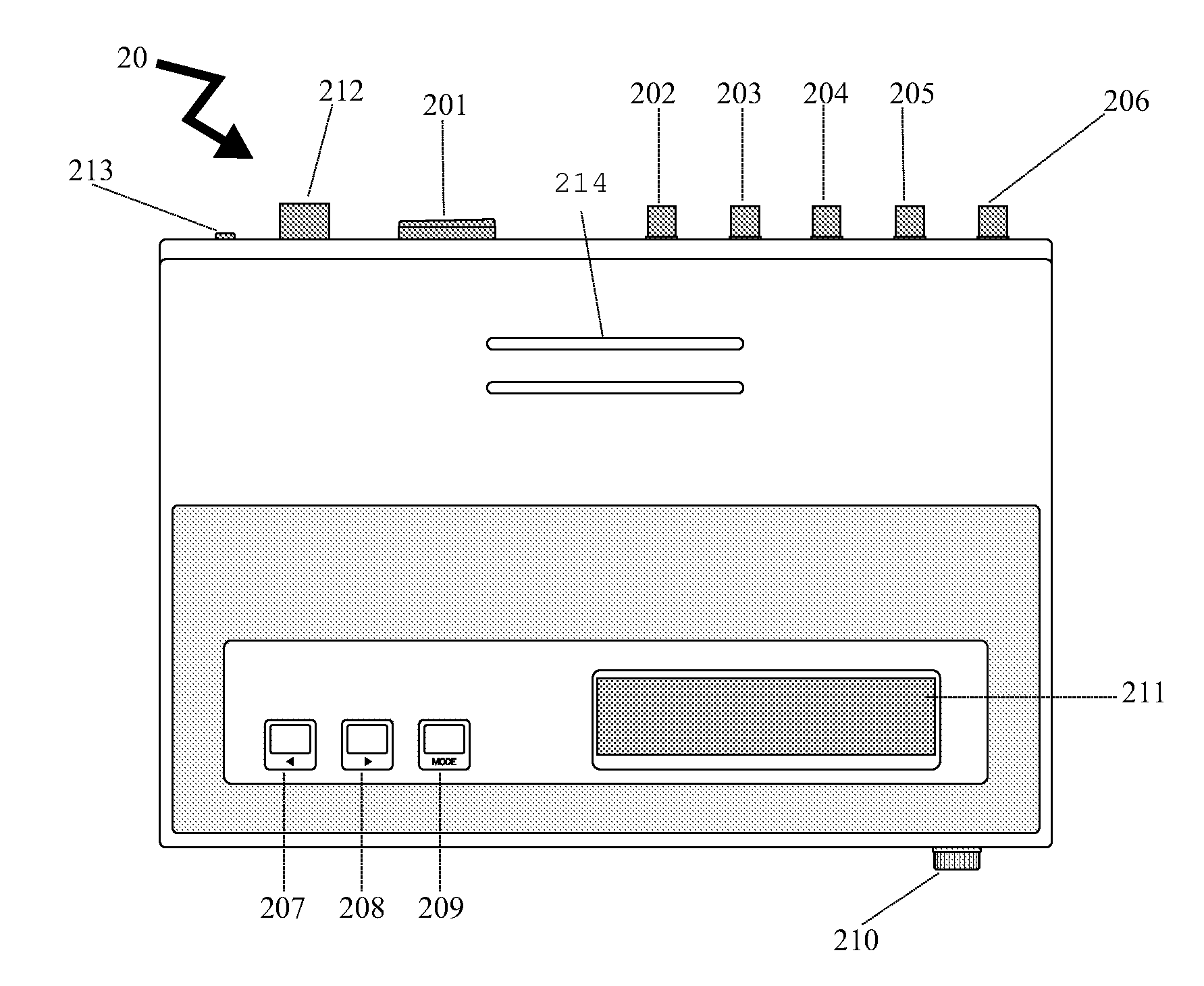

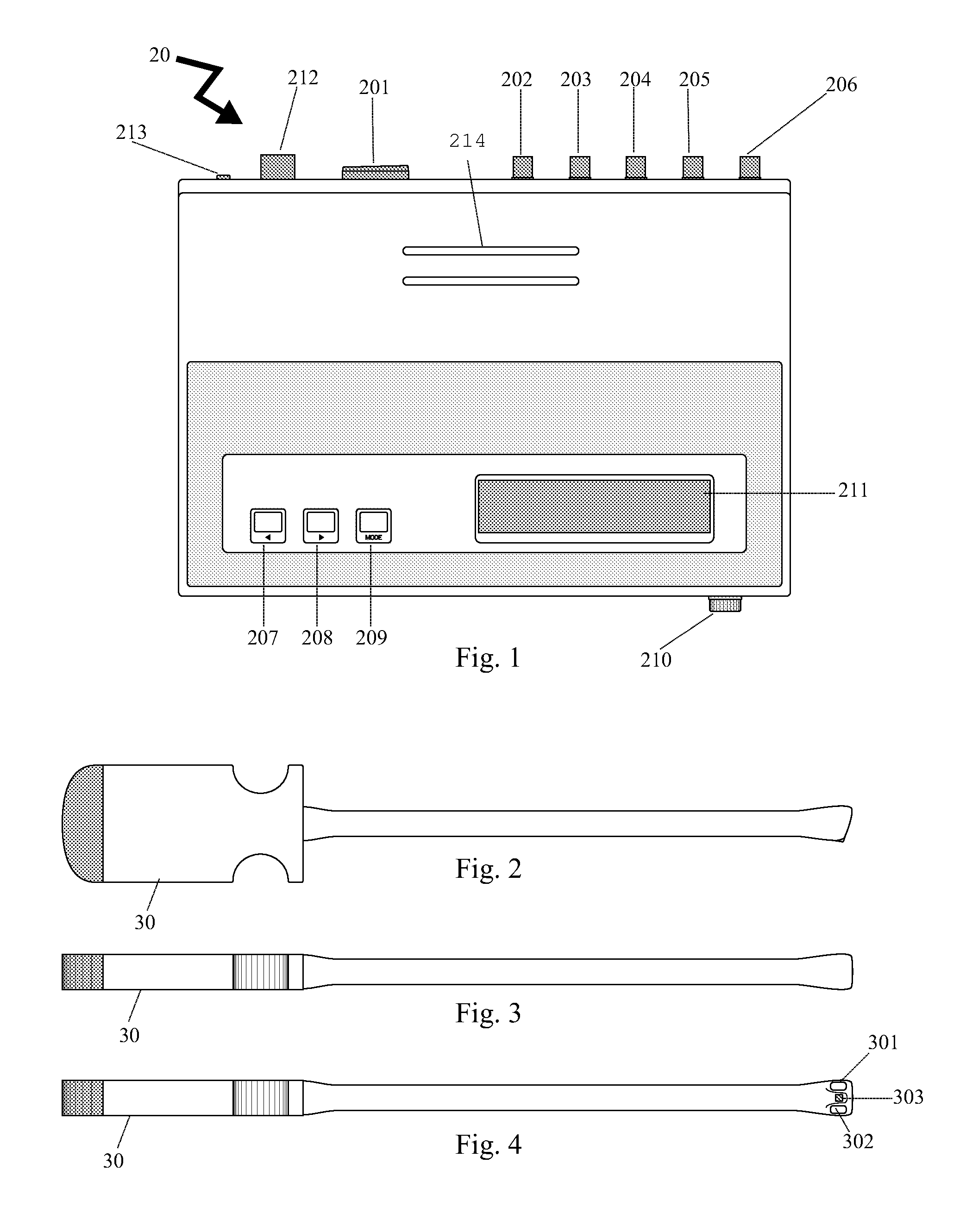

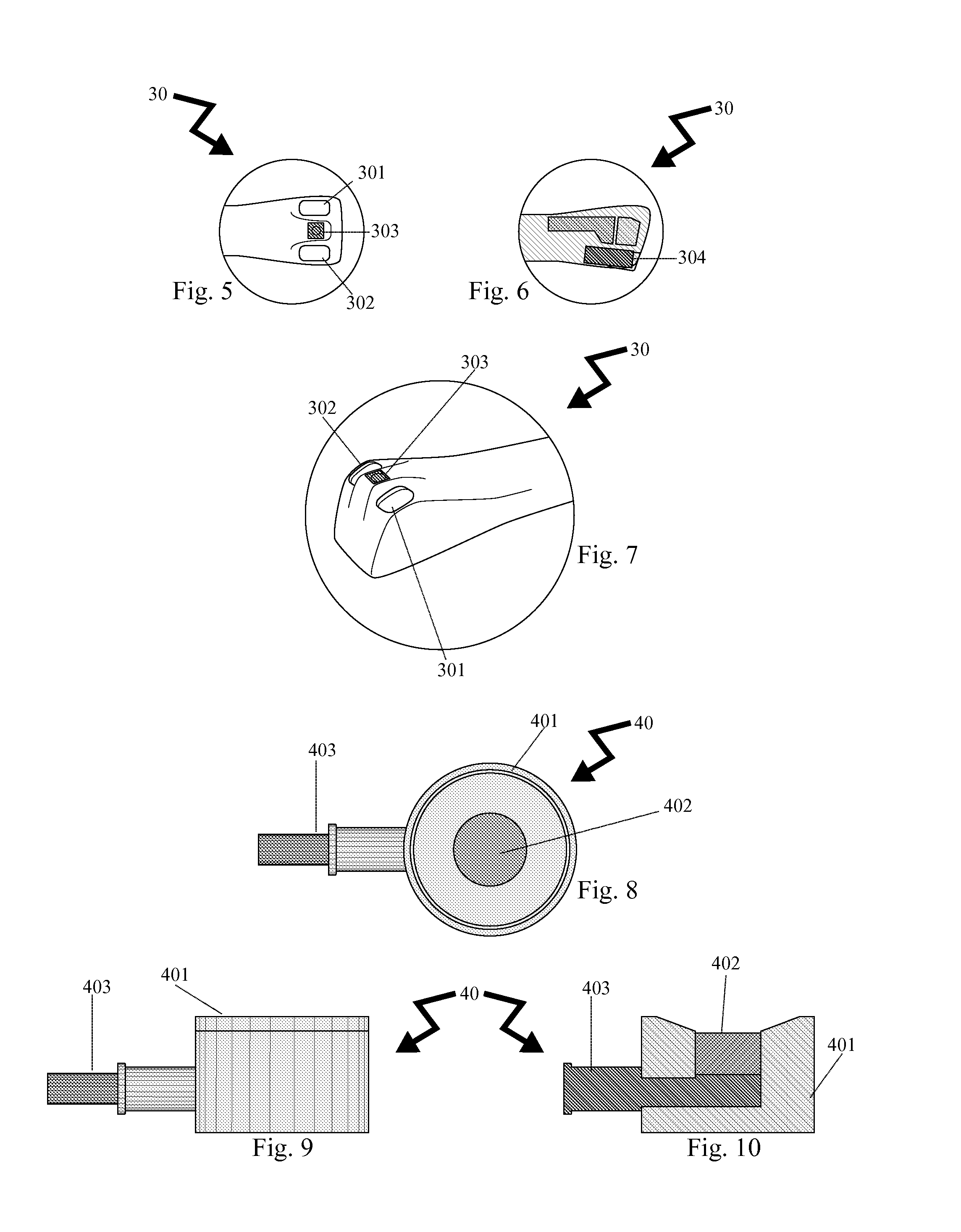

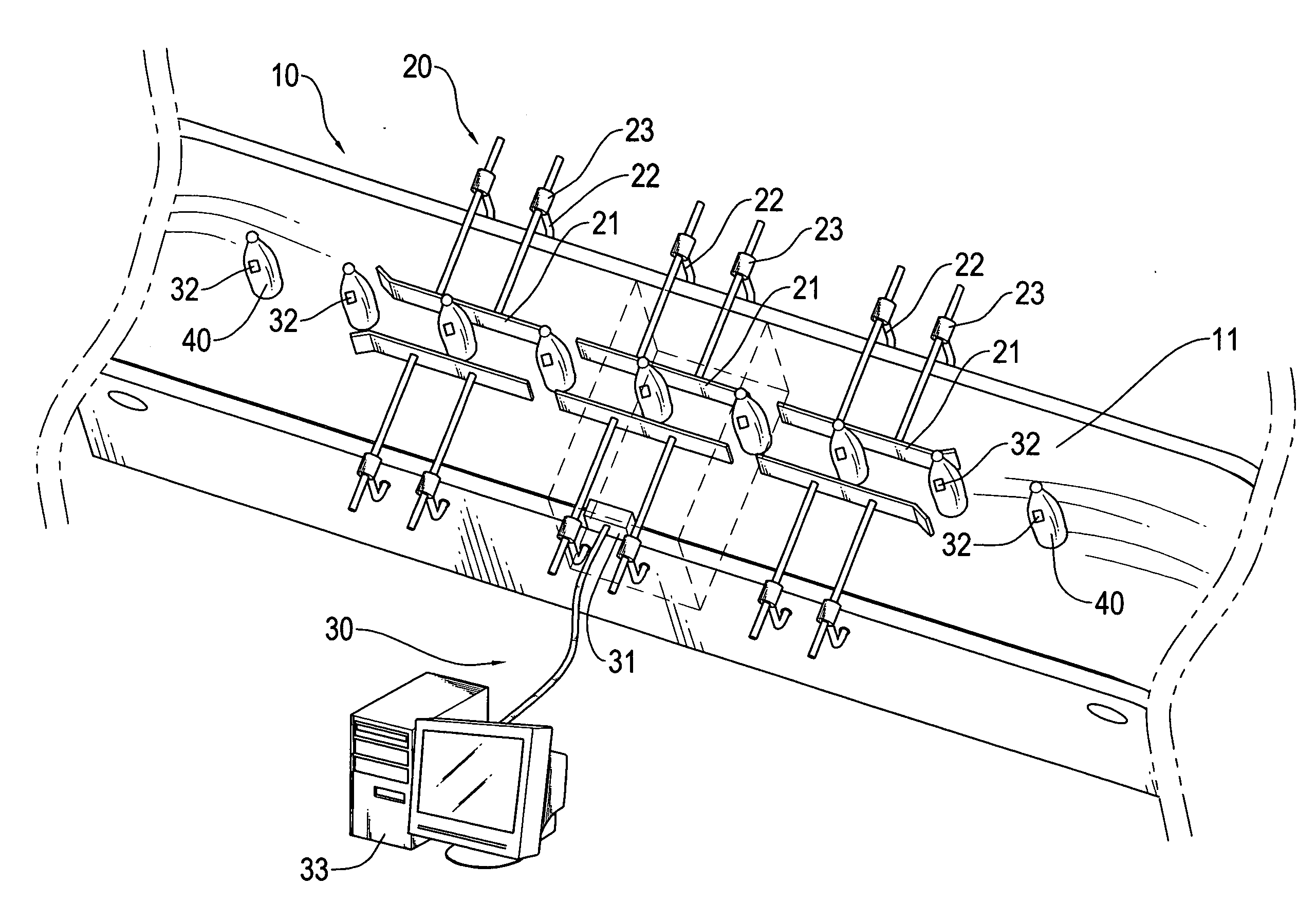

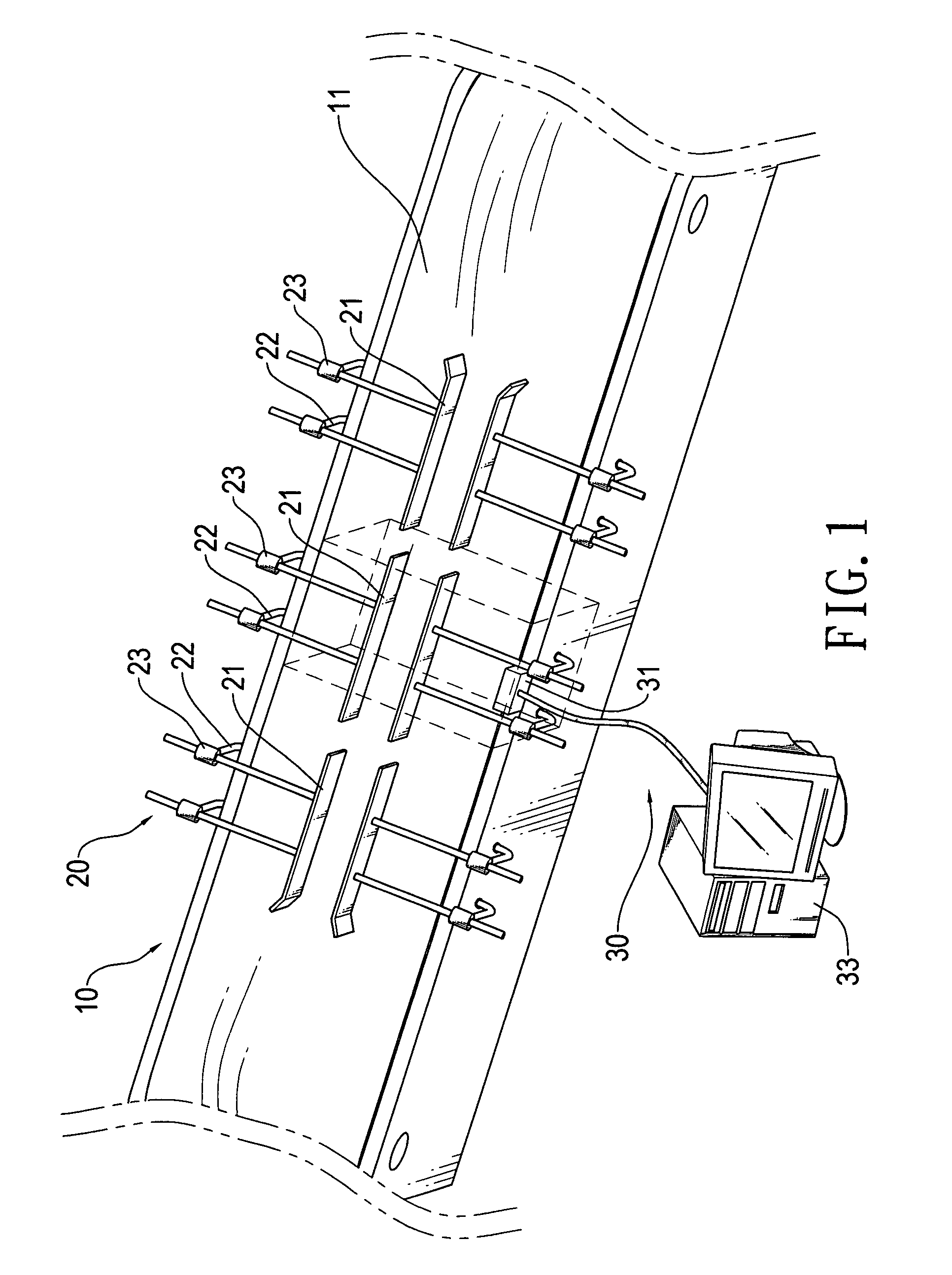

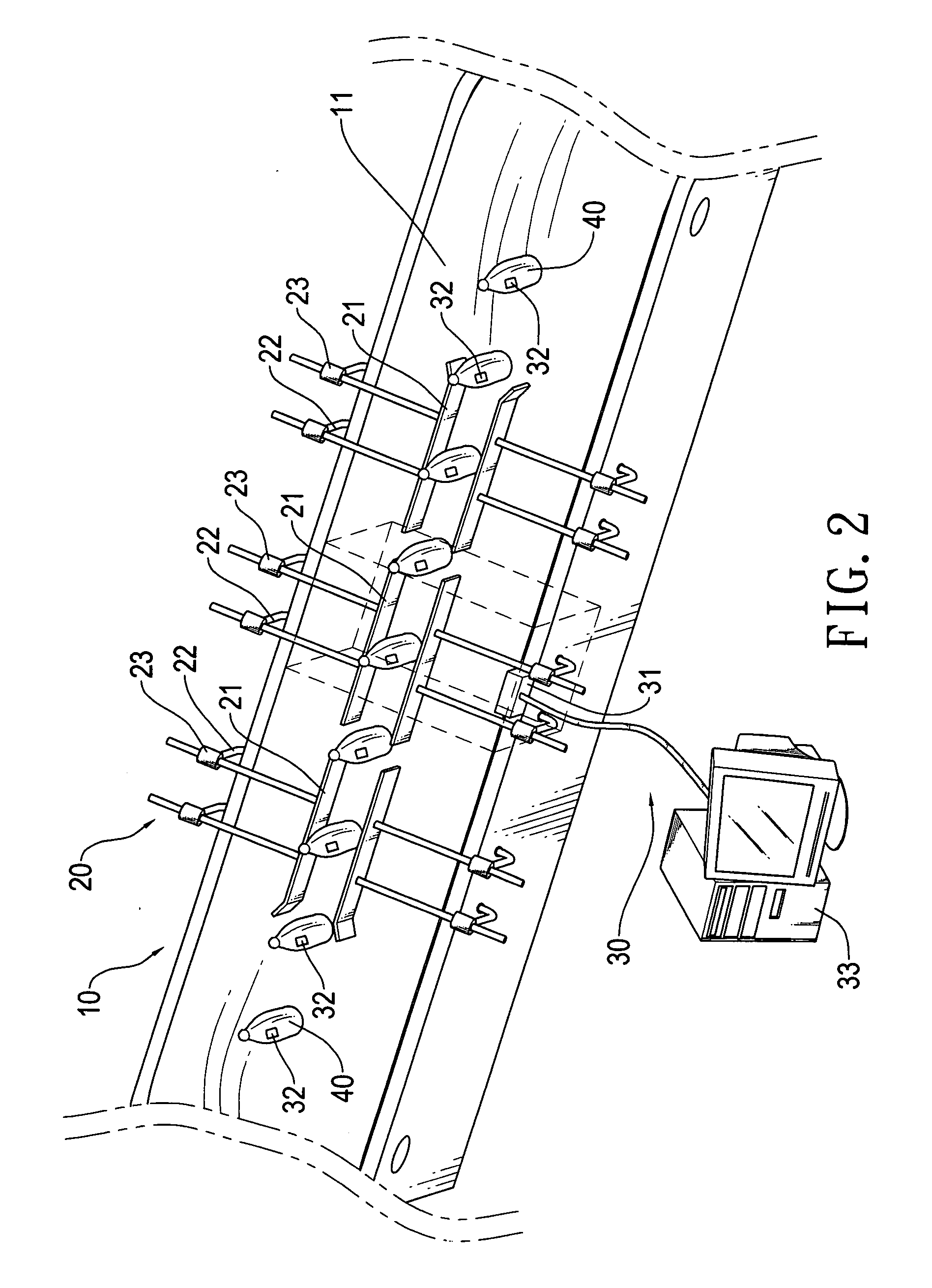

Electronic tag testing device and method

InactiveUS20080265031A1Good reproducibilityHigh-frequency performanceConveying record carriersSensing record carriersEngineeringUltimate tensile strength

An electronic tag testing device and method includes a feeding mechanism, a retaining mechanism and an R / W system. The feeding mechanism has a belt conveyer, the retaining mechanism has moving-guiding boards, guiding board-fixing bases and guiding board-adjusters, wherein one end of the moving-guiding board is connected to the guiding board-adjuster for adjusting the position of the moving-guiding board, one end of the guiding board-adjuster is connected to the guiding board-fixing base, the guiding board-fixing base is fixed under the belt conveyer for fixing the moving-guiding board, and the moving-guiding board is mounted on the belt conveyer of the feeding mechanism, and the R / W system includes a reader and an electronic tag, wherein the electronic tag is attached to an object to be measured, the reader is mounted on the conveyer mechanism for reading the data radiated from the electronic tag, thereby a signal strength from the electronic tag as located at each portion on the outer surface of the object to be tested is detected to find a best attaching position for the electronic tag.

Owner:CHENG LOONG CORPORATION

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com