Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

95results about How to "Meet Timing Requirements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

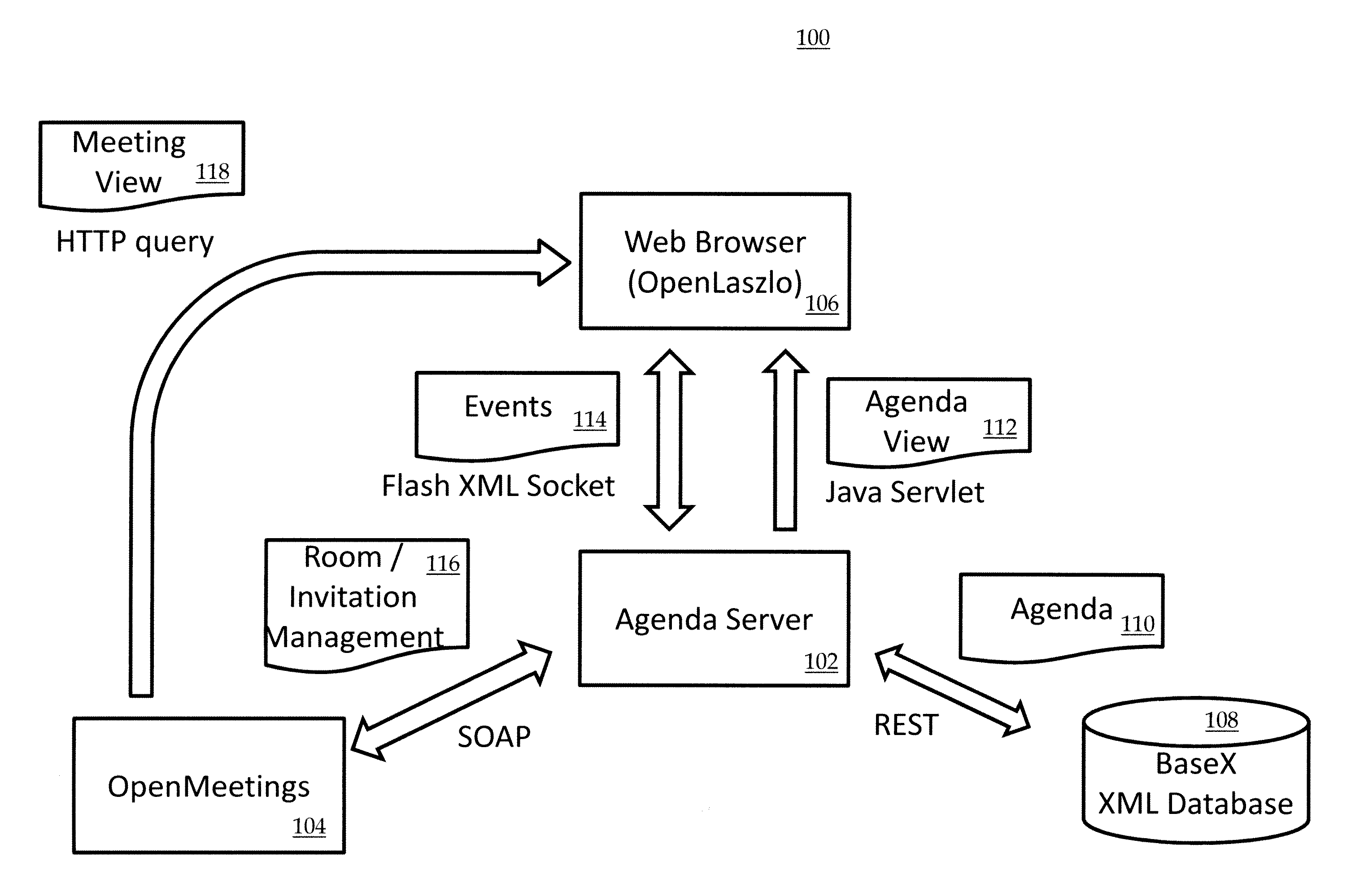

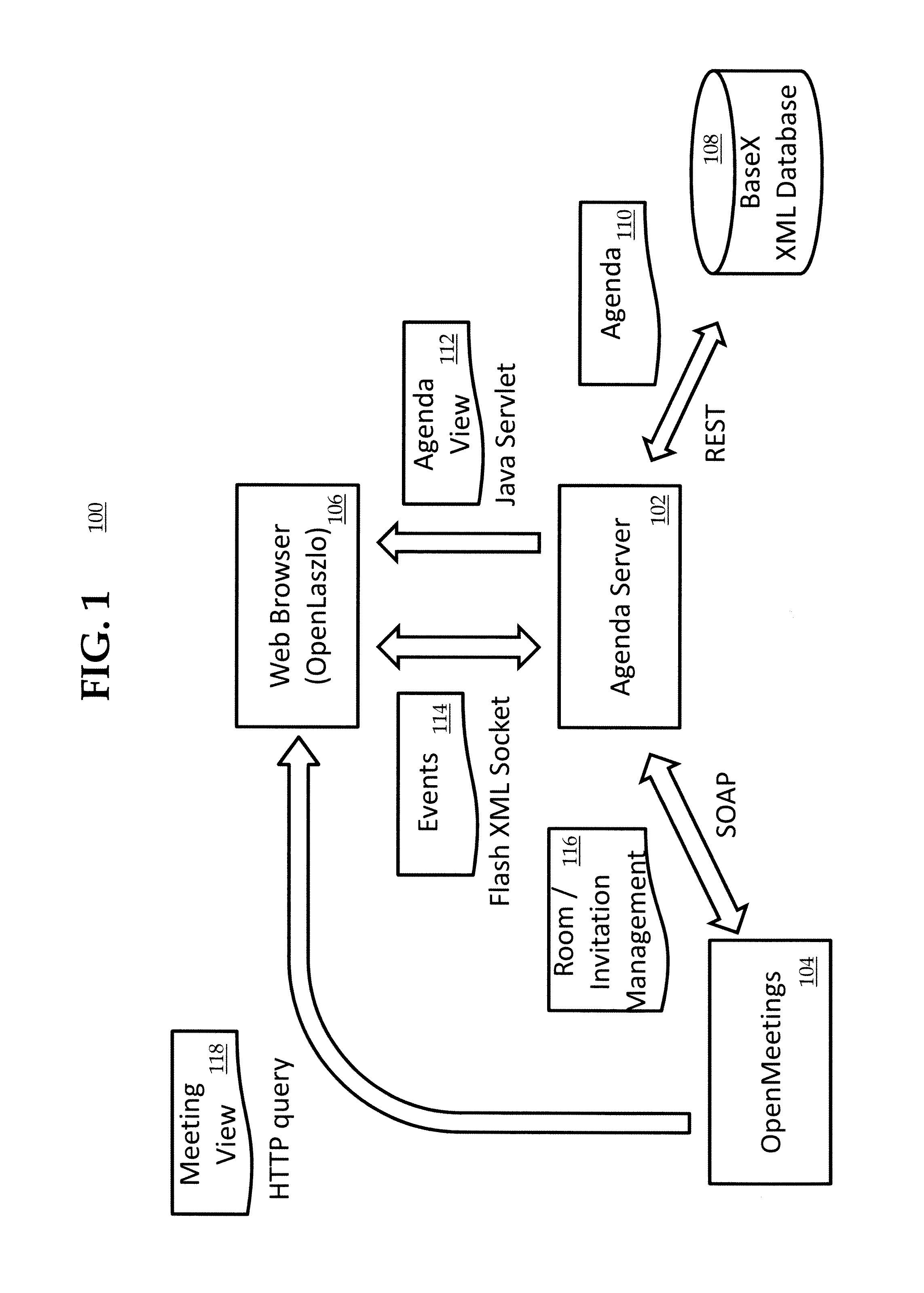

System and method for concurrent electronic conferences

ActiveUS20130254279A1Reduce probabilityEfficiently utilize timeTelevision conference systemsMultiple digital computer combinationsResource useDistributed computing

Method for scheduling and implementing an electronic meeting conducted among remotely-located users communicating with an agenda server, including: accepting a meeting agenda that includes a plurality of topics, a quorum, an identification of resources used by each topic, an identification of data used by each topic, and an identification of data produced by each topic; partitioning the meeting agenda into at least a first and second group of topics; searching for data dependencies between the first and second groups of topics; searching for resource dependencies between the first and second groups of topics; if data dependencies or resource dependencies are found between the first and second groups of topics, then repartitioning the meeting agenda until the data dependencies and resource dependencies between the first and second groups of topics are reduced below a predetermined dependency threshold; and concurrently scheduling and executing the first and second groups of topics.

Owner:AVAYA INC

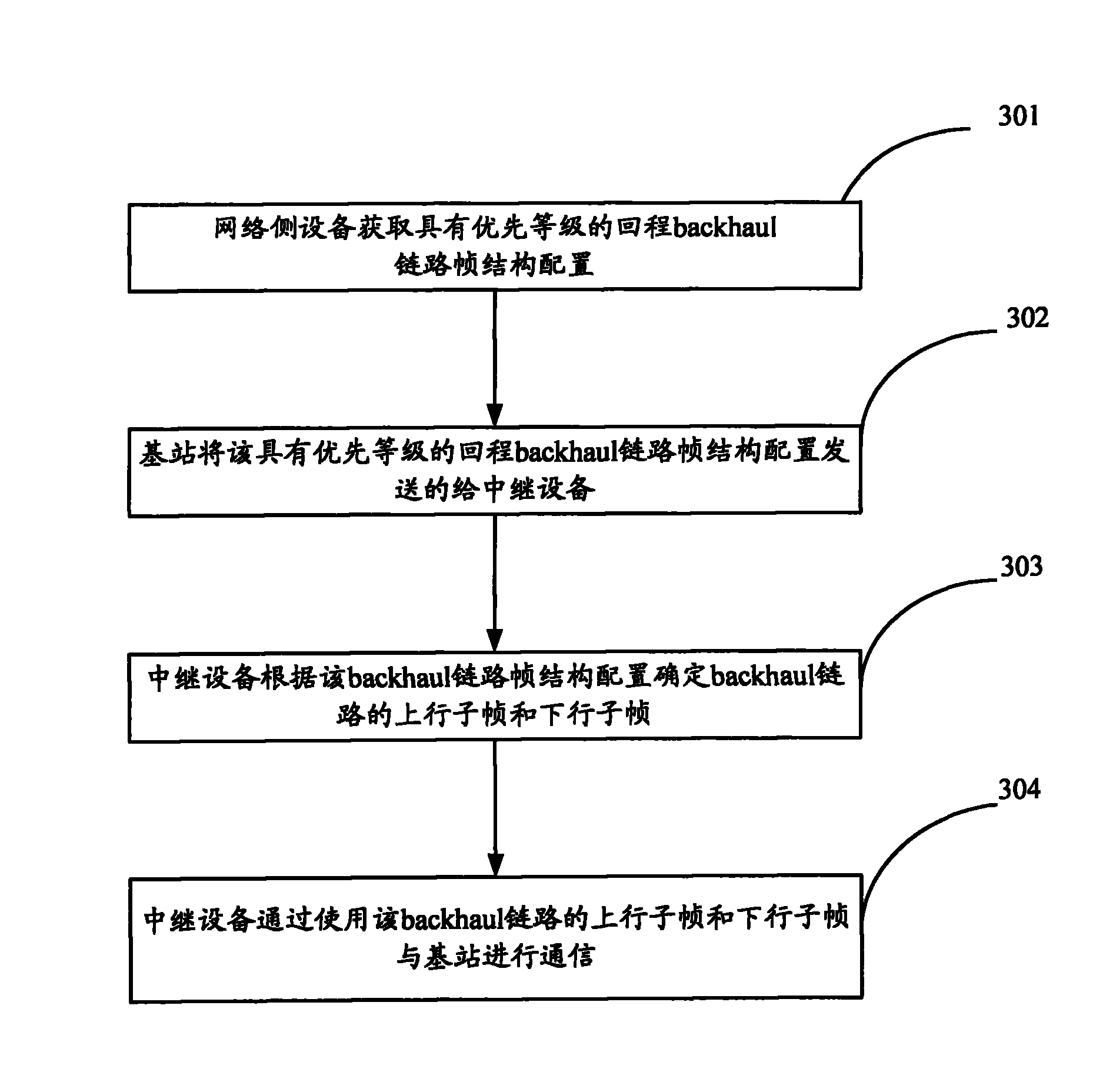

Method, equipment and system for configuring frame structure of backhaul link

The invention discloses a method for configuring the frame structure of a backhaul link, which comprises that: relay equipment receives the configuration, with priority, of the frame structure of the backhaul link from network side equipment; the relay equipment determines an uplink sub-frame and a downlink sub-frame of the backhaul link according to the configuration of the frame structure of the backhaul link; and the relay equipment communicates with the network side equipment by using the uplink sub-frame and the downlink sub-frame of the backhaul link. In the method, the frame structure of the backhaul link is configured according to the frame structure in an access link, so the influence of the frame structure of the backhaul link on the timing relationships of conventional hybrid auto repeat requests (HARQ) is minimized, the timing requirements of the conventional HARQ are met and different frame structures of the backhaul link can be selected according to application needs.

Owner:DATANG MOBILE COMM EQUIP CO LTD

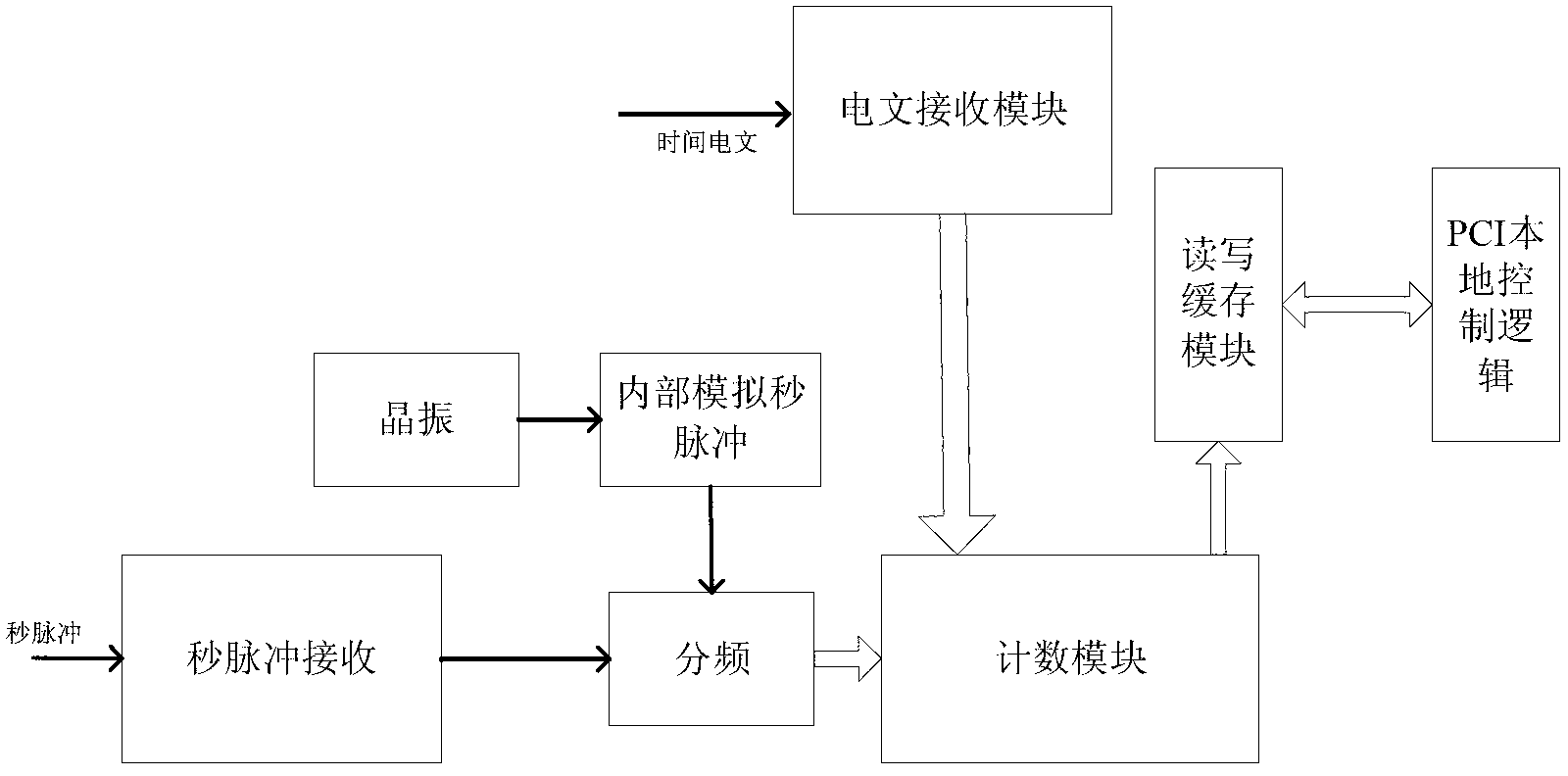

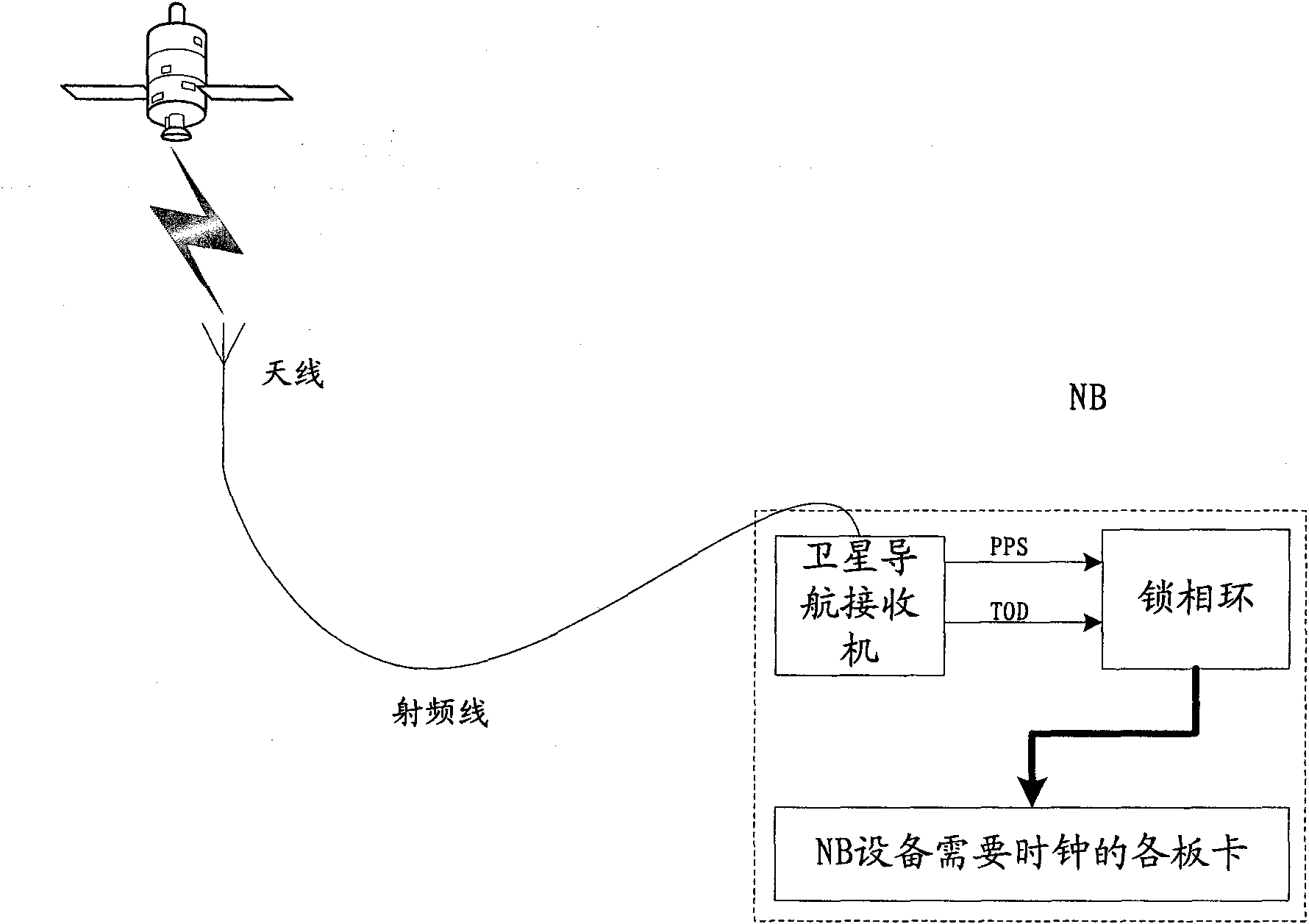

High-precision GPS (global position system) distributive time-service method based on ping-pong buffer and message mechanism

InactiveCN103076737AAchieving Clock SynchronizationDoes not affect time synchronization accuracyTime-division multiplexRadio-controlled time-piecesVIT signalsSatellite

The invention provides a high-precision GPS (global position system) distributive time-service method based on ping-pong buffer and a message mechanism. Clock synchronization among special equipment in a space remote control system is realized by a precise clock synchronization policy of hardware on time; and a GPS satellite synchronous clock serves as a clock source, and the time of each piece of special equipment is checked periodically by second pulse. Time information processing operation is completely finished in an FPGA (Field Programmable Gate Array), so that the time synchronization precision of the special equipment is not affected and the normal work of application programs of the special equipment is not intervened. A time-service time source also supports an IRIG-B (Inter Range Instrumentation Group) code time service, wherein the time frame speed of an IRIG-B type code is 1 frame / second, and 100-bit information can be transmitted. After a B type code is decoded, a 1c / s pulse signal, a 10c / s pulse signal, a 100c / s pulse signal. a 1,000c / s pulse signal, BCD (Binary-Coded Decimal) encoding time information and control function information can be acquired, and the synchronization precision can be up to dozens of nanosecond.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

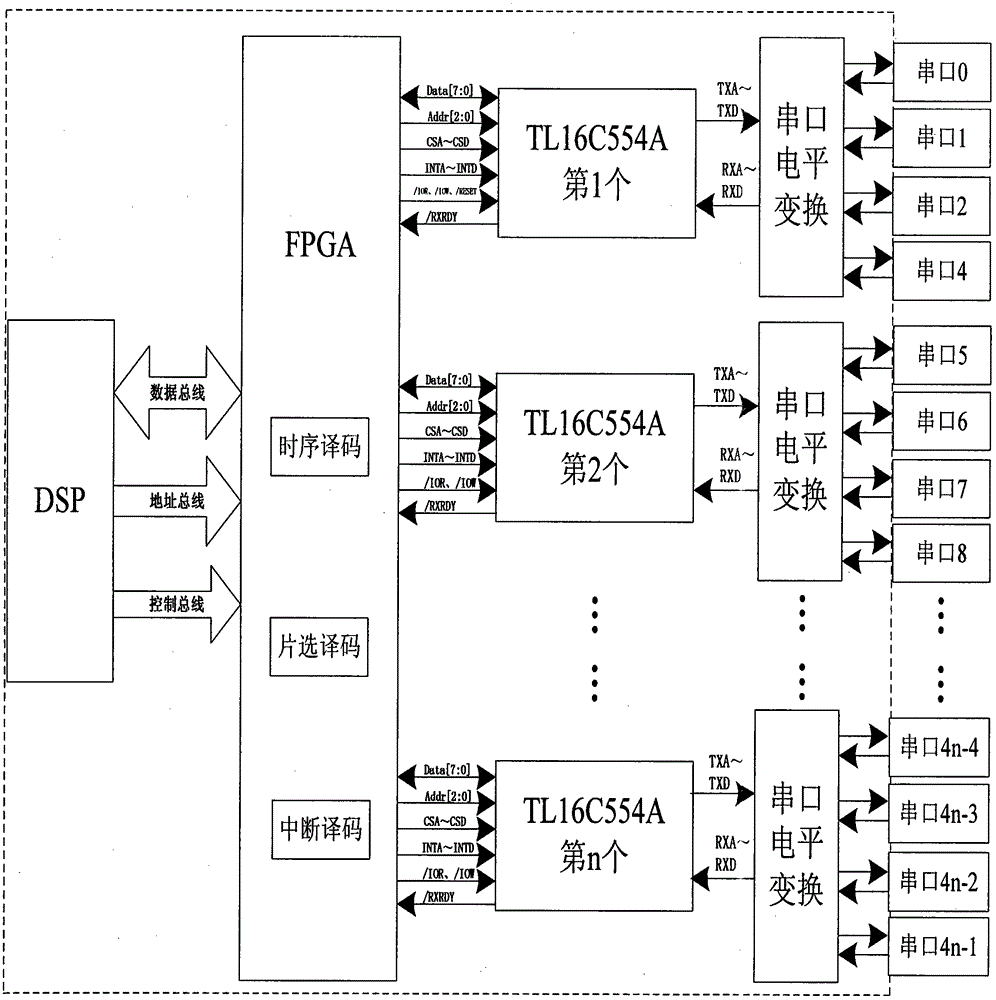

Multi-serial port extension method based on FPGA and TL16C554A

ActiveCN104866452AMeet Timing RequirementsThe number of extended serial ports can be changed flexiblyElectric digital data processingAsynchronous serial communicationManagement unit

Owner:哈尔滨工业大学(鞍山)工业技术研究院

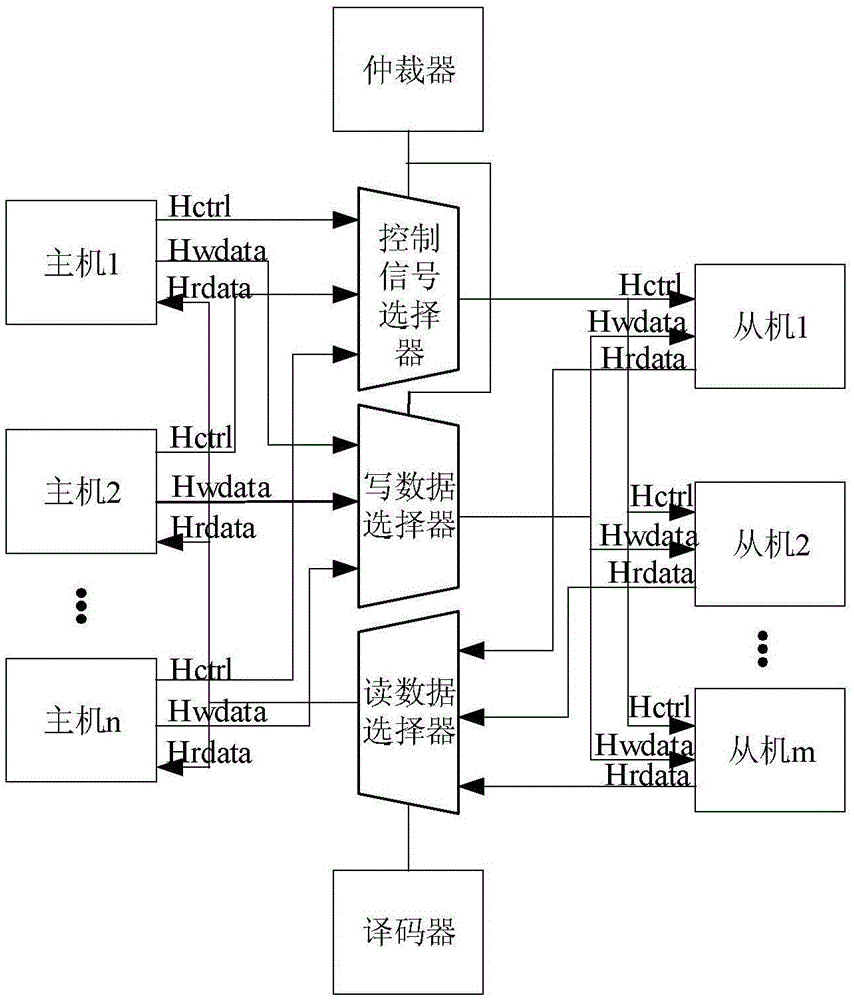

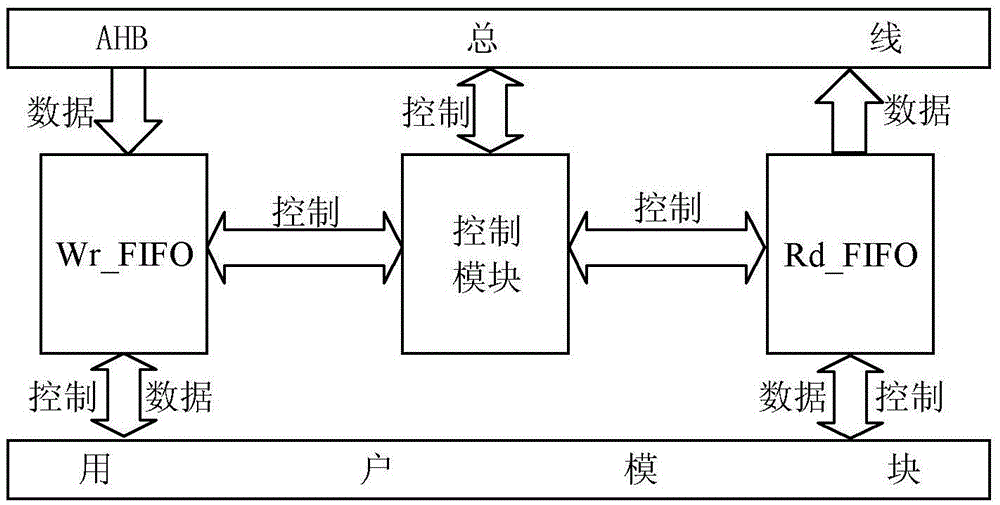

AHB interface system for stream data transmission

InactiveCN105573951AMeet Timing RequirementsVersatilityElectric digital data processingData streamBurst transmission

Aiming to solve the problem that an IP module cannot be matched with an on-chip bus of an SOC (System On Chip) because current methods cannot provide a universal interface, the invention provides an AHB interface system for stream data transmission. The AHB interface system for stream data transmission comprises a master control module, a register set module, a decoding control module, an abnormality detection module, a burst transmission monitoring module, an early termination judgment module, a block transmission processing module, an Rd_FIFO module (read FIFO module) and a Wr_FIFO module (write FIFO module) . The AHB interface system for stream data transmission is applied to the field of integrated circuits.

Owner:HARBIN UNIV OF SCI & TECH

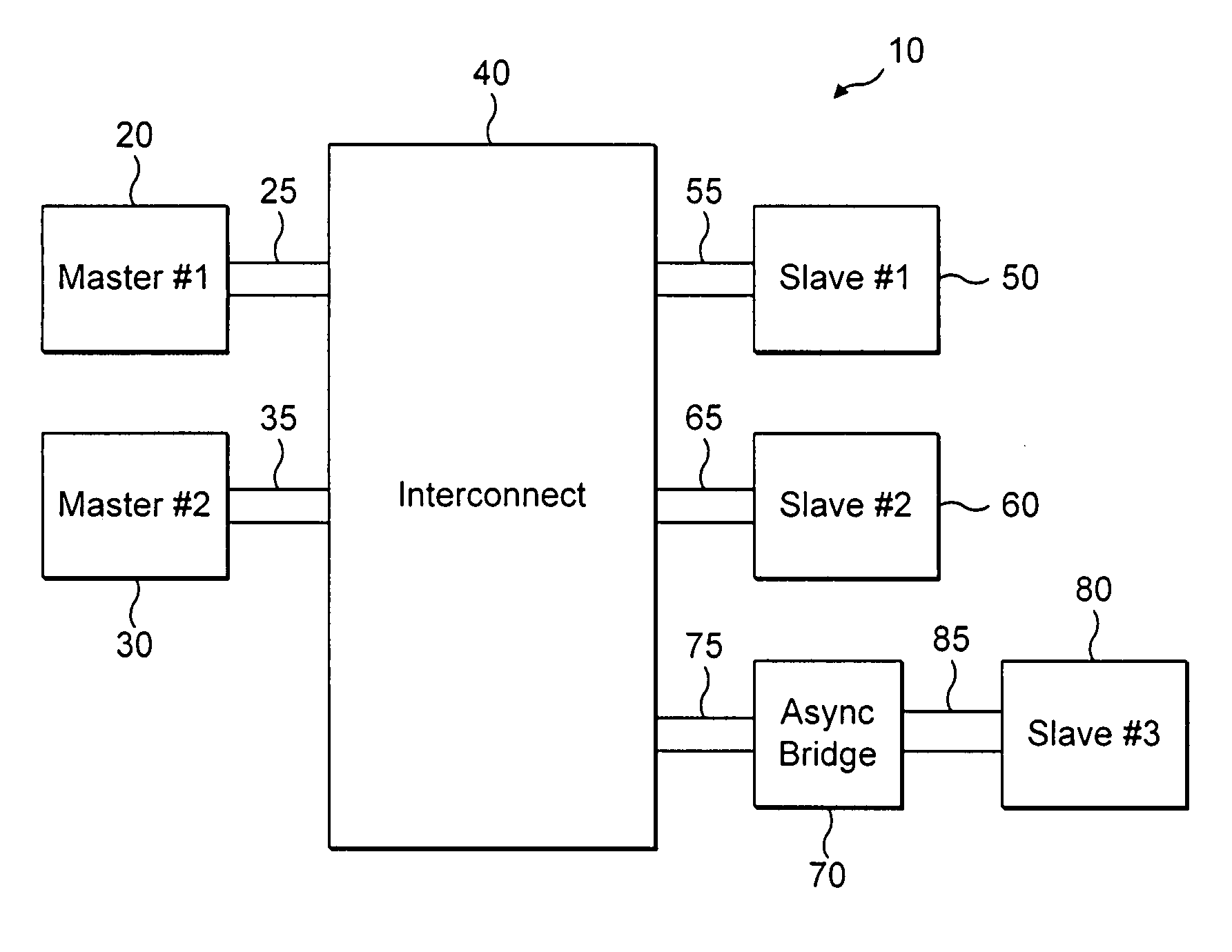

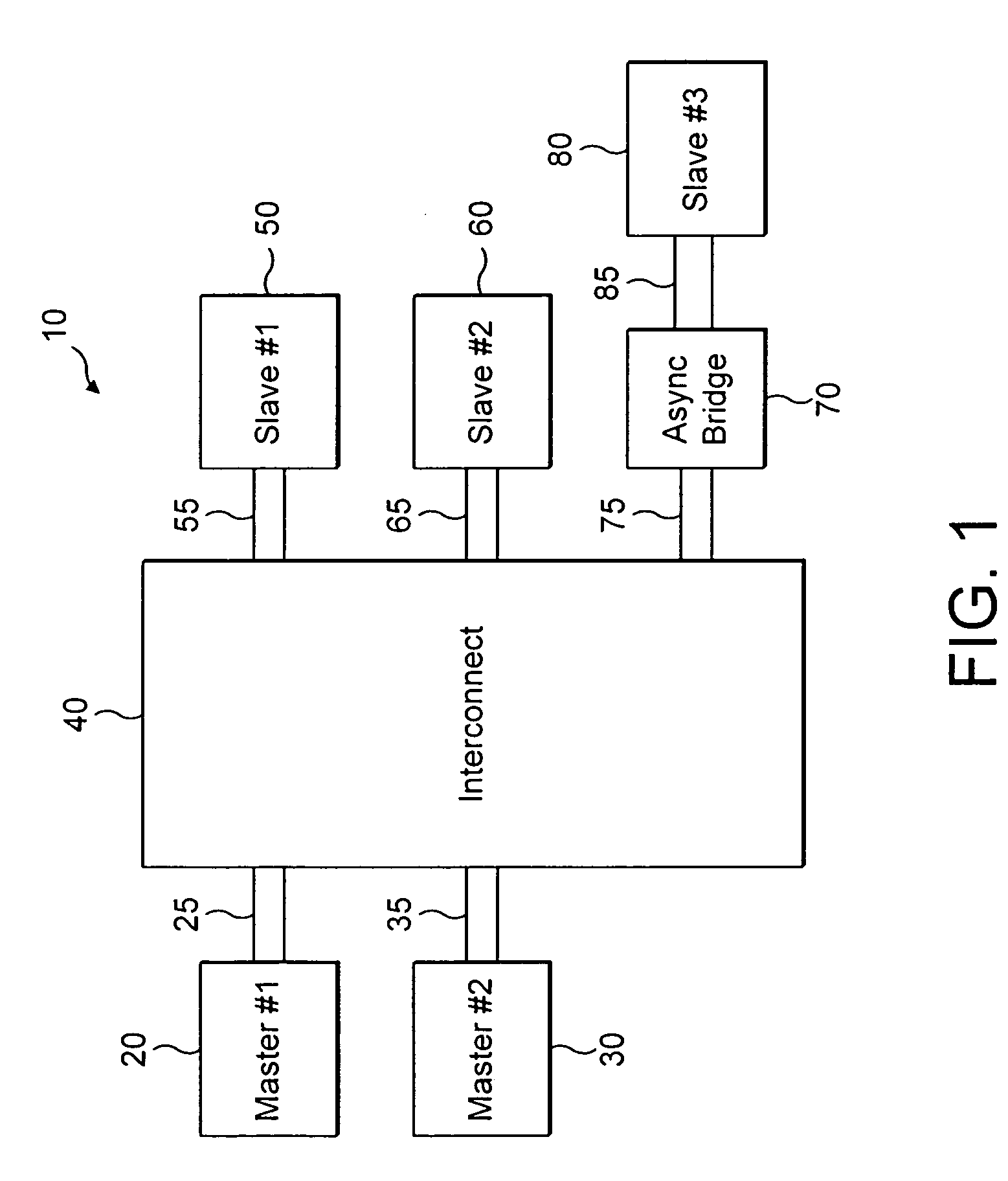

Handling of write transactions in a data processing apparatus

ActiveUS20050273536A1Reduce complexityAvoid the needInput/output processes for data processingEmbedded systemData processing

A data processing apparatus and method of handling write transactions in such an apparatus is provided. The apparatus has a plurality of devices, and bus circuitry providing connection paths between the plurality of devices. At least one of the devices has a bus master interface operable to generate write transactions for output via the bus circuitry, whilst at least one of the devices has a bus slave interface operable to receive the write transactions from the bus circuitry. A write transaction includes transferring a write address from a bus master interface to a bus slave interface and separately transferring write data from the bus master interface to the bus slave interface. In accordance with embodiments of the present invention, the bus master interface is allowed to generate a write transaction such that the write data is received at the bus slave interface before the associated write address. This leads to a significant decrease in the complexity of the apparatus.

Owner:ARM LTD

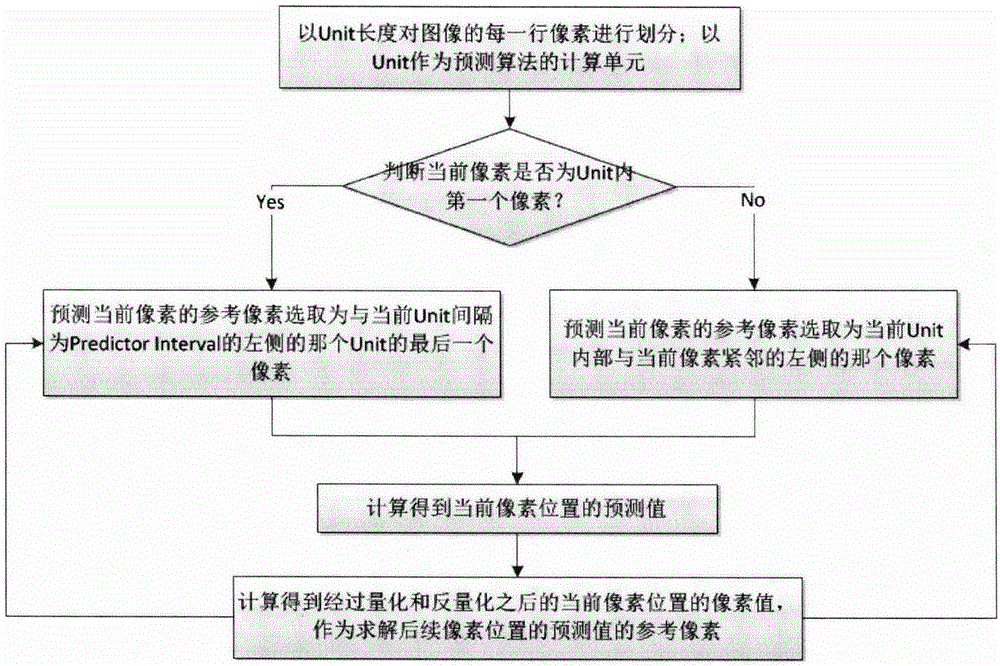

Real-time digital image compression prediction method and system

ActiveCN105208394AMeet Design ComplexityReduce Design ComplexityDigital video signal modificationImage resolutionPrediction interval

The invention discloses a real-time digital image compression prediction method, facilitating realization of a digital circuit and capable of performing time sequence optimization, based on prediction. Based on the prediction method, according to the image resolution, realization difficulty of the digital circuit and trade-off of compression efficiency, numerical values of a group of unit and prediction interval are selected. Higher is the image resolution, higher is the requirement for a time sequence of the digital circuit, at the moment, and the numerical values of the unit and prediction interval can be appropriately increased; according to the values of the selected unit and prediction interval and the position of the unit where a current pixel is located, corresponding reference pixels are selected for calculating the prediction value of the current pixel. By the adoption of the prediction method, the requirement for the time sequence of the digital circuit in a chip can be lowered, high practical value is achieved, and the method is expected to be applied to integrated circuits needing real-time video stream compression and decompression.

Owner:CHIPONE TECH BEIJINGCO LTD

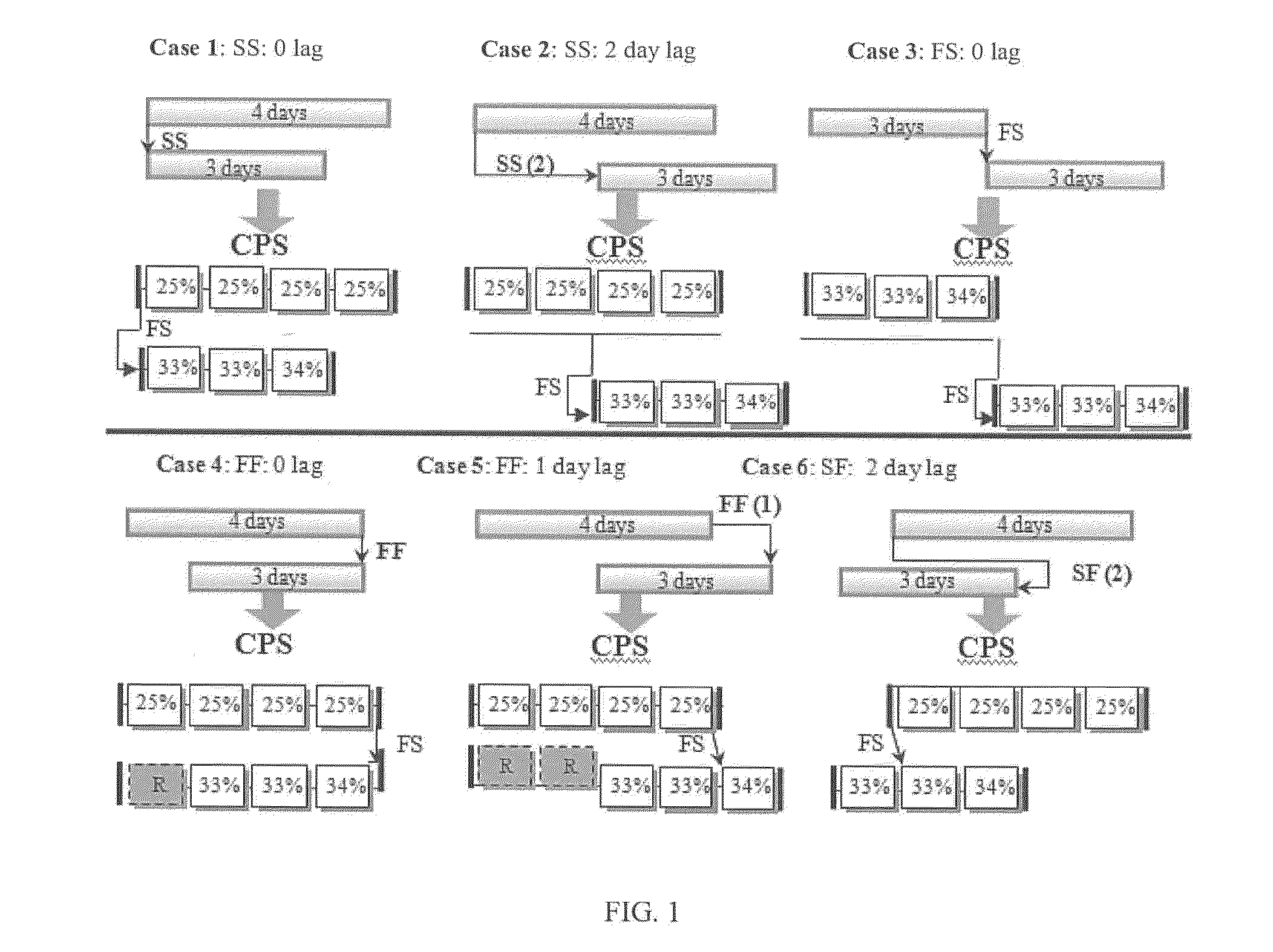

Method for critical path scheduling of activity time segments

A project management scheduling method applies critical path scheduling to separate the duration of each activity of the project into a group of segmented time segments attached to each other. The computer implemented method converts all activity relationships into finish-to-start between time segments without lead or lag times and corrects float and critical path calculations. Additional time segments representing daily events having either a positive or negative effect on time segment duration can be inputted and the project schedule adjusted accordingly. The method can also be employed in the conversion of existing critical path method scheduling systems.

Owner:HEGAZI TAREK MOHAMED MOHAMED

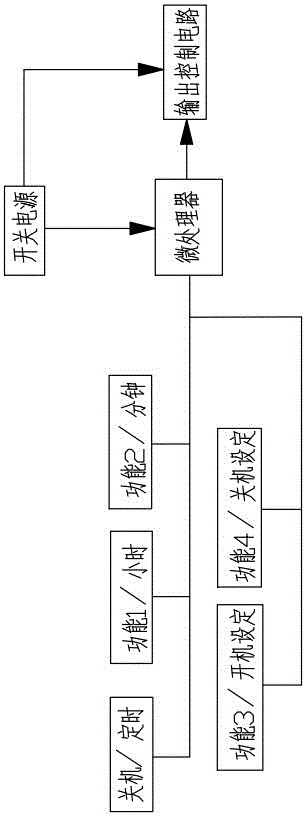

Method for setting fixed-time power on and off of electrical appliance device with microprocessor

InactiveCN102722114ASimple structureAccurate settingProgramme control in sequence/logic controllersReal-time clockTime switch

The invention discloses a method for setting fixed-time power on and off of an electrical appliance device with a microprocessor, which is suitable for a device with the microprocessor. An applied device comprises a key control circuit, a switch power supply, the microprocessor and an output control circuit, wherein the key control circuit comprises a power off key and four function keys. The method comprises the following steps of: (1) powering on the microprocessor; (2) switching the functions of keys; (3) setting multi-period timing; and (4) determining whether the timing setting is completed or not, and timing by a system; and presetting a circulation time T1 by the system. According to the method disclosed by the invention, the setting for the fixed-time power on and off in multiple periods can be carried out, the keys are not added, and a display screen and a real-time clock circuit are not needed.

Owner:宁波毕士达智能洁具有限公司

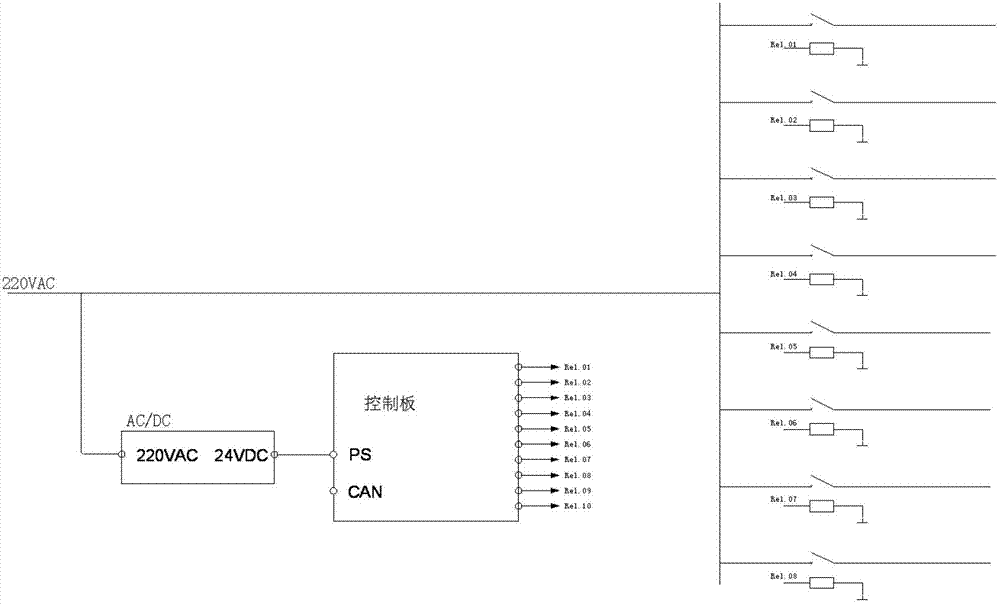

An intelligent power distribution timing sequence device based on self diagnosis

ActiveCN103592855APrecise positioningIntelligent fastProgramme control in sequence/logic controllersEffective solutionElectricity

The invention relates to an intelligent power distribution timing sequence device based on self diagnosis. After the timing sequence device is powered up, 220V alternating current is converted by a power supply circuit into +5V power that can be accepted by a controller. After operates, the controller reads a parameter stored in a data storage circuit firstly and configures the CAN bus node address of the timing sequence device with a bus address configuration circuit. Then, a self-diagnosis circuit is powered up to execute self diagnosis. After a normal state is diagnosed, the timing sequence device enters a power distribution mode to query states. According to different power distribution timing sequence of different vehicle-mounted instrument devices, the power distribution mode and the power distribution timing sequence are stored through the data storage circuit. In the meantime, load voltage, current, and frequency which are acquired by a data acquiring circuit are uploaded to a host computer through a bus communication circuit in order to monitor the load voltage, current, and the frequency parameters in real time. The intelligent power distribution timing sequence device has advantages of fast response speed, a strong anti-interference capability, high signal acquiring precision, and good universality, and provides a new effective solution for unattended power distribution of multipath AC load.

Owner:BEIJING INST OF SPACE LAUNCH TECH +1

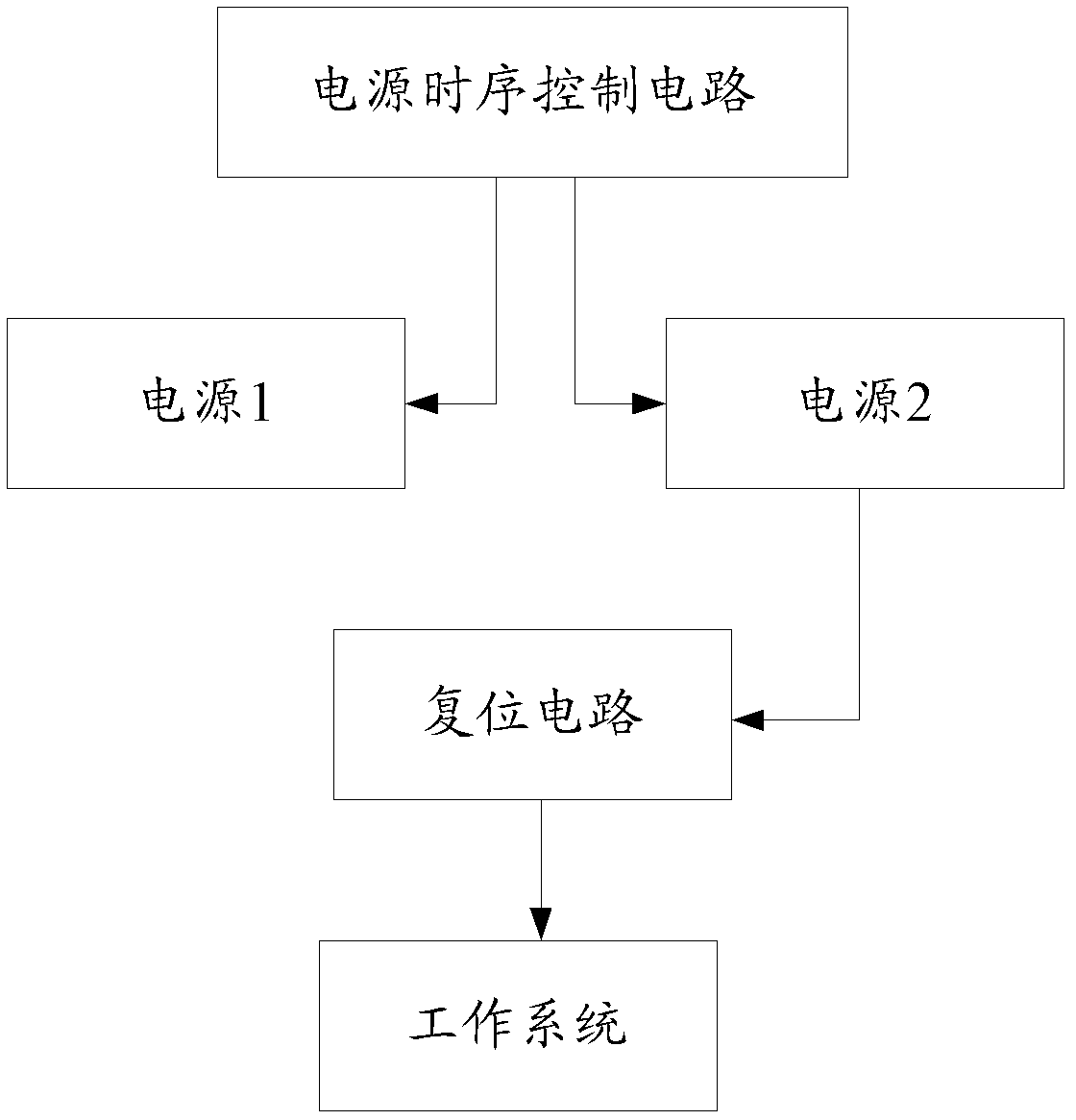

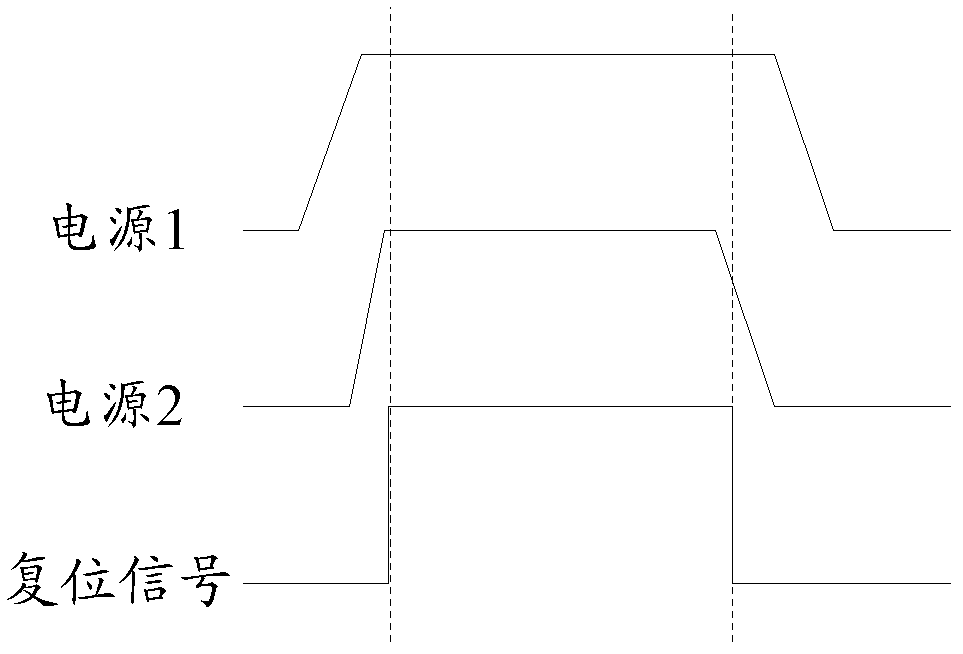

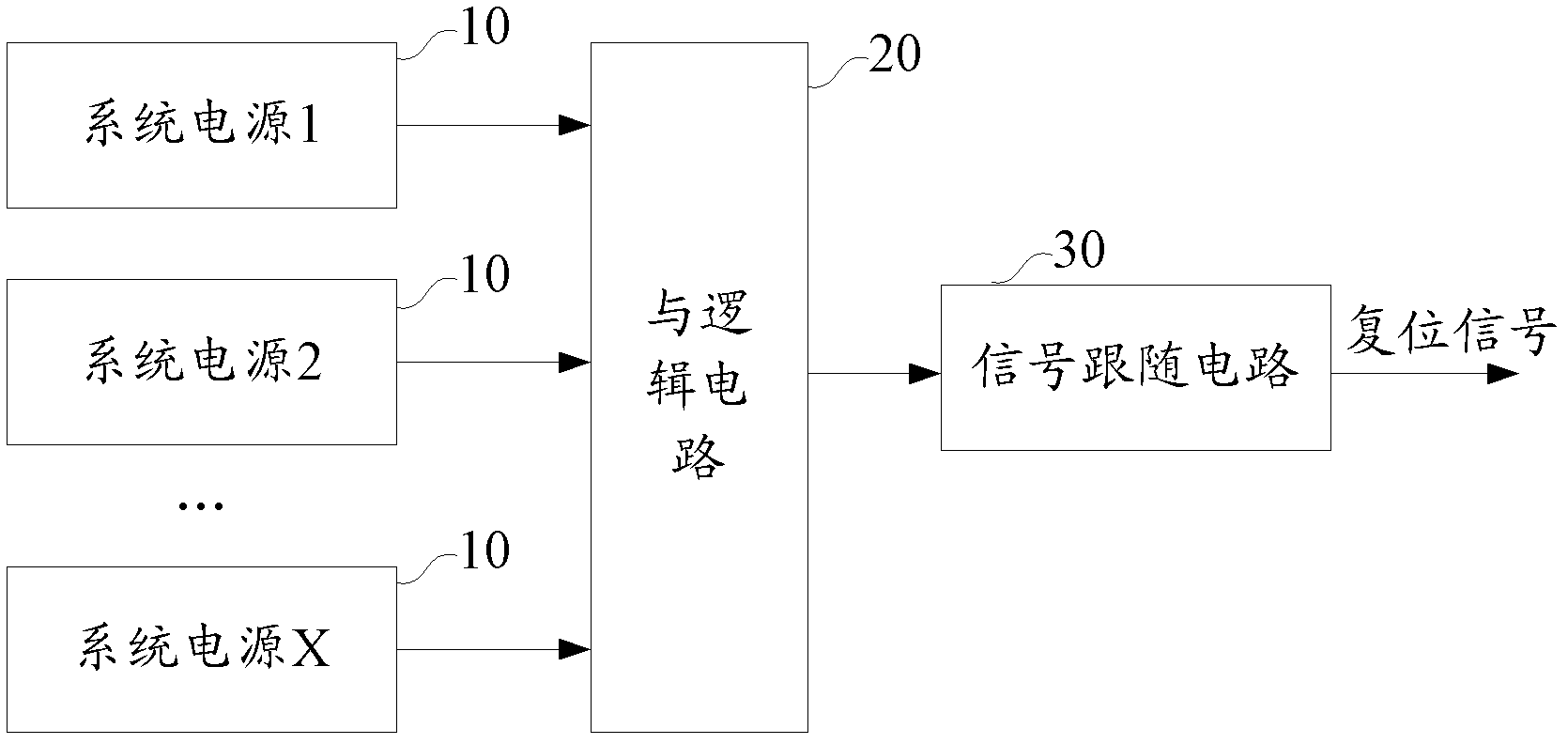

Reset circuit for multi-power-supply system

InactiveCN102522968ASimple designMeet Timing RequirementsElectronic switchingSequence controlControl system

The invention discloses a reset circuit for a multi-power-supply system, which comprises a logic circuit and a signal follower circuit connected with the logic circuit, wherein the multiple system power supplies of the multi-power-supply system are connected in parallel to the logic circuit. When voltage value output by any one of the multiple system power supplies is lower than a preset reset threshold voltage, the logic circuit generates an initial reset voltage signal and outputs the initial reset voltage signal to the signal follower circuit. The signal follower circuit performs voltage follower processing to the initial reset voltage signal so as to generate and output a reset signal. The reset circuit for the multi-power-supply system uses at least two system power supplies already existing in the multi-power-supply system for a reset work signal of the reset circuit, is capable of meeting the requirement for timing sequence of the reset signal in the multi-power-supply system, removes an existing timing sequence control circuit used for controlling the system power supplies, simplifies design of the reset circuit of the whole system, and meanwhile improves reliability of reset timing sequence of the reset signal provided by the system.

Owner:TCL TECH ELECTRONICS (HUIZHOU) CO LTD

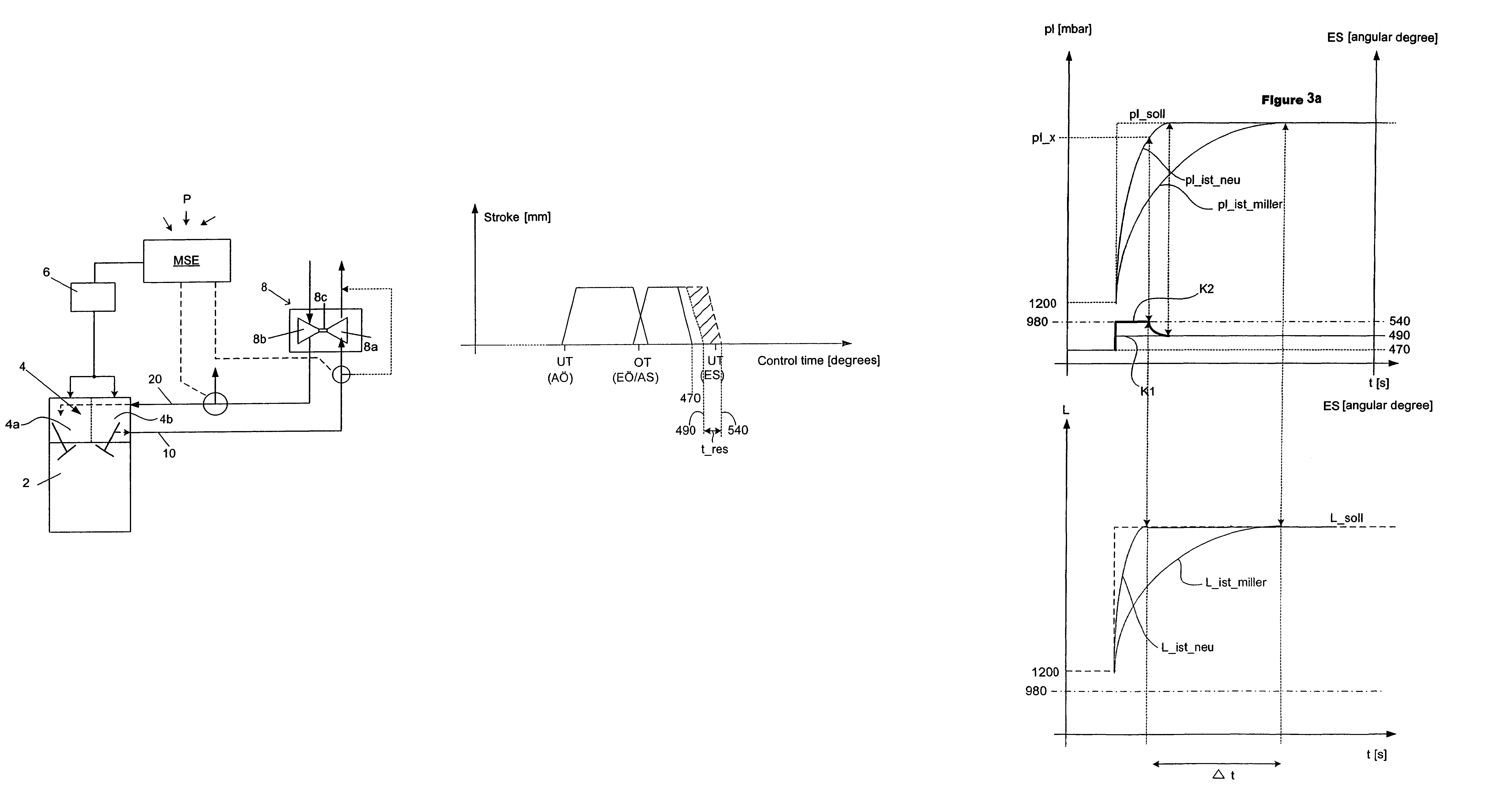

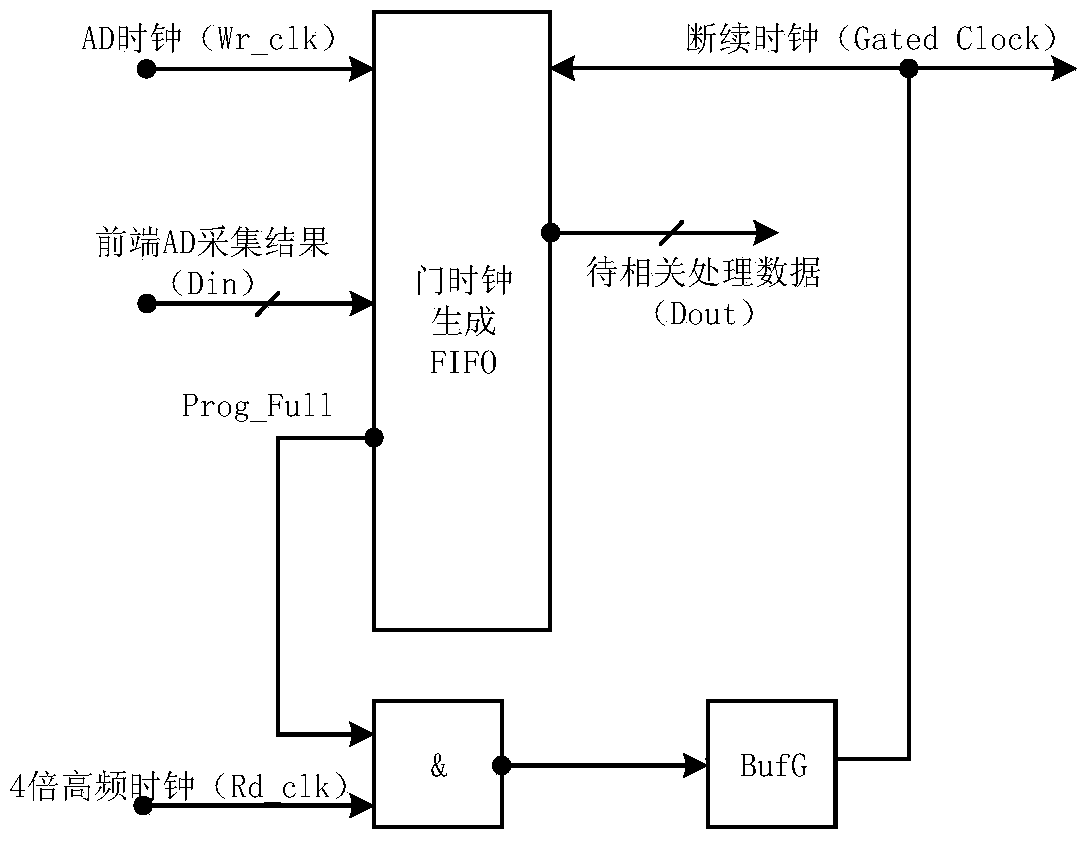

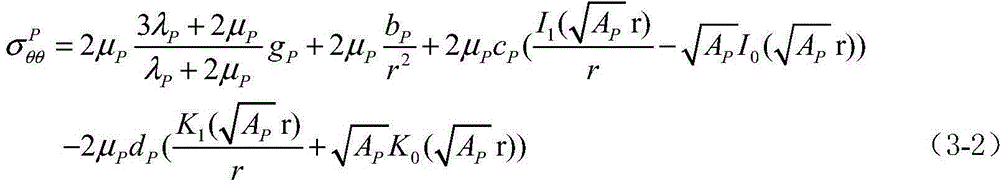

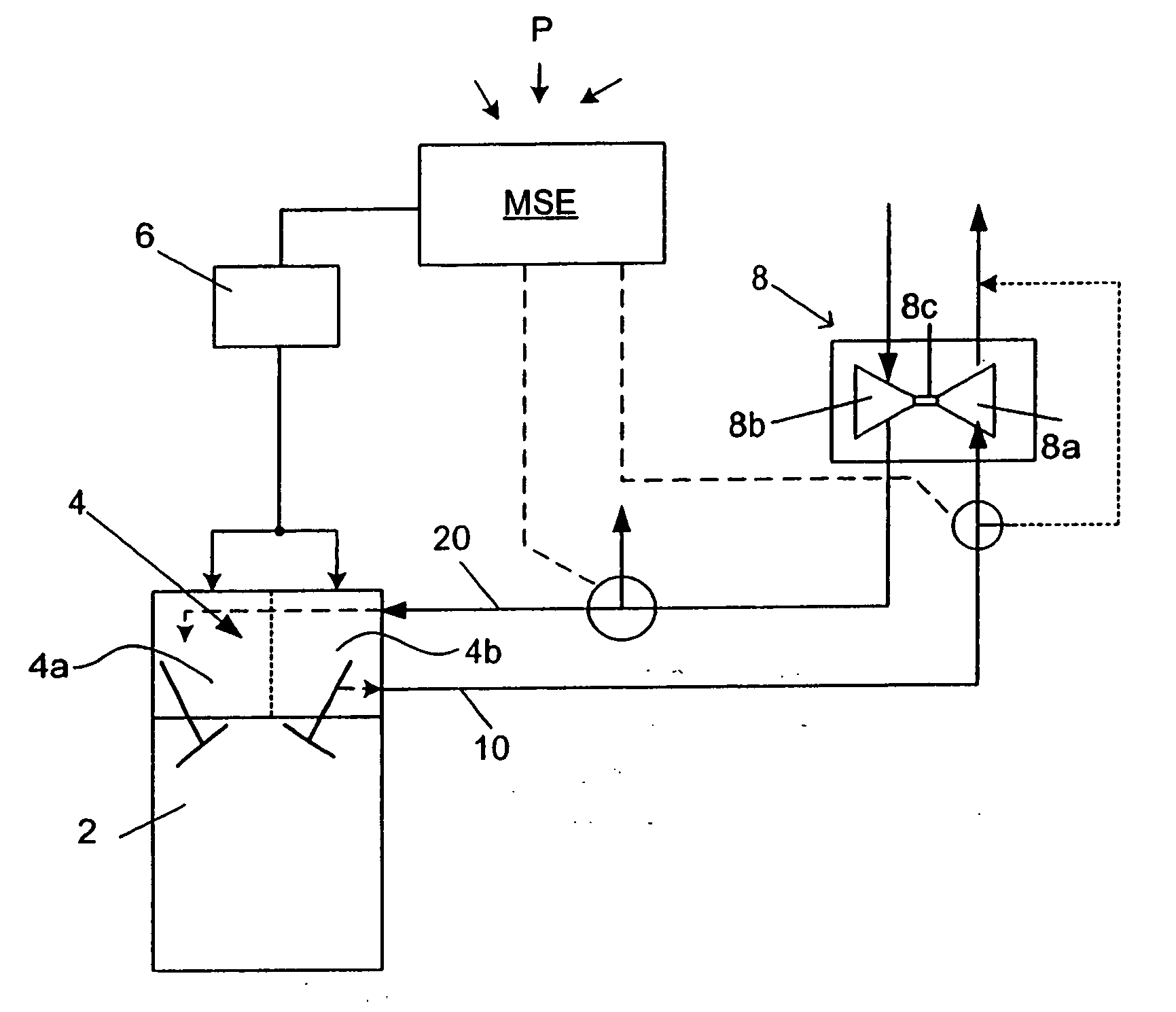

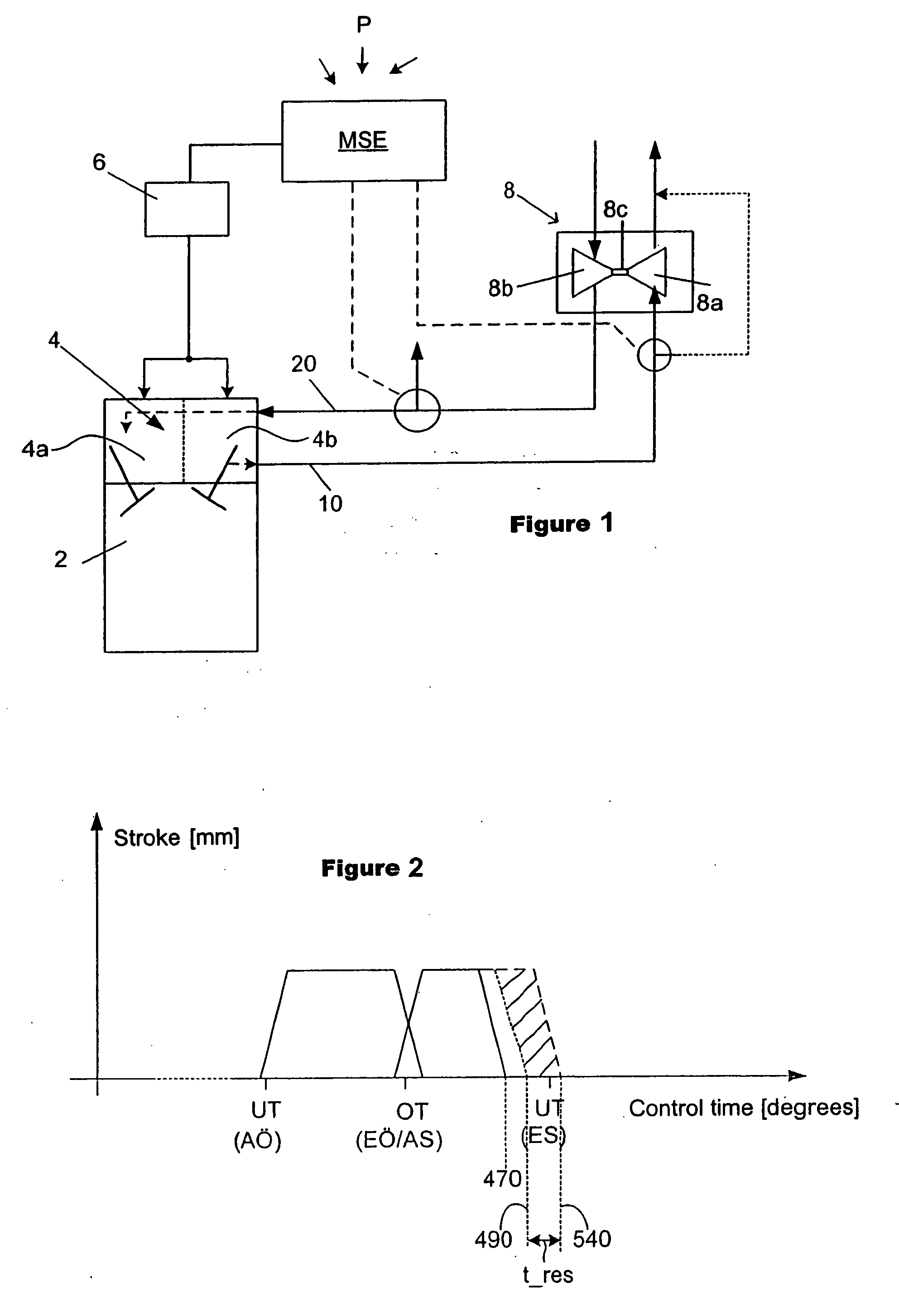

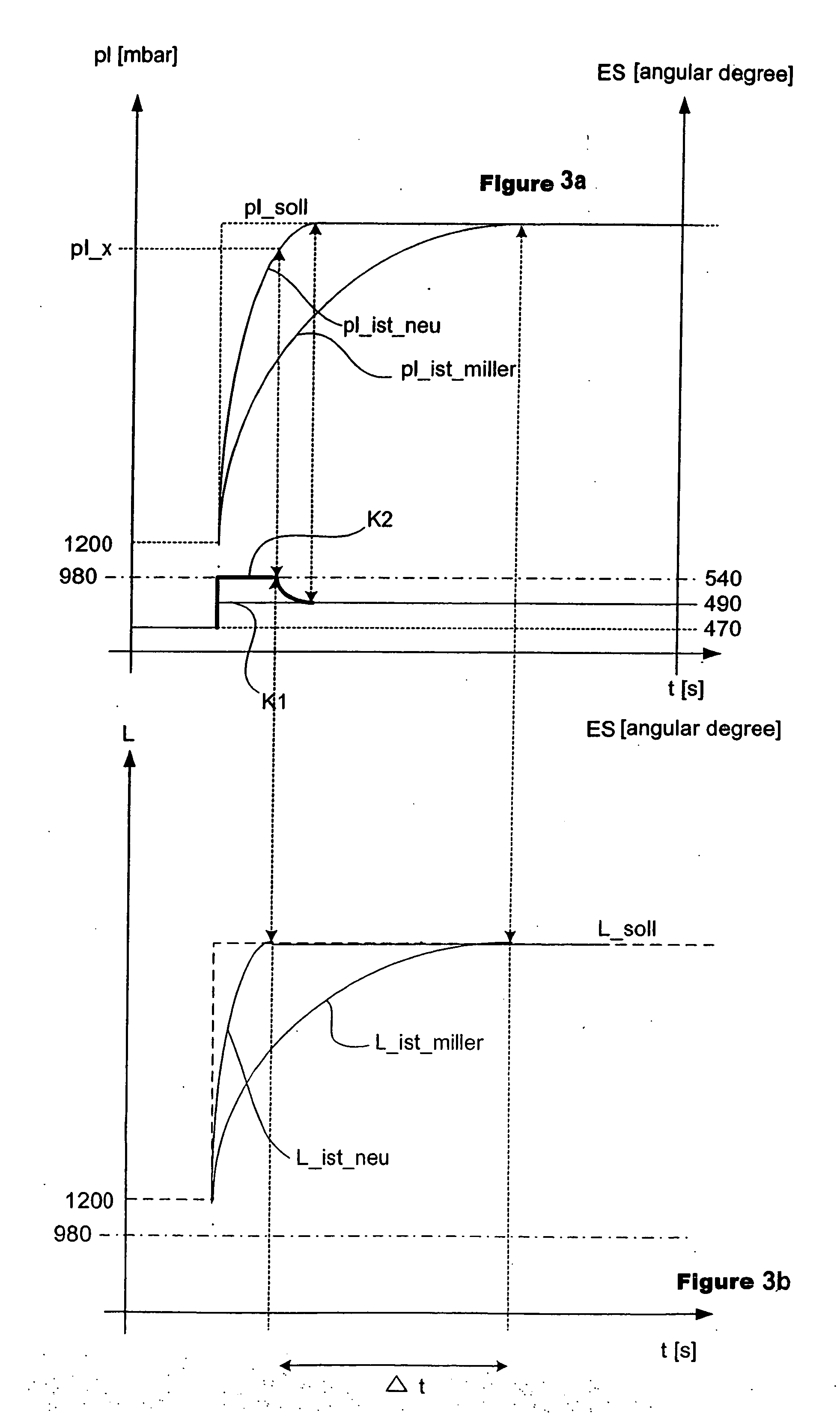

Method for operation of an internal combustion engine

ActiveUS7360514B2Improves non-steady-state response behaviorMeet Timing RequirementsValve arrangementsElectrical controlExternal combustion engineTurbocharger

A process for operating an internal combustion engine with a charging device such as a turbocharger and with an intake valve drive mechanism which is variable with respect to its intake valve control times and / or its intake valve stroke. Upon recognition of a positive charge requirement during the operation of the charging device, the at least one variable intake valve drive mechanism is driven in such a manner that an available stroke reserve and / or intake closure control time reserve is utilized to increase the charge amount introduced into an engine cylinder.

Owner:BAYERISCHE MOTOREN WERKE AG

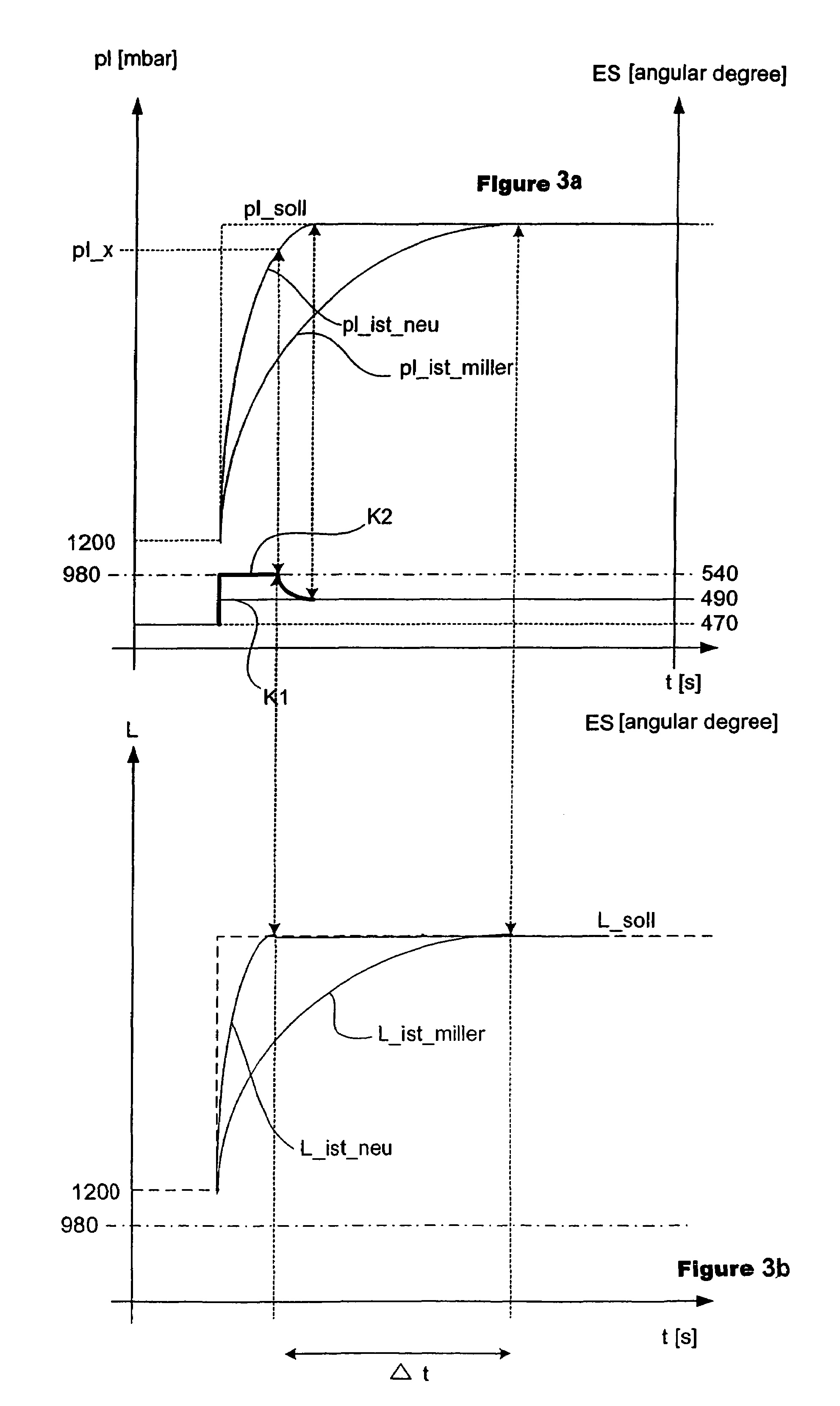

OLED driving power supply and electronic product

ActiveCN110880294ARealize the shapeRealize thinner and lighter shapeStatic indicating devicesMechanical engineeringElectric signal

The invention discloses an OLED driving power supply and an electronic product. The driving power supply comprises a main power supply board, a mainboard and an on-screen power supply board. Wherein the main power supply board is electrically connected with the mainboard and the on-screen power supply board. The main power supply board is used for outputting a first electric signal and a second electric signal to the on-screen power supply board according to the first enable signal sent by the mainboard; and the on-screen power panel is used for sequentially outputting a VDD electric signal and an EVDD electric signal according to the first electric signal and the second electric signal so as to lighten the OLED screen. A traditional power panel framework is changed into a split main powerpanel and on-screen power panel framework, so that the driving power supply is lighter and thinner on the basis of meeting strict time sequence control, and the lightening and thinning of the shape of an electronic product are facilitated.

Owner:SHENZHEN SKYWORTH RGB ELECTRONICS CO LTD

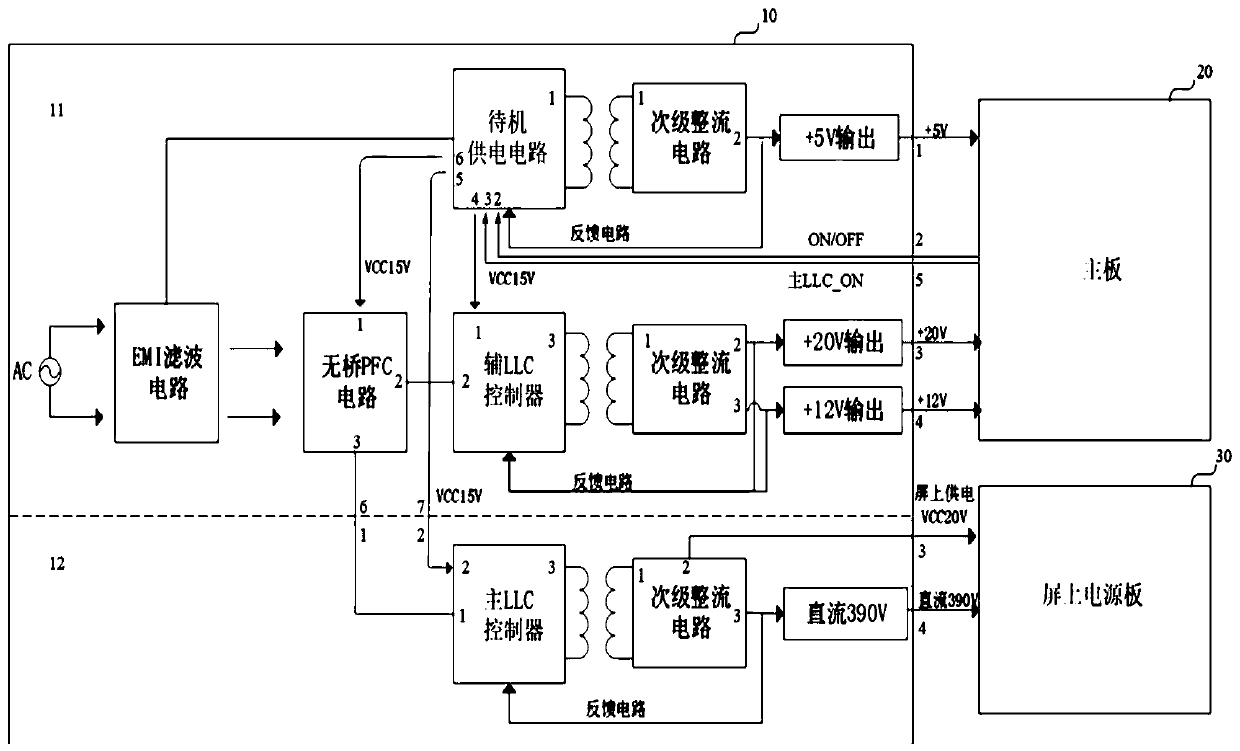

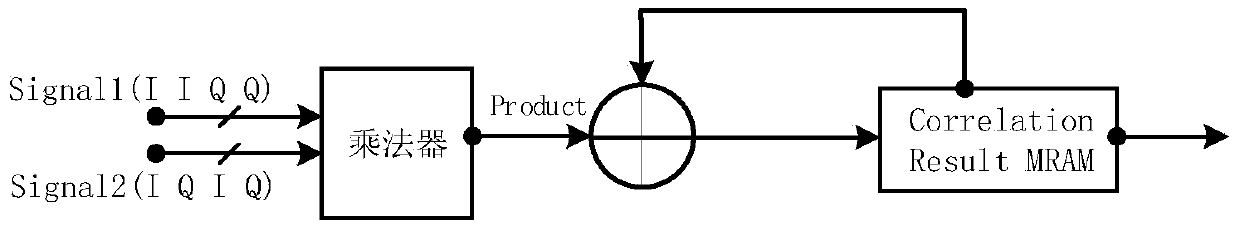

Multi-channel digital correlator in comprehensive aperture microwave remote sensing radiometer

InactiveCN103995255AReduce resource consumptionReduce complexityDirection finders using radio wavesRadio wave reradiation/reflectionData aggregatorRadiometer

The invention provides a multi-channel digital correlator in a comprehensive aperture microwave remote sensing radiometer. The multi-channel digital correlator is mainly formed by a gated clock generation unit, a delay distribution unit, a plurality of sedentary correlation units and a data aggregation unit which are connected in sequence. The gated clock generation unit enables FIFO full marking signals to be used as the enabled end and controls a high frequency clock Rd_clk which is four times of a low frequency clock Wr_clk on the radiometer to be connected and disconnected so that an interrupted clock can be formed, and the interrupted clock is used as a read clock of the FIFO and a processor clock of the delay distribution unit and the sedentary correlation units. The delay distribution unit conducts delay distribution on received signals of a plurality of channels and then transmits the signals to the sedentary correlation units. Preceding stage correlation units of the sedentary correlation units conduct time sharing and multi-correlation operation on the received signals, and backward stage correlation units of the sedentary correlation units conduct accumulation output on operation results of the preceding stage correlation units corresponding to the backward stage correlation units. The data aggregation unit is used for converting the parallel output correlation results of the sedentary correlation units into serial data flow output results.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

System and method for concurrent electronic conferences

ActiveUS9292814B2Improve subject matter schedulingEfficient use of timeSpecial service provision for substationTelevision conference systemsDistributed computingResource use

Method for scheduling and implementing an electronic meeting conducted among remotely-located users communicating with an agenda server, including: accepting a meeting agenda that includes a plurality of topics, a quorum, an identification of resources used by each topic, an identification of data used by each topic, and an identification of data produced by each topic; partitioning the meeting agenda into at least a first and second group of topics; searching for data dependencies between the first and second groups of topics; searching for resource dependencies between the first and second groups of topics; if data dependencies or resource dependencies are found between the first and second groups of topics, then repartitioning the meeting agenda until the data dependencies and resource dependencies between the first and second groups of topics are reduced below a predetermined dependency threshold; and concurrently scheduling and executing the first and second groups of topics.

Owner:AVAYA INC

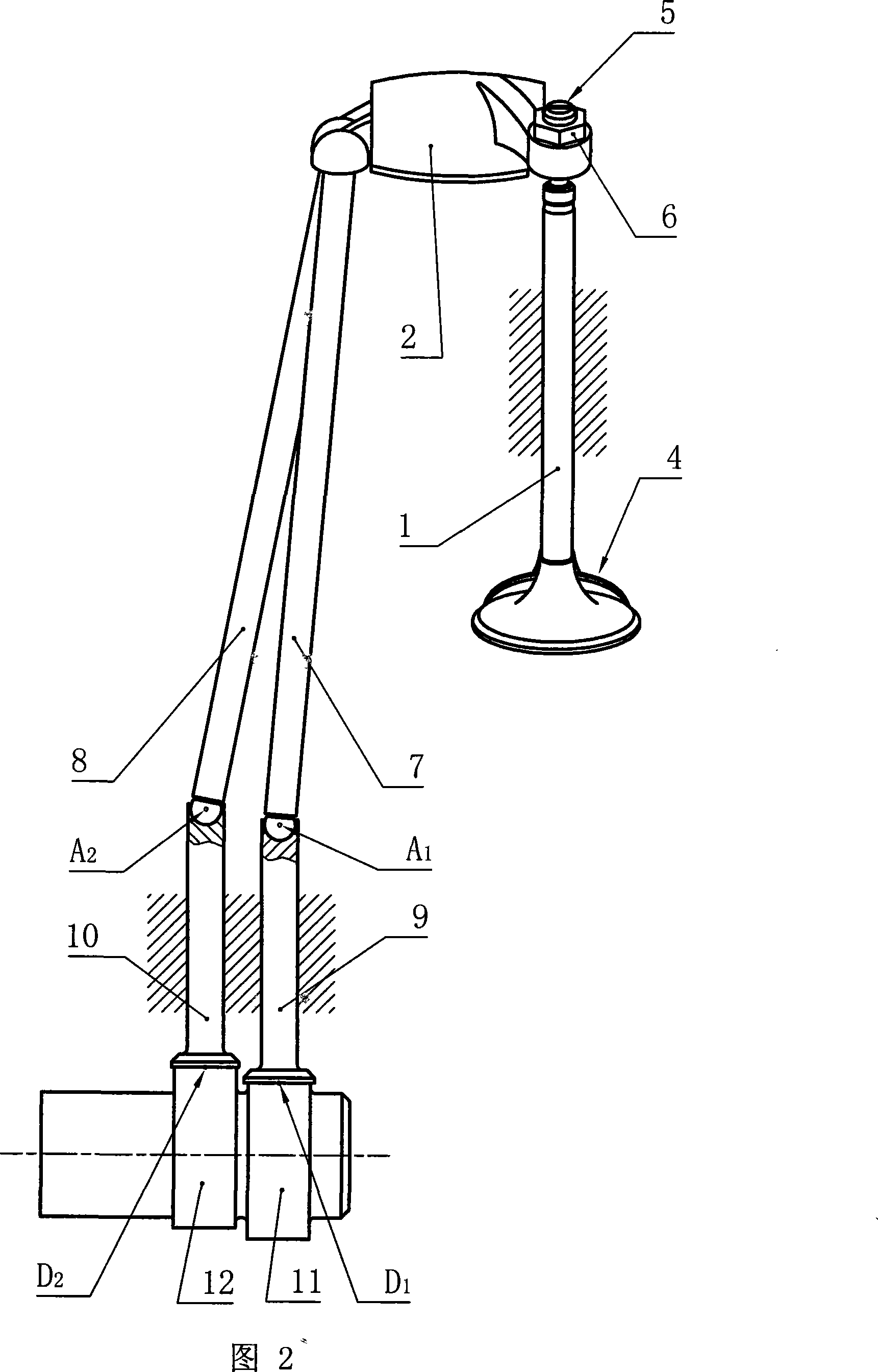

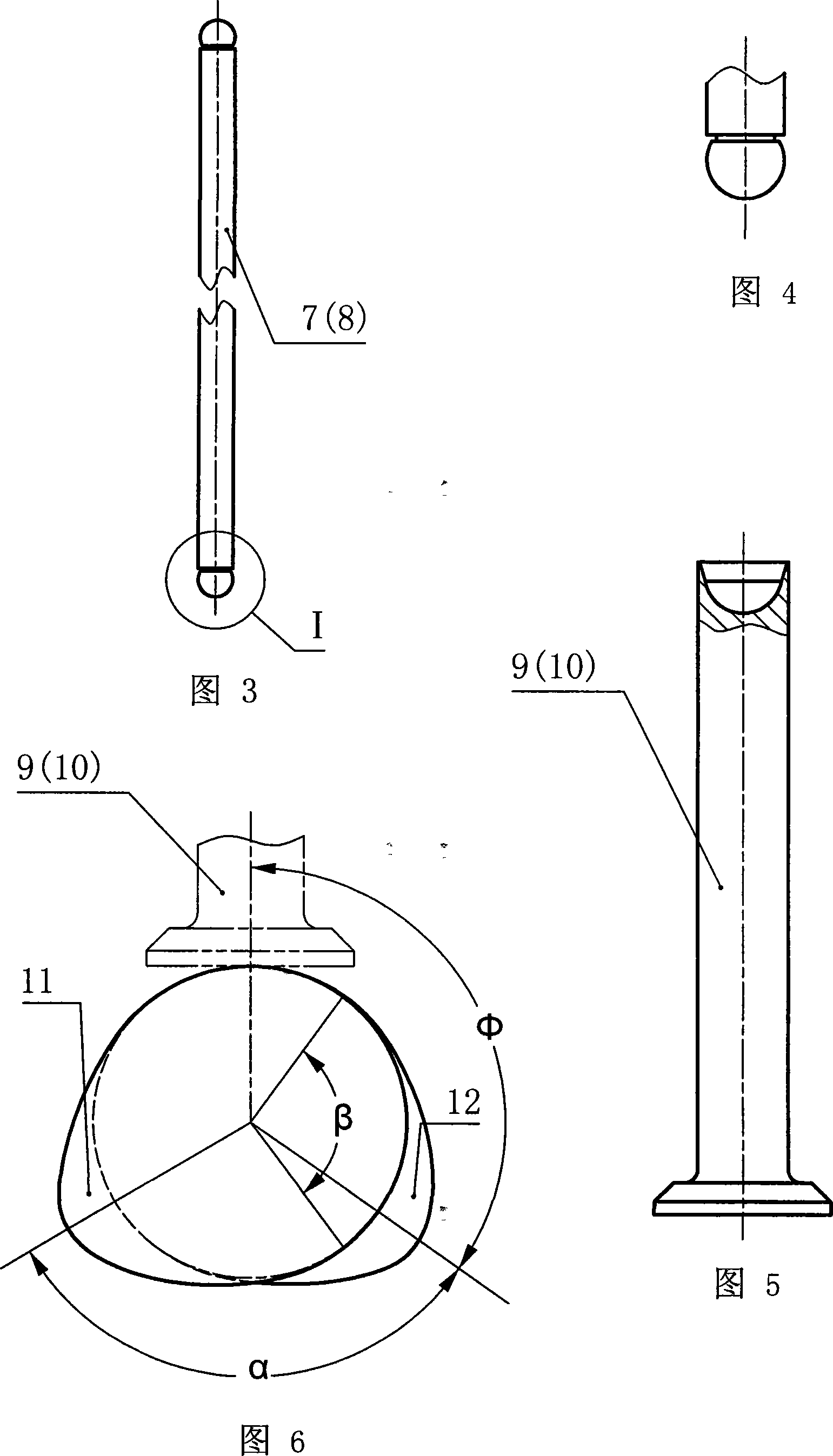

Cam axle underneath type valve mechanism of motorcycle engine

InactiveCN101158296AEliminate overconstraintsReduce gas distribution noiseValve drivesMachines/enginesLine segmentRocker arm

The invention provides a camshaft underslung valve mechanism of a motorcycle engine, comprising a camshaft, an air inlet jogger, an air outlet jogger, an air inlet rocker arm, an air outlet rocker arm, an air inlet valve and an air outlet valve. The camshaft of the invention is provided with an air inlet cam and an air outlet cam which respectively push the air inlet jogger and the air outlet jogger by an air inlet tappet and an air outlet tappet with a disc-shaped flat bottom; the axis line of the air inlet tappet and the air outlet tappet are orthogonal with the axis line of the camshaft. The cam profiles of the air inlet cam and the air outlet cam are respectively formed by connecting nine line segments with smooth transition of a line head and a line tail. Therefore, the invention has the advantages of high timing exactness of air inlet and air outlet, good continuity in inlet and outlet processes without mutation of the inertia force, good force transmission performance of a driven part, and high transmission efficiency. The power and the torque of the engine can be improved by 10% to 13%, and the noise can be reduced by about 10dB.

Owner:CHONGQING UNIV

Implementation method and device for reducing low-threshold units, equipment and storage medium

ActiveCN112214097AReduce power consumptionImprove stabilityGenerating/distributing signalsTiming marginPathPing

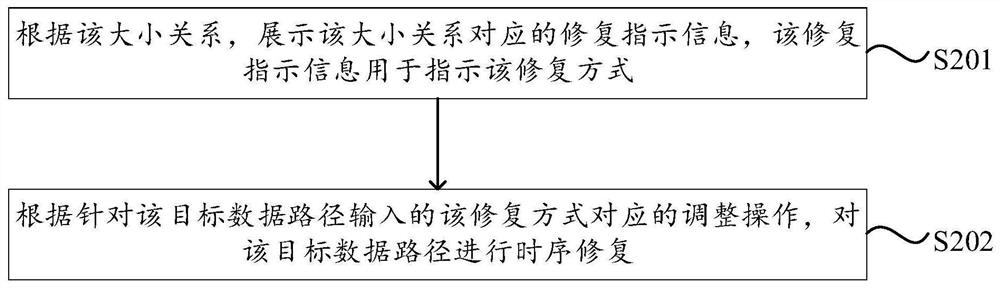

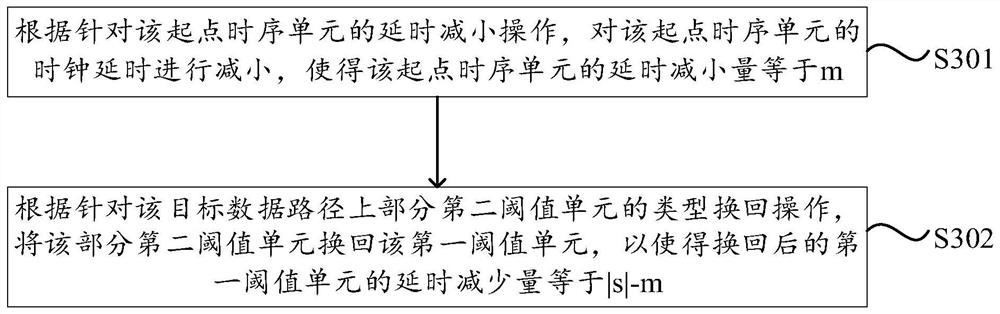

The invention provides an implementation method and device for reducing low threshold units, equipment and a storage medium, and relates to the technical field of integrated circuits. The method comprises the steps: replacing all first threshold units in an integrated circuit with second threshold units, wherein the first threshold units are low threshold units, and the second threshold units arestandard threshold units or high threshold units; obtaining a first timing margin of the data path after unit replacement; determining a target data path of which the first time sequence allowance isnegative; obtaining a second time sequence margin of the data path where the starting point time sequence unit reaching the target data path is located, and a third time sequence margin of the data path where the terminal point time sequence unit starting from the target data path is located; according to the size relationship among the first time sequence allowance, the second time sequence allowance and the third time sequence allowance, performing time sequence repair on the target data path by adopting a repair mode corresponding to the size relationship. According to the method disclosedin the invention, the time sequence requirement of the integrated circuit can be met by using the least low threshold units.

Owner:PHYTIUM TECH CO LTD

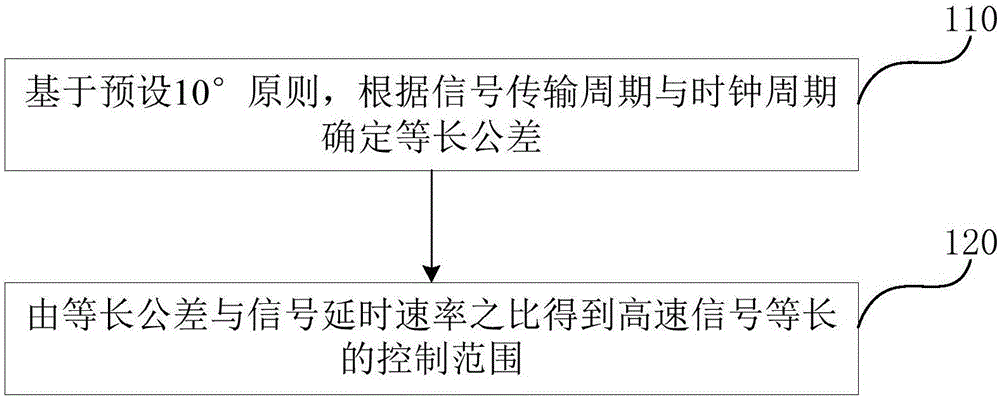

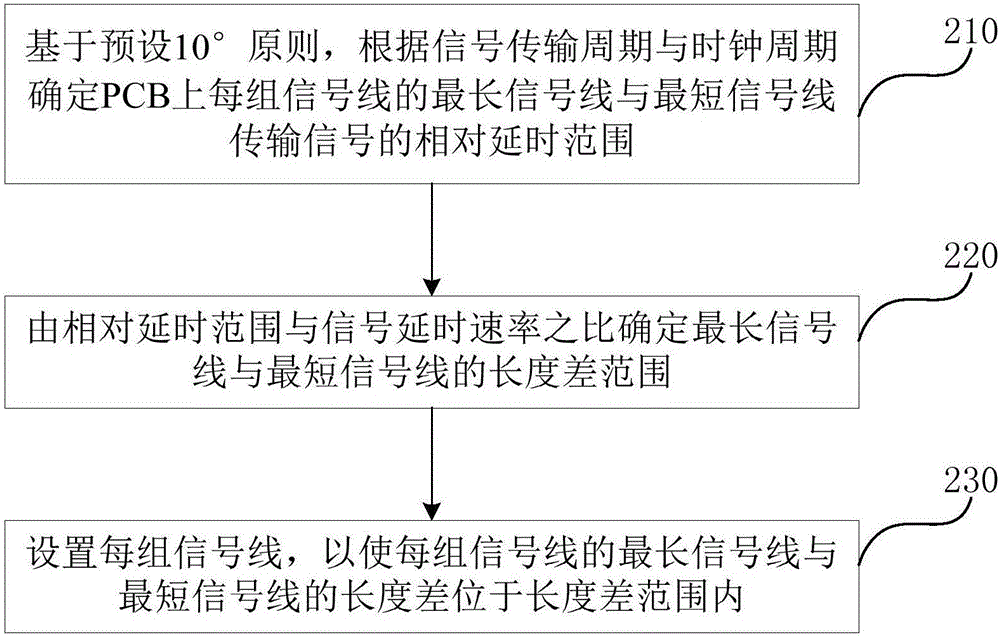

High-speed signal equal-length control algorithm, PCB (Printed Circuit Board) wiring method and PCB

ActiveCN107526893AImprove work efficiencyMeet Timing RequirementsSpecial data processing applicationsCritical signalTime delays

The invention discloses a high-speed signal equal-length control algorithm, a PCB (Printed Circuit Board) wiring method and a PCB. The high-speed signal equal-length control algorithm comprises the following steps that: on the basis of a preset 10-degree principle, according to a signal transmission period and a click period, determining equal-length tolerance to meet a system time sequence requirement; and through a ratio of the equal-length tolerance and a signal time delay rate, obtaining a high-speed signal equal-length control range. By use of the embodiment of the invention, on the basis of the preset 10-degree principle, the high-speed signal equal-length control range is calculated, a design principle and an algorithm with theoretical support can be provided for traditional high-speed circuit PCB design for carrying out key signal equal-length processing so as to be simple and practical, and the working efficiency of PCB design engineers can be greatly improved while the system time sequence requirement is met.

Owner:LUXSHARE PRECISION INDUSTRY (CHUZHOU) CO LTD

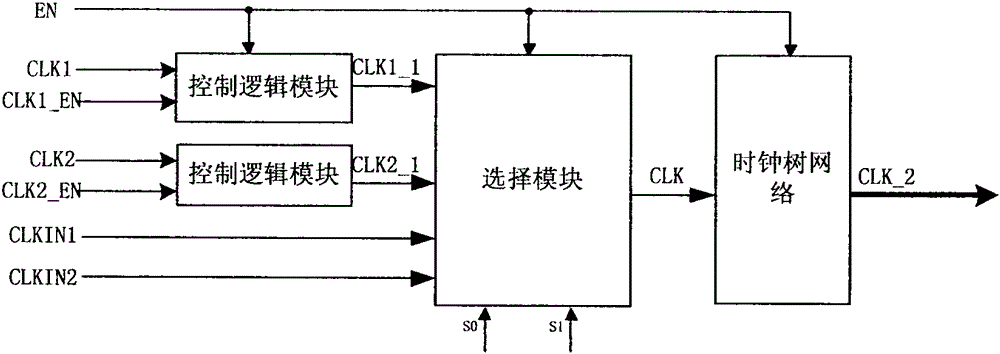

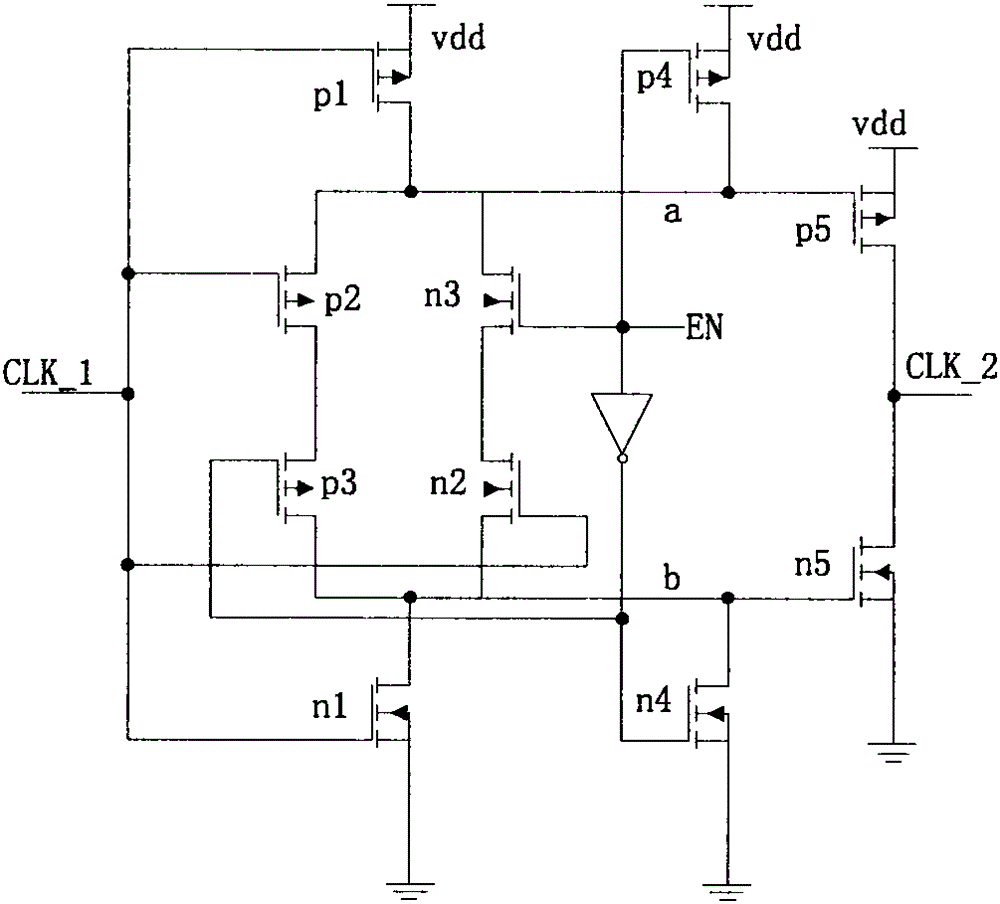

FPGA clock network design

InactiveCN106547929AMeet Timing RequirementsEliminate noise interferenceSpecial data processing applicationsCouplingFiltration

The invention puts forwards a scheme for FPGA clock network design for a programmable logic device. In order to meet the requirement for timing sequences by obtaining smaller clock skew, a design scheme for netted trees is adopted for the clock network. Clock burrs can be eliminated by filtration due to a push-pull structure added to a leaf unit. Noise interference caused by coupling and parasitic effect is eliminated so that stable waves are generated. In addition, configurable design is carried out on the clock network and is compatible to ordinary programmable devices.

Owner:马云利

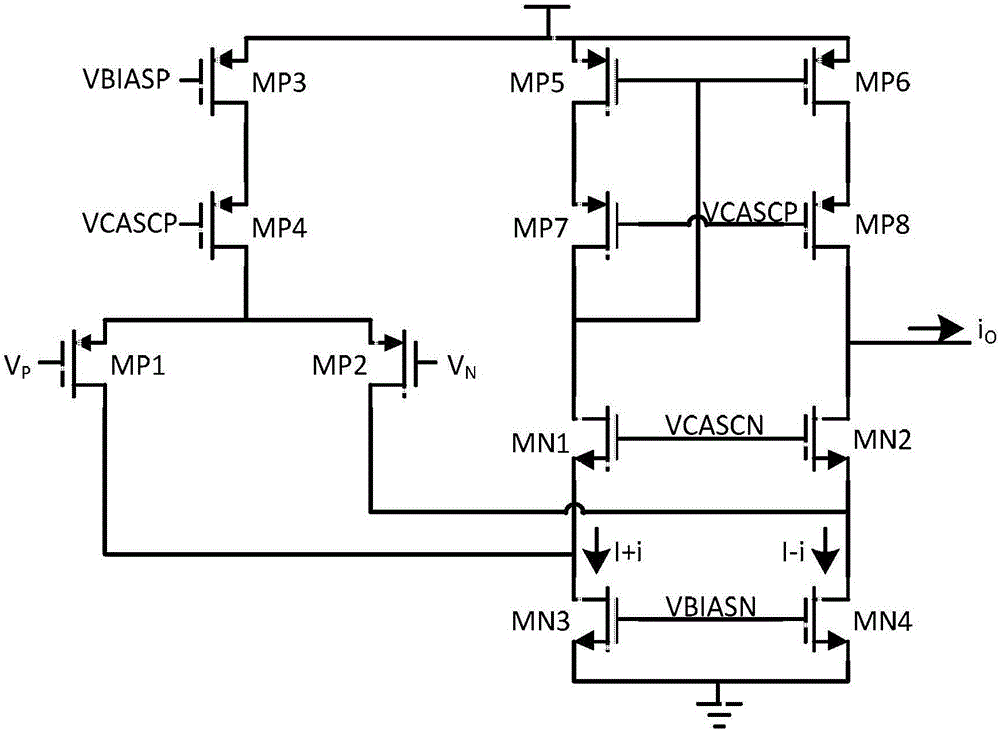

Operational transconductance amplifier applicable to infrared detector circuit

InactiveCN106208992AImprove transconductanceHigh gainPush-pull amplifiersPhase-splittersCircuit complexityPush pull

The invention discloses an operational transconductance amplifier applicable to an infrared detector circuit. An application environment of the operational transconductance amplifier is a front-end amplification circuit of an infrared reading circuit, which is composed of an input stage, a bias stage and an output stage, wherein the input stage is a push-pull structure connected to a differential inverter, which is composed of two PMOS transistors and two NMOS transistors; relatively high input transconductance can be used for forming relatively high gain and bandwidth; the bias stage is a cascode structure, which is composed of two PMOS transistors and two NMOS transistors, and used for increasing the gain and power supply rejection ratio; the output stage is a cascode current mirror, which is composed of four PMOS transistors and four NMOS transistors; by means of the structure, relatively high output impedance can also be provided while current is output; furthermore, due to the current mirror structure, a common-mode feedback structure can be prevented from being used; and thus, the circuit complexity is reduced. The operational transconductance amplifier disclosed by the invention overcomes the problems of low gain of a five-transistor unit structure, small bandwidth of a folding cascode structure and the like, and satisfies time sequence requirements of an infrared reading post-stage circuit.

Owner:TIANJIN UNIV

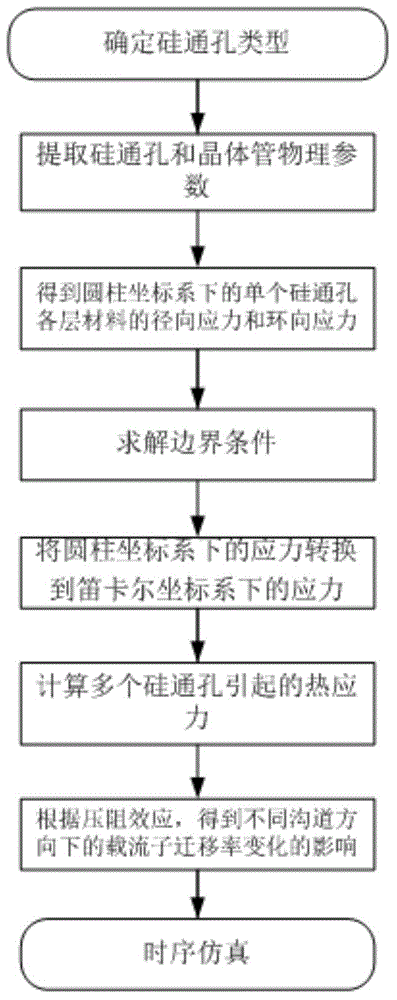

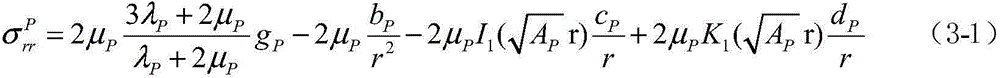

Static timing analysis method for thermal stress circuit with silicon through holes

ActiveCN104965955AResearch results are accurateAccurate researchSpecial data processing applicationsStress distributionStatic timing analysis

he invention belongs to a static timing analysis method for a thermal stress circuit with silicon through holes. The method comprises the following steps of: (1) determining the types of the silicon through holes used in a circuit; (2) extracting the physical parameters of all layers of materials and transistors in the silicon through holes in the circuit; (3) obtaining the radial stress and hoop stress of all layers of materials of single silicon through hole in a cylindrical-coordinate system; (4) solving the boundary conditions of all coefficients in a stress expression; (5) converting the stress under the cylindrical-coordinate system into the stress under a cartesian coordinate system; (6) obtaining total thermal stress distribution caused by a plurality of silicon through holes according to a linear superposition norm; (7) calculating the influence on the change of carrier mobility in different channel directions; and (8) adding the change of carrier mobility to a Gate-level netlist of the circuit, and operating PrimeTime to carry out the static timing analysis under a timing constraint condition, so as to obtain the conditions of longest path time delay and timing sequence allowance change of the circuit.

Owner:XIDIAN UNIV

Method for operation of an internal combustion engine

ActiveUS20070068156A1Improves non-steady-state response behaviorMeet Timing RequirementsValve arrangementsElectrical controlTurbochargerInternal combustion engine

A process for operating an internal combustion engine with a charging device such as a turbocharger and with an intake valve drive mechanism which is variable with respect to its intake valve control times and / or its intake valve stroke. Upon recognition of a positive charge requirement during the operation of the charging device, the at least one variable intake valve drive mechanism is driven in such a manner that an available stroke reserve and / or intake closure control time reserve is utilized to increase the charge amount introduced into an engine cylinder.

Owner:BAYERISCHE MOTOREN WERKE AG

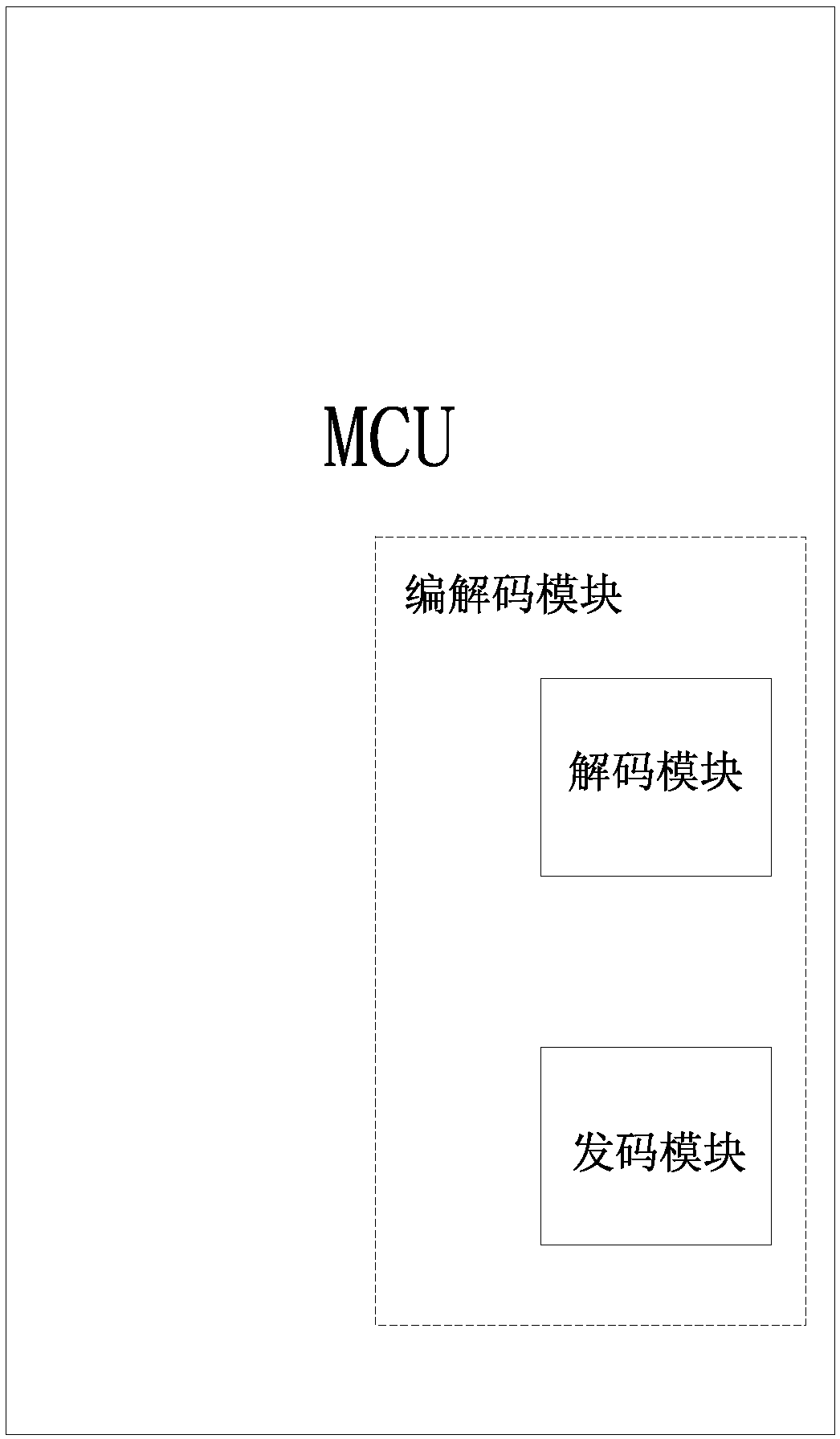

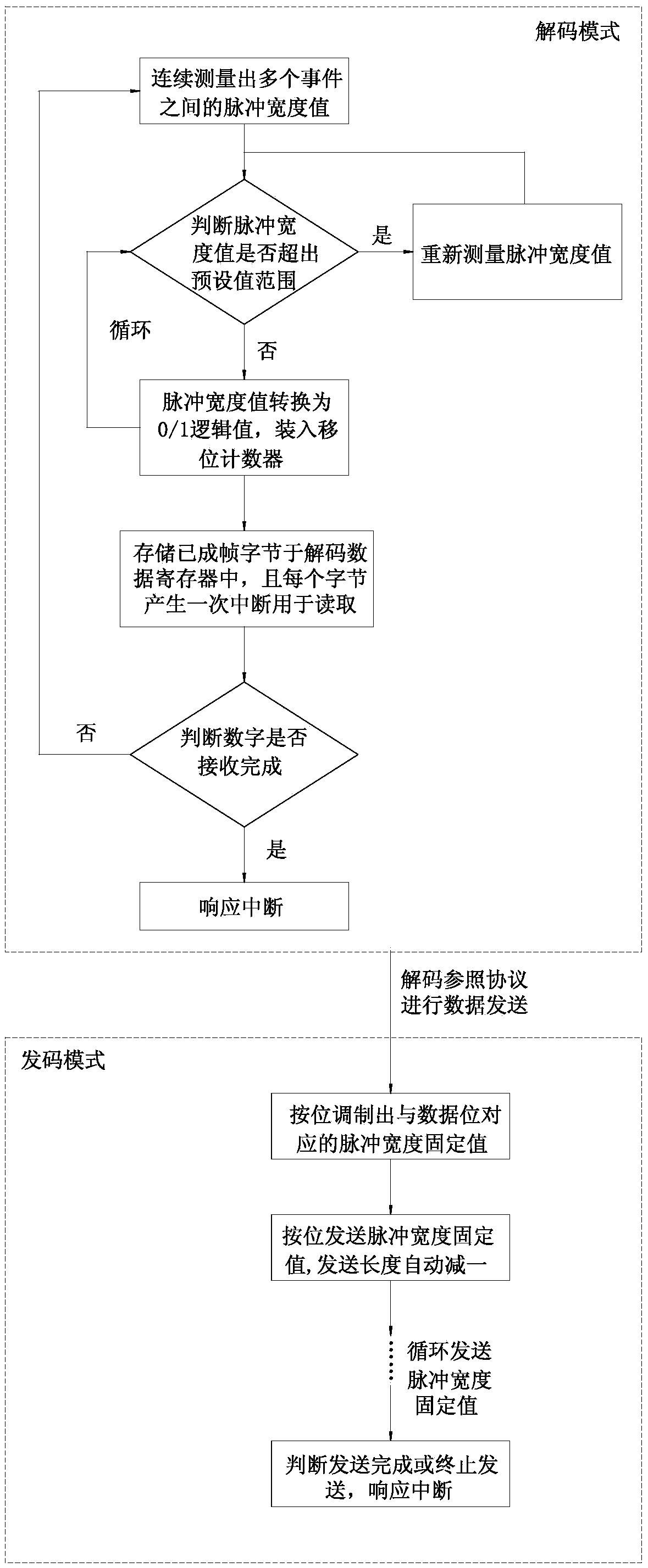

Hardware encoding and decoding method built in MCU for realizing industrial bus communication

ActiveCN108958114AOvercoming the problem of different delay timesReduced effectProgramme controlComputer controlDecoding methodsProcessor register

The invention discloses a hardware encoding and decoding method built in an MCU for realizing industrial bus communication. The method comprises an encoding and decoding module built in an MCU. The encoding and decoding module is composed of a decoding module and a code transmitting module, wherein the decoding module is used for measuring pulse widths among a plurality of events, analyzing the pulse widths into digital signals and storing the digital signals in a decoded data register of the MCU; the code transmitting module is used for modulating the digital signals into corresponding pulsewidth data, storing the pulse width data in the code transmitting data register of the MCU, and transmitting the pulse width data in the form of high-low level. A self-designed decoding mode and a self-designed code transmitting mode are adopted to realize encoding and decoding of industrial bus pulse signals. In this way, the method fundamentally solves the technical problems existing in conventional modes, can ensure the timing of bus communication, can reduce development difficulties and costs, is high in encoding and decoding accuracy, and ensures the stability, consistency and signal transmission distance of the system as a whole. Therefore, the method is suitable for popularization and application.

Owner:SICHUAN SAIKE SECURITY TECH CO LTD +1

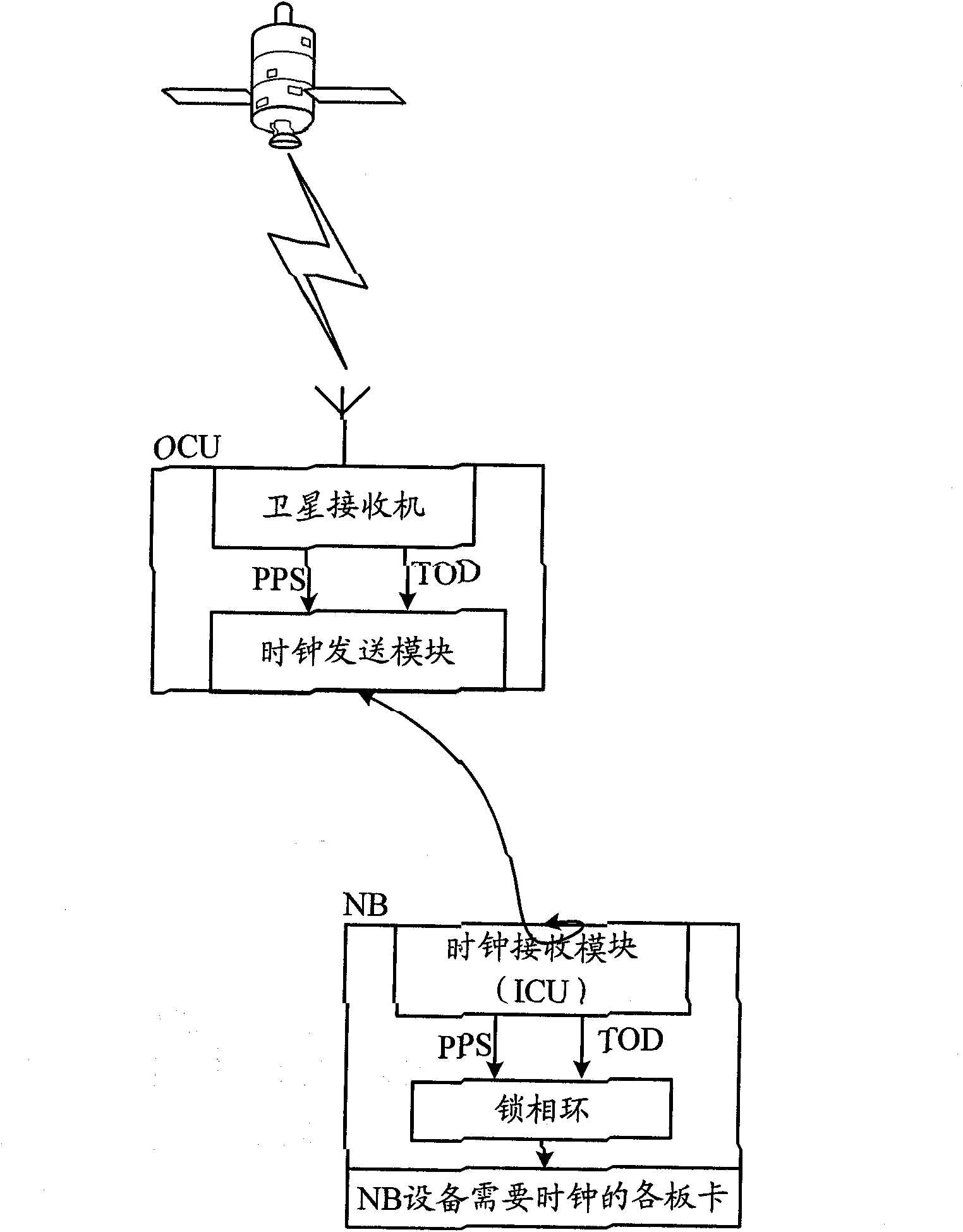

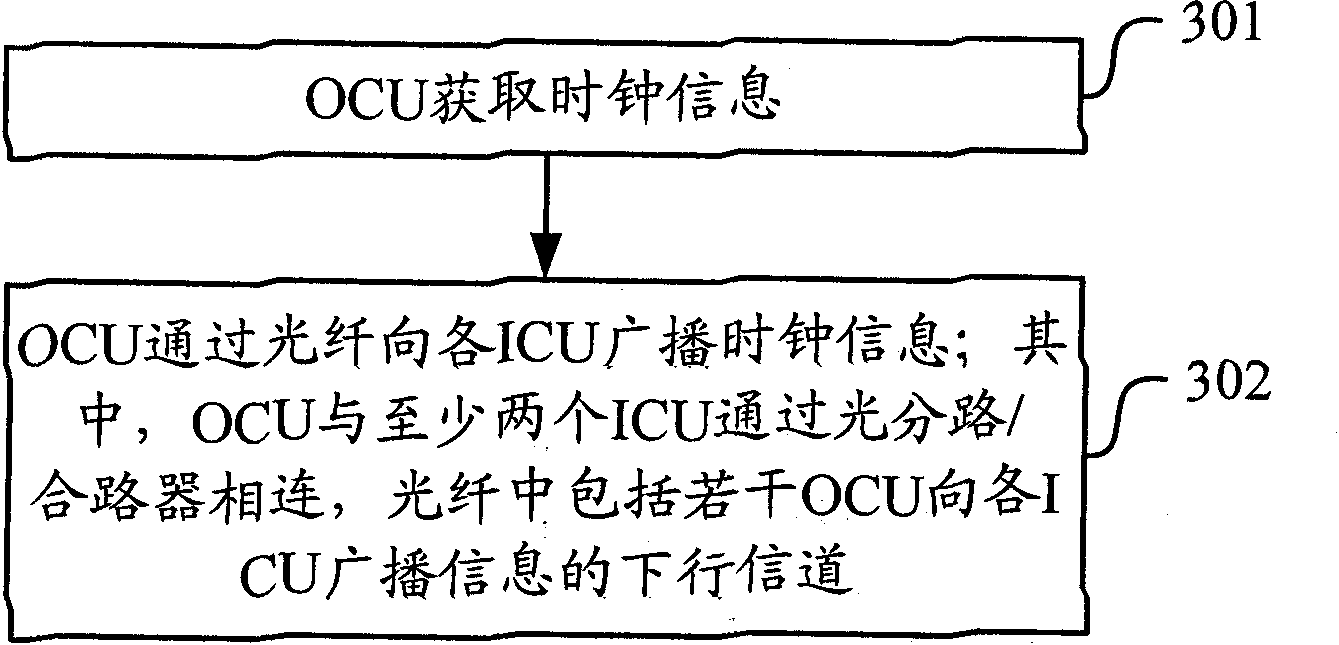

Point-to-point remote clock transmission method and equipment

InactiveCN102014478ASolve the limited transmission distanceReduce in quantitySynchronisation arrangementRadio transmission for post communicationCable transmissionRadio frequency

The invention discloses a point-to-point remote clock transmission method and equipment. The equipment comprises an outdoor clock unit for acquiring clock information and indoor clock units, wherein the outdoor clock unit broadcasts clock information to all indoor clock units through optical fibers; the outdoor clock unit is connected with at least two indoor clock units through an optical branching device / combiner, and the optical fibers comprise a plurality of downstream channels by which the outdoor clock unit broadcasts information to all indoor clock units. The invention can make optical fiber transmission distance reach 40km at least, effectively solve the problem of limited radio frequency cable transmission distance, achieve the purpose for providing time service for multiple base stations with one satellite receiver, reduce satellite receiver number and save cost.

Owner:CHINA ACAD OF TELECOMM TECH

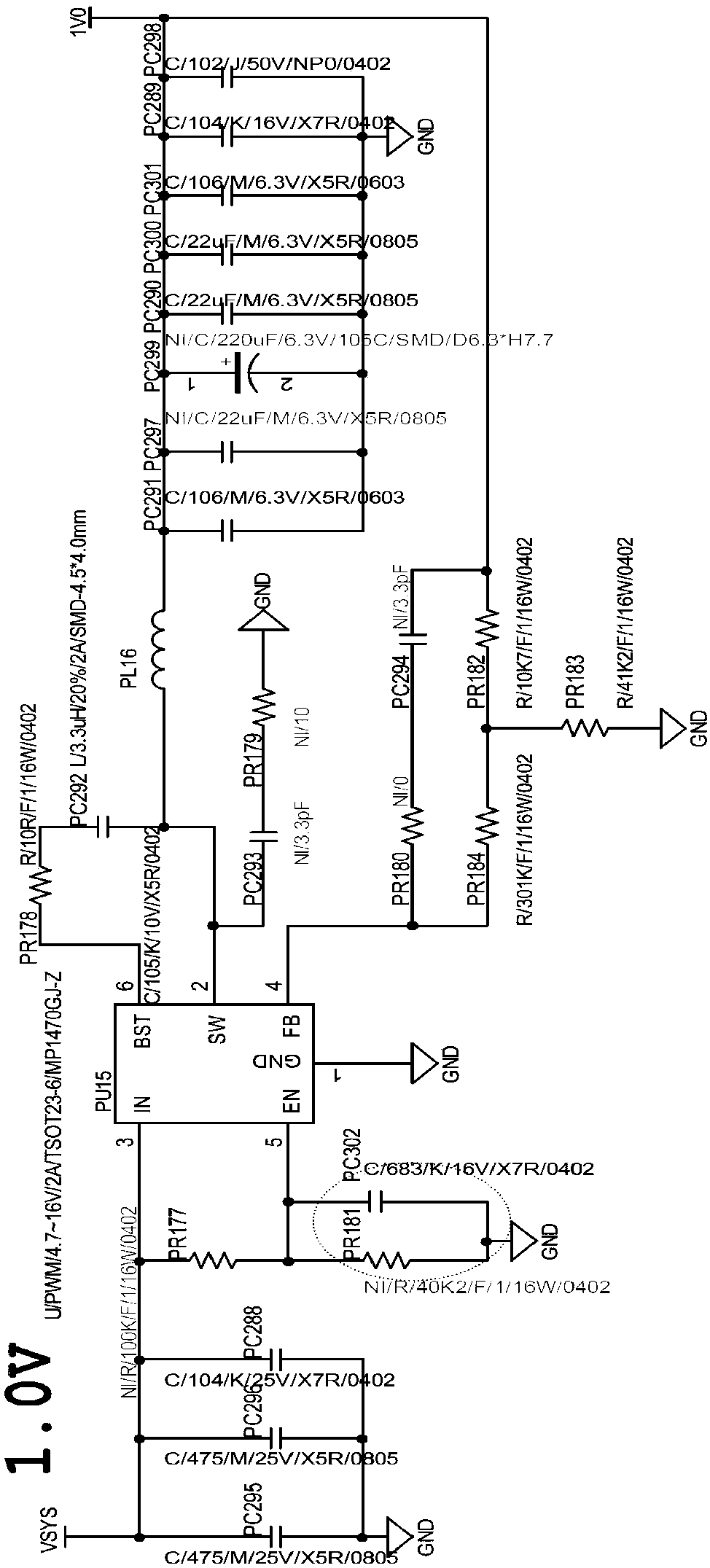

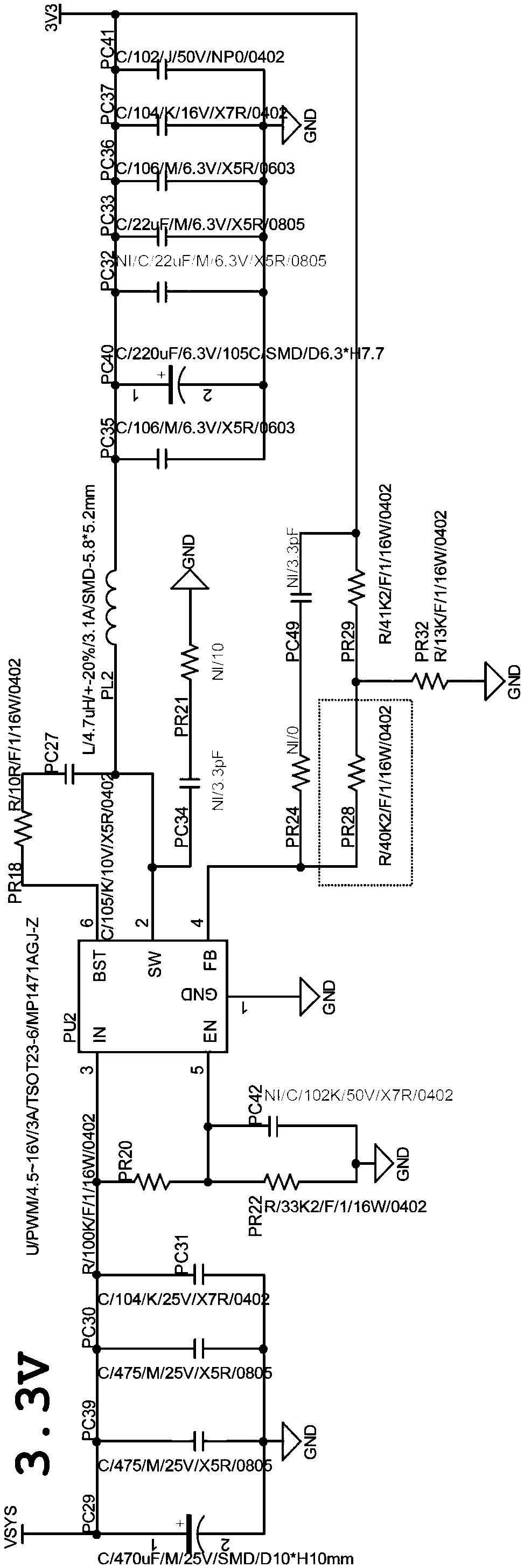

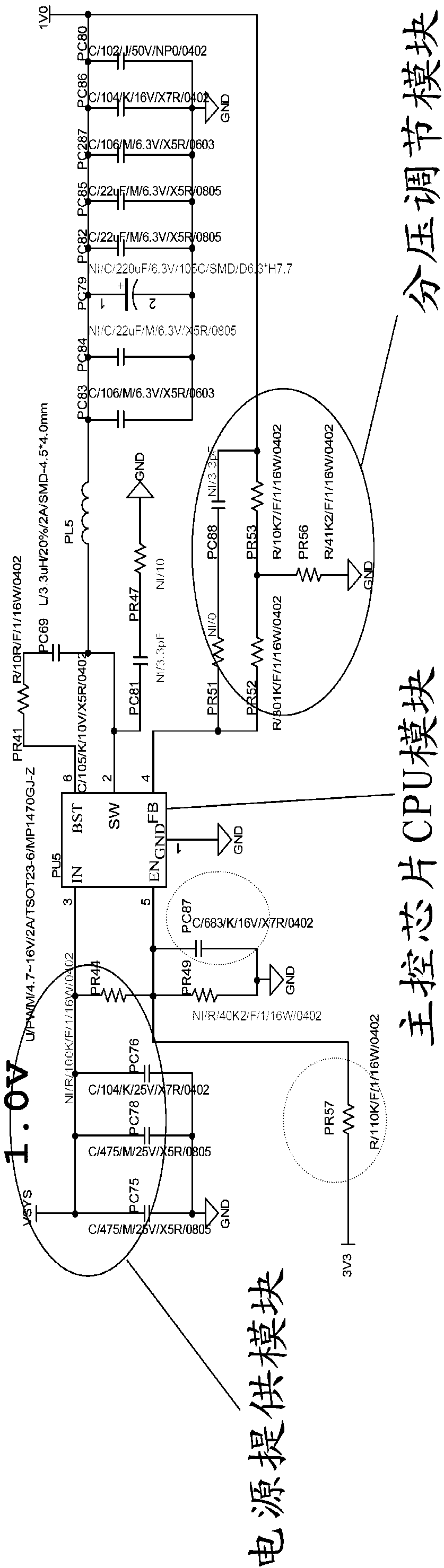

Power switch sequential circuit

PendingCN108052193AMeet Timing RequirementsVolume/mass flow measurementPower supply for data processingPower switchingEngineering

The invention relates to a power switch sequential switch. The circuit comprises a power supply module, a master control chip CPU module and a voltage-dividing regulating module. The power switch sequential circuit has the advantages that time sequence requirements between power switches can be satisfied fundamentally, and a new solution is provided for regulating the time sequence problem of a power supply; a good and convenient time sequence solution is provided for different circuits, the solution can be shared by complex CPU chips, and wide application range is achieved.

Owner:SHANGHAI GONGJIN COMM TECH

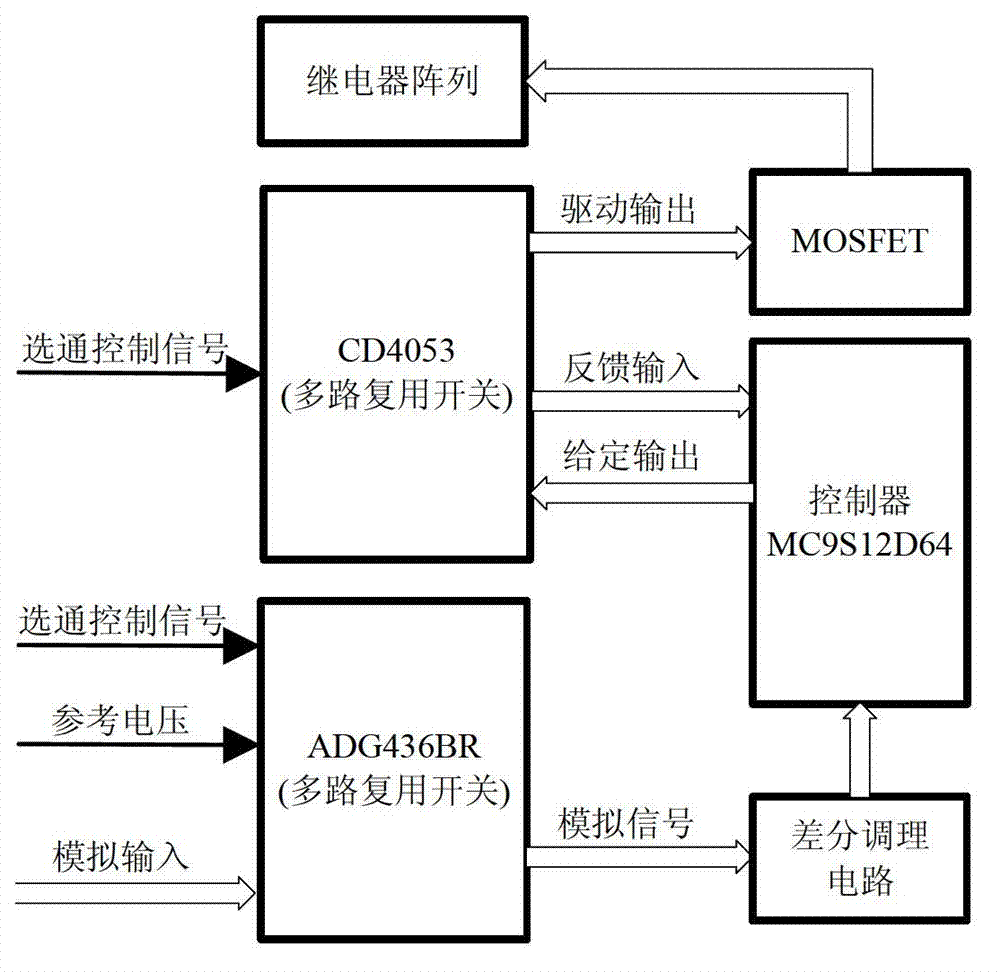

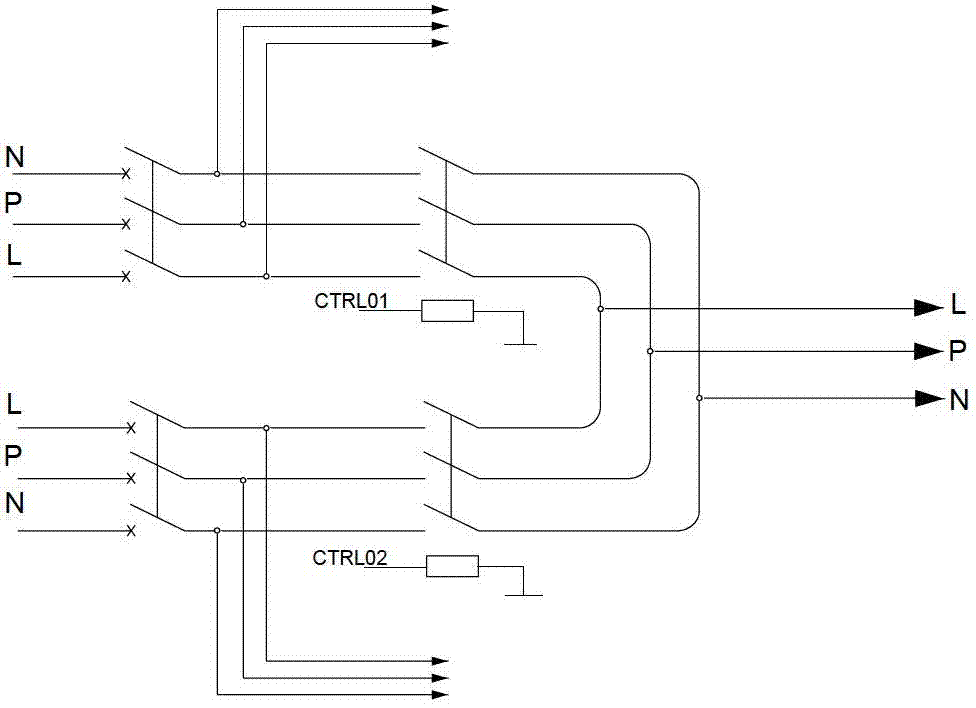

Vehicle Intelligent Power Distribution Control System

ActiveCN103532219BRealize intelligent monitoring functionMeet Timing RequirementsEmergency power supply arrangementsDistribution controlControl system

Owner:BEIJING INST OF SPACE LAUNCH TECH +1

Optimization method and device for sub-threshold circuit design

ActiveCN110135098AMeet Timing RequirementsReduce waste of power consumptionCAD circuit designEnergy efficient computingSub thresholdUnit device

The invention provides an optimization method and device for a sub-threshold circuit design.. Query data of a logic unit under different threshold voltages are preset, and the query data comprise device parameters-delay data; delay analysis is carried out on a to-be-optimized sub-threshold circuit; for a to-be-optimized path with unmatched delay, device parameters of a logic unit in a path are adjusted to perform deplay optimization; adjusted device parameters are determined through preset query data during optimization, meanwhile, the device parameters of each logic unit in the delay circuitto be optimized are changed by adopting different threshold voltages, and finally, tthe unit device parameters corresponding to each logic unit in the delay circuit to be optimized under the condition of minimum power consumption are taken as an optimization result. Therefore, power consumption is reduced while delay optimization is carried out.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

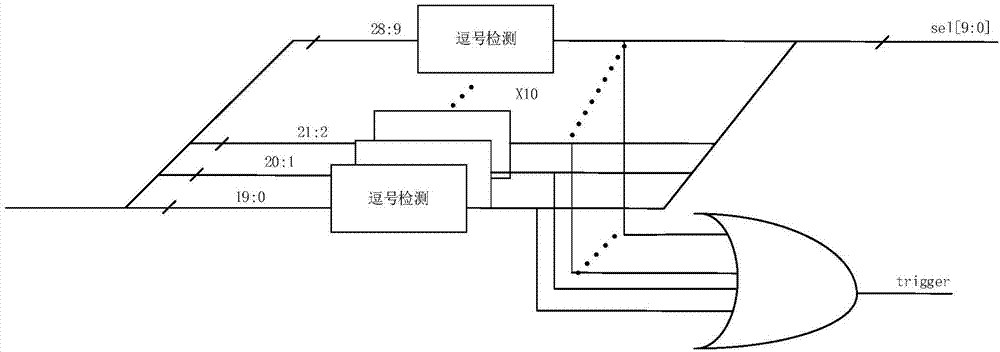

Comma detection and word alignment method and system suitable for JESD204B protocol

ActiveCN106933767AMeet Timing RequirementsElectric digital data processingProcessor registerShift sequence

The invention discloses a comma detection and word alignment method and system suitable for a JESD204B protocol. The method comprises the following steps that: utilizing a first register and a second register to independently cache input N bits of data; taking N bits of data from the first register, carrying out preset-frequency shifting on the taken N bits of data, and obtaining a N-bit shifting sequence after shifting is carried out each time; detecting an integral comma detection code in each shifting sequence to determine the position information of the comma detection code; after the position information of the comma detection code is detected, generating a shifting address according to a state machine, wherein the length of the shifting address is the same with the length of the position information of the comma detection code; and according to the shifting address, carrying out shifting on 2N-bit data in the first register and the second register to obtain word alignment data. By use of the technical scheme provided by the invention, a 12.5Gbps rate requirement stipulated by the JESD204B protocol can be met.

Owner:重庆湃芯创智微电子有限公司

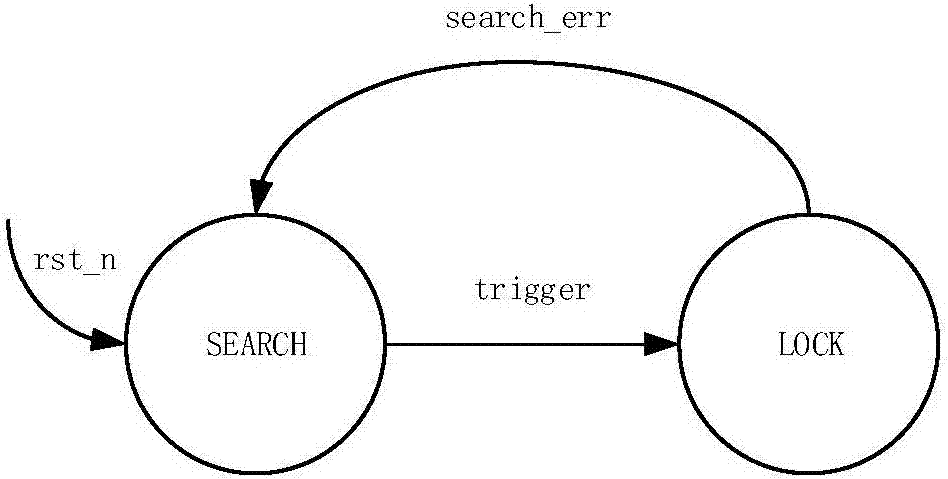

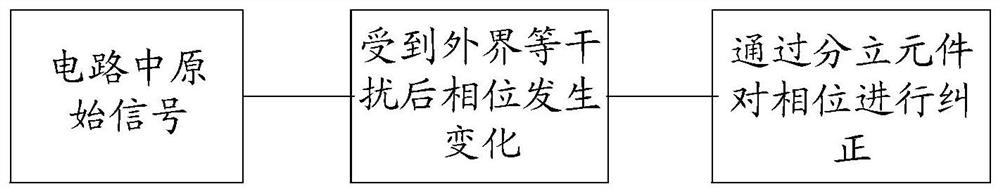

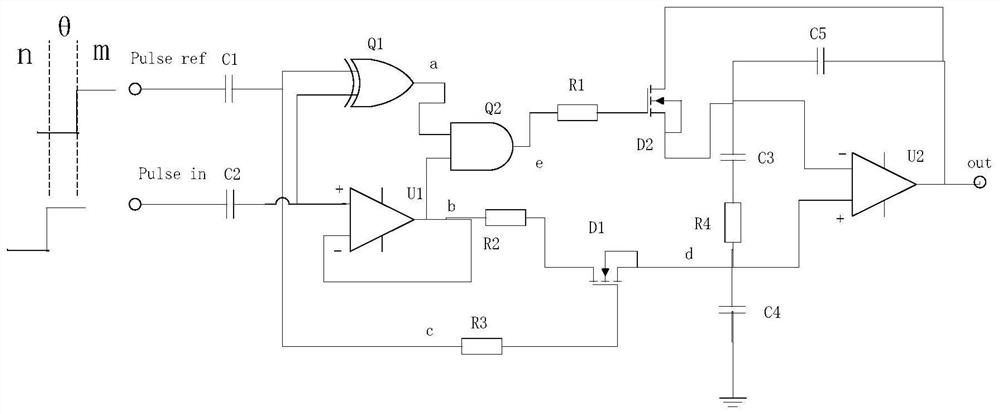

Phase self-correcting circuit

ActiveCN111817701AReduce manufacturing costLow pricePulse automatic controlDelay compensationPhase correctionEngineering

The invention discloses a phase self-correcting circuit. The phase self-correcting circuit comprises a trigger signal operation module and a signal phase correcting module, the trigger signal operation module and the signal phase correction module are both composed of a plurality of discrete components. The trigger signal operation module is used for performing logical operation on the input phasestandard reference signal and the actual transmission signal to obtain a target trigger signal of the trigger signal phase correction module; the signal phase correction module is used for outputtinga self-correction transmission signal with the same waveform as the phase standard reference signal based on the trigger mode of the target trigger signal and the actual transmission signal; the phase self-correction of the actual transmission signal is realized, so that the change of the signal phase caused by various external reasons is automatically corrected, the time sequence requirement ina long-distance transmission scene is met, and the whole circuit is simple in structure, high in universality and low in manufacturing cost.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

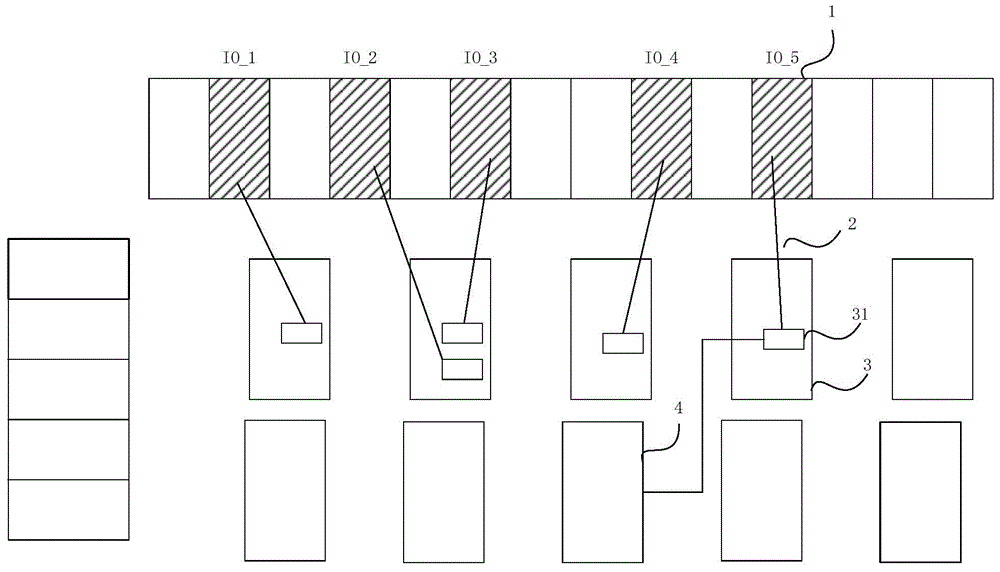

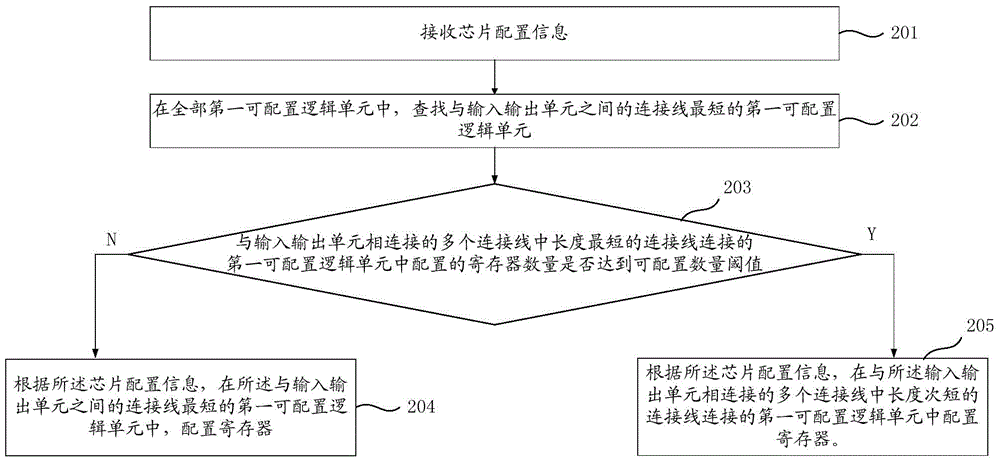

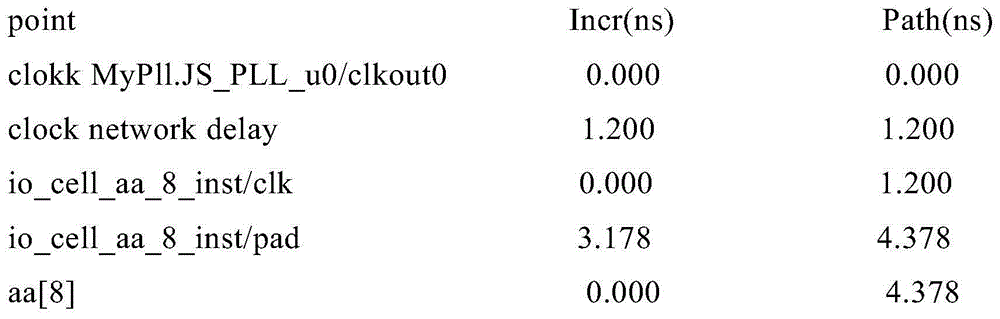

Interface structure and configuration method of FPGA (field programmable gate array) chip

ActiveCN104678815AMeet Timing RequirementsLower latencyProgramme controlComputer controlProcessor registerFpga chip

The invention relates to an interface structure and a configuration method of an FPGA (field programmable gate array) chip. The structure comprises an input and output unit, connecting wires and a first configurable logic unit, wherein the input and output unit is used for receiving chip configuration information sent by the outside, the first configurable logic unit is connected with the input and output unit through the connecting wire, and in addition, a register is configured in the first configurable logic unit connected with the shortest connecting wire in the plurality of connecting wires connected with the input and output unit according to the chip configuration information received by the input and output unit.

Owner:CAPITAL MICROELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com