FPGA clock network design

A clock network, clock technology, applied in computing, special data processing applications, instruments, etc., can solve problems such as complex circuit design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011] The present invention will be described in detail below in conjunction with the accompanying drawings and examples.

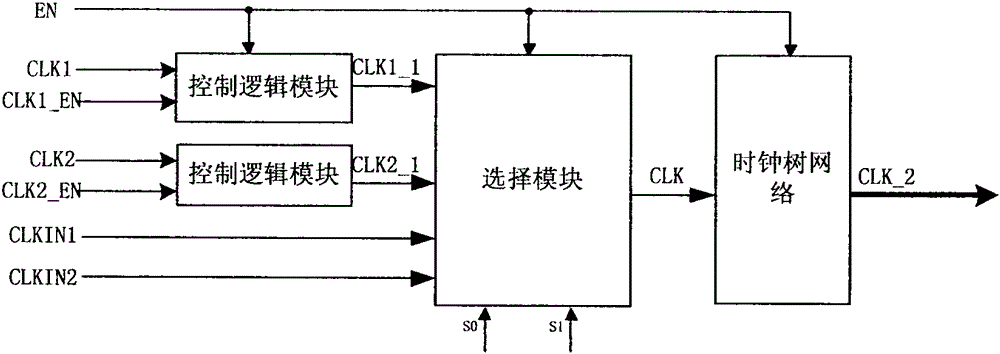

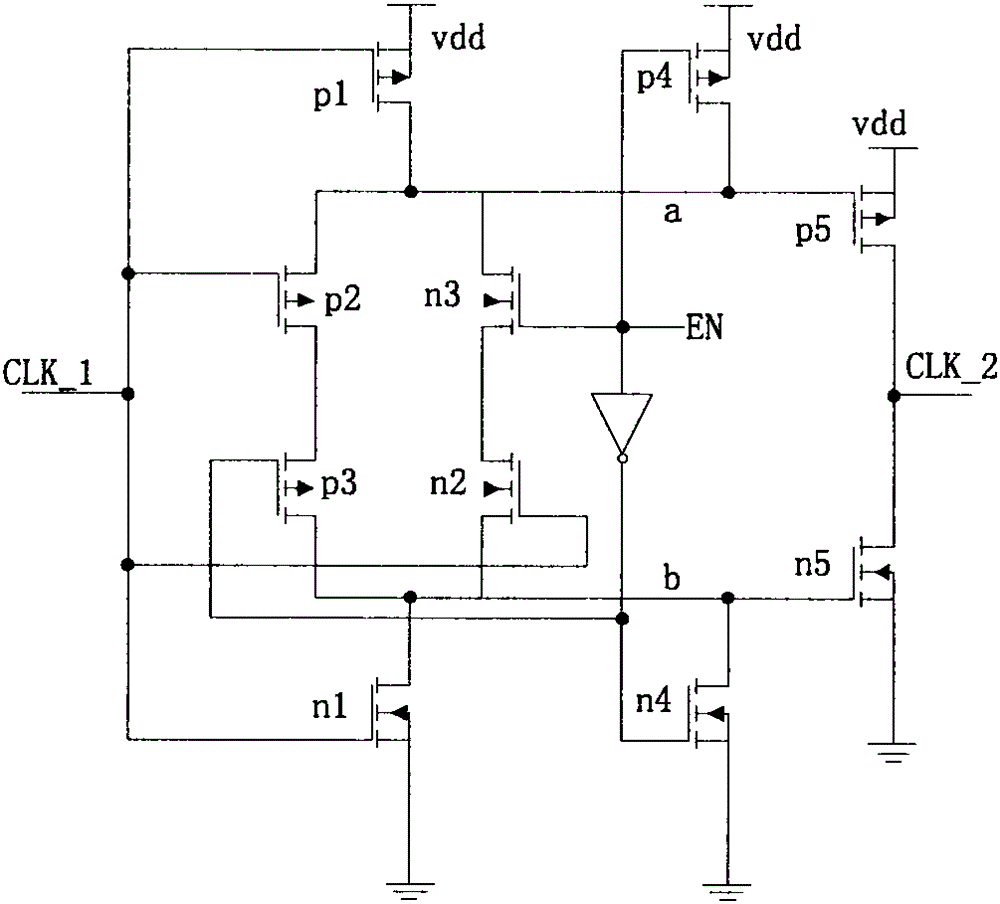

[0012] figure 1 As shown, the architecture of the clock network is designed. Since the clock signal runs through the entire chip, when the chip is working, the clock signal jumps periodically at the clock input end of the storage unit, and the driven load capacitance is very large, resulting in large power consumption. With the help of the global control signal EN, the clock is turned off when the programmable logic device is in the programming state or in the sleep mode to reduce dynamic power consumption. The user divides the frequency of the external clock CLK1 and CLK2 by programming to obtain the internal clock CLKIN1 and CLKIN2 of the desired frequency. After the external clock passes through the gate control circuit and the adjustment circuit of the conversion time, the selection module selects the clock channel with the internal clock. The select...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com