Static timing analysis method for thermal stress circuit with silicon through holes

A static timing analysis, through-silicon via technology, applied in the field of microelectronics, can solve problems such as inapplicability to circuits containing multiple types of through-silicon vias, reduced accuracy of carrier mobility changes, and reduced accuracy of thermal stress.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0083] Specific embodiments of the present invention will be described in detail below.

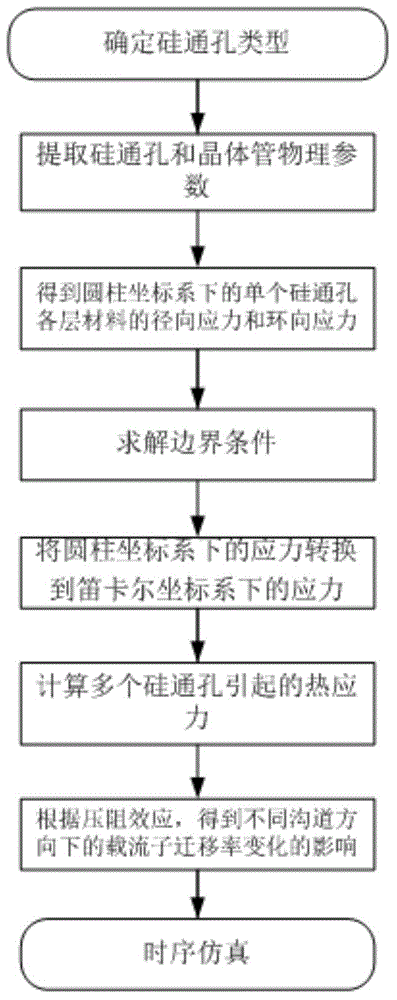

[0084] Such as figure 1 As shown, the static timing analysis method for circuits with thermal stress through silicon vias includes the following steps:

[0085] (1) Determine the type of TSV used in the circuit;

[0086] (2) According to the type of TSV, extract the material of each layer of the TSV used and the physical parameters of the transistor from the circuit;

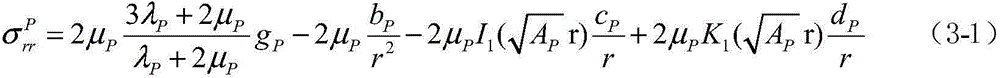

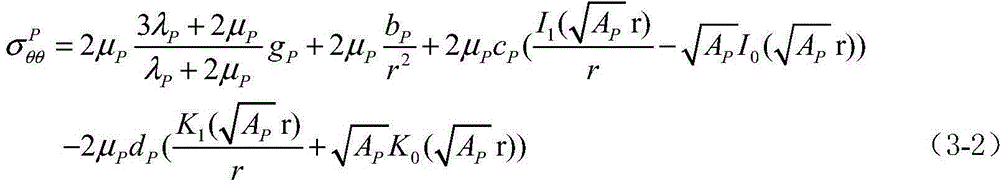

[0087] (3) According to the physical parameters of each layer material of TSV, the radial stress of each layer material of a single TSV in the cylindrical coordinate system is obtained by using the mathematical model of stress and hoop stress

[0088] σ r r P = 2 μ P 3 λ P + 2 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com