10-bit ultra-low-power successive approximation register analog-to-digital converter based on charge redistribution

A successive approximation, analog-to-digital converter technology, applied in analog/digital conversion, code conversion, instruments, etc., can solve the problems of increased power consumption and low precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0074]In order to make the technical problems, technical solutions and advantages to be solved by the present invention clearer, the following will describe in detail with reference to the drawings and specific embodiments.

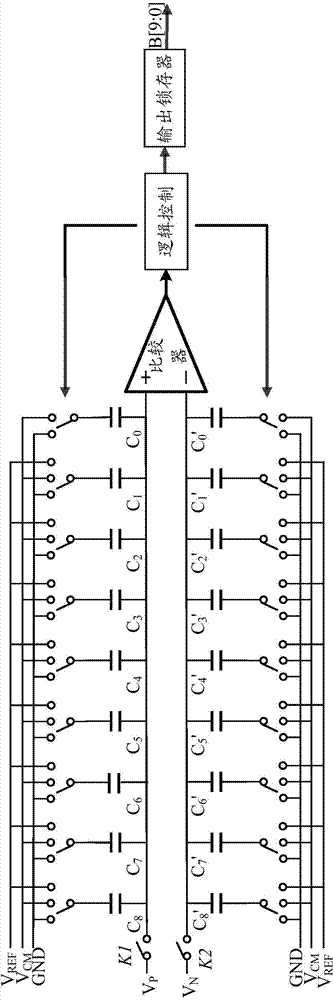

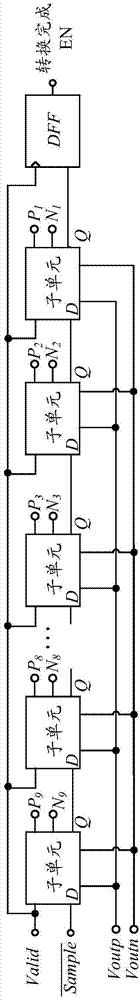

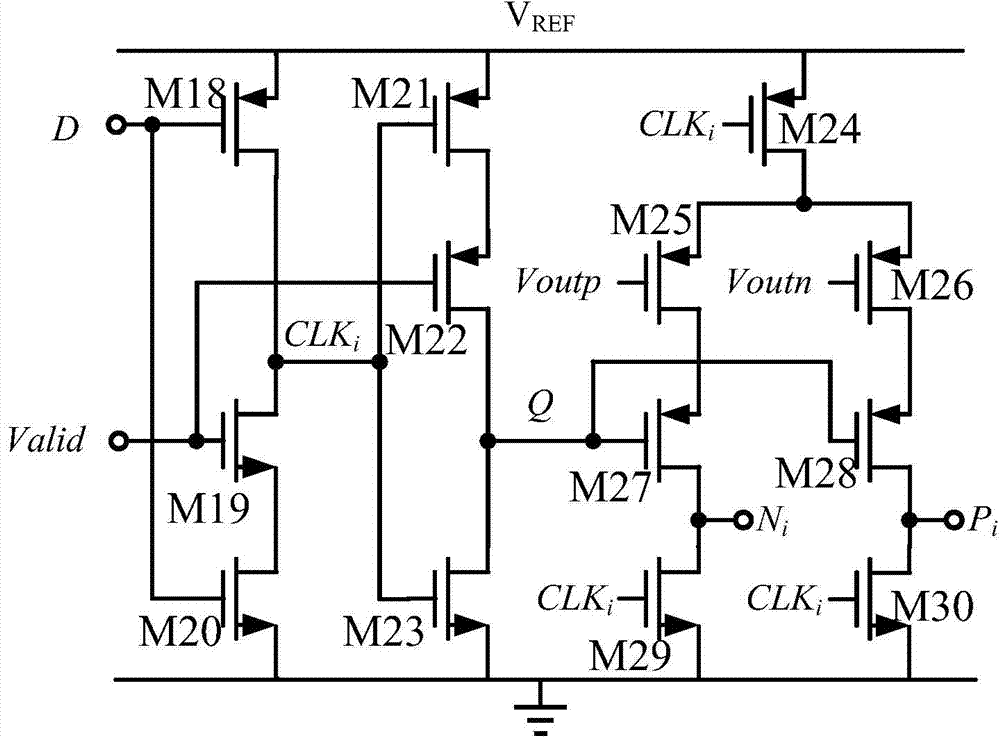

[0075] The present invention provides a 10-bit ultra-low power successive approximation analog-to-digital converter based on charge redistribution, and controls the switching timing of the switching of the capacitor switch of the differential capacitor array to select the connection voltage through the output terminal of the successive approximation control logic, The area and power consumption of the capacitor array can be greatly saved, and half of the capacitor can also be saved by applying the last redundant capacitor to the analog-to-digital conversion.

[0076] like Figures 1 to 11 As shown, the 10-bit ultra-low power successive approximation analog-to-digital converter based on charge redistribution provided by the embodiment of the present invent...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com