Semiconductor transistor structure and preparation method thereof

A semiconductor and transistor technology, applied in the field of semiconductor transistor structure and its preparation, to achieve the effect of reducing the value of parasitic capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0066] see Figure 2a-2m , the preparation method of the semiconductor transistor structure provided in this embodiment includes the following steps:

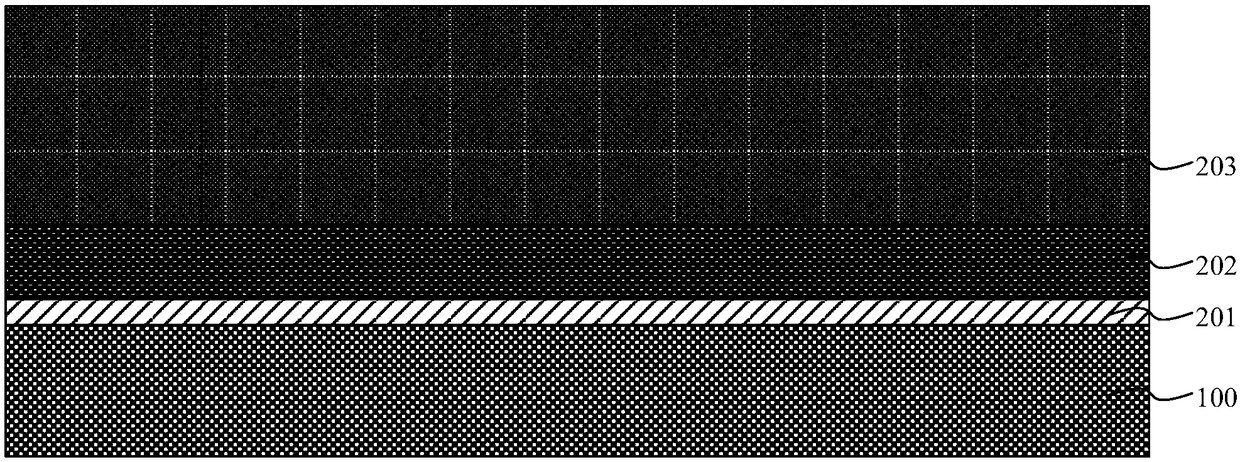

[0067] S11 as Figure 2a As shown, a gate dielectric layer 201 , a gate conductive layer 202 and an insulating protection layer 203 are sequentially formed on a semiconductor substrate 100 . Specifically, the semiconductor substrate 100 can be a silicon substrate; an oxide layer can be oxidized on the surface of the silicon substrate as the gate dielectric layer 201, with a thickness of 1-10 nm; A 60nm tungsten metal conductive film and a 50-300nm thick silicon nitride film are used as the gate conductive layer 202 and the insulating protection layer 203 respectively.

[0068] S12 as Figure 2b As shown, a gate pattern is defined, and a gate component is formed on the semiconductor substrate 100 by photolithography, and the gate component includes a gate dielectric layer 201, a gate conductive layer 202 on the gate dielectri...

Embodiment 2

[0080] see Figures 3a-3e , the preparation method of the semiconductor transistor structure provided in this embodiment includes the following steps:

[0081] S21 sequentially forming a gate dielectric layer 201 , a gate conductive layer 202 and an insulating protection layer 203 on the semiconductor substrate 100 .

[0082] S22 defines a gate pattern, and forms a gate component on the semiconductor substrate 100 by photolithography, and the gate component includes a gate dielectric layer 201, a gate conductive layer 202 on the gate dielectric layer 201, and An insulating protection layer 203 located on the gate conductive layer 202 .

[0083] S23 Form the first isolation layer 301, the sacrificial layer 302' and the second isolation layer 303 sequentially from the inside to the outside on the side wall of the gate assembly; the first isolation layer 301, the sacrificial layer 302', the second isolation layer 303, and etch to remove excess material after each vapor depositi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com