Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

6487results about "Pulse manipulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

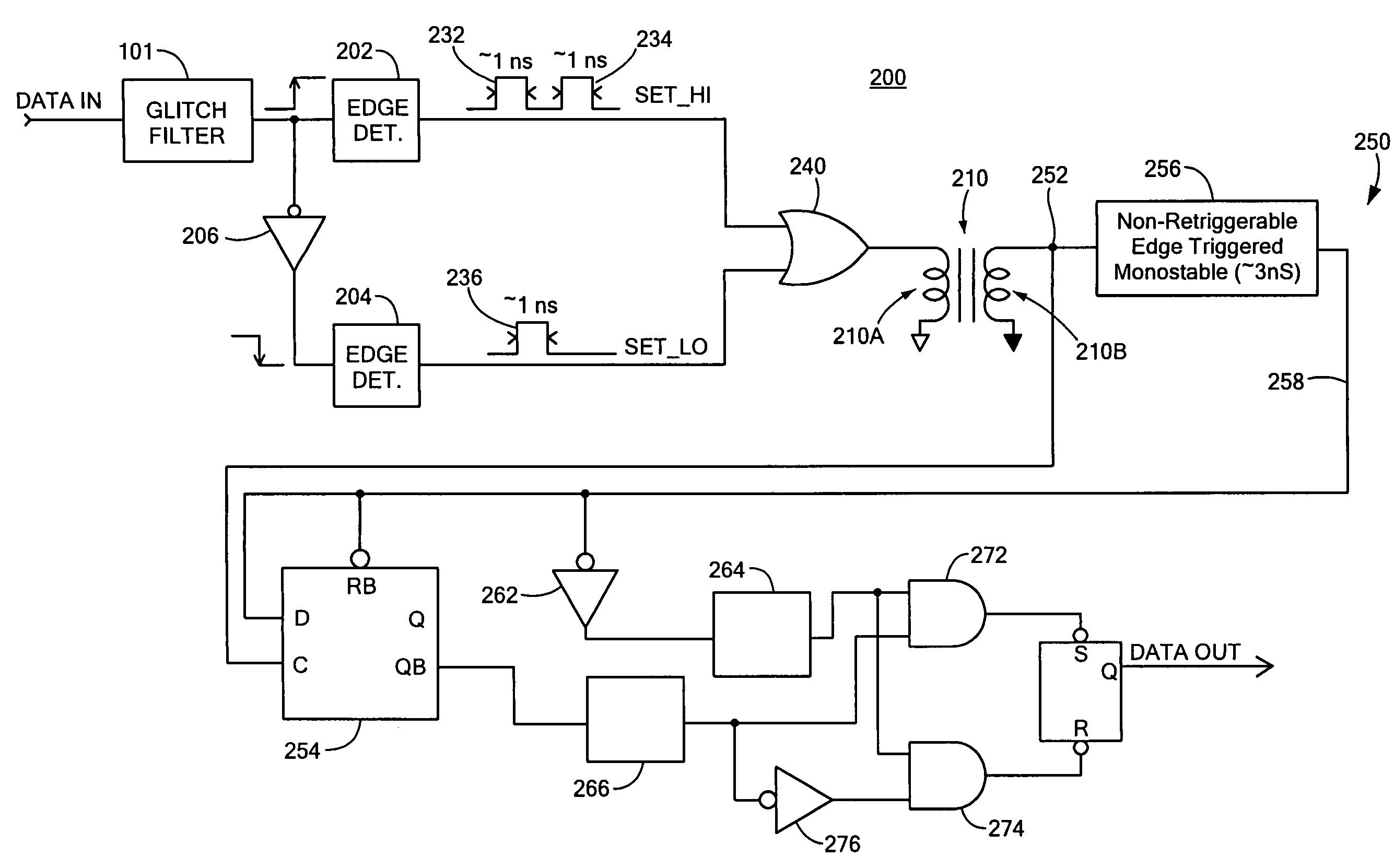

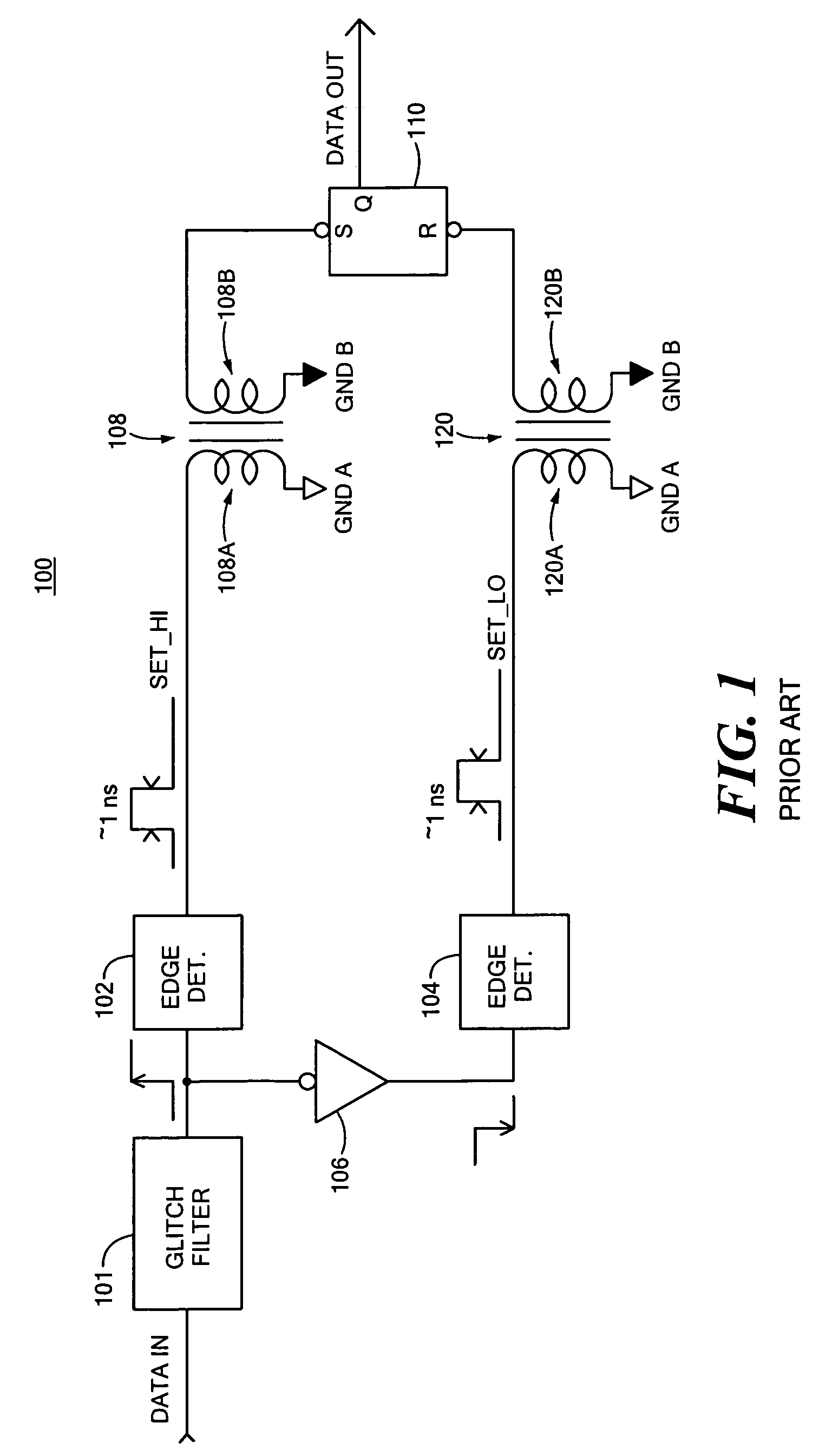

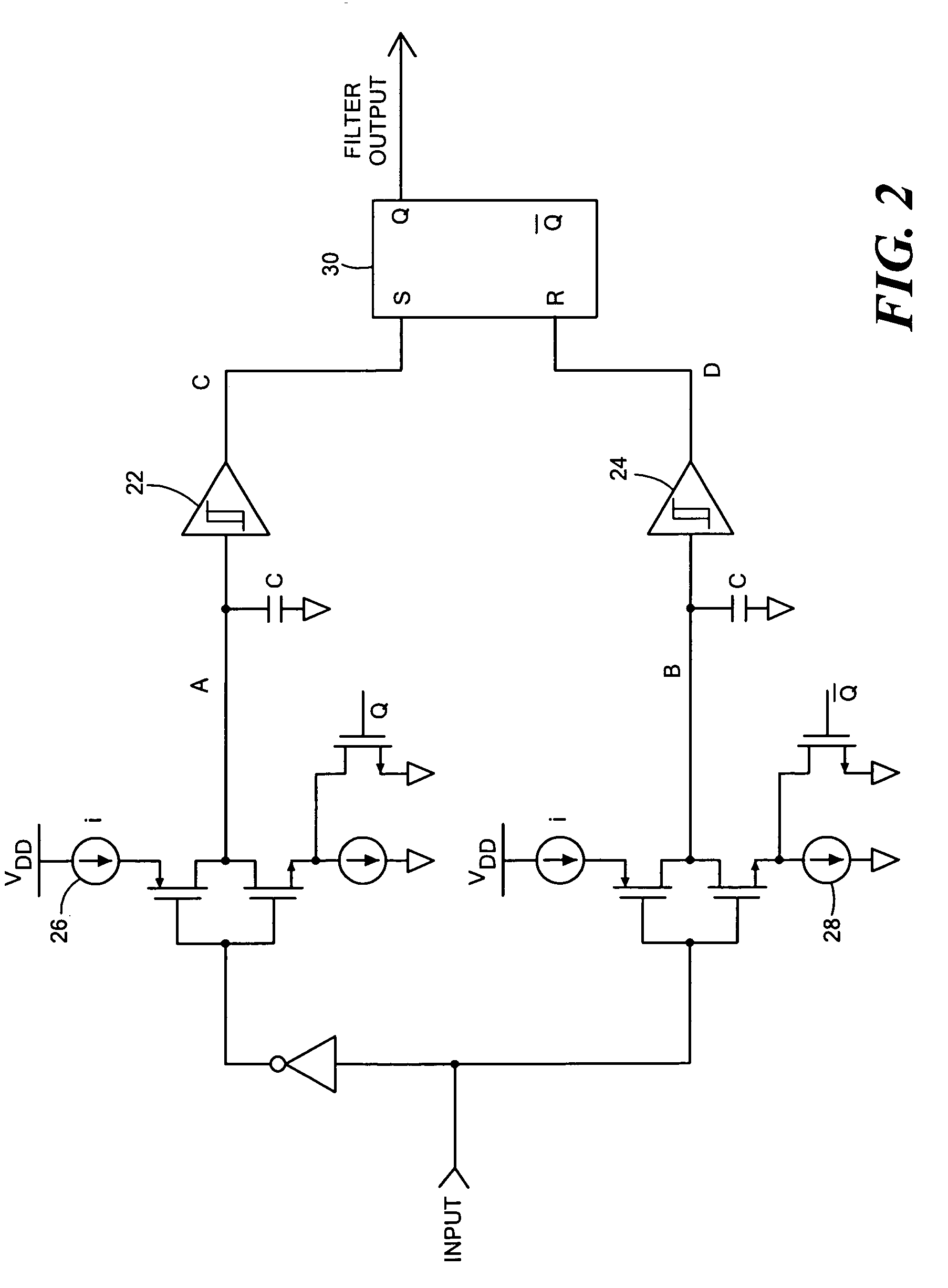

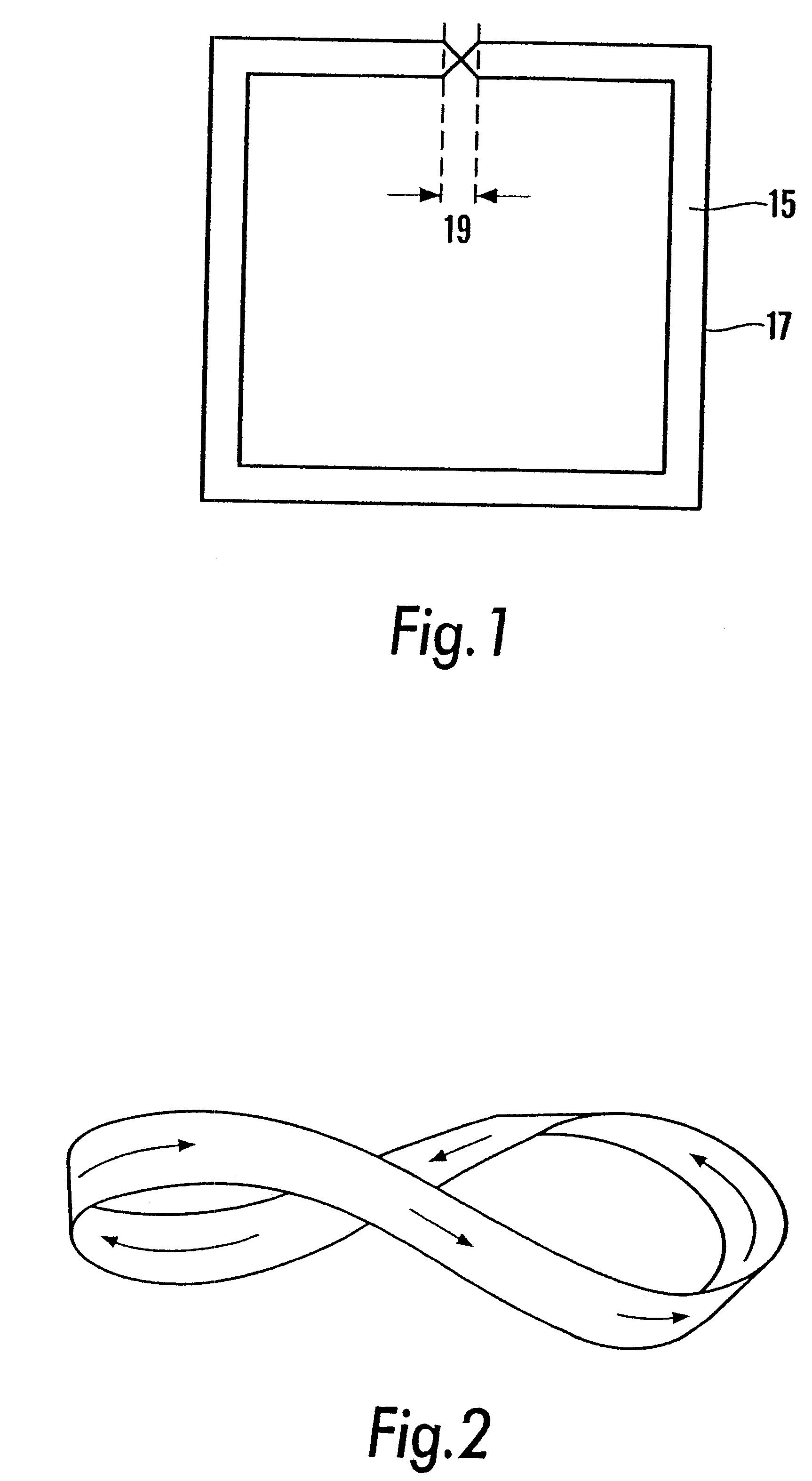

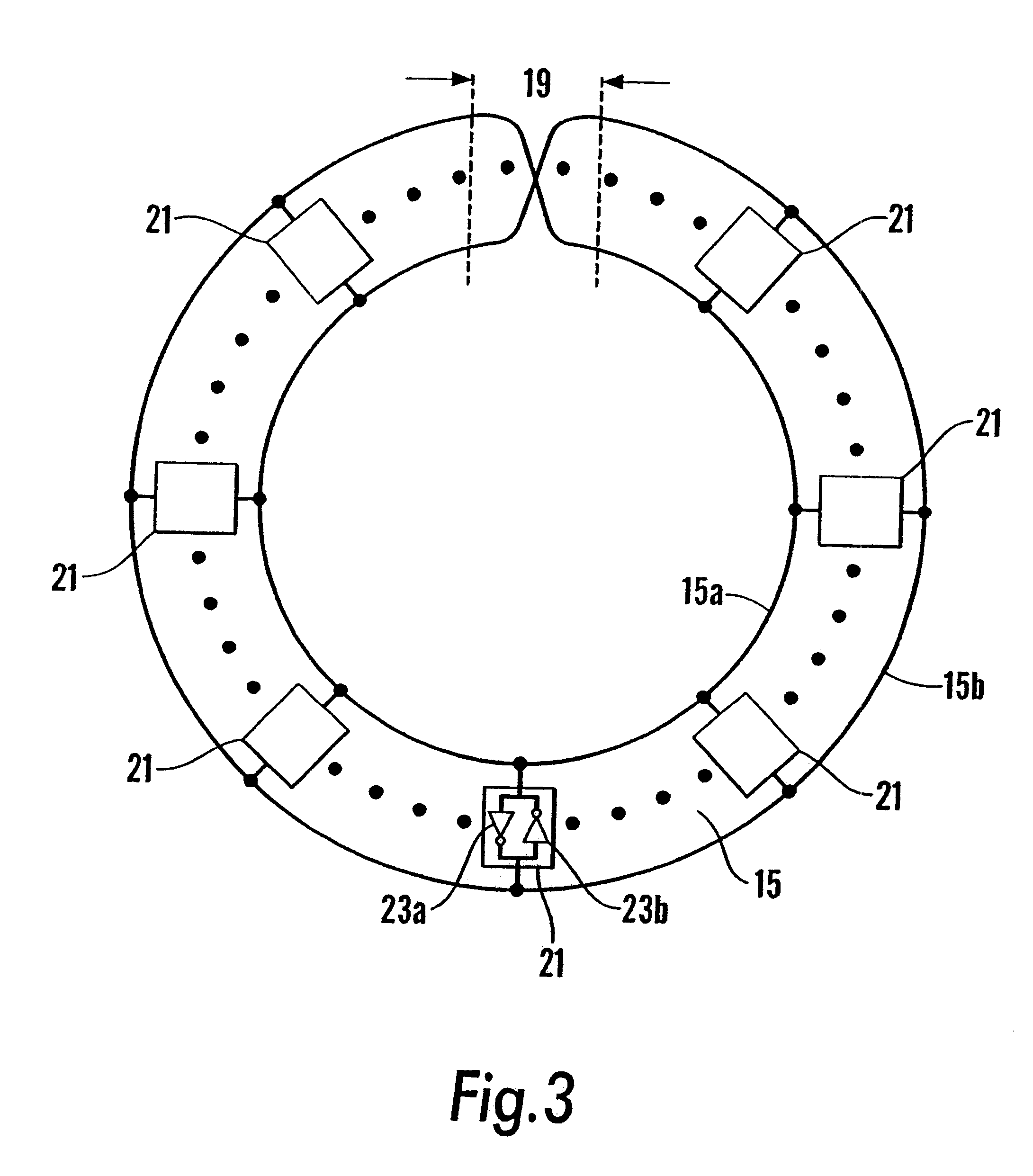

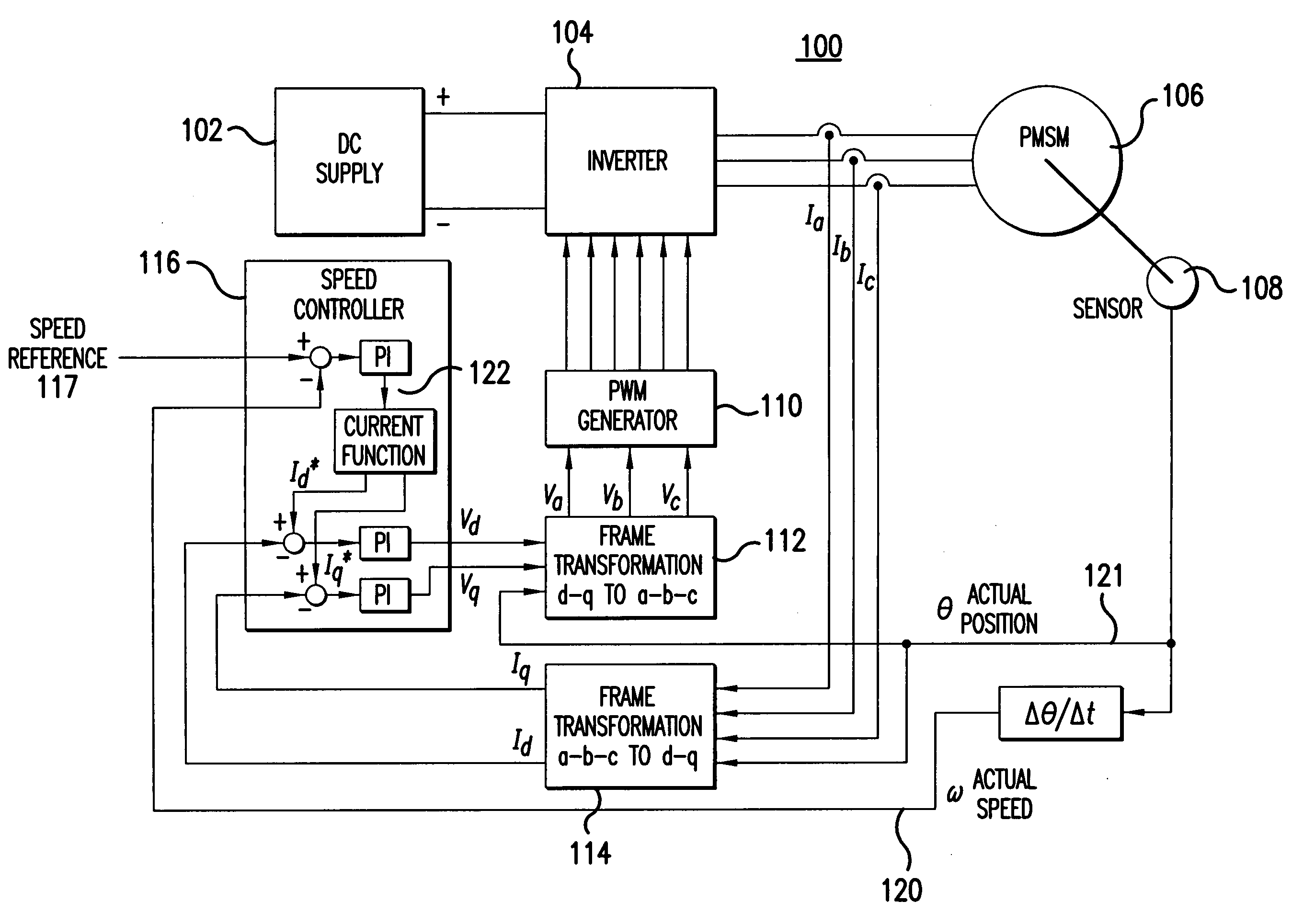

Signal isolators using micro-transformers

ActiveUS7075329B2Reliability increasing modificationsSemiconductor/solid-state device detailsTransformerEngineering

A logic signal isolator comprising a transformer having a primary winding and a secondary winding; a transmitter circuit which drives said primary winding in response to a received logic signal, such that in response to a first type of edge in the logic signal, a signal of a first predetermined type is supplied to the primary winding and in response to a second type of edge in the logic signal, a signal of a second predetermined type is supplied to said primary winding, the primary winding and the transmitter being referenced to a first ground; and the secondary winding being referenced to a second ground which is galvanically isolated from the first ground and said secondary winding supplying to a receiver circuit signals received in correspondence to the signals provided to the primary winding, the receiver reconstructing the received logic signal from the received signals.

Owner:ANALOG DEVICES INC

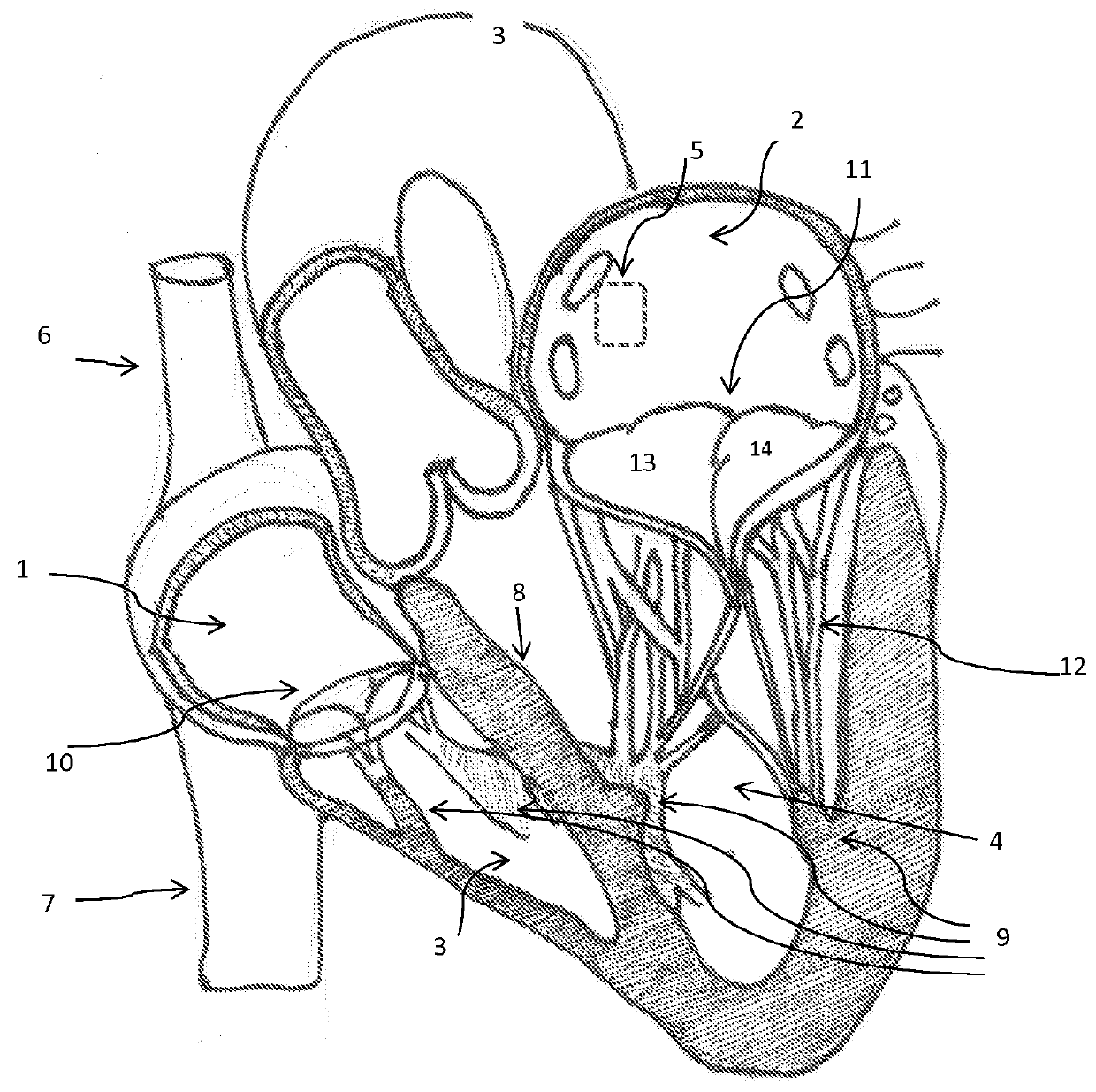

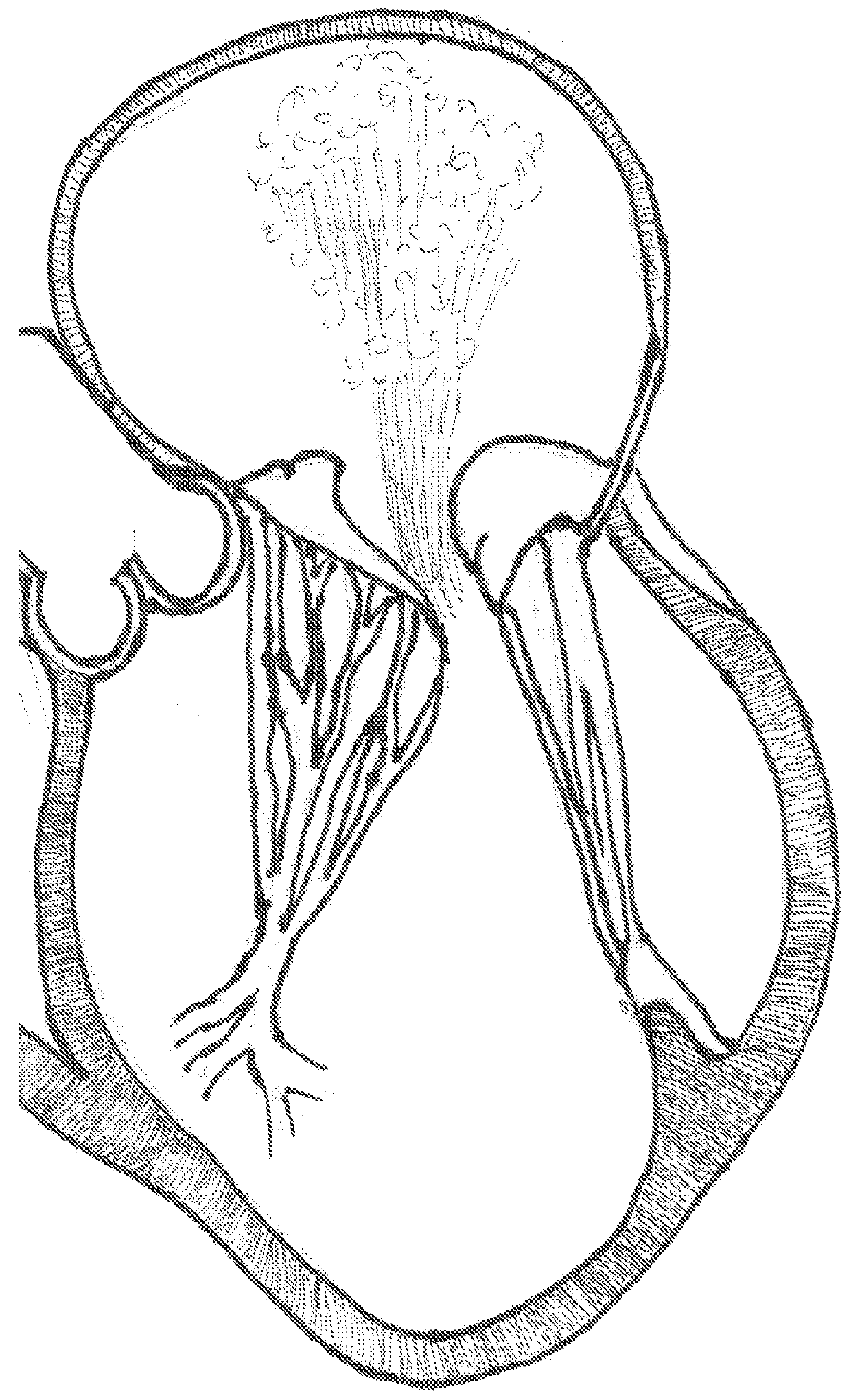

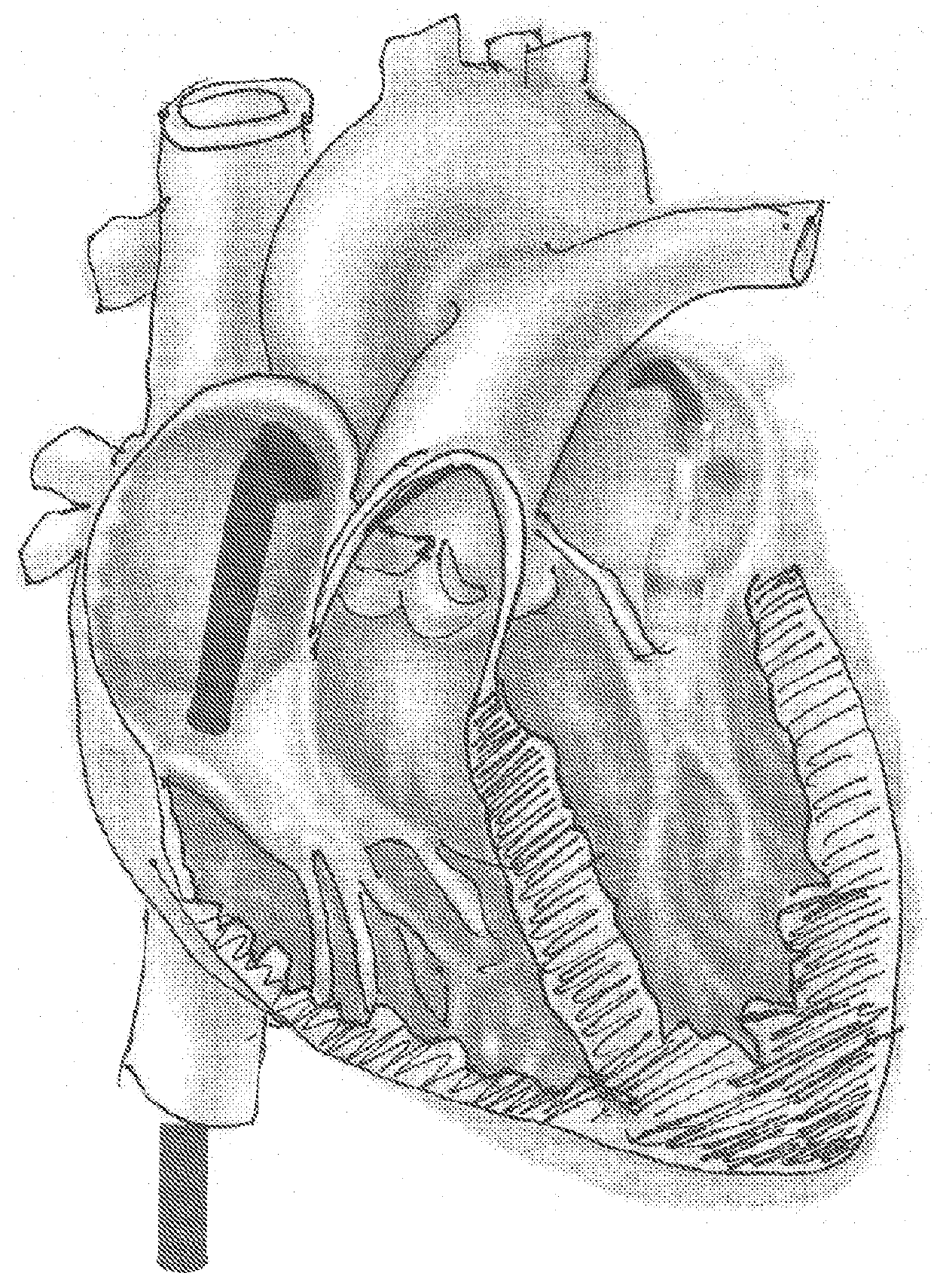

Catheter-guided replacement valves apparatus and methods

ActiveUS20160030171A1Reduced overall height dimensionMinimize intrusionStentsHeart valvesStructure and functionCatheter

The present invention is a replacement mitral valve suitable for catheter-based deployment. The replacement mitral valve has structure and dimensions that are uniquely suited to engage the annulus surrounding the native mitral valve and to restore normal function to a diseased valve. The invention describes the structures and functions of a replacement mitral valve and methods that are adapted for minimally invasive, catheter-based deployment of the valve.

Owner:NAVIGATE CARDIAC STRUCTURES

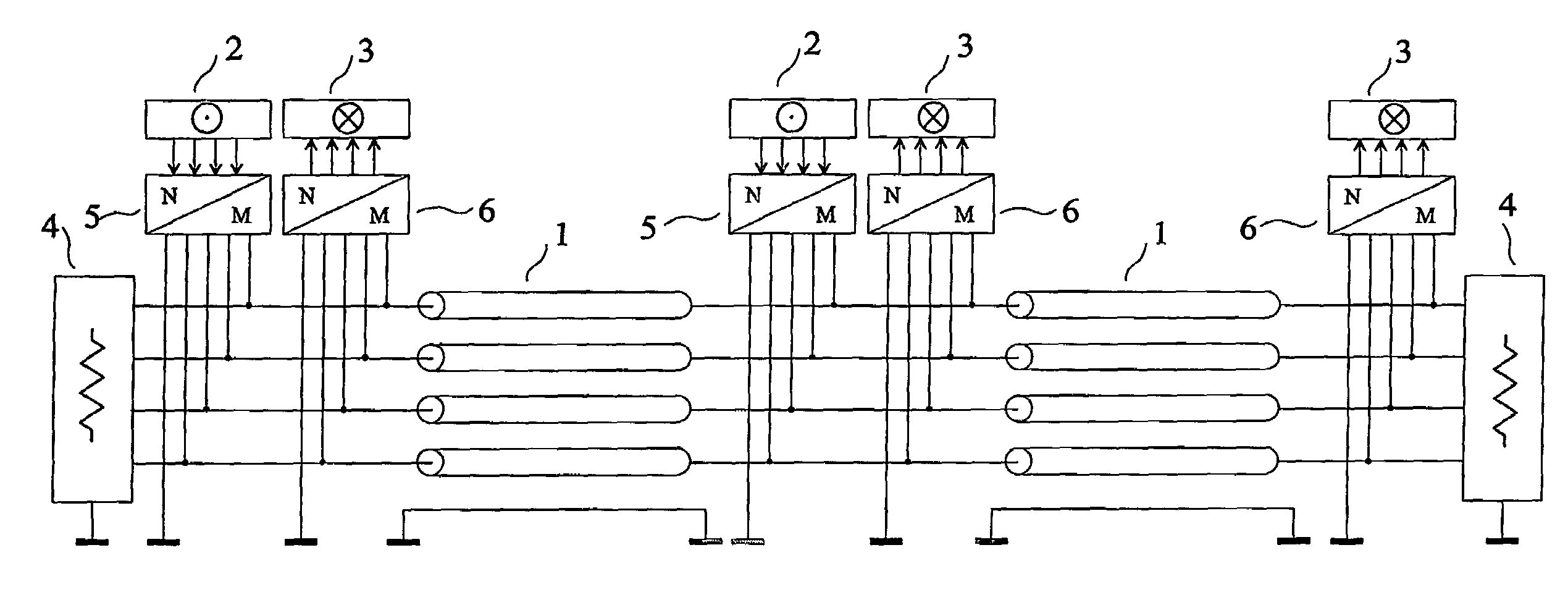

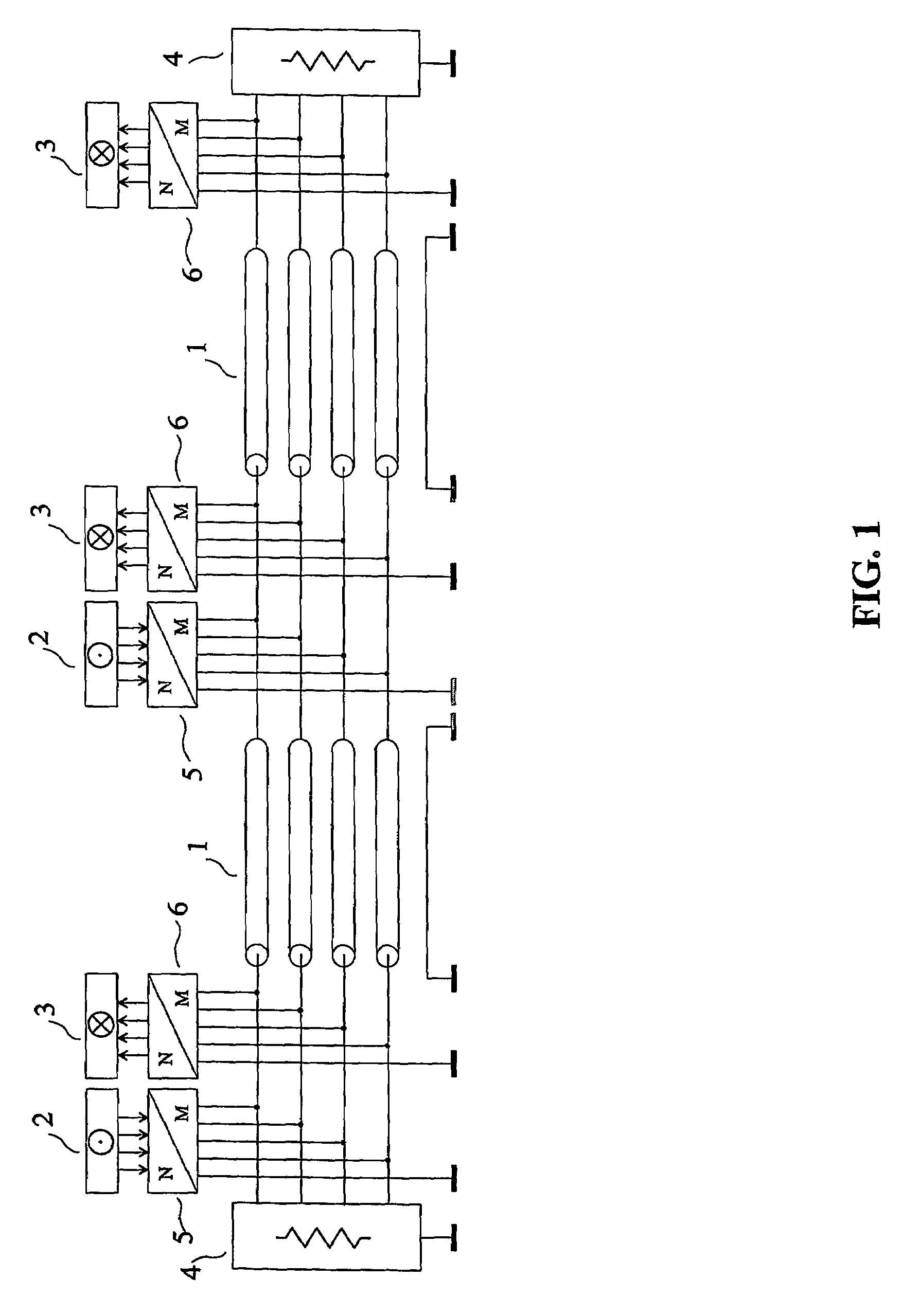

Method and device for transmission without crosstalk

ActiveUS7408426B2Simplifying the transmitting circuits and/or the receiving circuitsSimplification of the transmitting circuits and/or the receiving circuitsReliability increasing modificationsDc network circuit arrangementsElectrical conductorInterconnection

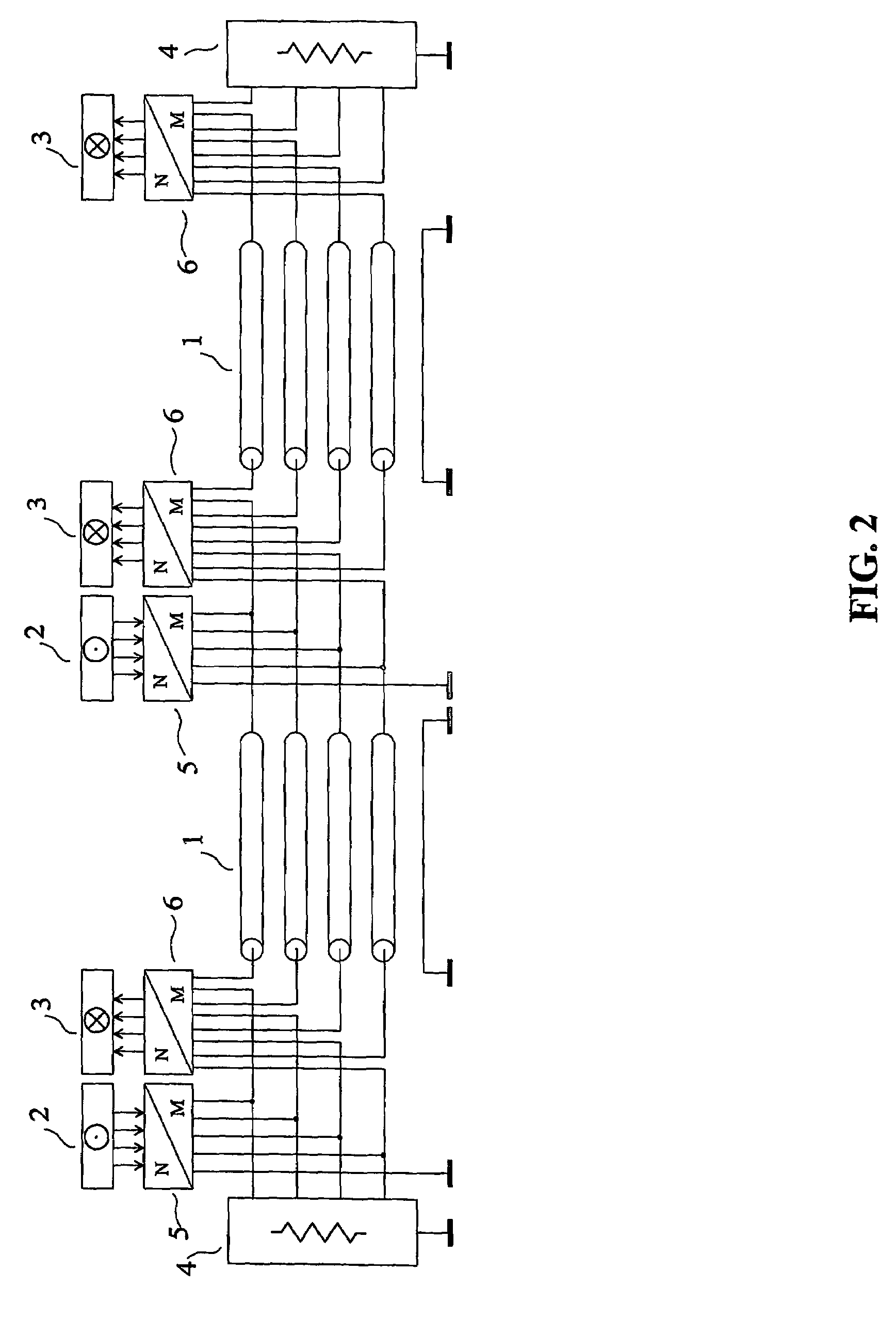

The invention relates to a method and a device for transmission without crosstalk in interconnections used for sending a plurality of signals, such as the interconnections made with flat multiconductor cables, or with the tracks of a printed circuit board, or inside an integrated circuit. An interconnection with four parallel transmission conductors plus a reference conductor has each of its ends connected to a termination circuit. The transmitting circuit receives at its input the signals of the four channels of the source and its output terminals are connected to the conductors of the interconnection. The receiving circuit(s) input terminals are connected to the conductors of the interconnection, and its four output channels are connected to the destination. The signals of the four channels of an active source are sent to the four channels of the destination, without noticeable crosstalk.

Owner:S AQUA SEMICONDUCTOR LLC

RF notch filter having multiple notch and variable notch frequency characteristics

InactiveUS6020783AReduce signalingImproved noise attenuationMultiple-port networksOscillations generatorsBandpass filteringFrequency spectrum

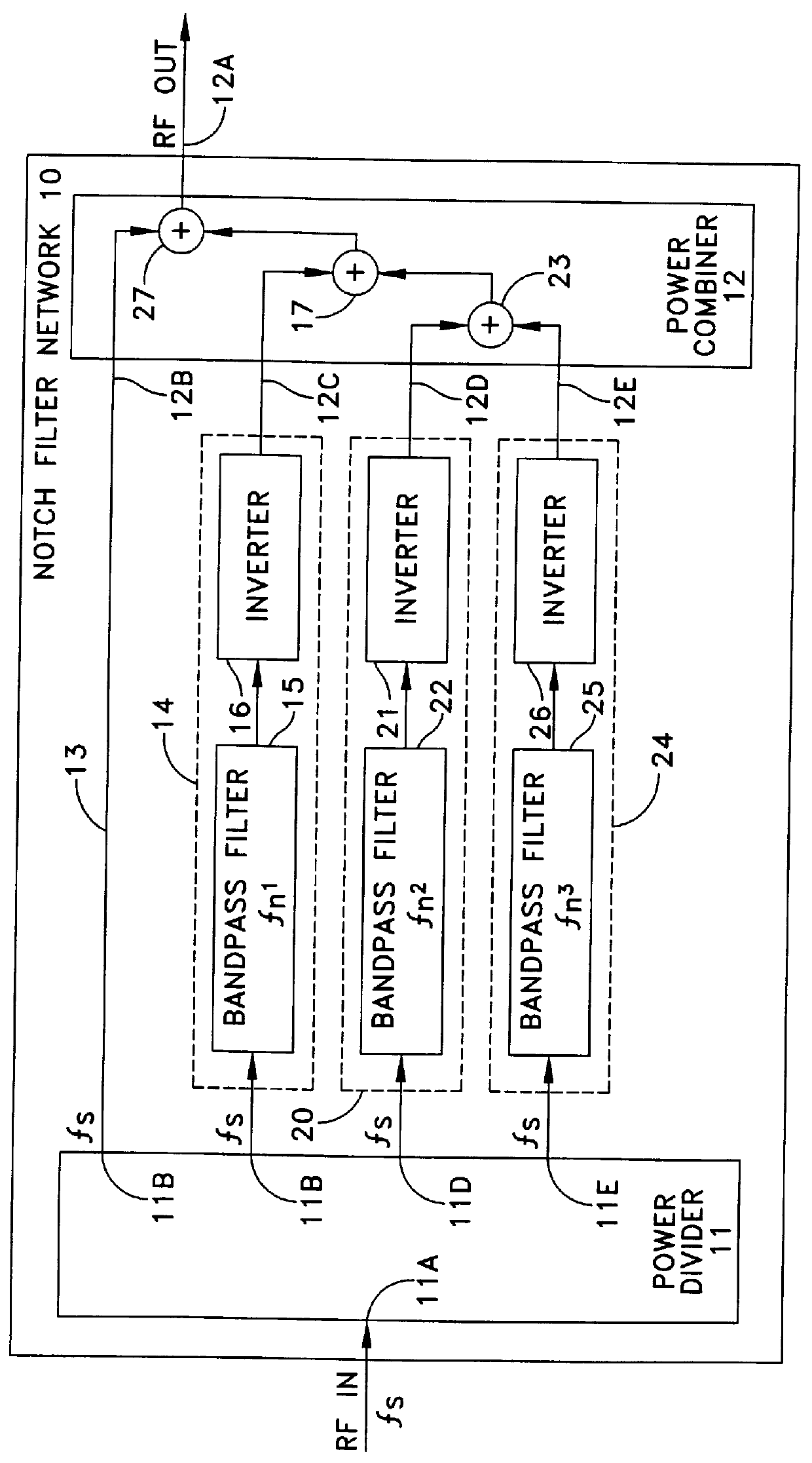

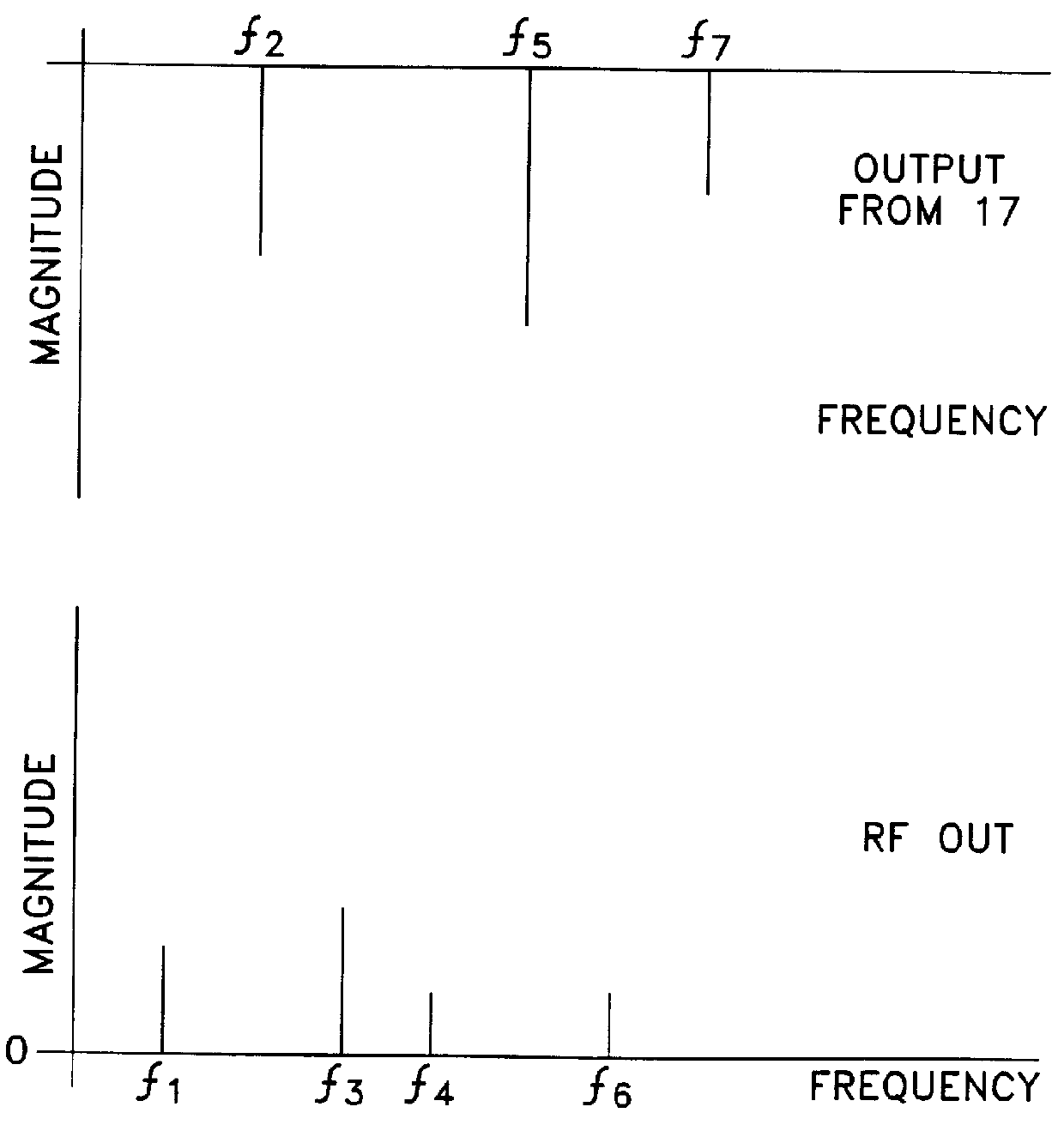

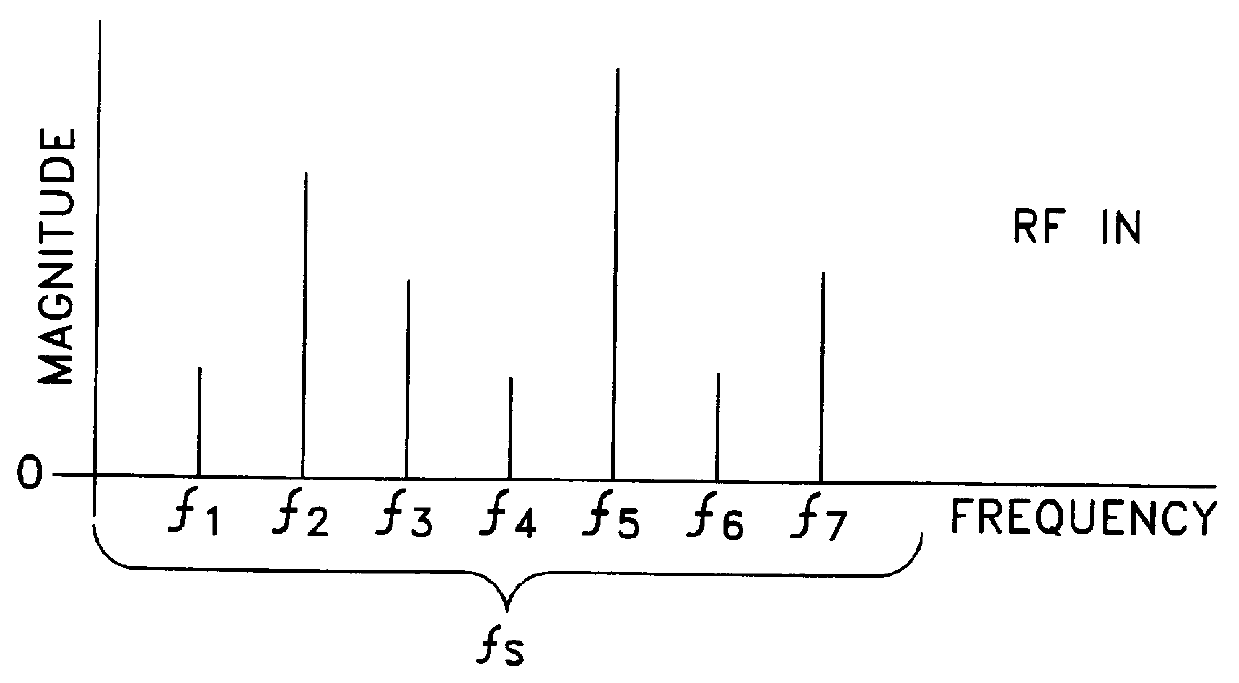

A filter network having the capability of establishing multiple, tunable notch frequencies. A notch filter path is established for each notch frequency and includes a bandpass filter and inverter. An input RF signal covering a wide frequency range is applied to all the notch filter paths. Each notch filter path produces an output spectrum that is equal in magnitude and 180.degree. out of phase with respect to an undesired frequency spectrum. A combiner circuit combines the outputs of each notch filter path in parallel with the RF input signal to produce an RF output signal with all desired spectra unchanged and all undesired spectra attenuated.

Owner:SIGNAL TECH CORP

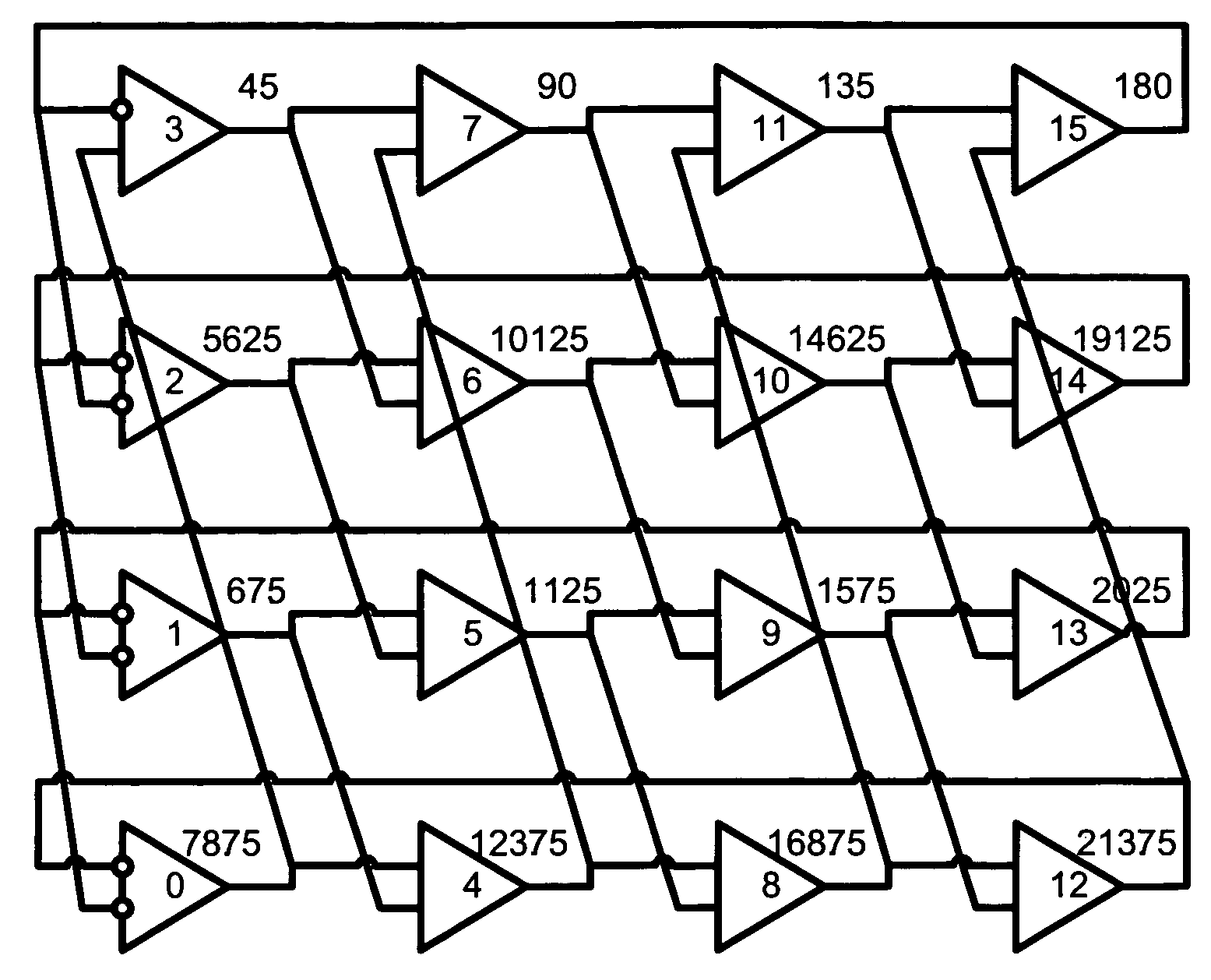

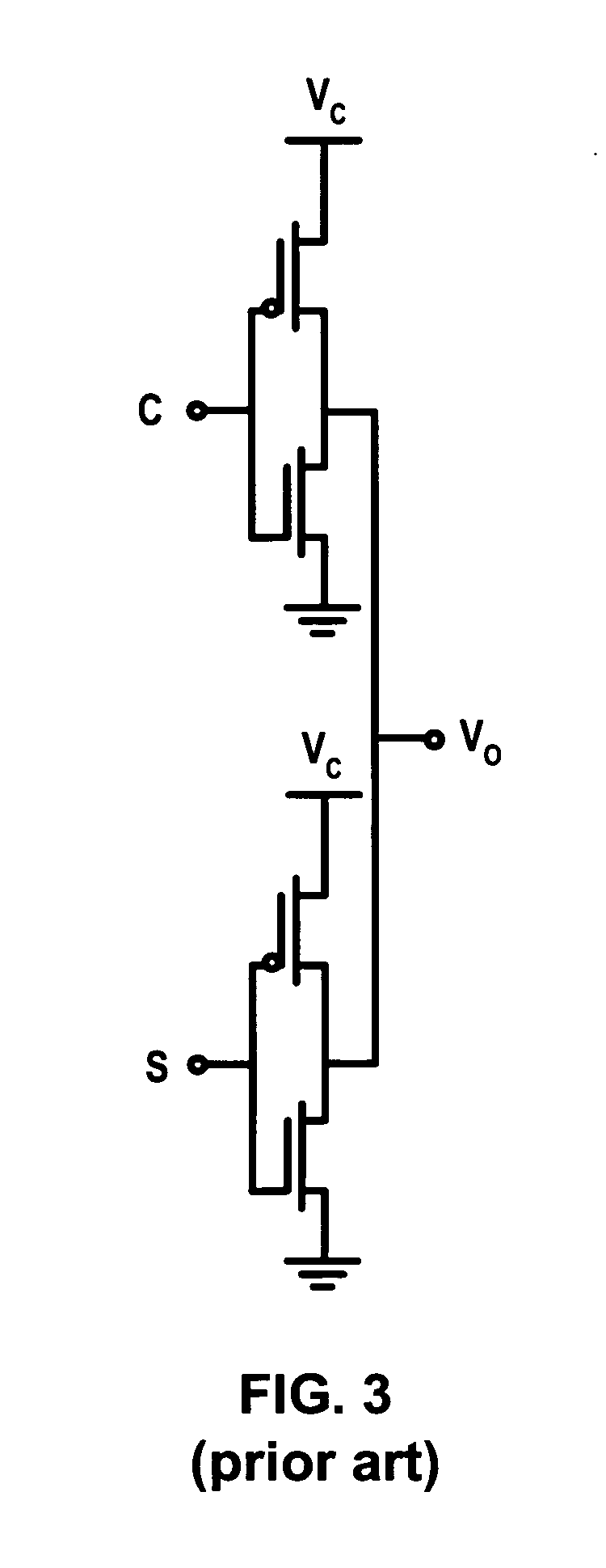

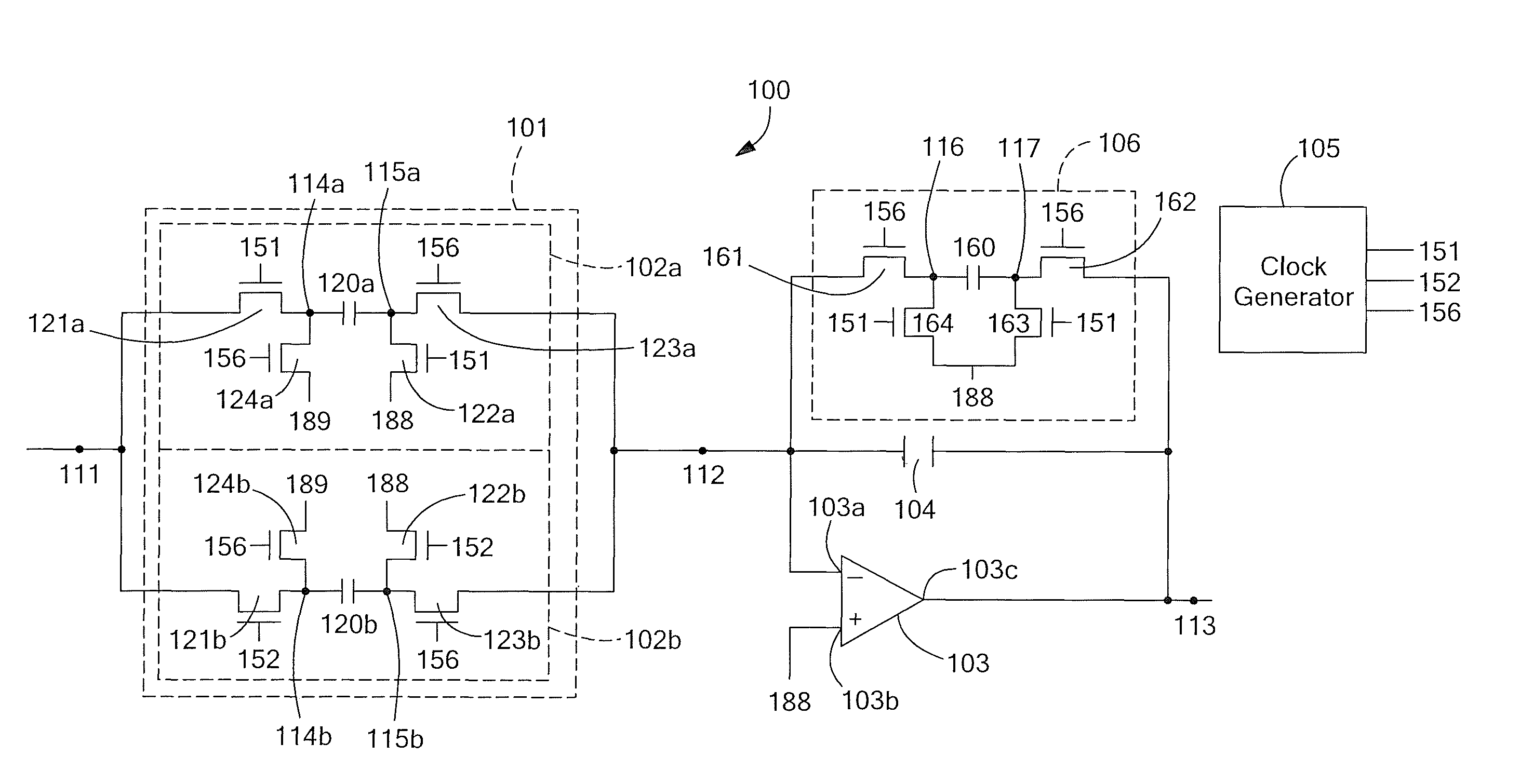

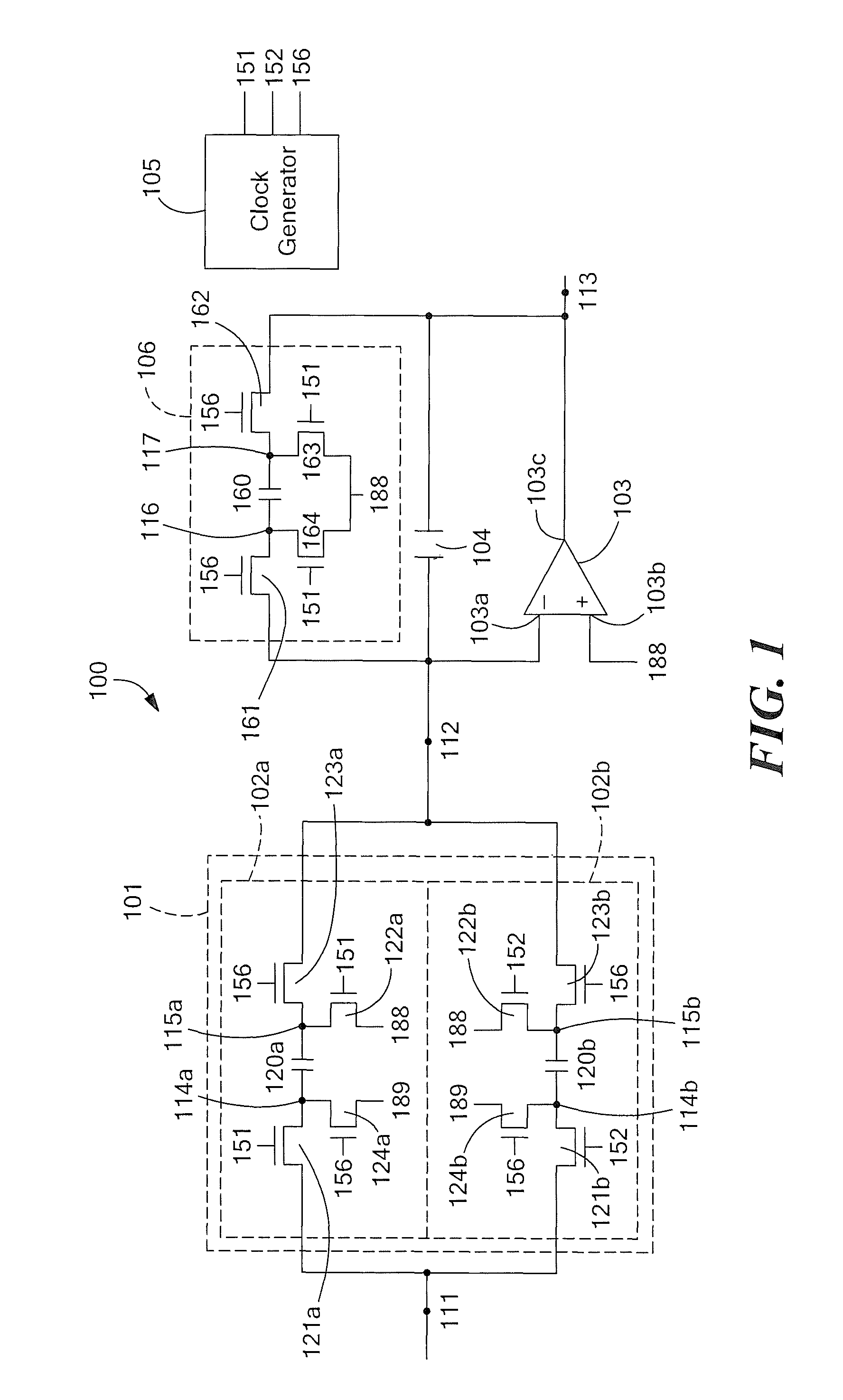

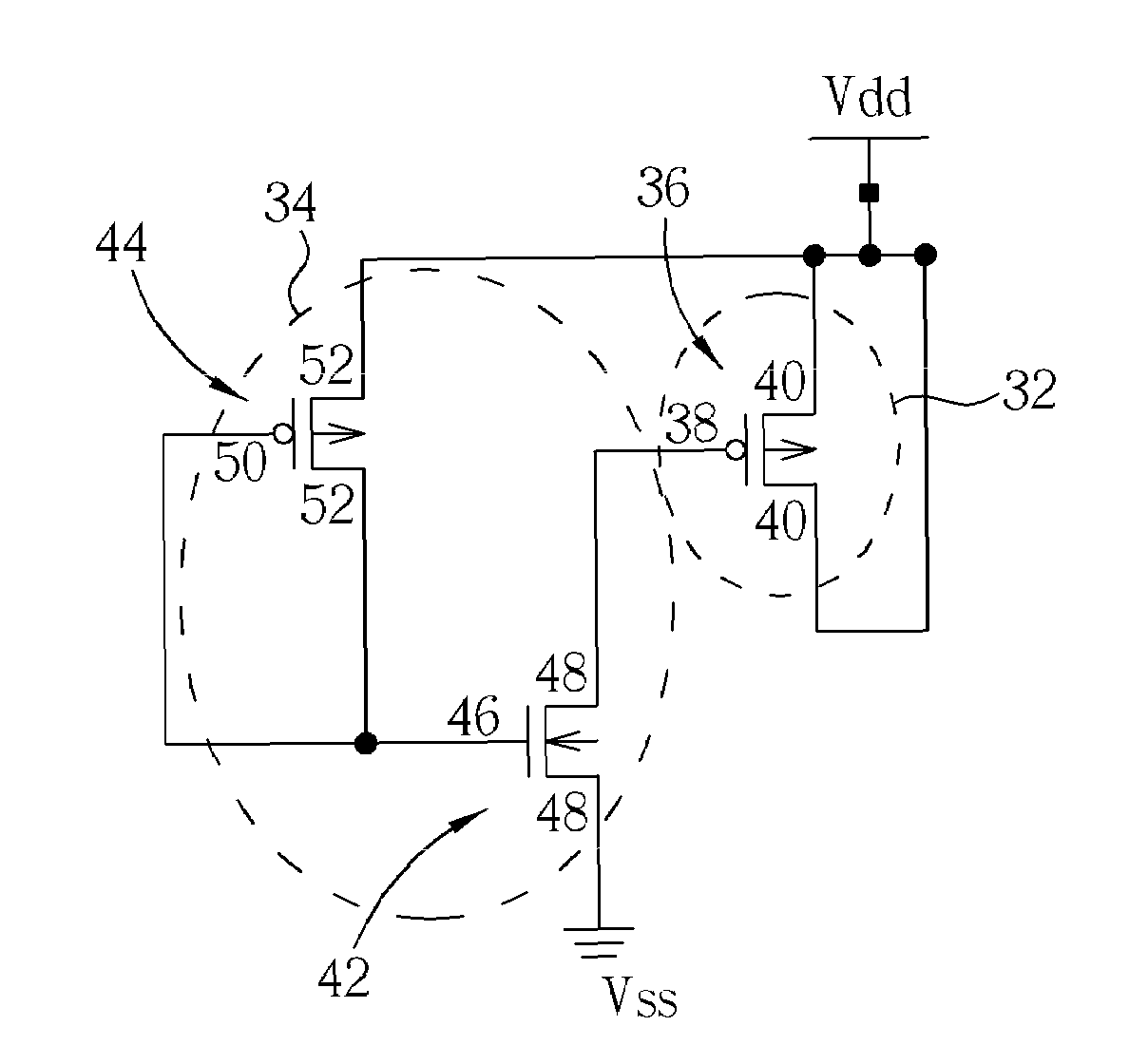

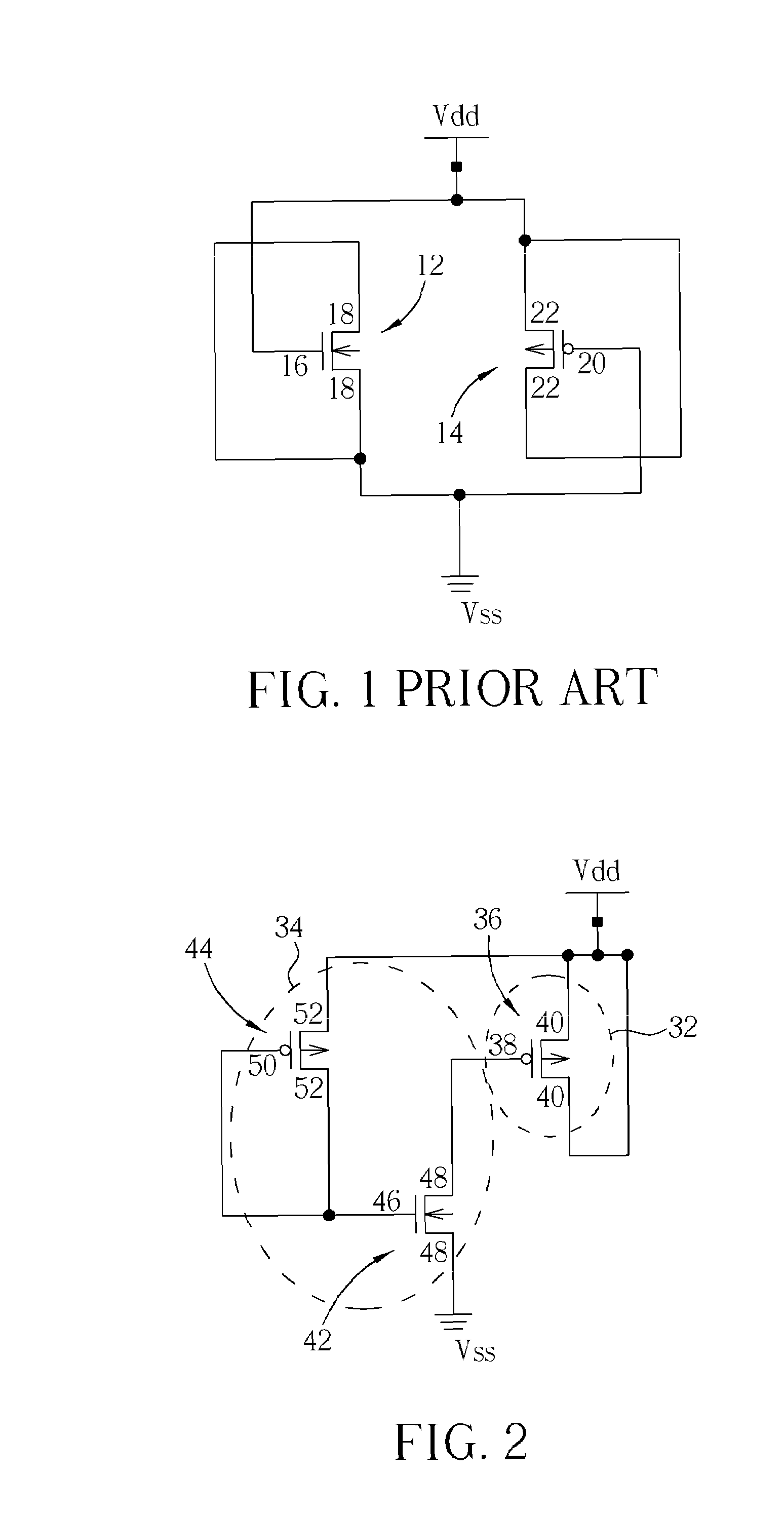

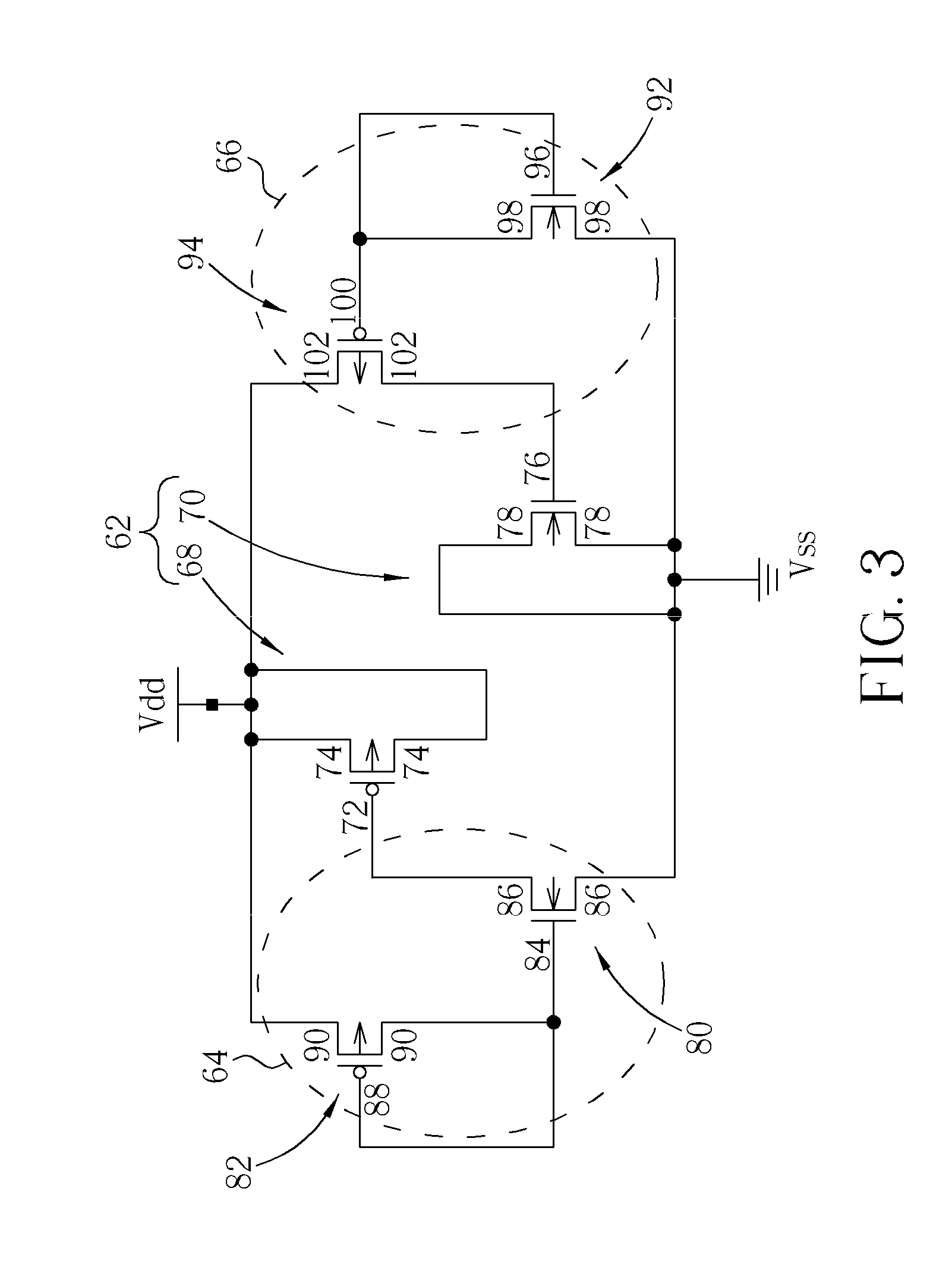

Array oscillator and polyphase clock generator

InactiveUS20060001496A1Increase speedReduce jitterPulse automatic controlPulse generation by logic circuitsMOSFETMultiplexing

The present invention relates generally to array oscillator circuits for use as phase delay generators. More particularly, the present invention relates to a novel array oscillator for providing a plurality of phases which have stable phase relationships. The present invention is particularly applicable to the generation of poly-phase clocks for receivers of very high speed interfaces which employ an over-sampling technique, or multiplexing, and for high speed logic. The array oscillator according to the invention comprises at least one ring oscillator having a plurality of at least two interconnected buffer stages including at least one, or any integer odd number of inverting stages and a series of non-inverting stages, wherein the buffer stages are formed of N-type MOSFET transistors.

Owner:ACUID +1

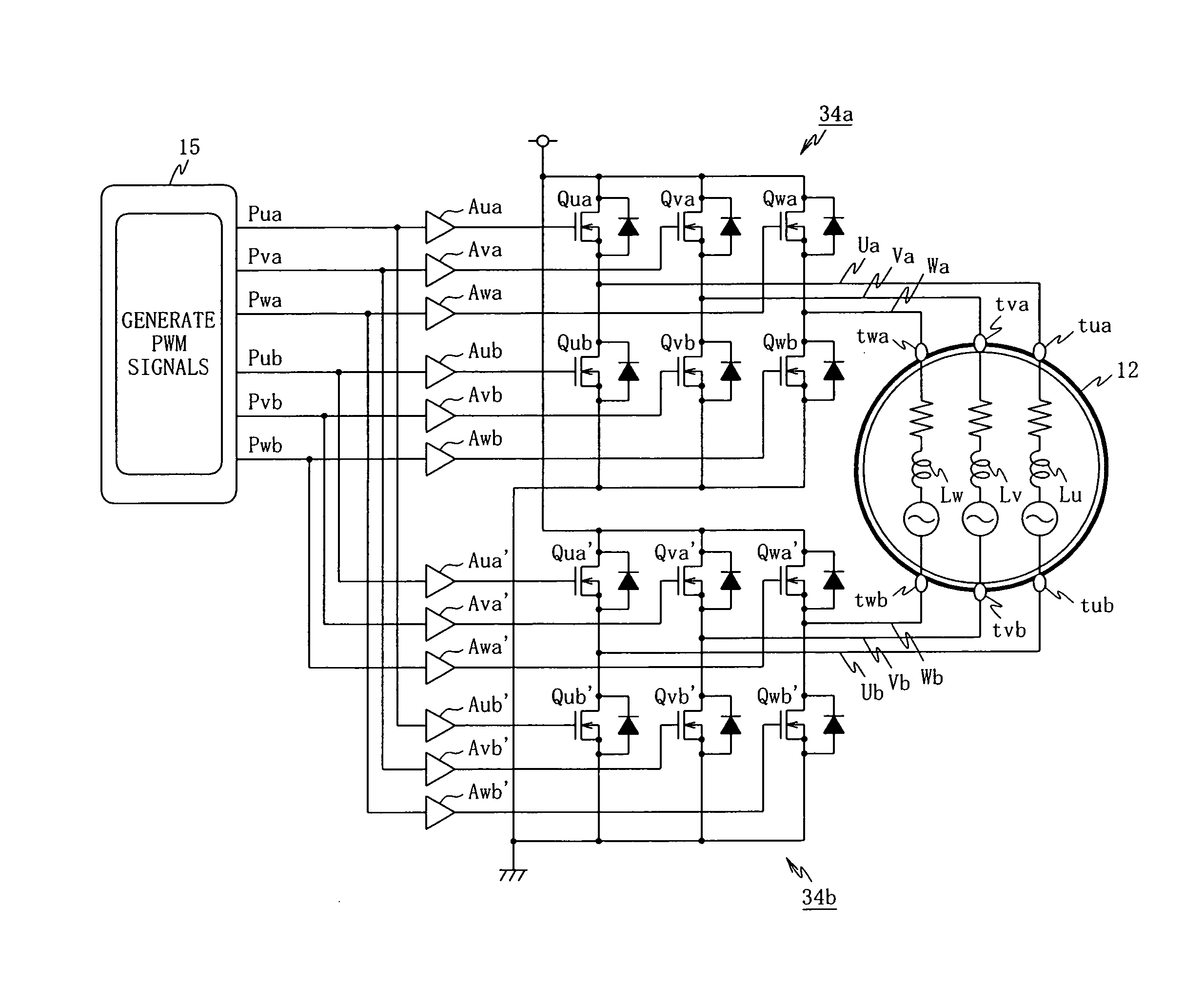

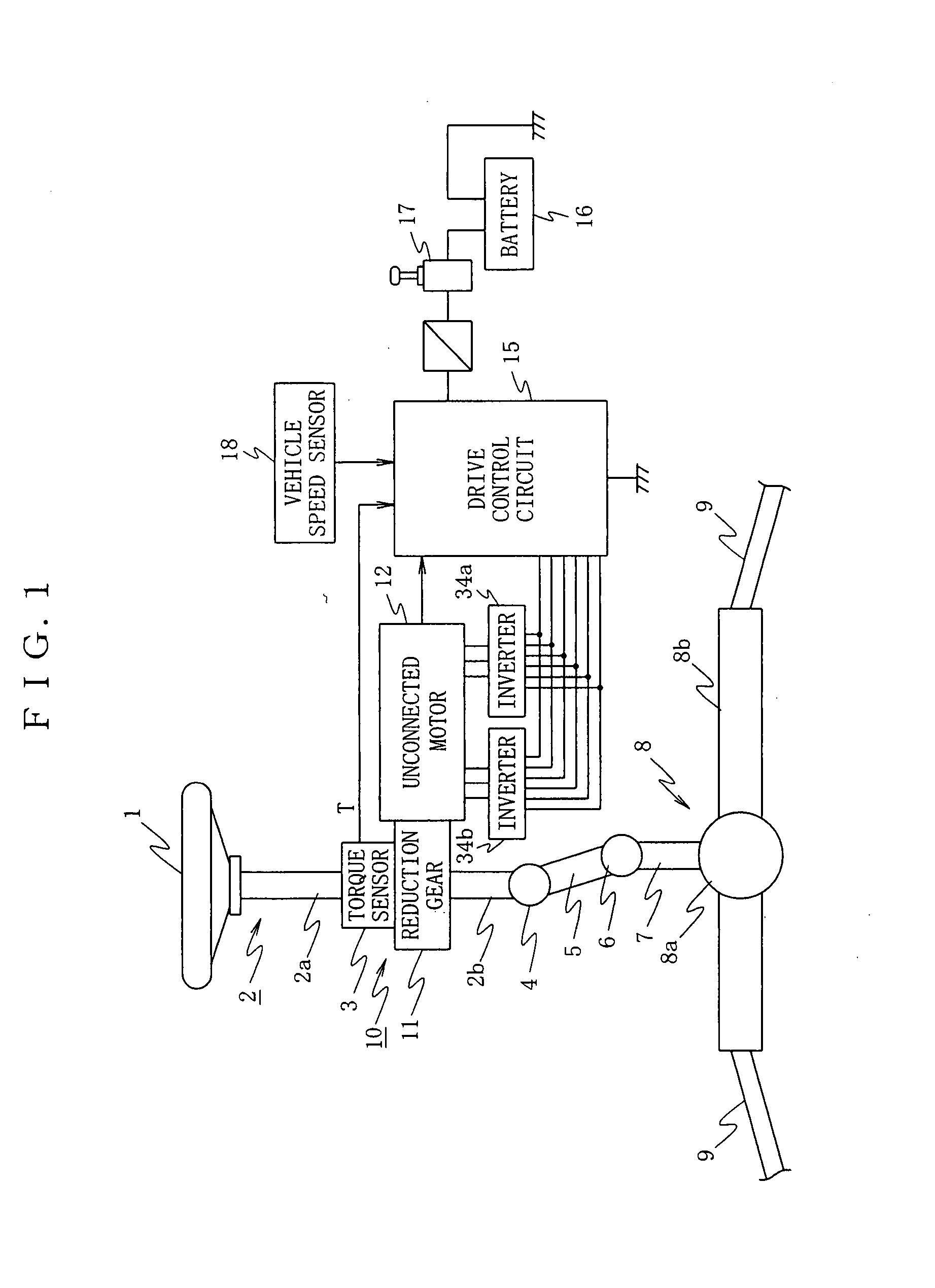

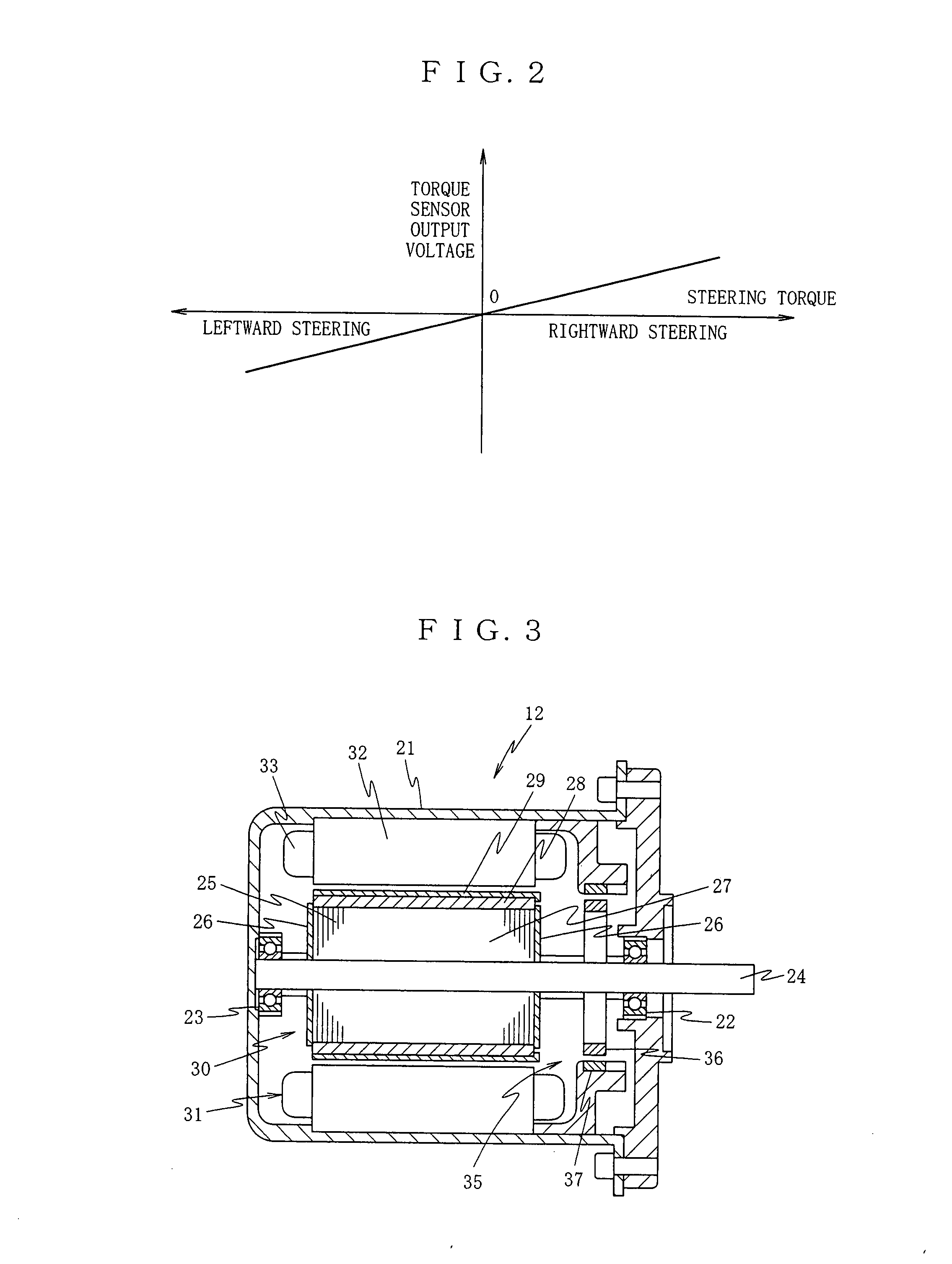

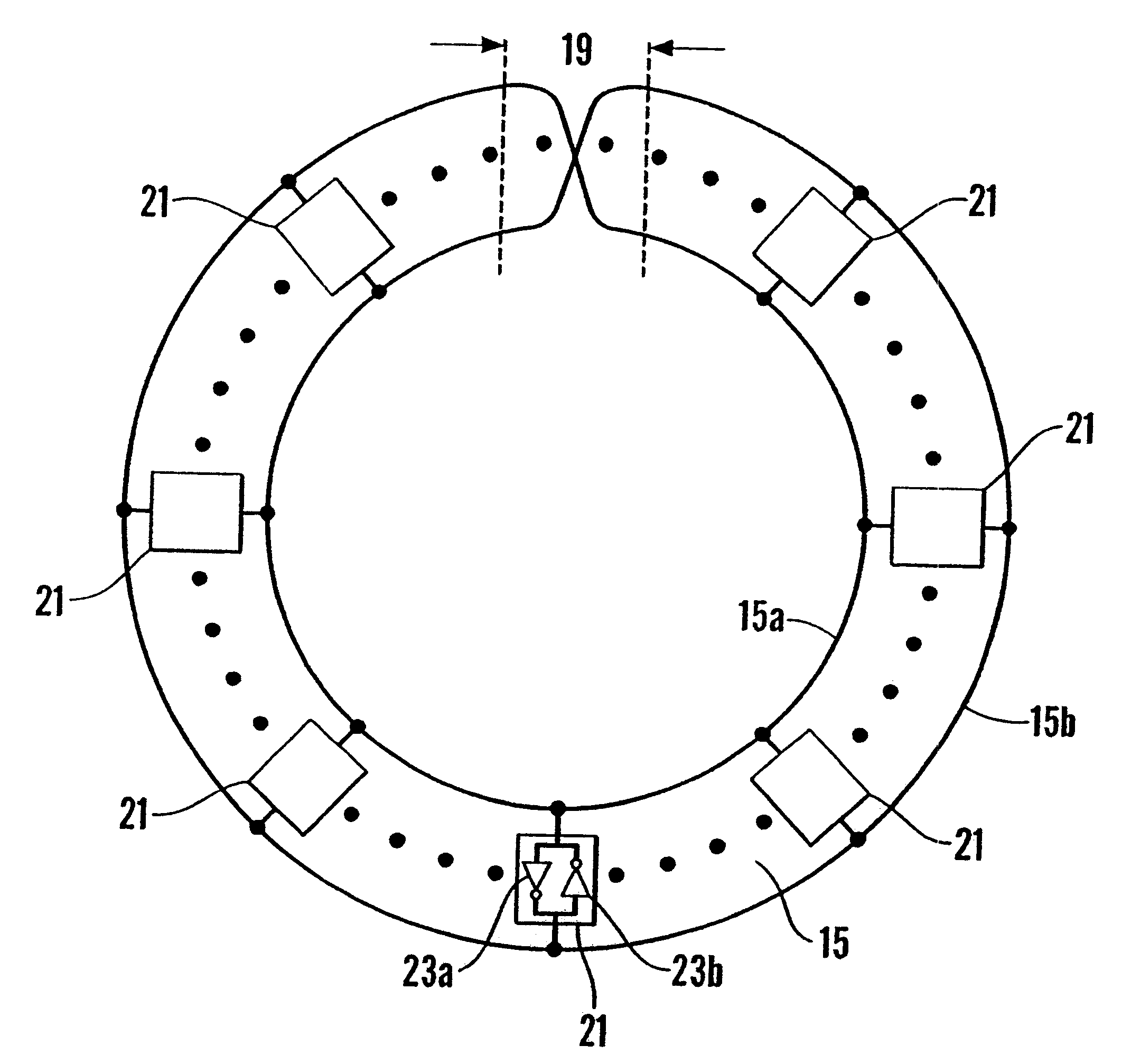

Unconnected Motor, Drive Control Device Thereof, And Electric Power Steering Device Using Drive Control Device Of Unconnected Motor

InactiveUS20080067960A1Constant gainIncreased current consumptionMotor/generator/converter stoppersSynchronous motors startersElectric power steeringControl signal

A drive control device of an unconnected motor capable of resolving power shortage and increasing motor output without using a boost circuit, and an electric power steering device using the unconnected motor. The drive control device comprises an unconnected motor (12) having a rotor in which permanent magnets are allocated and a stator opposing the rotor, in which armature winding Lu to Lw of a plurality (N number) of phases are independently arranged, a pair of inverter circuits (34a, 34b) individually connected to both ends of each armature winding, and a drive control circuit (15) which drives the pair of inverter circuits (34a, 34b) with a predetermined number (e.g. 2N) of PWM drive control signals.

Owner:NSK LTD

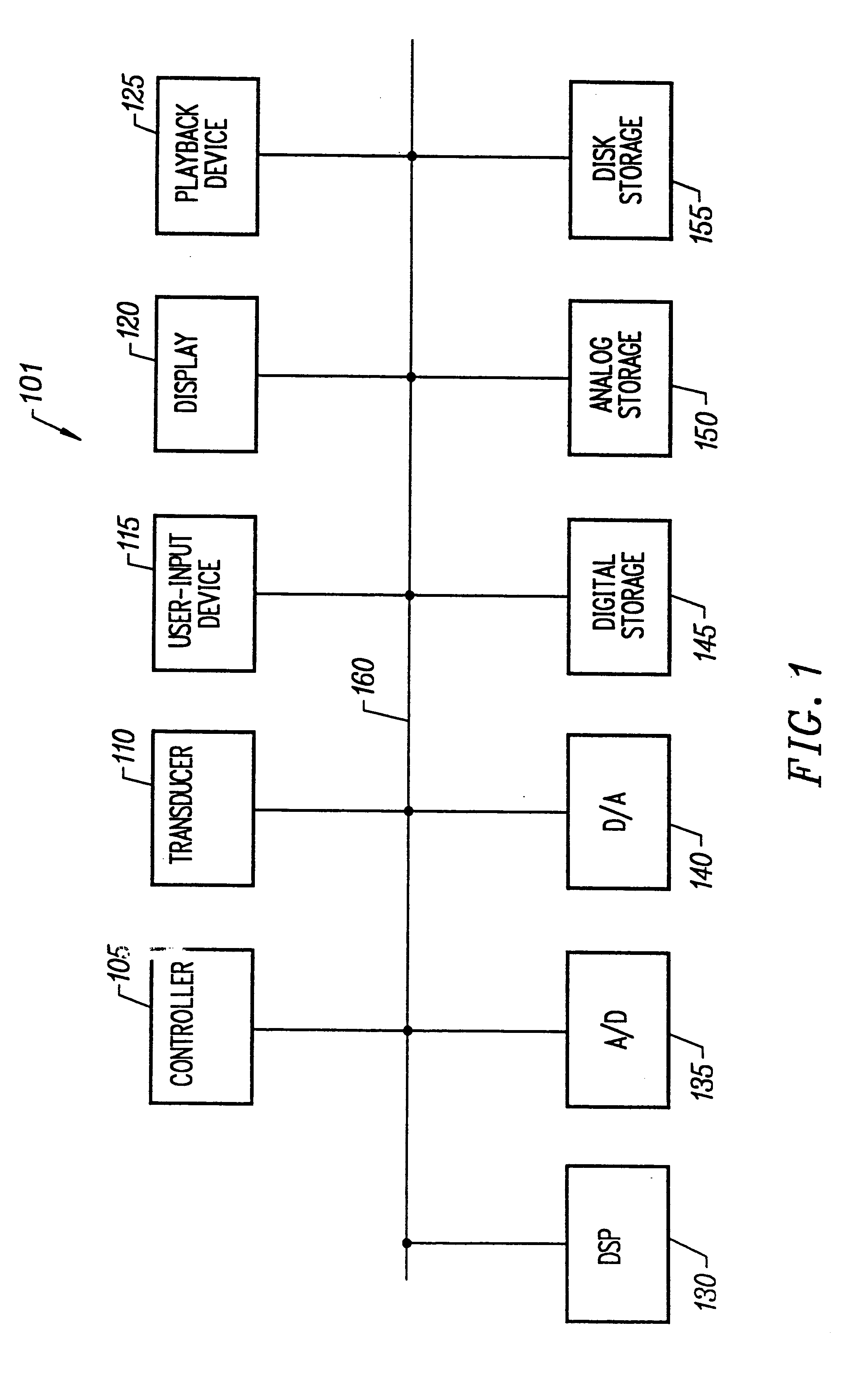

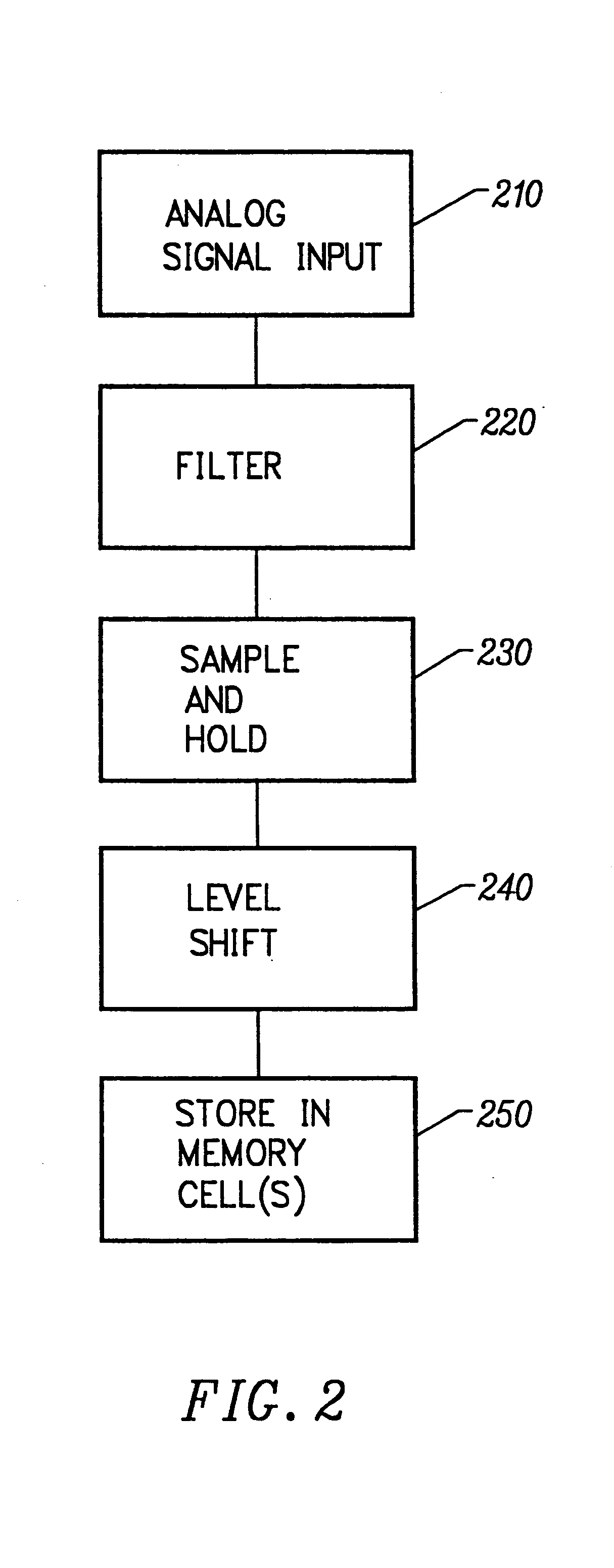

Adjustable level shifter circuits for analog or multilevel memories

InactiveUS6184726B1Prolong lifeImprove reliabilityPulse automatic controlElectric analogue storesMultilevel memoryEngineering

Level shifter circuits are used to configure analog or multilevel memory cells. A level shifter circuit generates an output voltage that is above the input voltage by an offset voltage value. The magnitude of this offset voltage or the relationship between the input and output voltages of the level shifter is adjustable or programmably selectable. Adjustments can be made after the integrated circuits is fabricated and packaged. Adjustments are made by configuring bits of data in the integrated circuit to indicate the offset voltage or other parameters. These configuration bits are implemented using latches, flip-flops, registers, memory cells, or other storage circuits.

Owner:SANDISK CORP

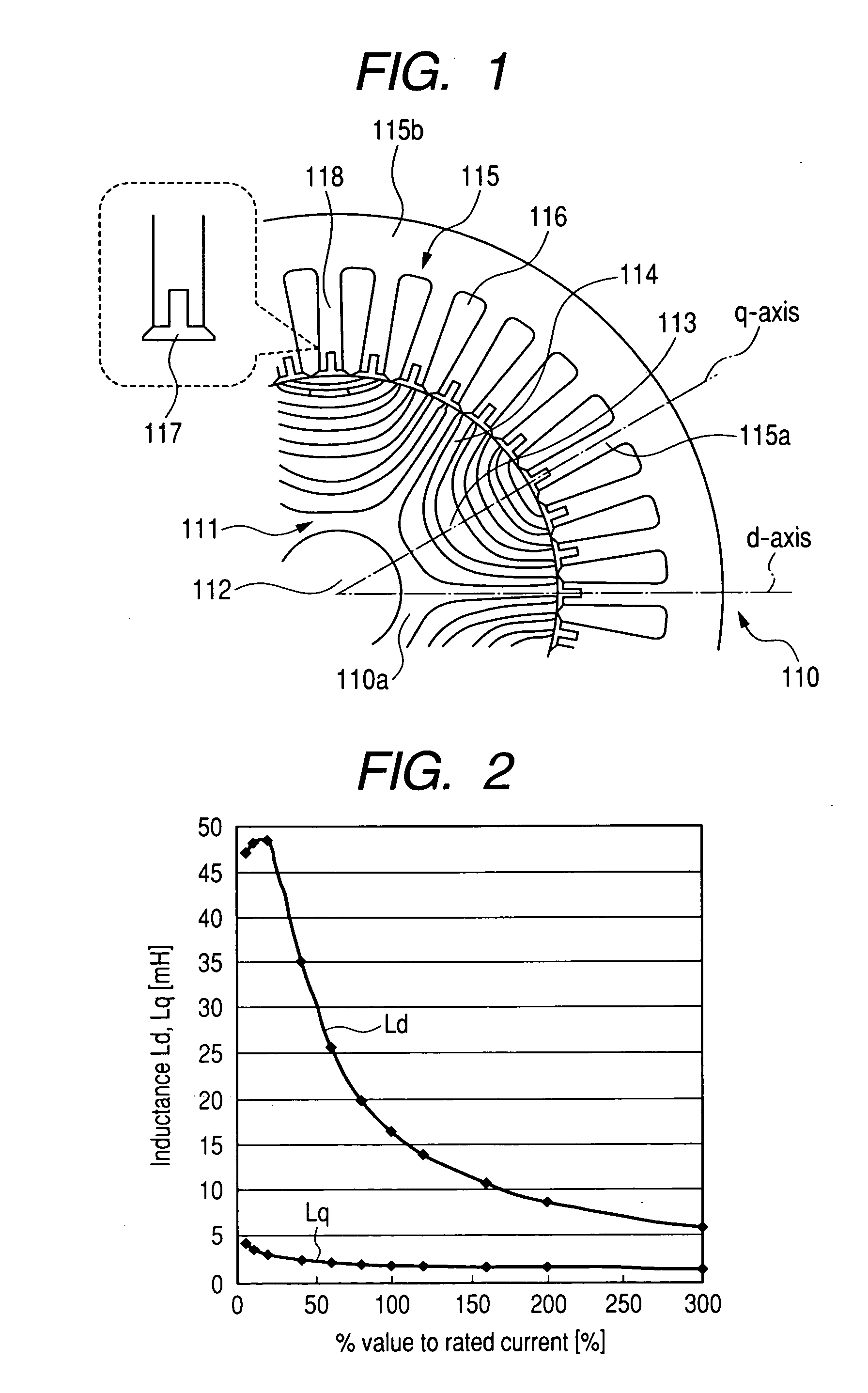

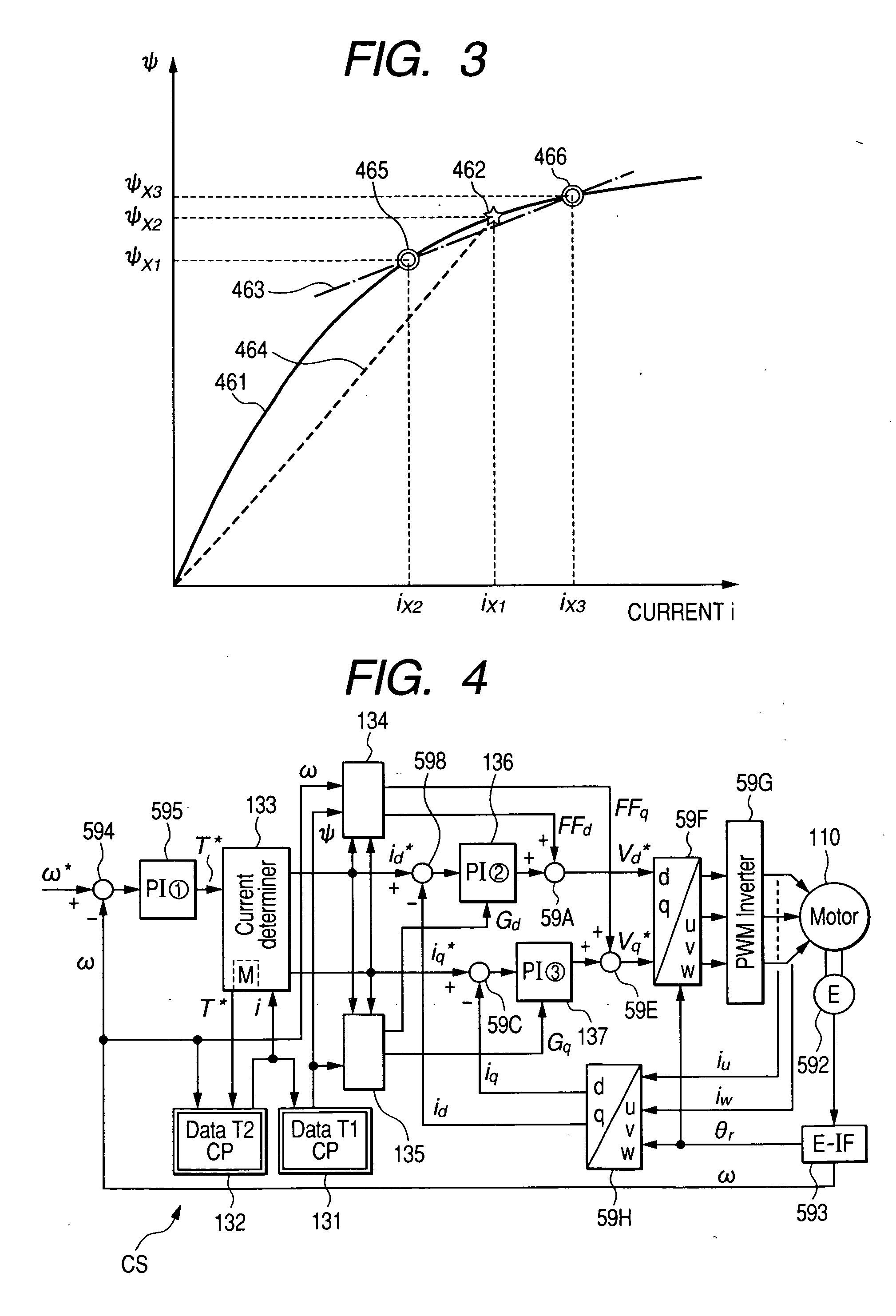

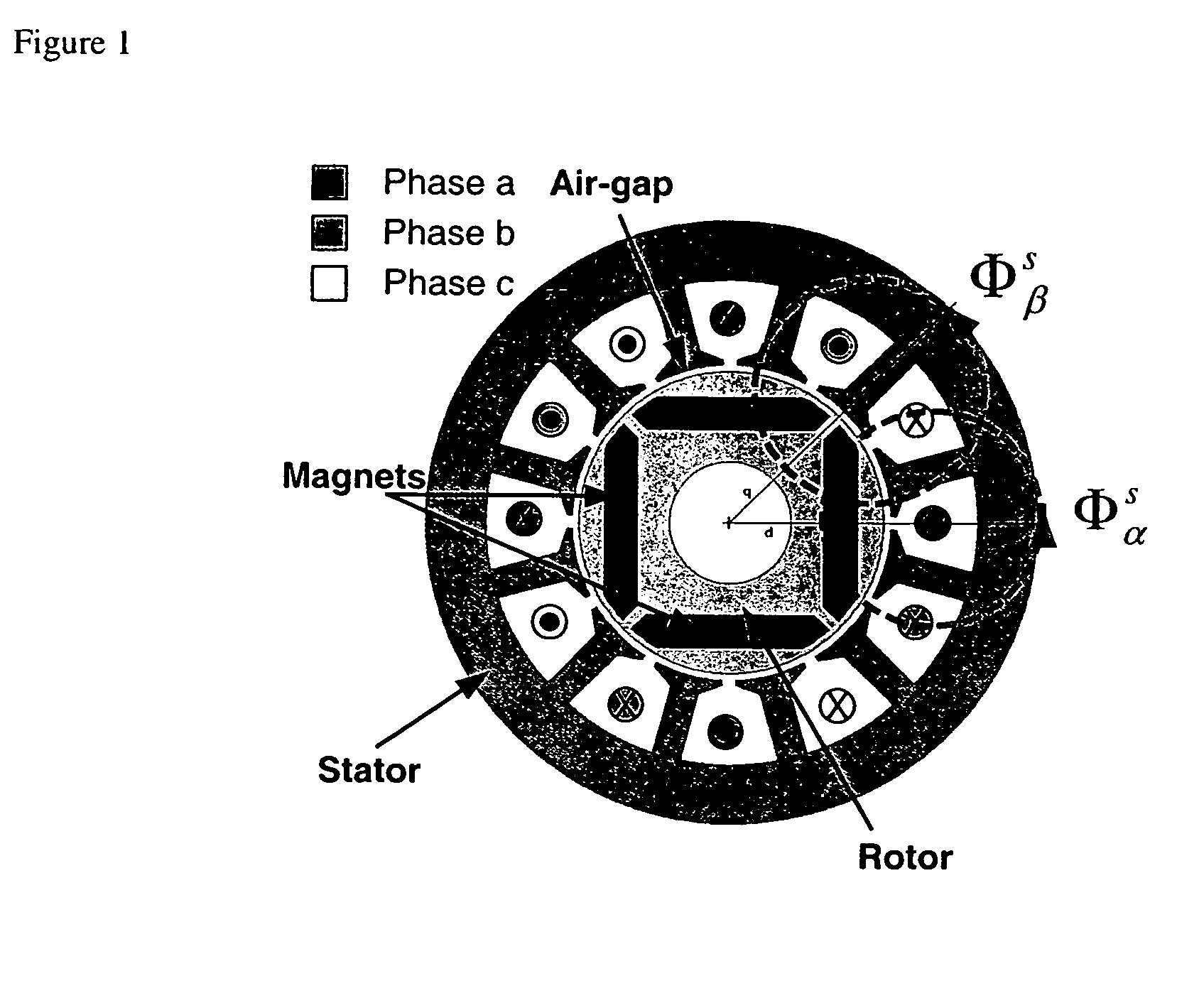

System and method for controlling motor using parameter associated with magnetic flux

InactiveUS20080129243A1Reliably graspTorque ripple controlSynchronous motors startersDriving currentOperating point

A control method for a motor that rotates based on flux linkages to a winding member of the motor when the winding member is energized by a drive current is provided. The method includes storing magnetic-state information indicative of a relationship between each of a plurality of predetermined operating points of the drive current and a magnetic-state parameter associated with the flux linkages. The method includes obtaining at least one of command information associated with an operating state of the motor and detection information associated with the operating state of the motor. The method includes referencing the magnetic-state information with the use of the obtained at least one of the command information and detection information to obtain a value of the magnetic-state parameter based on a result of the reference. The method includes controlling an output of the motor based on the obtained value of the magnetic-state parameter.

Owner:DENSO CORP

Electronic circuitry

InactiveUS6556089B2Short fallShort riseDelay lines pulse generationPulse automatic controlCMOSBipolar signal

Timing signal generation and distribution are combined in operation of a signal path exhibiting endless electromagnetic continuity affording signal phase inversion and having associated regenerative active means. Two-or more-phases of substantially square-wave bipolar signals arise directly in travelling wave transmission-line embodiments compatible with semiconductor fabrication including CMOS. Coordination by attainable frequency synchronism with phase coherence for several such oscillating signal paths has intra-IC inter-IC and printed circuit board impact.

Owner:ANALOG DEVICES INC

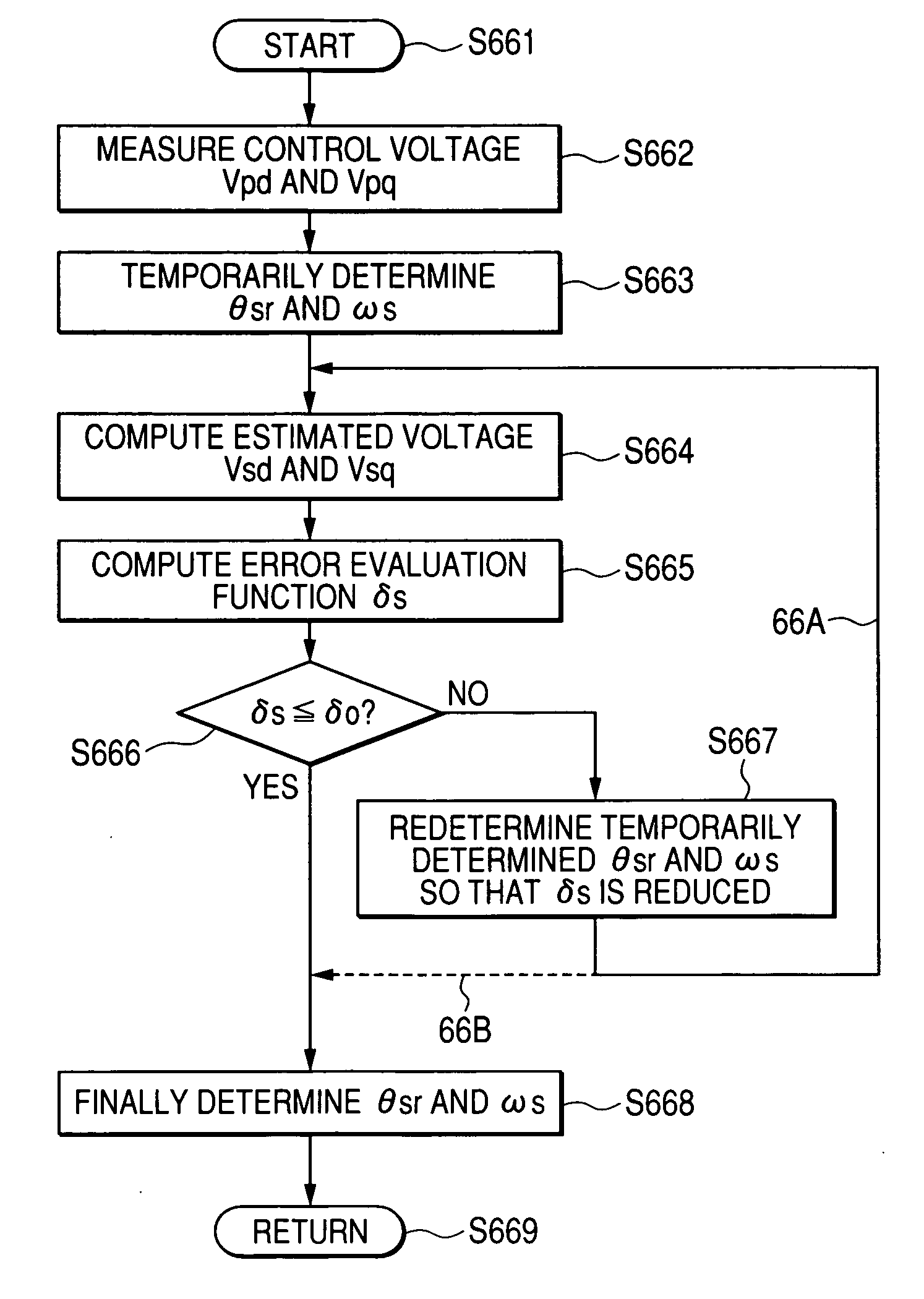

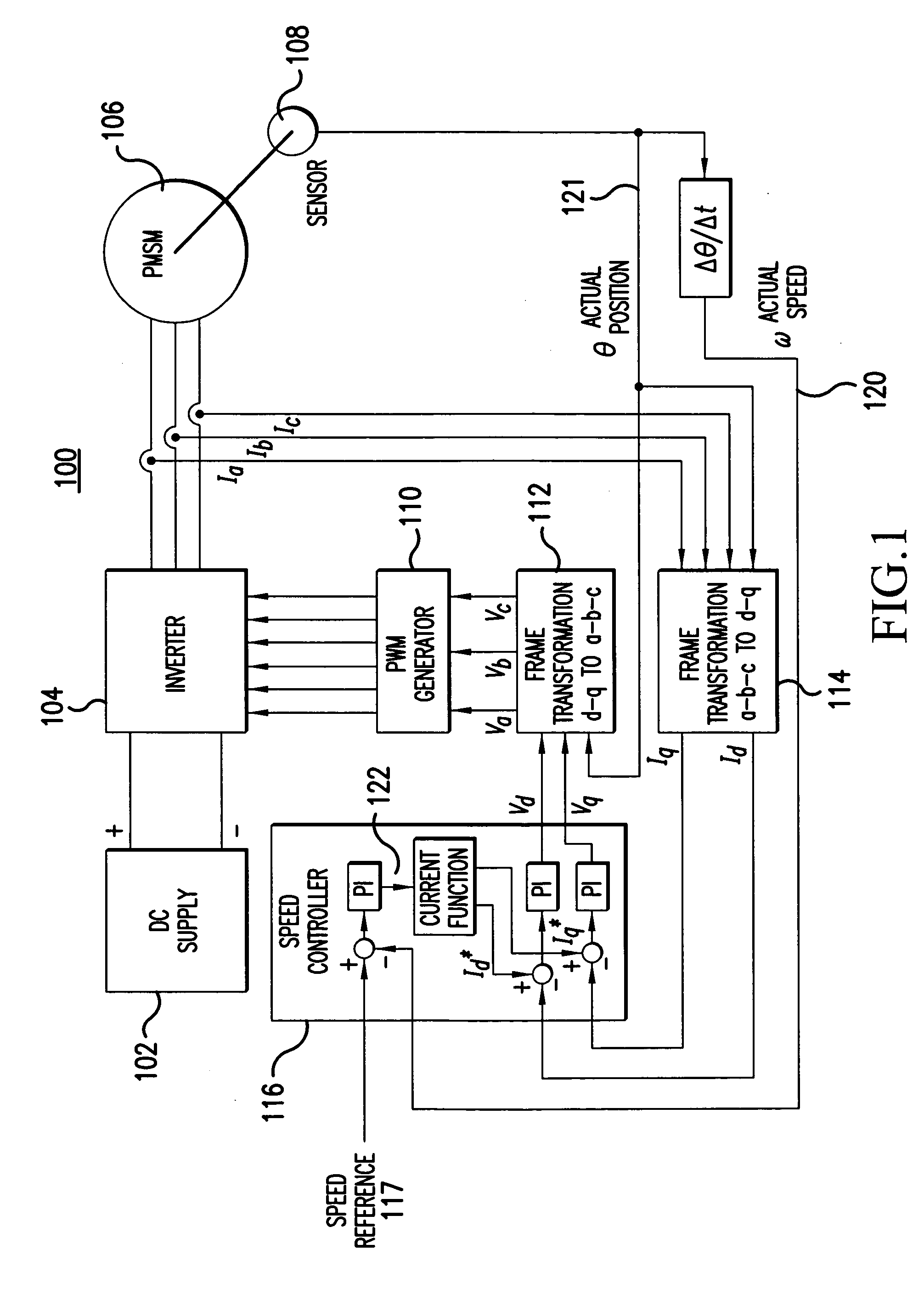

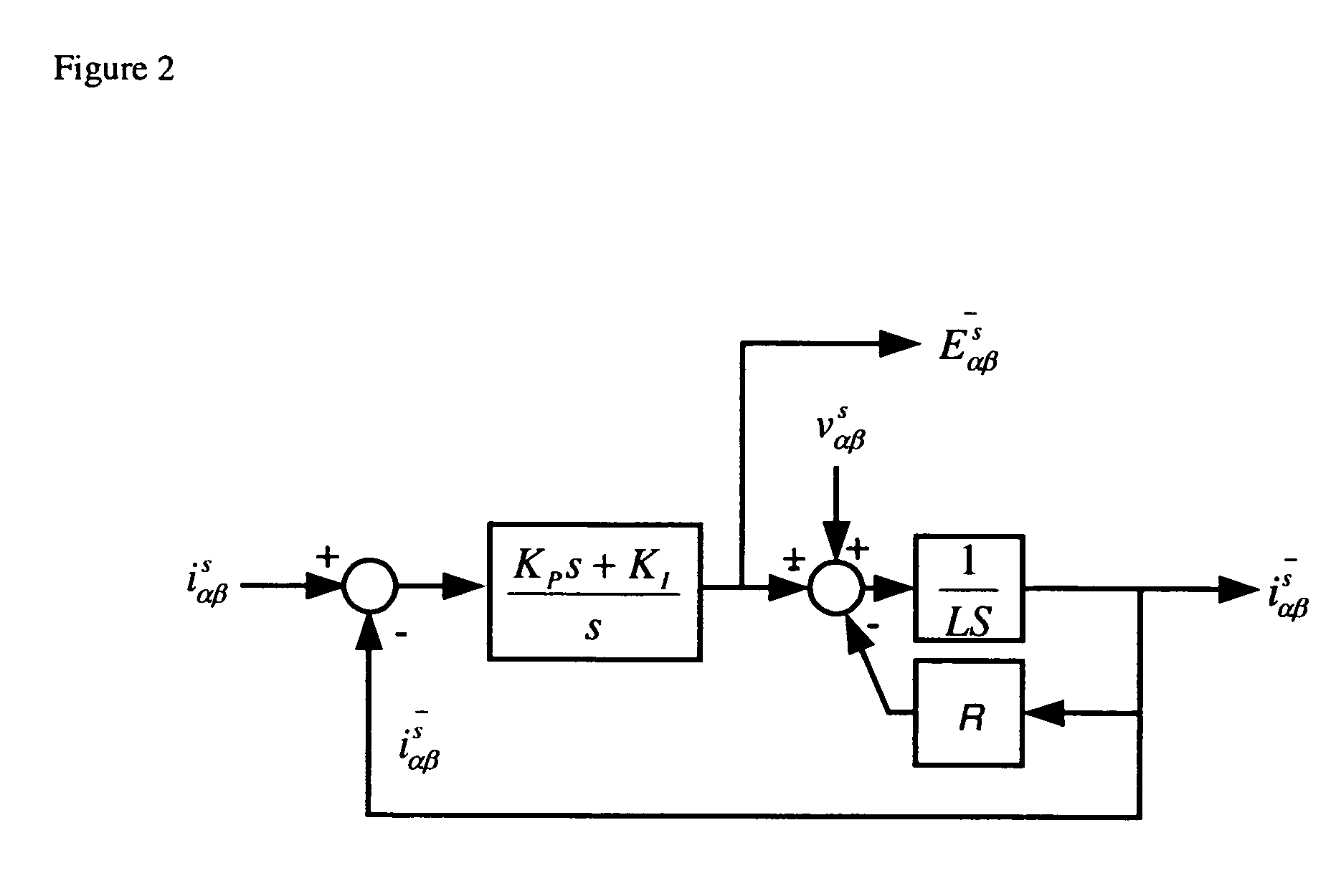

Sensorless control method and apparatus for a motor drive system

InactiveUS20050007044A1Quick calculationAccurate predictionDC motor speed/torque controlAC motor controlKaiman filterControl power

A method and apparatus provide a state observer control system 600 for a motor 106 that uses an extended Kalman filter 330 to predict initial rotor position and afterwards accurately predict rotor position and / or speed under variable types of loading conditions. A control system model 300 is generated that allows variable setting of an initial rotor position to generate estimated rotor position and speed as outputs. The control system model 300 includes an EKF (extended Kalman filter) estimator 330, speed controller 322, a current controller 324, and a variable load component 310. During operation, EKF estimator 330 estimates rotor speed 327 and position 333 based on reference voltages 402, 404 and currents 1325 generated by speed and current controllers 322, 324 and input from frame transformers 326, 328. Additionally, the reference currents and voltages 402, 404, 1325 are frame-transformed to be used as feedback signals 418, 346 in the system 600 and as drive signals to control power to be applied to a motor load 602.

Owner:HONEYWELL INT INC

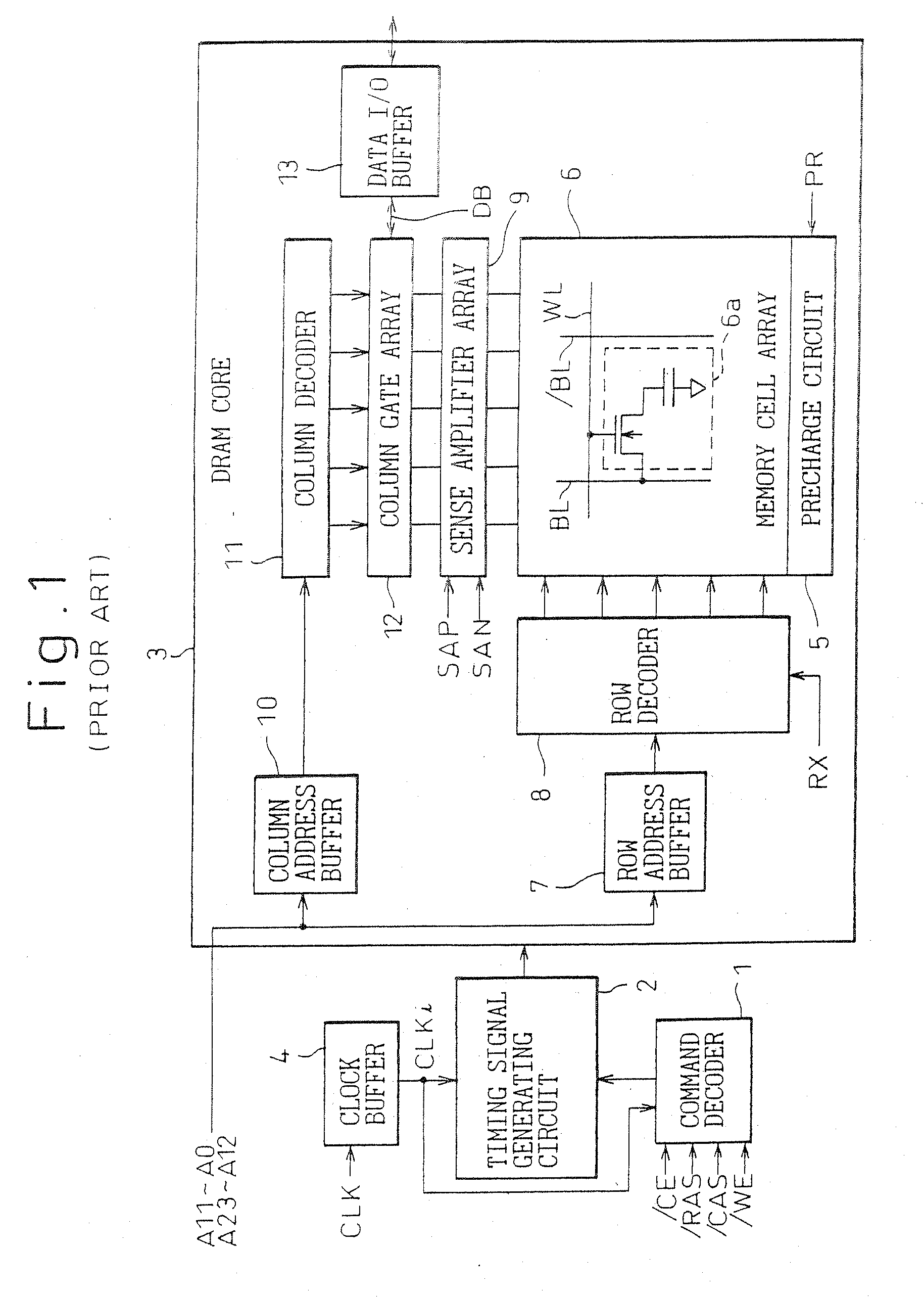

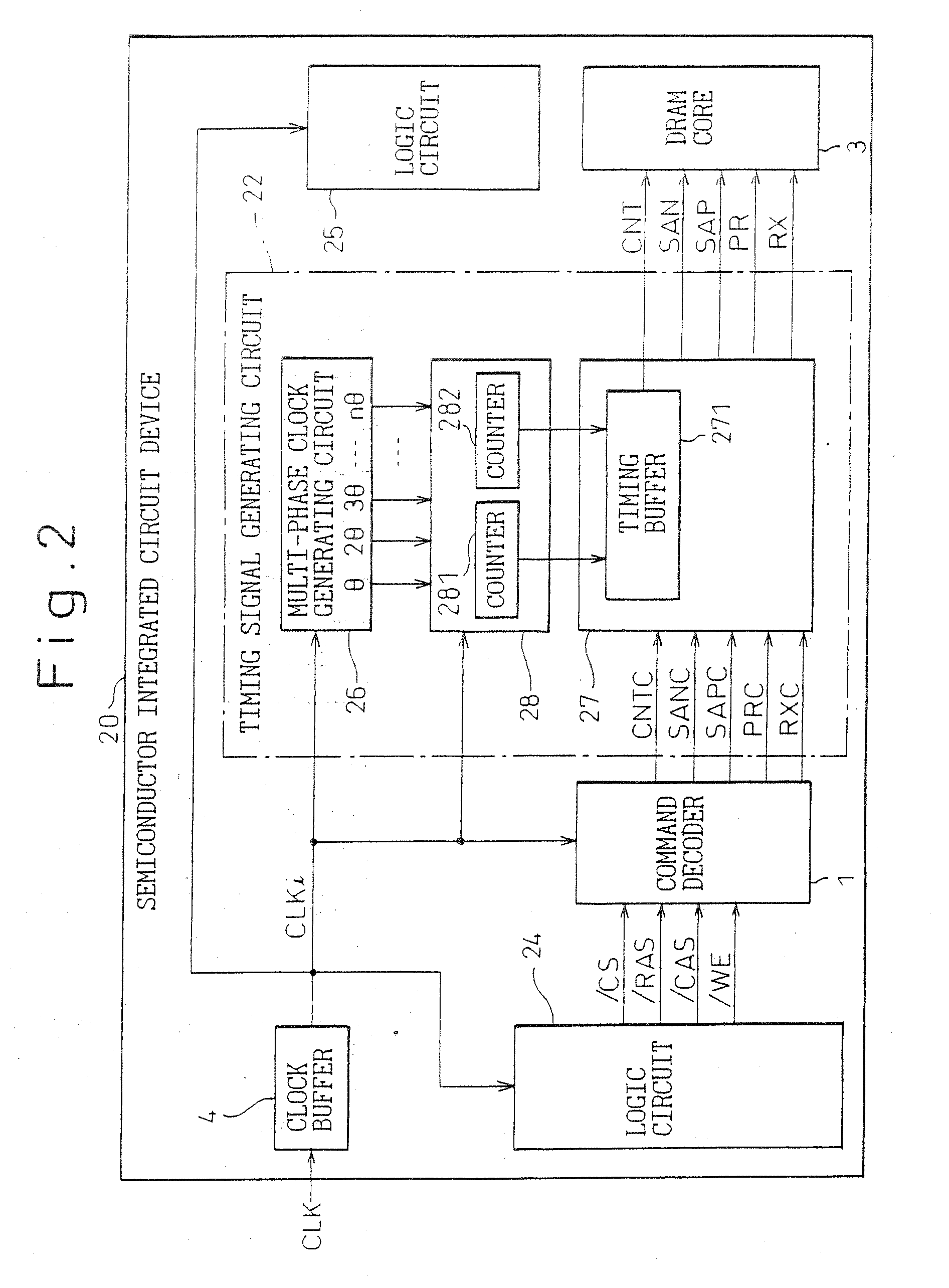

Timing Signal Generating Circuit, Semiconductor Integrated Circuit Device and Semiconductor Integrated Circuit System to which the Timing Signal Generating Circuit is Applied, and Signal Transmission System

InactiveUS20090195281A1High adjustment accuracySimple circuitPulse automatic controlError detection/correctionControl signalEngineering

Owner:FUJITSU LTD

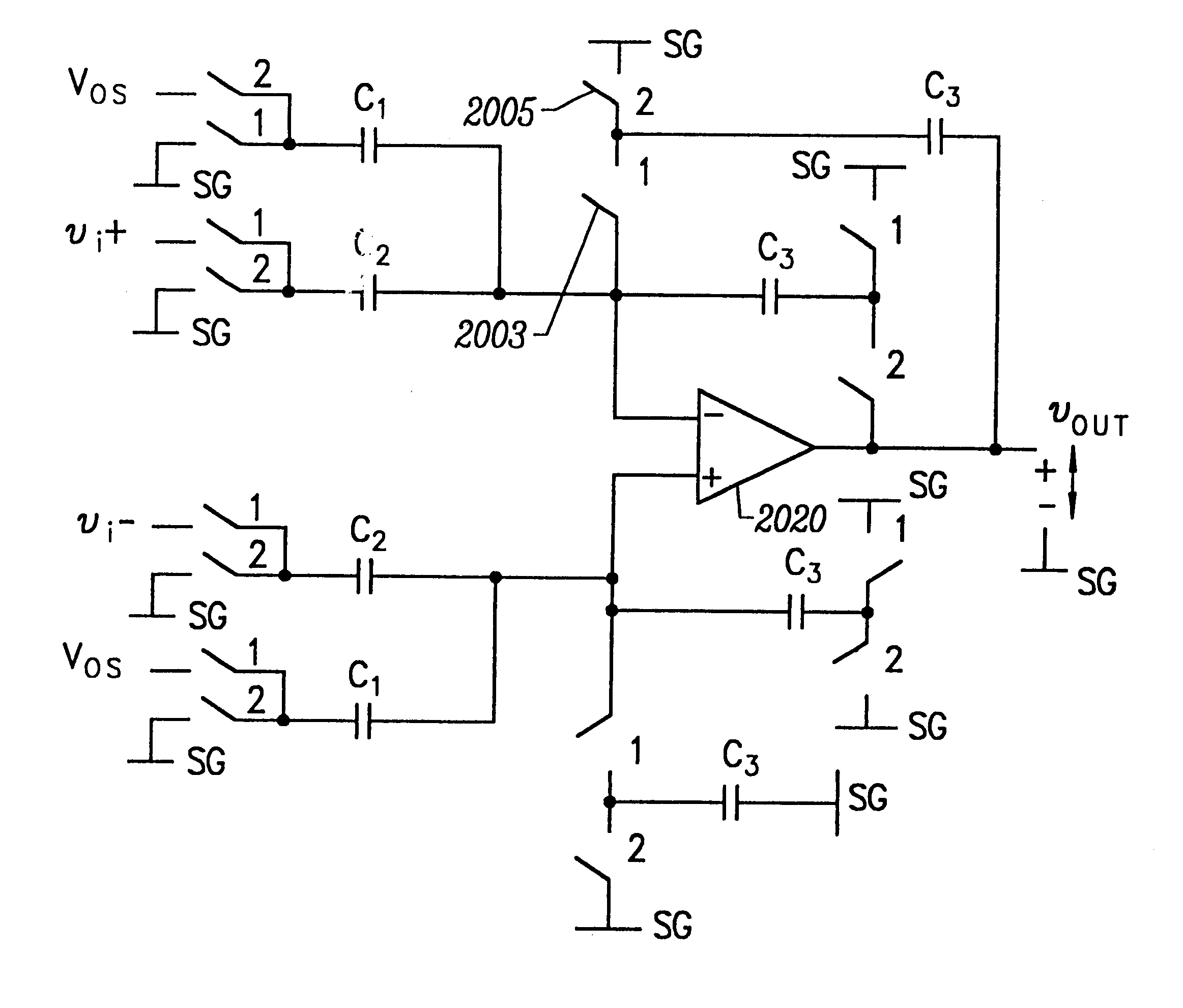

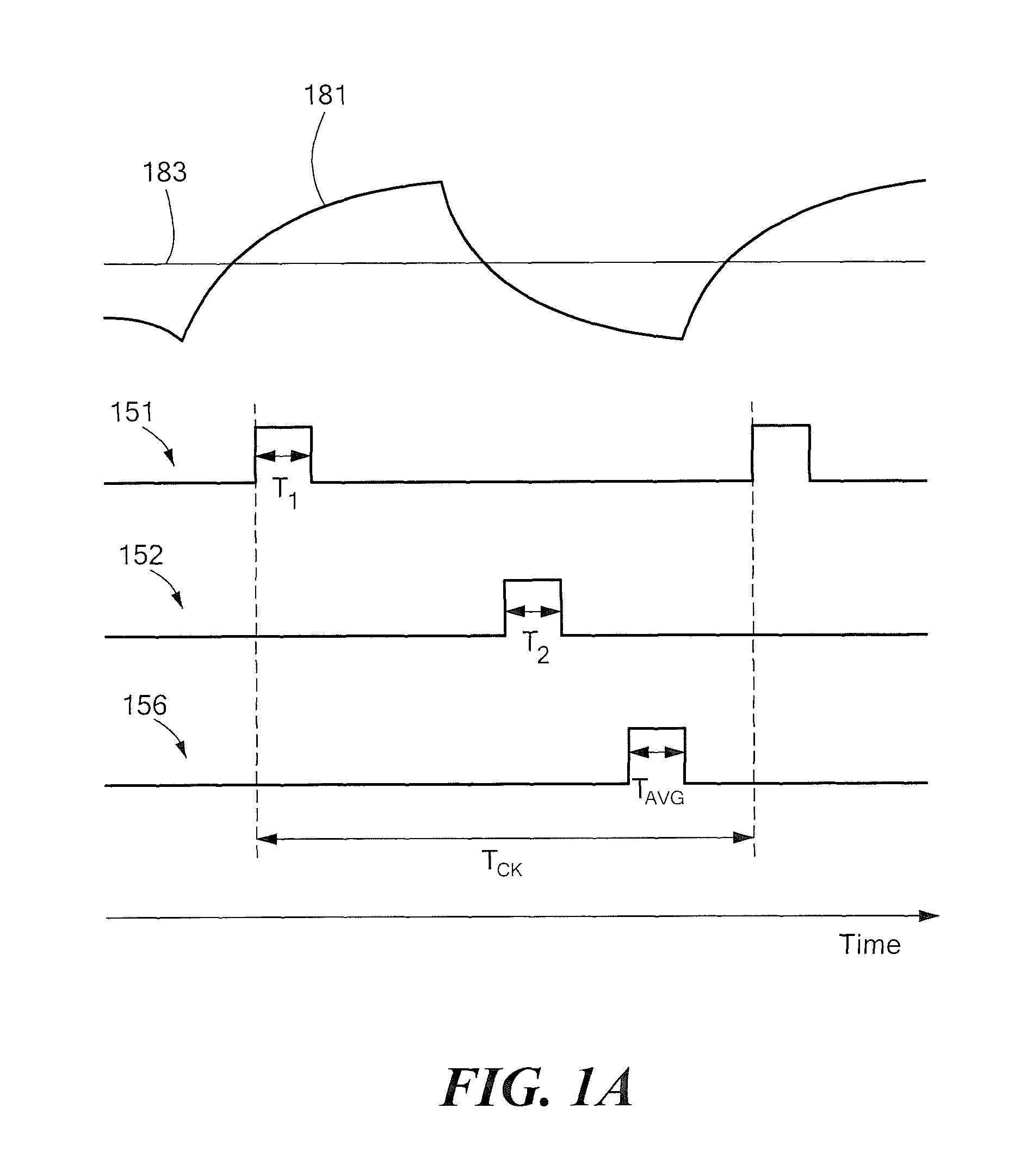

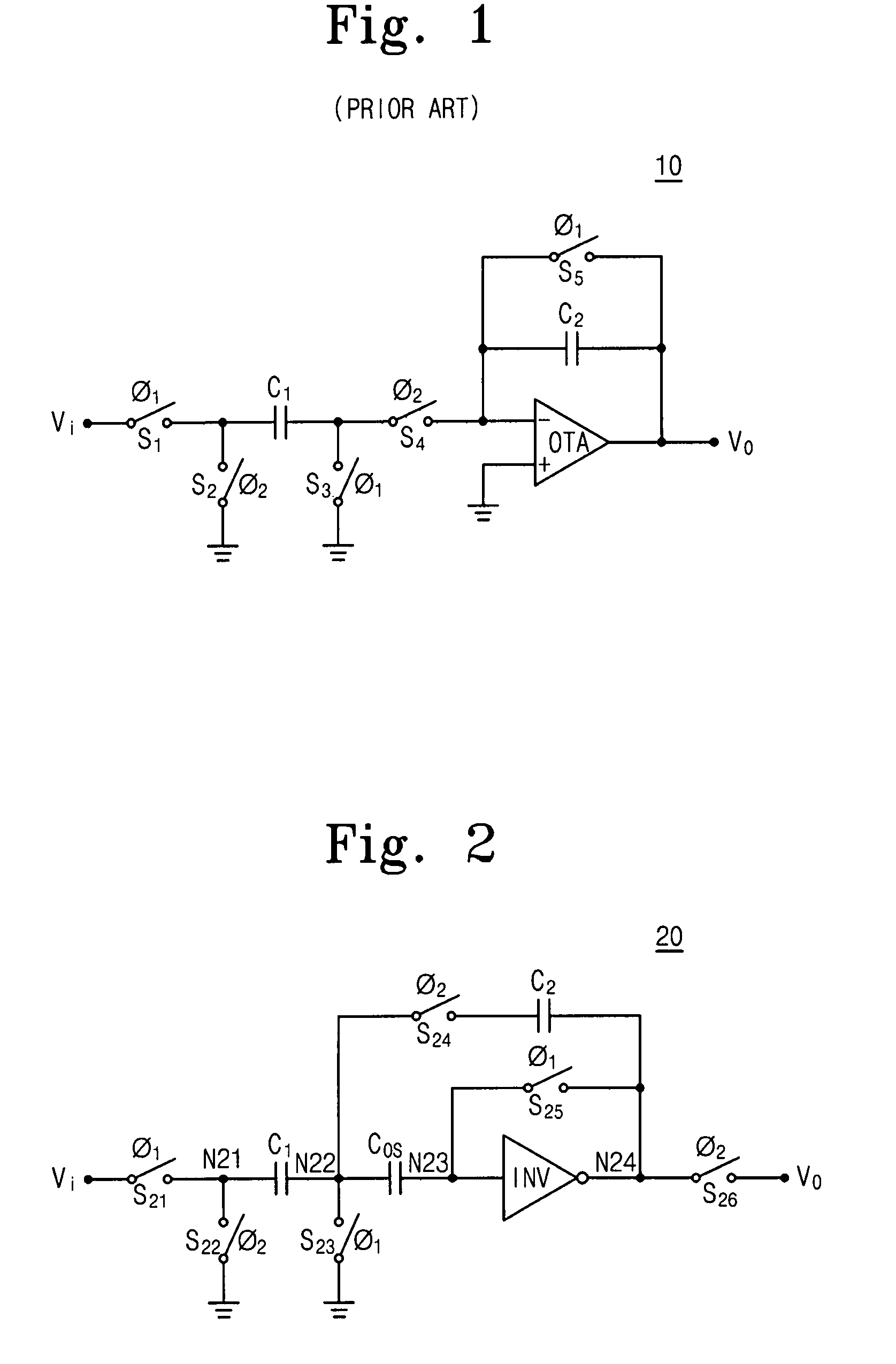

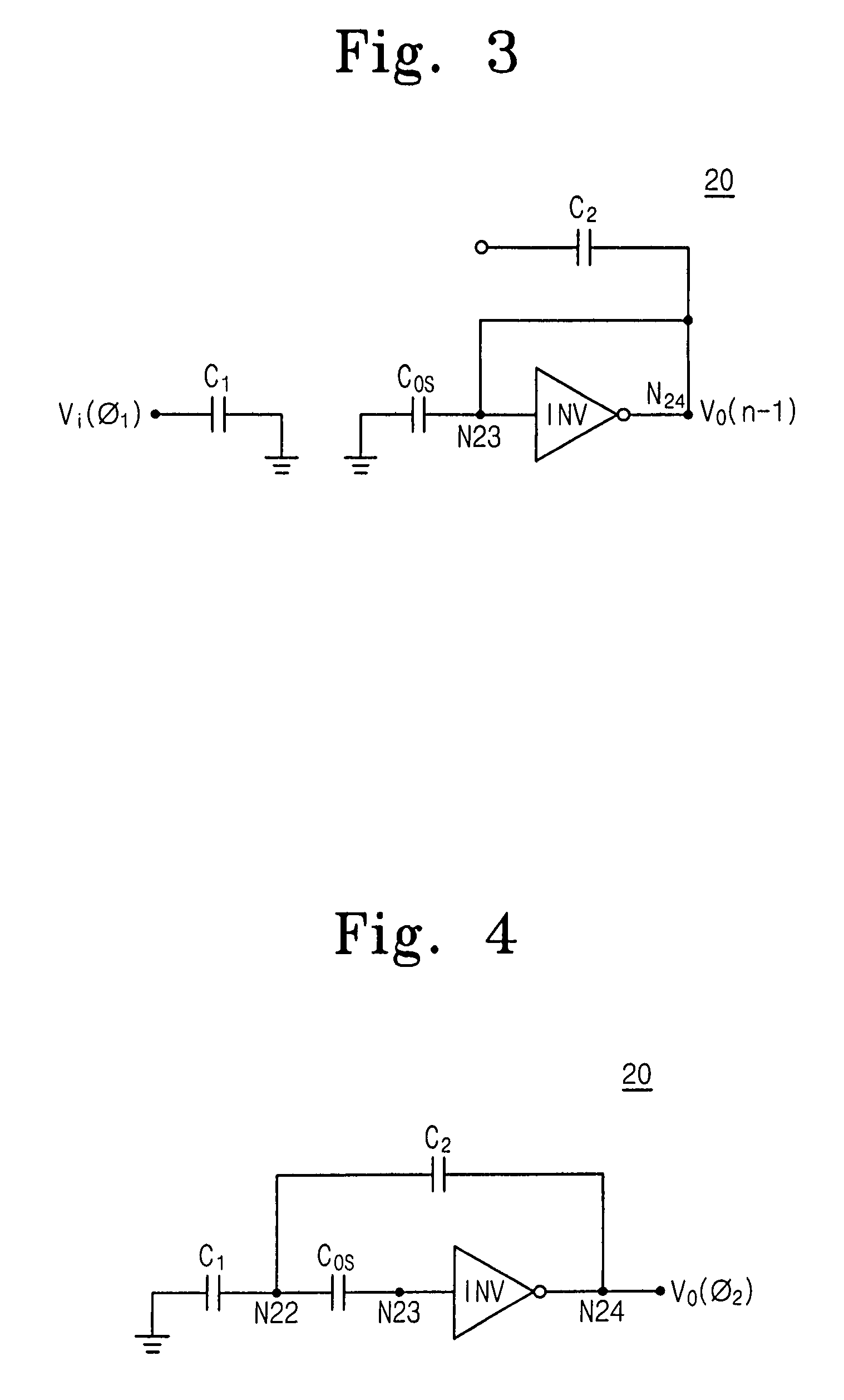

Switched capacitor notch filter

ActiveUS7990209B2Eliminate needLow pass filterSwitched capacitor networksOscillations generatorsCapacitanceTime segment

A switched capacitor notch filter for sampling an input signal using multiple sampling capacitors and multiple non-overlapping time periods. The charge from the sampling capacitors is averaged and transferred to the filter output during another non-overlapping time period.

Owner:ALLEGRO MICROSYSTEMS INC

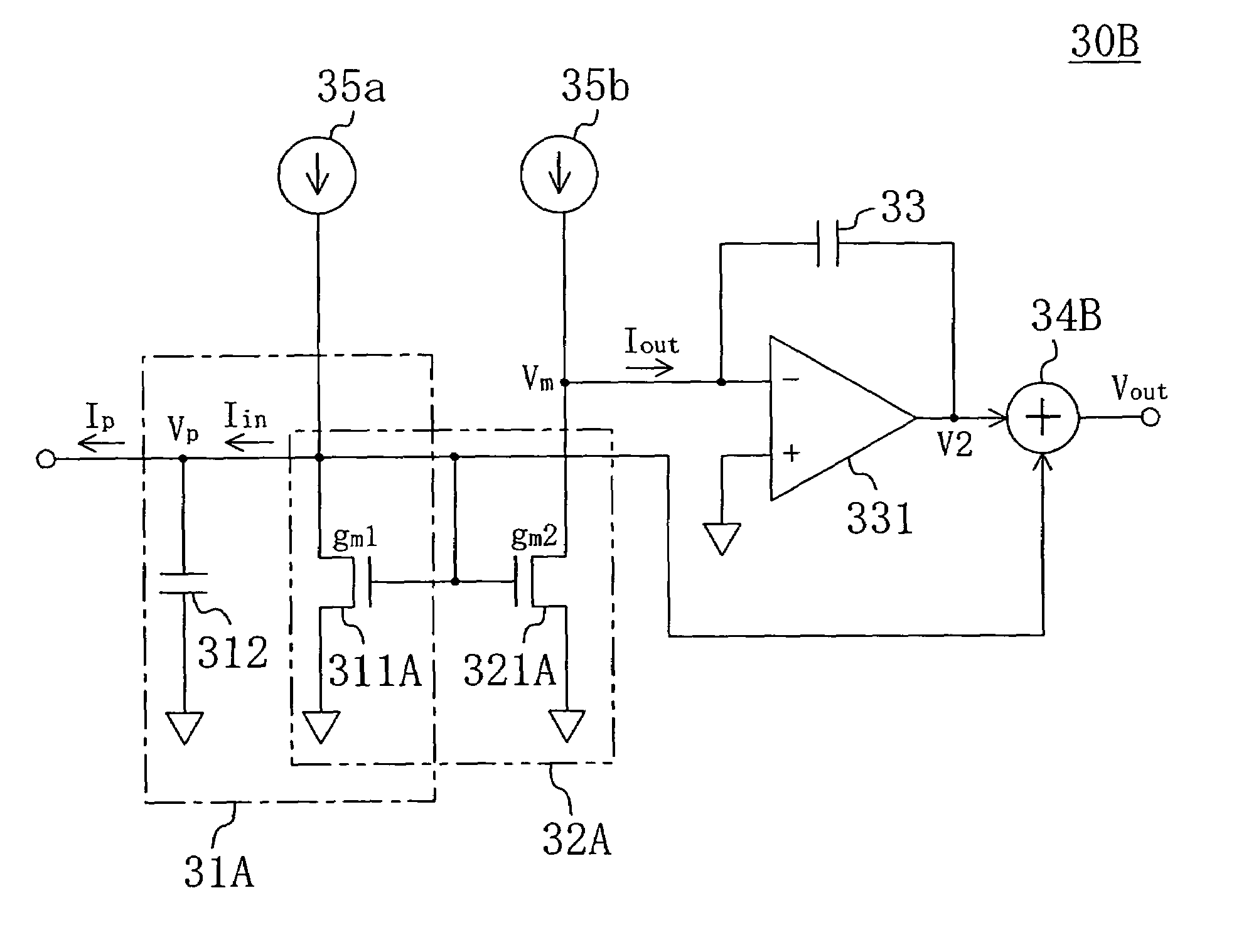

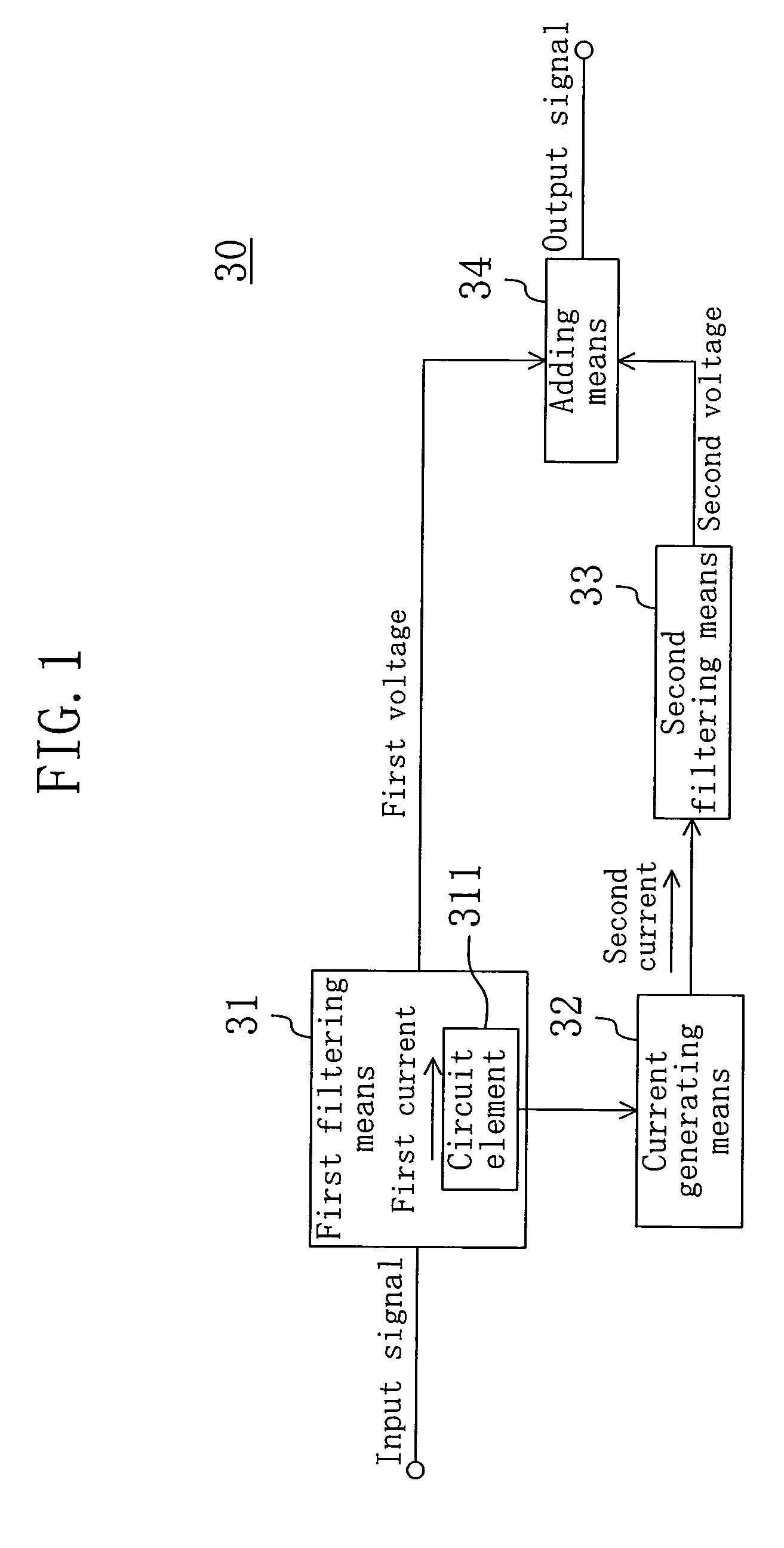

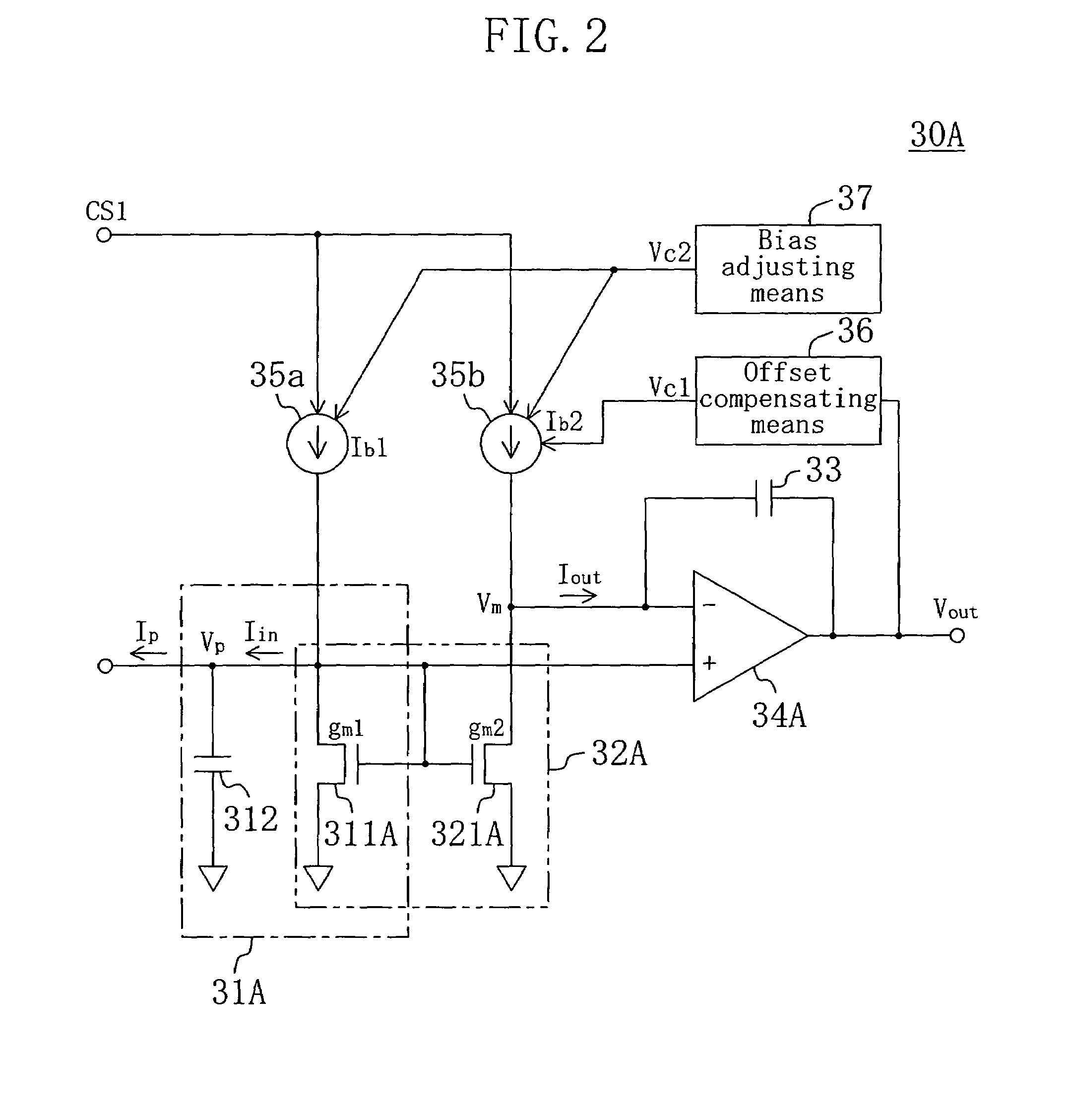

Low-pass filter for a PLL, phase-locked loop and semiconductor integrated circuit

InactiveUS7030688B2Reduce circuit sizeReduce circuit areaPulse automatic controlOscillations generatorsLoop filterBand-pass filter

The invention provides a low-pass filter suitably used as a loop filter for a PLL or a DLL that has a filtering characteristic equivalent to that of a conventional one and can be realized in a smaller circuit area. The low-pass filter includes first filtering means (31) for accepting, as an input, an input signal to the low-pass filter and outputting a first voltage; a circuit element (311) included in the first filtering means (31) for allowing a first current to flow in accordance with the first voltage; current generating means (32) for generating a second current at a given rate to the first current; second filtering means (33) for accepting, as an input, the second current and outputting a second voltage; and adding means (34) for adding the first voltage and the second voltage and outputting an output signal of the low-pass filter, in which the second current is set to be smaller than the first current.

Owner:PANASONIC CORP

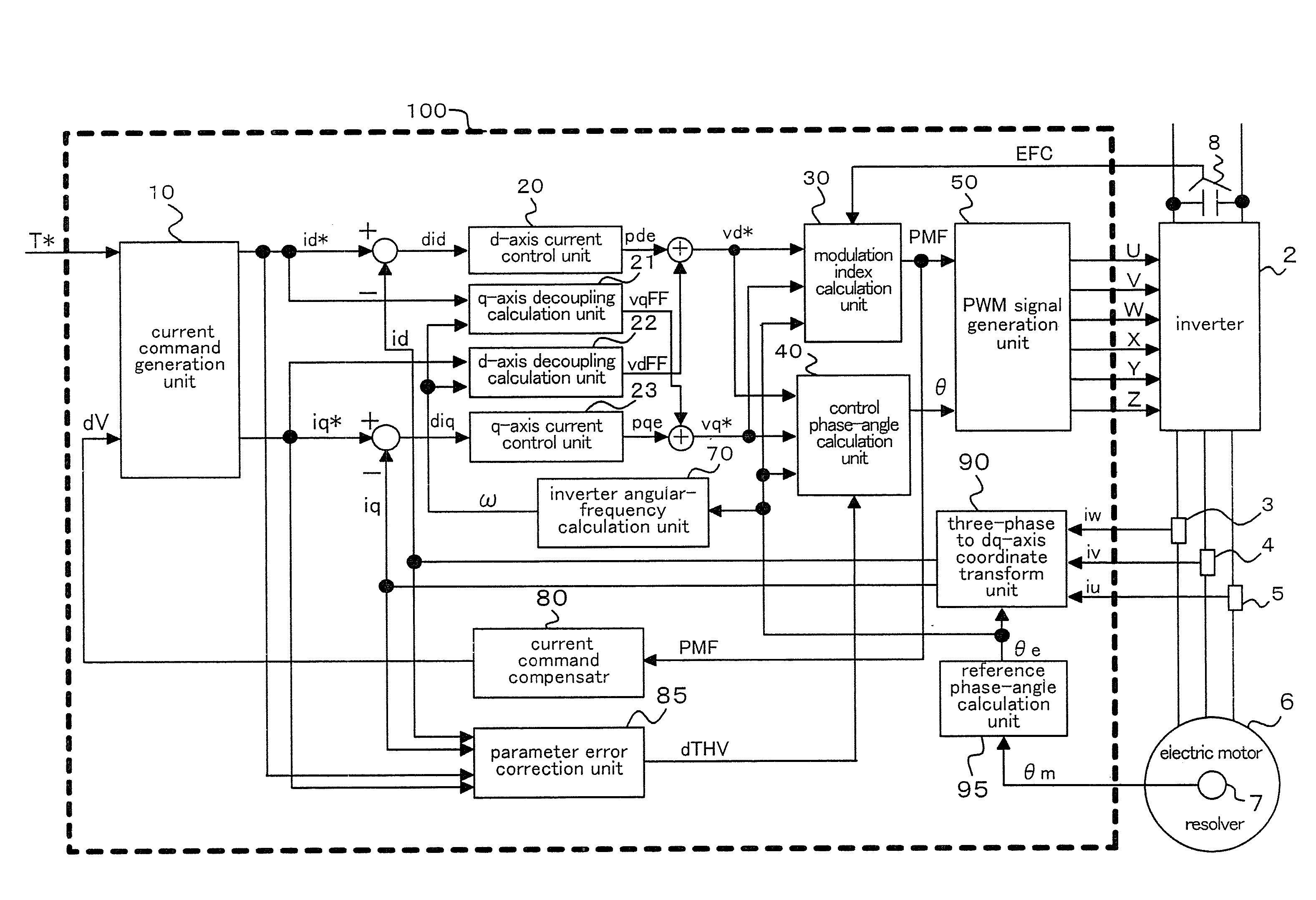

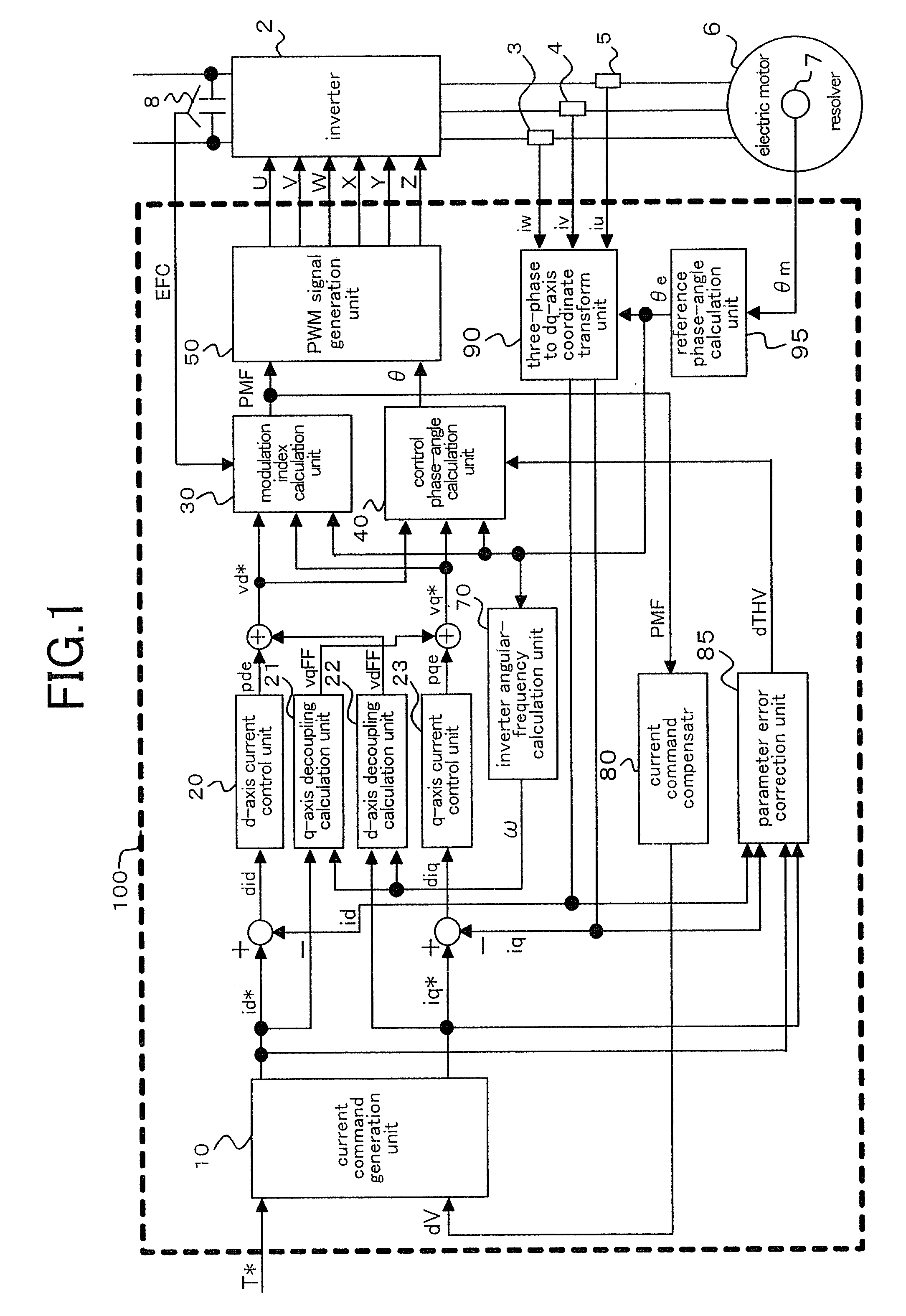

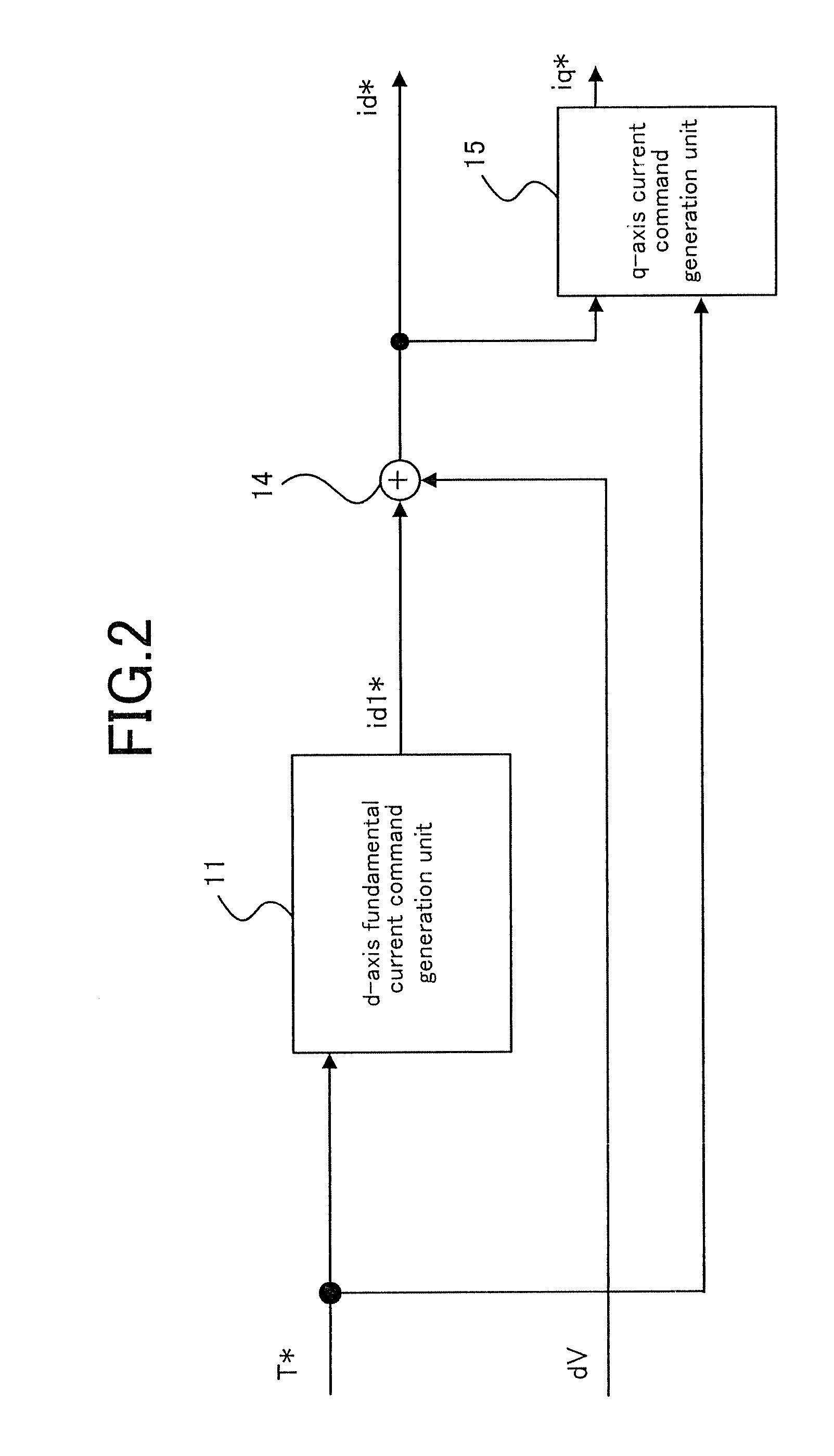

Vector controller for permanent-magnet synchronous electric motor

InactiveUS20100066283A1High speed rangeIncrease rangeDC motor speed/torque controlAC motor controlPermanent magnet synchronous motorPulsed mode

A method of controlling a current command by comparing voltage with a set value needs to vary the set value depending on voltage fluctuation, which involves taking a complicated control. A vector controller for a permanent-magnet synchronous electric motor, according to the present invention, can realize with a simplified configuration a field-weakening operation in a one-pulse mode in a high speed range by providing a current command compensator that corrects a current command by a corrected current command calculated based on a modulation index.

Owner:MITSUBISHI ELECTRIC CORP

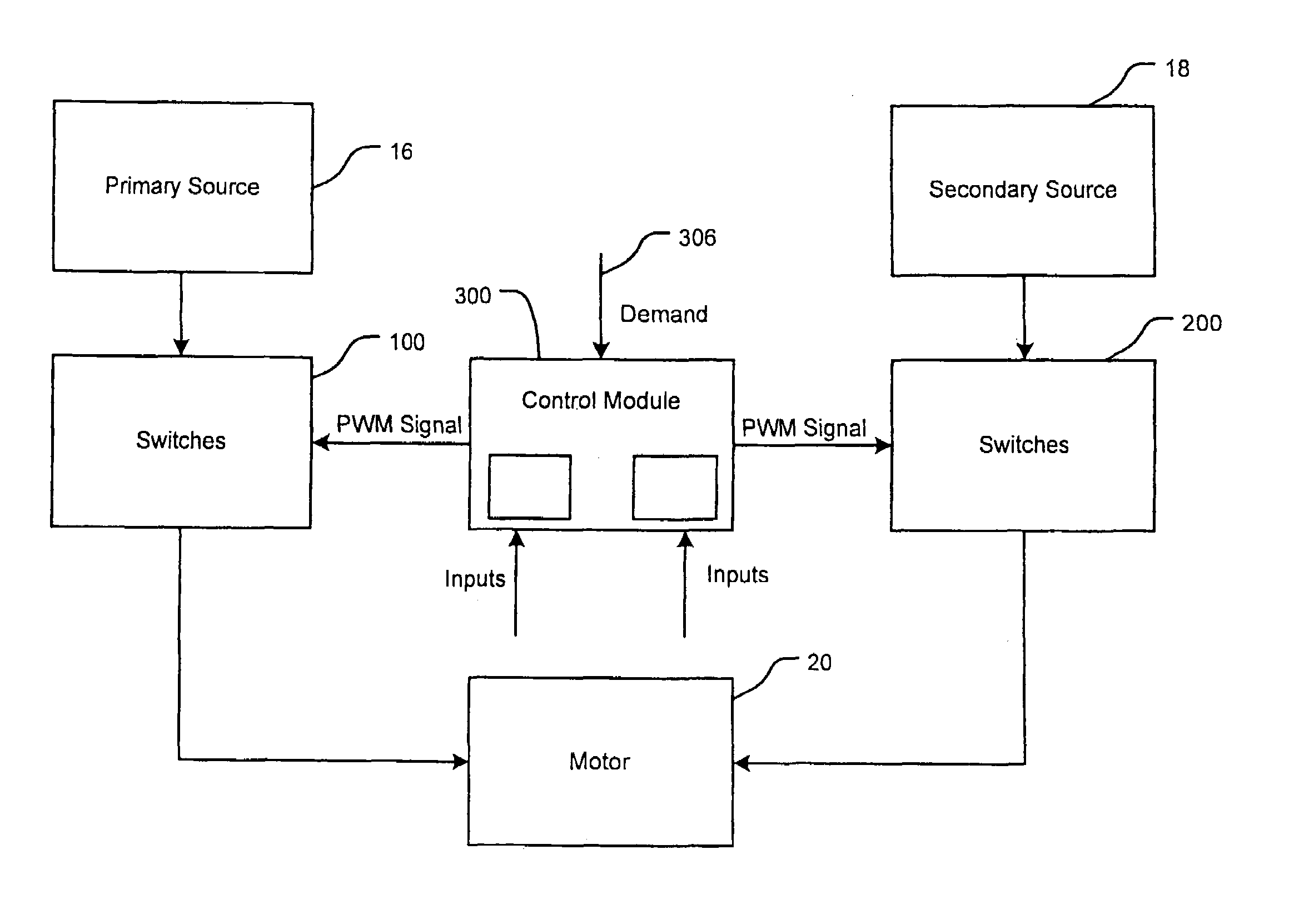

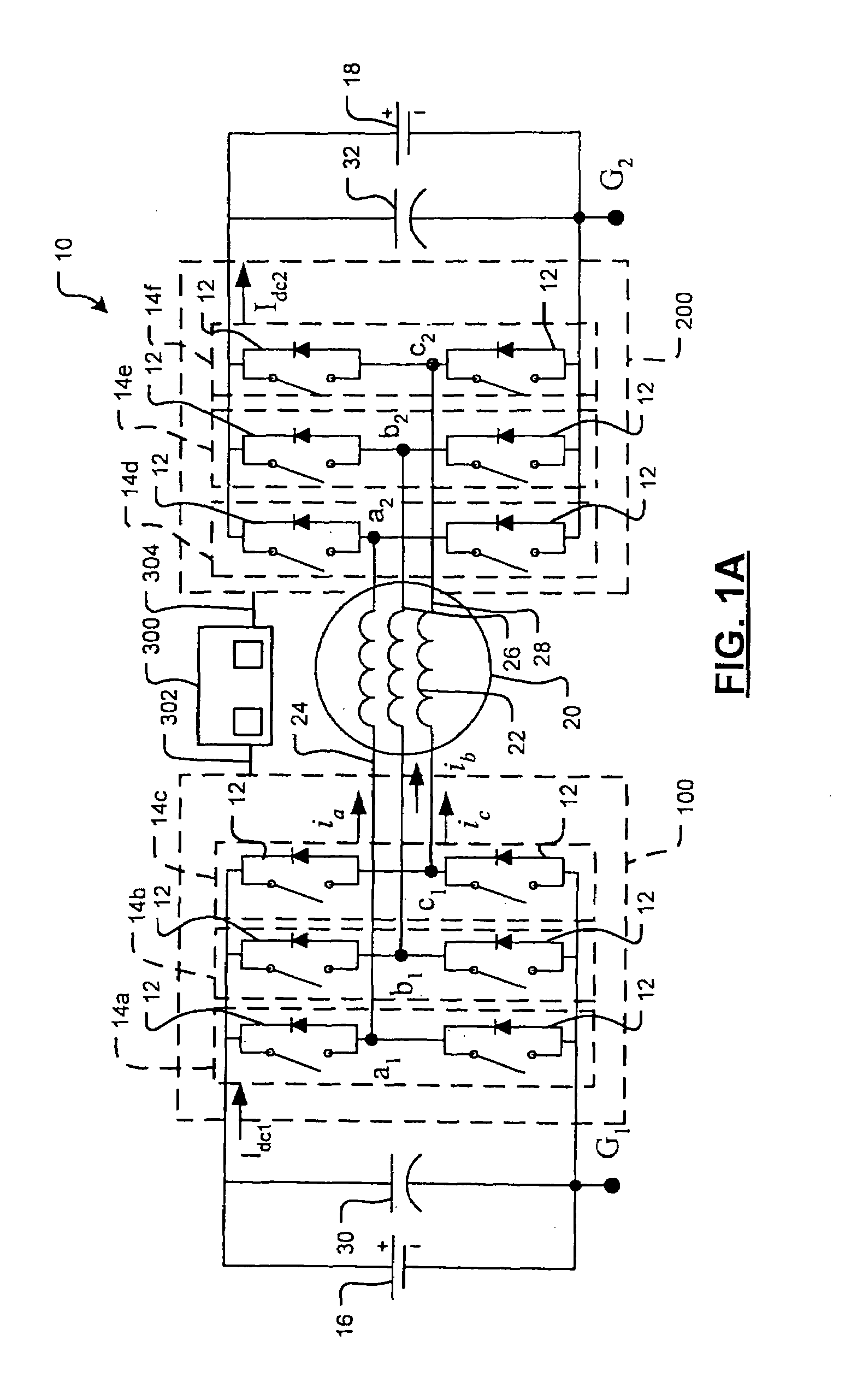

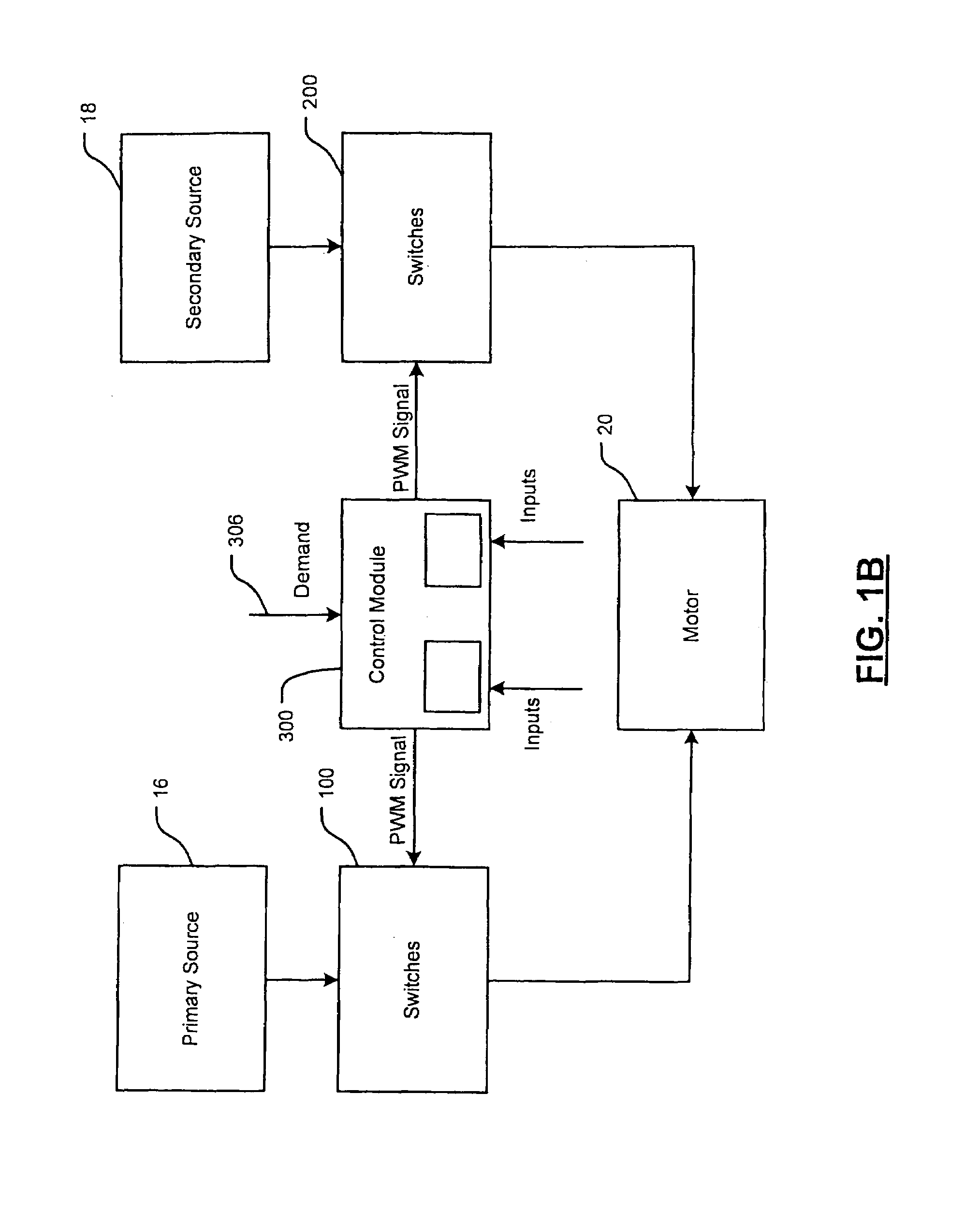

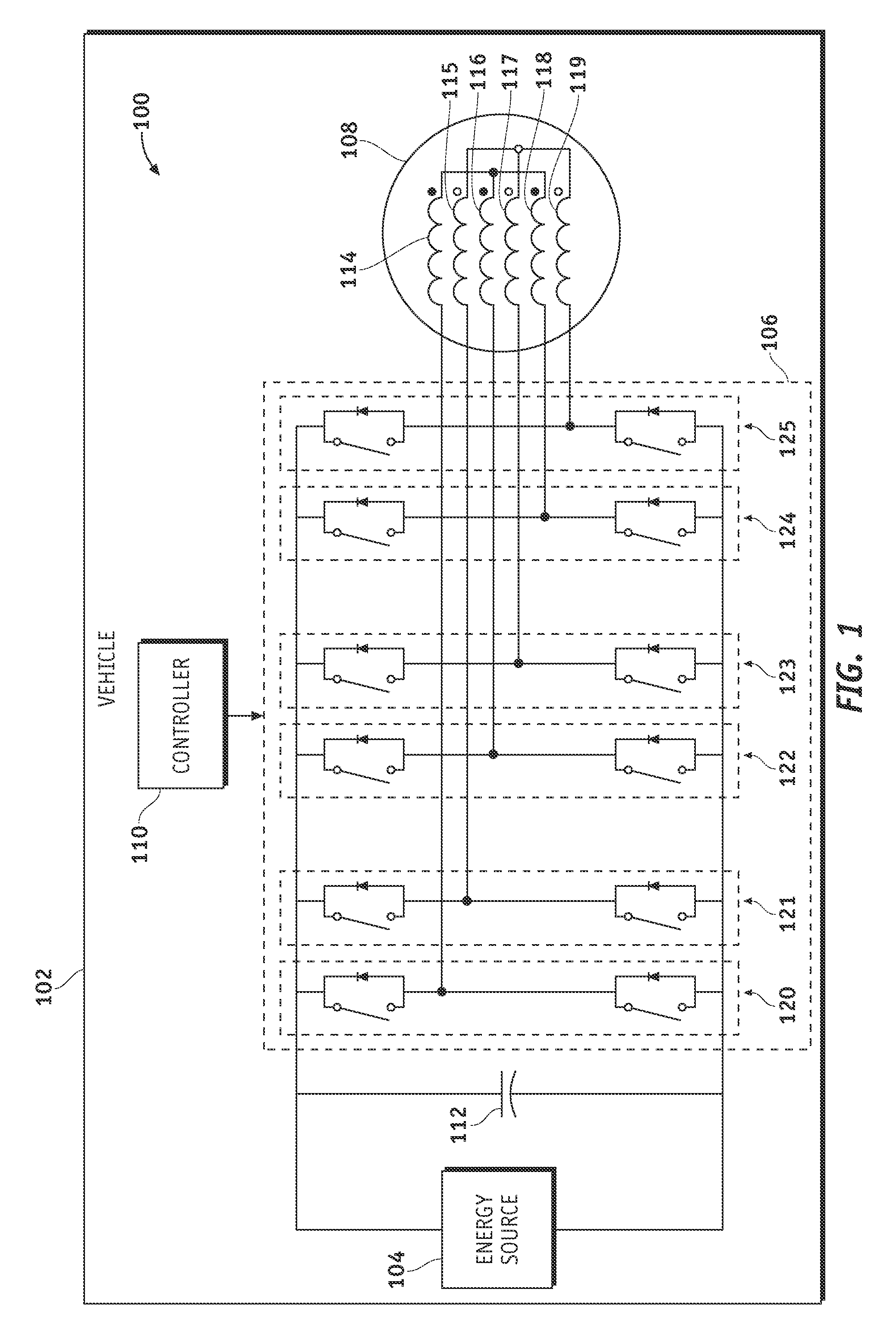

Unified power control method of double-ended inverter drive systems for hybrid vehicles

A method of providing a unified power control of a motor including providing a first inverter system, a second inverter system, and a motor coupled therebetween; coupling the first inverter system coupled to a first energy source; coupling the second inverter system coupled to a secondary energy source; generating a first pulse width modulated signal; and generating a second pulse width modulated signal. The first inverter system and the second inverter system are driven with the first pulse width modulated signal and the second pulse width modulated signal respectively in order to control a fundamental component of an output voltage of the first inverter system and the second inverter system to control the motor.

Owner:GM GLOBAL TECH OPERATIONS LLC

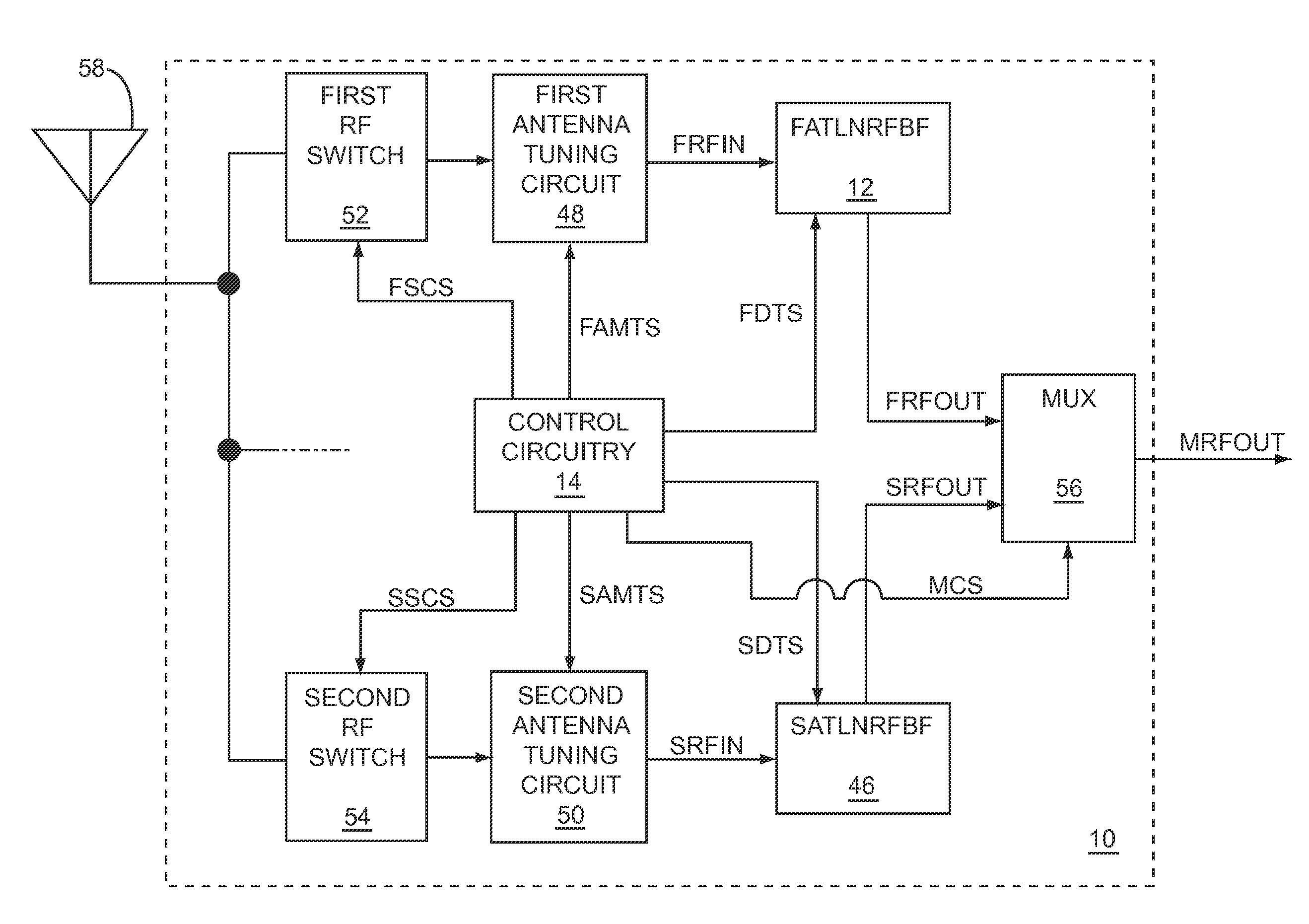

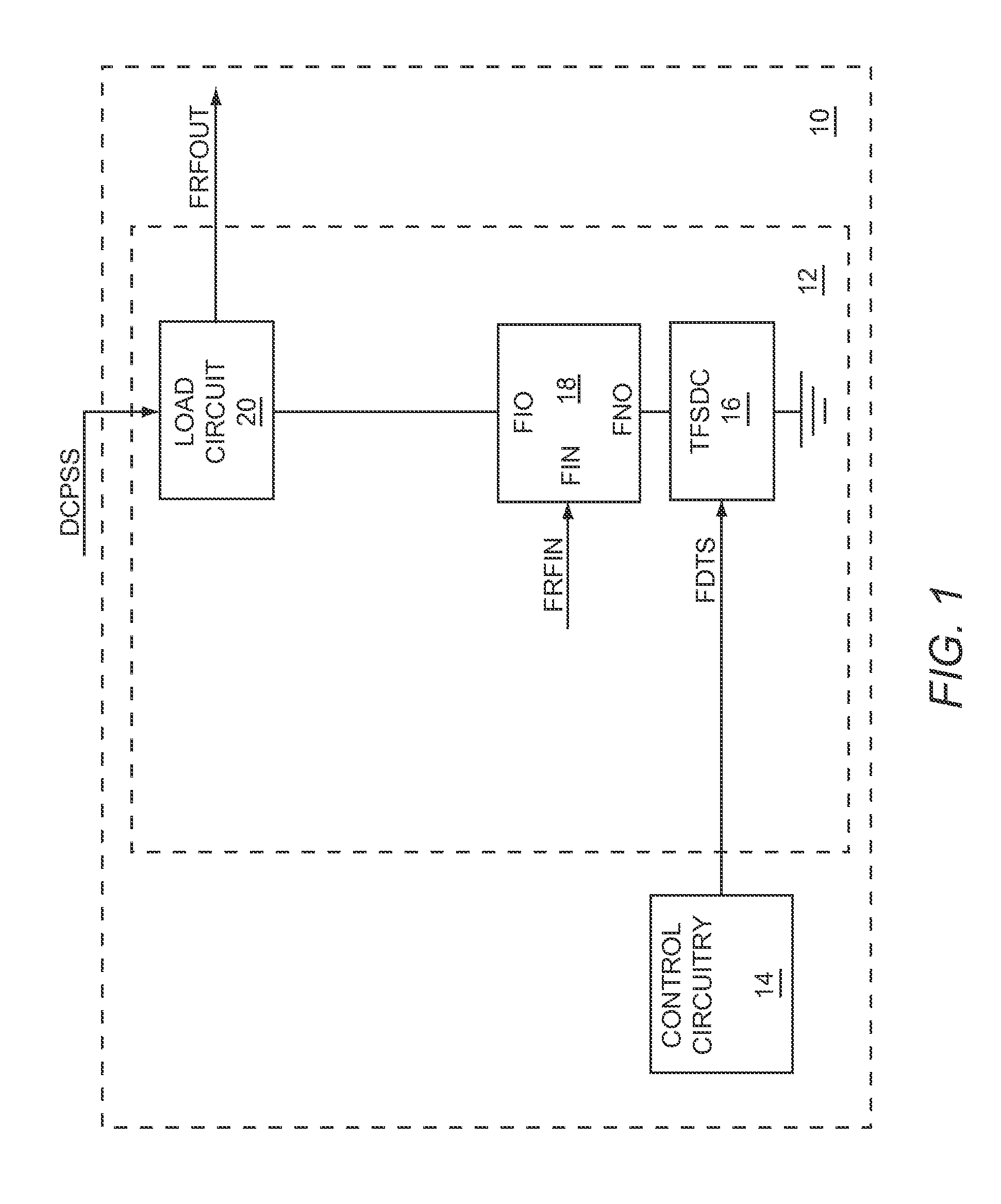

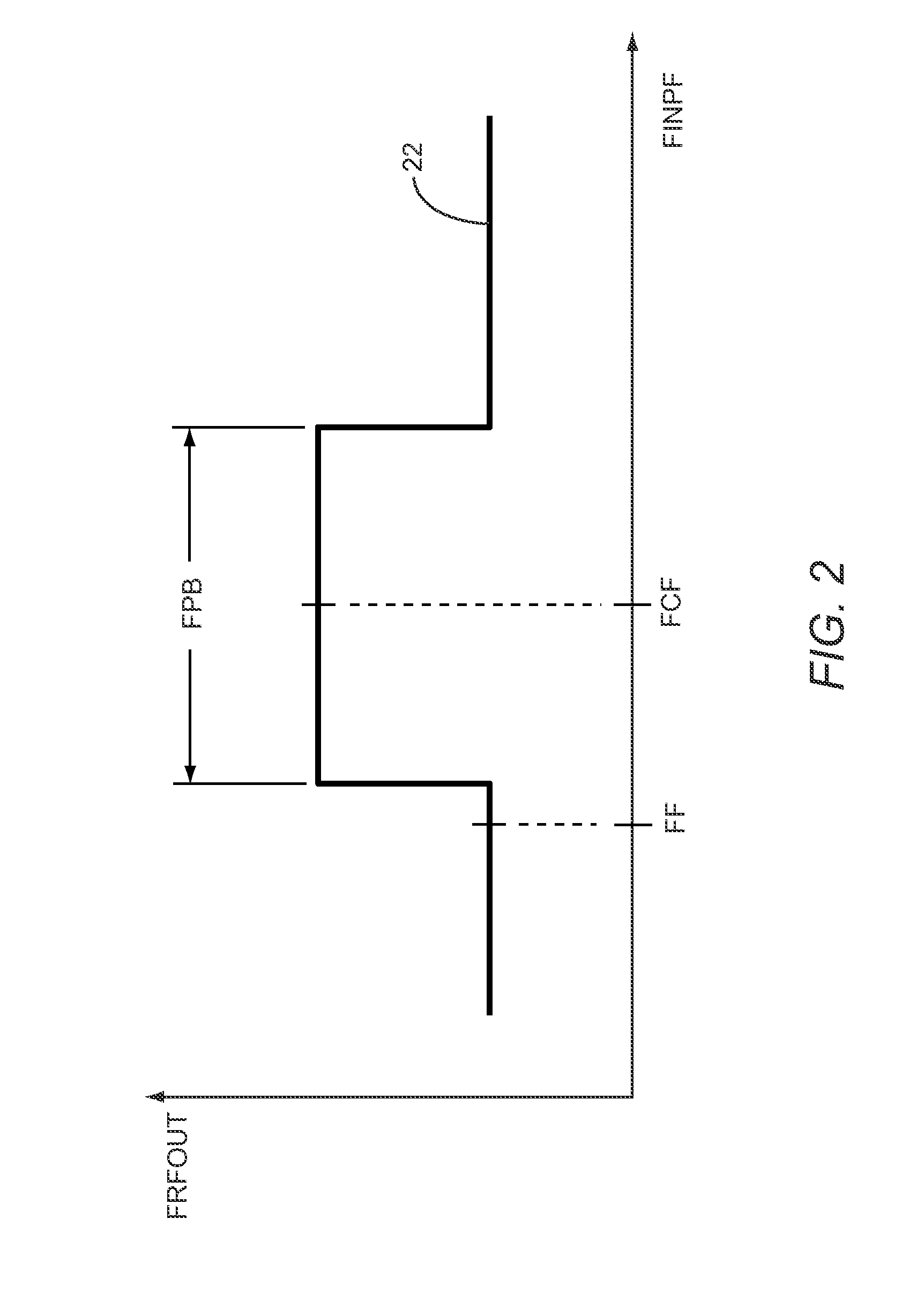

Using degeneration in an active tunable low-noise radio frequency bandpass filter

ActiveUS8314653B1Easy to FeedbackReduce gainSwitched capacitor networksAmplifier with semiconductor-devices/discharge-tubesLow noiseBandpass filtering

The present disclosure relates to a first active tunable low-noise RF bandpass filter that includes at least a first transistor element and a tunable frequency selective degeneration circuit coupled to a first non-inverting output of the first transistor element. The first active tunable low-noise RF bandpass filter combines low noise amplifier (LNA) and tunable bandpass filter functionalities into a single active RF bandpass filter. The tunable frequency selective degeneration circuit uses degeneration at frequencies outside of a passband of the active RF bandpass filter to increase feedback, thereby decreasing gain of the active RF bandpass filter. By decreasing the gain, linearity of the active RF bandpass filter may be improved in the presence of strong interfering RF signals, thereby enabling elimination of passive bandpass filter elements, such as surface acoustic wave (SAW) and bulk acoustic wave (BAW) filters, without degrading reception of in-band RF signals.

Owner:QORVO US INC

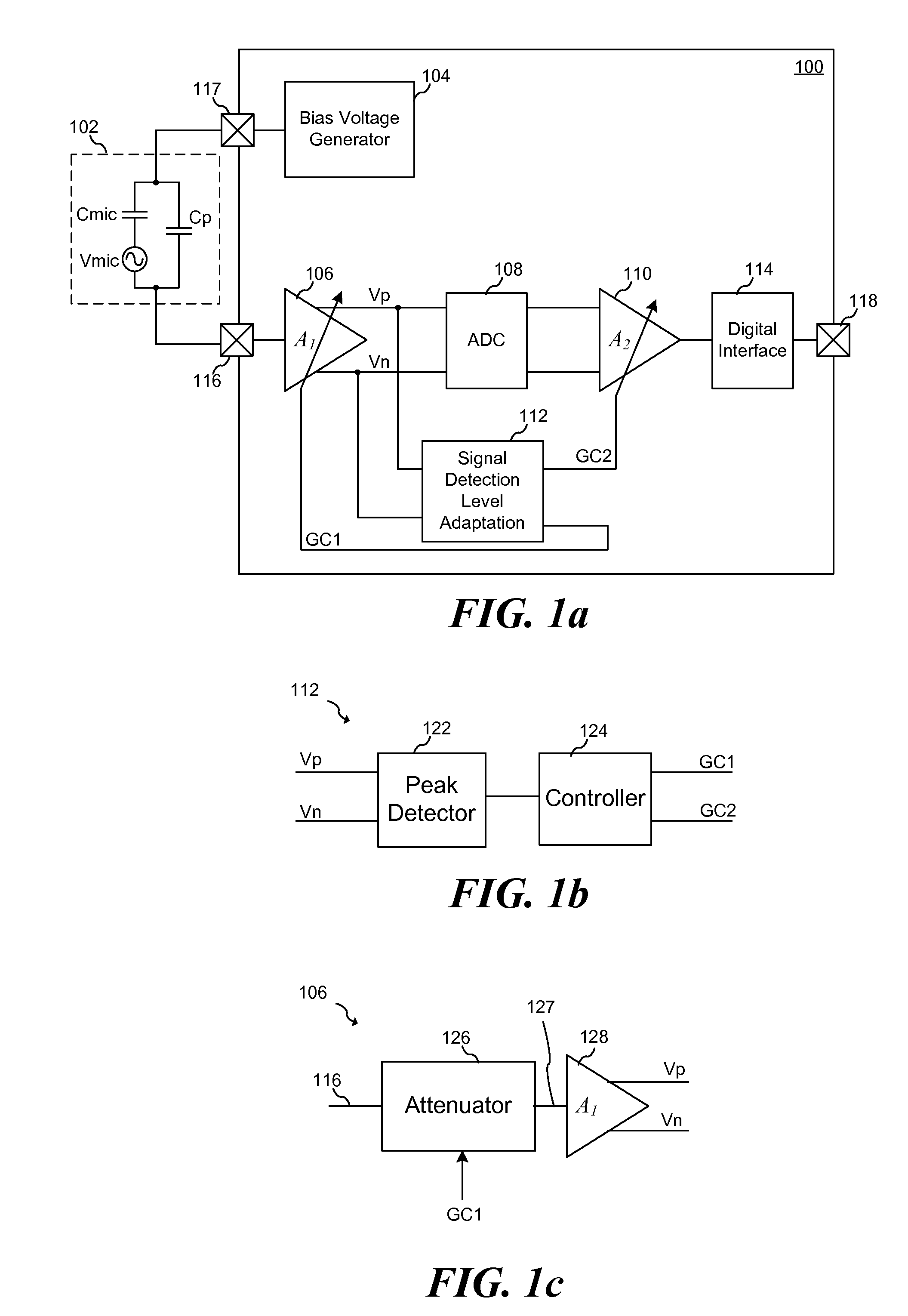

System and Method for High Input Capacitive Signal Amplifier

ActiveUS20130271307A1Electric signal transmission systemsVolume compression/expansion having semiconductor devicesCapacitanceAudio power amplifier

In accordance with an embodiment, a method includes determining an amplitude of an input signal provided by a capacitive signal source, compressing the input signal in an analog domain to form a compressed analog signal based on the determined amplitude, converting the compressed analog signal to a compressed digital signal, and decompressing the digital signal in a digital domain to form a decompressed digital signal. In an embodiment, compressing the analog signal includes adjusting a first gain of an amplifier coupled to the capacitive signal source, and decompressing the digital signal comprises adjusting a second gain of a digital processing block.

Owner:INFINEON TECH AG

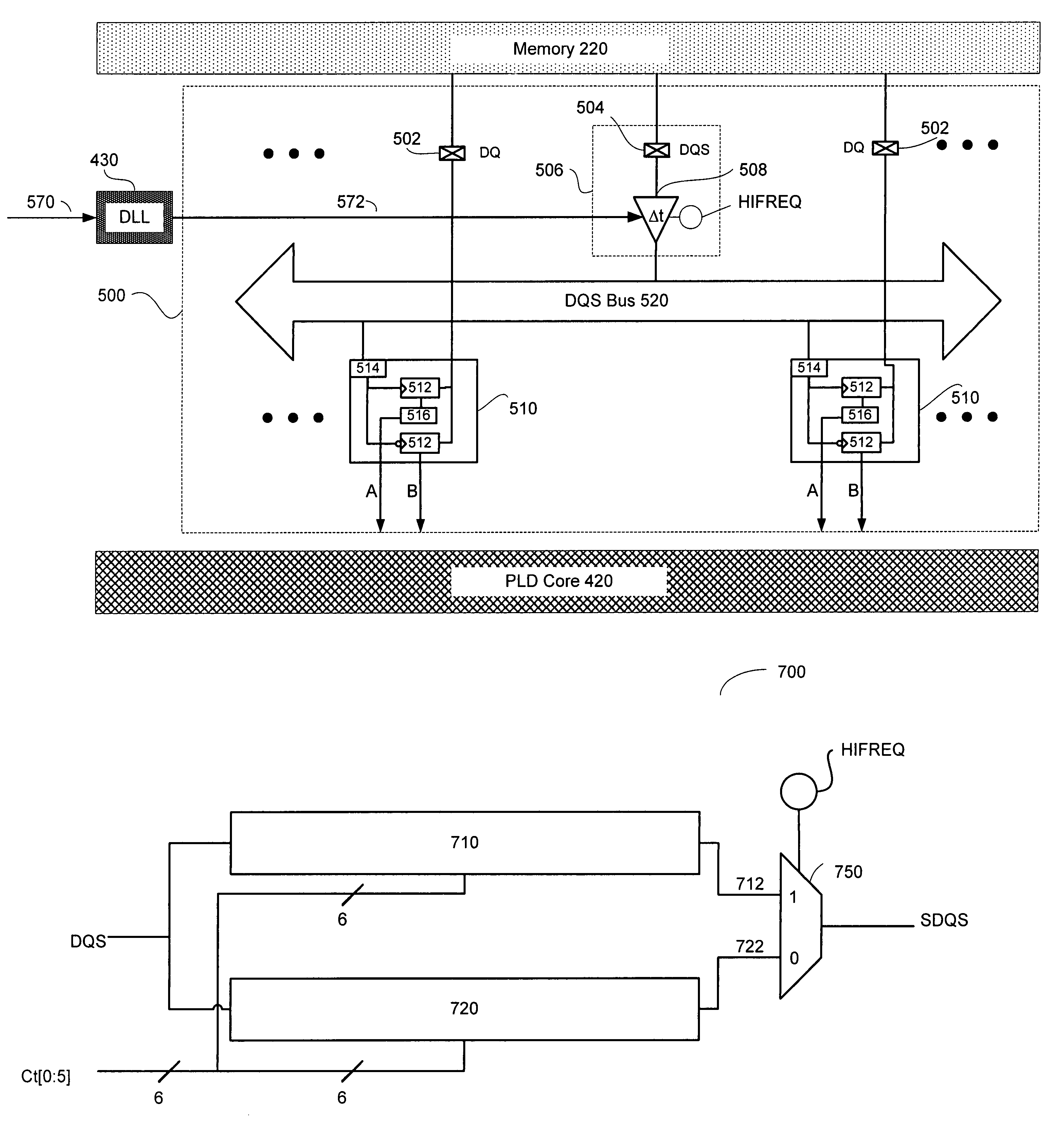

Memory interface phase-shift circuitry to support multiple frequency ranges

The present invention provides a phase shift circuit that supports multiple frequency ranges. The phase shift circuit receives a plurality of control bits and causes a phase shift in a received signal, the phase shift corresponding to a number of time steps, the number depending on the control bits, and the time step is selected from a plurality of different time steps based on a frequency range associated with the received signal.

Owner:BROOKE LAWRENCE L +1

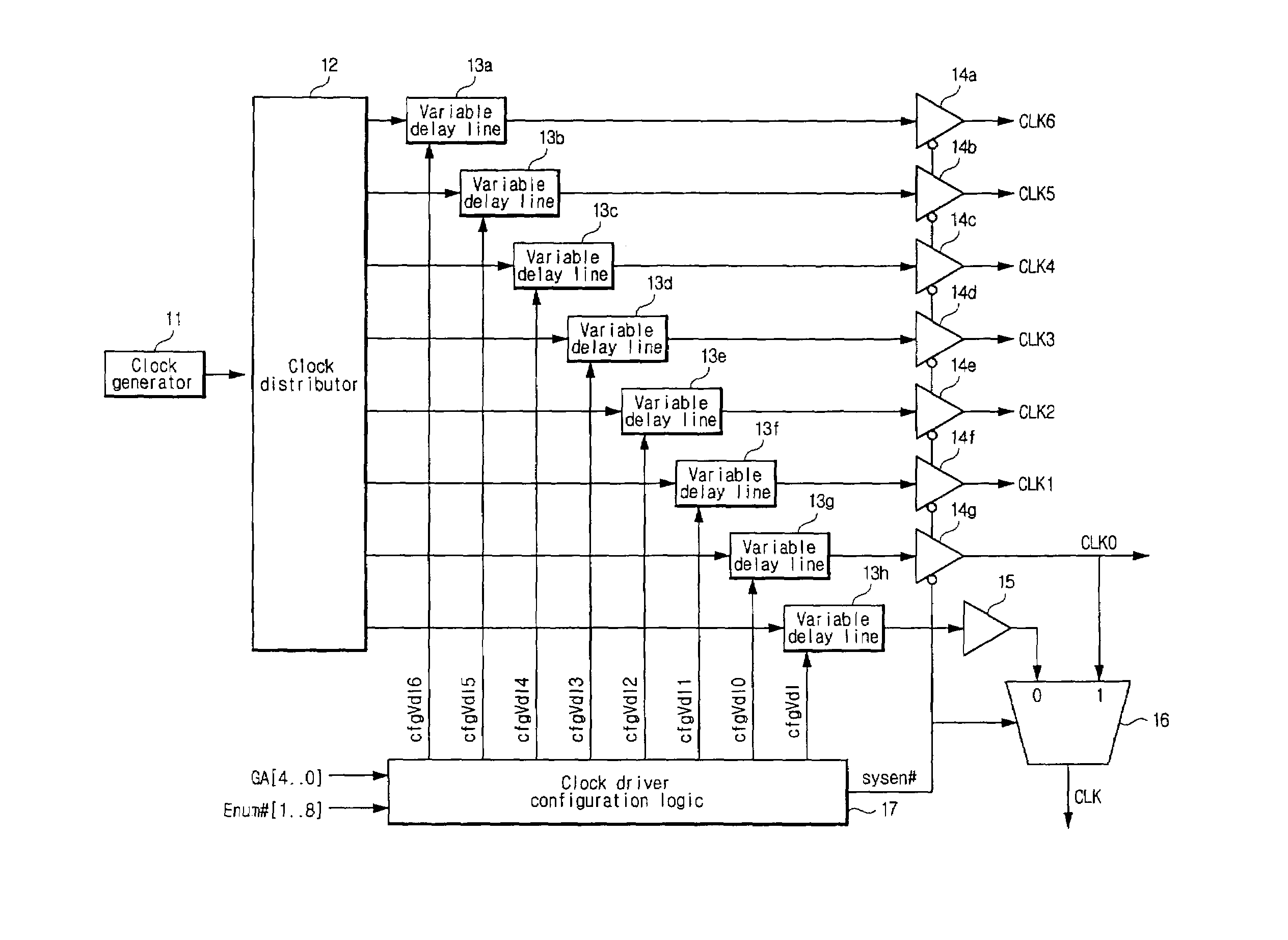

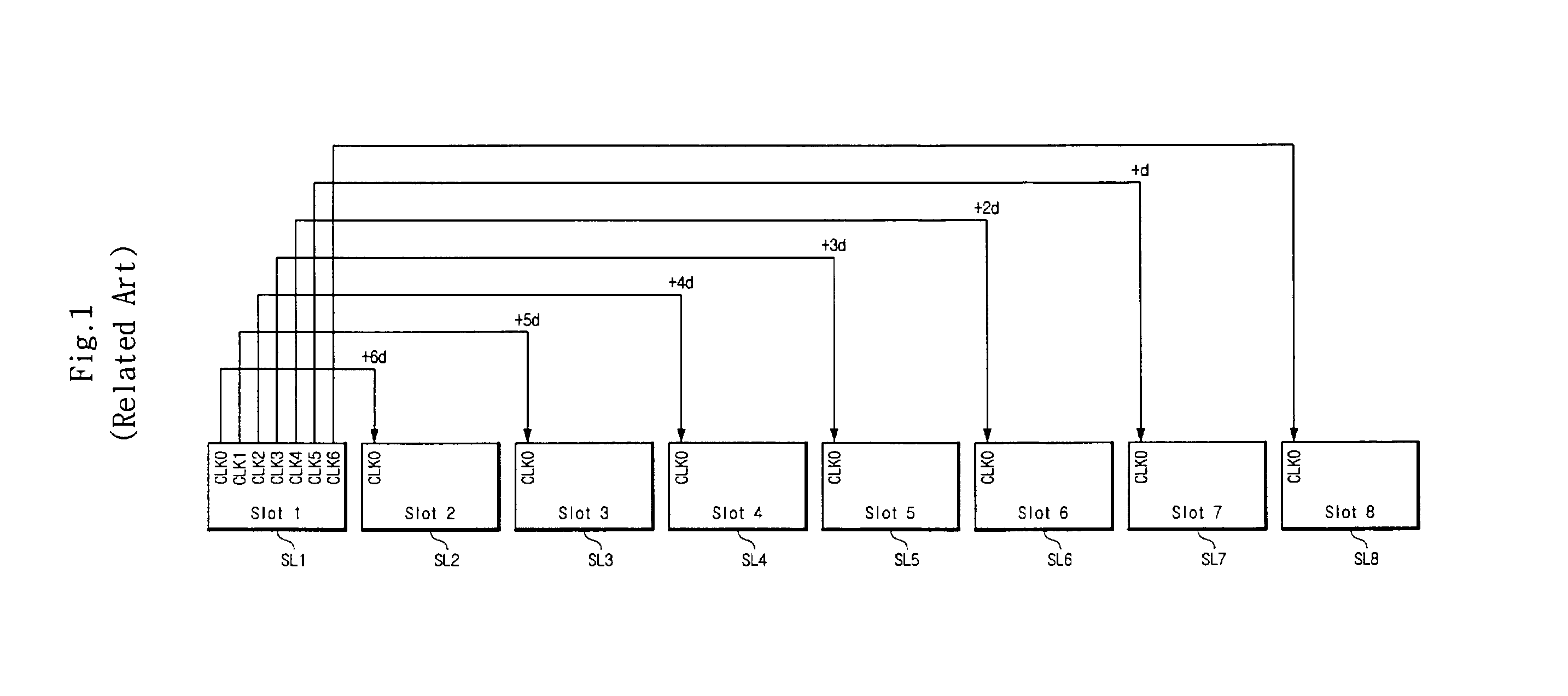

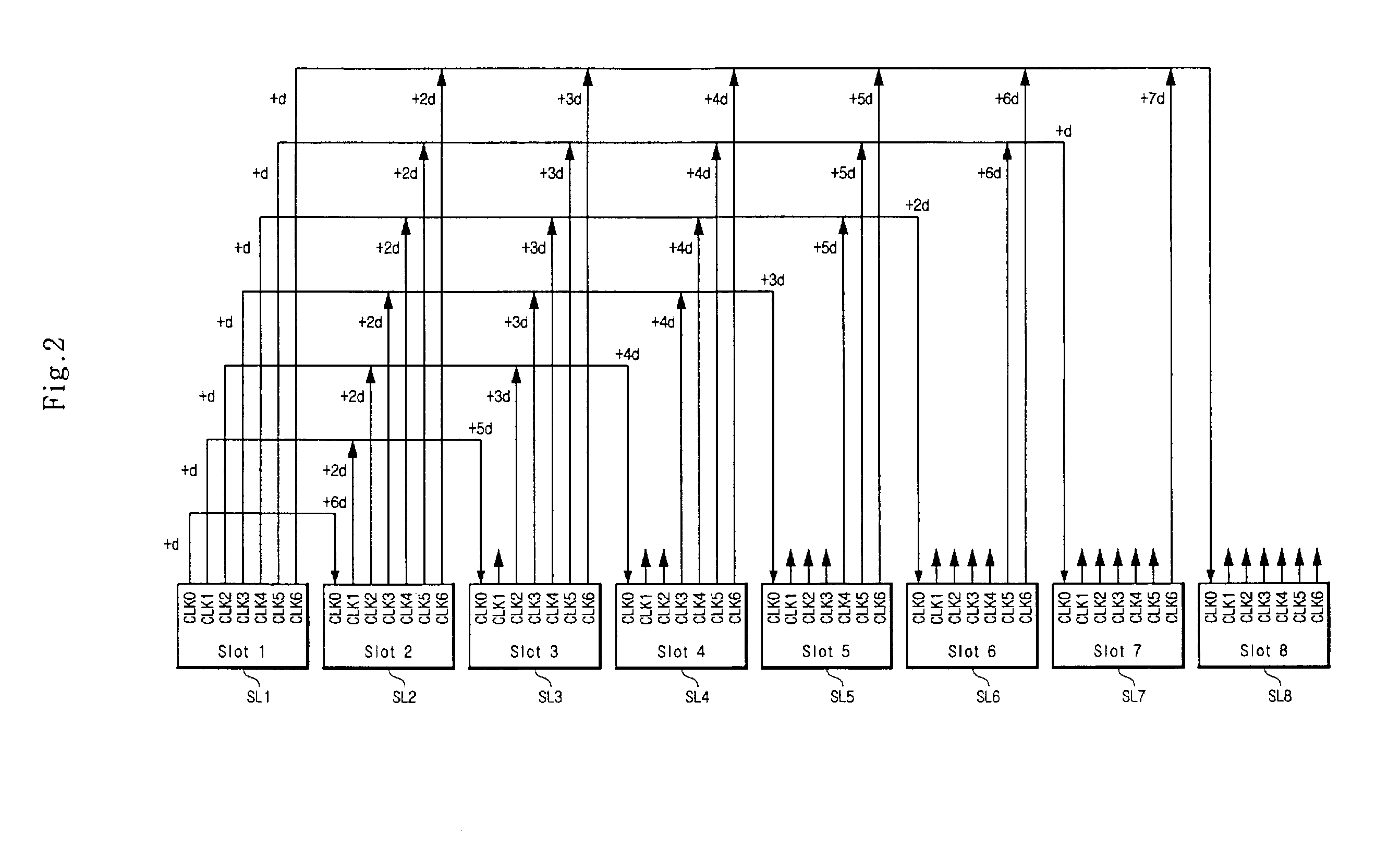

Clock distribution device and method in compact PCI based multi-processing system

InactiveUS7100066B2Skew of the clock transmitted to each slot may be minimizedMinimize skewTelevision system detailsPulse automatic controlHandling systemEmbedded system

Disclosed is a clock distribution device and method in a compact PCI system based multi-processing system. A compact PCI based multi-processing system preferably includes processing signals upon mounting various circuit boards on multiple slots, even if the location of the system slot is varied, the skew of clocks transmitted to the other slots may be minimized. Accordingly, the system may be configured in a flexible manner because of such variability of the system slot's location. Further, the system may be efficiently repaired and maintained because it is possible to easily and quickly take measures in response to any failure occurring on the board mounted on the system slot.

Owner:LG ERICSSON

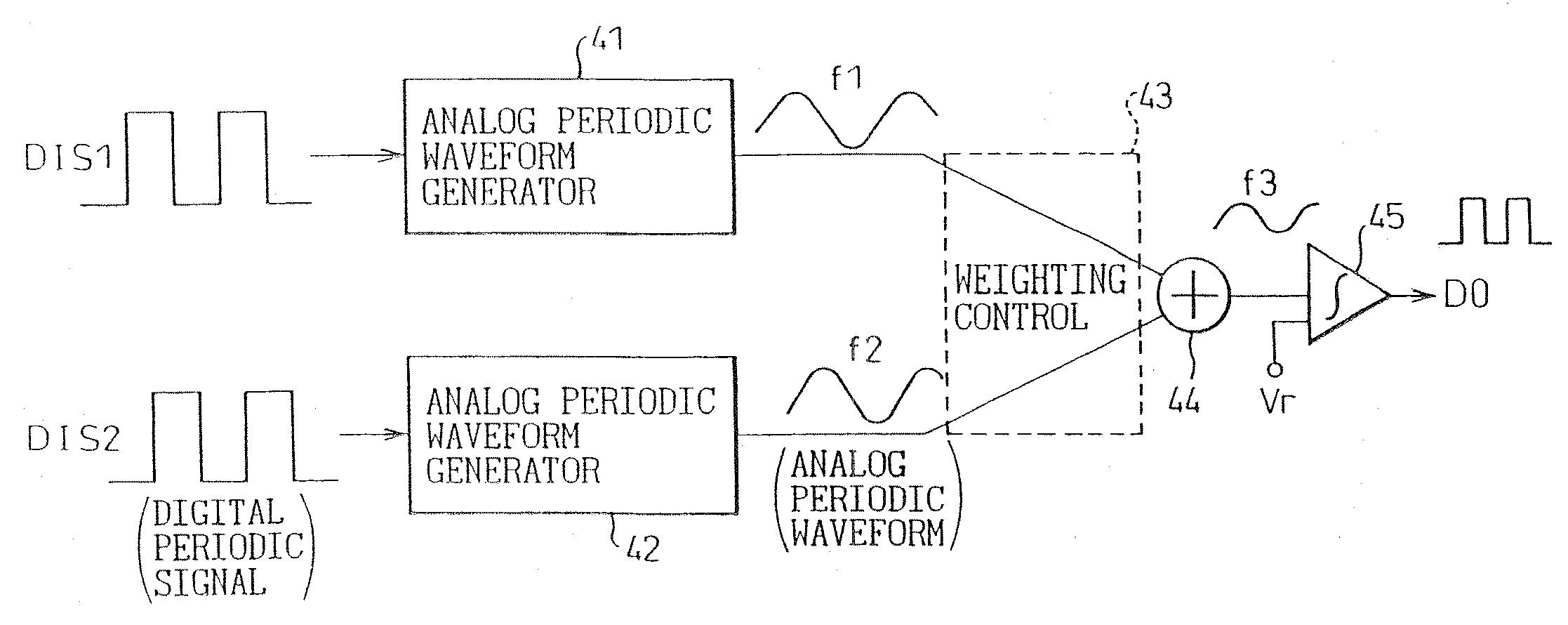

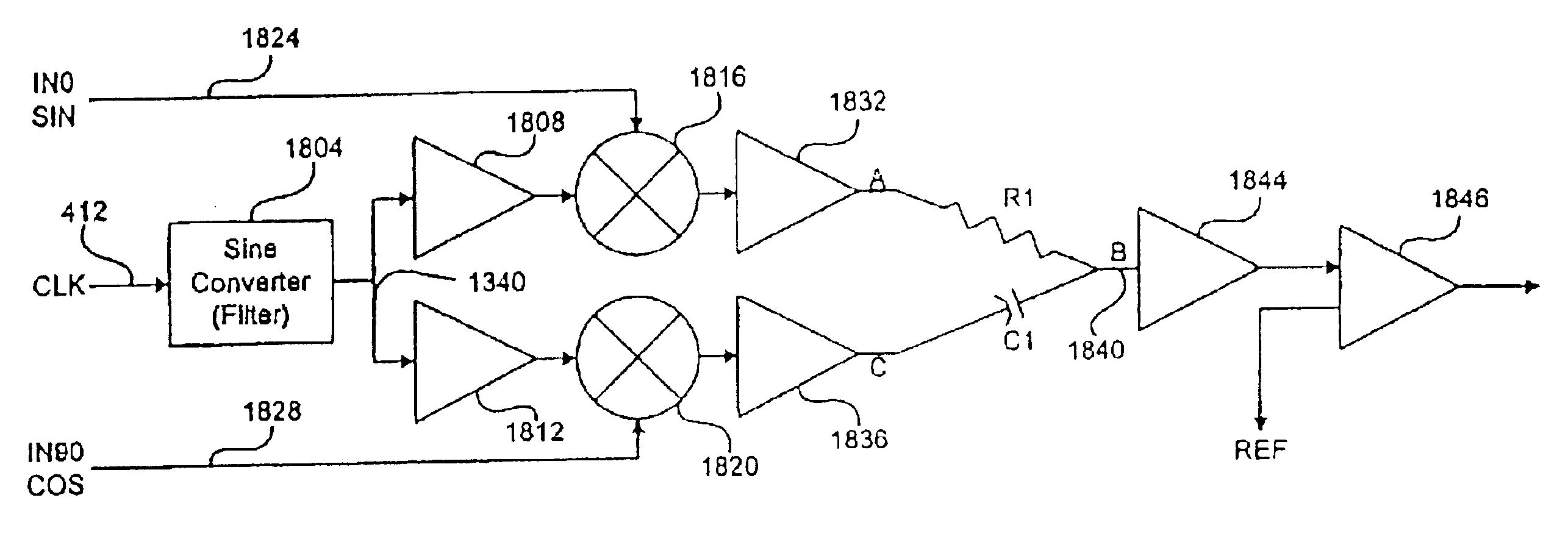

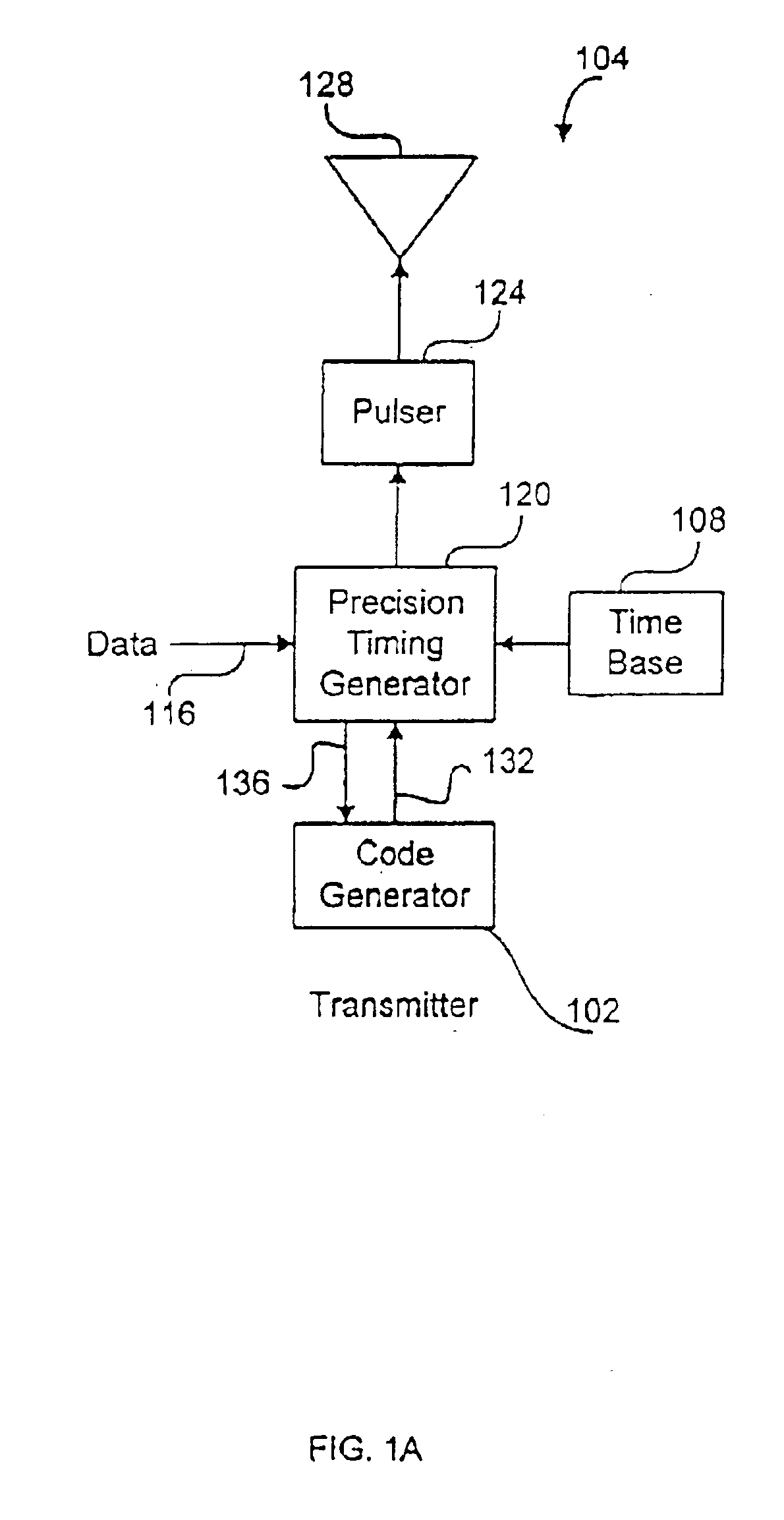

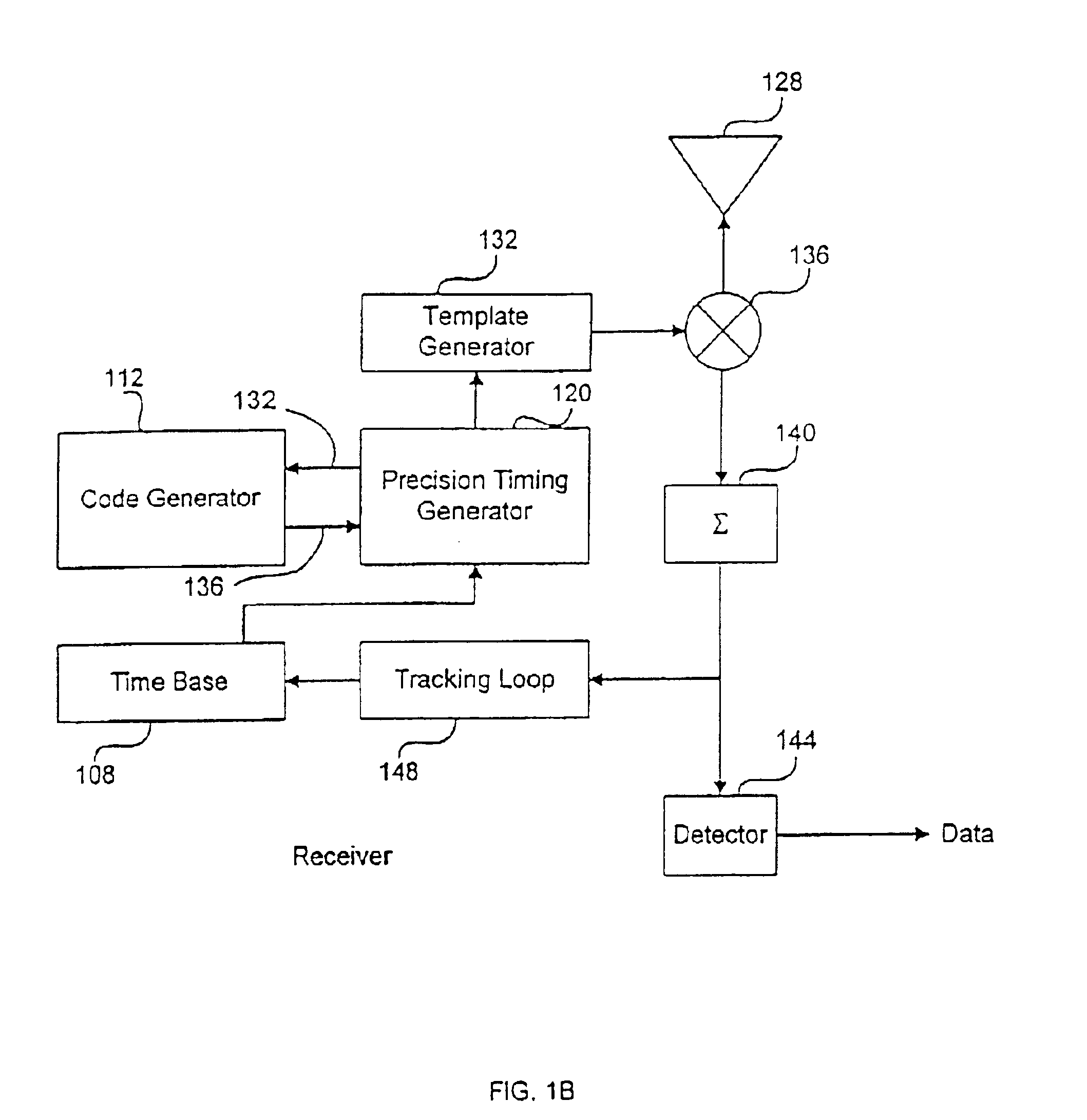

Precision timing generator apparatus and associated methods

InactiveUS6950485B2Overcome problemsPulse automatic controlTime-division multiplexTiming generatorPhase shifted

A precision timing generator includes a combiner that provides a timing signal by combining a coarse timing signal and a fine timing signal derived from a phase-shifted sinusoidal signal that has a desired phase shift. The coarse timing generator generates the coarse timing signal from a clock signal and a timing command input. The fine timing generator includes a sinusoidal-signal generator that receives the clock signal and generates a sinusoidal signal. The fine timing generator also includes a phase shifter that receives the sinusoidal signal and the timing command input and shifts the phase of the sinusoidal signal based on the timing input to generate the phase shifted sinusoidal signal.

Owner:ALEREON

Filler circuit cell

ActiveUS7705666B1Logic circuits characterised by logic functionOscillations generatorsVoltage sourceDecoupling capacitor

A filler circuit cell is disclosed. The filler circuit cell includes a decoupled capacitor, a tie low circuit and a tie high circuit. The decoupled capacitor includes a first NMOS transistor and a first PMOS transistor, in which the source / drain of the first NMOS transistor is connected to a second voltage source and the source / drain of the first PMOS transistor is connected to a first voltage source. The tie low circuit includes a second NMOS transistor and a second PMOS transistor and the tie high circuit includes a third NMOS transistor and a third PMOS transistor.

Owner:UNITED MICROELECTRONICS CORP

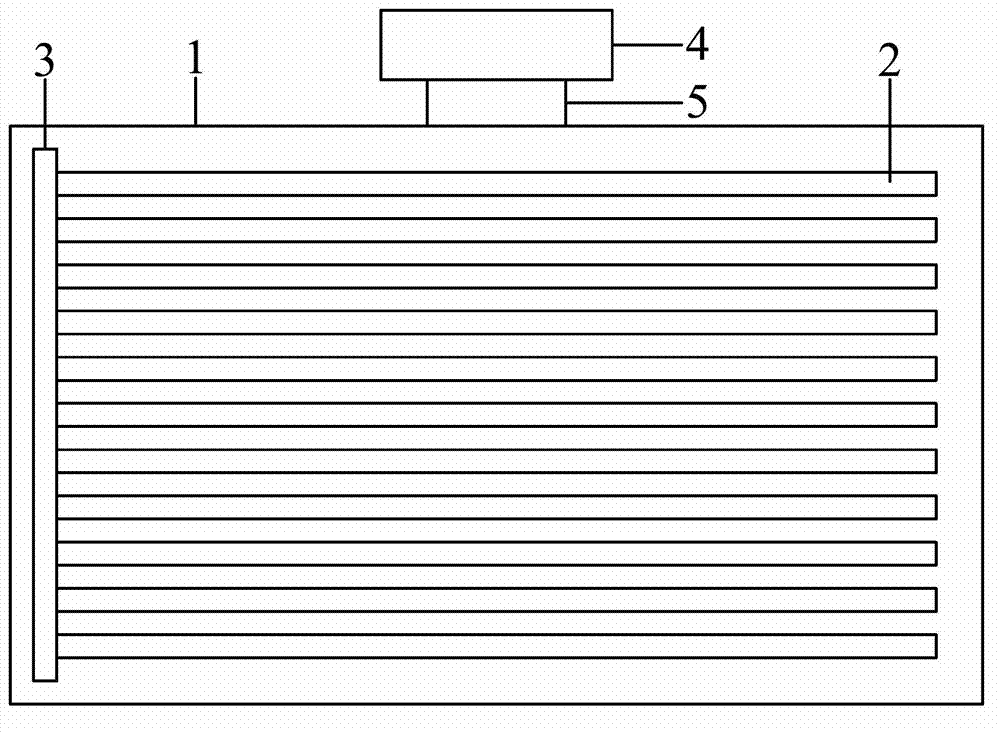

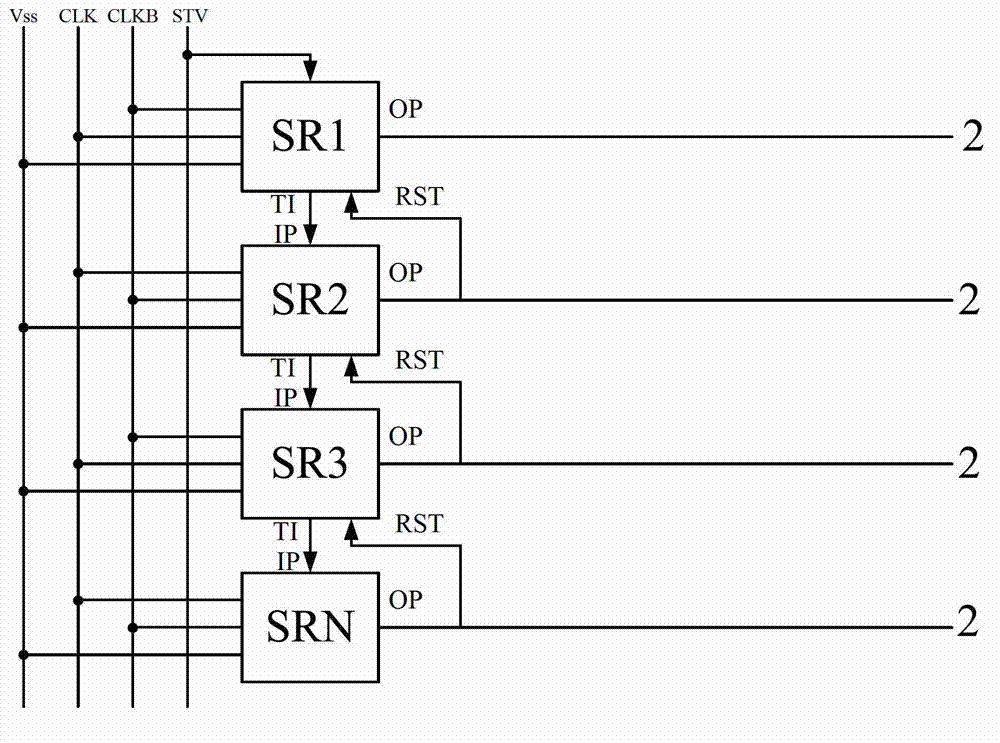

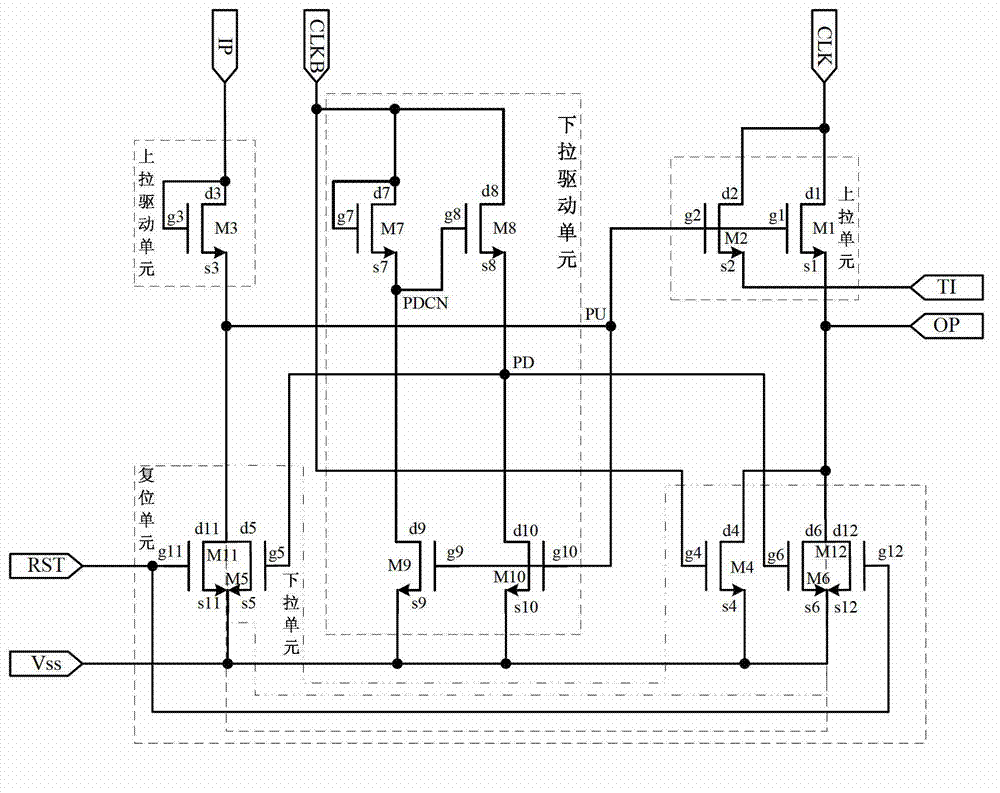

Gate driving circuit, display module and displayer

ActiveCN103050106AReduce power consumptionReduce loadStatic indicating devicesDigital storageShift registerDisplay device

The invention discloses a gate driving circuit, a display module and a displayer, which belong to the field of display and are designed for solving the problem of larger power consumption of the display module in the prior art. The gate driving circuit is used for driving a gate of a thin-film transistor corresponding to the connected a gate line. The gate driving circuit comprises at least two shifting registers which are connected in a step-by-step manner; each shifting register comprises a first output end and a second output end; the first output end is connected with an enabling signal input end of the next-step shifting register so as to output an enabling signal to the next-step shifting register; and the second output end is connected with the gate line so as to apply a gate driving signal of the thin-film transistor on the gate by the gate line.

Owner:BOE TECH GRP CO LTD +1

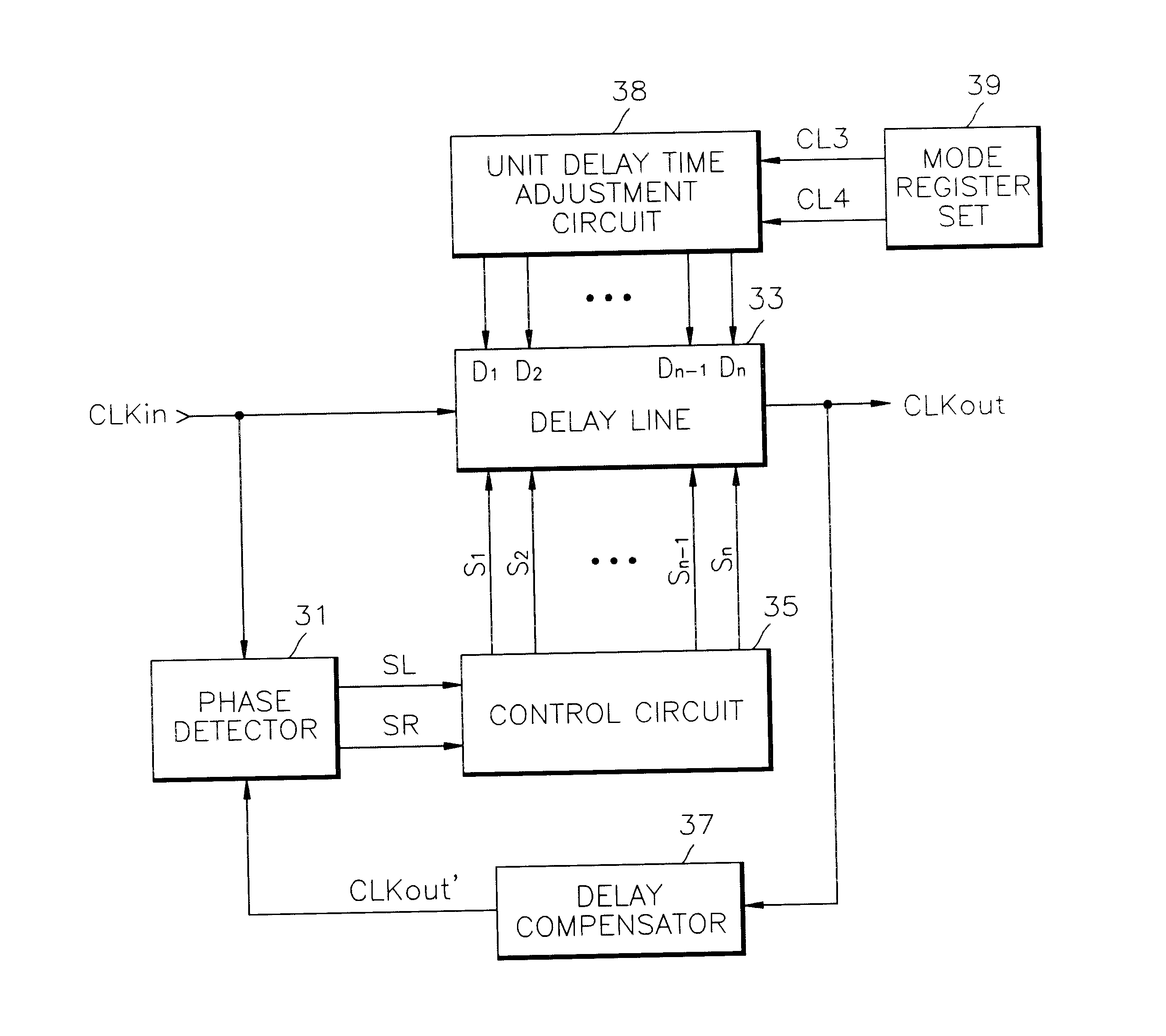

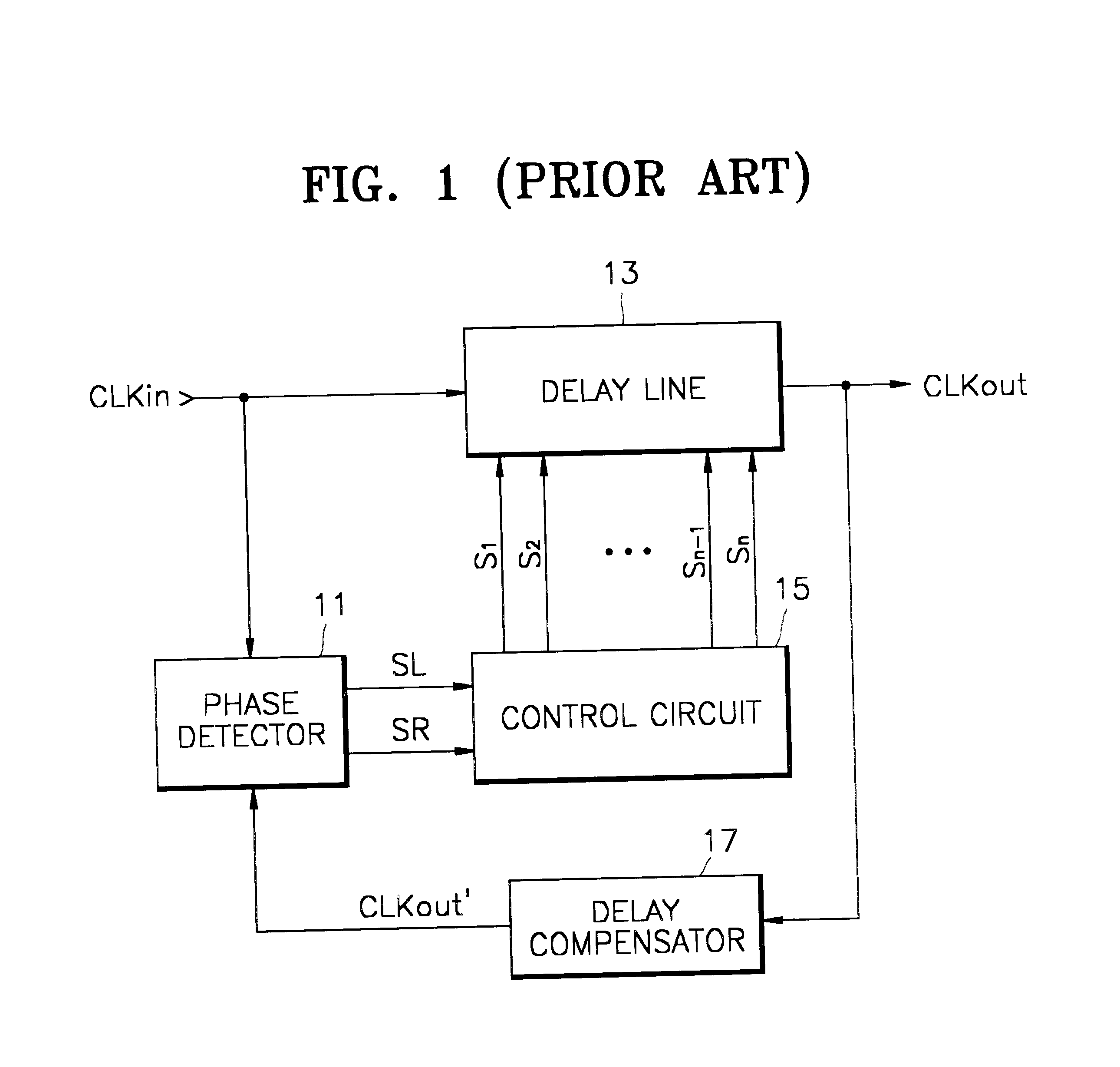

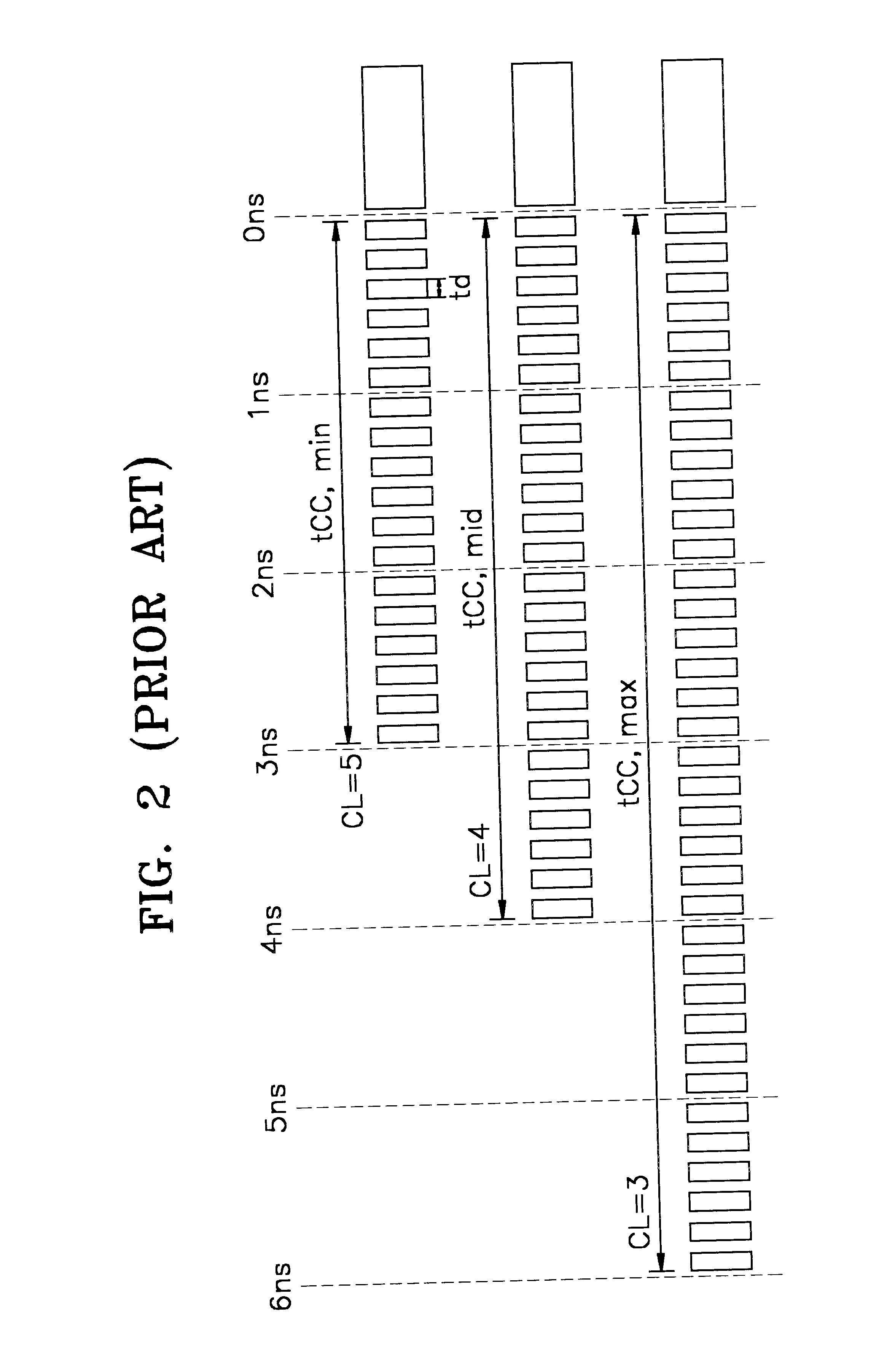

Delay locked loop circuit and method having adjustable locking resolution

A delay line receives an input clock signal and includes a cascaded plurality of unit delay circuits. A mode register set stores a value indicative of a column-address-strobe (CAS) latency of the memory device, and an adjustment circuit varies a delay time of the unit delay circuits according to the CAS latency stored in the mode register set. A phase detector detects a phase difference between the input clock signal and an output clock signal of the delay line, and a control circuit which controls an enabled state of the unit delay circuits according to an output of said phase detector.

Owner:SAMSUNG ELECTRONICS CO LTD

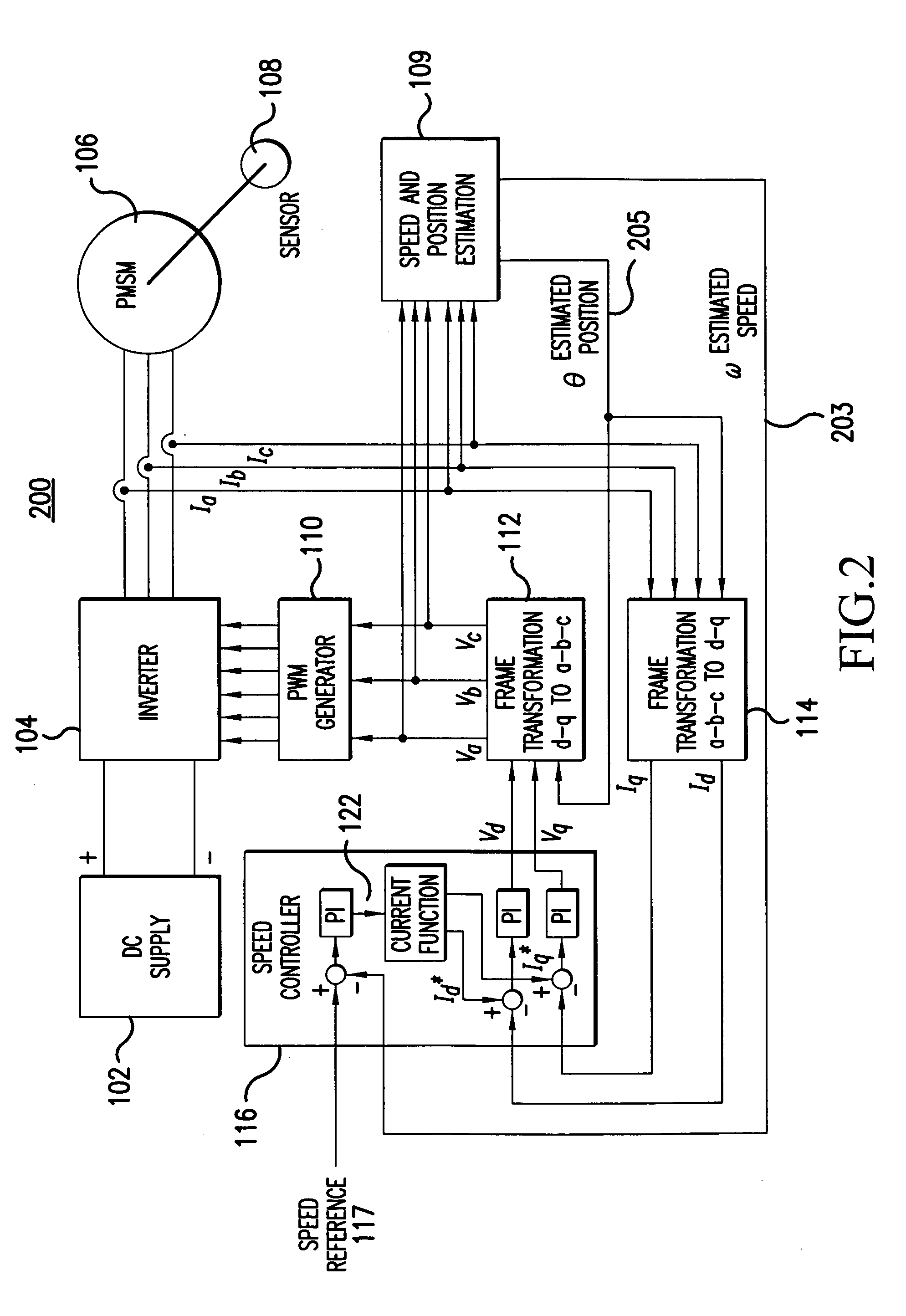

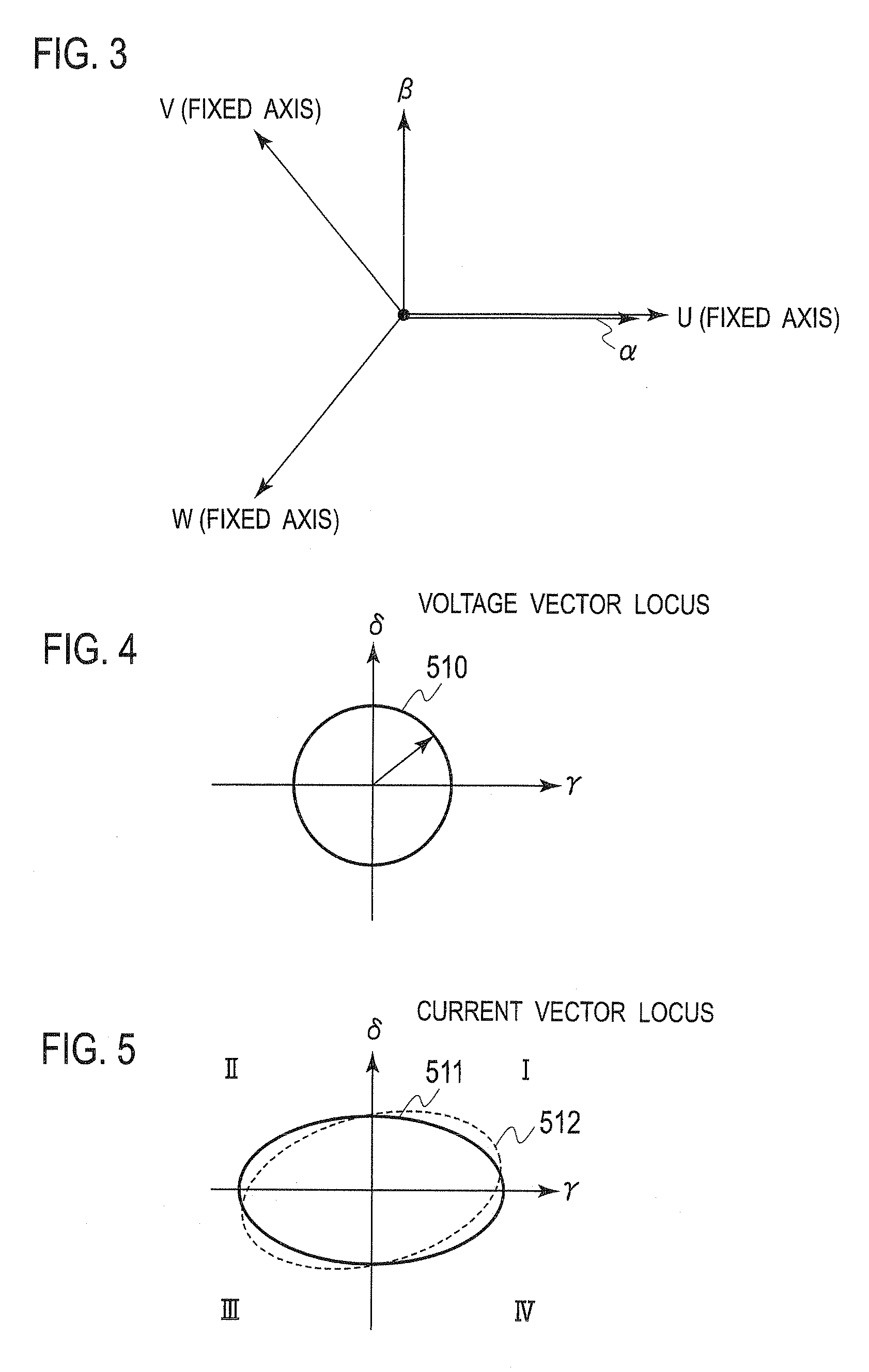

Position sensorless drive for permanent magnet synchronous motors

ActiveUS20050151502A1AC motor controlSynchronous motors startersLow speedPermanent magnet synchronous motor

A sensorless motor control algorithm that single-handedly permits operation over the entire speed range from low speed to high speed. This “fusion” algorithm seamlessly fuses the position data generated respectively by high speed and low speed sensorless algorithms. The resulting sensorless drive permits effective position sensorless operation over the entire speed range of a PM motor.

Owner:INFINEON TECH AMERICAS CORP

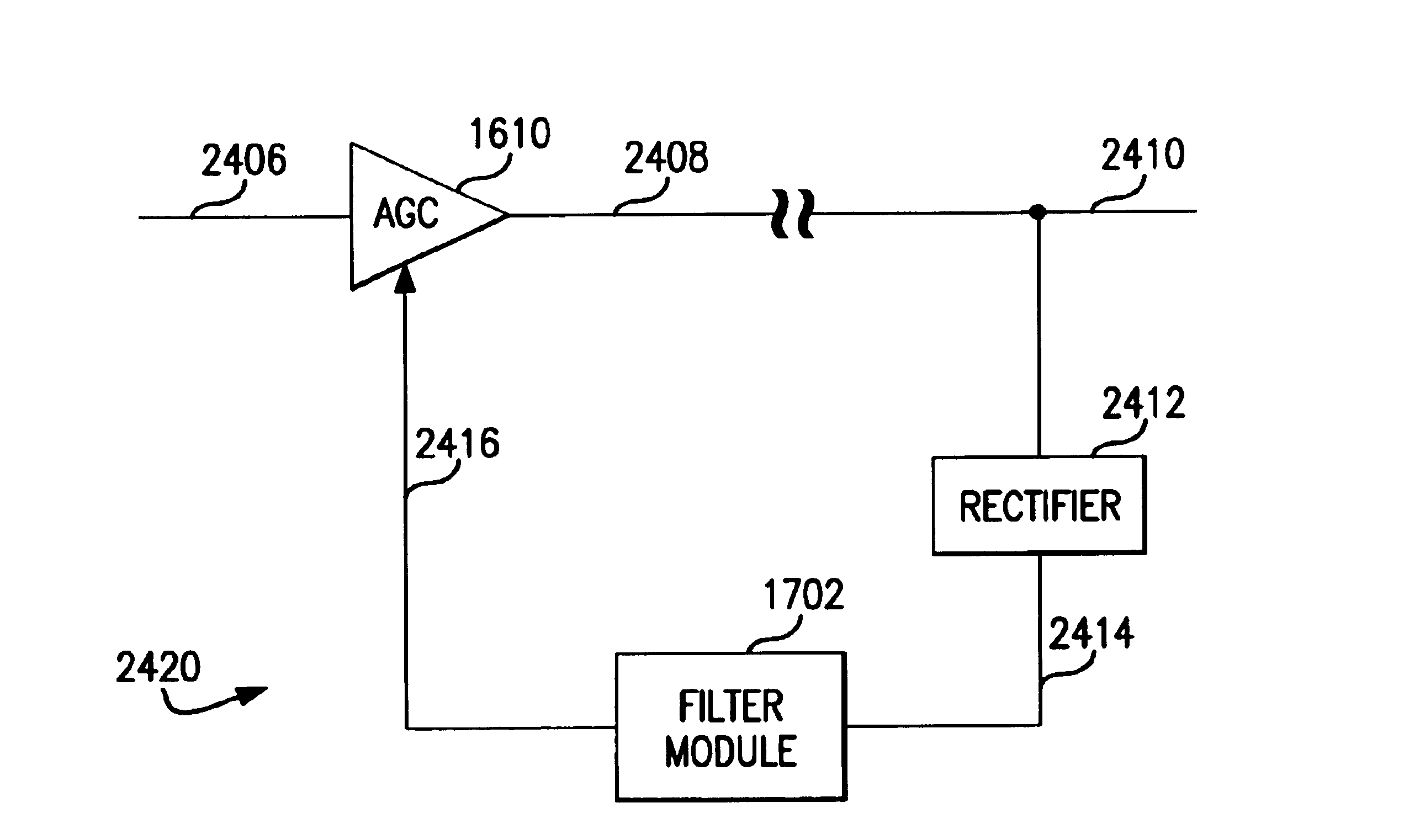

Method and apparatus for DC offset removal in a radio frequency communication channel

A filter module for reducing a DC offset voltage in a radio frequency communication channel is described. A first capacitor is coupled between a first differential input node and a first differential output node. A second capacitor is coupled between a second differential input node and a second differential output node. An active variable resistor is coupled between the first differential output node and the second differential output node. The active variable resistor receives a control signal. The control signal adjusts the value of the active variable resistor, which adjusts the frequency response of the filter module. The rate at which the filter module reduces DC offset voltages is thereby adjusted. The filter module is also adaptable to single-ended applications.

Owner:PARKER VISION INC

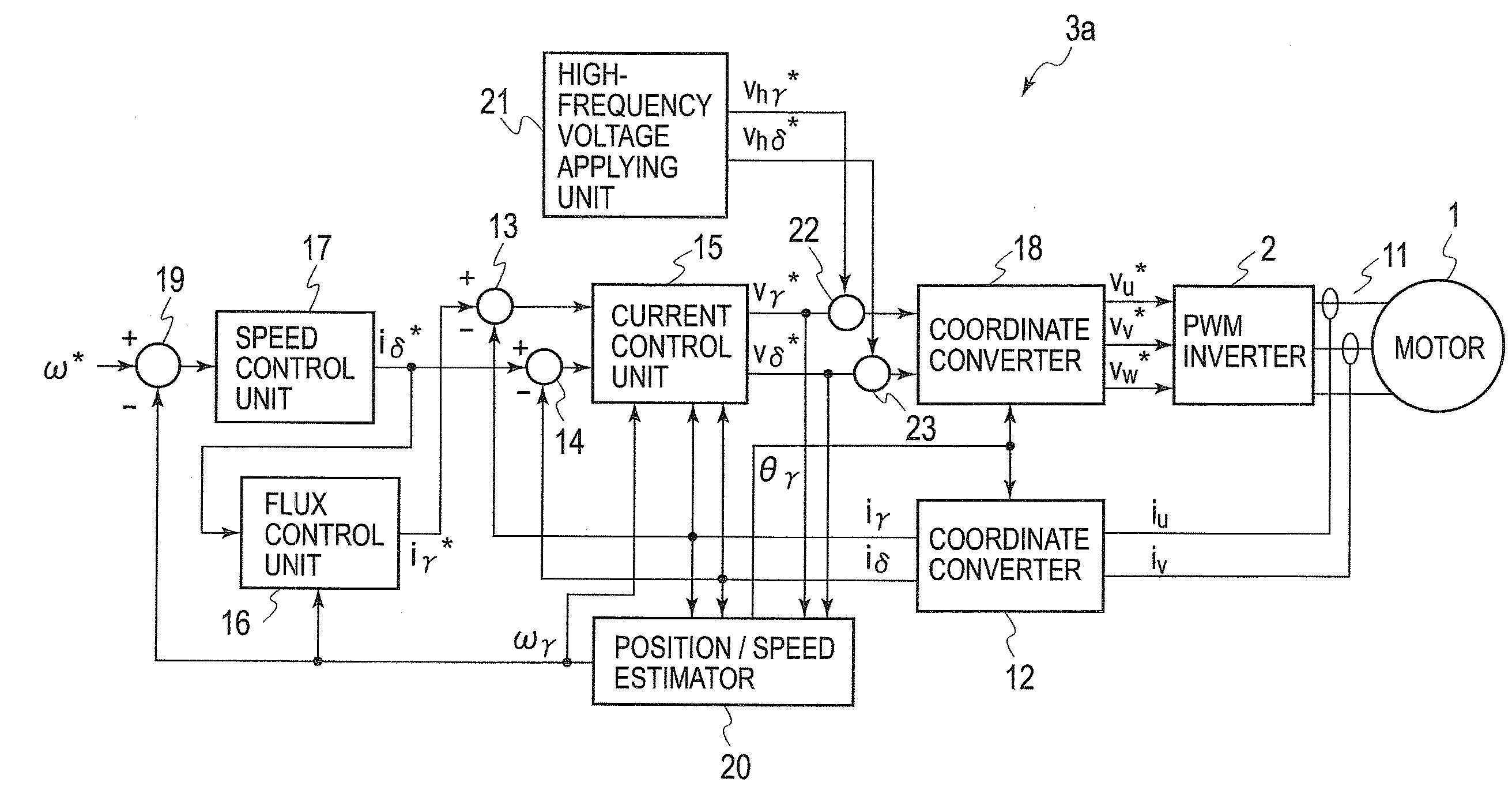

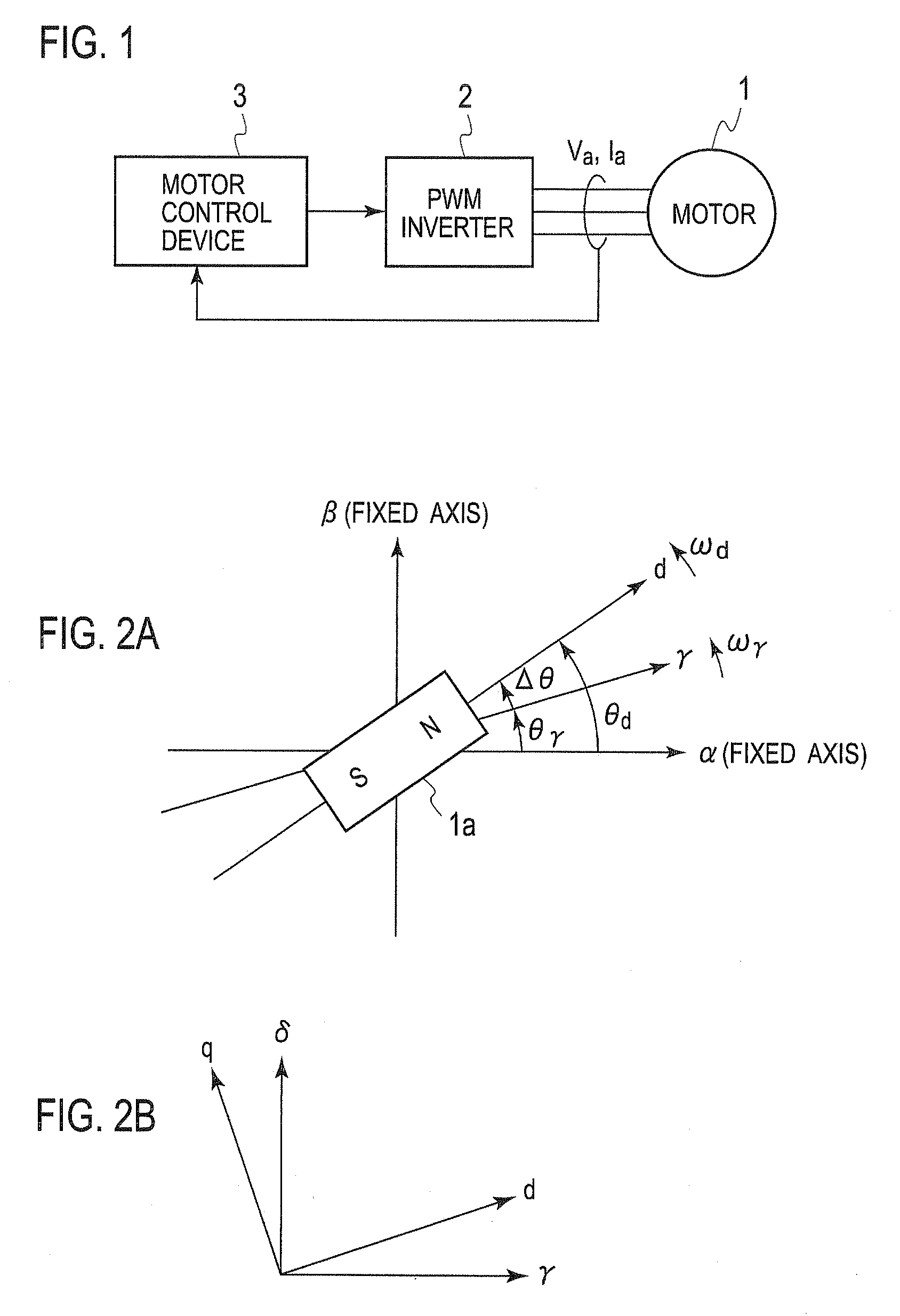

Motor Control Device

ActiveUS20100045218A1Stable positionShort amount of timeSynchronous motors startersVector control systemsMagnetic polesEngineering

To estimate an initial magnetic pole position in a short time, estimated axes for control that correspond to the d-axis and the q-axis are set as the γ-axis and the d-axis, and a high frequency rotation voltage or alternating voltage on the γδ coordinate system is applied to the motor. A high frequency current ih that flows in the motor due to the application of the high frequency voltage is extracted from a detected motor current (armature current) and a direct current component (ihγ×ihd)DC of a product of the γ-axis and d-axis components of the high frequency current ih is derived. On the other hand, the γ′-axis component ichγ and the δ′-axis component ichd of the high frequency current ih that are shifted by p / 4 in electric angle from the γ-axis and the d-axis are obtained and a direct current component of their product (ichγ×ichd)DC is obtained. Thereafter, the magnetic pole position is estimated by computing the axial error Δθ between the γ-d axes utilizing the two direct current components.

Owner:SANYO ELECTRIC CO LTD

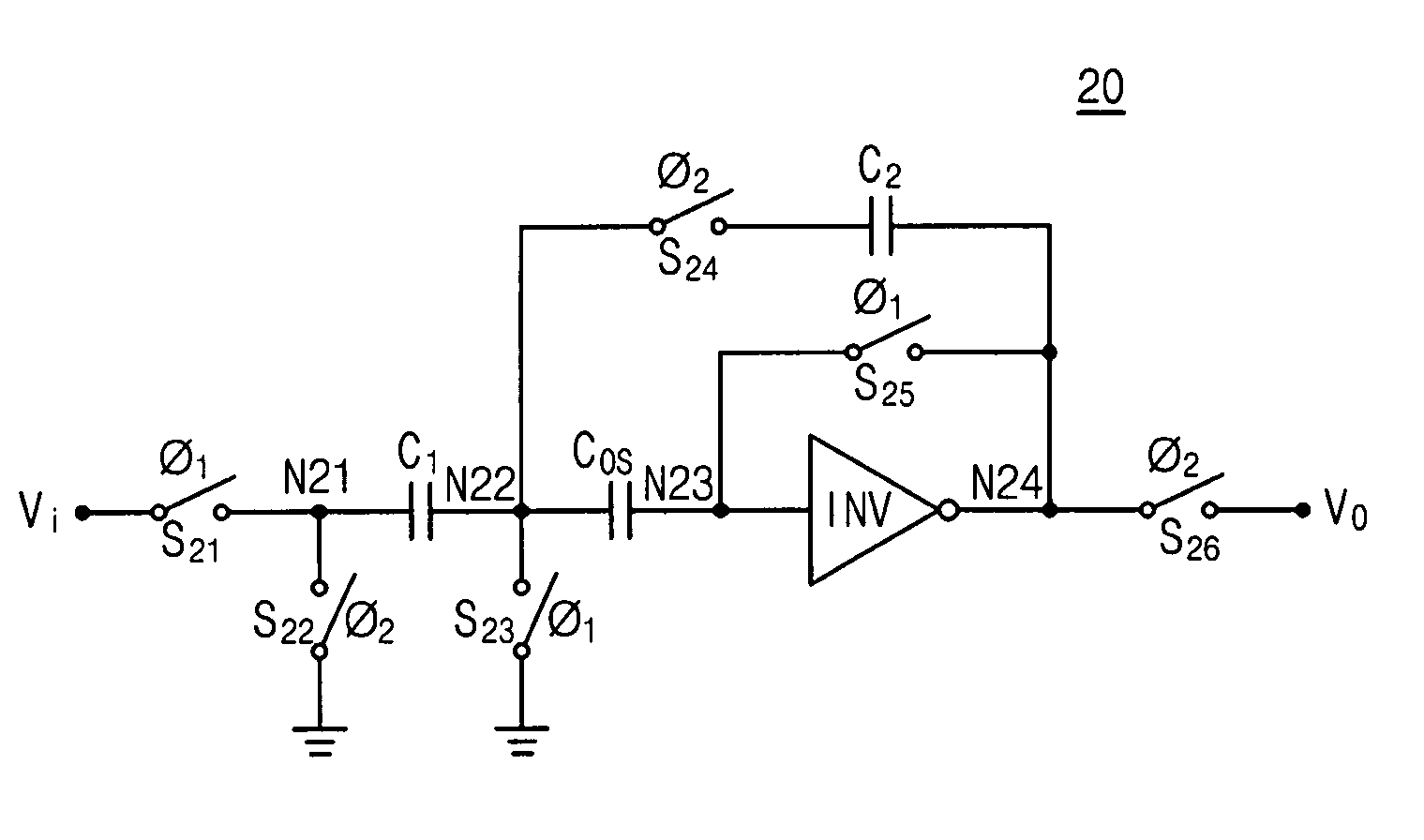

Switched capacitor circuit with inverting amplifier and offset unit

ActiveUS7800427B2Reduce power consumptionReduce circuit areaAmplifier modifications to reduce non-linear distortionComputing operations for integral formationCapacitanceAudio power amplifier

A switched capacitor circuit includes an amplifier, a charging unit, an offset unit, and an integrating unit. The charging unit is coupled between an input node and a first node, and is for accumulating charge corresponding to an input signal during a sampling mode. The offset unit is coupled between the first node and an input of the amplifier, and is for maintaining the first node to be a virtual ground during an integrating mode. The integrating unit is coupled between the first node and an output of the amplifier, and is for receiving charge from the charging unit during the integrating mode.

Owner:SAMSUNG ELECTRONICS CO LTD +1

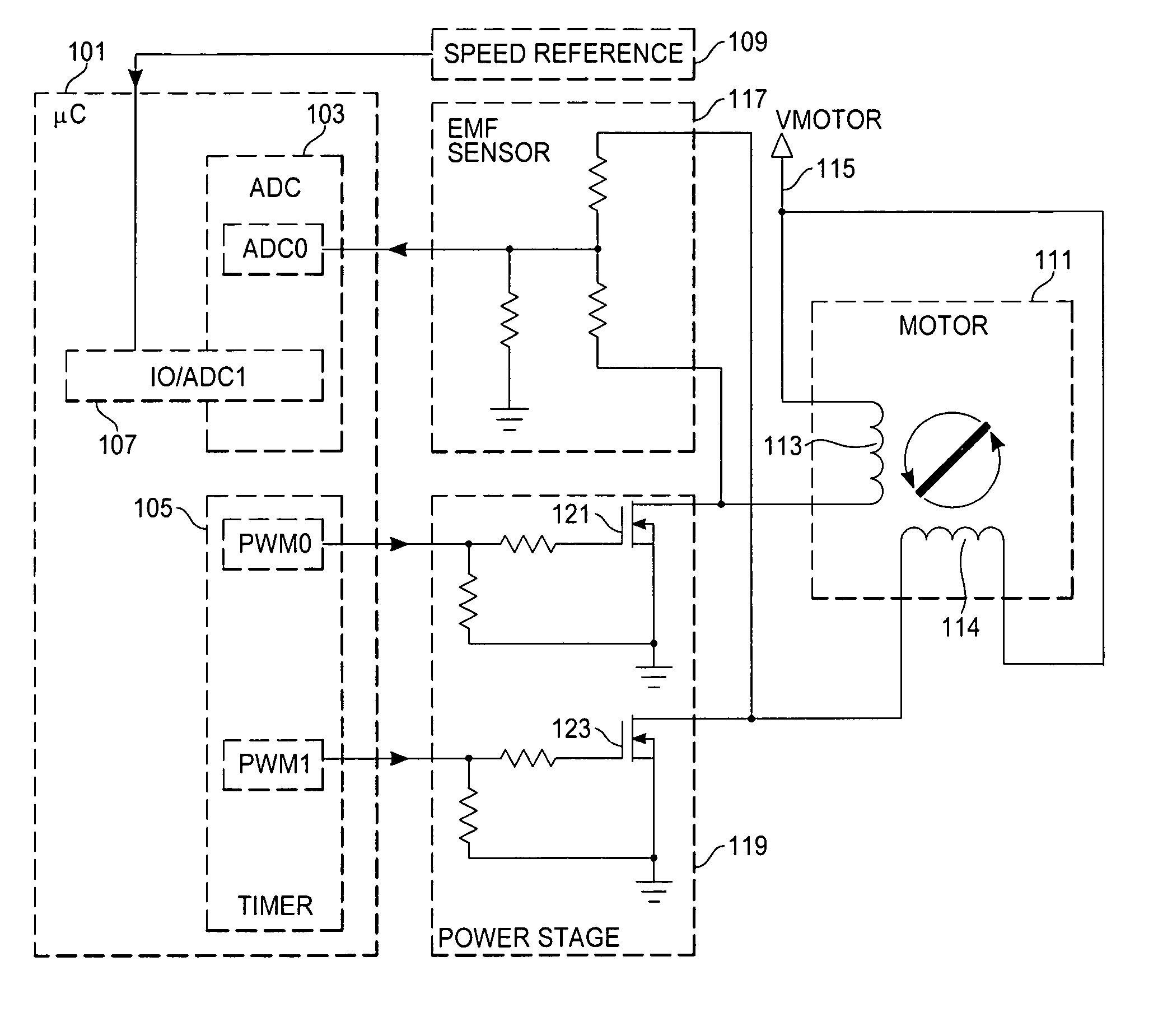

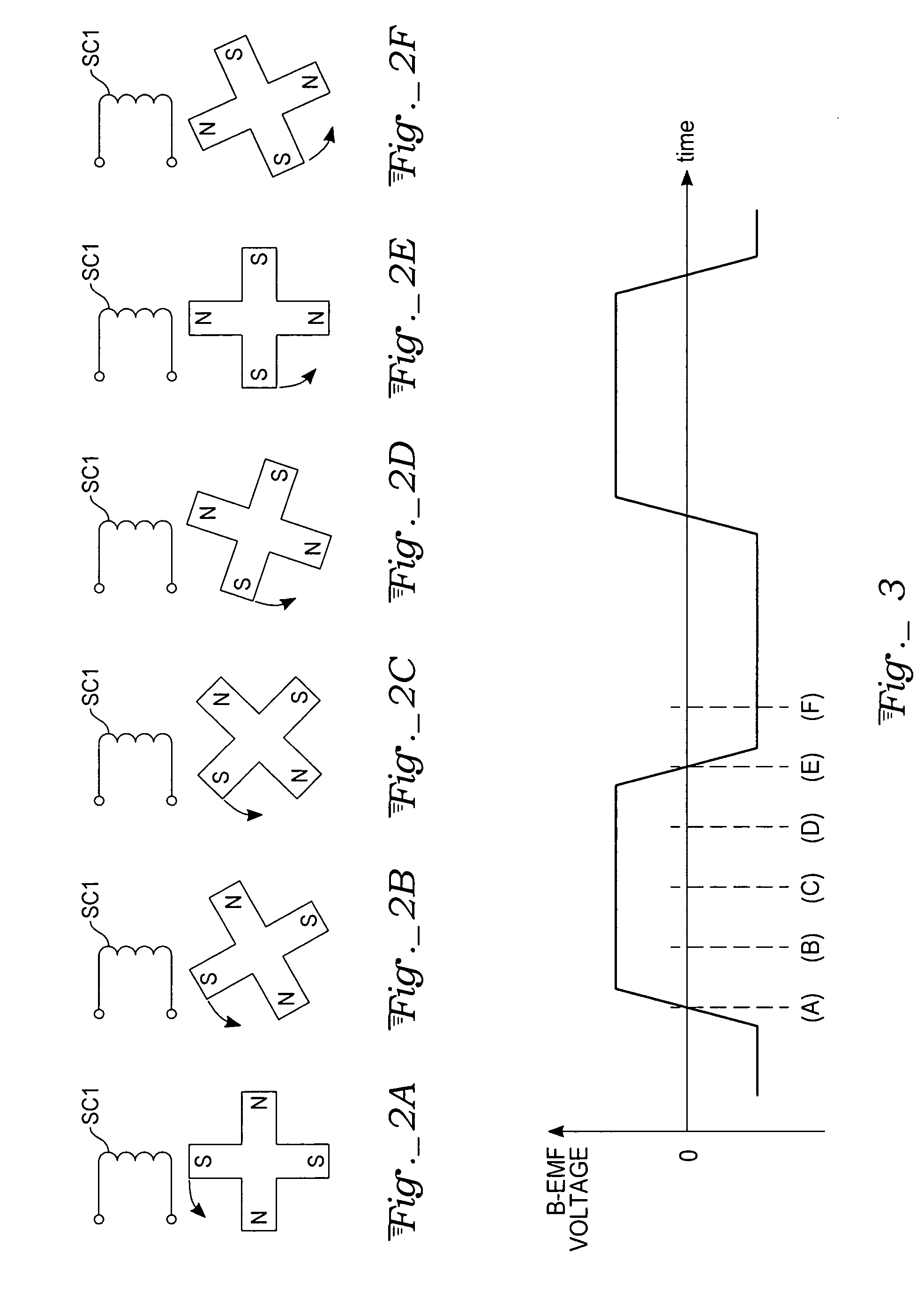

Sensorless control of two-phase brushless DC motor

A motor control system for a two-phase brushless DC motor uses measured EMF voltage from the passive set of stator coils to control commutation. A microcontroller receives the EMF voltage measurement and compares it to a threshold voltage value, which may be speed-dependent for advance commutation at high motor speeds. A match of the EMF voltage measurement with the threshold value triggers commutation of the drive to the opposite set of stator coils. The microcontroller also has an up-down counter timer whose count value is compared to an external speed reference. Each match of the count value triggers a transition in a pulse-width modulated (PWM) drive signal. The duty cycle of the PWM signal establishes an average drive voltage that controls motor speed.

Owner:ATMEL CORP

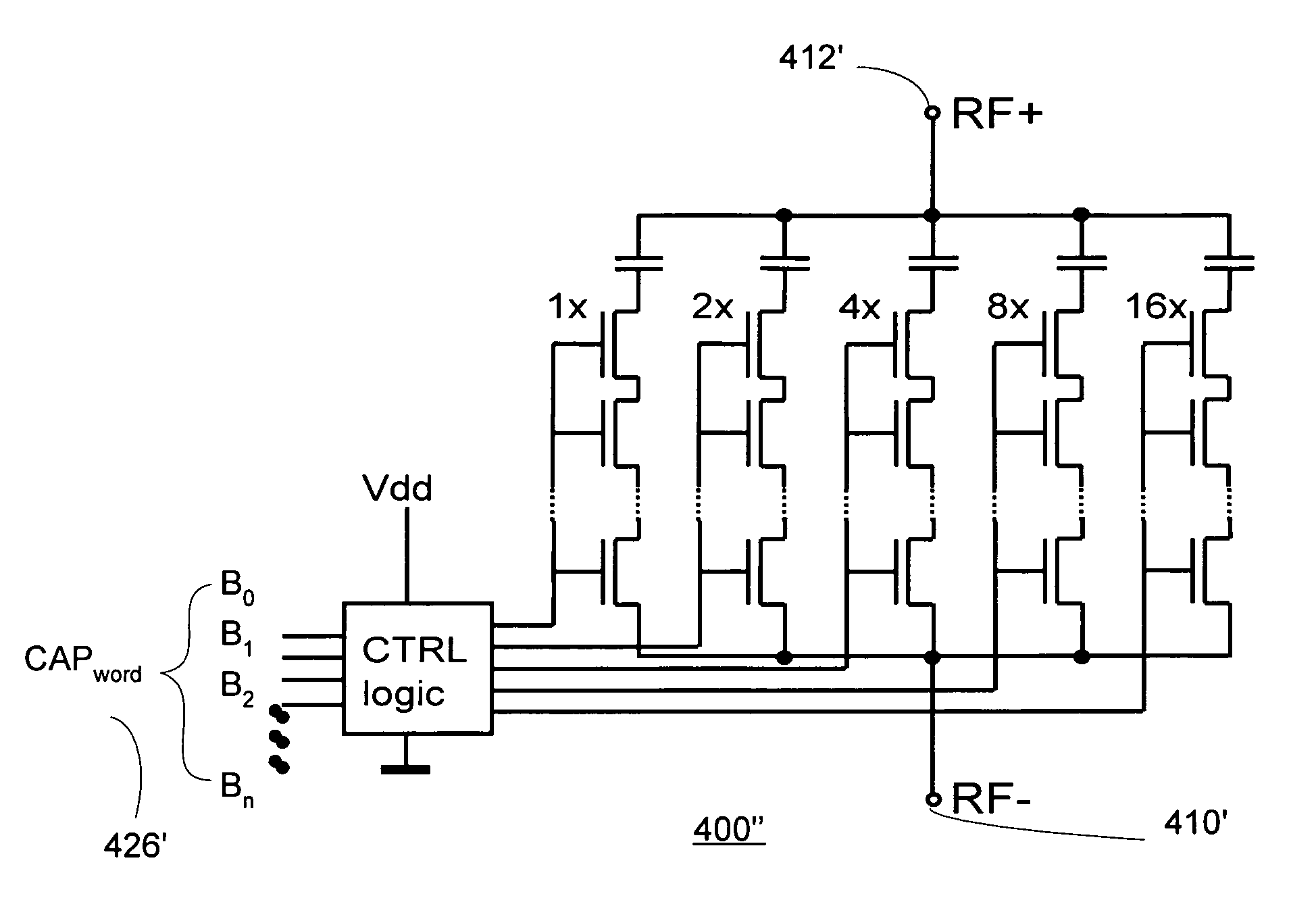

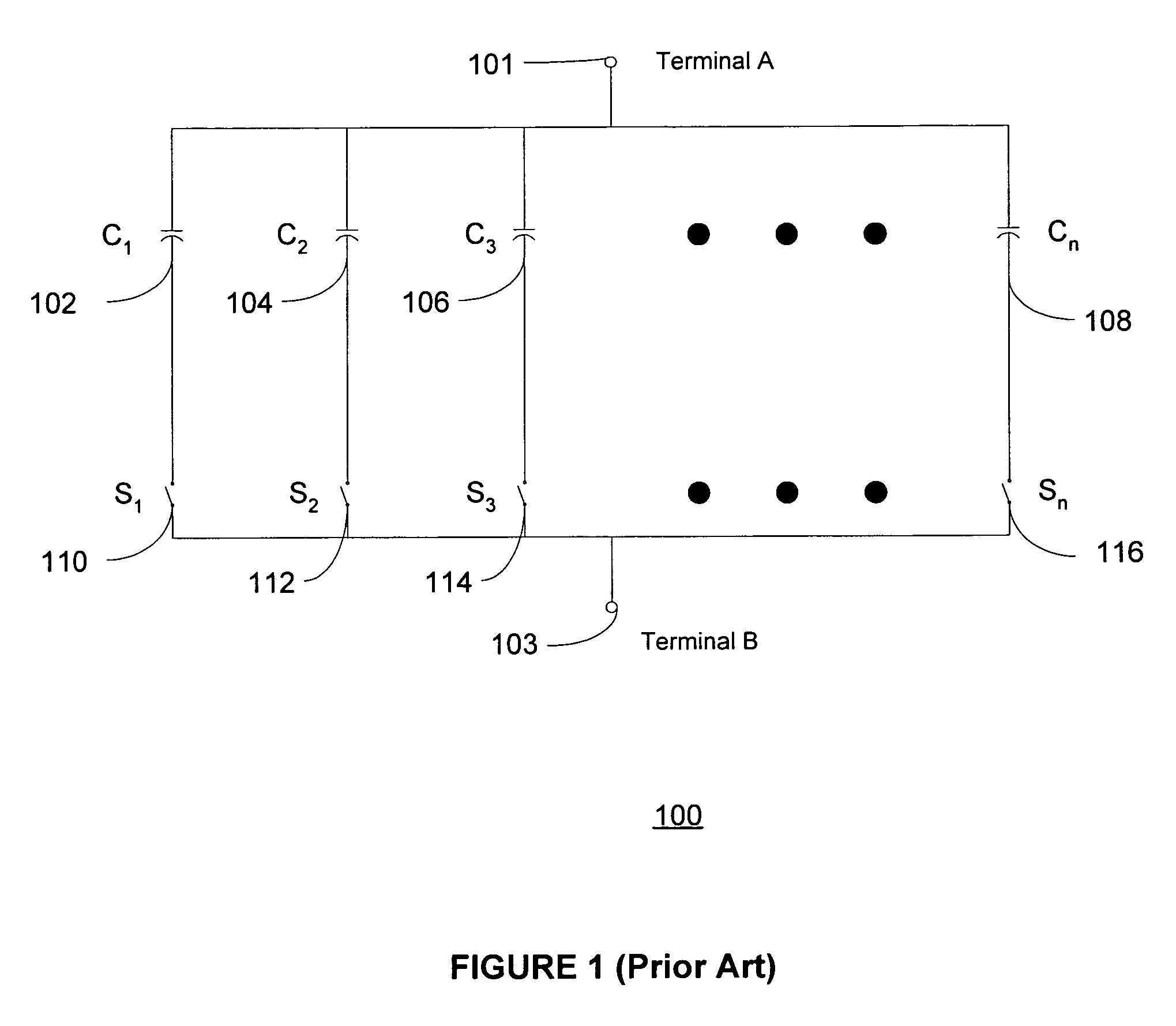

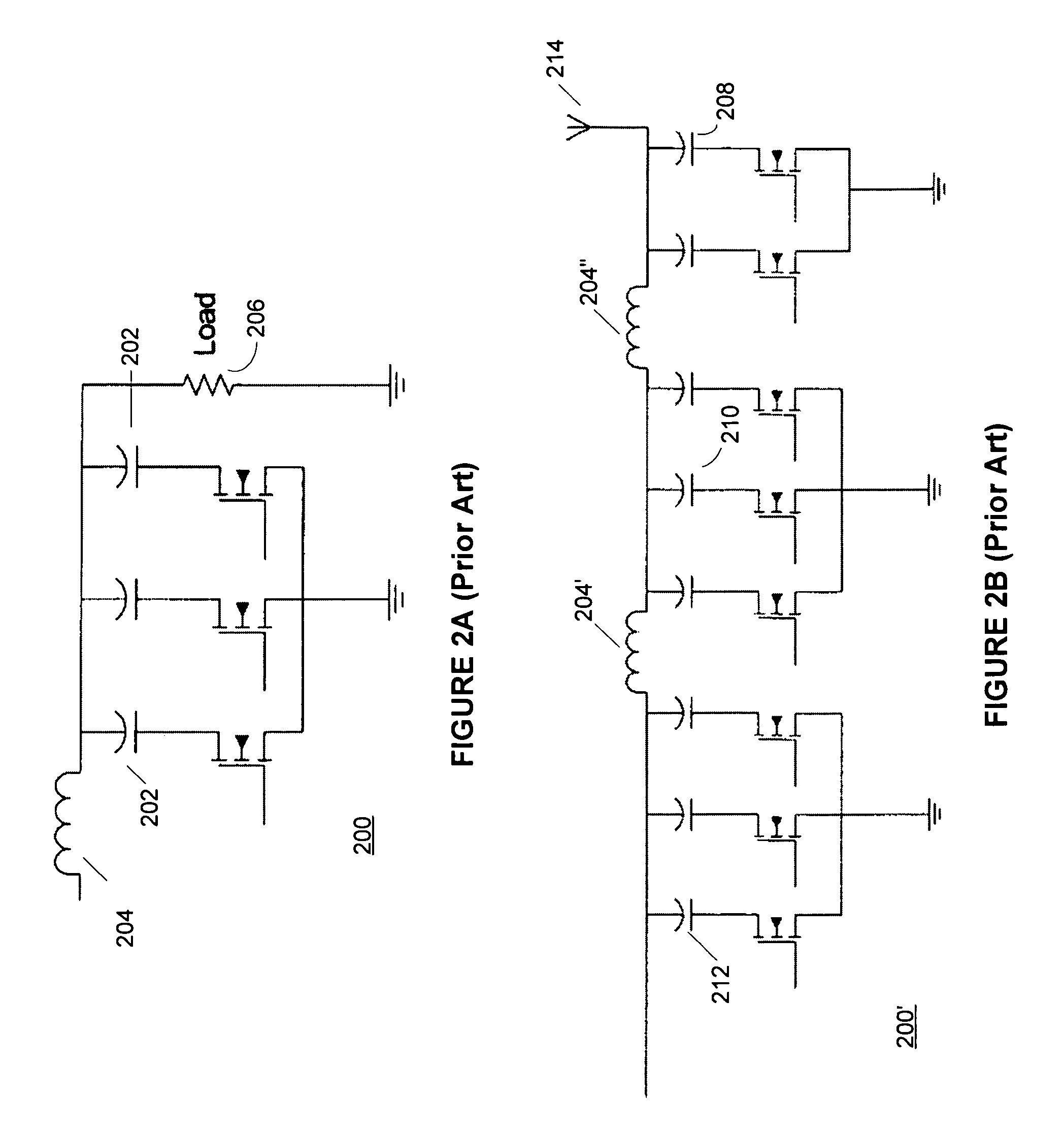

Method and apparatus for use in digitally tuning a capacitor in an integrated circuit device

ActiveUS9024700B2Easy to controlHigh Power Handling CapabilityMultiple-port networksImpedence matching networksCapacitanceLeast significant bit

Owner:PSEMI CORP

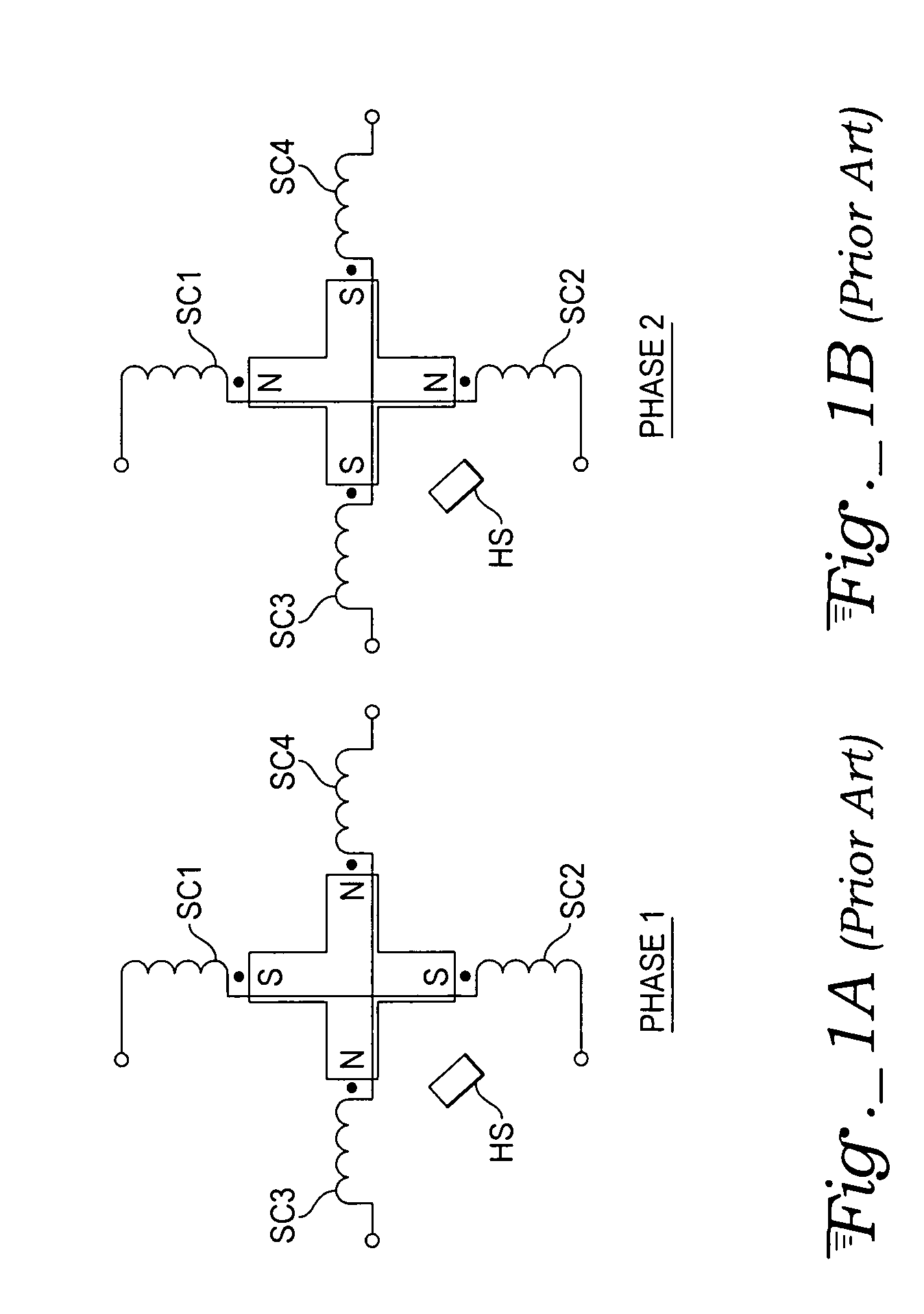

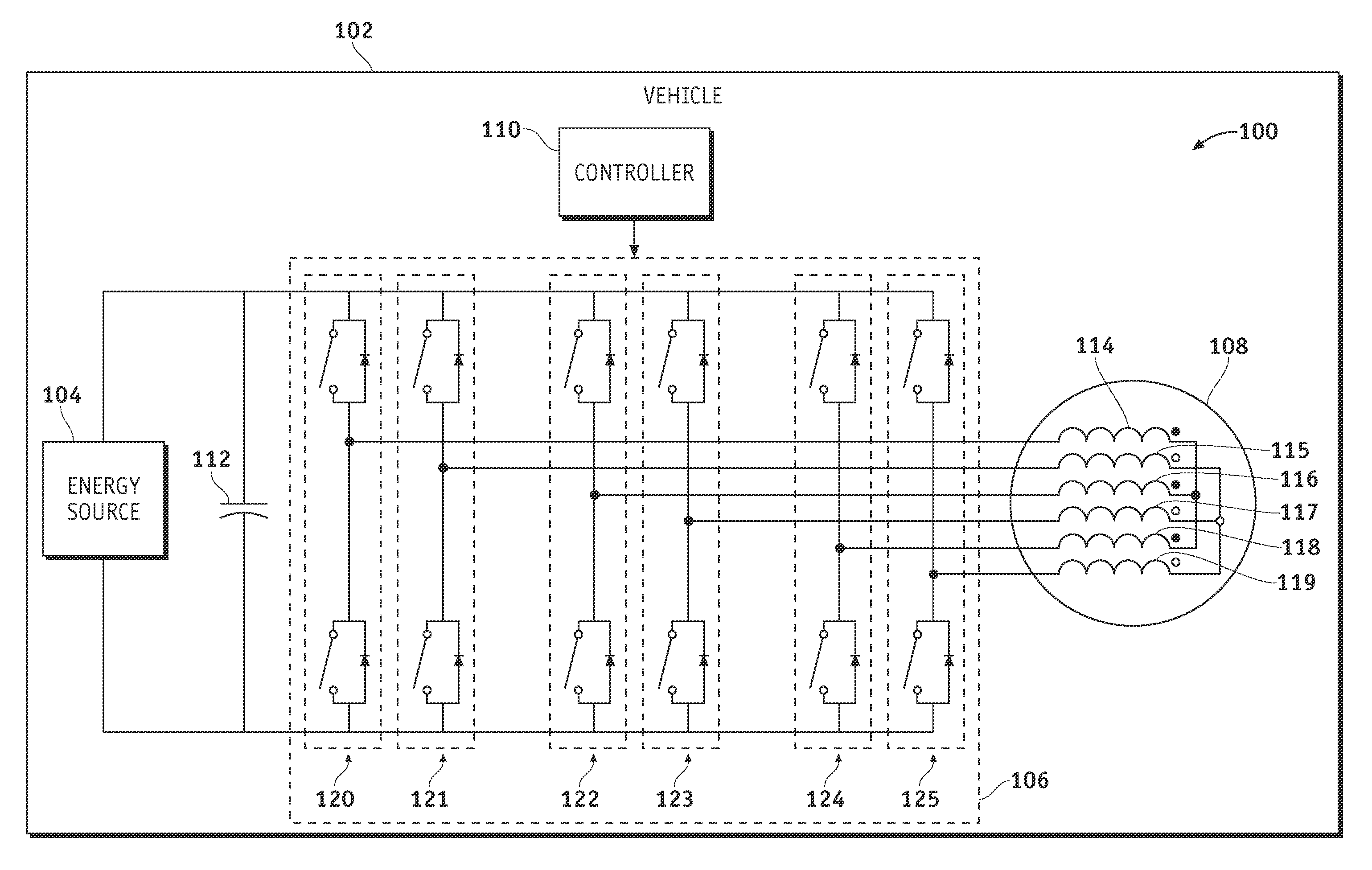

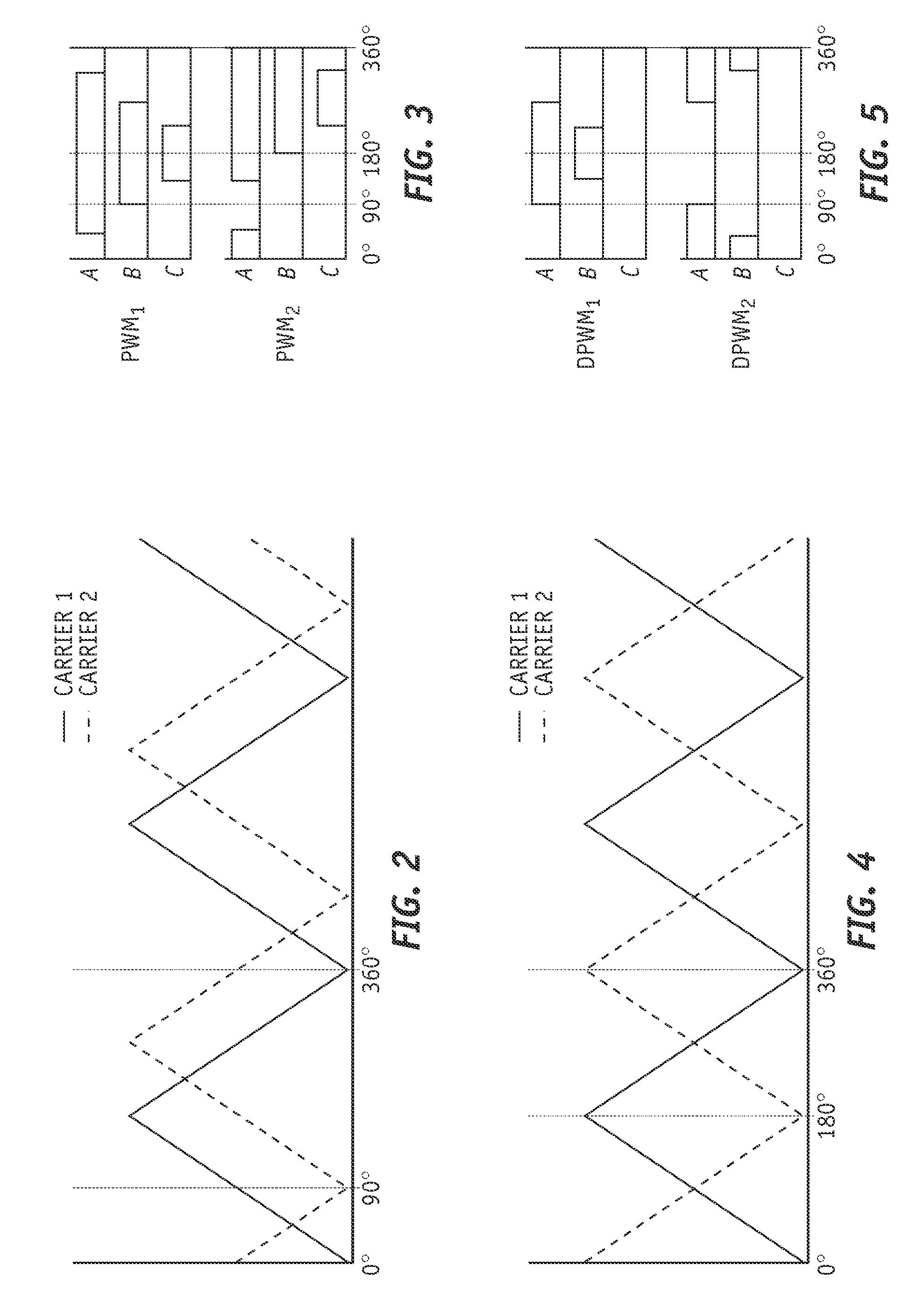

Electrical system using phase-shifted carrier signals and related operating methods

An automotive drive system and methods for making the same are provided. The system includes a three-phase motor and an inverter module. The three-phase motor includes a first set of windings each having a first magnetic polarity; and a second set of windings each having a second magnetic polarity that is opposite the first magnetic polarity. The first set of windings being electrically isolated from the second set of windings. The inverter module includes a first set of phase legs and a second set of phase legs. Each one of the first set of phase legs is coupled to a corresponding phase of the first set of windings, and each one of the second set of phase legs is coupled to a corresponding phase of the second set of windings.

Owner:GM GLOBAL TECH OPERATIONS LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com