Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

280results about "Switched capacitor networks" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

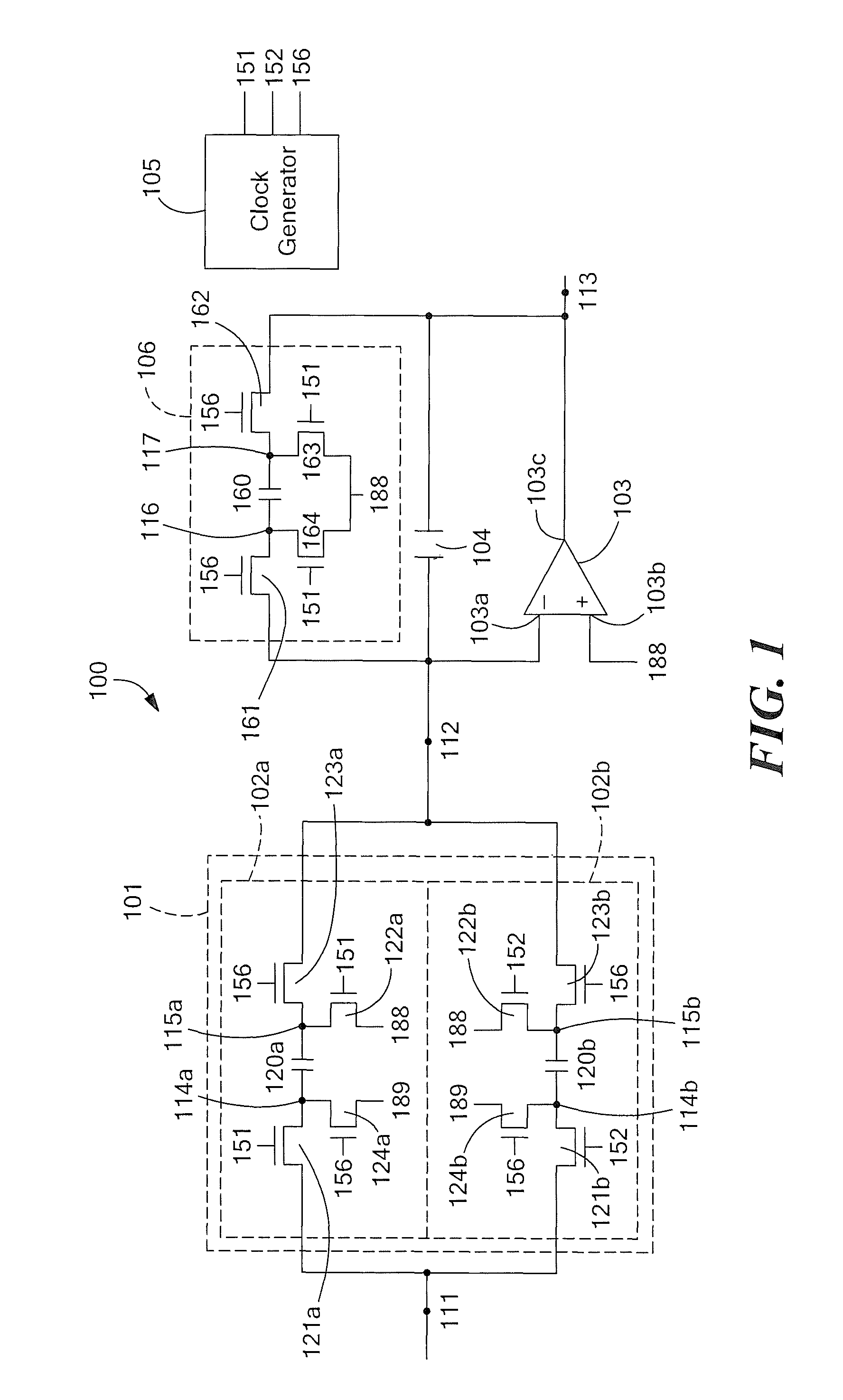

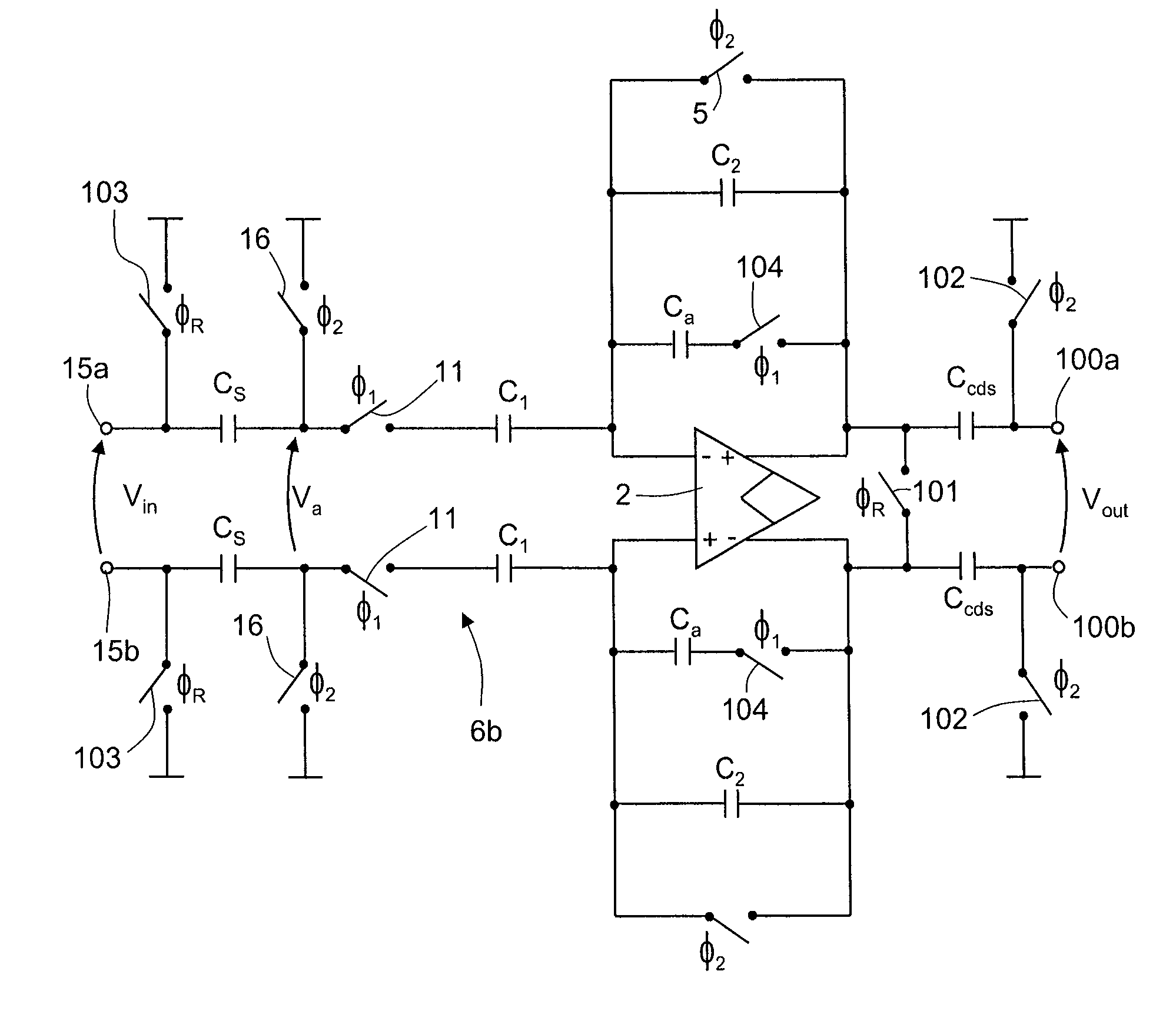

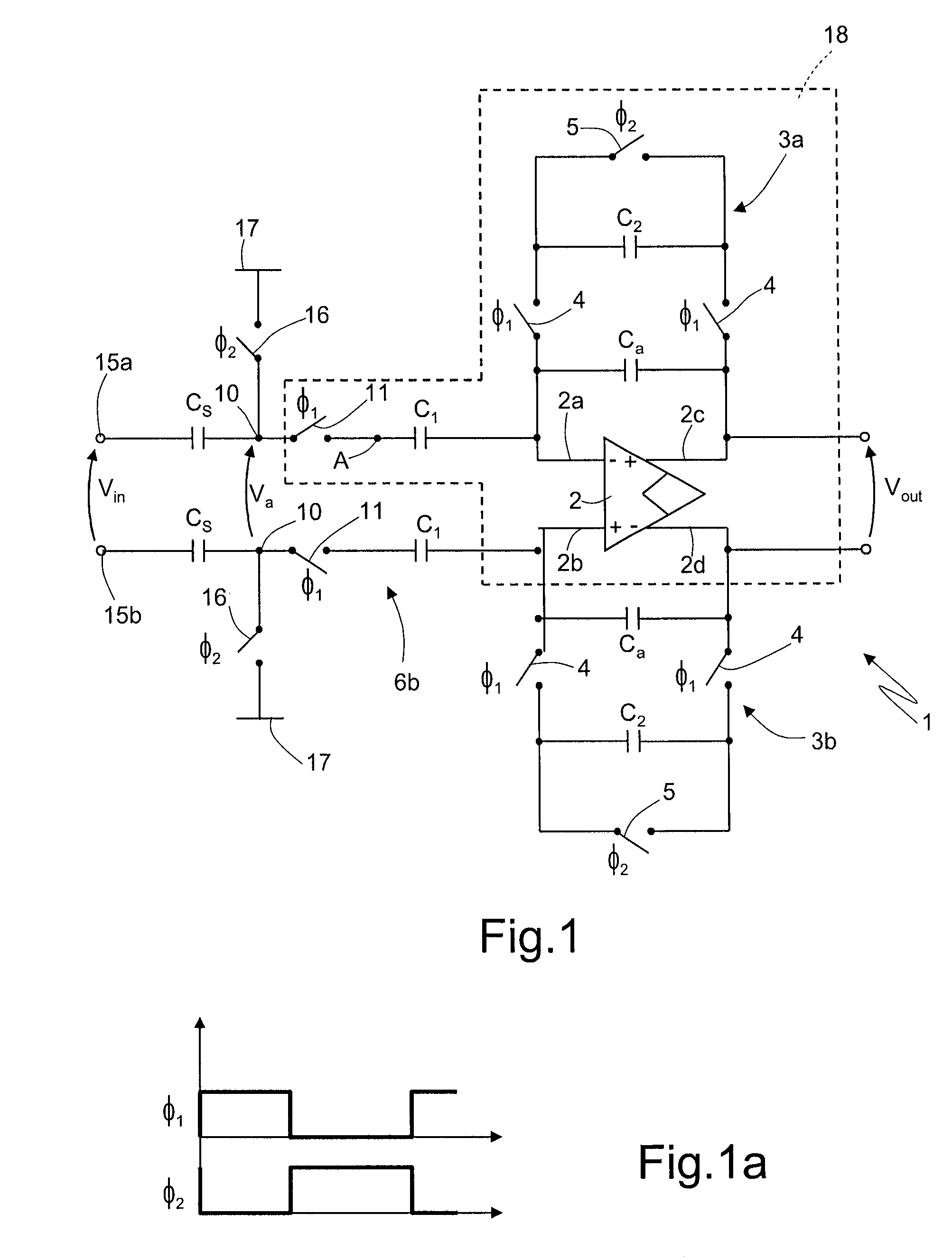

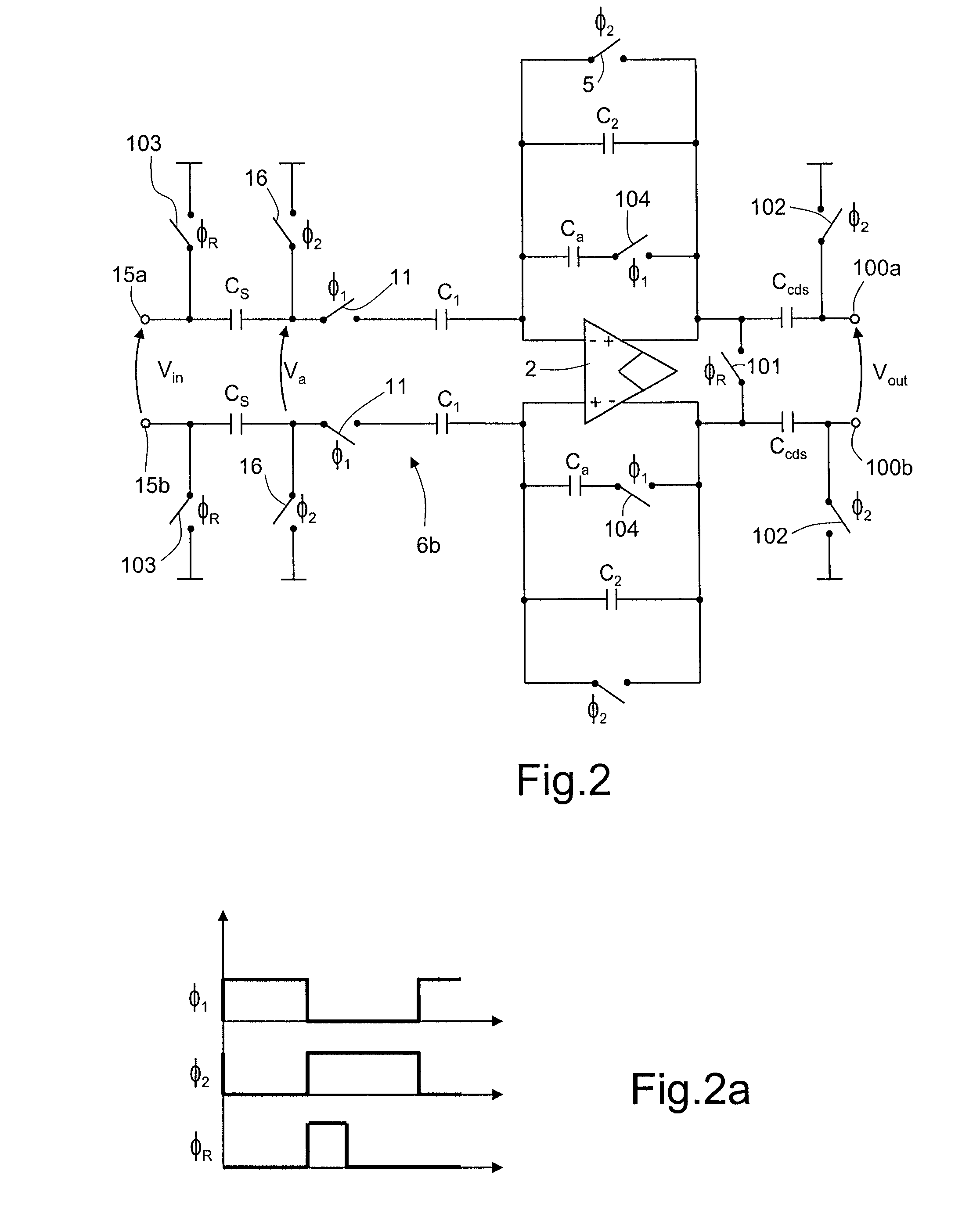

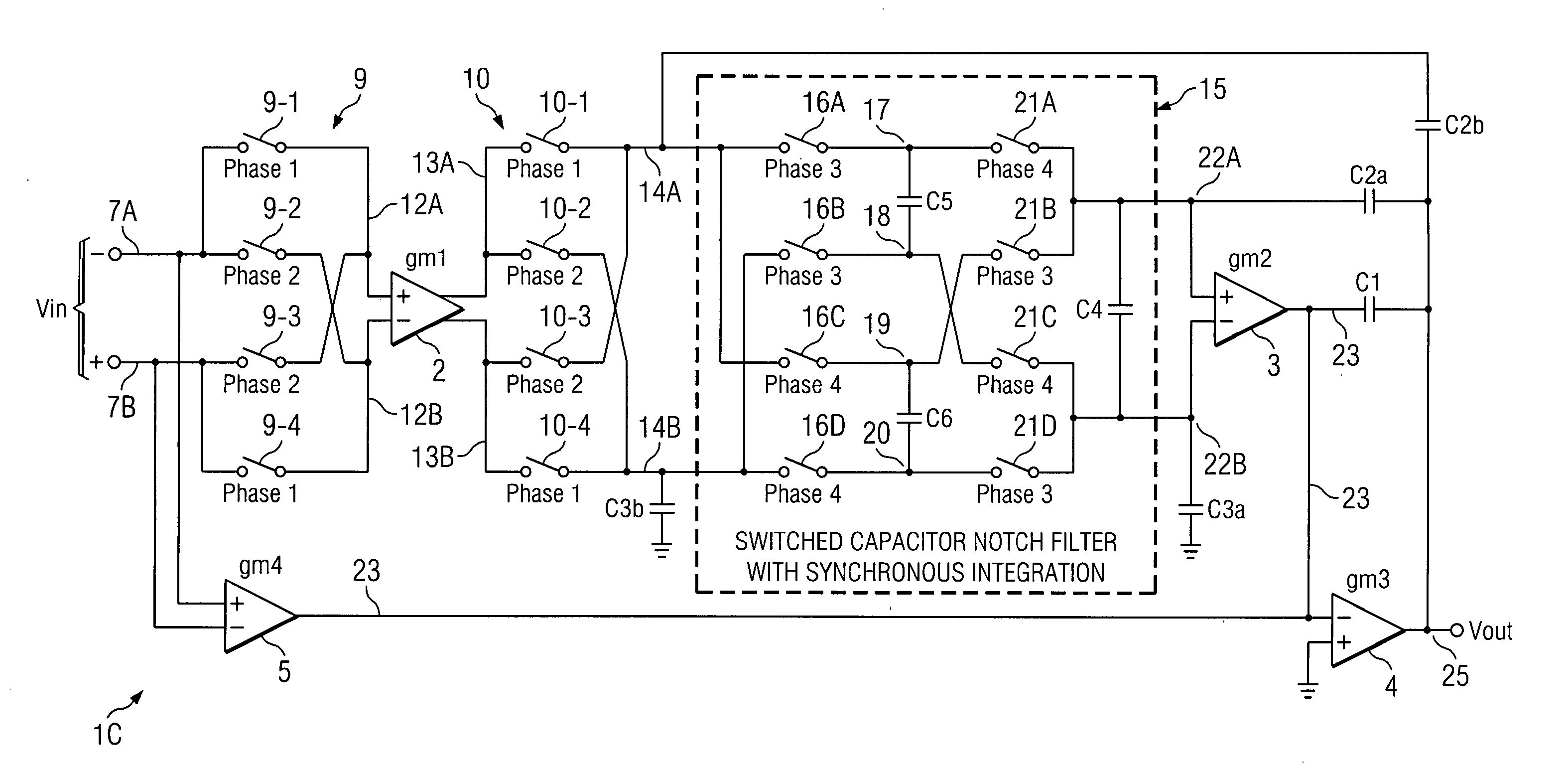

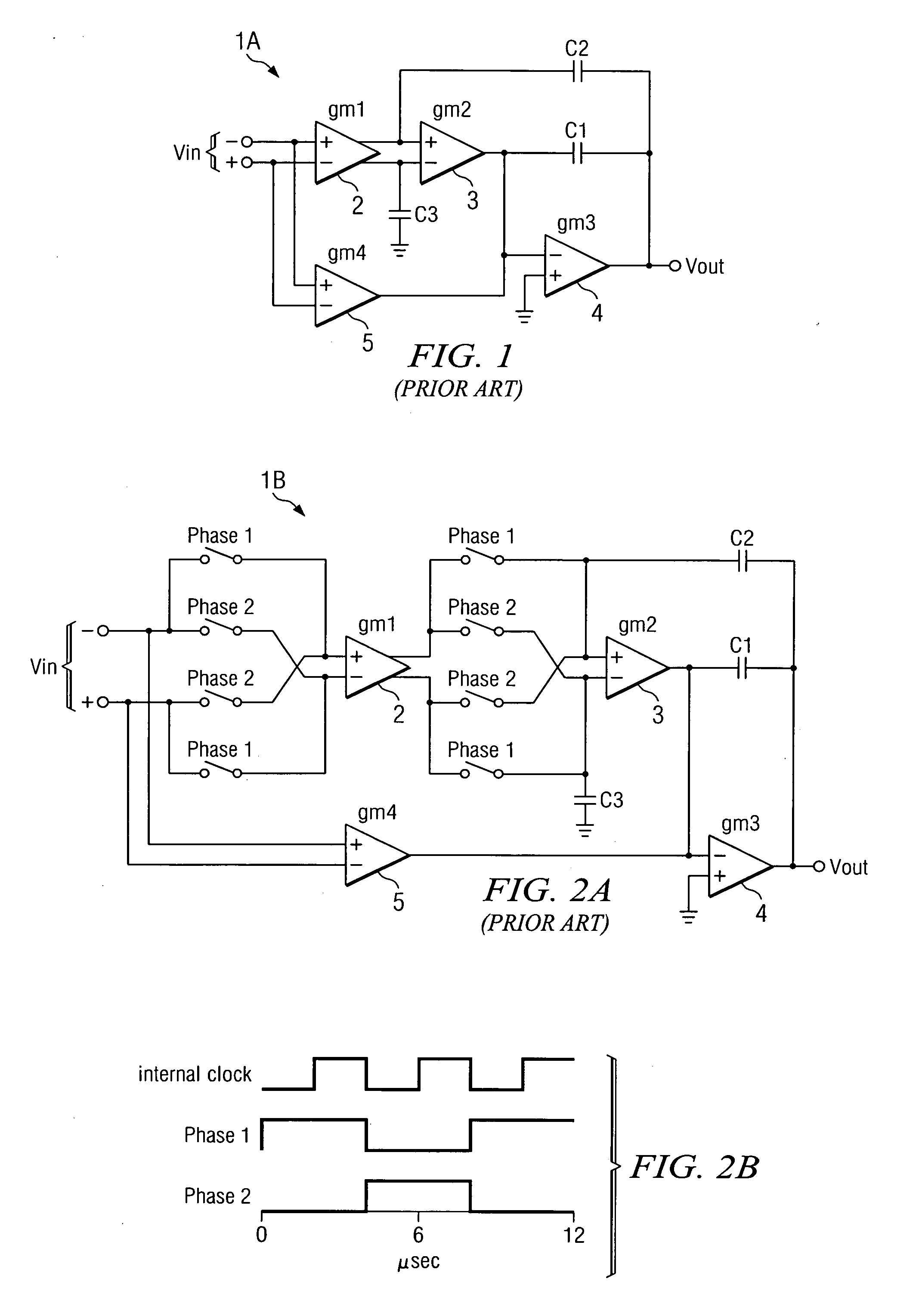

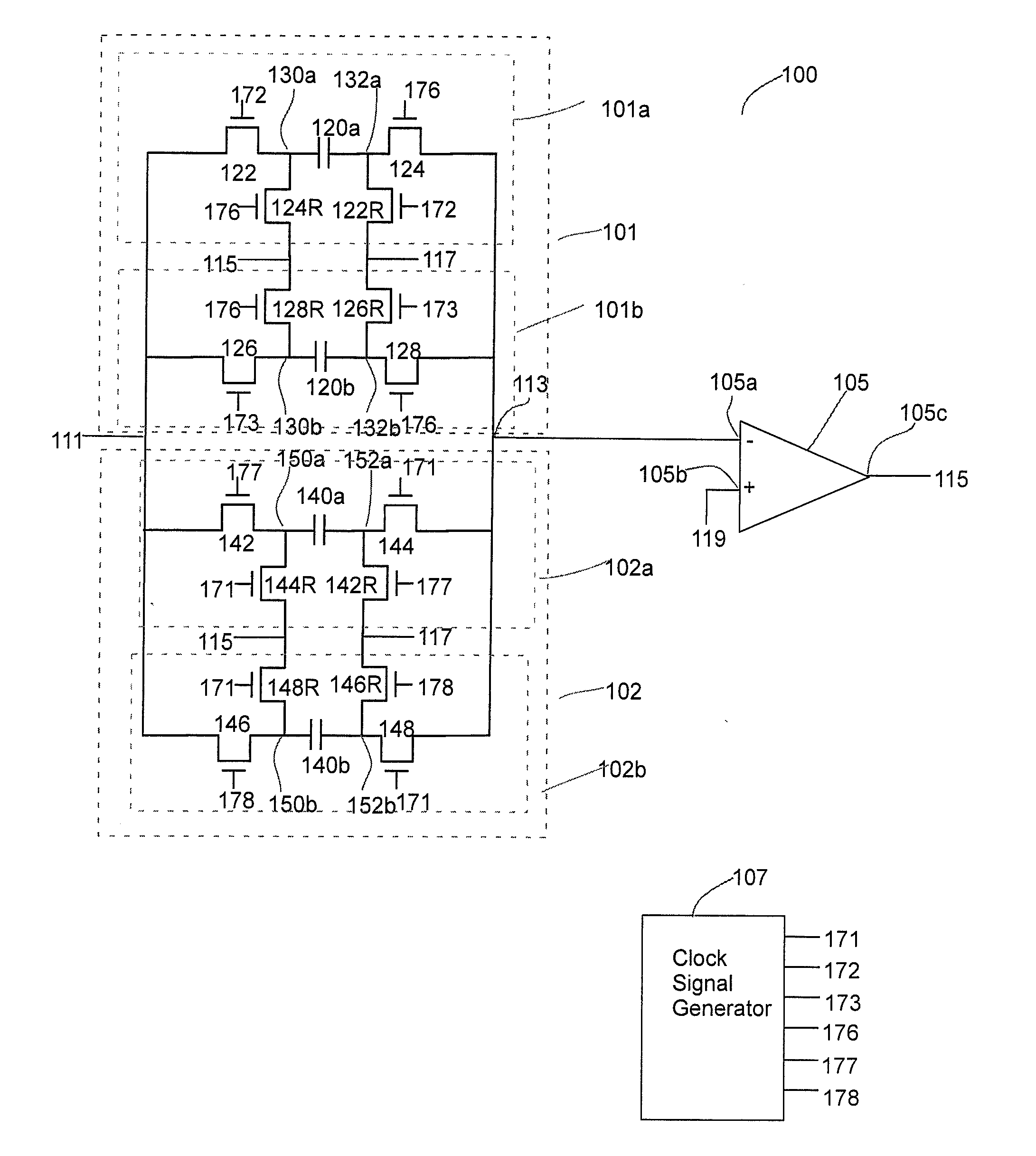

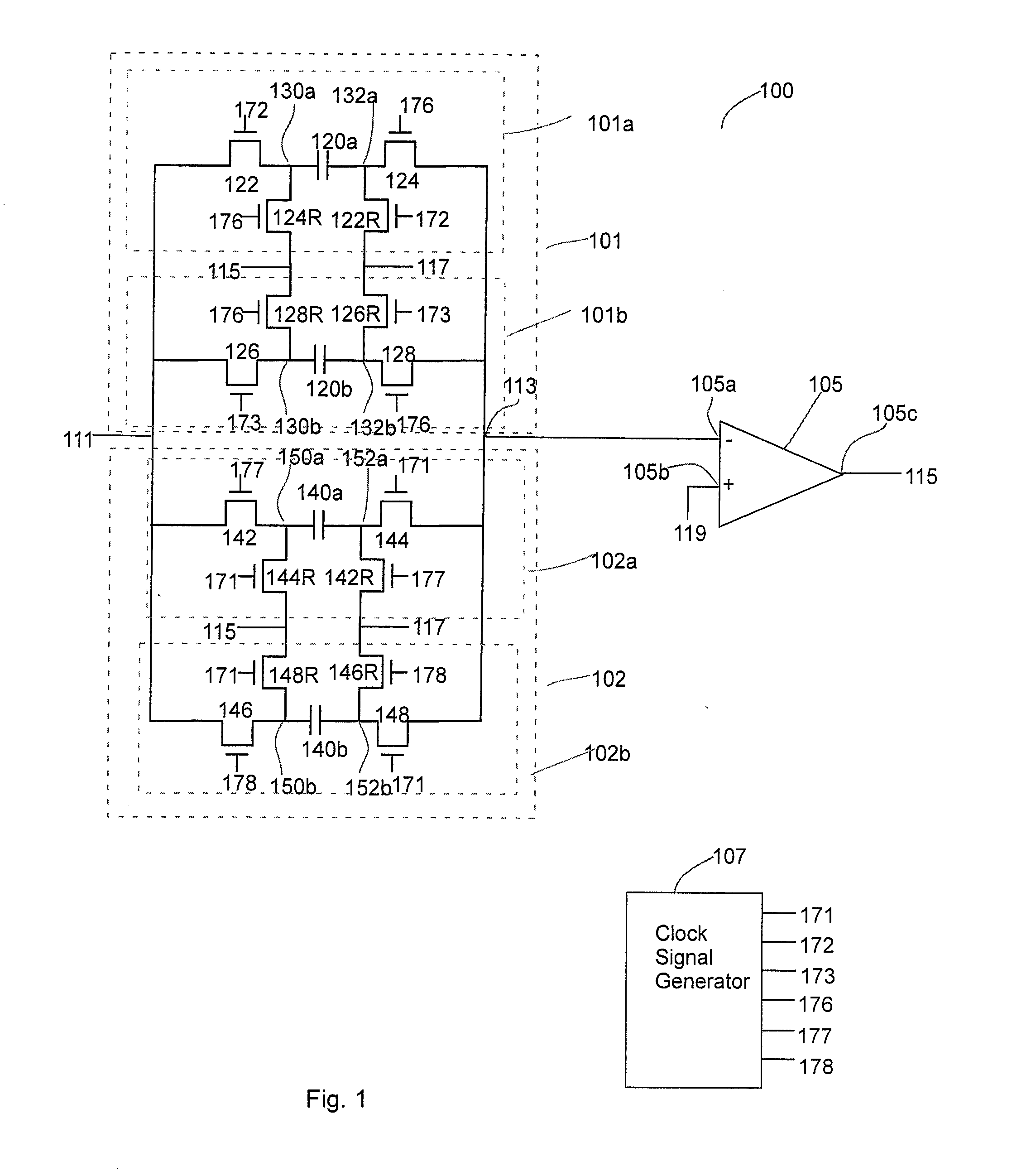

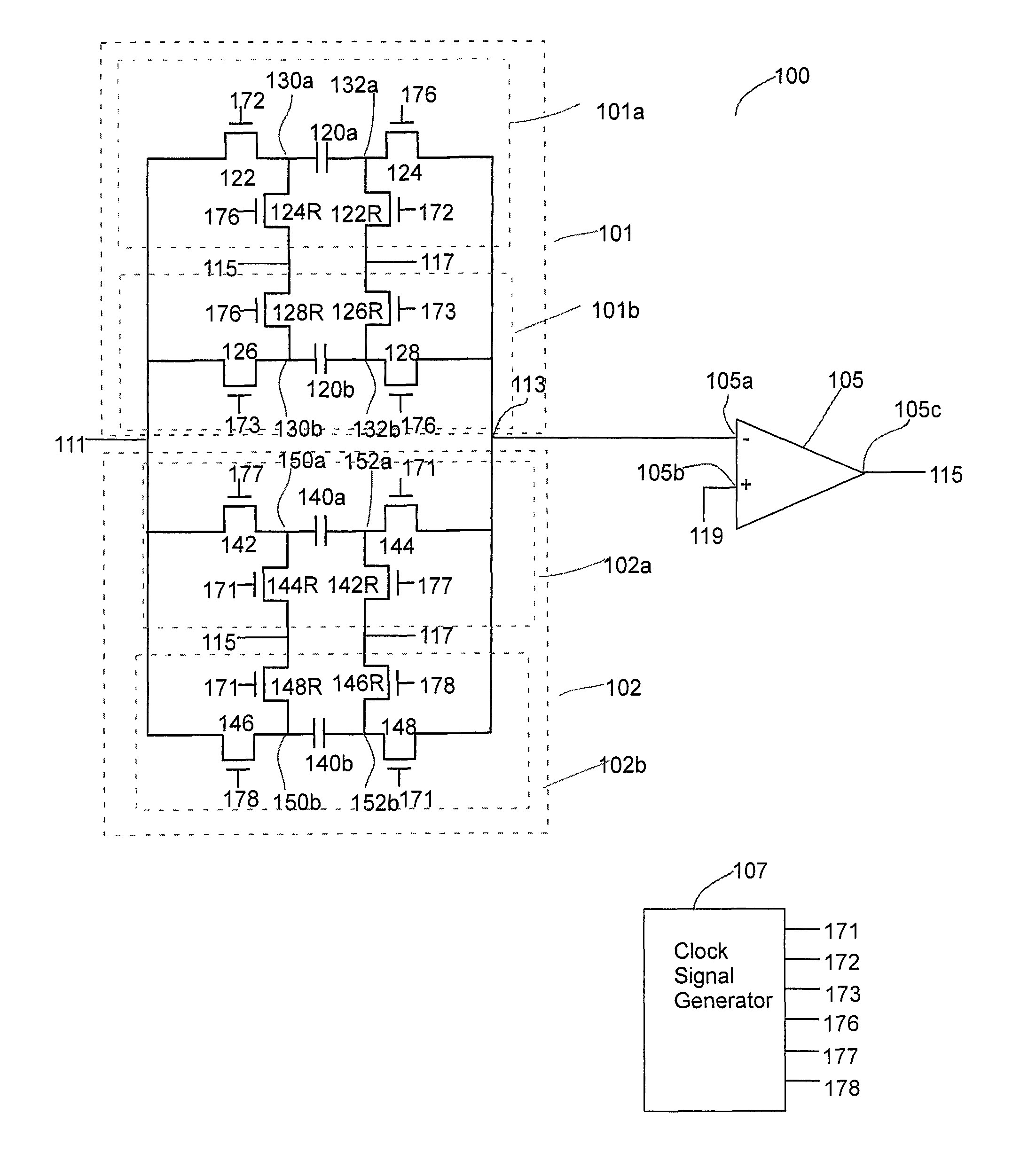

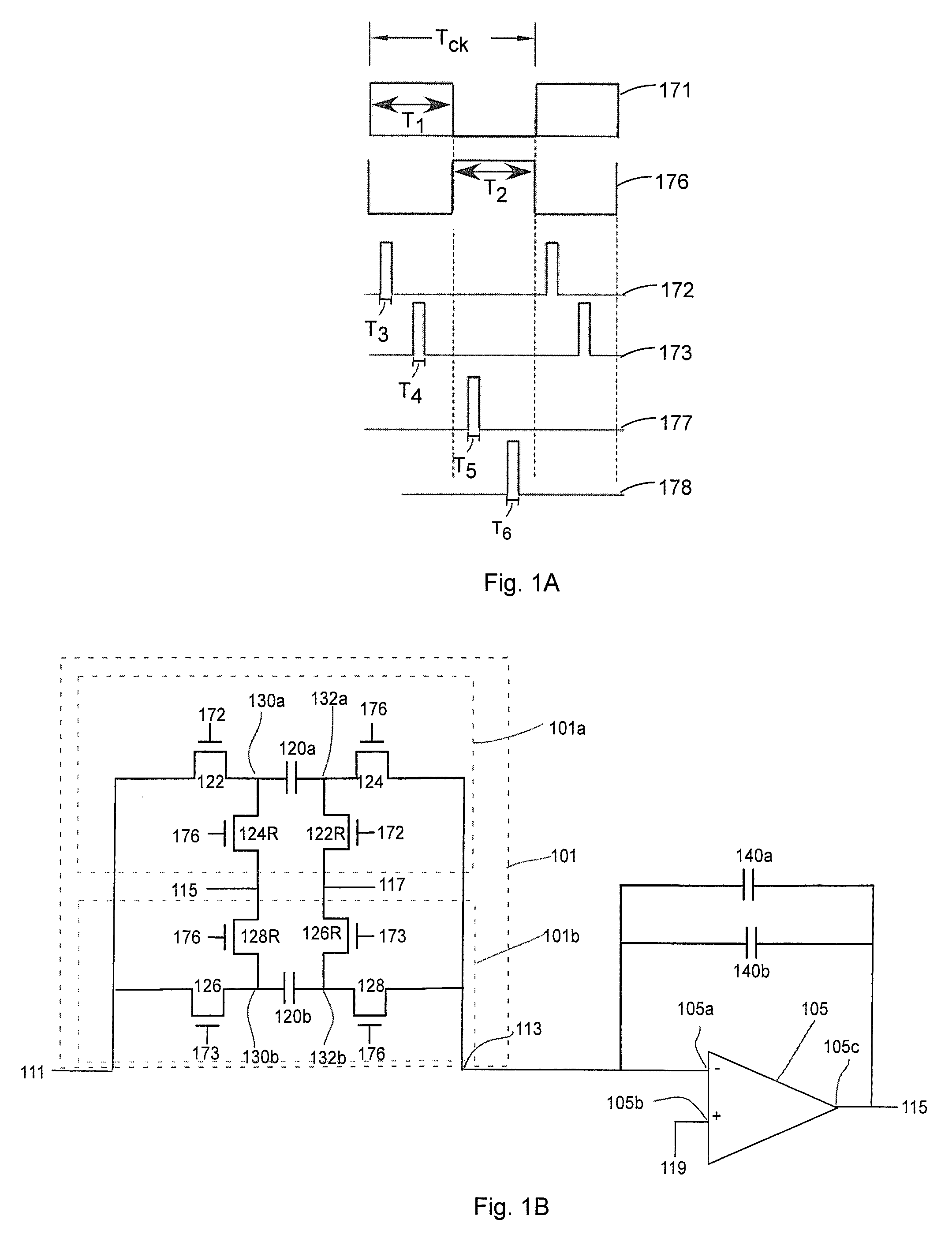

Notch filter for ripple reduction in chopper stabilized amplifiers

ActiveUS7292095B2Reduce ripple noiseFast signalAmplifier modifications to reduce noise influenceAmplifier modifications to raise efficiencyAudio power amplifierEngineering

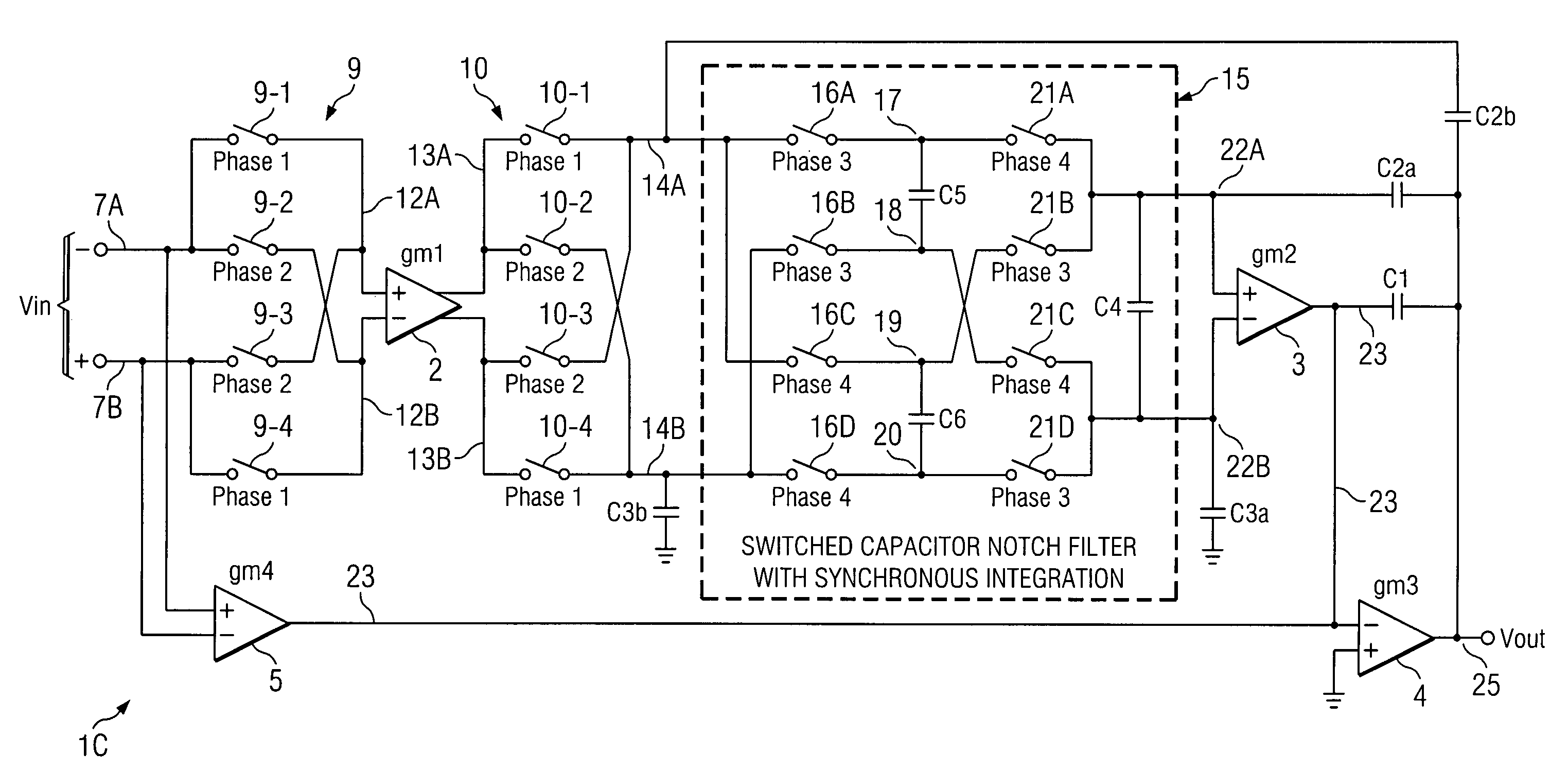

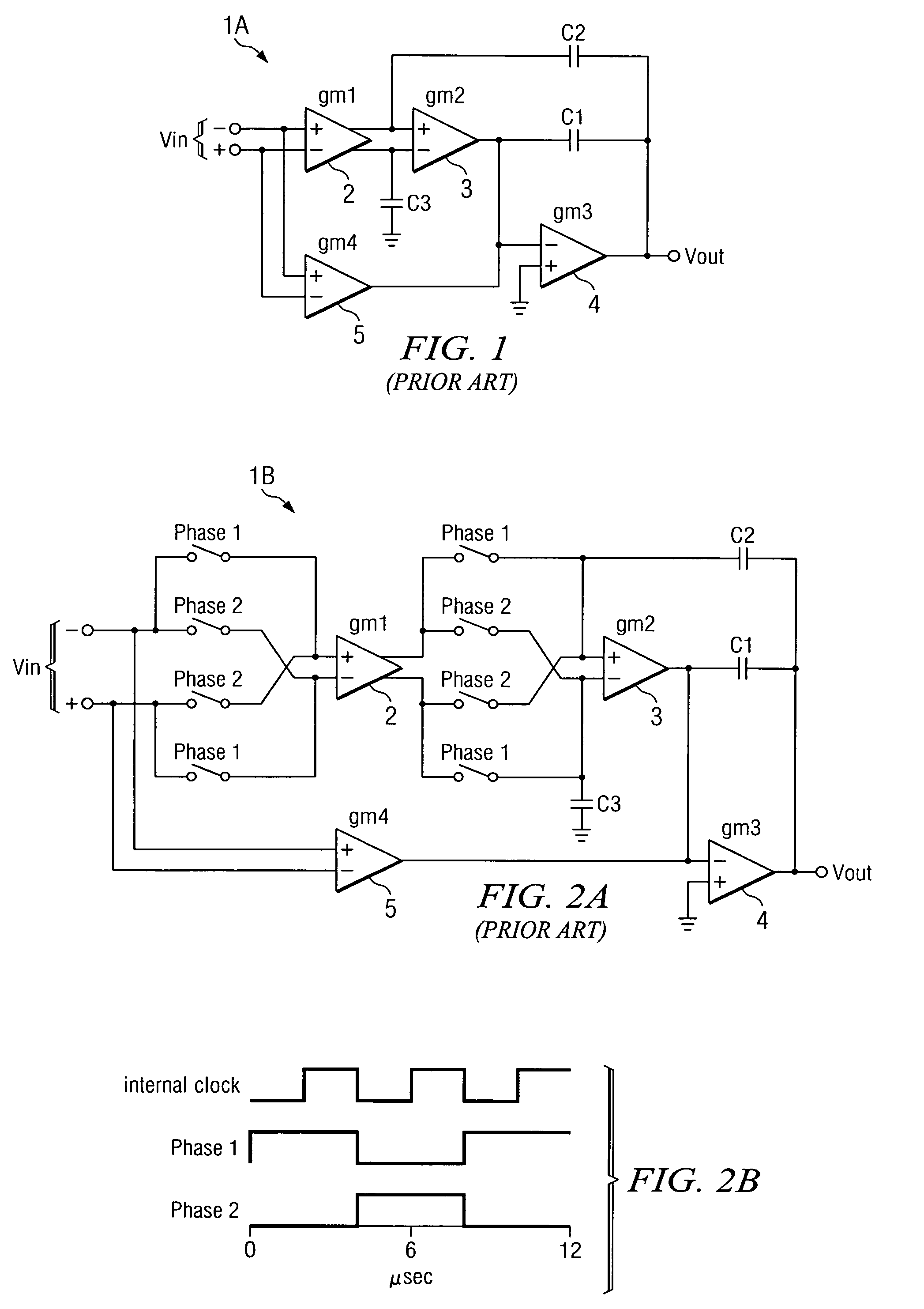

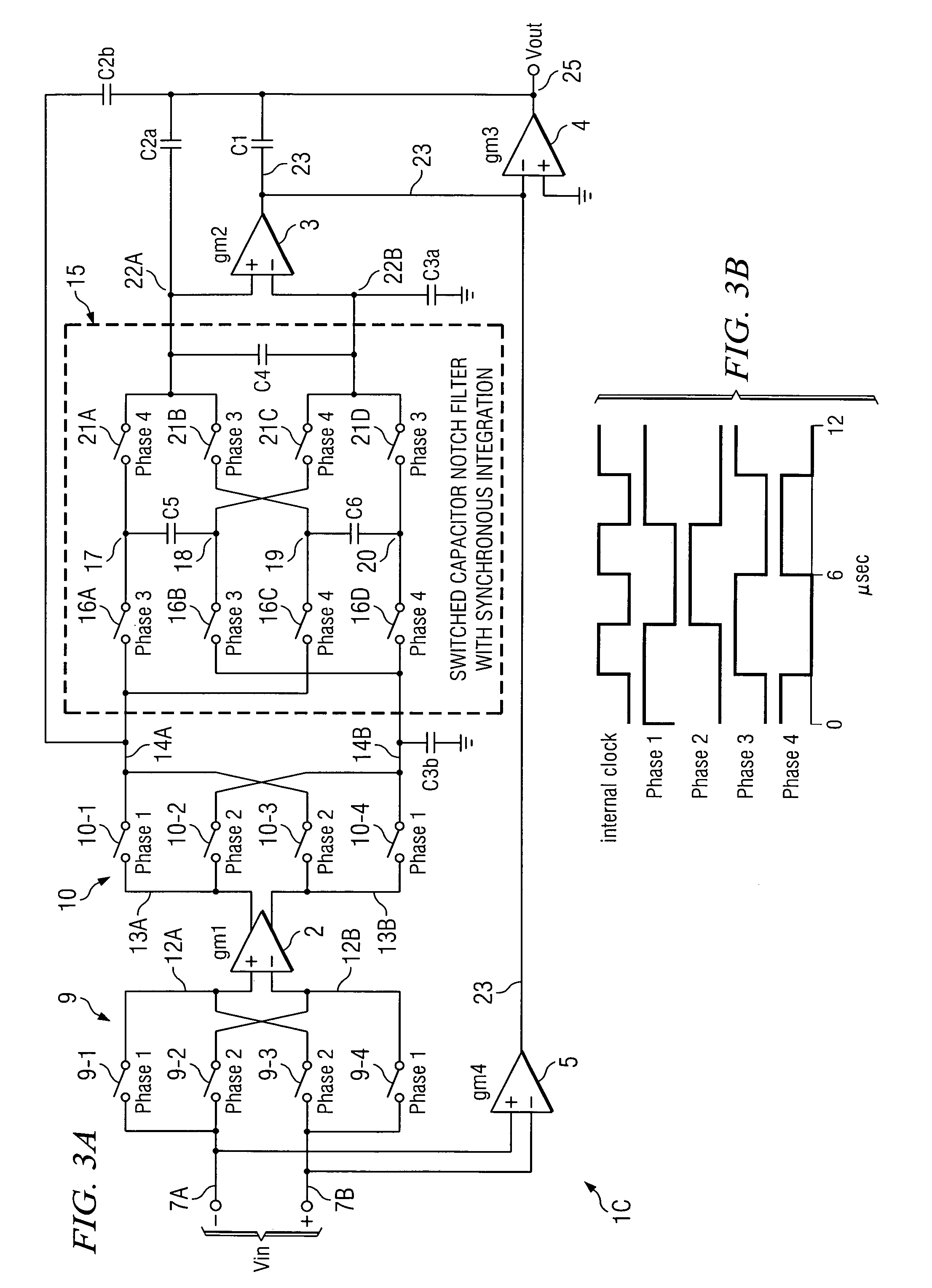

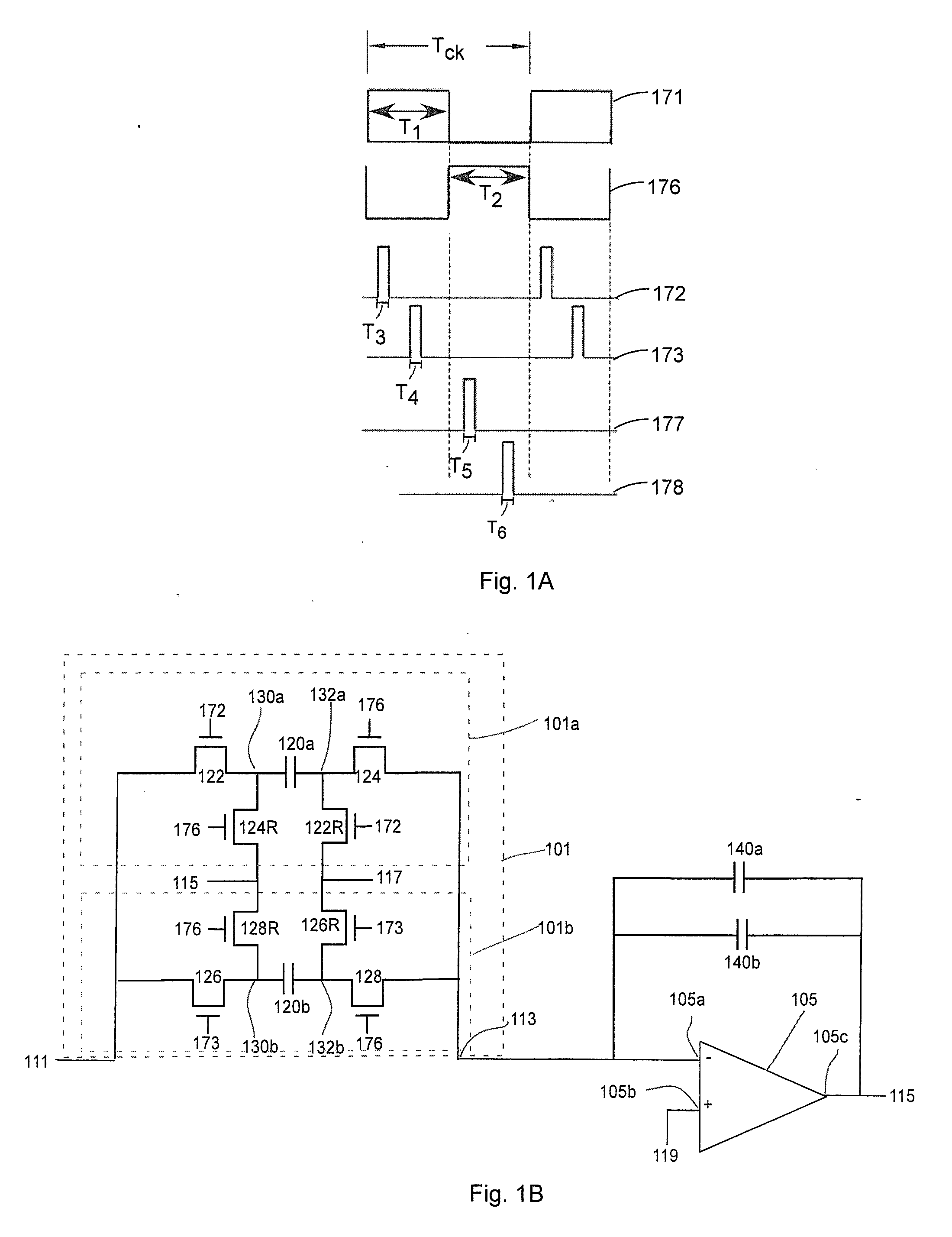

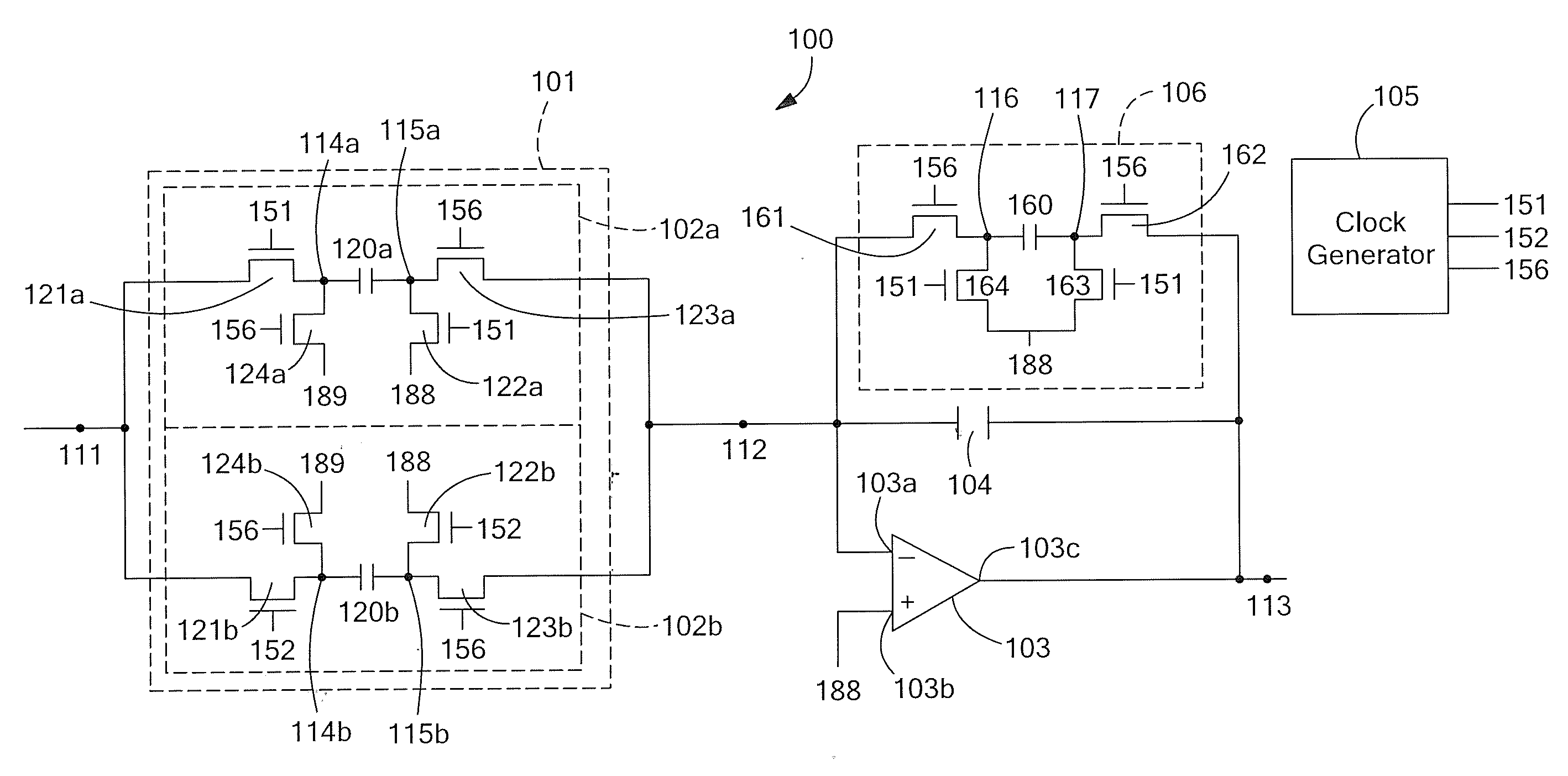

A chopper-stabilized amplifier receiving an input signal includes a first operational transconductance amplifier having an input chopper and an output chopper for chopping an output signal produced by the first operational transconductance amplifier. A switched capacitor notch filter filters the chopped output signal by operating synchronously with the chopping frequency of output chopper to filter ripple voltages that otherwise would be produced by the output chopper. In one embodiment, a second operational transconductance amplifier amplifies the notch filter output. The input signal is fed forward, summed with the output of the second operational transconductance amplifier, and applied to the input of a fourth operational transconductance amplifier. Ripple noise and offset are substantially reduced.

Owner:TEXAS INSTR INC

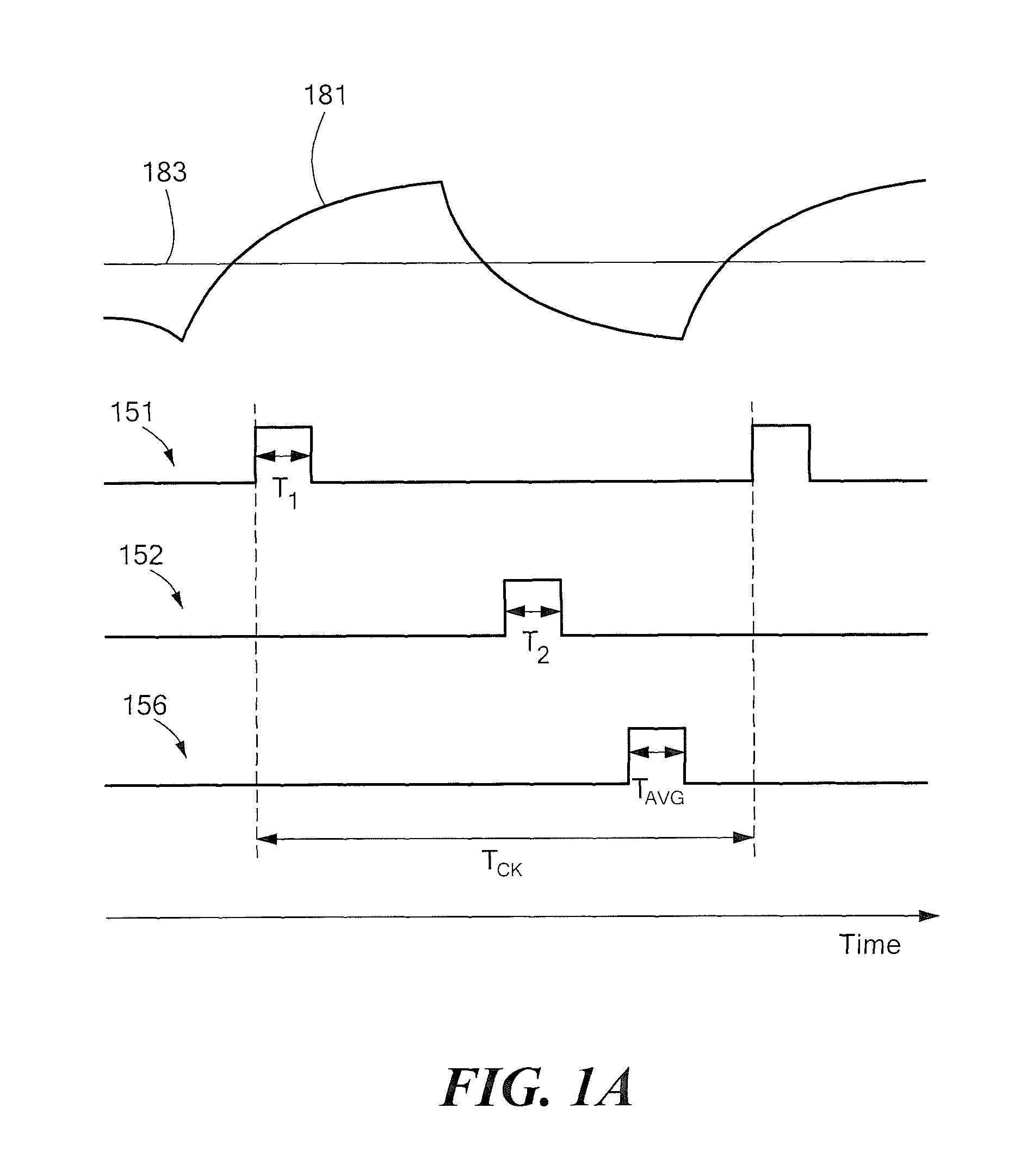

Switched capacitor notch filter

ActiveUS7990209B2Eliminate needLow pass filterSwitched capacitor networksOscillations generatorsCapacitanceTime segment

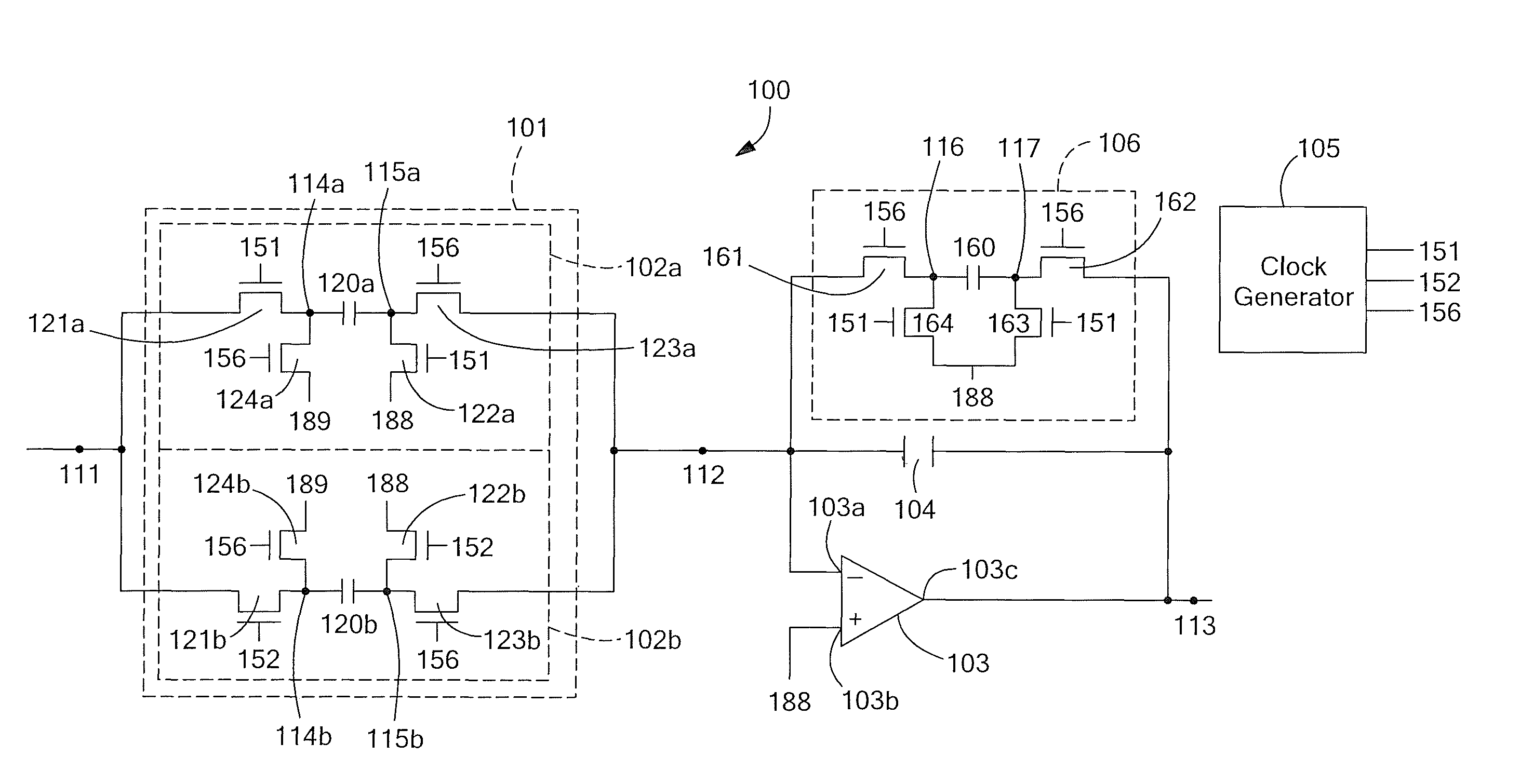

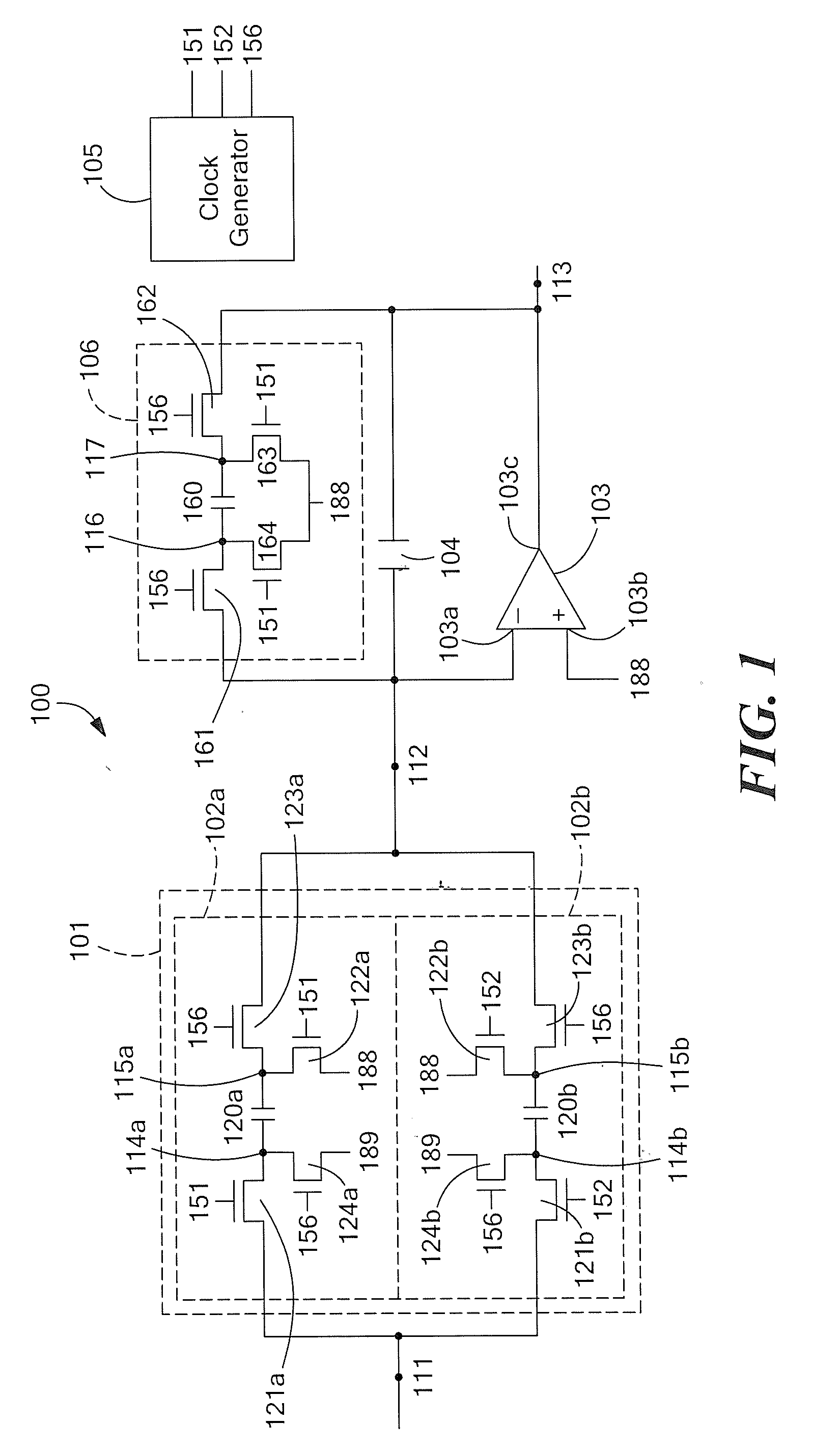

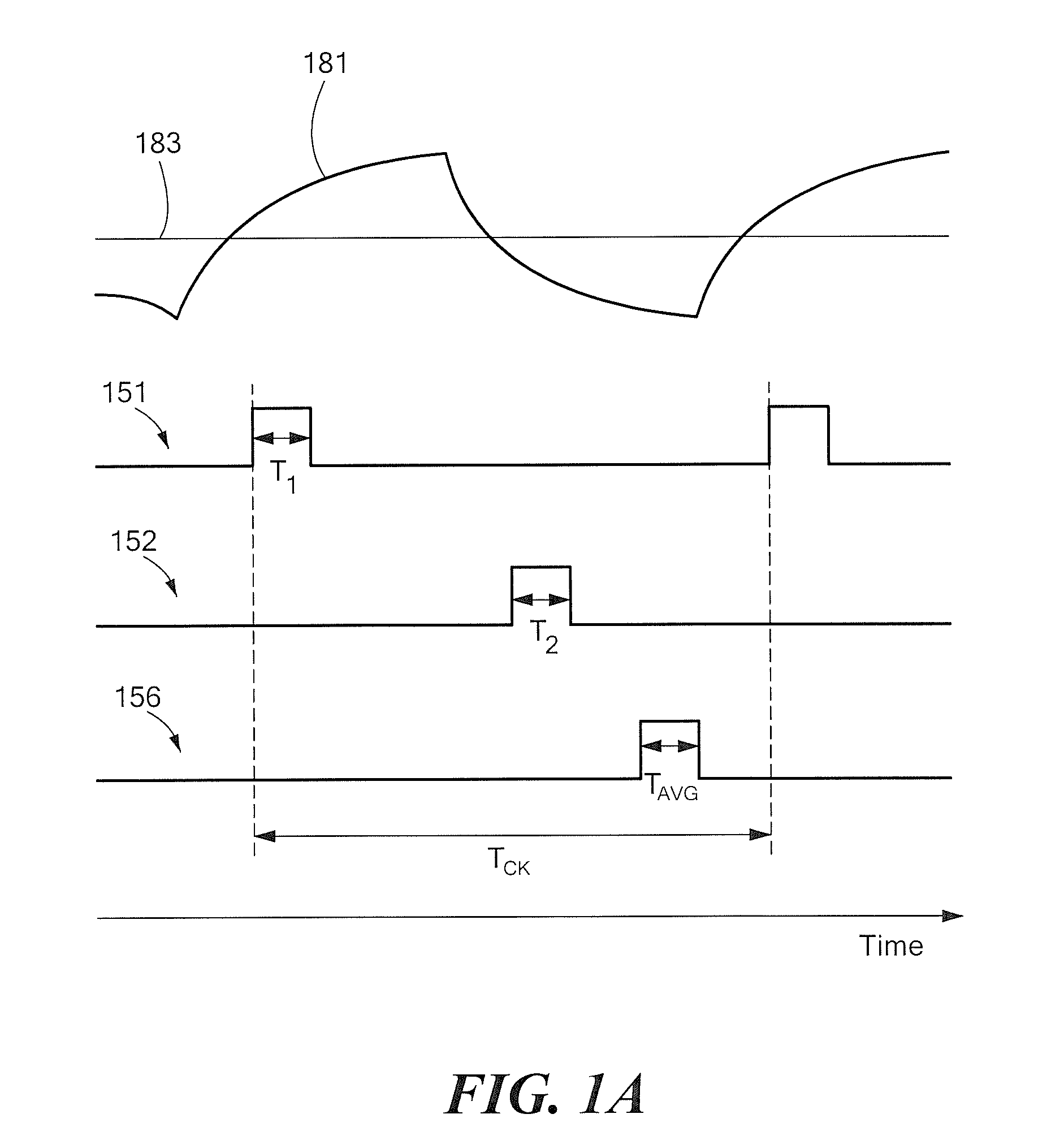

A switched capacitor notch filter for sampling an input signal using multiple sampling capacitors and multiple non-overlapping time periods. The charge from the sampling capacitors is averaged and transferred to the filter output during another non-overlapping time period.

Owner:ALLEGRO MICROSYSTEMS INC

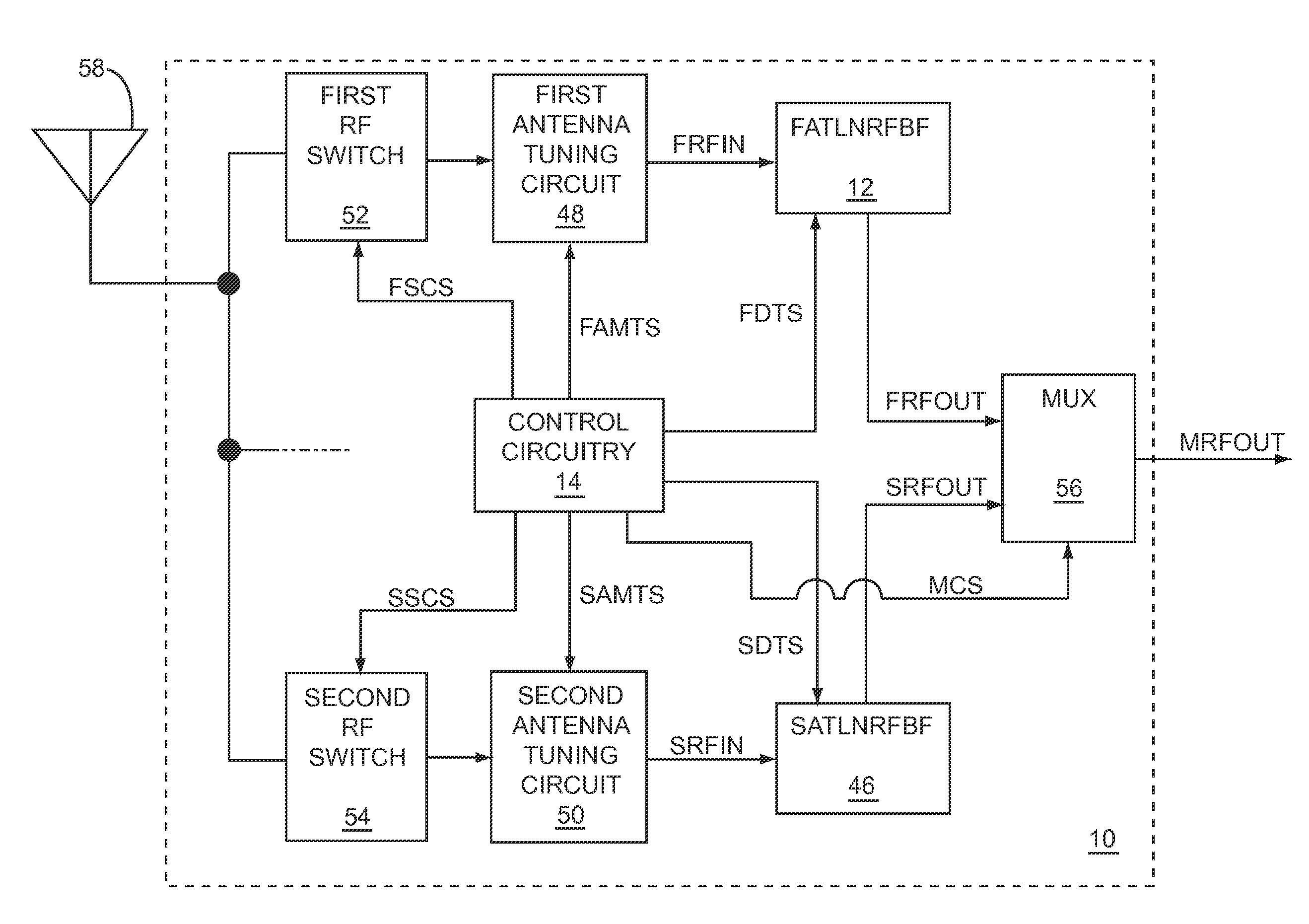

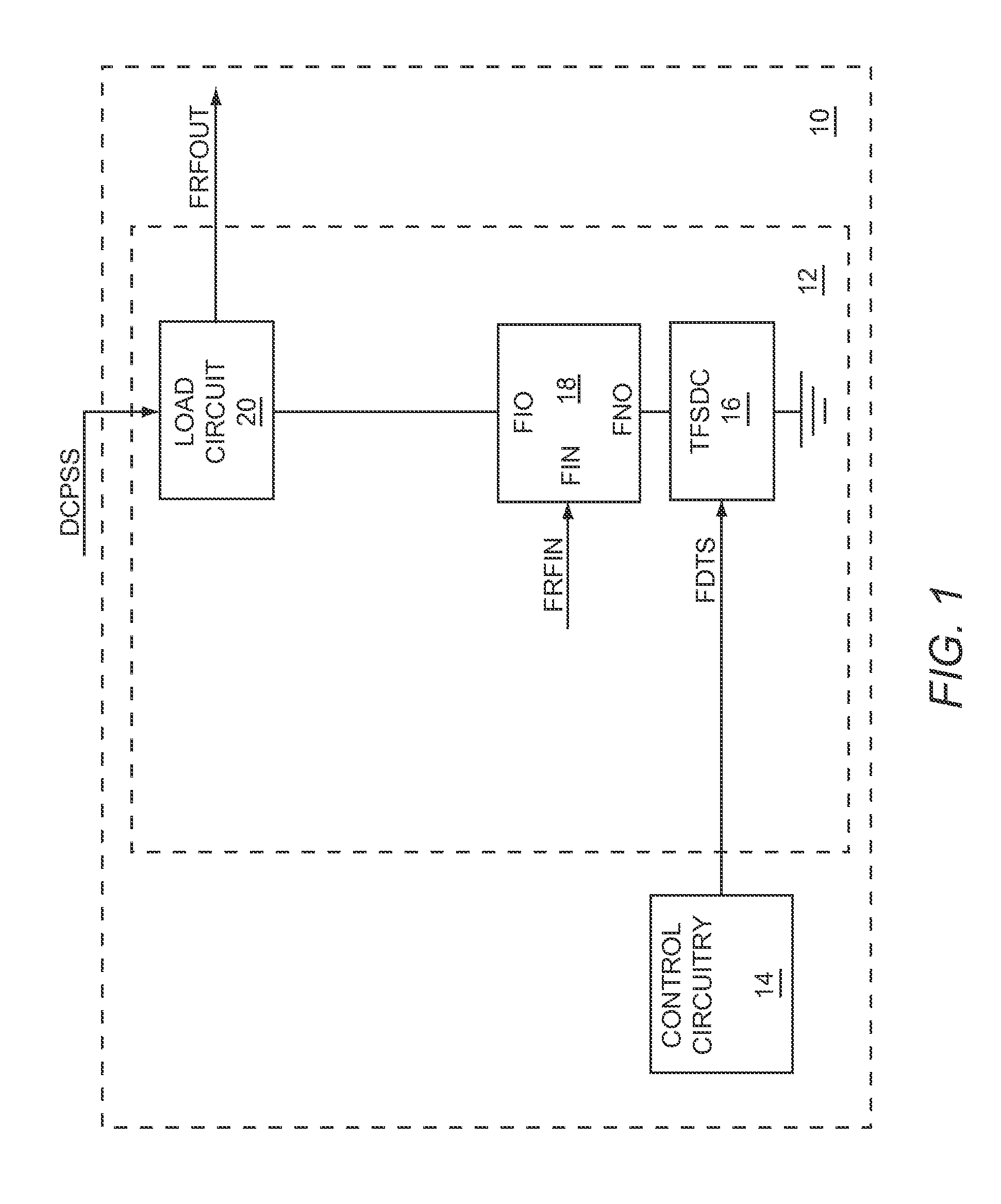

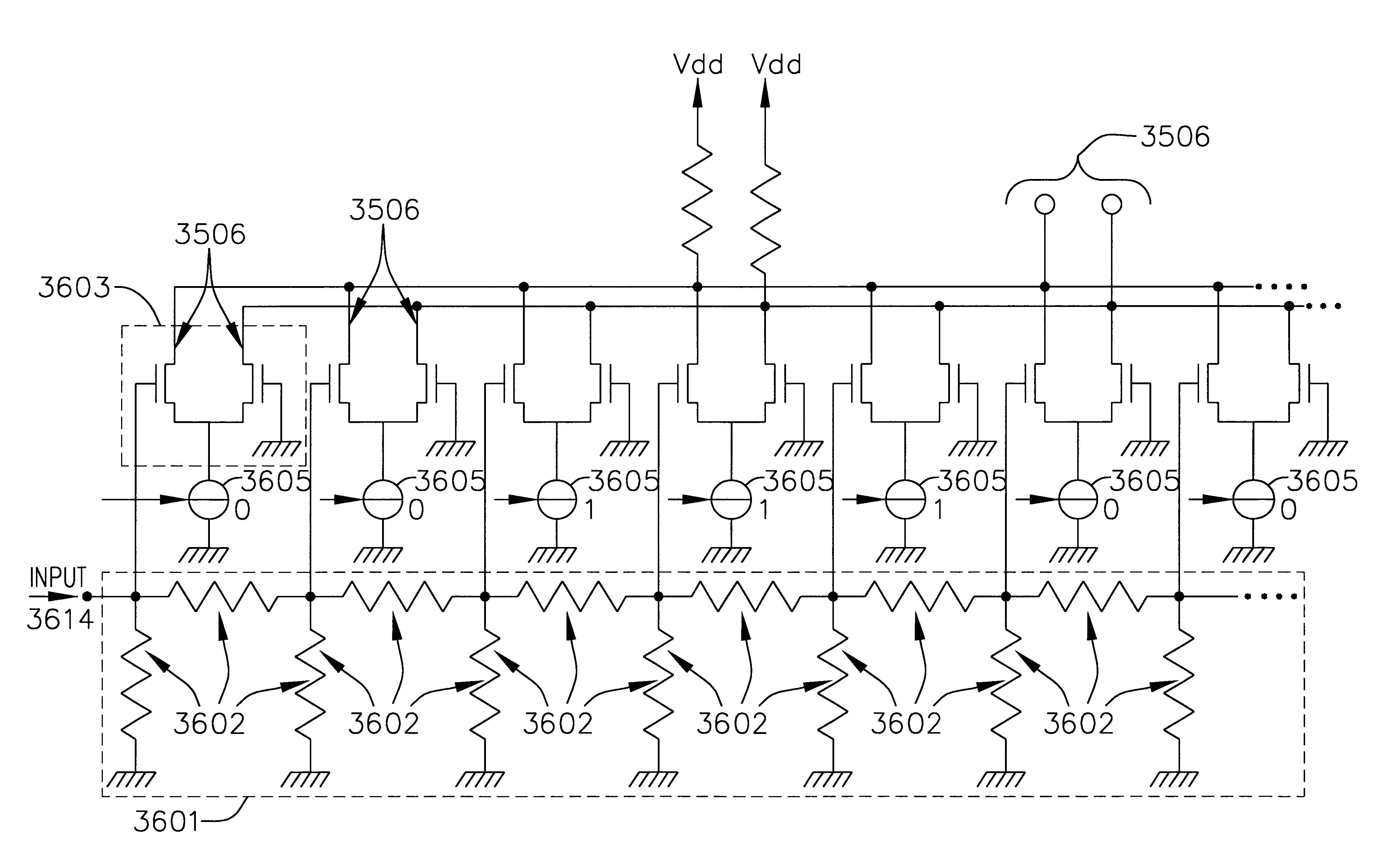

Using degeneration in an active tunable low-noise radio frequency bandpass filter

ActiveUS8314653B1Easy to FeedbackReduce gainSwitched capacitor networksAmplifier with semiconductor-devices/discharge-tubesLow noiseBandpass filtering

The present disclosure relates to a first active tunable low-noise RF bandpass filter that includes at least a first transistor element and a tunable frequency selective degeneration circuit coupled to a first non-inverting output of the first transistor element. The first active tunable low-noise RF bandpass filter combines low noise amplifier (LNA) and tunable bandpass filter functionalities into a single active RF bandpass filter. The tunable frequency selective degeneration circuit uses degeneration at frequencies outside of a passband of the active RF bandpass filter to increase feedback, thereby decreasing gain of the active RF bandpass filter. By decreasing the gain, linearity of the active RF bandpass filter may be improved in the presence of strong interfering RF signals, thereby enabling elimination of passive bandpass filter elements, such as surface acoustic wave (SAW) and bulk acoustic wave (BAW) filters, without degrading reception of in-band RF signals.

Owner:QORVO US INC

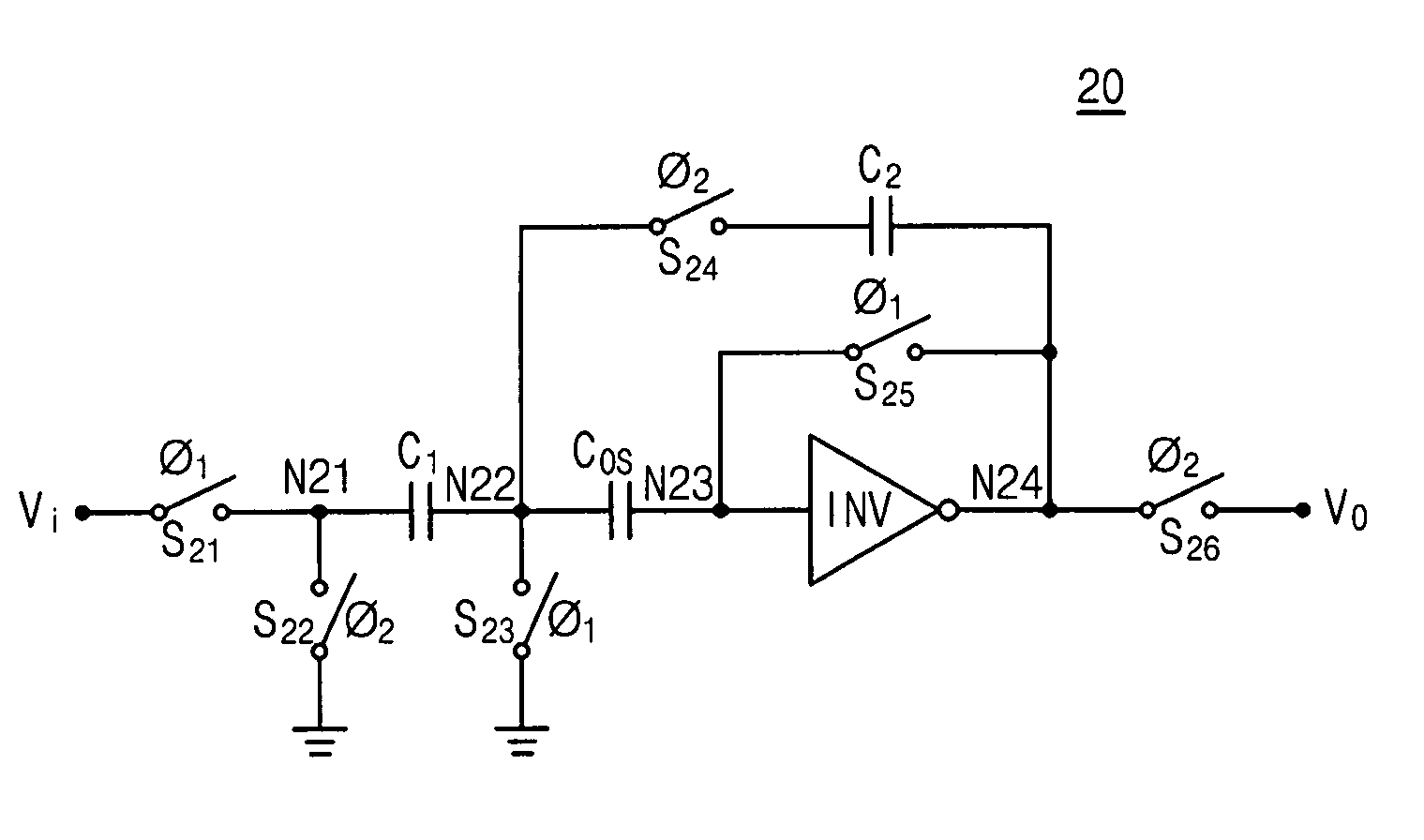

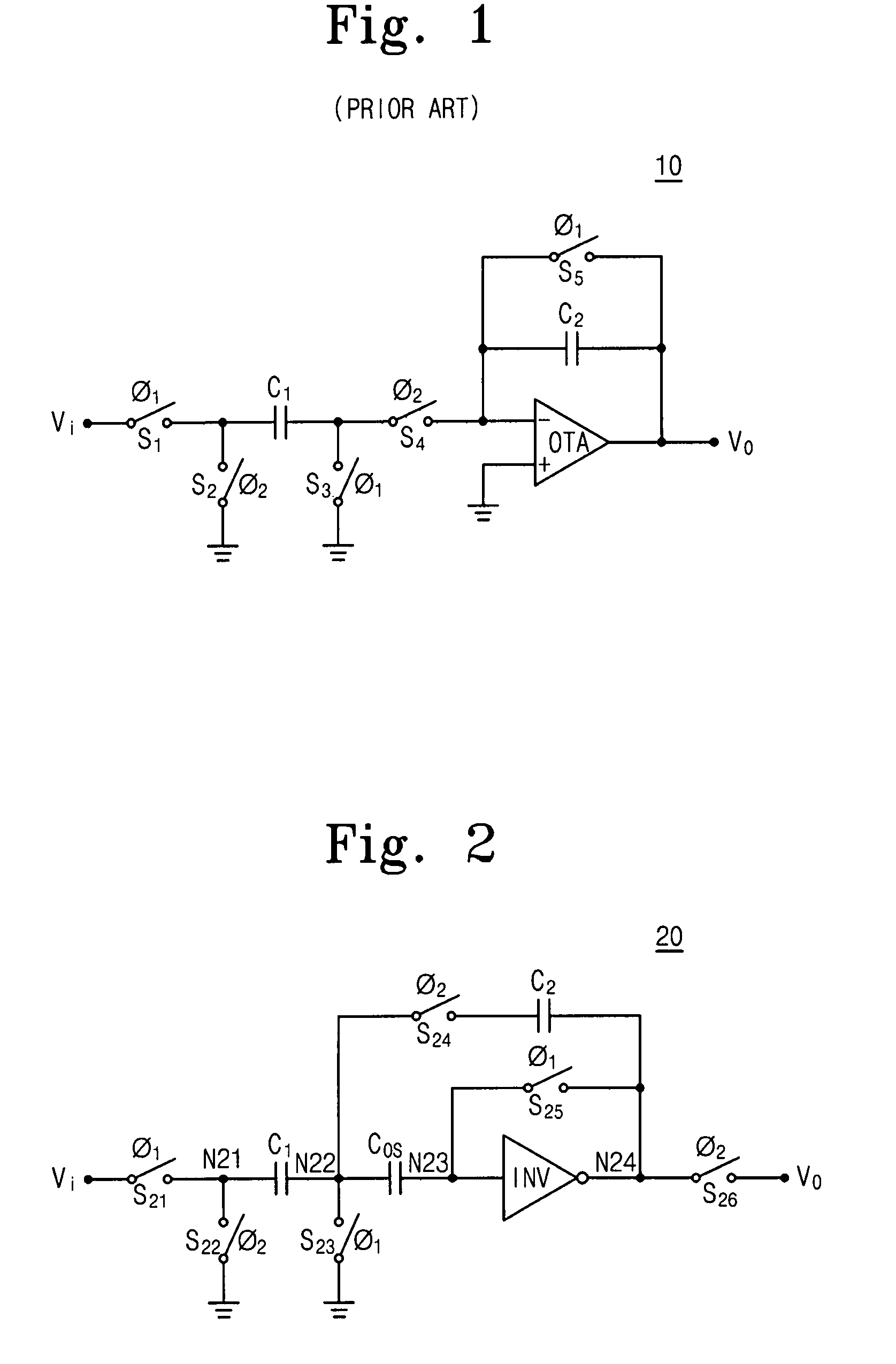

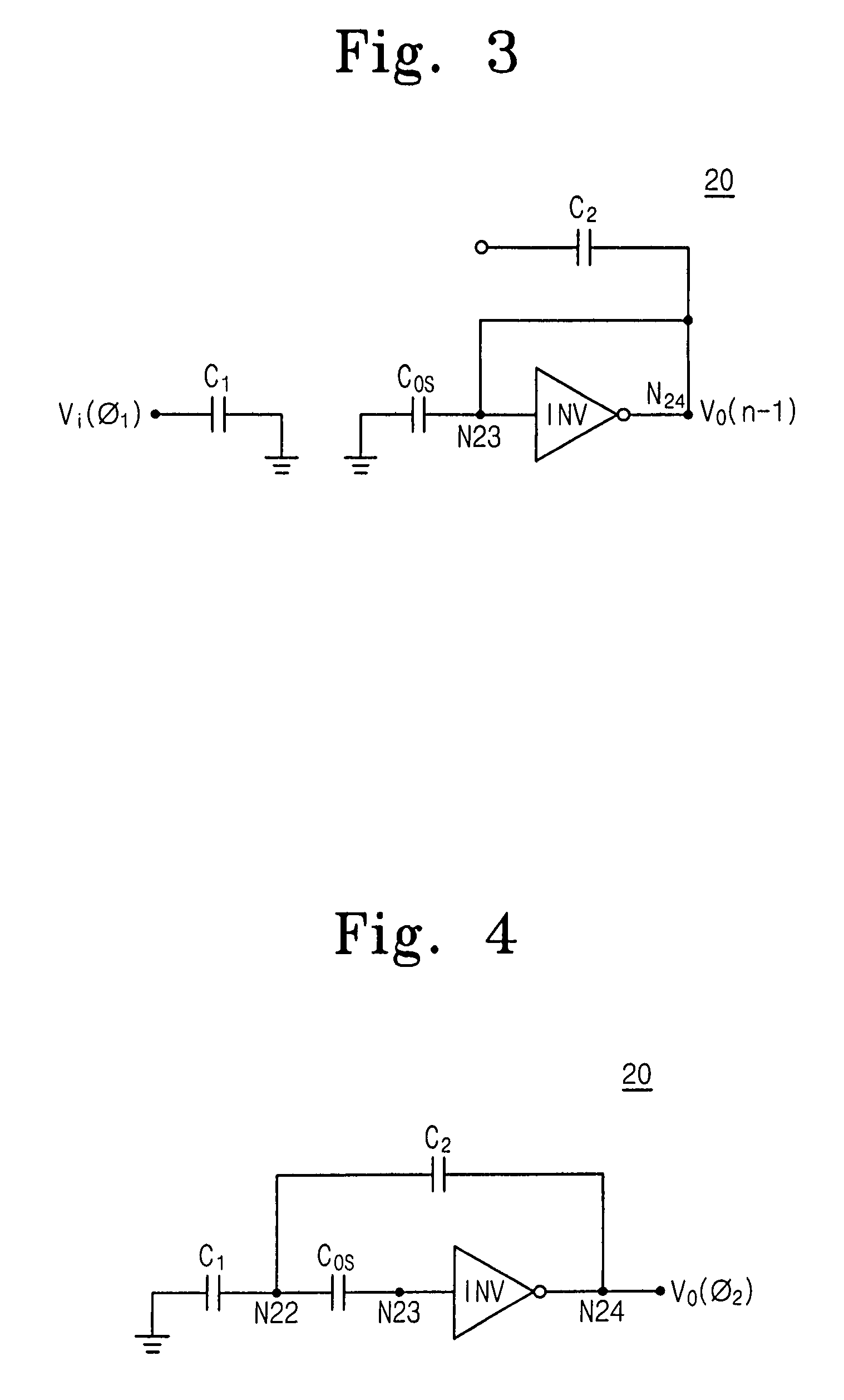

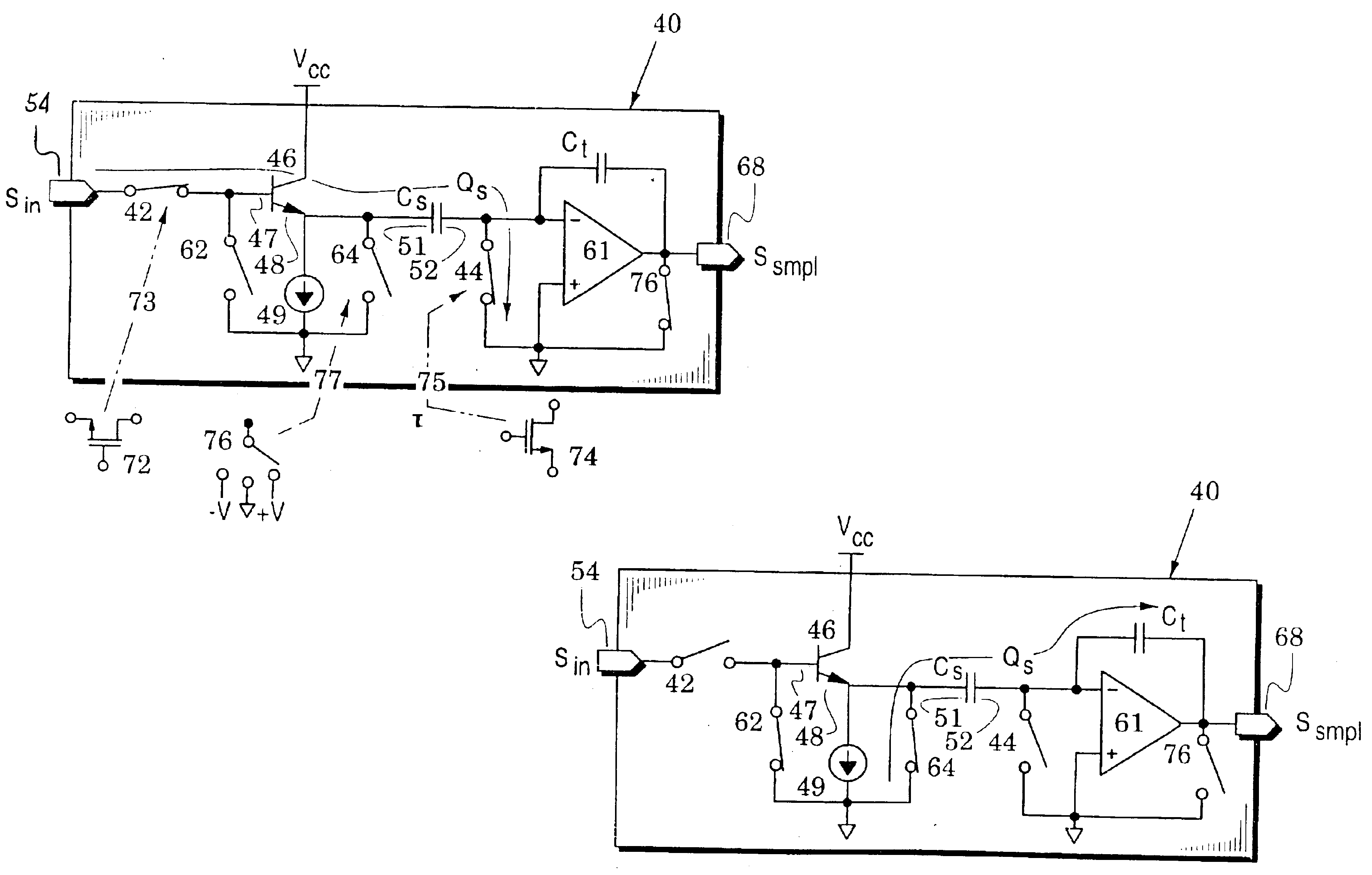

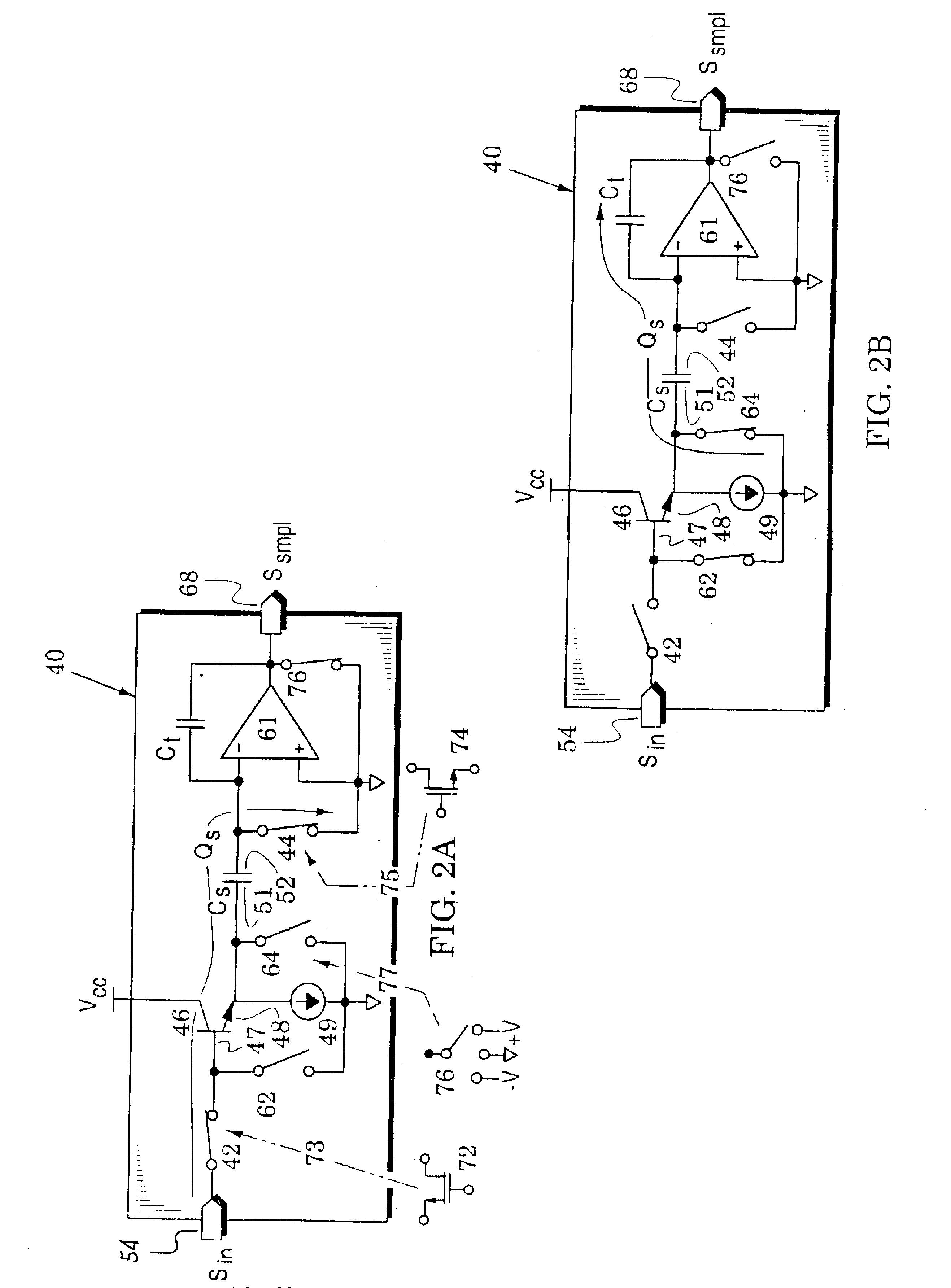

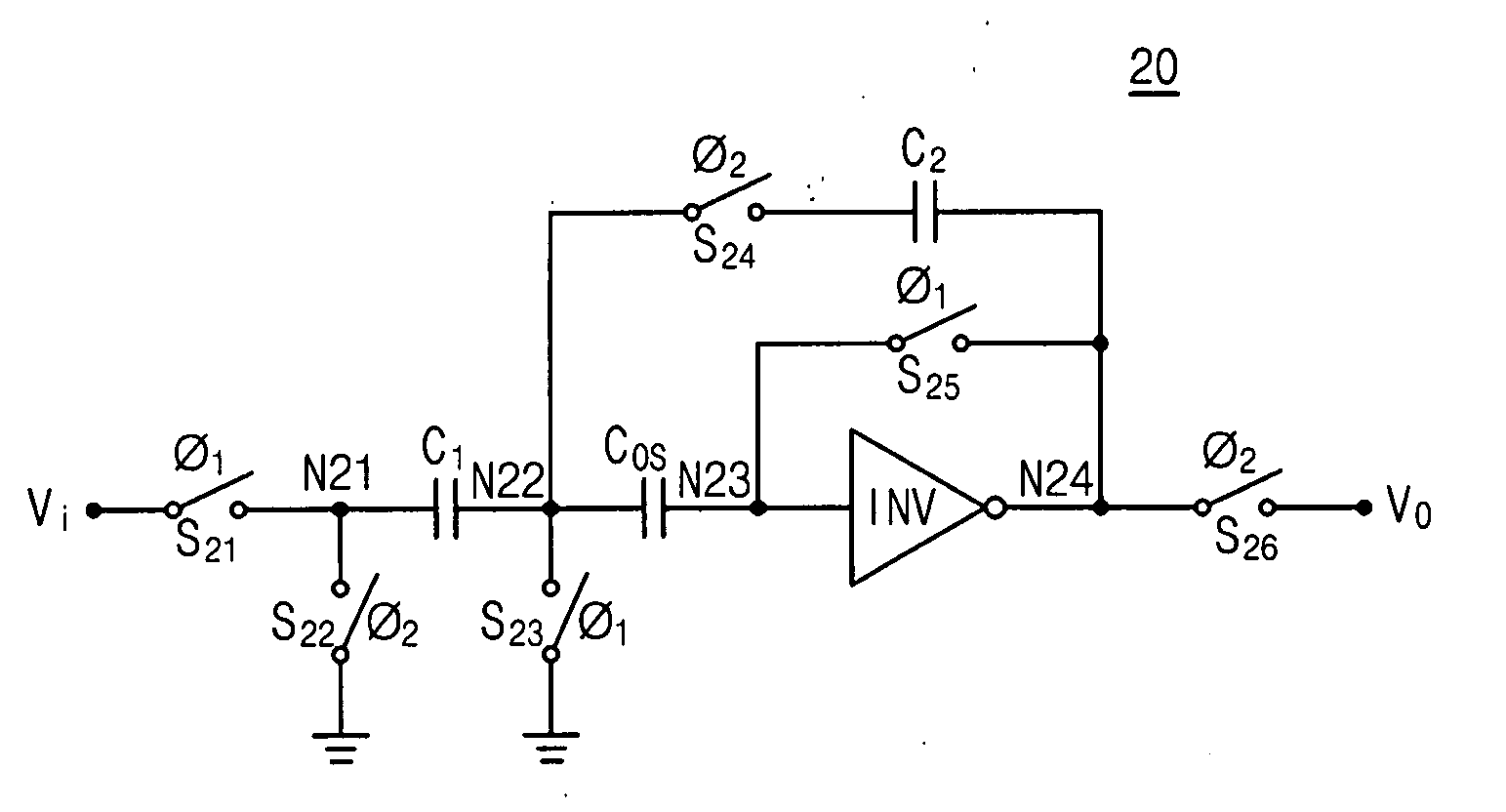

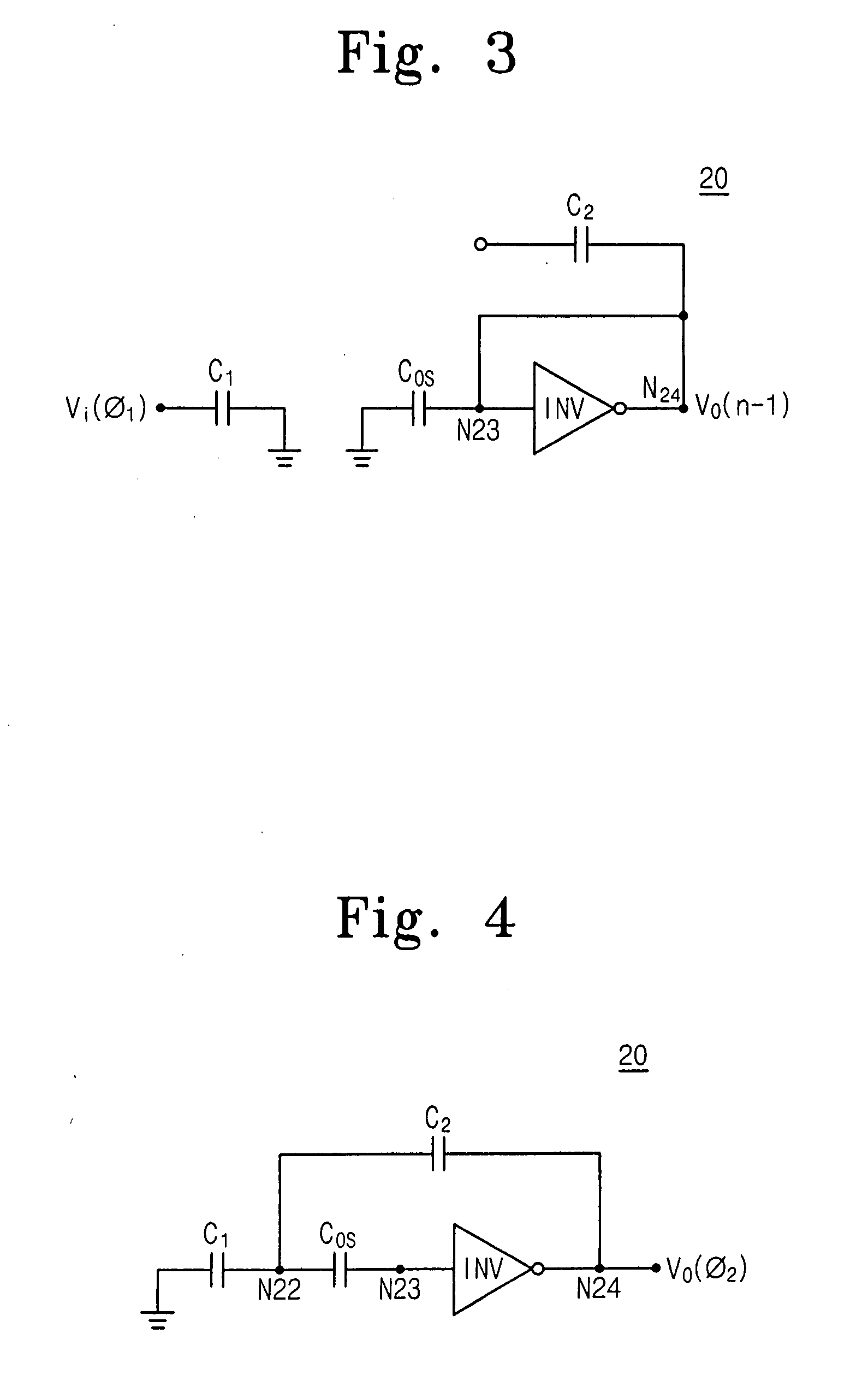

Switched capacitor circuit with inverting amplifier and offset unit

ActiveUS7800427B2Reduce power consumptionReduce circuit areaAmplifier modifications to reduce non-linear distortionComputing operations for integral formationCapacitanceAudio power amplifier

A switched capacitor circuit includes an amplifier, a charging unit, an offset unit, and an integrating unit. The charging unit is coupled between an input node and a first node, and is for accumulating charge corresponding to an input signal during a sampling mode. The offset unit is coupled between the first node and an input of the amplifier, and is for maintaining the first node to be a virtual ground during an integrating mode. The integrating unit is coupled between the first node and an output of the amplifier, and is for receiving charge from the charging unit during the integrating mode.

Owner:SAMSUNG ELECTRONICS CO LTD +1

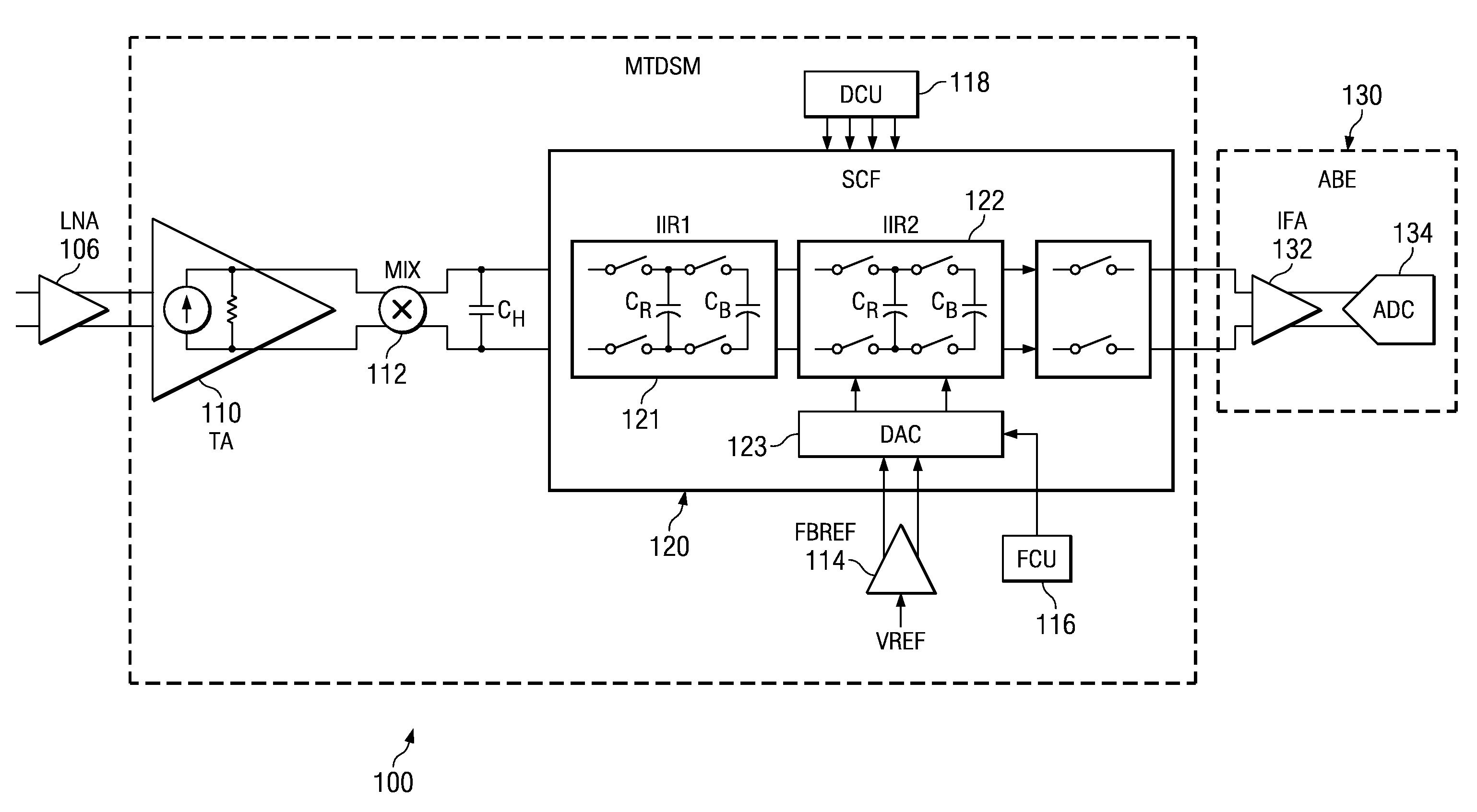

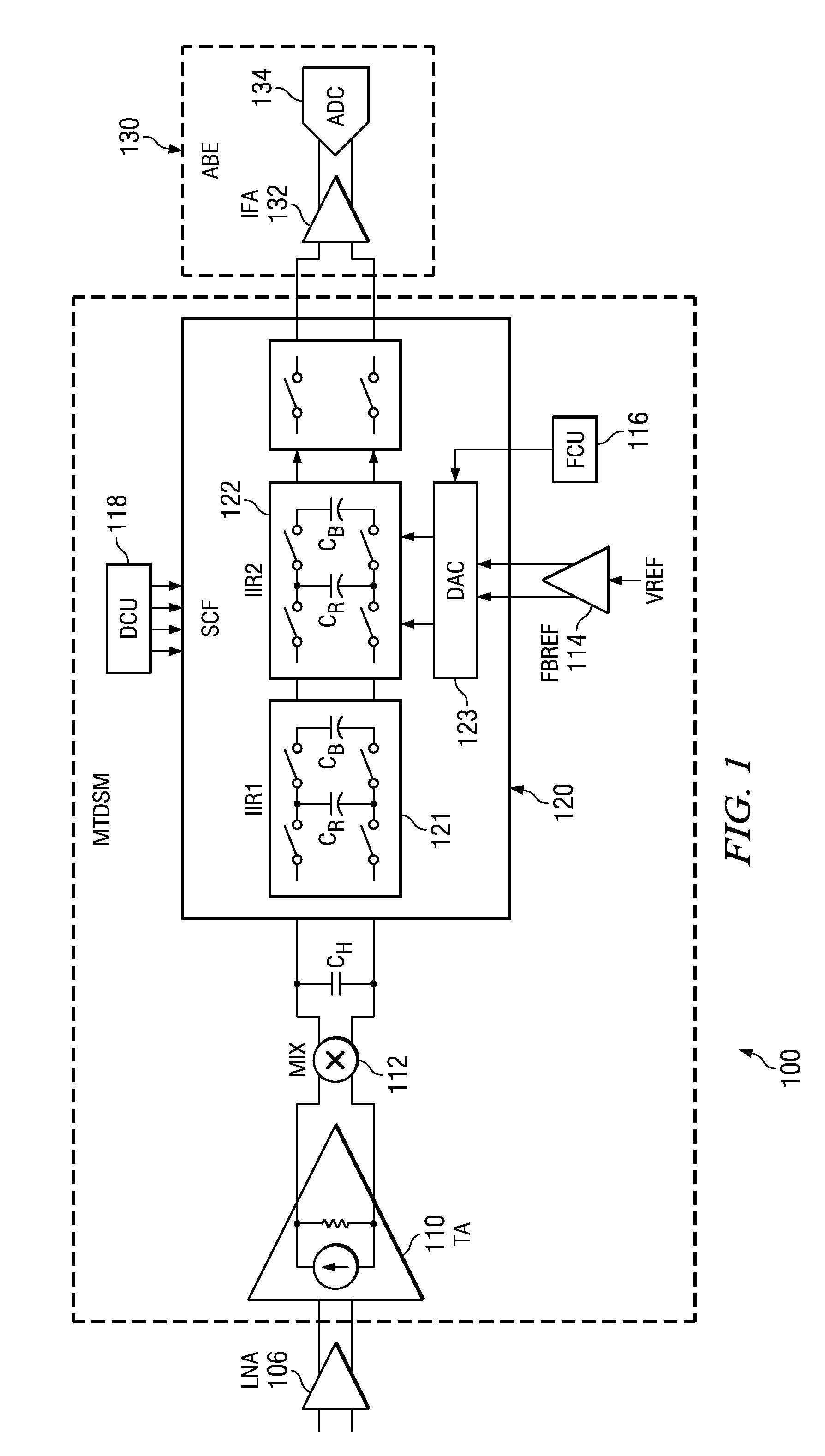

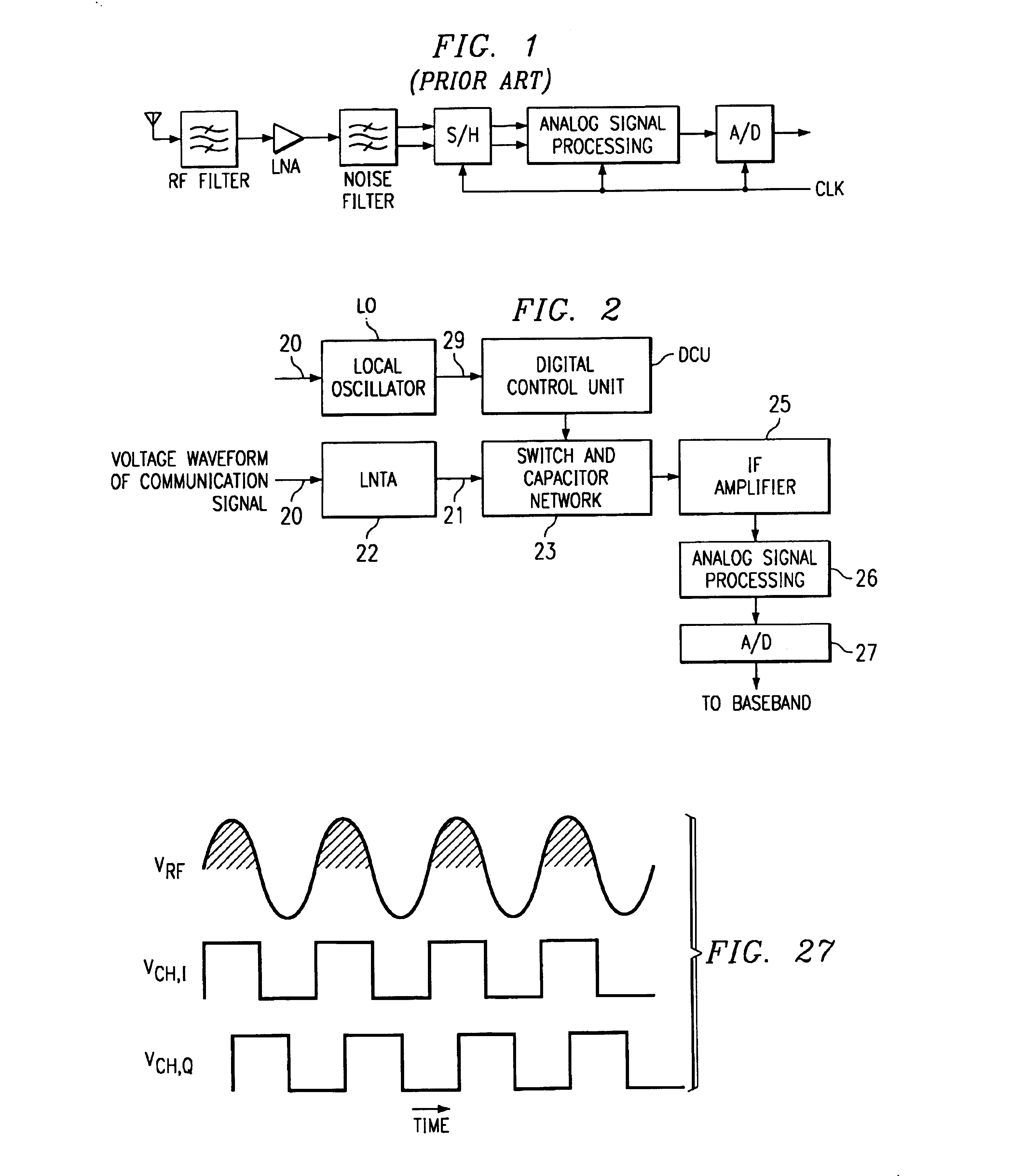

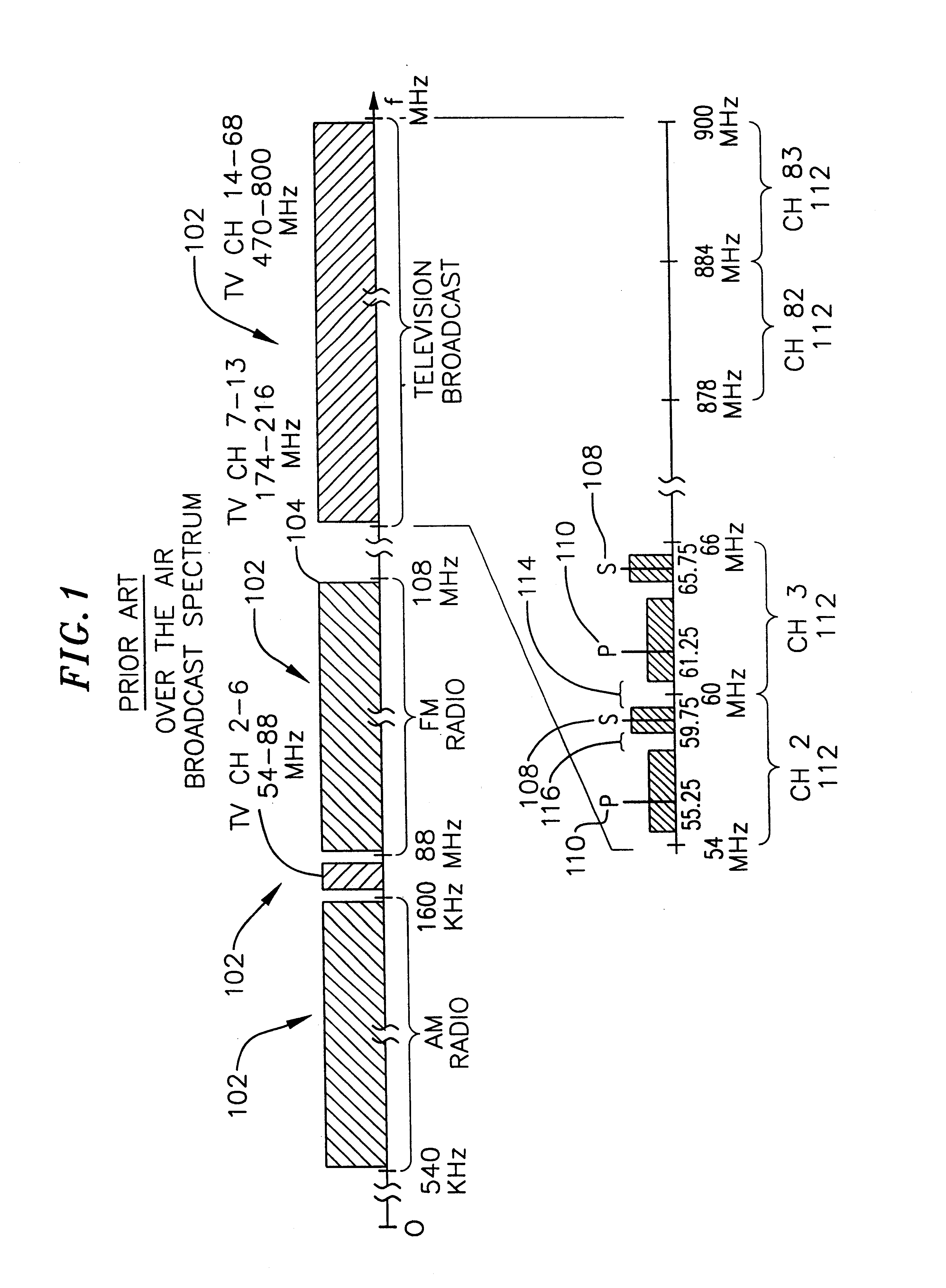

Multi-Tap Direct Sub-sampling Mixing System for Wireless Receivers

ActiveUS20090002066A1Transversal filtersSwitched capacitor networksHybrid systemAudio power amplifier

A multi-tap direct sub-sampling mixing system for wireless receivers is provided with a dynamically configurable passive switched capacitor filter. A front end amplifier is connected to receive a signal. The passive switched capacitor filter is connected to receive the amplified signal and has an output for providing a filtered signal. The switched capacitor filter has at least two sections that are each operable as a pole, wherein a first section of the at least two sections has sets of at least two stacked capacitors interconnected with a set of switches operable to amplify in input voltage provided to an input of the first section in response to operation of the set of switches; and a back end section connected to the output of the switched capacitor filter to receive the filtered signal.

Owner:TEXAS INSTR INC

Integrated switchless programmable attenuator and low noise amplifier

InactiveUS6879816B2Multiple-port active networksSwitched capacitor networksCapacitanceLocal oscillator signal

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

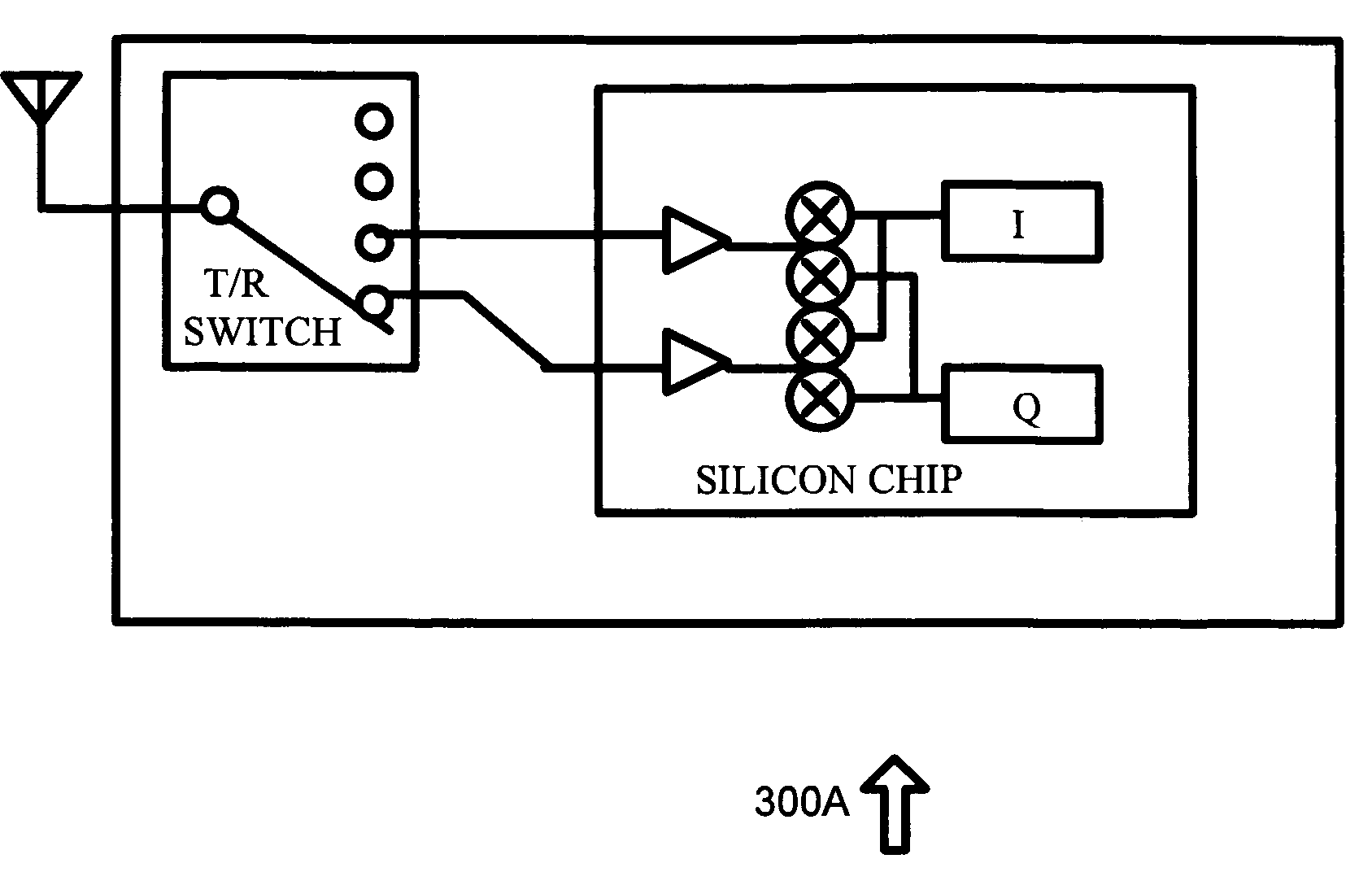

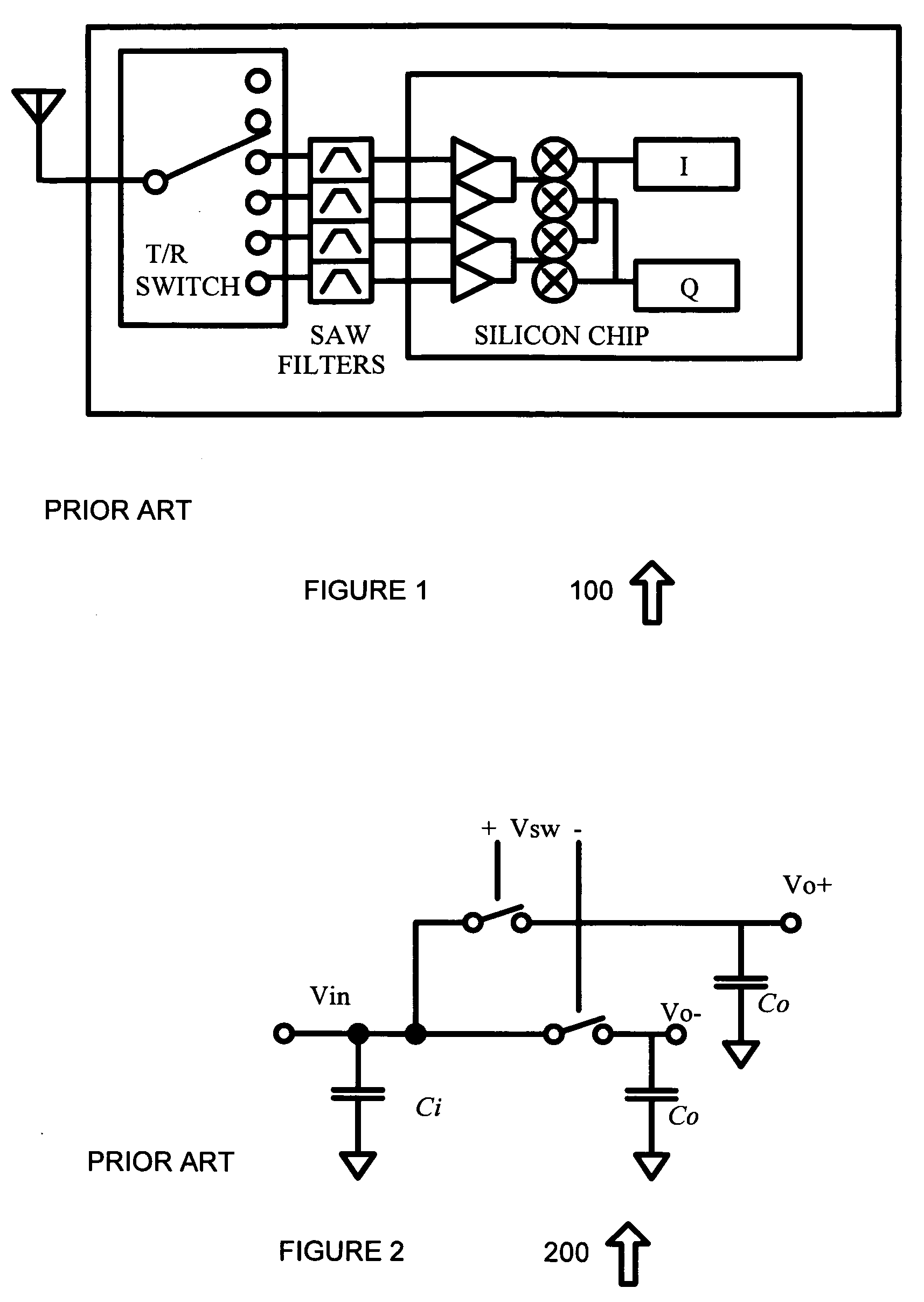

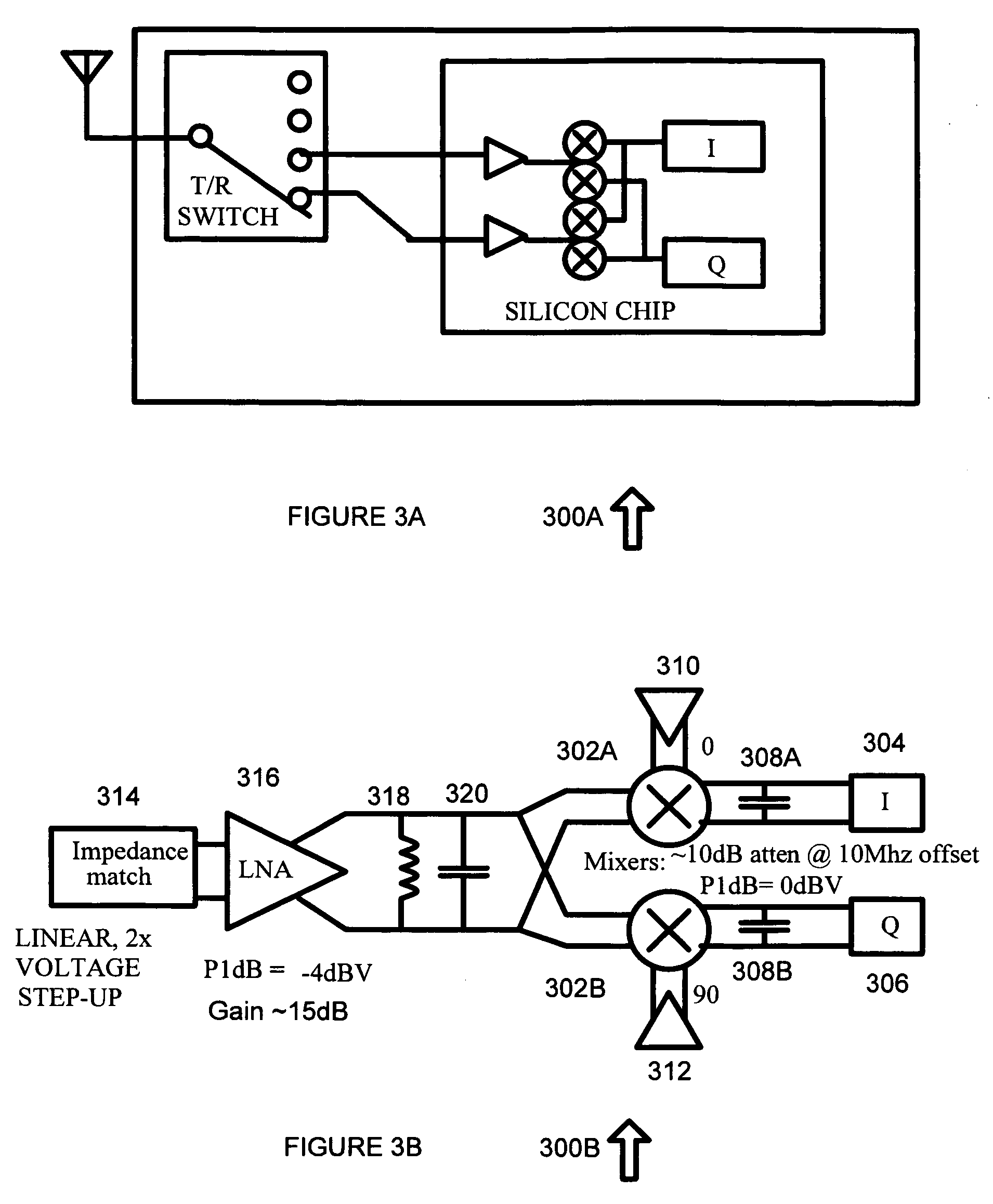

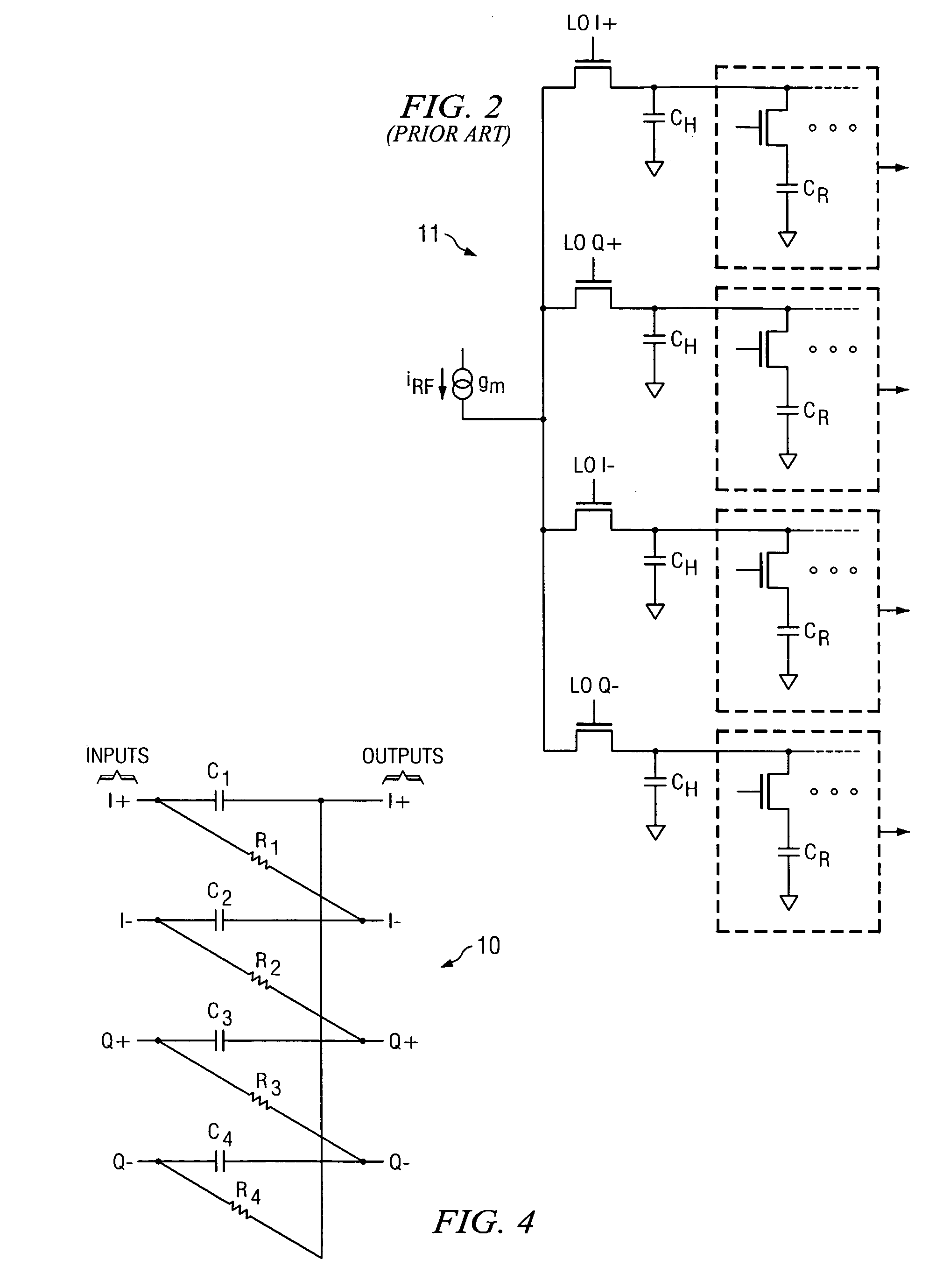

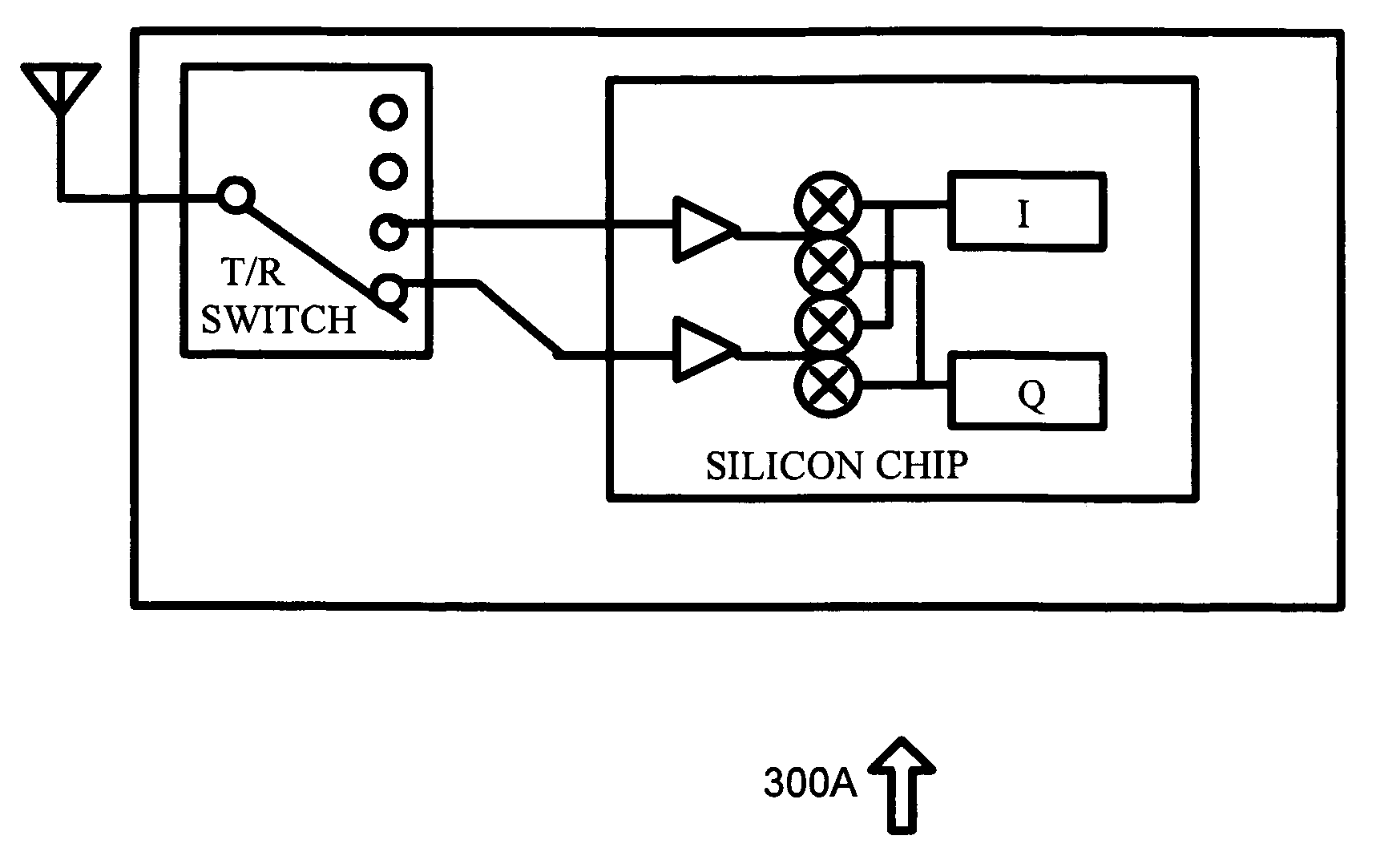

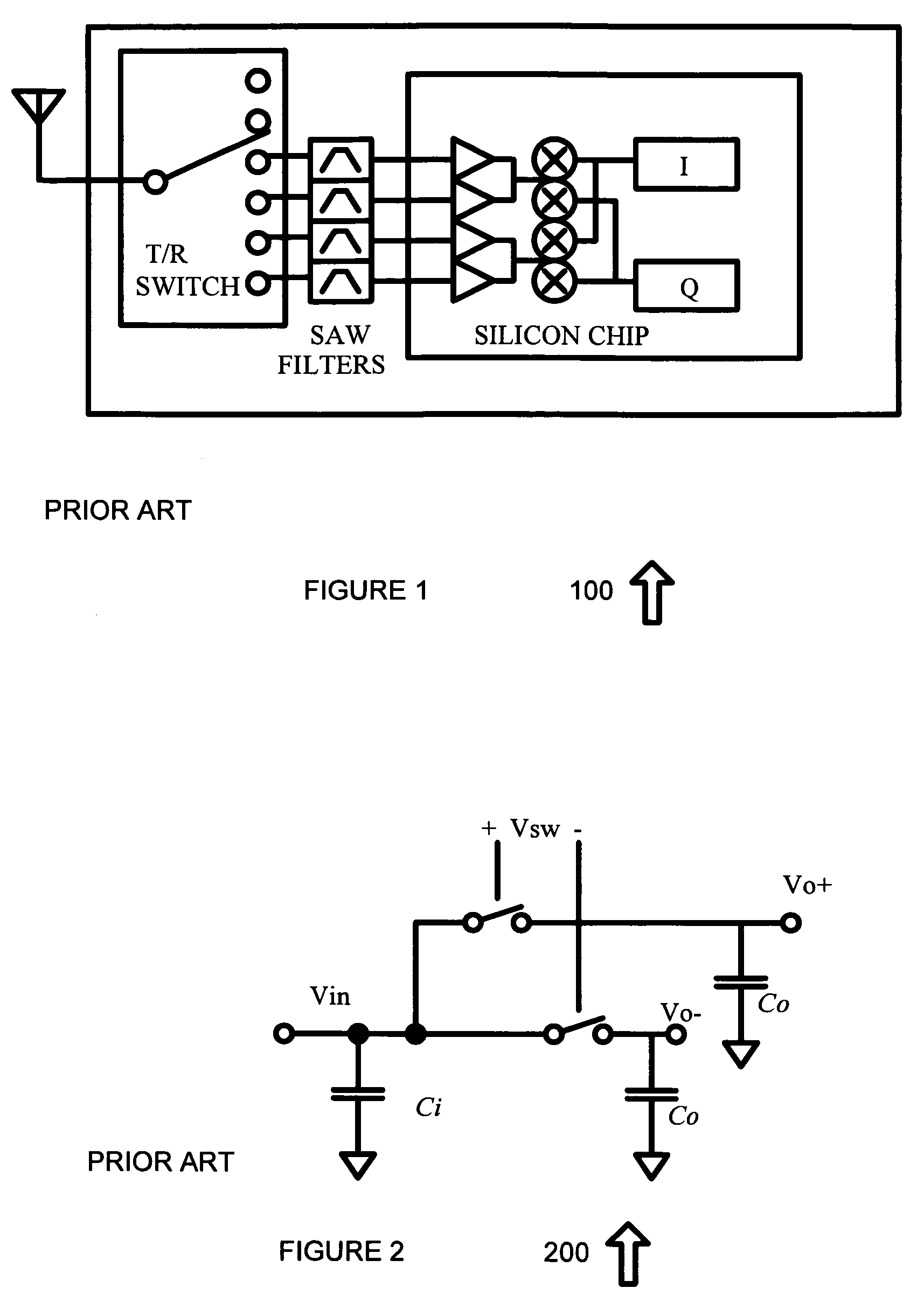

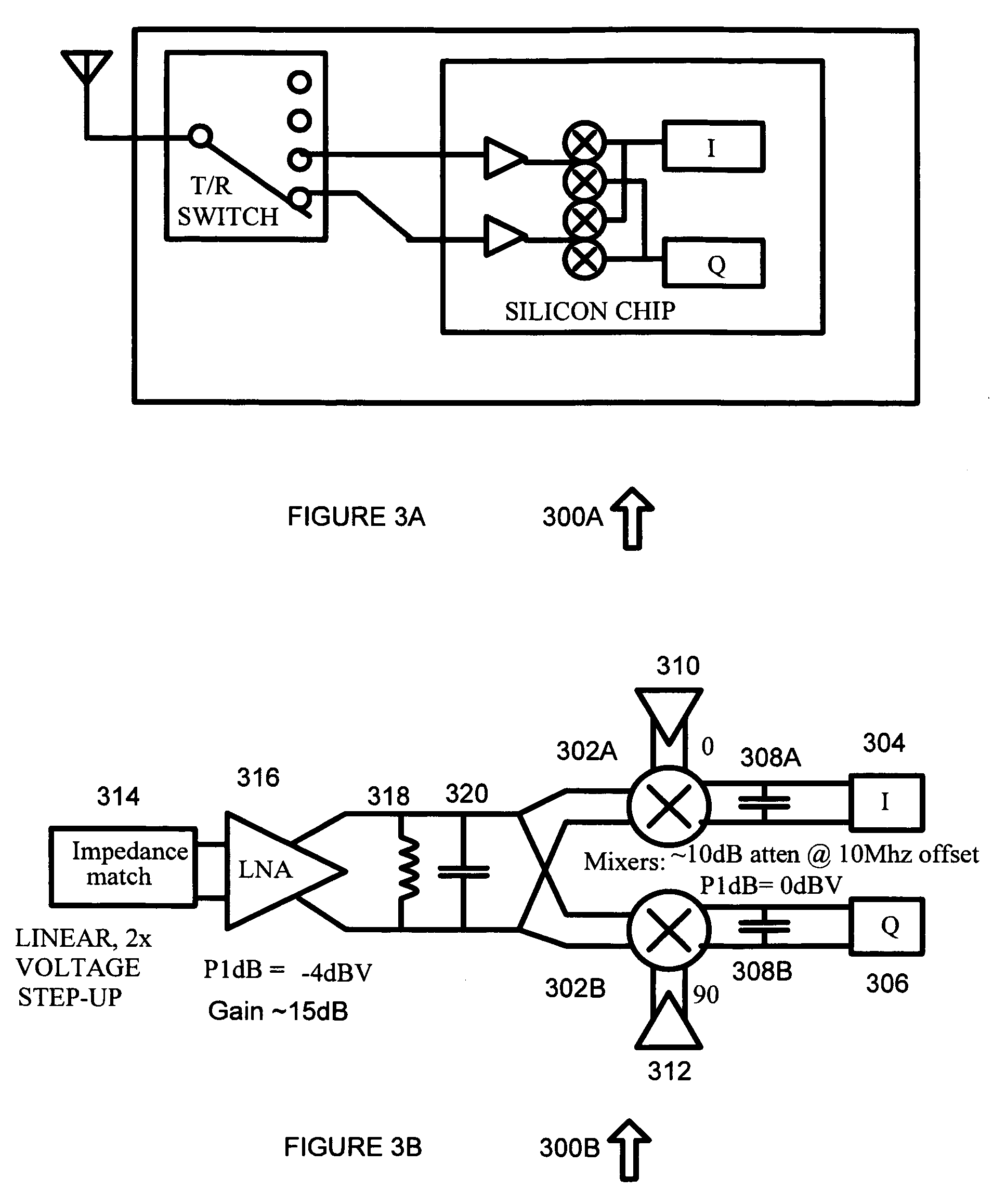

High dynamic range time-varying integrated receiver for elimination of off-chip filters

ActiveUS20050164669A1Improve linearityLow costModulation transference balanced arrangementsSwitched capacitor networksQuadrature mixerOutput impedance

A quadrature mixer with an LO input is provided. The quadrature mixer receives a signal having a frequency FLO and a signal input having a frequency FSIG, and has an output that comprises an output impedance that is high at frequencies of |FLO−FSIG | and |FLO+FSIG| and low at other. A mixer coupled to the output impedance interacts with the output impedance such that an impedance presented at the signal input is high for signals at FSIG if FSIG is a predetermined signal frequency, and low at other frequencies.

Owner:MEDIATEK INC

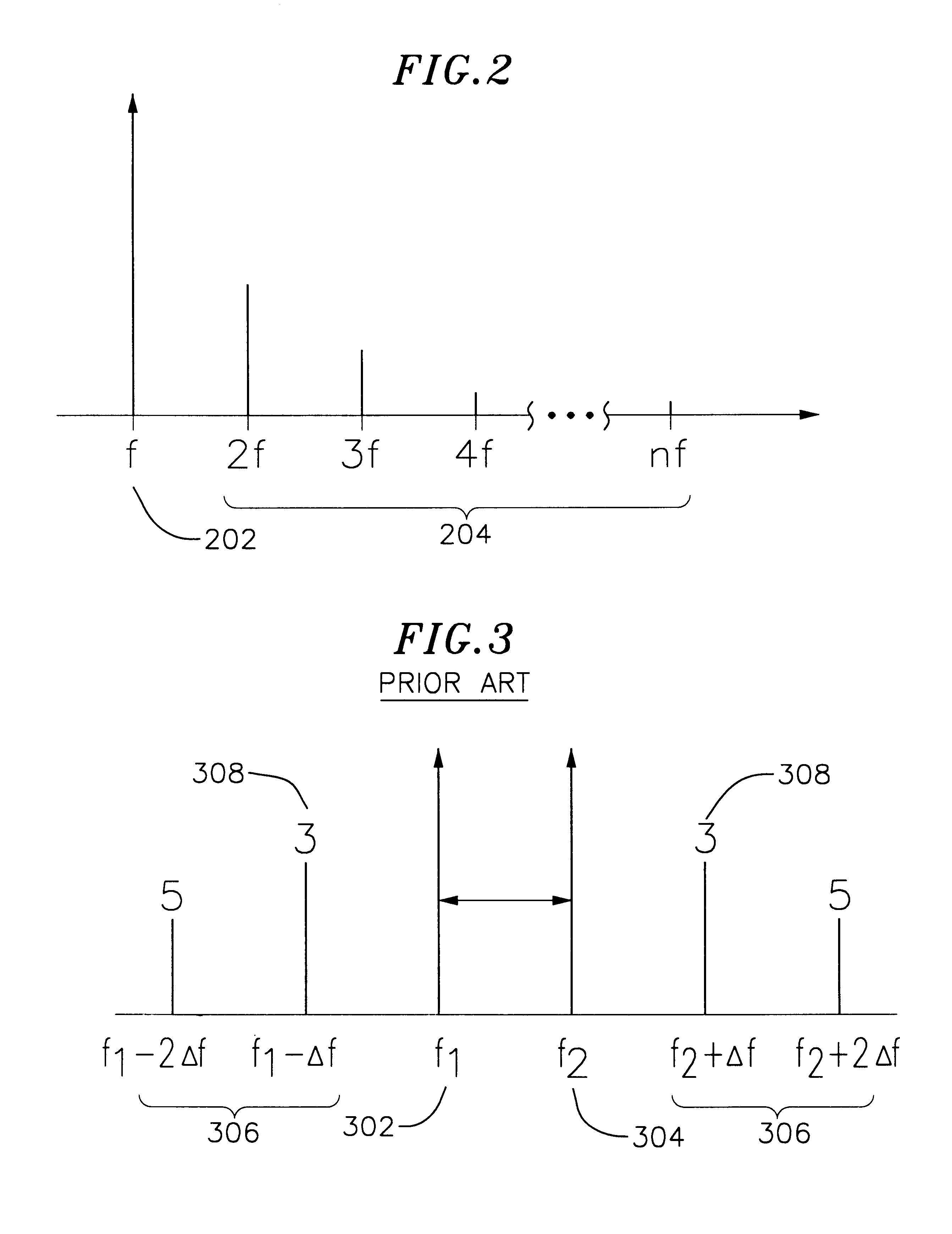

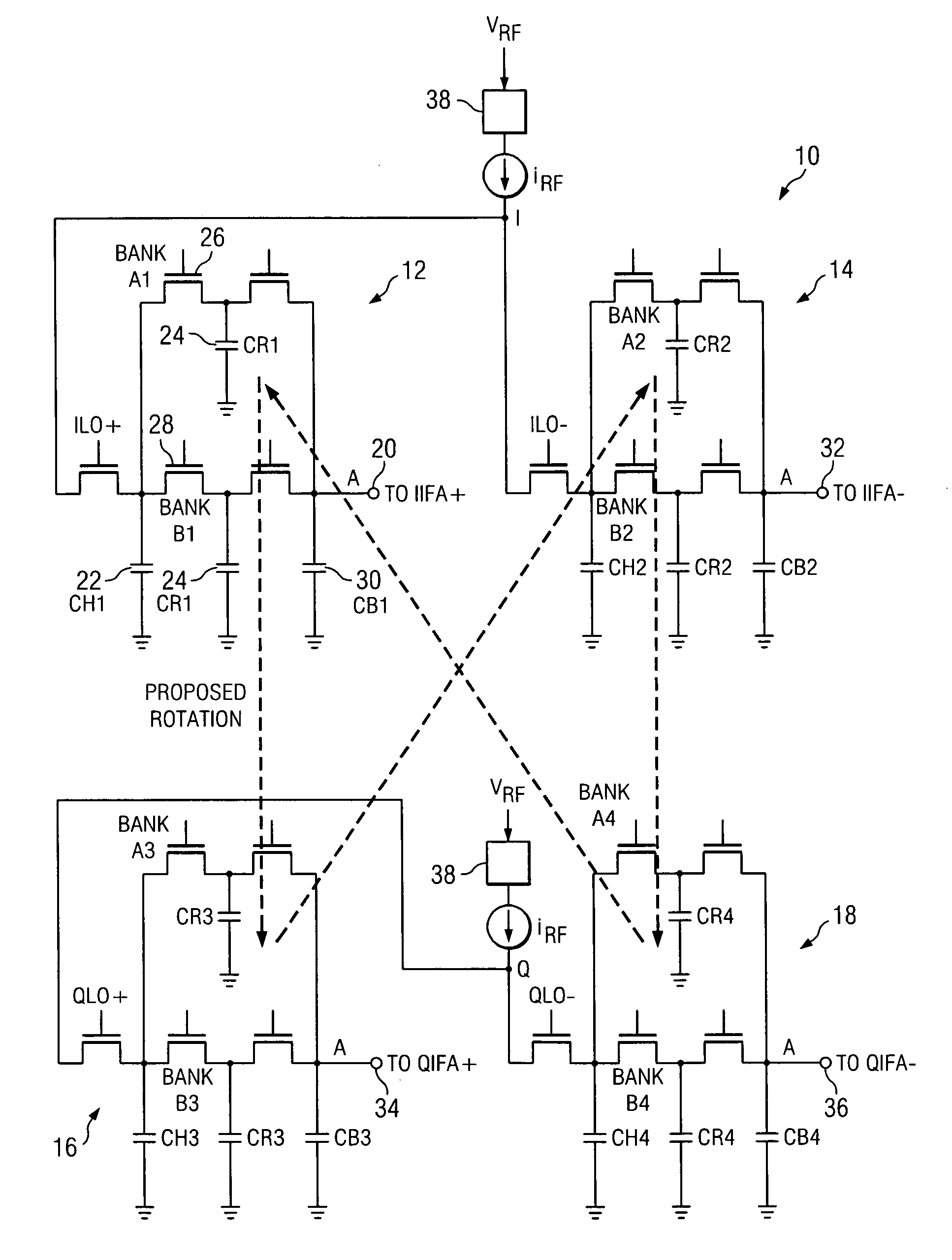

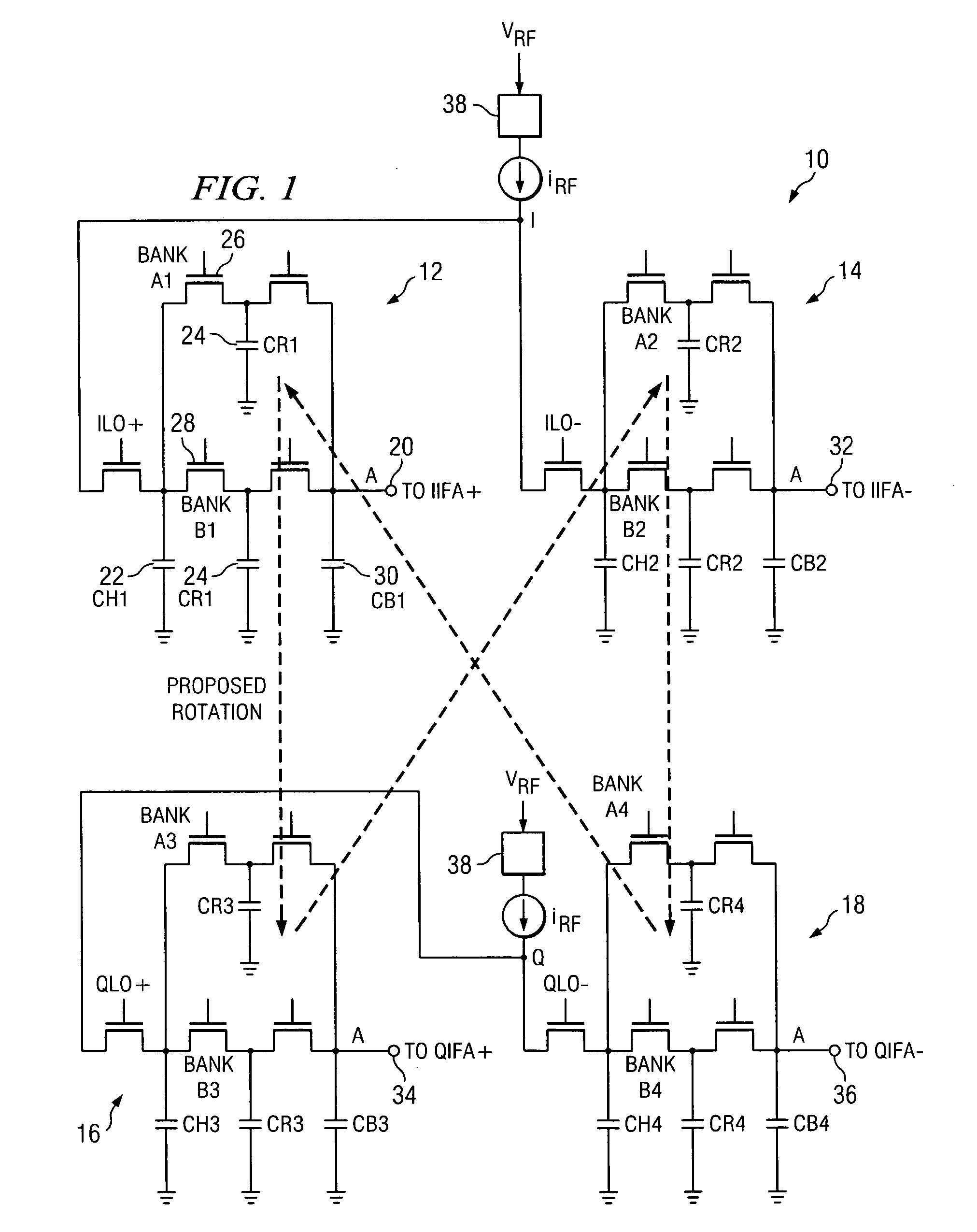

Image reject filtering in a direct sampling mixer

InactiveUS20050233725A1Reduced dynamic rangeReduce areaMultiple-port networksSwitched capacitor networksPattern recognitionFrequency mixer

Disclosed are methods, circuits and systems for image reject filtering in a multi-tap direct sampling mixer (MTDSM) of an IF or RF system. Disclosed is the use of rotating capacitors among the in-phase and quadrature branches of a signal processing system. The exchange of information among the branches of the I and Q channels is used in the implementation of a complex filter. Embodiments using cascaded multiple stages of the complex filter to provide higher order complex filters are also disclosed.

Owner:TEXAS INSTR INC

High dynamic range time-varying integrated receiver for elimination of off-chip filters

ActiveUS7460844B2Improve linearityLow costModulation transference balanced arrangementsSwitched capacitor networksQuadrature mixerOutput impedance

A quadrature mixer with an LO input is provided. The quadrature mixer receives a signal having a frequency FLO and a signal input having a frequency FSIG, and has an output that comprises an output impedance that is high at frequencies of |FLO−FSIG | and |FLO+FSIG| and low at other. A mixer coupled to the output impedance interacts with the output impedance such that an impedance presented at the signal input is high for signals at FSIG if FSIG is a predetermined signal frequency, and low at other frequencies.

Owner:MEDIATEK INC

Switched-capacitor structures with enhanced isolation

ActiveUS6859159B2Increase upstreamIncrease downstream isolationElectric signal transmission systemsElectric spark ignitersEngineeringSwitched capacitor

Switched-capacitor structures are provided that reduce distortion and noise in their processed signals because they increase isolation between structural elements and ensure that selected elements are securely turned off in one mode and quickly turned on in another mode.

Owner:ANALOG DEVICES INC

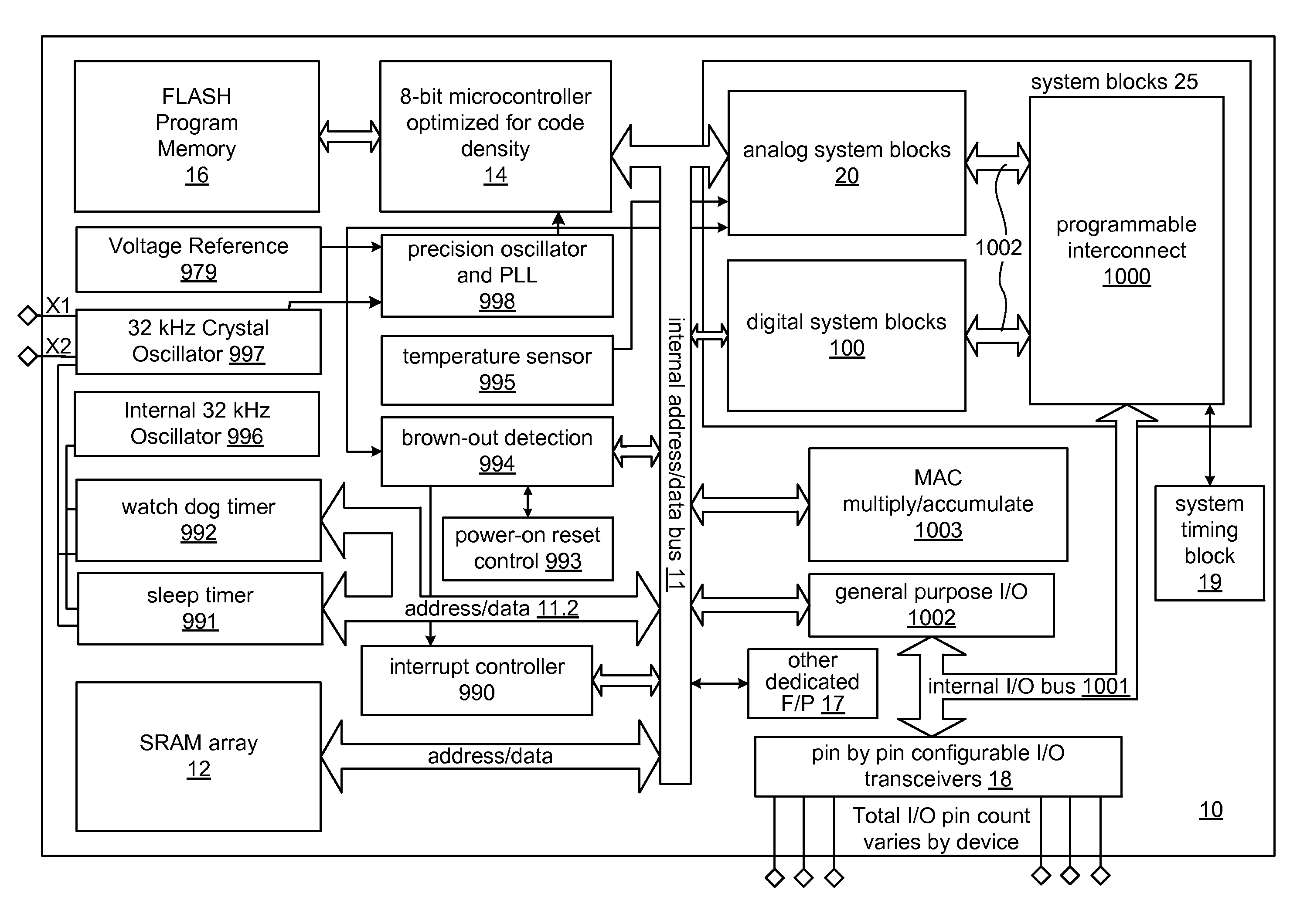

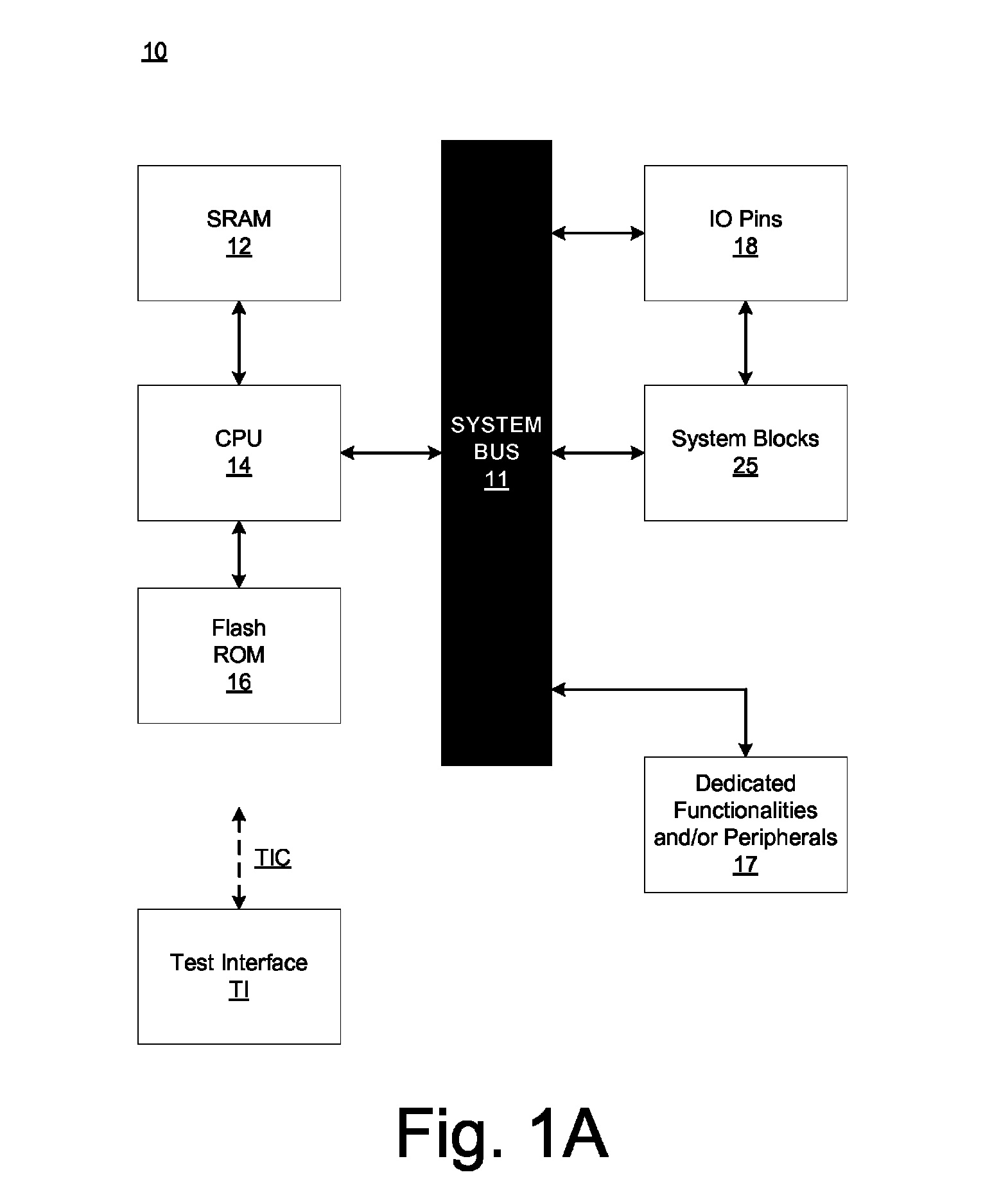

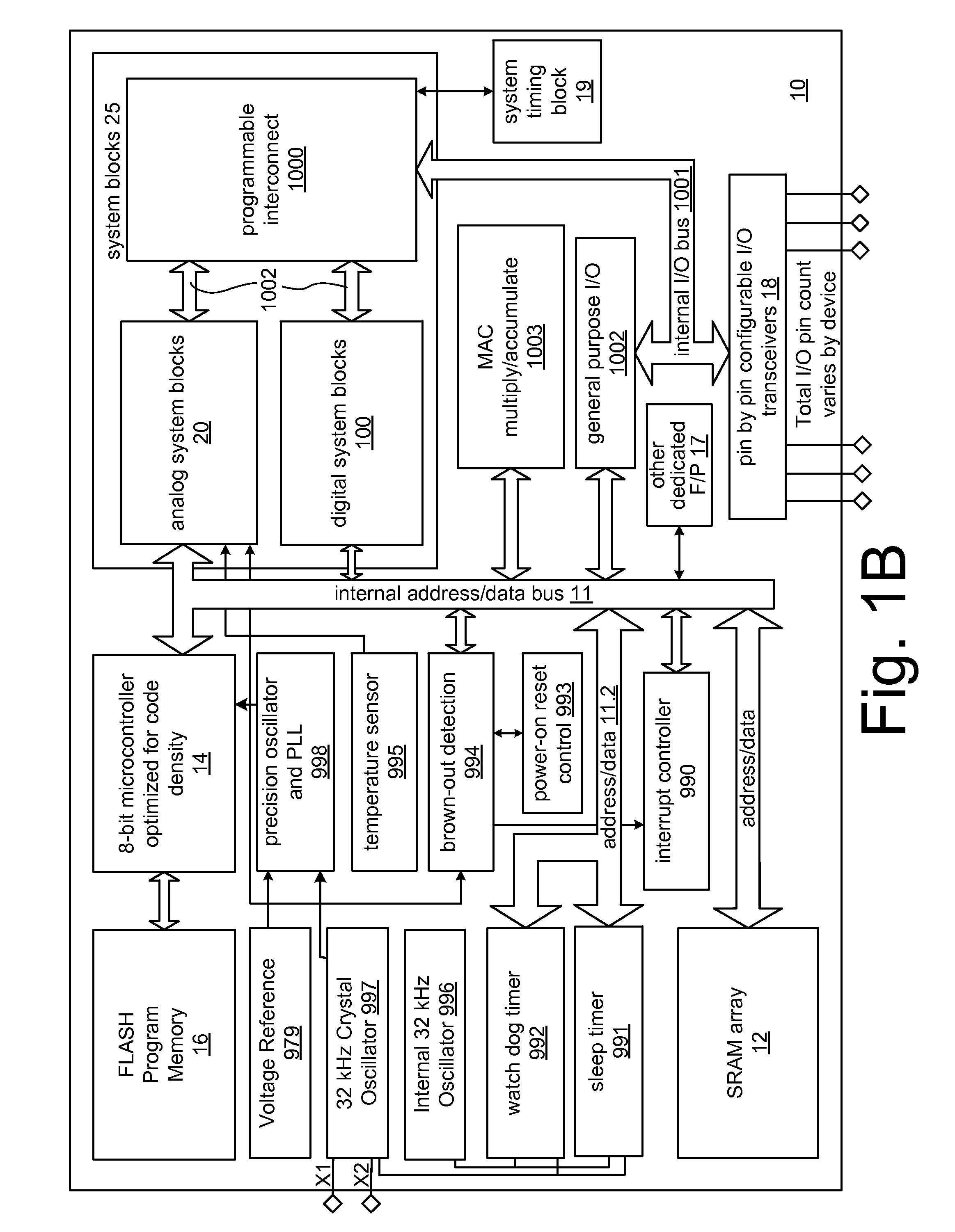

Programmable microcontroller architecture

ActiveUS8176296B2Little timeInexpensive and simple to and applyProgramme controlDigital technique networkController architectureMicrocontroller

Embodiments of the present invention are directed to a microcontroller device having a microprocessor, programmable memory components, and programmable analog and digital blocks. The programmable analog and digital blocks are configurable based on programming information stored in the memory components. Programmable interconnect logic, also programmable from the memory components, is used to couple the programmable analog and digital blocks as needed. The advanced microcontroller design also includes programmable input / output blocks for coupling selected signals to external pins. The memory components also include user programs that the embedded microprocessor executes. These programs may include instructions for programming the digital and analog blocks “on-the-fly,” e.g., dynamically. In one implementation, there are a plurality of programmable digital blocks and a plurality of programmable analog blocks.

Owner:MONTEREY RES LLC

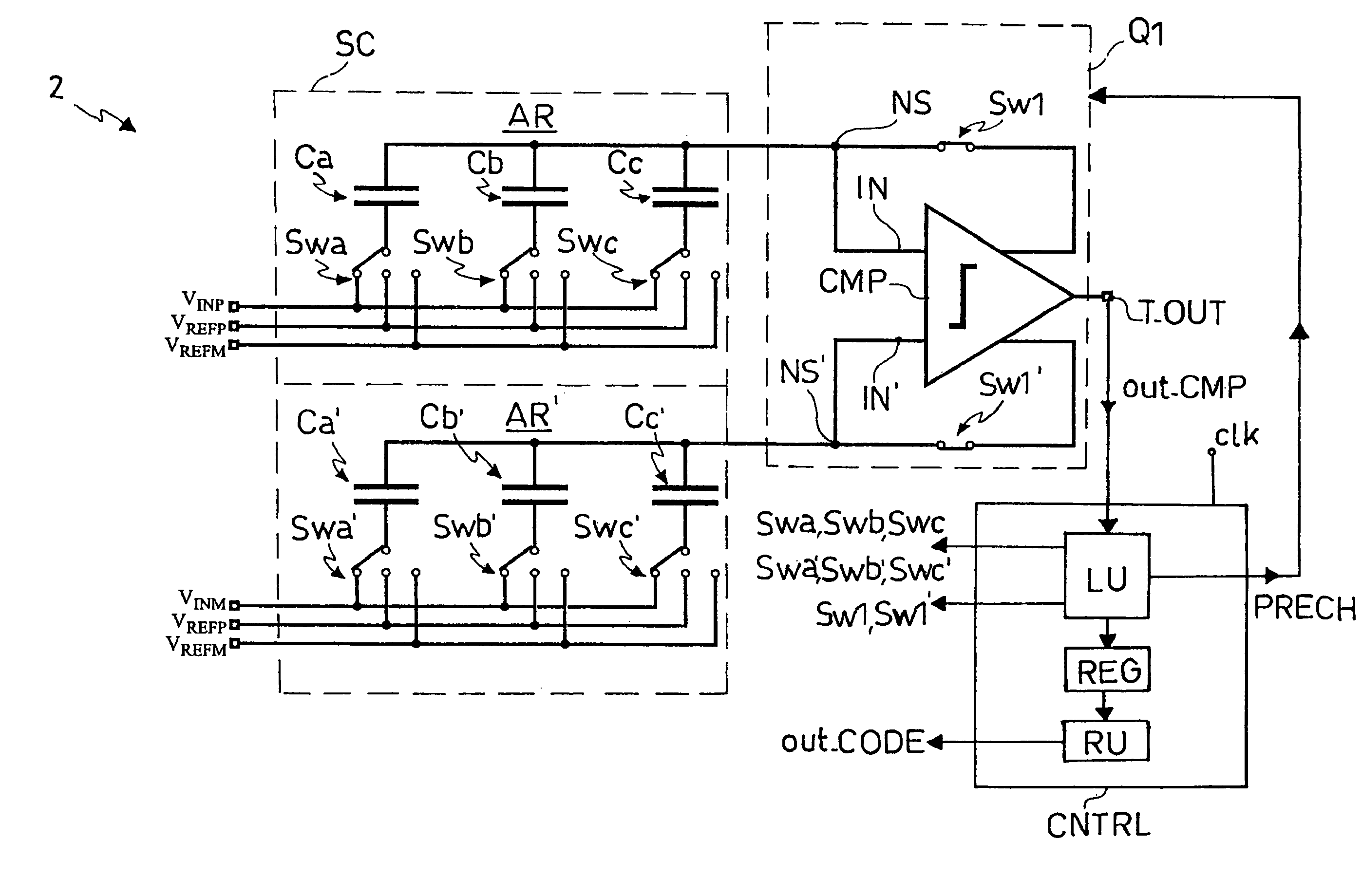

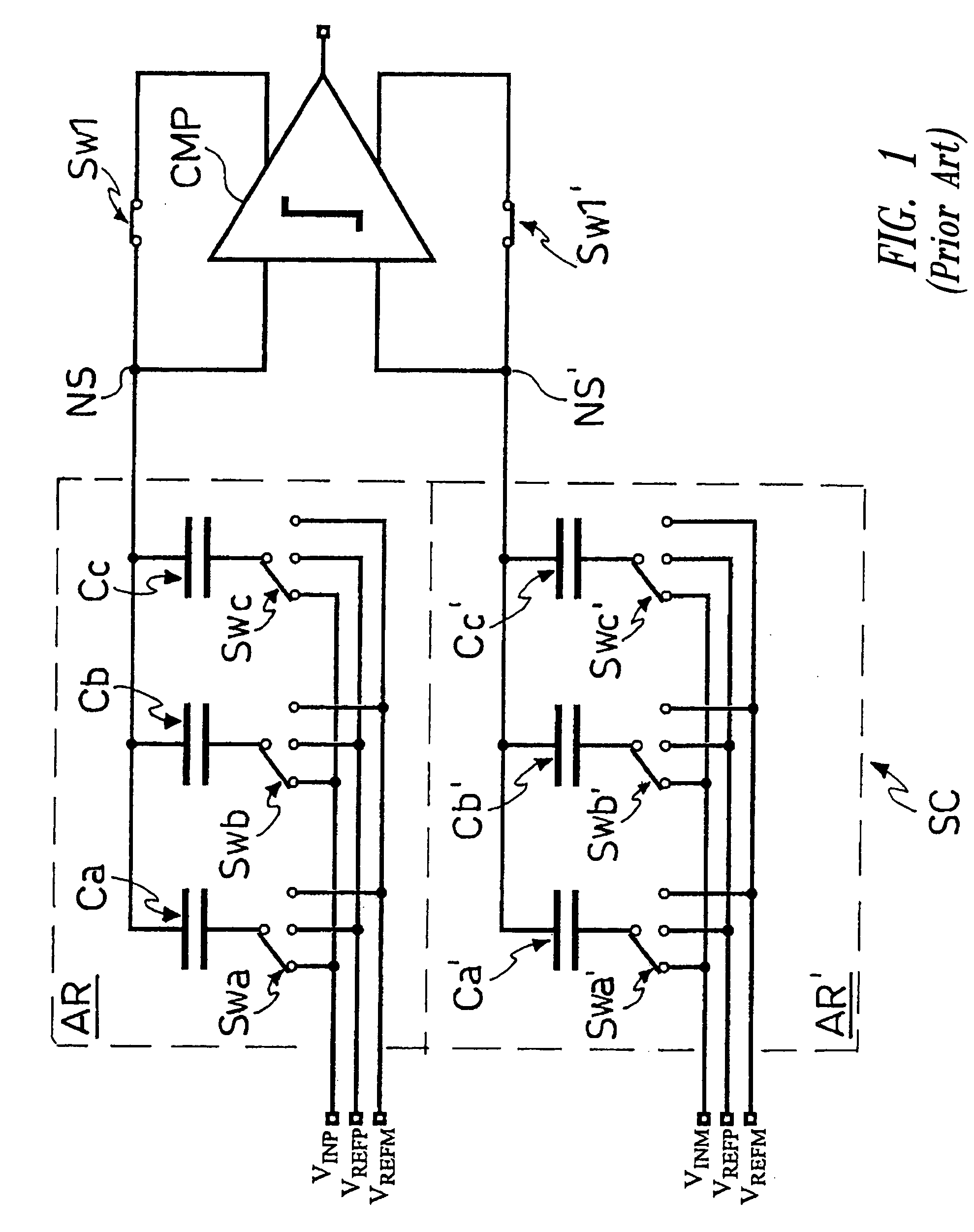

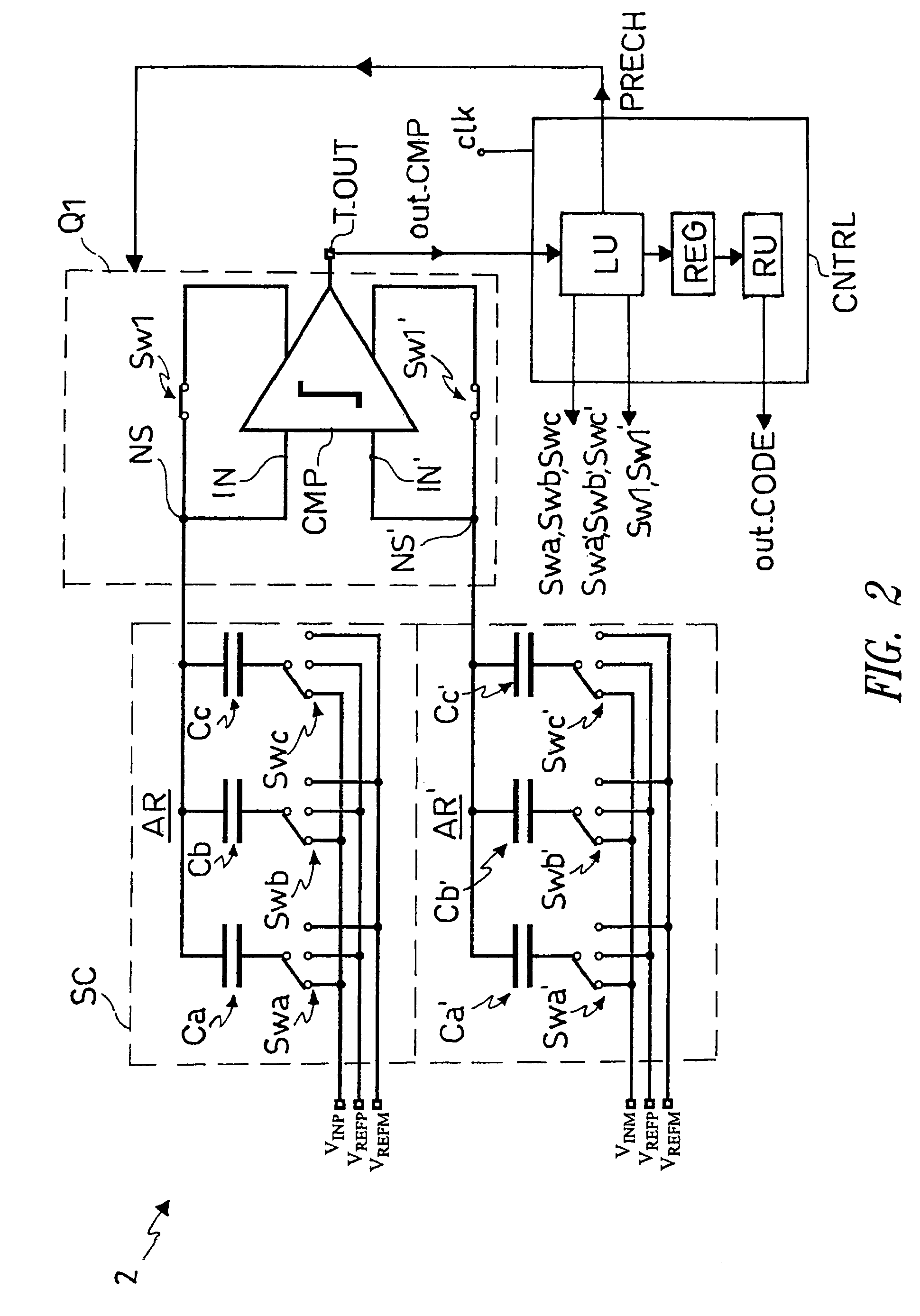

Switched-capacitor band-pass filter of a discrete-time type, in particular for cancelling offset and low-frequency noise of switched-capacitor stages

ActiveUS8497746B2Eliminate offsetReduce flicker noiseComputing operations for integral formationMultiple-port networksCapacitanceAudio power amplifier

A band-pass filter made up by an operational amplifier and by an input circuit. The input circuit is formed by a capacitive filtering element, connected to the input of the operational amplifier; a coupling switch, coupled between an input node and the capacitive filtering element; a capacitive sampling element, coupled between the input of the filter and the input node; and a sampling switch, coupled between the input node and a reference-potential line. The coupling switch and the input sampling switch close in phase opposition according to a succession of undesired components sampling and sensing steps, so that the capacitive sampling element forms a sampler for sampling the undesired component in the undesired components sampling step, in the absence of the component of interest, and forms a subtractor of the undesired components from the input signal in the sensing step.

Owner:STMICROELECTRONICS SRL

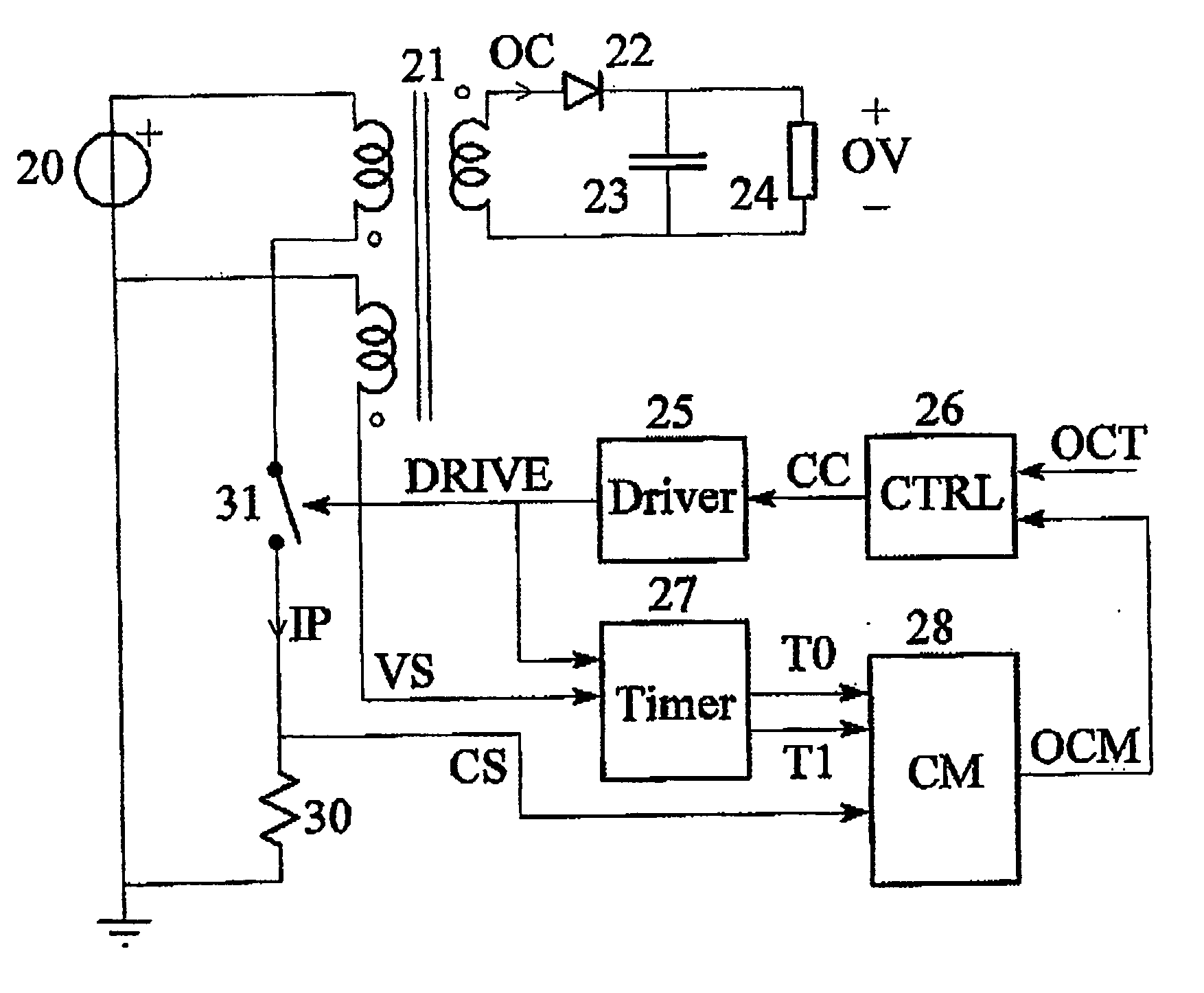

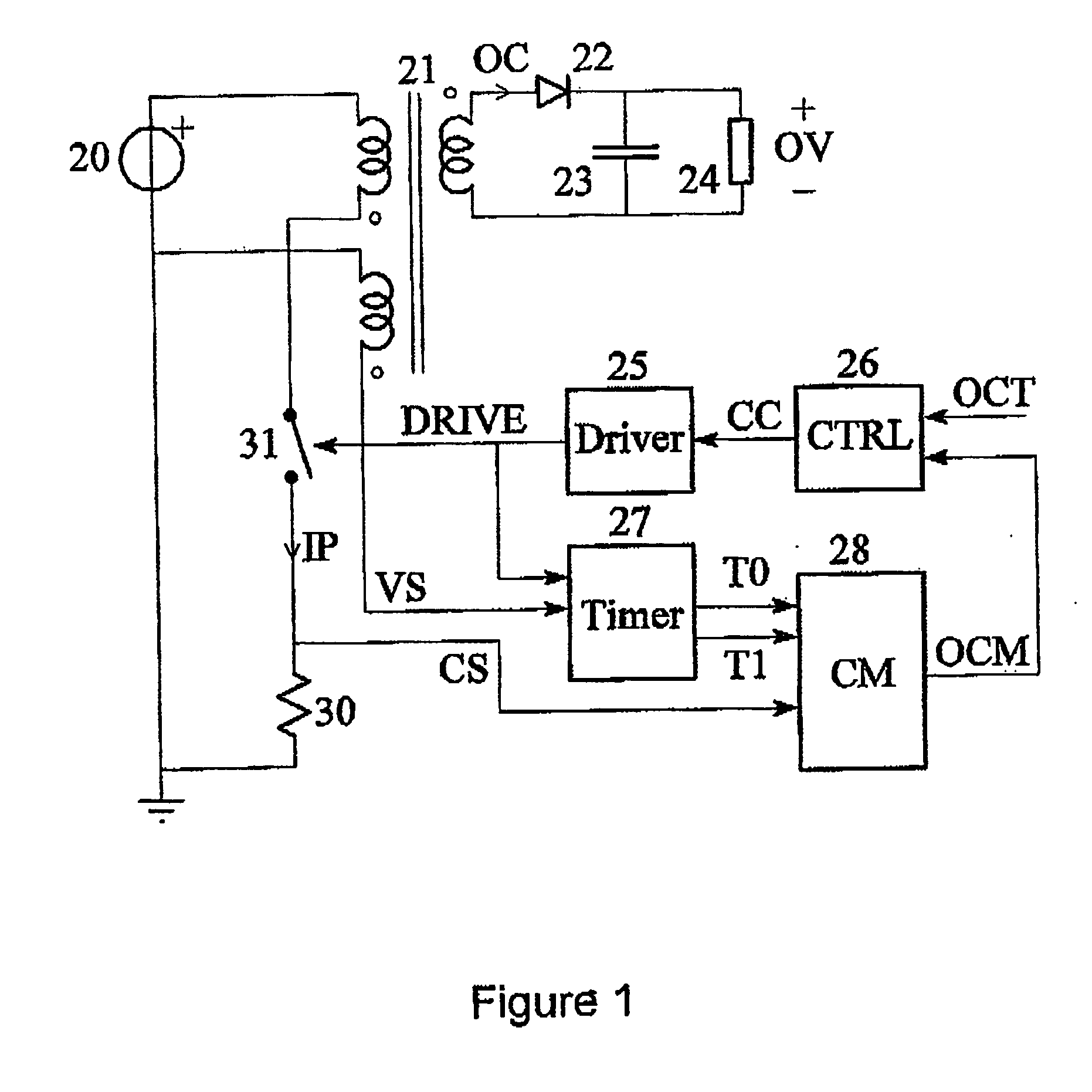

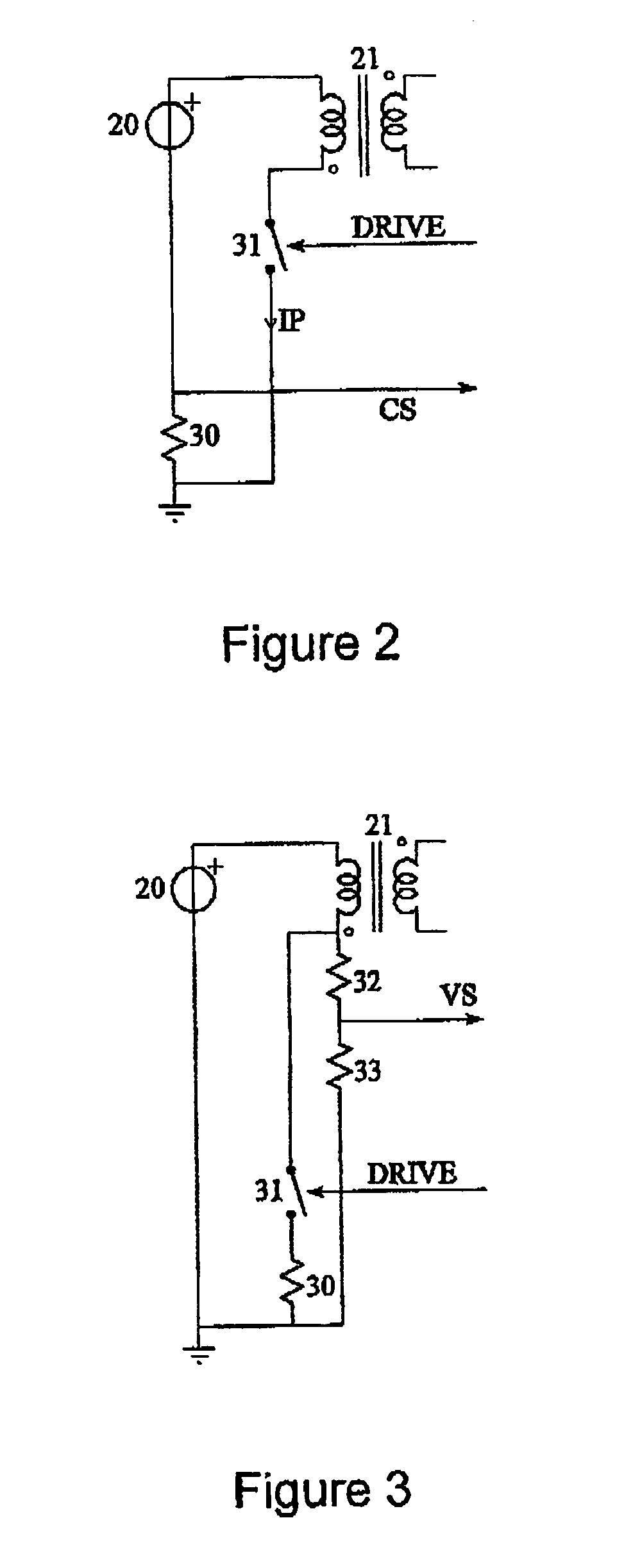

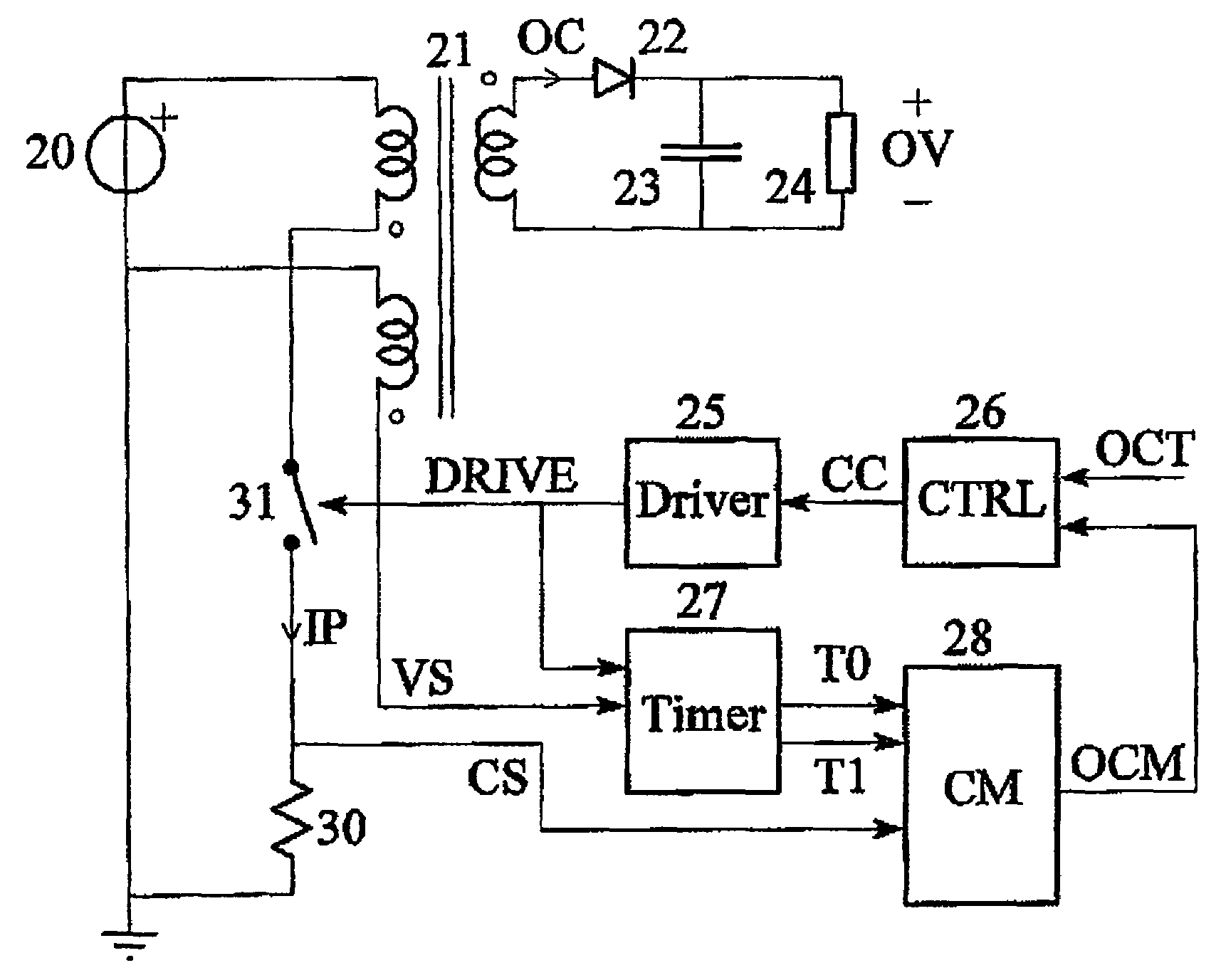

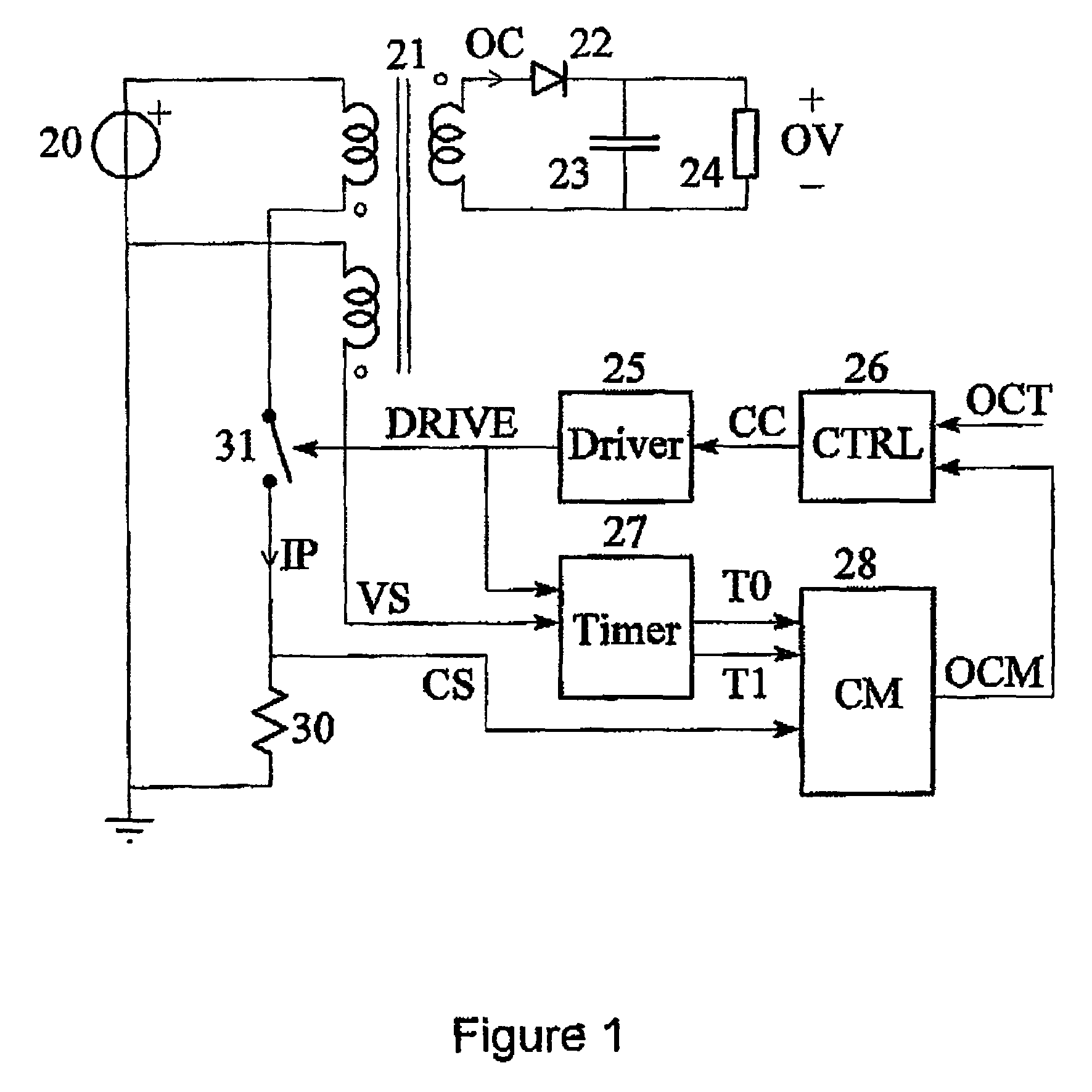

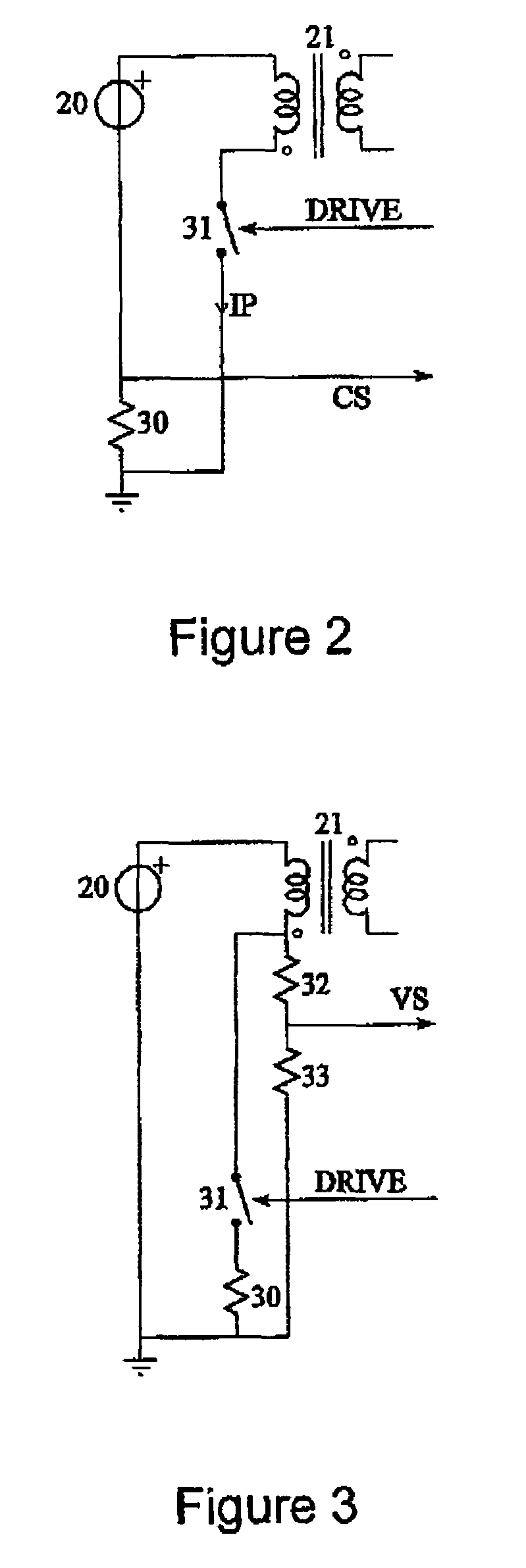

Switch mode power supply systems

InactiveUS20080007977A1Increase rmsConstant lengthCurrent/voltage measurementSwitched capacitor networksAverage currentTransformer

Methods and apparatus for sensing the output current in a switch mode power supply (SMPS) using primary side sensing are described. A module senses a current in a primary winding of a transformer and a voltage on a primary or auxiliary winding of the transformer, and which includes a multiplier coupled to an output of a signal averager averaging a primary winding current and to an output of a timing signal generator using the sensed voltage to signal when a secondary winding is powering an output of the SMPS, to multiply an averaged current sense signal by a fraction of a total cycle period of said SMPS during which the secondary winding is providing power to provide a signal estimating an output current of the SMPS.

Owner:POWER INTEGRATIONS INC

Notch filter for ripple reduction in chopper stabilized amplifiers

ActiveUS20070170981A1Reduce ripple noiseFast signalAmplifier modifications to reduce noise influenceAmplifier modifications to raise efficiencyAudio power amplifierEngineering

A chopper-stabilized amplifier receiving an input signal includes a first operational transconductance amplifier having an input chopper and an output chopper for chopping an output signal produced by the first operational transconductance amplifier. A switched capacitor notch filter filters the chopped output signal by operating synchronously with the chopping frequency of output chopper to filter ripple voltages that otherwise would be produced by the output chopper. In one embodiment, a second operational transconductance amplifier amplifies the notch filter output. The input signal is fed forward, summed with the output of the second operational transconductance amplifier, and applied to the input of a fourth operational transconductance amplifier. Ripple noise and offset are substantially reduced.

Owner:TEXAS INSTR INC

Hybrid low-pass sigma-delta modulator

A hybrid loop filter includes an integrator having an input and an output wherein the output forms an output of the hybrid loop filter, a plurality of transconductance amplifiers having an input and an output wherein each output of the plurality of transconductance amplifiers is coupled to the input of the integrator, a switched capacitor low pass chain having an input and a plurality of branches wherein each of the plurality of branches is coupled to the input of a separate one of said plurality of transconductance amplifiers, and a feedthrough branch having an input and an output wherein the input is coupled to the input of the switched capacitor low pass chain to form an input of said hybrid loop filter, and the output is coupled to the input of a separate one of the plurality of transconductance amplifiers.

Owner:SONIC INNOVATIONS

Switched capacitor circuit with inverting amplifier and offset unit

ActiveUS20080116966A1Reduce power consumptionReduce circuit areaComputing operations for integral formationAmplifier modifications to reduce non-linear distortionAudio power amplifierSample Mode

A switched capacitor circuit includes an amplifier, a charging unit, an offset unit, and an integrating unit. The charging unit is coupled between an input node and a first node, and is for accumulating charge corresponding to an input signal during a sampling mode. The offset unit is coupled between the first node and an input of the amplifier, and is for maintaining the first node to be a virtual ground during an integrating mode. The integrating unit is coupled between the first node and an output of the amplifier, and is for receiving charge from the charging unit during the integrating mode.

Owner:SAMSUNG ELECTRONICS CO LTD +1

Switched capacitor notch filter with fast response time

ActiveUS20110221518A1Eliminate needSwitched capacitor networksActive element networkCapacitanceTime segment

A switched capacitor notch filter for sampling an input signal using multiple sampling capacitors during multiple non-overlapping time periods. The charge from one set of sampling capacitors is averaged and transferred to the filter output during one non-overlapping time and the charge from another set of sampling capacitors is averaged and transferred to the filter output during a second non-overlapping time period.

Owner:ALLEGRO MICROSYSTEMS INC

Switched capacitor notch filter

ActiveUS20100321105A1Eliminate needSwitched capacitor networksOscillations generatorsCapacitanceTime segment

A switched capacitor notch filter for sampling an input signal using multiple sampling capacitors and multiple non-overlapping time periods. The charge from the sampling capacitors is averaged and transferred to the filter output during another non-overlapping time period.

Owner:ALLEGRO MICROSYSTEMS INC

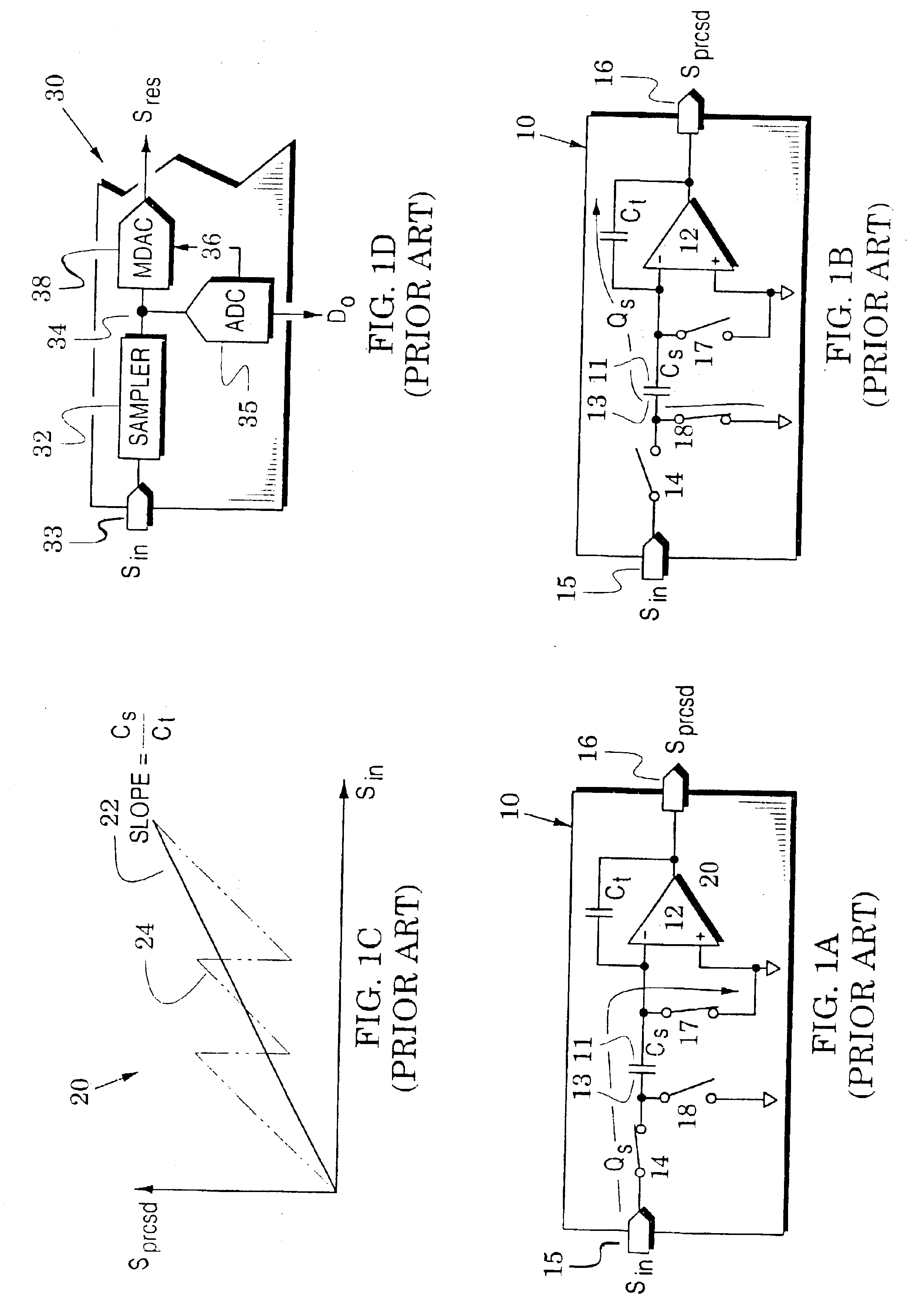

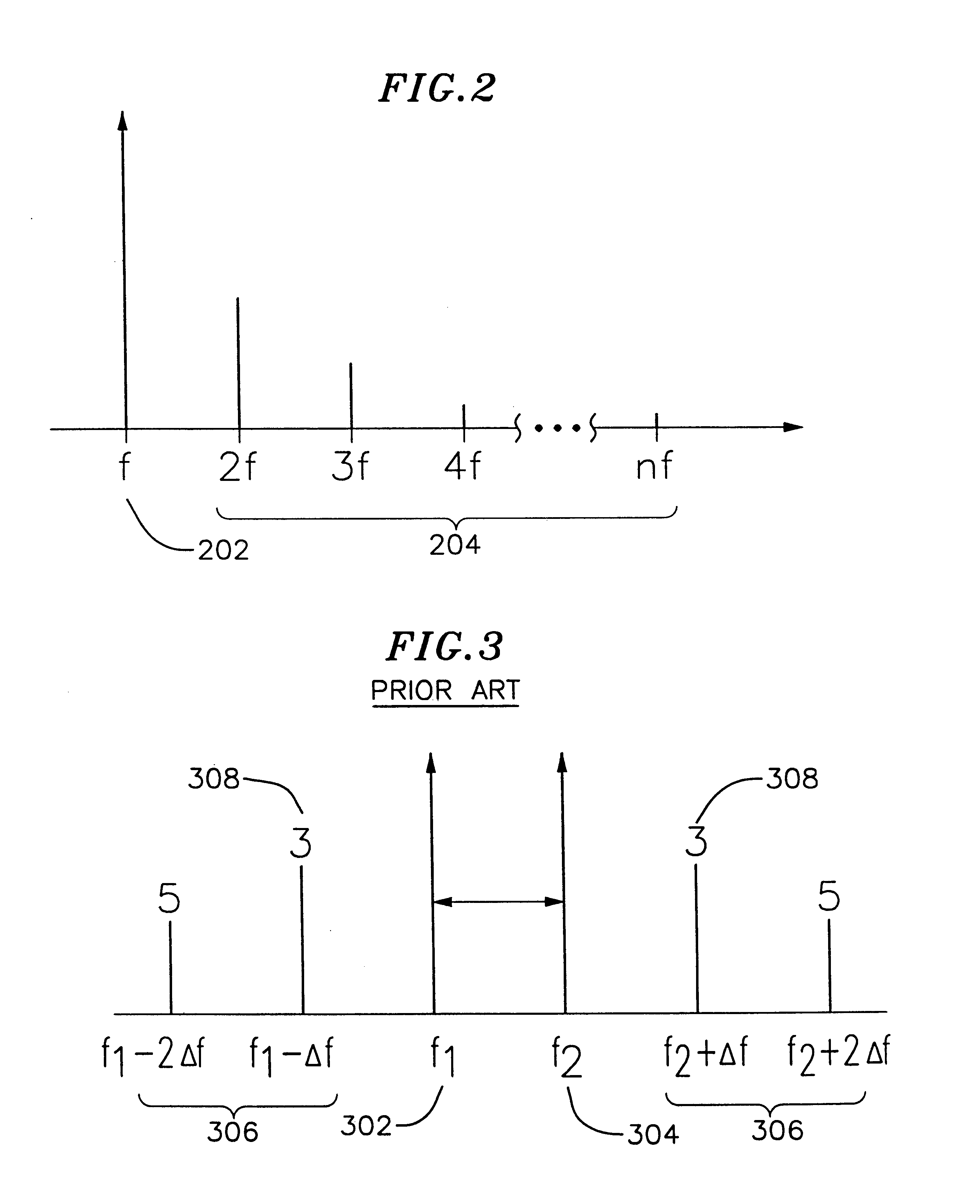

Subsampling communication receiver architecture with relaxed IFA readout timing

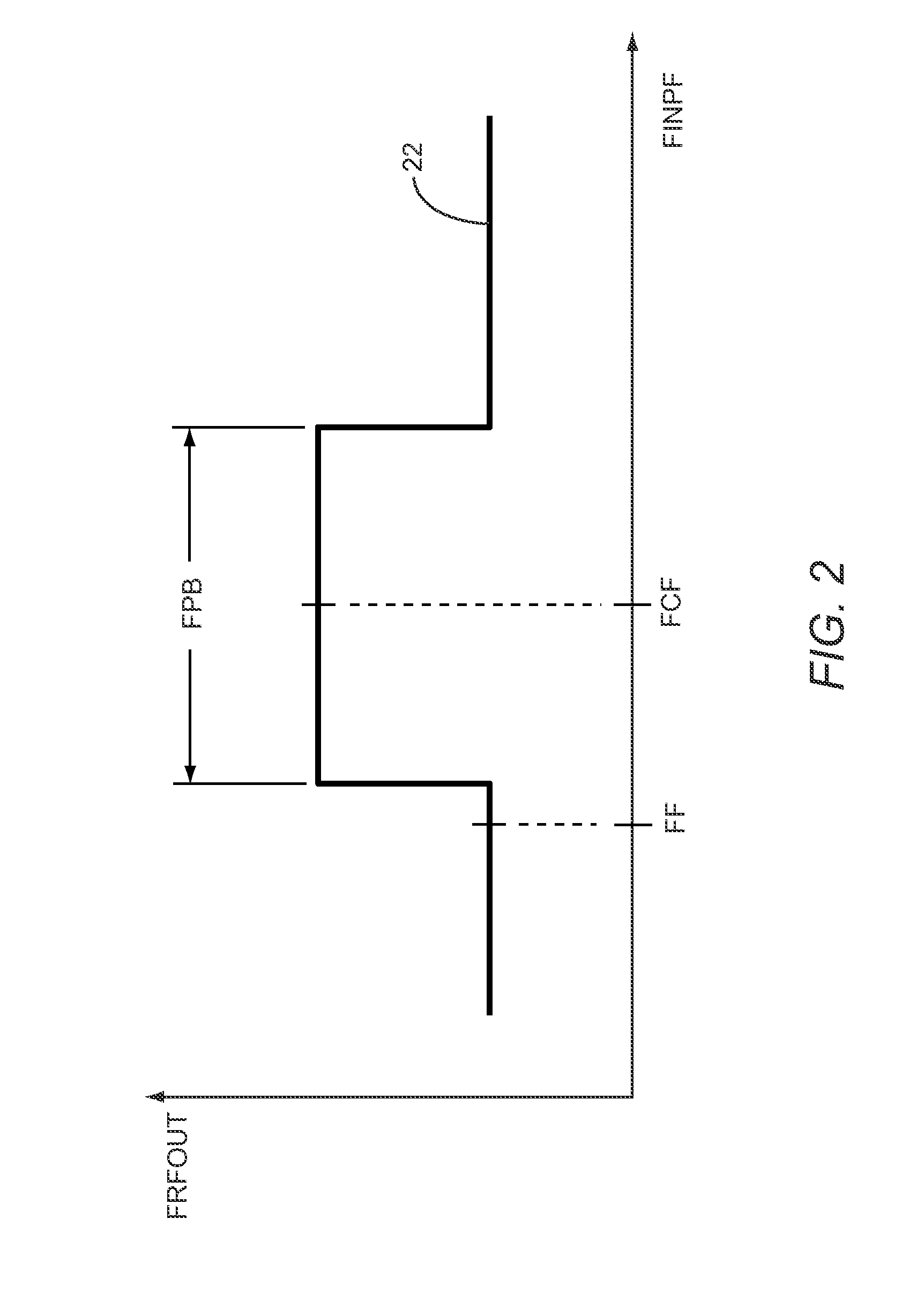

A first periodic voltage waveform (20) is downconverted into a second periodic voltage waveform (35, 36). A plurality of temporally distinct samples (SA1, SA2, . . . ) respectively indicative of areas under corresponding fractional-cycles of the first voltage waveform are obtained. The samples are combined to produce the second voltage waveform, and are also manipulated to implement a filtering operation such that the second voltage waveform represents a downconverted, filtered version of the first voltage waveform. The second waveform is driven by an amplifier stage (25), and the second waveform can be advantageously constructed so as to permit the amplifier stage to perform internal resets, offset corrections and other ancillary amplifier stage adjustments without losing information in the first waveform.

Owner:TEXAS INSTR INC

Digitally controlled analog RF filtering in subsampling communication receiver architecture

A first periodic voltage waveform (20) is downconverted into a second periodic voltage waveform (35, 36). A plurality of temporally distinct samples (SA1, SA2, . . . ) respectively indicative of areas under corresponding half-cycles of the first voltage waveform are obtained. The samples are combined to produce the second voltage waveform, and are also manipulated to implement a filtering operation such that the second voltage waveform represents a downconverted, filtered version of the first voltage waveform.

Owner:TEXAS INSTR INC

Switch mode power supply systems

InactiveUS7342812B2Constant lengthSignificant valueCurrent/voltage measurementAc-dc conversionTransformerAverage current

Methods and apparatus for sensing the output current in a switch mode power supply (SMPS) using primary side sensing are described. A module senses a current in a primary winding of a transformer and a voltage on a primary or auxiliary winding of the transformer, and which includes a multiplier coupled to an output of a signal averager averaging a primary winding current and to an output of a timing signal generator using the sensed voltage to signal when a secondary winding is powering an output of the SMPS, to multiply an averaged current sense signal by a fraction of a total cycle period of said SMPS during which the secondary winding is providing power to provide a signal estimating an output current of the SMPS.

Owner:POWER INTEGRATIONS INC

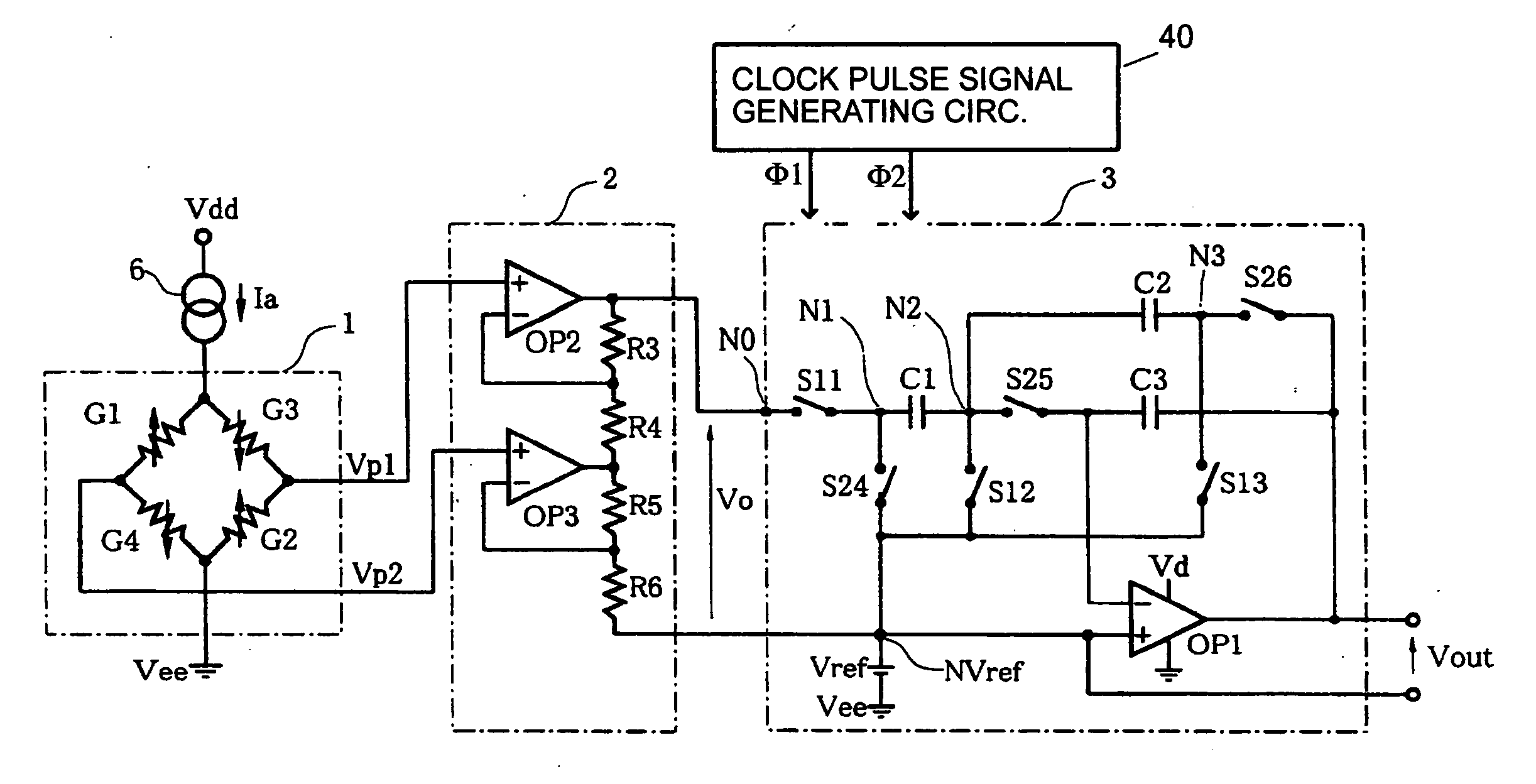

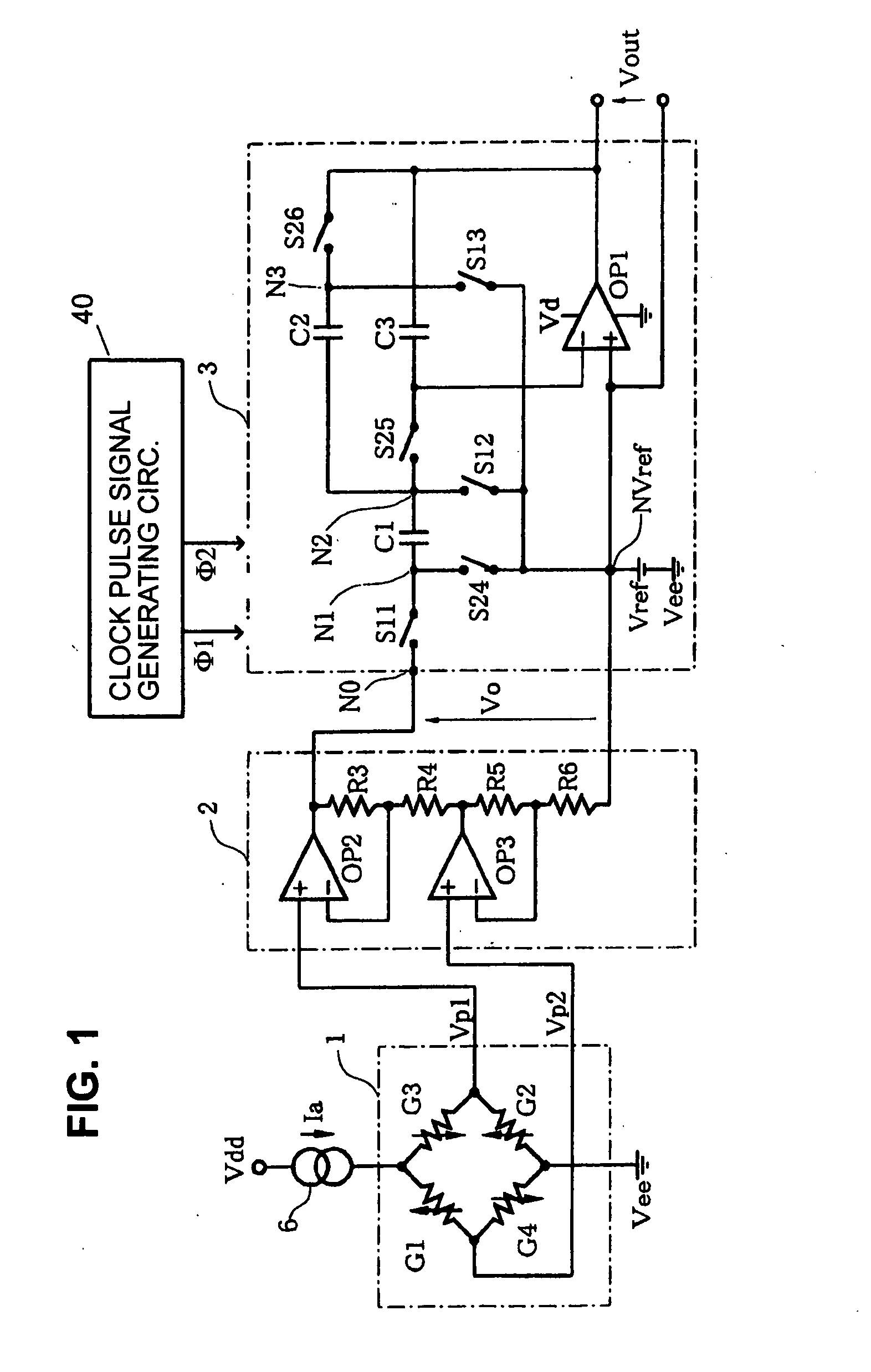

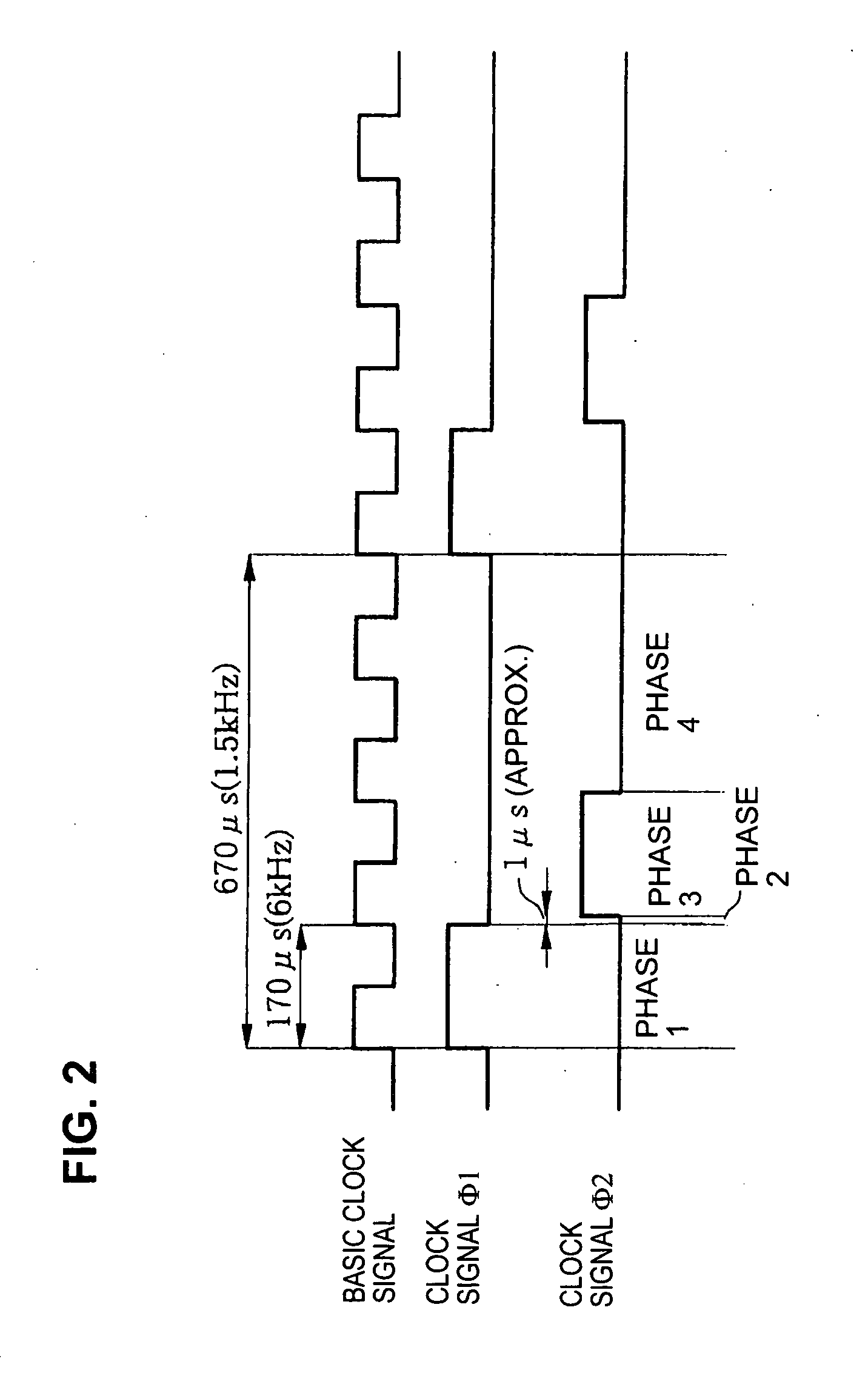

Switched-capacitor low-pass filter and semiconductor pressure sensor apparatus incorporating the filter

ActiveUS20040174209A1Fluid pressure measurement using ohmic-resistance variationSwitched capacitor networksCapacitanceBand-pass filter

A low-pass filter configured as a switched capacitor circuit in which capacitor charge switching is performed by 2-phase clock signals that control respective sets of switching elements, wherein an interval between a first-phase clock signal pulse and a succeeding second-phase clock signal pulse, during which no charging / discharging of capacitors should occur, is made as short as possible while ensuring that the two sets of switching elements cannot enter the ON state simultaneously. A low cut-off frequency can thereby be achieved, while using very small capacitor values.

Owner:DENSO CORP

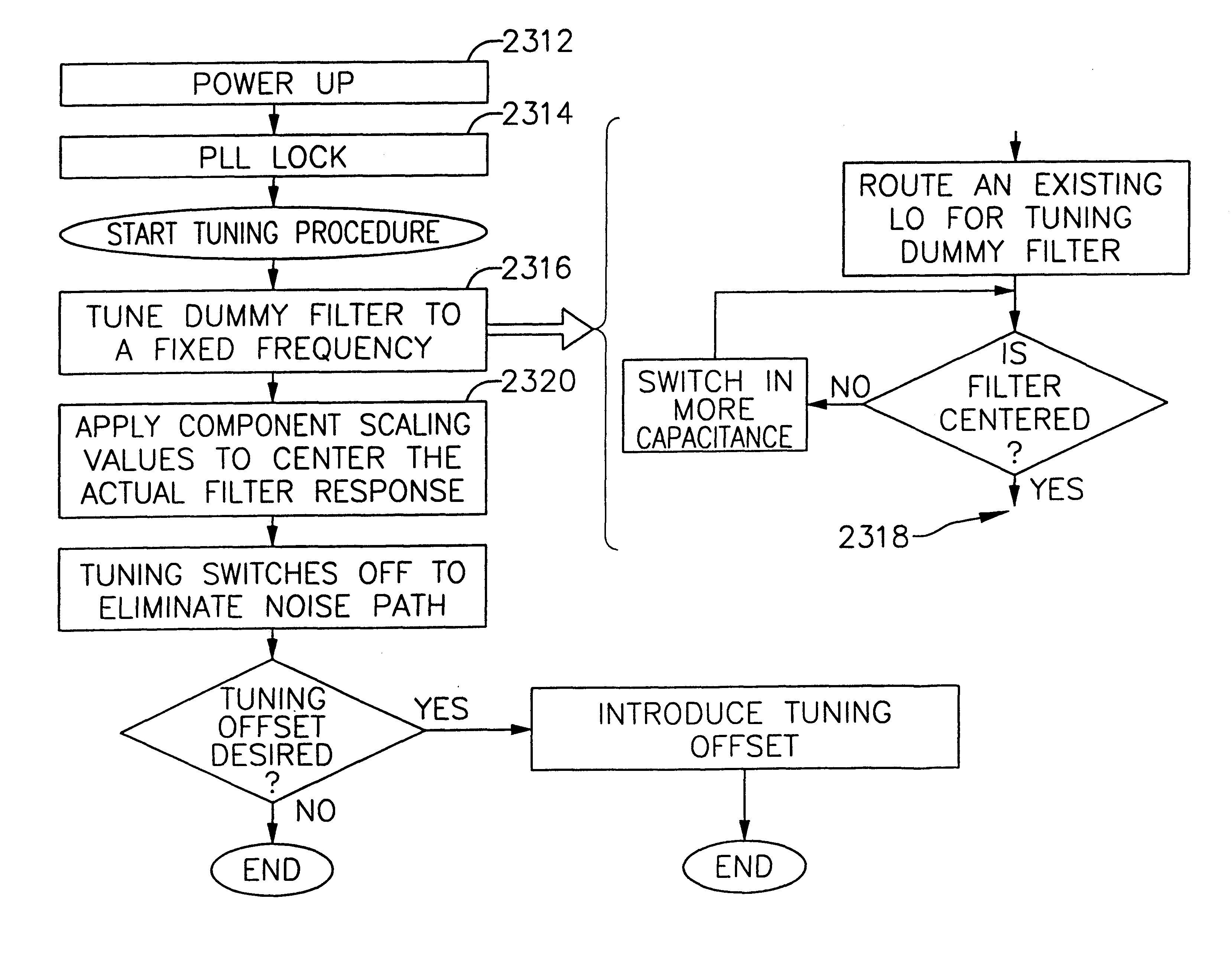

System and method for on-chip filter tuning

InactiveUS6865381B2Low selectivityMultiple-port active networksSolid-state devicesCapacitanceFilter tuning

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH INT SALES PTE LTD

Switched capacitor notch filter with fast response time

ActiveUS8416014B2Eliminate needActive element networkSwitched capacitor networksCapacitanceTime segment

A switched capacitor notch filter for sampling an input signal using multiple sampling capacitors during multiple non-overlapping time periods. The charge from one set of sampling capacitors is averaged and transferred to the filter output during one non-overlapping time and the charge from another set of sampling capacitors is averaged and transferred to the filter output during a second non-overlapping time period.

Owner:ALLEGRO MICROSYSTEMS INC

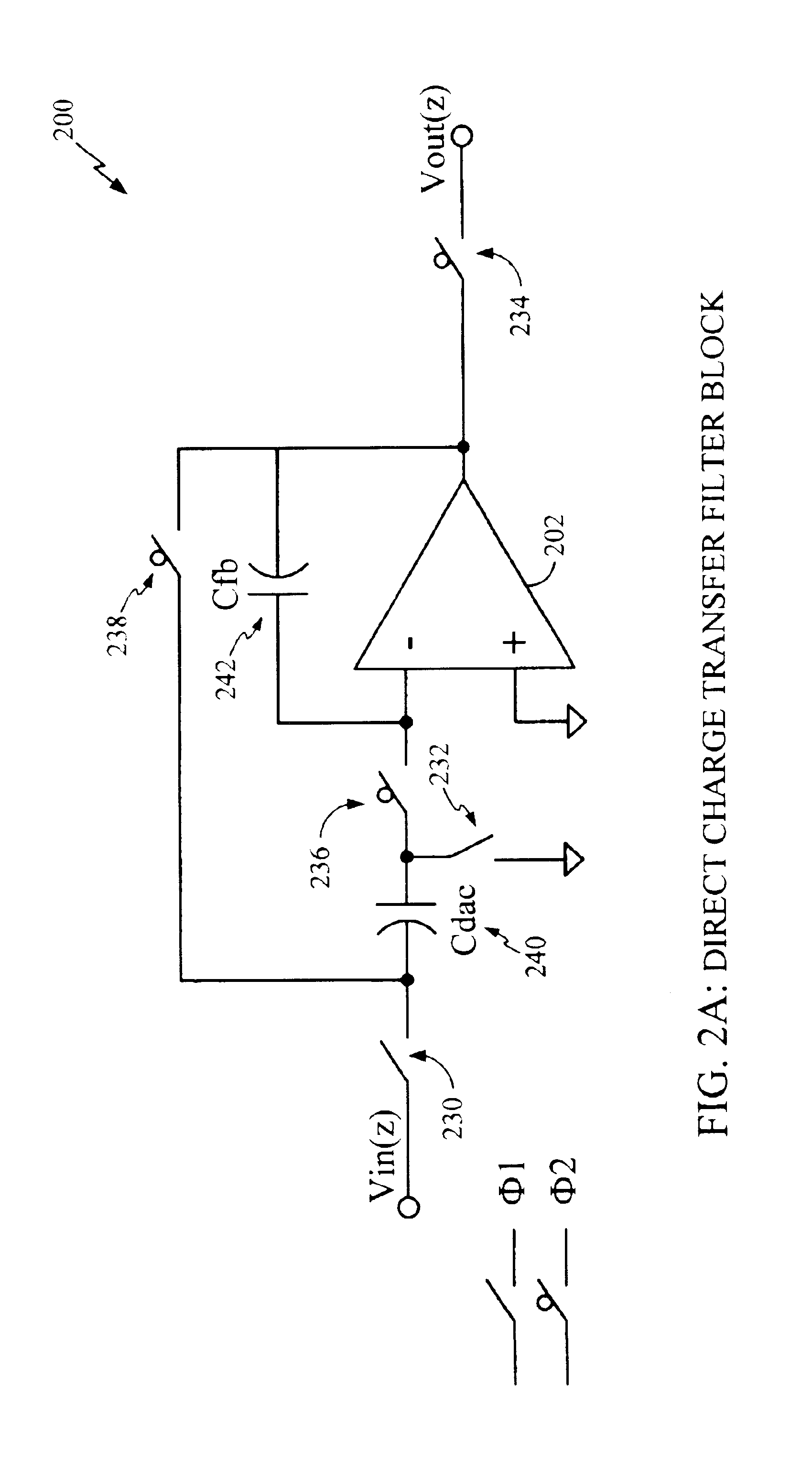

Digital to analog converter augmented with direct charge transfer techniques

InactiveUS6956515B2Electric signal transmission systemsAnalogue conversionDigital analog converterTransfer technique

A digital to analog converter augmented with Direct Charge Transfer (DCT) techniques. A digital to analog converter augmented with DCT and CDS techniques. A digital to analog converter augmented with Postfilter Droop Compensation.

Owner:QUALCOMM INC

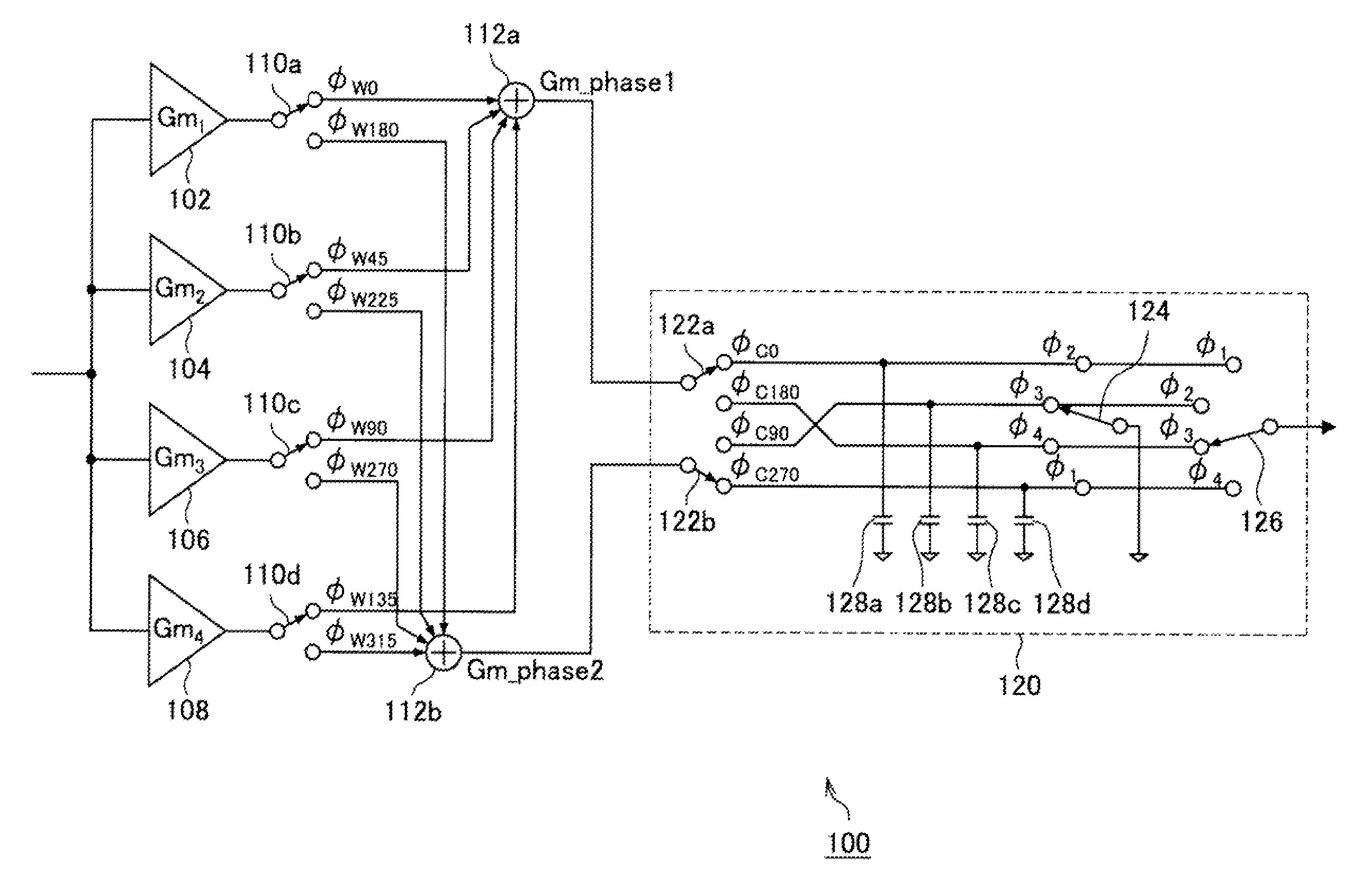

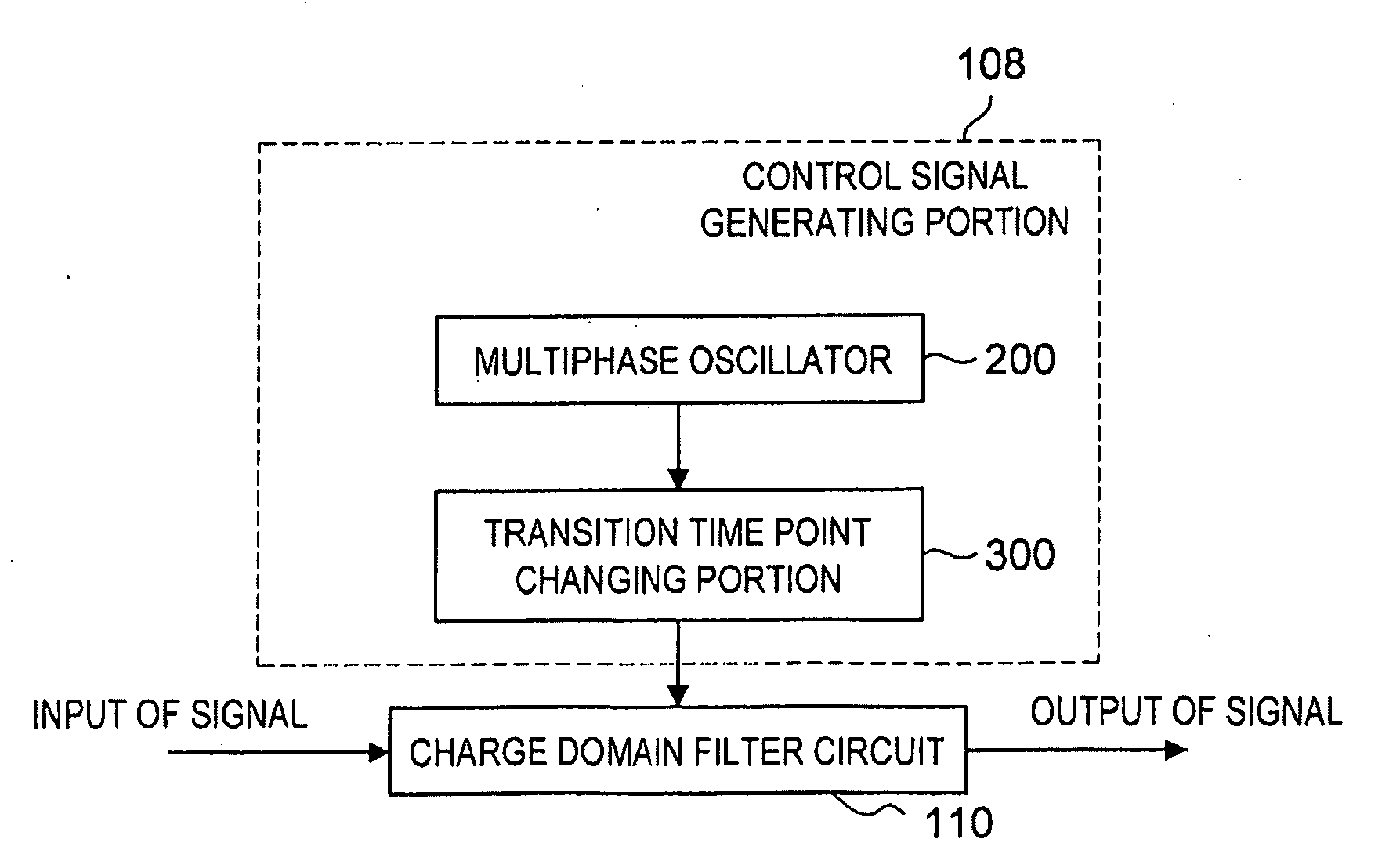

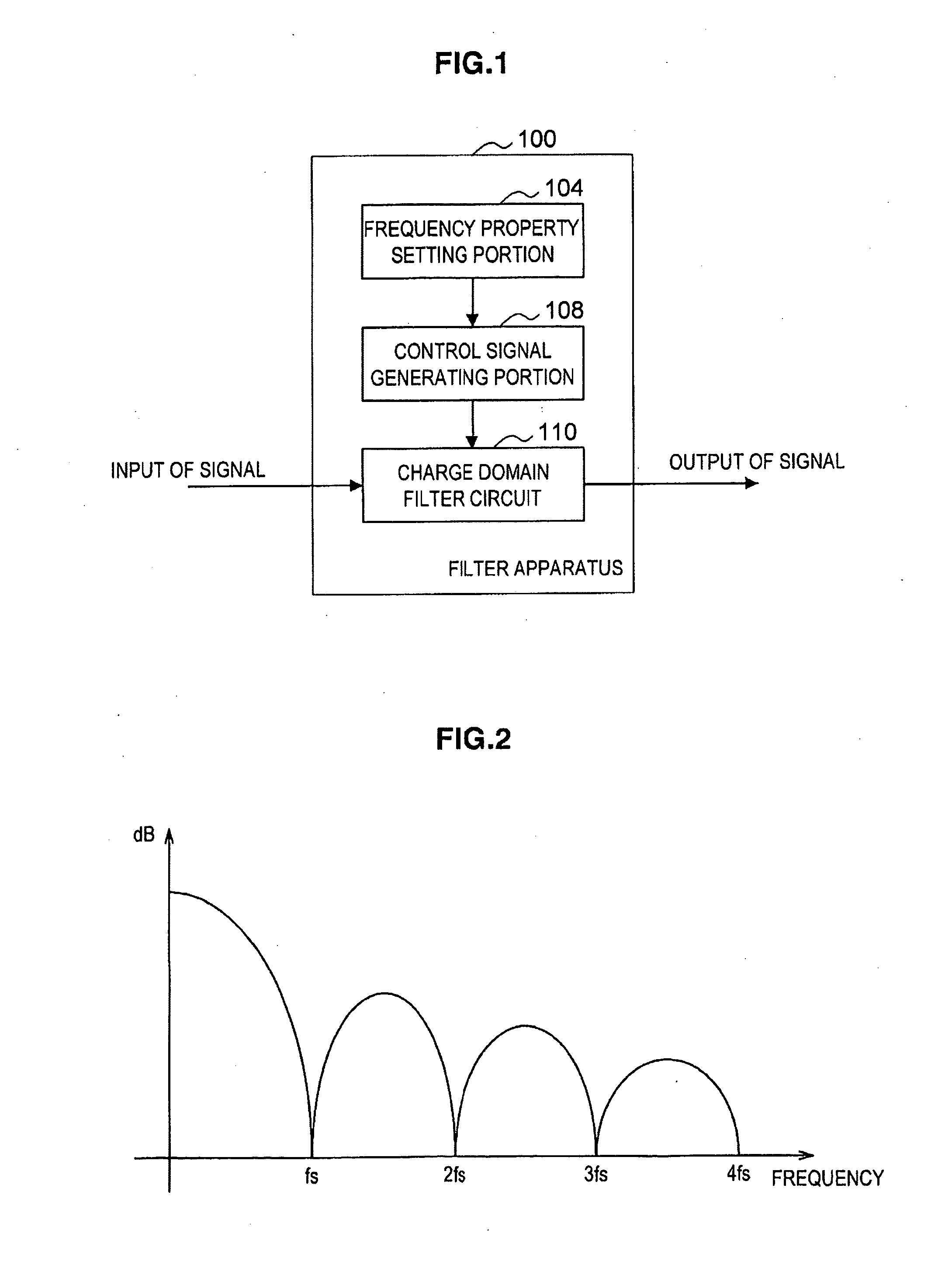

Charge Domain Filter Device

InactiveUS20080007326A1Pass efficientlyTransversal filtersSwitched capacitor networksImpulse responseCapacitor

There is provided a charge domain filter device including a plurality of transconductors each of which converts an input voltage to a current and outputs the current and a filter unit that filters output signals from said plurality of transconductors by repeatedly charging and discharging a plurality of capacitors, wherein an impulse response of the charge domain filter device is obtained through convolution of a first impulse corresponding to a charge time length over which said capacitors are charged and a second impulse corresponding to each of said plurality of transconductors.

Owner:SONY CORP

Switched capacitance circuit and analog/digital converter including said circuit

InactiveUS20050258998A1Multiple input and output pulse circuitsElectric signal transmission systemsCapacitanceEngineering

A switched capacitance circuit including: a switched capacitance section, capable of receiving as input a signal and carrying out a sampling of said signal, the section comprising at least one group of capacitors each of which has a terminal connected to a common node; at least an operational stage including at least an input terminal connected to said common node, the operational stage providing a current to said common node for charging said group of capacitors during a sampling time interval of said signal. The circuit further includes an auxiliary circuit connected to said common node and capable of being activated / deactivated by an enabling signal for injecting a further current into said common node and increasing the current provided to said common node during at least one time interval equal to a fraction of said sampling interval.

Owner:ST ERICSSON SA

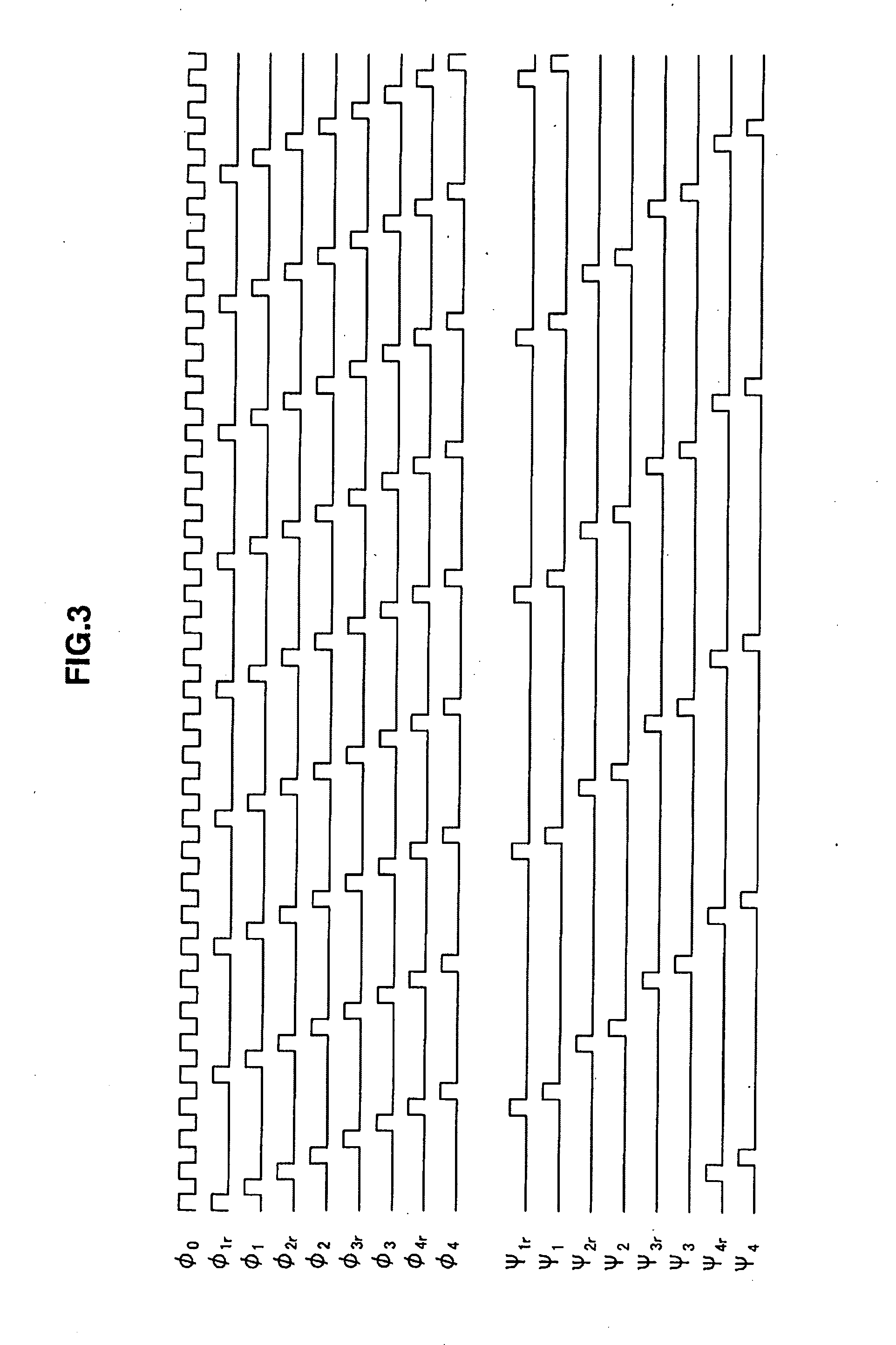

Signal generating appartus, filter apparatus, signal generating method and filtering method

InactiveUS20090015306A1Reduce power consumptionCounting chain synchronous pulse countersSwitched capacitor networksEngineeringSignal transition

There is provided a signal generating apparatus including: a multiphase oscillating portion for generating a number of base signals having the same frequency and a predetermined phase difference of which the signal level transitions between a first level and a second level, and where periods during which the signal level of any given base signal is at the first level and the signal level of the next base signal having the predetermined phase delay relative to the given base signal is at the first level overlap; and a transition time point changing portion for generating a pulse signal by changing the time point when each base signal transitions from the first level to the second level to a time point before the next base signal transitions from the second level to the first level.

Owner:SONY CORP

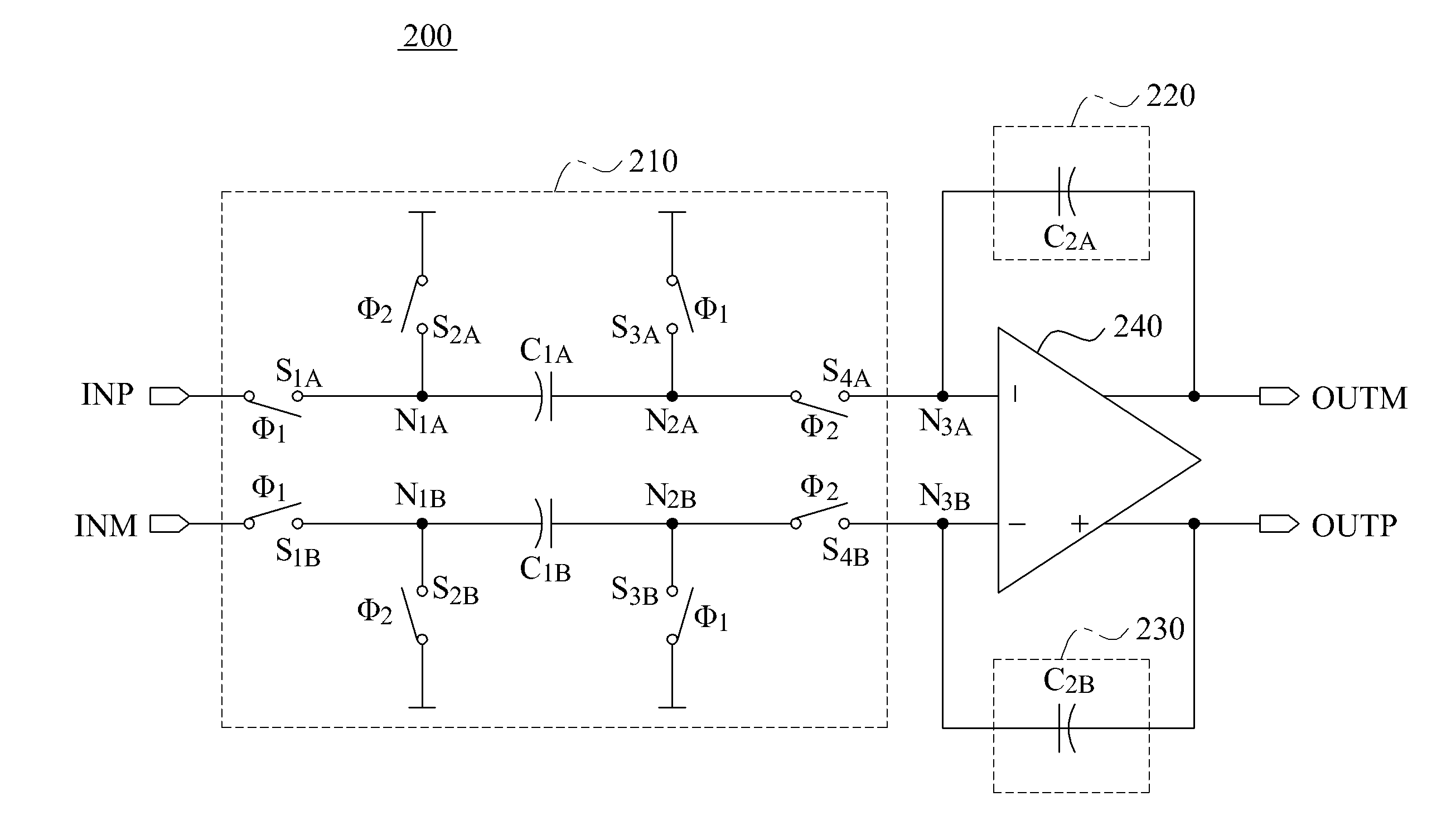

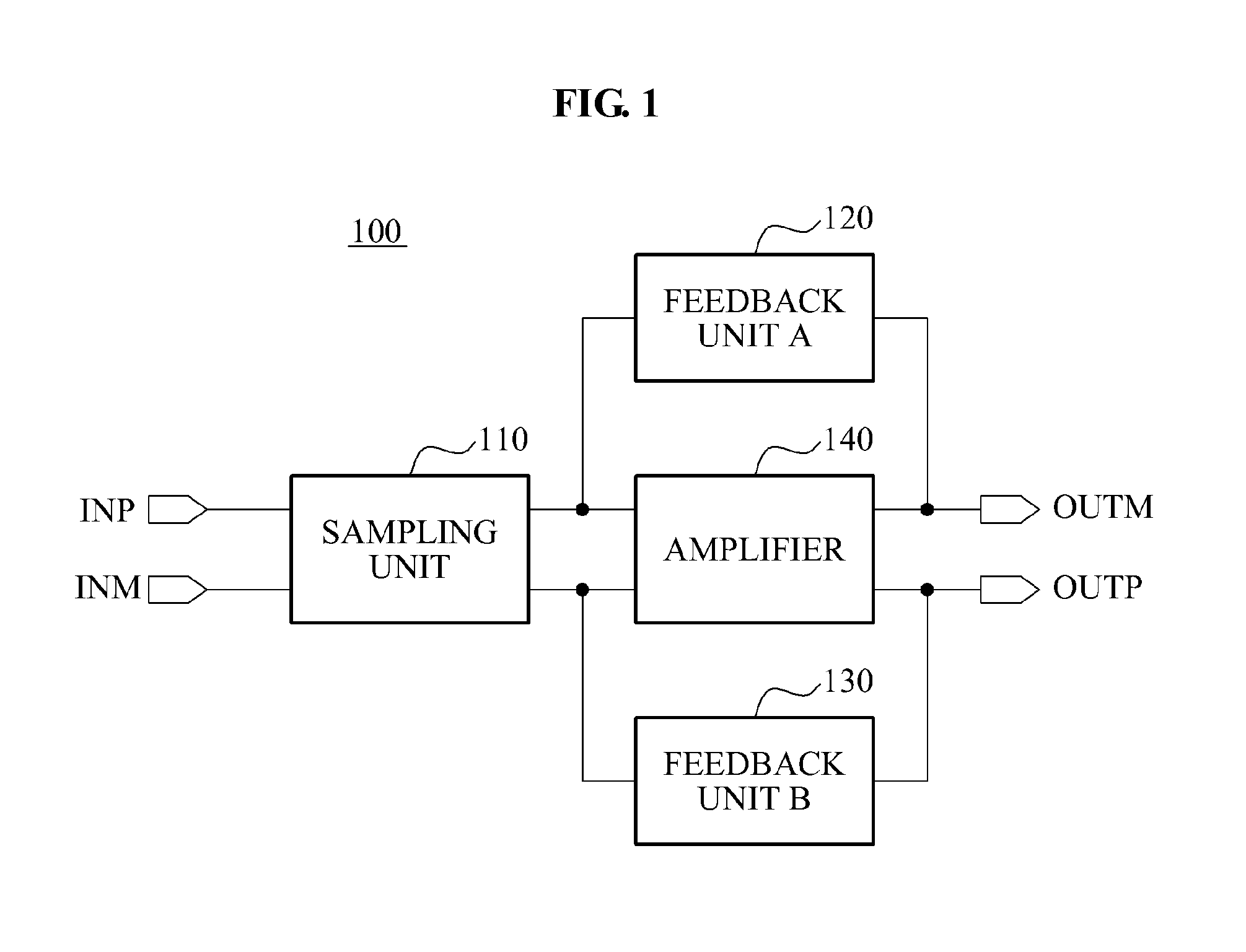

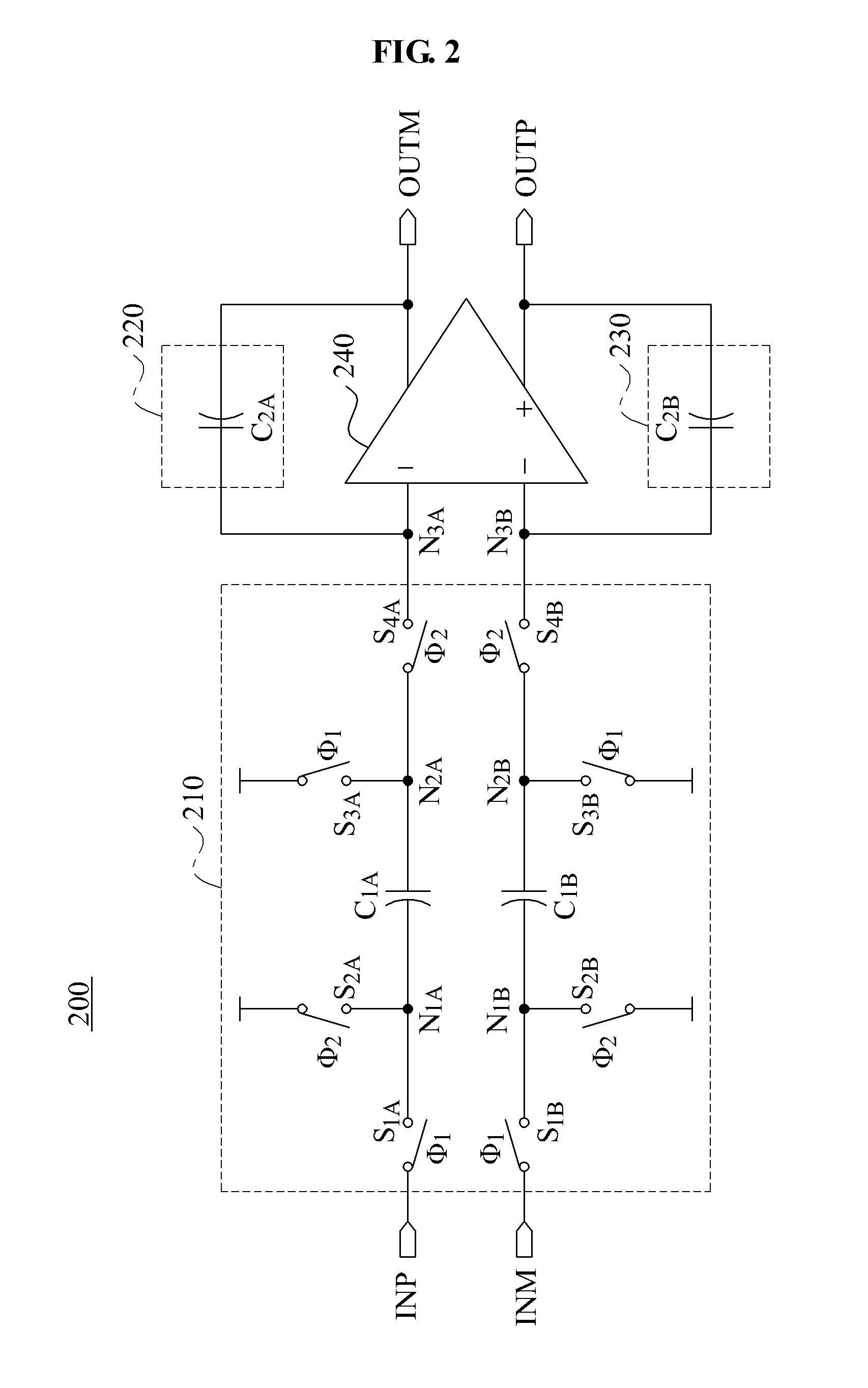

Switched capacitor circuit

ActiveUS20120229204A1Reduce areaReduce power consumptionCharge amplifiersSwitched capacitor networksCapacitanceEngineering

According to the present invention, a switched capacitor circuit comprises: an inverting amplifier for removing the offset by using a chopper stabilization circuit; a sampling unit which is connected between an input terminal and the inverting amplifier; and a feedback unit which is connected to the inverting amplifier in parallel.

Owner:IND ACADEMIC CORP FOUND YONSEI UNIV

Charge Domain Filter Circuit

InactiveUS20090134938A1Reconfigurable filter characteristicsReduce power consumptionMultiple-port networksTransversal filtersCapacitanceEngineering

A charge domain filter circuit includes a first signal output portion, at least one second signal output, portion, a third signal output portion, and an adder portion. The first signal output portion outputs a first signal that is sampled at a specified time interval. Each second signal, output portion outputs a second signal that is sampled after a specified delay after the first signal is sampled. Where a plurality of the second signal output portions is included, the second signals are sampled in succession. The third signal output portion outputs a third signal that is sampled after a specified delay after the last second signal is sampled. The adder portion adds the first, second, and third signals together and outputs the result. The capacitance ratio of the sampling capacitors in the first signal output portion and the second signal output portion is one of continuously or discretely varied.

Owner:SONY CORP

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com