Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1434 results about "Subtractor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics, a subtractor can be designed using the same approach as that of an adder. The binary subtraction process is summarized below. As with an adder, in the general case of calculations on multi-bit numbers, three bits are involved in performing the subtraction for each bit of the difference: the minuend (Xᵢ), subtrahend (Yᵢ), and a borrow in from the previous (less significant) bit order position (Bᵢ). The outputs are the difference bit (Dᵢ) and borrow bit Bᵢ₊₁. The subtractor is best understood by considering that the subtrahend and both borrow bits have negative weights, whereas the X and D bits are positive. The operation performed by the subtractor is to rewrite Xᵢ-Yᵢ-Bᵢ (which can take the values -2, -1, 0, or 1) as the sum -2Bᵢ₊₁+Dᵢ.

Arithmetic processing apparatus

InactiveUS7412470B2MiniaturizationReduce power consumptionDigital data processing detailsPicture reproducers using cathode ray tubesProcessor registerComputer science

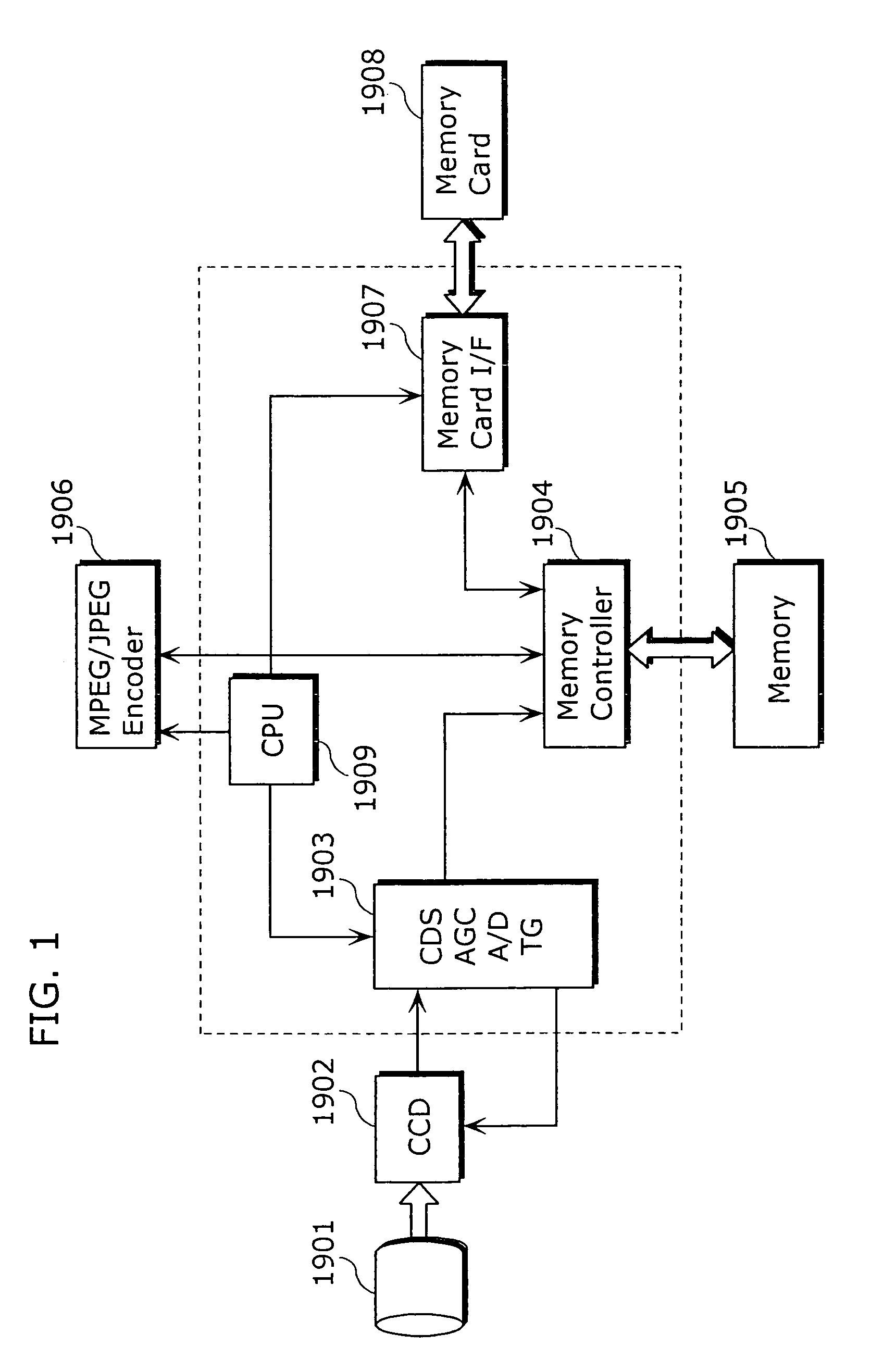

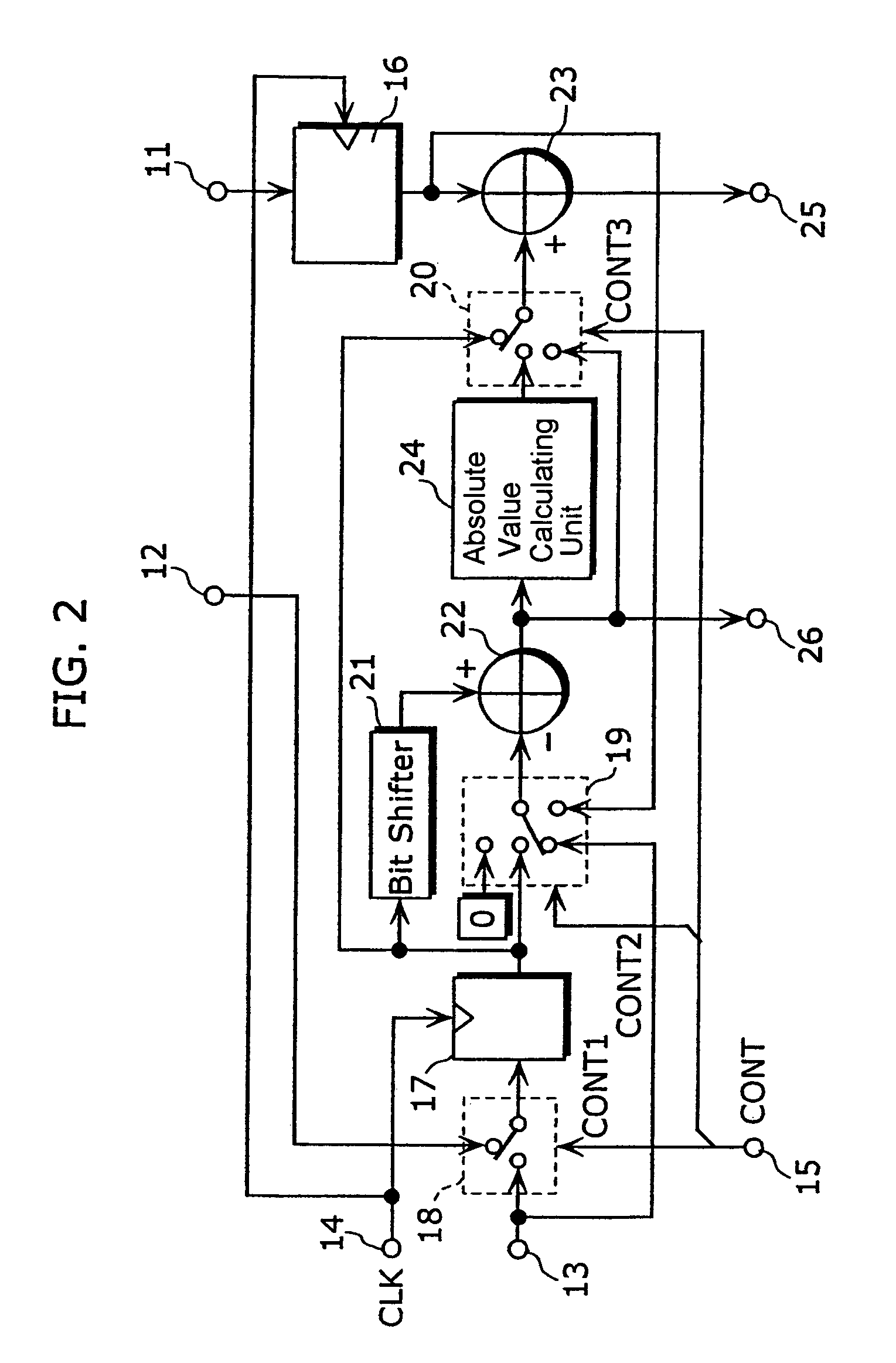

The arithmetic processing apparatus of the present invention is an arithmetic processing apparatus that can be reconfigured in accordance with a processing mode and has a plurality of arranged unit arithmetic circuits. Each unit arithmetic circuit includes at least one input terminal, at least one output terminal, a first register which holds data, an adder which calculates a sum of two pieces of data, a second register which holds data, a bit shifter which shifts data left or right, a subtractor which calculates a difference between two pieces of data, an absolute value calculating unit which calculates an absolute value of data, and a path setting unit which sets a path according to the processing mode connecting among these circuit elements.

Owner:GK BRIDGE 1

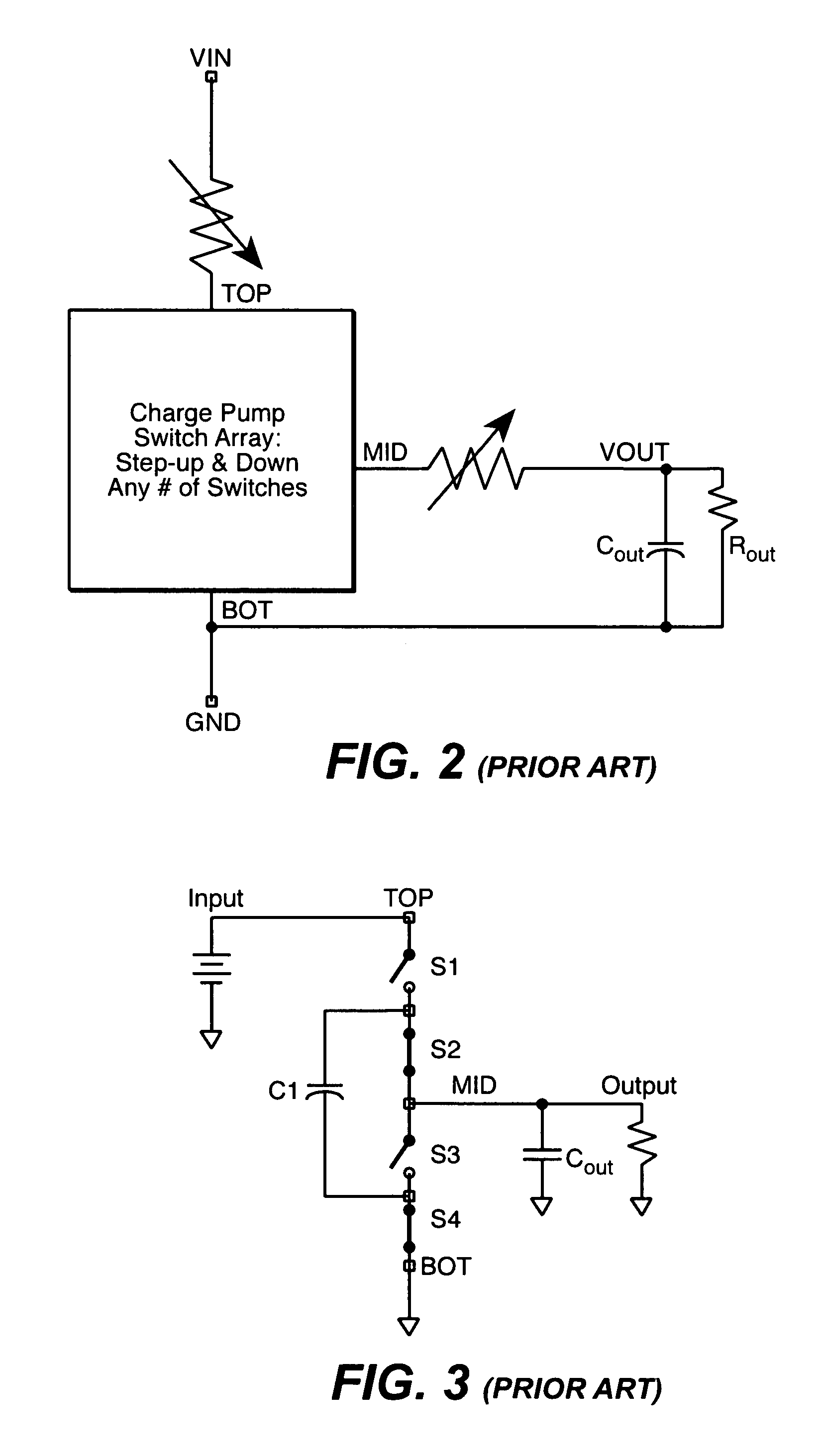

Digital loop for regulating DC/DC converter with segmented switching

InactiveUS6995995B2Save areaReduce rippleEmergency protective circuit arrangementsAc-dc conversionA d converterVoltage regulation

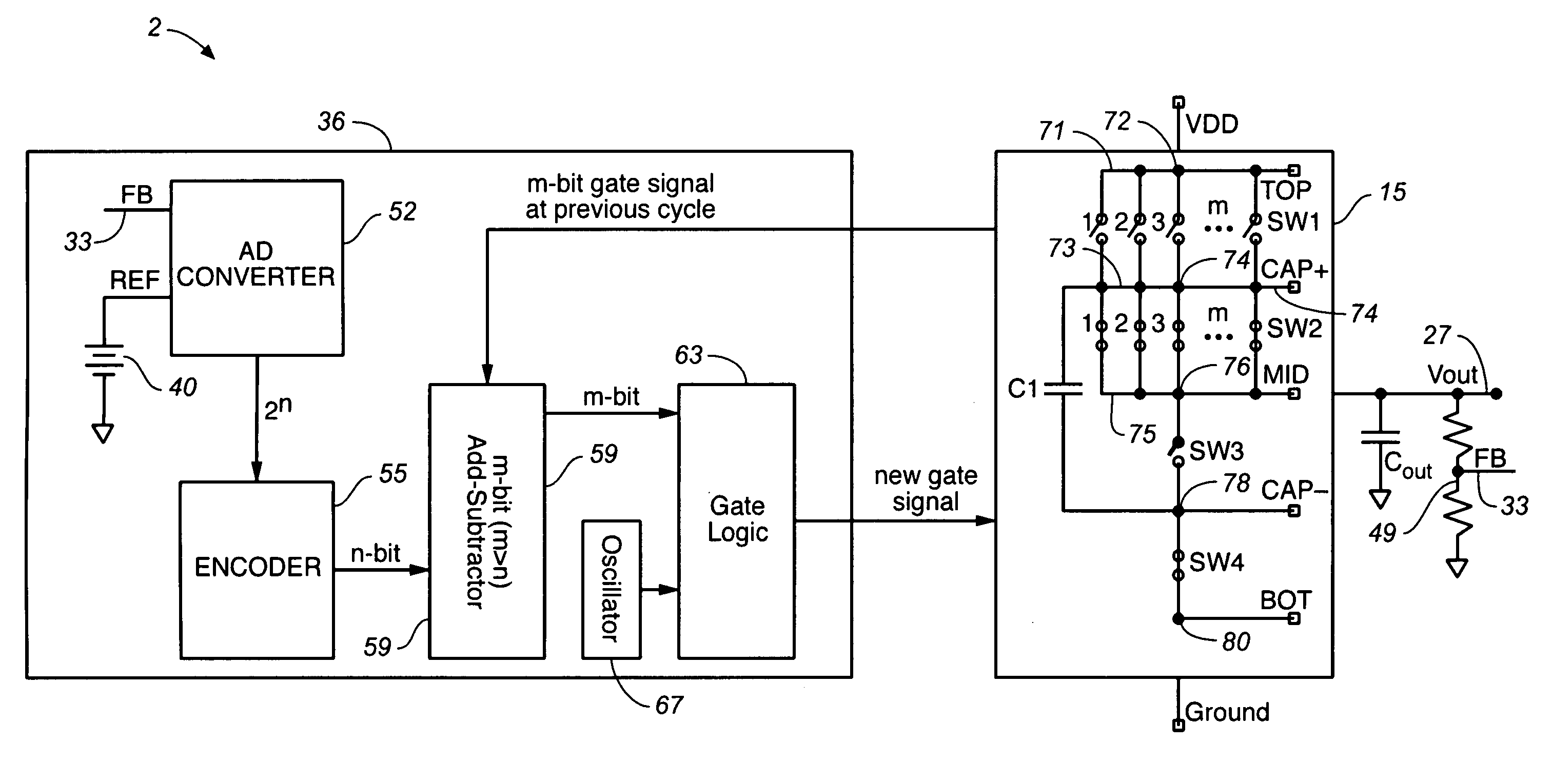

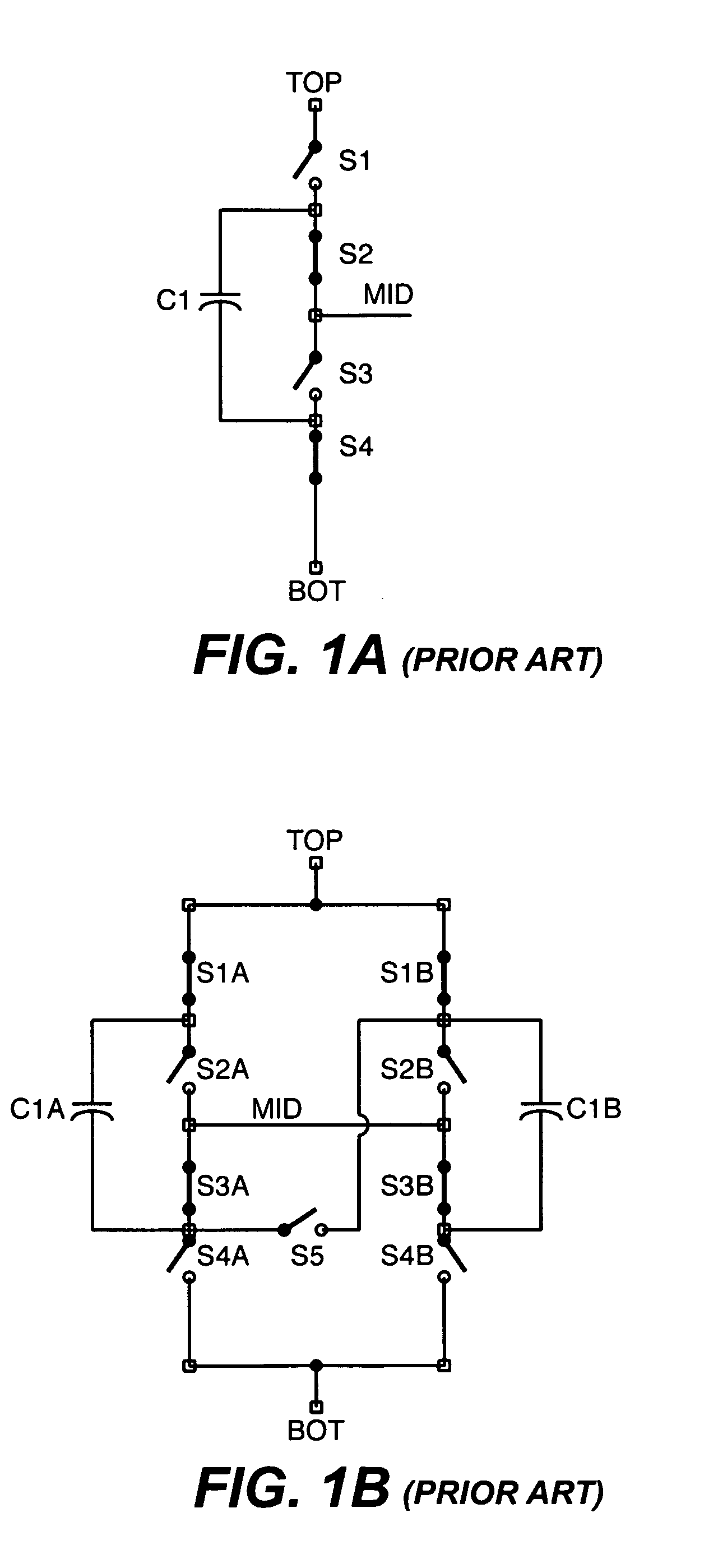

A power control circuit is provided containing a switch array, which includes segmented switches, a flying capacitor, an output voltage terminal, a feedback loop, and a digital voltage regulator block. The digital voltage regulator block includes an A / D converter, an encoder, an add-subtractor, and a gate logic. These power control circuits do not include pass transistors. A method is also provided, where the charge pumps of the power control circuit are operated in two-phase cycles including a charging phase and a pumping phase. The power control circuit is controlled in both of these phases, thereby reducing the ripple of the output voltage.

Owner:SEMICON COMPONENTS IND LLC

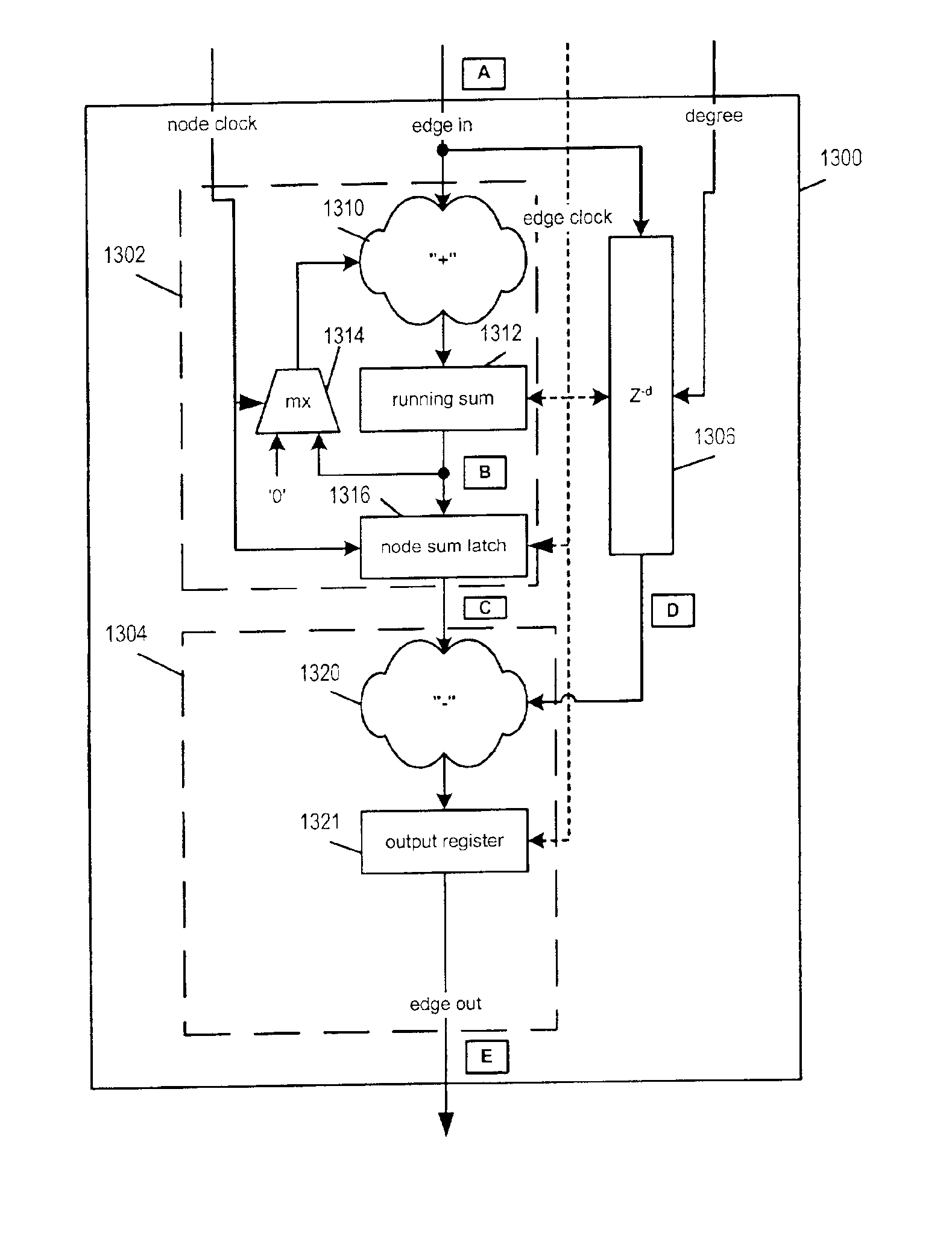

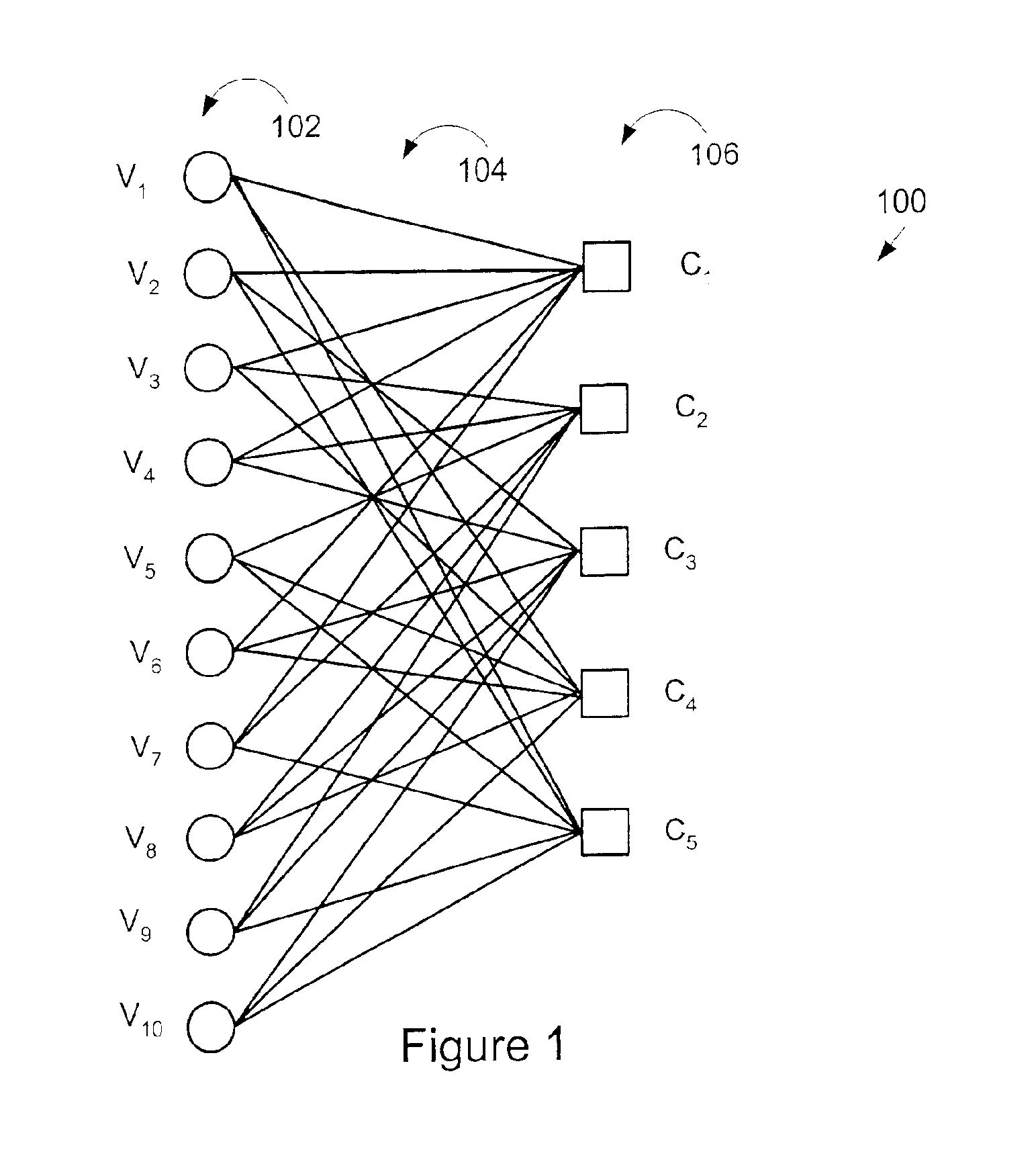

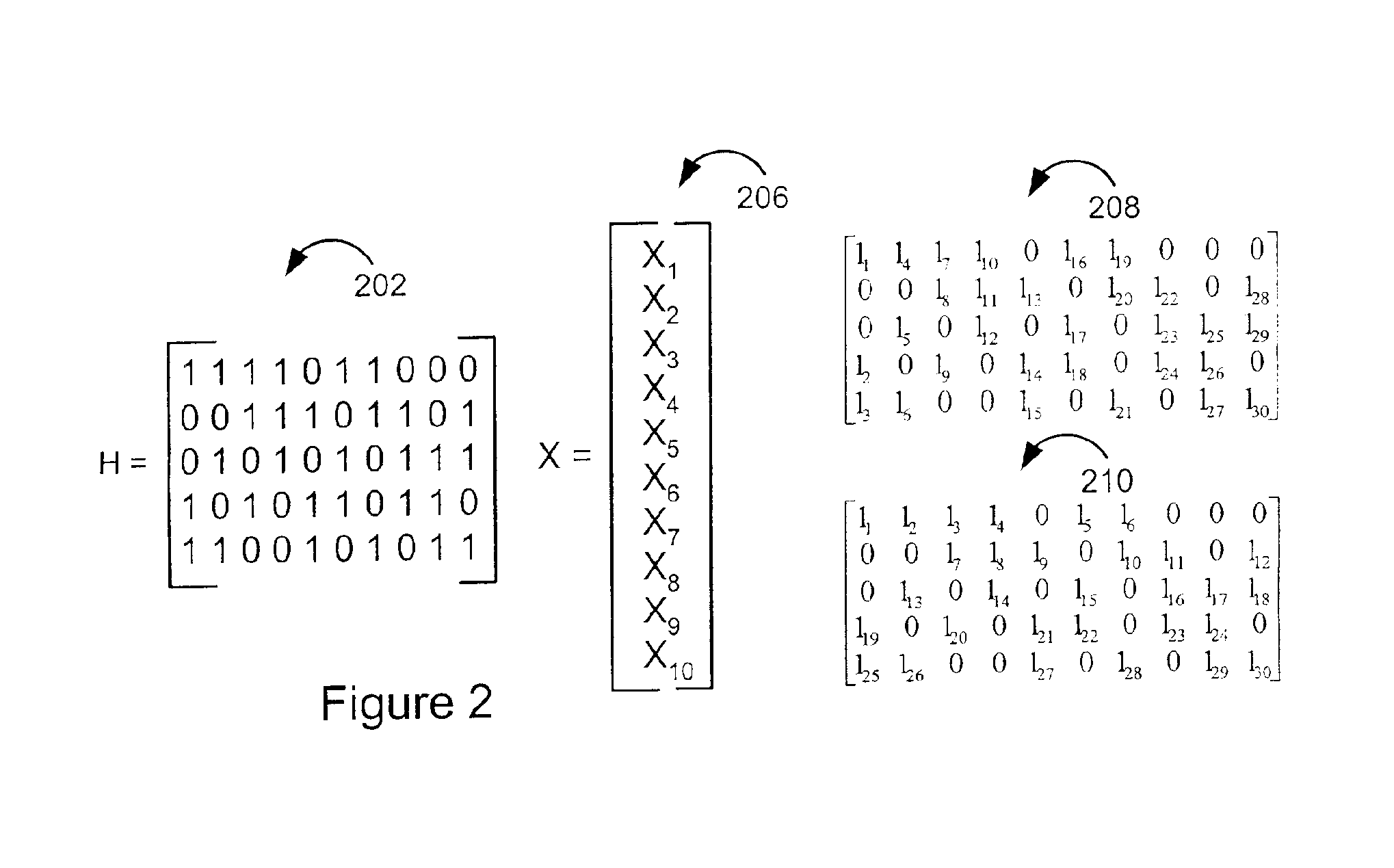

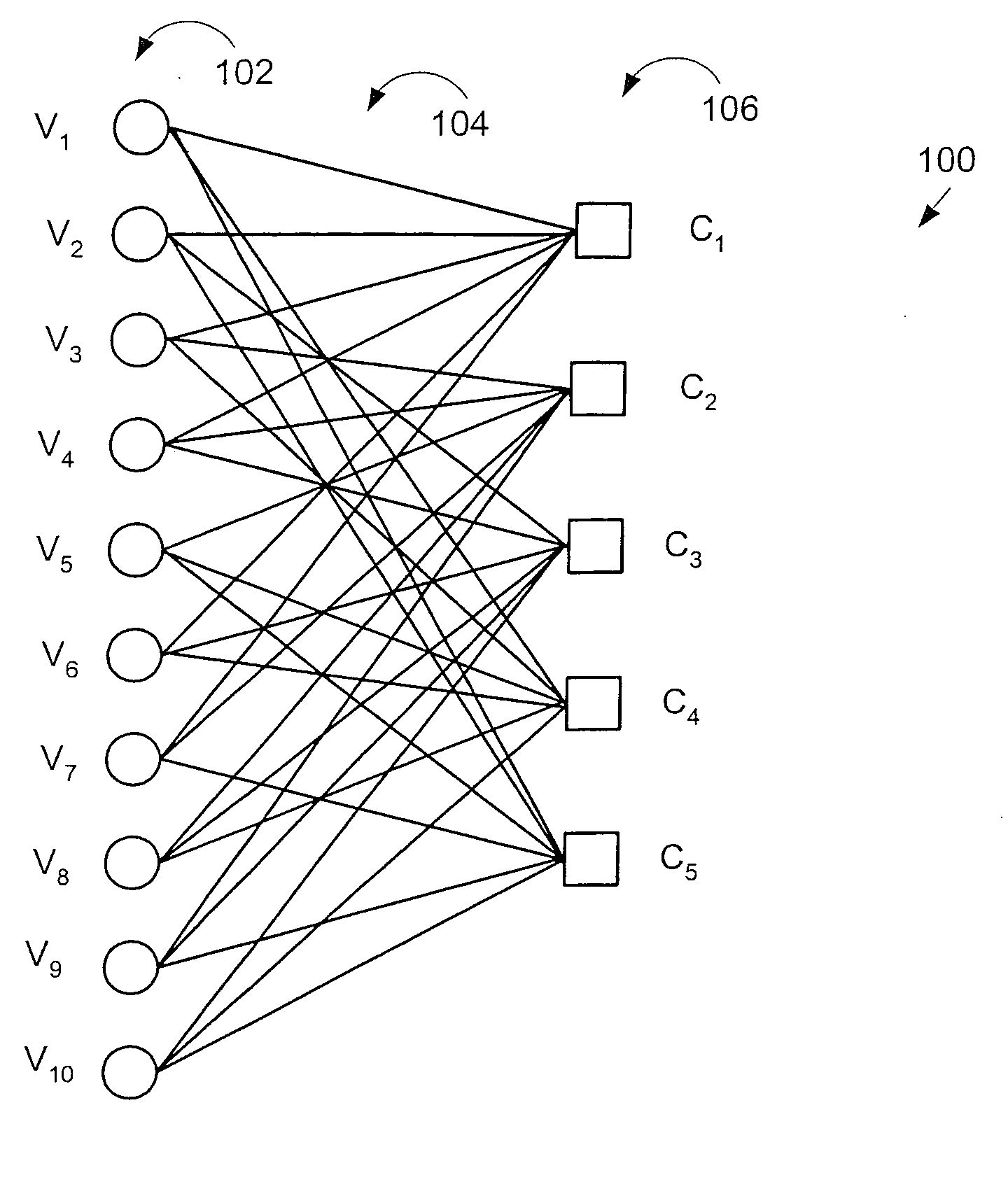

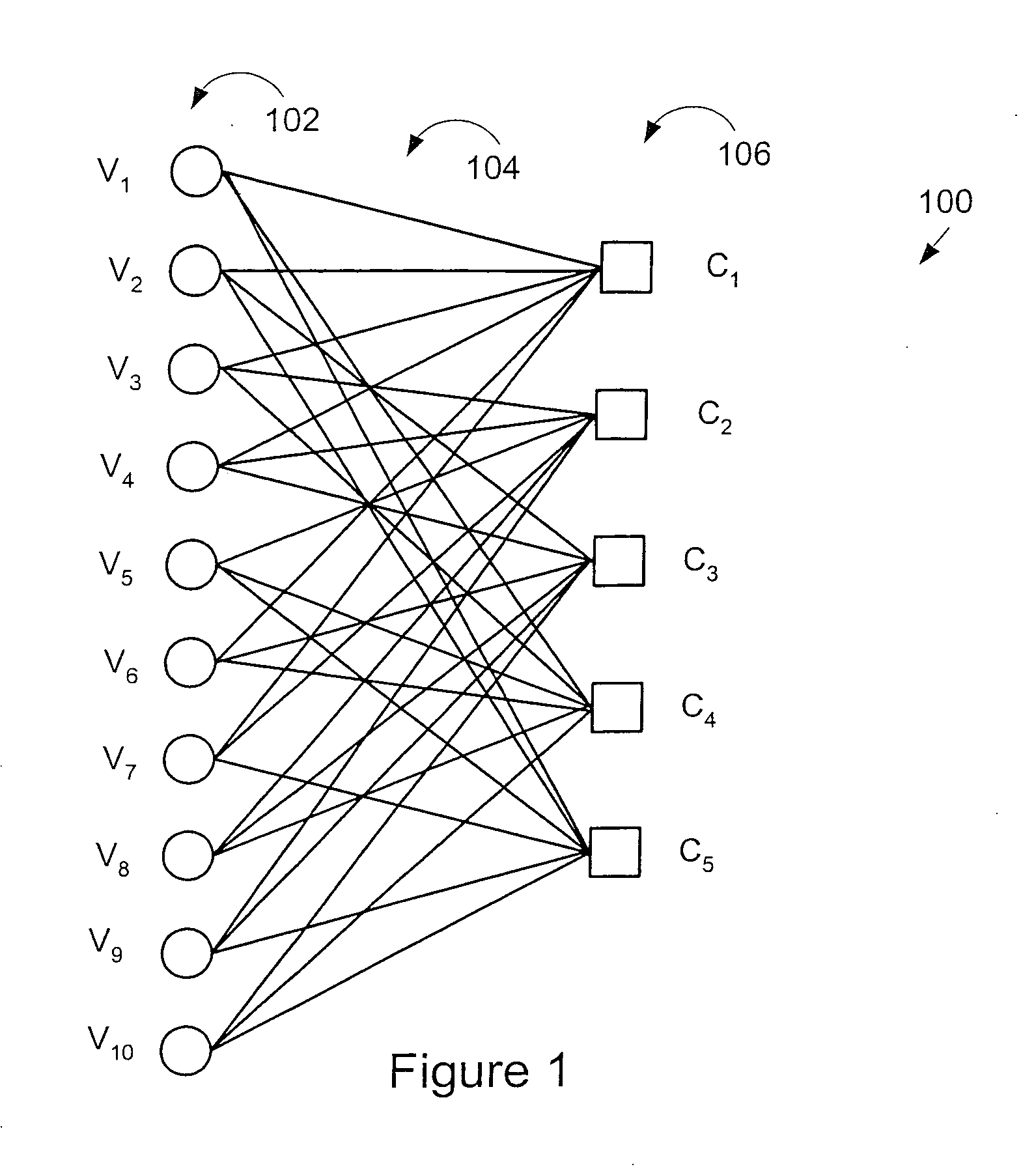

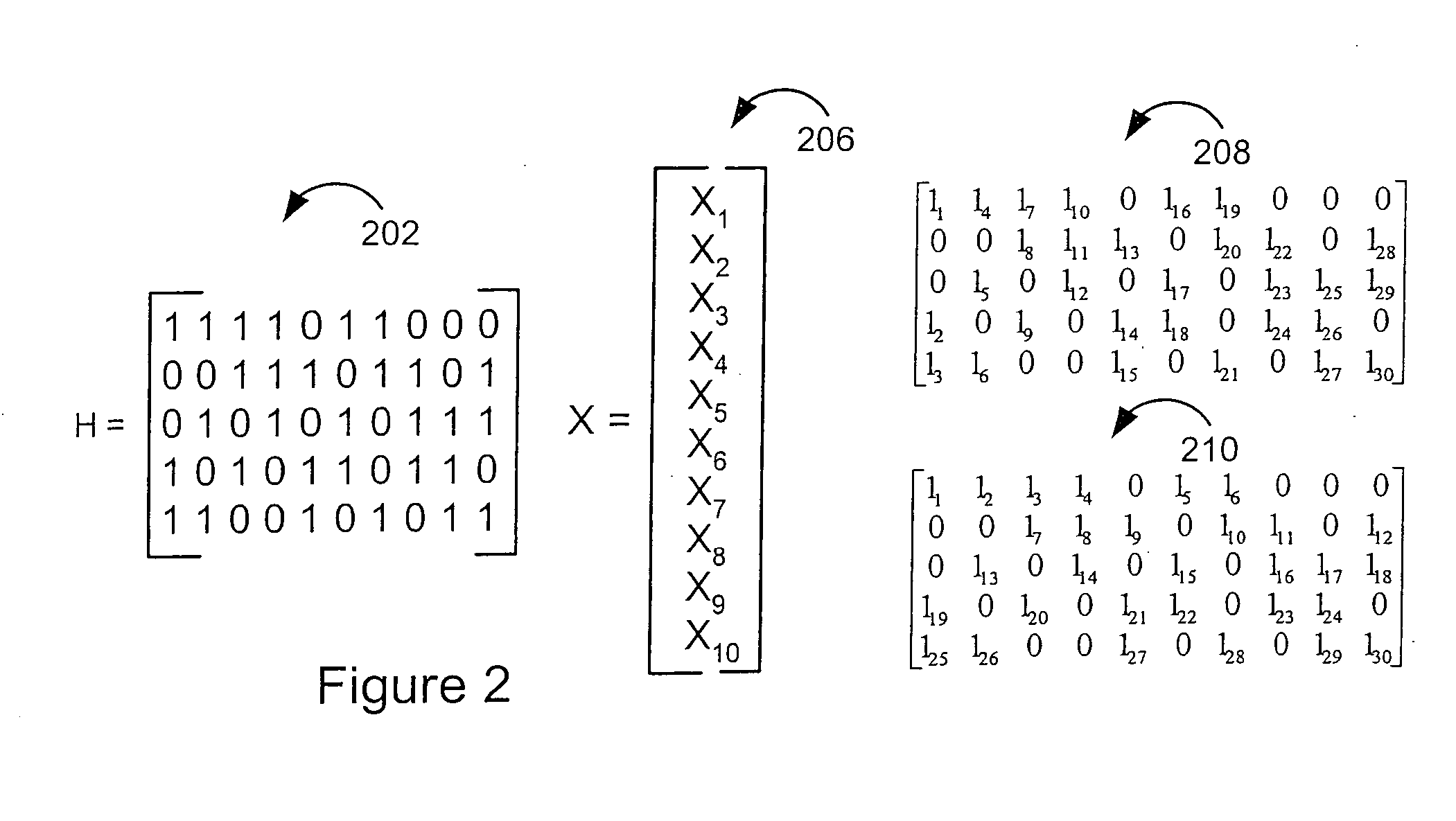

Node processors for use in parity check decoders

InactiveUS6938196B2Big errorCompensating for such errorError prevention/detection by using return channelOther decoding techniquesComputer moduleMessage processing

Techniques for implementing message passing decoders, e.g., LDPC decoders, are described. To facilitate hardware implementation messages are quantized to integer multiples of ½ ln2. Messages are transformed between more compact variable and less compact constraint node message representation formats. The variable node message format allows variable node message operations to be performed through simple additions and subtractions while the constraint node representation allows constraint node message processing to be performed through simple additions and subtractions. Variable and constraint nodes are implemented using an accumulator module, subtractor module and delay pipeline. The accumulator module generates an accumulated message sum. The accumulated message sum for a node is stored and then delayed input messages from the delay pipeline are subtracted there from to generate output messages. The delay pipeline includes a variable delay element making it possible to sequentially perform processing operations corresponding to nodes of different degrees.

Owner:QUALCOMM INC

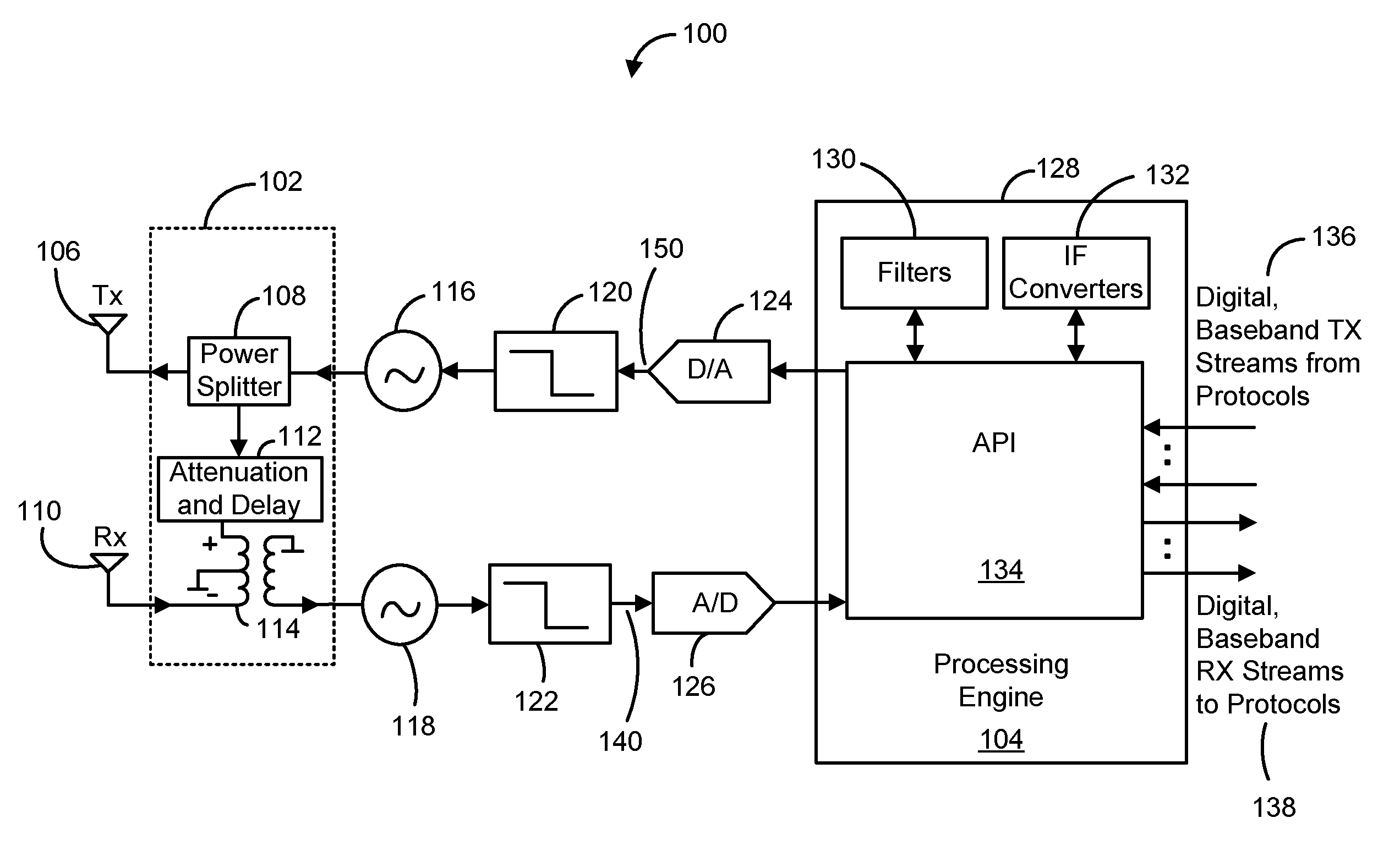

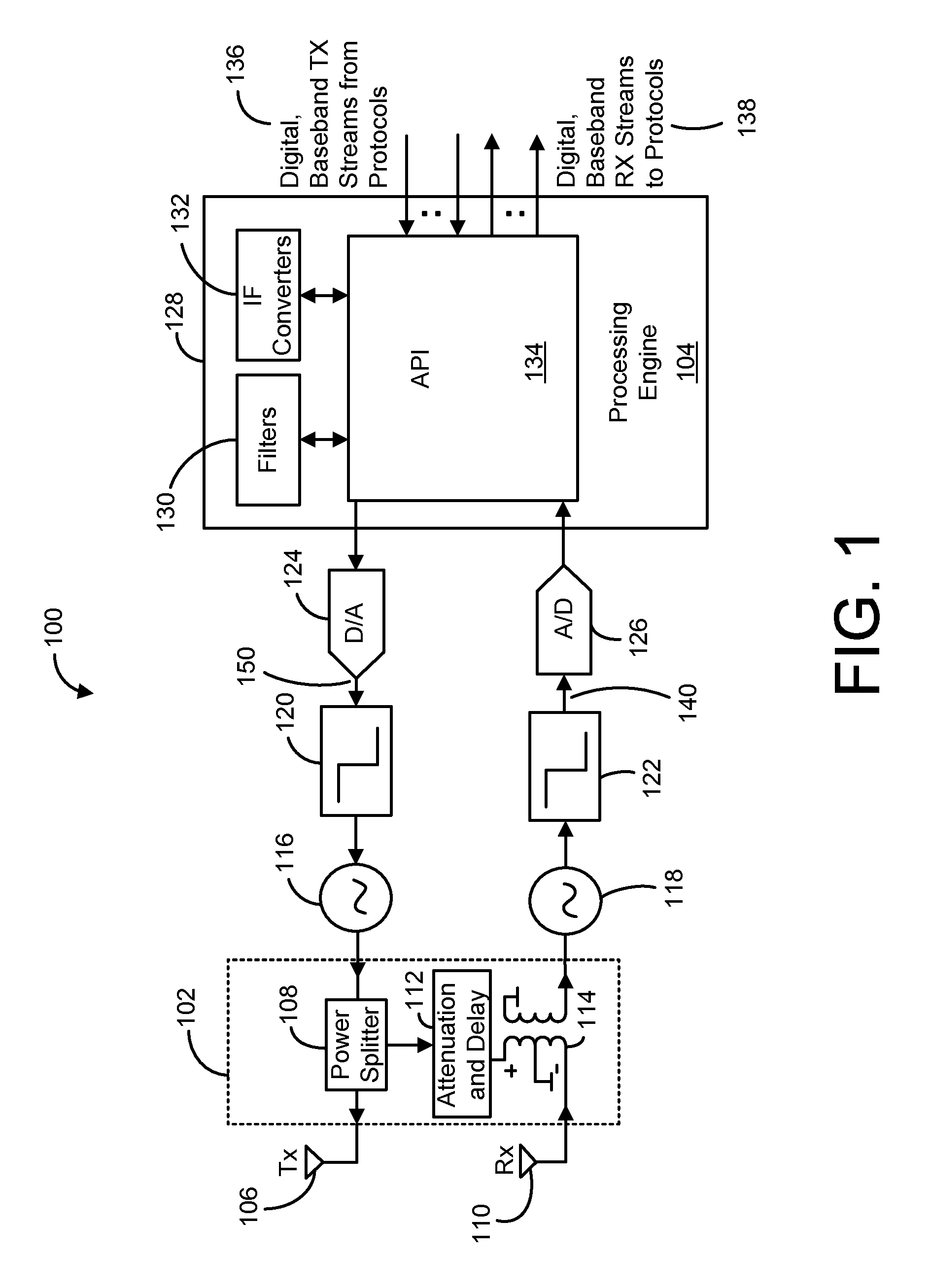

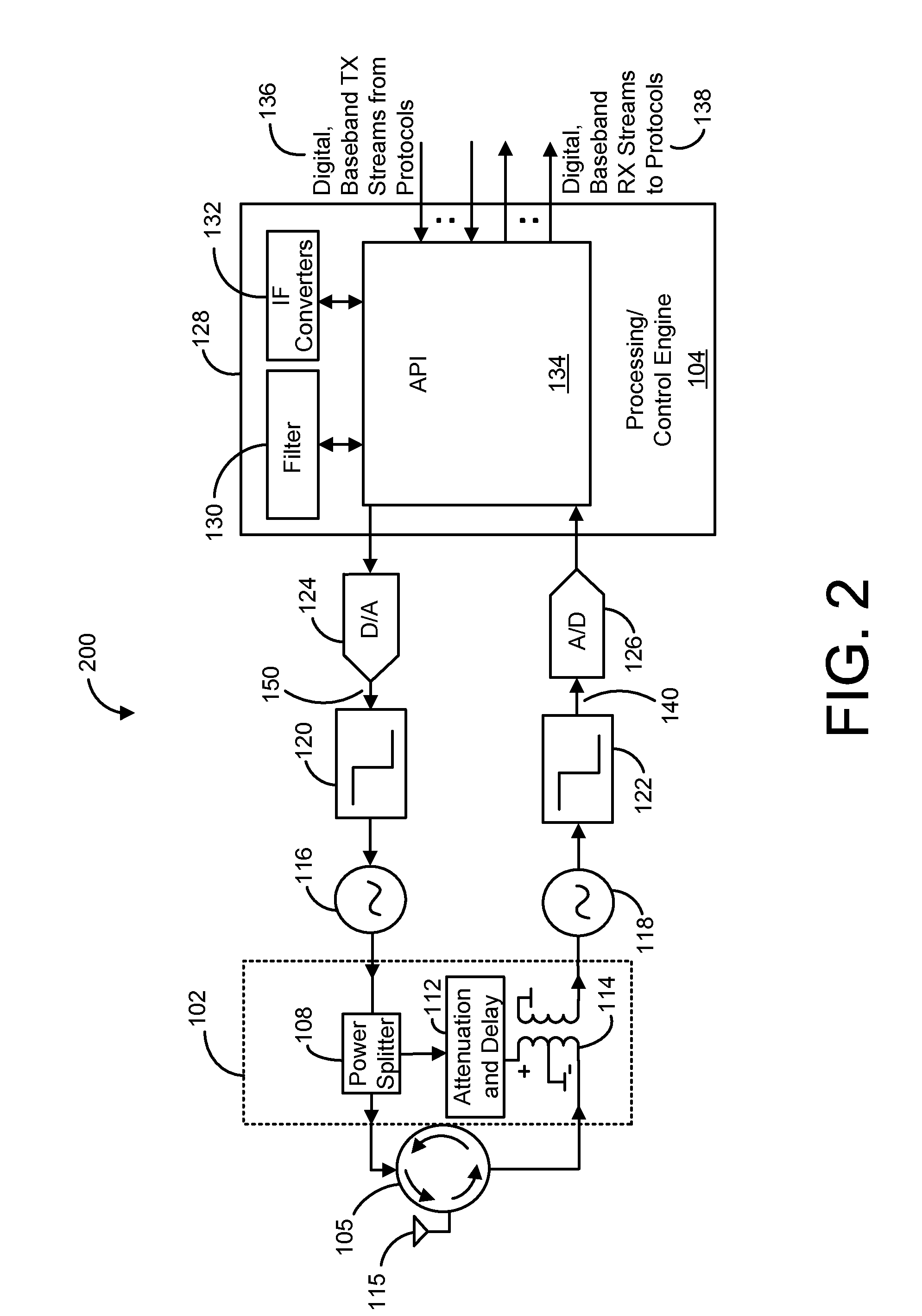

Systems and methods for cancelling interference using multiple attenuation delays

ActiveUS20130301488A1Reducing self-interference signalTransmission control/equalisingUltrasound attenuationSelf interference

A wireless communication device includes, in part, at least one antenna for receiving or transmitting a signal, and a cancelation circuit adapted to cancel or reduce the self-interference signal. The cancelation circuit includes, in part, a control block, N delay and attenuation paths, a combiner, and a subtractor. Each path includes a delay element and a variable attenuator whose attenuation level varies in response to a control signal generated by the control block. Each path receives a sample of the transmit signal and generates a delayed and attenuated (weighted) version of the sample signal. The combiner combines the N delayed and weighted versions of the sample signal to construct a signal representative of the self-interference signal. The subtractor subtracts the constructed signal from the received signal thereby the cancel or reduce the self-interference signal therefrom.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

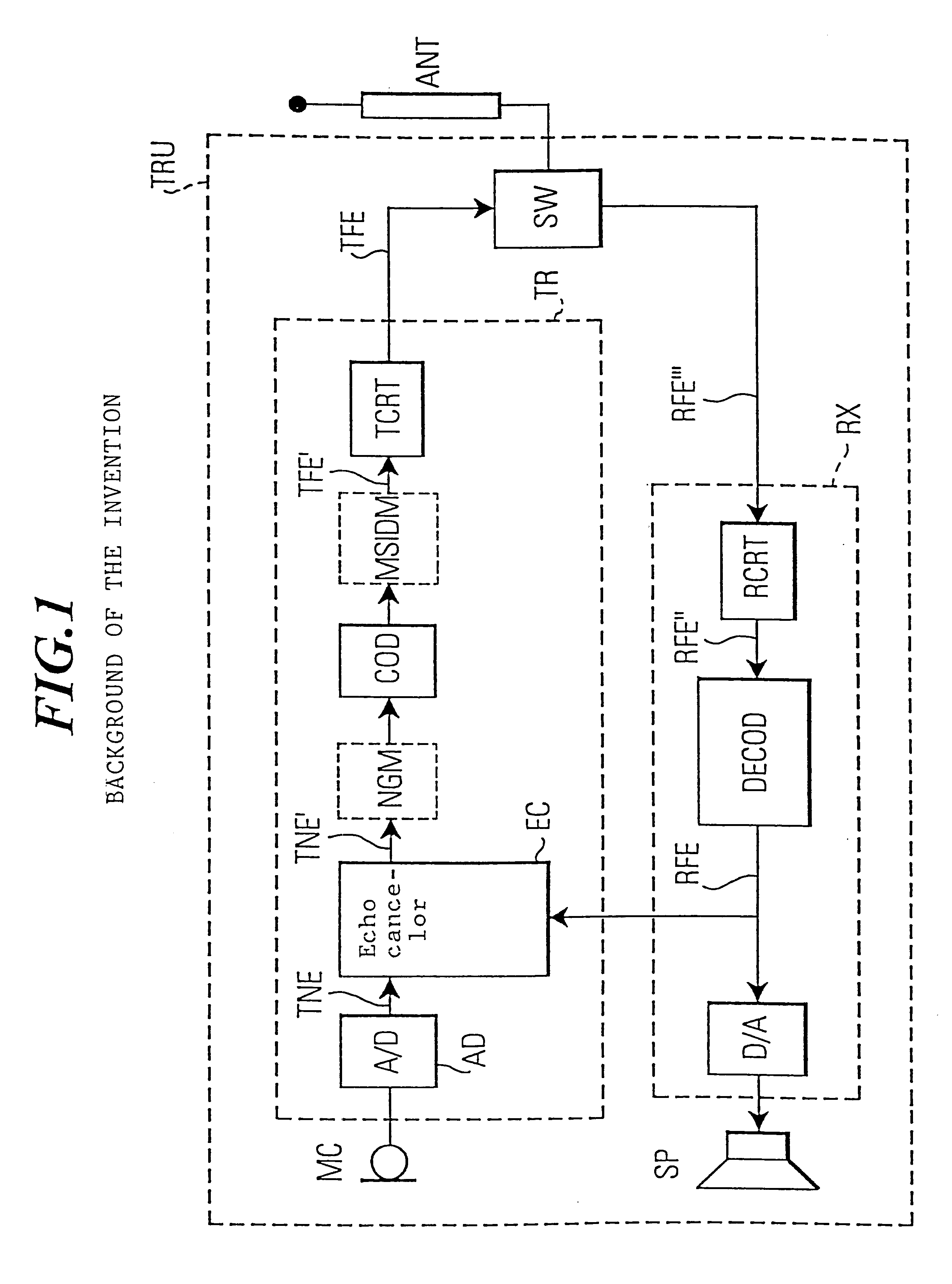

Echo cancellation device for cancelling echos in a transceiver unit

InactiveUS6597787B1Effectively cancellingTwo-way loud-speaking telephone systemsEcho effect reductionNoise generationAdaptive filter

An echo cancellation device (ECD) comprises an echo canceller (EC) including a transfer function estimator (EST, H) and a subtractor (ADD) and a residual echo suppression device (G, ADD2). The residual echo suppression device (G) comprises a residual echo filter (G) having an adjustable filter function (g). This filter function (g) can be adapted to either remove from the subtractor output (TNE') the spectral characteristics relating to the reception signal (RFE) and / or to emphasize in the subtractor output signal (TNE') a background signal spectral content relating to the transmission signal (TNE). A noise generation means (NGM') can be provided at the output of the adaptable filter (G) for injecting a noise process in to the filter output signal (TNE') prior to a speech coding in a speech coder (COD). The noise process masks in the filter output signal a spectral content relating to the reception signal (RFE).

Owner:TELEFON AB LM ERICSSON (PUBL)

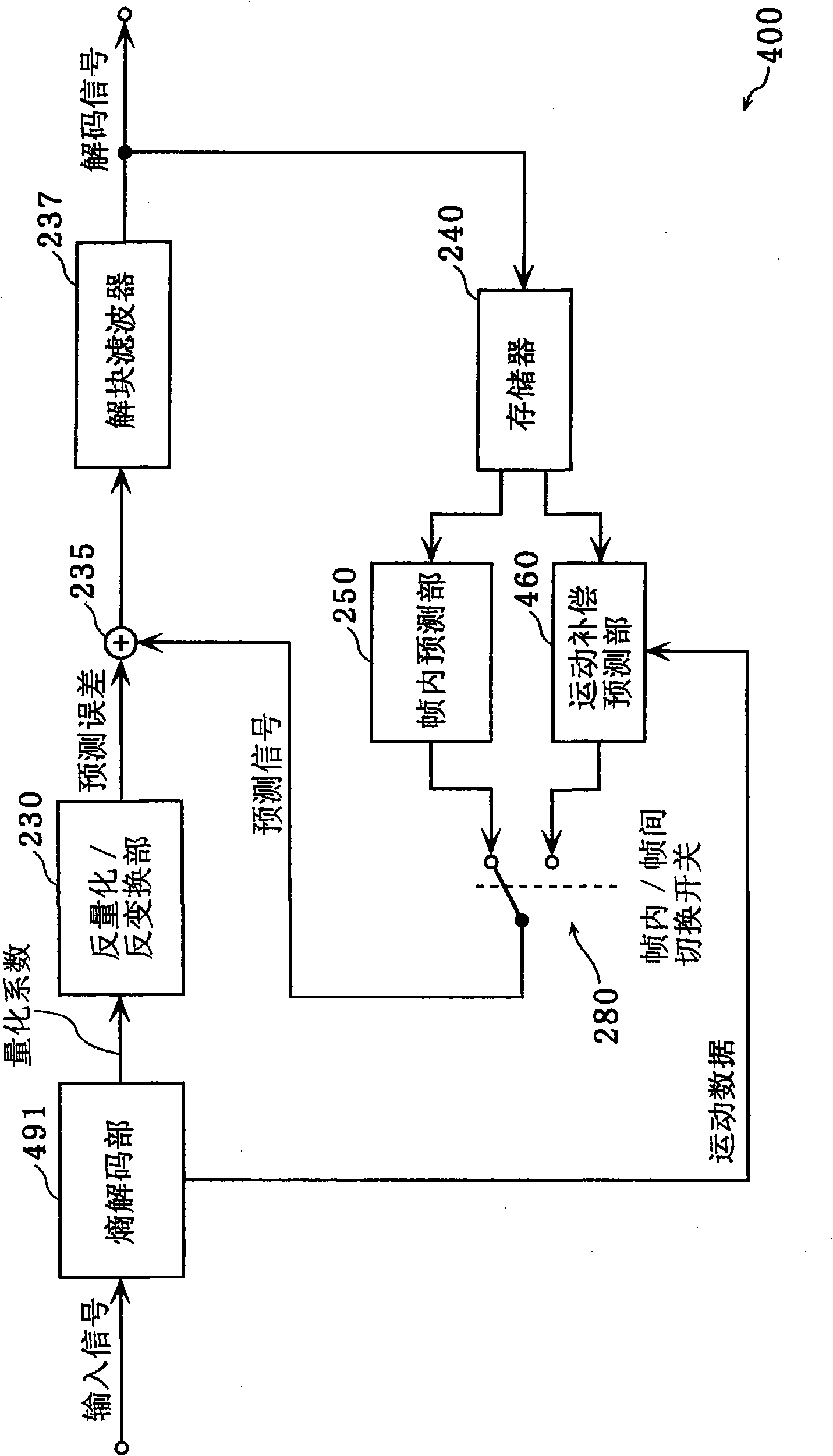

Intra-coding apparatus and method

An intra-coding apparatus and method for coding an image including a plurality of macroblocks are provided. The intra-coding apparatus includes an intra-frame prediction unit determining an intra prediction mode using border pixels on borders between a current macroblock to be coded and adjacent macroblocks and generating a predicted macroblock corresponding to the current macroblock in the determined intra prediction mode; a subtractor outputting a difference between the current macroblock and the predicted macroblock; a transformation / quantization unit transforming the difference into a frequency band signal and quantizing the frequency band signal; and a coding unit coding a quantization result.

Owner:KOREA POLYTECHNIC UNIV IND ACADEMIC COOPERATION FOUND

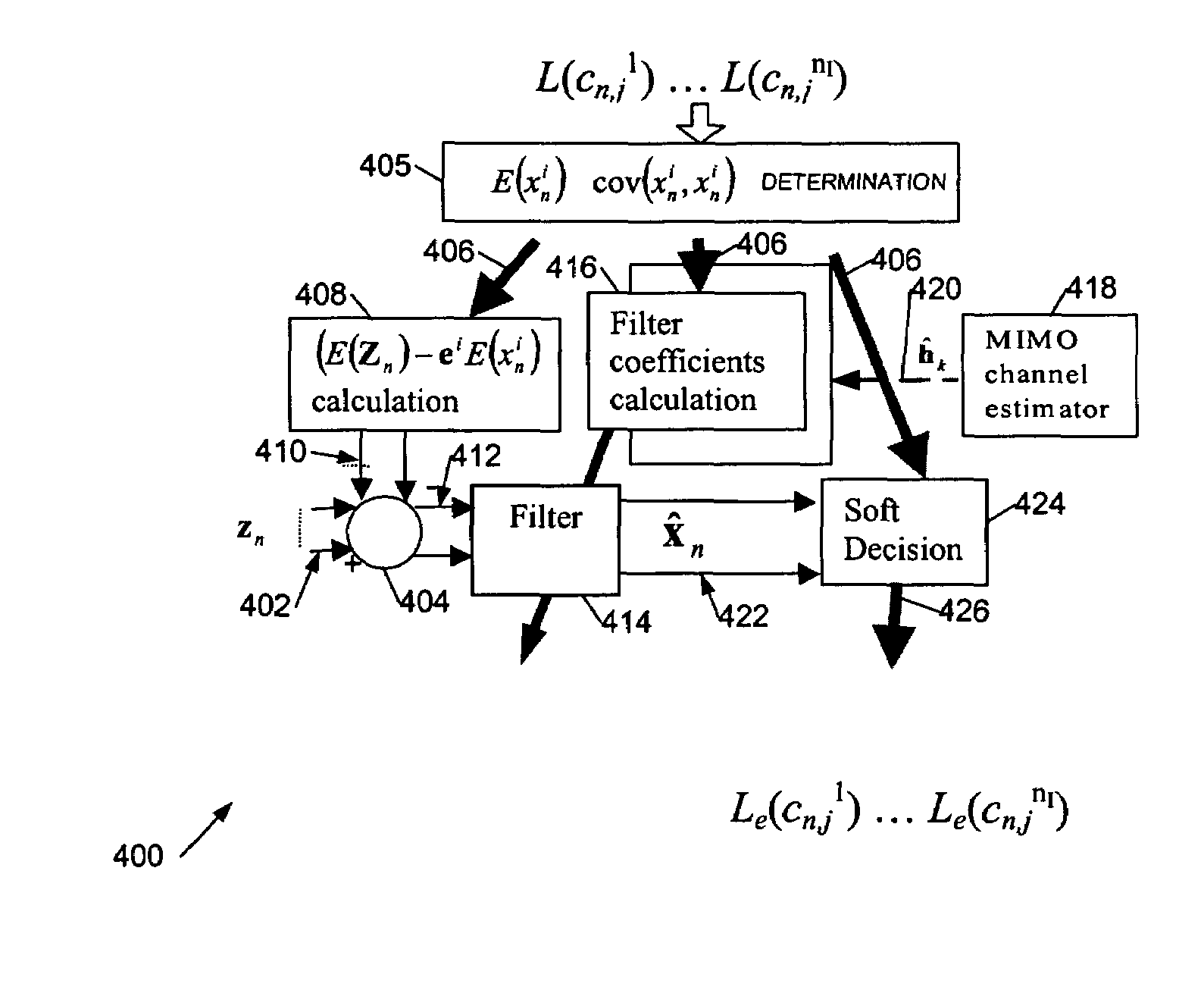

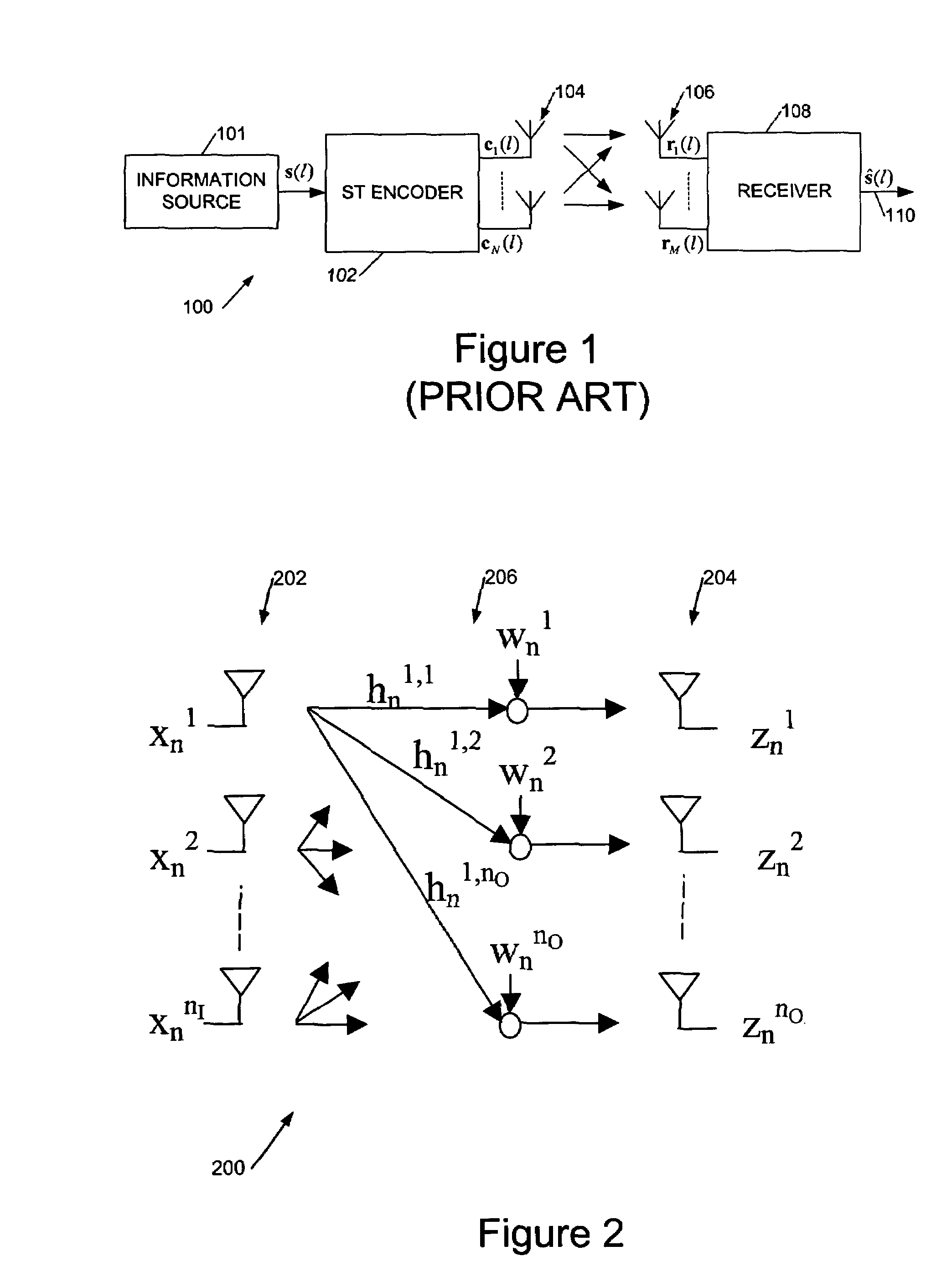

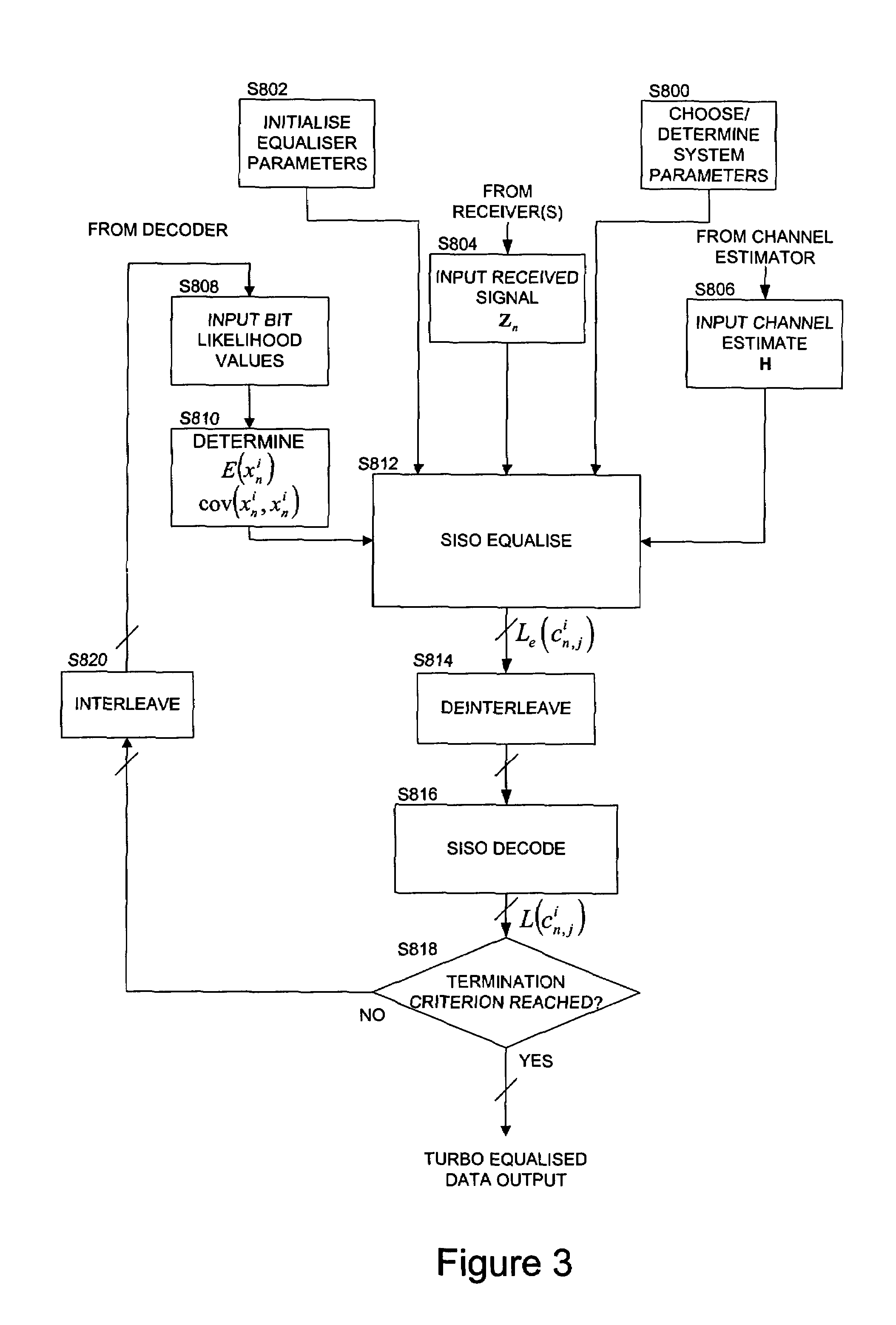

Equalisation apparatus and methods

InactiveUS7333540B2Reduce ISIIncrease the lengthMultiple-port networksResonant long antennasCovarianceComputer science

The invention relates to apparatus, methods and computer program code for equalisation. A soft-in-soft-out (SISO) equaliser for use in a receiver for receiving data from a transmitter configured to transmit data from a plurality of transmit antennas simultaneously is described. The equaliser comprises at least one received signal input for inputting a received signal; a plurality of likelihood value inputs, one for each transmit antenna, for inputting a plurality of decoded signal likelihood values from a SISO decoder; a processor configured to determine from said plurality of signal likelihood values an estimated mean and covariance value for a signal from each of said transmit antennas; an expected signal determiner coupled to said processor to determine an expected received signal value using said mean values; a subtractor coupled to said received signal input to subtract said expected received signal value from said received signal to provide a compensated signal; a filter coupled to said subtractor to filter said compensated signal to provide a plurality of estimated transmitted signal values, one for each said transmit antenna; a filter coefficient determiner coupled to said processor to determine coefficients of said filter using said covariance values; and an output stage coupled to said filter to output a plurality of transmitted signal likelihood values, one for each said transmit antenna, for input to said SISO decoder.

Owner:KK TOSHIBA

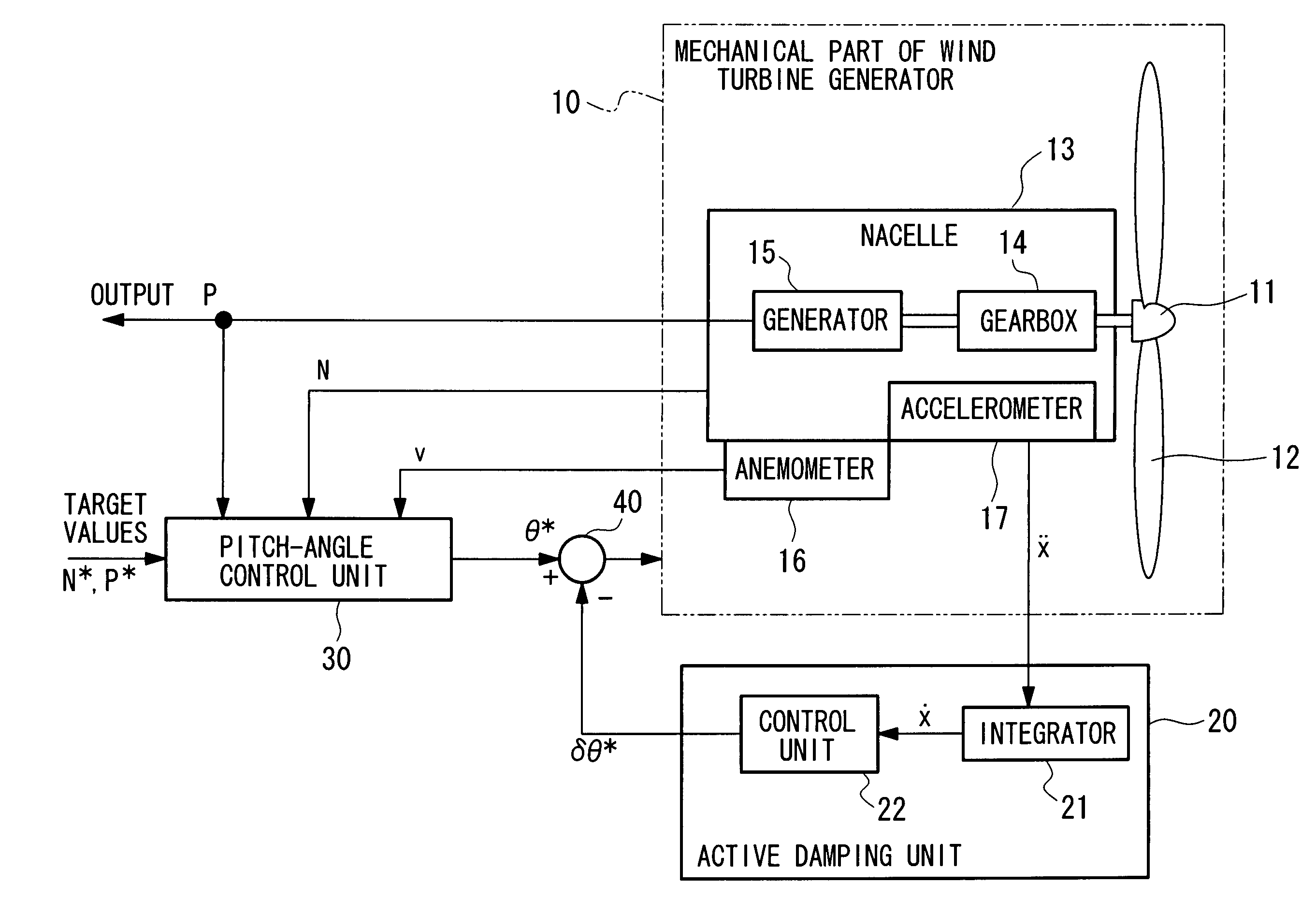

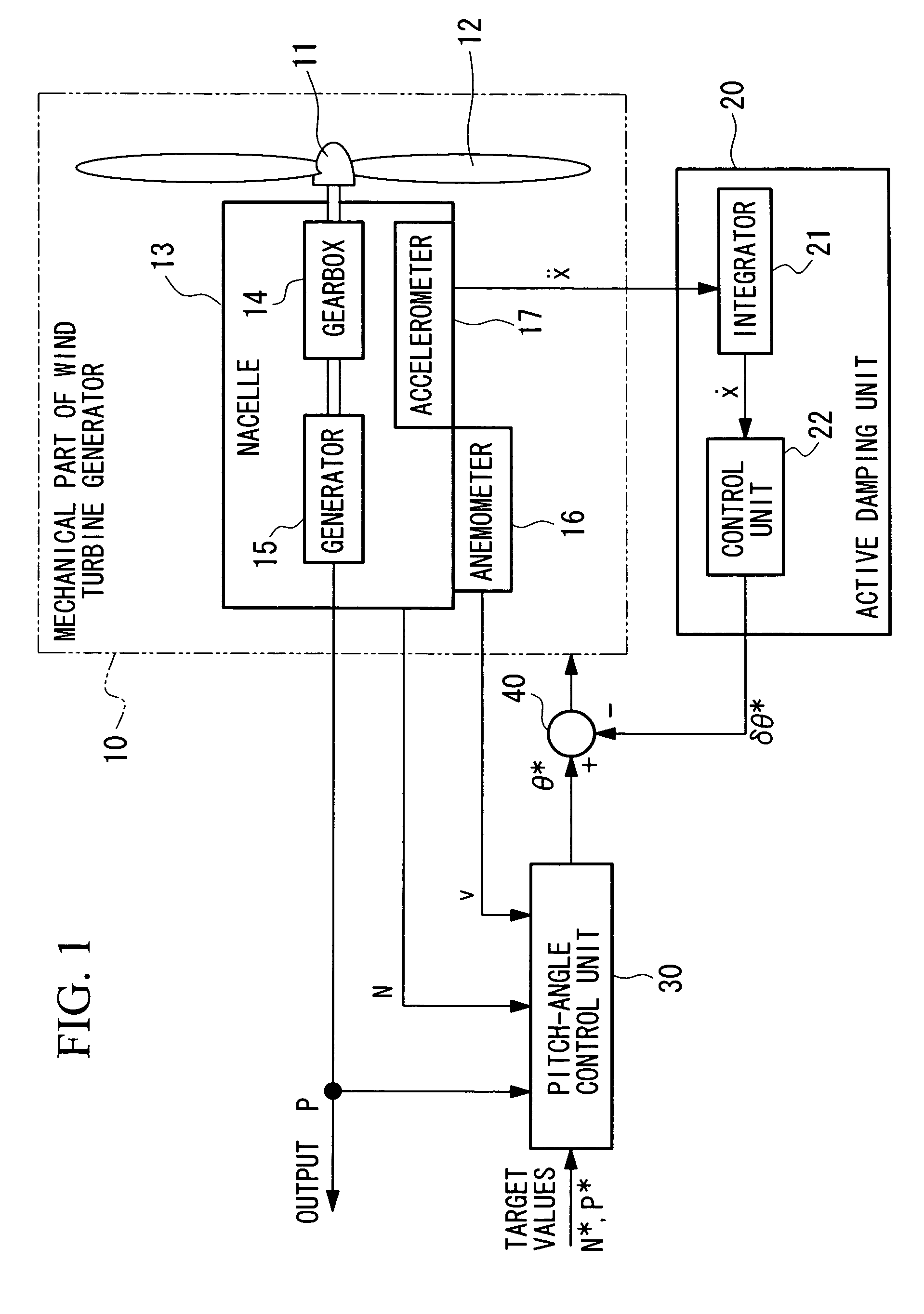

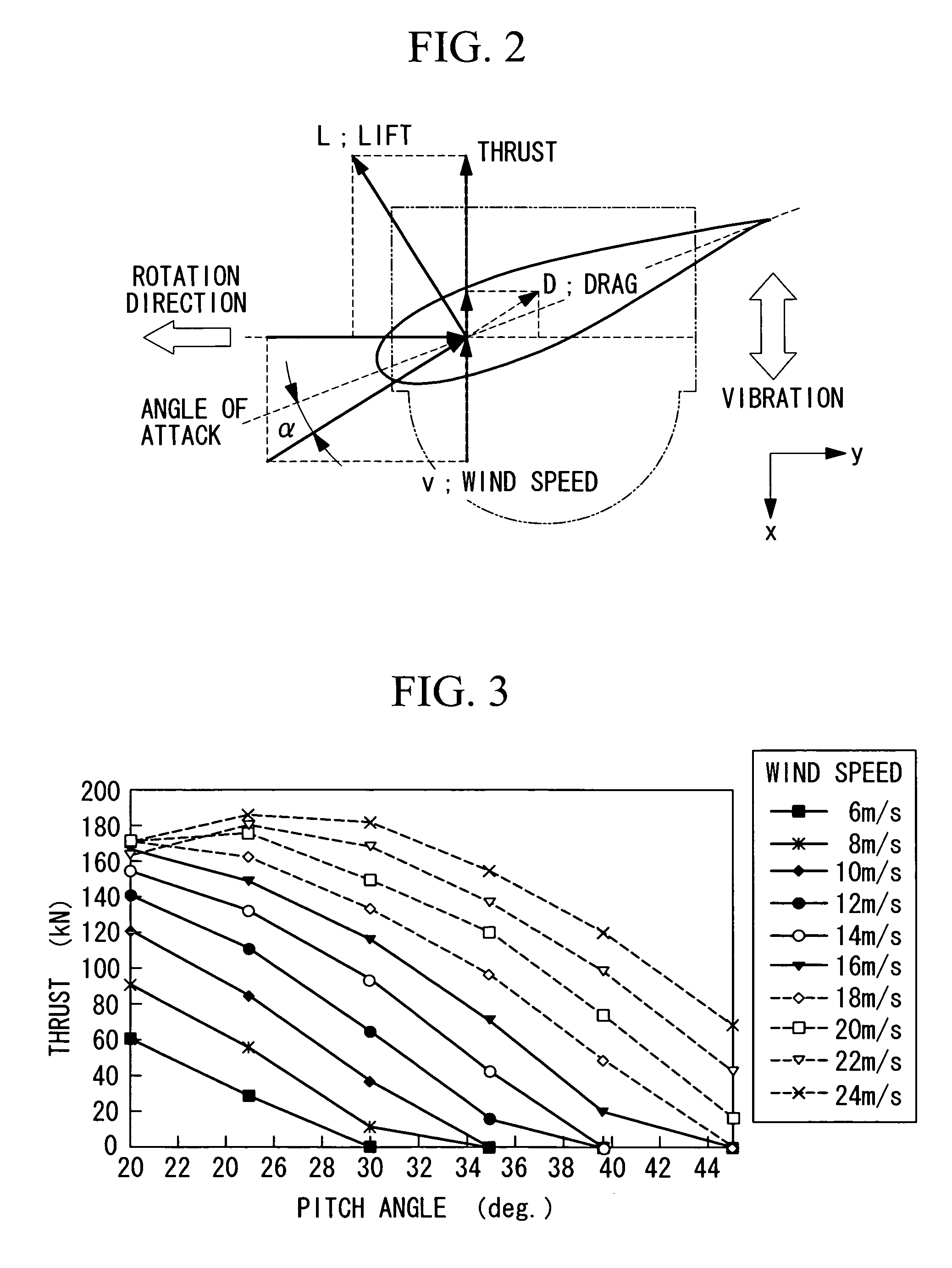

Wind Turbine Generator, Active Damping Method Thereof, and Windmill Tower

A wind turbine generator, an active damping method thereof, and a windmill tower in which vibrations of the wind turbine generator itself or the windmill tower can be reduced at low cost are provided. The acceleration due to vibrations of a nacelle (13) is detected with an accelerometer (17) attached to the nacelle (13). In an active damping unit (20), a pitch angle of windmill blades (12) for generating a thrust on the windmill blades (12) so as to cancel out the vibrations of the nacelle (13) is calculated on the basis of the acceleration, and the pitch angle is output as a blade-pitch-angle command δθ* for damping. On the other hand, in a pitch-angle control unit (30), a pitch angle of the windmill blades (12) for controlling the output to be a predetermined value is calculated, and the pitch angle is output as a blade-pitch-angle command θ* for output control. The blade-pitch-angle command δθ* for damping is combined with the blade-pitch-angle command θ* for output control using a subtracter (40). The pitch angle of the windmill blades is controlled on the basis of the resulting blade-pitch-angle command after combining.

Owner:MITSUBISHI HEAVY IND LTD

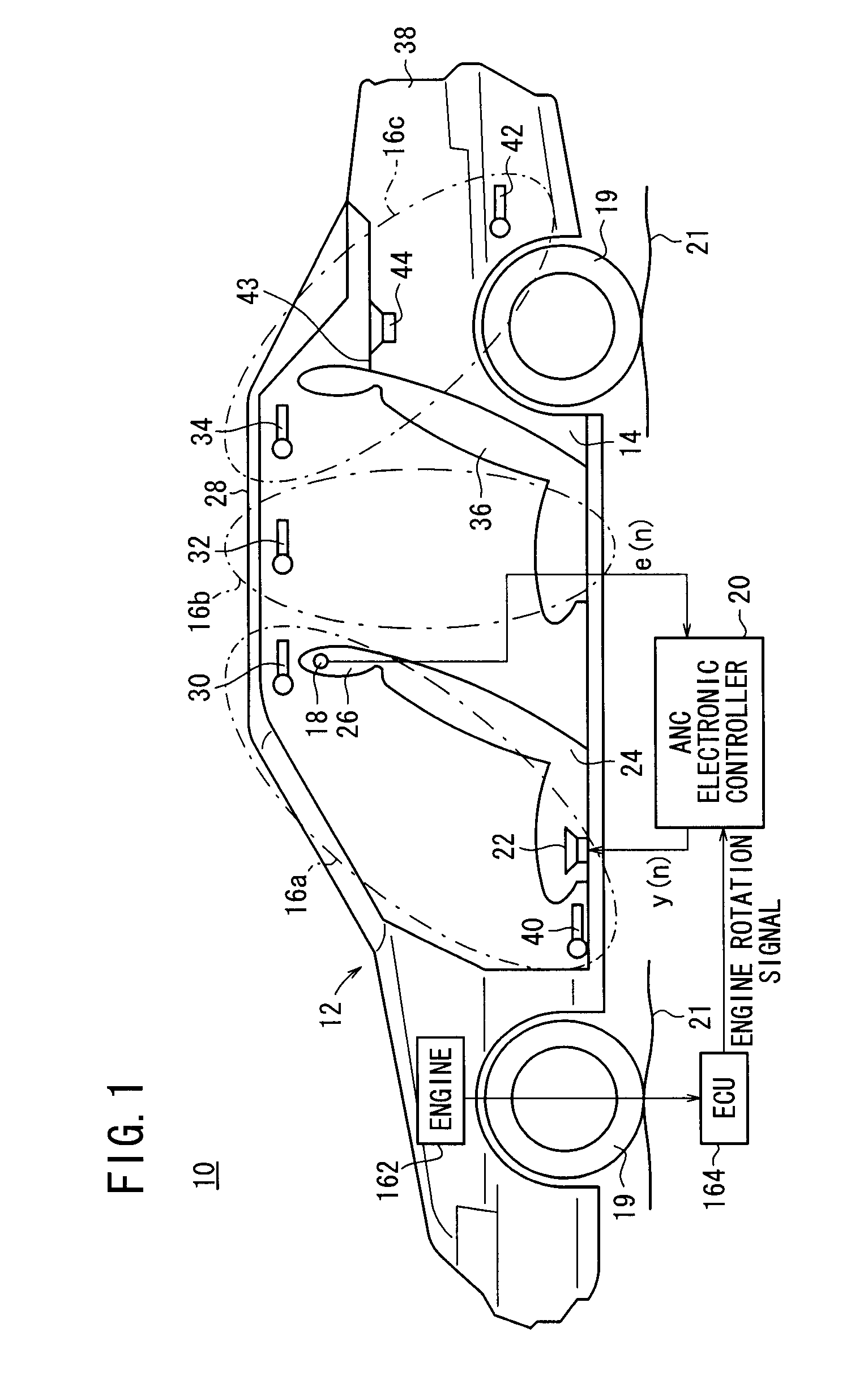

Active noise control apparatus

InactiveUS20080240457A1Lighten the computational burdenReduce manufacturing costEar treatmentNoise generationNoise controlControl signal

A subtractor subtracts an echo canceling signal Ĉ·yl(n−1) from a canceling error signal e(n) to estimate a residual noise to be silenced at the position of a microphone, and outputs a first basic signal x1(n) representing the residual noise. A first control circuit section generates a first control signal y1(n) based on the first basic signal x1(n) and a second basic signal x2(n) that is generated by delaying the first basic signal x1(n) by a time Z−n. A second circuit section generates a second control signal y2(n) based on the first basic signal x1(n) and an engine rotation signal.

Owner:HONDA MOTOR CO LTD

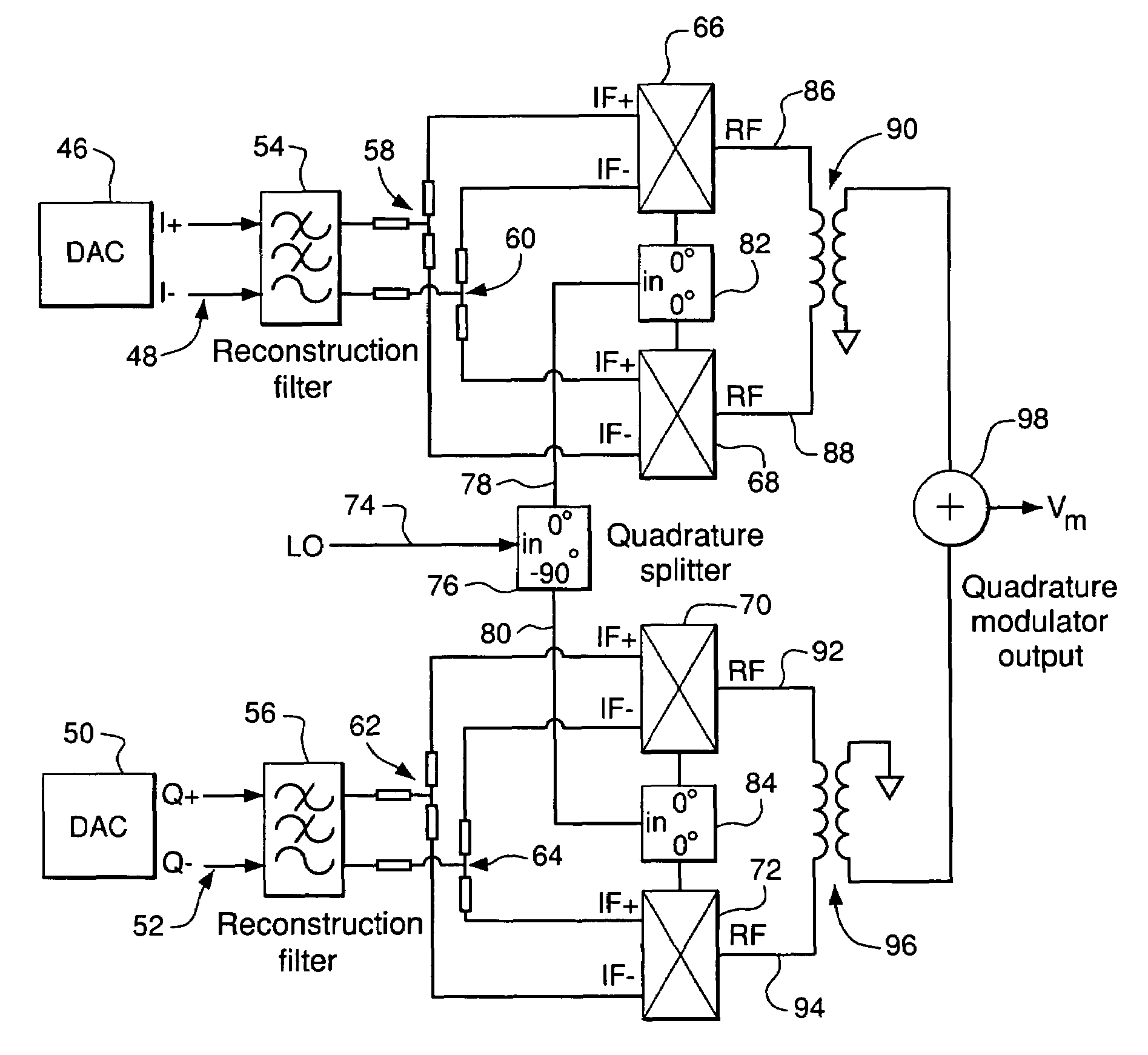

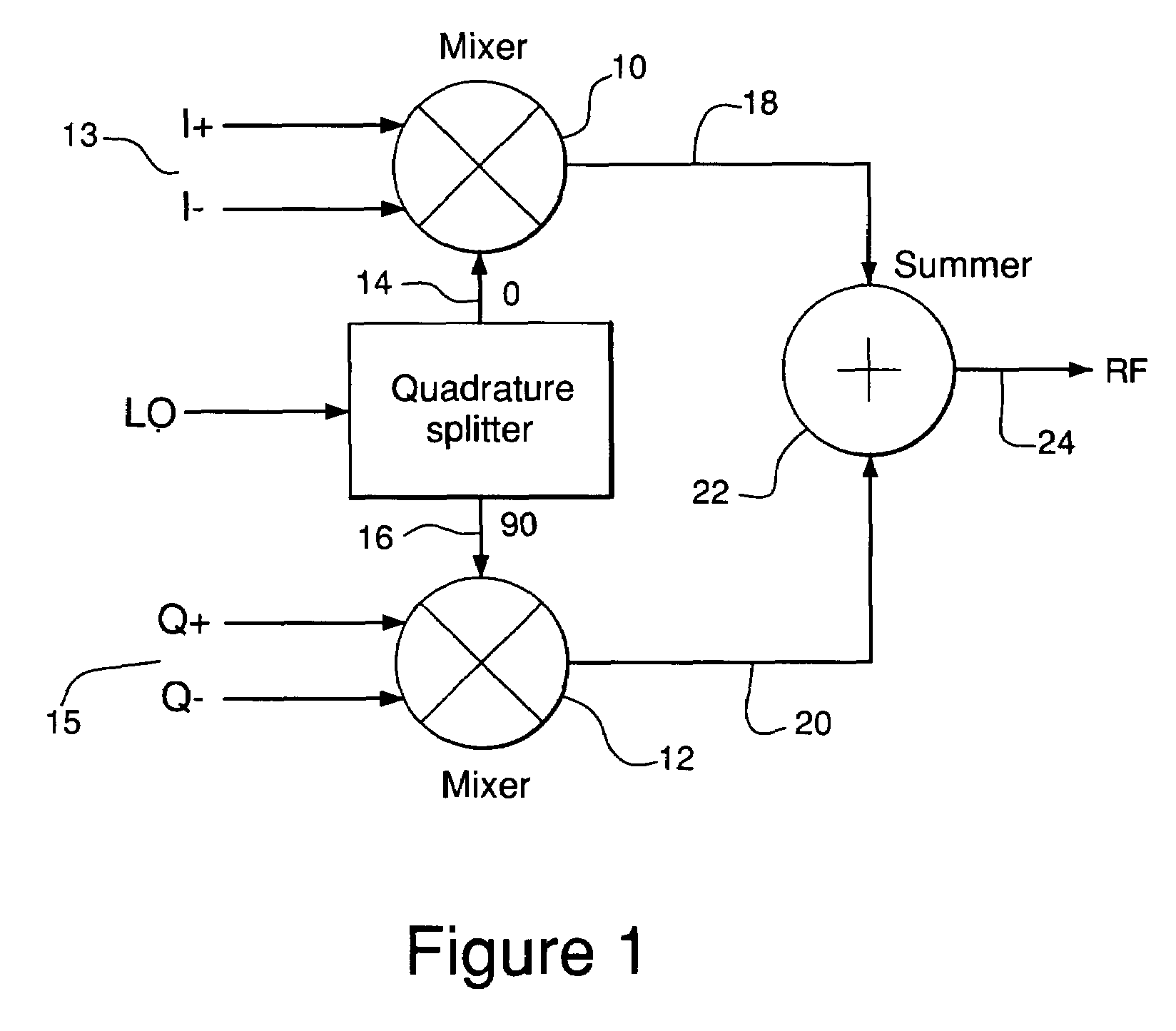

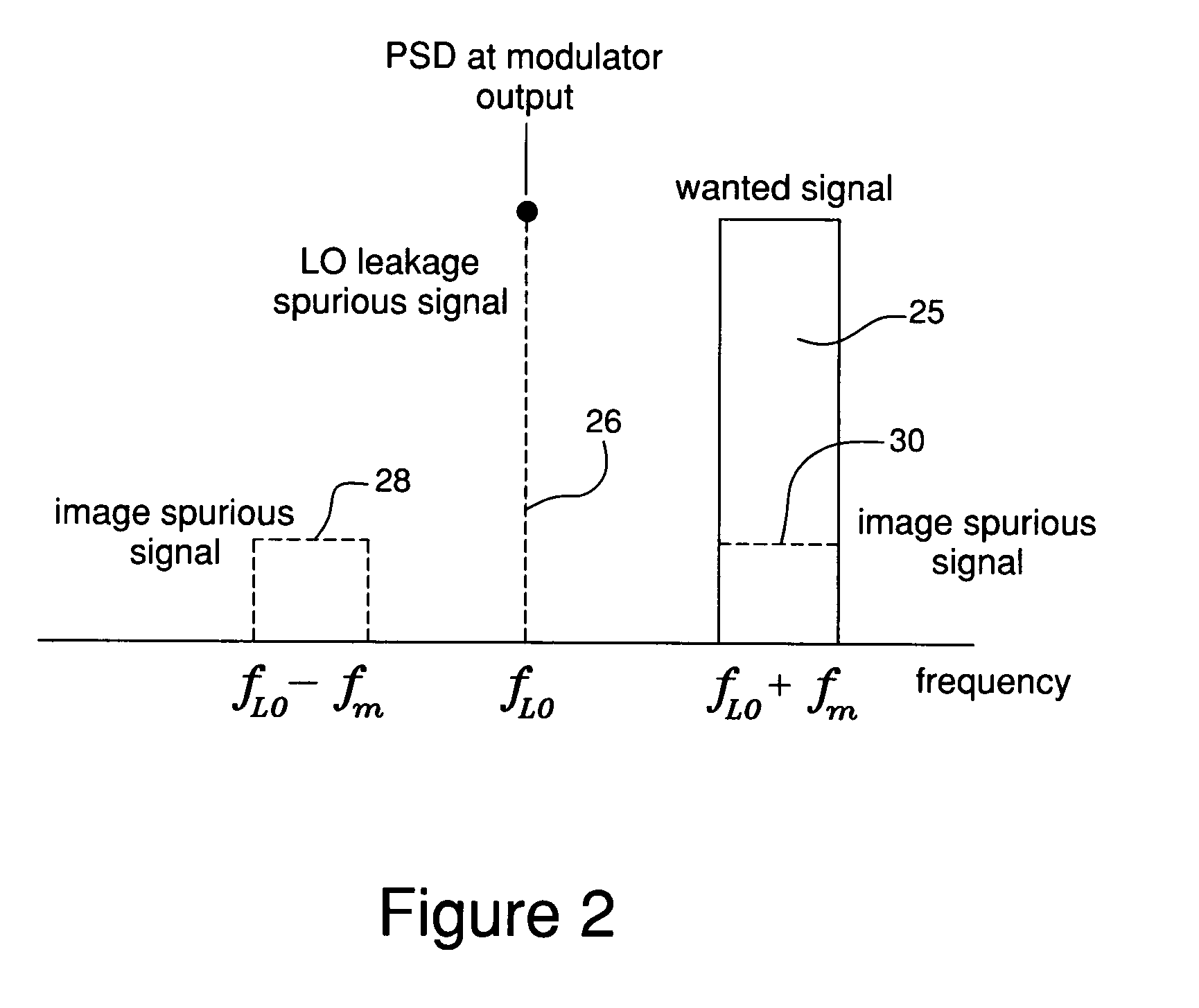

Frequency conversion techniques using antiphase mixing

InactiveUS7336940B2Modulation with suppressed carrierMultiple carrier systemsFrequency conversionFrequency mixer

A frequency upconverter using mixers operating on one or more signals and inverted versions thereof and a subtractor, such as a balun, for subtractively combining the mixer outputs to produce an upconverted signal.

Owner:ANDREW LLC

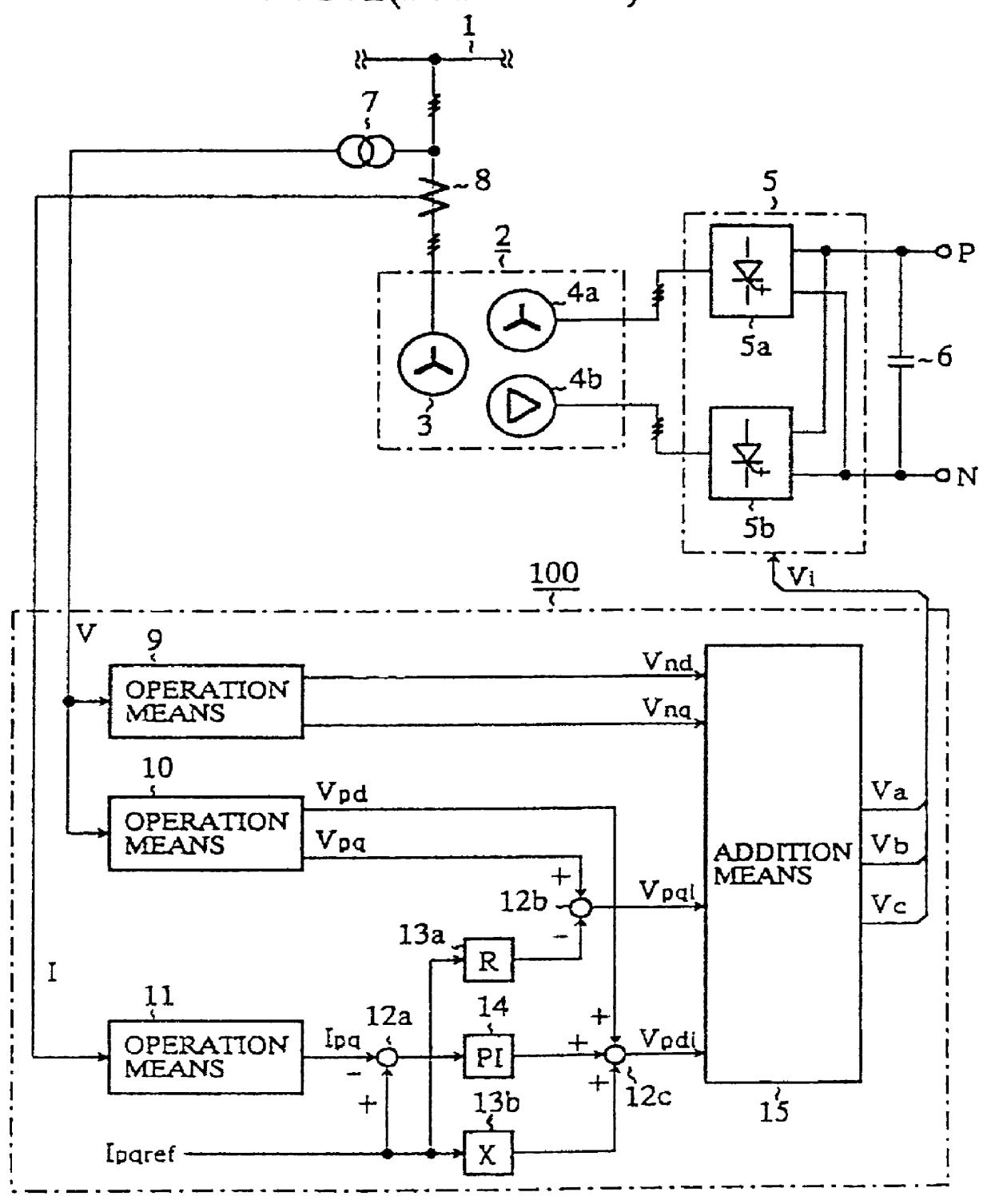

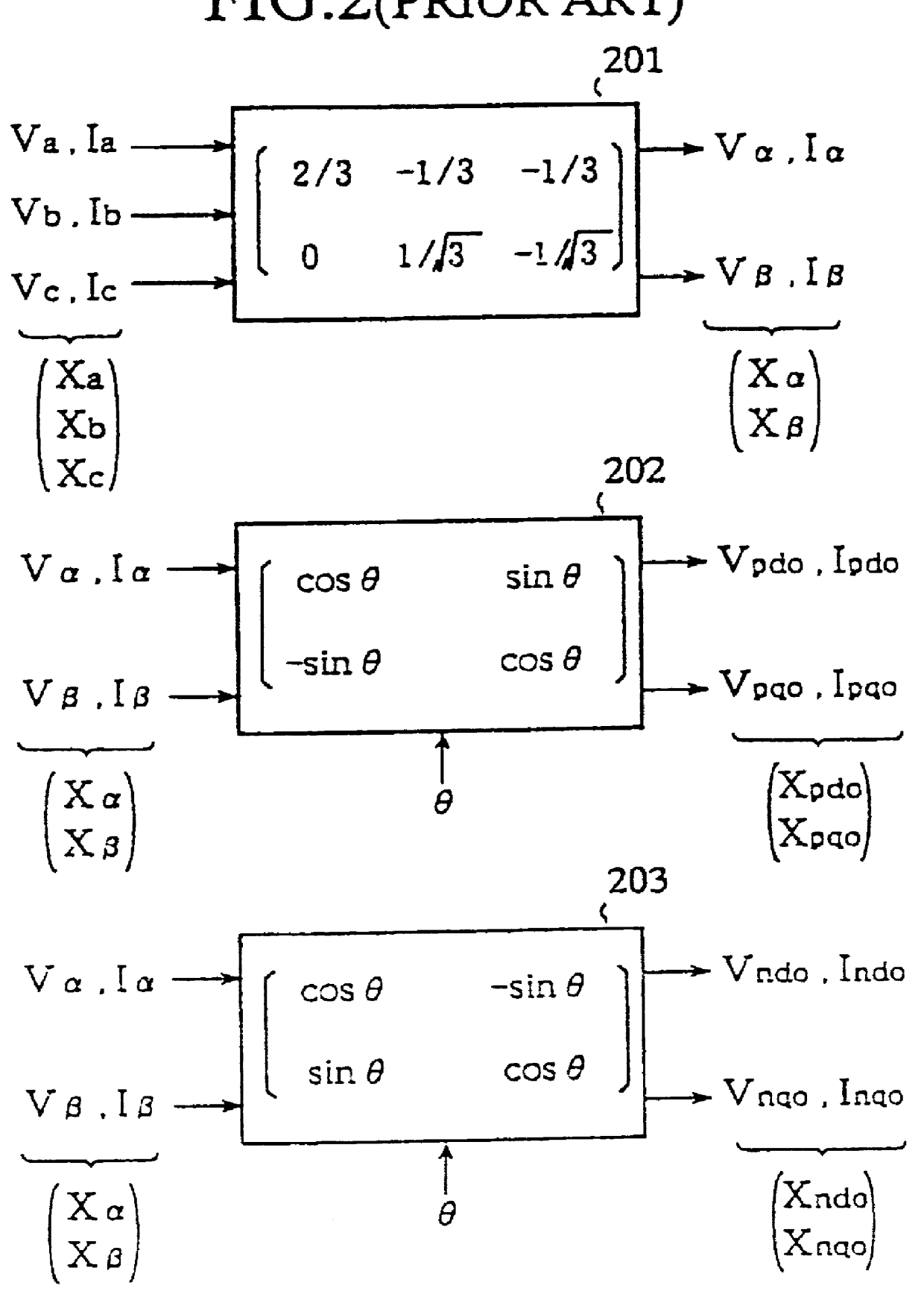

Power conversion apparatus

A power conversion apparatus includes a current component control section which outputs q axis and d axis negative-sequence components and q axis and d axis positive-sequence components based on a detected current value or a voltage value, a current component control which compares a current component with the current instruction value from an instruction value generator and outputs to an adder / subtractor the result, a converter converting a control signal output from the adder / subtractor into three-phase components, and an adder adding these three-phase components to respective phases and outputting the result to a power conversion section.

Owner:MITSUBISHI ELECTRIC CORP

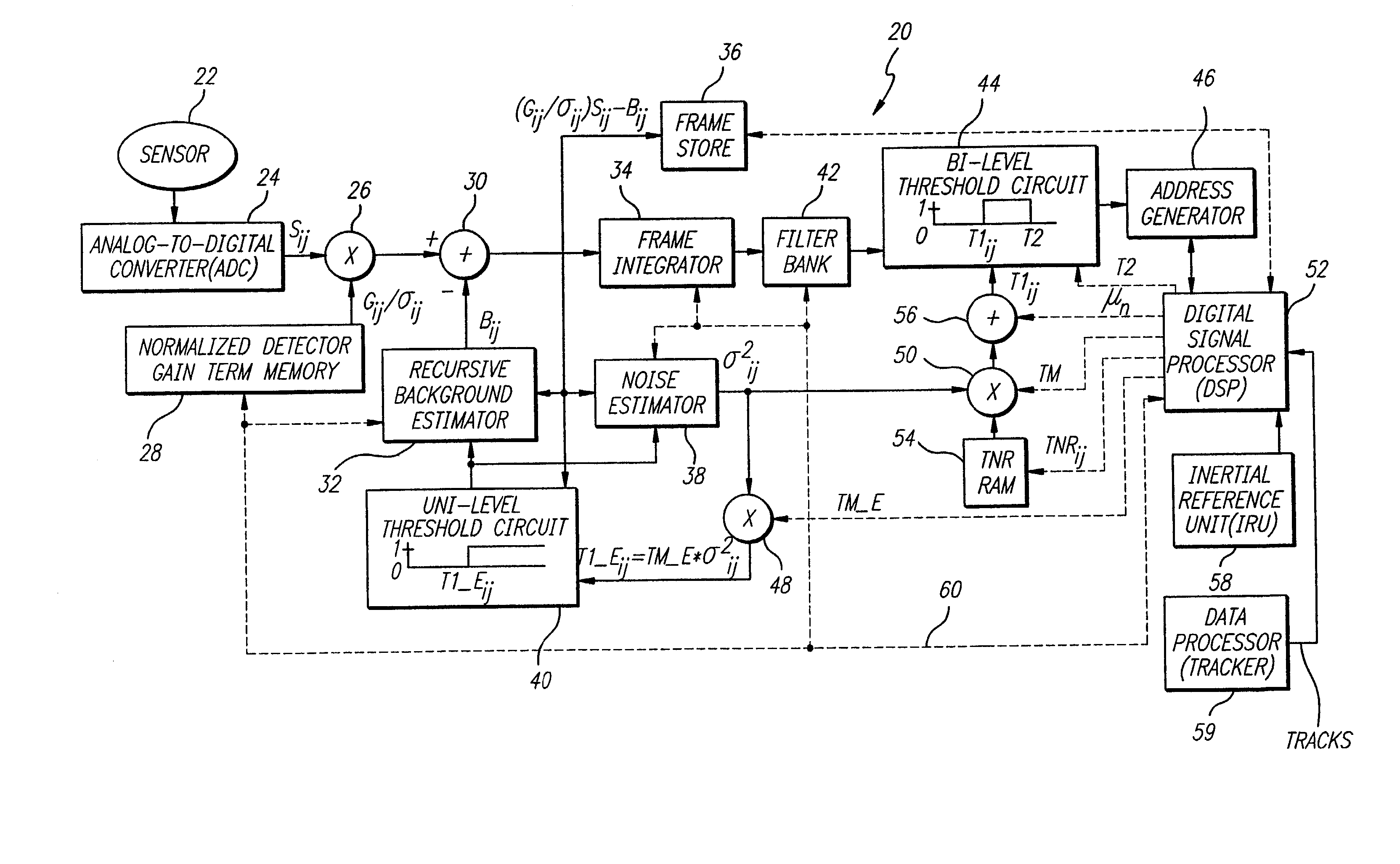

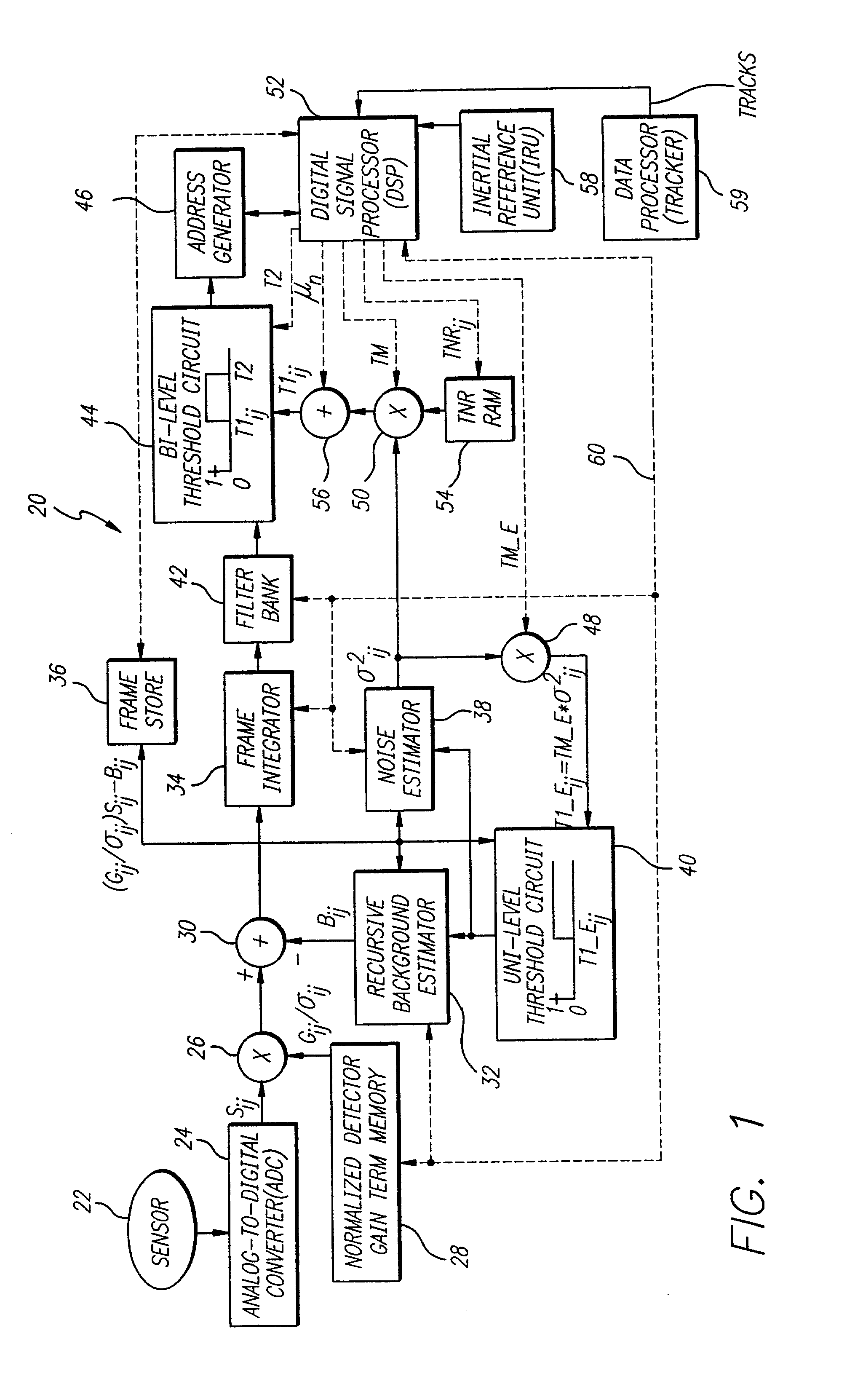

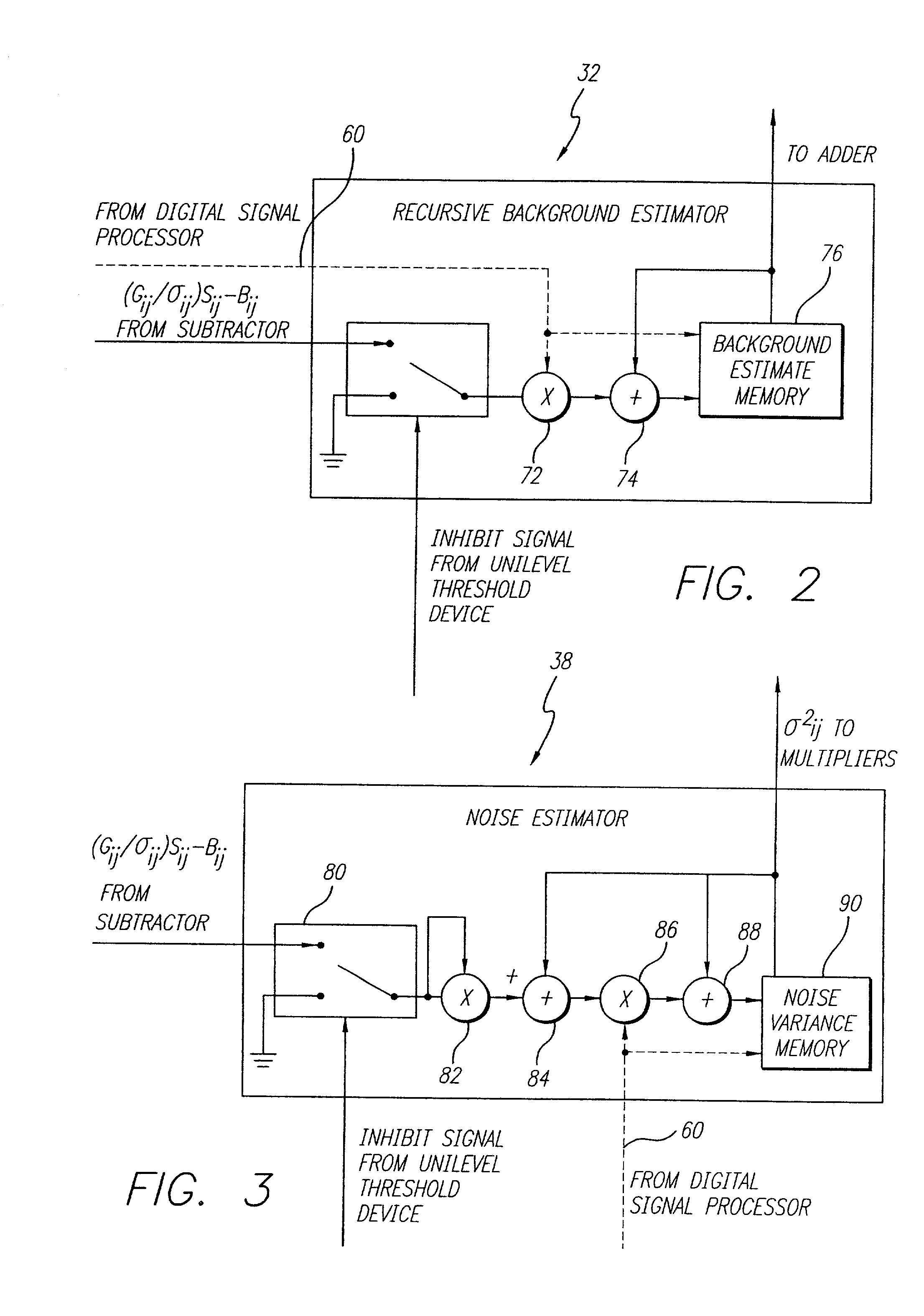

Accurate target detection system

InactiveUS20020084414A1Television system detailsMaterial analysis by optical meansElectricityIntegrator

An accurate target detection system. The system includes a sensor (22) that receives electromagnetic signals and provides electrical signals in response thereto. A non-uniformity correction circuit (28, 38, 52) corrects non-uniformities in the sensor (22) based on the electrical signals and provides calibrated electrical signals in response thereto. A third circuit (30, 32, 34, 38, 42, 44, 52) determines if a target signal is present within the calibrated electrical signals and provides a target detection signal in response thereto. A fourth circuit (38, 40, 48) selectively activates or deactivates the non-uniformity correction circuit (28, 38, 52) based on the target detection signal. In a specific embodiment, the sensor (22) is an array of electromagnetic energy detectors (22), each detector providing an electrical detector output signal The non-uniformity correction circuit (28, 38, and 52) includes circuit for compensating for gain, background, and noise non-uniformities (28, 38, and 52) in the electromagnetic energy detectors. The non-uniformity correction circuit (28, 38, and 52) includes a detector gain term memory (28) for storing detector gain compensation values. The detector gain compensation values are normalized by noise estimates unique to each of the detectors. The third circuit (30, 32, 34, 38, 42, 44, and 52) includes a signal enhancement circuit for reducing noise (34, 42) in the calibrated electrical signals. The third circuit (30, 32, 34, 38, 42, 44, and 52) includes a noise estimation circuit (32, 38) that estimates noise in each of the detector output signals and provides noise estimates in response thereto. The noise estimation circuit (32, 38) further includes a noise estimator circuit (38) and a recursive background estimator (32). The third circuit (30, 32, 34, 38, 42, 44, 52) further includes a subtractor (30) for subtracting background from the calibrated electrical signals and providing background subtracted signals in response thereto. The signal enhancement circuit (34, 42) includes a frame integrator circuit for adding frames of image data (34), each frame containing data corresponding to the background subtracted signals and providing summed frames in response thereto. The third circuit (30, 32, 34, 38, 42, 44, 52) includes a first threshold circuit (44) for comparing the filtered signal to a first threshold and a second threshold and providing a threshold exceedance signal if the filtered signal is between the first threshold and the second threshold.

Owner:RAYTHEON CO

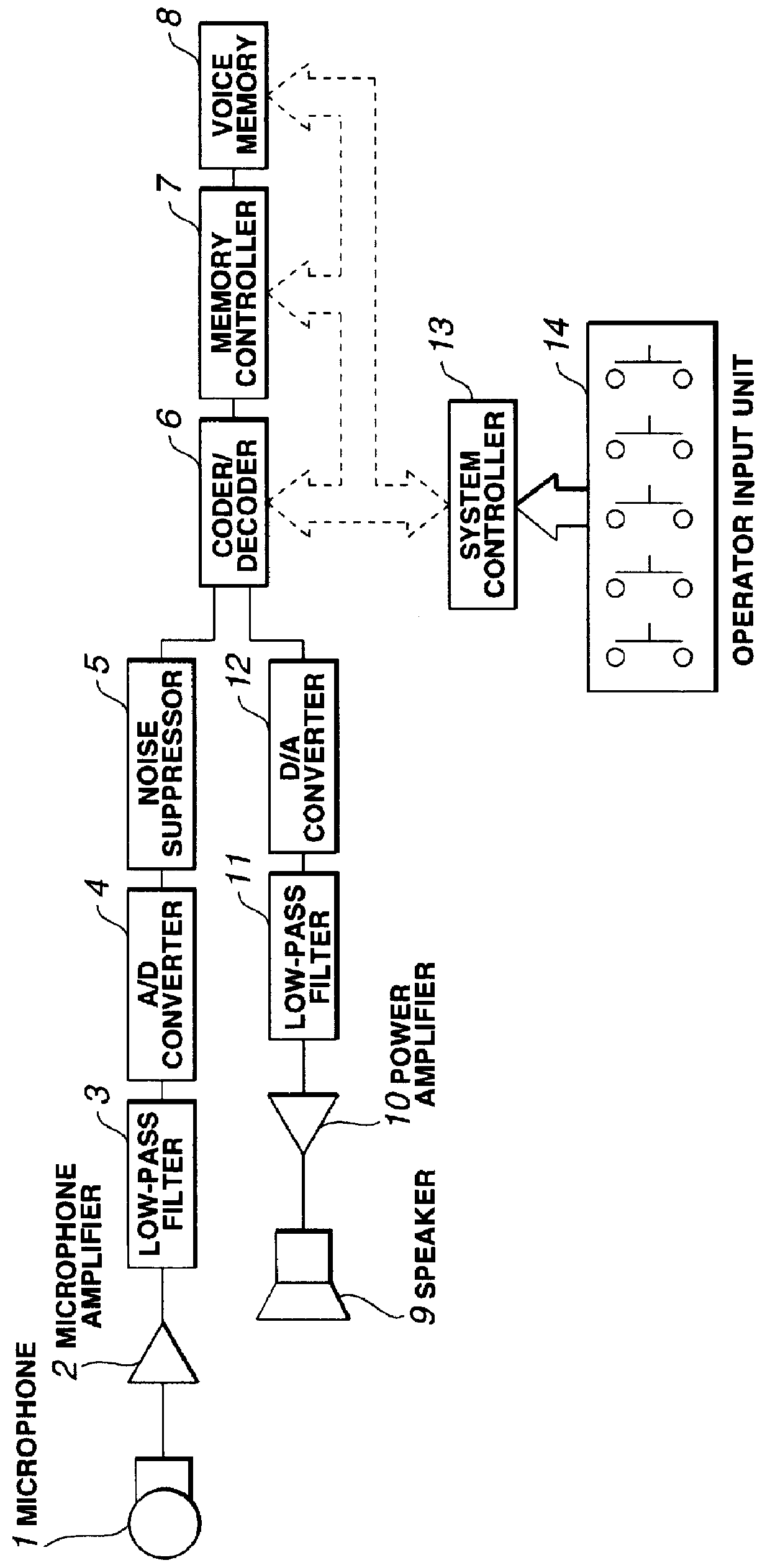

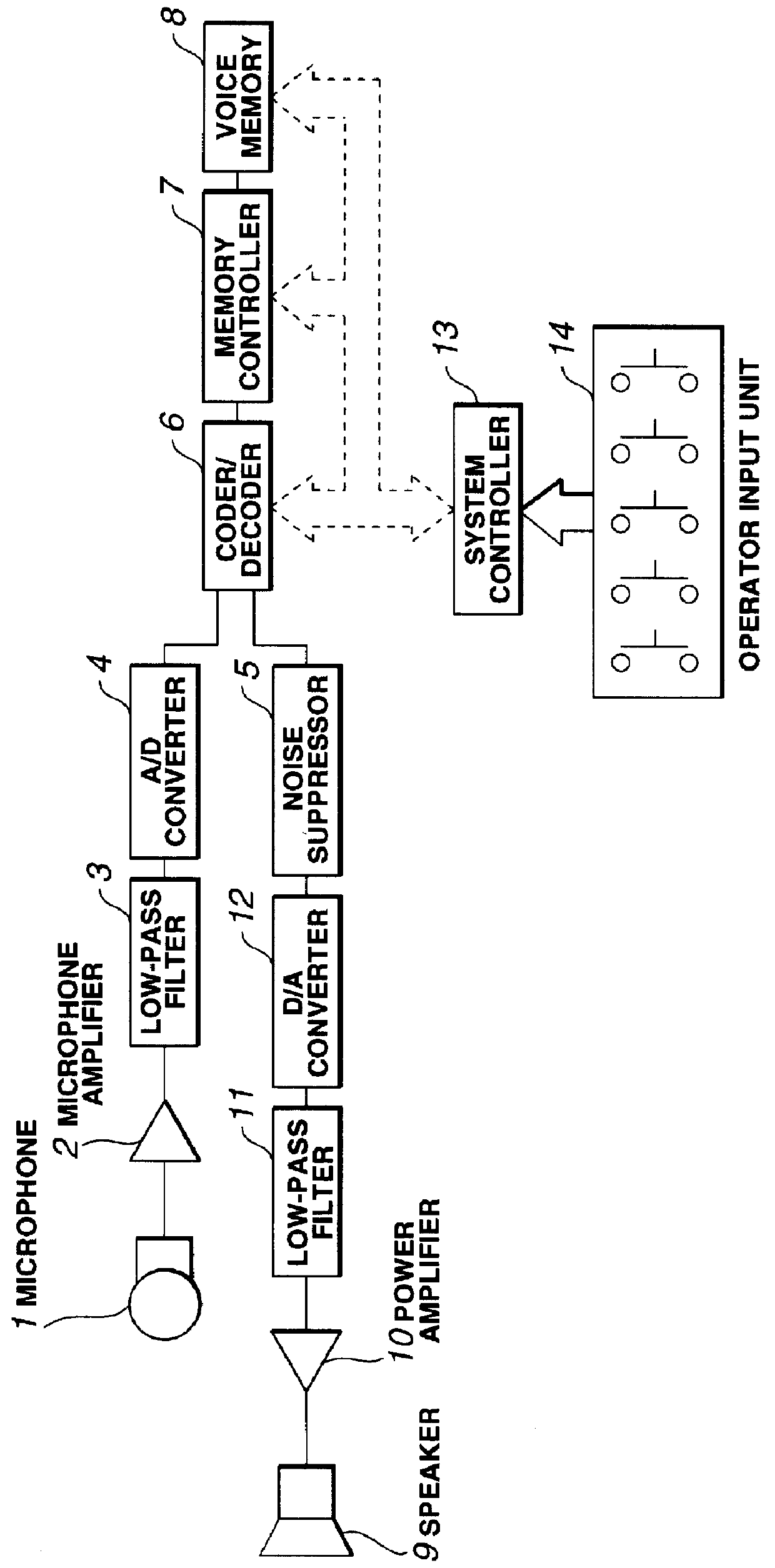

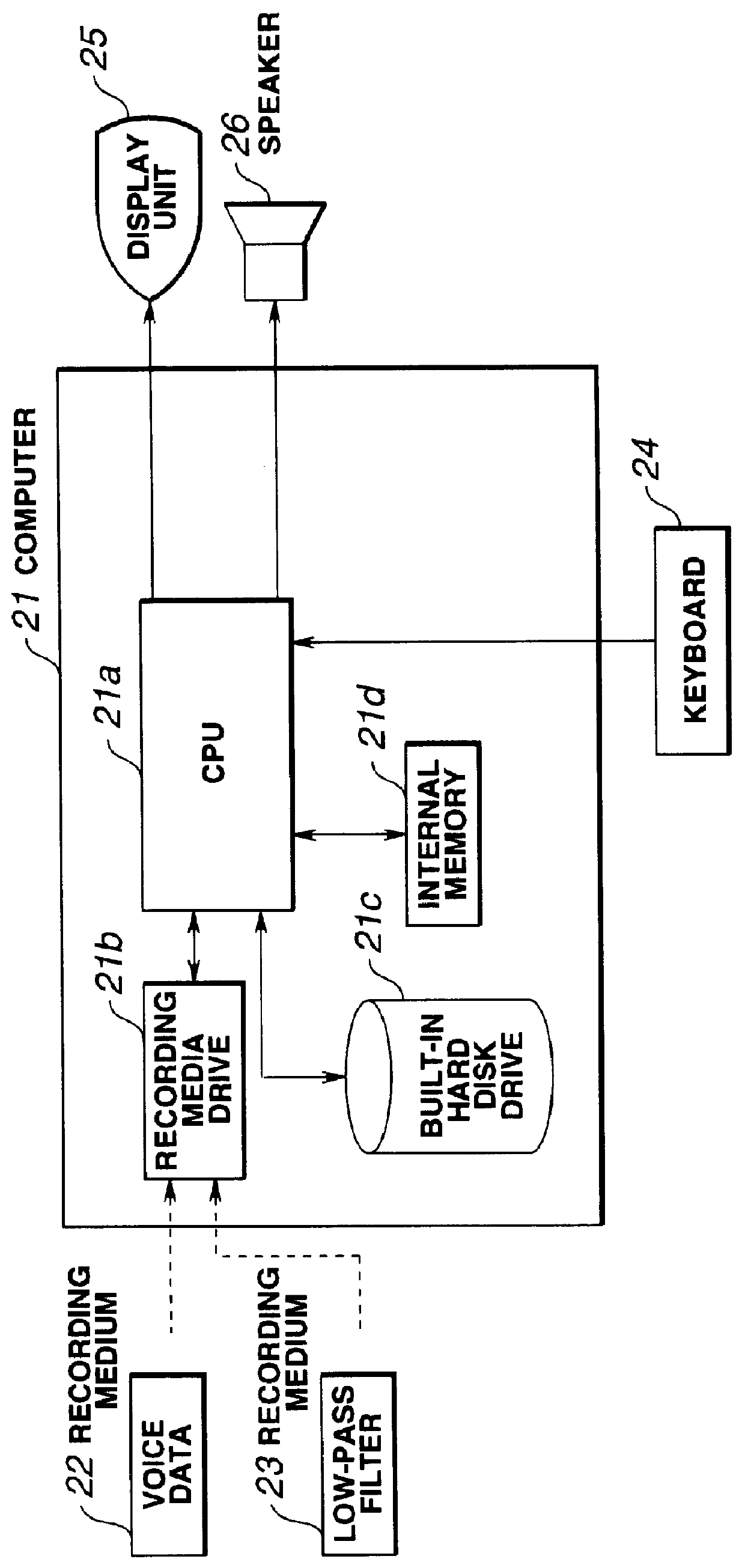

Noise suppression apparatus and recording medium recording processing program for performing noise removal from voice

InactiveUS6044341AIncreasing auditory sound qualityImprove sound qualitySpeech recognitionTransmission noise suppressionDiscriminatorFrequency spectrum

A noise suppression apparatus of the present invention includes a voice / non-voice discriminator for discriminating a frame signal divided into frames having a predetermined length; a Fourier transform unit for converting a frame signal into a spectrum; a noise spectrum estimation unit for estimating a noise spectrum of a frame judged as a non-voice signal; an amplitude spectrum subtractor for subtracting the product of an estimated noise spectrum and a predetermined coefficient from a spectrum obtained by the transform unit; an auditory correction noise adder for adding aa auditory correction noise spectrum to a spectrum outputted from the subtractor; and an inverse Fourier transform unit for performing inverse Fourier transform to an output of the adder. The noise suppression apparatus further includes a negative amplitude value counter for counting the number of frequency components in an output of the subtractor whose amplitude values are negative; a subtraction coefficient setting unit for gradually decreasing a subtraction coefficient unit the counted value becomes not more than a predetermined value; an inverse Fourier transform unit for performing inverse Fourier transform to an output of the counter; and a noise spectrum estimation unit for calculating spectrum information of noise in the frame signal using different spectrum information according to the current type of frame signal.

Owner:OLYMPUS CORP

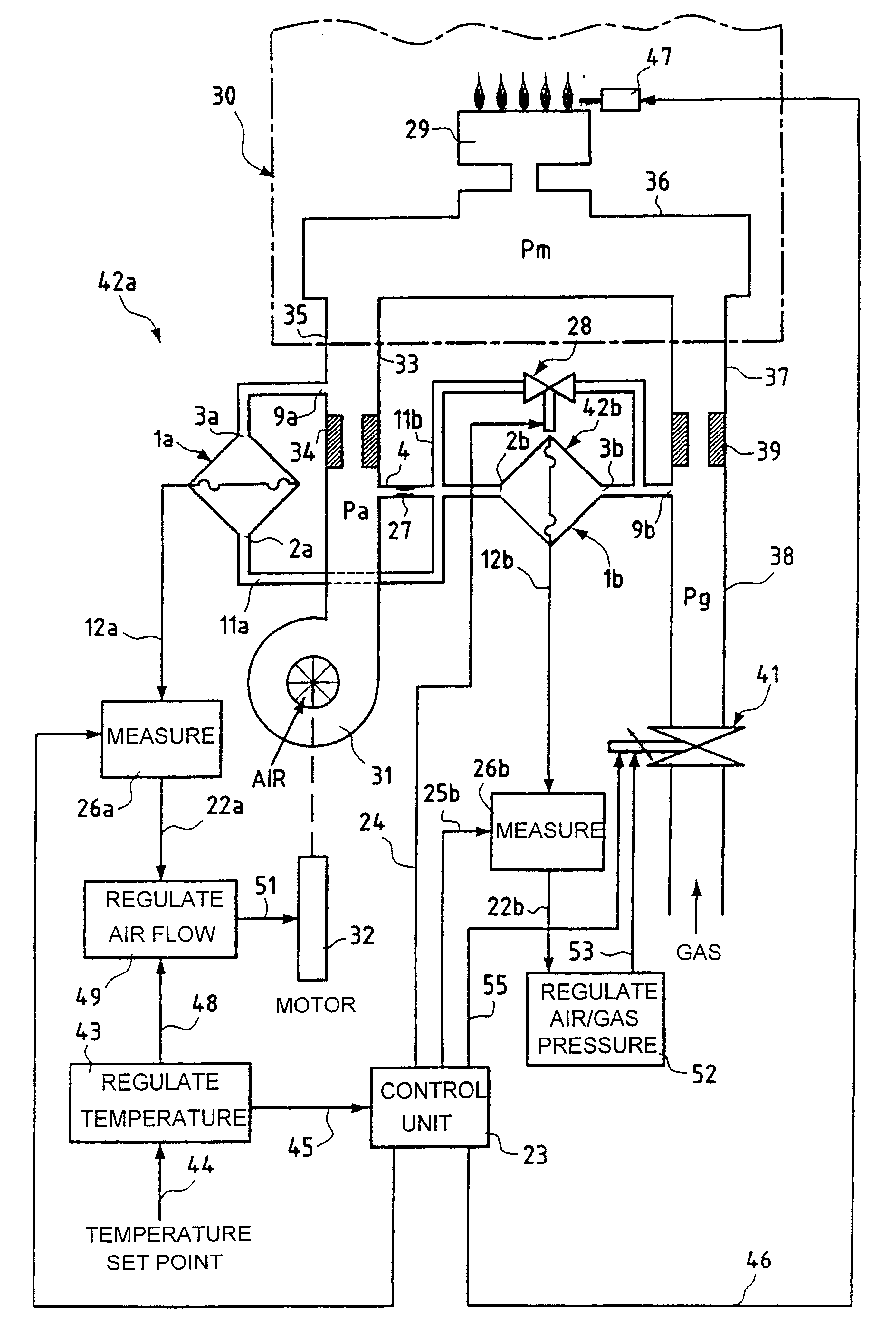

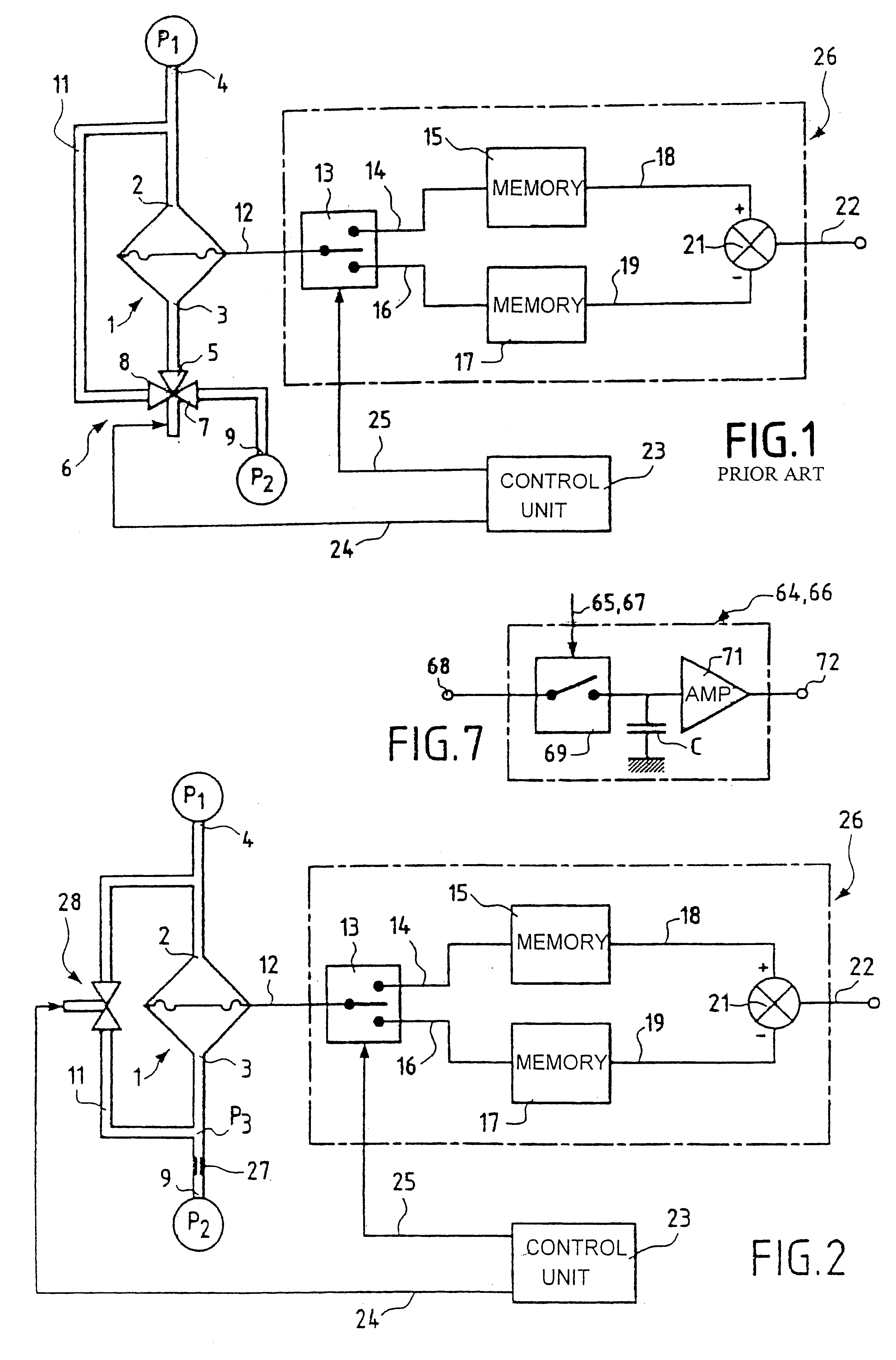

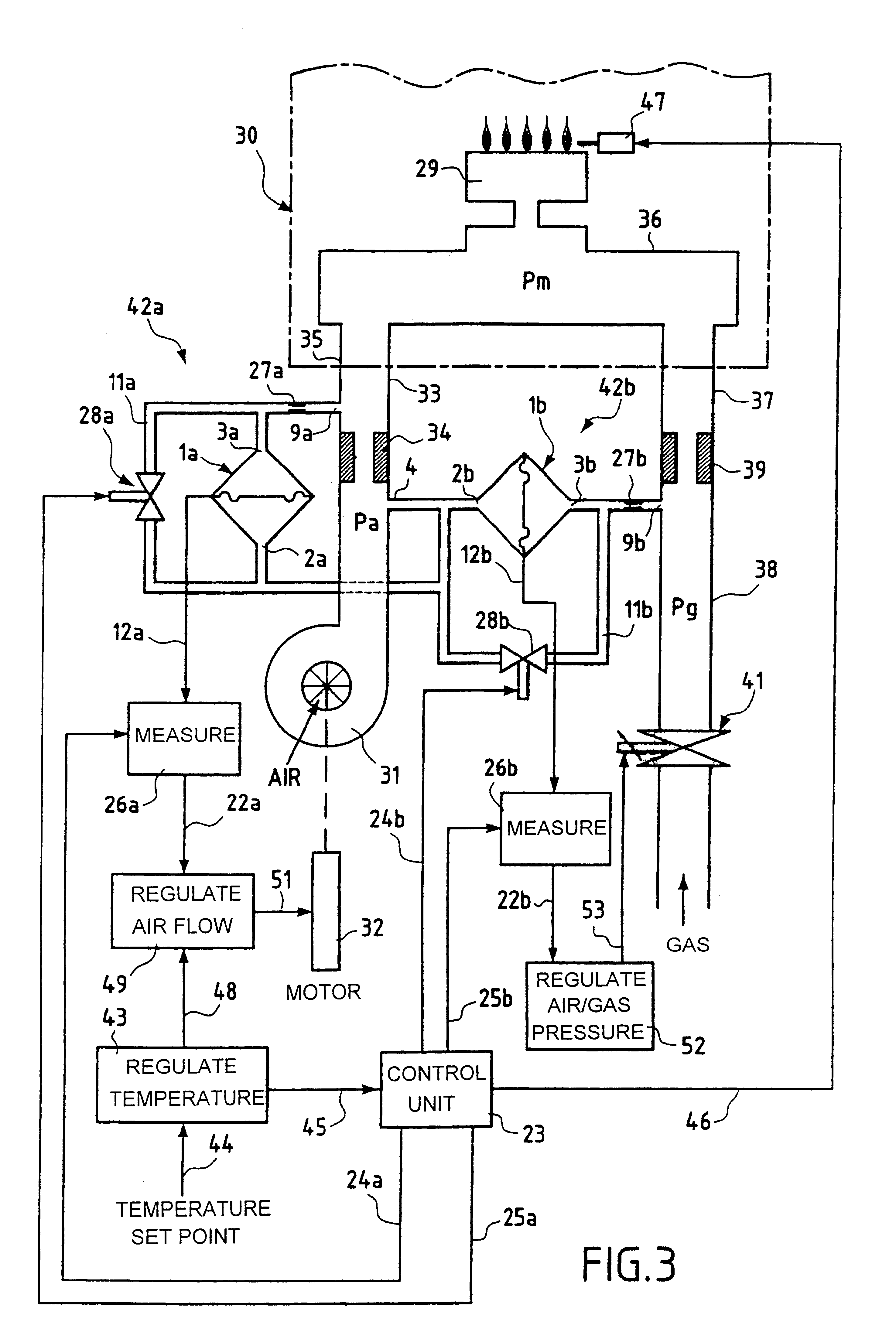

System for active regulation of the air/gas ratio of a burner including a differential pressure measuring system

InactiveUS6533574B1Simpler and less-costlyLess costlyFuel supply regulationCombustion ventilatorsCombustorDifferential pressure

The system for active regulation of the air / gas ratio of a burner comprises one or two differential pressure measuring systems each of which has a differential pressure sensor with two inlet orifices. The orifices are respectively connected to pressure ports in one of which there is a calibrated throttling orifice. The regulator system comprises a 2-channel valve which, when closed, isolates the two inlet orifices from each other, and, when open, connects them to each other. A measurement circuit is provided and has memory means for storing at least two values of the output signal of the sensors, a control unit for switching the valve and controlling the storage of a first value of an output signal of the sensor in the memory means when the valve is closed and the storage of a second value of the output signal of the sensor when the valve is open, and subtractor means for calculating the difference between the two stored values of the output signal of the sensor and thereby eliminating any drift. In a preferred variant, the regulator system includes only one differential pressure measuring system.

Owner:A THEOBALD

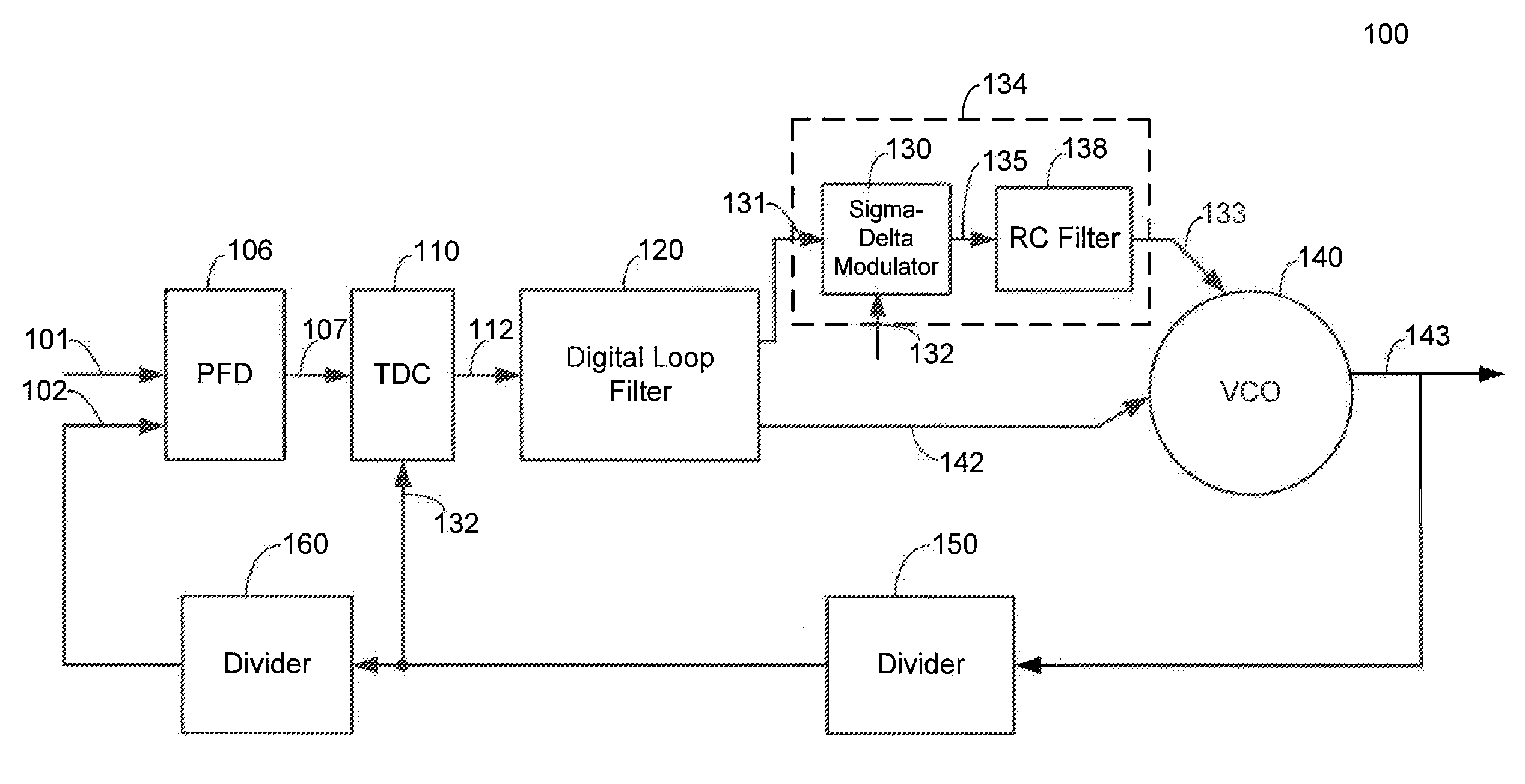

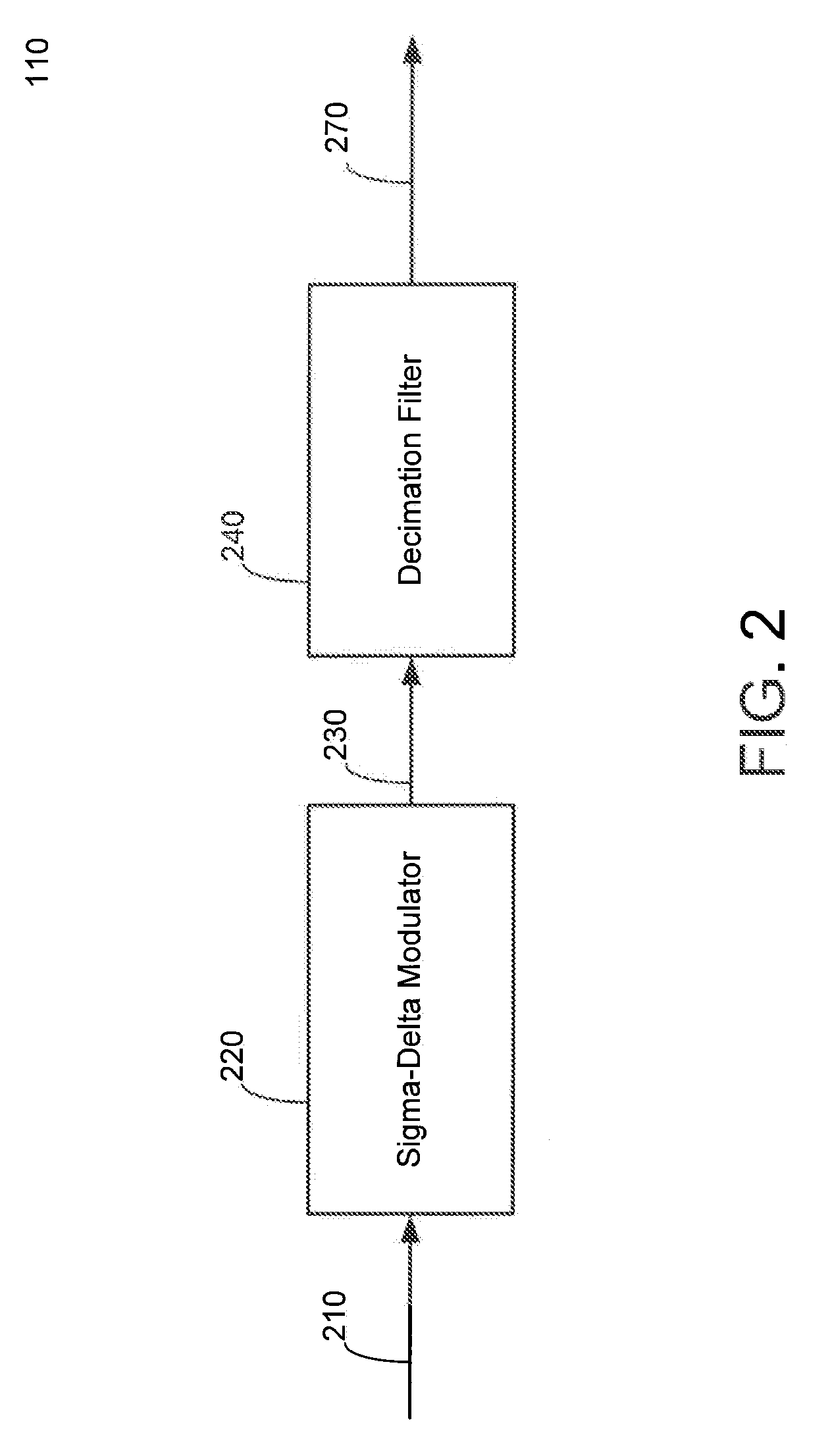

Systems, Circuits, and Methods for a Sigma-Delta Based Time to Digital Converter

ActiveUS20130257494A1Electric signal transmission systemsPulse automatic controlIntegratorEngineering

Systems, methods, and circuits provide a time to digital converter comprising a sigma-delta modulator. The sigma-delta based time to digital converter may receive an analog signal representing a phase error between a reference clock signal and a feedback clock signal and generate a digital signal representing the phase error. The sigma-delta modulator may comprise a subtractor, an integrator, a feedback path, and a quantizer. The subtractor may receive the analog signal and subtract a feedback signal from the analog signal and the integrator may integrate the output of the subtractor. The sigma-delta modulator may accumulate a voltage or a charge over a capacitor as pulses are received from the analog signal and after a number of clock cycles, the capacitor may be discharged to generate a pulse in an output signal.

Owner:AVAGO TECH INT SALES PTE LTD

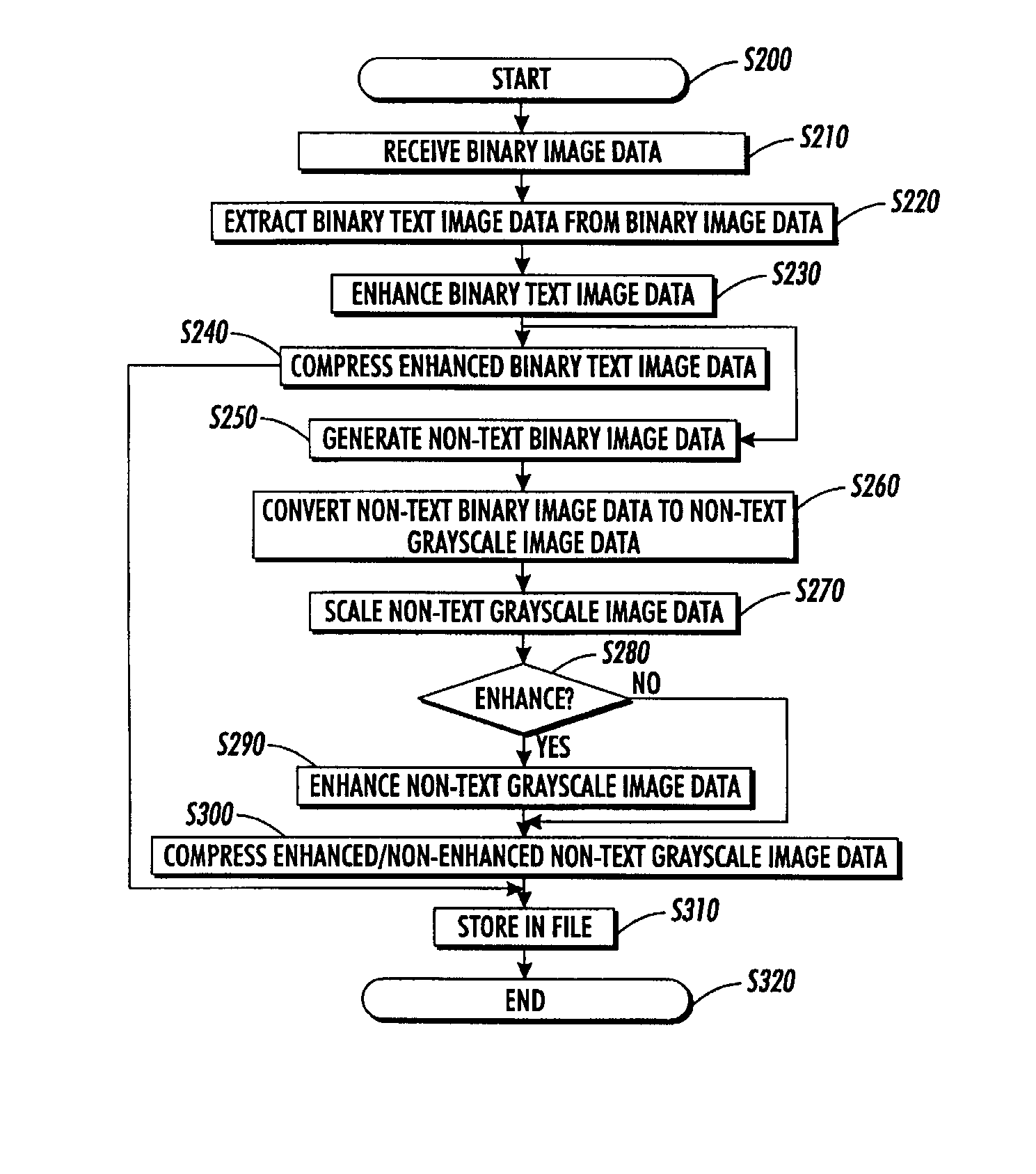

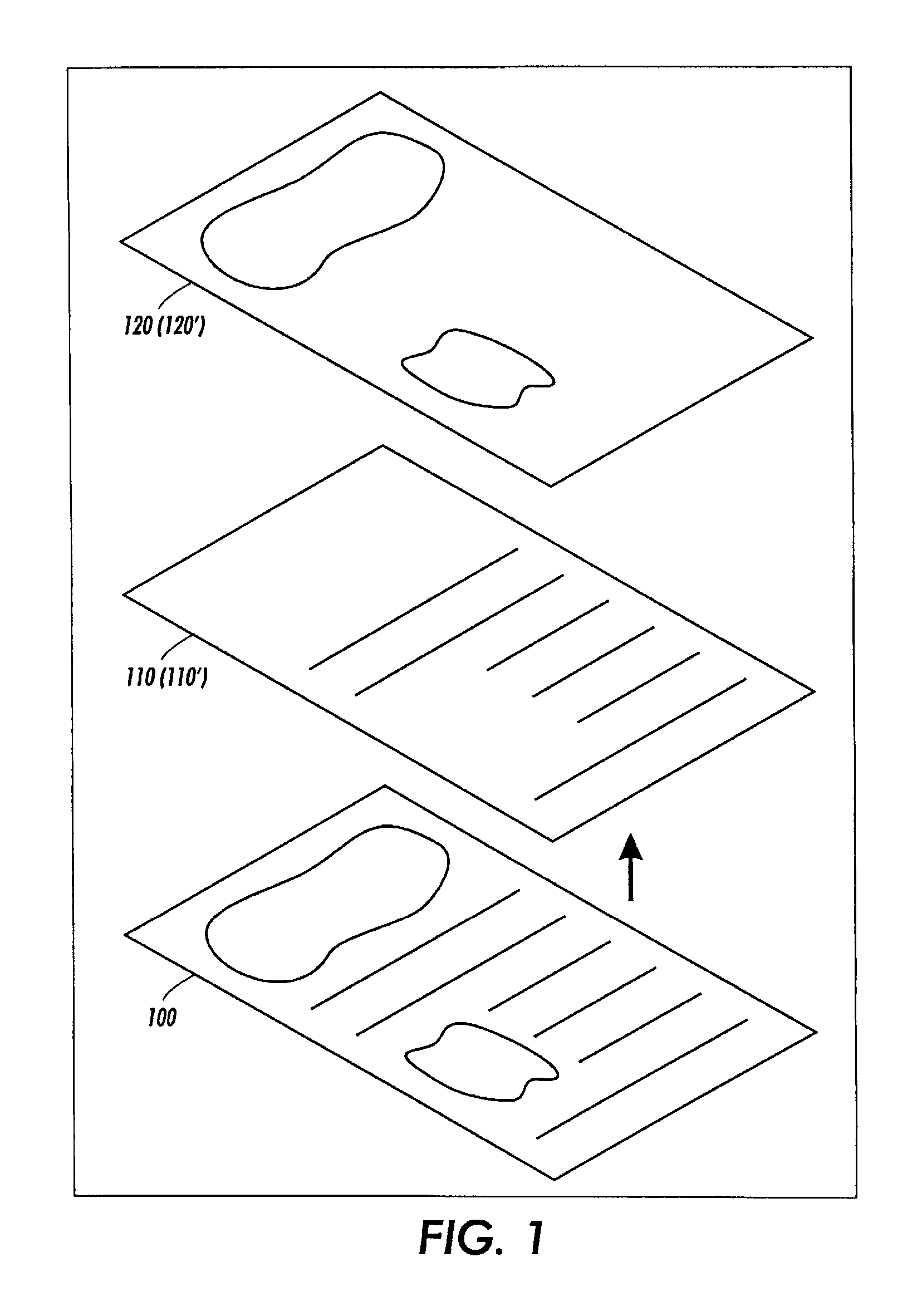

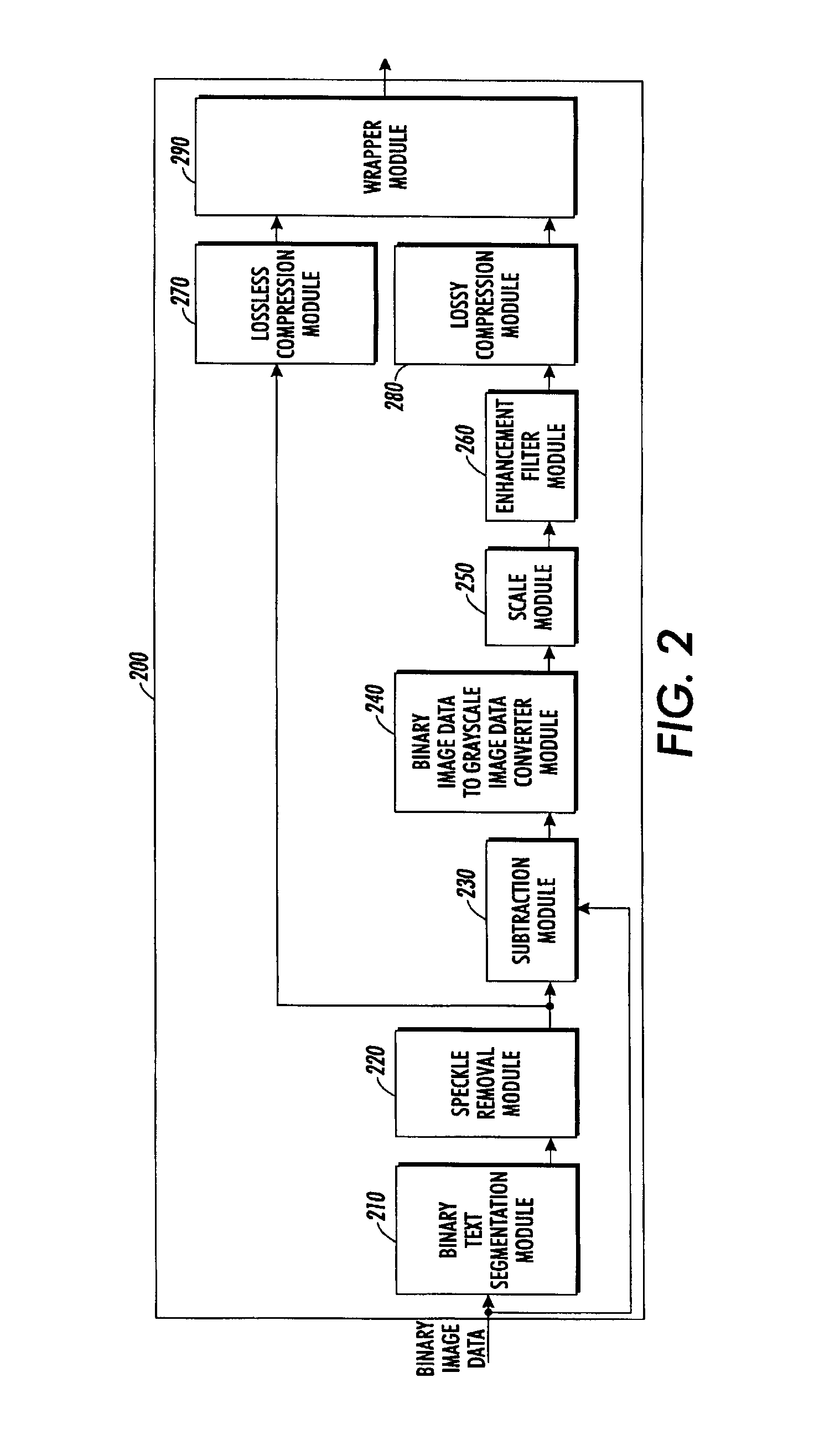

Reformatting binary image data to generate smaller compressed image data size

InactiveUS20050244060A1Stable changeEnhancing binary image data image dataCharacter and pattern recognitionPulse conversionComputer visionImaging data

In various exemplary embodiments, systems include a segmentor to segment text binary image data to a first plane. A subtractor subtracts text binary image from binary image data to generate a non-text binary image data in a second plane. A converter converts non-text binary image data in the second plane into non-text gray scale image data in the second plane. A first compressor compresses the text gray scale image data in the first plane. A second compressor compresses the non-text gray scale mage in the second plane.

Owner:XEROX CORP

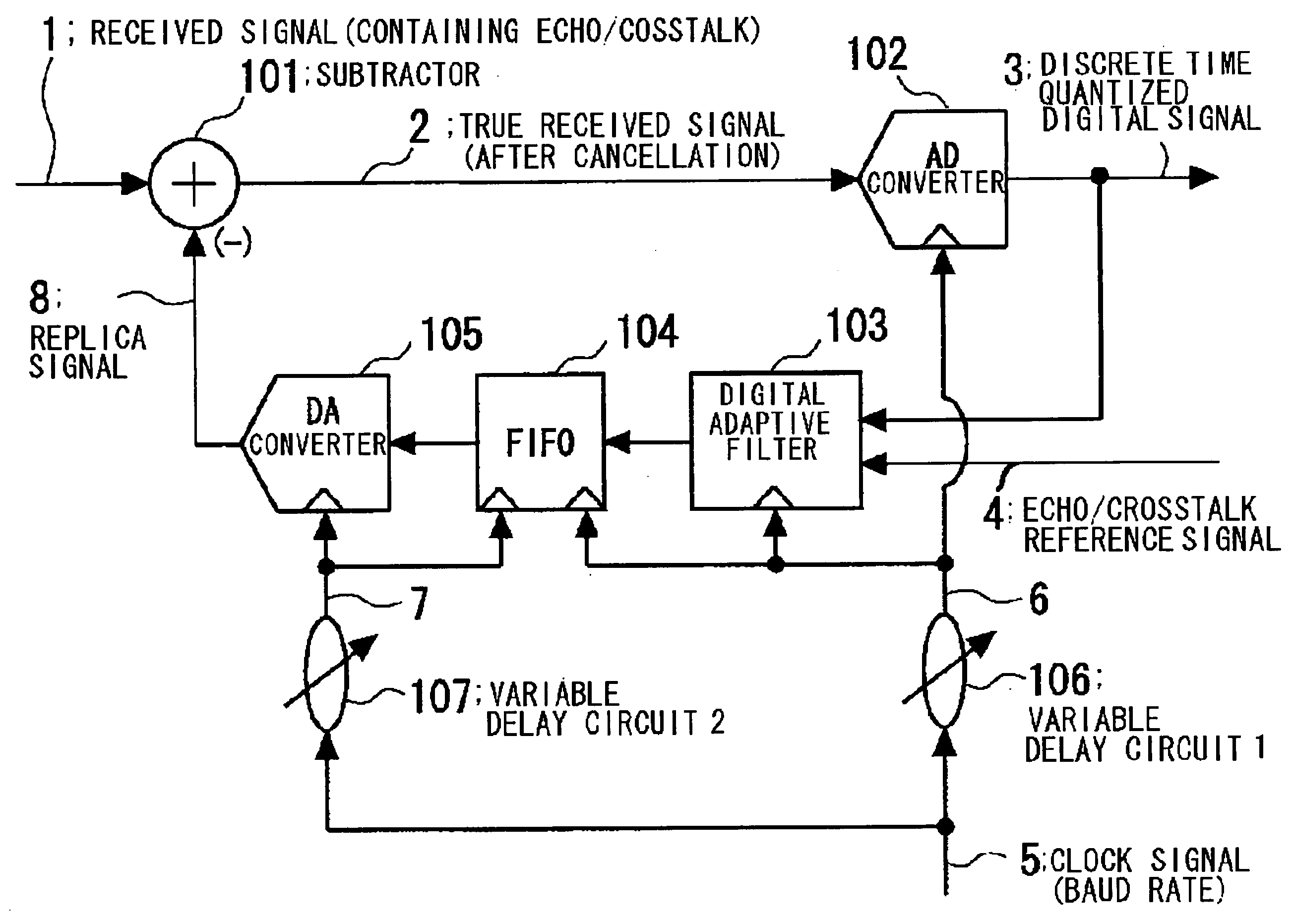

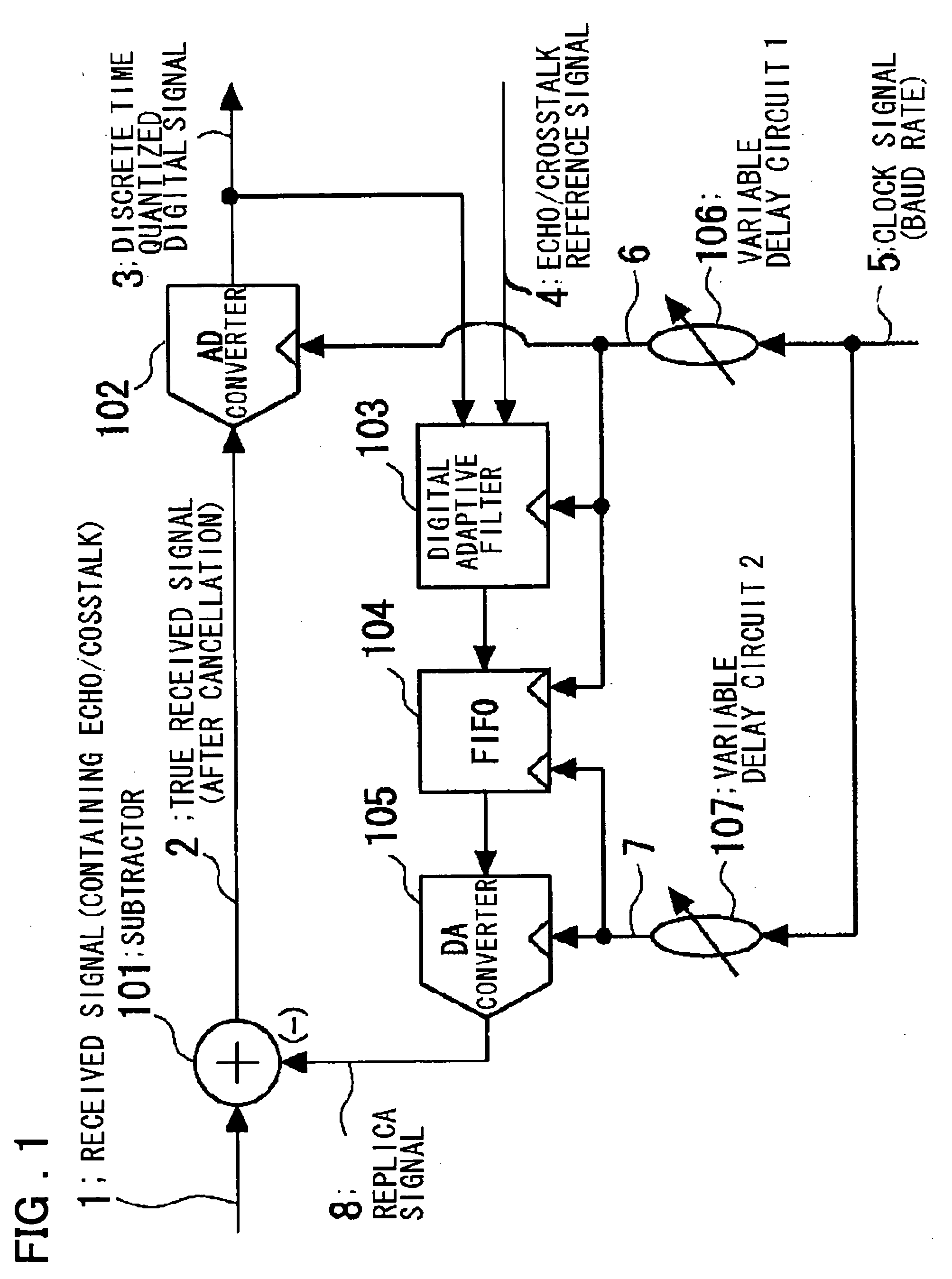

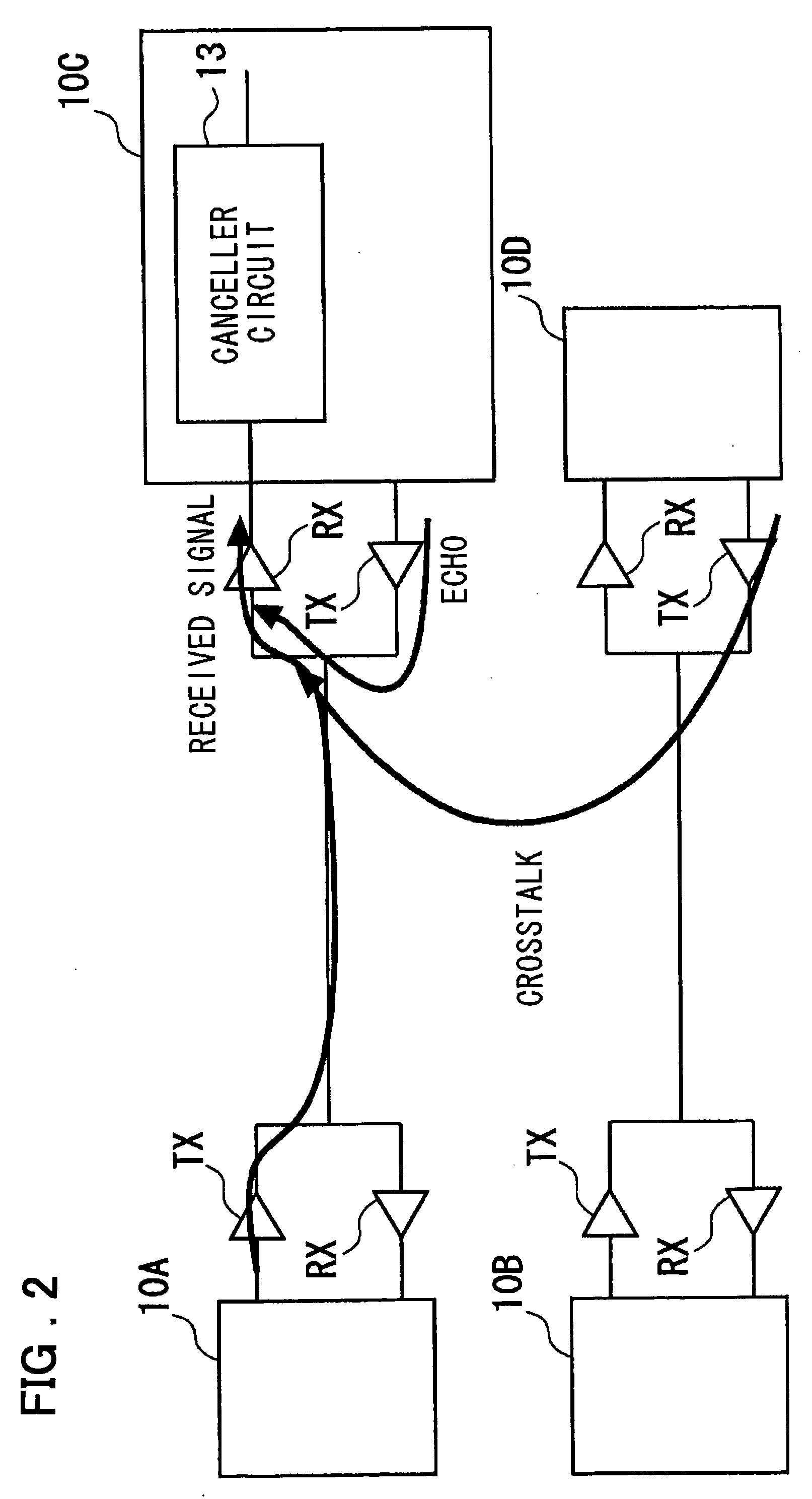

Canceller circuit and controlling method

InactiveUS20050099967A1Easy to integrateAdaptive networkCross-talk reductionAdaptive filterEngineering

Disclosed is a device in which overasampling is not needed and in which the echo / crosstalk of a continuous time analog waveform may be canceled at a baud rate. There are provided a continuous time analog subtractor, an AD converter for converting an analog signal from a subtractor to a digital signal, an adaptive filter receiving a digital output signal from the AD converter and an echo / crosstalk reference signal and having adaptively variable filter coefficients, a FIFO in which a digital output signal from the FIFO is written in first-in first-out and in which a write and read clocks are interchanged, a D / A converter for converting the digital output signal from the FIFO to an analog signal to output the analog signal, and first and second variable delay circuits for variably delaying an input clock signal to output the delayed signals as first and second clock signals. The first clock signal is supplied to the AD converter, adaptive filter and to the FIFO, while the second clock signal is supplied to the FIFO and to the DA converter as sampling clock. A received signal, containing the echo-crosstalk, and a replica signal of the echo-crosstalk, output from the D / A converter, is supplied to the subtractor. A true received signal, which is the received signal from which the echo / crosstalk has been cancelled, is supplied to the AD converter.

Owner:RENESAS ELECTRONICS CORP

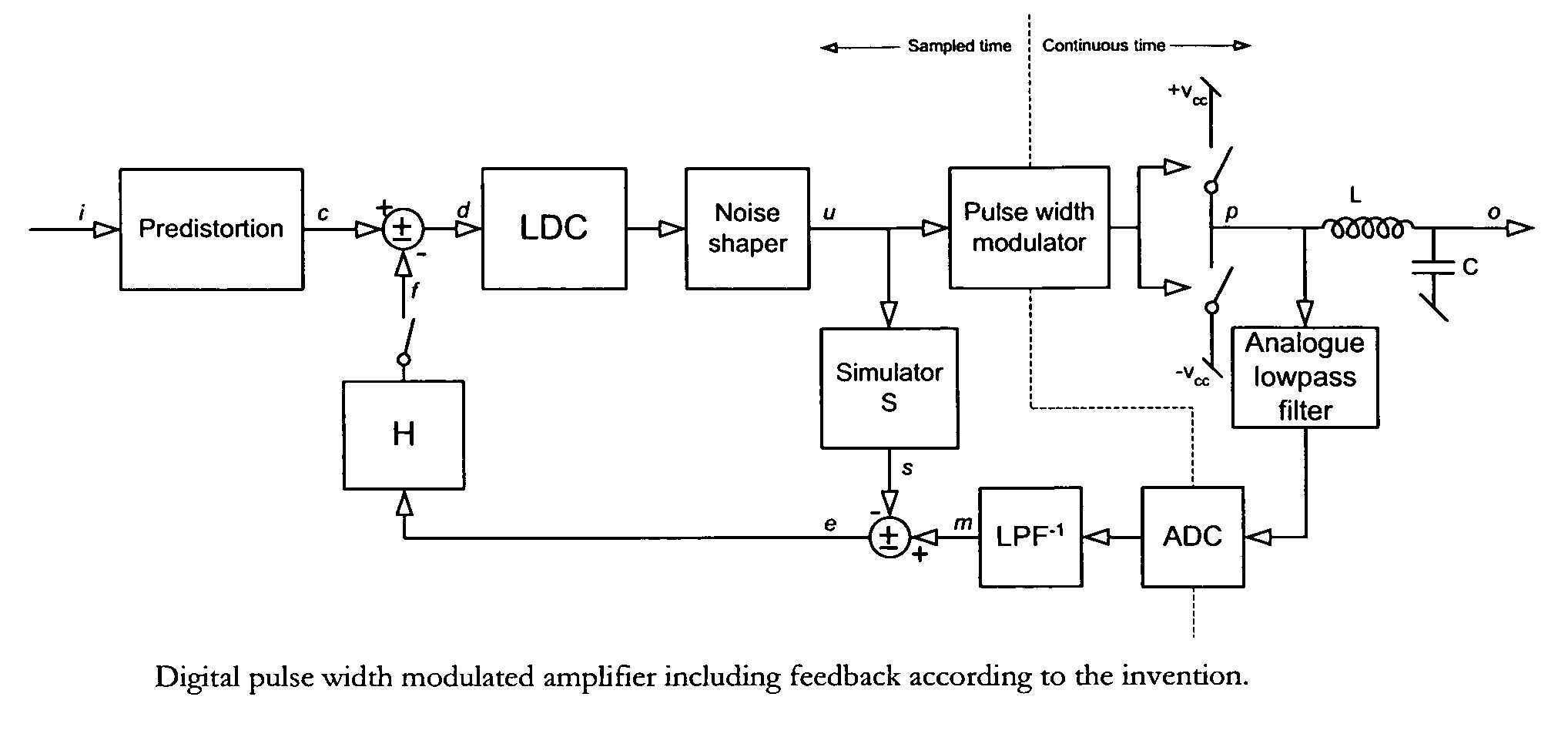

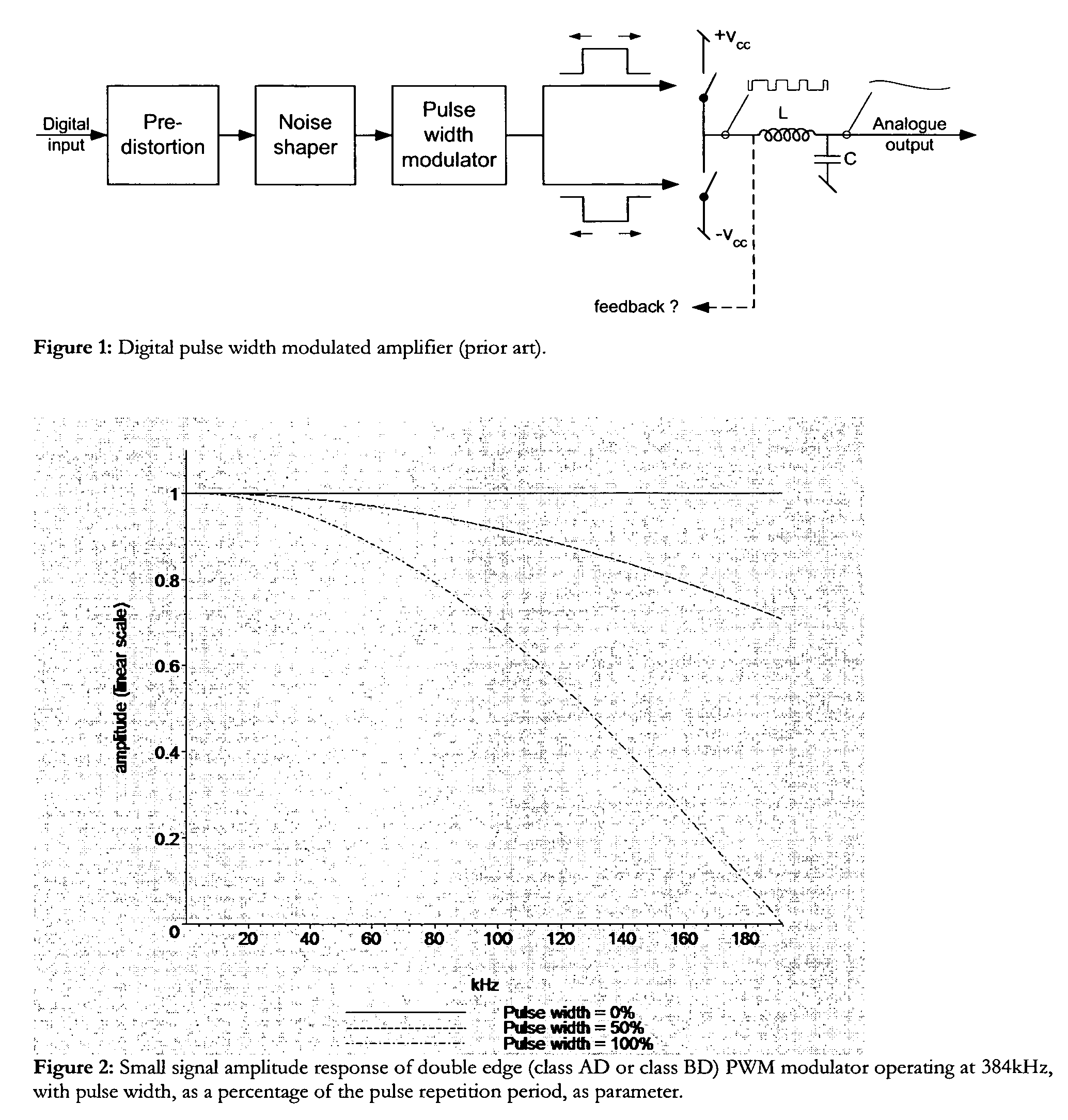

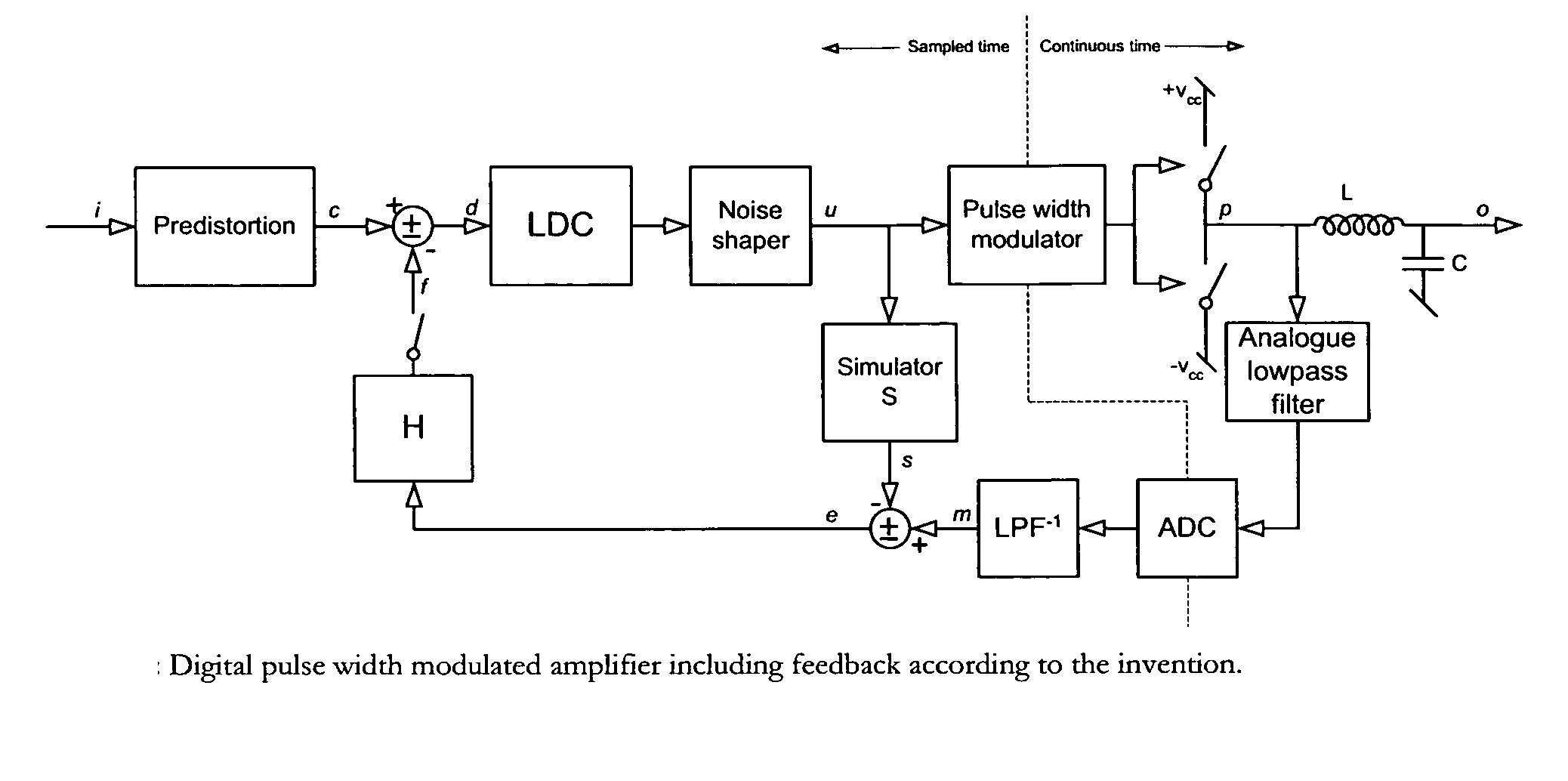

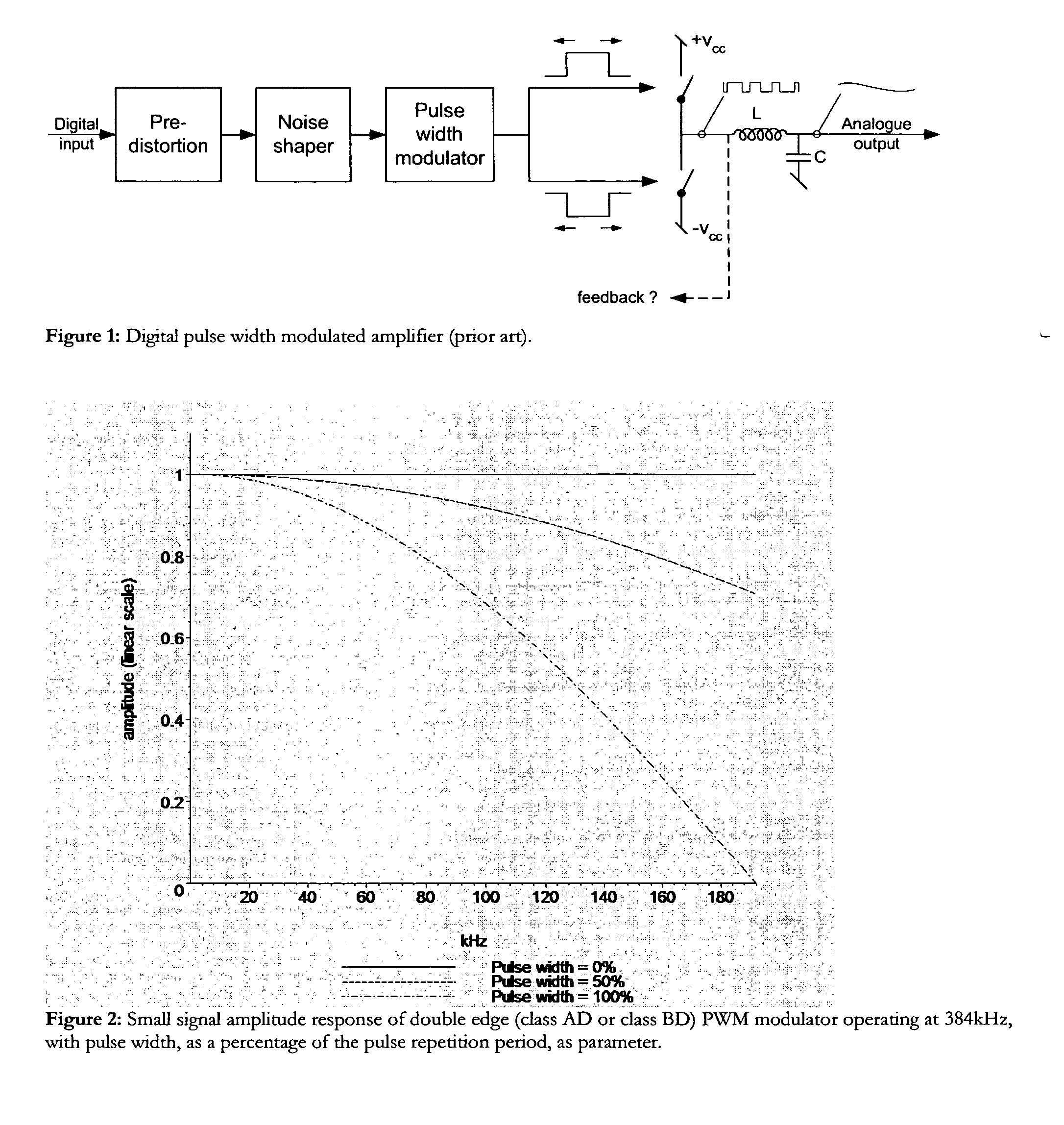

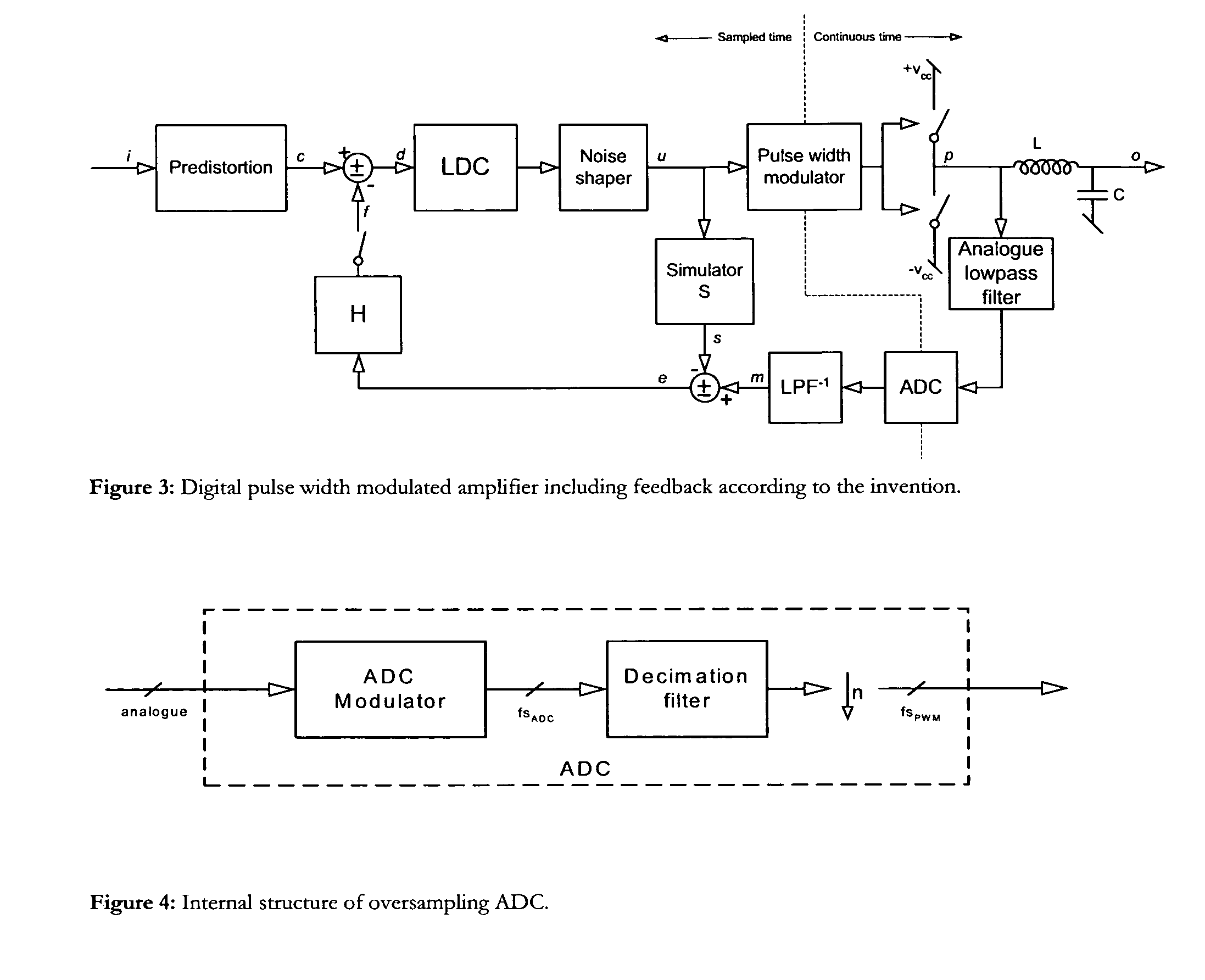

Digital PWM amplifier with simulation-based feedback

InactiveUS7286009B2Compensation delayAmplifier modifications to reduce non-linear distortionNegative-feedback-circuit arrangementsAudio power amplifierNoise shaping

Systems and methods for performance improvements in digital switching amplifiers using simulation-based feedback. In one embodiment, a digital pulse width modulation (PWM) amplifier includes a signal processing plant configured to receive and process an input audio signal. The amplifier also includes a simulator configured to model processing of audio signals by the plant. The outputs of the plant and the simulator are provided to a subtractor, the output of which is then added to the input audio signal as feedback. The plant may consist of a modulator and power switch, a noise shaper, or any other type of plant. An analog-to-digital converter (ADC) may be provided to convert the output audio signal to a digital signal for input to the subtractor. Filtering may be implemented before or after the ADC, and a decimator may be placed after the ADC if it is an oversampling ADC.

Owner:INTERSIL INC

Video coding method and video decoding method

InactiveCN101822061ATelevision systemsDigital video signal modificationPattern recognitionVideo encoding

Owner:PANASONIC CORP

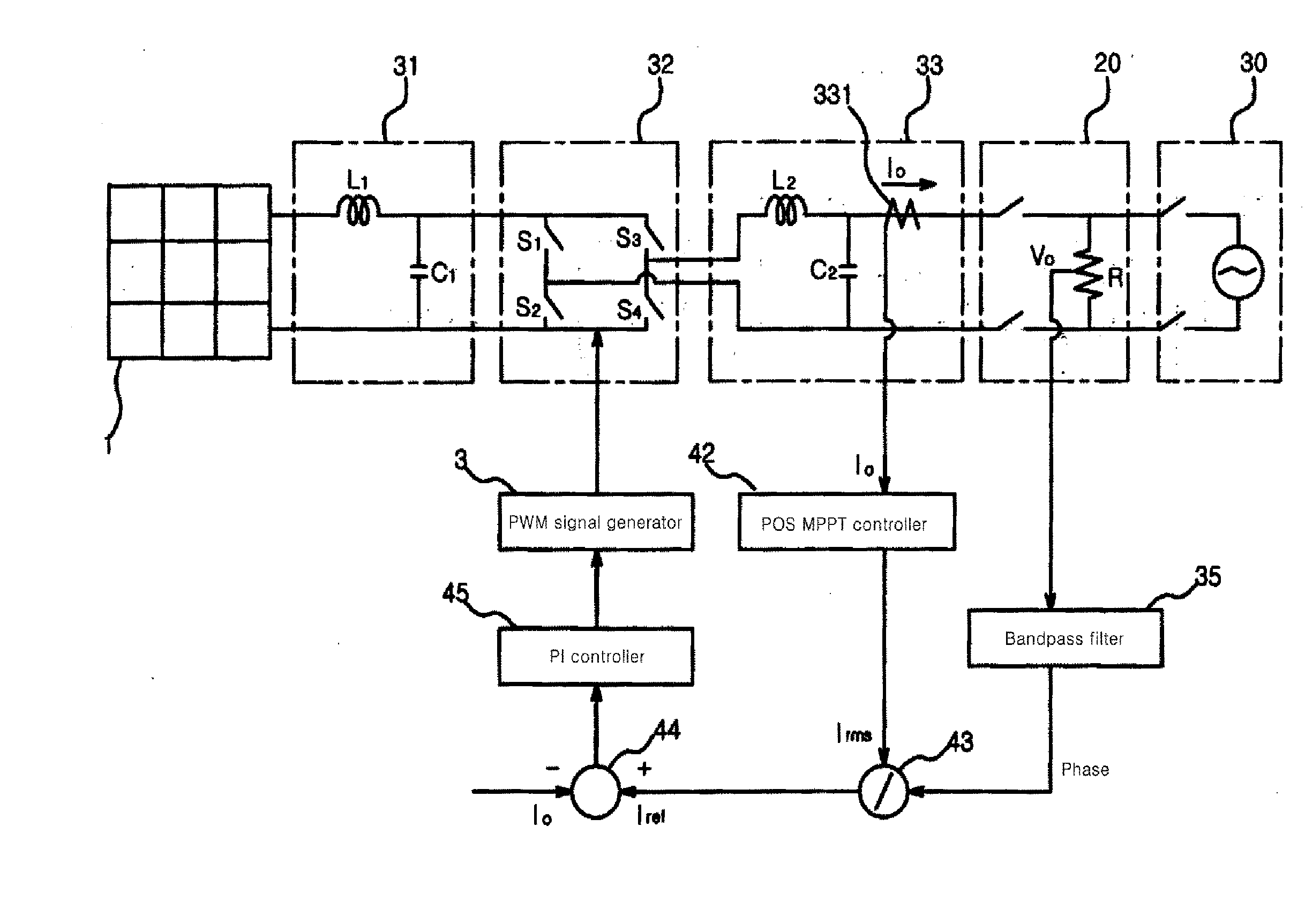

Controlling Apparatus of a Power Converter of Single-Phase Current For Photovoltaic Generation System

InactiveUS20080278983A1Insufficient ratioReduce installation costsBatteries circuit arrangementsBoards/switchyards circuit arrangementsBandpass filteringReference current

A control apparatus of a single-phase power converter for a photovoltaic power generation system is disclosed, including a POS MPPT controller for calculating a rating current by applying a POS MPPT control method to an output current detected through a current transformer of a single-phase AC filter, a bandpass filter for filtering only signals of a low-frequency band from a load, a single-phase reference current generator for producing a reference current by matching a phase of the current from the POS MPPT controller to a phase from the bandpass filter, a single-phase current subtractor for subtracting an output current of a current transformer from the reference current calculated by the single-phase reference current generator to thereby calculate a difference current between the output current of the current transformer and the reference current, a PI controller for outputting a control signal, corresponding to the difference current from the single-phase current subtractor, to a PWM signal generator, and the PWM signal generator for generating a PWM phase control signal corresponding to the control signal from the PI controller.

Owner:CHANG WON NAT UNIV BUSINESS ADMINISTRATION

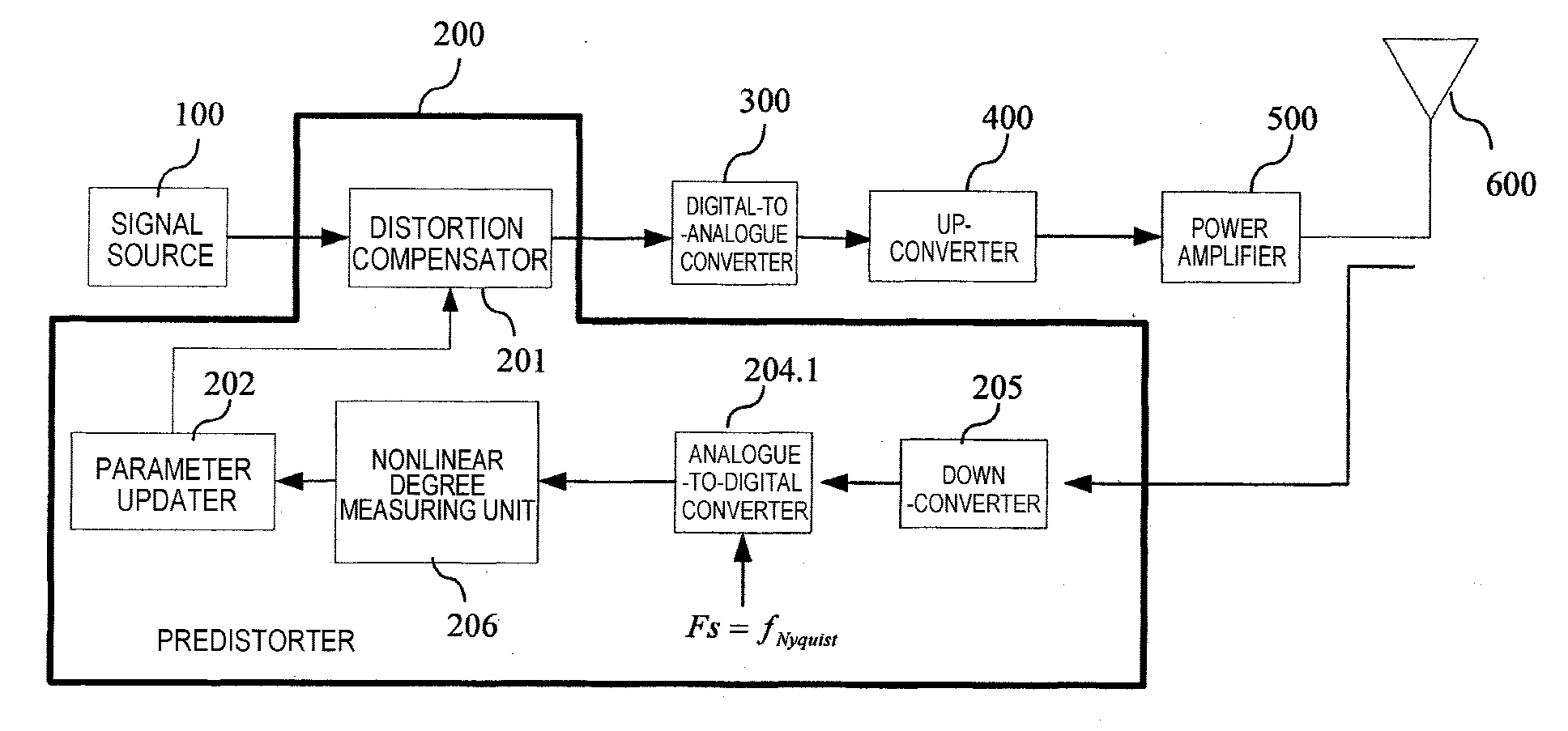

Nonlinear Degree Measuring Apparatus And Method For A Power Amplifier, Predistortion Compensation Apparatus

InactiveUS20100039100A1Low costReduce power consumptionNegative-feedback-circuit arrangementsCurrent/voltage measurementMeasurement deviceAudio power amplifier

This invention relates to a nonlinear degree measuring apparatus and method for a power amplifier, and a predistortion compensation apparatus. The nonlinear degree measuring apparatus comprises a delayer (304), for delaying inputted pilot frequency data; a subtracter (305), for subtracting, from the pilot frequency data delayed by the delayer, subsequently inputted pilot frequency data; a power calculating unit (306), for calculating an instantaneous power of an outputted signal from the subtracter (305); and an averager (307), for averaging the instantaneous power calculated by the power calculating unit (306) to obtain an averaged power.

Owner:FUJITSU LTD

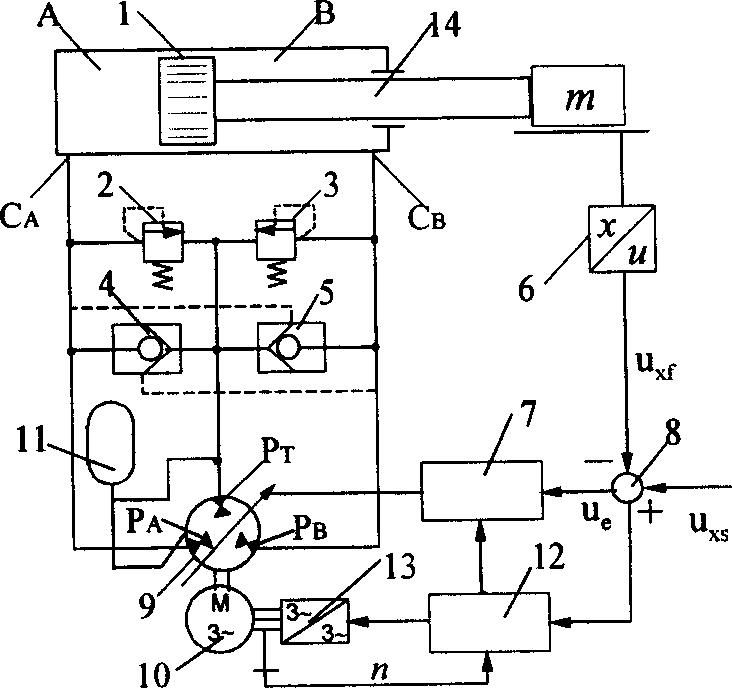

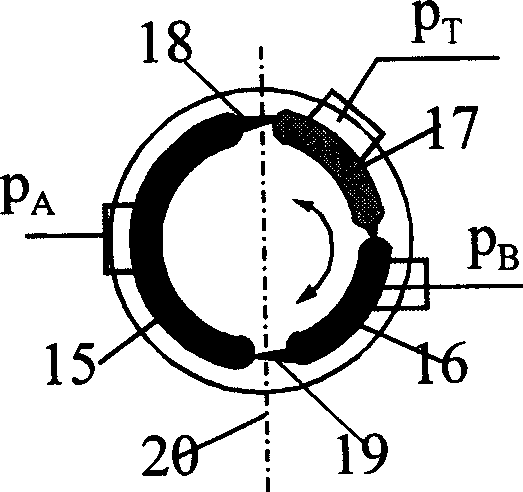

Closed electrohydraulic controlling system

InactiveCN1818382AControl movementPromote sportsFluid-pressure actuatorsPump controlHydraulic cylinderControl system

A closed electro-hydraulic control system comprised a differential hydraulic cylinder, two safety valves, a small path fluid one-way valve, a displacement transducer, a subtractor, two controllers, a hydraulic pump, a prime motor, a low-pressure oil-supply system and a rotational speed governor. The hydraulic pump has three oil ports connected with a rod-free cavity, a rod cavity of the differential hydraulic cylinder and the low-pressure oil-supply system separately.

Owner:TAIYUAN UNIV OF TECH

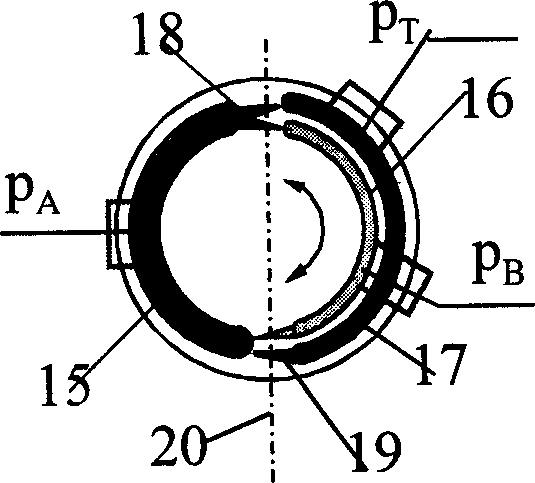

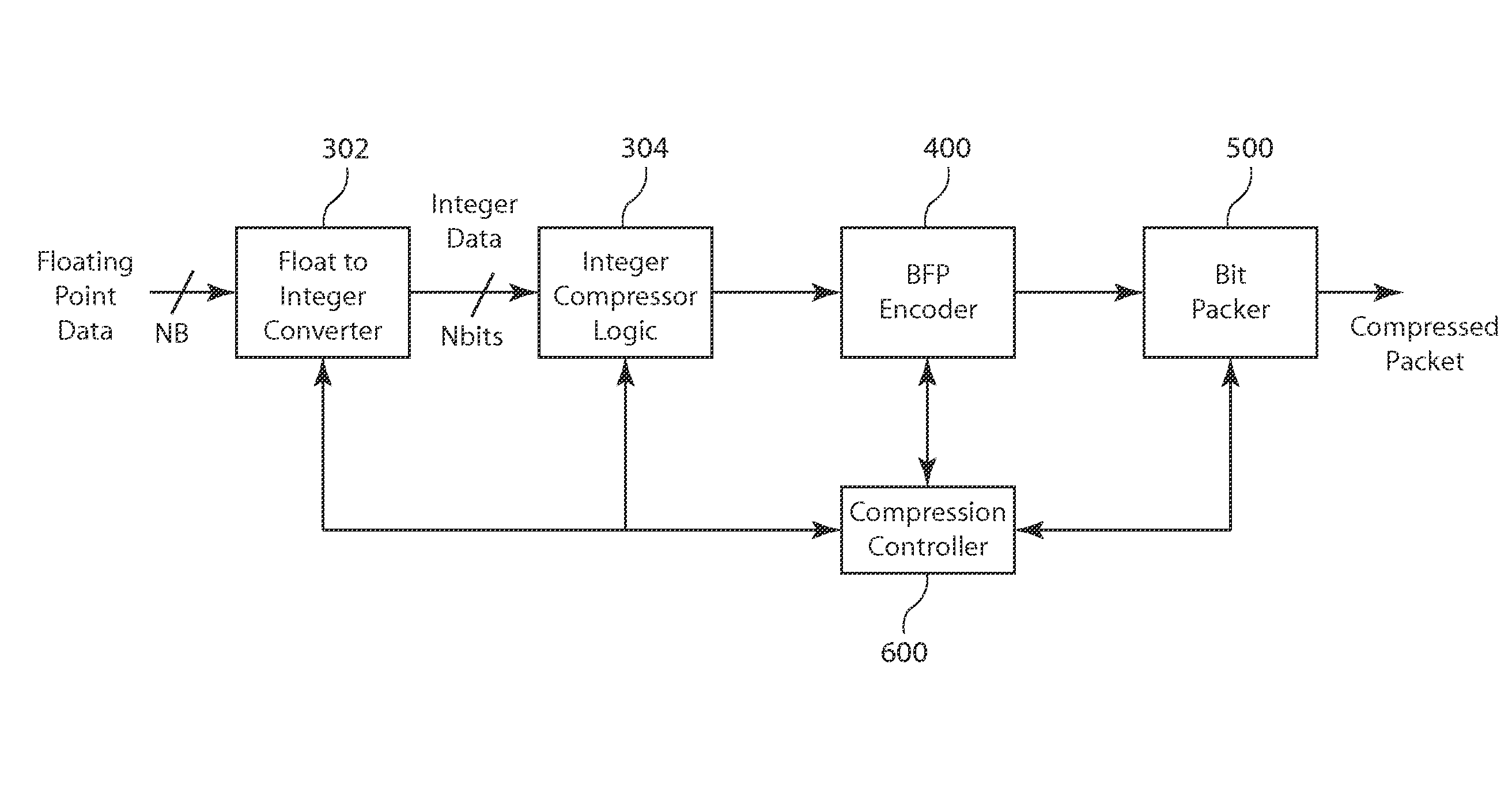

Conversion and compression of floating-point and integer data

ActiveUS20130262539A1Efficient data transferEfficient compressionDigital data processing detailsDigital computer detailsData compressionNetwork packet

Compression and decompression of numerical data can apply to floating-point or integer samples. Floating-point samples are converted to integer samples and the integer samples are compressed and encoded to produce compressed data for compressed data packets. For decompression, the compressed data retrieved from compressed data packets are decompressed to produce decompressed integer samples. The decompressed integer samples may be converted to reconstruct floating-point samples. Adaptive architectures can be applied for integer compression and decompression using one or two FIFO buffers and one or two configurable adder / subtractors. Various parameters can adapt the operations of adaptive architectures as appropriate for different data characteristics. The parameters can be encoded for the compressed data packet. This abstract does not limit the scope of the invention as described in the claims.

Owner:ALTERA CORP

Digital PWM amplifier with simulation-based feedback

InactiveUS20070152750A1Compensation delayAmplifier modifications to reduce non-linear distortionGain controlEngineeringAnalog-to-digital converter

Systems and methods for performance improvements in digital switching amplifiers using simulation-based feedback. In one embodiment, a digital pulse width modulation (PWM) amplifier includes a signal processing plant configured to receive and process an input audio signal. The amplifier also includes a simulator configured to model processing of audio signals by the plant. The outputs of the plant and the simulator are provided to a subtractor, the output of which is then added to the input audio signal as feedback. The plant may consist of a modulator and power switch, a noise shaper, or any other type of plant. An analog-to-digital converter (ADC) may be provided to convert the output audio signal to a digital signal for input to the subtractor. Filtering may be implemented before or after the ADC, and a decimator may be placed after the ADC if it is an oversampling ADC.

Owner:INTERSIL INC

Node processors for use in parity check decoders

InactiveUS20050257124A1Solve the lack of resolutionSimple calculationError correction/detection using multiple parity bitsCode conversionMessage processingMessage passing

Techniques for implementing message passing decoders, e.g., LDPC decoders, are described. To facilitate hardware implementation messages are quantized to integer multiples of ½ ln2. Messages are transformed between more compact variable and less compact constraint node message representation formats. The variable node message format allows variable node message operations to be performed through simple additions and subtractions while the constraint node representation allows constraint node message processing to be performed through simple additions and subtractions. Variable and constraint nodes are implemented using an accumulator module, subtractor module and delay pipeline. The accumulator module generates an accumulated message sum. The accumulated message sum for a node is stored and then delayed input messages from the delay pipeline are subtracted there from to generate output messages. The delay pipeline includes a variable delay element making it possible to sequentially perform processing operations corresponding to nodes of different degrees.

Owner:QUALCOMM INC

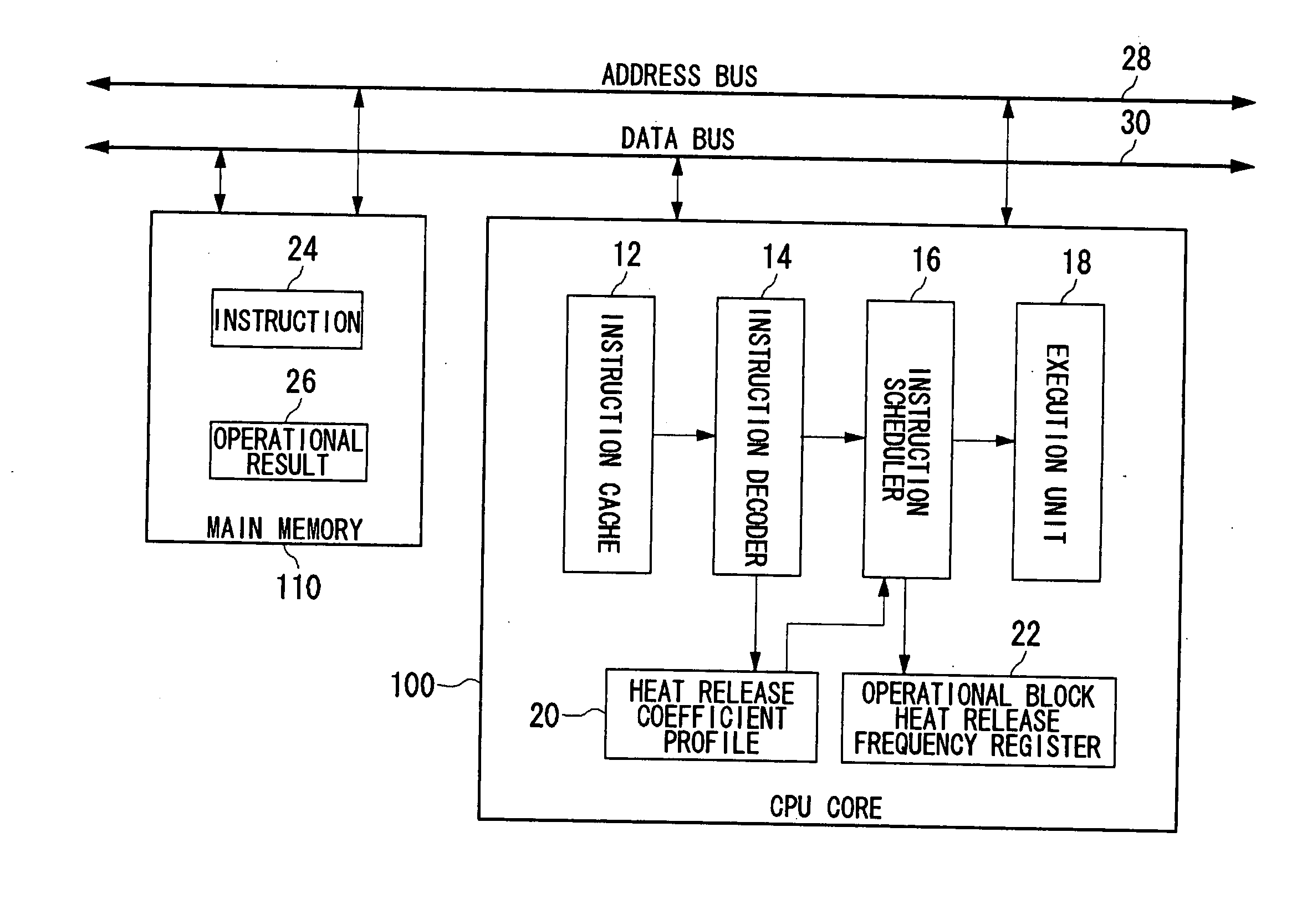

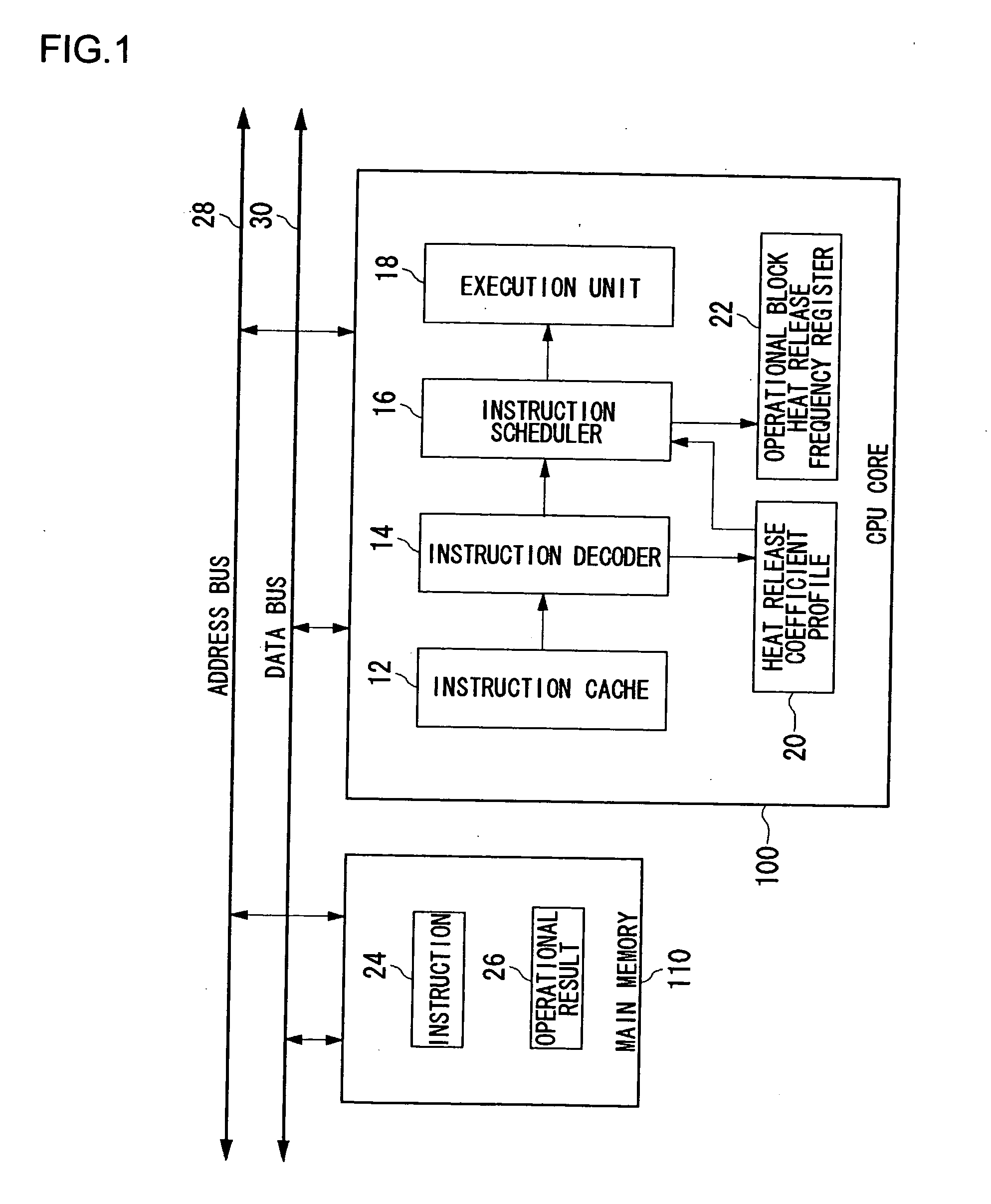

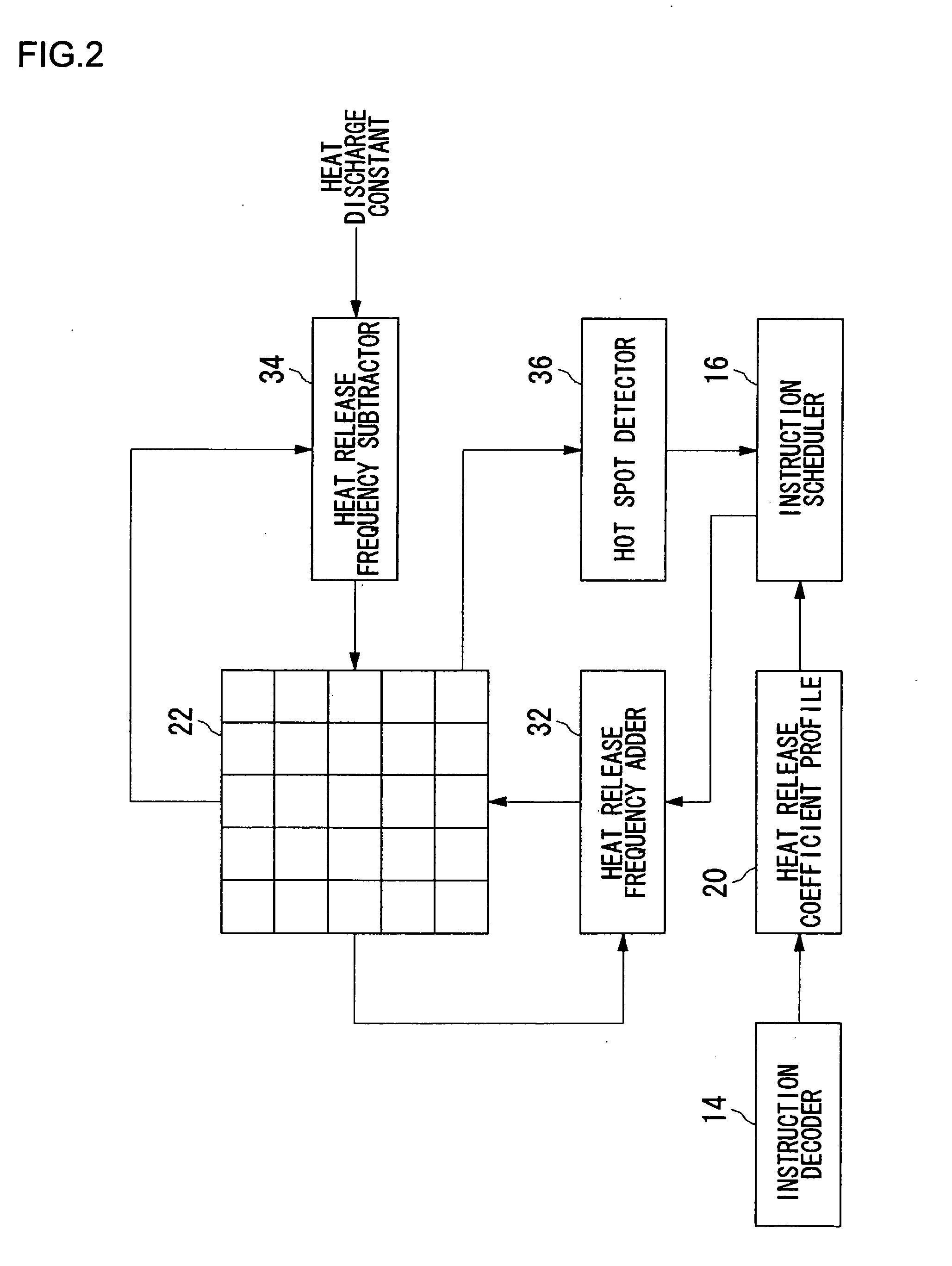

Processor, multiprocessor system, processor system, information processing apparatus, and temperature control method

InactiveUS20070198134A1Avoid misuseWithout incurring degradation in processor performanceEnergy efficient ICTResource allocationTemperature controlInformation processing

An instruction decoder identifies, for each instruction, an operational block involved in the execution of the instruction and an associated heat release coefficient. The instruction decoder stores identified information in a heat release coefficient profile. An instruction scheduler schedules the instructions in accordance with the dependence of the instructions on data. A heat release frequency adder cumulatively adds the heat release coefficient to the heat release frequency of the operational block held in the operational block heat release frequency register as the execution of the scheduled instructions proceeds. A heat release frequency subtractor subtracts from the heat release frequency of the operational blocks in the operational block heat release frequency register in accordance with heat discharge that occurs with time. A hot spot detector detects an operational block with its heat release frequency, held in the operational block heat release frequency register, exceeding a predetermined threshold value as a hot spot. The instruction scheduler delays the execution of the instruction involving for its execution the operational block identified as a hot spot.

Owner:SONY COMPUTER ENTERTAINMENT INC

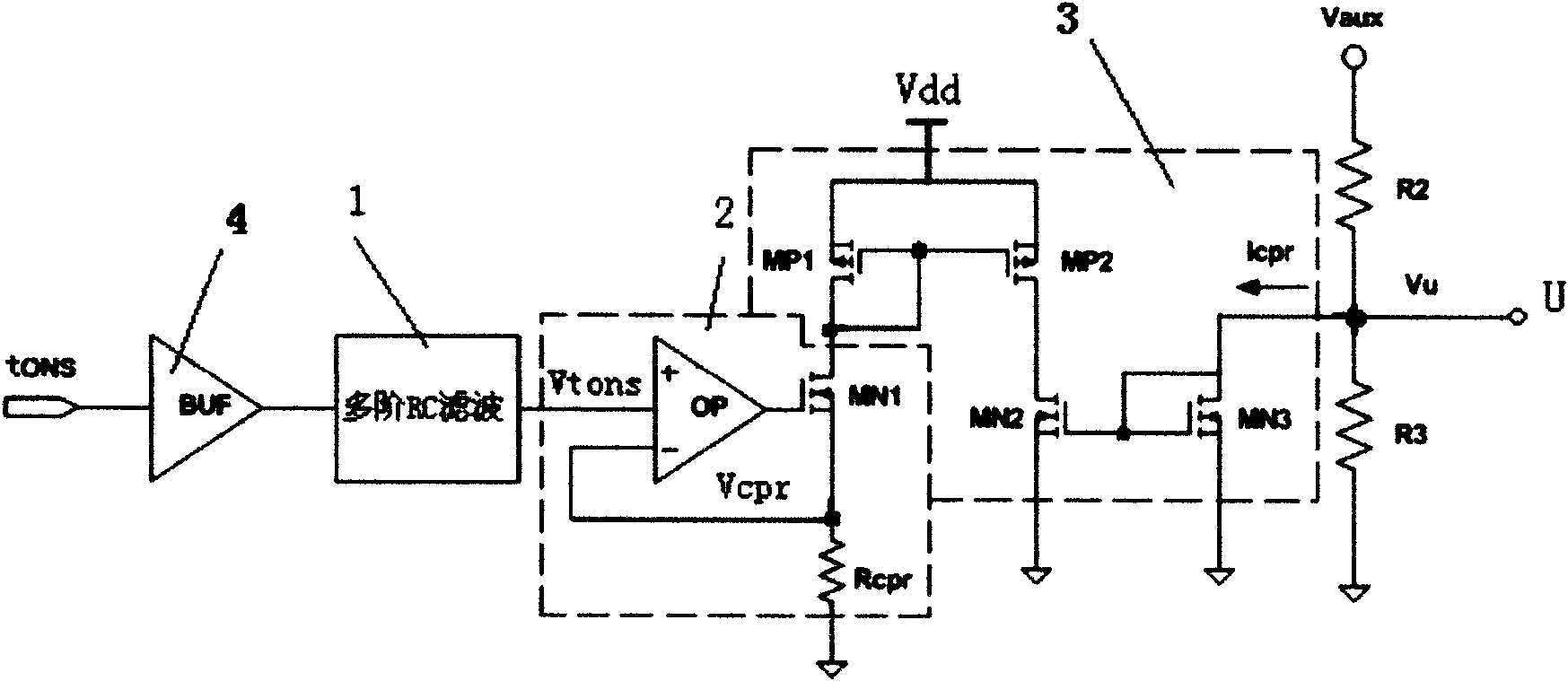

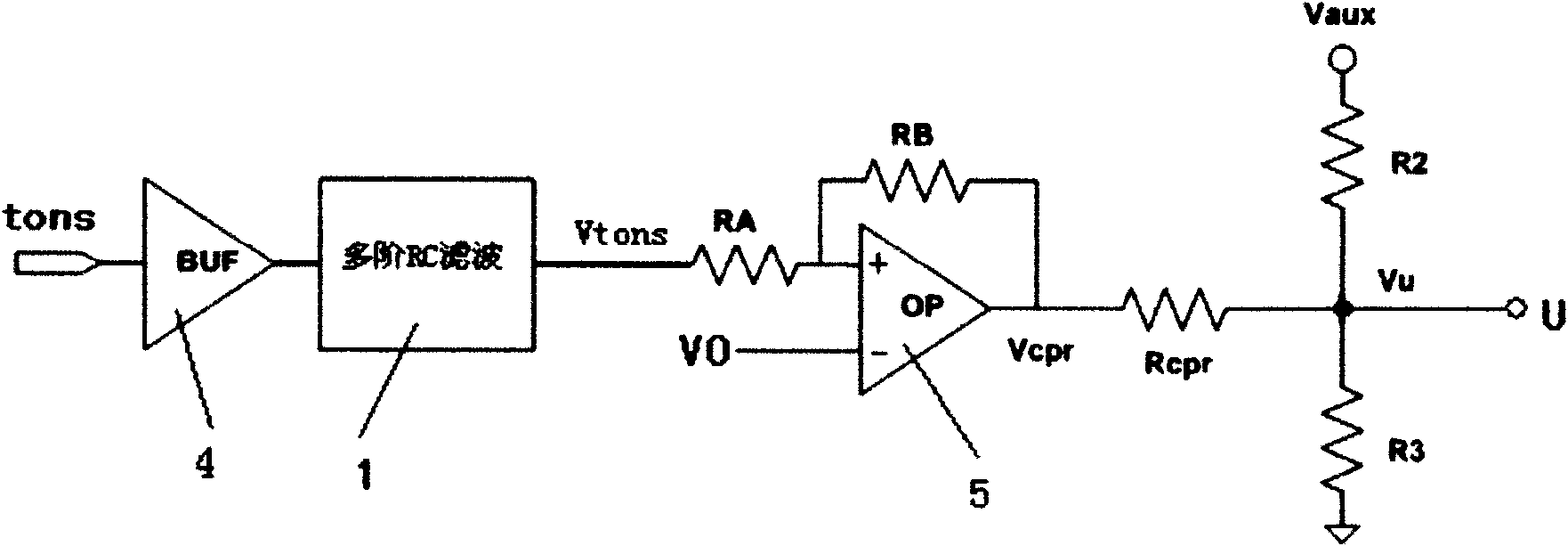

Line loss compensation circuit for switch power supply

InactiveCN101860243AImprove performanceSimple structureAc-dc conversionCapacitanceElectrical resistance and conductance

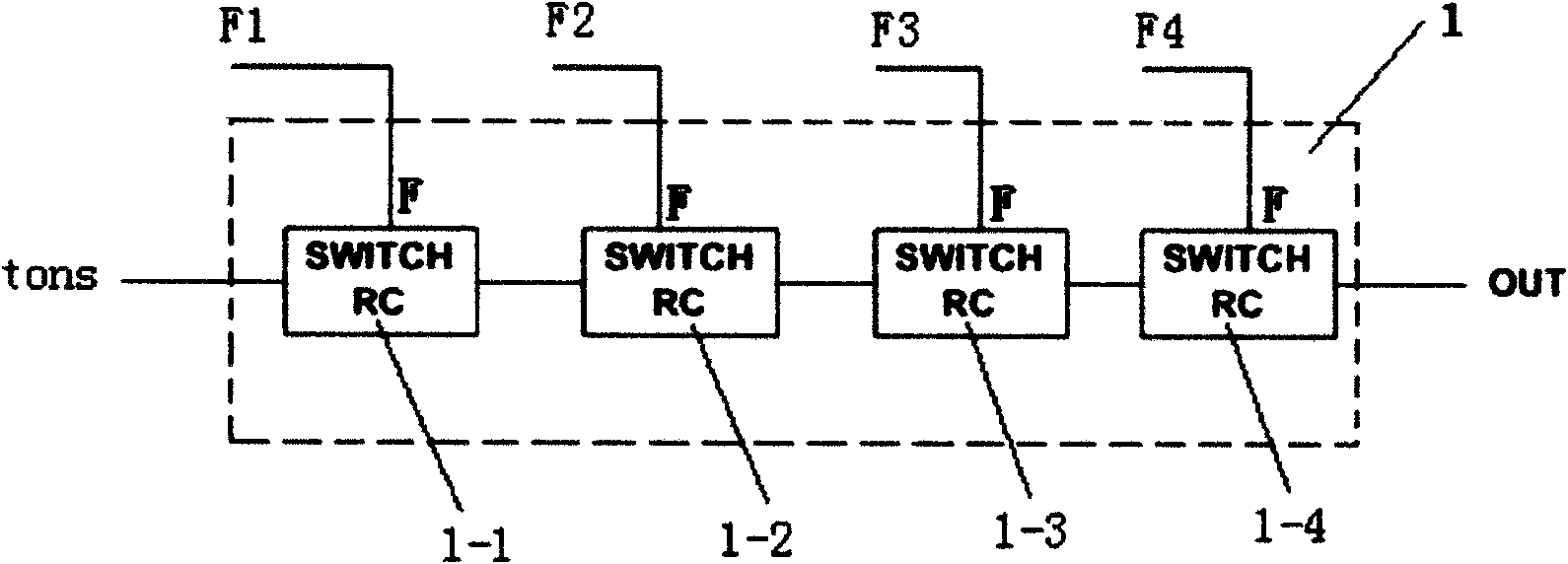

The invention relates to a line loss compensation circuit for a switch power supply, which is divided into a current-type line loss compensation circuit and a voltage-type line loss compensation circuit, wherein the current-type circuit comprises a multi-stage RC low pass filter, a voltage / current switching circuit and a current mirroring circuit, and the voltage-type circuit comprises a multi-stage RC low pass filter, a subtractor and a compensating resistance. The invention can produce a compensating current of Icpr or a compensating voltage of Vcpr which is proportionable to an output current of Iout, and the compensating current or the compensating voltage is used for offsetting voltage drop of an output wire caused by change of Iout, thereby recovering voltage stabilizing control function of a control loop to secure constant output. The invention has the advantages of skilful design idea and simple circuit and is easy to realize. The improvement of the invention is that: the switch RC filter is adopted to greatly reduce volume of an electric capacity of the RC filter, thereby facilitating integration, further improving circuit performance and simplifying circuit structure, and strengthening operation reliability of the switch power supply.

Owner:西安英洛华微电子有限公司

Parameter generation for interleavers

ActiveUS7590917B2Data representation error detection/correctionCode conversionAlgorithmRandom pattern

An interleaver parameter generator circuit used to calculate and generate on an as needed basis interleaver parameters for interleaving blocks of information of varying lengths in accordance with a pseudorandom pattern defined by the 3GPP standard. The interleaver parameter generator circuit calculates and generates the defined interleaver parameters based on an input parameter that represents the length of the block of information to be interleaved. At least one of the defined parameters is calculated and generated using a decomposed form of its definition. The interleaver parameter generator circuit uses well known circuit blocks such as multipliers, subtractors, Compare-and-Select circuits and other circuits to calculate and generate the defined parameters.

Owner:RPX CORP +1

Receiving apparatus in OFDM transmission system

InactiveUS7362832B2Easy to codeIncrease in the BER can be suppressedError preventionLine-faulsts/interference reductionTransfer systemGuard interval

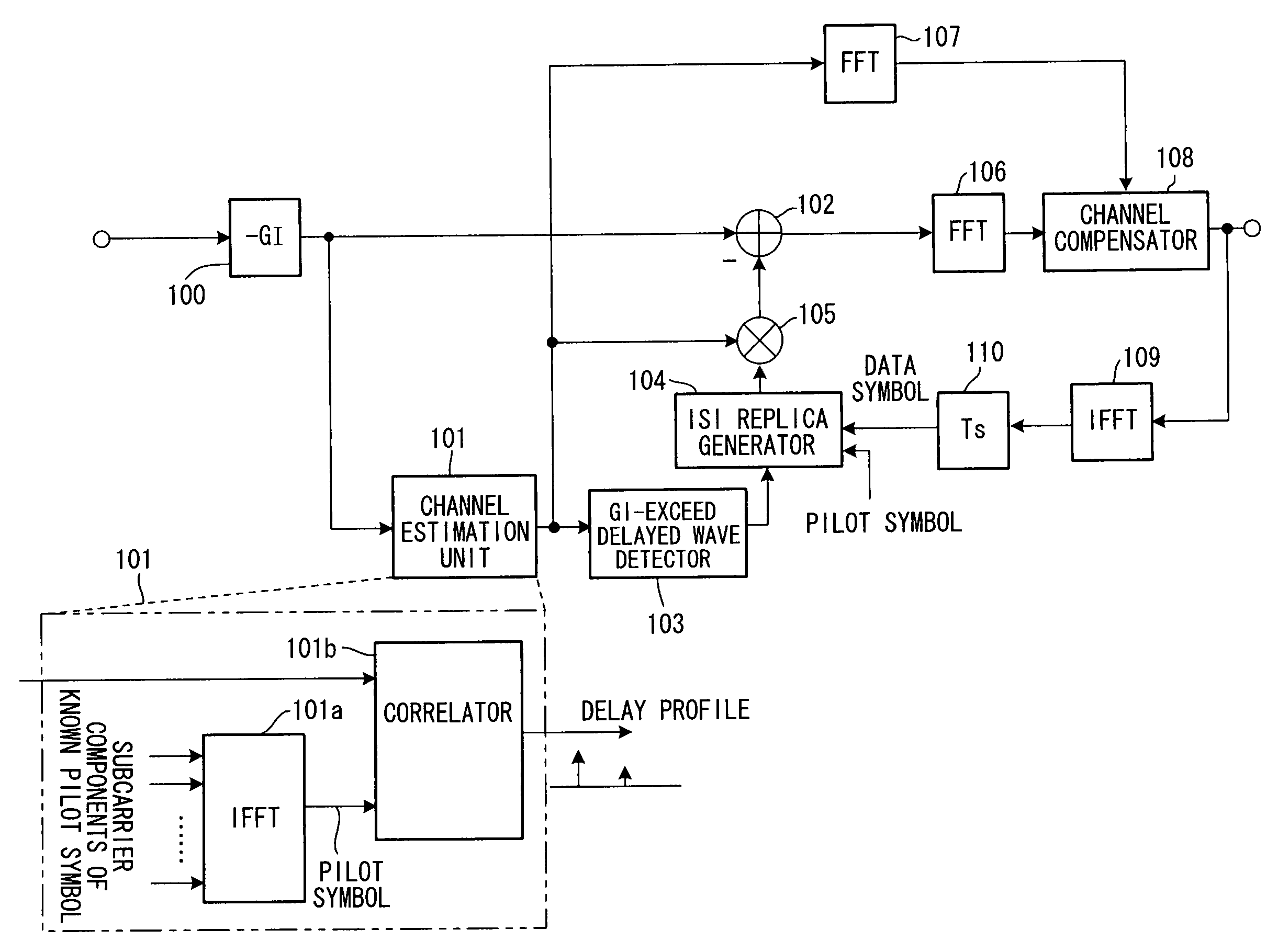

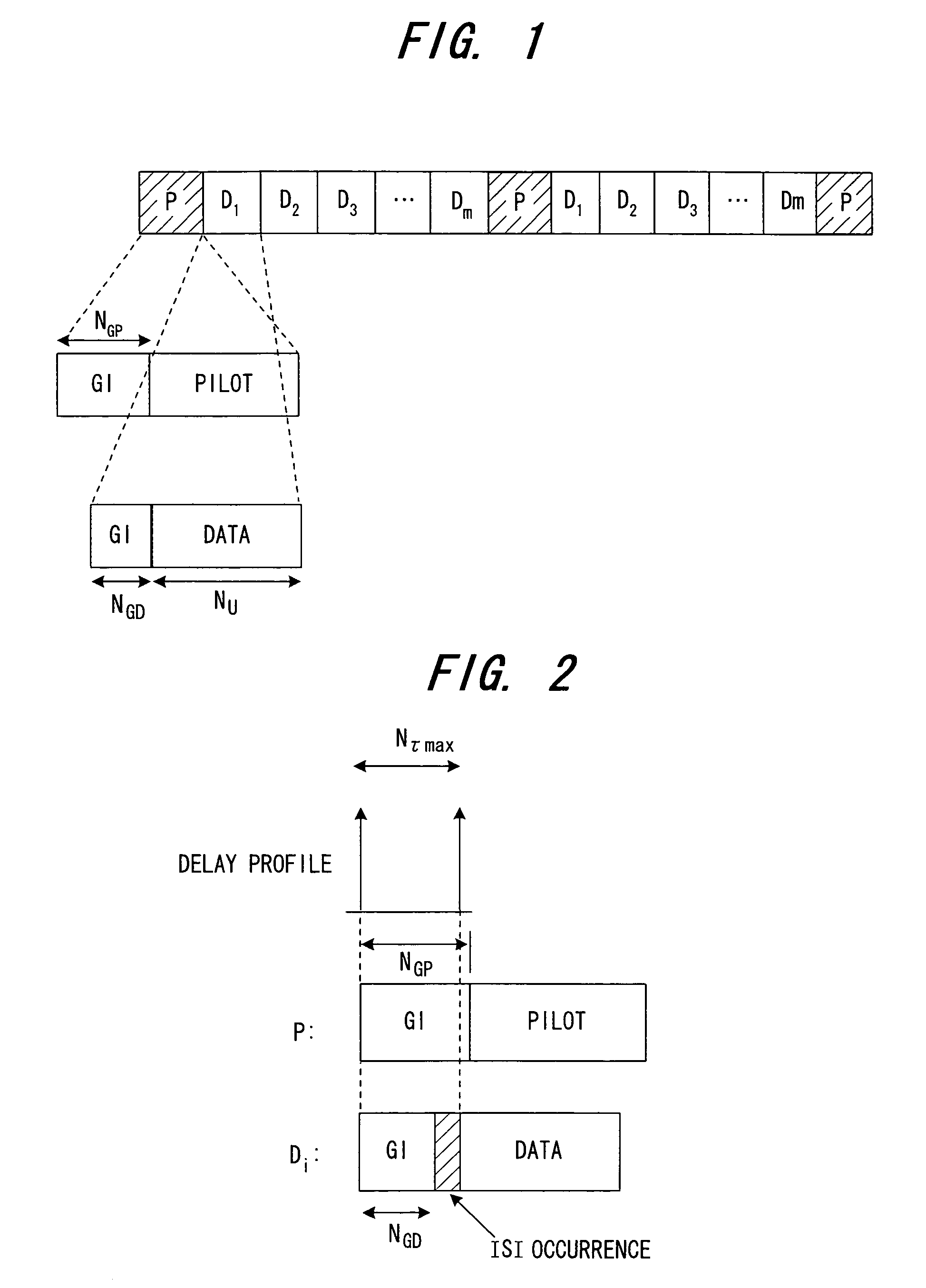

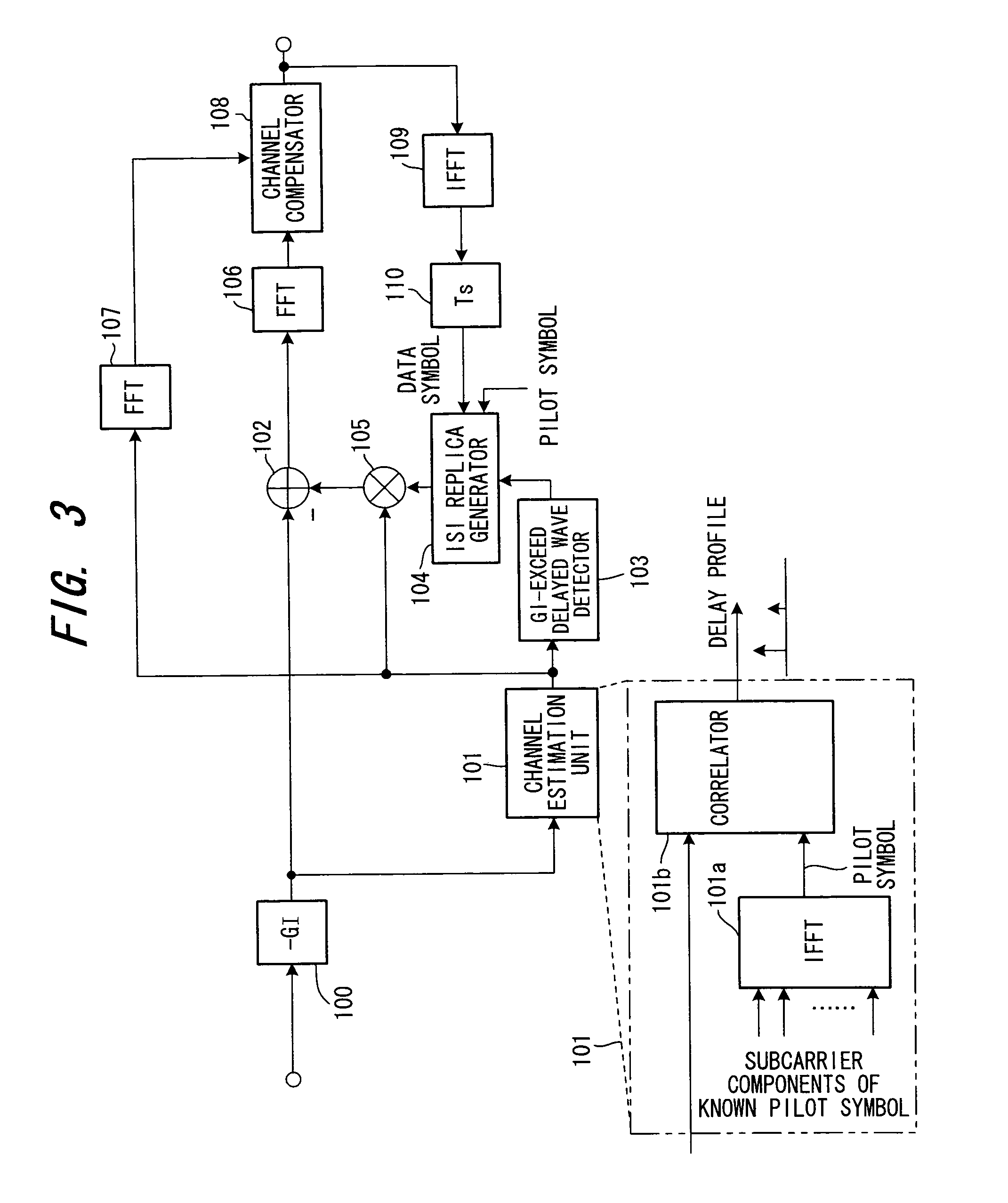

A receiving apparatus in an OFDM transmission system includes a channel estimation unit (101) for measuring a delay profile of a delayed wave having a delay greater than a guard interval of data; a guard-interval-exceed delayed wave detector (103) for detecting, from the delay profile as an intersymbol interference (ISI) portion, a delay-time portion greater than the guard interval of the data; a ISI replica generator (104) for generating, as the ISI replica, a time-waveform portion of a known symbol conforming to the ISI portion, or a time-waveform portion of the preceding symbol; subtractor (102) for subtracting the ISI replica from a receive signal; and an FFT arithmetic unit (106) for demodulating data by applying FFT processing to the result of subtraction.

Owner:FUJITSU LTD

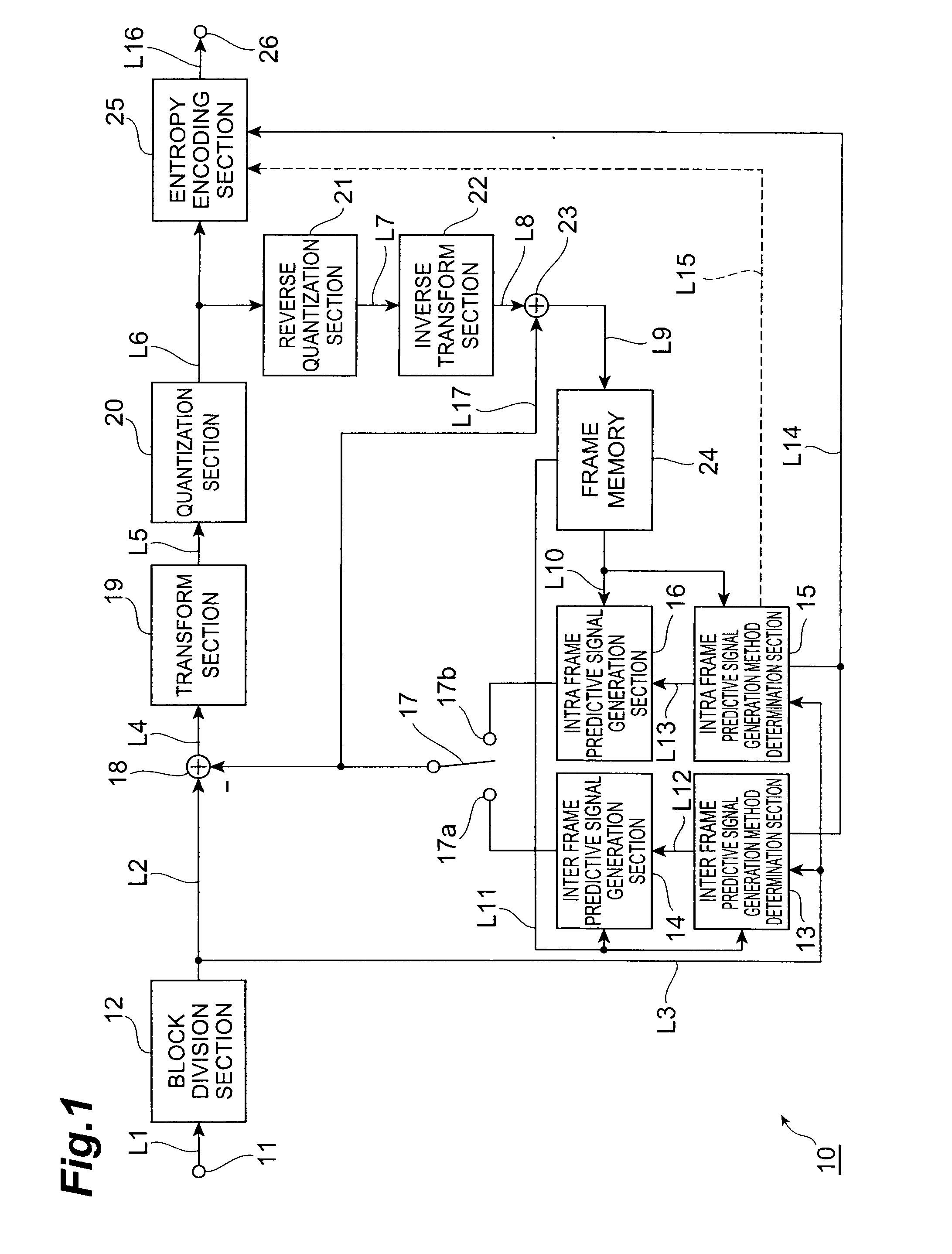

Image prediction encoding device, image prediction decoding device, image prediction encoding method, image prediction decoding method, image prediction encoding program, and image prediction decoding program

InactiveUS20090232206A1Reducing predictive method-related mode informationEasy to handleColor television with pulse code modulationColor television with bandwidth reductionSignal onPredictive methods

An image predictive encoding device including an intra frame predictive signal generation method determination section that determines, for adjacent areas including regenerated pixel signals and adjacent to the target area, a predictive method derived on the basis of data corresponding to the adjacent areas as an R mode predictive method or an L mode predictive method, an intra frame predictive signal generation section that generates an intra frame predictive signal on the basis of the R mode predictive method thus determined, and a subtractor, a transform section, a quantization section, and an entropy encoding section that encode a residual signal of a pixel signal of the target area on the basis of the generated intra frame predictive signal.

Owner:NTT DOCOMO INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com