Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

709 results about "Time-to-digital converter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

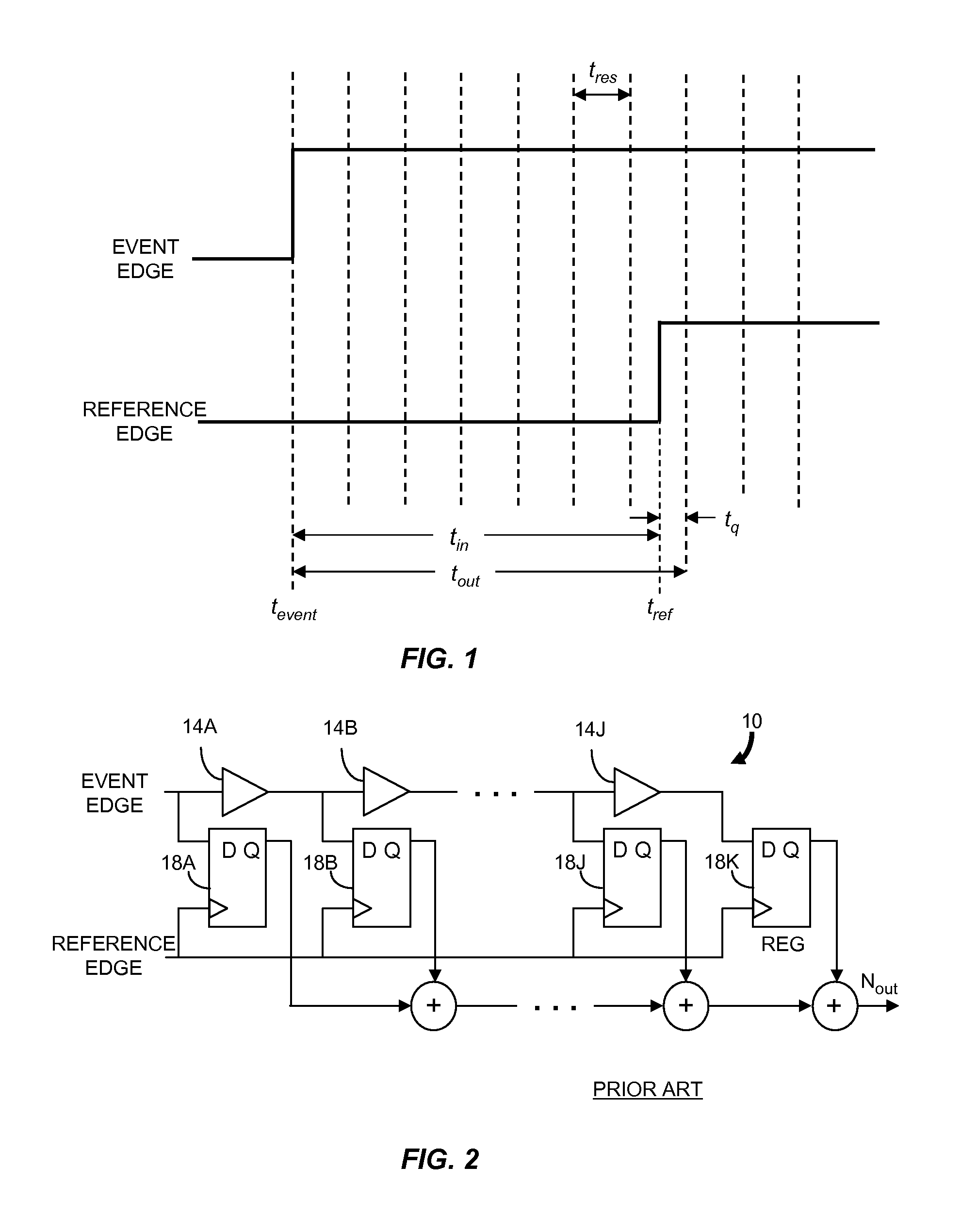

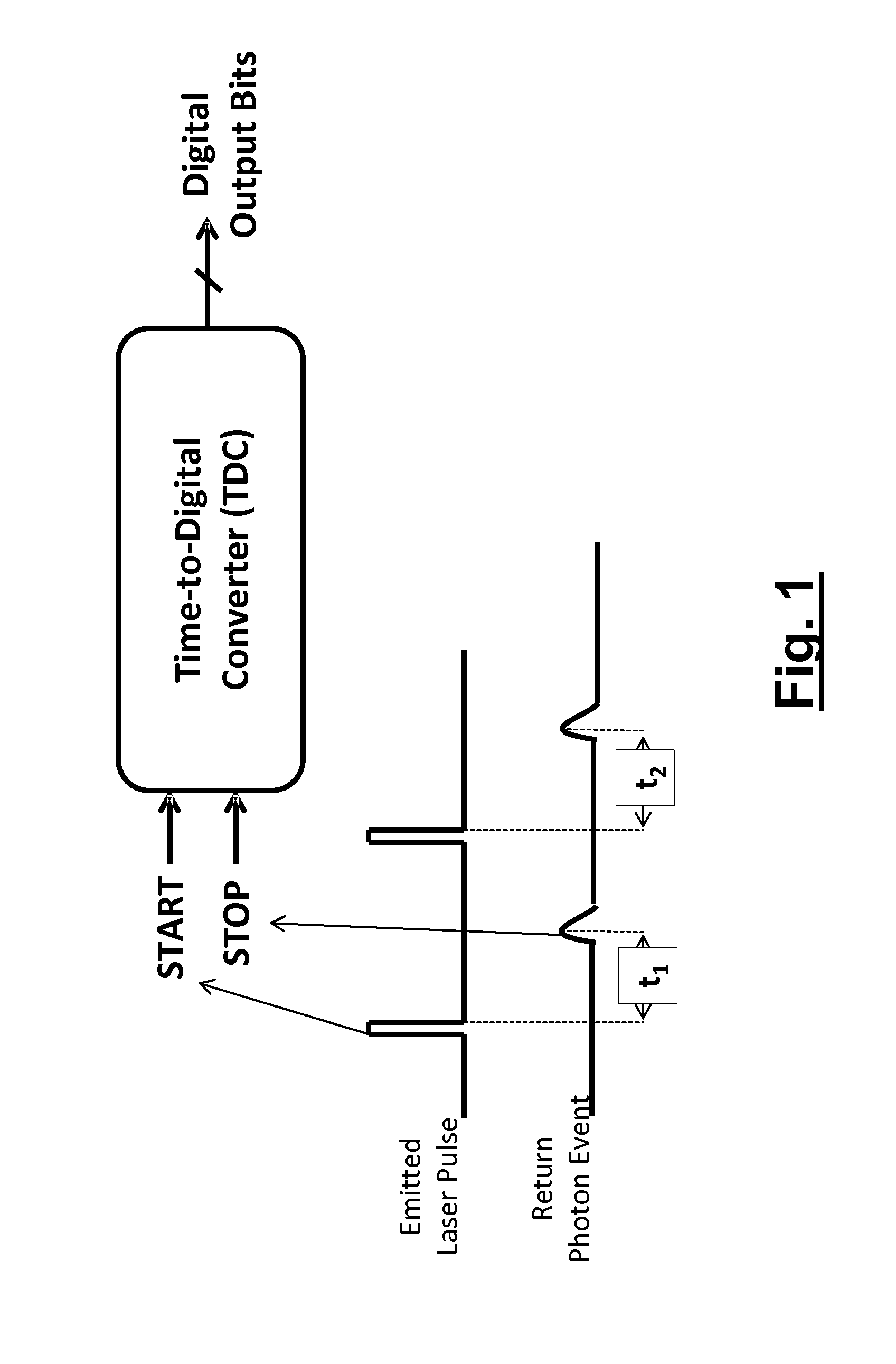

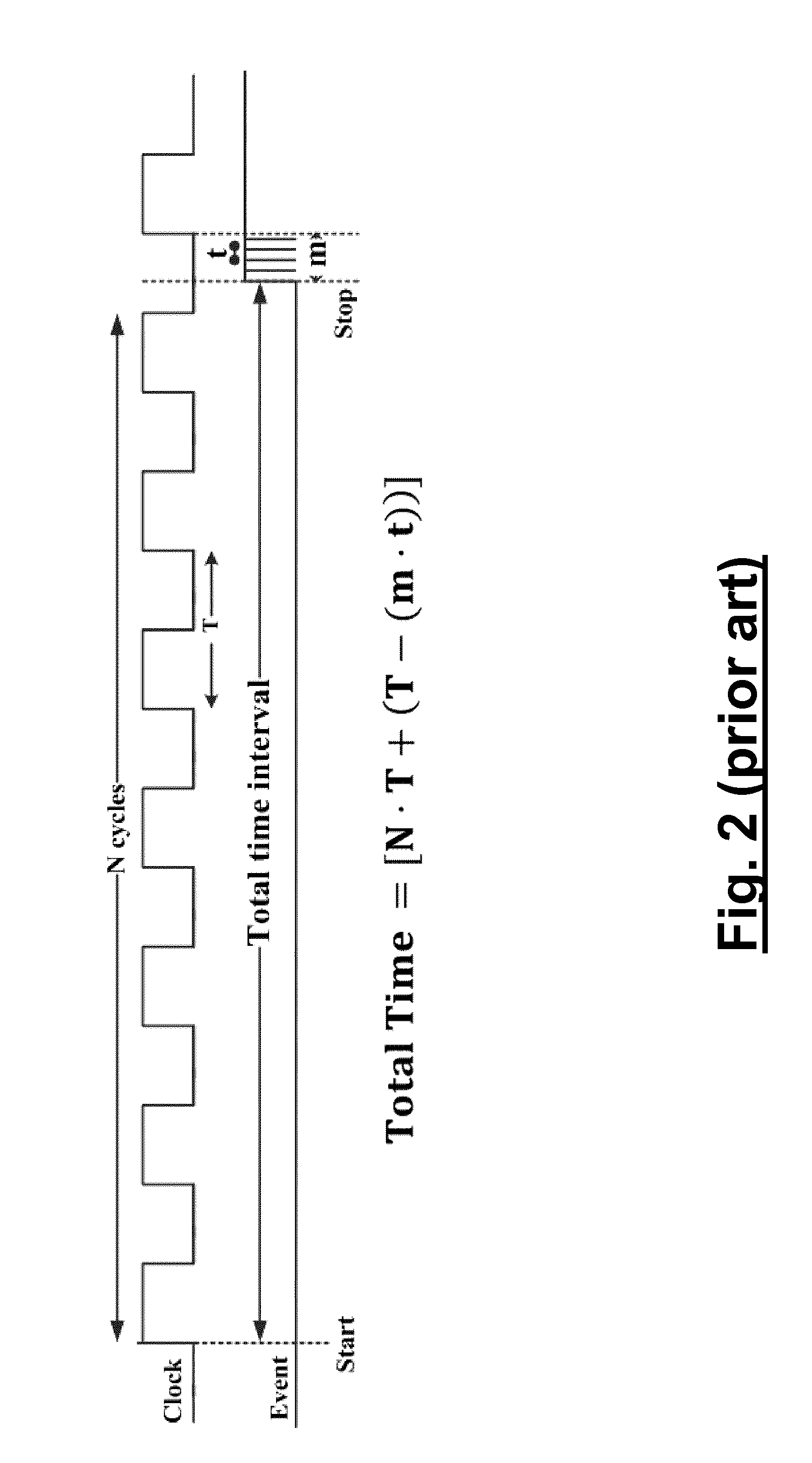

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.

Cost-effective lidar sensor for multi-signal detection, weak signal detection and signal disambiguation and method of using same

InactiveUS20140211194A1Low costOptical rangefindersElectromagnetic wave reradiationSignal qualityEngineering

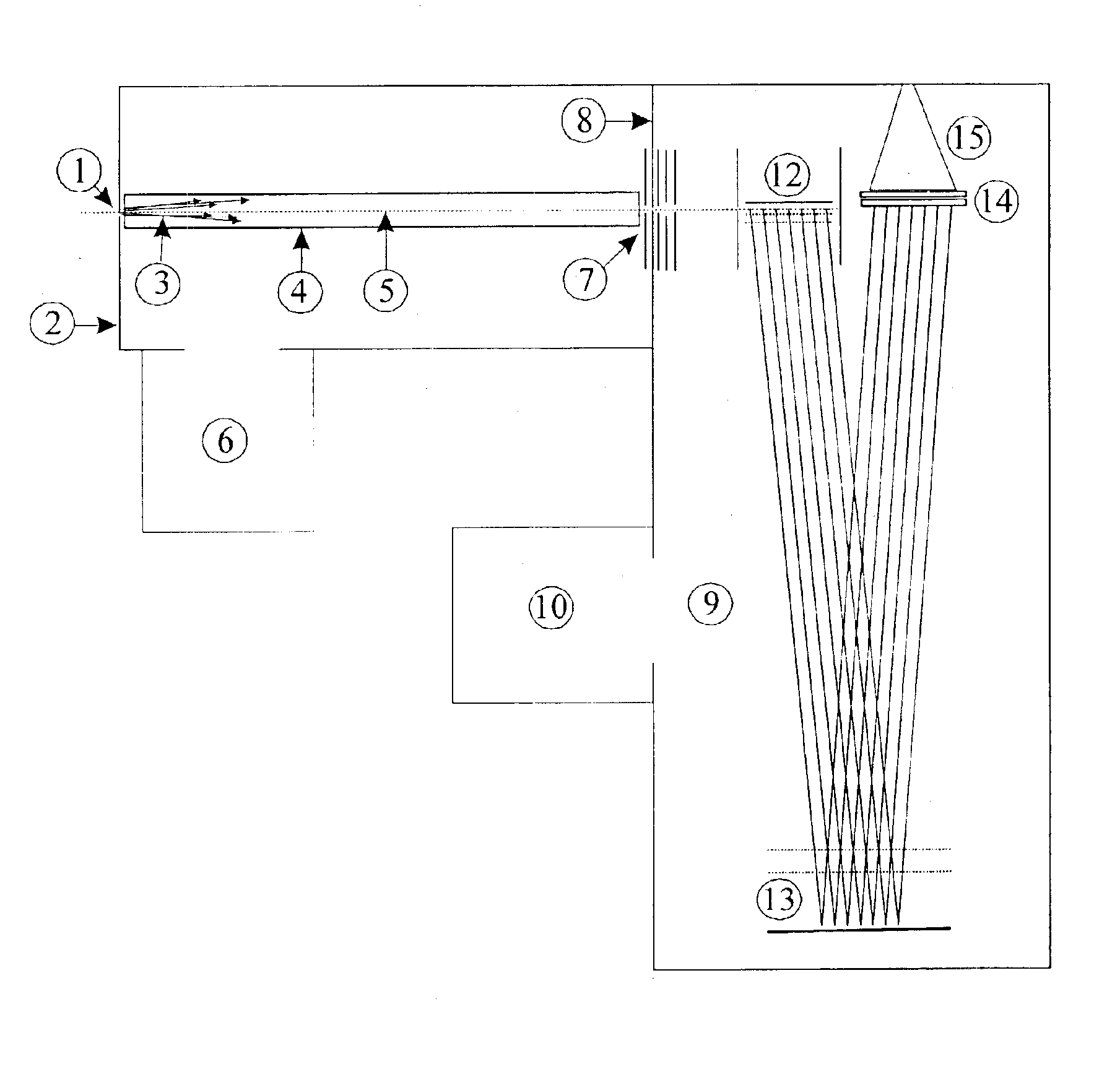

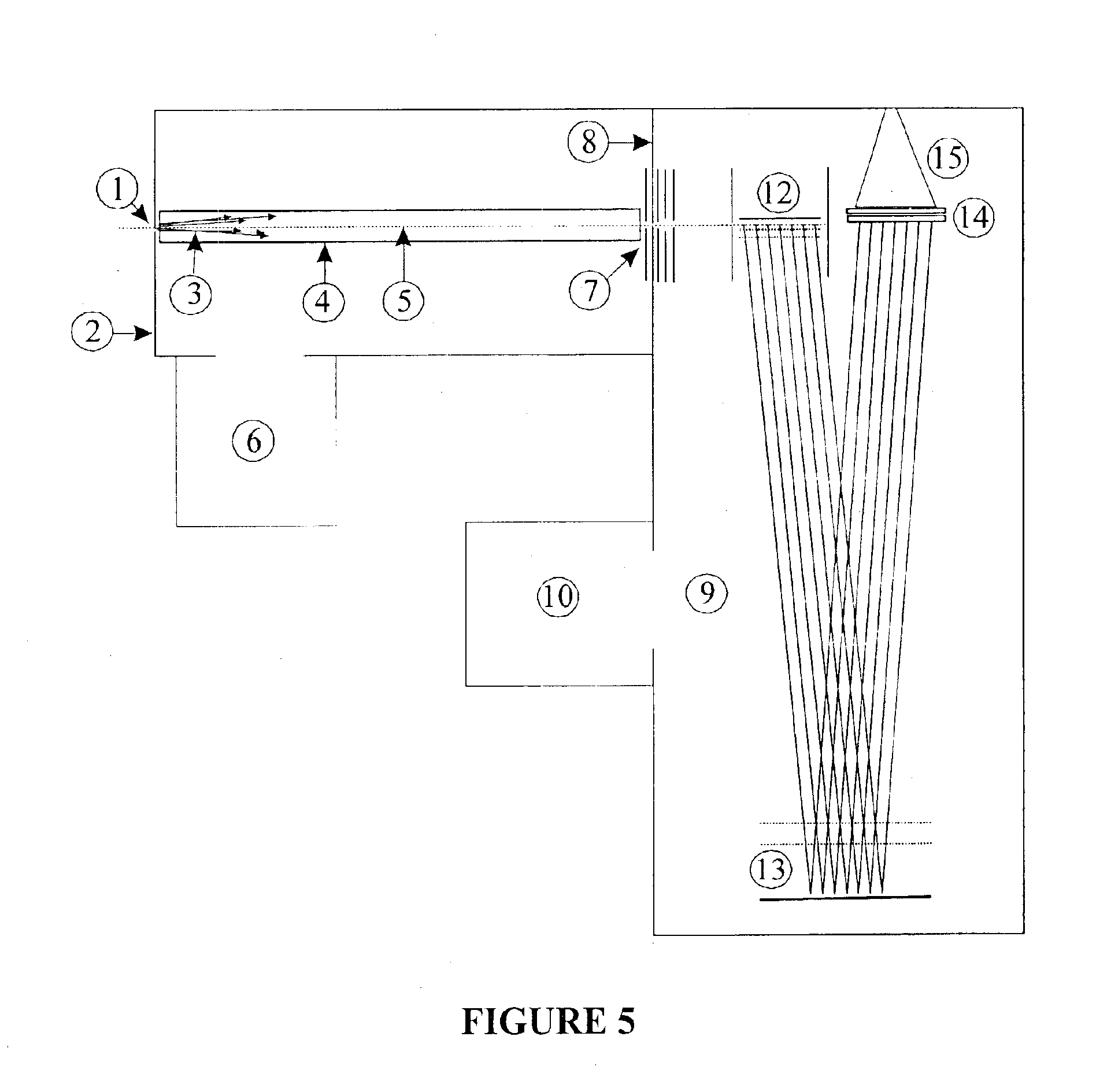

A lidar-based apparatus and method are used for multi-signal detection, weak signal detection and signal disambiguation through waveform approximation utilizing a multi-channel time-to-digital converter (TDC) electronic circuit, with each TDC having an individually adjustable voltage threshold. This advanced TDC-based pulse width time-of-flight (ToF) approach achieves the low cost associated with the TDC-based pulse width ToF approach while solving the signal quality issues associated with the standard single-threshold TDC-based approach.

Owner:QUANERGY SYST

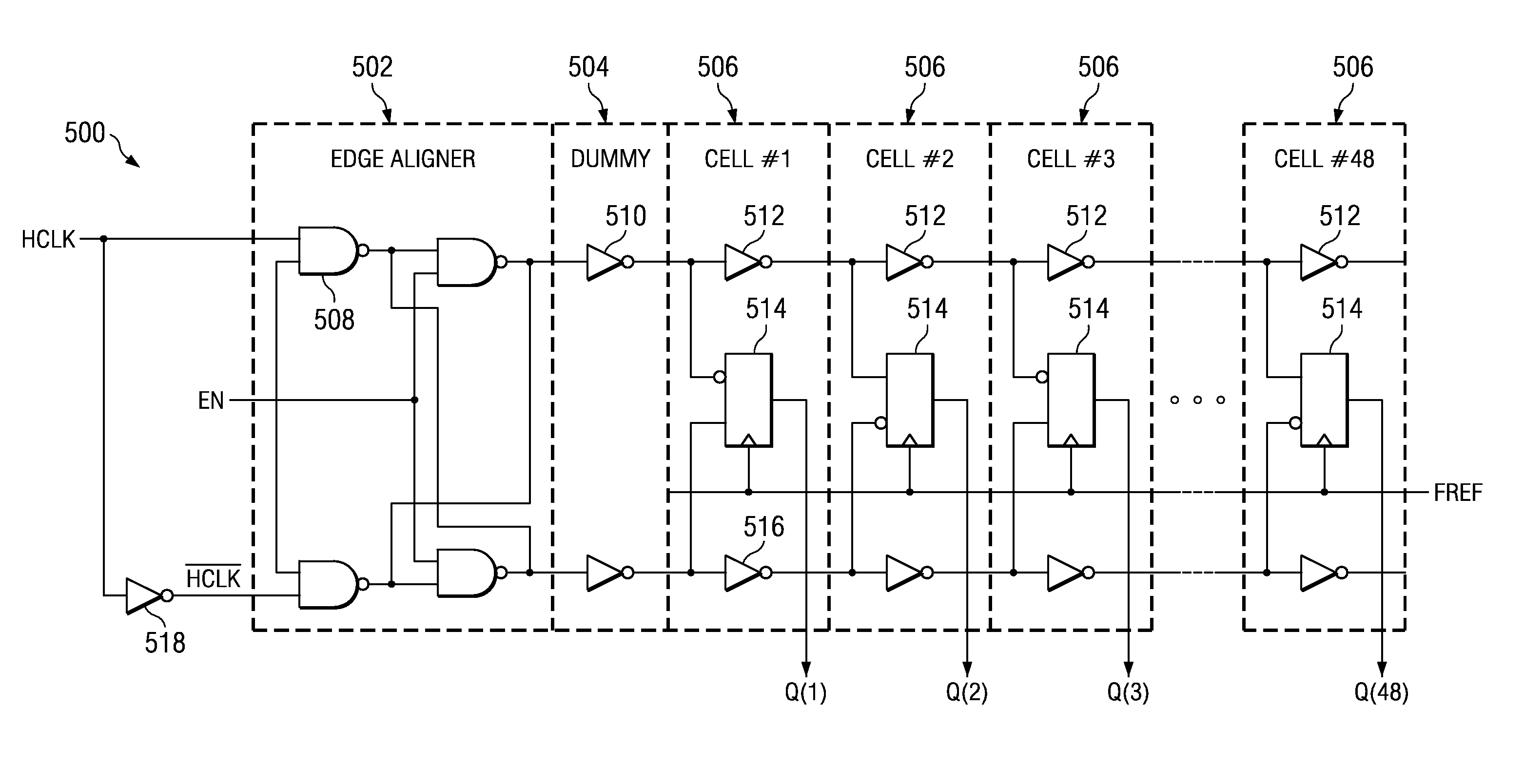

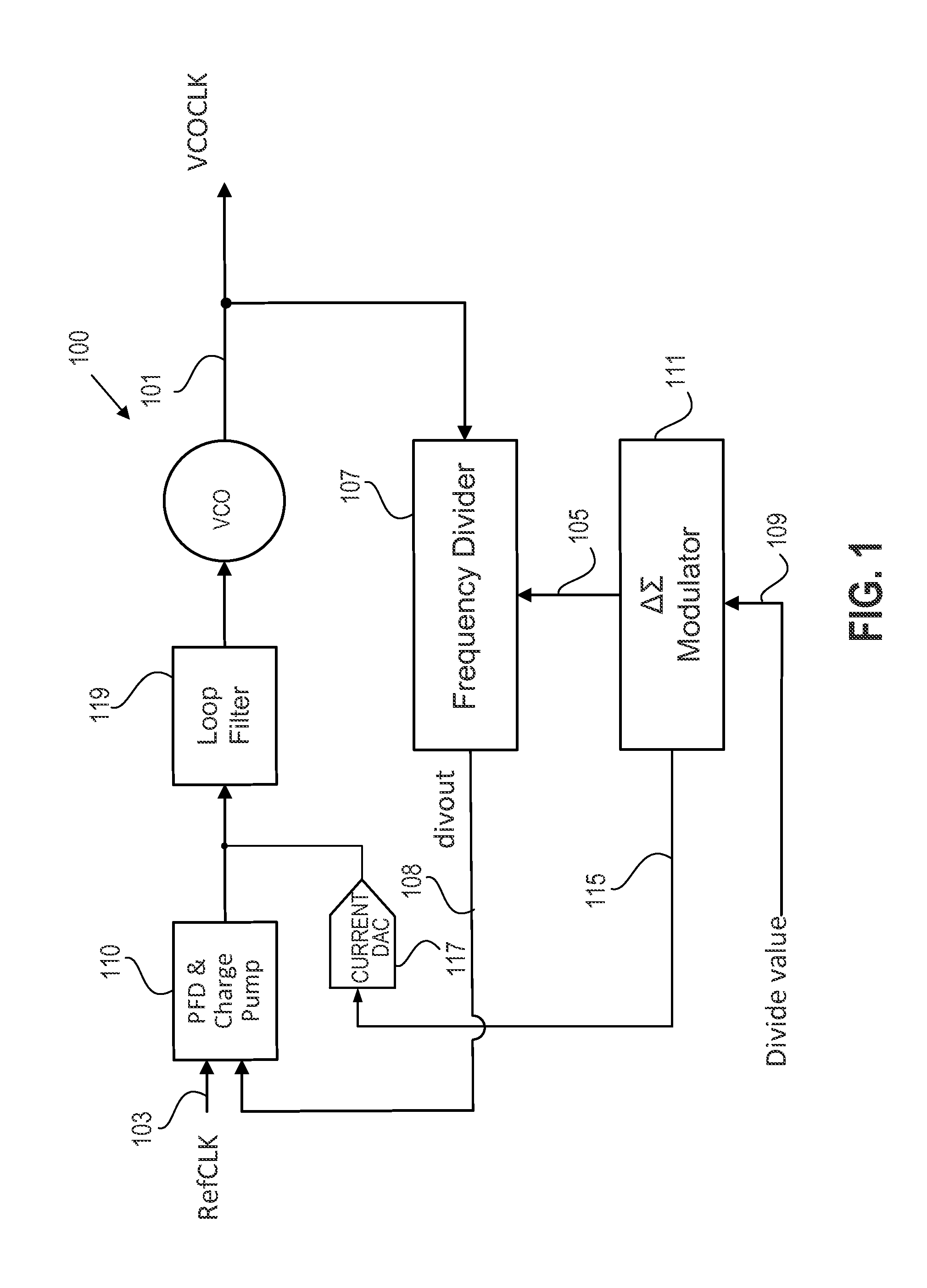

Circuit for high-resolution phase detection in a digital RF processor

ActiveUS20060103566A1Less sensitiveReduce power consumptionElectric signal transmission systemsPulse automatic controlEngineeringDigital converter

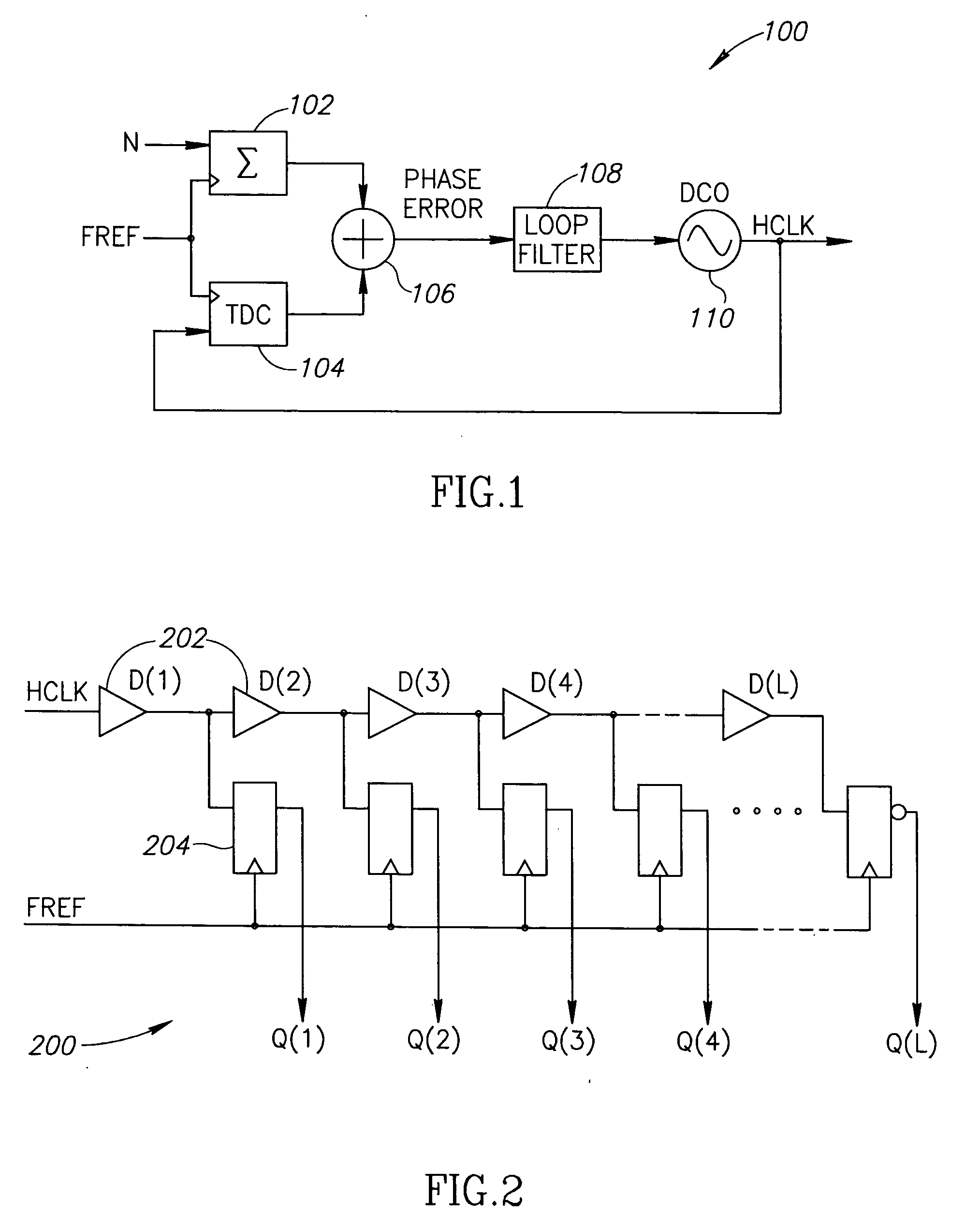

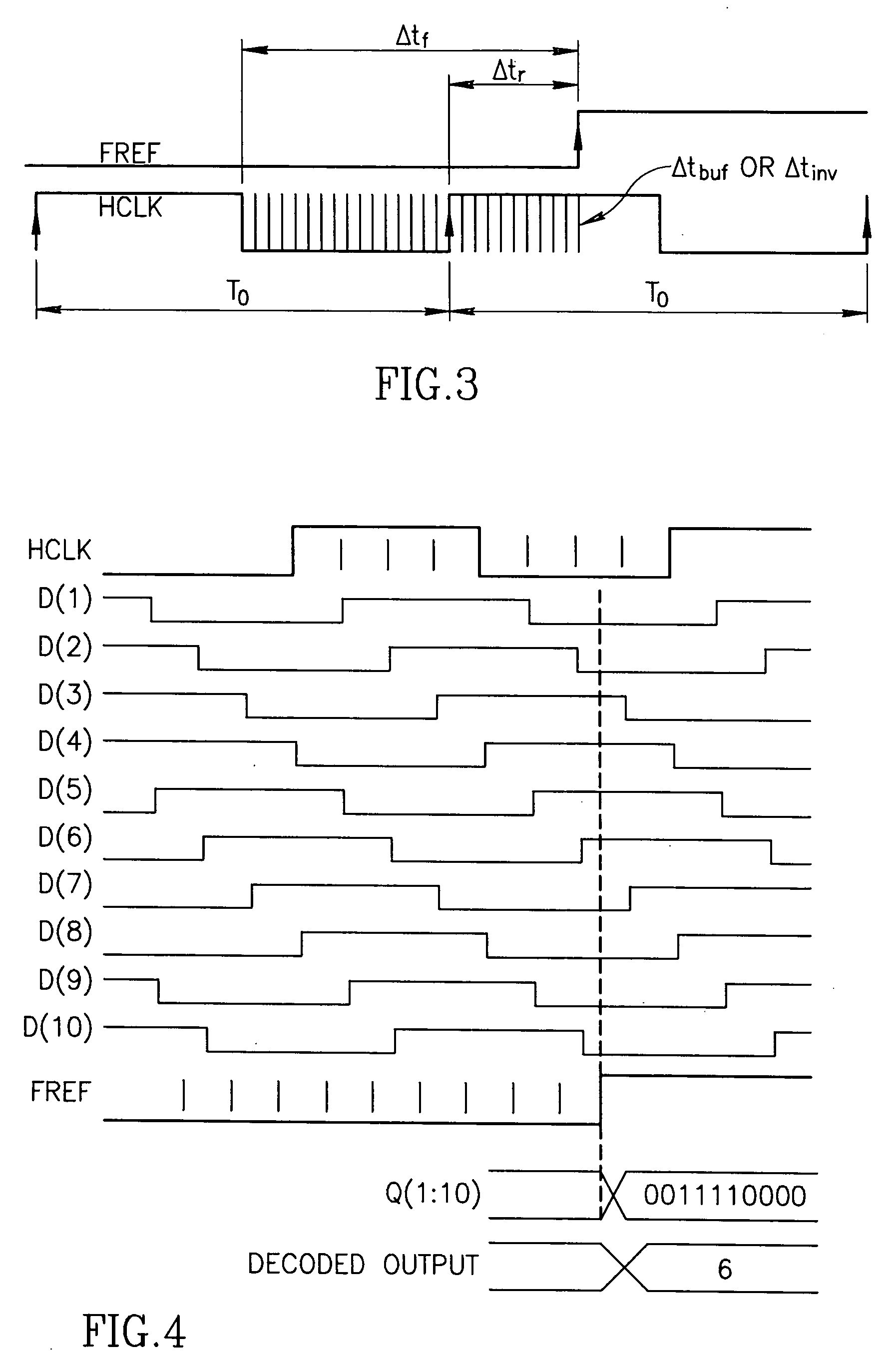

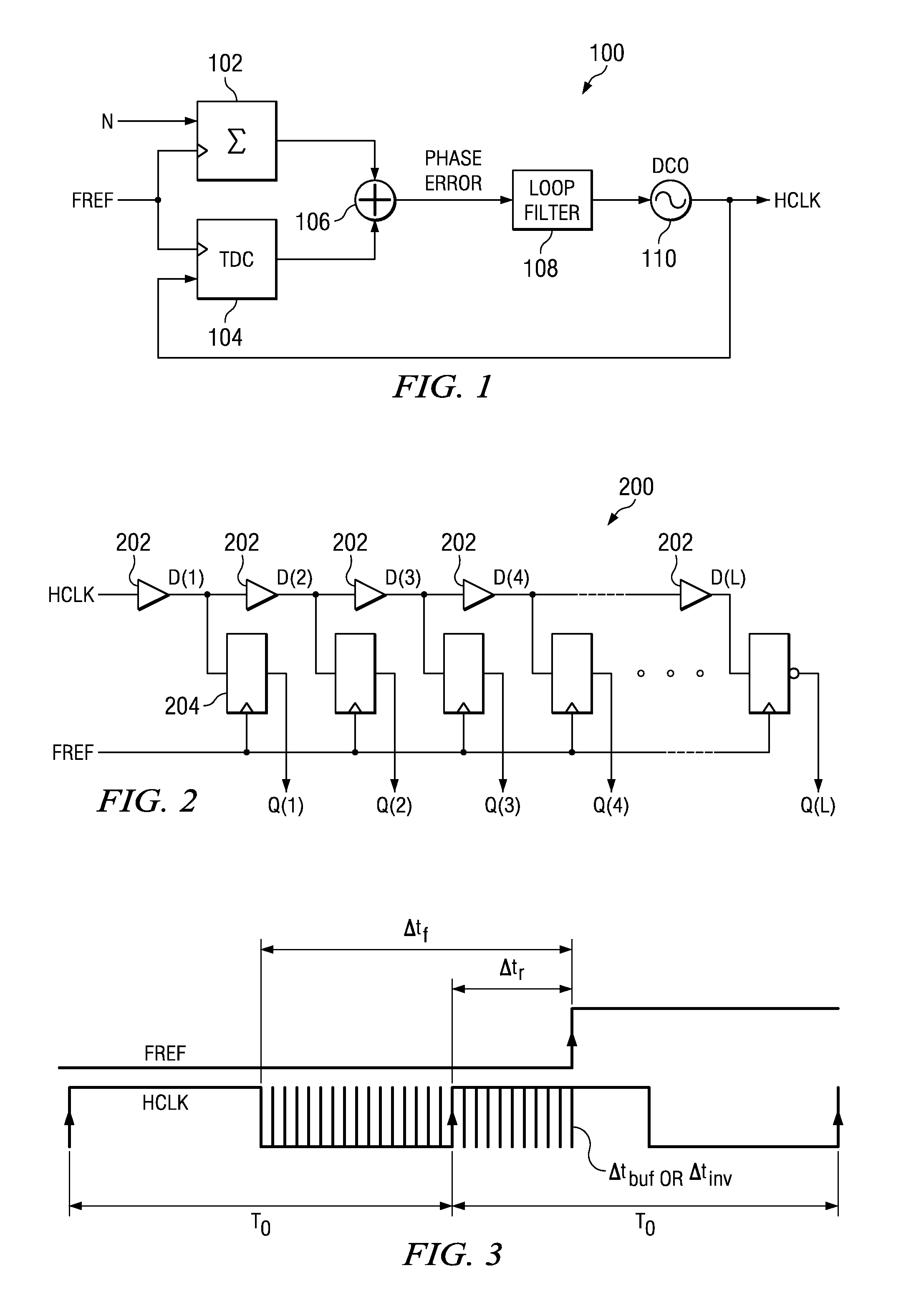

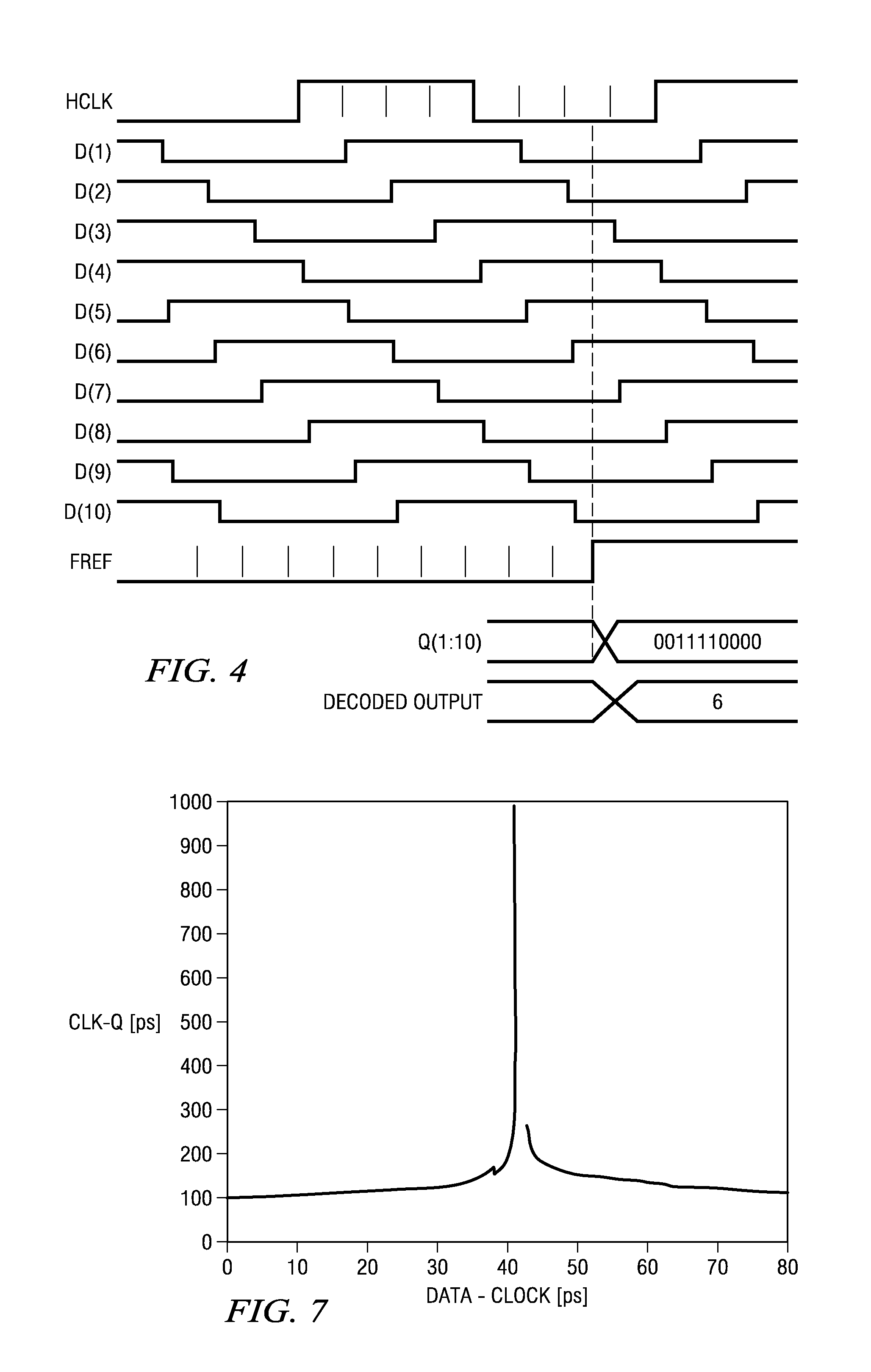

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC

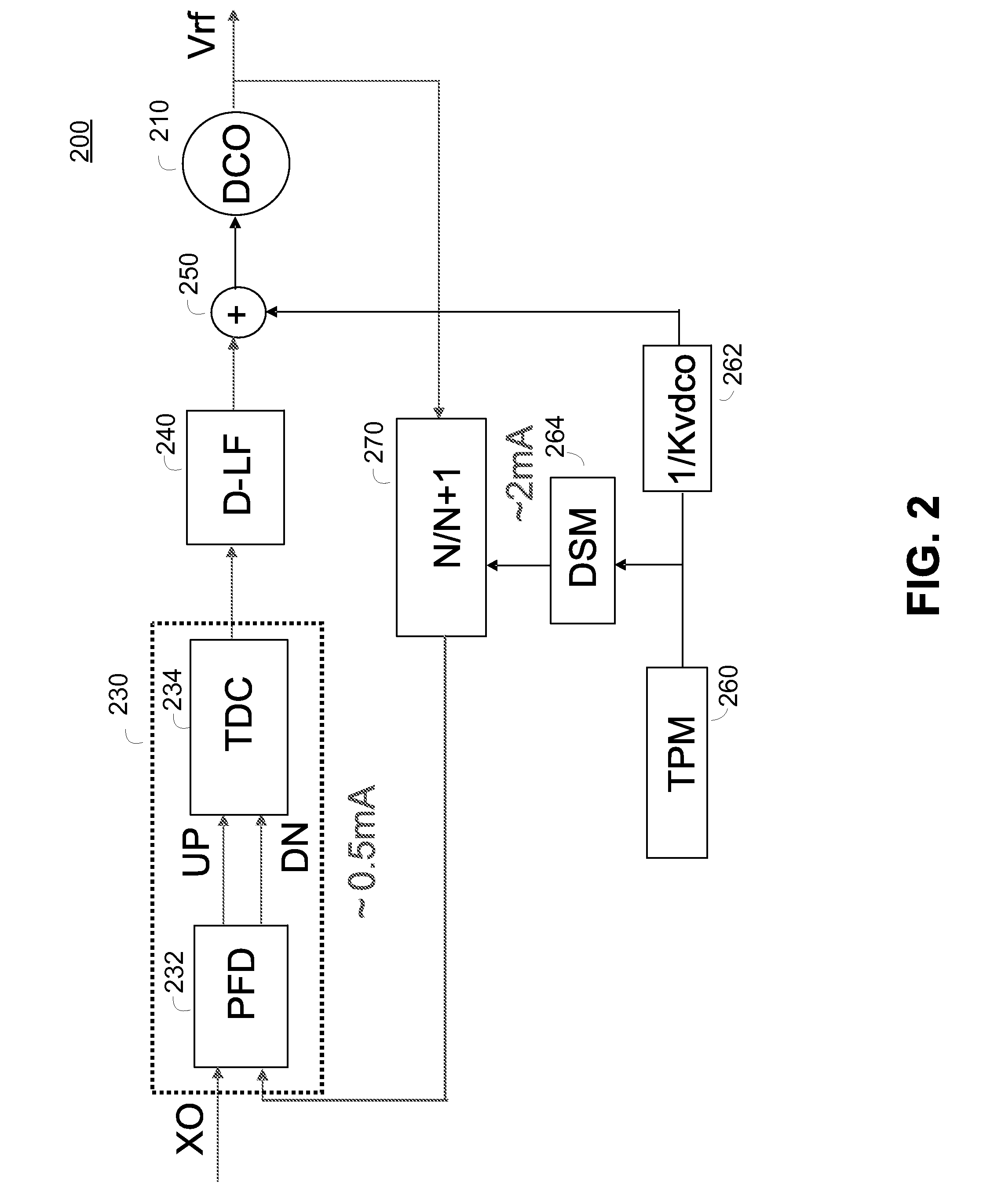

Phase to digital converter in all digital phase locked loop

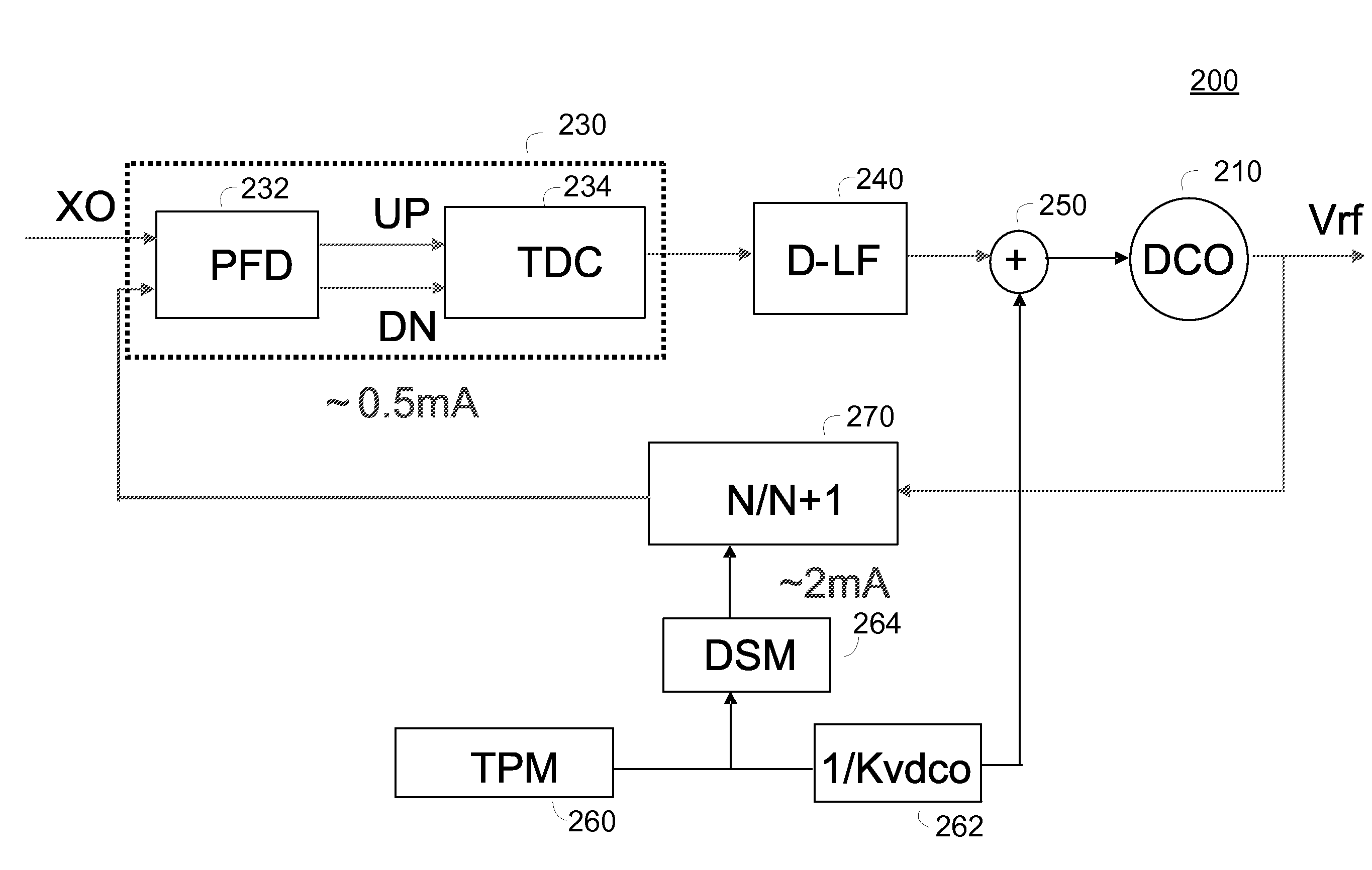

ActiveUS20090256601A1Low power operationLower requirementElectric signal transmission systemsPulse automatic controlDigital down converterReference Period

A phase to digital converter, all digital phase locked loop, and apparatus having an all digital phase locked loop are described herein. The phase to digital converter includes a phase to frequency converter driving a time to digital converter. The time to digital converter determines a magnitude and sign of the phase differences output by the phase to frequency converter. The time to digital converter utilizes tapped delay lines and looped feedback counters to enable measurement of small timing differences typical of a loop tracking process and large timing differences typical of an loop acquisition process. The tapped delay lines permit the measurement of fractions of a reference period and enable lower power operation of the phase to digital converter by reducing requirements on the speed of the reference clock.

Owner:QUALCOMM INC

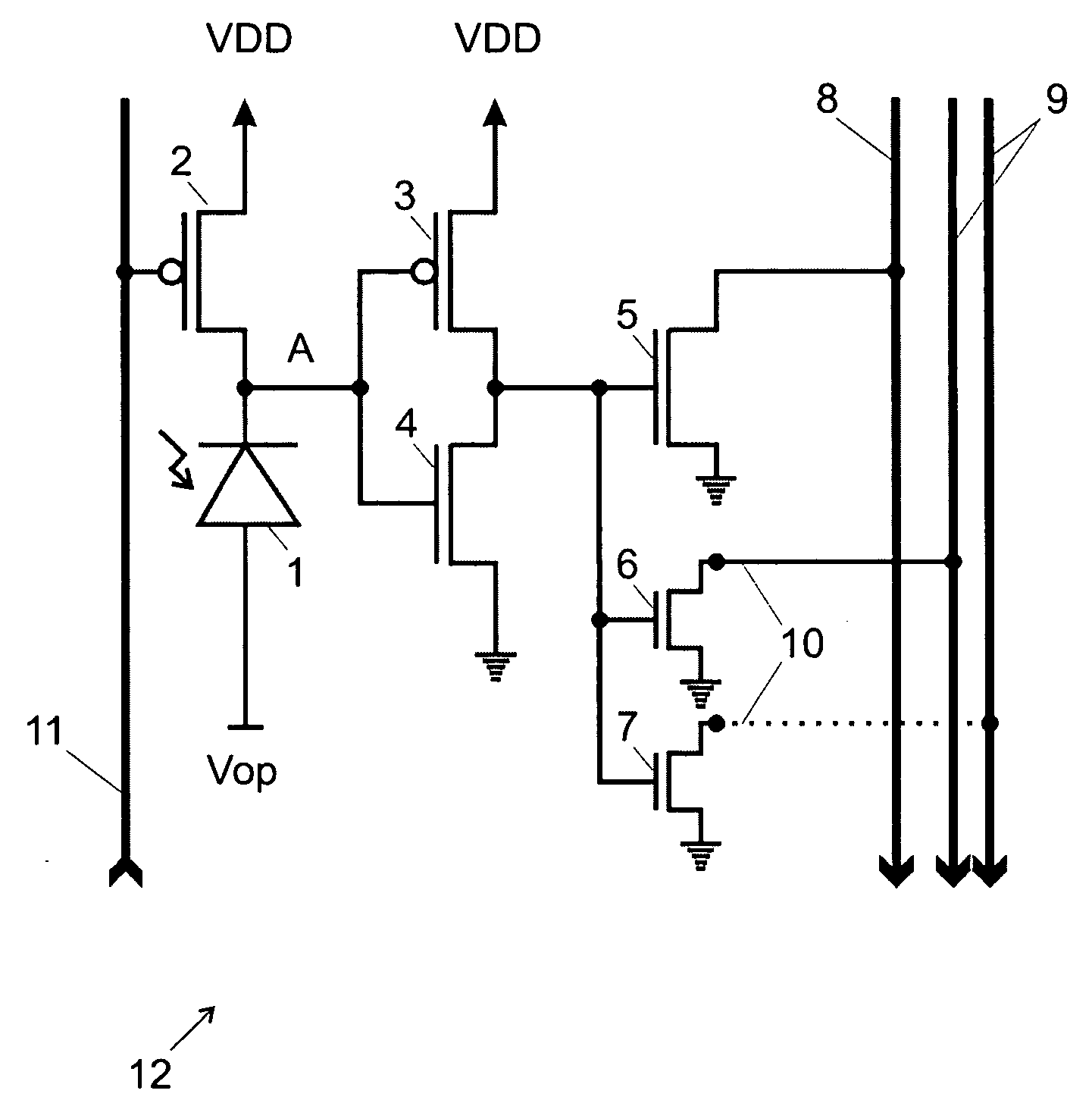

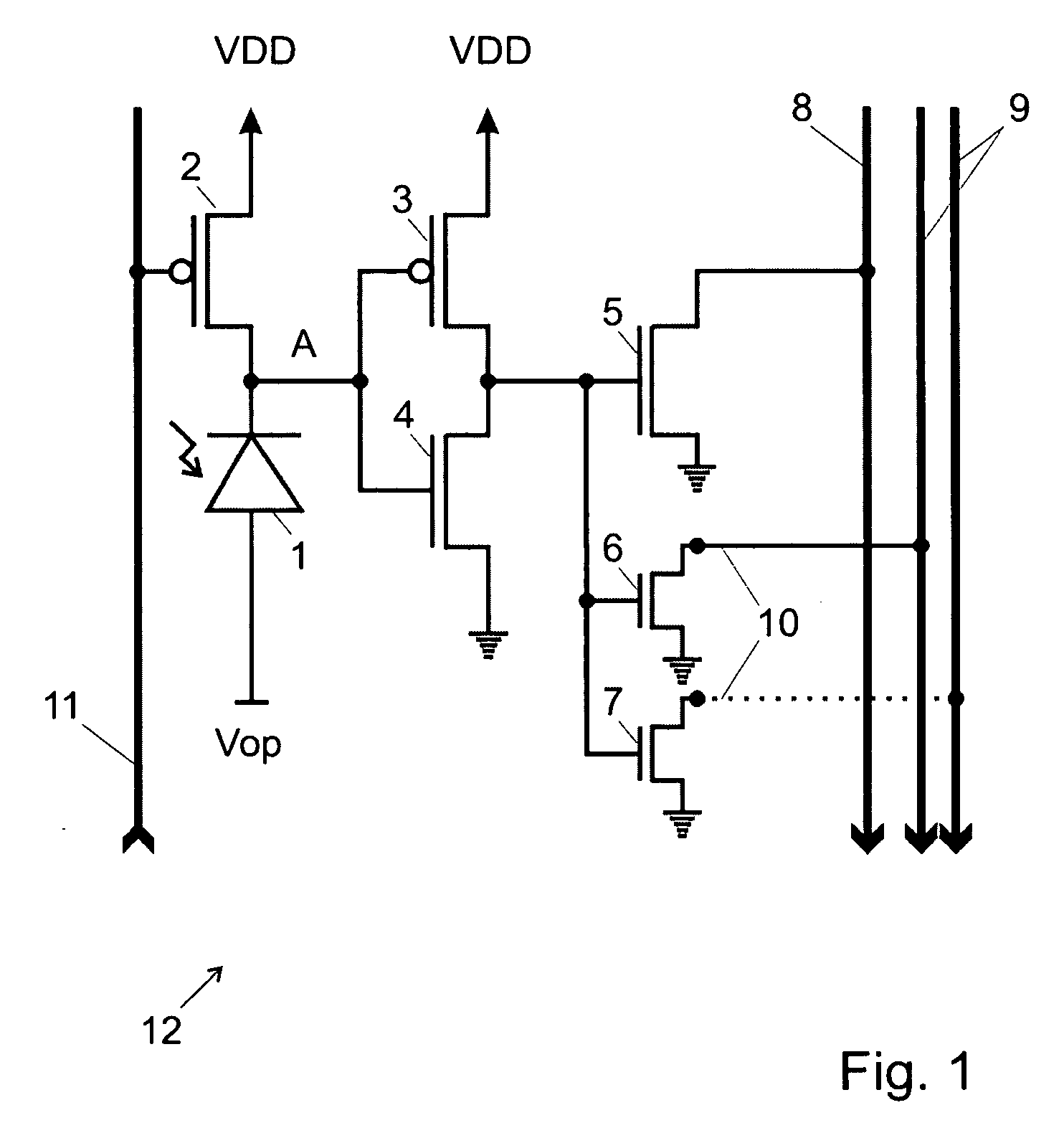

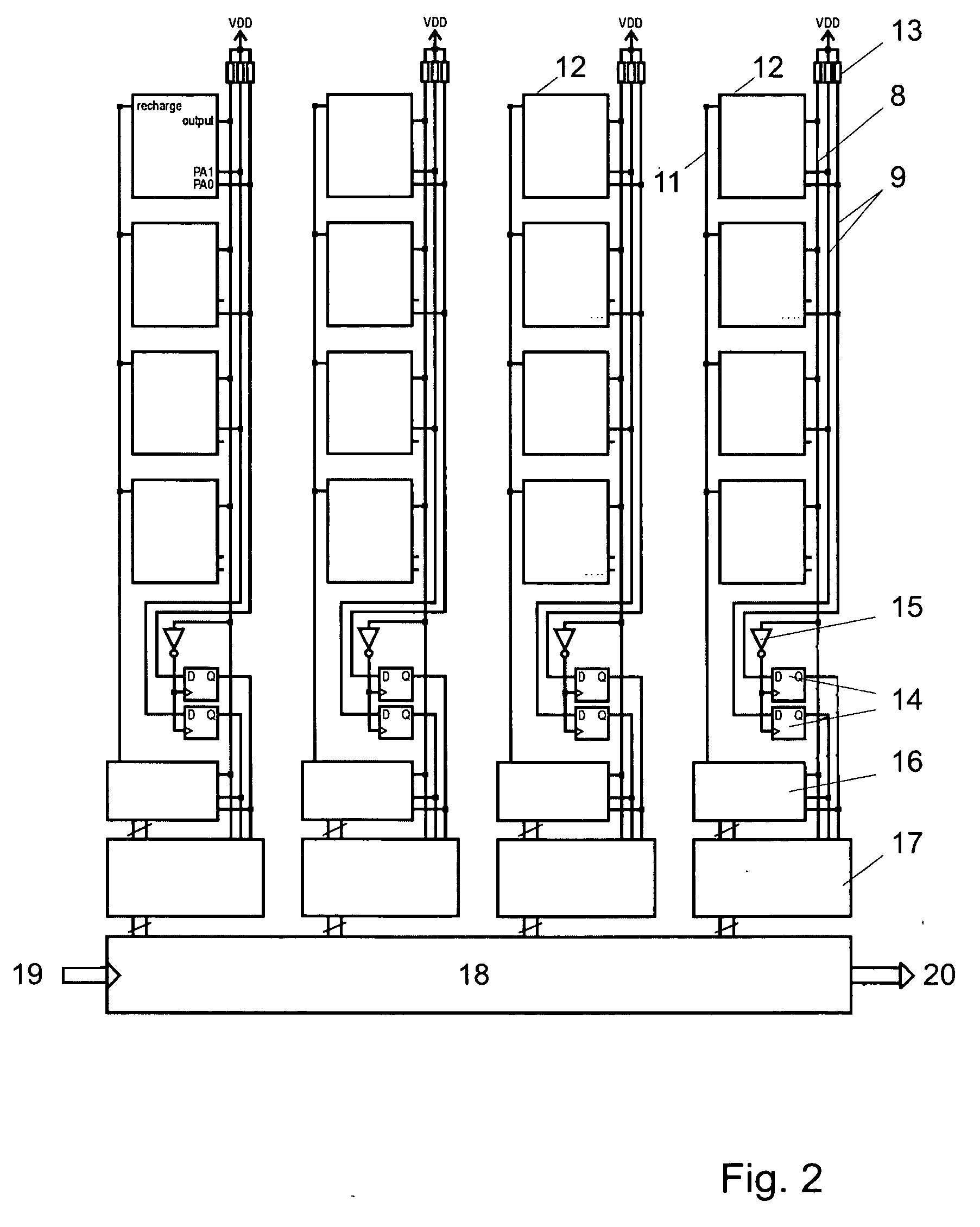

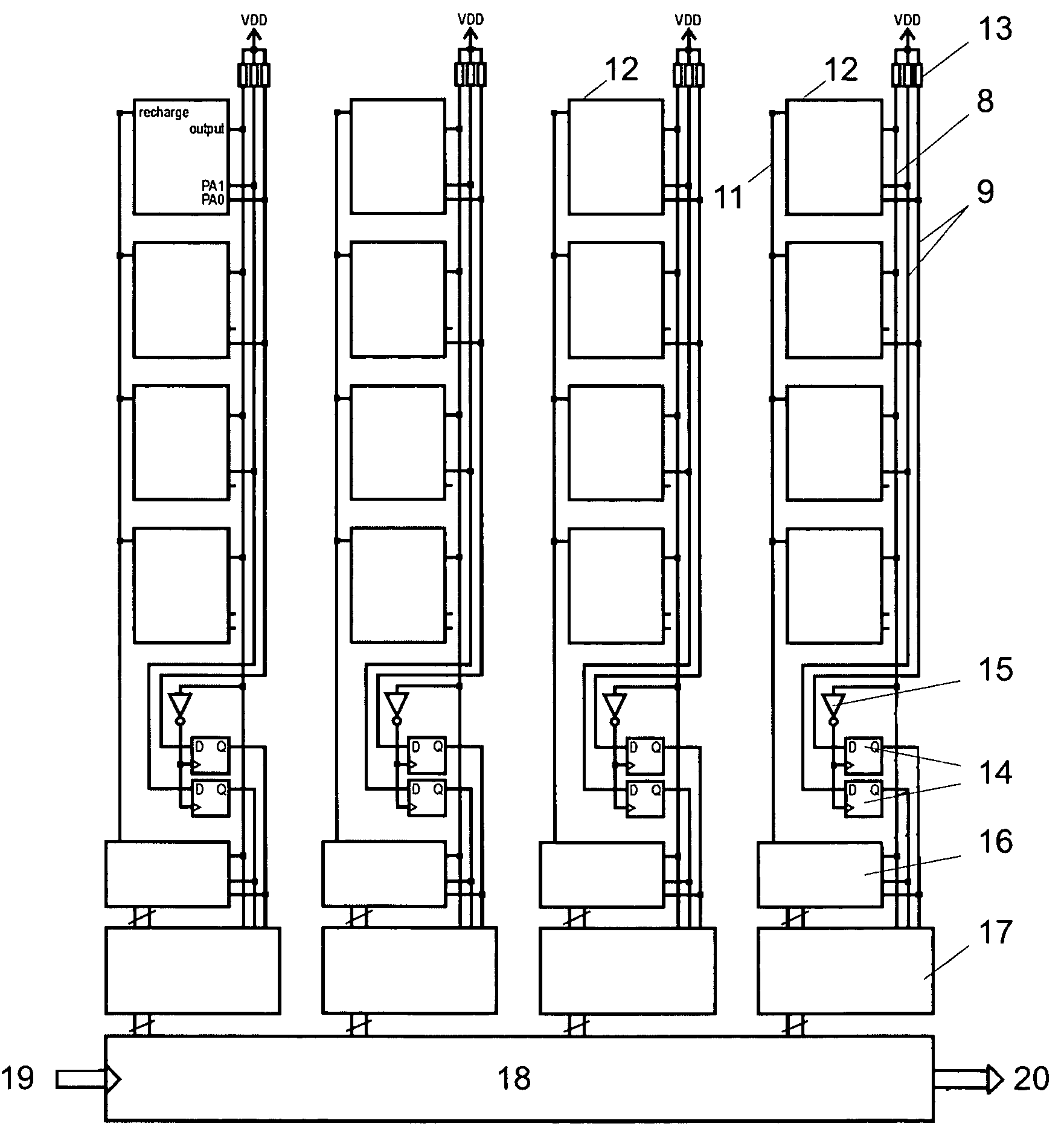

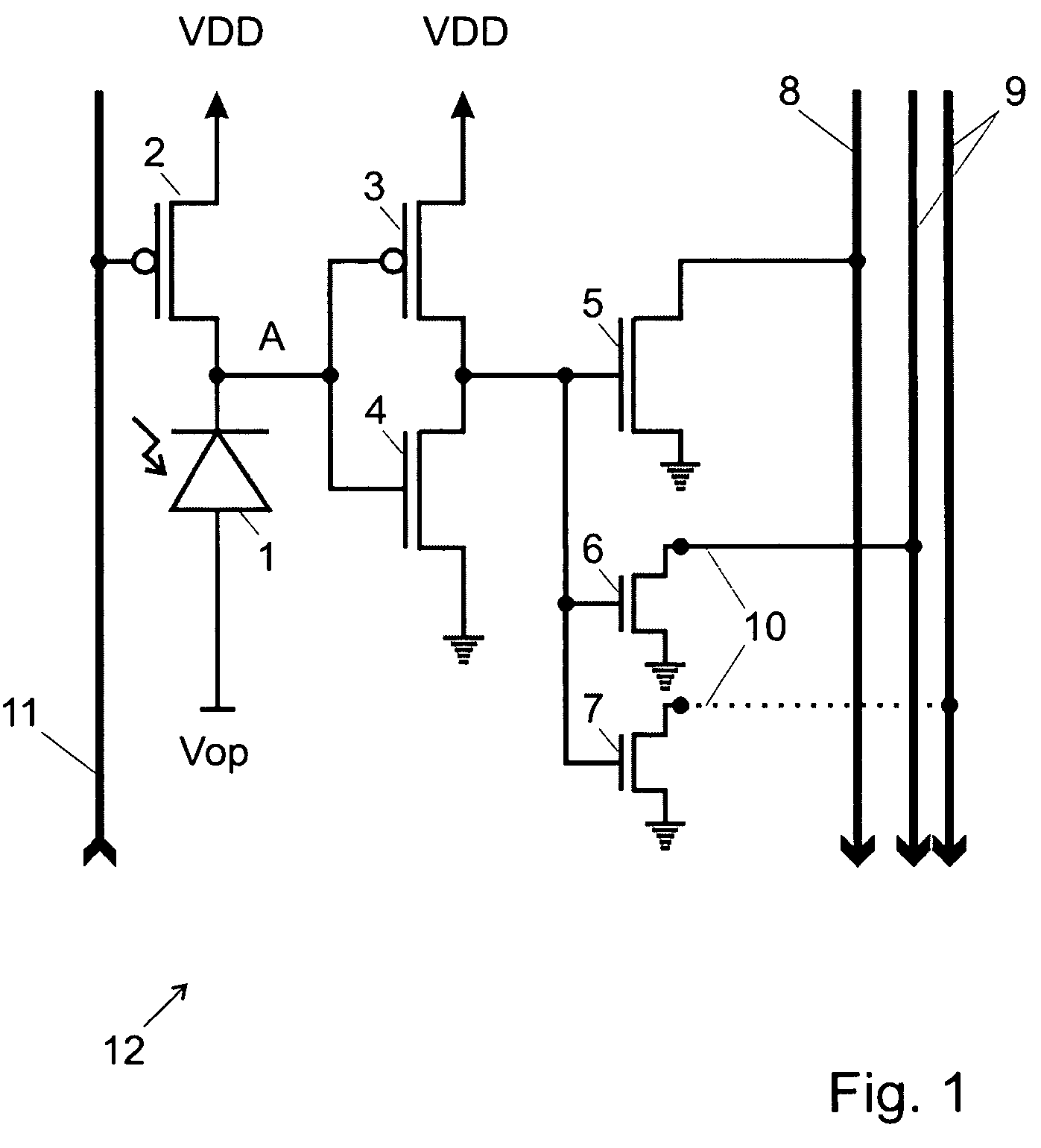

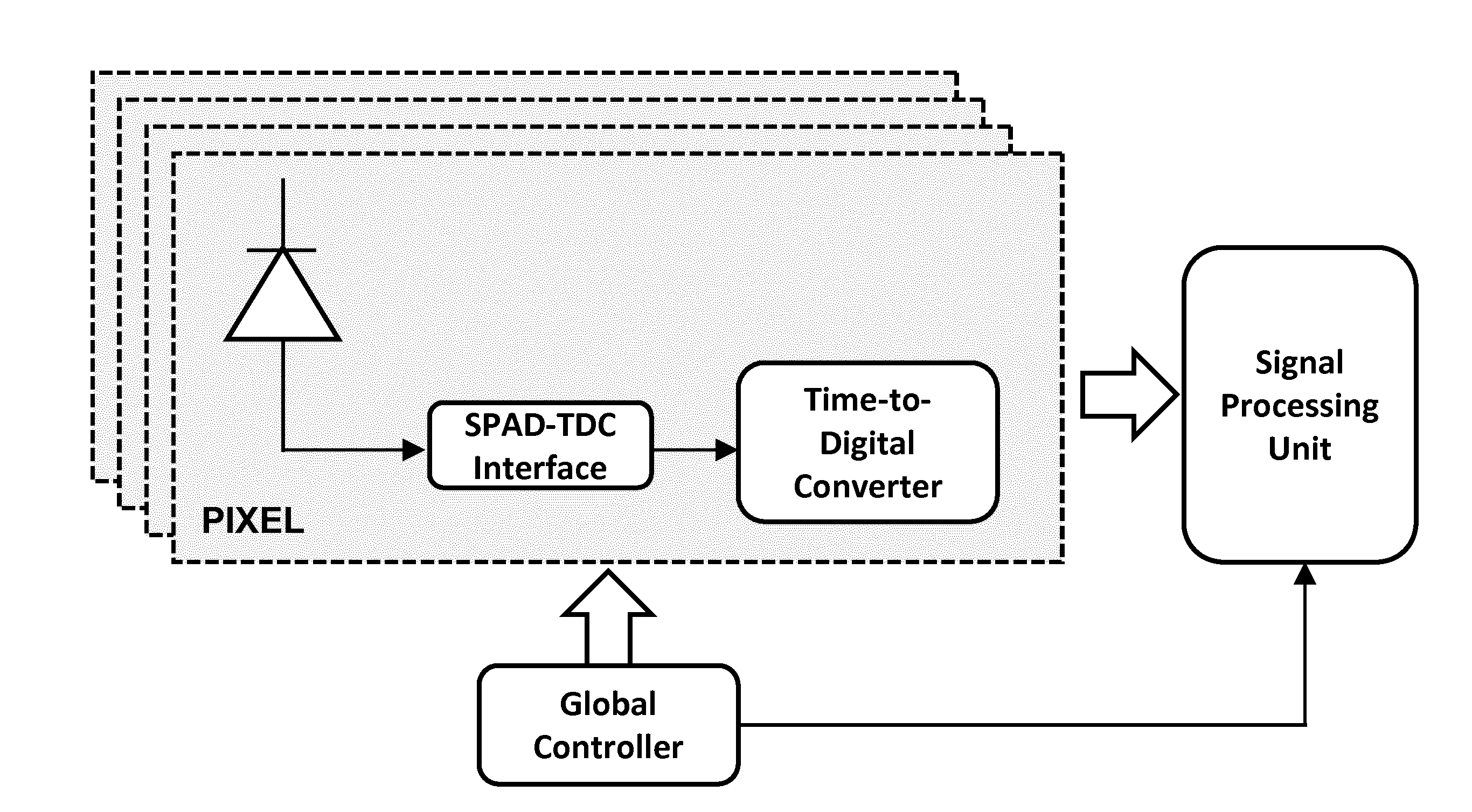

Integrated circuit comprising an array of single photon avalanche diodes

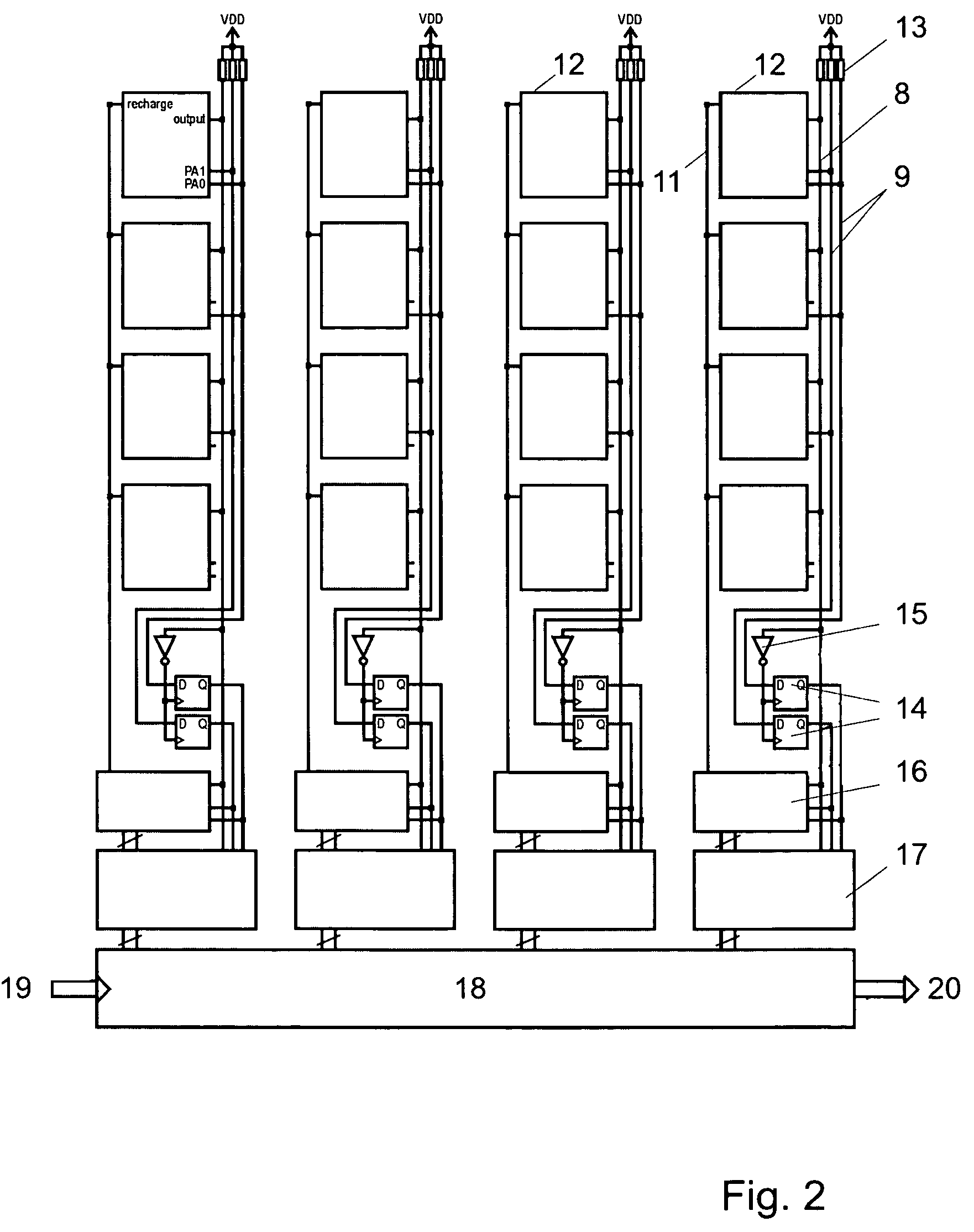

ActiveUS20060202129A1Improve performanceReduce power consumptionMaterial analysis by optical meansElectromagnetic wave reradiationSingle-photon avalanche diodeTransformer

An integrated circuit (1) has an array of single photon avalanche diodes (SPADS), a plurality of read-out circuits, each SPADS being coupled to one read-out circuit, wherein at least some of the read-out circuits comprise time-to-digital converters (TDC) and / or a digital asynchronous counter. The plurality of SPADS are coupled to one single read-out circuit. The read-out circuit may have a transformer for decoupling the SPAD from other parts of the read-out circuit.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

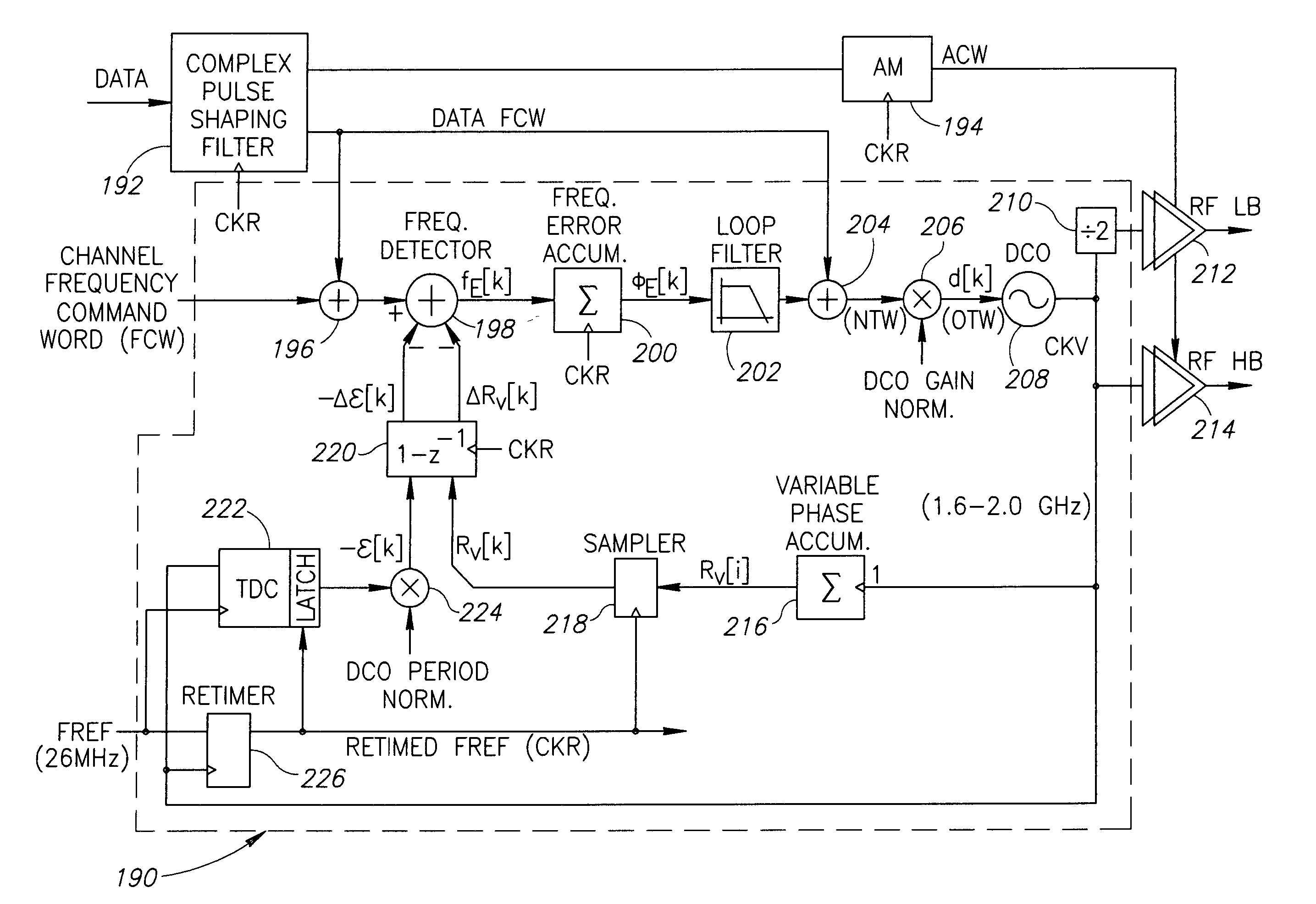

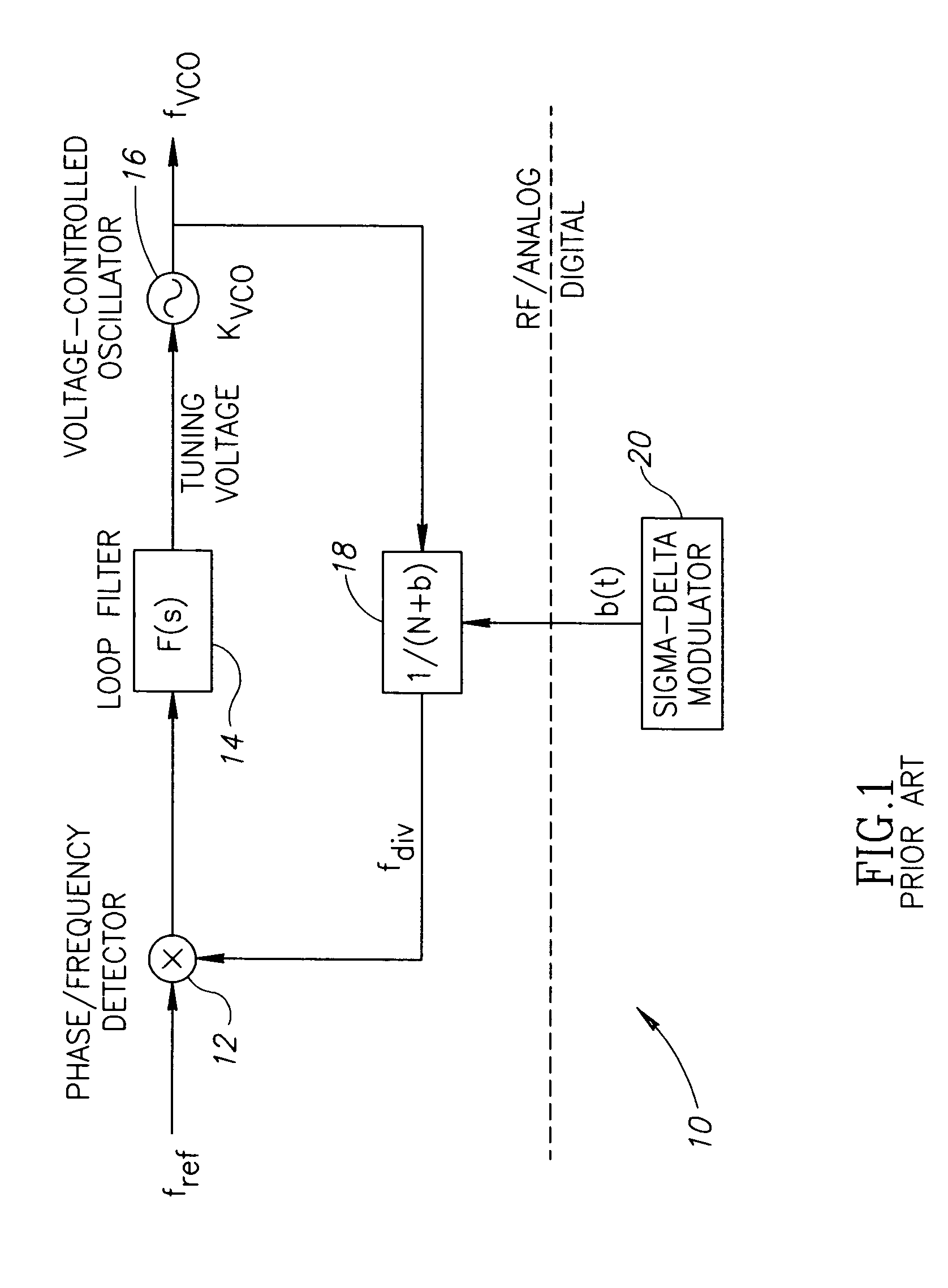

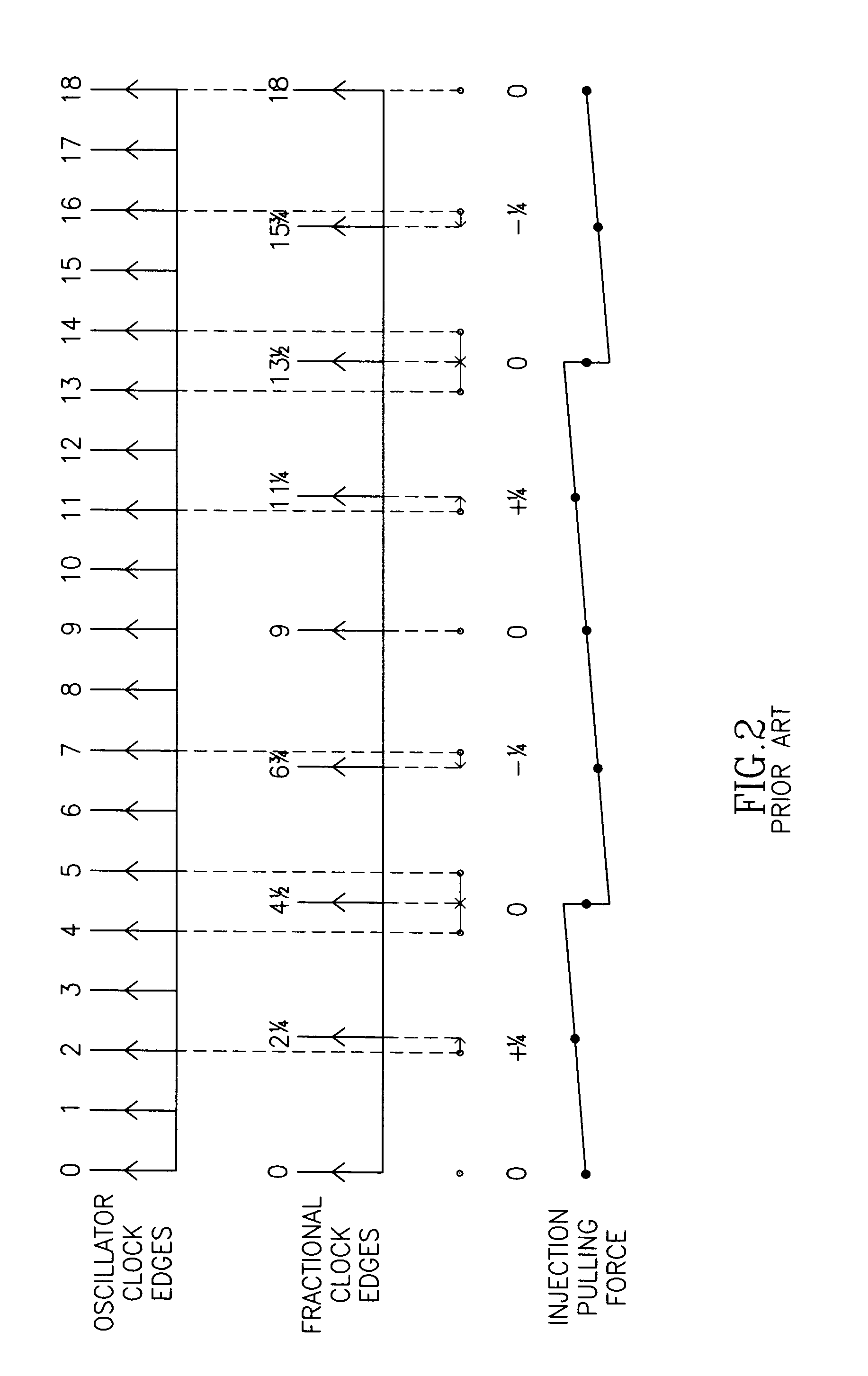

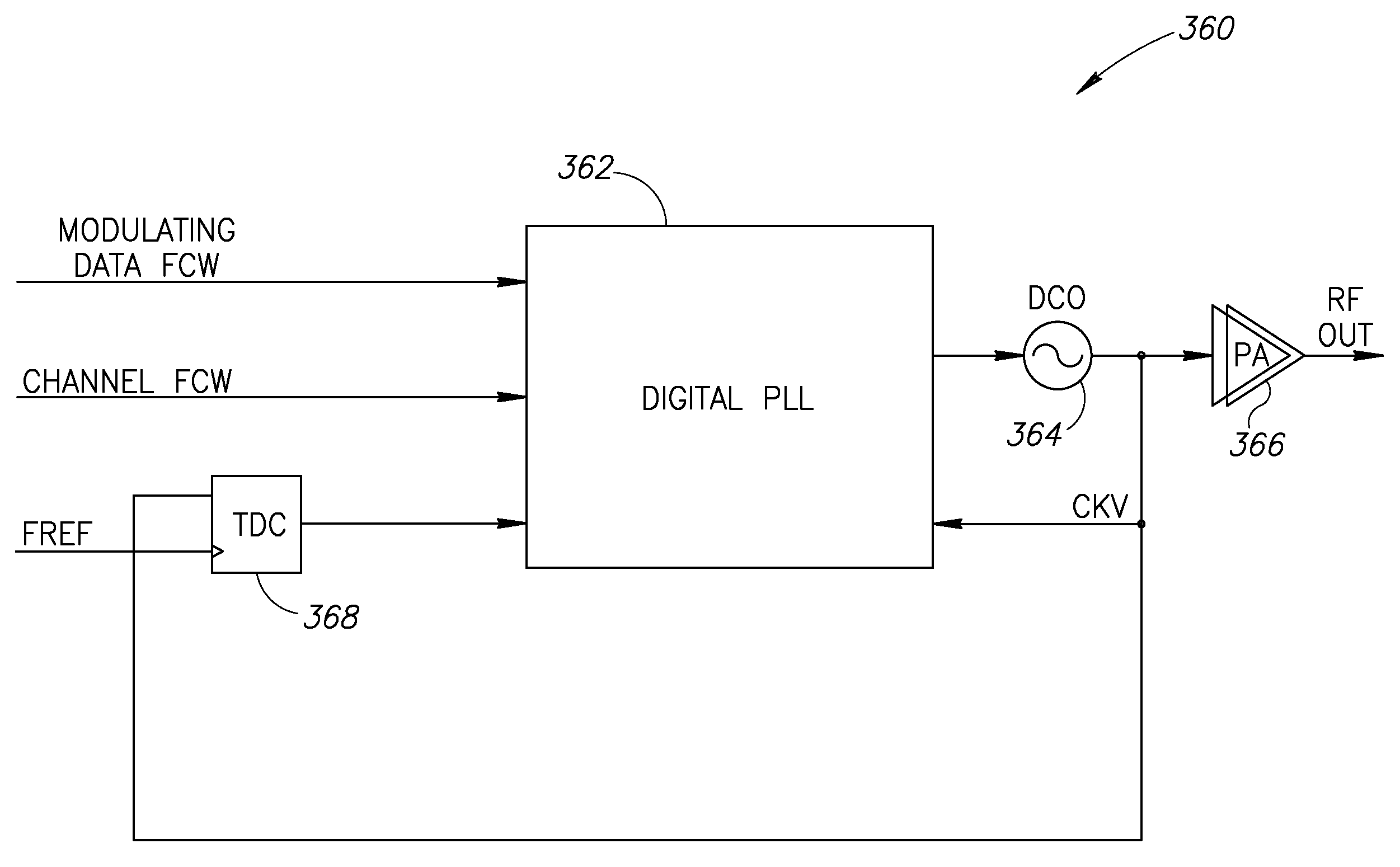

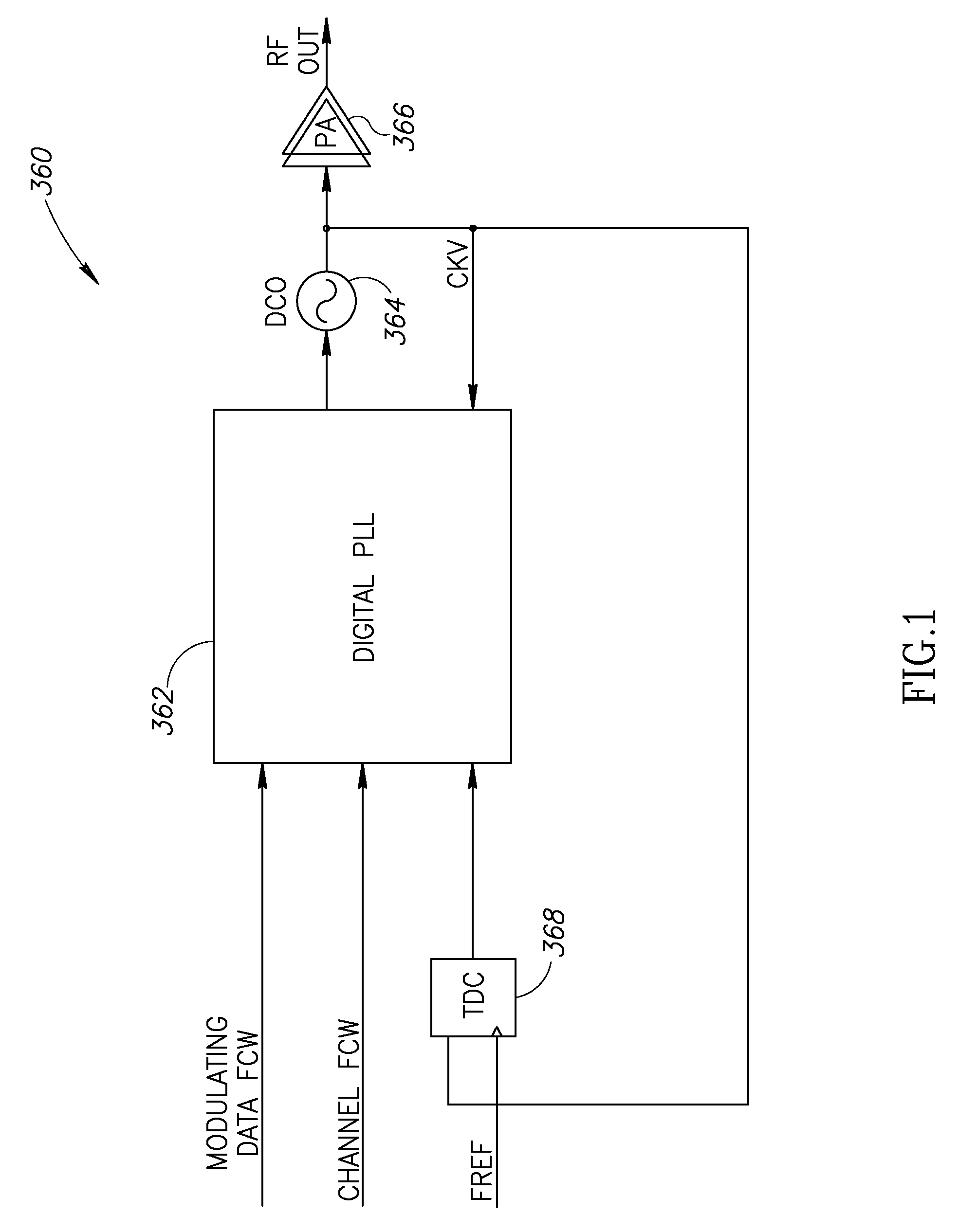

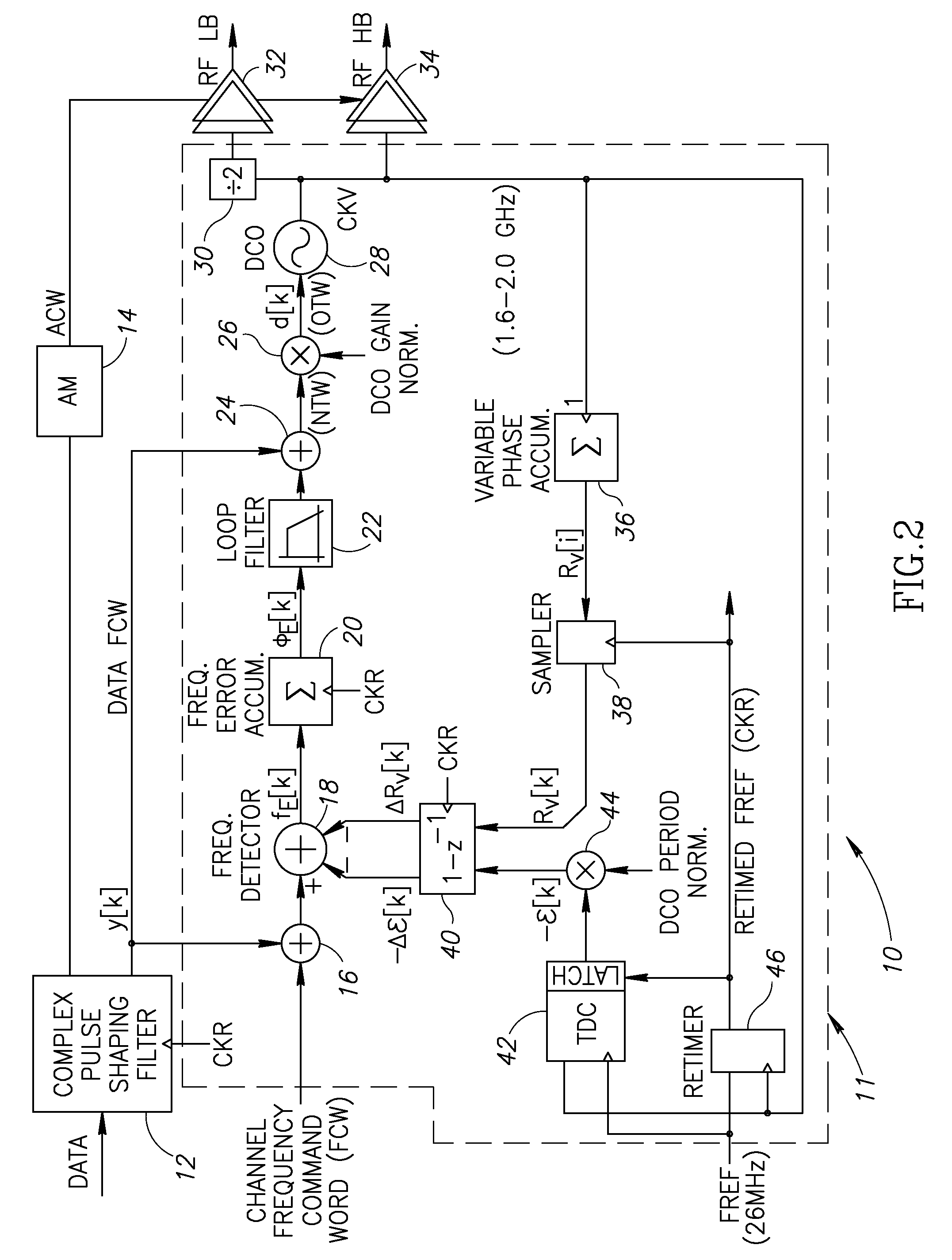

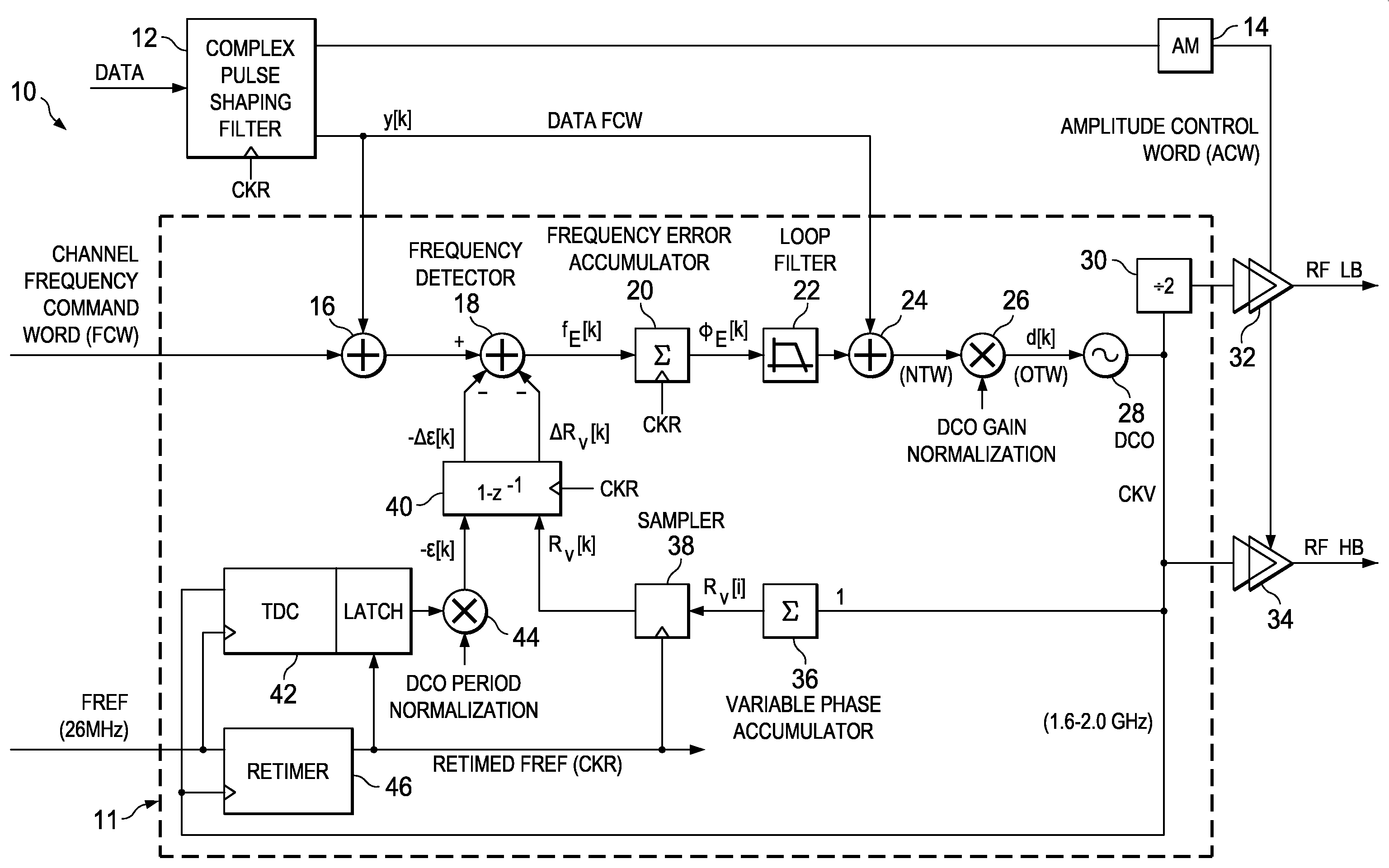

Apparatus for and method of noise suppression and dithering to improve resolution quality in a digital RF processor

InactiveUS20050186920A1Cancel noiseAvoid it happening againPulse automatic controlAngle modulationImage resolutionEngineering

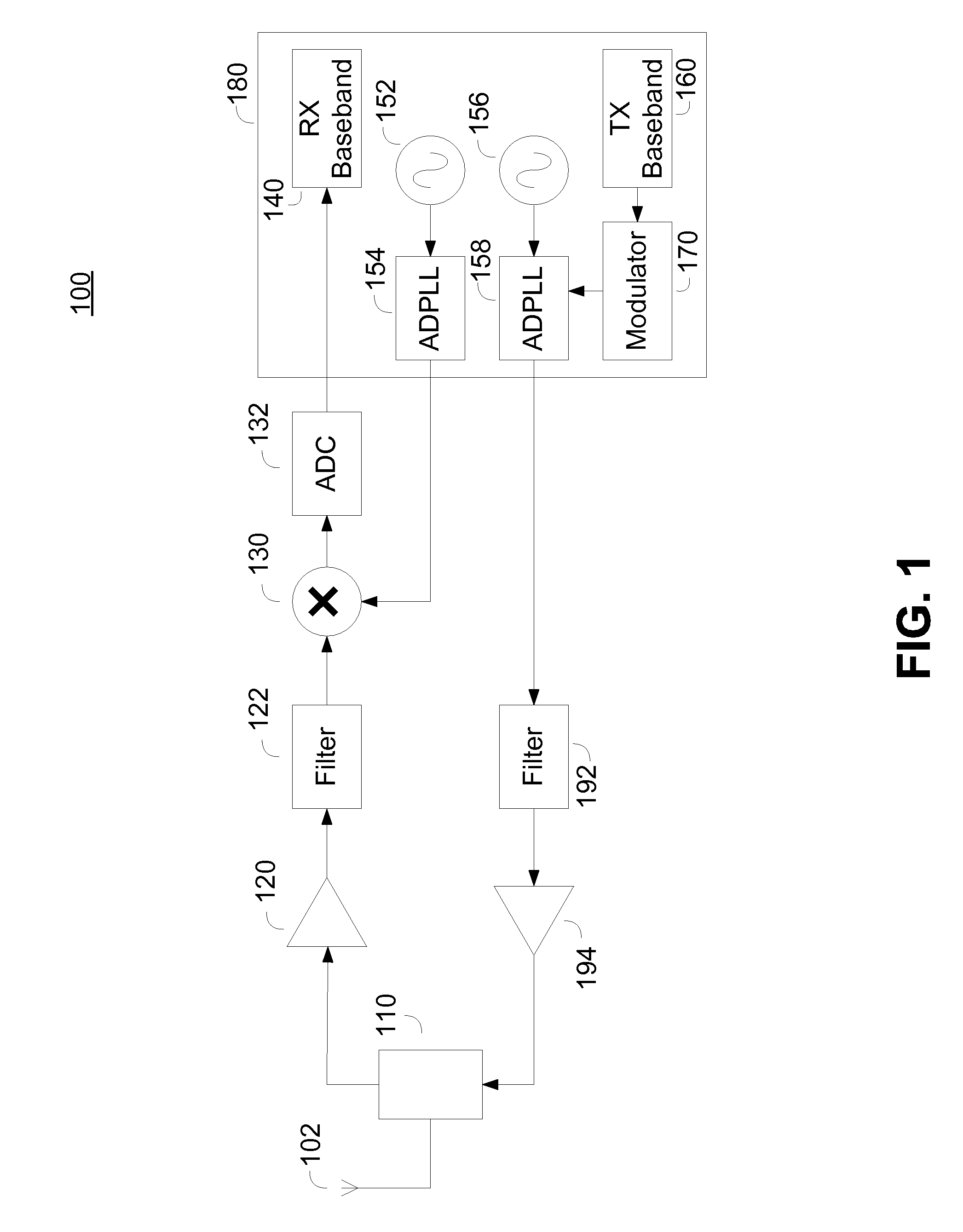

A novel apparatus for and a method of noise and spurious tones suppression in a digital RF processor (DRP). The invention is well suited for use in highly integrated system on a chip (SoC) radio solutions that incorporate a very large amount of digital logic circuitry. The noise suppression scheme eliminates the noise caused by various on chip interference sources transmitted through electromagnetic, power, ground and substrate paths. The noise suppression scheme permits an all digital PLL (ADPLL) to operate in such a way to avoid generating the spurs that would normally be generated from the injection pulling effect of interfering sources on the chip. The frequency reference clock is retimed to be synchronous to the RF oscillator clock and used to drive the entire digital logic circuitry of the DRP. This ensures that the different clock edges throughout the system will not exhibit mutual drift. A method of improving the resolution quality of a time to digital converter within the ADPLL is also taught. The method dithers the reference clock by passing it through a delay circuit that is controlled by a sigma-delta modulator. The dithered reference clock reduces the affect on the phase noise at the output of the ADPLL due to ill-behaved quantization of the TDC timing estimation.

Owner:TEXAS INSTR INC

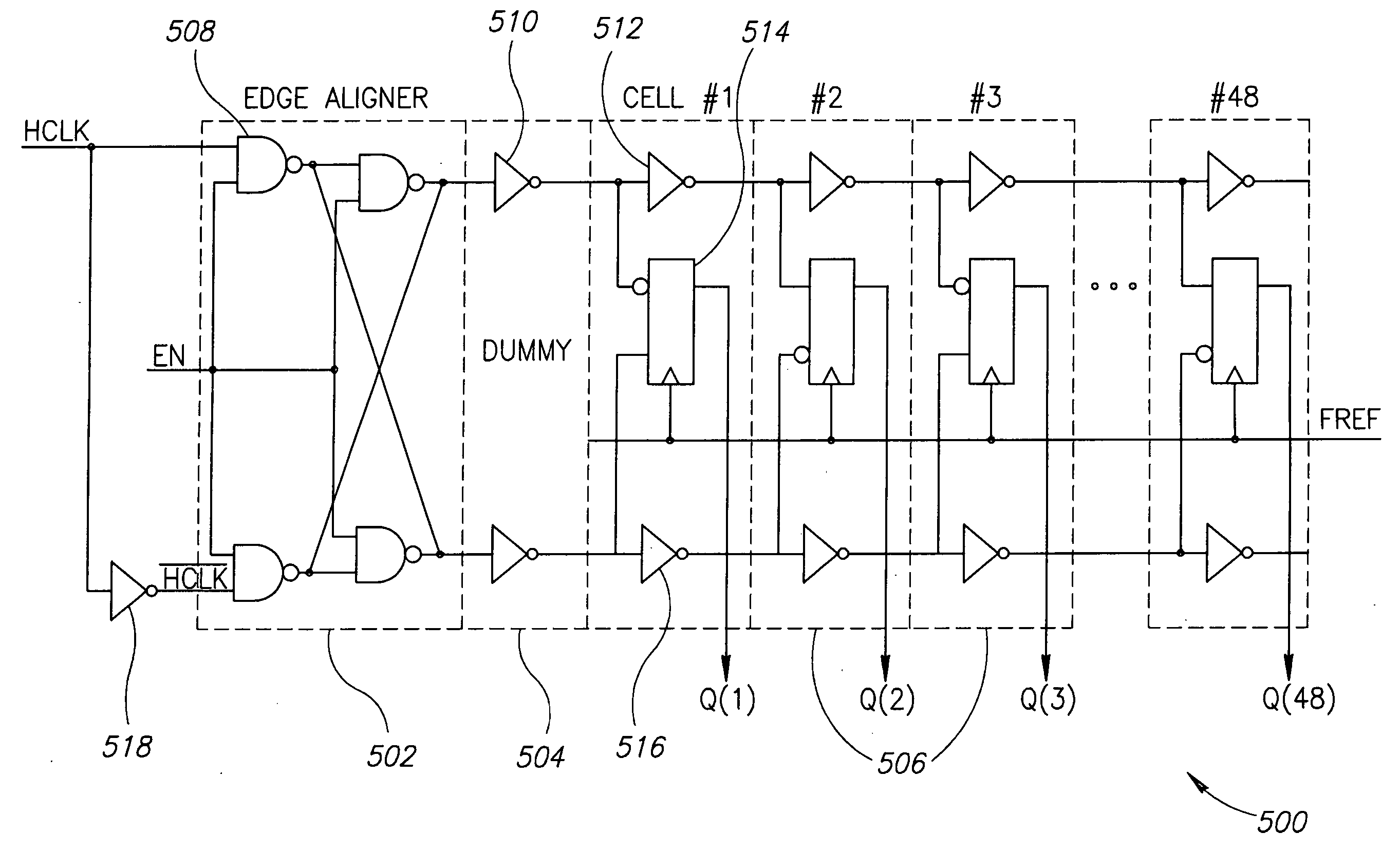

Circuit for high-resolution phase detection in a digital RF processor

ActiveUS7205924B2Less sensitiveReduce power consumptionElectric signal transmission systemsModulated-carrier systemsDigital converterCmos process

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC

Integrated circuit comprising an array of single photon avalanche diodes

ActiveUS7547872B2Reduce in quantityImprove fill factorTelevision system detailsTelevision system scanning detailsSingle-photon avalanche diodeTransformer

Owner:FASTREE 3D SA

Adaptive spectral noise shaping to improve time to digital converter quantization resolution using dithering

ActiveUS20080068236A1High resolutionHigh frequency noiseElectric signal transmission systemsAnalogue conversionFrequency spectrumNoise shaping

A novel and useful apparatus for and method of improving the quantization resolution of a time to digital converter in a digital PLL using noise shaping. The TDC quantization noise shaping scheme is effective to reduce the TDC quantization noise to acceptable levels especially in the case of integer-N channel operation. The mechanism monitors the output of the TDC circuit and adaptively generates a dither (i.e. delay) sequence based on the output. The dither sequence is applied to the frequency reference clock used in the TDC which adjusts the timing alignment between the edges of the frequency reference clock and the RF oscillator clock. The dynamic alignment changes effectively shape the quantization noise of the TDC. By shaping the quantization noise, a much finer in-band TDC resolution is achieved resulting in the quantization noise being pushed out to high frequencies where the PLL low pass characteristic effectively filters it out.

Owner:TEXAS INSTR INC

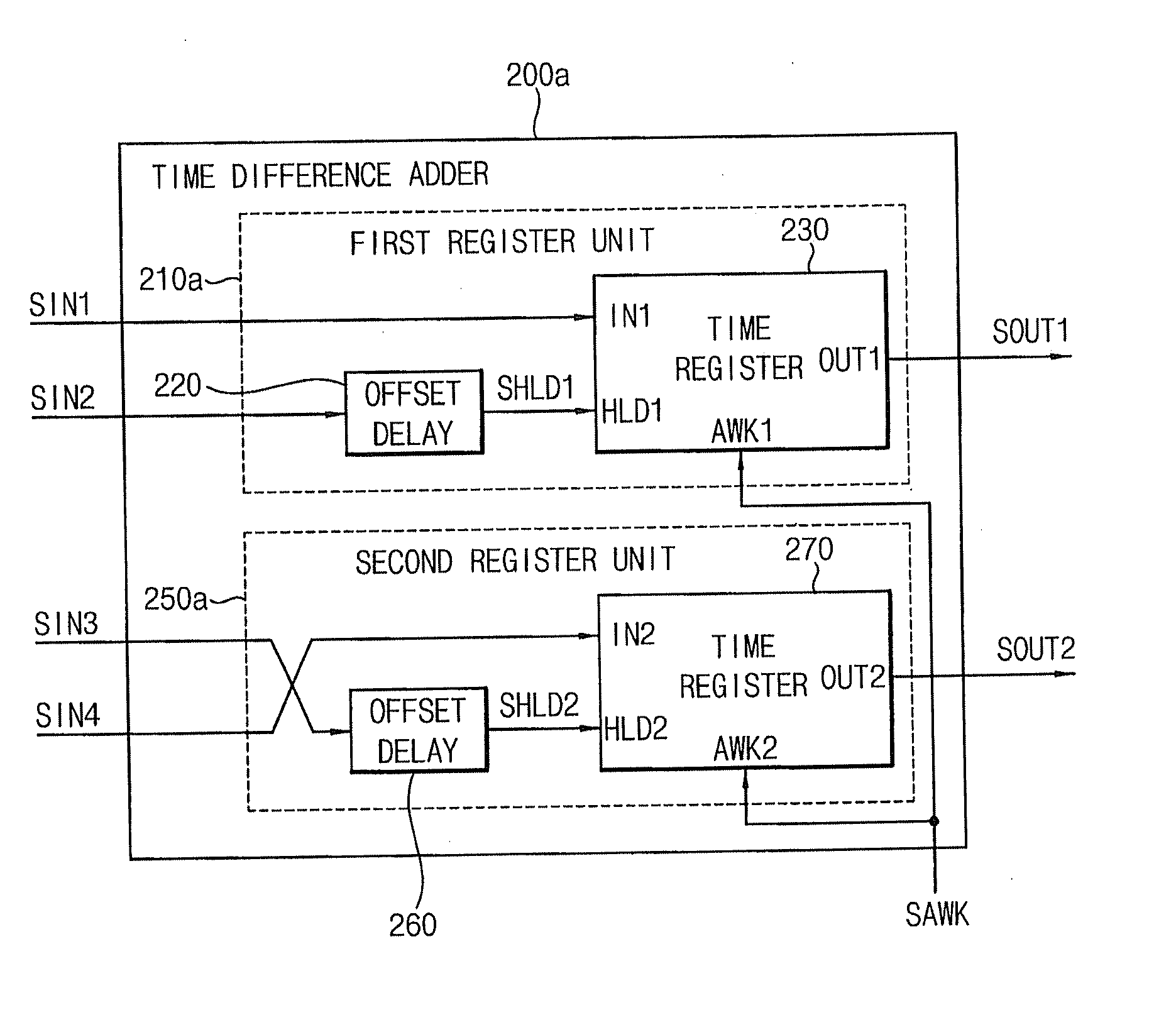

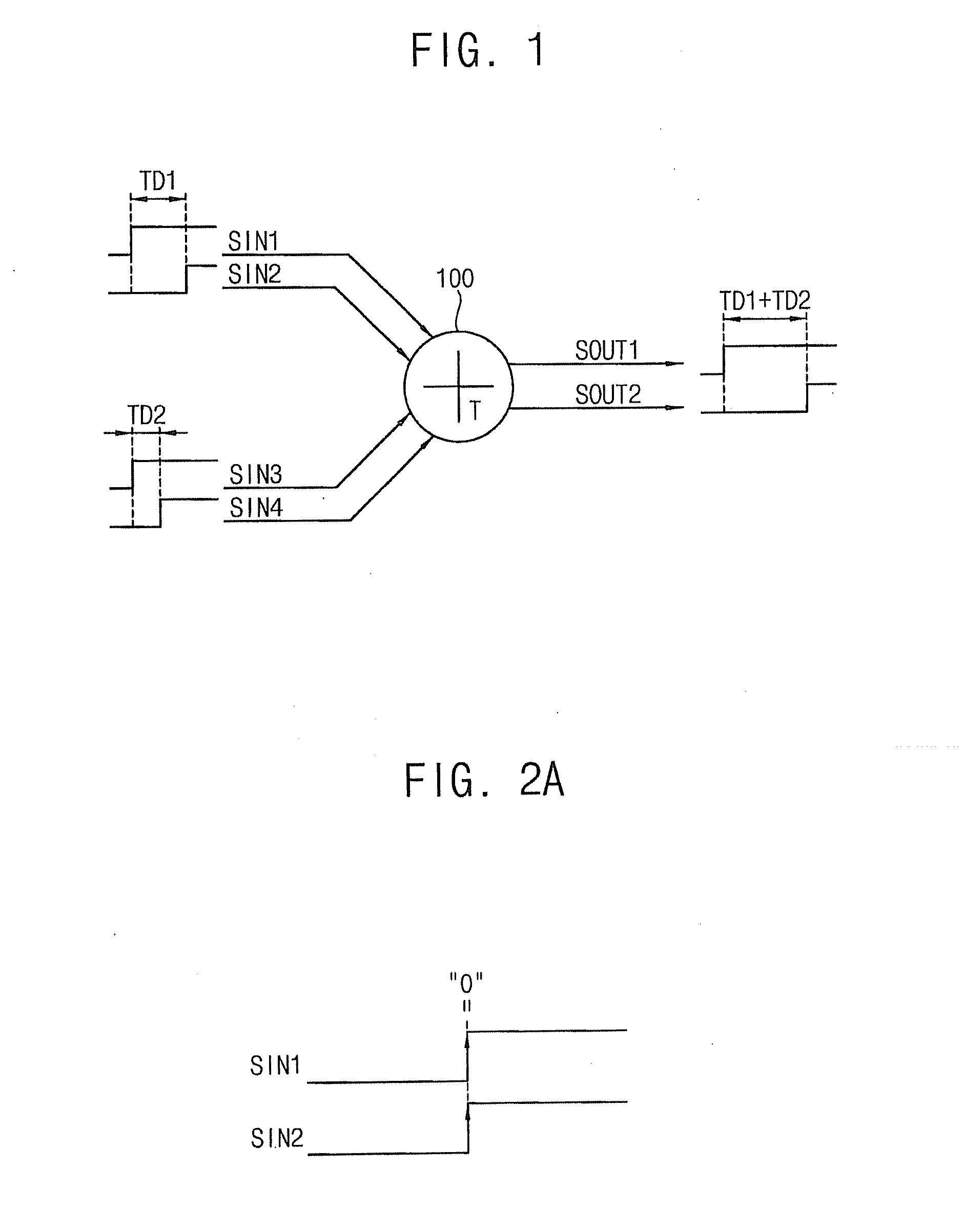

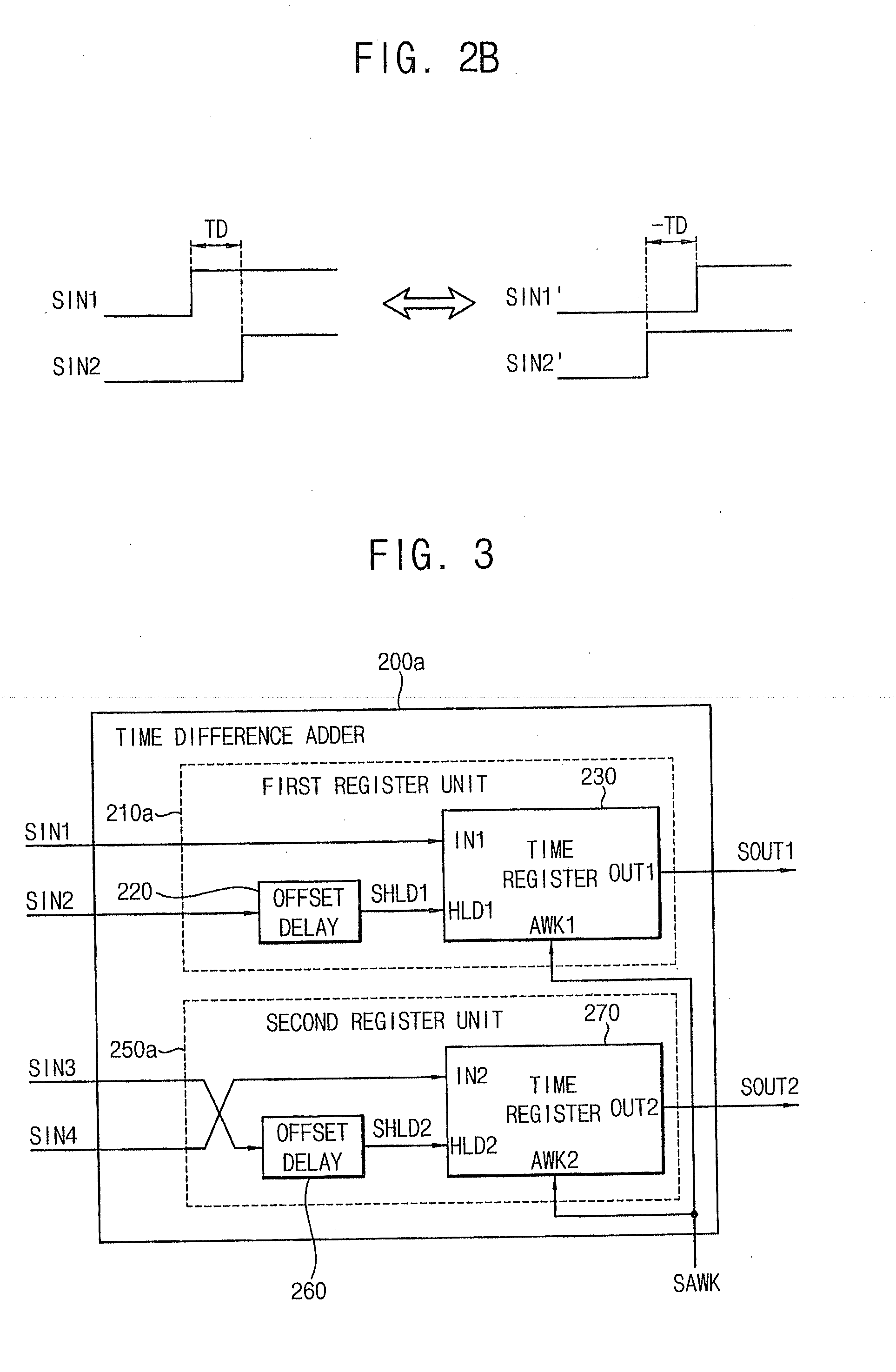

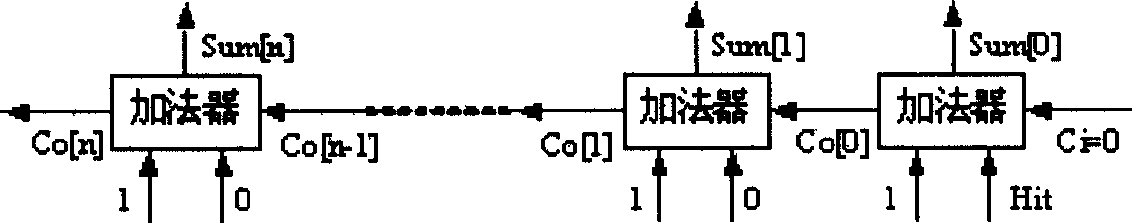

Time difference adders, time difference accumulators, sigma-delta time-to-digital converters, digital phase locked loops and temperature sensors

ActiveUS20120306553A1Computations using contact-making devicesPulse automatic controlDigital down converterProcessor register

A time difference adder included in a system-on-chip (SOC) includes a first register unit and a second register unit. The first register unit is configured to receive first and second input signals having a first time difference, and generate a first output signal in response to a first signal. The second register unit is configured to receive third and fourth input signals having a second time difference, and generate a second output signal having a third time difference with respect to the first output signal in response to the first signal. The third time difference corresponds to a sum of the first time difference and the second time difference.

Owner:SAMSUNG ELECTRONICS CO LTD

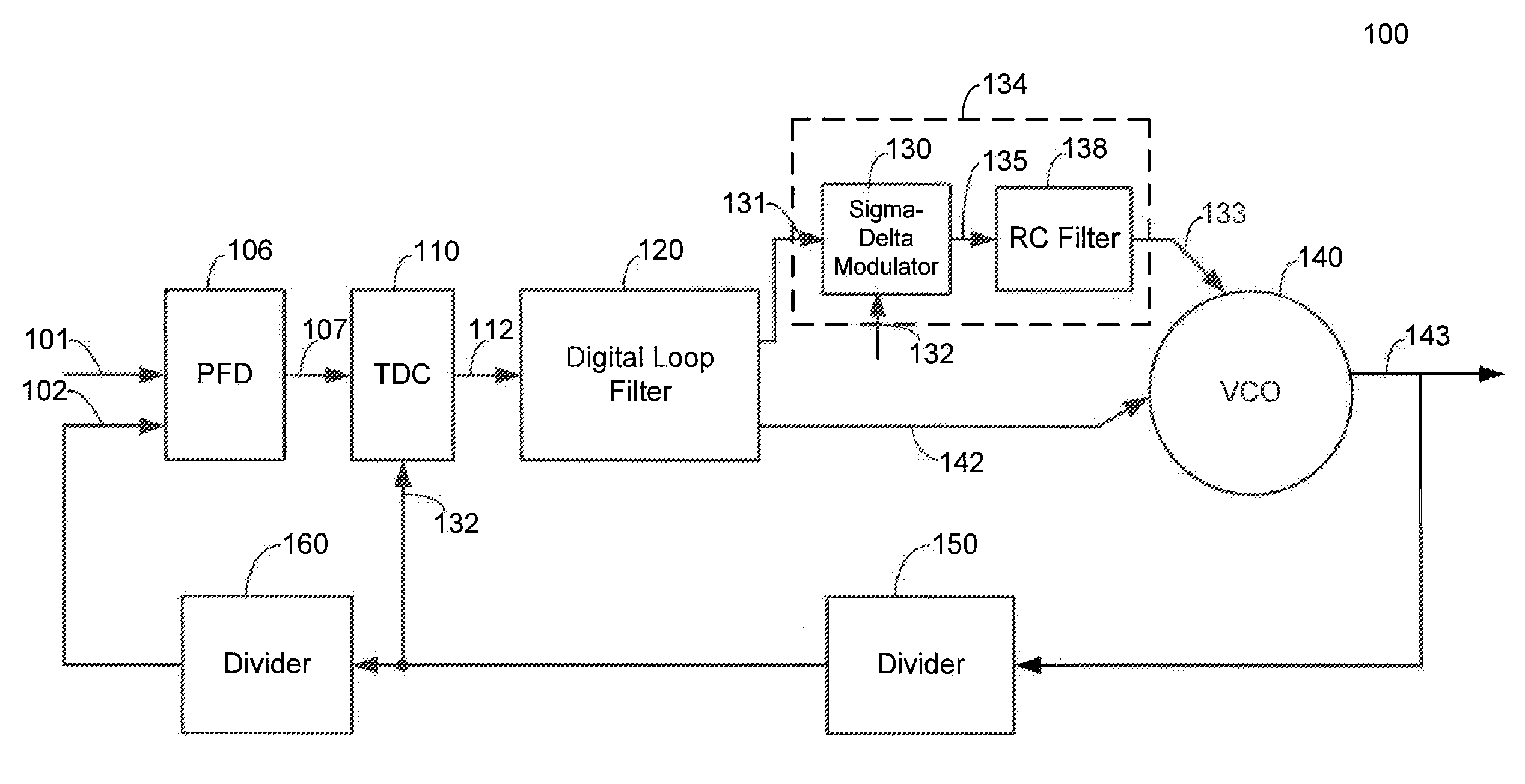

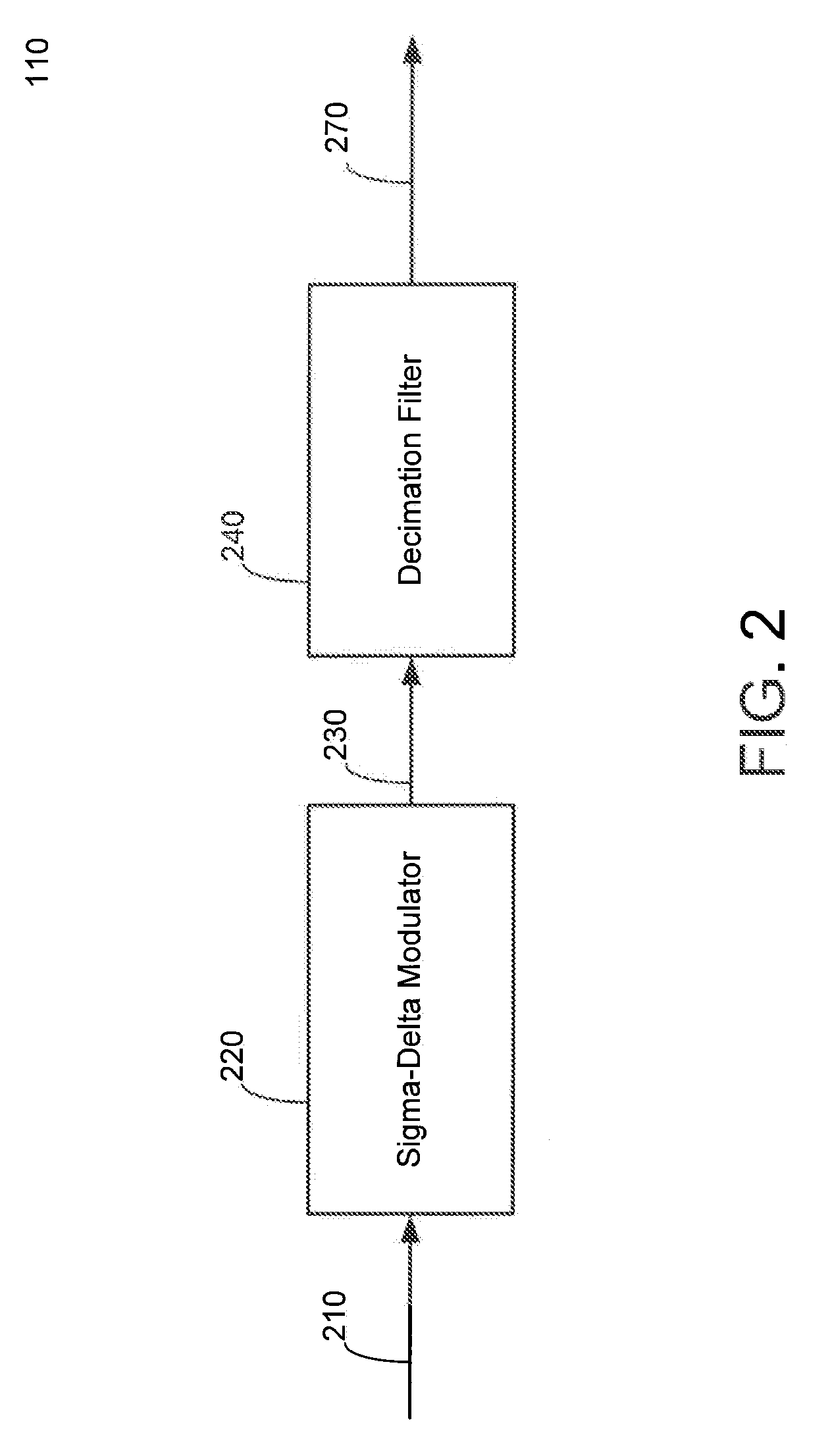

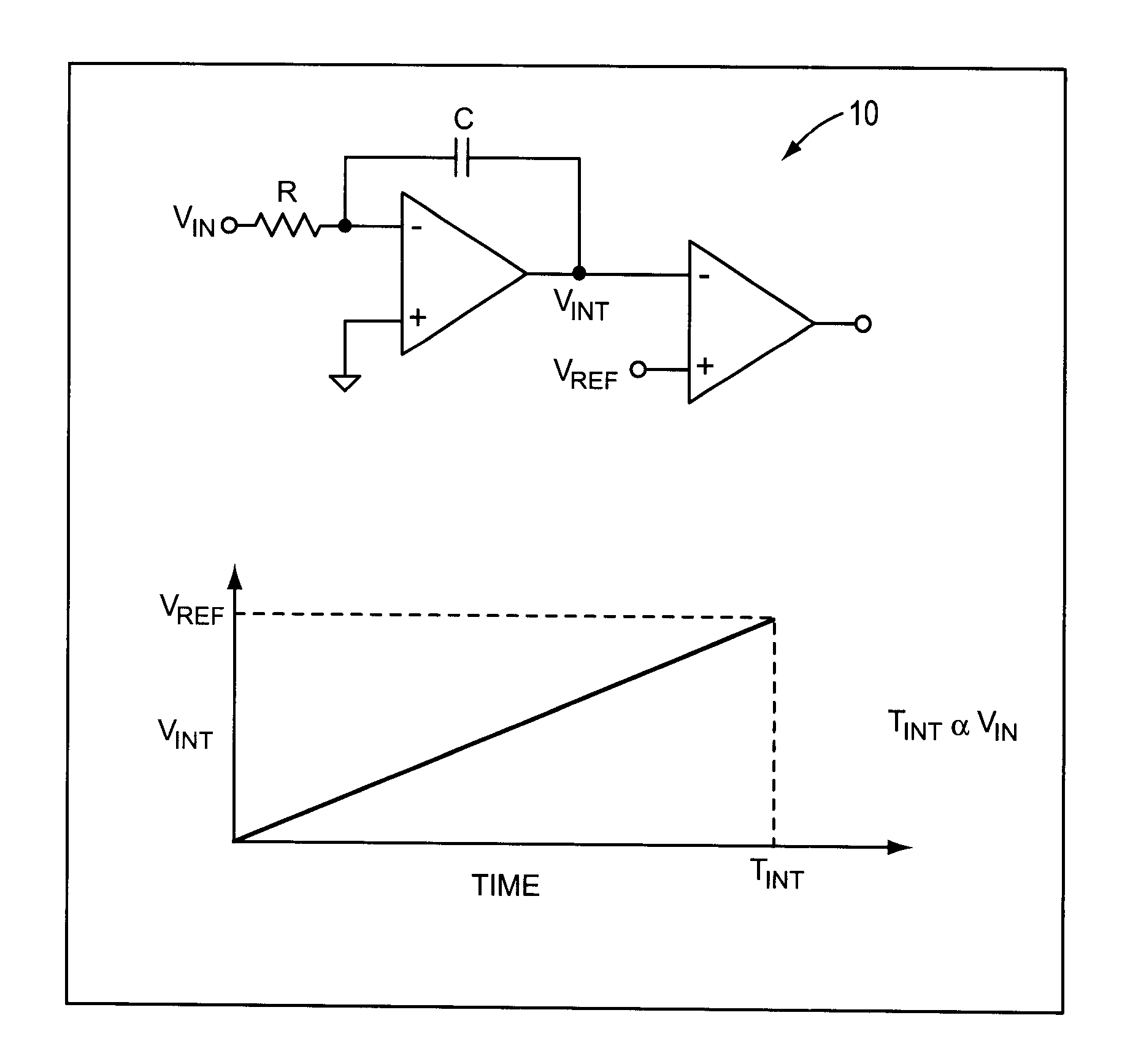

Systems, Circuits, and Methods for a Sigma-Delta Based Time to Digital Converter

ActiveUS20130257494A1Electric signal transmission systemsPulse automatic controlIntegratorEngineering

Systems, methods, and circuits provide a time to digital converter comprising a sigma-delta modulator. The sigma-delta based time to digital converter may receive an analog signal representing a phase error between a reference clock signal and a feedback clock signal and generate a digital signal representing the phase error. The sigma-delta modulator may comprise a subtractor, an integrator, a feedback path, and a quantizer. The subtractor may receive the analog signal and subtract a feedback signal from the analog signal and the integrator may integrate the output of the subtractor. The sigma-delta modulator may accumulate a voltage or a charge over a capacitor as pulses are received from the analog signal and after a number of clock cycles, the capacitor may be discharged to generate a pulse in an output signal.

Owner:AVAGO TECH INT SALES PTE LTD

Adaptive spectral noise shaping to improve time to digital converter quantization resolution using dithering

ActiveUS7570182B2Quantization noise resolutionReduce noiseElectric signal transmission systemsAnalogue conversionFrequency spectrumNoise shaping

Owner:TEXAS INSTR INC

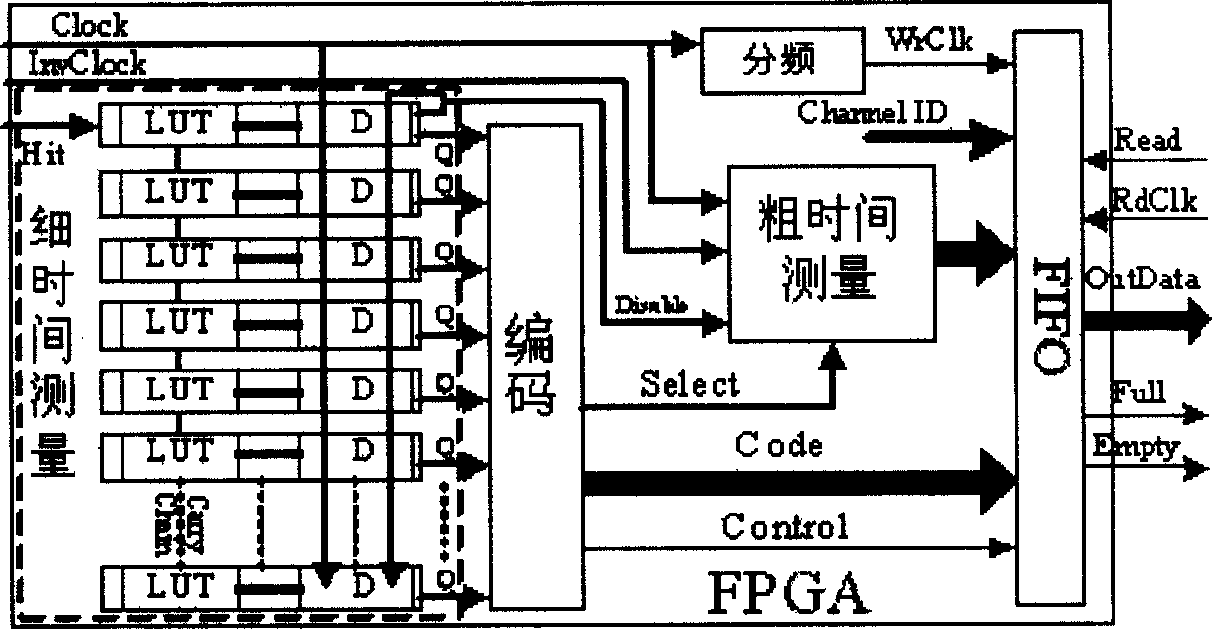

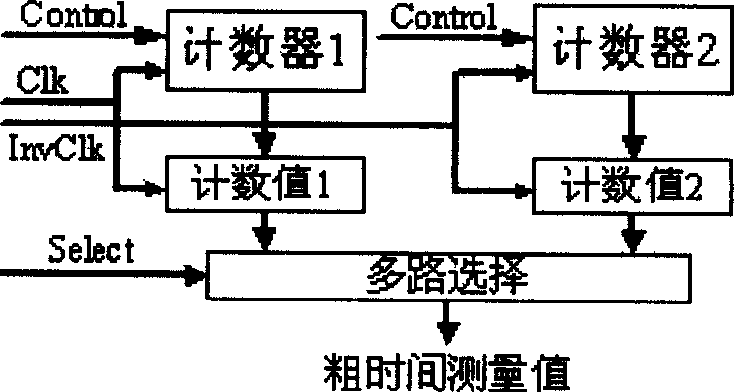

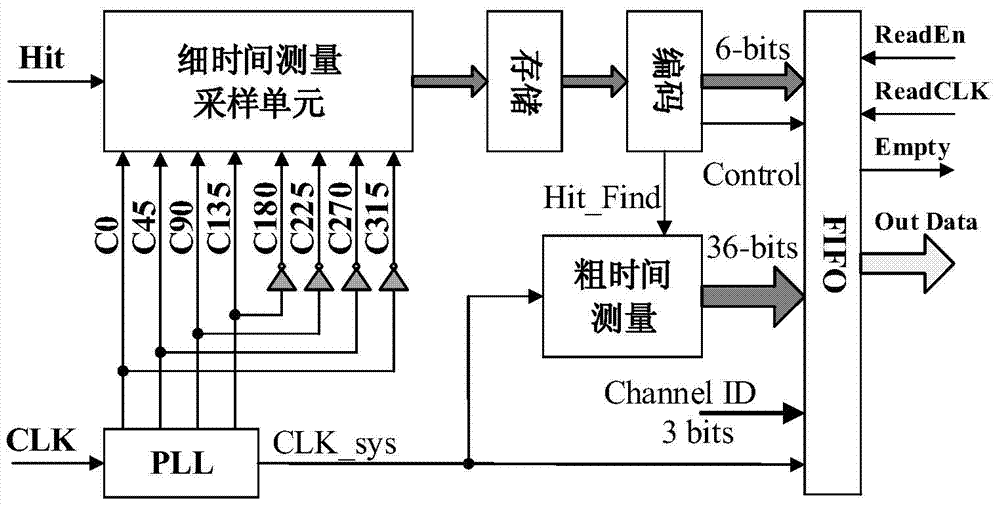

Time digital converter based on RPGA and its conversion method

InactiveCN1719353AFlexible useSimple designElectric unknown time interval measurementProgramme control in sequence/logic controllersDigital converterComputer science

The present invention relates to a time / digital converter based on FPGA and its conversion method, belonging to the field of time measurement technology. Said converter includes the following components: fine time measurement unit, coding unit, coarse time measurement unit and data buffer storage unit. The main application of said invention is to make high accuracy time measurement, it can be used in the fields of basis research and various application researches.

Owner:UNIV OF SCI & TECH OF CHINA

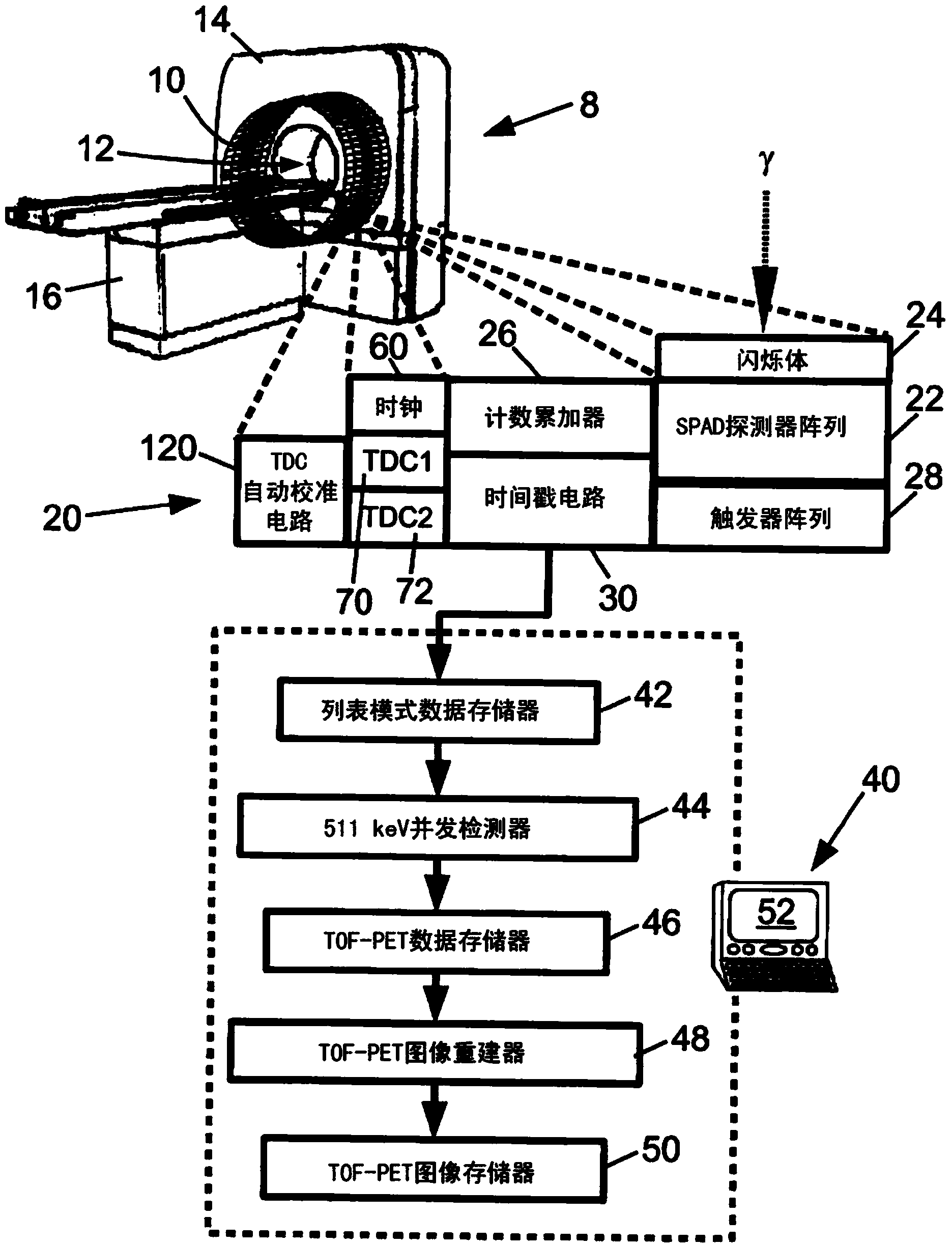

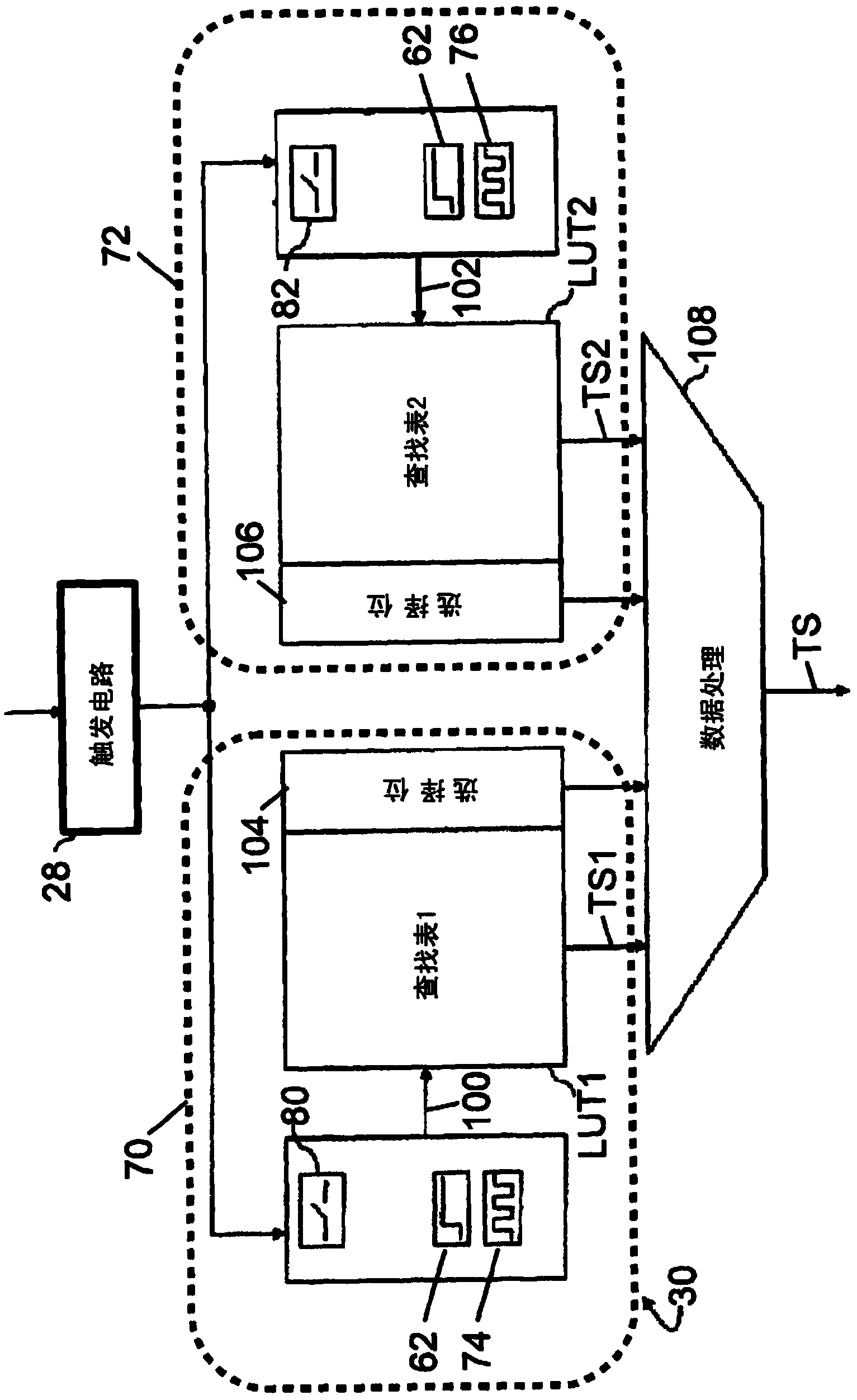

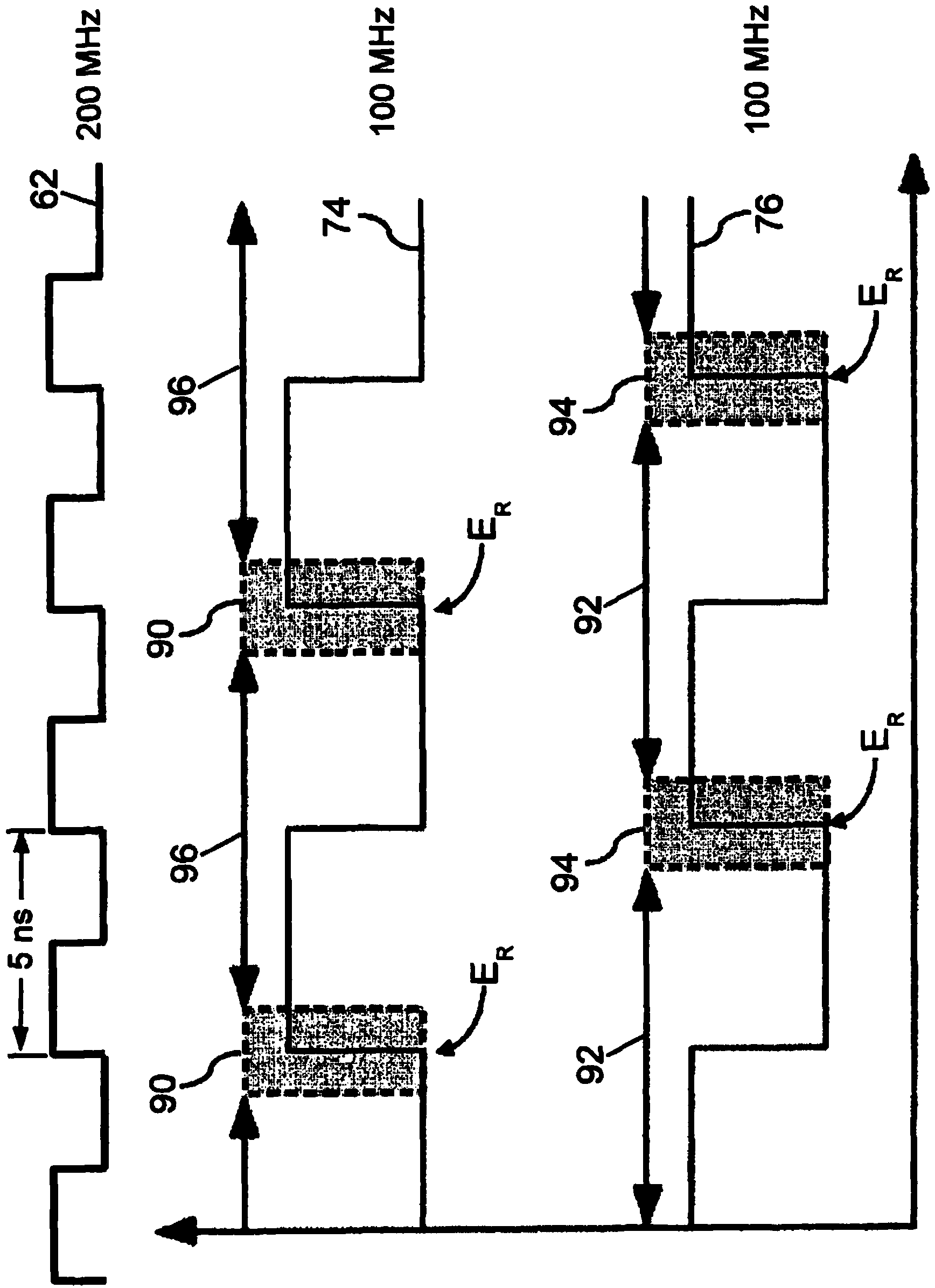

Detector array with time-to-digital conversion having improved temporal accuracy

ActiveCN103460072AImprove time resolutionAccurate time-of-flight PET imagingTomographyX/gamma/cosmic radiation measurmentDetector arrayDigital converter

A detector (22) detects an event. First and second time-to-digital converters(TDCs) (70, 72) generate first and second time stamps (TS1, TS2) for the detection of the event. The first TDC and the second TDC are both synchronized with a common clock signal (62) that defines a fixed time offset between the second TDC and the first TDC. An autocalibration circuit (120) adjusts the first TDC and the second TDC to keep the time difference between the second time stamp and the first time stamp equal to the fixed time offset between the second TDC and the first TDC. The detector may be a detector array, and trigger circuitry (28) propagates a trigger signal from a triggering detector of the array of detectors to the first and second TDC's. Skew correction circuitry (132, 134, 136, 142, 60, 162) adjusts a timestamp (TS) based on which detector is the triggering detector.

Owner:KONINKLJIJKE PHILIPS NV

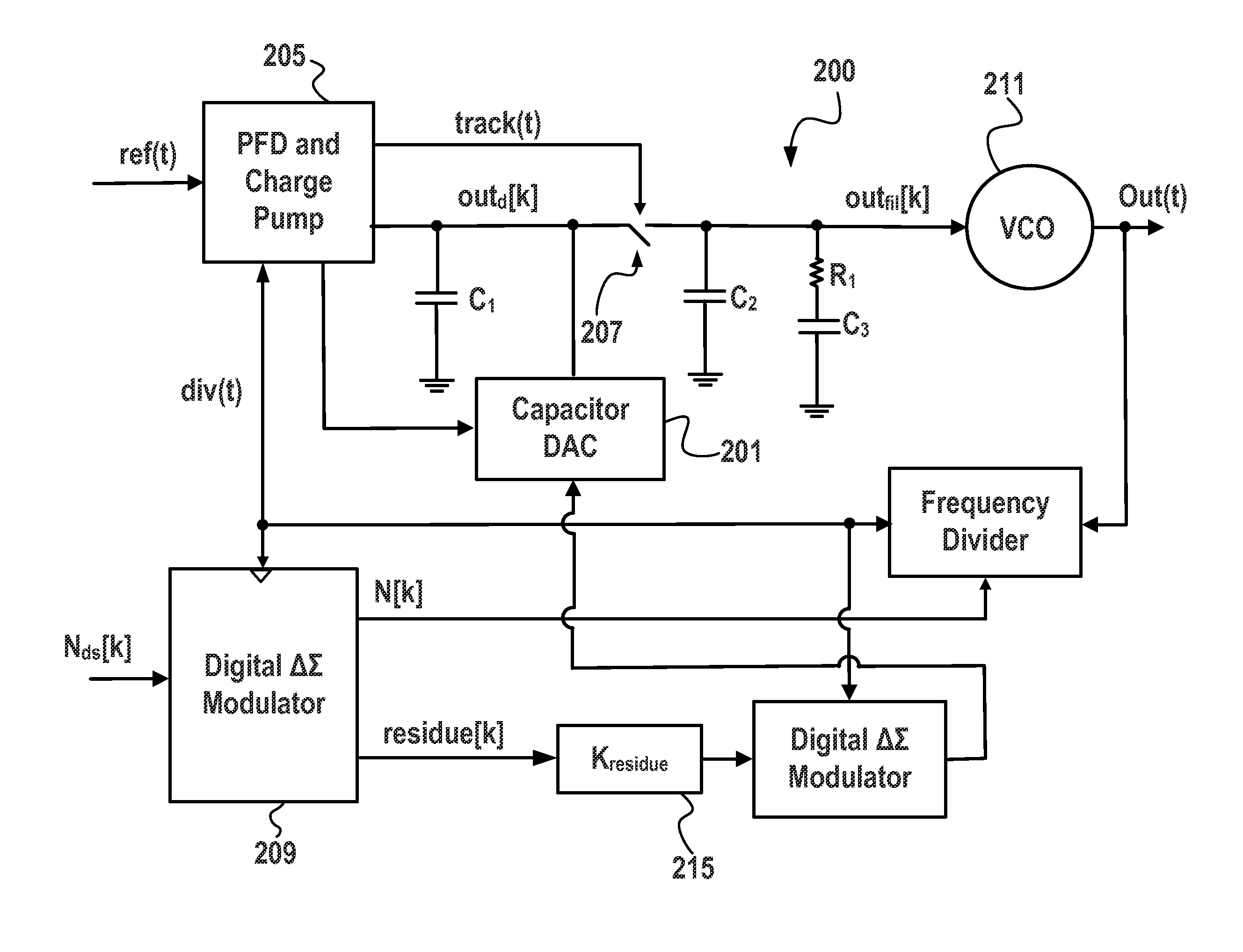

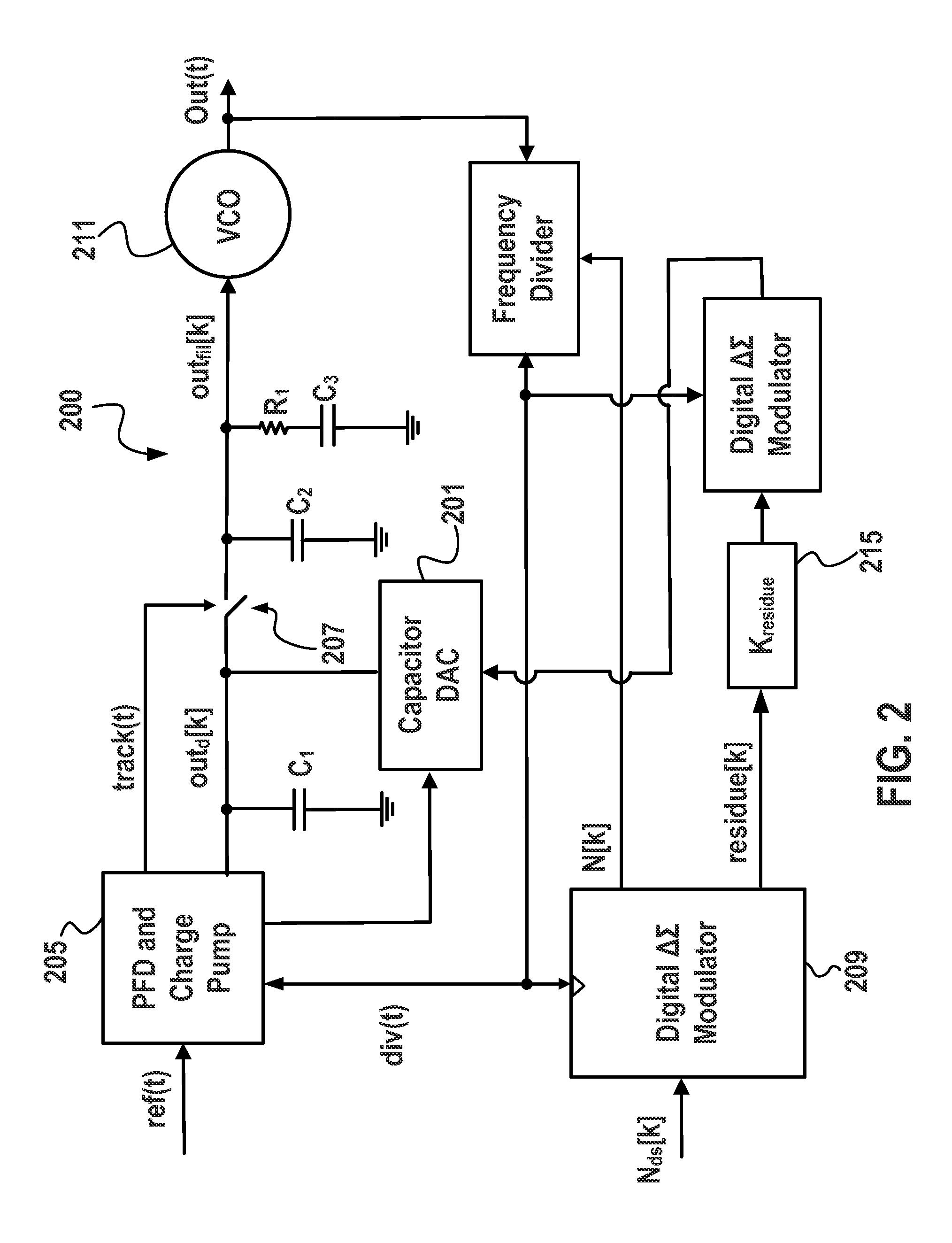

Cancellation of delta-sigma quantization noise within a fractional-n PLL with a nonlinear time-to-digital converter

ActiveUS20150145571A1Reduce quantization noisePulse automatic controlAnalogue conversionEngineeringGreek letter sigma

A fractional-N phase-locked loop (PLL) includes a nonlinear time to digital converter that generates a digital representation of a phase error corresponding to a time difference between a feedback signal of the fractional-N PLL and a reference signal. A nonlinear quantization noise cancellation circuit supplies a correction signal to ensure that the generated digital representation has reduced quantization noise. The correctional signal may be applied in the analog or digital domain.

Owner:SKYWORKS SOLUTIONS INC

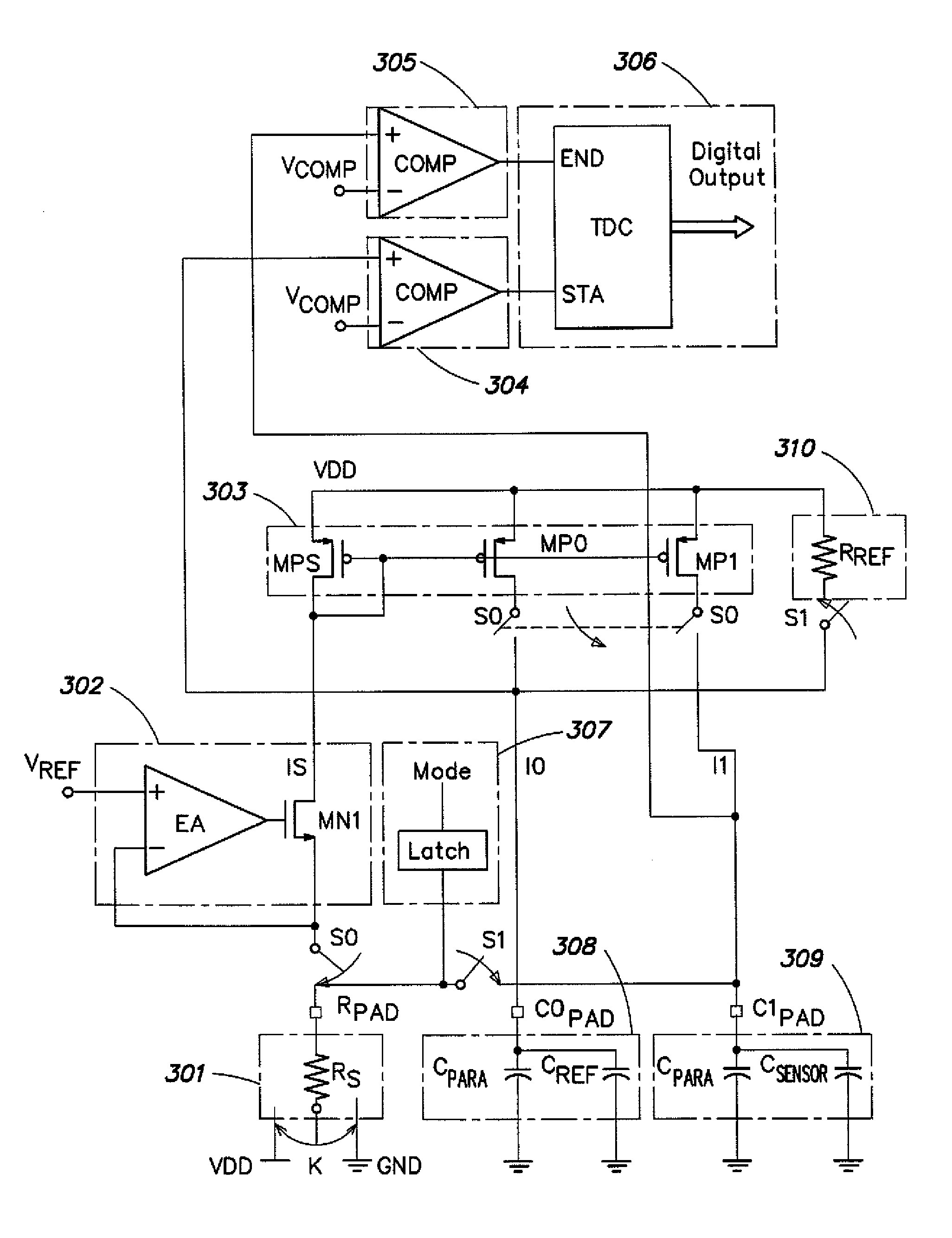

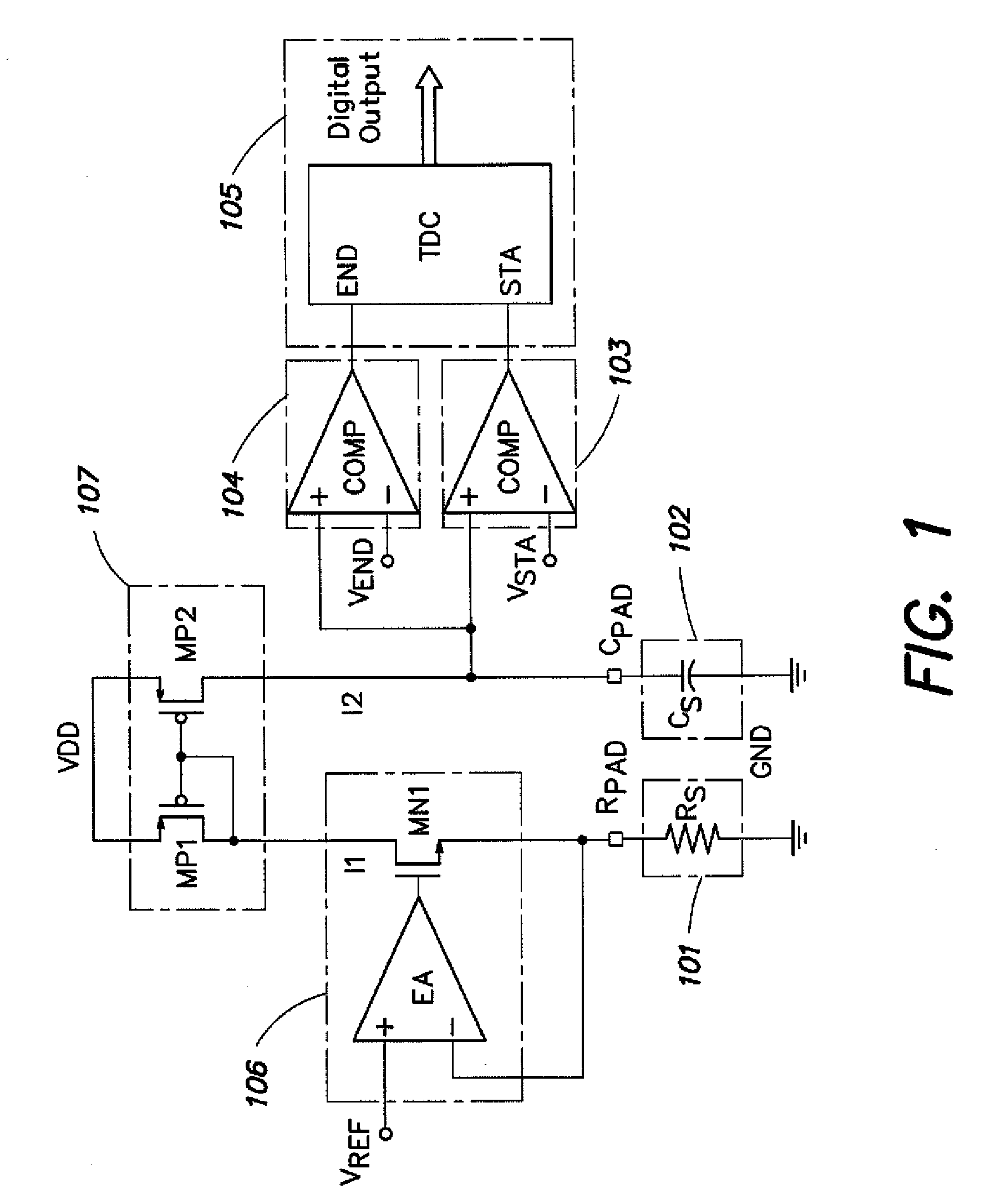

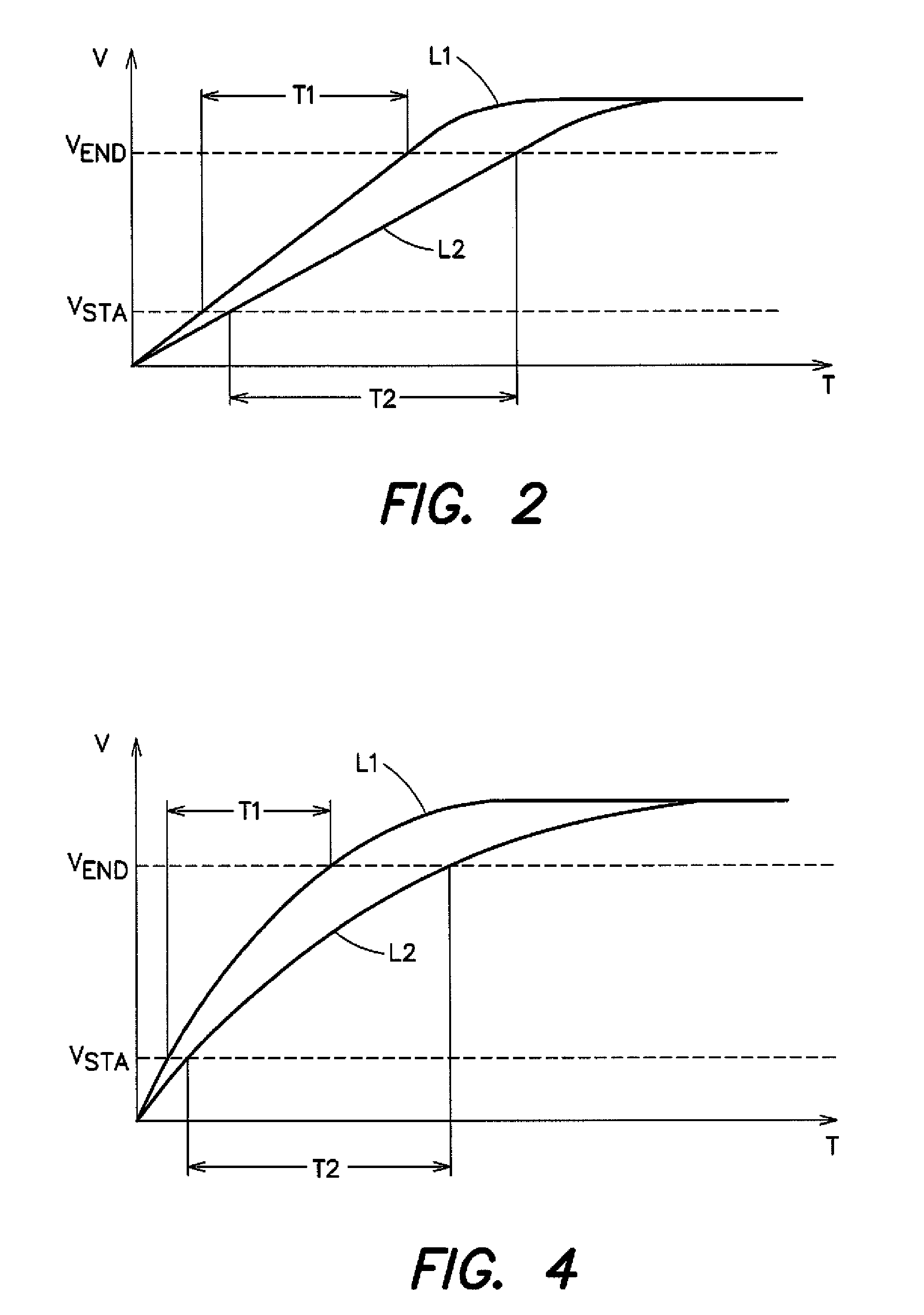

Adaptive capacitive touch sense control circuit

InactiveUS20090108914A1Improve abilitiesSimple structureResistance/reactance/impedenceElectronic switchingCapacitanceVoltage source

An adaptive capacitive touch sense control circuit includes a voltage buffer, a current setting resistor, a current mirror, a capacitor, a start comparator, an end comparator and a time-to-digital converter. The capacitor is connected with the current setting resistor. The circuit further includes a latch with a first control switch and a second control switch. The current setting resistor is switched between the ground and a voltage source through a switching element, so that when the current setting resistor is grounded, the first control switch is closed and the second control switch is opened, and when the current setting resistor is connected with the voltage source, the second control switch is closed and the first control switch is opened. An adaptive charging mode is adopted to sense a capacitance variation with a great ability of interference recognition, a simple structure, low power consumption and real time processing.

Owner:CHIPHOMER TECH SHANGHAI

Fractional-N Frequency Synthesizer Incorporating Cyclic Digital-To-Time And Time-To-Digital Circuit Pair

ActiveUS20160056827A1Low spuriousReduce power consumptionPower saving provisionsElectric signal transmission systemsFrequency spectrumFrequency synthesizer

A novel and useful look-ahead time to digital converter (TDC) that is applied to an all digital phase locked loop (ADPLL) as the fractional phase error detector. The deterministic nature of the phase error during frequency / phase lock is exploited to achieve a reduction in power consumption of the TDC. The look-ahead TDC circuit is used to construct a cyclic DTC-TDC pair which functions to reduce fractional spurs of the output spectrum in near-integer channels by randomly rotating the cyclic DTC-TDC structure so that it starts from a different point every reference clock thereby averaging out the mismatch of the elements. Associated rotation and dithering methods are also presented. The ADPLL is achieved using the look-ahead TDC and / or cyclic DTC-TDC pair circuit.

Owner:SHORT CIRCUIT TECH LLC

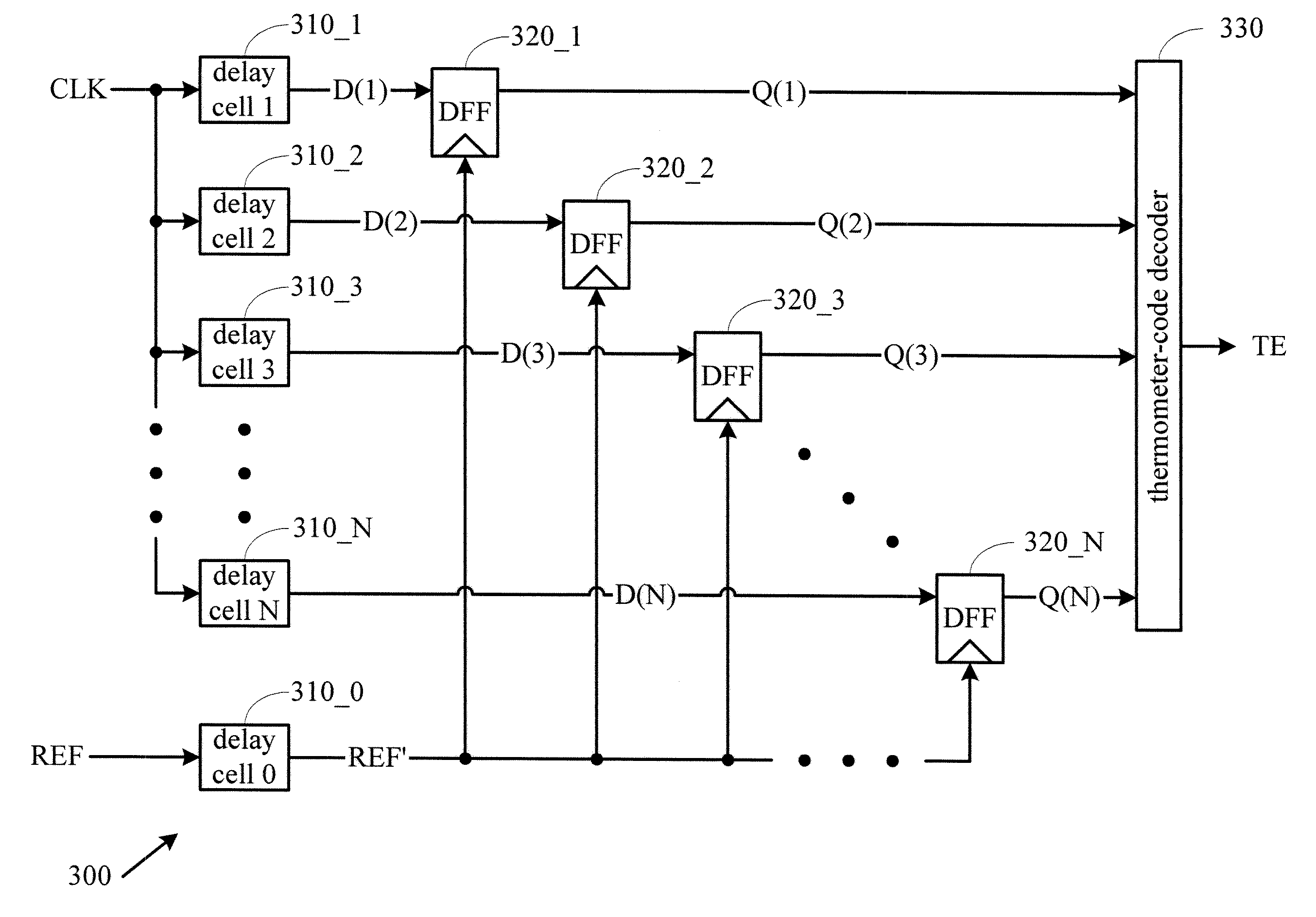

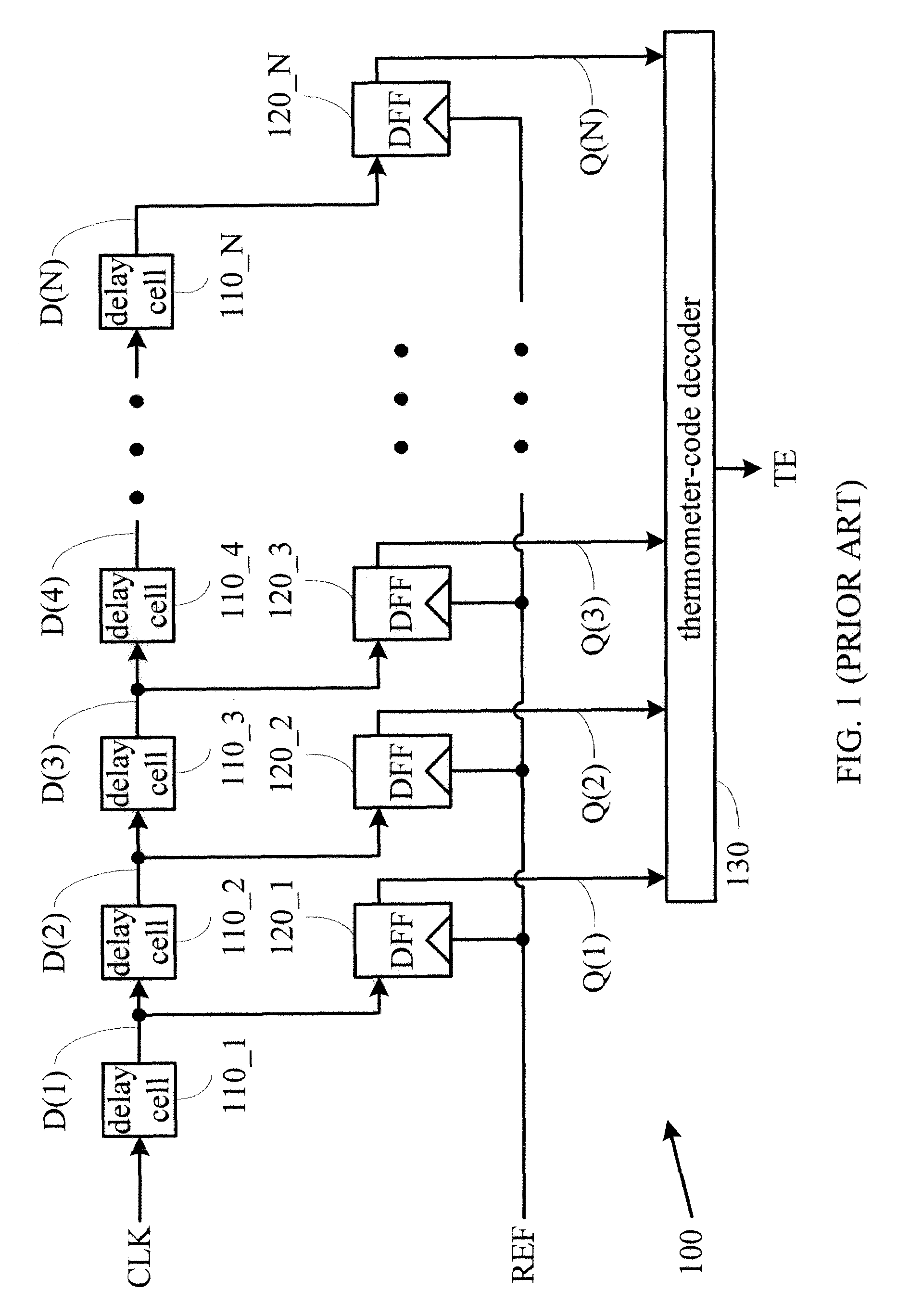

High resolution time-to-digital converter and method thereof

ActiveUS20070273569A1High resolutionElectric signal transmission systemsAnalogue-digital convertersDigital converterTime-to-digital converter

A time-to-digital converter (TDC) is disclosed, the TDC comprising: a plurality of parallel circuits for receiving a common first clock and for generating a plurality of delayed clocks; a plurality of sampling circuits for receiving and sampling said delayed clocks at an edge of a second clock to generate a plurality of decisions, respectively; and a decoder for receiving said decisions and for generating a digital output accordingly.

Owner:REALTEK SEMICON CORP

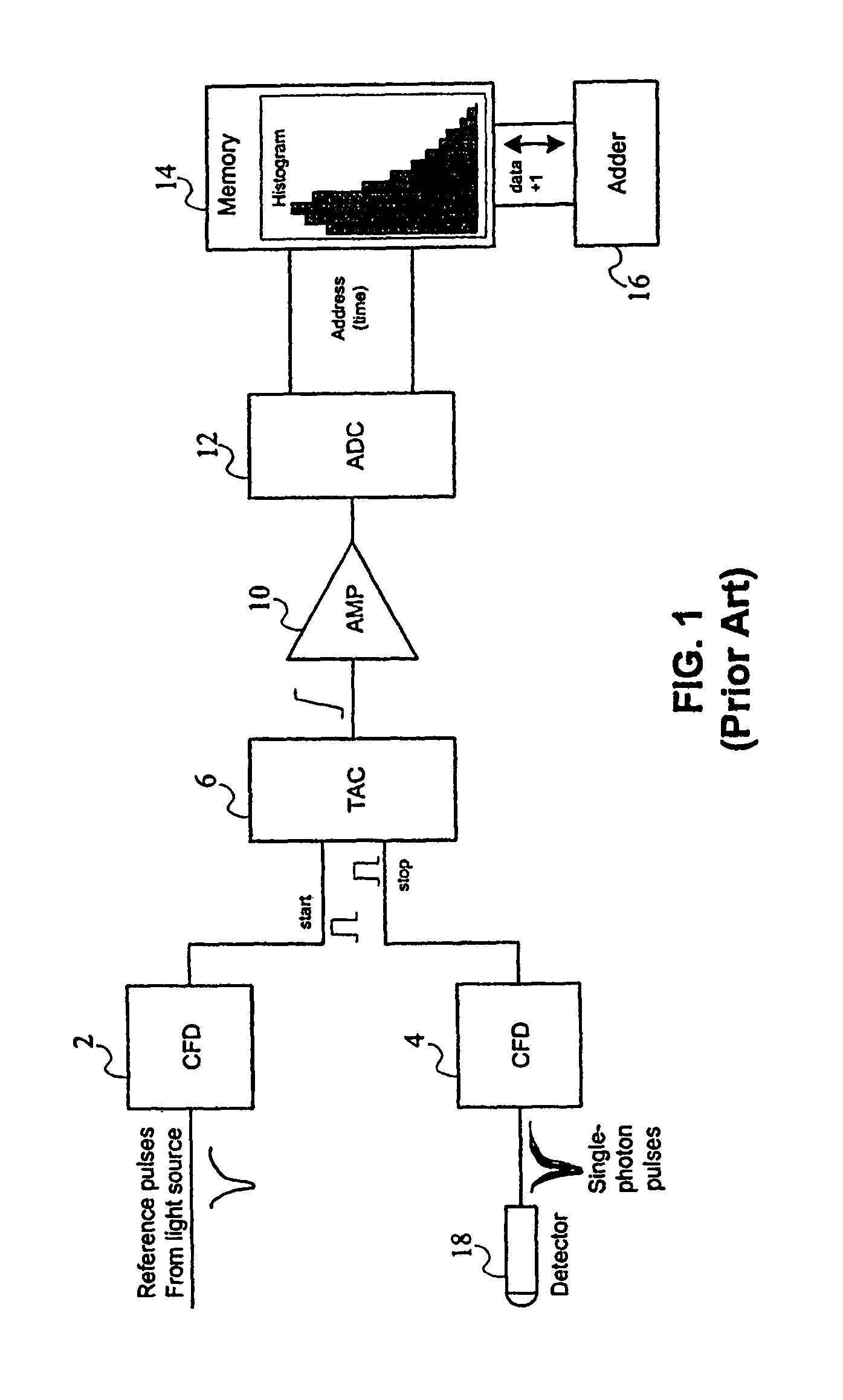

High resolution detection for time-of-flight mass spectrometers

InactiveUS6870156B2High resolutionInhibit transferSpectrometer detectorsTime-of-flight spectrometersEngineeringMass analyzer

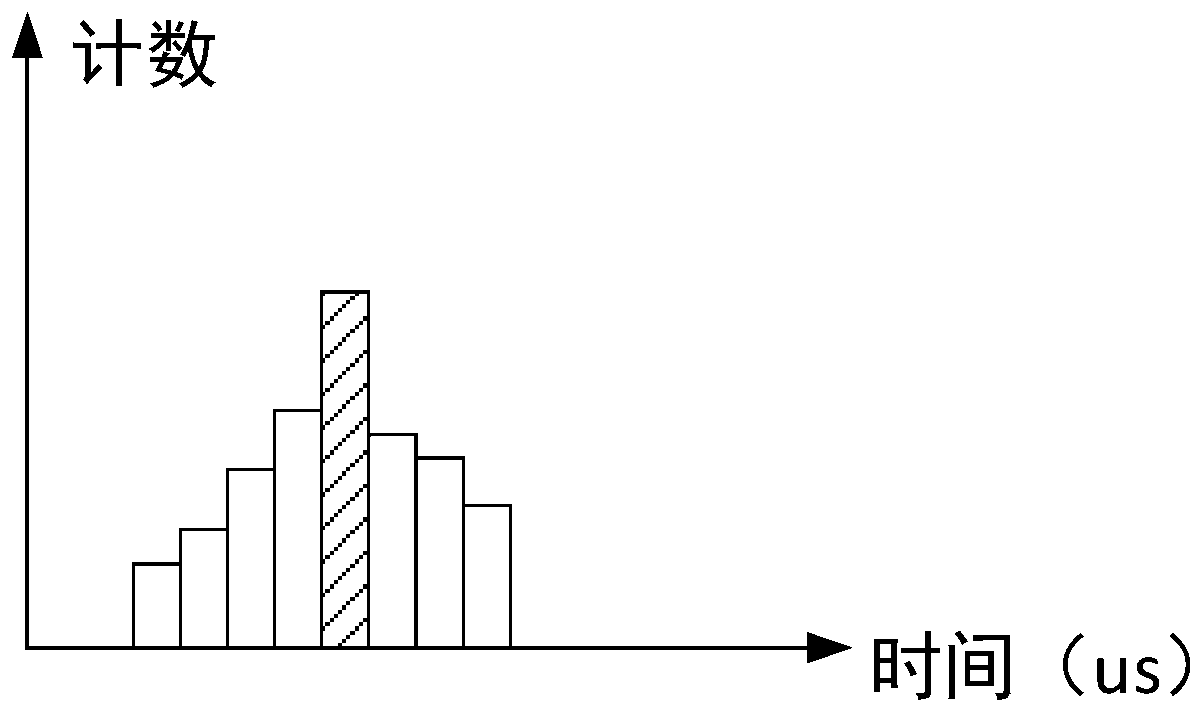

The invention covers a method for detecting ions in high resolution time-of-flight mass spectrometers which operate with secondary electron multiplier multichannel plates and in which many single spectra are acquired and added to produce a sum spectrum. The invention involves (a) using an analog digital converter (ADC) for converting electron currents from secondary electron multipliers, instead of a time-to-digital converter (TDC) which was previously used for highest possible signal resolution, (b) performing a separate rapid peak recognition procedure for the ion signals of each spectrum by a fast calculation method, thereby collecting flight time and intensity value pairs for the ion peaks, and (c) constructing a time-of-flight / intensity histogram, which is further processed as a composite time-of-flight spectrum. The invention retains the significantly higher measurement dynamics of an ADC and achieves the improved resolution capability of a TDC, but without showing the latter's known signal distortion due to dead times.

Owner:BRUKER DALTONIK GMBH & CO KG

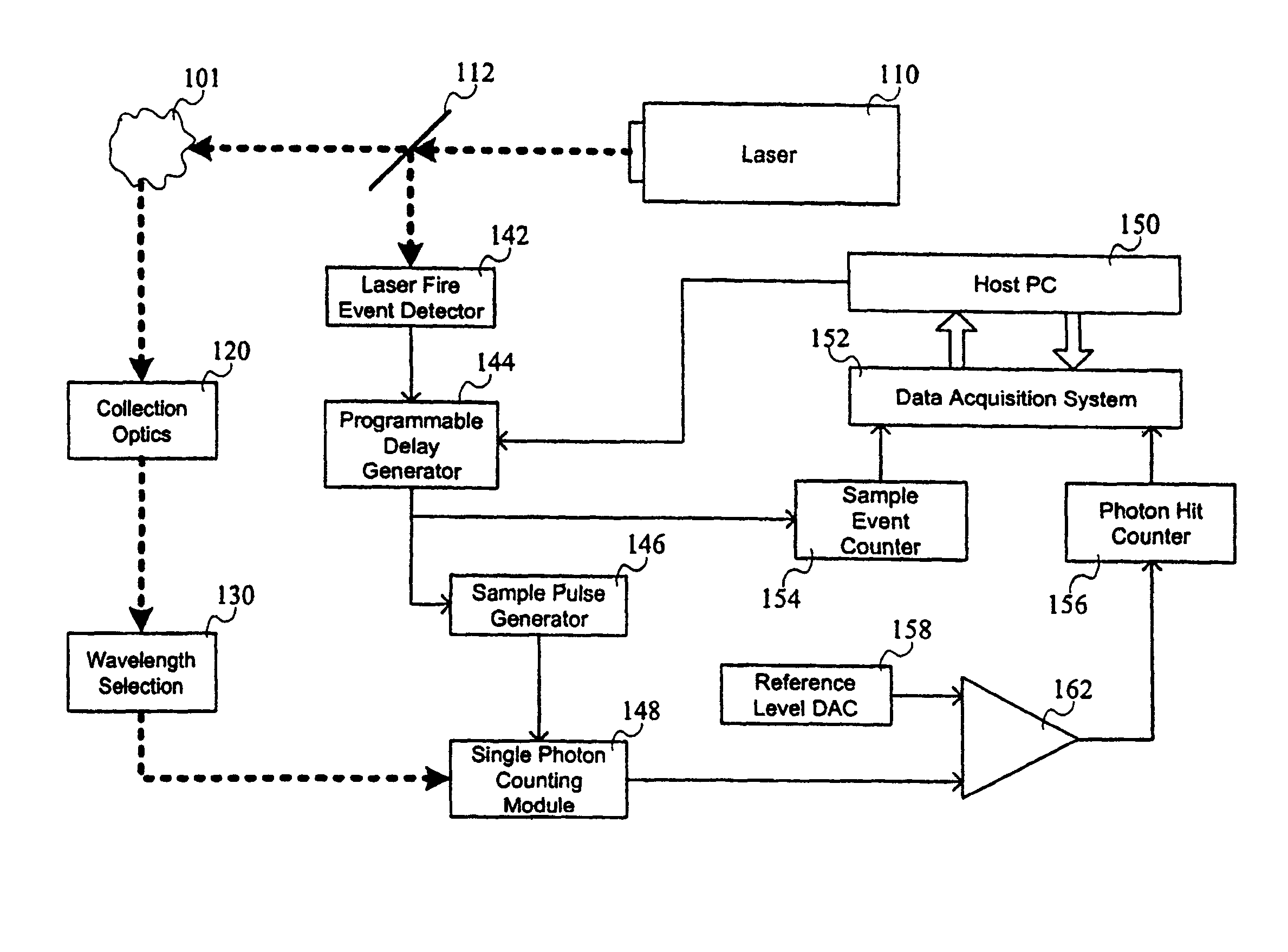

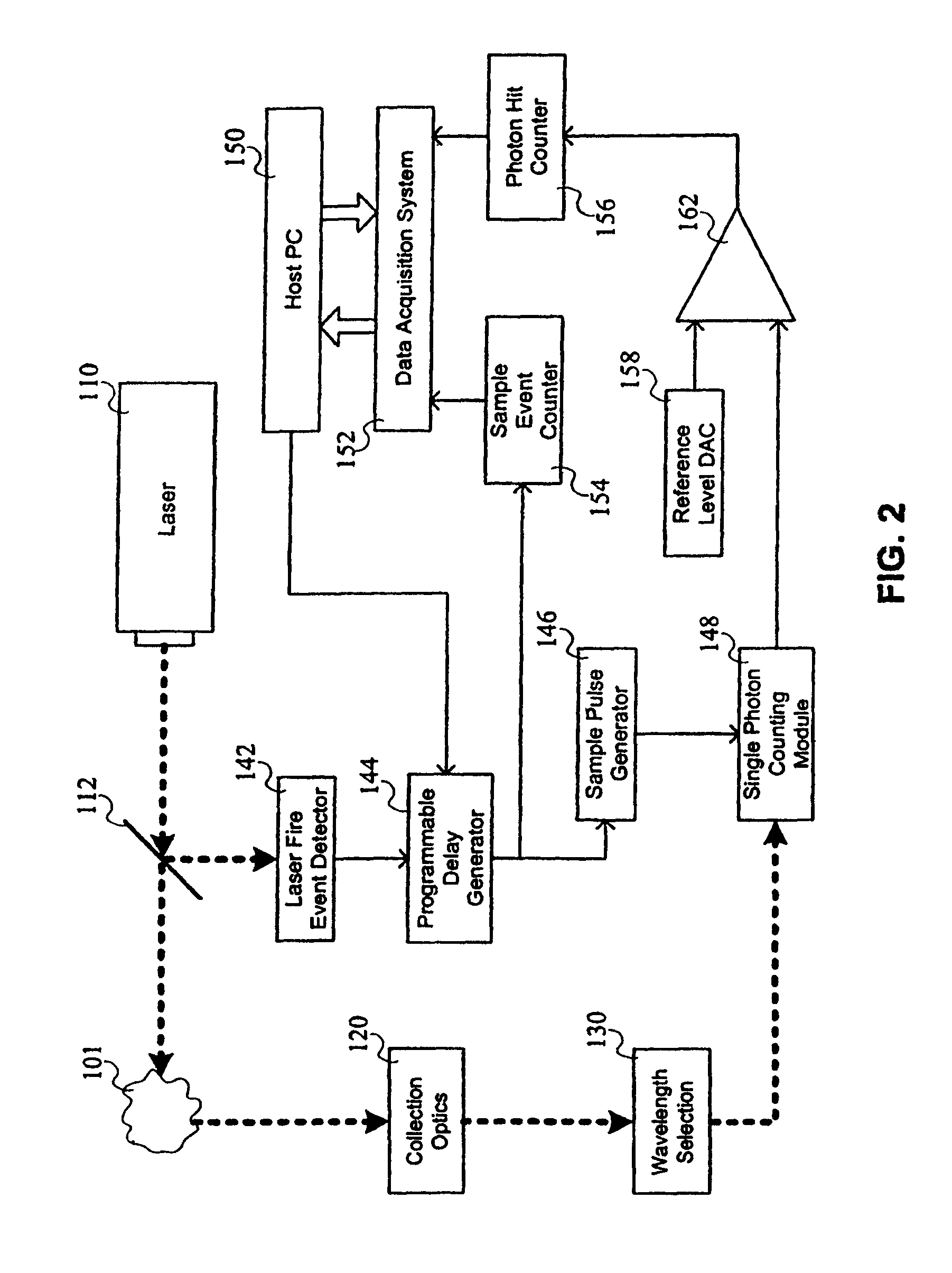

Time correlated single photon counting by time to digital conversion

A time correlated single photon counting system having a time to digital converter triggered by a laser fire event detector and the reception of a single photon. The system may be used for chemical agent detection based on Rayleigh scattering using optical time domain reflectometry techniques. The system may also be used for Raman detection using frequency to time transformations.

Owner:OPTECH VENTURES

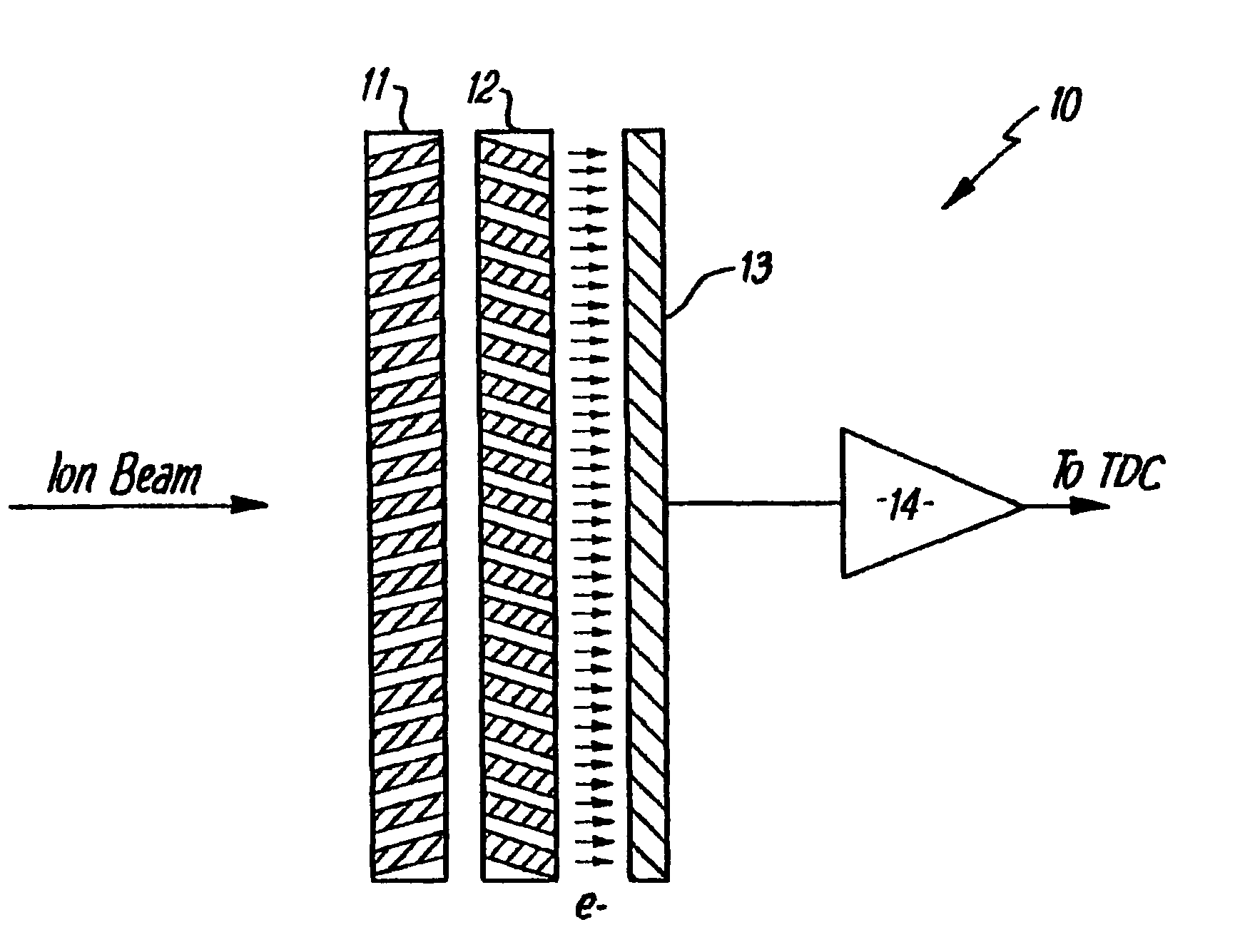

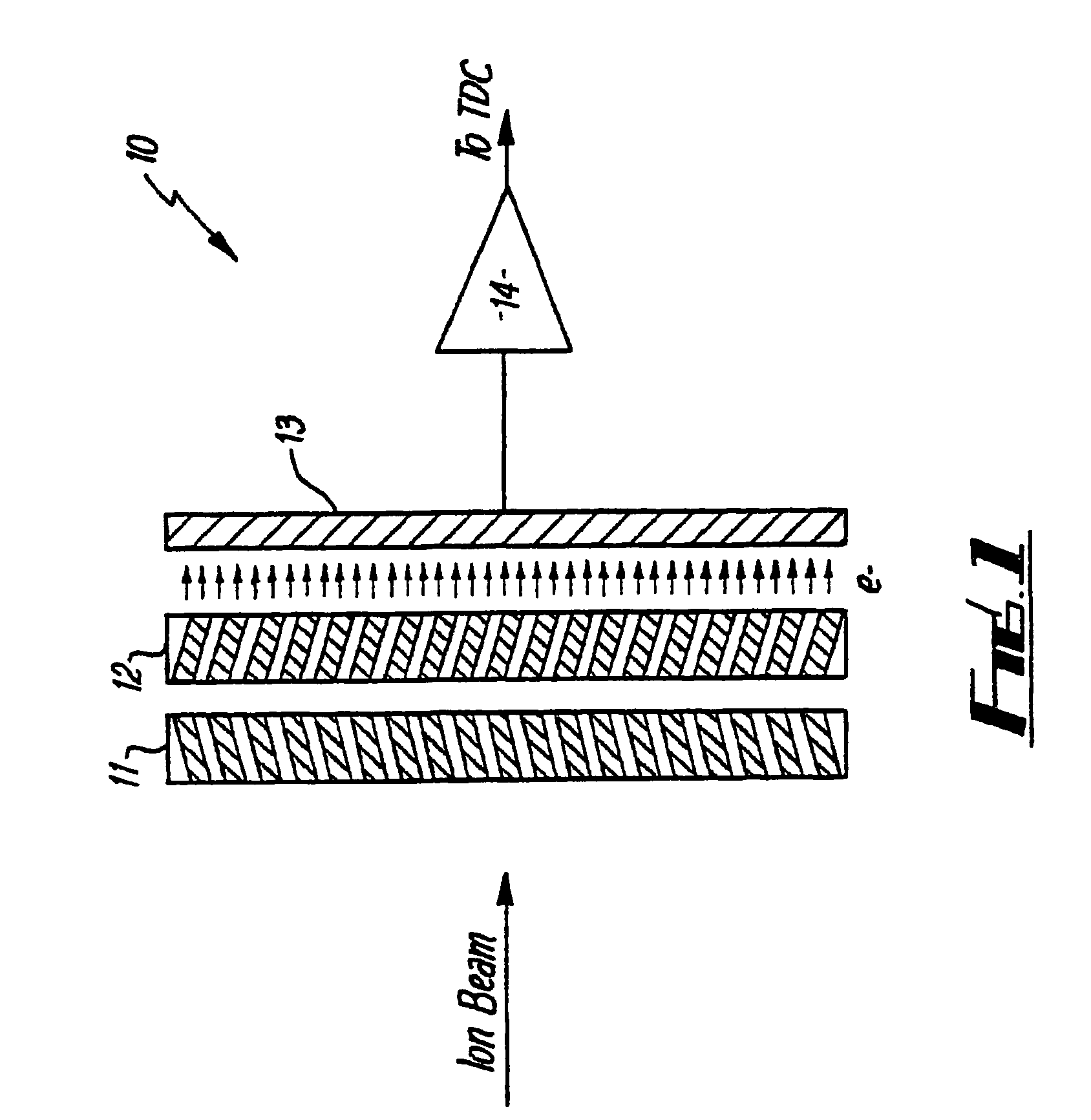

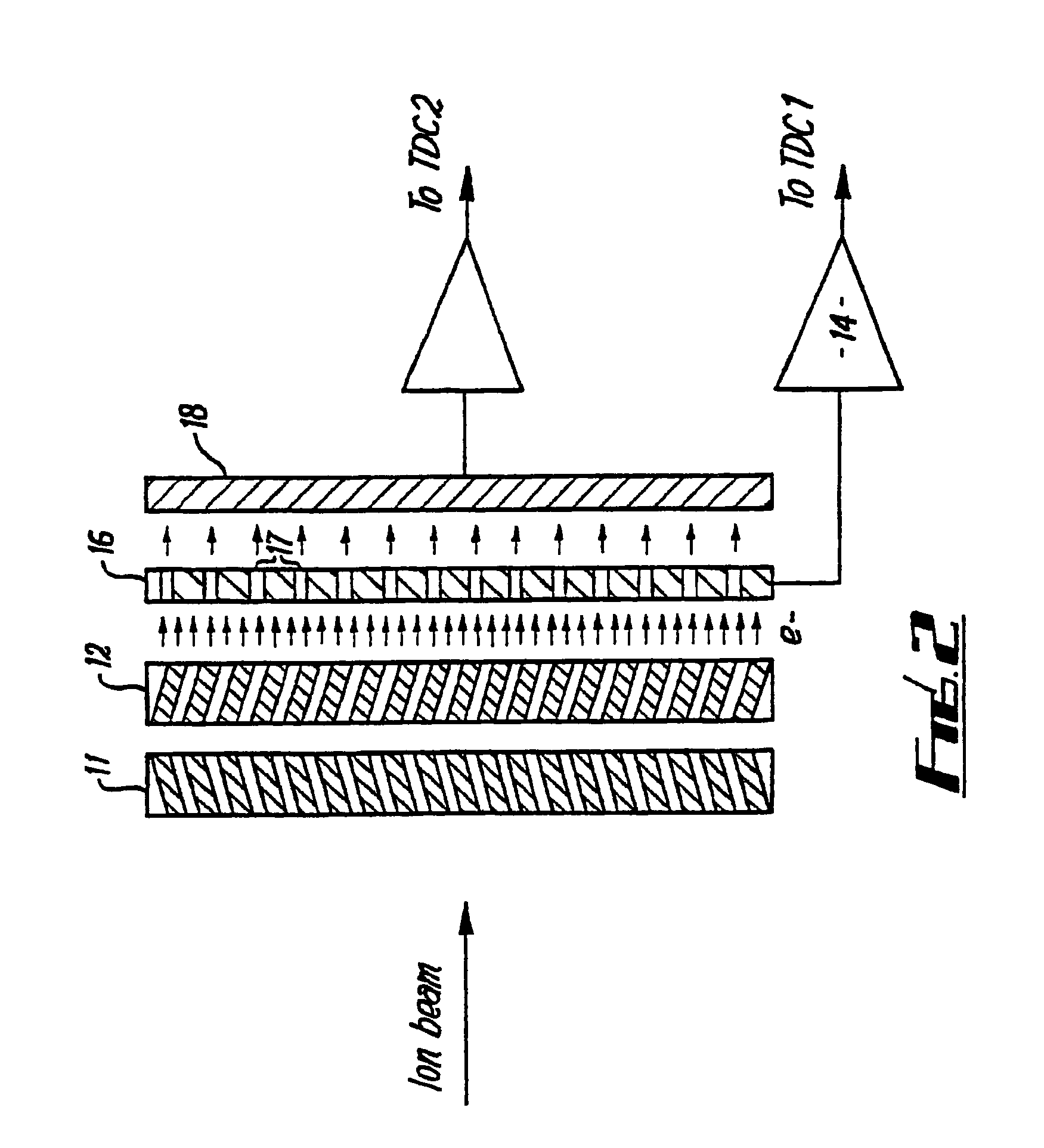

High dynamic range mass spectrometer

InactiveUS6969847B2Reduce the numberImprove dynamic rangeThermometer detailsTime-of-flight spectrometersUltrasound attenuationA d converter

A mass spectrometer comprises an ion source which produces an ion beam from a substance to be analysed and a detector to detect a quantity of ions incident thereon. The detector includes two elements (16, 18) each of which detect a part of the quantity of ions and an attenuation device attenuates the quantity of ions reaching one of the detector elements. At least one of the detector elements (16, 18) is connected to a time to digital converter (TDC) to allow counting of the ions and at least one of the detector elements is connected in parallel to both a time to digital converter (TDC) and an analogue to digital converter (ADC).

Owner:THERMO FINNIGAN

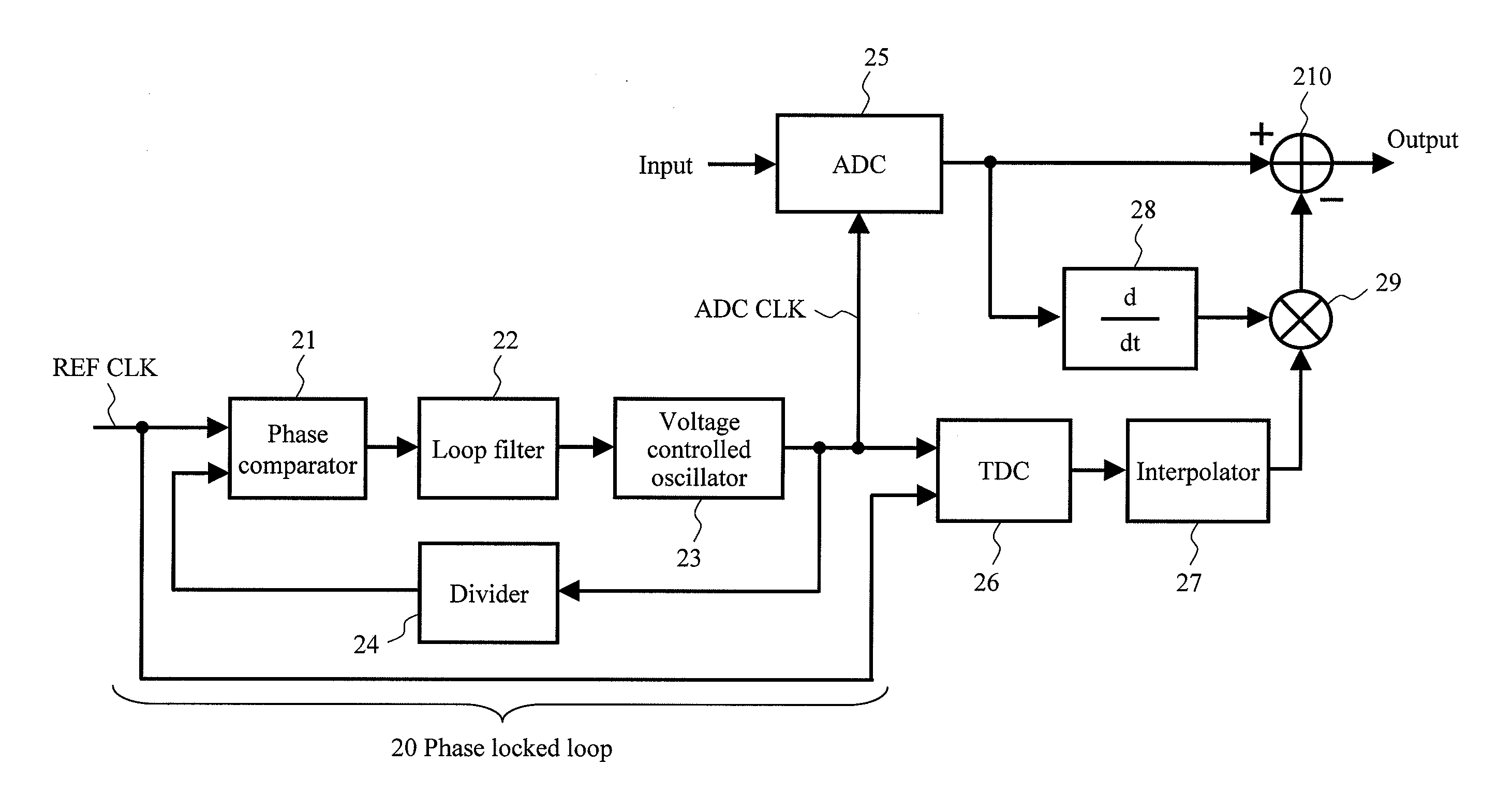

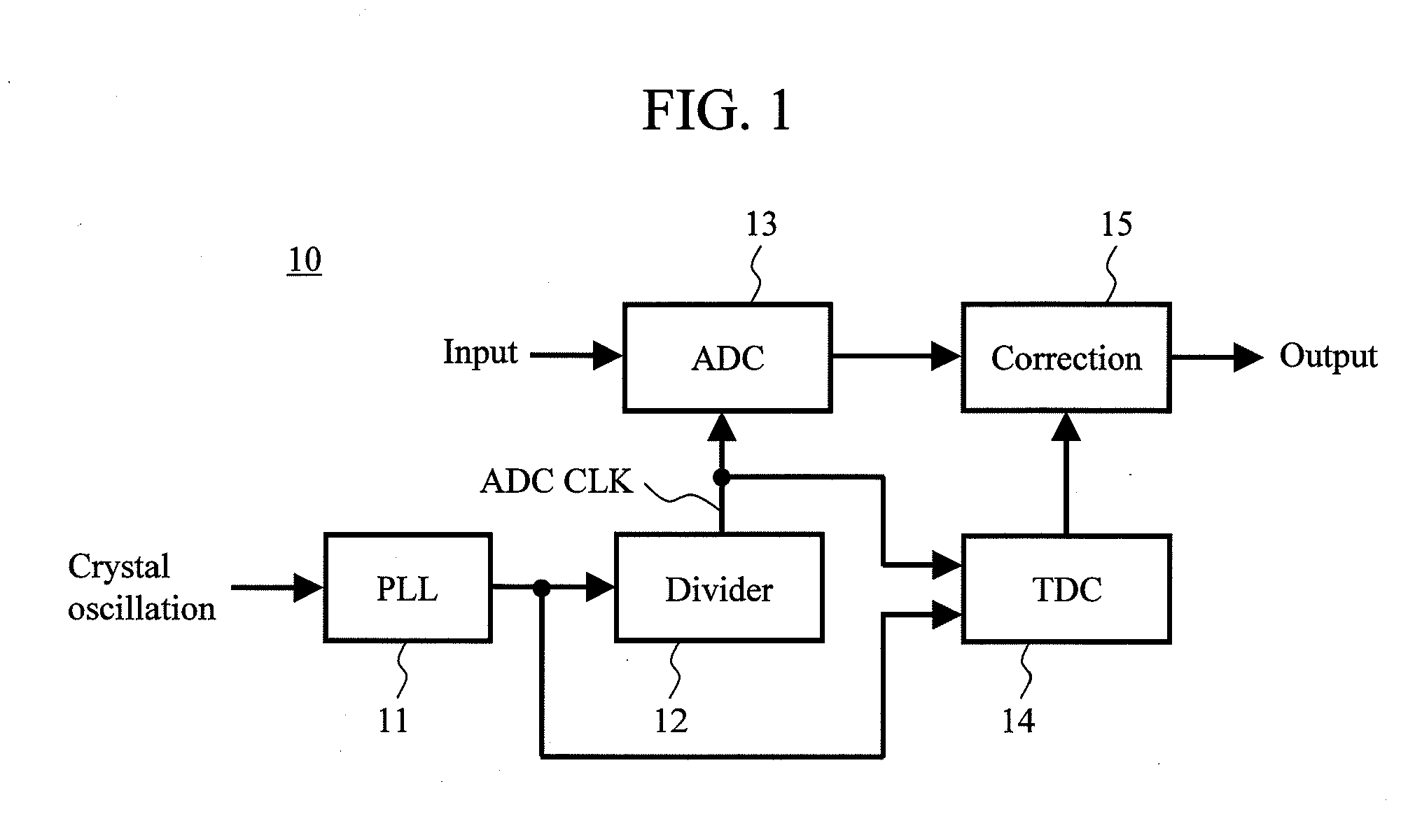

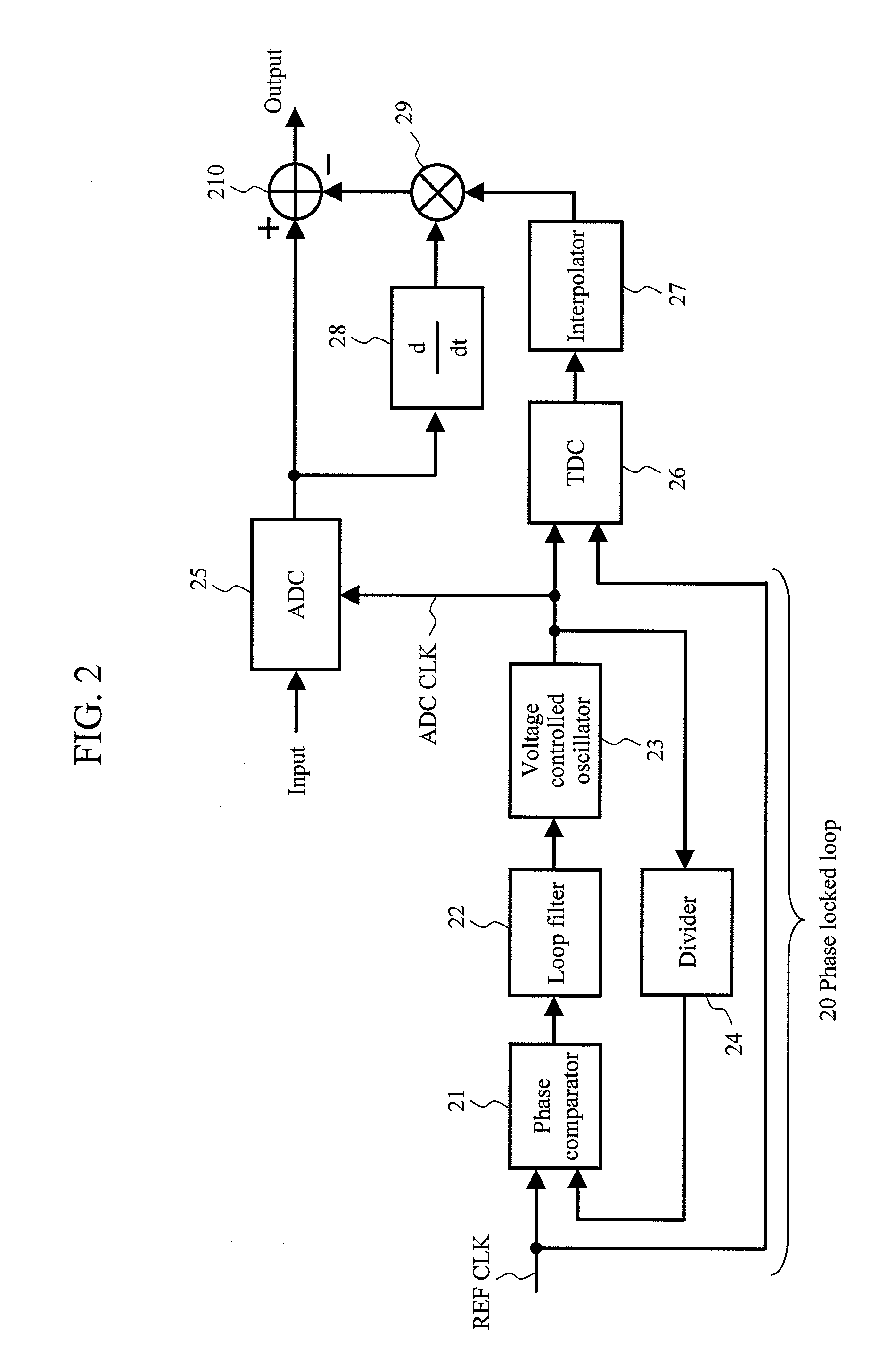

Analog-to-digital converter and wireless receiver

InactiveUS20130058437A1Electric signal transmission systemsModulated-carrier systemsLow jitterEngineering

The influence of a jitter of a sampling clock of an analog-to-digital converter is digitally corrected at low power consumption.The sampling clock of the analog-to-digital converter is generated by a phase locked loop (PLL) using a reference clock, which has a lower frequency and lower jitter than the sampling clock, as a source oscillation. A time-to-digital converter (TDC) converts a timing error at a timing where the sampling clock and the reference clock are synchronized with each other into a digital value. Incidentally, a timing error at a sampling timing where the reference clock is not present is generated by interpolating a detected timing error. Thus, a jitter value of the sampling clock at each sampling timing is obtained. A sampling voltage error is calculated from the jitter value and the output of the analog-to-digital converter is digitally corrected.

Owner:HITACHI LTD

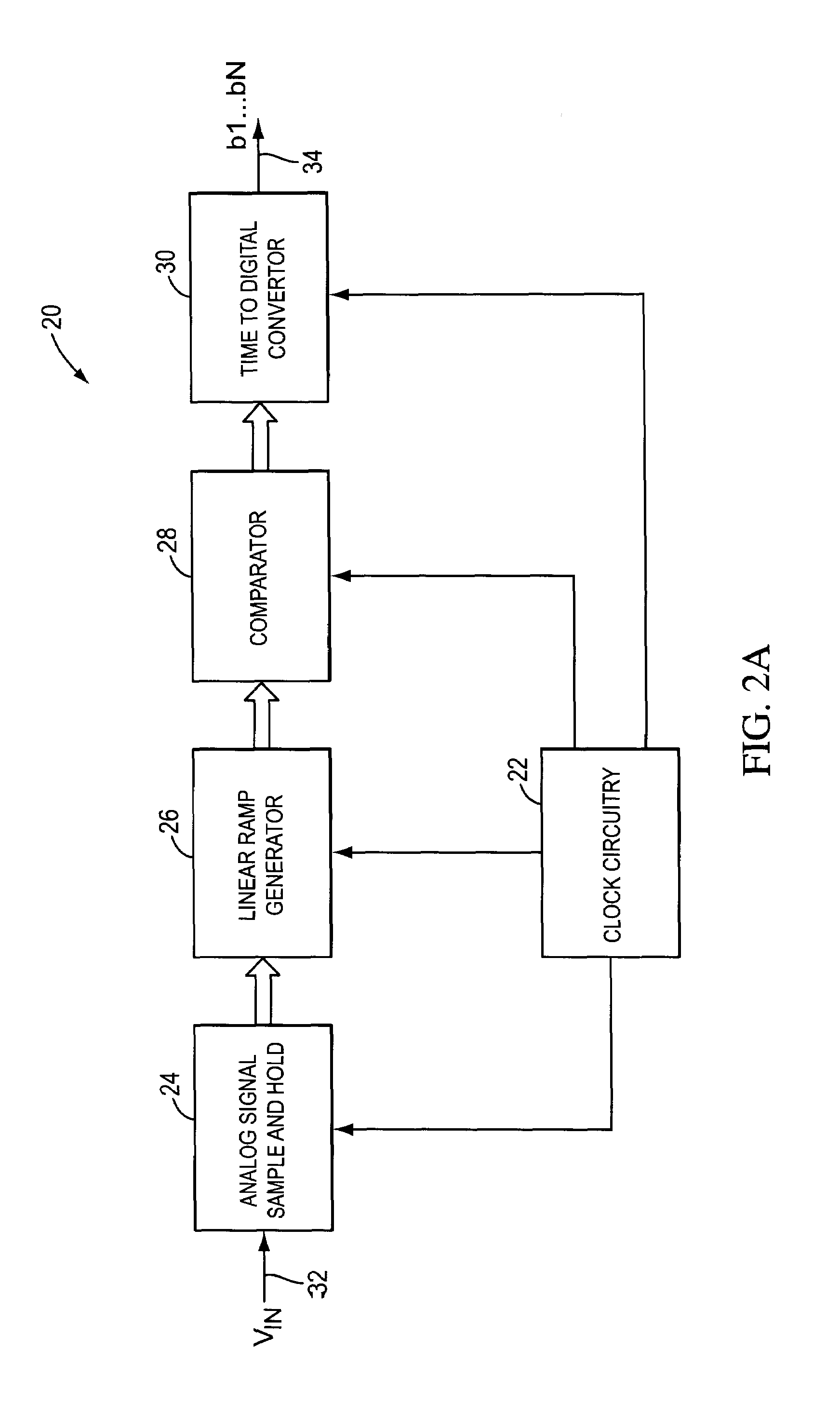

Rotary clock flash analog to digital converter system and method

ActiveUS7609756B2Electric signal transmission systemsPulse automatic controlDigital down converterEngineering

System and method for converting an analog voltage to a digital signal. The system includes an input voltage sampler, a ramp generator, a comparator, a time-to-digital converter (TDC), and a multiphase oscillator, preferably a rotary traveling wave oscillator, that provides the critical system timing. The phases of the multiphase oscillator define a sampling interval during which the input voltage is sampled and held and a conversion interval during which the ramp generator, comparator, and TDC operate to convert the sampled voltage to the digital signal. The TDC samples at times provided by the phases of the multiphase oscillator to form the bits of the digital signal. The sampler, ramp generator, and comparator can be constructed from multiple fragments, one of which is selectable for calibration while the rest of the fragments are joined for normal operation. Multiple converters can be interleaved to increase the sampling rate.

Owner:ANALOG DEVICES INC

Rotary clock flash analog to digital converter system and method

ActiveUS20080272952A1Electric signal transmission systemsPulse automatic controlDigital down converterEngineering

System and method for converting an analog voltage to a digital signal. The system includes an input voltage sampler, a ramp generator, a comparator, a time-to-digital converter (TDC), and a multiphase oscillator, preferably a rotary traveling wave oscillator, that provides the critical system timing. The phases of the multiphase oscillator define a sampling interval during which the input voltage is sampled and held and a conversion interval during which the ramp generator, comparator, and TDC operate to convert the sampled voltage to the digital signal. The TDC samples at times provided by the phases of the multiphase oscillator to form the bits of the digital signal. The sampler, ramp generator, and comparator can be constructed from multiple fragments, one of which is selectable for calibration while the rest of the fragments are joined for normal operation. Multiple converters can be interleaved to increase the sampling rate.

Owner:ANALOG DEVICES INC

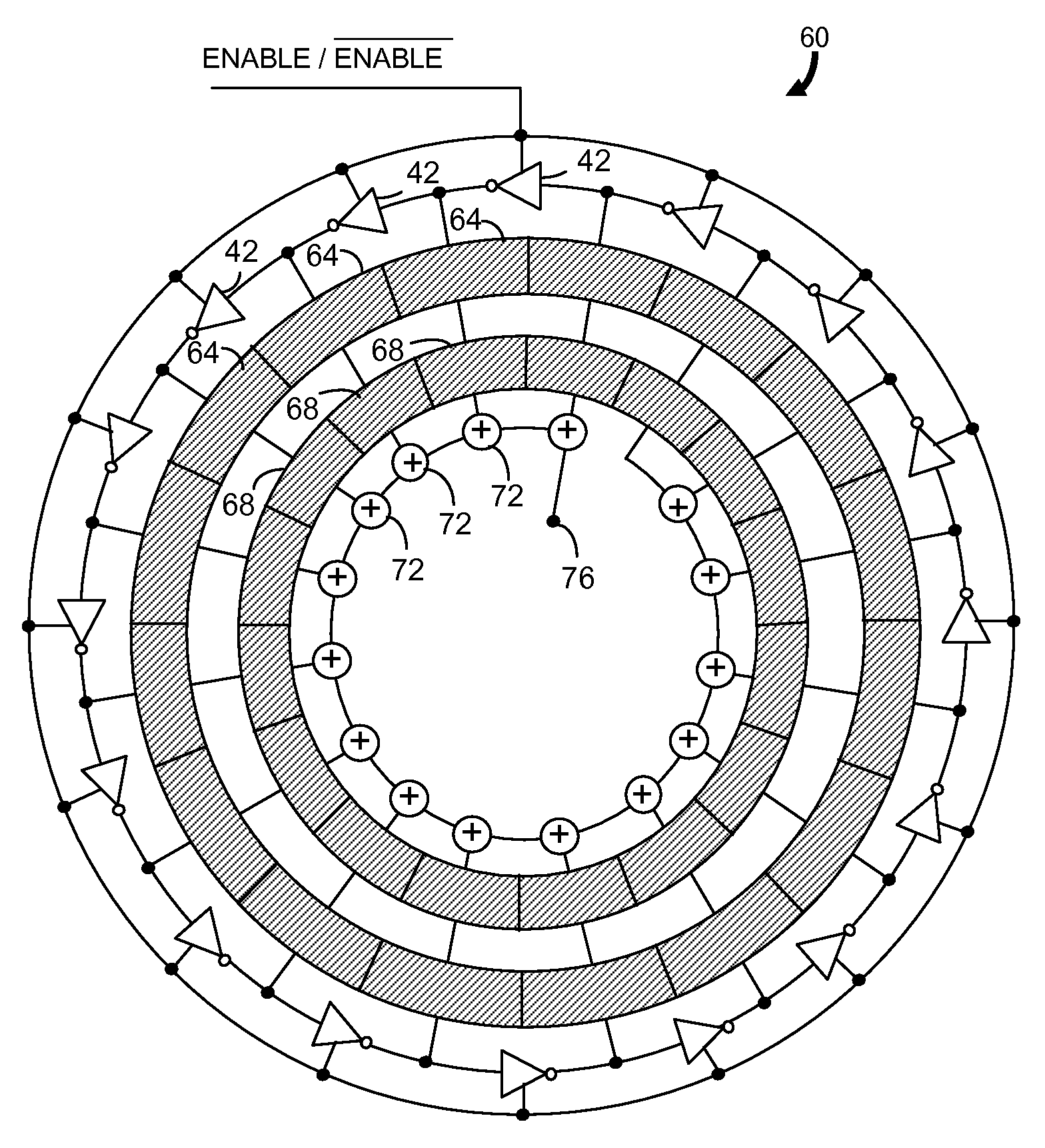

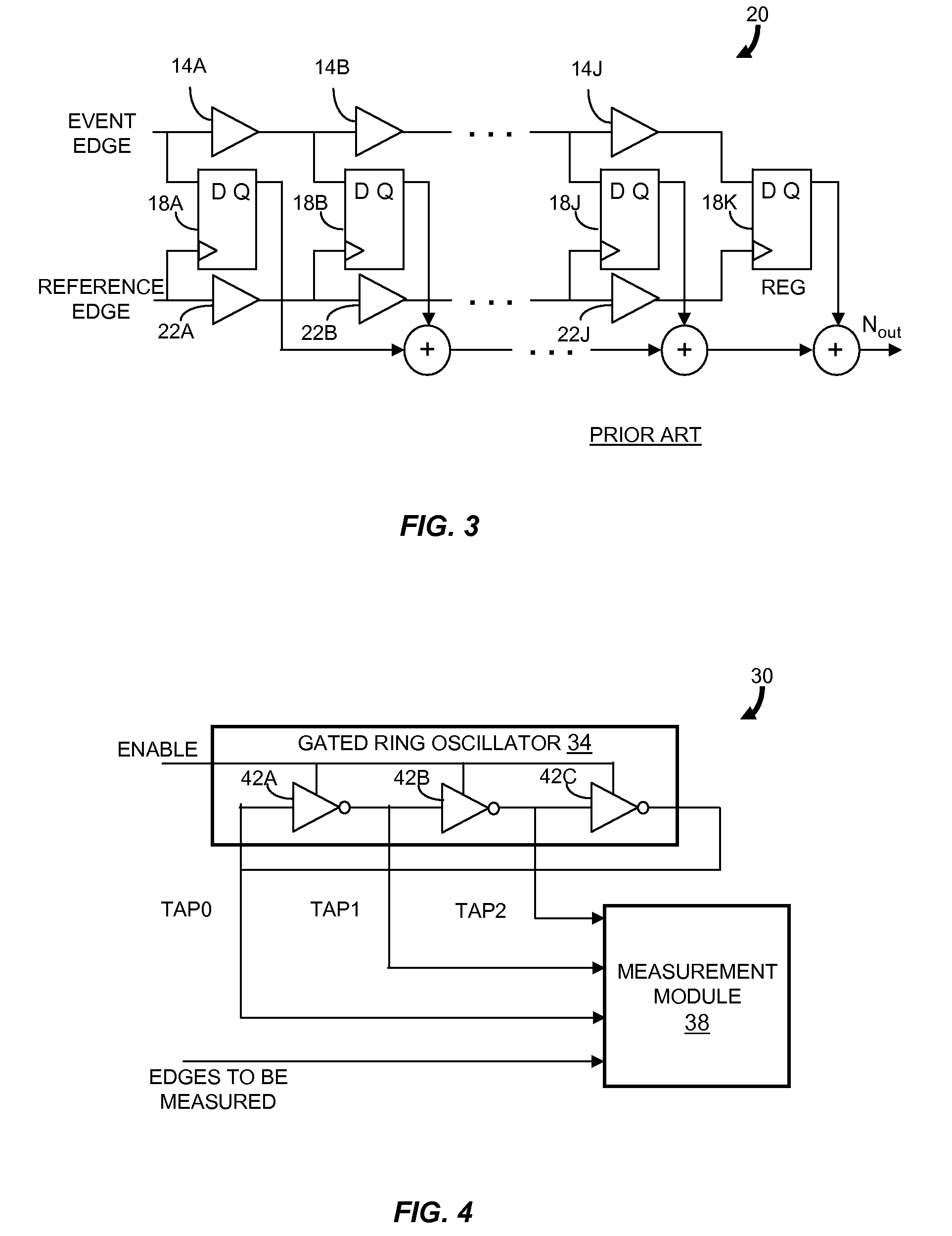

Gated ring oscillator for a time-to-digital converter with shaped quantization noise

ActiveUS20080069292A1Resolution timeContinuously circulated pulse countersCounting chain synchronous pulse countersImage resolutionNoise shaping

Described is a compact, lower power gated ring oscillator time-to-digital converter that achieves first order noise shaping of quantization noise using a digital implementation. The gated ring oscillator time-to-digital converter includes a plurality of delay stages configured to enable propagation of a transitioning signal through the delay stages during an enabled state and configured to inhibit propagation of the transitioning signal through the delay stages during a disabled state. Delay stages are interconnected to allow sustained transitions to propagate through the delay stages during the enabled state and to preserve a state of the gated ring oscillator time-to-digital converter during the disabled state. The state represents a time resolution that is finer than the delay of at least one of the delay stages. A measurement module determines the number of transitions of the delay stages.

Owner:MASSACHUSETTS INST OF TECH

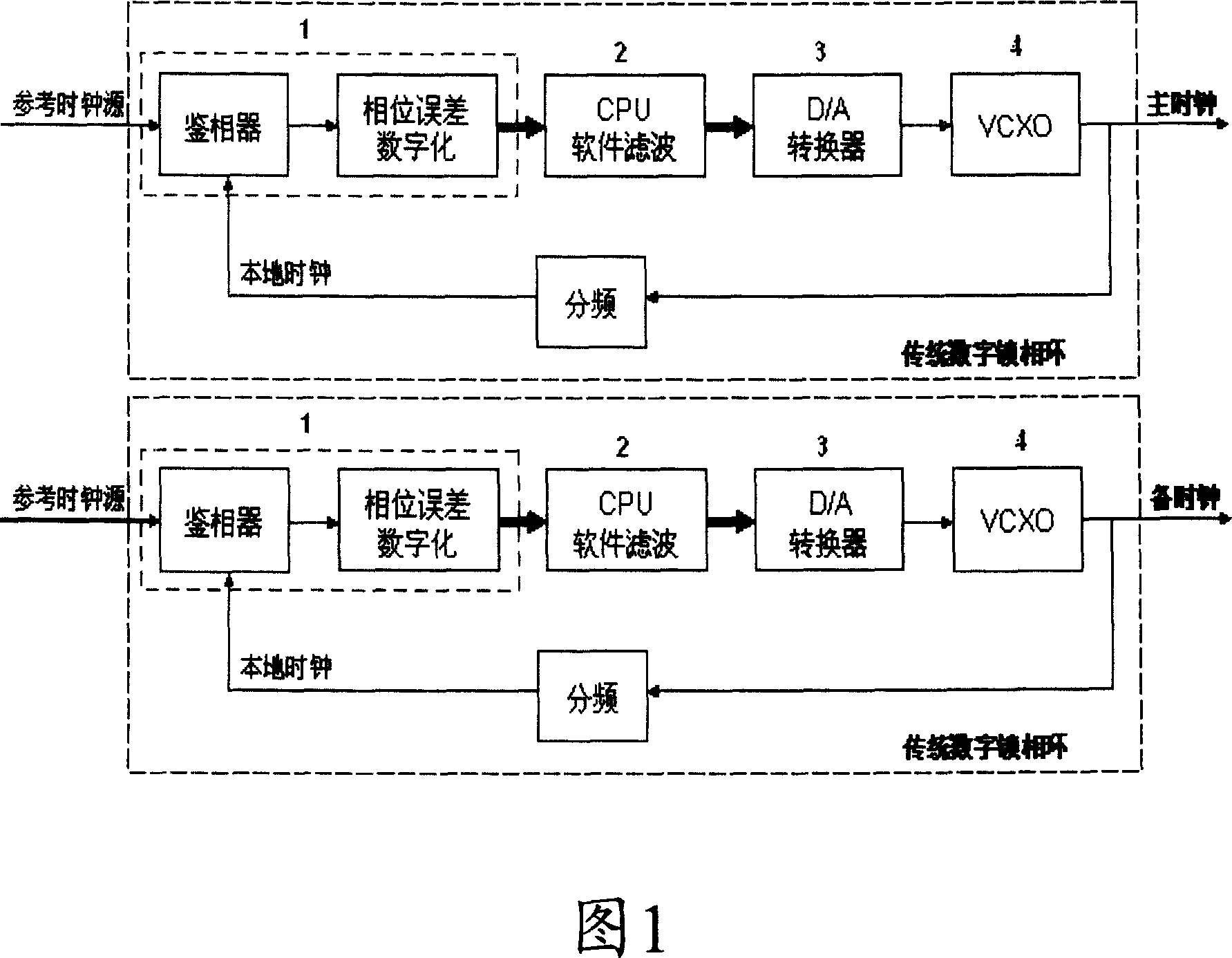

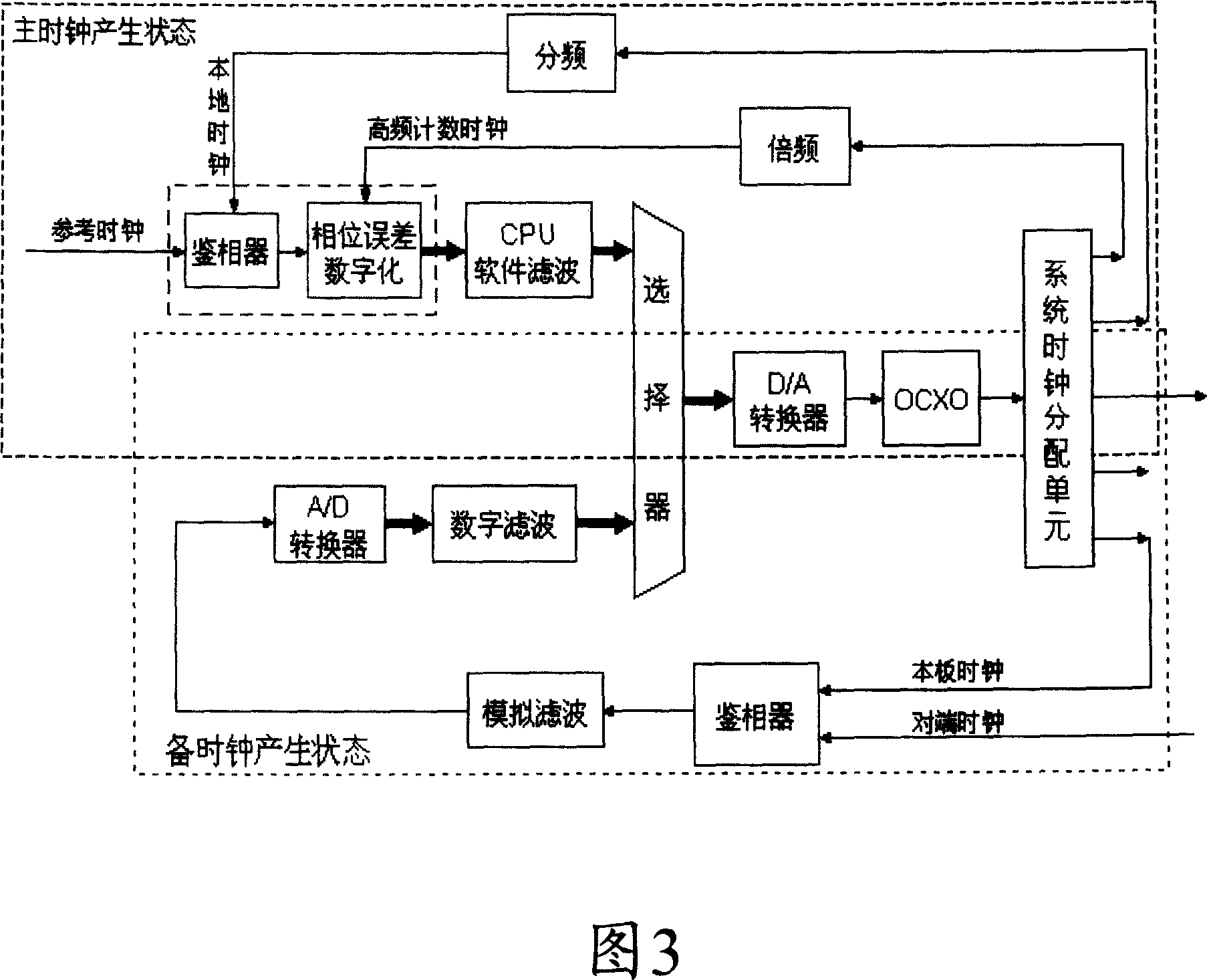

A digital phase lock loop device for smooth switching of clock phase and its method

InactiveCN101079630ASimple structureEasy to integratePulse automatic controlPhase differenceEngineering

The invention discloses a digital locked ring device to realize clock phase smooth conversion, which is characterized by the following: the reference source processes the selected reference clock according to master spare pattern; the time digital converses the reference clock and phase difference from local clock of frequency divider into the corresponding coded digital code to realize phase demodulation and phase difference digitalization to be transmitted to CPU filter and locked processing unit the proceed linear phase disposal, low-pass digital filter disposal, locked disposal, which outputs the digital phased error signal to the digifax converser as corresponding analog voltage-controlled value, in order to control the corresponding vibrating frequency output by voltage-controlled crystal oscillator; the frequency is processed by frequency divider to transmit the local clock with the same frequency as reference frequency to time digital converter. The invention realizes high-precision error control of main spare systems, which is convenient to integrate chip with high reliability and integration level.

Owner:ZTE CORP

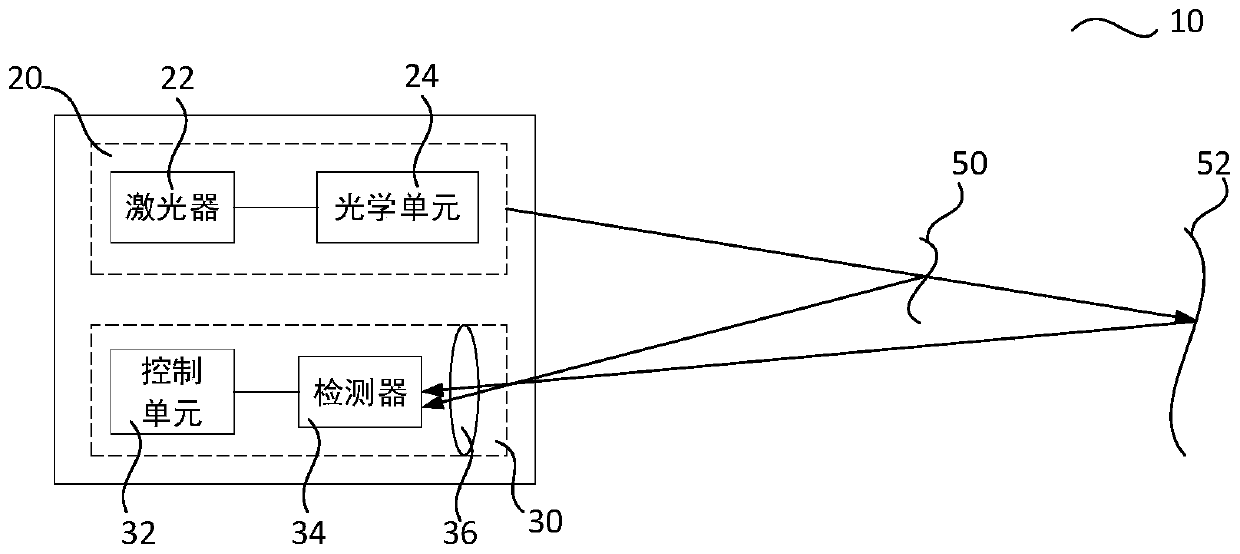

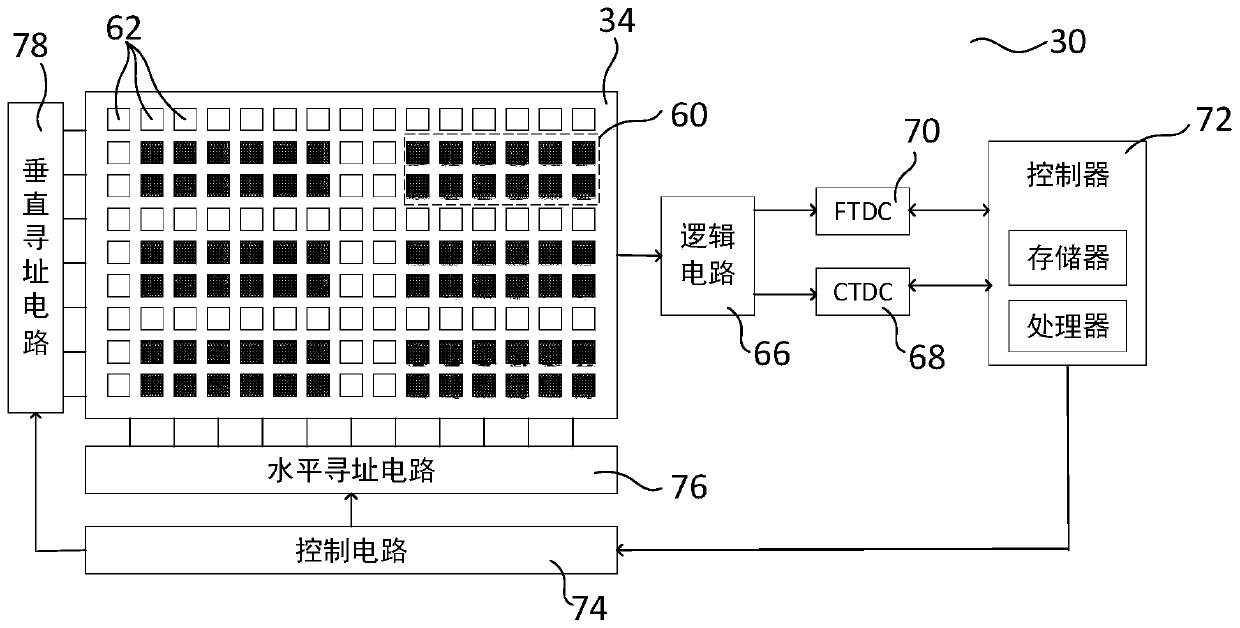

Time-of-flight-based distance detection system and method

ActiveCN110609293AAvoid inaccurate measurementsAvoid power consumptionElectromagnetic wave reradiationParallaxDistance detection

The invention discloses a time-of-flight-based distance detection system comprising a laser transmitting module and a laser receiving module, wherein the laser receiving module comprises a detector and a control unit; the laser transmitting module transmits a laser pulse sequence to a target, and the detector receives the photons reflected by the target and outputs a response signal; the control unit comprises a time-to-digital converter and a controller; the controller is used to control the time-to-digital converter to measure a first TOF value and a second TOF value, wherein the first TOF value is used to match the pre-defined corresponding relationship to regulate the working state of SPAD in the selected area of the detector array, and the second TOF value is used to calculate the distance between the target and the system. The invention performs a two-step test on a target object to obtain an accurate TOF value of the target object, which can overcome inaccurate measurement caused by parallax, and avoid power consumption and noise caused by excessive SPAD work.

Owner:ORADAR TECH CO LTD

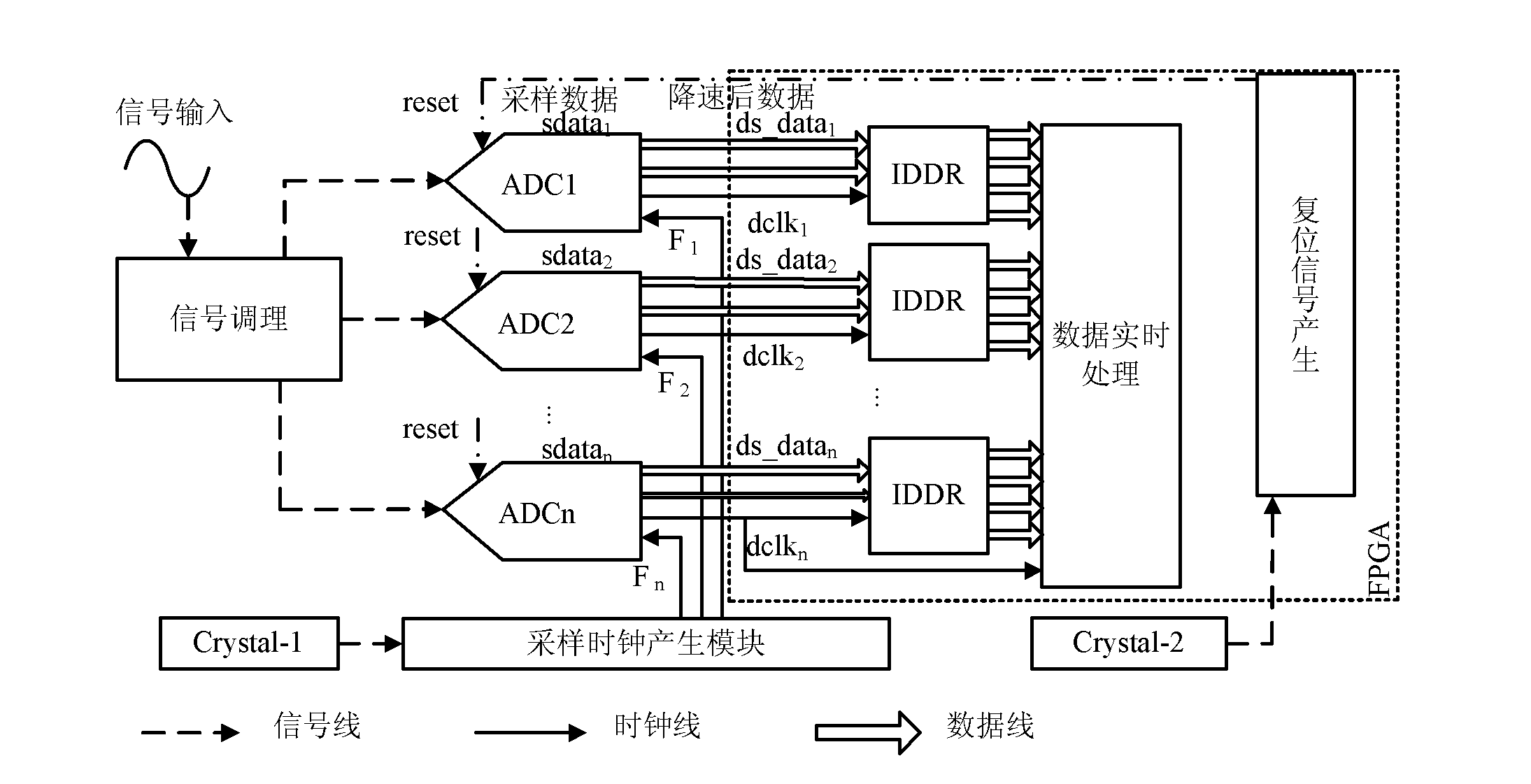

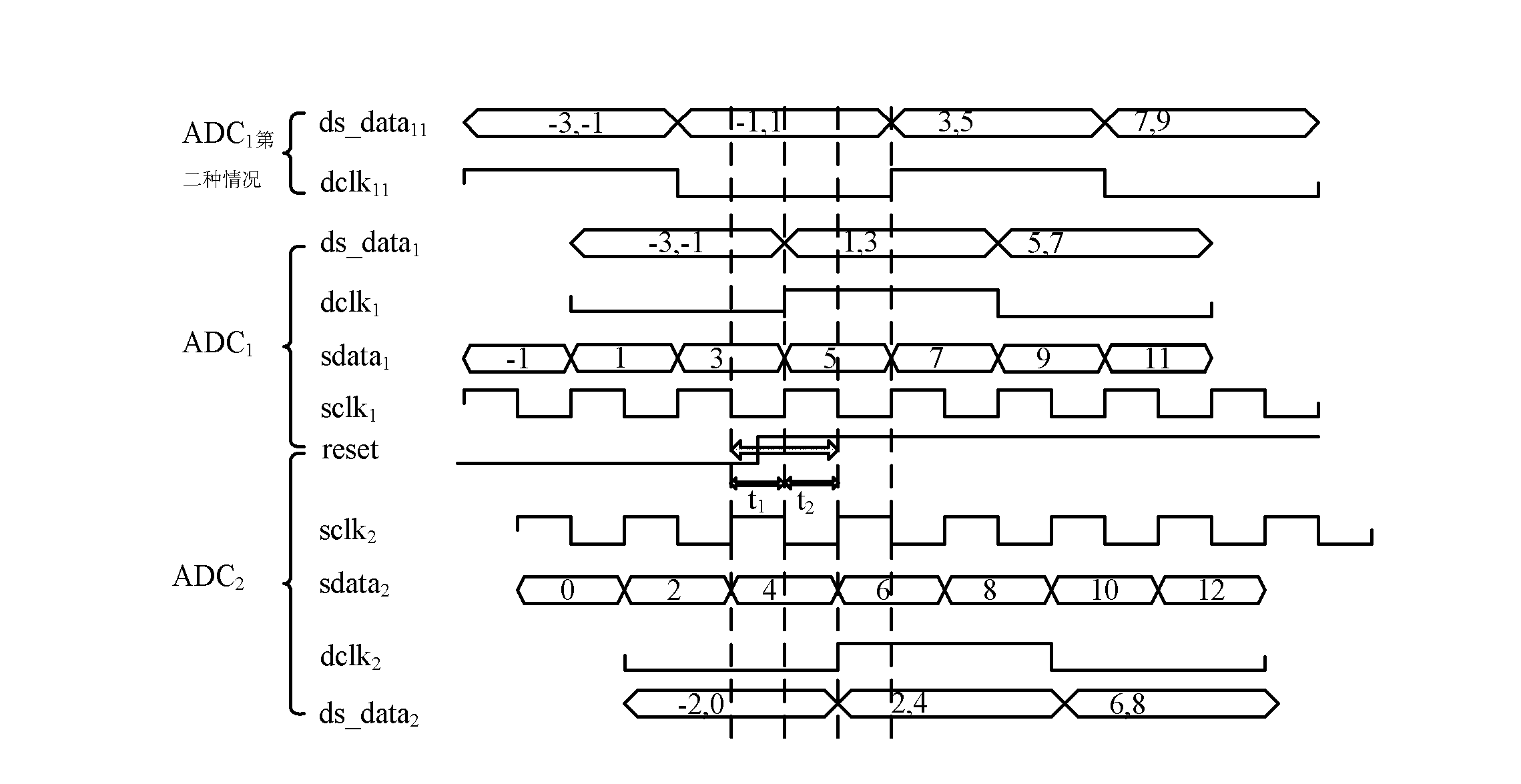

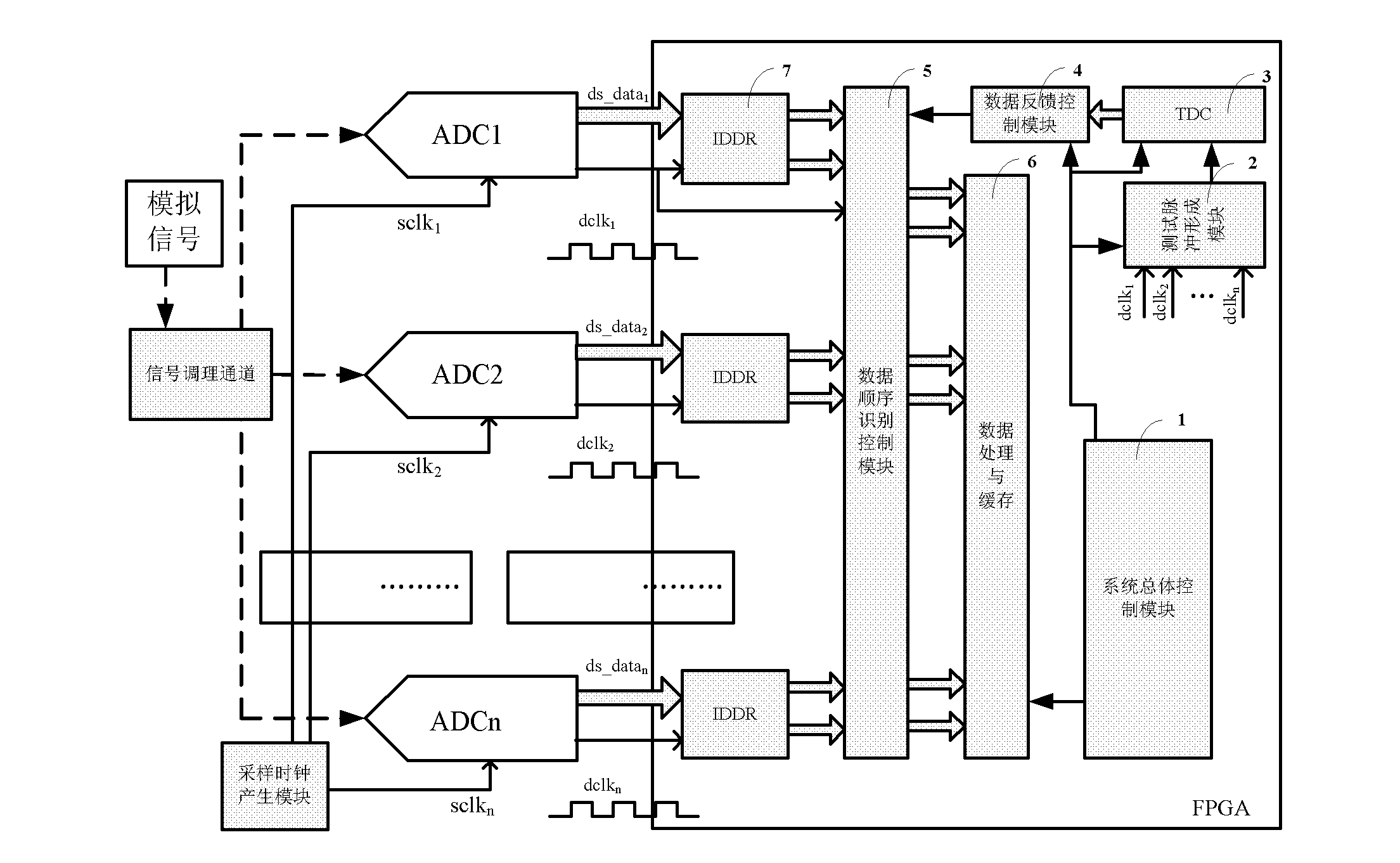

Data synchronous identification device of multiple analog-to-digital converter (ADC) high-speed data acquisition system

ActiveCN102497210AIncrease sampling rateGuaranteed uptimeAnalogue/digital conversion calibration/testingData synchronizationDigital down converter

The invention discloses a multi-analog-to-digital converter (ADC) high-speed time alternating acquisition system with a data synchronous identification function. Phase relation between multiple ADC data synchronous clocks is measured by adding a test pulse forming module, a high-precision time interval measuring unit, a data feedback control module and a data sequence identification module, and the sequence of sampled data is fed back and controlled according to a measuring result, so real-time correct splicing of parallel time alternating sampling data sequences is realized, reliable guarantee is provided to the processing of sampled data at the rear end, the stable operation of the system is effectively ensured, and the technology lays a firm foundation for construction of a multi-ADC acquisition system with higher sampling rate.

Owner:成都菁汇科技有限公司

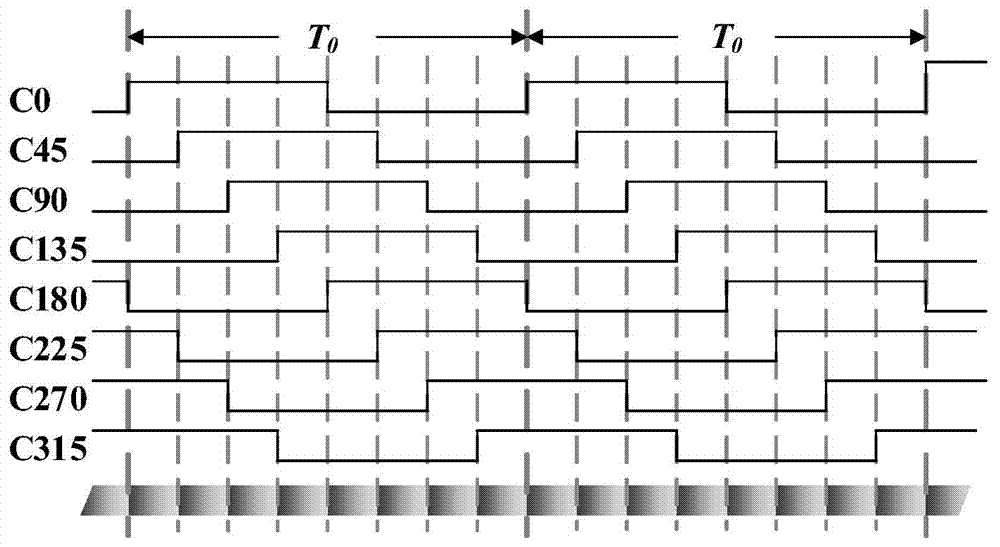

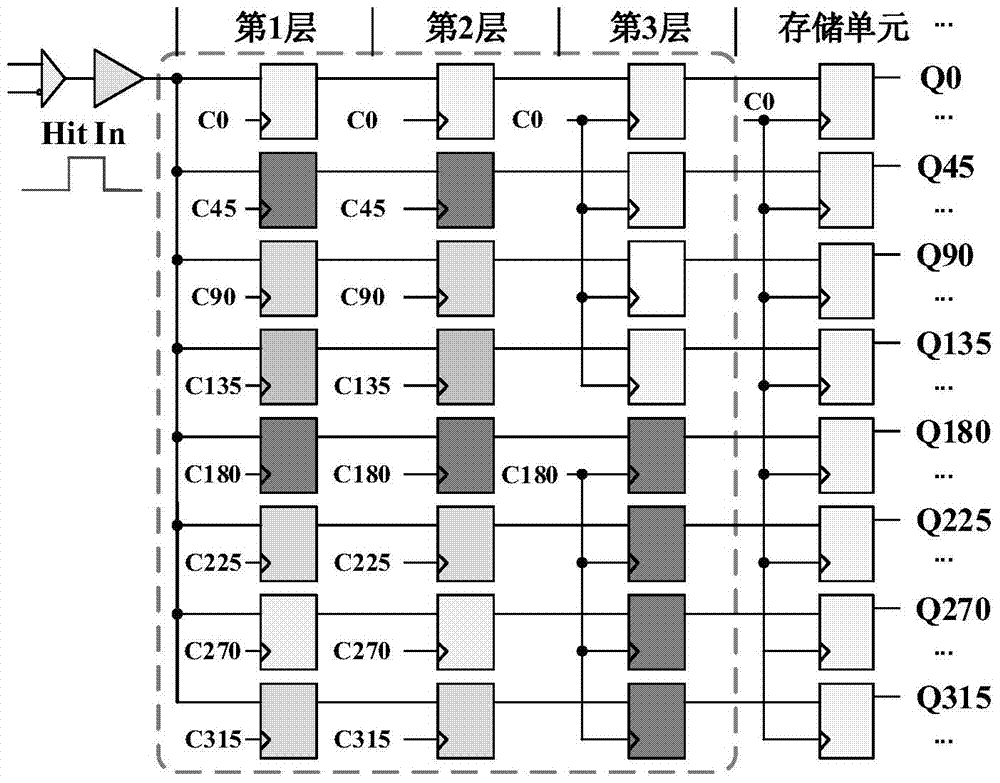

High-precision and high-integrality time-digital converter based on FPGA (Field Programmable Gate Array), and implementation method

ActiveCN103472712AFlexible useFlexibleElectric unknown time interval measurementDigital down converterPhase splitting

The invention provides a high-precision and high-integrality time-digital converter based on an FPGA (Field Programmable Gate Array), and an implementation method. The time-digital converter comprises a fine time measuring unit, wherein the fine time measuring unit consists of a time alternate sampling unit, a multi-stage sampling data buffering unit and a snapshot and encoding unit. The invention aims to provide the high-integrality precision time-digital converter based on an FPGA. Innovation points lie in that: a fine time measuring part adopts a technology of a latch snapshot and rapid encoding combined architecture based on phase splitting clock alternate sampling, multi-stage sampling data caching and cached multi-stage sampling data. The high-precision and high-integrality time-digital converter has the characteristics of simple structure, design flexibility, high portability, short measuring dead time, large dynamic range, low cost, flexible interface and the like, and can be applied to the fields of aerospace, space research, communication, biomedicine, earth dynamics, relativity research and the like.

Owner:UNIV OF SCI & TECH OF CHINA

Rapid locking method for full digital phase-locked loop

ActiveCN101640533AShort lock timeReduce forecast errorPulse automatic controlDiscriminatorPhase difference

The invention relates to a rapid locking method for a full digital phase-locked loop, which is used for locking the frequency of the full digital phase-locked loop comprising a phase detection discriminator, a time-to-digit converter, a digital filter, a digital controlled oscillator and a frequency divider in a short time. The method is characterized by comprising the following steps: finding a control word controlling the frequency of the digital controlled oscillator by a designed algorithm; dividing the frequency of a clock output by the digital controlled oscillator which is controlled bythe control word to obtain a divided-frequency clock with the frequency approximate to a reference clock frequency; and then, controlling the digital controlled oscillator to lock based on a phase difference between the reference clock and the divided-frequency clock which are distinguished by the phase detection discriminator. The full digital phase-locked loop is provided with a rapid frequencycapture loop and a phase-locked loop which alternately work, i.e. firstly, the rapid frequency capture loop finishes frequency capture, and then, the phase-locked loop finishes accurate locking.

Owner:SOUTHEAST UNIV

Time-to-digital converter and method therefor

ActiveUS20140232827A1Reduce power consumptionTelevision system detailsPower saving provisionsDigital down converterDigital converter

Time-to-digital converter system including: an event detector configured for detecting an event and generating an event detection signal upon detection of the event; and a time-to-digital converter coupled or connectable to the event detector and including a fine resolution part configured for counting fine time intervals, organized such that the fine resolution part is activated in response to the event detection signal and deactivated in response to a reference clock. 3D imager including an array of pixels, with in each pixel such a time-to-digital converter system, and further including a reference clock generator.

Owner:FASTREE 3D BV

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com