Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

175results about "Multiple-port active networks" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

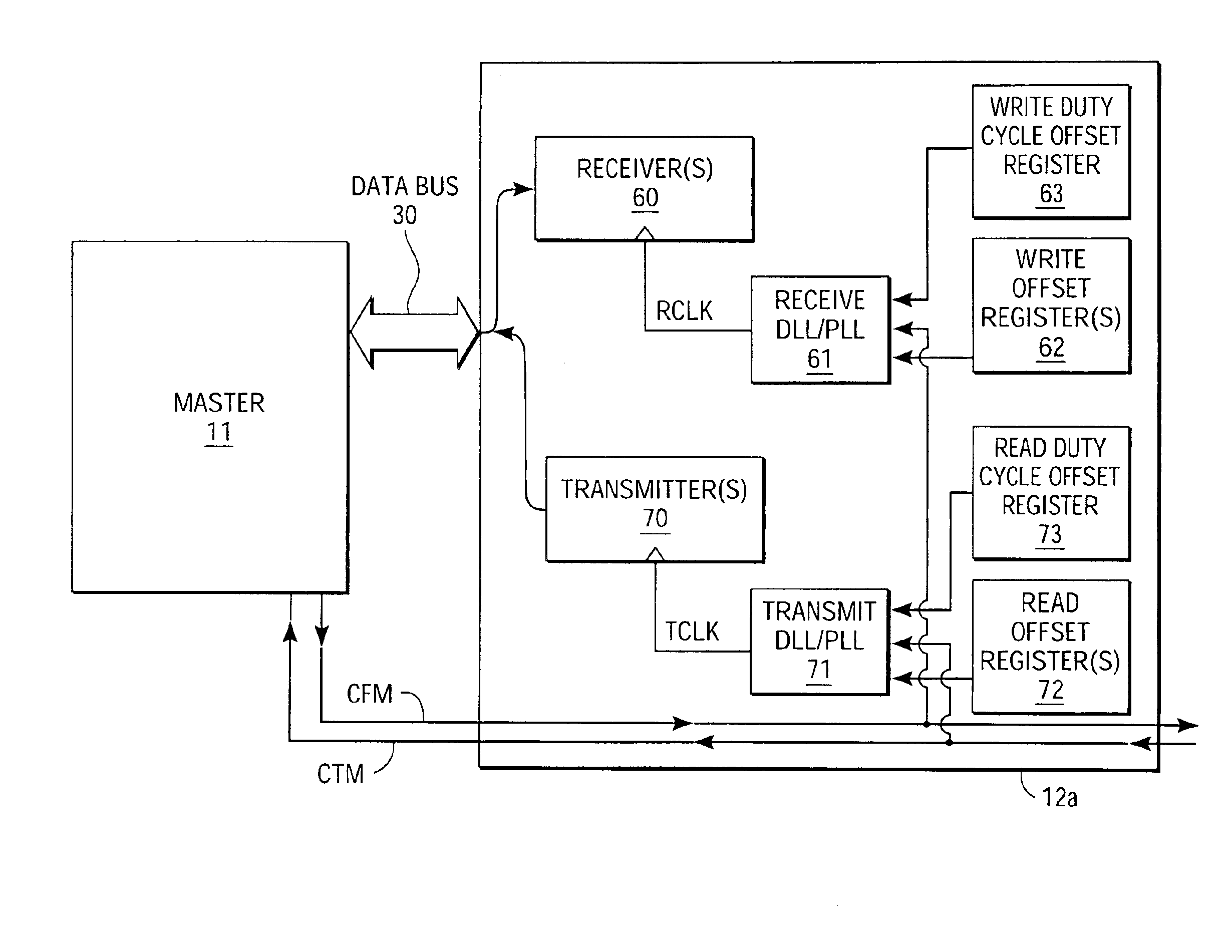

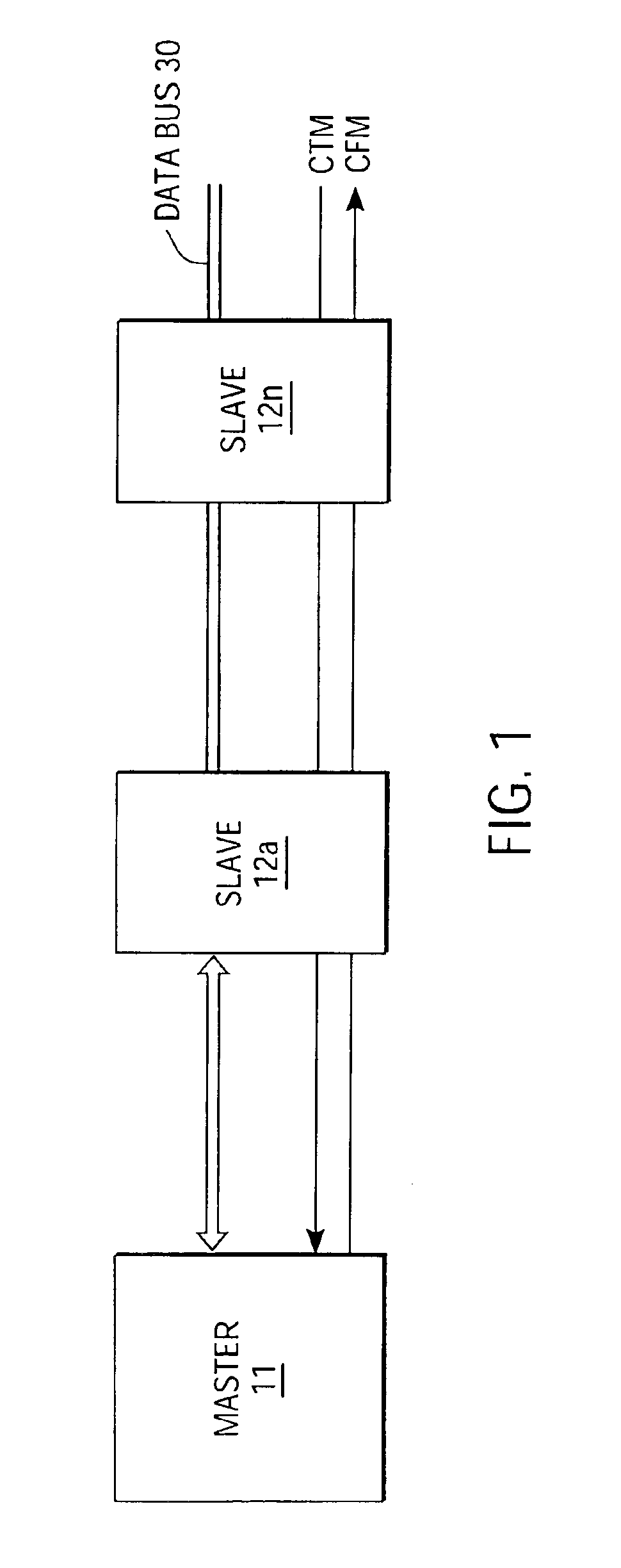

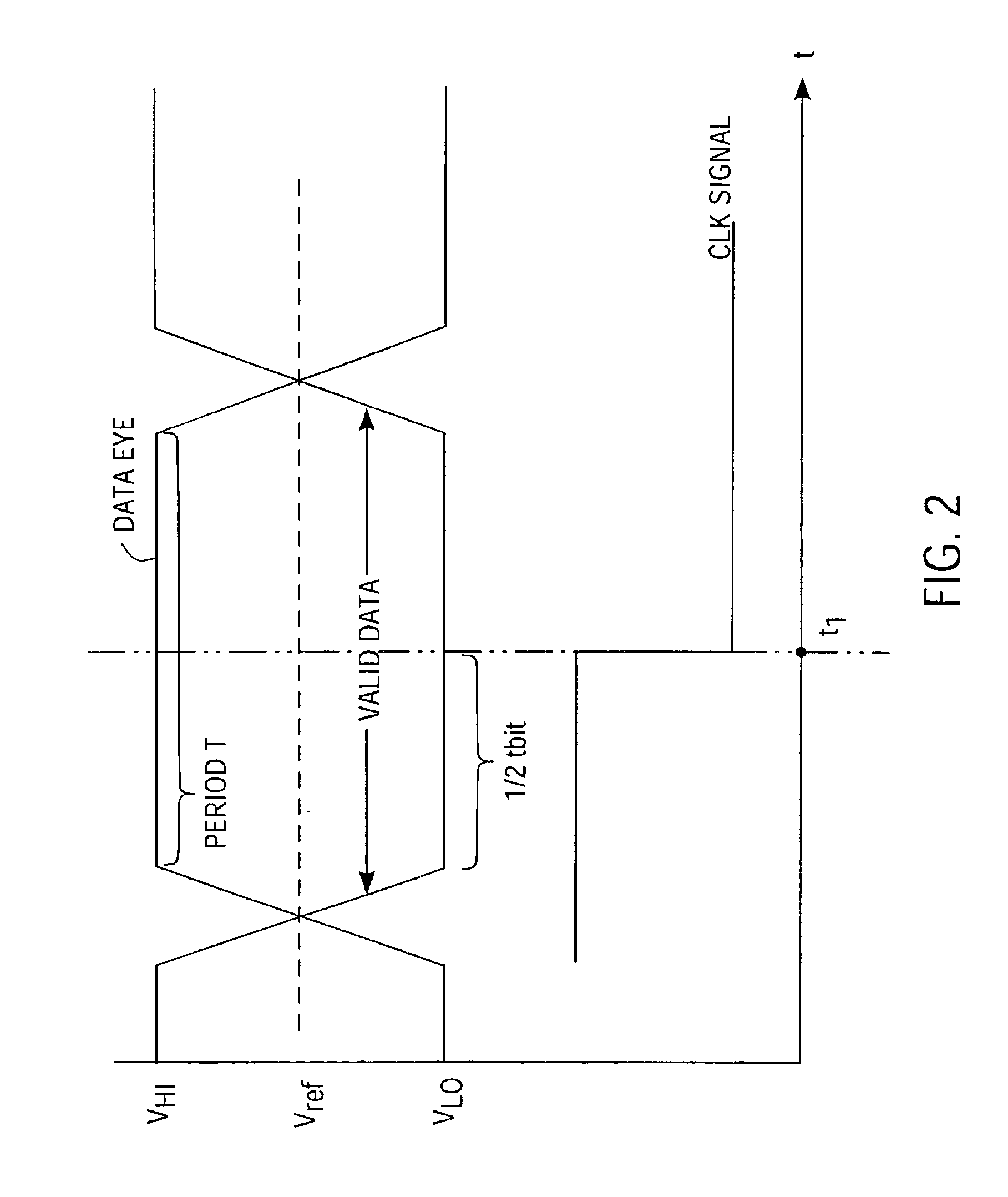

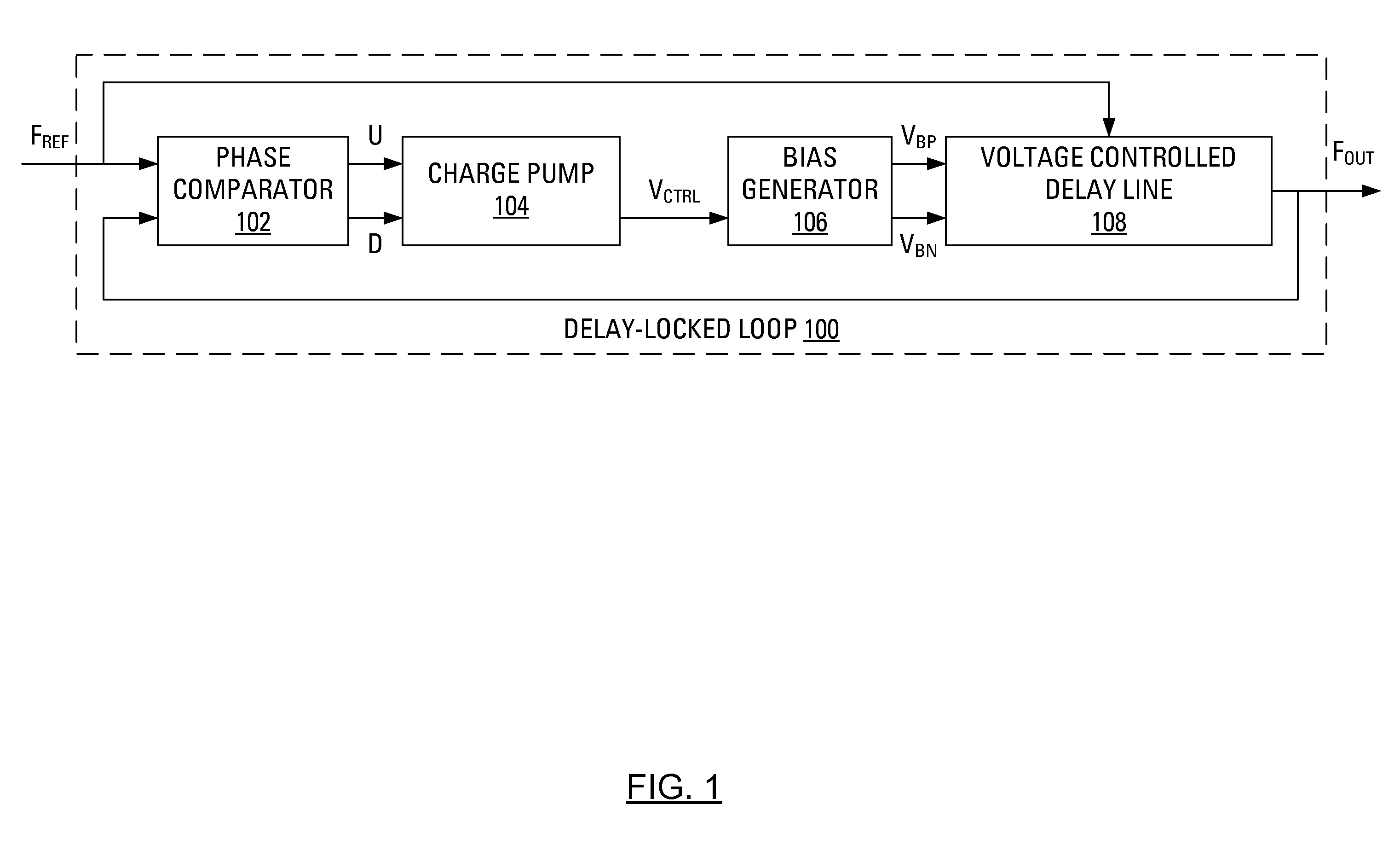

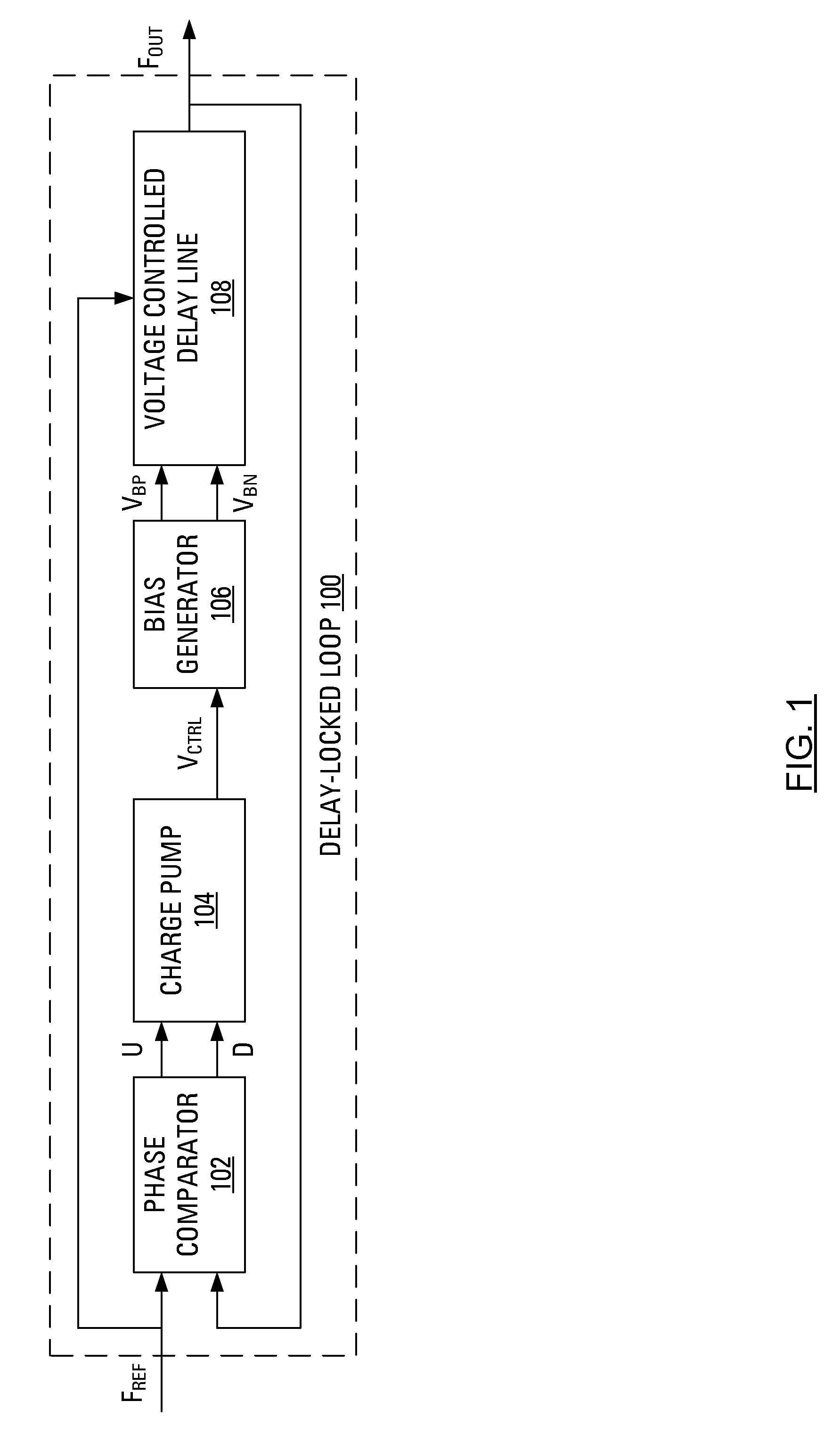

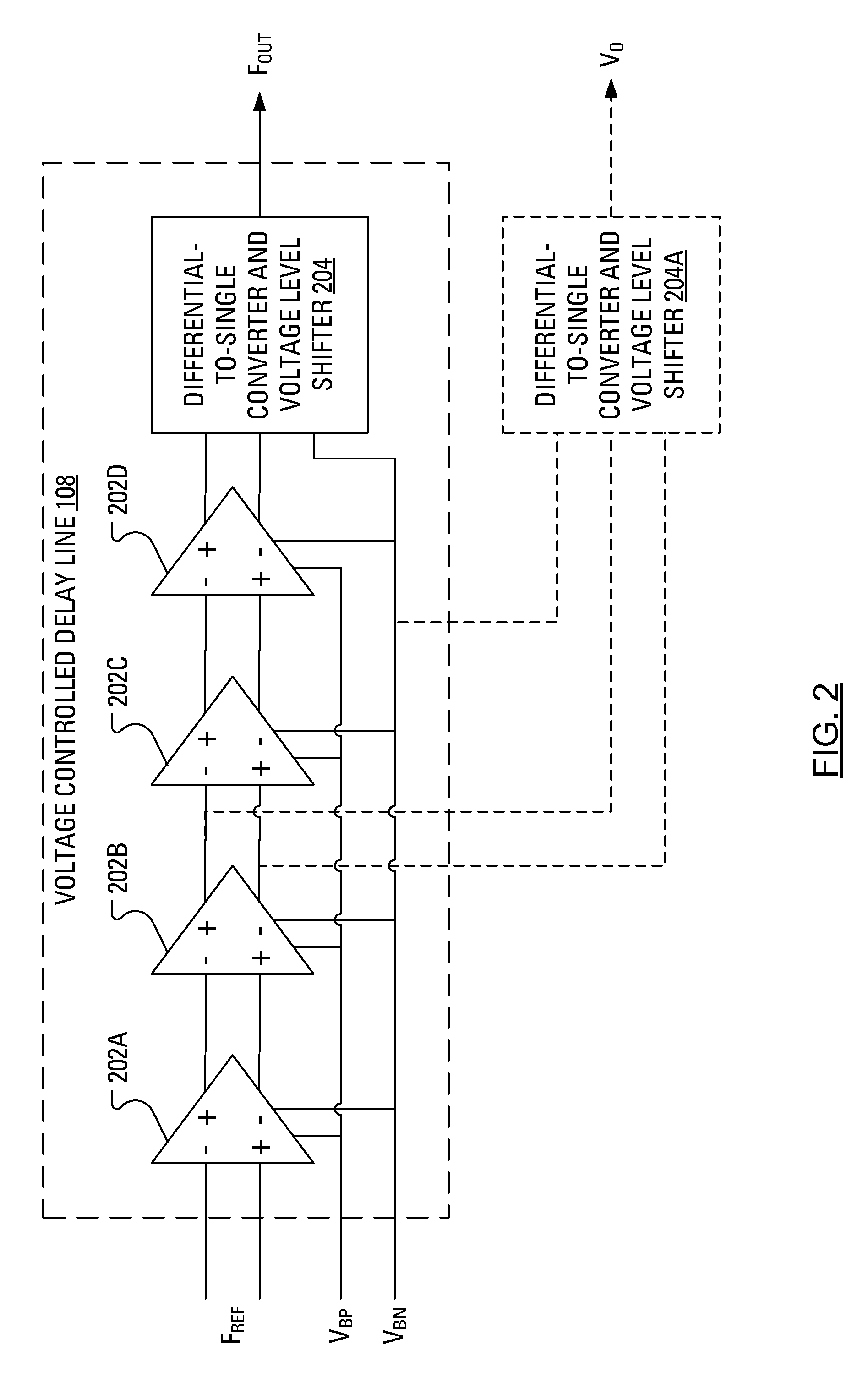

Integrated circuit with timing adjustment mechanism and method

InactiveUS6950956B2Multiple-port active networksModulated-carrier systemsComputer scienceIntegrated circuit

An integrated circuit device includes a receiver, a register and a clock circuit. The receiver samples data from an external signal line in response to an internal clock signal. The register stores a value that represents a timing offset to adjust the time at which the data is sampled. The clock circuit generates the internal clock signal such that the internal clock signal maintains a controlled timing relationship with respect to an external clock signal. The clock circuit includes an interpolator that phase mixes a set of reference clock signals such that the internal clock signal is phase offset in accordance with the value.

Owner:RAMBUS INC

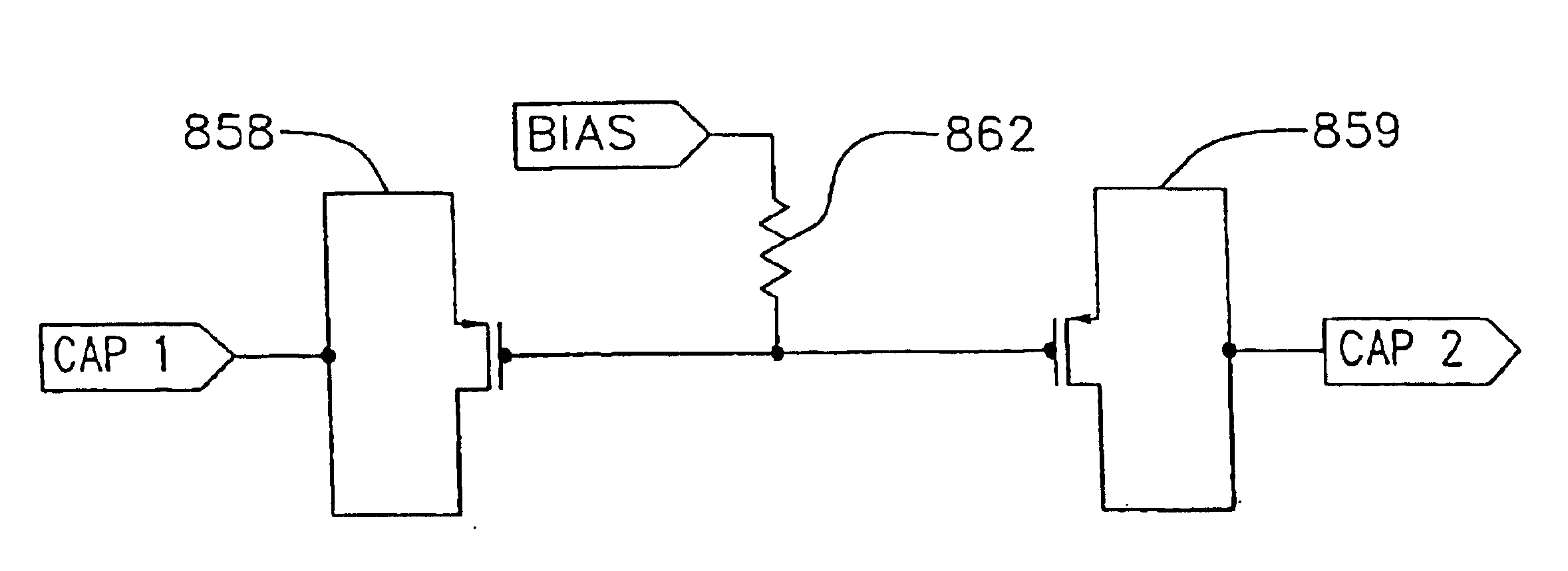

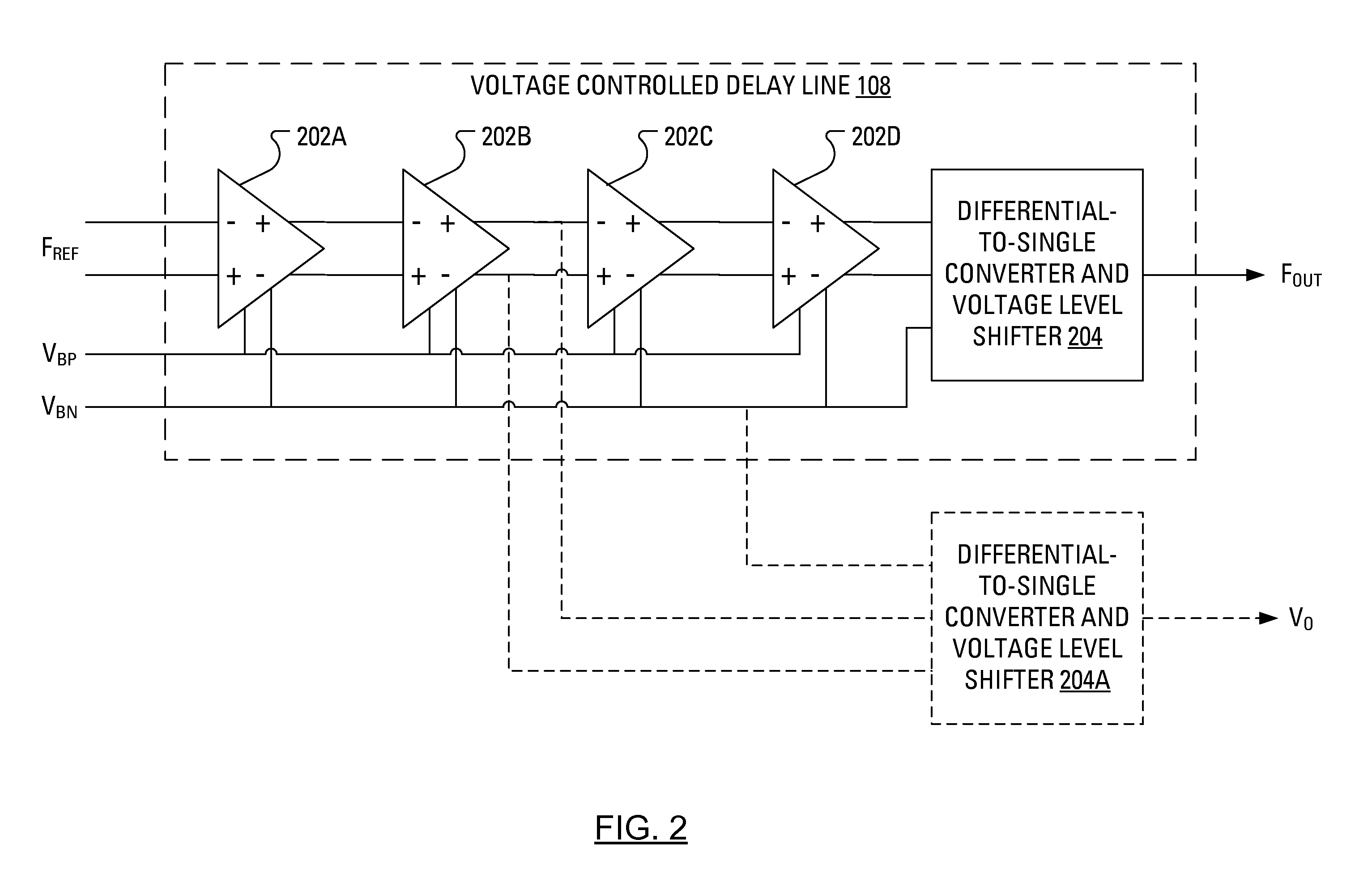

Adaptive radio transceiver with floating MOSFET capacitors

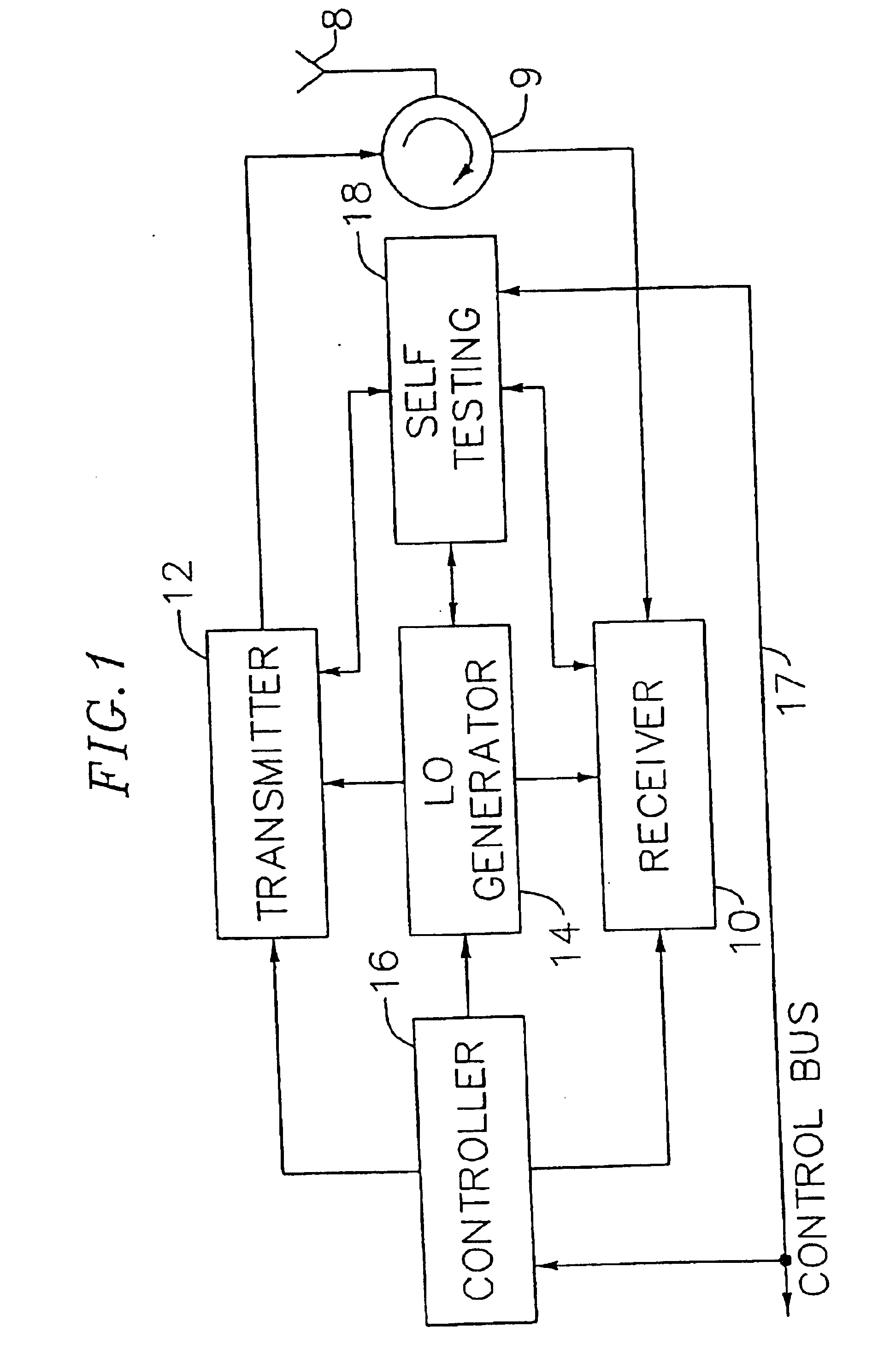

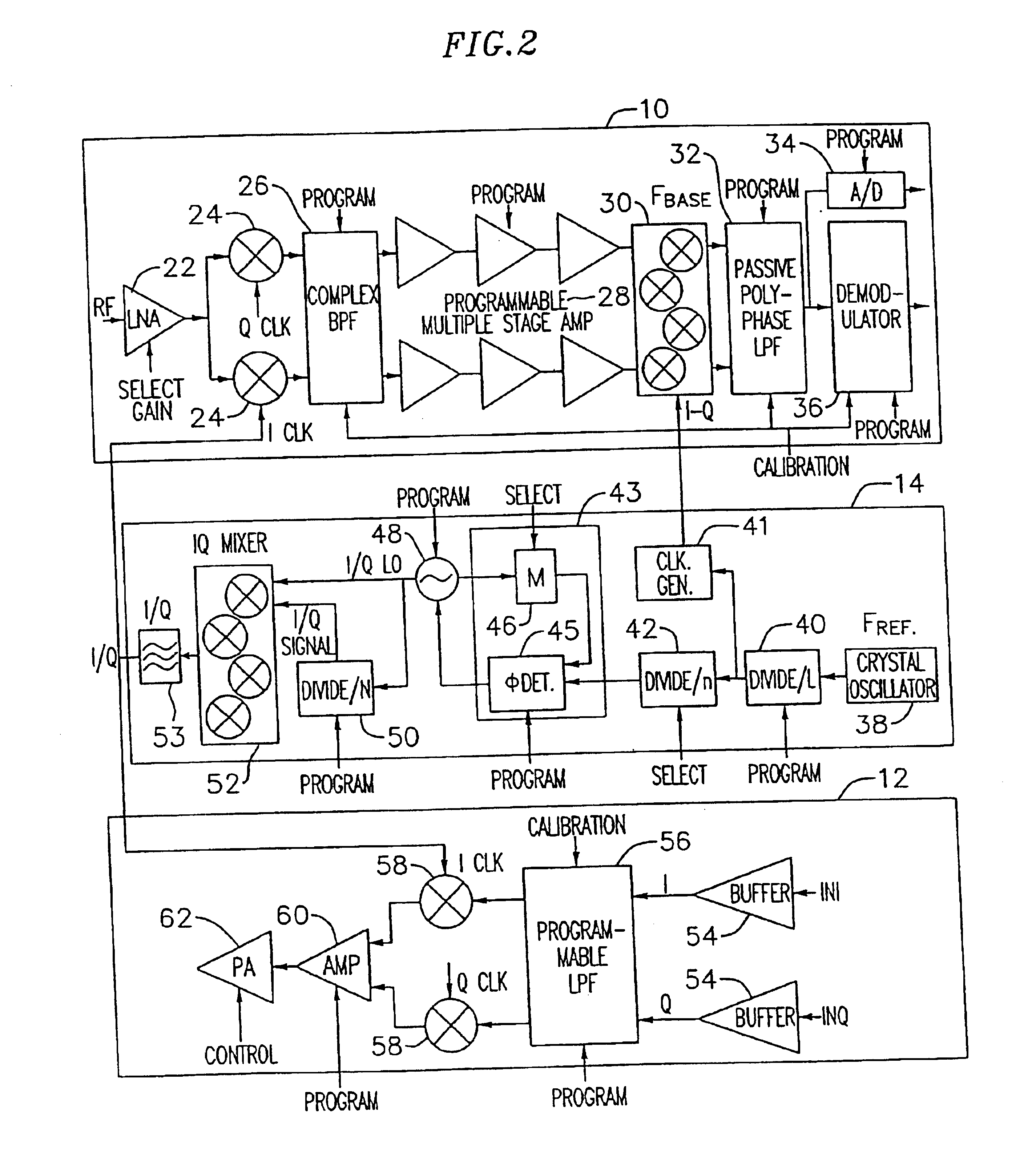

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH INT SALES PTE LTD

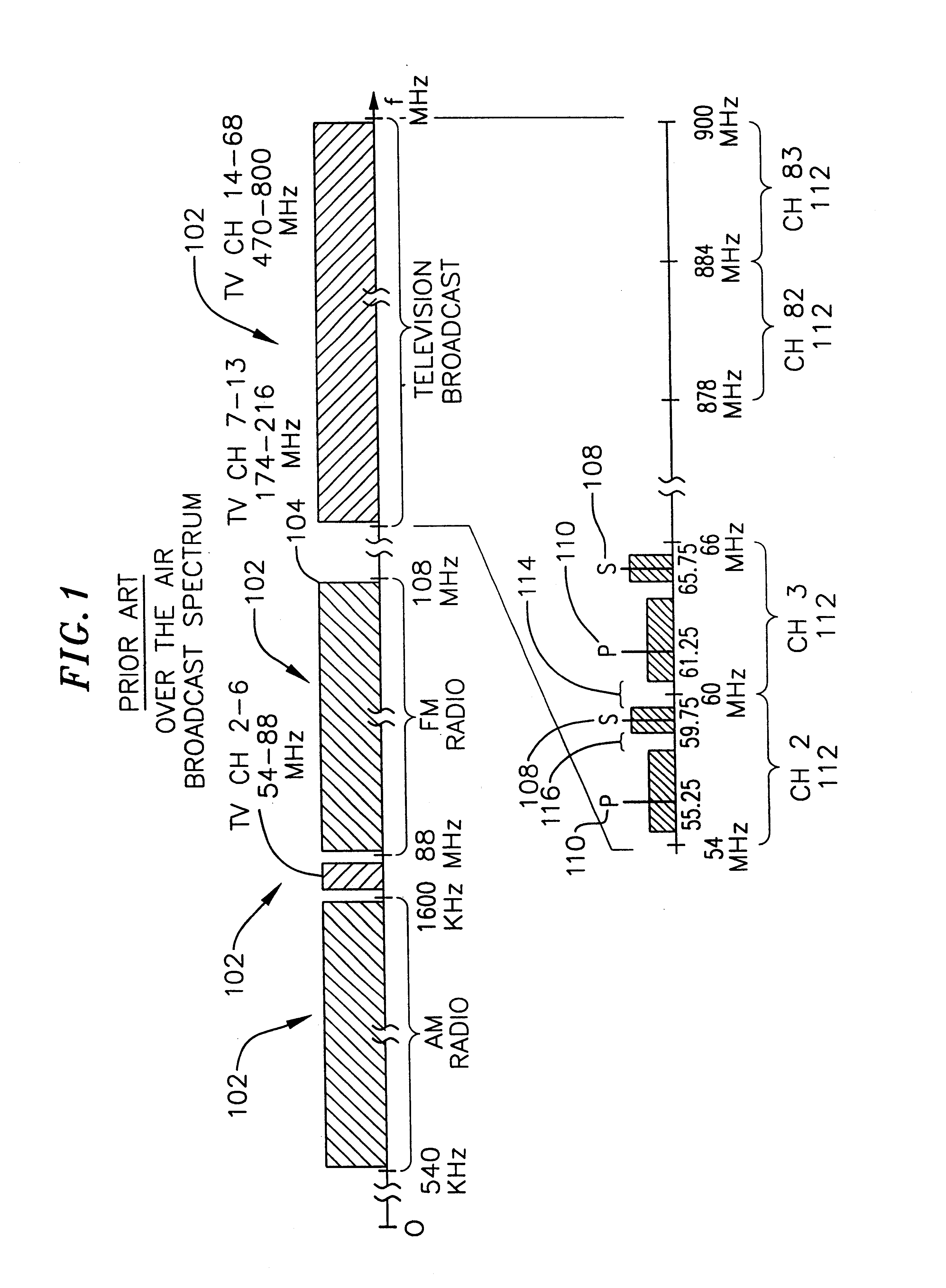

Integrated switchless programmable attenuator and low noise amplifier

InactiveUS6879816B2Multiple-port active networksSwitched capacitor networksCapacitanceLocal oscillator signal

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

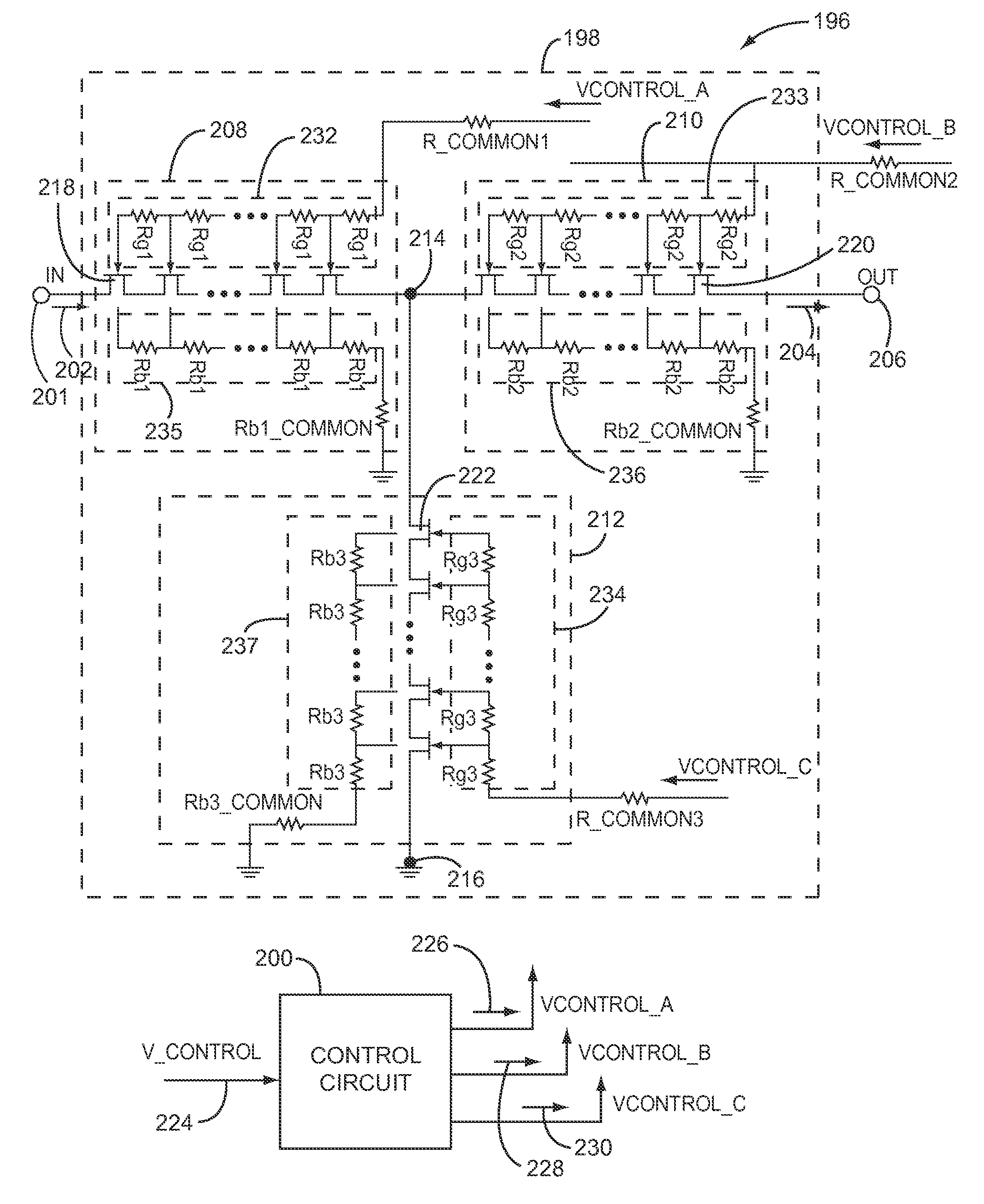

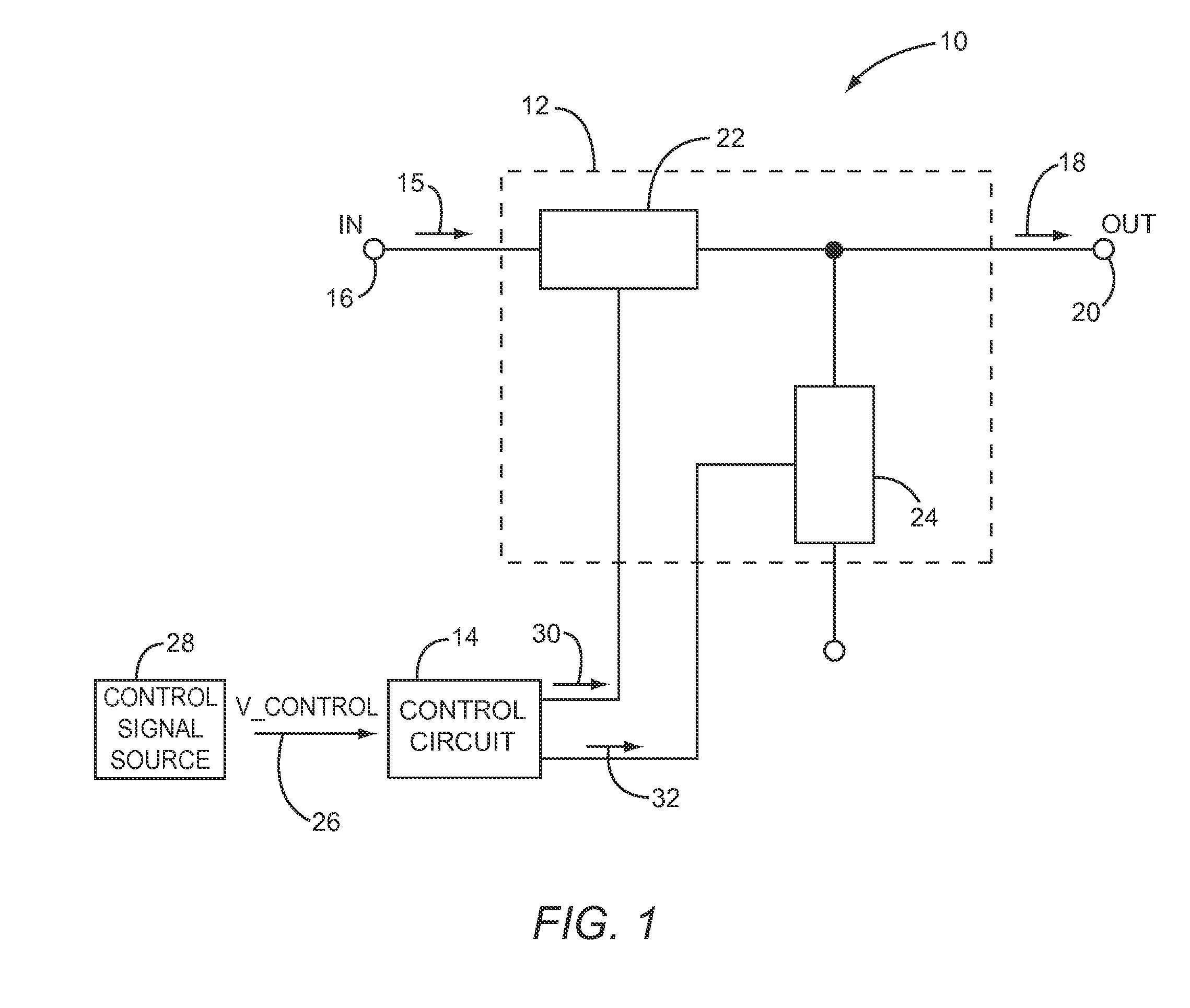

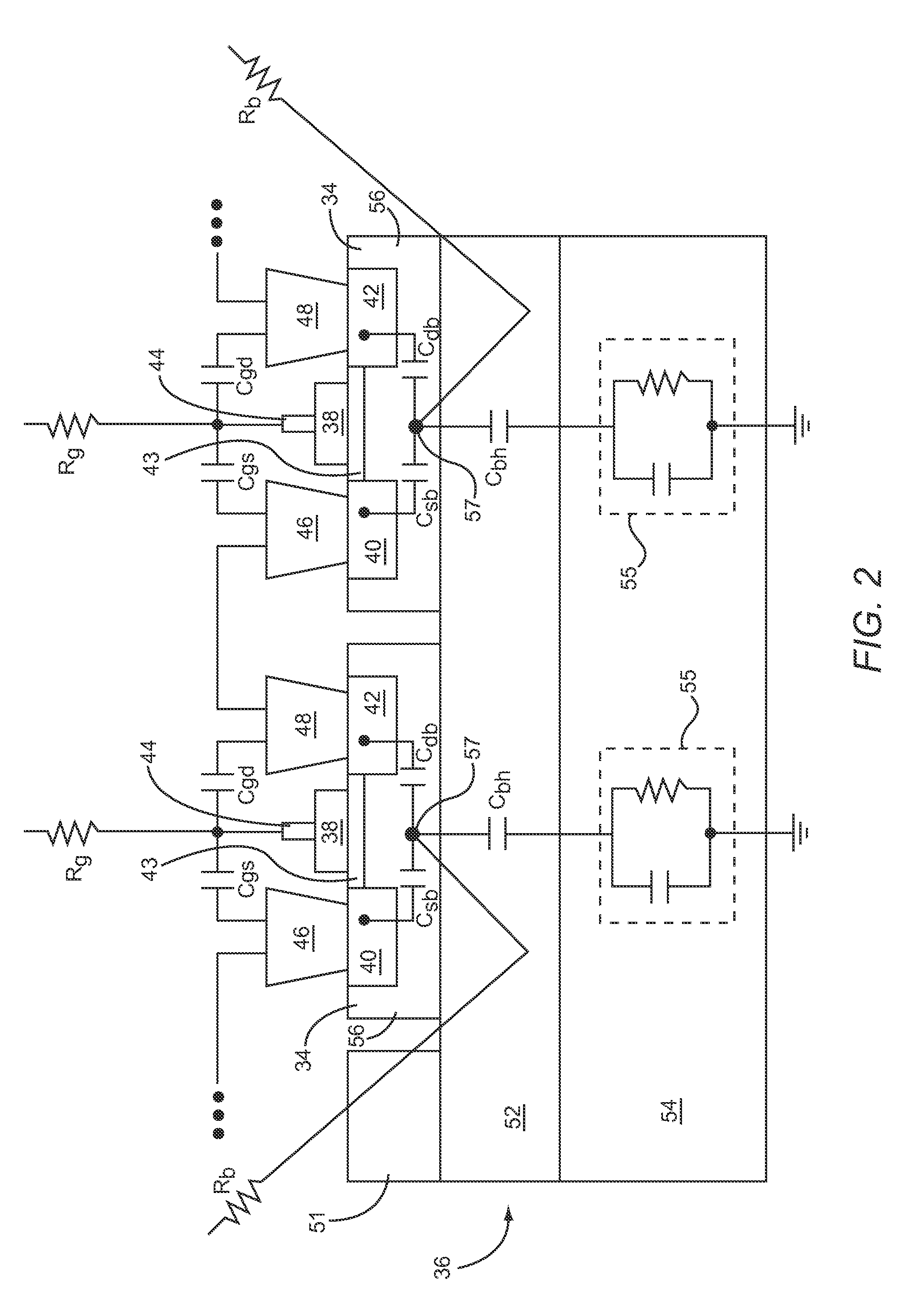

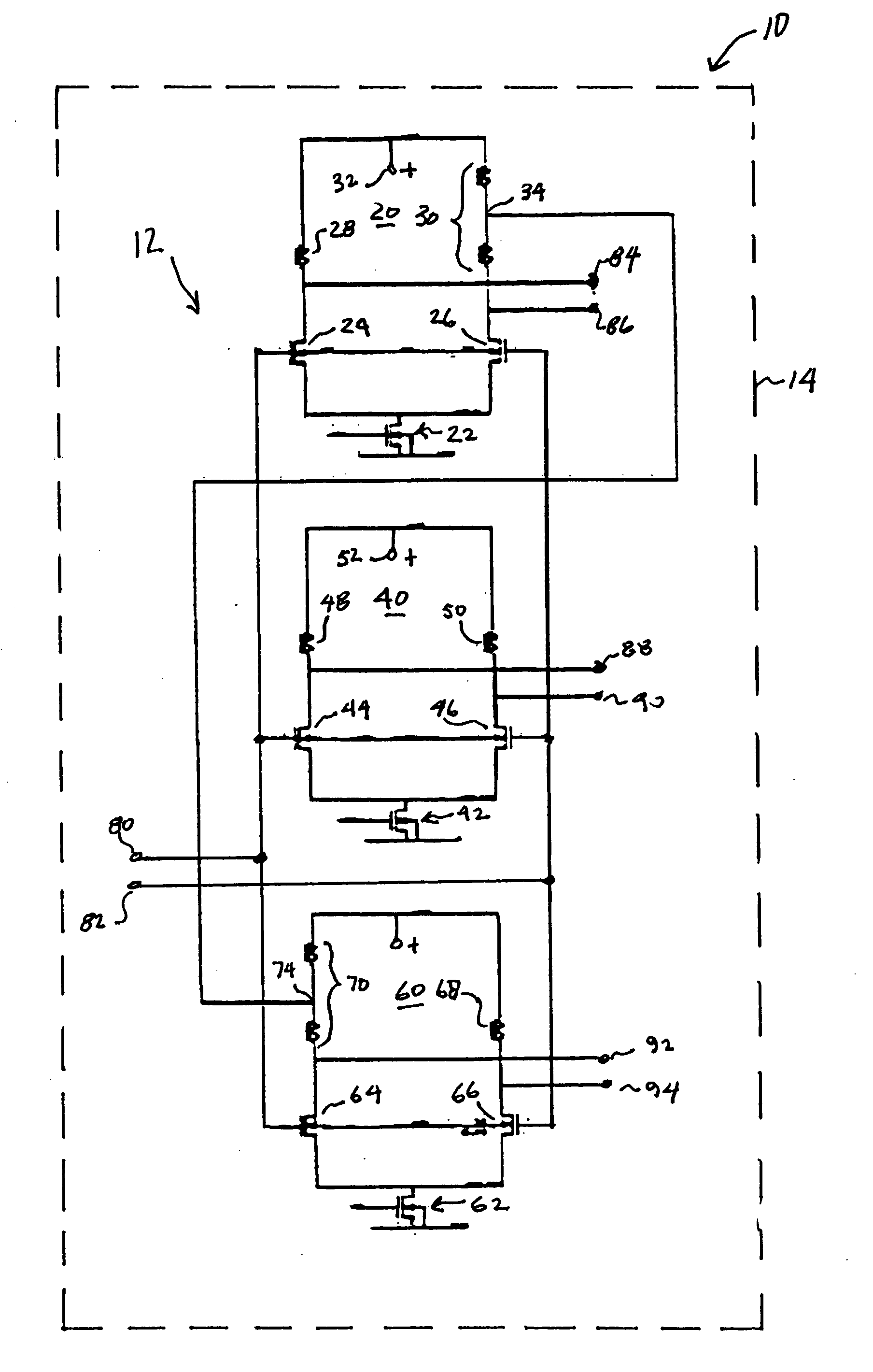

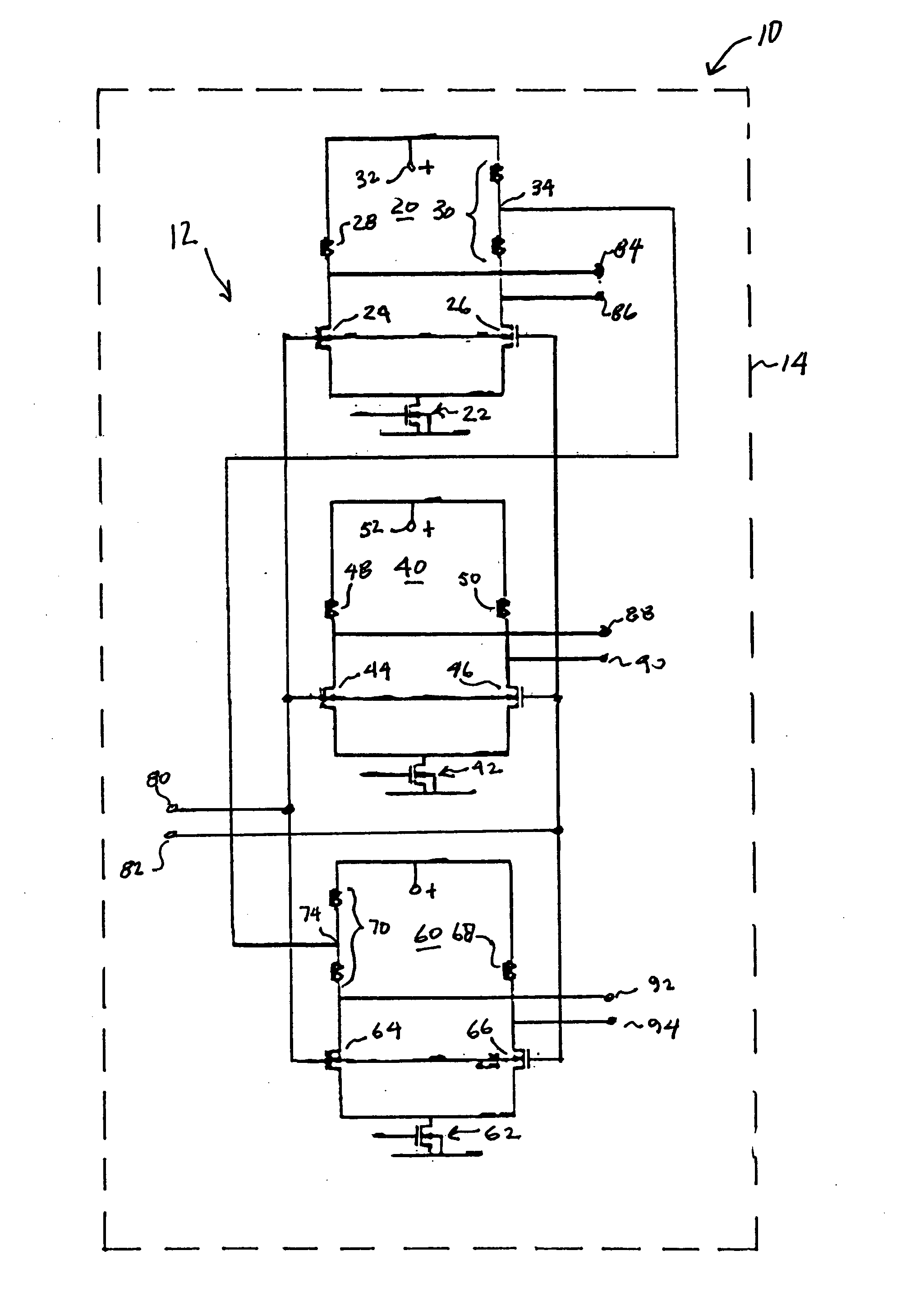

Variable attenuator having stacked transistors

ActiveUS20110148501A1Reduce distortion problemsWide bandwidthMultiple-port active networksPulse automatic controlUltrasound attenuationAttenuation coefficient

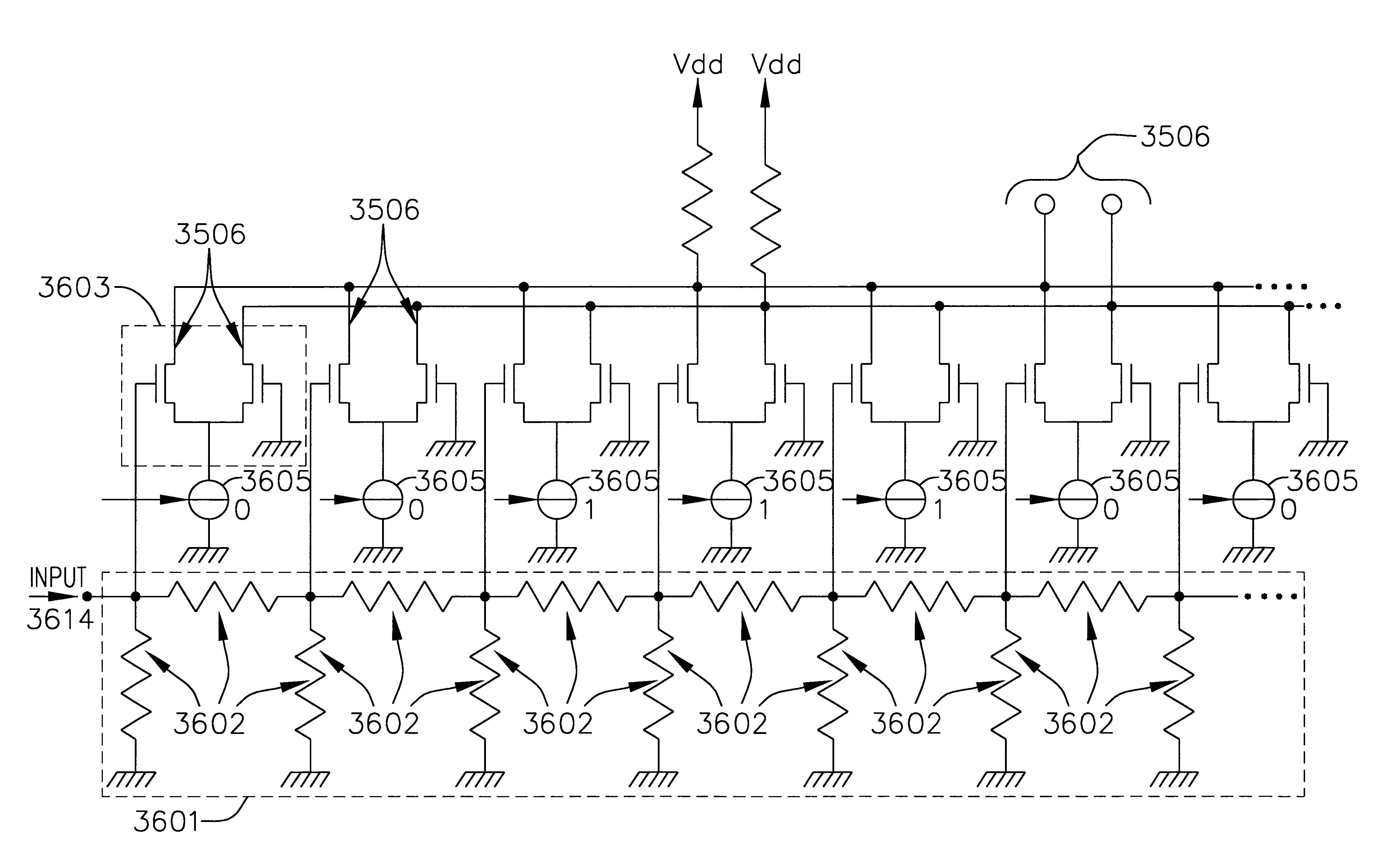

In one embodiment, a variable attenuator is disclosed having an attenuation circuit and a control circuit. The attenuation circuit may include a first series connected attenuation circuit segment and a shunt connected attenuation circuit segment, as well as additional attenuation circuit segments. Each attenuation circuit segment includes a stack of transistors that are coupled to provide the attenuation circuit segment with a variable impedance level having a continuous impedance range. In this manner, the control circuit may be operably associated with the stack of transistors in each attenuation circuit segment to control the variable attenuation level of the variable attenuator.

Owner:QORVO US INC

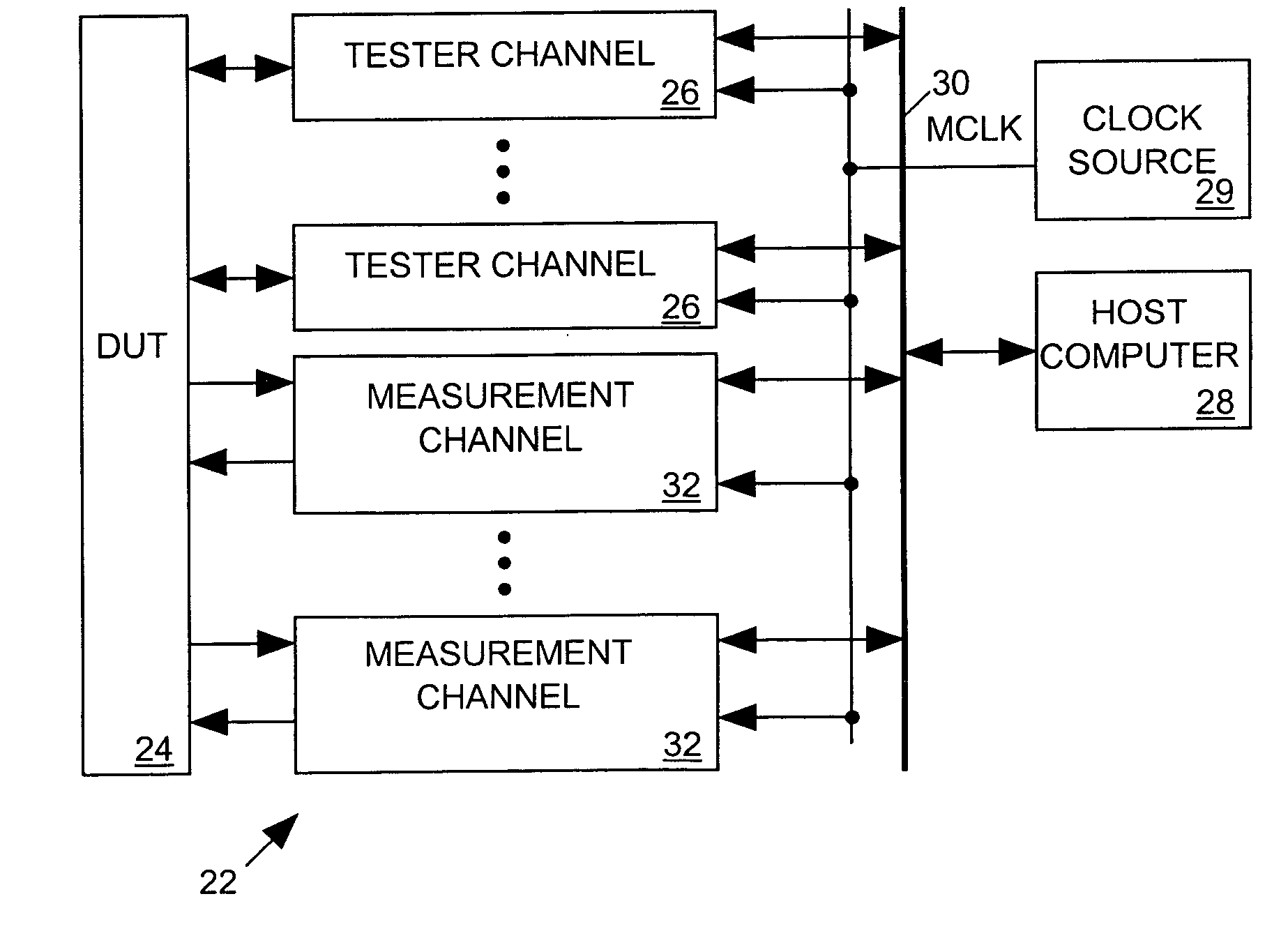

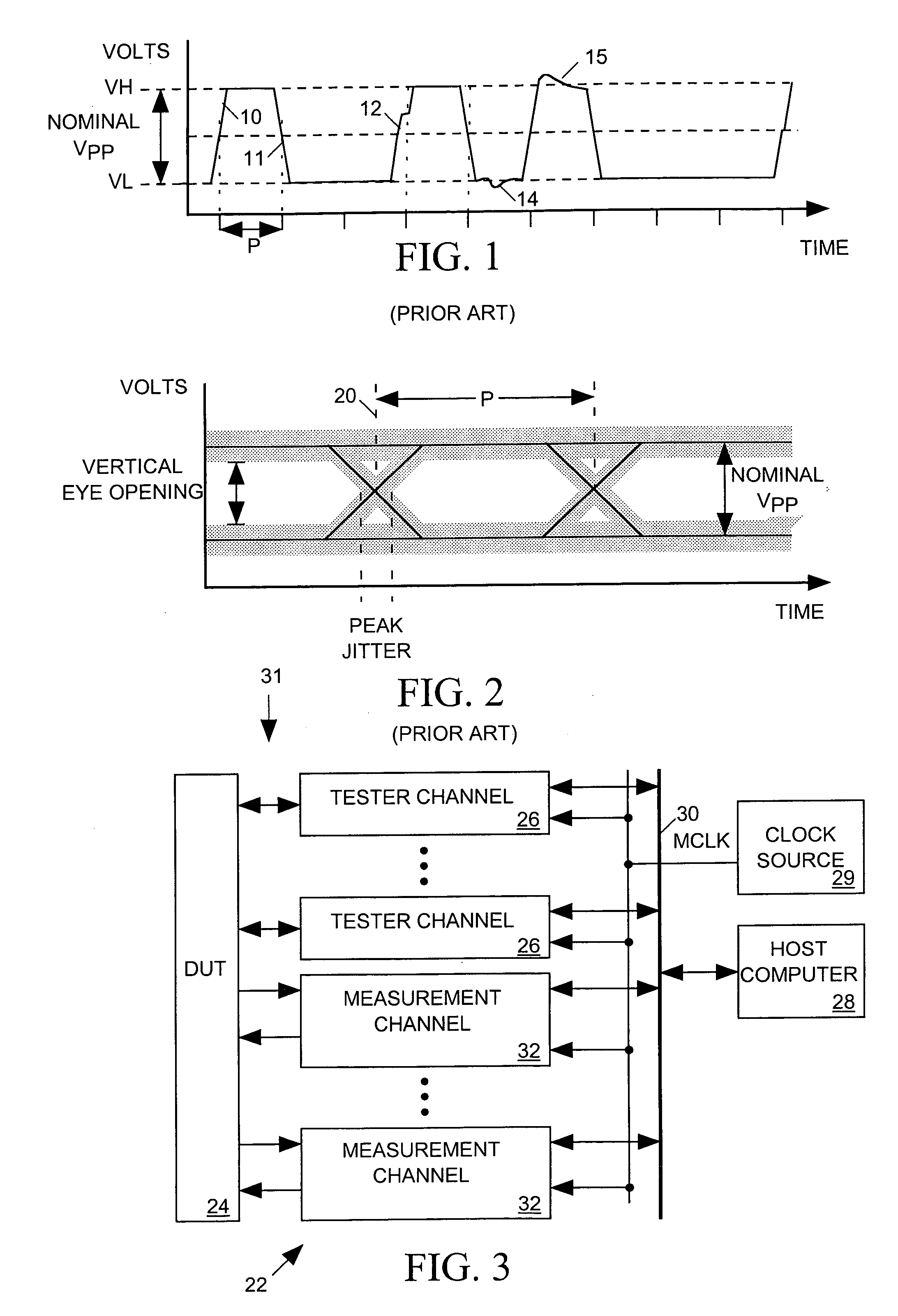

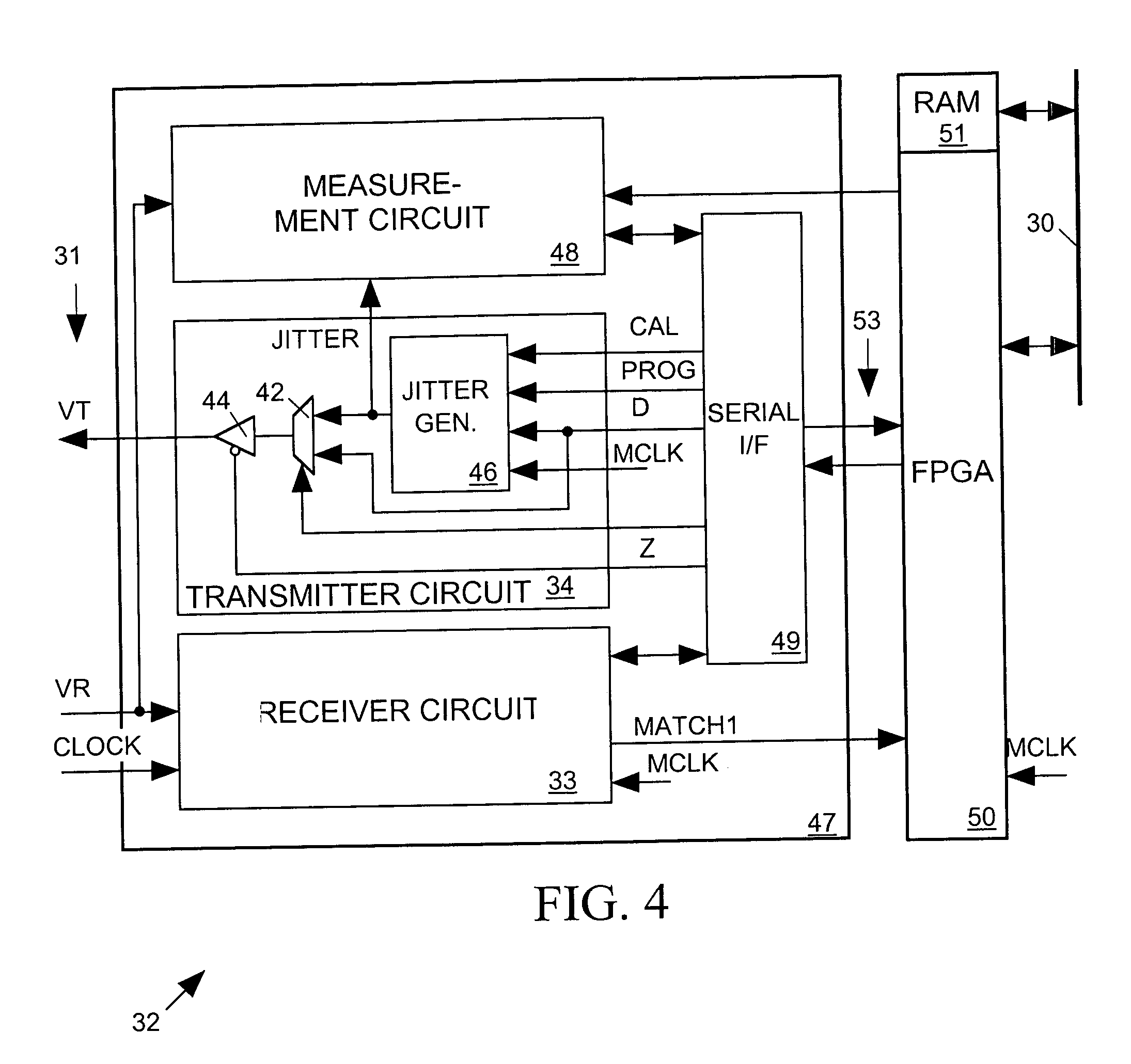

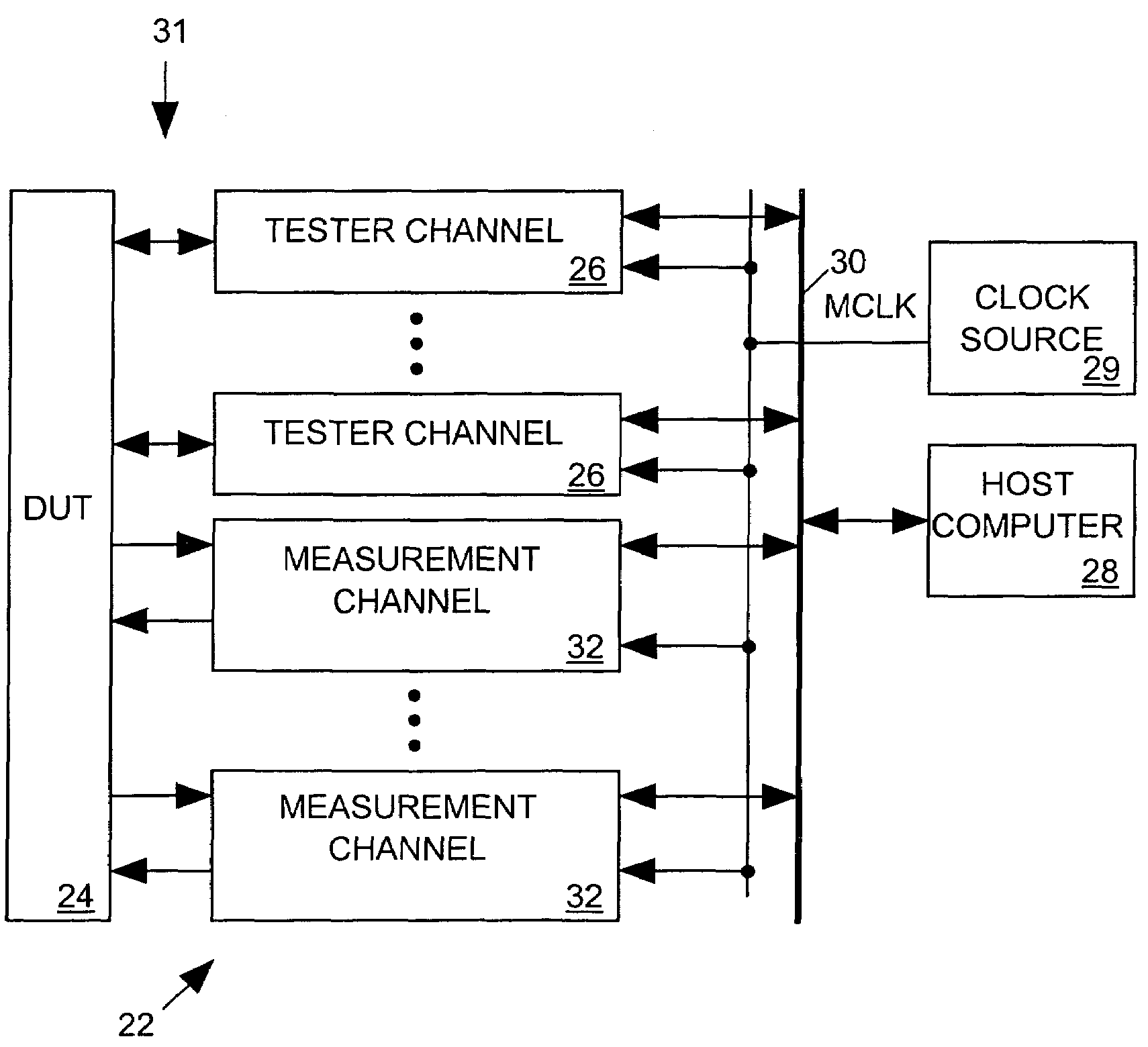

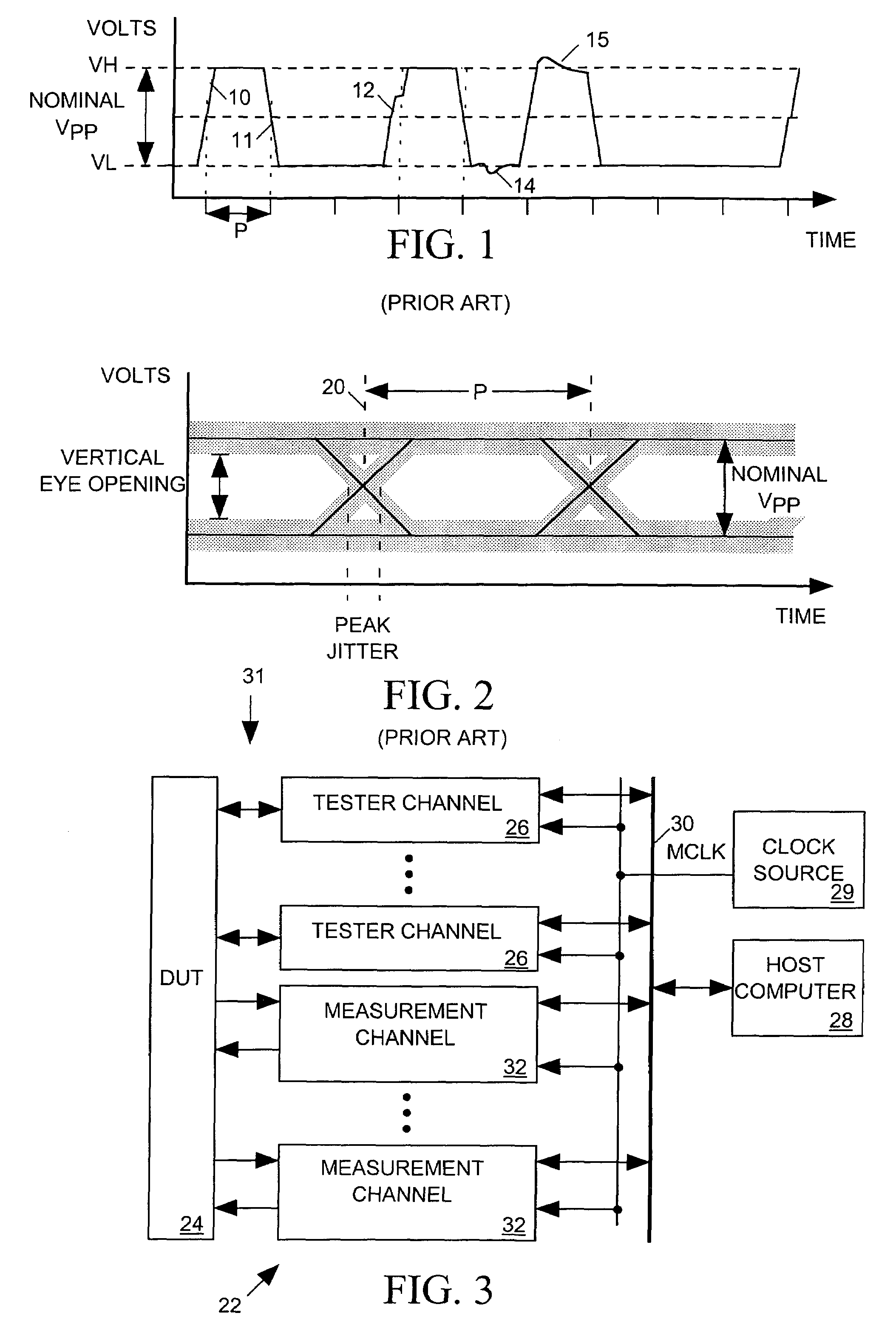

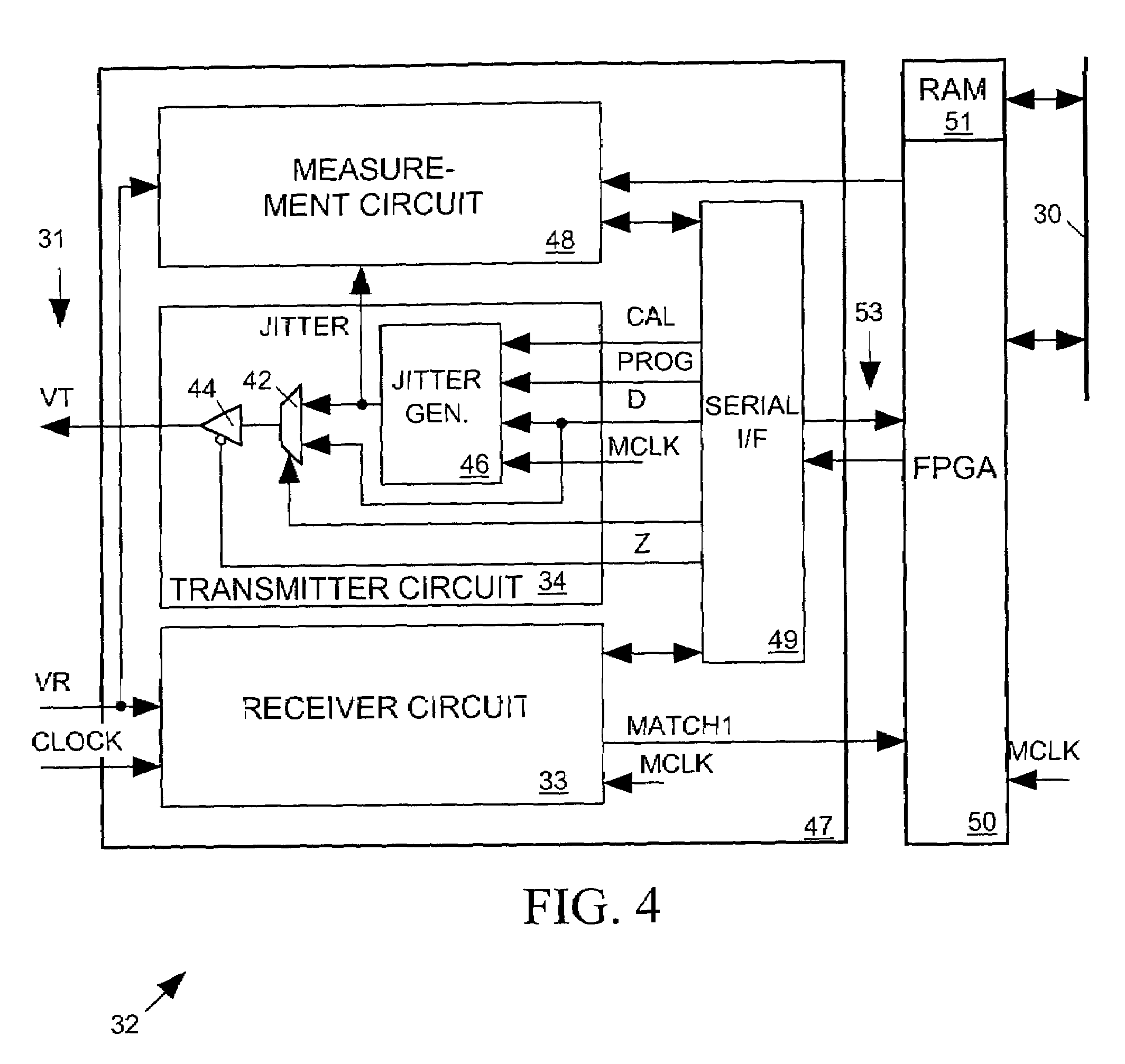

Apparatus for jitter testing an IC

InactiveUS20050097420A1Minimizing delay and noiseTime indicationMultiple-port active networksVoltage referenceProcess measurement

An integrated circuit tester channel includes an integrated circuit (IC) for adding a programmably controlled amount of jitter to a digital test signal to produce a DUT input signal having a precisely controlled jitter pattern. The IC also measures periods between selected edges of the same or different ones of the DUT output signal, the DUT input signal, and a reference clock signal. Additionally, when the DUT input and output signals convey repetitive patterns, the IC can measure the voltage of the DUT input out output signal as selected points within the pattern by comparing it to an adjustable reference voltage. Processing circuits external to the IC program the IC to provide a specified amount of jitter to the test signal, control the measurements carried out by the measurement circuit, and process measurement data to determine the amount of jitter and other characteristics of the DUT output signal, and to calibrate the jitter in the DUT input signal.

Owner:CREDENCE SYSTEMS

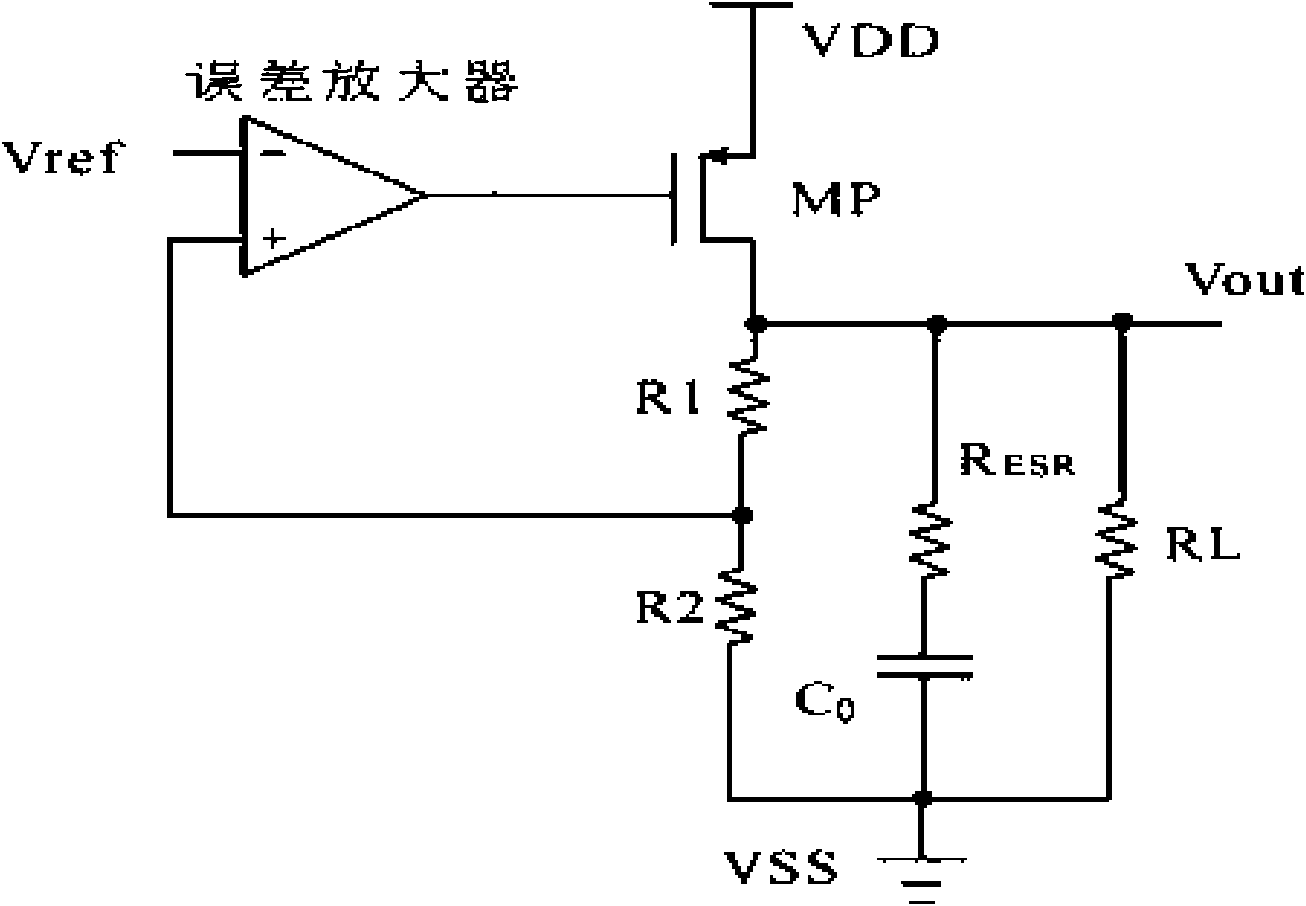

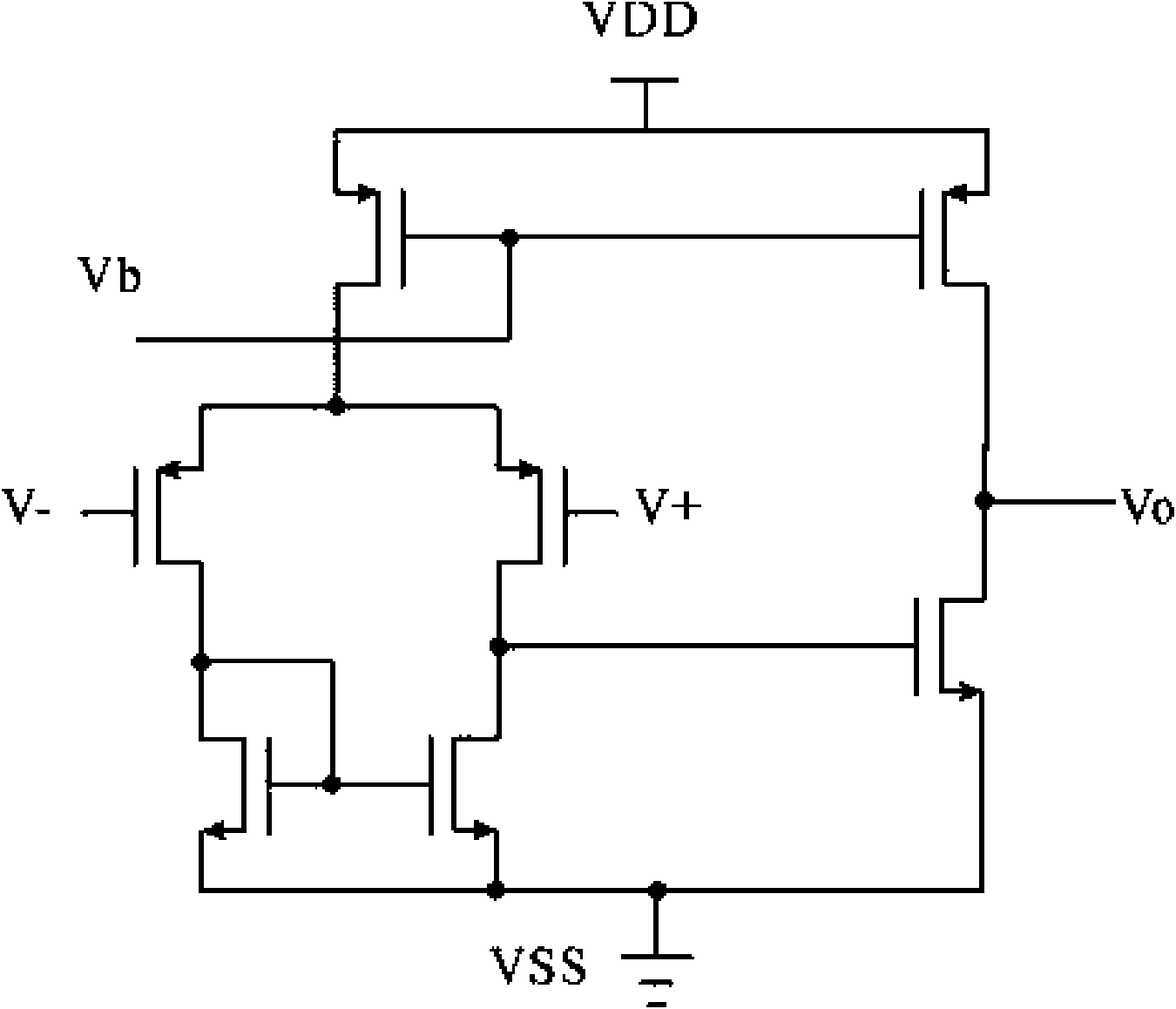

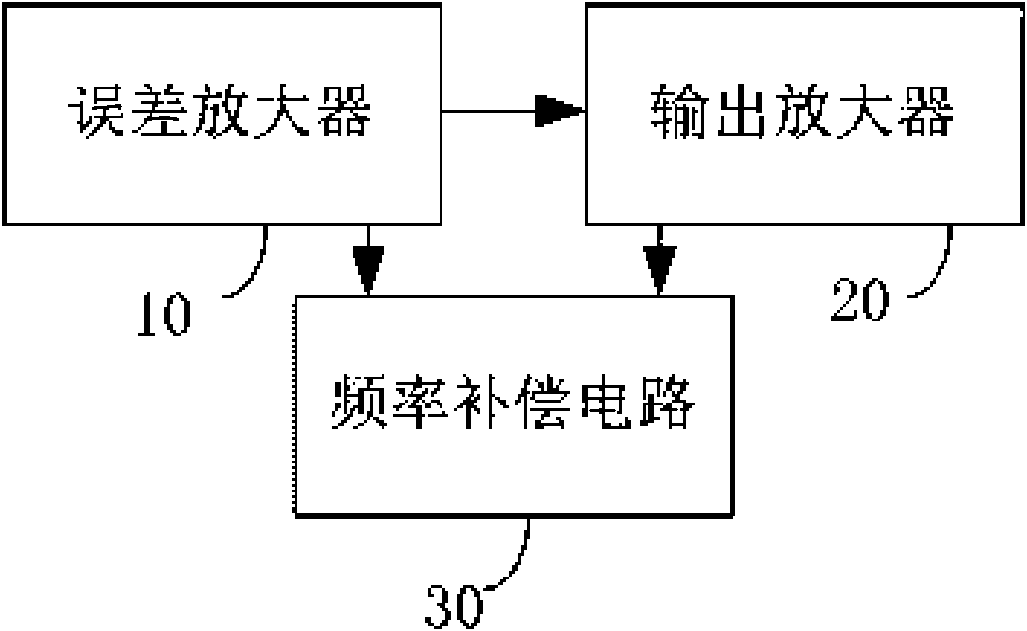

Low-voltage difference voltage adjuster

ActiveCN101667046AGood power supply rejection ratio performanceReduce the numberMultiple-port active networksAmplififers with field-effect devicesCapacitanceFrequency compensation

The invention discloses a low-voltage difference voltage adjuster, belonging to the technical field of an electronic circuit. The low-voltage difference voltage adjuster comprises an error amplifier,an output amplifier and a frequency compensating circuit, wherein the error amplifier is a first-class folding cascode amplifier, the output amplifier is coupled with the error amplifier, receives control voltage and comprises a transistor and two divider resistors which are connected in series; the frequency compensating circuit is respectively coupled with the error amplifier and the output amplifier; and the frequency compensating circuit comprises a voltage-controlling current source circuit consisting of at least one transistor and at least one compensating capacitor coupled with the voltage-controlling current source circuit. The low-voltage difference voltage adjuster can solves the problems that the current voltage adjuster has larger compensating capacitance and can not carry outon-chip integration, can provide complete chip integration, has good voltage-suppression specific characteristic, reduce the number of the compensating capacitance and simplify the compensating circuit.

Owner:灿芯创智微电子技术(北京)有限公司

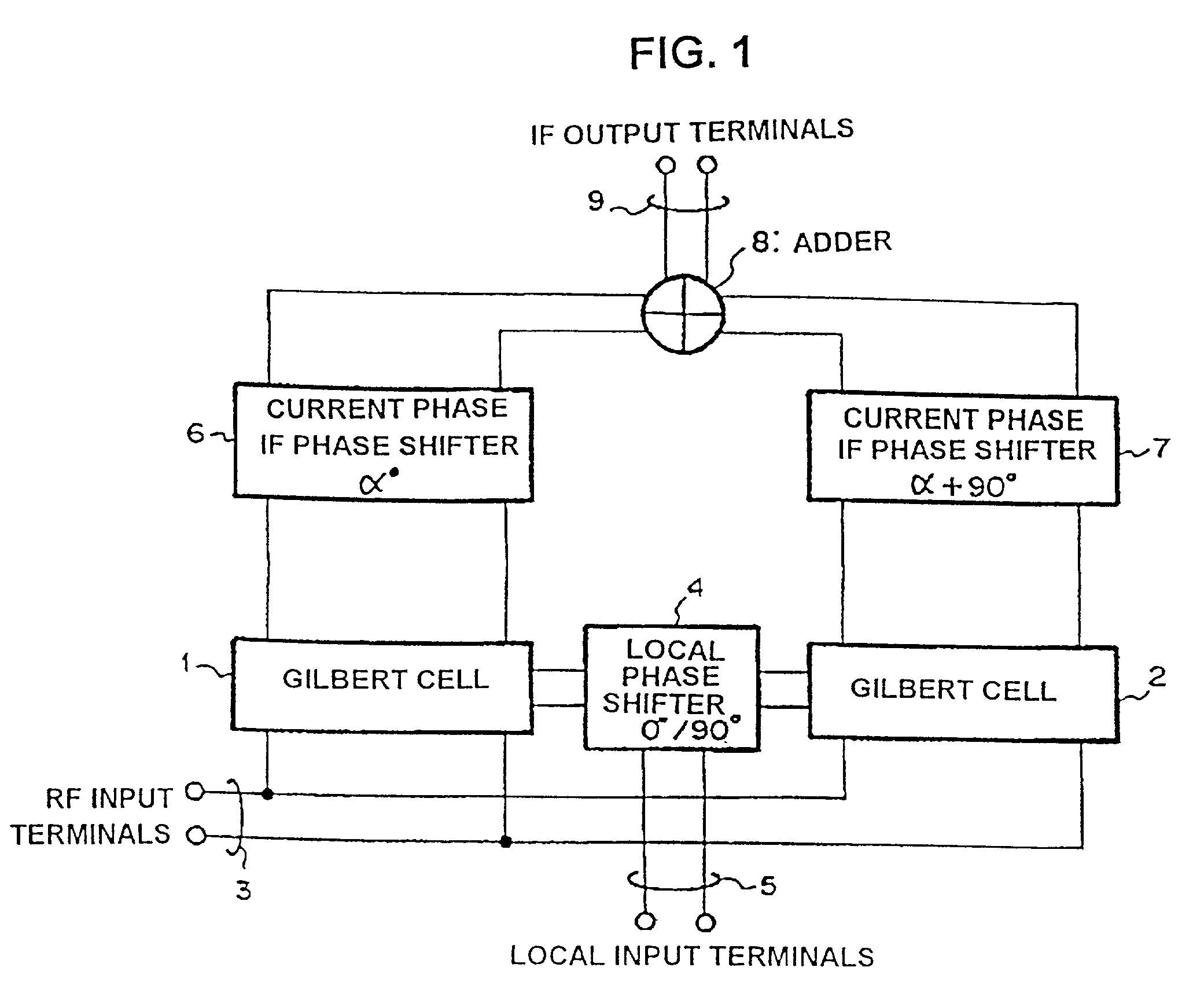

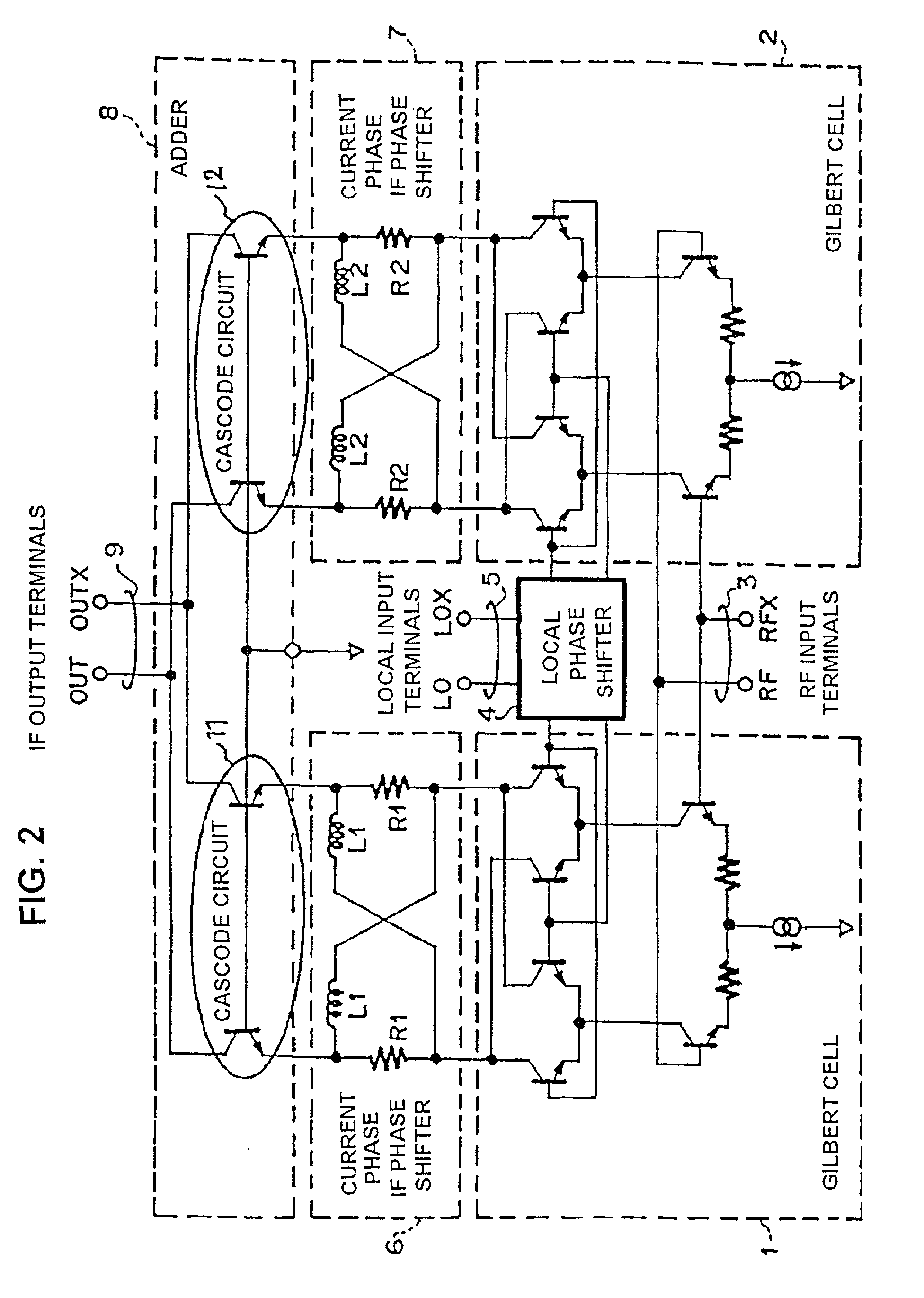

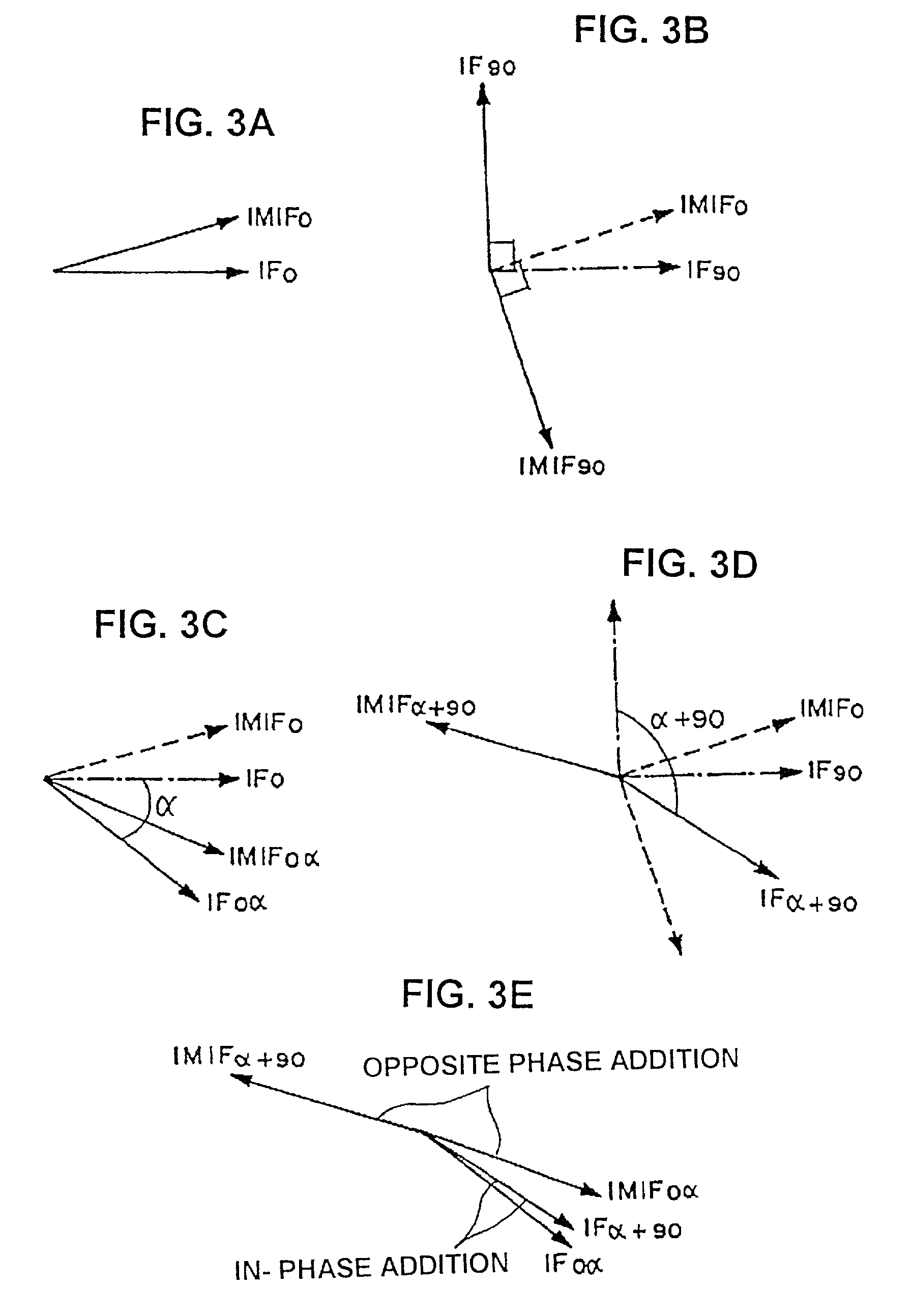

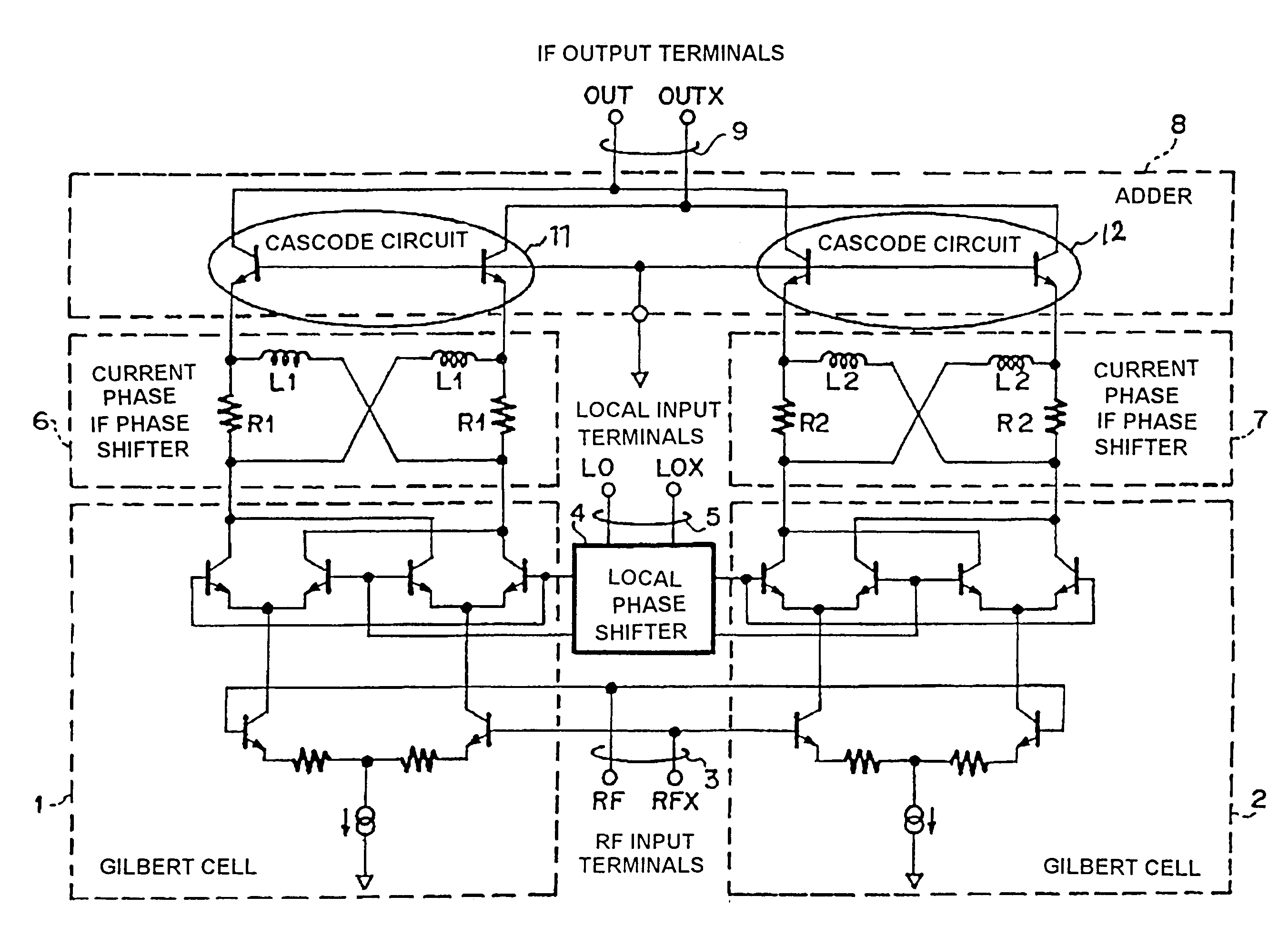

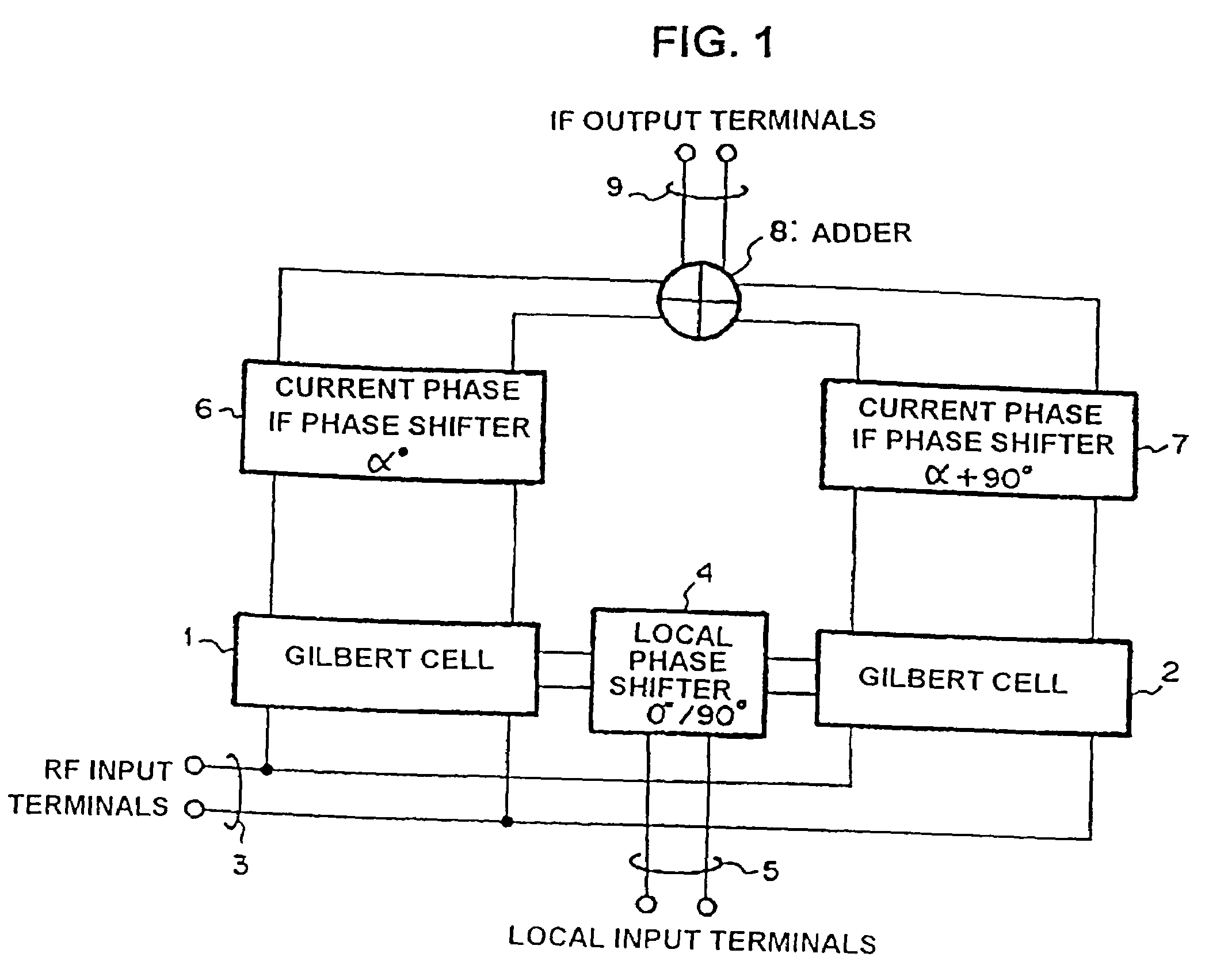

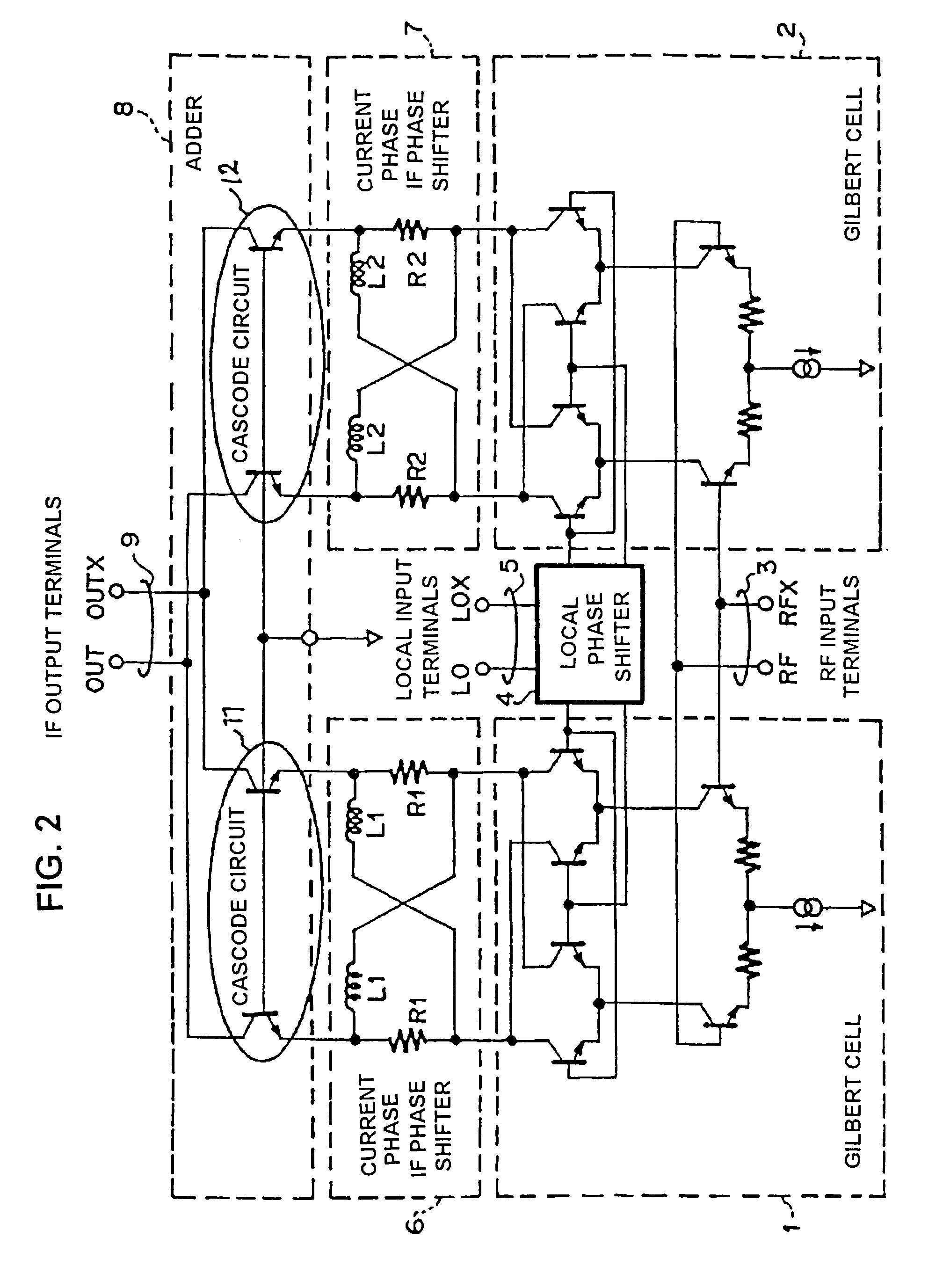

Image rejection mixer

An object of the present invention is to lower the power dissipation of the image rejection mixer. The image rejection mixer includes distribution means supplied with local signals having a phase difference to distribute the local signals, first and second mixing means for mixing the distributed local signals and RF signals having a phase difference and outputting respective IF current signals, phase shift means for shifting in phase the respective mixed IF current signals so as to provide them with a relative phase difference of 90 degrees, and addition means for adding the respective phase shifted intermediate frequency current signals. The phase shift means shifts the phases of the respective IF current signals outputted from the first and second mixing means.

Owner:RENESAS ELECTRONICS CORP

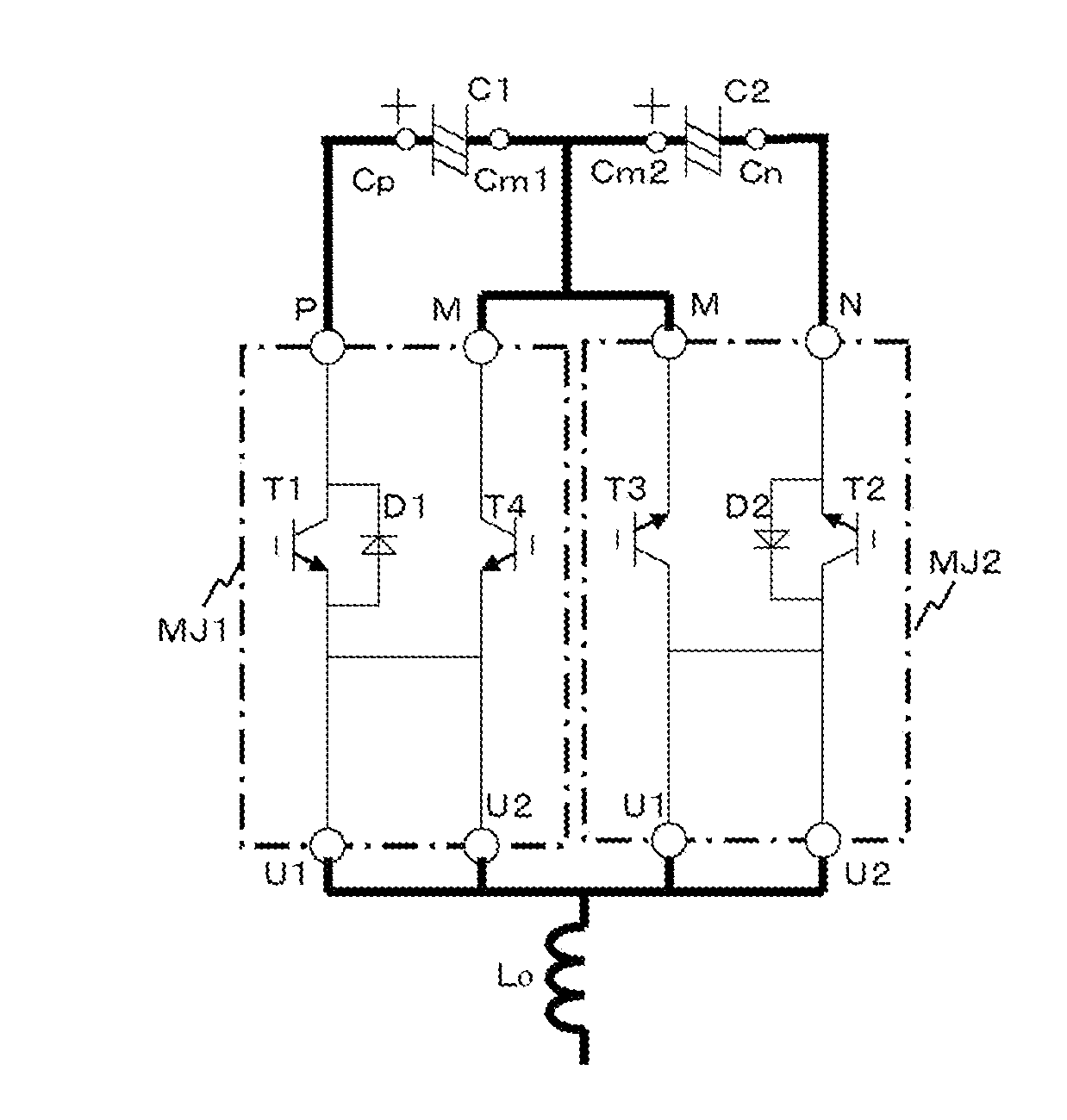

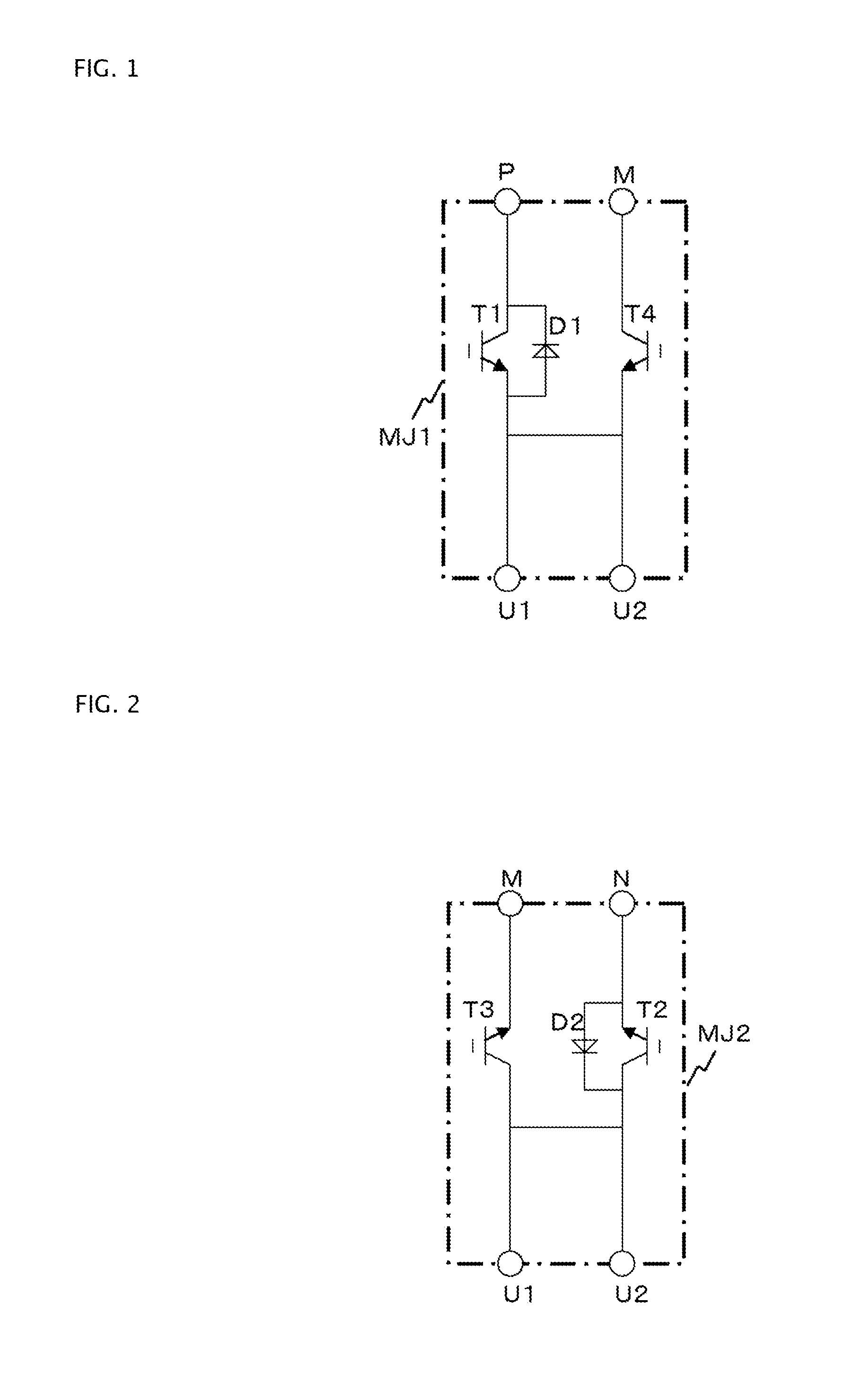

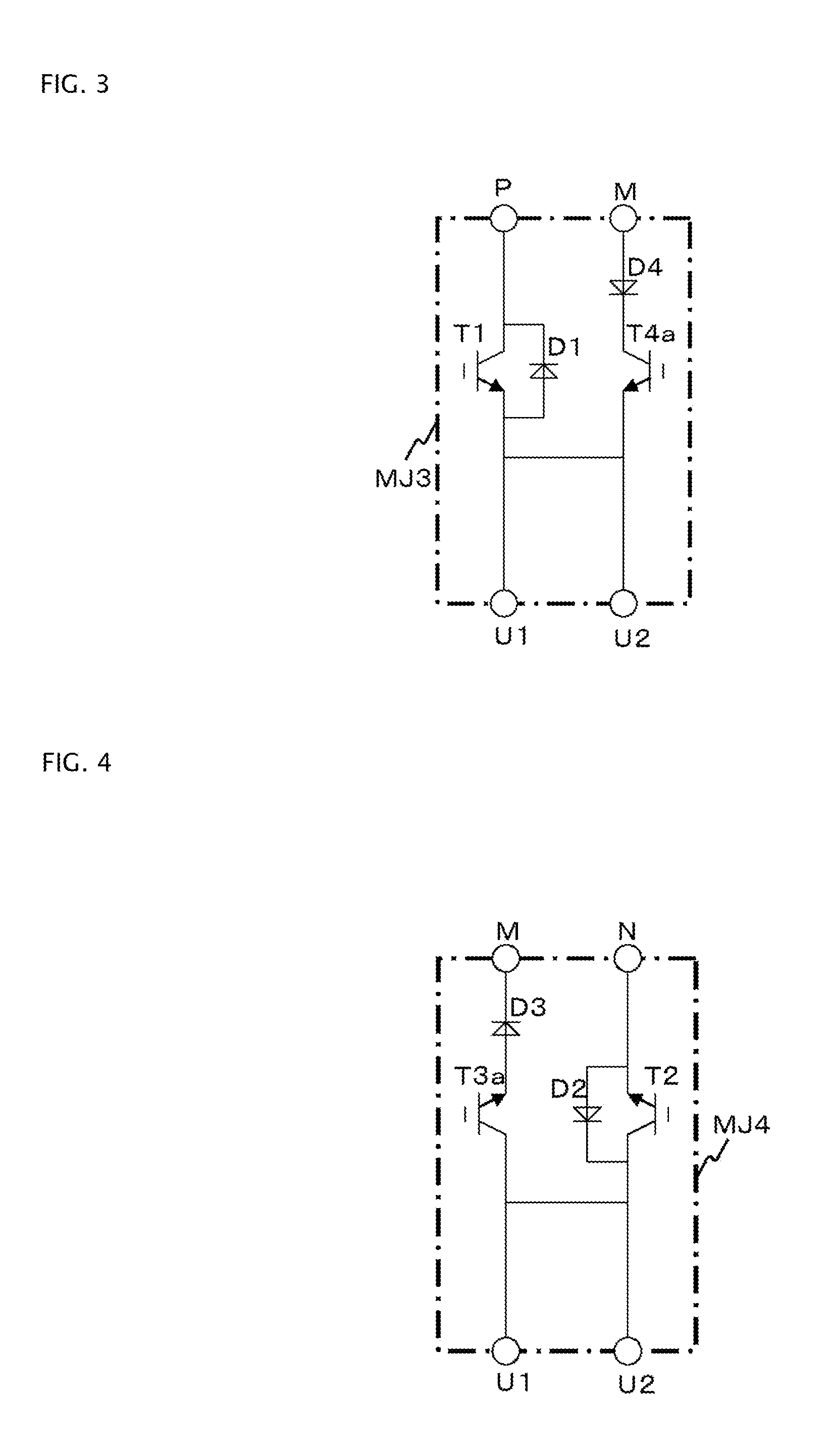

Power semiconductor device and power conversion system using the device

ActiveUS20110242866A1Reduce wire inductanceCurb valueMultiple-port active networksConversion constructional detailsPower semiconductor deviceConverters

Aspects of the invention are related to a power semiconductor module applied to a multi-level converter circuit with three or more levels of voltage waveform. Aspects of the invention can include a first IGBT to which a diode is reverse parallel connected and a second IGBT having reverse blocking voltage whose emitter is connected to the emitter of the first IGBT are housed in one package, and each of the collector of the first IGBT, the collector of the second IGBT, and the connection points of the emitter of the first IGBT and the emitter of the second IGBT, is an external terminal.

Owner:FUJI ELECTRIC CO LTD

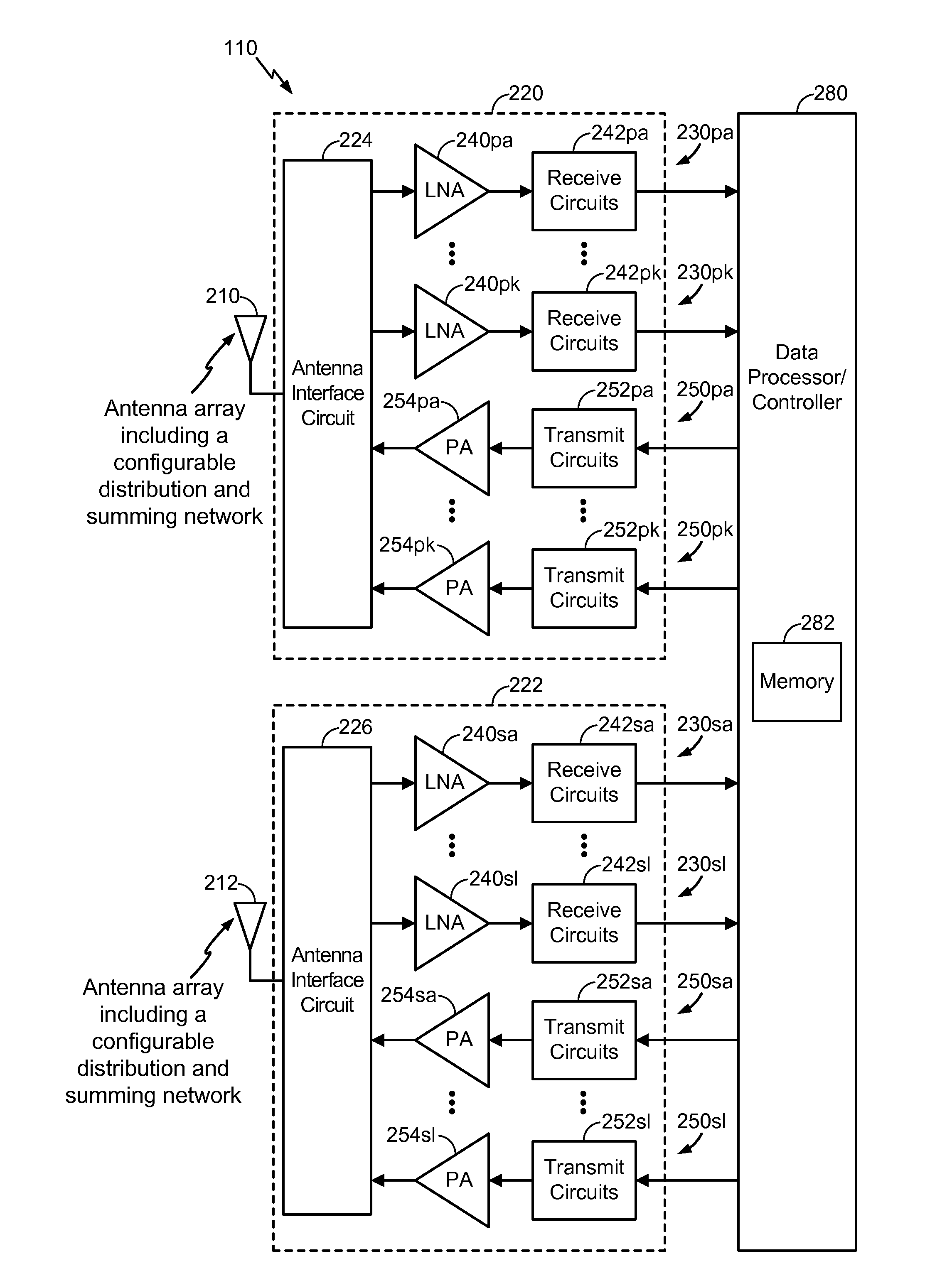

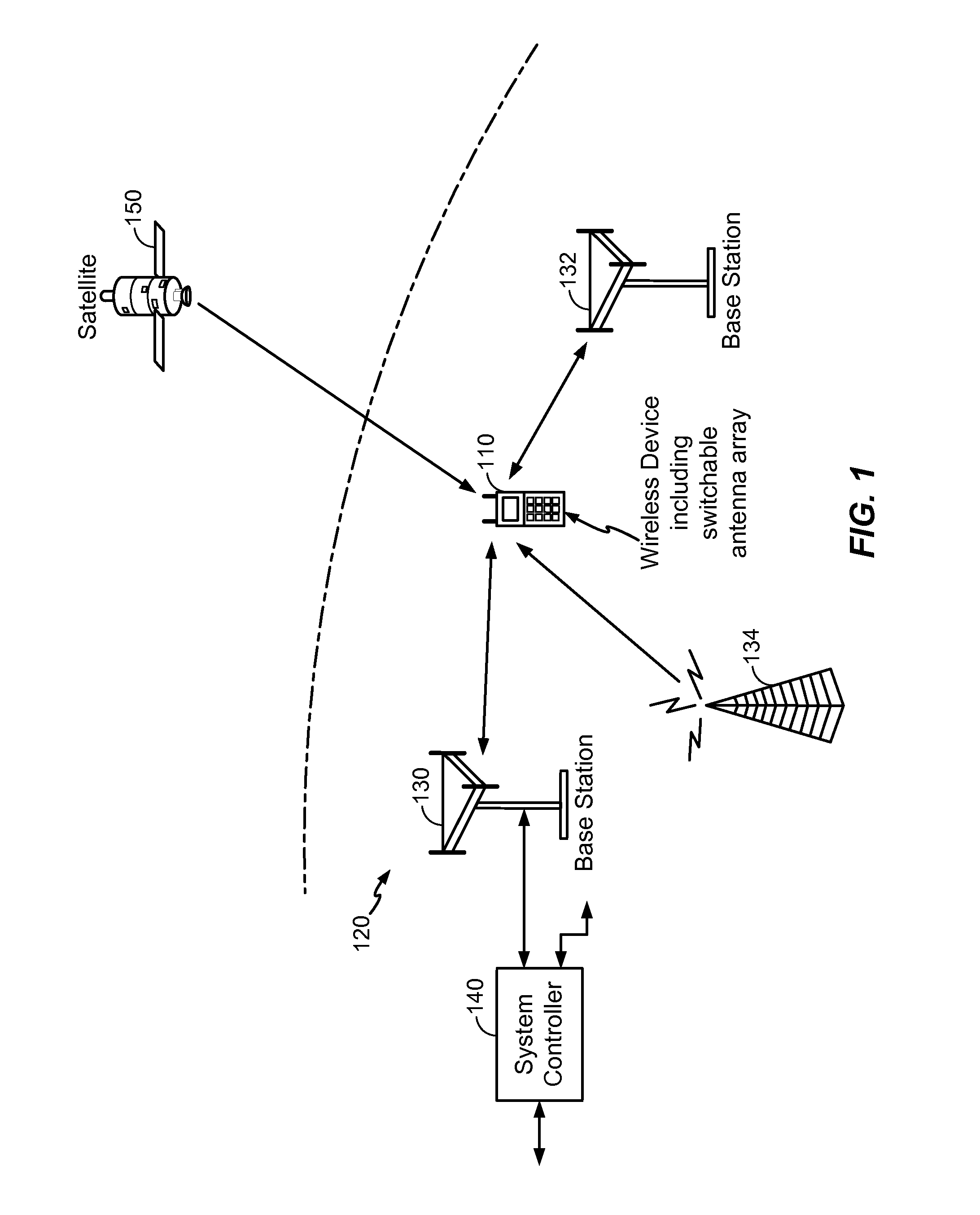

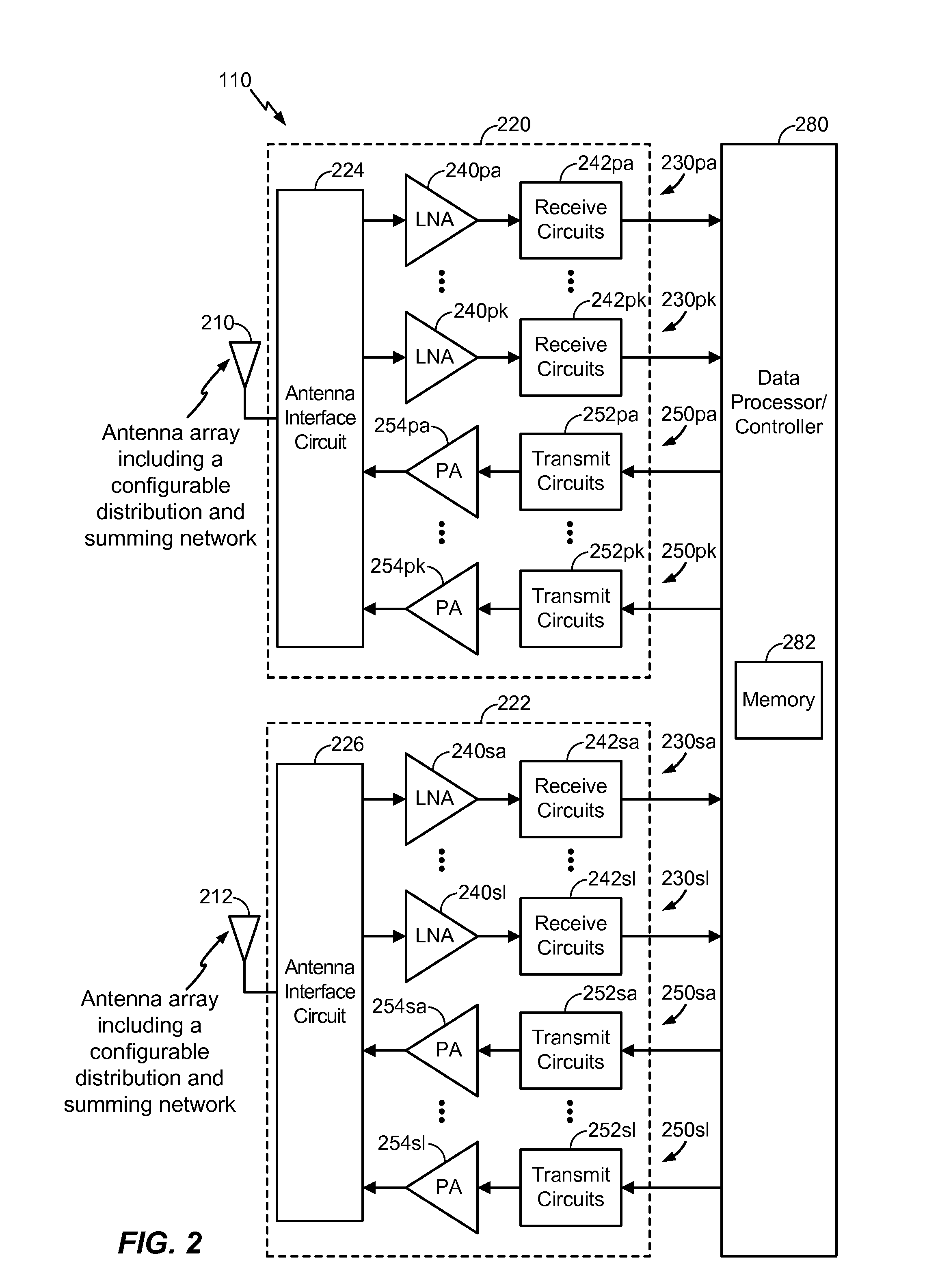

Switchable antenna array

Owner:QUALCOMM INC

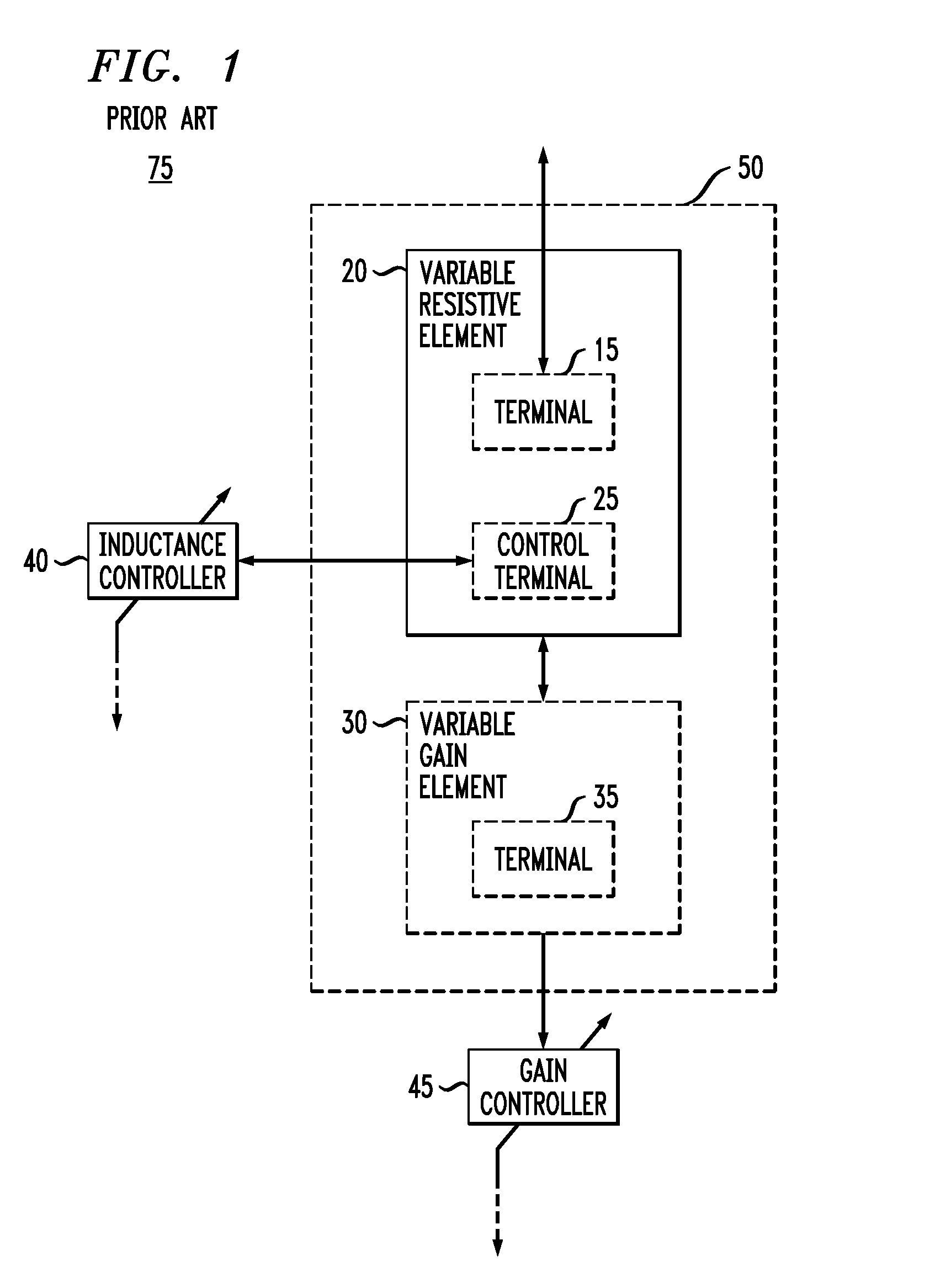

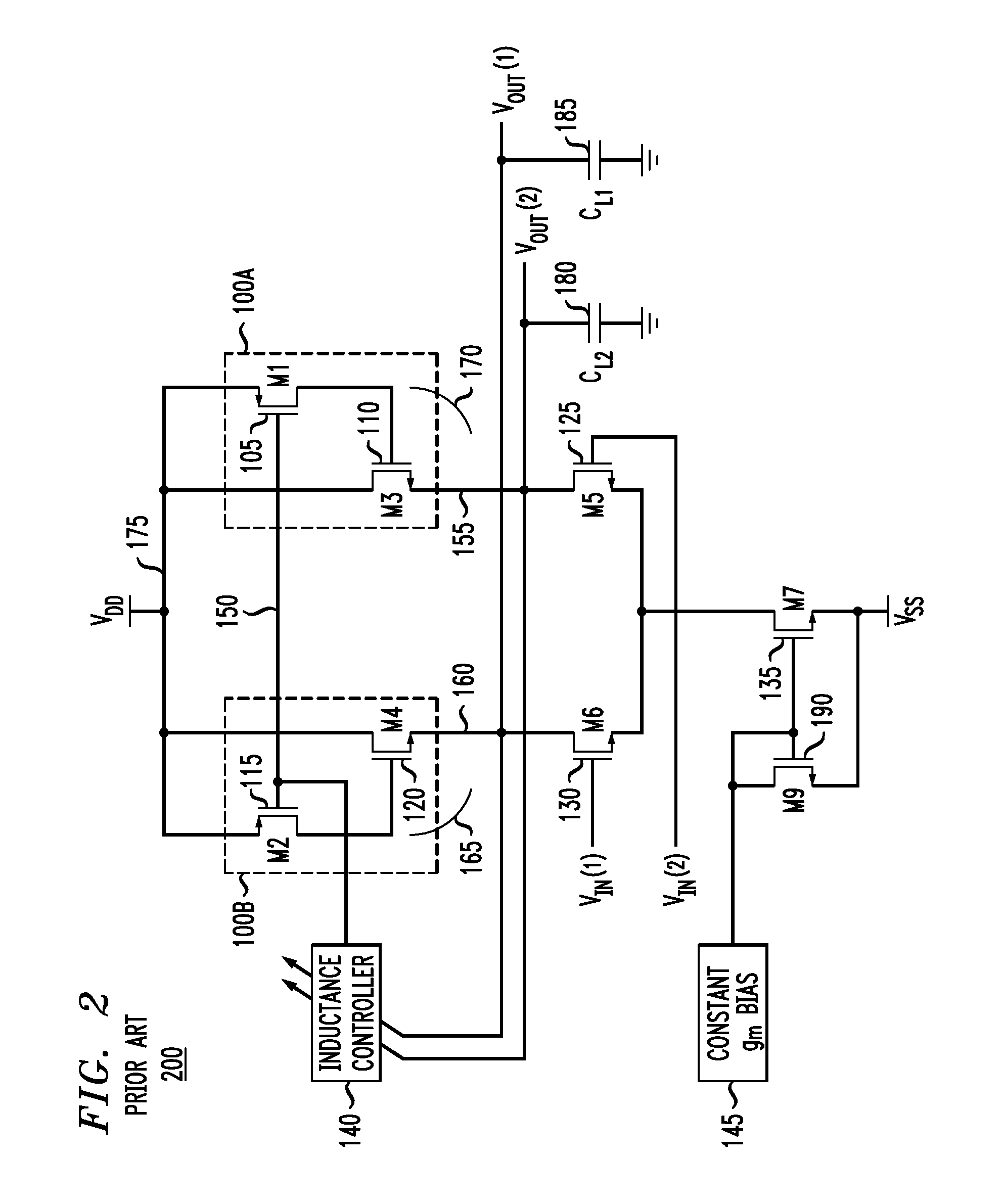

Methods and apparatus for programmable active inductance

ActiveUS20080204171A1Improve linearityMultiple-port active networksNetwork simulating reactancesResistive circuitsInductor

Methods and apparatus are provided for programmable active inductance. The disclosed active inductor devices provide a tunable bandwidth with improved linearity. The disclosed active inductors have a variable frequency response corresponding to a variable inductance of the active inductor. The active inductor comprises a variable resistive circuit having an effective resistance, wherein the variable resistive circuit is comprised of at least one resistor that can be selectively bypassed in the variable resistive circuit to vary the effective resistive. The active inductor has an inductance that can be varied by varying the effective resistance.

Owner:AVAGO TECH INT SALES PTE LTD

Image rejection mixer

InactiveUS6999746B2Reduce power consumptionReduced in noise and distortionMultiple-port networksTelevision system detailsPhase shiftedRelative phase

An image rejection mixer of reduced power dissipation includes a signal distributor supplied with local signals having a phase difference to distribute the local signals, a first and a second signal mixer for mixing the distributed local signals and RF signals having a phase difference and outputting respective IF current signals, a phase shifter for shifting in phase the respective mixed IF current signals so as to provide them with a relative phase difference of 90 degrees, and a signal adder for adding the respective phase shifted intermediate frequency current signals. The shifter shifts the phases of the respective IF current signals outputted from the first and the second signal mixers.

Owner:RENESAS ELECTRONICS CORP

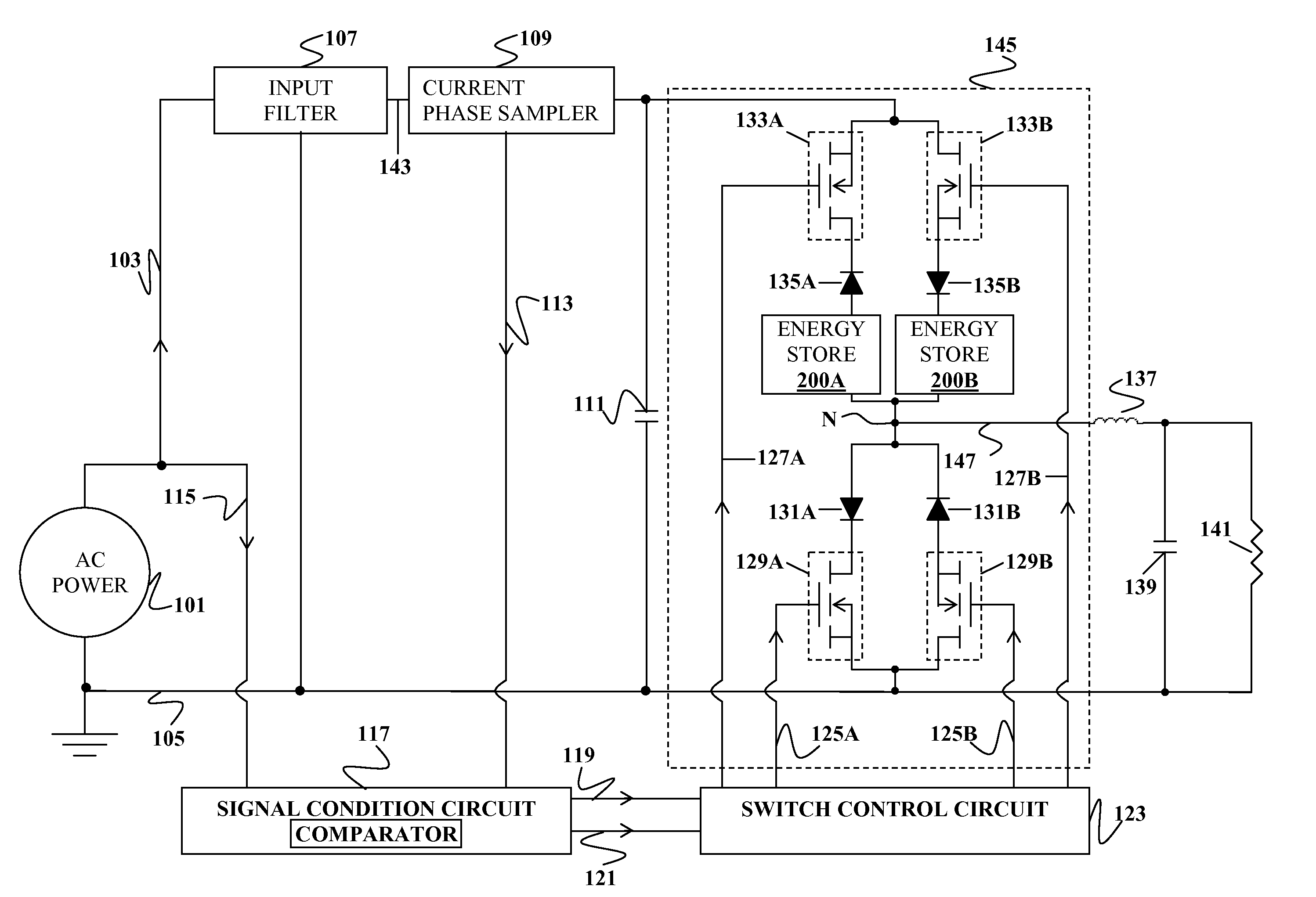

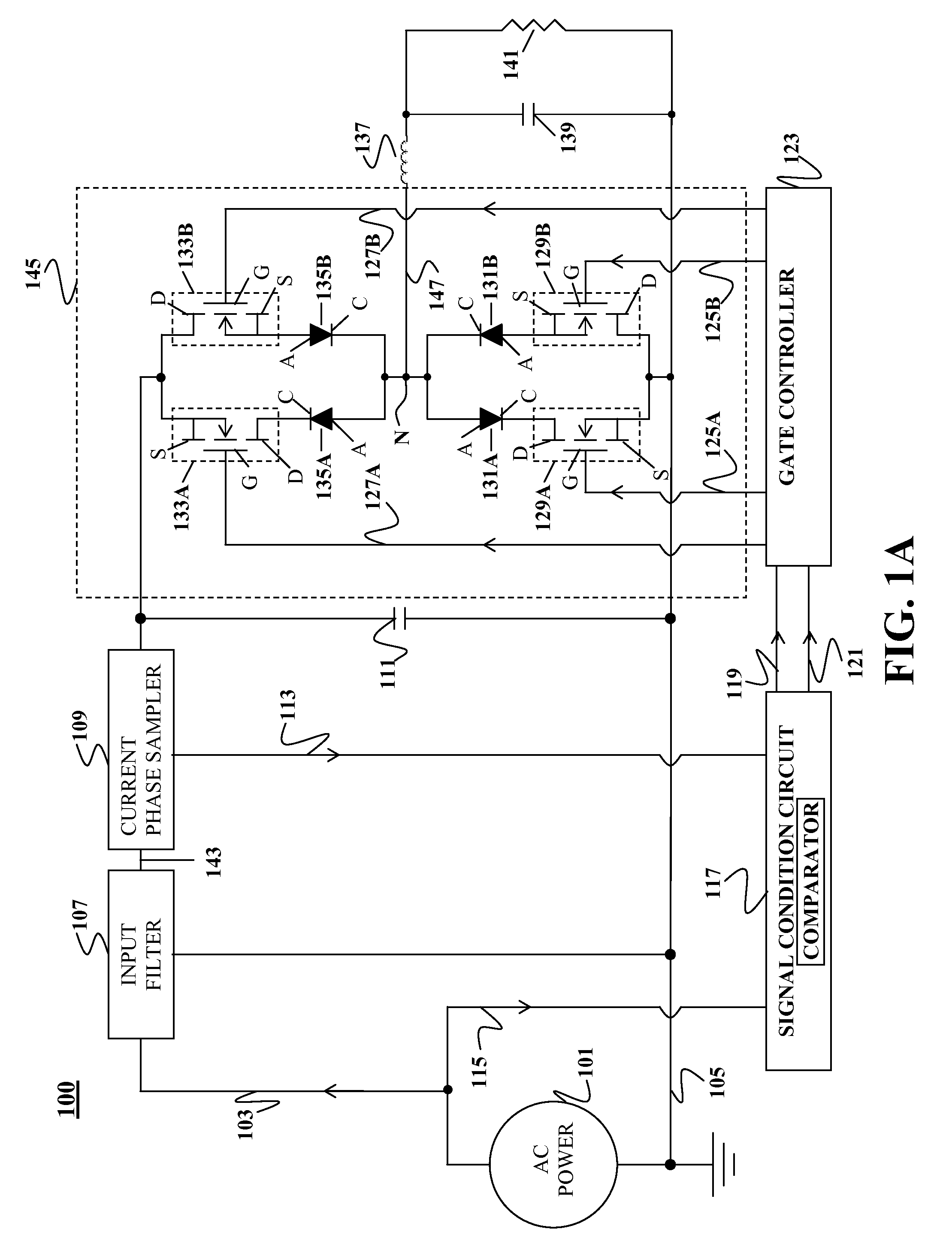

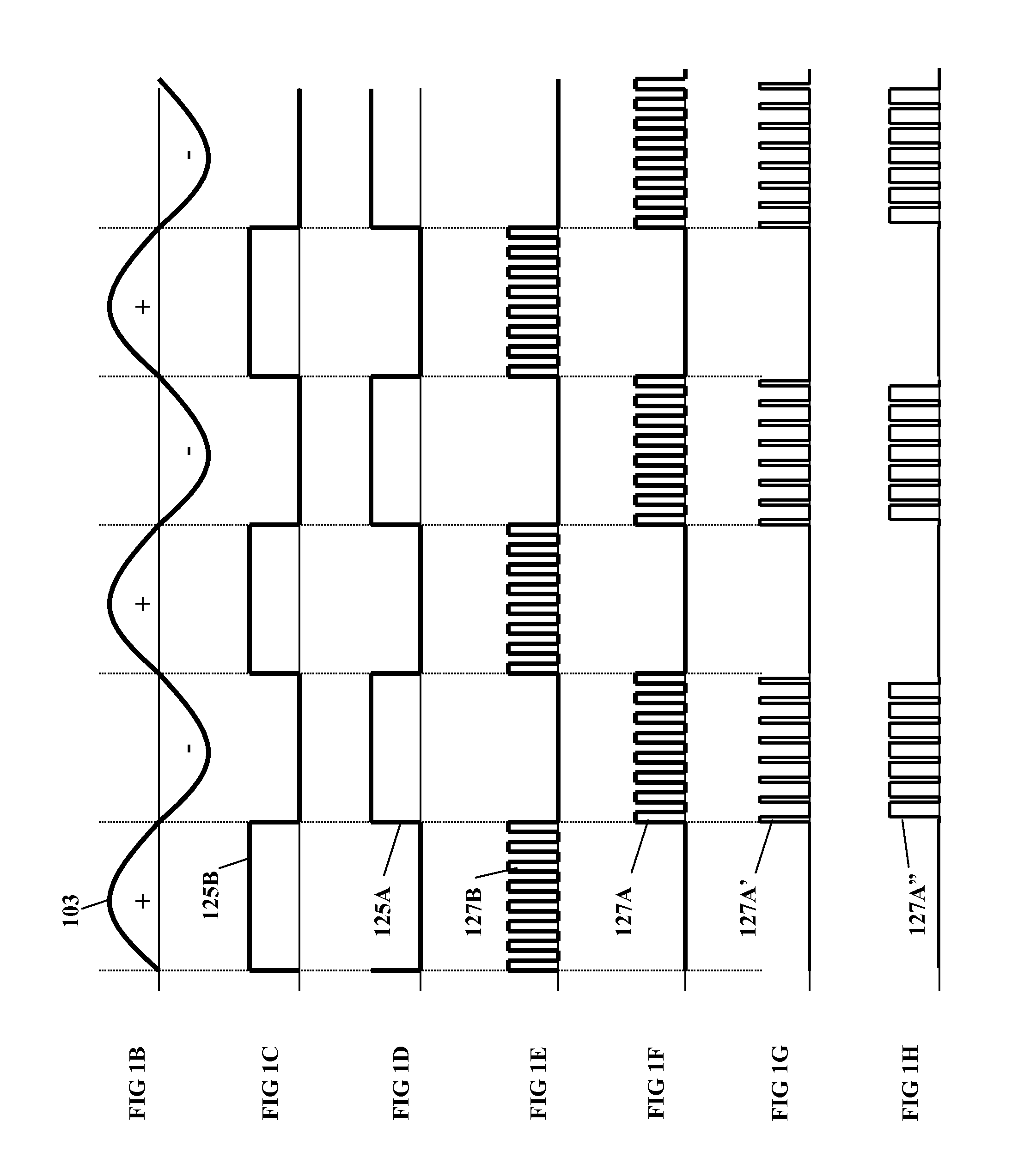

Voltage control and power factor correction in ac induction motors

A voltage control circuit is disclosed. A power factor corrector may utilize the control circuit to provide power factor correction for an AC induction motor. An AC induction motor system may combine the power factor correct with an AC induction motor.

Owner:POWERS JOHN E +1

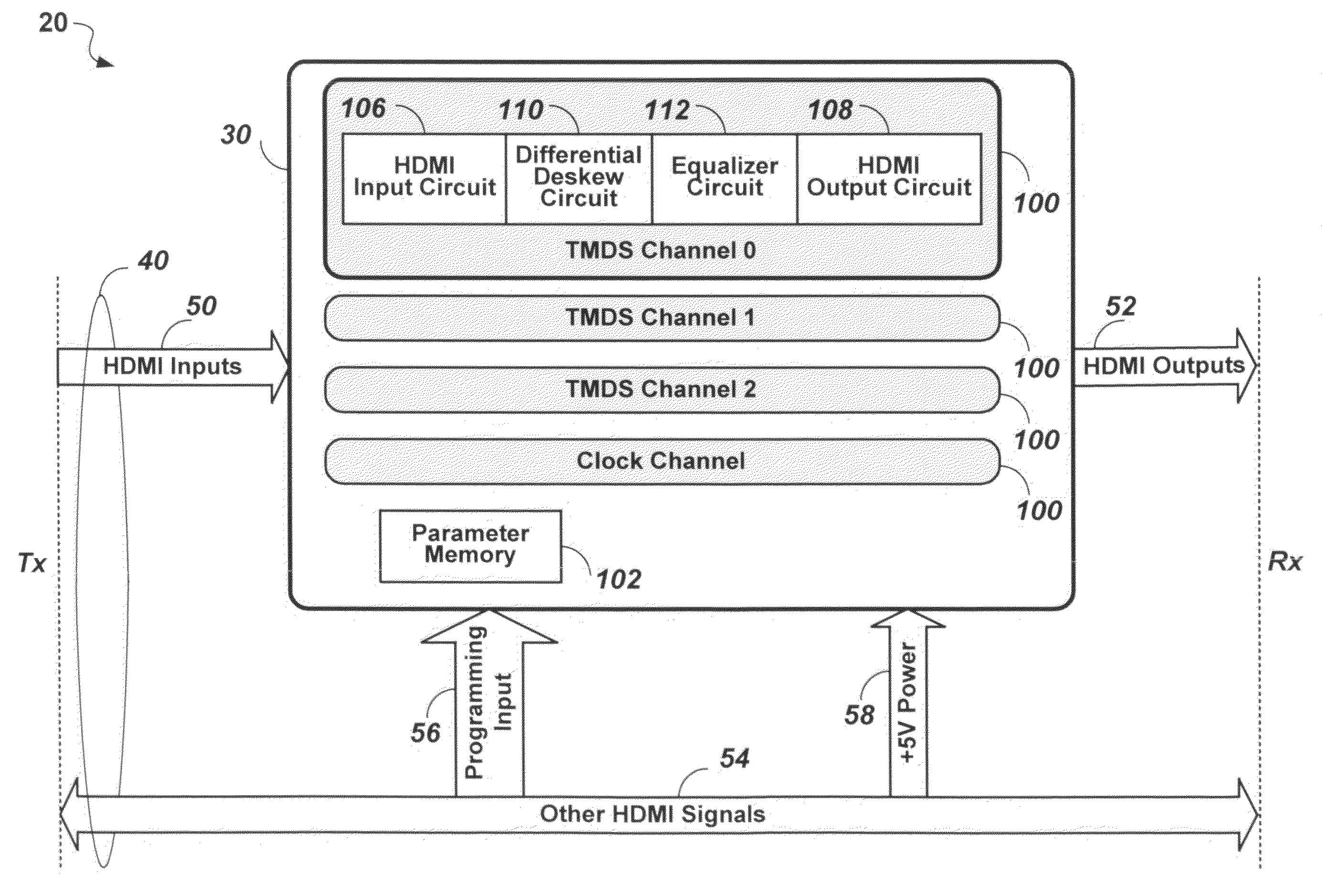

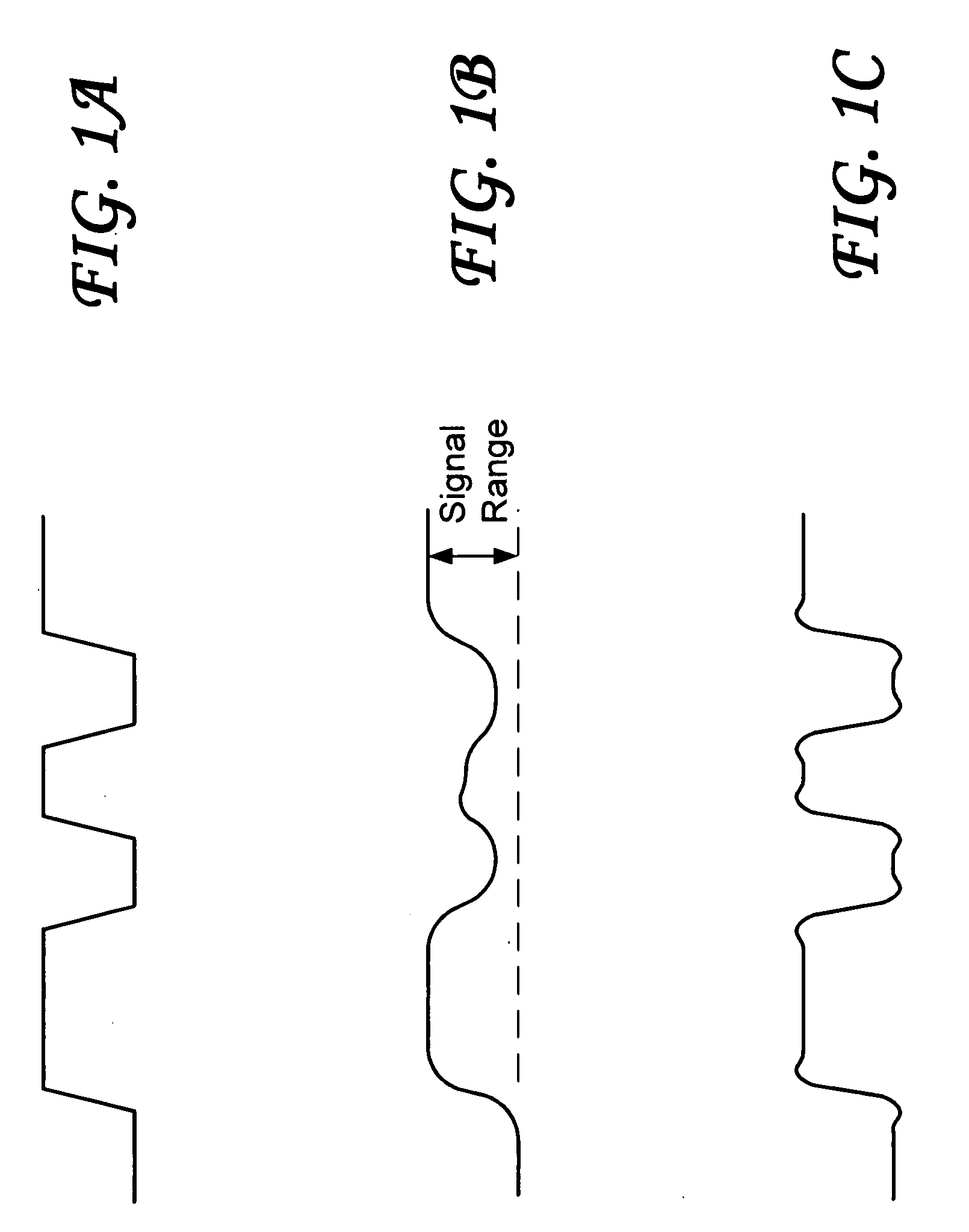

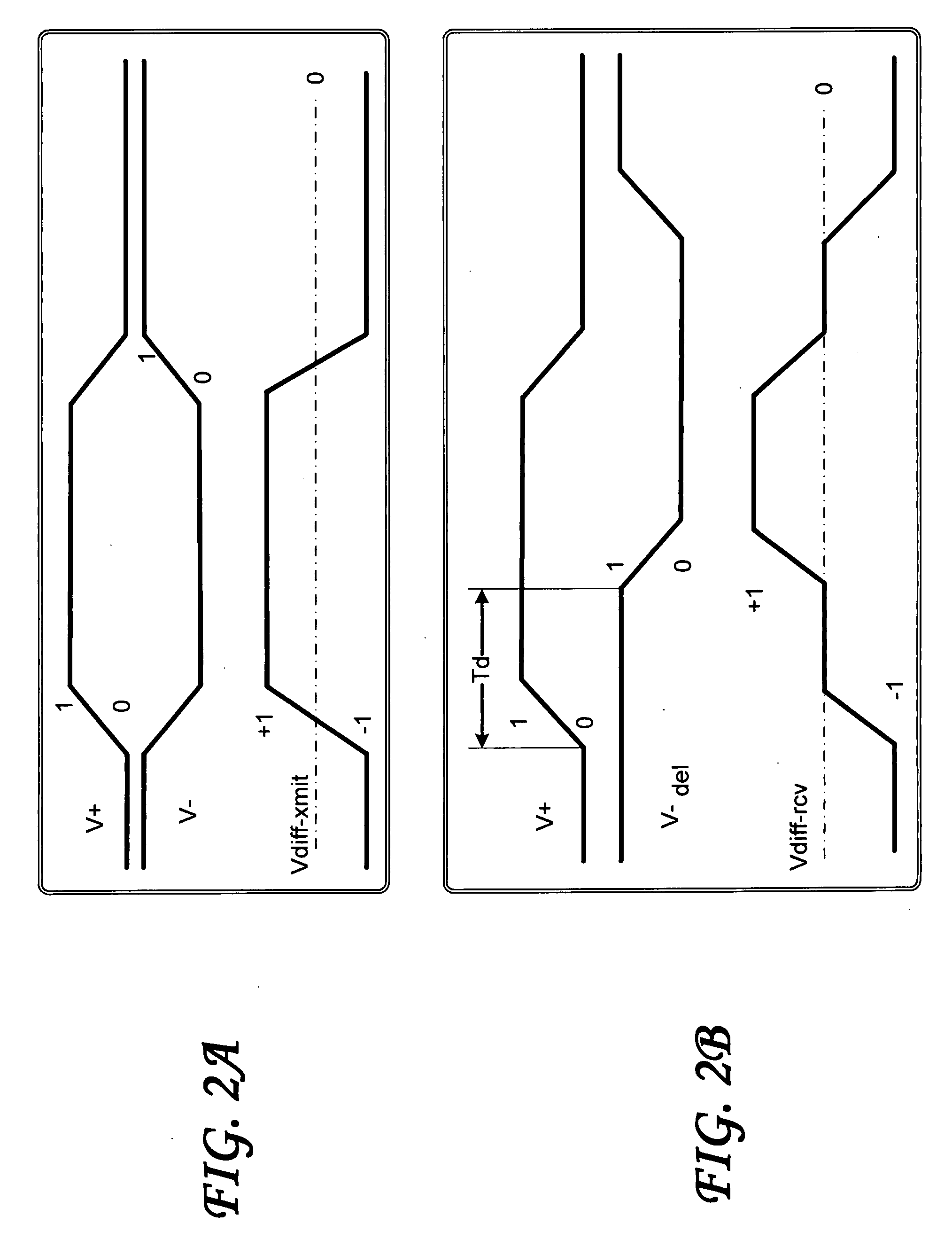

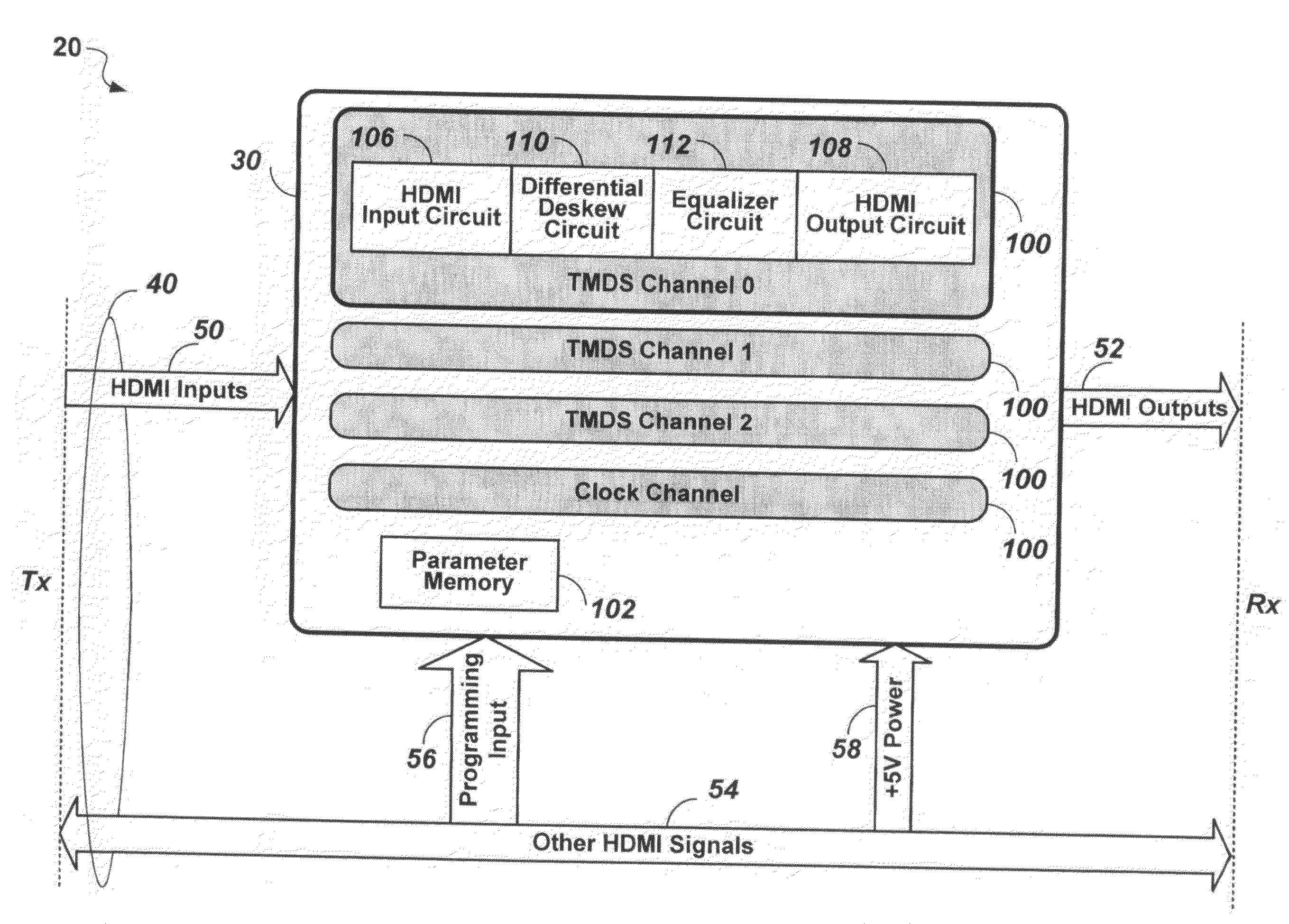

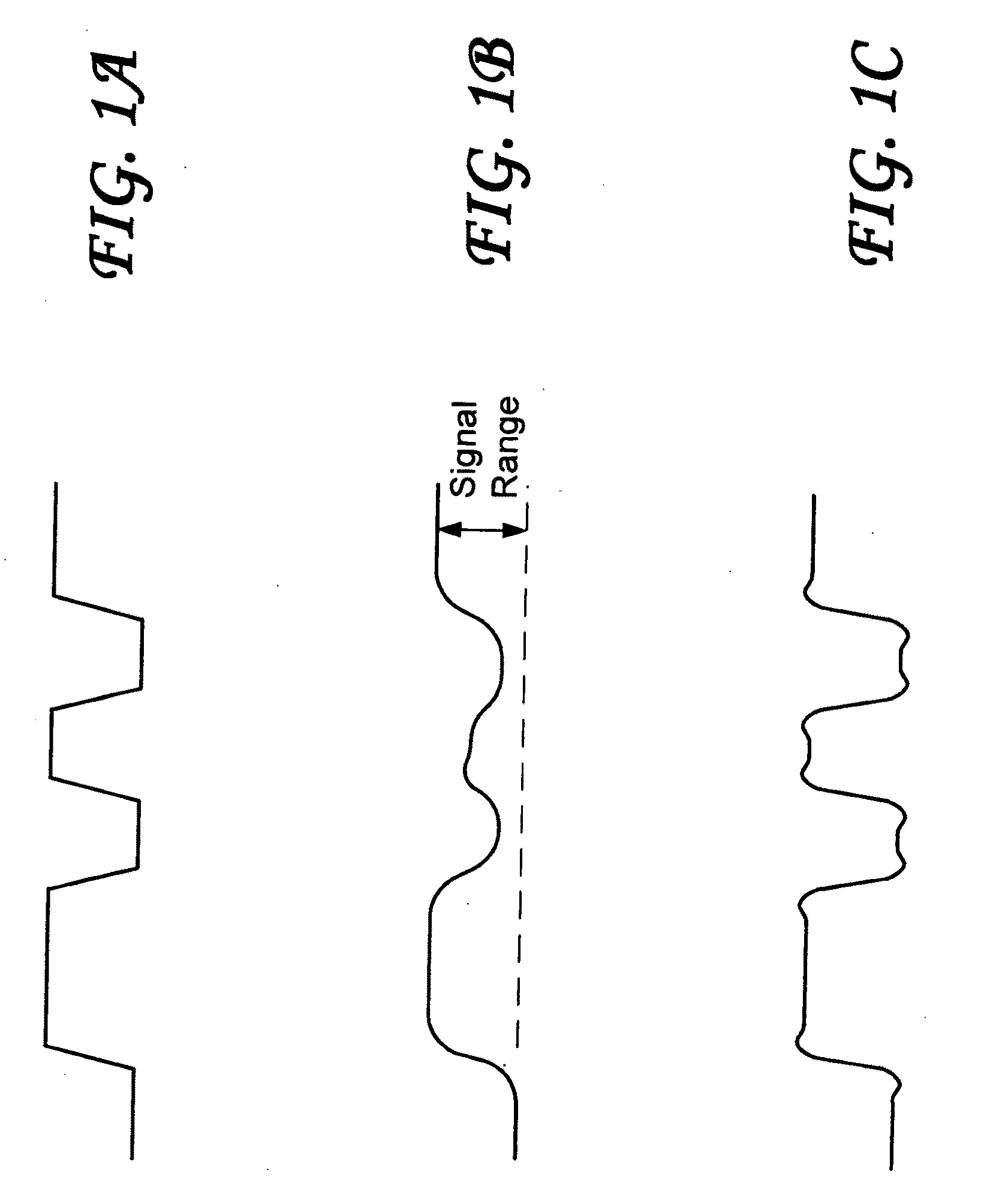

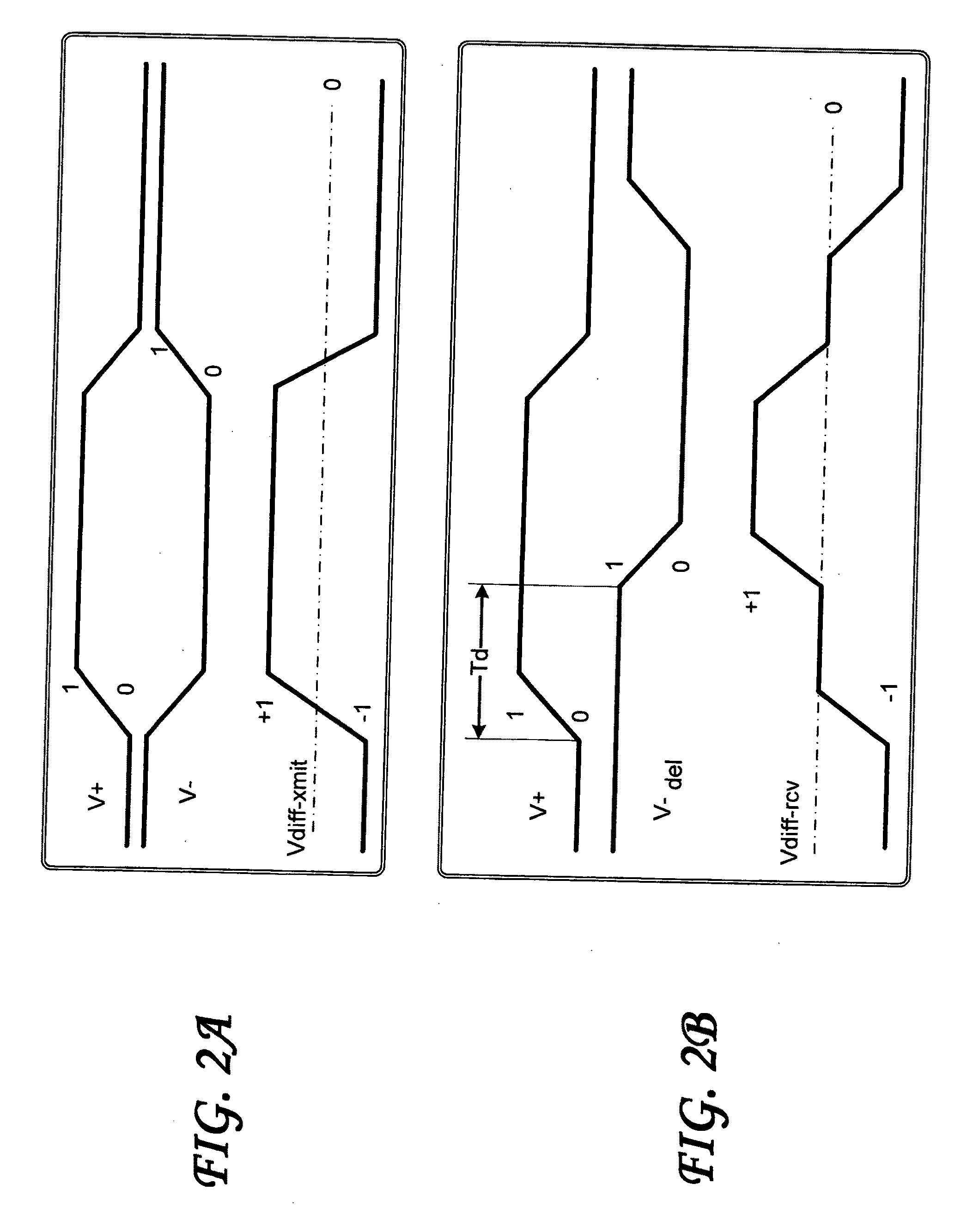

Programmable high-speed cable with printed circuit board and boost device

ActiveUS20080106312A1Quality improvementMultiple-port active networksDigital data processing detailsDifferential signalingEngineering

An HDMI cable carries high speed encoded data which are transmitted differentially over data channels, along with a clock. High-frequency loss and differential skew within a differential signal may be compensated by analog circuits embedded in the cable. These embedded circuits are tuned at production for best performance by observing the quality of the recovered analog signal. The embedded circuits are powered by a combination of power sources, both carried within the cable, and harvested from the high-speed signals themselves.

Owner:REDMERE TECH

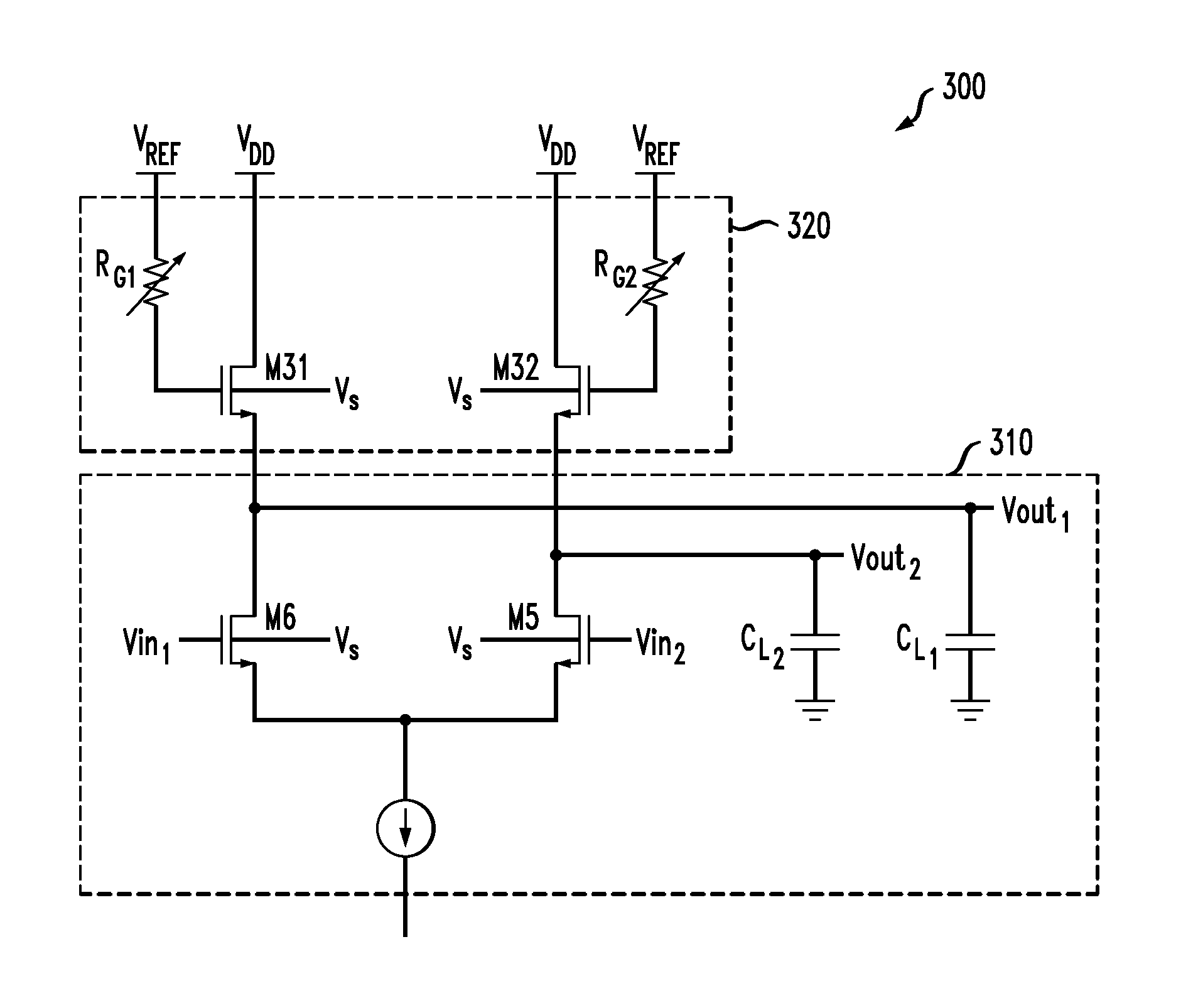

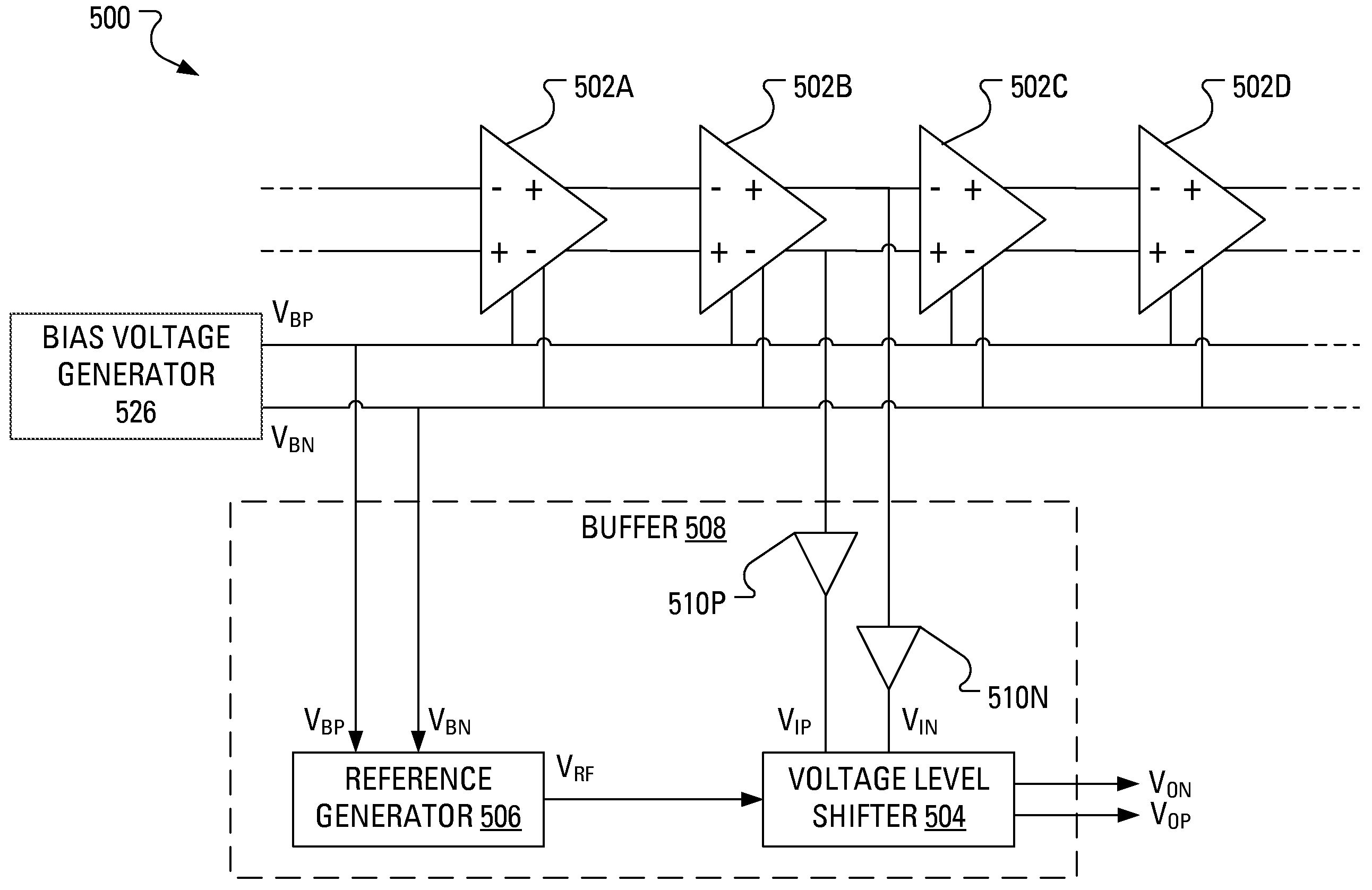

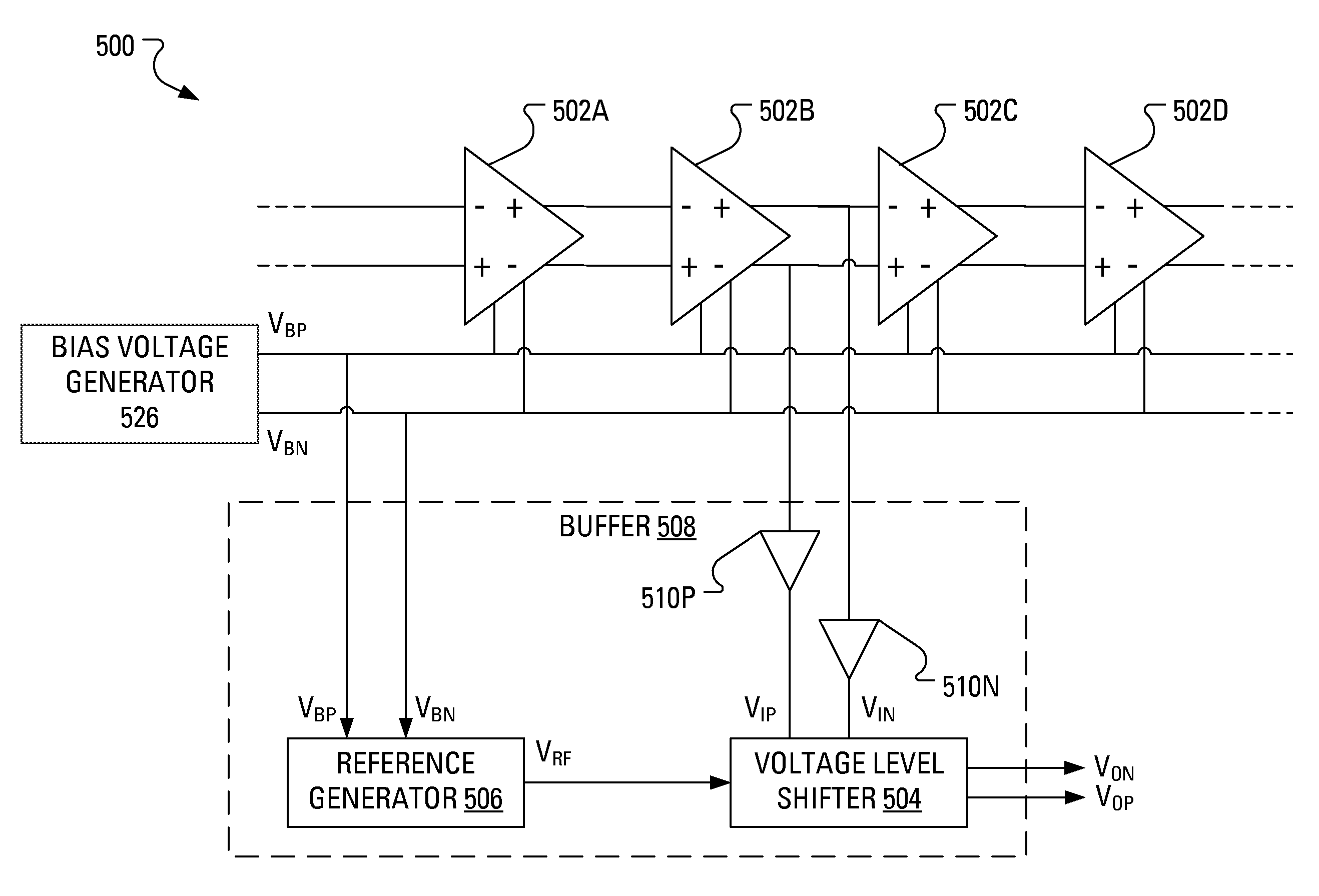

Voltage level shifter and buffer using same

ActiveUS20080265970A1Delay minimizationReduce power consumptionMultiple-port active networksPulse automatic controlDc currentVoltage reference

A voltage level shifter with an input transistor pair, a cross-coupled load chain transistor pair and a pair of current sources, effects reduced power consumption through the use of the cross-coupled load chain transistor pair to minimize the DC current component present in known voltage level shifters. In specific embodiments, feedback elements may be used to minimize delays in signal transitions. A reference voltage that corresponds to a current capability of the input transistor pair may be used to regulate the current sources in the load chain. Changes in a swing of the input signal voltage received by the input transistor pair may be reflected in corresponding changes to the reference voltage. The voltage level shifter may be of particular use in a buffer.

Owner:MOSAID TECH

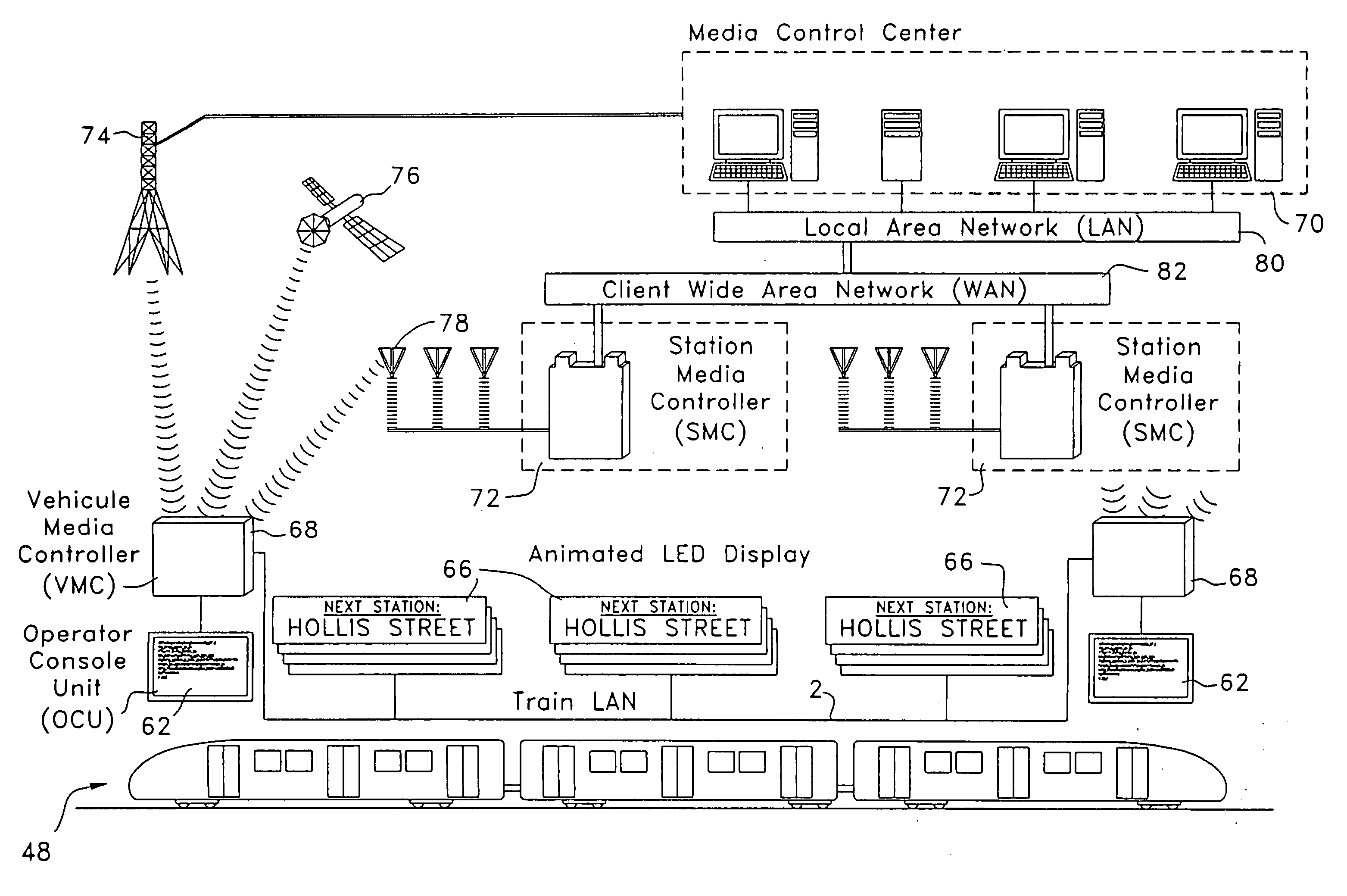

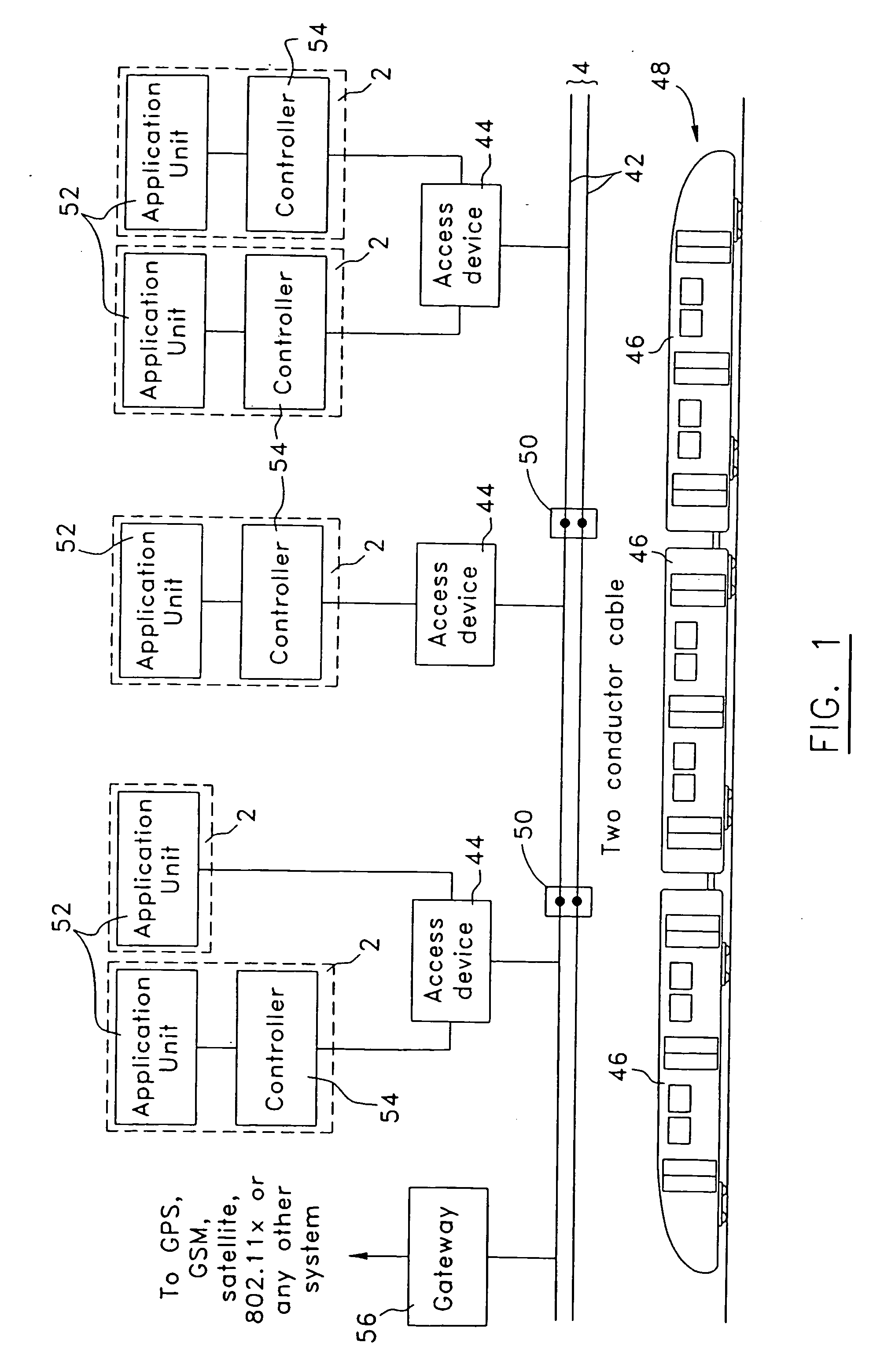

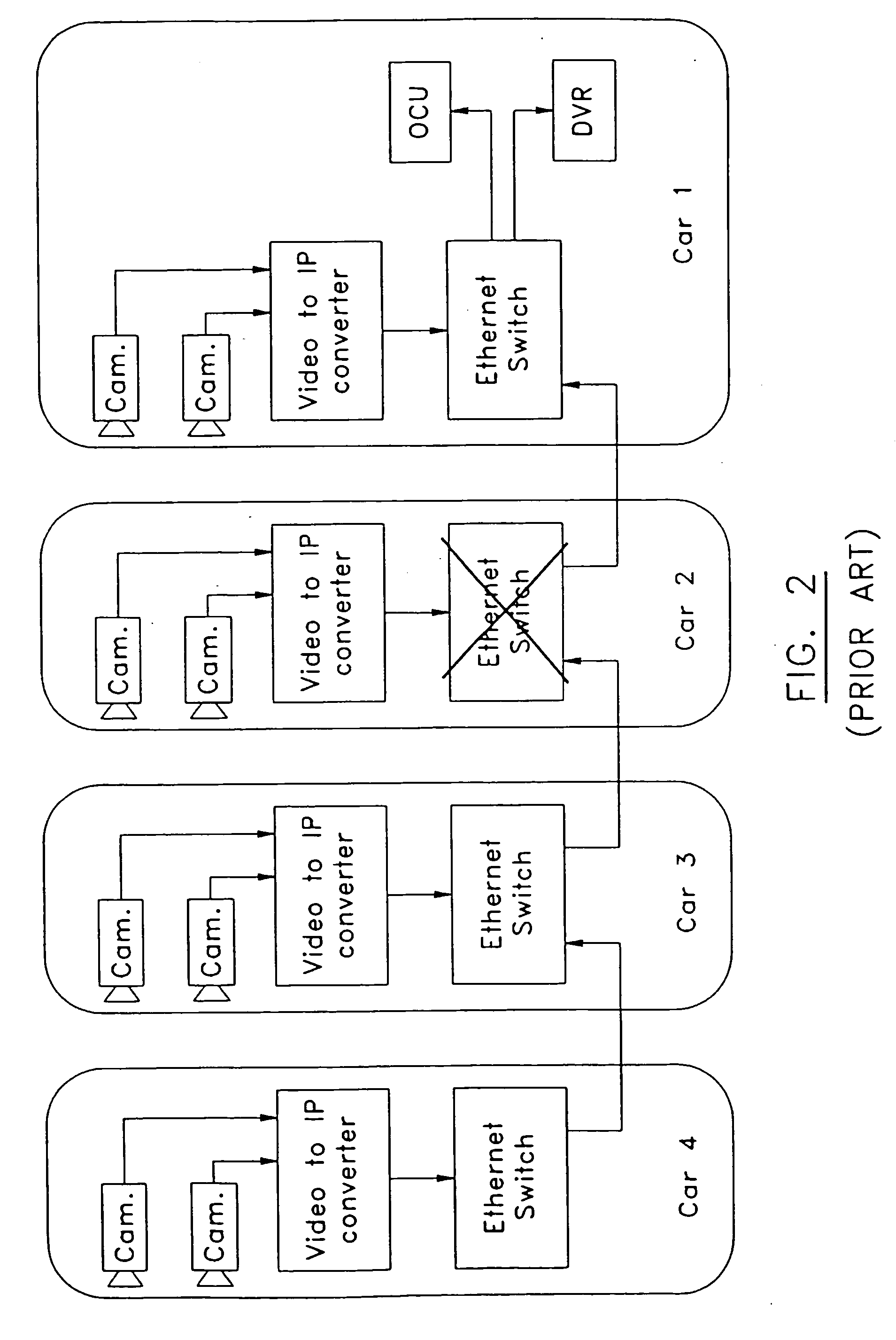

Ruggedized Analog Front-End for a Network Communicative Device in a Railway-Like Environment

InactiveUS20080298384A1Improve protectionImprove reliabilityMultiple-port active networksModulated-carrier systemsEnergy transferAudio power amplifier

A ruggedized analog front-end for interconnecting a network communicative device to a two-conductor based network operable in a train-like or other harsh environment. The front-end has a coupling circuit having first and second coupling channels providing isolation, impedance matching and energy transfer between a common mode filter circuit connectable to the two-conductor based network, and an amplifier and an attenuator respectively connectable to output and input of the network communicative device. The front-end has a power supply circuit for operative power supply of electronic components of the analog front-end.

Owner:ALSTOM CANADA

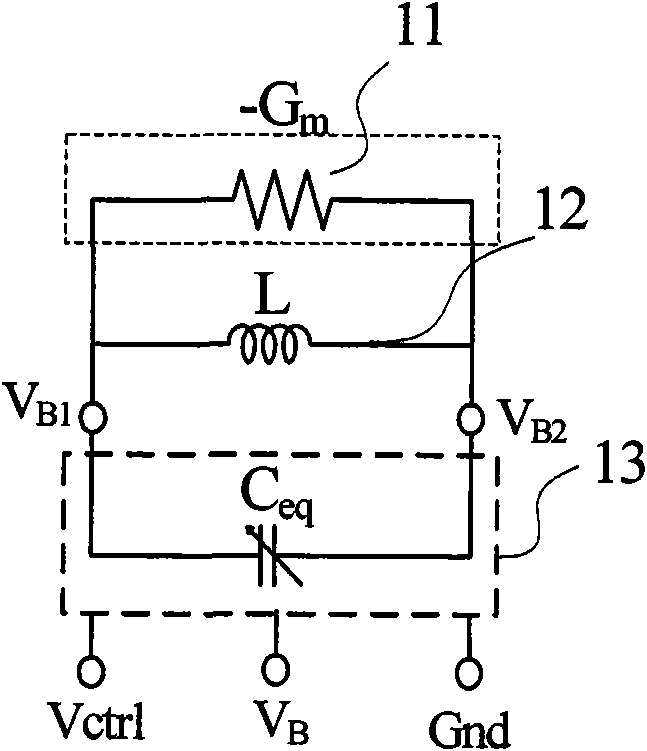

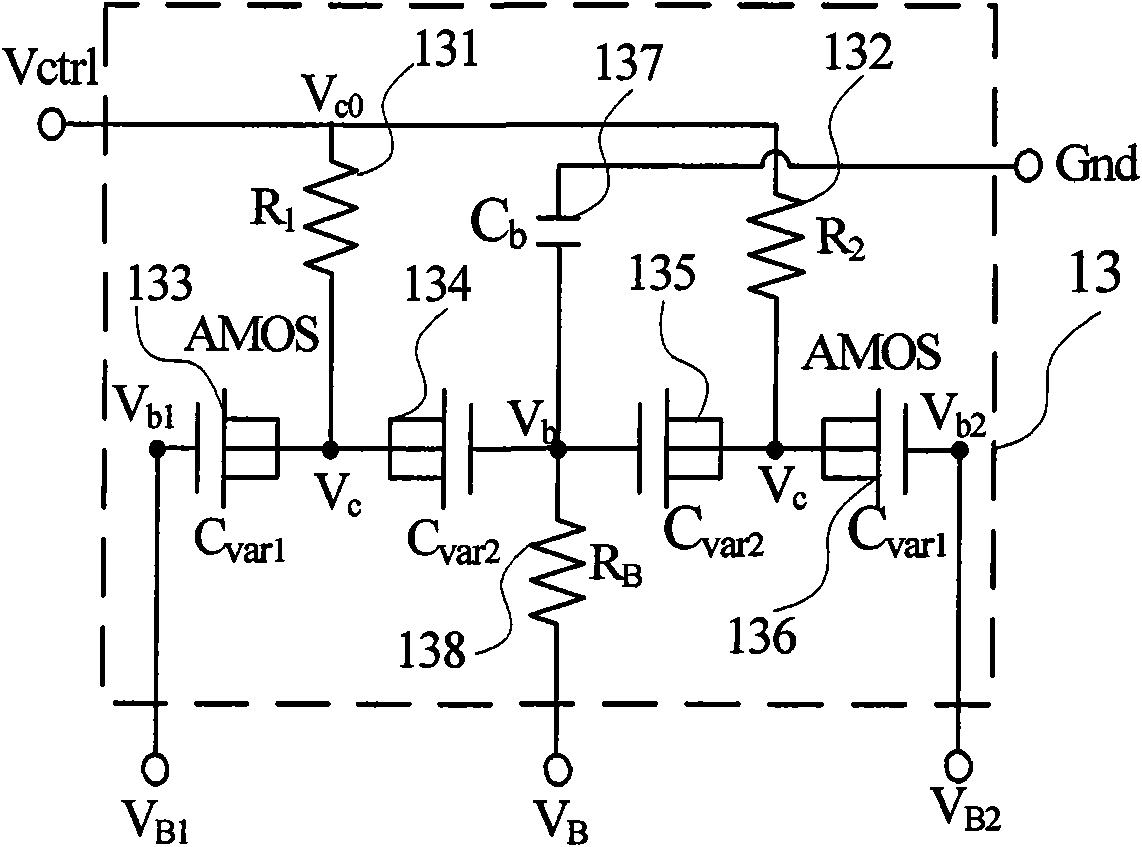

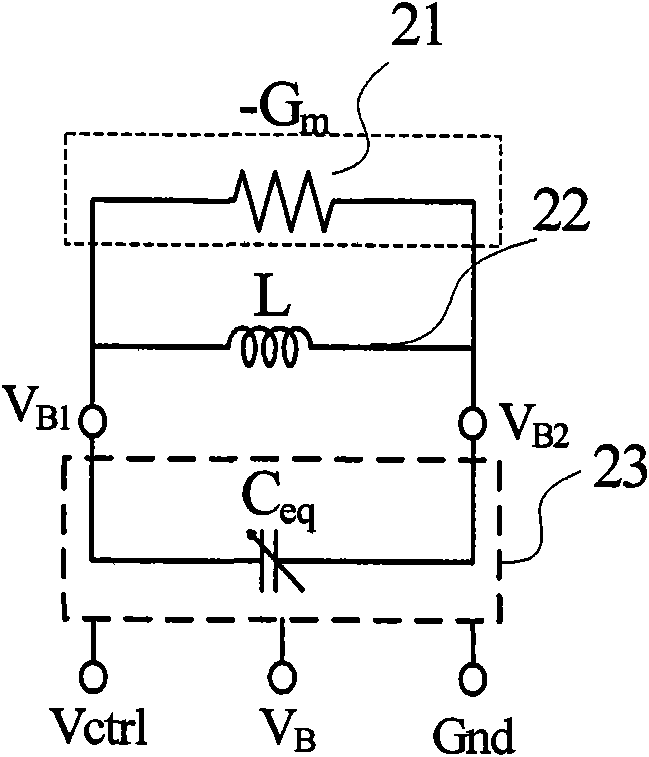

VCO tuning curve compensation method and module thereof

ActiveCN101944880ALarge tuning rangeImprove stabilityMultiple-port active networksOscillations generatorsCapacitanceLow-pass filter

The invention provides a VCO tuning curve compensation method. In the method, a negative resistance amplifier and an inductor are connected with both ends of a variable capacitor to form a parallel-connection structure, wherein the variable capacitor structure is a five-end AMOS capacitance network, and one end is a tuning curve compensation control end of the AMOS capacitance network, which changes the equivalent capacitance of the AMOS capacitance network by adjusting the DC voltage of a control end to obtain an approximate linearized change curve with respect to VCO output frequency and VCO control voltage, thereby realizing the VCO tuning curve compensation, improving the VCO stability and enabling a VCO circuit module to work in the area having a higher Q value. The invention also provides a VCO circuit module of a differential circuit structure formed by the method. The AMOS capacitance network comprises four AMOS varactors and one RC low-pass filter, wherein the four AMOS varactors are connected in series two by two and are symmetrically arranged, and the specific arrangement mode includes grid electrode series connection and substrate series connection. The VCO module performs voltage control on the AMOS varactors to change the oscillator frequency, and realizes the tuning curve compensation to enable the frequency tuning curve to be approximately linearized by changing the DC voltage of the compensation control end of the tuning curve, thereby realizing a larger frequency tuning range.

Owner:杭州中科微电子有限公司

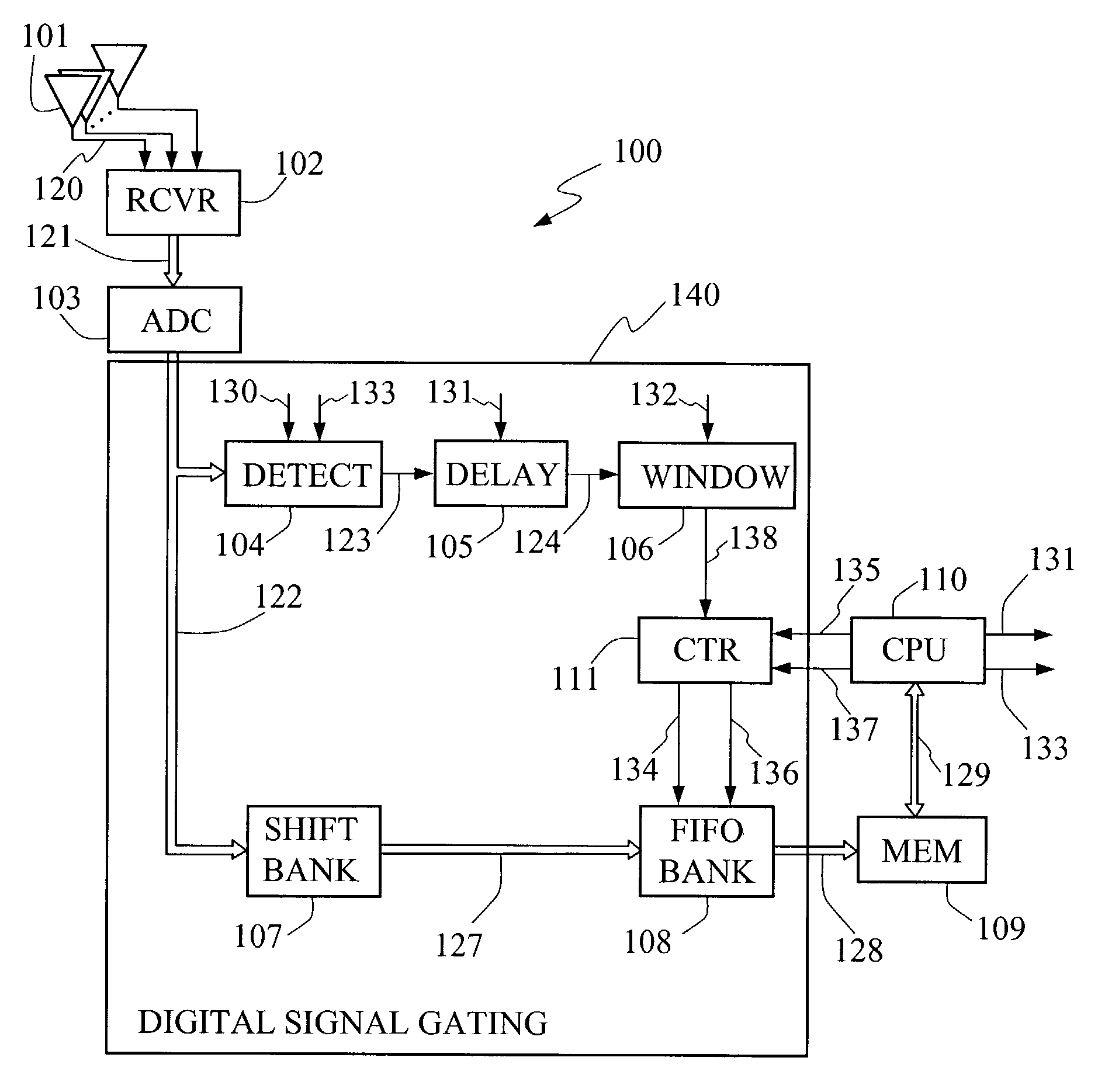

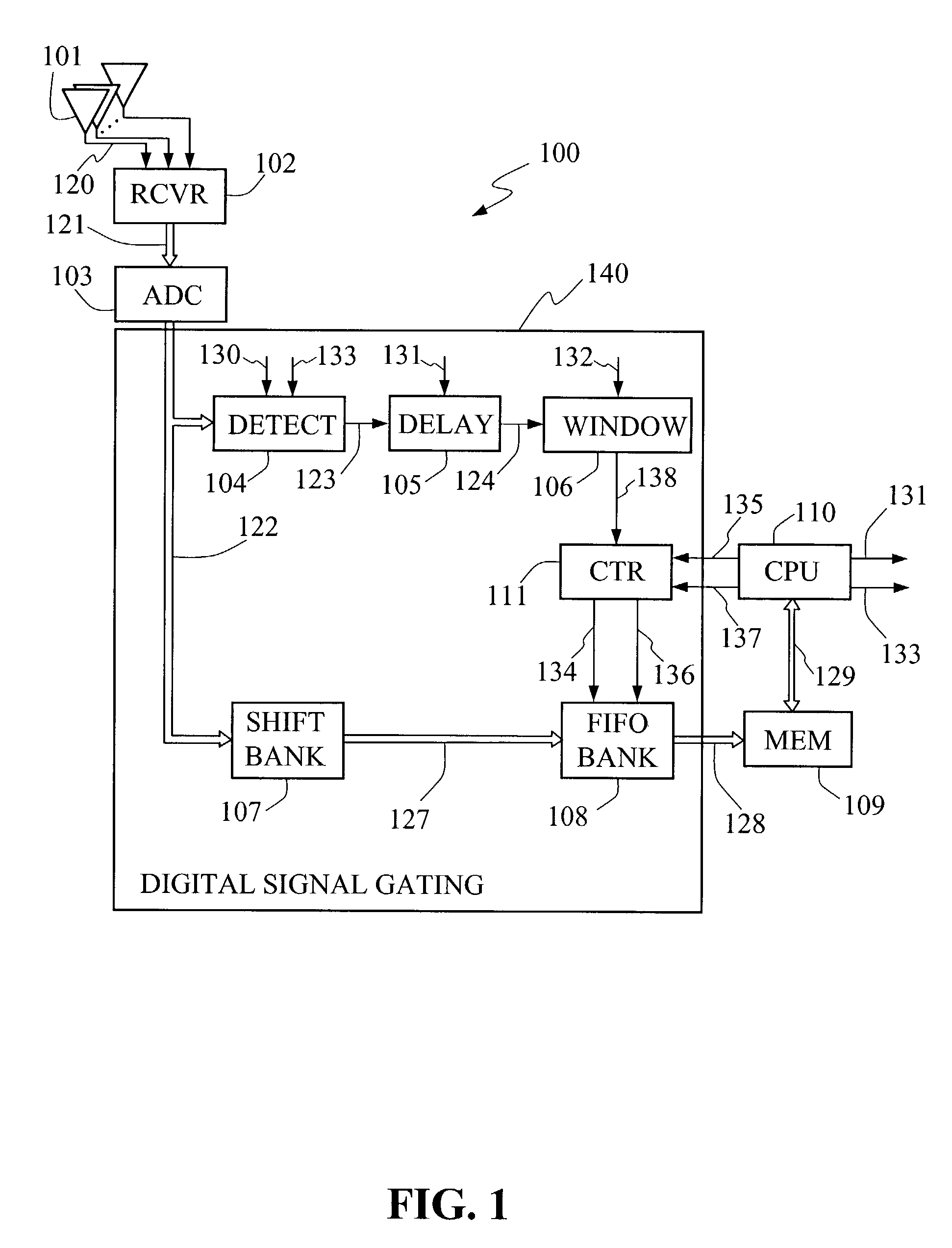

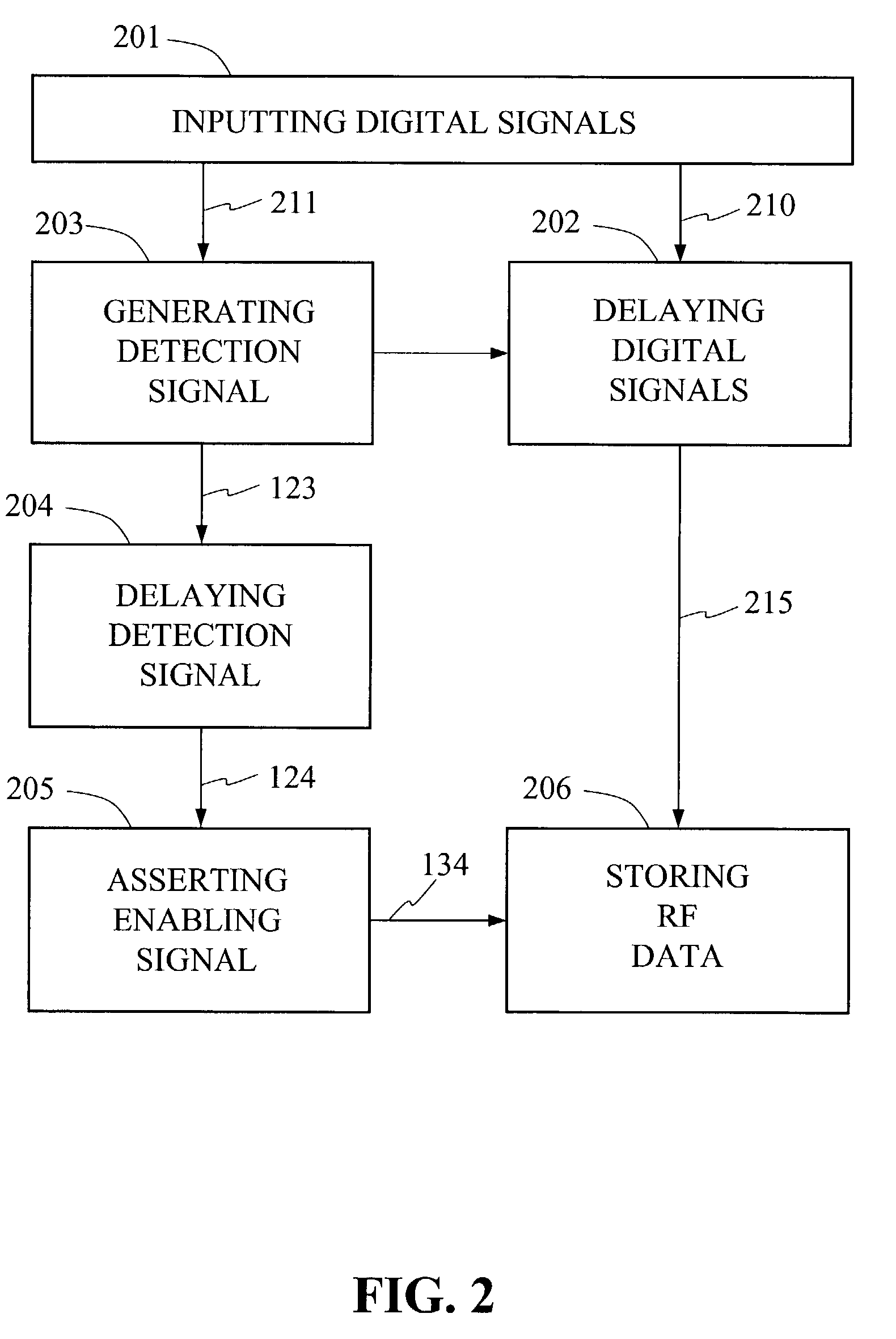

Digital signal gating apparatus and method in a pulse receiver system

ActiveUS7082172B1High noise rejection thresholdAccurate measurementOptical radiation measurementMultiple-port active networksComputer scienceDigital signal

A digital signal gating method and apparatus of a preprocessor in a detection system wherein the detection system includes a central processing unit, a main memory and a receiver, whereby the apparatus and method bifurcate received digital signals, delays them along a first path while subjecting the digital signals along a second path to detection, delay, and thresholding and thereby generates a gating signal from the second path so that digital signals of the first path, including pre-threshold amplitudes, may be recorded.

Owner:NORTHROP GRUMMAN SYST CORP

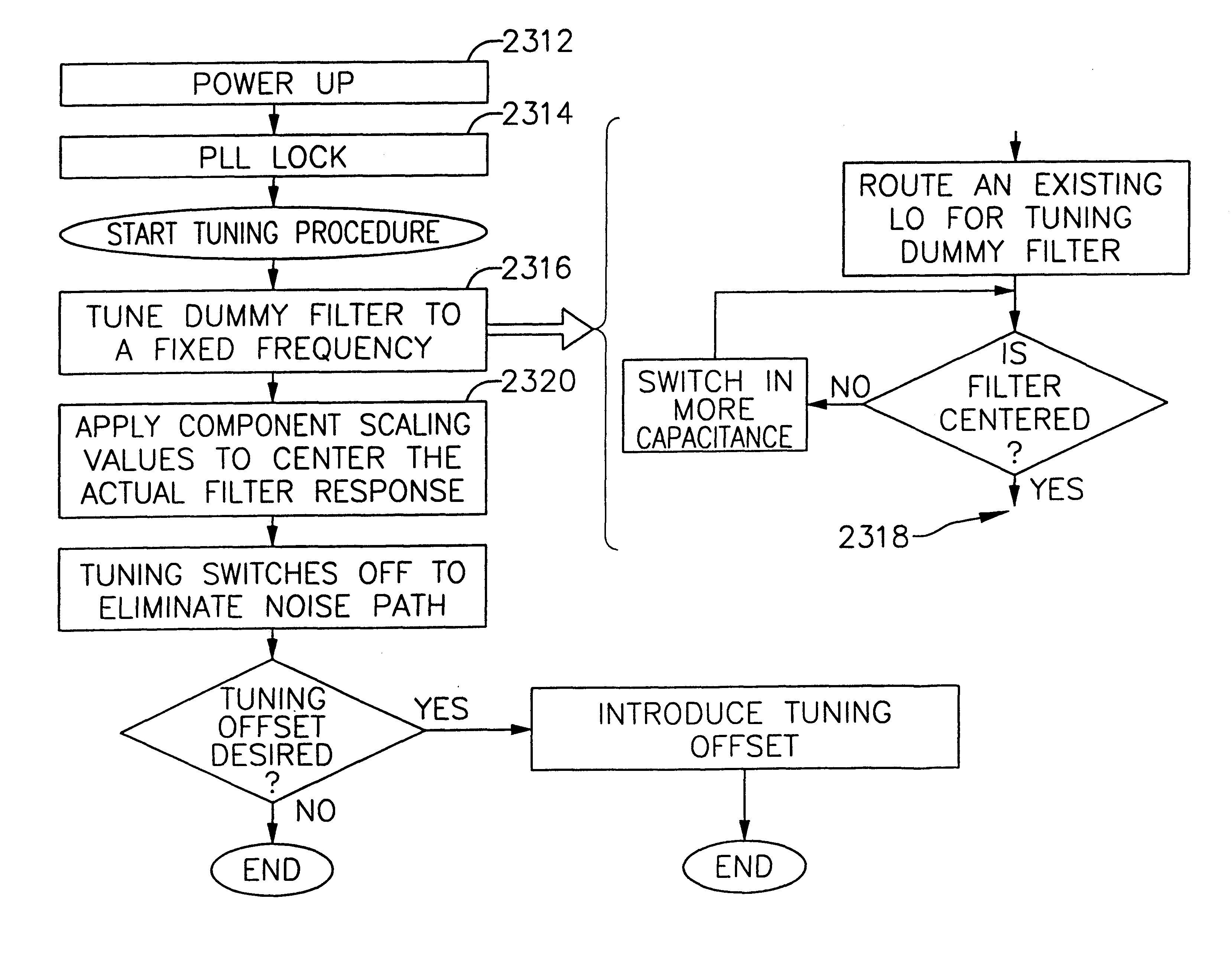

System and method for on-chip filter tuning

InactiveUS6865381B2Low selectivityMultiple-port active networksSolid-state devicesCapacitanceFilter tuning

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH INT SALES PTE LTD

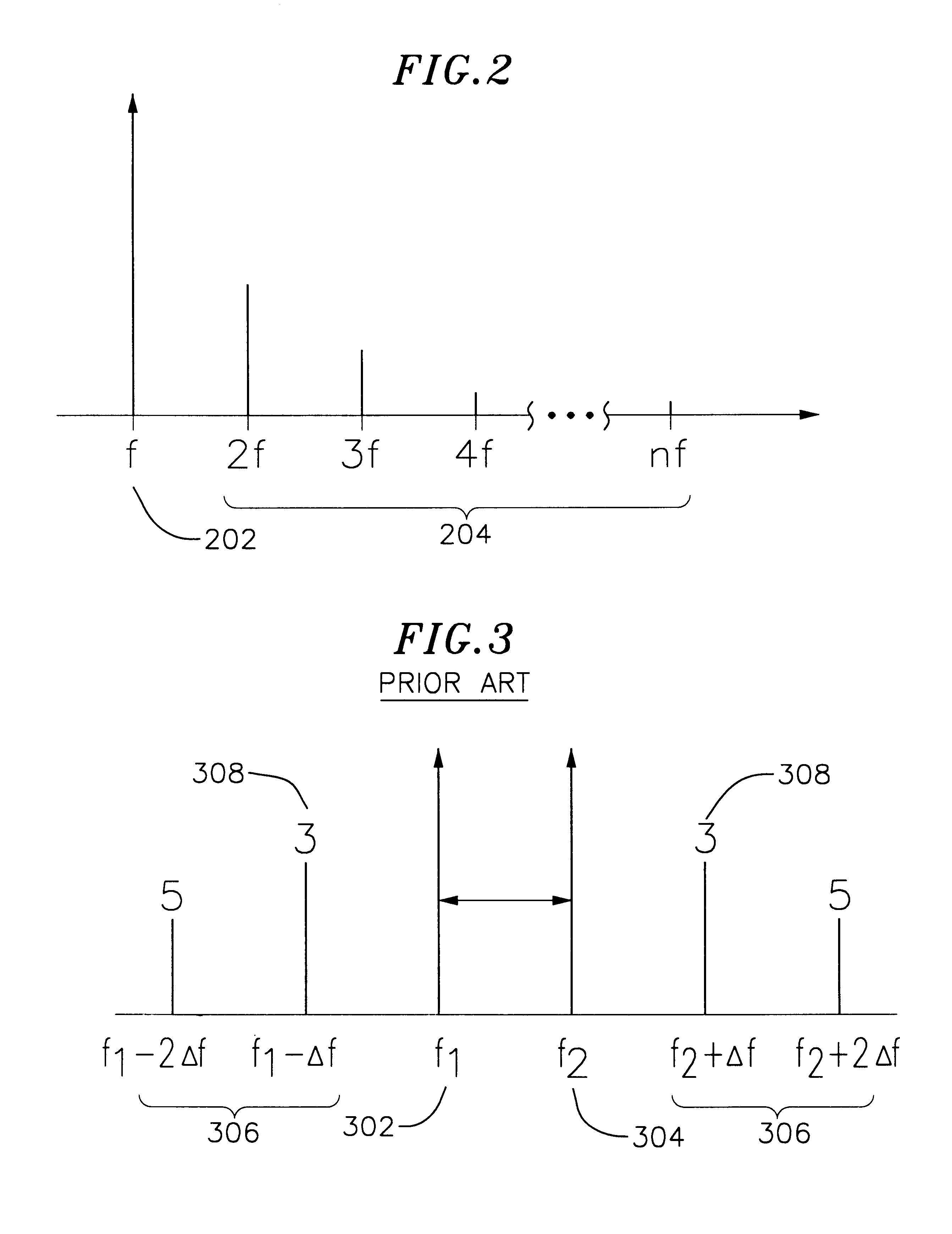

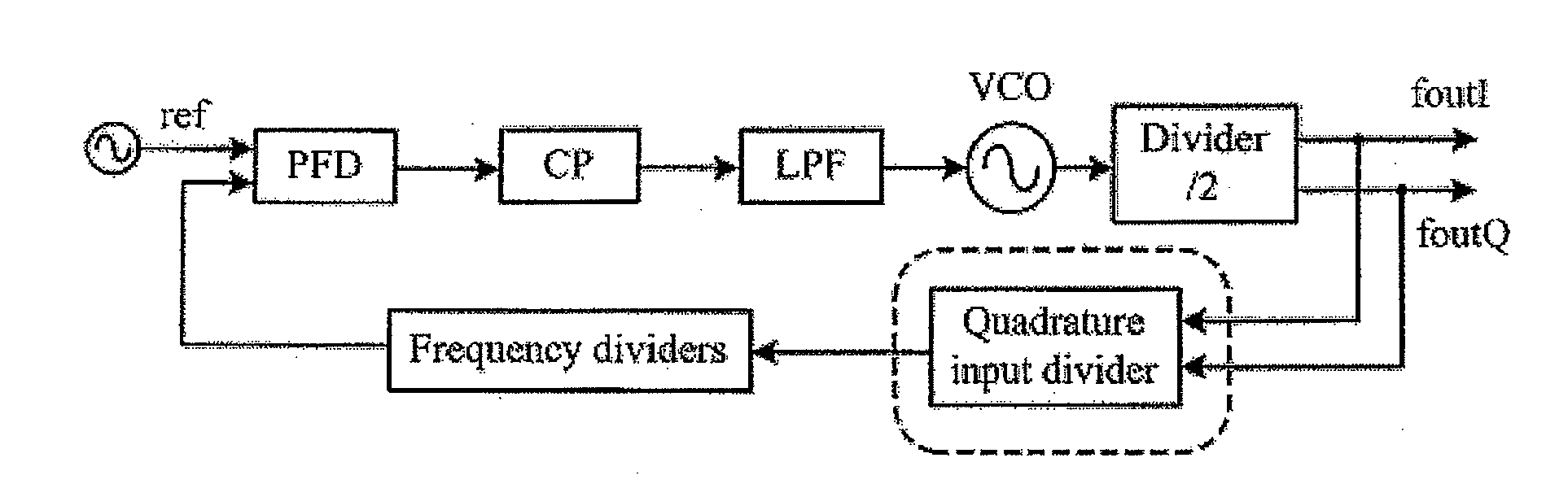

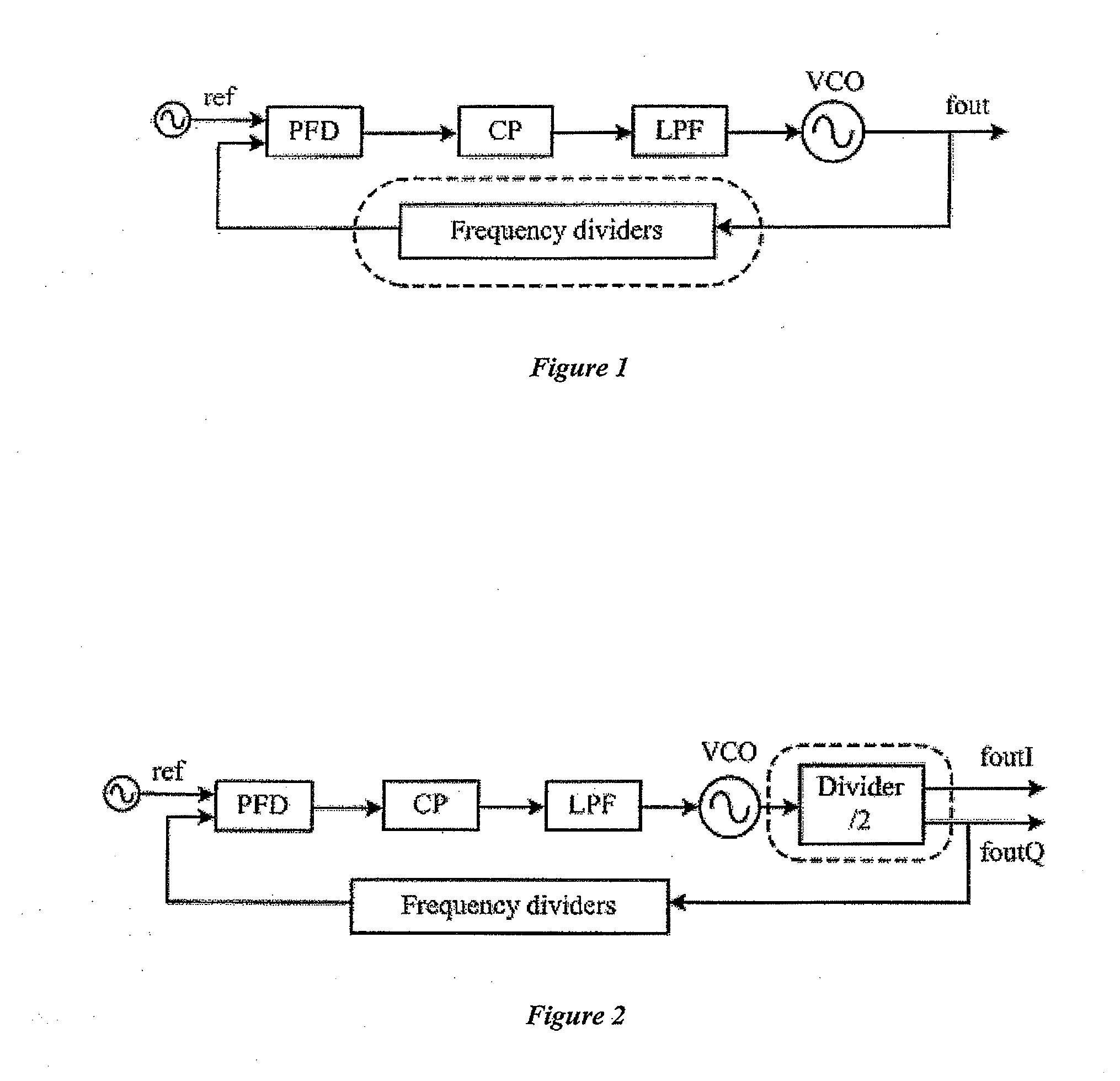

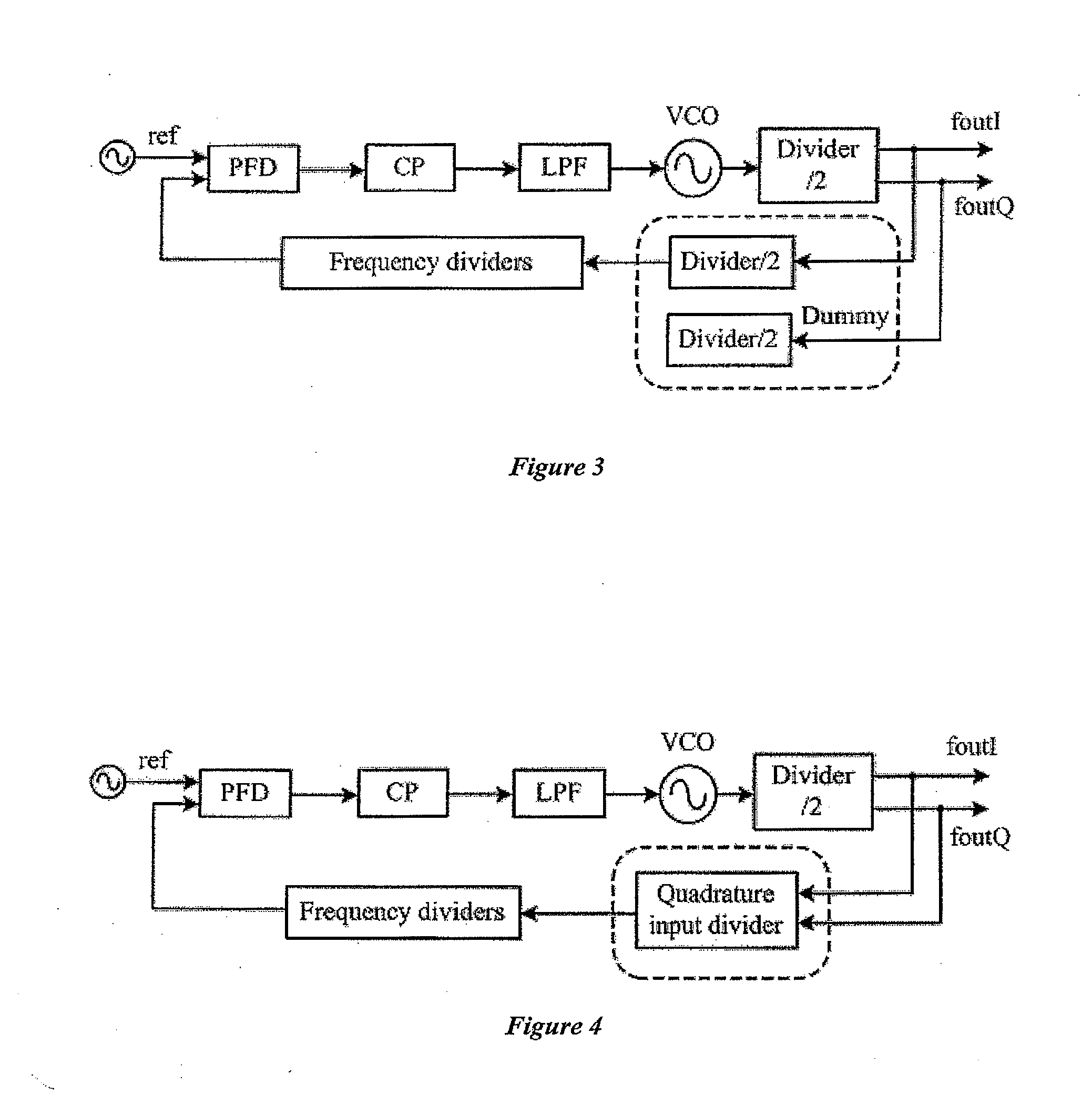

Quadrature-input, quadrature-output, divider and phase locked loop, frequency synthesiser or single side band mixer

ActiveUS20090068975A1Accurate operationMultiple-port active networksModulated-carrier systemsHarmonicFrequency mixer

The present invention relates to a quadrature divider which may be used in a phase locked loop or frequency synthesiser or with a single side band mixer. According to a preferred embodiment the divider takes a quadrature input and has a quadrature output. The divider has four analog mixers 1, 2, 3 and 4. The first two mixers 1, 2 take the in-phase quadrature input, while the second mixers 3, 4 take the quadrature-phase quadrature input. The outputs and feedback loops of the mixers are properly arranged such that the in-phase and quadrature-phase outputs of the divider have a determinisitic phase sequence relationship based on the phase sequence relationship of the corresponding quadrature inputs. Third order harmonics may be minimised or reduced by addition or subtraction of the mixer outputs. As the divider is able to take a quadrature input, there is no need for a dummy divider in the phase locked loop, thus saving space and power.

Owner:THE HONG KONG UNIV OF SCI & TECH

PAM-4 data slicer having symmetrical offset

InactiveUS20050008099A1Multiple-port active networksModulated-carrier systemsComparators circuitsEngineering

A PAM-4 data slicer includes first, second, and third comparators which provide first, second, and third thresholds, respectively. Each of the comparators has an offset. The first and third comparators have an offset generating arrangement at their outputs to provide the first and third comparator circuits with symmetrical offsets.

Owner:CALLAHAN CELLULAR L L C

Voltage level shifter and buffer using same

ActiveUS7679418B2Delay minimizationReduce power consumptionMultiple-port active networksPulse automatic controlDc currentEngineering

Owner:MOSAID TECH

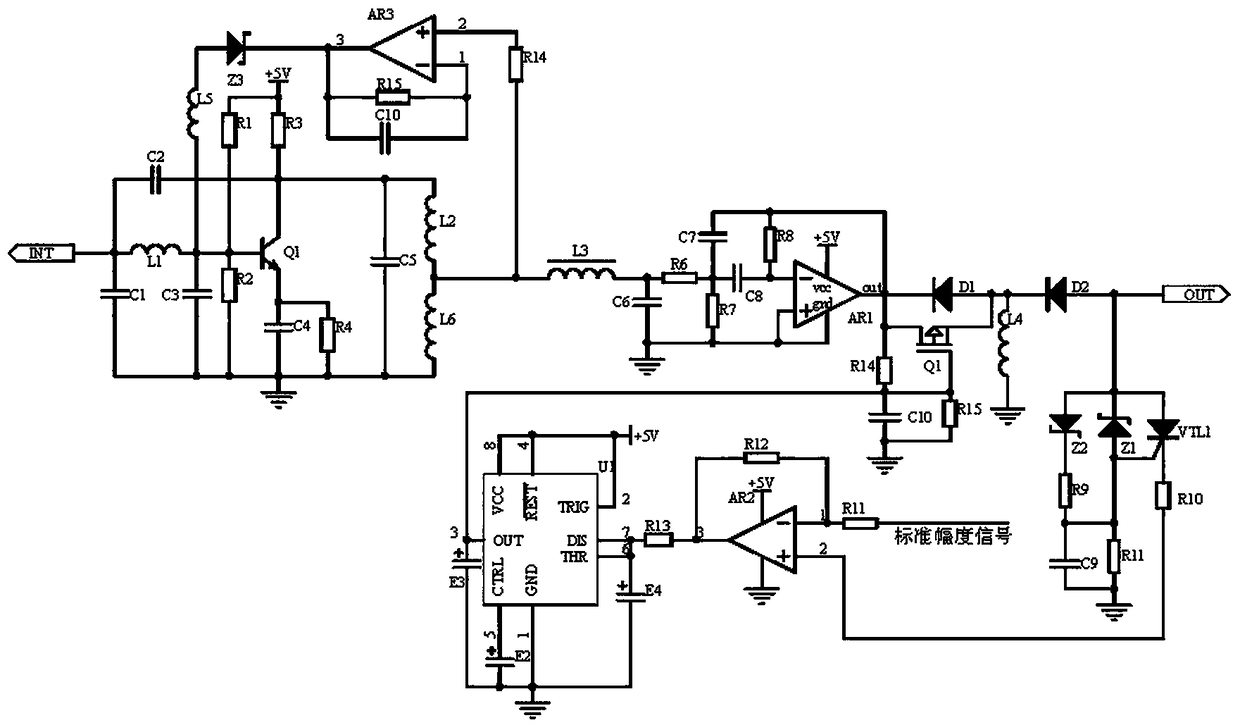

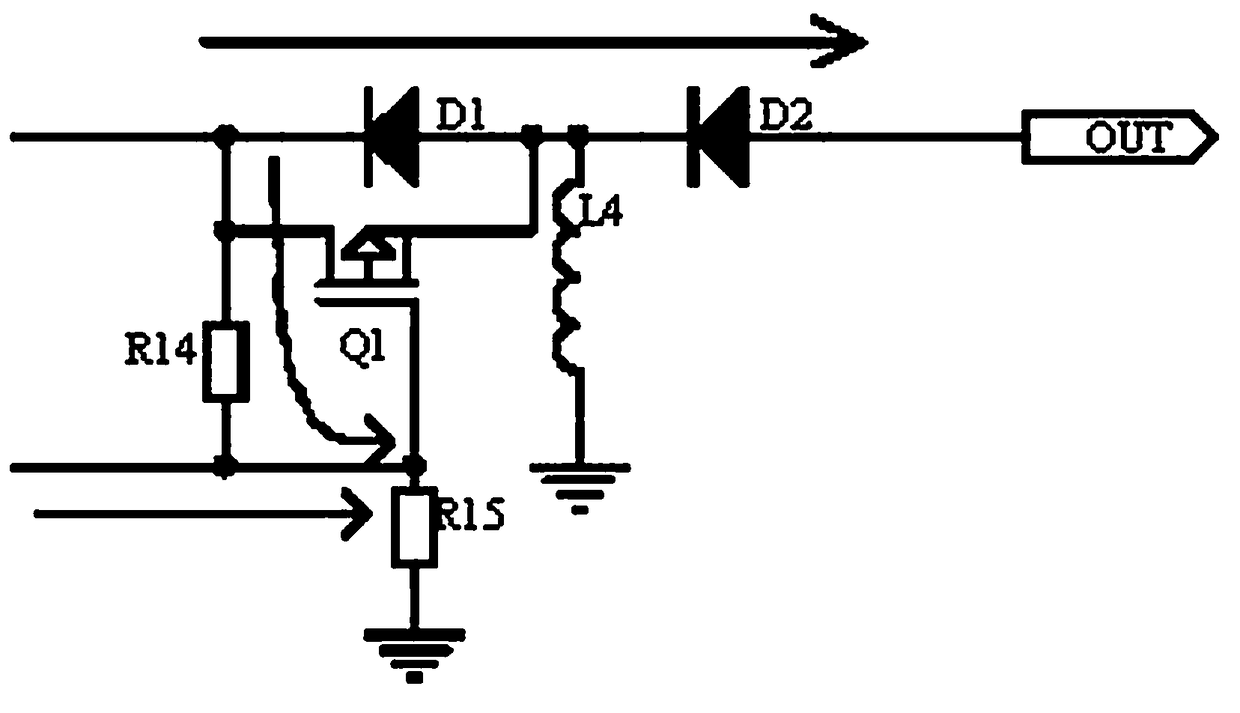

A Network Information Analysis System

PendingCN108988820ACompensating for signal attenuation issuesEfficient receptionMultiple-port active networksSpecial data processing applicationsBandpass filteringInformation analysis

The invention discloses a network information analysis system, a weak signal, which is received by the regenerative receiving circuit and is in the network information transmission channel is treatedby the oscillator with transistor Q1 as the core to generate positive feedback, distortion compensation and primary amplification are performed, wherein an operational amplifier AR3 is used to feedback a primary amplified signal, the accuracy of distortion compensation is improved, at that same time, the signal meeting the post-stage circuit amplitude and frequency Requirement is output, and then enters the filter circuit, the noise interference is filtered by LC filter circuit, and other frequency signal interference is avoided by a bandpass filter, the signal enters a signal amplitude modulation circuit, and boosting second-order amplitude modulation is performed by a Boost circuit. When the output signal is abnormal, the thyristor is on, the signal enters the subtractor and outputs adifference signal, which is converted into a PWM signal to be coupled to the gate of the MOS transistor Q1 to control the on or off of the MOS transistor Q1, so as to control the accuracy of the second-order amplitude modulation. the problems that the signal in the network information transmission channel is distorted and the attenuation can not be effectively received by the terminal server canbe effectively solved.

Owner:北京易用时代科技有限公司

Programmable high-speed cable with printed circuit board and boost device

ActiveUS20090153209A1Multiple-port active networksDigital data processing detailsDifferential signalingAnalog signal

An HDMI cable carries high speed encoded data which are transmitted differentially over data channels, along with a clock. High-frequency loss and differential skew within a differential signal may be compensated by analog circuits embedded in the cable. These embedded circuits are tuned at production for best performance by observing the quality of the recovered analog signal. The embedded circuits are powered by a combination of power sources, both carried within the cable, and harvested from the high-speed signals themselves. Methods are provided for deskewing, equalizing, and boosting the differential signals in the embedded circuits that are mounted on a PCB.

Owner:REDMERE TECH

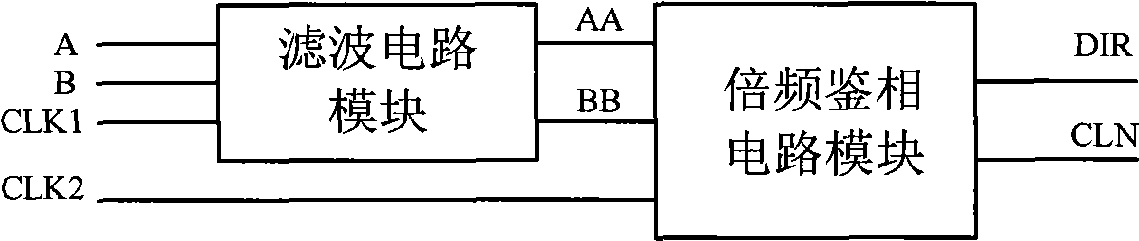

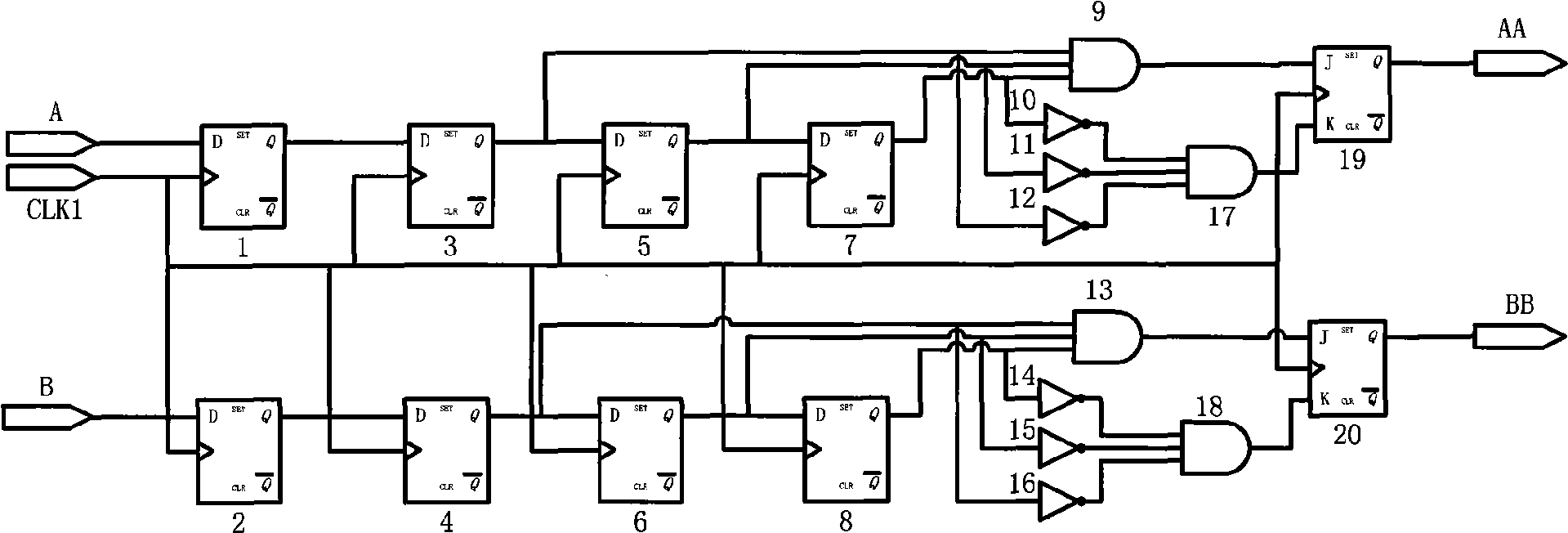

Orthogonal signal frequency-multiplication phase-demodulation logic circuit with filter function

InactiveCN101534109AWith filter functionSave spaceMultiple-port active networksUsing electrical meansComputer moduleEngineering

The invention discloses an orthogonal signal frequency-multiplication phase-demodulation logic circuit with filter function, which mainly comprises a filter circuit module and a frequency-multiplication phase-demodulation circuit module, wherein the filter circuit module consists of eight D triggers, six phase inverters, four three-way AND gates and two JK triggers, an input end of the module receives two paths of orthogonal coding signals needing to be filtered respectively, and an output of the module has two paths of orthogonal signals filtered by the corresponding orthogonal coding signals; and the frequency-multiplication phase-demodulation circuit module consists of two XOR gates and five D triggers, an input end of the module receives two paths of signals needing phase demodulation respectively, and an output end of the module has phase-demodulation signals and fourfold frequency signals. The circuit combines filter and frequency-multiplication phase demodulation, is simple and reliable, can solve the problem of subsequent data processing error caused by signal interference, can be downloaded to a programmable chip such as CPLD or FPGA and the like, saves the space of a circuit board, is convenient to debug, and has reliable performance and utility value.

Owner:ZHEJIANG UNIV

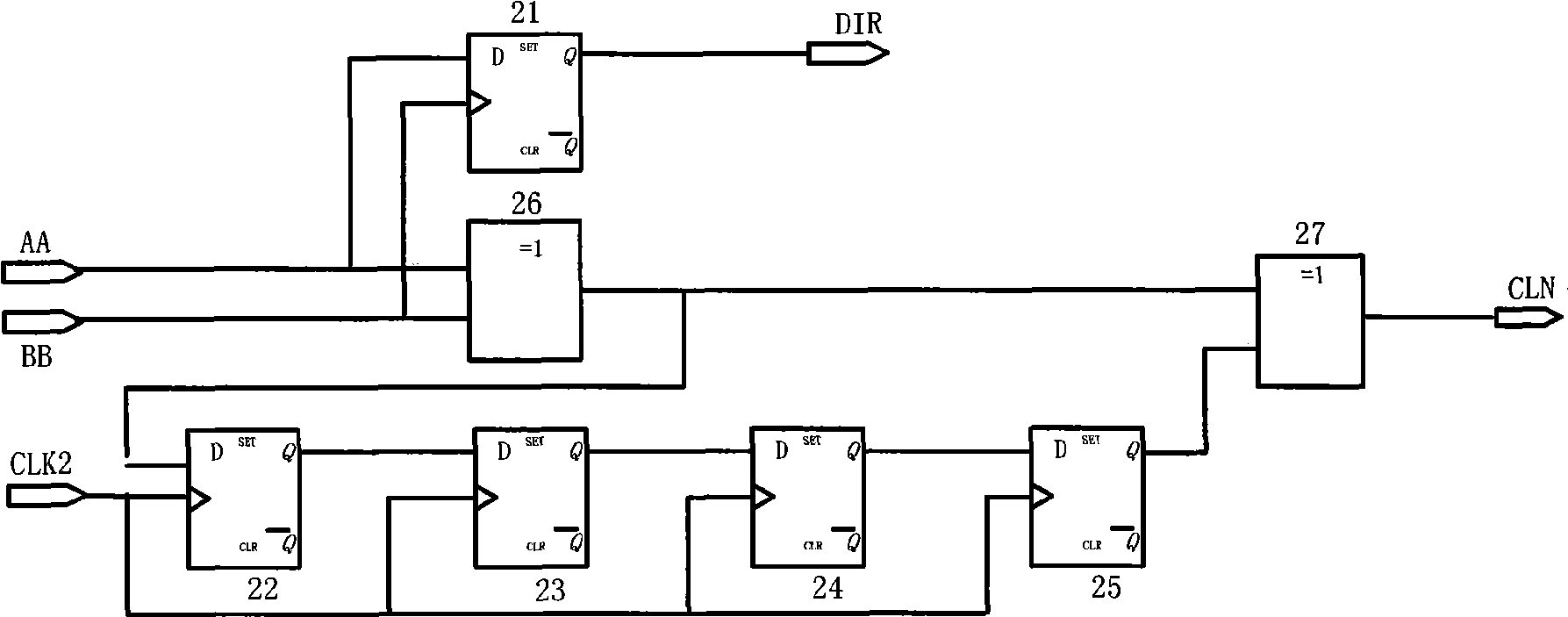

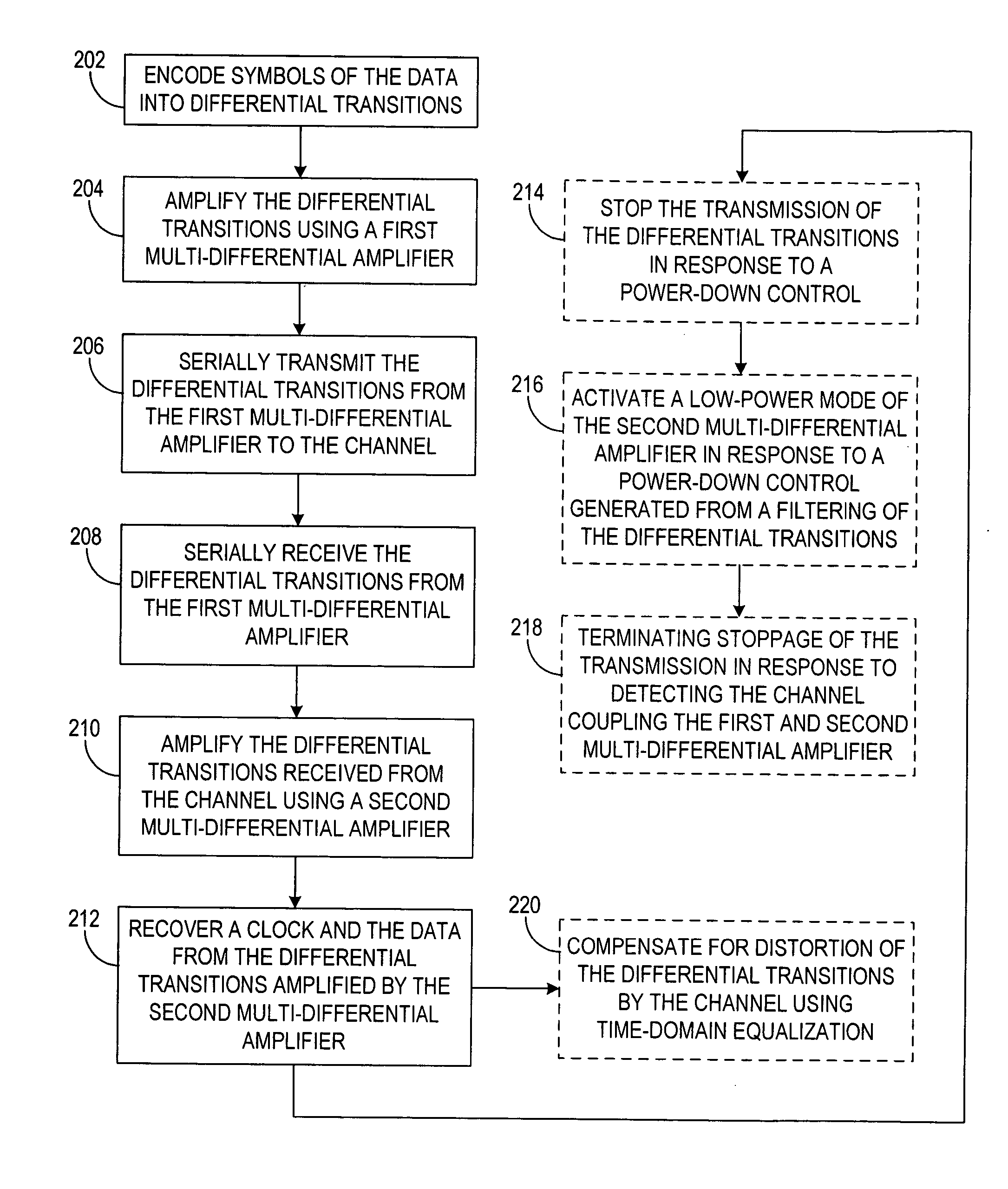

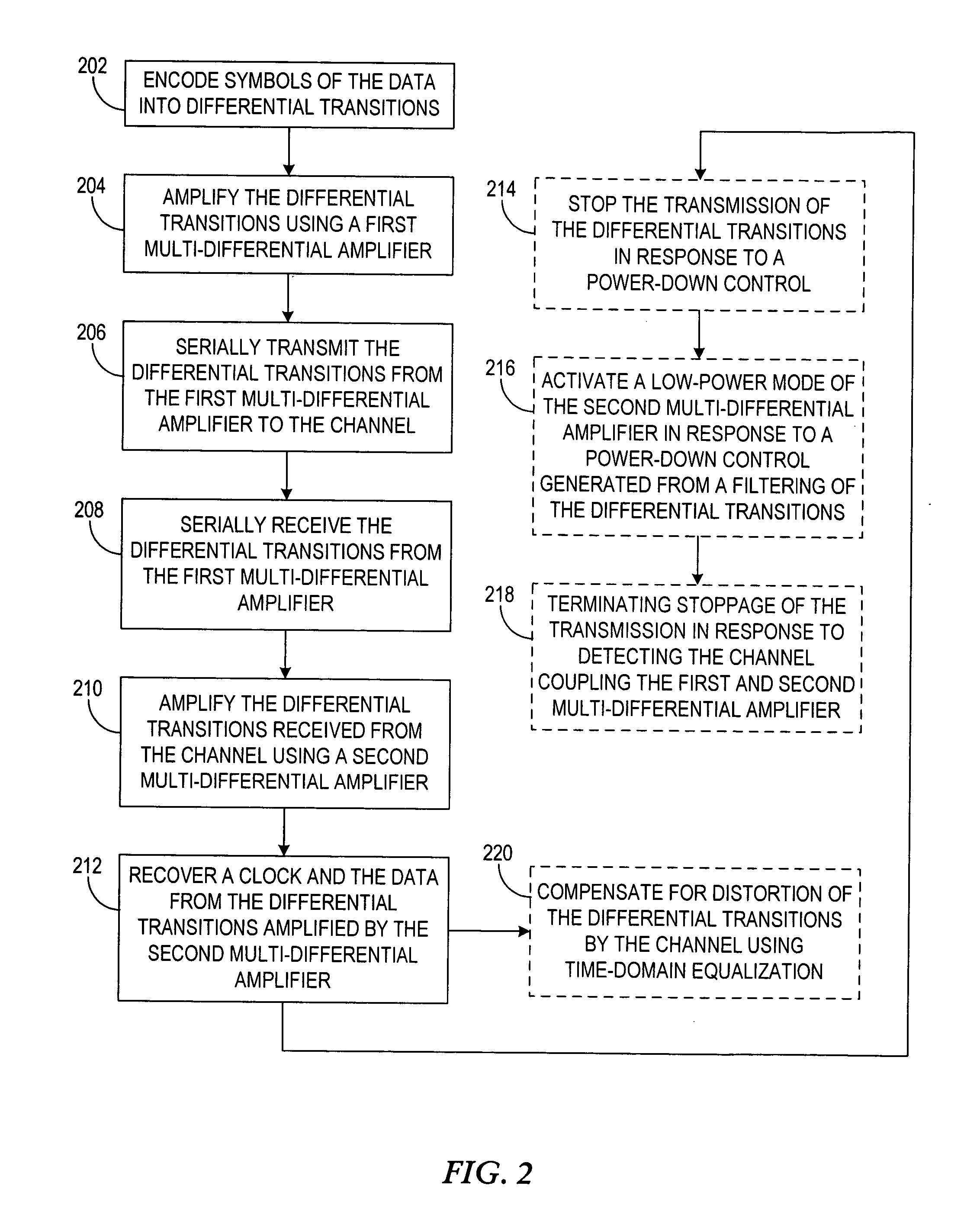

Circuits and methods for a multi-differential embedded-clock channel

ActiveUS20070014340A1Multiple-port active networksElectric analogue storesInterface circuitsDifferential amplifier

An interface circuit for a multi-differential embedded-clock channel for communicating data provides efficient utilization of the bandwidth of the channel. The interface circuit includes at least four first signals, at least four second signals, and a multi-differential amplifier. The multi-differential amplifier is coupled to the first and second signals. The multi-differential amplifier is adapted to generate the second signals by amplifying, for all combinations of two of the first signals, differential transitions between the two of the first signals. Each of a plurality of symbols of the data has a corresponding one of the differential transitions, and the differential transitions are serially communicated through the channel.

Owner:MCGEE JAMES RIDENOUR

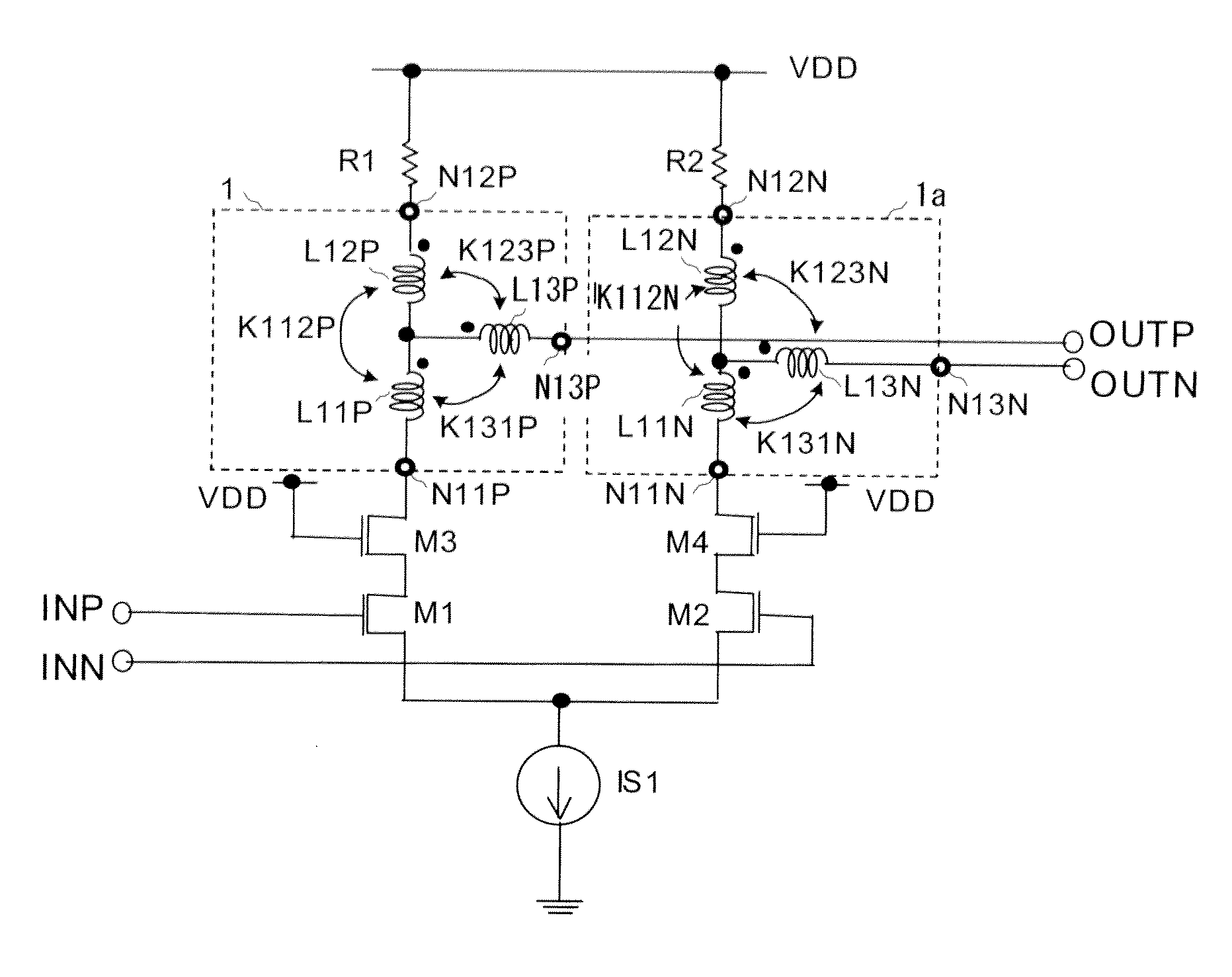

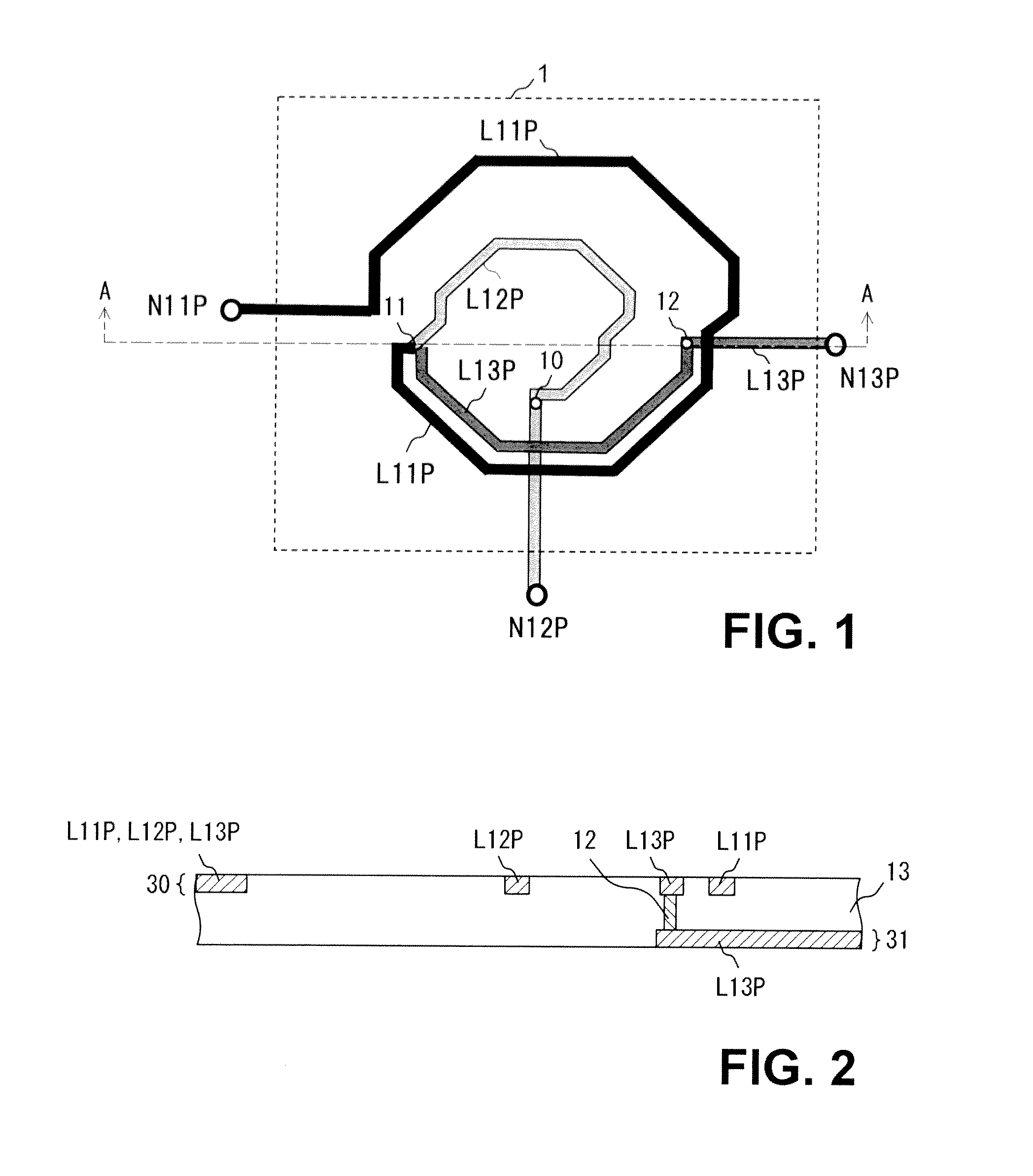

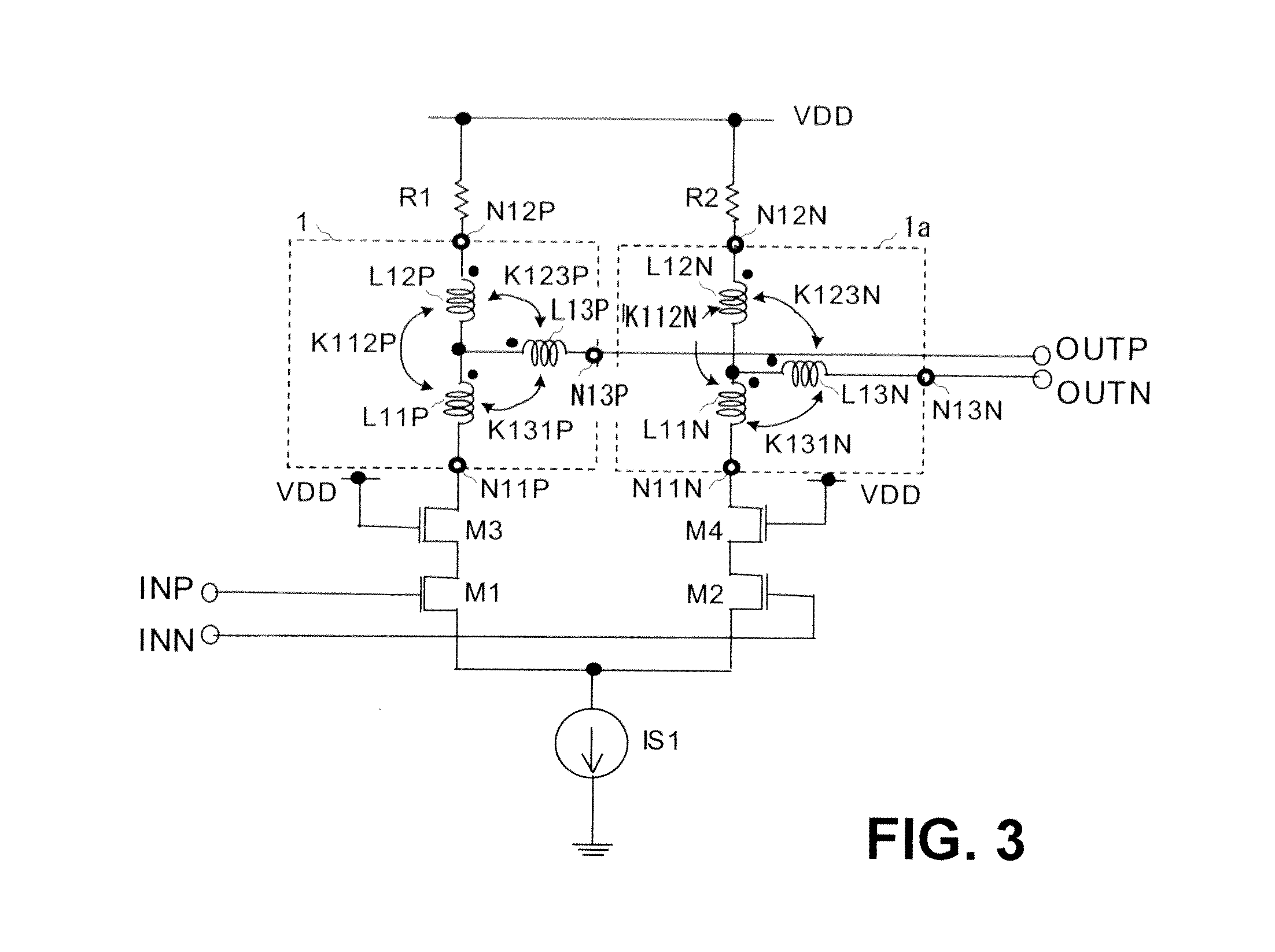

Inductor

InactiveUS20150035625A1Enhance band extension effectImprove scalabilityMultiple-port active networksSemiconductor/solid-state device detailsInductorEngineering

An inductor (1) includes an inductor (L11P) formed into the shape of a spiral on the outer circumference of an inductor region and having a start point connected to a terminal (N11P), an inductor (L12P) formed into the shape of a spiral on the inner circumference of the inductor region and having a start point at the end point of the inductor (L11P) and an end point connected to a terminal (N12P), and an inductor (L13P) formed into the shape of a spiral in a region sandwiched between the inductor (L11P) and the inductor (L12P) and having a start point at a node between the inductor (L11P) and the inductor (L12P) and an end point connected to a terminal (N13P).

Owner:NIPPON TELEGRAPH & TELEPHONE CORP +1

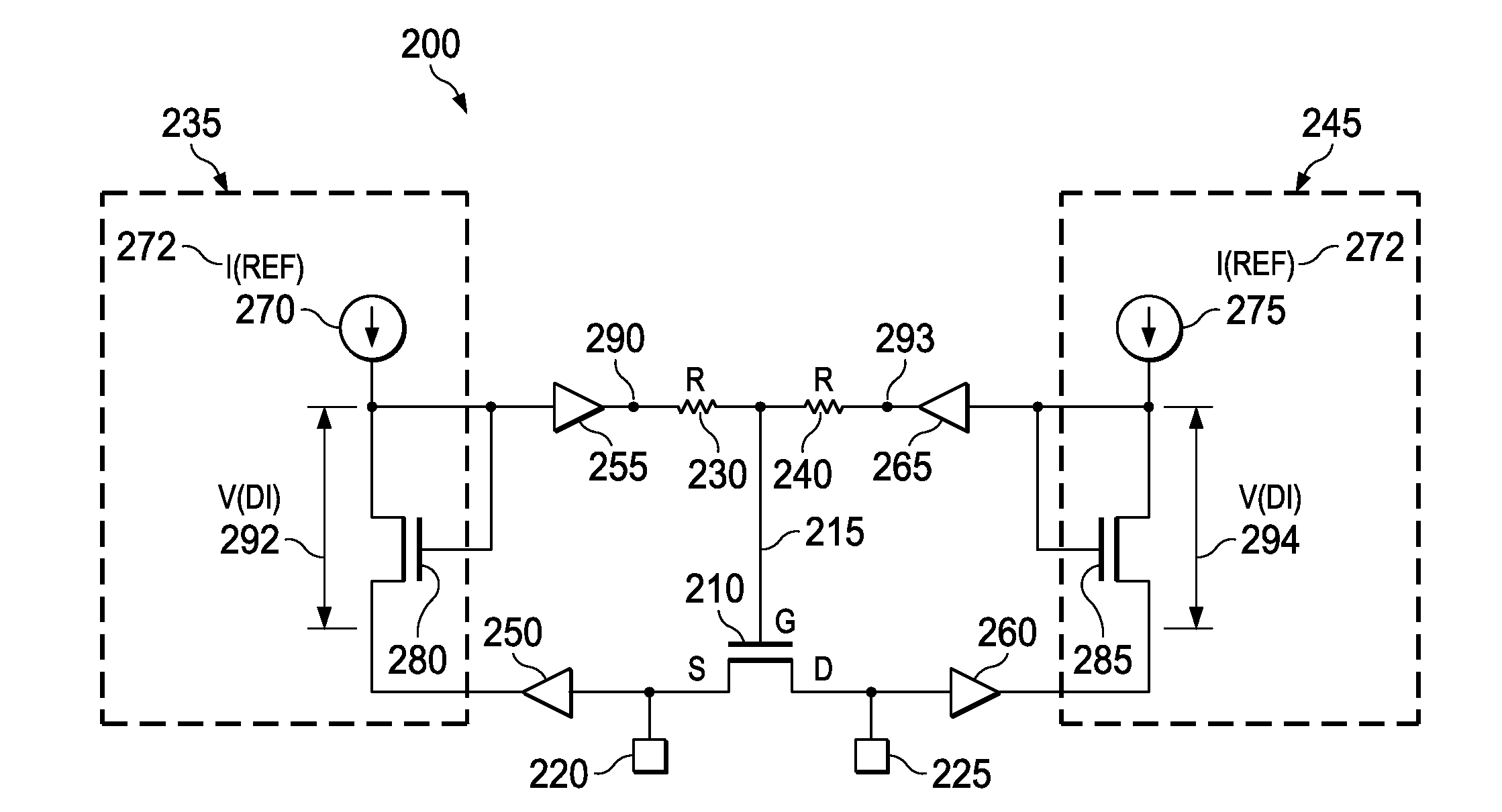

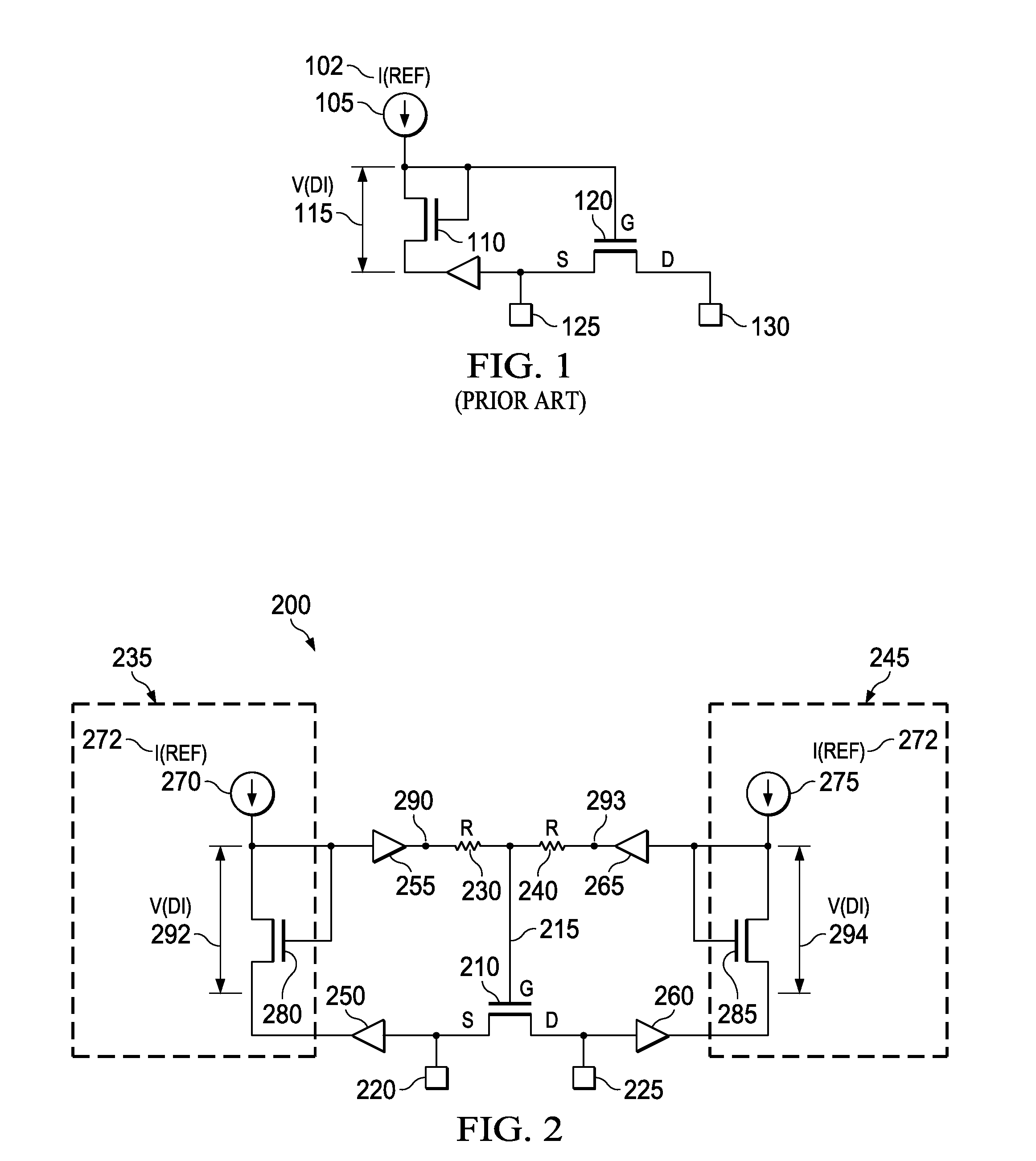

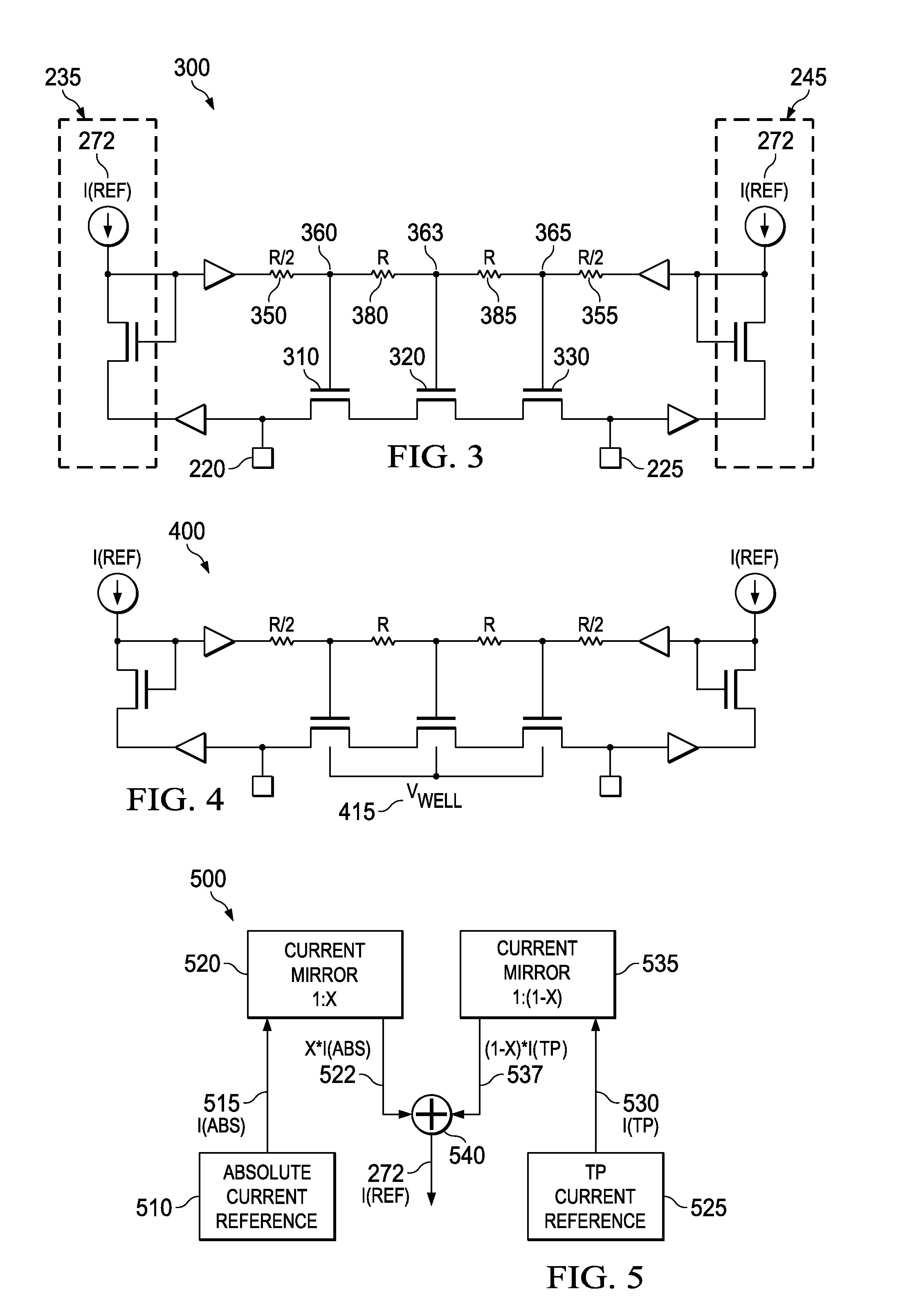

Mos resistor apparatus and methods

Apparatus and methods disclosed herein implement a MOS resistor using the current channel of a MOS transistor. The MOS resistance R(DS) is dependent upon MOS transistor geometry and nominal gate voltage. MOS resistor terminal-to-gate voltages are averaged and applied to the MOS transistor gate such as to maintain the MOS resistor terminal voltage to current ratio, resulting in a substantially constant R(DS). R(DS) is also compensated for temperature and process variations by adjusting gate voltages via negative feedback methods.

Owner:TEXAS INSTR INC

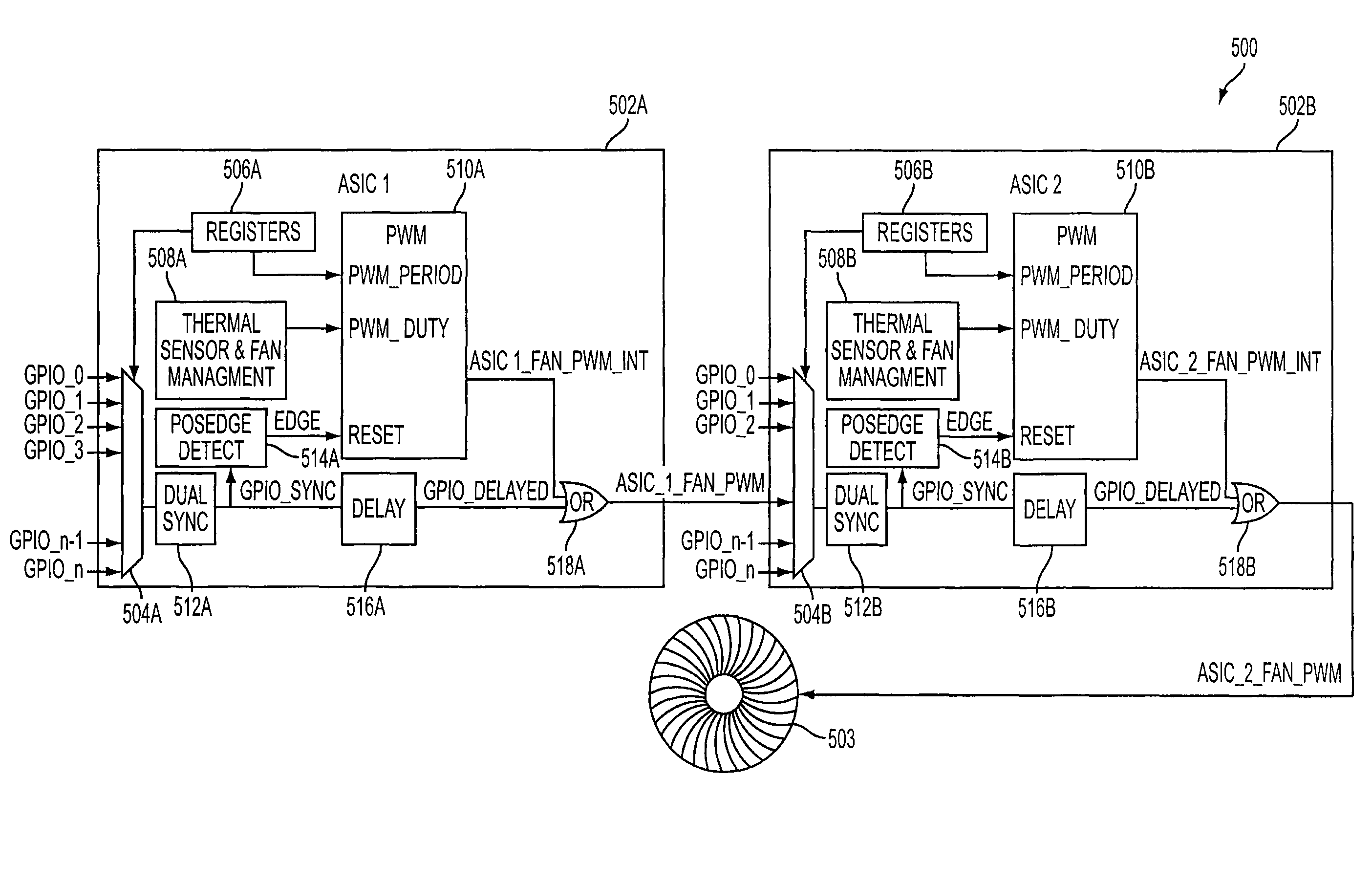

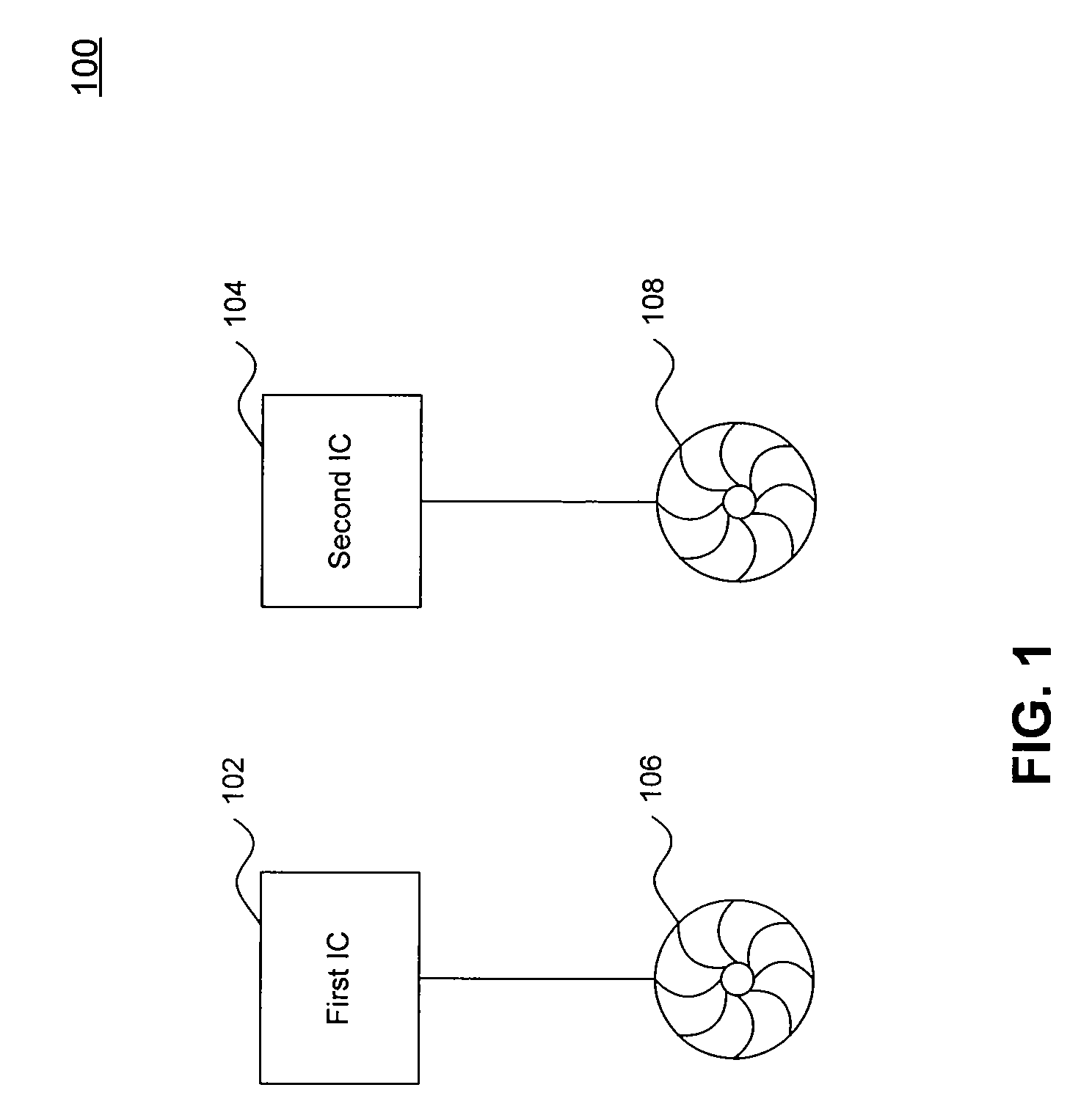

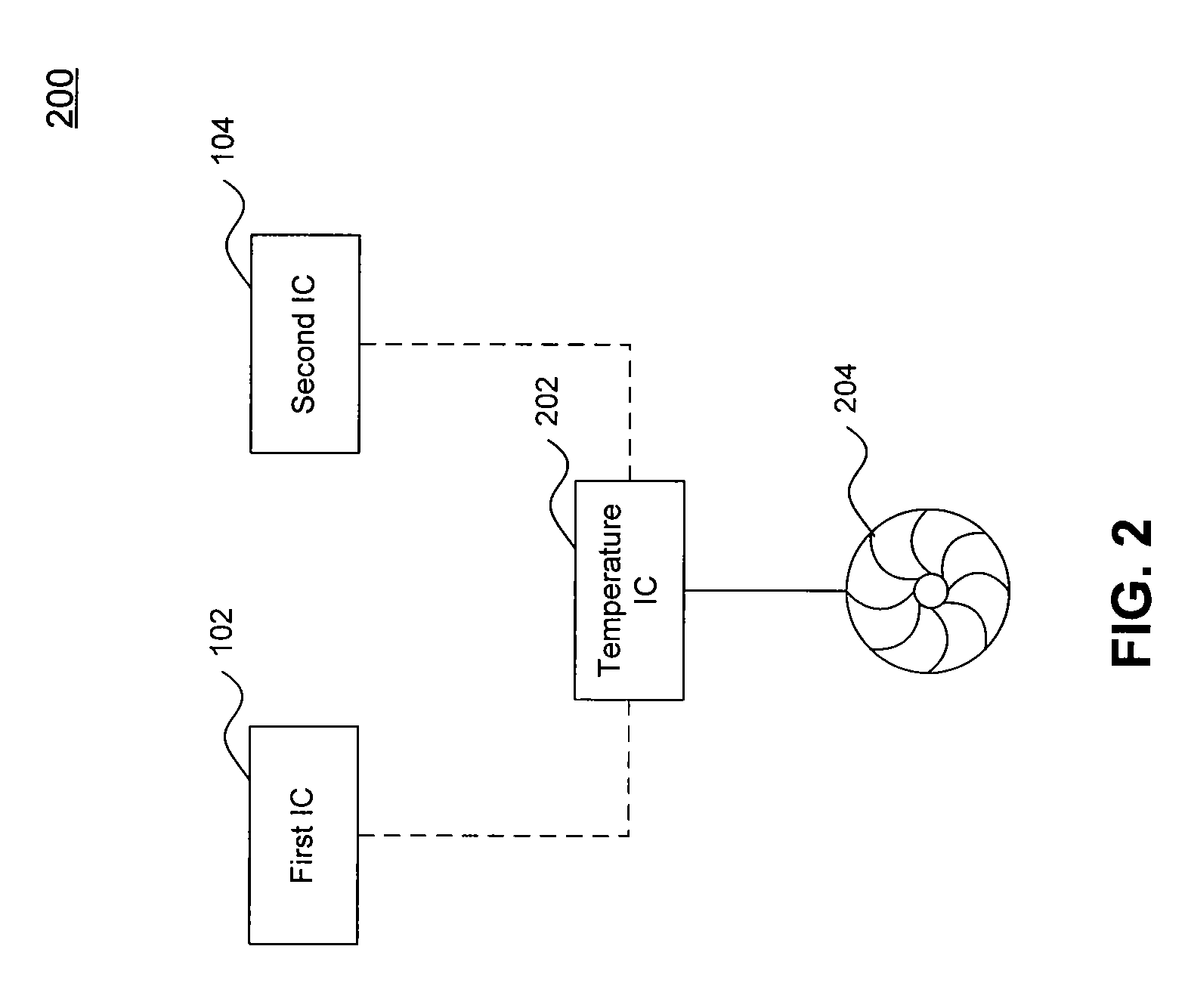

Apparatus and method for providing cooling to multiple components

In an embodiment, an integrated circuit includes an input configured to receive a first control signal and an output module configured to generate an output signal based at least on the first control signal and a second control signal generated based at least on a measured temperature of the IC. The output signal is configured to control a cooling device.

Owner:ADVANCED MICRO DEVICES INC

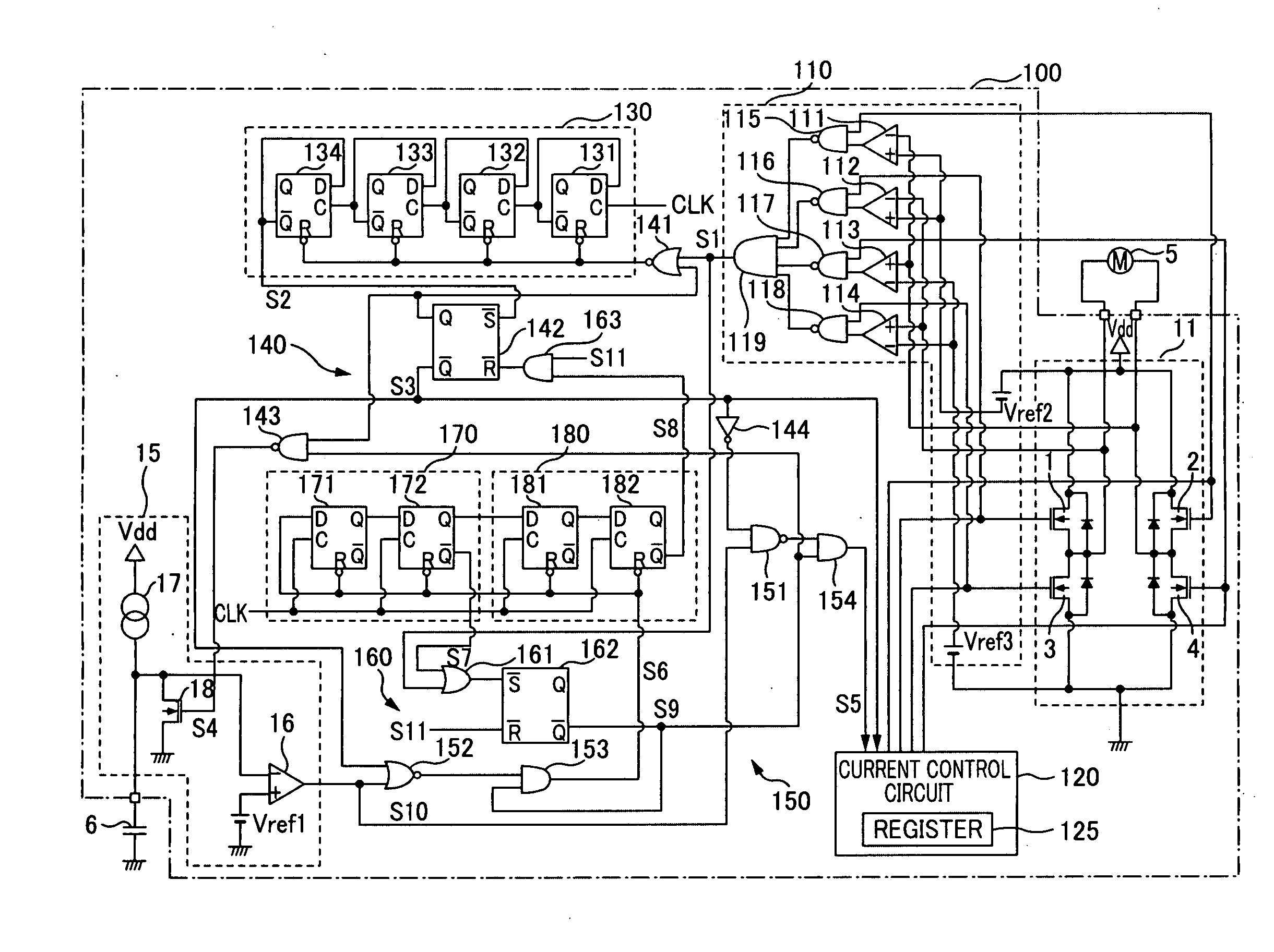

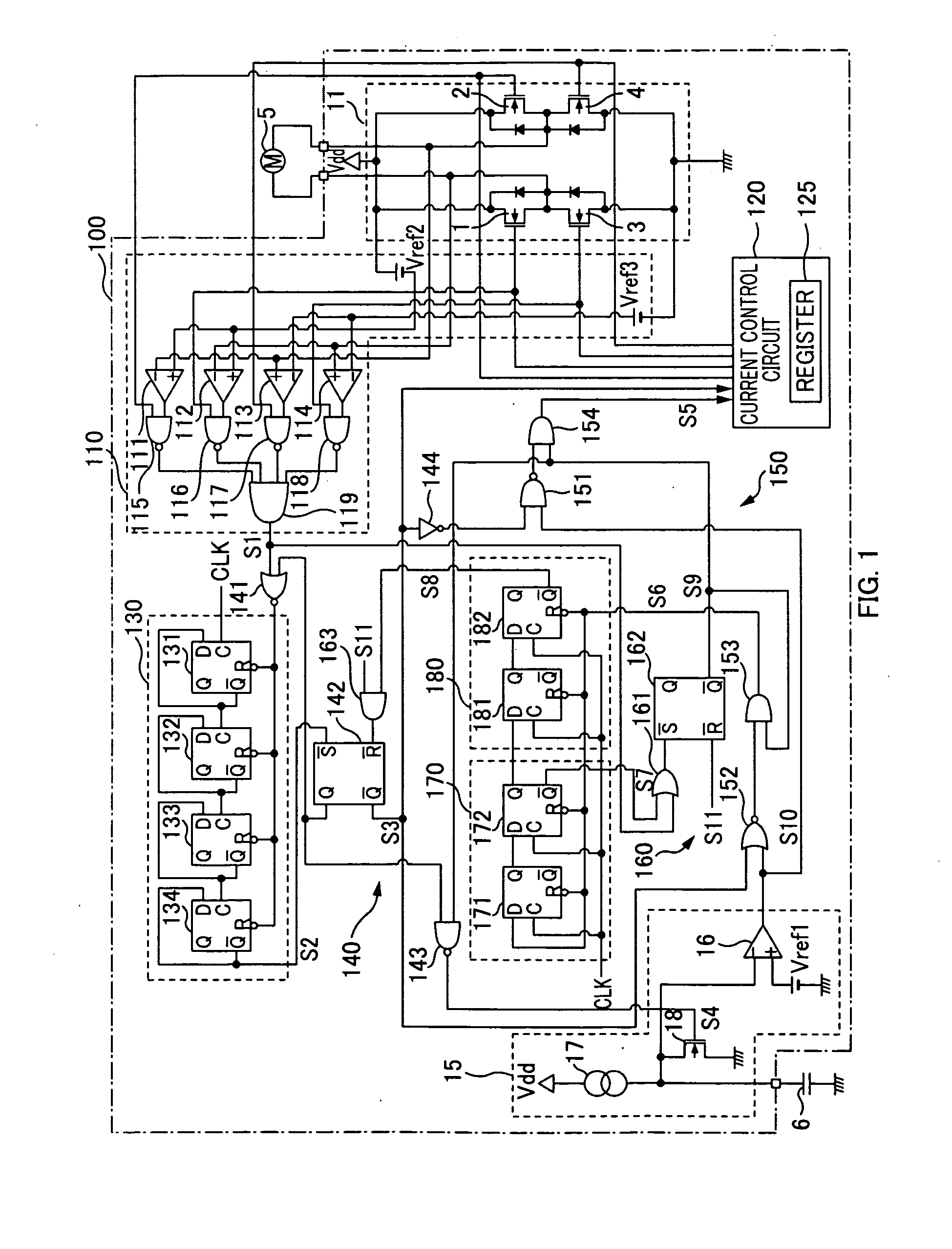

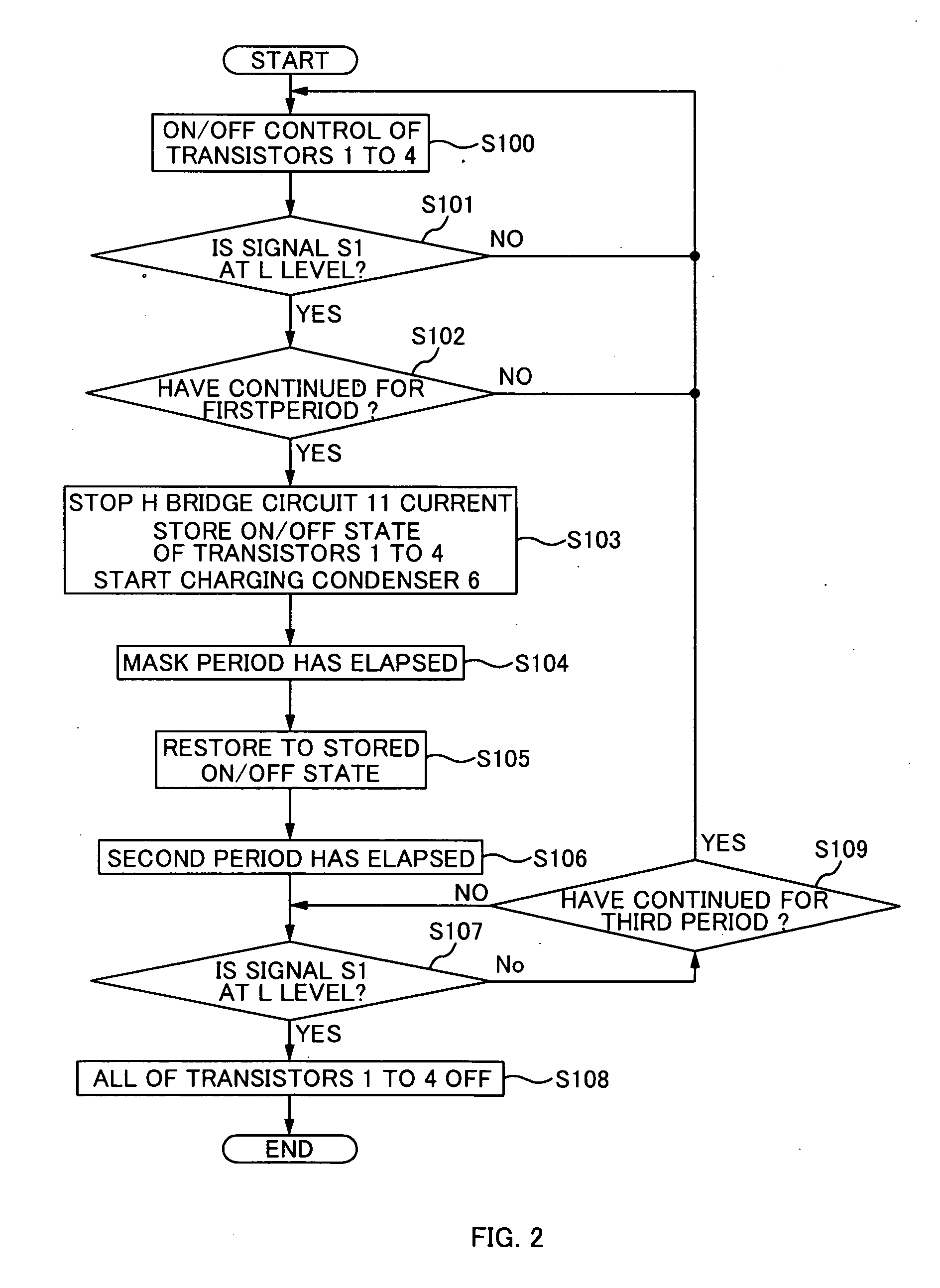

Motor drive circuit

A motor-drive circuit comprising: a current-passage-control circuit to perform ON / OFF control of a drive transistor connected to a motor coil to pass current through the motor coil; an overcurrent-state-detection circuit to detect whether current passing through the drive transistor is in an overcurrent state where the current exceeds a predetermined threshold value; a charging and discharging circuit to start charging a capacitor in response to detecting the overcurrent state by the overcurrent-state-detection circuit and subsequently discharge the capacitor in response to not detecting the overcurrent state; and an overcurrent-protection-control circuit to stop the ON / OFF control to turn off the drive transistor, for an elapsed charging period for a charging voltage of the capacitor at a predetermined voltage to exceed a threshold voltage, and determine whether to perform such an overcurrent-protection-control as to turn off the drive transistor by detection of the overcurrent state, after the charging period has elapsed.

Owner:SEMICON COMPONENTS IND LLC

Apparatus for jitter testing an IC

InactiveUS7627790B2Minimizing delay and noiseTime indicationMultiple-port active networksProcess measurementVoltage reference

An integrated circuit tester channel includes an integrated circuit (IC) for adding a programmably controlled amount of jitter to a digital test signal to produce a DUT input signal having a precisely controlled jitter pattern. The IC also measures periods between selected edges of the same or different ones of the DUT output signal, the DUT input signal, and a reference clock signal. Additionally, when the DUT input and output signals convey repetitive patterns, the IC can measure the voltage of the DUT input out output signal as selected points within the pattern by comparing it to an adjustable reference voltage. Processing circuits external to the IC program the IC to provide a specified amount of jitter to the test signal, control the measurements carried out by the measurement circuit, and process measurement data to determine the amount of jitter and other characteristics of the DUT output signal, and to calibrate the jitter in the DUT input signal.

Owner:CREDENCE SYSTEMS

Popular searches

Color television details Digital storage Television signal transmission by single/parallel channels Memory architecture accessing/allocation Color television with pulse code modulation Color television with bandwidth reduction Error detection/correction Digital computer details Voltage-current phase angle Single output arrangements

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com