Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

257 results about "Multilevel memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

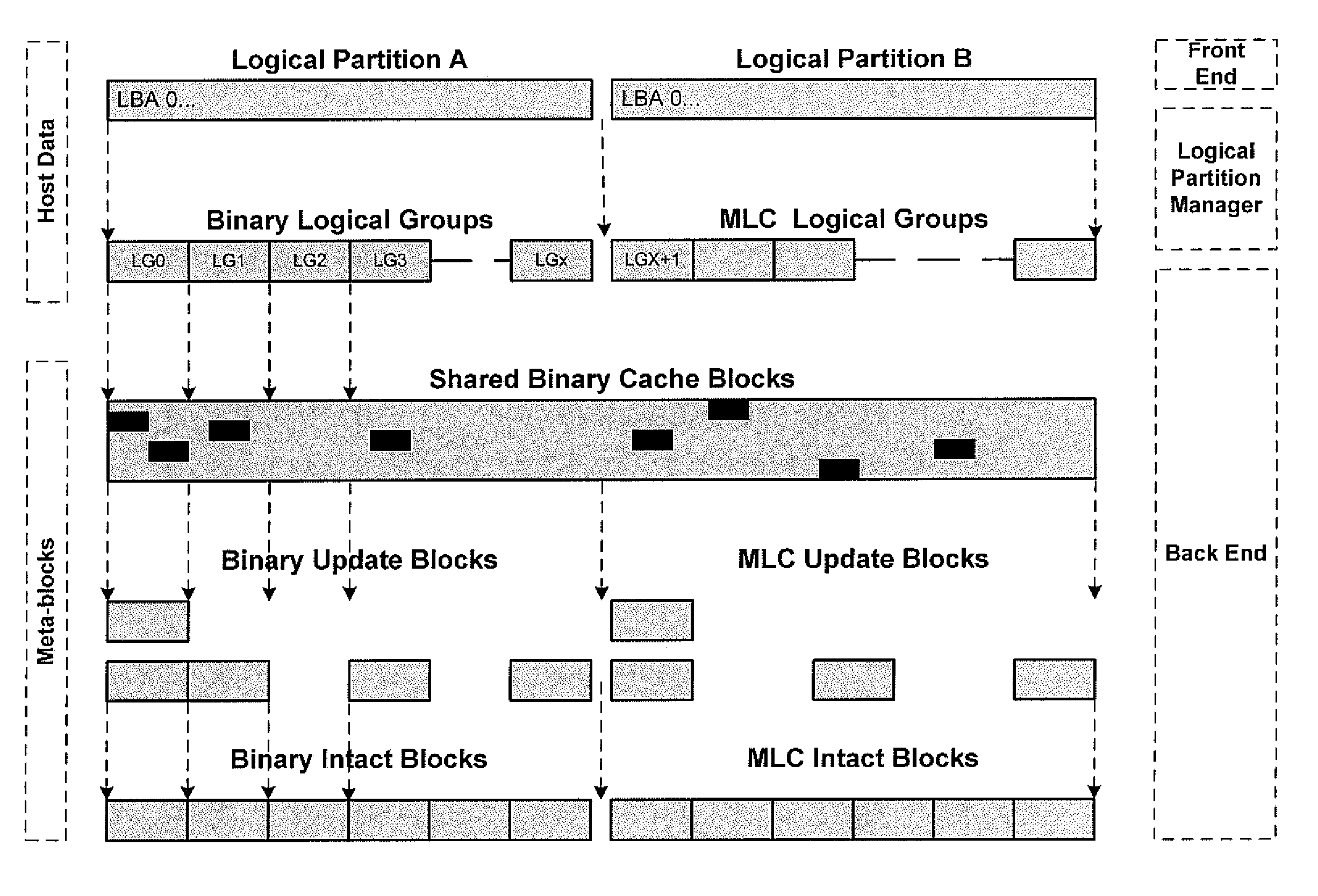

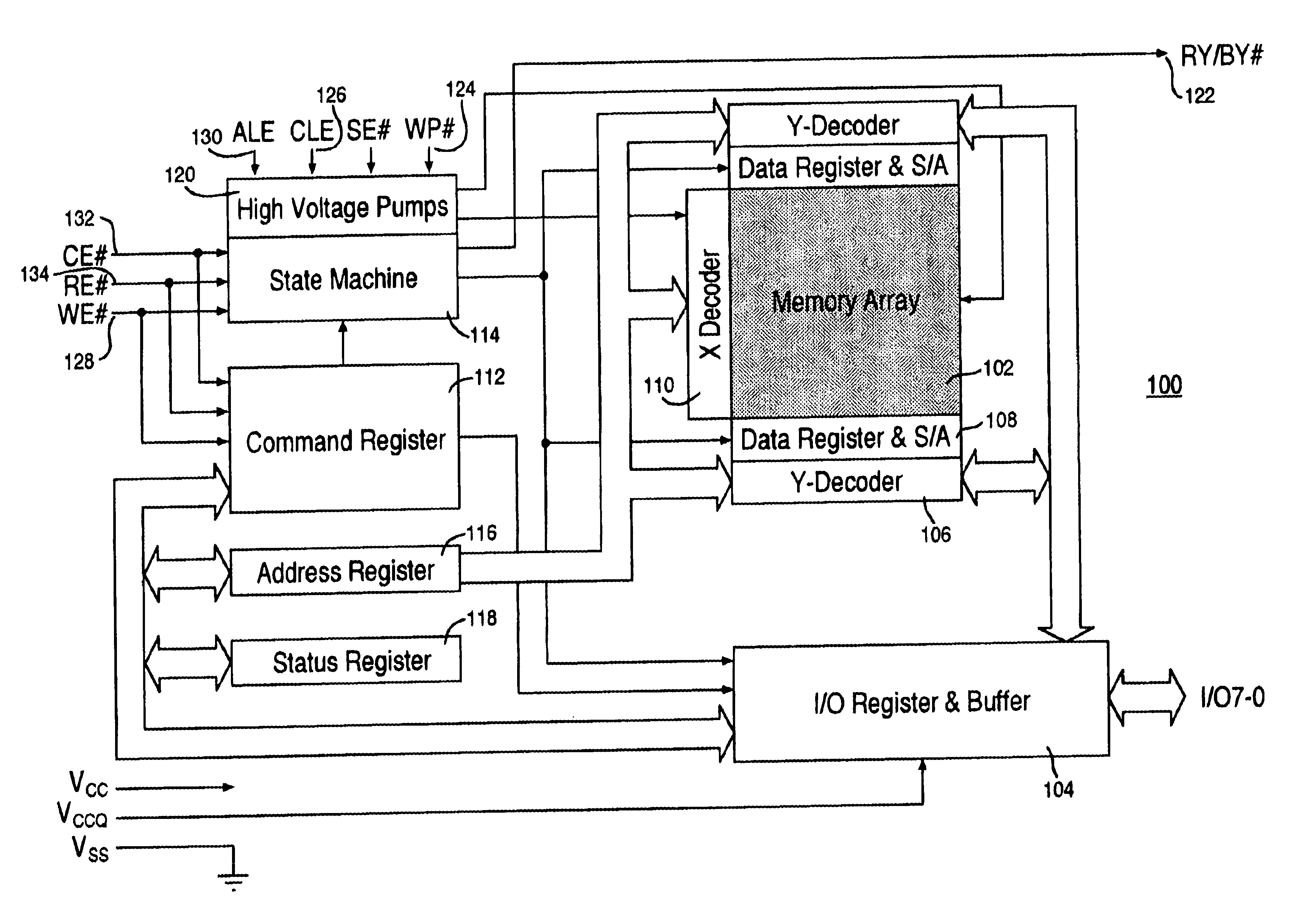

Non-Volatile Memory and Method With Write Cache Partitioning

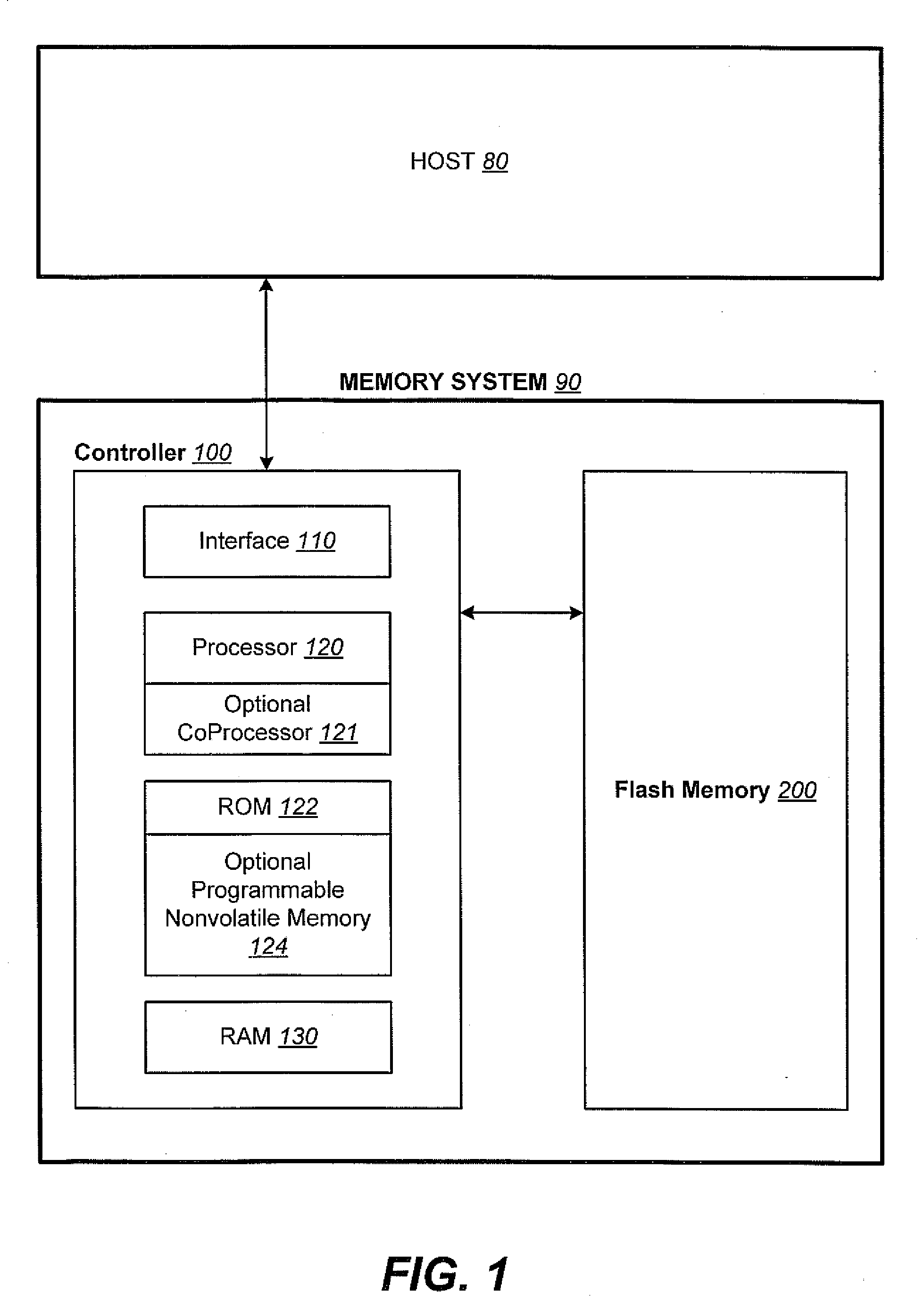

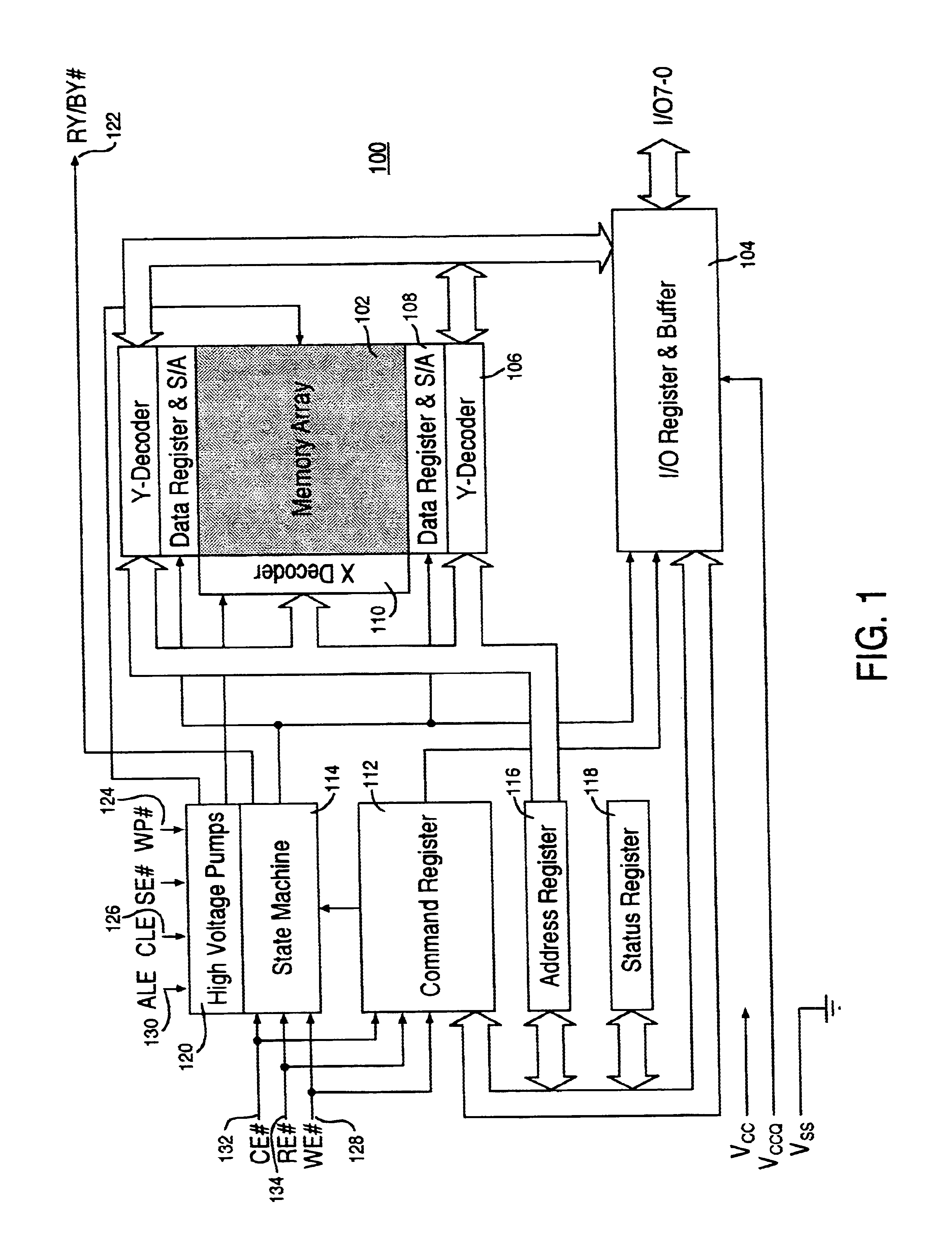

ActiveUS20100172180A1Faster and robust write and read performanceIncrease burst write speedMemory architecture accessing/allocationRead-only memoriesMultilevel memoryGranularity

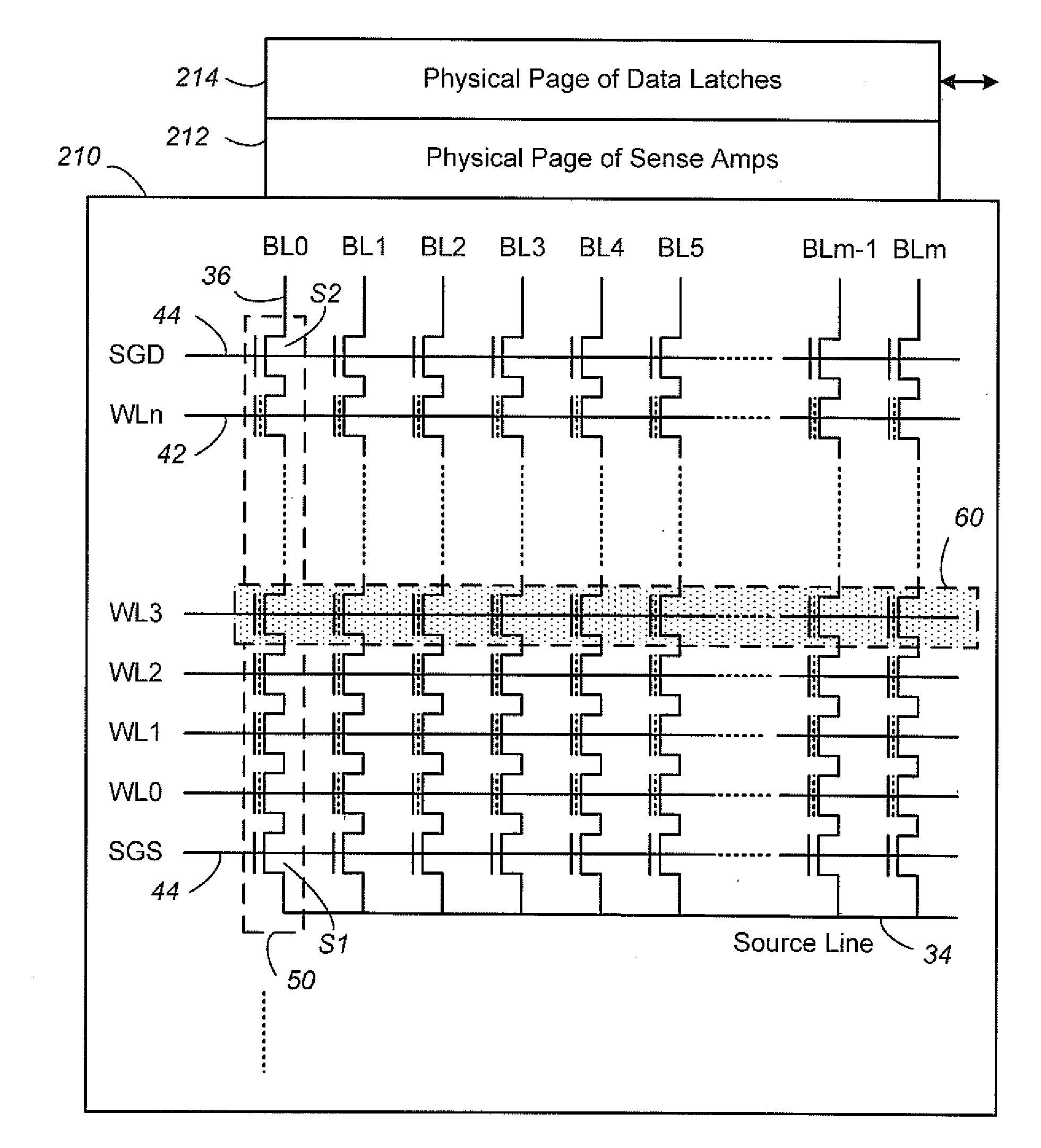

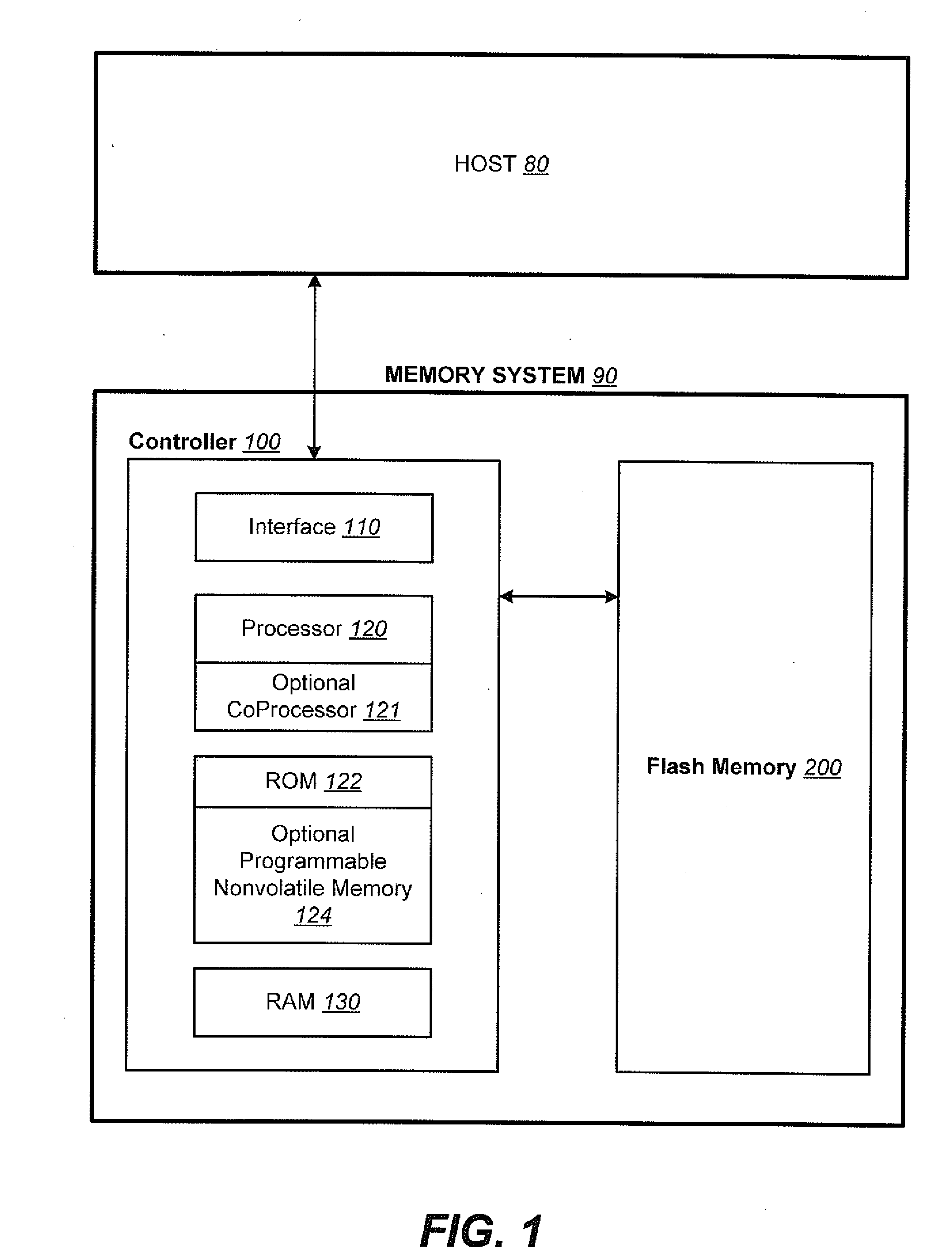

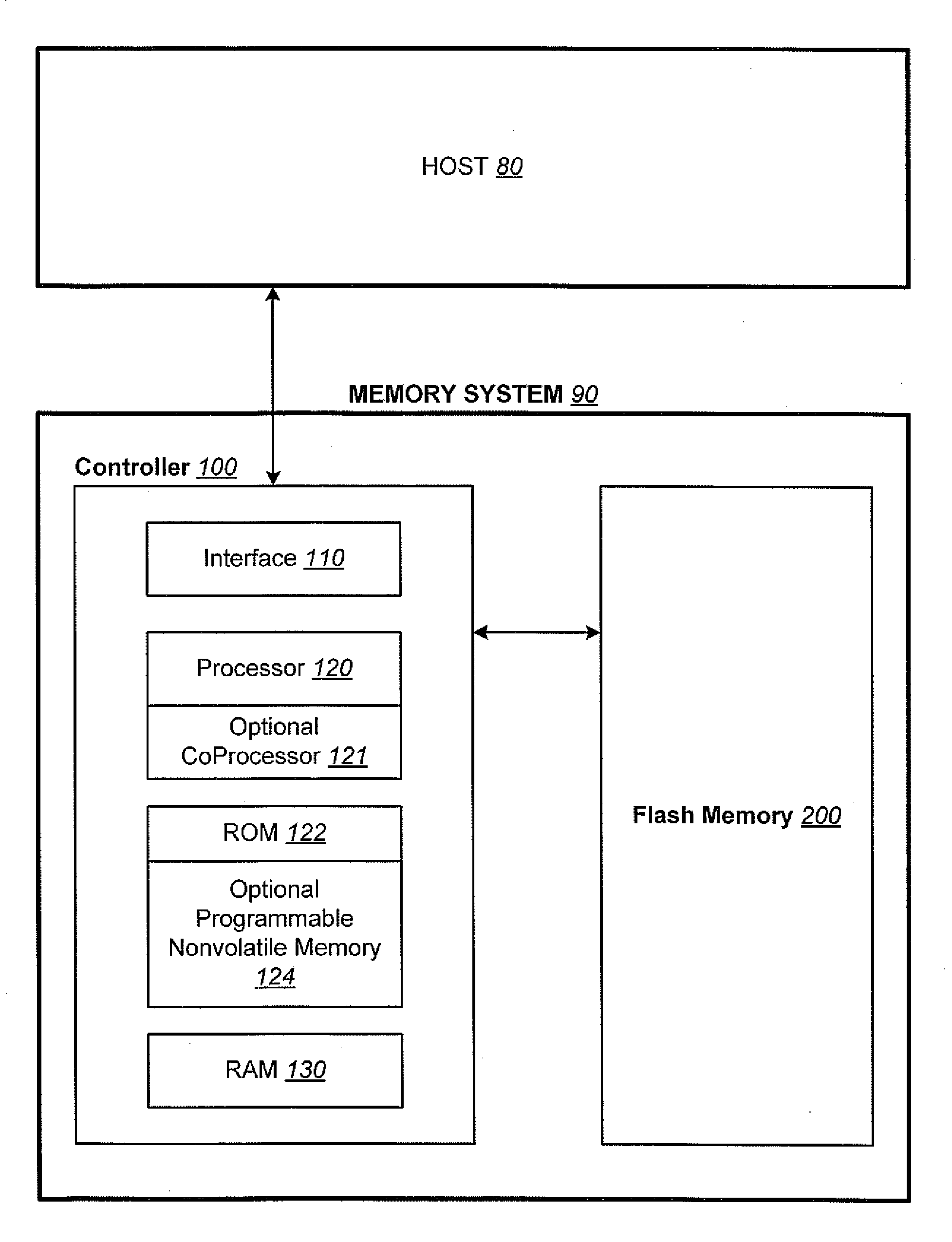

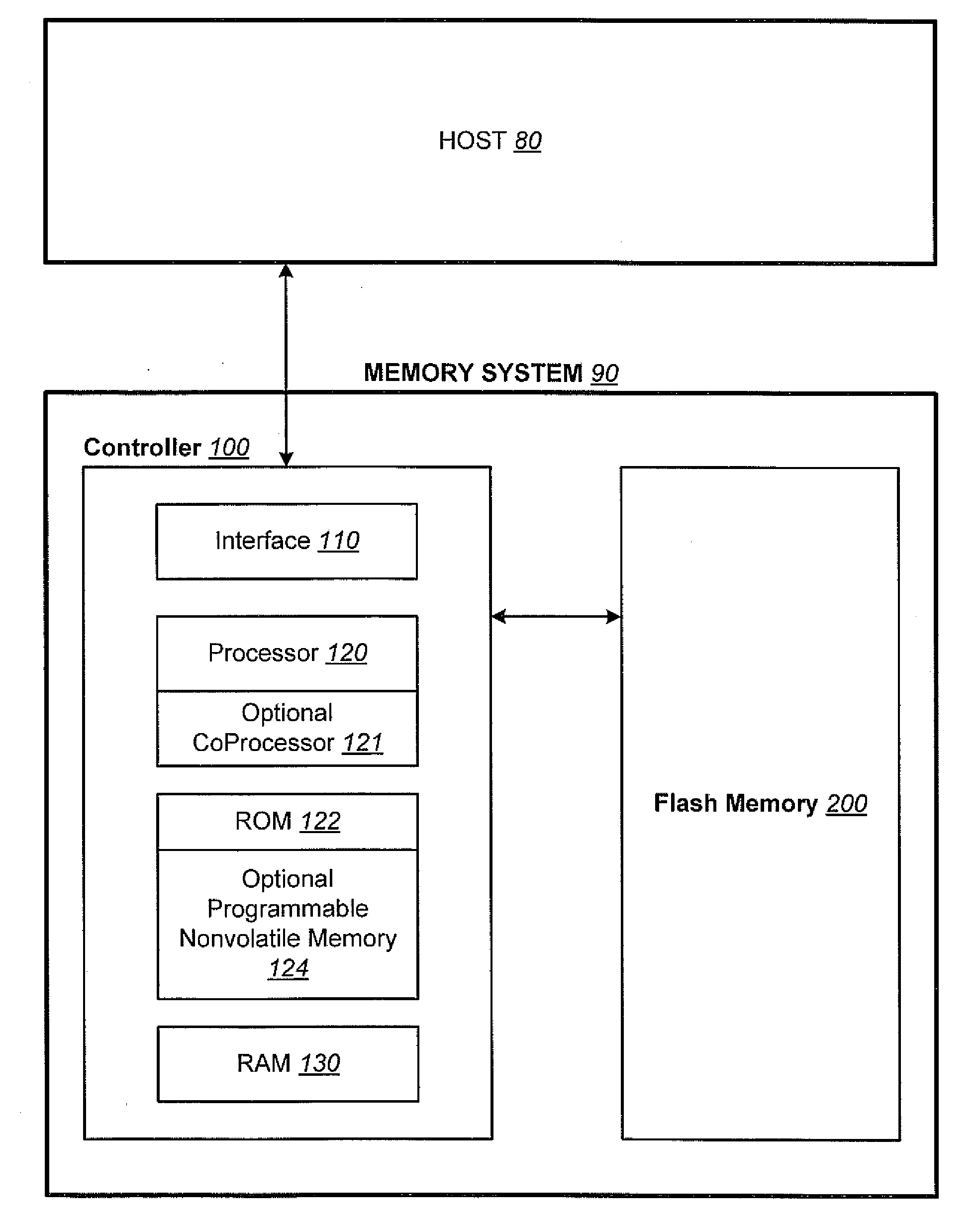

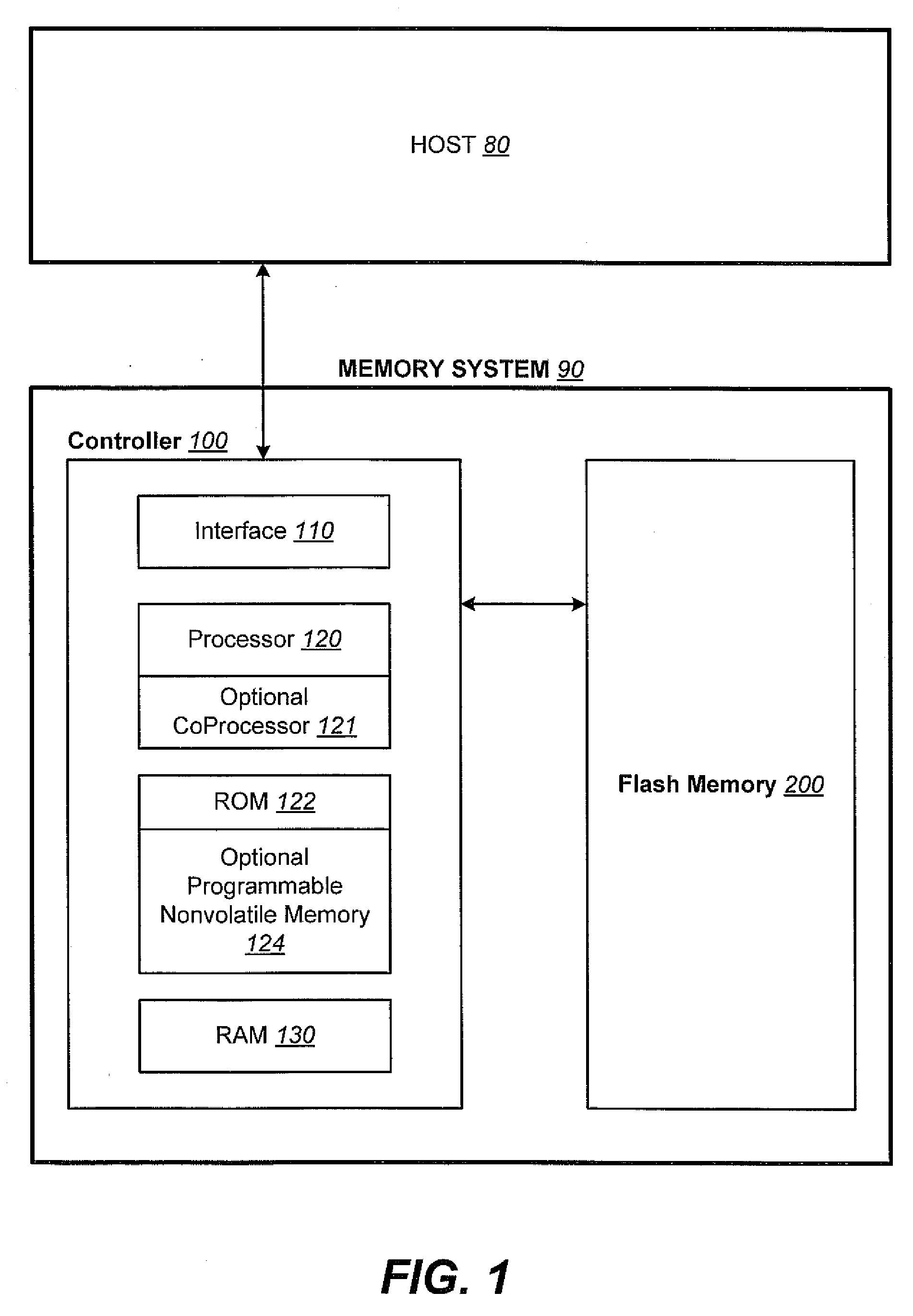

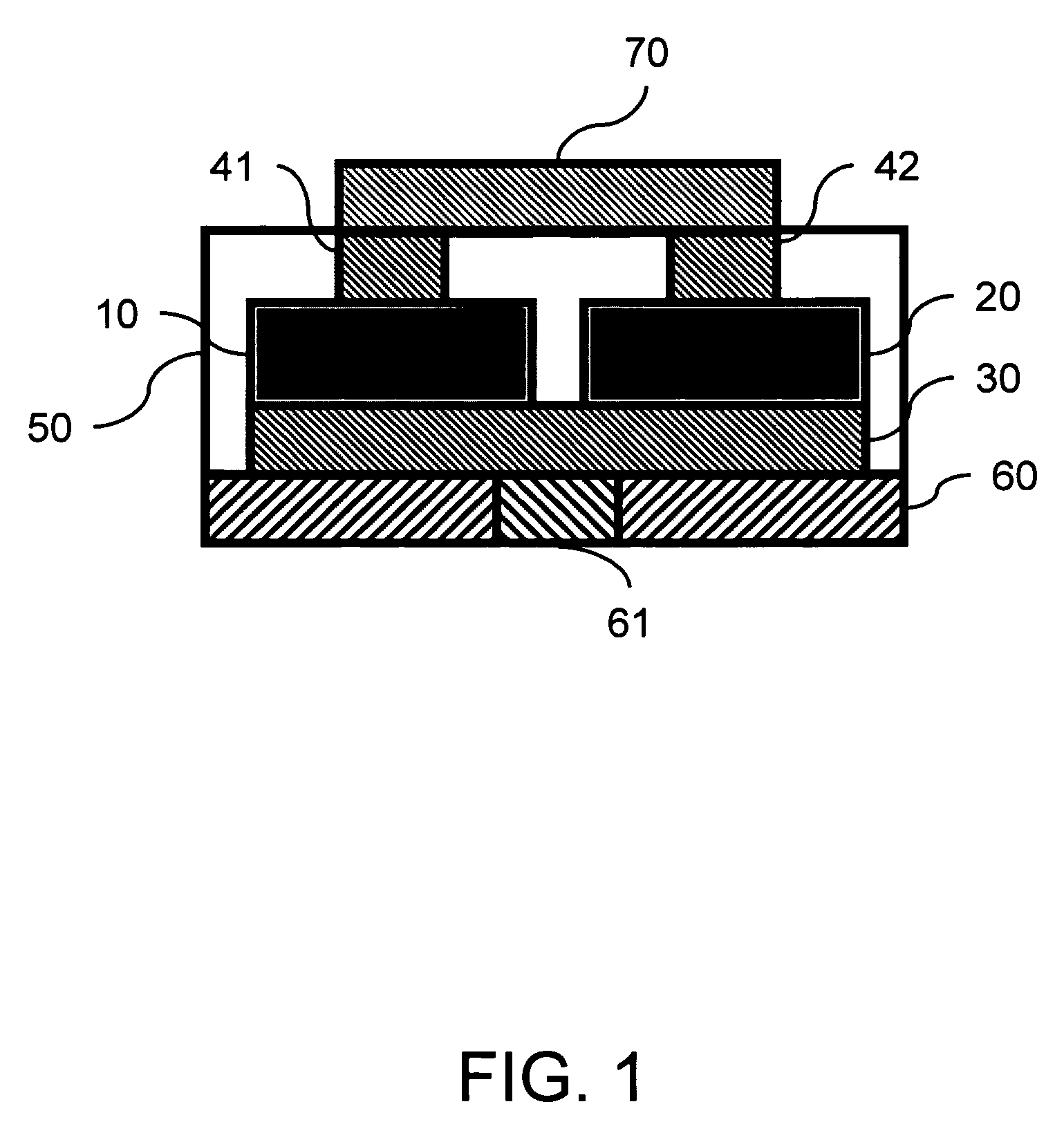

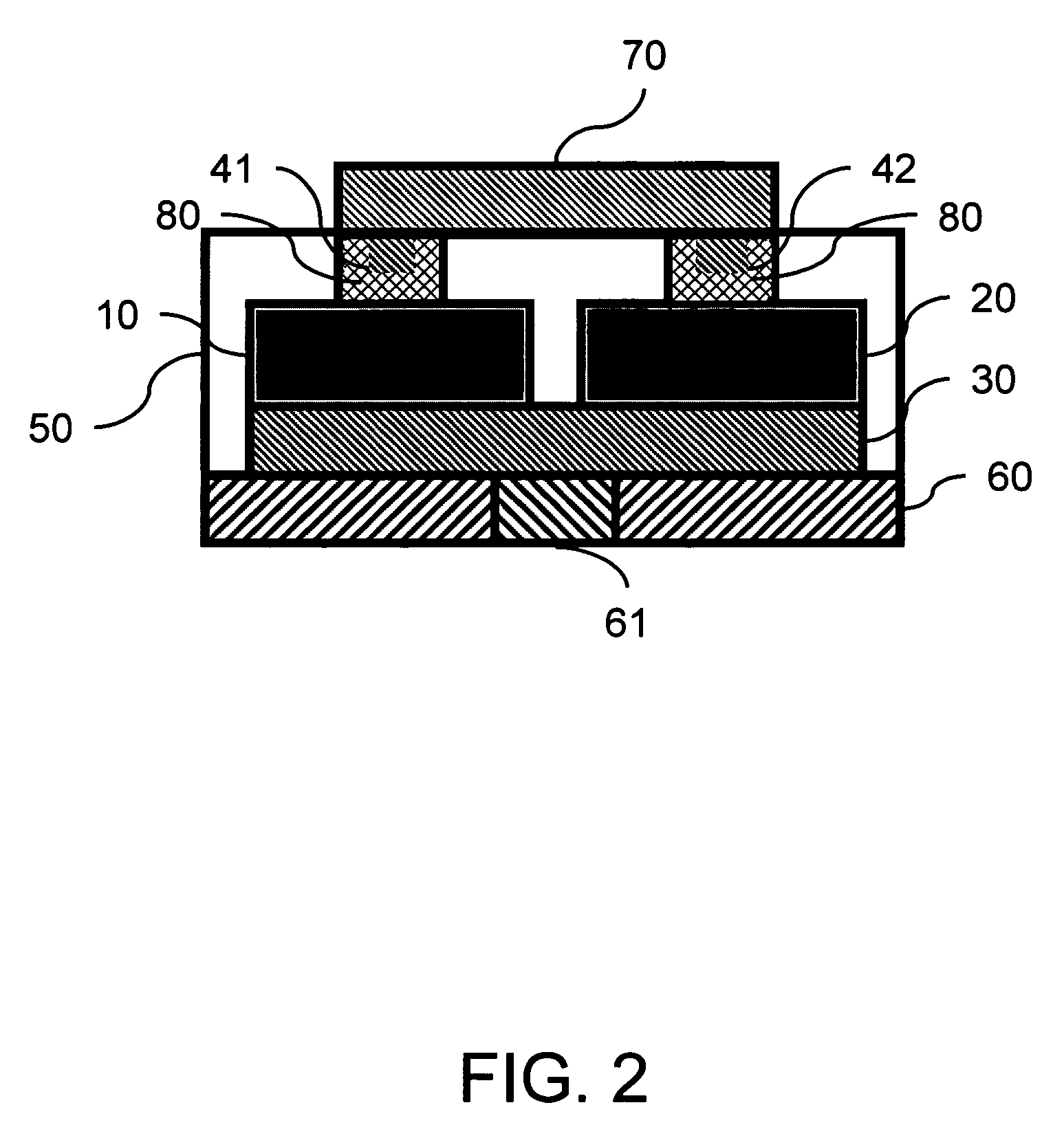

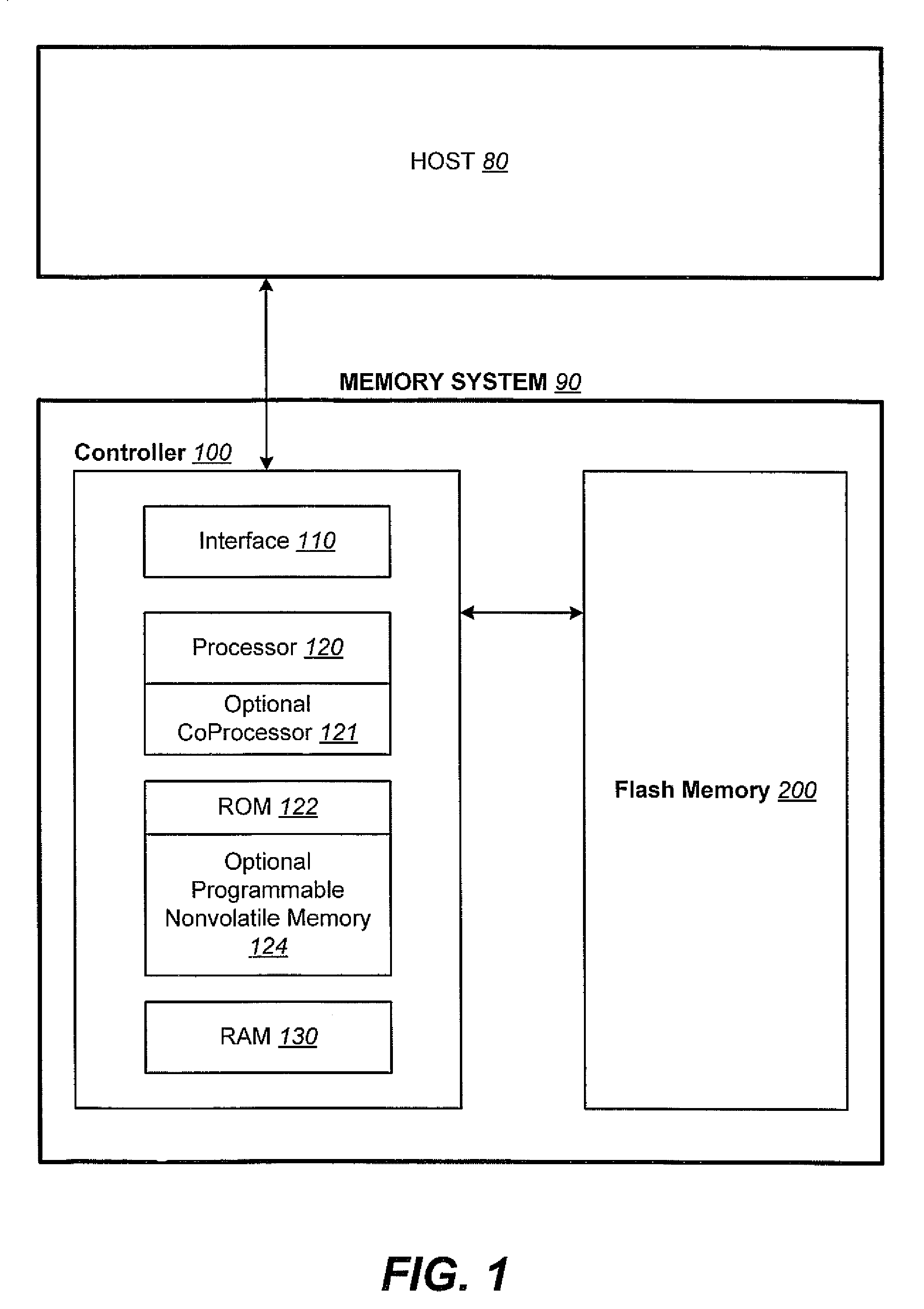

A portion of a nonvolatile memory is partitioned from a main multi-level memory array to operate as a cache. The cache memory is configured to store at less capacity per memory cell and finer granularity of write units compared to the main memory. In a block-oriented memory architecture, the cache has multiple functions, not merely to improve access speed, but is an integral part of a sequential update block system. Decisions to write data to the cache memory or directly to the main memory depend on the attributes and characteristics of the data to be written, the state of the blocks in the main memory portion and the state of the blocks in the cache portion.

Owner:SANDISK TECH LLC

Non-Volatile Memory and Method With Write Cache Partition Management Methods

InactiveUS20100174847A1Faster and robust write and read performanceIncrease burst write speedMemory architecture accessing/allocationMemory adressing/allocation/relocationGranularityMultilevel memory

A portion of a nonvolatile memory is partitioned from a main multi-level memory array to operate as a cache. The cache memory is configured to store at less capacity per memory cell and finer granularity of write units compared to the main memory. In a block-oriented memory architecture, the cache has multiple functions, not merely to improve access speed, but is an integral part of a sequential update block system. The cache memory has a capacity dynamically increased by allocation of blocks from the main memory in response to a demand to increase the capacity. Preferably, a block with an endurance count higher than average is allocated. The logical addresses of data are partitioned into zones to limit the size of the indices for the cache.

Owner:SANDISK TECH LLC

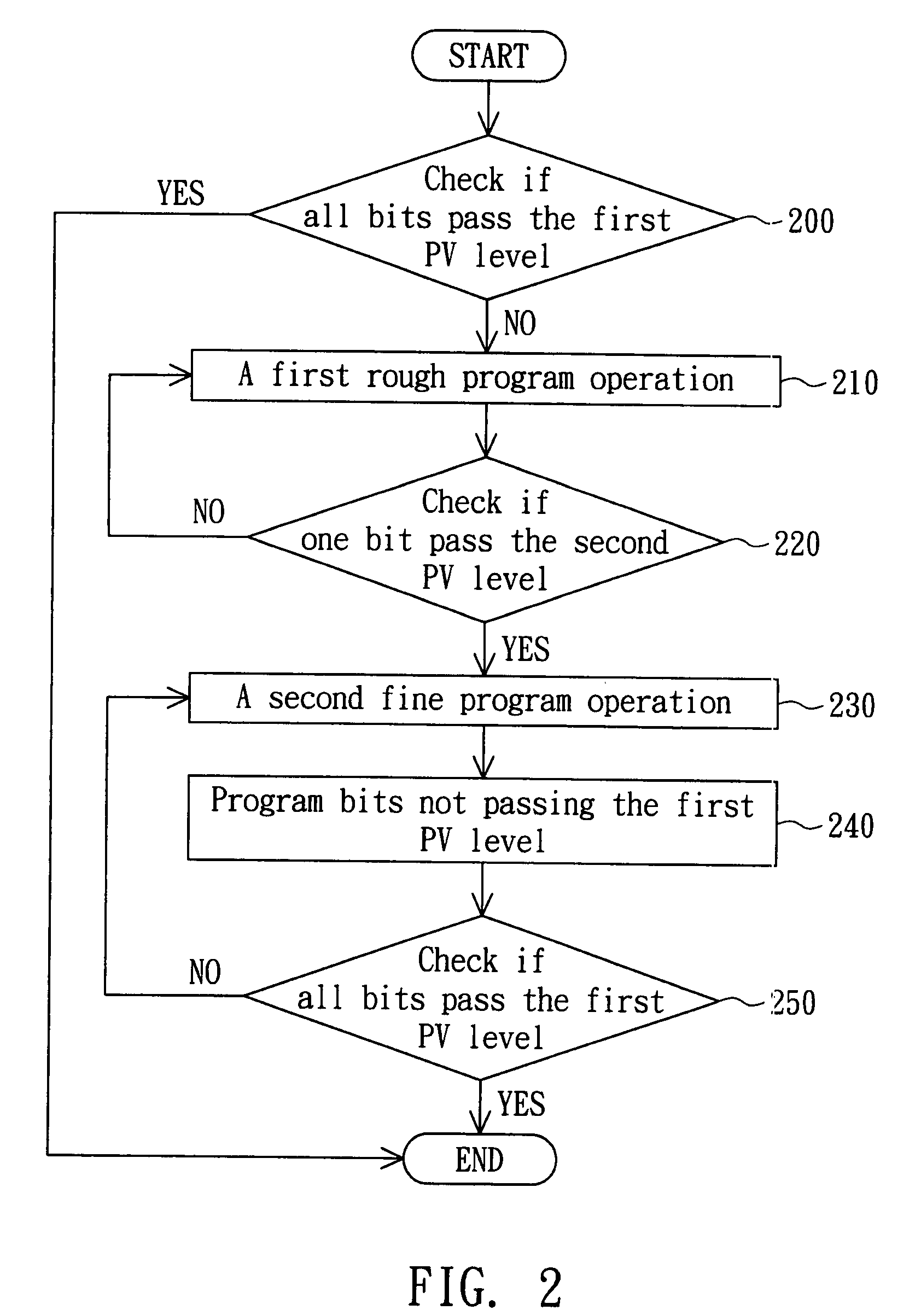

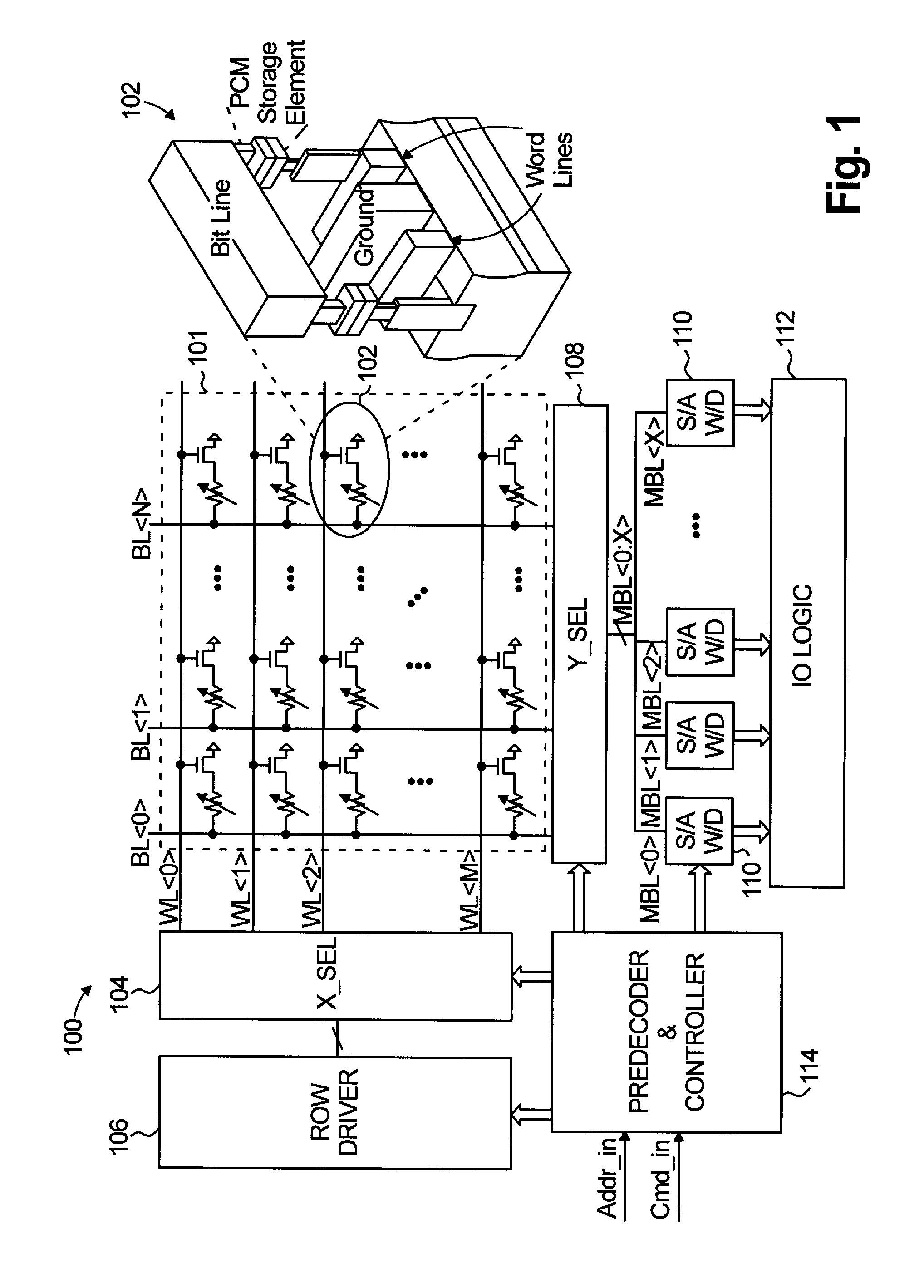

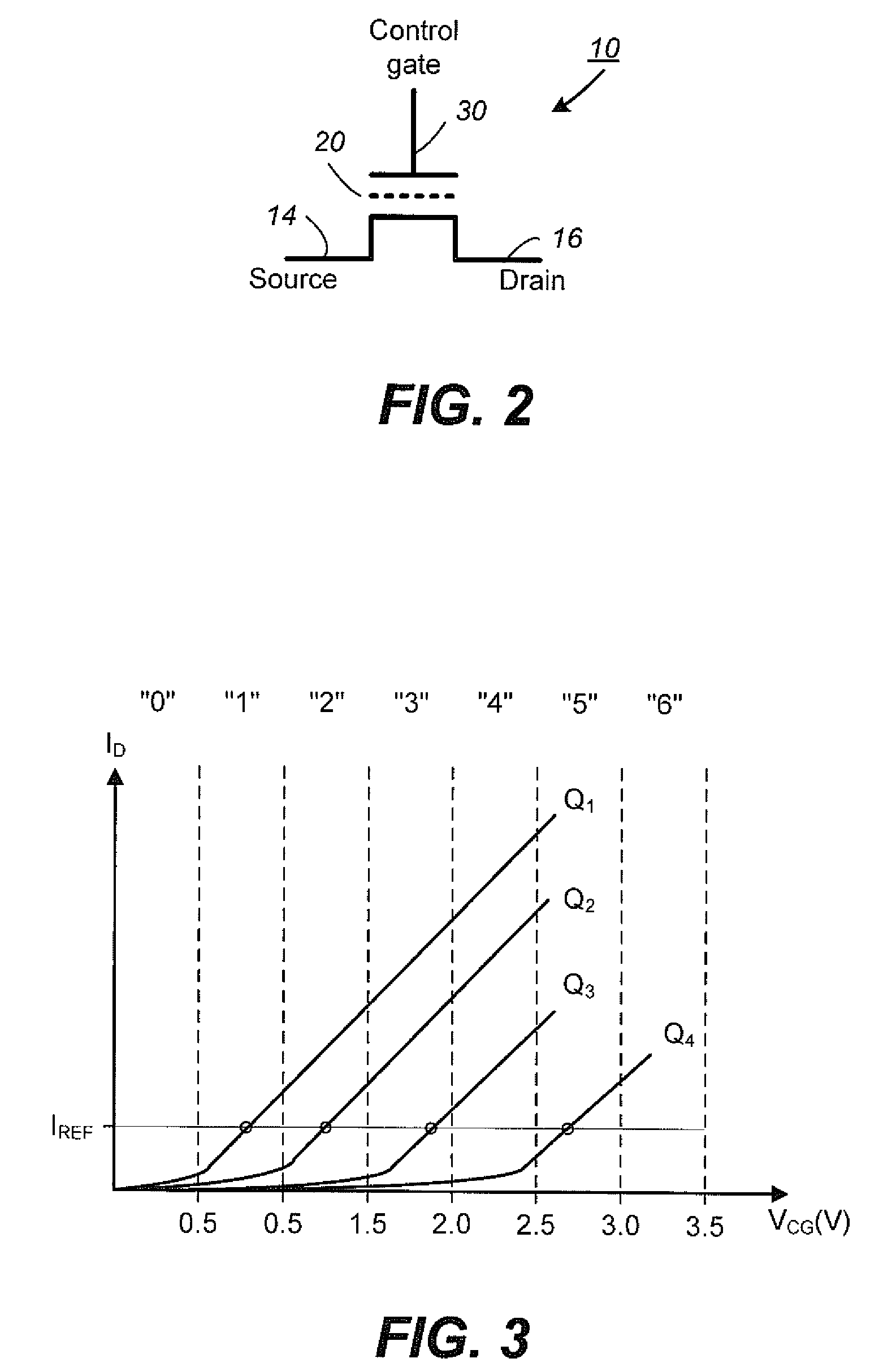

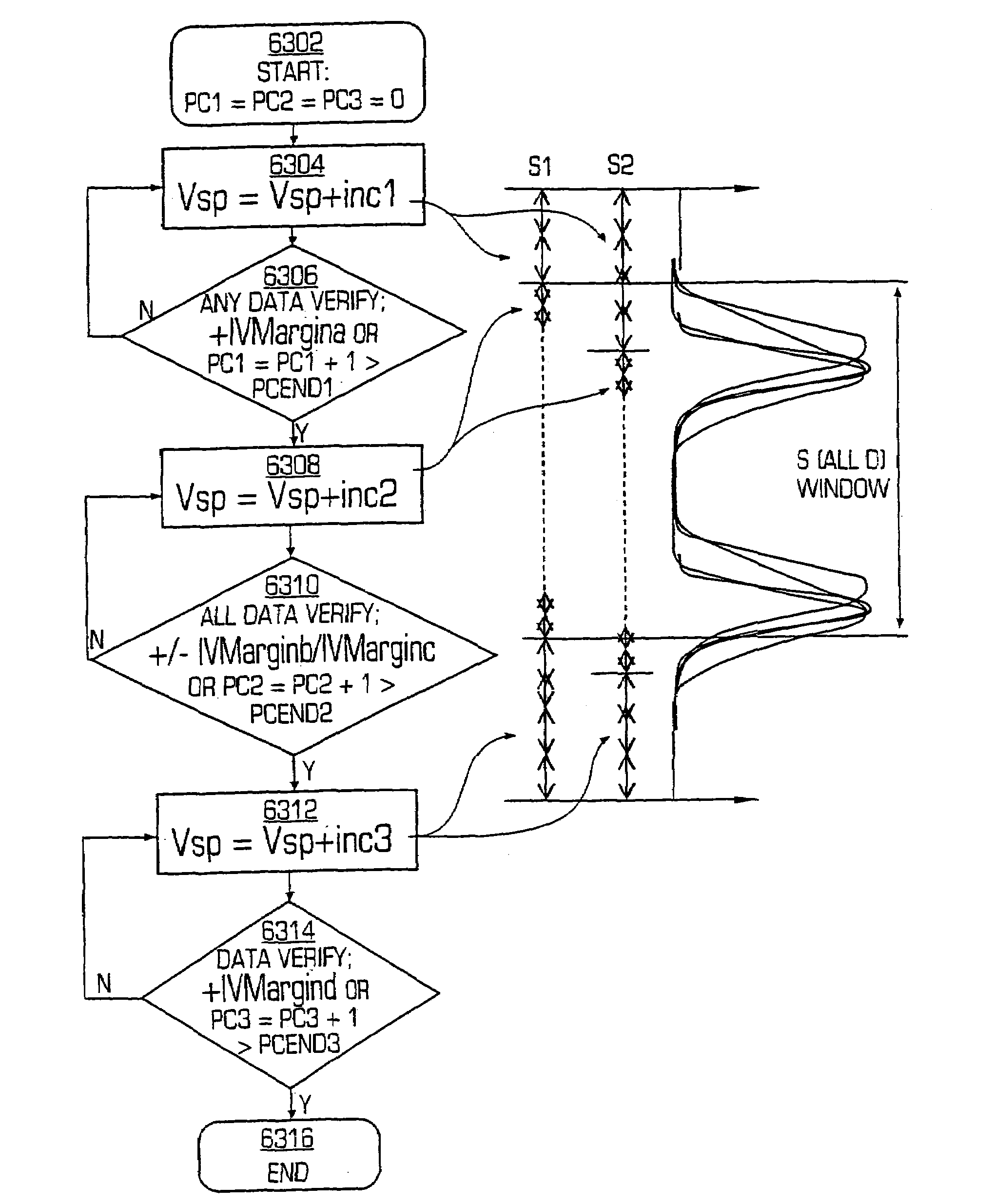

Method for programming a multilevel memory

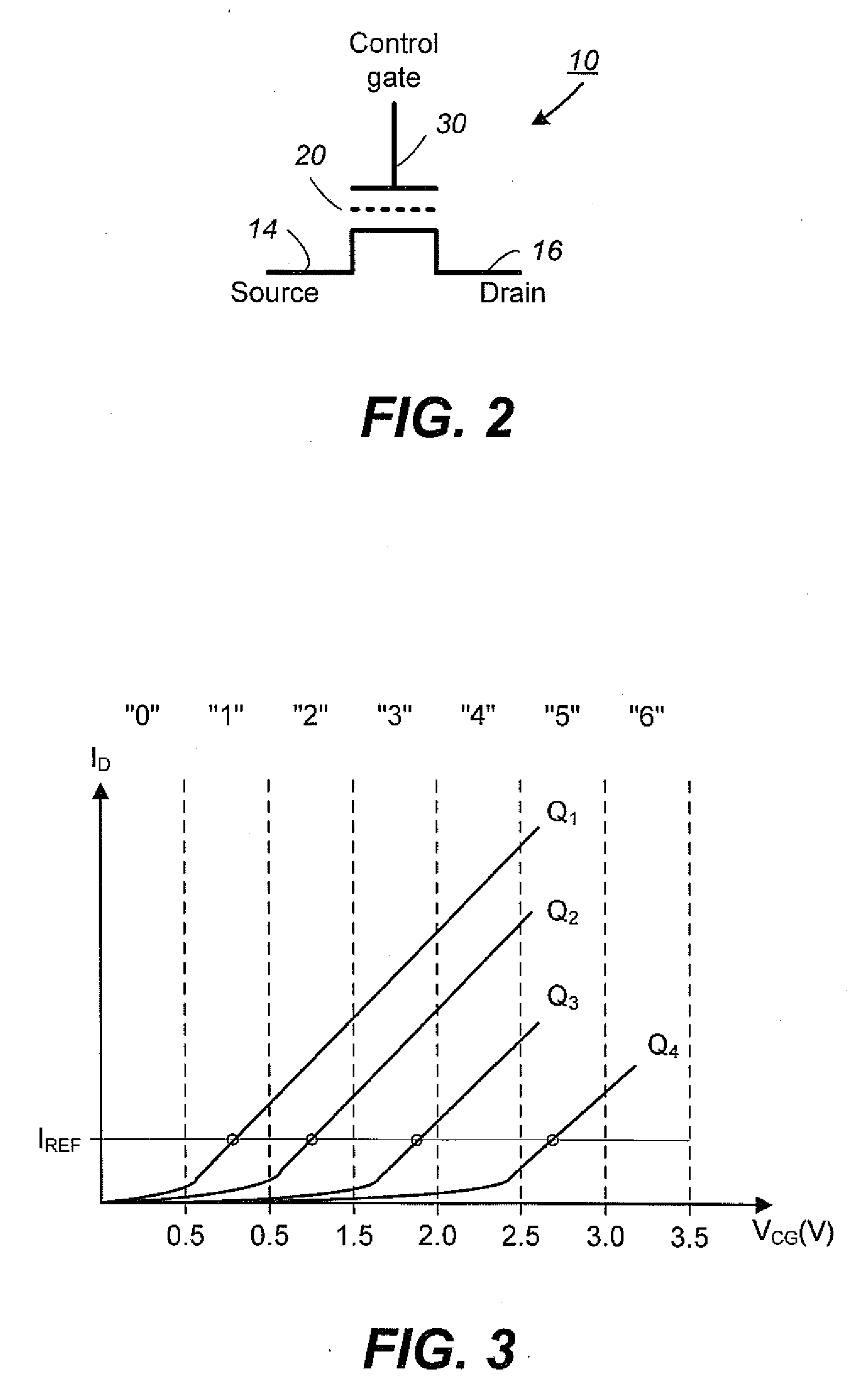

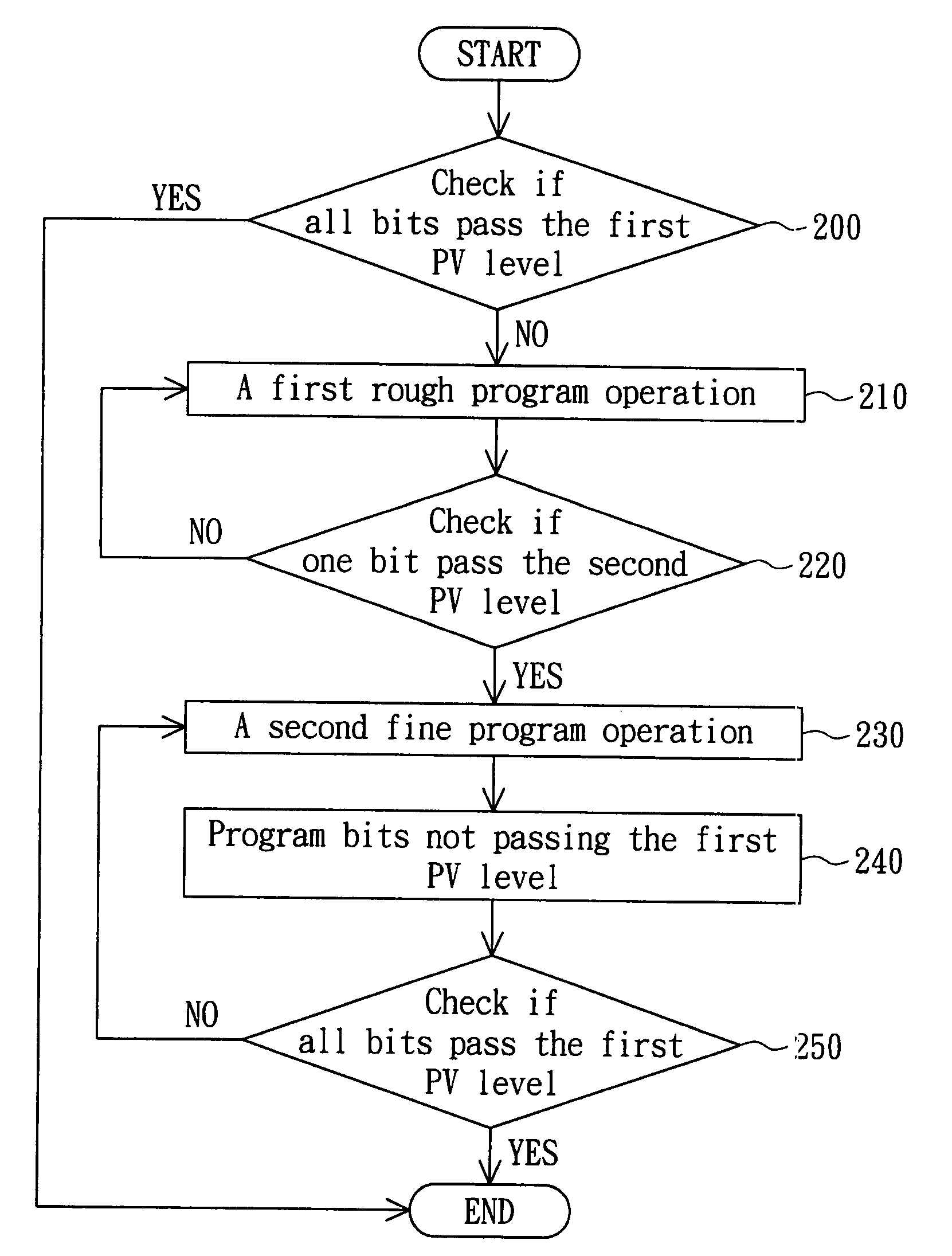

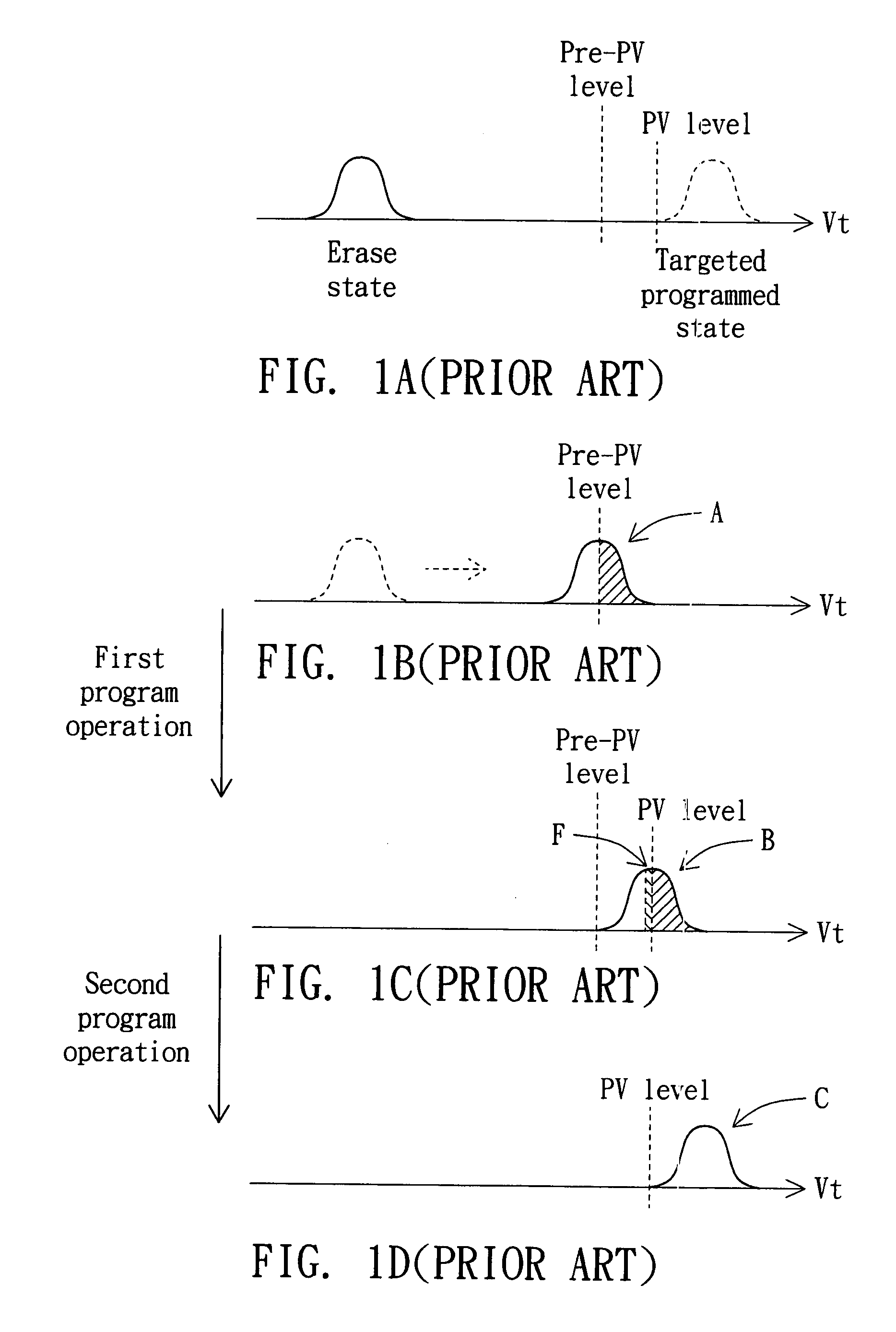

ActiveUS7447068B2Tightening the program distributionReduce bit error rateRead-only memoriesDigital storageGoal programmingMultilevel memory

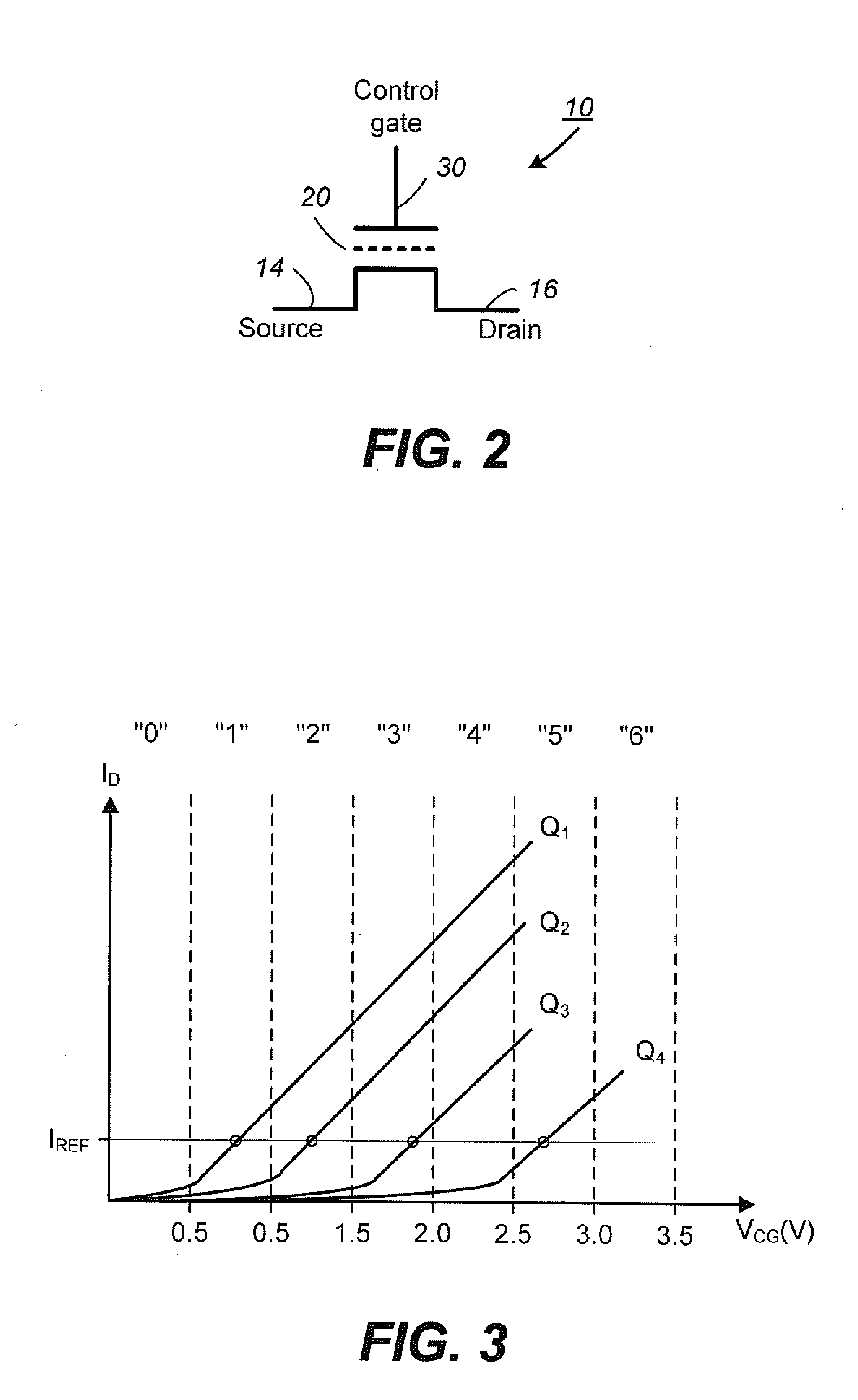

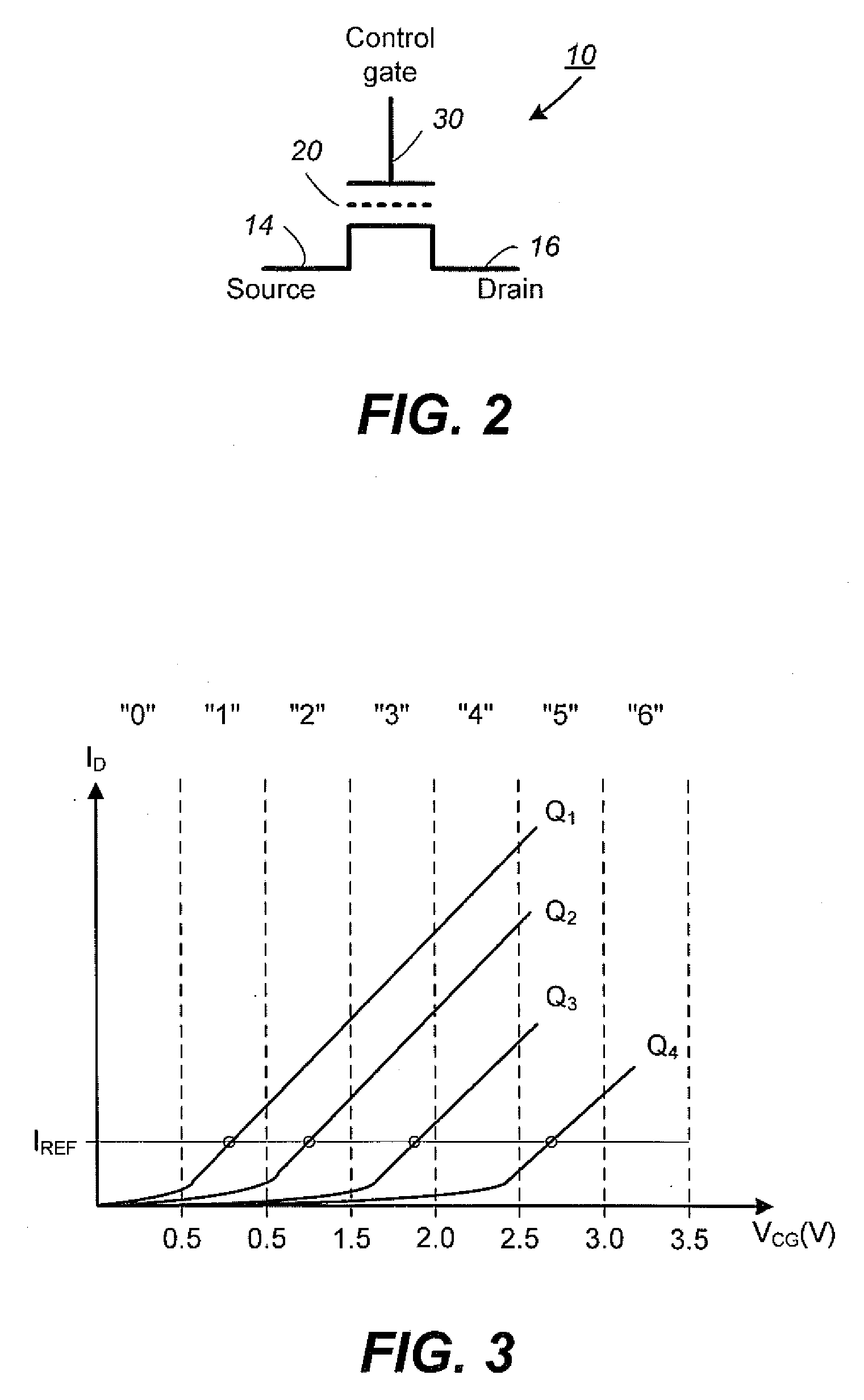

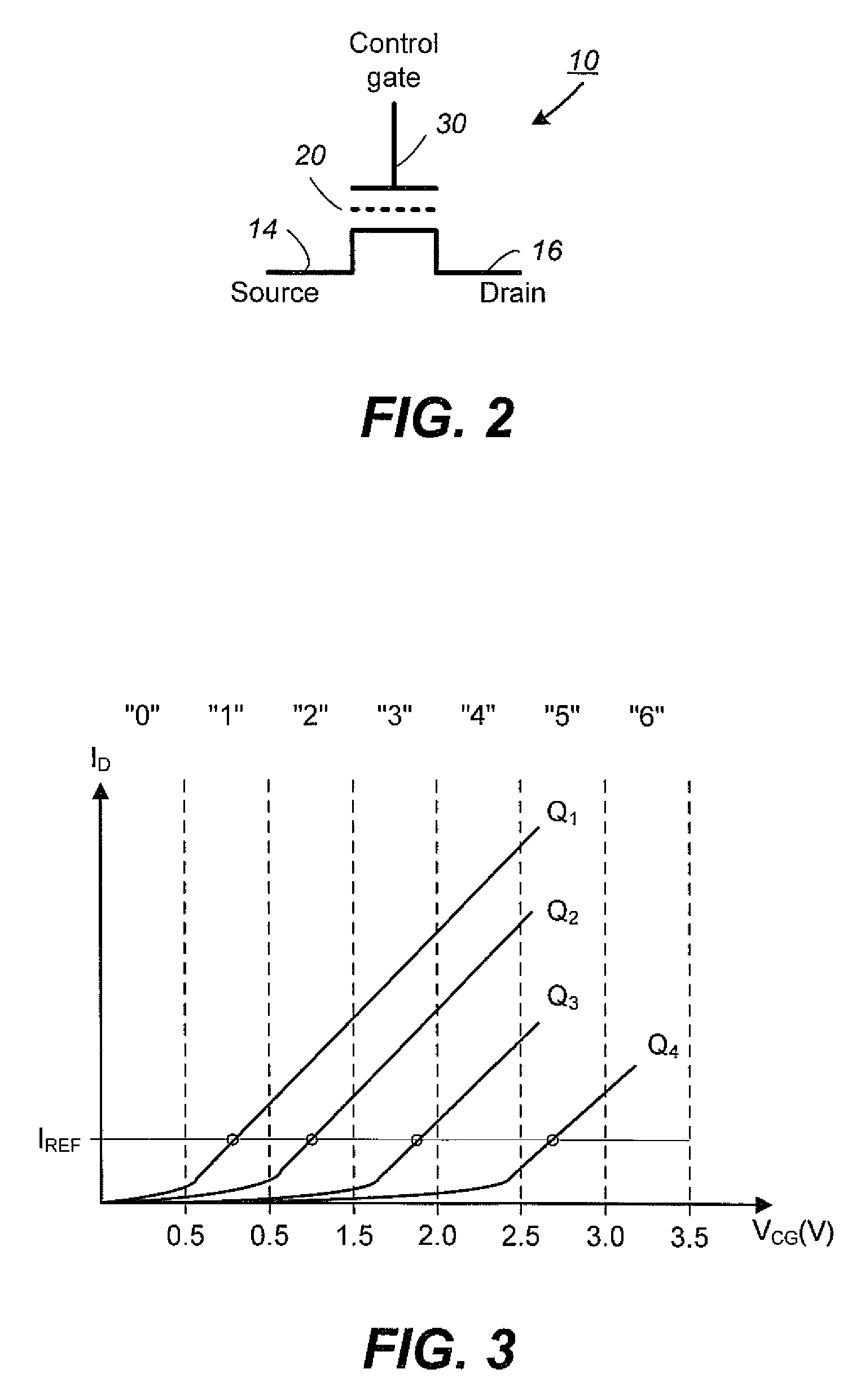

A method for programming a MLC memory is provided. The MLC memory has a number of bits, and each bit has a number of programmed states. Each programmed state has a first PV level. The method comprises programming the bits of the memory having a Vt level lower than the first PV level of the targeted programmed state such that at least one bit of them has a Vt level larger than a second PV level corresponding to a targeted programmed state, wherein the second PV level of the targeted programmed state is larger than the corresponding first PV level; and programming only the bits of the memory with a Vt level lower than the first PV level of the targeted programmed state such that each of them has a Vt level larger than the first PV level of the targeted programmed state.

Owner:MACRONIX INT CO LTD

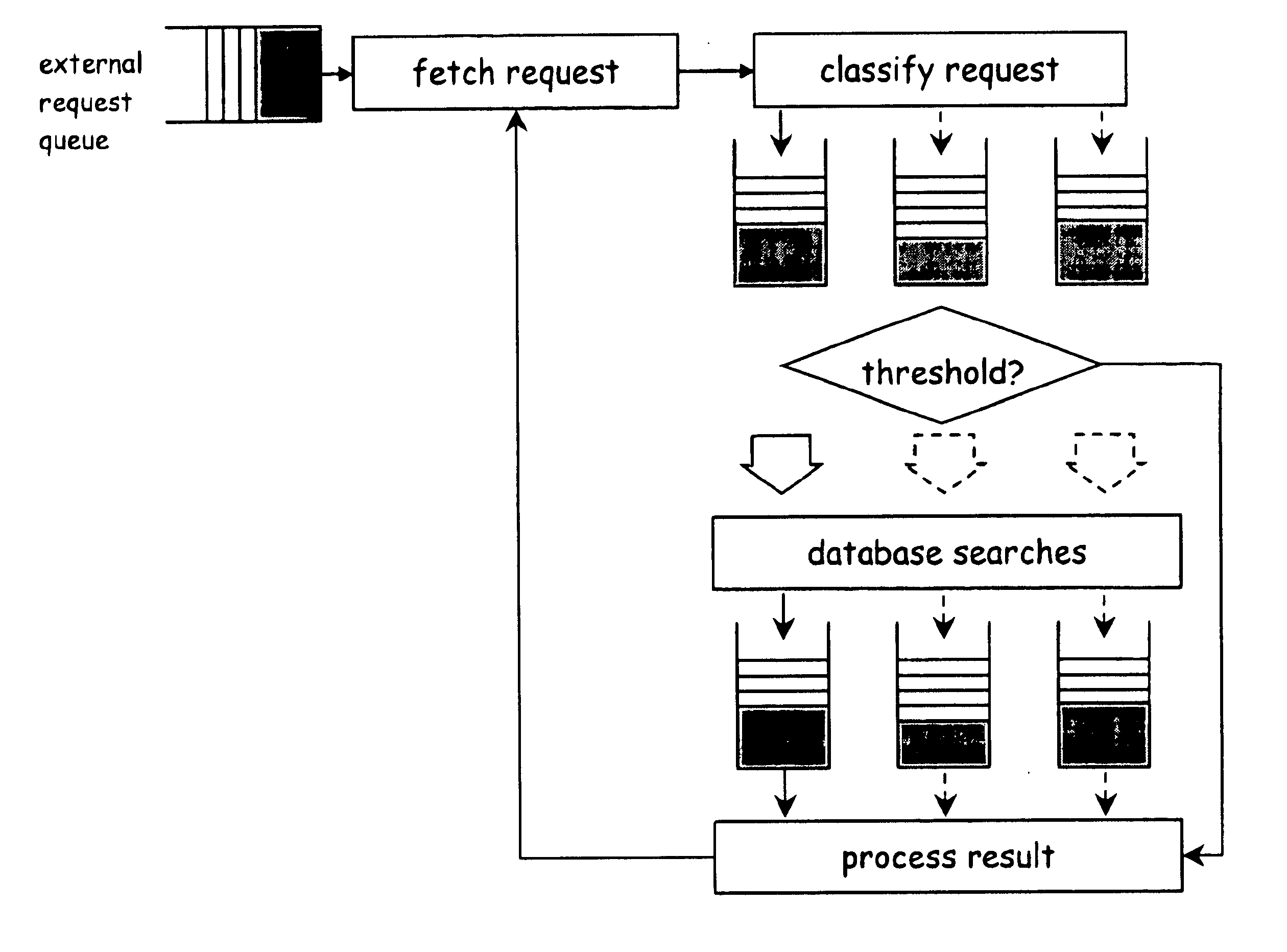

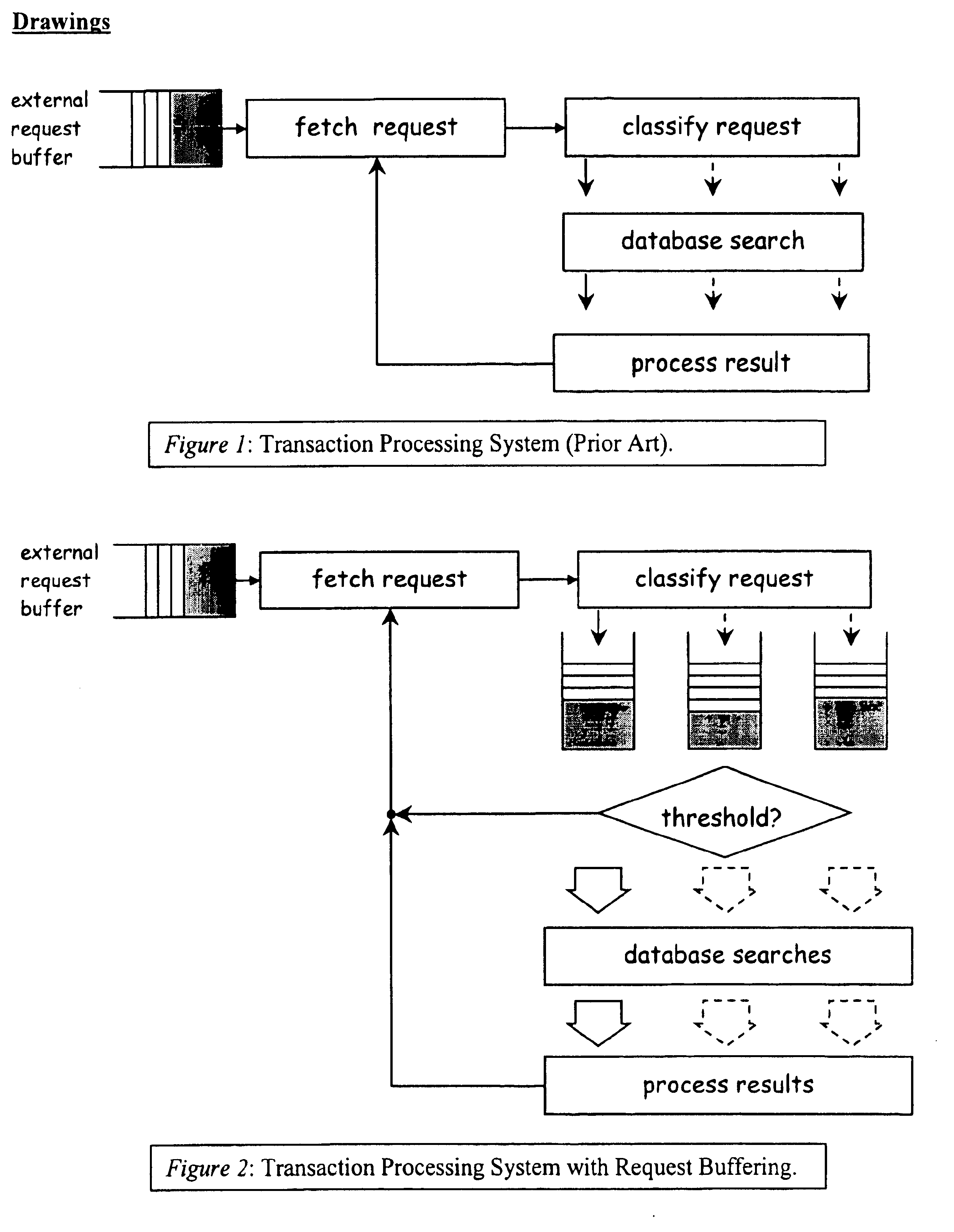

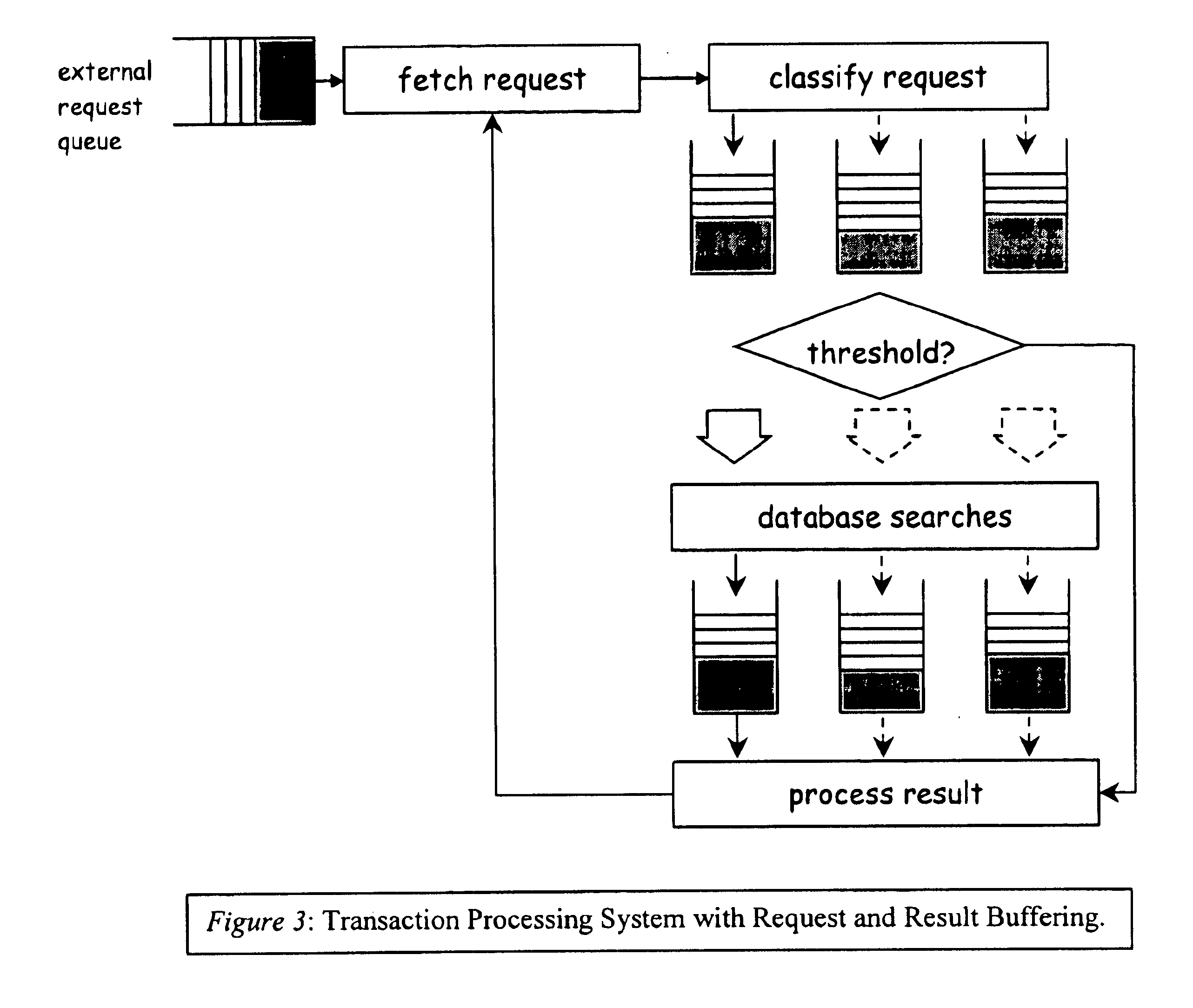

Method and apparatus for prefetching recursive data structures

InactiveUS6848029B2Improve cache hit ratioPotential throughput of the computer systemMemory architecture accessing/allocationMemory adressing/allocation/relocationApplication softwareCache hit rate

Computer systems are typically designed with multiple levels of memory hierarchy. Prefetching has been employed to overcome the latency of fetching data or instructions from or to memory. Prefetching works well for data structures with regular memory access patterns, but less so for data structures such as trees, hash tables, and other structures in which the datum that will be used is not known a priori. The present invention significantly increases the cache hit rates of many important data structure traversals, and thereby the potential throughput of the computer system and application in which it is employed. The invention is applicable to those data structure accesses in which the traversal path is dynamically determined. The invention does this by aggregating traversal requests and then pipelining the traversal of aggregated requests on the data structure. Once enough traversal requests have been accumulated so that most of the memory latency can be hidden by prefetching the accumulated requests, the data structure is traversed by performing software pipelining on some or all of the accumulated requests. As requests are completed and retired from the set of requests that are being traversed, additional accumulated requests are added to that set. This process is repeated until either an upper threshold of processed requests or a lower threshold of residual accumulated requests has been reached. At that point, the traversal results may be processed.

Owner:DIGITAL CACHE LLC +1

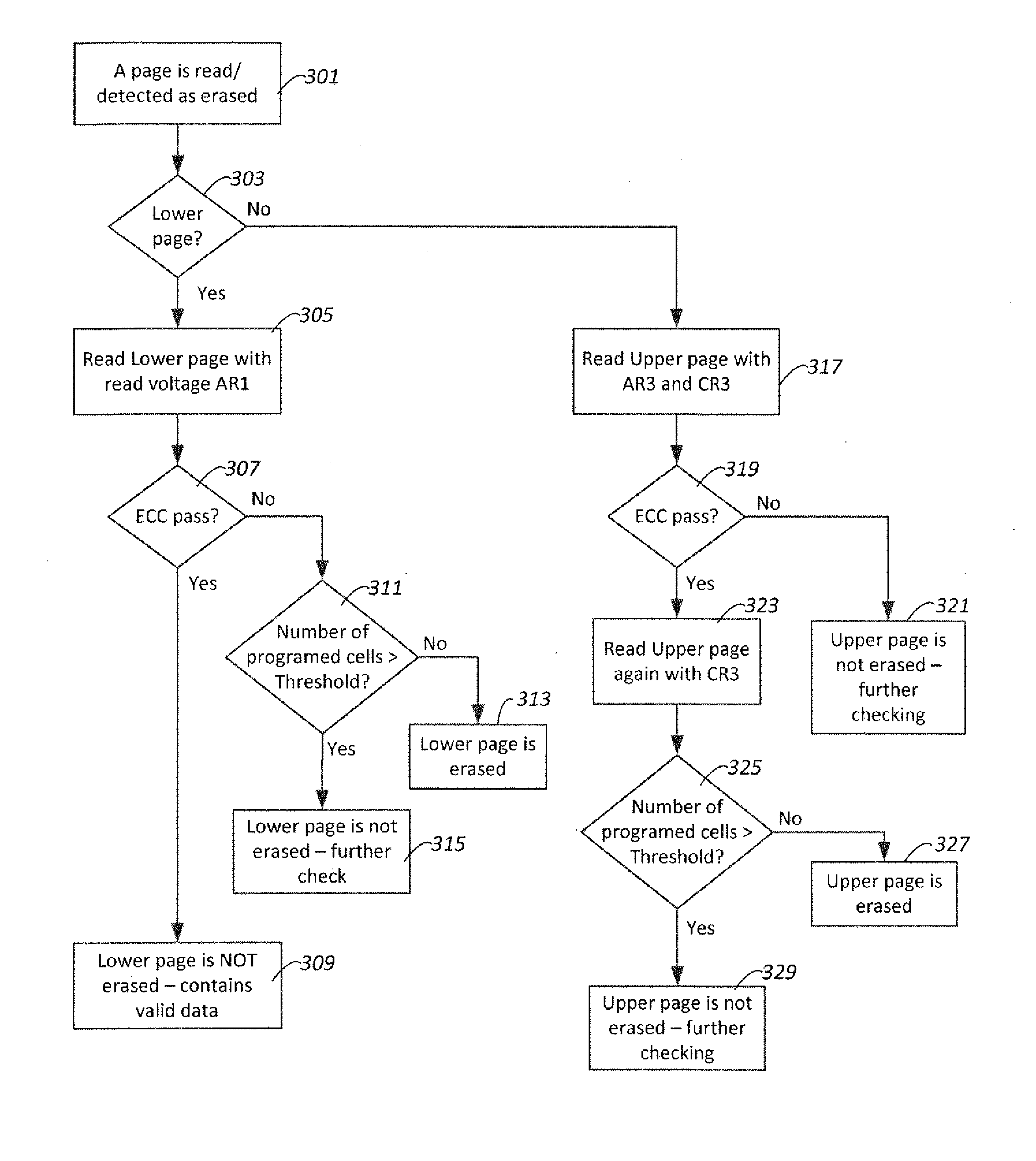

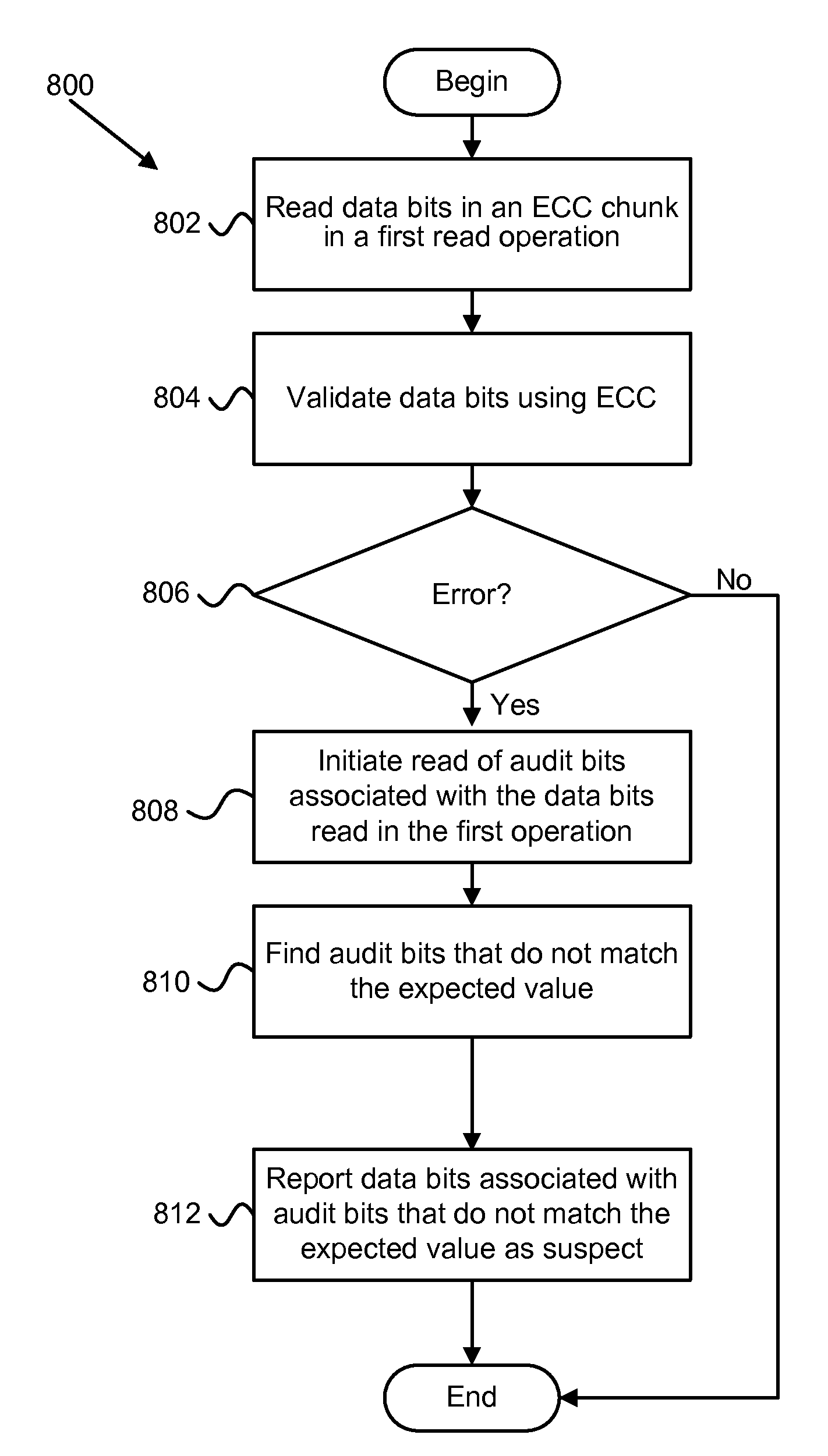

Erased Page Confirmation in Multilevel Memory

ActiveUS20140075252A1Error detection/correctionRead-only memoriesMultilevel memoryTwo-step verification

In a multi-level cell memory array, a flag that indicates that a logical page is unwritten is subject to a two-step verification. In a first verification step, the logical page is read, and ECC decoding is applied. If the first verification step indicates that the logical page is unwritten, then a second verification step counts the number of cells that are not in an unwritten condition.

Owner:SANDISK TECH LLC

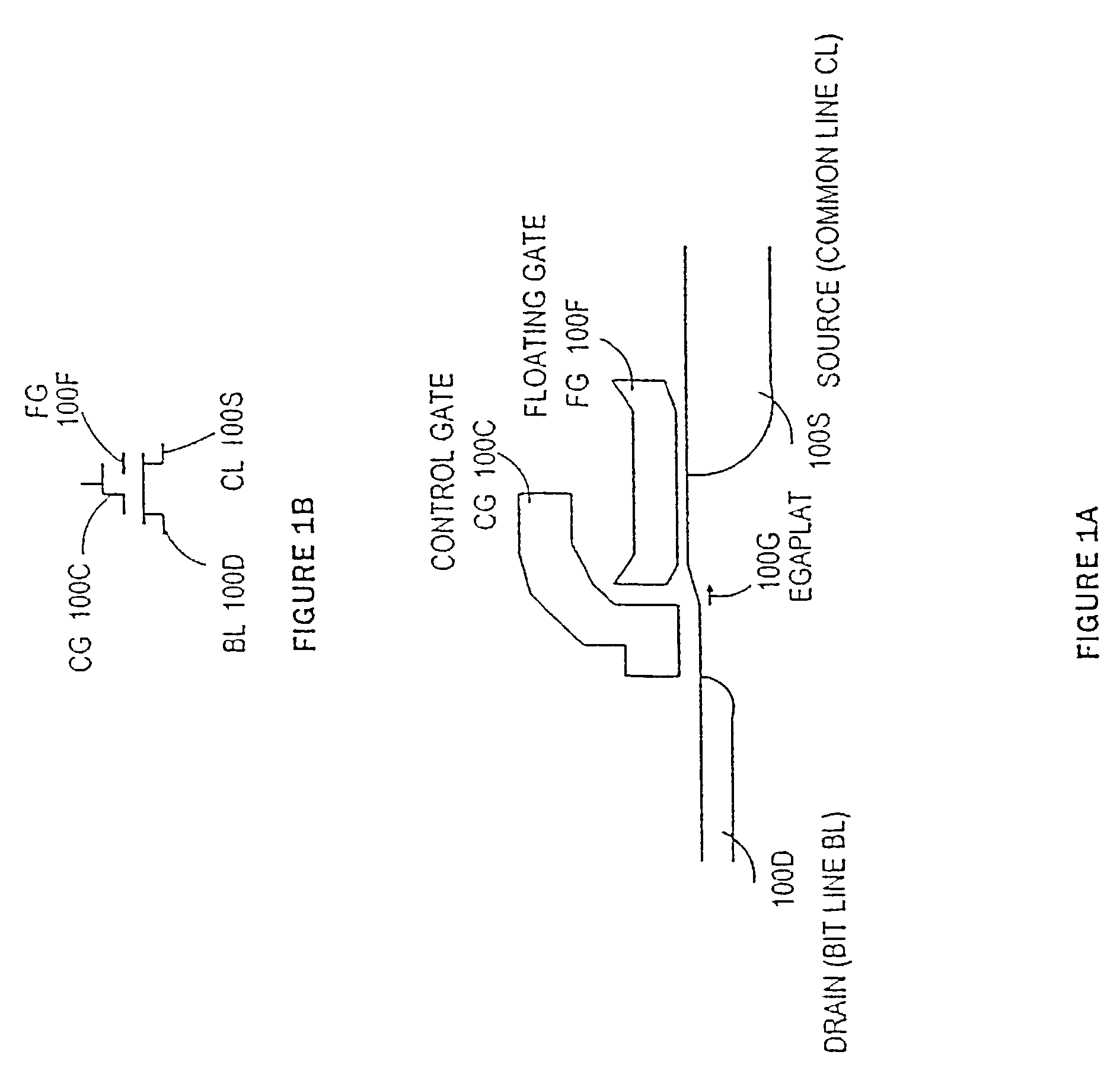

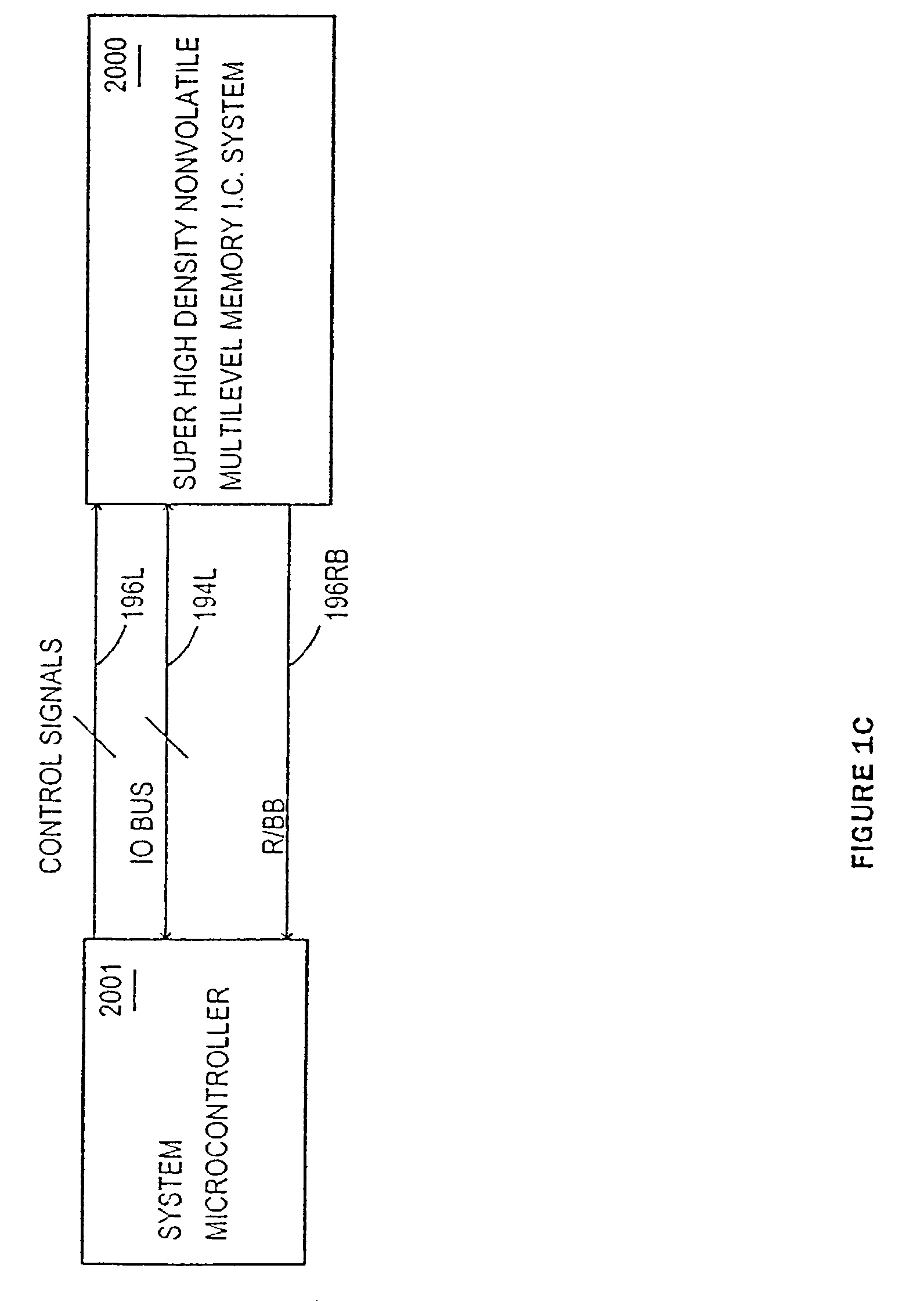

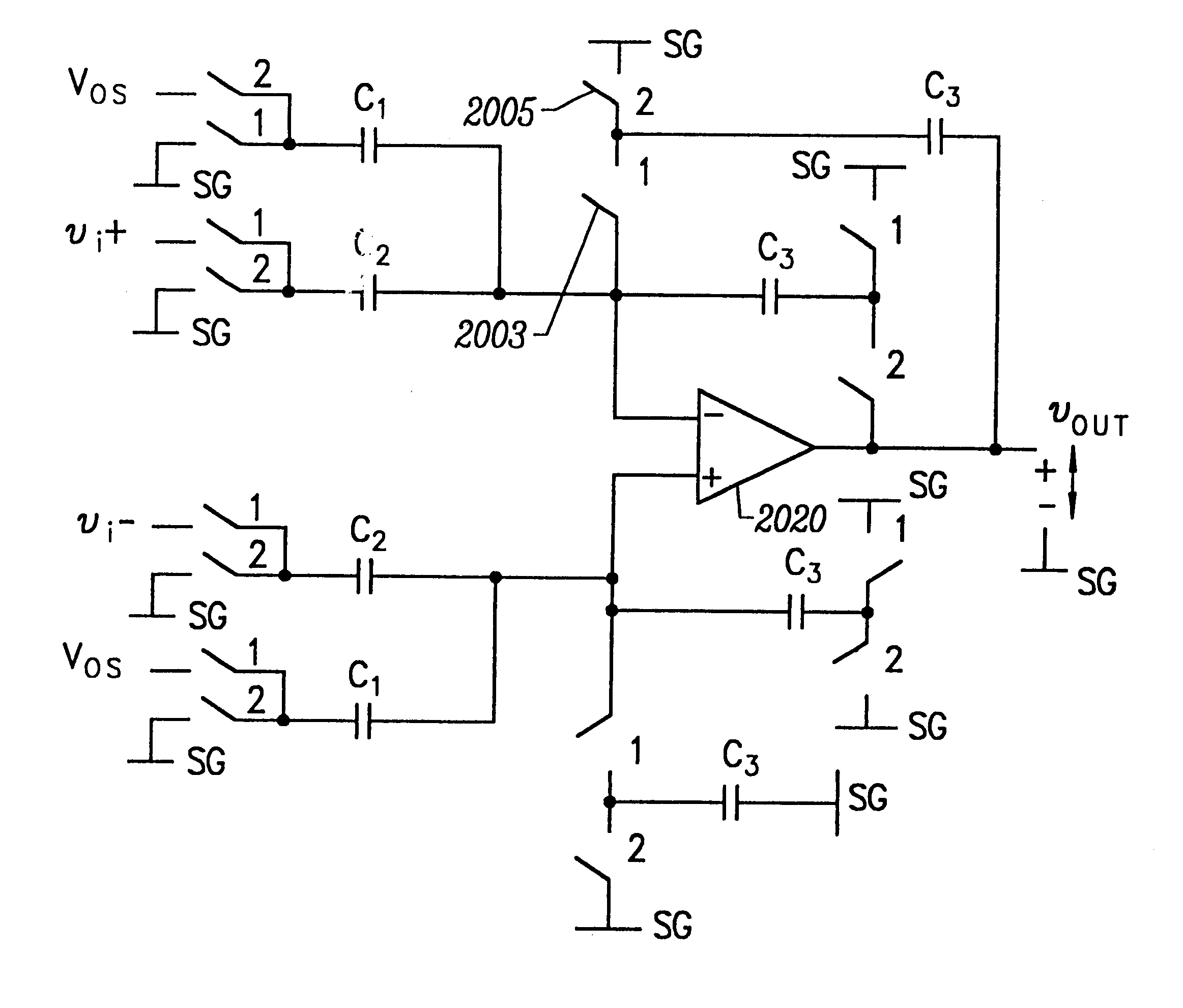

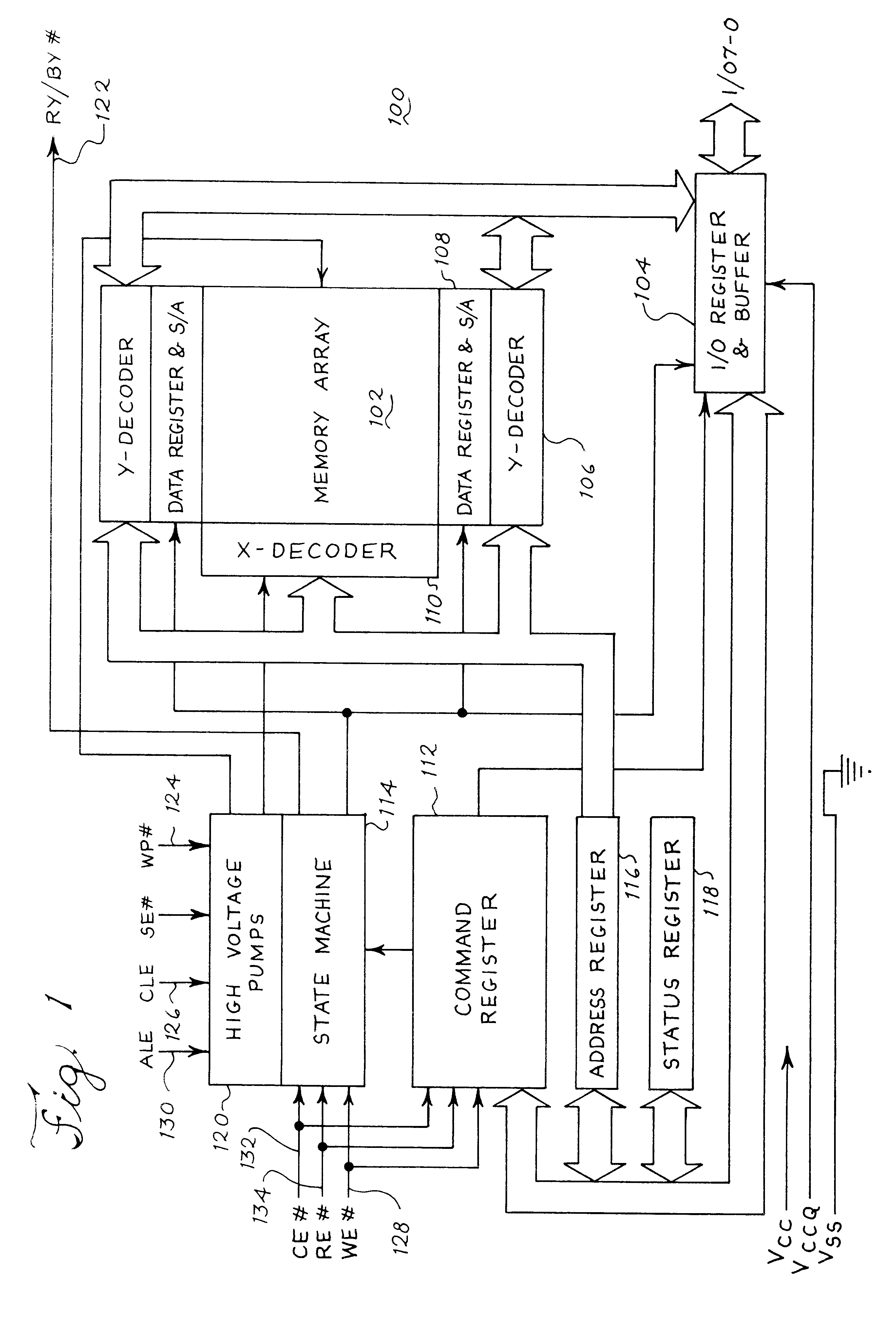

Digital multilevel memory system having multistage autozero sensing

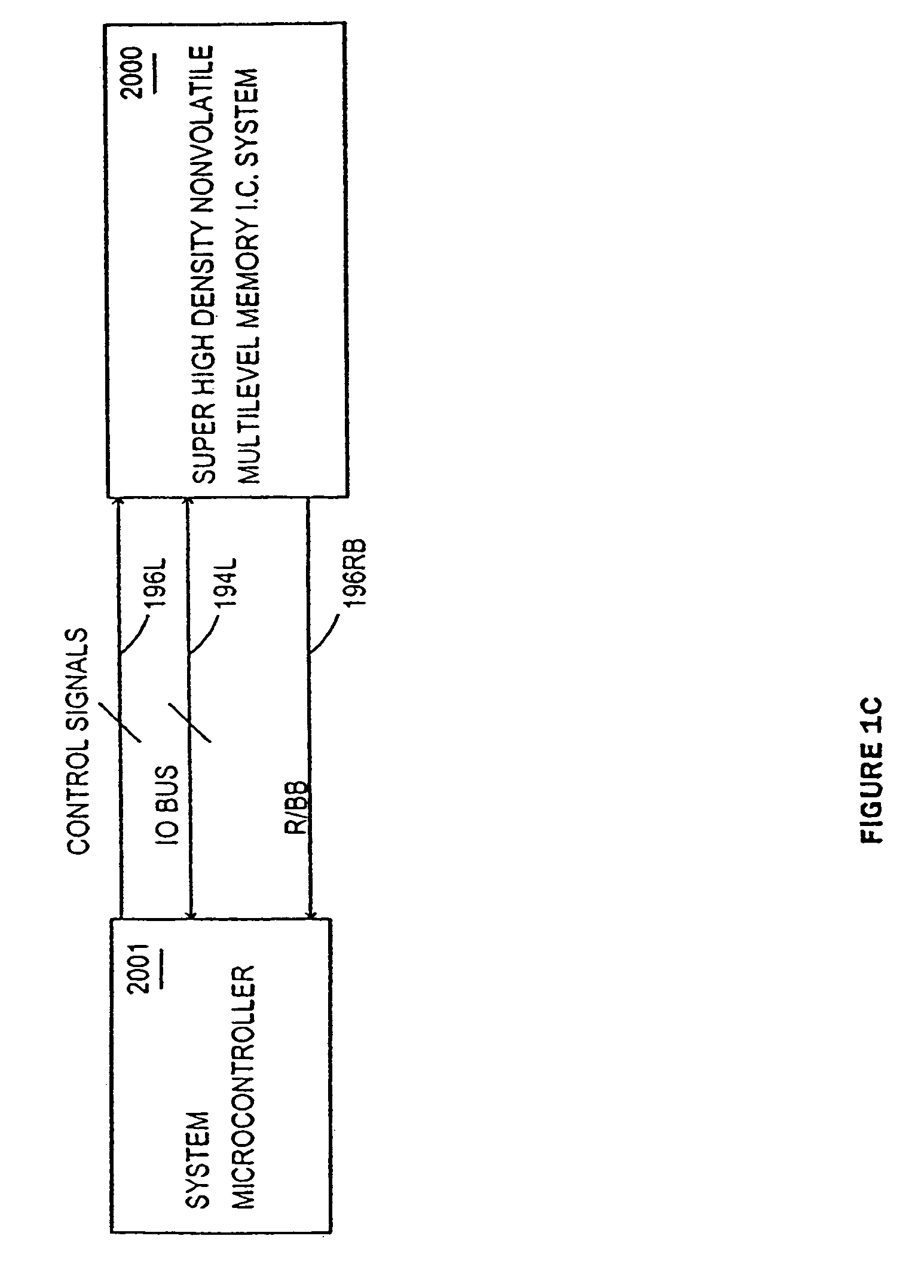

A digital multibit non-volatile memory integrated system includes autozero multistage sensing. One stage may provide local sensing with autozero. Another stage may provide global sensing with autozero. A twisted bitline may be used for array arrangement. Segment reference may be used for each segment. The system may read data cells using a current sensing one or two step binary search. The system may use inverse voltage mode or inverse current mode sensing. The system may use no current multilevel sensing. The system may use memory cell replica sensing. The system may use dynamic sensing. The system may use built-in byte redundancy. Sense amplifiers capable of sub-volt (<<1V) sensing are described.

Owner:SILICON STORAGE TECHNOLOGY

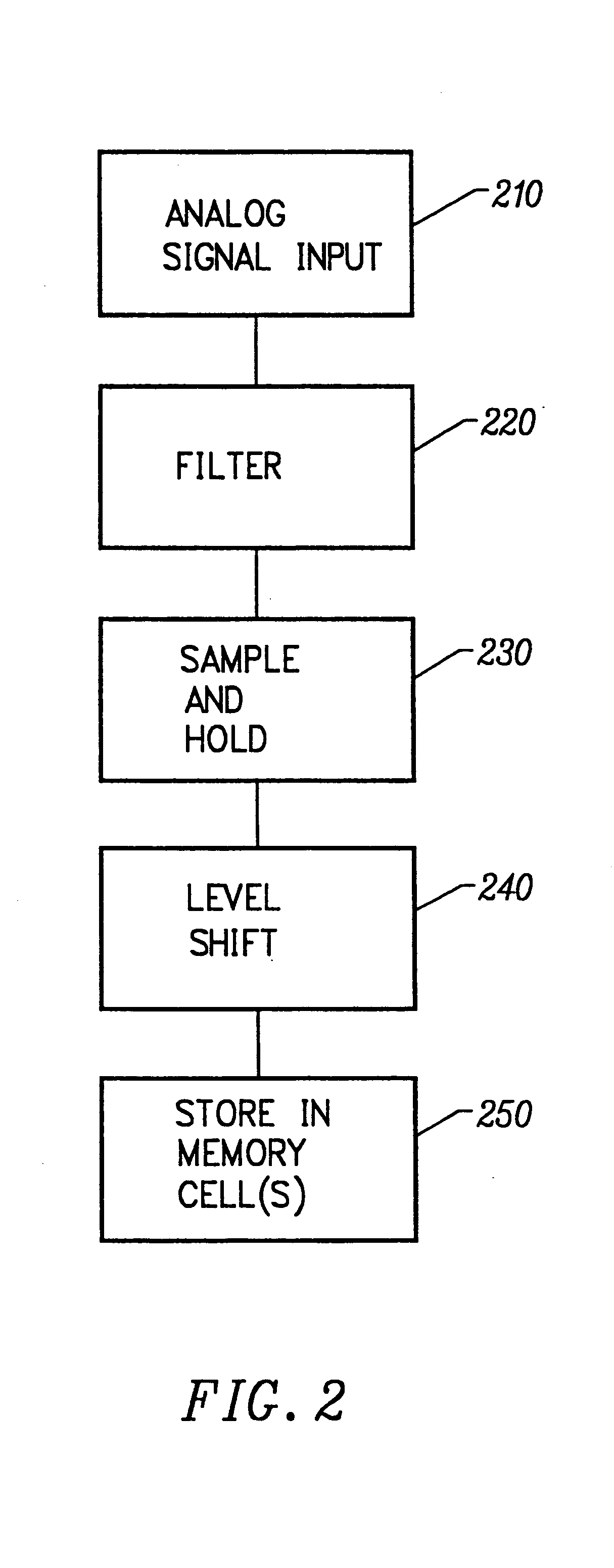

Adjustable level shifter circuits for analog or multilevel memories

InactiveUS6184726B1Prolong lifeImprove reliabilityPulse automatic controlElectric analogue storesMultilevel memoryEngineering

Level shifter circuits are used to configure analog or multilevel memory cells. A level shifter circuit generates an output voltage that is above the input voltage by an offset voltage value. The magnitude of this offset voltage or the relationship between the input and output voltages of the level shifter is adjustable or programmably selectable. Adjustments can be made after the integrated circuits is fabricated and packaged. Adjustments are made by configuring bits of data in the integrated circuit to indicate the offset voltage or other parameters. These configuration bits are implemented using latches, flip-flops, registers, memory cells, or other storage circuits.

Owner:SANDISK CORP

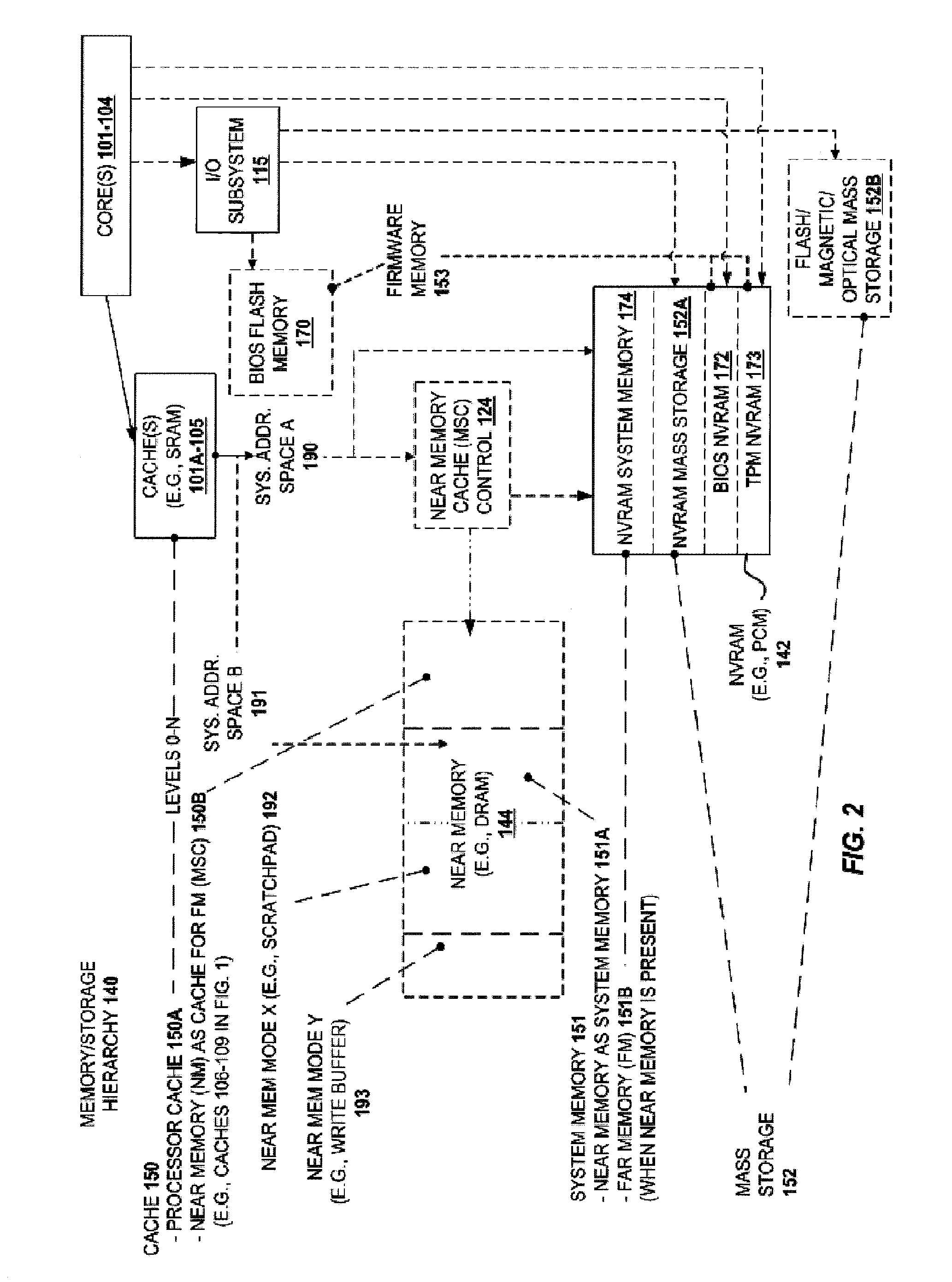

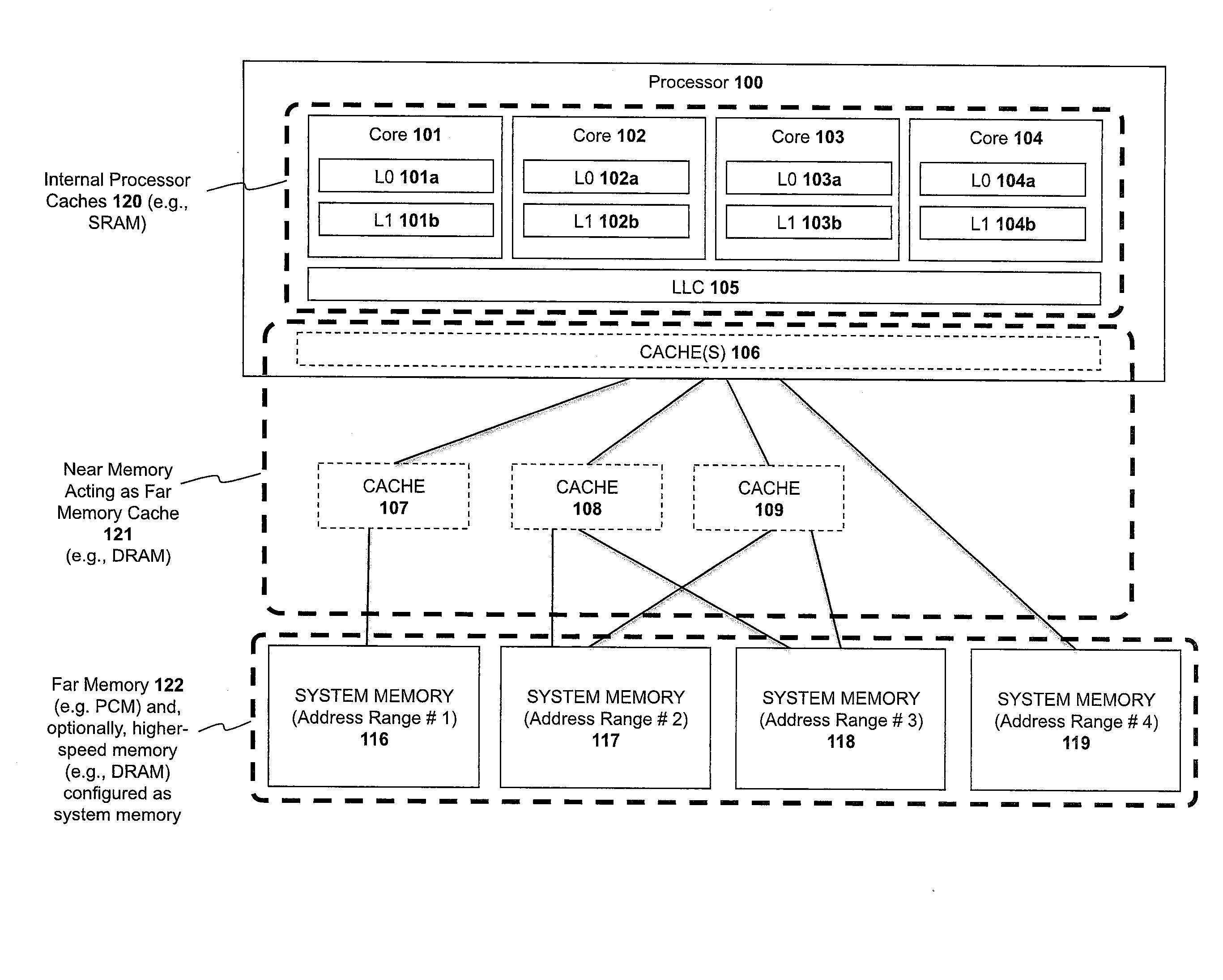

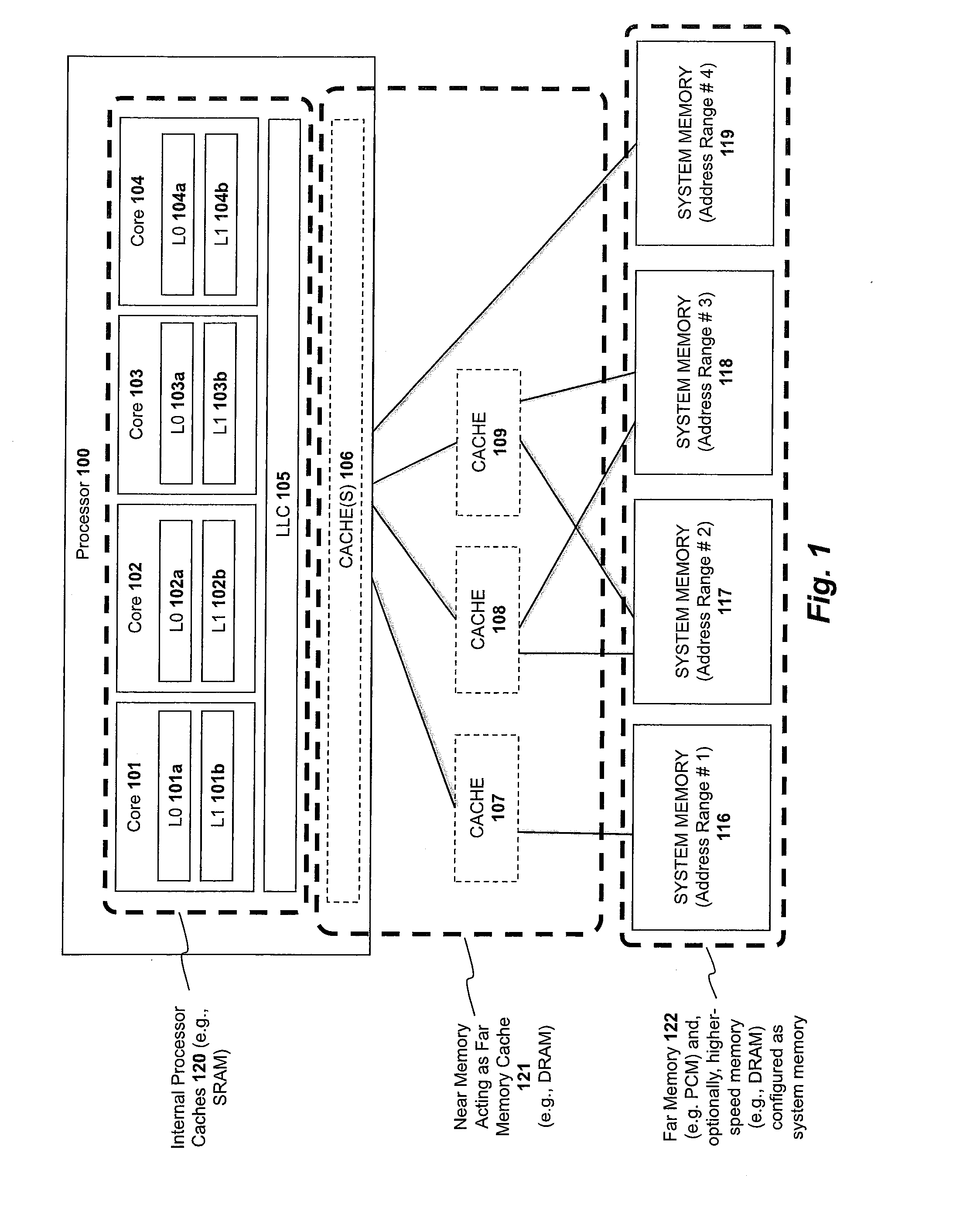

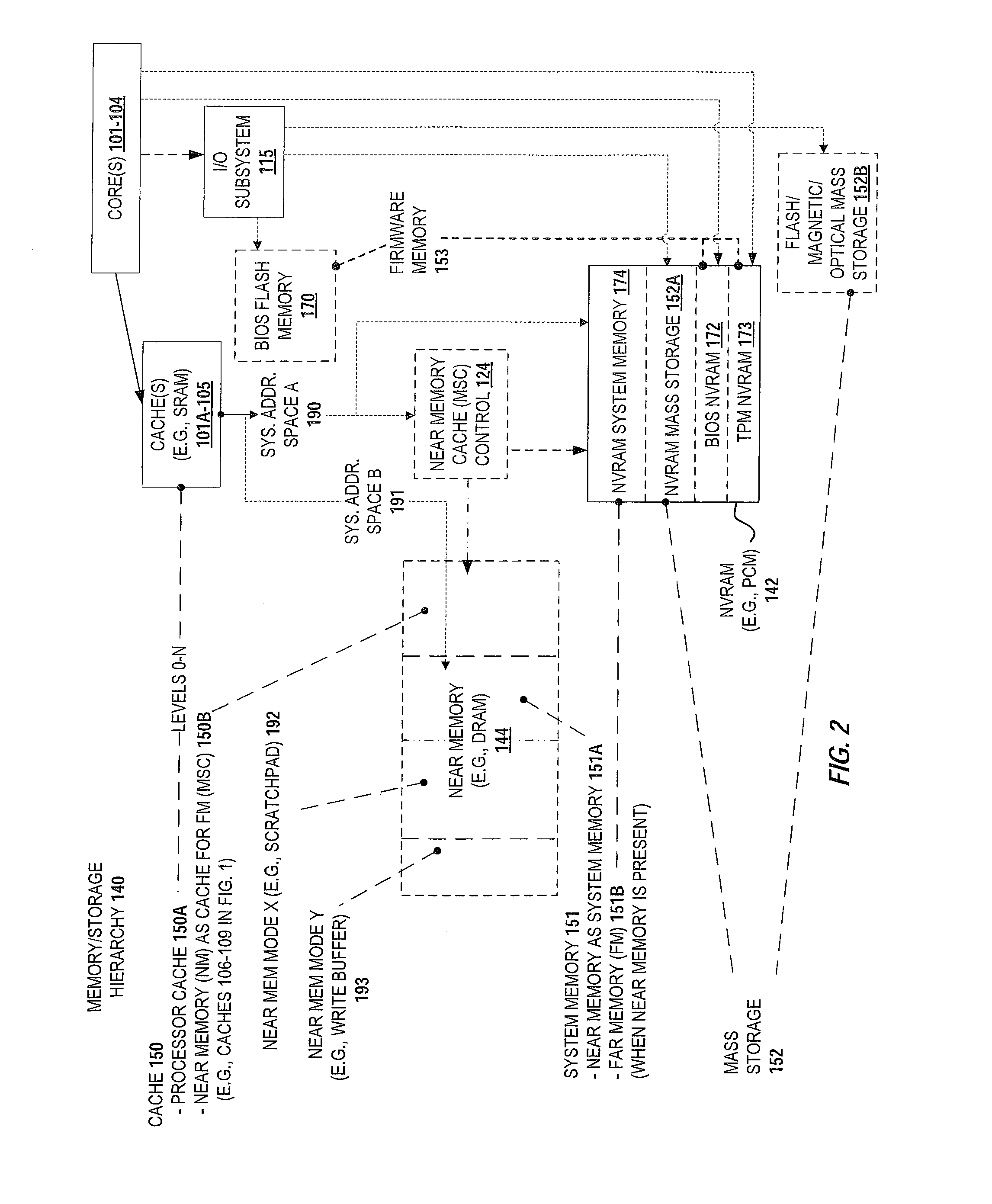

Dynamic partial power down of memory-side cache in a 2-level memory hierarchy

ActiveUS20140304475A1Memory architecture accessing/allocationMemory adressing/allocation/relocationMemory hierarchyMultilevel memory

A system and method are described for flushing a specified region of a memory side cache (MSC) within a multi-level memory hierarchy. For example, a computer system according to one embodiment comprises: a memory subsystem comprised of a non-volatile system memory and a volatile memory side cache (MSC) for caching portions of the non-volatile system memory; and a flush engine for flushing a specified region of the MSC to the non-volatile system memory in response to a deactivation condition associated with the specified region of the MSC.

Owner:INTEL CORP

Nonvolatile Memory With Write Cache Having Flush/Eviction Methods

ActiveUS20100174846A1Faster and robust write and read performanceIncrease burst write speedMemory architecture accessing/allocationEnergy efficient ICTGranularityMultilevel memory

A portion of a nonvolatile memory is partitioned from a main multi-level memory array to operate as a cache. The cache memory is configured to store at less capacity per memory cell and finer granularity of write units compared to the main memory. In a block-oriented memory architecture, the cache has multiple functions, not merely to improve access speed, but is an integral part of a sequential update block system. Decisions to archive data from the cache memory to the main memory depend on the attributes of the data to be archived, the state of the blocks in the main memory portion and the state of the blocks in the cache portion.

Owner:SANDISK TECH LLC

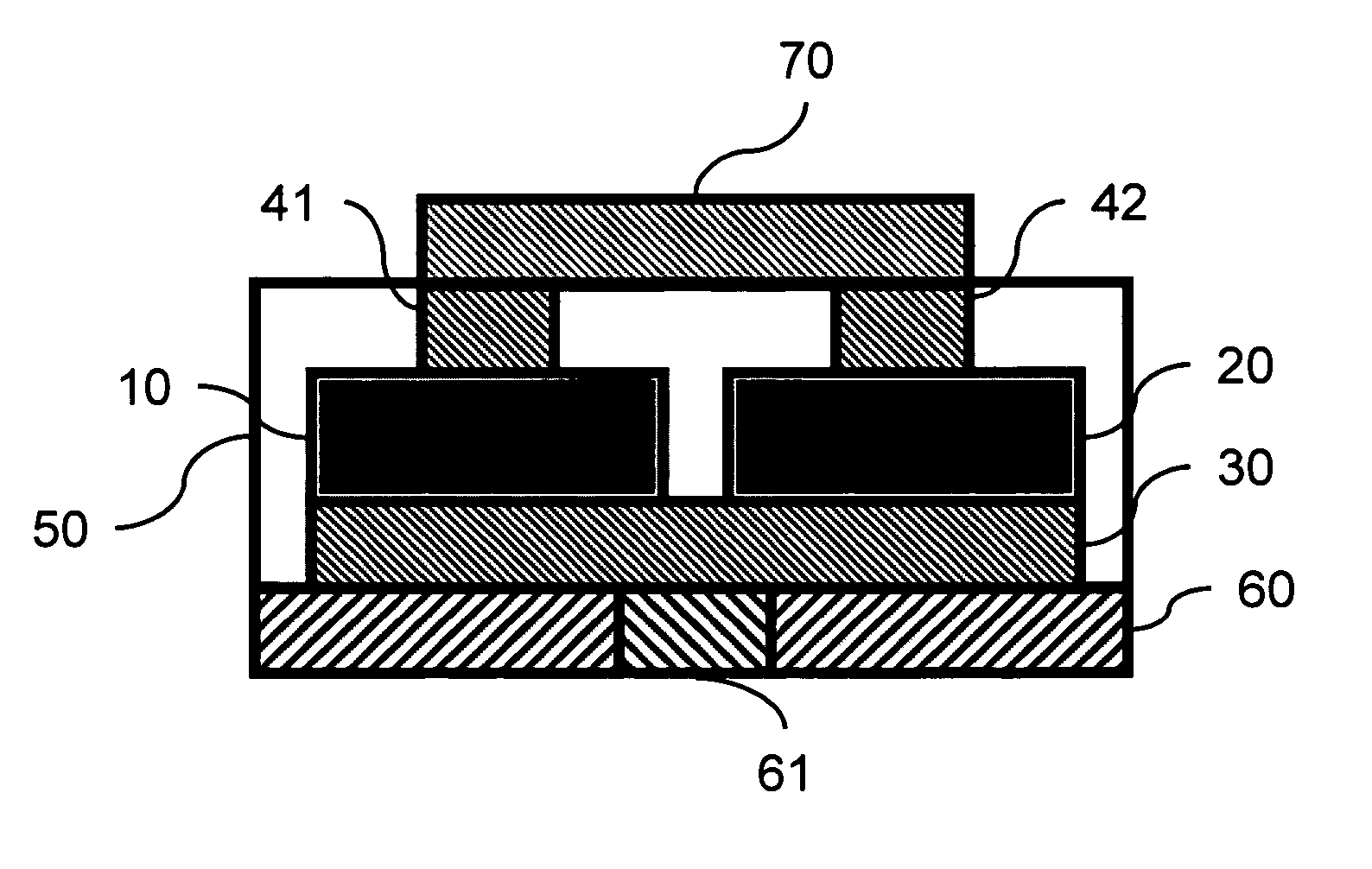

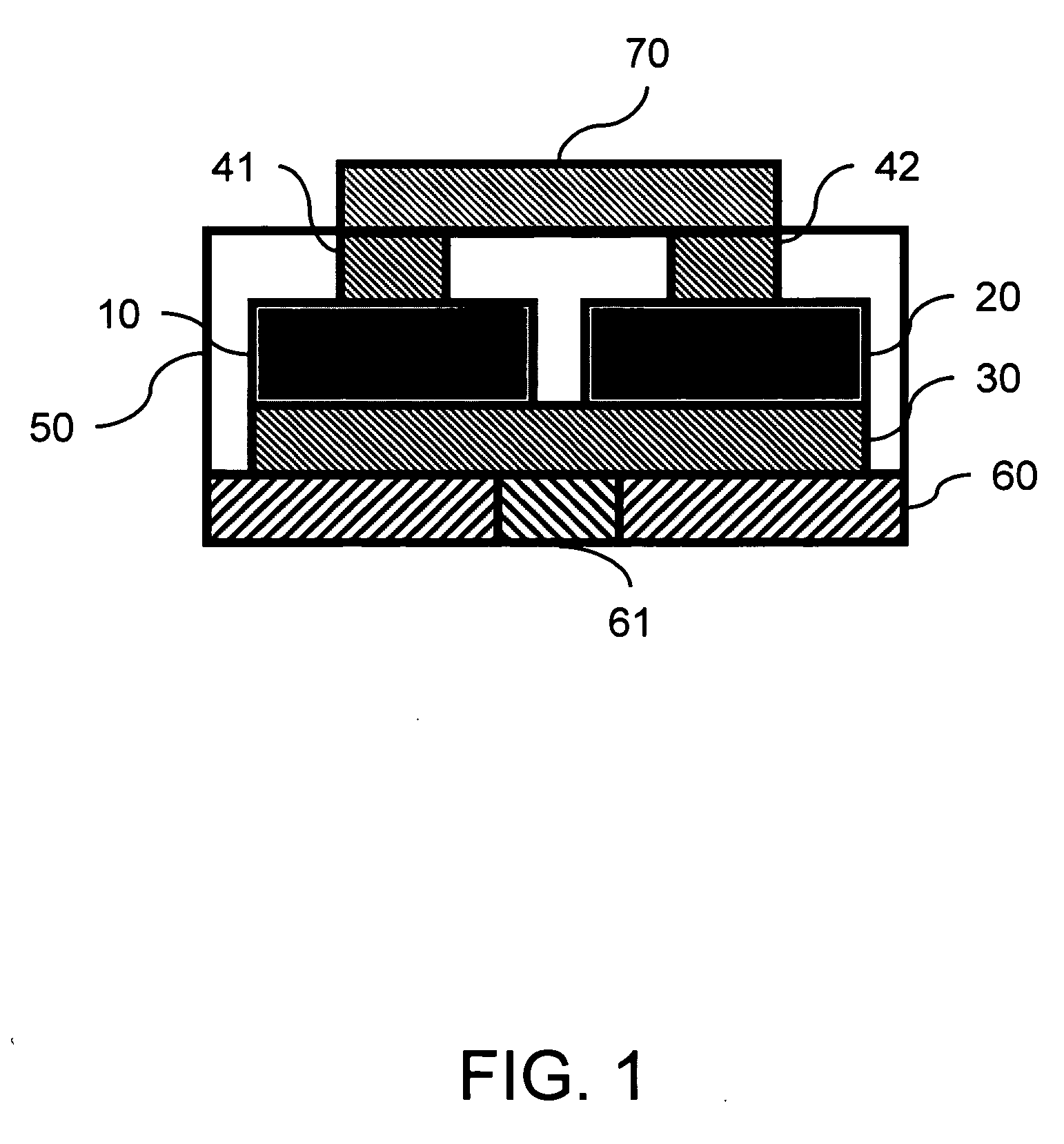

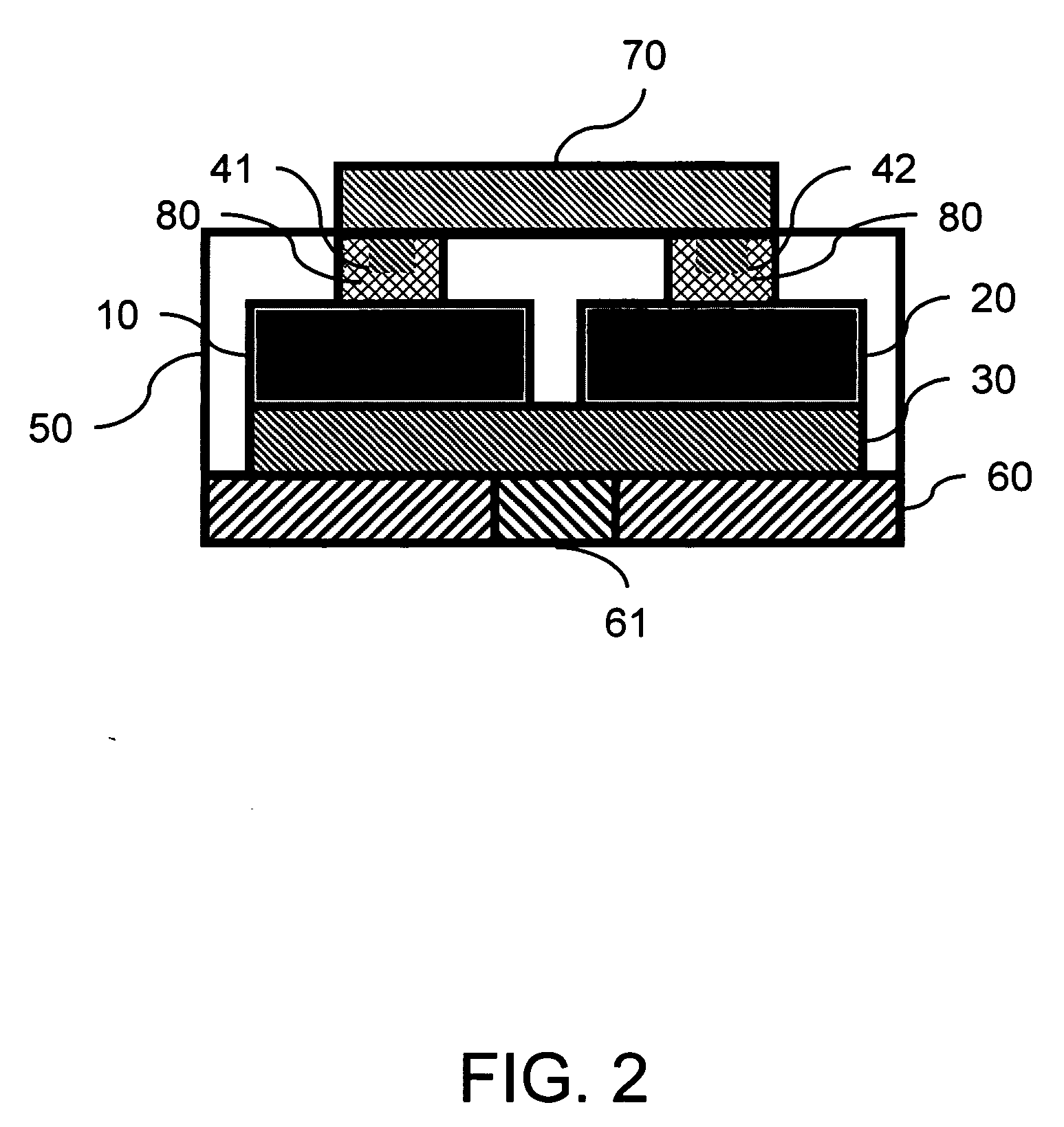

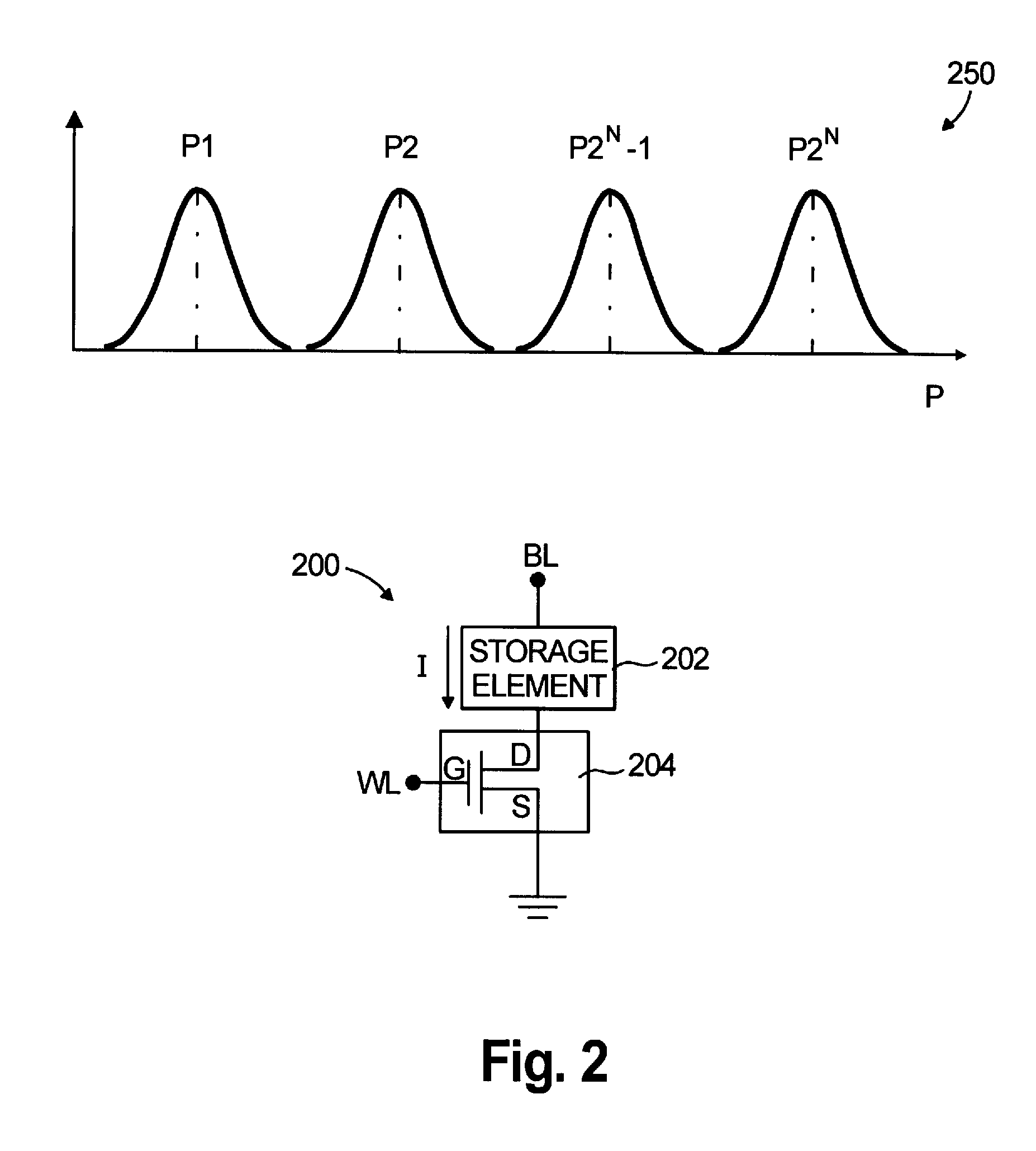

Multilevel phase-change memory element and operating method

A multilevel phase change memory element and operating method and electrodes, which are configured in a parallel structure to form a memory cell. A voltage-drive mode is employed to control and drive the memory element such that multilevel memory states may be achieved by imposing different voltage levels. The provided multilevel phase-change memory element has more bits and higher capacity than that of a memory element with a single phase-change layer.

Owner:IND TECH RES INST

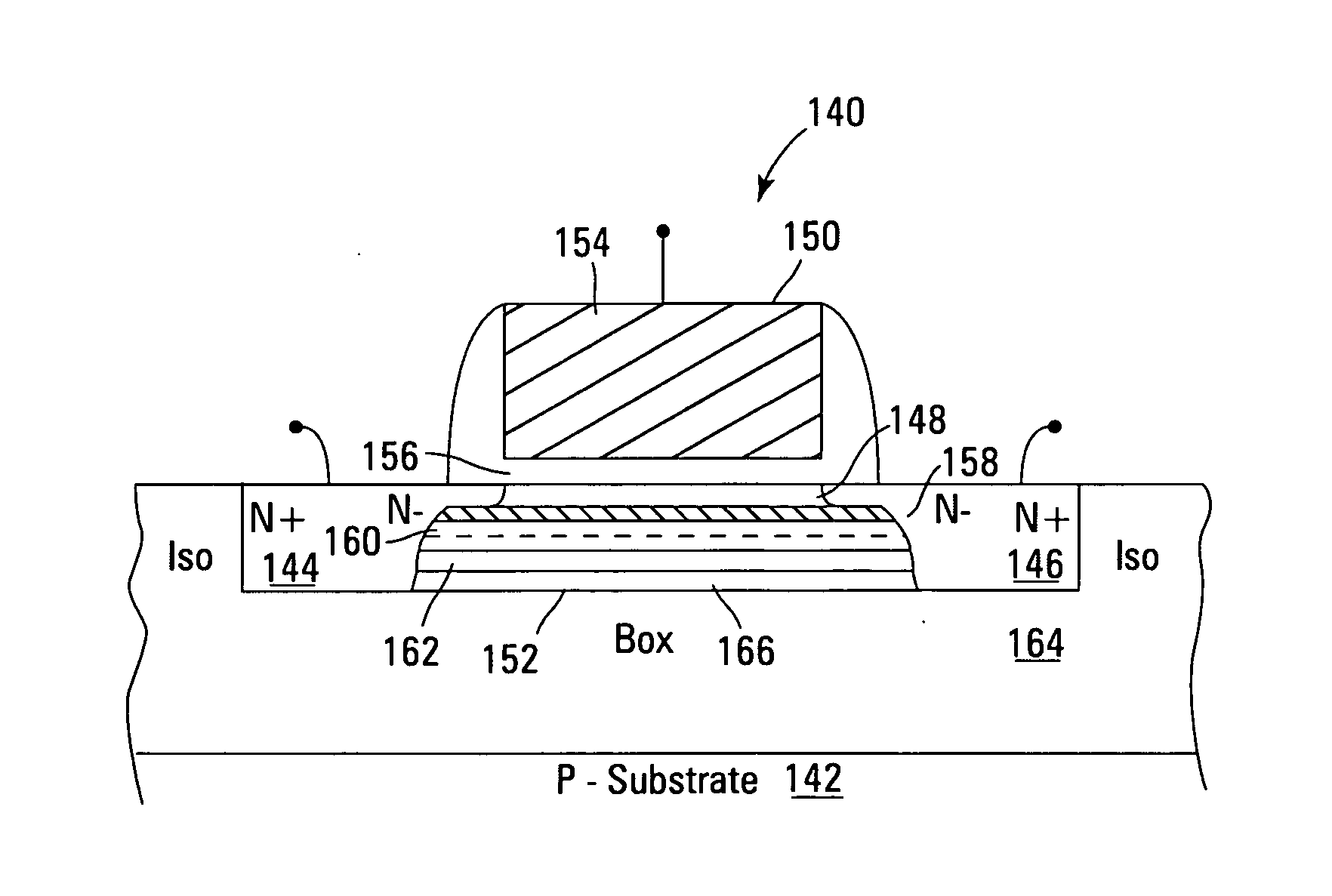

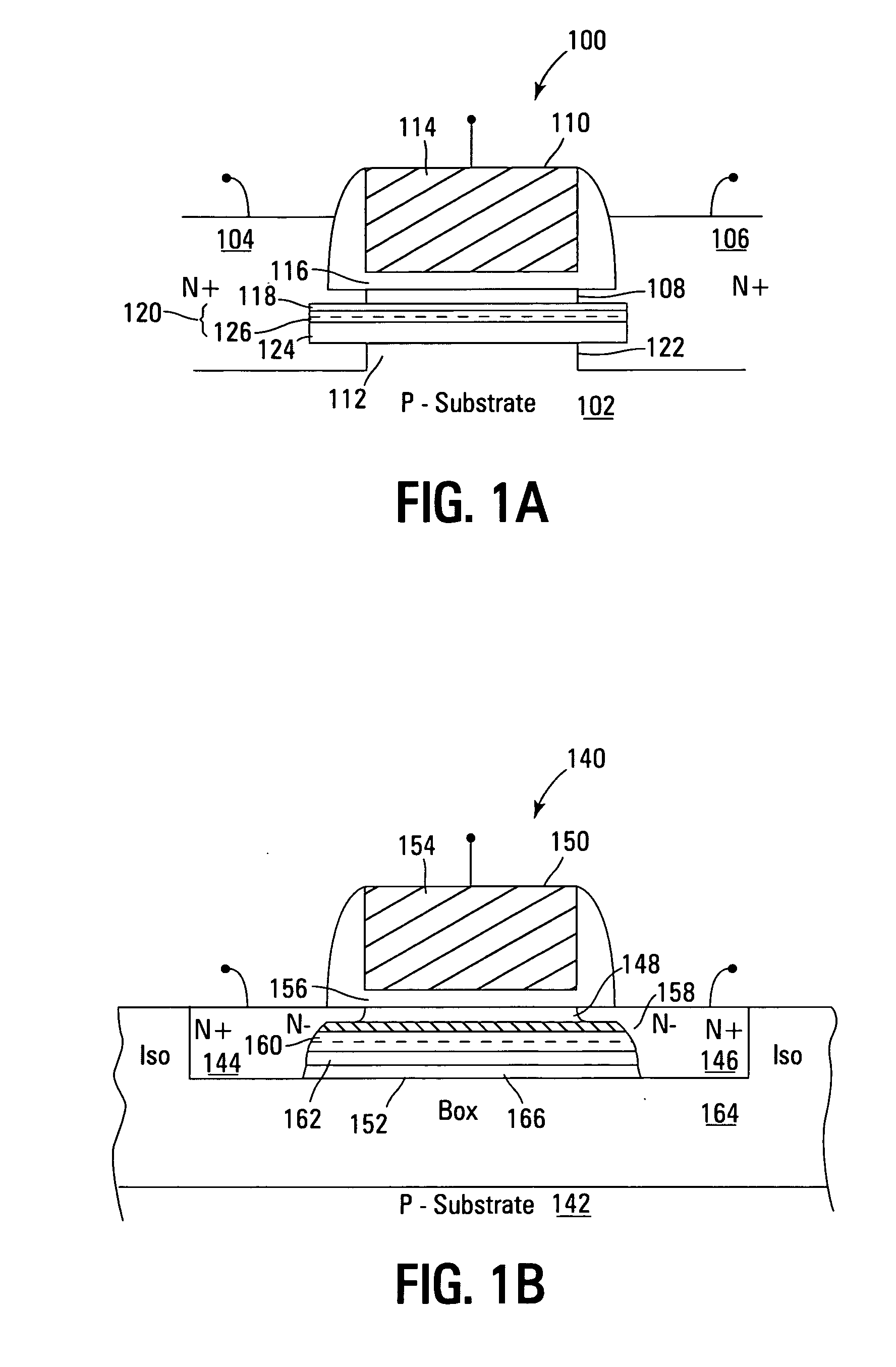

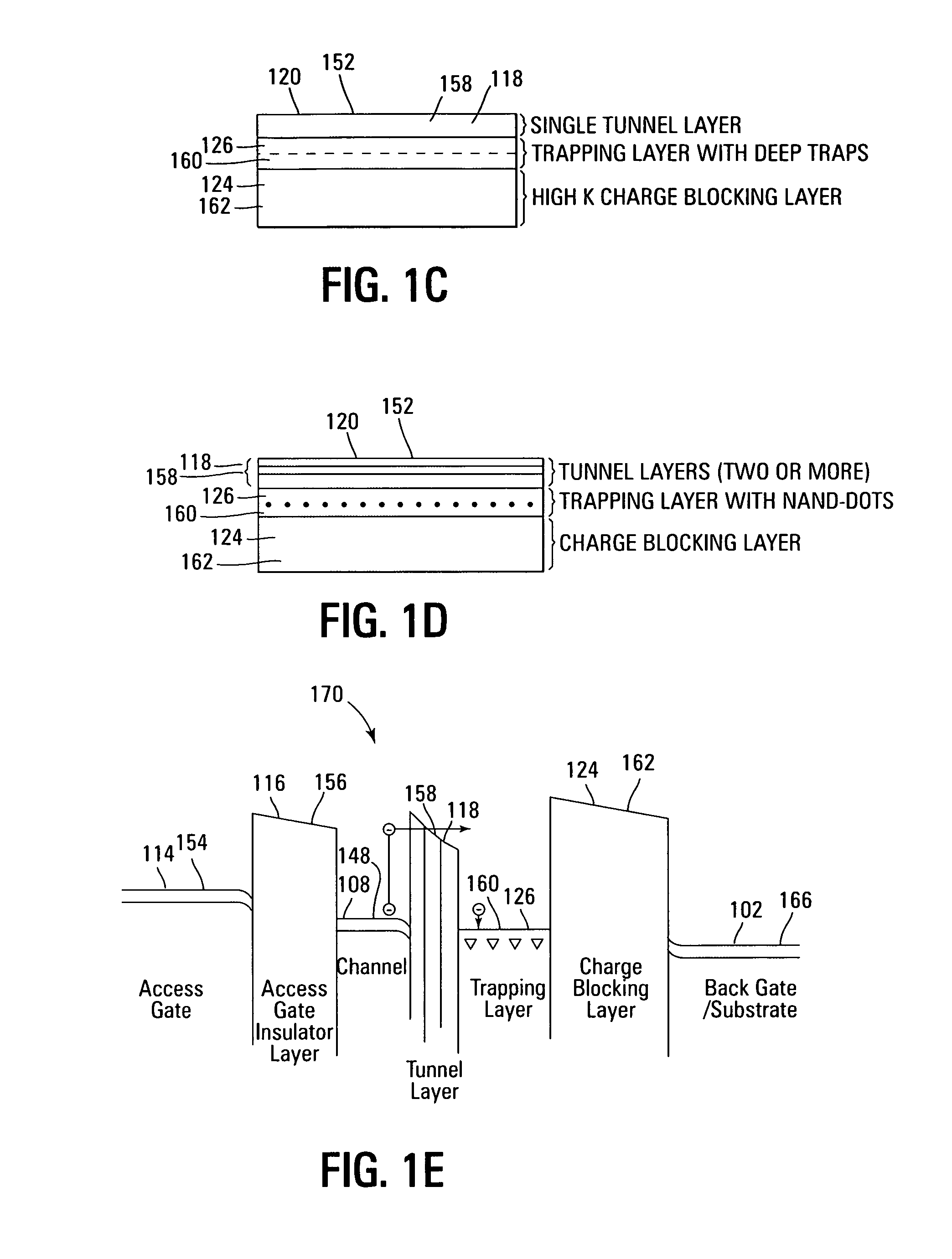

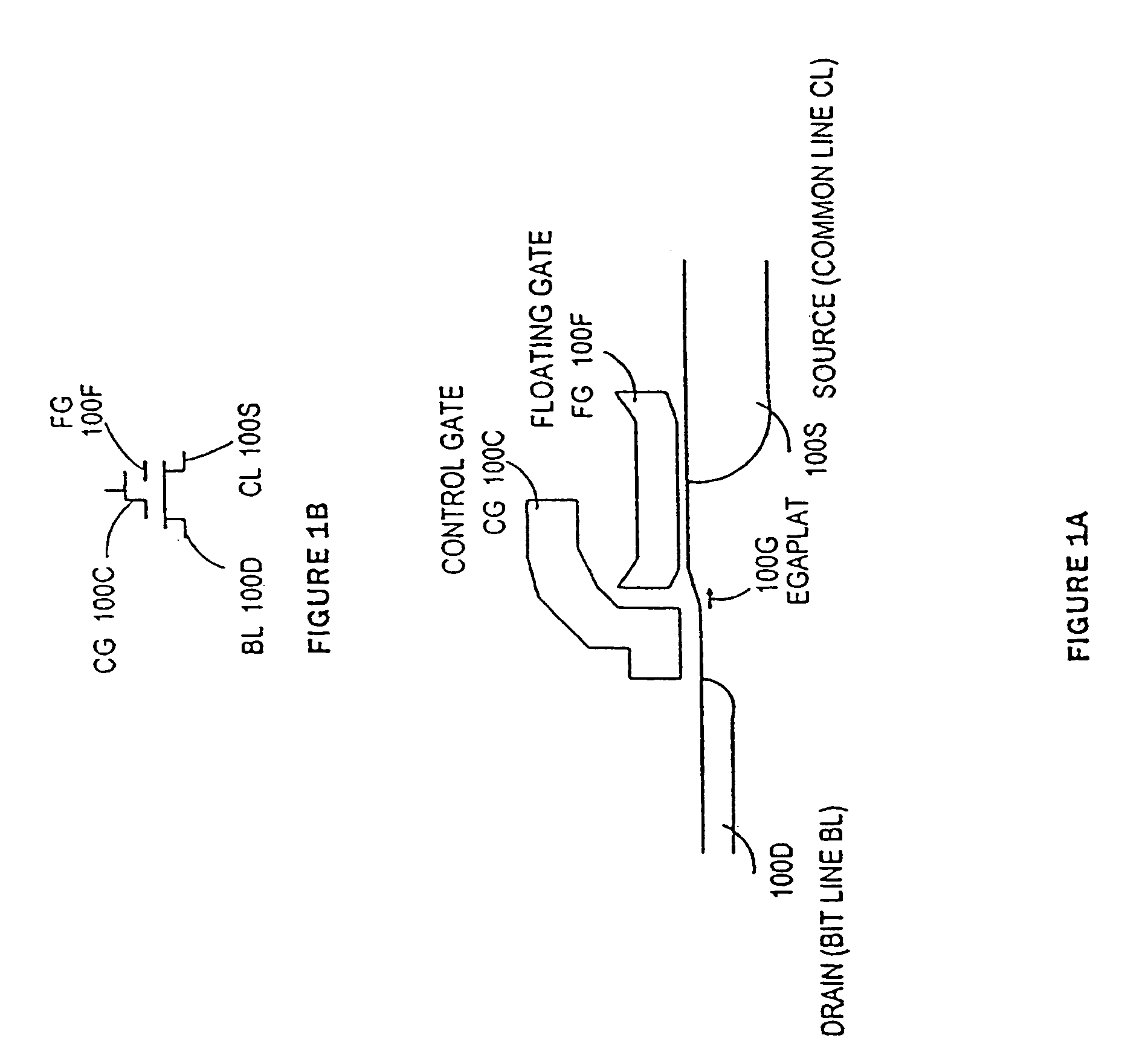

Back-side trapped non-volatile memory device

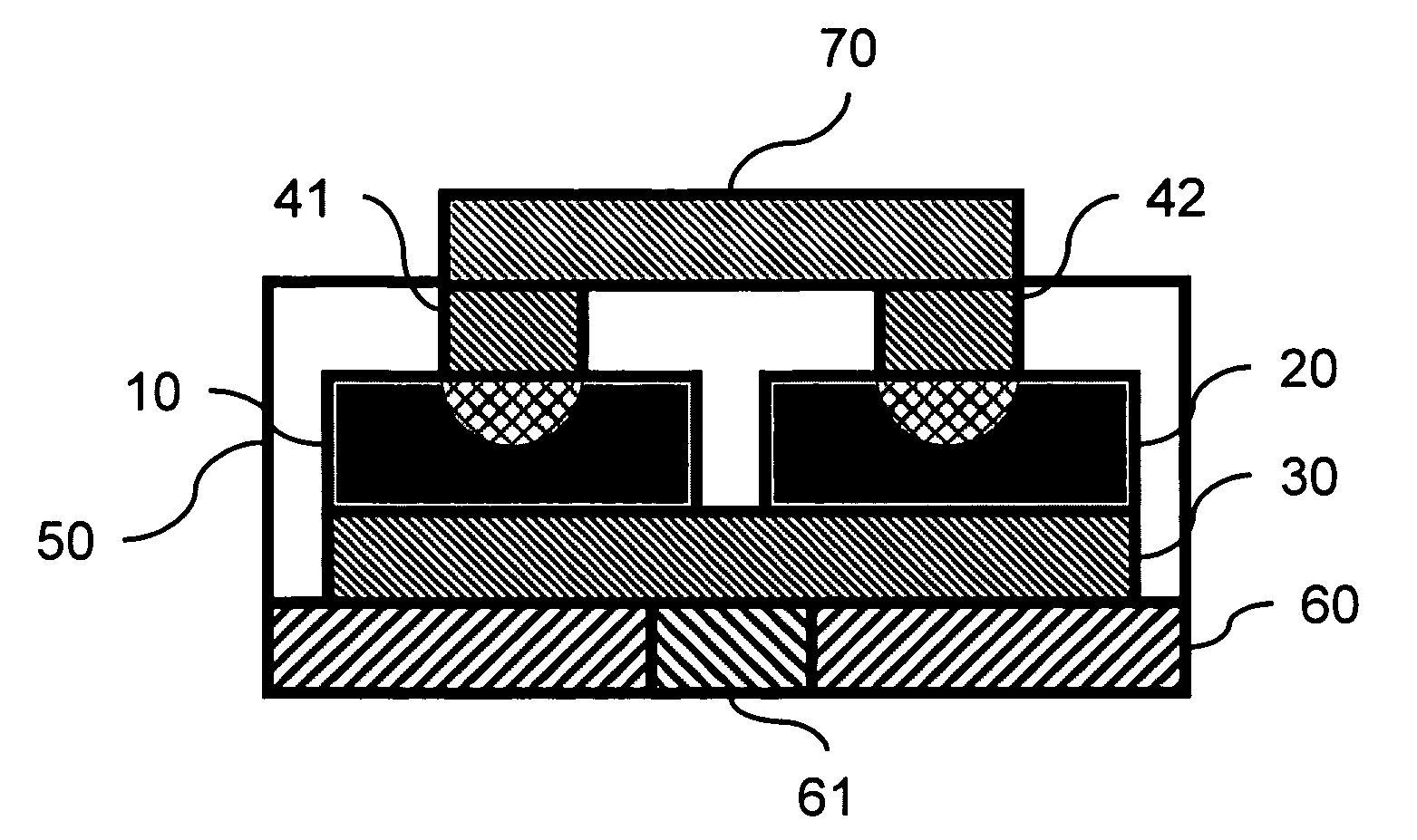

ActiveUS20060284236A1Efficient eraseReduce voltageNanoinformaticsSolid-state devicesCharge retentionHigh energy

Non-volatile memory devices and arrays are described that utilize back-side trapped floating node memory cells with band-gap engineered gate stacks with asymmetric tunnel barriers. Embodiments of the present invention allow for direct tunneling programming and efficient erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention and reduces the possibility of damage to the channel / insulator interface. The direct tunneling program and efficient erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and leakage issues and enhancing device lifespan. Memory device embodiments of the present invention are presented that are arranged in NOR or NAND memory architecture arrays. Memory cell embodiments of the present invention also allow multiple levels of bit storage in a single memory cell, and allow for programming and erase with reduced voltages.

Owner:MICRON TECH INC

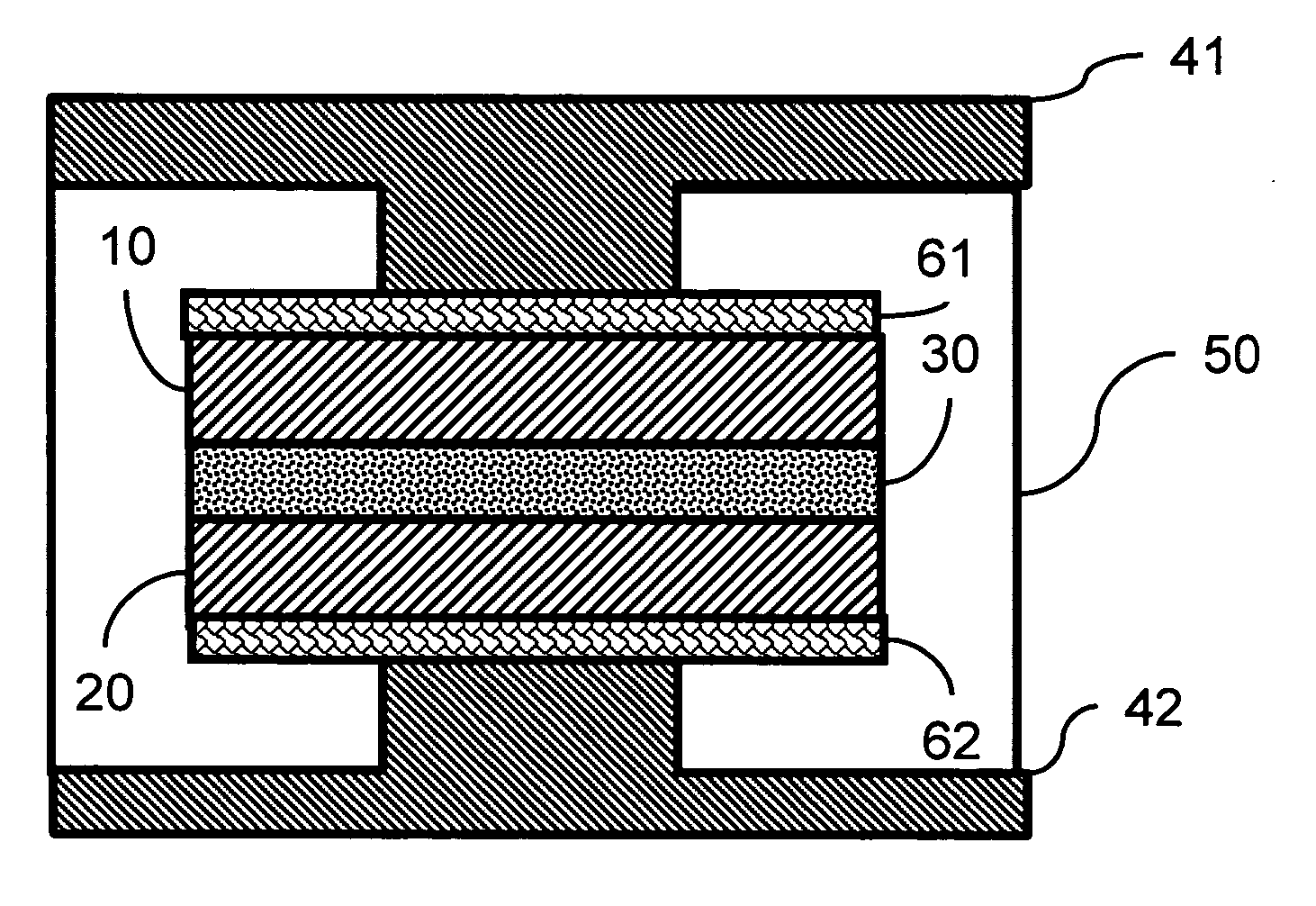

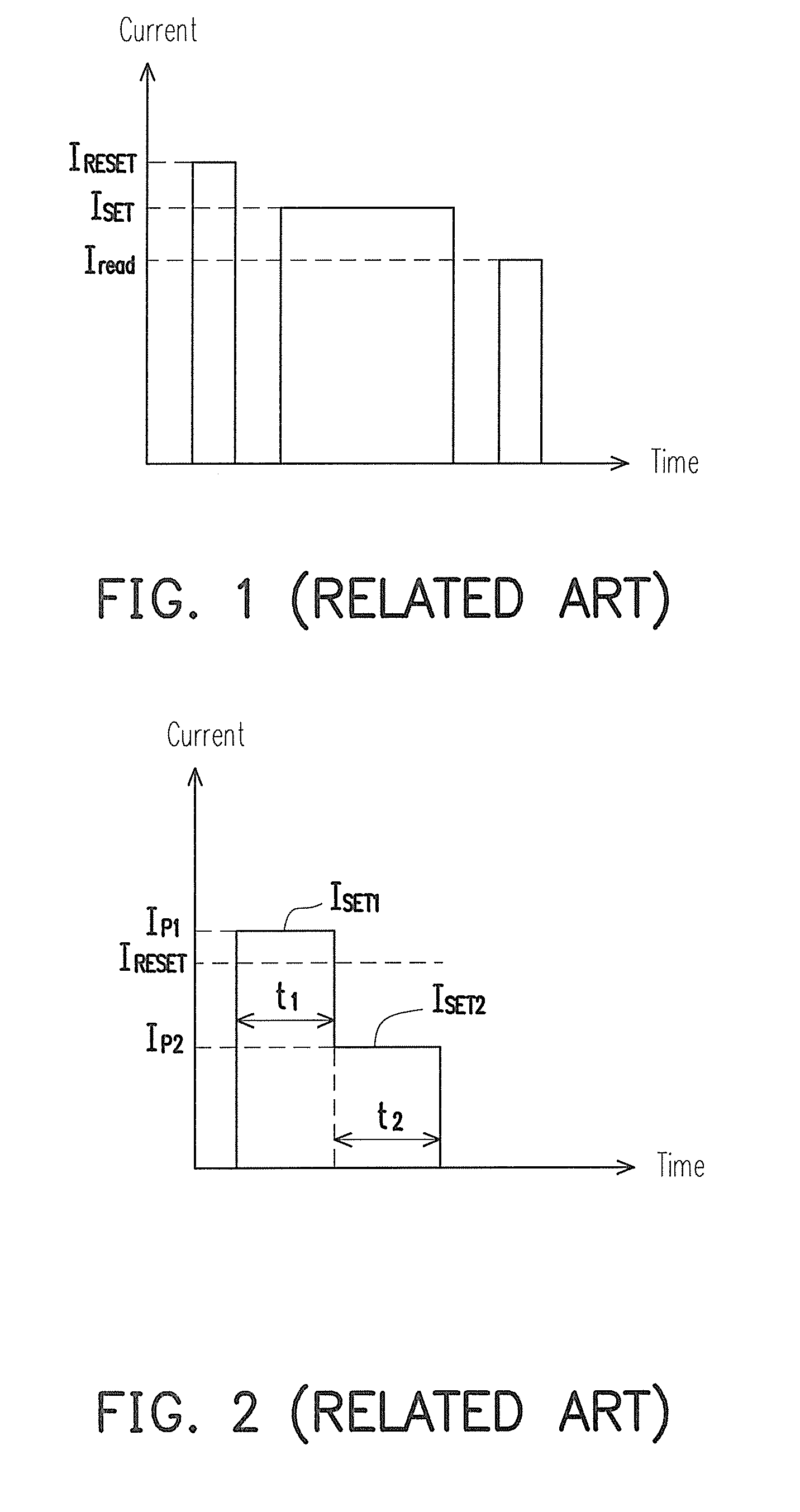

Multilevel phase-change memory, manufacturing and status transferring method thereof

InactiveUS20060077741A1Reduce areaIncrease memory densityElectrical apparatusDigital storagePhase-change memoryMultilevel memory

A multilevel phase-change memory, manufacturing method and status transferring method thereof. The phase-change memory includes two phase-change layers and electrodes, which are configured in a series structure to form a memory cell. A current-drive mode is employed to control and drive the memory such that multilevel memory states may be achieved by imposing different current levels. The provided multilevel phase-change memory has more bits and higher capacity than that of the memory with a single phase-change layer. Furthermore, the series structure may reduce the cell area and the device volume.

Owner:IND TECH RES INST

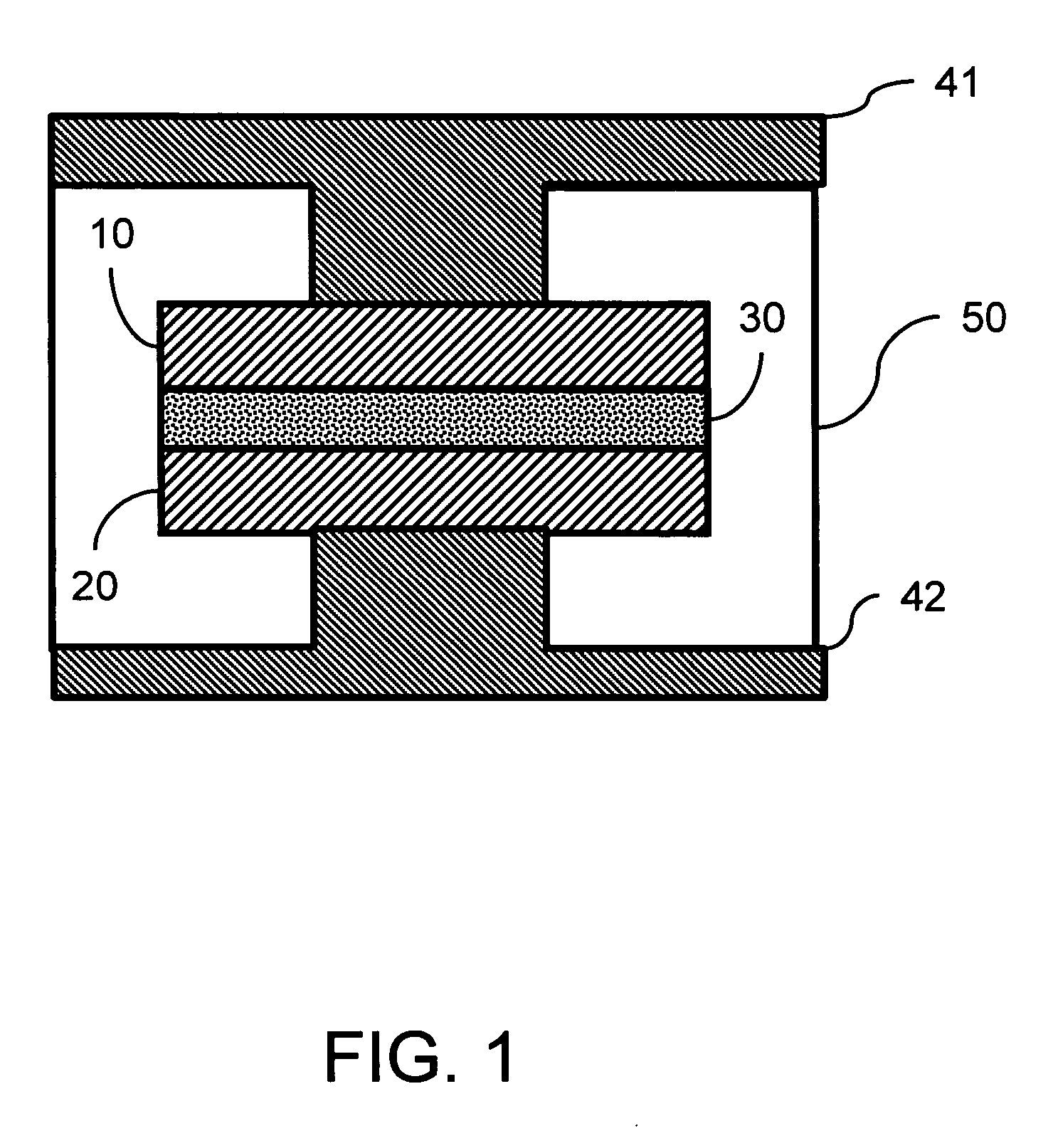

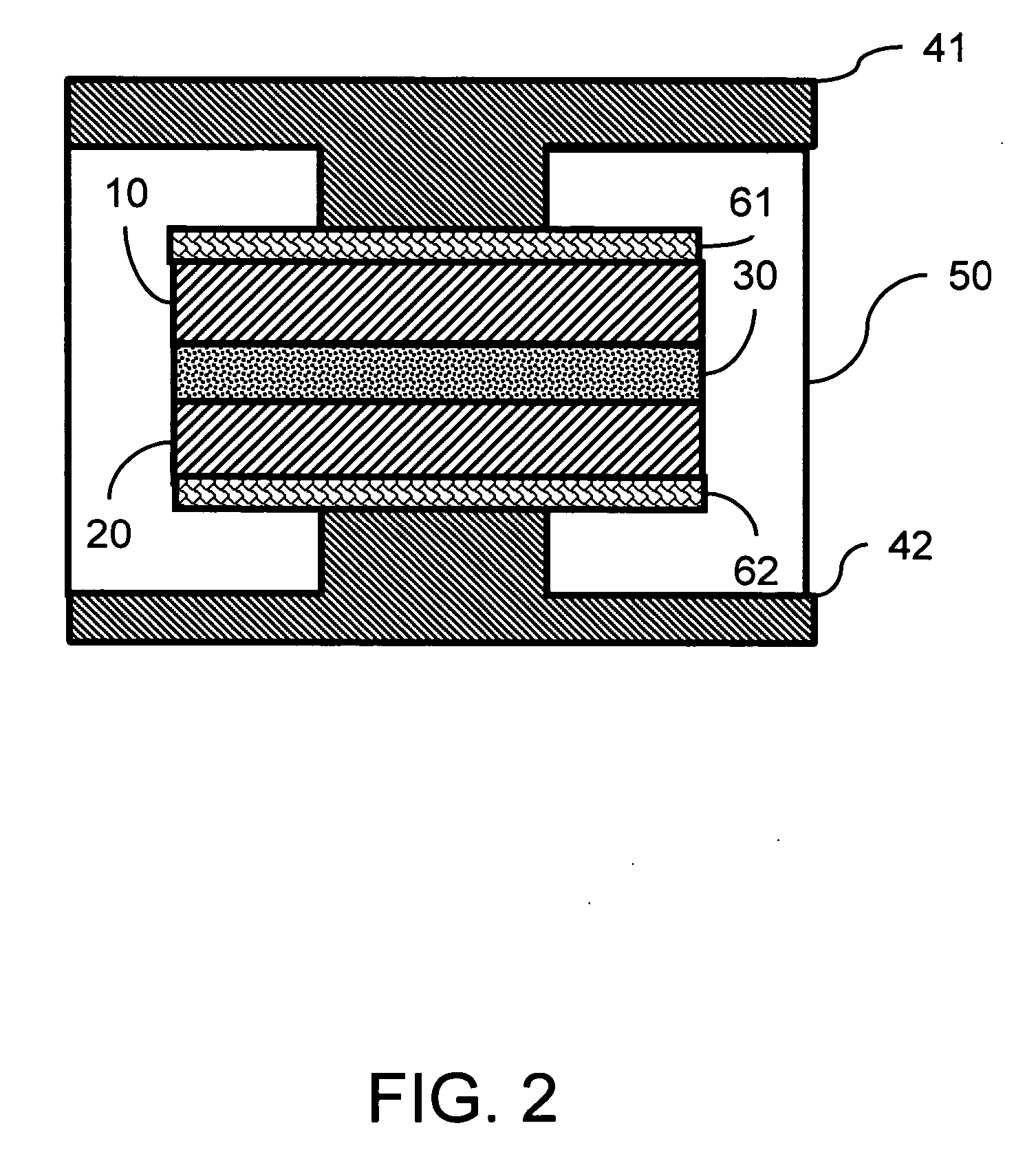

Multilevel phase-change memory, operating method and manufacture method thereof

A multilevel phase-change memory, operating method and manufacturing method thereof. The phase-change memory includes two phase-change layers and electrodes, which are configured in a parallel structure to form a memory cell. A voltage-drive mode is employed to control and drive the memory such that multilevel memory states may be achieved by imposing different voltage levels. The provided multilevel phase-change memory has more bits and higher capacity than that of the memory with a single phase-change layer.

Owner:IND TECH RES INST

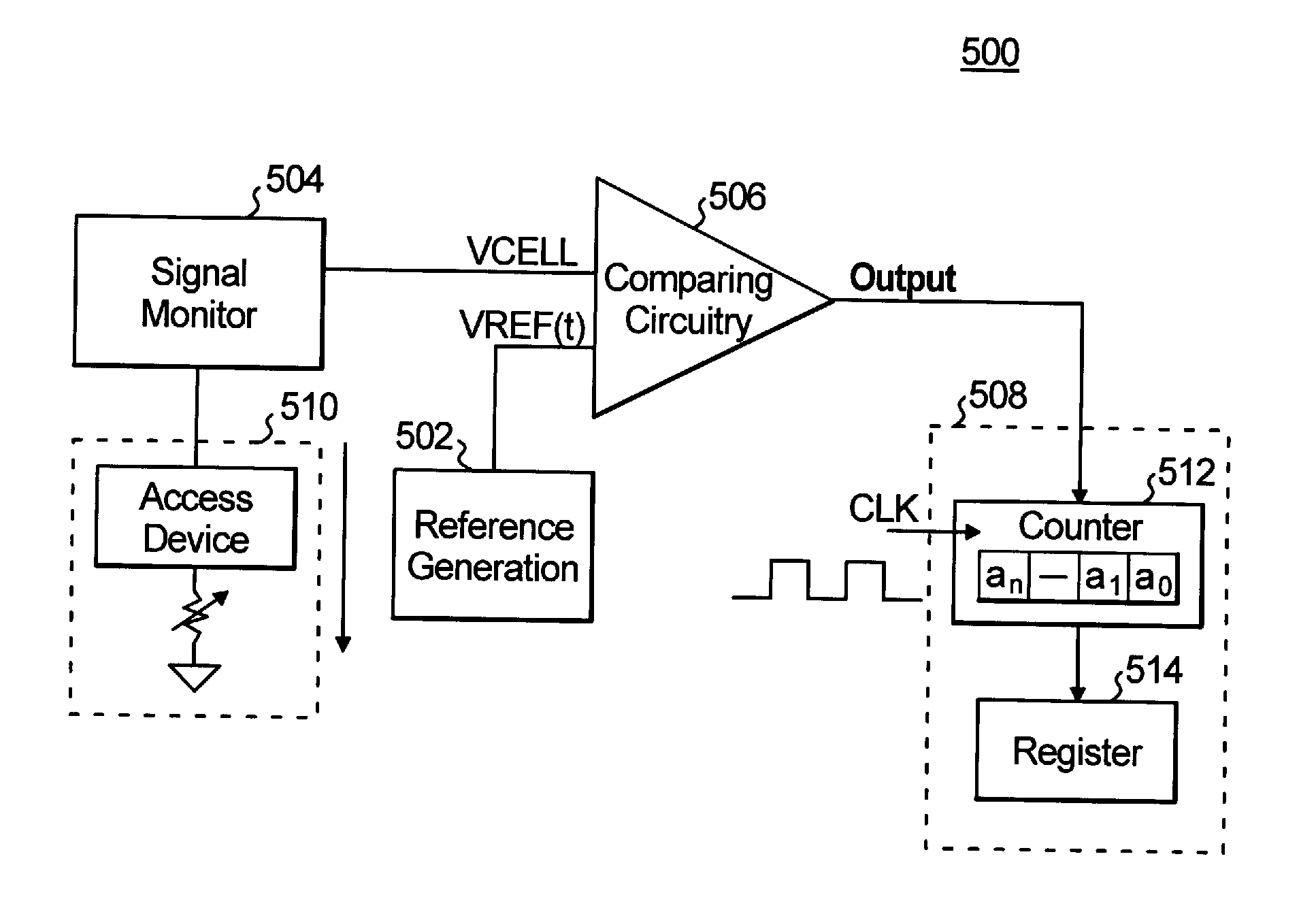

Reconfigurable Multi-level Sensing Scheme for Semiconductor Memories

ActiveUS20120063195A1Simple structureReduce chip areaDigital storageTemporal changeMultilevel memory

A method for sensing at least one parameter indicative of a logical state of a multi-level memory cell includes the steps of: measuring the parameter of the multi-level memory cell; comparing the measured parameter of the multi-level memory cell with a prescribed reference signal, the reference signal having a value which varies as a function of time; and storing a time value corresponding to a point in time at which the reference signal is substantially equal to the measured parameter of the multi-level memory cell, the stored time value being indicative of a sensed logical state of the multi-level memory cell.

Owner:GLOBALFOUNDRIES US INC

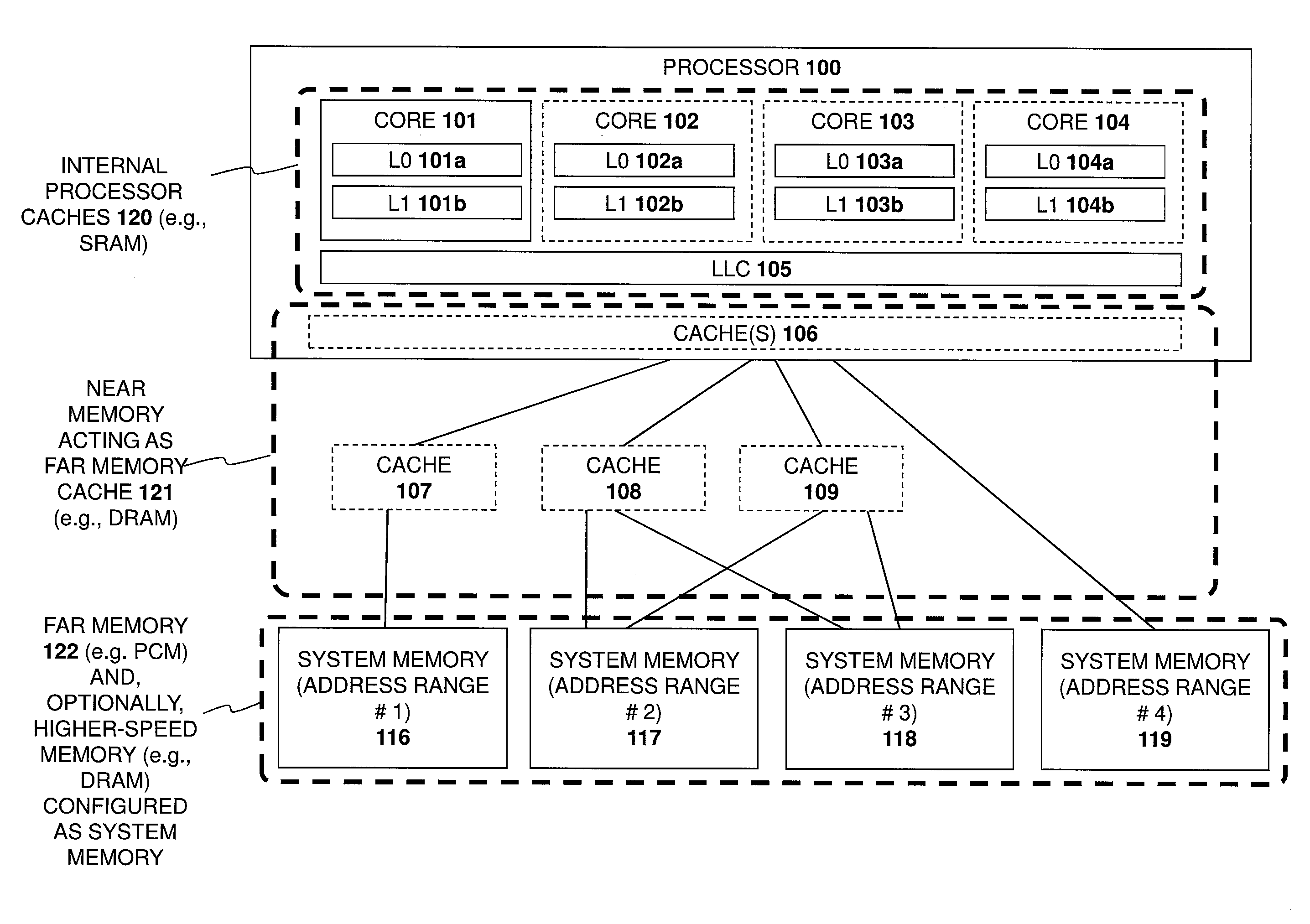

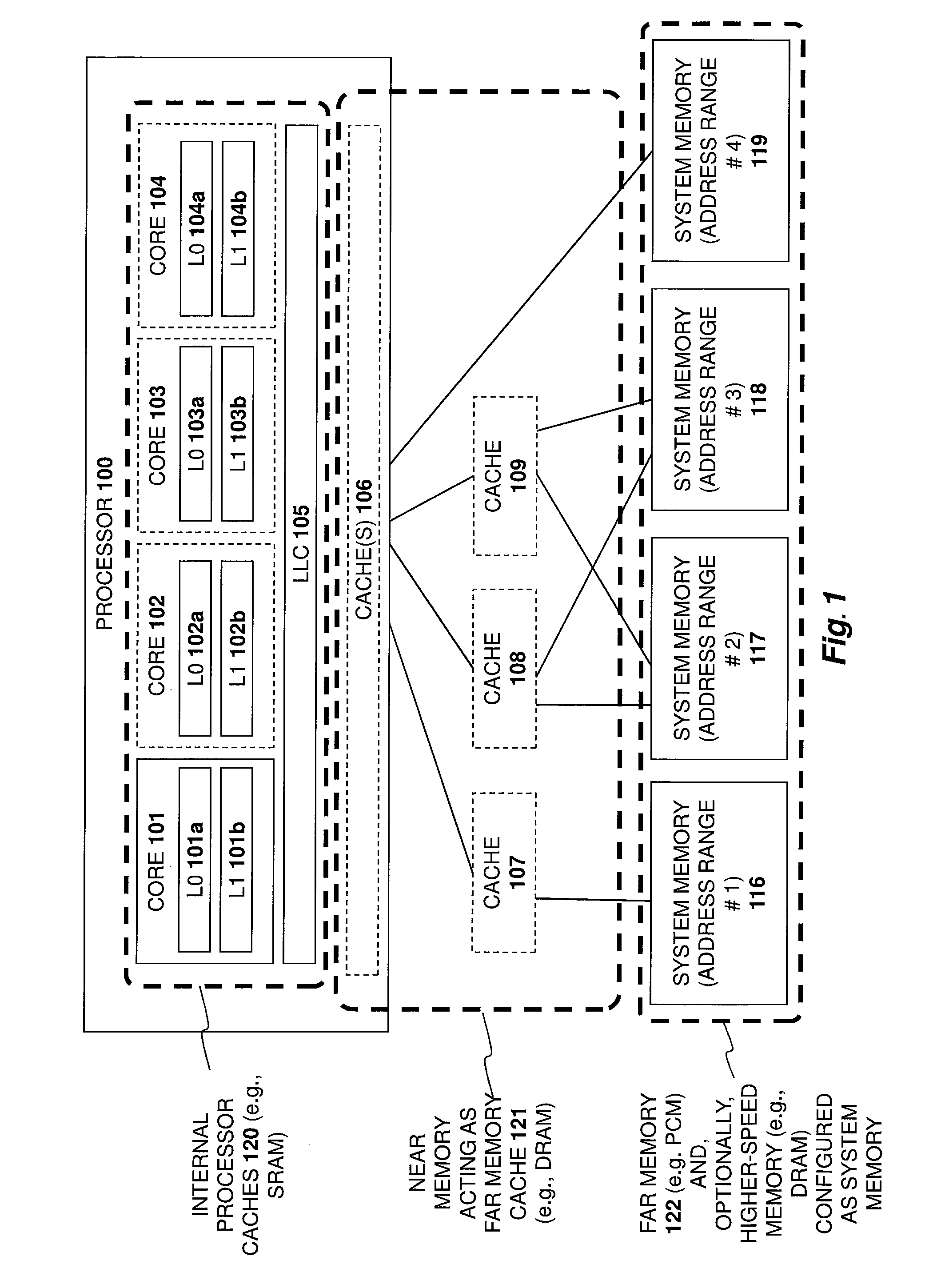

Apparatus and method for implementing a multi-level memory hierarchy having different operating modes

ActiveUS20130268728A1Memory architecture accessing/allocationMemory adressing/allocation/relocationMemory hierarchyMultilevel memory

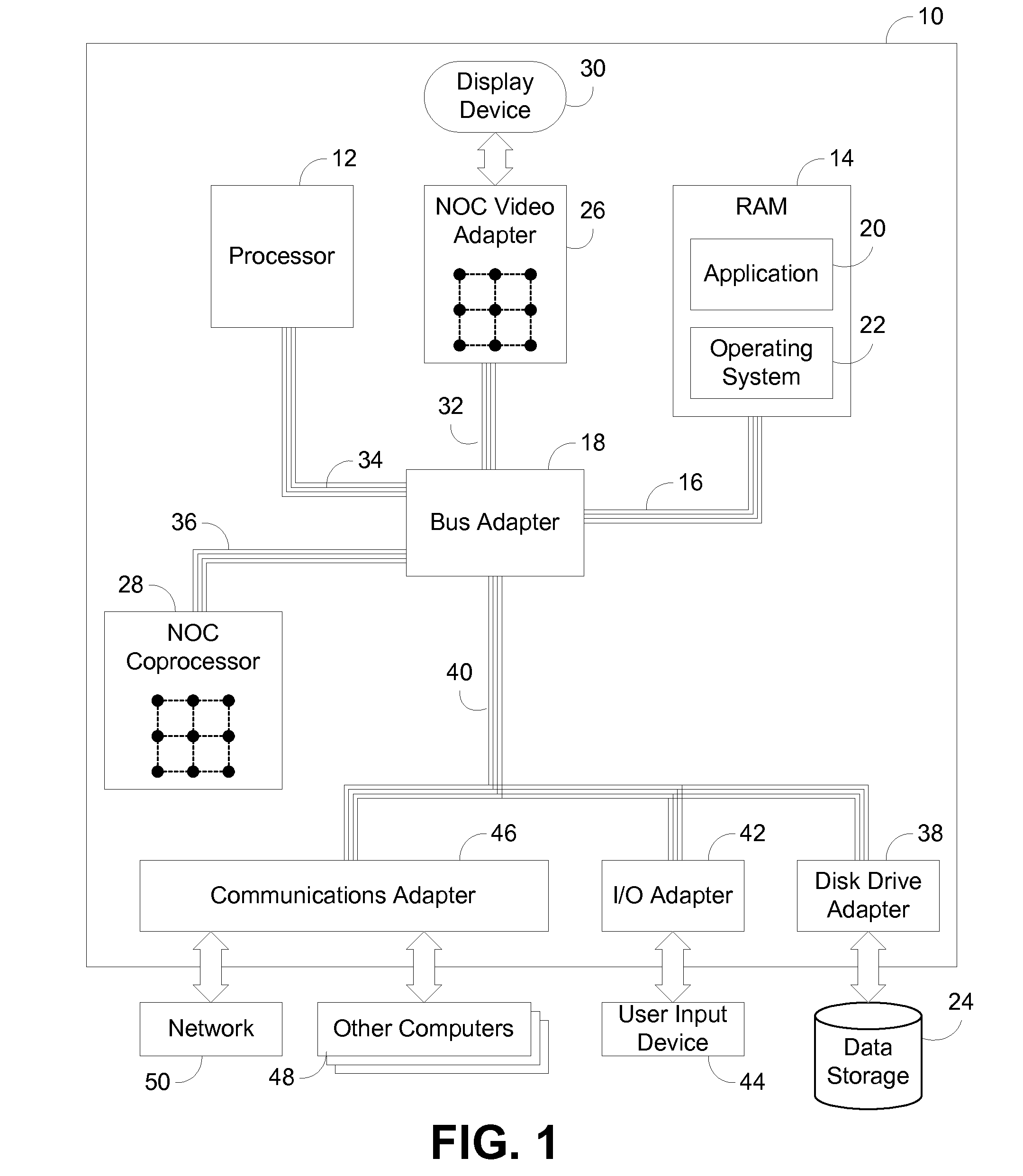

A system and method are described for integrating a memory and storage hierarchy including a non-volatile memory tier within a computer system. In one embodiment, PCMS memory devices are used as one tier in the hierarchy, sometimes referred to as “far memory.” Higher performance memory devices such as DRAM placed in front of the far memory and are used to mask some of the performance limitations of the far memory. These higher performance memory devices are referred to as “near memory.” In one embodiment, the “near memory” is configured to operate in a plurality of different modes of operation including (but not limited to) a first mode in which the near memory operates as a memory cache for the far memory and a second mode in which the near memory is allocated a first address range of a system address space with the far memory being allocated a second address range of the system address space, wherein the first range and second range represent the entire system address space.

Owner:SK HYNIX NAND PROD SOLUTIONS CORP

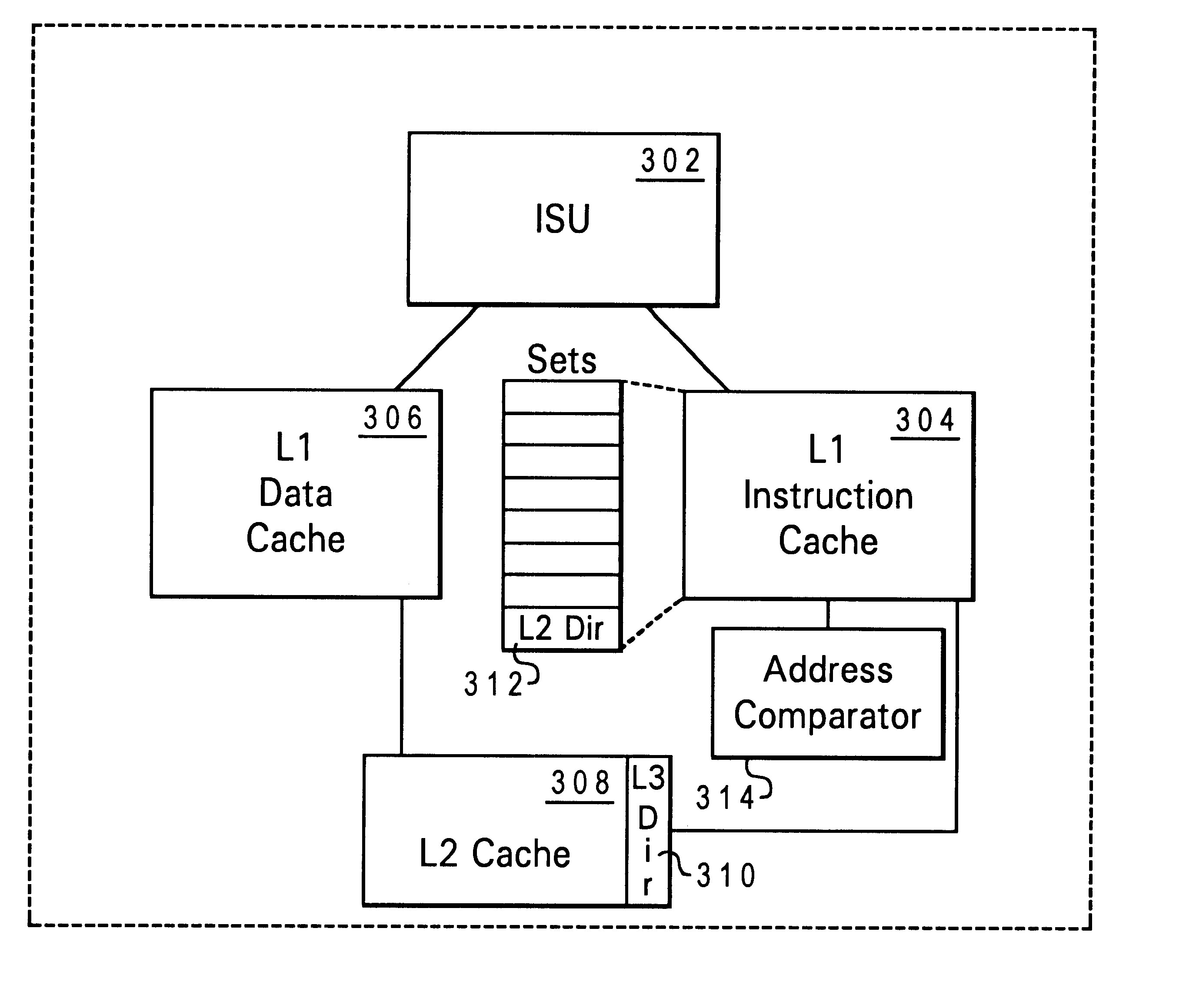

Integrated cache and directory structure for multi-level caches

A method of operating a multi-level memory hierarchy of a computer system and an apparatus embodying the method, wherein multiple levels of storage subsystems are used to improve the performance of the computer system, each next higher level generally having a faster access time, but a smaller amount of storage. Values within a level are indexed by a directory that provides an indexing of information relating the values in that level to the next lower level. In a preferred embodiment of the invention, the directories for the various levels of storage are contained within the next higher level, providing a faster access to the directory information. Cache memories used as the highest levels of storage, and one or more sets are allocated out of that cache memory for containing a directory of the next lower level of storage. An address comparator which is used to compare entries in a directory to address values is directly coupled to the set or sets used for the directory, reducing the time needed to compare addresses in determining whether an address is present in the cache.

Owner:IBM CORP

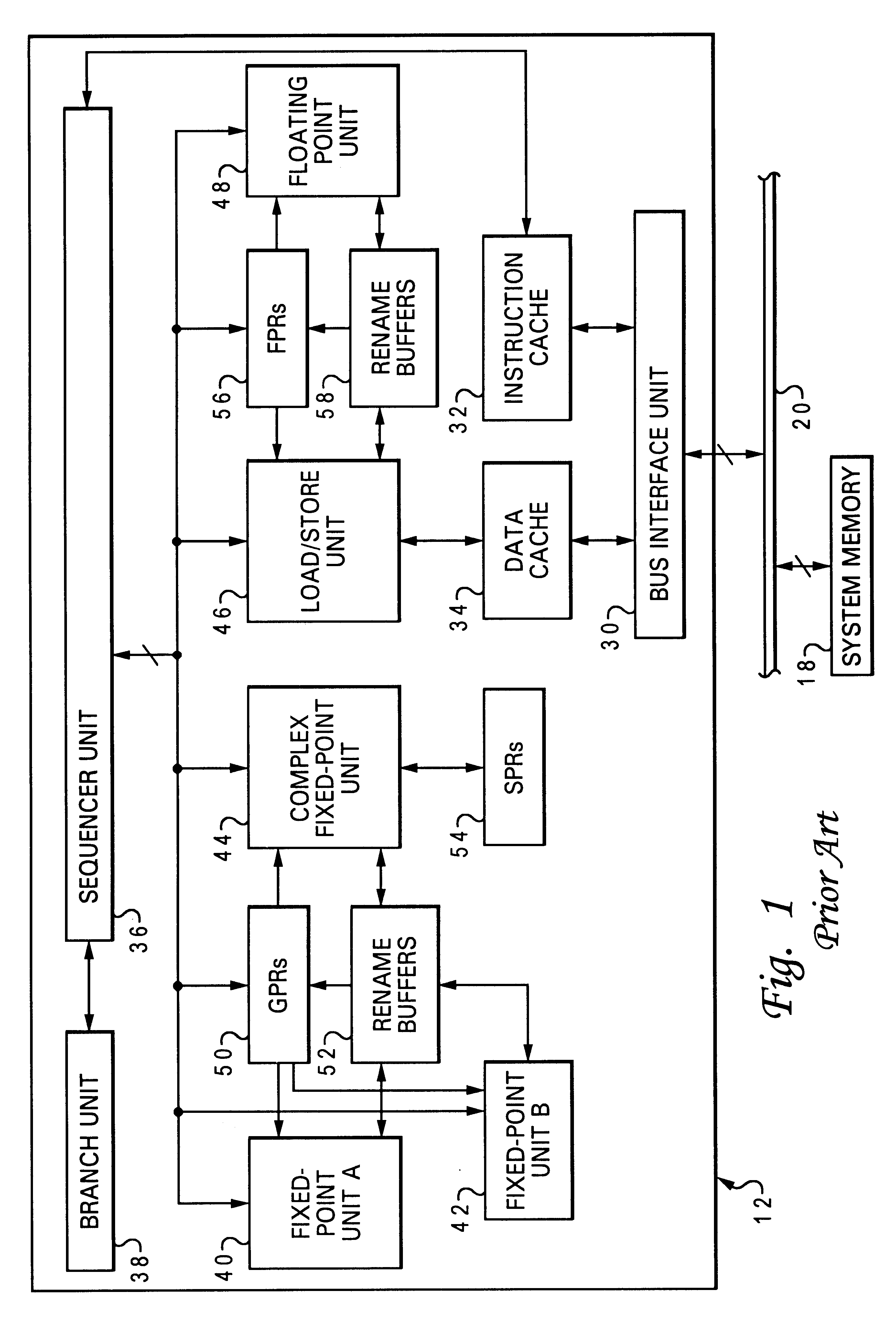

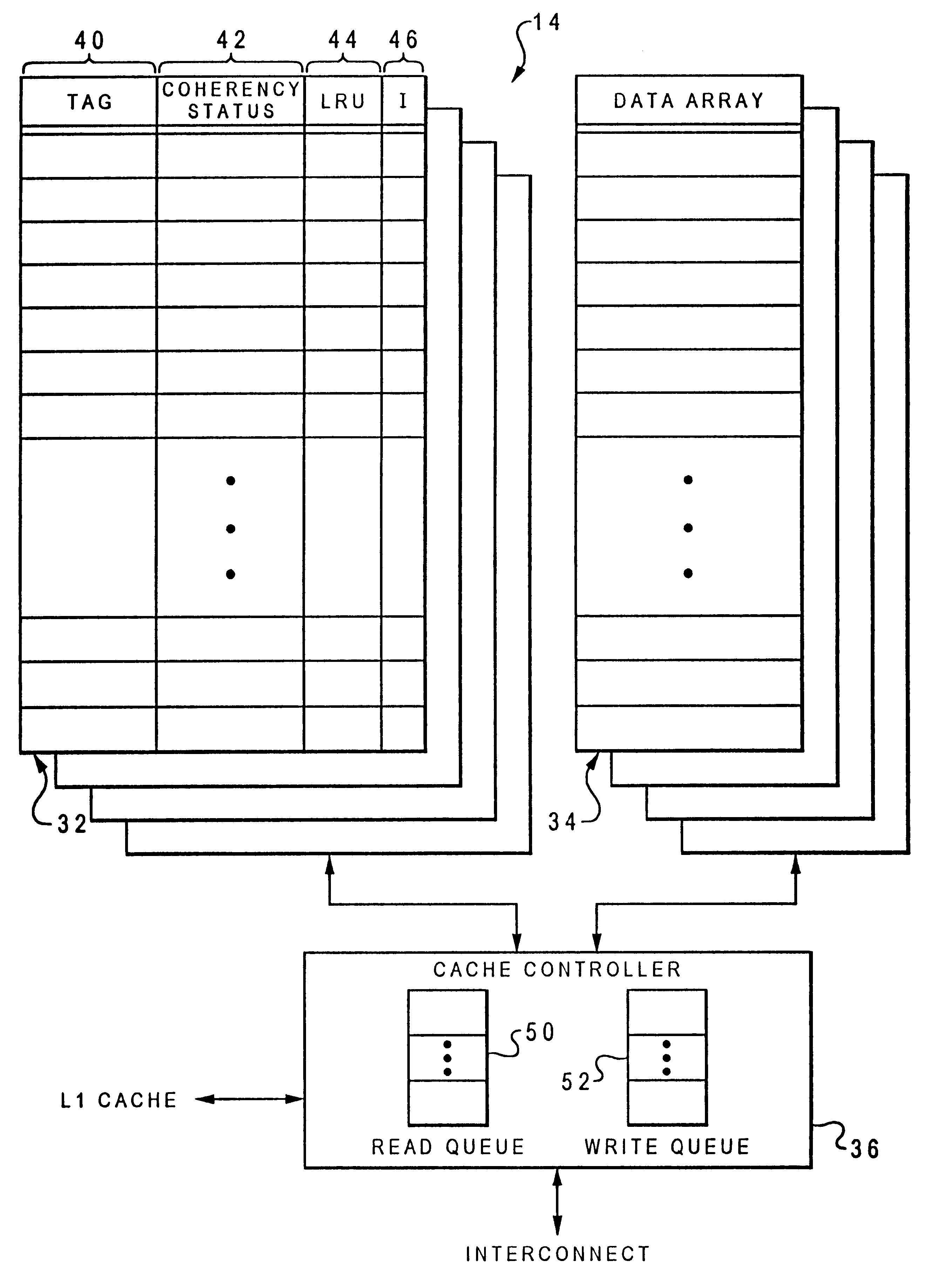

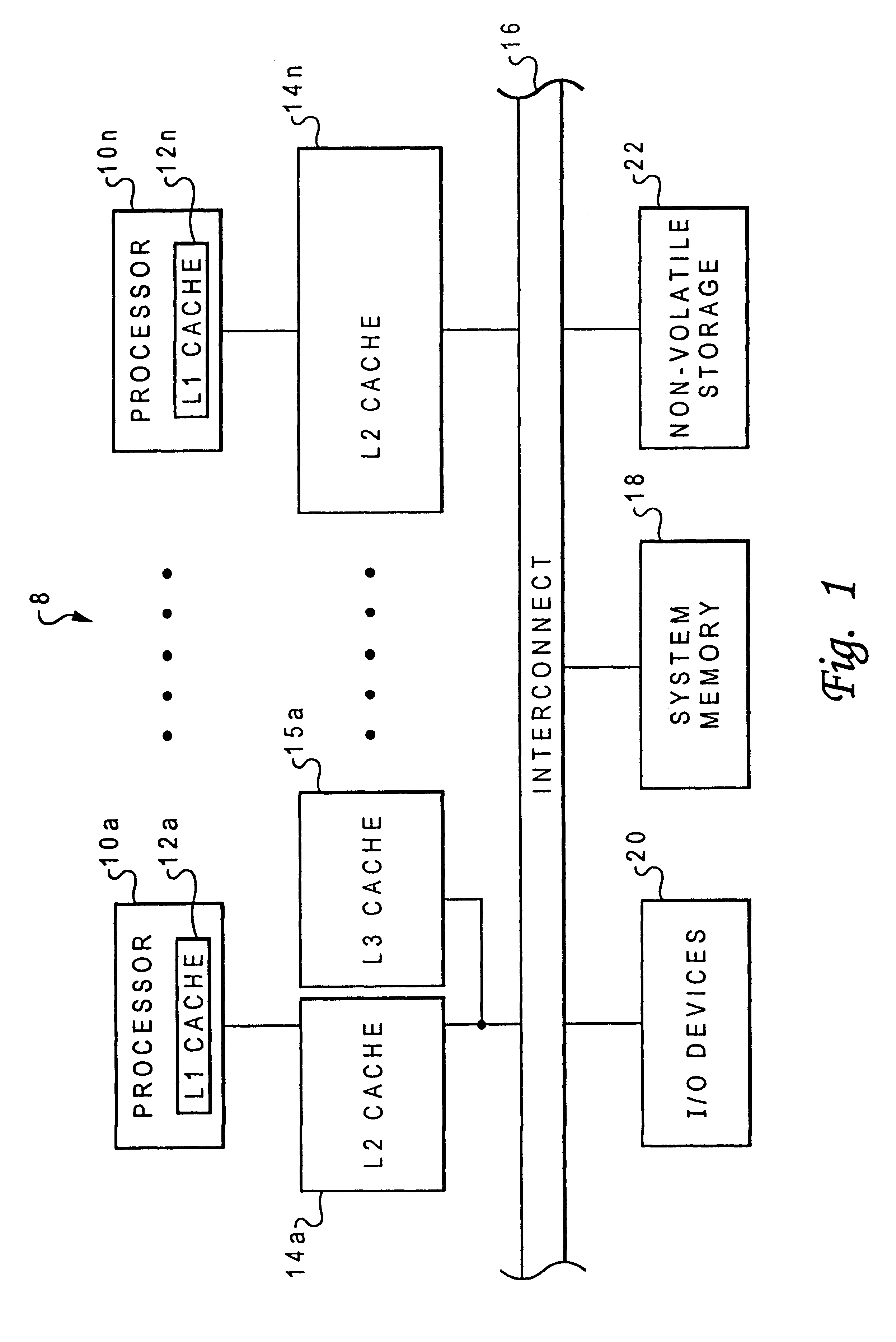

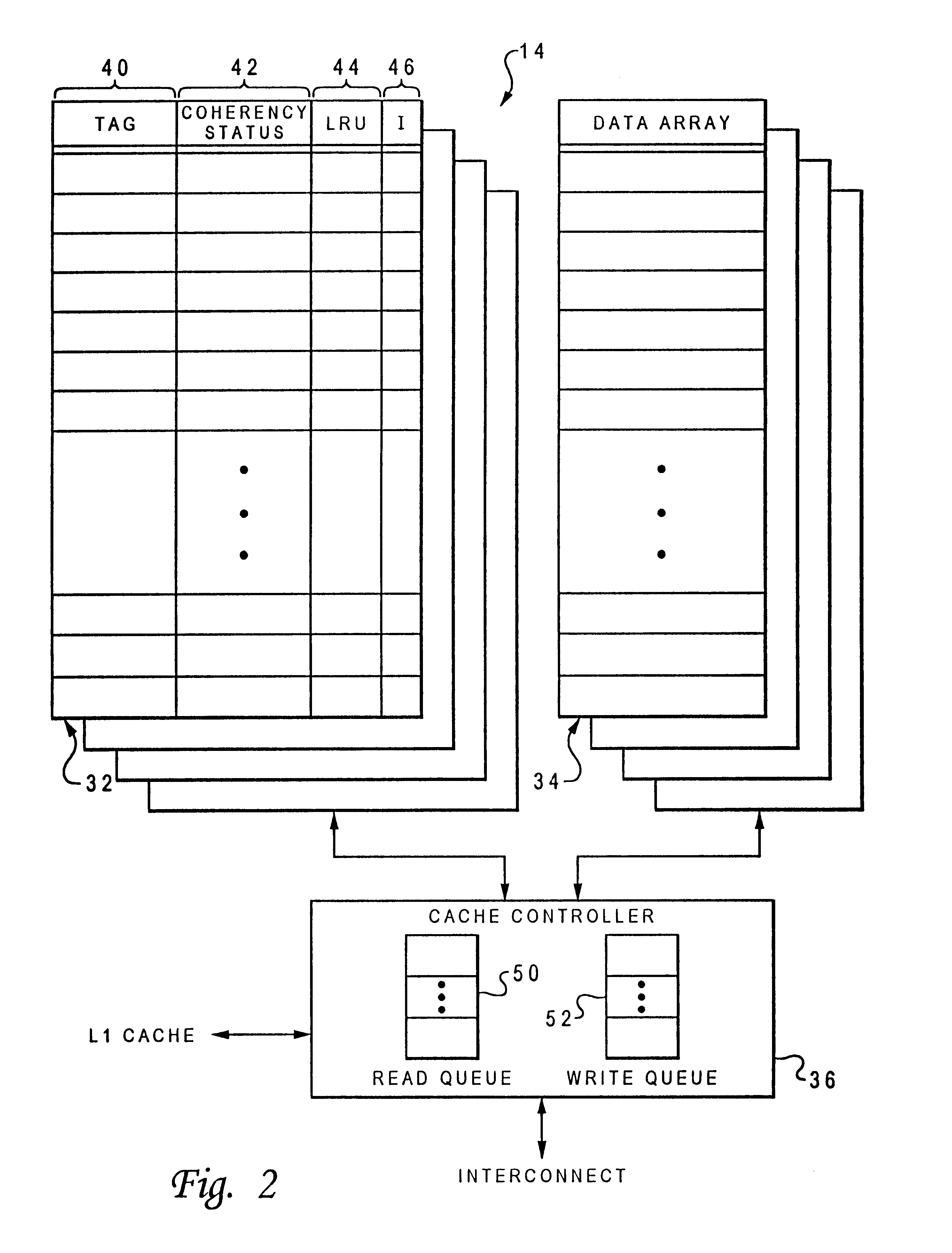

Cache coherency protocol for a data processing system including a multi-level memory hierarchy

InactiveUS6192451B1Memory adressing/allocation/relocationUnauthorized memory use protectionData processing systemMemory hierarchy

A data processing system and method of maintaining cache coherency in a data processing system are described. The data processing system includes a plurality of caches and a plurality of processors grouped into at least first and second clusters, where each of the first and second clusters has at least one upper level cache and at least one lower level cache. According to the method, a first data item in the upper level cache of the first cluster is stored in association with an address tag indicating a particular address. A coherency indicator in the upper level cache of the first cluster is set to a first state that indicates that the address tag is valid and that the first data item is invalid. Similarly, in the upper level cache of the second cluster, a second data item is stored in association with an address tag indicating the particular address. In addition, a coherency indicator in the upper level cache of the second cluster is set to the first state. Thus, the data processing system implements a coherency protocol that permits a coherency indicator in the upper level caches of both of the first and second clusters to be set to the first state.

Owner:IBM CORP

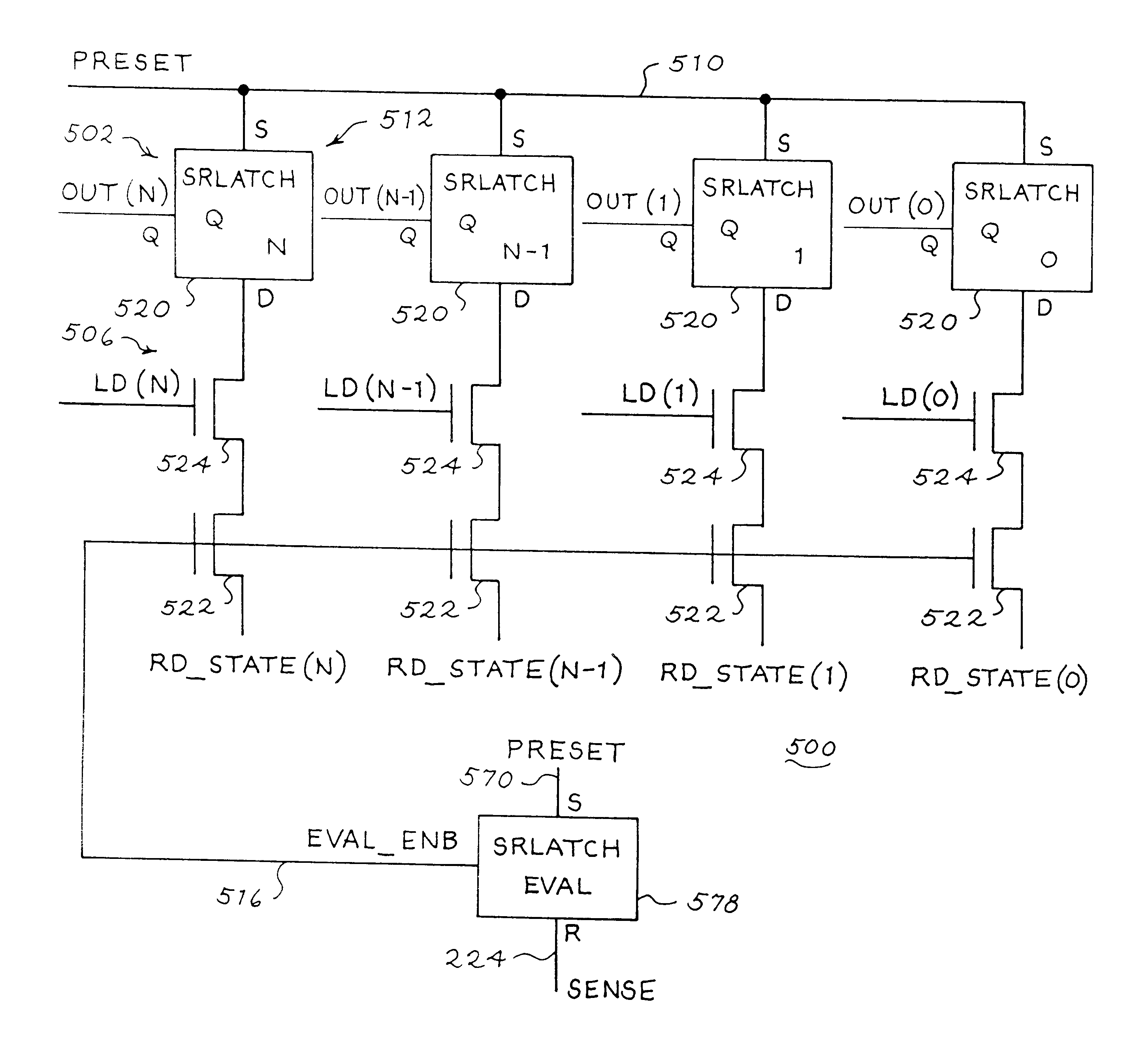

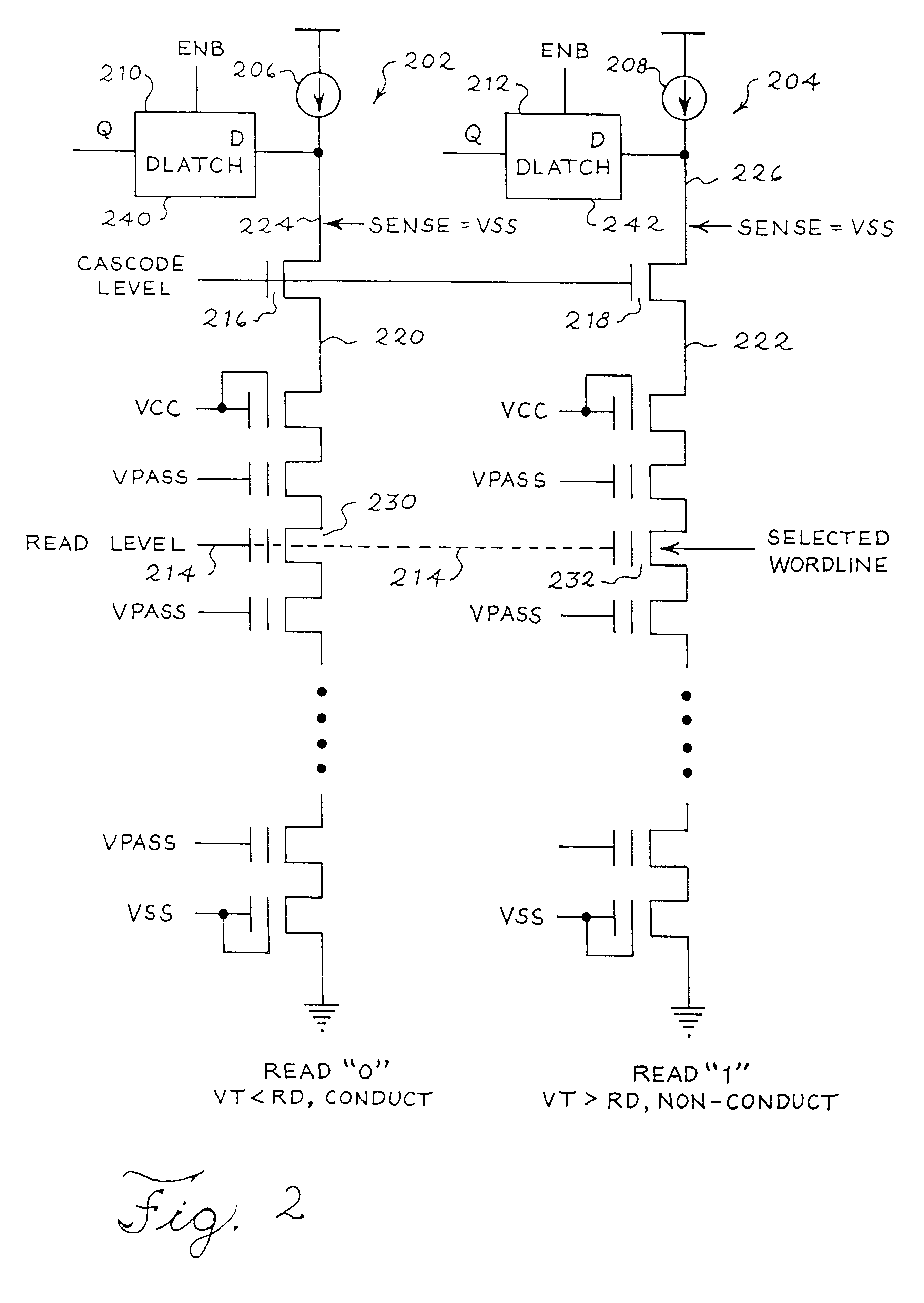

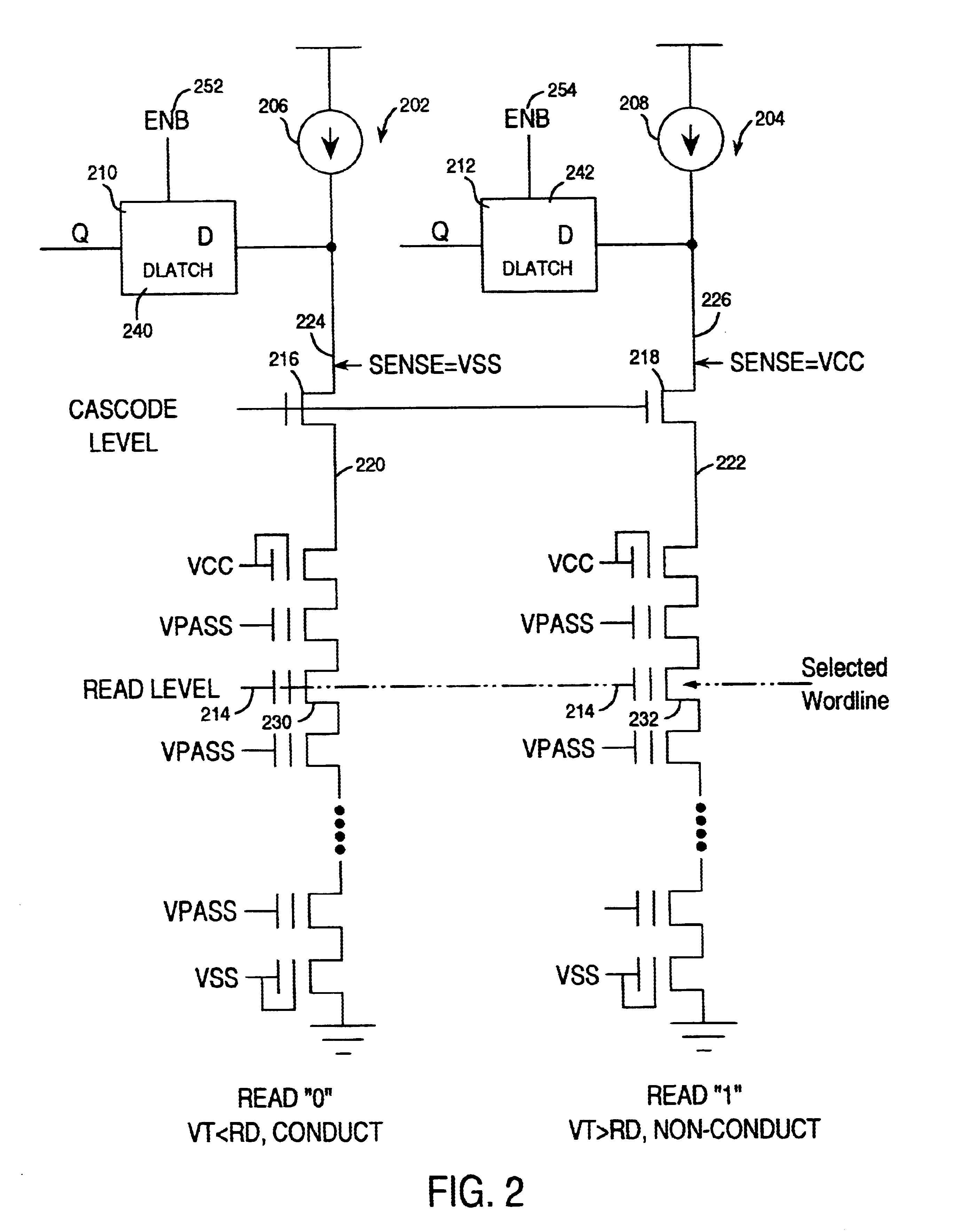

Descending staircase read technique for a multilevel cell NAND flash memory device

A multi-level memory includes an array of memory cells accessible through respective word lines and bit lines a control circuit controlling embedded operations of the memory and a read voltage generating circuit to generate a descending staircase read voltage to a word line associated with a selected memory cell under control of the control circuit. The multi-level memory further includes a read circuit including a latch circuit, and a switch circuit responsive to an evaluate / enable signal to selectively store a read state signal in the latch circuit in response to a sense signal generated from application of the descending staircase read voltage to the word line associated with the selected memory cell.

Owner:VALLEY DEVICE MANAGEMENT

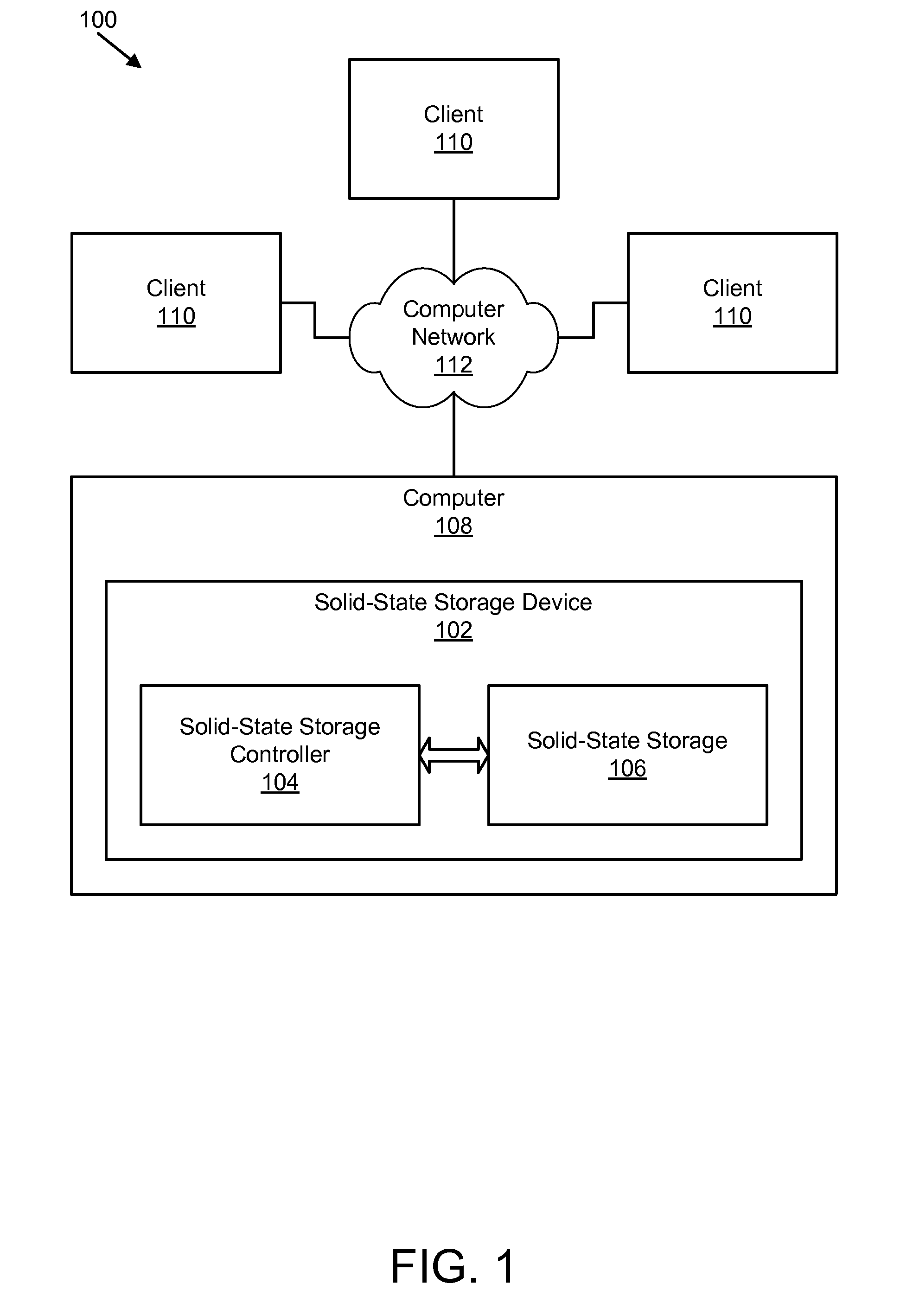

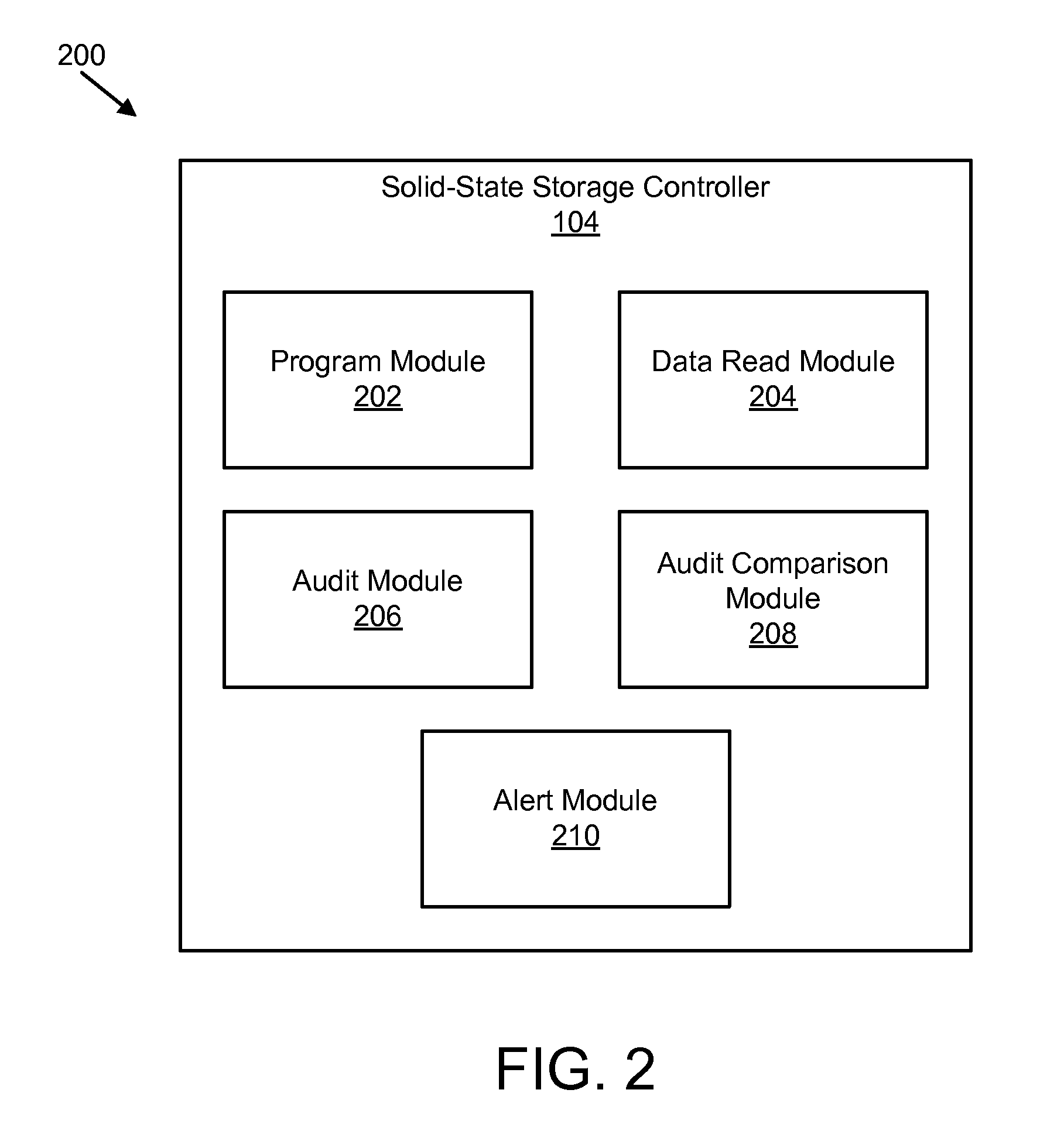

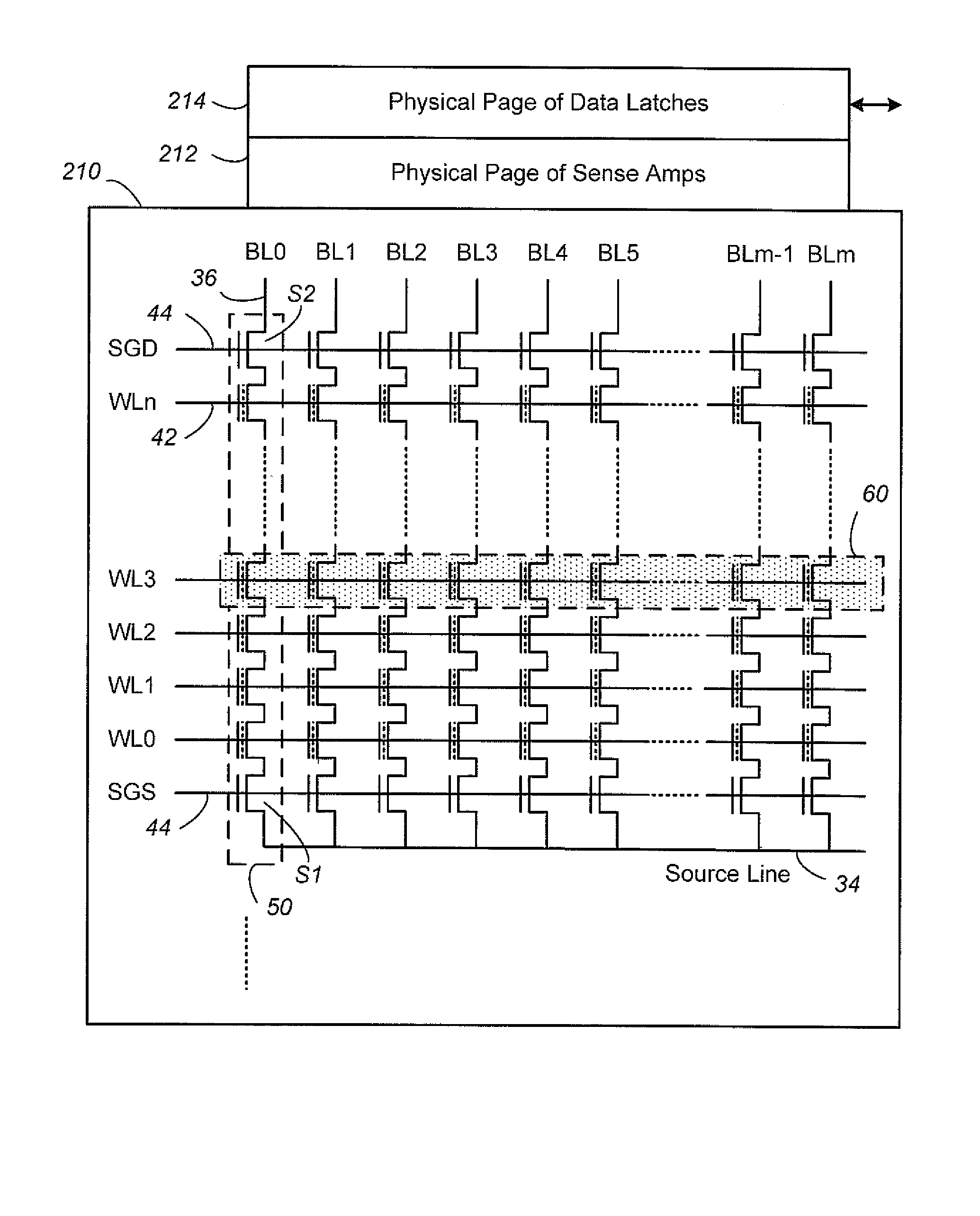

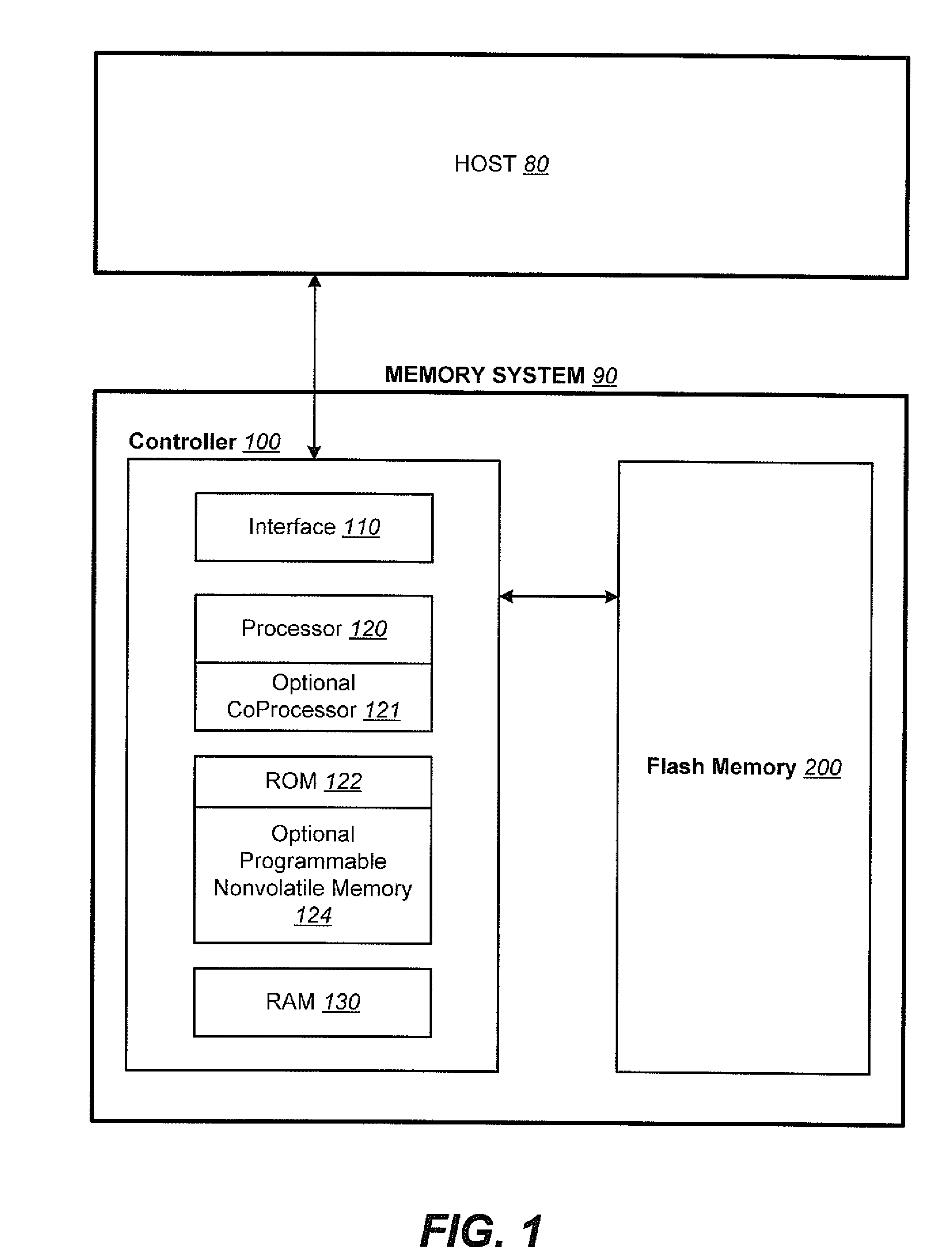

Apparatus, system, and method for using multi-level cell solid-state storage as single-level cell solid-state storage

ActiveUS20100235715A1Increase guard bandLow reliabilityMemory loss protectionRead-only memoriesSolid-state storageMultilevel memory

An apparatus, system, and method are disclosed for storing information in a storage device that includes multi-level memory cells. The method involves storing data that is written to the storage device in the LSBs of the multi-level memory cells, and storing audit data in the MSBs of the multi-level memory cells. The audit data can be read separately from the data and used to determine whether or not there has been any unintended drift between states in the multi-level cells. The audit data may be used to correct data when the errors in the data are too numerous to be corrected using error correction code (ECC). The audit data may also be used to monitor the general health of the storage device. The monitoring process may run as a background process on the storage device. The storage device may transition the multi-level memory cells to operate as single-level memory cells.

Owner:SANDISK TECH LLC

Non-volatile memory and method with write cache partitioning

ActiveUS8094500B2Faster and robust write and read performanceIncrease burst write speedMemory architecture accessing/allocationRead-only memoriesGranularityMultilevel memory

A portion of a nonvolatile memory is partitioned from a main multi-level memory array to operate as a cache. The cache memory is configured to store at less capacity per memory cell and finer granularity of write units compared to the main memory. In a block-oriented memory architecture, the cache has multiple functions, not merely to improve access speed, but is an integral part of a sequential update block system. Decisions to write data to the cache memory or directly to the main memory depend on the attributes and characteristics of the data to be written, the state of the blocks in the main memory portion and the state of the blocks in the cache portion.

Owner:SANDISK TECH LLC

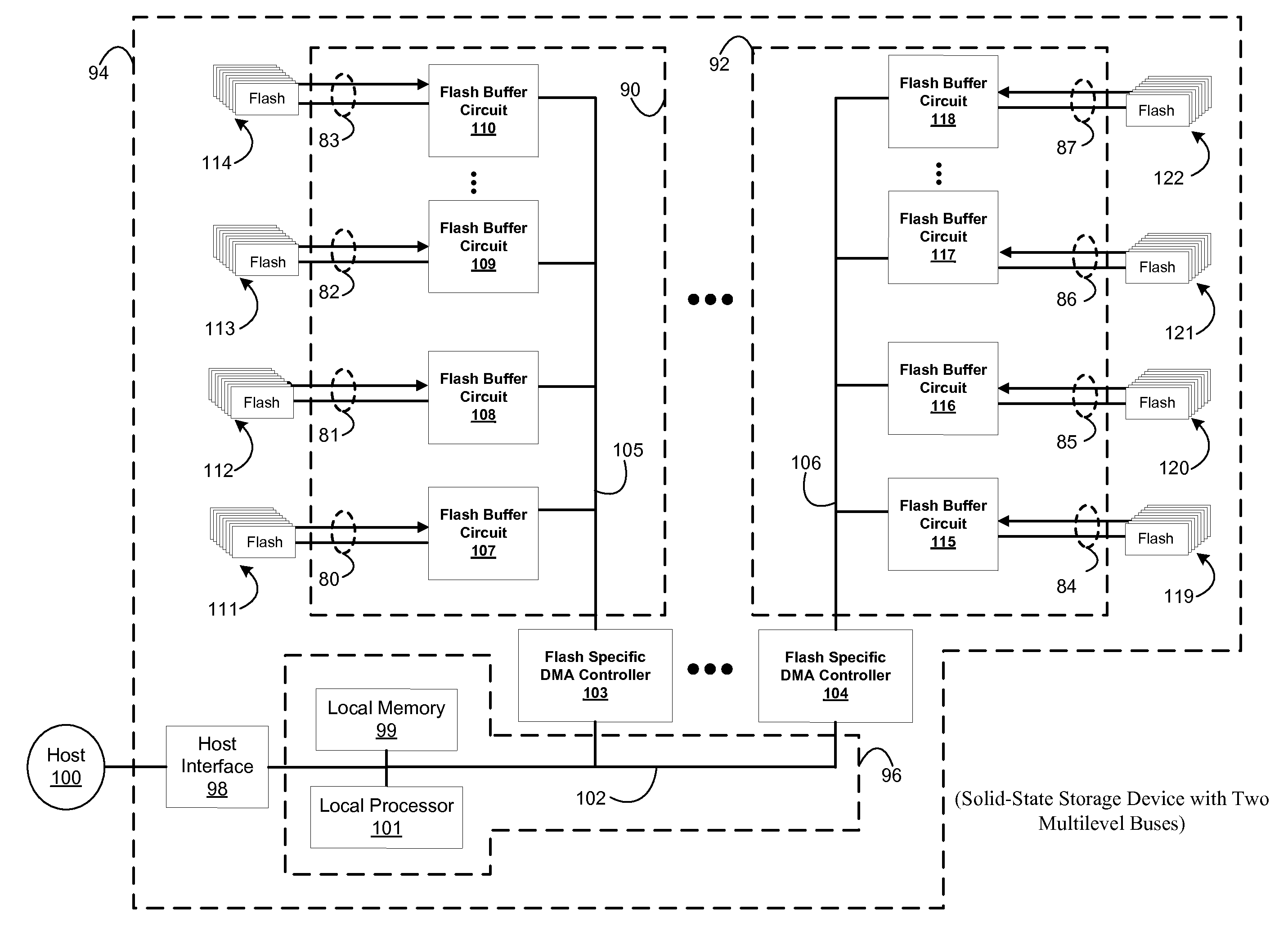

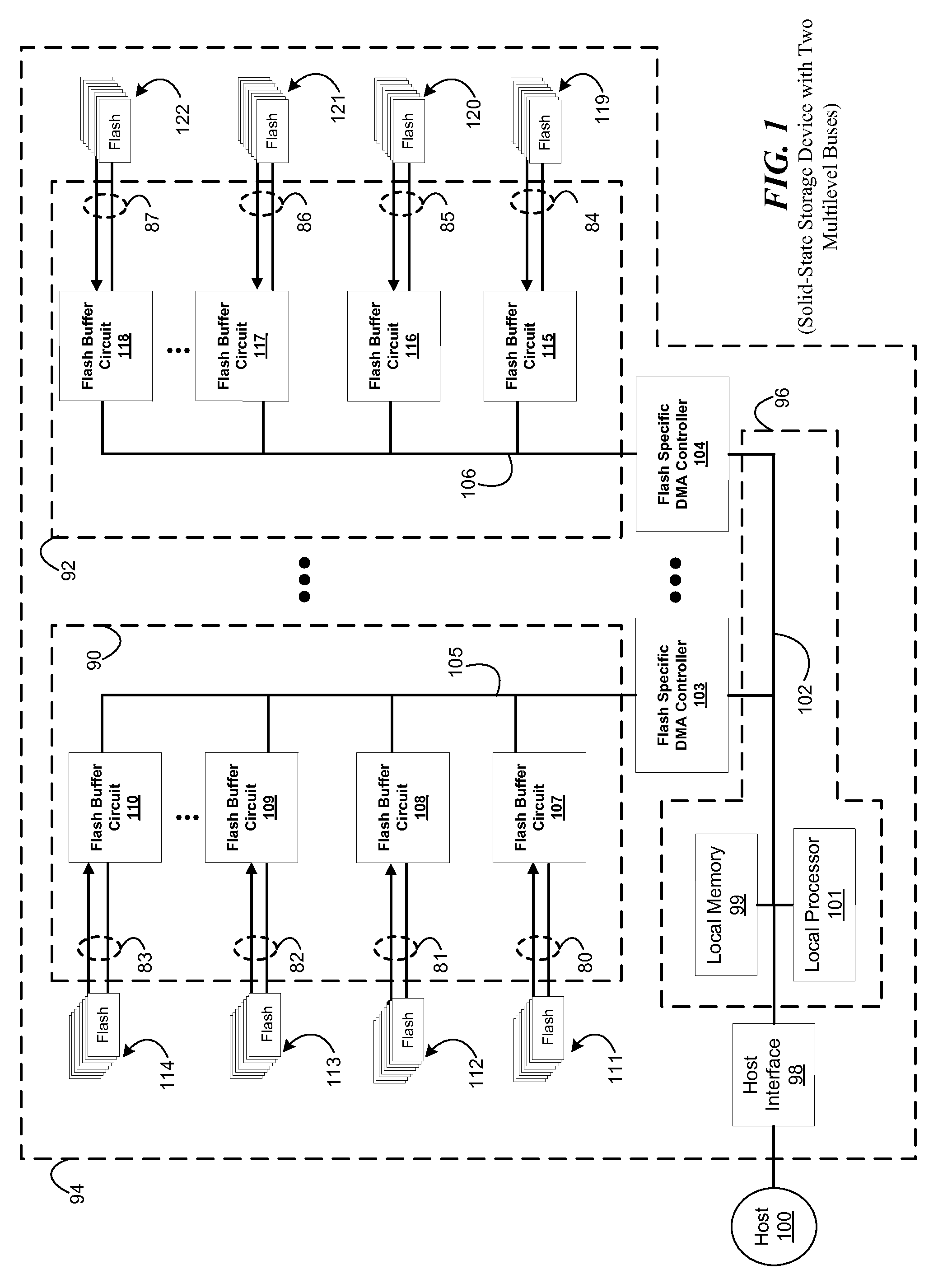

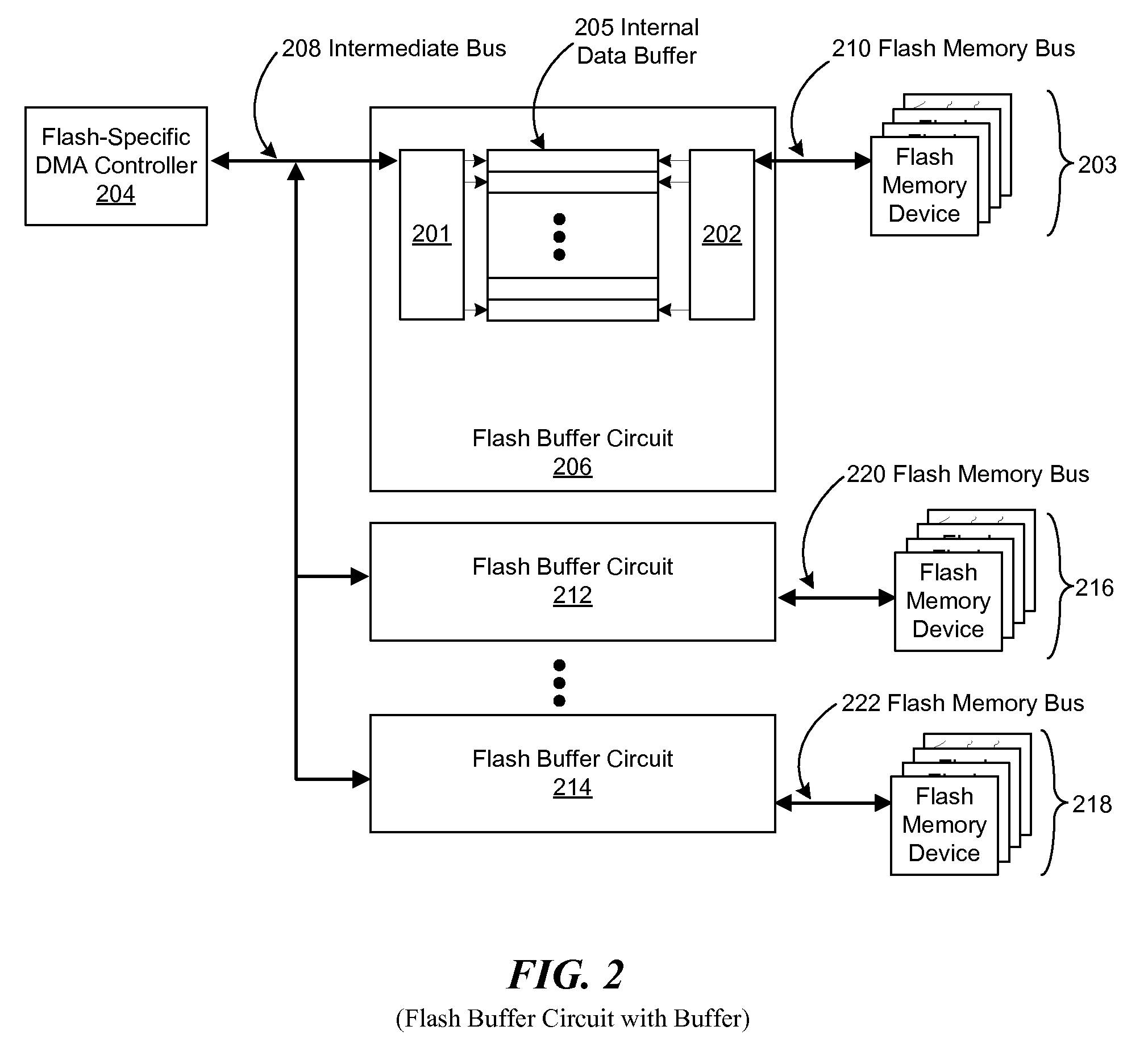

Multilevel memory bus system for solid-state mass storage

InactiveUS8447908B2Specific program execution arrangementsMemory systemsMass storageMultilevel memory

The present invention relates to a multilevel memory bus system for transferring information between at least one DMA controller and at least one solid-state semiconductor memory device, such as NAND flash memory devices or the like. This multilevel memory bus system includes at least one DMA controller coupled to an intermediate bus; a flash memory bus; and a flash buffer circuit between the intermediate bus and the flash memory bus. This multilevel memory bus system may be disposed to support: an n-bit wide bus width, such as nibble-wide or byte-wide bus widths; a selectable data sampling rate, such as a single or double sampling rate, on the intermediate bus; a configurable bus data rate, such as a single, double, quad, or octal data sampling rate; CRC protection; an exclusive busy mechanism; dedicated busy lines; or any combination of these.

Owner:BITMICRO LLC

Non-volatile memory and method with write cache partition management methods

InactiveUS8244960B2Faster and robust write and read performanceIncrease burst write speedMemory architecture accessing/allocationMemory systemsGranularityMultilevel memory

A portion of a nonvolatile memory is partitioned from a main multi-level memory array to operate as a cache. The cache memory is configured to store at less capacity per memory cell and finer granularity of write units compared to the main memory. In a block-oriented memory architecture, the cache has multiple functions, not merely to improve access speed, but is an integral part of a sequential update block system. The cache memory has a capacity dynamically increased by allocation of blocks from the main memory in response to a demand to increase the capacity. Preferably, a block with an endurance count higher than average is allocated. The logical addresses of data are partitioned into zones to limit the size of the indices for the cache.

Owner:SANDISK TECH LLC

Processing Unit Incorporating L1 Cache Bypass

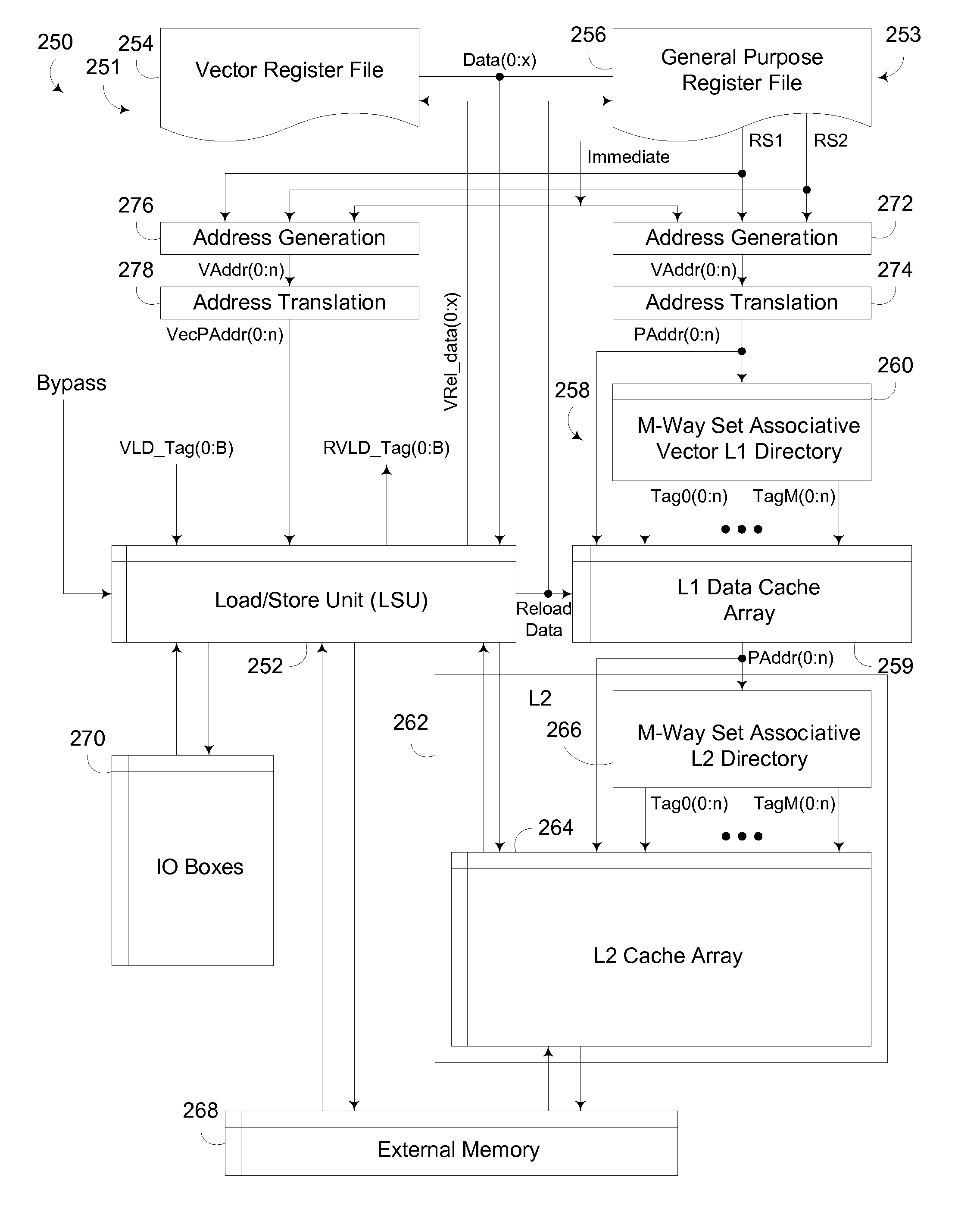

InactiveUS20090182944A1Reduce the possibilityMemory adressing/allocation/relocationMultilevel memoryMemory architecture

A circuit arrangement and method bypass the storage of requested data in a higher level cache of a multi-level memory architecture during the return of the requested data to a requester, while caching the requested data in a lower level cache. For certain types of data, e.g., data that is only used once and / or that is rarely modified or written back to memory, bypassing storage in a higher level cache reduces the likelihood of the requested data casting out frequently used data from the higher level cache. By caching the data in a lower level cache, however, the lower level cache can still snoop data requests and return requested data in the event the data is already cached in the lower level cache.

Owner:IBM CORP

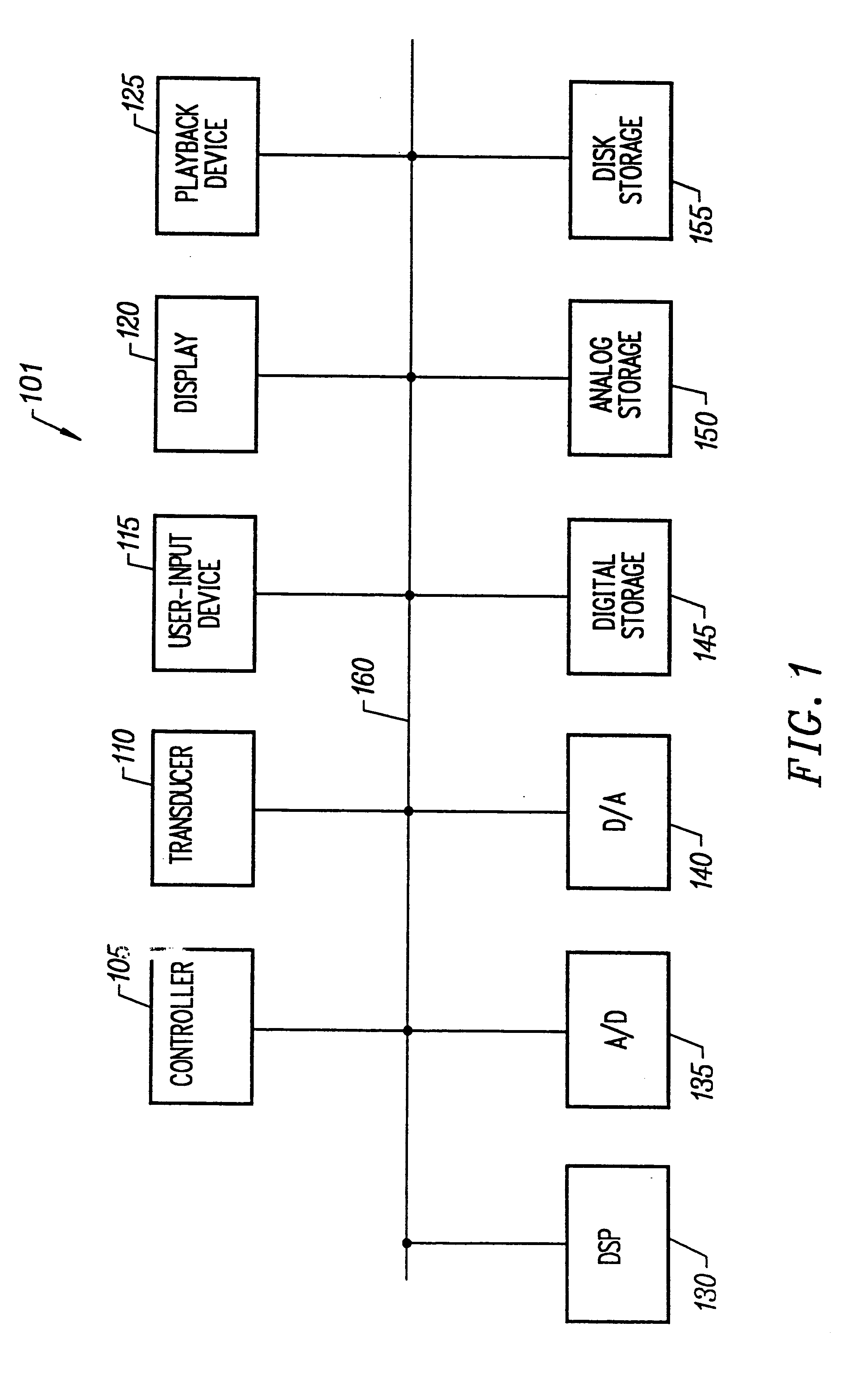

Apparatus, method, and system for flash memory

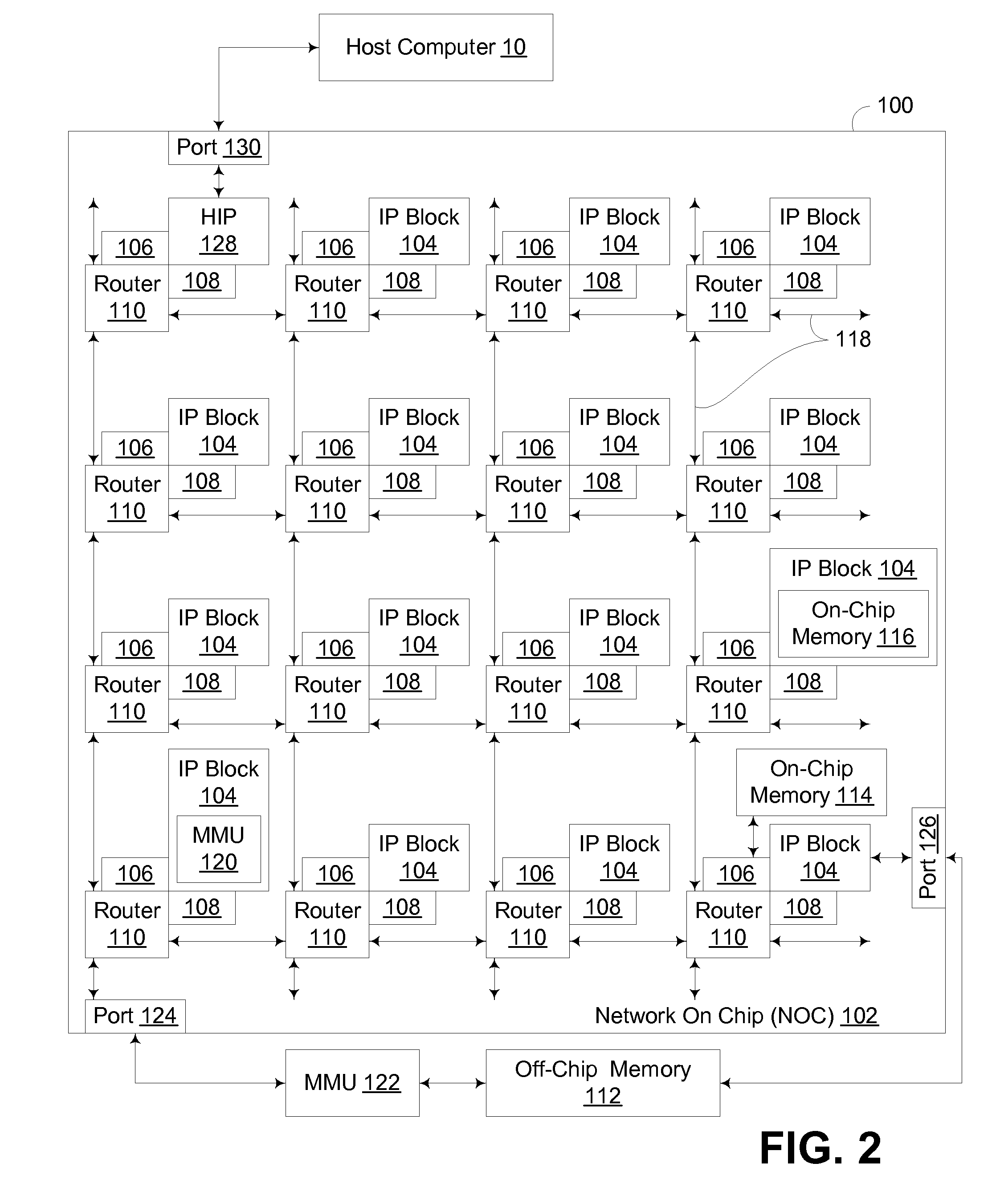

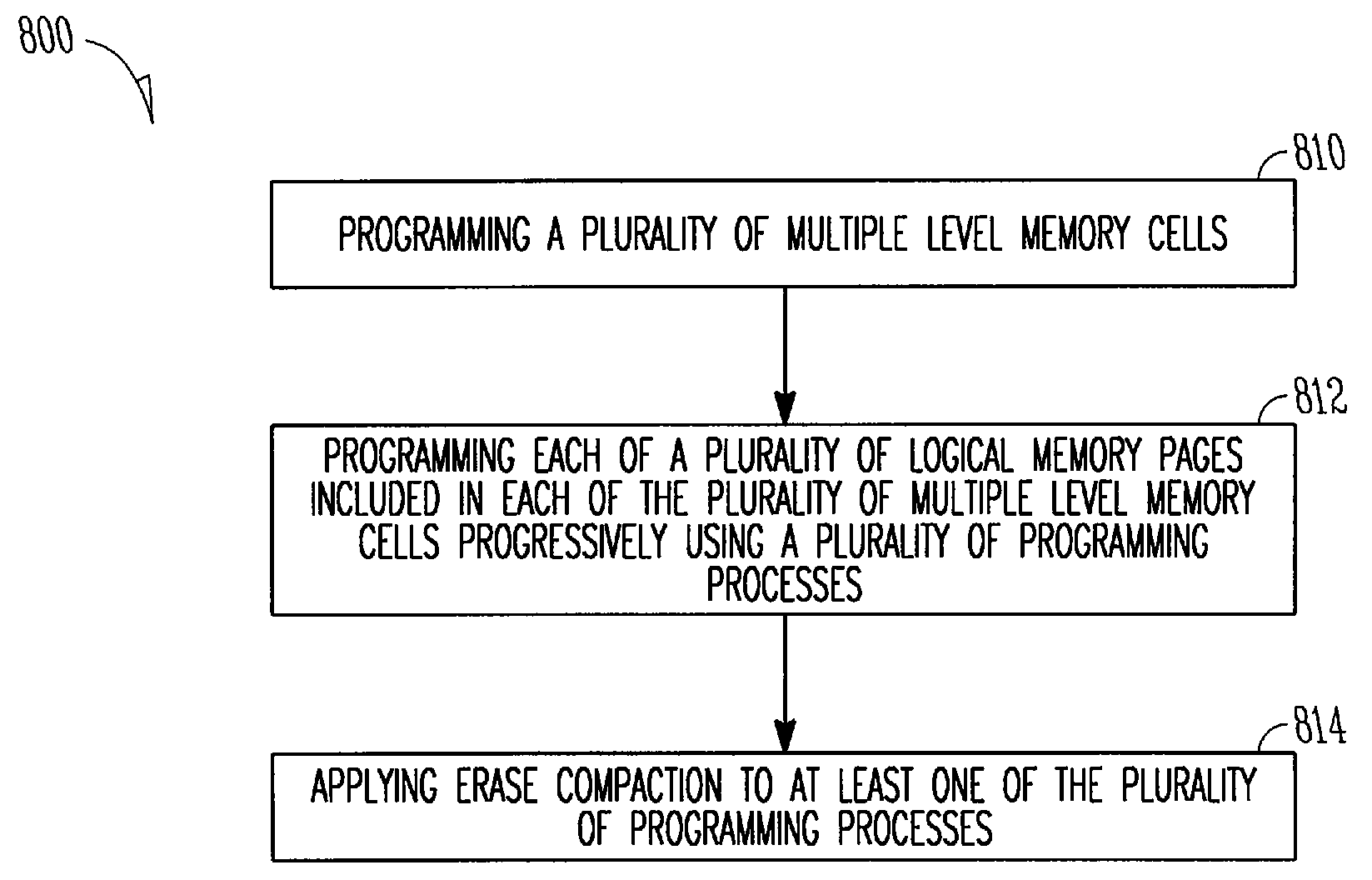

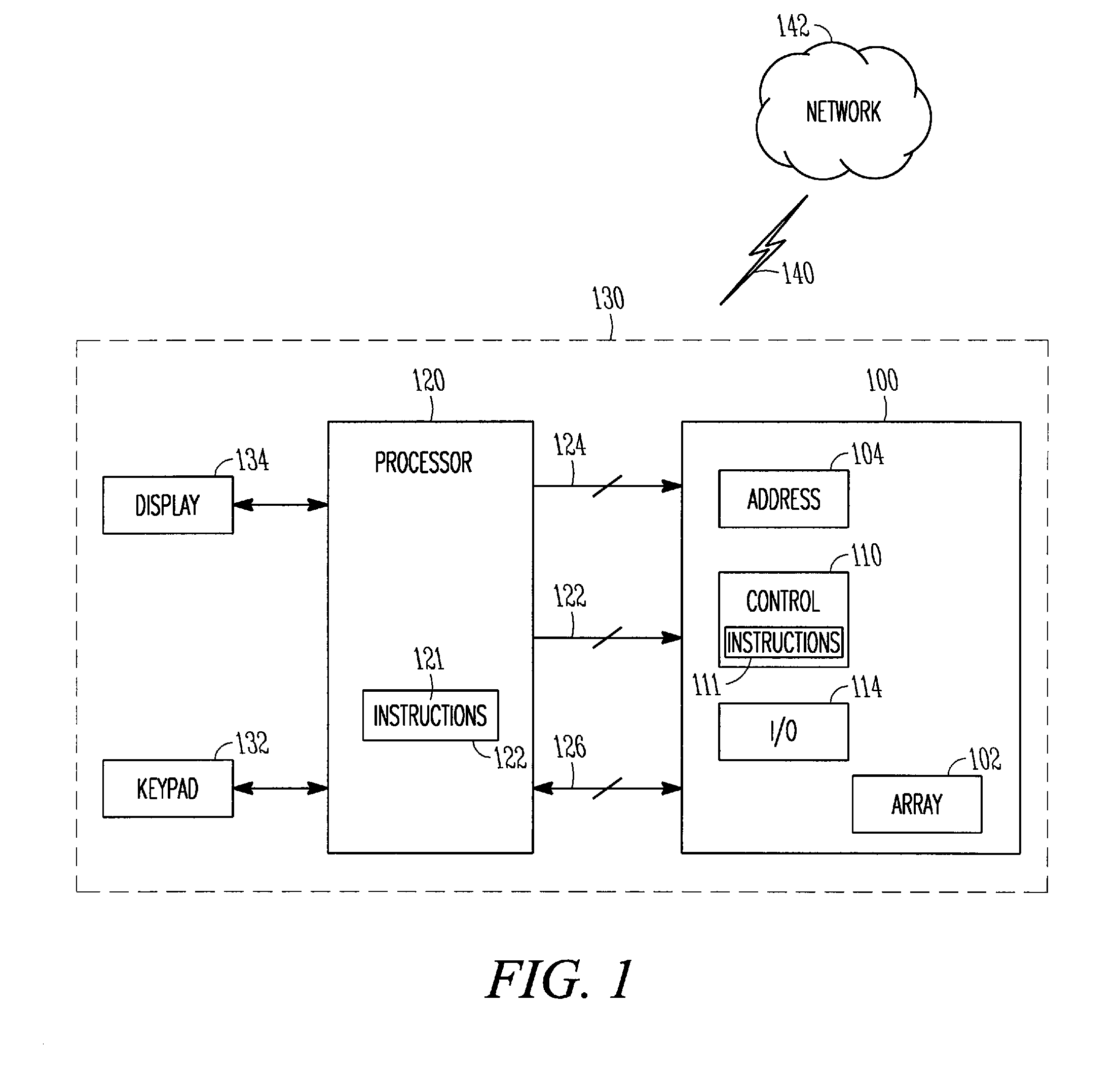

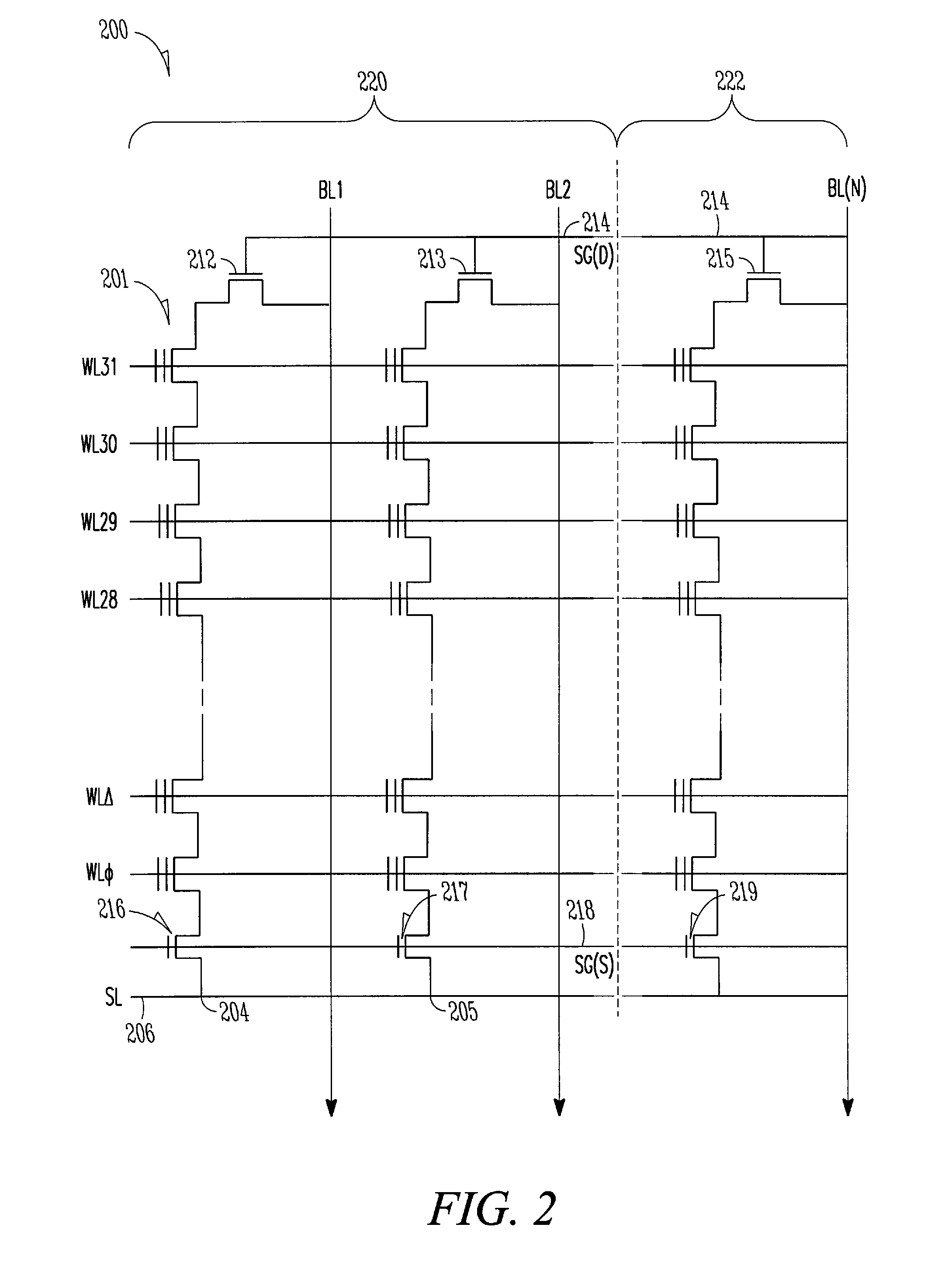

Methods, apparatus, systems, and data structures are disclosed, including a plurality of multiple level memory cells, each of the plurality of multiple level memory cells coupled to one of a plurality of wordlines and each of the plurality of multiple level memory cells including a plurality of logical memory pages; a control circuit coupled to the plurality of wordlines, the control circuit operable to progressively program each of the plurality of multiple level memory cells in at least one sequence including separation of the programming of a first logical memory page and a second logical memory page in any one of the plurality of multiple level memory cells by at least N−1 programming operations to memory cells either coupled to a different wordline or included in a different logical even page or a different logical odd page.

Owner:INTEL NDTM US LLC

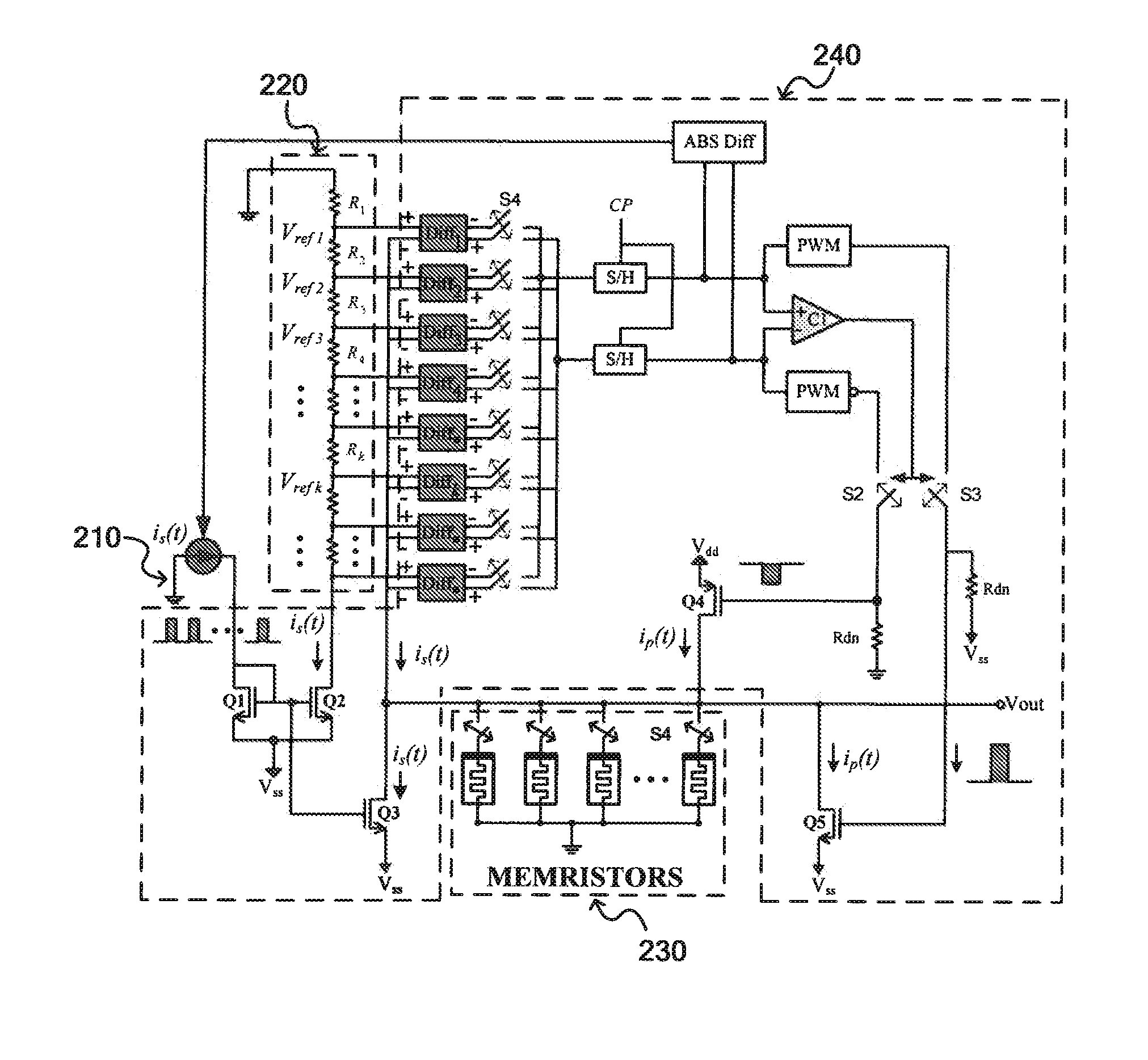

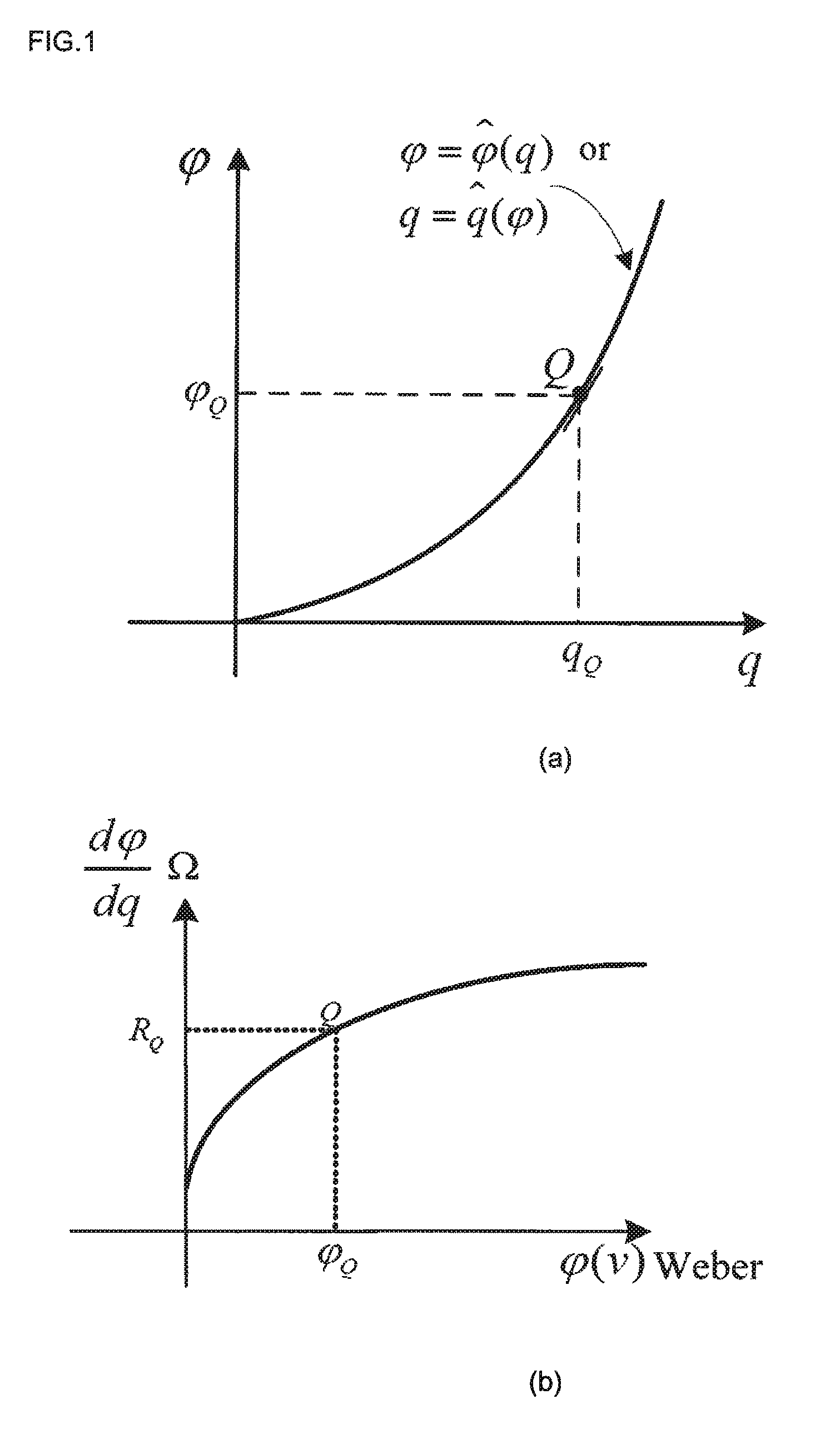

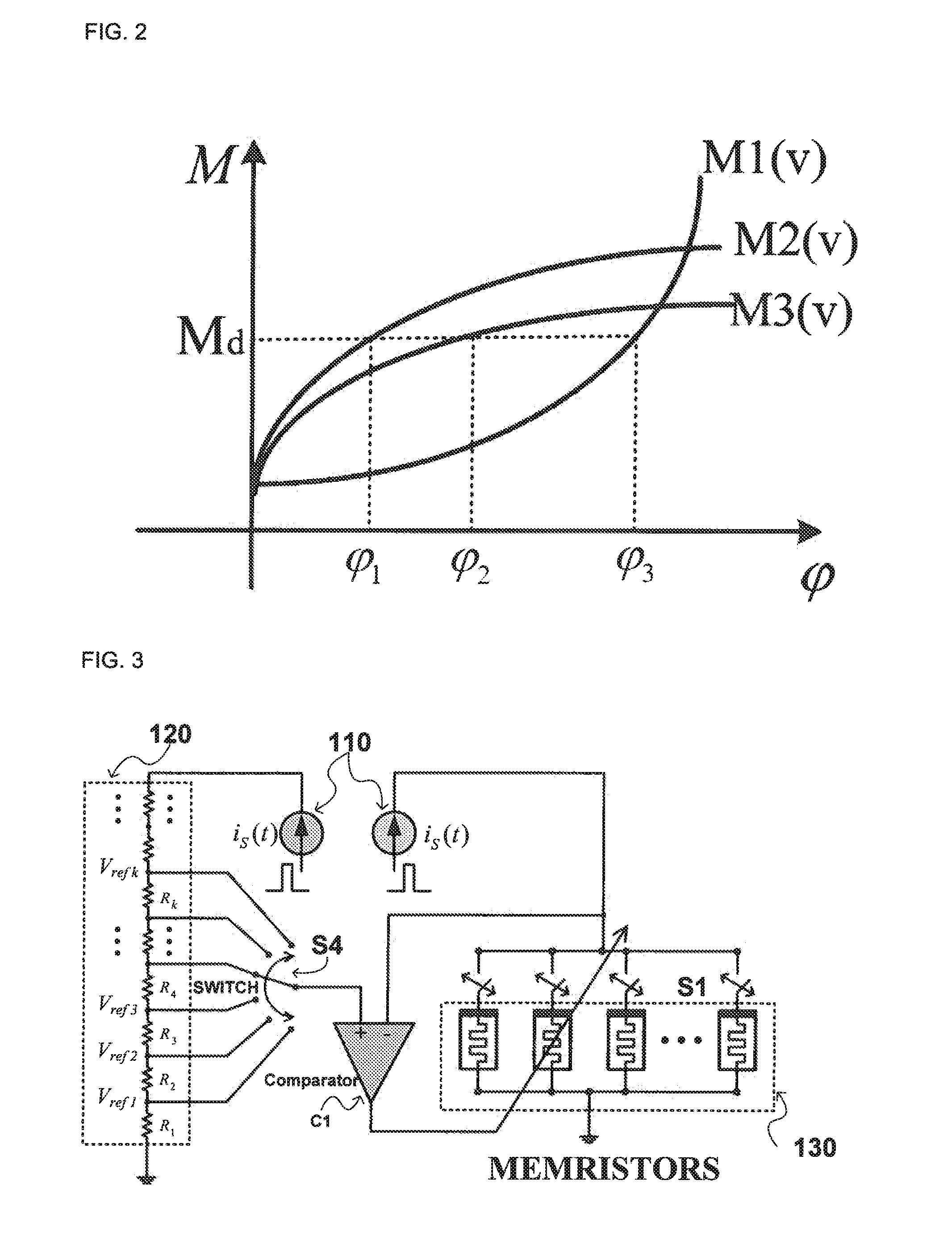

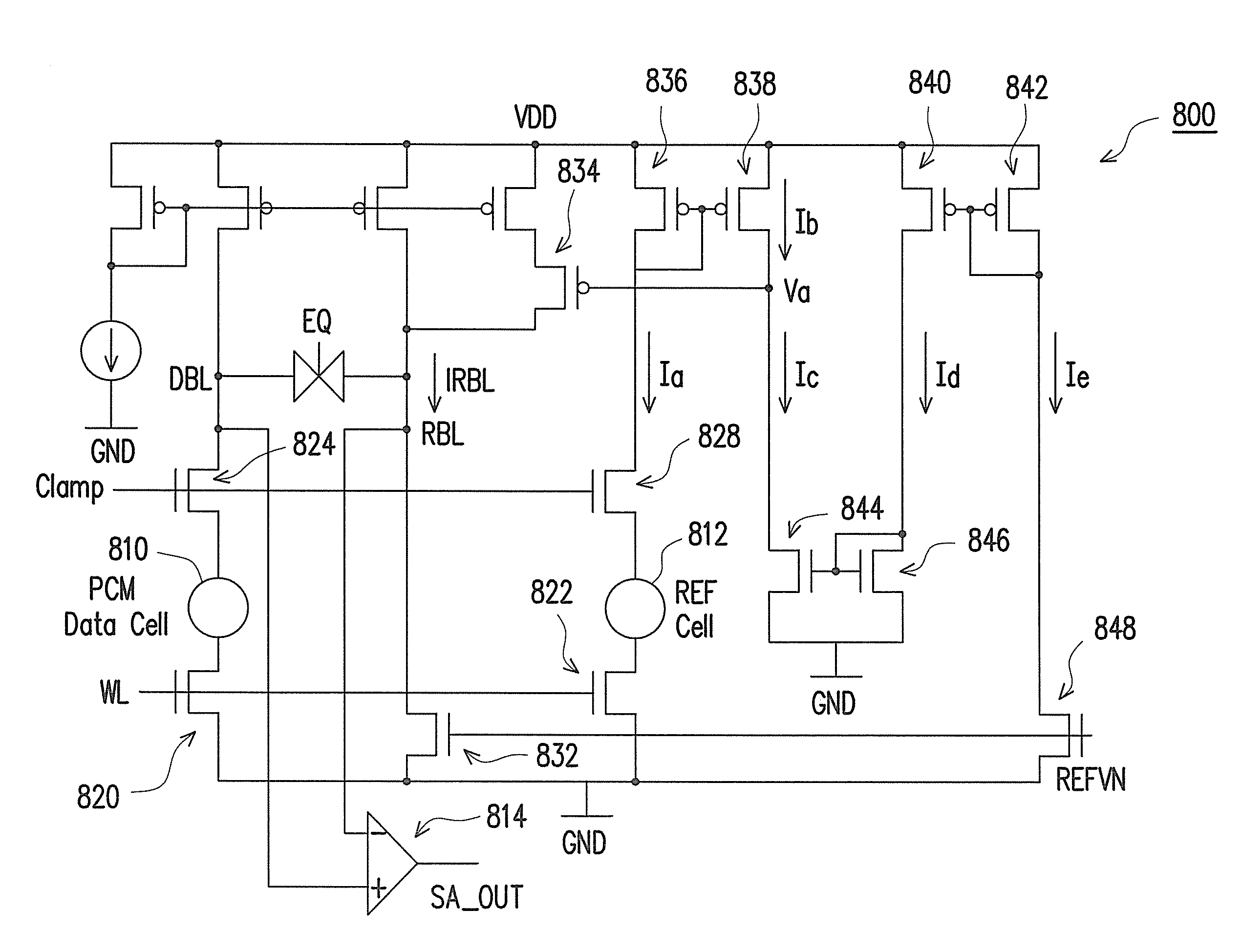

Method of implementing memristor-based multilevel memory using reference resistor array

The present invention relates to a memristor, and more particularly, to a method of implementing a memristor-based multilevel memory using a reference resistor array and a write-in circuit and a read-out / restoration circuit for the memristor-based multilevel memory, in which a memristor can be used as a multilevel memory. In the present invention, a reference resistance value is written in a selected memristor of a memristor array by applying repeatedly the current pulses of which widths are proportional to the difference between the resistances of the selected memristor and the selected node of the reference resistor array.

Owner:IND COOP FOUND CHONBUK NAT UNIV +1

Ascending staircase read technique for a multilevel cell NAND flash memory device

A method for resolving data to one stored level of N possible stored levels in a multi-level memory includes receiving an access address associated with a memory location of the multi-level memory and applying an ascending staircase read voltage to a word line associated with the access address. The method further includes detecting a sense signal produced on a sense line associated with the access address in response to the stored level and a value of the staircase read voltage, for each value of the ascending staircase read voltage, storing data responsive to the sense signal, and after application of a final value of the ascending staircase read voltage, producing an N-bit value corresponding to the one stored level stored in the memory location.

Owner:MONTEREY RES LLC

Seek window verify program system and method for a multilevel non-volatile memory integrated circuit system

A memory comprises a plurality of digital multilevel memory cells. A window of valid data voltages for accessing the said plurality of digital multilevel memory cells is detected. The window may be detected by incrementing a first programming voltage to program data in the plurality of memory cells and verifying whether the data in at least one of said plurality of memory cells is properly programmed. The incrementing and verifying may be repeated until data is verified to be properly programmed in one of said plurality of memory cells. The data in each memory cell of said plurality of memory cells is verified. The verification may be by incrementing a second programming voltage, and verifying whether data in each memory cell is properly programmed within a margin. The incrementing and verifying is repeated for each memory cell outside of the margin.

Owner:SILICON STORAGE TECHNOLOGY

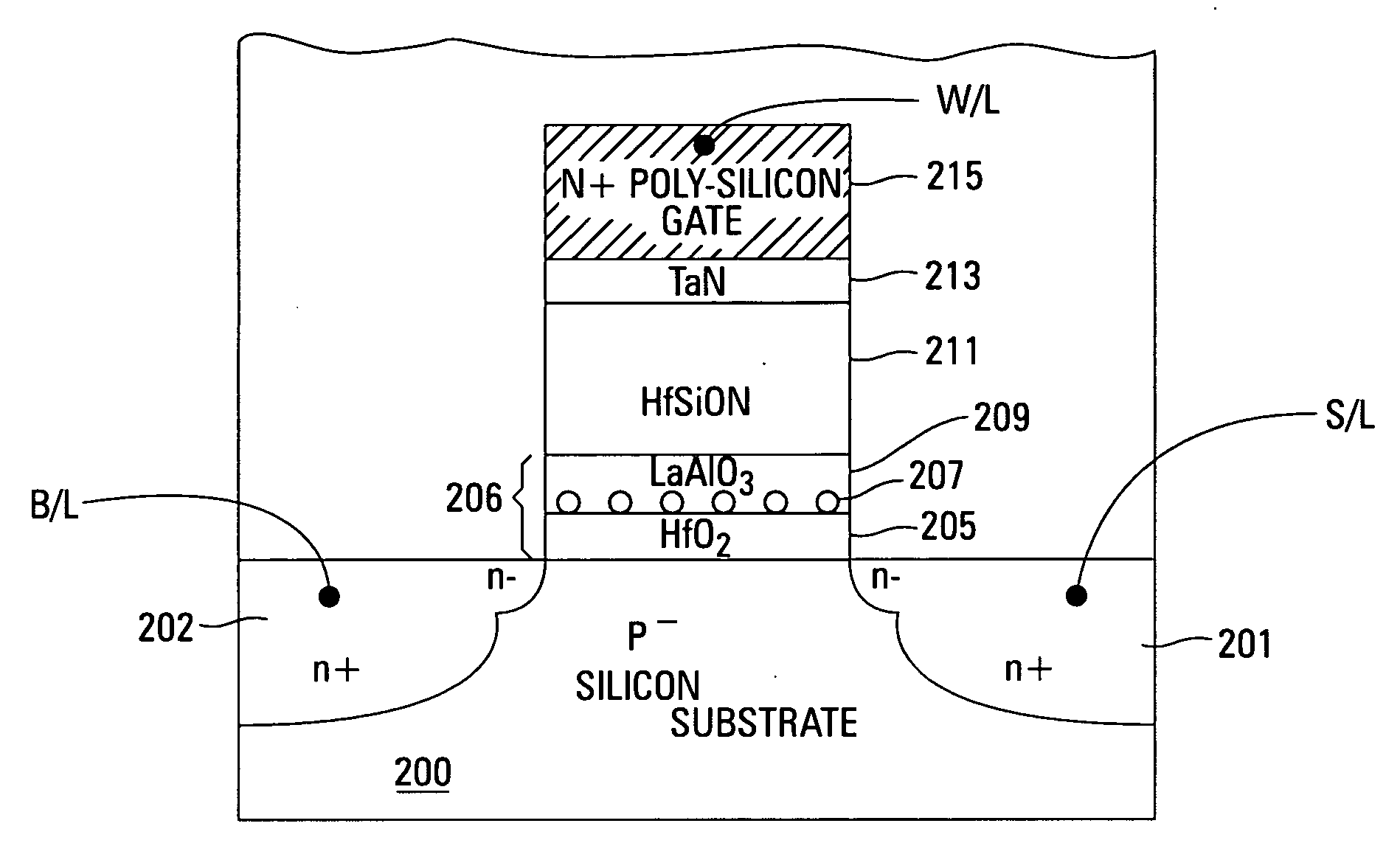

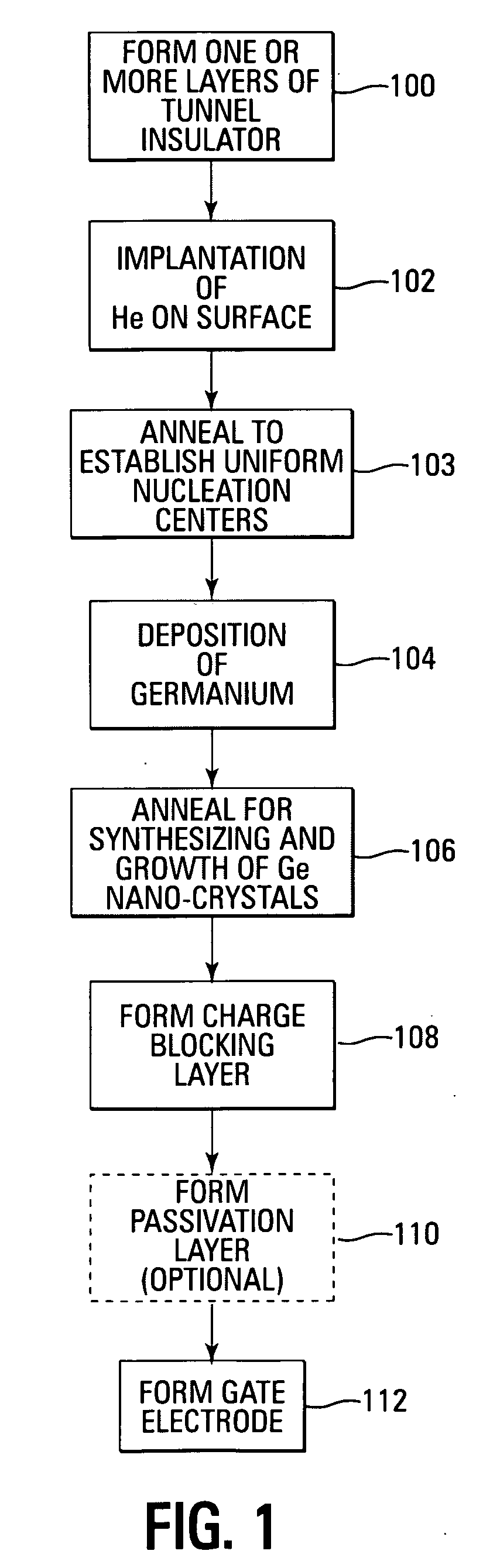

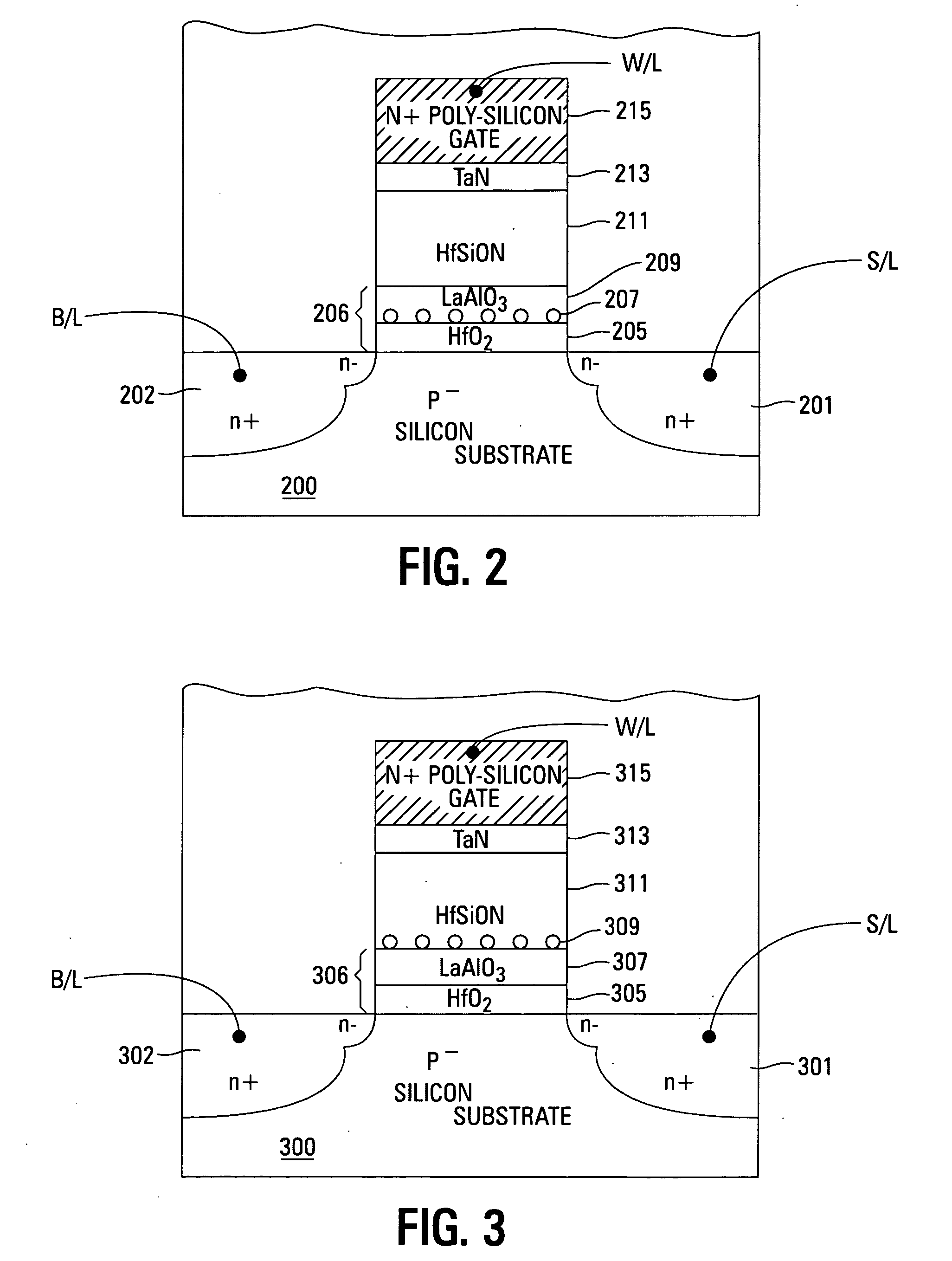

Scalable multi-functional and multi-level nano-crystal non-volatile memory device

ActiveUS20070052011A1Great non-volatilityEvenly distributedNanoinformaticsSolid-state devicesTrappingMultilevel memory

A multi-functional and multi-level memory cell is comprised of a tunnel layer formed over a substrate. In one embodiment, the tunnel layer is comprised of two layers such as HfO2 and LaAlO3. A charge blocking layer is formed over the tunnel layer. In one embodiment, this layer is formed from HfSiON. A control gate is formed over the charge blocking layer. A discrete trapping layer is embedded in either the tunnel layer or the charge blocking layer, depending on the desired level of non-volatility. The closer the discrete trapping layer is formed to the substrate / insulator interface, the lower the non-volatility of the device. The discrete trapping layer is formed from nano-crystals having a uniform size and distribution.

Owner:MICRON TECH INC

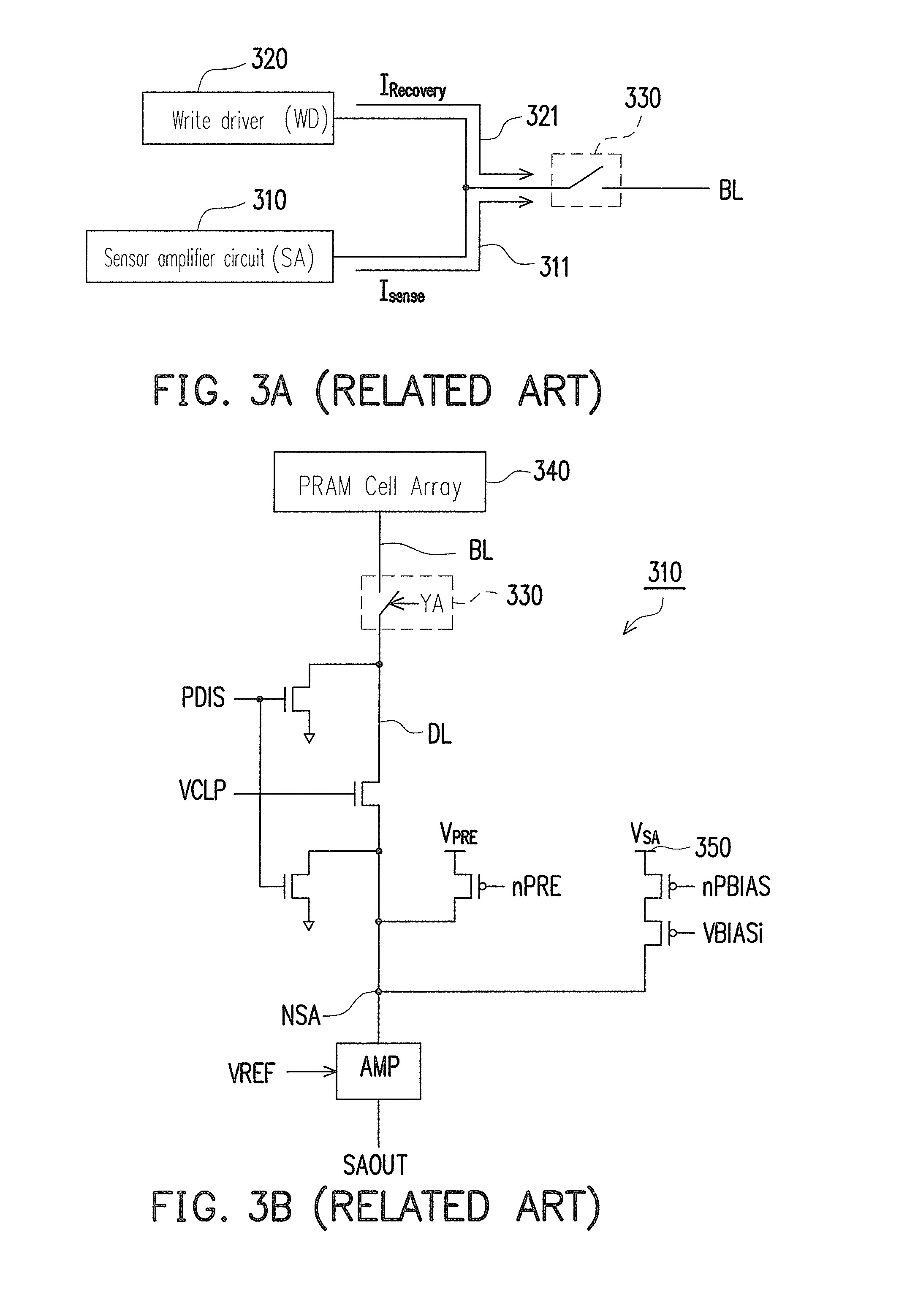

Voltage compensation circuit, multi-level memory device with the same, and voltage compensation method for reading the multi-level memory device

A voltage compensation circuit, a multi-level memory device with the same, and a voltage compensation method for reading the multi-level memory device are provided. When a memory cell is read, a reference voltage applied to the memory device is adjusted according to variation of characteristics of a drift resistance of a reference cell. The increased value of the reference voltage (i.e. a voltage difference) corresponds to a resistance variation caused by a drift condition. The drift compensation mechanism is adaptive to a compensation circuit of a read driver of the memory device, which can compensate variation of the voltage level when data is read from the memory cell. When the resistance drift occurs, a drift amount is calculated and is added to the reference voltage, in order to avoid the error in judgement caused by the resistance drift when the stored data is read out.

Owner:IND TECH RES INST

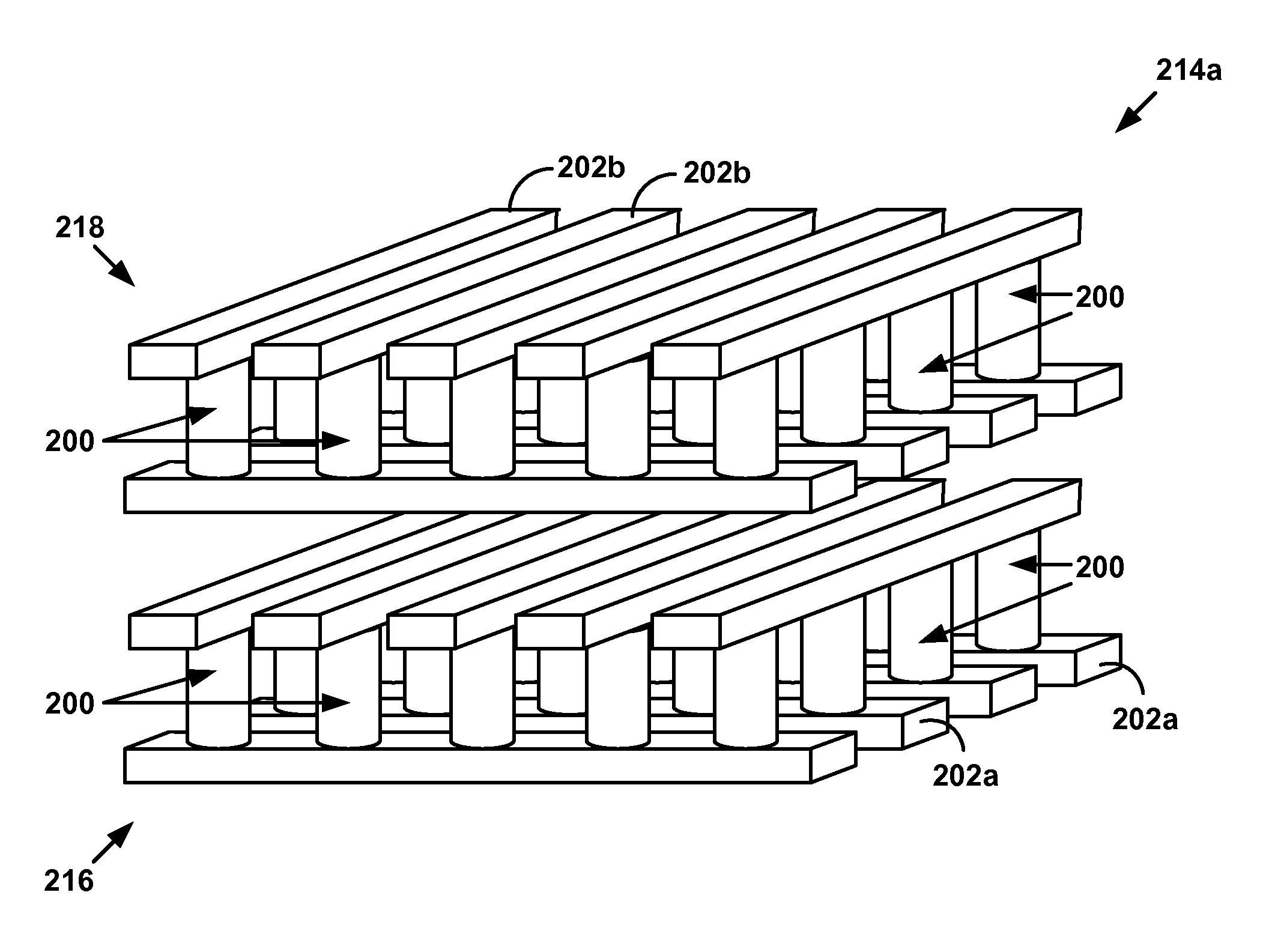

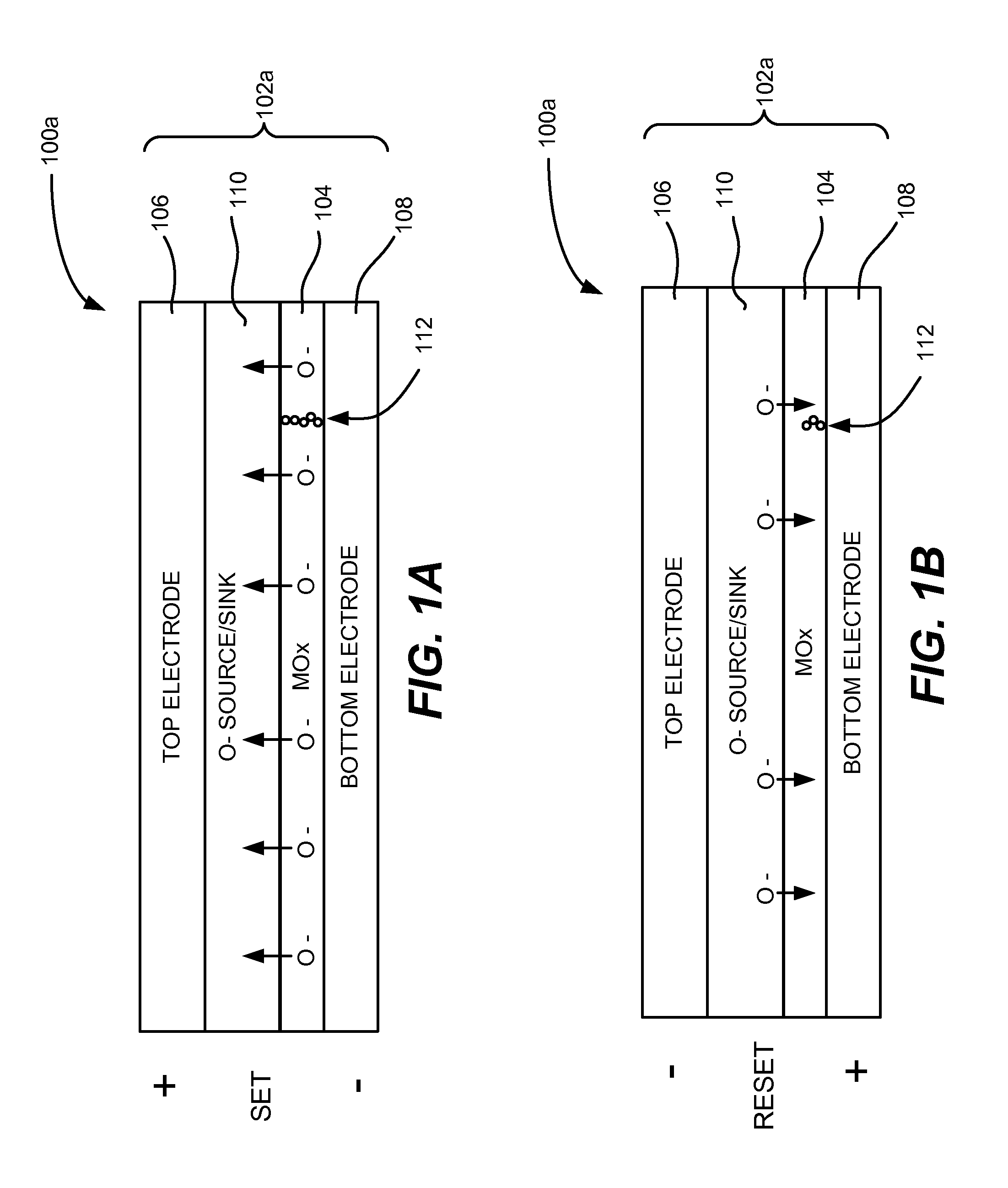

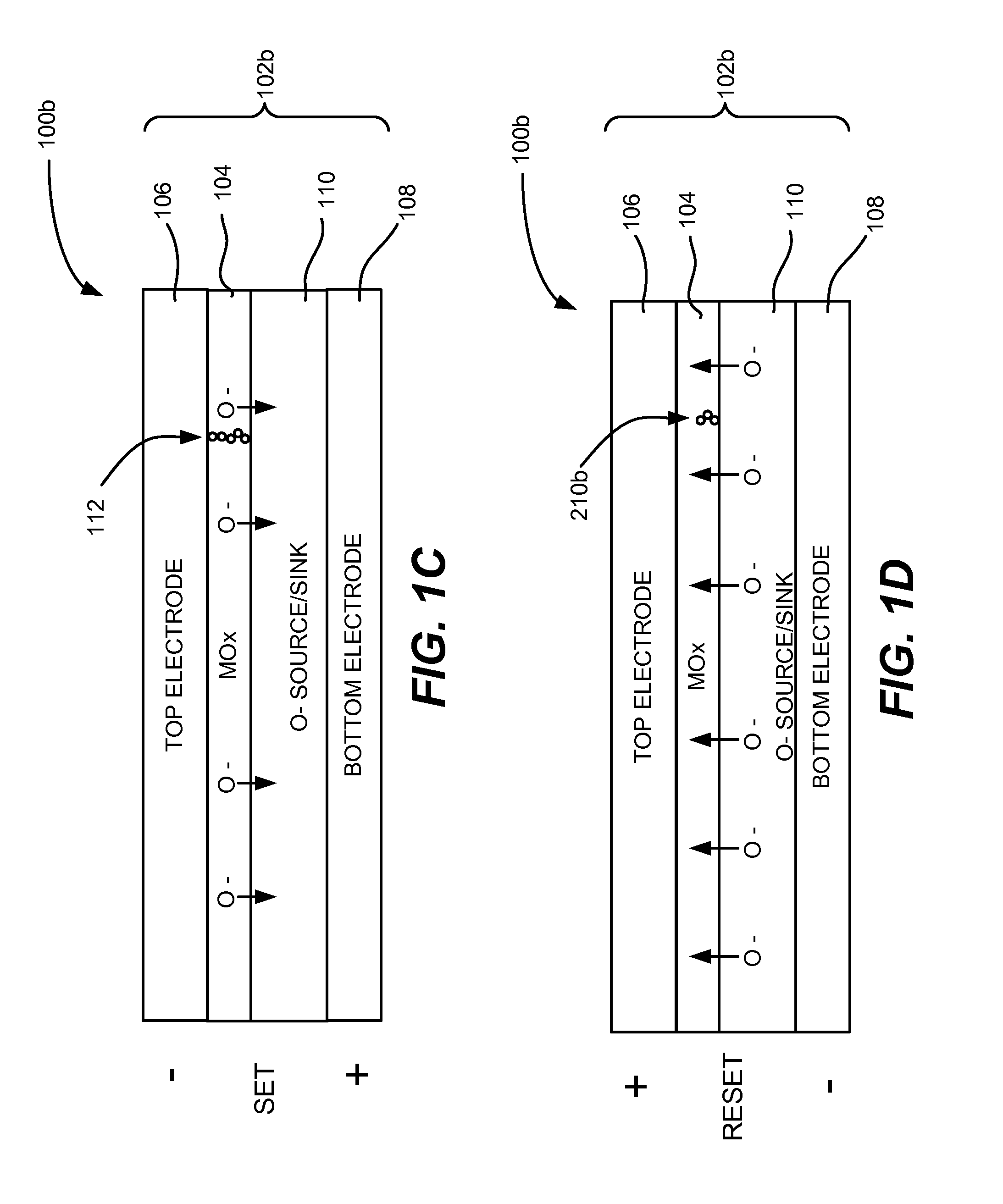

Multi-level memory arrays with memory cells that employ bipolar storage elements and methods of forming the same

ActiveUS20120091427A1Solid-state devicesSemiconductor/solid-state device manufacturingMultilevel memoryElectrical polarity

In some embodiments, a memory array is provided that includes (1) a first memory cell having (a) a first conductive line; (b) a first bipolar storage element formed above the first conductive line; and (c) a second conductive line formed above the first bipolar storage element; and (2) a second memory cell formed above the first memory cell and having (a) a second bipolar storage element formed above the second conductive line; and (b) a third conductive line formed above the second bipolar storage element. The first and second memory cells share the second conductive line; the first bipolar storage element has a first storage element polarity orientation within the first memory cell; the second bipolar storage element has a second storage element polarity orientation within the second memory cell; and the second storage element polarity orientation is opposite the first storage element polarity orientation. Numerous other aspects are provided.

Owner:SANDISK TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com