PDN alternating current noise analysis method for a three-dimensional integrated circuit

An integrated circuit and AC noise technology, applied in the field of electronics, can solve the problems of inaccurate AC noise, slow analysis speed of AC noise, inaccurate results of AC noise, etc., and achieve fast analysis speed, accurate measurement of AC noise and accurate AC noise. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be described in detail below in conjunction with the accompanying drawings.

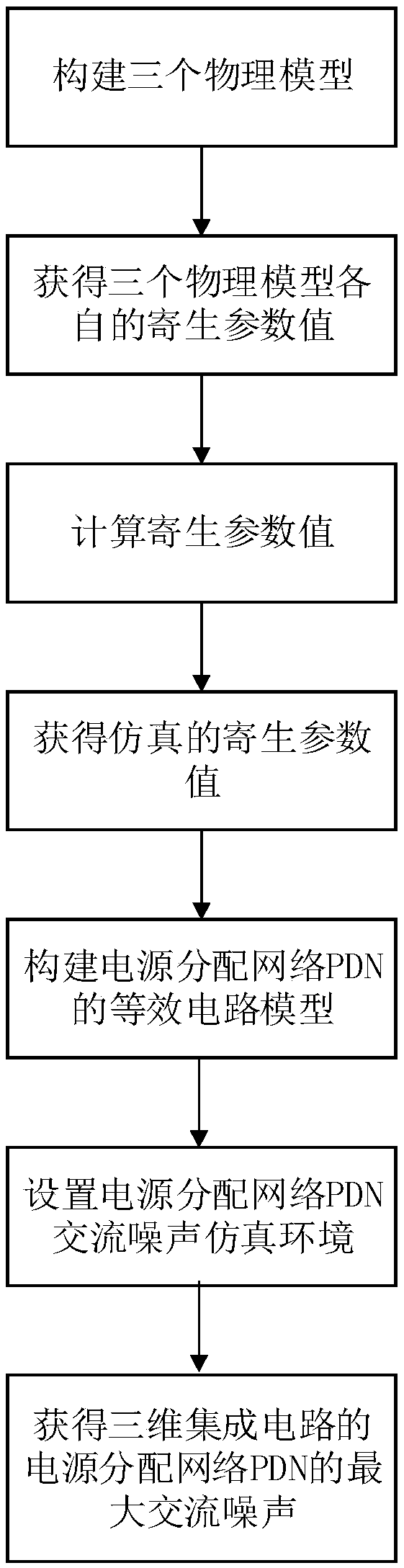

[0035] Refer to attached figure 1 , the implementation steps of the present invention are described in detail.

[0036] Step 1, construct three physical models.

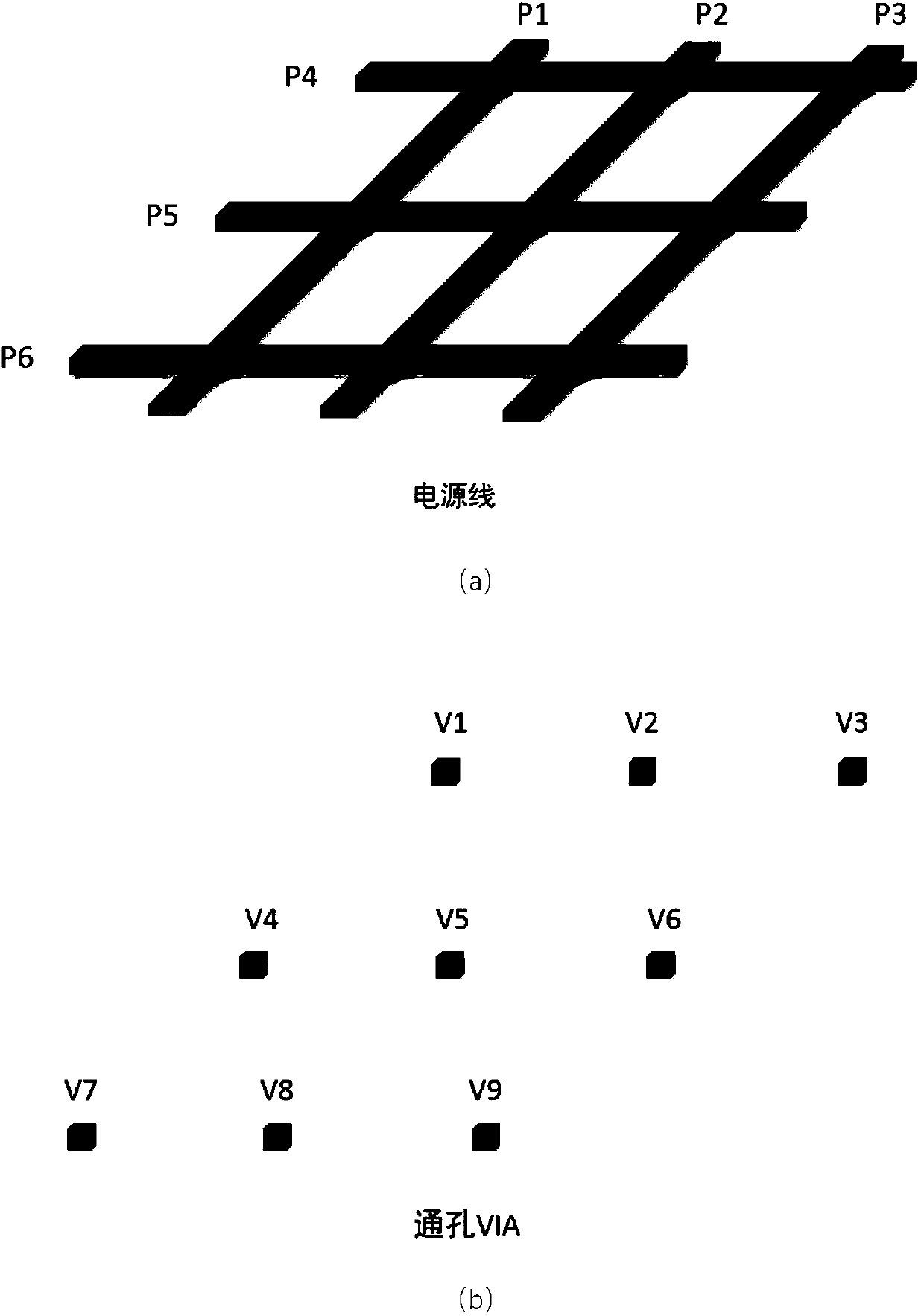

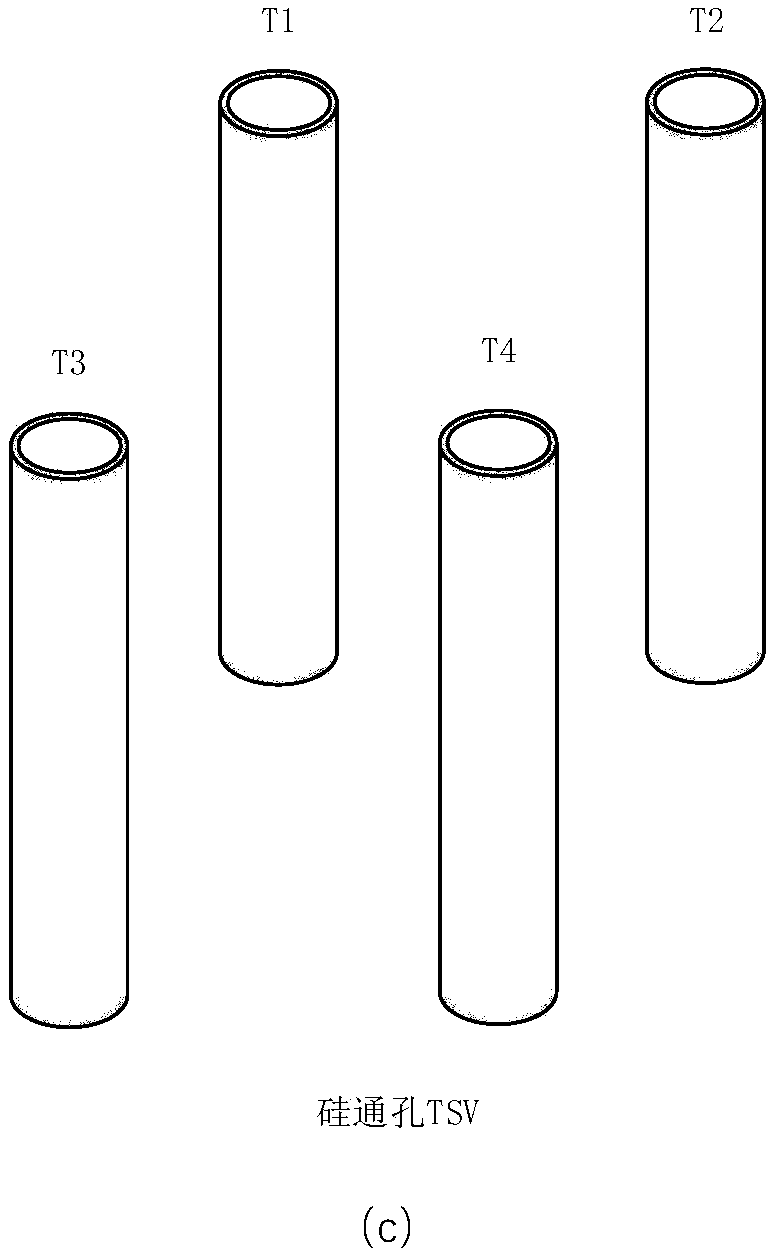

[0037]The process information such as the power line in the power distribution network of the three-dimensional integrated circuit, the length, width, height, and material of the through-silicon via TSV and VIA are input into the electromagnetic simulation software to obtain three physical models.

[0038] Step 2, obtain the respective parasitic parameter values of the three physical models.

[0039] Using the electromagnetic parameter extraction function of the electromagnetic simulation software, the parasitic parameter values of the three physical models of the power line, through-silicon via TSV and through-hole VIA in the power distribution network of the three-dimensional integrated circuit are ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com