Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2010results about "Cyclic codes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

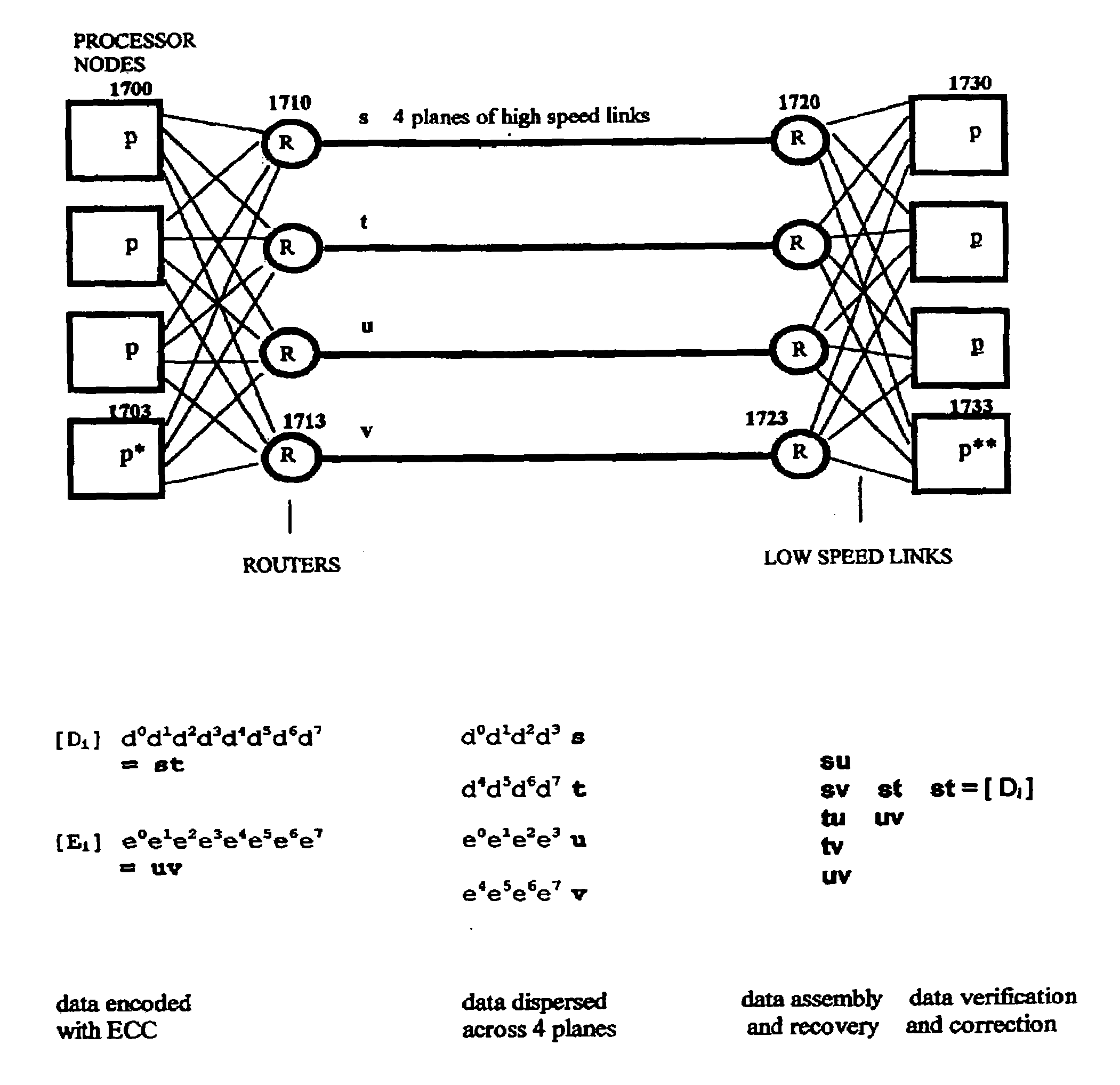

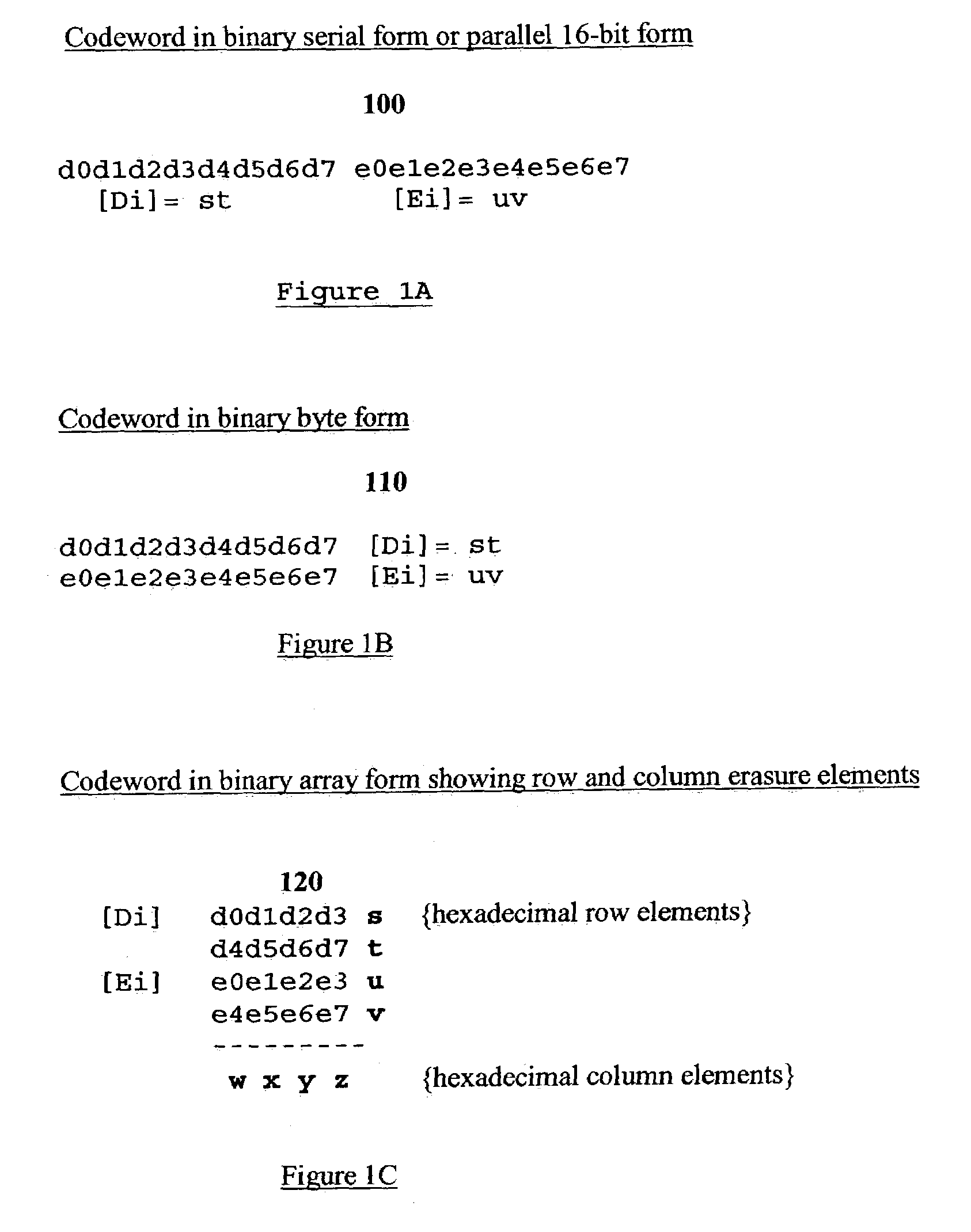

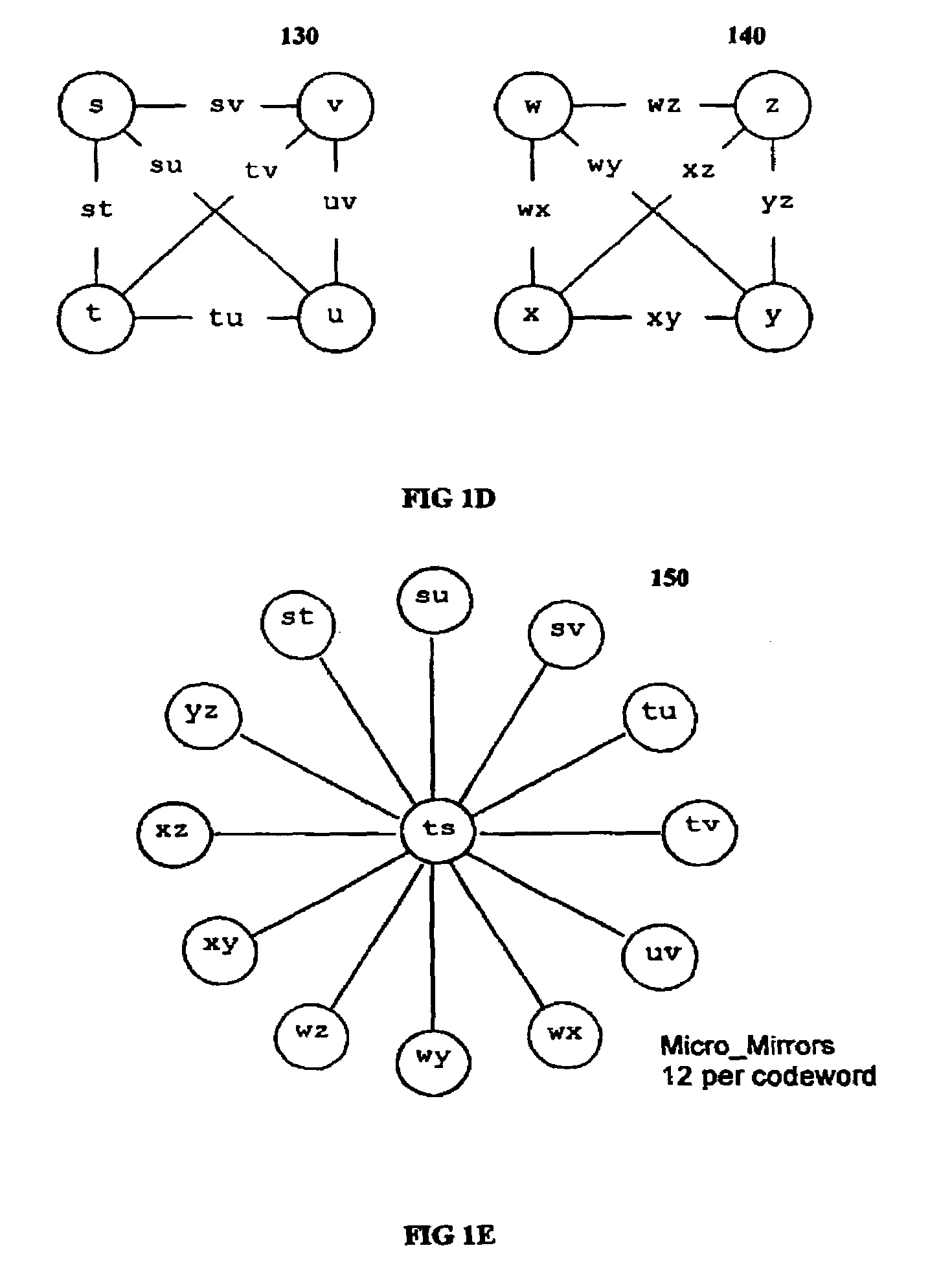

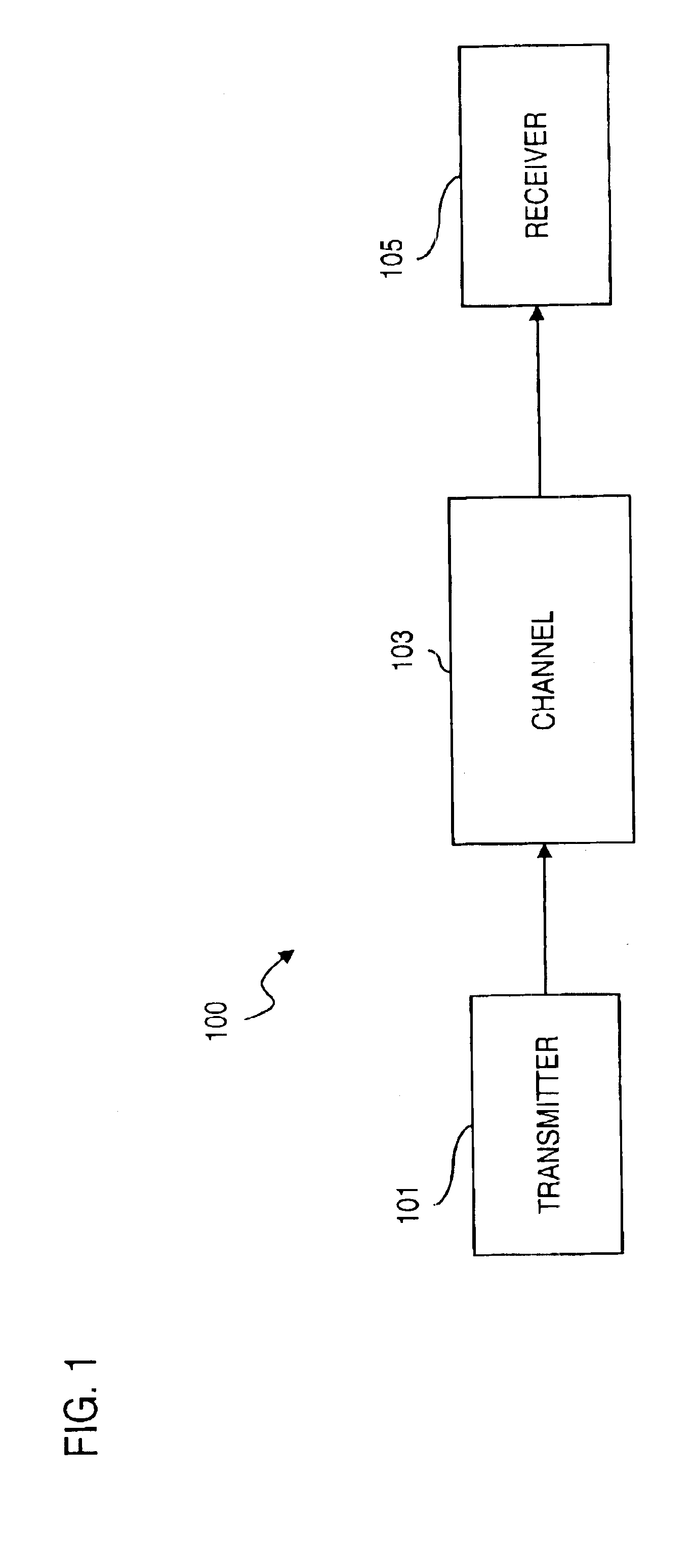

Multi-dimensional data protection and mirroring method for micro level data

ActiveUS7103824B2Detection errorLow common data sizeCode conversionCyclic codesData validationData integrity

The invention discloses a data validation, mirroring and error / erasure correction method for the dispersal and protection of one and two-dimensional data at the micro level for computer, communication and storage systems. Each of 256 possible 8-bit data bytes are mirrored with a unique 8-bit ECC byte. The ECC enables 8-bit burst and 4-bit random error detection plus 2-bit random error correction for each encoded data byte. With the data byte and ECC byte configured into a 4 bit×4 bit codeword array and dispersed in either row, column or both dimensions the method can perform dual 4-bit row and column erasure recovery. It is shown that for each codeword there are 12 possible combinations of row and column elements called couplets capable of mirroring the data byte. These byte level micro-mirrors outperform conventional mirroring in that each byte and its ECC mirror can self-detect and self-correct random errors and can recover all dual erasure combinations over four elements. Encoding at the byte quanta level maximizes application flexibility. Also disclosed are fast encode, decode and reconstruction methods via boolean logic, processor instructions and software table look-up with the intent to run at line and application speeds. The new error control method can augment ARQ algorithms and bring resiliency to system fabrics including routers and links previously limited to the recovery of transient errors. Image storage and storage over arrays of static devices can benefit from the two-dimensional capabilities. Applications with critical data integrity requirements can utilize the method for end-to-end protection and validation. An extra ECC byte per codeword extends both the resiliency and dimensionality.

Owner:HALFORD ROBERT

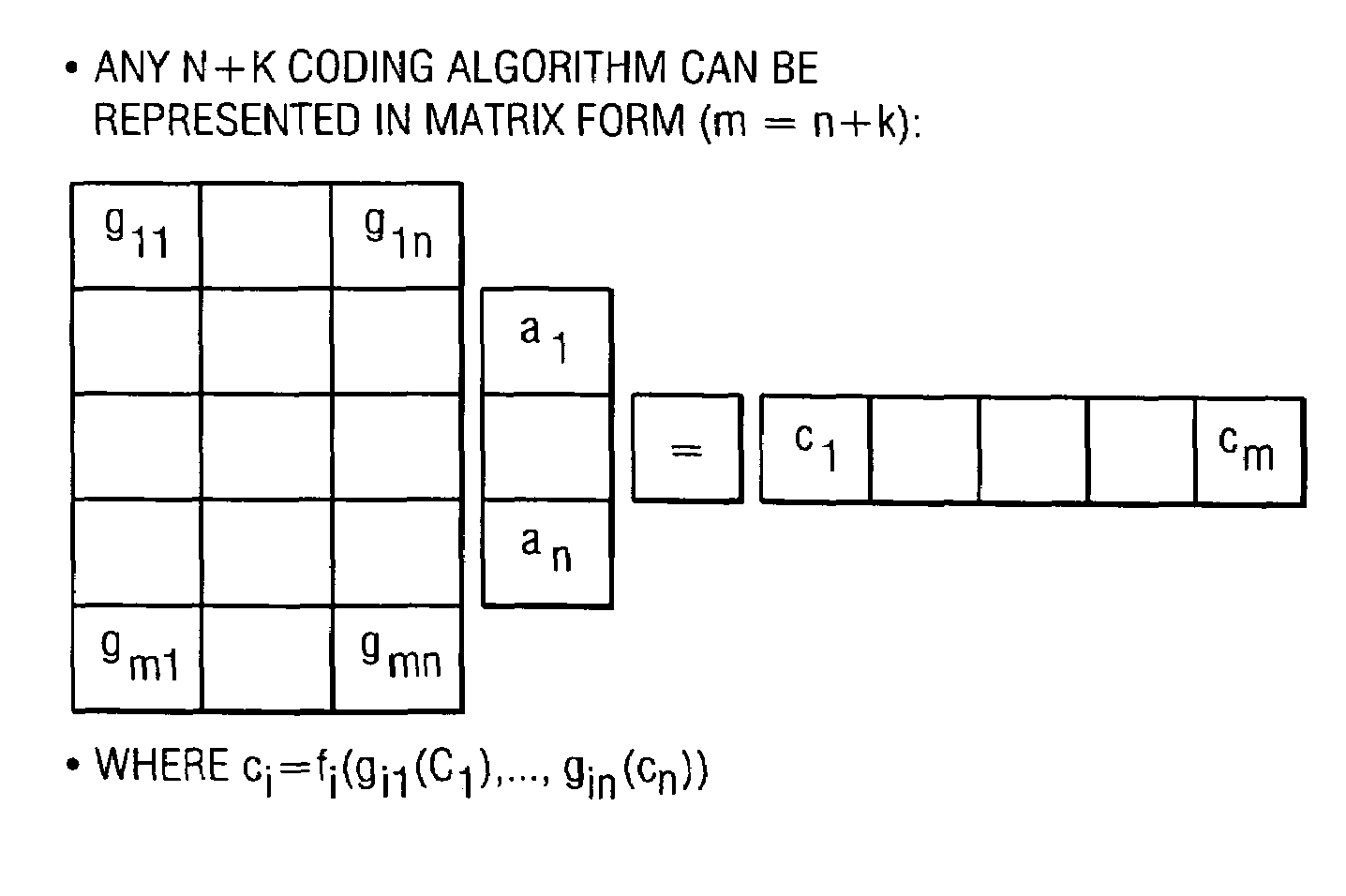

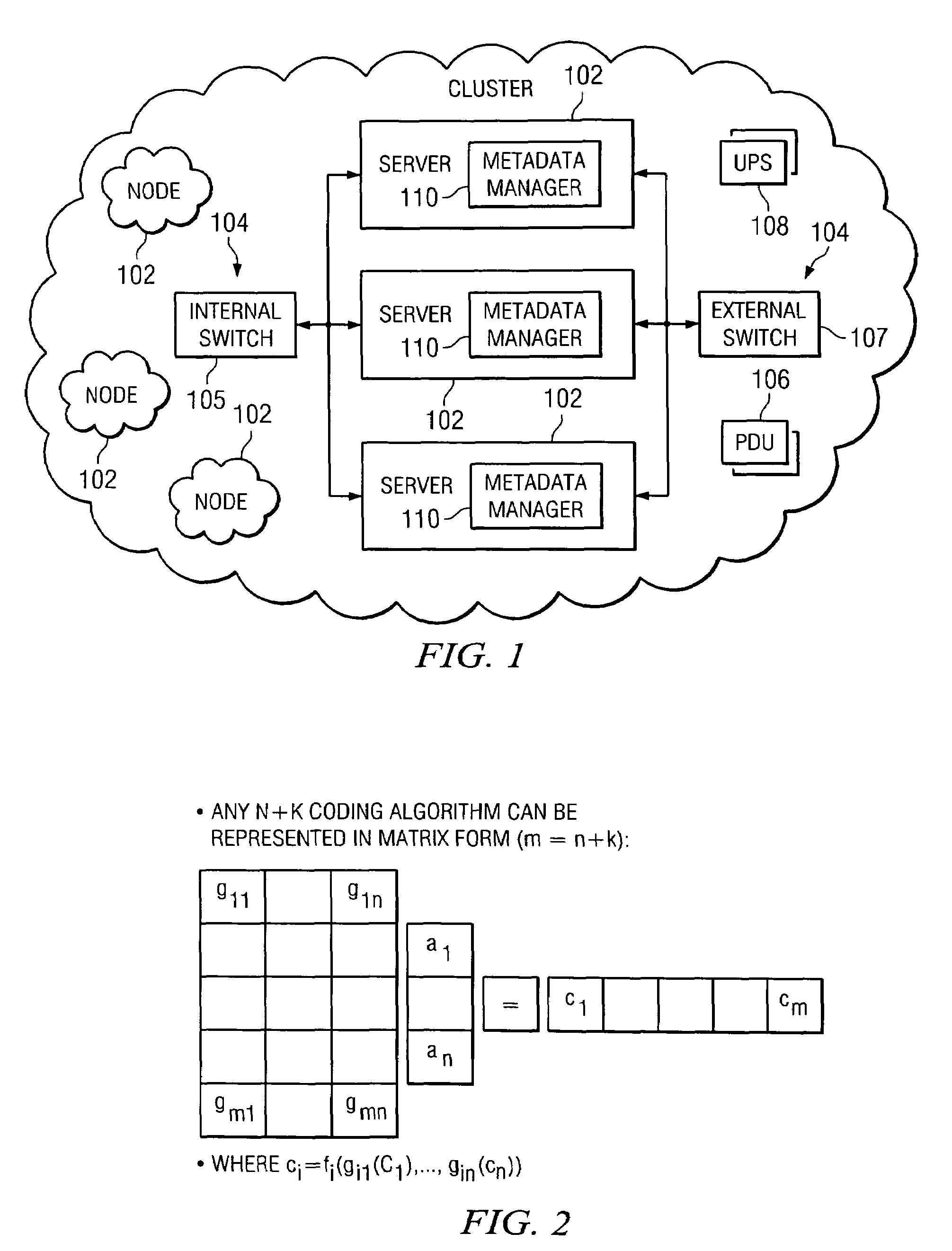

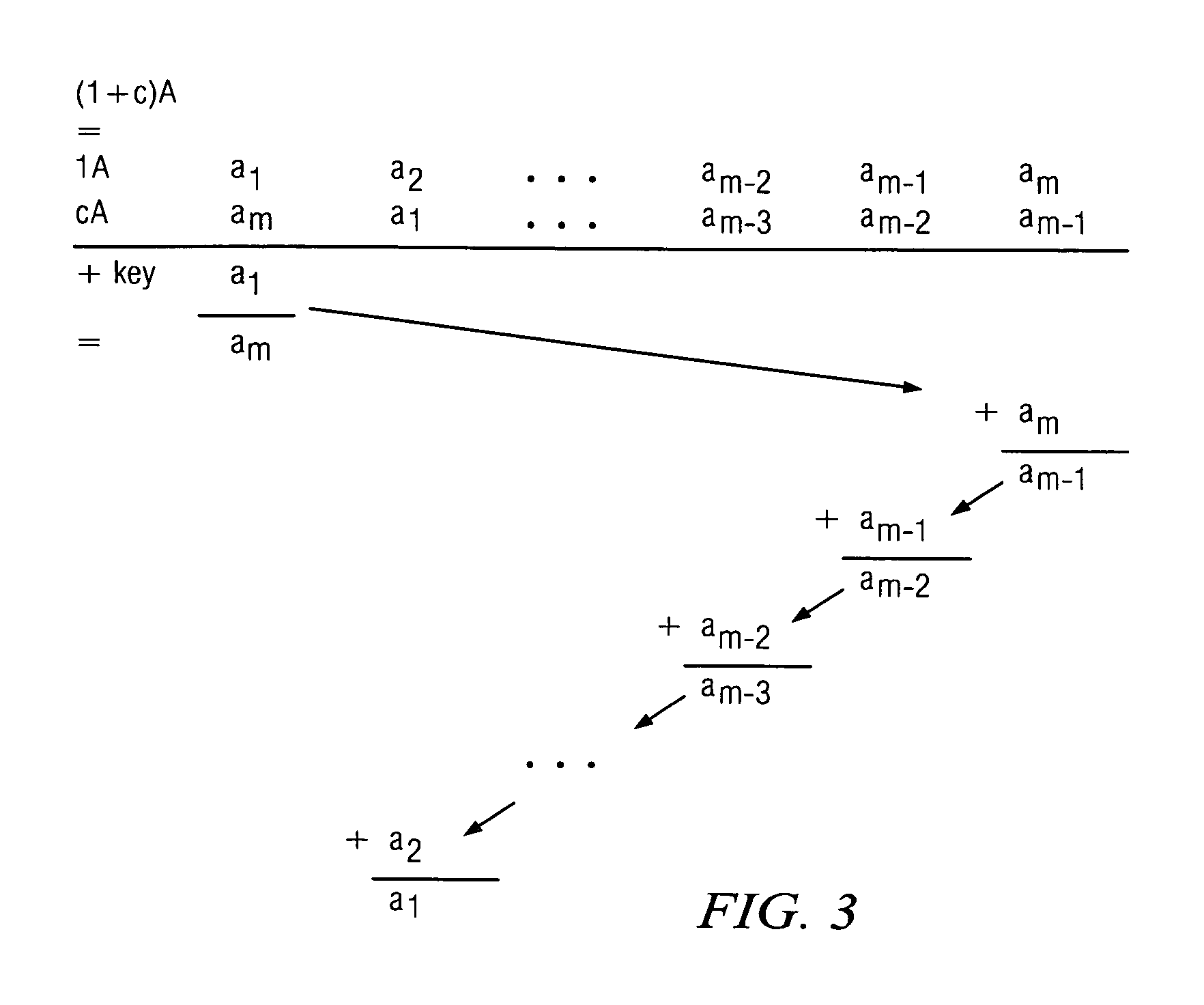

Fixed content distributed data storage using permutation ring encoding

InactiveUS7240236B2Highly available and reliable and persistent storageError correction/detection using multiple parity bitsCode conversionCoding blockDatabase

A file protection scheme for fixed content in a distributed data archive uses computations that leverage permutation operators of a cyclic code. In an illustrative embodiment, an N+K coding technique is described for use to protect data that is being distributed in a redundant array of independent nodes (RAIN). The data itself may be of any type, and it may also include system metadata. According to the invention, the data to be distributed is encoded by a dispersal operation that uses a group of permutation ring operators. In a preferred embodiment, the dispersal operation is carried out using a matrix of the form [IN<sub2>—< / sub2>C] where IN is an n×n identity sub-matrix and C is a k×n sub-matrix of code blocks. The identity sub-matrix is used to preserve the data blocks intact. The sub-matrix C preferably comprises a set of permutation ring operators that are used to generate the code blocks. The operators are preferably superpositions that are selected from a group ring of a permutation group with base ring Z2.

Owner:HITACHI VANTARA CORP

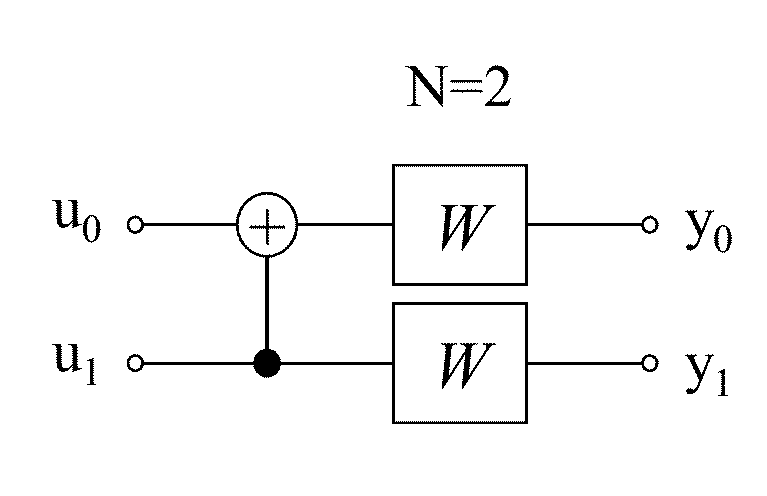

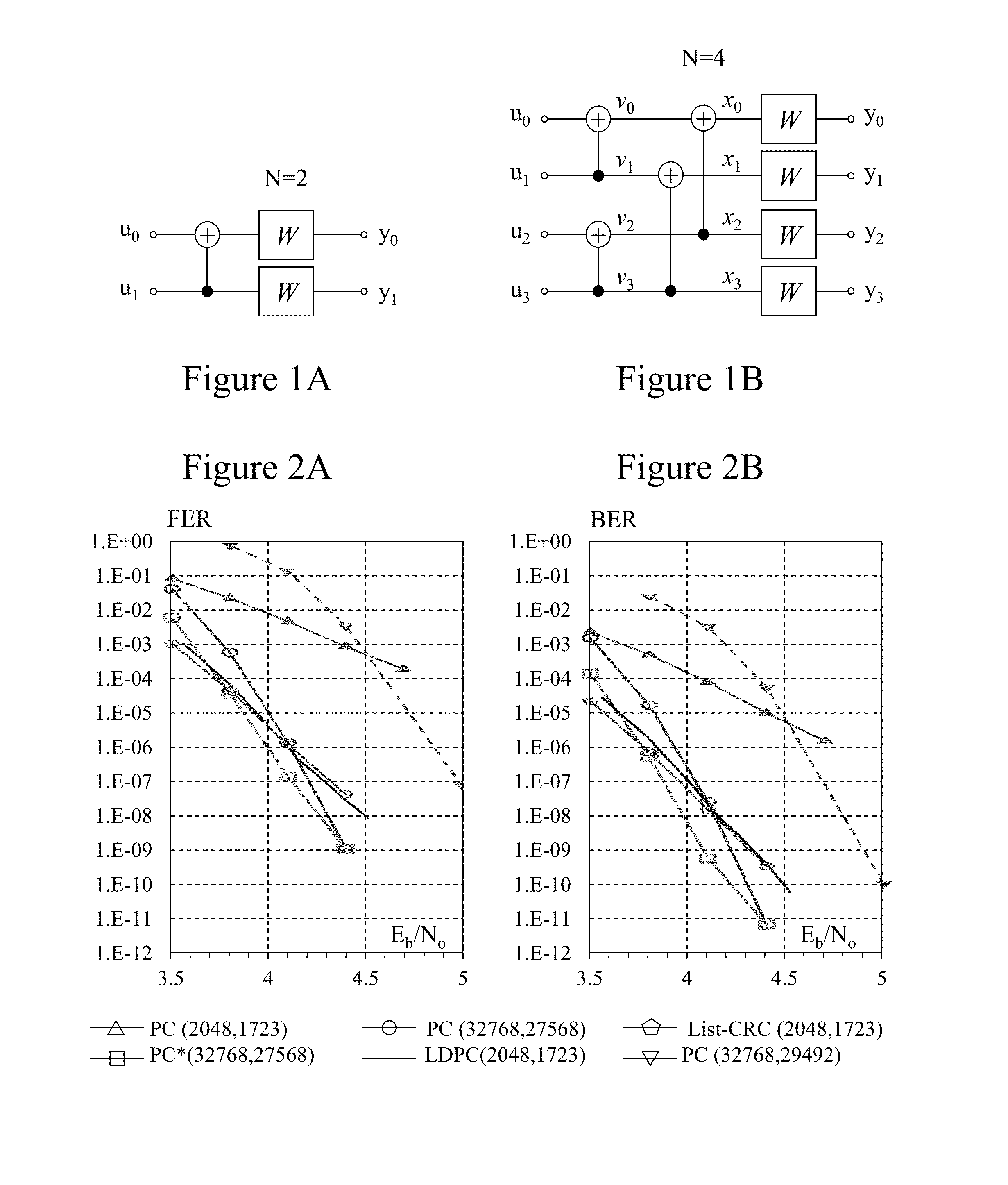

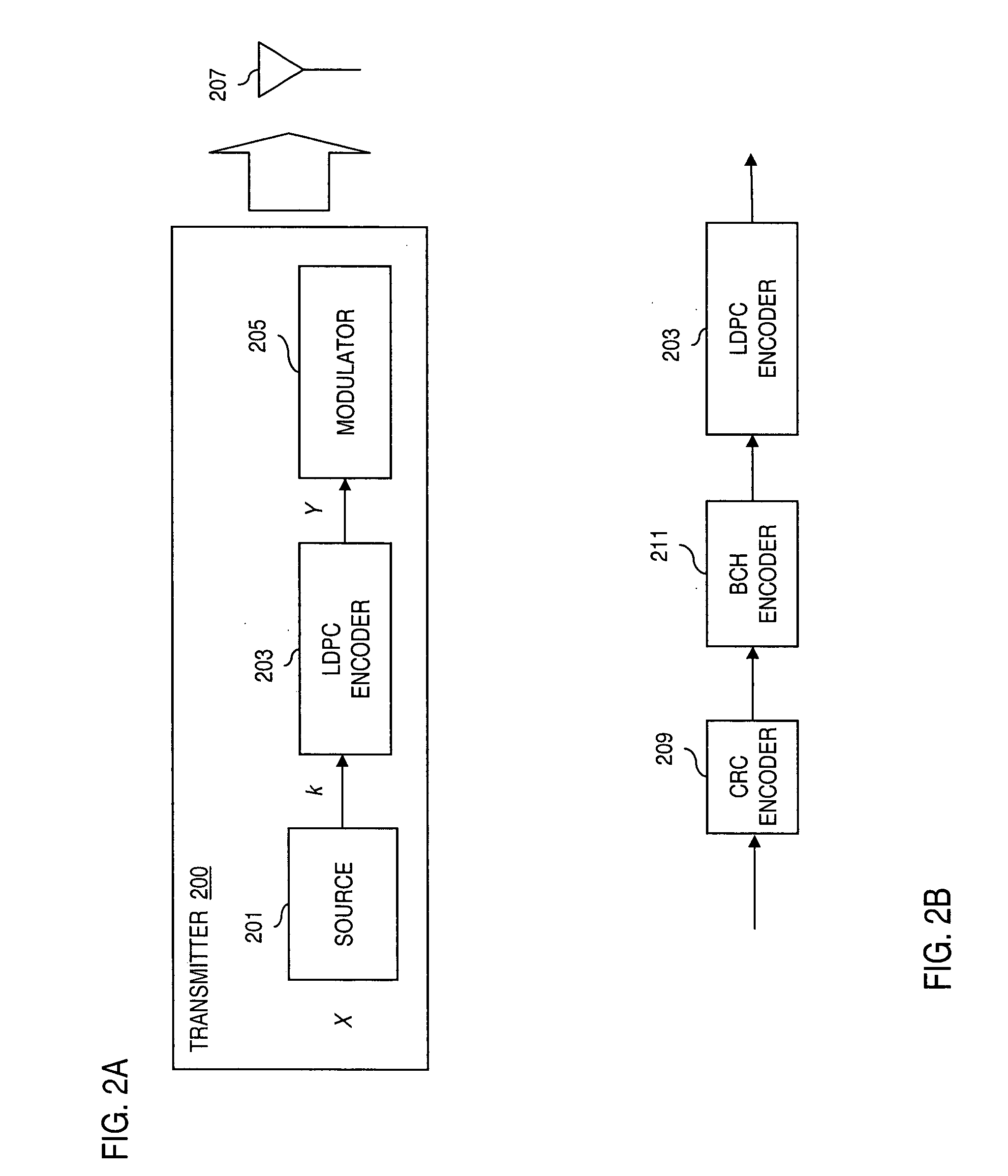

Flexible polar encoders and decoders

Modern communication systems must cope with varying channel conditions and differing throughput constraints. Polar codes despite being the first error-correcting codes with an explicit construction to achieve the symmetric capacity of memoryless channels are not currently employed against other older coding protocols such as low-density parity check (LDPC) codes as their performance at short / moderate lengths has been inferior and their decoding algorithm is serial leading to low decoding throughput. Accordingly techniques to address these issues are identified and disclosed including decoders that decode constituent codes without recursion and / or recognize classes of constituent directly decodable codes thereby increasing the decoder throughput. Flexible encoders and decoders supporting polar codes of any length up to a design maximum allow adaptive polar code systems responsive to communication link characteristics, performance, etc. whilst maximizing throughput. Further, designers are provided flexibility in implementing either hardware or software implementations.

Owner:POLAR TECH

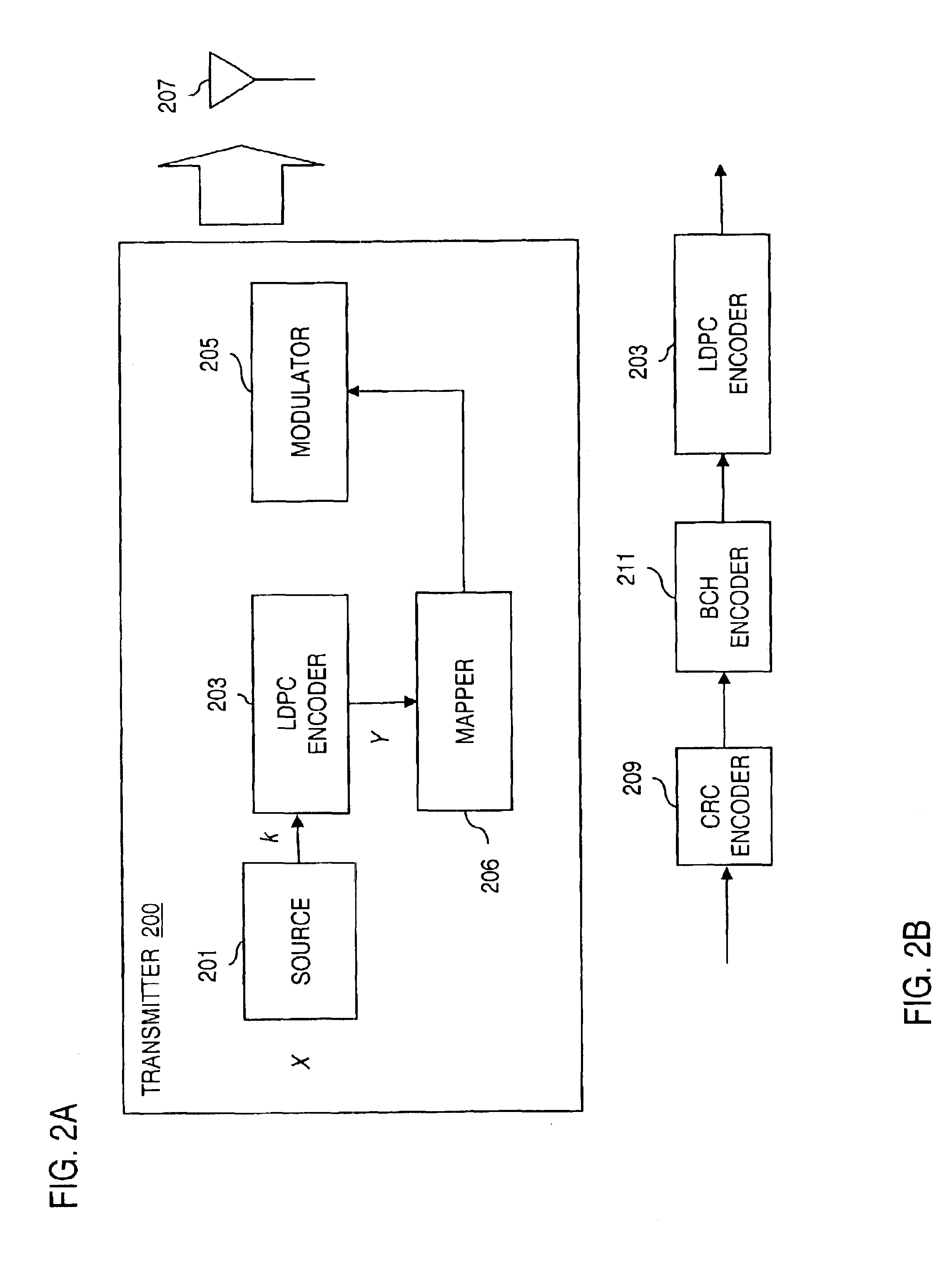

Method and system for providing low density parity check (LDPC) encoding

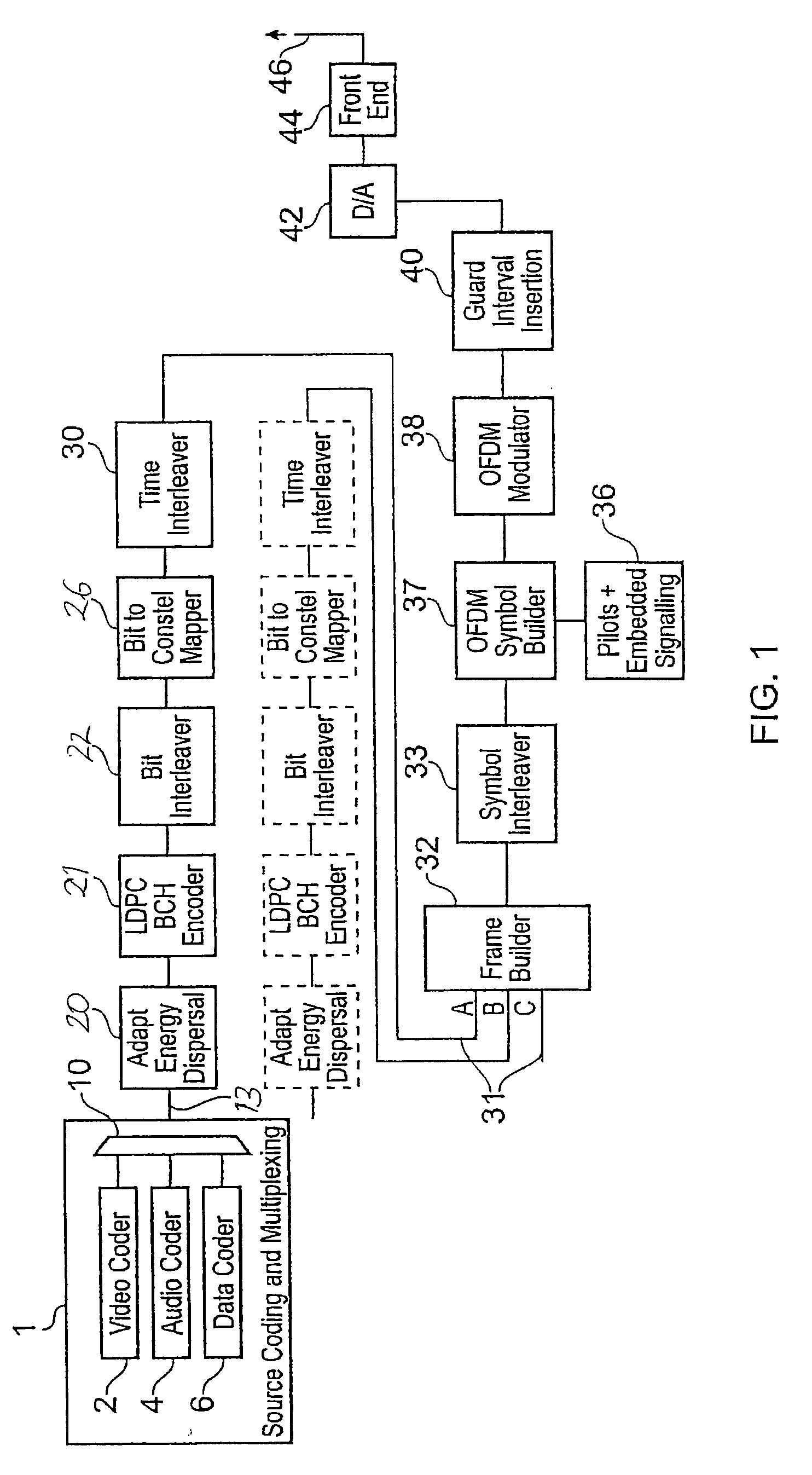

ActiveUS7191378B2Readily apparentInterconnection arrangementsError correction/detection using LDPC codesAlgorithmParity-check matrix

An approach is provided for a method of encoding structure Low Density Parity Check (LDPC) codes. Memory storing information representing a structured parity check matrix of Low Density Parity Check (LDPC) codes is accessed during the encoding process. The information is organized in tabular form, wherein each row represents occurrences of one values within a first column of a group of columns of the parity check matrix. The rows correspond to groups of columns of the parity check matrix, wherein subsequent columns within each of the groups are derived according to a predetermined operation. An LDPC coded signal is output based on the stored information representing the parity check matrix.

Owner:DTVG LICENSING INC

Data processing apparatus and method

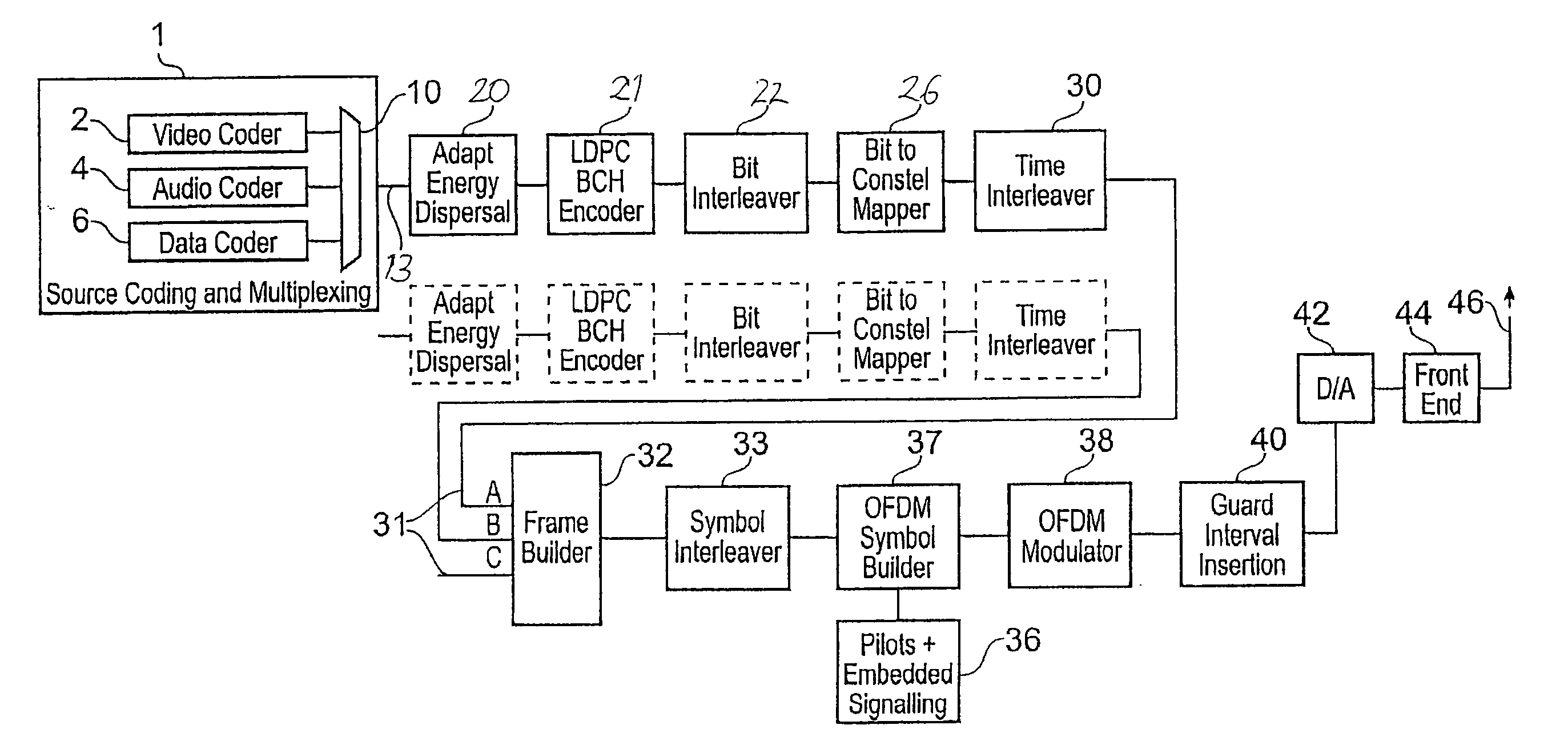

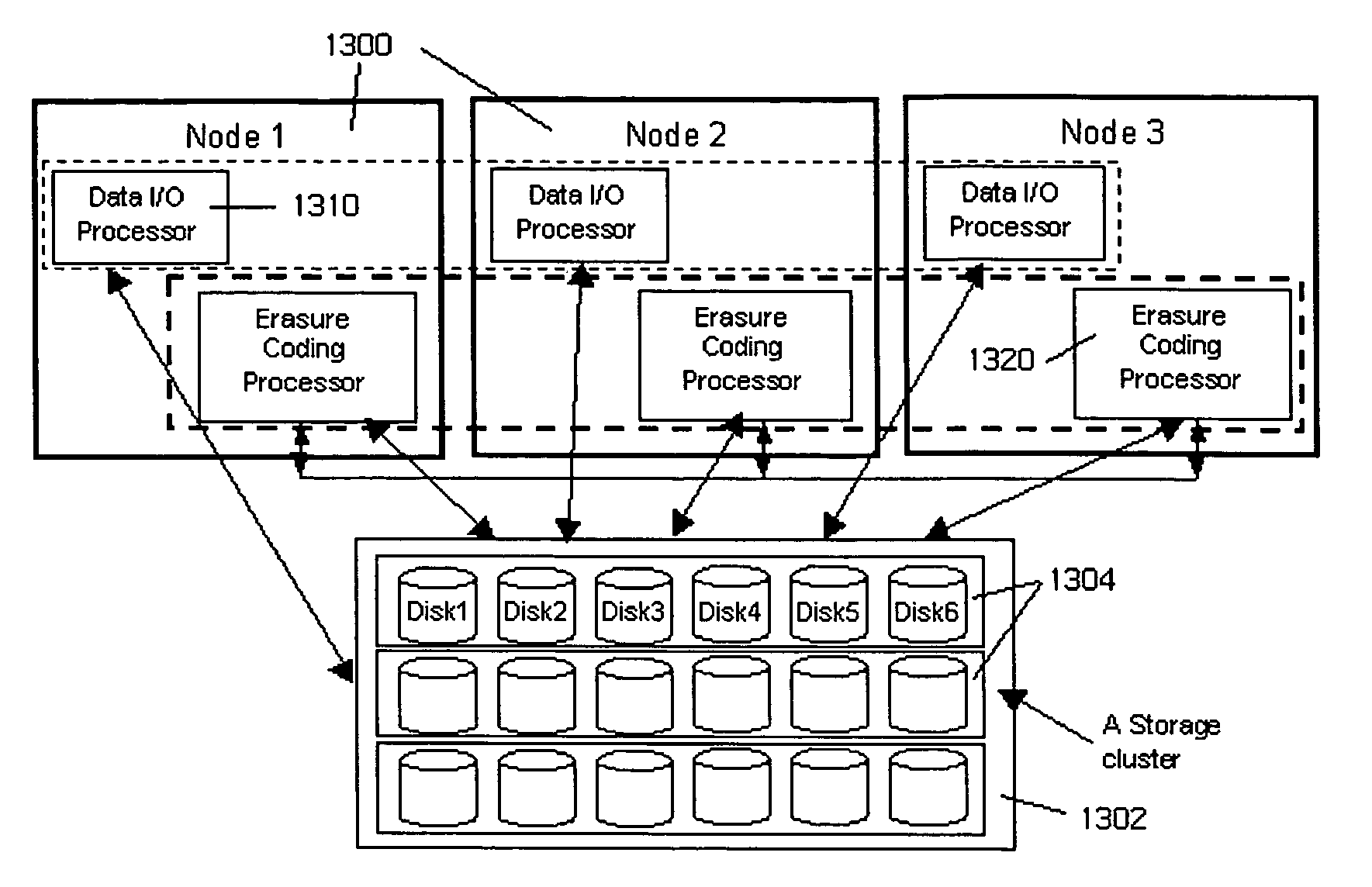

ActiveUS20090125780A1Improve performanceLow Density Parity Check (LDPCTransmission path divisionError detection/correctionCarrier signalTheoretical computer science

A data processing apparatus communicates data bits on a predetermined number of sub-carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processing apparatus comprises a parity interleaver operable to perform parity interleaving on Low Density Parity Check (LDPC) encoded data bits obtained by performing LDPC encoding according to a parity check matrix of an LDPC code including a parity matrix corresponding to parity bits of the LDPC code, the parity matrix having a stepwise structure, so that a parity bit of the LDPC encoded data bits is interleaved to a different parity bit position. A mapping unit maps the parity interleaved bits onto data symbols corresponding to modulation symbols of a modulation scheme of the OFDM sub-carrier signals. A symbol interleaver is arranged in operation to read-into a symbol interleaver memory the predetermined number of data symbols for mapping onto the OFDM sub-carrier signals, and to read-out of the interleaver memory the data symbols for the OFDM sub-carriers to effect the mapping, the read-out being in a different order than the read-in, the order being determined from a set of addresses, with the effect that the data symbols are interleaved on the sub-carrier signals. The set of addresses are generated by an address generator which has been optimised to interleave the data symbols on to the sub-carrier signals of the OFDM carrier signals for a given operating mode of the OFDM system, such as a 32K operating mode for DVB-T2 or DVB-C2.

Owner:SATURN LICENSING LLC

Method for lock-free clustered erasure coding and recovery of data across a plurality of data stores in a network

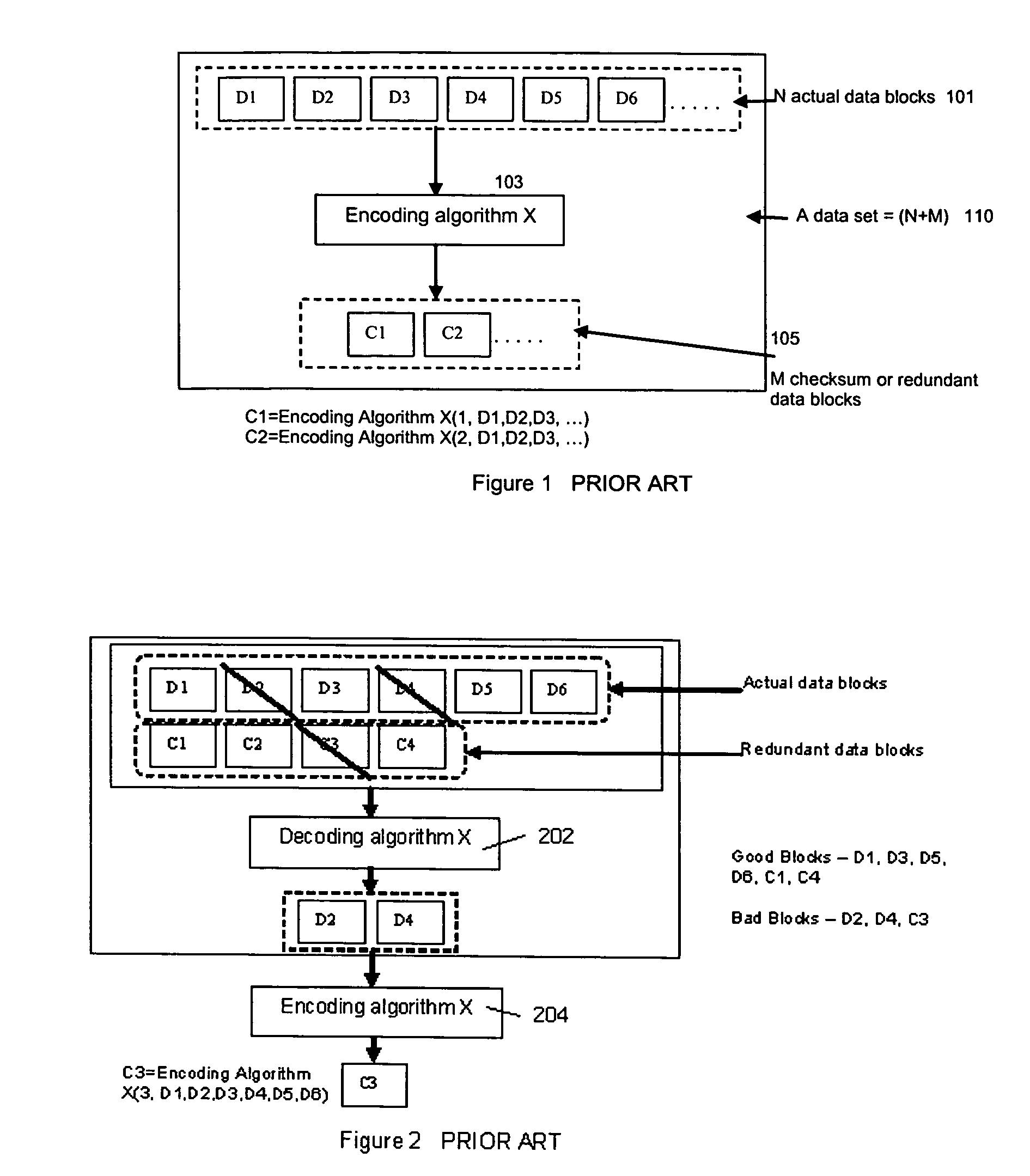

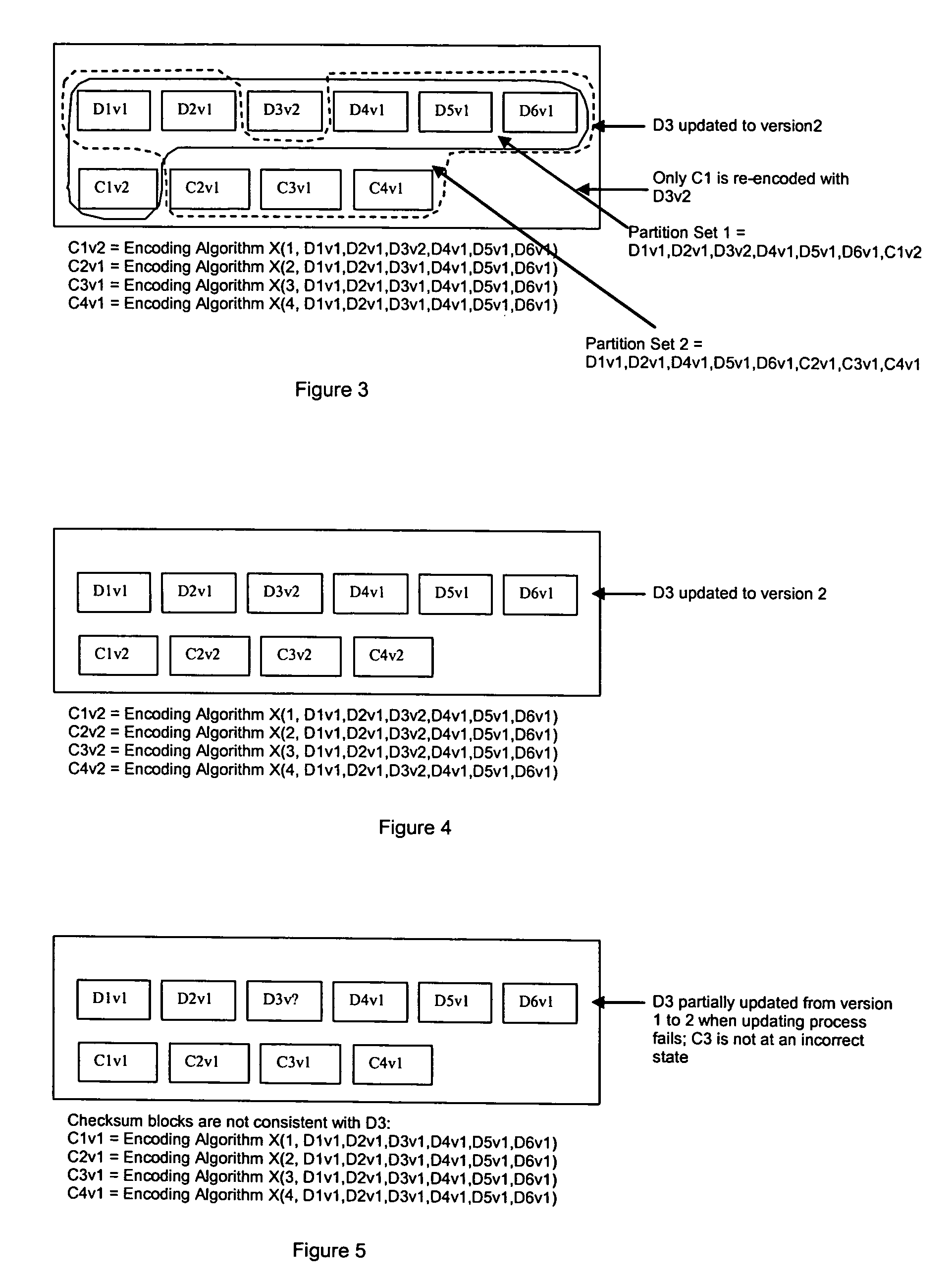

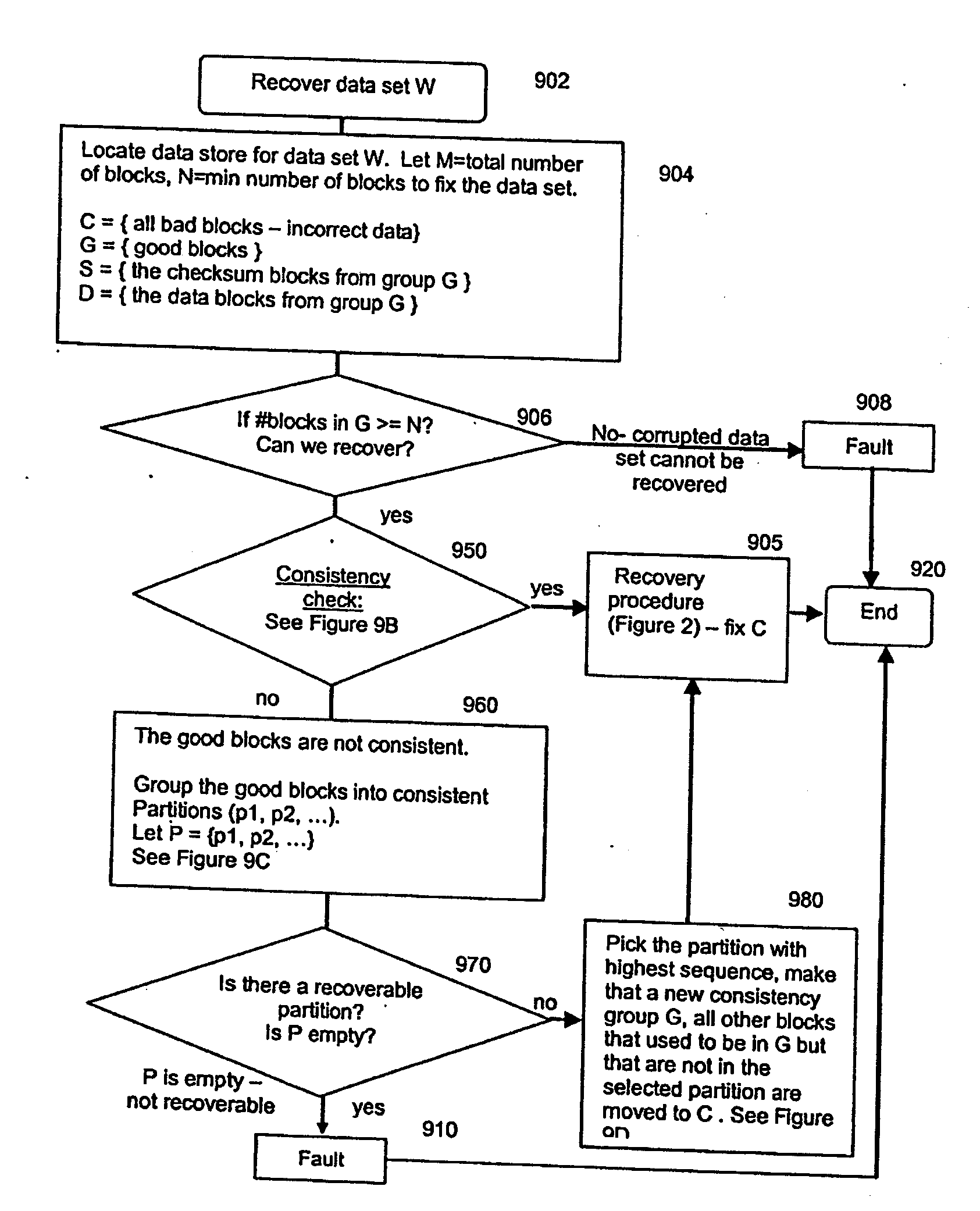

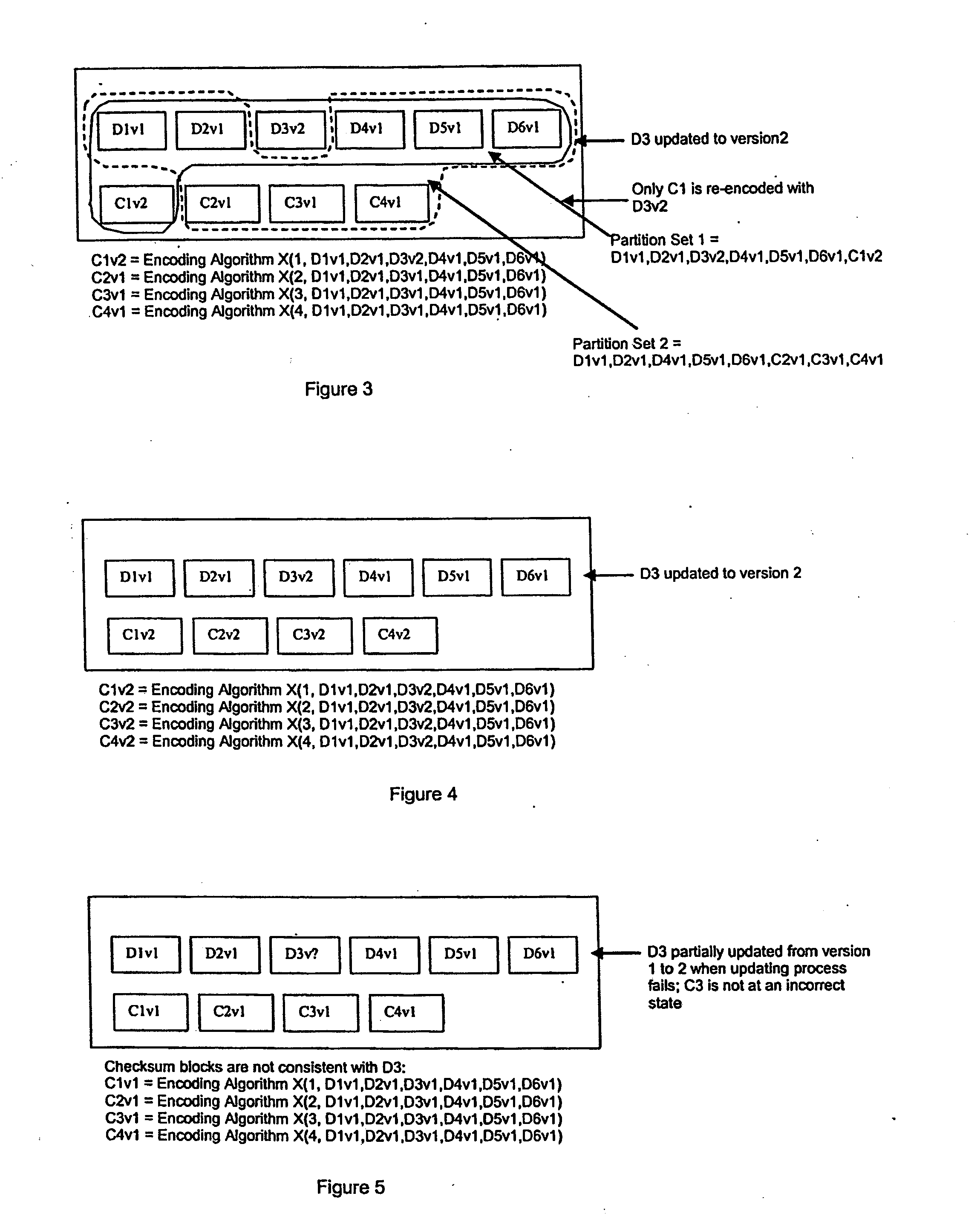

ActiveUS7681105B1Maintain data consistencyEffective applicationError detection/correctionCode conversionData storingData store

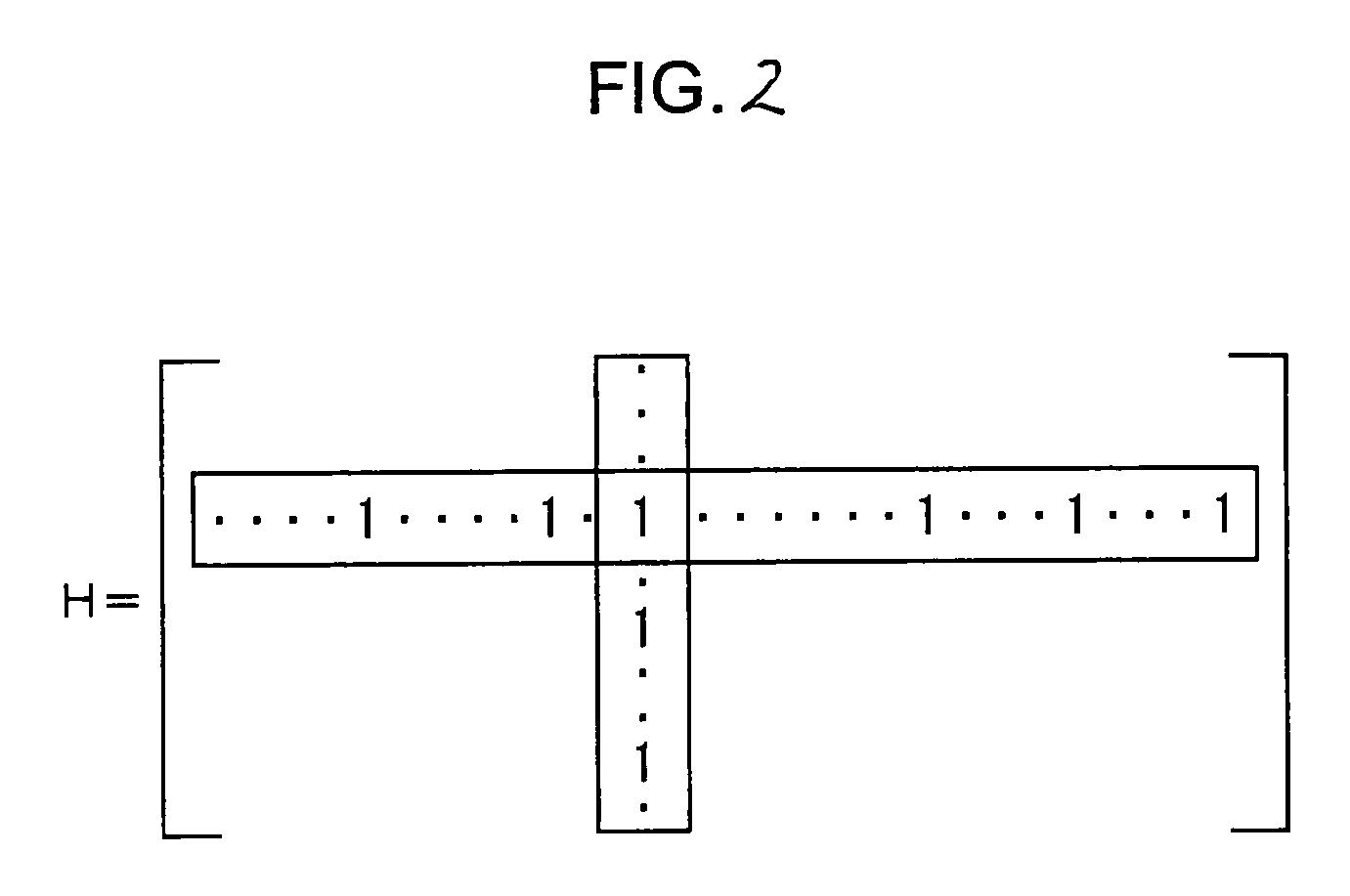

The present invention provides a distributed clustering method to allow multiple active instances of consistency management processes that apply the same encoding scheme to be cooperative and function collectively. The techniques described herein facilitate an efficient method to apply an erasure encoding and decoding scheme across dispersed data stores that receive constant updates. The technique can be applied on many forms of distributed persistent data stores to provide failure resiliency and to maintain data consistency and correctness.

Owner:QUEST SOFTWARE INC

Method for lock-free clustered erasure coding and recovery of data across a plurality of data stores in a network

ActiveUS20100162076A1Maintain data consistencyEfficient methodCode conversionCyclic codesData storingData store

The present invention provides a distributed clustering method to allow multiple active instances of consistency management processes that apply the same encoding scheme to be cooperative and function collectively. The techniques described herein facilitate an efficient method to apply an erasure encoding and decoding scheme across dispersed data stores that receive constant updates. The technique can be applied on many forms of distributed persistent data stores to provide failure resiliency and to maintain data consistency and correctness.

Owner:QUEST SOFTWARE INC

Iterative decoder employing multiple external code error checks to lower the error floor

InactiveUS7310768B2Code conversionError correction/detection by combining multiple code structuresError checkDegree of certainty

Owner:ENTROPIC COMM INC

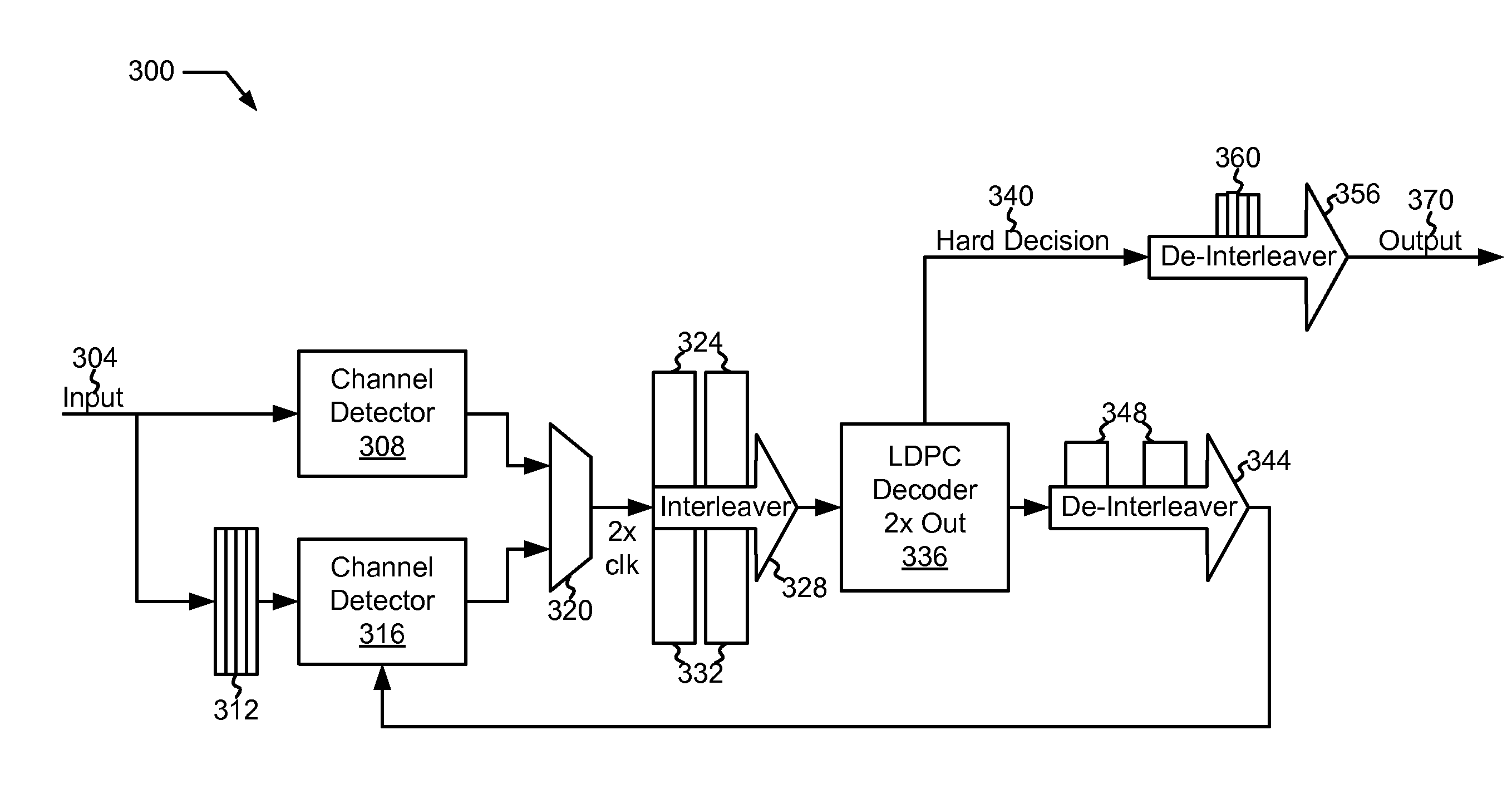

Systems and Methods for Queue Based Data Detection and Decoding

Various embodiments of the present invention provide systems and methods for data processing. For example, a variable iteration data processing system is disclosed that includes at least a first detector, a second detector, a decoder, and a queuing buffer. The first detector is operable to perform a data detection on an input data set at a first time. The decoder receives a derivation of an output from the first detector and performs a decoding process. Where the decoding process fails to converge, the decoder output is passed to the second detector for a subsequent detection and decoding process at a second time.

Owner:AVAGO TECH INT SALES PTE LTD

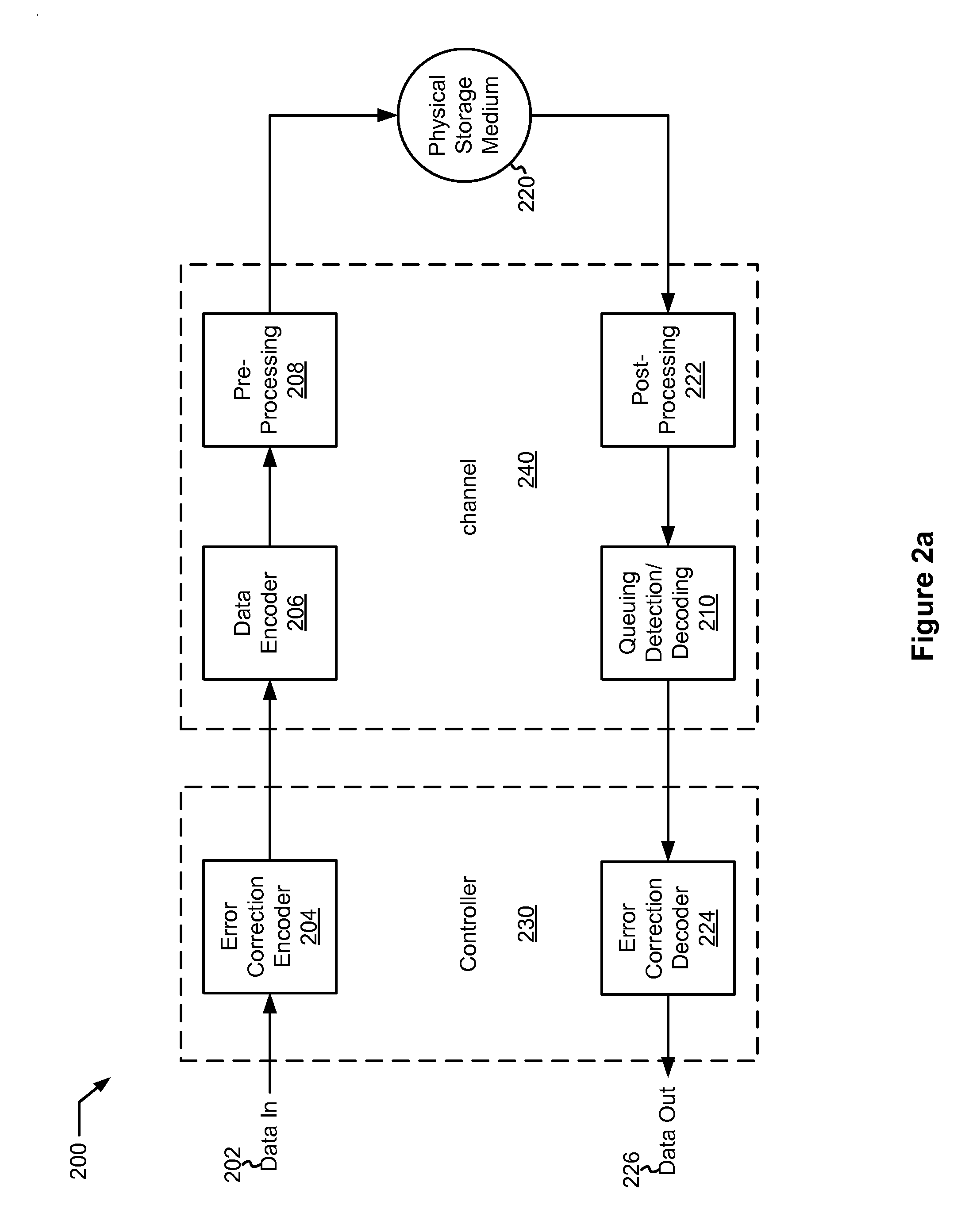

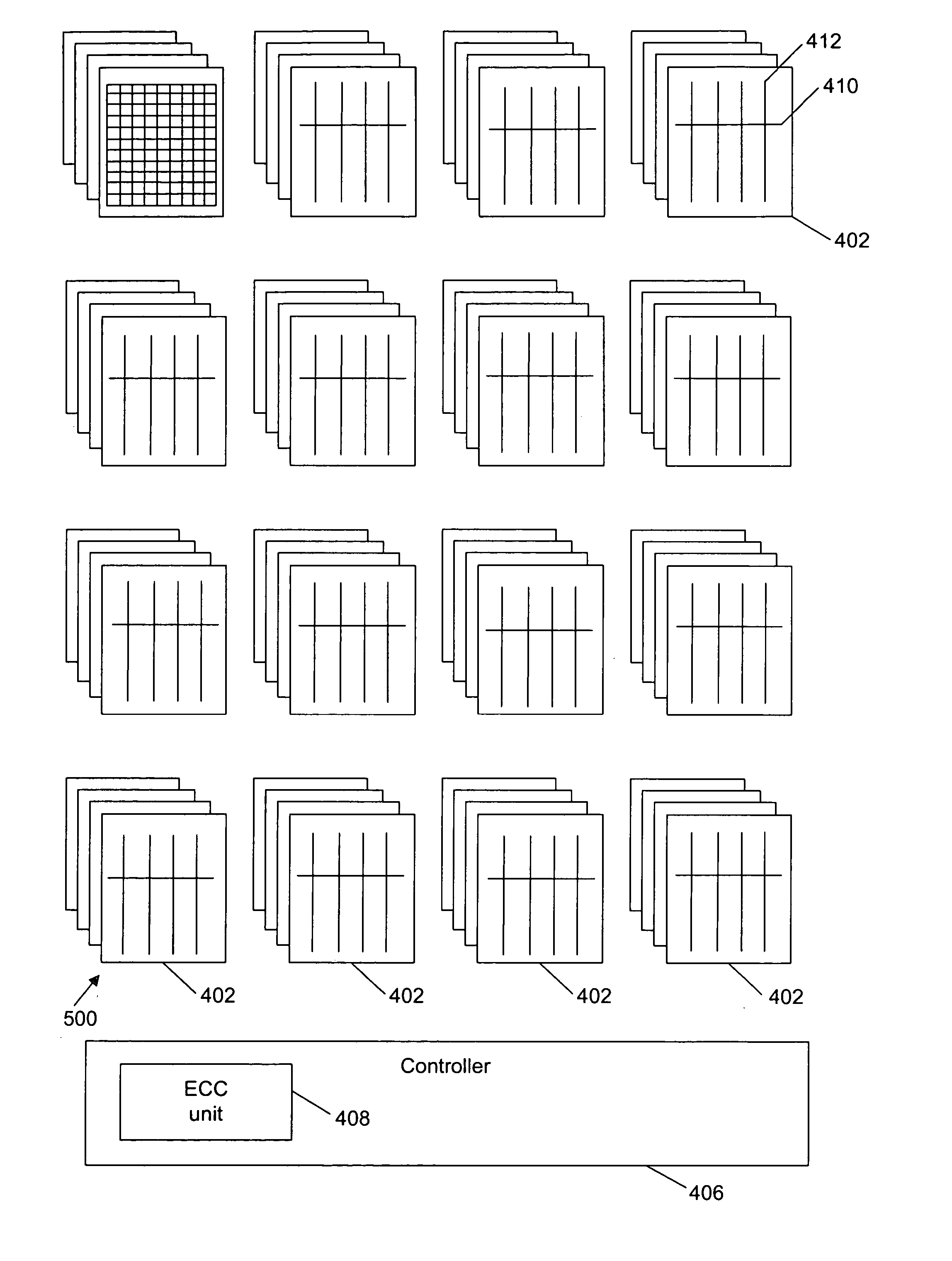

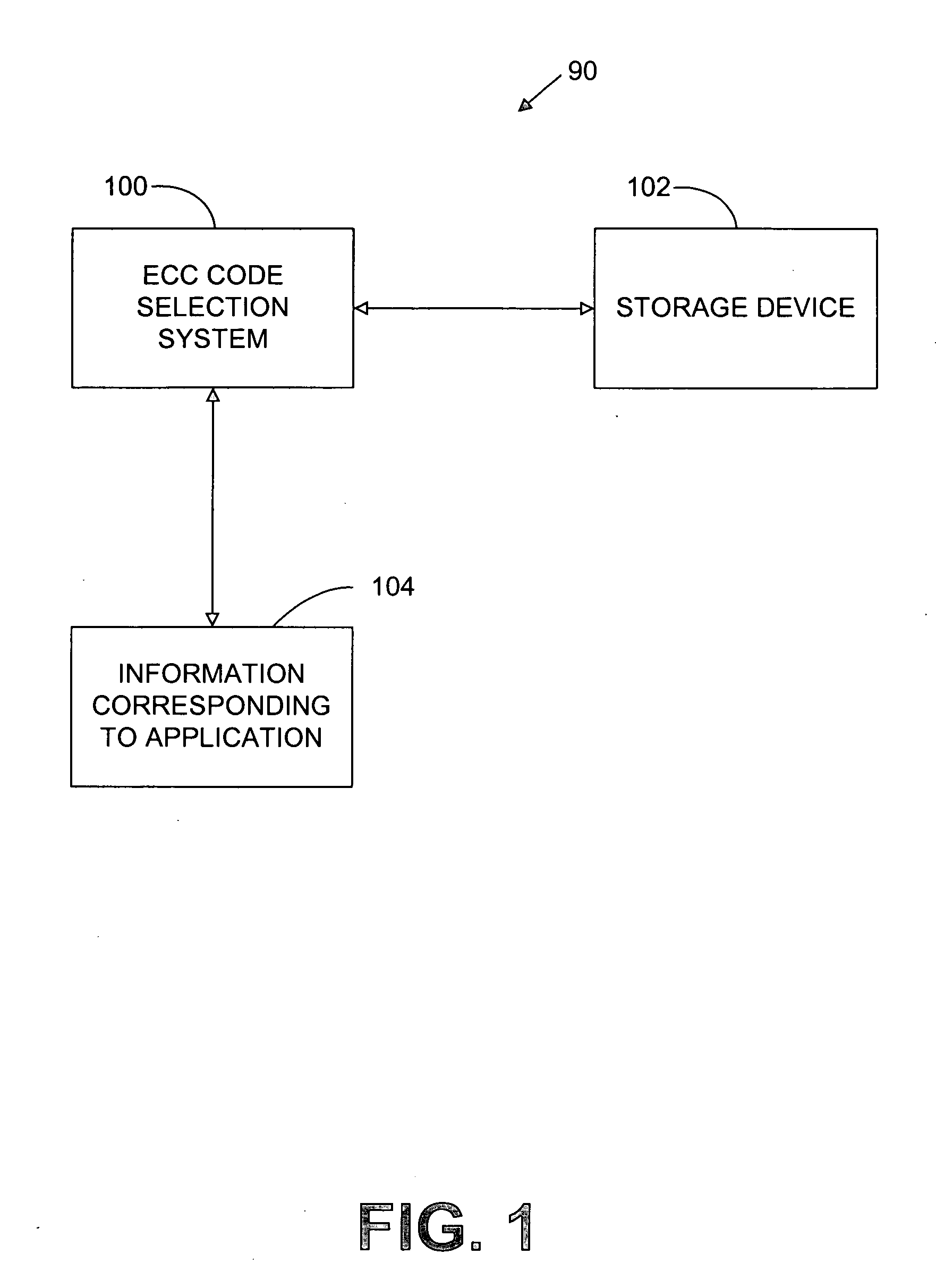

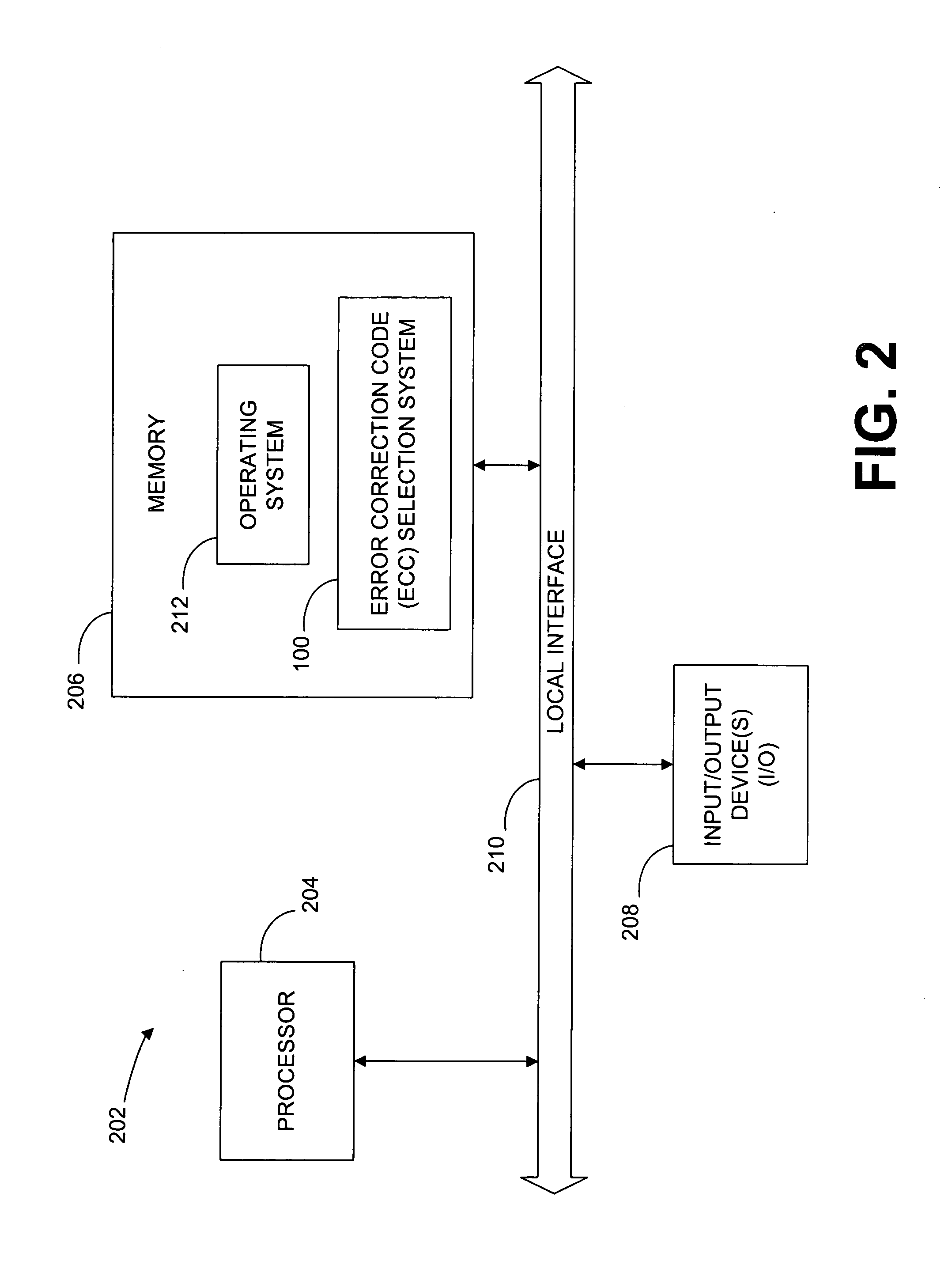

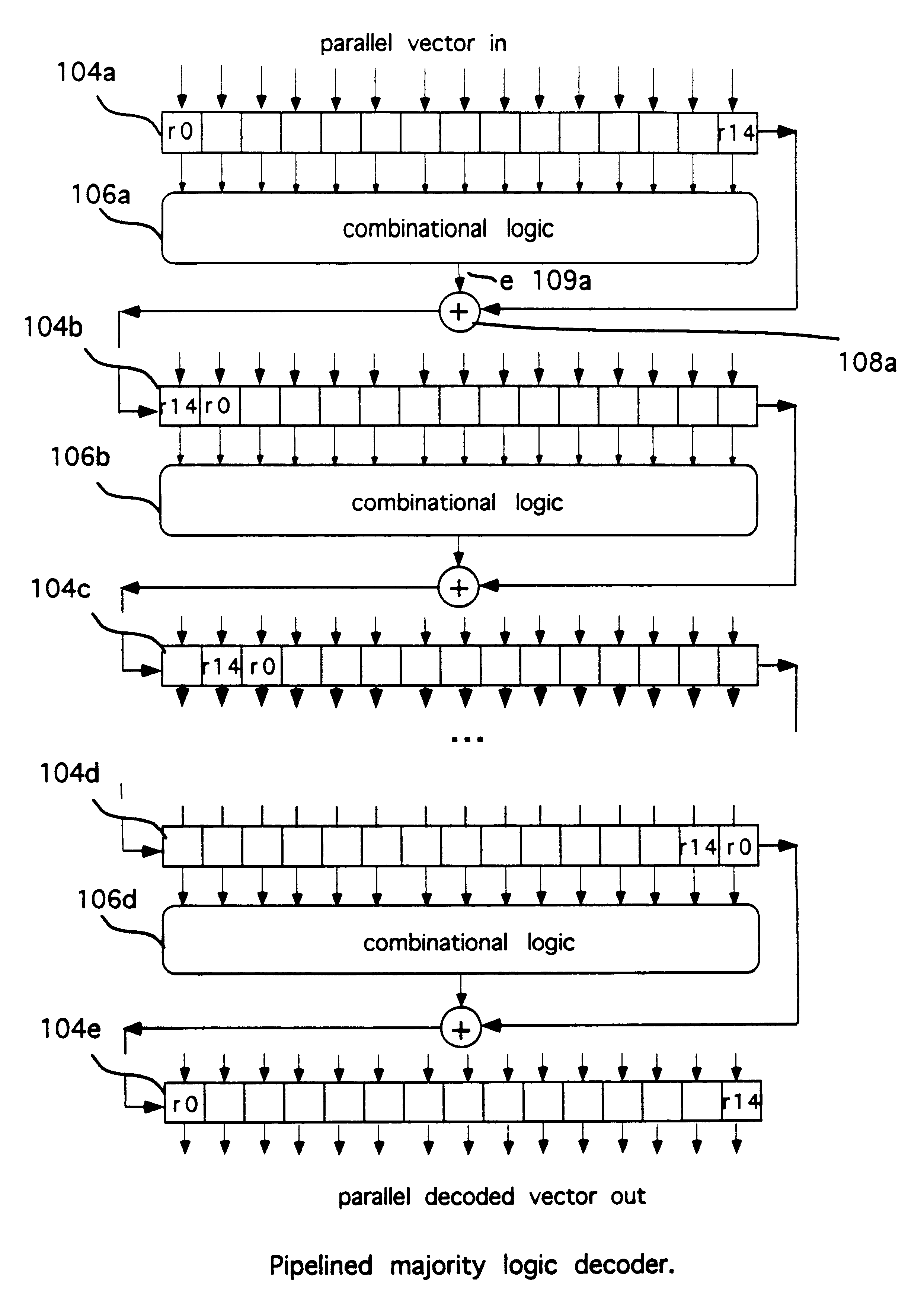

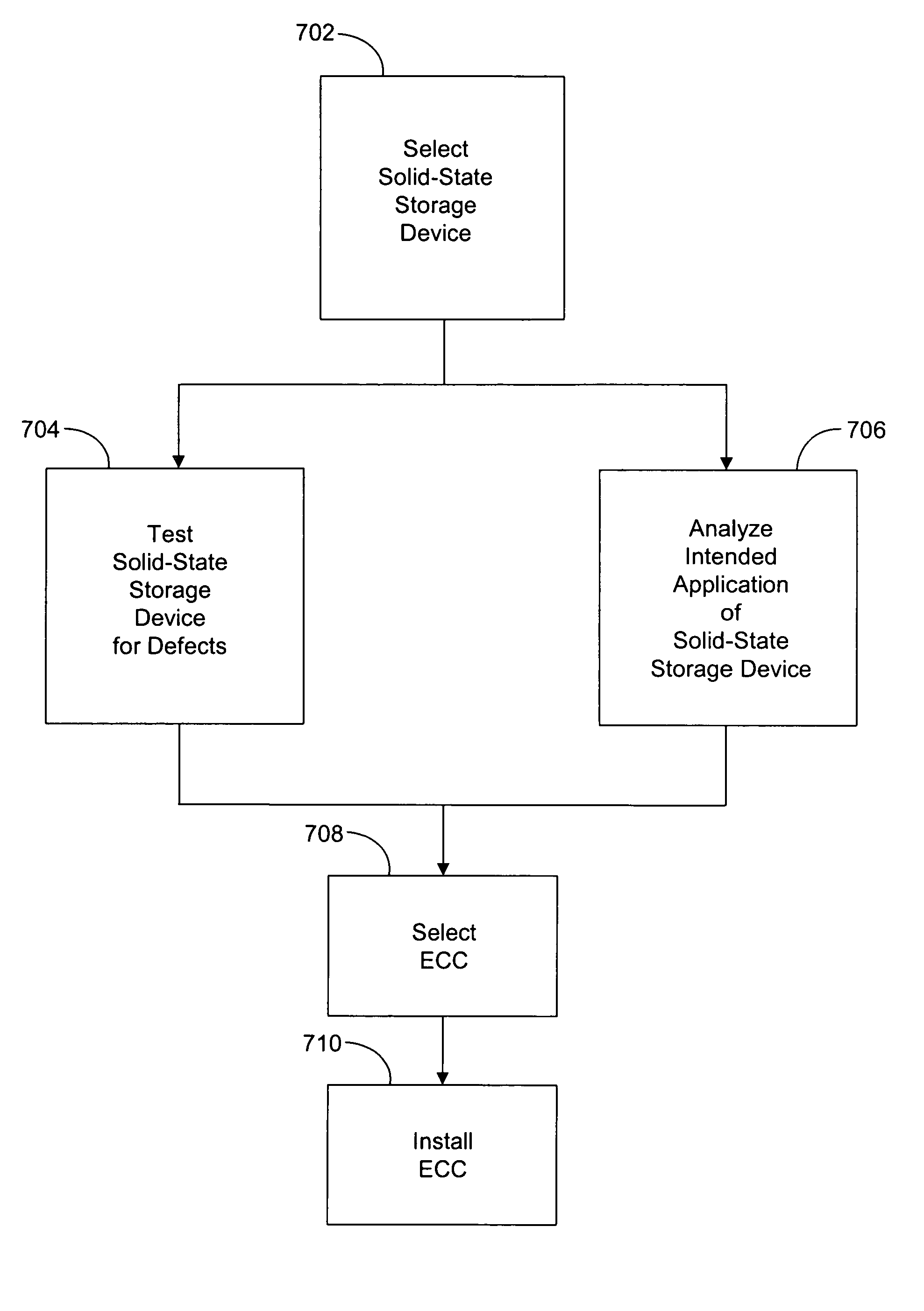

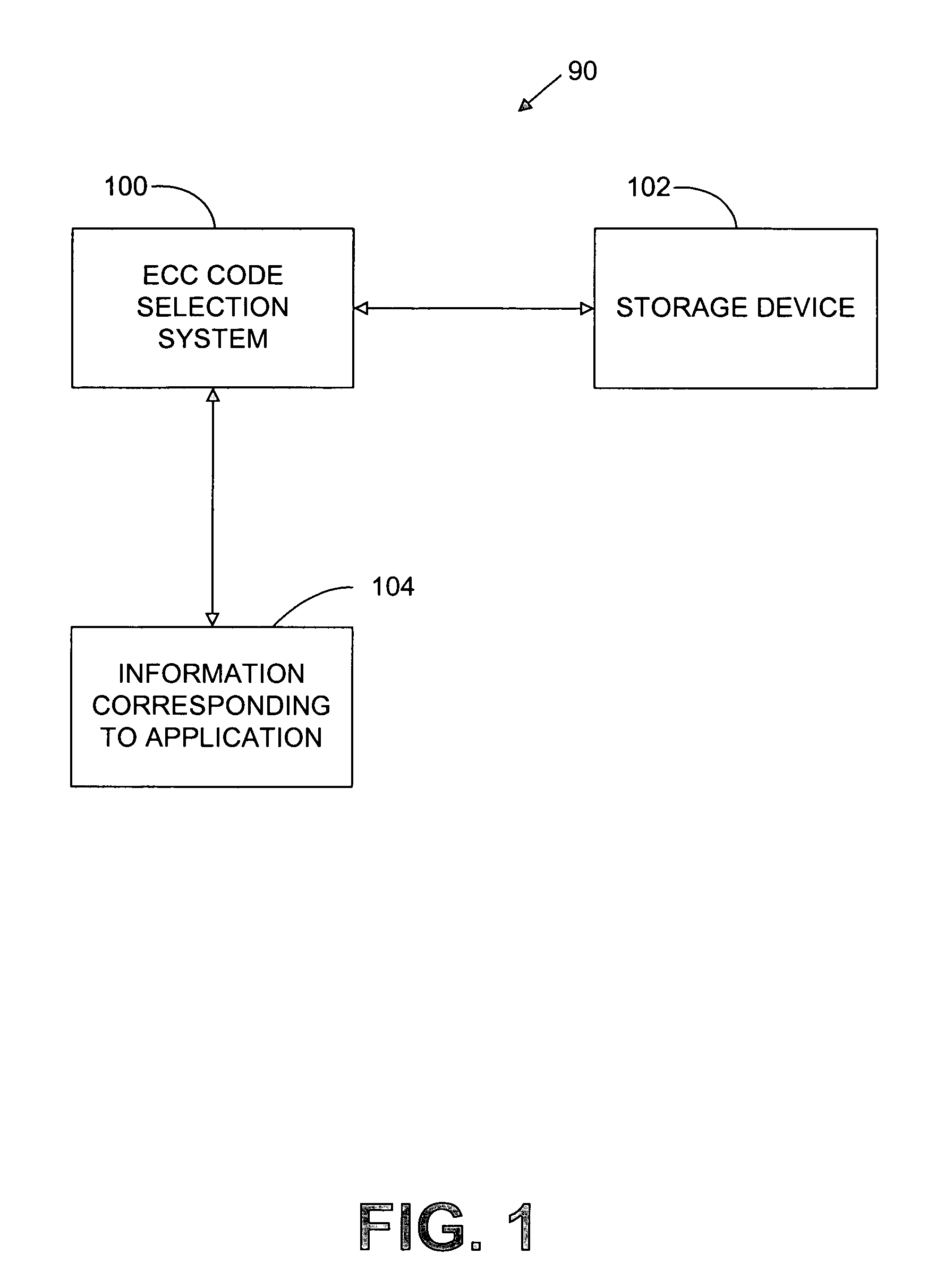

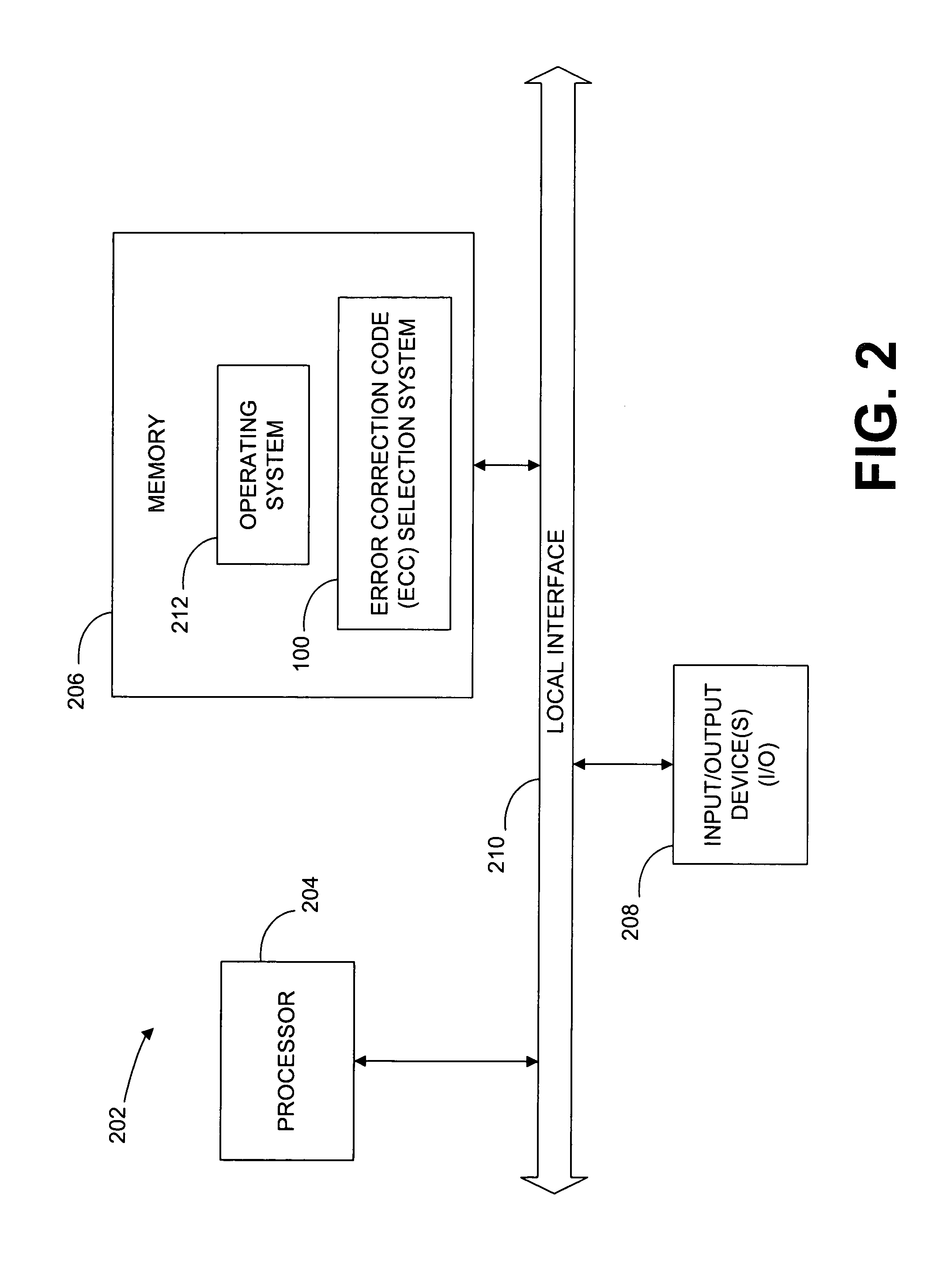

System and method for configuring a solid-state storage device with error correction coding

A system for configuring solid-state storage devices comprises a solid-state storage device and an error correction code (ECC) selection system. The ECC selection system is configured to automatically select a set of error correction code based on an error rate of the storage device. The ECC selection system is further configured to install the selected set of error correction code in the solid-state storage device.

Owner:SK HYNIX INC

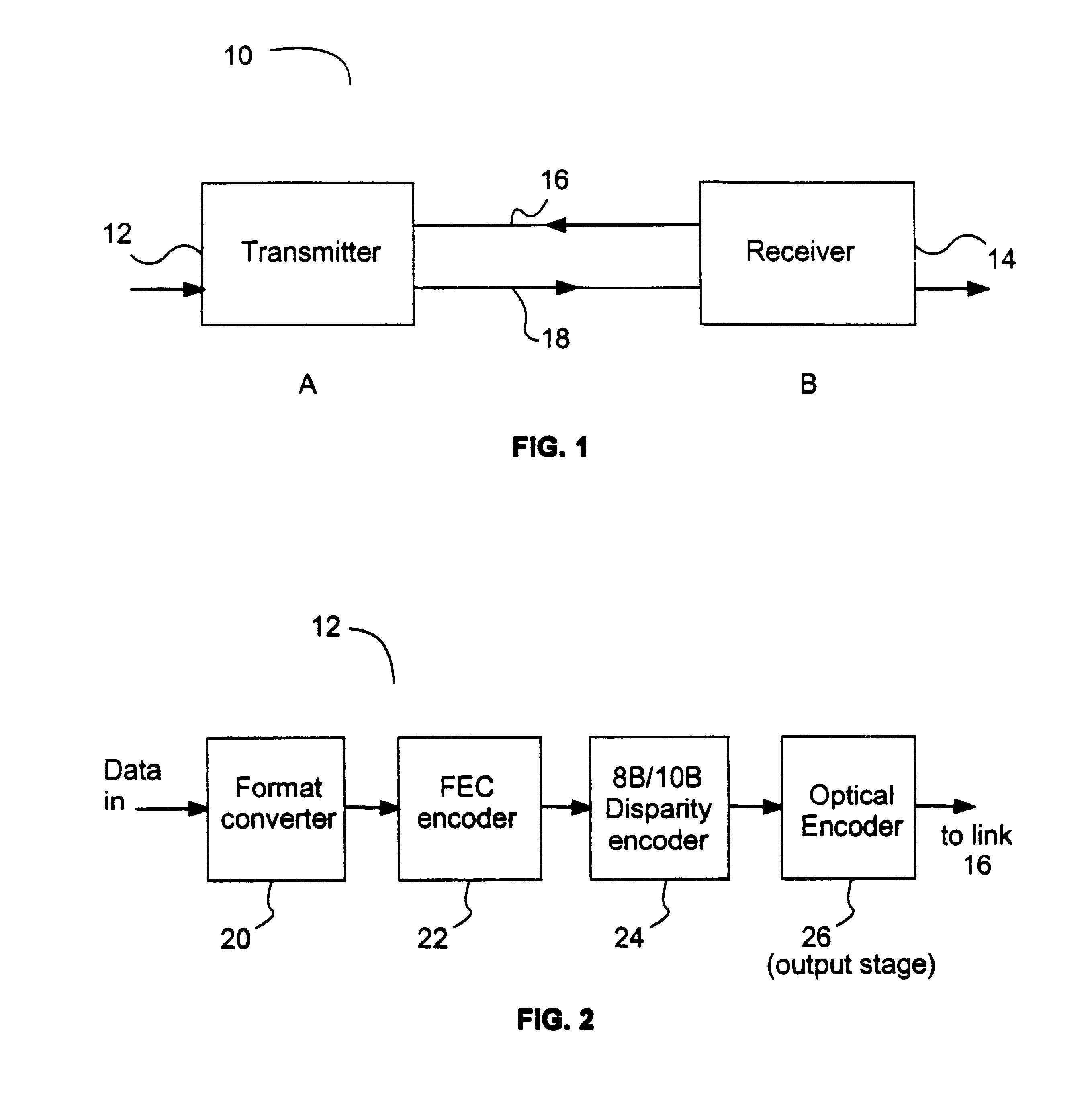

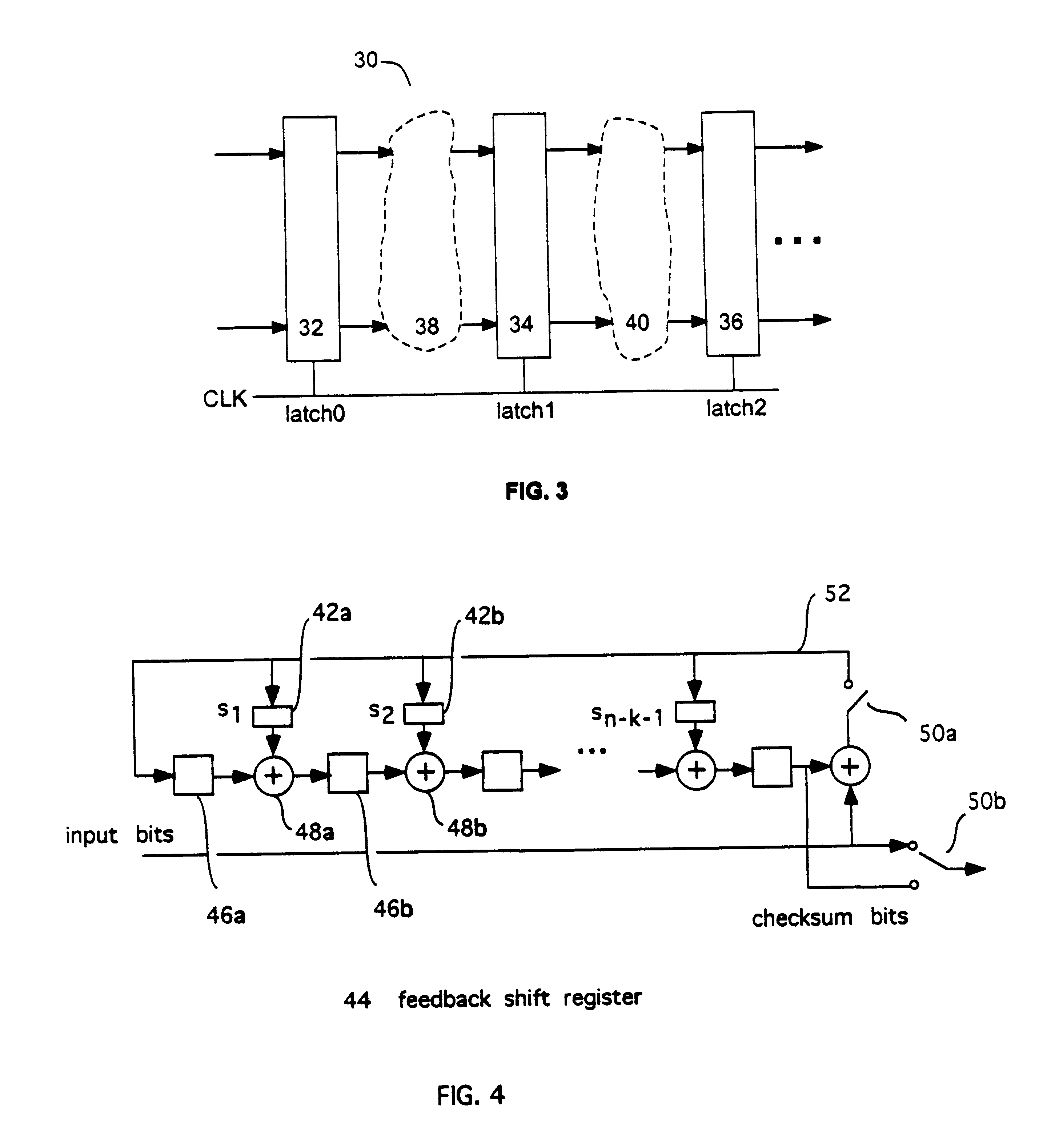

Transmitter, receiver, and coding scheme to increase data rate and decrease bit error rate of an optical data link

InactiveUS6851086B2Increase capacityIncrease bitrateError prevention/detection by using return channelError detection/correctionData packData rate

Transmitters, receivers, and coding schemes to increase data rate and decrease bit error rate of an optical data link are disclosed. Data is transmitted across the link with a less than nominal bit error rate (BER), by encoding the data using a forward error correction (FEC) code or by requesting retransmission of transmitted packets in error. Data is transmitted at a speed that introduces errors at a rate that is in excess of the nominal BER but that may be corrected using the FEC code or retransmission so that the data may be received with less than the nominal BER. The data rate is increased as the link operating speed is increased beyond the overhead required by the FEC codes or retransmission. High speed FEC encoders and decoders facilitating such transmission are disclosed.

Owner:SZYMANSKI TED

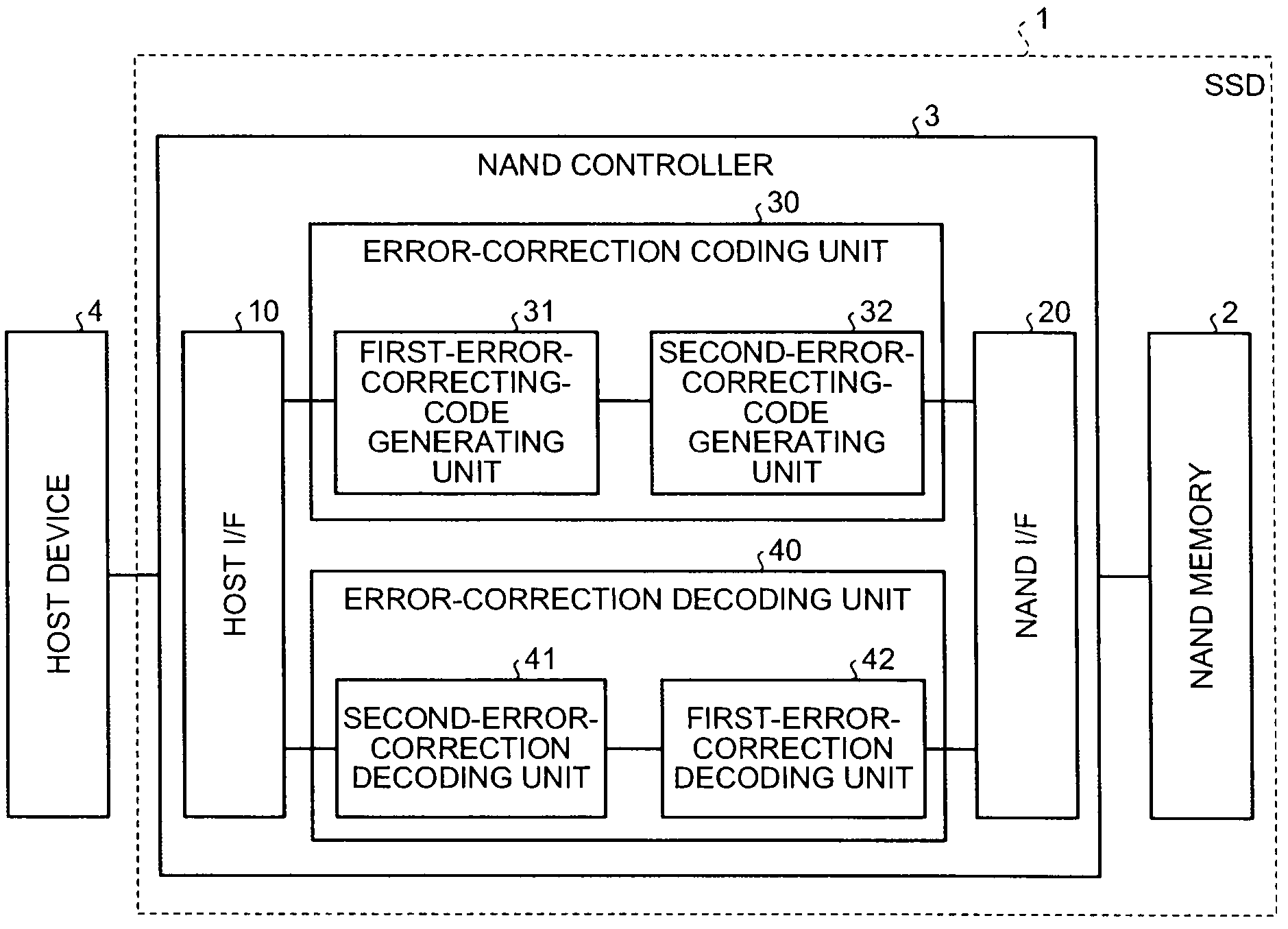

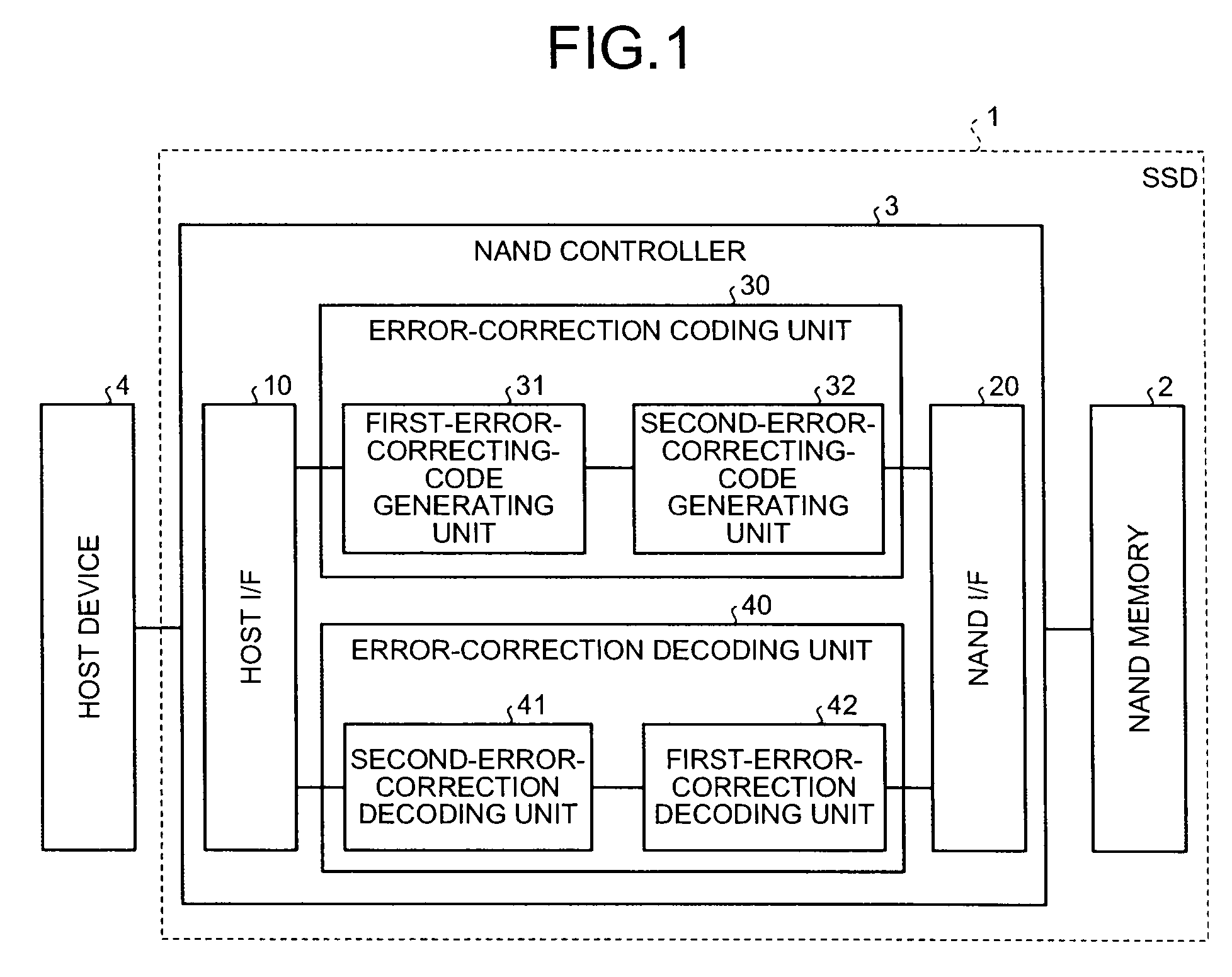

Error correcting device and error correcting method

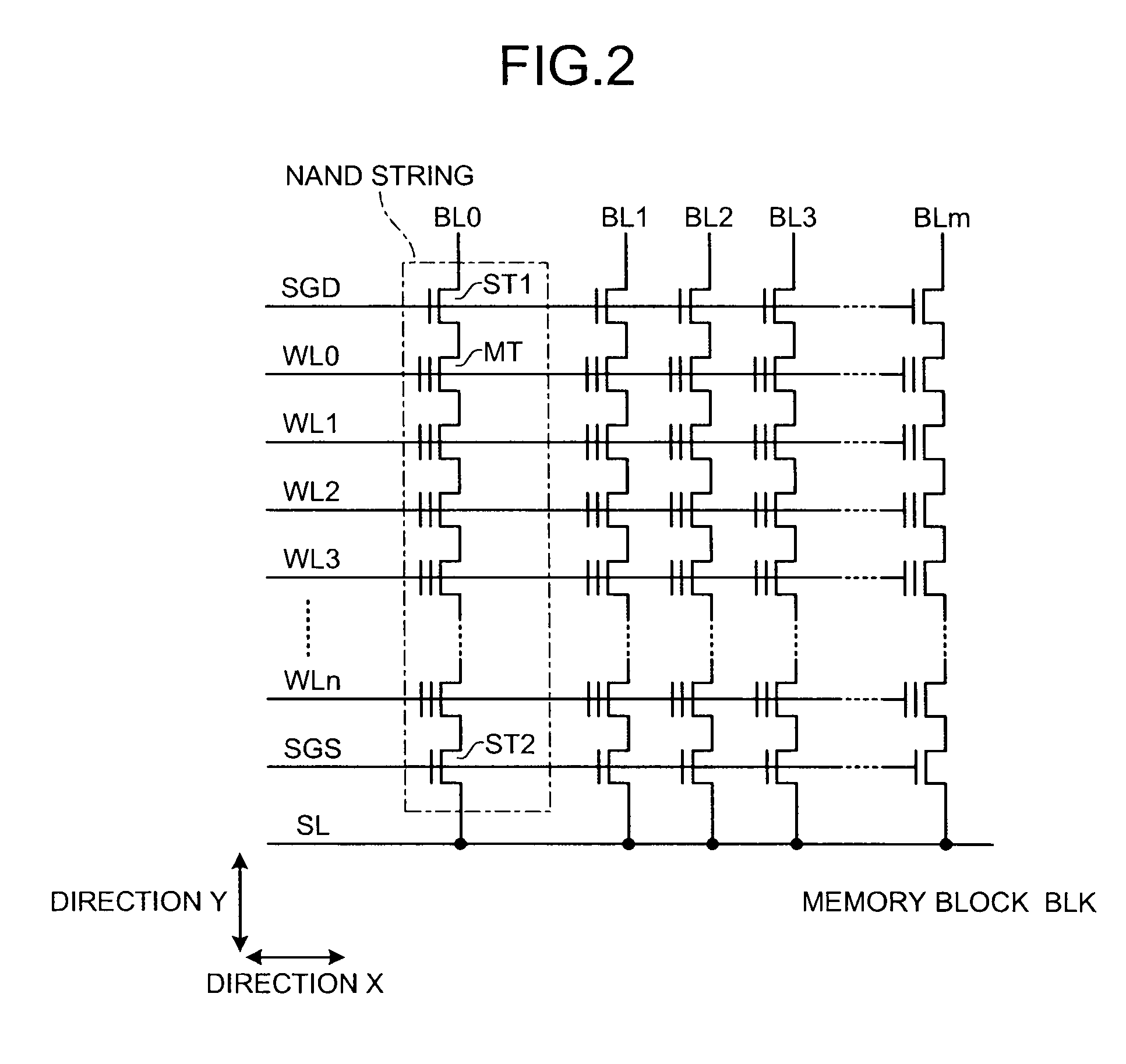

An error correcting device for correcting erroneous data included in data read out from a nonvolatile memory includes a determining unit that determines whether the data read out from the nonvolatile memory include an error beyond an error correcting capability of the error correcting device. When the determining unit has determined that an error beyond the error correcting capability exists, the error correcting device does not perform the correction of the error.

Owner:KK TOSHIBA

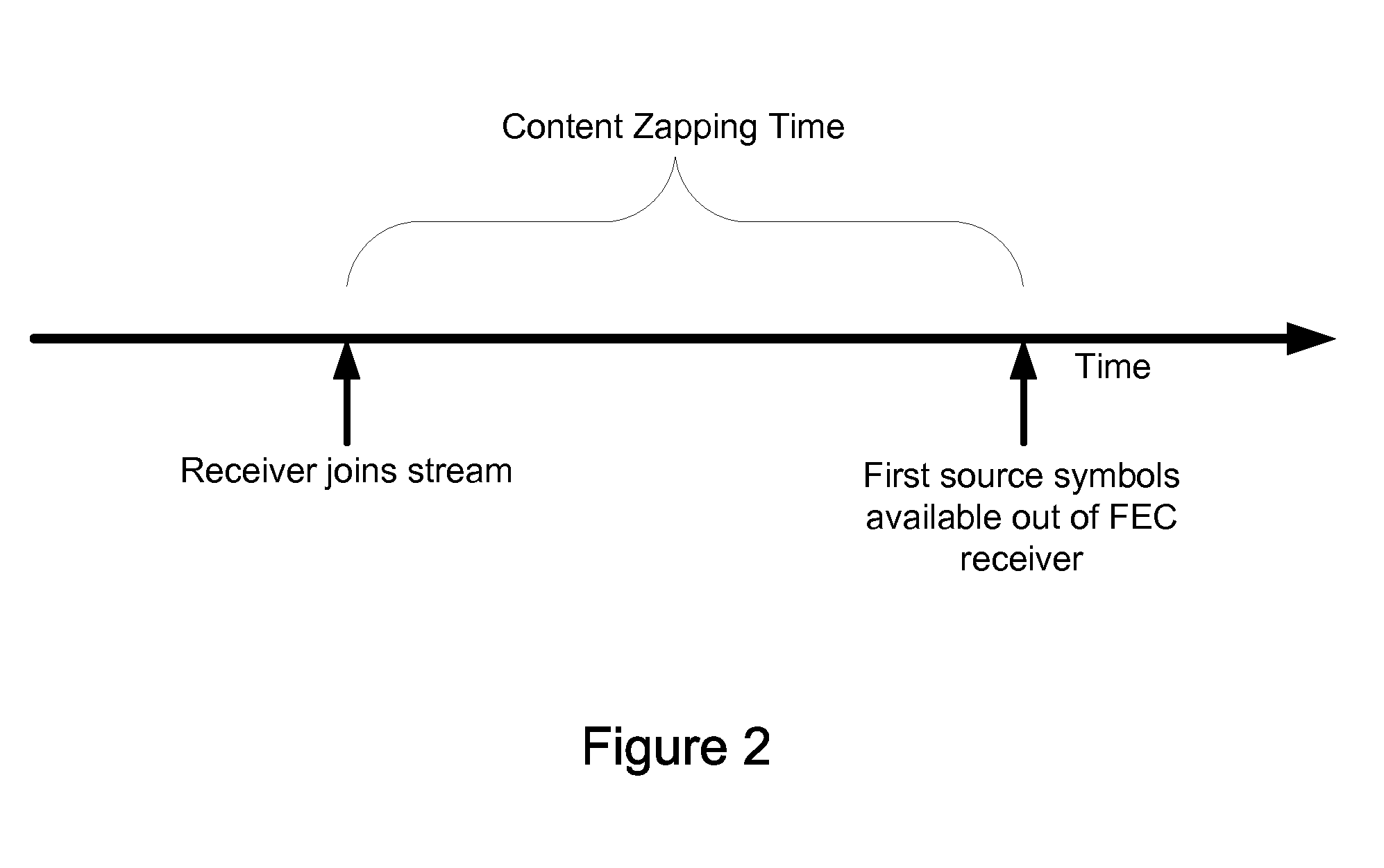

Dynamic stream interleaving and sub-stream based delivery

ActiveUS20080256418A1Convenient amountLoss of protectionFault responseCode conversionPacket lossCommunications system

A communications system can provide methods of dynamically interleaving streams, including methods for dynamically introducing greater amounts of interleaving as a stream is transmitted independently of any source block structure to spread out losses or errors in the channel over a much larger period of time within the original stream than if interleaving were not introduced, provide superior protection against packet loss or packet corruption when used with FEC coding, provide superior protection against network jitter, and allow content zapping time and the content transition time to be reduced to a minimum and minimal content transition times. Streams may be partitioned into sub-streams, delivering the sub-streams to receivers along different paths through a network and receiving concurrently different sub-streams at a receiver sent from potentially different servers. When used in conjunction with FEC encoding, the methods include delivering portions of an encoding of each source block from potentially different servers.

Owner:QUALCOMM INC

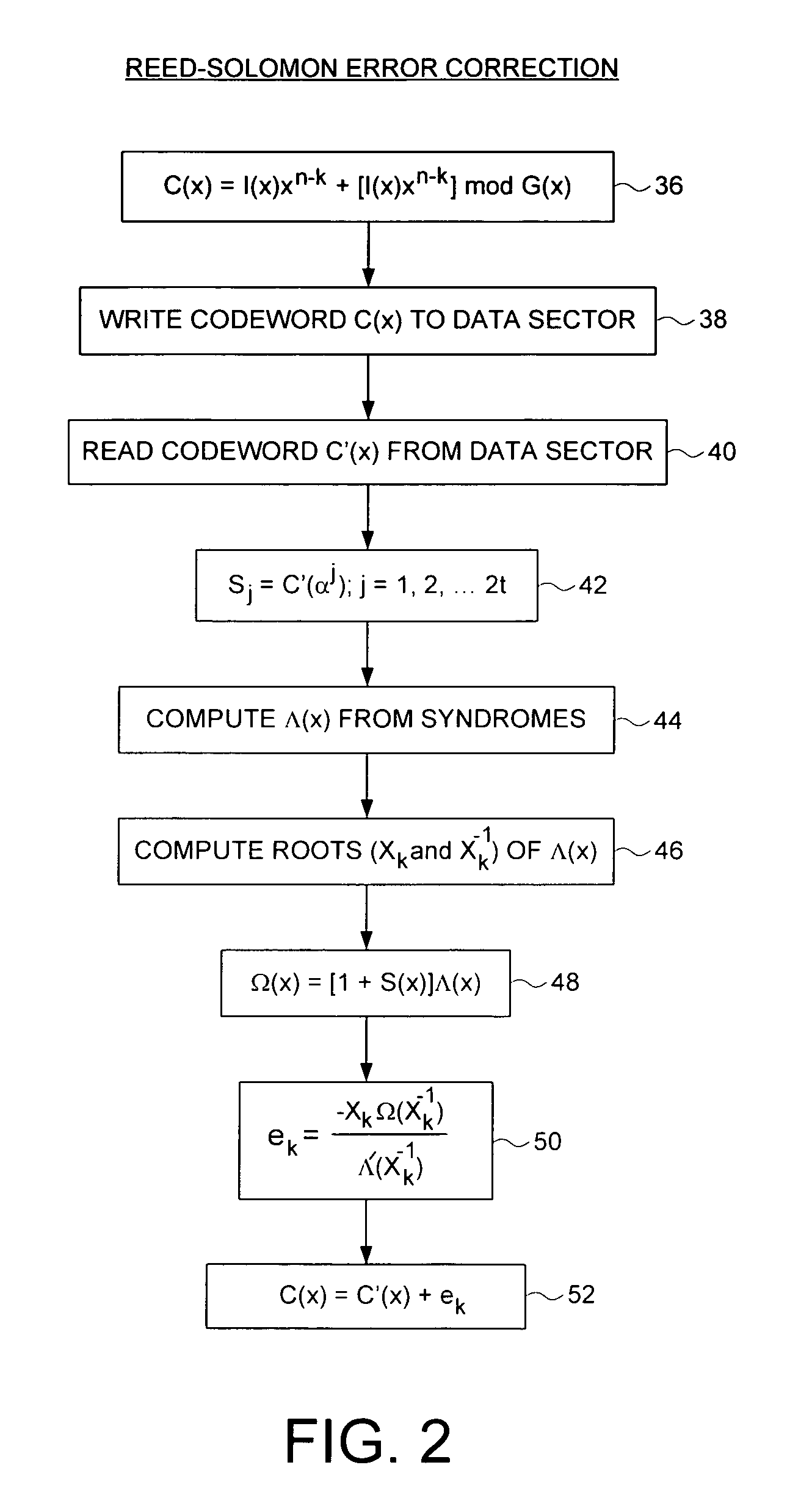

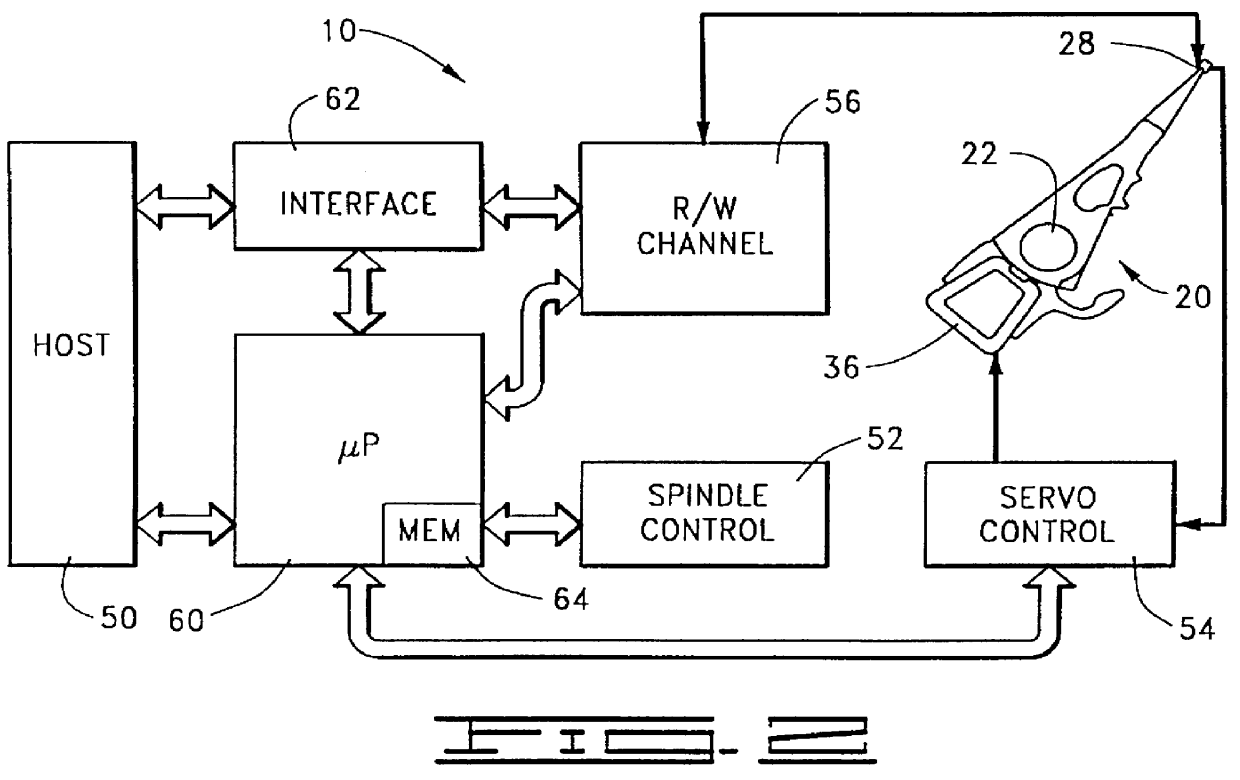

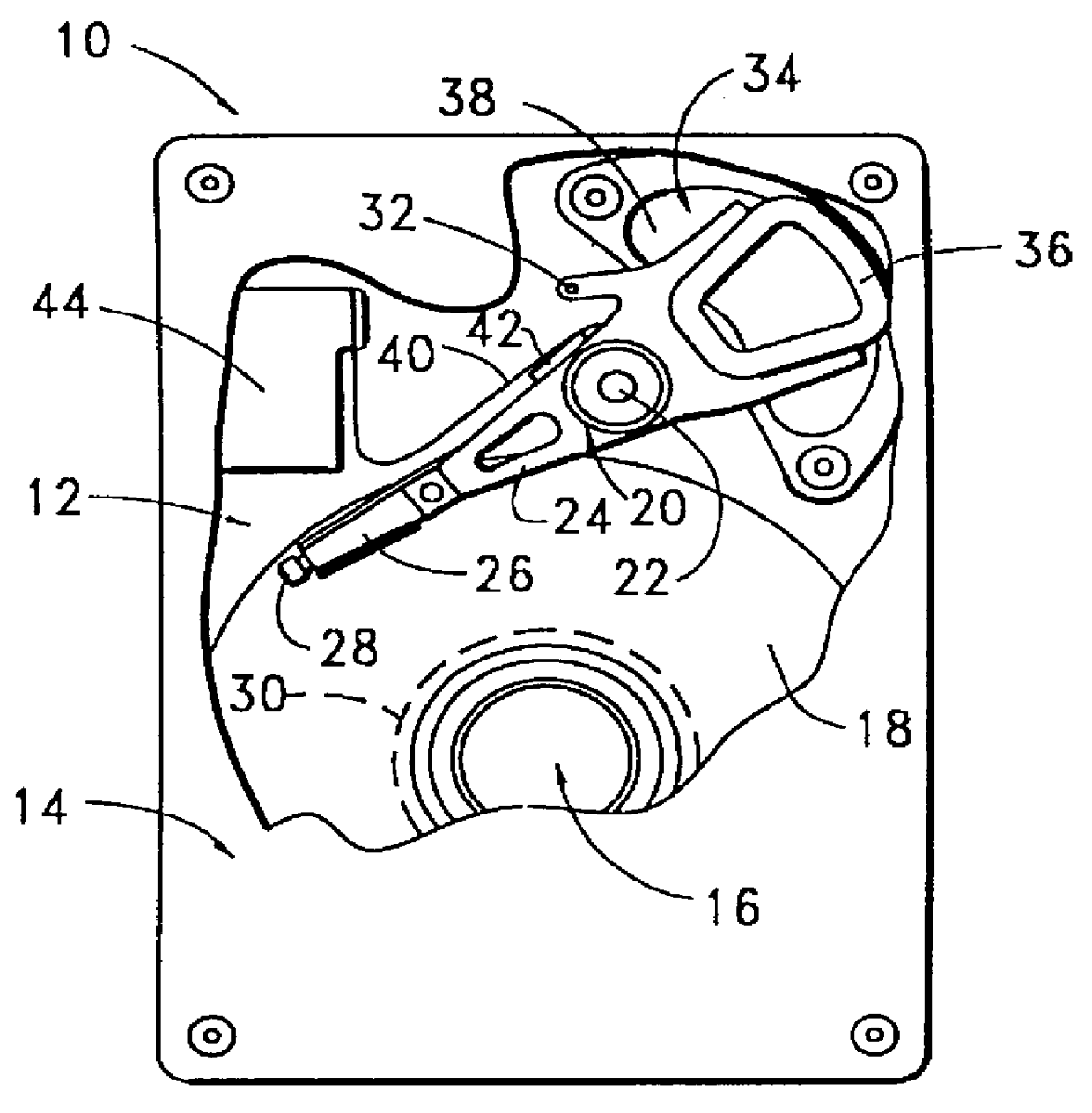

Disk drive employing error threshold counters to generate an ECC error distribution

A disk drive is disclosed comprising a head actuated over a disk. A redundancy generator generates a plurality of redundancy symbols appended to user data to form a codeword C(x) written to a selected data sector on the disk. During a read operation, a syndrome generator generates a plurality of error syndromes in response to a received codeword C′(x) generated by reading the selected data sector. An error detector, responsive to the error syndromes, detects a number of errors in the received codeword C′(x), and a plurality of counters count a number of times the number of errors falls within a predetermined plurality of ranges to thereby provide a distribution of the errors. The error distribution is used, for example, for selecting a track density or ECC depth, or for failure prediction or defect mapping.

Owner:WESTERN DIGITAL TECH INC

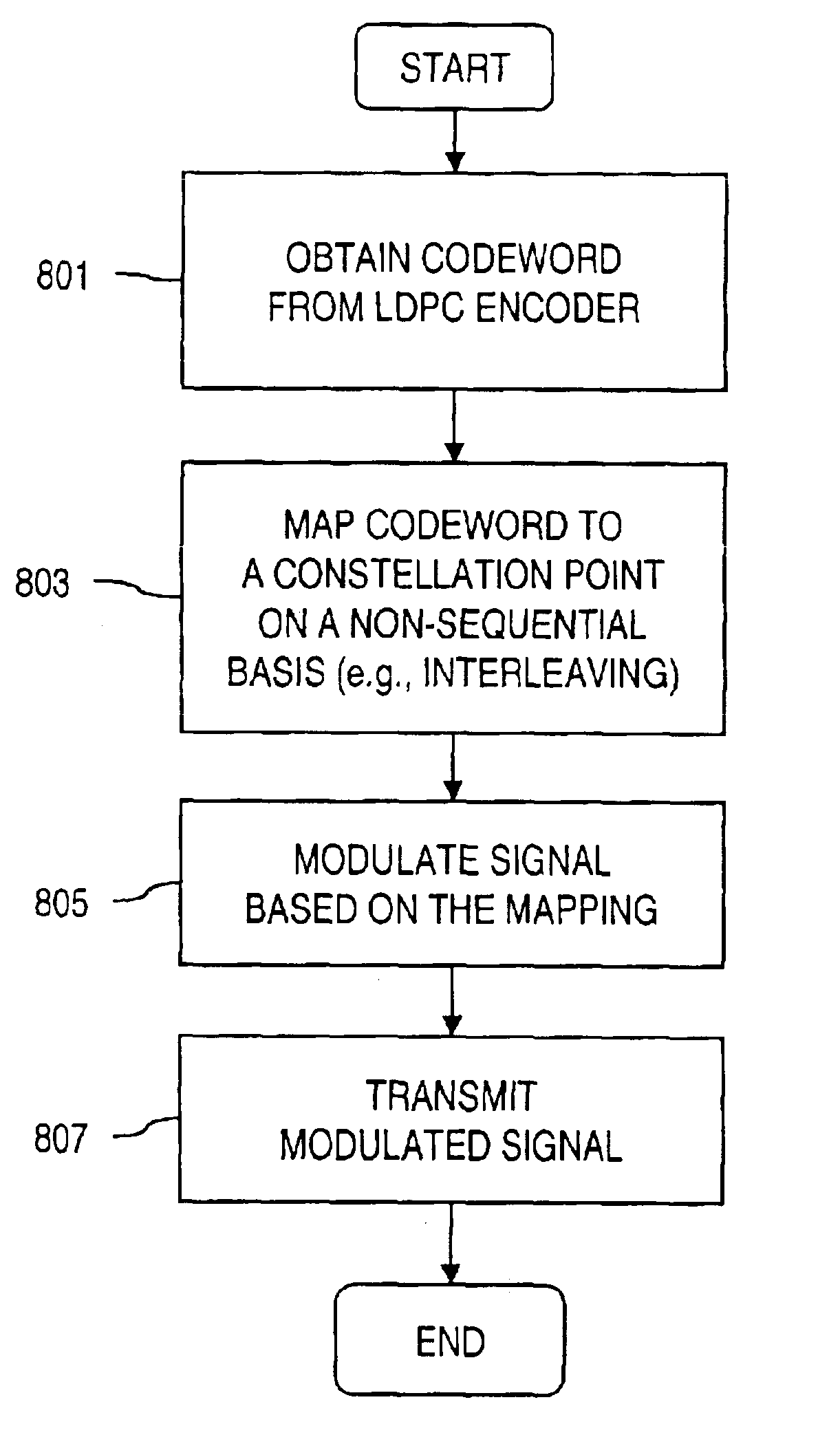

Bit labeling for amplitude phase shift constellation used with low density parity check (LDPC) codes

InactiveUS6963622B2Improve performanceError correction/detection using LDPC codesCode conversionParity-check matrixEngineering

An approach is provided for bit labeling of a signal constellation. A transmitter generates encoded signals using, according to one embodiment, a structured parity check matrix of a Low Density Parity Check (LDPC) code. The transmitter includes an encoder for transforming an input message into a codeword represented by a plurality of set of bits. The transmitter includes logic for mapping non-sequentially (e.g., interleaving) one set of bits into a higher order constellation (Quadrature Phase Shift Keying (QPSK), 8-PSK, 16-APSK (Amplitude Phase Shift Keying), 32-APSK, etc.), wherein a symbol of the higher order constellation corresponding to the one set of bits is output based on the mapping.

Owner:DTVG LICENSING INC

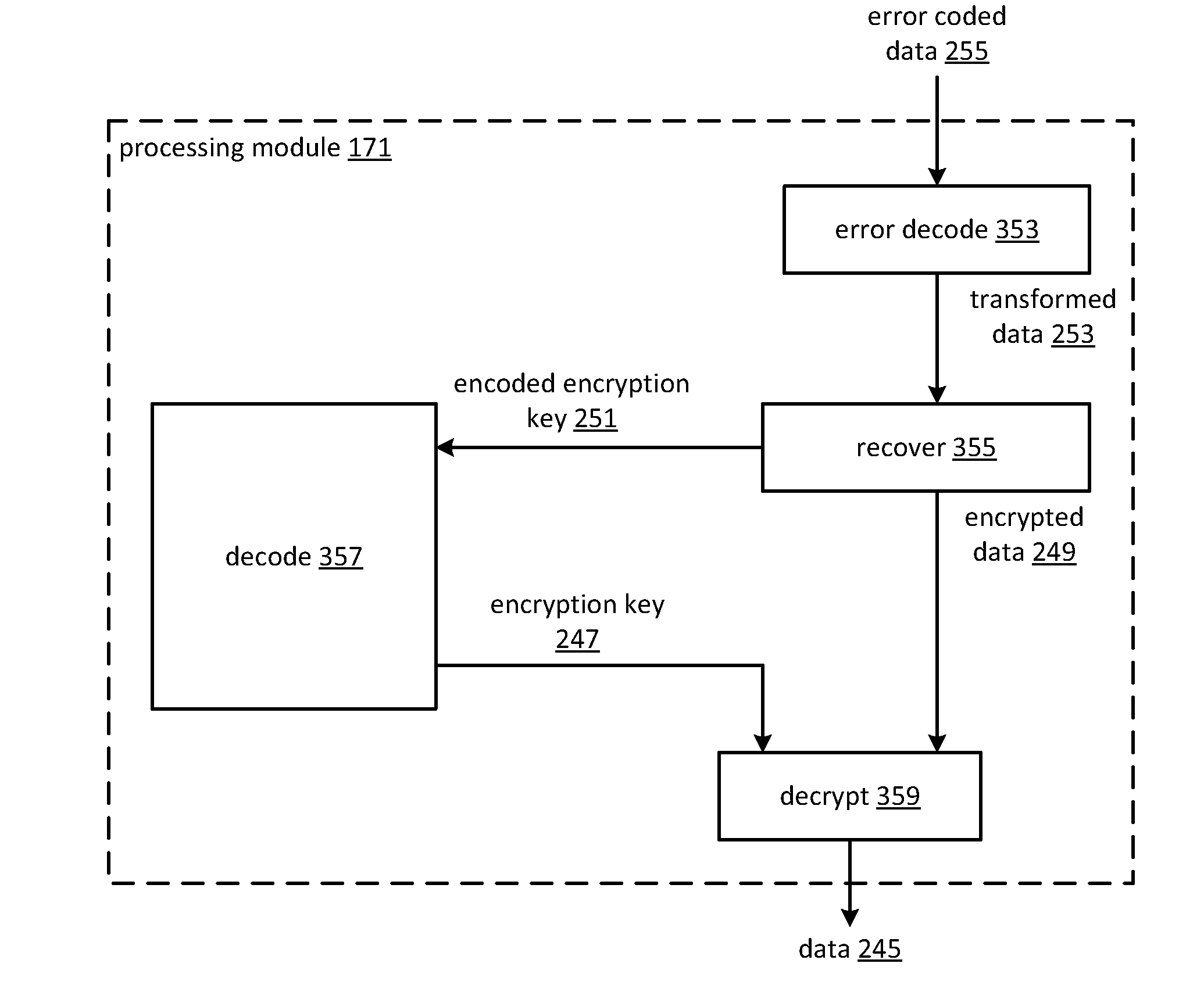

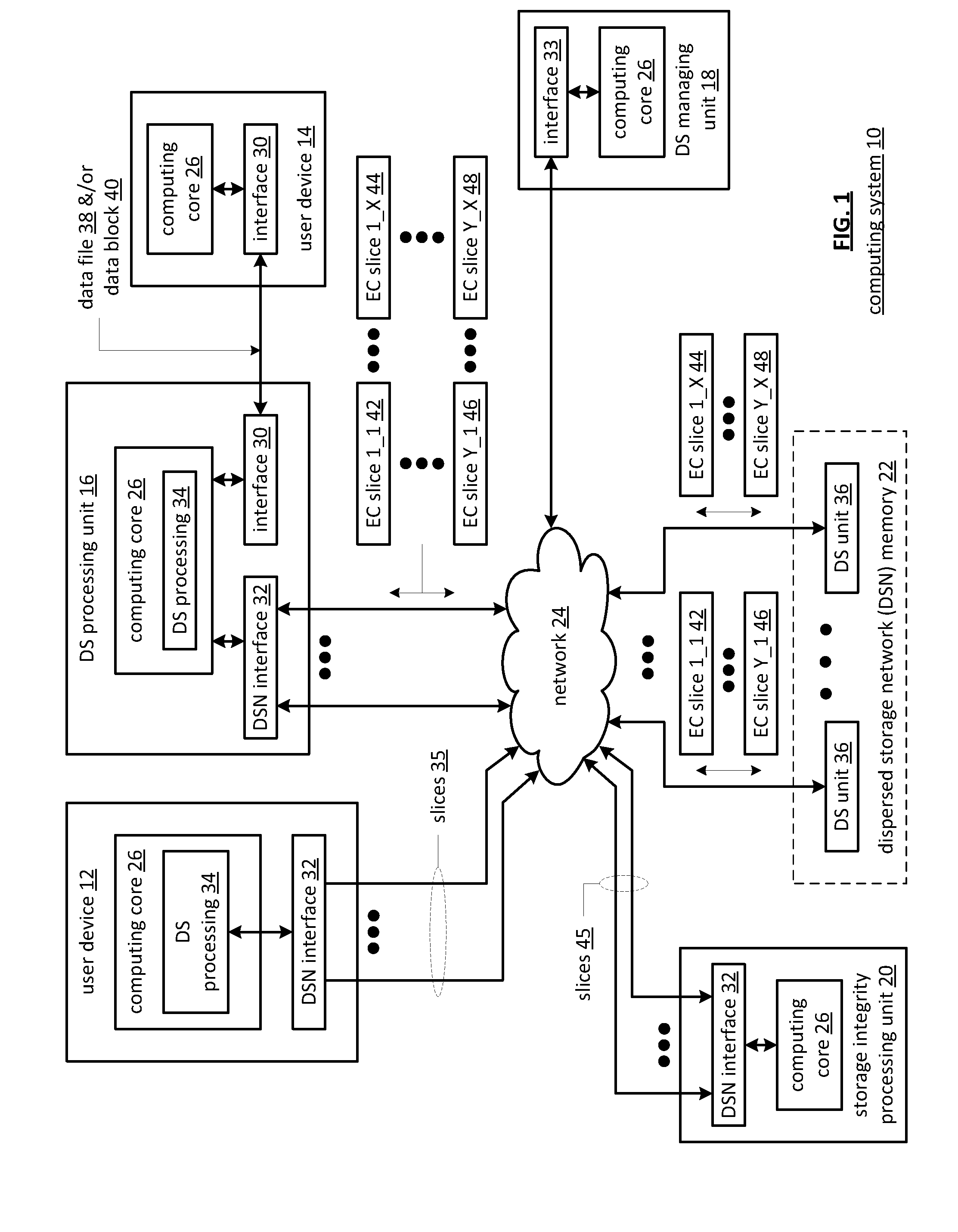

Dispersed data storage system data decoding and decryption

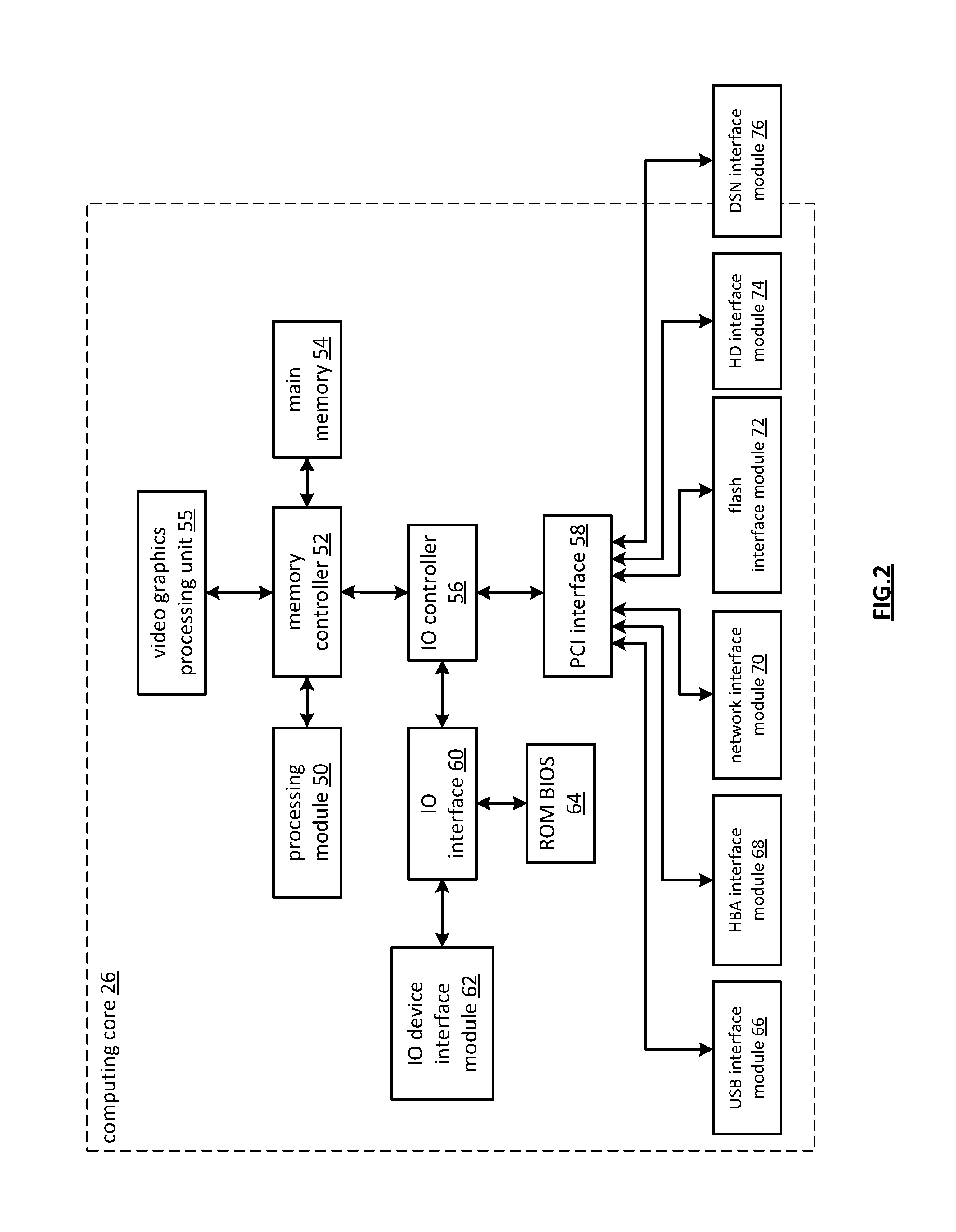

ActiveUS20100269008A1Error correction/detection using convolutional codesError preventionComputer hardwareComputer module

A computing system retrieves securely stored encrypted and encoded data from a dispersed data storage system. The computing system includes a processing module and a plurality of storage units. The processing module includes an error decoder and a decryptor and to decode and decrypt the encrypted and encoded data retrieved from the dispersed data storage system utilizing a read command to the storage units. The storage units retrieve the encrypted and encoded data and send the encrypted and encoded data to the processing module when receiving the read command.

Owner:PURE STORAGE

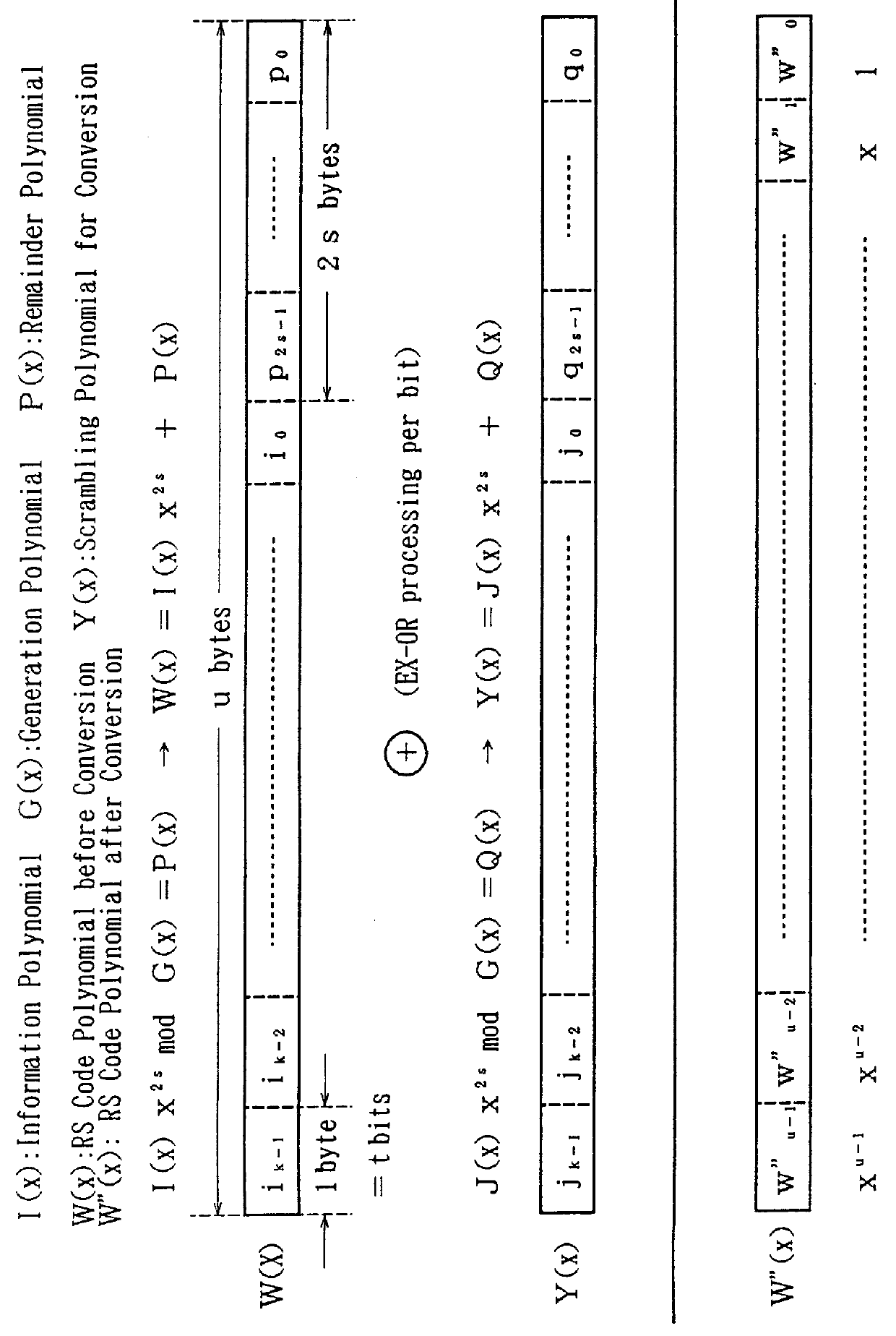

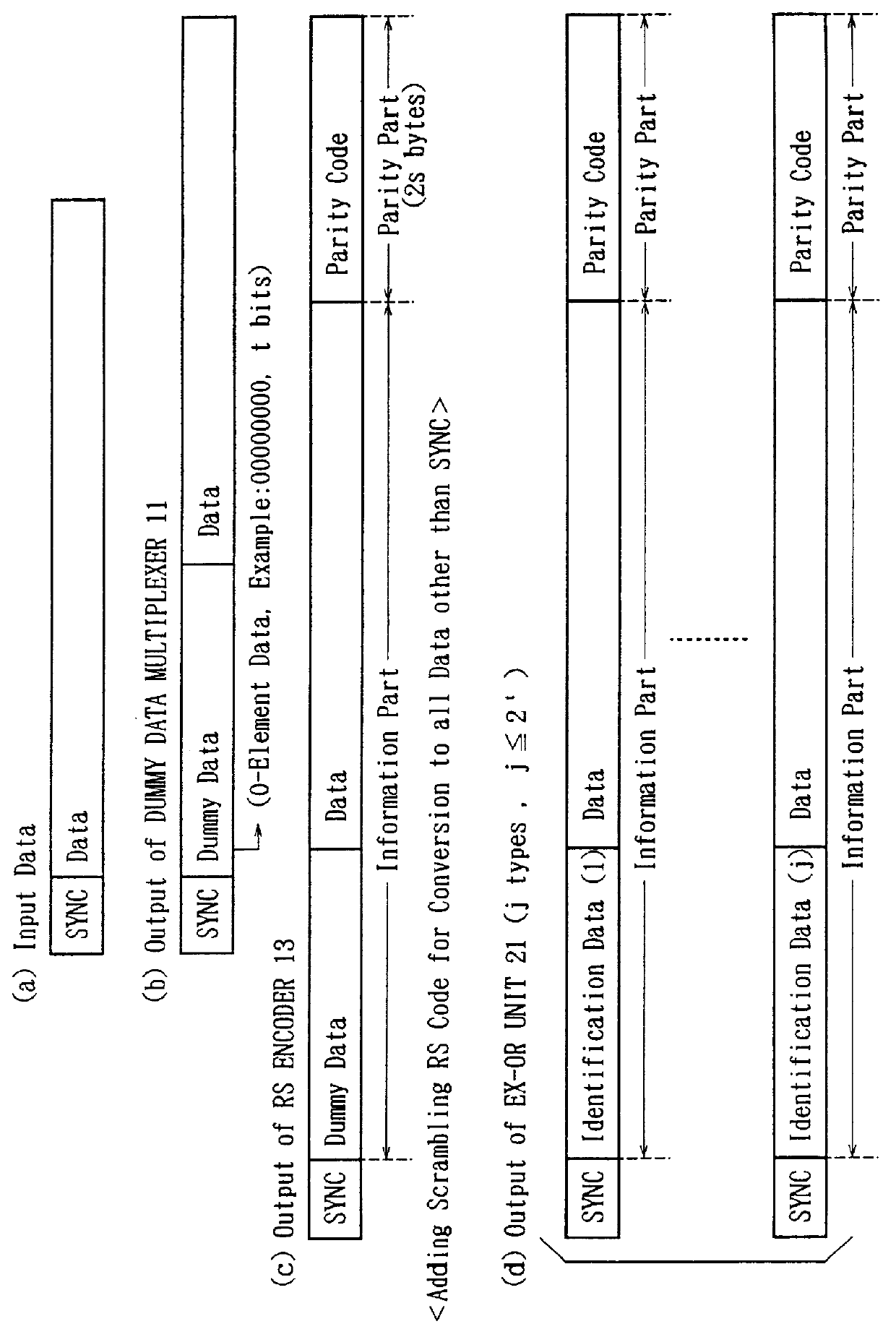

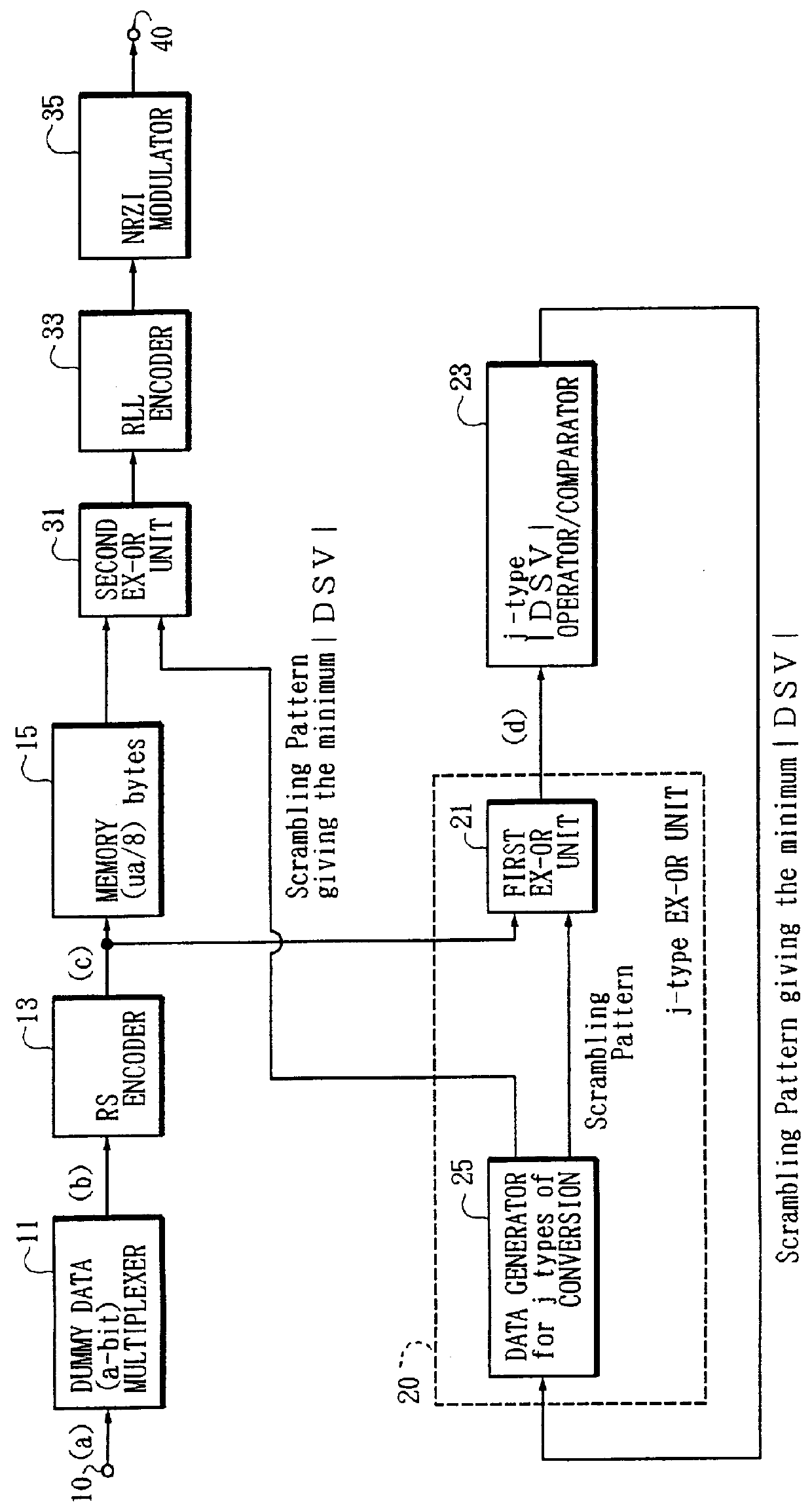

Digital modulation and demodulation

A digital modulator which inputs a data stream to convert to a channel bit stream. The multiplexed data block is generated by multiplexing dummy data to any position within each data block cut out of the data stream one by one. The first Reed-Solomon code is generated by Reed-Solomon-encoding the multiplexed data block as an information part. A plurality of second Reed-Solomon codes are generated by adding a plurality of Reed-Solomon codes for scrambling each of which has identification data showing its scrambling pattern in the same position as that of the dummy data, and the code length of information part and parity part is the same as the first Reed-Solomon code. The second Reed-Solomon code in which the characteristics becomes desirable after modulation among the plurality of the second Reed-Solomon codes is set for output.

Owner:SANYO ELCETRIC CO LTD +1

Method and apparatus for fault tolerant data storage on photographs

InactiveUS6859225B1Increase in sizeTelevision system detailsRecord information storageDigital dataImaging processing

A method of printing digital data onto a photograph using infra-red ink and using an ink jet printing process is disclosed. The data can store the details of an image taken by a camera, which has been transformed by a proprietary image processing program, loaded separately into the camera, along with a copy of the program, the data being recorded in a fault tolerant form enabling the copying or recovery of the transformed photograph or of the original thereof notwithstanding damage thereto.

Owner:GOOGLE LLC

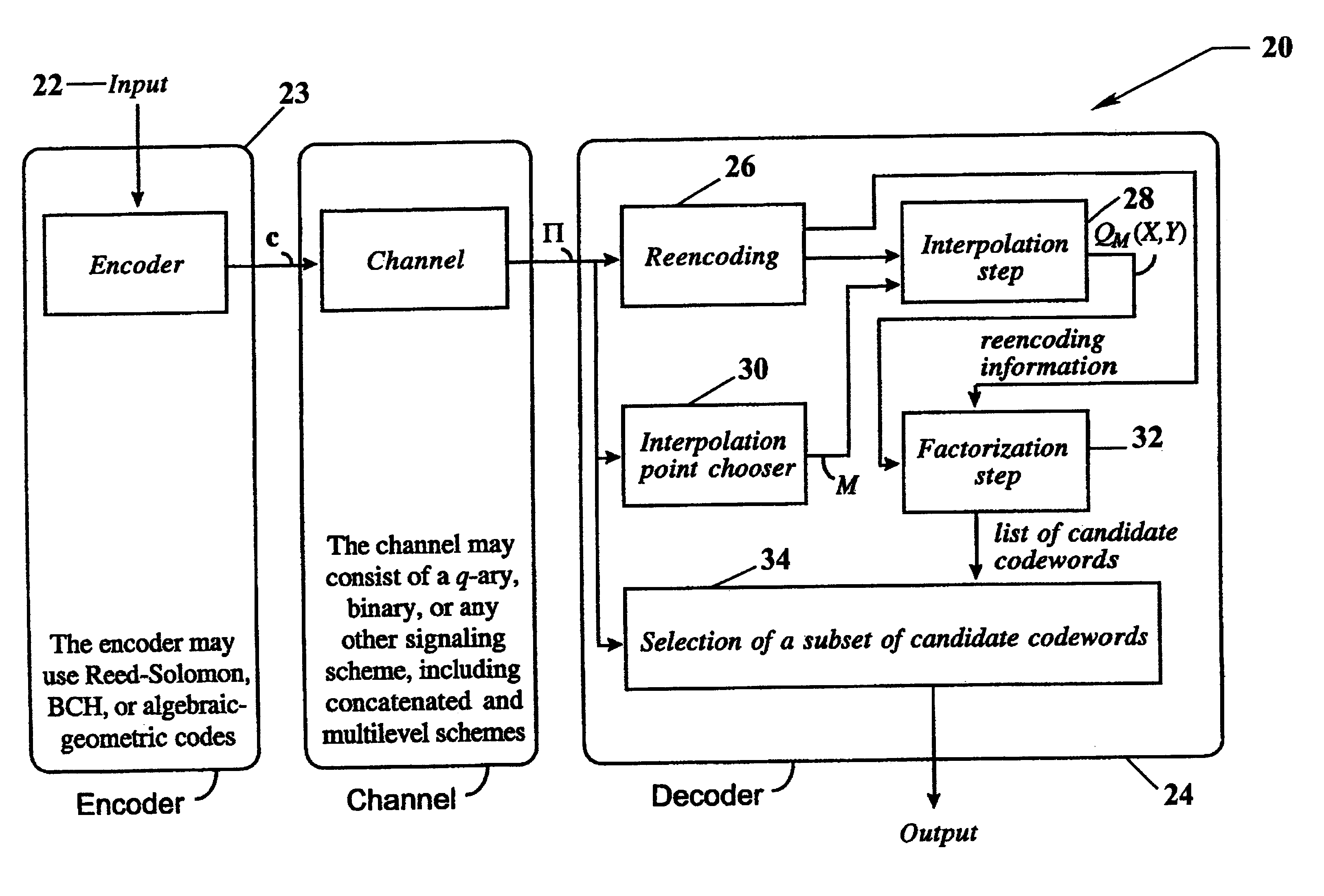

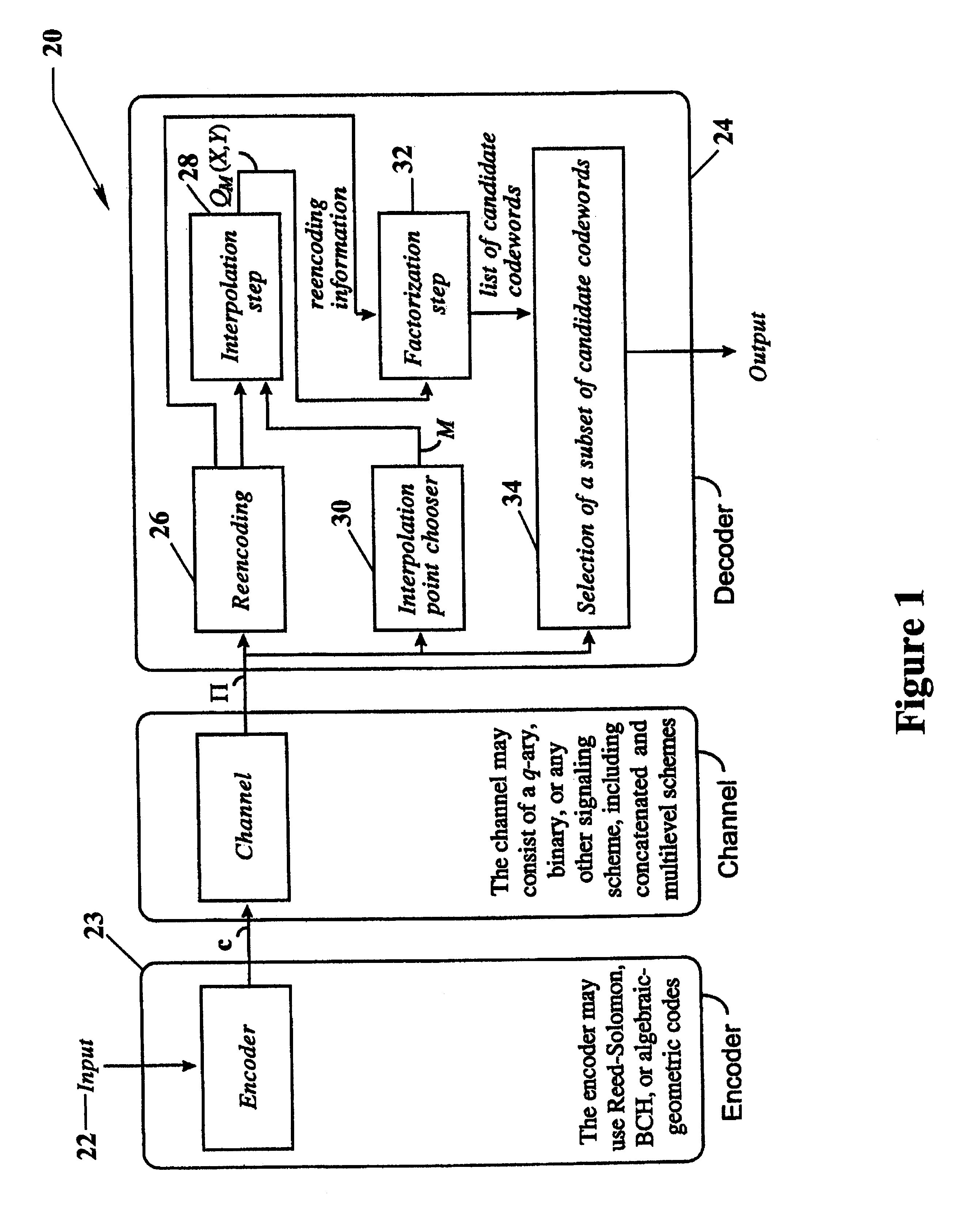

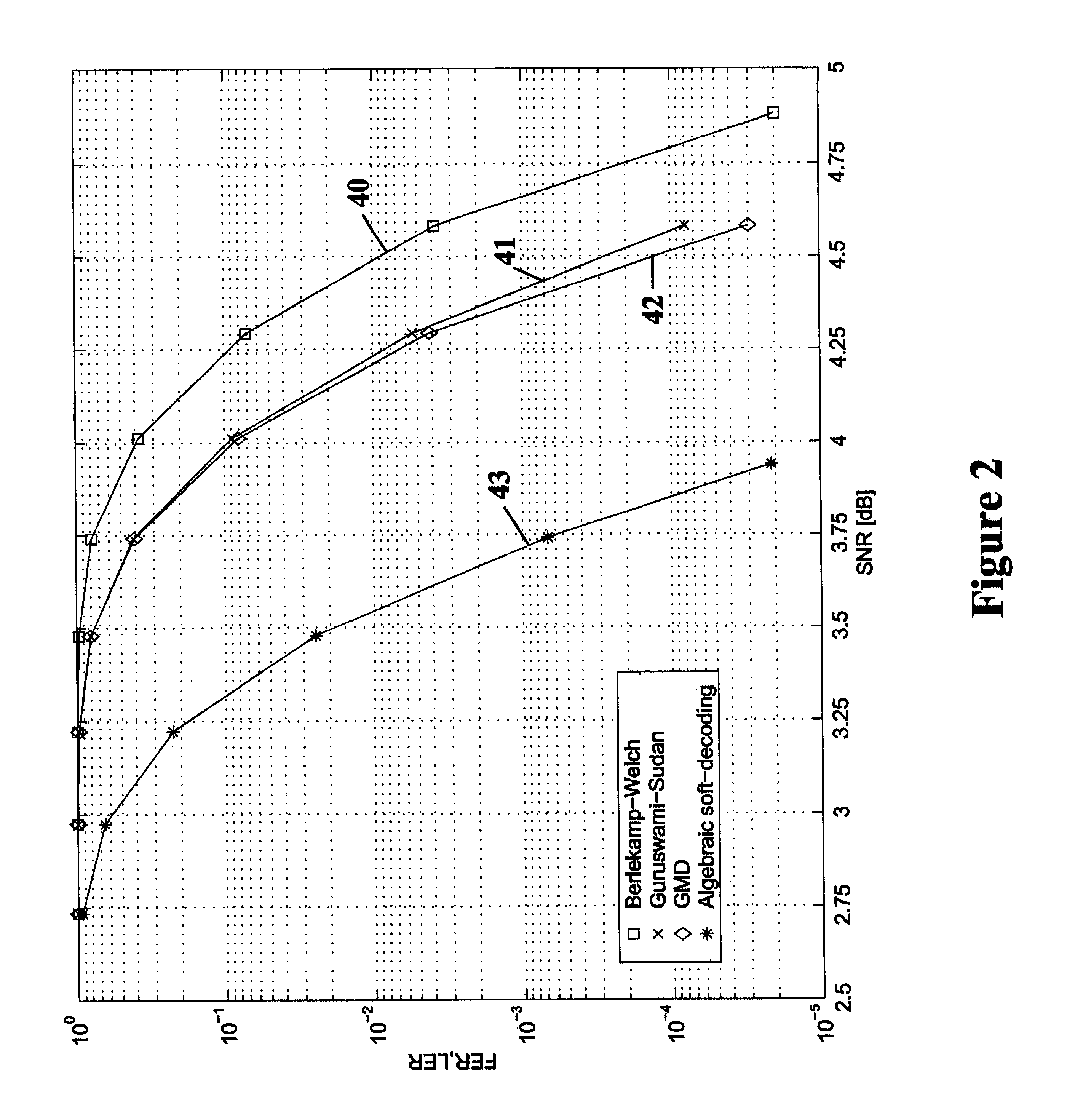

Algebraic soft decoding of reed-solomon codes

InactiveUS6634007B1Maximizes the expected scoreMaximizing the expected scoreOther decoding techniquesAlgebraic geometric codesDecoding methodsRound complexity

An algorithmic soft-decision decoding method for Reed-Solomon codes proceeds as follows. Given the reliability matrix Pi showing the probability that a code symbol of a particular value was transmitted at each position, computing a multiplicity matrix M which determines the interpolation points and their multiplicities. Given this multiplicity matrix M, soft interpolation is performed to find the non-trivial polynomial Q<HIL><PDAT>M< / SB><PDAT>(X,Y) of the lowest (weighted) degree whose zeros and their multiplicities are as specified by the matrix M. Given this non-trivial polynomial Q<HIL><PDAT>M< / SB><PDAT>(X,Y), all factors of Q<HIL><PDAT>M< / SB><PDAT>(X,Y) of type Y-f(X) are found, where f(X) is a polynomial in X whose degree is less than the dimension k of the Reed-Solomon code. Given these polynomials f(X), a codeword is reconstructed from each of them, and the most likely of these codewords selected as the output of the algorithm. The algorithmic method is algebraic, operates in polynomial time, and significantly outperforms conventional hard-decision decoding, generalized minimum distance decoding, and Guruswami-Sudan decoding of Reed-Solomon codes. By varying the total number of interpolation points recorded in the multiplicity matrix M, the complexity of decoding can be adjusted in real time to any feasible level of performance. The algorithmic method extends to algebraic soft-decision decoding of Bose-Chaudhuri-Hocquenghem codes and algebraic-geometry codes.< / PTEXT>

Owner:MIND FUSION LLC

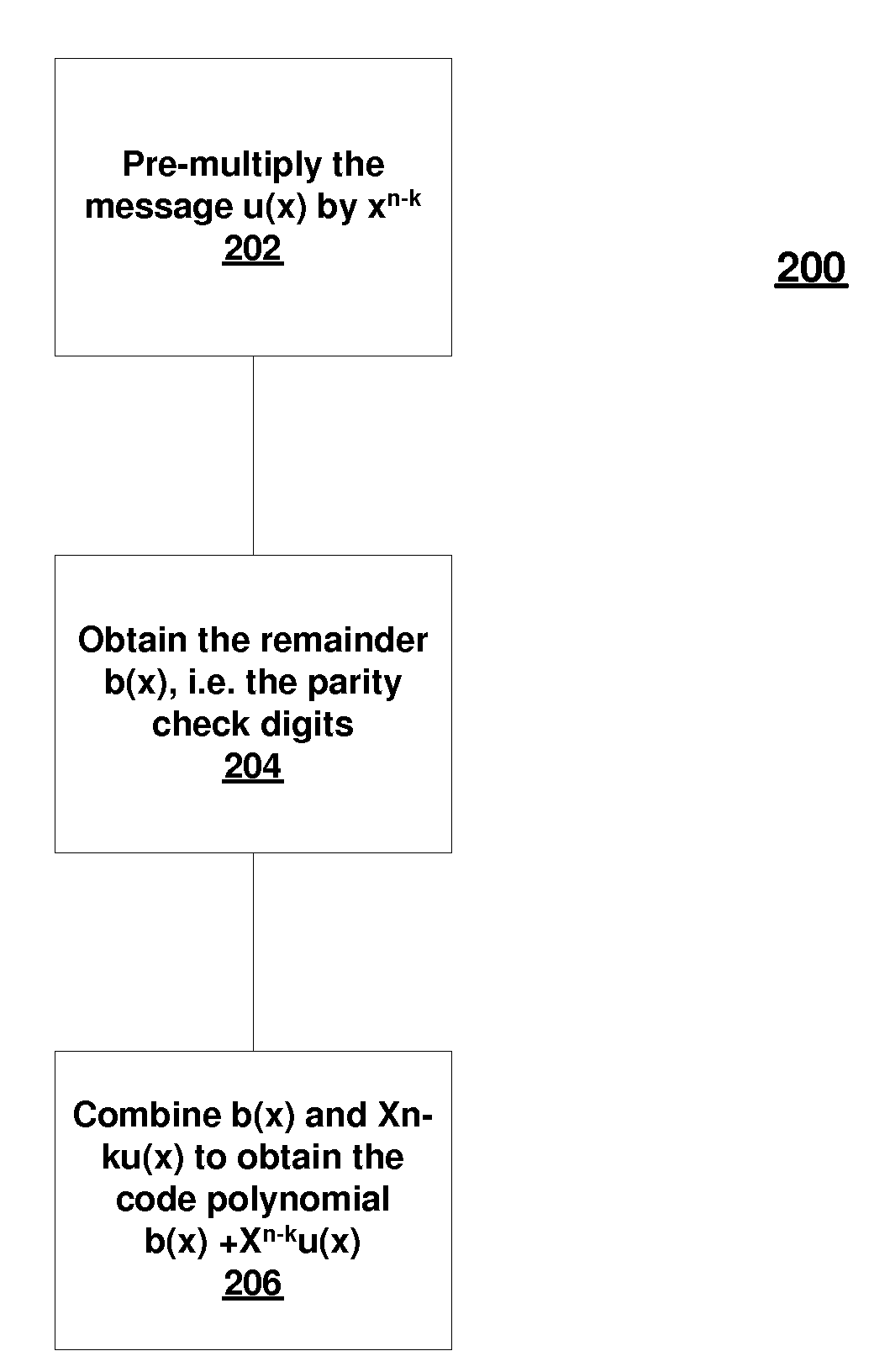

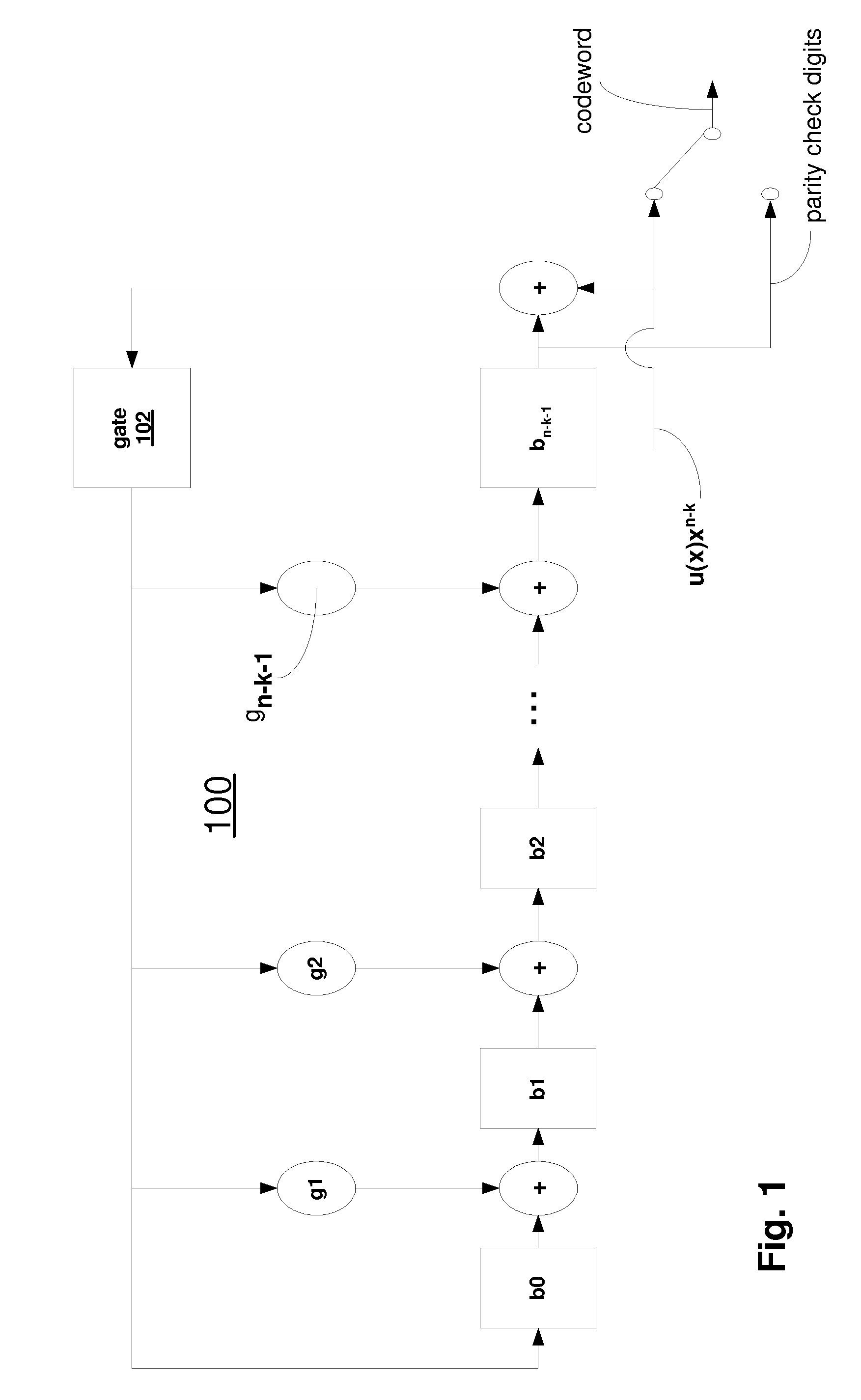

Bch code with 256 information bytes and up to 8 bytes of parity check elements

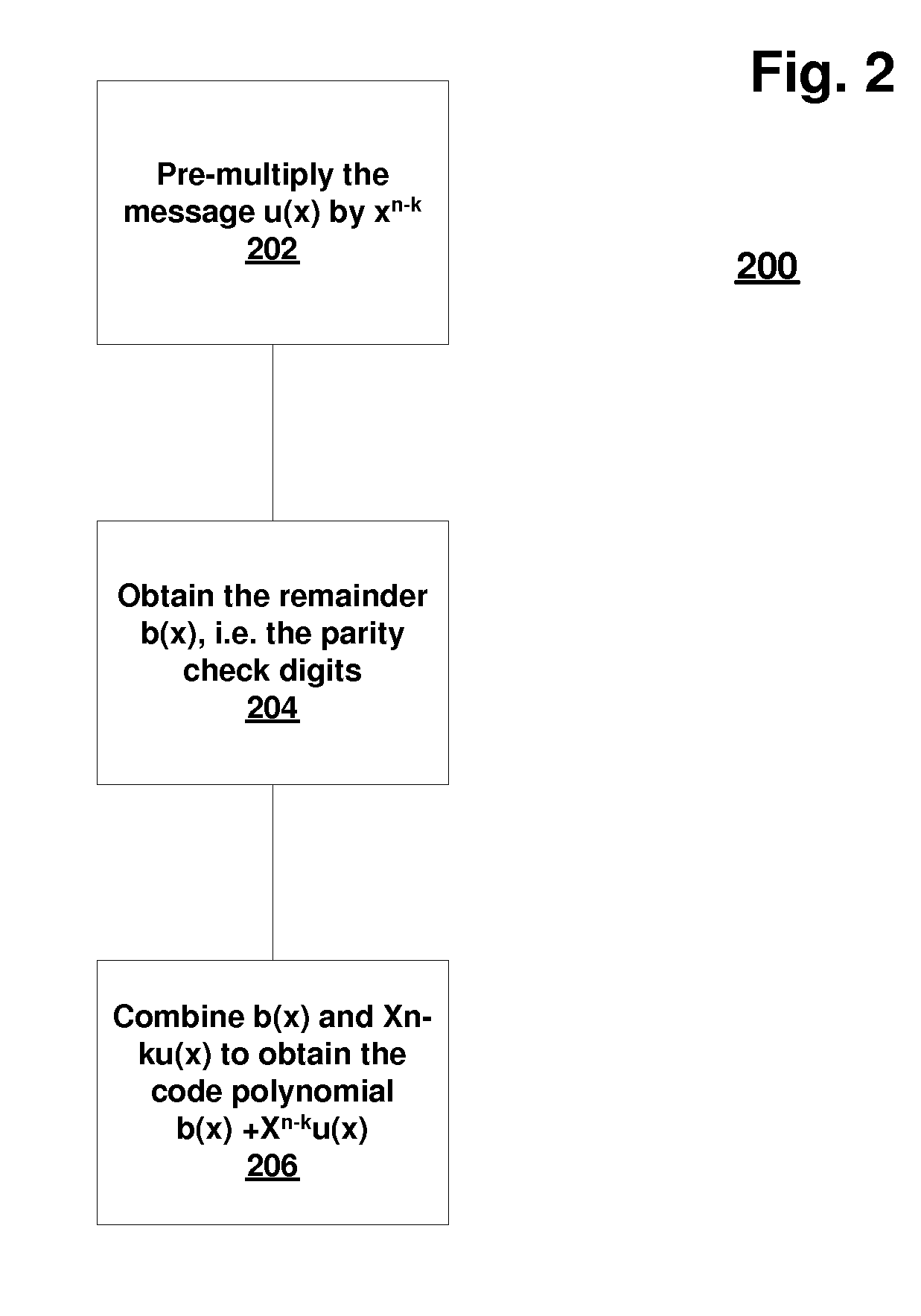

A coding system comprises pre-multiply the message u(x) by Xn−k. Obtain the remainder b(x), i.e. the parity check digits. And combine b(x) and Xn−ku(x) to obtain the code polynomial. A decoding method comprises calculating a syndrome; finding an error-location polynomial; and computing a set of error location numbers.

Owner:LEGEND SILICON

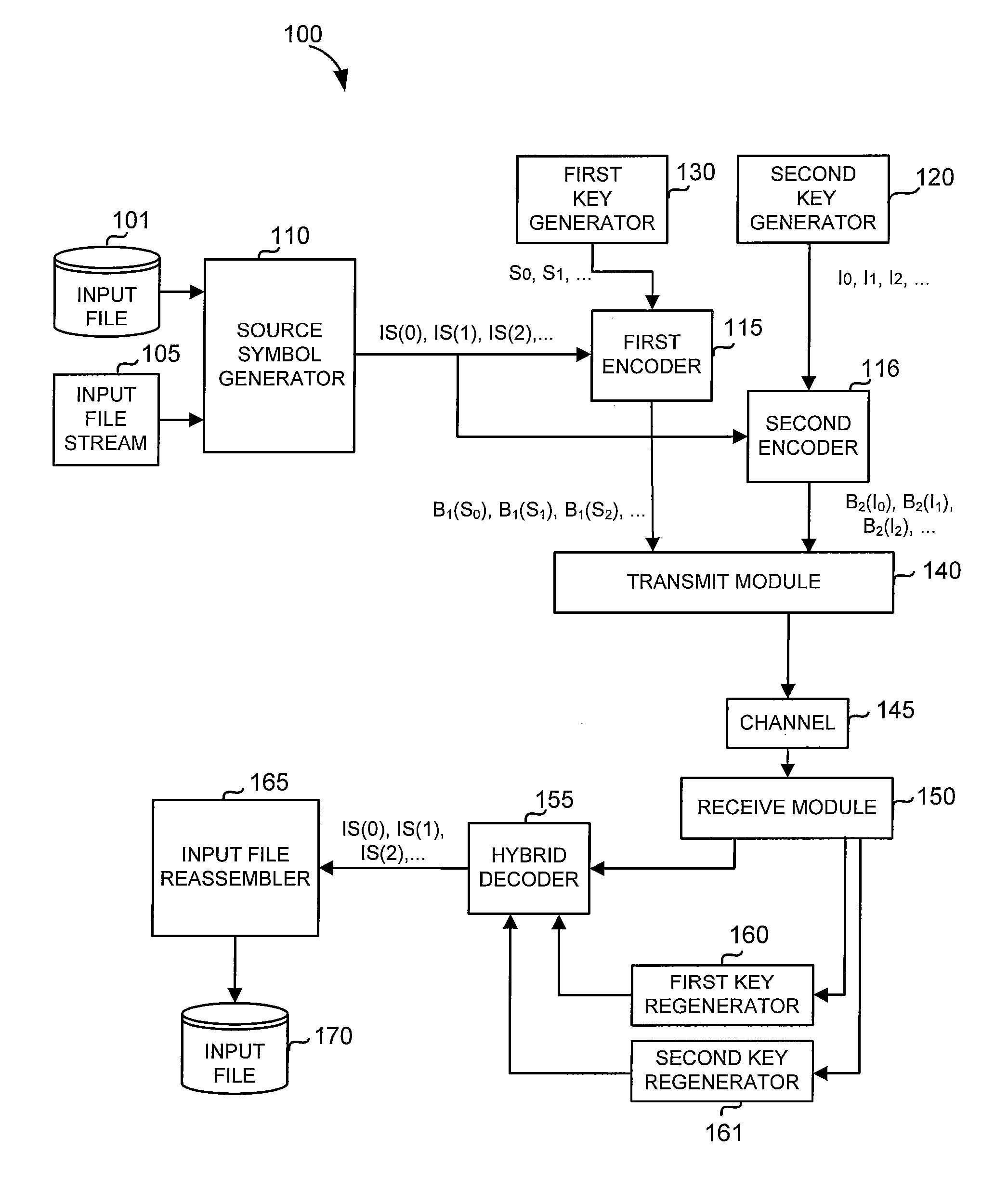

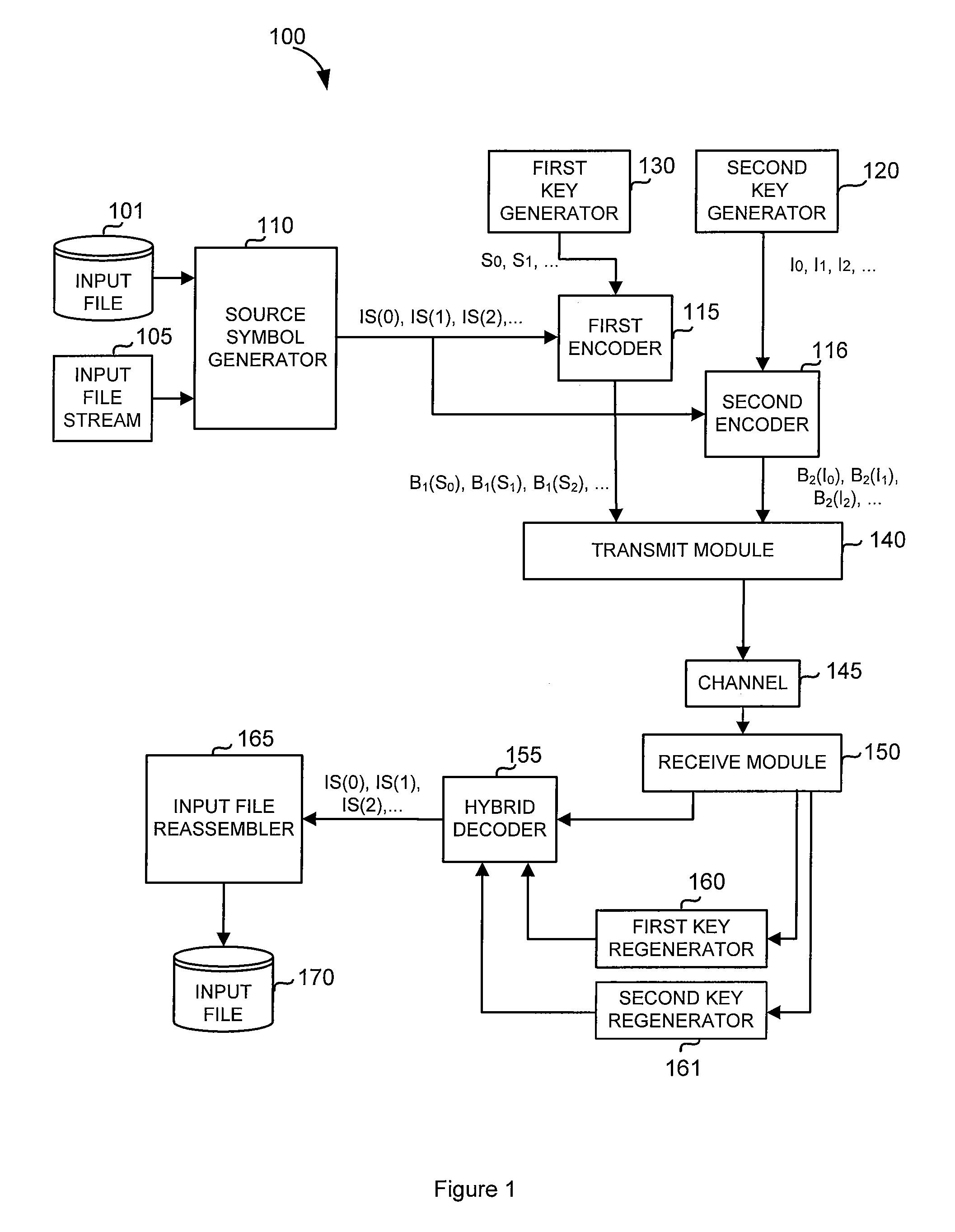

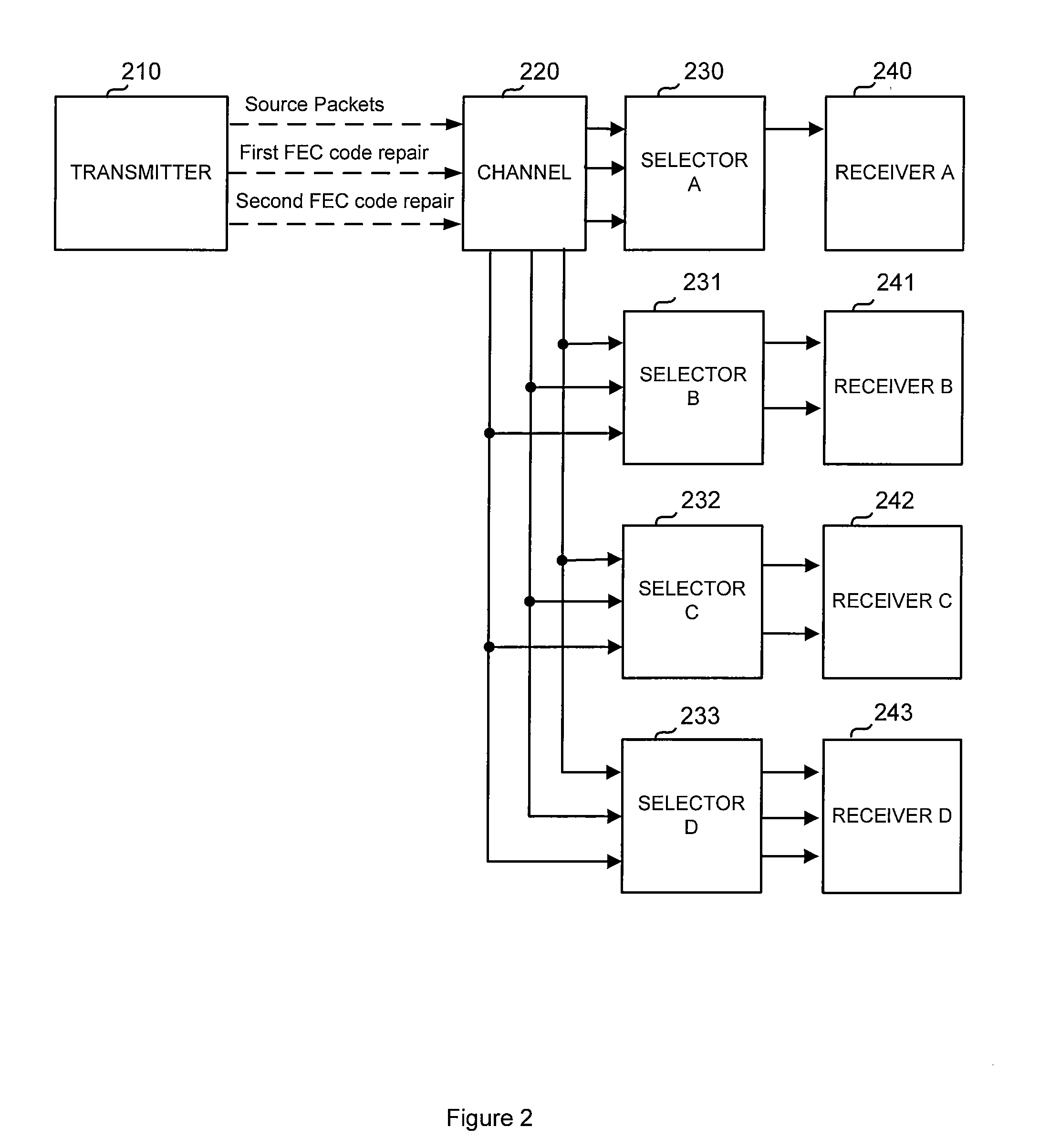

Code generator and decoder for communications systems operating using hybrid codes to allow for multiple efficient users of the communications systems

InactiveUS20070300127A1Error protectionImprove errorError preventionCode conversionComputer hardwareCommunications system

A method of encoding data for transmissions from a source to a destination over a communications channel is provided. The method operates on an ordered set of source symbols and may generate zero or more redundant symbols from the source symbols, wherein data is encoded in a first step according to a simple FEC code and in a second step, data is encoded according to a second FEC code, more complex than the first FEC code. The first FEC code and / or the second FEC code might comprise coding known in the art. These steps result in two groups of encoded data in such a way that a low-complexity receiver may make use of one of the groups of encoded data while higher complexity receivers may make use of both groups of encoded data.

Owner:QUALCOMM INC

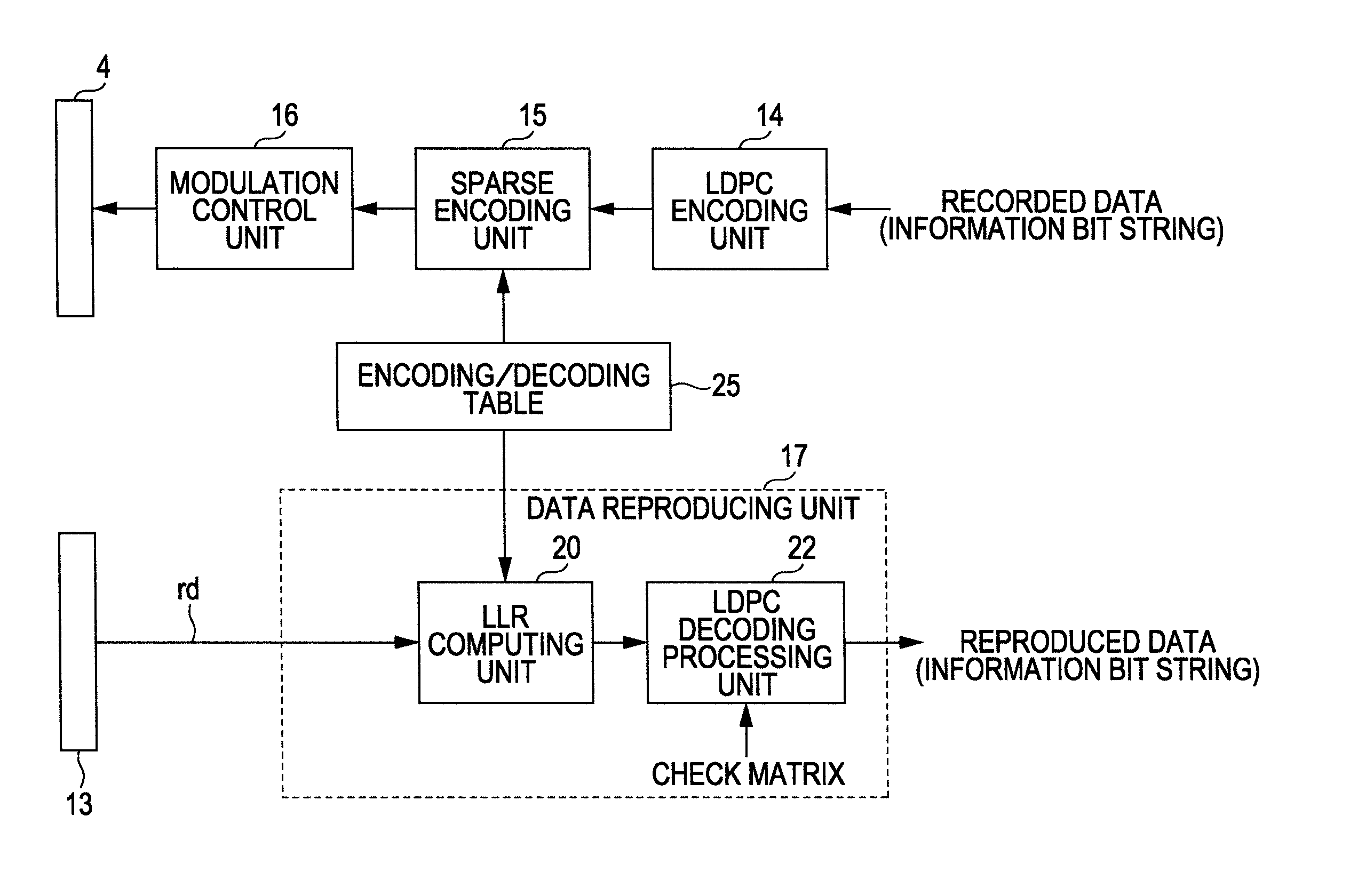

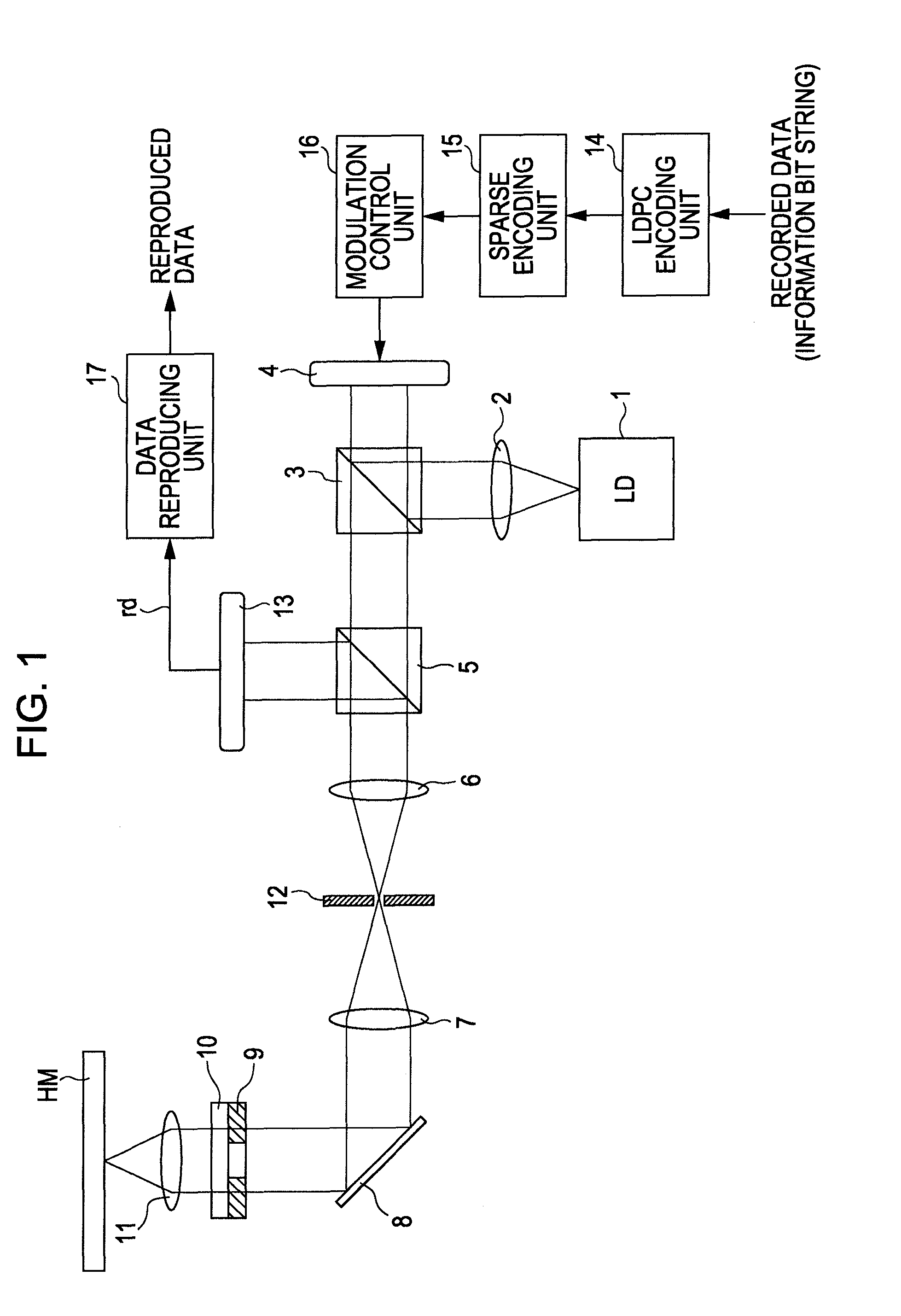

Data modulating device and method thereof

InactiveUS8365035B2Reliable valueGreat likelihoodError prevention/detection by using return channelJoint error correctionTheoretical computer scienceHamming distance

A data modulating device includes: an LDPC encoding unit configured to execute LDPC encoding; and a balance encoding unit configured to input a data string subjected to encoding by the LDPC encoding unit as data to be encoded, and convert k bits of this data to be encoded into balance code made up of m-bit block data; with the balance encoding unit executing balance encoding of said data to be encoded using a data conversion table subjected to mapping so that a set of the k-bit data patterns of which the Hamming distance is 1 corresponds to a set of block data of which the Hamming distance is 2.

Owner:SONY CORP

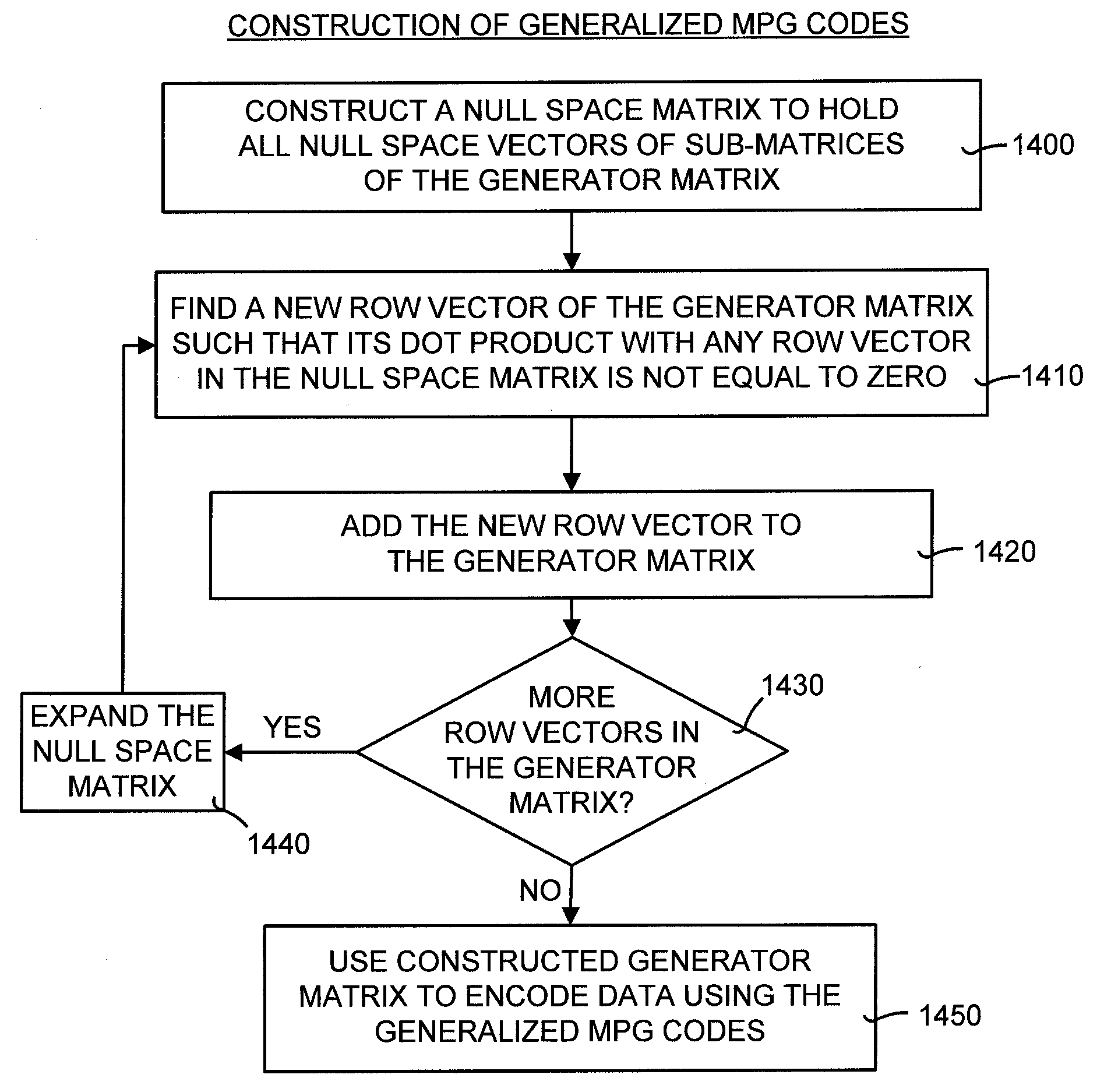

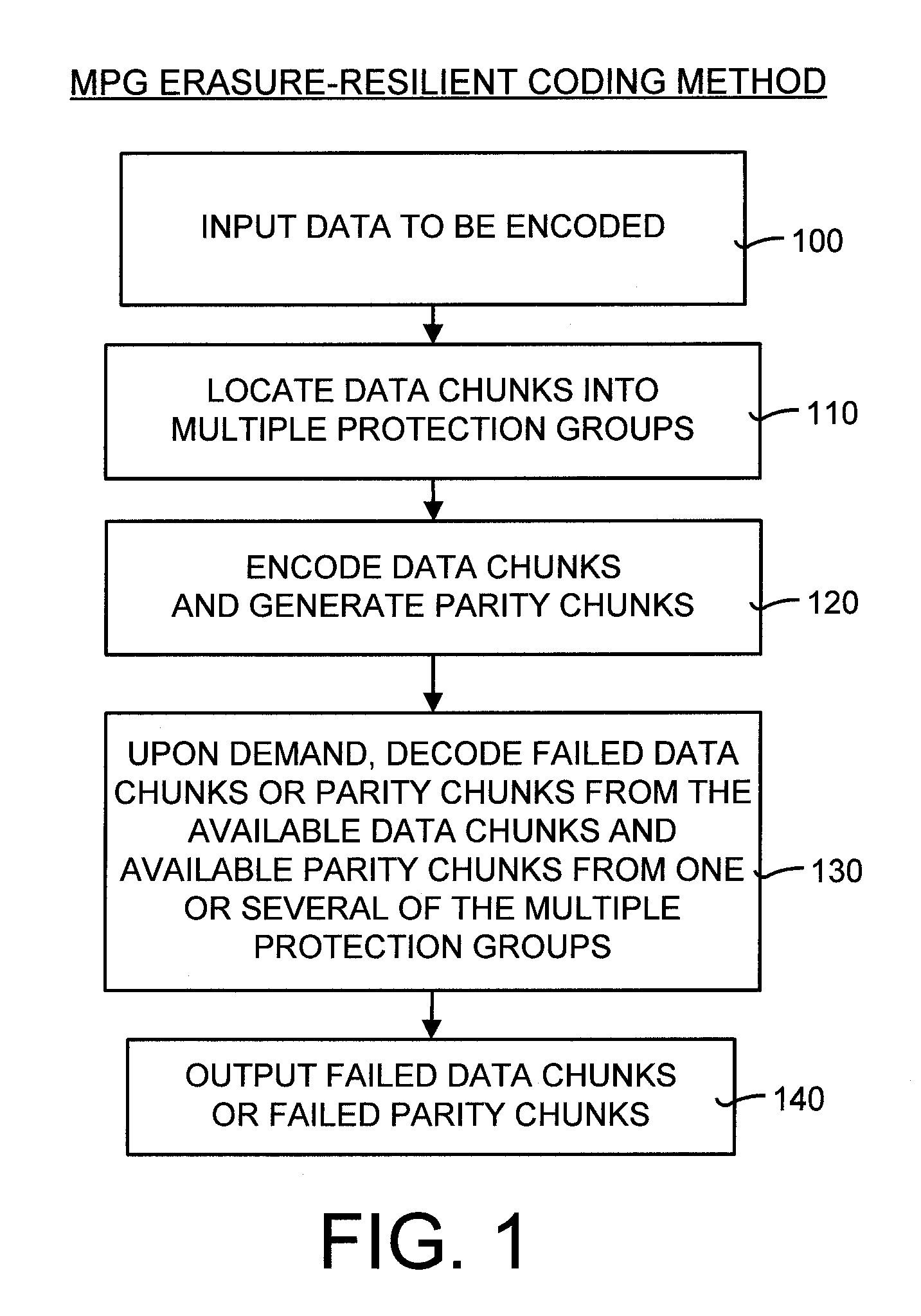

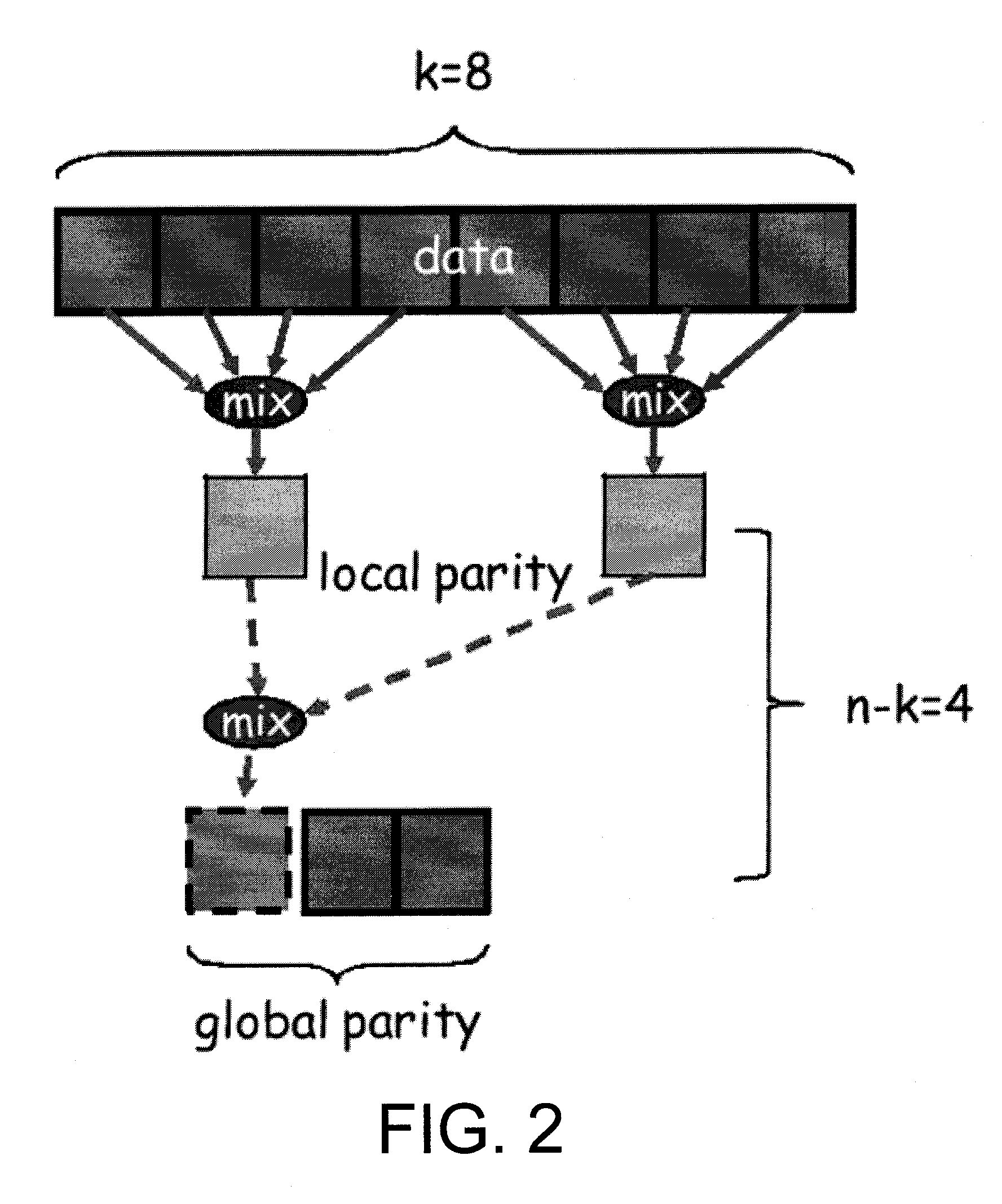

Multiple protection group codes having maximally recoverable property

InactiveUS20080222481A1Reduce access overheadCode conversionCyclic codesTheoretical computer scienceGroup code

Owner:MICROSOFT TECH LICENSING LLC

System and method for configuring a solid-state storage device with error correction coding

ActiveUS7210077B2Memory loss protectionUnequal/adaptive error protectionSolid-state storageSelection system

Owner:SK HYNIX INC

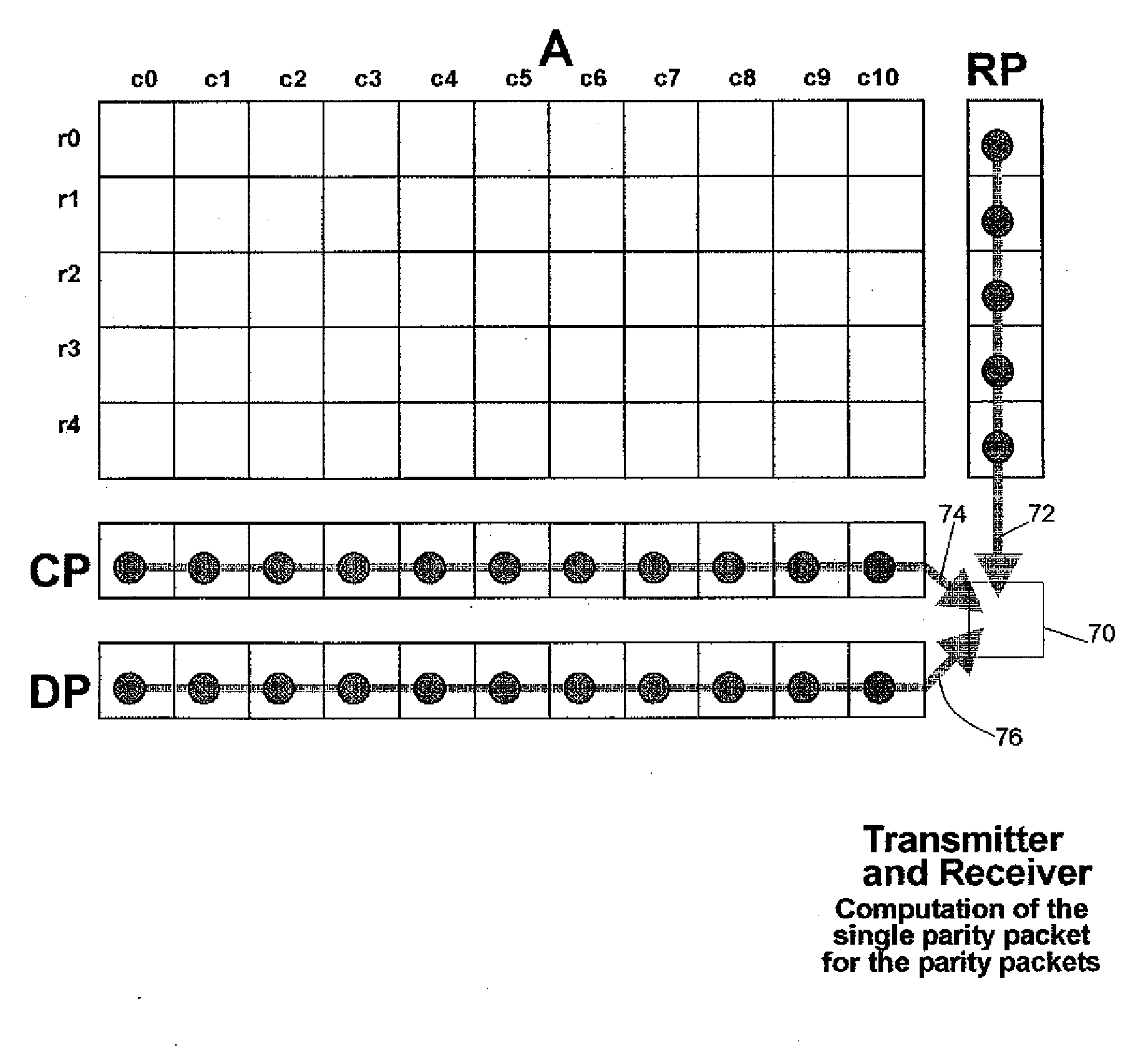

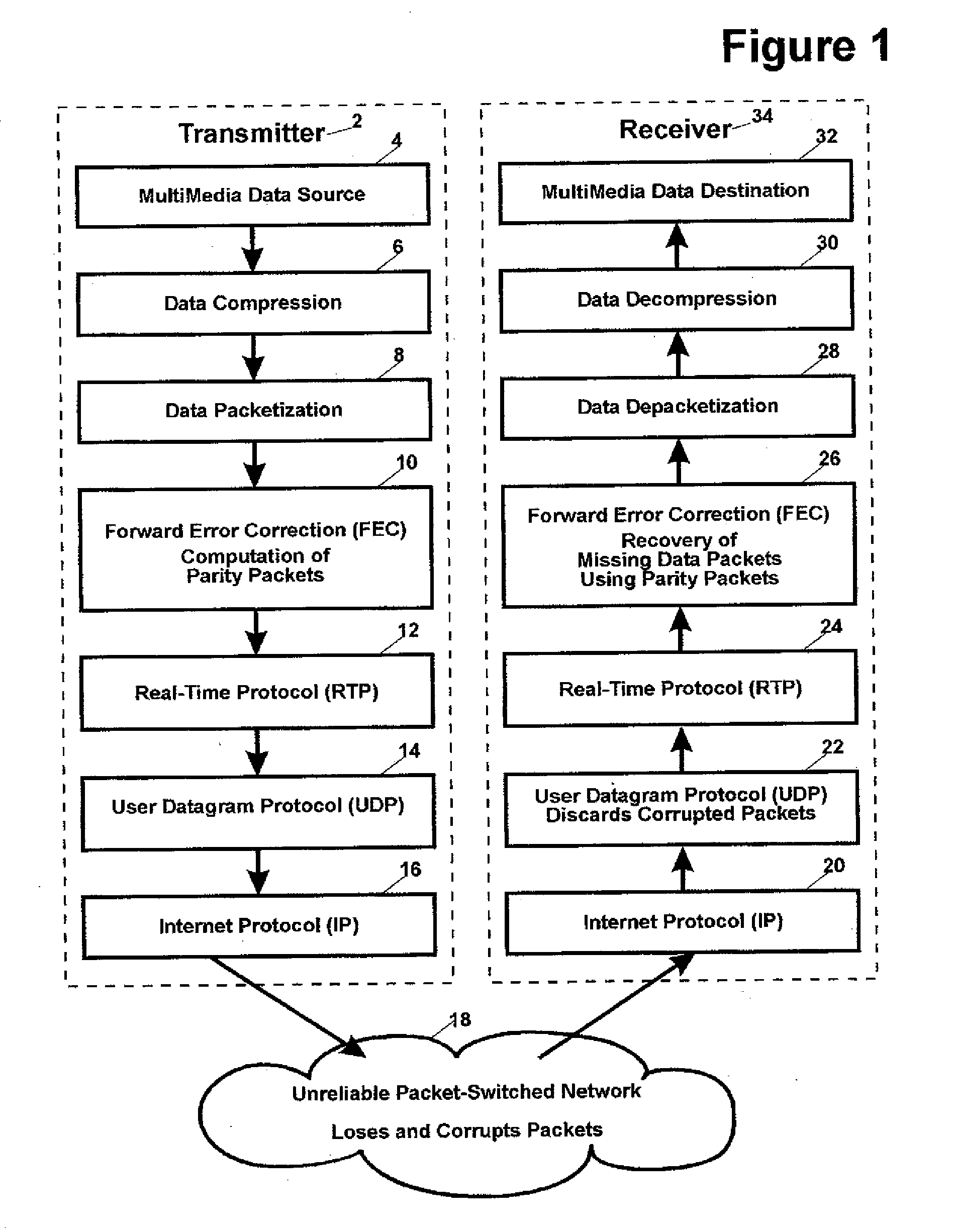

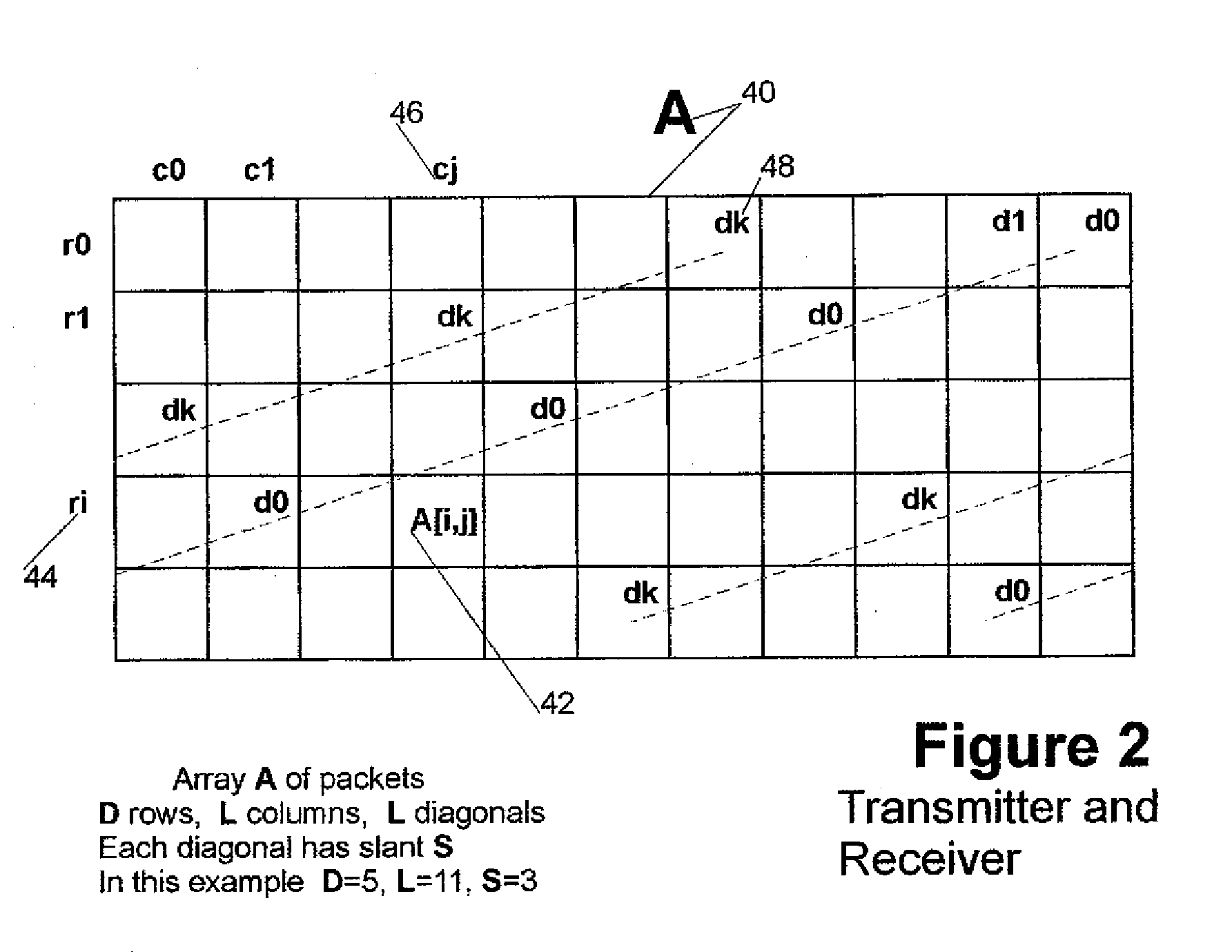

Forward error correction for burst and random packet loss for real-time multi-media communication

ActiveUS20090193314A1Less powerFlexibility of deploymentError correction/detection using convolutional codesError preventionMissing dataPacket loss

This invention relates generally to a packet recovery algorithm for real-time (live) multi-media communication over packet-switched networks, such as the Internet. Such multi-media communication includes video, audio, data or any combination thereof. More specifically, the invention comprises a forward error correction (FEC) algorithm that addresses both random and burst packet loss and errors, and that can be adjusted to tradeoff the recoverability of missing packets and the latency incurred. The transmitter calculates parity packets for the rows, columns and diagonals of a block of multi-media data packets using the exclusive or (XOR) operation and communicates the parity packets along with the multi-media data packets to the receiver. The receiver uses the parity packets to recover missing multi-media data packets in the block. The FEC algorithm is designed to be able to recover long bursts of consecutive missing data packets. If some parity packets are missing, they too can be recovered using an extra single parity packet, so that they can be used to recover other missing data packets. The invention applies to both one-way real-time streaming applications and two-way real-time interactive applications, and to both wired and wireless networks. The invention retains backwards compatibility with existing standards governing FEC for professional video over IP networks.

Owner:NEVION EURO

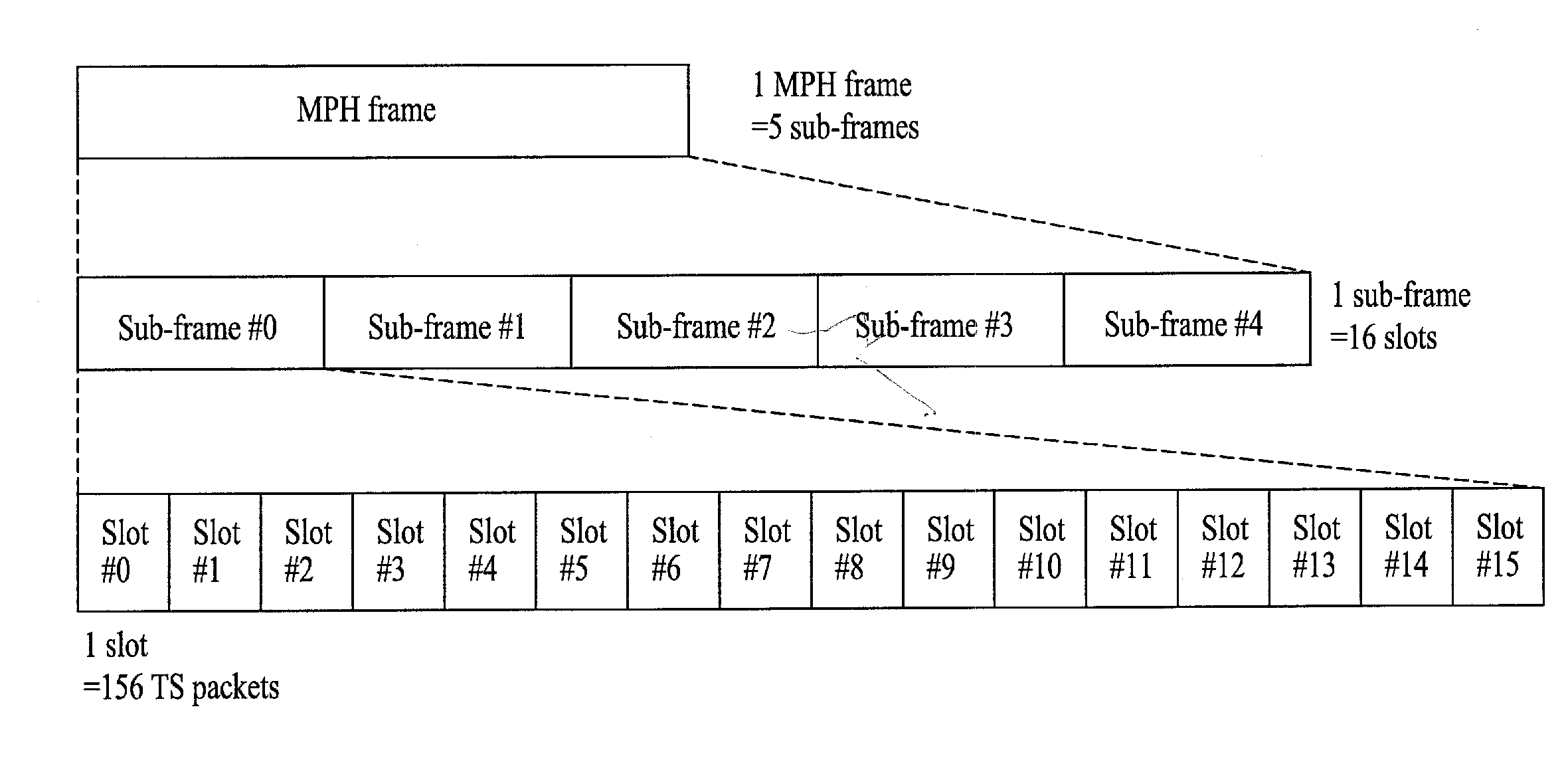

Digital broadcast system for transmitting/receiving digital broadcast data, and data processing method for use in the same

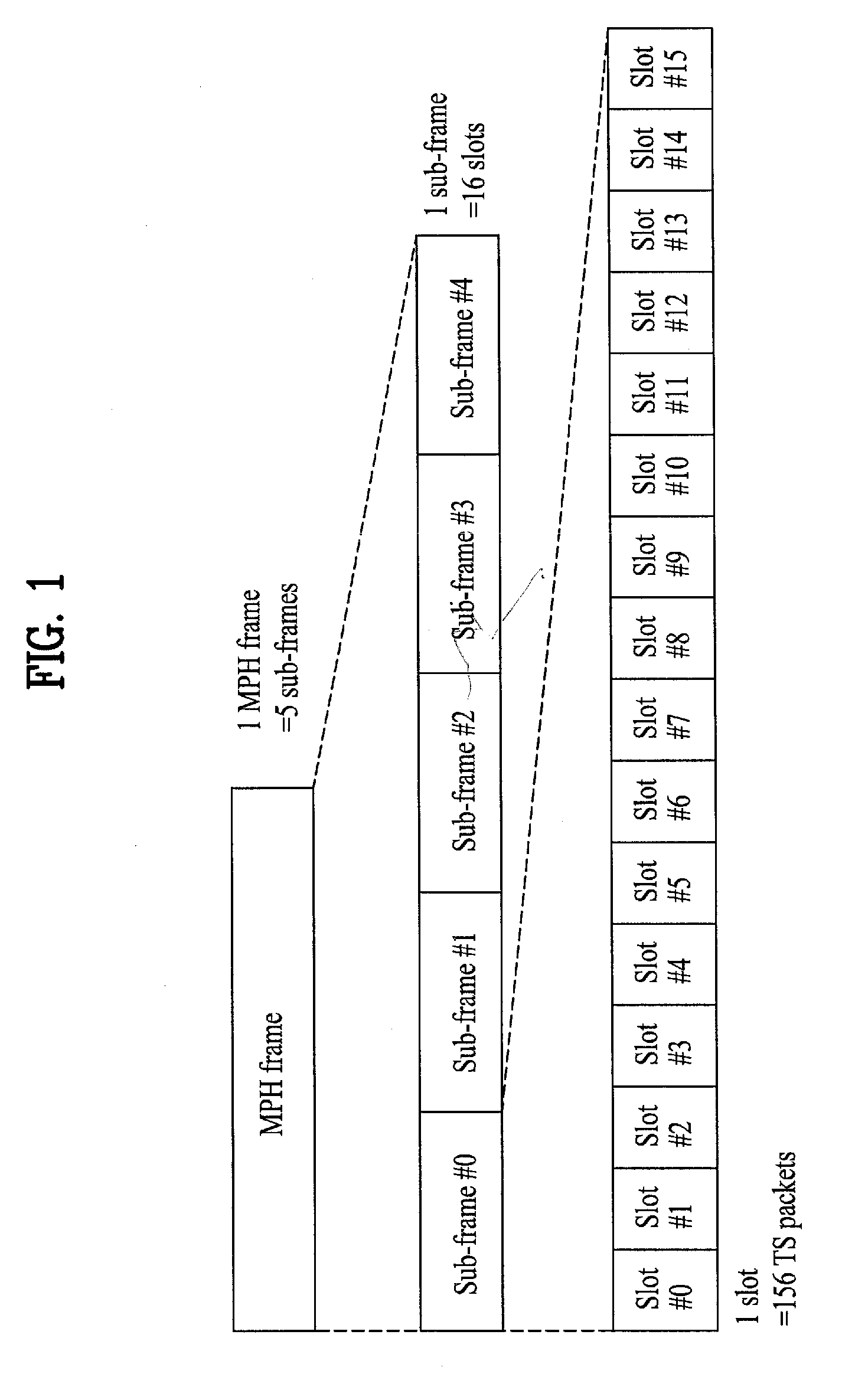

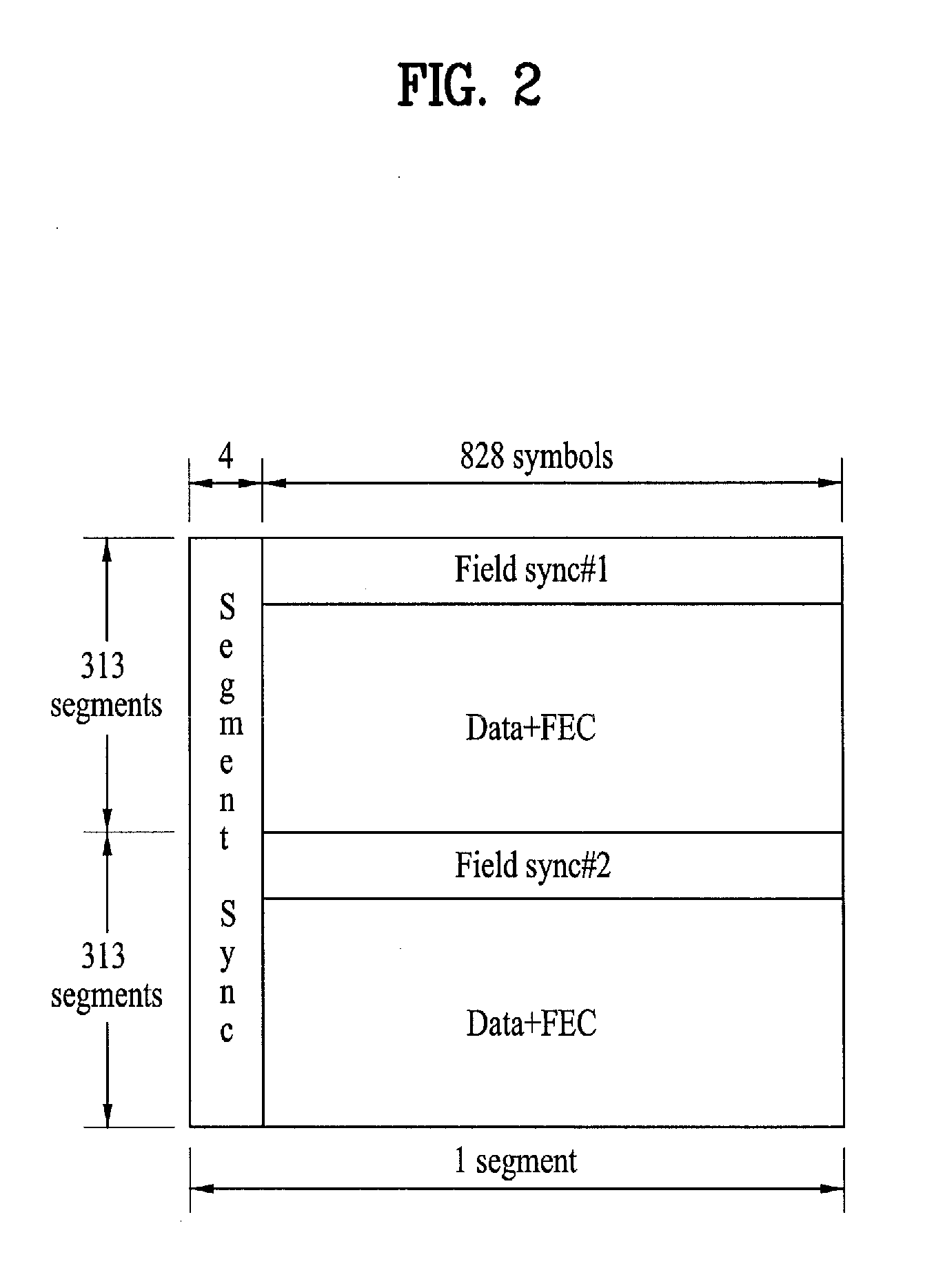

ActiveUS20090175218A1Strong resistanceImprove performanceTransmission systemsCode conversionMobile businessBroadcast data

A digital broadcast system having storing resistance to errors generated during the transmission of mobile service data, and a data processing method are disclosed. The digital broadcast system additionally encodes mobile service data. As a result, the mobile service data has strong resistance to a channel variation and noise, and at the same time the system can quickly cope with the channel variation.

Owner:LG ELECTRONICS INC

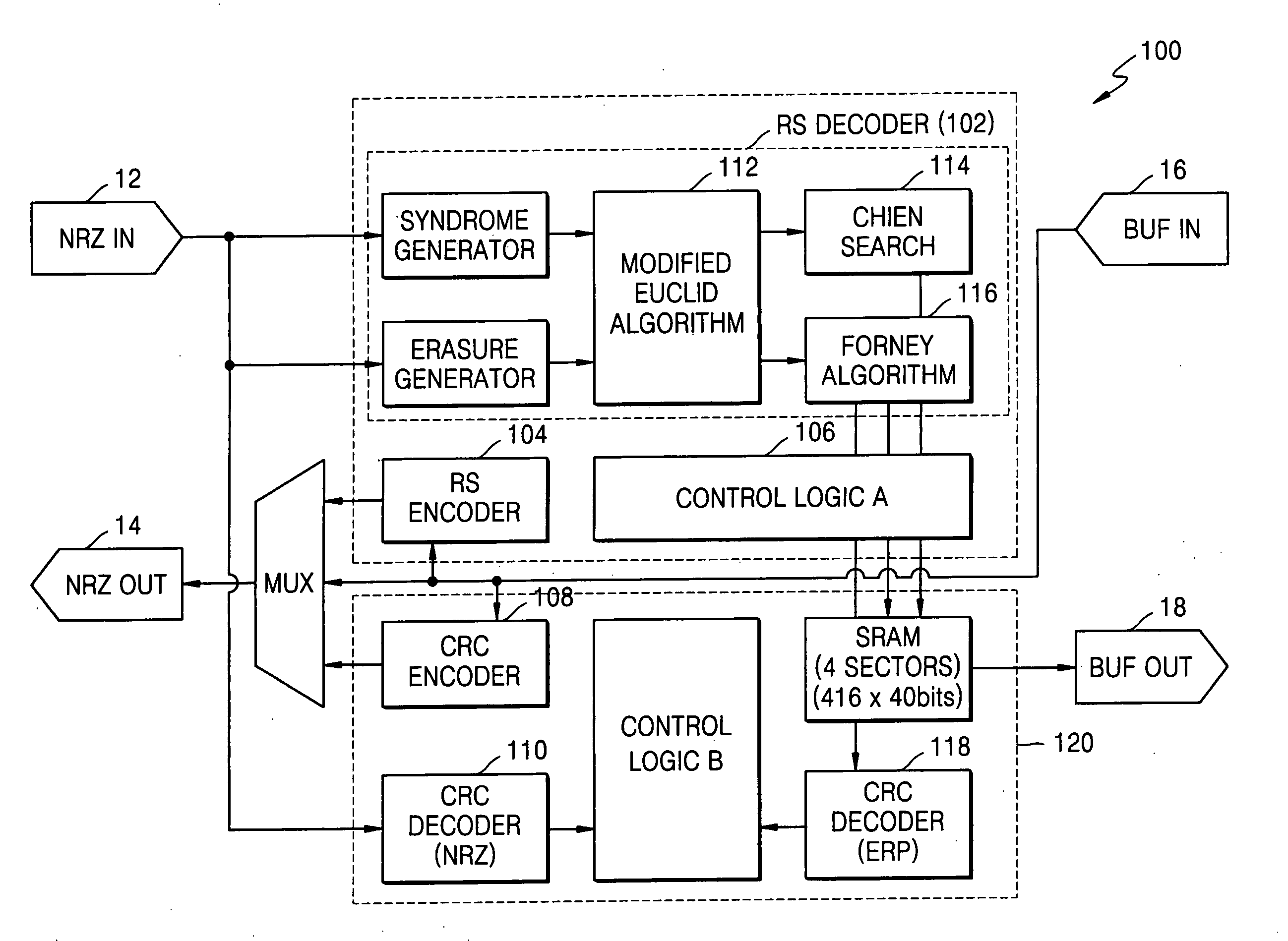

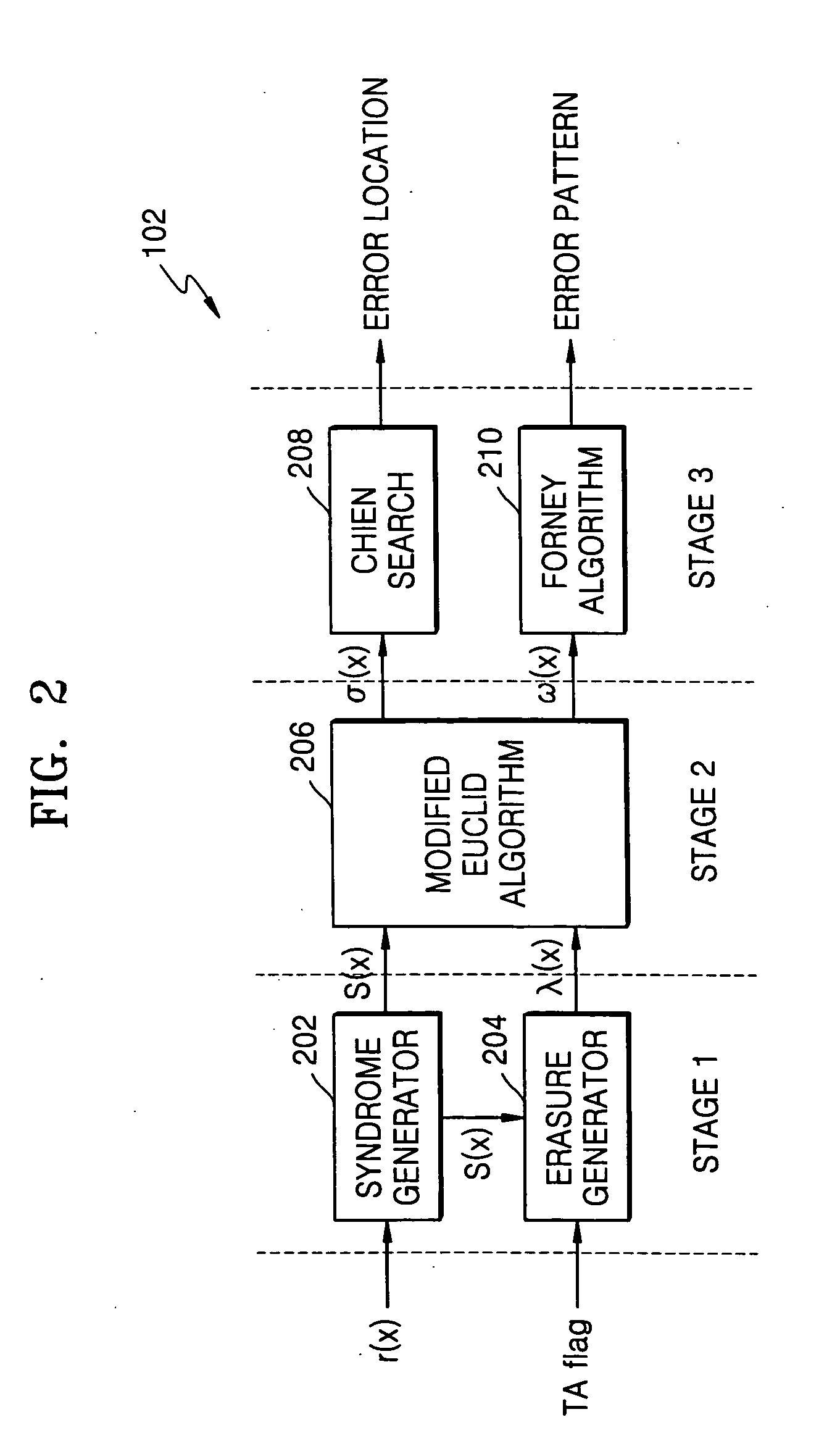

Forward Chien search type Reed-Solomon decoder circuit

ActiveUS20050172208A1Reduce aggregation timeShorten the timeCode conversionCyclic codesError locationReed solomon decoder

A Reed-Solomon decoder includes a Chien search circuit to receive an error location polynomial function, performs Chien search, and finds an error location; a Forney algorithm circuit to receives an error pattern polynomial function and find an error pattern; and, a seed generator circuit to indicates a seed value corresponding to a codeword length for the input data. A Chien search is performed to obtain and outputs exponential terms related to variables for the polynomials, wherein the Chien search is performed in the same computational direction as an order for the input data.

Owner:SAMSUNG ELECTRONICS CO LTD

Read error recovery utilizing ECC and read channel quality indicators

PCT No. PCT / US97 / 04906 Sec. 371 Date Oct. 21, 1997 Sec. 102(e) Date Oct. 21, 1997 PCT Filed Mar. 27, 1997 PCT Pub. No. WO97 / 43835 PCT Pub. Date Nov. 20, 1997An apparatus and method for recovering from read errors detected by a read channel (70) in a sequence of data read from a disc (18) of a disc drive (10) by using read channel quality indicators to determine the appropriateness of using error correction in combination with other corrective actions utilized in the recovery process. Upon the detection of an uncorrected error in the retrieved data, the disc drive (10) enters a read error recovery routine wherein one or more corrective actions (102, 122) are applied in an effort to resolve the error. One of the channel quality indicators comprises a channel quality measurement (108, 128) determined as the sum of the square of the sampled data bit error values recovered during the read operation. When the channel quality measurement is at or below a threshold value indicative that the probability of passing undetected erroneous data is at an acceptable level (110, 130), error correction is applied to the data (112, 138); otherwise, error correction is disallowed (118, 140). Additional channel quality indicators comprise erasure pointers (132) which identify a particular set of symbols that are suspected of containing a read error. In such a case, the disc drive determines that the total number of symbols identified by the erasure pointers is below a predetermined erasure threshold before applying error correction (134, 136, 138), the erasure threshold selected to be within the correction capability of error correction circuitry 90.

Owner:SEAGATE TECH LLC

Packet based ATM CRC-32 calculator

A method and apparatus for detecting errors in a data packet being transmitted as a set of smaller data cells by performing operations on the Cyclic Redundancy Check (CRC) values of the individual cells. An error detection apparatus initializes a memory area with a first value. The apparatus generates a CRC value for a first data cell. The apparatus combines the first value and the CRC value for the first cell in a XOR operation and the apparatus stores the result in a memory location. For subsequent cells in the data packet, the apparatus generates a cell CRC value, shifts the value in the memory location twelve times, and replaces the shifted value in the memory location with a new value generated from a XOR operation performed on the shifted value and the cell CRC value. The apparatus compares the final value in the memory location with an end comparison value and generates an error signal if the final and comparison values are different.

Owner:VITESSE SEMICONDUCTOR CORPORATION

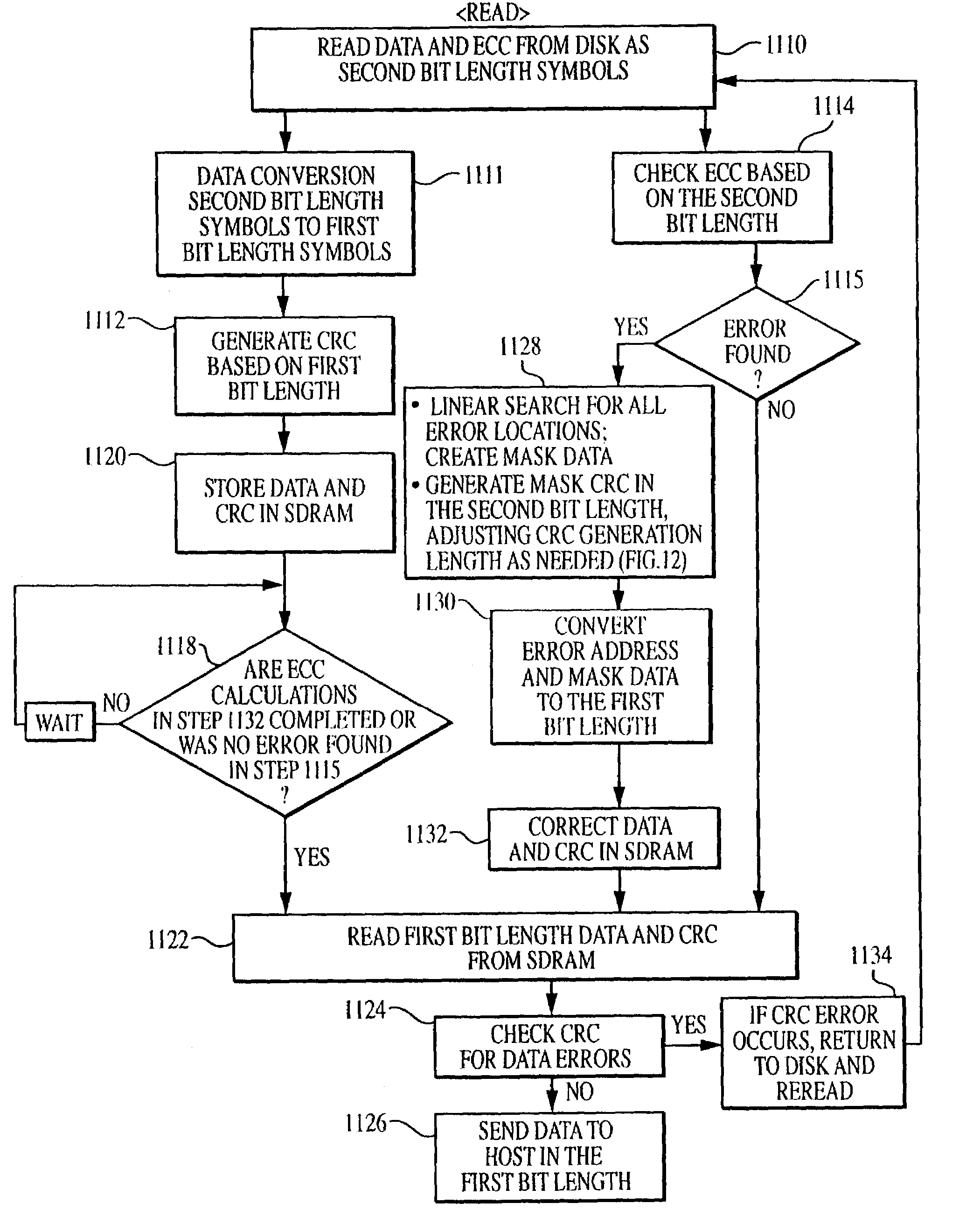

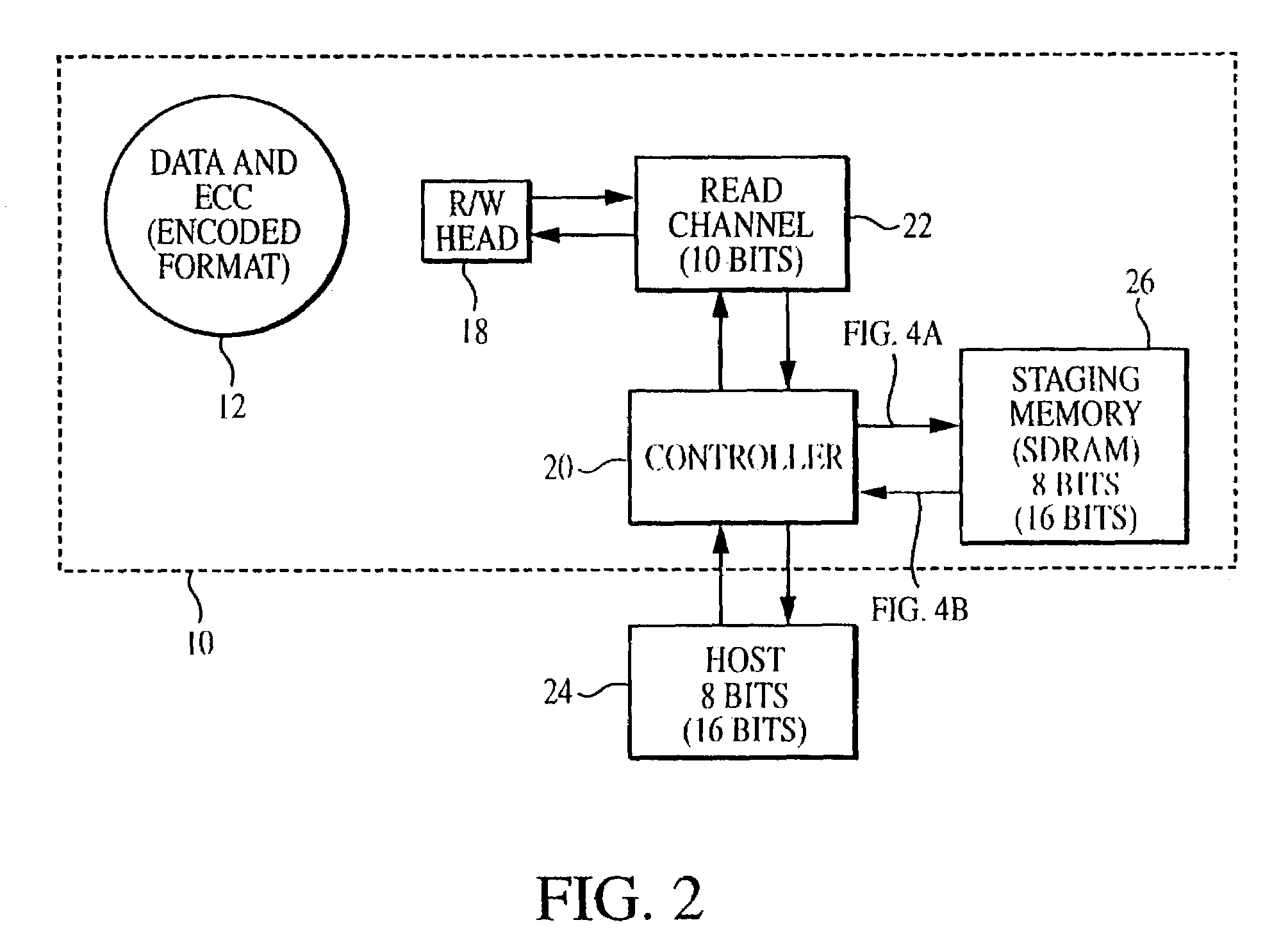

Methods and apparatus for correcting data and error detection codes on the fly

When data is read from a disk and stored in volatile memory, check bits are generated and stored in the memory using an algorithm such as cyclical redundancy check (CRC). The CRC algorithm operates on the basis of the bit length in which the data is organized, such as 8 bits. If the data has errors, an error correction code (ECC) algorithm is used to correct the data errors, but the ECC algorithm operates on the basis of symbols having a different bit length, such as 10 bits. To avoid having to re-read the data from the volatile memory to adjust the CRC value, the CRC algorithm is executed on selected mask data developed by the ECC algorithm, the CRC algorithm being executed on the basis of the second bit length to generate a CRC mask. The CRC mask corrects the stored CRC value.

Owner:TOSHIBA STORAGE DEVICE CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com