Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

159 results about "Error floor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

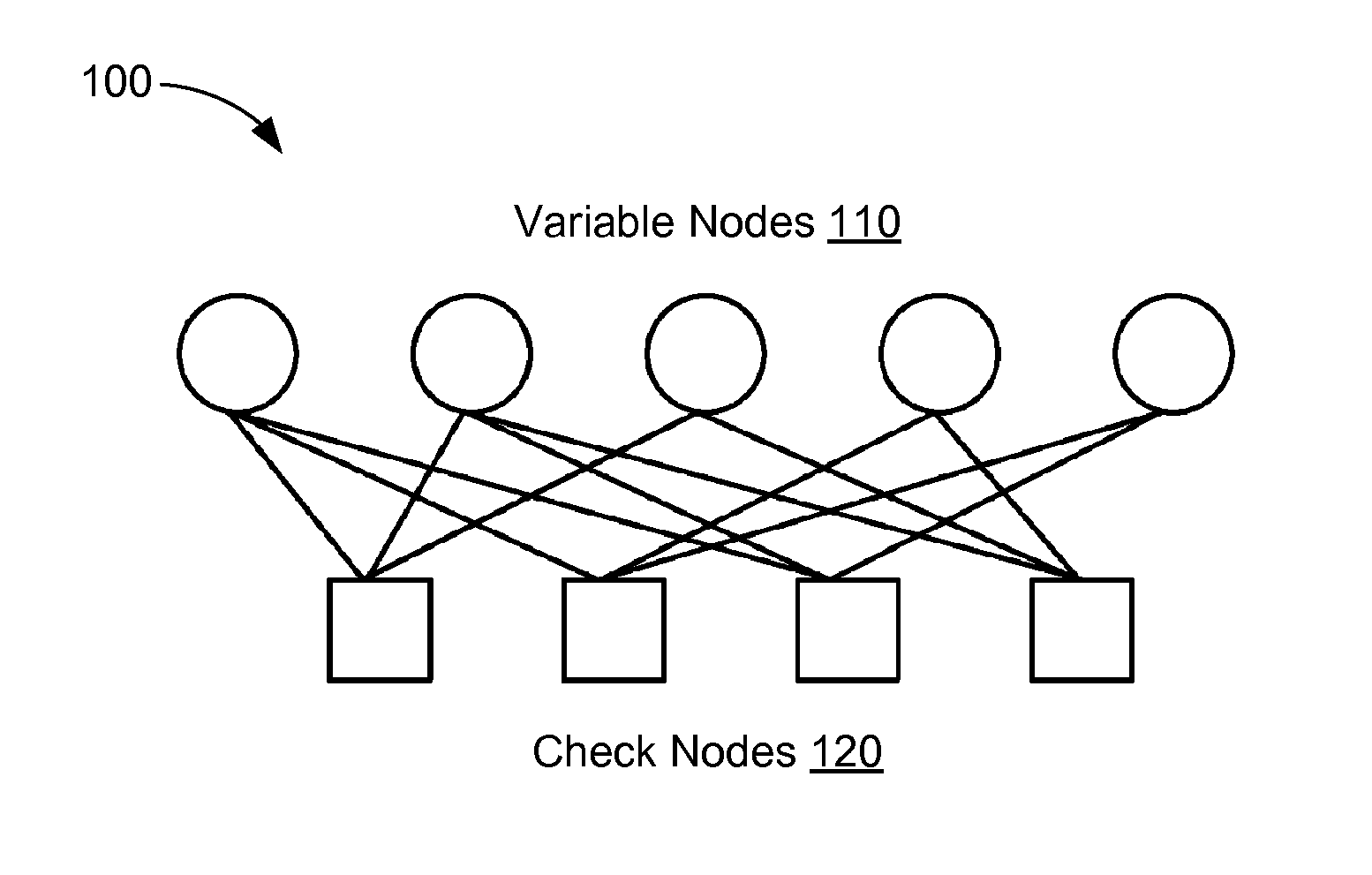

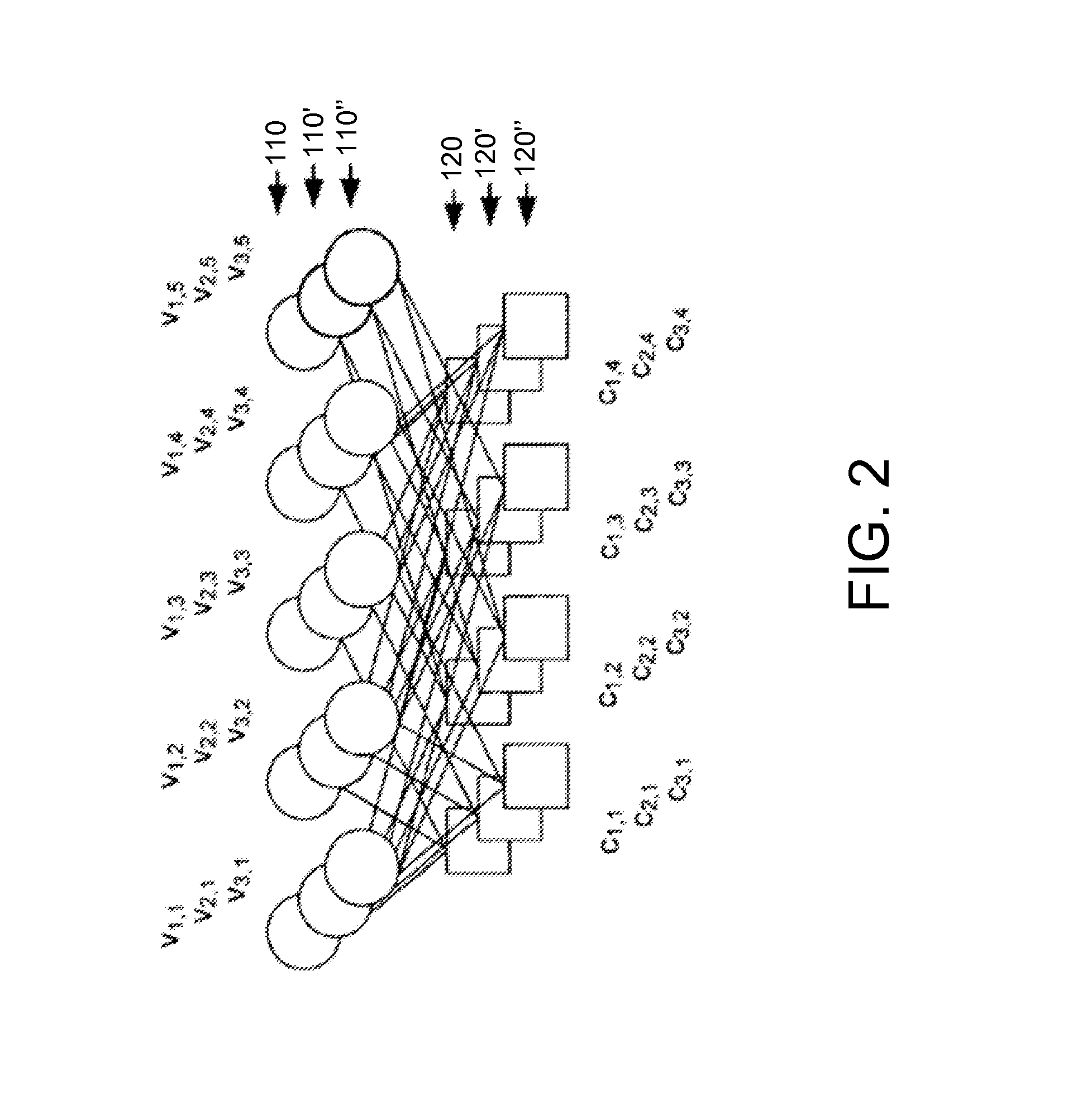

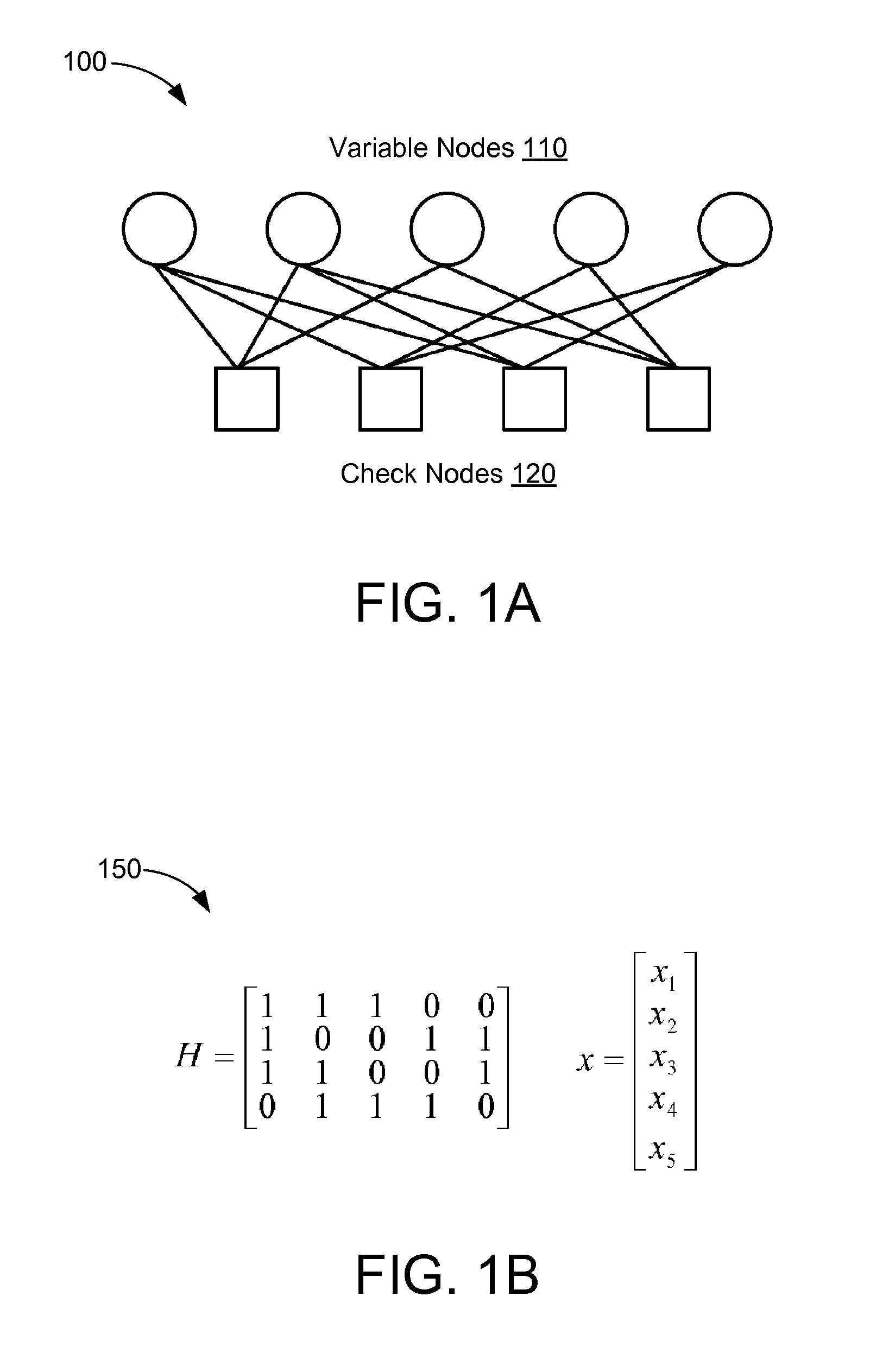

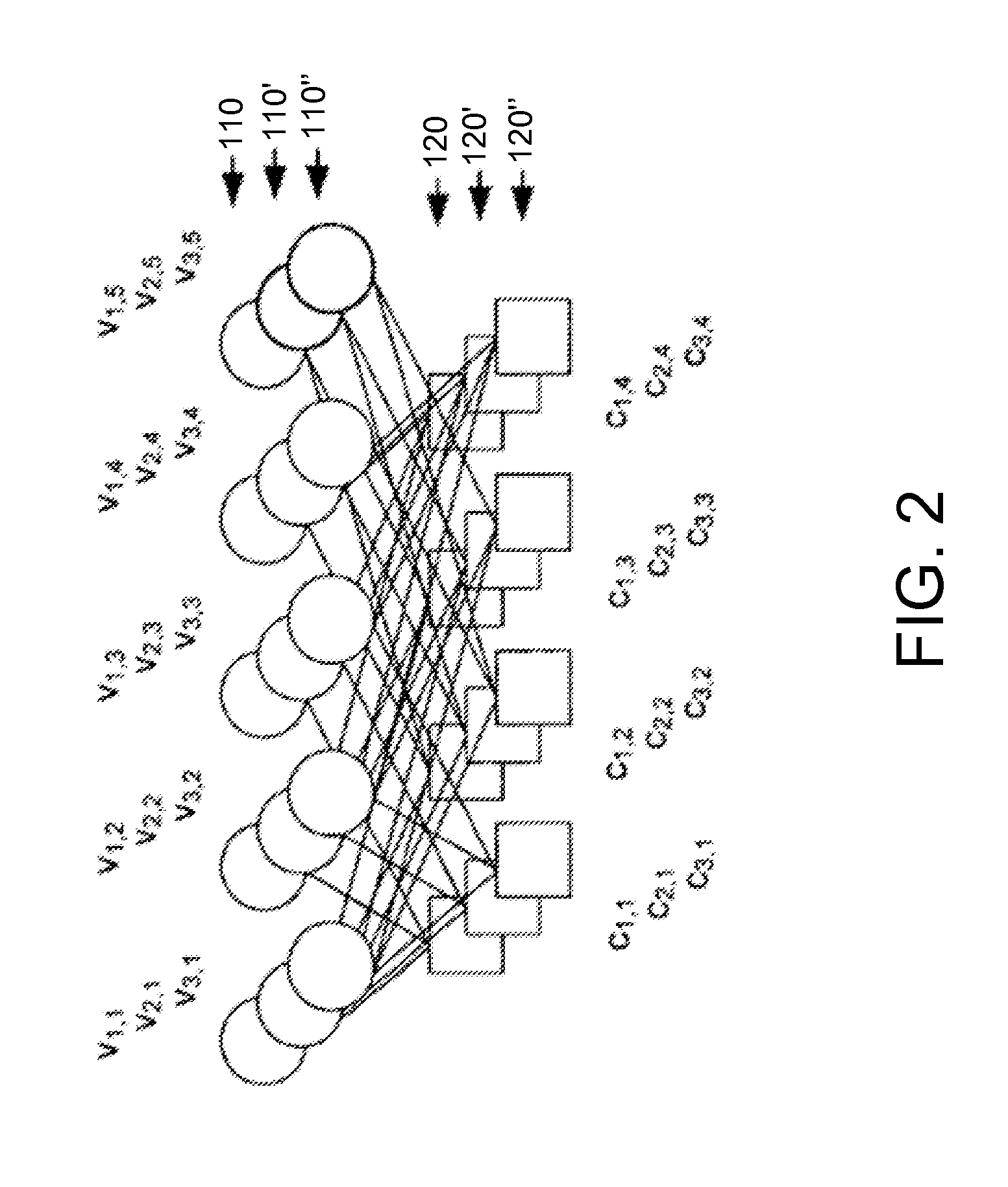

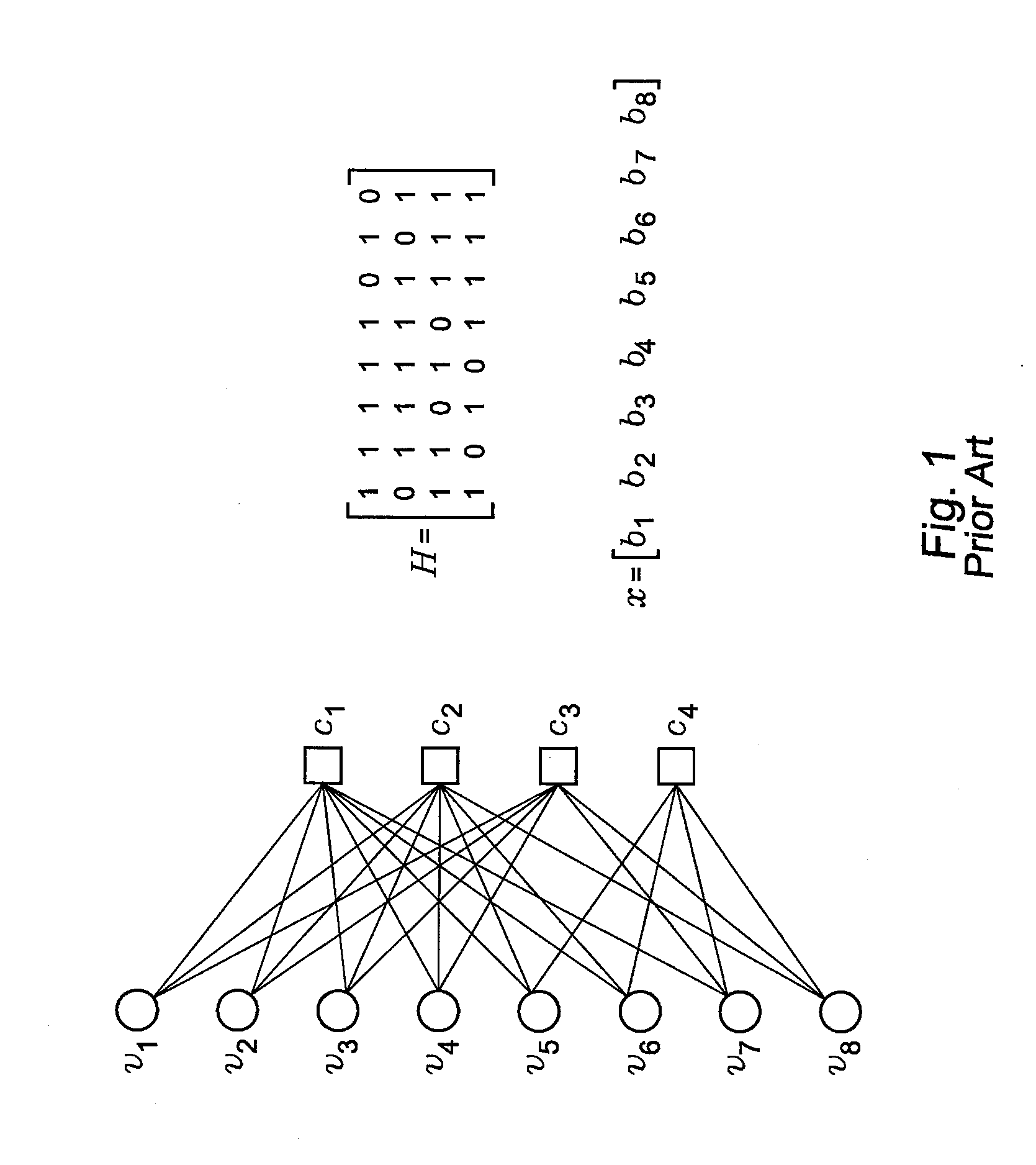

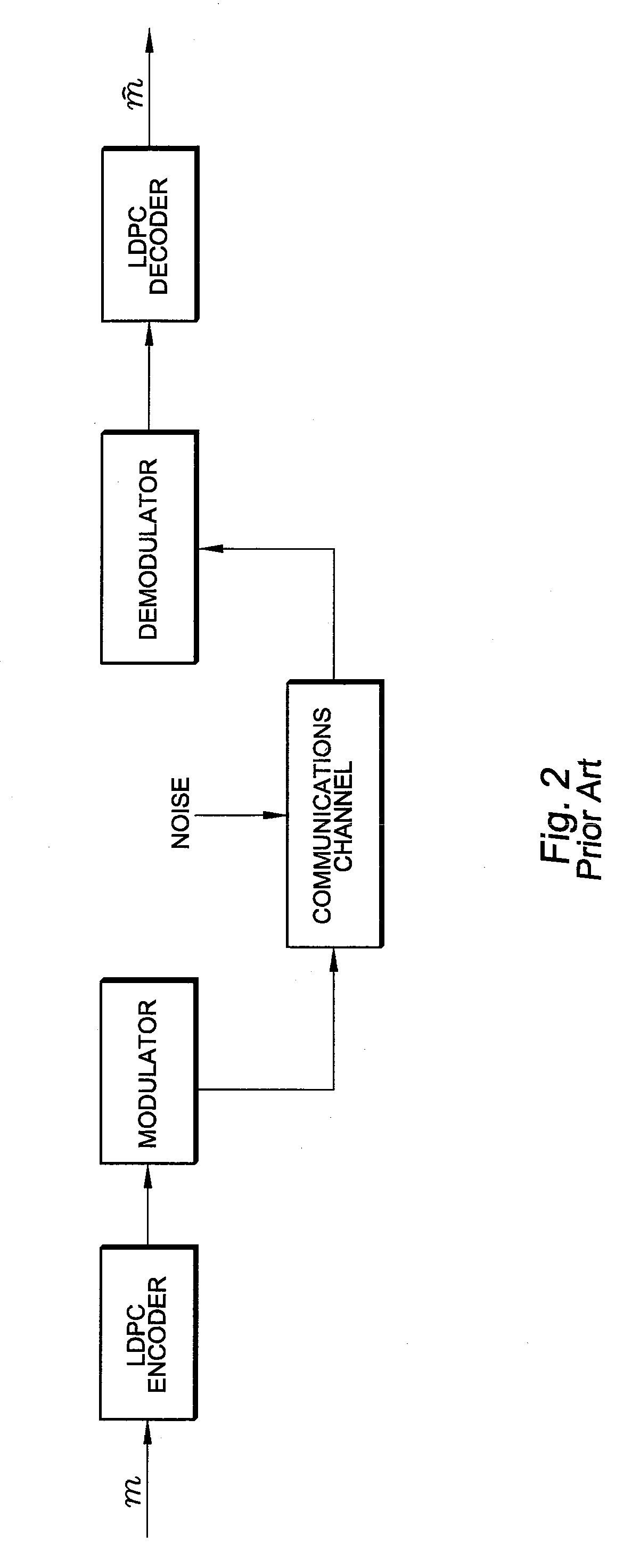

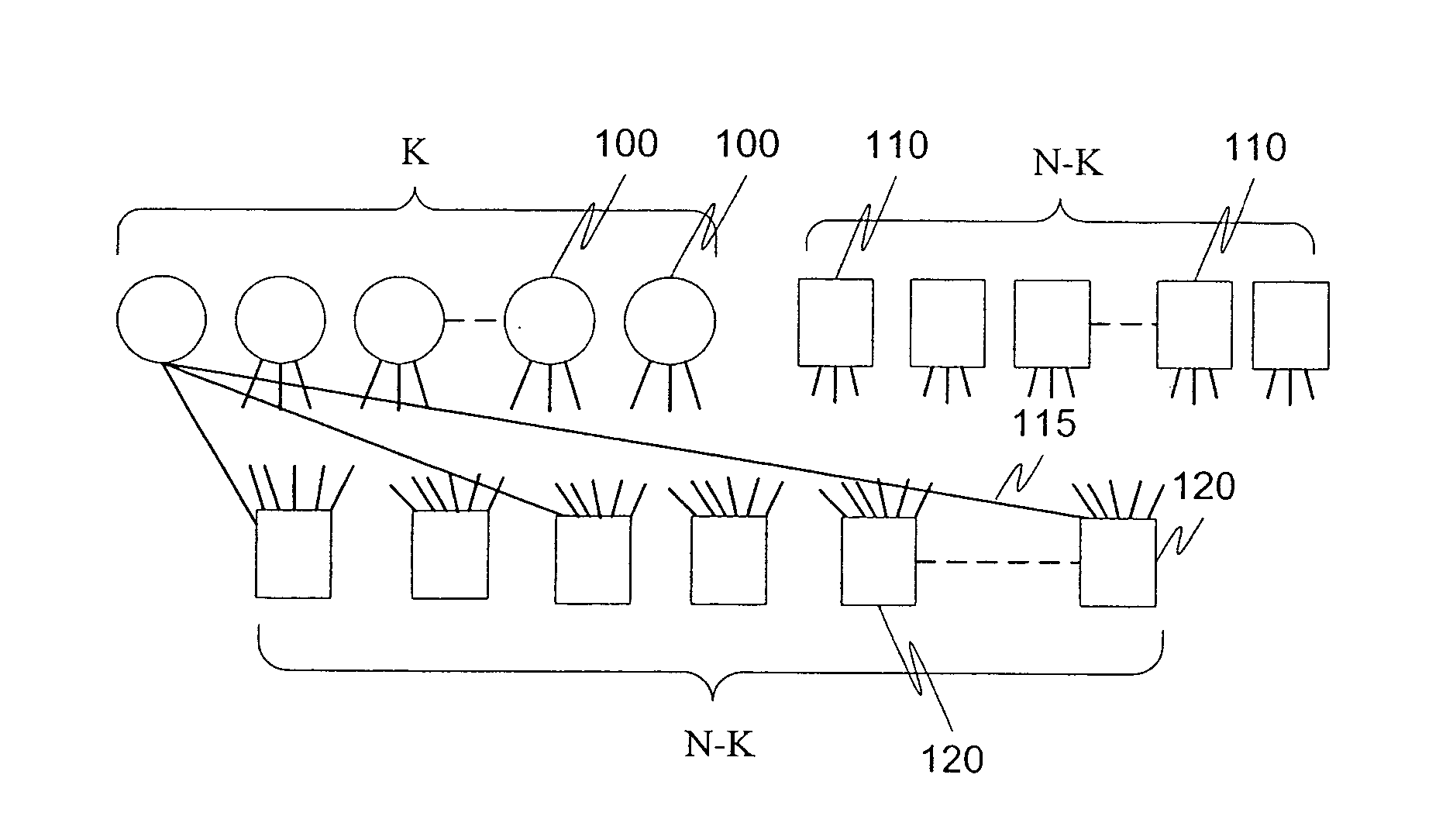

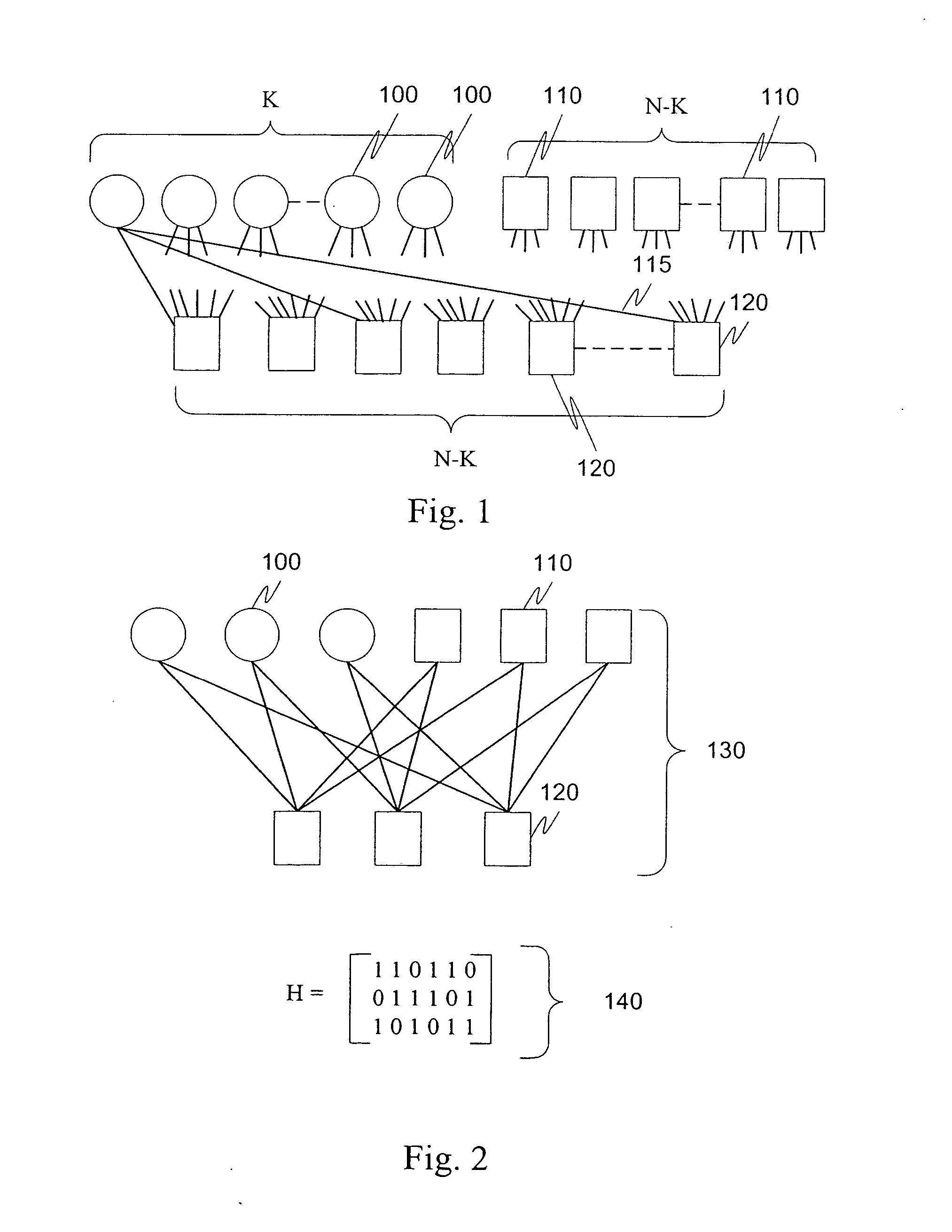

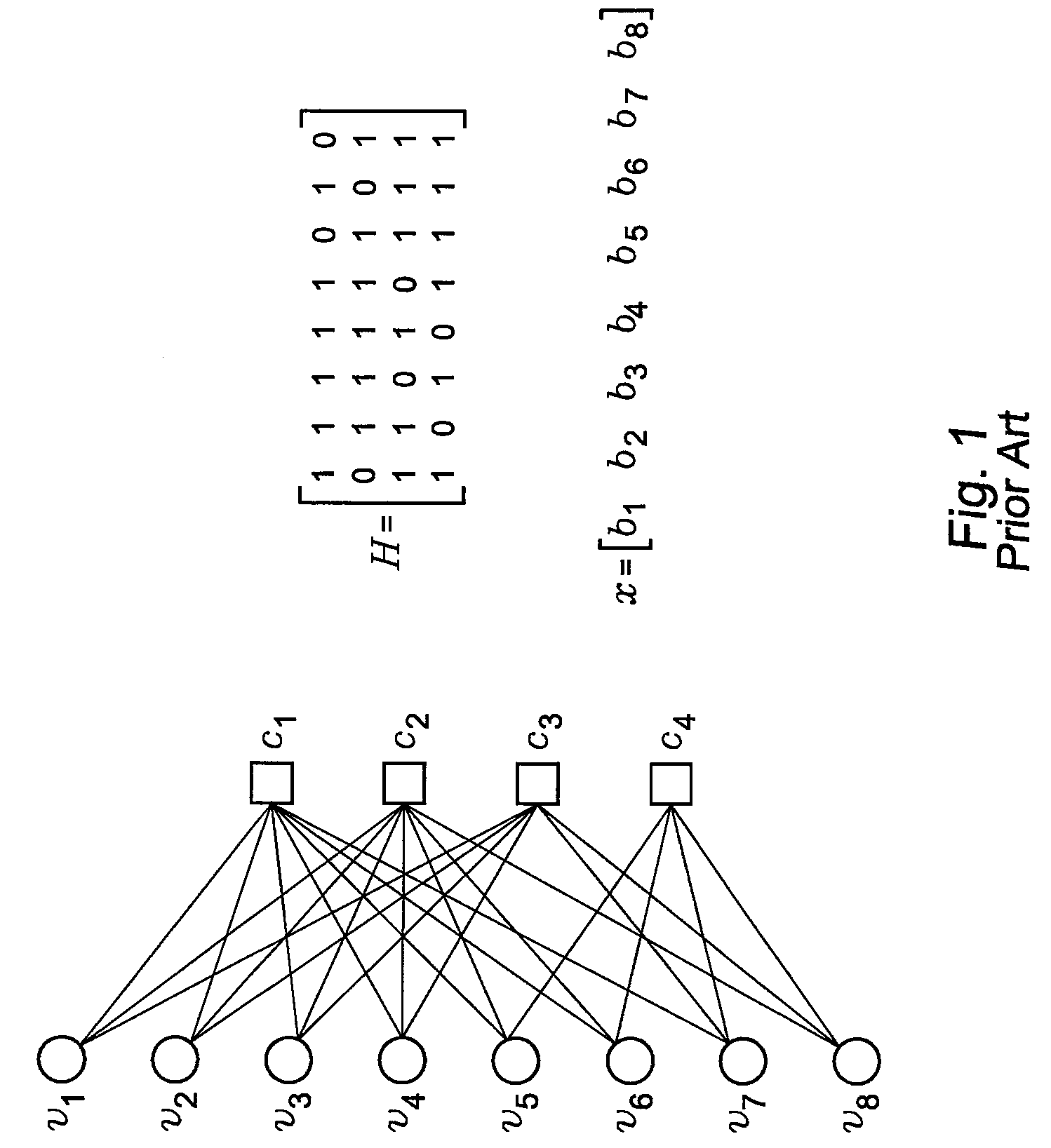

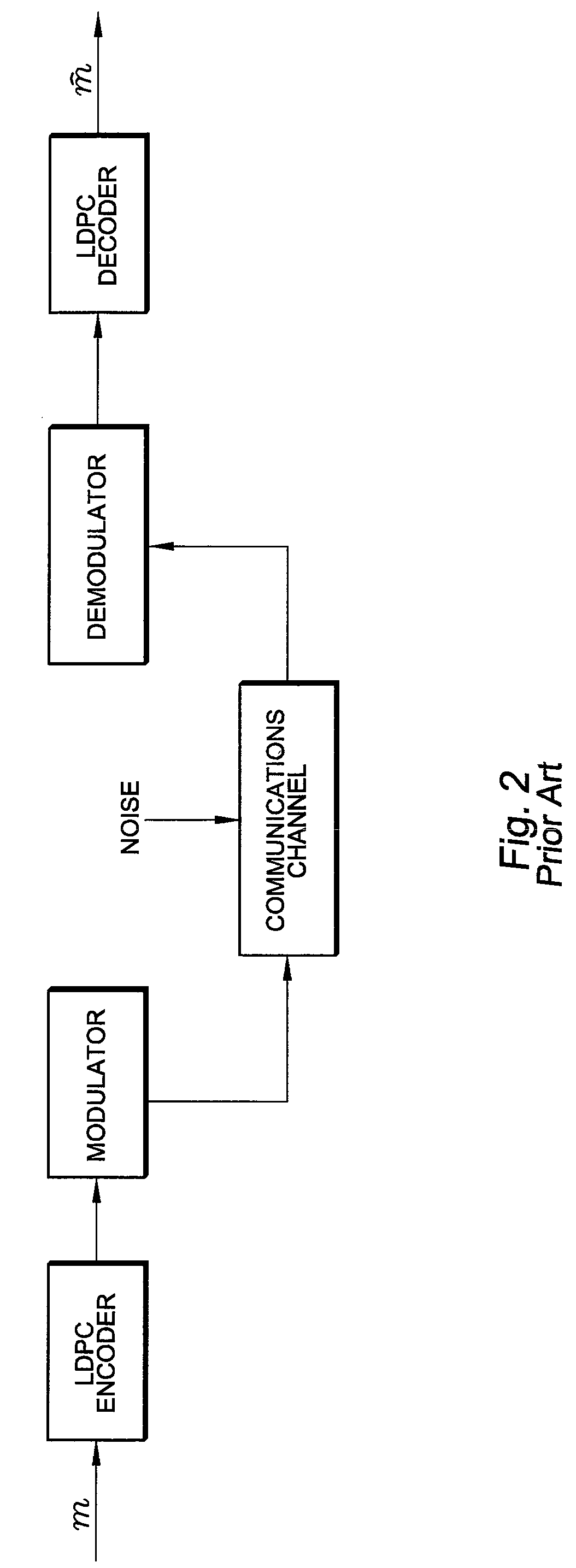

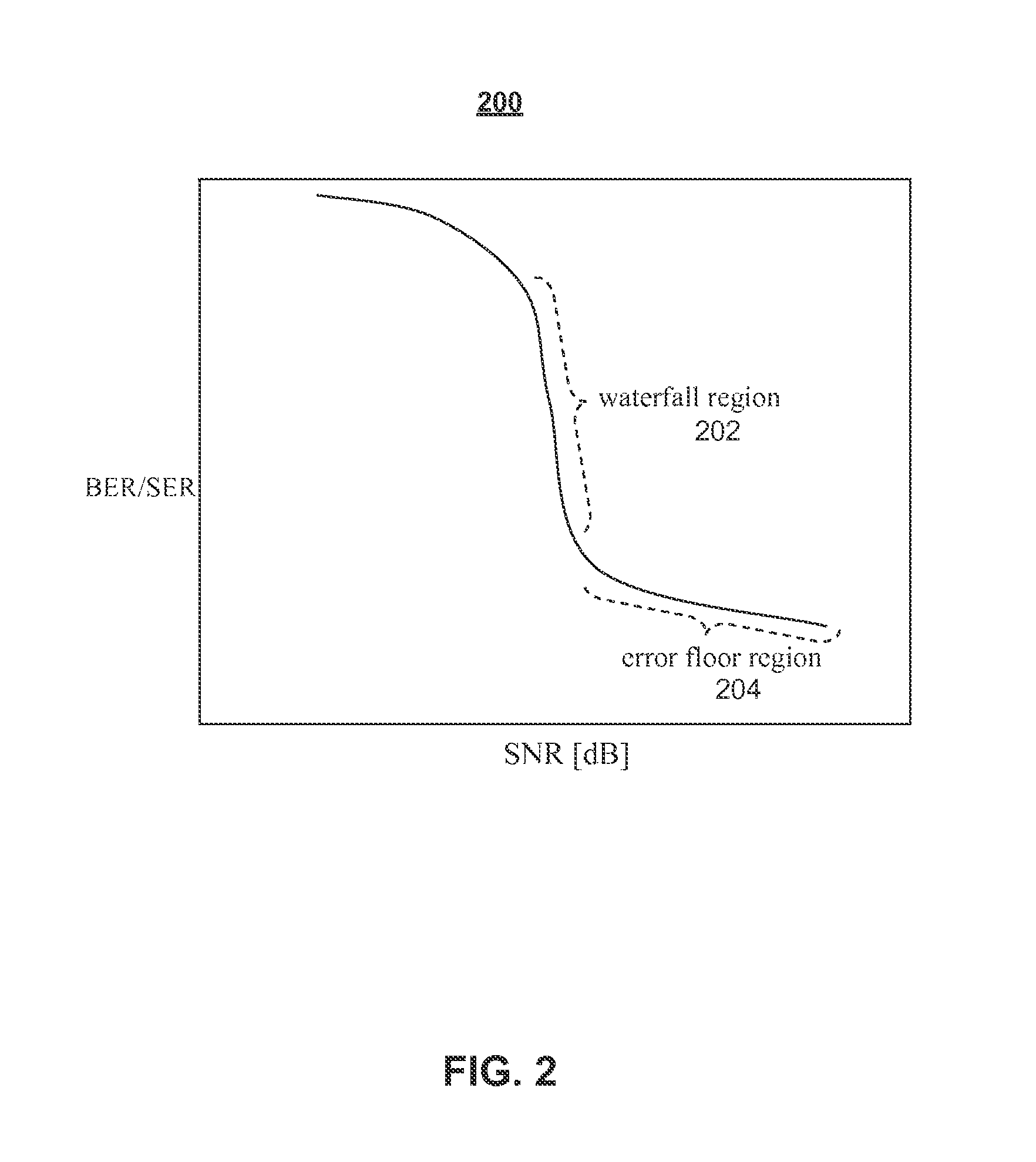

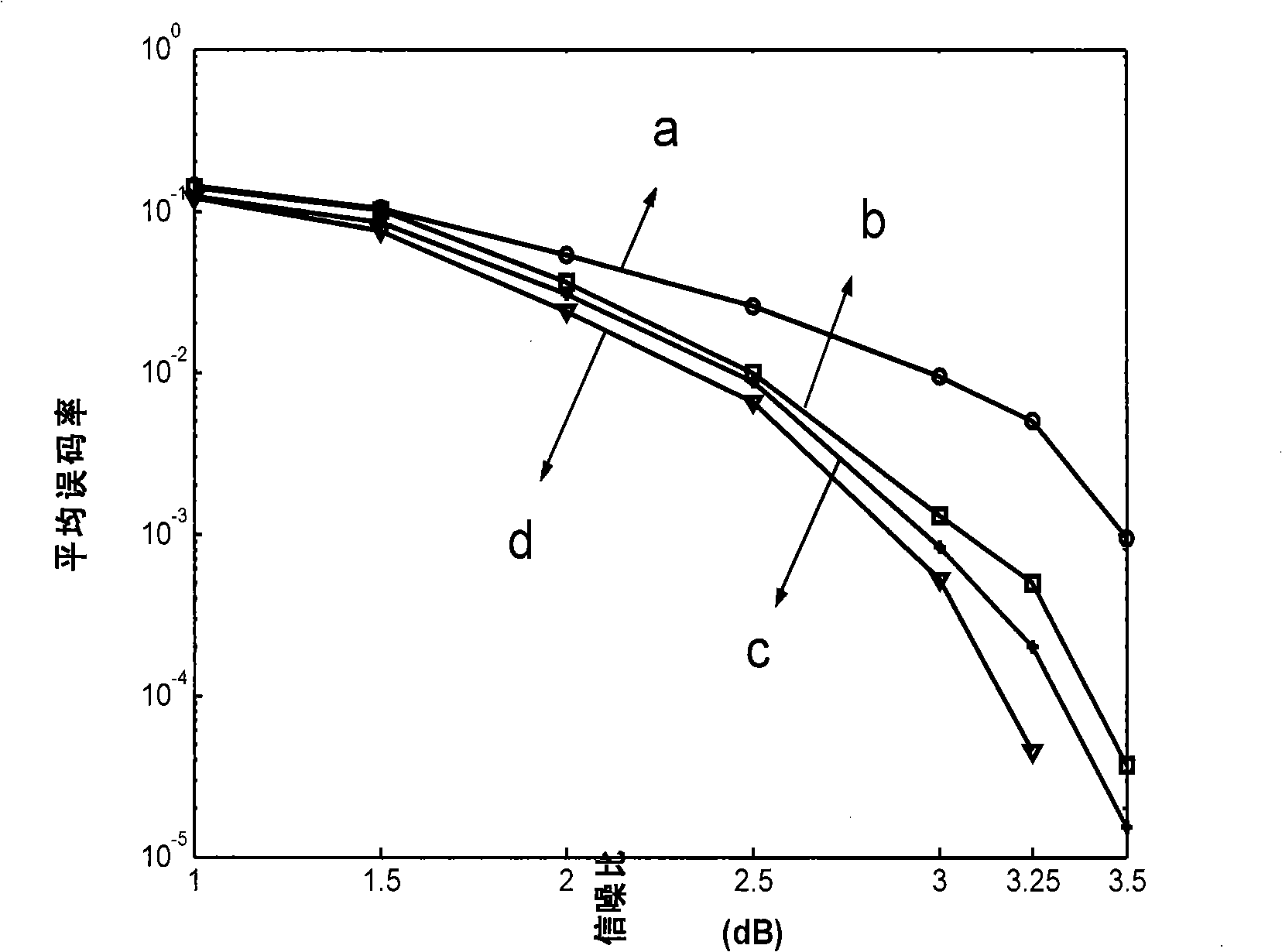

The error floor is a phenomenon encountered in modern iterated sparse graph-based error correcting codes like LDPC codes and turbo codes. When the bit error ratio (BER) is plotted for conventional codes like Reed–Solomon codes under algebraic decoding or for convolutional codes under Viterbi decoding, the BER steadily decreases in the form of a curve as the SNR condition becomes better. For LDPC codes and turbo codes there is a point after which the curve does not fall as quickly as before, in other words, there is a region in which performance flattens. This region is called the error floor region. The region just before the sudden drop in performance is called the waterfall region.

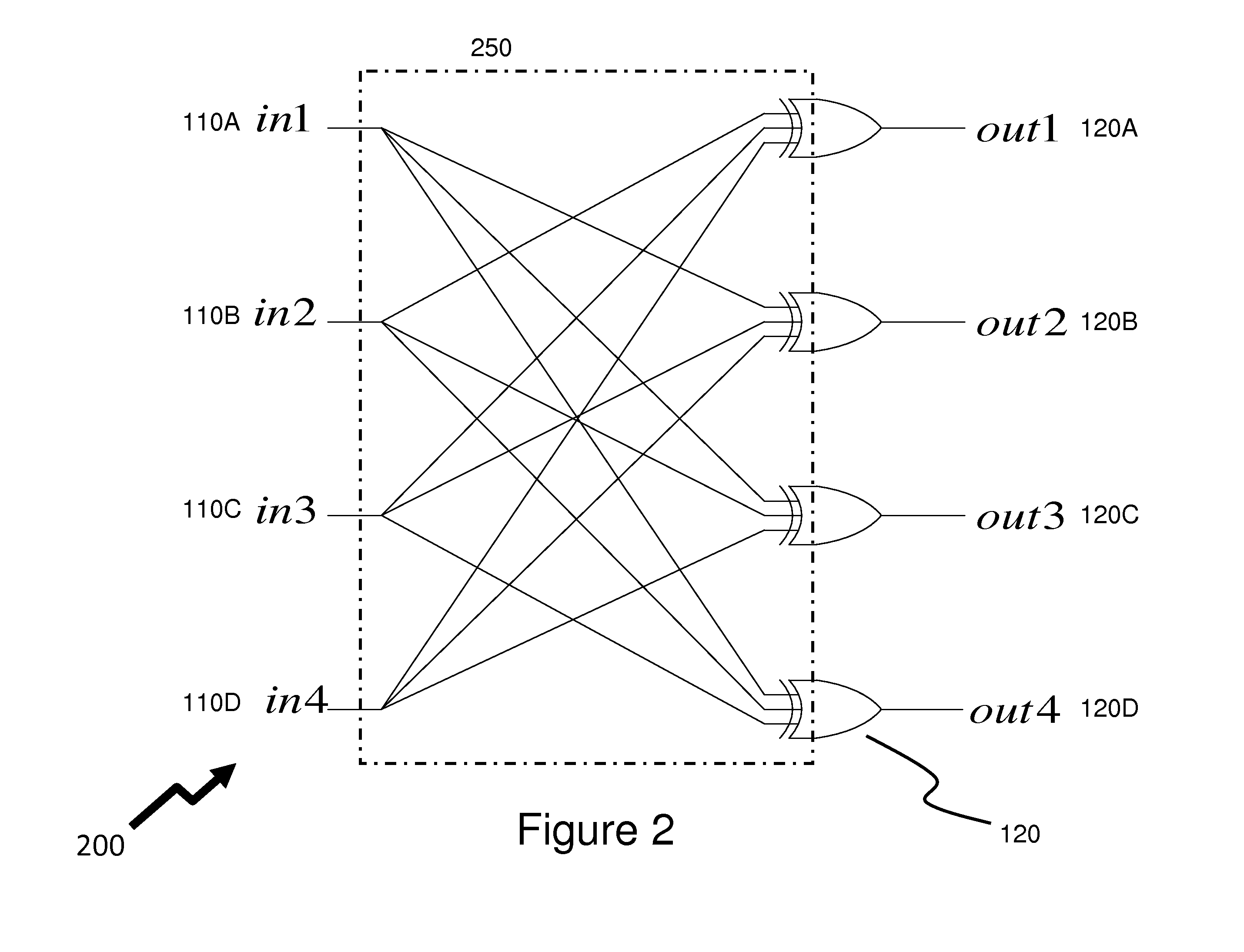

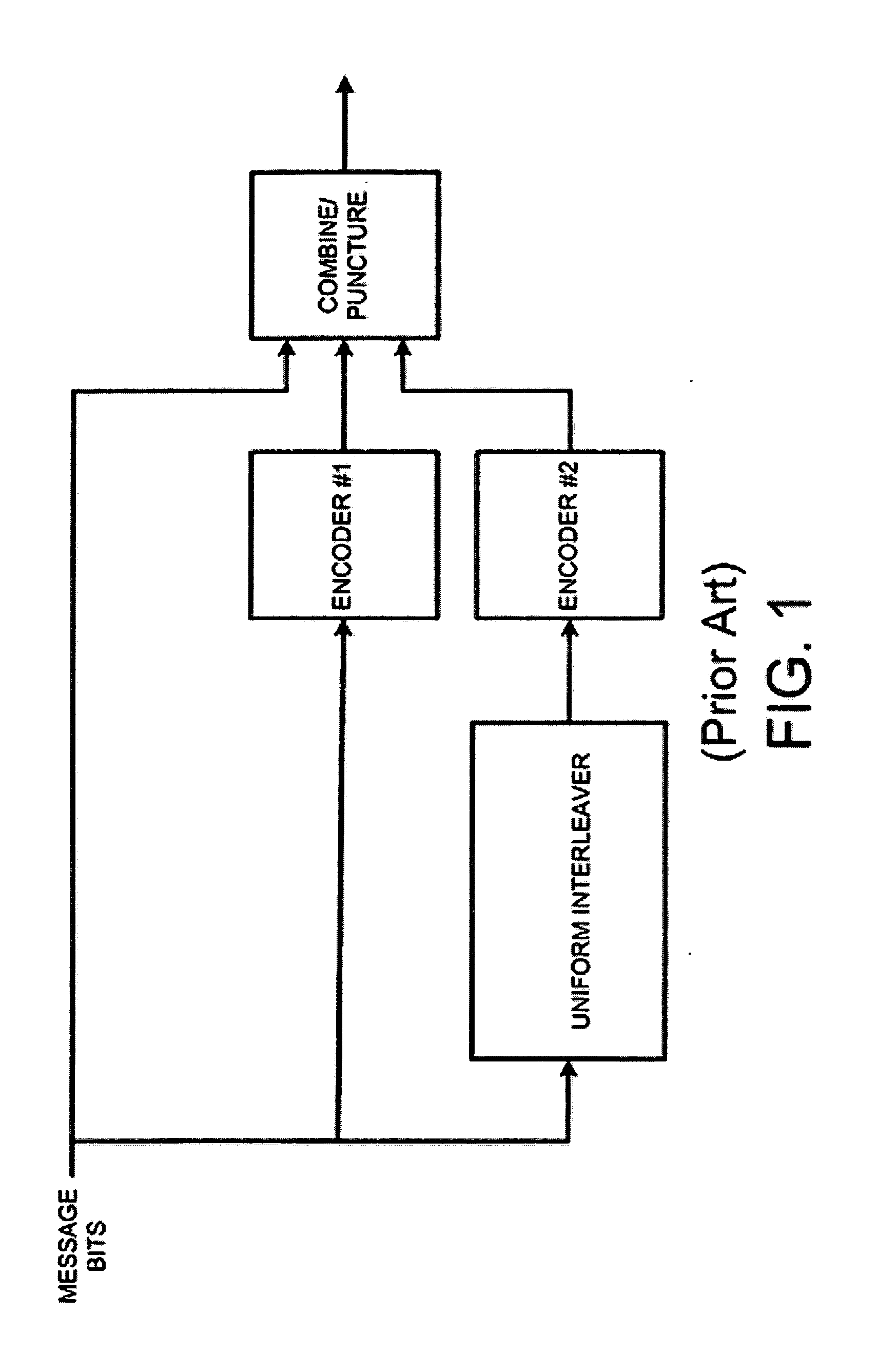

Iterative decoder employing multiple external code error checks to lower the error floor

InactiveUS7310768B2Code conversionError correction/detection by combining multiple code structuresError checkDegree of certainty

Owner:ENTROPIC COMM INC

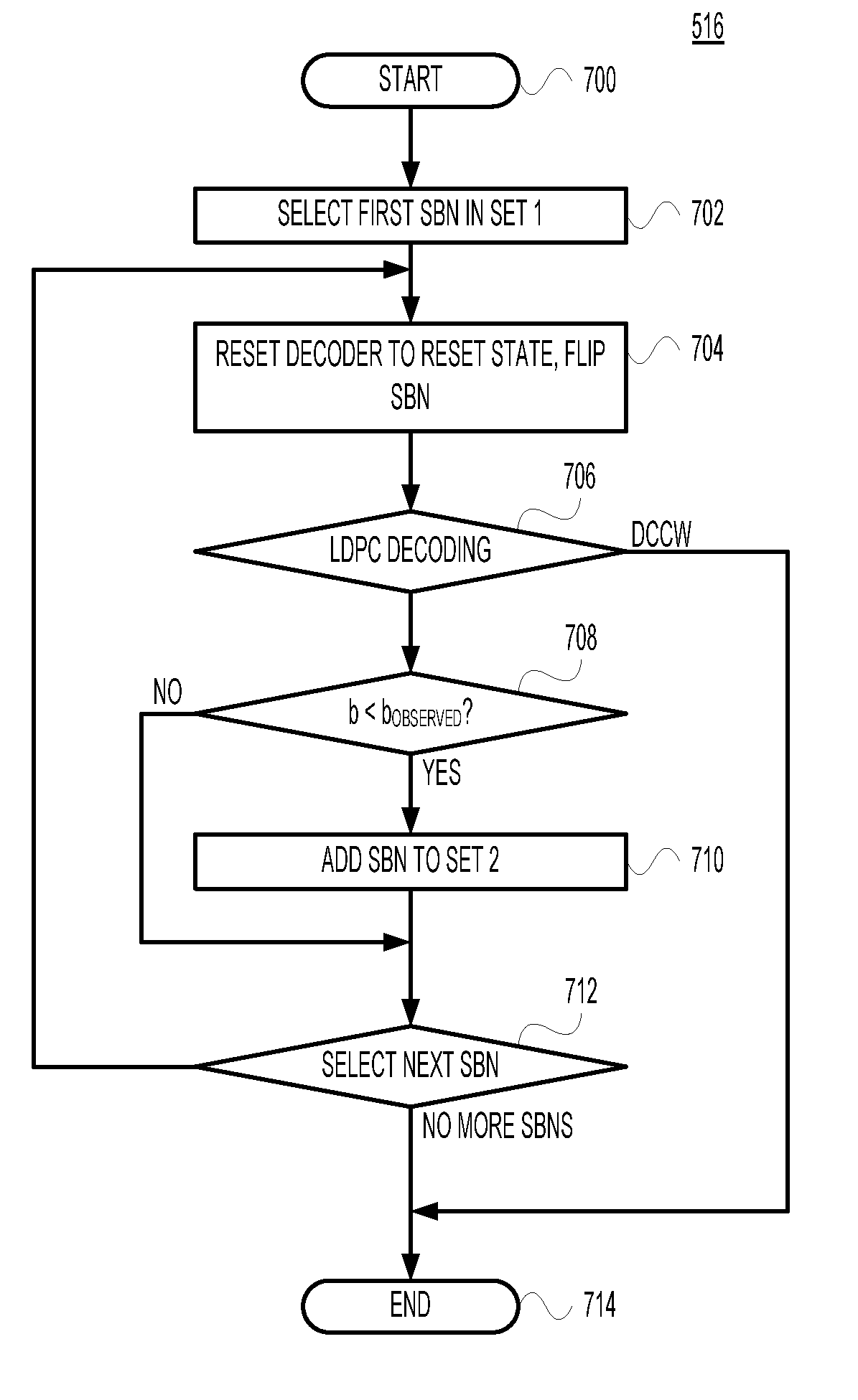

Error-floor mitigation of LDPC codes using targeted bit adjustments

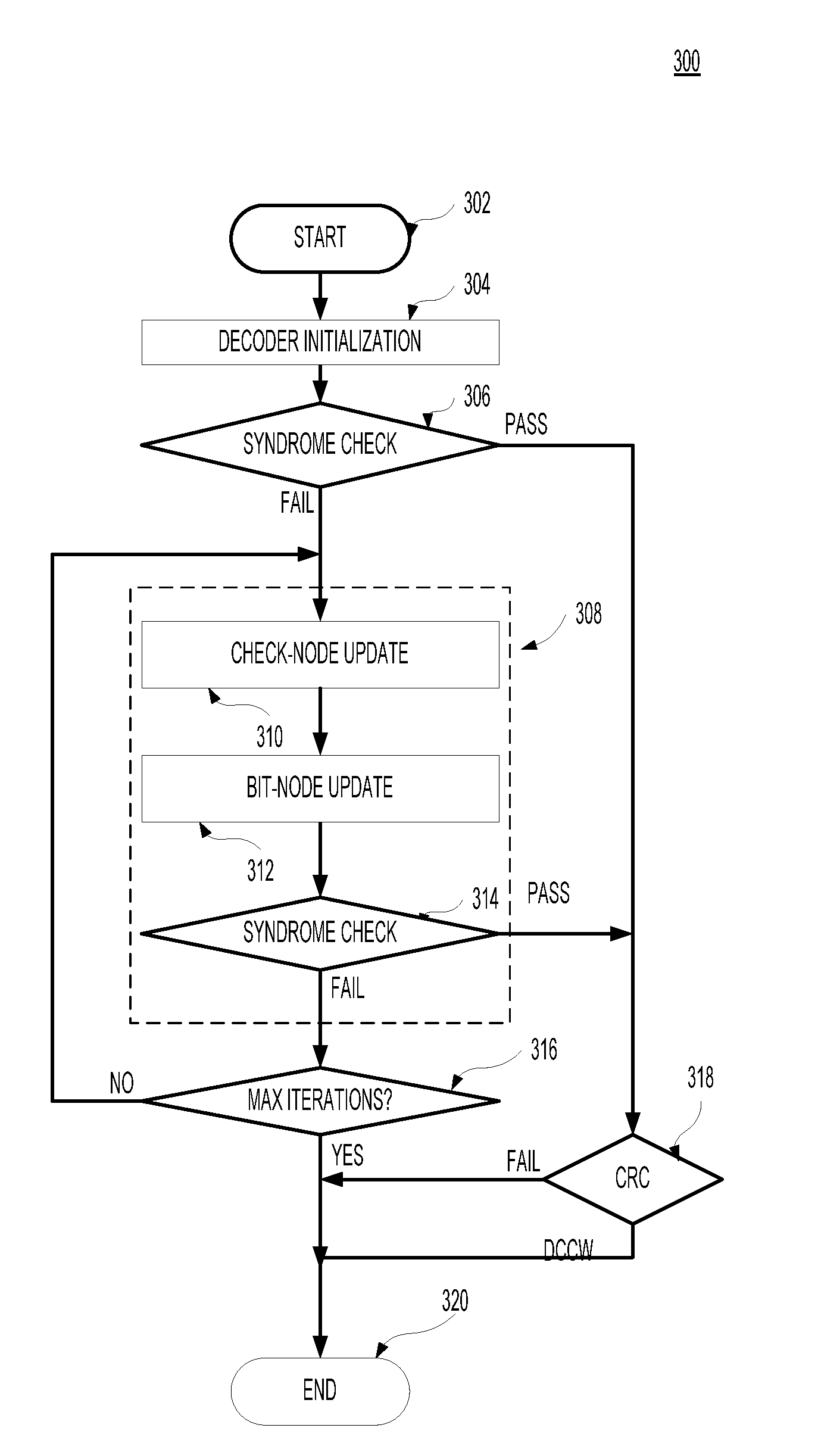

Embodiments of the present invention are methods for breaking one or more trapping sets in a near codeword of a failed graph-based decoder, e.g., an LDPC decoder. The methods determine, from among all bit nodes associated with one or more unsatisfied check nodes in the near codeword, which bit nodes, i.e., the suspicious bit nodes or SBNs, are most likely to be erroneous bit nodes. The methods then perform a trial in which the values of one or more SBNs are altered and decoding is re-performed. If the trial does not converge on the decoded correct codeword (DCCW), then other trials are performed until either (i) the decoder converges on the DCCW or (ii) all permitted combinations of SBNs are exhausted. The starting state of a particular trial, and the set of SBNs available to that trial may change depending on the results of previous trials.

Owner:AVAGO TECH INT SALES PTE LTD

Methods and apparatus for reducing error floors in message passing decoders

ActiveUS7237181B2Reduce the numberReduce quality problemsError preventionError correction/detection using multiple parity bitsComputer hardwareEdge states

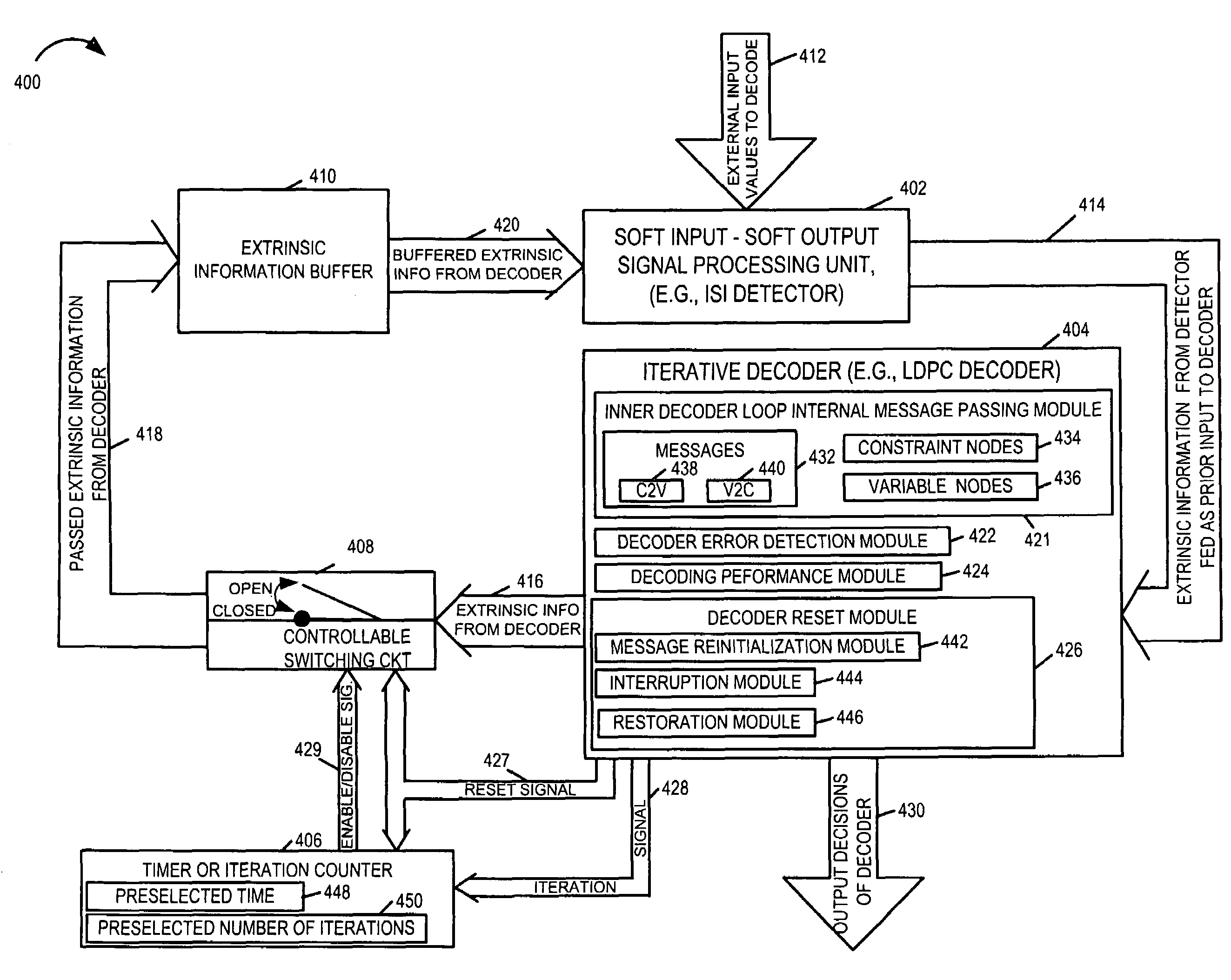

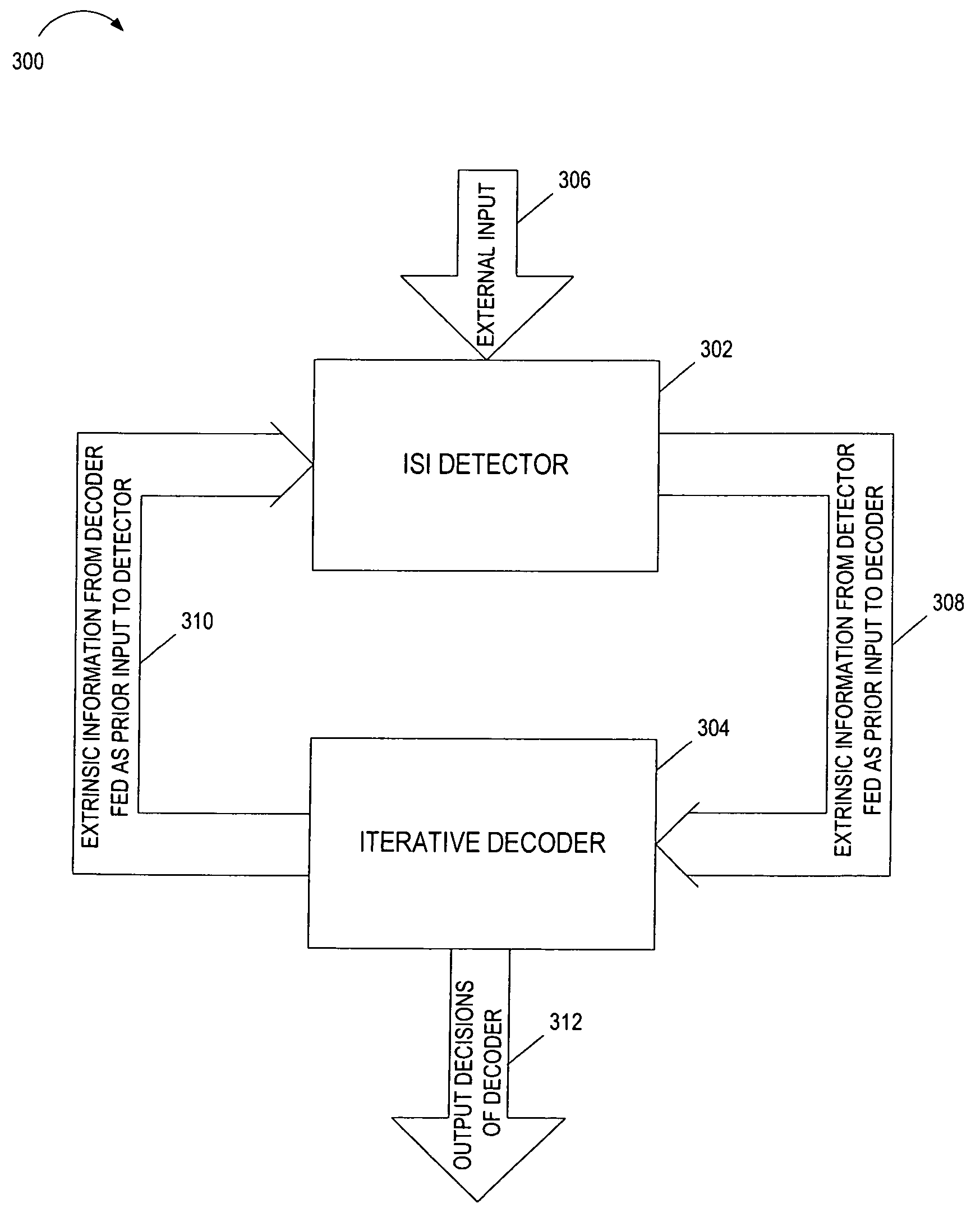

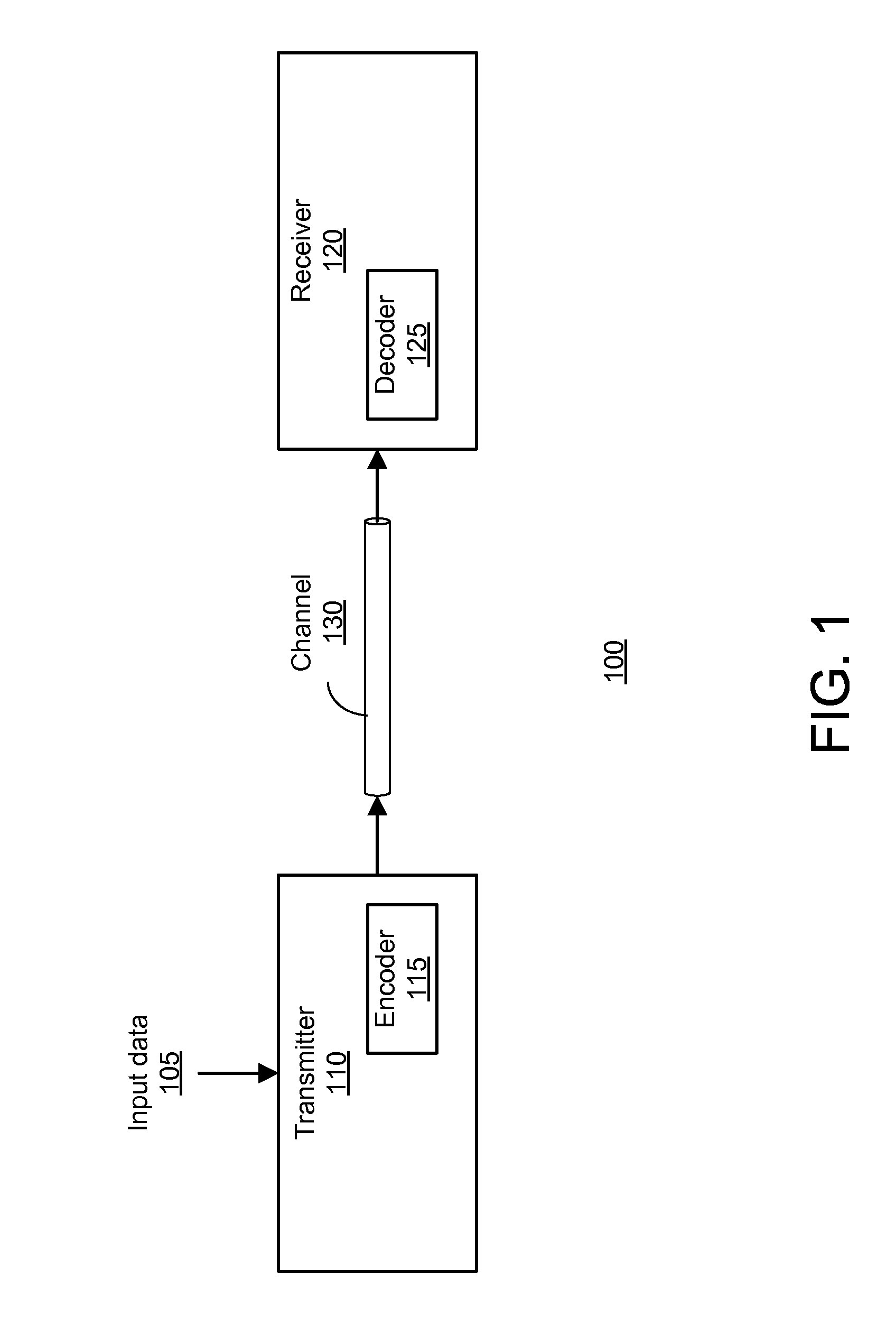

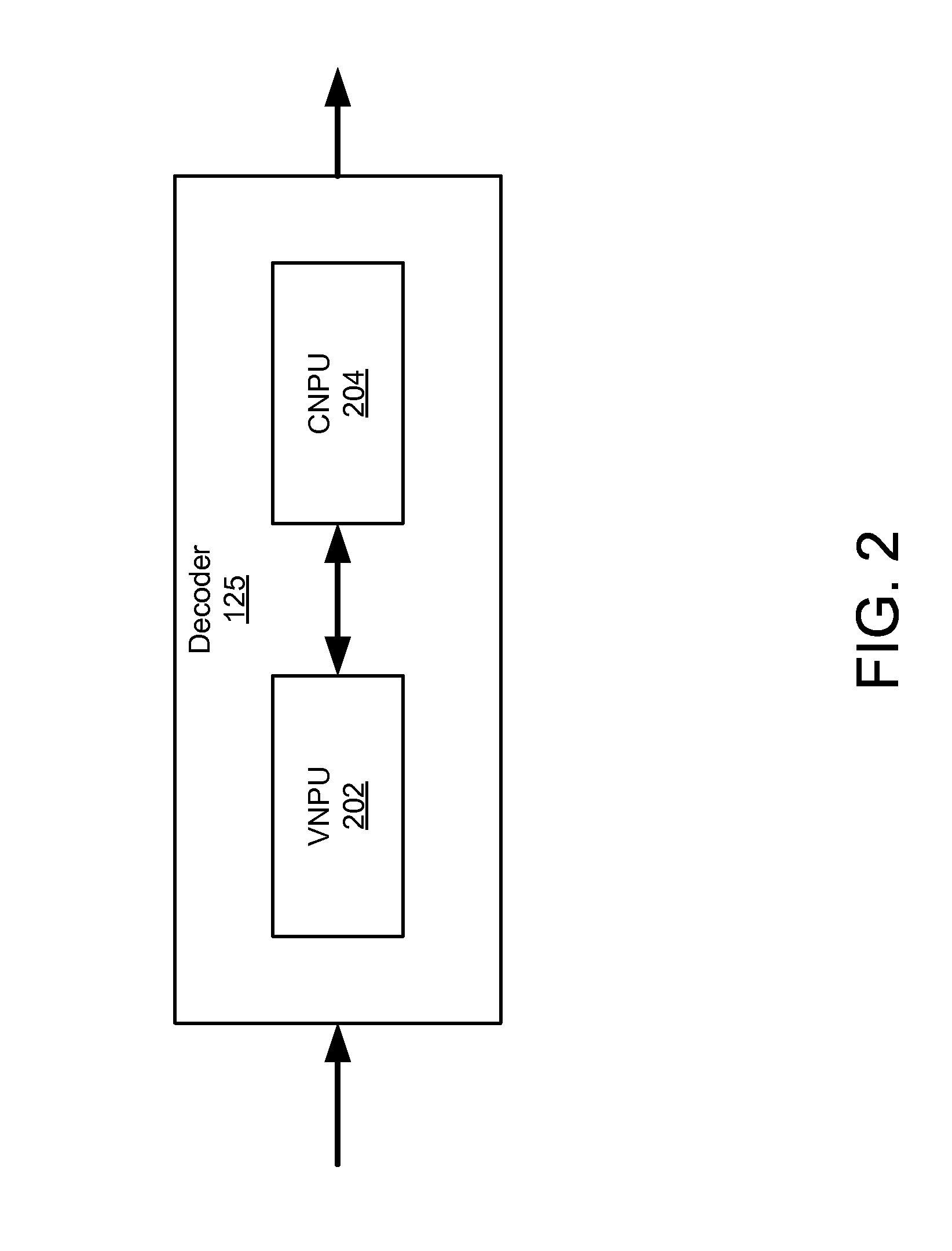

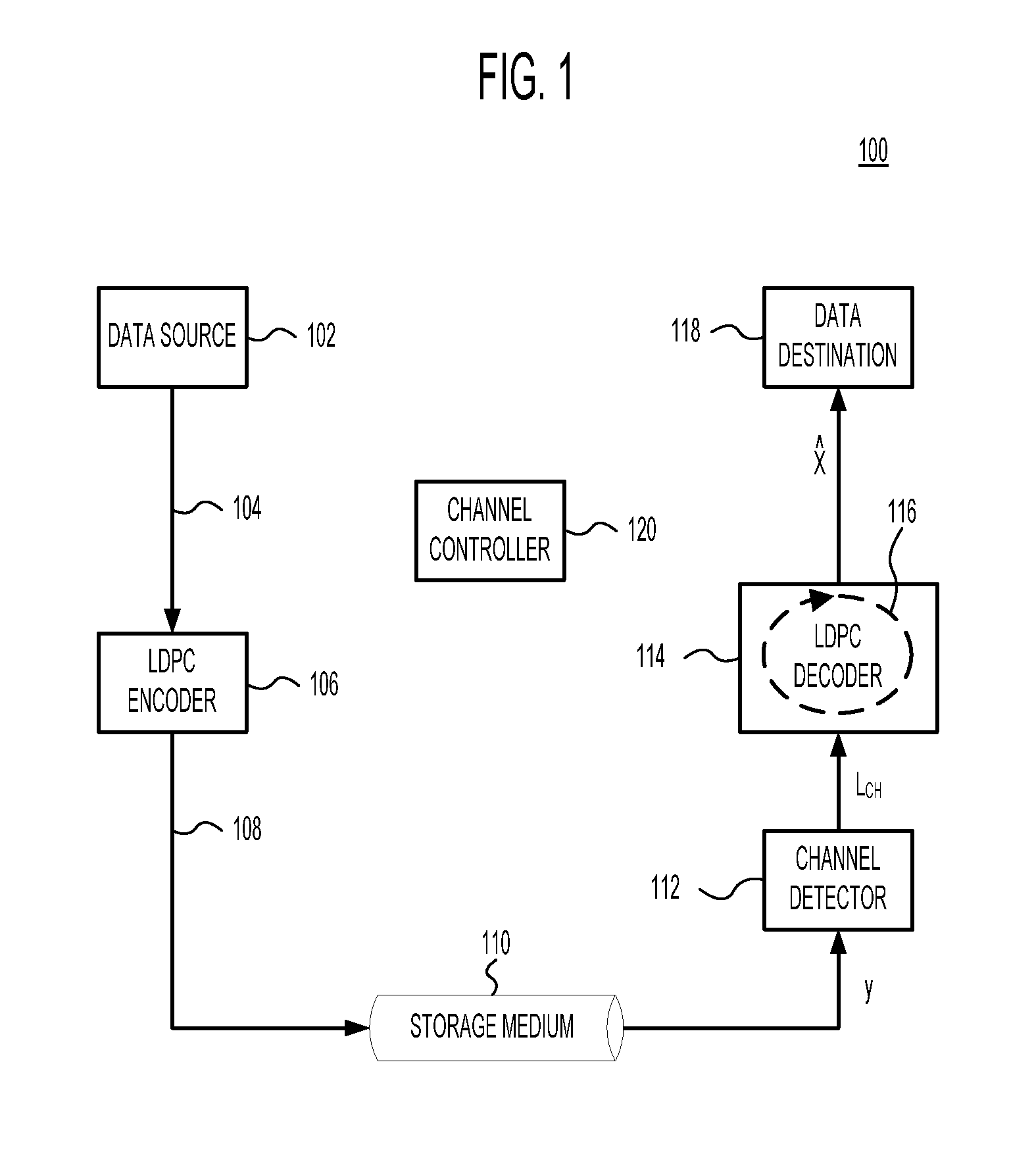

An iterative message passing decoder, e.g., an LDPC decoder, operating in conjunction with a soft input-soft output signal processing unit, e.g., an ISI detector, has an error floor performance region influenced by the decoder's sub-optimal message passing nature. Error floor reduction is achieved by a simple message re-initialization mechanism. Decoder edge states, e.g., constraint to variable node messages in decoder memory, are reinitialized, e.g., for an iteration, during the decoding after soft values provided by signal processing unit have improved. During the message re-initialization and for some subsequent amount of iterative decoder processing, extrinsic information fed back from the decoder to the signal processing unit and / or soft values delivered to the decoder from the signal processing unit, in an outer communications loop, is temporarily frozen, e.g., using a switch and a buffer. Then, the outer communications loop is restored as the decoding continues, achieving improved decoding performance.

Owner:QUALCOMM INC

Method of error floor mitigation in low-density parity-check codes

ActiveUS20120266040A1Improve performanceError correction/detection using LDPC codesCode conversionComputer hardwareMaximum magnitude

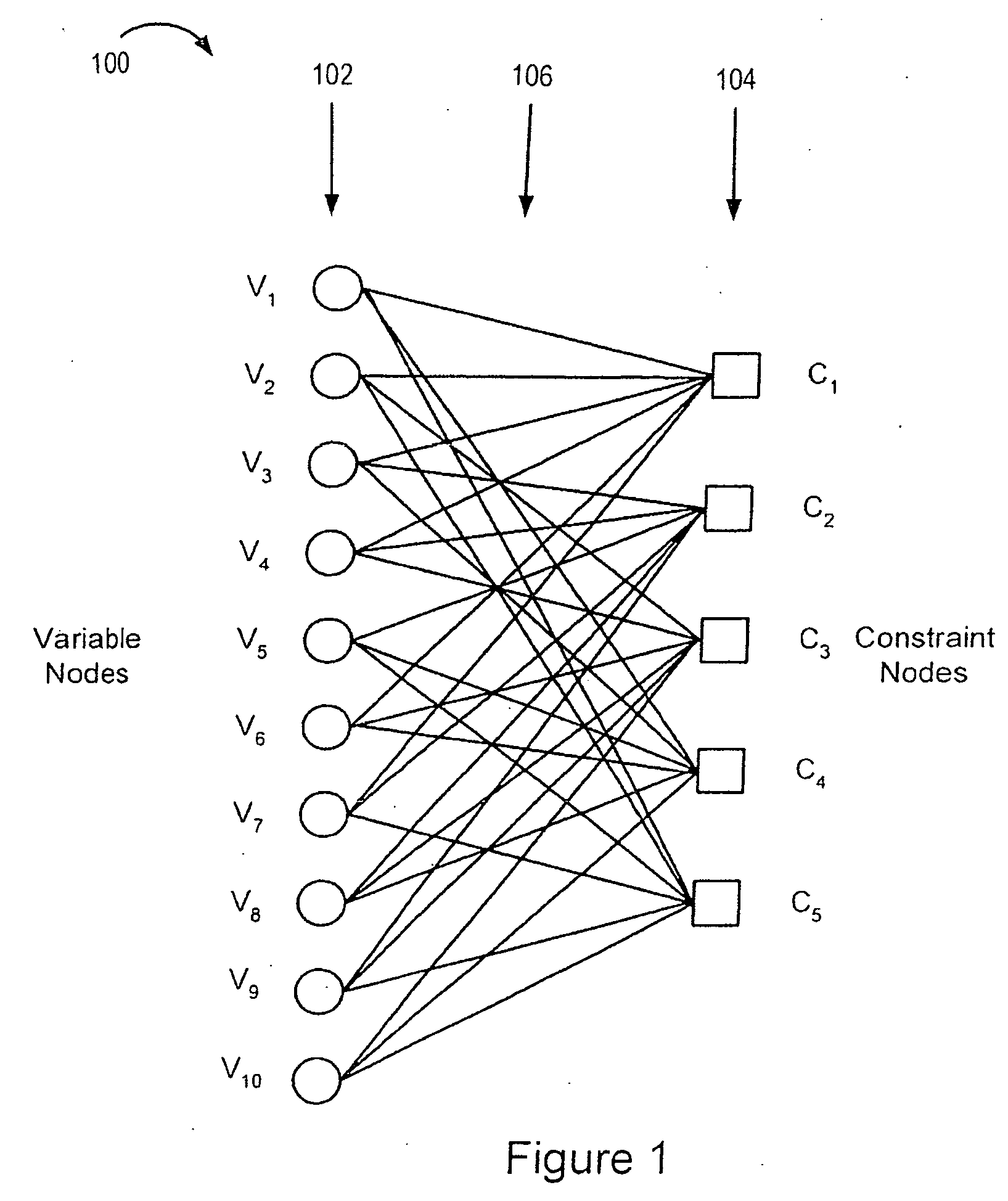

A digital communication decoding method for low-density parity-check coded messages. The decoding method decodes the low-density parity-check coded messages within a bipartite graph having check nodes and variable nodes. Messages from check nodes are partially hard limited, so that every message which would otherwise have a magnitude at or above a certain level is re-assigned to a maximum magnitude.

Owner:CALIFORNIA INST OF TECH

Method and system for decoding

ActiveUS20120054576A1Improve performanceIncreased complexityCode conversionError correction/detection using block codesValue setCommunication link

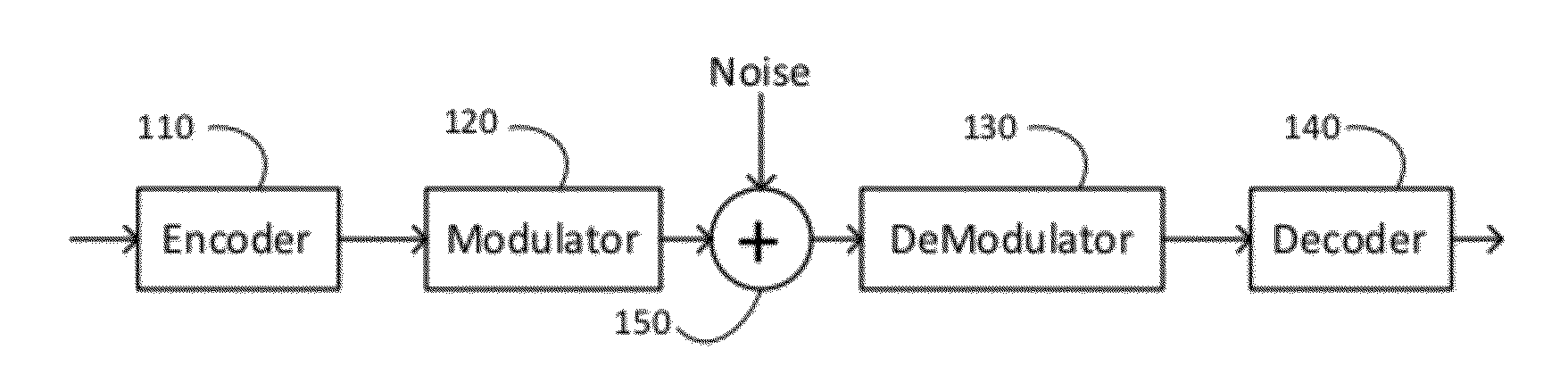

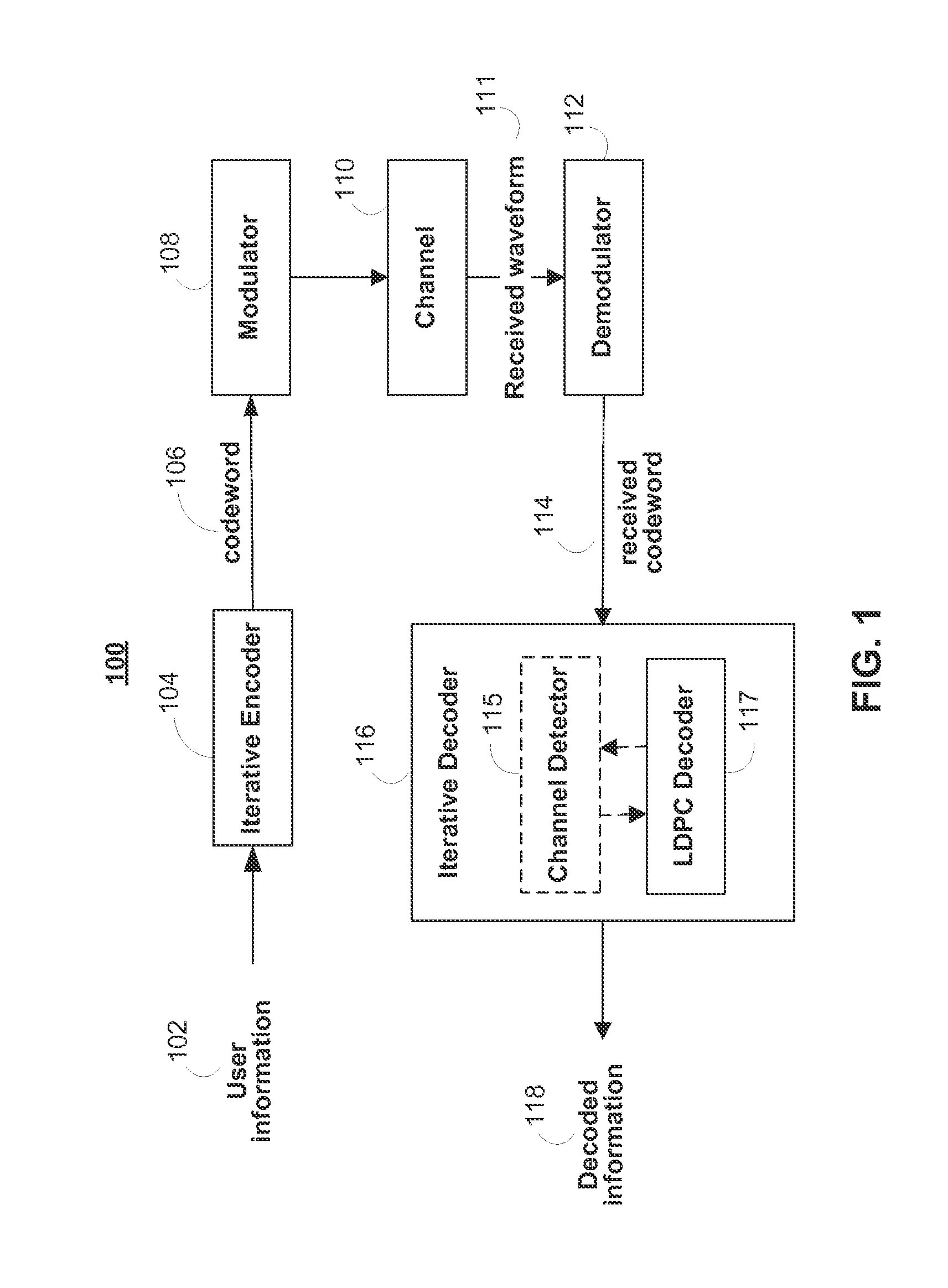

Low-Density Parity-Check (LDPC) codes offer error correction at rates approaching the link channel capacity and reliable and efficient information transfer over bandwidth or return-channel constrained links with data-corrupting noise present. They also offer performance approaching channel capacity exponentially fast in terms of the code length, linear processing complexity, and parallelism that scales with code length. They also offer challenges relating to decoding complexity and error floors limiting achievable bit-error rates. Accordingly encoders with reduced complexity, reduced power consumption and improved performance are disclosed with various improvements including simplifying communications linking multiple processing nodes by passing messages where pulse widths are modulated with the corresponding message magnitude, delaying a check operation in dependence upon variable node states, running the decoder multiple times with different random number generator seeds for a constant channel value set, and employing a second decoder with a randomizing component when the attempt with the first decoder fails.

Owner:POLAR TECH

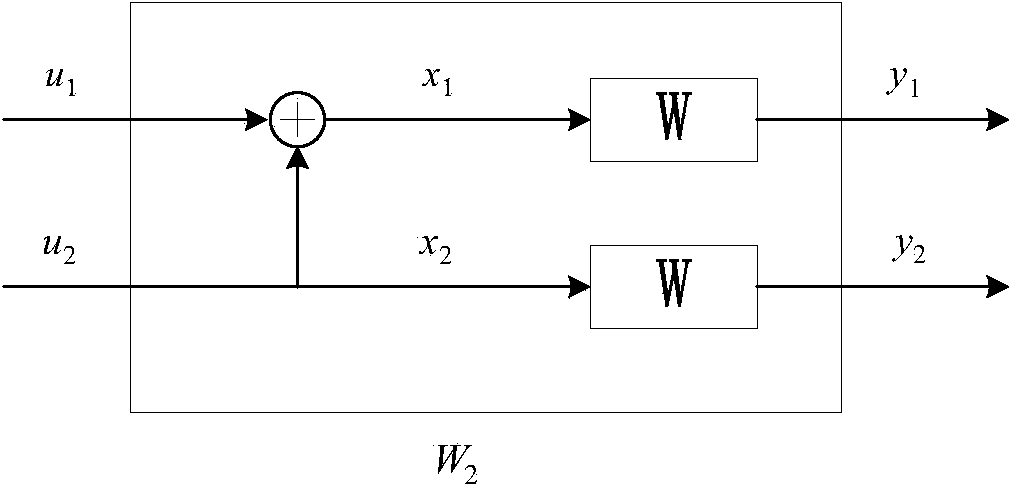

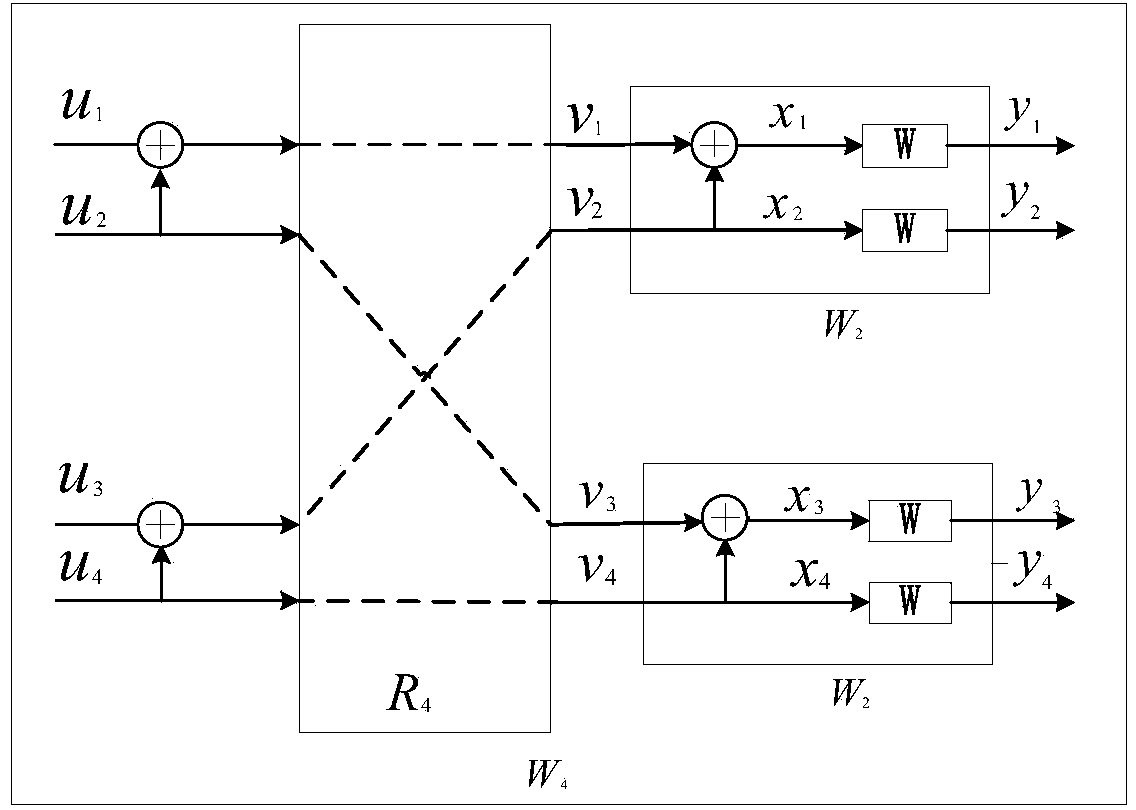

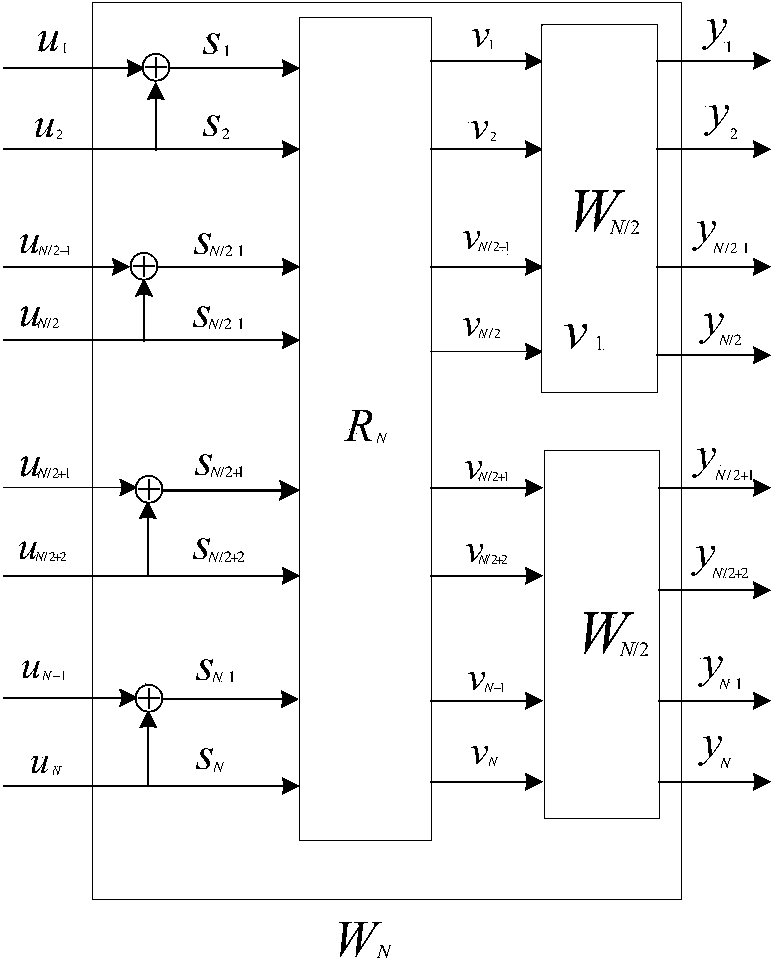

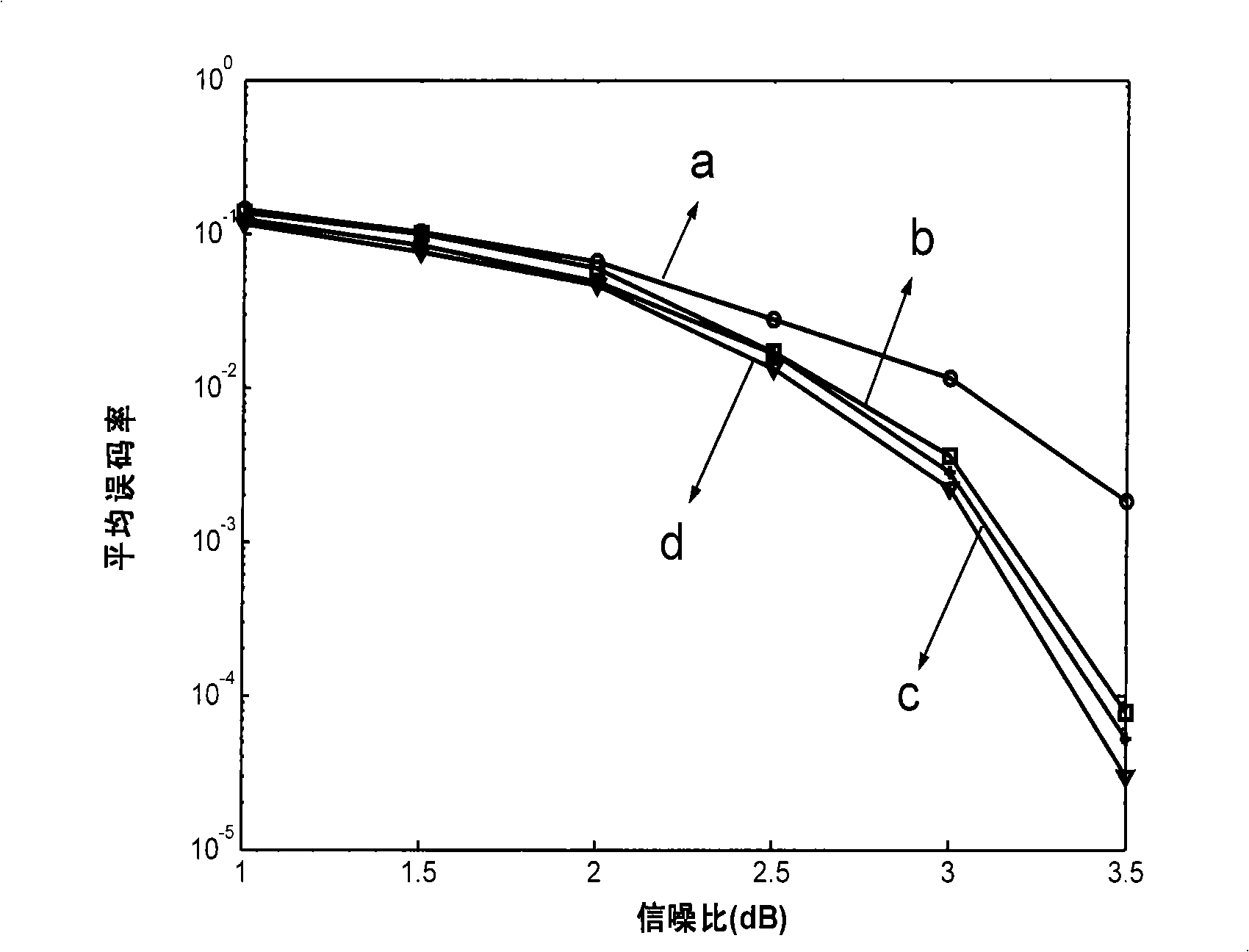

Method for constructing Polar-LDPC concatenated codes

InactiveCN103746708AReduce complexityReduce bit error rateError correction/detection using multiple parity bitsCode conversionInformation transmissionCoding decoding

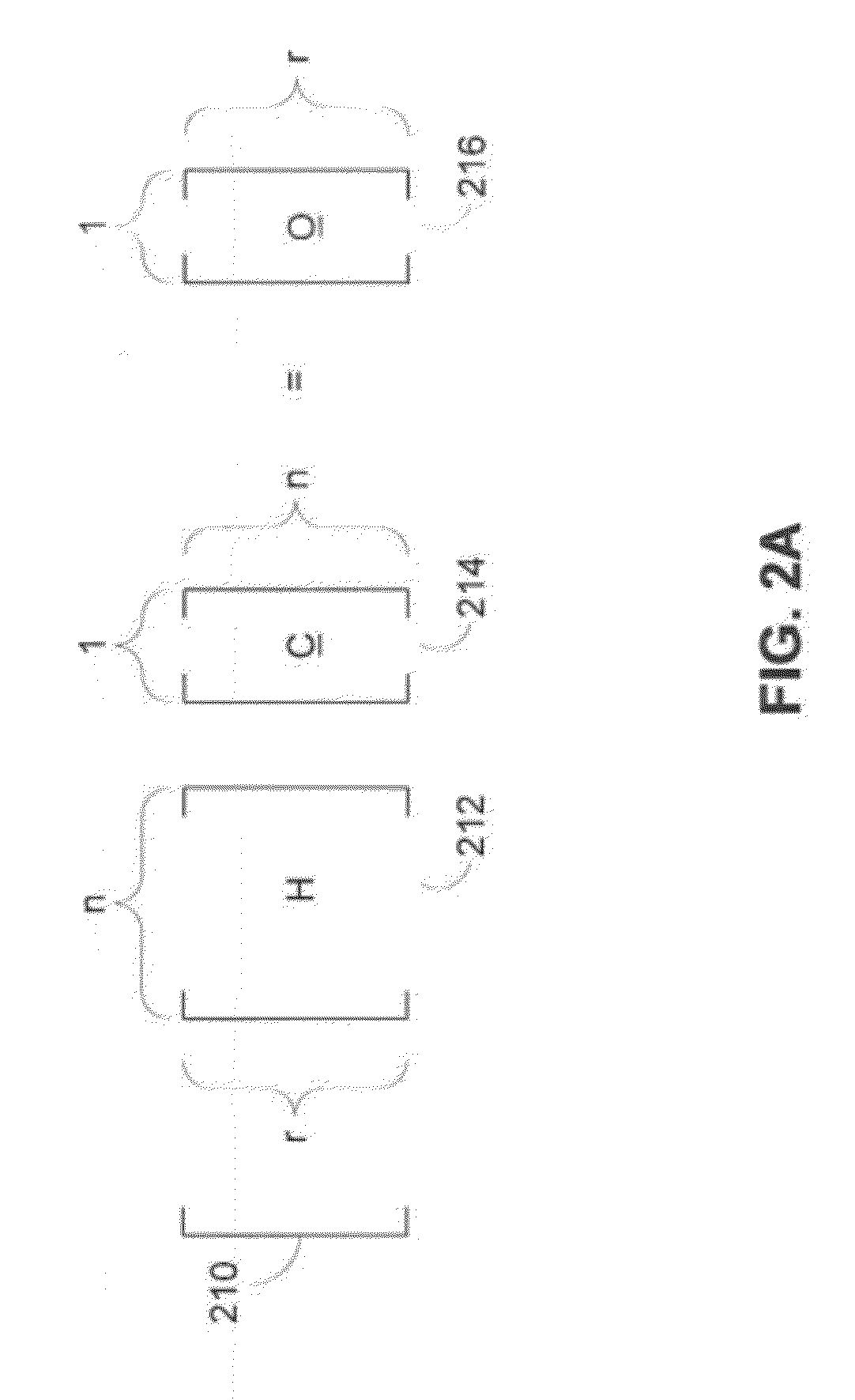

The invention provides a method for constructing Polar-LDPC concatenated codes. The method serially concentrates Polar codes as outer codes and LDPC codes as inner codes and is characterized by comprising the following steps of (1) carrying out coding operation of an information sequence (img file='DDA000402432330000011.TIF' wi='63' he='64' / ) through a generated matrix according to encoding rules of Polar codes to obtain an information sequence (img file='DDA000402432330000012.TIF' wi='86' he='81' / ); (2) encoding an information sequence (img file='DDA000402432330000013.TIF' wi='66' he='84' / ) after Polar code encoding according to LDPC codes to obtain an information sequence (img file='DDA000402432330000014.TIF' wi='88' he='64' / ) to be sent to a channel for information transmission; (3) receiving an information sequence (img file='DDA000402432330000015.TIF' wi='105' he='80' / ) from the channel and sending the information sequence to LDPC code decoding, and decoding the information sequence using a BP iterative decoding algorithm to obtain an information sequence (img file='DDA000402432330000016.TIF' wi='95' he='84' / ); and (4) sending an information sequence (img file='DDA000402432330000017.TIF' wi='64' he='67' / ) obtained after LDPC code decoding and sending the information sequence to a Polar code decoder to obtain an information sequence (img file='DDA000402432330000018.TIF' wi='96' he='72' / ) using a continuous deletion decoding algorithm. The novel concatenated codes have better decoding performances and fewer error floors, and can be applied to fields of deep space communication, image transmission and the like.

Owner:CHINA AGRI UNIV

Methods and apparatus for reducing error floors in message passing decoders

ActiveUS20050138520A1Reduce the numberReduce quality problemsError preventionError correction/detection using multiple parity bitsComputer hardwareMessage passing

An iterative message passing decoder, e.g., an LDPC decoder, operating in conjunction with a soft input-soft output signal processing unit, e.g., an ISI detector, has an error floor performance region influenced by the decoder's sub-optimal message passing nature. Error floor reduction is achieved by a simple message re-initialization mechanism. Decoder edge states, e.g., constraint to variable node messages in decoder memory, are reinitialized, e.g., for an iteration, during the decoding after soft values provided by signal processing unit have improved. During the message re-initialization and for some subsequent amount of iterative decoder processing, extrinsic information fed back from the decoder to the signal processing unit and / or soft values delivered to the decoder from the signal processing unit, in an outer communications loop, is temporarily frozen, e.g., using a switch and a buffer. Then, the outer communications loop is restored as the decoding continues, achieving improved decoding performance.

Owner:QUALCOMM INC

Phase pulse system and method for bandwidth and energy efficient continuous phase modulation

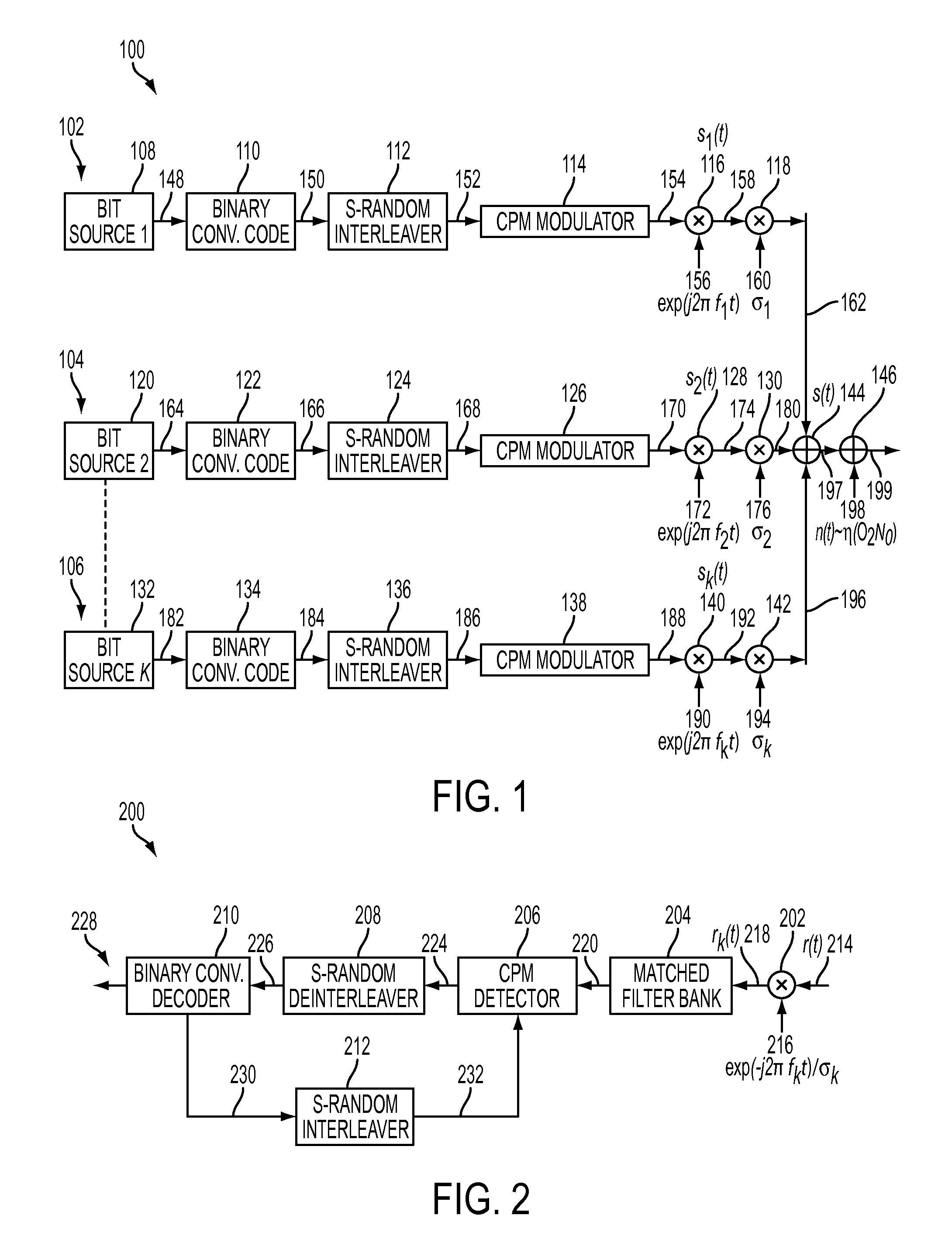

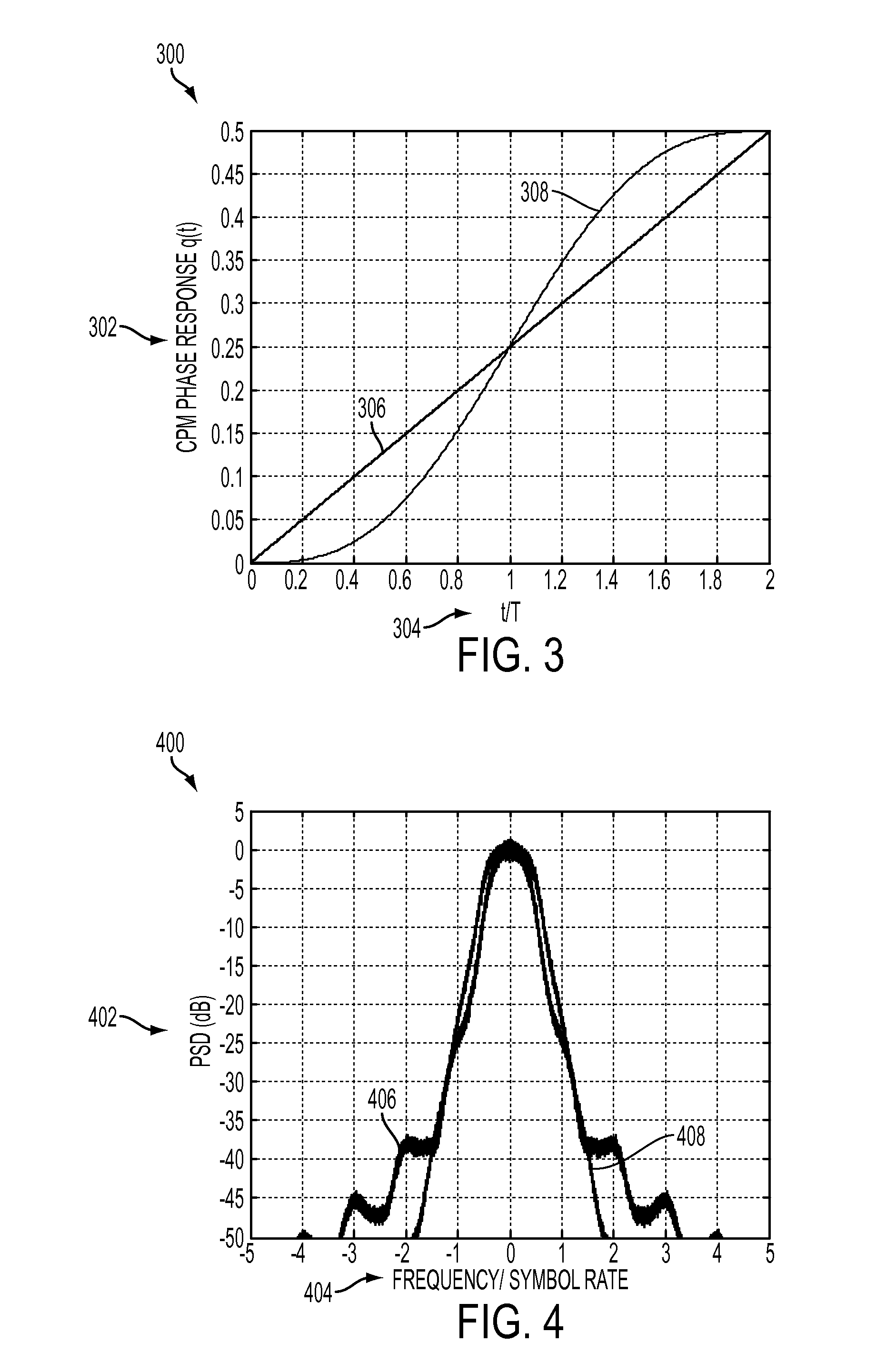

ActiveUS20110275338A1Improve performanceImprove bandwidth efficiencyError preventionAngle modulation detailsSide lobePulse shaping

A new pulse shape for CPM is introduced which is obtained by a linear combination of well-known RC and REC pulse shapes. The new pulse shape addresses the tradeoff between the width of the PSD main lobe and the rate of decay of the side lobe to improve the coded performance of multi-carrier systems affected by ACI. Also, a methodology is proposed to design and evaluate the performance of the new pulse shape for multi-carrier, coded systems based on the modulation constrained capacity. Furthermore, a binary convolutional code and the CPM modulator are concatenated using an S-random bit interleaver to lower the error floor. Finally, Laurent representation of the new pulse shape is suggested such that by retaining only the principal pulses at the receiver, complexity of the receiver can be reduced.

Owner:HUGHES NETWORK SYST

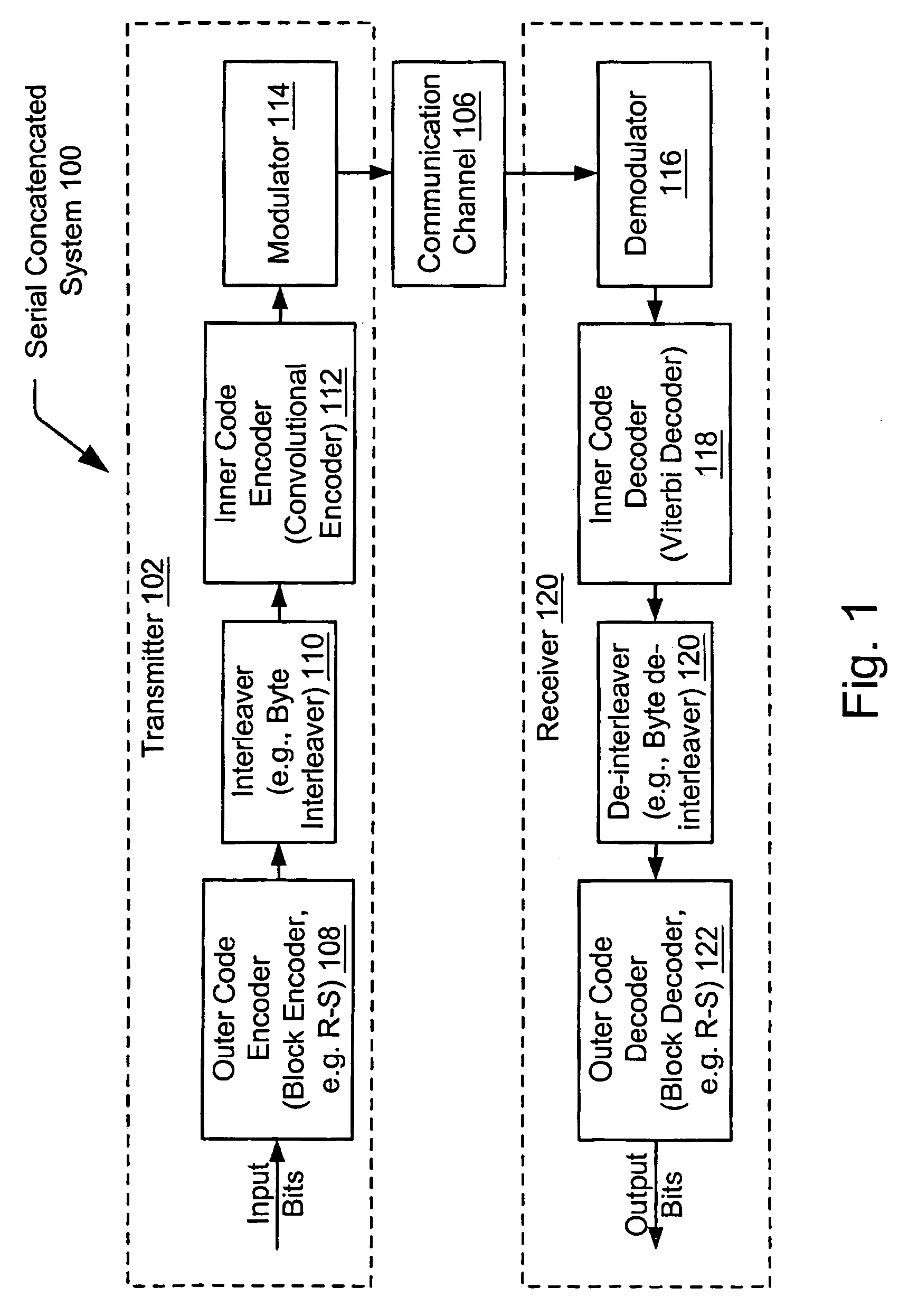

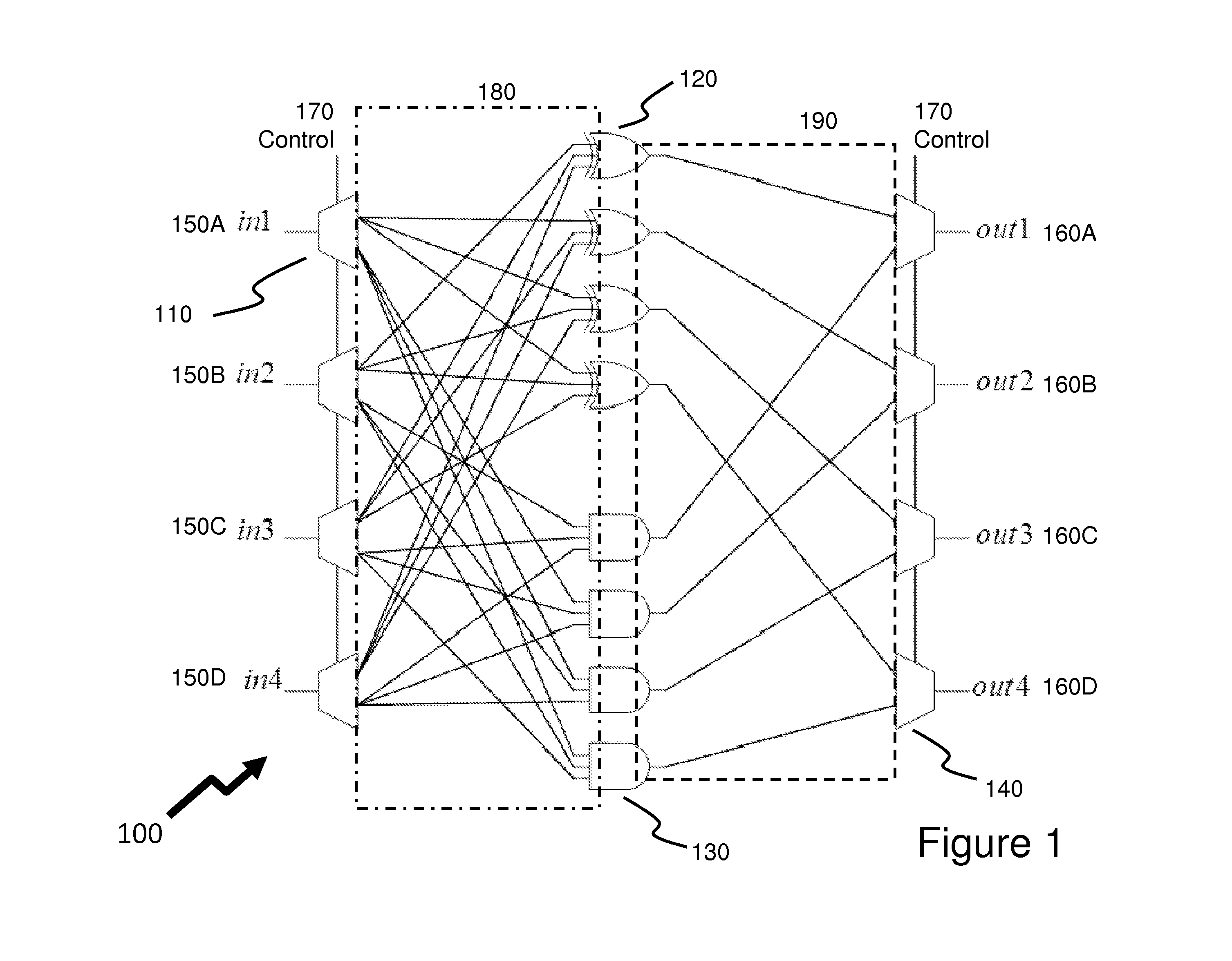

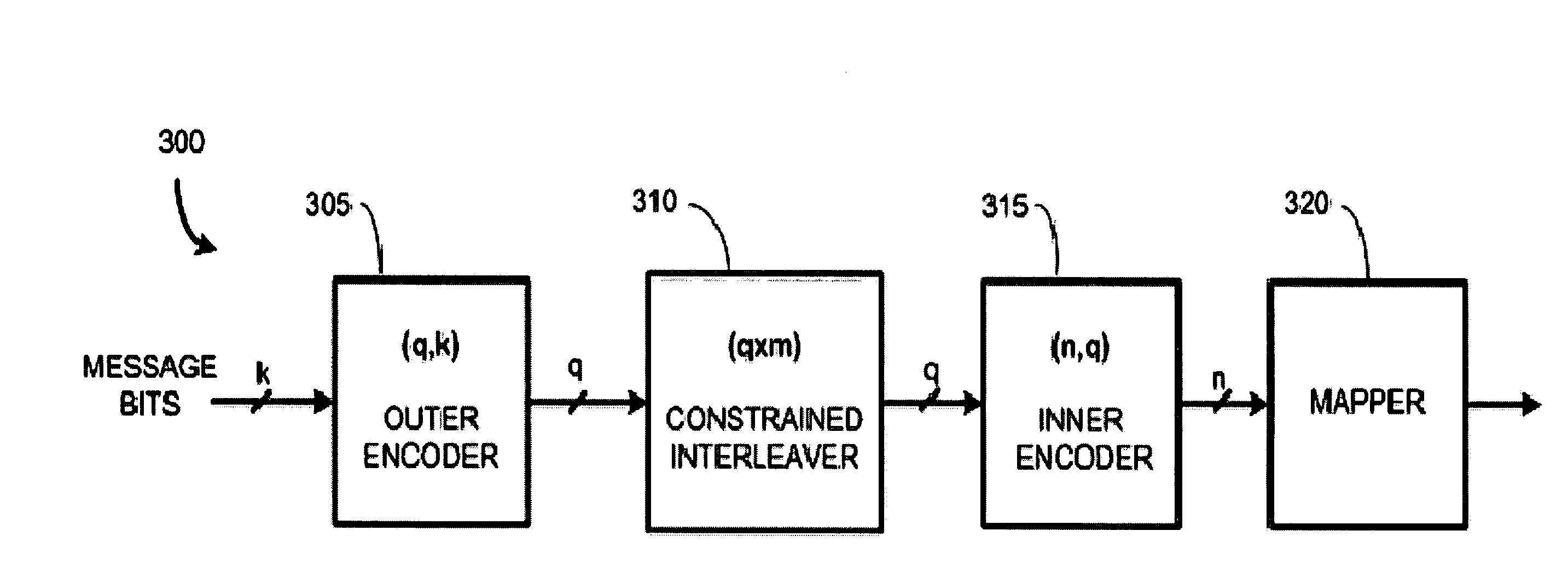

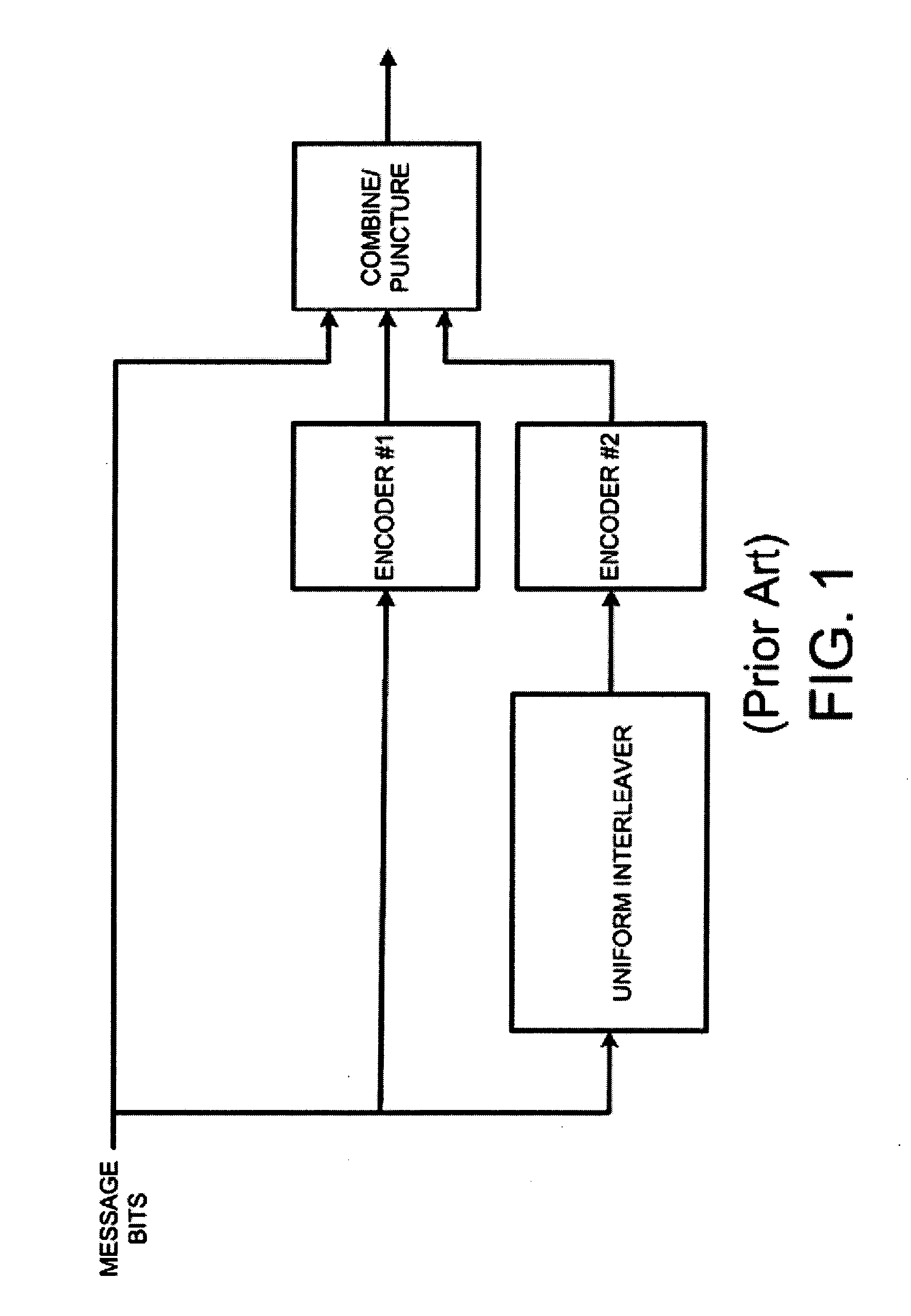

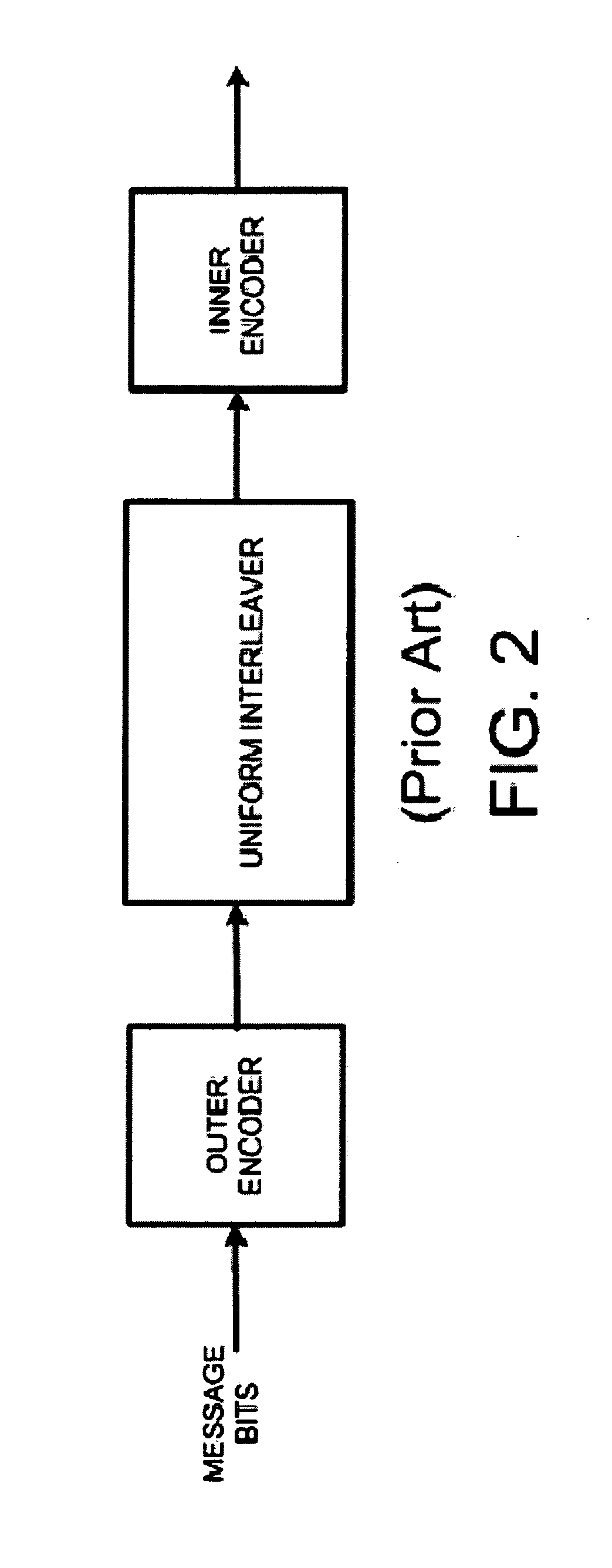

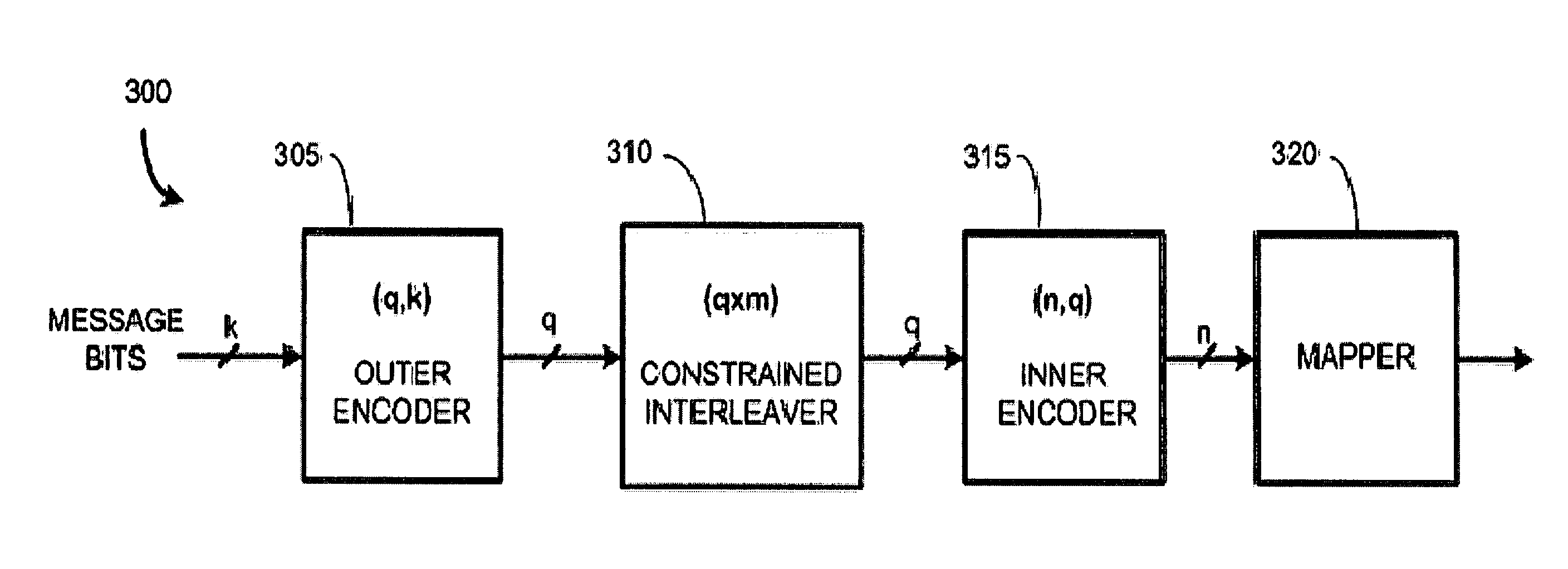

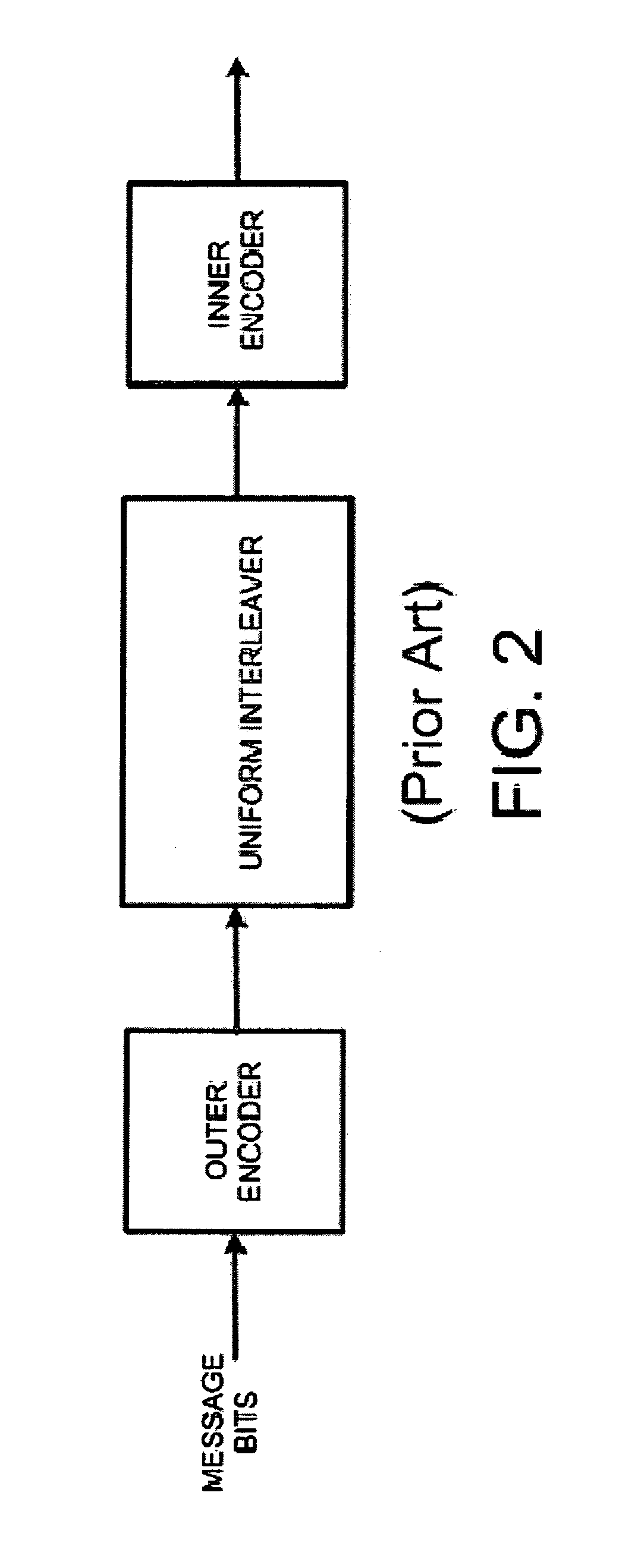

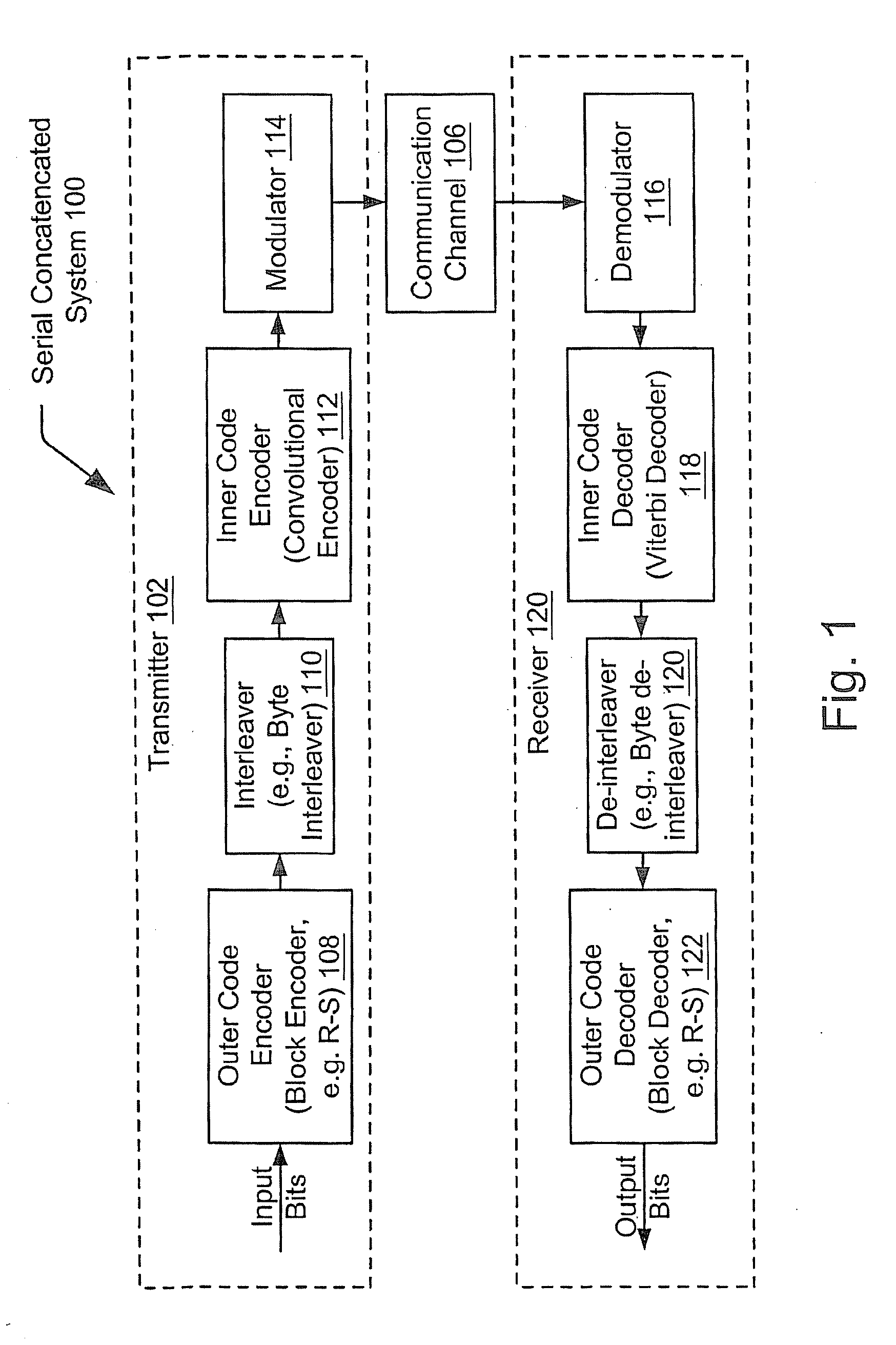

Encoding and decoding using constrained interleaving

InactiveUS20120063533A1Reduce measurementEfficient implementationAmplitude-modulated carrier systemsAmplitude demodulationSimple componentNoise margin

Serially-concatenated codes are formed in accordance with the present invention using a constrained interleaver. The constrained interleaver cause the minimum distance of the serial concatenated code to increase above the minimum distance of the inner code alone by adding a constraint that forces some or all of the distance of the outer code onto the serially-concatenated code. This allows the serially-concatenated code to be jointly optimized in terms of both minimum distance and error coefficient to provide significant performance advantages. These performance advantages allow a noise margin target to be achieved using simpler component codes and a much shorter interleaver than was needed when using prior art codes such as Turbo codes. Decoders are also provided. Both encoding and decoding complexity can be lowered, and interleavers can be made much shorter, thereby shortening the block lengths needed in receiver elements such as equalizers and other decision-directed loops. Also, other advantages are provided such as the elimination of a error floor present in prior art serially-concatenated codes. That allows the present invention to achieve much higher performance at lower error rates such as are needed in optical communication systems.

Owner:TRELLIS PHASE COMM LP

Error-correction decoder employing multiple check-node algorithms

ActiveUS20100241921A1Strong influence on error-floor characteristics of the LDPC codeImprove featuresError preventionTransmission systemsComputer scienceError floor

In one embodiment, an LDPC decoder has a controller and one or more check-node units (CNUs). The CNUs generate check-node messages using a scaled min-sum algorithm, an offset min-sum algorithm, or a scaled and offset min-sum algorithm. Initially, the controller selects a scaling factor and an offset value. The scaling factor may be set to one for no scaling, and the offset value may be set to zero for no offsetting. If the decoder is unable to correctly decode a codeword, then (i) the controller selects a new scaling and / or offset value and (ii) the decoder attempts to correctly decode the codeword using the new scaling and / or offset value. By changing the scaling factor and / or offset value, LDPC decoders of the present invention may be capable of improving error-floor characteristics over LDPC decoders that use only fixed or no scaling factors or fixed or no offsetting factors.

Owner:AVAGO TECH INT SALES PTE LTD

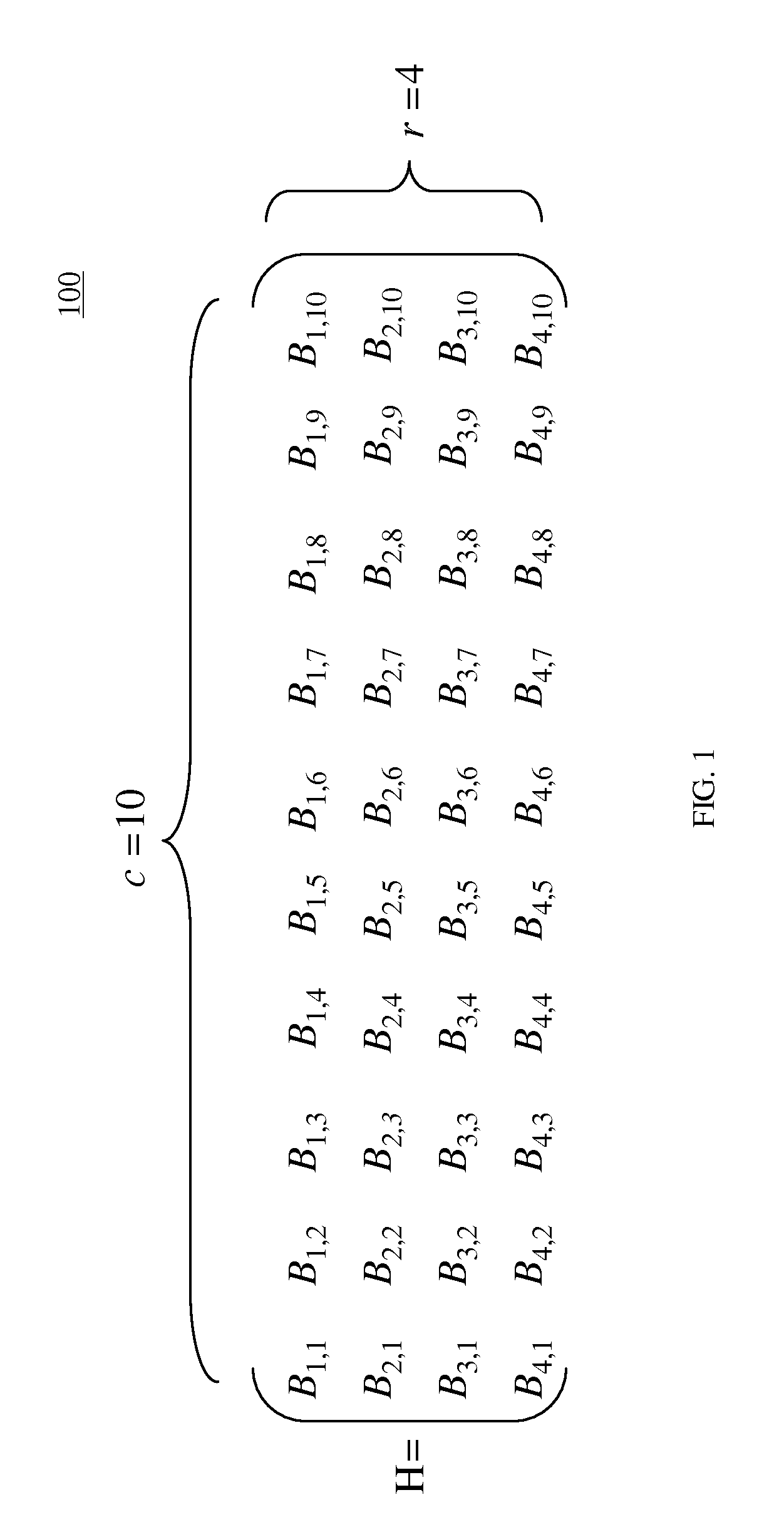

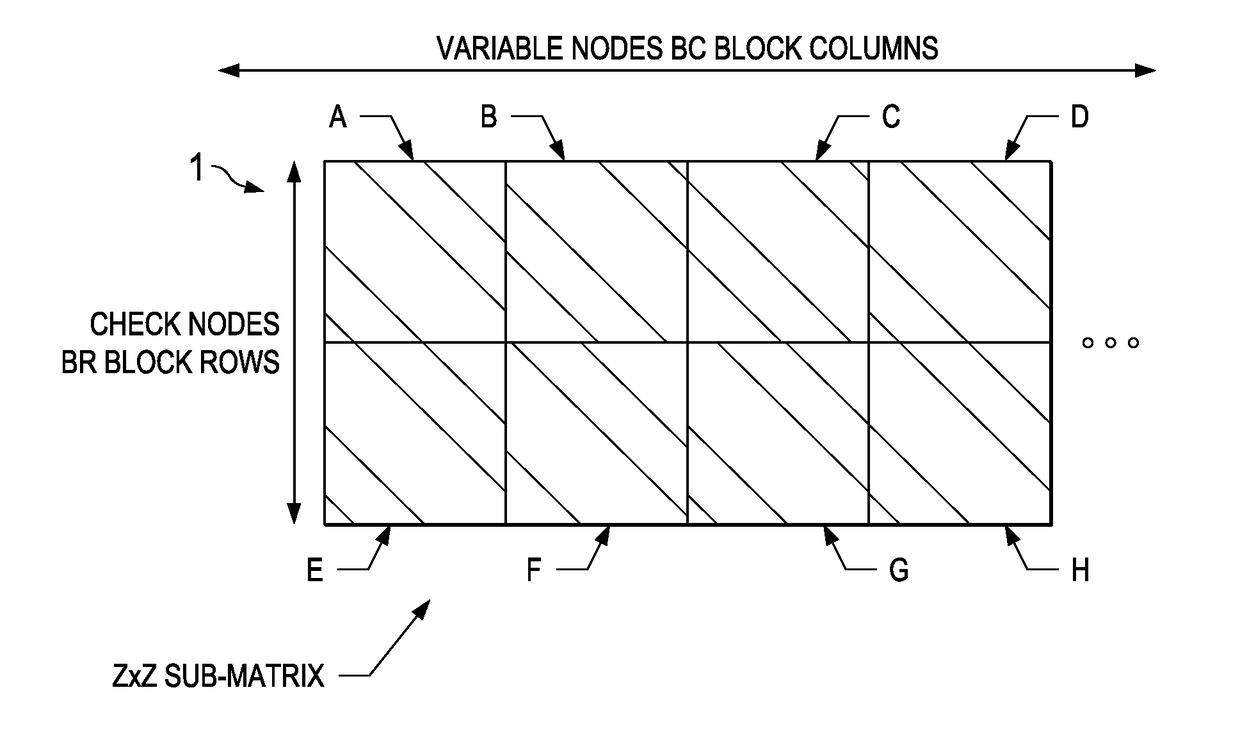

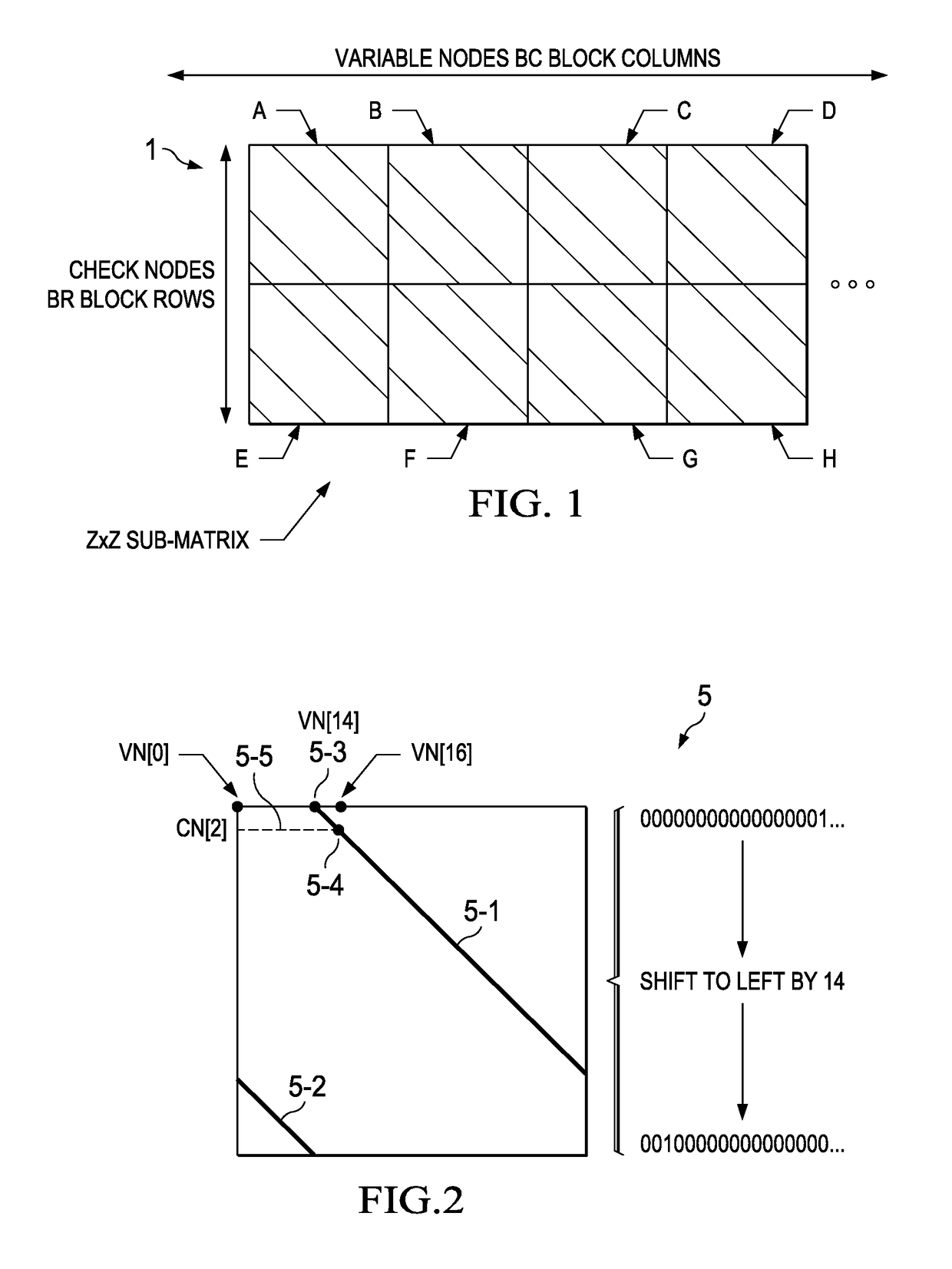

LDPC design for high parallelism, low error floor, and simple encoding

ActiveUS20140229789A1Yield with good performanceHigh error floorError correction/detection using multiple parity bitsChecking code calculationsTheoretical computer scienceData encoding

A method of data encoding is disclosed. An encoder receives a set of information bits and performs an LDPC encoding operation on the set of information bits to produce a codeword based on a matched lifted LDPC code. The matched lifted LDPC code is based on a commutative lifting group and includes a number of parity bits and a submatrix to determine values of the parity bits. An order of the lifting group (Z) corresponds with a size of the lifting. A determinant of the submatrix is a polynomial of the form: ga+(g0+gL)P, where g0 is the identity element of the group, g0=gL2<sup2>k< / sup2>, and P is an arbitrary non-zero element of a binary group ring associated to the lifting group.

Owner:QUALCOMM INC

LDPC design for high rate, high parallelism, and low error floor

InactiveUS20140229788A1Increase the number ofImprove encoding performanceError correction/detection using multiple parity bitsCode conversionMultiple edgesHigh rate

A method of data encoding is disclosed. An encoder receives a set of information bits and performs a lifted LDPC encoding operation on the information bits to produce a codeword. The encoder then punctures all lifted bits of the codeword that correspond to one or more punctured base bits of a base LDPC code used for the LDPC encoding operation. The base LDPC code has no multiple edges, and the one or more punctured base bits are those that correspond with one or more punctured base nodes, respectively, of the base LDPC code. For some embodiments, the one or more punctured base nodes correspond to one or more degree 2 variable nodes.

Owner:QUALCOMM INC

Non-Concatenated FEC Codes for Ultra-High Speed Optical Transport Networks

ActiveUS20120221914A1Improves decoding processAvoid delayError preventionChecking code calculationsUltra high speedParallel computing

A decoder performs forward error correction based on quasi-cyclic regular column-partition low density parity check codes. A method for designing the parity check matrix reduces the number of short-cycles of the matrix to increase performance. An adaptive quantization post-processing technique further improves performance by eliminating error floors associated with the decoding. A parallel decoder architecture performs iterative decoding using a parallel pipelined architecture.

Owner:MARVELL ASIA PTE LTD

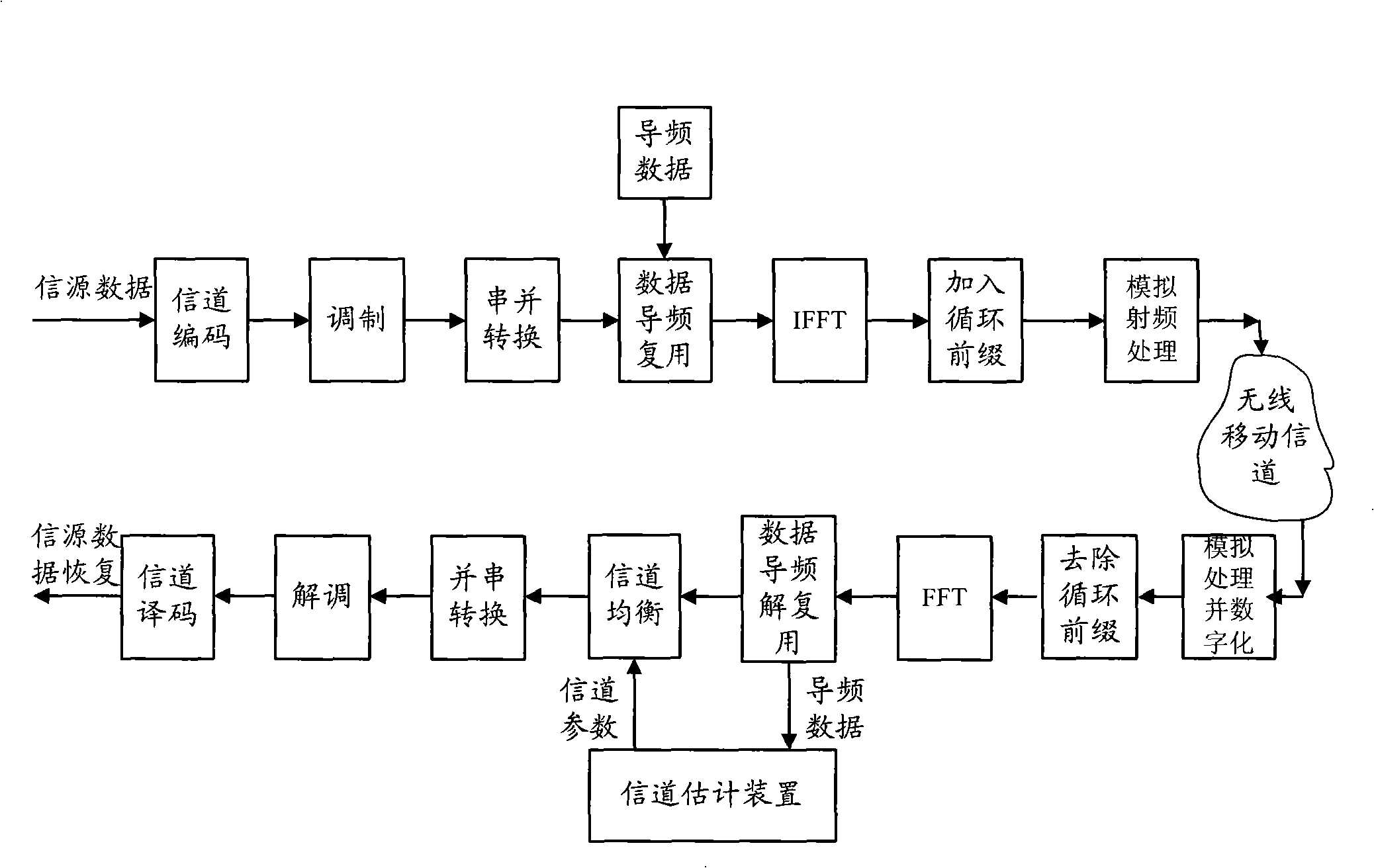

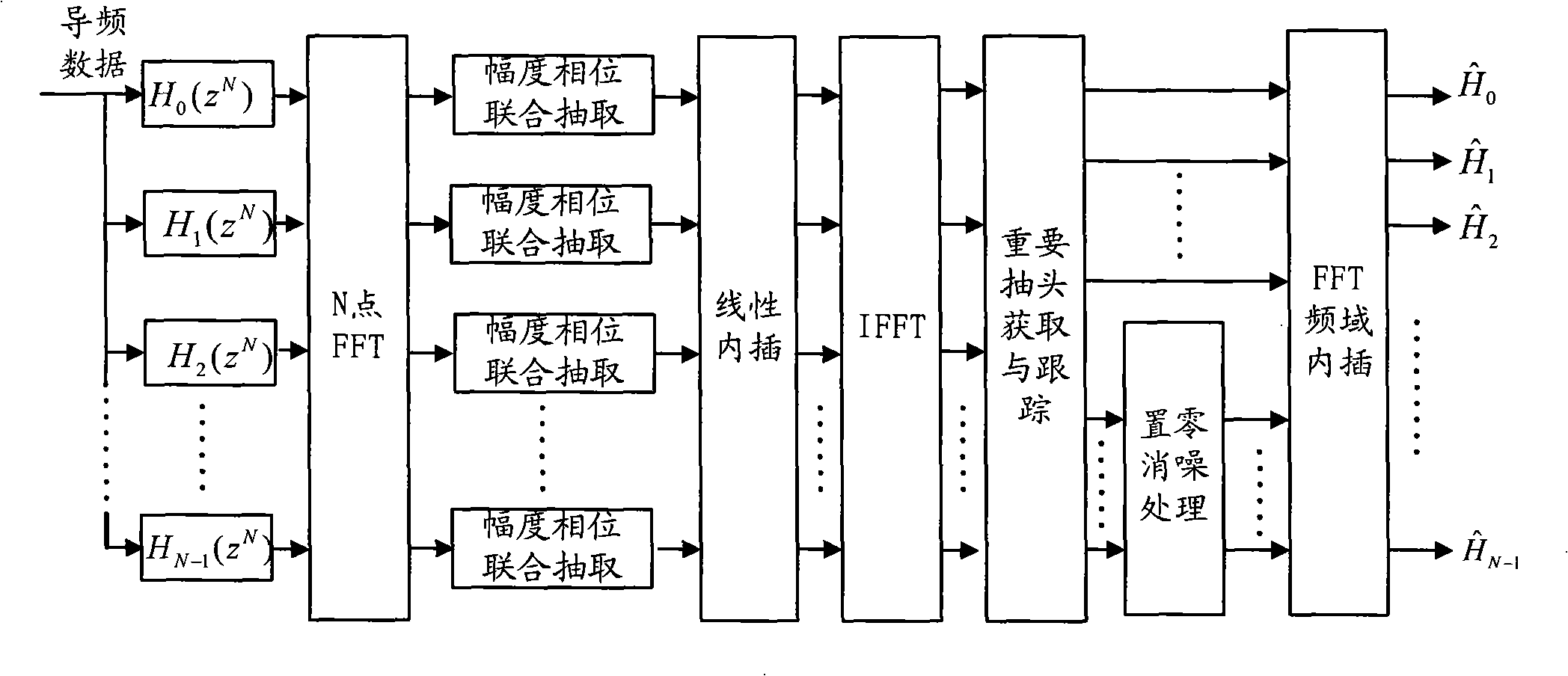

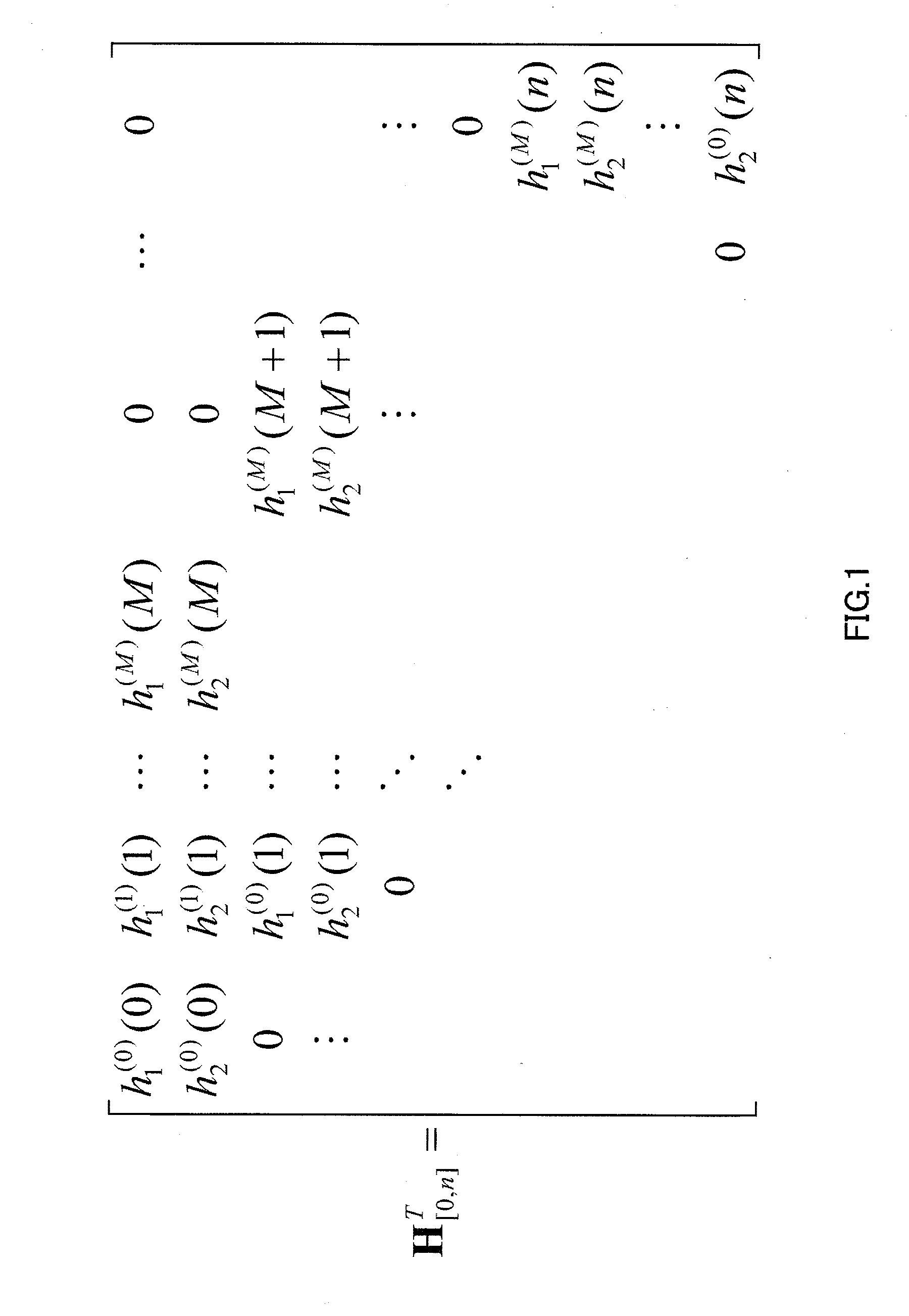

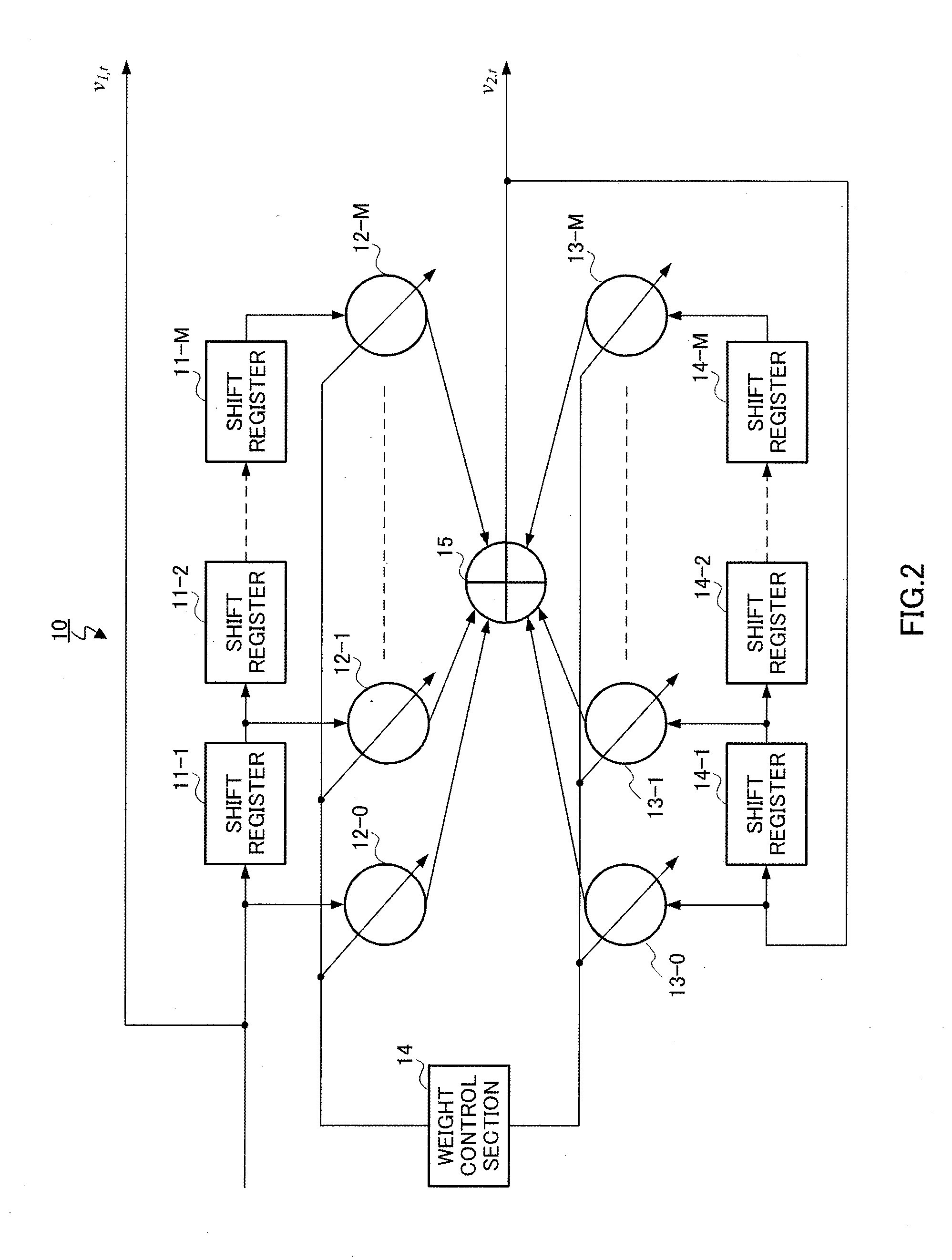

An OFDM time shift channel measuring method

InactiveCN101267421AImprove meter accuracyReduce computational complexityBaseband system detailsMulti-frequency code systemsChannel parameterCarrier signal

The invention provides an OFDM time-varying channel measuring method, comprising the following steps: generating complex exponential pilot frequency data having the same central frequency point as that of an OFDM sampling sub-carrier, multiplexing the data with data to be transmitted at a transmitting terminal in comb-like format, sending the pilot frequency data received by a receiving terminal in corresponding pilot frequency positions to a multi-phase filter bank realized by N points FFT, amplitude phase united extracting the data outputted by each corresponding passage to obtain initial channel frequency measuring data on a corresponding pilot frequency sub-carrier, obtaining initial channel frequency measuring data on all pilot frequency sub-carriers by linear interpolating, performing IFFT, and acquiring and tracking L-point important taps in time frequency. Finally, the L-point important taps coefficients are zero padded and FFT processed, interpolation in frequency domain is carried out to obtain channel parameters in all sub-carriers positions. By filtering noise by multi-phase filter, the measuring accuracy of parameters of an OFDM time-varying channel in low Signal-to-Noise condition is improved, and the invention has the characteristic of low bit error floor.

Owner:SHANGHAI UNIV

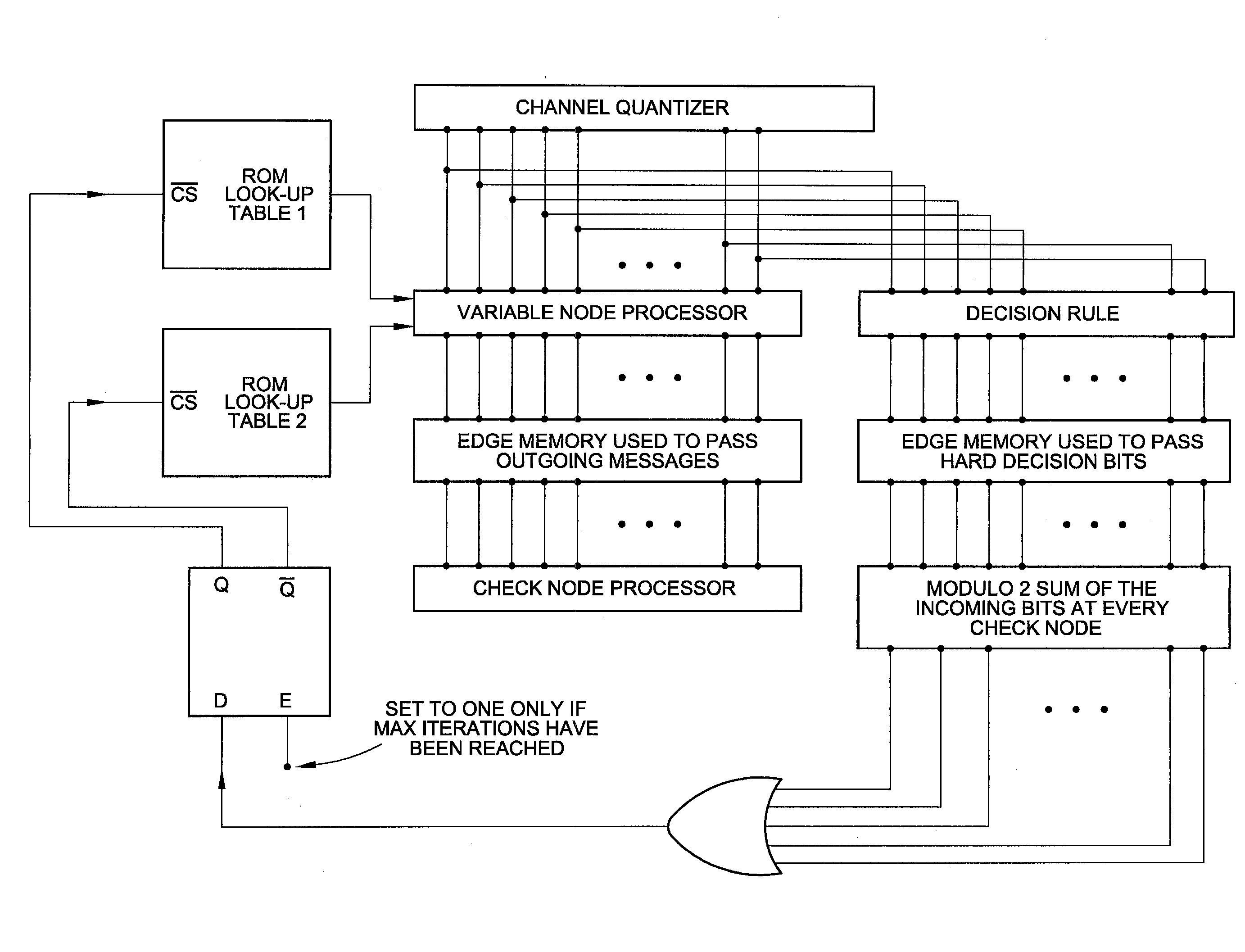

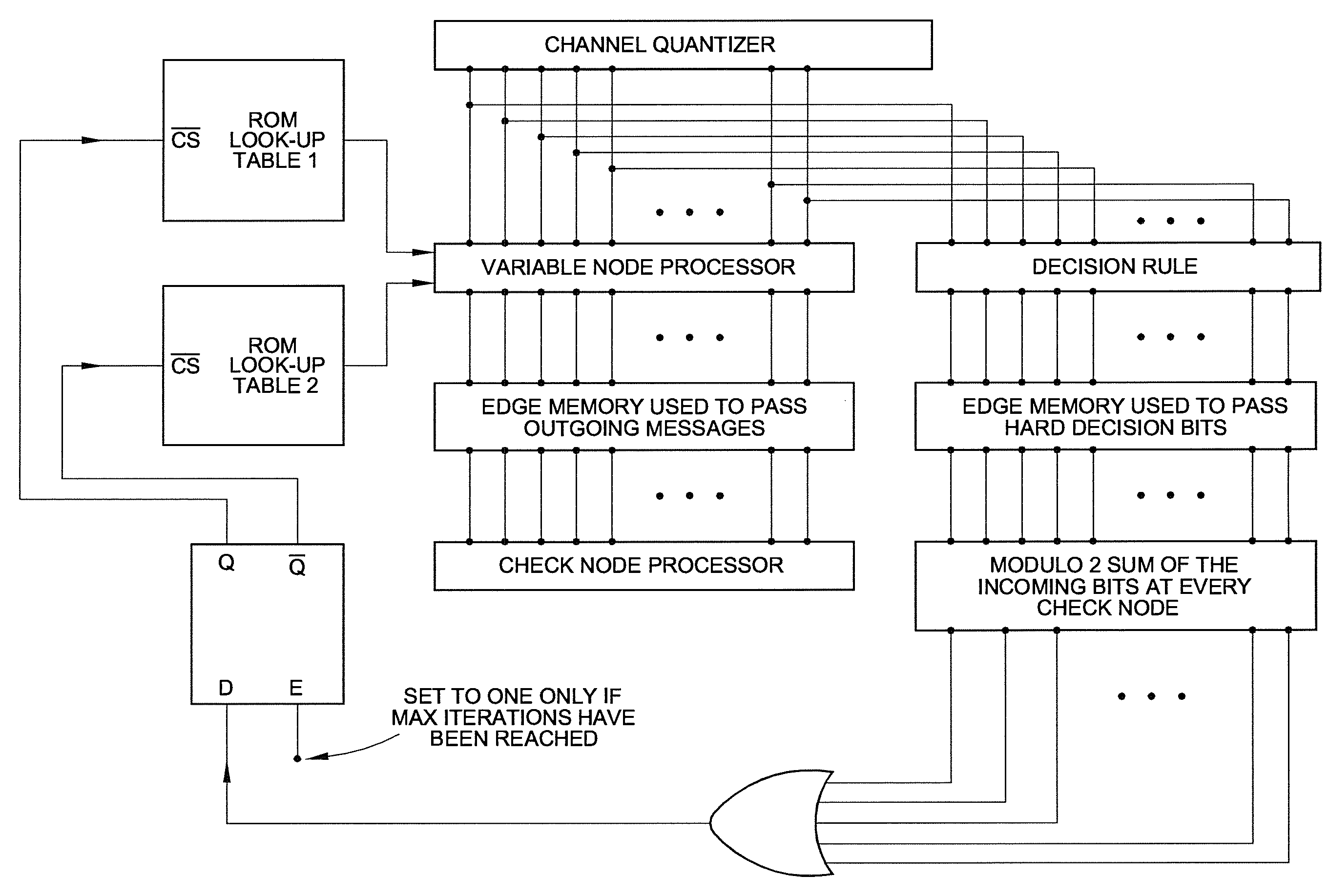

Low complexity finite precision decoders and apparatus for LDPC codes

ActiveUS20110087946A1Improving message-passing processLow failure rateCode conversionError correction/detection using block codesNODALRound complexity

In this invention, a new class of finite precision multilevel decoders for low-density parity-check (LDPC) codes is presented. These decoders are much lower in complexity compared to the standard belief propagation (BP) decoder. Messages utilized by these decoders are quantized to certain levels based on the number of bits allowed for representation in hardware. A message update function specifically defined as part of the invention, is used to determine the outgoing message at the variable node, and the simple min operation along with modulo 2 sum of signs is used at the check node. A general methodology is provided to obtain the multilevel decoders, which is based on reducing failures due to trapping sets and improving the guaranteed error-correction capability of a code. Hence these decoders improve the iterative decoding process on finite length graphs and have the potential to outperform the standard floating-point BP decoder in the error floor region. The description and apparatus of 3-bit decoders for column-weight three LDPC codes is also presented.

Owner:STMICROELECTRONICS SRL +2

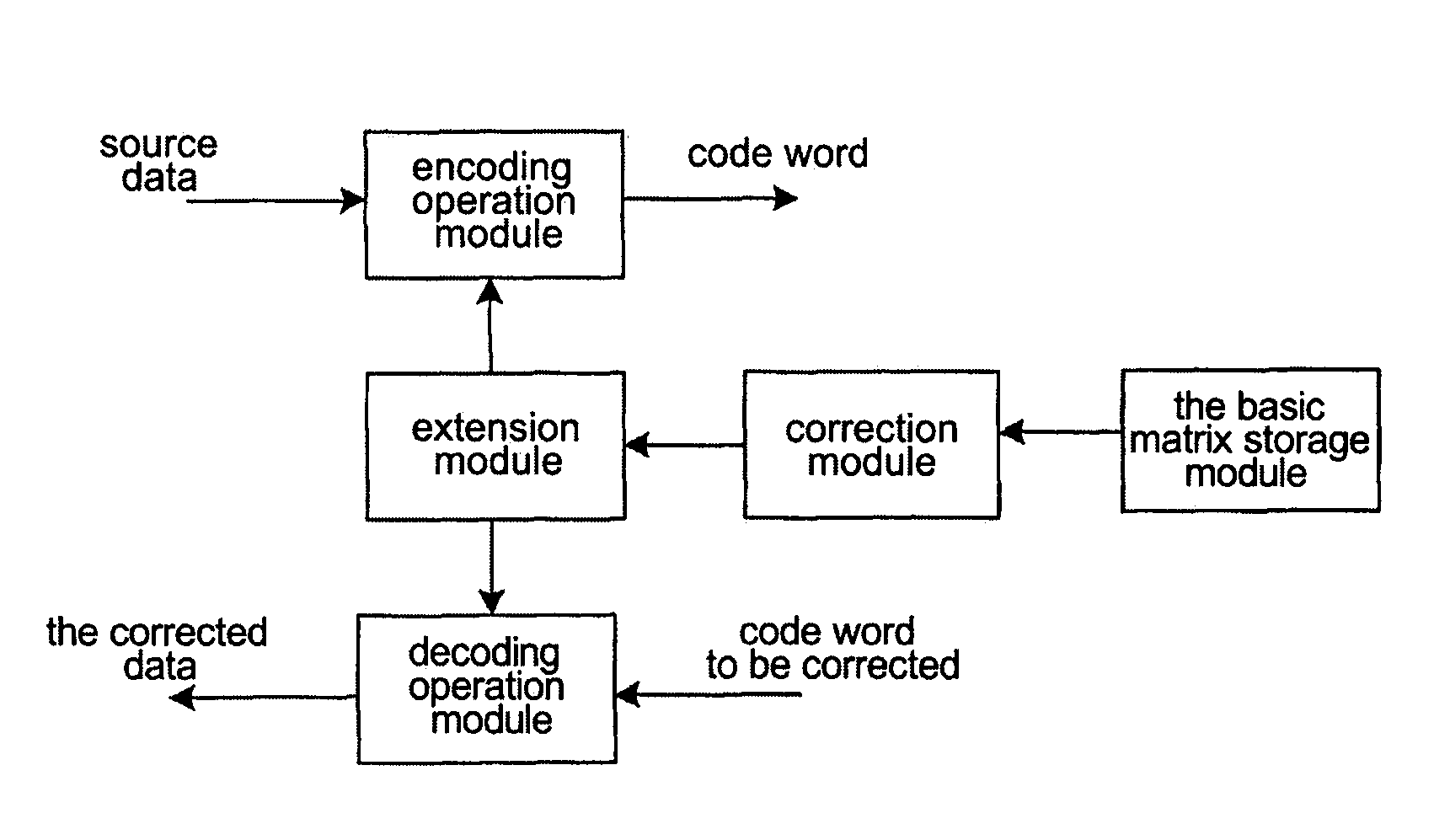

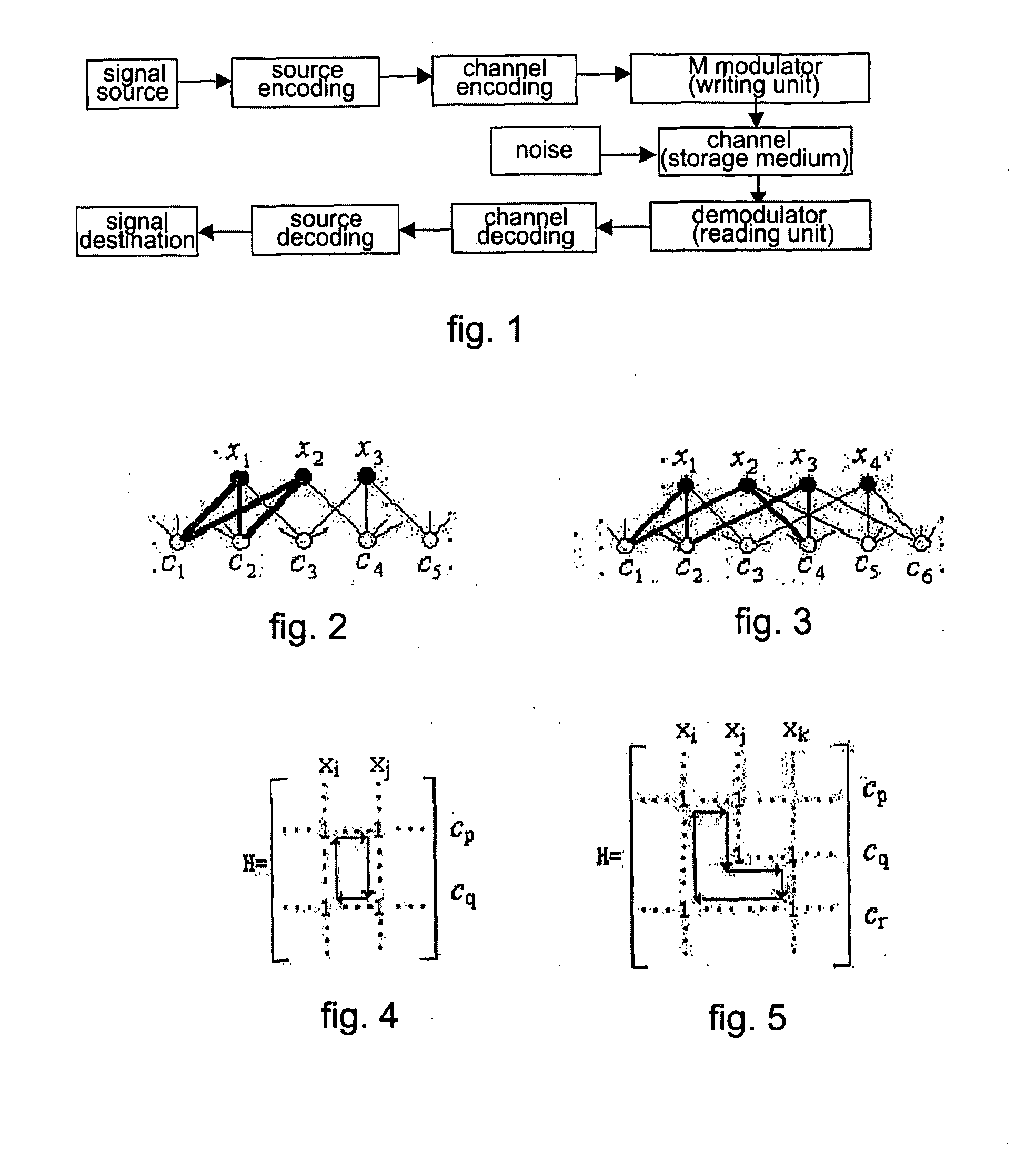

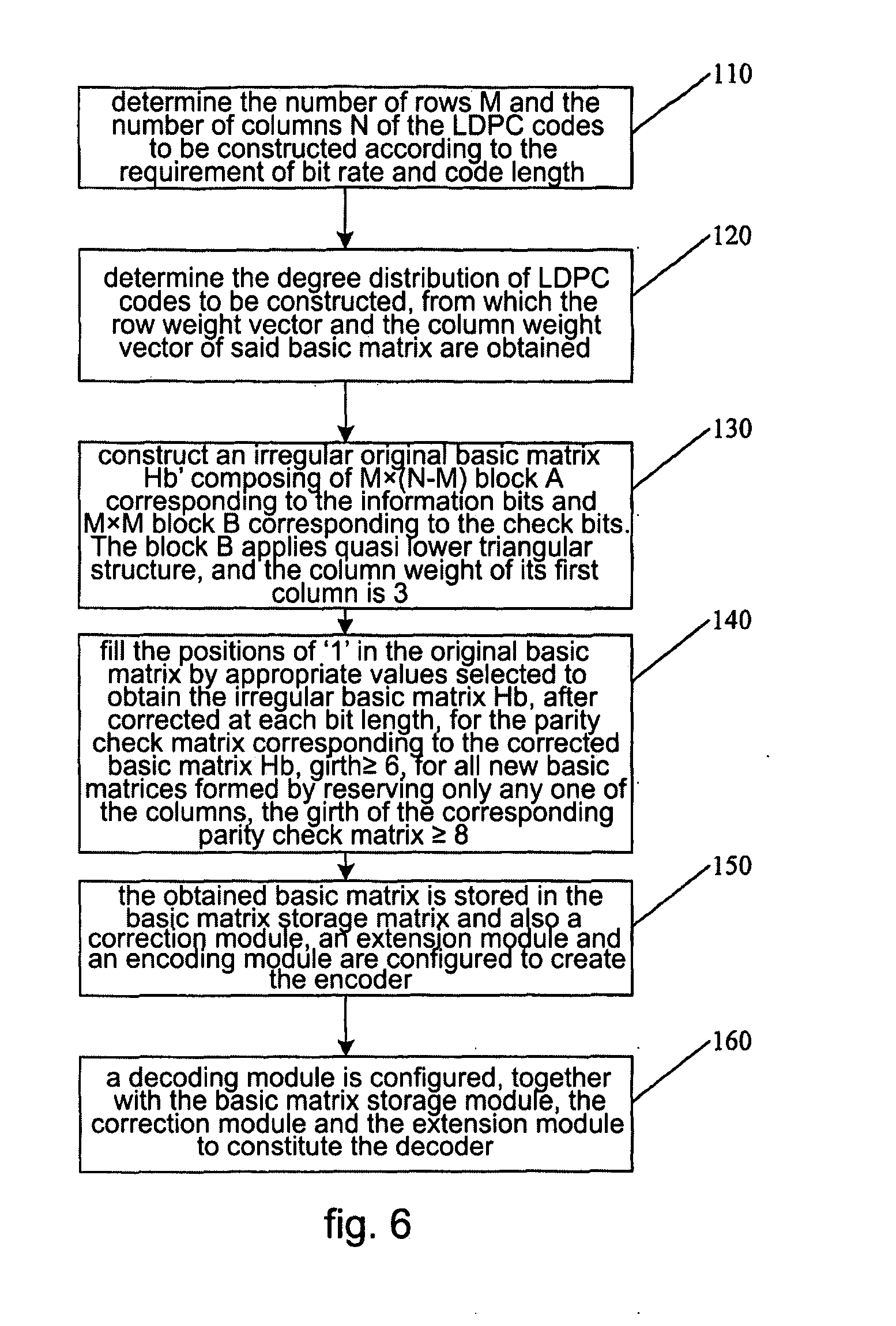

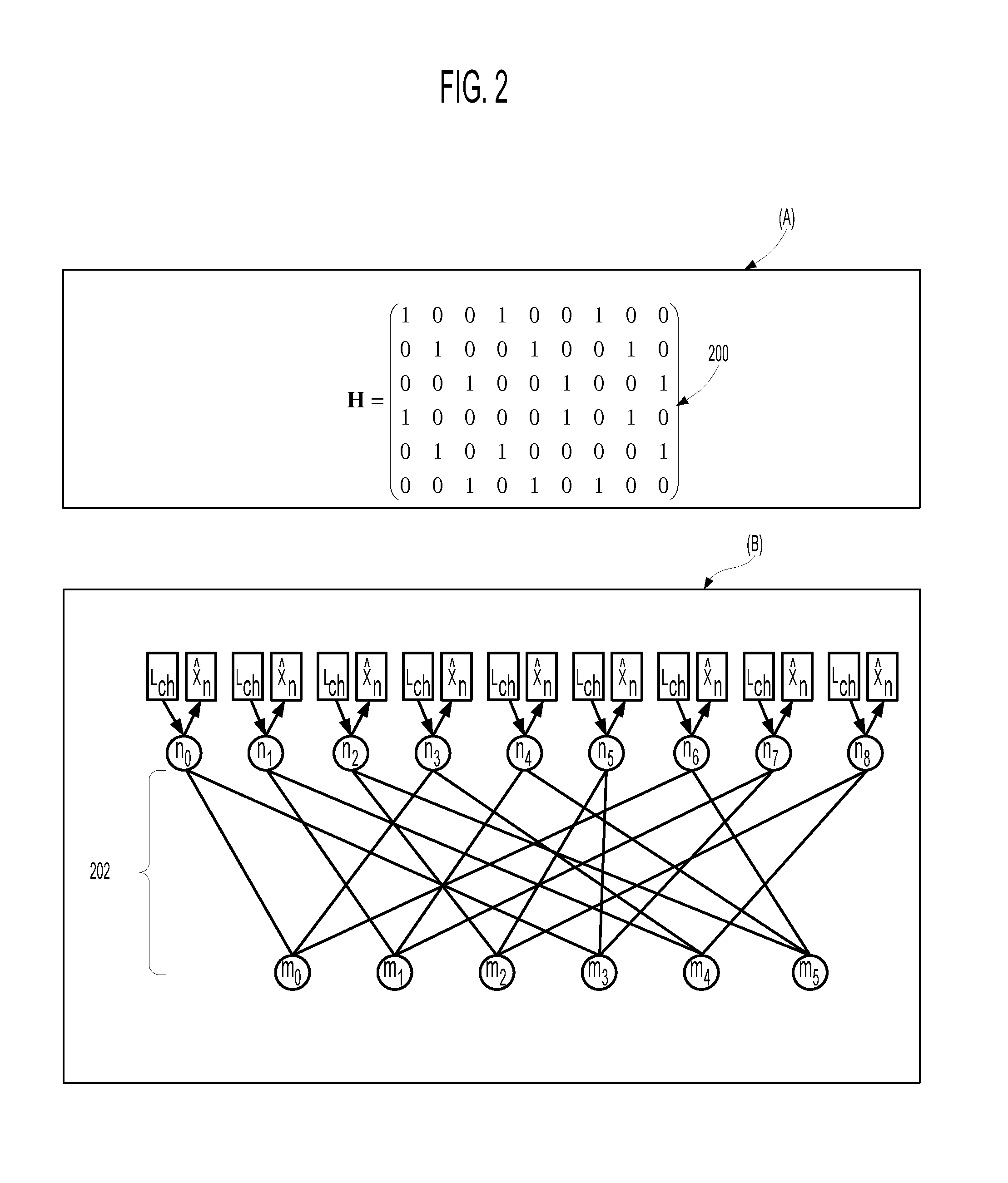

Basic Matrix Based on Irregular Ldpc, Codec and Generation Method Thereof

ActiveUS20080168324A1Eliminate phenomenonSpeed up the fallError detection/correctionParty-line systemsEssential matrixEuclidean vector

Basic matrix based on irregular LDPC codes, codec and generation method thereof. The codec includes an encoding / decoding operation module and a basic matrix storage module. In the stored basic matrix Hb, for all girths with length of 4, any element of i, j, k or l constituting the girths in anti-clockwise or clockwise always satisfies inequality: mod(i−j+k−l, z)≠0, wherein z is the extension factor. When generating the basic matrix, firstly the number of rows M, number of columns N, and weight vectors of the rows and columns are determined, an irregularly original basic matrix is constructed; then the position of ‘1’ is filled by a value chosen from set {0, 1, 2, . . . , z−1} to obtain the basic matrix Hb, which is made to satisfy the above-mentioned inequality. The basic matrix Hb obtained by storing, which is configured with corresponding encoding / decoding operation module, constitutes the desired encoder / decoder. The encoder / decoder according to the present invention can effectively eliminate error-floor phenomenon of LDPC codes and accelerate the falling speed of BER curve.

Owner:ZTE CORP

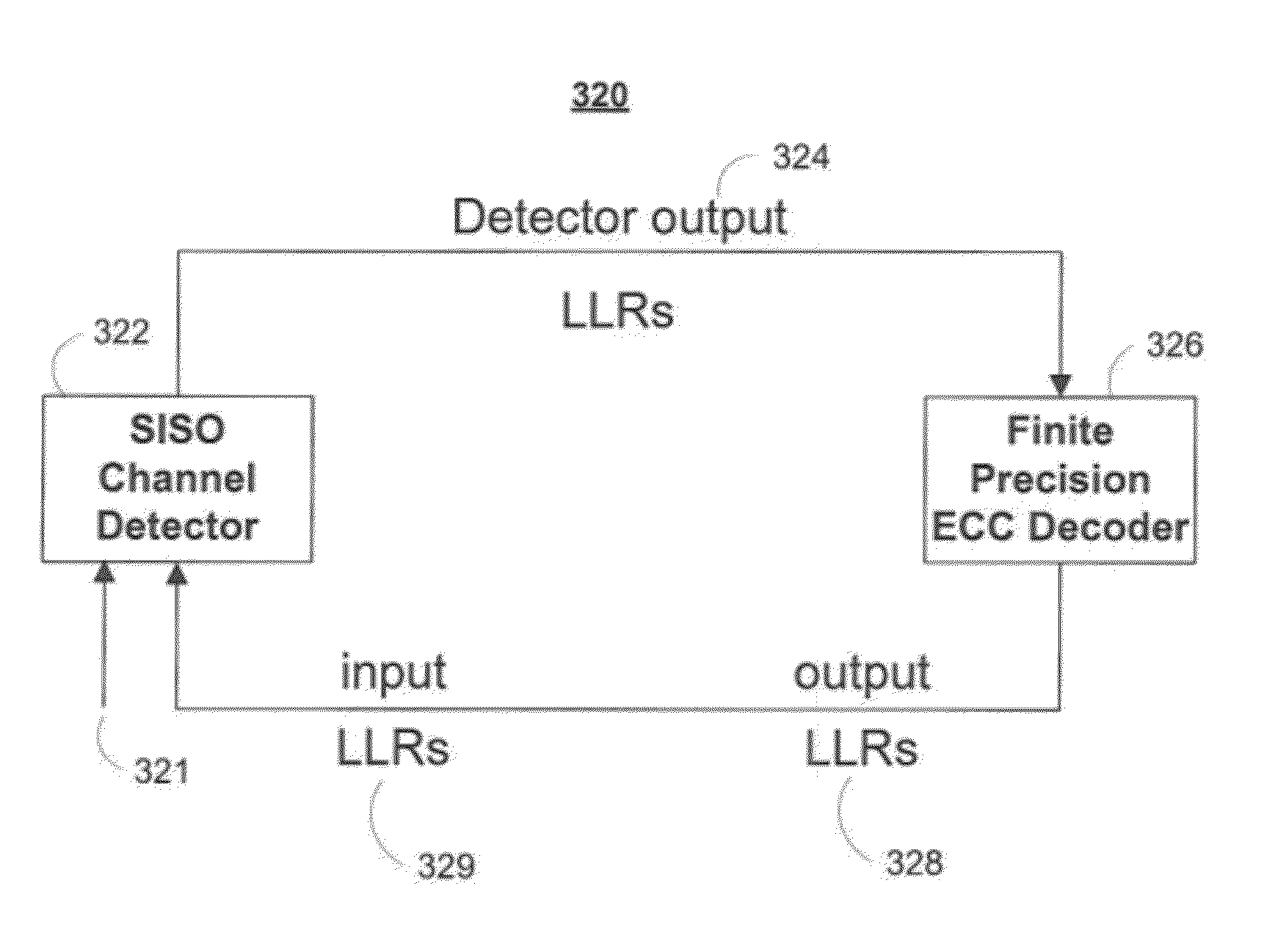

Optimizing error floor performance of finite-precision layered decoders of low-density parity-check (LDPC) codes

ActiveUS8291292B1Improve performanceAvoid mistakesCode conversionNon-redundant fault processingLow densityComputer science

Systems and methods are provided for selecting precisions during iterative decoding with a low-density parity check (LDPC) decoder in order to maximize LDPC code's performance in the error floor region. The selection of the precision of the messages may be done in such a way as to avoid catastrophic errors and to minimize the number of near-codeword errors during the decoding process. Another system and method to avoid catastrophic errors in the layered (serial) LDPC decoder is provided. Lastly, a system and method that select precisions and provide circuitry that optimizes the exchange of information between a soft-input, soft-output (SISO) channel detector and an error correction code (ECC) decoder for channels with memory is provided.

Owner:MARVELL ASIA PTE LTD

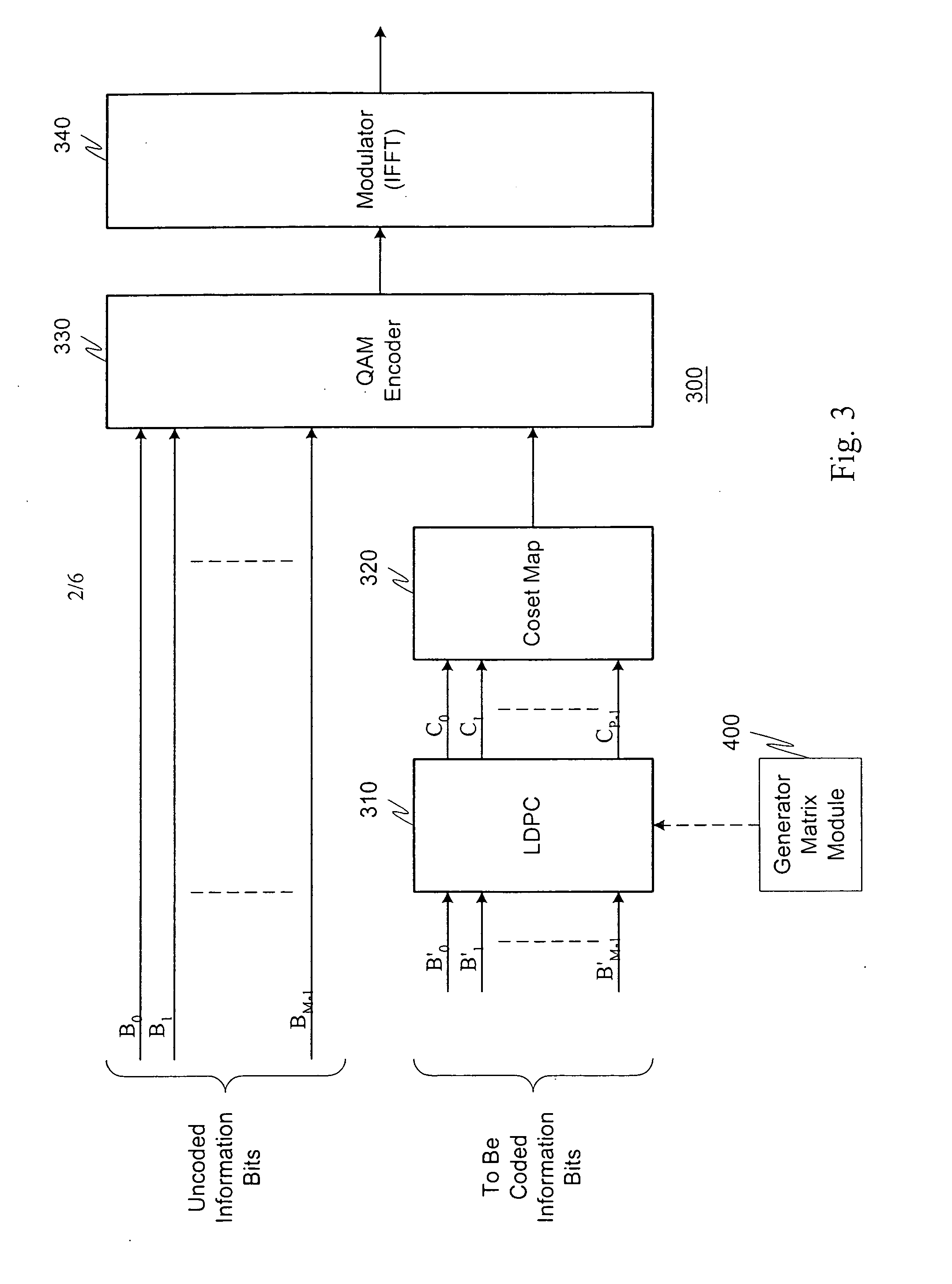

Systems and methods for LDPC coded modulation

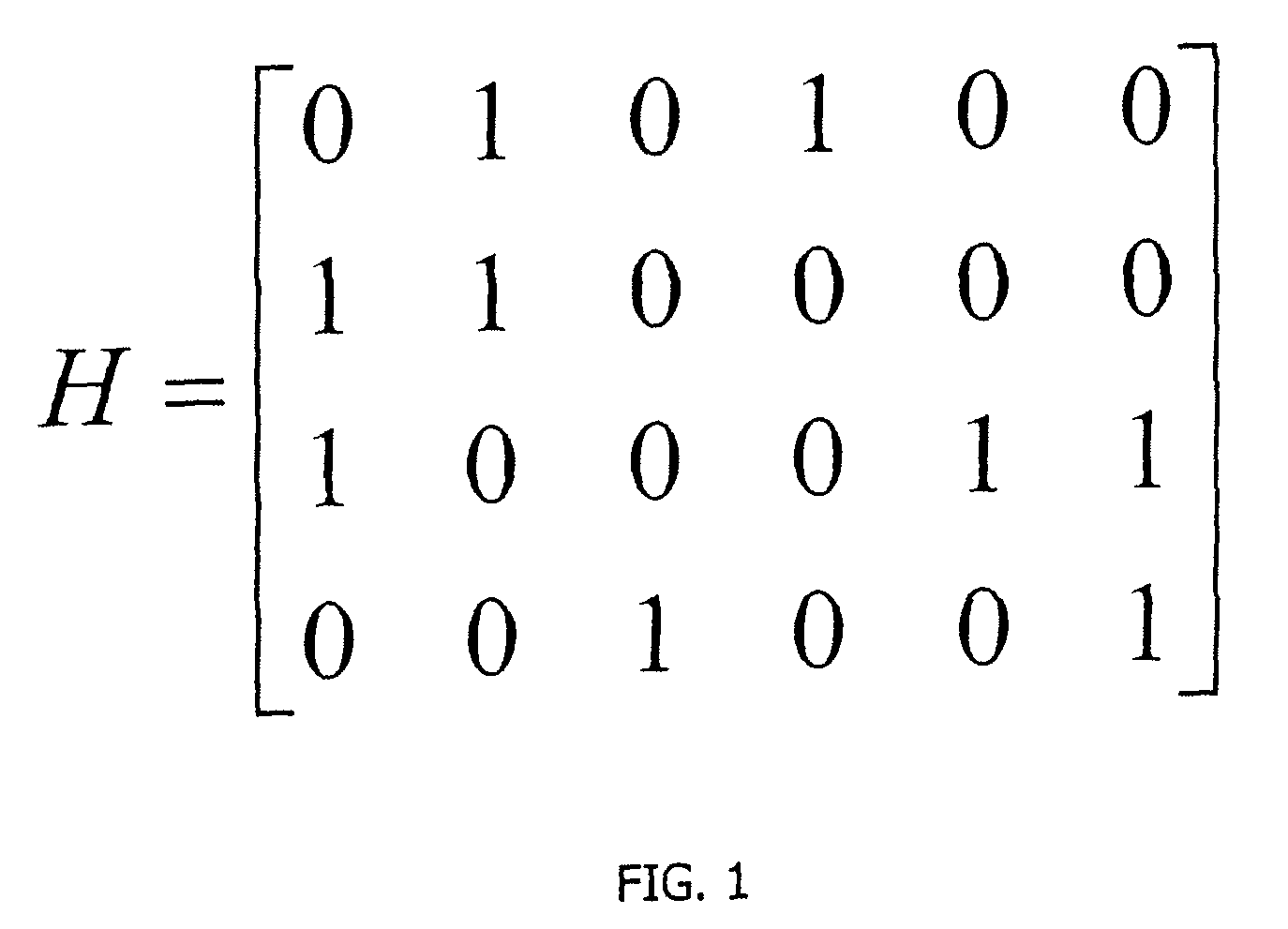

InactiveUS20050229088A1Improve performanceHigh gainError preventionError correction/detection using block single space codingTheoretical computer scienceParity-check matrix

Typical forward error correction methods employ Trellis Code Modulation. By substituting low density parity check coding in place of the convolution code as part of a combined modulation and encoding procedure, low density parity check coding and modulation can be performed. The low density parity check codes have no error floor, no cycles, an equal bit error rate for the information bits and the parity bits, and timely construction of both a parity check matrix with variable codeword size and a generator matrix is possible.

Owner:AWARE INC

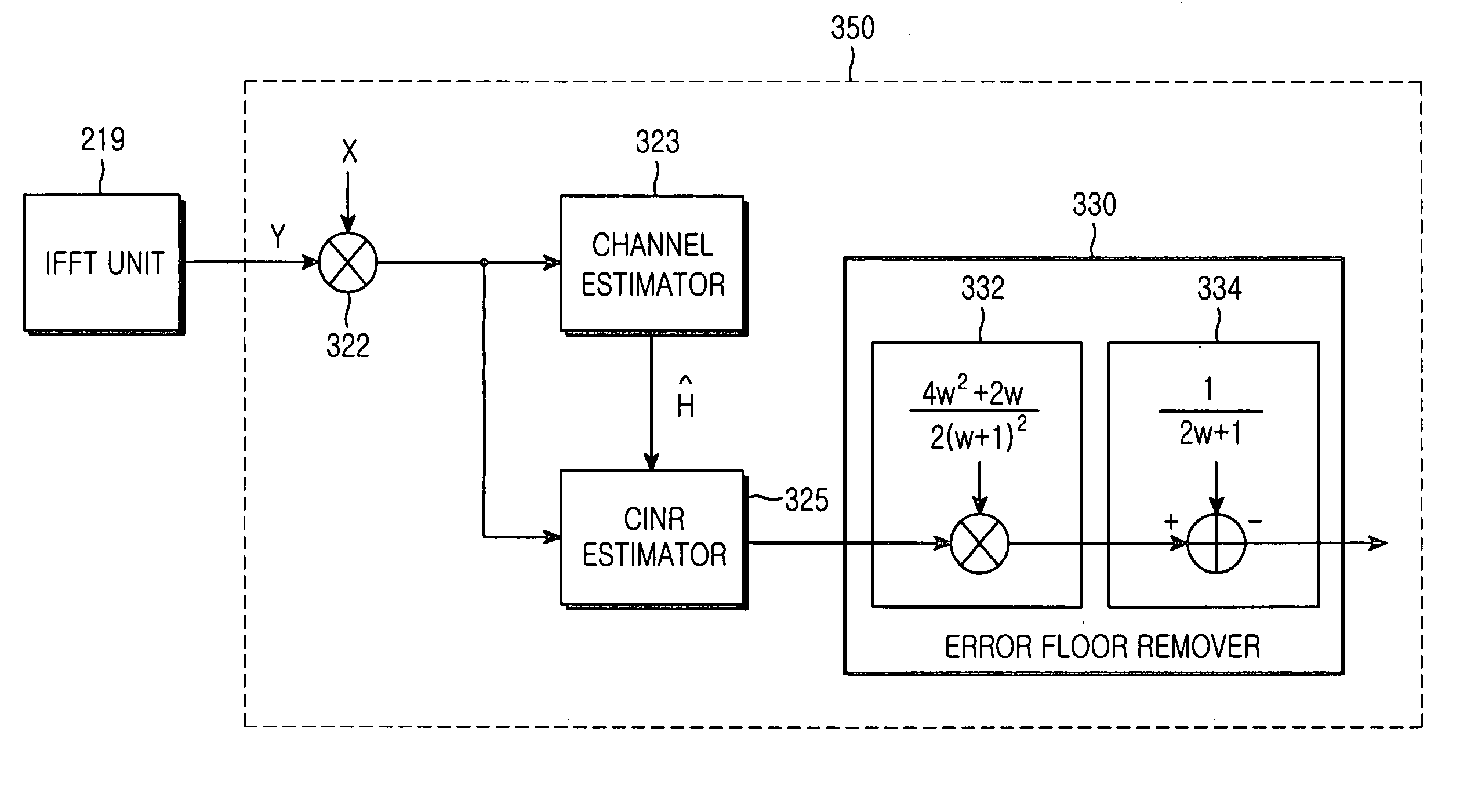

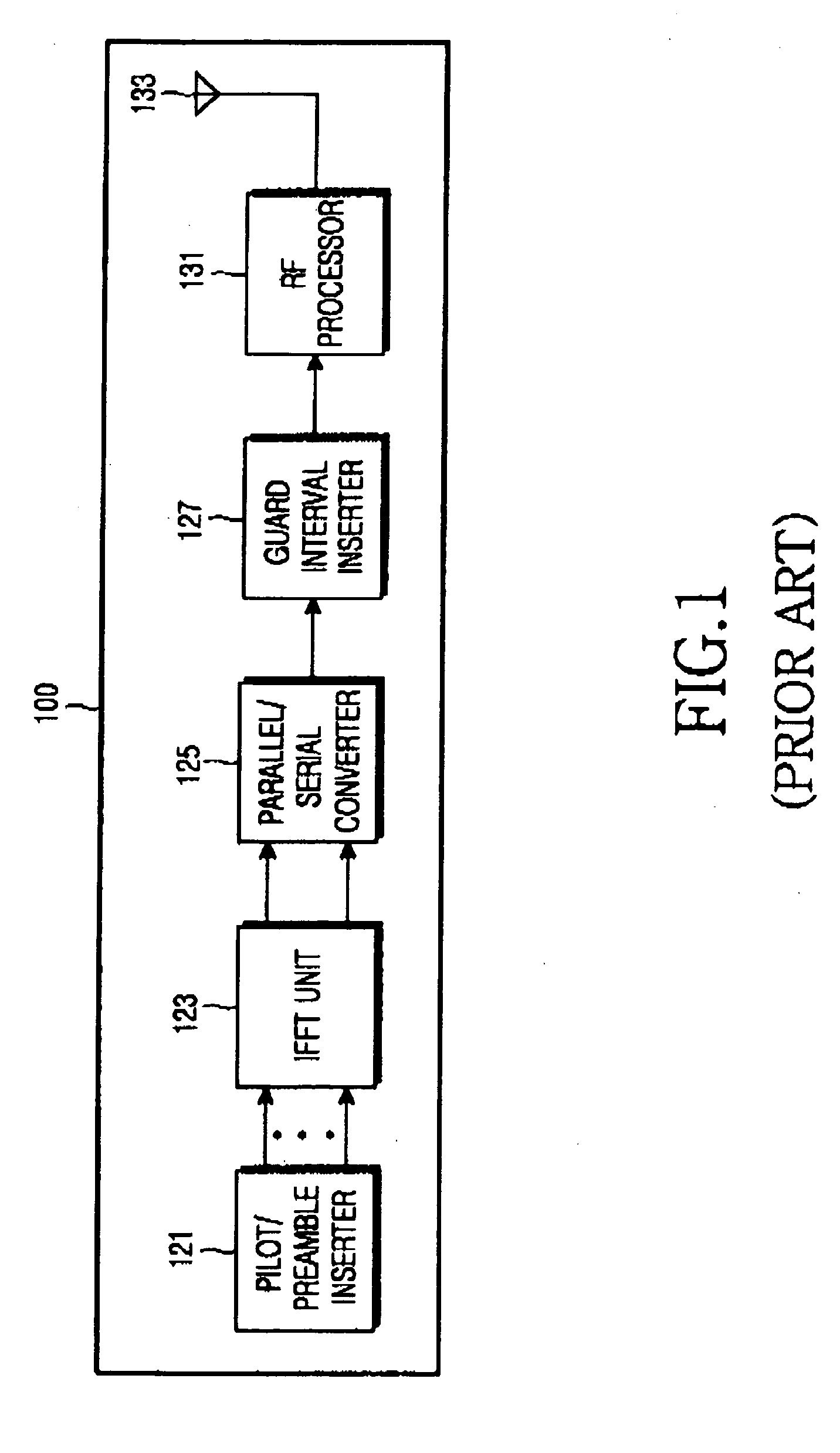

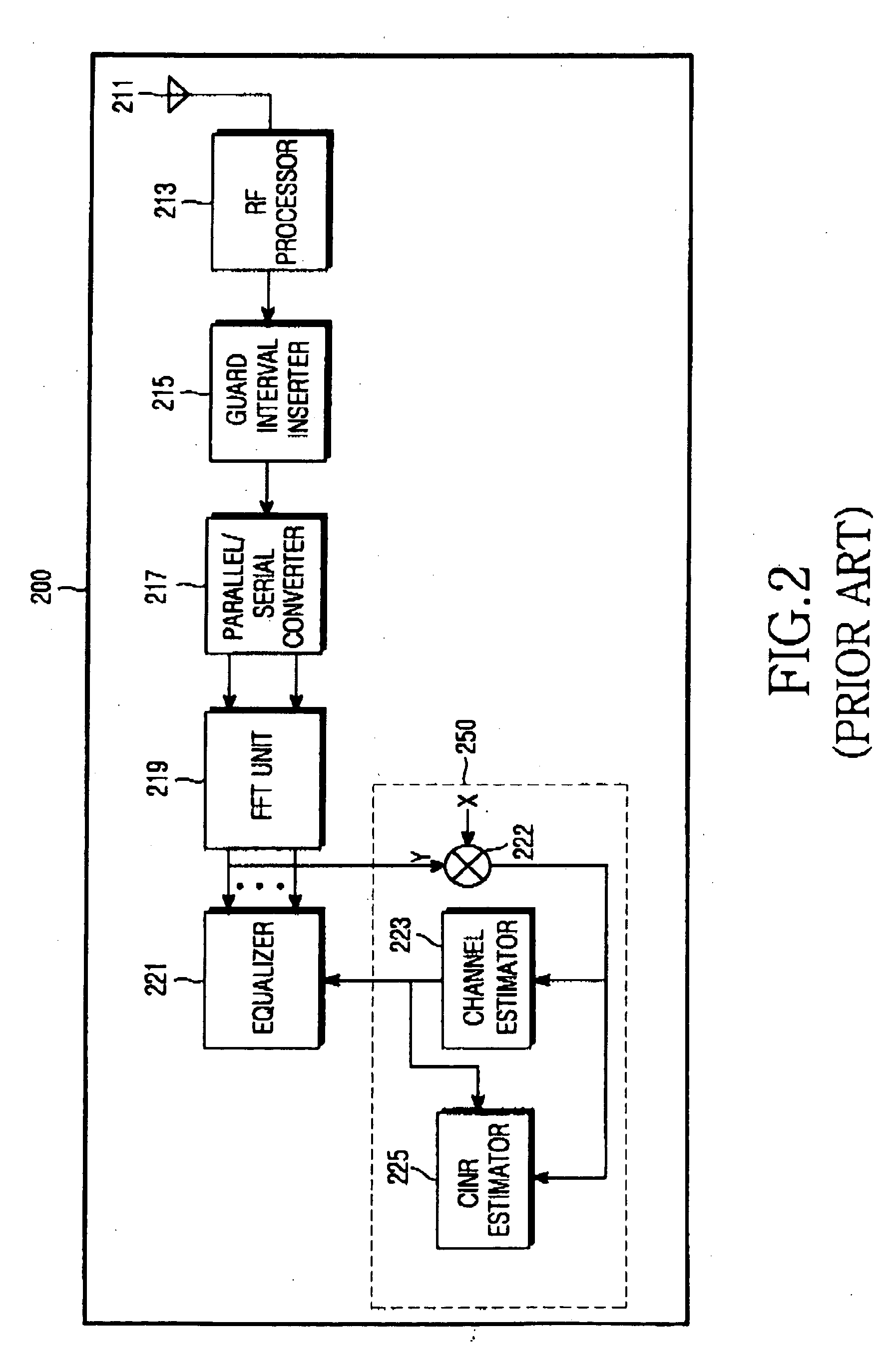

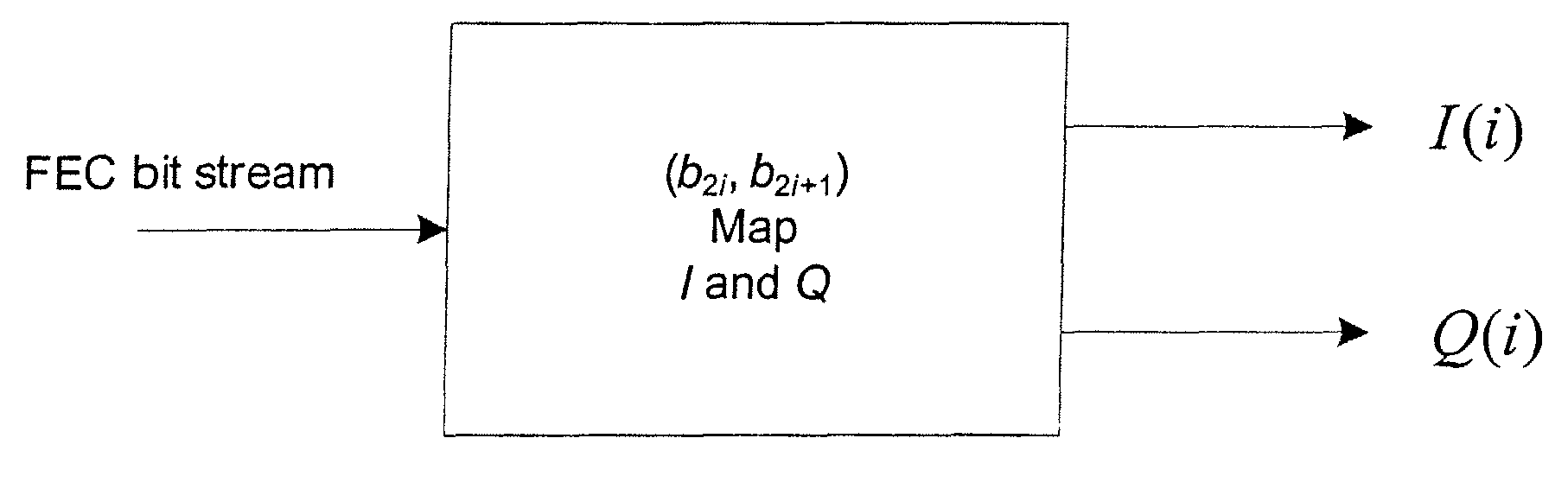

Apparatus and method for estimating a carrier to interference and noise ratio in a communication system

ActiveUS20050265489A1Accurate estimateError preventionFrequency-division multiplexCommunications systemCarrier signal

An apparatus and a method for estimating a carrier to interference and noise ratio (CINR) in a communication system. The CINR value is precisely estimated by removing the error floor value, which is caused by the inaccurate sliding average window SAW channel estimation value, from the CINR estimation value. Since the CINR value is precisely estimated, performance of the adaptive power control or the adaptive modulation and coding device is improved.

Owner:SAMSUNG ELECTRONICS CO LTD

Interleaving scheme for an LDPC coded QPSK/8PSK system

ActiveUS8230299B2Good thresholdReduce transmit powerData representation error detection/correctionOther decoding techniquesLow densityComputer science

Owner:AVAILINK

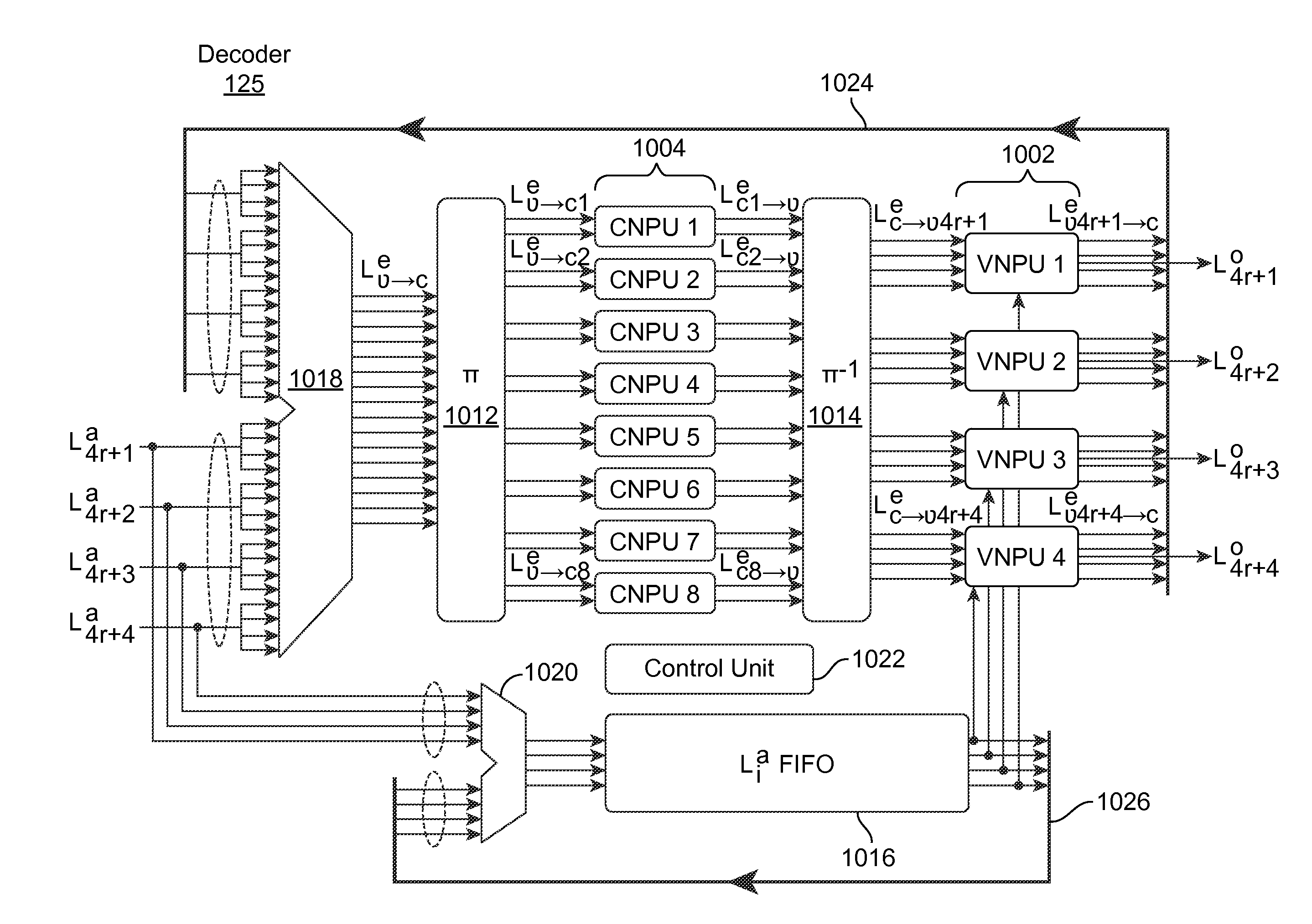

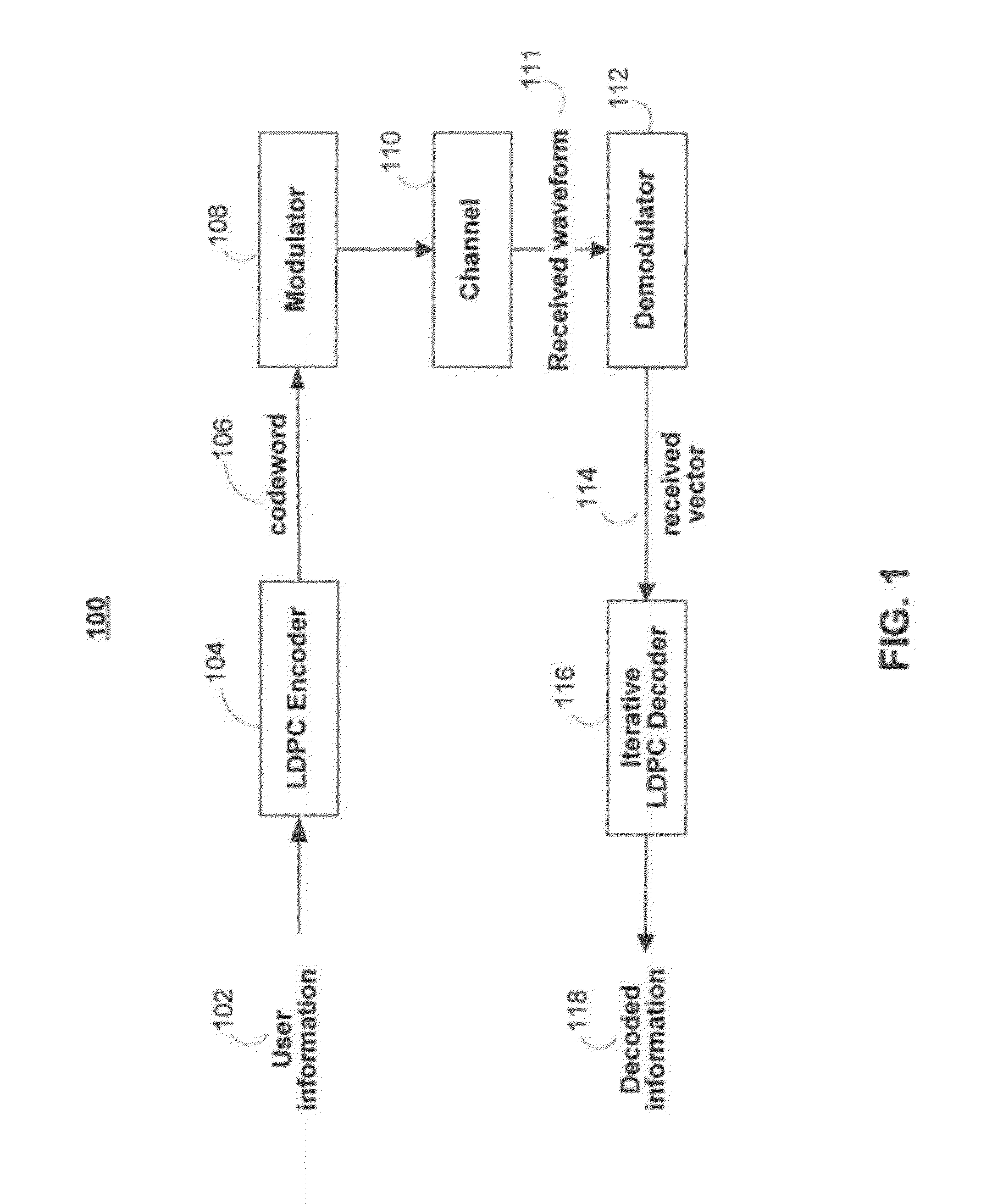

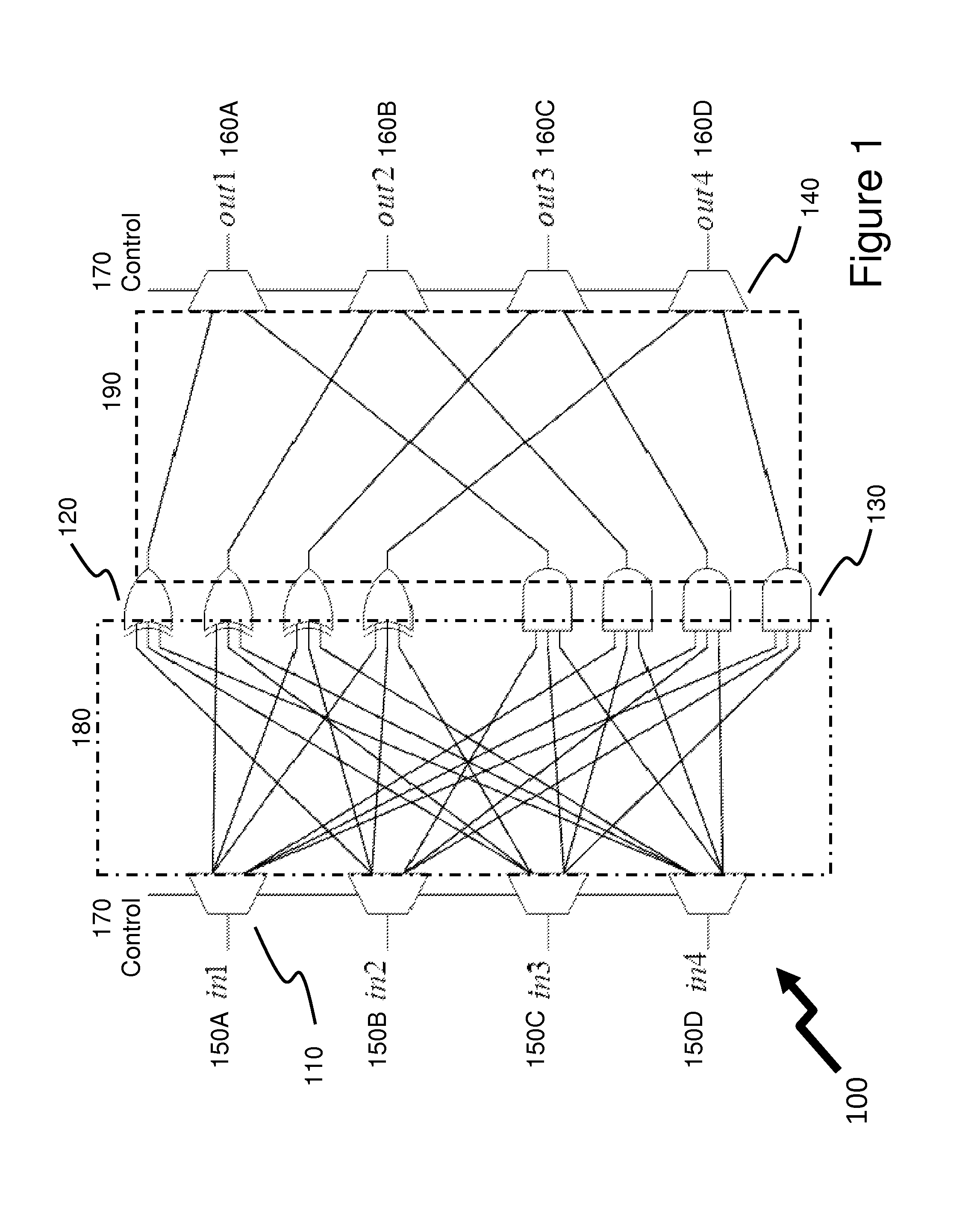

Method and system for decoding

ActiveUS8677227B2Improve performanceIncreased complexityCode conversionCoding detailsDecoding methodsCommunication link

Low-Density Parity-Check (LDPC) codes offer error correction at rates approaching the link channel capacity and reliable and efficient information transfer over bandwidth or return-channel constrained links with data-corrupting noise present. They also offer performance approaching channel capacity exponentially fast in terms of the code length, linear processing complexity, and parallelism that scales with code length. They also offer challenges relating to decoding complexity and error floors limiting achievable bit-error rates. Accordingly encoders with reduced complexity, reduced power consumption and improved performance are disclosed with various improvements including simplifying communications linking multiple processing nodes by passing messages where pulse widths are modulated with the corresponding message magnitude, delaying a check operation in dependence upon variable node states, running the decoder multiple times with different random number generator seeds for a constant channel value set, and employing a second decoder with a randomizing component when the attempt with the first decoder fails.

Owner:POLAR TECH

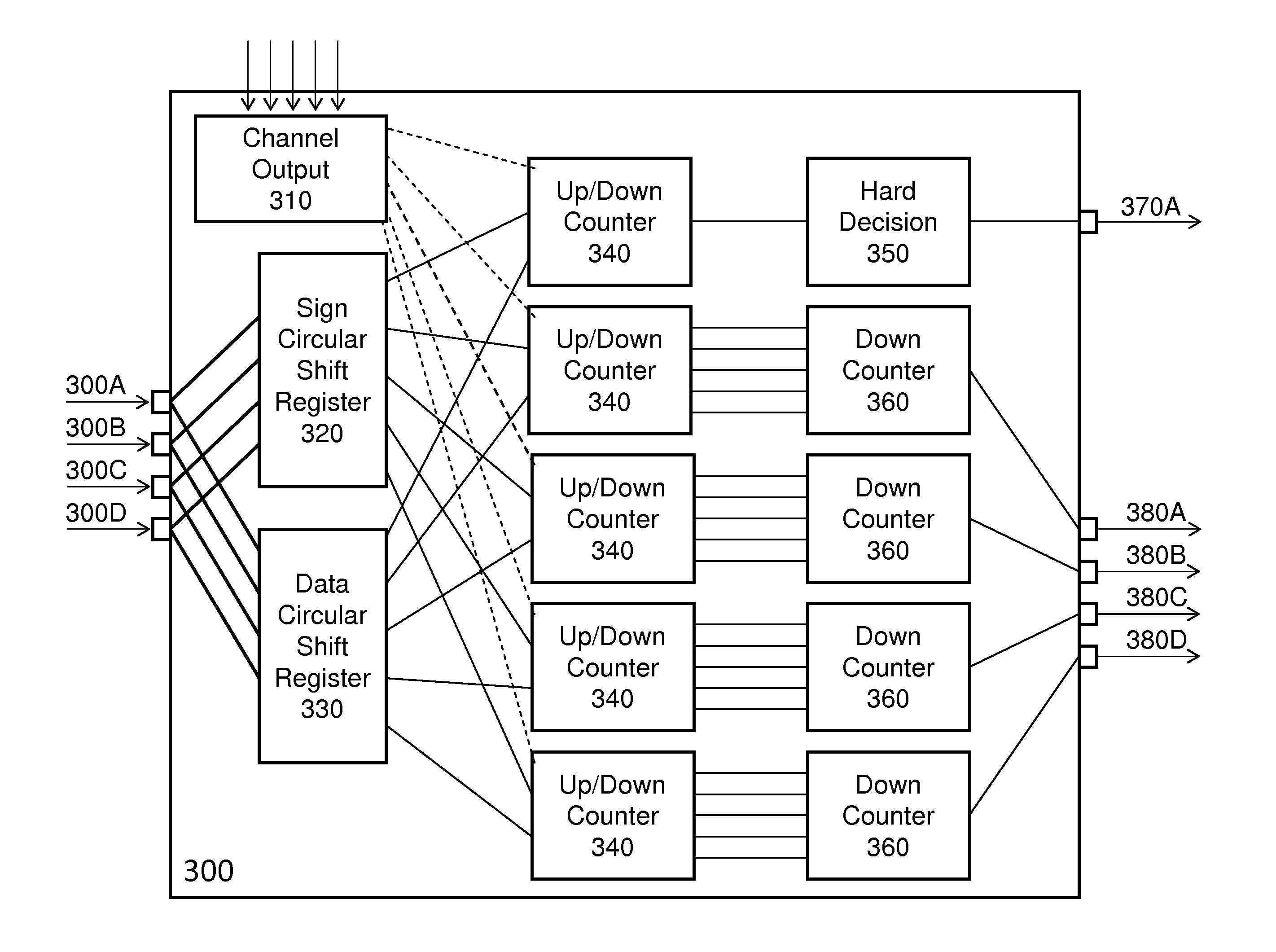

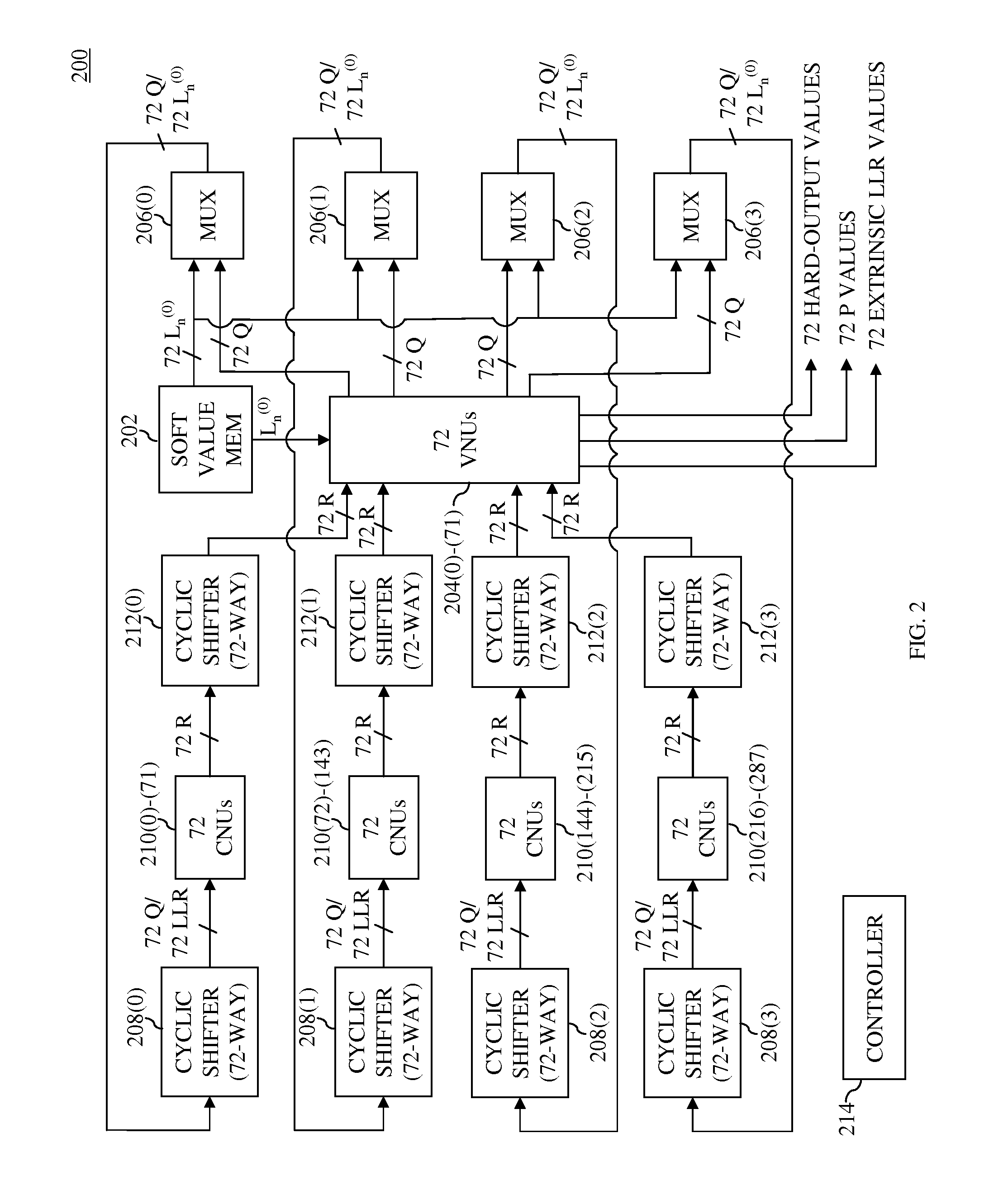

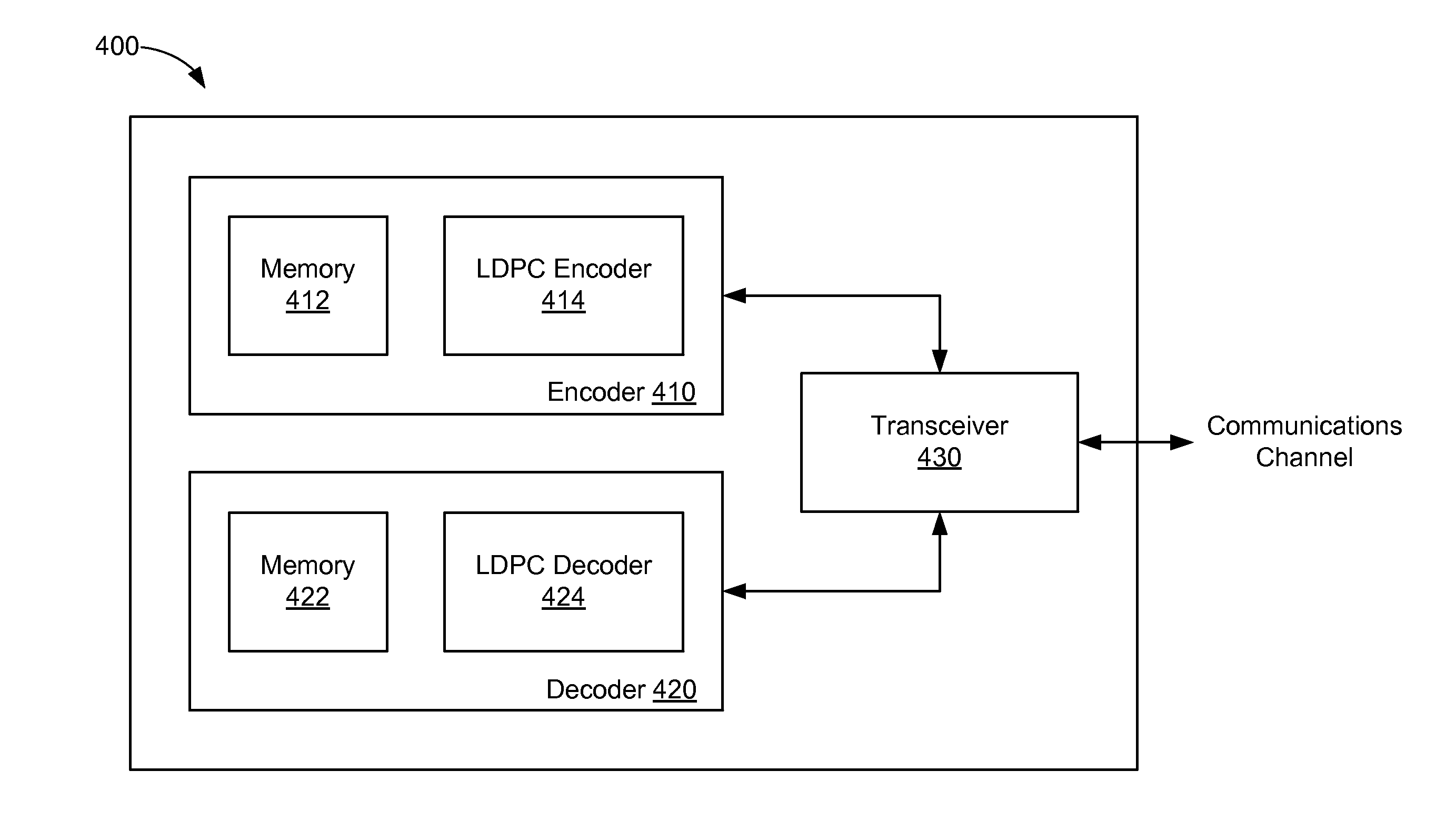

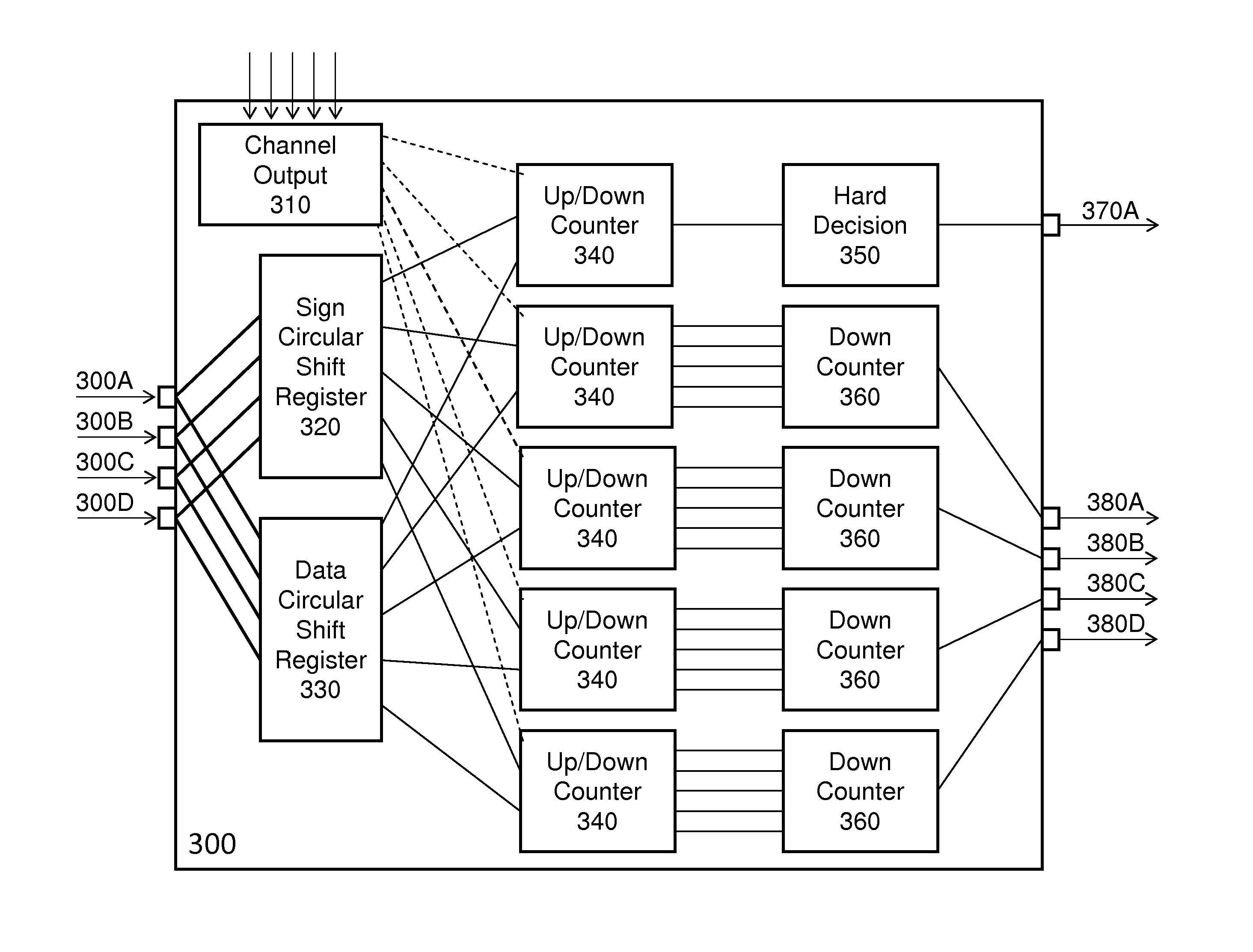

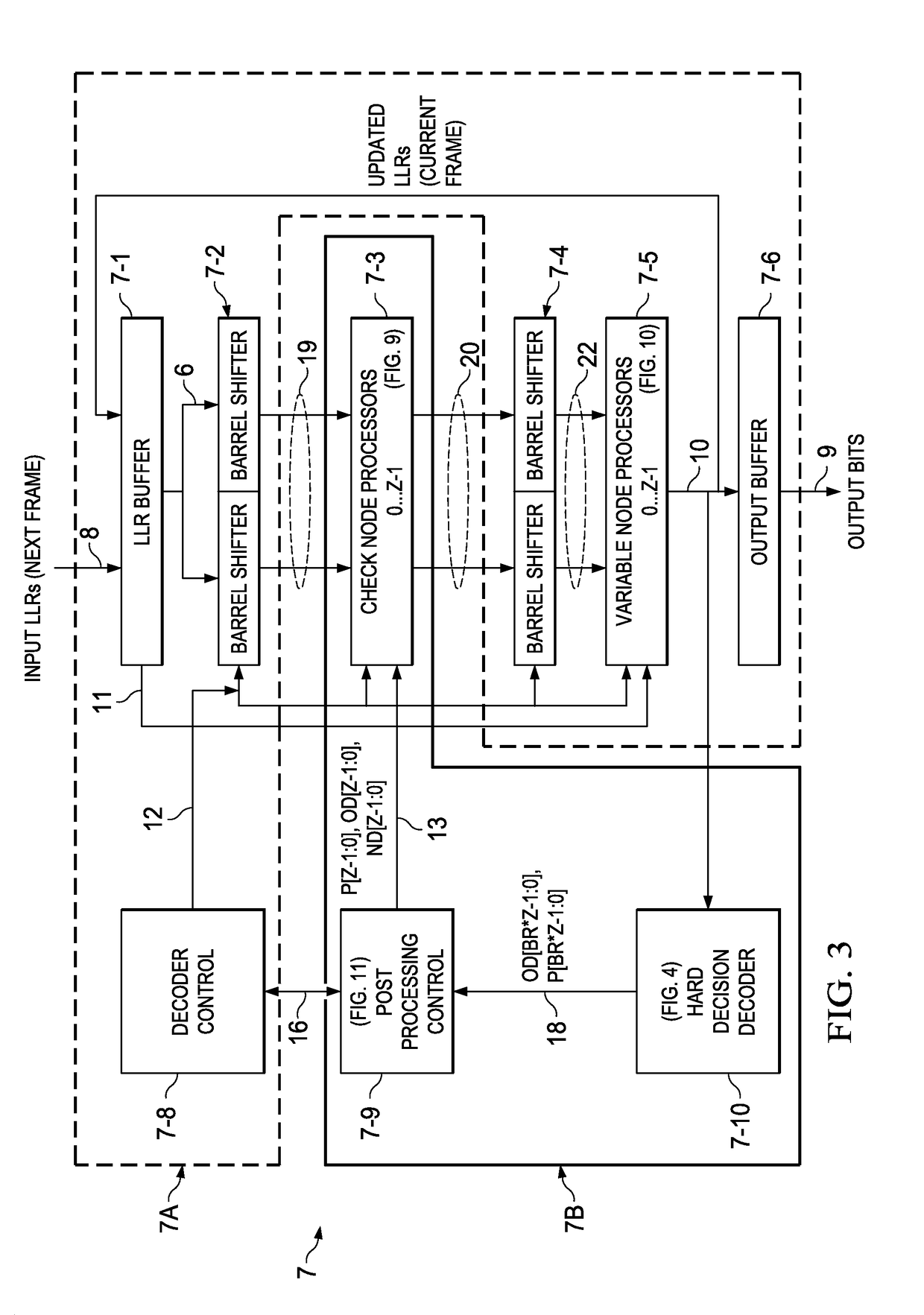

LDPC post-processor architecture and method for low error floor conditions

ActiveUS20170149446A1Reduce error rateSolve the real problemError correction/detection using multiple parity bitsCode conversionComputer architecturePost processor

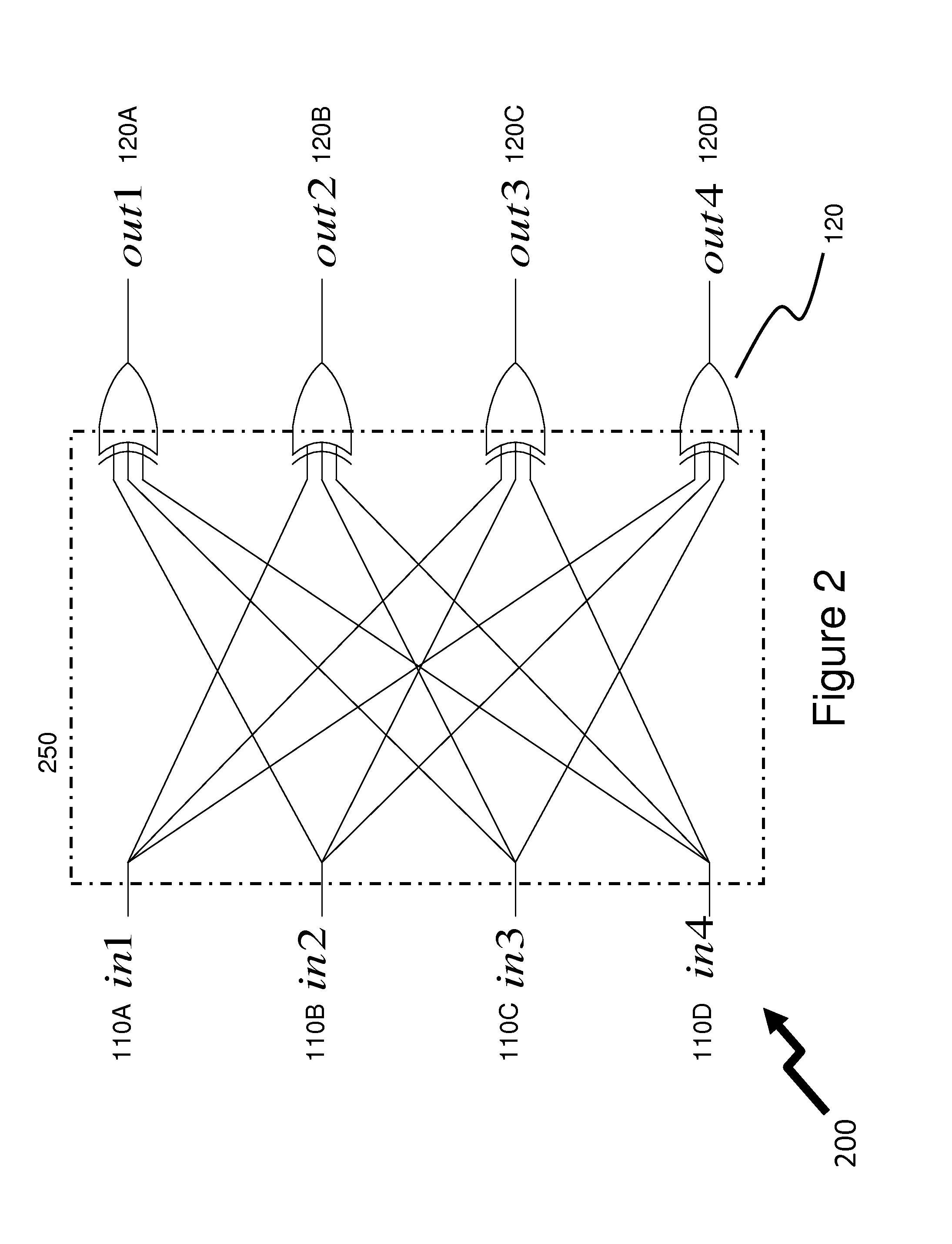

Post-processing circuitry for LDPC decoding includes check node processor for processing shifted LLR values, a hard decision decoder circuitry for receiving processed LLR information and performing parity checks on the processed LLR information. Post-processing control circuitry controls updating of LLR information in the check node processor. The check node processor, hard decision decoder, and control circuitry cooperate to identify check nodes with unsatisfied parity checks after an iteration cycle, identify neighborhood variable nodes that are connected with unsatisfied check nodes, identify satisfied check nodes which are connected to neighborhood variable nodes, and modify messages from neighborhood variable nodes to satisfied check nodes if needed to introduce perturbations to resolve decoding errors. Neighborhood identification circuitry determines which variable nodes are connected with unsatisfied check nodes, that have failed a parity check, and produces a signal indicating which variable nodes are connected to unsatisfied check nodes.

Owner:TEXAS INSTR INC

Encoding and decoding using constrained interleaving

InactiveUS20150039966A1Reduce measurementEfficient implementationCode conversionError correction/detection by combining multiple code structuresNoise marginSimple component

Serially-concatenated codes are formed in accordance with the present invention using a constrained interleaver. The constrained interleaver cause the minimum distance of the serial concatenated code to increase above the minimum distance of the inner code alone by adding a constraint that forces some or all of the distance of the outer code onto the serially-concatenated code. This allows the serially-concatenated code to be jointly optimized in terms of both minimum distance and error coefficient to provide significant performance advantages. These performance advantages allow a noise margin target to be achieved using simpler component codes and a much shorter interleaver than was needed when using prior art codes such as Turbo codes. Decoders are also provided. Both encoding and decoding complexity can be lowered, and interleavers can be made much shorter, thereby shortening the block lengths needed in receiver elements such as equalizers and other decision-directed loops. Also, other advantages are provided such as the elimination of a error floor present in prior art serially-concatenated codes. That allows the present invention to achieve much higher performance at lower error rates such as are needed in optical communication systems.

Owner:TRELLIS PHASE COMM LP

Low complexity finite precision decoders and apparatus for LDPC codes

ActiveUS8458556B2Improving message-passing processLow failure rateCode conversionCoding detailsNODALRound complexity

In this invention, a new class of finite precision multilevel decoders for low-density parity-check (LDPC) codes is presented. These decoders are much lower in complexity compared to the standard belief propagation (BP) decoder. Messages utilized by these decoders are quantized to certain levels based on the number of bits allowed for representation in hardware. A message update function specifically defined as part of the invention, is used to determine the outgoing message at the variable node, and the simple min operation along with modulo 2 sum of signs is used at the check node. A general methodology is provided to obtain the multilevel decoders, which is based on reducing failures due to trapping sets and improving the guaranteed error-correction capability of a code. Hence these decoders improve the iterative decoding process on finite length graphs and have the potential to outperform the standard floating-point BP decoder in the error floor region. The description and apparatus of 3-bit decoders for column-weight three LDPC codes is also presented.

Owner:STMICROELECTRONICS SRL +2

Iterative decoder employing multiple external code error checks to lower the error floor

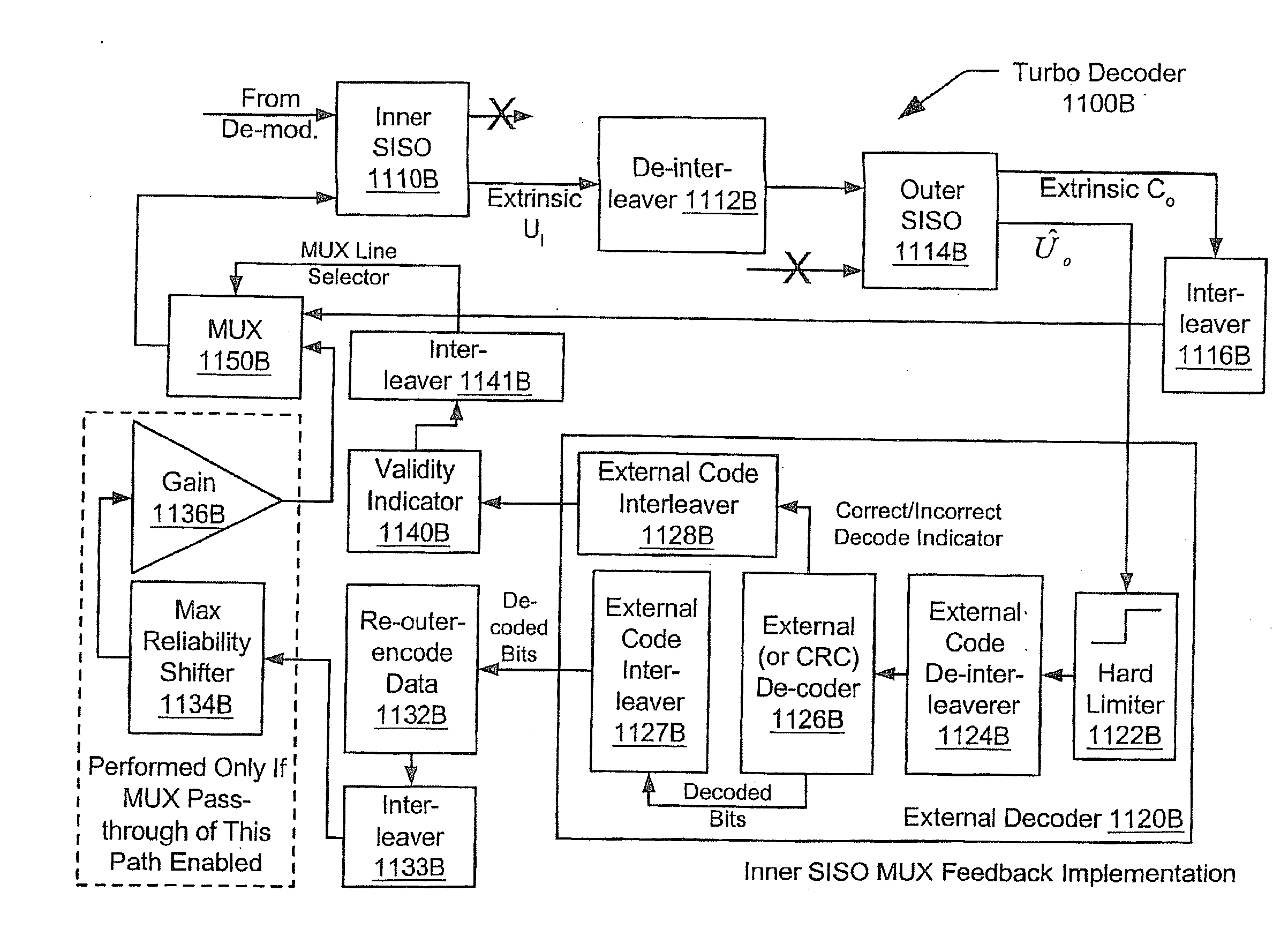

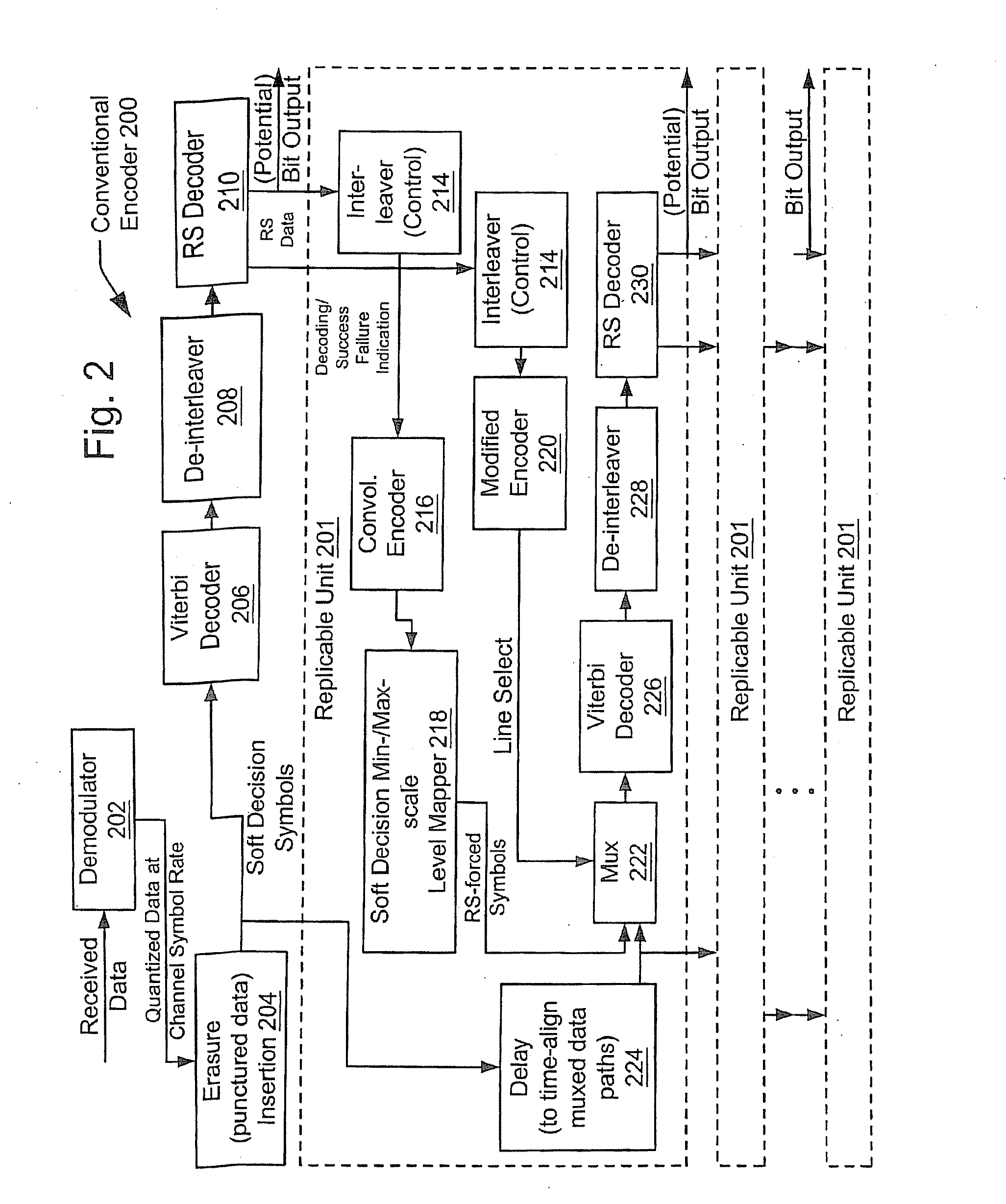

Iterative decoder employing multiple external code error checks to lower the error floor and / or improve decoding performance. Data block redundancy, sometimes via a cyclic redundancy check (CRC) or Reed Solomon (RS) code, enables enhanced iterative decoding performance. Improved decoding performance is achieved during interim iterations before the final iteration. A correctly decoded CRC block, indicating a decoded segment is correct with a high degree of certainty, assigns a very high confidence level to the bits in this segment and is fed back to inner and / or outer decoders (with interleaving, when appropriate) for improved iterative decoding. High confidence bits may be scattered throughout inner decoded frames to influence other bit decisions in subsequent iterations. Turbo decoders typically operate relatively well at regions where the BER is high; the invention improves iterative decoder operation at lower BERs, lowering the ‘BER floor’ that is sometimes problematic with conventional turbo decoders.

Owner:ENTROPIC COMM INC

Systems and methods for detection and correction of error floor events in iterative systems

InactiveUS8938660B1Data representation error detection/correctionCode conversionAlgorithmTime segment

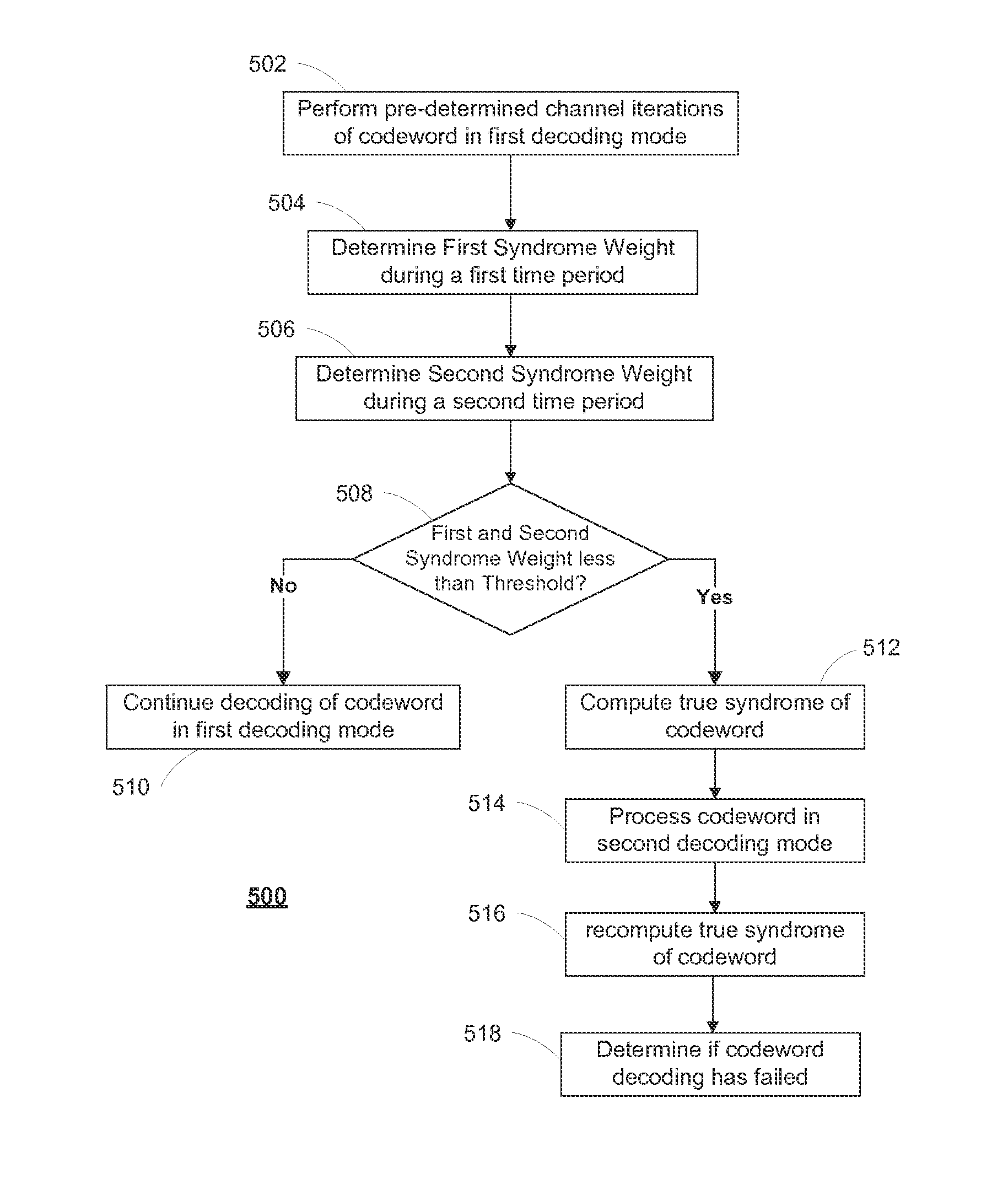

Methods and apparatuses are provided for decoding a codeword using an iterative decoder. The iterative decoder, in a first decoding mode, performs a number of channel iterations on the codeword, determines a first syndrome weight after a first time period, and determines a second syndrome weight after a second time period. Each channel iteration includes an iteration of the channel detector and at least one iteration of the inner iterative decoder. The iterative decoder, in a second decoding mode, determines a true syndrome of the codeword, and processes the codeword based on the true syndrome of the codeword. The codeword is processed using the second decoding mode in response to determining that the first and second determined syndrome weights are less than a syndrome weight threshold.

Owner:MARVELL INT LTD

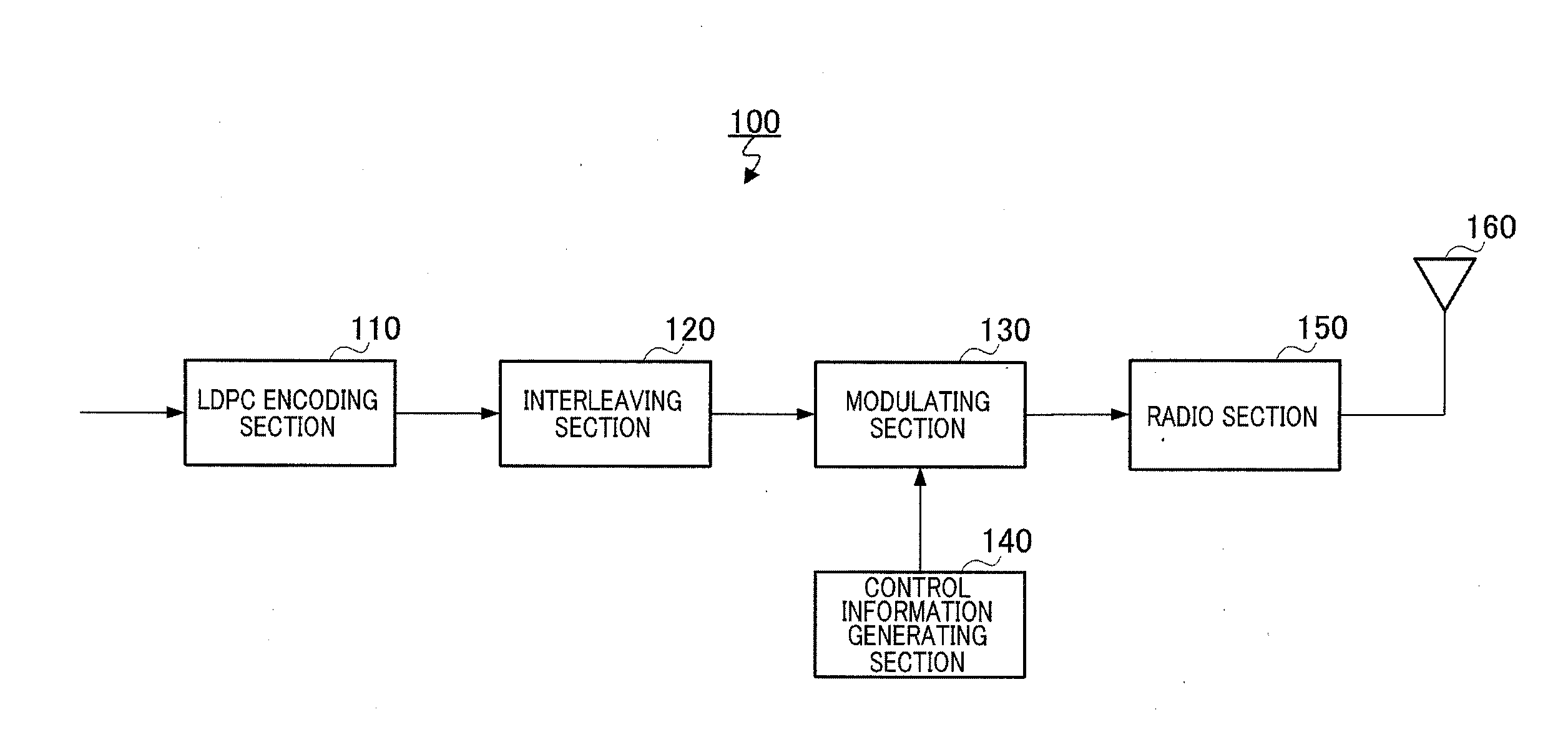

Encoding device and decoding device

ActiveUS20110138258A1Improve error floorImprove errorError correction/detection using convolutional codesOther decoding techniquesAlgorithmConvolutional code

An encoding device and decoding device for improving an error floor while taking advantage of the features of a convolutional code capable of encoding / decoding an information sequence with an arbitrary length are disclosed. An error correction encoding section (110) is provided with an LDPC-CC encoder (111) and an LDPC-BC encoder (112). The LDPC-CC encoder (111) acquires an LDPC-CC code word sequence by applying LDPC-CC encoding to a transmission information sequence. The LDPC-BC encoder (112) acquires a parity sequence by applying LDPC-BC encoding to the LDPC-CC code word sequence. The LDPC-CC encoder (111) further applies the LDPC-CC encoding to the parity sequence.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

Decoding method for LDPC channel code

InactiveCN101345532AImprove Calibration AccuracyImprove decoding performanceError preventionError correction/detection using multiple parity bitsSignal-to-noise ratio (imaging)Coding decoding

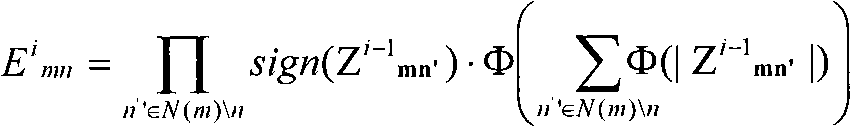

The present invention discloses a decoding method for LDPC channel coding, belongs to field of digital communication technology. In the method, comparing all information receiving from checking node to choose minimum value (Min1) and sub-minimum value (Min2); obtaining checking node update result according to minimum and decoding method, correcting update result by multiplicative dynamic factor omega whose value is determined by span of sub-minimum value received by checking node and varied according to sub-minimum value in each coding iteration to promote correction accuracy and to improve decoding performance, obtaining relative low error floor under high signal-noise ratio. Emulation results indicates that little calculated amount is needed to increase for standard LDPC code of short code length. The inventive decoding performance is better than NMS and OMS algorithm so as to solve contradiction of LDPC code decoding complexity and performance.

Owner:SUZHOU UNIV

Error-floor mitigation of codes using write verification

Executed when a channel input (e.g., LDPC) codeword is written to a storage medium, a write-verification method (i) compares the channel input codeword to the written codeword, (ii) identifies any erroneous too bits, and (iii) stores the erroneous-bit indices to a record in a table. At some later time, the written codeword is read and sent to a decoder. If the decoder fails with a near codeword, a write-error recovery process searches the table and retrieves the erroneous-bit information. The codeword bits at those indices are adjusted, and the modified codeword is submitted to further processing.

Owner:AVAGO TECH INT SALES PTE LTD

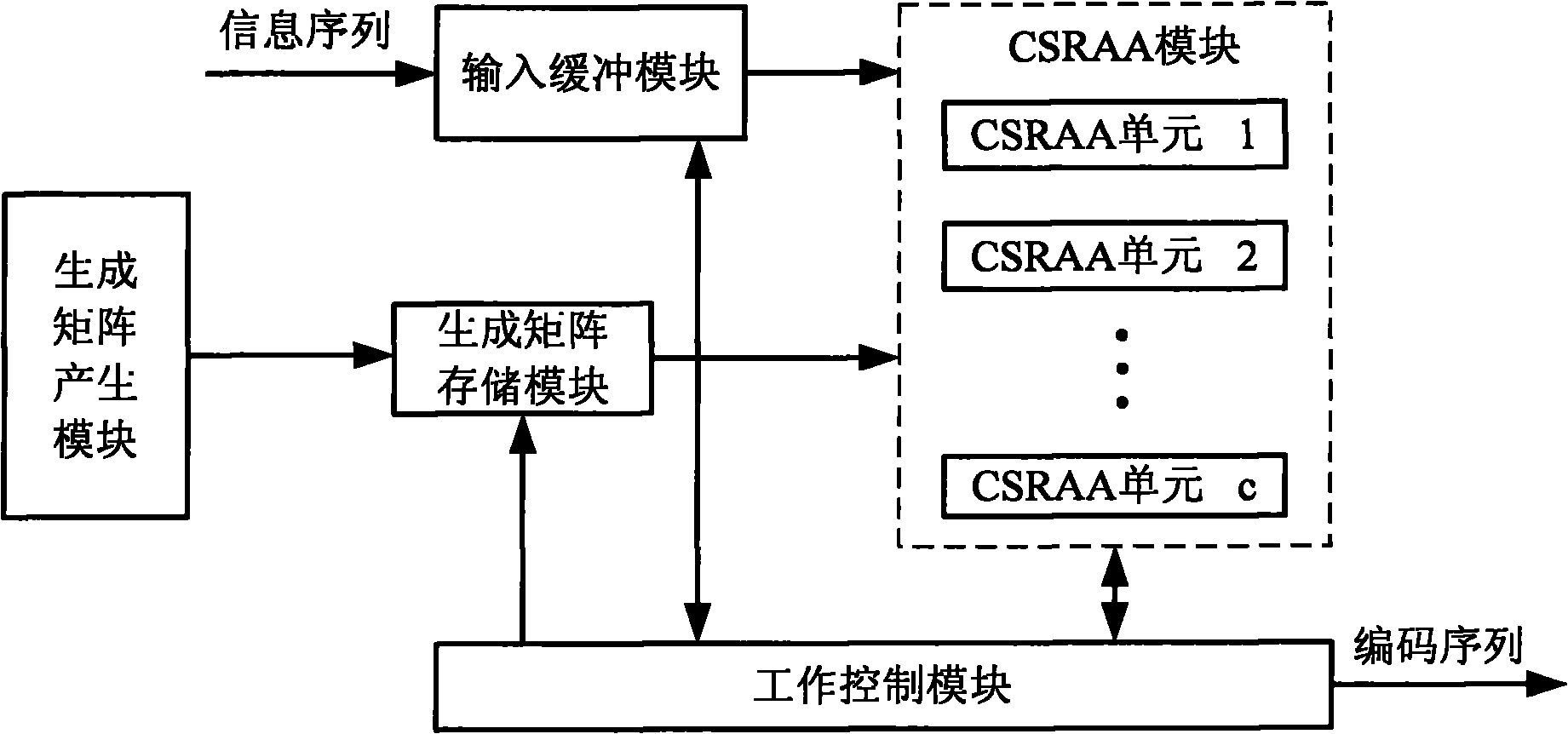

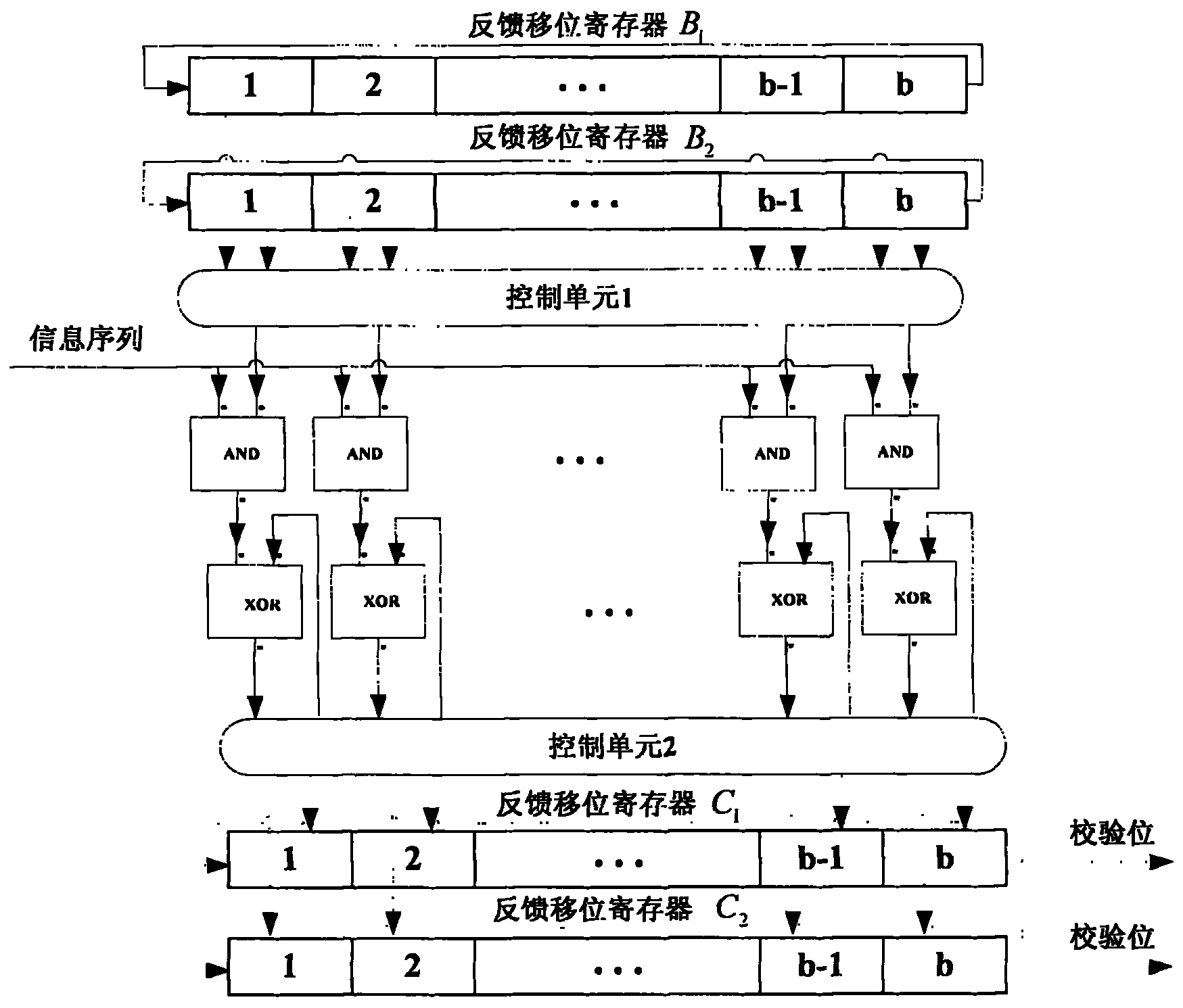

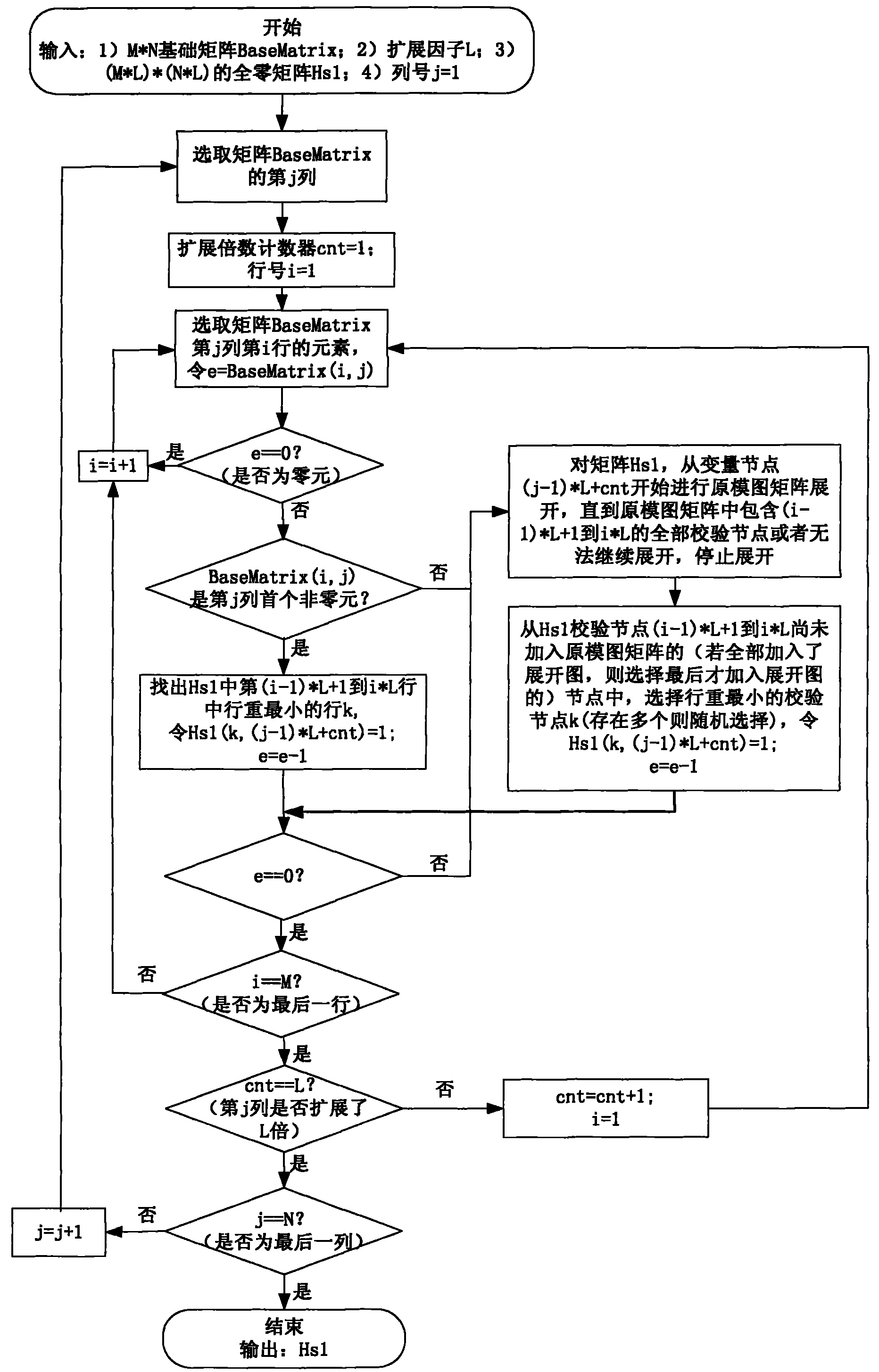

QC-LDPC (quasi-cyclic low-density parity-check codes) coder and coding method

ActiveCN102088294ALow decoding thresholdImprove performanceError correction/detection using multiple parity bitsLow-density parity-check codeSemantic routing

The invention relates to a QC-LDPC (quasi-cyclic low-density parity-check codes) coder which is characterized by comprising: a working control module, an input buffer module, a generated matrix storing module, a generated matrix generating module and a CSRAA (clustering semantic routing advanced algorithm) module. Simultaneously, the invention further provides a coding method implemented via the coder. According to the invention, code length and code rate can be flexibly selected, and a QC-LDPC code having low coding threshold and low error floor is generated.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com