Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

35 results about "Message passing decoding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Node processors for use in parity check decoders

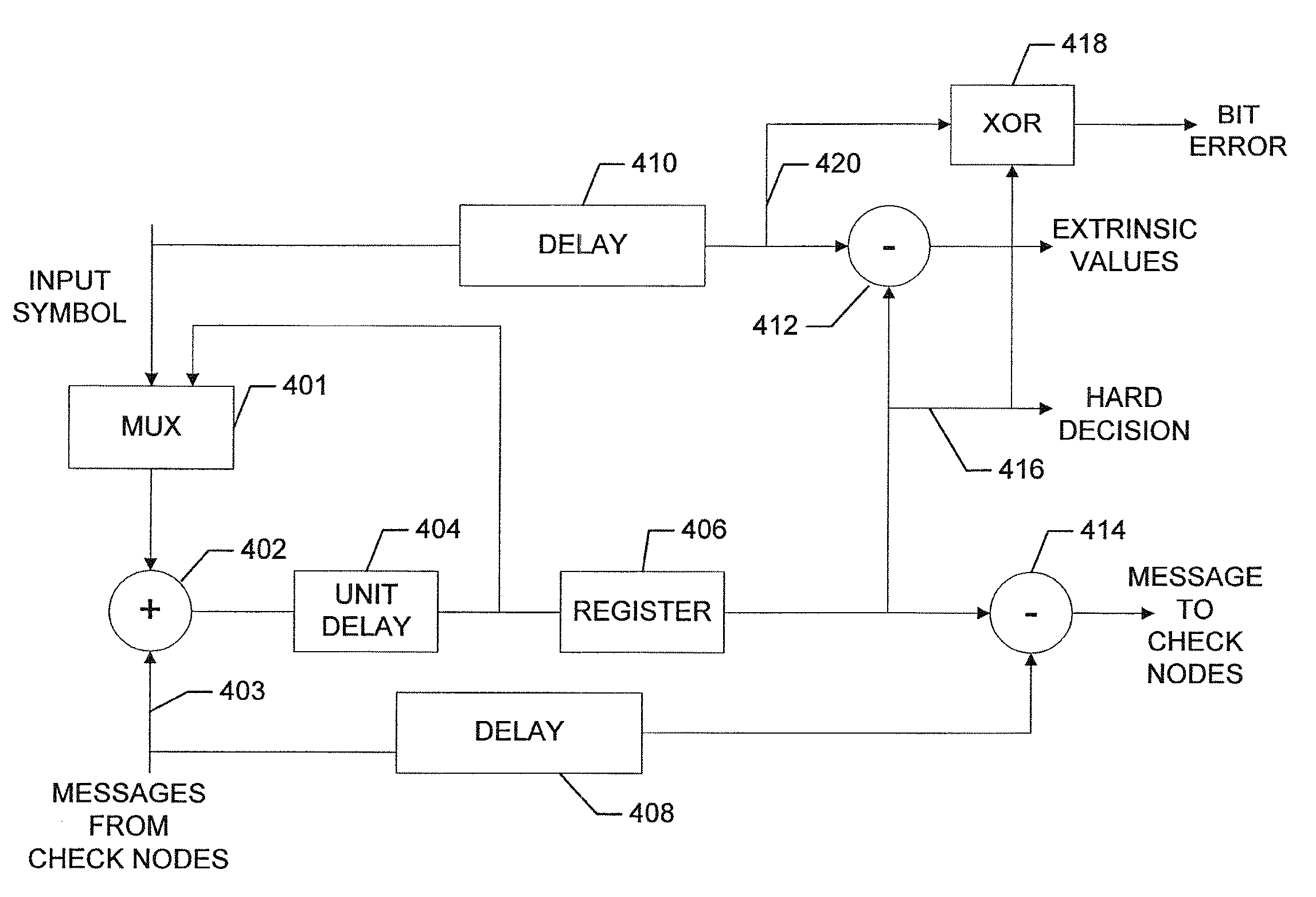

InactiveUS6938196B2Big errorCompensating for such errorError prevention/detection by using return channelOther decoding techniquesComputer moduleMessage processing

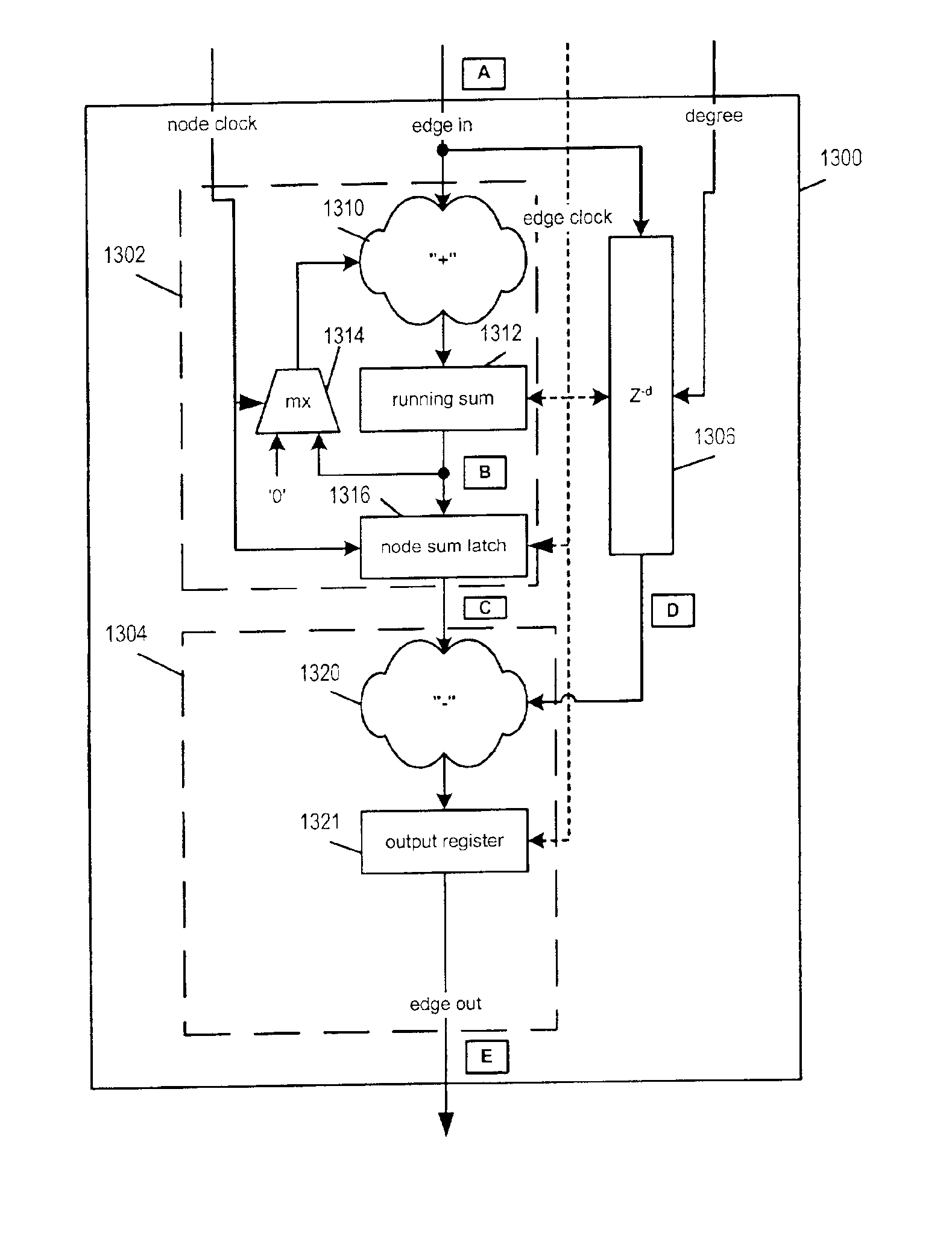

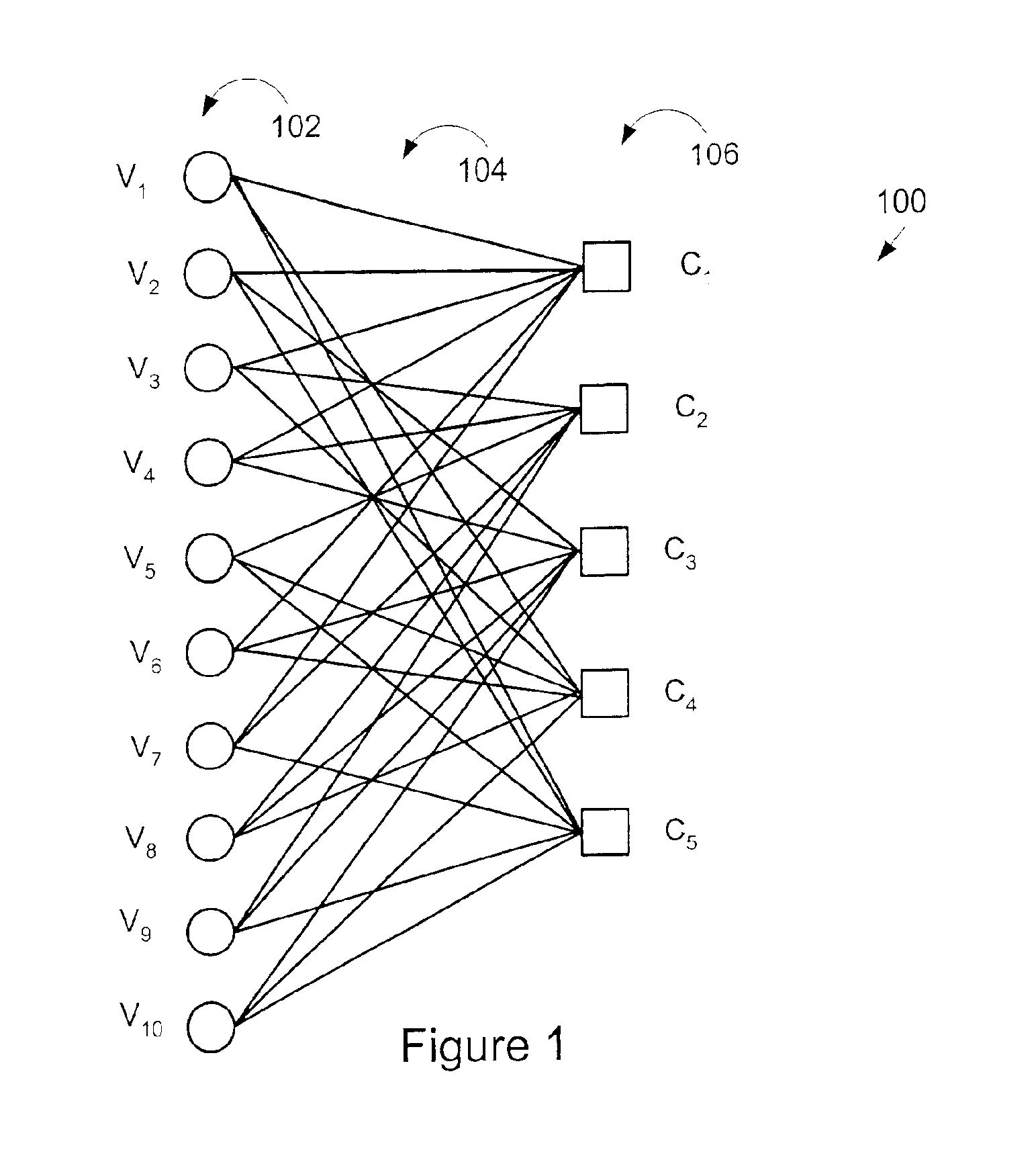

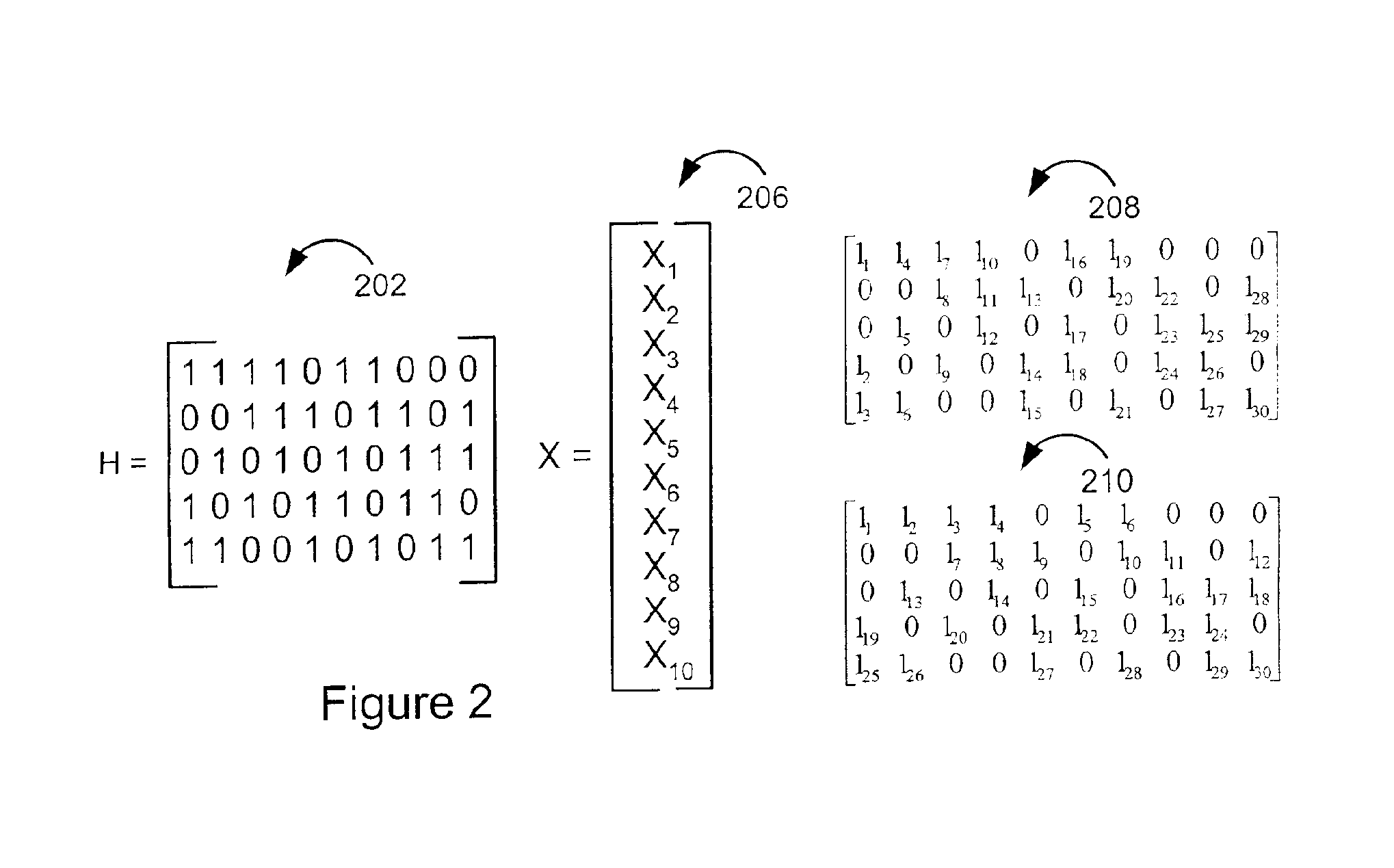

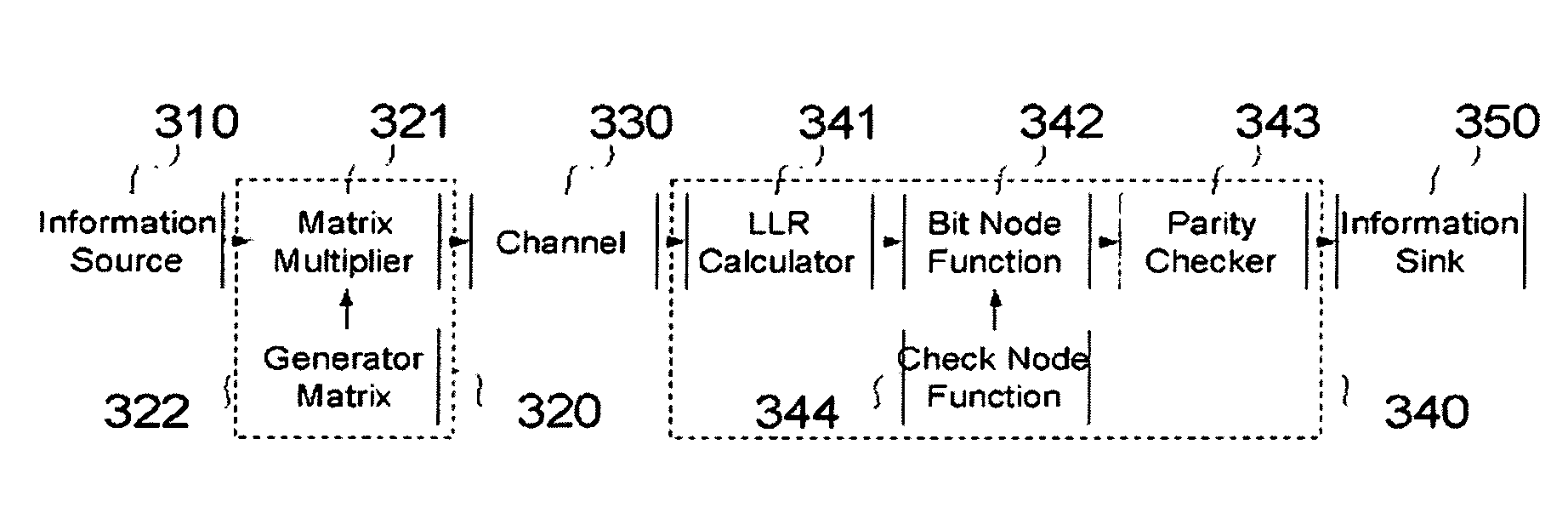

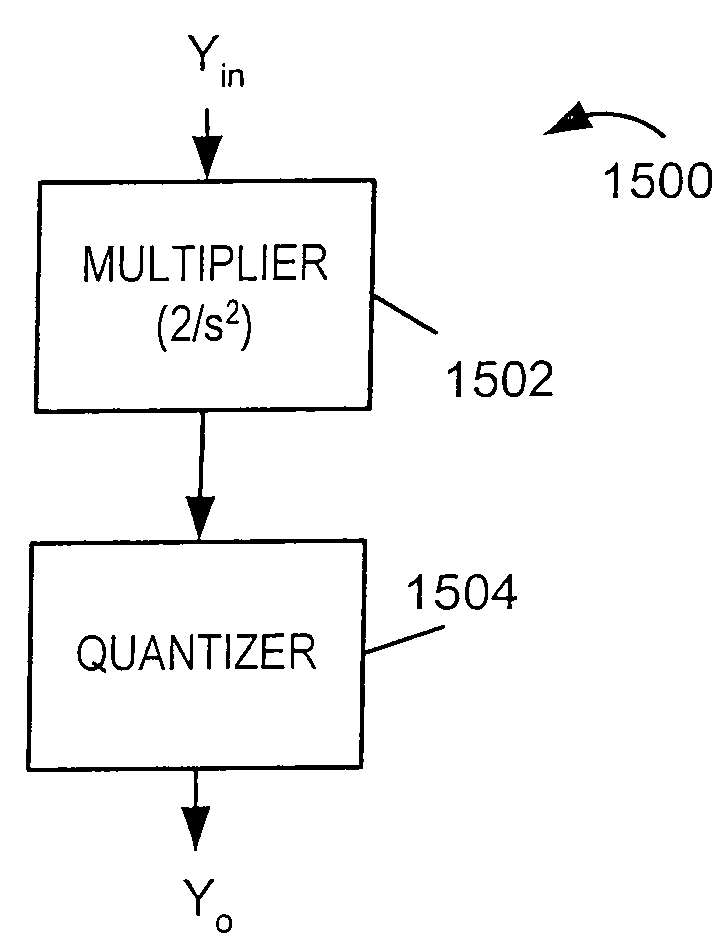

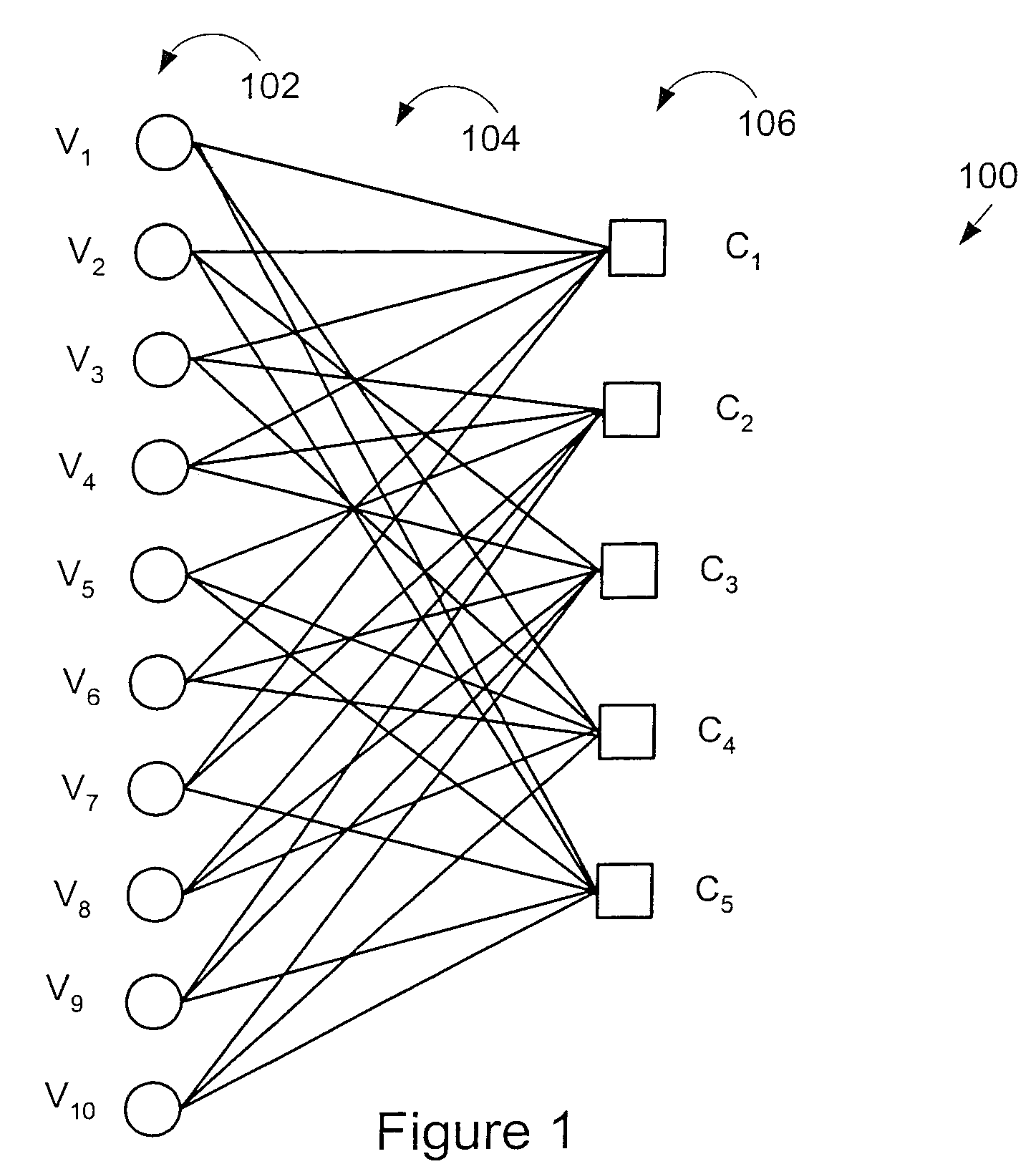

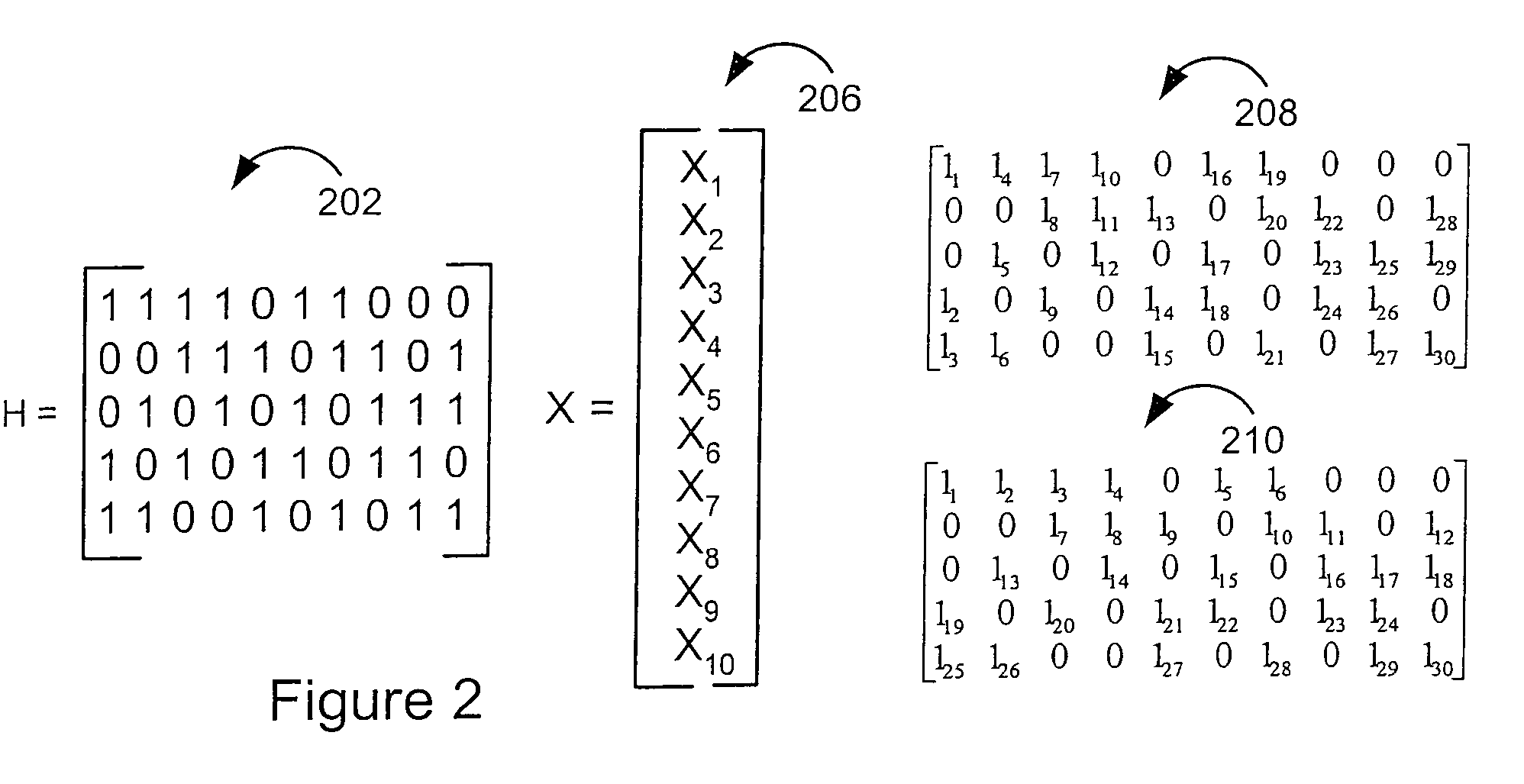

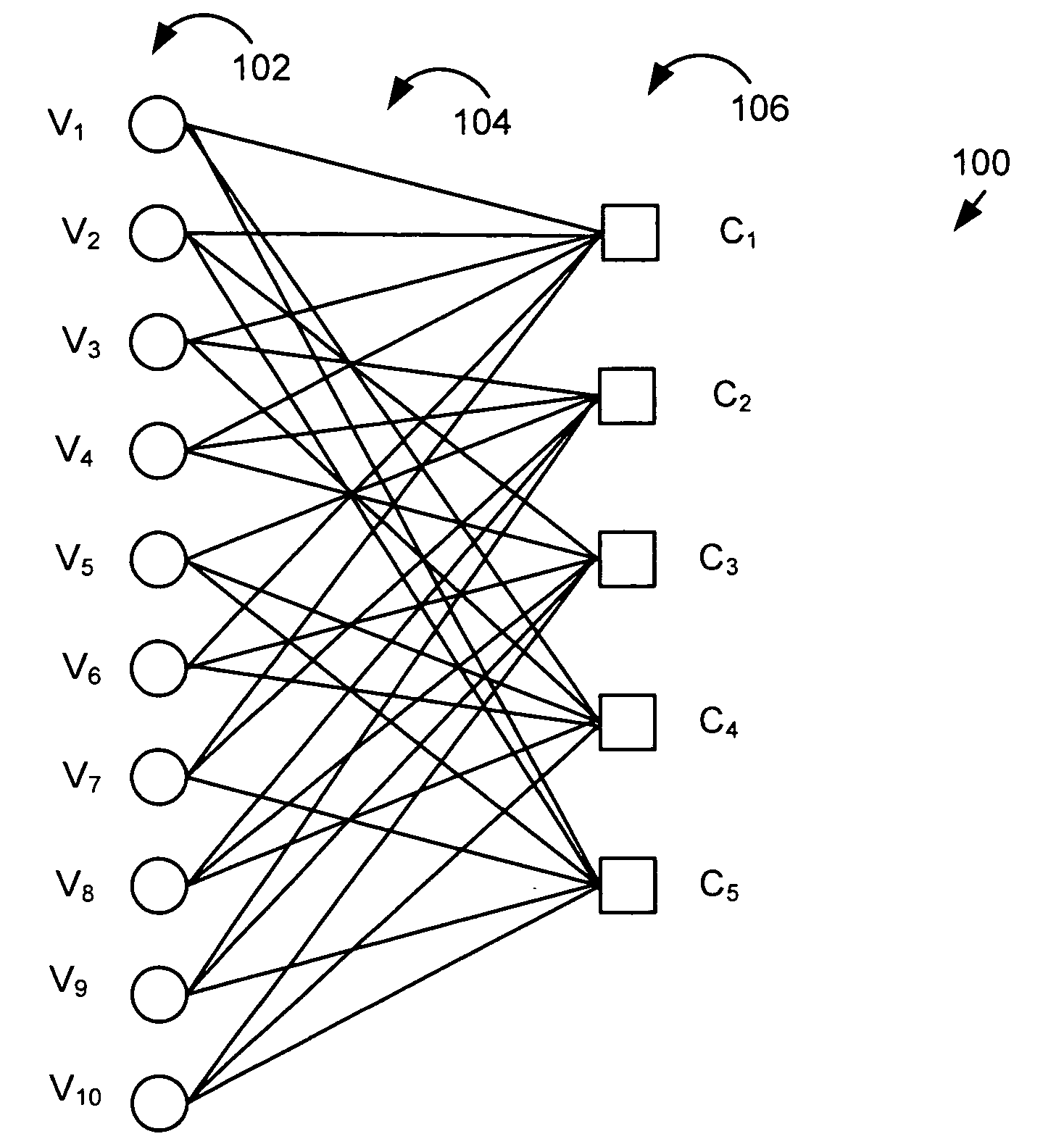

Techniques for implementing message passing decoders, e.g., LDPC decoders, are described. To facilitate hardware implementation messages are quantized to integer multiples of ½ ln2. Messages are transformed between more compact variable and less compact constraint node message representation formats. The variable node message format allows variable node message operations to be performed through simple additions and subtractions while the constraint node representation allows constraint node message processing to be performed through simple additions and subtractions. Variable and constraint nodes are implemented using an accumulator module, subtractor module and delay pipeline. The accumulator module generates an accumulated message sum. The accumulated message sum for a node is stored and then delayed input messages from the delay pipeline are subtracted there from to generate output messages. The delay pipeline includes a variable delay element making it possible to sequentially perform processing operations corresponding to nodes of different degrees.

Owner:QUALCOMM INC

Methods and apparatus for reducing error floors in message passing decoders

ActiveUS7237181B2Reduce the numberReduce quality problemsError preventionError correction/detection using multiple parity bitsComputer hardwareEdge states

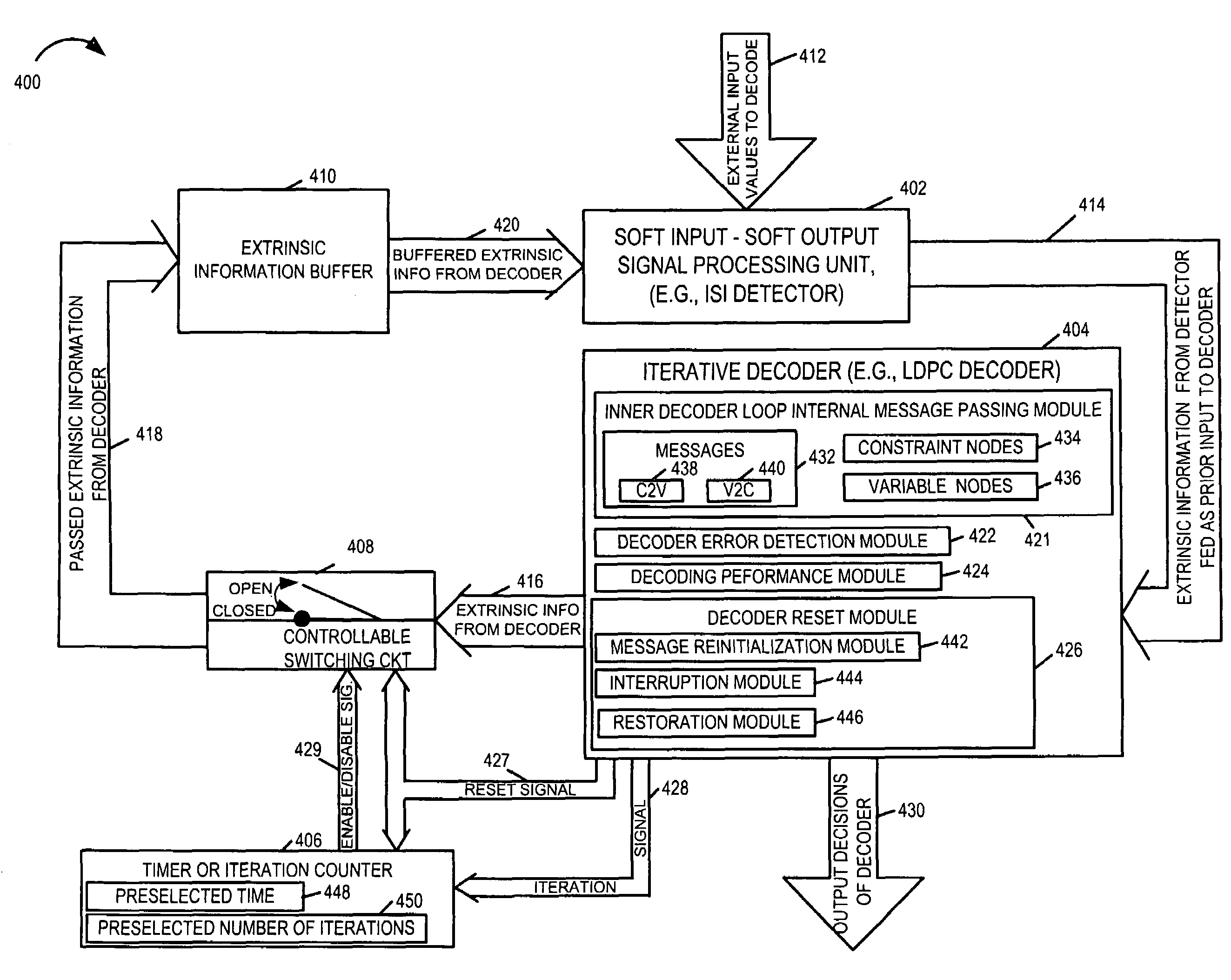

An iterative message passing decoder, e.g., an LDPC decoder, operating in conjunction with a soft input-soft output signal processing unit, e.g., an ISI detector, has an error floor performance region influenced by the decoder's sub-optimal message passing nature. Error floor reduction is achieved by a simple message re-initialization mechanism. Decoder edge states, e.g., constraint to variable node messages in decoder memory, are reinitialized, e.g., for an iteration, during the decoding after soft values provided by signal processing unit have improved. During the message re-initialization and for some subsequent amount of iterative decoder processing, extrinsic information fed back from the decoder to the signal processing unit and / or soft values delivered to the decoder from the signal processing unit, in an outer communications loop, is temporarily frozen, e.g., using a switch and a buffer. Then, the outer communications loop is restored as the decoding continues, achieving improved decoding performance.

Owner:QUALCOMM INC

Simplified message-passing decoder for low-density parity-check codes

InactiveUS7178081B2Reduce approximation errorReduce errorsError preventionError detection/correctionHardware structureComputer hardware

Disclosed is an implementation method for simplifying a complicated message-passing function in a decoder for decoding block codes encoded with low-density parity-check (LDPC) codes and only using a summator and a shifter to simplify the hardware structure of the decoder, in which method the input interval of the message-passing function for binary representation of a message input is divided and the respective divided intervals are linearized to allow the calculation of the output of the message-passing function without using a memory. Based on the fact that the message-passing function is similar in structure to an exponential function, the linearized intervals are set to make the maximum value expressible in each digit of the binary representation as the boundary of the intervals.

Owner:ELECTRONICS & TELECOMM RES INST

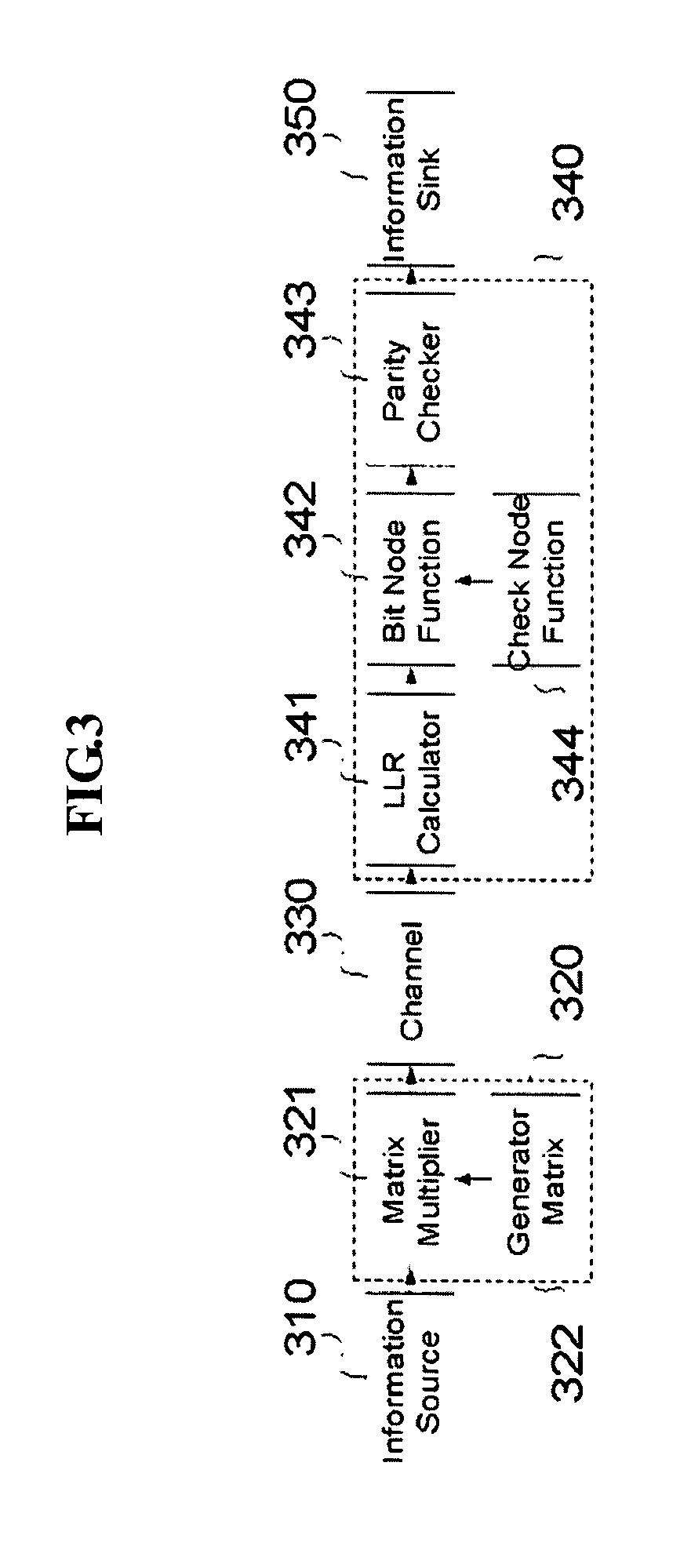

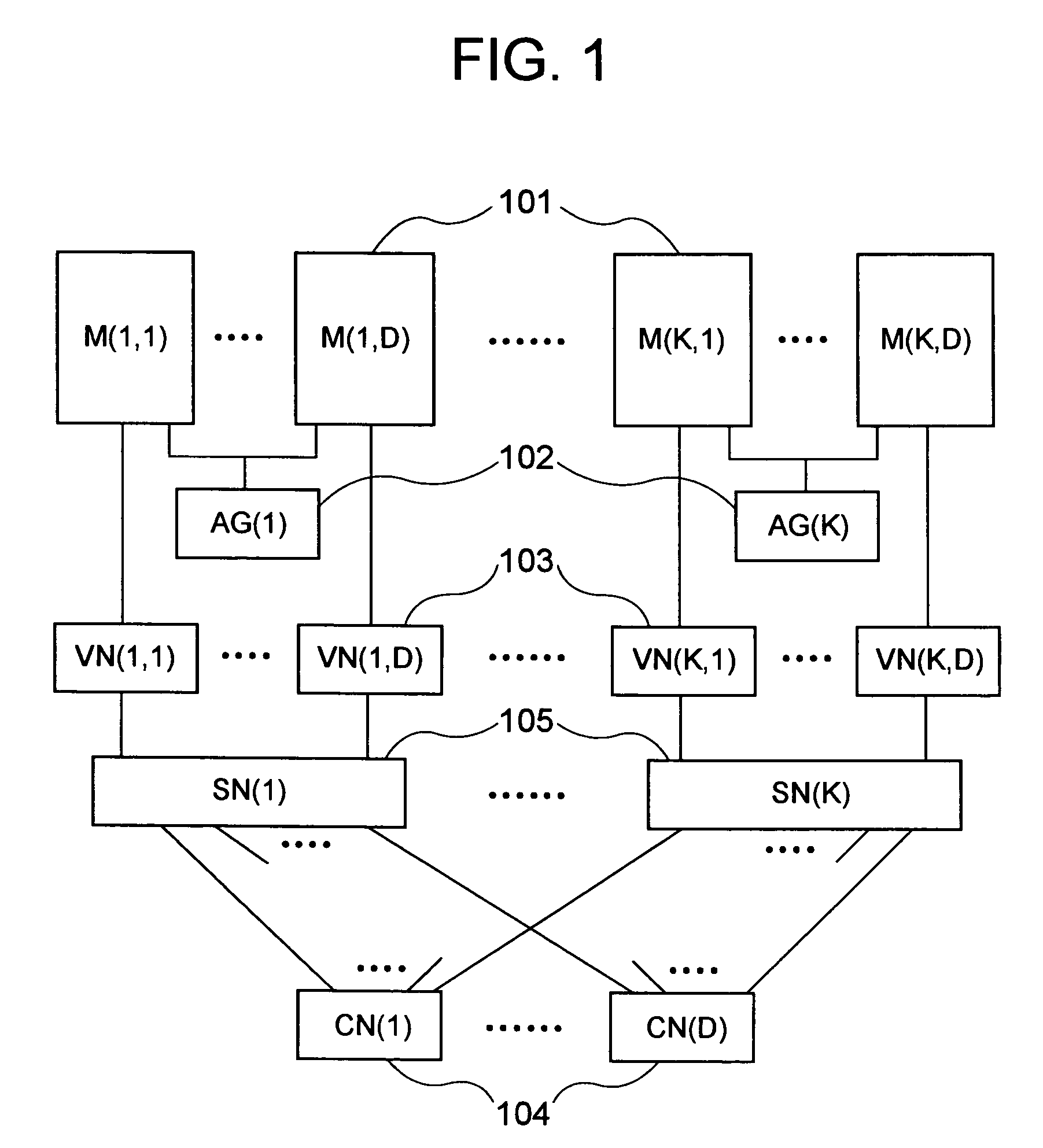

Device, program, and method for decoding LDPC codes

ActiveUS7373581B2Simpler and flexibleError preventionTransmission systemsAddress generation unitMessage passing decoding

A parallel decoder, which is simpler and more flexible than conventional devices, is provided in decoding device for a LDPC code. The present invention includes a plurality of memory units for storing a received value and a message generated during a Message-Passing decoding, a plurality of variable node function units, a plurality of check node function units, a plurality of address generation units for generating an address of each of memory units, and a plurality of shuffle network units for determining a connection between variable node function units and check node function units. An address generation unit generates an address on the basis of a plurality of permutations. Each shuffle network unit is connected to some of the variable node function units. This connection is determined on the basis of a plurality of permutations. A change of the permutations in the address generation units and a change of the permutations in the shuffle network units are performed in the same cycle in a decoding process.

Owner:NEC CORP

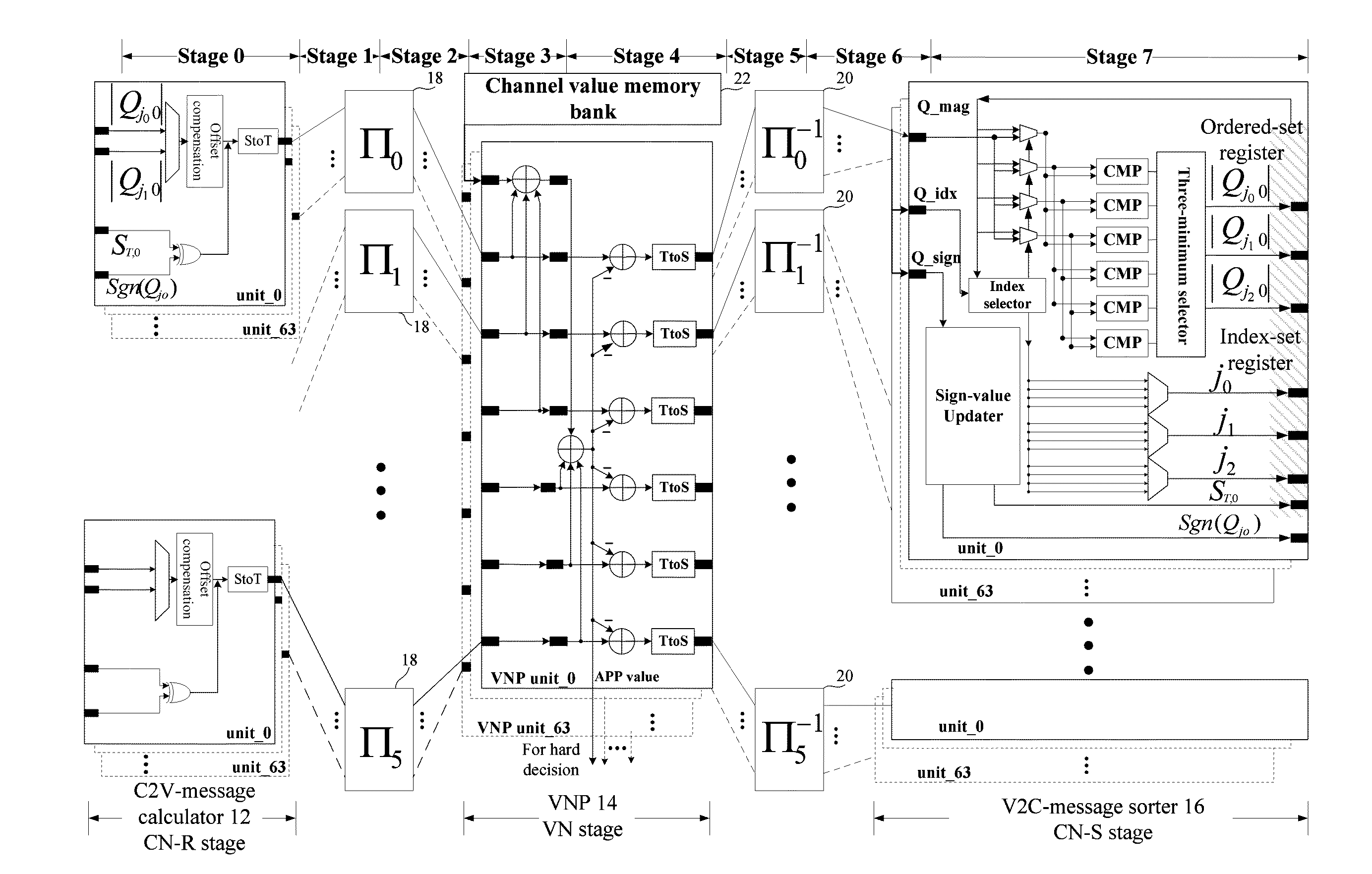

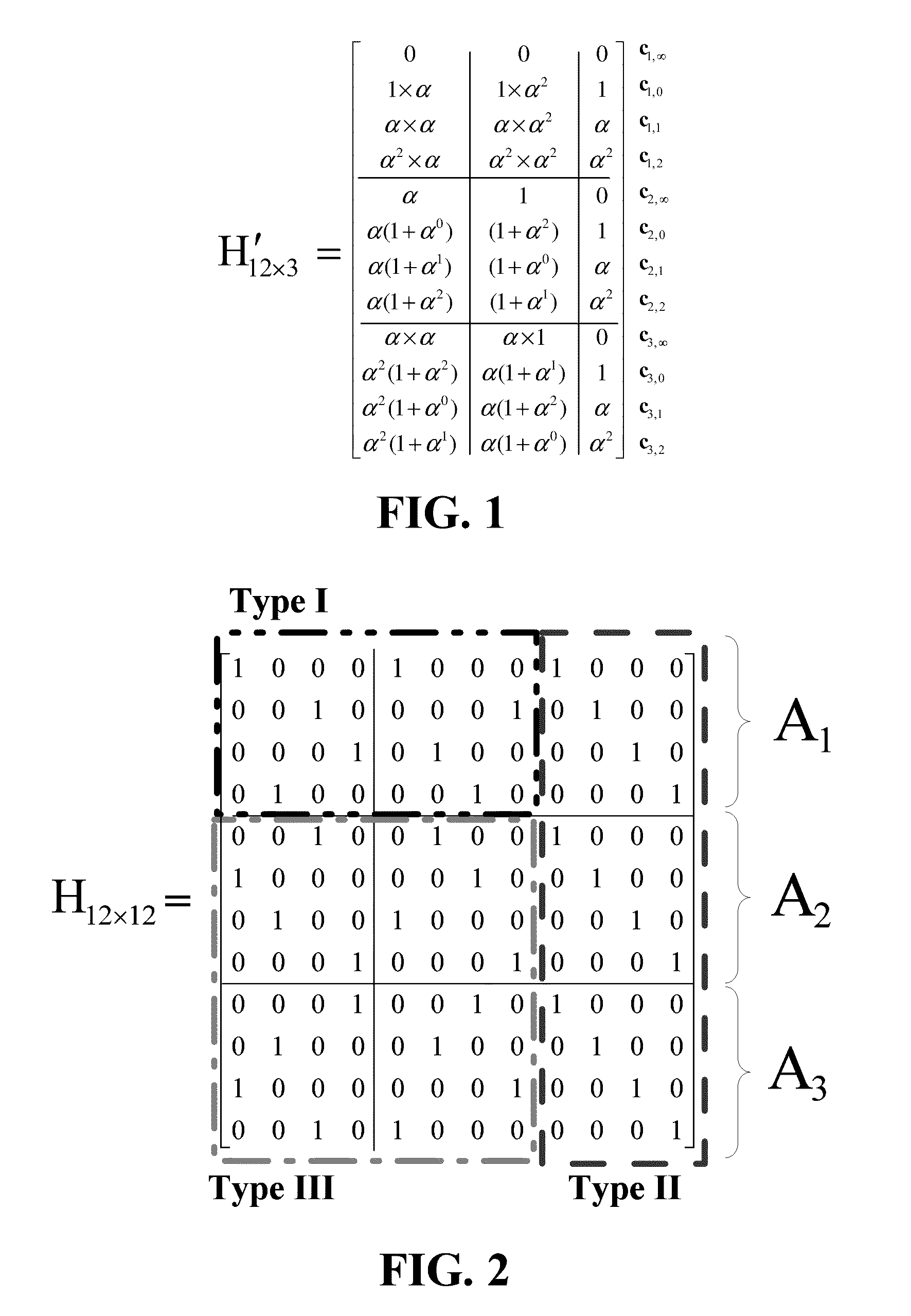

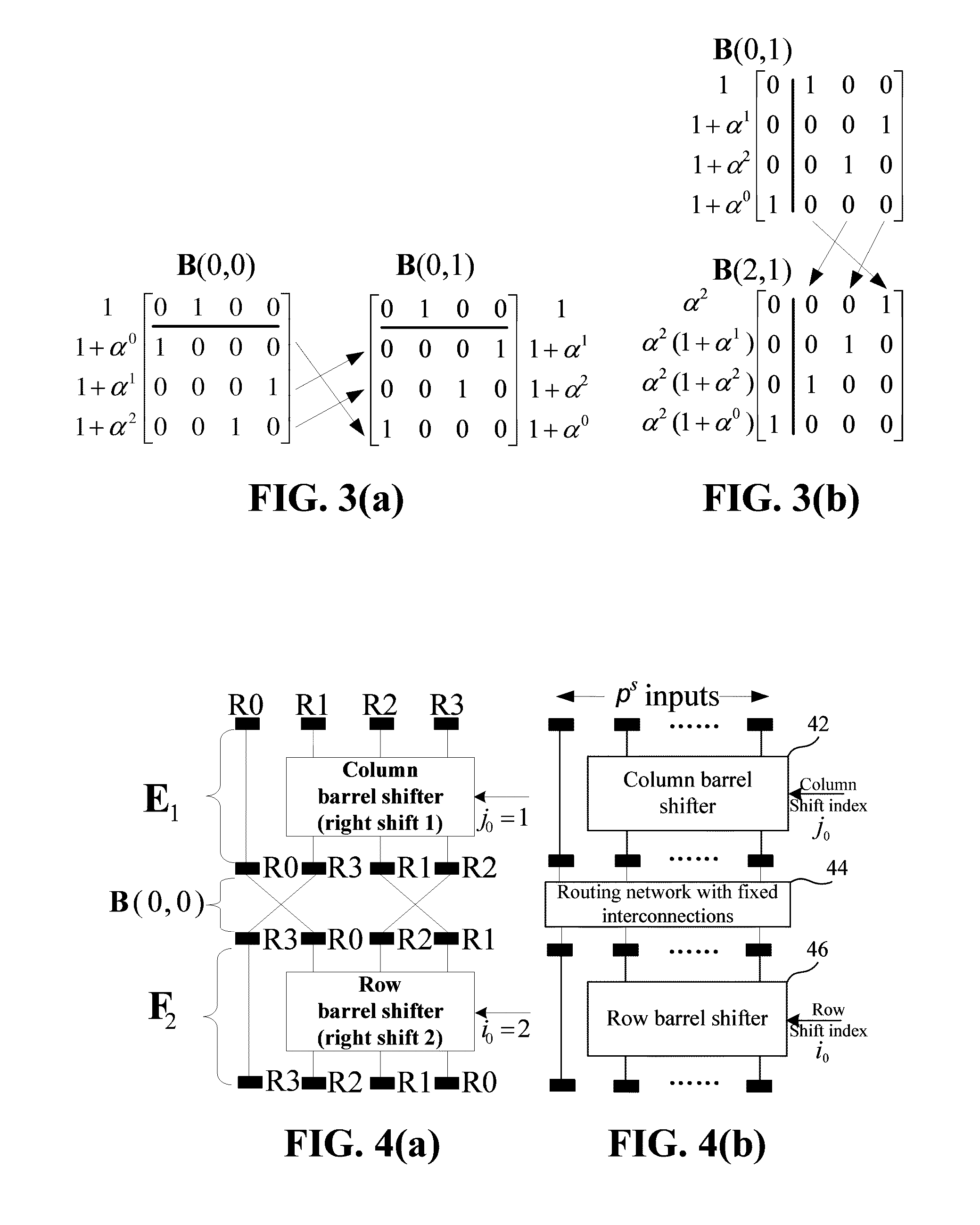

Decoder and decoding method for low-density parity check codes constructed based on reed-solomon codes

ActiveUS20110126078A1Easy to useMitigate increase in implementation complexityCode conversionError correction/detection by combining multiple code structuresComputer architectureLow density

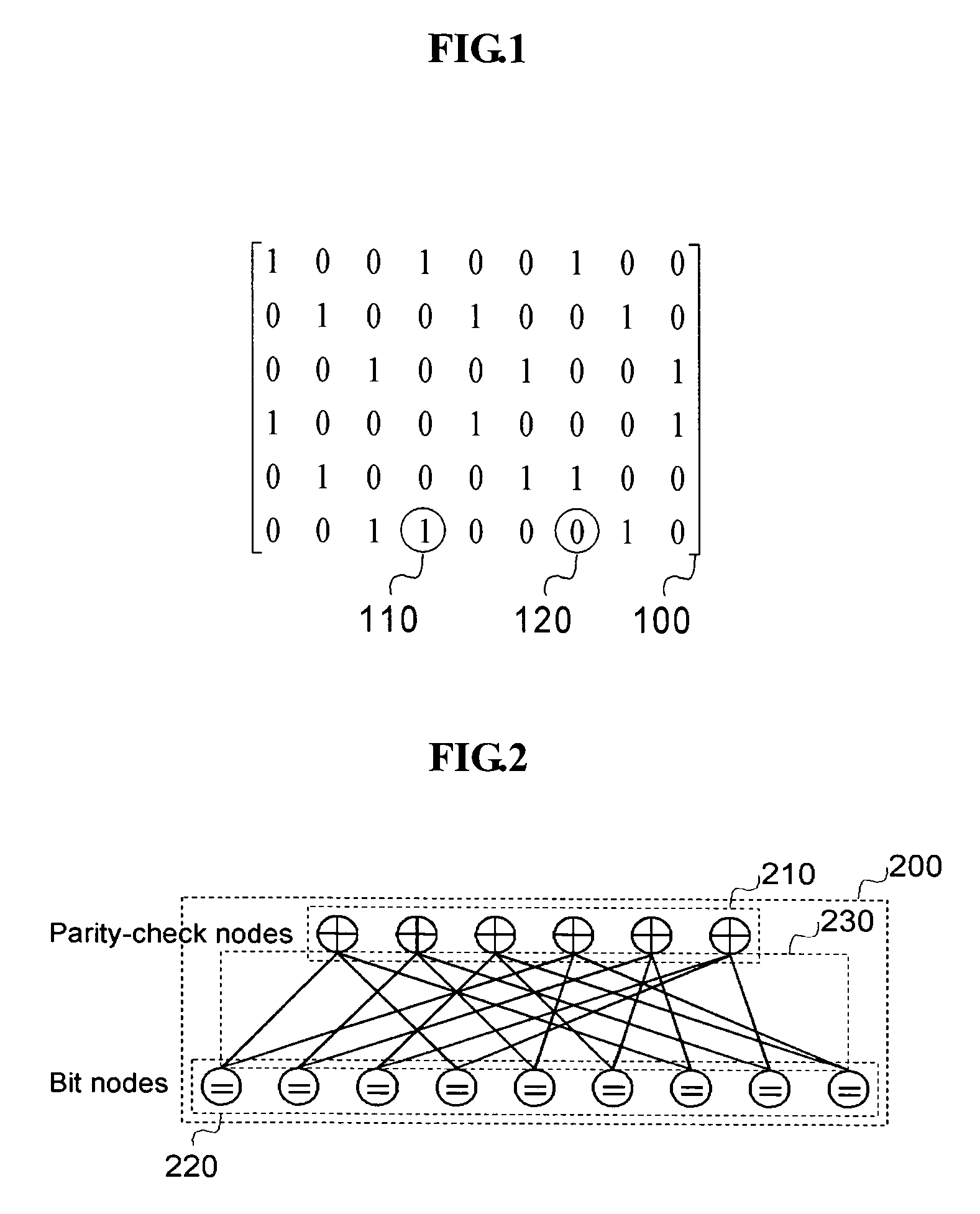

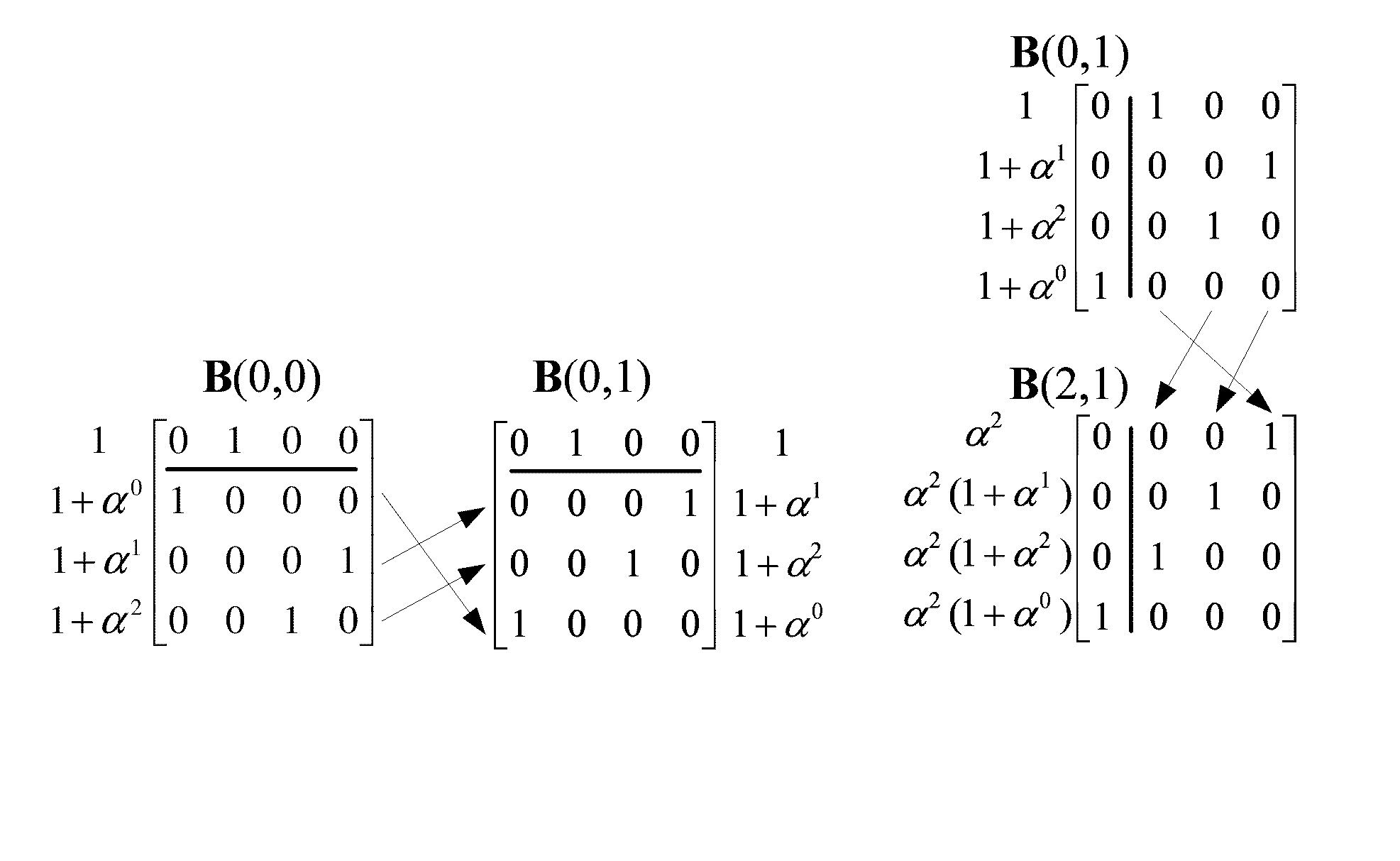

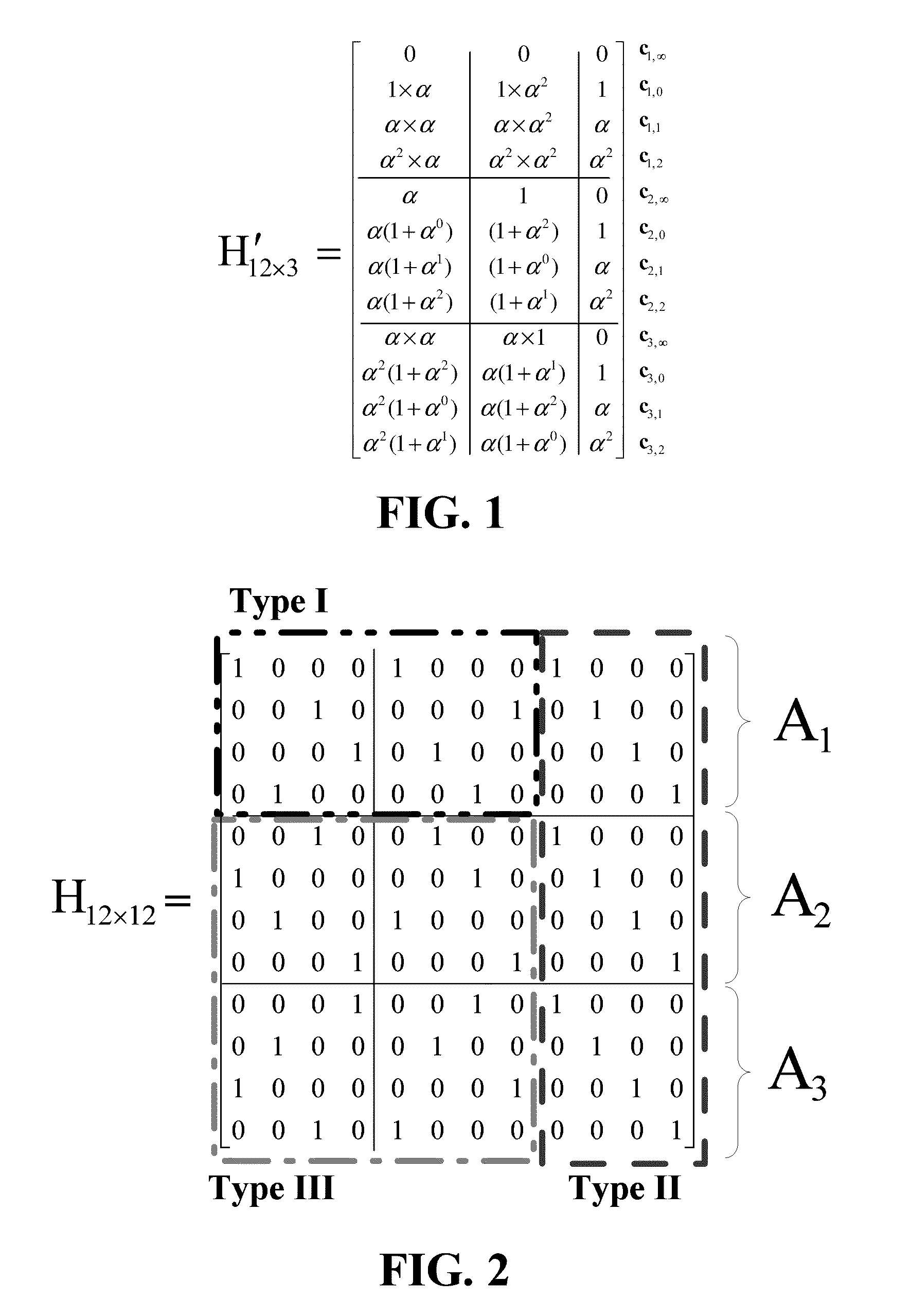

Configurable permutators in an LDPC decoder are provided. A partially-parallel architecture combined with the proposed permutators is used to mitigate the increase in implementation complexity for the multi-mode function. To overcome the difficulty in efficient implementation of a high-throughput decoder, the variable nodes are partitioned into several groups, and each group is processed sequentially in order to shorten the critical-path delay and, hence, increase the maximum operating frequency. In addition, shuffled message-passing decoding can be adopted in decoders according to the invention to increase the convergence speed, which reduces the number of iterations required to achieve a given bit-error-rate performance.

Owner:NATIONAL TSING HUA UNIVERSITY

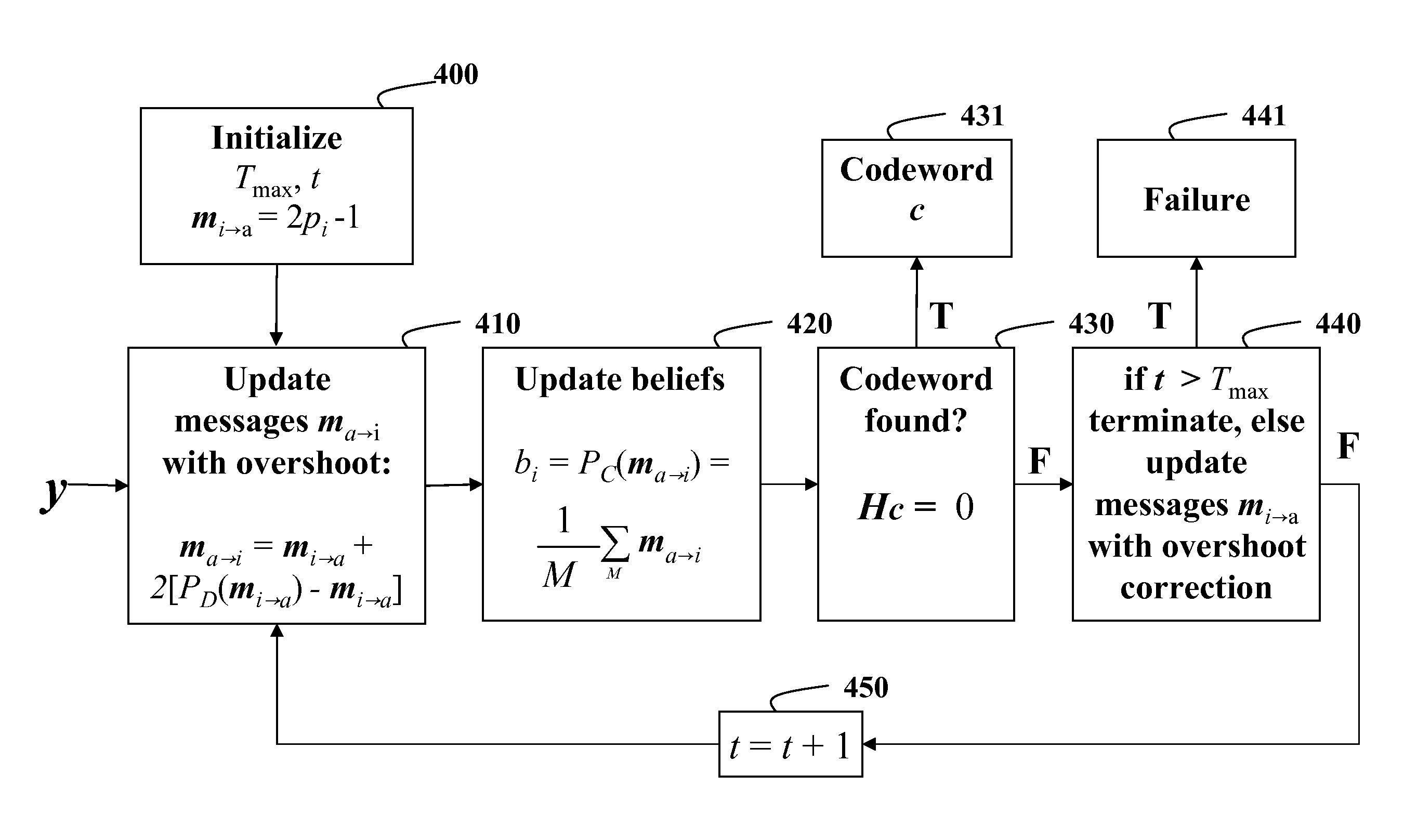

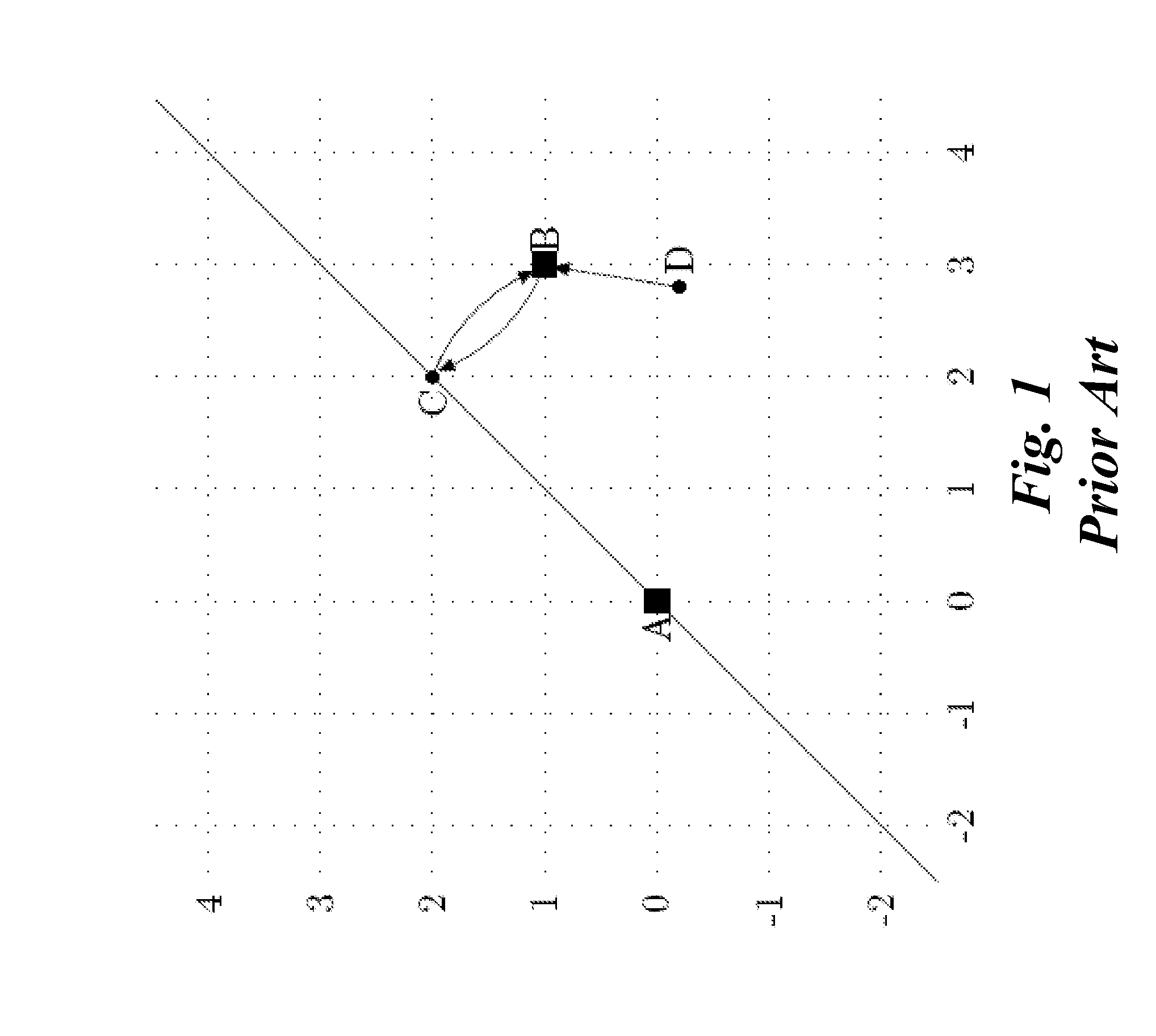

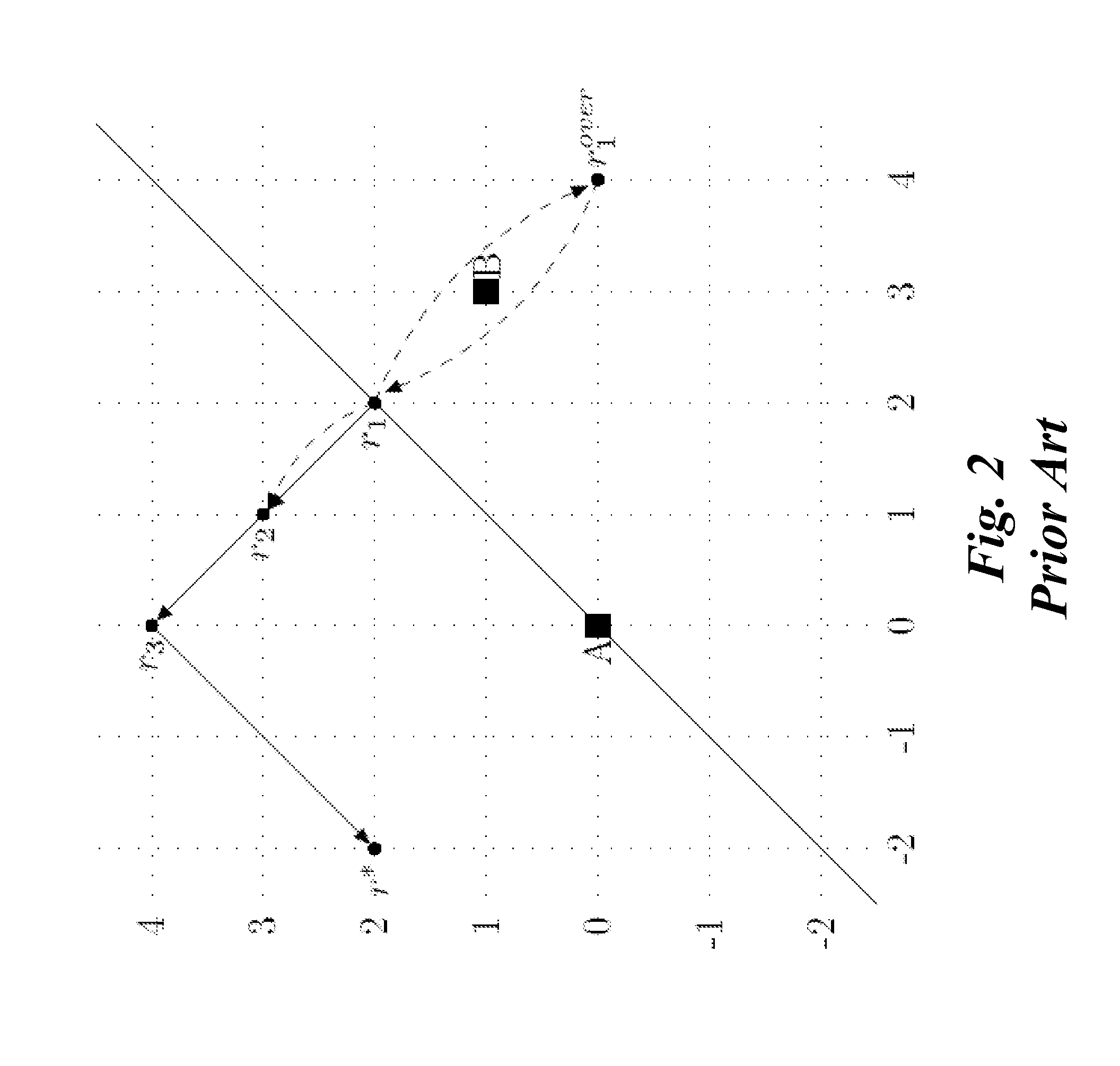

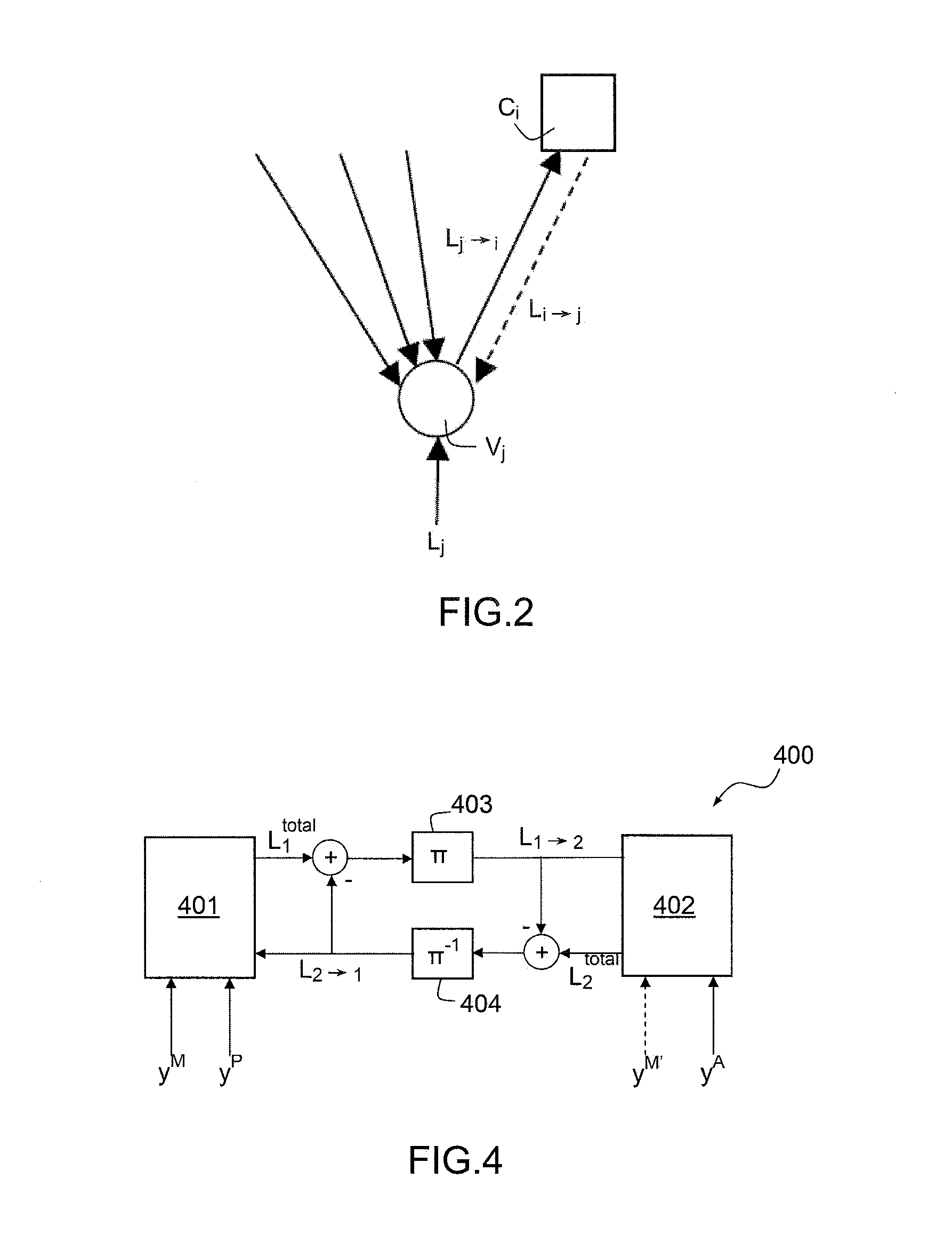

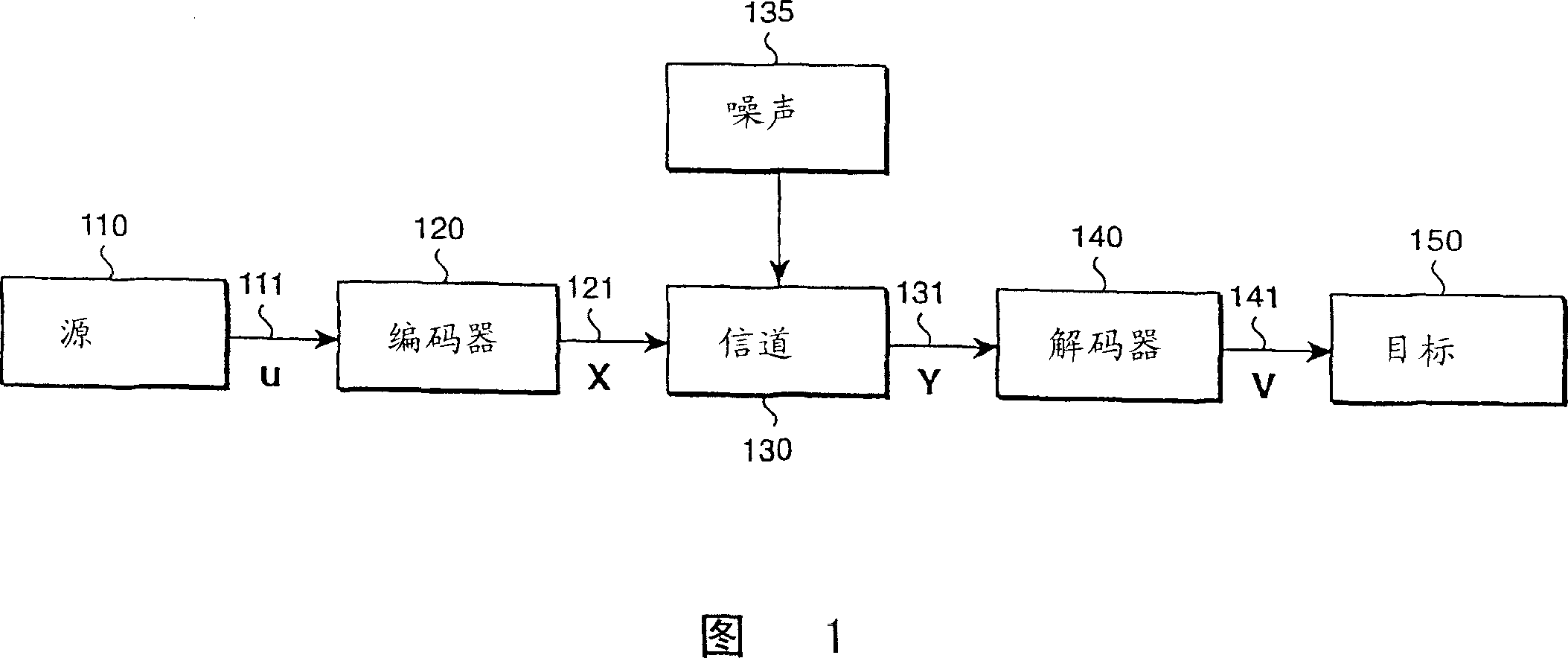

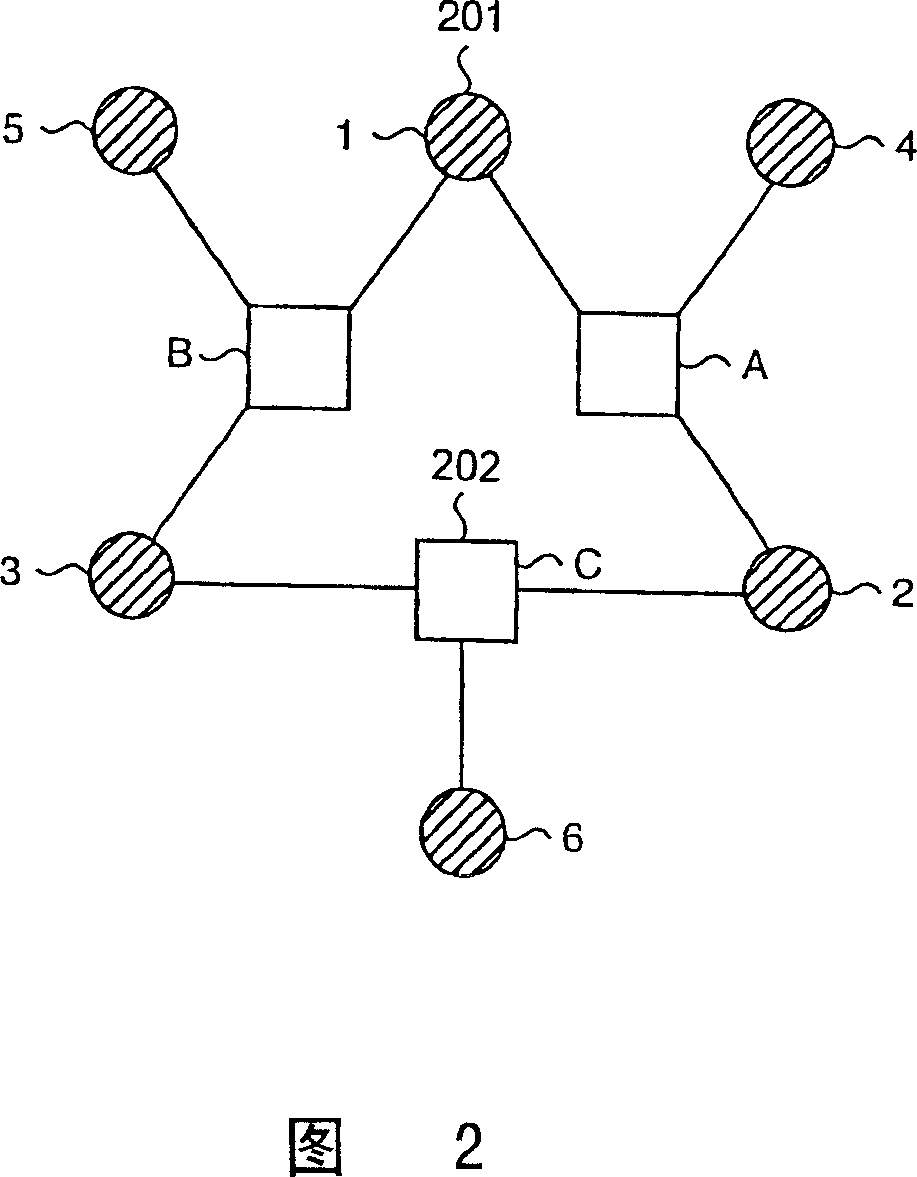

Method and System for Decoding Graph-Based Codes Using Message-Passing with Difference-Map Dynamics

InactiveUS20110041029A1Increase heightImprove errorDigital data processing detailsCode conversionDifference-map algorithmTheoretical computer science

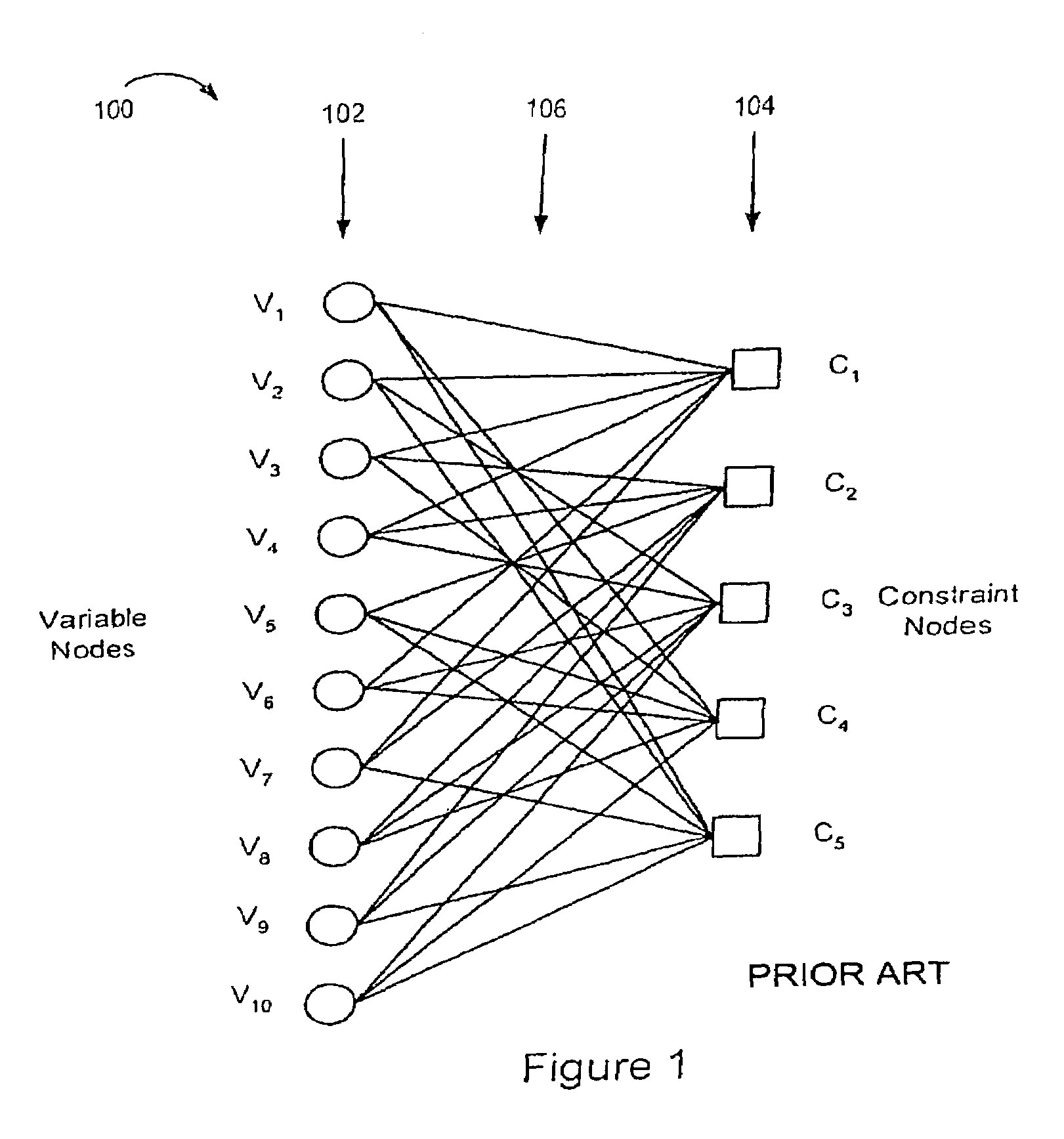

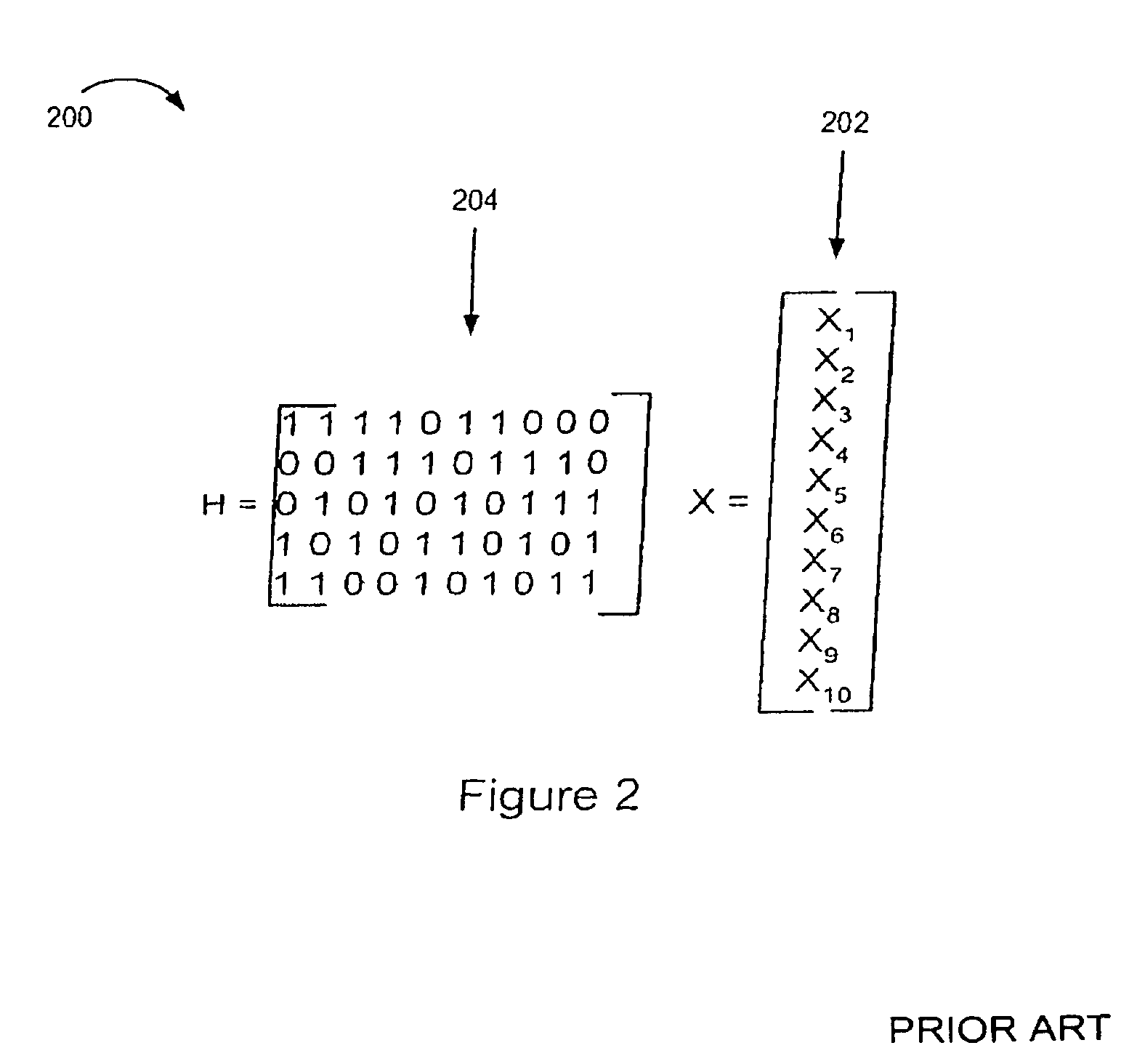

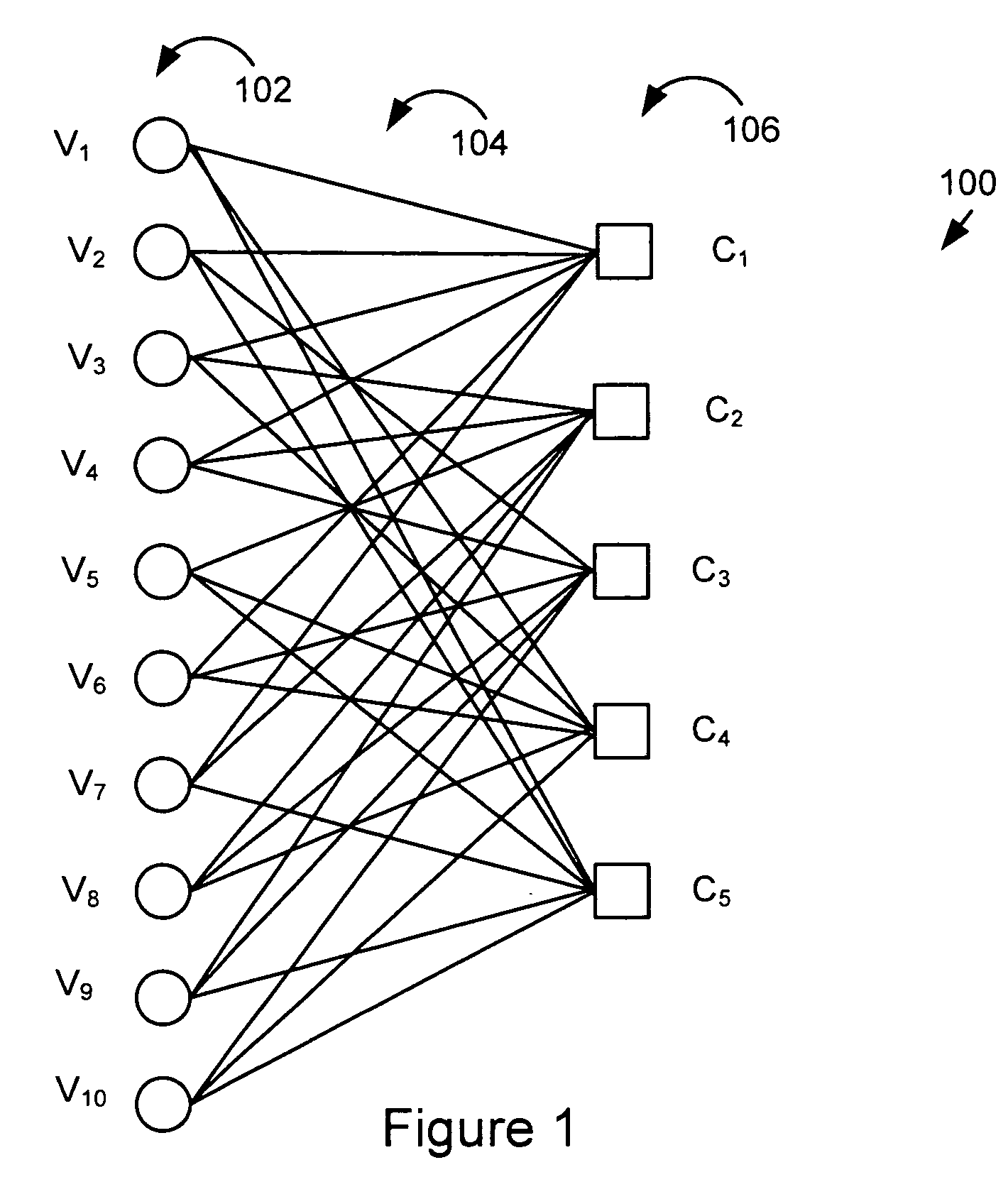

A code to be decoded by message-passing is represented by a factor graph. The factor graph includes variable nodes indexed by i and constraint nodes indexed by a connected by edges for transferring messages mi→a outgoing from the variable nodes to the constraint nodes and messages ma→i incoming from the constraint nodes to the variable nodes. The messages mi→a are initialized based on beliefs bi of a received codeword. The messages ma→i are generated by overshooting the messages mi→a at the constraint nodes. The beliefs bi are updated at the variable nodes using the messages ma→i. The codeword is outputted if found, otherwise, the messages mi→a are updated using a correction for the overshooting.

Owner:MITSUBISHI ELECTRIC RES LAB INC

Bit error detector for iterative ECC decoder

Owner:SEAGATE TECH LLC

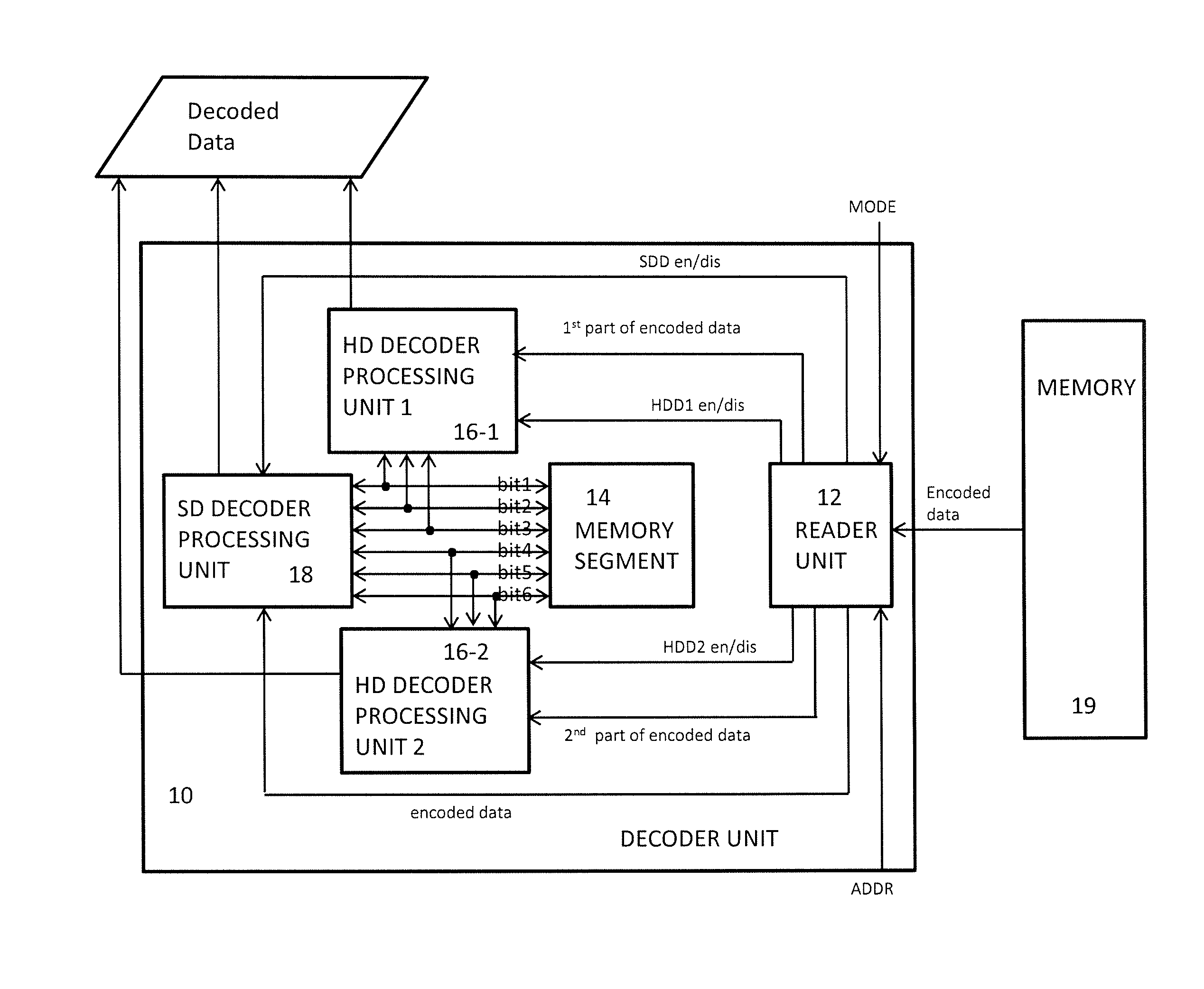

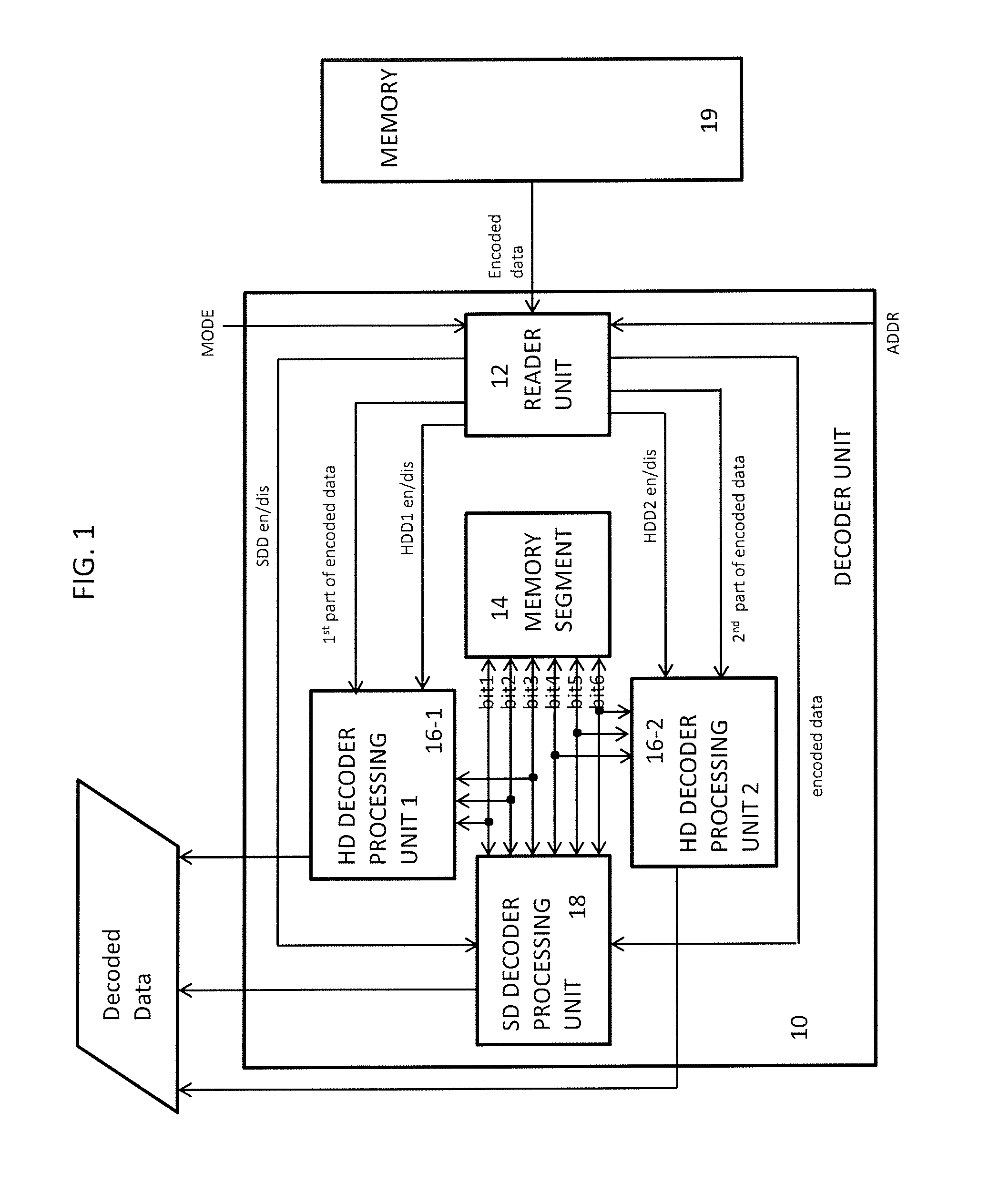

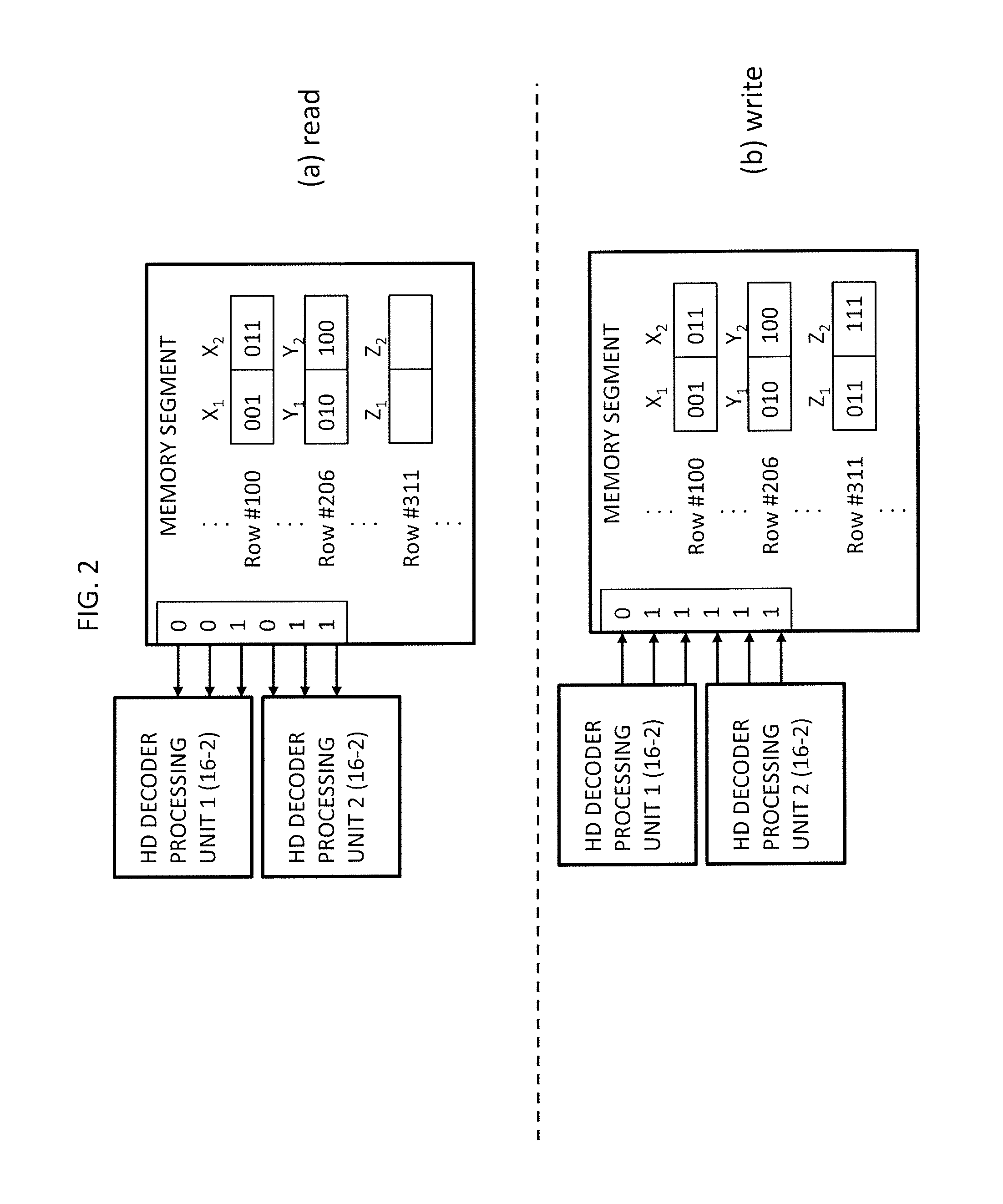

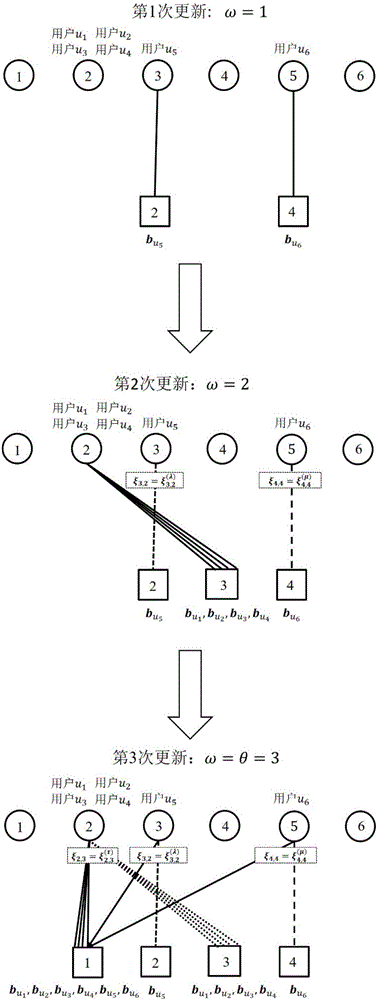

Soft and hard decision message-passing decoding

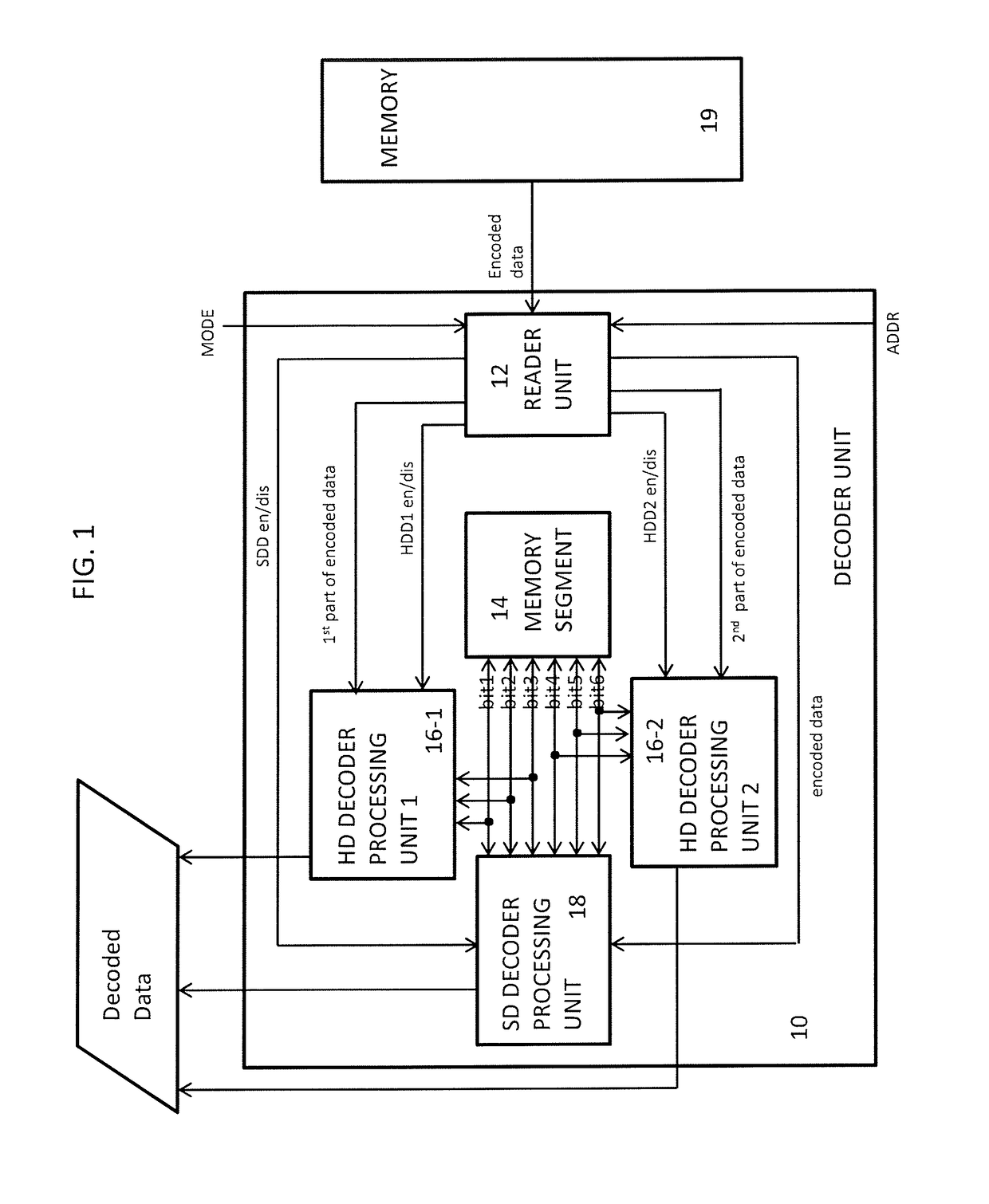

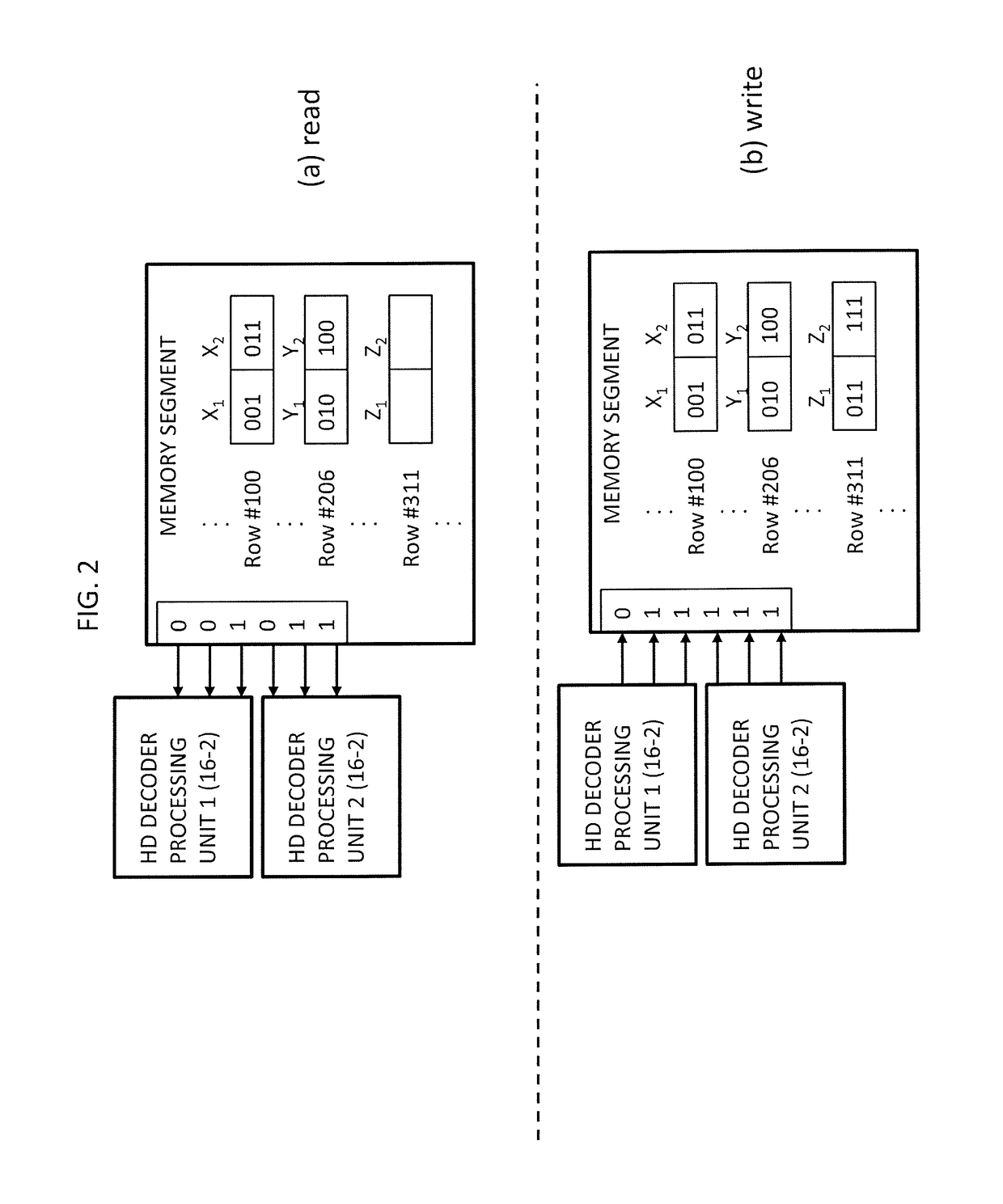

ActiveUS20150263760A1Error correction/detection using multiple parity bitsCode conversionProcessing elementLocal memories

A decoder unit is configured to perform a decoding on encoded data. The decoder unit includes a data bus comprising a number N of data lines, a local memory configured to store messages for a message-passing decoding and communicate the messages across the data bus, a plurality of first decoder processing units, wherein each first decoder processing unit is configured to perform the message-passing decoding by communicating with the local memory using a number A of the data channels, and a plurality of second decoder processing units, where each second decoder processing unit is configured to perform the message-passing decoding by communicating with the local memory using a number B of the data lines. N is at least two, A and B are less than or equal to N, and A is different from B.

Owner:SAMSUNG ELECTRONICS CO LTD

Node processors for use in parity check decoders

InactiveUS7673223B2Simple calculationSolve the lack of resolutionError correction/detection using multiple parity bitsCode conversionComputer moduleMessage processing

Techniques for implementing message passing decoders, e.g., LDPC decoders, are described. To facilitate hardware implementation messages are quantized to integer multiples of ½ ln2. Messages are transformed between more compact variable and less compact constraint node message representation formats. The variable node message format allows variable node message operations to be performed through simple additions and subtractions while the constraint node representation allows constraint node message processing to be performed through simple additions and subtractions. Variable and constraint nodes are implemented using an accumulator module, subtractor module and delay pipeline. The accumulator module generates an accumulated message sum. The accumulated message sum for a node is stored and then delayed input messages from the delay pipeline are subtracted there from to generate output messages. The delay pipeline includes a variable delay element making it possible to sequentially perform processing operations corresponding to nodes of different degrees.

Owner:QUALCOMM INC

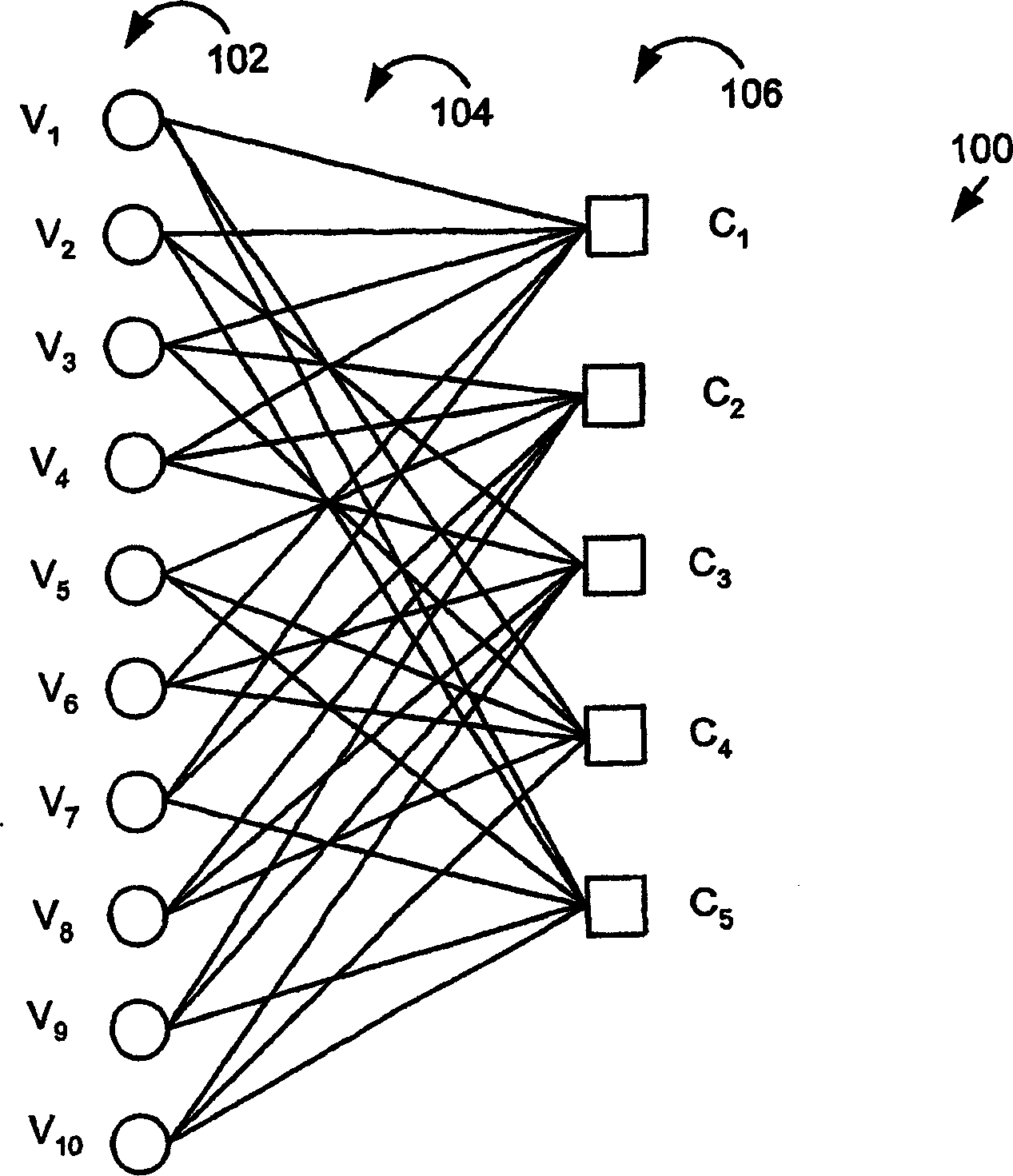

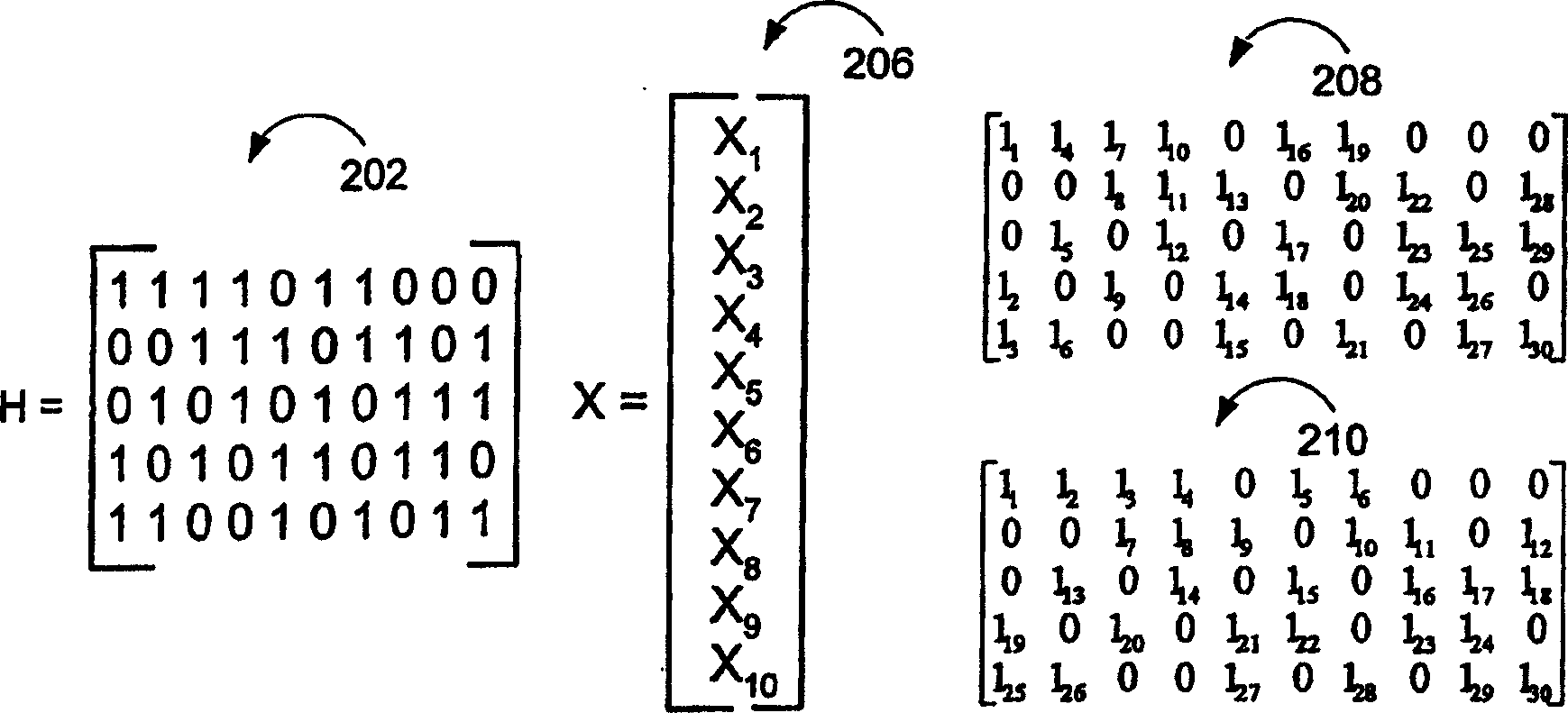

Methods and apparatus for decoding LDPC codes

InactiveUS20060242093A1Improve decoding efficiencyImprove efficiencyError correction/detection using multiple parity bitsDigital computer detailsLow densityMessage passing

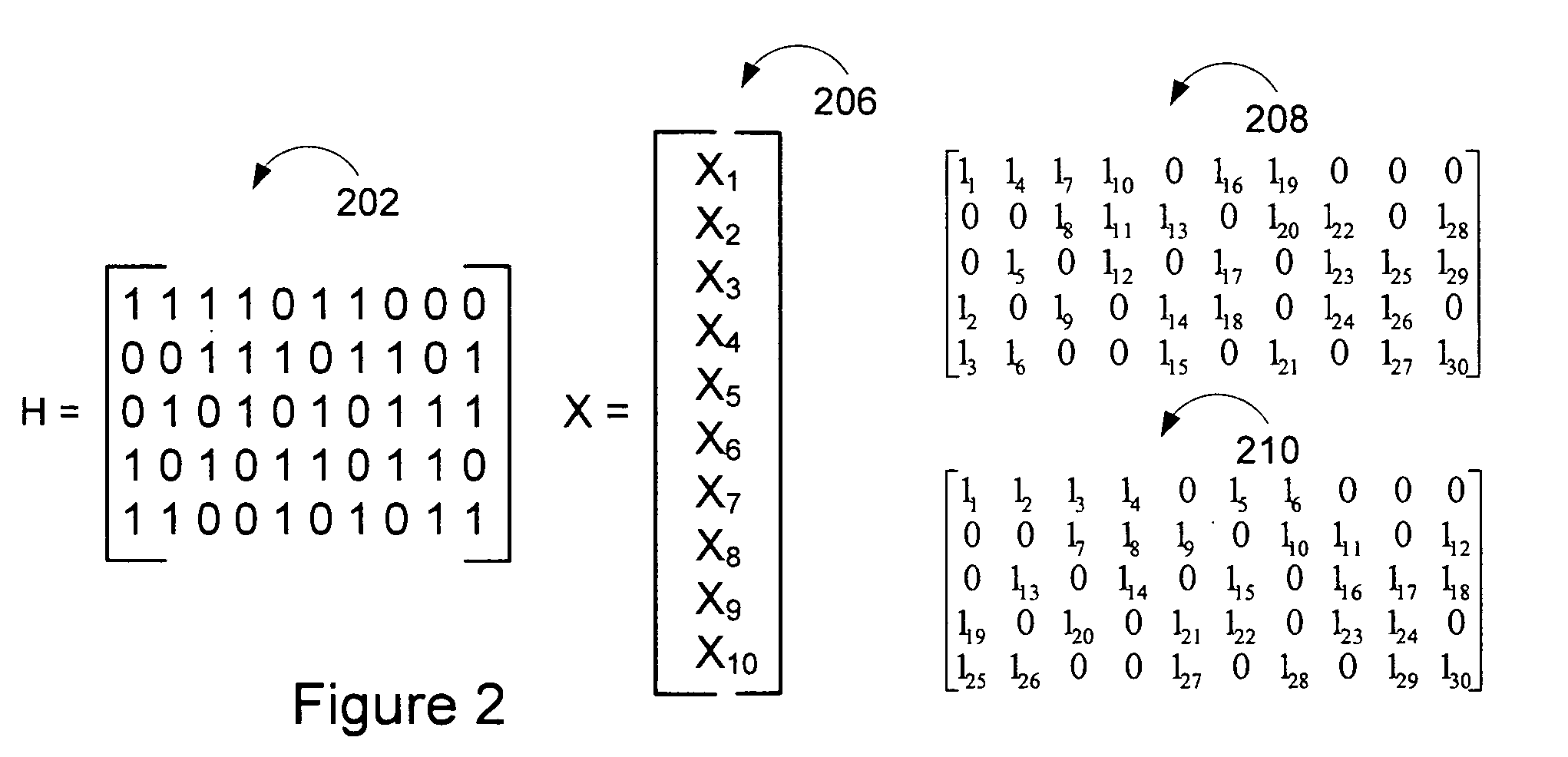

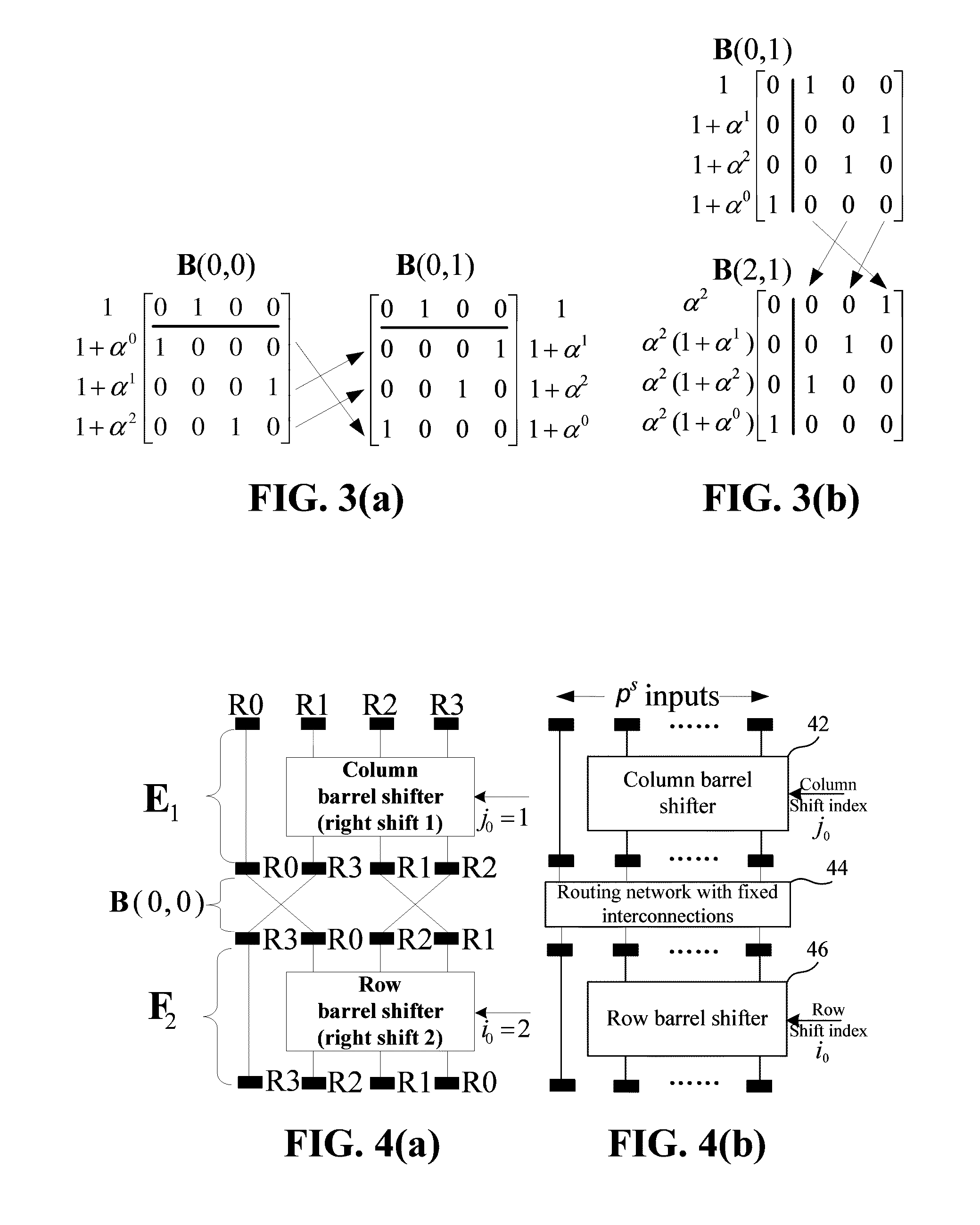

Methods and apparatus for decoding codewords using message passing decoding techniques which are particularly well suited for use with low density parity check (LDPC) codes and long codewords are described. The described methods allow decoding graph structures which are largely comprised of multiple identical copies of a much smaller graph. Copies of the smaller graph are subject to a controlled permutation operation to create the larger graph structure. The same controlled permutations are directly implemented to support message passing between the replicated copies of the small graph. Messages corresponding to individual copies of the graph are stored in a memory and accessed in sets, one from each copy of the graph, using a SIMD read or write instruction. The graph permutation operation may be implemented by simply reordering messages, e.g., using a cyclic permutation operation, in each set of messages read out of a message memory so that the messages are passed to processing circuits corresponding to different copies of the small graph.

Owner:QUALCOMM INC

Decoder and decoding method for low-density parity check codes constructed based on reed-solomon codes

ActiveUS8549375B2Easy to useMitigate increase in implementation complexityError preventionCode conversionComputer architectureRound complexity

Configurable permutators in an LDPC decoder are provided. A partially-parallel architecture combined with the proposed permutators is used to mitigate the increase in implementation complexity for the multi-mode function. To overcome the difficulty in efficient implementation of a high-throughput decoder, the variable nodes are partitioned into several groups, and each group is processed sequentially in order to shorten the critical-path delay and, hence, increase the maximum operating frequency. In addition, shuffled message-passing decoding can be adopted in decoders according to the invention to increase the convergence speed, which reduces the number of iterations required to achieve a given bit-error-rate performance.

Owner:NATIONAL TSING HUA UNIVERSITY

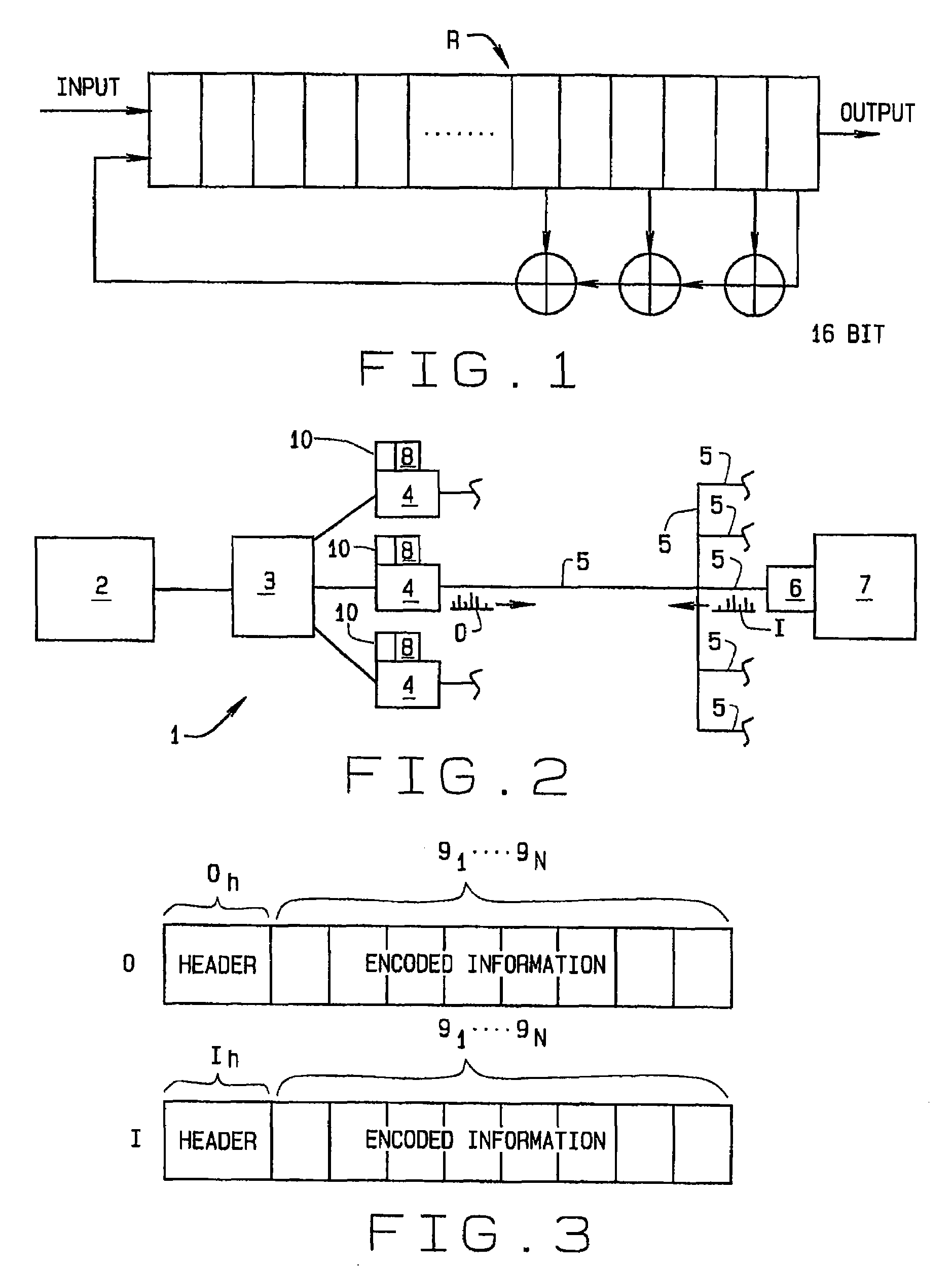

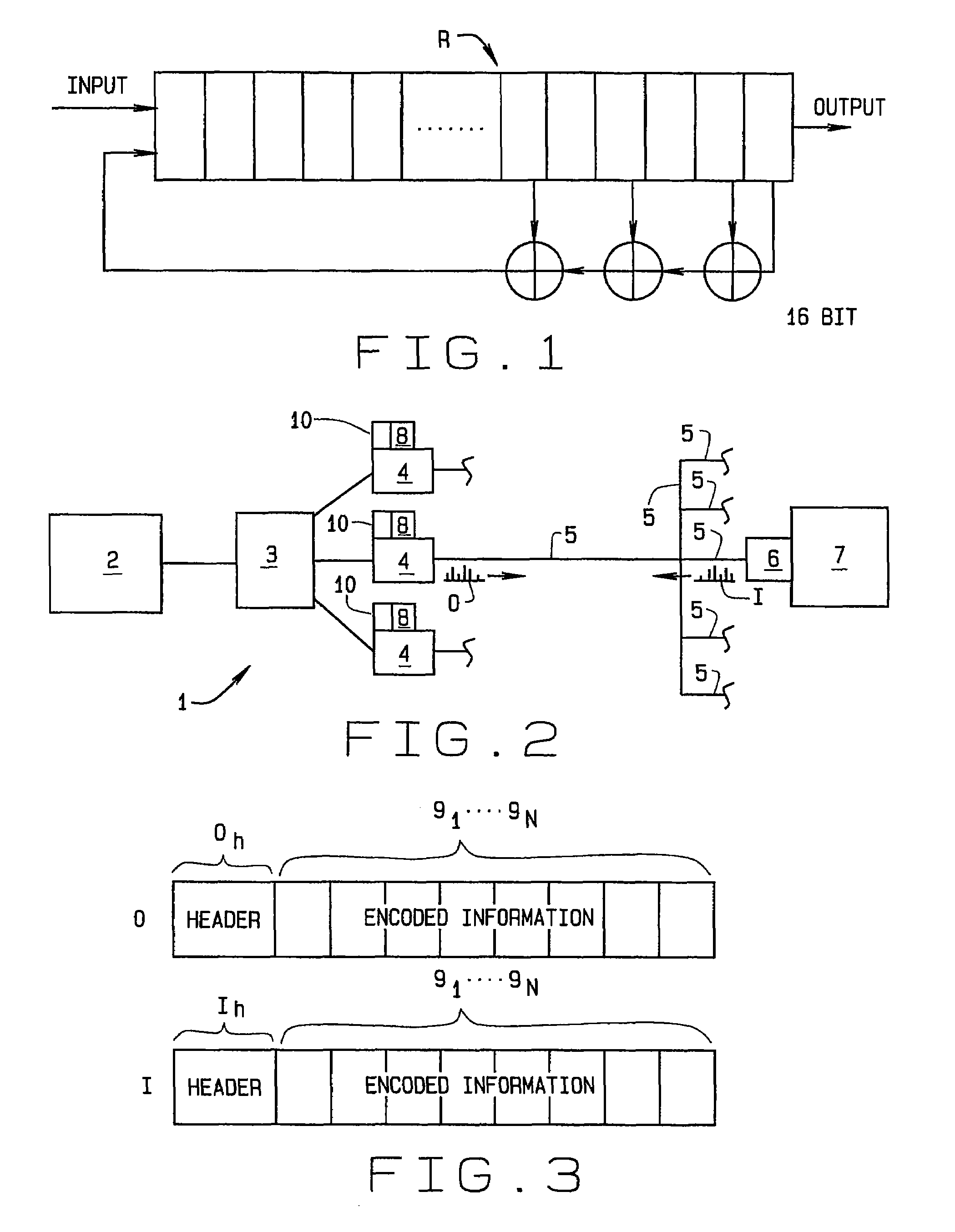

Method of correcting message errors using cycle redundancy checks

InactiveUS20090259917A1Improve performanceReduction in packet error rateCode conversionError detection onlyParity-check matrixMessage passing

A method of correcting errors in a message transmitted over a digital communication channel, where the message was encoded using a CRC for purposes of error detection. A parity-check matrix representation of the CRC is computed for any fixed-length message, and that parity-check matrix is combined with the parity-check matrix for any error correcting code that used in conjunction with the CRC. The combined parity-check matrix is extended using sparsification algorithms to allow it to work well under a message passing decoder (MPD). Received messages are decoded using the message passing decoder, making it possible to correct more errors than if the CRC were decoded in a conventional manner.

Owner:SPENCER QUENTIN

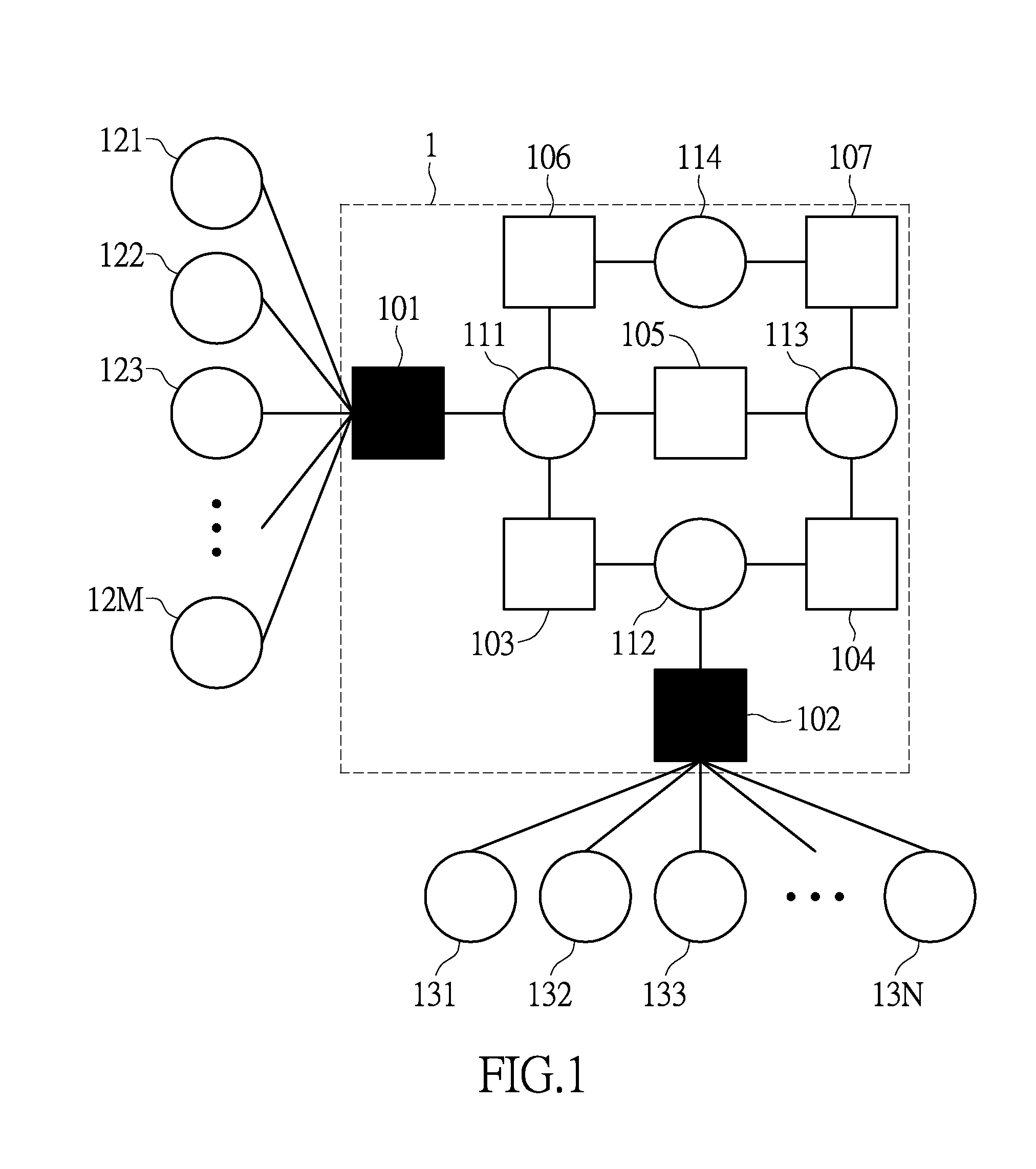

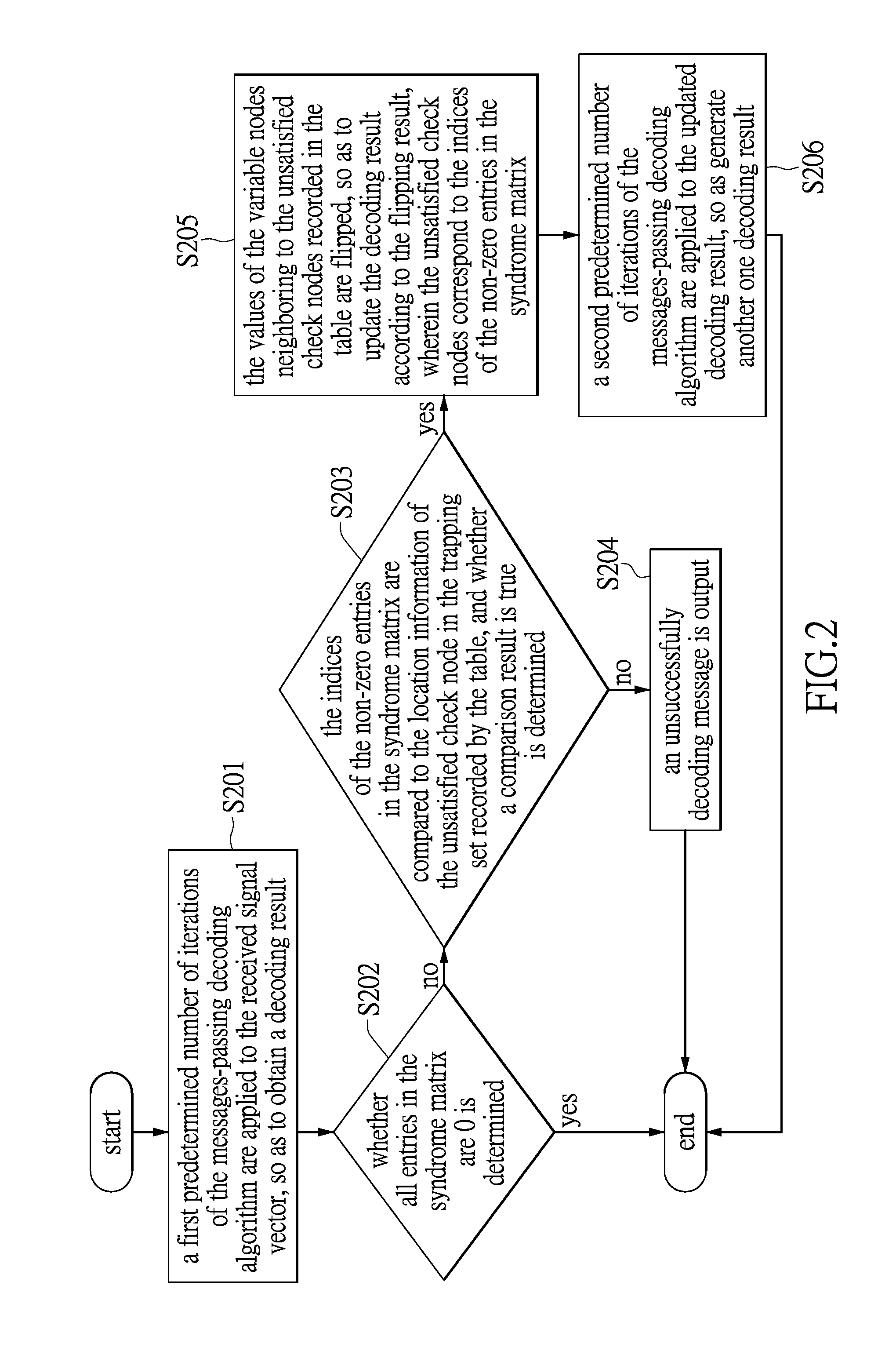

Decoding method of low density parity check code and information storing method in the decoding method

InactiveUS20160294416A1Reduce hardware costsReduce storage space costsError correction/detection using multiple parity bitsCode conversionTrappingComputer science

A decoding method of a LDPC comprises following steps. A first predetermined number of iterations of a messages-passing decoding algorithm are applied to a received signal vector, so as to attempt to decode a transmitted (or stored) codeword. Whether the decoding result converges to a valid codeword is determined by observing whether the decoding result makes all check nodes satisfied or not. When the decoding result does not converge to a valid codeword, the value of at least one of the variable nodes neighboring to one of the un-satisfied check node is be adjusted to a non-zero value, wherein the selected variable node is included in a trapping set. Then, a second predetermined number of iterations of the messages-passing decoding algorithm are applied to the updated decoding result to generate another one decoding result, and whether the other one decoding result converges to a valid codeword is checked.

Owner:NATIONAL TSING HUA UNIVERSITY

Method of correcting message errors using cyclic redundancy checks

ActiveUS20080040644A1Improve performanceReduction in packet error rateCode conversionError detection onlyParity-check matrixMessage passing

A method of correcting errors in a message transmitted over a digital communication channel, where the message was encoded using a CRC for purposes of error detection. A parity-check matrix representation of the CRC is computed for any fixed-length message, and that parity-check matrix is combined with the parity-check matrix for any error correcting code that used in conjunction with the CRC. The combined parity-check matrix is extended using sparsification algorithms to allow it to work well under a message passing decoder (MPD). Received messages are decoded using the message passing decoder, making it possible to correct more errors than if the CRC were decoded in a conventional manner.

Owner:ACLARA TECH LLC

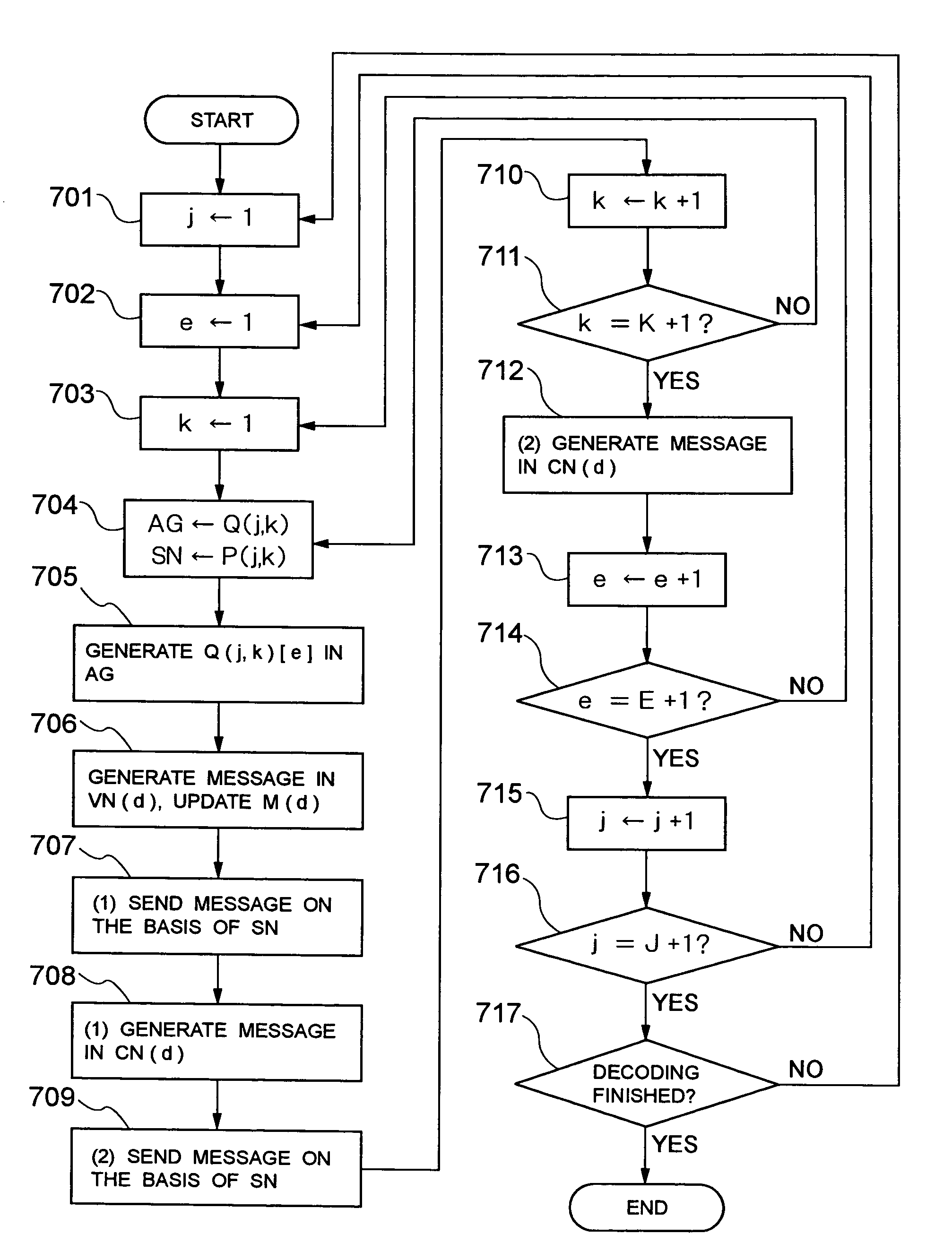

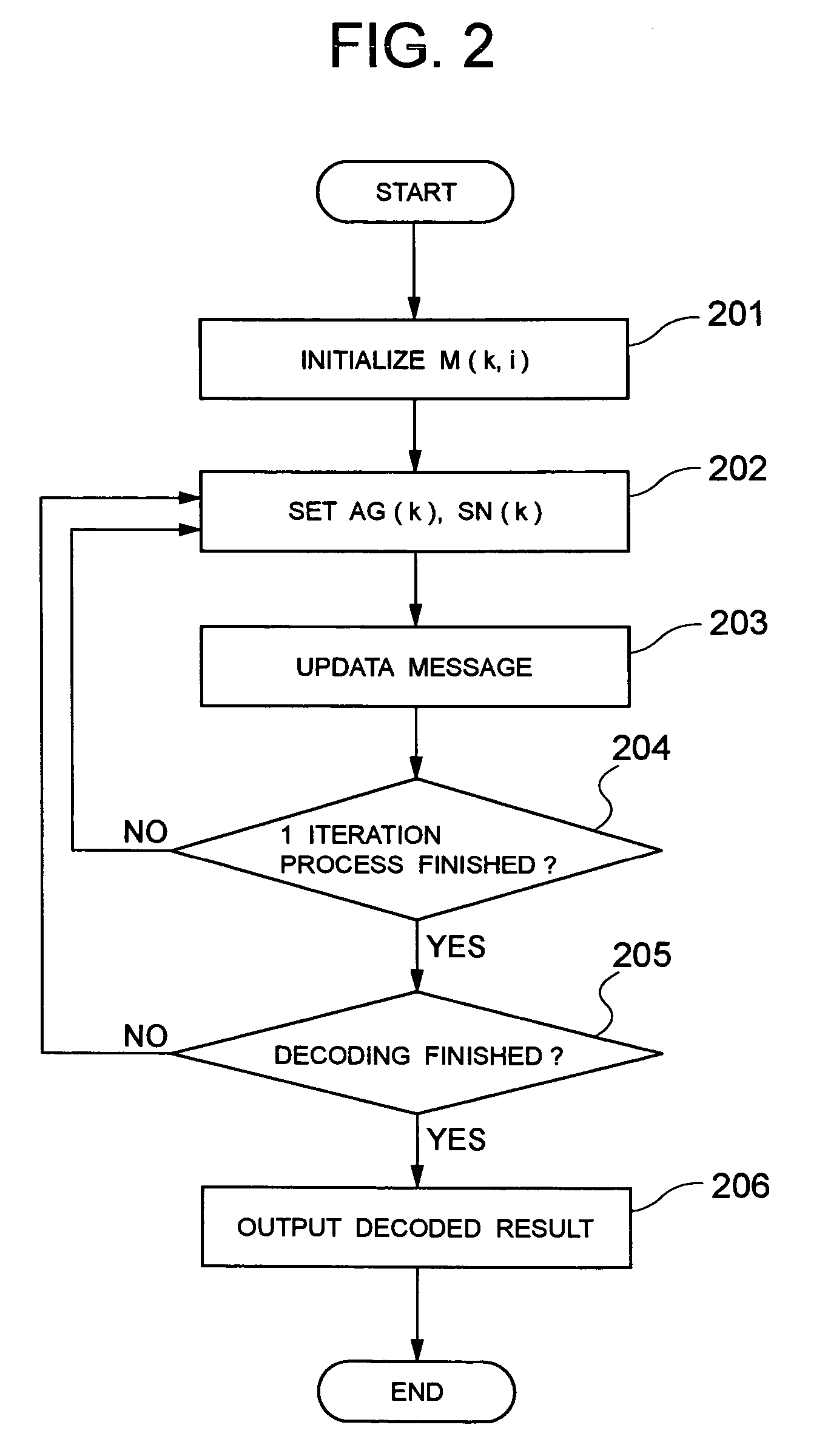

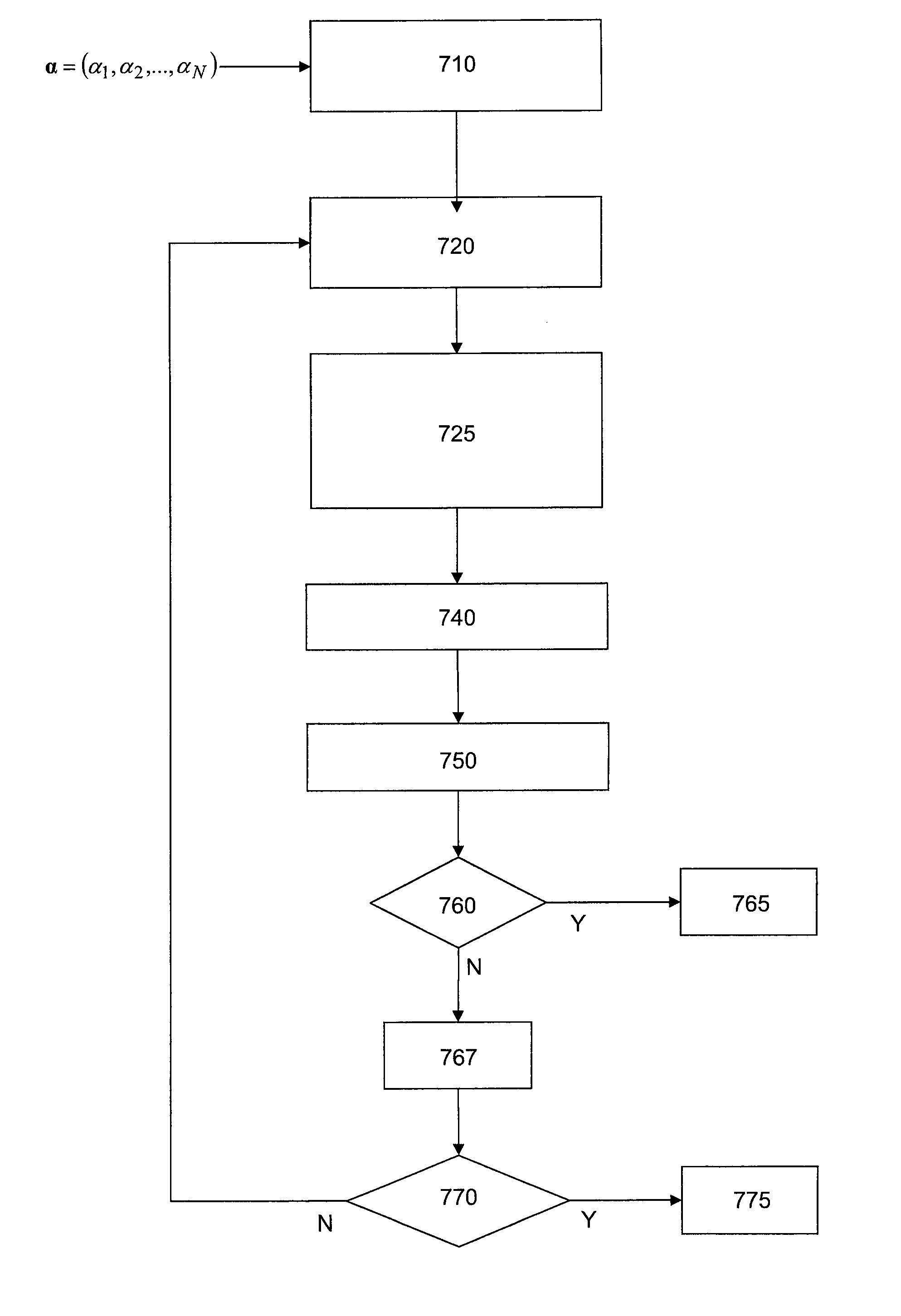

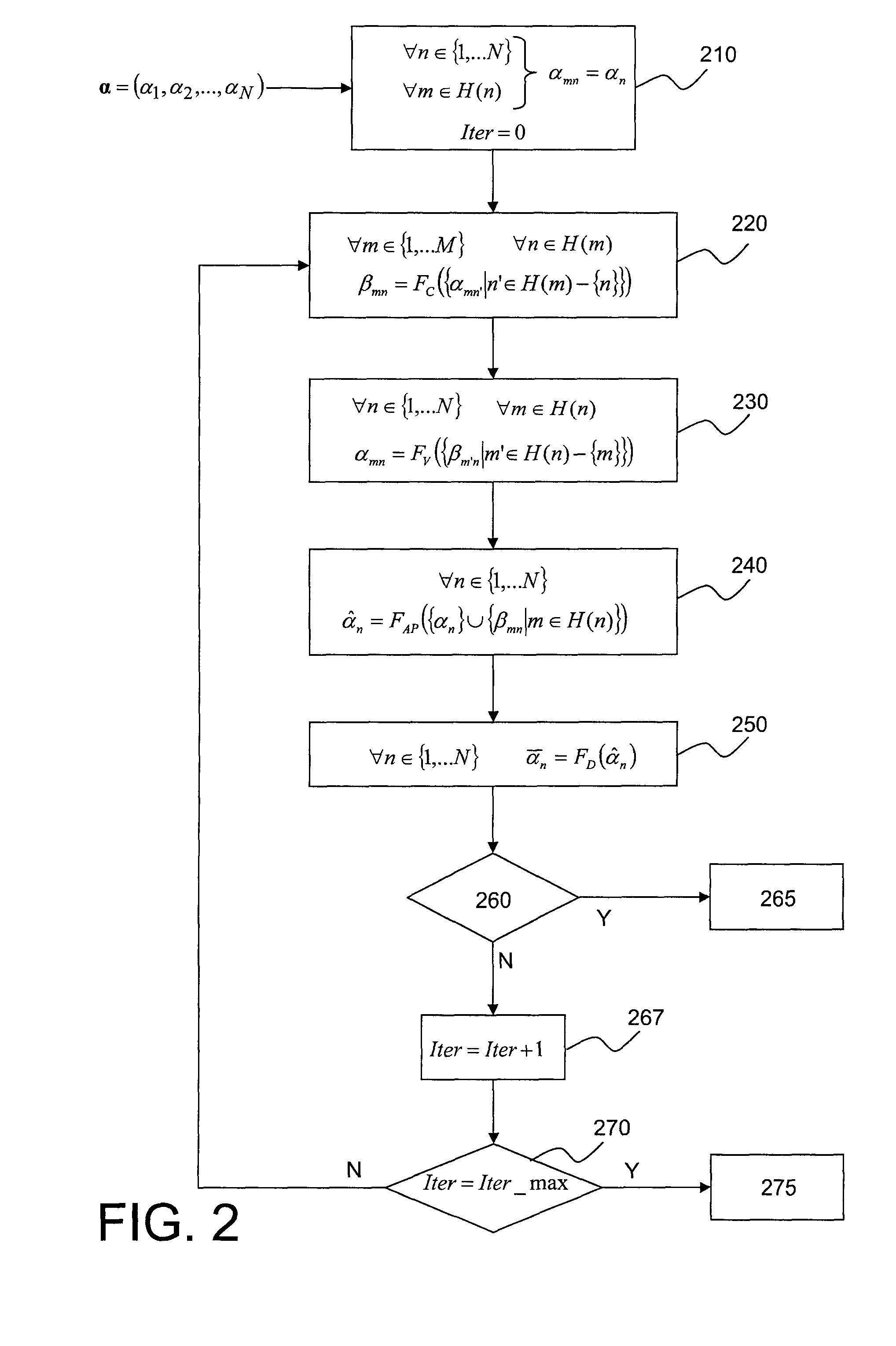

Method of decoding by message passing with scheduling depending on neighbourhood reliability

InactiveUS8245115B2Error correction/detection using multiple parity bitsCode conversionDecoding methodsDependability

The invention relates to an iterative method by message passing for decoding of an error correction code that can be displayed in a bipartite graph comprising a plurality of variable nodes and a plurality of check nodes. For each iteration in a plurality of decoding iterations of said method:variable nodes or check nodes are classified (720) as a function of the corresponding degrees of reliability of decoding information available in the neighborhoods (Vn(d),Vm(d)) of these nodes, a node with a high degree of reliability being classified before a node with a low degree of reliability;each node thus classified (725) passes at least one message (αmn,βmn) to an adjacent node, in the order defined by said classification.The invention also relates to a computer program designed to implement said decoding method.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

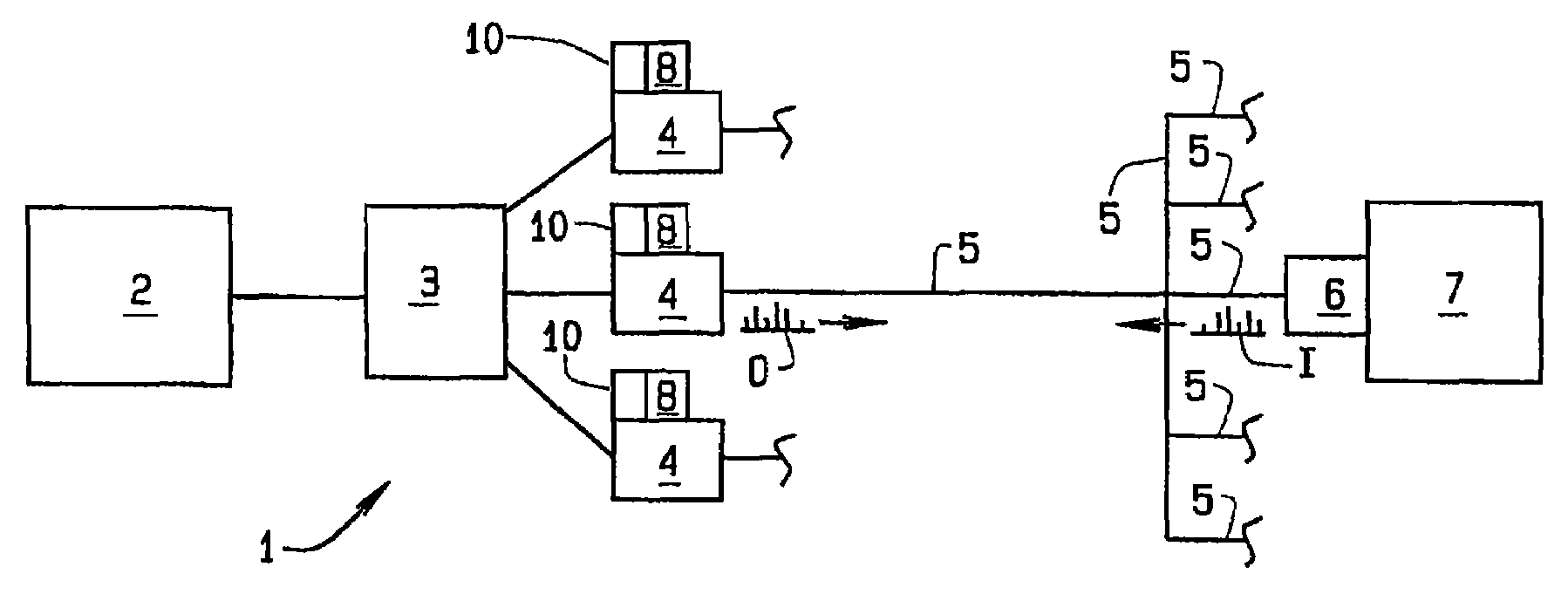

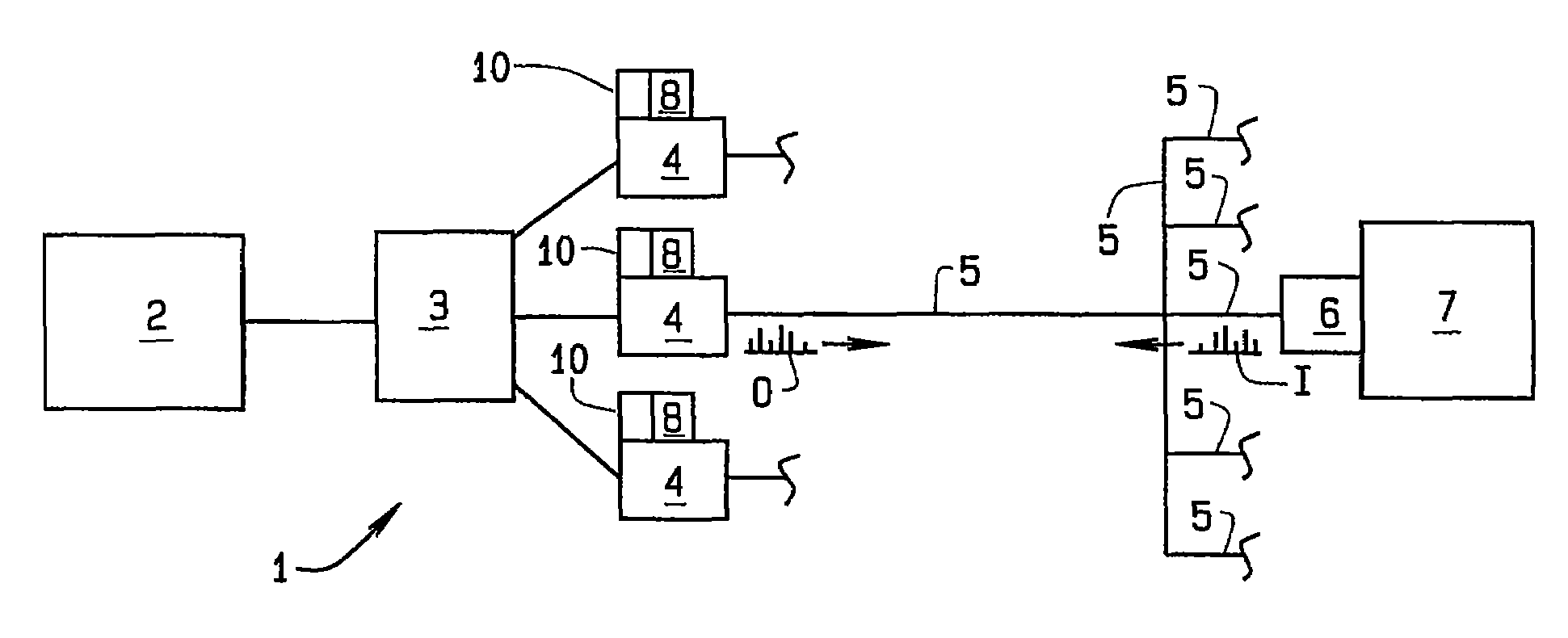

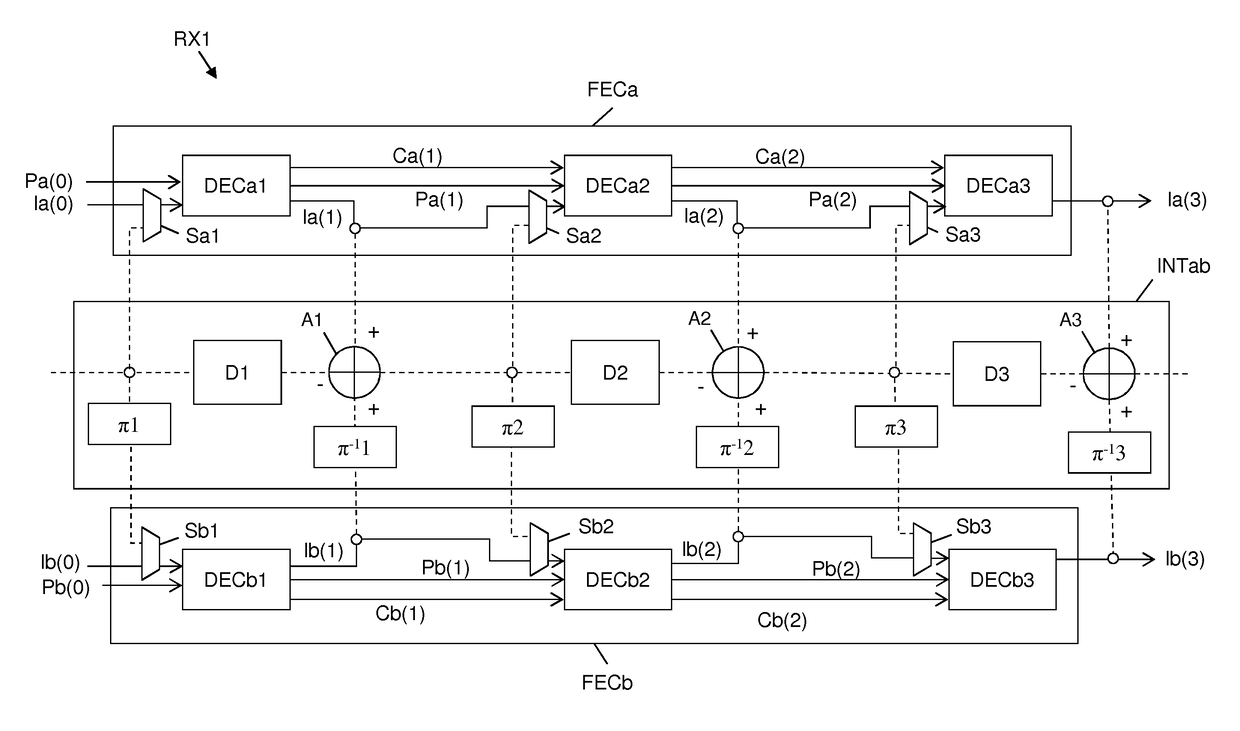

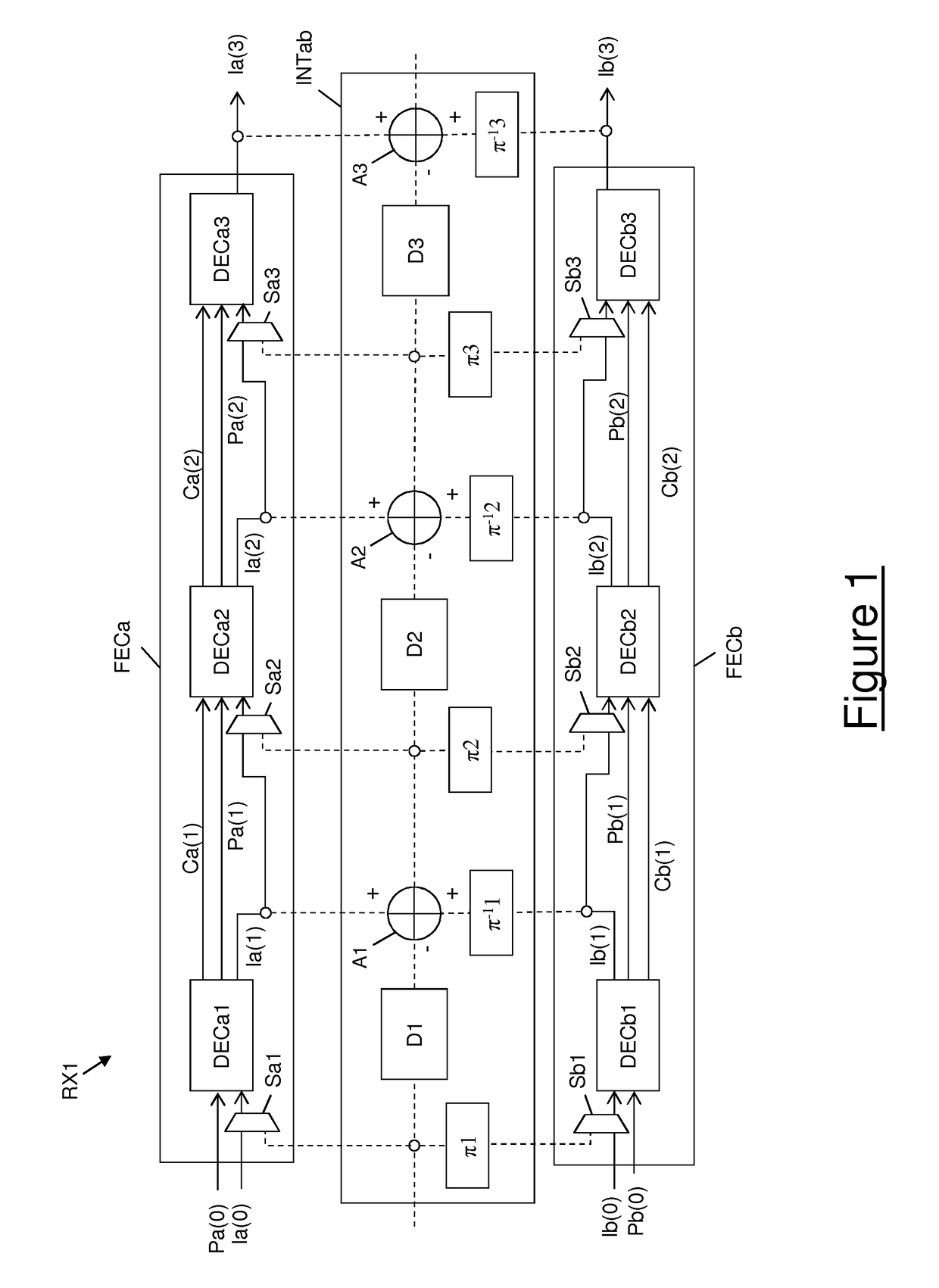

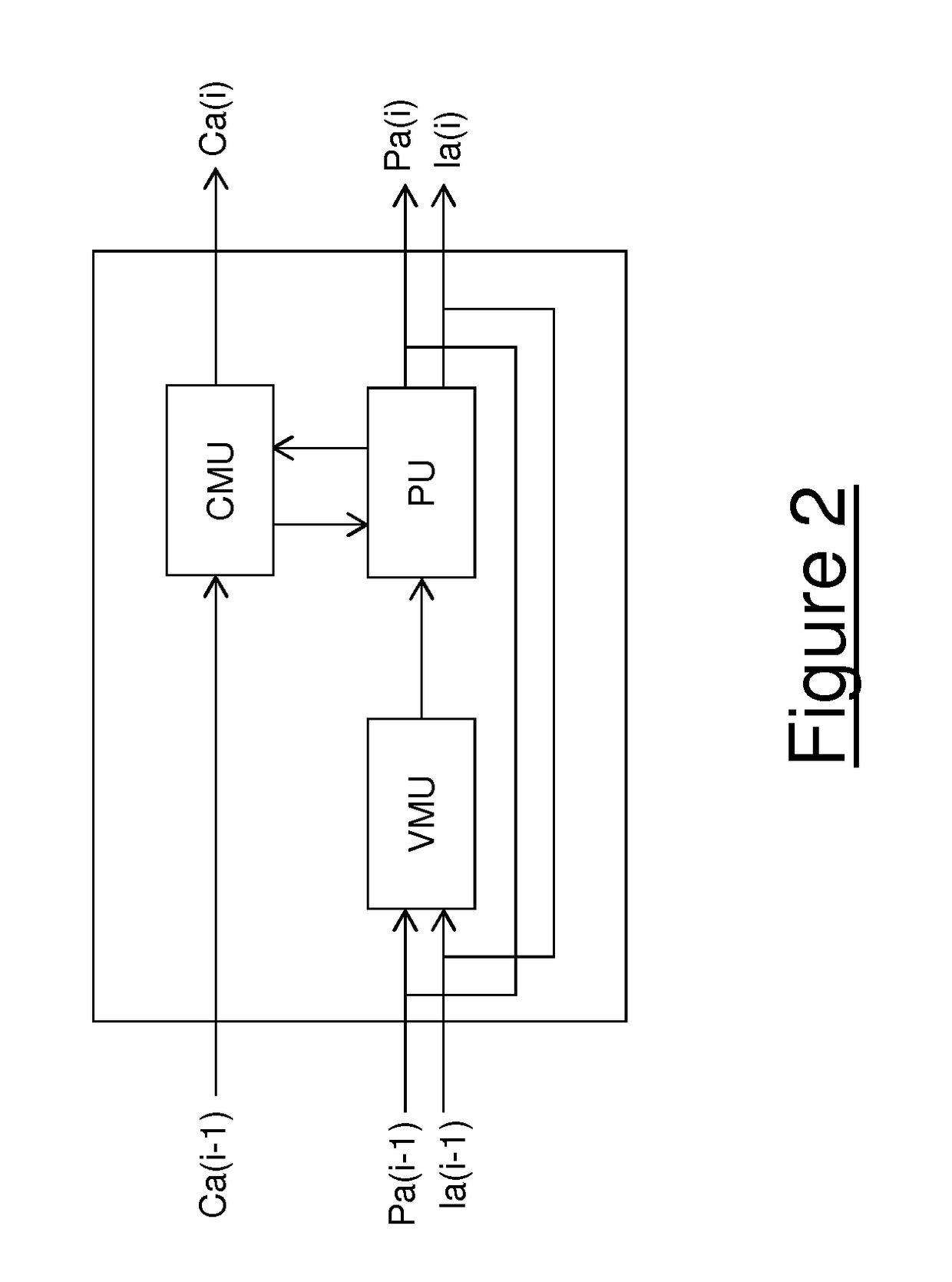

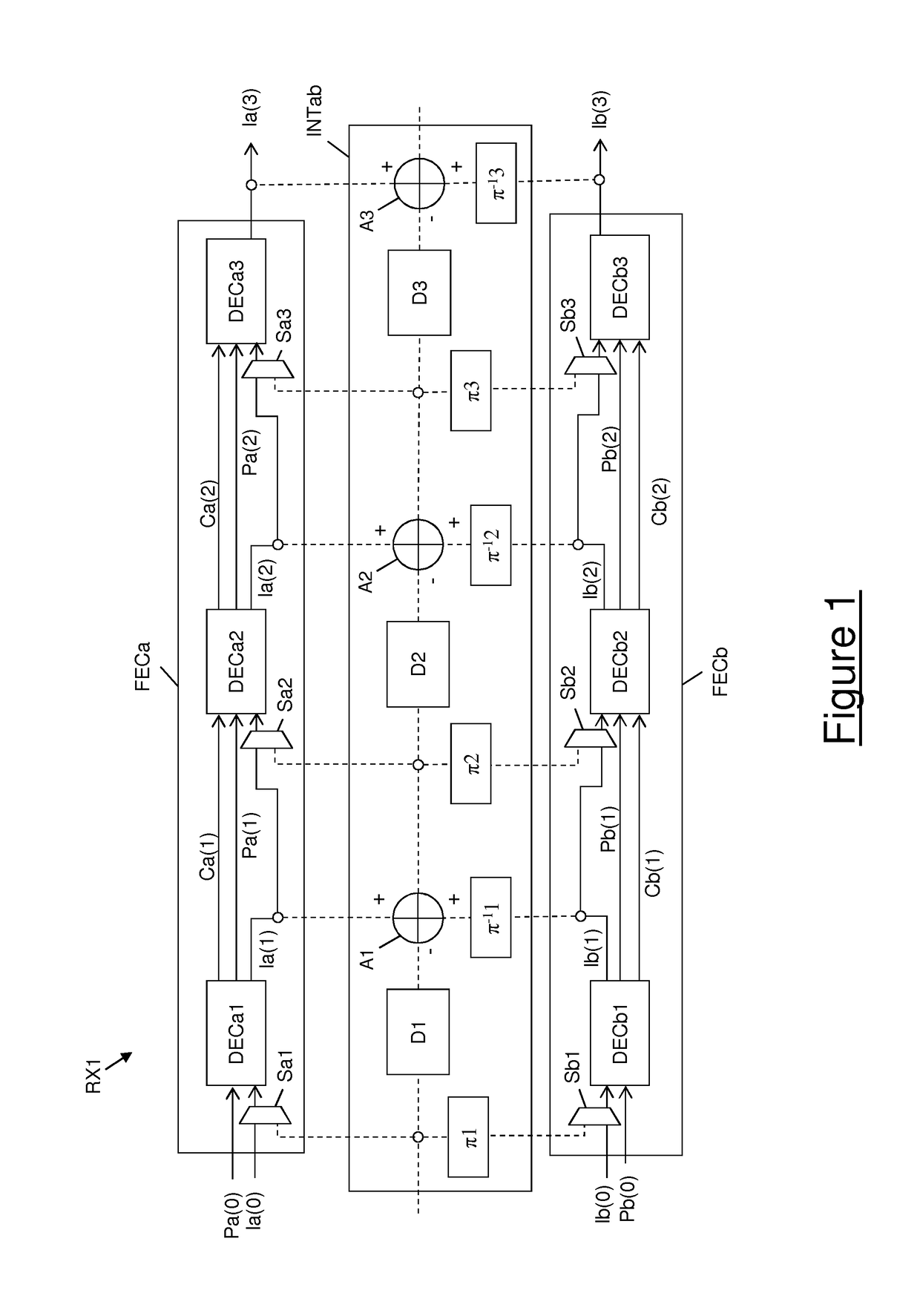

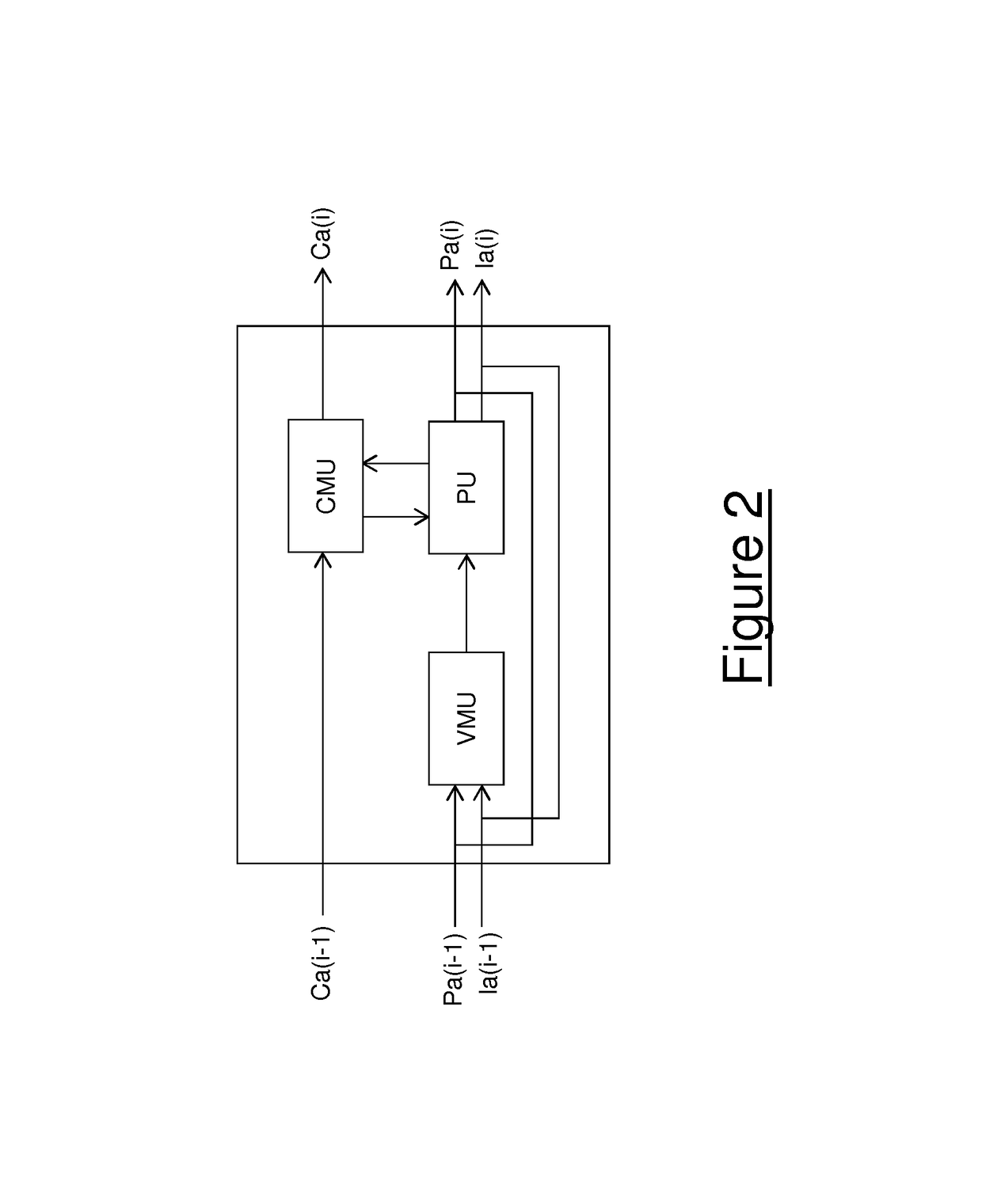

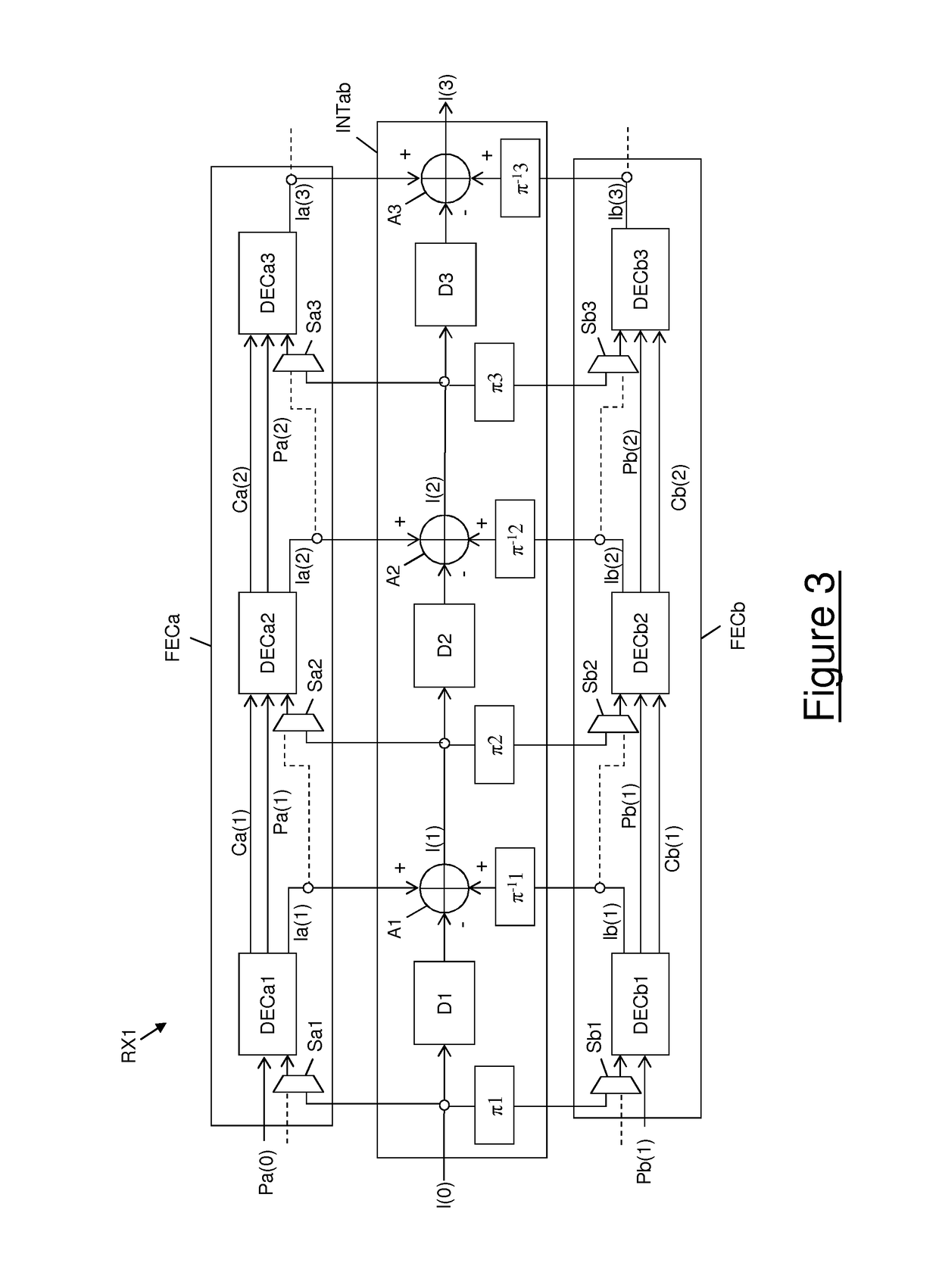

Optical coherent receiver with forward error correction

ActiveUS20170244515A1OptimizationIncrease the number ofOther decoding techniquesError correction/detection using multiple parity bitsComputer architectureForward error correction

It is disclosed an optical coherent receiver comprising a number of decoding blocks configured to implement iterations of a FEC iterative message-passing decoding algorithm. The decoding blocks are distributed into two (or more) parallel chains of cascaded decoding blocks. The receiver also comprises an intermediate circuit interposed between the two parallel chains. The optical coherent receiver is switchable between (i) a first operating mode, in which the intermediate circuit is inactive and the two parallel chains separately implement the FEC message-passing decoding algorithm on respective client channels; and (ii) a second operating mode, in which the intermediate circuit is active and the two parallel chains jointly implement the FEC message-passing decoding algorithm on a same client channel, by cooperating through the intermediate circuit.

Owner:ALCATEL LUCENT SAS

Method and System for Decoding Graph-Based Codes Using Message-Passing with Difference-Map Dynamics

InactiveUS20110041033A1Increase heightImprove errorDigital data processing detailsCode conversionDifference-map algorithmTheoretical computer science

A code to be decoded by message-passing is represented by a factor graph. The factor graph includes variable nodes indexed by i and constraint nodes indexed by a connected by edges for transferring messages mi→a outgoing from the variable nodes to the constraint nodes and messages ma→i incoming from the constraint nodes to the variable nodes. The messages mi→a are initialized based on beliefs bi of a received codeword. The messages ma→i are generated by overshooting the messages mi→a at the constraint nodes. The beliefs bi are updated at the variable nodes using the messages ma→i. The codeword is outputted if found, otherwise, the messages mi→a are updated using a correction for the overshooting.

Owner:MITSUBISHI ELECTRIC RES LAB INC

Methods and apparatus for decoding ldpc codes

InactiveCN1825771AEasy to useQuick checkError correction/detection using multiple parity bitsCode conversionInformation transmissionComputer science

The invention relates to a method for executing parity check information transmission decodes operation, and relative device, wherein said device comprises: one information source for supplying at least one group with Z k-bit information from at least L groups of any Z k-bit information, while Z is positive integer higher than 1, K and L are non-zero positive integer; and node processor which comprises several node processing units, while each unit is used to execute parity check limit node processing operation or / and parity check variable node processing operation, and one switch connecting said information source and the node processing unit. And switch is used to transmit Z k-bit groups between information sources and the node processors, to respond the switch control information to rearrange the information of at least one group.

Owner:QUALCOMM INC

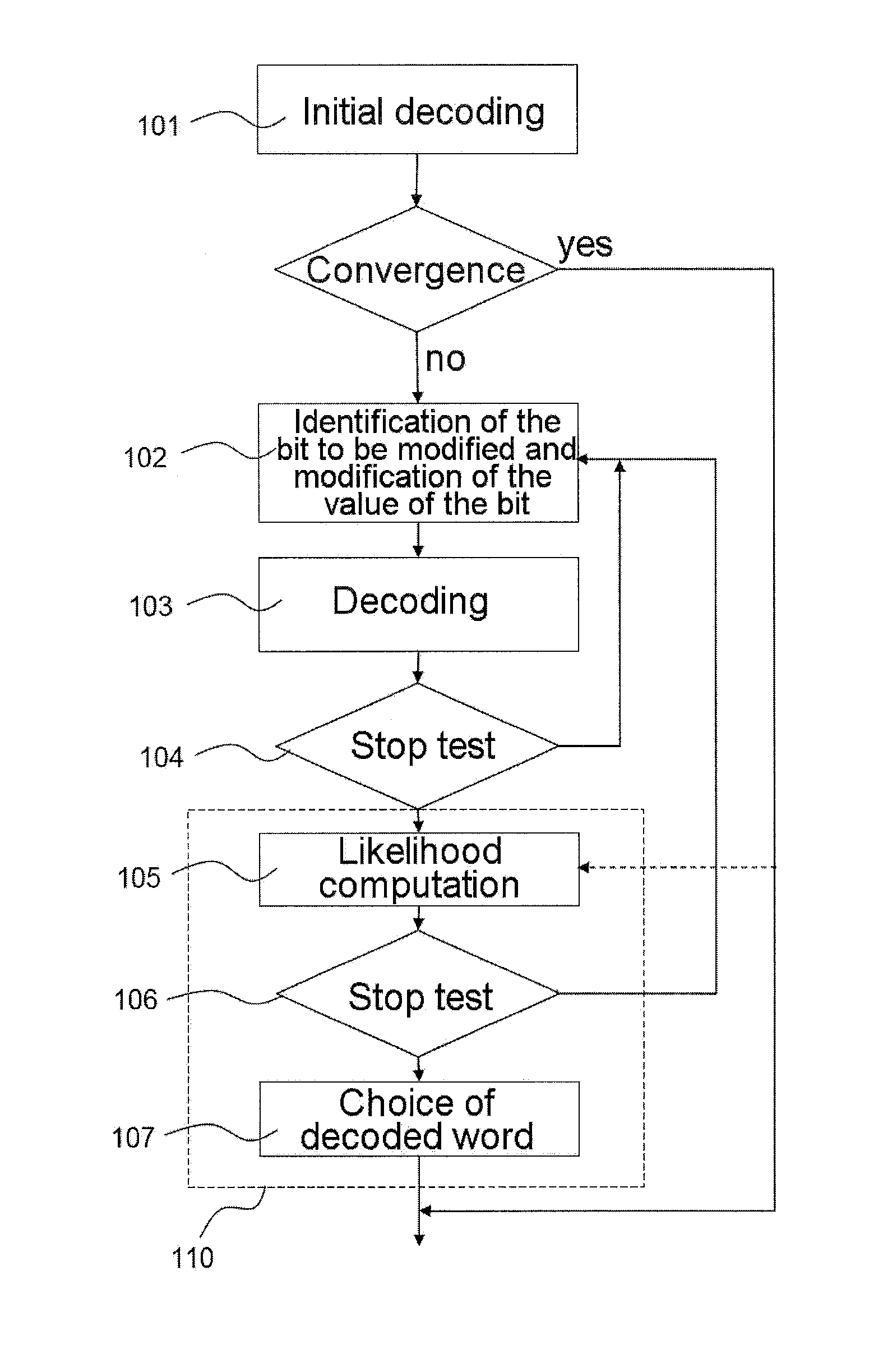

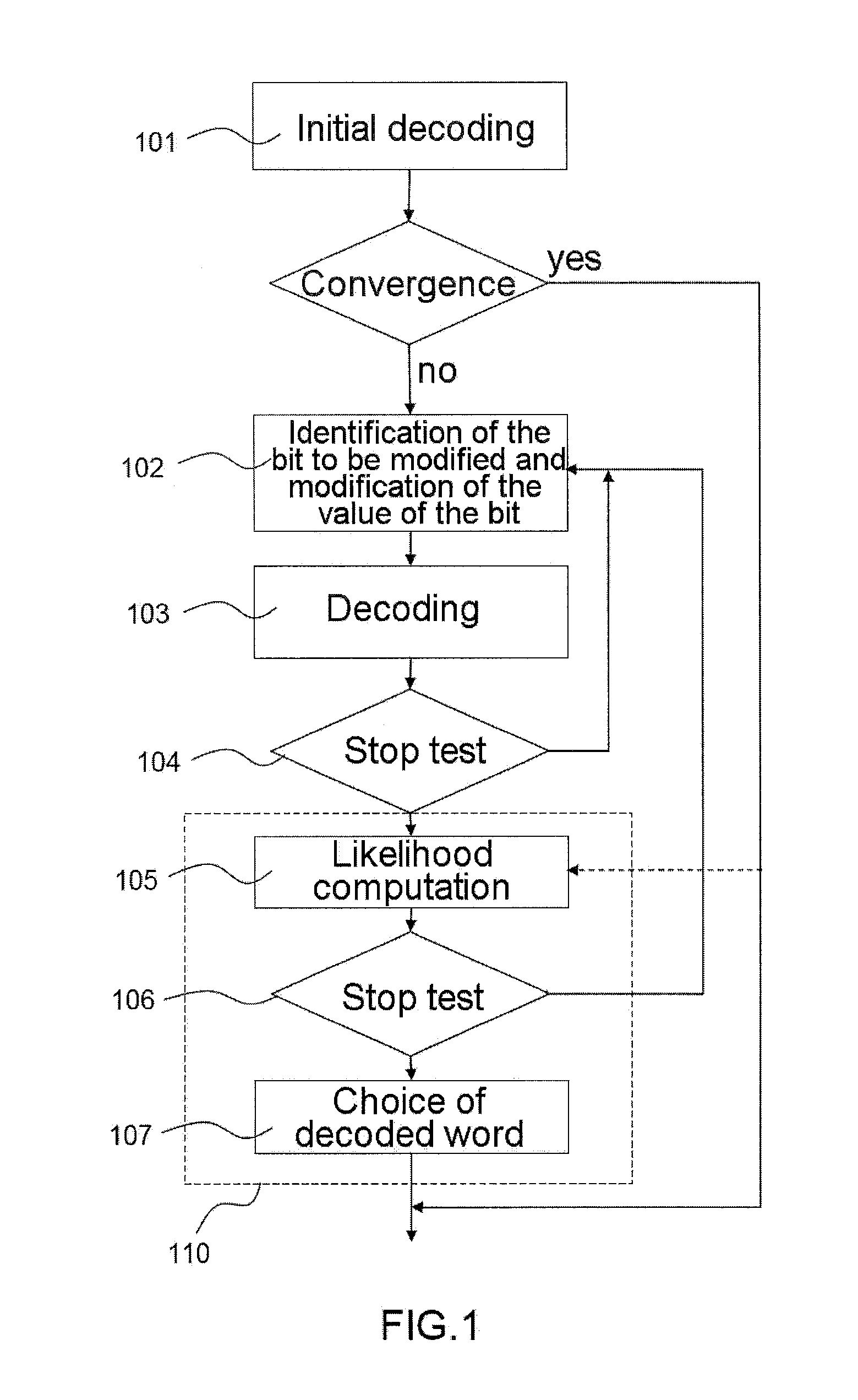

Method for decoding a correcting code with message passing, in particular for decoding LDPC codes or turbo codes

ActiveUS20150039959A1Possible to performImprove reliabilityError correction/detection using multiple parity bitsCode conversionComputer hardwareMessage passing

A method for iteratively decoding a word of a correcting code by an iterative decoding algorithm in the course of which, for each bit of said code word, at least one extrinsic information item is generated at each iteration, includes the following steps: an initial step of decoding by means of said iterative decoding algorithm; simultaneously, for each bit of said code word, a step of developing a criterion representing the number of oscillations of at least one extrinsic information item or of one extrinsic information item with regard to another extrinsic information item; if the decoding does not converge; a step of modifying the value of the bit of said code word for which said number of oscillations is highest; and, an additional step of decoding said at least one modified code word by means of said iterative decoding algorithm.

Owner:THALES SA

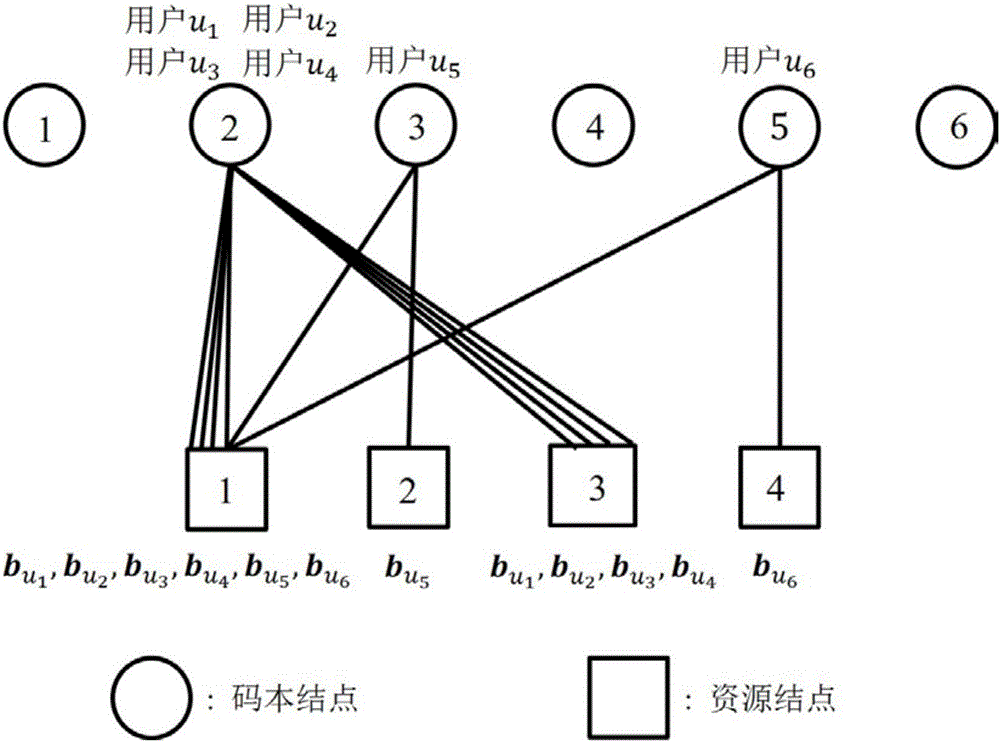

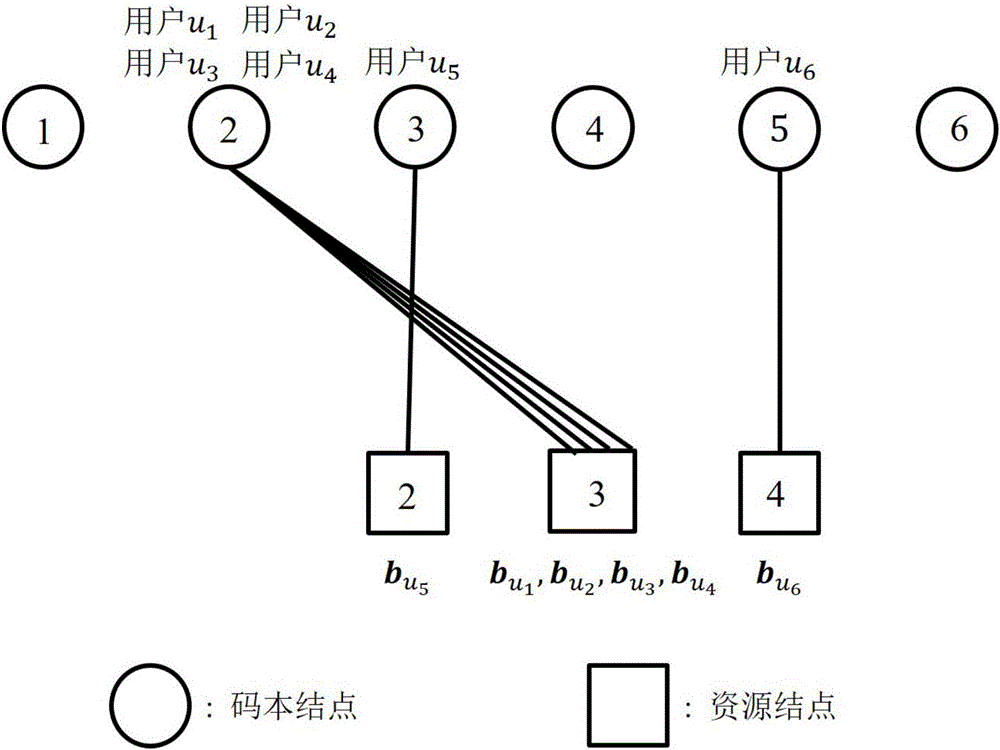

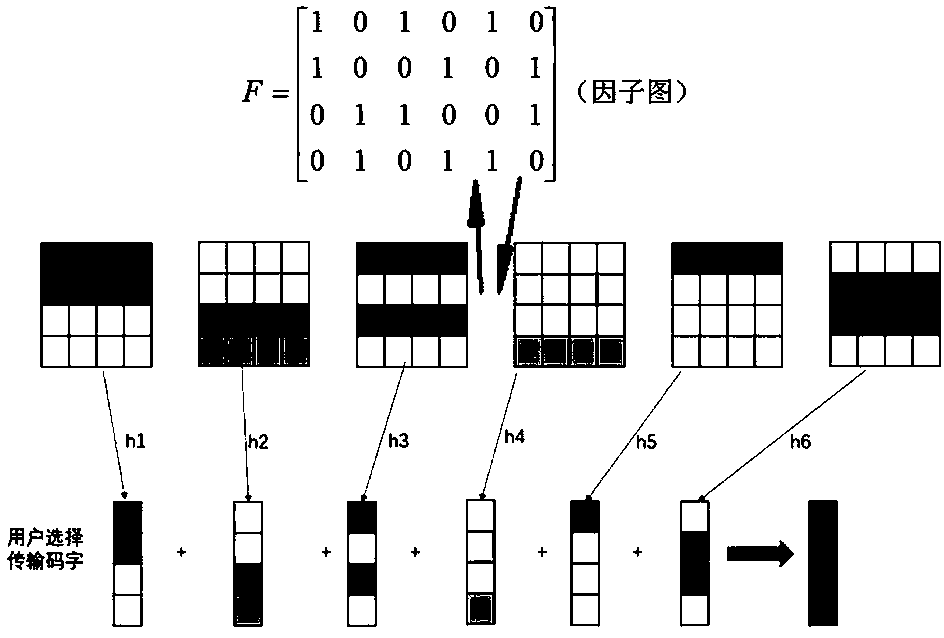

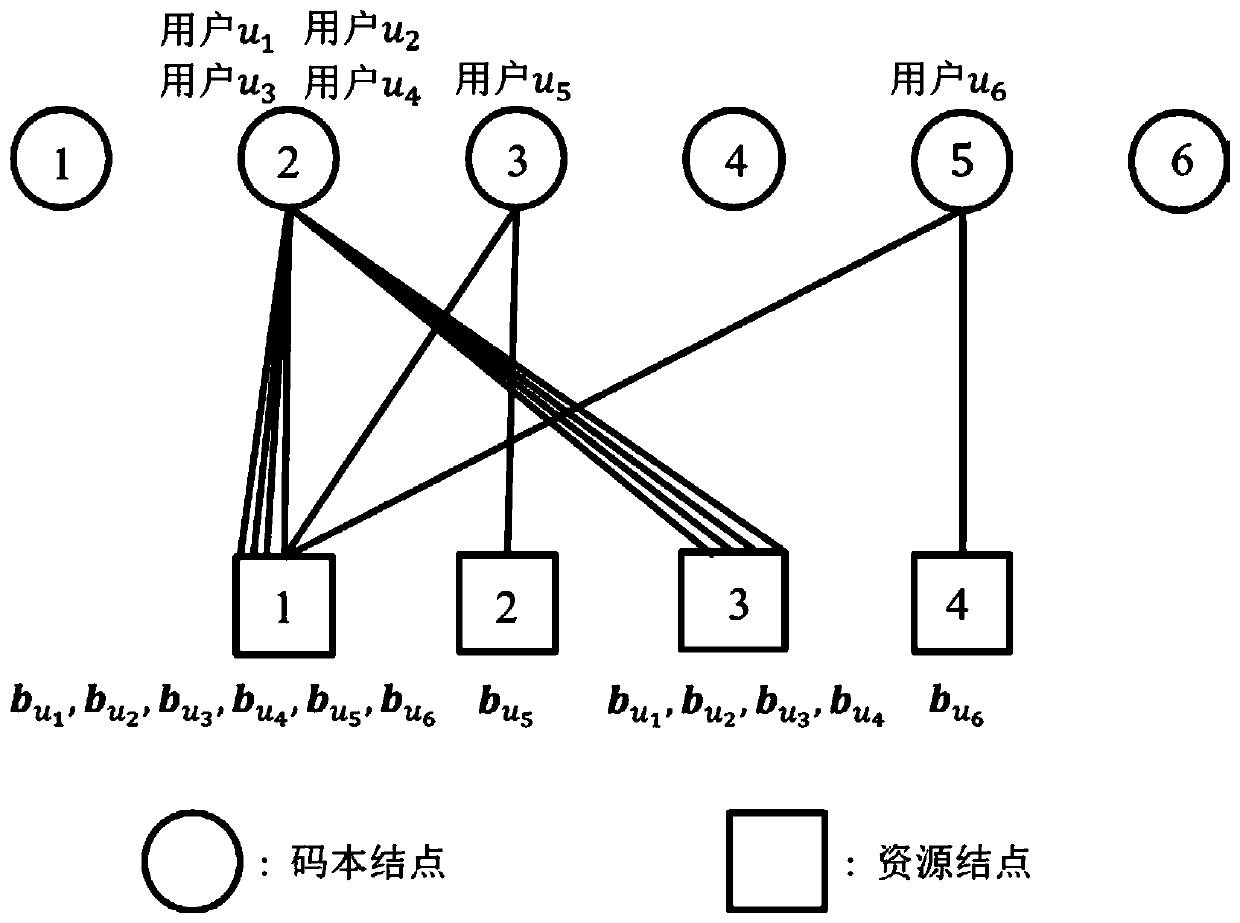

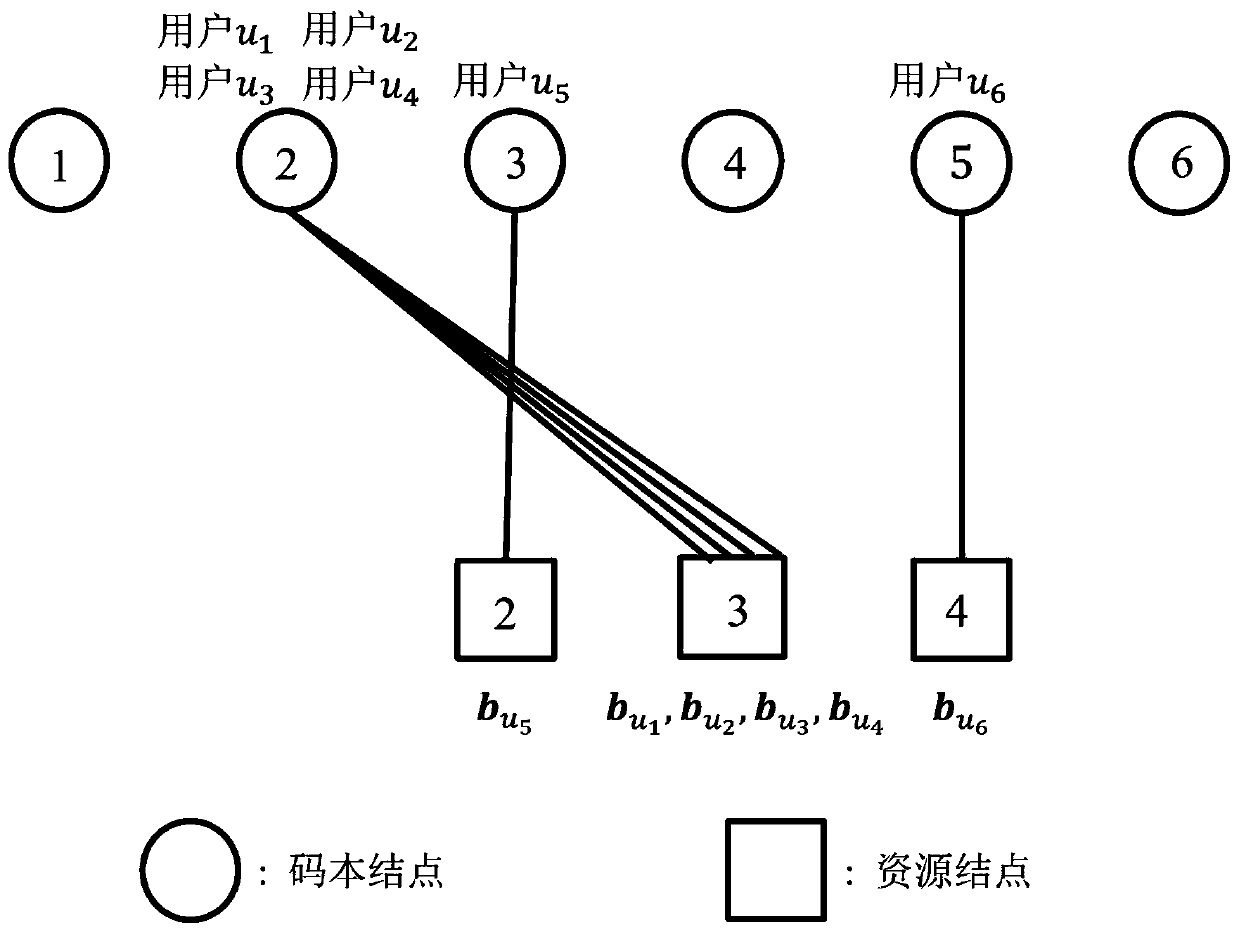

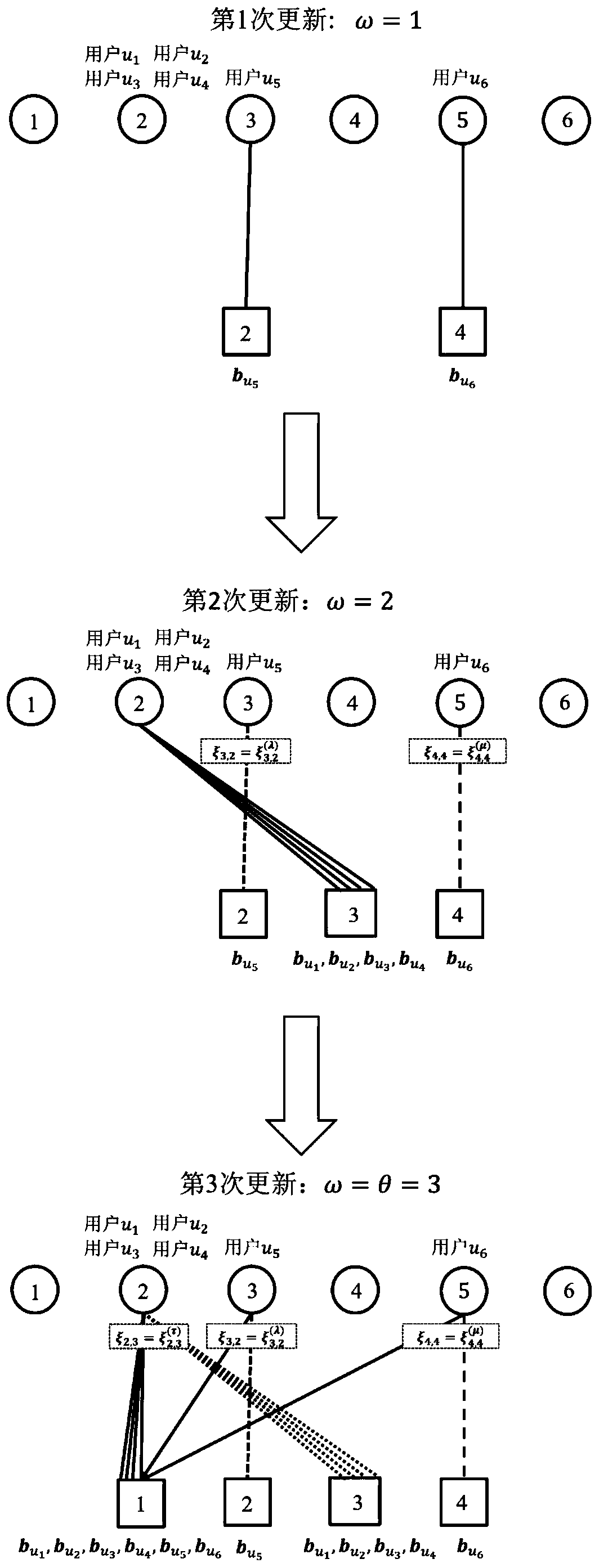

Low-complexity message passing decoding algorithm based on factor graph evolution in sparse code multiple access

ActiveCN106712900AImprove performanceReduce decoding delayForward error control useMultiple carrier systemsRound complexitySymbol of a differential operator

The invention provides a low-complexity message passing decoding algorithm based on factor graph evolution. A factor graph is simplified to realize low-complexity decoding, the degrees of resource nodes are classified at first, all resource nodes are removed at first, then the low-degree nodes are added to the factor graph for decoding gradually, therefore the evolution of the factor graph is realized, the obtained symbol experience information is stored, when the high-degree nodes are added to the factor graph subsequently, the high complexity of the traditional message passing algorithm under codebook collision can be greatly reduced by means of the hard judgment of a part of symbols by using the experience information, thereby reducing the decoding delay and further improving the performance expression of SCMA, in addition, by means of different settings of an update step length and a final update value of the factor graph, different compromise situations between the decoding accuracy and the decoding complexity can be obtained, and thus the algorithm is applicable to the actual application demands more flexibly.

Owner:TSINGHUA UNIV

Soft and hard decision message-passing decoding

ActiveUS9621188B2Other decoding techniquesError correction/detection using multiple parity bitsComputer architectureMessage delivery

Owner:SAMSUNG ELECTRONICS CO LTD

Method for acquiring a gold sequence by double iterative decoding

ActiveUS20160061961A1Active radio relay systemsSatellite radio beaconingMinimum weightComputer science

A method for acquiring a Gold code, obtained as a sum of a first M-sequence (x) and a second M-sequence (yi), the first M-sequence being generated by a first generator polynomial (gx) and the second M-sequence being generated by a second generator polynomial (gy), the weight of the first generator polynomial being lower than the weight of the second generator polynomial, the acquiring method involving a first step of message passing decoding according to a first bipartite graph the edges of which are determined by the coefficients of the first generator polynomial, a decimation step using a predetermined decimation factor, and a second step of message passing decoding according to a second bipartite graph the edges of which are determined by a third generator polynomial having a minimum weight generating a third M-sequence having the same length as that of the second M-sequence.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

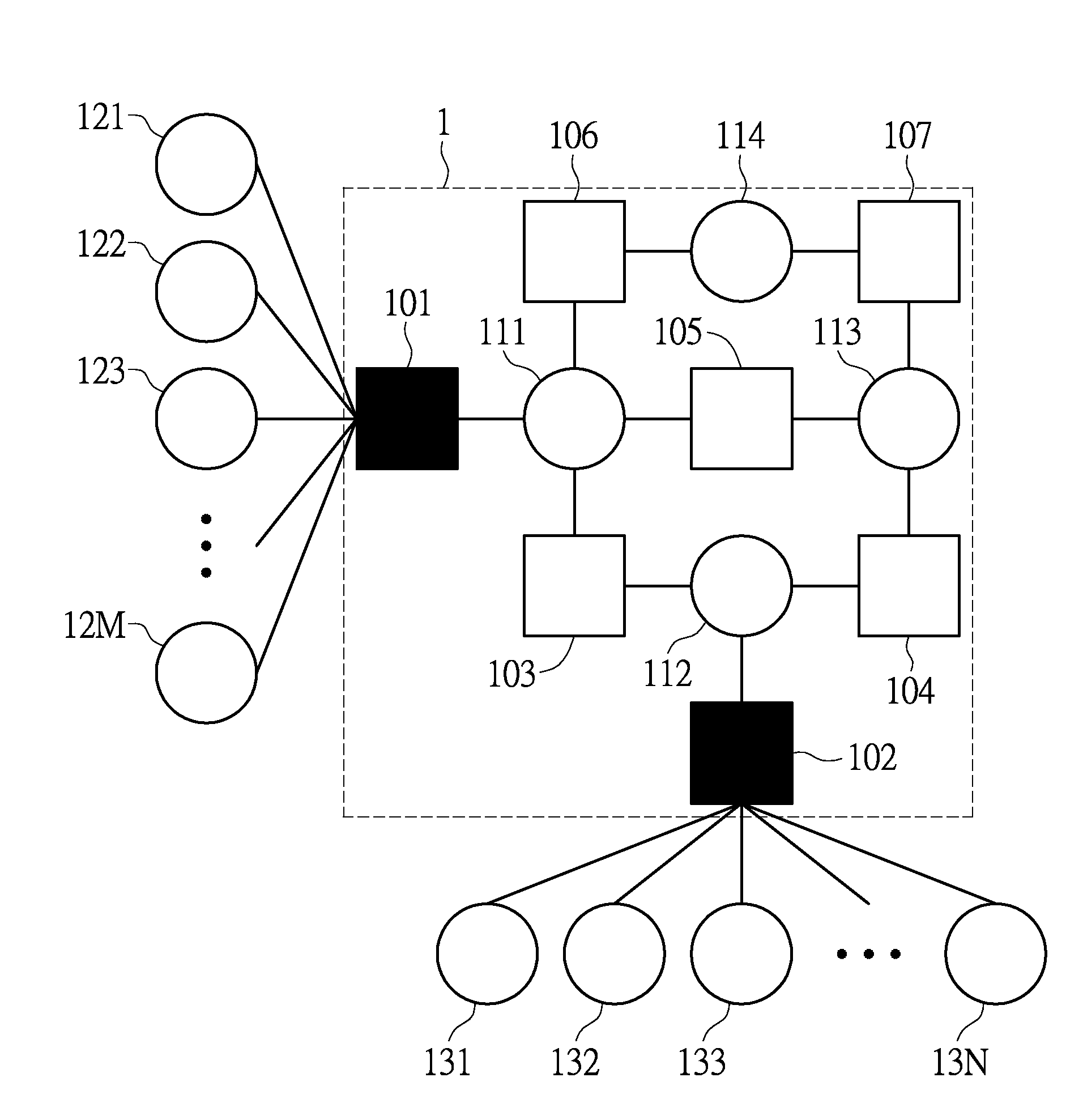

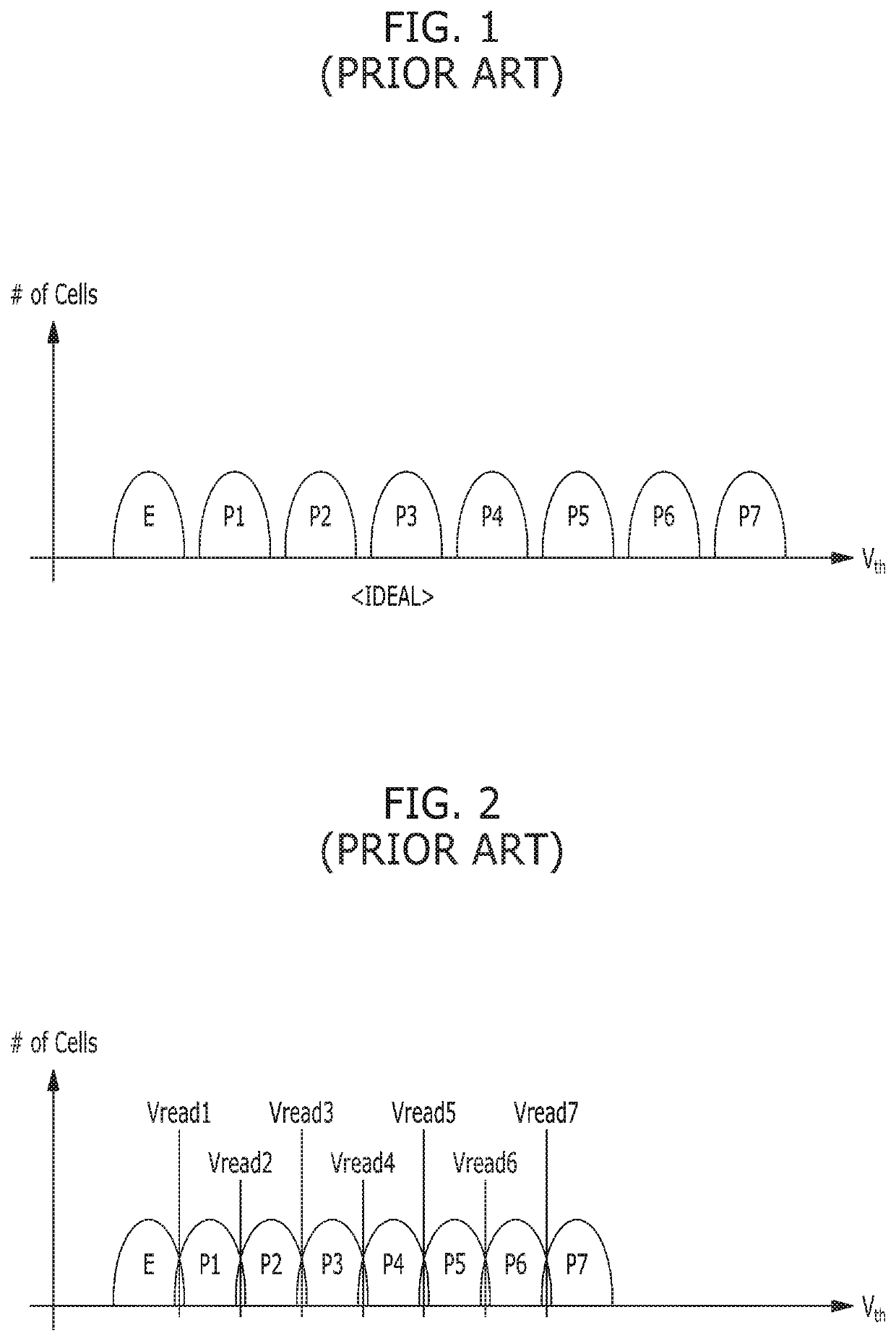

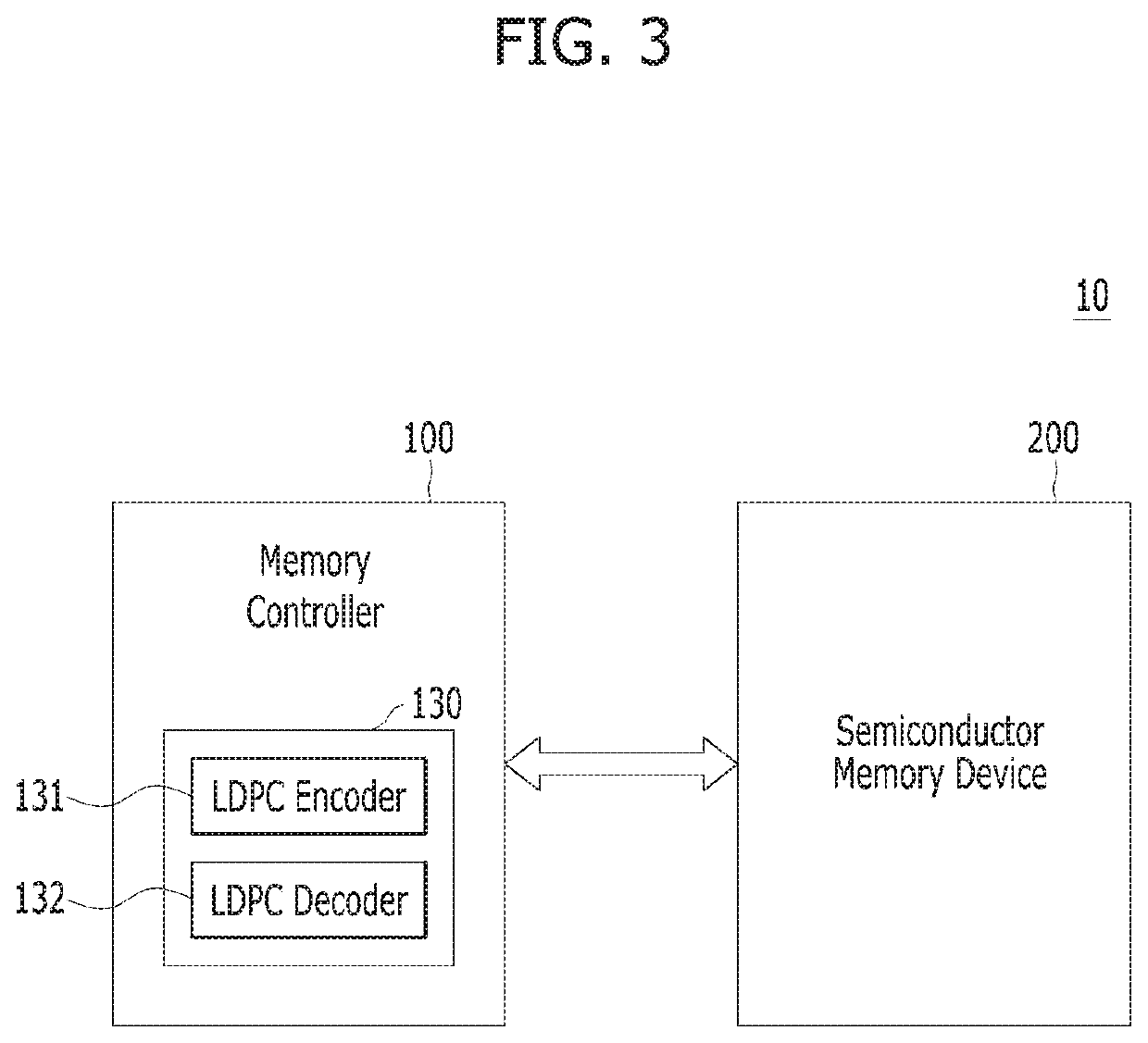

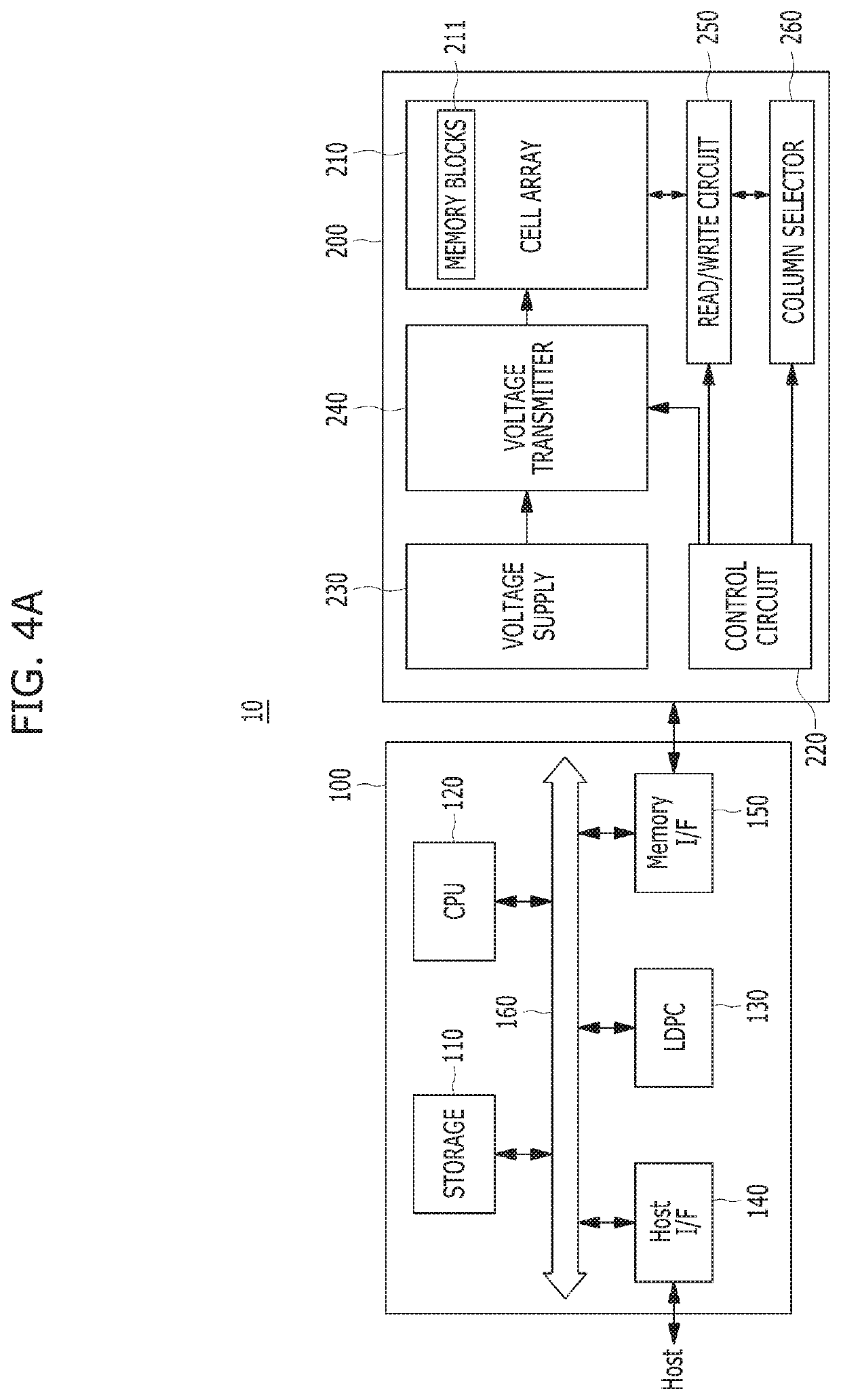

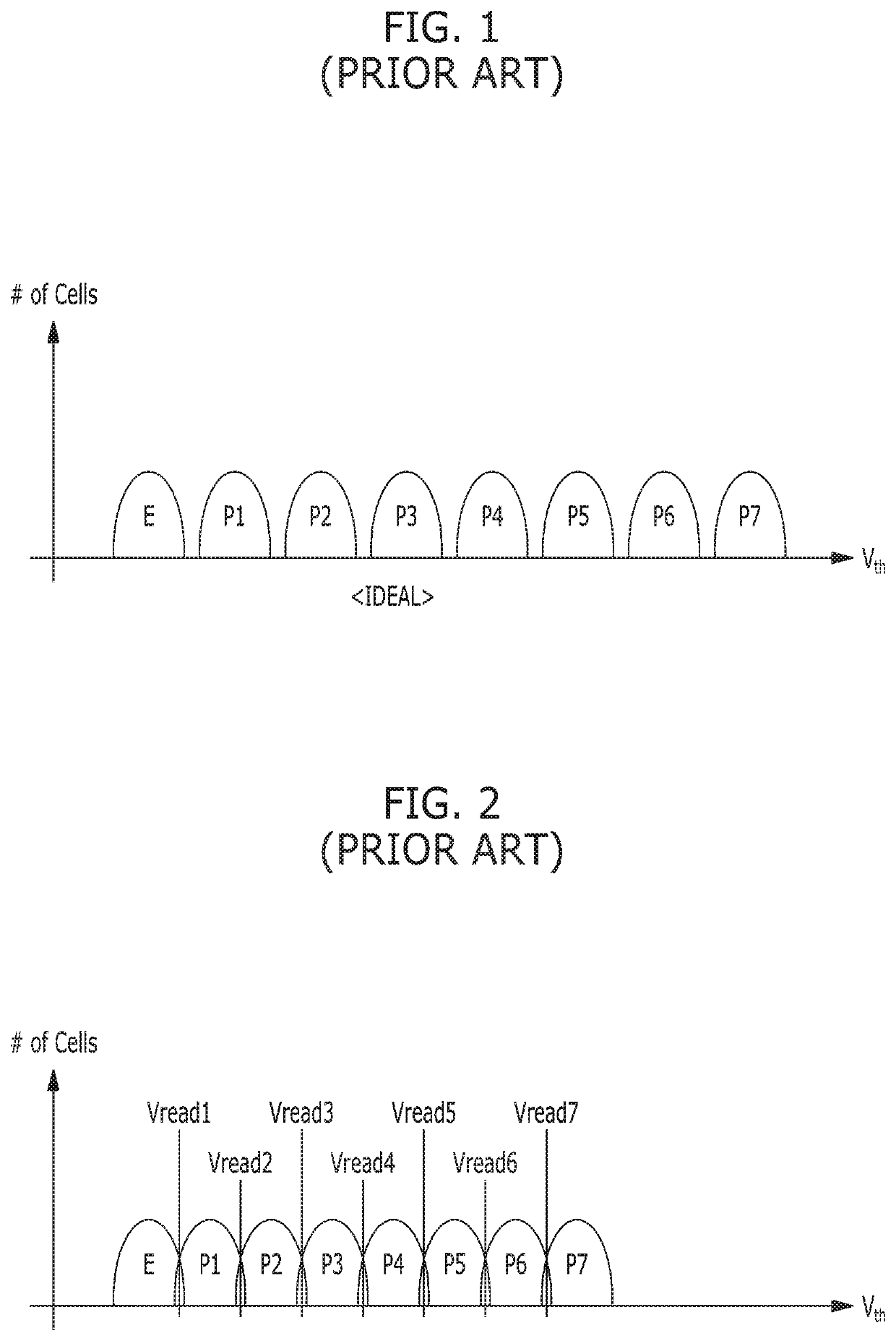

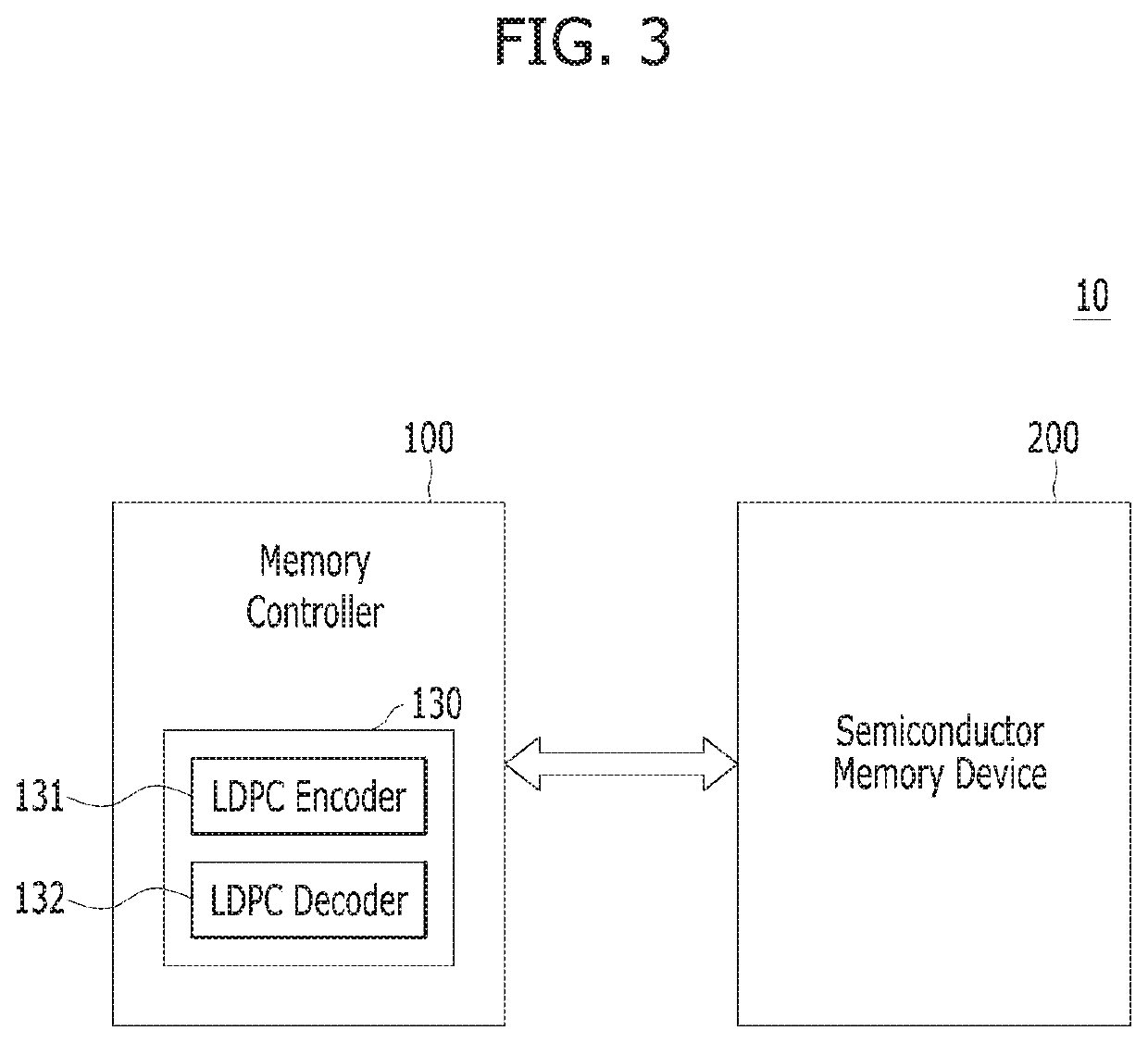

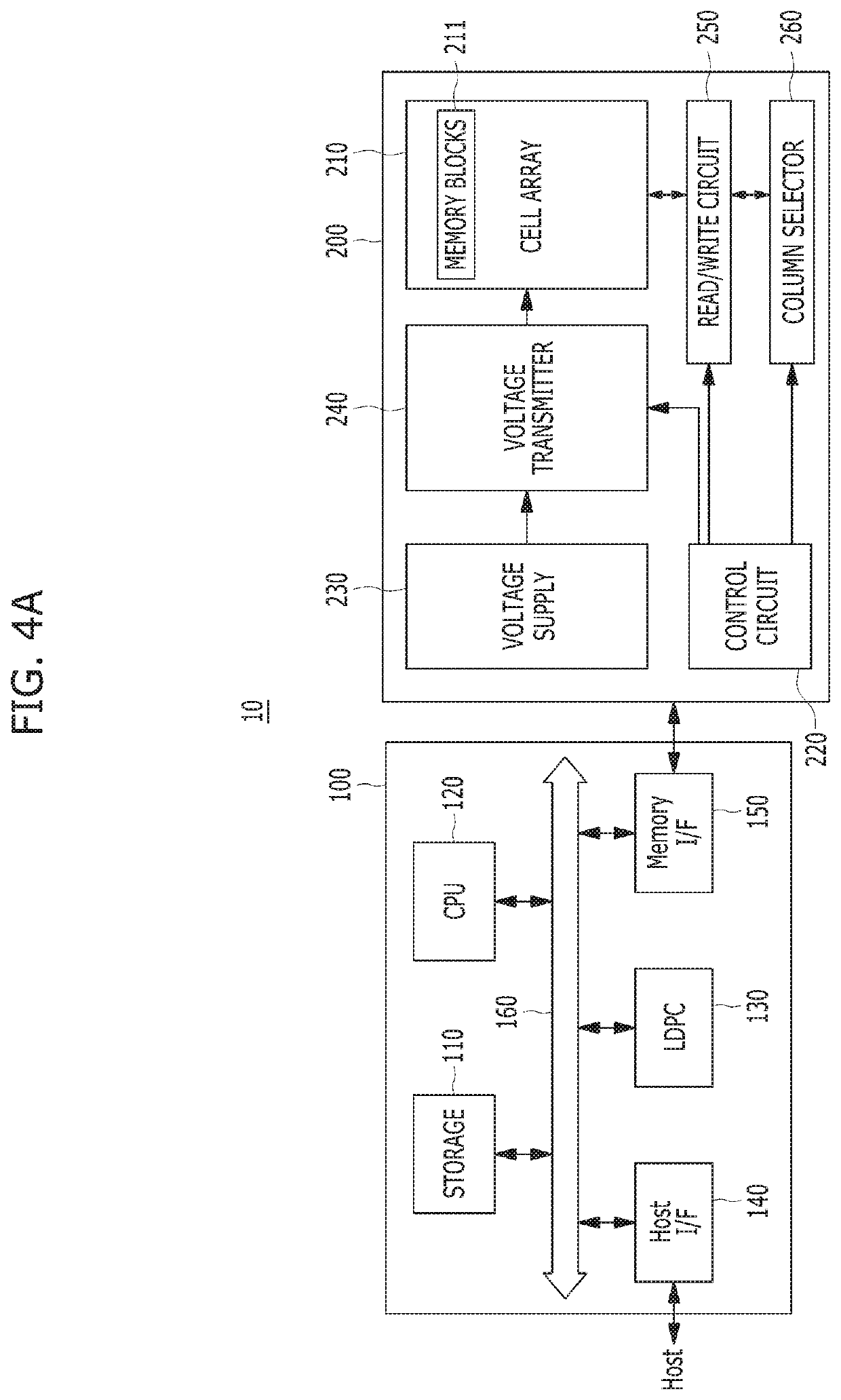

LDPC decoder, semiconductor memory system and operating method thereof

ActiveUS20200218607A1Improve performanceError correction/detection using multiple parity bitsCode conversionAlgorithmEngineering

A semiconductor memory system including: a semiconductor memory device suitable for storing a codeword; and an LDPC decoder suitable for decoding the codeword to generate decoded data, wherein the LDPC decoder includes: a message passing decoding component suitable for performing a first decoding operation of decoding the codeword, and calculating the minimum value among numbers of UCNs; and an error path detection component suitable for detecting error path candidates using a tree in which each of UCNs corresponding to the minimum value is set to a root node, sorting the detected error path candidates in ascending order of maximum LLRs, resetting symbol values and LLRs of variable nodes in the error path candidates, and providing the message passing decoding unit with information on the reset symbol values and LLRs.

Owner:SK HYNIX INC +1

Method for acquiring a gold sequence by double iterative decoding

A method for acquiring a Gold code, obtained as a sum of a first M-sequence (x) and a second M-sequence (yi), the first M-sequence being generated by a first generator polynomial (gx) and the second M-sequence being generated by a second generator polynomial (gy), the weight of the first generator polynomial being lower than the weight of the second generator polynomial, the acquiring method involving a first step of message passing decoding according to a first bipartite graph the edges of which are determined by the coefficients of the first generator polynomial, a decimation step using a predetermined decimation factor, and a second step of message passing decoding according to a second bipartite graph the edges of which are determined by a third generator polynomial having a minimum weight generating a third M-sequence having the same length as that of the second M-sequence.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

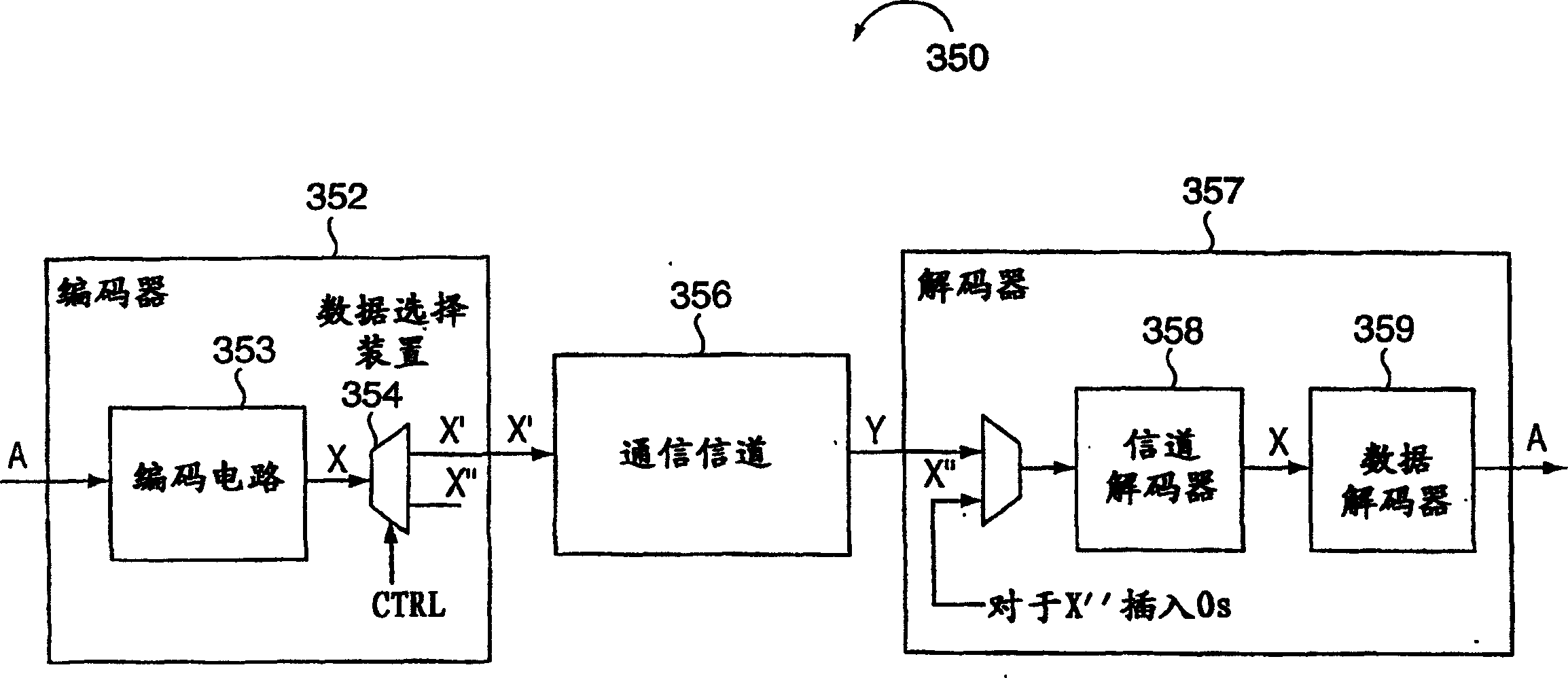

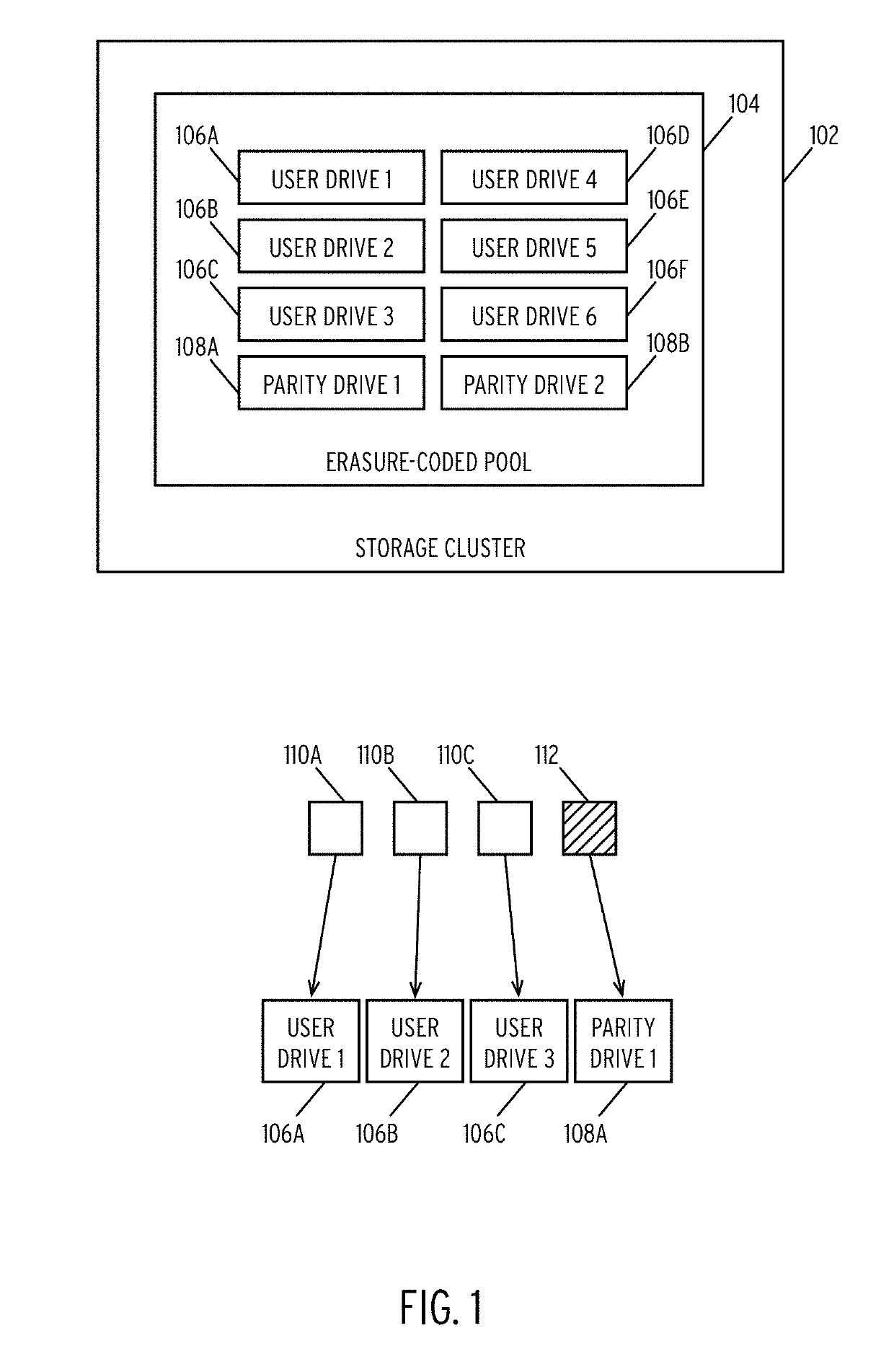

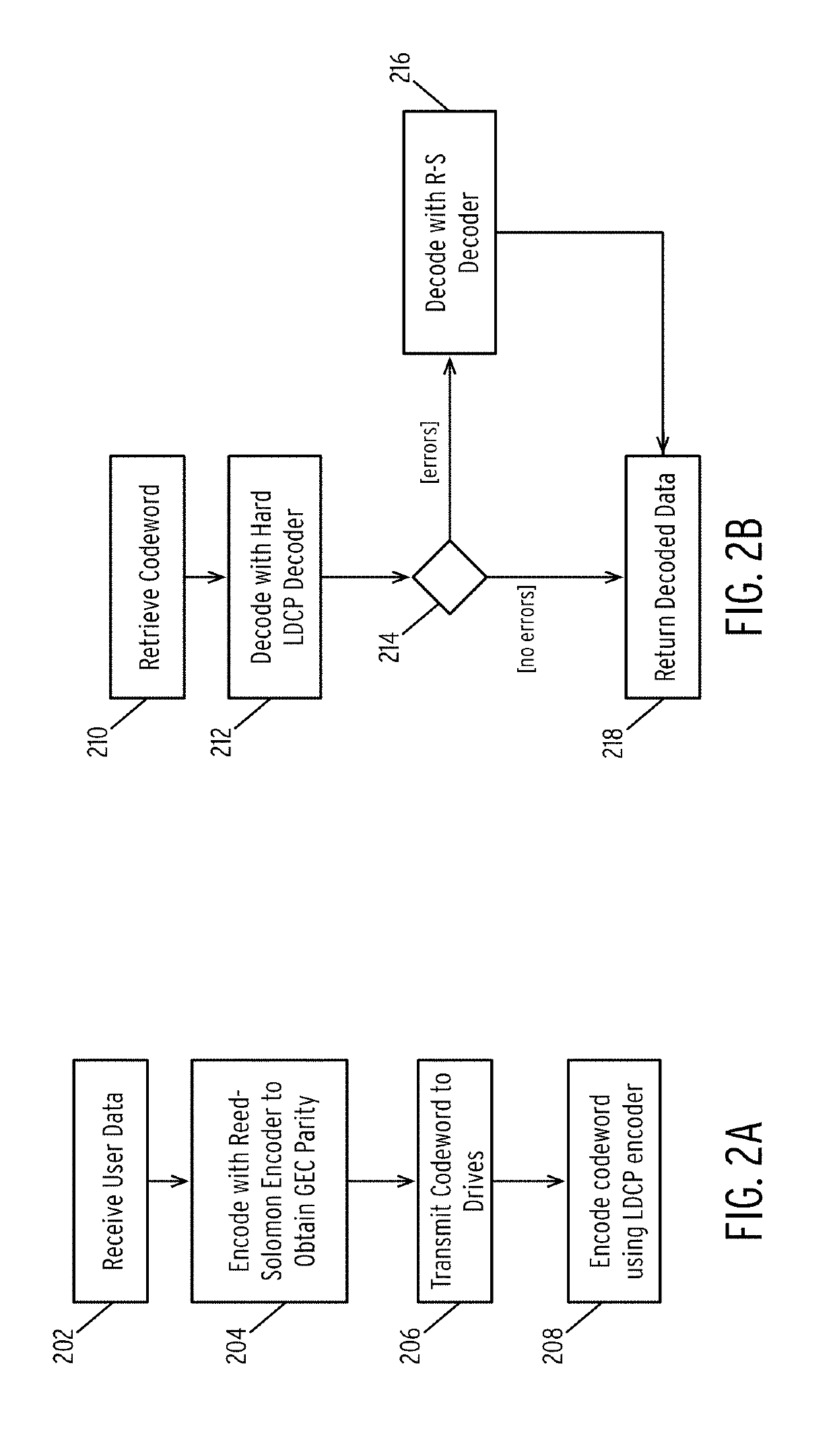

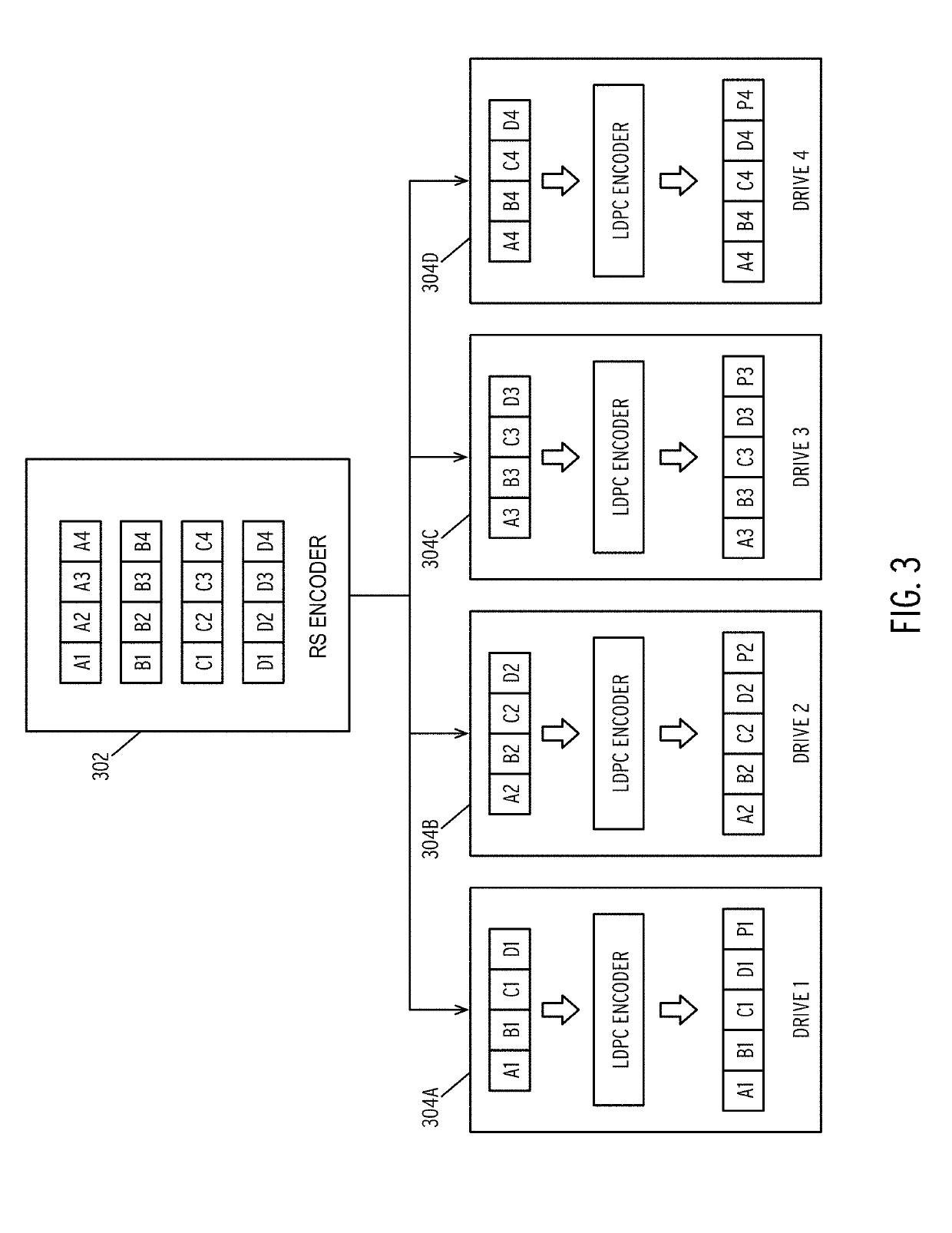

Iterative message-passing decoding with global code embedded with local code in time-division manner for fault tolerance improvement

ActiveUS20190245563A1Other decoding techniquesError detection/correctionFault toleranceSoft information

The disclosed embodiments are directed to systems, devices, and methods for iterative message-passing decoding. In one embodiment, a method is disclosed comprising decoding a first codeword at a storage device using a detector and a decoder, the first codeword comprising a set of symbols from a first set of codewords; assigning, via the decoding, a set of confidence levels for each symbol in the first codeword; transmitting, by the storage device, the confidence levels to an iterative decoder; generating, by the iterative decoder, a second codeword based on the set of confidence levels, the second codeword excluding at least one symbol in the set of symbols; and iteratively decoding, by the iterative decoder, the second codeword using an erasure decoder; and transmitting, by the iterative decoder, soft information generated by the erasure decoder to the storage device for subsequent decoding by the storage device.

Owner:ALIBABA GRP HLDG LTD

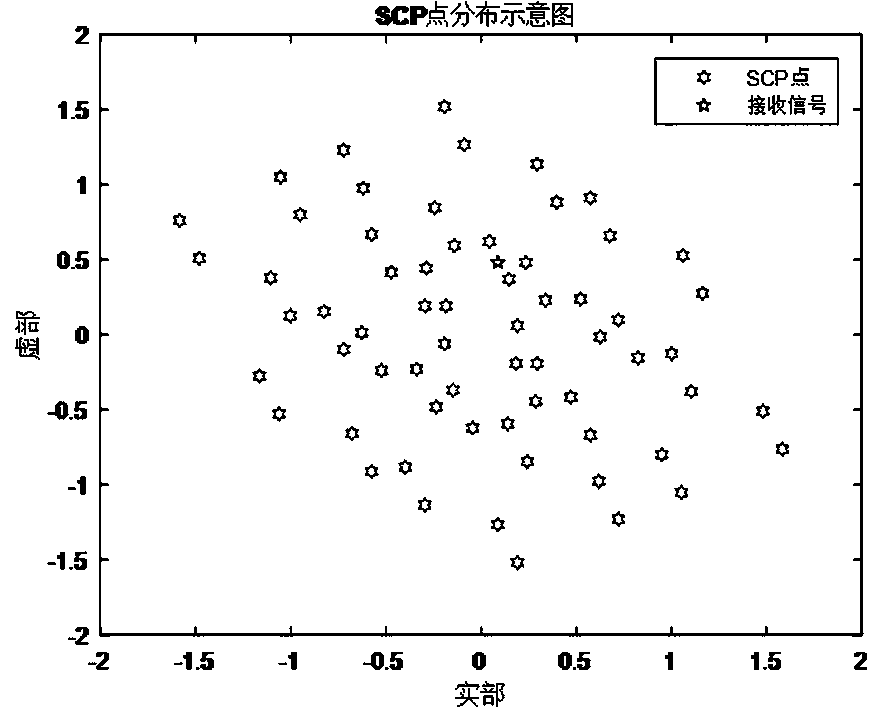

Message passing decoding algorithm in SCMA system

ActiveCN109586848AReduce operational complexityHighlight substantive featuresError preventionAlgorithmMessage passing

The present invention provides a message passing decoding algorithm based on a Euclidean distance threshold (ET-MPA) in an SCMA system. The message passing algorithm (MPA) used in the decoding end ofthe SCMA system will calculate a large number of useless overlapping codewords in the decoding process to increase the complexity, the solution is to perform pursuant deletion of overlapping codewordpoints (SCP) to be operated prior to the MPA algorithm iterative operation, and to divide the overlapping codewords selected for subsequent operations into reliable sets; and the rest of unreliable collection is discarded and does not participate in subsequent operations. Thus, the number of overlapping codewords and the number of calculations required to be calculated by the message passing algorithm in the second stepare greatly reduced compared to the original message passing algorithm (MPA). At the same time, since the overlapping codewords which have almost no influence on decoding are discarded when the overlapping codewords are deleted, the decoding performance provided by the invention is basically consistent with the performance of the original message passing algorithm.

Owner:NANJING UNIV OF POSTS & TELECOMM

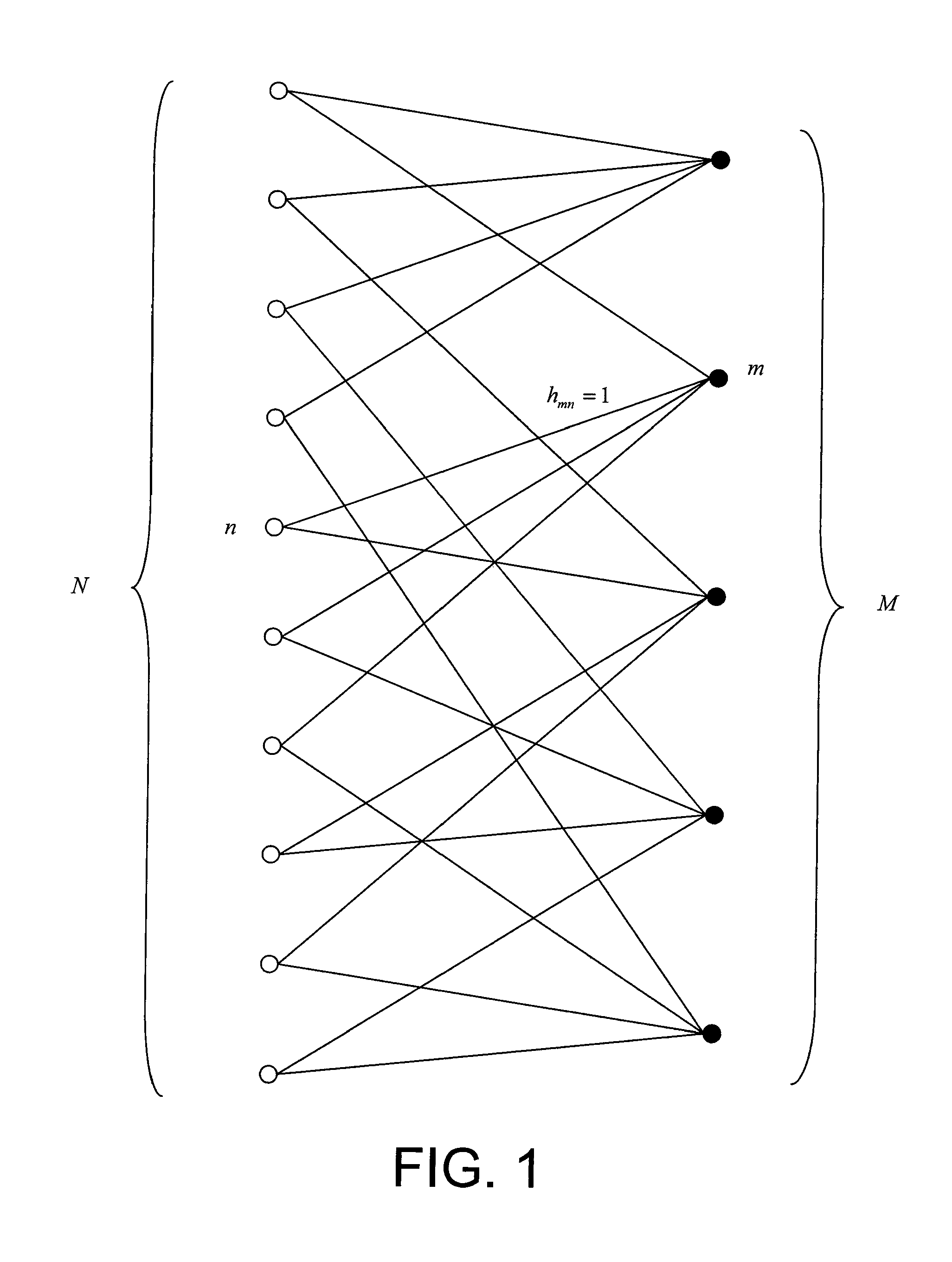

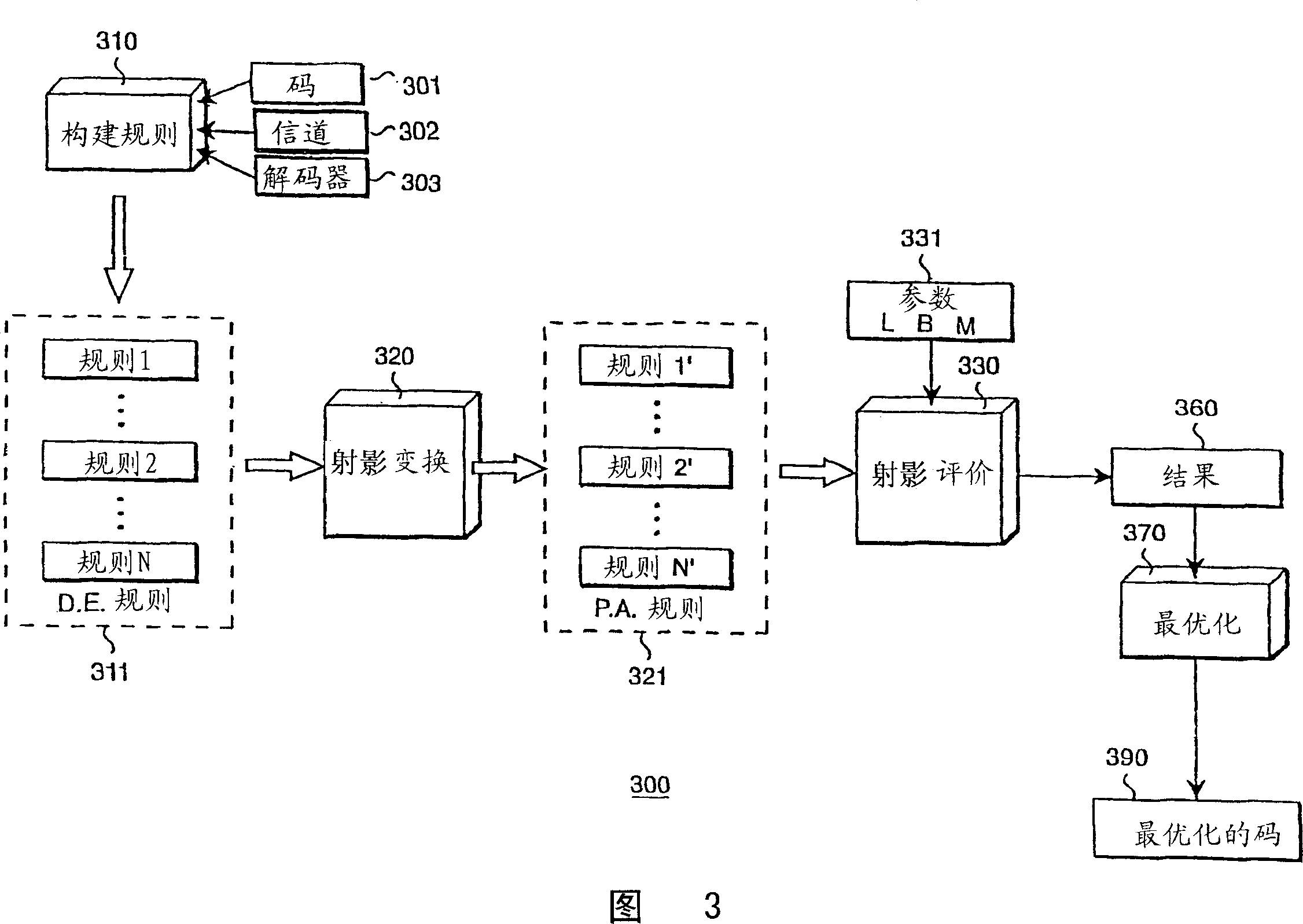

Evaluating and optimizing error-correcting codes using projective analysis

InactiveCN1312846COther decoding techniquesError correction/detection using multiple parity bitsAlgorithmParity-check matrix

A method evaluates and optimizes an error-correcting code to be transmitted through a noisy channel and to be decoded by an iterative message-passing decoder. The error-correcting code is represented by a parity check matrix which is modeled as a bipartite graph having variable nodes and check nodes. A set of message passing rules is provided for the decoder. The decoder is analyzed to obtain a set of density evolution rules including operators and operands which are then transformed to projective operators and projected operands to generate a set of projective message passing rules. The projective message passing rules are applied iteratively to the error-correcting code modeled by the bipartite graph until a termination condition is reached. Error rates of selected bits of the error-correcting code are then determined by evaluating the corresponding operands. The error rates can be passed to an optimizer to optimize the error-correcting code.

Owner:MITSUBISHI ELECTRIC CORP

Optical coherent receiver with forward error correction

ActiveUS10193568B2OptimizationIncrease the number ofOther decoding techniquesError correction/detection using multiple parity bitsComputer architectureForward error correction

It is disclosed an optical coherent receiver comprising a number of decoding blocks configured to implement iterations of a FEC iterative message-passing decoding algorithm. The decoding blocks are distributed into two (or more) parallel chains of cascaded decoding blocks. The receiver also comprises an intermediate circuit interposed between the two parallel chains. The optical coherent receiver is switchable between (i) a first operating mode, in which the intermediate circuit is inactive and the two parallel chains separately implement the FEC message-passing decoding algorithm on respective client channels; and (ii) a second operating mode, in which the intermediate circuit is active and the two parallel chains jointly implement the FEC message-passing decoding algorithm on a same client channel, by cooperating through the intermediate circuit.

Owner:ALCATEL LUCENT SAS

A Low-Complexity Message Passing Decoding Algorithm Based on Factor Graph Evolution in Sparse Code Multiple Access

ActiveCN106712900BImprove performanceReduce decoding delayForward error control useMultiple carrier systemsRound complexitySymbol of a differential operator

The invention provides a low-complexity message passing decoding algorithm based on factor graph evolution. A factor graph is simplified to realize low-complexity decoding, the degrees of resource nodes are classified at first, all resource nodes are removed at first, then the low-degree nodes are added to the factor graph for decoding gradually, therefore the evolution of the factor graph is realized, the obtained symbol experience information is stored, when the high-degree nodes are added to the factor graph subsequently, the high complexity of the traditional message passing algorithm under codebook collision can be greatly reduced by means of the hard judgment of a part of symbols by using the experience information, thereby reducing the decoding delay and further improving the performance expression of SCMA, in addition, by means of different settings of an update step length and a final update value of the factor graph, different compromise situations between the decoding accuracy and the decoding complexity can be obtained, and thus the algorithm is applicable to the actual application demands more flexibly.

Owner:TSINGHUA UNIV

LDPC decoder, semiconductor memory system and operating method thereof

ActiveUS10997021B2Improve performanceError correction/detection using multiple parity bitsCode conversionAlgorithmEngineering

A semiconductor memory system including: a semiconductor memory device suitable for storing a codeword; and an LDPC decoder suitable for decoding the codeword to generate decoded data, wherein the LDPC decoder includes: a message passing decoding component suitable for performing a first decoding operation of decoding the codeword, and calculating the minimum value among numbers of UCNs; and an error path detection component suitable for detecting error path candidates using a tree in which each of UCNs corresponding to the minimum value is set to a root node, sorting the detected error path candidates in ascending order of maximum LLRs, resetting symbol values and LLRs of variable nodes in the error path candidates, and providing the message passing decoding unit with information on the reset symbol values and LLRs.

Owner:SK HYNIX INC +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com