Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

149 results about "Decimation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

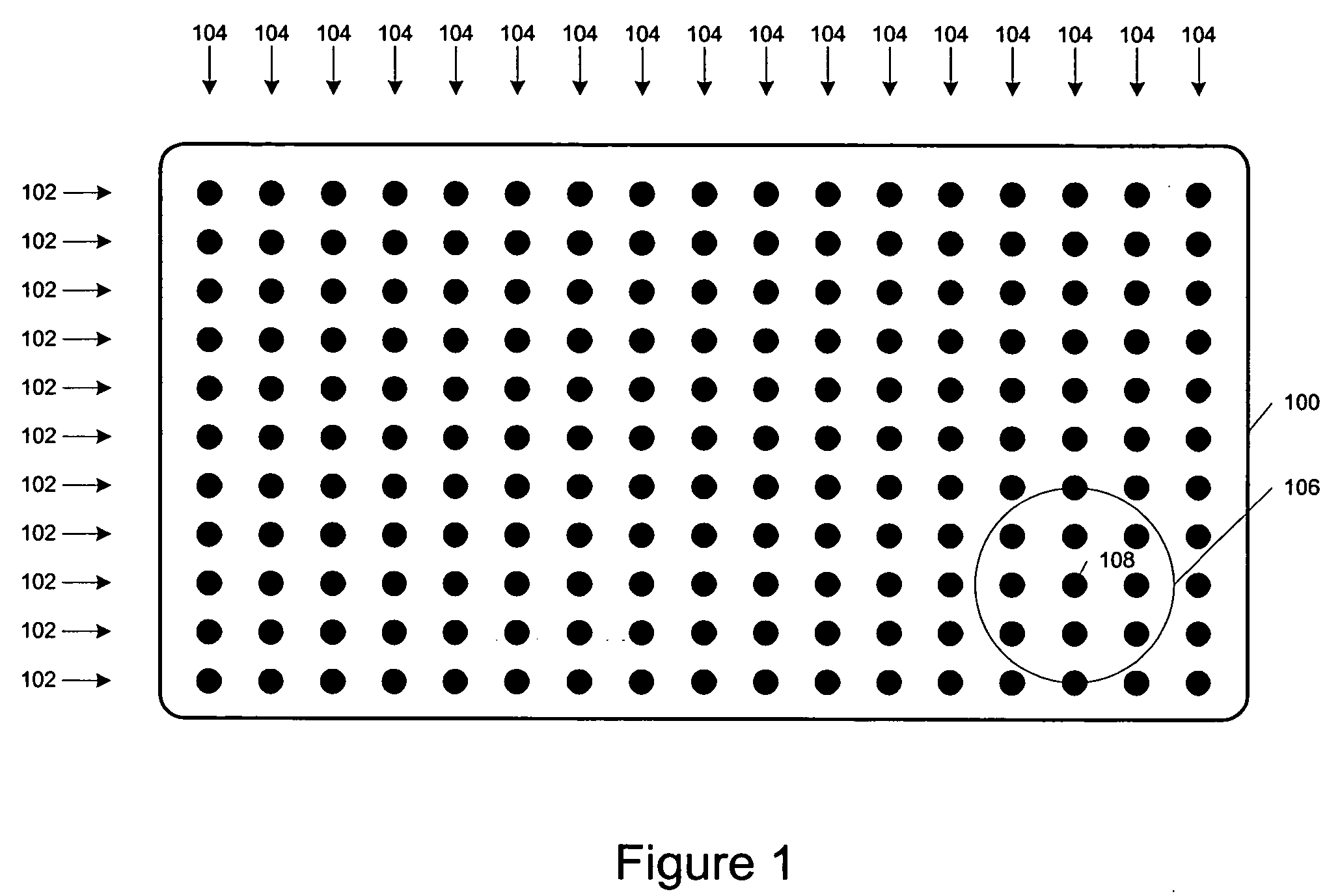

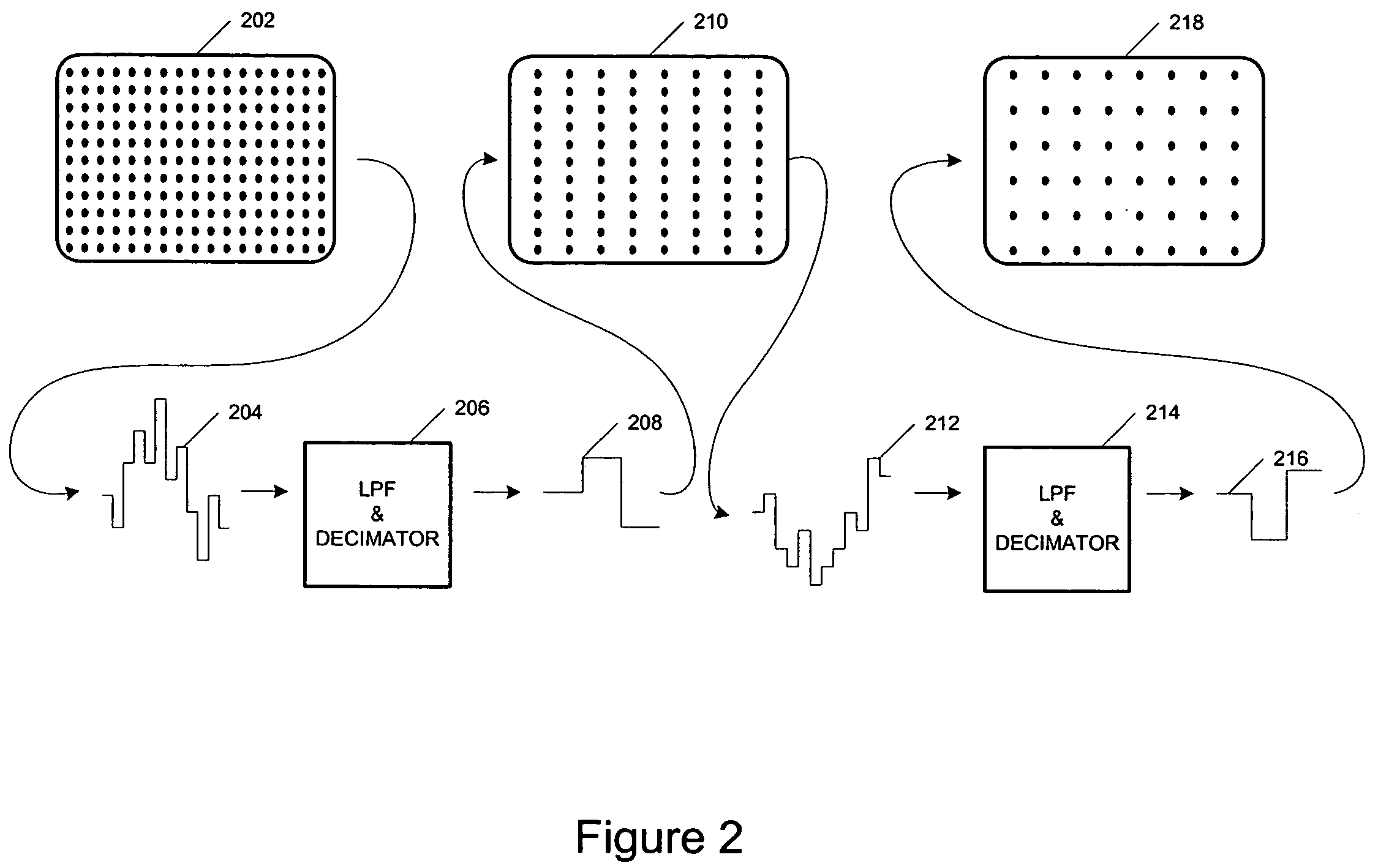

Inventor

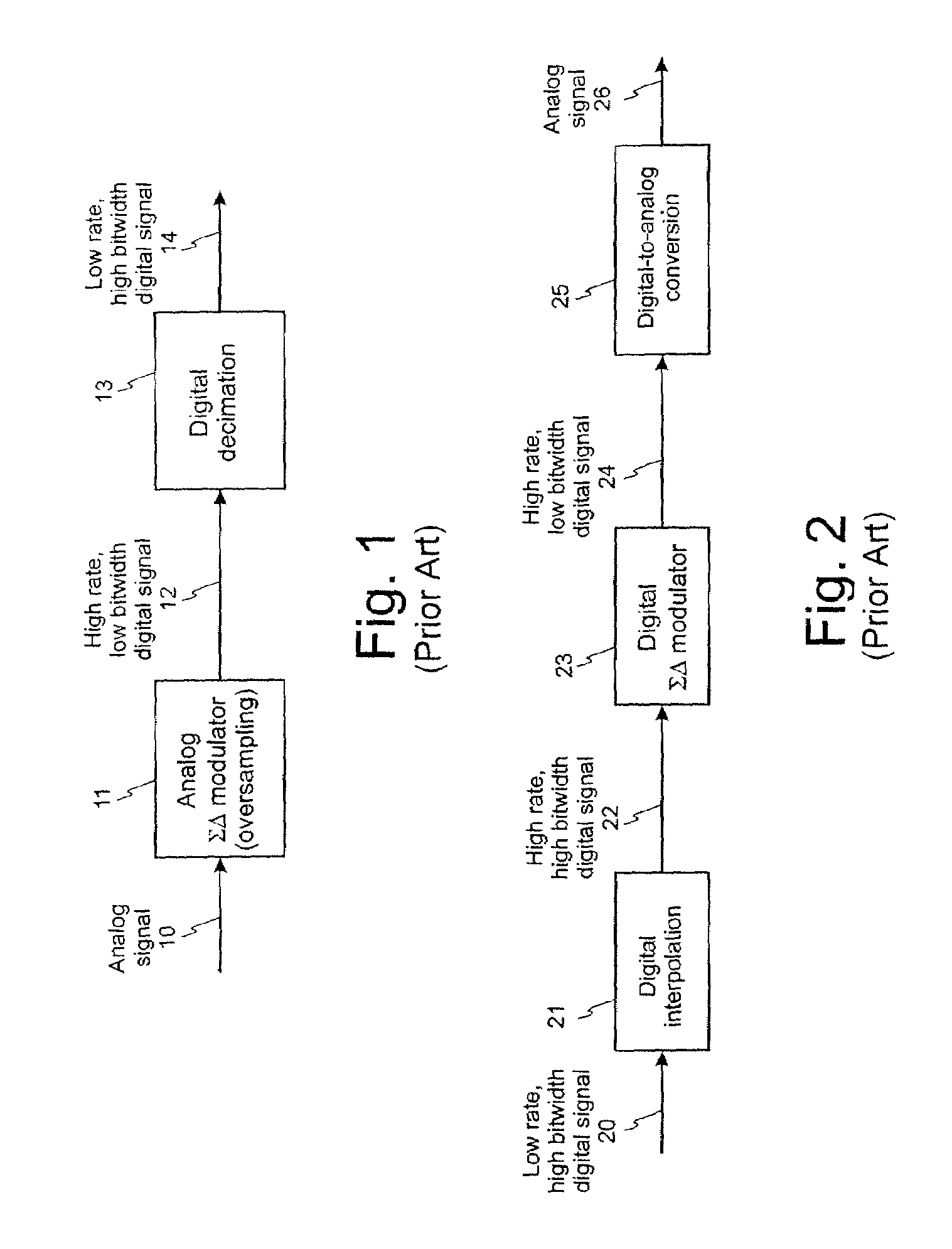

In digital signal processing, downsampling and decimation are terms associated with the process of resampling in a multi-rate digital signal processing system. Both terms are used by various authors to describe the entire process, which includes lowpass filtering, or just the part of the process that does not include filtering. When downsampling (decimation) is performed on a sequence of samples of a signal or other continuous function, it produces an approximation of the sequence that would have been obtained by sampling the signal at a lower rate (or density, as in the case of a photograph). The decimation factor is usually an integer or a rational fraction greater than one. This factor multiplies the sampling interval or, equivalently, divides the sampling rate. For example, if compact disc audio at 44,100 samples/second is decimated by a factor of 5/4, the resulting sample rate is 35,280. A system component that performs decimation is called a decimator.

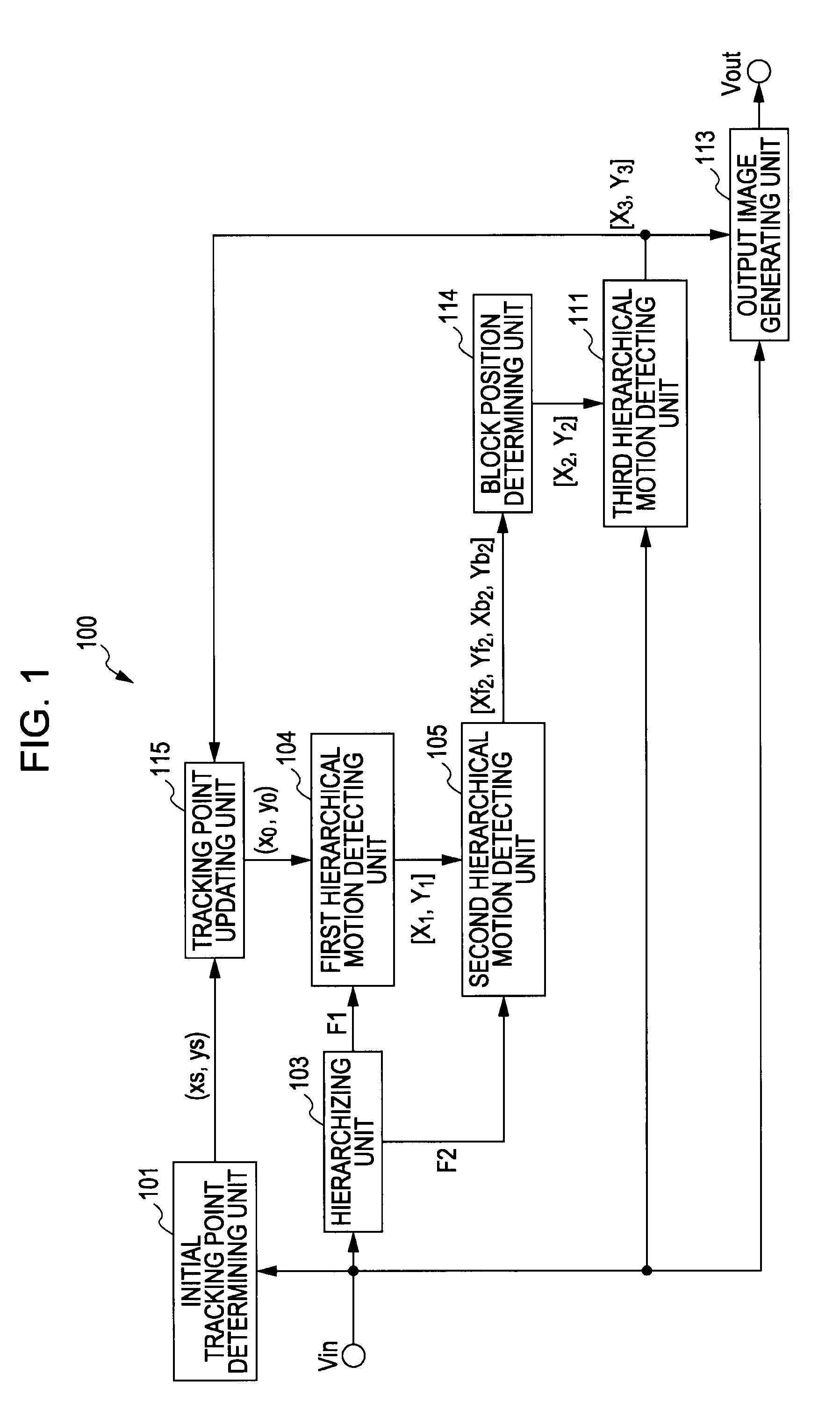

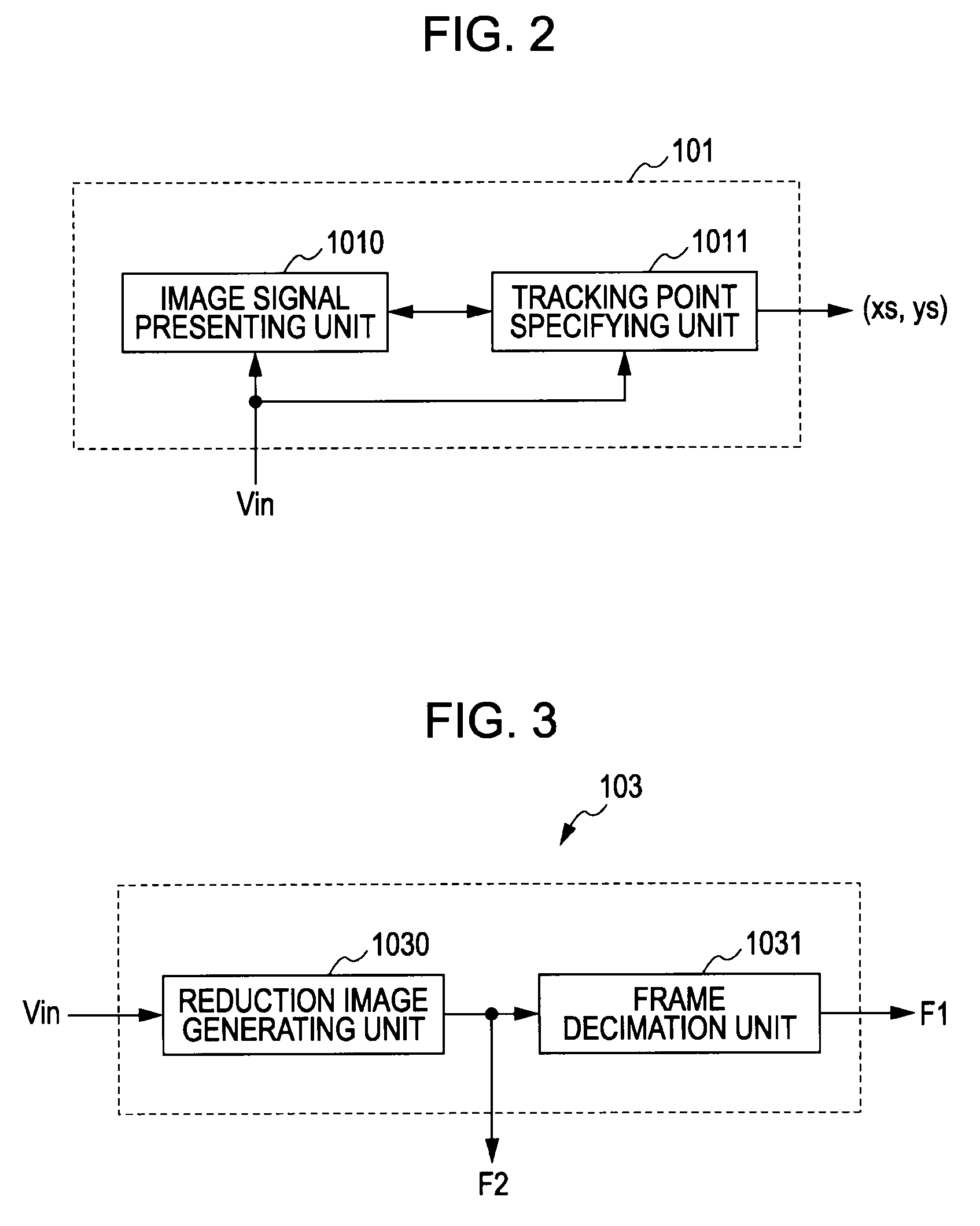

Tracking point detecting device and method, program, and recording medium

A tracking point detecting device includes: a frame decimation unit for decimation the frame interval of a moving image configured of multiple frame images continuing temporally; a first detecting unit for detecting, of two consecutive frames of the decimated moving image, a temporally-subsequent frame pixel corresponding to a predetermined pixel of a temporally-previous frame; a forward-direction detecting unit for detecting the pixel corresponding to a predetermined pixel of a temporally-previous frame of the decimated moving image, at each of the decimated frames in the same direction as time; an opposite-direction detecting unit for detecting the pixel corresponding to the detected pixel of a temporally-subsequent frame of the decimated moving image, at each of the decimated frames in the opposite direction of time; and a second detecting unit for detecting a predetermined pixel of each of the decimated frames by employing the pixel positions detected in the forward and opposite directions.

Owner:SONY CORP

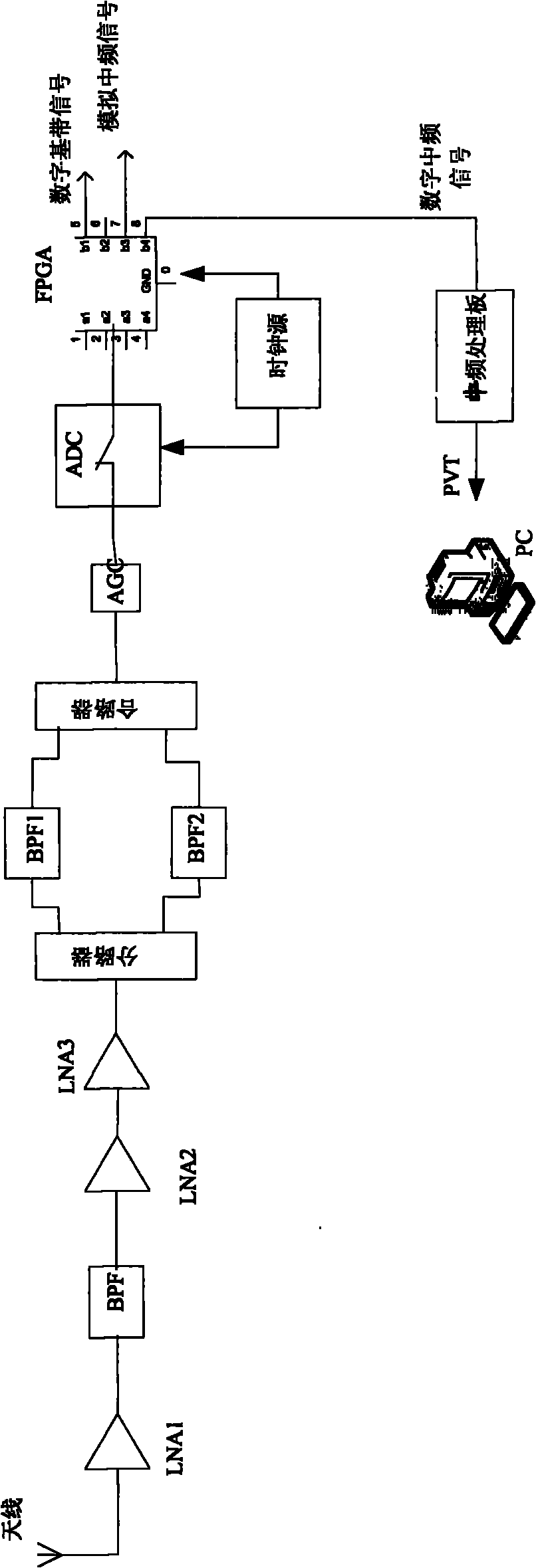

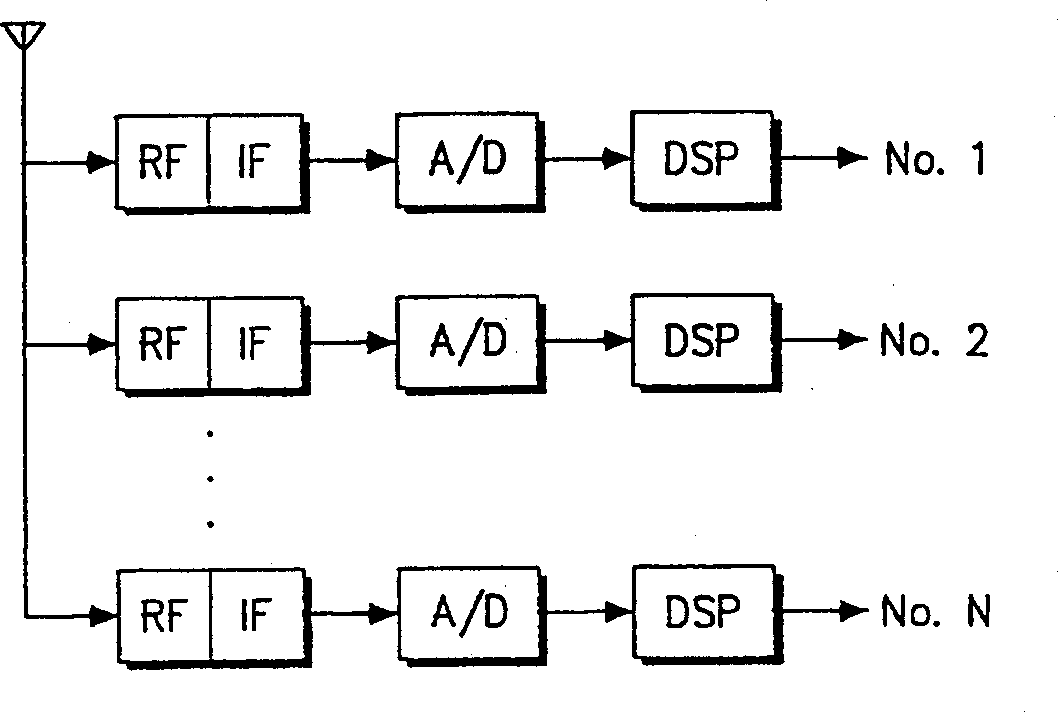

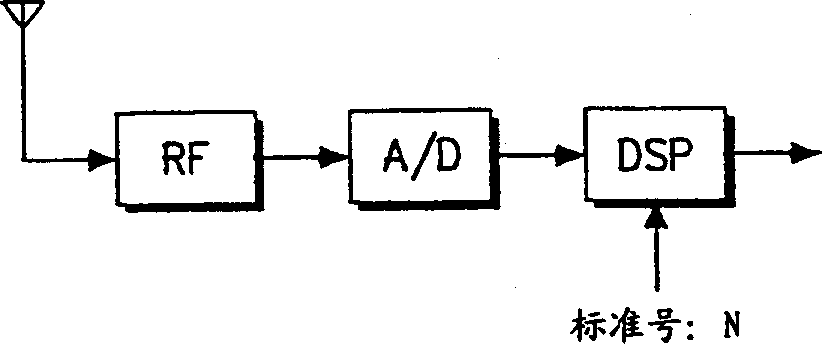

Method for constructing fully-digital GNSS compatible navigation receiver

InactiveCN101833100AImplement integrated receptionReduce occupancySatellite radio beaconingIntermediate frequencyDigital radio

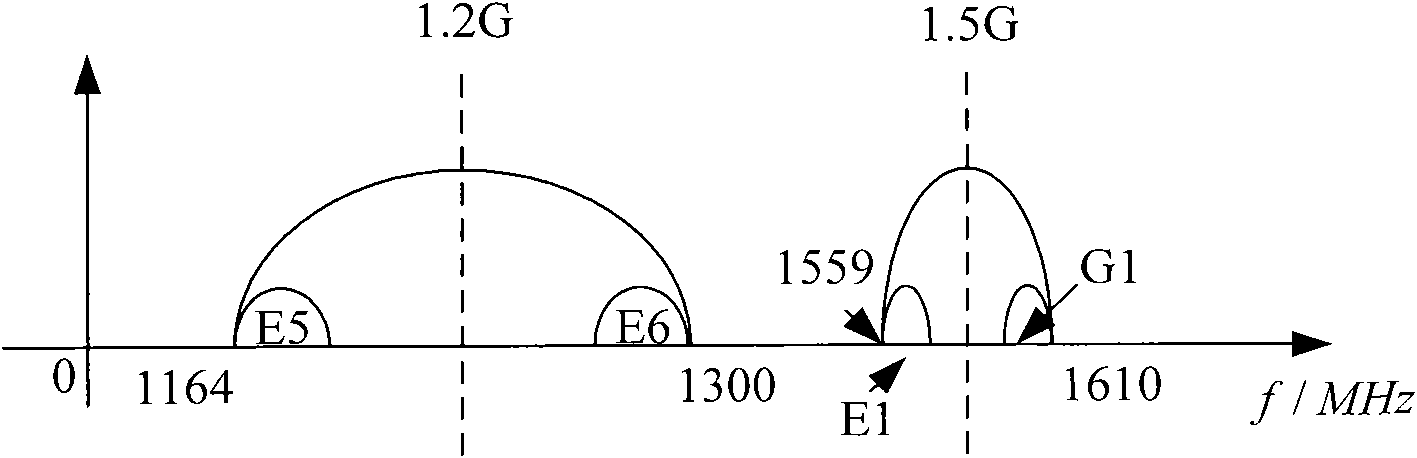

The invention relates to a method for constructing a fully-digital GNSS compatible navigation receiver, which comprises four steps: I, constructing a receiving link in accordance with actual needs by taking the characteristics of satellite signals, performance indexes and current device level into comprehensive consideration; II, choosing a proper A / D chip and a proper time clock source to complete direct radio frequency sampling and constructing a sampling rate in accordance with bandwidth sampling requirements; III, constructing a filter decimation network to reduce the sampling rate, completing the down-conversion of the radio frequency, converting the frequency of the bandwidth satellite navigation signals near 1.2G and 1.5G two frequency points down to a low medium frequency under a condition of a high sampling rate, and finally outputting a sampling time clock and a GNSS medium frequency signal; and IV, constructing digital radio frequency front end and rear end medium frequencyreceiver interfaces for making the receiver compatible with other medium frequency receiver. The thought of using software radio realizes the collective receiving of full-range GNSS satellite navigation signals; and the medium frequency receivers can complete navigation solution and output measurement values, so multi-system and multi-frequency point compatible navigation is realized. The method has an application and development prospect in the technical field of communication.

Owner:BEIHANG UNIV

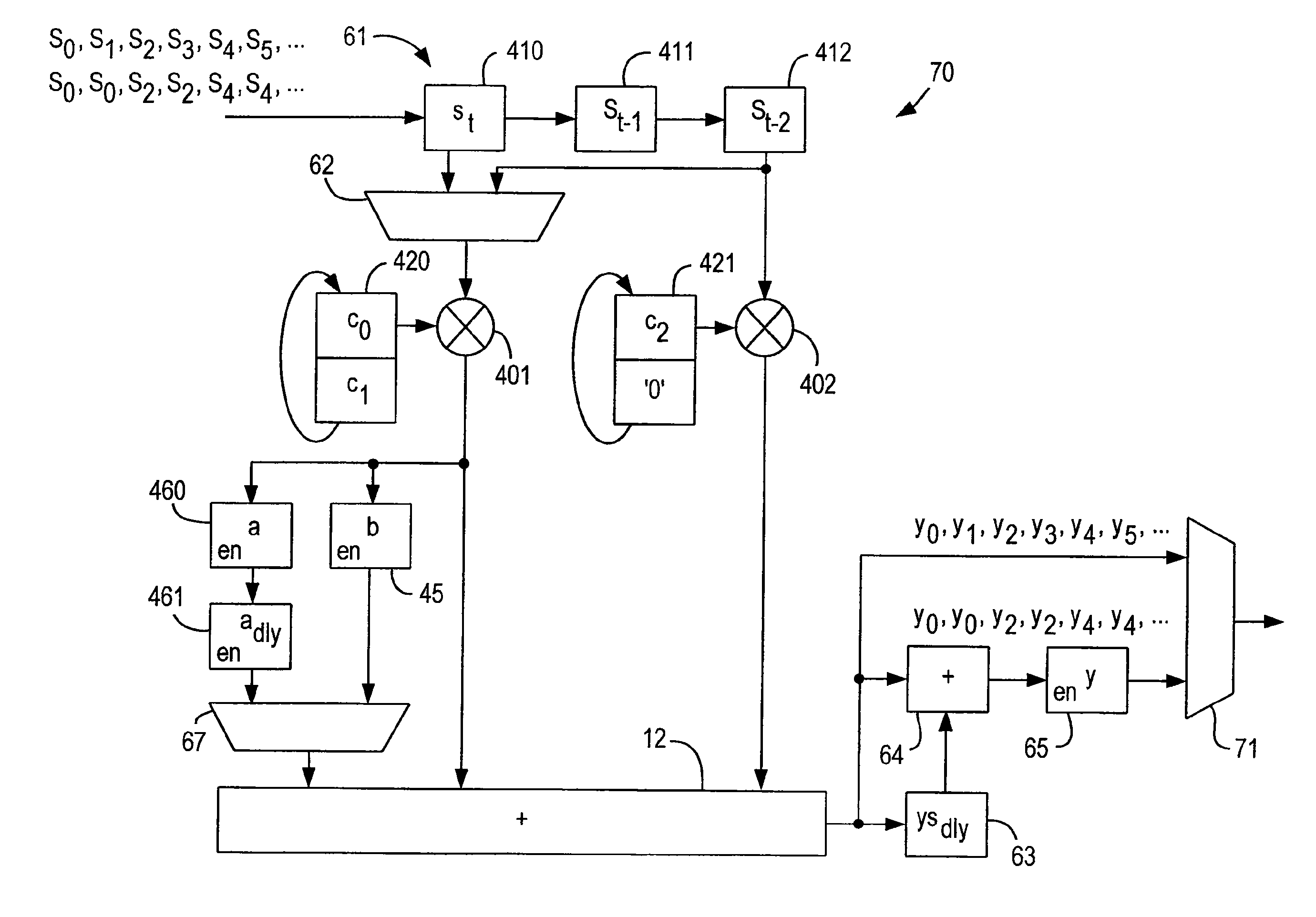

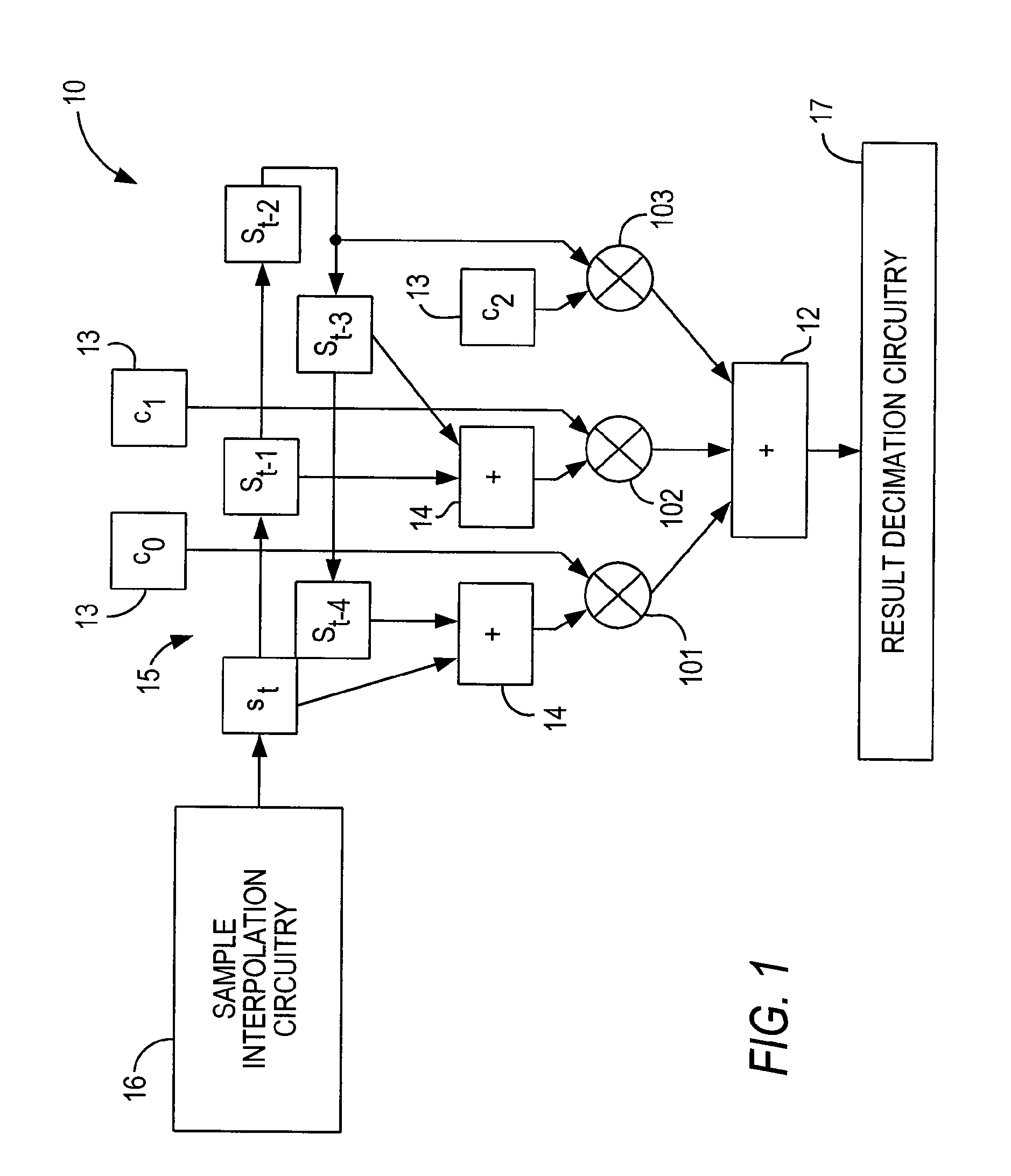

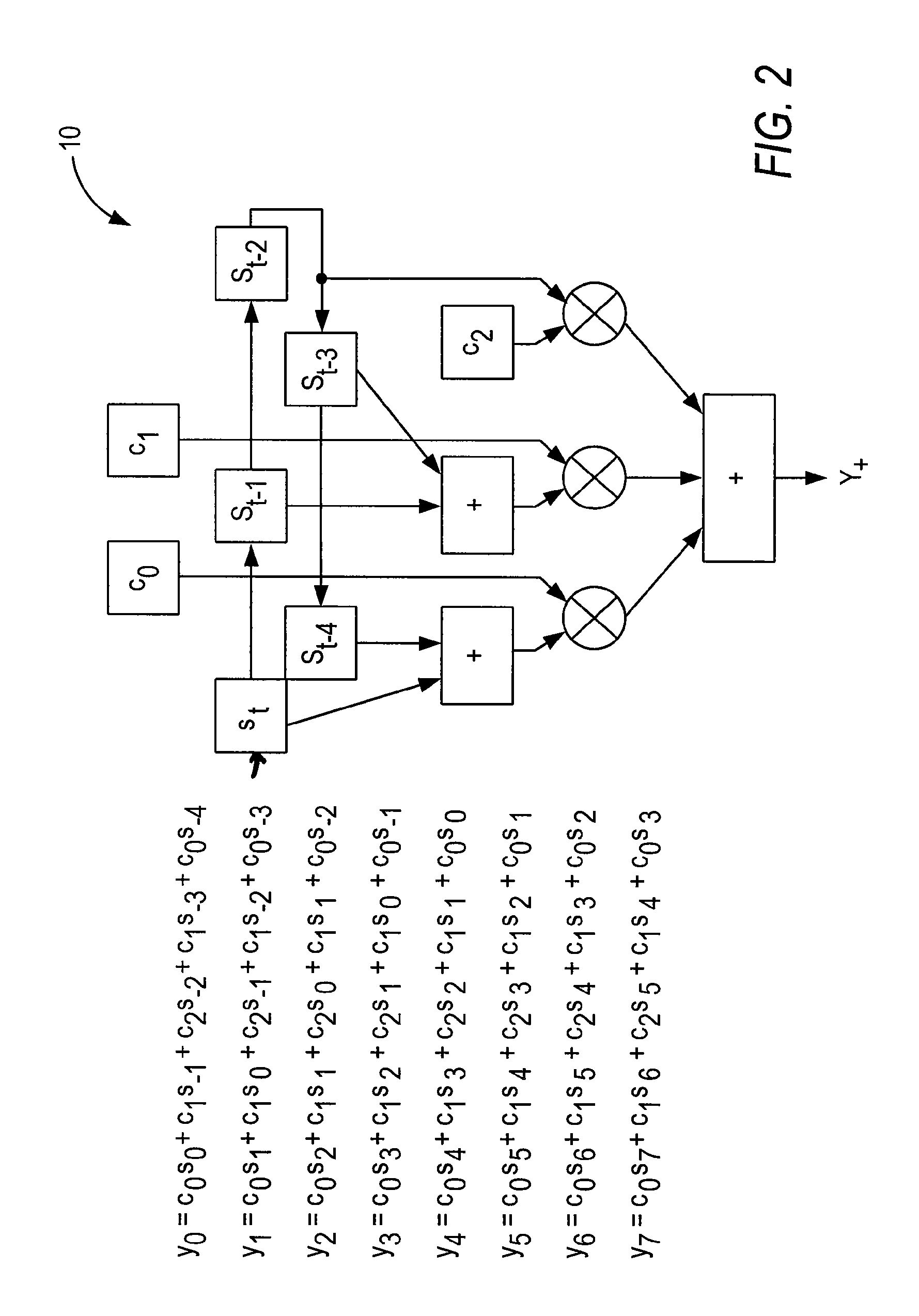

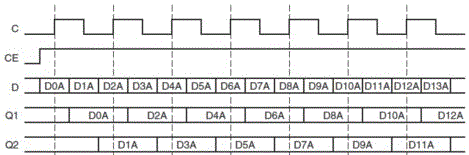

Combined interpolation and decimation filter for programmable logic device

InactiveUS7814137B1Digital technique networkComplex mathematical operationsFinite impulse responseMultiplexing

A programmable logic device can be configured as a finite impulse response (FIR) filter capable of operating in either interpolation mode or decimation mode and of switching between those modes at run time. The FIR filter structure can be mapped onto a specialized processing block of the programmable logic device that includes multipliers and adders for adding the products of the multipliers. The FIR filter structure minimizes the number of multipliers used by reusing various calculations that are repeated as a result of the interpolation or decimation operation, using multiplexers or other run-time-controllable selectors to select which current or stored multiplier outputs to use.

Owner:ALTERA CORP

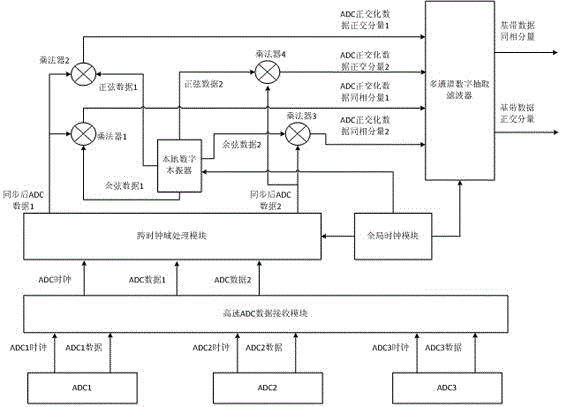

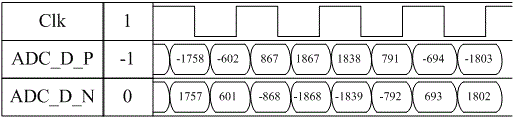

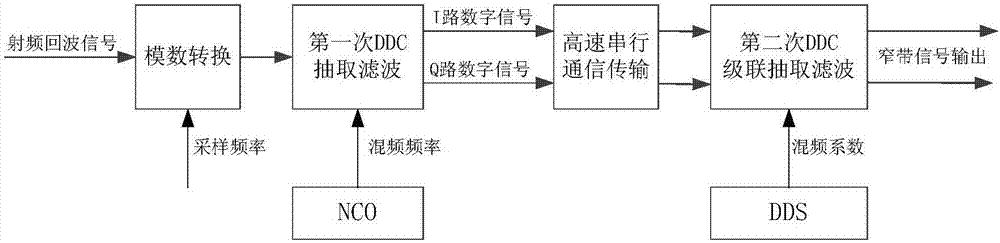

Method and system for realizing ultrahigh-speed digital orthogonal down conversion and decimation filtering in FPGA

InactiveCN105915241ANot subject to debuggingStrong upgradeabilityDigital technique networkTransmissionNumerical controlData rate

The invention discloses a method and a system for realizing ultrahigh-speed digital orthogonal down conversion and decimation filtering in an FPGA. The system comprises the components of a plurality of ADC sampling chips, a high-speed ADC data receiving module, an over-clock processing module, a global clock module, a local numerical control oscillator and a multichannel digital decimation filter. The designed working frequency of the traditional FPGA is hard to exceed 200MHz. According to the method and the system, a numerical control oscillator (NCO) and the digital decimation filter as core parts in orthogonal down conversion are improved; furthermore through reasonably restraining layout and wiring of the FPGA, highest sampling rate above 500Msps and output baseband data rate above 125MHz can be ensured on a common FPGA device. Furthermore the method and the device can support simultaneous parallel sampling of multiple paths of ADC data, thereby adapting with a multichannel data receiving occasion.

Owner:XINYANG NORMAL UNIVERSITY

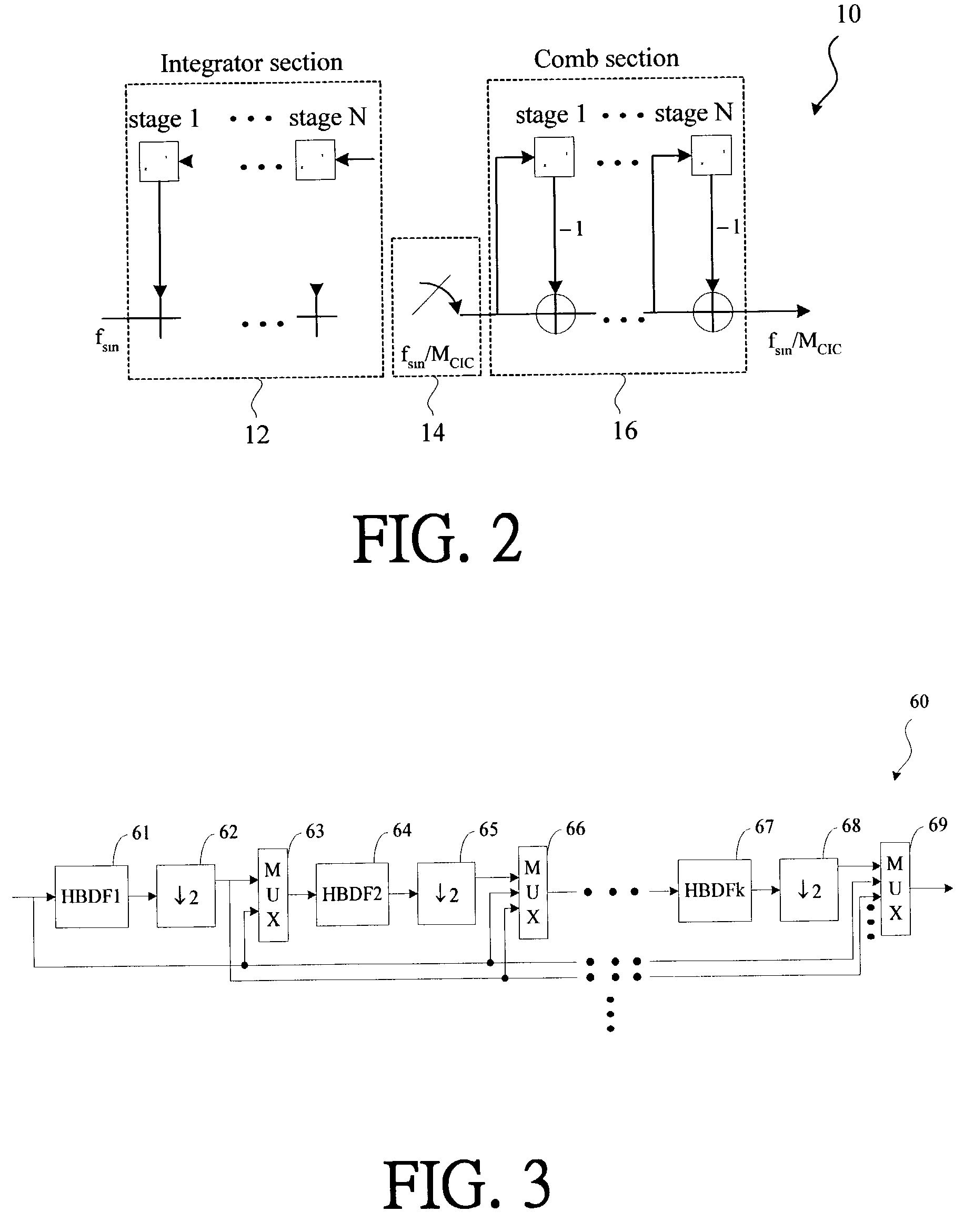

Optimized filter parameters design for digital IF programmable downconverter

InactiveUS6993464B2Avoid Complexity and DifficultySimple designDigital technique networkAnalogue computers for electric apparatusSpectral responseFrequency spectrum

The present invention discloses a method for finding an optimized filter parameters design to meet input specifications and hardware constraints in accordance with a typical single channel digital IF programmable downconverter. Said typical single channel digital IF programmable downconverter comprises four stages, including a high speed down-sampling stage, a spectral shaping stage, a rate matching stage and an oversampling stage. According to input specifications, said method firstly determines a number of Halfband interpolation filters used in said oversampling stage, secondly obtains optimized parameters for a CIC decimation filter and a Halfband decimation filter in said high speed down-sampling stage, using as many Halfband decimation filters as possible. Then determine if it is necessary to use re-sampling FIR filter for rate matching. Finally, use various function window to design programmable FIR filter for spectral shaping, obtains an overall synthesized spectral response which meets input specifications.

Owner:CHUNGHWA TELECOM CO LTD

Continuous-time sigma-delta analog-to-digital converter with capacitor and/or resistance digital self-calibration means for rc spread compensation

ActiveUS20100219997A1Good conditionReduce capacitanceElectric signal transmission systemsAnalogue conversionCapacitanceIntegrator

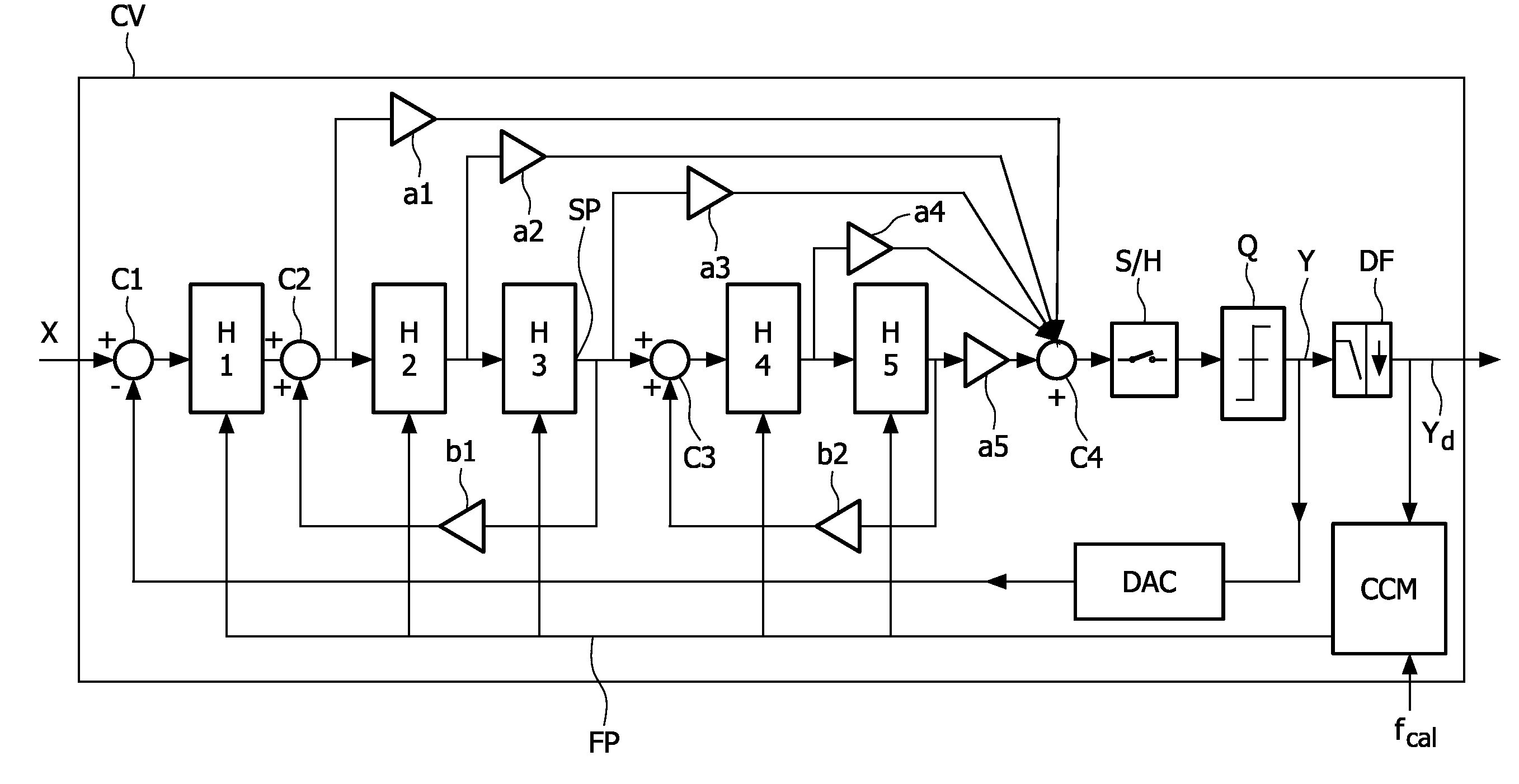

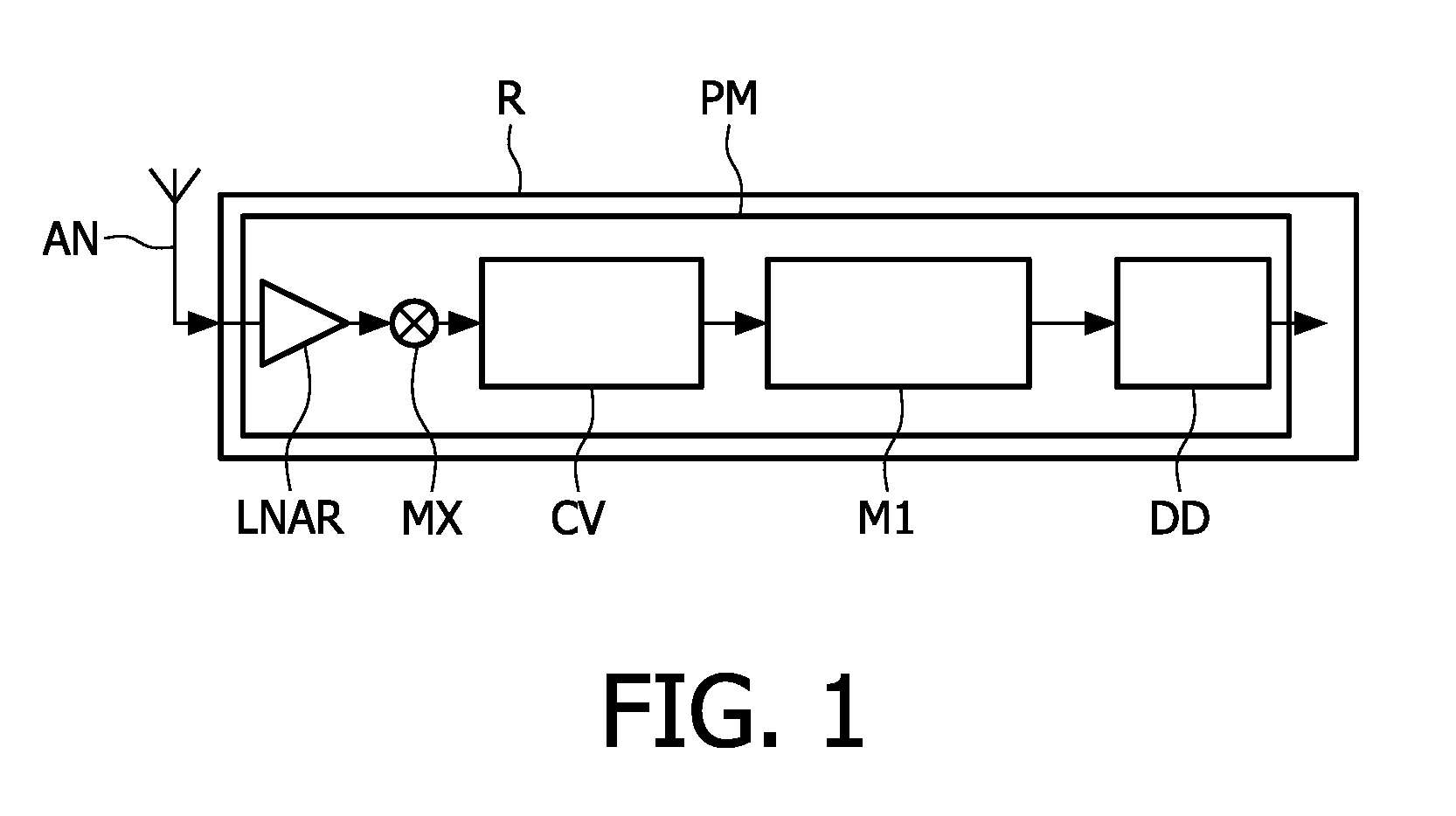

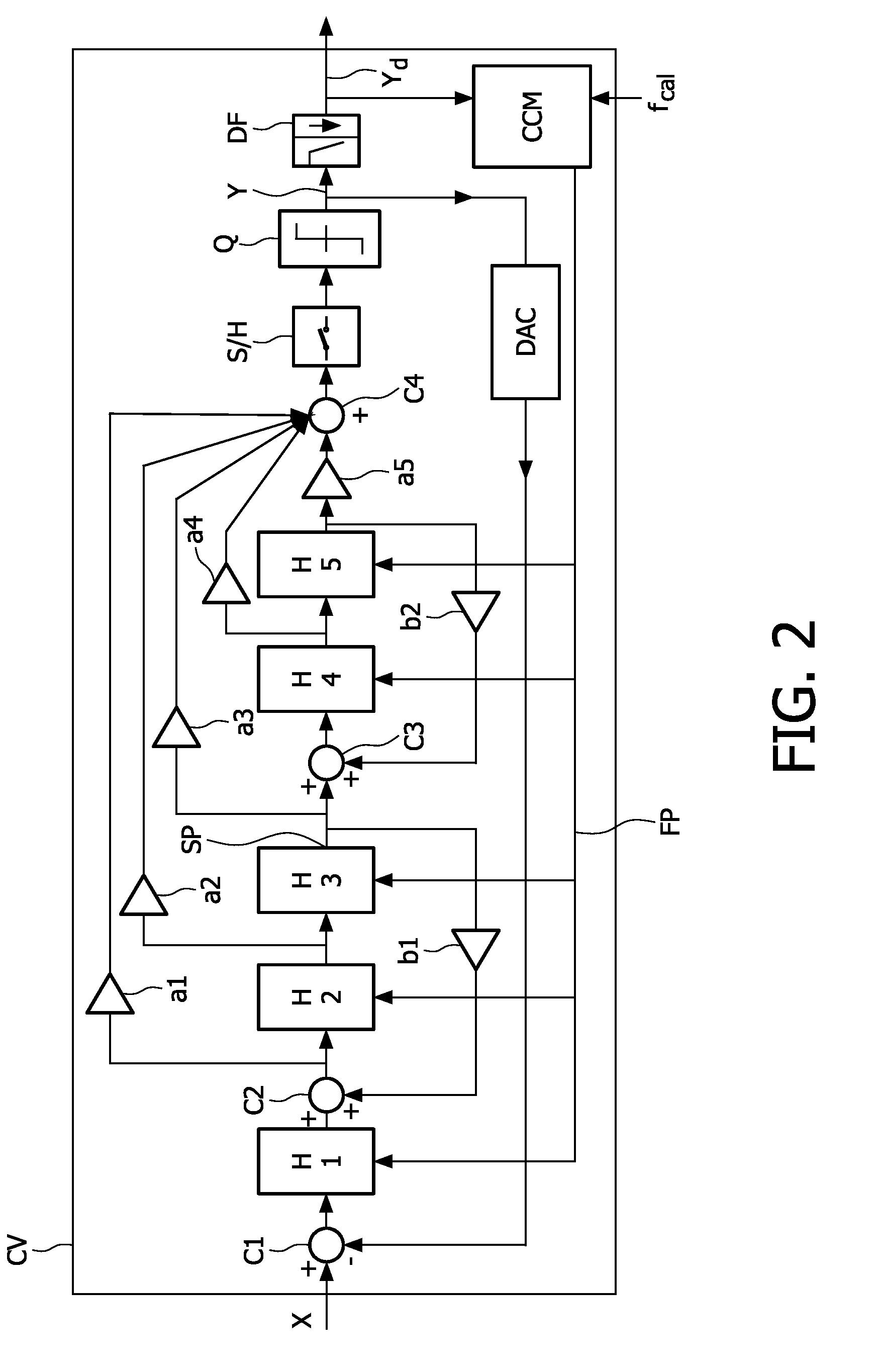

A continuous-time sigma-delta analog-to-digital converter (CV) comprises i) a signal path (SP) comprising at least one combiner (C1) for combining analog signals to convert with feedback analog signals, at least two integrators (H1, H5), mounted in series, to integrate the combined analog signals, a quantizer (Q) for converting the integrated signals into digital signals, and a decimation filter (DF) for filtering digital signals, and ii) a feedback path (FP) comprising at least a digital-to-analog converter (DAC) for converting the digital signals output by the quantizer (Q) into feedback analog signals intended for the combiner (C1). Each integrator (H1, H5) comprises variable capacitance means arranged to be set in chosen states define by the values of a digital word, to present chosen capacitances. The converter (CV) also comprises a self-calibration control means (CCM) arranged a) to generate a digital word with a chosen first value, b) to estimate an in-band noise IBN(n) from the filtered digital signals and to compare this IBN(n) to the preceding IBN(n-1), c) to modify the digital word value to decrease the capacitance of each integrator from a chosen decrement when IBN(n) is smaller than IBN(n-1), d) to iterate steps b) and c) till IBN(n) be greater than IBN(n-1), and to choose as calibration digital word value the value corresponding to IBN(n-1) to set the calibration state of the variable capacitance means.

Owner:NXP BV

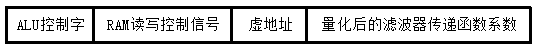

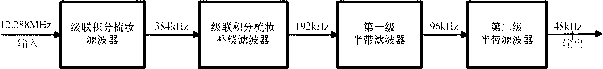

Method for implementing low-cost low-power-consumption programmable multistage FIR filter

InactiveCN103269212ASolve cost bottlenecksImprove performanceDigital technique networkDecimationIntegrated circuit

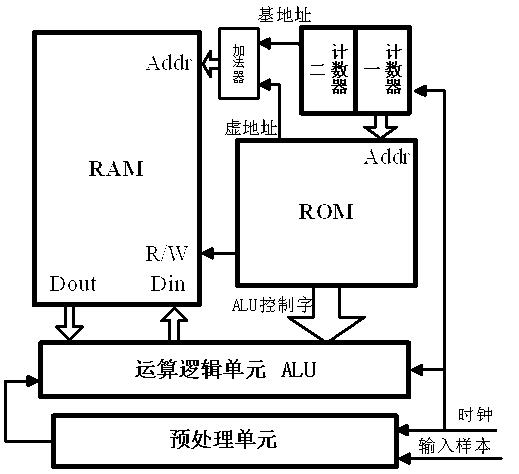

The invention relates to a method for implementing a multistage FIR filter in the field of an integrated circuit. The method for implementing the multistage FIR filter relates to an arithmetic unit, a control unit and a software environment for conducting programming configuration on the control unit. The arithmetic unit comprises a pretreatment unit, an ALU and a storage unit RAM, a transfer function of the filter is calculated through time division multiplexing, the mode that data in the RAM are flexibly read by changing addresses is adopted, and therefore a large quantity of data transfer power consumption in a typical filter implementation method is saved. The control unit comprises a storage unit ROM and a plurality of counters and summing units, commands and coefficients in the transfer function of the filter are provided for the arithmetic unit, therefore, filtering arithmetic of the arithmetic unit is finished in specific control step-by-step numbers, and a filtering result is acquired. The software environment conducts the programming configuration on the control unit according to performance parameters of the filter, and therefore a custom-made FIR filter suitable for application requirements is acquired. The method for implementing the multistage FIR filter can be mainly used for achieving a multistage FIR decimation filter, a multistage FIR interpolation filter and a multistage FIR same-speed filter, the function that the area can reach the minimum level of documents which have been published internationally can be achieved, and the method for implementing the multistage FIR filter has the advantages of greatly reducing the power consumption and customizing products according to the application requirements.

Owner:QUANZHOU TIANLONG ELECTRONICS SCI & TECHCO

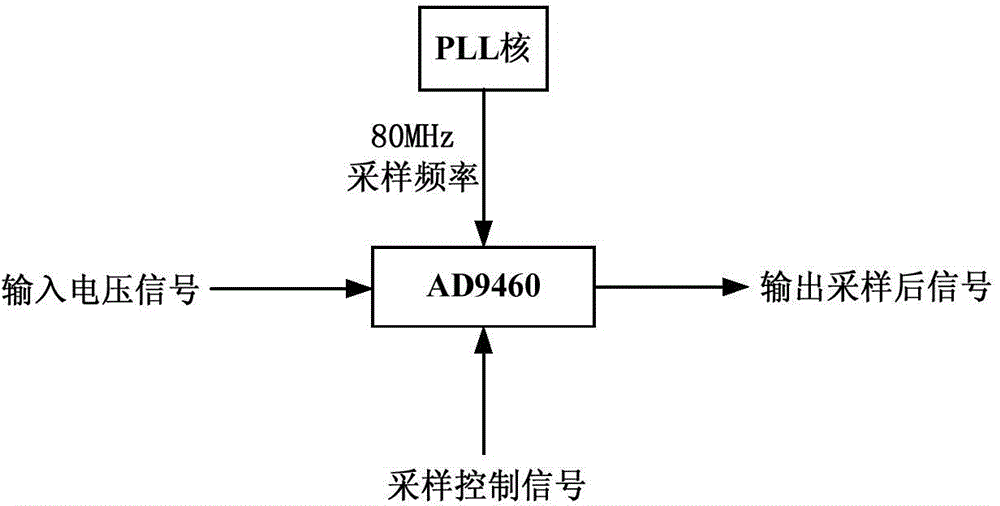

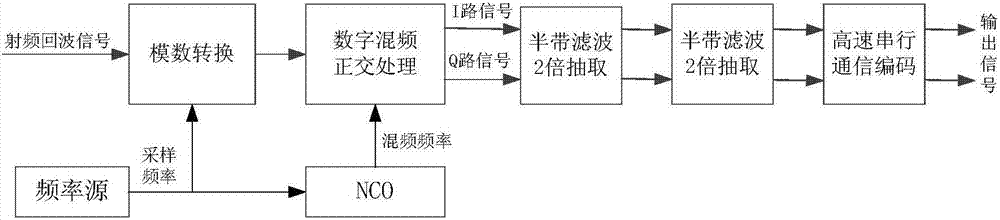

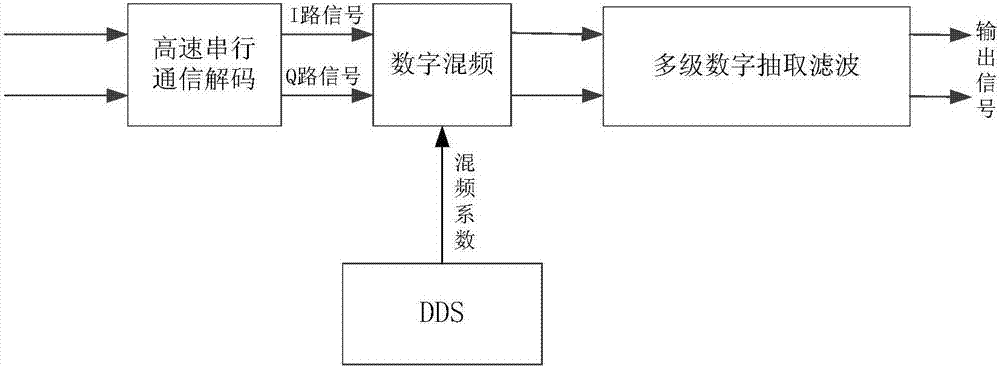

FPGA (field programmable gate array) based digital intermediate frequency coherent marine radar receiving and processing system

InactiveCN104793189AReduce noise interferenceAdapt to IF processing requirementsWave based measurement systemsRadar systemsLow distortion

The invention relates to the field of radar engineering and a radar system of intermediate frequency coherent, in particular to an FPGA (field programmable gate array) based digital intermediate frequency coherent marine radar receiving and processing system. The system comprises an intermediate frequency amplifier module connected with the output end of a receiver radio-frequency front-end, and is characterized by further comprising an A / D (analog / digital) sampling chip and an under-digital frequency conversion module, the under-digital frequency conversion module comprises digital-controlled oscillator, a low-pass filter and a digital decimation filter which are based on FPGA and are arranged in sequence; intermediate frequency power signals outputted by the receiver radio-frequency front-end are converted into voltage signals via the intermediate frequency amplifier module and then transmitted to the A / D sampling chip, and the voltage signals are acquired and transmitted to the under-digital frequency conversion module. The system is simple in structure and high in flexibility, image-frequency rejection ratio of I / Q signals is increased as compared with I / Q baseband signals respectively acquired with a simulation conversion method, and the system has the advantages of low drift, low distortion and the like, and useful information in return signals can be extracted to the greatest extent to be used for subsequent radar signal processing operations.

Owner:NANJING UNIV OF INFORMATION SCI & TECH

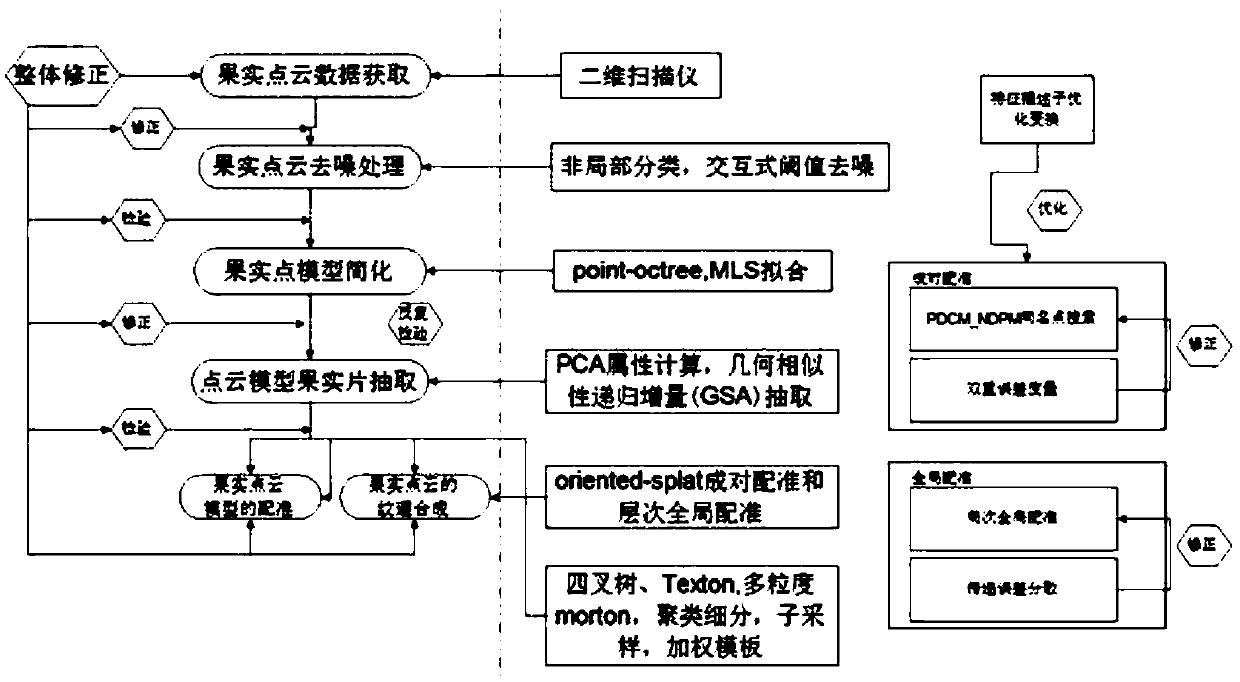

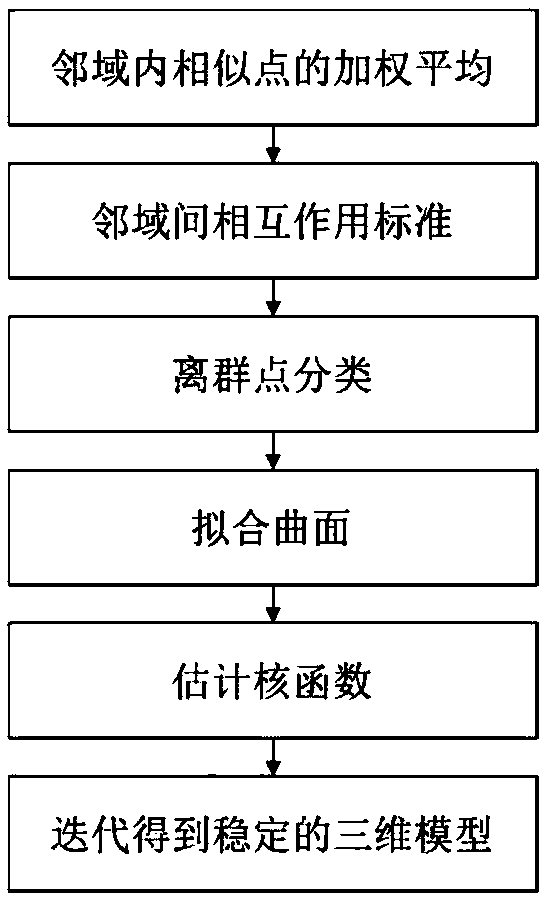

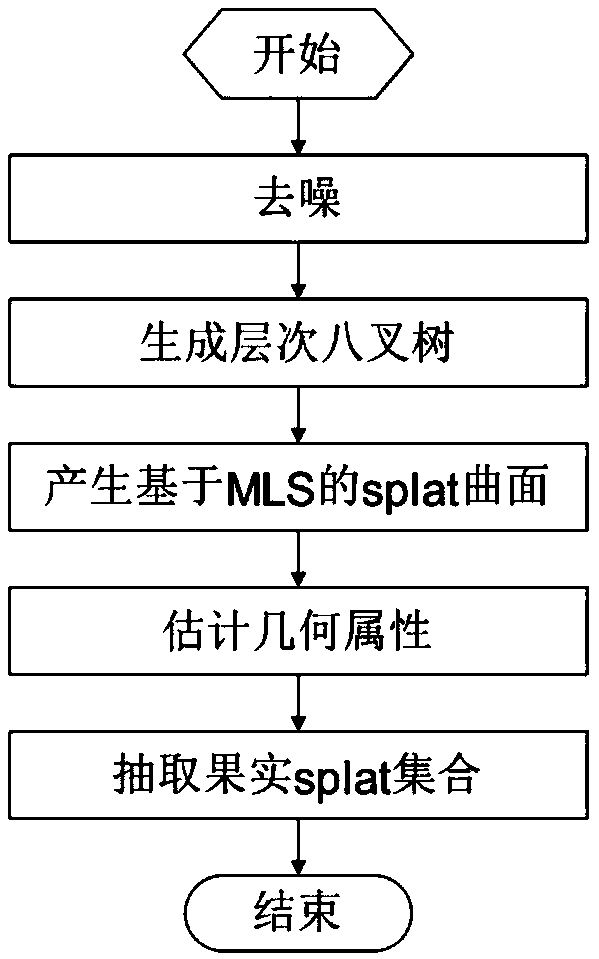

A fruit three-dimensional digitization method based on point cloud

ActiveCN109544681ASimplified Texture Image Segmentation MethodMake up for roughnessImage enhancementImage analysisPattern recognitionPoint cloud

The invention discloses a fruit three-dimensional digitization method based on point cloud, which comprises the following steps: 1) acquiring fruit point cloud data by using a portable laser three-dimensional scanner; 2) adopting non-local classification, interactive threshold denoising and decimation; 3) Using point-octree, MLS fitting to simplify the fruit point model; 4) extracting fruit slicesof that point cloud model through PCA attribute calculation and recursive increment of geometrical similarity; 5) Registering fruit point cloud models by oriented-splat team registration and hierarchical global registration;; 6) performing texture synthesis of fruit point cloud based on texton sub-sampling weighted template. This method reconstructs the real fruits in the growing process, and proposes some methods and algorithms such as denoising, extraction, registration and direct texture synthesis, which make up for the shortcomings of rough effect, low coding efficiency and large storagespace of direct texture synthesis on the current point model.

Owner:NORTHWEST A & F UNIV +1

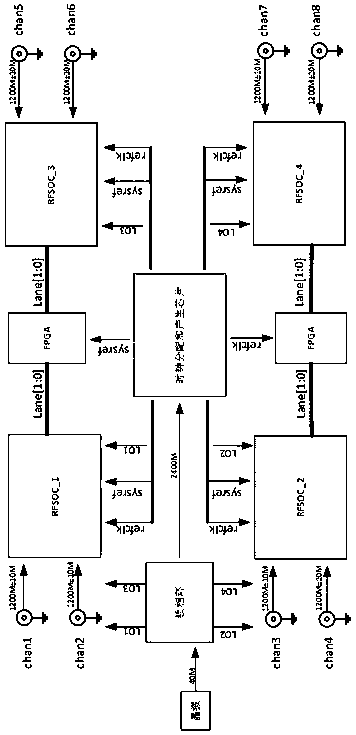

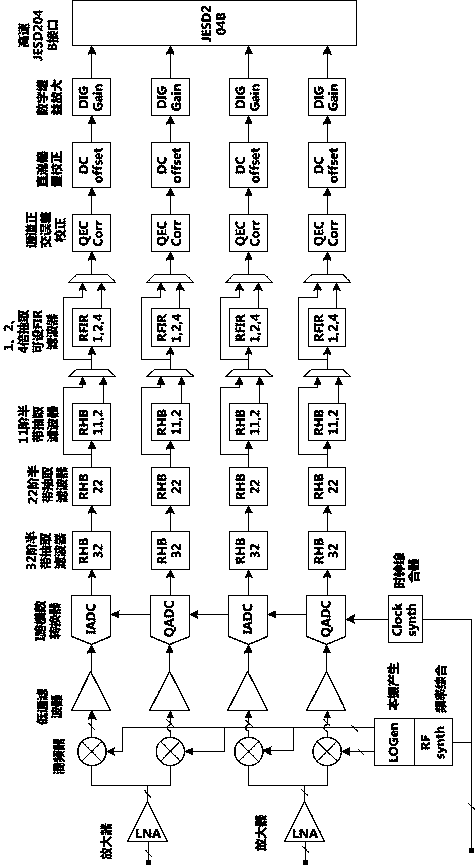

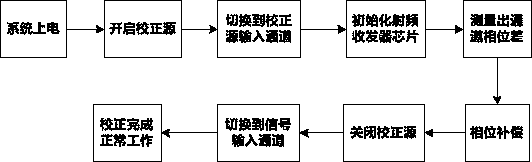

Multichannel phase measuring system and method based on radio frequency transceiver chip

ActiveCN108667466ARealize data interactionRealize functionTransmitters monitoringReceivers monitoringIntermediate frequencyFpga implementations

The invention discloses a multichannel phase measuring system and method based on a radio frequency transceiver chip. The system is realized by adopting the radio frequency transceiver chip and an FPGA mainly. The radio frequency transceiver chip is utilized for receiving analog radio frequency signals of eight channels, processing procedures such as analog mixing, zero intermediate frequency sampling, digital decimation filtering and digital signal correction are completed, a single radio frequency transceiver chip can complete RF signal processing to two channels, and digital-analog integrated design is completely realized. The FPGA mainly completes implementation of a phase measuring algorithm and control and parameter loading operations of the radio frequency transceiver chip. The system also adopts a JESD204B high-speed serial interface for realizing a data interaction and synchronizing function between the FPGA and the radio frequency transceiver chip, is simple in design and lowin cost and can realize a 0-6G wideband phase measuring function of multiple channels, phase measuring accuracy reaches less than 0.1 degree, and the system and the method which are disclosed by theinvention can be widely applied to the fields of radars, communication, industrial control and the like.

Owner:CHENGDU TIGER MICROWAVE TECH

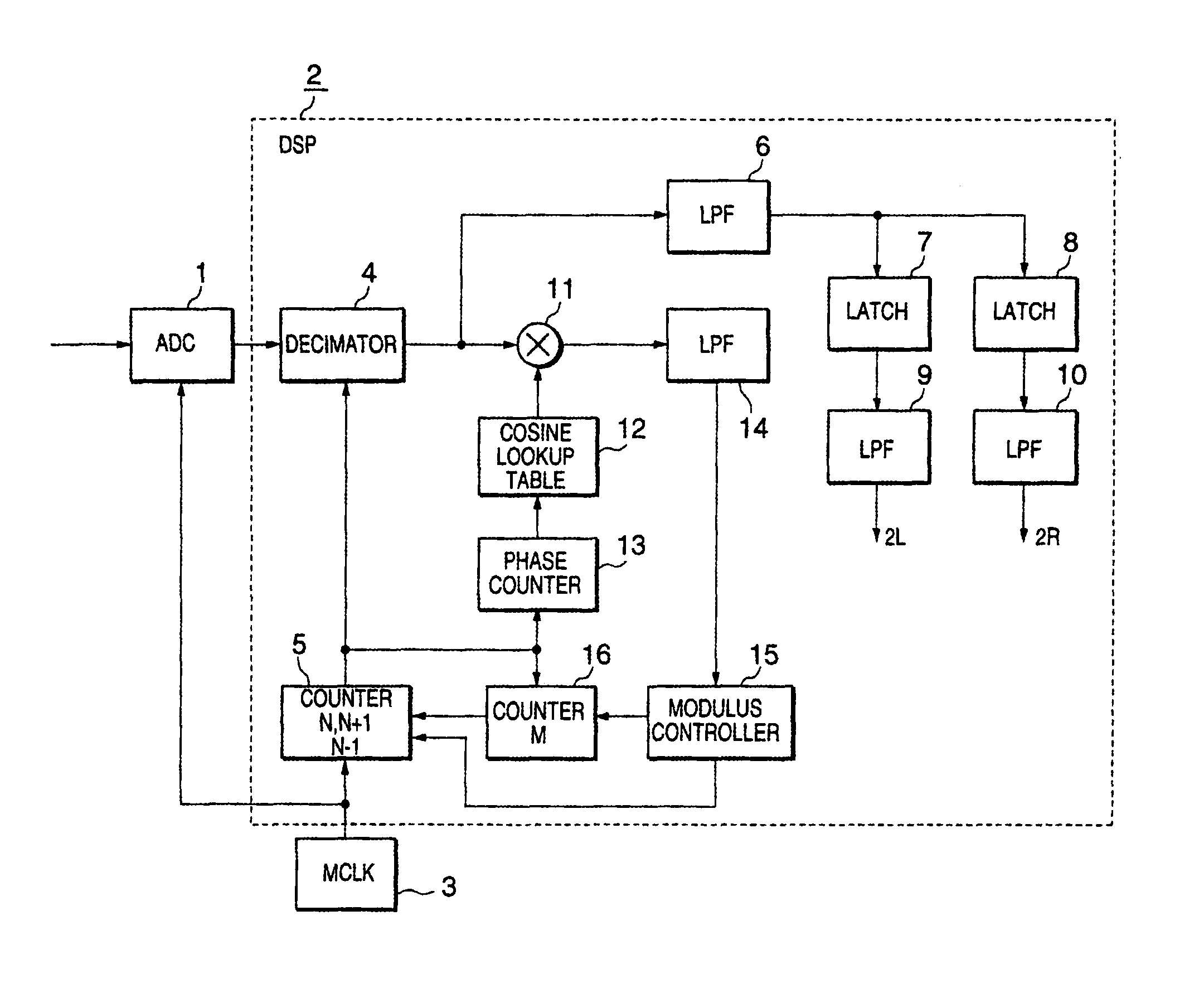

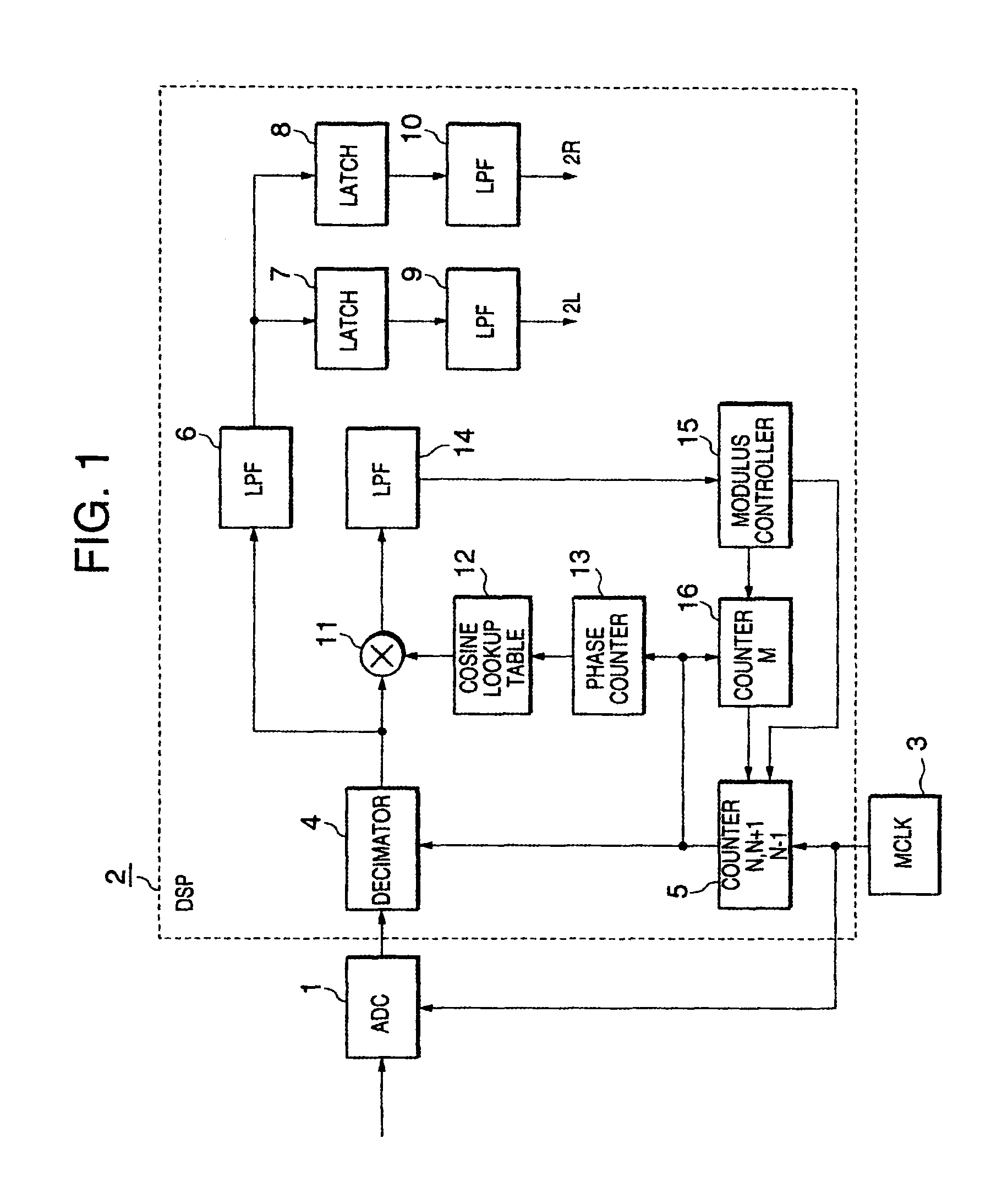

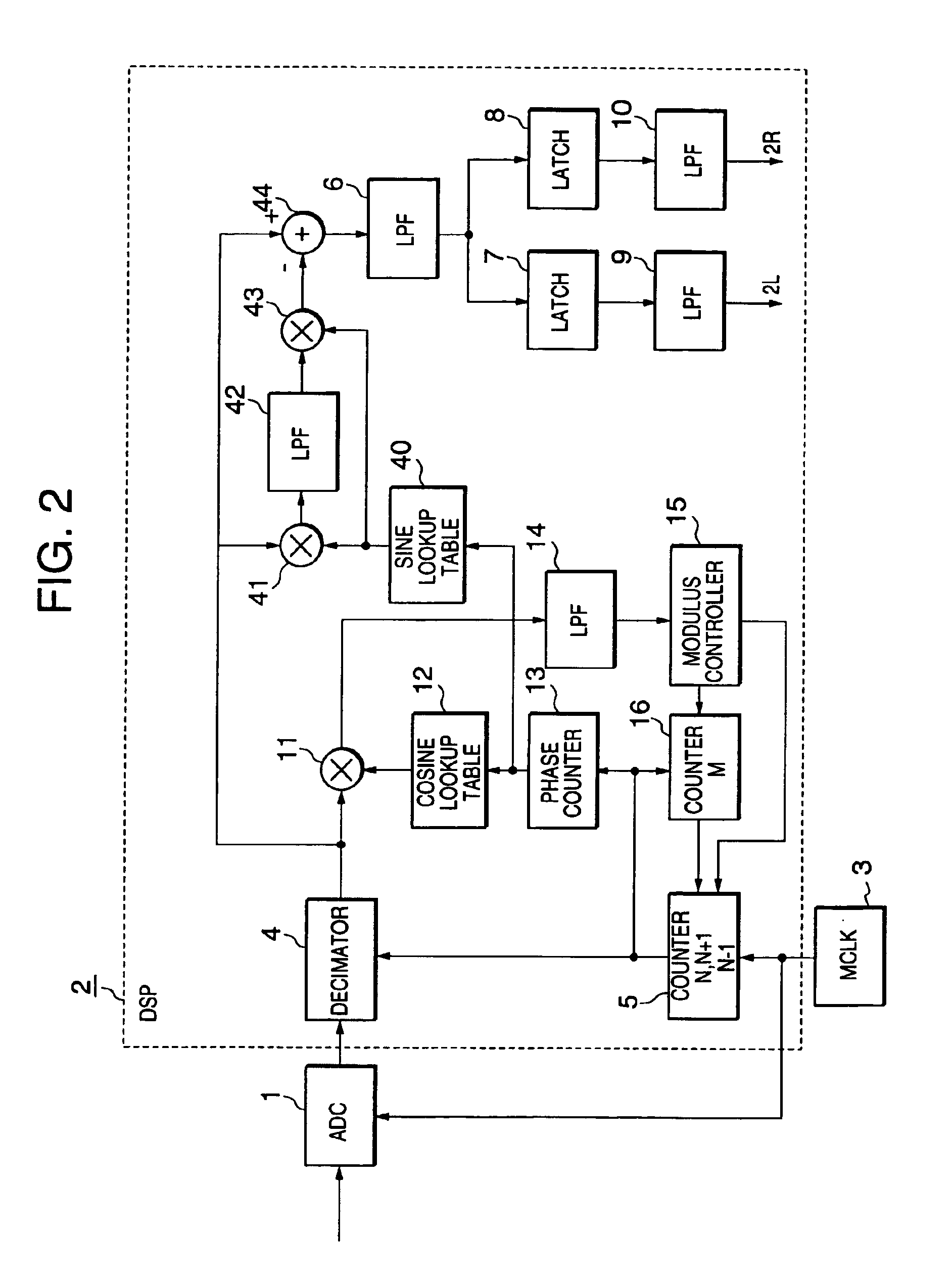

All-digital FM stereo demodulator and demodulation method

InactiveUS6901146B1Easy to implementPerformance requirementBroadcast circuit arrangementsTransmissionAudio frequencyComputer science

A stereo composite signal including a pilot signal is demodulated by processing input samples to obtain internal samples having variable sampling timings, synchronizing these sampling timings with the pilot signal, and digitally processing the internal samples to obtain stereo audio data. The internal samples may be obtained from the input samples by decimation or interpolation. Since the sampling frequency and sampling timing of the input samples do not have to be precisely controlled, no voltage-controlled oscillator is needed, and the demodulator can easily be incorporated into a monolithic integrated circuit.

Owner:MITSUBISHI ELECTRIC CORP

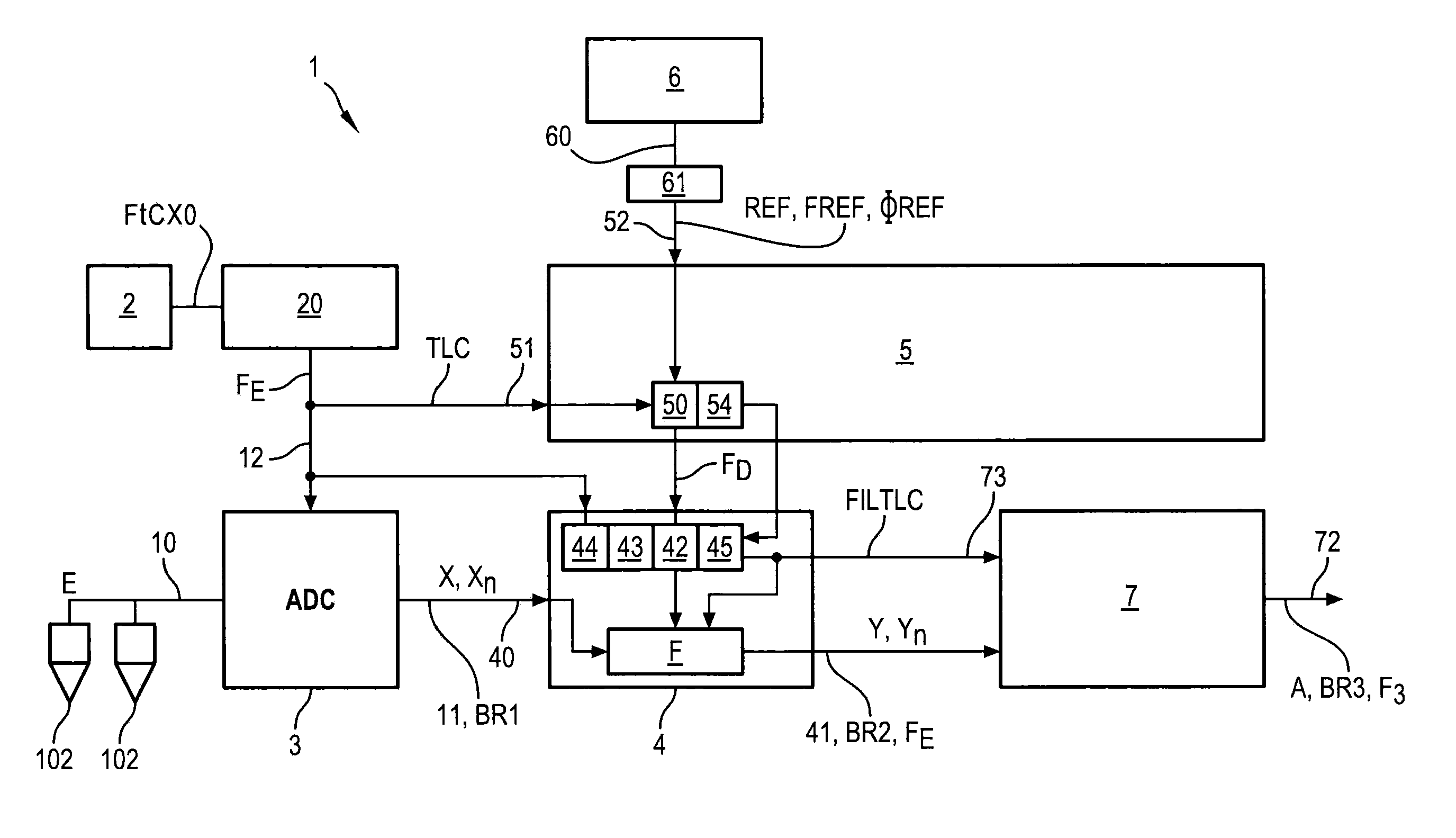

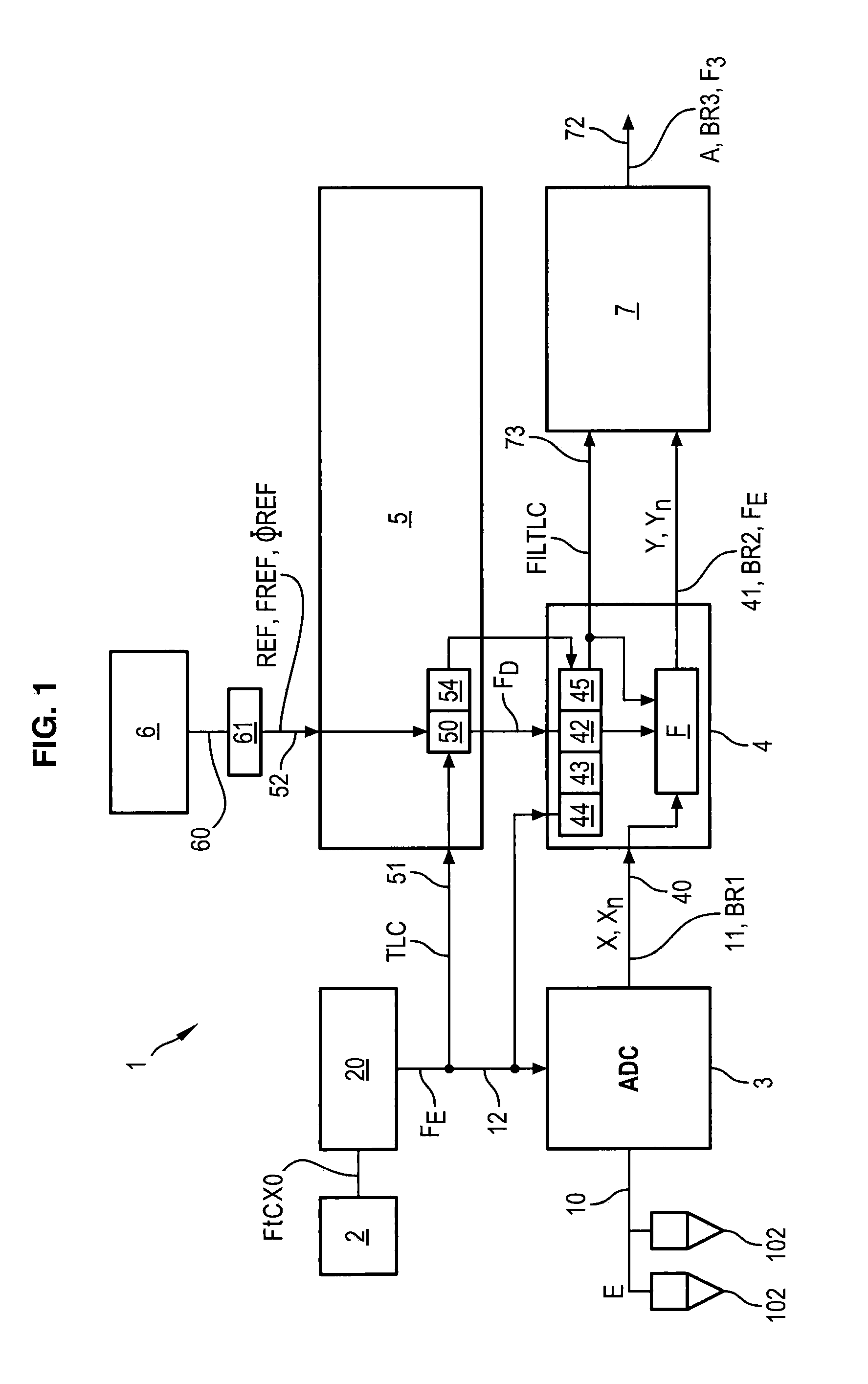

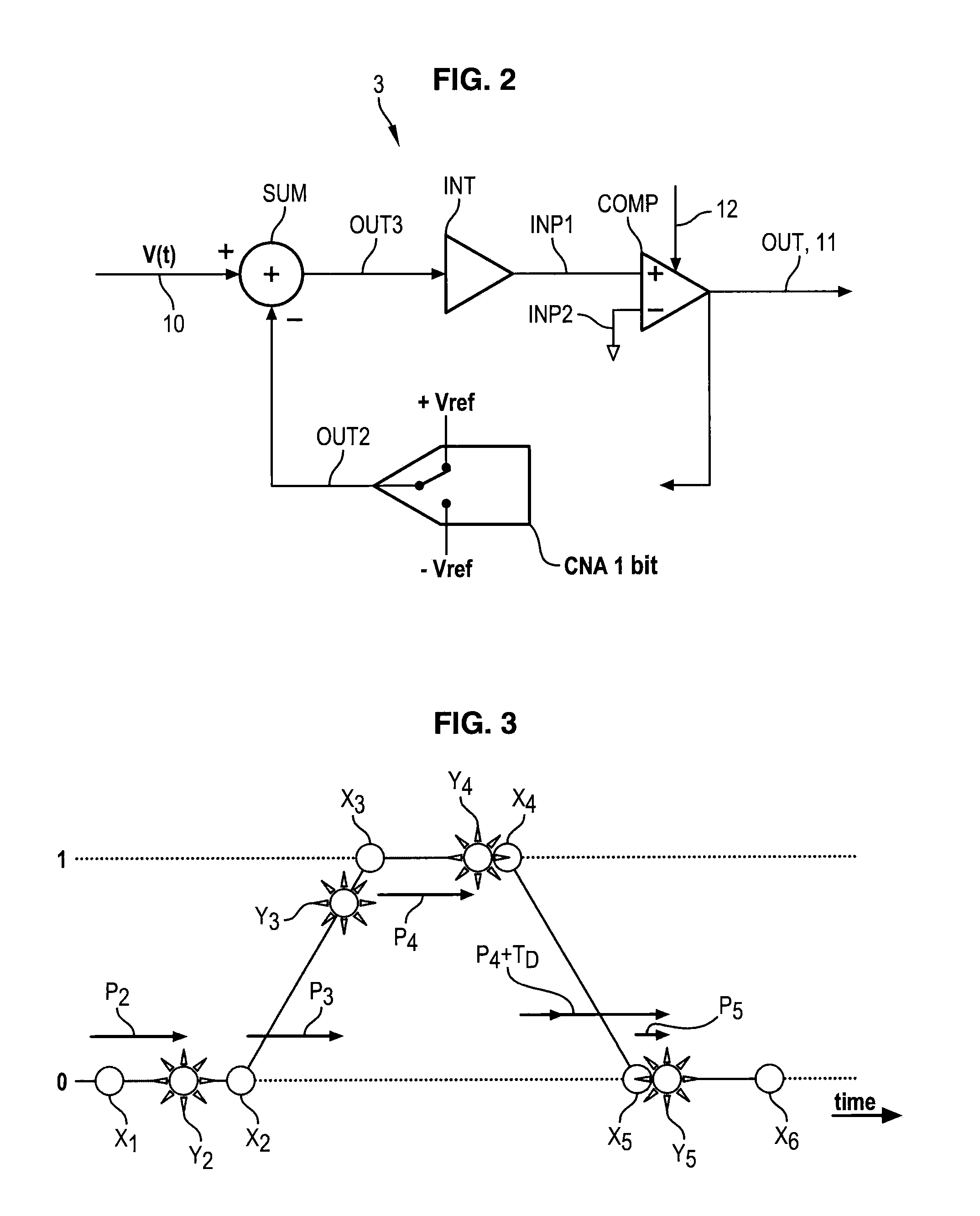

Data acquisition apparatus and method

ActiveUS20100198561A1High computational loadHigh degreeAmplifier modifications to reduce noise influenceDigital computer detailsDigital dataData acquisition

The disclosure concerns a data acquisition apparatus and method. According to the disclosure,a first means providing a series of first digital sampled data (X) at an imperfect sampling frequency (FE) provided by a local clock (2) comprises sigma-delta modulation means (3) arranged to produce said series of first digital sigma-delta modulated data (X),a second gauging means (50) for measuring the frequency error of the local clock (2) in view of a reference clock (6),a third means for correcting the first data based at least on the measured frequency error, which comprises at least an interpolation means (4) to produce second digital data (Y) based on at least an interpolation of said first series (X) and compensating the measured frequency error (FD), and at least a decimation filter (7) for producing third digital data (A) based on said second digital data (Y),are provided.

Owner:SERCEL INC

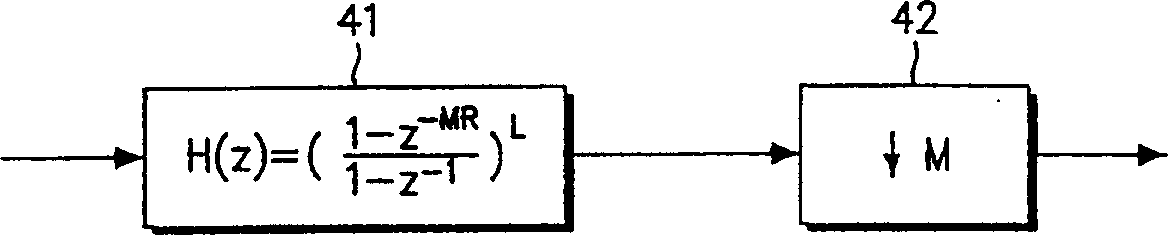

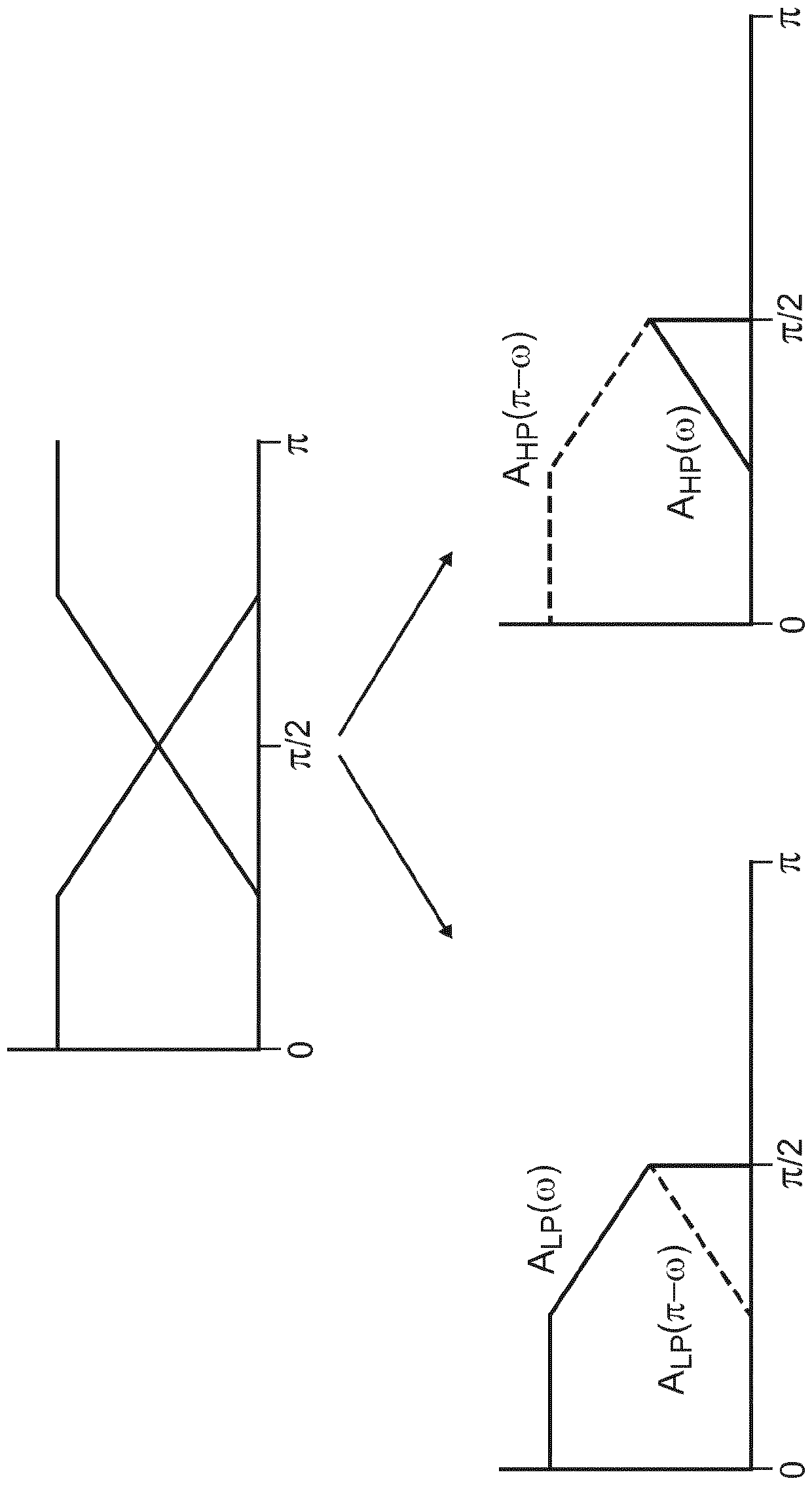

Decimation filtering apparatus and method

InactiveCN1285975APassband dropDigital technique networkAnalogue conversionFinite impulse responseIntegrator

A decimation filtering apparatus using interpolated second order polynomials compensates for a droop caused by a CIC (Cascaded Integrator-Comb) filter (51). The decimation filter includes a CIC decimation filter (51) for decimation filtering the sampling signal to downconvert a sampling signal; an ISOP filter (53) for monotonically increasing an output of the CIC decimation filter (51) to compensate for a passband droop caused by the CIC decimation filter (51); a multistage halfband filter (55) including at least one modified halfband filter for 1 / 2 decimating a signal output from the ISOP filter (53), the multistage halfband filter (55) decimating the signal output from the ISOP filter (53) to downconvert the signal; and a programmable FIR (Finite Impulse Response) filter (57) for compensating for a passband droop of a signal output from the multistage halfband filter (55).

Owner:SAMSUNG ELECTRONICS CO LTD

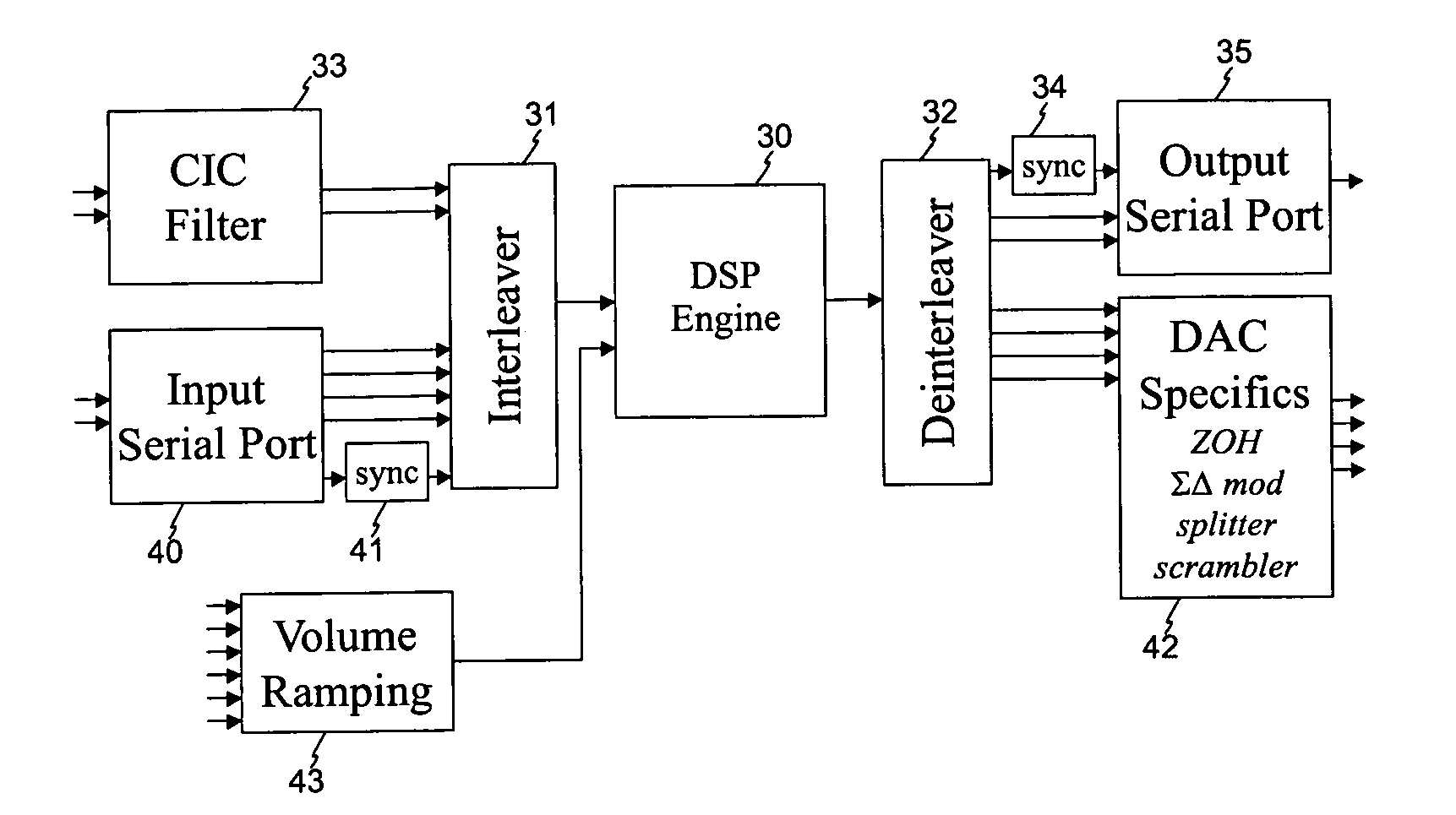

Audio signal processing

Owner:KONINKLJIJKE PHILIPS NV

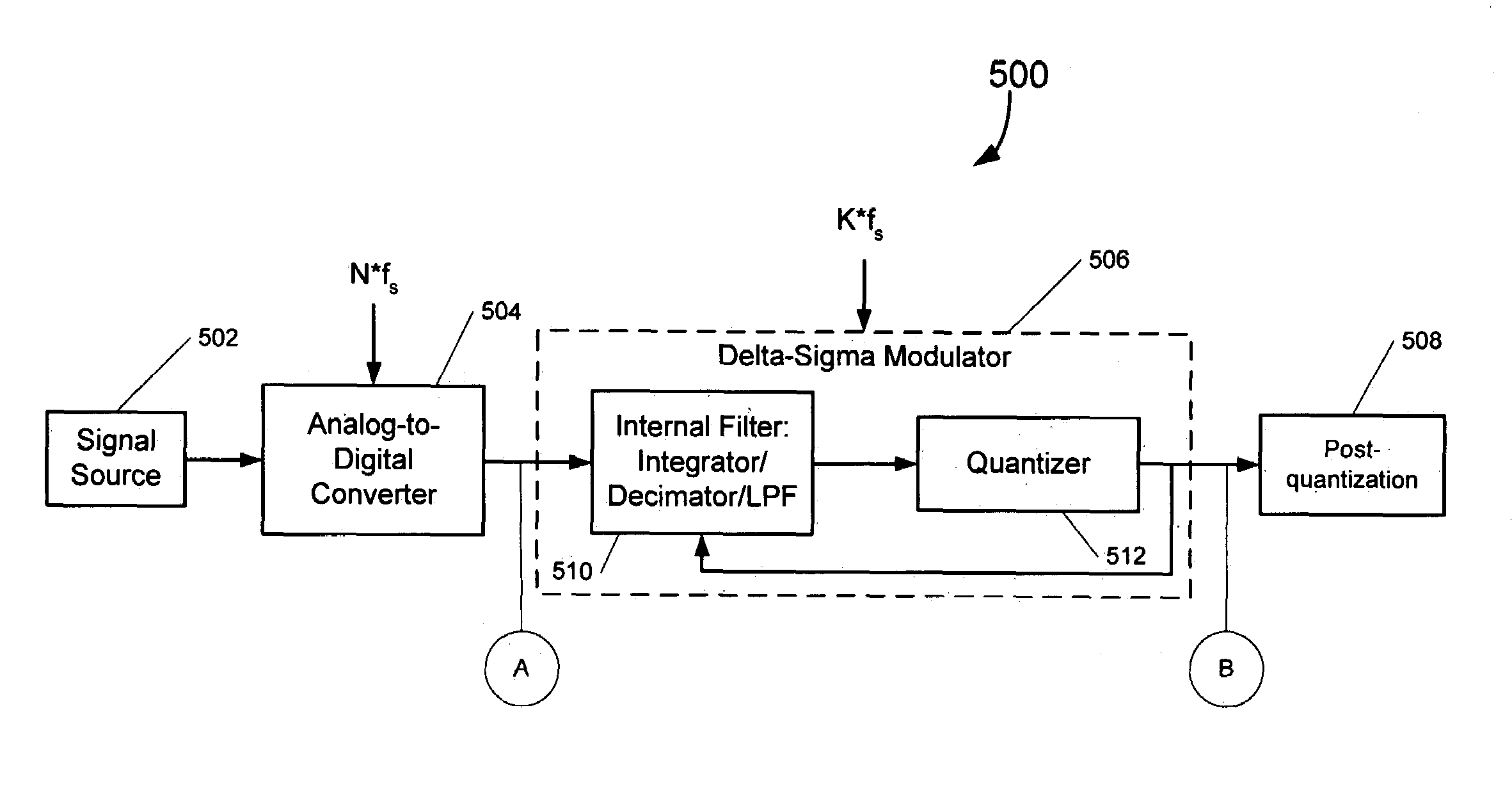

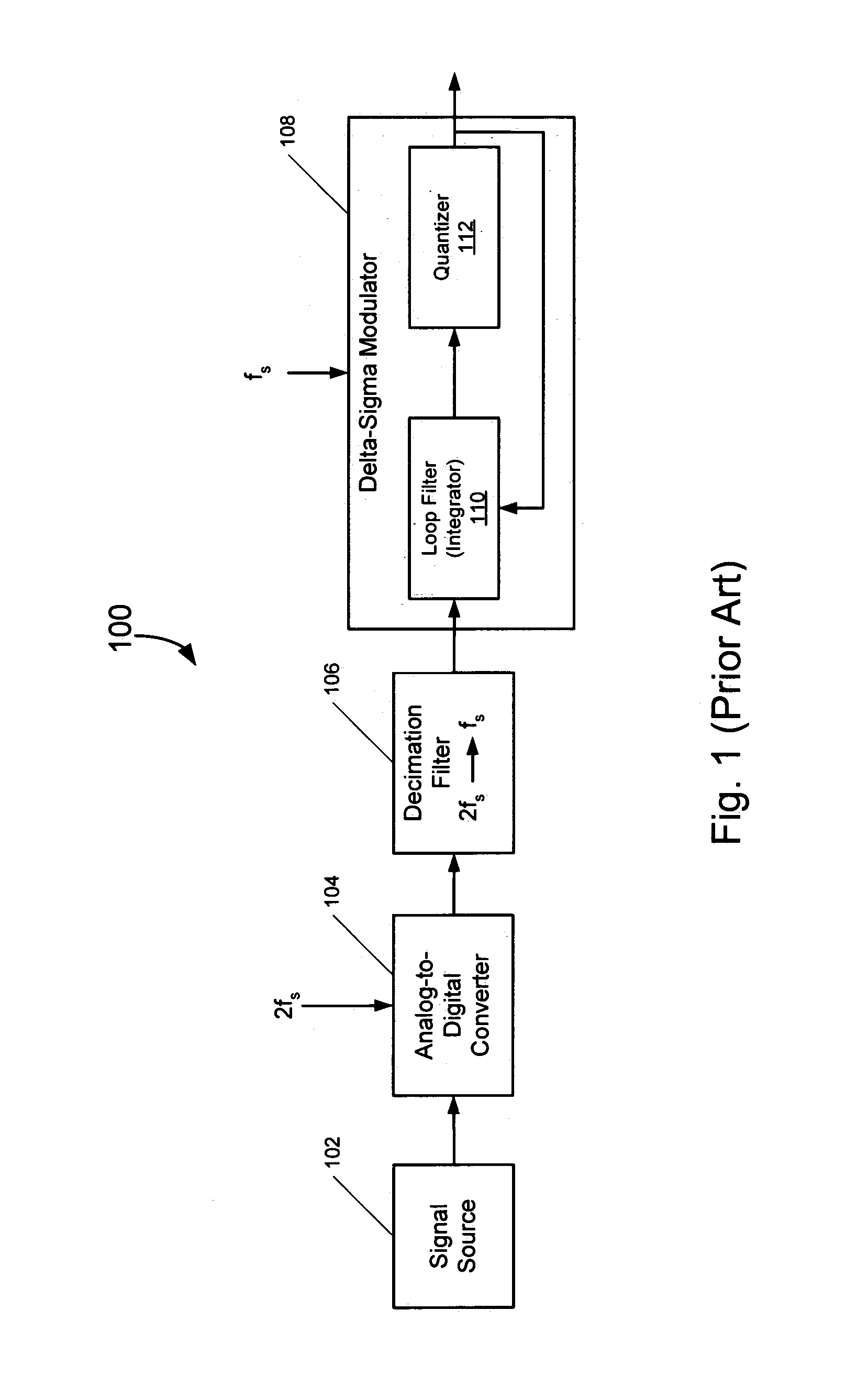

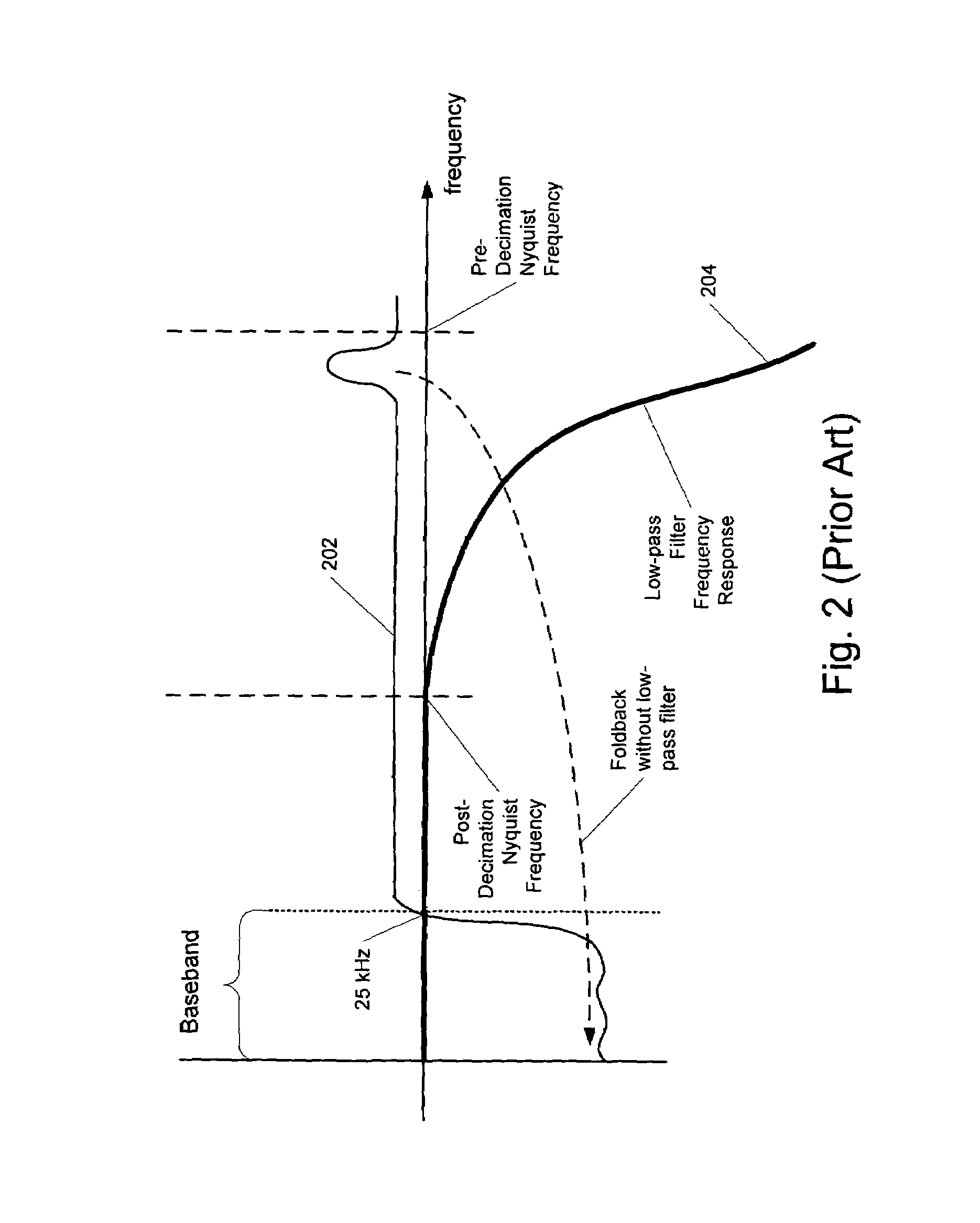

Delta sigma modulator with integral decimation

ActiveUS7212137B2Electric signal transmission systemsAnalogue conversionDigital signal processingSoftware engineering

Owner:CIRRUS LOGIC INC

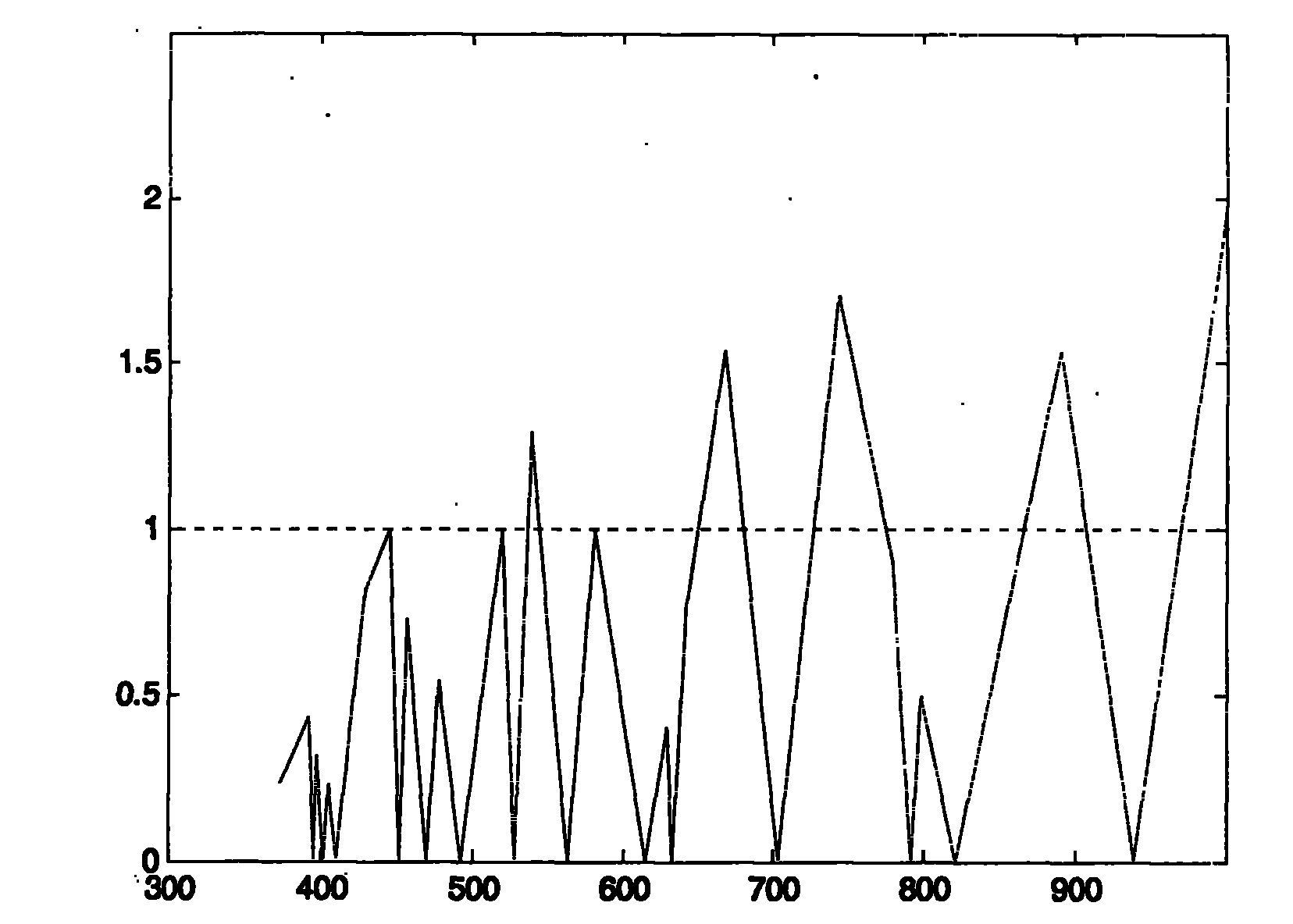

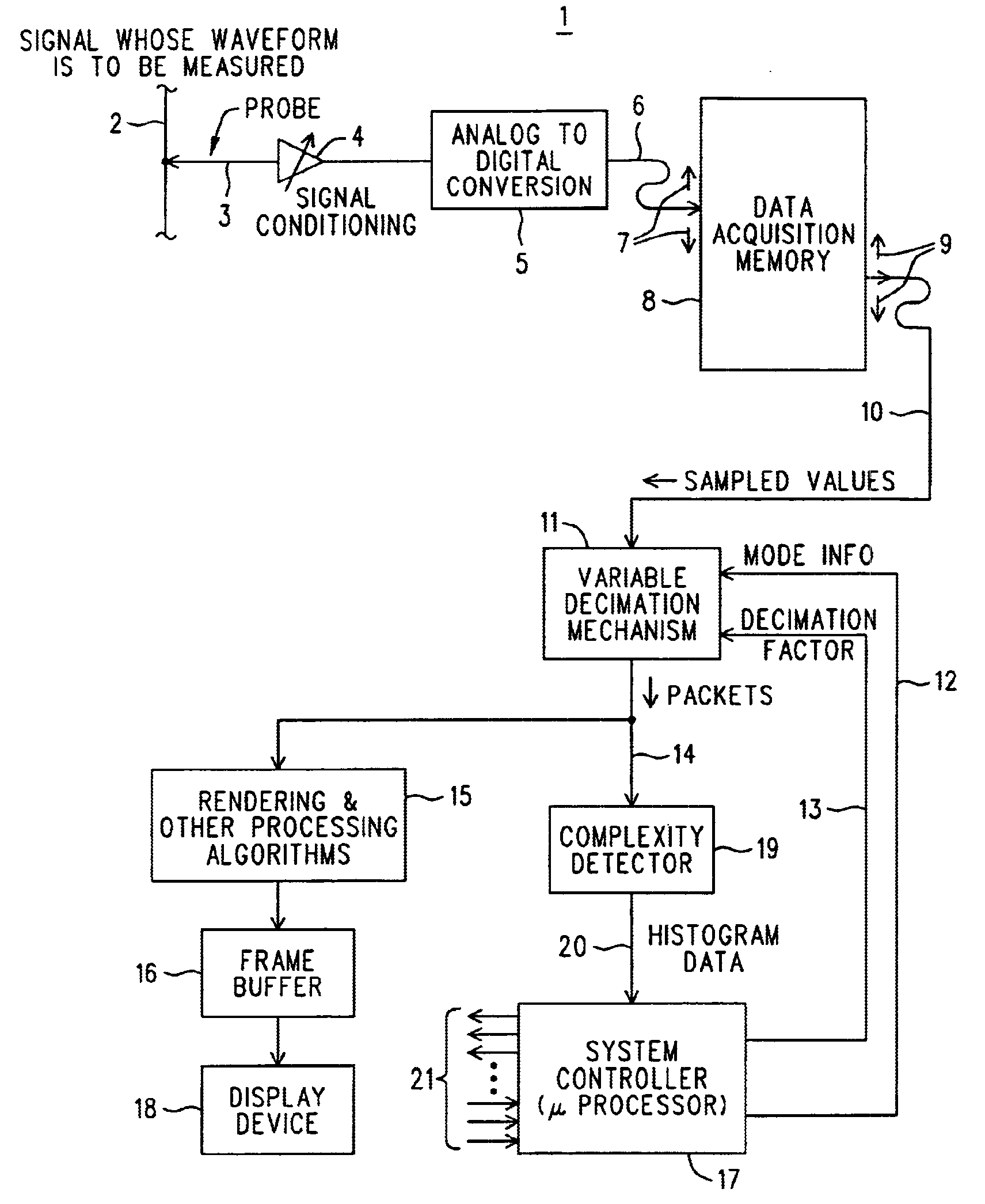

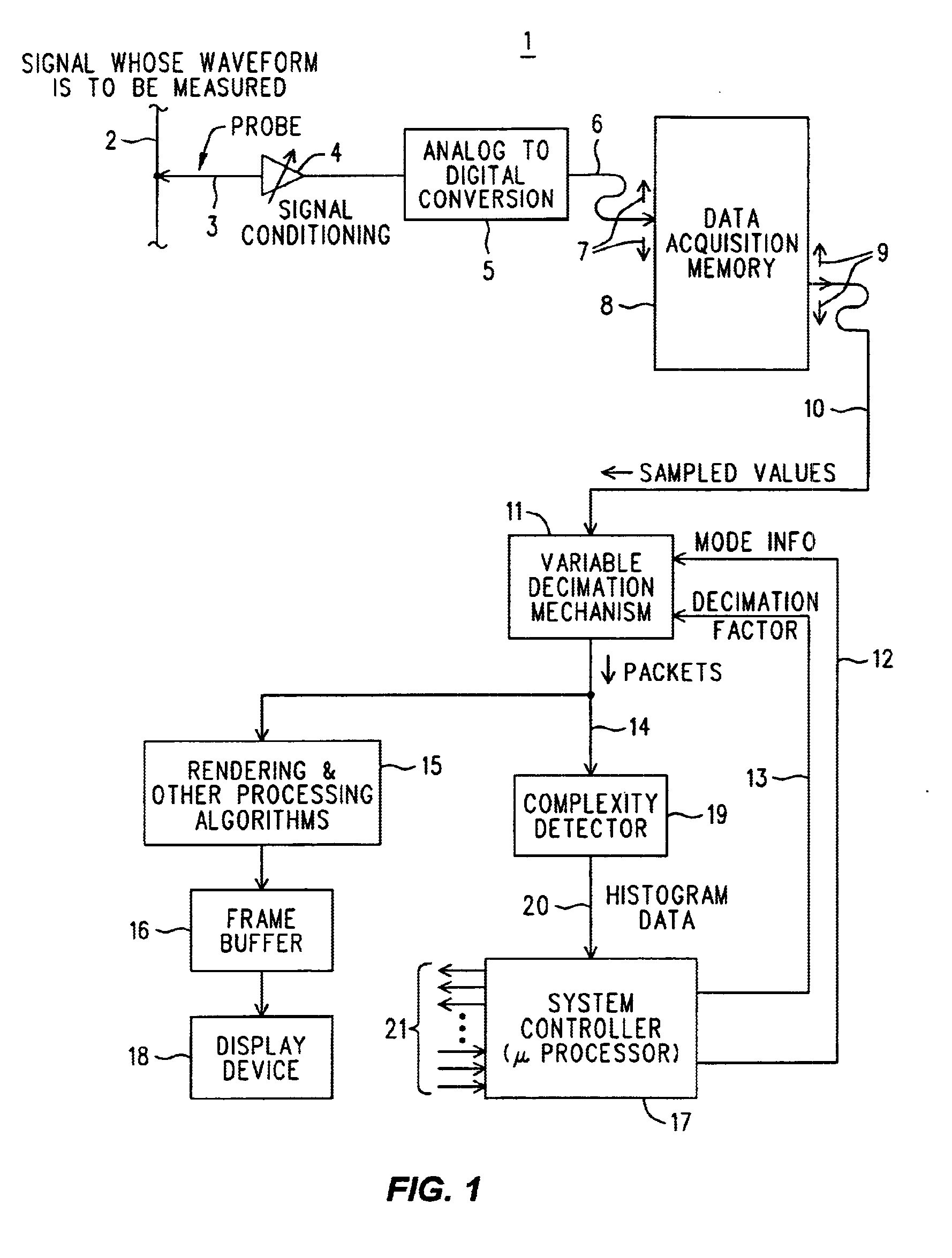

Waveform complexity detector

InactiveUS6934646B2Digital variable displayDrawing from basic elementsNetwork packetComputer science

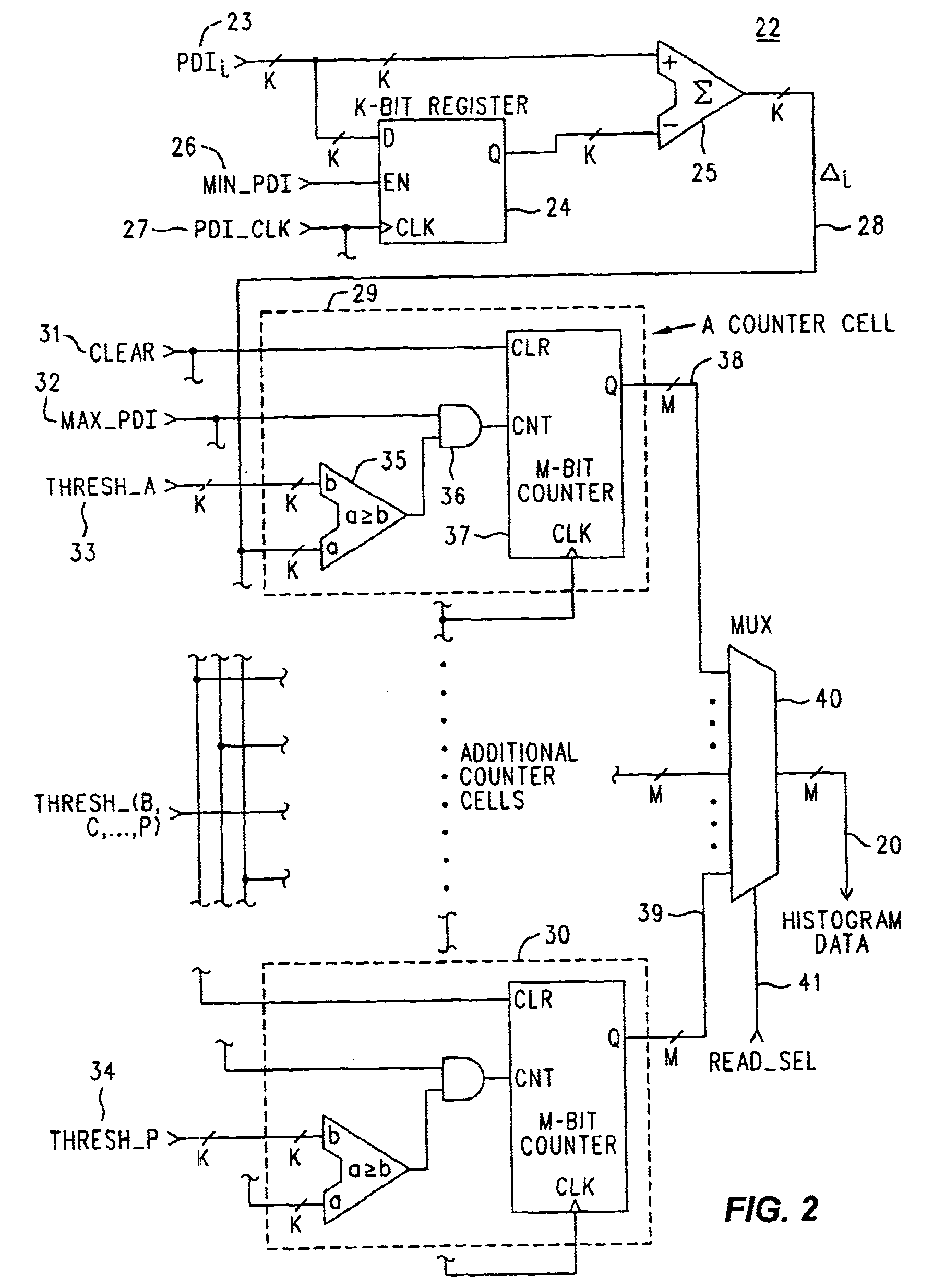

Trial decimations are performed on an acquired waveform. Each trial produces a sequence of packets applied to a complexity detection circuit. Each packet contains a decimation value to be used in place of acquisition values to be suppressed along a decimation sample width. Each packet also includes the maximum and minimum values that occurred within the associated decimation sample. A plurality of counters record for a trial decimation the number of instances when the differences in waveform extremes exceed a corresponding plurality of selected thresholds. Complexity introduced by decimation will tend to produce waveforms having larger voltage excursions over the region of suppressed acquisition samples. The data in the counters is processed to produce a suite of histograms examined to select a decimation factor that does not introduce significant additional complexity.

Owner:AGILENT TECH INC

Cascade digital filter anti-communication jamming method based on P band radio frequency sampling

InactiveCN108008359AImprove anti-interference abilityAchieve out-of-band rejectionWave based measurement systemsTransmissionFrequency spectrumRadio frequency

The invention relates to the field of radar against active jamming and particularly relates to a cascade digital filter anti-communication jamming method based on P band radio frequency sampling. Direct bandpass sampling digitalization is carried out on radio frequency echo signals received by the radar through an ADC chip, the sampled digital signals are subjected to digital down conversion, after digital mixing and multilevel decimation filter, needed baseband signals are obtained, and besides, spectrum aliasing is not introduced, high performance digital filter out-of-band rejection abilityis achieved, communication jamming outside an operating frequency point can be filtered out, and requirements of target detection display are met. Same frequency band communication jamming by radar sidelobe entering can be effectively restrained, the radar against jamming ability is enhanced, and a detected and extracted picture is improved.

Owner:WUHAN BINHU ELECTRONICS

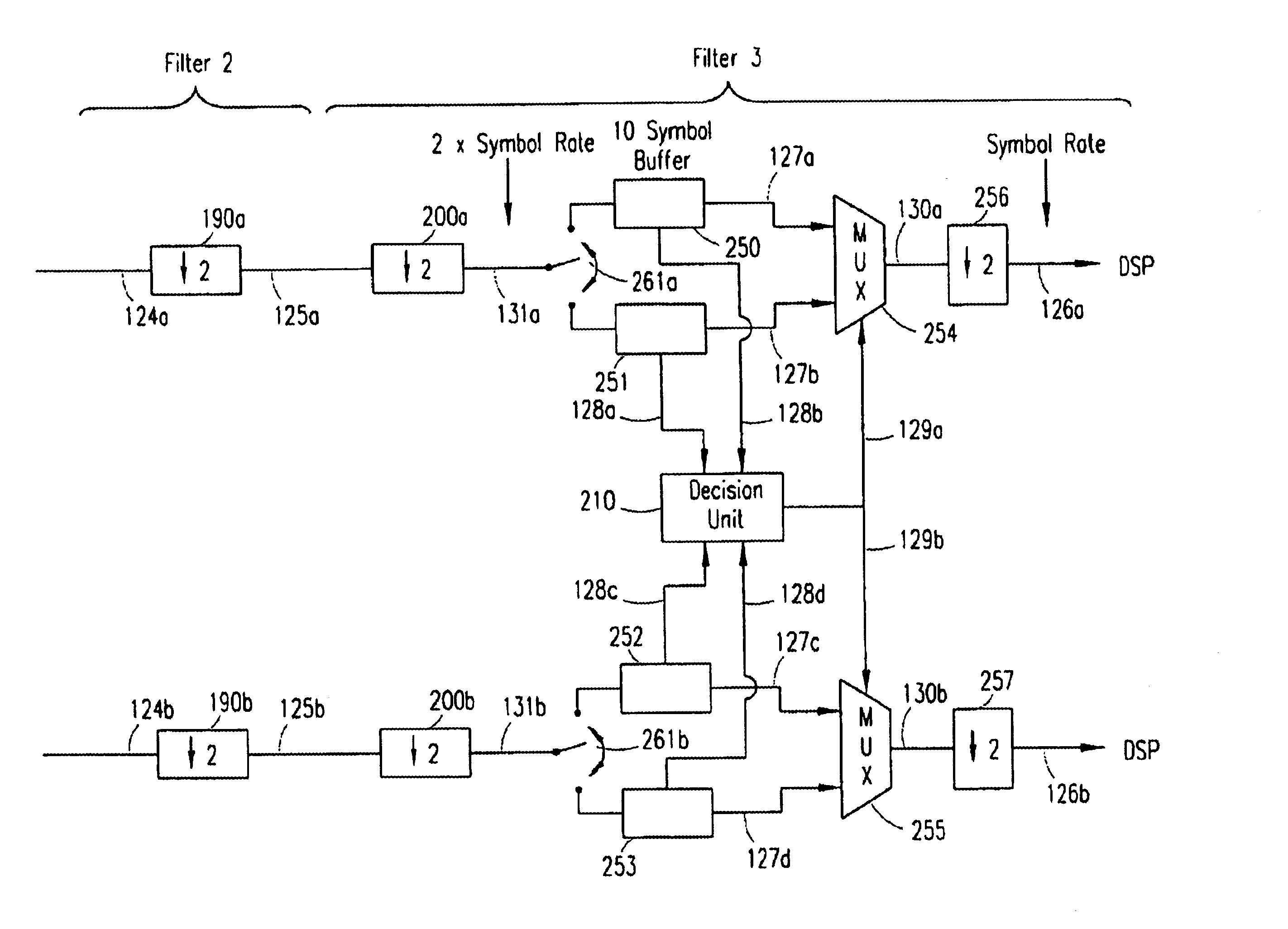

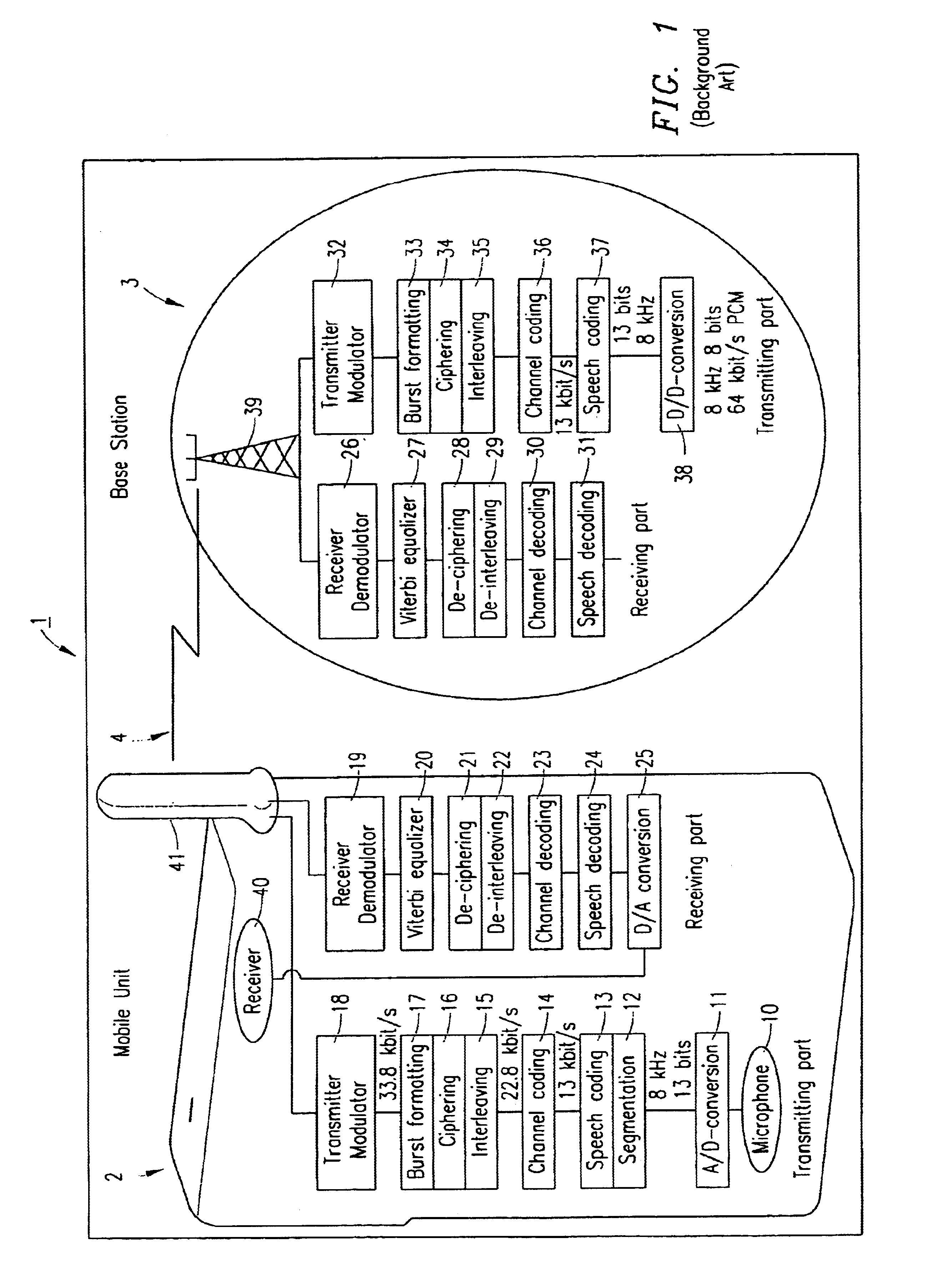

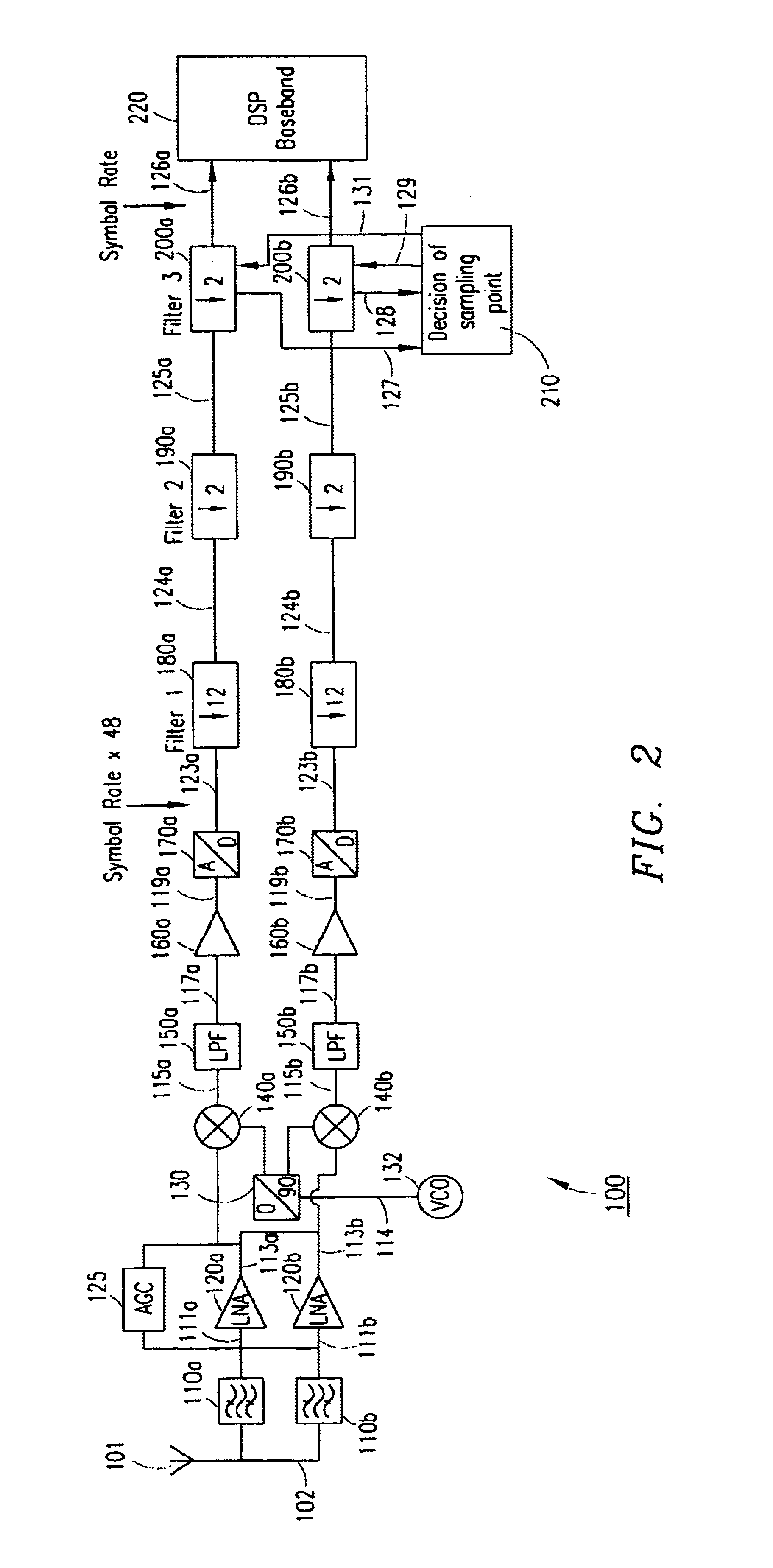

Technique for demodulating a linear modulated data signal in a communications system

InactiveUS6904104B1Reduce complexityEfficient and cost-effectiveSynchronisation error detectionDc level restoring means or bias distort correctionCommunications systemData signal

A receiver section recovers the in-phase and quadrature components of a linear modulated data signal. The in-phase signal is sampled and quantized producing an in-phase sample stream, and the quadrature phase signal is sampled and quantized producing a quadrature sample stream. The in-phase sample stream and the quadrature sample stream are both over-sampled at a rate of N times a symbol rate of the data signal. A decimation section filters the quantized in-phase sample stream and the quantized quadrature sample stream to produce a reduced in-phase sample stream and a reduced quadrature sample stream at a rate of M times the symbol rate, wherein M is less than or equal to N. A decision component calculates the magnitude of a combination of an in-phase sample and a quadrature sample at M corresponding sample points in the reduced in-phase sample stream and the reduced quadrature sample stream, respectively, and then forms an in-phase symbol stream and a quadrature symbol stream using the in-phase sample and the quadrature sample, respectively, associated with the sample point having a largest magnitude.

Owner:UNWIRED PLANET

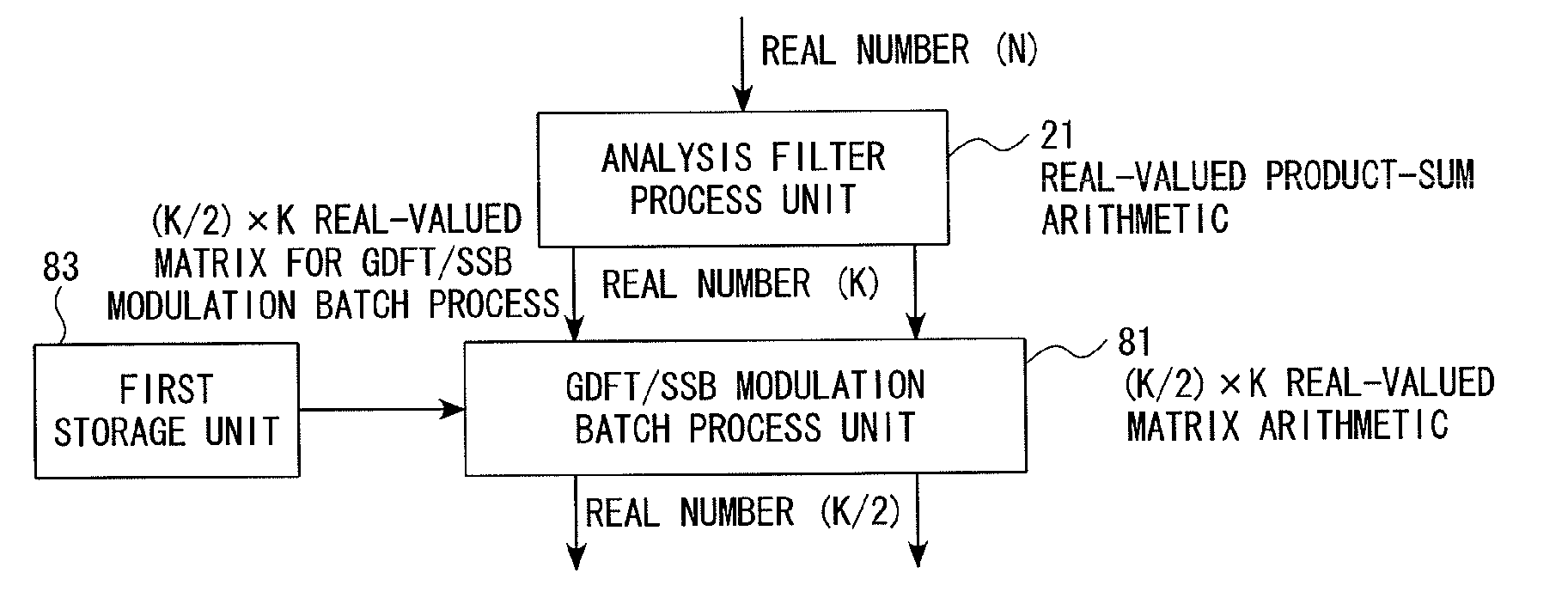

Signal processing device, echo canceller, and signal processing method

InactiveUS20100150365A1Accuracy deterioratesEar treatmentDigital technique networkVIT signalsUsage analysis

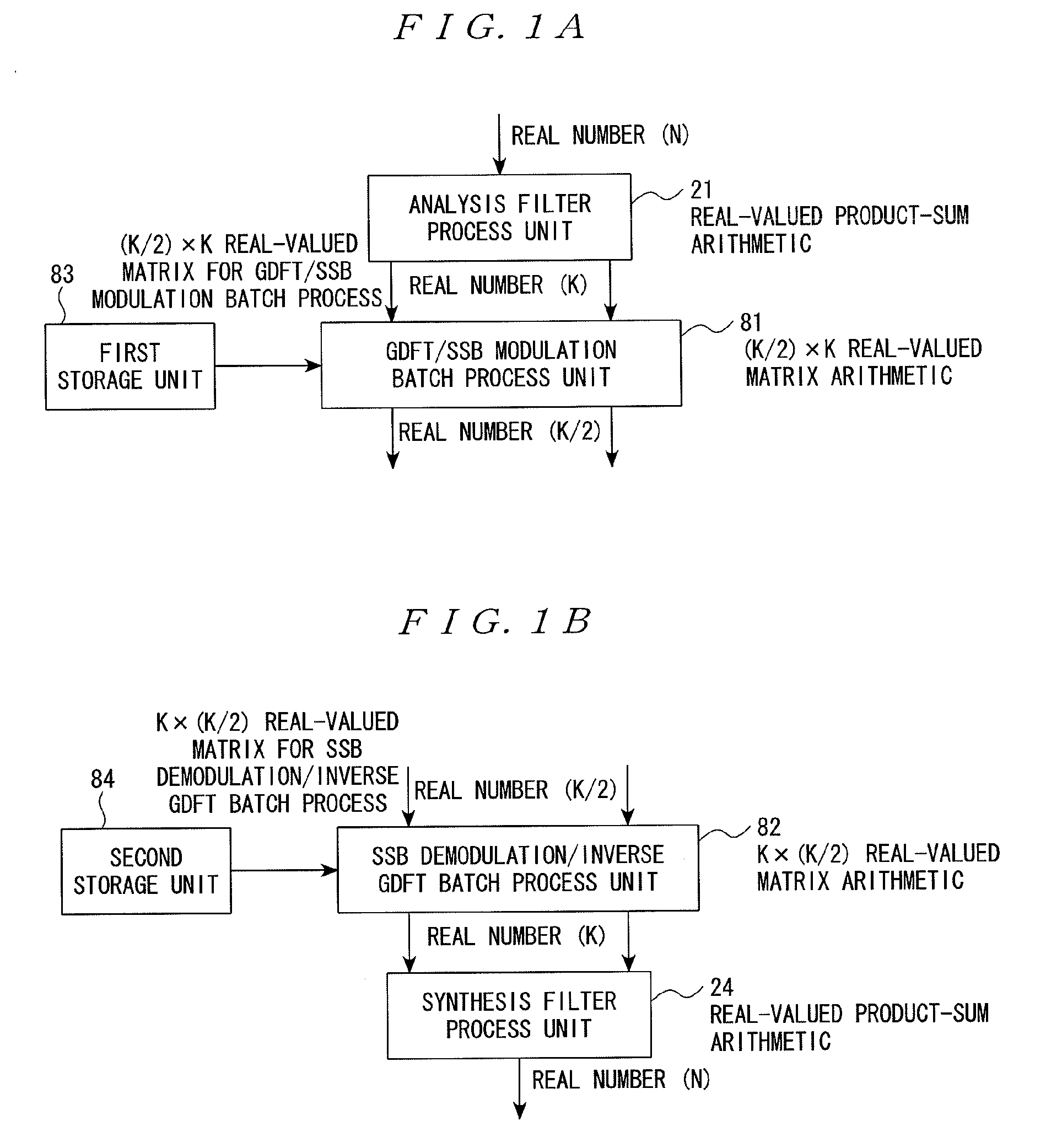

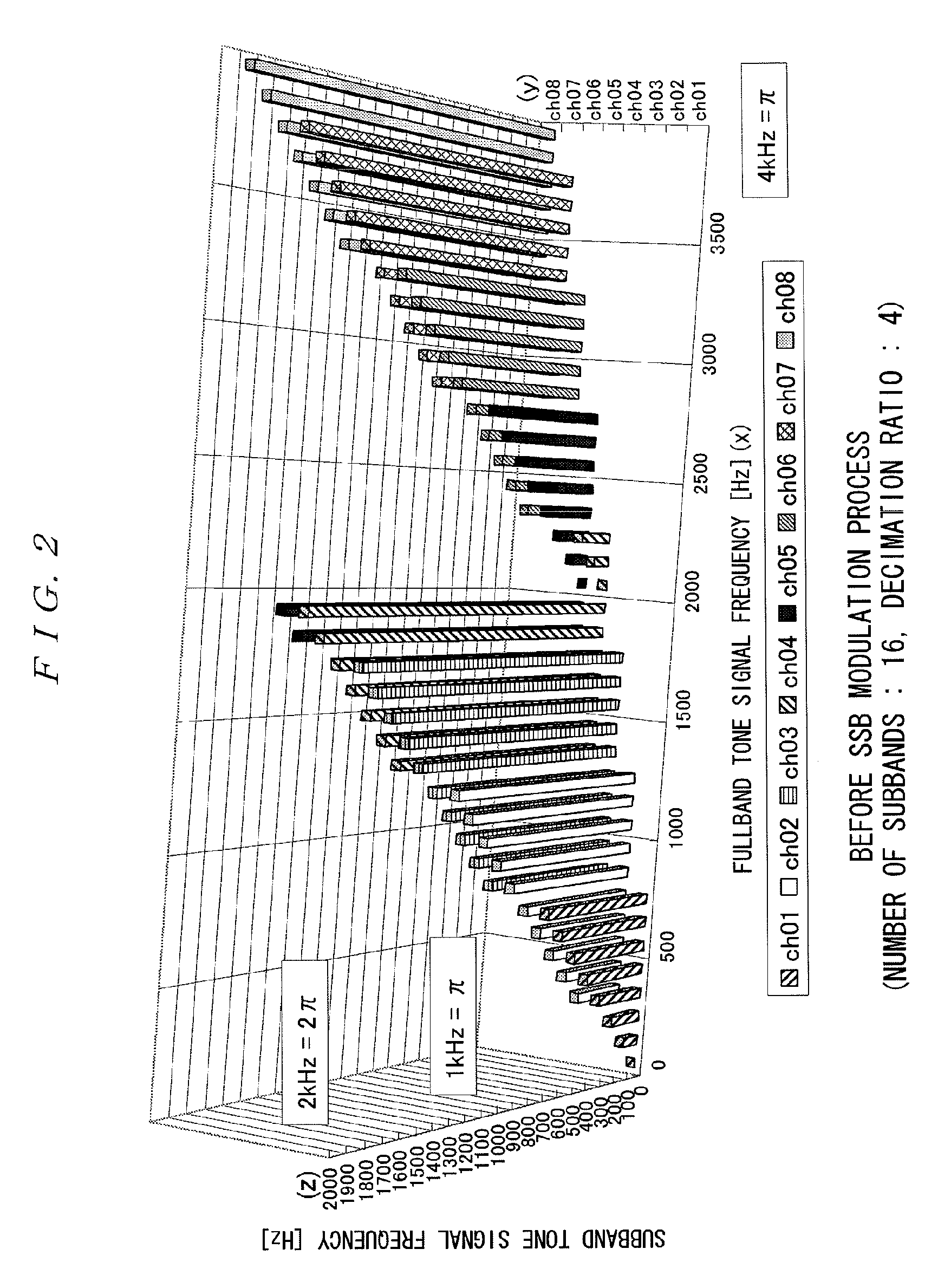

If K=4N, wherein K is a number of subbands and N is a decimation ratio, an analysis filter process unit 21 is used to perform an analysis filter process for every N samples of real-valued input data and output K samples of real-valued data. A GDFT / SSB modulation batch process unit (81) performs a GDFT process and an SSB modulation process on the outputted data by using a real-valued matrix calculation using a (K / 2)×K real-valued matrix to output 1 sample×(K / 2) channel of real-valued subbands data. Moreover, an SSB demodulation / inverse GDFT batch process unit (82) performs an SSB demodulation process and an inverse GDFT process on 1 sample×(K / 2) channel of real-valued subbands data by a real-valued matrix calculation using a K×(K / 2) real-valued matrix and outputs K samples of real-valued data. The outputted data is subjected to a synthesis filter process by a synthesis filter process unit (24) to output N samples of real-valued data.

Owner:ASAHI KASEI KOGYO KK

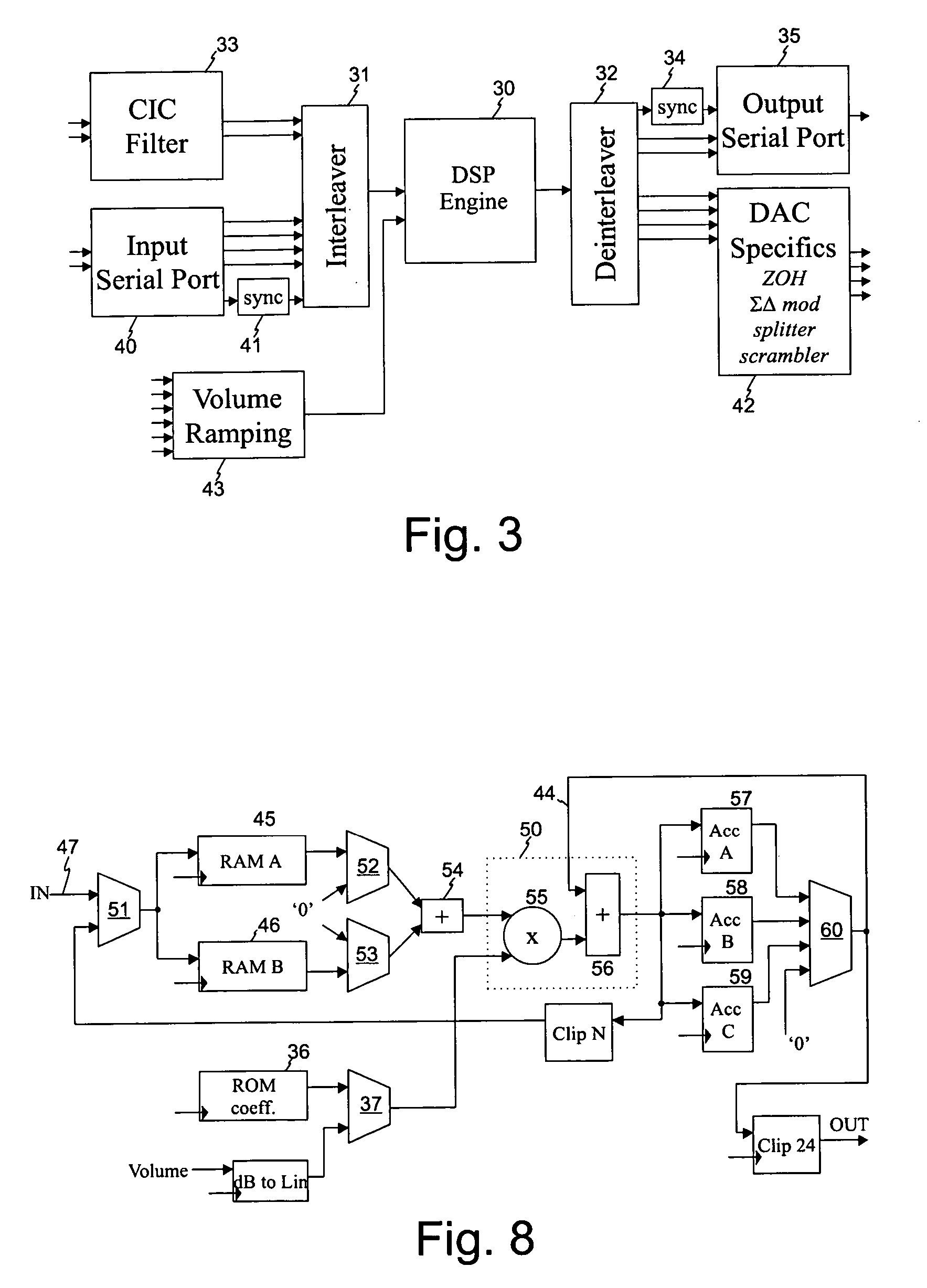

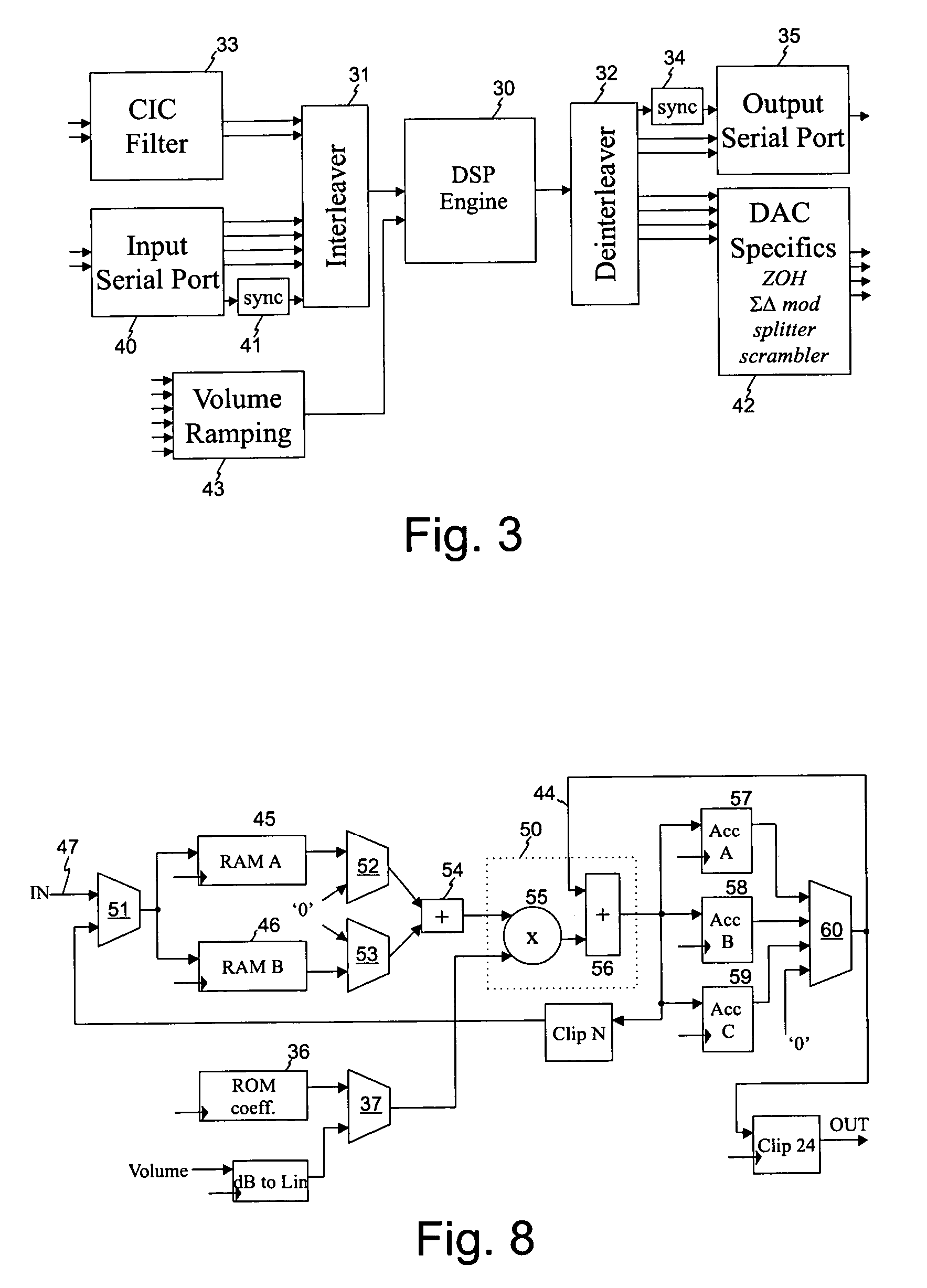

Digital signal processor optimized for interpolation and decimation

ActiveUS20060087466A1Reducing die spaceAvoid overwritingElectric signal transmission systemsDigital technique networkDigital signal processingFilter (signal processing)

A digital signal processor receives samples of a first digital signal which is to be decimated and samples of a second digital signal which is to be interpolated. A digital signal processing engine performs a decimation function on samples of the first digital signal and an interpolation function on samples of the second digital signal on a time-shared basis. The digital signal processor has a first dual memory space for storing the samples of the first digital signal and a second dual memory space for storing the samples of the second digital signal. Outputs retrieved from a dual memory space are pre-added and applied to a multiplication and accumulation stage which operates on the pre-added outputs and a filter coefficient of a digital filter.

Owner:ANALOG DEVICES INC

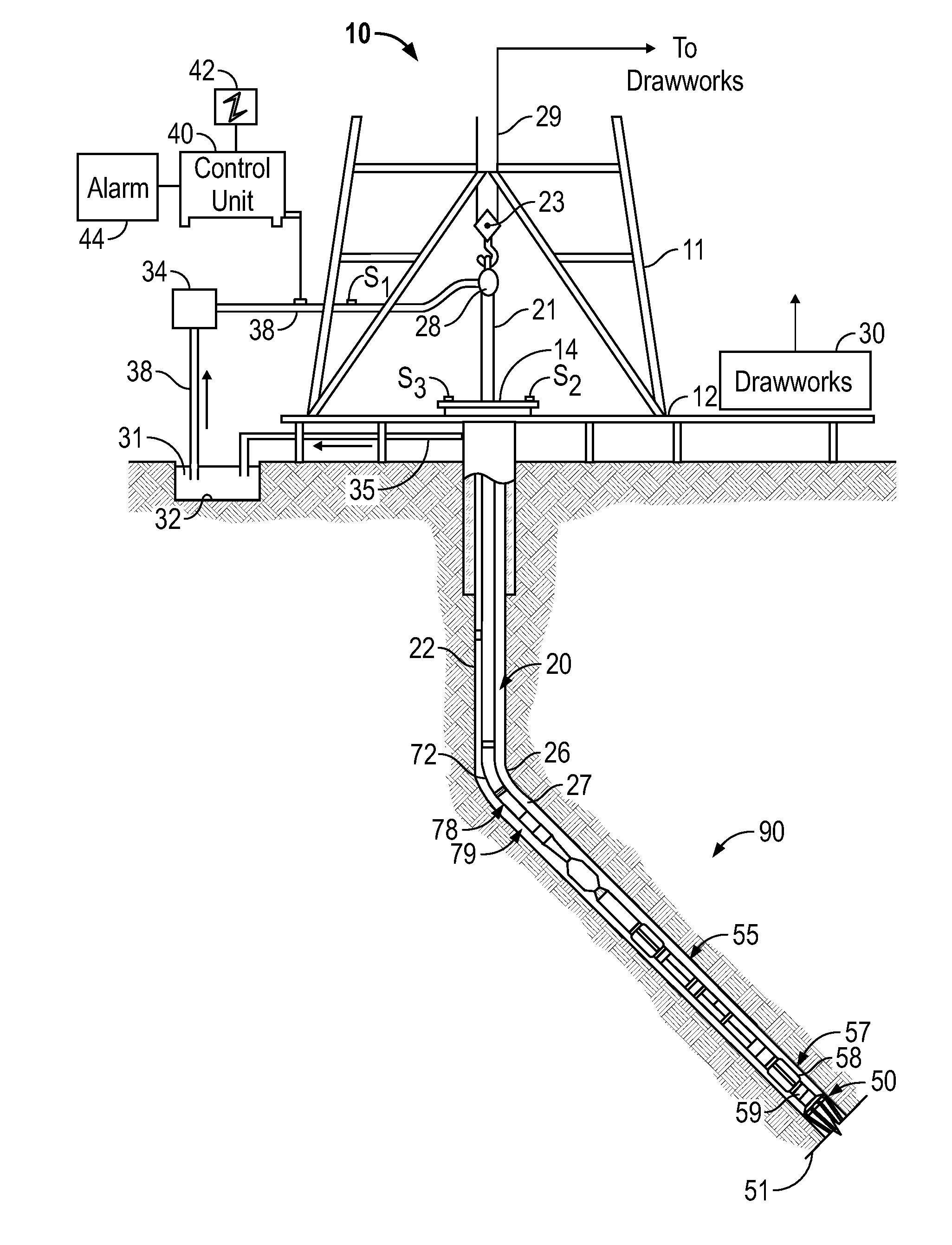

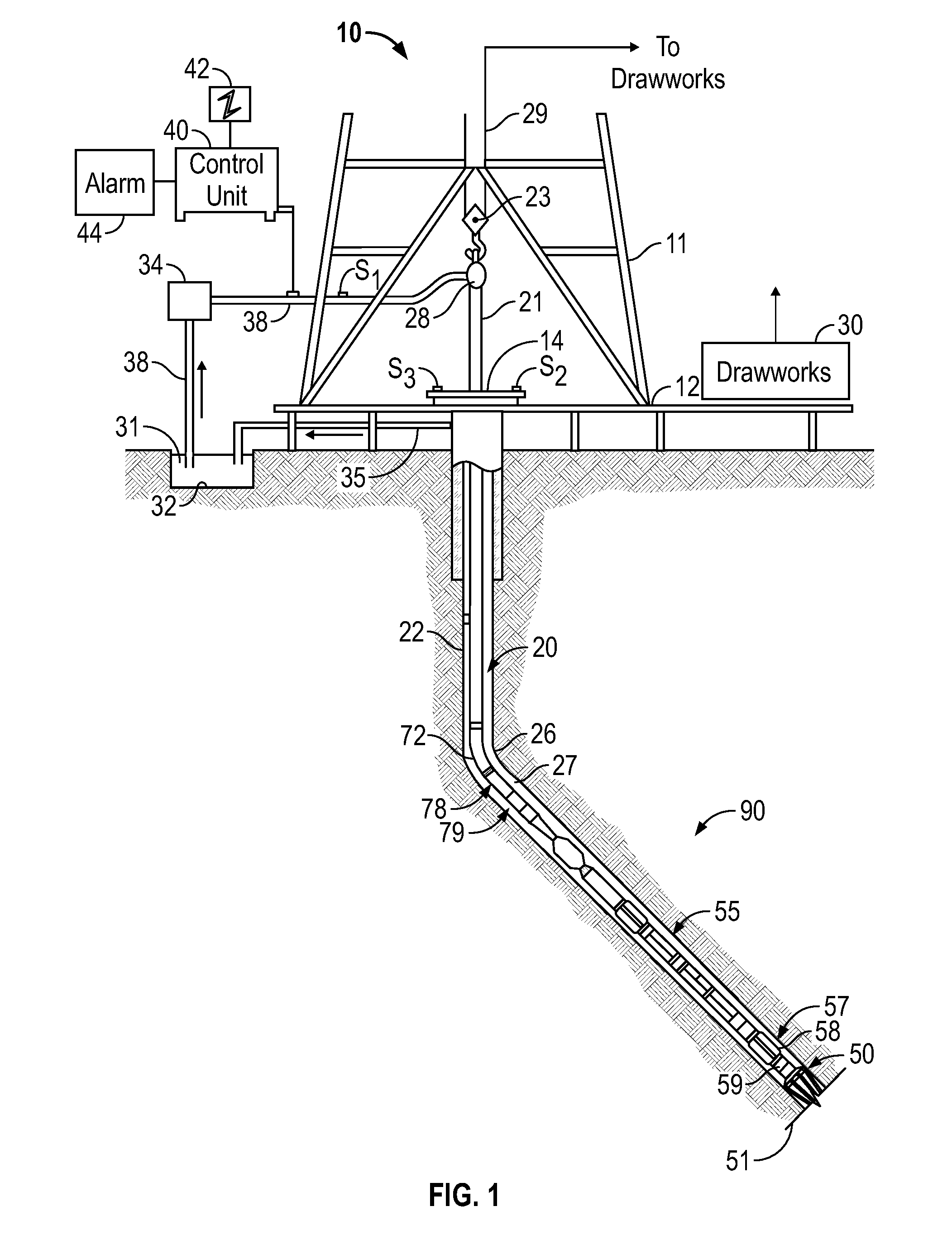

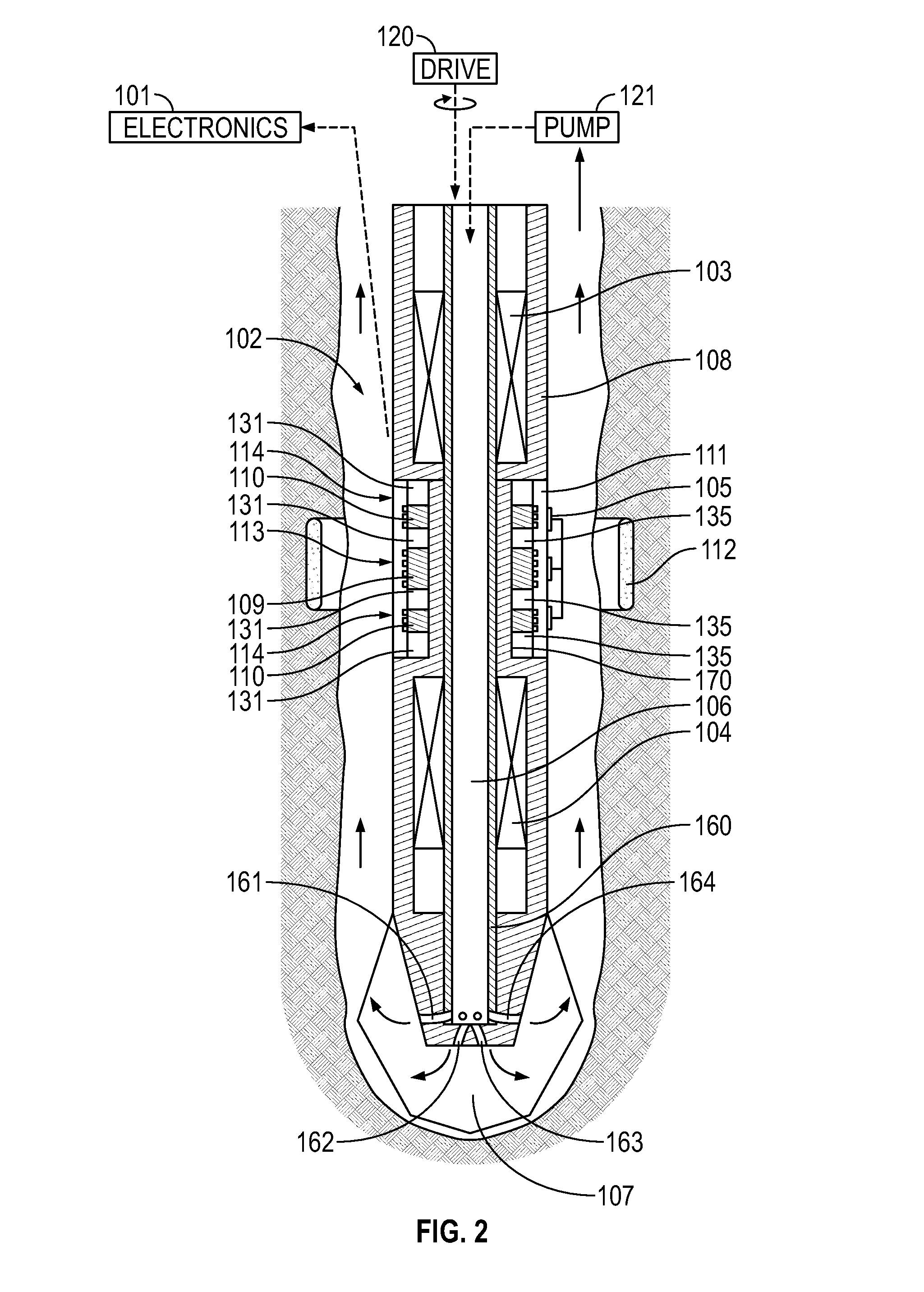

Non-uniform echo train decimation

ActiveUS20130207814A1Reduced data setReduce decreaseElectric/magnetic detection for well-loggingSurveyData setEngineering

Method and apparatus using at least one process to reduce a data set using a data adaptive down-sampling scheme comprising a plurality of non-uniform down-sampling factors. The method may include separating the data set into a plurality of data windows, where each of the plurality of data windows corresponds to one of the plurality of non-uniform data-sampling factors; applying the down-sampling factors, and transmitting the reduced data set from a downhole location to the surface. The data set may include an NMR echo train. The apparatus may include an NMR tool configured to acquire NMR data and at least one processor configured to perform the method.

Owner:BAKER HUGHES INC

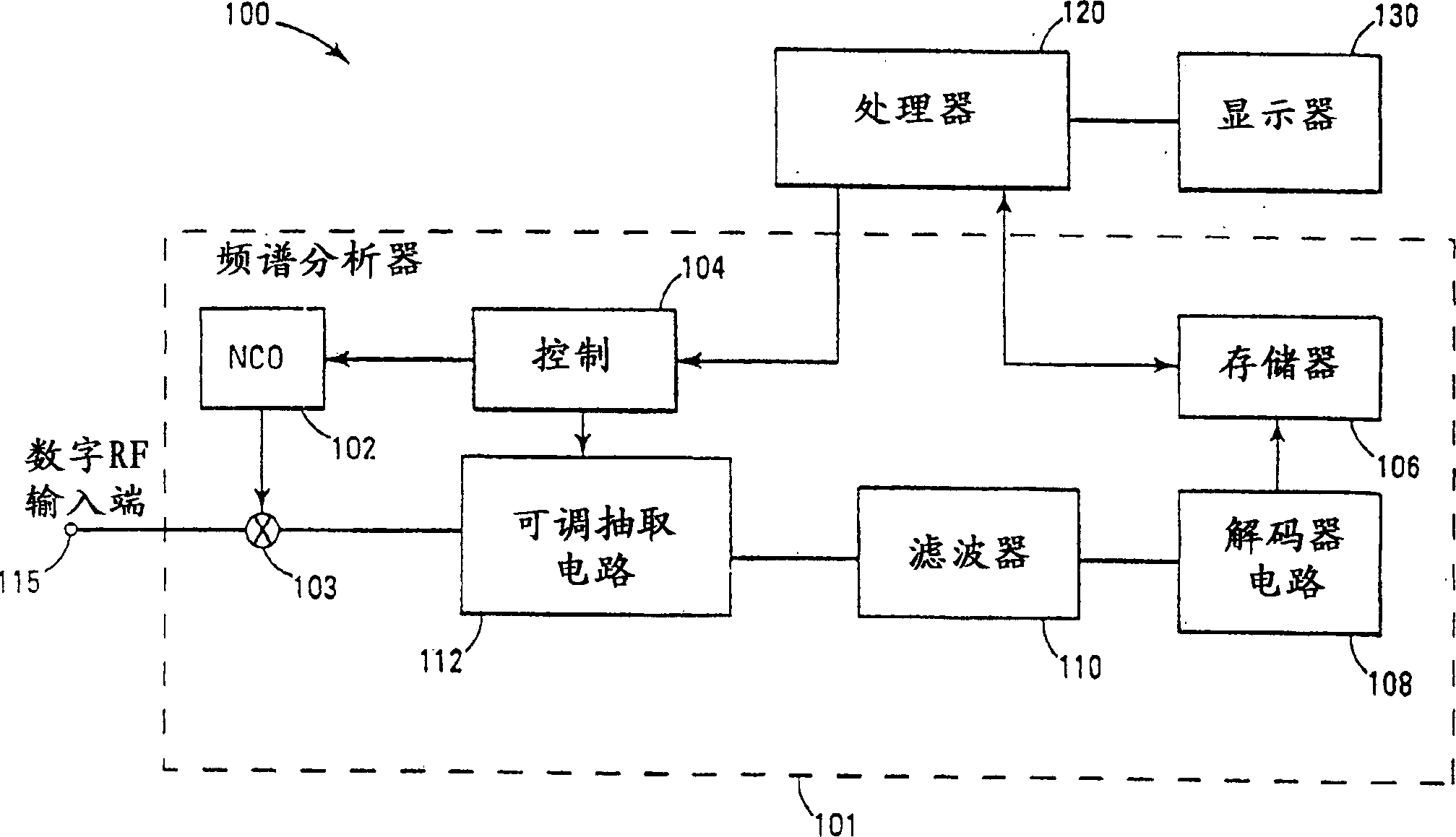

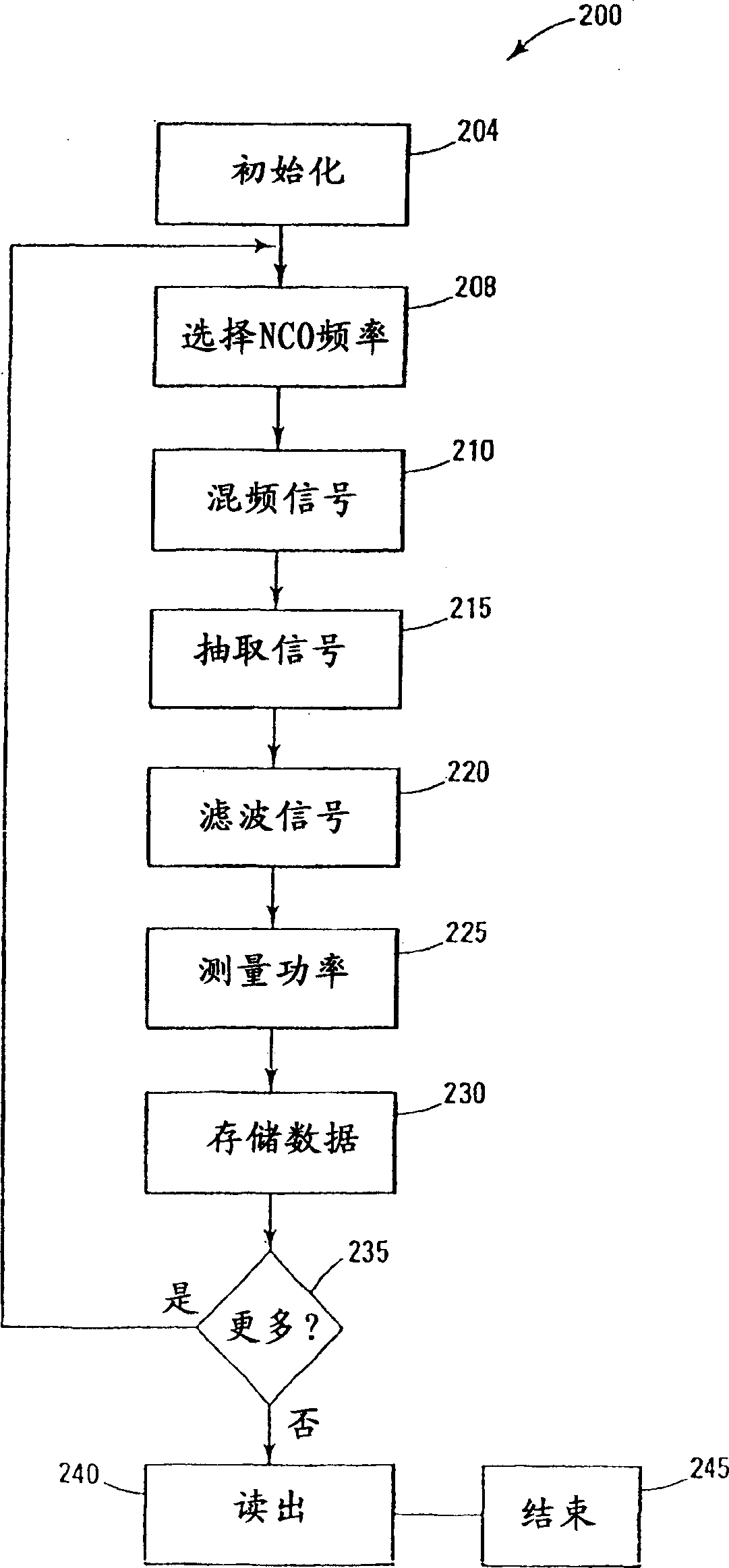

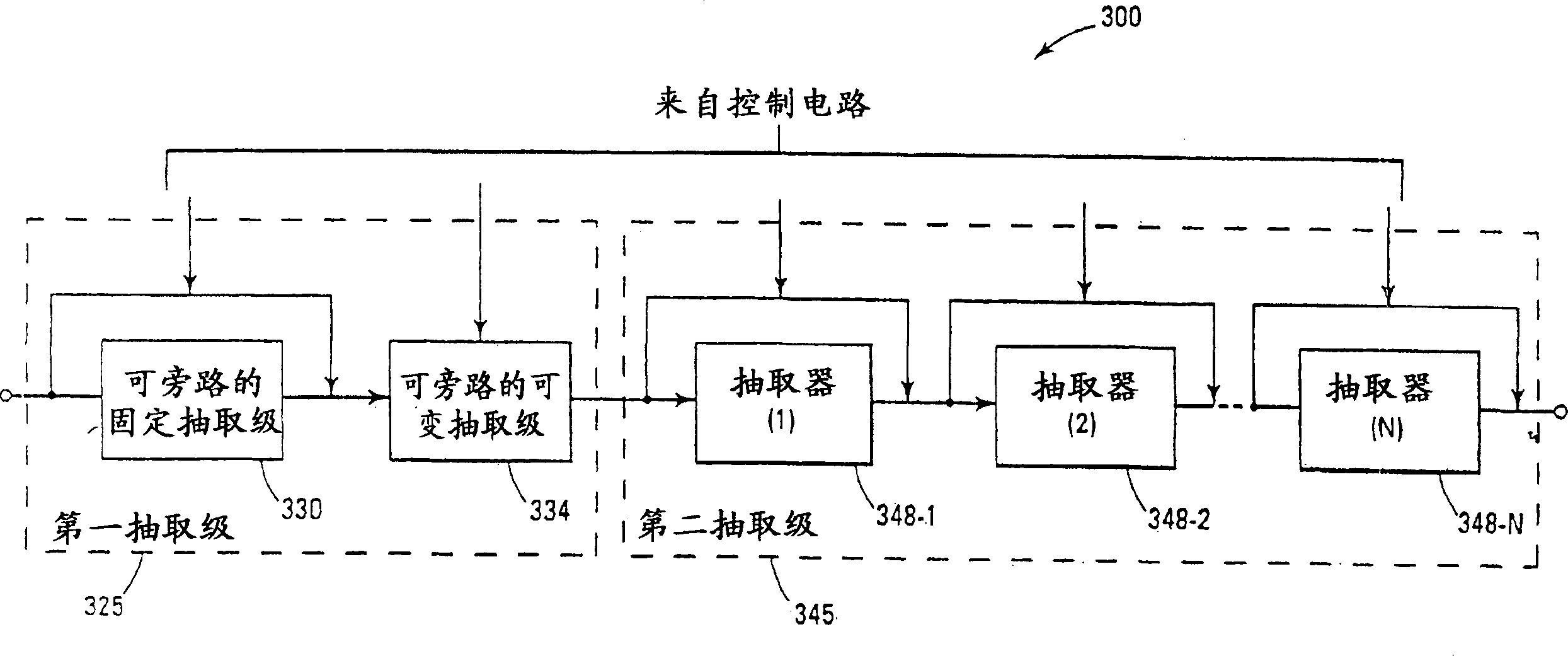

Monitoring upstream frequency band

The spectrum analyzer includes an input (115) adapted to receive an input signal and a mixer (30), coupled to the input. The mixer is adapted to produce a down converted signal from the input signal. The spectrum analyzer further includes an adjustable decimation circuit (112), coupled to the mixer, that selectively decimates the down converted signal, a decoder (108), coupled to the mixer, that selectively controls the frequency of the down converted signals from the mixer to measure power over a frequency spectrum of the input signal.

Owner:ADC BROADBAND ACCESS SYST

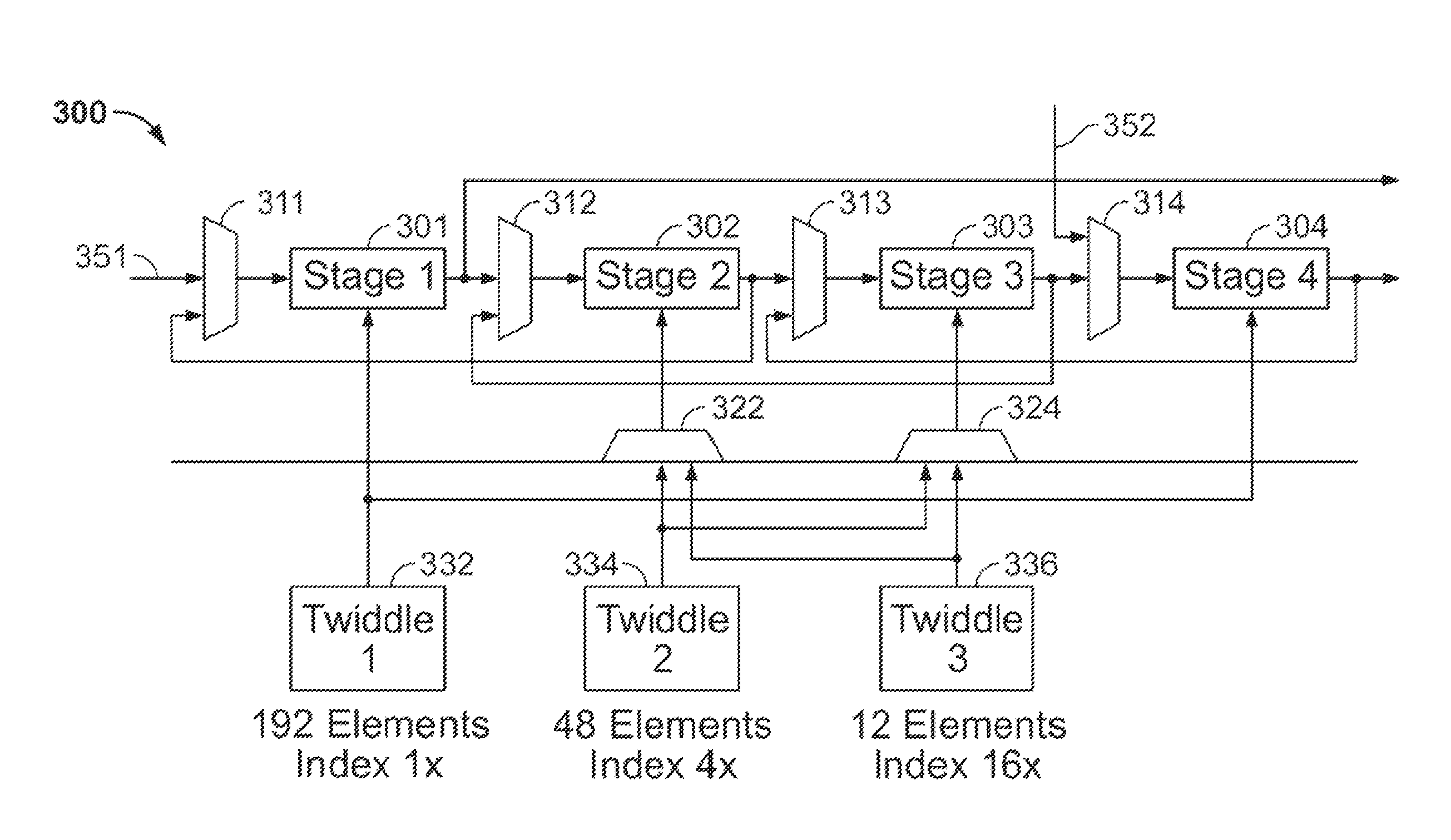

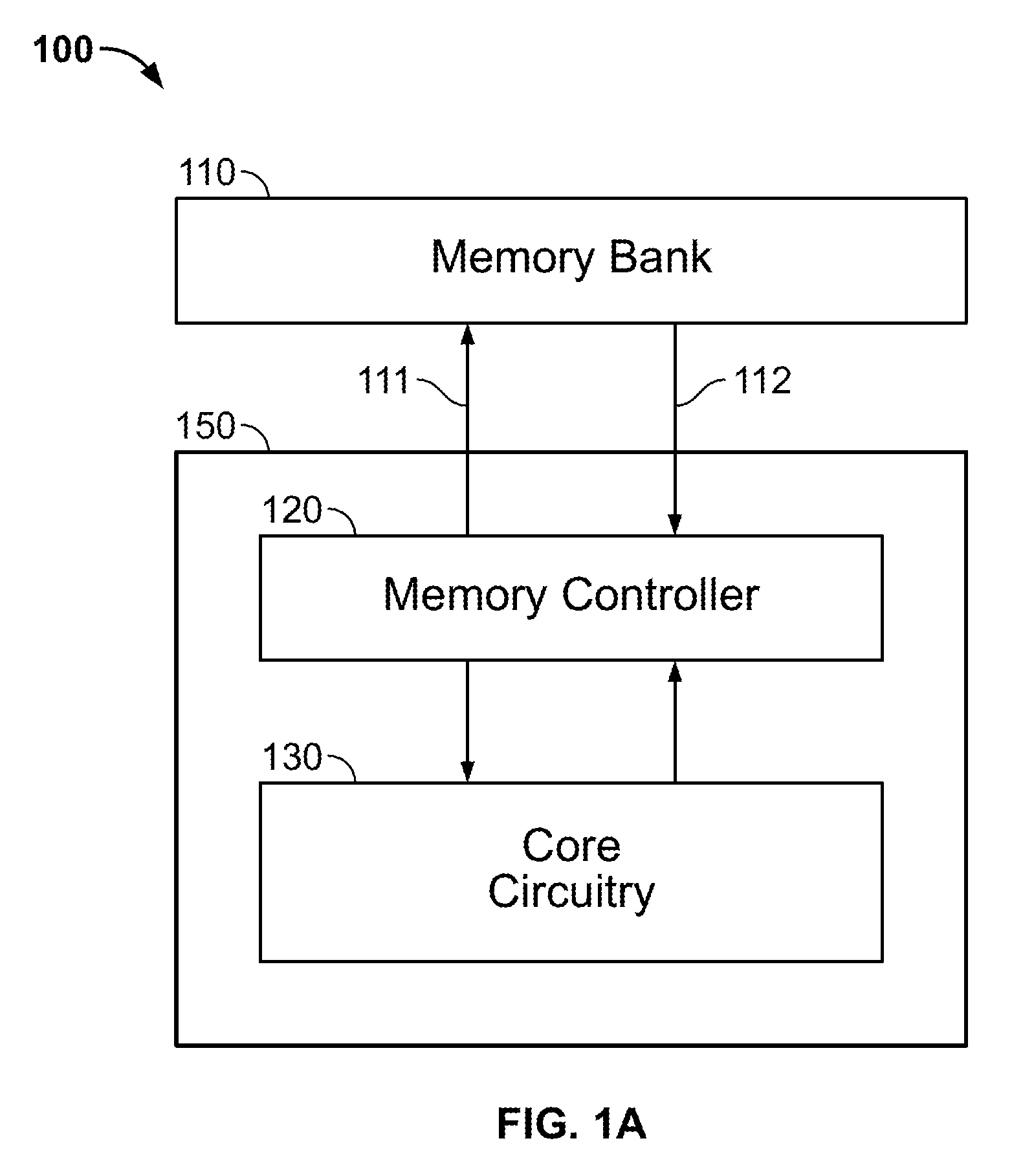

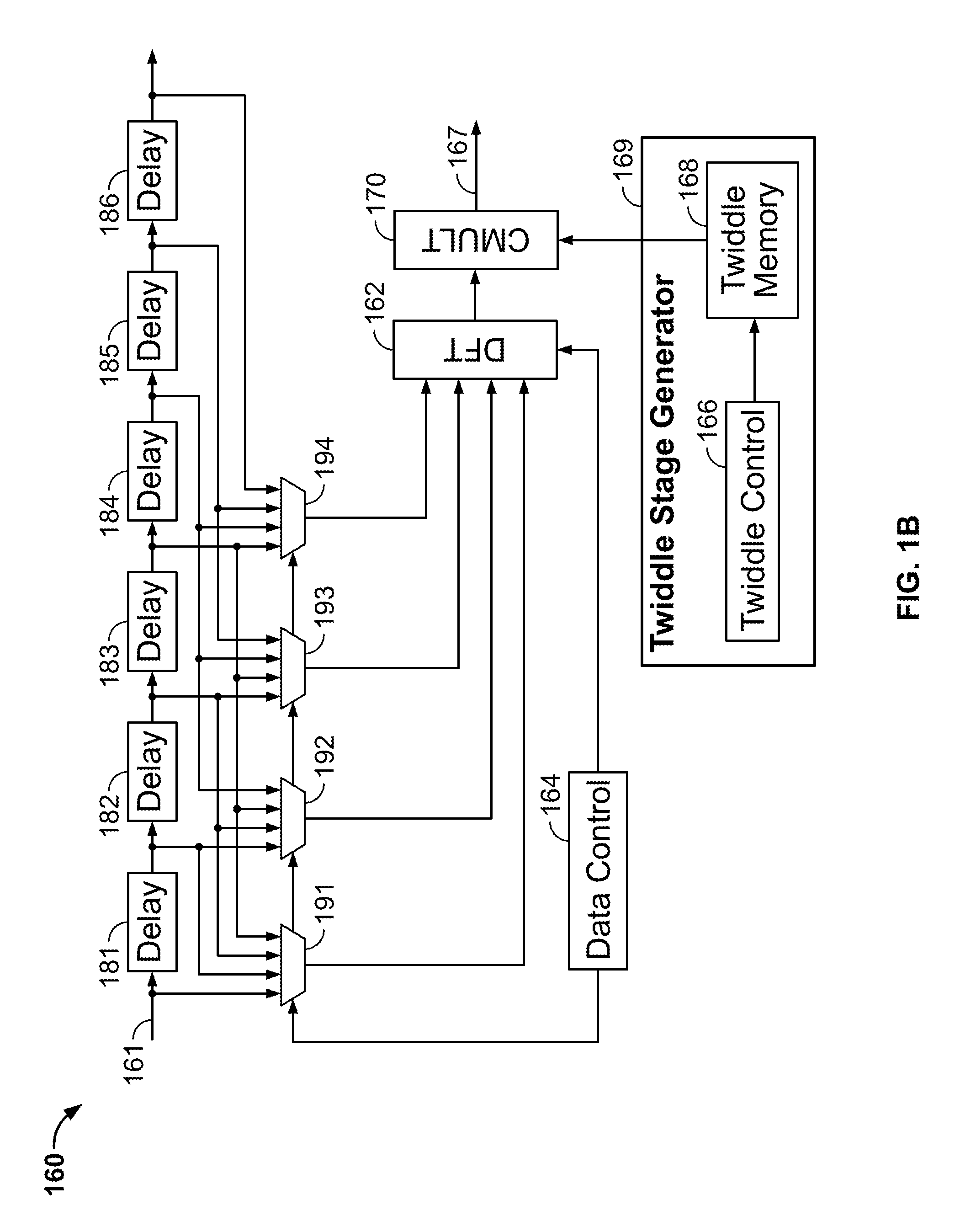

Bidirectional fast fourier transform in an integrated circuit device

Methods and systems for performing Fast Fourier Transform (FFT) operations are disclosed. A plurality of cascaded stages compute a selectable one of a forward decimation-in-frequency (DFT) FFT operation in a forward direction from an ith stage to a jth stage, and a reverse DFT FFT operation in a reverse direction from the jth stage to the ith stage. The reduction in time and resource usage from employing the disclosed bidirectional DIF FFT architectures may significantly increase performance of DIF applications, for example, ones that involve streaming FFTs.

Owner:ALTERA CORP

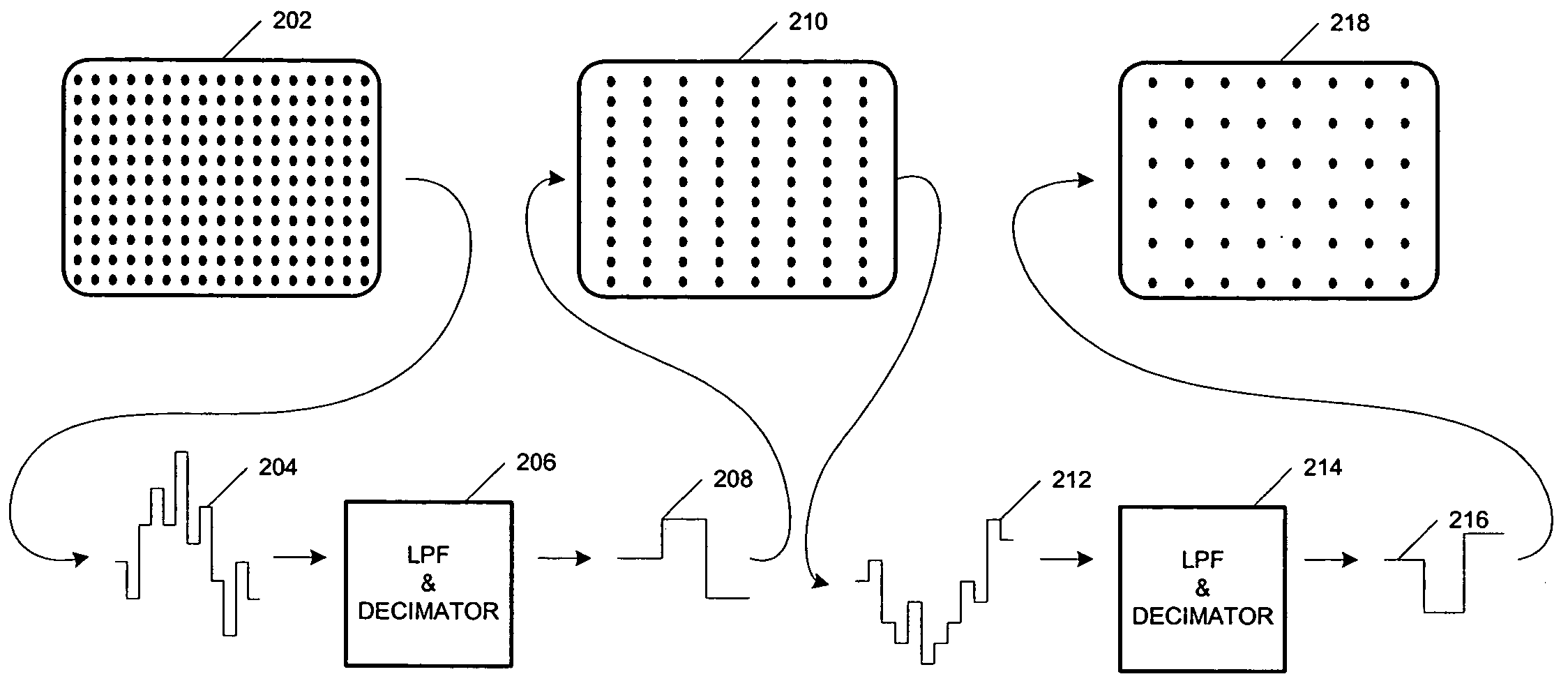

Systems and methods for image enhancement in multiple dimensions

ActiveUS7668390B2Improve real-time performanceReduce data volumeImage enhancementTelevision system detailsMulti dimensional dataLow spatial frequency

A multi-dimensional data enhancement system uses large kernel filtering, decimation, and interpolation, in multi-dimensions to enhance the multi-dimensional data in real-time. The multi-dimensional data enhancement system is capable of performing large kernel processing in real-time because the required processing overhead is significantly reduced. The reduction in processing overhead is achieved through the use of low pass filtering and decimation that reduces the amount of data that needs to be processed in order to generate an unsharp mask comprising low spatial frequencies that can be used to process the data in a more natural way.

Owner:Z MICROSYST

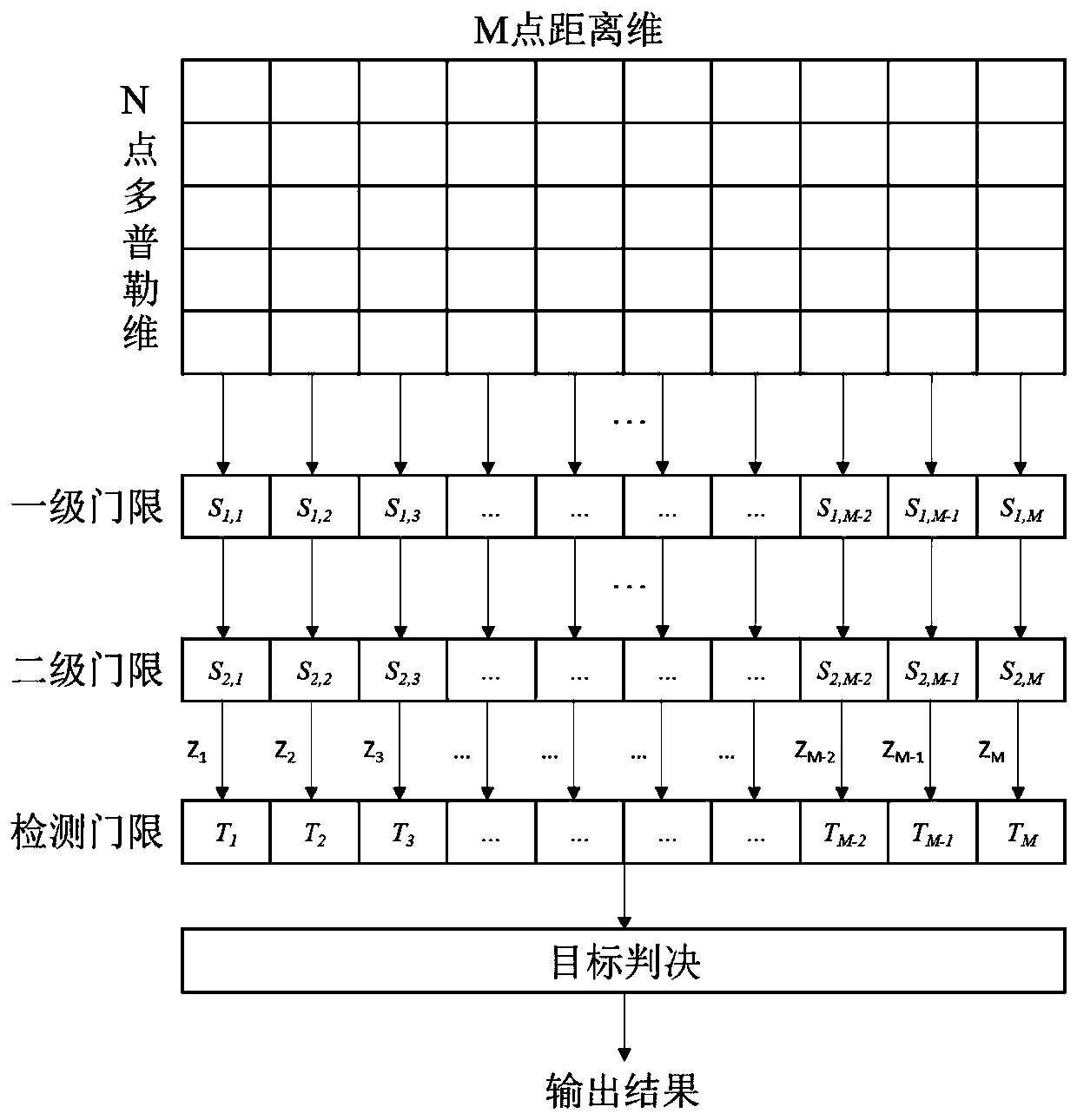

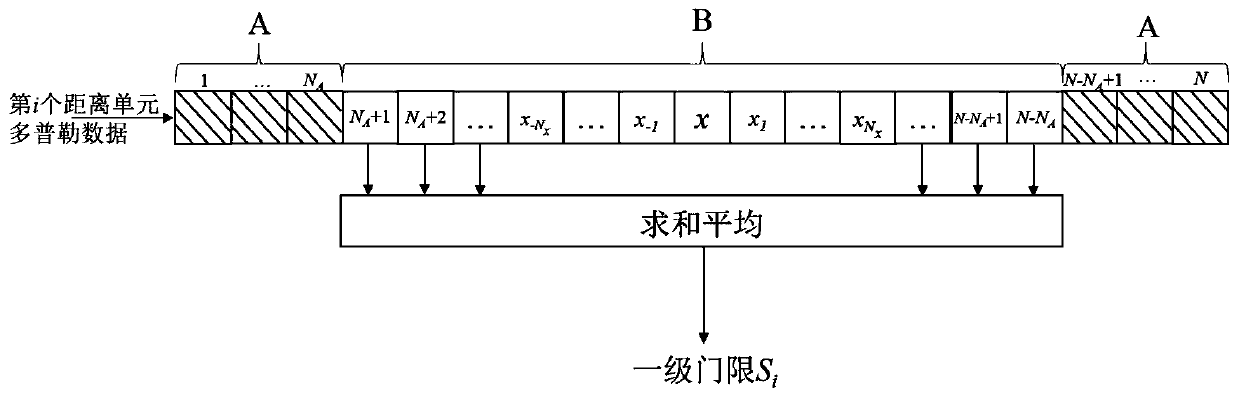

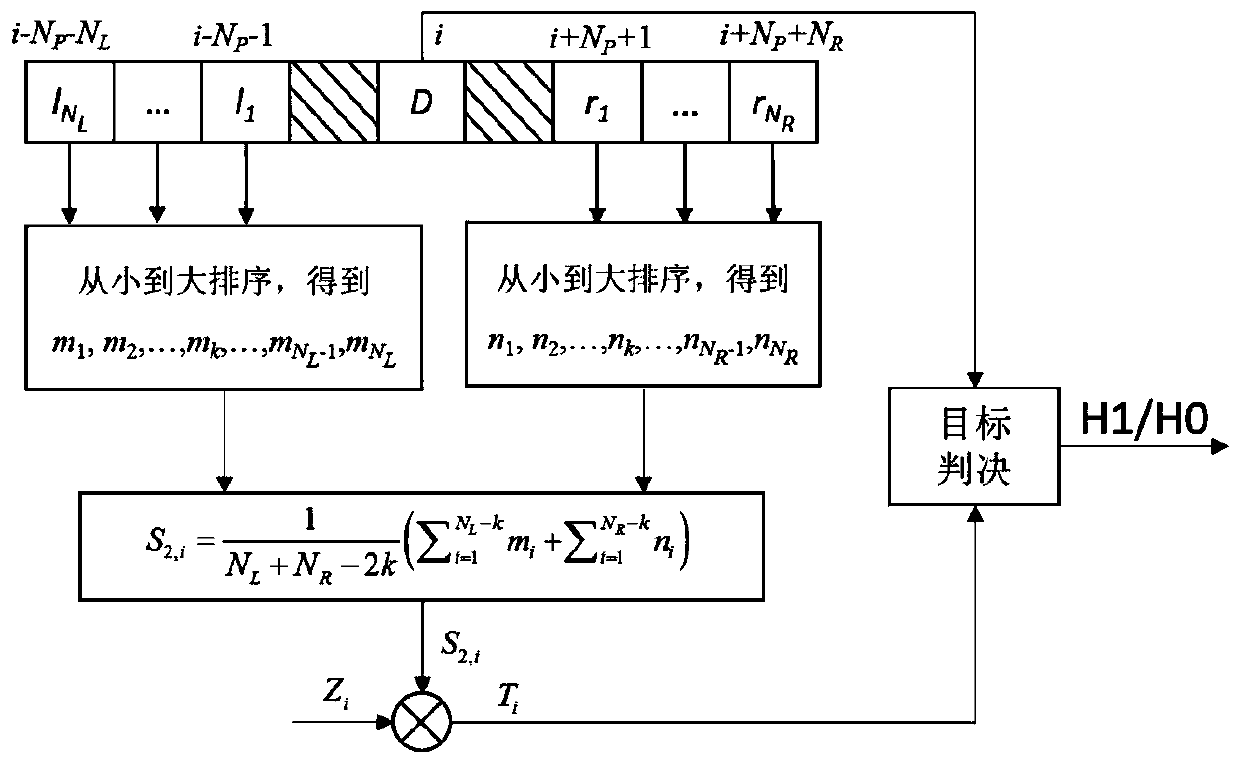

Two-stage threshold constant false alarm detection algorithm under strong ground clutter

PendingCN111157953AMeet real-time requirementsImprove discovery rateWave based measurement systemsRadar systemsFalse alarm

The invention discloses a two-stage threshold constant false alarm detection algorithm under strong ground clutters. Radar receiving echoes are subjected to down-conversion, decimation filtering, pulse compression and phase-coherent accumulation to form distance-Doppler two-dimensional data; and a two-stage threshold deletion average CFAR detection algorithm is adopted to determine the position ofthe target in the two-dimensional data, namely distance and Doppler information. Aiming at the problems of the ground reconnaissance radar CFAR detection technology, a two-stage threshold deletion average CFAR detection algorithm is designed, the discovery probability is improved, the false alarm probability is reduced, the calculation time is shortened, and the real-time requirement of a radar system is met.

Owner:NANJING UNIV OF SCI & TECH

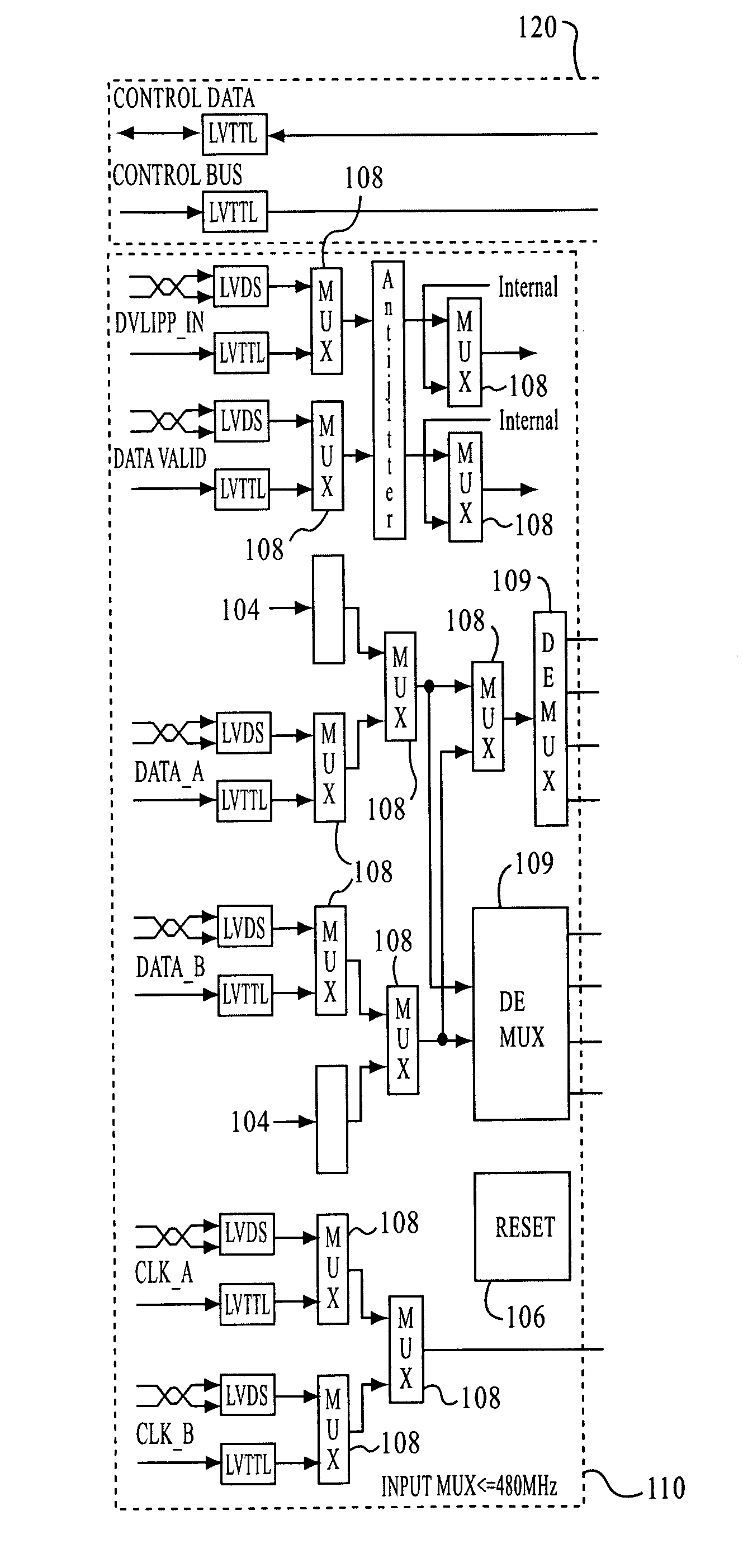

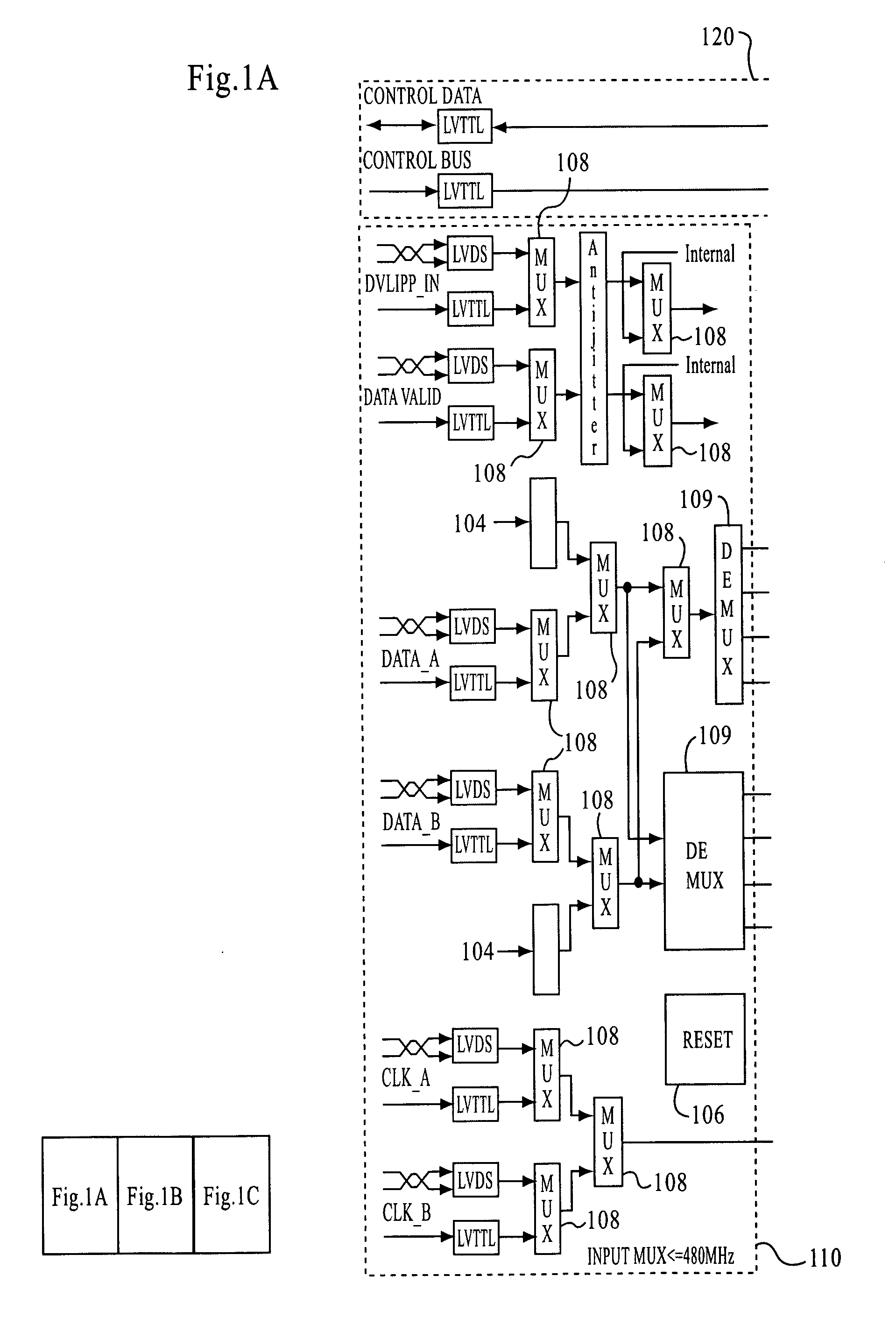

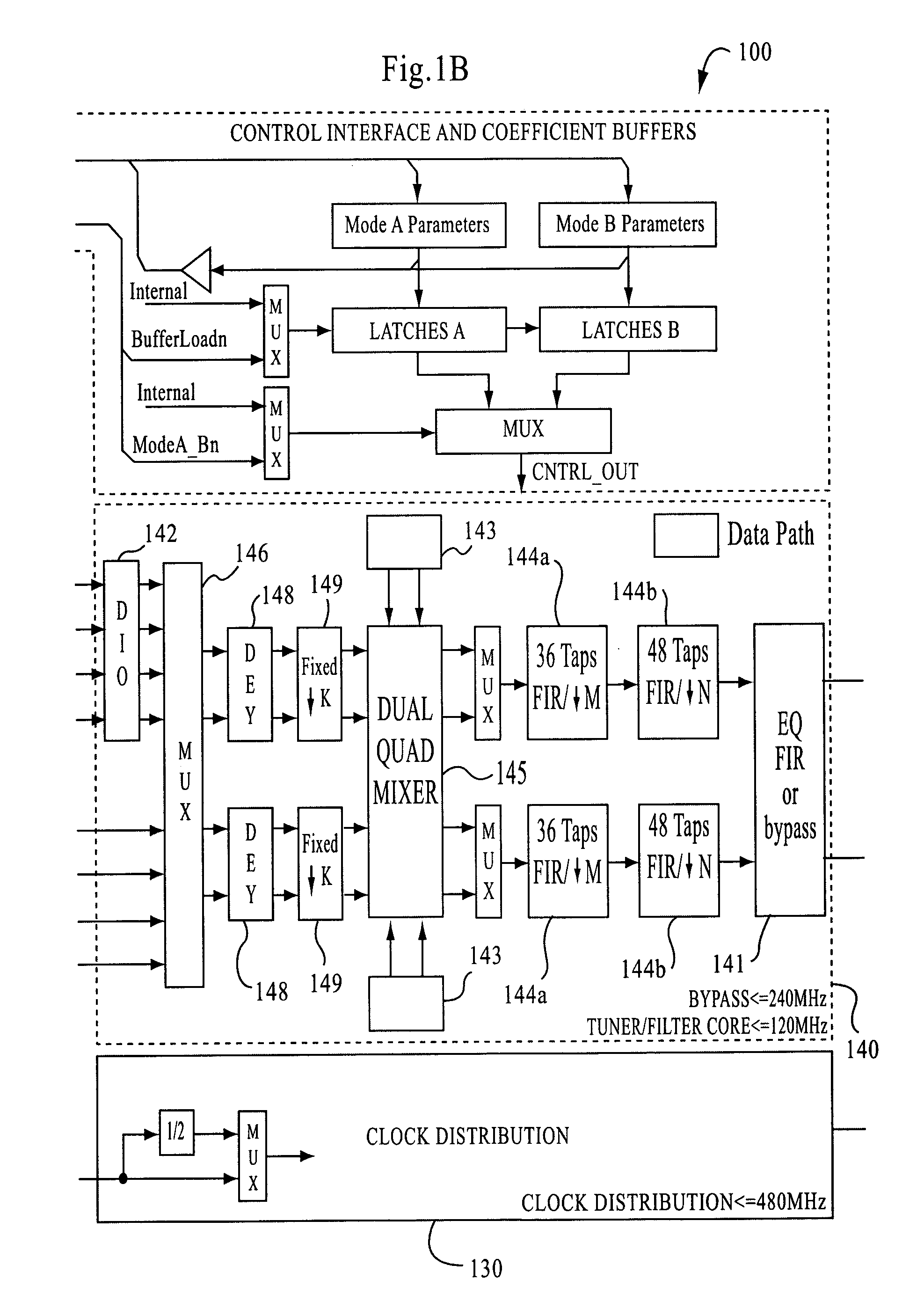

Wideband digital receiver architecture

InactiveUS20060290546A1Without loss of bandwidthElectric signal transmission systemsTransmissionEqualizationSingle chip

An integrated circuit architecture on a single chip, including a module for digital IQ generation; a module for LO synthesis; a digital mixing module; a multi-stage filtering and decimation module; a passband equalization module; an integration module; and a DC offset adjustment module.

Owner:NORTHROP GRUMAN CORP

Structure and method for carrying out A/D converter with multiple sampling rates and high accuracy

InactiveCN1585276AReduce noiseHigh precisionAnalogue-digital convertersPhysical parameters compensation/preventionFinite impulse responseData stream

The structure is composed of the decimation filter and the FIR filter. In the decimation filter, the input high-speed data stream is processed with frequency degression procedure and is converted into low speed data stream, after being filtered off the input signal, it is rectified into the quantified noise of high frequency. The FIR filter processes the result of the decimation filter with frequency compensation of passing band to reach the better accuracy. On the other hand, the transition band is steeper, thus makes the greater attenuation of the frequency.

Owner:珠海炬力集成电路设计有限公司

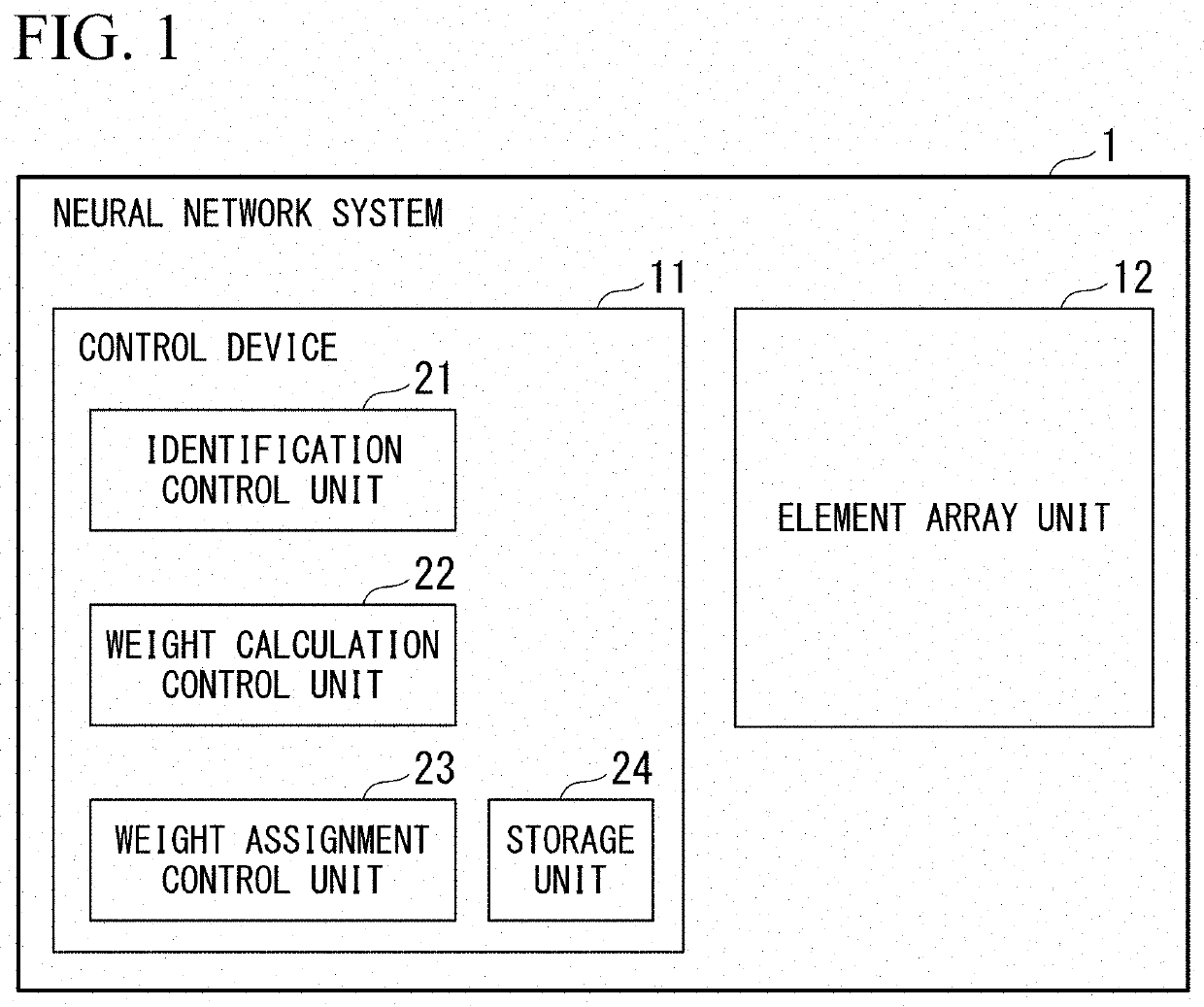

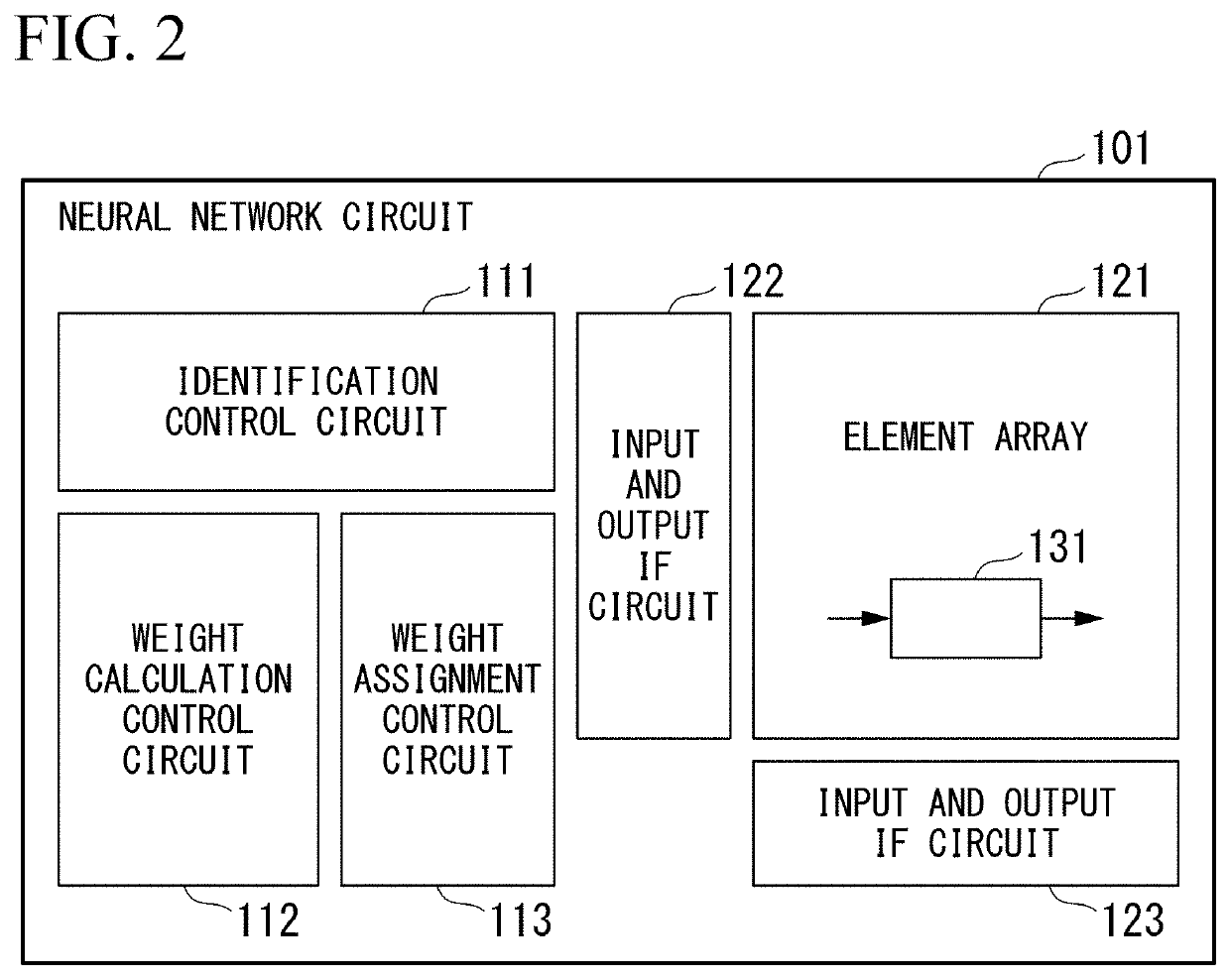

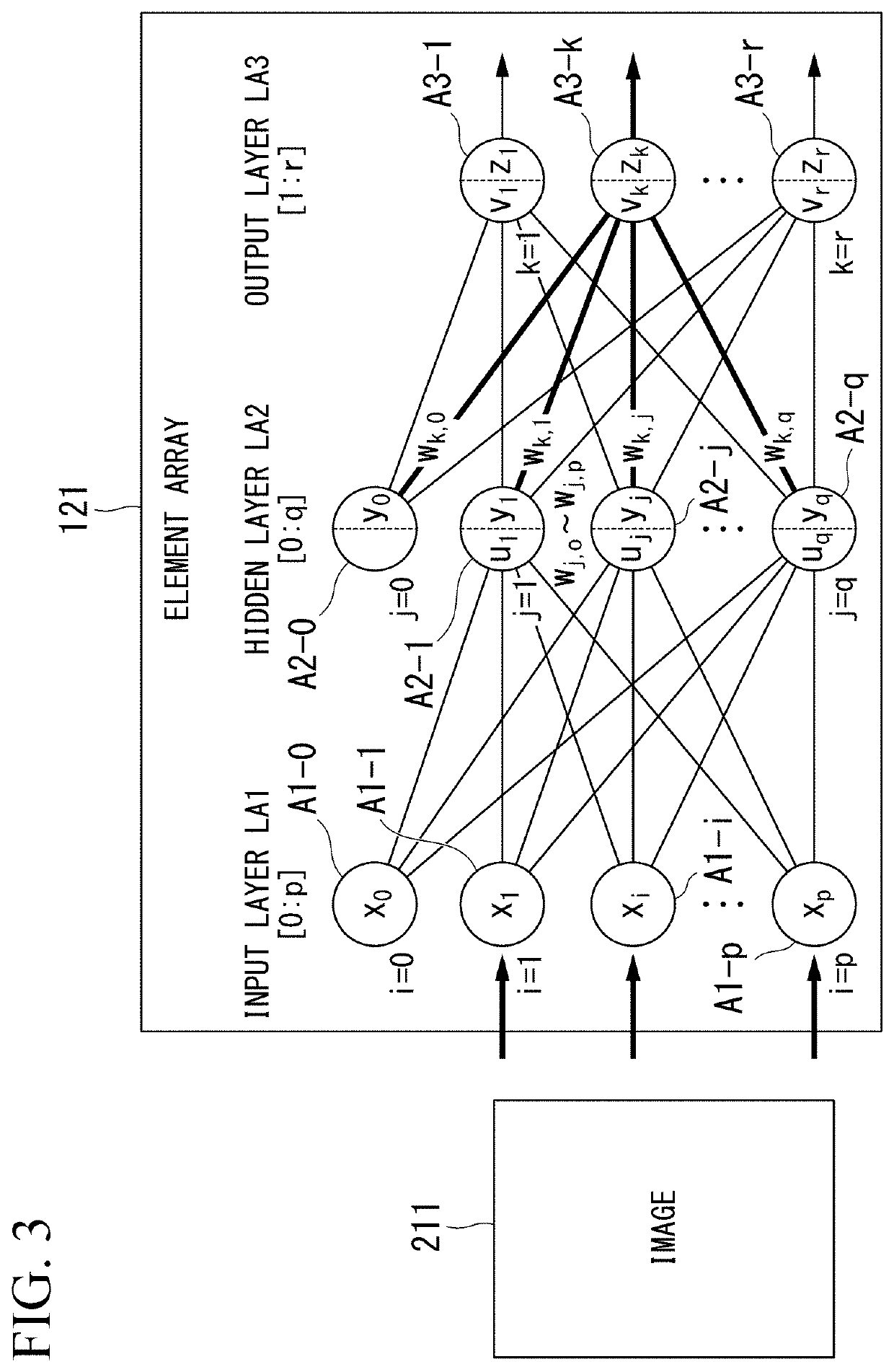

Neural network device, signal generation method, and program

ActiveUS20200293889A1Improve calculation timeCalculation time is increasedNeural architecturesPhysical realisationSignal onEngineering

A neural network device includes a decimation unit configured to convert a discrete value of an input signal to a discrete value having a smaller step number than a quantization step number of the input signal on the basis of a predetermined threshold value to generate a decimation signal a modulation unit configured to modulate a discrete value of the decimation signal generated by the decimation unit to generate a modulation signal indicating the discrete value of the decimation signal, and a weighting unit including a neuromorphic element configured to output a weighted signal obtained by weighting the modulation signal through multiplication of the modulation signal generated by the modulation unit by a weight according to a value of a variable characteristic.

Owner:TDK CORPARATION

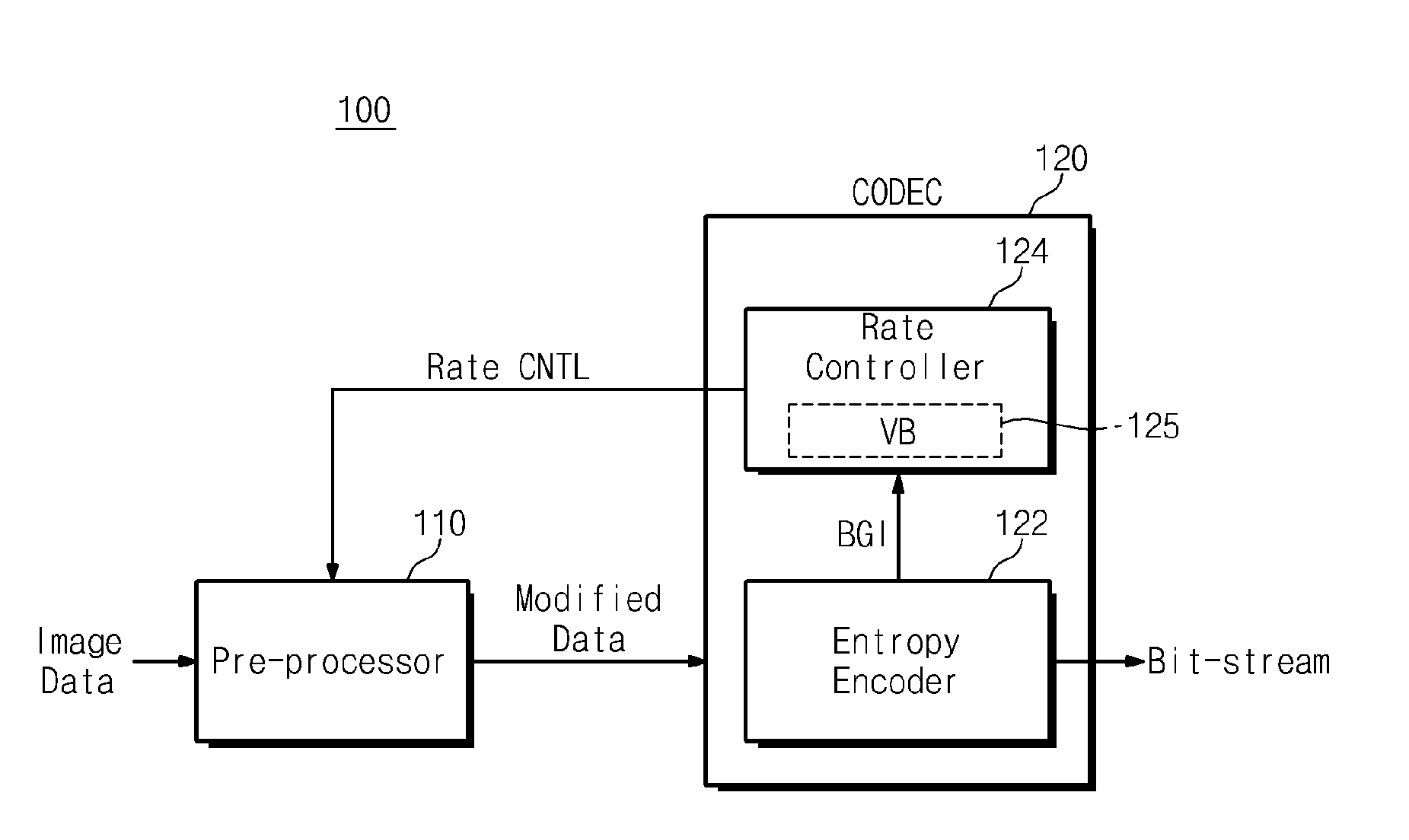

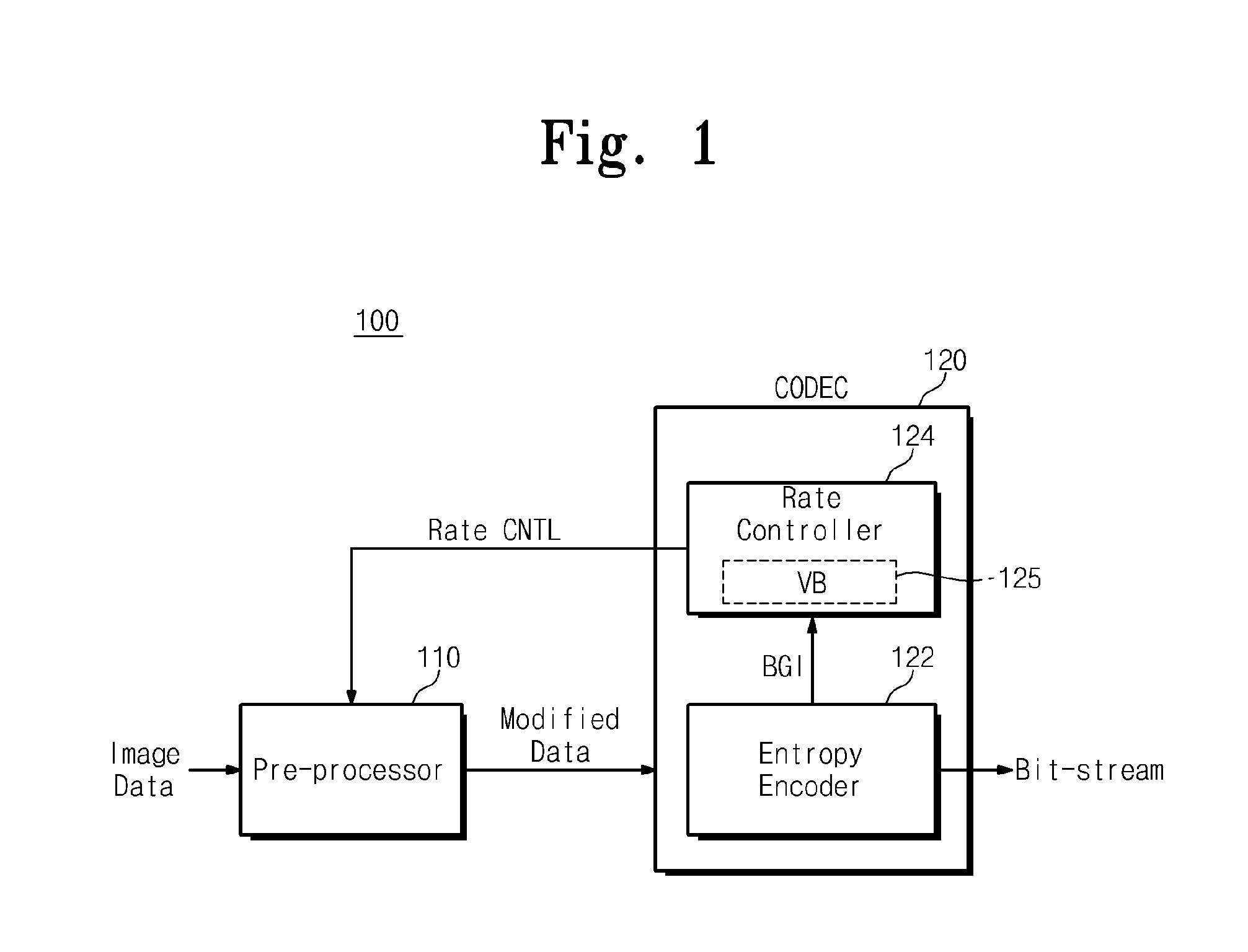

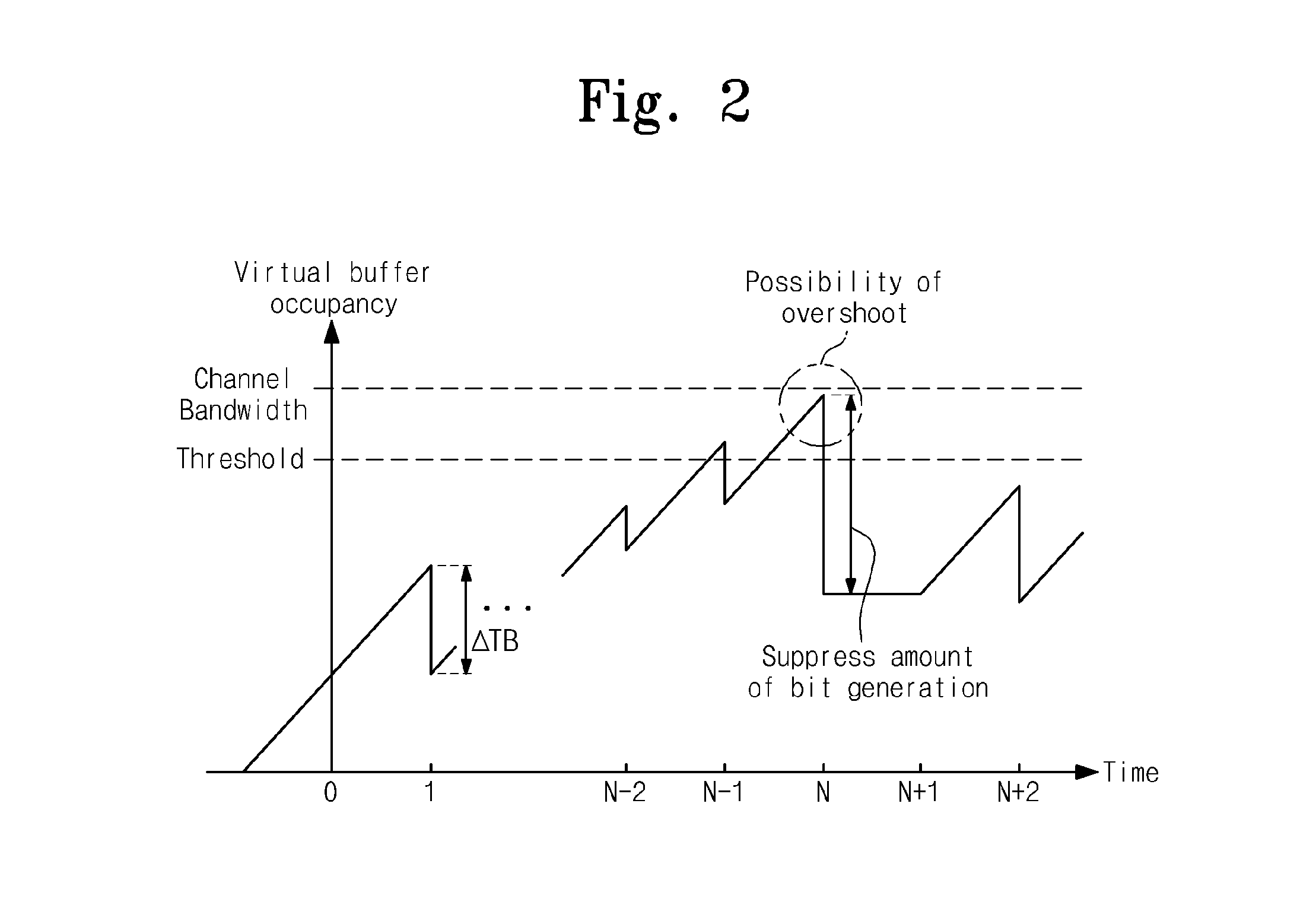

Video encoding device and encoding method thereof

InactiveUS20130301700A1Color television with pulse code modulationColor television with bandwidth reductionComputer hardwareVideo encoding

A video encoding device includes a codec unit to encode first image data to be output as a bitstream and to generate a rate control signal according to a result of the encoding and a pre-processor to perform a decimation operation on second image data successive to the first data and to transmit the second image data to the codec unit.

Owner:SAMSUNG ELECTRONICS CO LTD

Digital signal processor optimized for interpolation and decimation

ActiveUS7702710B2Avoid overwritingReduce spacingElectric signal transmission systemsDigital technique networkDigital signal processingFilter (signal processing)

A digital signal processor receives samples of a first digital signal which is to be decimated and samples of a second digital signal which is to be interpolated. A digital signal processing engine performs a decimation function on samples of the first digital signal and an interpolation function on samples of the second digital signal on a time-shared basis. The digital signal processor has a first dual memory space for storing the samples of the first digital signal and a second dual memory space for storing the samples of the second digital signal. Outputs retrieved from a dual memory space are pre-added and applied to a multiplication and accumulation stage which operates on the pre-added outputs and a filter coefficient of a digital filter.

Owner:ANALOG DEVICES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com