Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

201 results about "Bch coding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

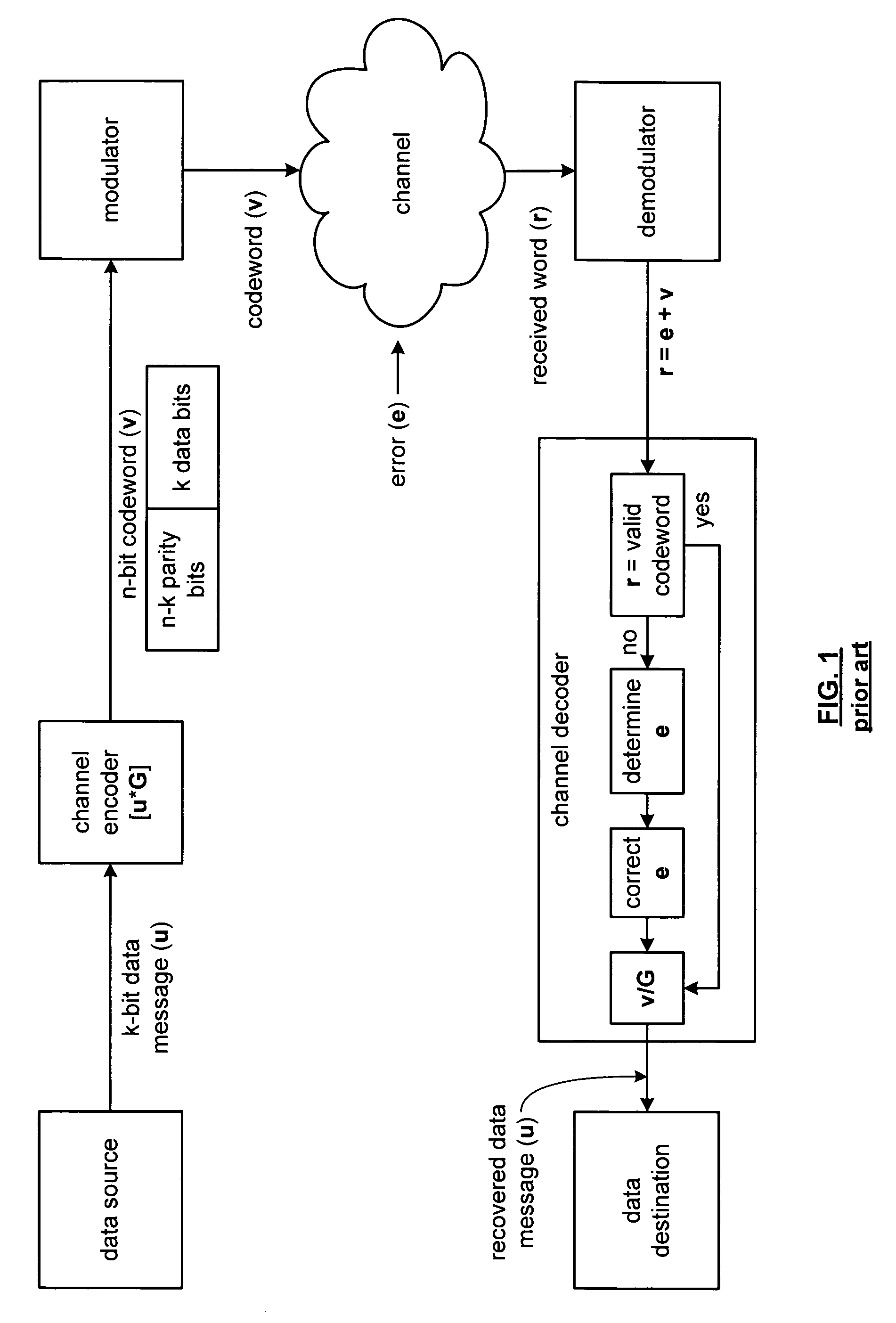

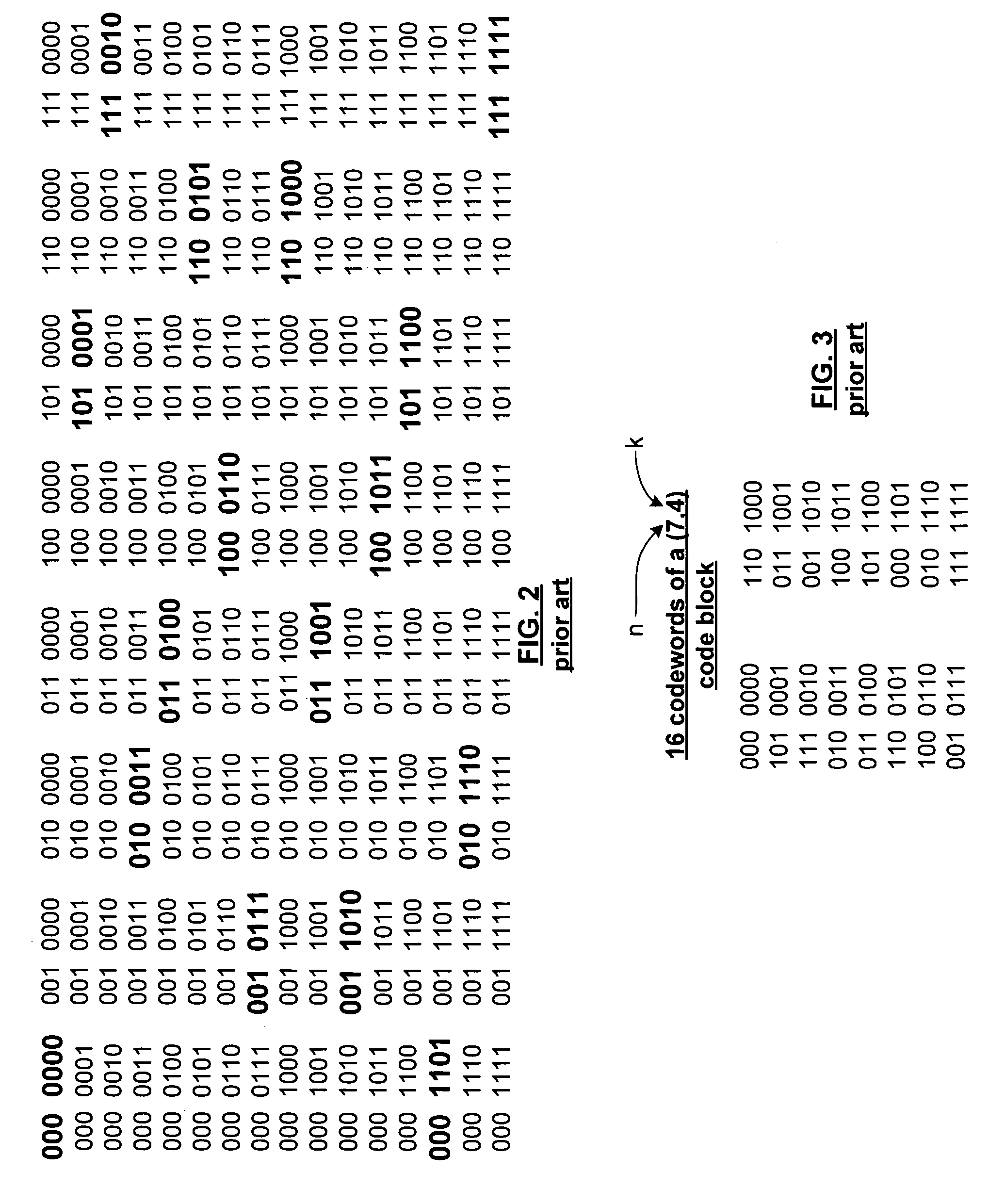

In coding theory, the BCH codes form a class of cyclic error-correcting codes that are constructed using finite fields. BCH codes were invented in 1959 by French mathematician Alexis Hocquenghem, and independently in 1960 by Raj Bose and D. K. Ray-Chaudhuri. The acronym BCH comprises the initials of these inventors' names.

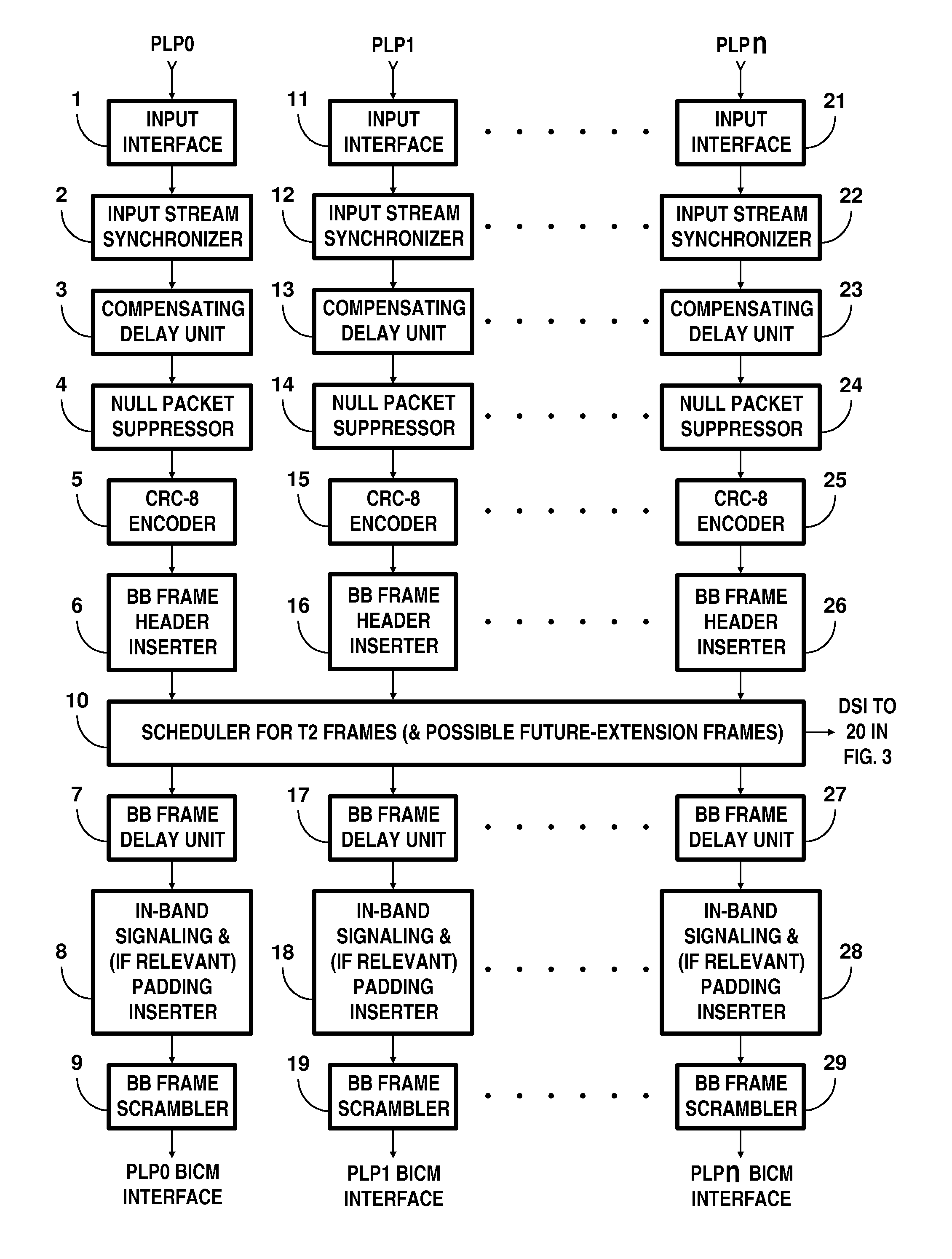

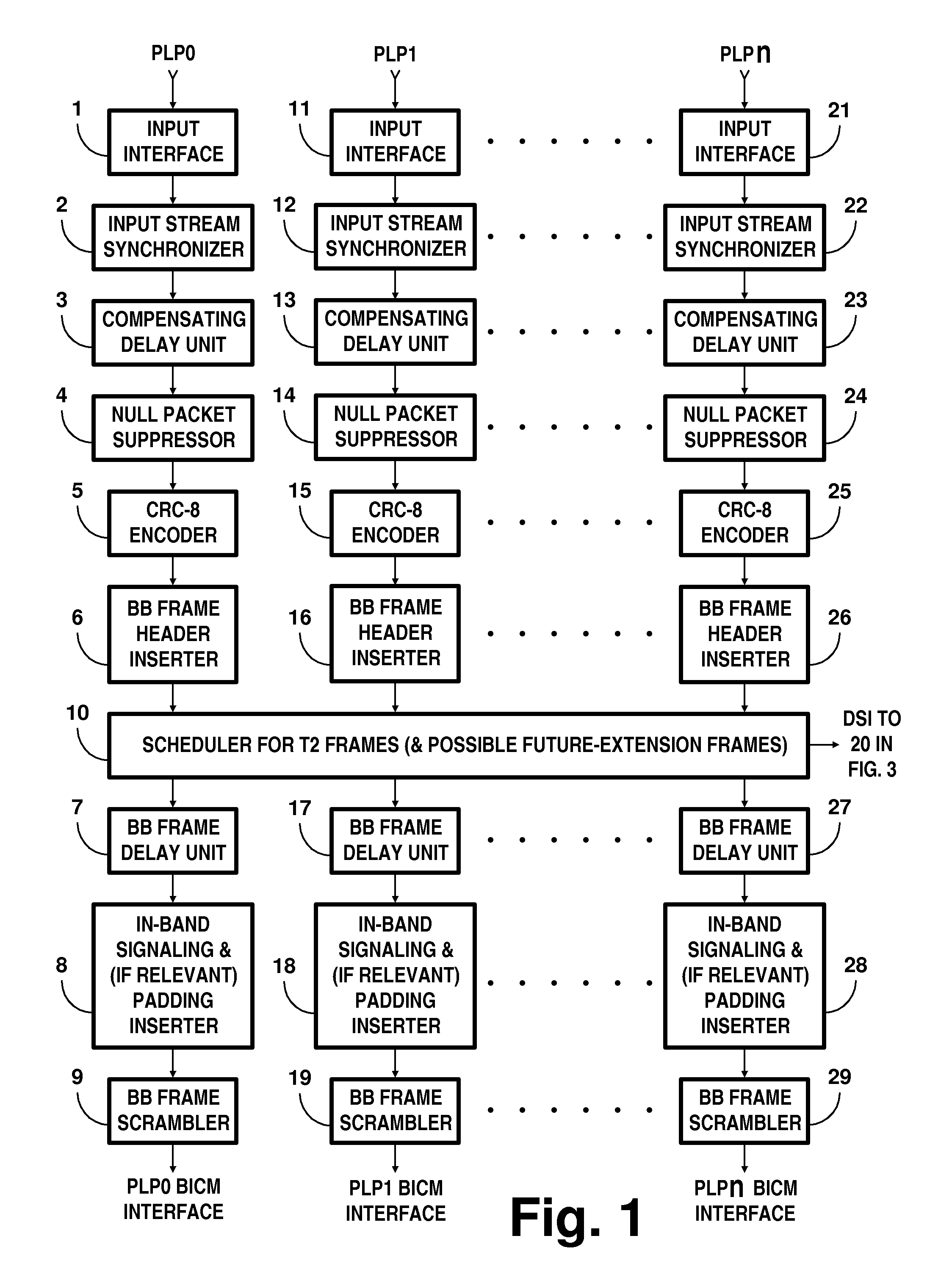

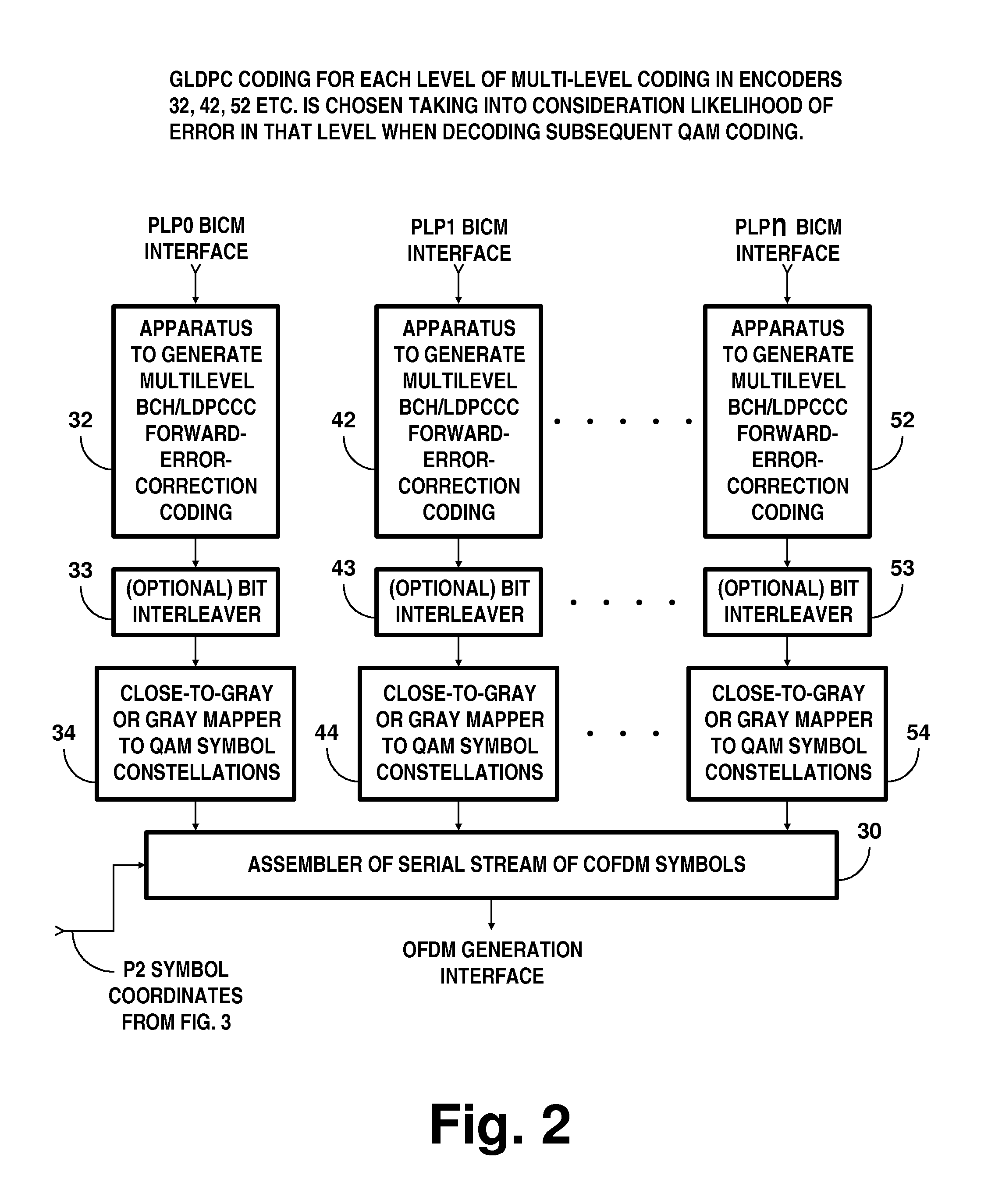

Digital television broadcasting system using coded orthogonal frequency-division modulation and multilevel LDPC convolutional coding

InactiveUS20150358648A1Facilitate parallel independent decodingError preventionError correction/detection using concatenated codesCarrier signalRadio frequency

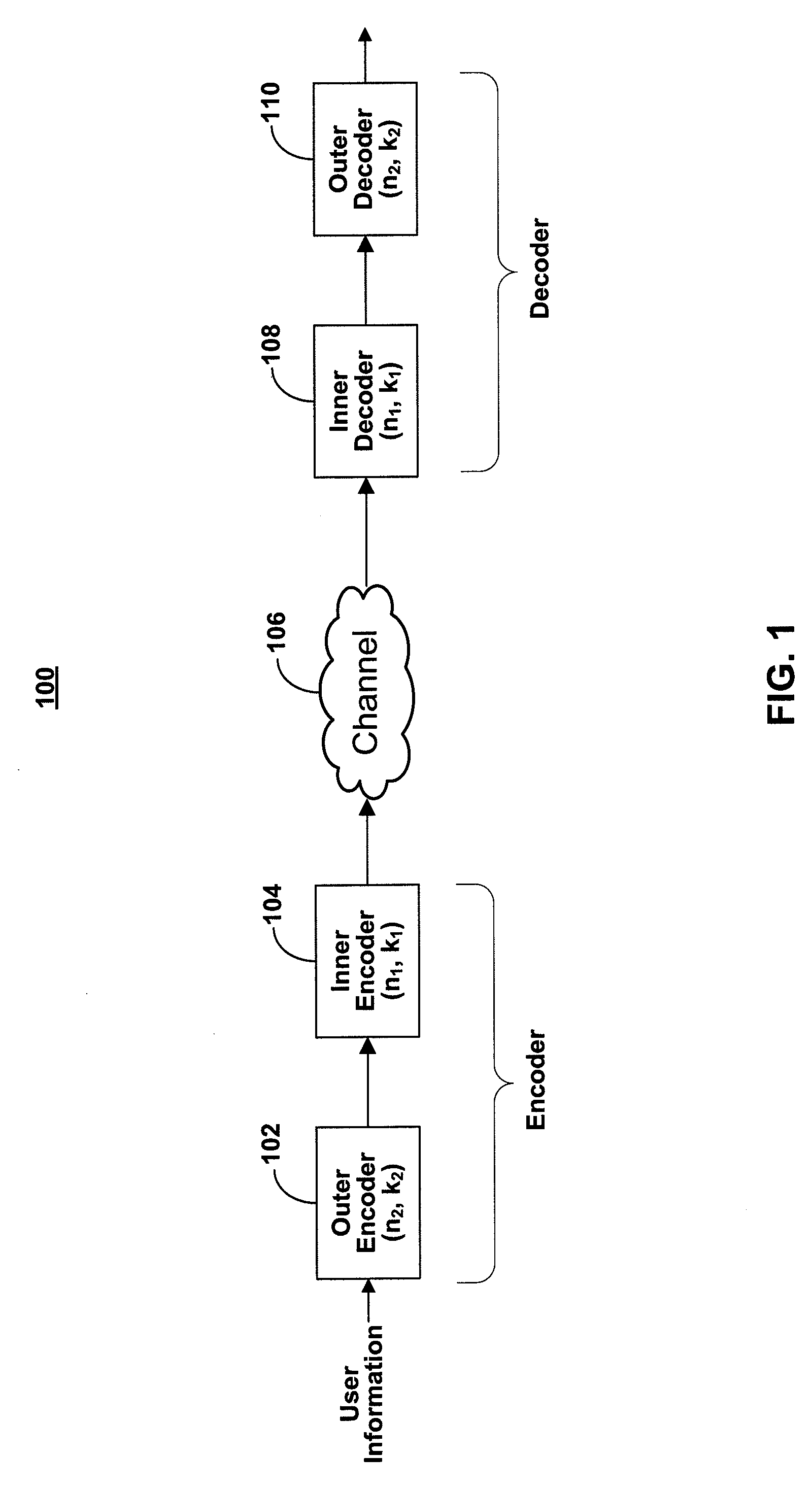

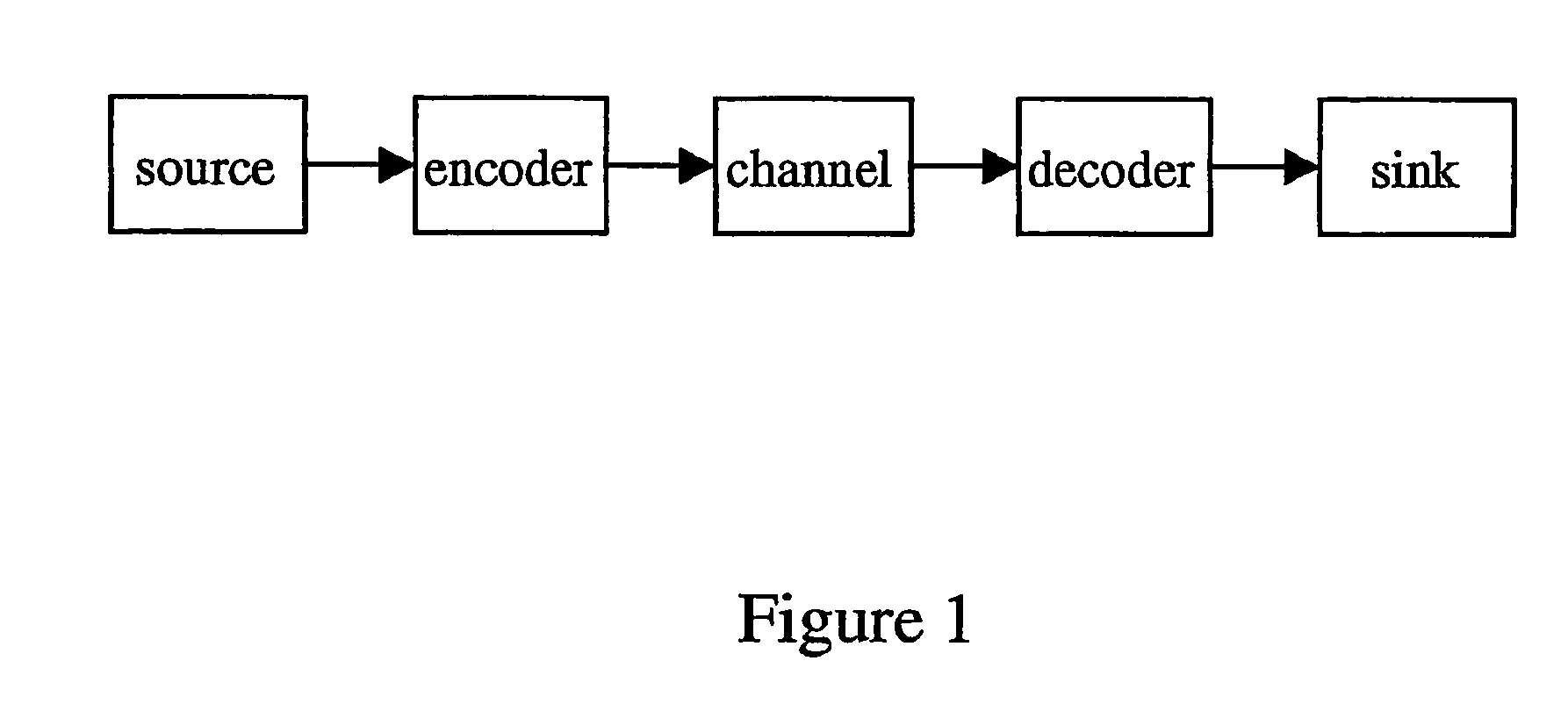

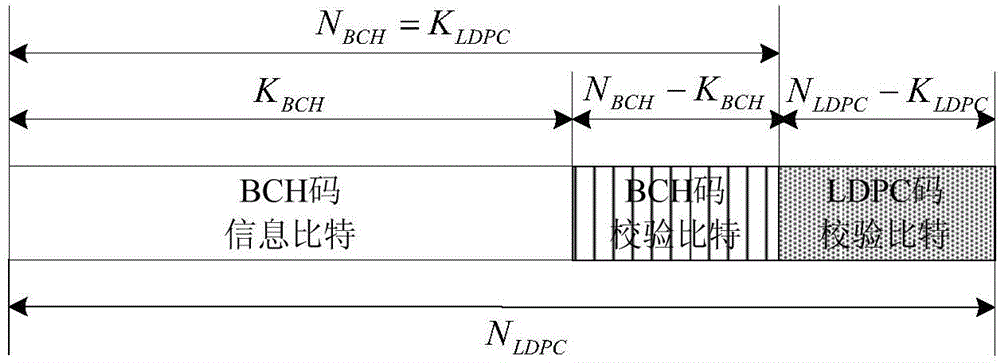

In transmitter apparatus for a digital television (DTV) broadcasting system, internet-protocol (IP) packets of digital television information are subjected to multilevel concatenated Bose-Chaudhuri-Hocquenghem (BCH) coding and low-density parity-check convolutional coding (LDPCCC) before being bit-interleaved and mapped to quadrature-amplitude-modulation (QAM) constellations. The QAM constellations are used in coded orthogonal frequency-division modulation (COFDM) of plural carrier waves up-converted to a radio-frequency broadcast television channel. In receiver apparatus for the DTV broadcasting system the results of de-mapping QAM constellations recovered from demodulating the COFDM carrier waves are de-interleaved, and the constituent LDPCCC codewords are decoded to recover constituent BCH codewords of the multilevel BCH coding. The constituent BCH codewords are decoded to correct remnant bit errors in them. Then, IP packets of digital television information are reconstituted from the systematic data bits in those BCH codewords.

Owner:LIMBERG ALLEN LEROY

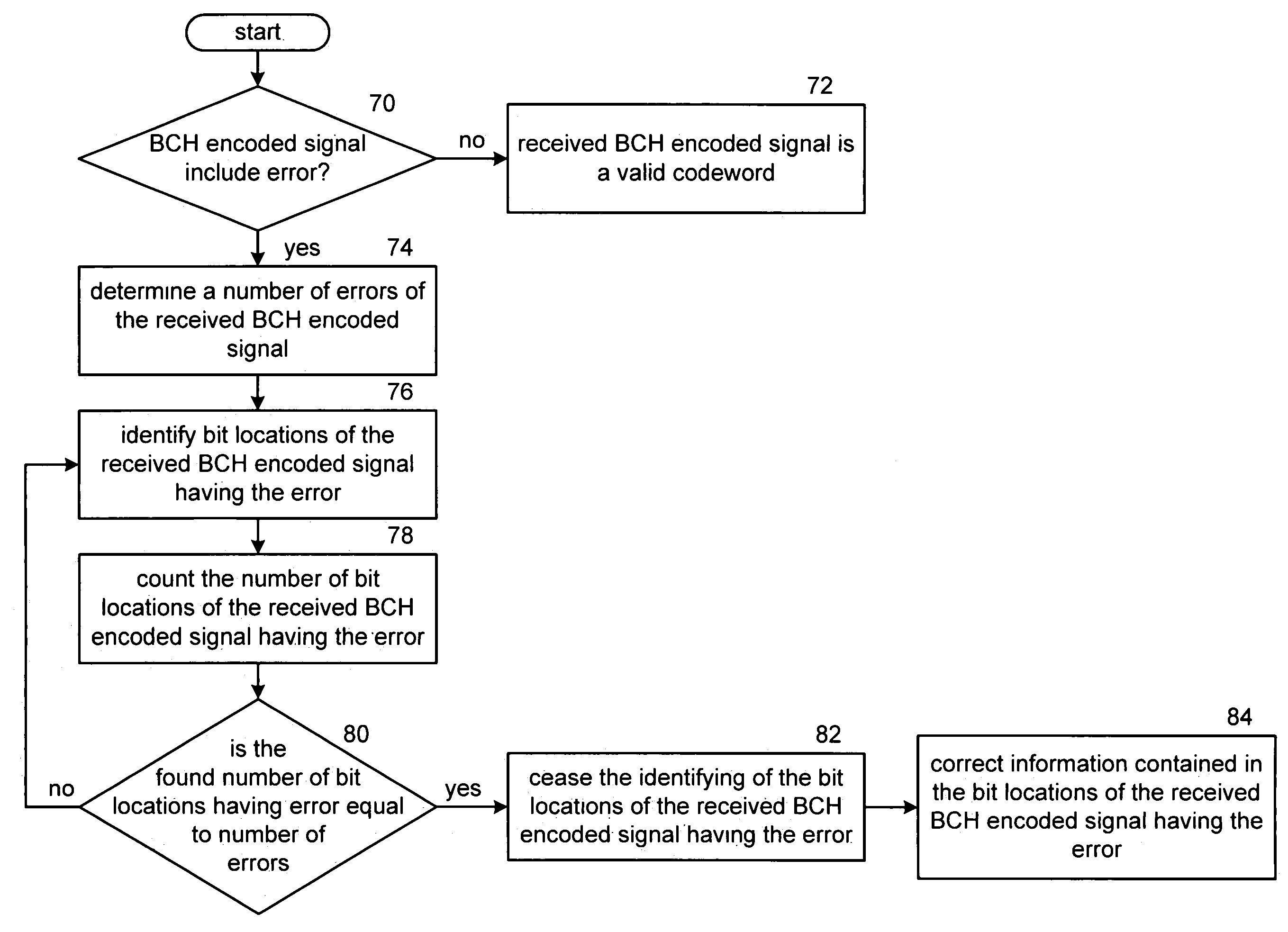

Decoding a received BCH encoded signal

InactiveUS7206992B2Reduce power consumptionSave powerError detection/correctionCode conversionComputer scienceBch coding

A method or apparatus for decoding of a BCH encoded signal begins by determining whether the received BCH encoded signal includes error. The decoding process continues when the received BCH encoded signal includes error by determining whether the error is correctable. This may be done by determining a number of errors of the received BCH encoded signal, identifying bit locations of the received BCH encoded signal having the error; counting the number of bit locations of the received BCH encoded signal having the error, comparing the number of errors to the number of bit locations of the received BCH encoded signal having the error, when the number of bit locations of the received BCH encoded signal having the error equals the number of errors, ceasing the identifying of the bit locations of the received BCH encoded signal having the error, and correcting information contained in the bit locations of the received BCH encoded signal having the error when the identifying of the bit locations is ceased.

Owner:AVAGO TECH INT SALES PTE LTD

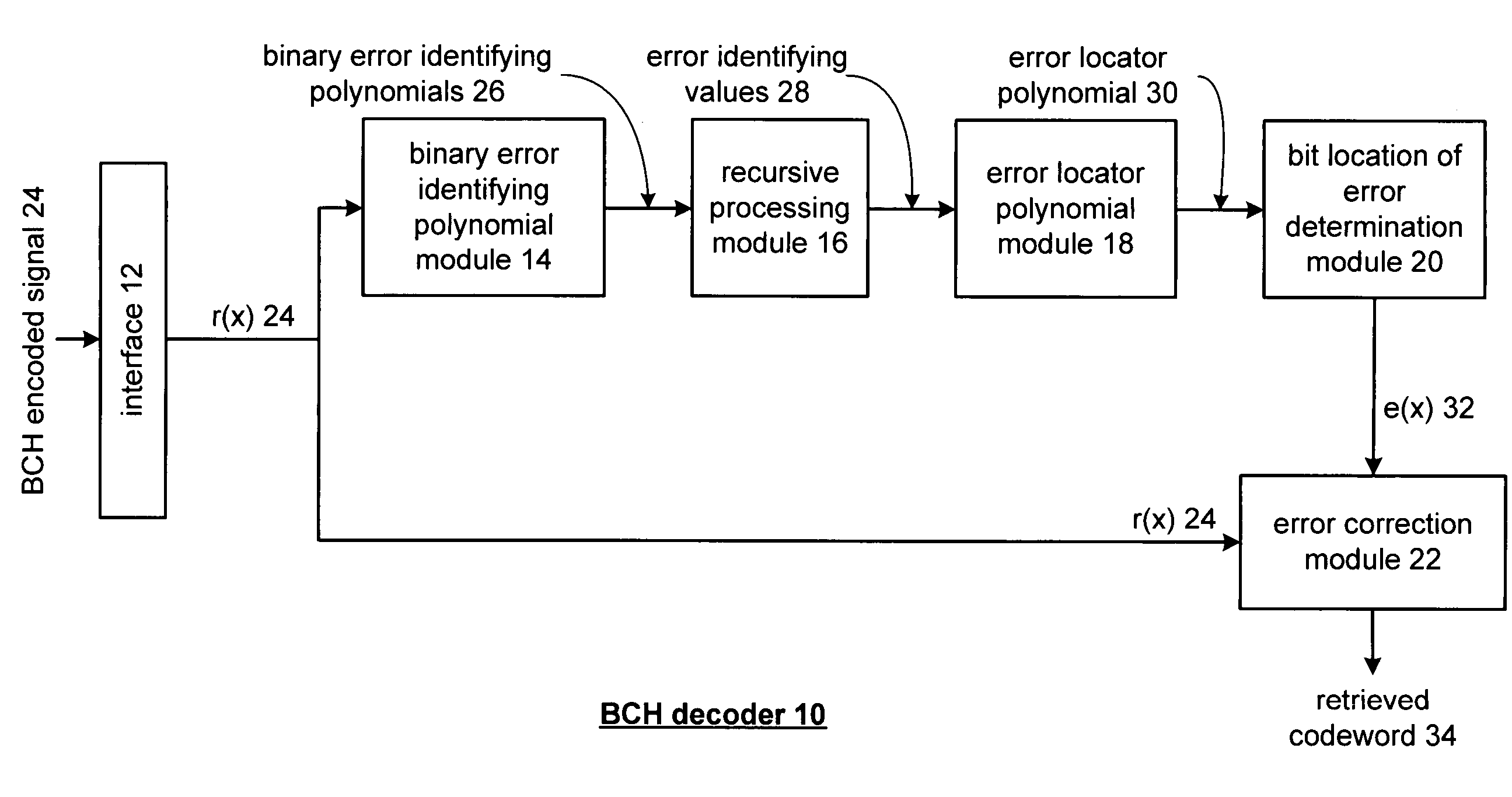

Parallel decoding of a BCH encoded signal

InactiveUS7237183B2Reduce the number of gatesBalance computing loadCode conversionCyclic codesComputer hardwareError identification

A method or apparatus for error identification of a BCH encoded signal includes processing that begins by receiving a BCH encoded signal in a binary polynomial format to produce a received polynomial. The processing then continues by converting the received polynomial into a plurality of error identifying polynomials. The processing then continues by recursively processing the plurality of binary error identifying polynomials to produce a plurality of error identifying values. The processing then continues by processing the plurality of error identifying values to produce an error locator polynomial that represents error in the received polynomial. The processing then continues by evaluating the error locator polynomial to identify the bit location of the error in the BCH encoded signal. The processing then continues by correcting the BCH encoded signal based on the bit location of the error.

Owner:AVAGO TECH INT SALES PTE LTD

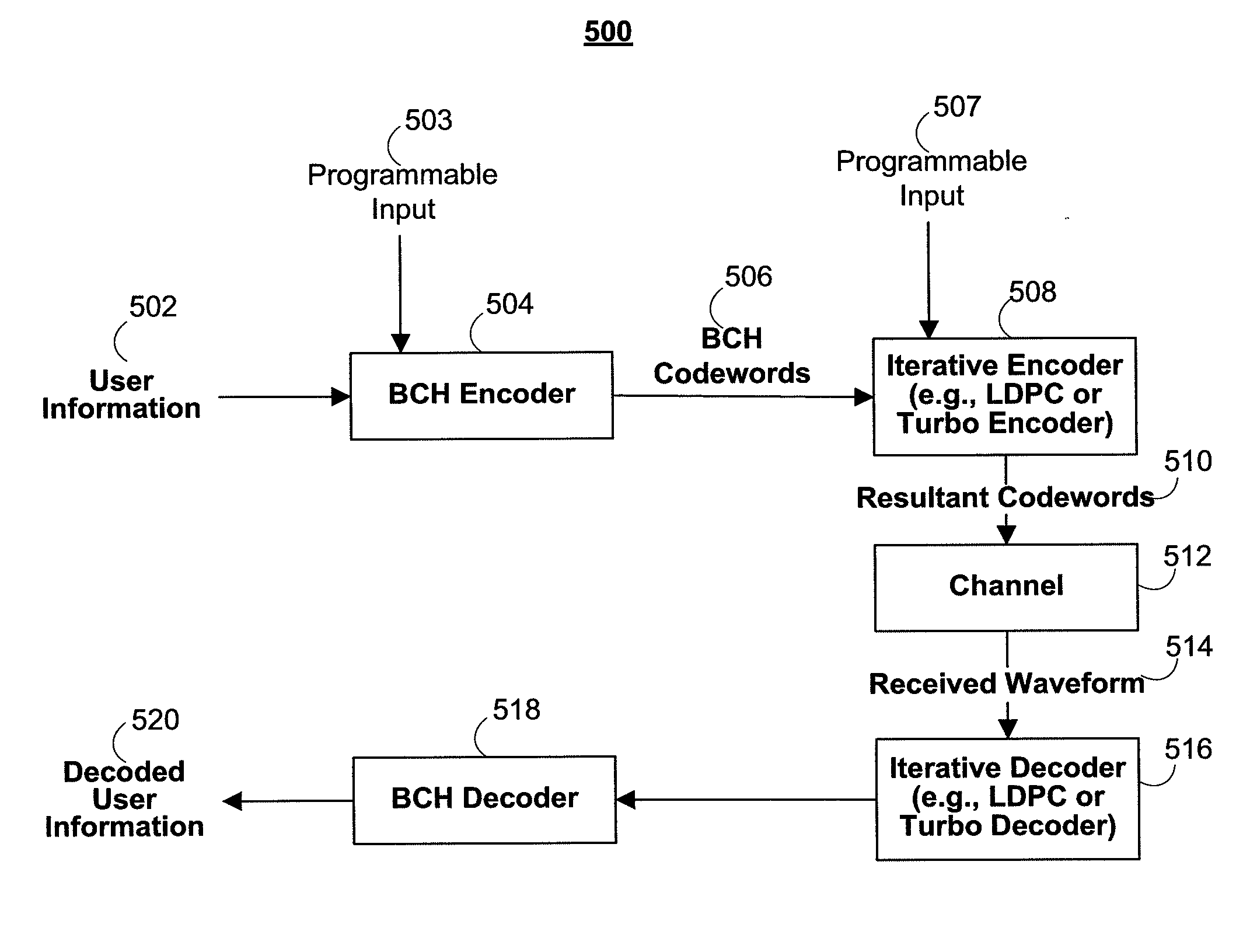

Concatenated codes for holographic storage

ActiveUS20080163026A1Robust implementationGood flexibilityError preventionTransmission systemsComputer hardwareHolographic storage

Systems and methods for constructing concatenated codes for data storage channels, such as holographic storage channels, are provided. The concatenated codes include an outer BCH code and an inner iteratively decodable code, such as an LDPC code or turbo code. The correction power and coding rate of one or both of the codes may be programmable based on the channel characteristics and the desired SNR coding gain. The correction power and / or coding rate of the inner and / or outer code may also be dynamically adjusted in real-time to compensate for time-varying error conditions on the channel.

Owner:MARVELL ASIA PTE LTD

System and method for coding a digital wrapper frame

ActiveUS7289530B1Improving parity codingCode conversionTime-division multiplexPacket communicationGroup communication systems

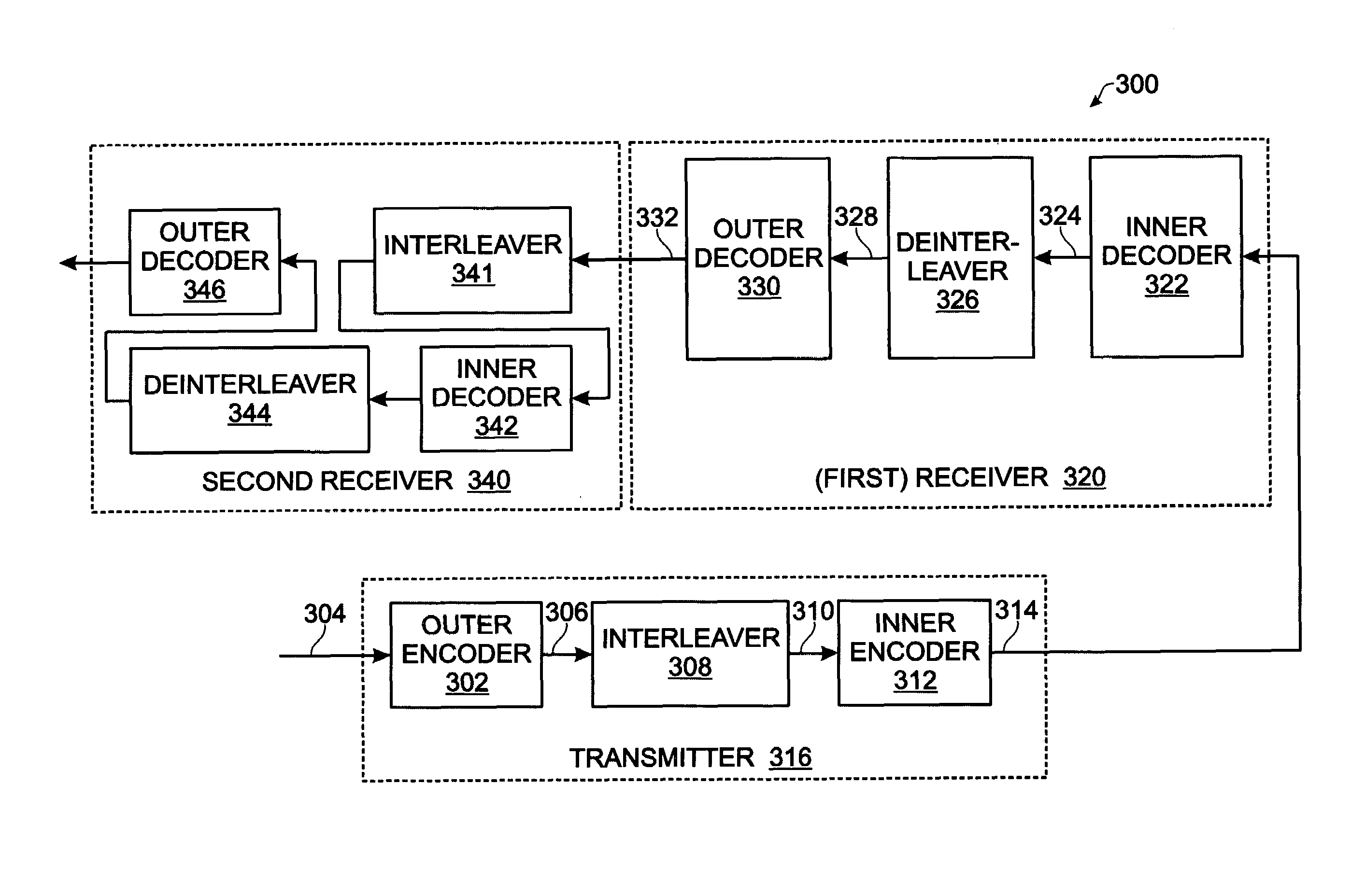

A system and method are provided for coding a frame in a packet communications system using a G.709 Digital Wrapper Frame format. The method comprises: accepting digital information; outer encoding the digital information with a Reed Solomon (RS) encoding scheme; interleaving the outer encoded information; inner encoding the interleaved information using a BCH encoding scheme; and, forming a G.709 Digital Wrapper frame including payload and parity bytes. More specifically, a standard DW superframe is formed with 122,368 bits of payload and 8192 bits of parity. The outer encoding process uses an RS(1023,1007) parent code. In one aspect, 15 groups of RS(781,765) and 1 group of RS(778,762) codewords are formed per superframe. The inner encoding process uses a BCH(2047,1959) parent code. In one aspect, 64 groups of BCH(2040,1952) codewords are formed per superframe.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

Encoding method and device thereof and decoding method and device thereof

InactiveCN101667887AHigh gainHigh forward error correctionForward error control useComputer hardwareData stream

The invention provides a forward error correction encoding method, comprising the following steps: encoding the data stream according to the Reed-Solomon (RS) rules; interweaving the data stream afterbeing encoded by RS to serve as the input data stream of the BCH encoding; and encoding the data stream after being interwoven according to the BCH rules. Accordingly, the invention also provides a forward error correction encoding device which is characterized by comprising an RS encoding module, an interweaving module and a BCH encoding module. Accordingly, the invention also provides a forwarderror correction decoding method, comprising the following steps: decoding the data stream according to the BCH rules; de-interweaving the data stream after being decoded by the BCH rules to serve asthe input data stream of the RS decoding; and decoding the data stream after being de-interwoven according to the RS rules. The invention provides a forward error correction device which is characterized by comprising a BCH decoding module, a de-interweaving module and an RS decoding module. The method and device above realize the forward error correction with higher gain.

Owner:ZTE CORP

Correction coding method for ground digital television broadcast

ActiveCN1925615AImprove performanceSimple structureTelevision systemsDigital video signal modificationComputer hardwareInformation transmission

This invention relates to earth digital television broadcast coding method in digital information transmission technique field, which comprises the following steps: diving transmission flow into 752 bit set and adding 261 zeros to get 1013 bit for BCH coding and removing front 261 bit to get BCH(762,752); forming one set of BCH(762,752) with certain number to generate matrix of LDPC(7493,3048),LDPC(7493,4572) or LDPC(7493,6096); deleting output 7493 bit front five correction bit to get final 7488 output bit.

Owner:TSINGHUA UNIV

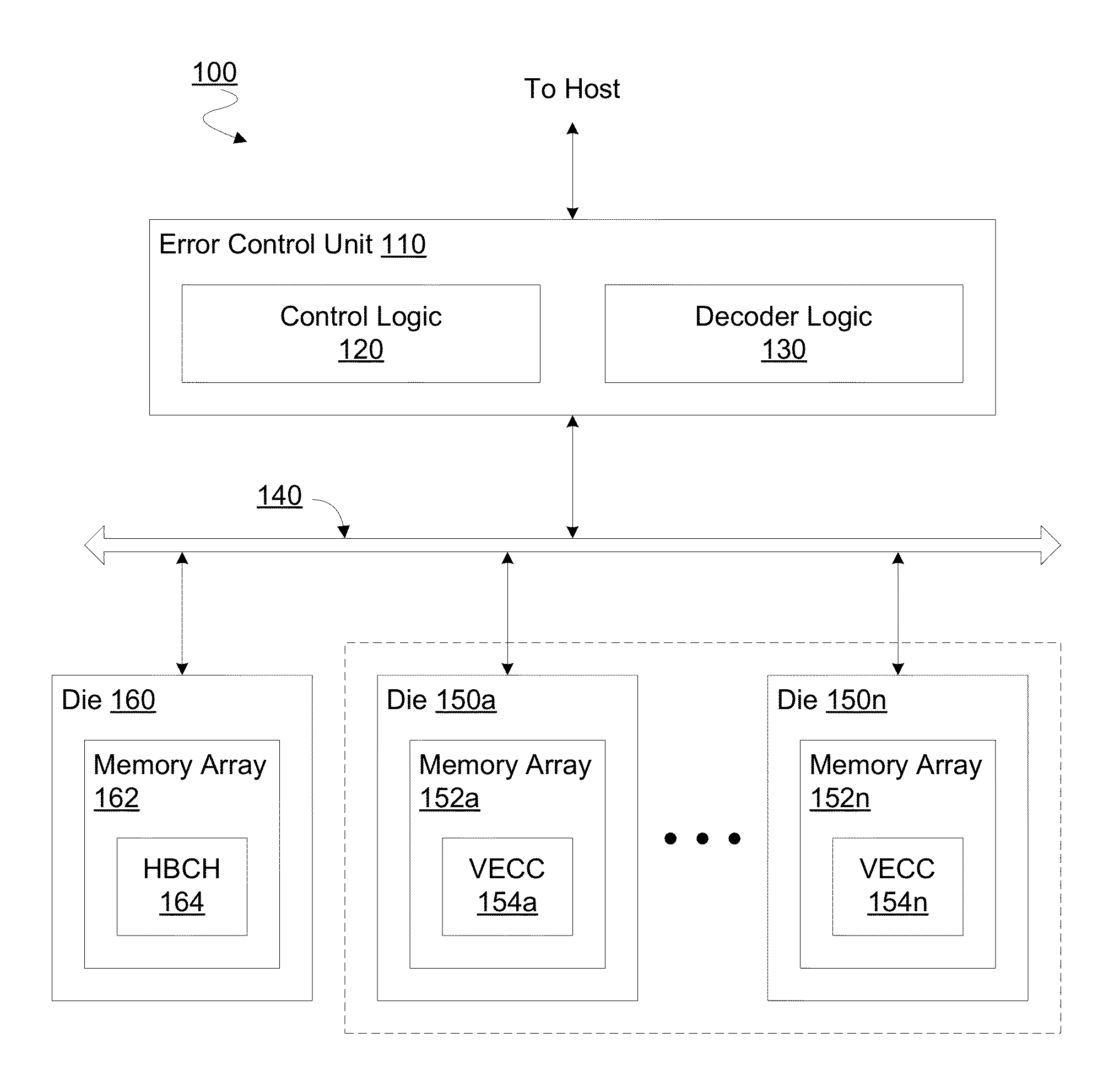

Method, apparatus and system for handling data faults

ActiveUS20140089758A1Error correction/detection using convolutional codesError detection/correctionControl logicData recovery

Techniques and mechanisms for handling data faults in a memory system which includes multiple integrated circuit (IC) dies, each die including a respective one of multiple memory arrays. In an embodiment, control logic monitors for a die failure of the multiple dies, and further monitors for a request to perform error correction for the multiple memory arrays. Each of the multiple memory arrays may store a respective vertical error correction code specific to data of that memory array. Another IC die may store a Bose, Ray-Chaudhuri, Hocquenghem (BCH) code of a horizontal codeword which spans the multiple memory arrays. In another embodiment, the BCH code is available to decode logic for data recovery operations in response to a die failure, where the BCH code is further available to the decode logic for error correction operations when all of the memory arrays are operative.

Owner:SK HYNIX NAND PROD SOLUTIONS CORP

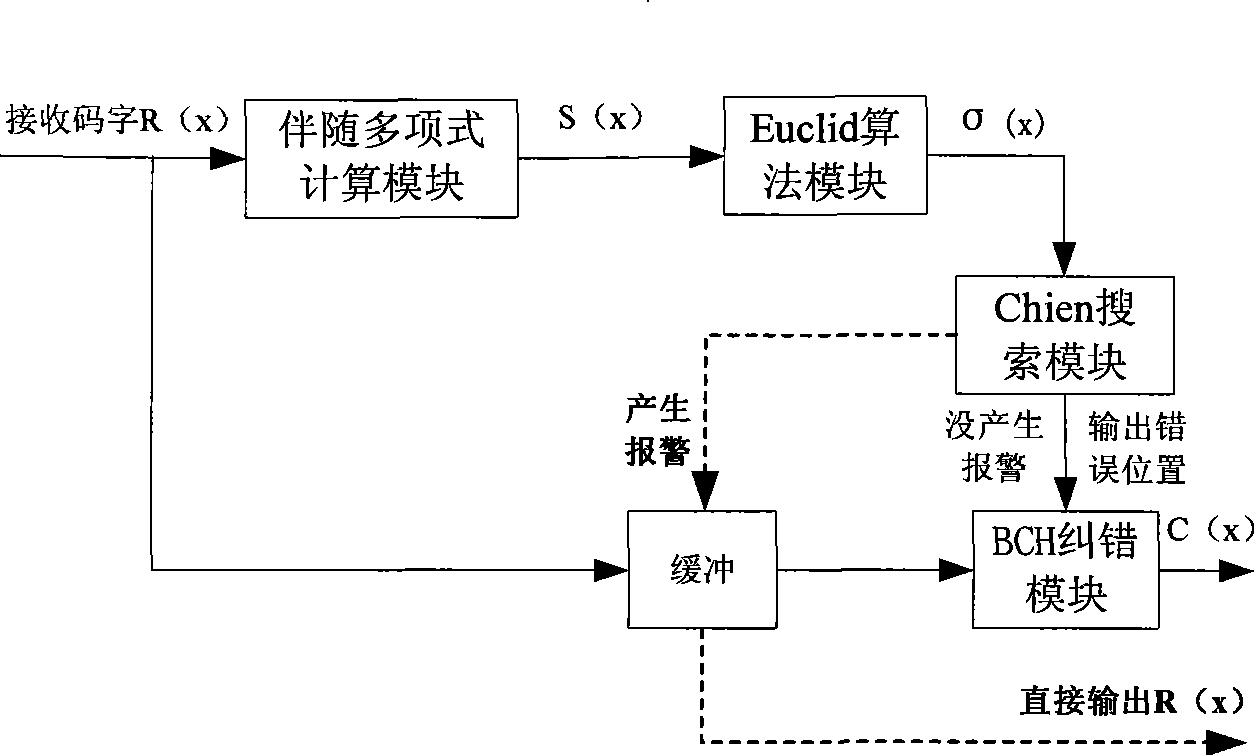

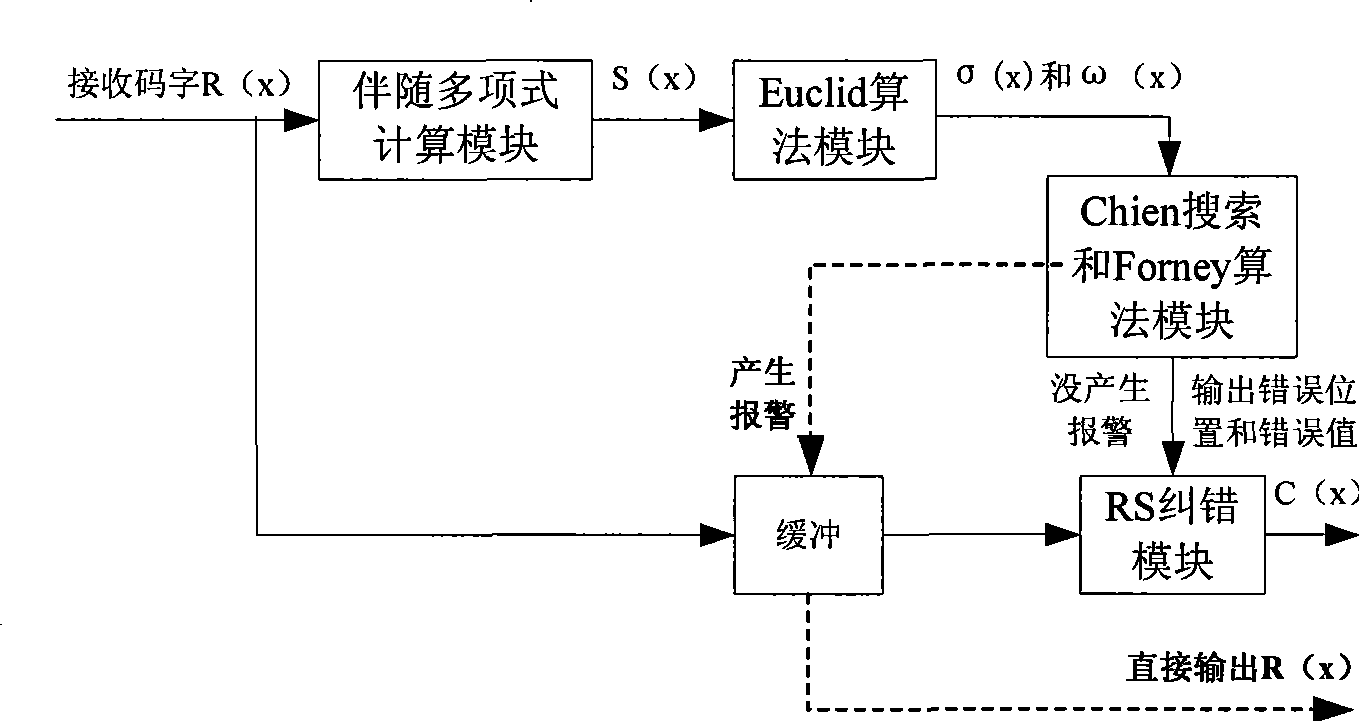

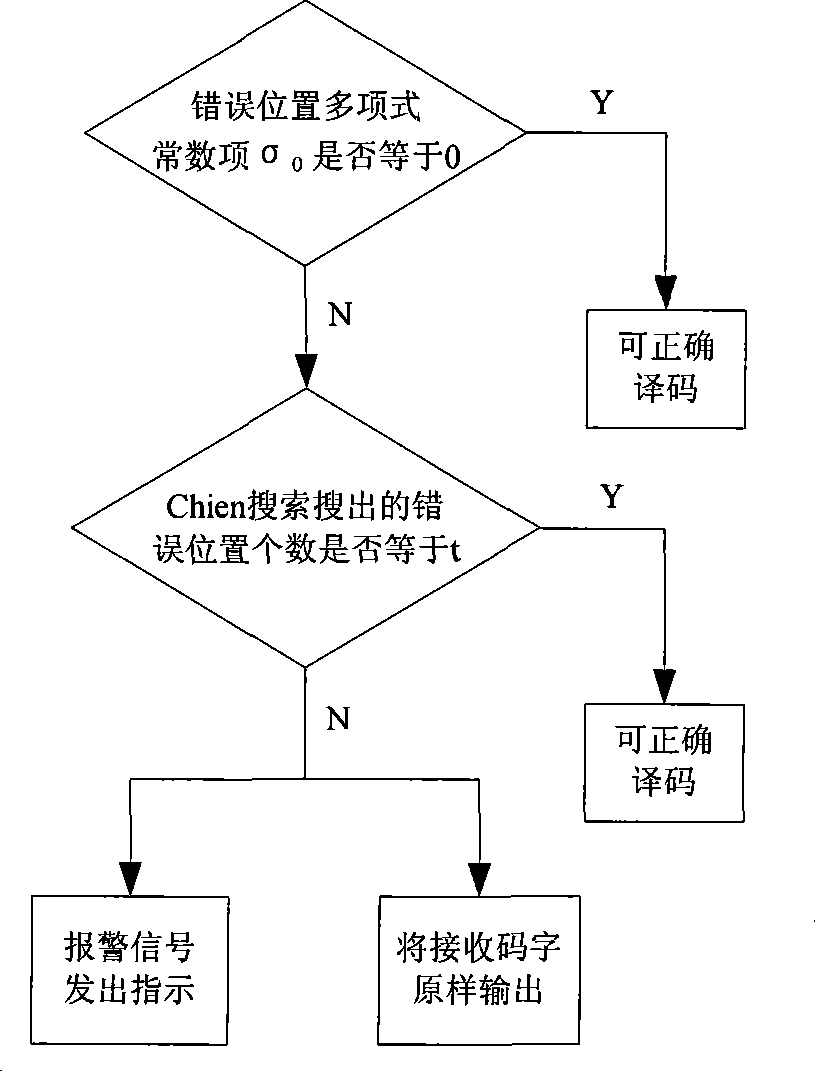

Decoding method for channel error correcting BCH code and RS code

ActiveCN101459431AReduce bit error rateAvoid the situation of "more correction and more error"Error preventionCyclic codesComputer hardwareCommunications system

The invention discloses an encoding method of a channel error correcting code BCH code and an RS code, belonging to the digital communication field, which comprises calculating an adjoint polynomial S(x) through a received code R(x), solving the Berlekamp key equation through the Euclid algorithm to obtain an error location polynomial sigma (x), and correctly encoding if the constant term sigma 0 in the error location polynomial sigma (x) is zero, or calculating the error locations and the relative error values through the Chien search if the constant term sigma 0 in the error location polynomial sigma (x) is not equal to 0, and being able to correctly encode if the number of searched error locations is equal to the largest error correcting capability thereof, or sending a warning indication signal whose error number of receiving signals exceeds the largest error correcting capability, and outputting original receiving codes. The encoding method avoids the condition that the more errors are corrected, the more errors existing when the receiving code error number exceeds the largest error correcting capability of the channel error correcting code, thereby reducing the error code rate of the whole communication system.

Owner:PEKING UNIV +1

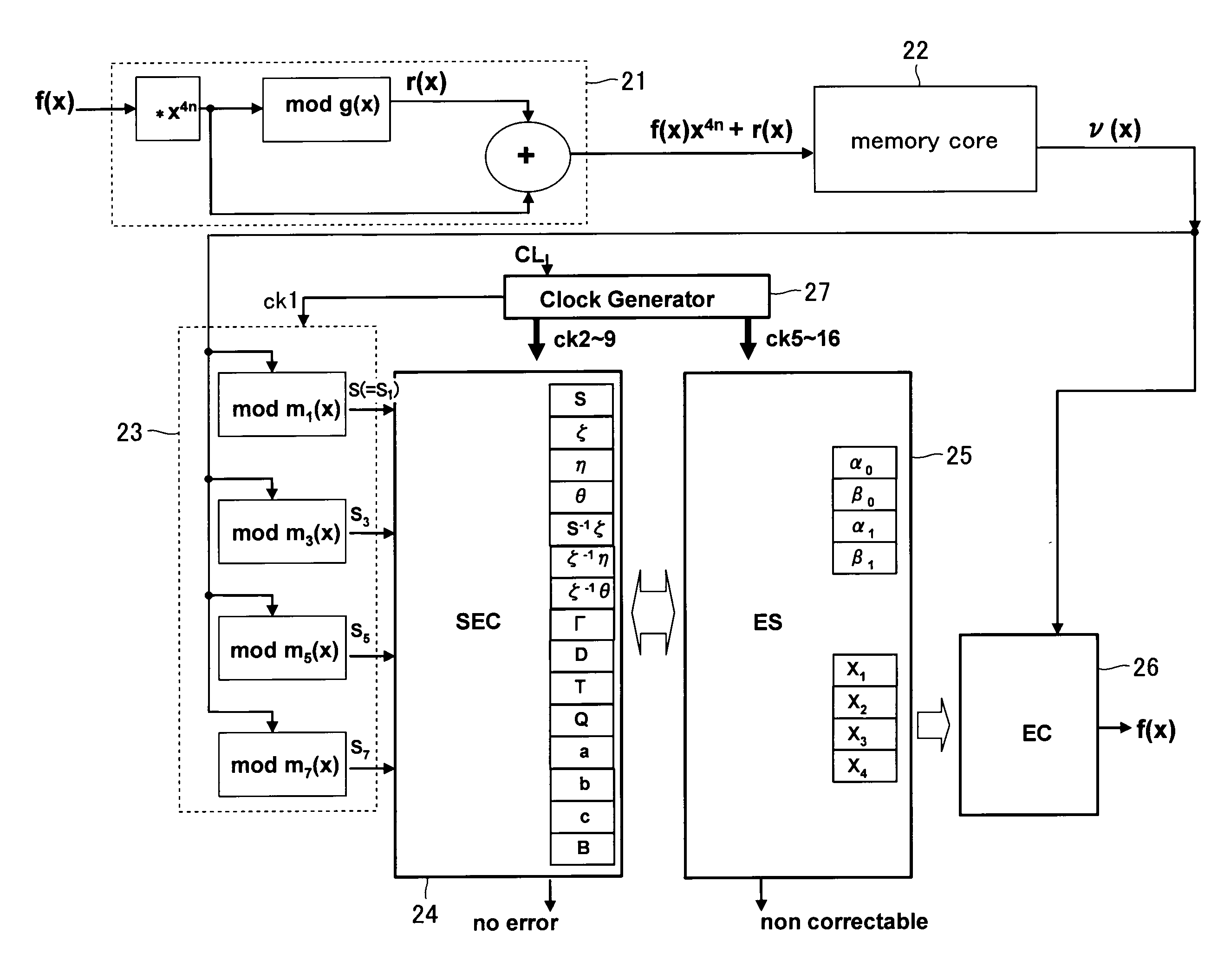

Memory device with error correction system

There is disclosed a memory device with an error detection and correction system formed therein, the error detection and correction system being configured to detect and correct errors in read out data by use of a BCH code, wherein the error detection and correction system is 4-bit error correctable, and searches error locations in such a way as to: divide an error location searching biquadratic equation into two or more factor equations; convert the factor equations to have unknown parts and syndrome parts separated from each other for solving them; and compare indexes of the solution candidates with those of the syndromes, the corresponding relationships being previously obtained as a table, thereby obtaining error locations.

Owner:KK TOSHIBA

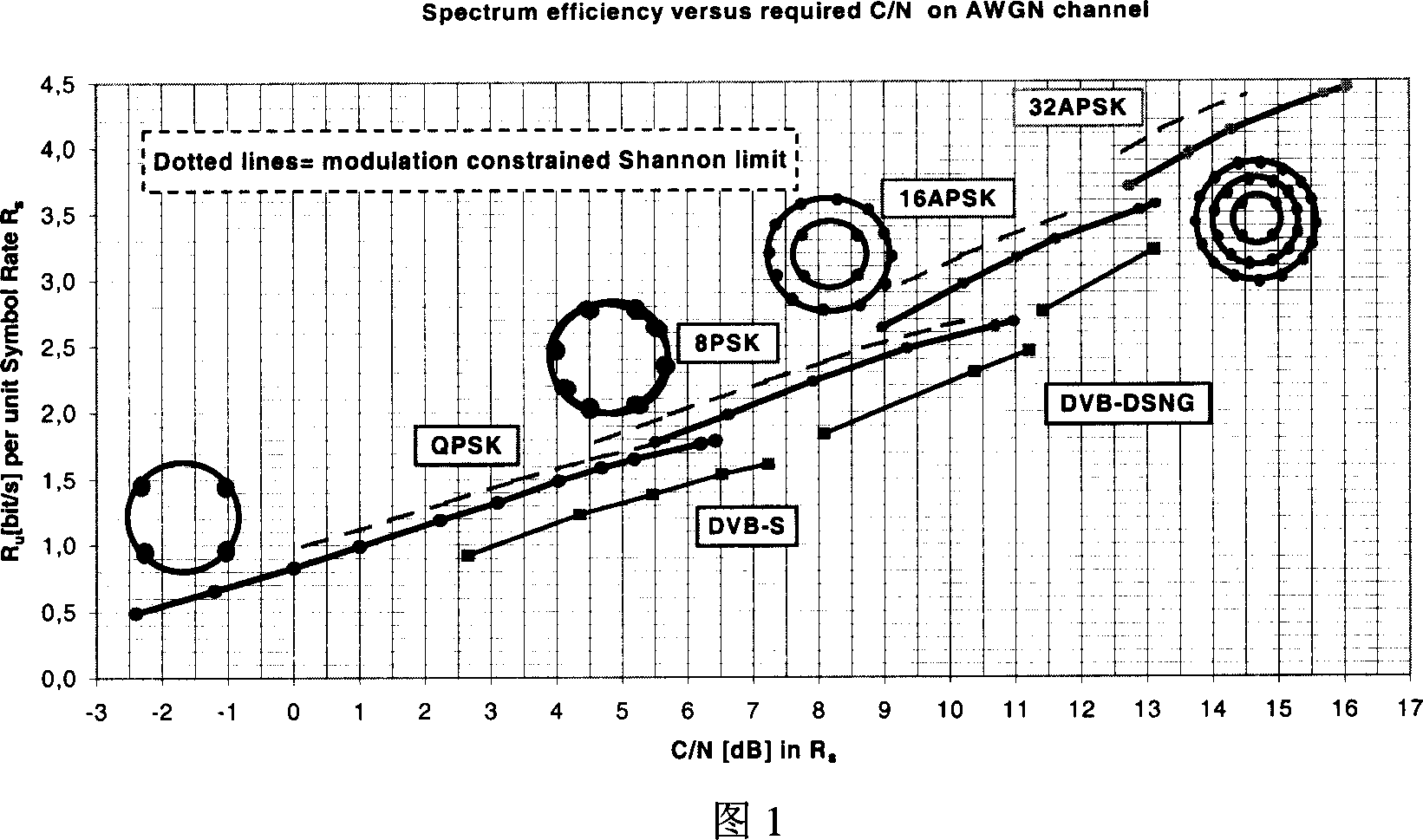

Adaptive Error Correcting Code for Data Communications Over a Plastic Optical Fibre

ActiveUS20120250785A1Less-efficient systemReduce in quantityError correction/detection using block single space codingUnequal/adaptive error protectionDigital dataThree level

An efficient coding and modulation system for transmission of digital data over plastic optical fibres is disclosed. The digital signal is coded by a three-level coset coding. The spectral efficiency of the system is configurable by selecting the number of bits to be processed in each of the levels. The first level applies to the digital data a binary BCH coding and performs coset partitioning by constellation mapping and lattice transformations. Similarly, second level applies another binary BCH coding, which may be performed selectably in accordance with the desired configuration by two BCH codes with substantially the same coding rate, operating on codewords of different sizes. The third level is uncoded. The second and third levels undergo mapping and lattice transformation. After an addition of the levels, a second-stage lattice transformation is performed to obtain a zero-mean constellation. The symbols output from such three-level coset coder are then further modulated.

Owner:KNOWLEDGE DEV FOR POF SL

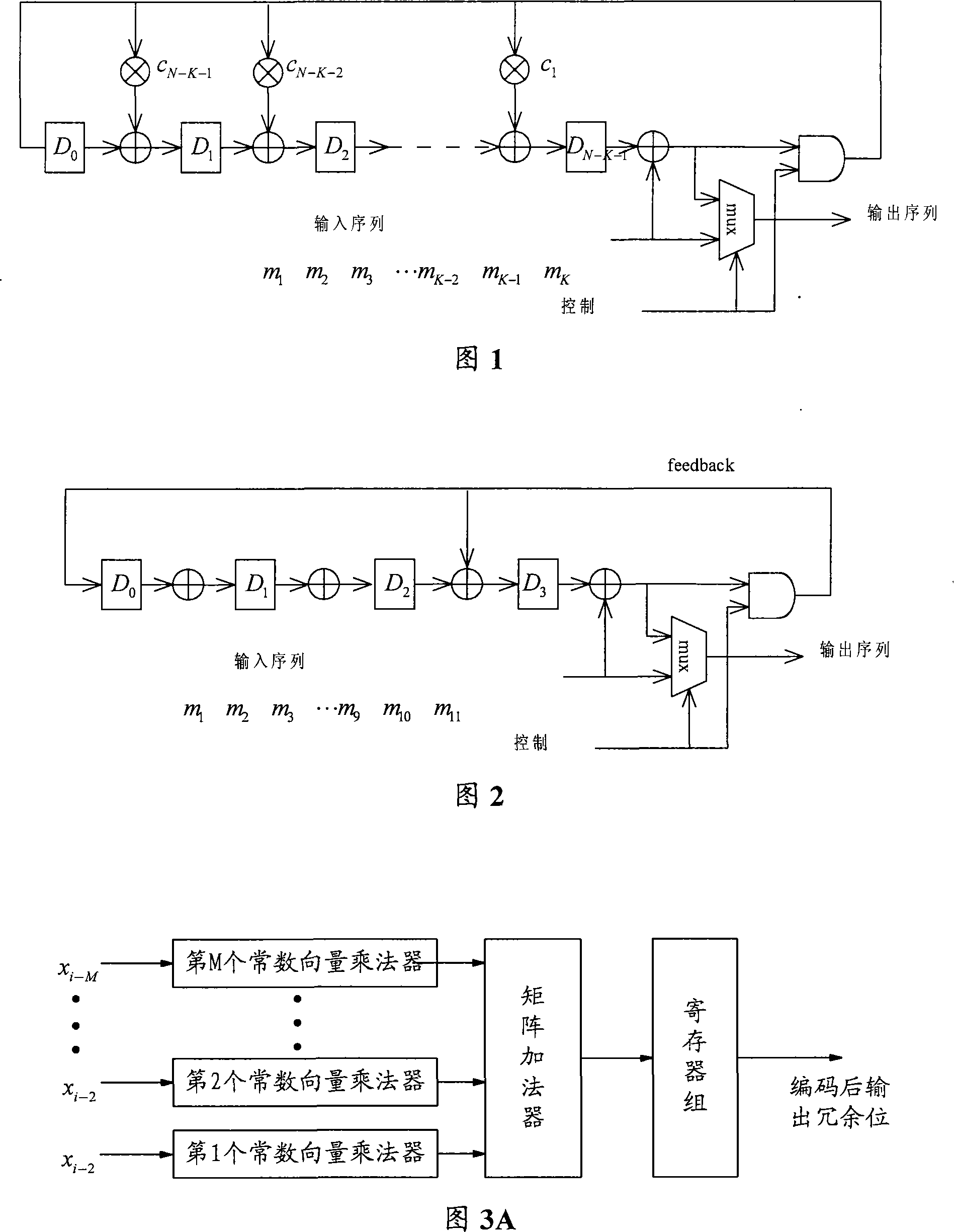

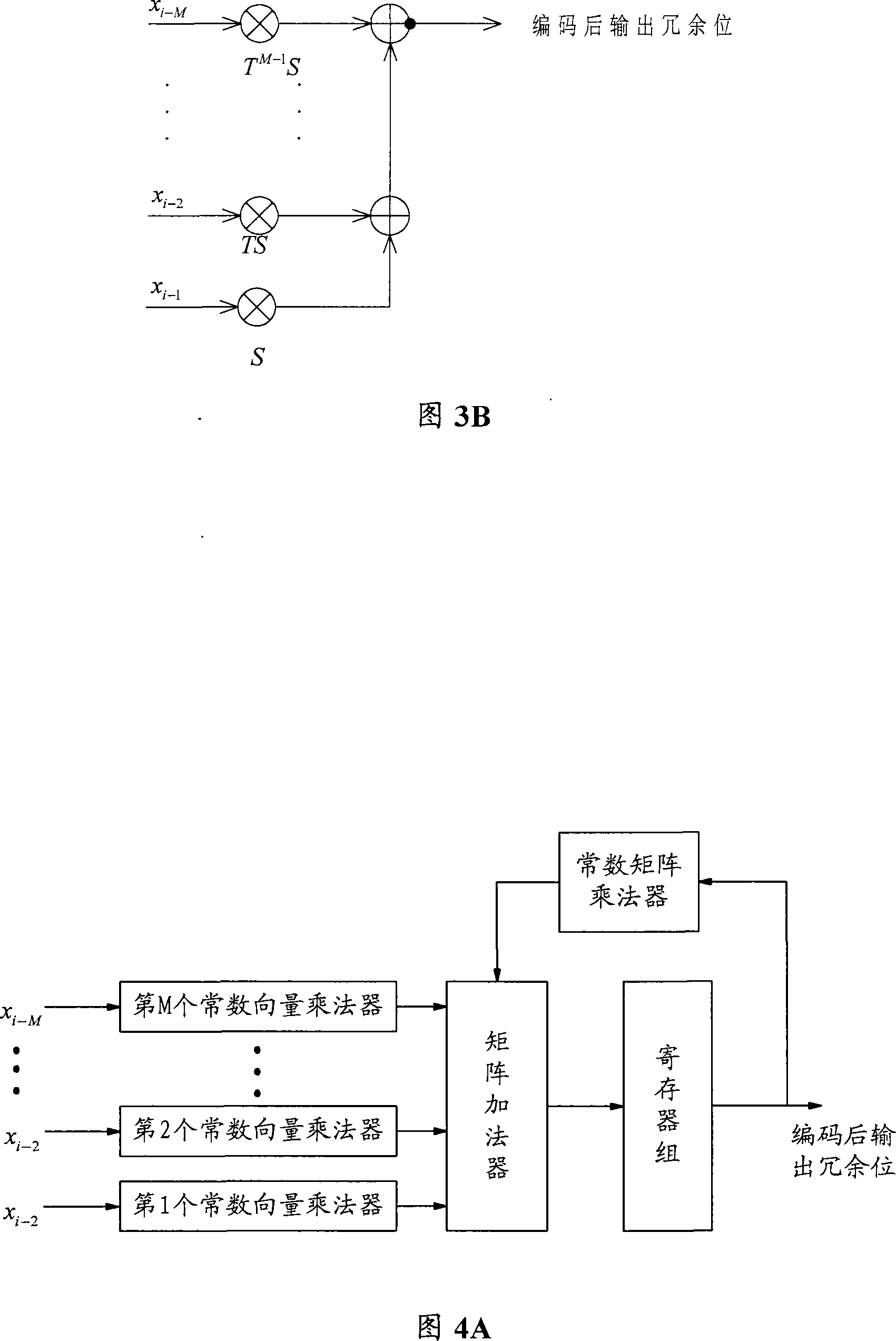

Circuit, encoder and method for encoding parallel BCH

ActiveCN101227194AControl fan-outFast operationError preventionCyclic codesResource consumptionProcessor register

The invention discloses a method for coding BCH in parallel, which comprises following steps: correspondingly multiplying input sequence {x1..., xi,..., xM} of current cycle respectively with a constant vector S, TS,..., TiS,..., TM-1S in turn, using the summation of the multiplication result as a first output, using the multiplication result of the last cycle output on a register group and a constant matrix TM as a second output, outputting the summation of the first output and the second output to the register group as the current cycle output of the register group, and obtaining final coding output through computing for certain quantity times of the steps. The method for coding BCH in parallel which is provided by the invention adopts an iterative algorithm, which has quicker arithmetic speed relative to a serial coding, eliminates lookup table compared with the parallel algorithm which is based on the lookup table, greatly reduces resource consumption, and effectively controls fan-out of a circuit. The invention also discloses a circuit and a coding device for coding BCH in parallel.

Owner:ACTIONS ZHUHAI TECH CO

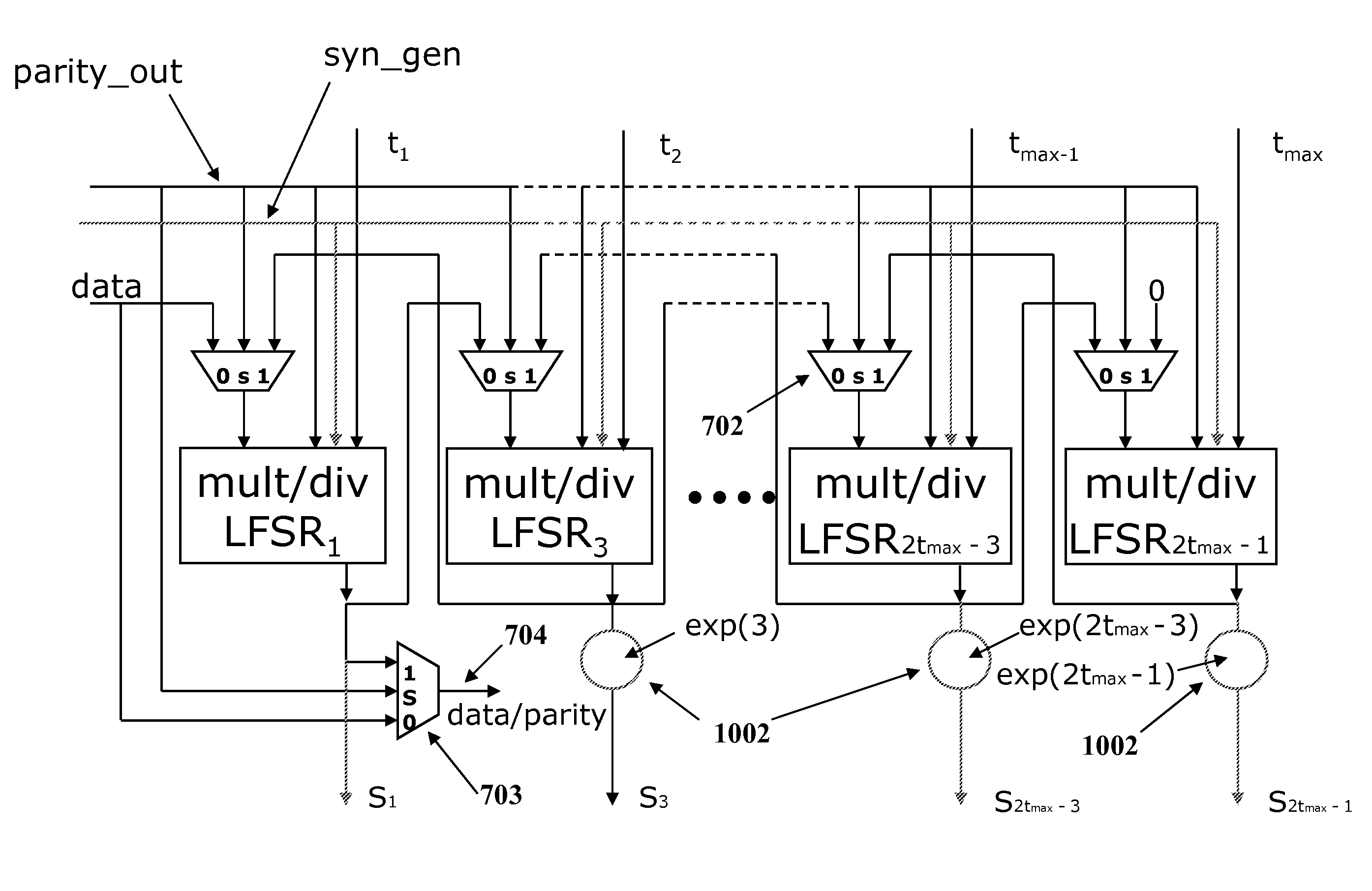

Programmable Error Correction Capability for BCH Codes

An embodiment of the invention relates to a BCH encoder formed with linear feedback shift registers (LFSRs) to form quotients and products of input polynomials with irreducible polynomials of a generator polynomial g(x) of the BCH encoder, with and without pre-multiplication by a factor xm. The BCH encoder includes multiplexers that couple LFSR inputs and outputs to other LFSRs depending on a data input or parity generation state. The BCH encoder can correct up to a selectable maximum number of errors in the input polynomials. The BCH encoder further includes LFSR output polynomial exponentiation processes to produce partial syndromes for the input data in a syndrome generation state. In the syndrome generation state the LFSRs perform polynomial division without pre-multiplication by the factor xm. The exponentiation processes produce partial syndromes from the resulting remainder polynomials of the input data block.

Owner:INFINEON TECH AG

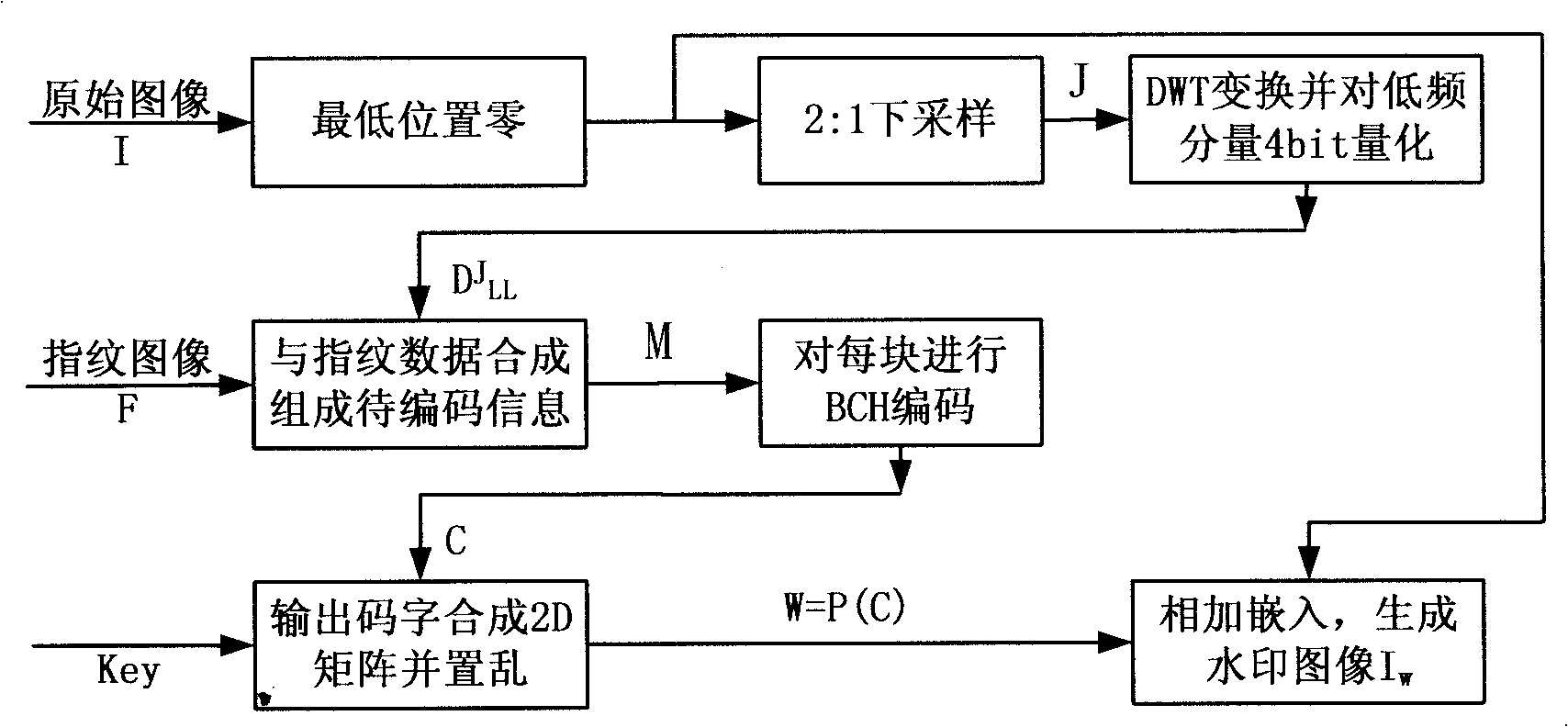

Method for generating and authenticating frailty watermark based on error correction encoding

InactiveCN101303725AEasy to manageImprove securityCharacter and pattern recognitionImage data processing detailsComputer hardwareError location

The invention discloses a generating method and an authentication method for a fragile watermarking by utilizing the theory of error-correcting codes. The generating method for the watermarking in the invention is that: carrying out wavelet transformation on a shrunken initial image and carrying out quantification on the low frequency coefficients of the wavelet transformation obtained by decomposing, then carrying out BCH coding on the formed binary data and the binary data comprising fingerprint binary data, then carrying out scrambling encryption on the binary data and the binary data comprising fingerprint binary data to from the final watermarking and embedding the final watermarking into the lowest bit of the original image. The authentication method for the watermarking includes: obtaining the lowest bit of the image to be authenticated, recovering the scrambling of the lowest bit and carrying out corresponding BCH decoding to obtain the information of the initial image, the fingerprint information and the information of the error position which are used for the complete authentication and copyright protection. When carrying out image authentication, the invention does not need the initial image as well as the initial watermarking information; the parameter management of the invention is simple. The invention can not only distinguish the tampering objects, preciously locate the tampering position and point out the tampering intensity, but also provide basis for the ownership problem of the copyright according to the embedded fingerprint information.

Owner:ZHEJIANG UNIV

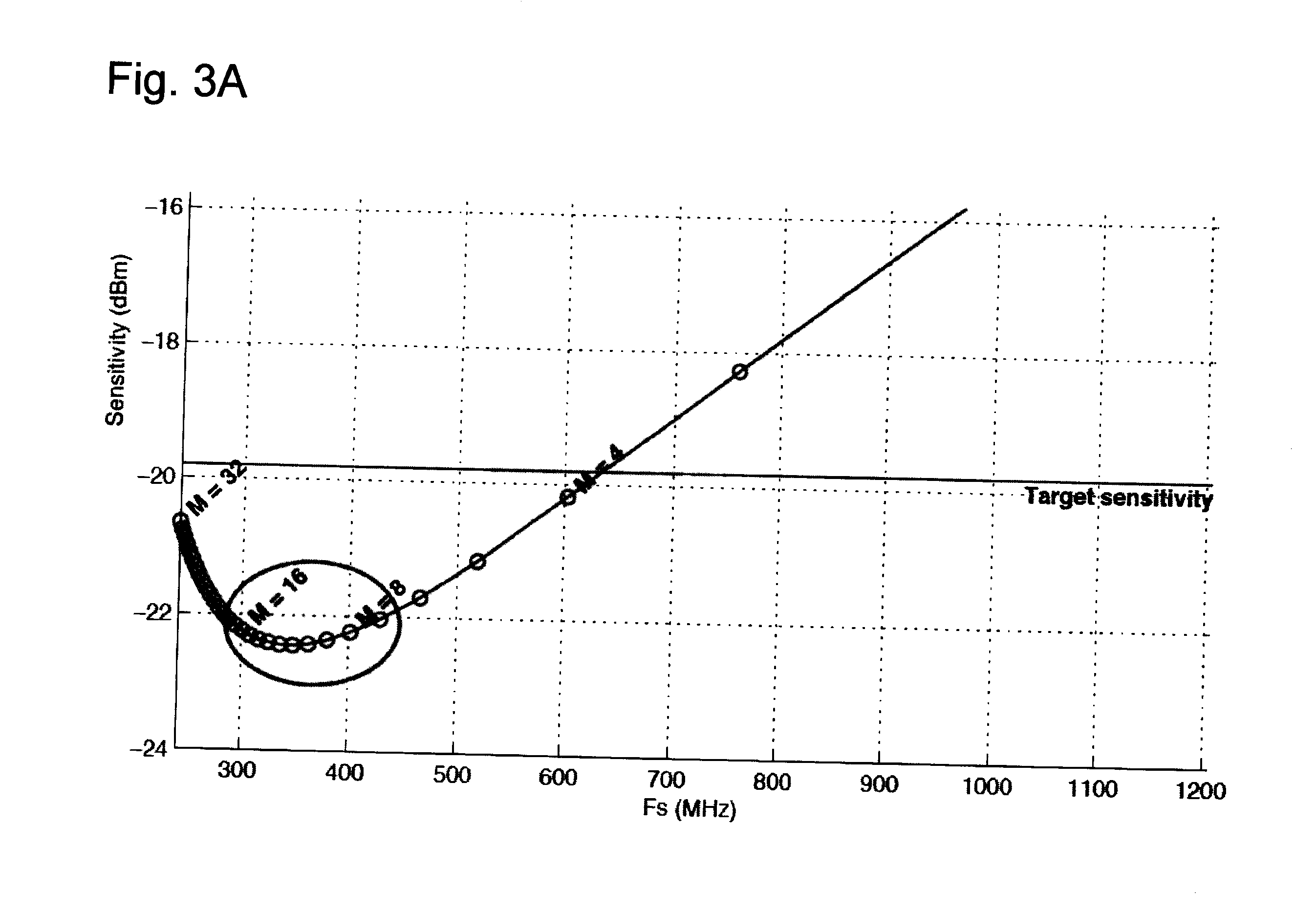

Two-level coset coding scheme for gigabit ethernet over plastic optical fiber

ActiveUS20160204873A1Lower latencyEasy to installError correction/detection using block single space codingError preventionDigital dataEngineering

An efficient coding and modulation system for transmission of digital data over plastic optical fibers with low latency. In particular, the digital signal is coded by means of a two-level coset coding. The first level applies to the digital data a binary shortened BCH coding and performs coset partitioning by means of constellation mapping and lattice transformations. The second level is uncoded but undergoes mapping and lattice transformation. After an addition of the two levels, a second-stage lattice transformation is performed so as to obtain a zero-mean constellation. The symbols output from such three-level coset coder are then further modulated.

Owner:KNOWLEDGE DEV FOR POF SL

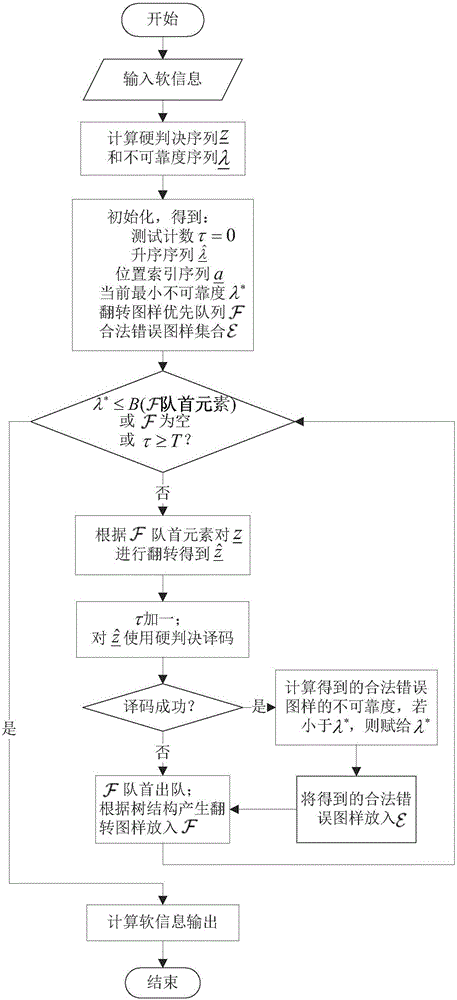

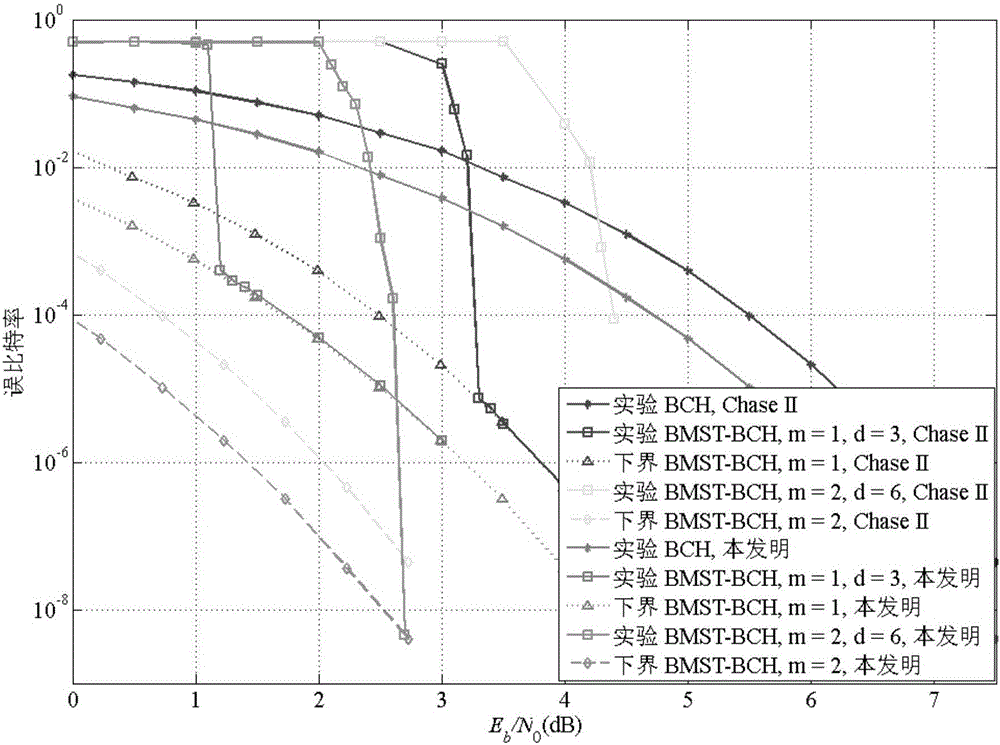

Packet Markov superposition coding method by taking binary BCH code as component code, and decoding method

ActiveCN106059596AKeep basic code rateSimplify the design processCyclic codesComputer architectureSuperposition coding

The invention belongs to the field of digital communication and digital storage, and discloses a packet Markov superposition coding method by taking a binary BCH code as a component code, and a decoding method. The binary BCH code having the code length of n, the information bit length of k and the error correcting capability of tmin is used as the component code; and a binary information sequence (u)u( / u) having the length of K=kBL is coded into a code (u)c( / u) having the length of N=nB(L+m). The invention further provides a soft iteration decoding method applicable to the packet Markov superposition coding method by taking the binary BCH code as the component code. The soft iteration decoding method comprises the following steps of: generating a turnover pattern according to a tree structure, judging whether a test process is ended or not and whether soft information output is calculated or not by using the lower bound of the unreliability of a potential legal error pattern, etc. According to the packet Markov superposition coding method and the decoding method thereof provided by the invention, the value of the coding memory length m is {1,2,3}; the net coding gain, which is greater than 10 dB, is provided at the bit error rate performance, which is as low as 10-10 to 10-15; and thus, the packet Markov superposition coding method and the decoding method thereof provided by the invention can be applied to a communication system having low bit error rate requirements, such as optical fibre communication.

Owner:SUN YAT SEN UNIV

Voice integrity protection method based on digital fingerprint

InactiveCN101847409AImprove the correct extraction rateImprove bit error correction capabilityError preventionSpeech analysisDecoding methodsComputer hardware

The present invention discloses a voice integrity protection method based on digital fingerprint, which develops a relatively perfect method for the realization of audio integrity protection. The method first provides a combined watermarked data coding / decoding method based on trellis coding, BCH coding and CRC coding to improve the error code correcting performance of a system, then a watermark extraction synchronizing method using an energy synchronization head signal as a positioning standard and re-synchronization as complementary means to realize an accurate positioning on watermark extraction operation, and finally a voice integrity protection method taking watermark information as a primary determination criterion and the abstract of the watermark information as an auxiliary determination criterion to realize the core technology of voice integrity validation; according to the method, the user can transparently embed voice integrity protection information into a voice signal in real time during normal communication.

Owner:BEIJING UNIV OF POSTS & TELECOMM

Forward error correction coding

InactiveUS7484165B2Increase overheadOvercome limitationsCode conversionError correction/detection by combining multiple code structuresComputer hardwareForward error correction

Owner:MARCONI COMM GMBH

Super forward error correction hardware decoding method and apparatus thereof

ActiveCN102170327AReduce design sizeSmall implementation scaleMultiplex system selection arrangementsError preventionComputer hardwareForward error correction

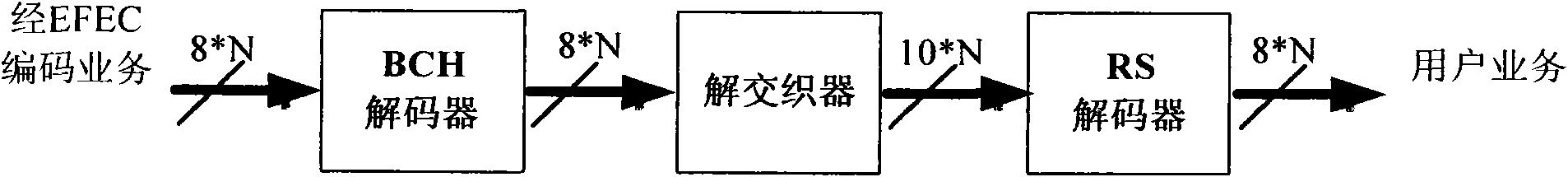

The invention discloses a super forward error correction hardware decoding method and an apparatus thereof. The hardware decoding method of the invention comprises the following steps of: adopting BCH (2040, 1952) code for calculating the syndrome of reception channel output data and solving the error position polynomial thereof; carrying out money search to determine the code element error position among BCH code words and accordingly correct the error, and completing decoding processing of the code elements of BCH code words one by one; carrying out interlacing processing every time the decoding of each internal code BCH code element is processed, calculating RS code word syndrome of the decoding result, solving error position polynomial and error value polynomial, carrying out money search according to the error position polynomial, determining the code element error position of the RS code word, calculating error value according to the error value polynomial and conducting error correction, completing the decoding of the code elements of RS code word one by one; and carrying out deinterlacing on output data, thereby obtaining SFEC decoding result. The invention can correctly realize the whole algorithm with hardware circuit of relatively small scale and improve the realization sequential speed of SFEC hardware.

Owner:FENGHUO COMM SCI & TECH CO LTD +1

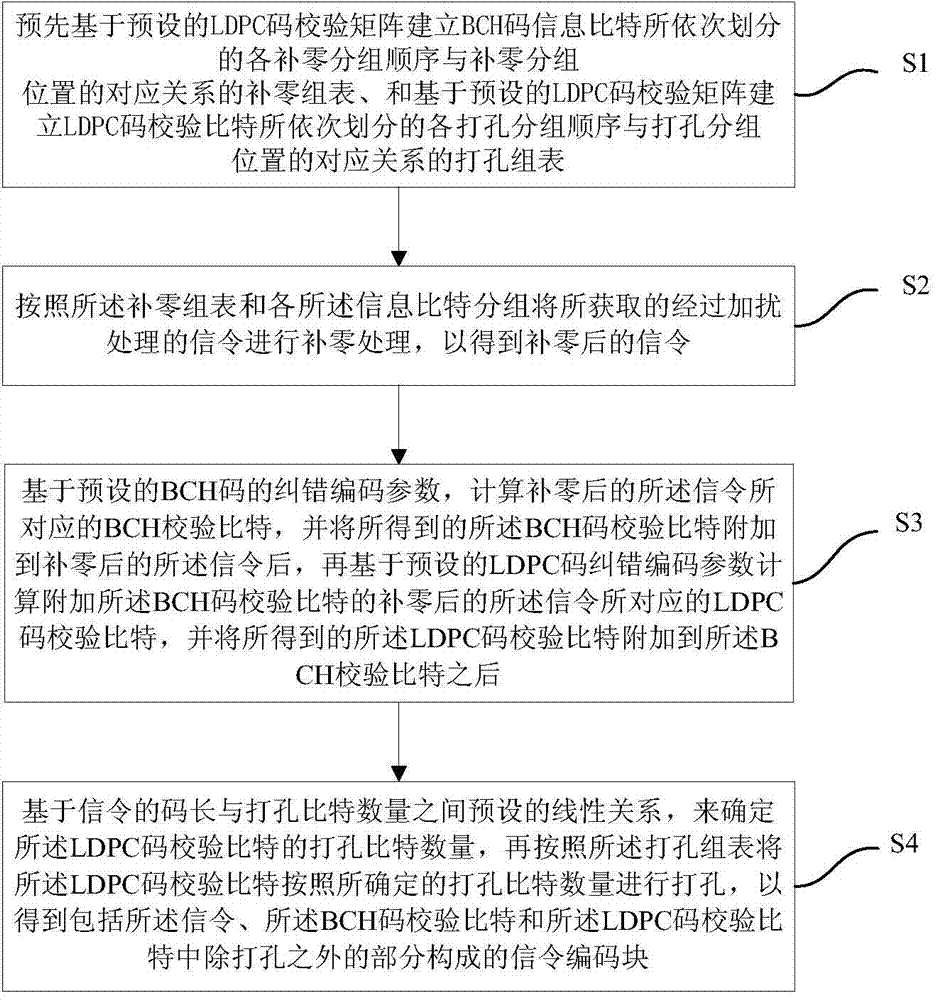

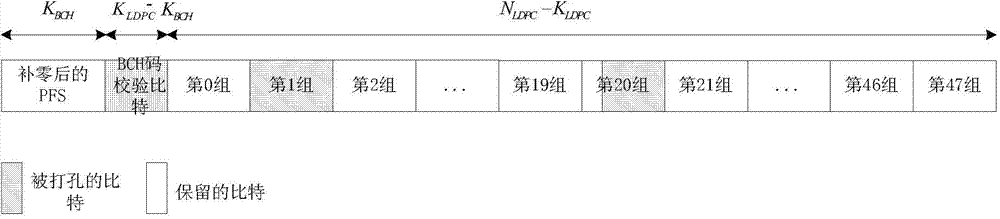

Signaling coding method and signaling coding system based on BCH code and short LDPC code cascading

The invention provides a signaling coding method and a signaling coding system based on BCH code and short LDPC code cascading. The method comprises the following steps: establishing a zero padding group table of the correspondence between the sequences of zero padding groups divided in turn and the positions of the zero padding groups based on a default LDPC code check matrix and establishing a punching group table of the correspondence between the sequences of punching groups divided in turn and the positions of the punching groups based on the default LDPC code check matrix; zero-padding an input signaling after scrambling treatment according to the zero padding group; sequentially calculating the BCH code check bit and the LPDC code check bit corresponding to the signaling after zero padding based on preset BCH code and LPDC code error correction coding parameters; and determining the number of punching bits of the LPDC code check bit based on the preset linear relationship between the code length of the signaling and the number of punching bits, and punching the LDPC code check bit according to the number and according to the punching group table.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

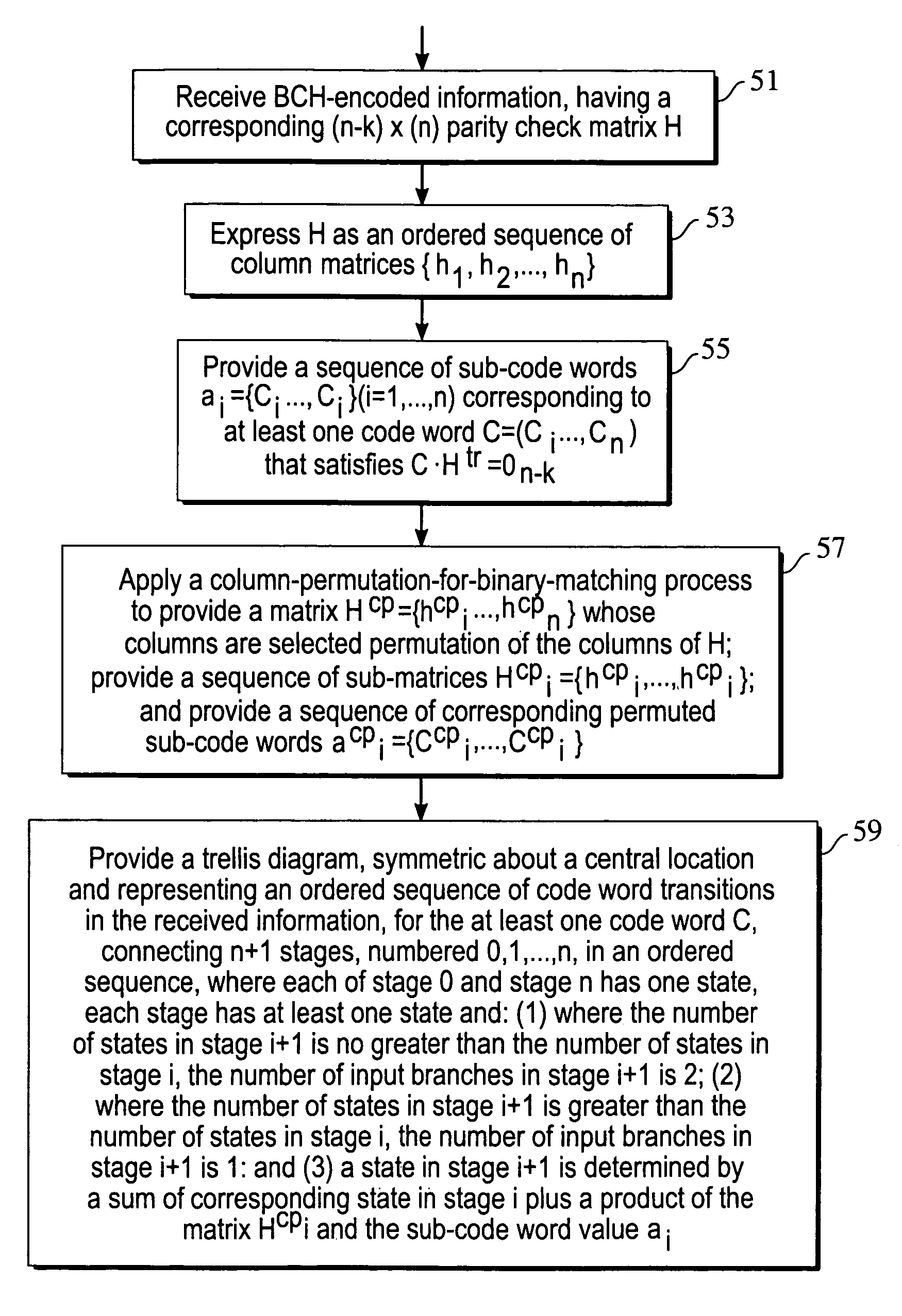

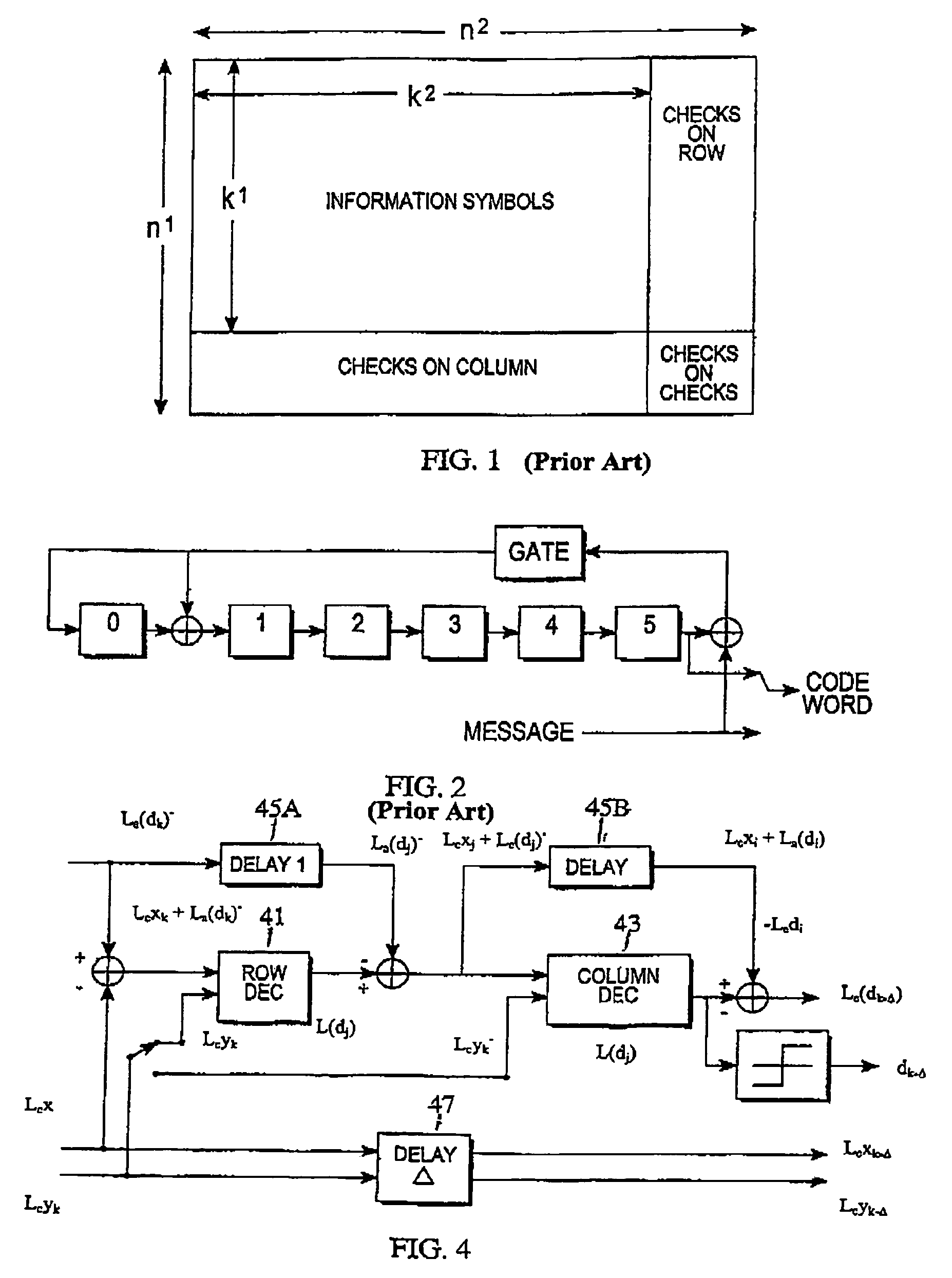

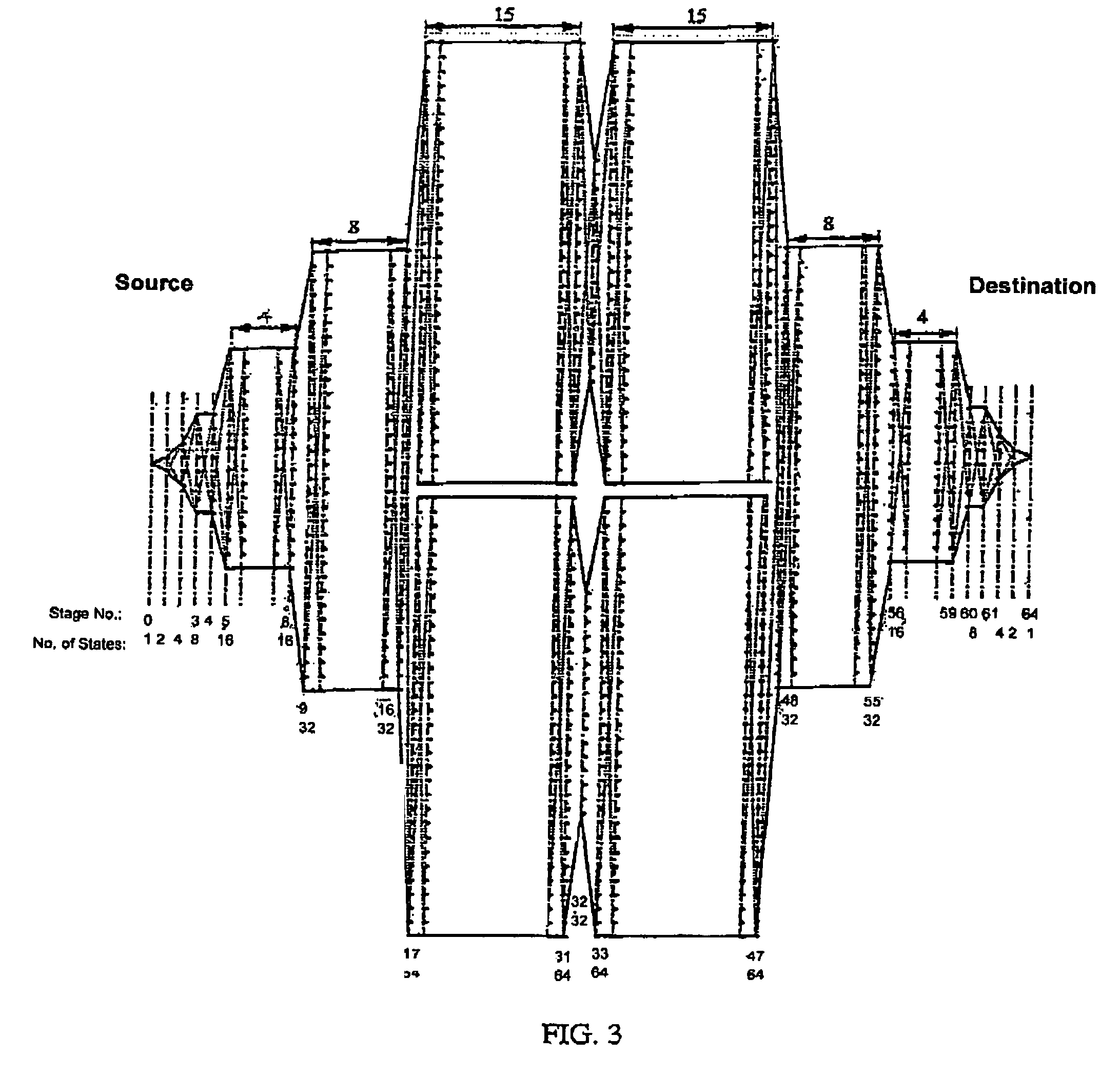

Trellis construction based on parity check matrix for BCH code

InactiveUS7266749B1Error prevention/detection by using return channelCode conversionTheoretical computer scienceParity-check matrix

A method for constructing a simplified trellis diagram for BCH-encoded information is disclosed. BCH-encoded information is received, having a corresponding parity check matrix H. The parity check matrix H is expressed as an ordered sequence of columns of matrices. A sequence of sub-code words is provided, corresponding to one or more code words, each satisfying a given condition. A matrix Hcp, having columns that are generated as a selected permutation of the columns of the matrix H through a column-permutation-for-binary-matching process, is provided, and a sequence of sub-matrices and a corresponding sequence of permuted sub-code words is provided. A trellis diagram, representing an ordered sequence of code word transitions in the received information and symmetric about a central location, is provided for each code word c, connecting n+1 stages, numbered i=0, 1, . . . , n, in an ordered sequence.

Owner:LEGEND SILICON

Method and apparatus for decoding shortened bch codes or reed-solomon codes

ActiveUS20090259921A1Improve efficiencyReduce in quantityCode conversionCyclic codesBerlekamp–Massey algorithmComputer engineering

The present invention proposes a method and apparatus for decoding BCH codes and Reed-Solomon codes, in which a modified Berlekamp-Massey algorithm is used to perform the decoding process and the efficiency of the decoder can be improved by re-defining the error locating polynomial as a reverse error locating polynomial, while the operation of the decoding process can be further realized by a common re-configurable module. Furthermore, the architecture of the decoder is consisted of a plurality of sets of re-configurable modules in order to provide parallel operations with different degrees of parallel so that the decoding speed requirement of the decoder in different applications can be satisfied.

Owner:NAT CHIAO TUNG UNIV

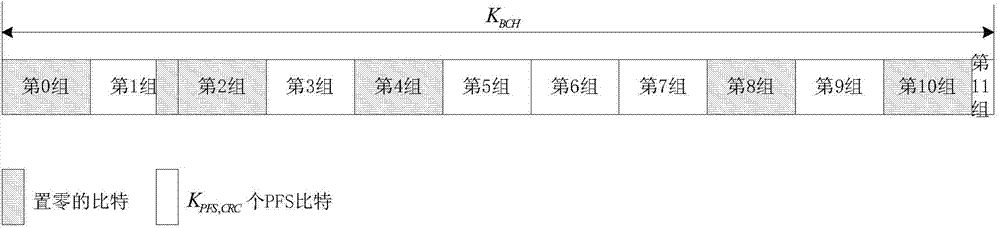

Method for encoding and modulating physical frame signaling channel in NGB-W system

ActiveCN104618067ASupport bitmapSupport generationSelective content distributionTransmission format adaptationCoding blockComputer hardware

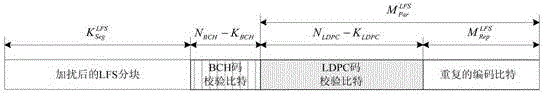

The invention discloses a method for encoding and modulating a physical frame signaling channel in an NGB-W system. The method comprises the following steps of: adding CRC (cyclic redundancy code) bits to physical frame signaling and scrambling the physical frame signaling; mapping the scrambled physical frame signaling into BCH (Broadcast Channel) code information bits; performing forward error correction coding to the BCH code information bits by BCH coding and LDPC (Low Density Parity Check) coding cascade methods; generating physical frame signaling check bits and forming physical frame signaling coding blocks; performing constellation mapping to the physical frame signaling coding blocks to generate BICM (Bit Interleaved Coded Modulation) blocks. The method is characterized in that a forward error correction coding solution with a reasonable structure and parameters, and LDPC codes including a QC-Raptor-Like structure and approaching a Claude Elwood Shannon threshold are adopted, and bit mapping of information with the changeable signaling length, code rate control and coding block generation can be supported; the physical frame signaling with the changeable length can be protected so that the transmission reliability of the physical frame signaling is relatively steady along with the change of the signaling length.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

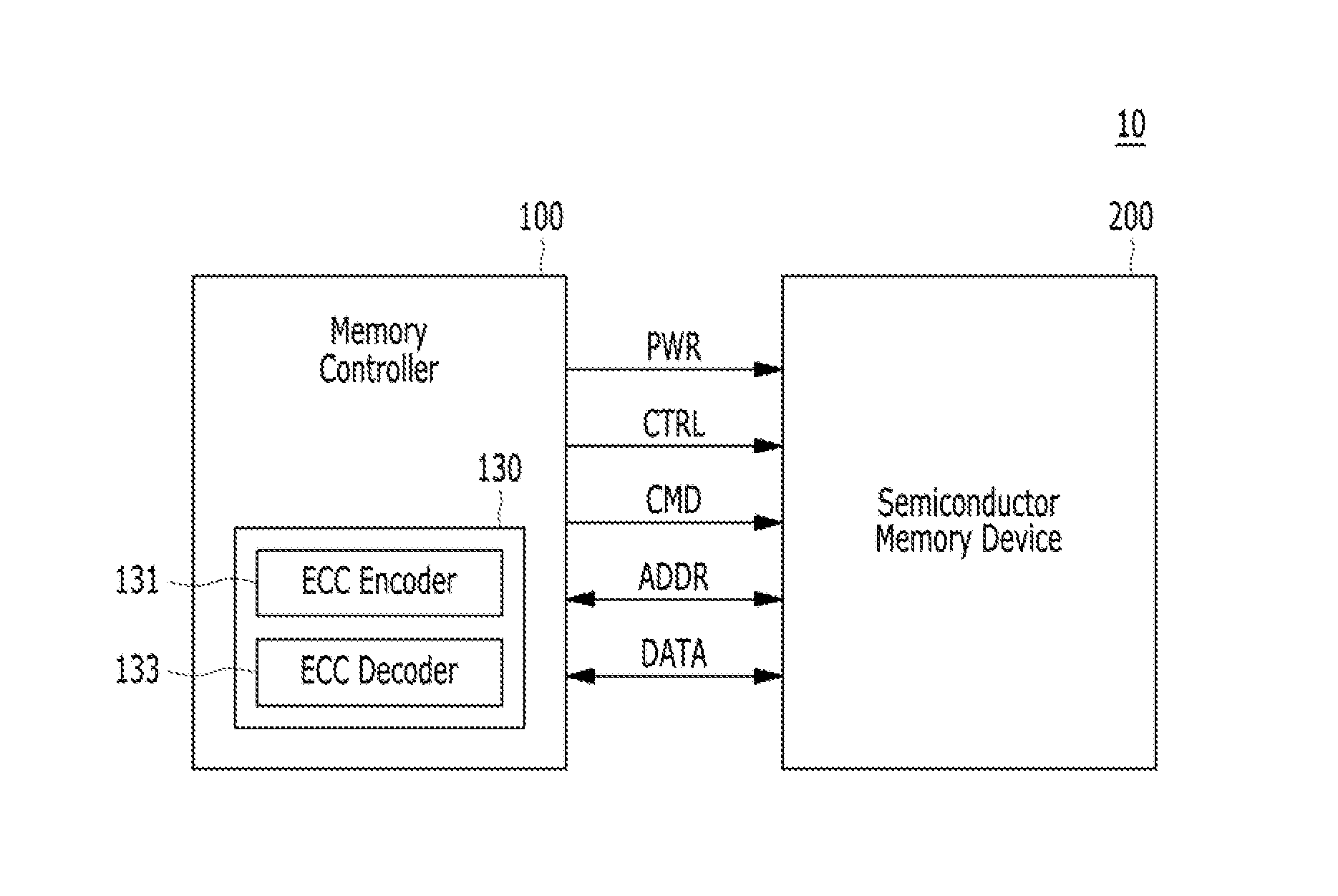

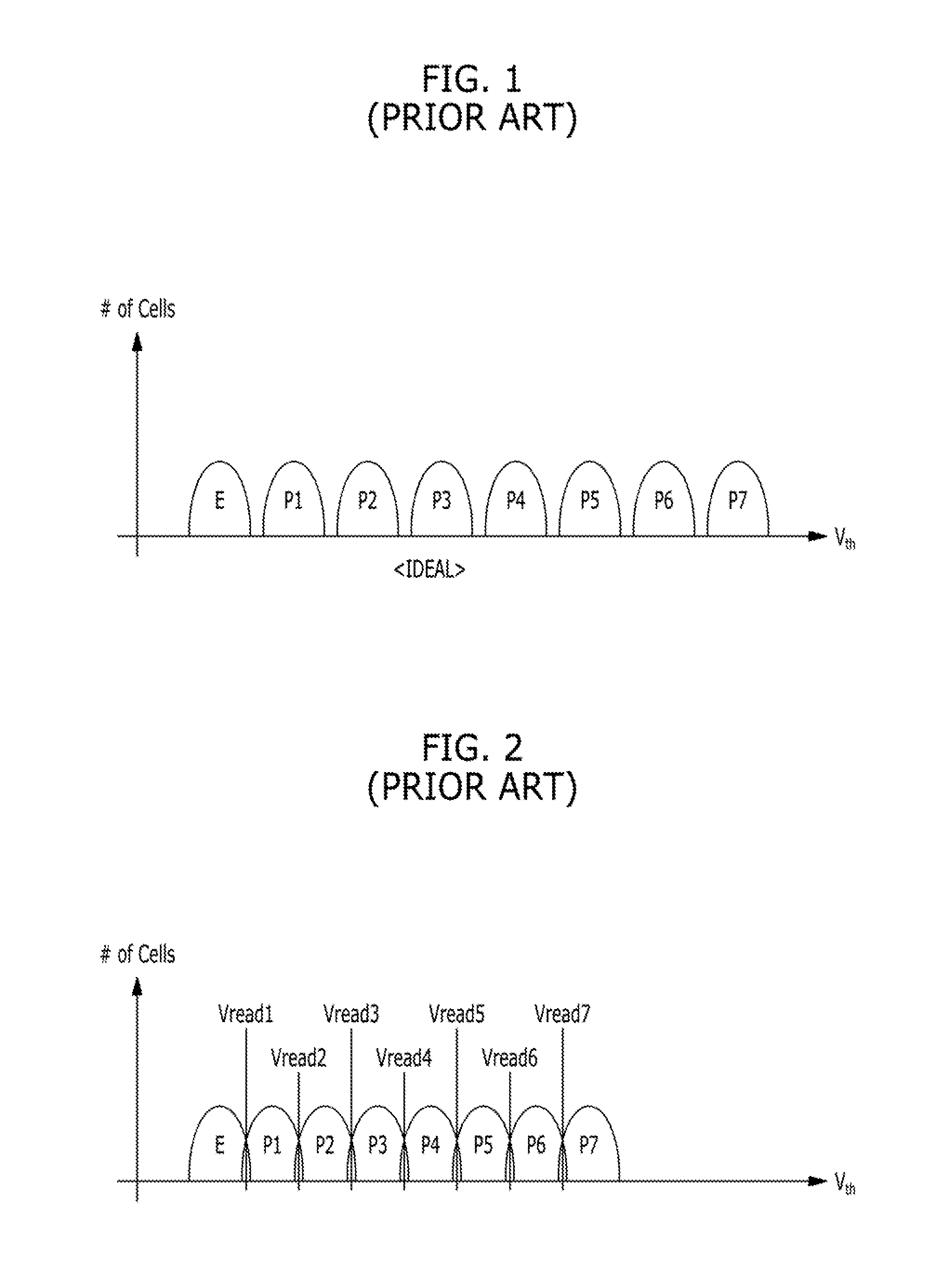

Controller, semiconductor memory system and operating method thereof

ActiveUS20160378596A1Accurate readingError correction/detection using convolutional codesError correction/detection using block single space codingSemiconductorComputer engineering

An operating method of a controller includes generating error reliability of data based on reliability information of one or more error-corrected bits of the data, wherein the data is read out from a semiconductor memory device and a hard decision ECC decoding to the data through a BCH code is determined as successful; and determining miscorrection of the data based on the error reliability.

Owner:SK HYNIX INC

Adaptive error correcting code for data communications over a plastic optical fibre

ActiveUS8634450B2Adapt effectivelyEasy to installError correction/detection using block single space codingUnequal/adaptive error protectionThree levelDigital data

An efficient coding and modulation system for transmission of digital data over plastic optical fibers is disclosed. The digital signal is coded by a three-level coset coding. The spectral efficiency of the system is configurable by selecting the number of bits to be processed in each of the levels. The first level applies to the digital data a binary BCH coding and performs coset partitioning by constellation mapping and lattice transformations. Similarly, second level applies another binary BCH coding, which may be performed selectably in accordance with the desired configuration by two BCH codes with substantially the same coding rate, operating on codewords of different sizes. The third level is uncoded. The second and third levels undergo mapping and lattice transformation. After an addition of the levels, a second-stage lattice transformation is performed to obtain a zero-mean constellation. The symbols output from such three-level coset coder are then further modulated.

Owner:KNOWLEDGE DEV FOR POF SL

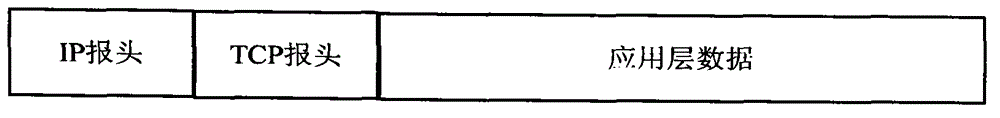

Real-time streaming media transmission protocol stack in multi-hop network

InactiveCN102984232AReduce redundancyIncrease the ability to resist sudden interferenceError preventionNetwork traffic/resource managementBroadcast channelsTransmission protocol

The invention discloses a real-time streaming media transmission protocol stack in a multi-hop network. A packet control layer and an error control layer are added to an existing transmission control protocol (TCP) / internet protocol (IP) stack. The real-time streaming media transmission protocol stack in the multi-hop network has the advantages that an IP header and a TCP header are compressed by the packet control layer, and the obtained compressed headers reduce data redundancy; the compressed headers are subjected to broadcast channel (BCH) encoding, the encoded headers are uniformly distributed to data portions, the resistance to burst interference of the headers is improved, a receiver can obtain accurate header information through BCH decoding, thereby packet loss and retransmission are avoided, and time delay caused by retransmission is reduced; and a cyclic redundancy check (CRC) single bit error correction based reed-solomon (RS) errors-and-erasures correcting encoding and decoding scheme of the error control layer is utilized, the good communication effect can be guaranteed under the channel with short burst as a majority and accompanied with a small quantity of random errors, and the time delay is excellently controlled.

Owner:XIDIAN UNIV +1

BCH code error correction method capable of adaptive error correction

InactiveCN102394114AImprove error correction performanceGuaranteed reliabilityStatic storageData errorSelf adaptive

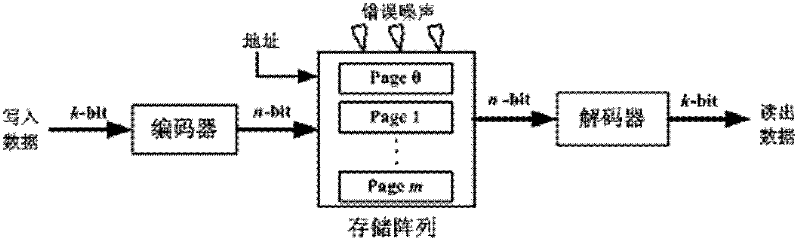

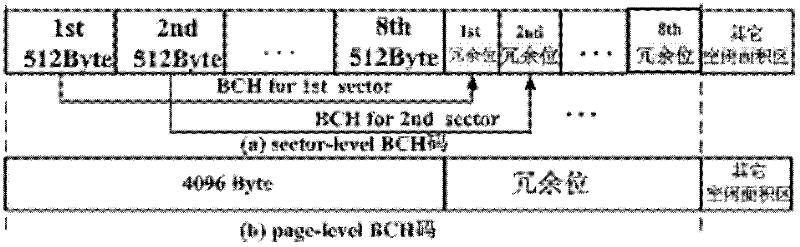

The invention discloses a BCH code error correction method capable of adaptive error correction, which belongs to the field of data error correction in non-volatile memories. The method comprises the following steps: 1) when a page programming erasing number of a NAND flash memory is less than or equal to a, selecting a sector-level BCH code as an error correcting code; 2) when the page programming erasing number of the NAND flash memory is more than a and less than b, selecting a page-level BCH code as an error correcting code; 3) when the page programming erasing number of the NAND flash memory is more than or equal to b, marking the page as an invalid page. The beneficial effect of the invention is that: when a sector-level BCH code is adopted, the response speed of the flash memory to a host is increased; when a page-level BCH code is adopted, the error correction performance is improved, and thus the service life of the flash memory is increased.

Owner:TSINGHUA UNIV

Method for encoding and modulating logical frame signaling channel in NGB-W system

ActiveCN104618072AImprove transmission reliabilitySupport transmissionError preventionSelective content distributionComputer hardwareBroadcast channels

The invention discloses a method for encoding and modulating a logical frame signaling channel in an NGB-W system. The method comprises the following steps of: adding CRC (cyclic redundancy code) bits to logical frame signaling and dividing the logical frame signaling into blocks; scrambling the logical frame signaling block; mapping the scrambled logical frame signaling block into BCH (Broadcast Channel) code information bits; performing forward error correction coding to the BCH code information bits; generating the coding block of the logical frame signaling block; generating logical frame signaling coding bit sequences; generating bit interleaving blocks; performing constellation mapping to the bit interleaving blocks to generate BICM (Bit Interleaved Coded Modulation) blocks. According to the method, the logical frame signaling with any length can be transmitted, so that the different-length logical frame signaling is basically uniform in transmission reliability; four levels of transmission reliability and transmission efficiency are selected under each modulating method.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

Quick double-error correction BCH code decoder

InactiveCN1561005AReduce complexityDecoding speed is fastError detection/correctionCode conversionControl signalError location

This invention discloses a BCH decoder for correcting double errors quickly working on GF(25) composed of an ad-joint computing circuit, an error number judgment circuit and an error location computing circuit connected sequently. The BCH code is BCH (N, N-10), code length N is any integer in 11-31. This method utilizes the feature of BCH code of correcting double mistakes to present a search method to compute the error location from the ad-joint result without the help of Chien method or ROM.

Owner:汇智系统股份有限公司 +1

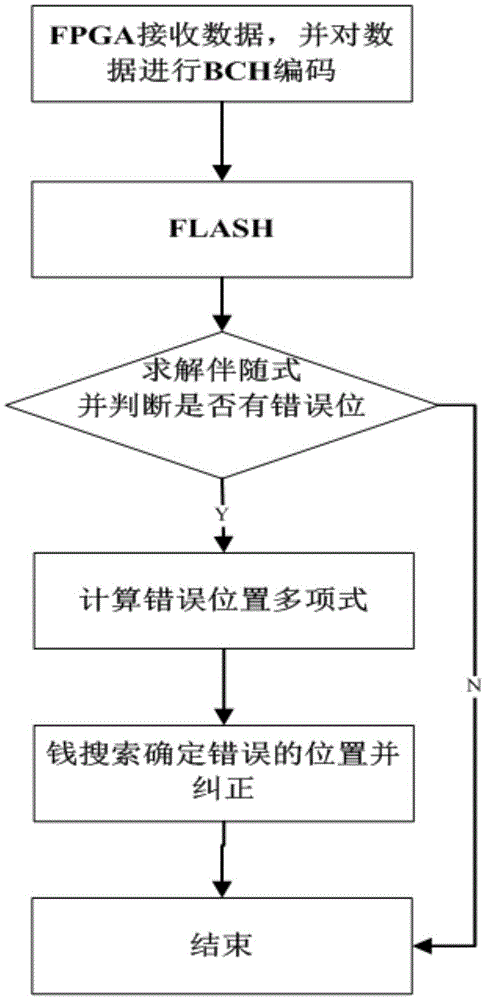

FPGA-based BCH encoding and decoding device and encoding and decoding method thereof

InactiveCN105553485AShort cycleReduce complexityCode conversionCyclic codesCheck digitError location

The invention discloses an FPGA-based BCH encoding and decoding method comprising the following steps: a receiving module receives signal data and sends the signal data to a BCH encoding module, the BCH encoding module encodes the signal data in a segmented manner to get r bit check digits corresponding to the signal data, and the signal data and the bit check digits are stored in a storage module; after the signal data and the parity bits are acquired from the storage module, BCH decoding is performed to get a code word polynomial R(x), Q syndromes of the code word polynomial R(x) are obtained on the basis, and an error location polynomial of error of the signal data in the storage process is obtained; and the root of the error location polynomial is solved according to the error location polynomial of error of the signal data in the storage process and a money search traversal algorithm, and the error data bit of the signal data in the storage process is corrected to get correct signal data stored in the storage module.

Owner:XIDIAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com