BCH code error correction method capable of adaptive error correction

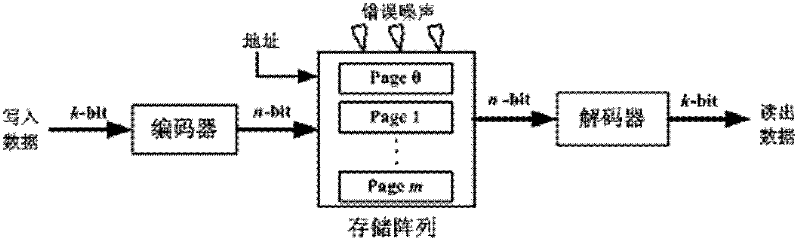

An error correction capability, BCH code technology, applied in the field of BCH code error correction, can solve the problems of reduced NAND flash memory life, reduced programming and erasing times, and reduced flash reliability. longevity and performance improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0040] Such as image 3 , Figure 5 As shown, the BCH code error correction method with adaptive error correction capability comprises the following steps:

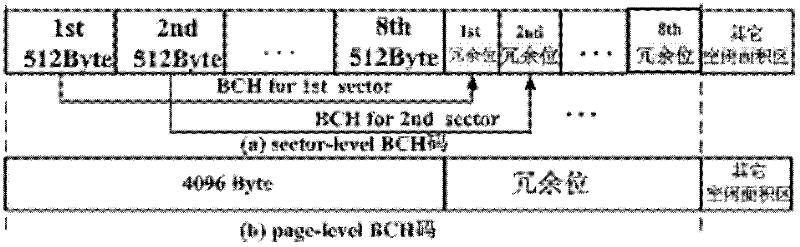

[0041] 1) When the NAND flash memory is first used, the number of page programming and erasing is small (less than or equal to a), and the bit error rate (BER) inside the flash memory is also small. At this time, the sector-level BCH code is selected (in sector (Sector) as the unit) as the error correction code of the NAND flash memory;

[0042] 2) With the continuous use of NAND flash memory, the number of page programming and erasing (P / E cycles) inside it continues to increase, and the bit error rate increases. When the number of page programming and erasing increases to a certain value (greater than a) When causing the number of bit errors to exceed the error correction capability of the original ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com